## 4.5V~36V、6A 昇降圧コンバータ

MAX26239/MAX26240

### 概要

MAX26239/MAX26240 は、H ブリッジ・スイッチを内蔵した小型の同期整流式昇降圧コンバータです。これらの IC は固定の出力電圧を生成できる他、3V~20V の範囲で外部調整可能な出力電圧を、出力電圧より高い入力電圧、低い入力電圧、あるいは等しい入力電圧から供給できます。これらの IC には、8.2A および 10A (代表値) の入力電流制限オプションが備わっており、入出力電圧比と動作周波数に応じて最大 6A の連続負荷電流をサポートできます。また、4.5V~36V の広い入力電圧範囲で動作します。

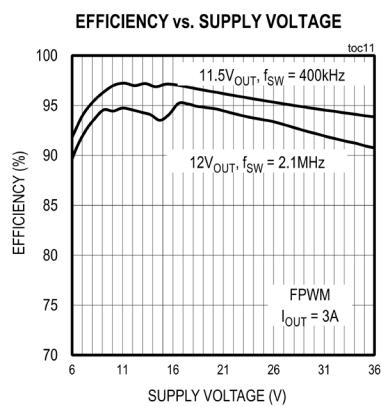

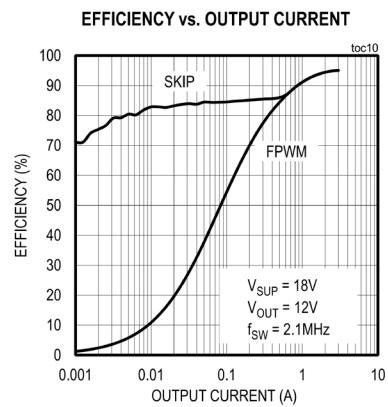

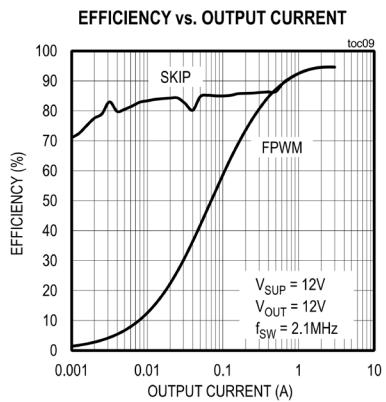

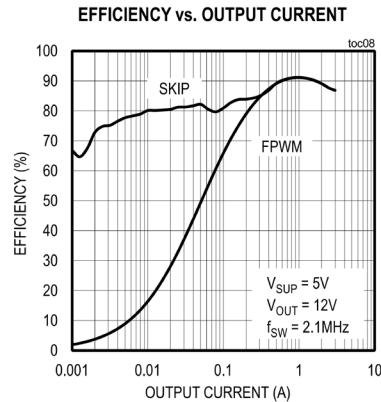

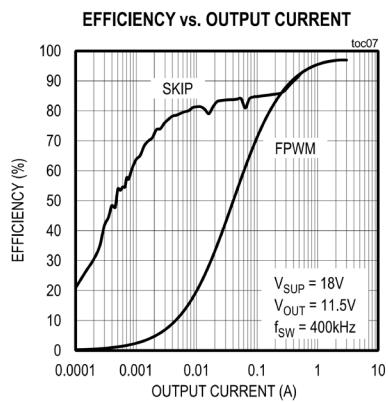

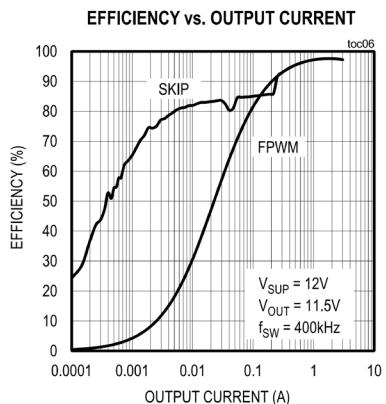

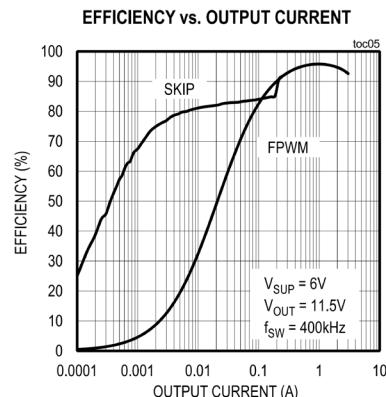

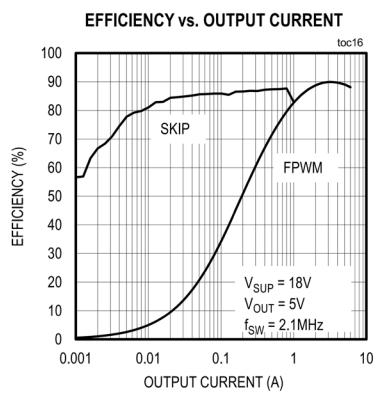

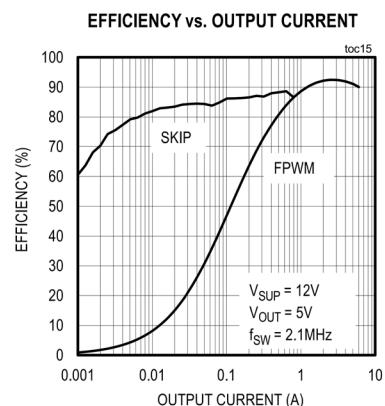

MAX26239/MAX26240 には 2 つのスイッチング周波数オプション (2.1MHz および 400kHz) があります。スイッチング周波数を最高の 2.1MHz に設定すると、小型の外付け部品が使用可能になります。出力リップルを抑えて、AM 帯域の干渉も防止できます。一方、スイッチング周波数を 400kHz にした場合は、効率が高まり、消費電力の問題を軽減できます。SYNC 入力では、超低自己消費電流でのスキップ・モード、強制固定周波数 PWM 動作、外部クロックへの同期という 3 つの動作モードを使用できます。これらの IC はスペクトラム拡散周波数変調を備えており、EMI 干渉を最小限に抑えることができます。

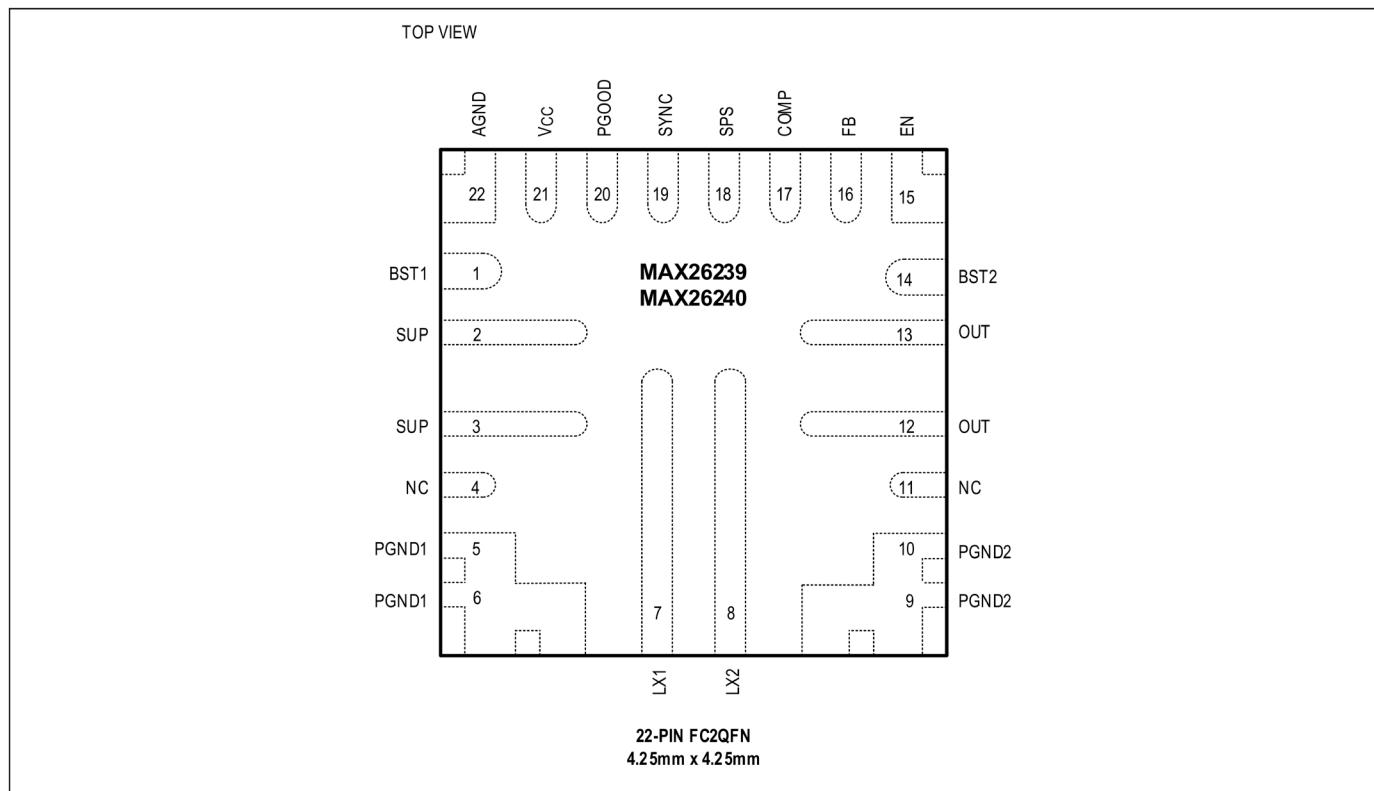

MAX26239/MAX26240 は、パワーOK (POK) インジケータ、低電圧ロックアウト、過電圧保護、サイクル単位の電流制限、サーマル・シャットダウンの機能を搭載しています。これらの IC は、小型 (4.25mm × 4.25mm × 0.75mm) の 22 ピン FC2QFN パッケージで提供されます。

### アプリケーション

- ポイントオブロード (POL) 電源

- 12V/24V 産業用アプリケーション

- 通信、サーバー、ネットワーク機器

### 機能と利点

- 厳しい品質要件と信頼性要件に対応

- 4.5V~36V の動作入力電圧範囲により、幅広い入力条件での動作が可能

- 最大 42V の入力トランジエントに対応可能

- EN ピンは最大 42V に対応

- 入力電流制限 : 8.2A/10A (代表値)

- 固定出力電圧および調整可能な出力電圧のオプション

- 温度範囲 : -40°C~+125°C

- 热特性が改善された高集積パッケージにより部品表コストと基板スペースを削減

- 内蔵 FET H ブリッジ・アーキテクチャ

- スイッチング周波数オプション : 2.1MHz/400kHz

- フェーズ・ロック・ループ (PLL) 周波数同期

- 放熱特性に優れた 22 ピン FC2QFN パッケージ

- 低自己消費電流により厳しい電流要件にも適合

- スタンバイ・モード時の自己消費電流 : 95µA

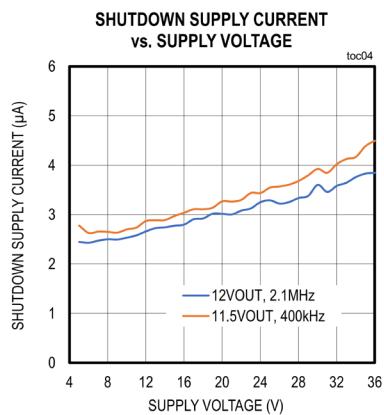

- 最大シャットダウン電流 : 10µA

- スイッチング周波数での EMI 放射を低減

- スペクトラム拡散機能の有効／無効を SPS ピンで制御

- 保護機能によってシステム信頼性を向上

- 電源低電圧ロックアウトおよび過熱に対する保護

- 出力 PGOOD インジケータ、過電圧、短絡に対する保護機能

型番はデータシートの末尾に記載されています。

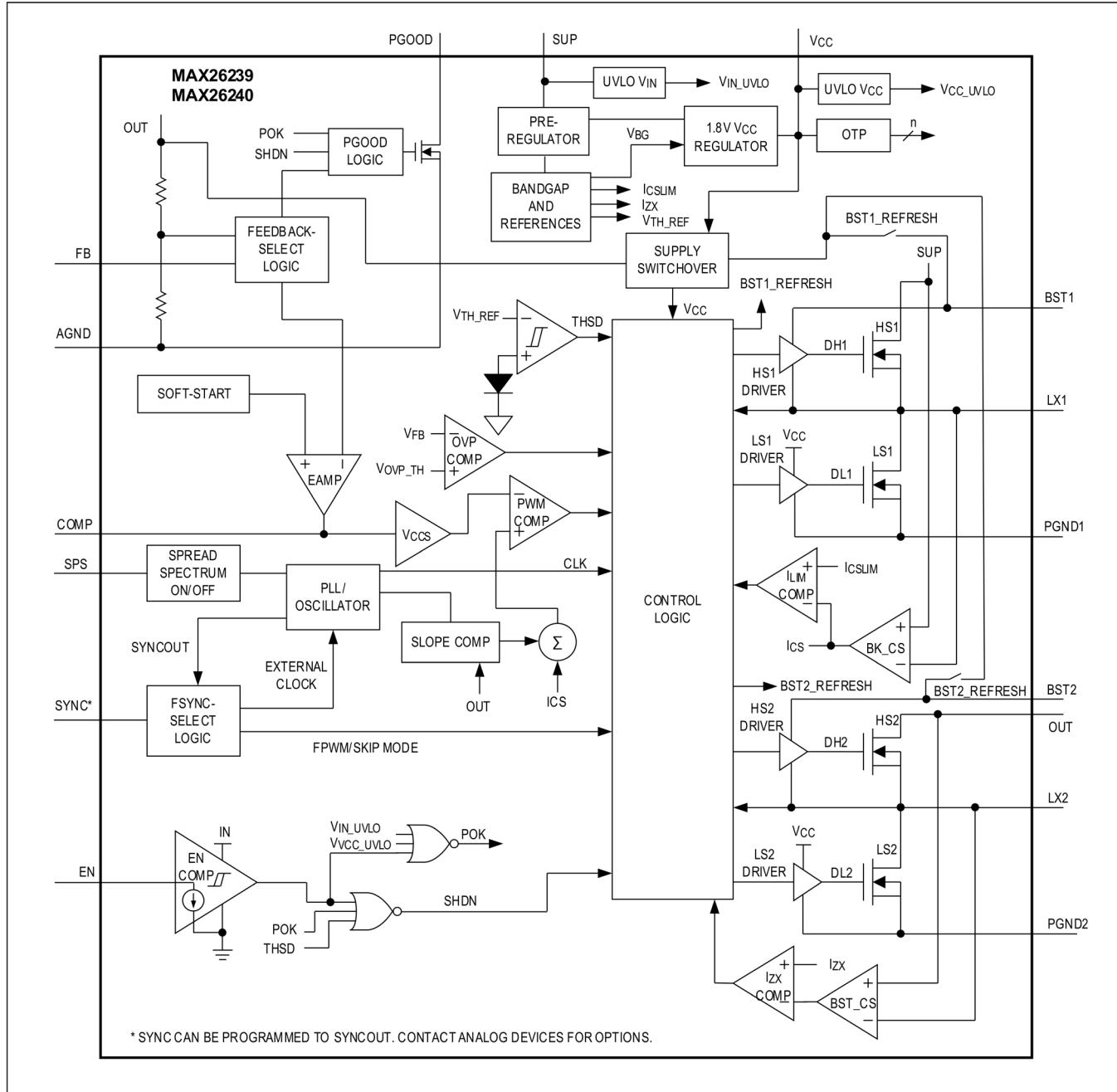

## 簡略化したブロック図

## 絶対最大定格

|                   |                              |

|-------------------|------------------------------|

| SUP、EN~AGND       | -0.3V~+42V                   |

| LX1~PGND1         | -0.3V~V <sub>SUP</sub> +0.3V |

| LX2~PGND2         | -0.3V~V <sub>OUT</sub> +0.3V |

| OUT~AGND          | -0.3V~+28V                   |

| BST1~LX1、BST2~LX2 | -0.3V~+2.2V                  |

| BST1~PGND1        | -0.3V~+44V                   |

| BST2~PGND2        | -0.3V~+30V                   |

| VCC、SPS~AGND      | -0.3V~+2.2V                  |

| COMP、FB~AGND      | -0.3V~V <sub>VCC</sub> +0.3V |

| PGND~AGND         | -0.3V~+0.3V                  |

|                                                                   |              |

|-------------------------------------------------------------------|--------------|

| SYNC、PGOOD~AGND                                                   | -0.3V~+6V    |

| ESD 保護                                                            |              |

| 人体モデル                                                             | ±2kV         |

| マシン・モデル                                                           | ±100V        |

| 連続消費電力 (T <sub>A</sub> = +70°C、+70°C を超えると 30mW/°C で<br>ディレーティング) | 2404mW       |

| 動作ジャンクション温度                                                       | -40°C~+150°C |

| 保管温度範囲                                                            | -65°C~+150°C |

| リード温度 (はんだ処理 10 秒)                                                | +300°C       |

| はんだ付け処理温度 (リフロー)                                                  | +260°C       |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## パッケージ情報

### 22 FC2QFN

| Package Code                                                             | F224A4FY+1                |                      |

|--------------------------------------------------------------------------|---------------------------|----------------------|

| Outline Number                                                           | <a href="#">21-100399</a> |                      |

| Land Pattern Number                                                      | <a href="#">90-100137</a> |                      |

| THERMAL PARAMETERS                                                       | 4-LAYER JEDEC BOARD       | 4-LAYER EV KIT BOARD |

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )                | 33.3°C/W                  | 22.4°C/W             |

| Junction-to-Case (top) Thermal Resistance (θ <sub>JCT</sub> )            | 6.8°C/W                   | —                    |

| Junction-to-Case (bottom) Thermal Resistance (θ <sub>JCB</sub> )         | 6.4°C/W                   | 7.5°C/W              |

| Junction-to-Board Thermal Resistance (θ <sub>JB</sub> )                  | 7.6°C/W                   | 9.6°C/W              |

| Junction-to-Top Thermal Characterization Parameter (Ψ <sub>JT</sub> )    | 3.3°C/W                   | 3.3°C/W              |

| Junction-to-Bottom Thermal Characterization Parameter (Ψ <sub>JB</sub> ) | 8.5°C/W                   | 9.4°C/W              |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、アナログ・デバイセズ社ウェブサイトのパッケージ・インデックスで確認してください。パッケージ・コードの「+」、「#」、「-」はRoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面はRoHS状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、[IC パッケージの熱特性評価](#)を参照してください。

## 電気的特性

(特に指定のない限り、V<sub>SUP</sub> = V<sub>EN</sub> = 14V、T<sub>J</sub> = -40°C~+150°C。代表値は T<sub>A</sub> = +25°C での値です。Note 1 と Note 2 参照。)

| PARAMETER               | SYMBOL                        | CONDITIONS                                   | MIN | TYP | MAX | UNITS |

|-------------------------|-------------------------------|----------------------------------------------|-----|-----|-----|-------|

| <b>SUP INPUT SUPPLY</b> |                               |                                              |     |     |     |       |

| SUP Voltage Range       | V <sub>SUP</sub>              | Initial startup                              | 4.5 |     | 36  | V     |

| Shutdown Supply Current | I <sub>SUP_SHUTDO</sub><br>WN | V <sub>EN</sub> = 0V, T <sub>A</sub> = +25°C |     | 5   | 10  | μA    |

(特に指定のない限り、 $V_{SUP} = V_{EN} = 14V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$ 。代表値は  $T_A = +25^{\circ}C$  での値です。Note 1 と Note 2 参照。)

| PARAMETER                                   | SYMBOL               | CONDITIONS                                                       | MIN           | TYP     | MAX   | UNITS     |

|---------------------------------------------|----------------------|------------------------------------------------------------------|---------------|---------|-------|-----------|

| Standby Supply Current                      | $I_{SUP\_STANDBY}$   | $V_{EN} = V_{SUP}$ , $V_{OUT} = 5V$ , no load, $V_{SYNC} = 0V$   |               | 95      |       | $\mu A$   |

| SUP Undervoltage Lockout                    | $V_{UVLO\_RISE}$     | $V_{SUP}$ rising                                                 |               | 4.2     | 4.45  | V         |

|                                             | $V_{UVLO\_FALL}$     | $V_{SUP}$ falling                                                |               |         | 1.9   |           |

| <b>V<sub>CC</sub> REGULATOR</b>             |                      |                                                                  |               |         |       |           |

| V <sub>CC</sub> Output Voltage              | $V_{VCC}$            | $V_{SUP} > 3.5V$ , $I_{VCC} = 1mA$ to $50mA$                     |               | 1.8     |       | V         |

| V <sub>CC</sub> Undervoltage Lockout        | $V_{UVLO\_VCC}$      | $V_{VCC}$ falling                                                |               | 1.6     |       | V         |

|                                             | $V_{UVLO\_VCC\_HYS}$ | $V_{VCC}$ hysteresis, <a href="#">Note 3</a>                     |               | 100     |       | mV        |

| V <sub>CC</sub> Short-Circuit Current Limit | $I_{VCC\_SC}$        | V <sub>CC</sub> shorted to AGND                                  |               | 50      |       | mA        |

| <b>BUCK-BOOST CONVERTER</b>                 |                      |                                                                  |               |         |       |           |

| Fixed Output Voltage                        | $V_{OUT\_5V}$        | $V_{FB} = V_{VCC}$                                               | 4.9           | 5.0     | 5.1   | V         |

|                                             | $V_{OUT\_11P5}$      | $V_{FB} = V_{VCC}$                                               | 11.27         | 11.5    | 11.73 |           |

| Soft-Start Ramp Time                        | $t_{SOFT\_START}$    |                                                                  |               | 2.5     |       | ms        |

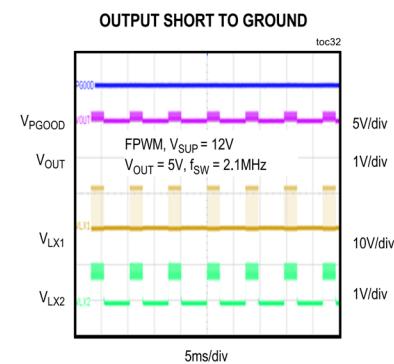

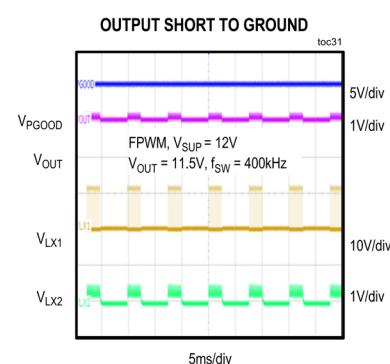

| Auto Retry Time                             | $t_{AUTO}$           | Auto retry time after an output short condition is detected      |               | 5       |       | ms        |

| Minimum ON Time                             | $t_{ON\_MIN}$        | In buck mode, $f_{SW} = 2.1MHz$                                  |               | 100     |       | ns        |

|                                             |                      | In buck mode, $f_{SW} = 400kHz$ , <a href="#">Note 3</a>         |               | 125     |       |           |

| Dead Time                                   | $t_{DEAD}$           | <a href="#">Note 3</a>                                           |               | 3       |       | ns        |

| LX1, LX2 Rise Time                          | $t_{LX\_RISE}$       | <a href="#">Note 3</a>                                           |               | 1.5     |       | ns        |

| LX1, LX2 Fall Time                          | $t_{LX\_FALL}$       | <a href="#">Note 3</a>                                           |               | 3       |       | ns        |

| <b>POWER MOSFET</b>                         |                      |                                                                  |               |         |       |           |

| DMOS On-Resistance                          | $R_{DSON\_DMOS}$     | $V_{VCC} = 1.8V$ , $I_{DSON} = 0.2A$                             |               | 20      | 35    | $m\Omega$ |

| LX1 Leakage Current                         | $I_{LX1\_LKG}$       | $V_{EN} = 0V$ , $V_{SUP} = V_{LX1} = 36V$ , $T_A = +25^{\circ}C$ |               |         | 5     | $\mu A$   |

| LX2 Leakage Current                         | $I_{LX2\_LKG}$       | $V_{EN} = 0V$ , $V_{LX2} = 12V$ , $T_A = +25^{\circ}C$           |               |         | 5     | $\mu A$   |

| <b>CURRENT SENSE</b>                        |                      |                                                                  |               |         |       |           |

| Current Limit                               | $I_{LIM}$            | 10A, <a href="#">Note 4</a>                                      | 8             | 10      | 12    | A         |

|                                             |                      | 8.2A                                                             | 6.8           | 8.2     | 9.5   |           |

| <b>ERROR AMPLIFIER</b>                      |                      |                                                                  |               |         |       |           |

| Regulated Feedback Voltage                  | $V_{FB}$             |                                                                  | 0.786         | 0.800   | 0.814 | V         |

| Feedback Leakage Current                    | $I_{FB\_LKG}$        | $V_{FB} = 0.8V$ , $T_A = +25^{\circ}C$                           |               | 0.02    | 1     | $\mu A$   |

| Transconductance (from FB to COMP)          | $g_m$                | $V_{FB} = 0.8V$ , $V_{VCC} = 1.8V$                               | 85            | 100     | 115   | $\mu S$   |

| <b>SWITCHING FREQUENCY</b>                  |                      |                                                                  |               |         |       |           |

| PWM Switching Frequency                     | $f_{SW}$             | 400kHz option                                                    | 350           | 400     | 450   | kHz       |

|                                             |                      | 2.1MHz option                                                    | 1.9           | 2.1     | 2.3   | MHz       |

| SYNC External Clock Input                   | $f_{SYNC}$           | Minimum sync pulse of 100ns                                      | 400kHz option | 280     | 520   | kHz       |

|                                             |                      |                                                                  | 2.1MHz option | 1.5     | 2.7   | MHz       |

| Spread Spectrum                             | SPS                  |                                                                  |               | $\pm 6$ |       | %         |

| <b>OUTPUT MONITORS</b>                      |                      |                                                                  |               |         |       |           |

(特に指定のない限り、 $V_{SUP} = V_{EN} = 14V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$ 。代表値は  $T_A = +25^{\circ}C$  での値です。Note 1 と Note 2 参照。)

| PARAMETER                           | SYMBOL              | CONDITIONS                                                | MIN | TYP | MAX | UNITS       |

|-------------------------------------|---------------------|-----------------------------------------------------------|-----|-----|-----|-------------|

| Output Overvoltage Threshold        | $V_{OUT\_OVP}$      | Detected with respect to $V_{FB}$ rising                  | 106 | 108 | 110 | %           |

| Output Overvoltage Hysteresis       | $V_{OUT\_OVP\_HYS}$ |                                                           |     | 3   |     | %           |

| PGOOD Threshold                     | $V_{PGOOD\_TH}$     | % of $V_{OUT}$ , $V_{OUT}$ rising                         | 92  | 94  | 96  | %           |

|                                     |                     | % of $V_{OUT}$ , $V_{OUT}$ falling                        | 91  | 93  | 95  |             |

| PGOOD Output Low Voltage            | $V_{PGOOD\_LOW}$    | $I_{SINK} = 1mA$                                          |     |     | 0.2 | V           |

| PGOOD Leakage Current               | $I_{PGOOD\_LKG}$    | $V_{PGOOD} = 5.5V$ , $T_A = +25^{\circ}C$                 |     |     | 1   | $\mu A$     |

| PGOOD Debounce Time                 | $t_{PGOOD\_DB}$     | Fault detection, rising and falling                       |     | 40  |     | $\mu s$     |

| <b>LOGIC INPUTS (EN, SYNC, SPS)</b> |                     |                                                           |     |     |     |             |

| Input High Level                    | $V_{HIGH}$          | Voltage rising                                            | 1.3 |     |     | V           |

| Input Low Level                     | $V_{LOW}$           | Voltage falling                                           |     |     | 0.5 | V           |

| Input Leakage Current (EN, SPS)     | $I_{IN\_LEAK}$      | $T_A = +25^{\circ}C$                                      |     |     | 1   | $\mu A$     |

| Input Leakage Current (SYNC)        | $I_{IN\_LEAK}$      | $T_A = +25^{\circ}C$ , $SYNC = 1.8V$ , $EN = \text{high}$ | 20  | 50  |     | $\mu A$     |

| <b>THERMAL SHUTDOWN</b>             |                     |                                                           |     |     |     |             |

| Thermal Shutdown Threshold          | $T_{SHDN}$          | <a href="#">Note 3</a>                                    |     |     | 175 | $^{\circ}C$ |

| Thermal Shutdown Hysteresis         | $T_{SHDN\_HYS}$     | <a href="#">Note 3</a>                                    |     |     | 20  | $^{\circ}C$ |

**Note 1:** 全ユニットを $+25^{\circ}C$ で100%出荷テストしています。温度限界は全て設計と特性評価により裏付けられています。

**Note 2:** このデバイスは、 $T_J = +125^{\circ}C$ で95,000時間、 $T_J = +150^{\circ}C$ で5,000時間、連続動作するように設計されています。

**Note 3:** これらの仕様については出荷テストを行っていませんが、設計により裏付けられています。

**Note 4:** 昇圧モードの電流制限。

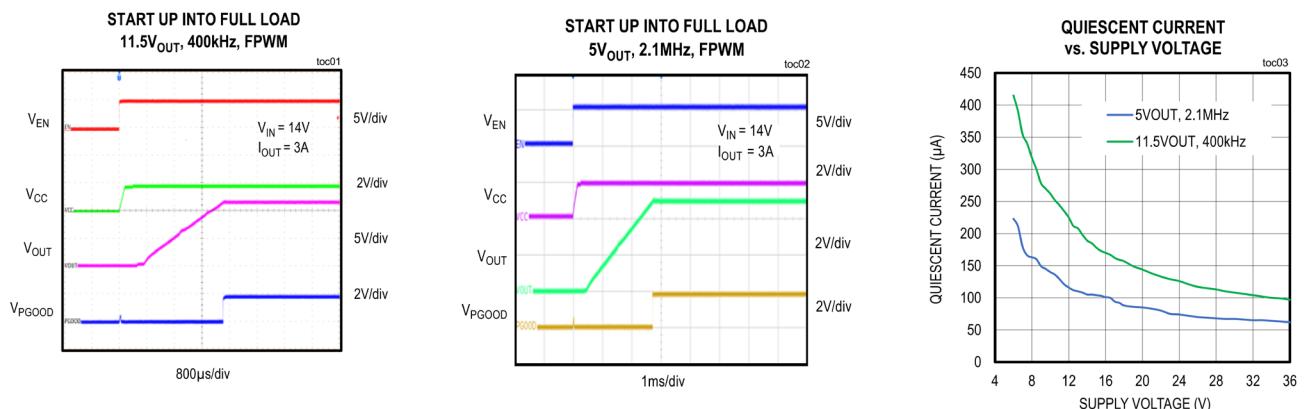

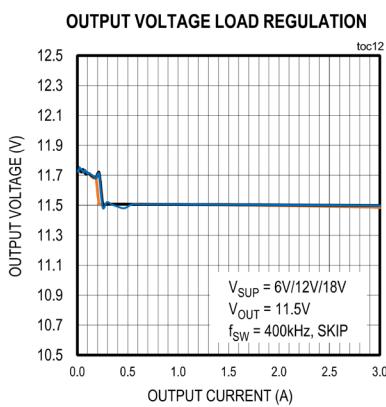

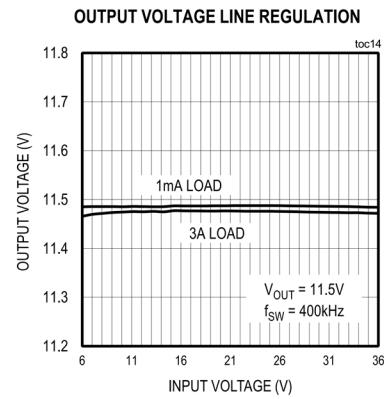

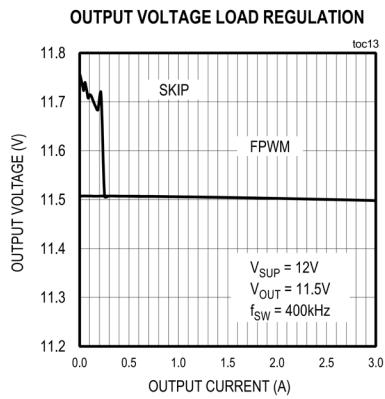

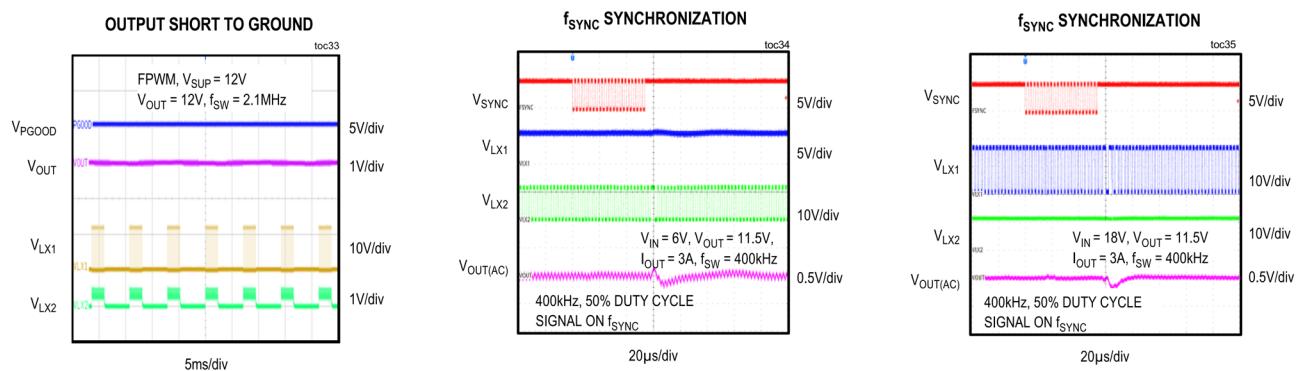

## 標準動作特性

(特に指定のない限り、 $T_A = +25^{\circ}C$ 。)

(特に指定のない限り、 $T_A = +25^\circ\text{C}$ 。)

(特に指定のない限り、 $T_A = +25^\circ\text{C}$ 。)

(特に指定のない限り、 $T_A = +25^\circ\text{C}$ 。)

## ピン配置

## 端子説明

| ピン   | 名称   | 説明                                                                                                |

|------|------|---------------------------------------------------------------------------------------------------|

| 1    | BST1 | スイッチング・ノード LX1 用のブートストラップ・コンデンサ接続。LX1 と BST1 の間に $0.1\mu\text{F}$ のセラミック・コンデンサを接続します。             |

| 2, 3 | SUP  | 昇降圧コンバータと内部 $V_{\text{CC}}$ LDO レギュレータの電源。 $4.7\mu\text{F}$ 以上のセラミック・コンデンサで SUP を PGND1 にバイパスします。 |

| 4    | NC   | 未接続。                                                                                              |

|        |                 |                                                                                                                                                                                                                                                          |

|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5, 6   | PGND1           | 降圧ローサイド FET LS1 の電源グランド接続。PGND1 と PGND2 をまとめて電源グランドに接続します。                                                                                                                                                                                               |

| 7      | LX1             | 昇降圧コンバータのスイッチング・ノード 1。LX1 をパワー・インダクタの一方の側に接続します。                                                                                                                                                                                                         |

| 8      | LX2             | 昇降圧コンバータのスイッチング・ノード 2。LX2 はパワー・インダクタのもう一方の側に接続します。                                                                                                                                                                                                       |

| 9, 10  | PGND2           | 昇圧ローサイド FET LS2 の電源グランド接続。PGND1 と PGND2 をまとめて電源グランドに接続します。                                                                                                                                                                                               |

| 11     | NC              | 未接続。                                                                                                                                                                                                                                                     |

| 12, 13 | OUT             | 昇降圧コンバータの出力。                                                                                                                                                                                                                                             |

| 14     | BST2            | スイッチング・ノード LX2 用のブートストラップ・コンデンサ接続。LX2 と BST2 の間に $0.1\mu\text{F}$ のセラミック・コンデンサを接続します。                                                                                                                                                                    |

| 15     | EN              | 高耐圧のイネーブル入力。EN をハイにすると昇降圧コンバータがイネーブルされます。                                                                                                                                                                                                                |

| 16     | FB              | 帰還入力。OUT と AGND の間に配置した抵抗分圧器に FB を接続して、3V~20V の範囲で出力電圧を調整します。固定出力電圧オプションに設定する場合は、FB を $V_{\text{CC}}$ に接続します。                                                                                                                                            |

| 17     | COMP            | エラー・アンプ出力。RC 補償ネットワークを COMP と AGND の間に接続して、制御ループを安定化します。                                                                                                                                                                                                 |

| 18     | SPS             | スペクトラム拡散 (SPS) 機能イネーブル入力。SPS をハイに接続すると、SPS 機能がイネーブルされ、ローに接続すると SPS 機能がディスエーブルされます。                                                                                                                                                                       |

| 19     | SYNC            | 外部クロック同期およびスキップ・モード/PWM モード制御入力。SYNC を AGND に接続するとスキップ・モードが有効になります。SYNC を $V_{\text{CC}}$ に接続すると PWM モードが有効になります。SYNC を有効な外部クロックに接続すると、昇降圧コンバータのスイッチング周波数が外部クロックに同期します。                                                                                  |

| 20     | PGOOD           | オープン・ドレインのパワーグッド・インジケータ。 $V_{\text{CC}}$ または 5.5V より低い正電圧に PGOOD を外付けの抵抗でブルアップすると、OUT 電圧の状態を正確に提示します。OUT 電圧がレギュレーション電圧の 93% (代表値) より下がると、PGOOD がローにアサートされます。OUT 電圧がレギュレーション電圧の 94% (代表値) より高くなると、PGOOD は高インピーダンスになります。ソフトスタート中とシャットダウン中も、PGOOD はローになります。 |

| 21     | $V_{\text{CC}}$ | 内部 1.8V レギュレータ出力。 $V_{\text{CC}}$ は $4.7\mu\text{F}$ 以上のセラミック・コンデンサでグランドにバイパスします。                                                                                                                                                                        |

| 22     | AGND            | アナログ・グランド。AGND、PGND1、PGND2 は、スター・グランド接続になるようにまとめて 1 点で接続します。                                                                                                                                                                                             |

## 詳細説明

MAX26239/MAX26240 は、小型の同期整流式昇降圧コンバータで、ハイサイド・スイッチとローサイド・スイッチを内蔵しています。これらの IC は、+4.5V~+36V の入力電圧で最大 6.0A を供給できるよう設計されており、無負荷時の自己消費電流はわずか 95 $\mu$ A です。MAX26239/MAX26240 は、通常動作入力範囲内で $\pm 2\%$ の正確な出力電圧を供給します。電圧品質は、PGOOD 信号を観察することで監視可能です。

MAX26239/MAX26240 は、固定の出力電圧および3V~20V の範囲のプログラマブルな出力電圧を出力できます。周波数は固定で、400kHz と 2.1MHz のオプションがあります。2.1MHz の周波数では、小型の外付け部品を使用でき、出力リップルが低減され、AM 干渉をなくすことができます。この IC は、軽負荷時には自動的にスキップ・モードに入り、無負荷時には 95 $\mu$ A という超低自己消費電流になります。EMI 放射エミッションを最小限に抑えるために、 $\pm 6\%$ のスペクトラム拡散周波数変調での動作が可能です。

## H ブリッジ動作

MAX26239/MAX26240 の H ブリッジ構成を [簡略化したブロック図](#) に示します。H ブリッジは、HS1、LS1、HS2、LS2 の 4 つのスイッチで構成されます。スイッチ HS1 と LS1 は直列に入力電圧に接続されており、スイッチ HS2 と LS2 は出力に接続されています。インダクタを LX1 と LX2 の間に接続します。入力電圧と出力電圧の比に応じて、降圧モード、昇圧モード、昇降圧モードの 3 つの動作モードがあります。

## 降圧モード

入力電圧が出力電圧よりはるかに高い場合、MAX26239/MAX26240 は純粋な降圧モードで動作します。このモードでは、スイッチ HS2 は常時オン、スイッチ LS2 は常時オフで、スイッチ HS1 と LS1 はスイッチング周波数でスイッチングします。IC はピーク電流モード制御方式を用いて、スイッチ HS1 と LS1 の ON パルス幅を決定します。スイッチ HS1 と LS1 は交互に切り替わり、同期整流式降圧コンバータのように動作します。

## 昇圧モード

入力電圧が出力電圧よりはるかに低い場合、MAX26239/MAX26240 は純粋な昇圧モードで動作します。このモードでは、スイッチ HS1 は常時オン、スイッチ LS1 は常時オフで、スイッチ HS2 と LS2 はスイッチング周波数でスイッチングします。MAX26240 はピーク電流モード制御方式を用いて、スイッチ HS2 と LS2 の ON パルス幅を決定します。スイッチ HS2 と LS2 は交互に切り替わり、同期整流式昇圧コンバータのように動作します。

## 昇降圧モード

入力電圧が出力電圧に近い場合、MAX26239/MAX26240 は昇降圧モードで動作します。昇降圧の遷移領域では、高い効率の維持と遷移領域での出力電圧レギュレーションに必要なため、4 つのスイッチ全てがスイッチング周波数でオン／オフします。

## リニア・レギュレータ出力 (V<sub>cc</sub>)

このデバイスには、1.8V のリニア・レギュレータ (V<sub>cc</sub>) が内蔵されており、内部回路ブロックに電力を供給します。V<sub>cc</sub> と GND の間に 4.7 $\mu$ F (以上) のセラミック・コンデンサを接続します。バイアス・レギュレータには、起動時には入力から電力が供給され、起動が完了すると出力からの供給に切り替わります。出力電圧が 1.8V 未満の場合、バイアス・レギュレータは常に入力から電力の供給を受けます。

## ソフトスタート

MAX26239/MAX26240 には 2.5ms のソフトスタート時間があります。ソフトスタート時間は、出力電圧をレギュレーション・ポイントに向けて強制的にランプ・アップすることによって、起動時の突入電流を制限するものです。ソフトスタートの上昇率は 2.5ms です。

## 電流制限／ヒップ・モード

デバイスは、出力での短絡および過負荷状態からデバイスを保護する電流制限機能を備えています。短絡または過負荷状態の場合、インダクタ電流がハイサイド MOSFET の電流制限スレッショルドに達するまで、ハイサイド MOSFET はオンのままでです。次に、コンバータはローサイド MOSFET をオンにして、インダクタ電流を減少させます。インダクタ電流がローサイド MOSFET の電流制限スレッショルドを下回ると、コンバータはハイサイド MOSFET を再びオンにします。このサイクルは、短絡または過負荷状態が解消されるまで繰り返されます。

デバイスが電流制限に達し、出力電圧が目標値の 50% を下回ると、ヒップ・モードが有効になり、出力が 5ms オフになった後、ソフトスタートで再び起動しようとします。

## パワーグッド出力 (PGOOD)

このデバイスには、オープン・ドレインのパワーグッド・インジケータ (PGOOD) があります。出力電圧が 93% (代表値) の立下がりスレッショルドより下がると、PGOOD はローにアサートされます。出力電圧が 94% (代表値) の立上がりスレッショルドより上ると、PGOOD はアサート解除されます。PGOOD はプルアップ抵抗を介して出力もしくは外部の I/O 電圧に接続します。

## 同期入力 (SYNC)

SYNC ピンは、動作モードの選択と周波数制御のために用いられる、ロジックレベルの入力です。SYNC を V<sub>CC</sub> または外部クロックに接続すると、強制固定周波数 (FPWM) 動作が有効になります。SYNC を GND に接続すると、自動スキップ・モード動作が有効になり、軽負荷時の効率が改善します。SYNC に与える外部クロックの周波数は、20%まで内部より高くあるいは低くすることができます。このデバイスは、2 周期内で外部クロックに同期します。2 クロック・サイクルより長く外部クロック信号が SYNC で検出されなければ、IC は内部クロック動作に切り替わります。

## システム・イネーブル (EN)

イネーブル制御入力 (EN) でデバイスを低電力シャットダウン・モードから起動します。EN は、V<sub>IN</sub> から低い側は 1.8V までの入力に対応可能です。EN で内蔵のリニア (V<sub>CC</sub>) レギュレータがオンになります。V<sub>CC</sub> が内部ロックアウト・スレッショルド (V<sub>UVLO\_VCC</sub> = 1.7V (代表値)) を超えると、コンバータが起動し、出力電圧はプログラムされたソフトスタート時間でランプ・アップします。

EN がロジックローの場合、デバイスはシャットダウンします。シャットダウンの間、V<sub>CC</sub> レギュレータとゲート・ドライバはオフになります。シャットダウン時は電力が最も低くなる状態で、自己消費電流は 5 $\mu$ A (代表値) に低下します。EN をハイに駆動すると、デバイスがシャットダウンから復帰します。

## スペクトラム拡散オプション (SPS)

SPS ピンがハイに接続されているとき、動作周波数はスイッチング周波数を中心に  $\pm 6\%$  の範囲で変動します。

デバイスが外部クロックに同期している場合は、内部のスペクトラム拡散は無効化されます。しかし、SYNC ピンの外部クロックはフィルタされないので、供給される外部クロックに存在する変調は (スペクトラム拡散のものを含み) そのまま通過します。

## サーマル・シャットダウン保護

サーマル・シャットダウンは、デバイスを過度な動作温度から保護するものです。ジャンクション温度が +175°C を超えると、内蔵センサーがコンバータをシャットダウンして、IC の温度が下がるようにします。ジャンクション温度が 20°C 下がると、センサーによって IC が再びオンになります。サーマル・シャットダウンでは電力のスイッチングのみがディスエーブルになり、V<sub>CC</sub> レギュレータや IC ロジックはサーマル・シャットダウン中もアクティブのままでです。

## アプリケーション情報

### インダクタの選択

インダクタの設計は、サイズ、効率、制御、帯域幅、コンバータの安定性などの兼ね合いで決まります。昇降圧アプリケーションでは、インダクタの適切な値を選択することが更に重要です。これは昇圧モードと昇降圧モードでは右半平面 (RHP) ゼロが存在するからです。インダクタンス値を大きくすると、MOSFET での実効値電流損失、インダクタのコア損失と巻線損失が低減します。一方、制御ループが低速になり、RHP ゼロの周波数が下がるため、安定性に懸念が生じる場合があります。

式 1、式 2、式 3 を使用し、降圧モード動作時と昇圧モード動作時の最大インダクタ電流に対するパーセンテージとしてのインダクタのピーク to ピーク電流リップルに基づいて、インダクタを選択します。一般的には、最大インダクタ電流の 40% のリップルが、速度と効率の間の良い妥協点になります。

式 1 :

$$L_{BUCK} = \frac{(V_{IN\_MAX} - V_{OUT}) \times V_{OUT}}{f_{SW} \times \Delta I_{LP-P} \times V_{IN\_MAX}}$$

ここで、

$V_{IN\_MAX}$  = 最大入力電圧

$V_{OUT}$  = 出力電圧

$\Delta I_{LP-P}$  = インダクタのピーク to ピーク電流リップル

$f_{SW}$  = スイッチング周波数

式 2 :

$$L_{BOOST} = \frac{(V_{OUT\_MAX} - V_{IN}) \times V_{IN}}{f_{SW} \times \Delta I_{LP-P} \times V_{OUT\_MAX}}$$

ここで、

$V_{IN}$  = 入力電圧

$V_{OUT\_MAX}$  = 最大出力電圧

$L_{BUCK}$  と  $L_{BOOST}$  の大きい方を選択して、インダクタンス  $L$  の最終値とします。インダクタンス  $L$  の最終値が選択されれば、式 3 を使用して実ピーク・インダクタ電流を計算し、飽和電流がピーク・インダクタ電流より約 20% 大きく、DC 抵抗 (DCR) が低いインダクタを選択します。

式 3 :

$$I_{L_{PEAK}} = \frac{V_{OUT} \times I_{OUT}}{V_{IN\_MIN} \times \eta} + \frac{V_{IN\_MIN} \times \left(1 - \frac{V_{IN\_MIN}}{V_{OUT}}\right)}{L \times f_{SW} \times 2}$$

ここで、

$V_{IN\_MIN}$  = 最小入力電圧

$I_{OUT}$  = 出力電流

$\eta$  = 電力変換効率

$L$  = インダクタ値

### 最大出力電流

MAX26239/MAX26240 はピーク・インダクタ電流を検出して出力電流を制限します。最大出力電流は動作条件と部品の選択により決定し、これがピーク・インダクタ電流に影響します。重負荷で出力電圧が高いとき、熱の制限が出力電流供給能力に影響します。 $\theta_{JA}$  を使用して特定の動作条件におけるジャンクション温度を見積もり、デバイスがサーマル・シャットダウンをトリガするかを判断します。

## 入力コンデンサ

入力コンデンサは、電源から引き出されるピーク電流を抑制し、回路のスイッチングに起因する入力のノイズおよび電圧リップルを低減します。降圧モードの動作では、入力コンデンサには高い不連続な入力電流が発生します。入力コンデンサの等価直列抵抗 (ESR) と容量によって、式4で計算されるピーク to ピーク電圧リップルが生じます。

式4：

$$\Delta V_{IN} = \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times I_{OUT} \times ESR + \frac{\left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times I_{OUT} \times V_{OUT}}{f_{SW} \times V_{IN} \times C_{IN}}$$

ここで、

ESR = 入力コンデンサの等価直列抵抗

I<sub>OUT</sub> = 出力電流

C<sub>IN</sub> = 入力コンデンサの容量

得られた最大入力電圧リップルに対し、式5で入力容量を計算します。

式5：

$$C_{IN} = \frac{\left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times I_{OUT} \times V_{OUT}}{(V_{IN} \times \Delta V_{IN} - (V_{IN} - V_{OUT}) \times I_{OUT} \times ESR) \times f_{SW}}$$

選択した入力コンデンサは、式6で計算される入力コンデンサの入力実効値電流を許容できるように設計されたものであることが必要です。

式6：

$$I_{CIN_{RMS}} = \frac{I_{OUT} \times \sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}}{V_{IN}}$$

ここで、

I<sub>CINRMS</sub> = 入力コンデンサを流れる実効値電流

V<sub>IN</sub> = 2 × V<sub>OUT</sub> のときに、式7の最大入力実効値電流が発生します。

式7：

$$I_{CIN_{RMS(MAX)}} = \frac{I_{OUT}}{2}$$

得られた実効値電流に対応できる入力コンデンサを選択します。コンデンサの ESR を流れる実効値電流によって電力損失が生じ、温度が上昇するからです。セラミック・コンデンサは、ESR と ESL が低く、サイズが小さく、高い電流リップルを許容することから、パルス的リップル電流のバイパス用に推奨されます。これにより、入力電圧におけるピーク to ピーク電圧リップルと電磁場干渉 (EMI) が低減します。

## 出力コンデンサ

昇圧モードでは、出力コンデンサには高い不連続なリップル電流が発生します。出力コンデンサの等価直列抵抗 (ESR) と容量によって、式8で計算される電圧リップルが生じます。

式8：

$$\Delta V_{OUT} = \frac{V_{OUT} \times I_{OUT} \times ESR}{V_{IN} \times \eta} + \frac{I_{OUT} \times \left(1 - \frac{V_{IN}}{V_{OUT}}\right)}{f_{SW} \times C_{OUT}}$$

ここで、

ESR = 出力コンデンサの等価直列抵抗

C<sub>OUT</sub> = 出力コンデンサの容量

得られた最大電圧リップルに対し、式9で出力容量を計算します。

式 9 :

$$C_{OUT} = \frac{(V_{OUT} - V_{IN}) \times V_{IN} \times I_{OUT} \times \eta}{(\Delta V_{OUT} \times V_{IN} \times \eta - V_{OUT} \times I_{OUT} \times ESR) \times V_{OUT} \times f_{SW}}$$

入力電圧が最小値に達し、出力電圧が最大値に達したとき、出力電圧が最大になります。

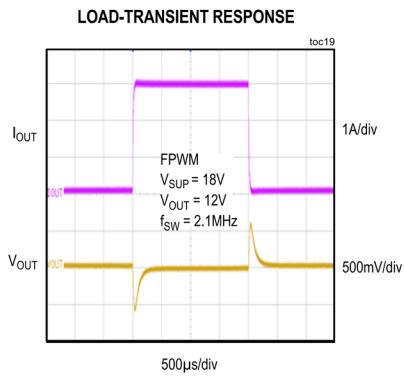

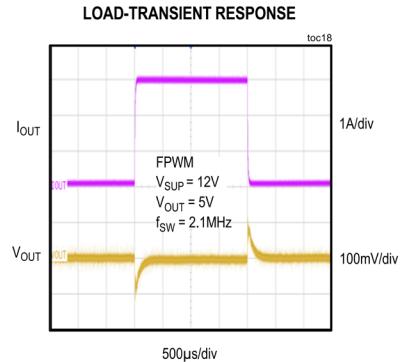

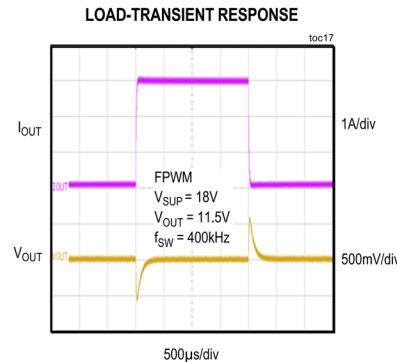

一方、出力容量は、負荷過渡応答の要求を満足するように選択します。負荷ステップ時に、出力電流はほぼ瞬時に変わるのでに対して、インダクタは遅い反応を示します。この遷移時間の間に、出力コンデンサから負荷充電の要求が課されるので、出力電圧にアンダーシュートが生じます。出力電圧での許容最大アンダーシュートに基づいてコンデンサを選択します。一般的には、ロード・トランジエントによる最も厳しい応答は、昇圧モードで発生します。許容されるアンダーシュートに対する出力容量は、昇圧モードでのロード・トランジエント条件で、式 10 によって計算されます。

式 10 :

$$C_{OUT} = \frac{\Delta I_{OUT}}{2 \times \pi \times \Delta V_{OUT_{US}} \times f_c}$$

ここで、

$f_c$  = クロスオーバー周波数

$\Delta I_{OUT}$  = トランジエント負荷ステップ

$\Delta V_{OUT_{US}}$  = 許容最大アンダーシュート

式 9 と式 10 の大きい方の値の出力容量を、出力容量  $C_{OUT}$  の最終値として選択すると、動作周波数における与えられた実効値電流に対応できます。セラミック・コンデンサは、ESR と ESL が低く、サイズが小さく、高い電流リップルを許容することから、パルス的なリップル電流のバイパス用に推奨されます。これにより、出力電圧におけるピーク to ピーク電圧リップルと電磁場干渉 (EMI) が低減します。出力コンデンサの実効値リップル電流は、式 11 を使用して計算します。

式 11 :

$$I_{COUT_{RMS}} = I_{OUT} \times \sqrt{\frac{V_{OUT} - V_{IN}}{V_{IN}}}$$

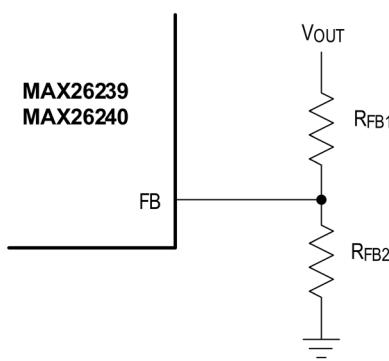

## 出力電圧の設定

FB を  $V_{CC}$  に接続すると、帰還ピン (FB) と AGND の間に配置された内部抵抗分圧器で設定される固定出力電圧がイネーブルされます。出力電圧を 3V~20V の範囲で外部調整するには、図 1 に示すように、出力 (OUT) から FB を経由して AGND に至る抵抗分圧器を接続します。 $R_{FB1}$  と  $R_{FB2}$  の値は式 12 を使用して計算します。

式 12 :

$$R_{FB1} = R_{FB2} \left[ \left( \frac{V_{OUT}}{V_{FB}} \right) - 1 \right]$$

ここで、

$V_{FB}$  = 0.8V (代表値)

$R_{FB2} < 50\text{k}\Omega$ 、一般的には  $10\text{k}\Omega$  に設定可

図 1. 出力電圧の外部調整

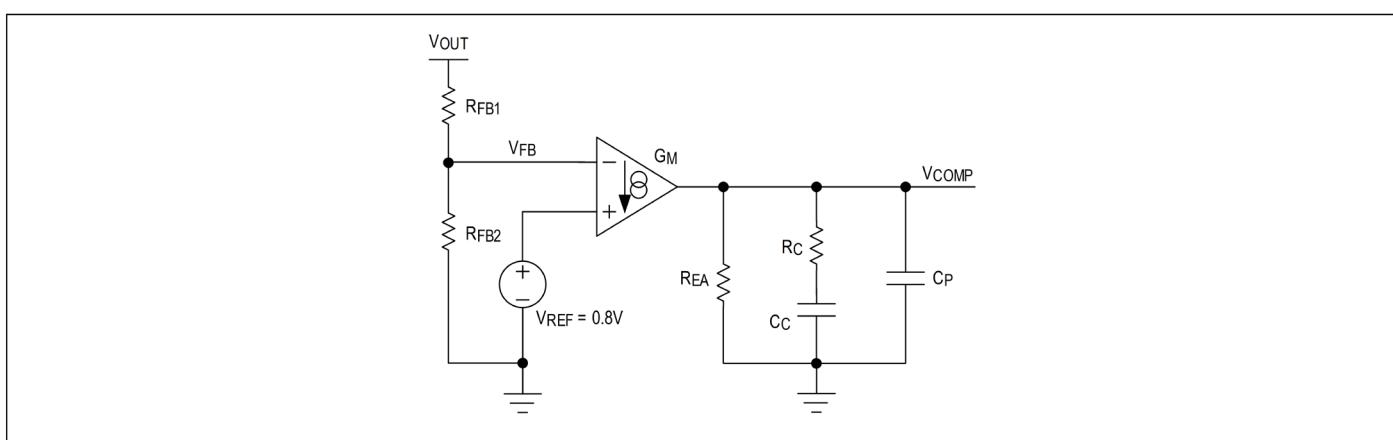

### エラー・アンプ補償設計

MAX26240 コンバータはトランスコンダクタンス・エラー・アンプを内蔵しており、その反転入力端子と出力端子を使用して、外付けでの周波数補償が可能です（図 2 参照）。

コントローラはピーク電流モード制御アーキテクチャを使用し、必要とされる電流が外付けインダクタを流れるようにして出力電圧を安定化します。電流モード制御により、インダクタと出力コンデンサに起因するフィードバック・ループのダブル・ポールが 2 つのシングル・ポールに分離されます。そのポールの 1 つは、コンバータの一般的な帯域幅を外れた高周波域に移動するため、シングル・ポール・システムになります。このため、ループの補償にはタイプ 2 のみが必要になるので、補償が容易になります。昇圧モードでは、更に電力段により右半面（RHP）ゼロが発生し、制御ループに位相遅延が追加されます。RHP ゼロがコンバータの安定性に有意な影響を及ぼすのを防止するためには、帯域幅が最も厳しい条件における RHP ゼロ周波数の約 1/5 になるように補償を設計します。

外部補償の設計では、最適な設計に至るために何回かの反復作業が必要です。高昇圧モードおよび重負荷条件 ( $V_{IN-MIN}$ ) での補償の設計では、RHP ゼロの周波数が低くなるため、注意が必要です。

最小の入力電圧と重負荷（高昇圧モード）で補償を設計するのが、降圧モードと昇圧モードの両方に対して補償を設計するための容易な方法です。この動作ポイントで、RHP ゼロが最低の周波数になります。帯域幅が RHP ゼロ周波数の 1/5 以下になるように補償を設計することで、RHP ゼロがコンバータの安定性に有意な影響を及ぼすのを防止できます。コンバータの閉ループ・ゲインは、コンバータの電力段のゲインとエラー・アンプのゲインの組み合わせで、電力段のポールとゼロは式 13 で計算されます。

式 13 :

$$f_{PBOOST} = \frac{1}{\pi \times R_{LOAD} \times C_{OUT}}$$

$$f_{ZESR} = \frac{1}{2 \times \pi \times ESR \times C_{OUT}}$$

$$f_{ZRHP} = \frac{R_{LOAD} \times (1 - D)^2}{2 \times \pi \times L}$$

また、エラー・アンプのポールとゼロは、式 14 で計算されます。

式 14 :

$$f_{P1EA} = \frac{1}{2 \times \pi \times (R_{EA} + R_C) \times C_C} \approx \frac{1}{2 \times \pi \times R_{EA} \times C_C}, \quad \text{if } R_{EA} \gg R_C$$

$$f_{P2EA} = \frac{1}{2 \times \pi \times R_C \times C_P}$$

$$f_{ZEA} = \frac{1}{2 \times \pi \times R_C \times C_C}$$

二二二

$R_{EA} = \sim 5M\Omega$ 、トランジスタコンダクタンス・エラー・アンプの出力インピーダンス

ESR = 出力コンデンサの等価直列抵抗

$R_{LOAD}$  = 负荷抵抗

コンバータの閉ループの目標帯域幅が、RHP ゼロの  $1/5$  になるように選択します。エラー・アンプのゼロは、帯域幅より十分低く配置し、クロスオーバー周波数  $f_c$  で十分な位相余裕を保つようにします。一般的には、トランスクンダクタンス・エラー・アンプのゼロは、電力段の低周波数ポール  $f_{P\text{BOOST}}$  の近くに配置します。トランスクンダクタンス・エラー・アンプの 2 つ目のポール  $f_{P\text{EA}}$  は、電力段の RHP ゼロの近くに配置します。この場合、補償ネットワークの抵抗 ( $R_C$ ) とコンデンサ ( $C_C, C_P$ ) は式 15 で計算されます。

式 15：

$$R_C = \frac{2 \times \pi \times R_i \times C_{OUT} \times V_{OUT} \times f_C}{(1 - D) \times G_m \times V_{REF}}$$

$$C_C = \frac{R_{LOAD} \times C_{OUT}}{2 \times R_C}$$

$$C_P = \frac{1}{2 \times \pi \times R_C \times f_{ZBHP}}$$

ここで、

$R_i = 50m\Omega$ 、電流検出抵抗

$G_M = 100\mu A/V$ 、トランスコンダクタ・エラー・アンプのゲイン

$f_C$  = 選択したクロスオーバ一周波数

$V_{REF} = 0.8V$ 、帰還電圧リファレンス

内部補償ネットワークを図2に示します。

図2. 補償ネットワーク

## PCB レイアウト時のガイドライン

低スイッチング損失とノイズのない安定した動作を実現するには、慎重な PCB レイアウトが欠かせません。ノイズ耐性と消費電力の改善には可能な限り多層基板を使用します。次のガイドラインに従って、PCB レイアウトを適切なものにしてください。

1. セラミック・バイパス・コンデンサを入力ピンおよび出力ピンの近くに配置して、高周波電流ループを最小化します。これにより、効率が改善し、放射エミッションが最低限になります。

2. V<sub>CC</sub>バイパス・コンデンサは、V<sub>CC</sub>ピンとAGNDピンの間に、ICに近づけて配置します。

3. グランド接続の距離が最小となるよう、入力コンデンサと出力コンデンサの方向を定めます。

4. 電源グランドとアナログ・グランドを可能な限り分離します。電源グランドとアナログ・グランドは、AGNDピンでスター・グランド接続により接続します。これにより、グランド電流ループが最小限になります。1か所のグランドのみを使用する場合には、アナログのリターン・シグナルと大電力の信号の間に適切なアイソレーションを保つことが必要です。

5. LXピンとBSTコンデンサの間のパターン・インダクタンスを最小化し、セラミック・ブートストラップ・コンデンサをBST1ピンとBST2ピンのできるだけ近くに配置します。

6. 大電力部品と高電流のパスを、影響を受けやすい補償およびフィードバック・ループのアナログ回路と分離します。これは、ノイズがアナログ信号に混入するのを防止するために重要です。

7. 大電流経路は、特にグランド端子では短くします。この方法は、安定したジッタのない動作に必須のものです。大電流のパス（入力コンデンサ、ハイサイドFET、インダクタ、出力コンデンサで構成される）は可能な限り短くします。

8. 電源パターンと負荷の接続は短く広くします。この方法は、高い効率を得るために必須のものです。銅層の厚い（1オンスよりは2オンス）PCBを用いると、全負荷効率と放熱性を改善できます。

9. アナログ信号のパターンは、高周波プレーンから離して配線します。これにより、デバイスにフィードバックされる、影響を受けやすい信号の品質を確保します。

10. 補償用部品はCOMPピンのできるだけ近くに配置します。

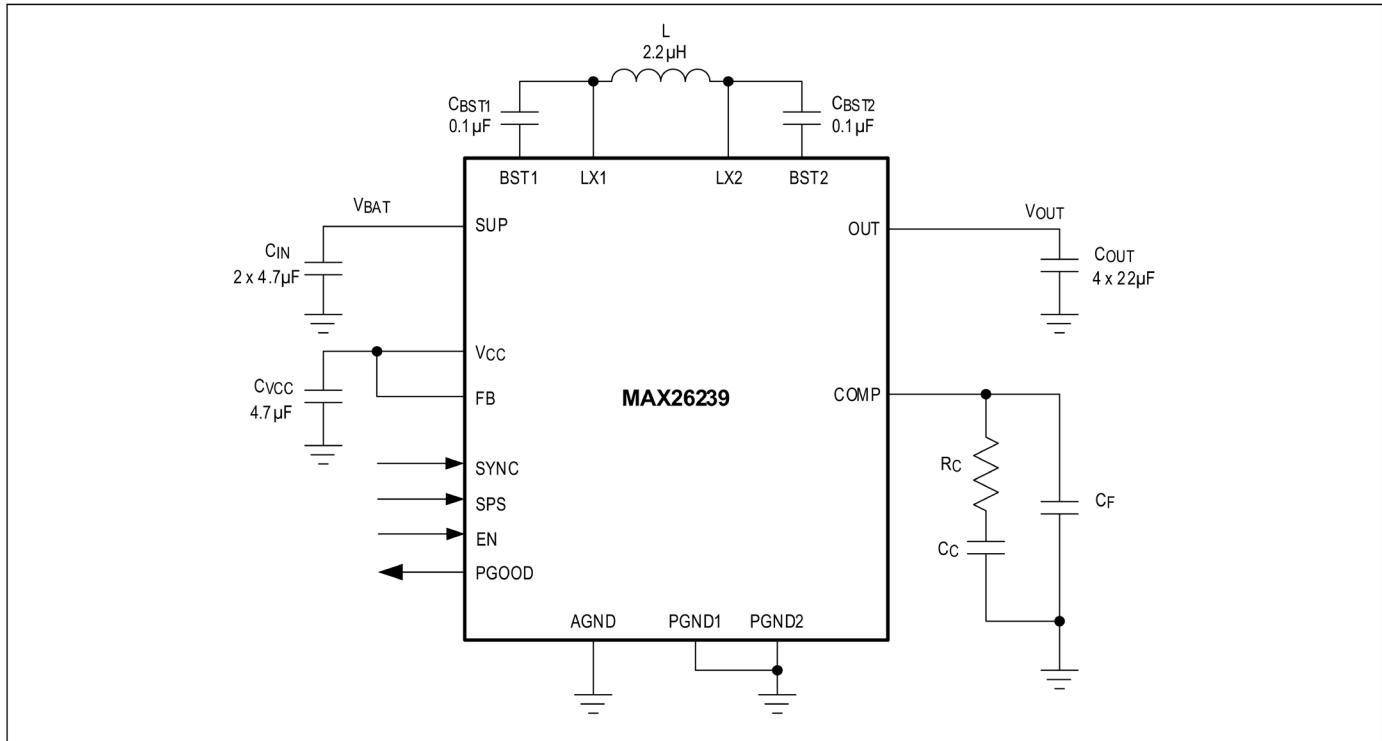

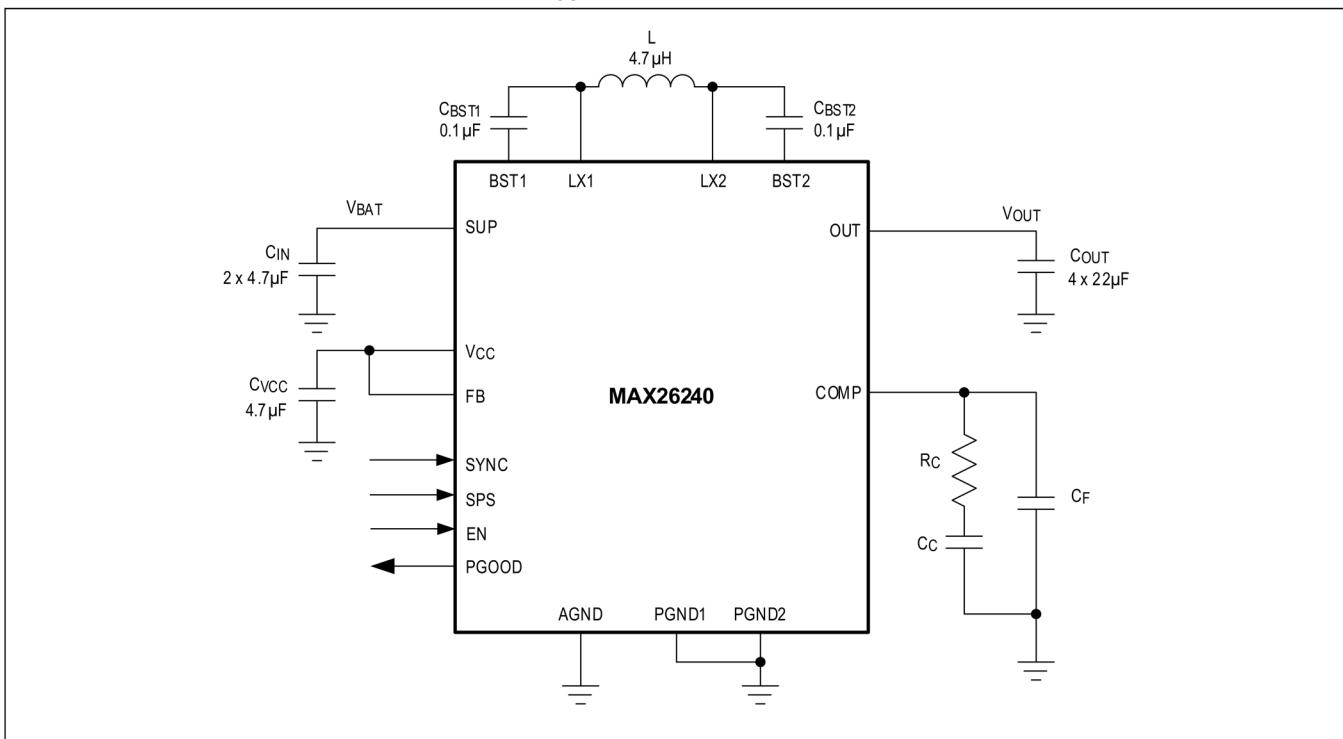

## 標準アプリケーション回路

2.1MHz アプリケーション回路 :  $I_{LIM} = 8.2A$ 、 $V_{OUT} = 5V$ 400kHz アプリケーション回路 :  $I_{LIM} = 10A$ 、 $V_{OUT} = 5V$

## 型番

| PART NUMBER    | CURRENT LIMIT<br>$I_{LIM}$ (A) | FIXED $V_{OUT}$<br>OPTIONS (V)** | ADJ<br>$V_{OUT}$ (V) | SWITCHING<br>FREQUENCY (kHz) |

|----------------|--------------------------------|----------------------------------|----------------------|------------------------------|

| MAX26239AFFAY+ | 8.2                            | 5                                | <6.5                 | 2100                         |

| MAX26239AFFBY+ | 8.2                            | 5                                | <6.5                 | 400                          |

| MAX26239AFFDY+ | 8.2                            | 10.5                             | >6.5                 | 2100                         |

| MAX26239AFFFY+ | 8.2                            | 11.5                             | >6.5                 | 400                          |

| MAX26240AFFAY+ | 10                             | 5                                | <6.5                 | 2100                         |

| MAX26240AFFBY+ | 10                             | 5                                | <6.5                 | 400                          |

| MAX26240AFFDY+ | 10                             | 10.5                             | >6.5                 | 2100                         |

+は鉛 (Pb) フリー／RoHS 準拠のパッケージであることを示します。

T = テープ & リール。

\*\*以下のようなオプションについては弊社にお問い合わせください。

- 3V~15V の固定  $V_{OUT}$  オプション

- SYNC 入力または出力

- PGOOD アサートの時間遅延オプション (5ms と 10ms)

## 改訂履歴

| 版数 | 改訂日   | 説明   | 改訂ページ |

|----|-------|------|-------|

| 0  | 10/23 | 初版発行 | -     |