# 300MHzデジタル プリディストーション・レシーバ

## 特長

- I/Q復調器、IFアンプ、および14ビット、310Mps

高速デュアルA/Dコンバータを内蔵

- 外付けハイパス・フィルタにより帯域幅を調整可能

- チャネルごとの300MHzローパス・フィルタ

- RF入力の周波数範囲: 0.7GHz ~ 4GHz

- 50ΩシングルエンドRFポート

- 50Ω差動LOポート

- 周波数特性の平坦度: 標準 1.3dB

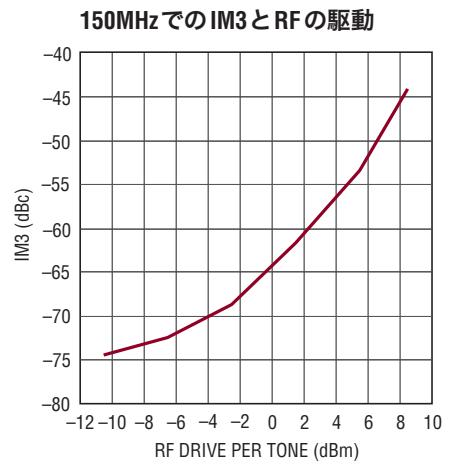

- -7dBFSでのIM3レベル: 66dBc

- -1dBFSでのSNR: 59dB

- DDR LVDSパラレル出力

- クロック・デューティ・サイクル・スタビライザ

- 低消費電力: 2.6W

- シャットダウン・モードとナップ・モード

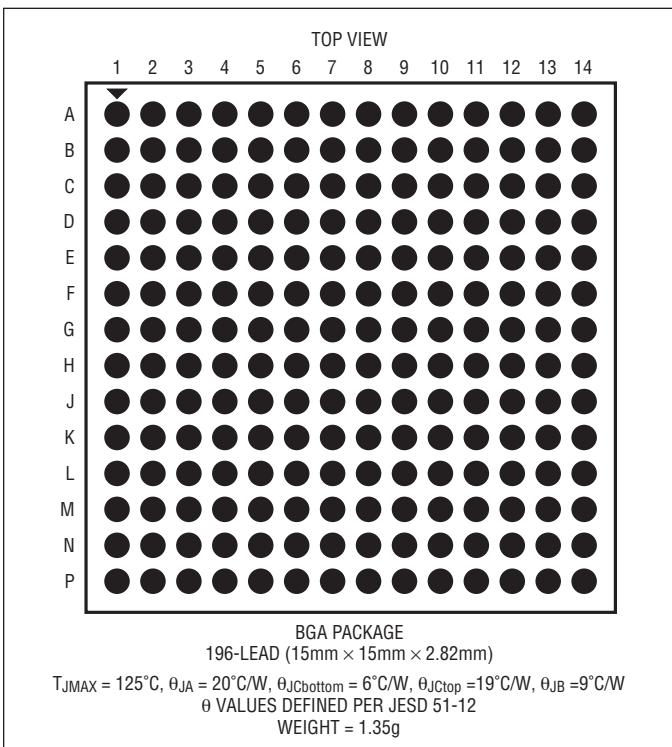

- 15mm×15mmのBGAパッケージ

## アプリケーション

- 電気通信機器

- 広帯域、低IFレシーバ

- デジタル・プリディストーション・レシーバ

- セルラ基地局

## 概要

LTM<sup>®</sup>9013は300MHzのデジタル・プリディストーション・レシーバです。このデバイスは、集積化システム・イン・パッケージ(SiP)技術を利用しておおり、高速14ビット・デュアルA/Dコンバータ、ローパス・フィルタ、差動利得段、および直交復調器を内蔵したμModule<sup>®</sup>(マイクロモジュール)レシーバです。

LTM9013はデジタル・プリディストーション・アプリケーションに最適であり、SNRが59dB、DCから300MHzまでの周波数特性の平坦度が1.3dBなどのAC性能を備えています。設計の柔軟性を高めるため、デバイスの外部でハイパス・フィルタまたは単純なAC結合を使用します。内蔵の広帯域トランスにより、RF入力で50Ωのシングルエンド・インターフェースが得られます。

5V電源が復調器に電力を供給し、3.3V電源がIFアンプに電力を供給するので、歪みを最小限に抑えることができます。1.8V電源により、A/Dコンバータの低消費電力動作が可能です。出力の電源が独立しているので、DDR LVDS出力で1.8Vのロジックを駆動できます。オプションのマルチプレクサにより、2つのチャネルが1つのデジタル出力バスを共用できます。また、オプションのクロック・デューティ・サイクル・スタビライザにより、広範なクロック・デューティ・サイクルにわたって最高速度で高性能を発揮できます。

LT、LT、LTC、LTM、μModule、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。

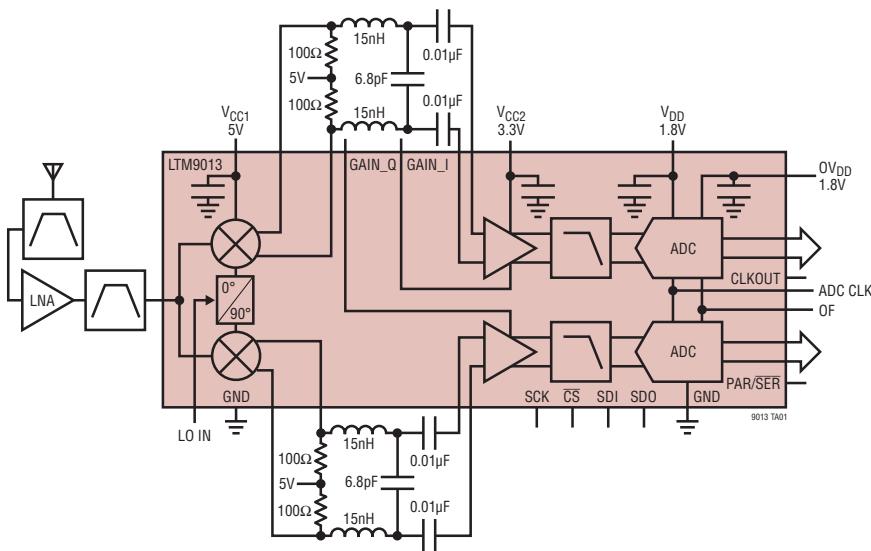

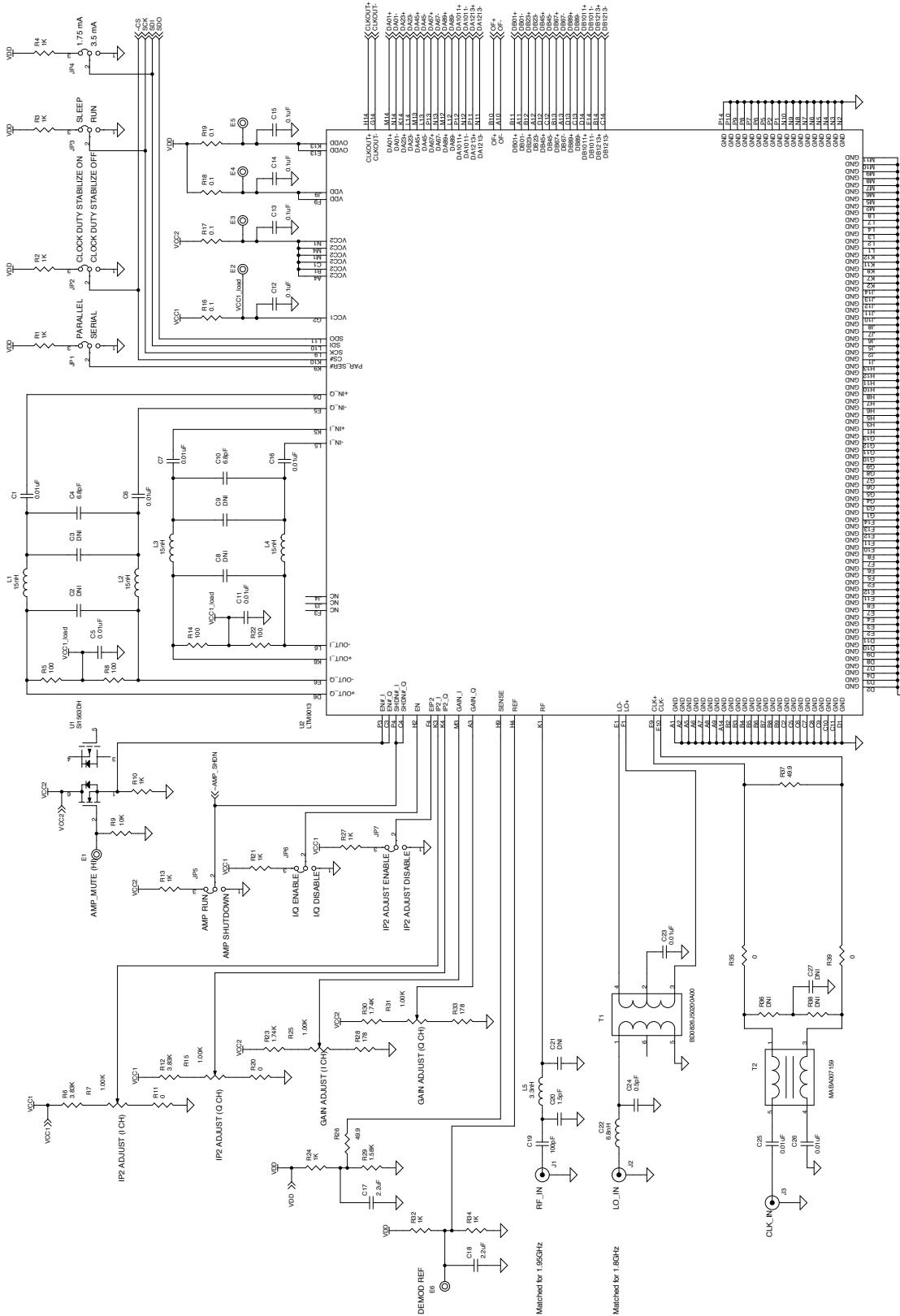

## 標準的応用例

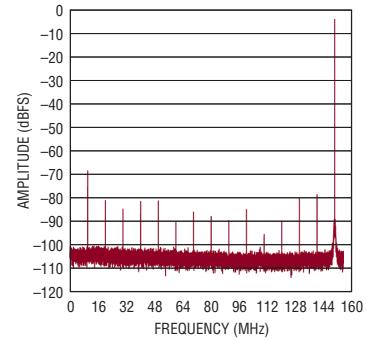

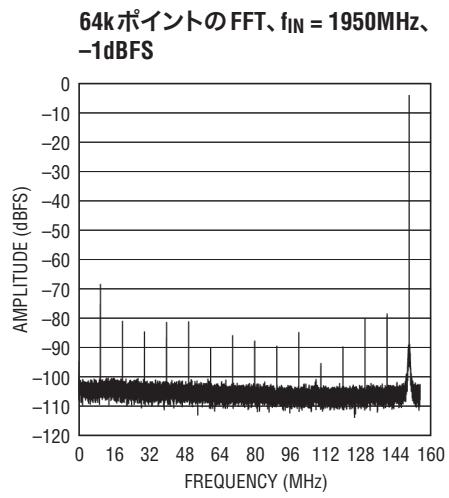

64kポイントのFFT、

$f_{IN} = 1950\text{MHz}$ 、-1dBFS

9013 TA01b

# LTM9013

## 絶対最大定格

(Note 1, 2)

### 電源電圧

$V_{CC1}$  ..... -0.3V ~ 5.5V

$V_{CC2}$  ..... -0.3V ~ 3.8V

$V_{DD}$ ,  $0V_{DD}$  ..... -0.3V ~ 2.0V

### アナログ入力電圧

EN, EIP2, REF, IP2I, IP2Q ..... -0.3V ~  $V_{CC1} + 0.3V$

PAR/SER, SENSE ..... -0.3V ~ ( $V_{DD} + 0.2V$ )

### デジタル入力電圧 (Note 3)

CLK<sup>+</sup>, CLK<sup>-</sup> ..... -0.3V ~ ( $V_{DD} + 0.3V$ )

### デジタル入力電圧 (Note 4)

CS, SDI, SCK ..... -0.3V ~ 3.9V

RF 入力の DC 電圧 ..... ±0.1V

LO<sup>+</sup>, LO<sup>-</sup> 入力の DC 電圧 ..... -0.3V ~  $V_{CC1} + 0.3V$

### アナログ入力電流

+IN\_I, -IN\_I, +IN\_Q, -IN\_Q ..... ±20mA

GAIN\_I, GAIN\_Q, EN\_I, EN\_Q, SHDN\_I,

SHDN\_Q ..... ±10mA

LO<sup>+</sup>, LO<sup>-</sup> の入力電力 ..... +10dBm

RF の入力電力 ..... +20dBm

### アナログ入力電力、連続的

+IN\_I, -IN\_I, +IN\_Q, -IN\_Q ..... +15dBm

### アナログ入力電力、100μs パルス

+IN\_I, -IN\_I, +IN\_Q, -IN\_Q ..... +20dBm

### アナログ出力電圧

+OUT\_I, -OUT\_I,

+OUT\_Q, -OUT\_Q ..... 2.5V ~  $V_{CC1} + 0.3V$

### デジタル出力電圧

SDO ..... -0.3V ~ 3.9V

SDO 以外 ..... -0.3V ~ ( $0V_{DD} + 0.3V$ )

### 動作温度範囲

LTM9013C ..... 0°C ~ 70°C

LTM9013I ..... -40°C ~ 85°C

保存温度範囲 ..... -55°C ~ 125°C

注意: このデバイスは、静電放電(ESD)の影響を受けやすい。

LTM9013 の RF 入力および LO 入力を扱う場合、適切な ESD 対策に従うことが非常に重要である。

## ピン配置

## 発注情報

| 無鉛仕上げ            | トレイ              | 製品マーキング*    | パッケージ                              | 温度範囲          |

|------------------|------------------|-------------|------------------------------------|---------------|

| LTM9013CY-AA#PBF | LTM9013CY-AA#PBF | LTM9013Y-AA | 196-Lead (15mm × 15mm × 2.8mm) BGA | 0°C to 70°C   |

| LTM9013IY-AA#PBF | LTM9013IY-AA#PBF | LTM9013Y-AA | 196-Lead (15mm × 15mm × 2.8mm) BGA | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

この製品はトレイでのみ供給されます。詳細については、<http://www.linear-tech.co.jp/packaging/> をご覧ください。

## 電気的特性

●は、全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $P_{RF} = -5\text{dBm}$ 、 $P_{LO} = 0\text{dBm}$  (Note 5, 7)。

| SYMBOL | PARAMETER                         | CONDITIONS                                                                      | MIN  | TYP                      | MAX | UNITS      |

|--------|-----------------------------------|---------------------------------------------------------------------------------|------|--------------------------|-----|------------|

|        | RF Input Frequency Range          | No External Matching (Mid Band)<br>with External Matching (Low Band, High Band) |      | 1.5 to 2.7<br>0.7 to 4.0 |     | GHz<br>GHz |

|        | LO Input Frequency Range          | No External Matching (Mid Band)<br>With External Matching (Low Band, High Band) |      | 1.5 to 2.7<br>0.7 to 4.0 |     | GHz<br>GHz |

|        | IF Frequency Range                |                                                                                 |      | 0.5 to 300               |     | MHz        |

|        | RF Input Return Loss              | $Z_0 = 50\Omega$ , 1.5GHz to 2.7GHz, Internally Matched                         |      | >10                      |     | dB         |

|        | LO Input Return Loss              | $Z_0 = 50\Omega$ , 1.5GHz to 2.7GHz, Internally Matched                         |      | >10                      |     | dB         |

|        | RF Input Power for -1dBFS         | RF = 2140MHz, LO = 1990MHz (Figure 14)                                          |      | -5                       |     | dBm        |

|        | LO Input Power                    |                                                                                 |      | -6 to +6                 |     | dBm        |

|        | I/Q Gain Mismatch                 | RF = 2140MHz, LO = 1990MHz (Figure 14)                                          |      | 0.15                     |     | dB         |

|        | I/Q Phase Mismatch                | RF = 2140MHz, LO = 1990MHz (Figure 14)                                          |      | 1                        |     | Deg        |

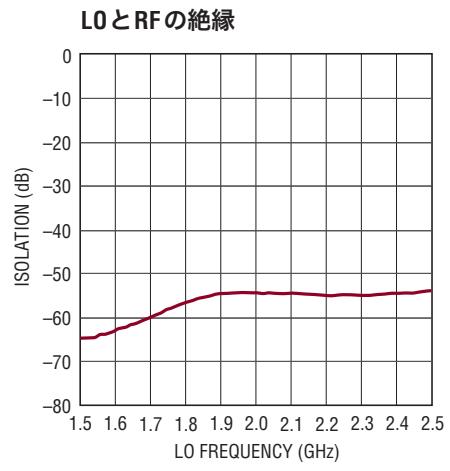

|        | LO to RF Leakage                  | LO = 1990MHz                                                                    |      | -55                      |     | dBm        |

|        | RF to LO Isolation                | RF = 2140MHz                                                                    |      | 58                       |     | dBm        |

|        | Gain Flatness (Notes 5, 6)        | $f_{IF} = 500\text{kHz}$ to 300MHz (Figure 14)                                  |      | 0.5                      |     | dB         |

|        | Lowpass Filter Cutoff Frequency   | 0.5dB Point                                                                     |      | 300                      |     | MHz        |

|        | Resolution (No Missing Codes)     |                                                                                 | ●    | 14                       |     | Bits       |

|        | Integral Linearity Error (Note 8) | Differential Analog Input                                                       |      | ±4.5                     |     | LSB        |

|        | Differential Linearity Error      | Differential Analog Input                                                       | -1   | ±0.35                    | 1   | LSB        |

|        | Offset Error (Note 9)             |                                                                                 | -186 | ±62                      | 186 | LSB        |

## ダイナミック精度

●は、全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $P_{RF} = -5\text{dBm}$ 、 $P_{LO} = 0\text{dBm}$ (Note 5, 7)。

| SYMBOL  | PARAMETER                                              | CONDITIONS                                                                  | MIN | TYP | MAX      | UNITS        |

|---------|--------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|----------|--------------|

| IIP3    | Input 3rd Order Intercept, 1 Tone                      | RF = 2140MHz, LO = 1990MHz                                                  |     | 30  |          | dBm          |

| IIP2    | Input 2nd Order Intercept, 1 Tone                      | RF = 2140MHz, LO = 1990MHz                                                  |     | 56  |          | dBm          |

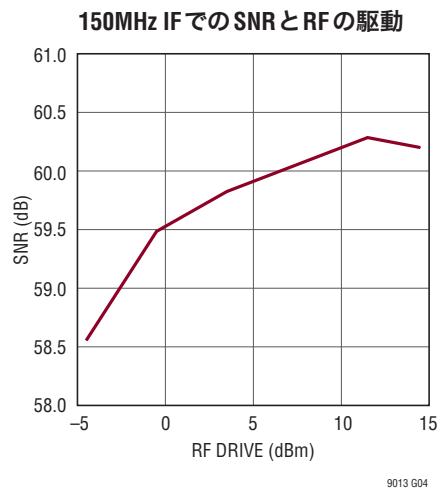

| SNR     | Signal-to-Noise Ratio at $-1\text{dBFS}$               | RF = 2140MHz, LO = 1990MHz (Figure 14)<br>$f_{IF} = 150\text{MHz}$ (Note 6) | ●   | 59  | 59<br>62 | dBFS<br>dBFS |

| SFDR    | Spurious Free Dynamic Range<br>2nd or 3rd Harmonic     | RF = 2140MHz, LO = 1990MHz (Figure 14)<br>$f_{IF} = 150\text{MHz}$ (Note 6) | ●   | 60  | 65<br>70 | dB<br>dB     |

|         | Spurious Free Dynamic Range<br>4th or Higher           | RF = 2140MHz, LO = 1990MHz (Figure 14)<br>$f_{IF} = 150\text{MHz}$ (Note 6) |     |     | 75<br>80 | dB<br>dB     |

| S/(N+D) | Signal-to-Noise Plus Distortion Ratio                  | RF = 2140MHz, LO = 1990MHz (Figure 14)<br>$f_{IF} = 150\text{MHz}$ (Note 6) | ●   | 58  | 58<br>61 | dBFS<br>dBFS |

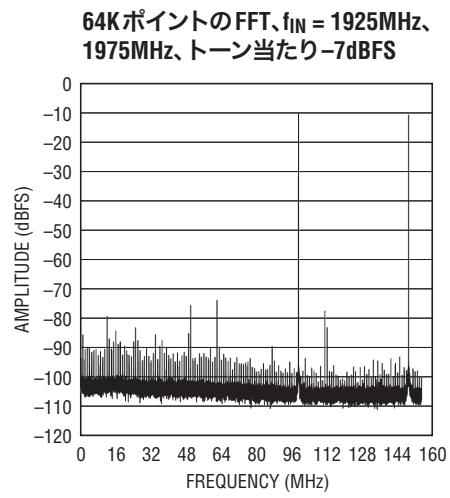

| IMD3    | Intermodulation Distortion at $-7\text{dBFS}$ per Tone | RF = 2140MHz and 2141MHz, LO = 1990MHz<br>(Figure 14)                       |     |     | 66       | dB           |

## アナログ入力とアナログ出力

●は、全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5, 7)。

| SYMBOL                                        | PARAMETER                                                     | CONDITIONS                                                                                        | MIN             | TYP  | MAX          | UNITS                                |

|-----------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------|------|--------------|--------------------------------------|

| <b>復調器調整入力(IP2I, IP2Q)</b>                    |                                                               |                                                                                                   |                 |      |              |                                      |

|                                               | Input Voltage                                                 |                                                                                                   | 0               | 1.3  |              | V                                    |

|                                               | Input Impedance                                               |                                                                                                   | 2  1            |      |              | $\text{k}\Omega  \text{pF}$          |

|                                               | Settling Time                                                 | For Step Input; Output with 90% of Final Value                                                    | 2               |      |              | $\mu\text{s}$                        |

| <b>復調器調整入力(REF)</b>                           |                                                               |                                                                                                   |                 |      |              |                                      |

|                                               | Input Voltage                                                 |                                                                                                   | 0.4             | 0.5  | 0.7          | V                                    |

|                                               | Input Impedance                                               |                                                                                                   | 8  1            |      |              | $\text{M}\Omega  \text{pF}$          |

| <b>アンプ・アナログ入力(+IN_I, -IN_I, +IN_Q, -IN_Q)</b> |                                                               |                                                                                                   |                 |      |              |                                      |

|                                               | Differential Input Resistance                                 | $V_{IN(DIFF)} = 100\text{mV}$                                                                     | 49              | 57   | 65           | $\Omega$                             |

|                                               | Input Common Mode Voltage                                     |                                                                                                   |                 | 640  |              | mV                                   |

|                                               | Minimum Input Frequency (3dB Corner)                          |                                                                                                   |                 | 500  |              | kHz                                  |

| <b>アンプ利得制御アナログ入力(GAIN_I, GAIN_Q)</b>          |                                                               |                                                                                                   |                 |      |              |                                      |

| $R_{IN}$                                      | Input Resistance                                              | $GAIN_I, GAIN_Q = 1.0\text{V}$ , $R_{IN} = 1\text{V}/\Delta I_{IL}$                               | ●<br>7.8<br>7.2 | 9.2  | 10.6<br>12.8 | $\text{k}\Omega$<br>$\text{k}\Omega$ |

| $I_{IL}$                                      | Input Low Current                                             | $GAIN_I, GAIN_Q = 0\text{V}$                                                                      | ●<br>-9<br>-10  | -5   | -1<br>-1     | $\mu\text{A}$<br>$\mu\text{A}$       |

|                                               | Gain Control Range                                            | $V_{GAIN} = 0.2\text{V}$ to $1.2\text{V}$                                                         | ●               | 27.5 | 29           | 30.5                                 |

|                                               | Temperature Coefficient of Gain at Fixed Gain Control Voltage |                                                                                                   |                 |      | -0.007       | $\text{dB}^\circ\text{C}$            |

|                                               | Gain Control Slope                                            | Gain Control Voltage = $0.2\text{V}$ to $1\text{V}$ , Slope of the Least-Square Fit Line          | ●               | 30.6 | 32.6         | 34.7                                 |

|                                               | Average Conformance Error to Gain Slope Line                  | Gain Control Voltage = $0.2\text{V}$ to $1\text{V}$ , Standard Error to the Least-Square Fit Line |                 |      | 0.12         | dB                                   |

|                                               | Maximum Conformance Error to Gain Slope Line                  | Gain Control Voltage = $0.2\text{V}$ to $1\text{V}$ , Maximum Error to the Least-Square Fit Line  |                 |      | 0.2          | dB                                   |

## アナログ入力とアナログ出力

●は、全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5, 7)。

| SYMBOL                                           | PARAMETER                     | CONDITIONS                                 | MIN | TYP                     | MAX | UNITS               |

|--------------------------------------------------|-------------------------------|--------------------------------------------|-----|-------------------------|-----|---------------------|

| <b>ADCアナログ入力(SENSE)</b>                          |                               |                                            |     |                         |     |                     |

|                                                  | Input Leakage Current         | $1.1\text{V} < \text{SENSE} < 1.2\text{V}$ |     | -1                      | 1   | $\mu\text{A}$       |

| <b>復調器アナログ出力(+OUT_I, -OUT_I, +OUT_Q, -OUT_Q)</b> |                               |                                            |     |                         |     |                     |

|                                                  | Common Mode Voltage           |                                            |     | $V_{CC1} - 1.5\text{V}$ |     | V                   |

|                                                  | Differential Output Impedance |                                            |     | $50\Omega  6$           |     | $\Omega  \text{pF}$ |

## デジタル入力とデジタル出力

●は、全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5, 7)。

| SYMBOL                     | PARAMETER                | CONDITIONS                                                  | MIN | TYP | MAX | UNITS            |

|----------------------------|--------------------------|-------------------------------------------------------------|-----|-----|-----|------------------|

| <b>復調器ロジック入力(EN, EIP2)</b> |                          |                                                             |     |     |     |                  |

| $V_{IH}$                   | High Level Input Voltage | $V_{CC} = 5\text{V}$                                        | ●   | 2   |     | V                |

| $V_{IL}$                   | Low Level Input Voltage  | $V_{CC} = 5\text{V}$                                        | ●   |     | 0.3 | V                |

|                            | Input Pull-Up Resistance | $V_{CC} = 5\text{V}, V_{EN} = 4.4\text{V}$ to $2.6\text{V}$ |     | 100 |     | $\text{k}\Omega$ |

|                            | EIP2 Input Current       | $EIP2 = 5\text{V}$                                          |     | 40  |     | $\mu\text{A}$    |

|                            | Turn-On Time             |                                                             |     | 0.2 |     | $\mu\text{s}$    |

|                            | Turn-Off Time            |                                                             |     | 0.8 |     | $\mu\text{s}$    |

### IおよびQチャネル・ロジック入力( $\overline{\text{EN}}_I, \overline{\text{EN}}_Q, \overline{\text{SHDN}}_I, \overline{\text{SHDN}}_Q$ )

|          |                          |                                                                                                                                  |   |     |     |                  |               |

|----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|------------------|---------------|

| $V_{IH}$ | High Level Input Voltage | $V_{CC} = 3.3\text{V}$                                                                                                           | ● | 2.2 |     | V                |               |

| $V_{IL}$ | Low Level Input Voltage  | $V_{CC} = 3.3\text{V}$                                                                                                           | ● |     | 0.8 | V                |               |

|          | Input Pull-Up Resistance | $V_{CC} = 3.3\text{V}, V_{EN\_I, EN\_Q} = 0\text{V}$ to $0.5\text{V}$                                                            |   | 100 |     | $\text{k}\Omega$ |               |

|          | Input High Current       | $\overline{\text{EN}}_I, \overline{\text{EN}}_Q = 2.2\text{V}, \overline{\text{SHDN}}_I, \overline{\text{SHDN}}_Q = 2.2\text{V}$ |   | -30 | -15 | -1               | $\mu\text{A}$ |

|          | Input Low Current        | $\overline{\text{EN}}_I, \overline{\text{EN}}_Q = 0.8\text{V}, \overline{\text{SHDN}}_I, \overline{\text{SHDN}}_Q = 0.8\text{V}$ |   | -60 | -30 | -1               | $\mu\text{A}$ |

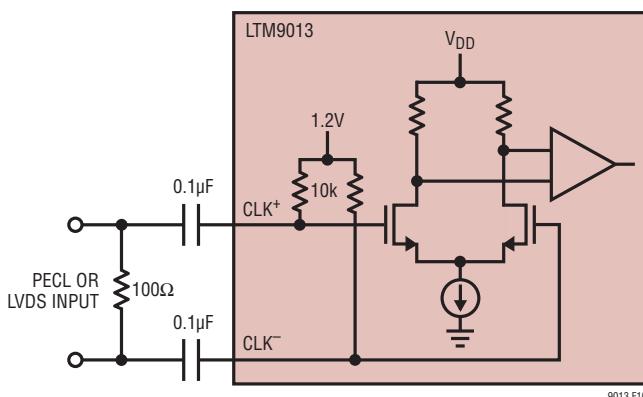

### ADCエンコード・クロック入力(CLK<sup>+</sup>, CLK<sup>-</sup>)

|  |                            |                                  |   |     |     |                  |

|--|----------------------------|----------------------------------|---|-----|-----|------------------|

|  | Differential Input Voltage | $V_{DD} = 1.8\text{V}$           | ● | 0.2 |     | V                |

|  | Common Mode Input Voltage  | Internally Set<br>Externally Set | ● | 1.2 | 1.5 | V                |

|  | Input Resistance           |                                  |   | 10  |     | $\text{k}\Omega$ |

|  | Input Capacitance          | (Note 10)                        |   | 2   |     | $\text{pF}$      |

### ADCロジック入力(SDI, SCK, CS)

|          |                          |                                       |   |     |     |               |

|----------|--------------------------|---------------------------------------|---|-----|-----|---------------|

| $V_{IH}$ | High Level Input Voltage | $V_{DD} = 1.8\text{V}$                | ● | 1.3 |     | V             |

| $V_{IL}$ | Low Level Input Voltage  | $V_{DD} = 1.8\text{V}$                | ● |     | 0.6 | V             |

|          | Input Current            | $V_{IN} = 0\text{V}$ to $3.6\text{V}$ | ● | -10 | 10  | $\mu\text{A}$ |

|          | Input Capacitance        | (Note 10)                             |   | 3   |     | $\text{pF}$   |

### ADCロジック入力(PAR/SER)

|  |                       |                               |  |    |   |               |

|--|-----------------------|-------------------------------|--|----|---|---------------|

|  | Input Leakage Current | $0 < \text{PAR/SER} < V_{DD}$ |  | -1 | 1 | $\mu\text{A}$ |

|--|-----------------------|-------------------------------|--|----|---|---------------|

### ADCロジック出力(SDO)

|  |                                    |                                                |   |     |    |               |

|--|------------------------------------|------------------------------------------------|---|-----|----|---------------|

|  | Logic Low Output Resistance to GND | $V_{DD} = 1.8\text{V}, \text{SDO} = 0\text{V}$ |   | 200 |    | $\Omega$      |

|  | Logic High Output Leakage Current  | $\text{SDO} = 0\text{V}$ to $3.6\text{V}$      | ● | -10 | 10 | $\mu\text{A}$ |

|  | Output Capacitance                 | (Note 10)                                      |   | 4   |    | $\text{pF}$   |

## デジタル入力とデジタル出力

●は、全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5, 7)。

| SYMBOL                           | PARAMETER                      | CONDITIONS                                                                | MIN    | TYP            | MAX            | UNITS          |          |

|----------------------------------|--------------------------------|---------------------------------------------------------------------------|--------|----------------|----------------|----------------|----------|

| データ出力( $0V_{DD} = 1.8\text{V}$ ) |                                |                                                                           |        |                |                |                |          |

|                                  | Differential Output Voltage    | 100Ω Differential Load, 3.5mA Mode<br>100Ω Differential Load, 1.75mA Mode | ●<br>● | 247<br>125     | 350<br>175     | 454<br>250     | mV<br>mV |

|                                  | Common Mode Output Voltage     | 100Ω Differential Load, 3.5mA Mode<br>100Ω Differential Load, 1.75mA Mode | ●<br>● | 1.125<br>1.125 | 1.250<br>1.250 | 1.375<br>1.375 | V<br>V   |

|                                  | On-Chip Termination Resistance | Termination Enabled, $0V_{DD} = 1.8\text{V}$                              |        |                | 100            |                | Ω        |

## 電源要件

●は、全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5, 7)。

| SYMBOL          | PARAMETER                                  | CONDITIONS                                                                                                            | MIN | TYP  | MAX  | UNITS |   |

|-----------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|---|

| $V_{CC1}$       | Demodulator and Amplifier Supply Voltage   |                                                                                                                       | ●   | 4.75 | 5.25 | V     |   |

| $V_{CC2}$       | Amplifier Analog Supply Voltage            |                                                                                                                       | ●   | 2.7  | 3.3  | 3.6   | V |

| $V_{DD}$        | ADC Analog Supply Voltage                  |                                                                                                                       | ●   | 1.74 | 1.8  | 1.9   | V |

| $0V_{DD}$       | ADC Digital Output Supply Voltage          |                                                                                                                       | ●   | 1.74 | 1.8  | 1.9   | V |

| $I_{CC1}$       | Demodulator and Amplifier Supply Current   |                                                                                                                       | ●   | 285  | 330  | mA    |   |

| $I_{CC1(SHDN)}$ | Demodulator and Amplifier Shutdown Current | $\text{EN} = 0\text{V}$ , $\text{EN}_I$ , $\text{EN}_Q = 3.3\text{V}$ , $\text{SHDN}_I$ , $\text{SHDN}_Q = 0\text{V}$ | ●   | 16   | 20   | mA    |   |

| $I_{CC2}$       | Amplifier Supply Current                   |                                                                                                                       | ●   | 132  | 160  | mA    |   |

| $I_{DD}$        | ADC Supply Current                         |                                                                                                                       | ●   | 335  | 385  | mA    |   |

| $I_{0VDD}$      | Digital Supply Current                     | 3.5mA Mode                                                                                                            |     | 80   | 90   | mA    |   |

|                 | ADC Sleep Power                            | ADC Programmed for Sleep Mode, No CLK                                                                                 |     | 5    |      | mW    |   |

|                 | Total Power Dissipation                    |                                                                                                                       |     | 2.6  |      | W     |   |

## タイミング特性

●は、全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5, 7)。

| SYMBOL       | PARAMETER                                     | CONDITIONS                                                                | MIN    | TYP        | MAX        | UNITS    |          |

|--------------|-----------------------------------------------|---------------------------------------------------------------------------|--------|------------|------------|----------|----------|

| $t_s$        | Sampling Frequency                            |                                                                           | ●      | 1          | 310        | MHz      |          |

| $t_L$        | CLK Low Time                                  | Duty Cycle Stabilizer Off (Note 10)<br>Duty Cycle Stabilizer On (Note 10) | ●<br>● | 1.5<br>1.2 | 1.6<br>1.6 | 50<br>50 | ns<br>ns |

| $t_H$        | CLK High Time                                 | Duty Cycle Stabilizer Off (Note 10)<br>Duty Cycle Stabilizer On (Note 10) | ●<br>● | 1.5<br>1.2 | 1.6<br>1.6 | 50<br>50 | ns<br>ns |

| $t_{JITTER}$ | Sample-and-Hold Acquisition Delay Time Jitter |                                                                           |        | 0.15       |            | ps RMS   |          |

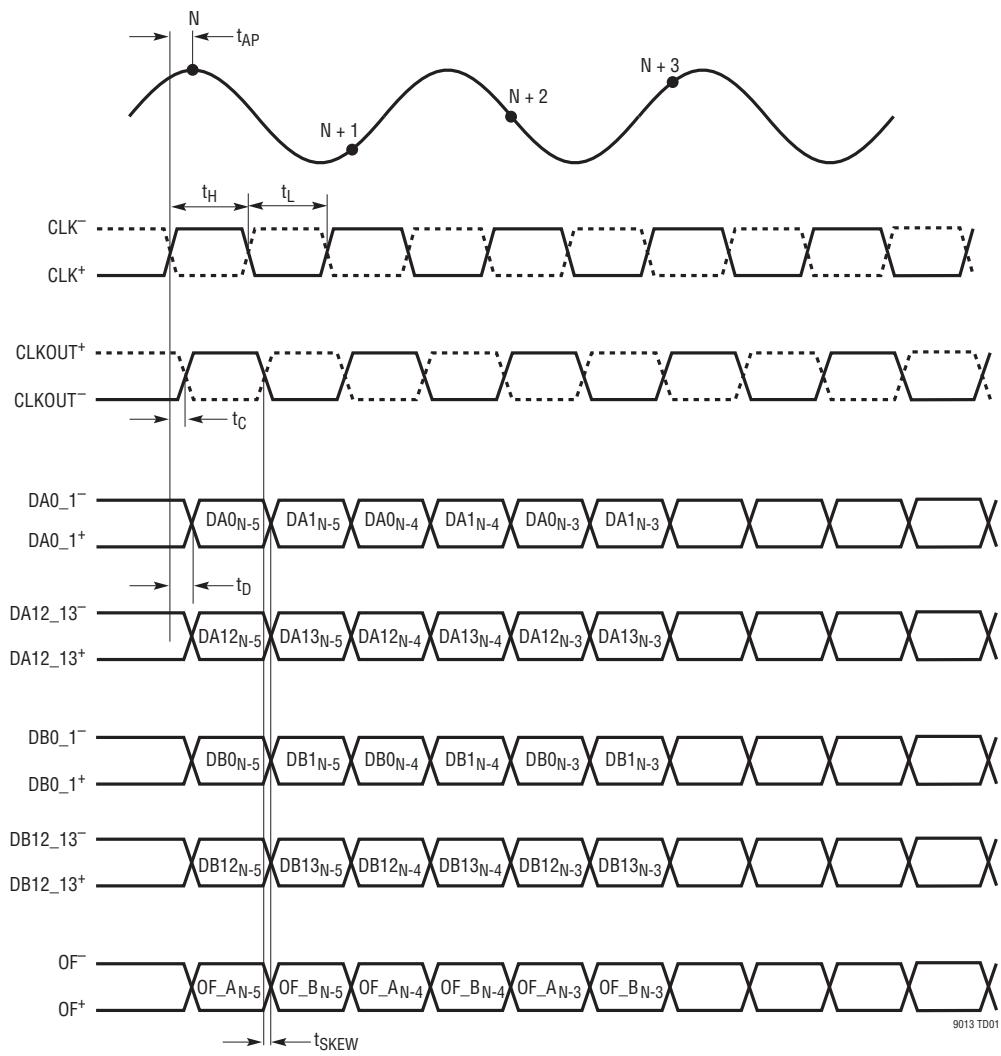

| $t_{AP}$     | Sample-and-Hold Acquisition Delay Time        |                                                                           |        | 1          |            | ns       |          |

## データ出力(Note 10)

|            |                     |                    |   |     |     |      |    |

|------------|---------------------|--------------------|---|-----|-----|------|----|

| $t_D$      | CLK to DATA Delay   | $C_L = 5\text{pF}$ | ● | 1.7 | 2   | 2.3  | ns |

| $t_C$      | CLK to CLKOUT Delay | $C_L = 5\text{pF}$ | ● | 1.3 | 1.6 | 2    | ns |

| $t_{SKEW}$ | DATA to CLKOUT Skew | $t_D - t_C$        | ● | 0.3 | 0.4 | 0.55 | ns |

## タイミング特性

●は、全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 5, 7)。

| SYMBOL                        | PARAMETER                     | CONDITIONS                                                                           | MIN    | TYP       | MAX | UNITS    |

|-------------------------------|-------------------------------|--------------------------------------------------------------------------------------|--------|-----------|-----|----------|

| <b>SPIポートのタイミング (Note 10)</b> |                               |                                                                                      |        |           |     |          |

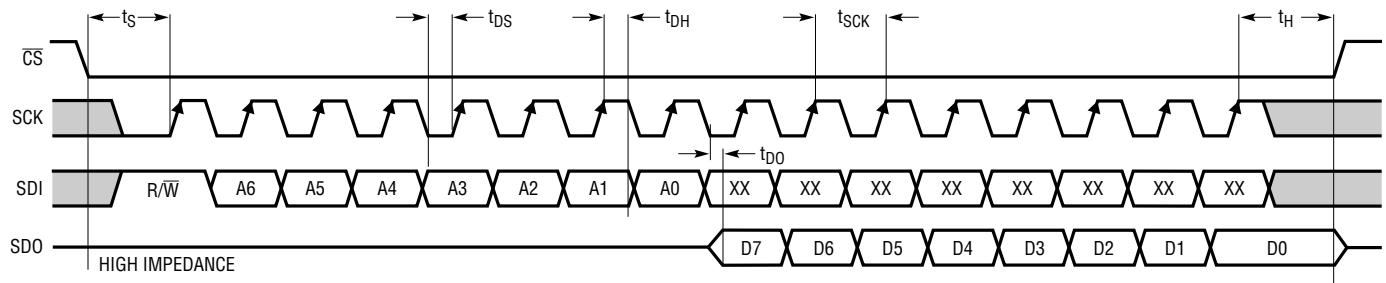

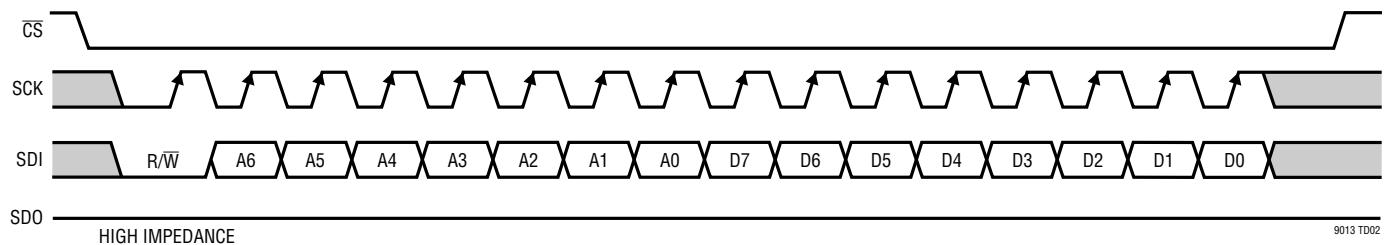

| t <sub>SCK</sub>              | SCK Period                    | Write Mode<br>Readback Mode $C_{SD0} = 20\text{pF}$ , $R_{PULLUP} = 2\text{k}\Omega$ | ●<br>● | 40<br>250 |     | ns<br>ns |

| t <sub>S</sub>                | $\bar{CS}$ to SCK Set-up Time |                                                                                      |        | 5         |     | ns       |

| t <sub>H</sub>                | SCK to $\bar{CS}$ Hold Time   |                                                                                      |        | 5         |     | ns       |

| t <sub>DS</sub>               | SDI Set-Up Time               |                                                                                      |        | 5         |     | ns       |

| t <sub>DH</sub>               | SDI Hold Time                 |                                                                                      |        | 5         |     | ns       |

| t <sub>DO</sub>               | SCK Falling to SDO Valid      | Readback Mode $C_{SD0} = 20\text{pF}$ , $R_{PULLUP} = 2\text{k}\Omega$               |        |           | 125 | ns       |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** 全ての電圧値は(注記がない限り) GND と OGND を接続したグランドを基準にしている。

**Note 3:** これらのピンの電圧を GND より低くすると、 $V_{DD}$  より高くすると、その電圧は内部のダイオードによってクランプされる。この製品は、GND より低いか、または  $V_{DD}$  より高い電圧で、ラッチアップを生じることなしに 100mA を超える入力電流を処理することができる。

**Note 4:** これらのピンの電圧を GND より低くすると、その電圧は内部のダイオードによってクランプされる。これらのピンの電圧を  $V_{DD}$  より高くしても、その電圧は内部のダイオードによってクランプされない。この製品は、GND より低い電圧で、ラッチアップを生じることなく 100mA を超える入力電流を処理することができる。

**Note 5:** テスト回路 1 を使用(「アプリケーション情報」セクションの図 14 の設計例を参照)。

**Note 6:**  $\pm IN_1$  ピンに適用される信号であり、アンプと A/D コンバータのみを測定する。

**Note 7:** 注記のない限り、 $V_{CC1} = 5\text{V}$ ,  $V_{CC2} = 3.3\text{V}$ ,  $V_{DD} = 1.8\text{V}$ ,  $EN = 5\text{V}$ ,  $\bar{EN}_I$ ,  $\bar{EN}_O = 0\text{V}$ ,  $GAIN_I$ ,  $GAIN_Q = 1.2\text{V}$ ,  $SHDN_I$ ,  $SHDN_Q = 3.3\text{V}$ ,  $SENSE = 1.15\text{V}$ ,  $f_S = 310\text{MHz}$ 。

**Note 8:** 積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 9:** DC オフセットは、モジュールに RF 入力信号も LO 入力信号も適用されていない場合の ADC 出力コード。

**Note 10:** 設計によって保証されているが、テストされない。

## 標準的性能特性

## ピン機能

### 電源ピン

**V<sub>CC1</sub>(ピンB7)**: 復調器とアンプ用のアナログ5V電源。既定動作範囲は4.75V～5.25Vです。このピンの電圧は、復調器とアンプにのみ電力を供給し、内部でGNDにバイパスされます。

**V<sub>CC2</sub>(ピンA2、A3、A12、A13、D1、D12)**: アンプ用のアナログ3.3V電源。既定動作範囲は2.7V～3.6Vです。V<sub>CC2</sub>は、内部でGNDにバイパスされます。

**V<sub>DD</sub>(ピンJ6、J9)**: A/Dコンバータ用のアナログ1.8V電源。既定動作範囲は1.74V～1.9Vです。V<sub>DD</sub>は、内部でGNDにバイパスされます。

**OV<sub>DD</sub>(ピンN5、N10)**: デジタル出力ドライバ用の1.8V正電源。既定動作範囲は1.74V～1.9Vです。OV<sub>DD</sub>は、内部でGNDにバイパスされます。

**GND**: アナログ・グランド。ピンの位置については、ピン配置表を参照してください。

### アナログ入力

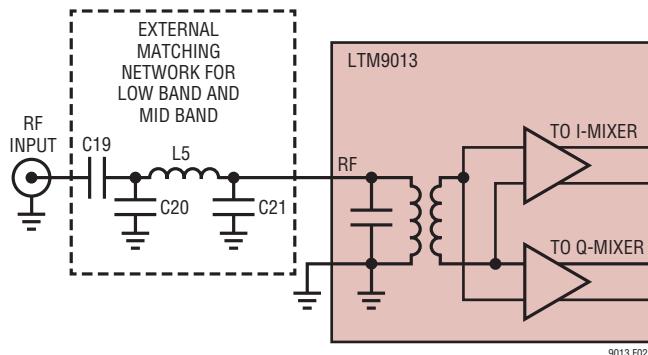

**RF(ピンA10)**: RF入力ピン。これは、終端された50Ωシングルエンド入力です。1.5GHz～2.7GHzの帯域の場合、外部マッチング・ネットワークは不要です。700MHz～1.5GHzまたは2.7GHz～4GHzの帯域でインピーダンスを50Ωに変換する場合、外付け直列インダクタ(および/またはシャント・コンデンサ)が必要になる場合があります(図2を参照)。RFのソースがDC遮断されていない場合、直列ブロッキング・コンデンサを使用する必要があります。そうしないと、デバイスが損傷する恐れがあります。

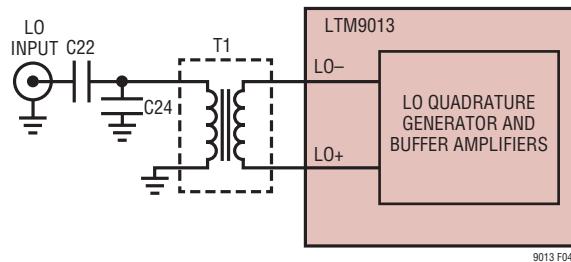

**LO<sup>+</sup>、LO<sup>-</sup>(ピンA6、A5)**: ローカル発振器の入力ピン。これは、終端された50Ω差動入力です。700MHz～1.5GHzまたは2.7GHz～4GHzの帯域でインピーダンスを50Ωに変換する場合、外付け直列インダクタ(および/またはシャント・コンデンサ)が必要になる場合があります(図4を参照)。LOのソースがDC遮断されていない場合、直列ブロッキング・コンデンサを使用する必要があります。そうしないと、デバイスが損傷する恐れがあります。

**+IN\_I、-IN\_I(ピンE10、E11)**: チャネルI信号入力。これは、アンプを駆動する差動入力です。これらのピンは、内部で生成されたDC電圧によってバイアスされます。これらのピンと+OUT\_I、-OUT\_Iの間で、直列ブロッキング・コンデンサが必要になります。

**+IN\_Q、-IN\_Q(ピンE4、E5)**: チャネルQ信号入力。これは、アンプを駆動する差動入力です。これらのピンは、内部で生成されたDC電圧によってバイアスされます。これらのピンと+OUT\_Q、-OUT\_Qの間で、直列ブロッキング・コンデンサが必要になります。

**GAIN\_I(ピンC12)**: Iチャネル利得制御入力。これは、アンプの利得を制御する入力です。このピンは、GNDに接続された10kΩの抵抗を使用して、内部で“L”に引き下げられます。利得制御スロープは、0.1V～1.1Vの利得制御範囲で約32dB/Vです。

**GAIN\_Q(ピンC1)**: Qチャネル利得制御入力。これは、アンプの利得を制御する入力です。このピンは、GNDに接続された10kΩの抵抗を使用して、内部で“L”に引き下げられます。利得制御スロープは、0.1V～1.1Vの利得制御範囲で約32dB/Vです。

**CLK<sup>+</sup>、CLK<sup>-</sup>(ピンJ5、K5)**: A/Dコンバータのクロック入力。CLK<sup>+</sup>の立ち上がりエッジで変換が開始されます。

**IP2\_I(ピンC10)**: IチャネルのIP2調整ピン。

**IP2\_Q(ピンD10)**: QチャネルのIP2調整ピン。

**REF(ピンD8)**: アナログ制御電圧ピンの電圧リファレンス入力。

**SENSE(ピンJ8)**: A/Dコンバータのリファレンス設定ピン。SENSEをV<sub>DD</sub>に接続すると、内部リファレンスと1.32Vの入力範囲が選択されます。

### アナログ出力

**+OUT\_I、-OUT\_I(ピンF10、F11)**: チャネルI信号出力。これは、復調器からの差動出力です。各ピンのDCバイアス・ポイントは、V<sub>CC1</sub>-1.5Vです。これらのピンには、V<sub>CC1</sub>へのプルアップとして、外部の100Ω抵抗またはインダクタが必要です。これらのピンと+IN\_I、-IN\_Iの間で、直列ブロッキング・コンデンサが必要になります。

**+OUT\_Q、-OUT\_Q(ピンF4、F5)**: チャネルQ信号出力。これは、復調器からの差動出力です。各ピンのDCバイアス・ポイントは、V<sub>CC1</sub>-1.5Vです。これらのピンには、V<sub>CC1</sub>へのプルアップとして、外部の100Ω抵抗またはインダクタが必要です。これらのピンと+IN\_Q、-IN\_Qの間で、直列ブロッキング・コンデンサが必要になります。

### 制御ピン

**EN(ピンB8)**: 復調器イネーブル・ピン。ENが“H”的場合(入力電圧が2.0Vよりも高い場合)、復調器はイネーブルされます。ENが“L”的場合(入力電圧が1.0Vよりも低い場合)、復調器はディスエーブルされます。イネーブル機能が不要な場合は、このピンをV<sub>CC1</sub>に接続してください。

**EIP2(ピンD6)**: 復調器IP2調整イネーブルピン。このピンは、GNDに接続された200kΩを使用して、内部で“L”に引き下げられます。EIP2が“H”的場合(入力電圧が2.0Vよりも高い場合)、IP2調整回路がイネーブルされます。EIP2が“L”的場合(入力電圧が1.0Vよりも低い場合)、IP2調整回路がディスエーブルされます。

**NC1、NC2、NC3(ピンC6、C9、D9)**: 接続しないでください。

## ピン機能

**EN\_I(ピンC14)**: 第1アンプIチャネル・イネーブル・ピン。このピンは、V<sub>CC2</sub>に接続された100kΩの抵抗を使用して、内部で“H”に引き上げられます。このピンを“L”電圧にアサートすると、アンプがイネーブルされます。イネーブル機能を使用しない場合は、このピンをGNDに接続します。

**EN\_Q(ピンC3)**: 第1アンプQチャネル・イネーブル・ピン。このピンは、V<sub>CC2</sub>に接続された100kΩの抵抗を使用して、内部で“H”に引き上げられます。このピンを“L”電圧にアサートすると、アンプがイネーブルされます。イネーブル機能を使用しない場合は、このピンをGNDに接続します。

**SHDN\_I(ピンD14)**: アンプIチャネル・シャットダウン・ピン。このピンは、V<sub>CC2</sub>に接続された100kΩの抵抗を使用して、内部で“H”に引き上げられます。このピンを“L”電圧にアサートすると、アンプがシャットダウンされます。非モノトニック出力信号動作を防ぐために、EN\_IピンとSHDN\_Iピンを正しくシーケンシングする必要があります。シャットダウン機能を使用しない場合は、このピンをV<sub>CC2</sub>に接続します。

**SHDN\_Q(ピンD3)**: アンプQチャネル・シャットダウン・ピン。このピンは、V<sub>CC2</sub>に接続された100kΩの抵抗を使用して、内部で“H”に引き上げられます。このピンを“L”電圧にアサートすると、アンプがシャットダウンされます。非モノトニック出力信号動作を防ぐために、EN\_QピンとSHDN\_Qピンを正しくシーケンシングする必要があります。シャットダウン機能を使用しない場合は、このピンをV<sub>CC2</sub>に接続します。

**SDI(ピンK11)**: シリアル・インターフェースのデータ入力。シリアル・プログラミング・モード(PAR/SER=GND)では、SDIはシリアル・インターフェースのデータ入力です。SDIのデータはSCKの立ち上がりエッジでモード制御レジスタにクロックインされます。パラレル・プログラミング・モード(PAR/SER=V<sub>DD</sub>)では、SDIは3.5mAまたは7.5mAのLVDS出力電流を選択します(表4を参照)。SDIは1.8V～3.3Vのロジックで駆動することができます。

**SCK(ピンJ11)**: シリアル・インターフェースのクロック入力。シリアル・プログラミング・モード(PAR/SER=GND)では、SCKはシリアル・インターフェースのクロック入力です。パラレル・プログラミング・モード(PAR/SER=V<sub>DD</sub>)では、SCKを使ってデバイスを低消費電力のスリープ・モードにすることができます(表4を参照)。SCKは1.8V～3.3Vのロジックで駆動することができます。

**CS(ピンK10)**: シリアル・インターフェースのチップ選択入力。シリアル・プログラミング・モード(PAR/SER=GND)では、CSはシリアル・インターフェースのチップ選択入力です。CSが“L”的とき、SCKはイネーブルされ、SDIのデータはモード制御レジスタにシフトします。パラレル・プログラミング・モード(PAR/SER=V<sub>DD</sub>)では、CSはクロック・デューティ・サイクル・スタビライ

ザを制御します(表4を参照)。CSは、1.8V～3.3Vのロジックで駆動できます。

**PAR/SER(ピンJ10)**: プログラミング・モード選択ピン。シリアル・プログラミング・モードをイネーブルするにはGNDに接続します。この場合、CS、SCK、SDI、SDOは、A/Dコンバータの動作モードを制御するシリアル・インターフェースになります。パラレル・プログラミング・モードをイネーブルするにはV<sub>DD</sub>に接続します。この場合、CS、SCK、SDI、SDOは、A/Dコンバータの(種類が限定された)動作モードを制御するパラレル・ロジック入力になります。PAR/SERはGNDまたはV<sub>DD</sub>に直接接続し、ロジック信号では駆動しないようにします。

## デジタル出力

**SDO(ピンL11)**: シリアル・インターフェースのデータ出力。シリアル・プログラミング・モード(PAR/SER=GND)では、SDOはオプションのシリアル・インターフェースのデータ出力です。SDOのデータは、モード制御レジスタから読み出してSCKの立ち下がりエッジでラッチすることができます。SDOはオープンドラインのNチャネルMOSFET出力で、2kΩの外付けプルアップ抵抗を1.8V～3.3Vに接続する必要があります。モード制御レジスタから読み出す必要がない場合は、プルアップ抵抗は不要であり、SDOは未接続のままでかまいません。

## LVDSデジタル出力

以下のピンは差動LVDS出力です。出力電流レベルは設定可能です。各LVDS出力対のピンの間にはオプションの内部100Ω終端抵抗があります。

**CLKOUT<sup>+</sup>、CLKOUT<sup>-</sup>(ピンP8、P7)**: A/Dコンバータのデータ出力クロック。

**DB0\_1-/DB0\_1+～DB12\_13-/DB12\_13+(ピンの位置については、ピン配置表を参照)**: QCチャネルのA/Dコンバータのダブルデータレート・デジタル出力。2つのデータ・ビットが各差動出力対に多重化されます。CLKOUT<sup>+</sup>が“L”的ときは、偶数データ・ビット(DB0、DB2、DB4、DB6、DB8、DB10、DB12)が現れます。CLKOUT<sup>+</sup>が“H”的ときは、奇数データ・ビット(DB1、DB3、DB5、DB7、DB9、DB11、DB13)が現れます。

**DA0\_1-/DA0\_1+～DA12\_13-/DA12\_13+(ピンの位置については、ピン配置表を参照)**: QCチャネルのA/Dコンバータのダブルデータレート・デジタル出力。2つのデータ・ビットが各差動出力対に多重化されます。CLKOUT<sup>+</sup>が“L”的ときは、偶数データ・ビット(DA0、DA2、DA4、DA6、DA8、DA10、DA12)が現れます。CLKOUT<sup>+</sup>が“H”的ときは、奇数データ・ビット(DA1、DA3、DA5、DA7、DA9、DA11、DA13)が現れます。

**OF<sup>+</sup>、OF<sup>-</sup>(ピンK2、K1)**: オーバーフロー/アンダーフロー出力。オーバーフローやアンダーフローが生じると、OF<sup>+</sup>は“H”になります。

## ピン機能

### ピン配置

|   | 1                 | 2                   | 3                   | 4                   | 5                           | 6                           | 7                   | 8                   | 9               | 10                | 11                | 12                  | 13                  | 14     |

|---|-------------------|---------------------|---------------------|---------------------|-----------------------------|-----------------------------|---------------------|---------------------|-----------------|-------------------|-------------------|---------------------|---------------------|--------|

| A | GND               | V <sub>CC2</sub>    | V <sub>CC2</sub>    | GND                 | L <sub>O</sub> <sup>-</sup> | L <sub>O</sub> <sup>+</sup> | GND                 | GND                 | RF              | GND               | V <sub>CC2</sub>  | V <sub>CC2</sub>    | GND                 |        |

| B | GND               | GND                 | GND                 | GND                 | GND                         | GND                         | V <sub>CC1</sub>    | EN                  | GND             | GND               | GND               | GND                 | GND                 | GND    |

| C | GAIN_Q            | GND                 | EN_Q                | GND                 | GND                         | NC1                         | GND                 | GND                 | NC2             | IP2_I             | GND               | GAIN_I              | GND                 | EN_I   |

| D | V <sub>CC2</sub>  | GND                 | SHDN_Q              | GND                 | GND                         | EIP2                        | GND                 | REF                 | NC3             | IP2_Q             | GND               | V <sub>CC2</sub>    | GND                 | SHDN_I |

| E | GND               | GND                 | GND                 | +IN_Q               | -IN_Q                       | GND                         | GND                 | GND                 | GND             | +IN_I             | -IN_I             | GND                 | GND                 | GND    |

| F | GND               | GND                 | GND                 | +OUT_Q              | -OUT_Q                      | GND                         | GND                 | GND                 | GND             | +OUT_I            | -OUT_I            | GND                 | GND                 | GND    |

| G | GND               | GND                 | GND                 | GND                 | GND                         | GND                         | GND                 | GND                 | GND             | GND               | GND               | GND                 | GND                 | GND    |

| H | GND               | GND                 | GND                 | GND                 | GND                         | GND                         | GND                 | GND                 | GND             | GND               | GND               | GND                 | GND                 | GND    |

| J | GND               | GND                 | GND                 | GND                 | CLK <sup>+</sup>            | V <sub>DD</sub>             | GND                 | SENSE               | V <sub>DD</sub> | PAR/SER           | SCK               | GND                 | GND                 | GND    |

| K | OF <sup>-</sup>   | OF <sup>+</sup>     | GND                 | GND                 | CLK <sup>-</sup>            | GND                         | GND                 | GND                 | GND             | CS                | SDI               | GND                 | GND                 | GND    |

| L | DB01 <sup>-</sup> | DB01 <sup>+</sup>   | GND                 | GND                 | GND                         | GND                         | GND                 | GND                 | GND             | SDO               | GND               | DA1213              | DA1213 <sup>+</sup> |        |

| M | DB23 <sup>-</sup> | DB23 <sup>+</sup>   | DB45 <sup>-</sup>   | DB45 <sup>+</sup>   | GND                         | GND                         | GND                 | GND                 | GND             | DA89 <sup>-</sup> | DA89 <sup>+</sup> | DA1011 <sup>-</sup> | DA1011 <sup>+</sup> |        |

| N | DB67 <sup>-</sup> | DB67 <sup>+</sup>   | DB89 <sup>-</sup>   | DB89 <sup>+</sup>   | OV <sub>DD</sub>            | GND                         | GND                 | GND                 | GND             | DA45 <sup>-</sup> | DA45 <sup>+</sup> | DA67 <sup>-</sup>   | DA67 <sup>+</sup>   |        |

| P | GND               | DB1213 <sup>+</sup> | DB1213 <sup>-</sup> | DB1011 <sup>+</sup> | DB1011 <sup>-</sup>         | GND                         | CLKOUT <sup>-</sup> | CLKOUT <sup>+</sup> | GND             | DA23 <sup>+</sup> | DA23 <sup>-</sup> | DA01 <sup>+</sup>   | DA01 <sup>-</sup>   | GND    |

部品を透かして見たBGAパッケージの上面図

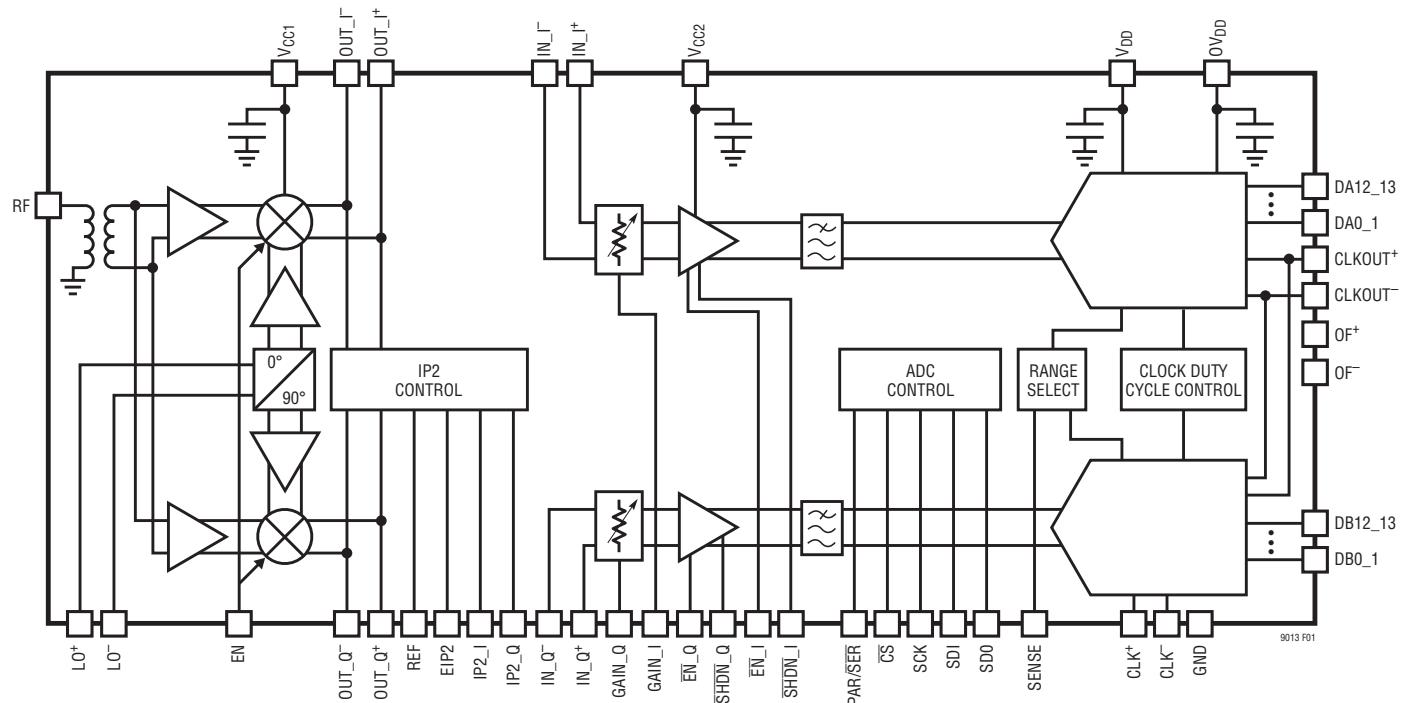

### ブロック図

図1. 機能ブロック図

## タイミング図

ダブルデータレート出力のタイミング、すべてのデータが差動LVDS

## タイミング図

SPI Port Timing (Readback Mode)

SPI Port Timing (Write Mode)

9013 TD02

## 動作

### 概要

LTM9013は、最大4GHzのRF入力周波数を備える無線インフラストラクチャなどの、デジタル・プリディストーション・レシーバ・アプリケーションを対象にする低IFレシーバです。このデバイスは、システム・イン・パッケージ(SiP)技術を活用して、高速14ビット・デュアルA/Dコンバータ、300MHzのローパス・フィルタ、1チャネルにつき1つの利得調整可能な低ノイズ差動アンプ、およびIP2調整付きI/Q復調器を統合したμModuleレシーバです。

以降のセクションでは、各部の動作の詳細について説明します。

### 復調器の動作

RF信号がRFトランスコンダクタンス・アンプの入力に適用され、次に、直交LO信号を使用して、I/Qベースバンド信号に復調されます。この直交LO信号は、高精度の90°C位相シフタによって、外部LOソースから内部で生成されます。

シングルエンドRFインターフェースをイネーブルするために、広帯域トランスがRF入力で内蔵されています。中周波数帯(1.5GHz～2.7GHz)では、RFポートとLOポートの両方は、内部で $50\Omega$ にマッチングされます。外付けのマッチング部品は不要です。低周波数帯(700MHz～1.5GHz)および高周波数帯(2.7GHz～4GHz)の場合、直列インダクタまたはシャント・コンデンサ(あるいは、その両方)を含む簡素なネットワークを、インピーダンス・マッチング・ネットワークとして使用できます。

### アンプの動作

LTM9013の各チャネルは、AC結合された、低ノイズ、低歪みの完全差動オペアンプ/ADCドライバの1段で構成されています。格段の後ろには、高速、高性能のオペアンプと高精度の受動部品を使用する、4極ローパス・フィルタが続きます。この段は、最大の利得と位相の平坦性を得るように設計されています。

LTM9013の可変利得アンプでは、可変利得特性を生成するために、補間にによるタップ減衰器回路アーキテクチャが採用されています。タップ減衰器は、バッファと出力アンプに入力されて、差動信号経路を形成します。この回路アーキテクチャは、良好なRF入力電力操作能力を提供するとともに、ほとんどのIF信号チェーン・アプリケーションにとって望ましい一定の出力ノイズと出力IP3特性を提供します。内部制御回路は、GAIN端子から利得制御信号を受け取り、これを、減衰器回路への適切な一連の制御信号に変換します。減衰器制御回路によって、デシベル・リニアの利得応答が、低速と高速の両方の移動入力制御信号に対して、利得の範囲全体で連続的かつモノトニックでありながら、非常に小さい入力インピーダンスの変動を示すことが保証されます。これらの設計上の配慮によって、 $\pm 0.1\text{dB}$ のリップルでの利得対VG特性、および、類似のデジタル・ステップ減衰器設計よりも緩やかな $0.5\mu\text{s}$ の利得応答時間が得られます。

多くの場合で見落とされるアナログ制御VGAの特性は、利得制御端子からのアップコンバートされた振幅変調(AM)ノイズです。VGAは、2象限乗算器として動作します。そのため、過剰なAMサイドバンド・ノイズの発生を防ぐために、最小限の注意が必要です。以下の表に、LTM9013回路からのベースラインとなる $20\text{nV}/\sqrt{\text{Hz}}$ に等価の入力制御ノイズの影響と、外部制御回路のノイズによるさらに高い結合入力ノイズの影響を示します。

| 制御入力の合計ノイズ電圧<br>(nV/ $\sqrt{\text{Hz}}$ ) | 最大利得に近い10kHzオフセット<br>でのピークAMノイズ(dBc/Hz) |

|-------------------------------------------|-----------------------------------------|

| 20                                        | -142                                    |

| 40                                        | -136                                    |

| 70                                        | -131                                    |

| 100                                       | -128                                    |

| 200                                       | -122                                    |

## 動作

表より、ベースラインとなる  $20\text{nV}/\sqrt{\text{Hz}}$  に等価の入力ノイズで、 $-142\text{dBc}/\text{Hz}$  の最悪の AM サイドバンドが発生していることがわかります。この値は、公称  $0\text{dBm}$  の出力信号に対する最大利得での  $-147\text{dBm}/\text{Hz}$  の出力ノイズフロアに近い値です。無視できないほどの AM サイドバンド・ノイズを防ぐために、通常は、入力制御ノイズ電圧を  $80\text{nV}/\sqrt{\text{Hz}}$  よりも小さくすることが推奨されます。オペアンプ制御回路の出力ノイズ電圧は、通常は  $80\text{nV}/\sqrt{\text{Hz}}$  未満ですが、一部の低電力 D/A コンバータの出力ノイズ電圧は、 $150\text{nV}/\sqrt{\text{Hz}}$  を超えます。 $100\text{nV}/\sqrt{\text{Hz}} \sim 150\text{nV}/\sqrt{\text{Hz}}$  の範囲内の出力ノイズを持つ D/A コンバータは、通常は適切な 2:1 または 3:1 の抵抗分割器ネットワークを出力で使用して調整され、それと同じ比率でノイズの振幅が抑えられます。アプリケーションで AM ノイズを最小にすることが重要な場合は、 $150\text{nV}/\sqrt{\text{Hz}}$  を超えるノイズを持つ D/A コンバータの使用を避ける必要があります。

### A/D コンバータの入力ネットワーク

アンプの出力段と A/D コンバータの入力段の間の受動ネットワークは、リップルが  $0.1\text{dB}$  の 4 次チェビシェフ・ローパス・フィルタ応答を提供します。

### コンバータの動作

LTM9013 は、 $1.8\text{V}$  単一電源で動作する  $310\text{Msps}$  の 2 チャネル、14 ビット A/D コンバータを備えています。このコンバータはパイプライン構成の 5 個の ADC 段を備えており、サンプリングされた入力は 5 サイクル後にデジタル値になります。アナログ入力は、VGA によって差動で駆動されます。最適性能を得るには、エンコード入力を差動で駆動する必要があります。デジタル出力はダブルデータレート LVDS です。シリアル SPI ポートを介してモード制御レジスタをプログラムすることにより、追加機能を選択することができます。

## アプリケーション情報

### RF入力

内蔵トランジスタと高直線性トランスクンダクタンス・アンプによって構成された、ミキサのRF入力を図2に示します。トランスクンダクタンスの1次側は、RF入力ピンに接続されています。トランスクンダクタンスの2次側はトランスクンダクタンス・アンプの差動入力に接続されています。どのような状況においても、外部DC電圧をRF入力ピンに加えないでください。トランスクンダクタンスの1次側に流れ込むDC電流は内蔵トランジスタに損傷を与える可能性があります。直列ブロッキング・コンデンサを使用して、RF入力ポートをRF信号源にAC結合する必要があります。

図2. RF入力インターフェース

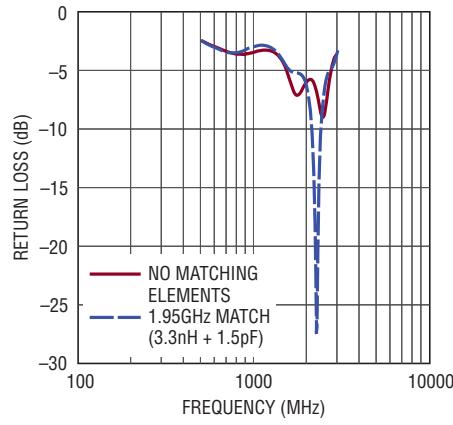

RF入力ポートは、1.5GHz～2.7GHzの広い周波数範囲で、通常は10dBよりも良い入力リターン損失で内部でマッチングされます。この周波数範囲では、外部マッチング・ネットワークは不要です。ただし、デバイスがさらに低い周波数で動作する場合は、図2に示すマッチング・ネットワークを使用して入力リターン損失を改善できます。図3に示すように、目的の周波数でマッチングする最適な入力インピーダンスを得るために、シャント・コンデンサC20、C21、および直列インダクタL5を選択できます。C19は、直列DCブロッキング・コンデンサとして機能します。

外部マッチング部品がない場合のRF入力インピーダンスとS11のパラメータを、表1に示します。

図3. 外部マッチングを使用したRF入力のリターン損失

表1. RF入力インピーダンス

| 周波数     | 大きさ  | 位相     | R     | X      |

|---------|------|--------|-------|--------|

| 500MHz  | 0.96 | 41.2   | 92.3Ω | -95.4Ω |

| 600MHz  | 0.93 | 50.6   | 85.3Ω | -62.0Ω |

| 700MHz  | 0.90 | 61.3   | 76.0Ω | -36.0Ω |

| 800MHz  | 0.81 | 71.3   | 66.9Ω | -17.6Ω |

| 900MHz  | 0.70 | 90.7   | 49.4Ω | 0.4Ω   |

| 1000MHz | 0.74 | 109.6  | 34.8Ω | 8.5Ω   |

| 1100MHz | 0.78 | 122.1  | 25.9Ω | 11.2Ω  |

| 1200MHz | 0.82 | 130.2  | 20.4Ω | 12.1Ω  |

| 1300MHz | 0.81 | 136.9  | 16.8Ω | 11.6Ω  |

| 1400MHz | 0.83 | 143.6  | 13.2Ω | 10.9Ω  |

| 1500MHz | 0.83 | 149.0  | 11.0Ω | 9.7Ω   |

| 1600MHz | 0.83 | 157.2  | 7.9Ω  | 7.7Ω   |

| 1700MHz | 0.84 | 165.3  | 5.8Ω  | 5.2Ω   |

| 1800MHz | 0.83 | 175.9  | 4.7Ω  | 1.5Ω   |

| 1900MHz | 0.84 | -173.1 | 4.8Ω  | -2.5Ω  |

| 2000MHz | 0.81 | -161.6 | 7.3Ω  | -6.2Ω  |

| 2100MHz | 0.81 | -150.2 | 10.9Ω | -9.2Ω  |

| 2200MHz | 0.78 | -141.5 | 15.2Ω | -10.5Ω |

| 2300MHz | 0.75 | -132.7 | 20.2Ω | -10.9Ω |

| 2400MHz | 0.73 | -129.9 | 22.2Ω | -10.6Ω |

| 2500MHz | 0.68 | -126.8 | 24.9Ω | -9.7Ω  |

| 2600MHz | 0.66 | -128.6 | 24.3Ω | -9.4Ω  |

| 2700MHz | 0.63 | -129.1 | 24.8Ω | -8.8Ω  |

| 2800MHz | 0.62 | -126.9 | 26.0Ω | -8.6Ω  |

| 2900MHz | 0.61 | -124.9 | 27.2Ω | -8.5Ω  |

| 3000MHz | 0.59 | -117.7 | 31.5Ω | -7.6Ω  |

9013f

## アプリケーション情報

### LO入力ポート

ミキサのLO入力インターフェースを図4に示します。入力は高精度直交位相シフタによって構成されており、I/Qミキサを駆動するLOバッファ・アンプ向けに位相を0°Cおよび90°CシフトさせたLO信号を生成します。どのような状況においても、外部DC電圧を入力ピンに加えないでください。トランジスタの1次側に流れ込むDC電流はトランジスタに損傷を与える恐れがあります。

図4. LO入力インターフェース

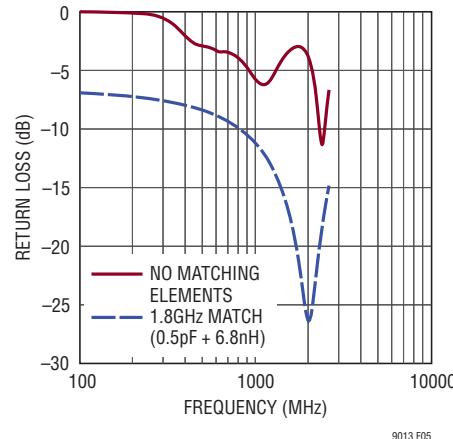

LO入力ポートは、1.5GHz～2.7GHzの広い周波数範囲で、通常は10dBよりも良い入力リターン損失で内部でマッチングされます。この周波数範囲では、外部マッチング・ネットワークは不要です。外部マッチング部品がない場合のLO入力インピーダンスとS11のパラメータを、表2に示します。この周波数範囲を外れる場合、直列コンデンサC22とシャント・コンデンサC24を使用して、インピーダンスのマッチングを改善できます。

図5. 外部マッチングを使用したLO入力のリターン損失

表2. LO入力インピーダンス

| 周波数     | 大きさ  | 位相     | R      | X      |

|---------|------|--------|--------|--------|

| 500MHz  | 0.71 | -70.3  | 67.7Ω  | 15.5Ω  |

| 600MHz  | 0.66 | -83.9  | 55.0Ω  | 3.6Ω   |

| 700MHz  | 0.66 | -97.1  | 44.5Ω  | -3.3Ω  |

| 800MHz  | 0.62 | -119.8 | 29.8Ω  | -8.3Ω  |

| 900MHz  | 0.55 | -144.9 | 20.2Ω  | -6.5Ω  |

| 1000MHz | 0.51 | -177.8 | 16.1Ω  | -0.4Ω  |

| 1100MHz | 0.48 | 146.5  | 22.2Ω  | 5.3Ω   |

| 1200MHz | 0.52 | 115.0  | 34.3Ω  | 6.1Ω   |

| 1300MHz | 0.57 | 87.9   | 51.6Ω  | -0.9Ω  |

| 1400MHz | 0.62 | 70.5   | 66.9Ω  | -12.4Ω |

| 1500MHz | 0.66 | 55.0   | 84.7Ω  | -30.5Ω |

| 1600MHz | 0.67 | 44.0   | 101.4Ω | -46.6Ω |

| 1700MHz | 0.69 | 34.1   | 123.7Ω | -67.4Ω |

| 1800MHz | 0.67 | 24.3   | 154.8Ω | -75.6Ω |

| 1900MHz | 0.66 | 15.5   | 193.5Ω | -70.8Ω |

| 2000MHz | 0.61 | 2.5    | 206.9Ω | -10.8Ω |

| 2100MHz | 0.55 | -10.2  | 163.1Ω | 24.2Ω  |

| 2200MHz | 0.46 | -34.3  | 101.7Ω | 21.3Ω  |

| 2300MHz | 0.34 | -63.8  | 65.5Ω  | 5.5Ω   |

| 2400MHz | 0.30 | -113.3 | 40.0Ω  | -2.5Ω  |

| 2500MHz | 0.33 | -164.3 | 25.8Ω  | -1.6Ω  |

| 2600MHz | 0.42 | 164.8  | 21.4Ω  | 2.2Ω   |

| 2700MHz | 0.51 | 140.5  | 23.1Ω  | 6.3Ω   |

| 2800MHz | 0.53 | 120.3  | 31.4Ω  | 6.7Ω   |

| 2900MHz | 0.52 | 101.7  | 42.2Ω  | 3.6Ω   |

| 3000MHz | 0.33 | 98.1   | 45.9Ω  | 1.3Ω   |

9013f

## アプリケーション情報

### IM2調整回路

LTM9013には、IチャネルとQチャネルのIM2レベルを個別に調整する回路も備わっています。EIP2ピンがロジック“H”的とき、この回路はイネーブルされ、IP2IとIP2Qのアナログ制御電圧入力はIM2レベルを調整することができます。IM2レベルはベースバンド帯域幅の大きな範囲にわたって効果的に最小化することができます。回路の有効なベースバンド周波数の上限は約200MHzです。この周波数範囲に収まるどんなIM2成分も最小化することができます。

### 可変利得アンプ

LTM9013は、1MHz～500MHzの範囲のアプリケーション周波数に対して最適化され、完全に差動でアナログ制御された高直線性可変利得アンプ(VGA)を備えています。VGAアーキテクチャは、31dBを超える利得制御範囲で一定のOIP3と一定の出力ノイズ・レベル(NF + 利得)を提供し、そのため利得全体で均一なスプリアス・フリー・ダイナミック・レンジ(SFDR)を示します。この一定のSFDR特性は、レシーバのIFチェーンで使用する場合に理想的です。

### 利得特性

LTM9013は、GAIN\_IとGAIN\_Qに加えられる制御電圧に対してデシベル・リニアである、連続的に調整可能な31dBの利得を提供します。次のようにして、正の利得制御スロープを簡単に実現できます。

利得制御電圧をGAIN\_I/GAIN\_Qピンに加えます。GAIN\_I/GAIN\_Qの電圧が増えると、利得が増加します。

この標準シングルエンド構成で接続した場合、アクティブ制御入力範囲は、0.1Vから1.1Vに拡張されます。適切な低出力抵抗を持つ抵抗分割器を使用して、この制御入力範囲を拡張できます。例えば、各1kの2つの直列抵抗は、実効500Ωのテブナン等価ソース抵抗(GAIN\_I/GAIN\_Q端子の10kの入力抵抗と比較して相対的に小さな負荷効果)を提供しながら、制御入力範囲を0.2Vから2.2Vに拡張します。

### IF入力ポート特性

アンプ入力は、動作周波数範囲全体で公称50Ωの差動入力インピーダンスを備えています。この入力インピーダンス特性は、差動減衰器回路から派生します。内部回路は、この減衰器回路へのIF接続を制御し、適切な同相DC電圧を生成します。

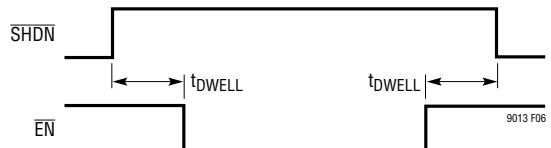

### イネーブル/シャットダウン

$\overline{EN}$ ピンと $\overline{SHDN}$ ピンは、各100kのプルアップ抵抗を介して $V_{CC2}$ に自己バイアスされます。そのため、出力アンプ信号経路がディスエーブルされて、既定のオープンピン状態で電源が投入されます。 $\overline{EN}$ ピンを“L”に引き下げるとき、減衰器回路から出力アンプを経由する信号経路が形成されます。 $\overline{EN}$ ピンは、基本的に高速なミューティング機能を提供します。一方、 $\overline{SHDN}$ ピンは、比較的低速な電源オン/オフ機能を提供します。

$\overline{SHDN}$ 機能を必要とするアプリケーションの場合、 $\overline{SHDN}$ 信号が遷移する前に、“H”の $\overline{EN}$ 電圧を使用して出力アンプ信号経路をディスエーブルすることが推奨されます。アンプをイネーブルする場合、VGAによる非モノトニック出力信号動作を回避するために、 $\overline{SHDN}$ の立ち上がり遷移と $\overline{EN}$ の立ち下り遷移の間で、最低5msのドウェル時間を許容します。 $\overline{SHDN}$ の立下り遷移の場合は逆の遅延シーケンスが推奨されますが、出力信号の振幅が $\overline{EN}$ ピンとは無関係に急に減少するため、あまり重要ではありません。

図6.

## アプリケーション情報

### ESD

アンプの入力は、すべてのピンで逆バイアスされたESDダイオードを使用して保護されます。いずれかのピンが、強制的に、正電源を超える電圧から1ダイオード電圧分低下するか、負電源を下回る電圧から1ダイオード電圧分低下した場合、それらのダイオードを経由して大電流が流れることができます。電流が10mA未満に維持されれば、デバイスに損傷は発生しません。

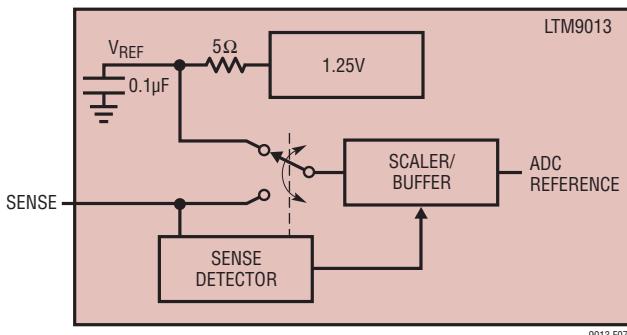

### リファレンス

LTM9013は、A/Dコンバータ用の1.25Vの電圧リファレンスを内蔵しています。内部リファレンスを使用する1.32Vの入力範囲の場合、SENSEをV<sub>DD</sub>に接続します。外部リファレンスを使用する1.32Vの入力範囲の場合は、1.25Vのリファレンス電圧をSENSEに印加します(図7)。規定の性能を実現するには、1.15Vのリファレンス電圧をSENSEに加えます。

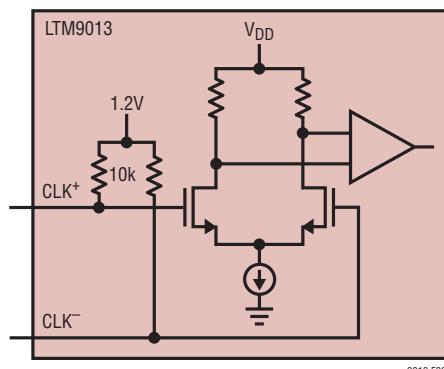

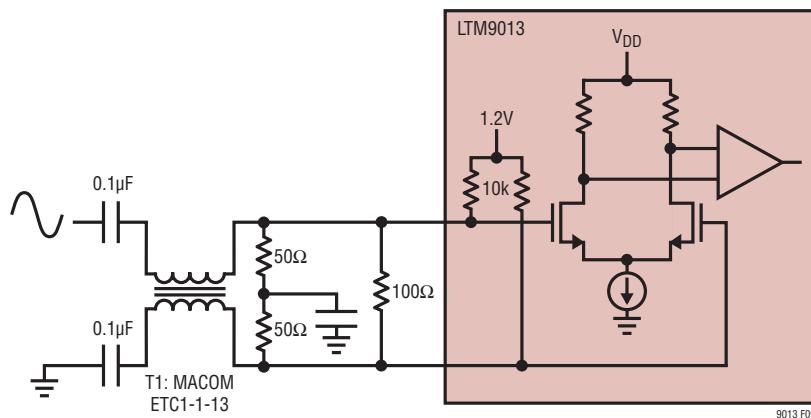

### エンコード入力

エンコード入力の信号品質は、A/Dコンバータのノイズ性能に大きく影響します。エンコード入力はアナログ信号として扱います。このため、回路基板上のデジタル・トレースに隣接して配線しないようにしてください。

エンコード入力は内部で10kΩの等価抵抗を介して1.2Vにバイアスされています(図8)。ドライバの同相範囲が1.1V～1.5Vの場合は、エンコード入力を直接ドライブすることが可能です。そうでなければ、トランジストまたはカップリング・コンデンサが必要です(図9と図10)。入力信号の最大(ピーク)電圧は決してV<sub>DD</sub> + 0.1Vを超えないように、または-0.1Vより低くならないようにします。

図7. リファレンス回路

図8. 等価エンコード入力回路

## アプリケーション情報

図9. 正弦波のエンコード回路

図10. PECLまたはLVDSのエンコード・ドライブ

### クロック・デューティ・サイクル・スタビライザ

良好な性能を得るために、エンコード信号のデューティサイクルは50% ( $\pm 5\%$ )にします。オプションのクロック・デューティ・サイクル・スタビライザ回路がインエーブルされていると、エンコードのデューティ・サイクルは30%～70%の間で変化することができ、デューティ・サイクル・スタビライザは内部のデューティ・サイクルを一定の50%に保ちます。デューティサイクル・スタビライザは、SPIレジスタA2(表5を参照)によって、または、パラレル・プログラミング・モードでは $\overline{CS}$ によってインエーブルされます。

サンプル・レートを迅速に変更する必要のあるアプリケーションでは、クロック・デューティサイクル・スタビライザをディスエーブルすることができます。この場合、クロックのデューティ・サイクルが50% ( $\pm 5\%$ )になるように注意してください。

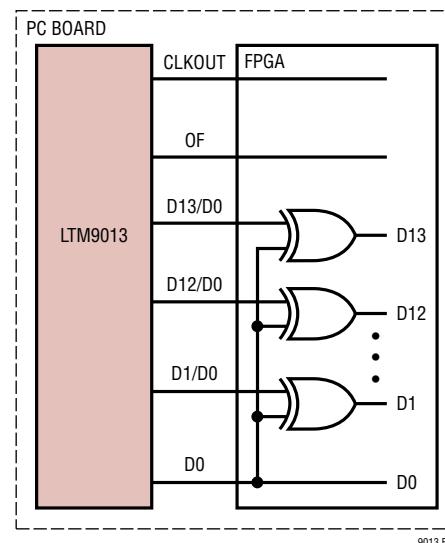

### デジタル出力

デジタル出力はダブルデータレートLVDS信号です。2つのデータ・ビットが各差動出力対に多重化されて出力されます。チャネルAには7つのLVDS出力対(DA0\_1+/DA0\_1-～DA12\_13-/DA12\_13+)、チャネルBには7つのLVDS出力対(DB0\_1+/DB0\_1-～DB12\_13-/DB12\_13+)があります。オーバーフロー( $OF^+/OF^-$ )およびデータ出力クロック(CLKOUT+/CLKOUT-)には、それぞれLVDS出力対が1つあります。両チャネルのオーバーフローは、 $OF^+/OF^-$ 出力対に多重化されることに注意してください。

デフォルトでは、出力は標準LVDSレベルです。すなわち、出力電流が3.5mA、出力同相電圧が1.25Vです。各LVDS出力対には外付けの100Ω差動終端抵抗が必要です。終端抵抗は、LVDSレシーバのできるだけ近くに配置してください。

### 設定可能なLVDS出力電流

デフォルトの出力ドライバ電流は3.5mAです。この電流は、モード制御レジスタA3をシリアル・モードでプログラムすることにより調整できます(表5を参照)。利用可能な電流レベルは、1.75mA、2.1mA、2.5mA、3mA、3.5mA、4mA、および4.5mAです。

## アプリケーション情報

### オプションのLVDSドライバの内部終端

ほとんどの場合、 $100\Omega$ の外付け終端抵抗を使用するだけでLVDSの優れた信号品質が得られます。さらに、モード制御レジスタA3をシリアルでプログラムすることにより、オプションの $100\Omega$ の内部終端抵抗をイネーブルすることができます。内部終端は、レシーバでの不完全な終端によって発生する反射を吸収するのに役立ちます。内部終端がイネーブルされると、同じ出力電圧振幅を維持するために、出力ドライバ電流は2倍になります。

### オーバーフロー・ビット

アナログ入力にオーバーレンジまたはアンダーレンジが生じると、オーバーフロー出力ビット(OF)はロジック“H”を出力します。オーバーフロー・ビットにはデータ・ビットと同じパイプライン待ち時間があります。OF出力はダブルデータレートです。CLKOUT<sup>+</sup>が“L”的ときは、チャネルAのオーバーフローを利用できます。CLKOUT<sup>+</sup>が“H”的ときは、チャネルBのオーバーフローを利用できます。

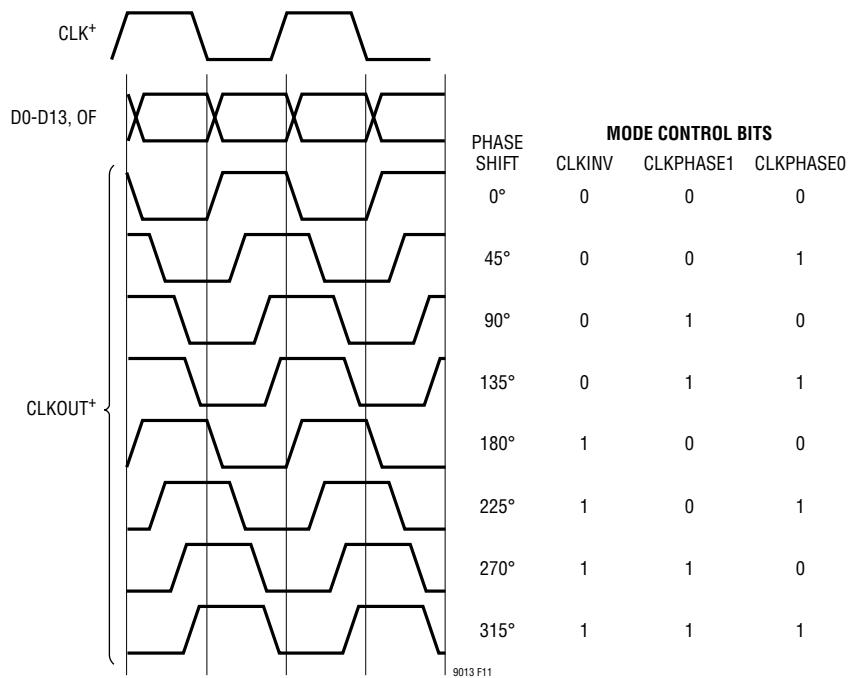

### 出力クロックの位相シフト

出力データをラッチするとき適切なセットアップ時間とホールド時間を与えるには、データ出力ビットに対して CLKOUT<sup>+</sup>信号の位相をシフトさせることが必要な場合があります。ほとんどのFPGAはこの機能を備えており、これが一般にタイミングを調整する最良のポイントです。

あるいは、A/Dコンバータはモード制御レジスタA2をシリアル・モードでプログラムすることにより、CLKOUT<sup>+</sup>/CLKOUT<sup>-</sup>信号の位相をシフトすることもできます。出力クロックは $0^\circ$ 、 $45^\circ$ 、 $90^\circ$ または $135^\circ$ の単位でシフトすることができます。位相シフト機能を使うには、クロック・デューティ・サイクル・スタビライザをオンにする必要があります。もう1つの制御レジスタ・ビットは、位相シフトとは関係なく、CLKOUT<sup>+</sup>とCLKOUT<sup>-</sup>の極性を反転させることができます。これら2つの機能を組み合わせると、 $45^\circ$ から $315^\circ$ までの位相シフトが可能になります(図11)。

図11. CLKOUTの位相シフト

## アプリケーション情報

### データ形式

アナログ入力電圧、デジタル・データ出力ビット、およびオーバーフロー・ビットの相互関係を表3に示します。デフォルトでは、出力のデータ形式はオフセット・バイナリです。モード制御レジスタA4をシリアル・モードでプログラムすることにより、2の補数形式を選択することができます。

表3. 出力コードと入力レベル

| +IN ~ -IN   | OF | D13 ~ D0<br>(オフセット・バイナリ) | D13 ~ D0<br>(2の補数) |

|-------------|----|--------------------------|--------------------|

| +Overflow   | 1  | 11 1111 1111 1111        | 01 1111 1111 1111  |

| +Full Scale | 0  | 11 1111 1111 1111        | 01 1111 1111 1111  |

|             | 0  | 11 1111 1111 1110        | 01 1111 1111 1110  |

| Mid-Scale   | 0  | 10 0000 0000 0001        | 00 0000 0000 0001  |

|             | 0  | 10 0000 0000 0000        | 00 0000 0000 0000  |

|             | 0  | 01 1111 1111 1111        | 11 1111 1111 1111  |

|             | 0  | 01 1111 1111 1110        | 11 1111 1111 1110  |

| -Full Scale | 0  | 00 0000 0000 0001        | 10 0000 0000 0001  |

| -Overflow   | 0  | 00 0000 0000 0000        | 10 0000 0000 0000  |

|             | 1  | 00 0000 0000 0000        | 10 0000 0000 0000  |

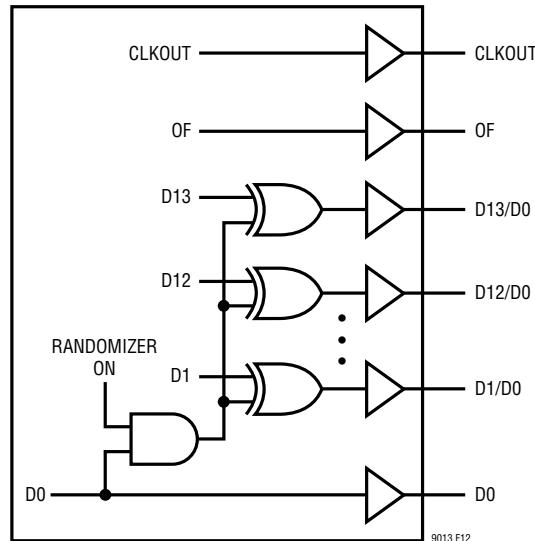

### デジタル出力ランダマイザ

A/Dコンバータのデジタル出力からの干渉は、場合によっては避けられません。デジタル干渉は、容量性結合や誘導性結合、あるいはグランド・プレーンを介した結合によって発生する可能性があります。結合係数がきわめて小さい場合でも、そのためにA/Dコンバータの出力スペクトルに不要なトーンが発生することがあります。デジタル出力をデバイスから伝送する前にランダム化することにより、これらの不要なトーンをランダム化し、それによって不要なトーン振幅を減少させることができます。

デジタル出力は、LSBと他のすべてのデータ出力ビットとの間で排他的論理演算を行うことによってランダム化されます。デコードするには逆の演算を行います。つまり、LSBと他の全てのビットとの間で排他的論理演算を行います。LSB、OF、およびCLKOUTの各出力は影響を受けません。モード制御レジスタA4をシリアル・モードでプログラムすることにより、出力ランダマイザをインエーブルすることができます。

図12. デジタル出力ランダマイザの等価機能

図13. ランダム化されたデジタル出力信号の復元

## アプリケーション情報

### 交互ビット極性

回路基板のデジタル帰還を減らすことがあるもう1つの機能は、交互ビット極性モードです。このモードがイネーブルされると、すべての奇数ビット(D1、D3、D5、D7、D9、D11、D13)が出力バッファの前で反転します。偶数ビット(D0、D2、D4、D6、D8、D10、D12)、OFおよびCLKOUTは影響を受けません。これにより、回路基板のグランド・プレーンのデジタル電流を減らし、(特に非常に小さなアナログ入力信号の場合)デジタル・ノイズを減らすことができます。

デジタル出力は、奇数ビット(D1、D3、D5、D7、D9、D11、D13)を反転させることにより、レシーバでデコードされます。交互ビット極性モードはデジタル出力ランダマイザからは独立しています。つまり、両方の機能を同時にオンすることも、両方の機能を同時にオフする事も可能ですが、交互ビット極性モードは、モード制御レジスタA4をシリアル・モードでプログラムすることによってイネーブルされます。

### デジタル出力のテストパターン

A/Dコンバータへのデジタル・インターフェースを回路内でテストできるようにするために、A/Dコンバータのデータ出力[OF、D13～D0]を強制的に既知の値にするいくつかのテスト・モードがあります。

オール1:すべての出力が1

オール0:すべての出力が0

交互:サンプルの出力がオール1からオール0に交互に変化する。

格子縞:サンプルの出力が101010101010101から0101010101010に交互に変化する。

デジタル出力のテスト・パターンは、モード制御レジスタA4をシリアル・モードでプログラムすることによってイネーブルされます。テストパターンがイネーブルされると、他のすべての形式設定モード(2の補数、ランダマイザ、交互ビット極性)がオーバーライドされます。

### 出力のディスエーブル

デジタル出力はモード制御レジスタA3をシリアル・モードでプログラムすることによってディスエーブルすることができます。OFおよびCLKOUTを含むすべてのデジタル出力がディスエーブルされます。高インピーダンスのディスエーブル・ステートは、長期間の休止状態を対象にしており、複数のコンバータ間でデータ・バスを多重化する用途向けには設計されていません。

### スリープ・モード

節電のため、A/Dコンバータをスリープ・モードにすることができます。スリープ・モードでは、A/Dコンバータ全体がパワーダウンし、電力消費は5mW未満になります。エンコード入力信号がディスエーブルされていないと、消費電力は(250Mspsで最大5mWまで)増加します。スリープ・モードは、モード制御レジスタA1(シリアル・プログラミング・モード)またはSCK(パラレル・プログラミング・モード)によってイネーブルされます。

シリアル・プログラミング・モードでは、チャネルAを通常動作状態にしたまま、チャネルBをディスエーブルすることもできます。

スリープ・モードから回復するのに要する時間は、V<sub>REF</sub>のバイパス・コンデンサの容量によって決まります。内部で使用される2.2μFの値では、A/Dコンバータは $0.1\text{ms} + 2500 \cdot t_p$ 経過後に安定化します。ここで、t<sub>p</sub>はサンプリング・クロックの周期です。

### ナップ・モード

ナップ・モードでは、A/Dコンバータのコアはパワーダウンしますが、内部リファレンス回路はアクティブなままで、より速くウェイクアップすることができます。ナップ・モードからの復帰には、最低でも100クロック・サイクルが必要です。ナップ・モードは、シリアル・プログラミング・モードでパワーダウン・レジスタA1によってイネーブルされます。

ナップ・モードからのウェイクアップ時間は、クロックが動作している場合だけ保証されます。そうでないと、「パワーダウン・ウェイクアップ」条件が適用されます。

## アプリケーション情報

### デバイスのプログラミング・モード

A/Dコンバータの動作モードはパラレル・インターフェースまたは簡単なシリアル・インターフェースのどちらでもプログラム可能です。シリアル・インターフェースの方が柔軟性が高く、選択可能なすべてのモードをプログラムできます。パラレル・インターフェースには制限が多く、プログラムできるのはよく使用される一部のモードのみです。

### パラレル・プログラミング・モード

パラレル・プログラミング・モードを使用するには、PAR/SERをV<sub>DD</sub>に接続します。CS、SCK、およびSDIの各ピンはバイナリ・ロジック入力で、特定の動作モードを設定します。これらのピンはV<sub>DD</sub>またはグランドに接続するか、あるいは1.8V、2.5V、または3.3VのCMOSロジックでドライブすることができます。表4に、CS、SCK、およびSDIで設定されるモードを示します。

表4. パラレル・プログラミング・モードの制御ビット(PAR/SER = V<sub>DD</sub>)

| ピン  | 説明                                                                                                                   |

|-----|----------------------------------------------------------------------------------------------------------------------|

| CS  | Clock Duty Cycle Stabilizer Control Bit<br>0 = Clock Duty Cycle Stabilizer Off<br>1 = Clock Duty Cycle Stabilizer On |

| SCK | Power Down Control Bit<br>0 = Normal Operation<br>1 = Sleep Mode (entire ADC is powered down)                        |

| SDI | LVDS Current Selection Bit<br>0 = 3.5mA LVDS Current Mode<br>1 = 1.75mA LVDS Current Mode                            |

### シリアル・プログラミング・モード

シリアル・プログラミング・モードを使用するには、PAR/SERをグランドに接続します。CS、SCK、SDIおよびSDOの各ピンは、A/Dコンバータの制御レジスタをプログラムするシリアル・インターフェースになります。データは16ビットのシリアル・ワードでレジスタに書き込まれます。データをレジスタから読み出して、レジスタの内容を検証することもできます。

シリアル・データ転送はCSが“L”になると開始されます。SDIピンのデータは、SCKの先頭から16番目までの立ち上がりエッジでラッチされます。先頭から16番目より後のSCKの立ち上がりエッジは無視されます。データ転送は、CSが再度“H”になると終了します。

16ビットの入力ワードの先頭ビットはR/Wビットです。次の7ビットはレジスタのアドレス(A6:A0)です。最後の8ビットはレジスタのデータ(D7:D0)です。

R/Wビットが“L”的場合、シリアル・データ(D7:D0)はアドレス・ビット(A6:A0)で設定されるレジスタに書き込まれます。R/Wビットが“H”的場合は、アドレス・ビット(A6:A0)によって設定されるレジスタ内のデータがSDOピンで読み出されます(タイミング図を参照)。読み出しコマンドの実行中、レジスタは更新されず、SDIのデータは無視されます。

SDOピンはオープン・ドレイン出力で、200Ωのインピーダンスでグランド電位まで引き込みます。レジスタのデータをSDOを介して読み出す場合は、2kの外付けプルアップ抵抗が必要です。シリアル・データが書き込み専用で読み出す必要がない場合は、SDOをフロート状態のままにしてもかまわないので、プルアップ抵抗は不要です。モード制御レジスタのマップを表5に示します。

### ソフトウェア・リセット

シリアル・プログラミングを使用する場合は、電源がオンして安定した後できるだけ早くモード制御レジスタをプログラムします。最初のシリアル・コマンドは、すべてのレジスタのデータ・ビットをロジック0にリセットするソフトウェア・リセットにする必要があります。ソフトウェア・リセットを行うには、レジスタA0(ビットD7)に1を書き込む必要があります。リセットが完了した後、ビットD7は自動的に再度ゼロに設定されます。このレジスタは書き込み専用です。

## アプリケーション情報

表5. シリアル・プログラミング・モードのレジスタ・マップ( $\overline{PAR/SER} = GND$ )。Xは未使用のビットを示す

レジスタ A0:リセット・レジスタ(アドレス 00h)、書き込み専用

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------|----|----|----|----|----|----|----|

| RESET | X  | X  | X  | X  | X  | X  | X  |

ビット7      **RESET**      ソフトウェア・リセット・ビット

0 = リセットをディスエーブル

1 = ソフトウェア・リセット。すべてのモード制御レジスタが00hにリセットされる。リセットが完了すると、このビットは自動的に0に戻る。

ビット6～0      不使用のビット

レジスタ A1:パワーダウン・レジスタ(アドレス 01h)

| D7 | D6 | D5 | D4 | D3    | D2  | D1  | D0 |

|----|----|----|----|-------|-----|-----|----|

| X  | X  | X  | X  | SLEEP | NAP | PDB | 0  |

ビット7～4      未使用、このビットは0として読み出される

ビット3      **SLEEP**

0 = 通常動作

1 = ADC全体をパワーダウン

ビット2      **NAP**

0 = 通常モード

1 = 両方のチャネルが低消費電力モード

ビット1      **PDB**

0 = 通常動作

1 = チャネルBをパワーダウン。チャネルAは通常動作。

ビット0      0に設定する必要がある

レジスタ A2:タイミング・レジスタ(アドレス 02h)

| D7 | D6 | D5 | D4 | D3     | D2        | D1        | D0  |

|----|----|----|----|--------|-----------|-----------|-----|

| X  | X  | X  | X  | CLKINV | CLKPHASE1 | CLKPHASE0 | DCS |

ビット7～4      未使用、このビットは0として読み出される

ビット3      **CLKINV** 出力クロック反転ビット

0 = 通常の CLKOUT の極性(タイミング図に示されているとおり)

1 = 反転した CLKOUT 極性

ビット2～1      **CLKPHASE1:CLKPHASE0** 出力クロックの位相遅延ビット

00 = CLKOUT の遅延なし(タイミング図に示されているとおり)

01 = CLKOUT<sup>+</sup>/CLKOUT<sup>-</sup> を 45°C(クロックの周期・1/8)だけ遅延

10 = CLKOUT<sup>+</sup>/CLKOUT<sup>-</sup> を 90°C(クロックの周期・1/4)だけ遅延

11 = CLKOUT<sup>+</sup>/CLKOUT<sup>-</sup> を 135°C(クロックの周期・3/8)だけ遅延

Note: CLKOUT 位相遅延機能を使う場合、クロック・デューティ・サイクル・スタビライザもオンする必要がある

ビット0      **DCS** クロック・デューティ・サイクル・スタビライザ・ビット

0 = クロック・デューティ・サイクル・スタビライザをオフ

1 = クロック・デューティ・サイクル・スタビライザをオン

## アプリケーション情報

### レジスタ A3:出力モード・レジスタ(アドレス 03h)

| D7 | D6 | D5 | D4     | D3     | D2     | D1     | D0     |

|----|----|----|--------|--------|--------|--------|--------|

| X  | X  | X  | ILVDS2 | ILVDS1 | ILVDS0 | TERMON | OUTOFF |

ビット 7～5 未使用、このビットは0として読み出される

ビット 4～2 **ILVDS2:ILVDS0** LVDS 出力電流ビット

000 = 3.5mA LVDS 出力ドライバ電流

001 = 4.0mA LVDS 出力ドライバ電流

010 = 4.5mA LVDS 出力ドライバ電流

011 = 未使用

100 = 3.0mA LVDS 出力ドライバ電流

101 = 2.5mA LVDS 出力ドライバ電流

110 = 2.1mA LVDS 出力ドライバ電流

111 = 1.75mA LVDS 出力ドライバ電流

ビット 1 **TERMON** LVDS 内部終端ビット

0 = 内部終端をオフ

1 = 内部終端をオン LVDS 出力ドライバ電流は ILVDS2:ILVDS0 によって設定される電流の2倍

ビット 0 **OUTOFF** デジタル出力モード制御ビット

0 = デジタル出力をイネーブル

1 = デジタル出力をディスエーブル(高インピーダンス)

### レジスタ A4:データ・フォーマット・レジスタ(アドレス 04h)

| D7       | D6       | D5       | D4  | D3 | D2      | D1   | D0       |

|----------|----------|----------|-----|----|---------|------|----------|

| OUTTEST2 | OUTTEST1 | OUTTEST0 | ABP | 0  | DTESTON | RAND | TWOSCOMP |

ビット 7～5 **OUTTEST2:OUTTEST0** デジタル出力のテストパターン・ビット

000 = 全デジタル出力が 0

001 = 全デジタル出力が 1

010 = 交互出力パターン 0F、D13～D0 は、000 0000 0000 0000 と 111 1111 1111 1111 を交互に出力

100 = チェッカーボード出力パターン。OF、D13～D0 は 101 0101 0101 0101 と 010 1010 1010 1010 を交互に出力

Note 1:他のビットの組み合わせは使用されない。

Note 2: チャネル A からのパターンとチャネル B からのパターンは同期していないことがある。

ビット 4 **ABP** 交互ビット極性モードの制御ビット

0 = 交互ビット極性モードをオフ

1 = 交互ビット極性モードをオン

ビット 3 0 に設定する必要がある

ビット 2 **DTESTON** デジタル出力テストパターンをイネーブル(ビット 7～5 によって設定)

0 = 通常モード

1 = デジタル出力テストパターンをイネーブル

ビット 1 **RAND** データ出力ランダマイザ・モード制御ビット

0 = データ出力ランダマイザ・モードをオフ

1 = データ出力ランダマイザ・モードをオン

ビット 0 **TWOSCOMP** 2 の補数モード制御ビット

0 = オフセット・バイナリのデータ形式

1 = 2 の補数のデータ形式

## アプリケーション情報

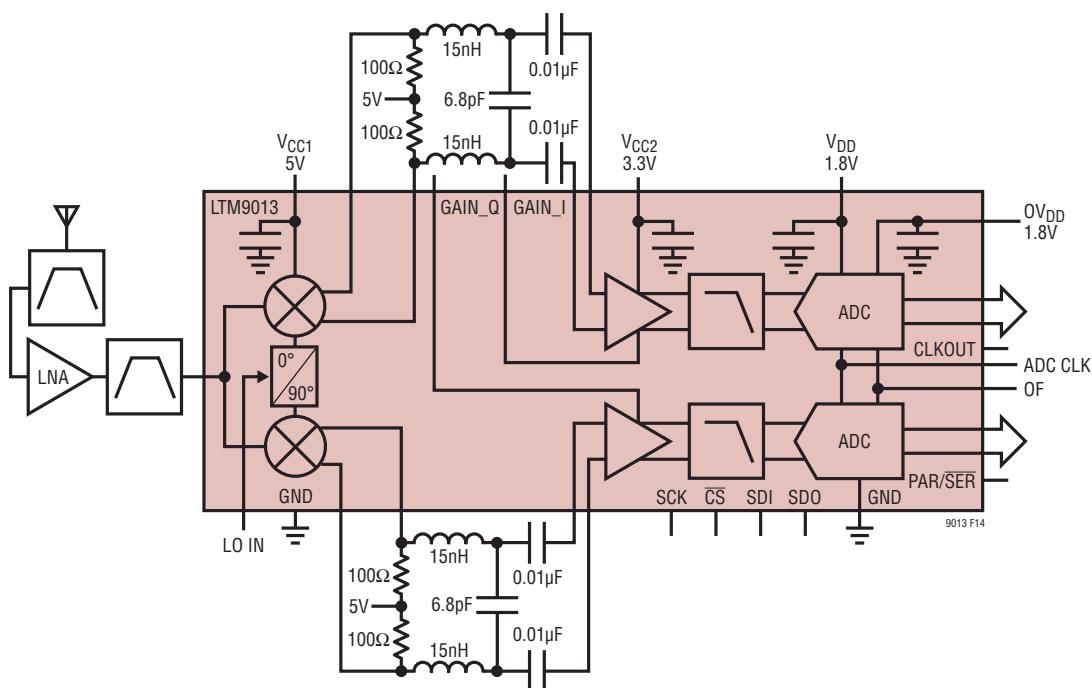

### 設計例

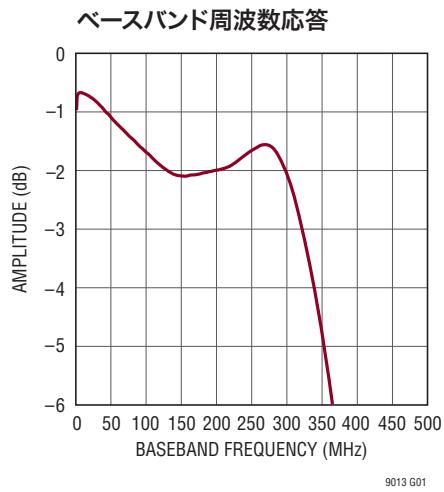

LTM9013では、アプリケーションに合わせて、ハイパス・コーナー周波数を調整できます。300MHzの内部ネットワークによって、0.5dBのローパス・コーナーが設定されます。外部ハイパス・ネットワークと内部ローパス・ネットワークをカスケード接続することによって、バンドパス特性を実現します。超低周波数のハイパス・コーナーの例を、図14に示します。

モジュール全体の標準的性能は次のとおりです。

IFパスバンド(1.5dB):1MHz～300MHz

-1dBFSの場合のRF入力:最大利得で-5dBm

-1dBFSでのSNR:59.1dB

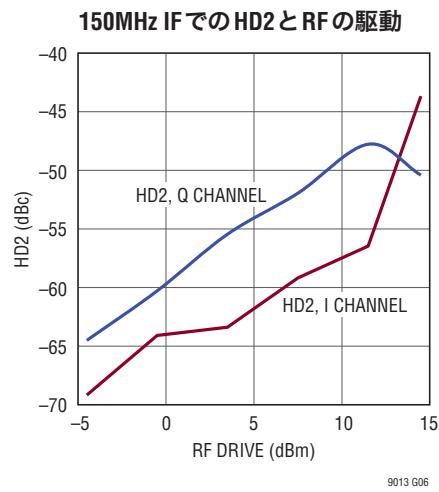

-1dBFSでのHD2:74dBc

1トーンあたり-7dBFSでのIMD3:-72dBc

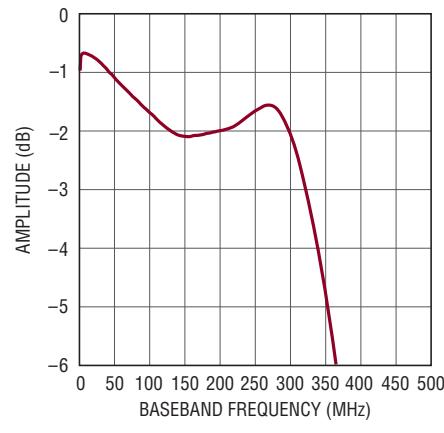

周波数応答を図15に示します。

図15. ベースバンド周波数応答

図14. 1MHzのハイパス・フィルタ設定

## アプリケーション情報

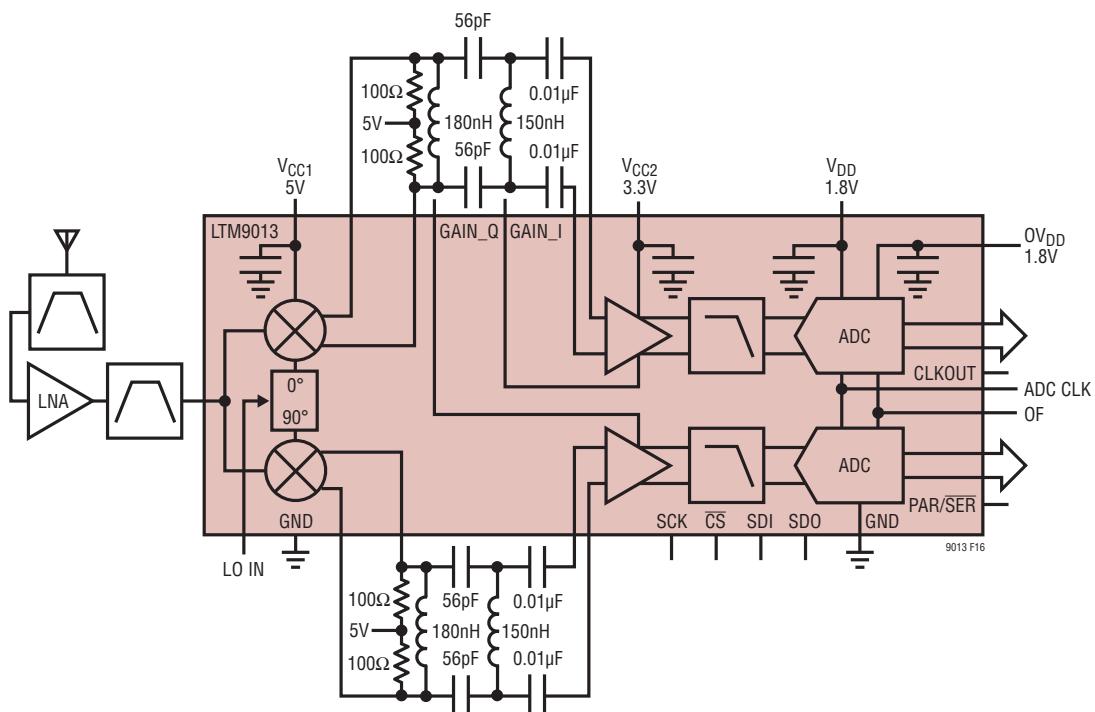

ハイパス・ポイントでさらに高い周波数コーナーを必要とするアプリケーションの場合、例えば図16に示すように、ネットワークを調整できます。

モジュール全体の標準的性能は次のとおりです。

IFパスバンド(1.0dB):55MHz～315MHz

-1dBFSの場合のRF入力:最大利得で-5dBm

-1dBFSでのSNR:59.1dB

-1dBFSでのHD2:74dBC

1トーンあたり-7dBFSでのIMD3:-72dBC

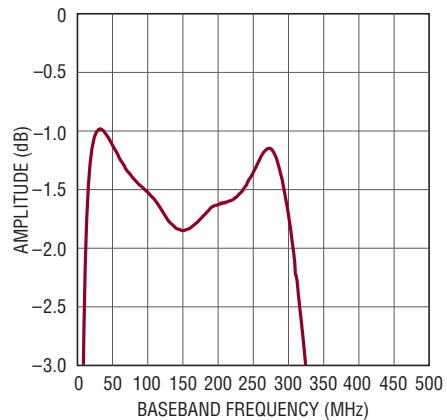

周波数応答を図17に示します。

9013 F17

図17. ベースバンド周波数応答

図16. 55MHzのハイパス・フィルタ設定

## アプリケーション情報

### 電源シーケンシング

V<sub>CC1</sub>ピンは、復調器に電圧を供給します。V<sub>CC2</sub>ピンは、アンプに電圧を供給します。アンプの出力段は、V<sub>CC1</sub>ピンからも供給されるため、電源シーケンスに注意することが重要です。アンプの損傷を避けるために、V<sub>CC1</sub>ピンに電力を供給する前に、V<sub>CC2</sub>ピンに電力を供給する必要があります。同じ理由により、V<sub>CC1</sub>ピンに電圧を加える前にアンプをイネーブルする必要があることにも注意してください。

### 接地とバイパス

LTM9013には、全く切れ目のないグランド・プレーンを備えたプリント回路基板が必要です。内部グランド・プレーンを備えた多層基板を推奨します。LTM9013のピン配置はフロースルー・レイアウトに最適化されているので、入力とデジタル出力間の相互反応が最小に抑えられます。連続的なグランド・パッドの列によって、デジタル信号線とアナログ信号線をできるだけ分離してレイアウトすることが容易になります。

LTM9013は、A/Dコンバータ(V<sub>DD</sub>)、ミキサ、アンプ(V<sub>CC</sub>)のデジタル(OV<sub>DD</sub>)電源が共通グランド(GND)に戻り、内部でバイパスされています。追加のバイパス容量はオプションです。これは、電源ノイズが大きい場合に必要になることがあります。

### 熱伝達

LTM9013から発生する熱の大部分は、底面のグランド・ピンを経由して伝達します。良好な電気的性能および熱的性能を得るには、すべてのグランド・ピンを、面積が十分大きなグランド・プレーンにできるだけ多くのビアを使用して接続することが重要です。

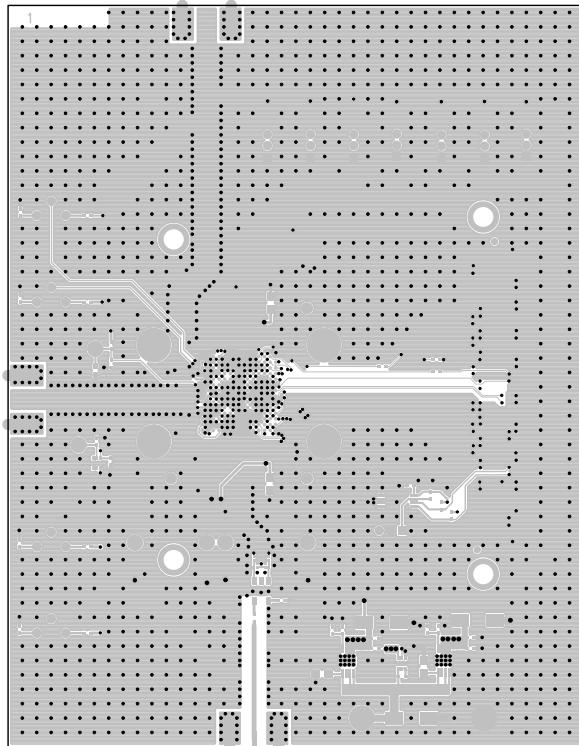

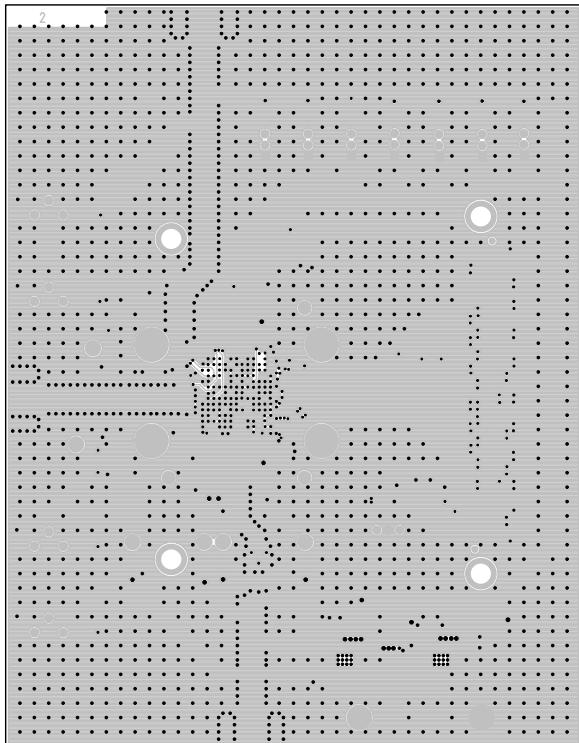

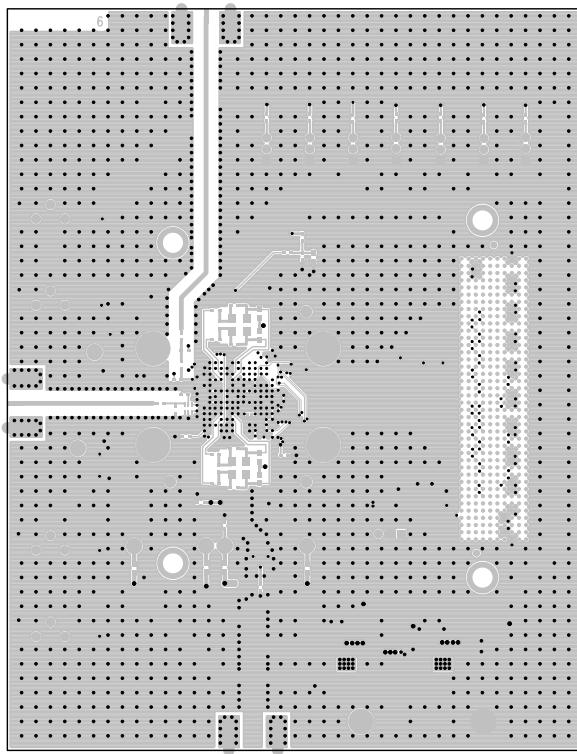

### 推奨レイアウト

LTM9013は集積密度が高いので、プリント回路基板のレイアウトが簡単です。ただし、電気的性能と熱的性能を最適化するにはいくつかのレイアウト上の配慮が依然として必要です。

- グランドには、プリント回路基板の大きな銅箔領域を使用します。これは、基板を介したパッケージの熱の放散を助け、影響を受けやすい基板上のアナログ信号のシールドに役立ちます。

- グランドで複数のビアを使用します。できるだけ多くのビアを使用すると、基板の熱的性能を高め、基板上で高周波のアナログ配線とデジタル配線を分離するために必要なバリアを作成できます。

- ビアを使用して高周波バリアを作成し、アナログ配線とデジタル配線をできるだけ分離します。これによってデジタル・フィードバックを減らして、LTM9013の信号・ノイズ比(SNR)とダイナミックレンジを低減することができます。

推奨レイアウトの良い例を図18～25に示します。

ペースト印刷の品質は、高歩留まりで組立品を生産するための重要な要因になります。タイプ3またはタイプ4印刷の無洗浄型半田ペーストを使用することを推奨します。半田付着の設計については、「プリント回路基板の組立と製造ガイドライン」に記載されたガイドラインに従ってください。

[BGAパッケージ:リニアテクノロジーのμModule BGAパッケージの組立に関する検討事項](#)

## 標準的應用例

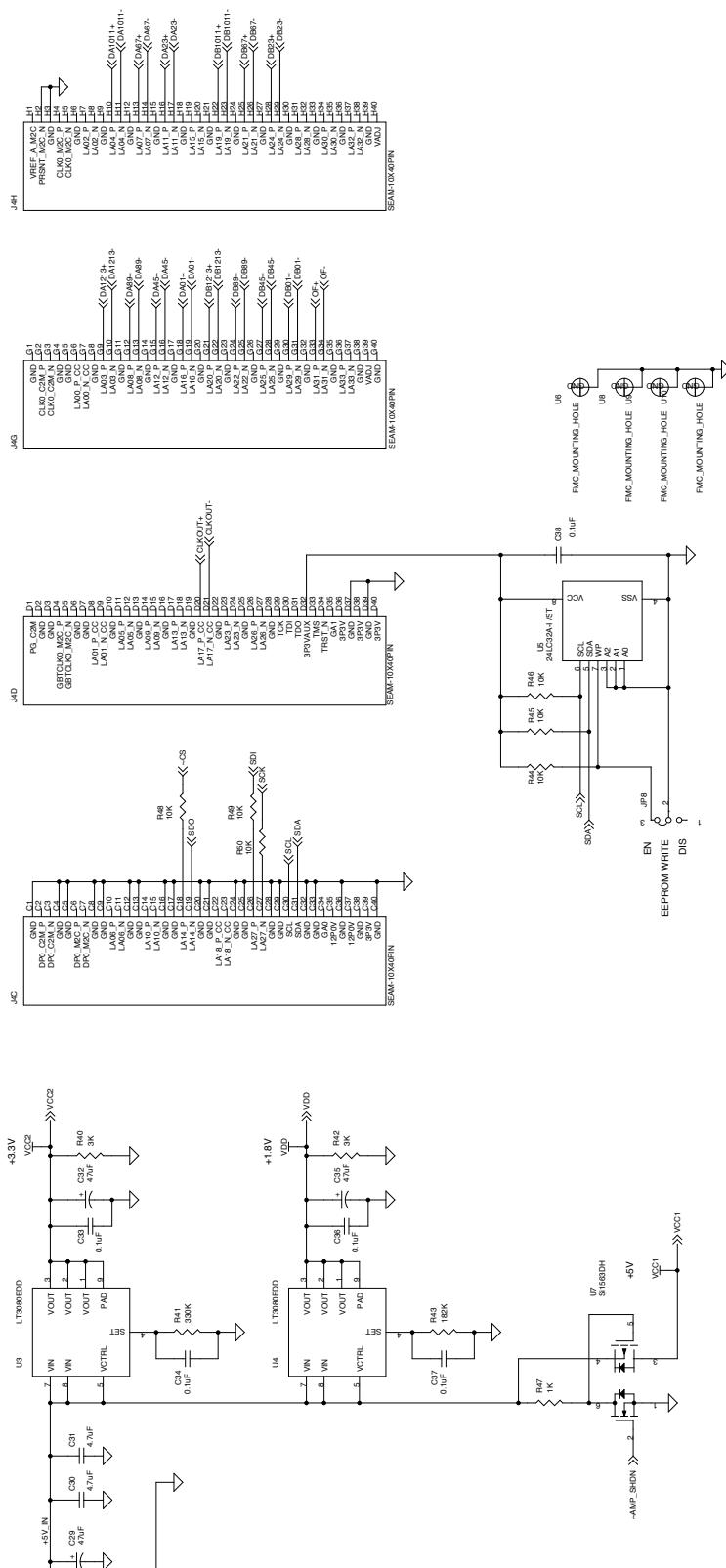

図18. 推奨レイアウトの回路図

## 標準的应用例

図19. 推奨レイアウトのその他の回路図の要素

## 標準的応用例

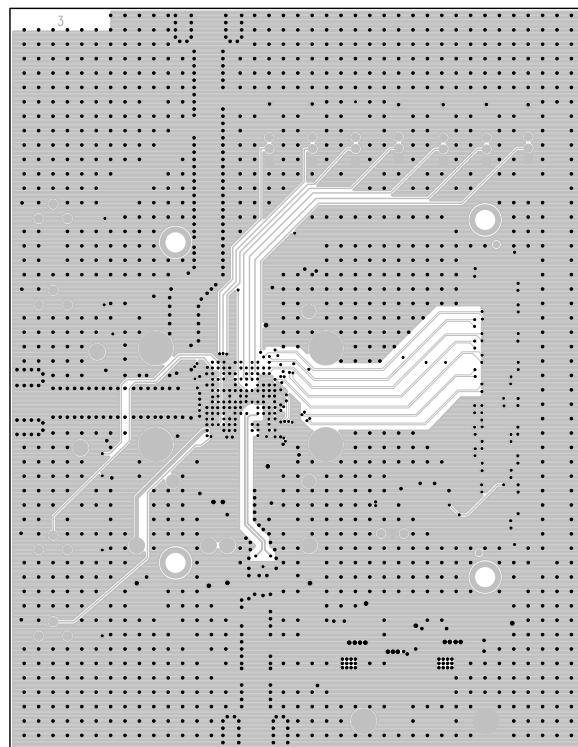

図20. 第1層

図21. 第2層

9013f

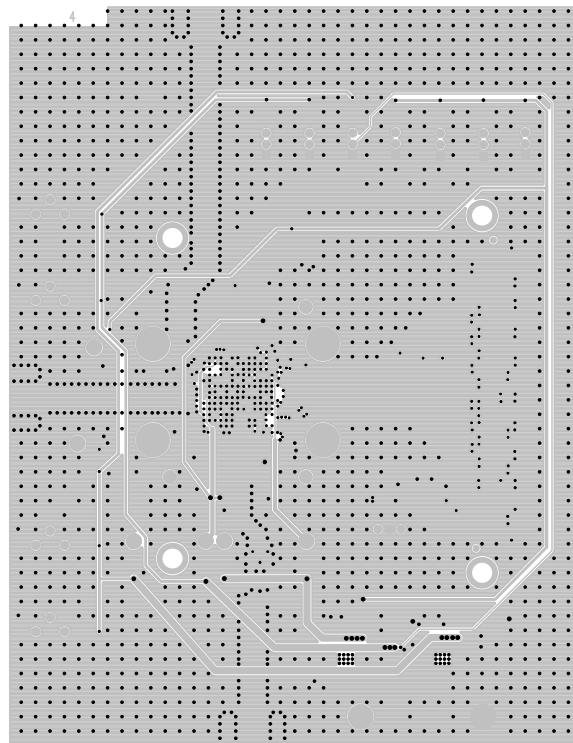

## 標準的応用例

図22. 第3層

図23. 第4層

9013f

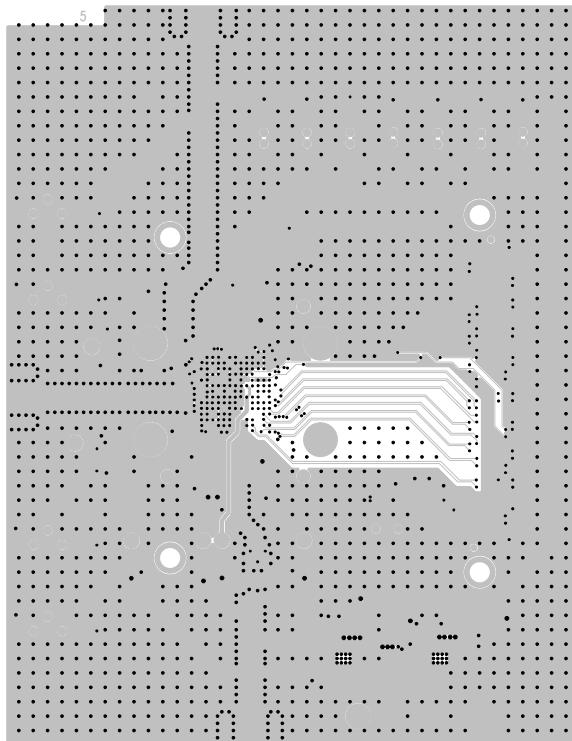

## 標準的応用例

図24. 第5層

図25. 第6層

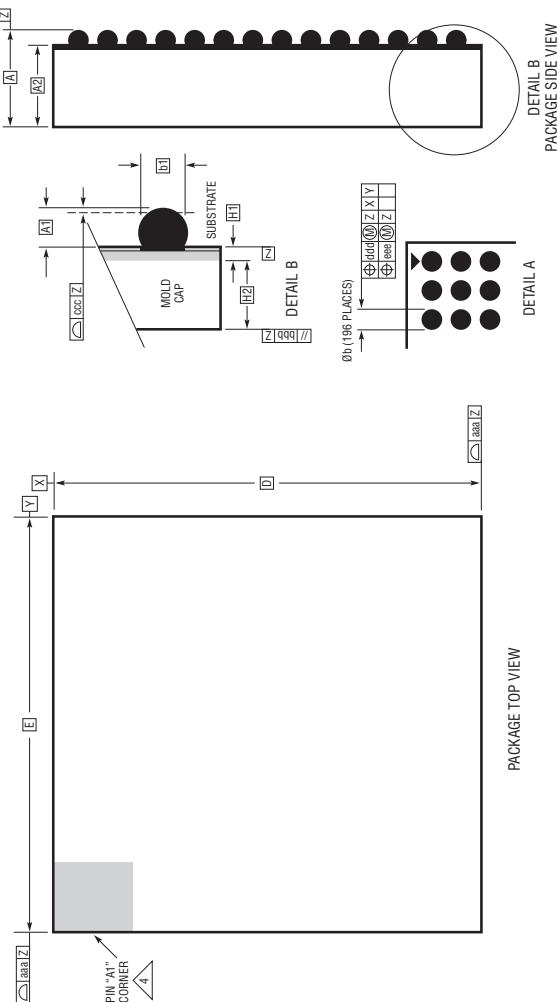

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**BGAパッケージ

196ピン(15mm×15mm×2.82mm)**

(Reference LTC DWG# 05-08-1907 Rev 0)

| SYMBOL                     | DIMENSIONS |      |      | NOTES |

|----------------------------|------------|------|------|-------|

|                            | MIN        | NOM  | MAX  |       |

| A                          | 2.62       | 2.82 | 3.02 |       |

| A1                         | 0.40       | 0.50 | 0.60 |       |

| A2                         | 2.22       | 2.32 | 2.42 |       |

| b                          | 0.55       | 0.60 | 0.65 |       |

| b1                         | 0.55       | 0.60 | 0.65 |       |

| D                          |            |      | 15.0 |       |

| E                          |            | 15.0 |      |       |

| e                          |            | 1.0  |      |       |

| F                          |            | 13.0 |      |       |

| G                          |            | 13.0 |      |       |

| H1                         | 0.22       | 0.32 | 0.42 |       |

| H2                         | 1.95       | 2.00 | 2.05 |       |

| aaa                        |            |      | 0.15 |       |

| bbb                        |            |      | 0.10 |       |

| ccc                        |            |      | 0.15 |       |

| ddd                        |            |      | 0.15 |       |

| eee                        |            |      | 0.08 |       |

| TOTAL NUMBER OF BALLS: 196 |            |      |      |       |

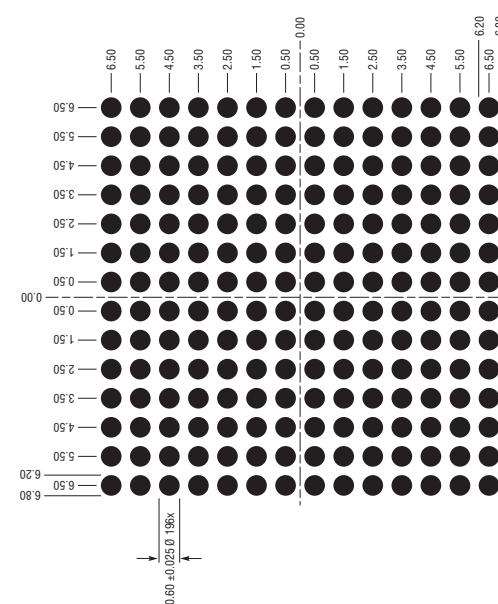

SUGGESTED PCB LAYOUT

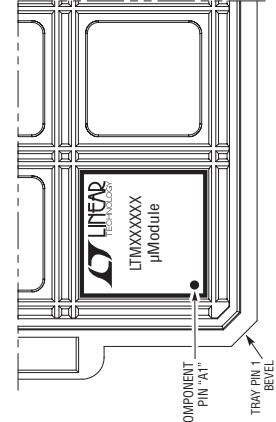

TOP VIEW

PACKAGE IN TRAY LOADING ORIENTATION

# LTM9013

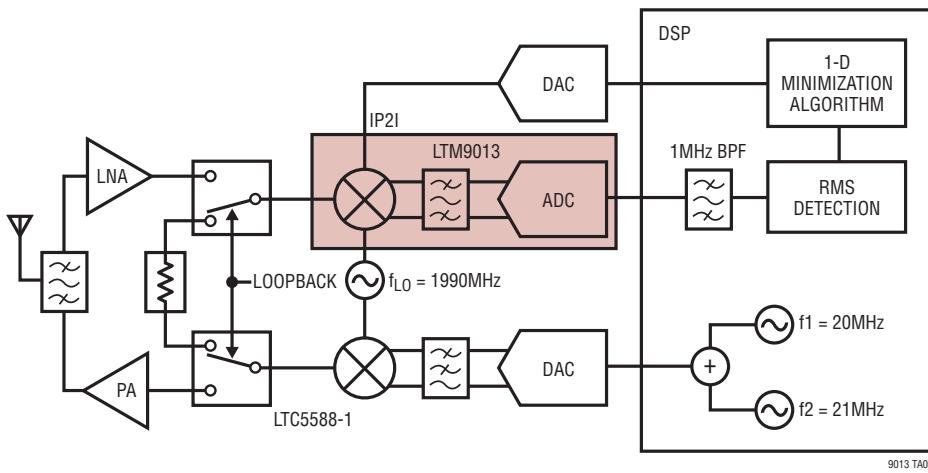

## 標準的応用例

IM2調整のブロック図|チャネルのみ示されている

9013 TA02

## 関連製品

| 製品番号                                 | 説明                                                   | 注釈                                                                           |

|--------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------|

| <b>A/Dコンバータ</b>                      |                                                      |                                                                              |

| LTC2208                              | 16ビット、130Msps、3.3V ADC、LVDS出力                        | 1250mW、SNR:77.7dB、SFDR:100dB、64ピンQFNパッケージ                                    |

| LTC2157-14/LTC2156-14/<br>LTC2155-14 | 14ビット、250Msps/210Msps/170Msps、1.8VデュアルADC、DDR LVDS出力 | 605mW/565mW/511mW、SNR:70dB、SFDR:90dB、9mm×9mm 64ピンQFNパッケージ                    |

| LTC2152-14/LTC2151-14/<br>LTC2150-14 | 14ビット、250Msps/210Msps/170Msps、1.8VシングルADC、DDR LVDS出力 | 338mW/316mW/290mW、SNR:70dB、SFDR:90dB、6mm×6mm 40ピンQFNパッケージ                    |

| LTC2158-14                           | 14ビット、310Msps、1.8VデュアルADC、DDR LVDS出力、低消費電力           | 724mW、SNR:68.8dB、SFDR:88dB、9mm×9mm 64ピンQFNパッケージ                              |

| <b>RFミキサ/復調器</b>                     |                                                      |                                                                              |

| LT5517                               | 40MHz～900MHz直接変換直交復調器                                | 高いIIP3:800MHzで21dBm、LO直交ジェネレータ内蔵                                             |

| LT5527                               | 400MHz～3.7GHz高直線性ダウンコンバーティング・ミキサ                     | IIP3:900MHzで24.5dBm、3.5Gで23.5dBm、NF:12.5dB、50ΩシングルエンドのRFポートとLOポート            |

| LT5575                               | 800MHz～2.7GHz直接変換直交復調器                               | 高いIIP3:900MHzで28dBm、LO直交ジェネレータ内蔵、RFおよびLOトランス内蔵                               |

| <b>アンプ/フィルタ</b>                      |                                                      |                                                                              |

| LTC6409                              | GBWが10GHzの1.1nV/ $\sqrt{\text{Hz}}$ 差動アンプ/ADCドライバ    | SFDR:88dB(100MHz)、グランドを含む入力範囲、電源電流:52mA、3mm×2mm QFNパッケージ                     |

| LTC6412                              | 800MHz、31dBレンジ、アナログ制御可変利得アンプ                         | 連続調整可能な利得制御、240MHzでのOIP3: 35dBm、ノイズフィギュア:10dB、4mm×4mm QFN-24パッケージ            |

| LTC6420-20                           | 300MHzのIF向け1.8GHz、低ノイズ、低歪み、デュアル差動ADCドライバ             | 固定利得:10V/V、全入力ノイズ:1nV/ $\sqrt{\text{Hz}}$ 、電源電流:80mA/アンプ、3mm×4mm QFN-20パッケージ |

| <b>レシーバ・サブシステム</b>                   |                                                      |                                                                              |

| LTM9002                              | 14ビット・デュアル・チャネルIF/ベースバンド・レシーバ・サブシステム                 | 高速ADC、パッシブ・フィルタ、および固定利得差動アンプを内蔵                                              |

| LTM9003                              | 12ビット・デジタル・プリディストーション・レシーバ                           | 12ビットADC、入力周波数範囲が0.4GHz～3.8GHzのダウンコンバーティング・ミキサ                               |