# 12ビット・デジタル プリディストーション レシーバ・サブシステム

## 特長

- デジタル・プリディストーション・アプリケーション向け

完全集積化レシーバ・サブシステム

- RF周波数範囲の広い(400MHz ~ 3.8GHz)

ダウンコンバーティング・ミキサ

- パスバンド・リップルが0.5dB未満の125MHz幅

バンドパス・フィルタ

- 分解能が最大12ビット、サンプルレートが最大

250Mspsの低消費電力ADC

- 入力ノイズフロア:-145.5dBm/Hz、IIP3:25.8dBm

- 総消費電力:1.5W

- 50ΩシングルエンドのRFポートおよびLOポート

- バイパス容量を内蔵、外付け部品が不要

- ADCのクロック・デューティ・サイクル・スタビライザ

- 11.25mm×15mm LGAパッケージ

## アプリケーション

- 送信監視バス・レシーバ

- デジタル・プリディストーション(DPD)レシーバ

- 広帯域レシーバ

- 広帯域計測

## 概要

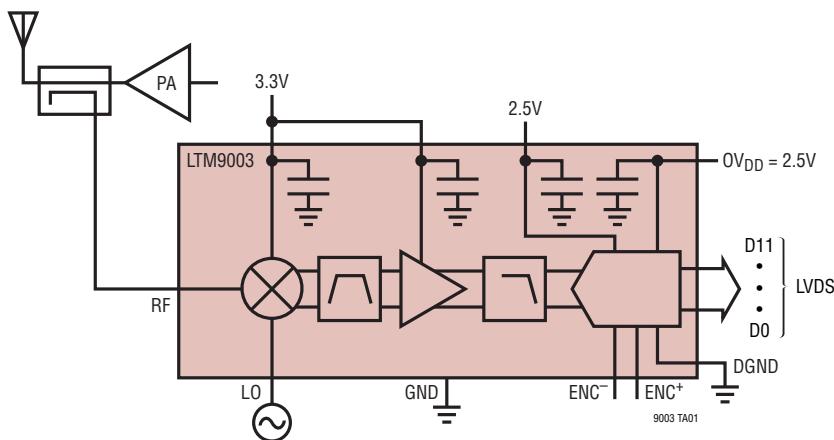

LTM<sup>®</sup>9003は、セルラー基地局の送信バス向けの12ビット・デジタル・プリディストーション・レシーバ・サブシステムです。集積化SiP (System in a Package) 技術を利用し、ダウンコンバーティング・ミキサ、広帯域フィルタおよびADCを内蔵しています。このシステムは、中間周波数(IF)が184MHz、信号帯域幅が最大125MHzになるように調整されています。12ビットADCは最大250Mspsのレートでサンプリングを行います。カスタム対応につきましては、弊社にお問い合わせください。

高信号レベルのダウンコンバーティング・アクティブ・ミキサは、高直線性でダイナミックレンジの広いIFサンプリング・アプリケーション向けに最適化されています。このデバイスは二重平衡ミキサをドライブする差動LOバッファ・アンプを内蔵しています。RF入力とLO入力にブロードバンド・トランスを搭載しており、シングルエンドの50Ωインターフェースを提供します。RF入力とLO入力は、1.1GHz~1.8GHzの範囲で50Ωに内部で整合しています。

CLK入力はコンバータ動作を制御し、差動またはシングルエンドでドライブ可能です。また、オプションのクロック・デューティ・サイクル・スタビライザにより、広範なクロック・デューティ・サイクルに対してフルスピードで高性能を実現できます。

、LT、LTC、LTM、Linear Technology、Linear のロゴおよび μModule はリニアテクノロジー社の登録商標です。他の全ての商標はそれぞれの所有者に所有権があります。5481178、6580258、6304066、6127815、6498466、6611131 を含む米国特許により保護されています。

## 標準的応用例

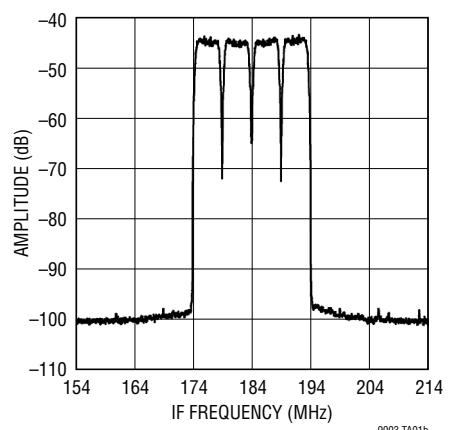

4チャネルWCDMA入力の2.14GHzでのFFT

9003 TA01b

# LTM9003

## 絶対最大定格

(Note 1,2)

電源電圧 ( $V_{CC1}$ )

LTM9003-AA ..... -0.3V~4V

LTM9003-AB ..... -0.3V~5.5V

電源電圧 ( $V_{CC2}$ ) ..... -0.3V~5.5V

電源電圧 ( $V_{DD}, 0V_{DD}$ ) ..... -0.3V~2.8V

デジタル出力のグランド電圧 (0GND) ..... -0.3V~1V

LO入力電力 (380MHz~4.2GHz) ..... 10dBm

LO入力のDC電圧 ..... -1V~( $V_{CC1}+1V$ )

RF入力電力 (400MHz~3.8GHz) ..... 15dBm

RF入力のDC電圧 ..... ±0.1V

MIX\_ENの電圧 ..... -0.3V~( $V_{CC1}+0.3V$ )

AMP\_ENの入力電流 ..... ±10mA

デジタル入力電圧 ..... -0.3V~( $V_{DD}+0.3V$ )

デジタル出力電圧 ..... -0.3V~(0V<sub>DD</sub>+0.3V)

動作周囲温度範囲

LTM9003CV ..... 0°C~70°C

LTM9003IV ..... -40°C~85°C

保存温度範囲 ..... -40°C~125°C

最大接合部温度 ..... 125°C

注意：RF入力とLO入力は静電気放電 (ESD) に敏感です。

LTM9003を扱うときは適切なESD対策をとることが非常に

重要です。

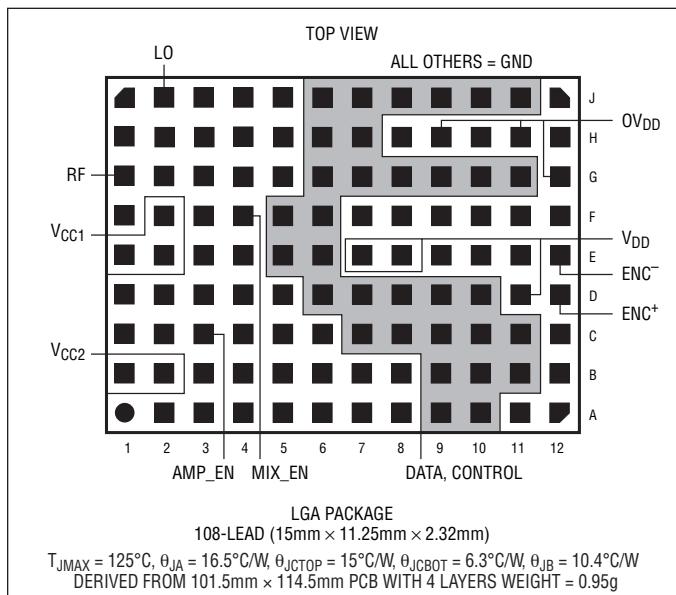

## ピン配置

## 発注情報

| 鉛フリー仕様           | トレイ              | 製品マーキング*    | パッケージ                                 | 温度範囲          |

|------------------|------------------|-------------|---------------------------------------|---------------|

| LTM9003CV-AA#PBF | LTM9003CV-AA#PBF | LTM9003 AA  | 108-Lead (11.25mm × 15mm × 2.3mm) LGA | 0°C to 70°C   |

| LTM9003IV-AA#PBF | LTM9003IV-AA#PBF | LTM9003V AA | 108-Lead (11.25mm × 15mm × 2.3mm) LGA | -40°C to 85°C |

| LTM9003CV-AB#PBF | LTM9003CV-AB#PBF | LTM9003 AB  | 108-Lead (11.25mm × 15mm × 2.3mm) LGA | 0°C to 70°C   |

| LTM9003IV-AB#PBF | LTM9003IV-AB#PBF | LTM9003V AB | 108-Lead (11.25mm × 15mm × 2.3mm) LGA | -40°C to 85°C |

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。\* 温度等級は出荷時のコンテナのラベルで識別されます。

鉛フリー製品のマーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

この製品はトレイでのみ供給されます。詳細については、<http://www.linear-tech.co.jp/packaging/> をご覧下さい。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| PARAMETER                 | CONDITIONS                                                                                     | MIN      | TYP          | MAX    | UNITS      |

|---------------------------|------------------------------------------------------------------------------------------------|----------|--------------|--------|------------|

| RF Input Frequency Range  | LTM9003-AA<br>No External Matching (Midband)<br>With External Matching (Low Band or High Band) | 400      | 1100 to 1800 | 3800   | MHz<br>MHz |

|                           | LTM9003-AB<br>No External Matching (Midband)<br>With External Matching (Low Band or High Band) | 400      | 1100 to 1800 | 3700   | MHz<br>MHz |

| LO Input Frequency Range  | LTM9003-AA<br>No External Matching<br>With External Matching                                   | 380      | 800 to 3500  |        | MHz<br>MHz |

|                           | LTM9003-AB<br>No External Matching<br>With External Matching                                   | 380      | 900 to 3500  |        | MHz<br>MHz |

| RF Input Return Loss      | $Z_0 = 50\Omega$ , 1100MHz to 1800MHz (No External Matching)<br>LTM9003-AA<br>LTM9003-AB       |          | >12<br>>12   |        | dB<br>dB   |

| LO Input Return Loss      | $Z_0 = 50\Omega$ , 900MHz to 3500MHz (No External Matching)<br>LTM9003-AA<br>LTM9003-AB        |          | >10<br>>10   |        | dB<br>dB   |

| RF Input Power for -1dBFS | LTM9003-AA<br>LTM9003-AB                                                                       |          | -1.7<br>-1.7 |        | dBm<br>dBm |

| LO Input Power            | 1200MHz to 4200MHz, LTM9003-AA or<br>1200MHz to 3500MHz, LTM9003-AB<br>380MHz to 1200MHz       | -8<br>-5 | -3<br>0      | 2<br>5 | dBm<br>dBm |

| LO to RF Leakage          | LTM9003-AA<br>$f_{LO} = 380\text{MHz}$ to 1600MHz<br>$f_{LO} = 1600\text{MHz}$ to 4000MHz      |          | <-50<br><-45 |        | dBm<br>dBm |

|                           | LTM9003-AB<br>$f_{LO} = 400\text{MHz}$ to 2100MHz<br>$f_{LO} = 2100\text{MHz}$ to 3200MHz      |          | <-44<br><-36 |        | dBm<br>dBm |

| RF to LO Isolation        | LTM9003-AA<br>$f_{RF} = 400\text{MHz}$ to 1700MHz<br>$f_{RF} = 1700\text{MHz}$ to 3800MHz      |          | >50<br>>42   |        | dB<br>dB   |

|                           | LTM9003-AB<br>$f_{RF} = 400\text{MHz}$ to 2200MHz<br>$f_{RF} = 2200\text{MHz}$ to 3700MHz      |          | >43<br>>38   |        | dB<br>dB   |

## コンバータ特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| PARAMETER                         | CONDITIONS     | MIN     | TYP  | MAX | UNITS |

|-----------------------------------|----------------|---------|------|-----|-------|

| Resolution (No Missing Codes)     |                | ●<br>12 |      |     | Bits  |

| Integral Linearity Error (Note 4) | IF = 184.32MHz |         | ±1   |     | LSB   |

| Differential Linearity Error      | IF = 184.32MHz |         | ±0.4 |     | LSB   |

# LTM9003

## フィルタの特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| PARAMETER            | CONDITIONS                             | MIN         | TYP | MAX | UNITS    |

|----------------------|----------------------------------------|-------------|-----|-----|----------|

| Center Frequency     |                                        | 184.32      |     |     | MHz      |

| Lower 3dB Bandedge   |                                        | 84          |     |     | MHz      |

| Upper 3dB Bandedge   |                                        | 304         |     |     | MHz      |

| Lower 20dB Stopband  |                                        | 40          |     |     | MHz      |

| Upper 20dB Stopband  |                                        | 450         |     |     | MHz      |

| Passband Flatness    | 129MHz to 239.6MHz<br>174MHz to 194MHz | 0.5<br>0.15 |     |     | dB<br>dB |

| Group Delay Flatness | 129MHz to 239.6MHz<br>174MHz to 194MHz | 1.2<br>0.1  |     |     | ns<br>ns |

| Absolute Delay       |                                        | 2.7         |     |     | ns       |

## ダイナミック精度

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL  | PARAMETER                                                                   | CONDITIONS                                                                                           | MIN       | TYP                     | MAX | UNITS                   |

|---------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------|-------------------------|-----|-------------------------|

| SNR     | Signal-to-Noise Ratio at $-1\text{dBFS}$                                    | RF = 1889MHz, LO = 1766MHz<br>RF = 1950MHz, LO = 1766MHz<br>RF = 2011MHz, LO = 1766MHz               | ●<br>141  | 143.6<br>143.6<br>143.6 |     | dB/Hz<br>dB/Hz<br>dB/Hz |

| IIP3    | Input 3rd Order Intercept, 2-Tone                                           | LTM9003-AA<br>RF = 1948MHz, 1952MHz, LO = 1766MHz                                                    |           | 27                      |     | dBm                     |

|         |                                                                             | LTM9003-AB<br>RF = 1948MHz, 1952MHz, LO = 1766MHz                                                    |           | 28                      |     | dBm                     |

| IIP2    | Input 2nd Order Intercept, 1-Tone                                           | LTM9003-AA<br>RF = 1950MHz, LO = 1766MHz                                                             |           | 61                      |     | dBm                     |

|         |                                                                             | LTM9003-AB<br>RF = 1950MHz, LO = 1766MHz                                                             |           | 61.4                    |     | dBm                     |

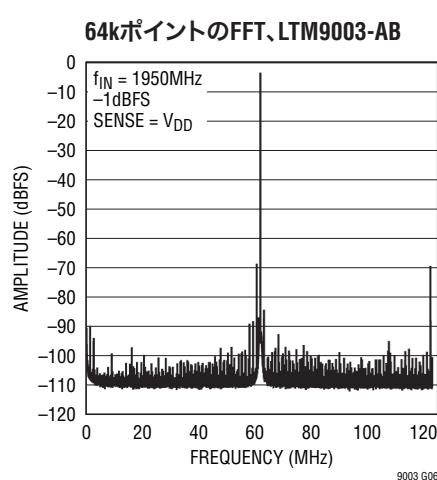

| SFDR    | Spurious Free Dynamic Range, 2nd or 3rd Harmonic at $-1\text{dBFS}$         | LTM9003-AA<br>RF = 1889MHz, LO = 1766MHz<br>RF = 1950MHz, LO = 1766MHz<br>RF = 2011MHz, LO = 1766MHz | ●<br>50.7 | 54.1<br>58.8<br>63.6    |     | dB<br>dB<br>dB          |

|         |                                                                             | LTM9003-AB<br>RF = 1889MHz, LO = 1766MHz<br>RF = 1950MHz, LO = 1766MHz<br>RF = 2011MHz, LO = 1766MHz | ●<br>52.0 | 57.3<br>62.4<br>66.3    |     | dB<br>dB<br>dB          |

| SFDR    | Spurious Free Dynamic Range, 4th or Higher at $-1\text{dBFS}$               | RF = 1889MHz, LO = 1766MHz<br>RF = 1950MHz, LO = 1766MHz<br>RF = 2011MHz, LO = 1766MHz               | ●<br>66.5 | 74<br>82<br>87          |     | dB<br>dB<br>dB          |

| S/(N+D) | Signal-to-Noise Plus Distortion Ratio at $-1\text{dBFS}$                    | RF = 1889MHz, LO = 1766MHz<br>RF = 1950MHz, LO = 1766MHz<br>RF = 2011MHz, LO = 1766MHz               | ●<br>50.3 | 54<br>58<br>60          |     | dB<br>dB<br>dB          |

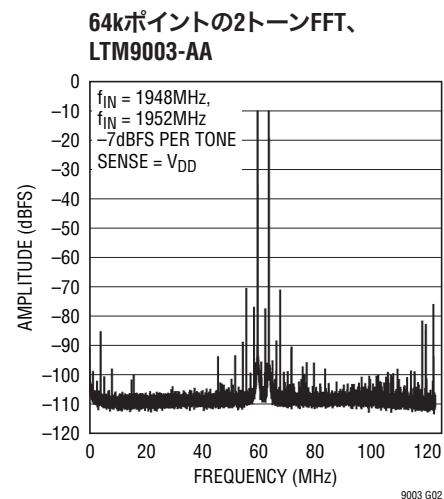

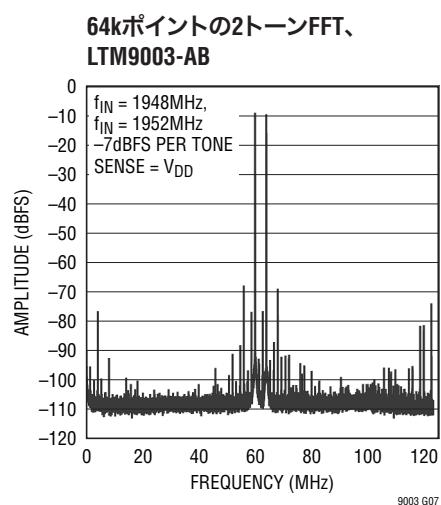

| IMD3    | Intermodulation Distortion at $-7\text{dBFS}$ per Tone                      | RF = 1950MHz, LO = 1766MHz                                                                           |           | -58                     |     | dB                      |

| ACPR    | Adjacent Channel Power Ratio at $2.4\text{dBm}$ per Carrier, Four Carriers  |                                                                                                      |           | 58.5                    |     | dB                      |

| ALTCP   | Alternate Channel Power Ratio at $2.4\text{dBm}$ per Carrier, Four Carriers |                                                                                                      |           | 63.3                    |     | dB                      |

## デジタル入力と出力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL                                    | PARAMETER                     | CONDITIONS                                                                 |        | MIN          | TYP        | MAX        | UNITS                          |

|-------------------------------------------|-------------------------------|----------------------------------------------------------------------------|--------|--------------|------------|------------|--------------------------------|

| <b>エンコード入力(ENC-, ENC+)</b>                |                               |                                                                            |        |              |            |            |                                |

| $V_{ID}$                                  | Differential Input Voltage    | (Note 5)                                                                   |        | 0.2          |            |            | V                              |

| $V_{ICM}$                                 | Common Mode Input Voltage     | Internally Set<br>Externally Set (Note 5)                                  | ●      | 1.2          | 1.5        | 2          | V                              |

| $R_{IN}$                                  | Input Resistance              | Single-Ended                                                               |        |              | 4.8        |            | $\Omega$                       |

| $R_{IN(DIFF)}$                            | Input Resistance              | Differential                                                               |        |              | 100        |            | $\Omega$                       |

| $C_{IN}$                                  | Input Capacitance             |                                                                            |        |              | 2          |            | pF                             |

| <b>ロジック入力( OE、SHDN )</b>                  |                               |                                                                            |        |              |            |            |                                |

| $V_{IH}$                                  | High Level Input Voltage      | $V_{DD} = 2.5\text{V}$                                                     | ●      | 1.7          |            |            | V                              |

| $V_{IL}$                                  | Low Level Input Voltage       | $V_{DD} = 2.5\text{V}$                                                     | ●      |              |            | 0.7        | V                              |

| $I_{IN}$                                  | Input Current                 | $V_{IN} = 0\text{V}$ to $V_{DD}$                                           | ●      | -10          |            | 10         | $\mu\text{A}$                  |

| $C_{IN}$                                  | Input Capacitance             | (Note 5)                                                                   |        |              |            | 3          | pF                             |

| <b>ミキサ・イネーブル</b>                          |                               |                                                                            |        |              |            |            |                                |

| $V_{IH}$                                  | High Level Input Voltage      | $V_{CC1} = 3.3\text{V}$ , LTM9003-AA<br>$V_{CC1} = 5\text{V}$ , LTM9003-AB | ●<br>● | 2.7<br>3     |            |            | V                              |

| $V_{IL}$                                  | Low Level Input Voltage       | $V_{CC1} = 3.3\text{V}$ , LTM9003-AA<br>$V_{CC1} = 5\text{V}$ , LTM9003-AB | ●<br>● |              |            | 0.3<br>0.3 | V                              |

| $I_{IN}$                                  | Input Current                 | $V_{IN} = 0\text{V}$ to $V_{CC1}$ , LTM9003-AA                             | ●      |              | 53         | 90         | $\mu\text{A}$                  |

|                                           | Turn-On Time                  |                                                                            |        |              |            | 2.8        | ms                             |

|                                           | Turn-Off Time                 |                                                                            |        |              |            | 2.9        | ms                             |

| <b>アンプ・イネーブル</b>                          |                               |                                                                            |        |              |            |            |                                |

| $V_{IH}$                                  | High Level Input Voltage      | $V_{CC2} = 3.3\text{V}$                                                    | ●      | 2            |            |            | V                              |

| $V_{IL}$                                  | Low Level Input Voltage       | $V_{CC2} = 3.3\text{V}$                                                    | ●      |              |            | 0.8        | V                              |

| $I_{IN}$                                  | Input Current                 | $V_{IN} = 0.8\text{V}$<br>$V_{IN} = 2\text{V}$                             | ●<br>● | -200<br>-150 | -85<br>-30 | 0<br>0     | $\mu\text{A}$<br>$\mu\text{A}$ |

| <b>制御入力(SENSE、MODE、LVDS)</b>              |                               |                                                                            |        |              |            |            |                                |

| $I_{SENSE}$                               | SENSE Input Leakage           | $0\text{V} < \text{SENSE} < 1\text{V}$                                     | ●      | -1           |            | 1          | $\mu\text{A}$                  |

| $I_{MODE}$                                | MODE Pull-Down Current to GND | See Pin Functions for Voltage Levels                                       |        |              | 7          |            | $\mu\text{A}$                  |

| $I_{LVDS}$                                | LVDS Pull-Down Current to GND | See Pin Functions for Voltage Levels                                       |        |              | 7          |            | $\mu\text{A}$                  |

| <b>ロジック出力(LVDSモード)</b>                    |                               |                                                                            |        |              |            |            |                                |

| <b><math>OV_{DD} = 2.5\text{V}</math></b> |                               |                                                                            |        |              |            |            |                                |

| $V_{OD}$                                  | Differential Output Voltage   | $100\Omega$ Differential Load                                              | ●      | 247          | 350        | 454        | mV                             |

| $V_{OS}$                                  | Output Common Mode Voltage    | $100\Omega$ Differential Load                                              | ●      | 1.125        | 1.250      | 1.375      | V                              |

# LTM9003

## 電源条件

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL          | PARAMETER                         | CONDITIONS                                          | MIN | TYP   | MAX | UNITS         |

|-----------------|-----------------------------------|-----------------------------------------------------|-----|-------|-----|---------------|

| $V_{CC1}$       | Mixer Supply Range                | LTM9003-AA (Note 6)<br>LTM9003-AB (Note 6)          | ●   | 2.9   | 3.3 | 3.6           |

|                 |                                   |                                                     | ●   | 4.5   | 5   | 5.25          |

| $V_{CC2}$       | Amplifier Supply Range            | (Note 6)                                            | ●   | 2.8   | 3.3 | 5.25          |

| $V_{DD}$        | ADC Analog Supply Voltage         | (Note 6)                                            | ●   | 2.375 | 2.5 | 2.625         |

| $I_{CC1}$       | Mixer Supply Current              | MIX_EN = 3V, LTM9003-AA<br>MIX_EN = 5V, LTM9003-AB  | ●   | 80    | 92  | mA            |

|                 |                                   |                                                     | ●   | 82    | 92  | mA            |

| $I_{CC1(SHDN)}$ | Mixer Shutdown Supply Current     | MIX_EN = 0V                                         | ●   |       | 100 | $\mu\text{A}$ |

| $I_{CC2}$       | Amplifier Supply Current          | AMP_EN = 3V                                         | ●   | 104   | 140 | mA            |

| $I_{CC2(SHDN)}$ | Amplifier Shutdown Supply Current | AMP_EN = 0V                                         | ●   | 3     | 5   | mA            |

| $I_{DD(ADC)}$   | ADC Supply Current                |                                                     | ●   | 285   | 320 | mA            |

| $P_{D(SHDN)}$   | ADC Shutdown Power                | SHDN = $V_{DD}$ , $\overline{OE} = V_{DD}$ , No CLK |     |       | 1.5 | mW            |

| $P_{D(NAP)}$    | ADC Nap Mode Power                | SHDN = $V_{DD}$ , $\overline{OE} = 0V$ , No CLK     |     |       | 30  | mW            |

## LVDS出力モード

|                 |                                   |                                                                                            |   |       |              |       |          |

|-----------------|-----------------------------------|--------------------------------------------------------------------------------------------|---|-------|--------------|-------|----------|

| $OV_{DD}$       | ADC Digital Output Supply Voltage |                                                                                            | ● | 2.375 | 2.5          | 2.625 | V        |

| $I_{OVDD(ADC)}$ | ADC Digital Output Supply Current |                                                                                            | ● | 58    | 74           | mA    |          |

| $P_{D(ADC)}$    | ADC Power Dissipation             |                                                                                            | ● | 858   | 985          | mA    |          |

| $P_{D(TOTAL)}$  | Total Power Dissipation           | SHDN = 0V, MIX_EN = AMP_EN = 3V, $f_{SAMPLE} = \text{MAX}$<br>(LTM9003-AA)<br>(LTM9003-AB) |   |       | 1465<br>1611 |       | mW<br>mW |

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 3)

| SYMBOL       | PARAMETER                                     | CONDITIONS                                                              | MIN    | TYP        | MAX    | UNITS      |

|--------------|-----------------------------------------------|-------------------------------------------------------------------------|--------|------------|--------|------------|

| $f_s$        | Sampling Frequency                            | (Note 6)                                                                | ●      | 1          | 250    | MHz        |

| $t_L$        | ENC Low Time                                  | Duty Cycle Stabilizer Off (Note 5)<br>Duty Cycle Stabilizer On (Note 5) | ●<br>● | 1.9<br>1.5 | 2<br>2 | 500<br>500 |

| $t_H$        | ENC High Time                                 | Duty Cycle Stabilizer Off (Note 5)<br>Duty Cycle Stabilizer On (Note 5) | ●<br>● | 1.9<br>1.5 | 2<br>2 | 500<br>500 |

| $t_{JITTER}$ | Sample-and-Hold Acquisition Delay Time Jitter |                                                                         |        |            | 95     | $f_{sRMS}$ |

| $t_{AP}$     | Sample-and-Hold Aperture Delay                |                                                                         |        |            | 0      | ns         |

| $t_{OE}$     | Output Enable Delay                           | (Note 5)                                                                | ●      |            | 5      | 10         |

### LVDS出力モード

|       |                     |                        |   |      |     |     |        |

|-------|---------------------|------------------------|---|------|-----|-----|--------|

| $t_D$ | ENC to DATA delay   | (Note 5)               | ● | 1    | 1.7 | 2.8 | ns     |

| $t_C$ | ENC to CLKOUT Delay | (Note 5)               | ● | 1    | 1.7 | 2.8 | ns     |

|       | DATA to CLKOUT Skew | $(t_C - t_D)$ (Note 5) | ● | -0.6 | 0   | 0.6 | ns     |

|       | Rise Time           |                        |   |      | 0.5 |     | ns     |

|       | Fall Time           |                        |   |      | 0.5 |     | ns     |

|       | Pipeline Latency    |                        |   |      | 5   |     | Cycles |

**Note 1 :** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2 :** 全ての電圧値は（注記がない限り）GNDとOGNDを結線したグランドを基準にしている。

**Note 3 :** 注記がない限り、 $V_{CC1} = V_{CC2} = 3.3V$  (LTM9003-AA) または  $V_{CC1} = 5V$ 、 $V_{CC2} = 3.3V$  (LTM9003-AB)、 $V_{DD} = 2.5V$ 、 $OV_{DD} = 2.5V$ 、 $f_{SAMPLE} = 250\text{MHz}$ 、入力範囲 =  $-1\text{dBFS}$ 、差動  $\text{ENC}^+/\text{ENC}^- = 2\text{V}_{\text{P-P}}$  の正弦波。

**Note 4 :** 積分非直線性は、伝達曲線に合致する「最善の直線」からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 5 :** 設計によって保証されているが、テストされない。

**Note 6 :** 推奨動作条件。

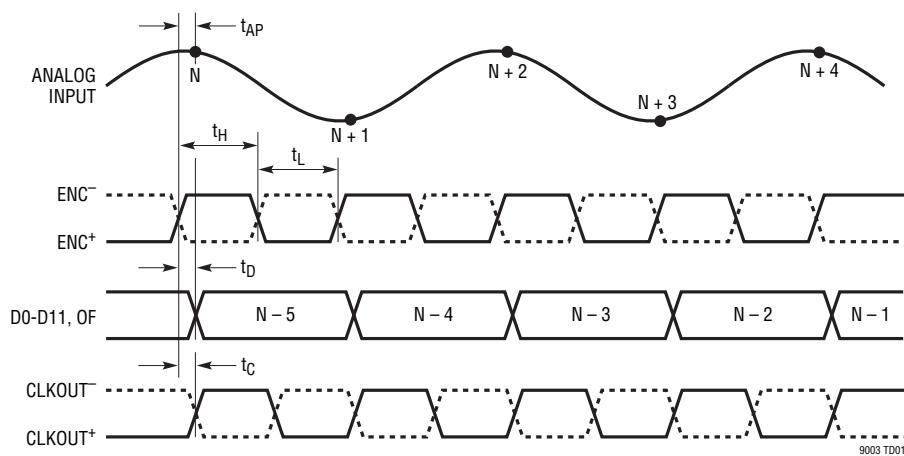

## タイミング図

LVDS出力モードのタイミング

全ての出力は差動でLVDSレベル

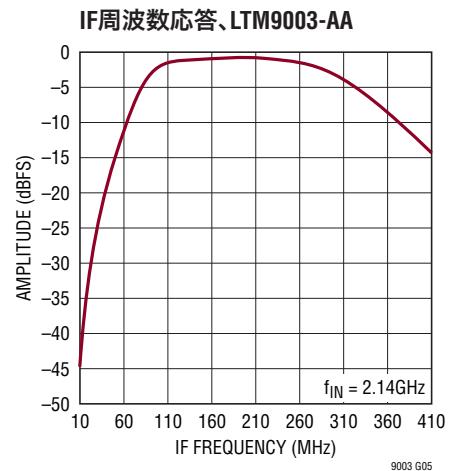

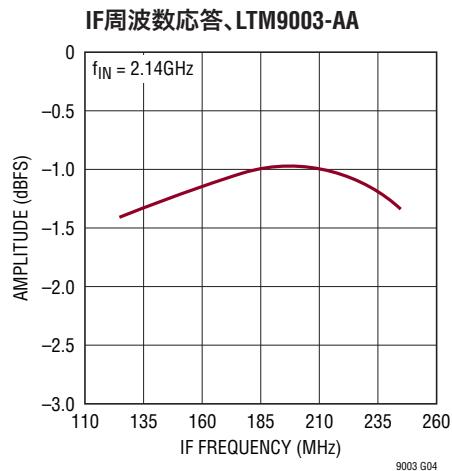

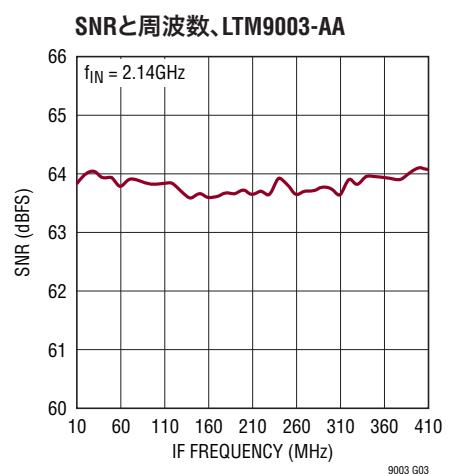

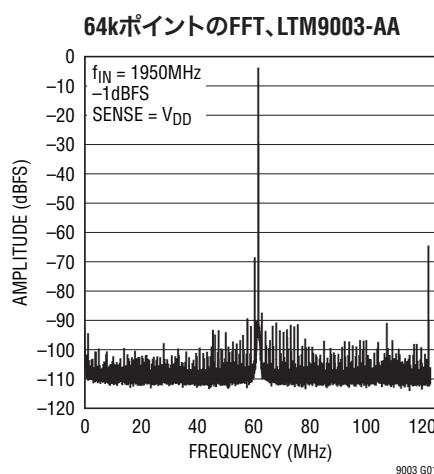

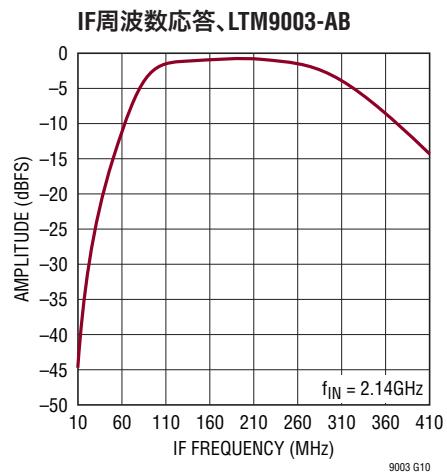

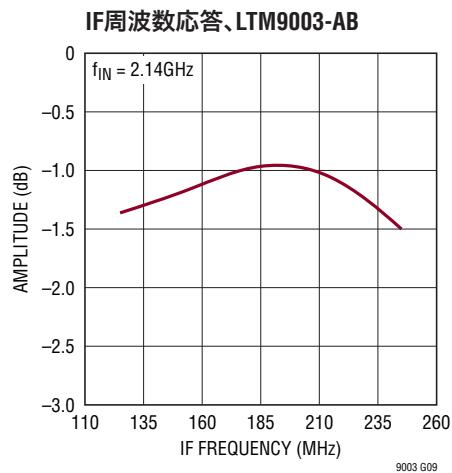

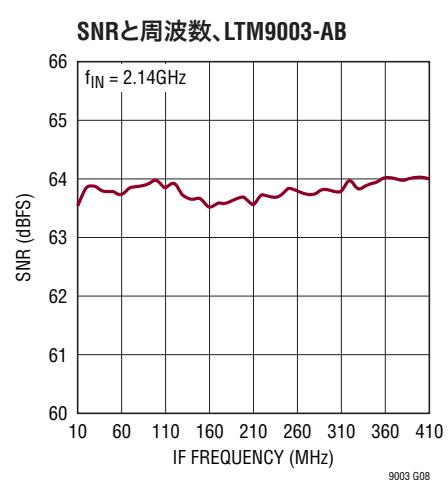

標準的性能特性  $T_A = 25^\circ\text{C}$

# LTM9003

標準的性能特性  $T_A = 25^\circ\text{C}$

## ピン機能

**V<sub>CC1</sub> (ピンE1、E2、F2)** : 3.3V (LTM9003-AA) または5V (LTM9003-AB) のミキサ用電源電圧。V<sub>CC1</sub>は内部でGNDにバイパスされています。

**V<sub>CC2</sub> (ピンB1、B2)** : 3.3Vのアンプ用電源電圧。V<sub>CC2</sub>は内部でGNDにバイパスされています。

**V<sub>DD</sub> (ピンD11、E7、E8)** : 2.5VのADC用電源電圧。V<sub>DD</sub>は内部でGNDにバイパスされています。

**OV<sub>DD</sub> (ピンG12、H9、H11)** : 出力ドライバ用2.5V電源。OV<sub>DD</sub>は内部でOGNDにバイパスされています。GND (位置については表を参照) : モジュールのグランド。

**OGND (ピンF12、H8、H10、H12、J12)** : 出力ドライバのグランド。

**RF (ピンG1)** : RF信号のシングルエンド入力。このピンは内部でRF入力トランジスタの1次側に接続されており、グランドへの小さなDC抵抗があります。RFソースがDCブロックされていない場合、直列にブロッキング・コンデンサを使う必要があります。RF入力は1.1GHz～1.8GHzで内部整合されています。簡単な外部整合を使うと、下は400MHzまで、上は3.8GHzまで動作可能です。

**LO (ピンJ2)** : ローカル発振器信号のシングルエンド入力。このピンは内部でLOトランジスタの1次側に接続されており、内部でDCブロックされています。外部にブロッキング・コンデンサは不要です。LO入力は0.9GHz～3.5GHzで内部整合されています。簡単な外部整合を使うと、下は380MHzまで動作可能です。

**MIX\_EN (ピンF4)** : ミキサ・イネーブル・ピン。MIX\_ENをV<sub>CC1</sub>に接続すると通常動作になります。MIX\_ENをGNDに接続すると、ミキサはディスエーブルされます。MIX\_ENピンはフロント状態のままにしないでください。

**AMP\_EN (ピンC3)** : アンプ・イネーブル・ピン。このピンは内部で標準30kの抵抗によってV<sub>CC2</sub>に引き上げられています。AMP\_ENをV<sub>CC2</sub>に接続すると通常動作になります。AMP\_ENをGNDに接続すると、アンプはディスエーブルされます。

**ENC<sup>+</sup> (ピンD12)** : ADCのエンコード入力。立ち上がりエッジで変換が開始されます。

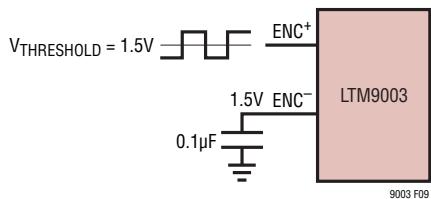

**ENC<sup>-</sup> (ピンE12)** : ADCのエンコード相補入力。立ち下がりエッジで変換が開始されます。シングルエンドのENCODE信号の場合、0.1μFのセラミック・コンデンサを使ってグランドにバイパスします。

**SHDN (ピンB11)** : ADCのシャットダウン・モードの選択ピン。SHDNとOEをGNDに接続すると通常動作になり、出力がイネーブルされます。SHDNをGNDに接続し、OEをV<sub>DD</sub>に接続すると通常動作になり、出力が高インピーダンスになります。SHDNをV<sub>DD</sub>に接続し、OEをGNDに接続するとナップ・モードになり、出力が高インピーダンスになります。SHDNとOEをV<sub>DD</sub>に接続するとスリープ・モードになり、出力が高インピーダンスになります。

**OE (ピンC11)** : 出力イネーブル・ピン。SHDNピンの機能を参照してください。

**MODE (ピンC7)** : 出力のフォーマットとクロック・デューティ・サイクル・スタビライザの選択ピン。MODEをGNDに接続すると、オフセット・バイナリの出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオフします。1/3V<sub>DD</sub>に接続すると、オフセット・バイナリの出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオンします。2/3V<sub>DD</sub>に接続すると、2の補数の出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオンします。V<sub>DD</sub>に接続すると、2の補数の出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオフします。

**SENSE (ピンG7)** : リファレンス・プログラミング・ピン。SENSEを1.25Vに接続すると、内部リファレンスと±0.5Vの入力レンジが選択されます。V<sub>DD</sub>に接続すると、内部リファレンスと±1Vの入力レンジが選択されます。0.5Vより大きく1Vより小さい外部リファレンスをSENSEに印加すると、±V<sub>SENSE</sub>の入力レンジが選択されます。±1Vが最大有効入力レンジです。

**LVDS (ピンD7)** : 出力モードの選択ピン。LVDSはV<sub>DD</sub>に接続します。

## デジタル出力

**D0<sup>-</sup>/D0<sup>+</sup>～D11<sup>-</sup>/D11<sup>+</sup> (ピン配置については表を参照)** : LVDSデジタル出力。全てのLVDS出力にはLVDSレシーバに差動100Ω終端抵抗が必要です。D11<sup>-</sup>/D11<sup>+</sup>がMSBです。

**CLKOUT<sup>-</sup>/CLKOUT<sup>+</sup> (ピンJ10/J11)** : LVDSデータが有効であることを示す出力。CLKOUT<sup>-</sup>の立ち上がりエッジ(CLKOUT<sup>+</sup>の立ち下がりエッジ)でデータをラッチします。

**OF<sup>-</sup>/OF<sup>+</sup> (ピンE5/F5)** : LVDSのオーバーフロー/アンダーフロー出力。オーバーフローやアンダーフローが生じると“H”になります。

# LTM9003

## ピン機能

### ピン配置

| J | GND              | LO               | GND    | GND    | GND | D9+  | D8-             | D6+             | D6-              | CLKOUT+ | CLKOUT-          | OGND             |

|---|------------------|------------------|--------|--------|-----|------|-----------------|-----------------|------------------|---------|------------------|------------------|

| H | GND              | GND              | GND    | GND    | GND | D9-  | D8+             | OGND            | OV <sub>DD</sub> | OGND    | OV <sub>DD</sub> | OGND             |

| G | RF               | GND              | GND    | GND    | GND | D10- | SENSE           | D7+             | D7-              | D5+     | D5-              | OV <sub>DD</sub> |

| F | GND              | V <sub>CC1</sub> | GND    | MIX_EN | OFP | D10+ | GND             | GND             | GND              | GND     | GND              | OGND             |

| E | V <sub>CC1</sub> | V <sub>CC1</sub> | GND    | GND    | OFN | D11- | V <sub>DD</sub> | V <sub>DD</sub> | GND              | GND     | GND              | ENC <sup>-</sup> |

| D | GND              | GND              | GND    | GND    | GND | D11+ | LVDS            | D4+             | D3+              | D1+     | V <sub>DD</sub>  | ENC <sup>+</sup> |

| C | GND              | GND              | AMP_EN | GND    | GND | GND  | MODE            | D4-             | D3-              | D1-     | OE               | GND              |

| B | V <sub>CC2</sub> | V <sub>CC2</sub> | GND    | GND    | GND | GND  | GND             | GND             | D2+              | D0+     | SHDN             | GND              |

| A | GND              | GND              | GND    | GND    | GND | GND  | GND             | GND             | D2-              | D0-     | GND              | GND              |

|   | 1                | 2                | 3      | 4      | 5   | 6    | 7               | 8               | 9                | 10      | 11               | 12               |

部品を透かして見たLGAパッケージの上面図

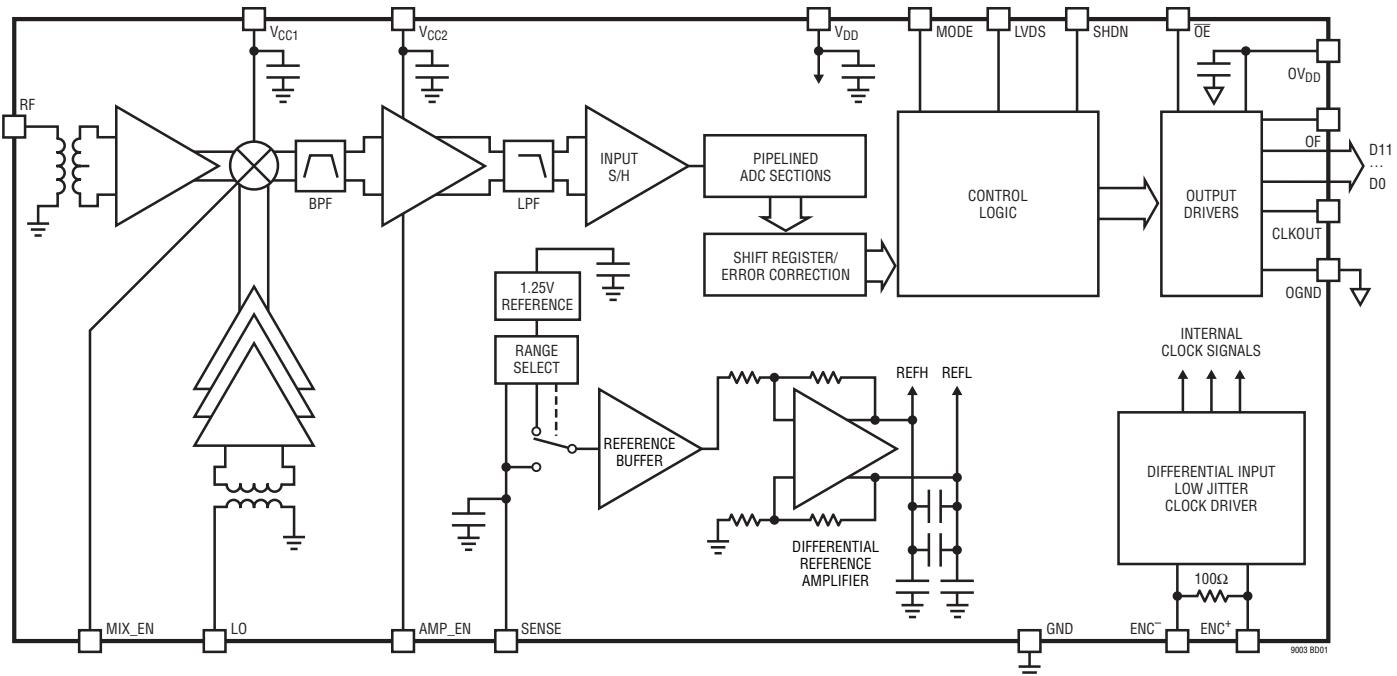

## ブロック図

図1. 簡略ブロック図

## 動作

### 概要

LTM9003は高集積システム・イン・パッケージ (SiP) であり、高速12ビットA/Dコンバータ、広帯域フィルタおよびアクティブ・ミキサを内蔵しています。LTM9003は、RF入力が最大3.8GHzまでの、IFサンプリング、デジタル・プリディストーション (DPD) アプリケーション (transmit observation path receiverとしても知られる) 向けに設計されています。代表的なアプリケーションには、マルチキャリア基地局やテレコムのテスト装置があります。

デジタル・プリディストーションは第三世代 (3G) のワイヤレス基地局に広く使われている技術で、パワー・アンプ (PA) の直線性を改善します。改善されたPAの直線性により、低消費電力のPAを使うことが可能になり、基地局の電力量が大幅に節約できます。DPDレシーバはPAの出力を捕捉し、それをデジタル化してから、歪みを解析することができる回路に戻します。次いで相補的な歪みが送信DACに導入され、それによって信号に予め歪みを与えます。

PAの直線性に影響する大きな要素の1つが奇数次の相互変調 (IM) 積によって生じる歪みです。デジタル化される帯域幅は、信号の帯域幅に、キャンセルされるIM積の次数をかけた値に等しくなります。たとえば、4キャリアWCDMAは20MHzの信号帯域幅を消費します。したがって、5次のIM積を捕捉するには100MHzが必要です。ナイキスト理論によれば、ADCのサンプルレートは少なくともその周波数の2倍であることが必要です。

ただし、捕捉される帯域幅を単純に2倍してサンプルレートを設定するのは最善策ではないことがあります。ADCの正確なサンプルレートと中間周波数 (IF) の選択はシステム内の他の要素に依存します。フィルタリングを簡単にするため、サンプルレートは多くの場合チップレートの整数倍に設定されます。WCDMAのチップレートは3.84MHzです。チップレートの64倍のADCのサンプルレートを選択すると245.76Mspsになります。IFをサンプルレート ( $f_S$ ) の3/4に設定すると184.32MHzになるので、帯域幅全体を2次ナイキスト領域に収めることができます。他の多くの周波数プランが可能です。

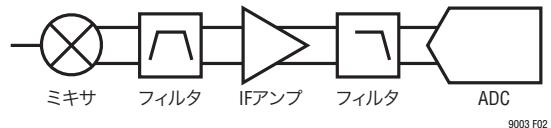

以下のセクションではLTM9003の各機能要素の動作をさらに詳細に説明します。SiPテクノロジーによりLTM9002はカスタム化が可能で、それについて「セミカスタム・オプション」のセクションで説明します。残りのセクションのアウトラインは図2に示されている基本的機能要素に従います。

図2. 基本的機能要素

予測されるであろうように、ミキサによってノイズ指数の計算が支配されます。全体の利得は、ミキサによって許容されるRF入力レベルを基準にしたADCのダイナミックレンジに対して最適化されています。等価カスケードノイズ指数は9.1dB (LTM9003-AA) および9.9dB (LTM9003-AB) です。バンドパス・フィルタはミキサに続く2次のLCフィルタで、アンプに続くローパス・フィルタはアンチエイリアスとノイズ制限の機能を果たします。

### セミカスタム・オプション

**μModule**構造は、アプリケーション固有の標準製品に新しいレベルの柔軟性を提供します。特定のアプリケーション向けに、標準的ADCとアンプの部品を（それらのプロセス・テクノロジーに関係なく）統合し、受動部品に適合させることができます。最初の例として、LTM9003-AAは最高250MHzのレートでサンプリングする12ビットADCを使って構成されています。システム全体の利得は約10.8dBです。IFはバンドパス・フィルタによって125MHzの帯域幅で184MHzに固定されています。RF範囲はローサイドLOにより1.1GHz～1.8GHzに整合しています。

ただし、リニアテクノロジーのセミカスタム開発プログラムにより他のオプションも可能です。リニアテクノロジーは、ほとんどどんなアプリケーションにも対応する、他の速度、分解能、IF範囲、利得およびフィルタ構成を提供するプログラムを用意しています。これらのセミカスタム・デザインは、適切に変更を加えた整合ネットワークと組み合わせた既存のADCとアンプを基礎にします。次いで、アプリケーションで定義された精確なパラメータに対して最終サブシステムがテストされます。最終的には、同じパッケージに完全に一体化され、精確にテストされ、最適化されたソリューションになります。セミカスタムのレシーバ・サブシステム・プログラムの詳細については、弊社にお問い合わせください。

### ダウンコンバーティング・ミキサ

ミキサ段は高直線性の二重平衡ミキサ、RFバッファ・アンプ、高速リミティングLOバッファアンプ、およびバイアス/イネーブル回路で構成されています。

## 動作

RF入力とLO入力は両方ともシングルエンドです。ローサイドまたはハイサイドのLOインジェクションを使うことができます。

ミキサのRF入力は内蔵トランスと高直線性の差動アンプによって構成されています。トランスの1次側端子はRF入力（ピンG1）とグランドに接続されています。トランスの2次側は内部でアンプの差動入力に接続されています。

ミキサのLO入力は内蔵トランスと高速リミティング差動アンプによって構成されています。最高の直線性と最低のノイズ指数を得るために、これらのアンプは精確にミキサをドライブするよう設計されています。

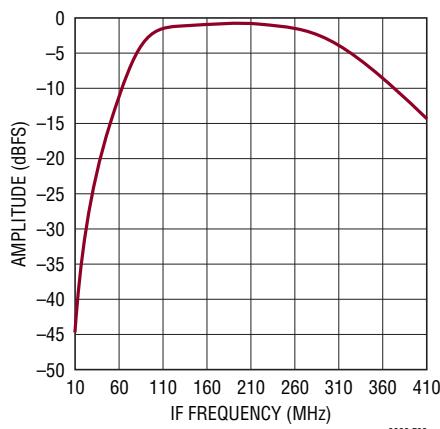

## 広帯域フィルタ

IFのフィタリングの大部分はミキサとIFアンプの間で行われます。このネットワークは2次のチェビシェフ・バンドパスの部分で、パスバンド・リップルが0.1dBに設計されています。3dB帯域幅は220MHzで、中心は184MHzです（図3を参照）。ADCの直前で追加のローパス・フィルタリングが行われます。このフィルタはコンバータに入ってくる帯域外ノイズの帯域を制限し、さらにIFアンプの出力をコンバータのサンプリング動作から絶縁するのに役立ちます。

図3. IFフィルタの応答

## A/D コンバータ

図1に示されているように、A/Dコンバータ（ADC）はCMOSパイプライン・マルチステップ・コンバータです。パイプライン構成の5個のADC段を備えており、サンプルされたアナログ入力は5サイクル後にデジタル値になります（タイミング図を参照）。エンコード入力は同相ノイズ耐性を改善するため差動です。ADCは差動のENC<sup>+</sup>/ENC<sup>-</sup>入力ピンの状態で定まる2つのフェーズで動作します。簡単にするため、ここでの説明では、ENC<sup>+</sup>がENC<sup>-</sup>より大きいときENCは“H”であると表現し、ENC<sup>+</sup>がENC<sup>-</sup>より小さいときENCは“L”であると表現します。

図1に示されているパイプライン構成の各段は、1個のADC、再構成DAC、および段間残余アンプを備えています。動作時、ADCは各段の入力を量子化し、量子化された値はDACによって入力から差し引かれ、残余を生じます。残余は残余アンプによって増幅されて出力されます。奇数段がその残余を出力しているとき偶数段がその残余を取得するように、またその逆になるように、後に続く段は位相がずれて動作します。

ENCが“L”的とき、アナログ入力はブロック図に示されている「入力S/H」内部の入力サンプル&ホールド・コンデンサに差動で直接サンプリングされます。ENCが“L”から“H”に遷移する瞬間、サンプルされた入力がホールドされます。ENCが“H”的間、ホールドされた入力電圧はS/Hアンプによってバッファされます。このS/Hアンプはパイプライン構成の最初のADC段をドライブします。最初の段はENCの“H”フェーズの間にS/Hの出力を取得します。ENCが再度“L”に戻るとき最初の段はその残余を出力し、この残余が2番目の段によって取得されます。同時に、入力のS/Hは再度アナログ入力を取得します。ENCが“H”に戻ると2番目の段はその残余を出力し、この残余が3番目の段によって取得されます。同様の過程が3番目と4番目の段で繰り返され、4番目の段の残余は最終評価のために5番目の段のADCに送られます。

初段に続く各ADC段にはフラッシュ誤差とアンプのオフセット誤差を調節するための追加範囲があります。ADCの全段からの結果は、出力バッファに送る前に、それらの結果を補正ロジックで適切に結合できるようにデジタル動作で同期させます。

## アプリケーション情報

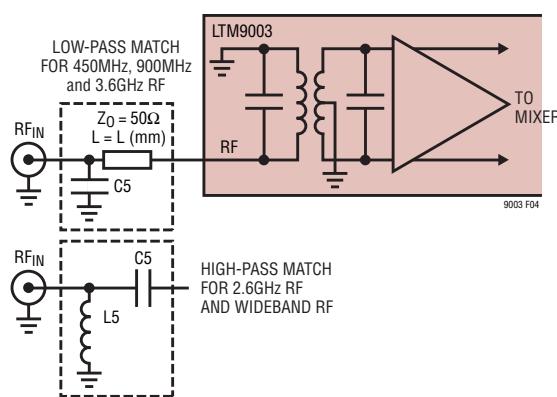

### RF入力ポート

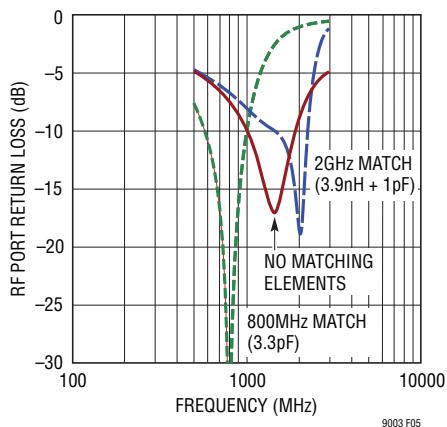

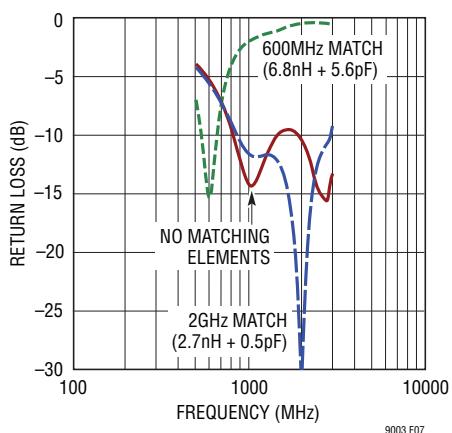

ミキサのRF入力は図4に示されており、1.1GHz～1.8GHzで内部整合されているので、この周波数範囲では外付け部品は不要です。図5に示されている入力リターン損失は帯域幅の両端で標準12dBです。帯域幅の低い方の端の入力整合は3.3pFのコンデンサをピンG1に直列に使って最適化することができます、0.8GHzのリターン損失が25dBを超えるまで改善されます。同様に、2GHzの整合は3.9nHのインダクタと1pFのシャント・コンデンサを直列に使って25dBを超えるまで改善することができます。これら3つの場合に測定したRF入力のリターン損失を図5に示します。

図4. RF入力回路

図5. 整合ありとなしの場合のRF入力リターン損失

この直列伝送ライン/シャント・コンデンサ整合トポロジーにより、回路基板のレイアウトを修正せずに、LTM9003を複数の周波数規格で使用することができます。レイアウトを小さくするには、直列伝送ラインを直列チップ・インダクタで置き換えることもできます。

周波数に対するRF入力インピーダンスおよびS11(外部整合部品なし)を表1に示します(ピンG1を基準)。これらのS11データをマイクロ波回路シミュレータを使ってカスタムの整合ネットワークを設計し、RF入力フィルタへの基板レベルのインターフェースをシミュレートすることができます。

表1a. RF入力インピーダンスと周波数(LTM9003-AA)

| FREQUENCY<br>(MHz) | INPUT IMPEDANCE | S11  |        |

|--------------------|-----------------|------|--------|

|                    |                 | MAG  | ANGLE  |

| 500                | 20.3+j7         | 0.57 | 143    |

| 600                | 23.6+j6.7       | 0.53 | 137.9  |

| 700                | 27.1+j6.1       | 0.48 | 132.7  |

| 800                | 30.8+j5.3       | 0.43 | 127    |

| 900                | 34.9+j4.2       | 0.38 | 120.4  |

| 1000               | 39.4+j2.9       | 0.33 | 112.6  |

| 1100               | 44.6+j1.4       | 0.28 | 102.8  |

| 1200               | 50.1            | 0.22 | 89.8   |

| 1300               | 56-j1           | 0.17 | 70.4   |

| 1400               | 61.5-j1.2       | 0.14 | 42.2   |

| 1500               | 66-j0.3         | 0.14 | 6.6    |

| 1600               | 68.7+j1.4       | 0.17 | -21.5  |

| 1700               | 69+j3.2         | 0.22 | -41    |

| 1800               | 67.5+j4.5       | 0.27 | -54    |

| 1900               | 64.3+j4.7       | 0.32 | -64.3  |

| 2000               | 60.8+j4.1       | 0.36 | -72.2  |

| 2100               | 56.7+j2.8       | 0.4  | -79.5  |

| 2200               | 52.7+j1.2       | 0.43 | -85.8  |

| 2300               | 48.6-j0.6       | 0.46 | -92.1  |

| 2400               | 44.7-j2.3       | 0.48 | -98    |

| 2500               | 40.8-j4         | 0.5  | -104.3 |

| 2600               | 37-j5.3         | 0.51 | -110.5 |

| 2700               | 33.1-j6.3       | 0.52 | -117.2 |

| 2800               | 29.4-j6.9       | 0.53 | -124.3 |

| 2900               | 26-j7           | 0.53 | -131.7 |

| 3000               | 22.9-j6.7       | 0.53 | -139.6 |

# LTM9003

## アプリケーション情報

表1b. RF入力インピーダンスと周波数(LTM9003-AB)

| FREQUENCY<br>(MHz) | INPUT IMPEDANCE | S11  |        |

|--------------------|-----------------|------|--------|

|                    |                 | MAG  | ANGLE  |

| 500                | 19.8+j7.3       | 0.59 | 143    |

| 600                | 22.7+j7         | 0.55 | 138.4  |

| 700                | 25.7+j6.6       | 0.51 | 133.9  |

| 800                | 28.8+j5.9       | 0.47 | 129.2  |

| 900                | 32.3+j5.1       | 0.42 | 123.9  |

| 1000               | 36.1+j3.9       | 0.38 | 117.9  |

| 1100               | 40.5+j2.6       | 0.32 | 110.6  |

| 1200               | 45.4+j1.1       | 0.26 | 101.3  |

| 1300               | 50.8-j0.2       | 0.2  | 87.6   |

| 1400               | 56.3-j0.9       | 0.15 | 65.6   |

| 1500               | 61.4-j0.7       | 0.12 | 27.5   |

| 1600               | 65.3+j0.5       | 0.14 | -13.1  |

| 1700               | 67.4+j2.4       | 0.19 | -37.9  |

| 1800               | 67.3+j4.1       | 0.25 | -52.4  |

| 1900               | 65.7+j5.1       | 0.31 | -61.9  |

| 2000               | 63.2+j5.2       | 0.37 | -68.9  |

| 2100               | 60.4+j4.7       | 0.42 | -74.4  |

| 2200               | 57.6+j3.7       | 0.46 | -79.1  |

| 2300               | 55+j2.6         | 0.49 | -83    |

| 2400               | 52.4+j1.3       | 0.51 | -86.7  |

| 2500               | 49.9            | 0.53 | -90.1  |

| 2600               | 47.4-j1.4       | 0.54 | -93.7  |

| 2700               | 44.8-j2.7       | 0.55 | -97.3  |

| 2800               | 41.9-j3.9       | 0.55 | -101.6 |

| 2900               | 39-j5           | 0.55 | -106.3 |

| 3000               | 35.7-j5.9       | 0.54 | -111.9 |

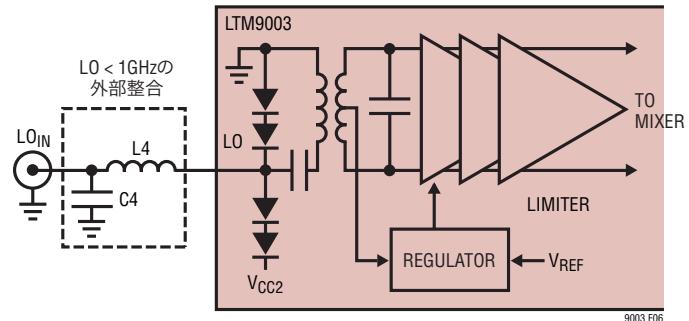

## LO 入力ポート

図6に示されているミキサのLO入力は、0.9GHz～3.5GHzで内部整合されています。LO入力の600MHz近くの整合には、図6に示されている直列インダクタ(L4) /シャント・コンデンサー(C4)のネットワークが必要です。同様に、2GHzの整合は、L4 = 2.7μH, C4 = 0.5pFを使って改善することができます。これら3つの場合に測定したLO入力のリターン損失を図7に示します。

アンプは数dBのLO入力電力の変動に対して順応するように設計されており、ミキサ性能の大きな変化は生じませんが、最適LOドライブは1.2GHzを超えるLO周波数では-3dBmです。1.2GHzより下では、-3dBmが依然として十分な換算利得と直線性を与えますが、最適ノイズ指数を得るには、0dBmのLOドライブを推奨します。

図6. LO入力回路

表2に記載されているポート・インピーダンスのデータを使って、カスタム整合ネットワークを設計することができます。このデータは外部整合を使わないLOピンを基準にしています。

表2a. LO入力インピーダンスと周波数(LTM9003-AA)

| FREQUENCY<br>(MHz) | INPUT IMPEDANCE | S11  |        |

|--------------------|-----------------|------|--------|

|                    |                 | MAG  | ANGLE  |

| 500                | 10.3-j6.1       | 0.73 | -159.1 |

| 600                | 9.7+j2.2        | 0.68 | 172.4  |

| 700                | 18.7+j8.2       | 0.64 | 141.8  |

| 800                | 37+j6.2         | 0.6  | 108.4  |

| 900                | 64.5-j9.9       | 0.59 | 72.7   |

| 1000               | 109.7-j42.2     | 0.6  | 38.3   |

| 1100               | 206.6-j35.9     | 0.63 | 7.9    |

| 1200               | 183.8+j70       | 0.66 | -17.1  |

| 1300               | 115.4+j59.4     | 0.68 | -37.3  |

| 1400               | 86.7+j35.2      | 0.7  | -53.7  |

| 1500               | 70.7+j18.5      | 0.71 | -67.4  |

| 1600               | 59.3+j7.4       | 0.7  | -79.2  |

| 1700               | 50.2+j0.2       | 0.7  | -89.7  |

| 1800               | 42.6-j4.5       | 0.68 | -99.6  |

| 1900               | 35.9-j7.2       | 0.66 | -109.2 |

| 2000               | 30.2-j8.3       | 0.63 | -118.9 |

| 2100               | 25.6-j8.1       | 0.59 | -129.2 |

| 2200               | 22.4-j6.7       | 0.54 | -140.3 |

| 2300               | 20.8-j4.6       | 0.48 | -152.3 |

| 2400               | 21.5-j2.1       | 0.42 | -165.5 |

| 2500               | 24.2            | 0.35 | -179.8 |

| 2600               | 28.9+j1.3       | 0.28 | 163.9  |

| 2700               | 35.3+j1.5       | 0.21 | 145.1  |

| 2800               | 42.6+j0.9       | 0.16 | 121.1  |

| 2900               | 50.3            | 0.12 | 88.6   |

| 3000               | 57.7-j0.6       | 0.1  | 45.8   |

9003f

## アプリケーション情報

表2b. LO入力インピーダンスと周波数(LTM9003-AB)

| FREQUENCY<br>(MHz) | INPUT IMPEDANCE | S11  |        |

|--------------------|-----------------|------|--------|

|                    |                 | MAG  | ANGLE  |

| 500                | 14.3 - j7.5     | 0.68 | -150.6 |

| 600                | 12.6 - j2.4     | 0.61 | -170.4 |

| 700                | 15.8 + j1.9     | 0.53 | 170.8  |

| 800                | 22.7 + j4.1     | 0.44 | 151.5  |

| 900                | 32.5 + j3.8     | 0.35 | 130.2  |

| 1000               | 44.2 + j1.3     | 0.25 | 104.9  |

| 1100               | 56.3 - j1.2     | 0.18 | 70.3   |

| 1200               | 66 - j1.3       | 0.15 | 26.4   |

| 1300               | 70.7 + j1       | 0.18 | -12.8  |

| 1400               | 69.9 + j3.1     | 0.21 | -37.8  |

| 1500               | 66 + j3.7       | 0.25 | -54.1  |

| 1600               | 61.8 + j3.3     | 0.27 | -65.5  |

| 1700               | 58.1 + j2.4     | 0.28 | -73.4  |

| 1800               | 54.9 + j1.5     | 0.29 | -79.8  |

| 1900               | 52.7 + j0.8     | 0.28 | -84.2  |

| 2000               | 50.7 + j0.2     | 0.28 | -88.5  |

| 2100               | 49.4 - j0.2     | 0.27 | -91.4  |

| 2200               | 47.8 - j0.5     | 0.25 | -95.5  |

| 2300               | 46.7 - j0.7     | 0.23 | -98.9  |

| 2400               | 45.7 - j0.8     | 0.2  | -103.3 |

| 2500               | 45.5 - j0.7     | 0.17 | -106.8 |

| 2600               | 46.4 - j0.4     | 0.13 | -107.1 |

| 2700               | 48.7 - j0.1     | 0.1  | -97.9  |

| 2800               | 50.9 + j0.1     | 0.09 | -84.2  |

| 2900               | 52.9 + j0.3     | 0.09 | -72.5  |

| 3000               | 54.6 + j0.5     | 0.11 | -66.7  |

図7. 整合ありとなしの場合のLO入力リターン損失

## ミキサ・イネーブル・インターフェース

ミキサをオンするのに必要な電圧は2.7Vです。ミキサをディスエーブルするには、イネーブル電圧が0.3Vより低くなければなりません。MIX\_ENピンをフロートさせたままにしておくと、ミキサはその最後の動作状態を保とうとします。したがって、イネーブル機能をこのように使用することは推奨できません。シャットダウン機能が不要なら、MIX\_ENピンを直接VCC1に接続します。

## アンプ・イネーブル・インターフェース

AMP\_ENは30k抵抗を介してVCC2に自己バイアスされています。アンプをディスエーブルするにはこのピンを0.8Vより下にする必要があります。

## ADCのクロック入力のドライブ

ADCのノイズ特性は、アナログ入力に依存するのと同程度にエンコード信号の質の良し悪しに依存することがあります。ENC<sup>+</sup>/ENC<sup>-</sup>入力は、主に同相ノイズ源に対して耐性をもたせるため、差動でドライブするように意図されています。各入力は4.8kの抵抗を通して1.5Vにバイアスされています。これらのバイアス抵抗はトランジスト結合のドライブ回路のDC動作点を設定し、シングルエンドのドライブ回路のロジック・スレッショルドを設定することができます。

エンコード信号に含まれるどんなノイズも新たなアーチャ・ジッタを生じ、このジッタは本来のADCアーチャ・ジッタにRMSとして追加されます。

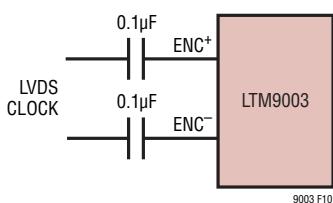

ジッタが重要な問題となる(高入力周波数) アプリケーションでは、以下の配慮が必要です。

1. 差動ドライブを使います。

2. できるだけ大きな振幅を使います。トランジスト結合の場合、高い巻線比を使って振幅を大きくします。

3. 正弦波信号でADCをクロック駆動する場合、エンコード信号にフィルタをかけて広帯域ノイズを減らします。

4. 両方のエンコード入力で容量と直列抵抗値をバランスさせ、どの結合ノイズも同相ノイズとして両方の入力に現わるようにします。エンコード入力の同相範囲は1.2V~2.0Vです。シングルエンドのドライブの場合、各入力はグランド~VDDの範囲でドライブすることができます。

## アプリケーション情報

図8. トランスでドライブされる $\text{ENC}^+$ / $\text{ENC}^-$

図9. シングルエンドのENCドライバ(低ジッタには推奨できない)

図10. LVDSを使ったENCドライブ

### 最大変換レートと最小変換レート

ADCの最大変換レートは250Mspsです。ADCが正常に動作するには、エンコード信号のデューティ・サイクルは50% ( $\pm 5\%$ ) である必要があります。各半周期は、十分なセトリング時間をADCの内部回路に与えて正常動作させるため、少なくとも1.9ns必要です。正確に50%のデューティ・サイクルを簡単に実現するには、トランスを使った、またはPECLやLVDSのような対称型差動ロジックを使った差動正弦波ドライブを使います。

サンプリング・レートの下限はサンプル&ホールド回路の垂下によって決まります。このADCのパイプライン・アーキテクチャでは、アナログ信号を小容量のコンデンサに保存します。接合部のリーク電流によりコンデンサが放電します。LTM9003の規定最小動作周波数は1Mspsです。

### クロック・デューティ・サイクル・スタビライザ

入力クロックのデューティ・サイクルが50%でない場合、オプションのクロック・デューティ・サイクル・スタビライザ回路を使うことができます。この回路は $\text{ENC}^+$ ピンの立ち上がりエッジを使って、アナログ入力をサンプルします。 $\text{ENC}^+$ の立ち下がりエッジは無視され、フェーズロック・ループにより内部で立ち下がりエッジが作られます。入力クロックのデューティ・サイクルは40%~60%の範囲で変化することができ、クロック・デューティ・サイクル・スタビライザは内部デューティ・サイクルを50%に保ちます。クロックが長時間オフすると、デューティ・サイクル・スタビライザ回路のPLLが入力クロックにロックするのに100クロック・サイクルを必要とします。クロック・デューティ・サイクル・スタビライザを使うには、外付け抵抗を使ってMODEピンを1/3 $V_{\text{DD}}$ または2/3 $V_{\text{DD}}$ に接続します。

### アンダーサンプリングのクロック・ソース

アンダーサンプリングでは、クロック・ソースに対して特に要求が厳しく、入力周波数が高いほどクロックのジッタや位相ノイズに対して敏感になります。フルスケール信号のSNRを70MHzで1dBだけ悪化させるクロック・ソースは、SNRを140MHzでは3dB、190MHzでは4.5dBだけ悪化させます。

クロック周波数の絶対精度が比較的重要ではなく、1つのADCだけが必要とされるケースでは、SaronixやVectronのようなベンダーのメタルキャン発振器をADCの近くに配置してADCに直接接続することができます。ADCまでいくらか距離がある場合、たとえ数分の1インチでも生じることのあるリングングを減らすために、ソースを終端することを推奨します。クロックが決して電源をオーバーシュートしないようにします。そうしないと性能が低下します。正弦波のクロック・ソースでない限り、クロック信号は狭帯域のバンド・フィルタを通さないでください。フィルタを通すと、標準的なデジタル・クロック信号に含まれる立ち上がり時間と立ち下がり時間のアーチファクトが位相ノイズに変換されるからです。

## アプリケーション情報

位相ノイズが最低の発振器はシングルエンドの正弦波出力を備えており、これらのデバイスの場合は、ADCの近くにフィルタを使用すると有効なことがあります。このフィルタはADCに近づけて配置して、往復の反射時間を短くするとともに、フィルタとADCの間のトレースが外部の影響を受けにくくします。

回路が近接位相ノイズに敏感であれば、発振器の電源とバッファが非常に安定している必要があります。そうでないと、電源による伝播遅延の変動が位相ノイズに変換されます。これらのクロック・ソースはデジタル・デバイスと見なされるかもしれません、それらをデジタル電源で動作させないでください。クロックがFPGAなどのデジタル・デバイスをドライブするのにも使用される場合、発振器とクロックのファンアウトに使われるデバイスをADCの近くに配置し、ADCへの配線を優先させます。FPGAへのクロック信号はドライバのところで直列に終端し、FPGAからの高周波ノイズがクロックのファンアウト・デバイスのサブストレートを乱すのを防ぎます。FPGAをプログラム可能な分周器として使用する場合、元の発振器を使って信号の時間合せを行う必要があり、タイミング調整用フリップ・フロップと発振器をADCに近づけて配置し、非常に静穏な電源から給電します。

複数のADCが存在する場合、またはクロック・ソースがいくらか離れている場合、クロックを差動で分配することを推奨します。これは、EMIの観点からだけでなく、(放射と、多層PCBのレイヤ間に存在するウェーブガイド内の伝播による) デジタル・ソースからのノイズを防ぐ観点からも推奨します。この差動対は一緒に近接させ、他の信号から離す必要があります。この差動対は(トレース間の距離の少なくとも3倍距離をとつて)両側に銅でガードを設け、1/4インチ以下の間隔でビアを使って接地します。

## デジタル出力

アナログ入力電圧、デジタル・データ・ビット、およびオーバーフロー・ビットの相互関係を表3に示します。

表3. 出力コードと入力電圧

| 入力<br>(SENSE = $V_{DD}$ ) | OF | D11~D0<br>(オフセット・バイナリ) | D11~D0<br>(2の補数) |

|---------------------------|----|------------------------|------------------|

| 過電圧                       | 1  | 1111 1111 1111         | 0111 1111 1111   |

| 最大                        | 0  | 1111 1111 1111         | 0111 1111 1111   |

|                           | 0  | 1111 1111 1110         | 0111 1111 1110   |

| 0.000000V                 | 0  | 1000 0000 0001         | 0000 0000 0001   |

|                           | 0  | 1000 0000 0000         | 0000 0000 0000   |

|                           | 0  | 0111 1111 1111         | 1111 1111 1111   |

|                           | 0  | 0111 1111 1110         | 1111 1111 1110   |

| 最小                        | 0  | 0000 0000 0001         | 1000 0000 0001   |

|                           | 0  | 0000 0000 0000         | 1000 0000 0000   |

| 低電圧                       | 1  | 0000 0000 0000         | 1000 0000 0000   |

## デジタル出力バッファ

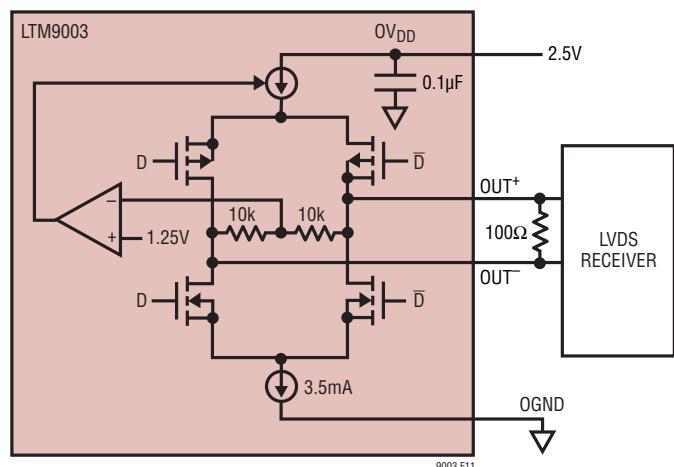

CMOS出力モードの1個の出力バッファの等価回路を図11に示します。3.5mAの電流が $OUT^+$ から $OUT^-$ に、またはその逆方向に振り向けられ、それにより、LVDSレシーバの100Ω終端抵抗両端に±350mVの差動電圧が生じます。帰還ループが同相出力電圧を1.25Vに安定化します。

図11. LVDSモードのデジタル出力

## アプリケーション情報

正しく動作するには、( $OF^+/OF^-$ または $CLKOUT^+/CLKOUT^-$ などの) 信号を使用しなくとも、各LVDS出力対には $100\Omega$ の外付け終端抵抗が必要です。ノイズを最小に抑えるには、PCボード上の各LVDS出力対のトレースは一緒に近接させて配置します。クロックのスキーを最小に抑えるため、すべてのLVDSのPCボード・トレースを同じ長さにします。

### データのフォーマット

LTM9003のパラレル・デジタル出力のフォーマットには、オフセット・バイナリ形式または2の補数を選択できます。フォーマットはMODEピンを使って選択します。MODEをGNDまたは $1/3V_{DD}$ に接続するとオフセット・バイナリの出力フォーマットが選択されます。MODEを $2/3V_{DD}$ または $V_{DD}$ に接続すると2の補数の出力フォーマットが選択されます。外部抵抗分割器を使って $1/3V_{DD}$ または $2/3V_{DD}$ のロジック値を設定することができます。MODEピンのロジック状態を表4に示します。

表4. MODEピンの機能

| MODEピン      | 出力フォーマット   | クロック・デューティ・サイクル・スタビライザ |

|-------------|------------|------------------------|

| 0           | ストレート・バイナリ | オフ                     |

| $1/3V_{DD}$ | ストレート・バイナリ | オン                     |

| $2/3V_{DD}$ | 2の補数       | オン                     |

| $V_{DD}$    | 2の補数       | オフ                     |

### オーバーフロー・ビット

オーバーフロー出力ビットはコンバータにオーバーレンジまたはアンダーレンジの信号が入力されていることを示します。 $OF^+/OF^-$ ピンの差動ロジック“H”はオーバーフローまたはアンダーフローを示します。

### 出力クロック

LTM9003には $ENC^+$ 入力を遅延させた信号がデジタル出力( $CLKOUT$ )として備わっています。この $CLKOUT$ ピンを使って、コンバータのデータをデジタル・システムに同期させることができます。これは正弦波のエンコードを使っているとき必要です。データは $CLKOUT^+/CLKOUT^-$ が立ち上がった直後に更新され、 $CLKOUT^+/CLKOUT^-$ の立ち下がりエッジでラッチすることができます。

### 出力ドライバの電源

$OV_{DD}$ は2.5V電源に接続し、 $OGND$ はGNDに接続します。

### 出力イネーブル

出力イネーブル・ピン( $\overline{OE}$ )を使って出力をディスエーブルすることができます。LVDS出力モードでは、 $\overline{OE}$ を“H”にすると、 $OF$ や $CLKOUT$ を含むすべてのデータ出力がディスエーブルされます。データのアクセス時間やバスの解放時間は、全速動作時に出力をイネーブルまたはディスエーブルするには遅すぎます。出力のHi-Z状態は長期の休止時に使うことを意図しています。

このHi-Z状態は真の開放回路ではありません。LVDS出力対を形成する出力ピンの間には $20k$ の抵抗があります。

### スリープ・モードとナップ・モード

節電のため、コンバータをシャットダウン・モードまたはナップ・モードにすることができます。SHDNをGNDに接続すると通常動作になります。SHDNを $V_{DD}$ に接続し、 $\overline{OE}$ を $V_{DD}$ に接続するとスリープ・モードになり、リファレンスを含む全ての回路がパワーダウンし、ADCの電力損失は標準で $1.5mW$ になります。スリープ・モードを抜け出すとき、リファレンスのコンデンサを再充電して安定化する必要があるので、出力データが有効になるまで数ミリ秒かかります。SHDNを $V_{DD}$ に接続し、 $\overline{OE}$ をGNDに接続するとナップ・モードになり、ADCの電力損失は標準で $30mW$ になります。ナップ・モードでは内蔵リファレンス回路はオンしたままなので、ナップ・モードからの回復はスリープ・モードからの回復よりも速く、標準で $100$ クロック・サイクルかかります。スリープとナップの両方のモードで全てのデジタル出力はディスエーブルされ、Hi-Z状態になります。

### 電源シーケンシング

$V_{CC1}$ ピンと $V_{CC2}$ ピンはそれぞれミキサとアンプに電源を与え、 $V_{DD}$ ピンはADCに電源を与えます。ミキサ、アンプおよびADCはLTM9003内の個別の集積回路です。別々のリニア・レギュレータが共通の入力電源を持っていれば、追加の電源シーケンシング回路なしに、それらを使うことができます。

## アプリケーション情報

### 接地とバイパス

LTM9003には全く切れ目の無いグランド・プレーンを備えたプリント基板が必要です。内部グランド・プレーンを備えた多層基板を推奨します。LTM9003のピン配置はフロースルーレイアウトに最適化されているので、入力とデジタル出力間の相互反応が最小に抑えられます。十分なグランド・パッドによりレイアウトが簡単になり、デジタル信号ラインとアナログ信号ラインをできるだけ分離することができます。

LTM9003は内部でバイパスされており、ADC ( $V_{DD}$ )、アンプ ( $V_{CC2}$ ) およびミキサ ( $V_{CC1}$ ) の各電源は共通グランド (GND) に戻ります。デジタル出力電源 ( $OV_{DD}$ ) はOGNDに戻ります。追加のバイパス・コンデンサはオプションで、電源ノイズが大きいと必要になることがあります。

### 熱伝達

LTM9003が発生する熱の大部分は底面のグランド・パッドを通って伝わります。電気的および熱的性能を良くするには、全てのグランド・ピンを面積が十分大きなグランド・プレーンにできるだけ多くのビアを使って接続することが重要です。

### 推奨レイアウト

LTM9003は高度に統合されているので、PCBボードのレイアウトが非常に簡単かつ容易です。ただし、電気的性能と熱的性能を最適化するにはいくつかのレイアウト上の配慮が依然として必要です。

- グランドにはPCBの大きな銅領域を使用します。これにより基板を通してパッケージ内部の熱が放散するのが助けられ、基板上の敏感なアナログ信号をシールドするのにも役立ちます。共通グランド (GND) と出力グランド (OGND) はLTM9003では電気的に絶縁されていますが、PCB上でデバイスの下で接続して共通リターン経路を与えることができます。

- 複数のグランド・ビアを使います。できるだけ多くのビアを使うと、基板の熱性能を改善するのに役立ち、基板上のアナログ・トレースとデジタル・トレースを高周波数で分離するのに必要なバリヤを形成します。

- ビアを使って高周波バリヤを作り、アナログ・トレースとデジタル・トレースをできるだけ分離します。これにより、LTM9003の信号対雑音比 (SNR) とダイナミックレンジを下げる可能性のあるデジタル・フィードバックが減少します。

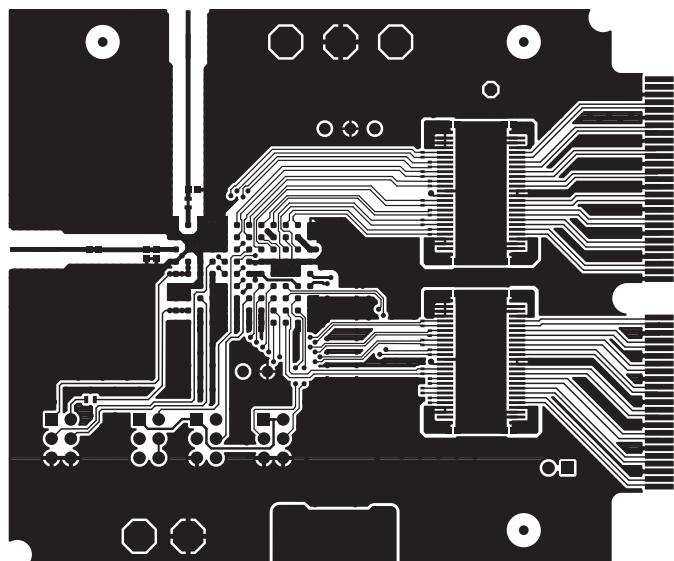

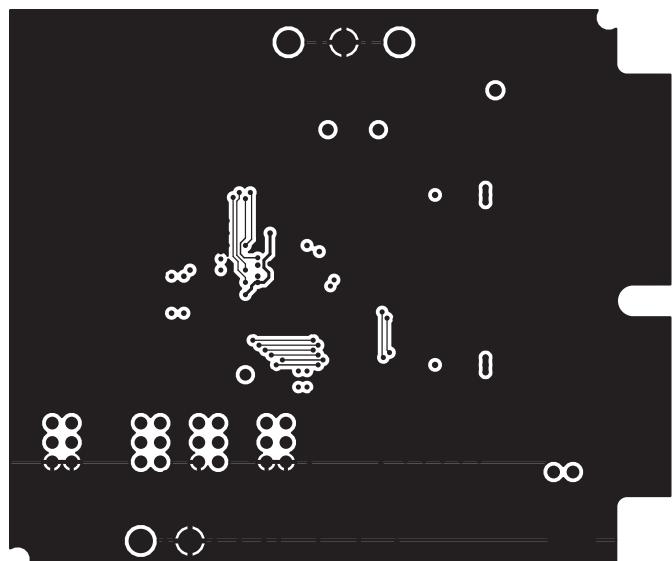

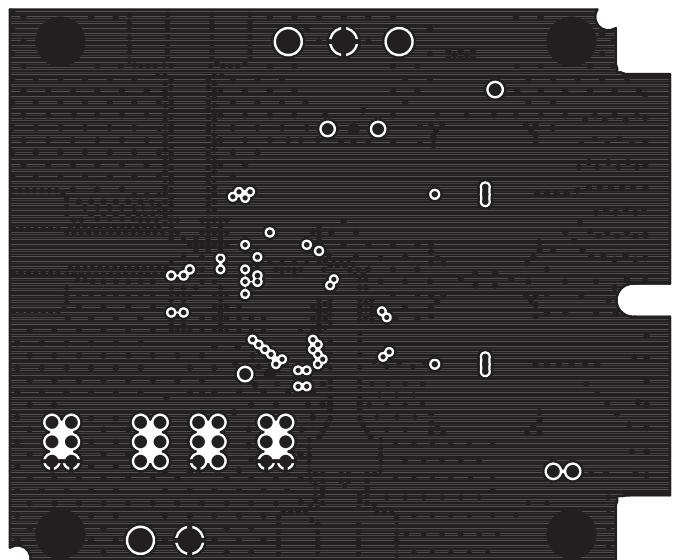

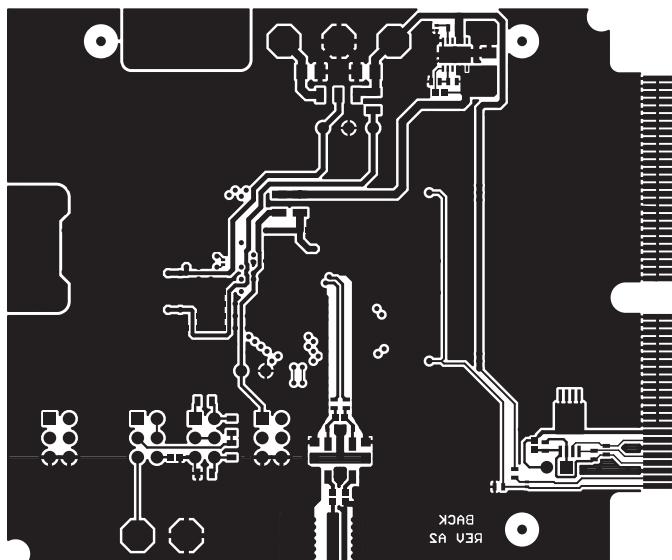

推奨レイアウトの良い例を図12～図15に示します。

ペースト印刷の品質は、高歩留りアセンブリにとって重要な要素です。タイプ3またはタイプ4を使って無洗浄半田ペーストを印刷することを推奨します。半田ステンシルは「アプリケーションノート100」で説明されているガイドラインに従ってデザインします。

LTM9003は鉛ベースまたは錫ベースの半田ペーストで使えるように金仕上げのパッドを採用しています。内部は鉛フリーで、JEDEC (e4) 標準規格に適合しています。材料表は[http://www.linear.com/leadfree/mat\\_dec.jsp](http://www.linear.com/leadfree/mat_dec.jsp)からオンラインで入手できます。

# LTM9003

## アプリケーション情報

図12. レイヤ1(部品側)

図13. レイヤ2

図14. レイヤ3

図15. 裏面

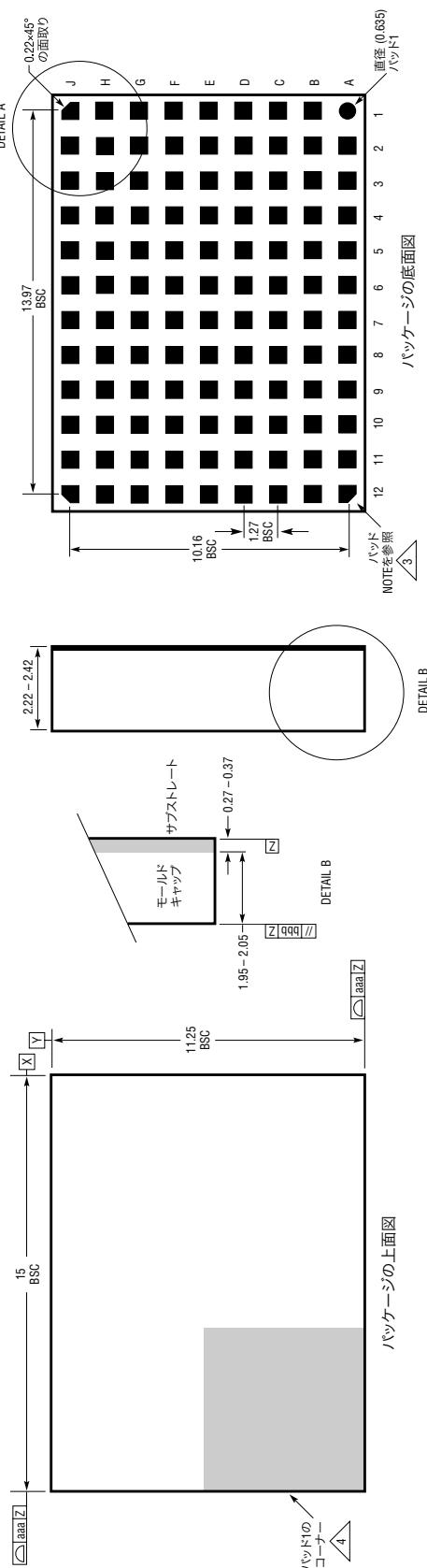

## パッケージ

**LGA パッケージ

108ピン(15mm×11.25mm×2.32mm)**

(Reference LTC DWG # 05-08-1757 Rev Ø)

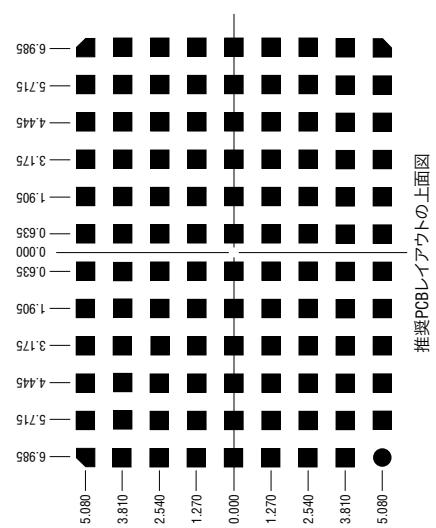

推奨PCBレイアウトの上面図

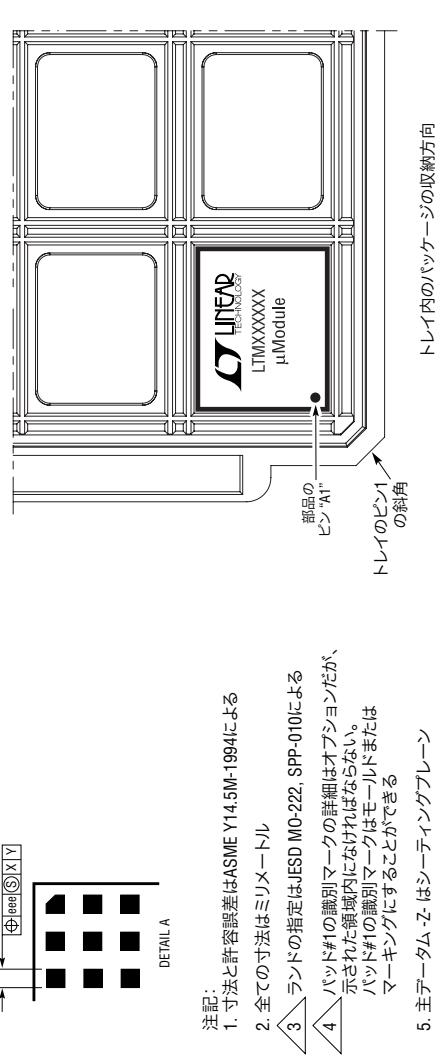

- トレイ内のパッケージの取納方向

- トレイの傾斜の斜角

- 部品のピンA

- 主データム-Z-はシーティングフレーン

6. パッドの総数: 108

LGA 108 0707 Rev 0

| 記号  | 許容誤差 |

|-----|------|

| aaa | 0.15 |

| bbb | 0.10 |

| eee | 0.05 |

# LTM9003

## 関連製品

| 製品番号       | 説明                                       | 注釈                                                                        |

|------------|------------------------------------------|---------------------------------------------------------------------------|

| LTC2240-10 | 10ビット、170Msps、2.5V ADC、LVDS出力            | 445mW、SNR:60.6dB、SFDR:78dB、64ピンQFN                                        |

| LTC2240-12 | 12ビット、170Msps、2.5V ADC、LVDS出力            | 445mW、SNR:65.5dB、SFDR:80dB、64ピンQFN                                        |

| LTC2241-10 | 10ビット、210Msps、2.5V ADC、LVDS出力            | 585mW、SNR:60.6dB、SFDR:78dB、64ピンQFN                                        |

| LTC2241-12 | 12ビット、210Msps、2.5V ADC、LVDS出力            | 585mW、SNR:65.5dB、SFDR:78dB、64ピンQFN                                        |

| LTC2242-10 | 10ビット、250Msps、2.5V ADC、LVDS出力            | 740mW、SNR:60.5dB、SFDR:78dB、64ピンQFN                                        |

| LTC2242-12 | 12ビット、250Msps、2.5V ADC、LVDS出力            | 740mW、SNR:65.4dB、SFDR:78dB、64ピンQFN                                        |

| LTC6410    | 入力インピーダンスを設定可能な差動IFアンプ                   | 1.4GHz、-3dB BW、6dB固定電圧利得(50Ωシステム)、OIP3:36dBm                              |

| LT5527     | 400MHz～3.7GHz、5V高信号レベル・ダウンコンバーティング・ミキサ   | IIP3:1.9GHzで23.5dBm、NF:12.5dB、シングルエンドのRFポートとLOポート                         |

| LT5557     | 400MHz～3.8GHzの3.3V高信号レベル・ダウンコンバーティング・ミキサ | IIP3:1.9GHzで24.7dBm、NF:11.7dB、シングルエンドのRFポートとLOポート、3.3V電源                  |

| LTM9001-AA | 16ビット、IF/ベースバンド・レシーバ・サブシステム              | 16ビット、130Msps ADC、利得が20dBのアンプ、アンチエイリアス・フィルタ、内部バイパス容量                      |

| LTM9002-AA | デュアル、14ビット、IF/ベースバンド・レシーバ・サブシステム         | デュアル、14ビット、125Msps ADC、利得が26dBのデュアル・アンプ、アンチエイリアス・フィルタ、利得調整用補助DAC、内部バイパス容量 |