## 特長

- 最大12個の直列に接続されたバッテリ・セルを測定

- スタック接続型アーキテクチャにより、数百個の接続されたセルをサポート可能

- isoSPI™インターフェースを内蔵

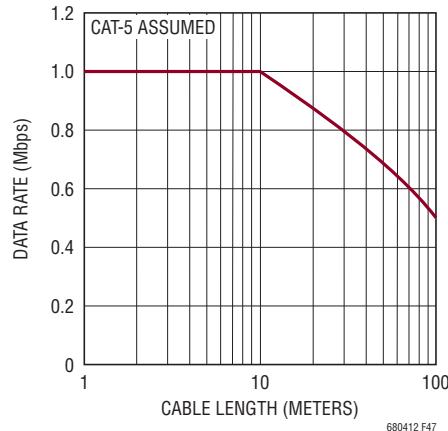

- 1Mbpsの絶縁型シリアル通信

- 1本のツイストペアケーブル使用し、最長100メートル

- EMIの影響を受けにくく、EMIの放射が少ない

- 全測定誤差:最大1.2mV

- システム内のすべてのセルを290μsで測定

- 電圧と電流の同期測定

- 周波数設定可能な3次ノイズ・フィルタを備えた16ビットΔΣ型A/Dコンバータ

- ISO26262準拠システムに対応した設計

- プログラム可能なタイマによるセルの受動式均等化機能

- 5つの汎用デジタル入出力またはアナログ入力:

- 温度などのセンサ入力

- I<sup>2</sup>CまたはSPIのマスターとして構成可能

- スリープ・モード時の消費電流:4μA

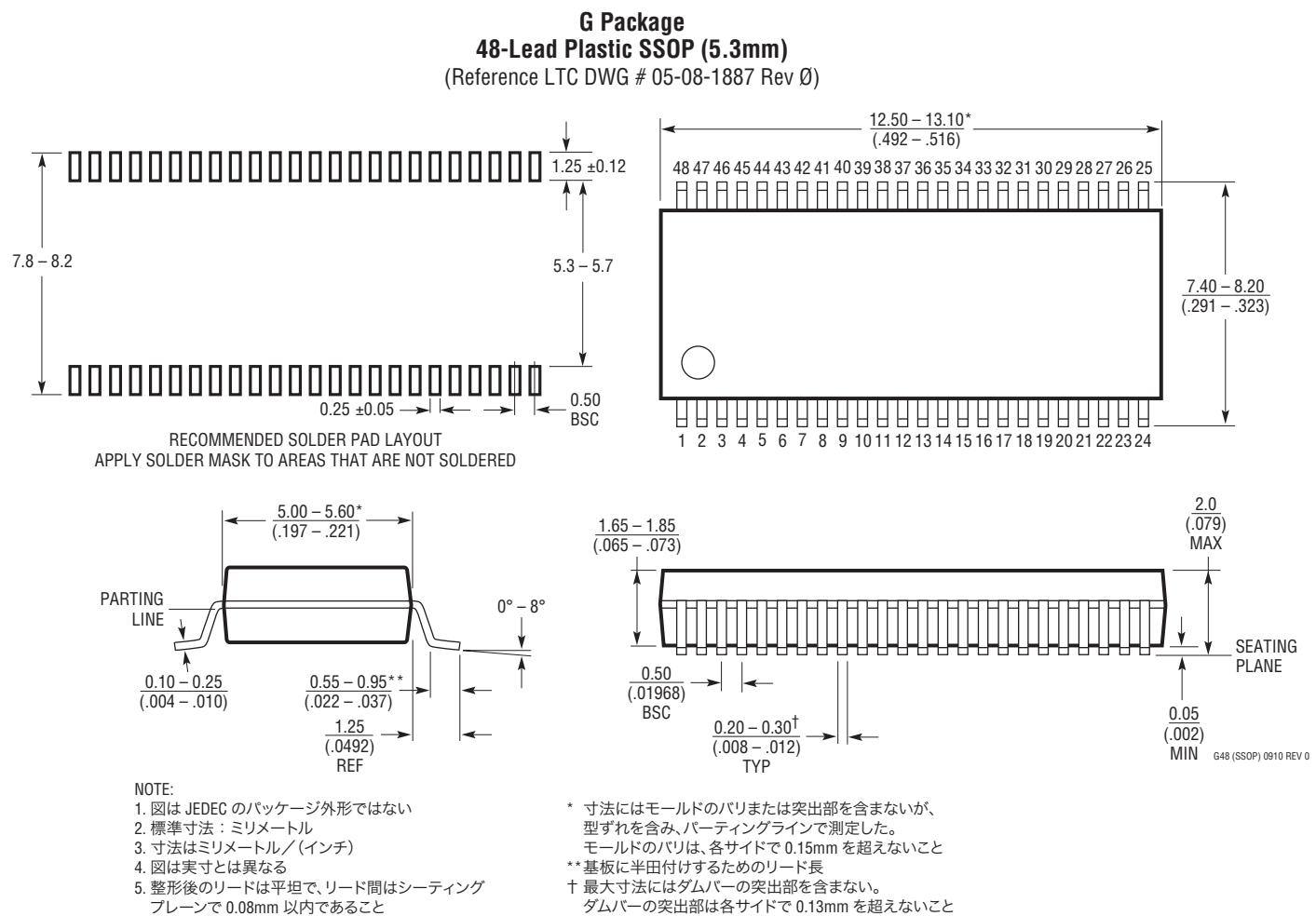

- 48ピンSSOPパッケージ

## アプリケーション

- 電気自動車およびハイブリッド車

- バックアップ・バッテリ・システム

- グリッド・エネルギー蓄積装置

- 大電力携帯機器

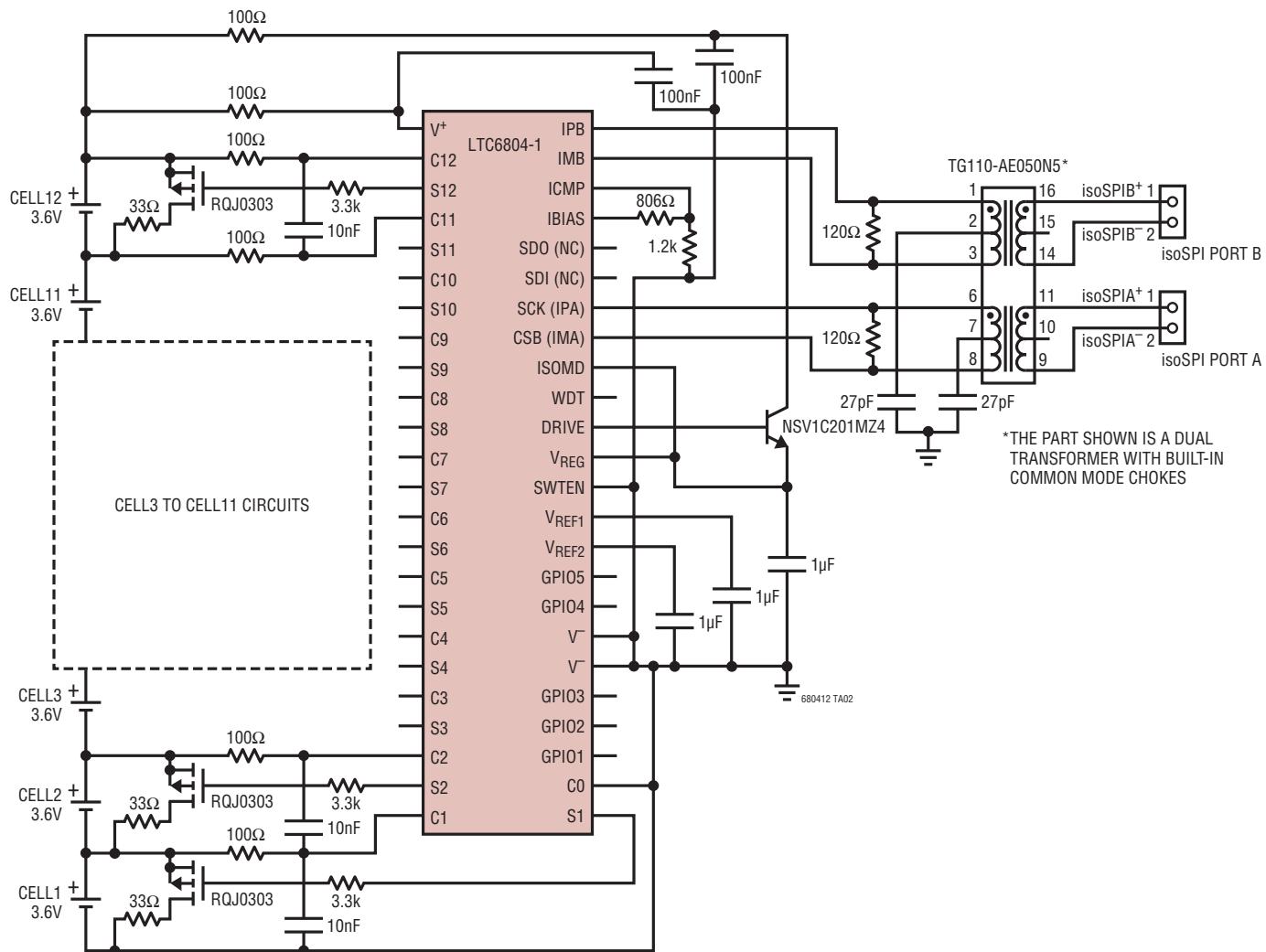

## 概要

LTC®6804は、最大12個の直列に接続されたバッテリ・セルを1.2mV未満の全測定誤差で測定する第3世代のマルチセル・バッテリ・スタック・モニタです。セルの測定範囲は0V～5Vなので、LTC6804はほとんどの科学的組成のバッテリに適しています。12セルの電圧は290μs以内にすべて取り込み可能であり、低めのデータ収集速度を選択することにより、ノイズ低減率を高めることができます。

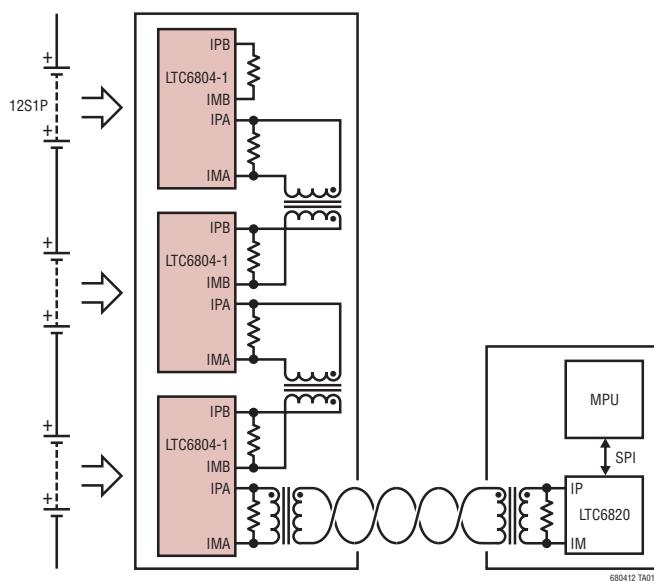

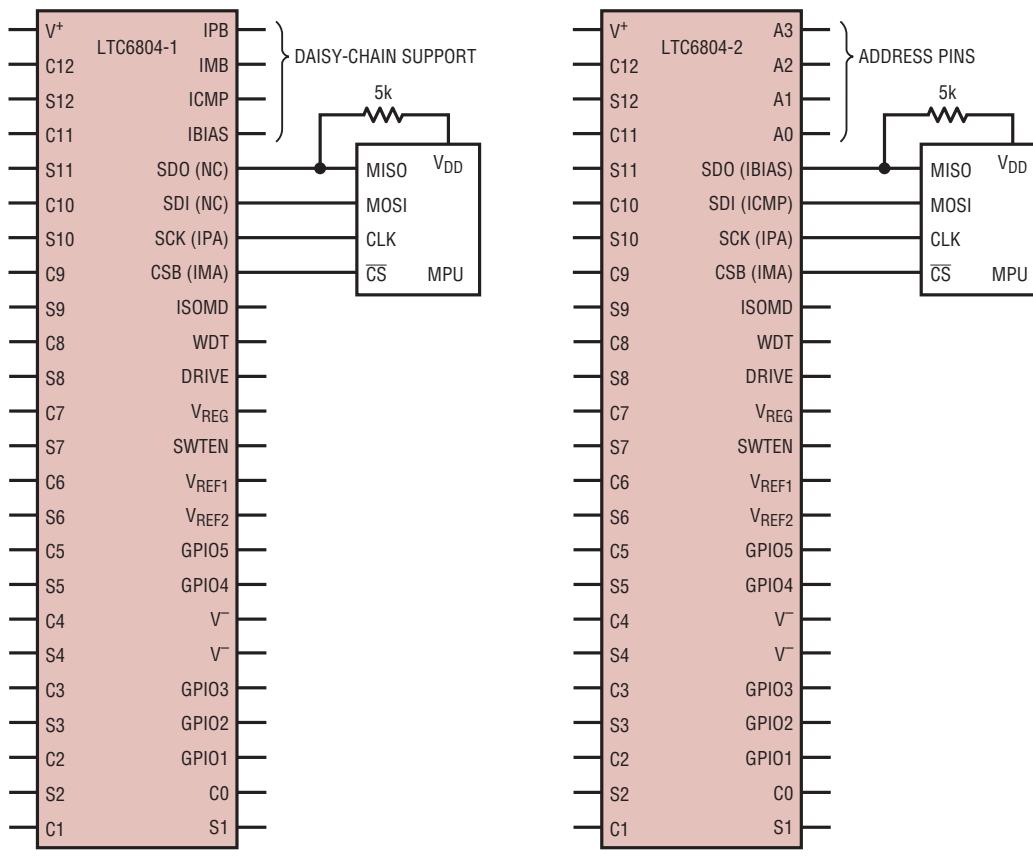

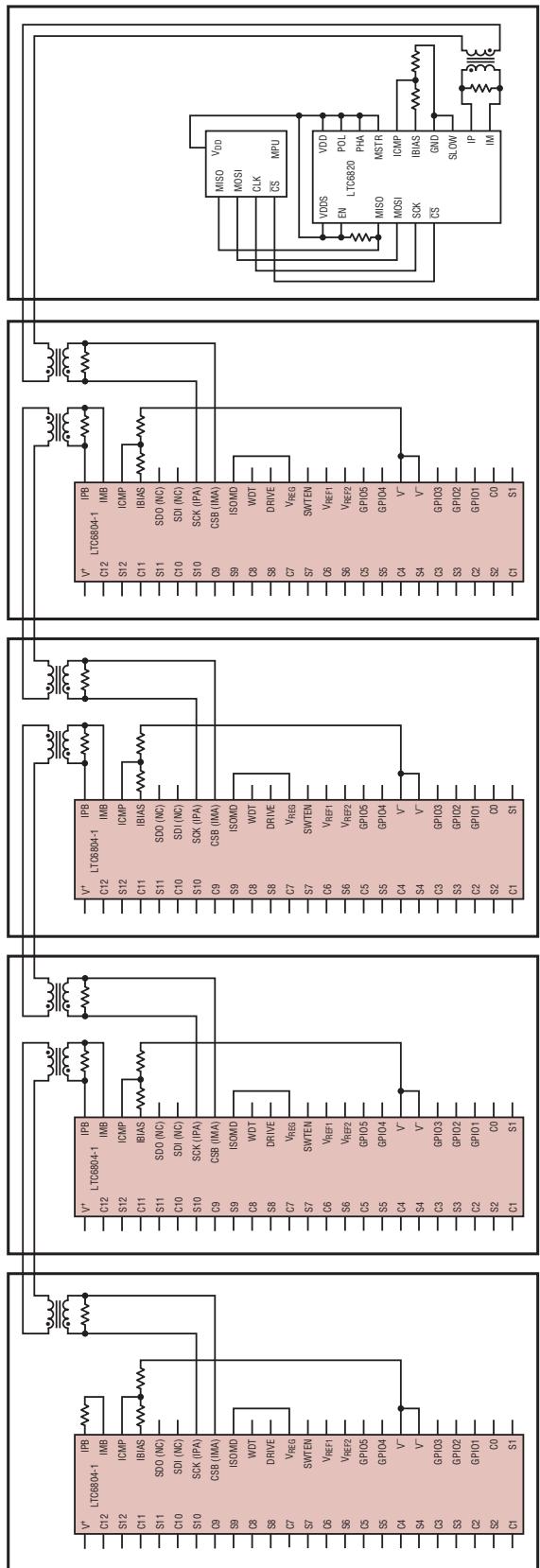

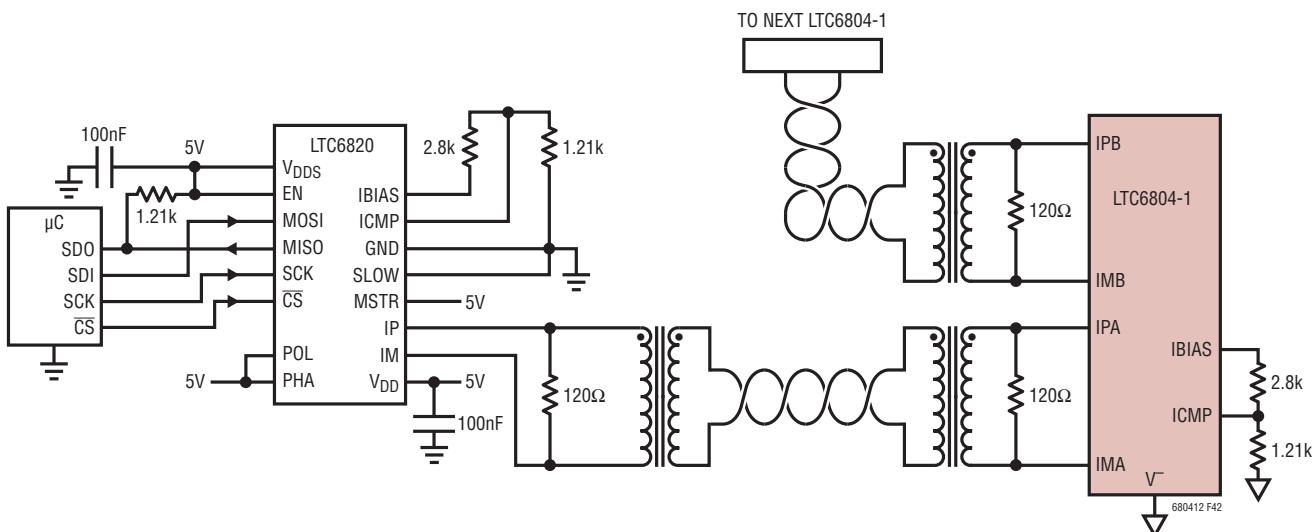

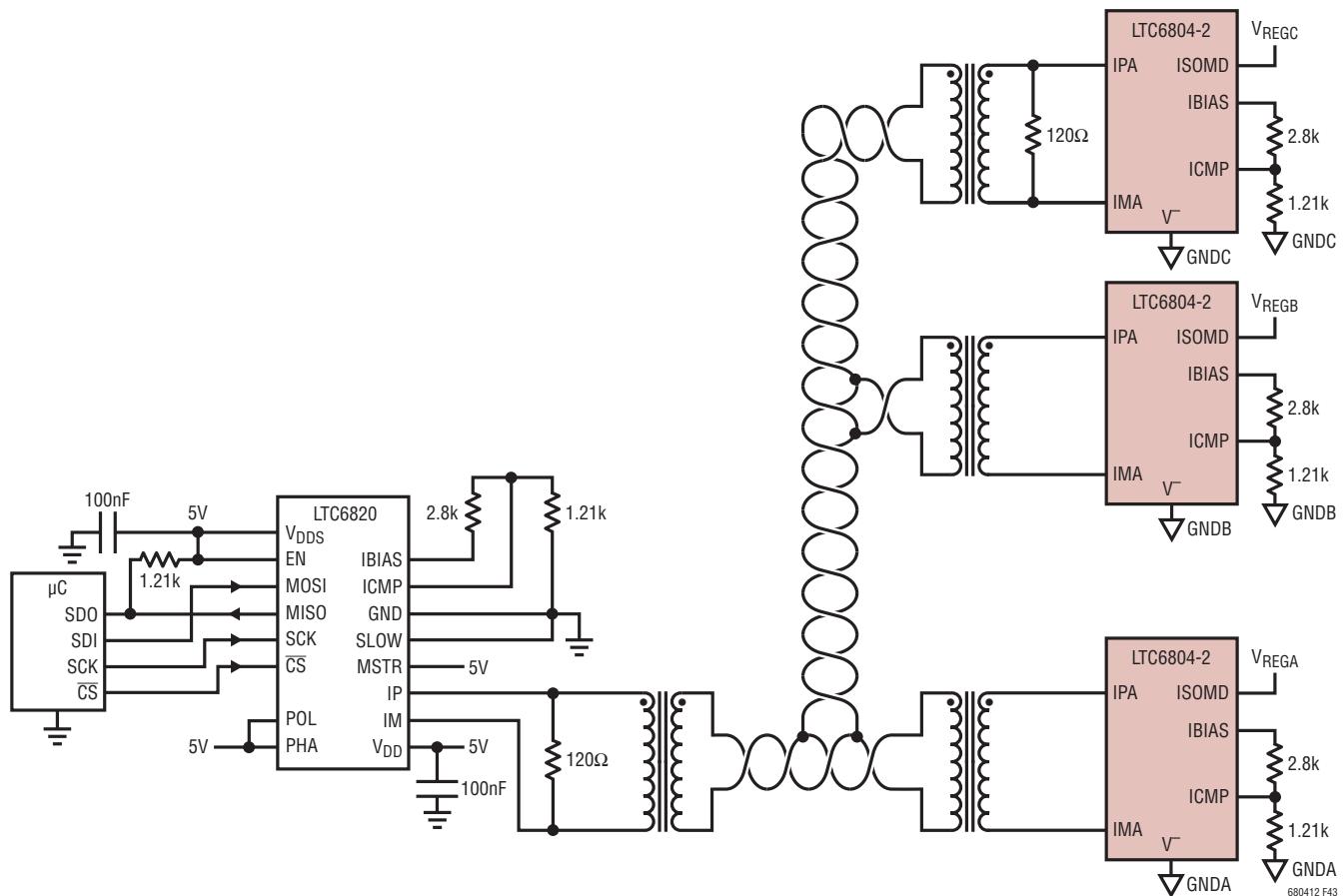

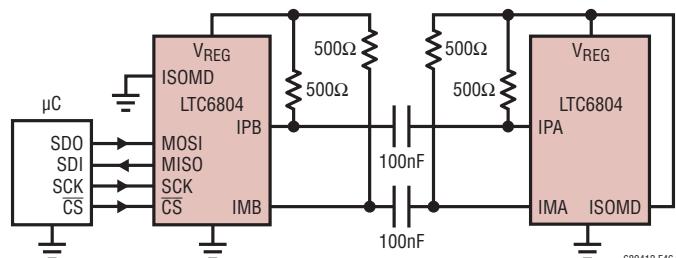

複数のLTC6804デバイスを直列に接続できるので、電圧が高く長いバッテリ列のセルを同時にモニタすることができます。各LTC6804は、電波の影響を受けない高速のローカル・エリア通信向けisoSPIインターフェースを備えています。LTC6804-1を使用すると、複数のデバイスがデジ털接続され、1つのホスト・プロセッサ接続ですべてのデバイスを接続できます。LTC6804-2を使用すると、複数のデバイスがホスト・プロセッサと並列に接続され、各デバイスにはアドレスが個別に指定されます。

その他の特長としては、受動式セル均等化機能、5Vレギュレータ内蔵、5つの汎用I/Oポートがあります。スリープ・モードでは、消費電流は4μAに減少します。LTC6804へは、電力をバッテリから直接供給することも、絶縁型電源から供給することもできます。

LT、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。isoSPIはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

## 標準的応用例

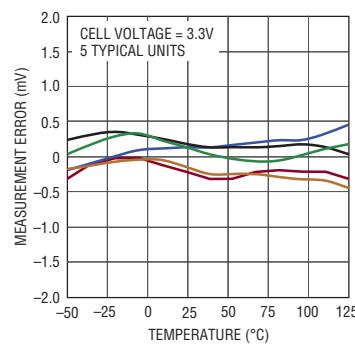

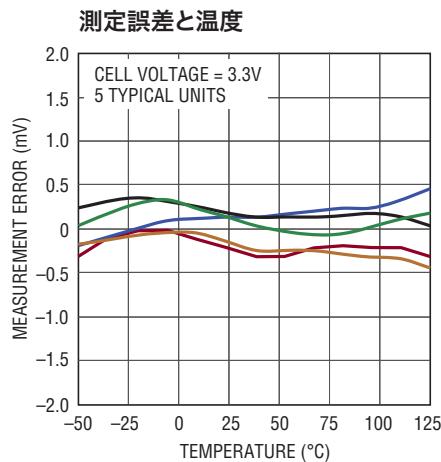

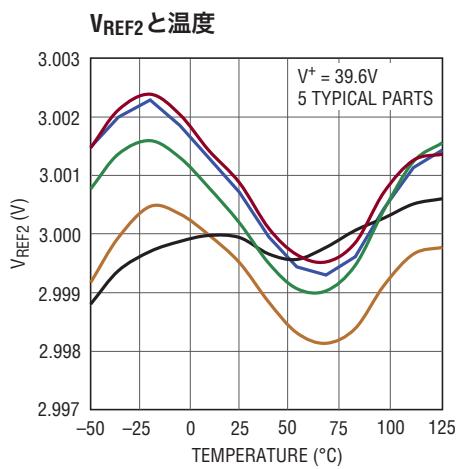

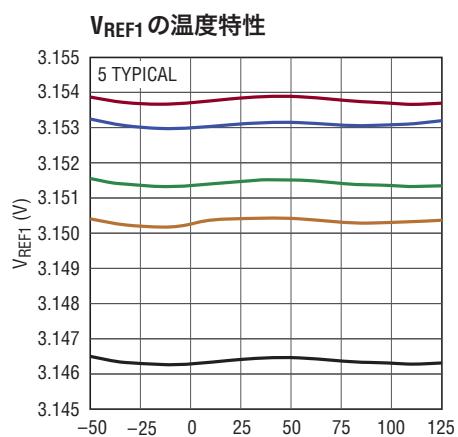

全測定誤差と

5つの代表的ユニットの温度

680412 TA01b

# LTC6804-1/LTC6804-2

---

## 目次

|                                            |    |                                |    |

|--------------------------------------------|----|--------------------------------|----|

| 特長                                         | 1  | プログラミング例                       | 52 |

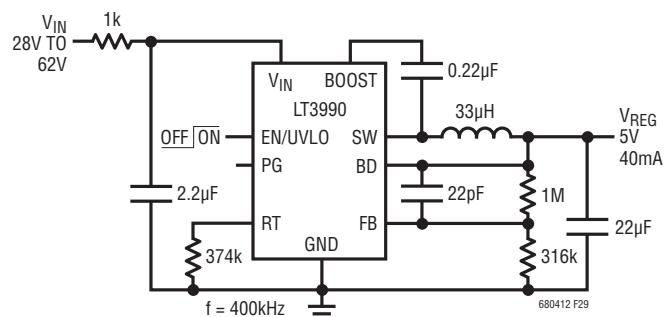

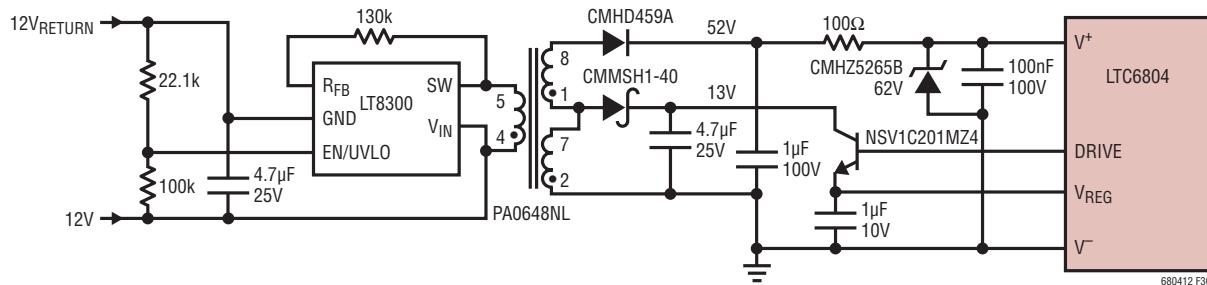

| アプリケーション                                   | 1  | 簡易リニア・レギュレータ                   | 56 |

| 標準的応用例                                     | 1  | 向上したレギュレータの電力効率                | 56 |

| 概要                                         | 1  | 完全に絶縁された電源                     | 57 |

| 絶対最大定格                                     | 3  | 外部温度プローブの読み取り                  | 57 |

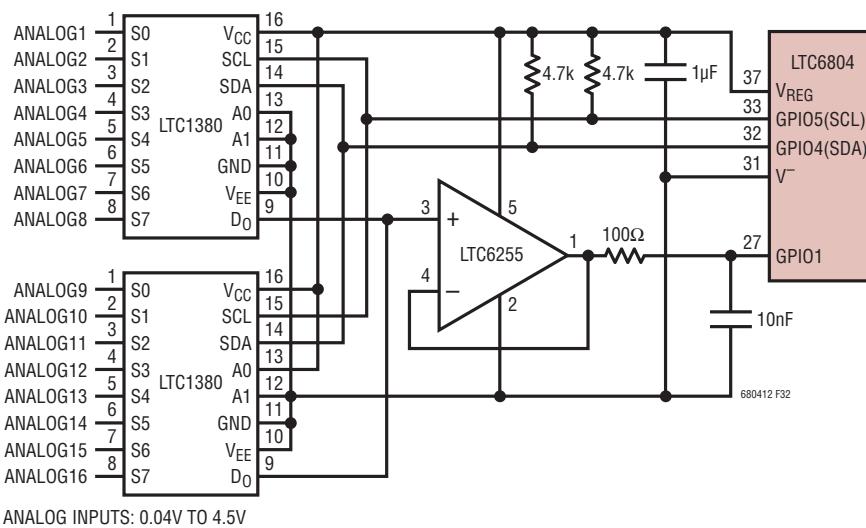

| ピン配置                                       | 3  | 補助測定入力の拡張                      | 58 |

| 発注情報                                       | 4  | 内部保護機能                         | 58 |

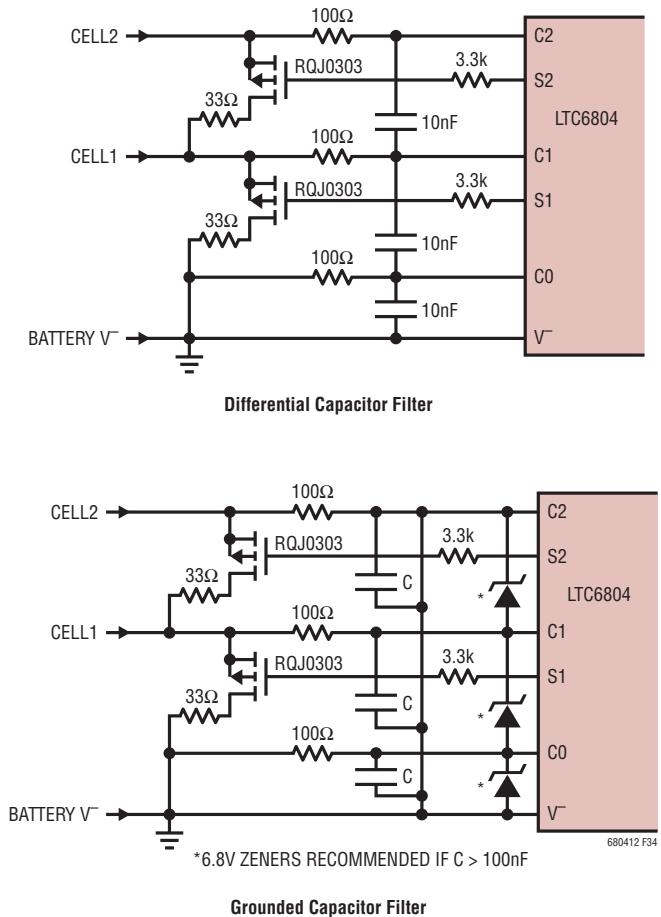

| 電気的特性                                      | 4  | セル入力とGPIO入力のフィルタリング            | 58 |

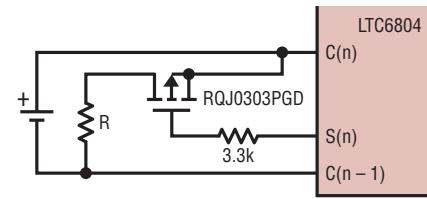

| ピン機能                                       | 17 | 内部MOSFETによるセル・バランシング           | 60 |

| ブロック図                                      | 18 | 外部MOSFETによるセル・バランシング           | 60 |

| 動作                                         | 20 | セル測定時の放電制御                     | 60 |

| ステートチャート図                                  | 20 | 電力損失とサーマル・シャットダウン              | 61 |

| LTC6804のコアのステートの説明                         | 20 | バランシング回路の検証方法                  | 61 |

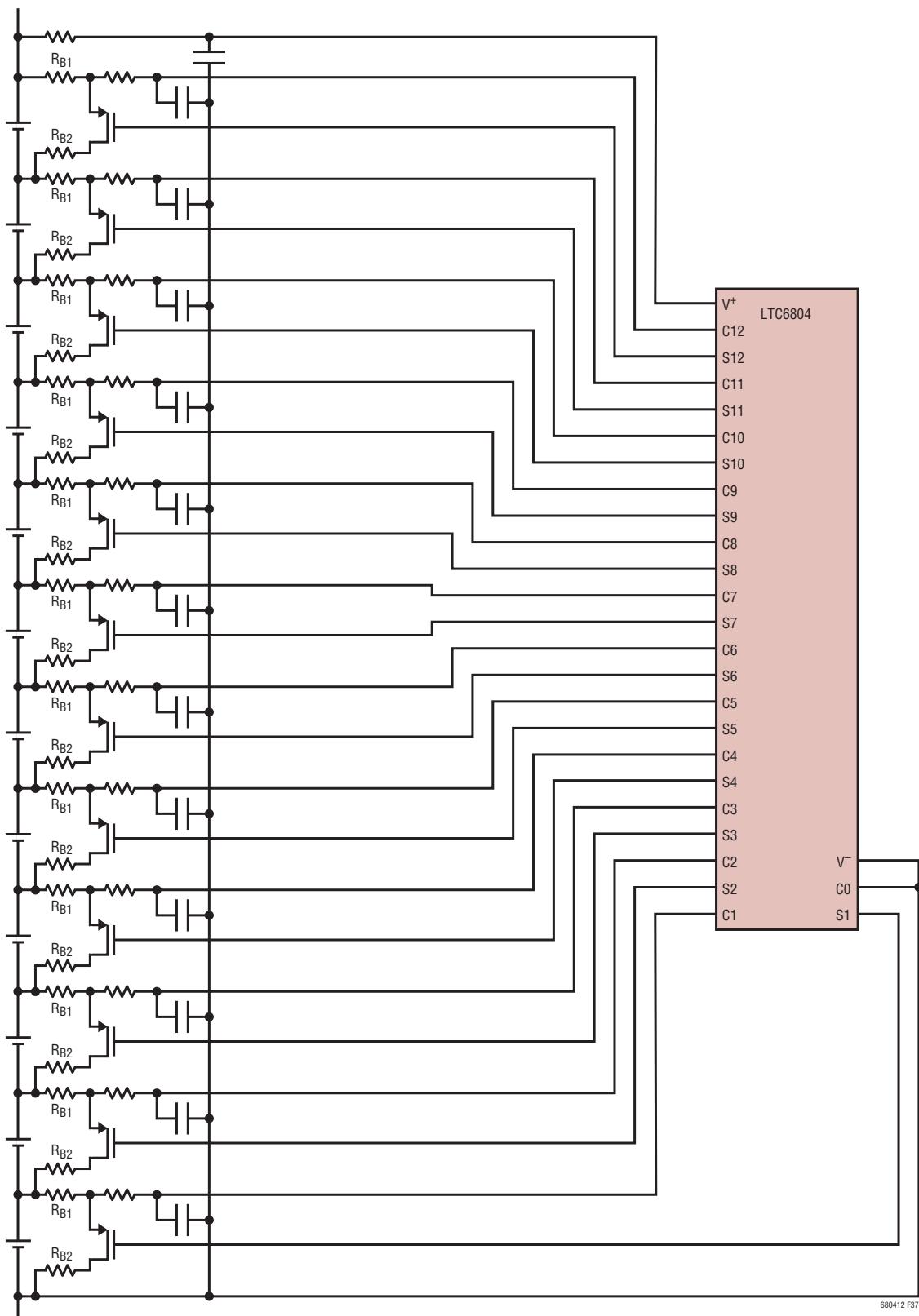

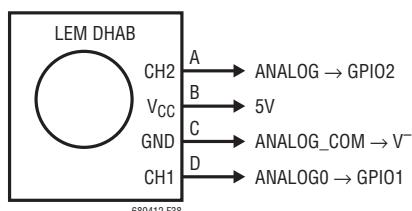

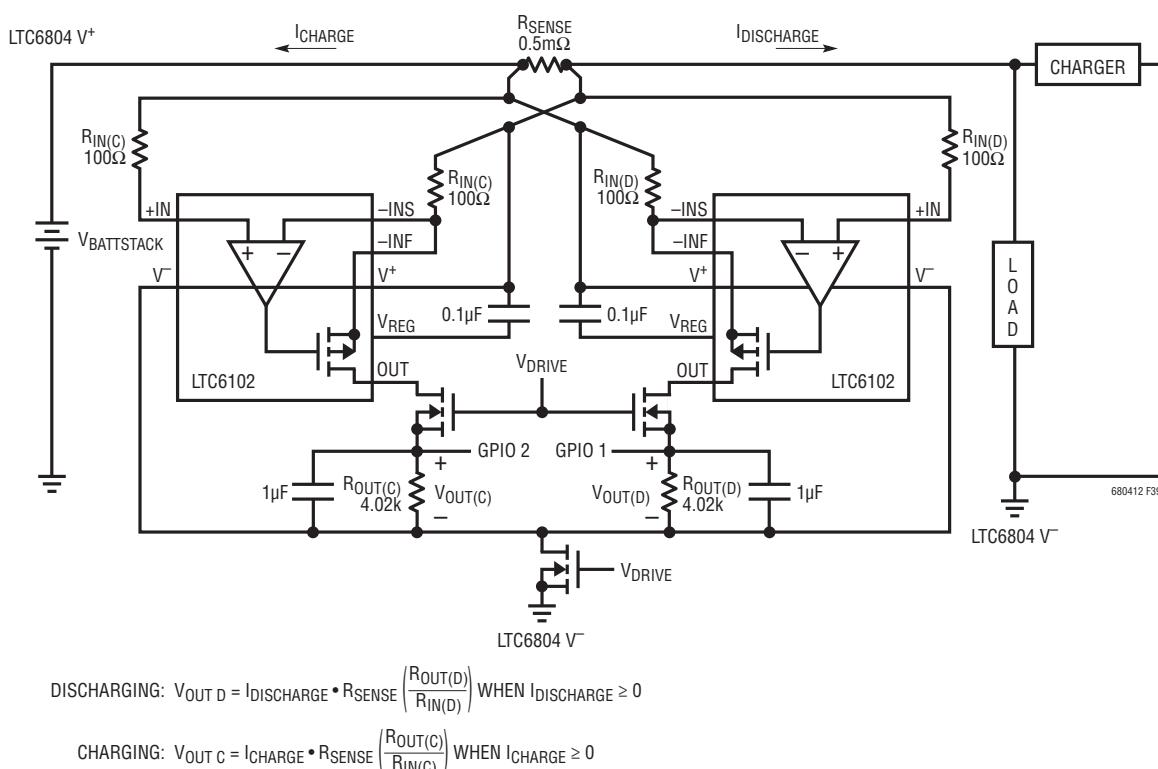

| isoSPIのステートの説明                             | 21 | ホール効果センサを使用した電流測定              | 64 |

| 消費電力                                       | 21 | シャント抵抗を使用した電流測定                | 64 |

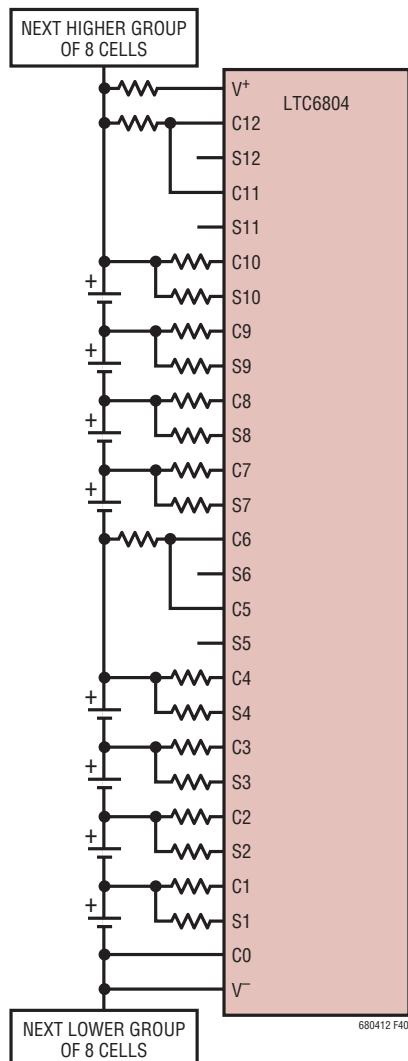

| AD変換器の動作                                   | 21 | 12個より少ないセルでのLTC6804の使用         | 65 |

| データ収集システムの診断                               | 26 | 同一PCB上の複数のLTC6804-1の接続         | 65 |

| ウォッチドッグとソフトウェア放電タイマ                        | 30 | isoSPIデータ・リンクを使用したMCUと         |    |

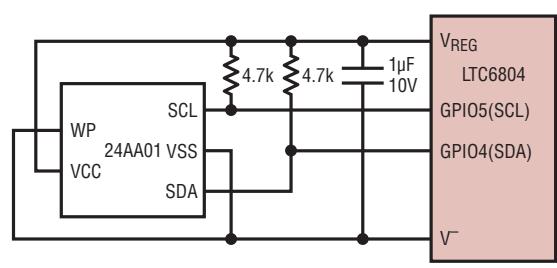

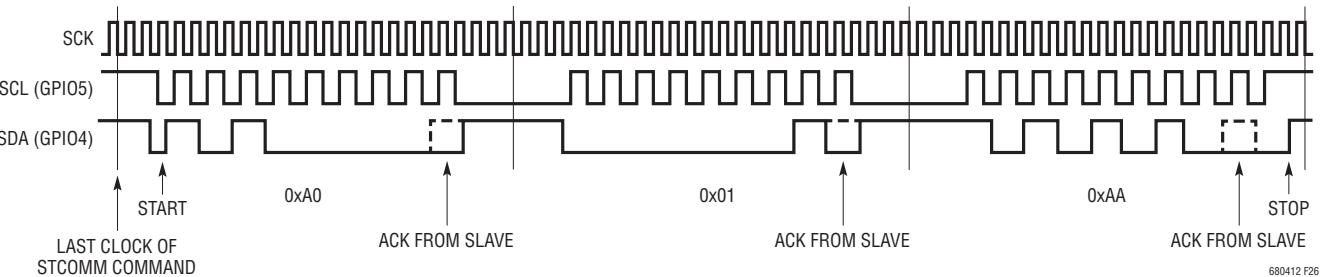

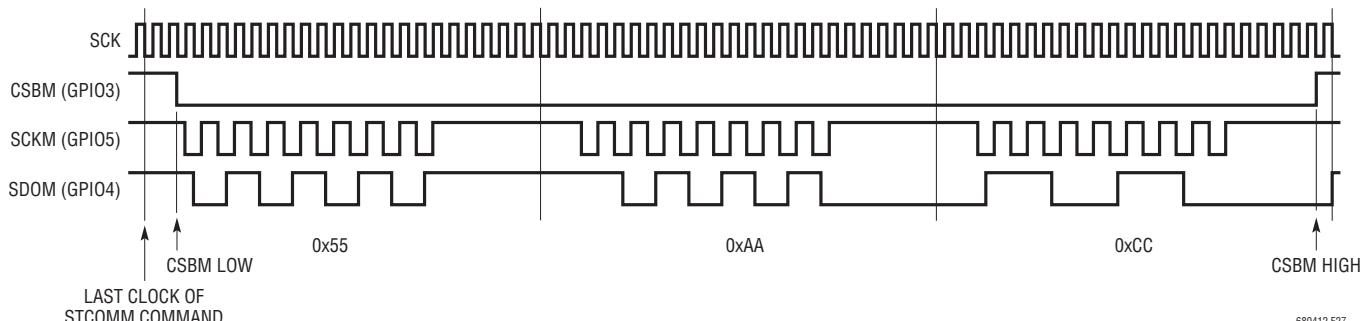

| GPIOSを使用したLTC6804でのI <sup>2</sup> C/SPIマスタ | 31 | LTC6804-1の接続                   | 65 |

| シリアル・インターフェースの概要                           | 35 | マルチドロップisoSPIリンクでのLTC6804-2の構成 | 65 |

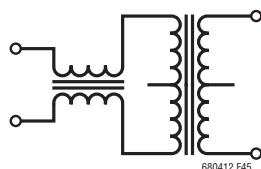

| 4線シリアル・ペリフェラル・インターフェース(SPI)の物理層            | 35 | トランス選択ガイド                      | 67 |

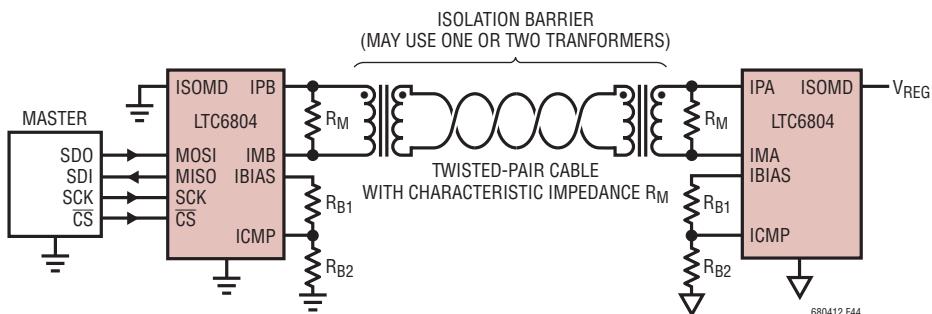

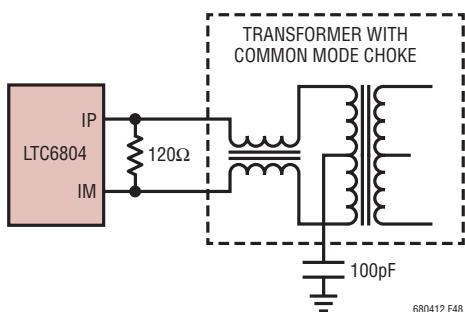

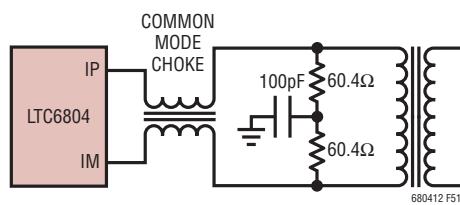

| 2線絶縁インターフェース(isoSPI)の物理層                   | 36 |                                |    |

| データ・リンク層                                   | 41 |                                |    |

| ネットワーク層                                    | 41 |                                |    |

|                                            |    | パッケージ                          | 71 |

|                                            |    | 標準的応用例                         | 72 |

|                                            |    | 関連製品                           | 72 |

680412f

## 絶対最大定格 (Note 1)

|                                         |                                 |

|-----------------------------------------|---------------------------------|

| 全電源電圧(V <sup>+</sup> ~ V <sup>-</sup> ) | 75V                             |

| 入力電圧(V <sup>-</sup> を基準)                |                                 |

| C0                                      | -0.3V ~ 0.3V                    |

| C12                                     | -0.3V ~ 75V                     |

| C(n)                                    | -0.3V ~ 最小(8 • n、75V)           |

| S(n)                                    | -0.3V ~ 最小(8 • n、75V)           |

| IPA、IMA、IPB、IMB                         | -0.3V ~ V <sub>REG</sub> + 0.3V |

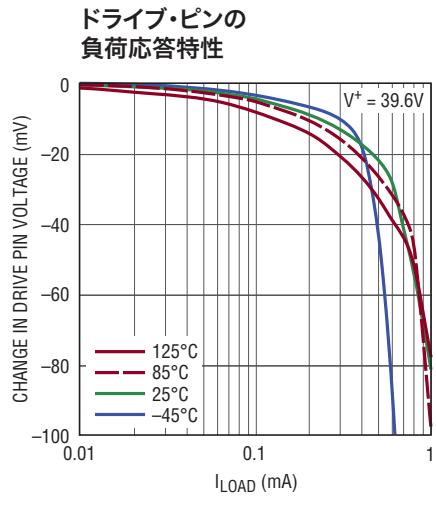

| DRIVEピン                                 | -0.3V ~ 7V                      |

| 他の全てのピン                                 | -0.3V ~ 6V                      |

| 入力間の電圧(Note 2)                          |                                 |

| C(n) ~ C(n - 1)                         | -0.3V ~ 8V                      |

| S(n) ~ C(n - 1)                         | -0.3V ~ 8V                      |

| C12 ~ C8                                | -0.3V ~ 25V                     |

| C8 ~ C4                                 | -0.3V ~ 25V                     |

| C4 ~ C0                                 | -0.3V ~ 25V                     |

端子の電流入力/出力

|                                        |          |      |

|----------------------------------------|----------|------|

| V <sub>REG</sub> 、IPA、IMA、IPB、IMB、S(n) | を除く全てのピン | 10mA |

| IPA、IMA、IPB、IMB                        |          | 30mA |

動作温度範囲

|          |               |

|----------|---------------|

| LTC6804I | -40°C ~ 85°C  |

| LTC6804H | -40°C ~ 125°C |

既定温度範囲

|          |               |

|----------|---------------|

| LTC6804I | -40°C ~ 85°C  |

| LTC6804H | -40°C ~ 125°C |

接合部温度.....150°C

保存温度.....-65°C ~ 150°C

リード温度(半田付け、10秒).....300°C

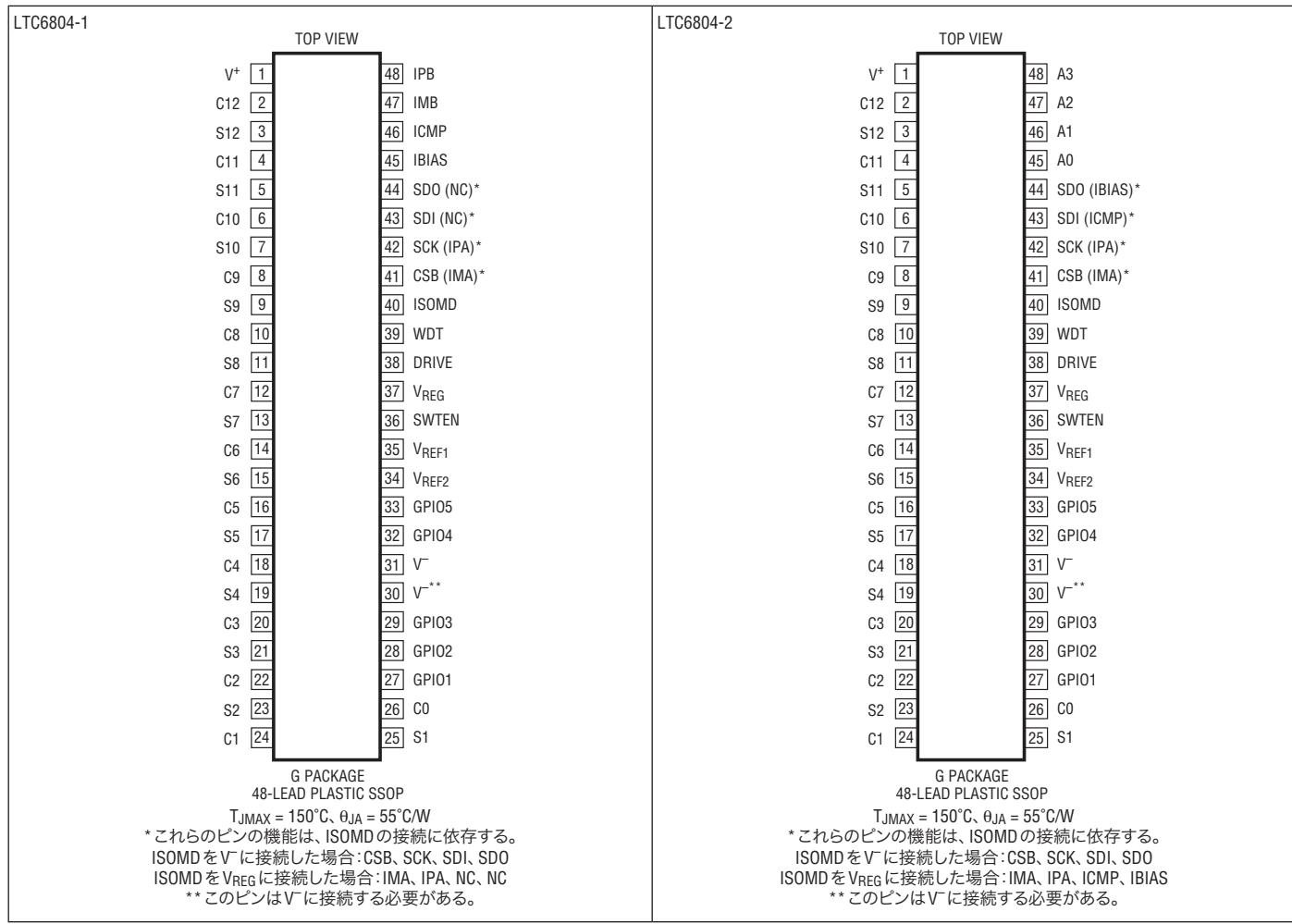

## ピン配置

# LTC6804-1/LTC6804-2

## 発注情報

| 無鉛仕上げ           | テープアンドリール         | 製品マーキング*   | パッケージ                | 規定温度範囲         |

|-----------------|-------------------|------------|----------------------|----------------|

| LTC6804IG-1#PBF | LTC6804IG-1#TRPBF | LTC6804G-1 | 48-Lead Plastic SSOP | -40°C to 85°C  |

| LTC6804HG-1#PBF | LTC6804HG-1#TRPBF | LTC6804G-1 | 48-Lead Plastic SSOP | -40°C to 125°C |

| LTC6804IG-2#PBF | LTC6804IG-2#TRPBF | LTC6804G-2 | 48-Lead Plastic SSOP | -40°C to 85°C  |

| LTC6804HG-2#PBF | LTC6804HG-2#TRPBF | LTC6804G-2 | 48-Lead Plastic SSOP | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。<sup>\*</sup> 温度等級は出荷時のコンテナのラベルで識別されます。非標準の鉛ベース仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、テスト条件は  $V^+ = 39.6\text{V}$ 、 $V_{\text{REG}} = 5.0\text{V}$ 。

| SYMBOL                                       | PARAMETER                                               | CONDITIONS | MIN        | TYP          | MAX       | UNITS  |

|----------------------------------------------|---------------------------------------------------------|------------|------------|--------------|-----------|--------|

| ADC の DC 仕様                                  |                                                         |            |            |              |           |        |

|                                              | Measurement Resolution                                  |            | ●          | 0.1          |           | mV/bit |

|                                              | ADC Offset Voltage                                      | (Note 2)   | ●          | 0.1          |           | mV     |

|                                              | ADC Gain Error                                          | (Note 2)   | ●          | 0.01<br>0.02 |           | %      |

| Total Measurement Error (TME) in Normal Mode | C(n) to C(n - 1), GPIO(n) to $V^- = 0$                  |            |            | $\pm 0.2$    |           | mV     |

|                                              | C(n) to C(n - 1) = 2.0                                  |            |            | $\pm 0.1$    | $\pm 0.8$ | mV     |

|                                              | C(n) to C(n - 1), GPIO(n) to $V^- = 2.0$                | ●          |            |              | $\pm 1.4$ | mV     |

|                                              | C(n) to C(n - 1) = 3.3                                  |            |            | $\pm 0.2$    | $\pm 1.2$ | mV     |

|                                              | C(n) to C(n - 1), GPIO(n) to $V^- = 3.3$                | ●          |            |              | $\pm 2.2$ | mV     |

|                                              | C(n) to C(n - 1) = 4.2                                  |            |            | $\pm 0.3$    | $\pm 1.6$ | mV     |

|                                              | C(n) to C(n - 1), GPIO(n) to $V^- = 4.2$                | ●          |            |              | $\pm 2.8$ | mV     |

|                                              | C(n) to C(n - 1), GPIO(n) to $V^- = 5.0$                |            |            | $\pm 1$      |           | mV     |

|                                              | Sum of Cells                                            | ●          | $\pm 0.2$  | $\pm 0.75$   |           | %      |

|                                              | Internal Temperature, T = Maximum Specified Temperature |            |            | $\pm 5$      |           | °C     |

|                                              | $V_{\text{REG}}$ Pin                                    | ●          | $\pm 0.1$  | $\pm 0.25$   |           | %      |

|                                              | $V_{\text{REF}2}$ Pin                                   | ●          | $\pm 0.02$ | $\pm 0.1$    |           | %      |

|                                              | Digital Supply Voltage $V_{\text{REGD}}$                | ●          | $\pm 0.1$  | $\pm 1$      |           | %      |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、テスト条件は $V^+ = 39.6\text{V}$ 、 $V_{\text{REG}} = 5.0\text{V}$ 。

| SYMBOL                                         | PARAMETER                                                | CONDITIONS          | MIN        | TYP        | MAX          | UNITS |    |

|------------------------------------------------|----------------------------------------------------------|---------------------|------------|------------|--------------|-------|----|

| Total Measurement Error (TME) in Filtered Mode | C(n) to C(n - 1), GPIO(n) to $V^- = 0$                   |                     |            | $\pm 0.1$  |              | mV    |    |

|                                                | C(n) to C(n - 1) = 2.0                                   |                     |            | $\pm 0.1$  | $\pm 0.8$    | mV    |    |

|                                                | C(n) to C(n - 1), GPIO(n) to $V^- = 2.0$                 | ●                   |            |            | $\pm 1.4$    | mV    |    |

|                                                | C(n) to C(n - 1) = 3.3                                   |                     |            | $\pm 0.2$  | $\pm 1.2$    | mV    |    |

|                                                | C(n) to C(n - 1), GPIO(n) to $V^- = 3.3$                 | ●                   |            |            | $\pm 2.2$    | mV    |    |

|                                                | C(n) to C(n - 1) = 4.2                                   |                     |            | $\pm 0.3$  | $\pm 1.6$    | mV    |    |

|                                                | C(n) to C(n - 1), GPIO(n) to $V^- = 4.2$                 | ●                   |            |            | $\pm 2.8$    | mV    |    |

|                                                | C(n) to C(n - 1), GPIO(n) to $V^- = 5.0$                 |                     |            | $\pm 1$    |              | mV    |    |

|                                                | Sum of Cells                                             | ●                   | $\pm 0.2$  | $\pm 0.75$ |              | %     |    |

|                                                | Internal Temperature, T = Maximum Specified Temperature  |                     |            | $\pm 5$    |              | °C    |    |

|                                                | $V_{\text{REG}}$ Pin                                     | ●                   | $\pm 0.1$  | $\pm 0.25$ |              | %     |    |

|                                                | $V_{\text{REF}2}$ Pin                                    | ●                   | $\pm 0.02$ | $\pm 0.1$  |              | %     |    |

|                                                | Digital Supply Voltage $V_{\text{REGD}}$                 | ●                   | $\pm 0.1$  | $\pm 1$    |              | %     |    |

| Total Measurement Error (TME) in Fast Mode     | C(n) to C(n - 1), GPIO(n) to $V^- = 0$                   |                     |            | $\pm 2$    |              | mV    |    |

|                                                | C(n) to C(n - 1), GPIO(n) to $V^- = 2.0$                 | ●                   |            | $\pm 4$    |              | mV    |    |

|                                                | C(n) to C(n - 1), GPIO(n) to $V^- = 3.3$                 | ●                   |            | $\pm 4.7$  |              | mV    |    |

|                                                | C(n) to C(n - 1), GPIO(n) to $V^- = 4.2$                 | ●                   |            | $\pm 8.3$  |              | mV    |    |

|                                                | C(n) to C(n - 1), GPIO(n) to $V^- = 5.0$                 |                     |            | $\pm 10$   |              | mV    |    |

|                                                | Sum of Cells                                             | ●                   | $\pm 0.3$  | $\pm 1$    |              | %     |    |

|                                                | Internal Temperature, T = Maximum Specified Temperature  |                     |            | $\pm 5$    |              | °C    |    |

|                                                | $V_{\text{REG}}$ Pin                                     | ●                   | $\pm 0.3$  | $\pm 1$    |              | %     |    |

|                                                | $V_{\text{REF}2}$ Pin                                    | ●                   | $\pm 0.1$  | $\pm 0.25$ |              | %     |    |

|                                                | Digital Supply Voltage $V_{\text{REGD}}$                 | ●                   | $\pm 0.2$  | $\pm 2$    |              | %     |    |

| I <sub>L</sub>                                 | Input Range                                              | C(n), n = 1 to 12   | ●          | C(n - 1)   | C(n - 1) + 5 | V     |    |

|                                                |                                                          | C <sub>0</sub>      | ●          | 0          |              |       |    |

|                                                |                                                          | GPIO(n), n = 1 to 5 | ●          | 0          | 5            | V     |    |

| I <sub>L</sub>                                 | Input Leakage Current When Inputs Are Not Being Measured | C(n), n = 0 to 12   | ●          | 10         | $\pm 250$    | nA    |    |

|                                                |                                                          | GPIO(n), n = 1 to 5 | ●          | 10         | $\pm 250$    | nA    |    |

|                                                | Input Current When Inputs Are Being Measured             | C(n), n = 0 to 12   |            |            | $\pm 2$      | μA    |    |

|                                                |                                                          | GPIO(n), n = 1 to 5 |            |            | $\pm 2$      | μA    |    |

|                                                | Input Current During Open Wire Detection                 |                     | ●          | 70         | 100          | 130   | μA |

# LTC6804-1/LTC6804-2

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、テスト条件は $V^+ = 39.6\text{V}$ 、 $V_{\text{REG}} = 5.0\text{V}$ 。

| SYMBOL                          | PARAMETER                                                                                                                                                   | CONDITIONS                                                           |                              | MIN   | TYP   | MAX   | UNITS                          |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------|-------|-------|-------|--------------------------------|

| 電圧リファレンスの仕様                     |                                                                                                                                                             |                                                                      |                              |       |       |       |                                |

| $V_{\text{REF}1}$               | 1st Reference Voltage                                                                                                                                       | $V_{\text{REF}1}$ Pin, No Load                                       | ●                            | 3.1   | 3.2   | 3.3   | V                              |

|                                 | 1st Reference Voltage TC                                                                                                                                    | $V_{\text{REF}1}$ Pin, No Load                                       |                              |       | 3     |       | $\text{ppm}/^\circ\text{C}$    |

|                                 | 1st Reference Voltage Hysteresis                                                                                                                            | $V_{\text{REF}1}$ Pin, No Load                                       |                              |       | 20    |       | ppm                            |

|                                 | 1st Reference Long Term Drift                                                                                                                               | $V_{\text{REF}1}$ Pin, No Load                                       |                              |       | 20    |       | $\text{ppm}/\sqrt{\text{kHr}}$ |

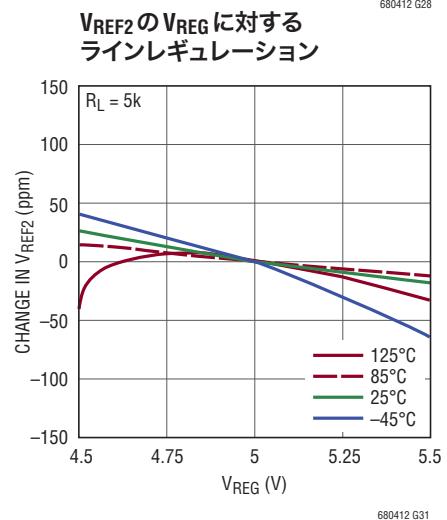

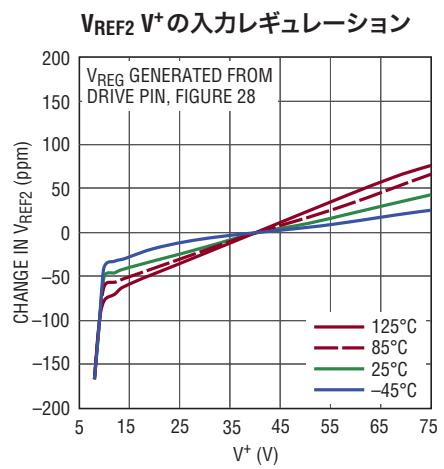

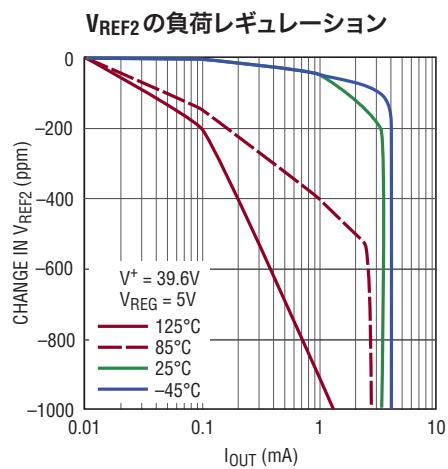

| $V_{\text{REF}2}$               | 2nd Reference Voltage                                                                                                                                       | $V_{\text{REF}2}$ Pin, No Load                                       | ●                            | 2.990 | 3     | 3.010 | V                              |

|                                 |                                                                                                                                                             | $V_{\text{REF}2}$ Pin, 5k Load to $V^-$                              | ●                            | 2.988 | 3     | 3.012 | V                              |

|                                 | 2nd Reference Voltage TC                                                                                                                                    | $V_{\text{REF}2}$ Pin, No Load                                       |                              |       | 10    |       | $\text{ppm}/^\circ\text{C}$    |

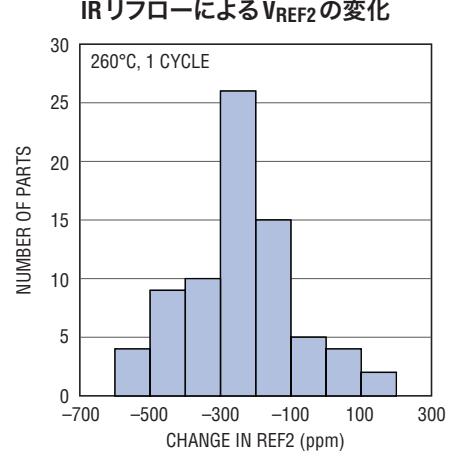

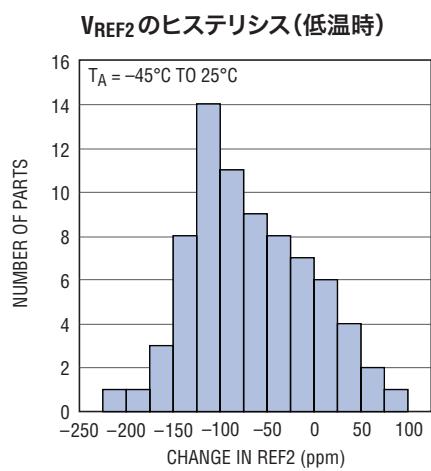

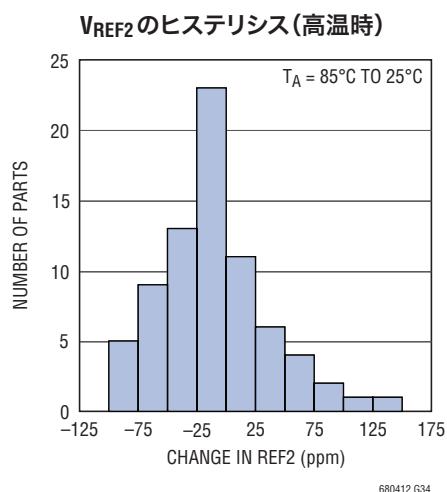

|                                 | 2nd Reference Voltage Hysteresis                                                                                                                            | $V_{\text{REF}2}$ Pin, No Load                                       |                              |       | 100   |       | ppm                            |

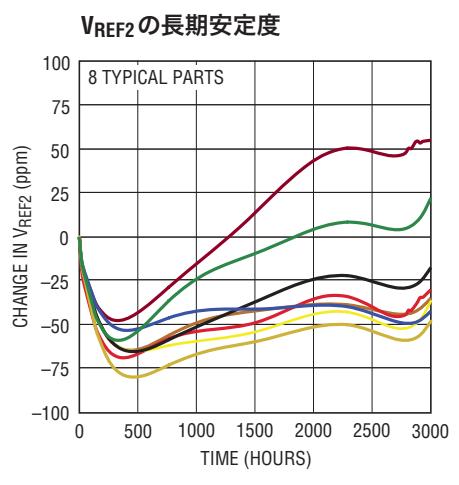

|                                 | 2nd Reference Long Term Drift                                                                                                                               | $V_{\text{REF}2}$ Pin, No Load                                       |                              |       | 60    |       | $\text{ppm}/\sqrt{\text{kHr}}$ |

| 一般DC仕様                          |                                                                                                                                                             |                                                                      |                              |       |       |       |                                |

| $I_{\text{YP}}$                 | $V^+$ Supply Current<br>(See Figure 1:LTC6804 Operation State Diagram)                                                                                      | State:Core = SLEEP, isoSPI = IDLE                                    | $V_{\text{REG}} = 0\text{V}$ |       | 3.8   | 6     | $\mu\text{A}$                  |

|                                 |                                                                                                                                                             |                                                                      | ●                            |       | 3.8   | 10    | $\mu\text{A}$                  |

|                                 |                                                                                                                                                             |                                                                      | $V_{\text{REG}} = 5\text{V}$ |       | 1.6   | 3     | $\mu\text{A}$                  |

|                                 |                                                                                                                                                             |                                                                      | ●                            |       | 1.6   | 5     | $\mu\text{A}$                  |

|                                 |                                                                                                                                                             | State:Core = STANDBY                                                 |                              |       | 18    | 32    | 50                             |

|                                 |                                                                                                                                                             |                                                                      | ●                            |       | 10    | 32    | 60                             |

|                                 |                                                                                                                                                             | State:Core = REFUP or MEASURE                                        |                              |       | 0.4   | 0.55  | 0.7                            |

|                                 |                                                                                                                                                             |                                                                      | ●                            |       | 0.375 | 0.55  | 0.725                          |

|                                 |                                                                                                                                                             |                                                                      |                              |       |       |       | mA                             |

|                                 |                                                                                                                                                             |                                                                      | ●                            |       |       |       | mA                             |

| $I_{\text{REG}(\text{CORE})}$   | $V_{\text{REG}}$ Supply Current<br>(See Figure 1:LTC6804 Operation State diagram)                                                                           | State:Core = SLEEP, isoSPI = IDLE                                    | $V_{\text{REG}} = 5\text{V}$ |       | 2.2   | 4     | $\mu\text{A}$                  |

|                                 |                                                                                                                                                             |                                                                      | ●                            |       | 2.2   | 6     | $\mu\text{A}$                  |

|                                 |                                                                                                                                                             | State:Core = STANDBY                                                 |                              |       | 10    | 35    | 60                             |

|                                 |                                                                                                                                                             |                                                                      | ●                            |       | 6     | 35    | 65                             |

|                                 |                                                                                                                                                             | State:Core = REFUP                                                   |                              |       | 0.2   | 0.45  | 0.7                            |

|                                 |                                                                                                                                                             |                                                                      | ●                            |       | 0.15  | 0.45  | 0.75                           |

|                                 |                                                                                                                                                             | State:Core = MEASURE                                                 |                              |       | 10.8  | 11.5  | 12.2                           |

|                                 |                                                                                                                                                             |                                                                      | ●                            |       | 10.7  | 11.5  | 12.3                           |

|                                 |                                                                                                                                                             |                                                                      |                              |       |       |       | mA                             |

|                                 |                                                                                                                                                             |                                                                      | ●                            |       |       |       | mA                             |

| $I_{\text{REG}(\text{isoSPI})}$ | Additional $V_{\text{REG}}$ Supply Current if isoSPI in READY/ACTIVE States<br>Note:ACTIVE State Current Assumes $t_{\text{CLK}} = 1\mu\text{s}$ , (Note 3) | LTC6804-2:ISOMD = 1,<br>$R_{\text{B}1} + R_{\text{B}2} = 2\text{k}$  | READY                        | ●     | 3.9   | 4.8   | 5.8                            |

|                                 |                                                                                                                                                             |                                                                      | ACTIVE                       | ●     | 5.1   | 6.1   | 7.3                            |

|                                 |                                                                                                                                                             | LTC6804-1:ISOMD = 0,<br>$R_{\text{B}1} + R_{\text{B}2} = 2\text{k}$  | READY                        | ●     | 3.7   | 4.6   | 5.6                            |

|                                 |                                                                                                                                                             |                                                                      | ACTIVE                       | ●     | 5.7   | 6.8   | 8.1                            |

|                                 |                                                                                                                                                             | LTC6804-1:ISOMD = 1,<br>$R_{\text{B}1} + R_{\text{B}2} = 2\text{k}$  | READY                        | ●     | 6.5   | 7.8   | 9.5                            |

|                                 |                                                                                                                                                             |                                                                      | ACTIVE                       | ●     | 10.2  | 11.3  | 13.3                           |

|                                 |                                                                                                                                                             | LTC6804-2:ISOMD = 1,<br>$R_{\text{B}1} + R_{\text{B}2} = 20\text{k}$ | READY                        | ●     | 1.3   | 2.1   | 3                              |

|                                 |                                                                                                                                                             |                                                                      | ACTIVE                       | ●     | 1.6   | 2.5   | 3.5                            |

|                                 |                                                                                                                                                             | LTC6804-1:ISOMD = 0,<br>$R_{\text{B}1} + R_{\text{B}2} = 20\text{k}$ | READY                        | ●     | 1.1   | 1.9   | 2.8                            |

|                                 |                                                                                                                                                             |                                                                      | ACTIVE                       | ●     | 1.5   | 2.3   | 3.3                            |

|                                 |                                                                                                                                                             | LTC6804-1:ISOMD = 1,<br>$R_{\text{B}1} + R_{\text{B}2} = 20\text{k}$ | READY                        | ●     | 2.1   | 3.3   | 4.9                            |

|                                 |                                                                                                                                                             |                                                                      | ACTIVE                       | ●     | 2.7   | 4.1   | 5.8                            |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、テスト条件は $V^+ = 39.6\text{V}$ 、 $V_{\text{REG}} = 5.0\text{V}$ 。

| SYMBOL                       | PARAMETER                       | CONDITIONS                                    | MIN | TYP | MAX | UNITS      |

|------------------------------|---------------------------------|-----------------------------------------------|-----|-----|-----|------------|

| $V_{\text{REG}}$             | $V^+$ Supply Voltage            | TME Specifications Met (Note 6)               | ●   | 11  | 40  | 55         |

|                              | $V_{\text{REG}}$ Supply Voltage | TME Supply Rejection < 1mV/V                  | ●   | 4.5 | 5   | 5.5        |

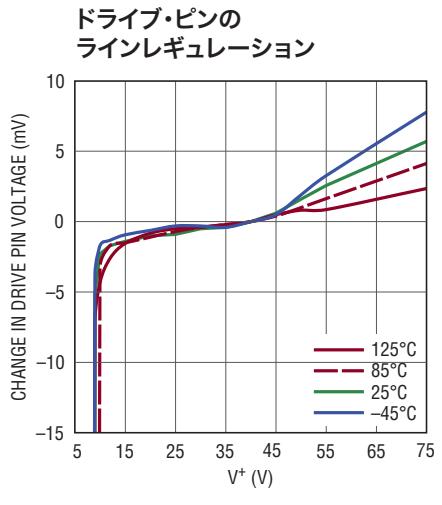

|                              | DRIVE output voltage            | Sourcing 1 $\mu\text{A}$                      | ●   | 5.4 | 5.6 | 5.8        |

|                              |                                 | Sourcing 500 $\mu\text{A}$                    | ●   | 5.2 | 5.6 | 6.0        |

|                              |                                 | Sourcing 500 $\mu\text{A}$                    | ●   | 5.1 | 5.6 | 6.1        |

| $V_{\text{REGD}}$            | Digital Supply Voltage          |                                               | ●   | 2.7 | 3.0 | 3.6        |

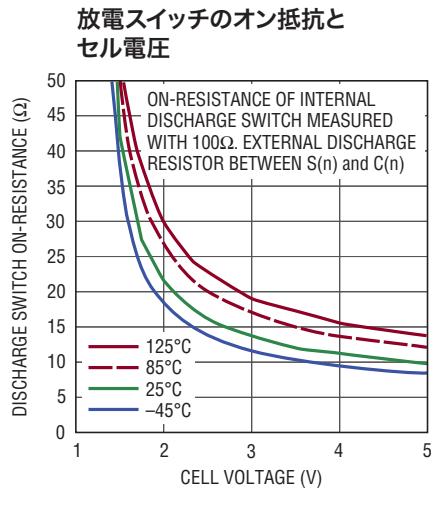

|                              | Discharge Switch ON Resistance  | $V_{\text{CELL}} = 3.6\text{V}$               | ●   | 10  | 25  | $\Omega$   |

| Thermal Shutdown Temperature |                                 |                                               | 150 |     |     |            |

| $V_{\text{OL(WDT)}}$         | Watchdog Timer Pin Low          | WDT Pin Sinking 4mA                           | ●   | 0.4 |     | $\text{V}$ |

| $V_{\text{OL(GPIO)}}$        | General Purpose I/O Pin Low     | GPIO Pin Sinking 4mA (Used as Digital Output) | ●   | 0.4 |     | $\text{V}$ |

### ADCのタイミング仕様

|                                                     |                                                                                             |                                                       |   |       |       |       |               |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------|---|-------|-------|-------|---------------|

| $t_{\text{CYCLE}}$<br>(Figure 3)                    | Measurement + Calibration Cycle<br>Time When Starting from the REFUP State in Normal Mode   | Measure 12 Cells                                      | ● | 2120  | 2335  | 2480  | $\mu\text{s}$ |

|                                                     |                                                                                             | Measure 2 Cells                                       | ● | 365   | 405   | 430   | $\mu\text{s}$ |

|                                                     |                                                                                             | Measure 12 Cells and 2 GPIO Inputs                    | ● | 2845  | 3133  | 3325  | $\mu\text{s}$ |

|                                                     | Measurement + Calibration Cycle<br>Time When Starting from the REFUP State in Filtered Mode | Measure 12 Cells                                      | ● | 183   | 201.3 | 213.5 | ms            |

|                                                     |                                                                                             | Measure 2 Cells                                       | ● | 30.54 | 33.6  | 35.64 | ms            |

|                                                     |                                                                                             | Measure 12 Cells and 2 GPIO Inputs                    | ● | 244   | 268.4 | 284.7 | ms            |

|                                                     | Measurement + Calibration Cycle<br>Time When Starting from the REFUP State in Fast Mode     | Measure 12 Cells                                      | ● | 1010  | 1113  | 1185  | $\mu\text{s}$ |

|                                                     |                                                                                             | Measure 2 Cells                                       | ● | 180   | 201   | 215   | $\mu\text{s}$ |

|                                                     |                                                                                             | Measure 12 Cells and 2 GPIO Inputs                    | ● | 1420  | 1564  | 1660  | $\mu\text{s}$ |

| $t_{\text{SKEW1}}$<br>(Figure 6)                    | Skew Time.The Time Difference between C12 and GPIO2 Measurements, Command = ADCVAX          | Fast Mode                                             | ● | 189   | 208   | 221   | $\mu\text{s}$ |

|                                                     |                                                                                             | Normal Mode                                           | ● | 493   | 543   | 576   | $\mu\text{s}$ |

| $t_{\text{SKEW2}}$<br>(Figure 3)                    | Skew Time.The Time Difference between C12 and C0 Measurements, Command = ADCV               | Fast Mode                                             | ● | 211   | 233   | 248   | $\mu\text{s}$ |

|                                                     |                                                                                             | Normal Mode                                           | ● | 609   | 670   | 711   | $\mu\text{s}$ |

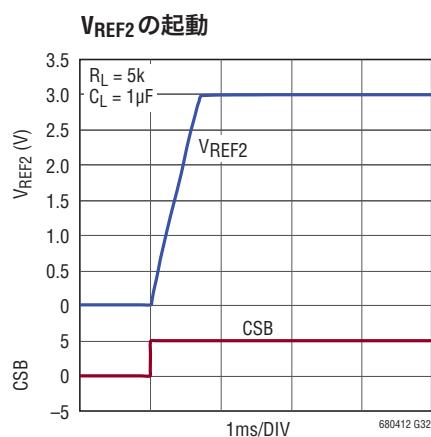

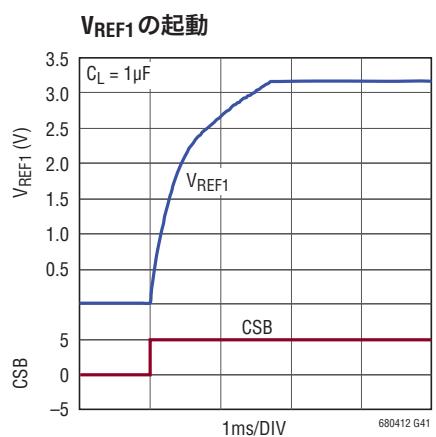

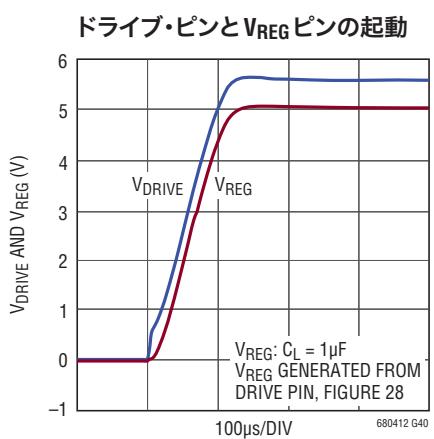

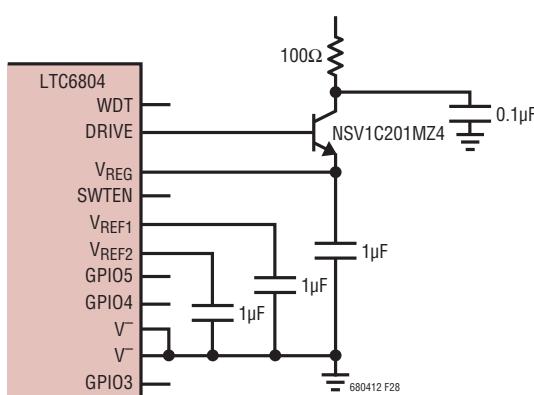

| $t_{\text{WAKE}}$                                   | Regulator Start-Up Time                                                                     | $V_{\text{REG}}$ Generated from Drive Pin (Figure 28) | ● | 100   |       | 300   | $\mu\text{s}$ |

| $t_{\text{SLEEP}}$                                  | Watchdog or Software Discharge Timer                                                        | SWTEN Pin = 0 or DCTO[3:0] = 0000                     | ● | 1.8   | 2     | 2.2   | sec           |

|                                                     |                                                                                             | SWTEN Pin = 1 and DCTO[3:0] ≠ 0000                    | ● | 0.5   |       | 120   | min           |

| $t_{\text{REFUP}}$<br>(Figure 1,<br>Figures 3 to 7) | Reference Wake-Up Time                                                                      | State:Core = STANDBY                                  | ● | 2.7   | 3.5   | 4.4   | ms            |

|                                                     |                                                                                             | State:Core = REFUP                                    | ● | 0     |       | ms    |               |

| $f_s$                                               | ADC Clock Frequency                                                                         |                                                       | ● | 3.0   | 3.3   | 3.5   | MHz           |

### SPIインターフェースのDC仕様

|                      |                                              |                                             |   |     |  |            |

|----------------------|----------------------------------------------|---------------------------------------------|---|-----|--|------------|

| $V_{\text{IH(SPI)}}$ | SPI Pin Digital Input Voltage High           | Pins CSB, SCK, SDI                          | ● | 2.3 |  | $\text{V}$ |

| $V_{\text{IL(SPI)}}$ | SPI Pin Digital Input Voltage Low            | Pins CSB, SCK, SDI                          | ● | 0.8 |  | $\text{V}$ |

| $V_{\text{IH(CFG)}}$ | Configuration Pin Digital Input Voltage High | Pins ISOMD, SWTEN, GPIO1 to GPIO5, A0 to A3 | ● | 2.7 |  | $\text{V}$ |

| $V_{\text{IL(CFG)}}$ | Configuration Pin Digital Input Voltage Low  | Pins ISOMD, SWTEN, GPIO1 to GPIO5, A0 to A3 | ● | 1.2 |  | $\text{V}$ |

# LTC6804-1/LTC6804-2

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、テスト条件は $V^+ = 39.6\text{V}$ 、 $V_{\text{REG}} = 5.0\text{V}$ 。

| SYMBOL                 | PARAMETER             | CONDITIONS                                 |   | MIN | TYP | MAX     | UNITS         |

|------------------------|-----------------------|--------------------------------------------|---|-----|-----|---------|---------------|

| $I_{\text{LEAK(DIG)}}$ | Digital Input Current | Pins CSB, SCK, SDI, ISOMD, SWTEN, A0 to A3 | ● |     |     | $\pm 1$ | $\mu\text{A}$ |

| $V_{\text{OL(SDO)}}$   | Digital Output Low    | Pin SDO Sinking 1mA                        | ● |     |     | 0.3     | V             |

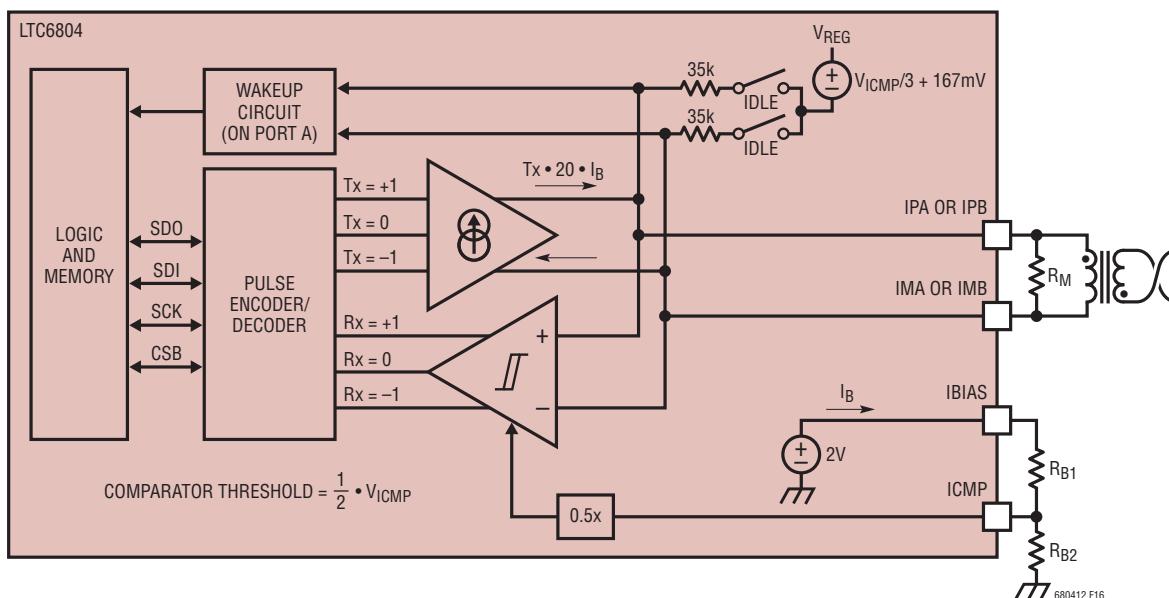

### isoSPIのDC仕様(図16を参照)

|                          |                                            |                                                                                                                  |   |          |          |                                                       |                  |

|--------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------|---|----------|----------|-------------------------------------------------------|------------------|

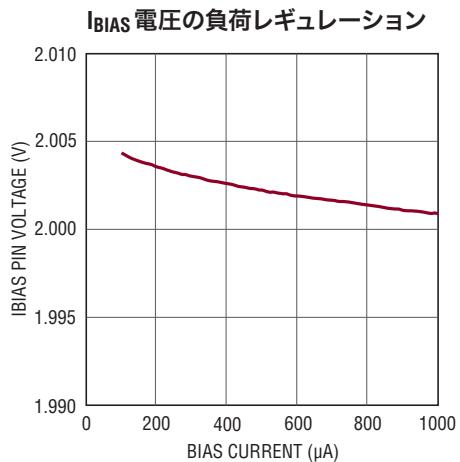

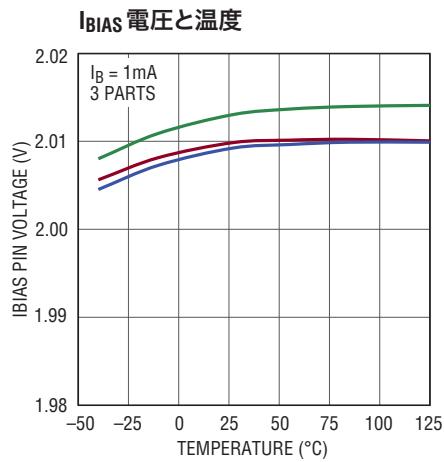

| $V_{\text{BIAS}}$        | Voltage on IBIAS Pin                       | READY/ACTIVE State<br>IDLE State                                                                                 | ● | 1.9<br>0 | 2.0      | 2.1                                                   | V<br>V           |

| $I_B$                    | Isolated Interface Bias Current            | $R_{\text{BIAS}} = 2\text{k}$ to $20\text{k}$                                                                    | ● | 0.1      |          | 1.0                                                   | mA               |

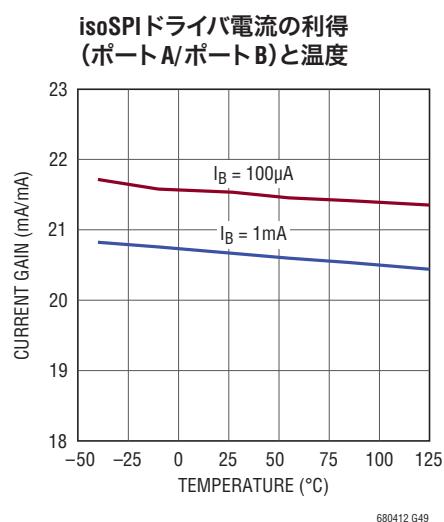

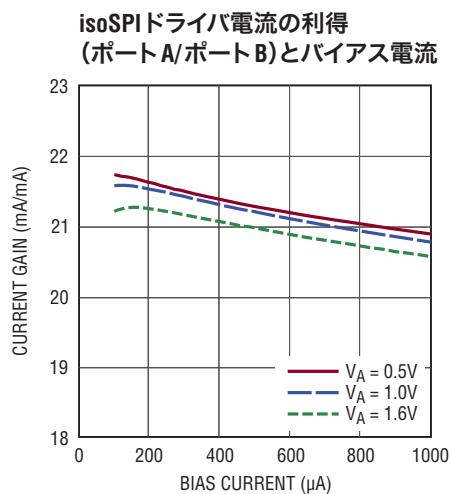

| $A_{IB}$                 | Isolated Interface Current Gain            | $V_A \leq 1.6\text{V}$                                                                                           | ● | 18<br>18 | 20<br>20 | 22<br>24.5                                            | mA/mA<br>mA/mA   |

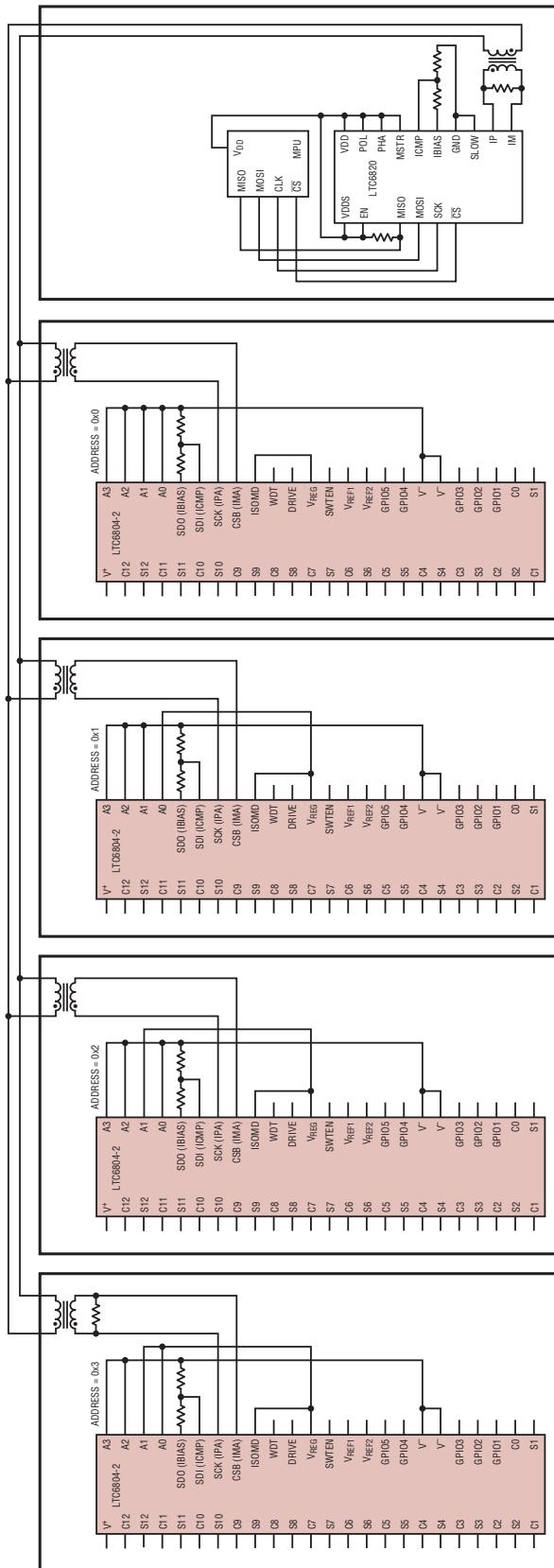

| $V_A$                    | Transmitter Pulse Amplitude                | $V_A =  V_{IP} - V_{IM} $                                                                                        | ● |          |          | 1.6                                                   | V                |

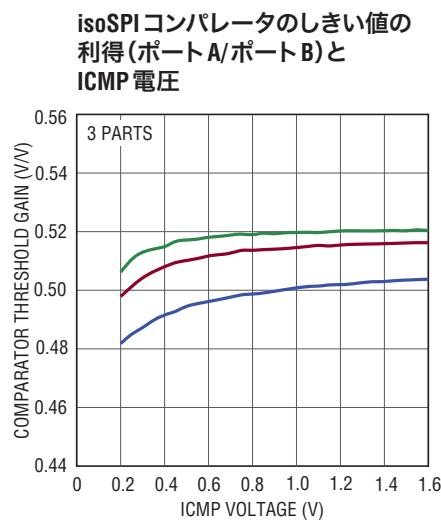

| $V_{\text{ICMP}}$        | Threshold-Setting Voltage on ICMP Pin      | $V_{\text{TCMP}} = A_{\text{TCMP}} \cdot V_{\text{ICMP}}$                                                        | ● | 0.2      |          | 1.5                                                   | V                |

| $I_{\text{LEAK(ICMP)}}$  | Input Leakage Current on ICMP Pin          | $V_{\text{ICMP}} = 0\text{V}$ to $V_{\text{REG}}$                                                                | ● |          |          | $\pm 1$                                               | $\mu\text{A}$    |

| $I_{\text{LEAK(IP/IM)}}$ | Leakage Current on IP and IM Pins          | IDLE State, $V_{IP}$ or $V_{IM} = 0\text{V}$ to $V_{\text{REG}}$                                                 | ● |          |          | $\pm 1$                                               | $\mu\text{A}$    |

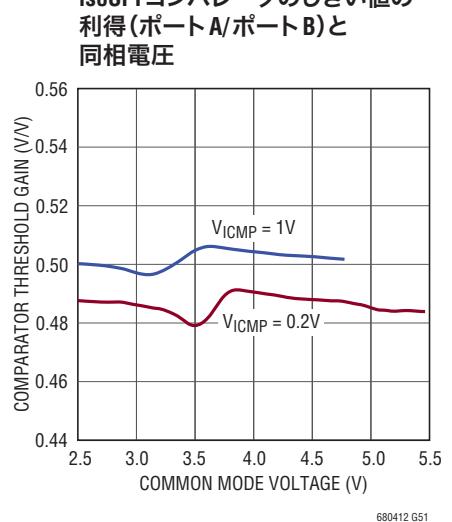

| $A_{\text{TCMP}}$        | Receiver Comparator Threshold Voltage Gain | $V_{CM} = V_{\text{REG}}/2$ to $V_{\text{REG}} - 0.2\text{V}$ , $V_{\text{ICMP}} = 0.2\text{V}$ to $1.5\text{V}$ | ● | 0.4      | 0.5      | 0.6                                                   | V/V              |

| $V_{CM}$                 | Receiver Common Mode Bias                  | IP/IM Not Driving                                                                                                |   |          |          | $(V_{\text{REG}} - V_{\text{ICMP}}/3 - 167\text{mV})$ | V                |

| $R_{\text{IN}}$          | Receiver Input Resistance                  | Single-Ended to IPA, IMA, IPB, IMB                                                                               | ● | 27       | 35       | 43                                                    | $\text{k}\Omega$ |

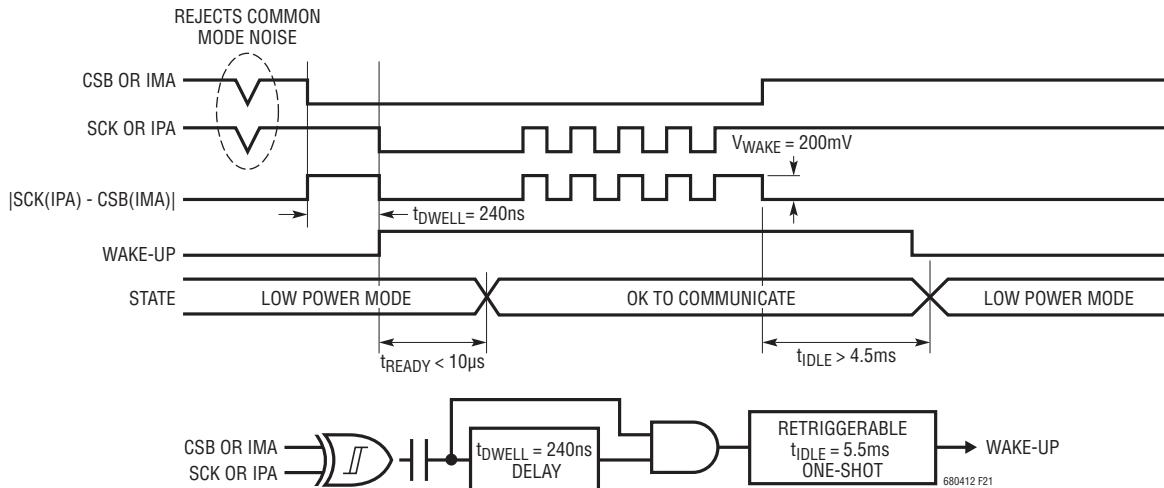

### isoSPIのアイドル/ウェイクアップ仕様(図21を参照)

|                    |                                                       |                                   |   |     |     |     |               |

|--------------------|-------------------------------------------------------|-----------------------------------|---|-----|-----|-----|---------------|

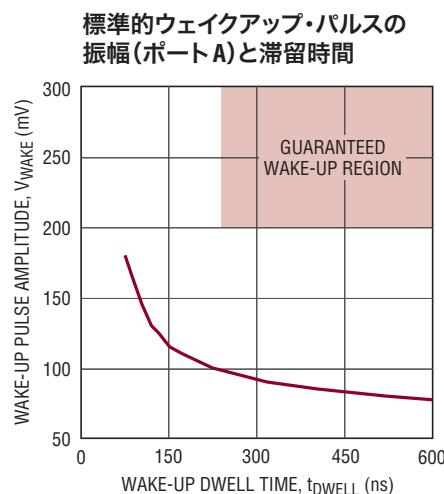

| $V_{\text{WAKE}}$  | Differential Wake-Up Voltage                          | $t_{\text{DWELL}} = 240\text{ns}$ | ● | 200 |     |     | mV            |

| $t_{\text{DWELL}}$ | Dwell Time at $V_{\text{WAKE}}$ Before Wake Detection | $V_{\text{WAKE}} = 200\text{mV}$  | ● | 240 |     |     | ns            |

| $t_{\text{READY}}$ | Startup Time After Wake Detection                     |                                   | ● |     |     | 10  | $\mu\text{s}$ |

| $t_{\text{IDLE}}$  | Idle Timeout Duration                                 |                                   | ● | 4.3 | 5.5 | 6.7 | ms            |

### isoSPIのパルス・タイミング仕様(図19を参照)

|                             |                                   |  |   |     |     |     |    |

|-----------------------------|-----------------------------------|--|---|-----|-----|-----|----|

| $t_{1/2PW(\text{CS})}$      | Chip-Select Half-Pulse Width      |  | ● | 120 | 150 | 180 | ns |

| $t_{\text{INV}(\text{CS})}$ | Chip-Select Pulse Inversion Delay |  | ● |     |     | 200 | ns |

| $t_{1/2PW(\text{D})}$       | Data Half-Pulse Width             |  | ● | 40  | 50  | 60  | ns |

| $t_{\text{INV}(\text{D})}$  | Data Pulse Inversion Delay        |  | ● |     |     | 70  | ns |

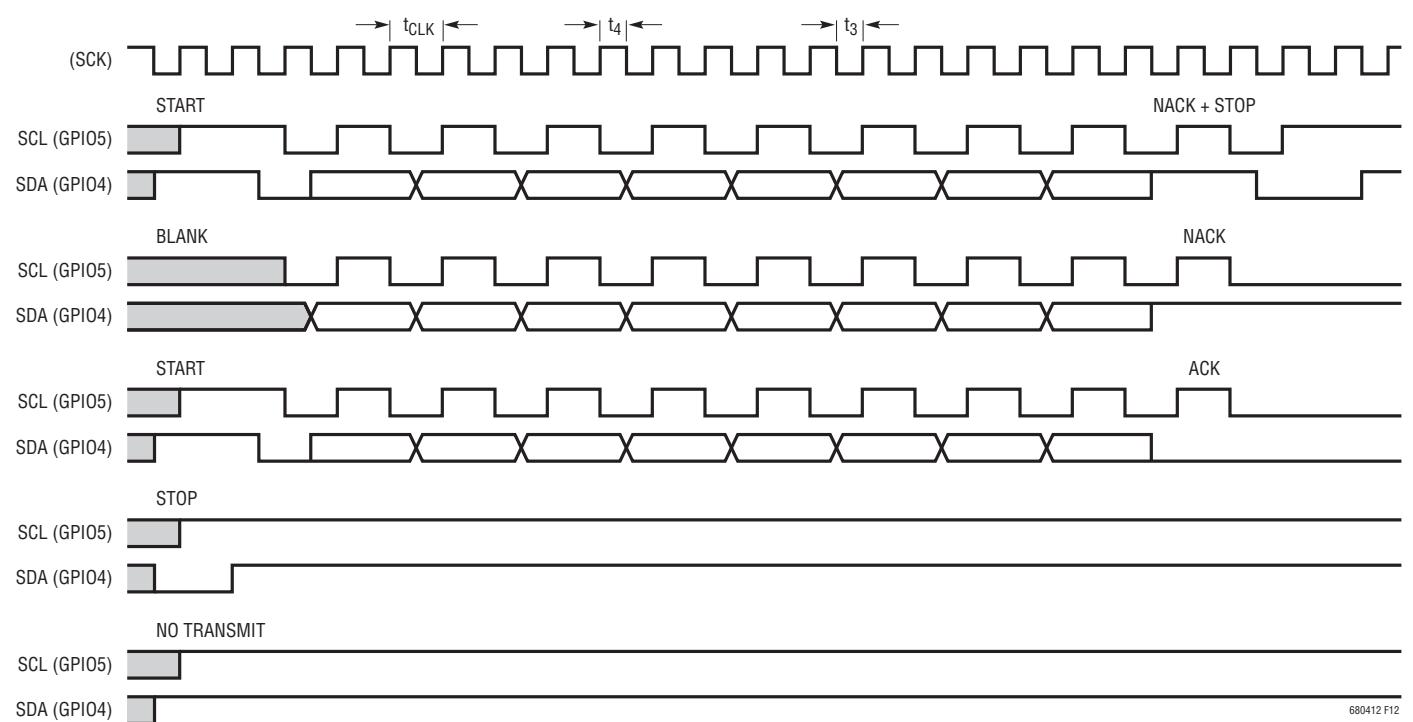

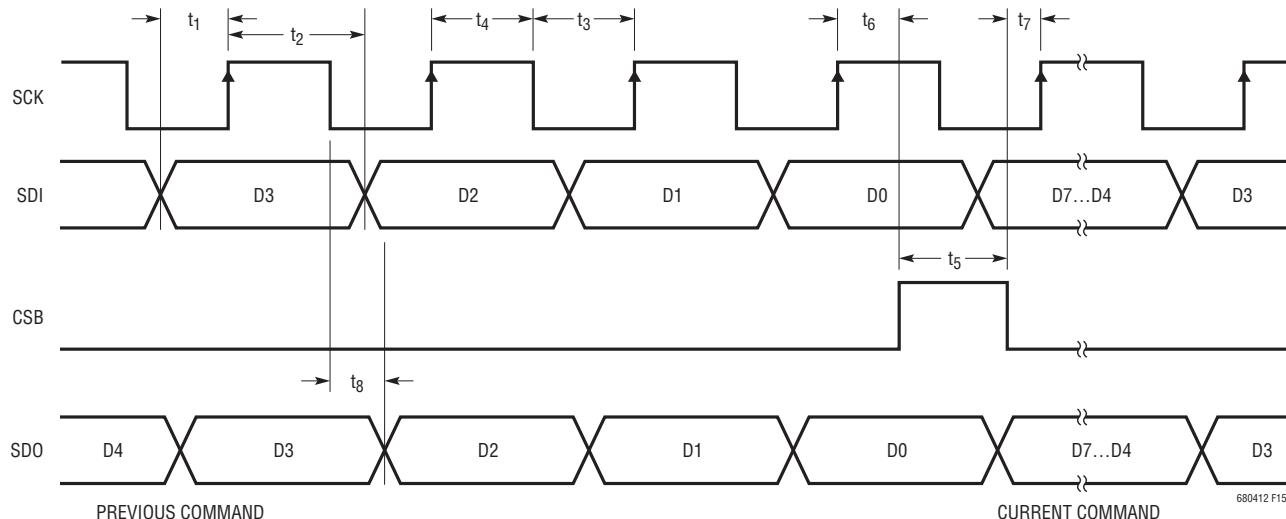

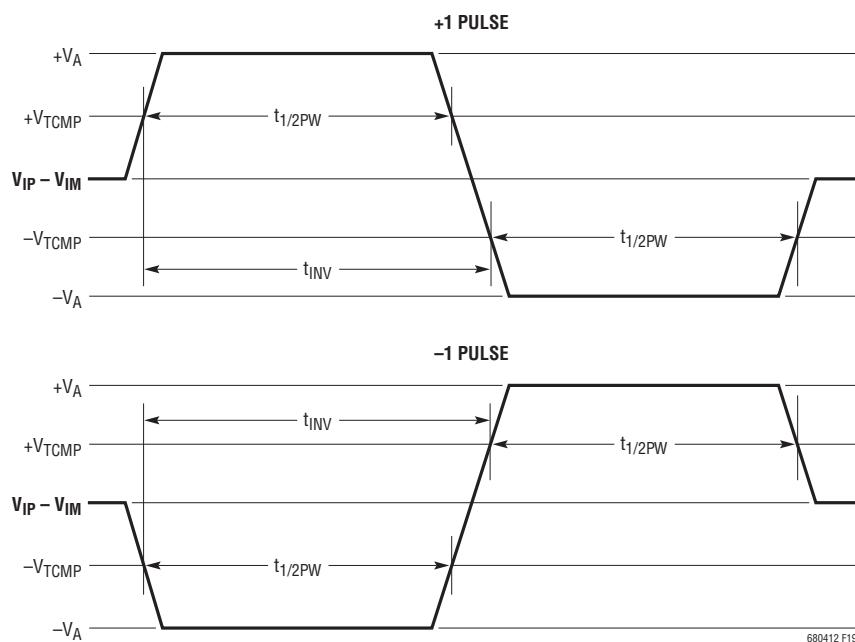

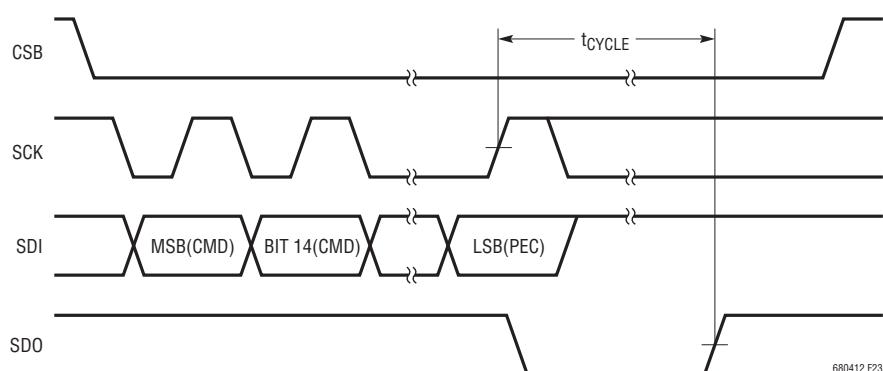

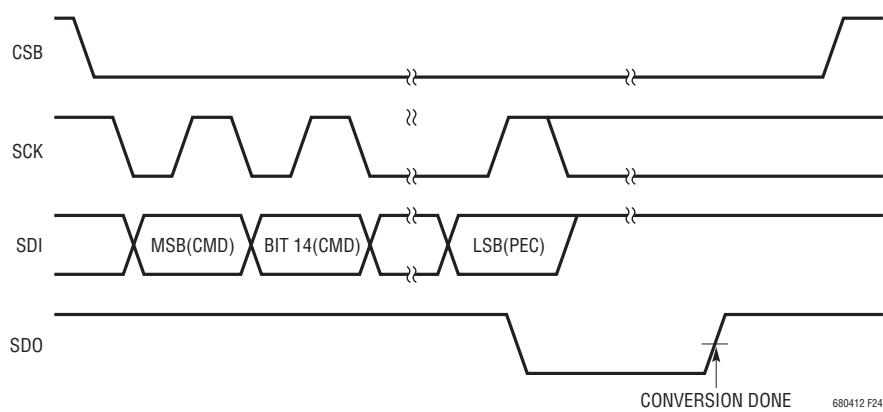

### SPIのタイミング要件(図15および図20を参照)

|                  |                                       |                                                |   |      |  |  |               |

|------------------|---------------------------------------|------------------------------------------------|---|------|--|--|---------------|

| $t_{\text{CLK}}$ | SCK Period                            | (Note 4)                                       | ● | 1    |  |  | $\mu\text{s}$ |

| $t_1$            | SDI Setup Time before SCK Rising Edge |                                                | ● | 25   |  |  | ns            |

| $t_2$            | SDI Hold Time after SCK Rising Edge   |                                                | ● | 25   |  |  | ns            |

| $t_3$            | SCK Low                               | $t_{\text{CLK}} = t_3 + t_4 \geq 1\mu\text{s}$ | ● | 200  |  |  | ns            |

| $t_4$            | SCK High                              | $t_{\text{CLK}} = t_3 + t_4 \geq 1\mu\text{s}$ | ● | 200  |  |  | ns            |

| $t_5$            | CSB Rising Edge to CSB Falling Edge   |                                                | ● | 0.65 |  |  | $\mu\text{s}$ |

| $t_6$            | SCK Rising Edge to CSB Rising Edge    | (Note 4)                                       | ● | 0.8  |  |  | $\mu\text{s}$ |

| $t_7$            | CSB Falling Edge to SCK Rising Edge   | (Note 4)                                       | ● | 1    |  |  | $\mu\text{s}$ |

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、テスト条件は $V^+ = 39.6\text{V}$ 、 $V_{\text{REG}} = 5.0\text{V}$ 。

| SYMBOL                        | PARAMETER                                 | CONDITIONS | MIN | TYP | MAX  | UNITS         |

|-------------------------------|-------------------------------------------|------------|-----|-----|------|---------------|

| <b>isoSPIのタイミング仕様(図19を参照)</b> |                                           |            |     |     |      |               |

| $t_8$                         | SCK Falling Edge to SDO Valid             | (Note 5)   | ●   |     | 60   | ns            |

| $t_9$                         | SCK Rising Edge to Short $\pm 1$ Transmit |            | ●   |     | 50   | ns            |

| $t_{10}$                      | CSB Transition to Long $\pm 1$ Transmit   |            | ●   |     | 60   | ns            |

| $t_{11}$                      | CSB Rising Edge to SDO Rising             | (Note 5)   | ●   |     | 200  | ns            |

| $t_{\text{RTN}}$              | Data Return Delay                         |            | ●   |     | 430  | 525           |

| $t_{\text{DSY}(\text{CS})}$   | Chip-Select Daisy-Chain Delay             |            | ●   |     | 150  | 200           |

| $t_{\text{DSY}(\text{D})}$    | Data Daisy-Chain Delay                    |            | ●   |     | 300  | 360           |

| $t_{\text{LAG}}$              | Data Daisy-Chain Lag (vs Chip-Select)     |            | ●   | 0   | 35   | 70            |

| $t_6(\text{GOV})$             | Data to Chip-Select Pulse Governor        |            | ●   | 0.8 | 1.05 | $\mu\text{s}$ |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに回復不可能な損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** ADCの仕様は全測定誤差の仕様によって保証されている。

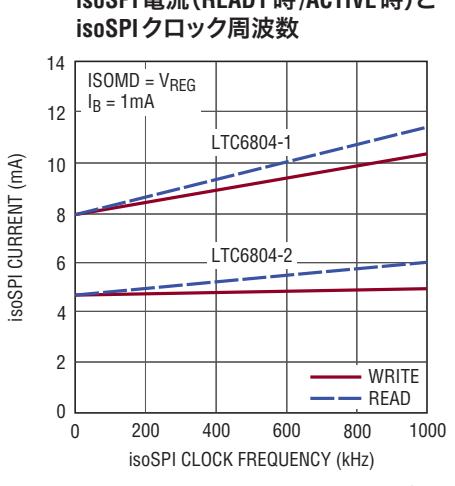

**Note 3:** ACTIVEステートの電流はDCの測定値から計算される。isoSPIポートに、データ1が50%、データ0が50%の連続的な1MHzの通信が存在する場合、ACTIVEステートの電流は、 $V_{\text{REG}}$ への追加平均消費電流になる。クロック・レートが遅くなるほど、消費電流が減少する。詳細については、「アプリケーション情報」のセクションを参照。

**Note 4:** これらのタイミング仕様はケーブルの遅延によって異なり、各方向に50nsの遅延を許容する。50nsは10mのCAT-5ケーブル(伝播速度が光速の66%)に対応する。これより長いケーブルを使用する場合は、遅延が大きくなる分、仕様を低減する必要がある。

**Note 5:** これらの仕様には、SDOの立ち上がり時間と立ち下がり時間は含まれない。立ち下がり時間(内部プルダウン・トランジスタのため標準で5ns)は問題ではないが、立ち上がりエッジの遷移時間 $t_{\text{rise}}$ はSDOピンでのプルアップ抵抗と負荷容量によって異なる。SDOがMCUのセットアップ時間要件を満たすように、時定数を選択する必要がある。

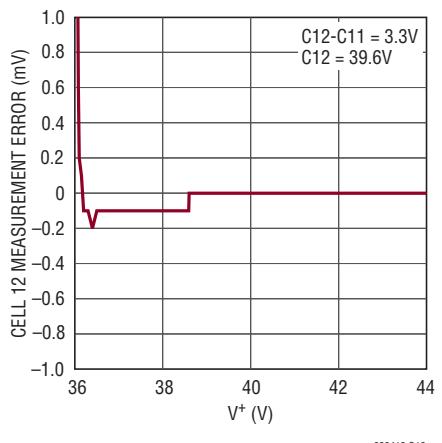

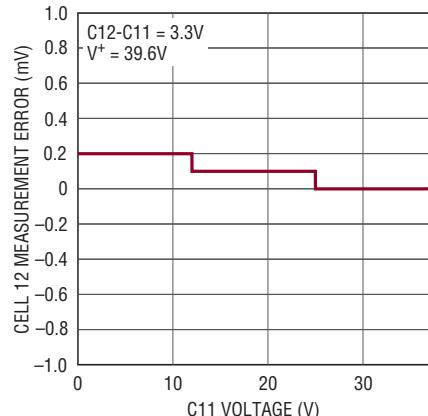

**Note 6:** 正確に測定するには、 $V^+$ が最大 $C(n)$ 電圧以上である必要がある。最上位セルの測定誤差と $V^+$ のグラフを参照。

# LTC6804-1/LTC6804-2

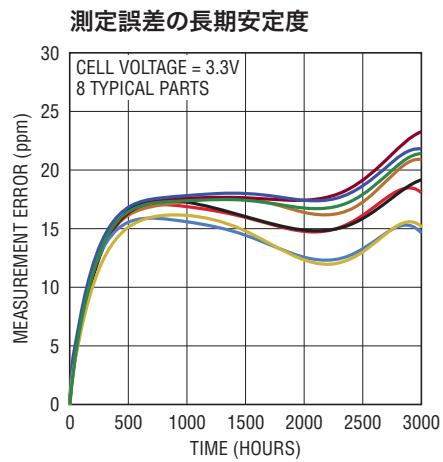

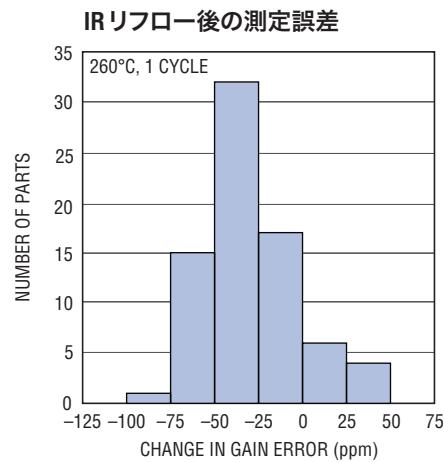

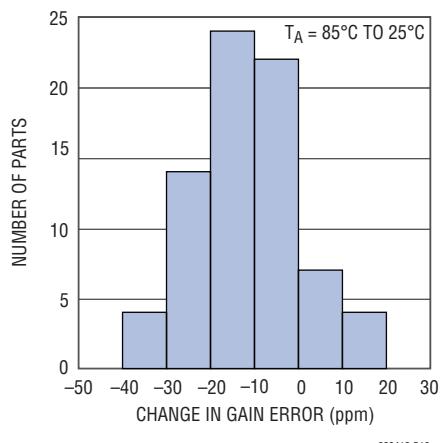

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

680412f

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

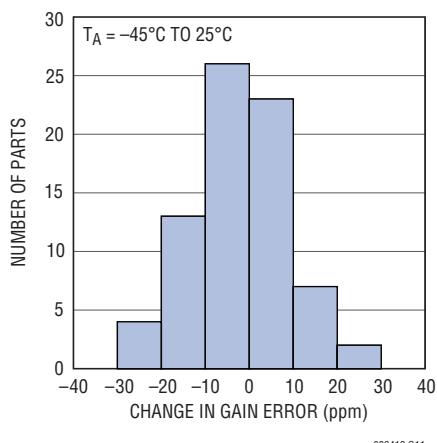

測定利得誤差のヒステリシス

(高温時)

測定利得誤差のヒステリシス

(低温時)

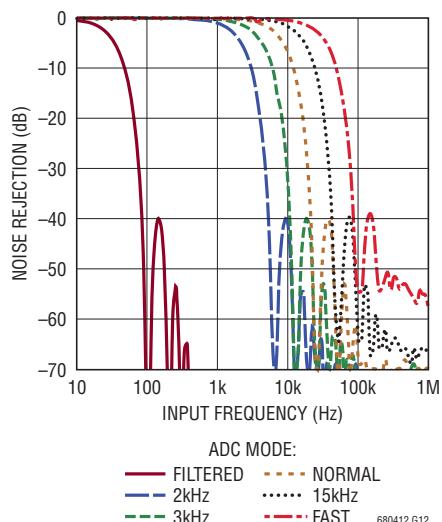

ノイズ・フィルタ応答性

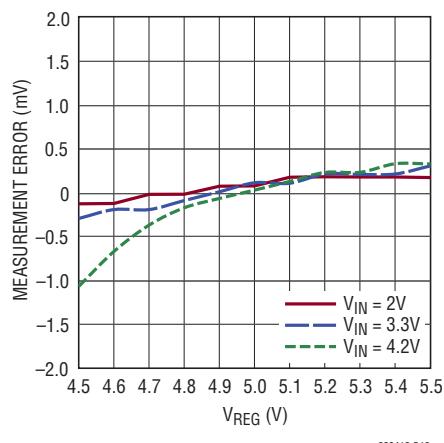

測定誤差と  $V_{\text{REG}}$

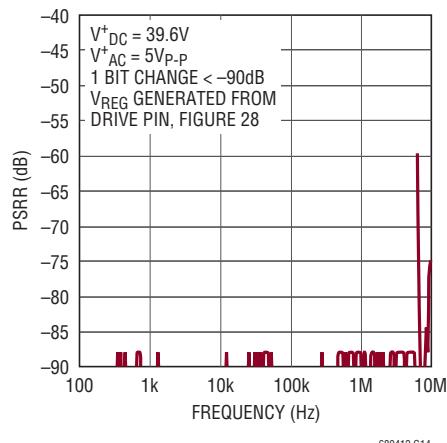

測定誤差  $V^+$  PSRR と周波数

測定誤差  $V_{\text{REG}}$  PSRR と周波数

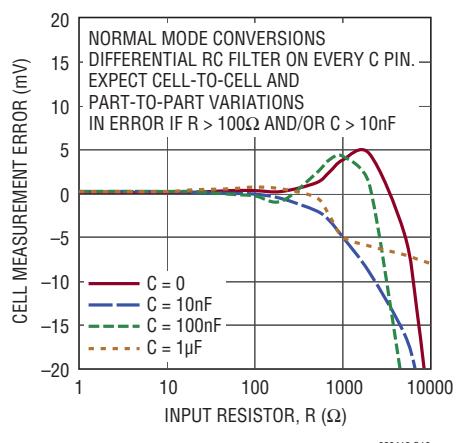

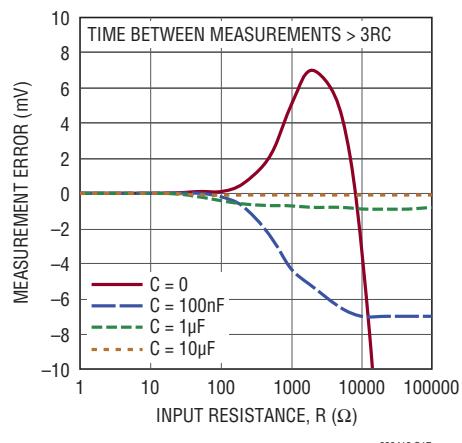

電圧の測定誤差と入力 RC 値

GPIO の測定誤差と入力 RC 値

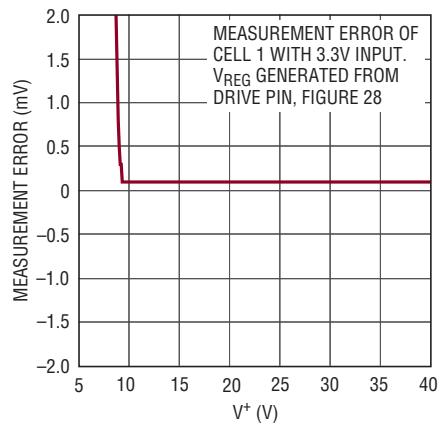

最上位セルの測定誤差と  $V^+$

# LTC6804-1/LTC6804-2

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

セル電圧の測定誤差と同相電圧

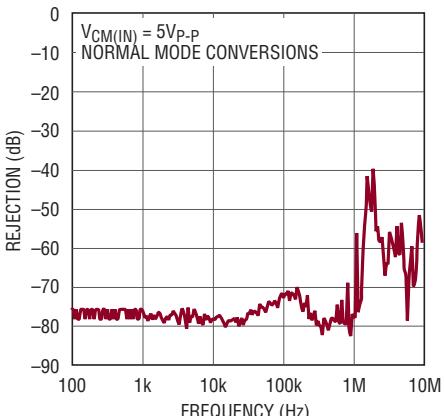

セル電圧の測定 CMRR と周波数

測定誤差と  $V^+$

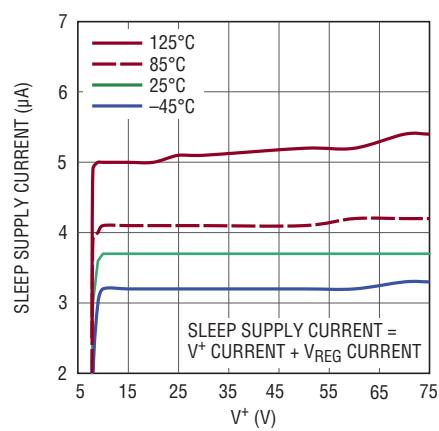

スリープ時消費電流と  $V^+$

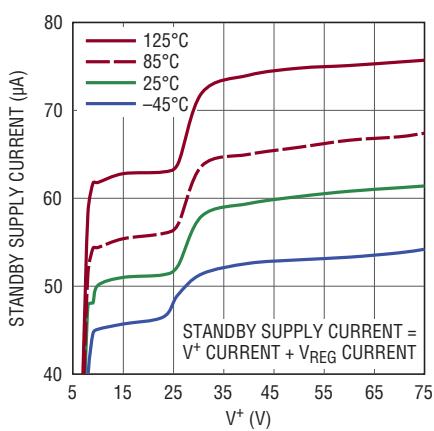

スタンバイ時消費電流と  $V^+$

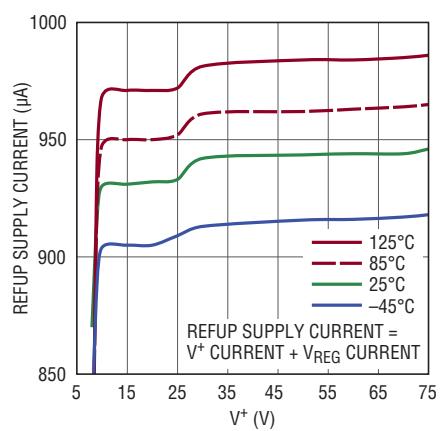

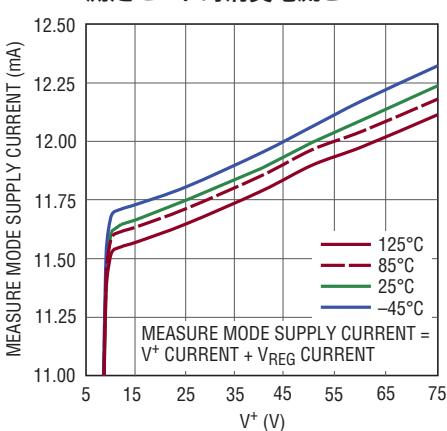

REFUP 消費電流と  $V^+$

測定モード時消費電流と  $V^+$

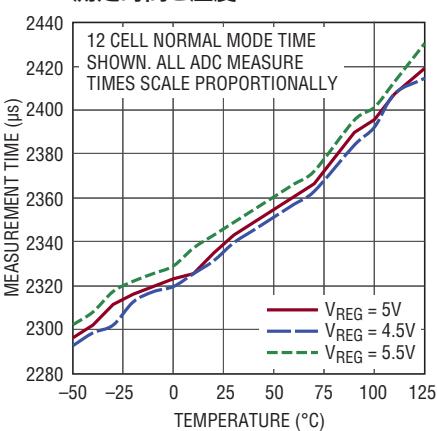

測定時間と温度

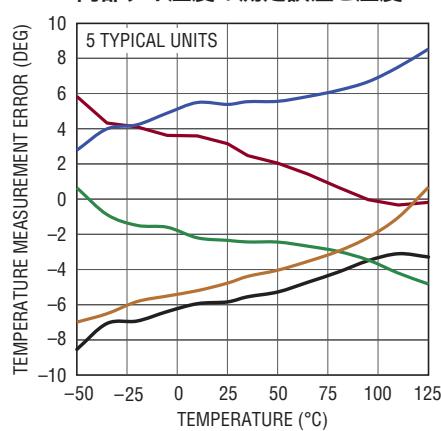

内部ダイ温度の測定誤差と温度

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

# LTC6804-1/LTC6804-2

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

# LTC6804-1/LTC6804-2

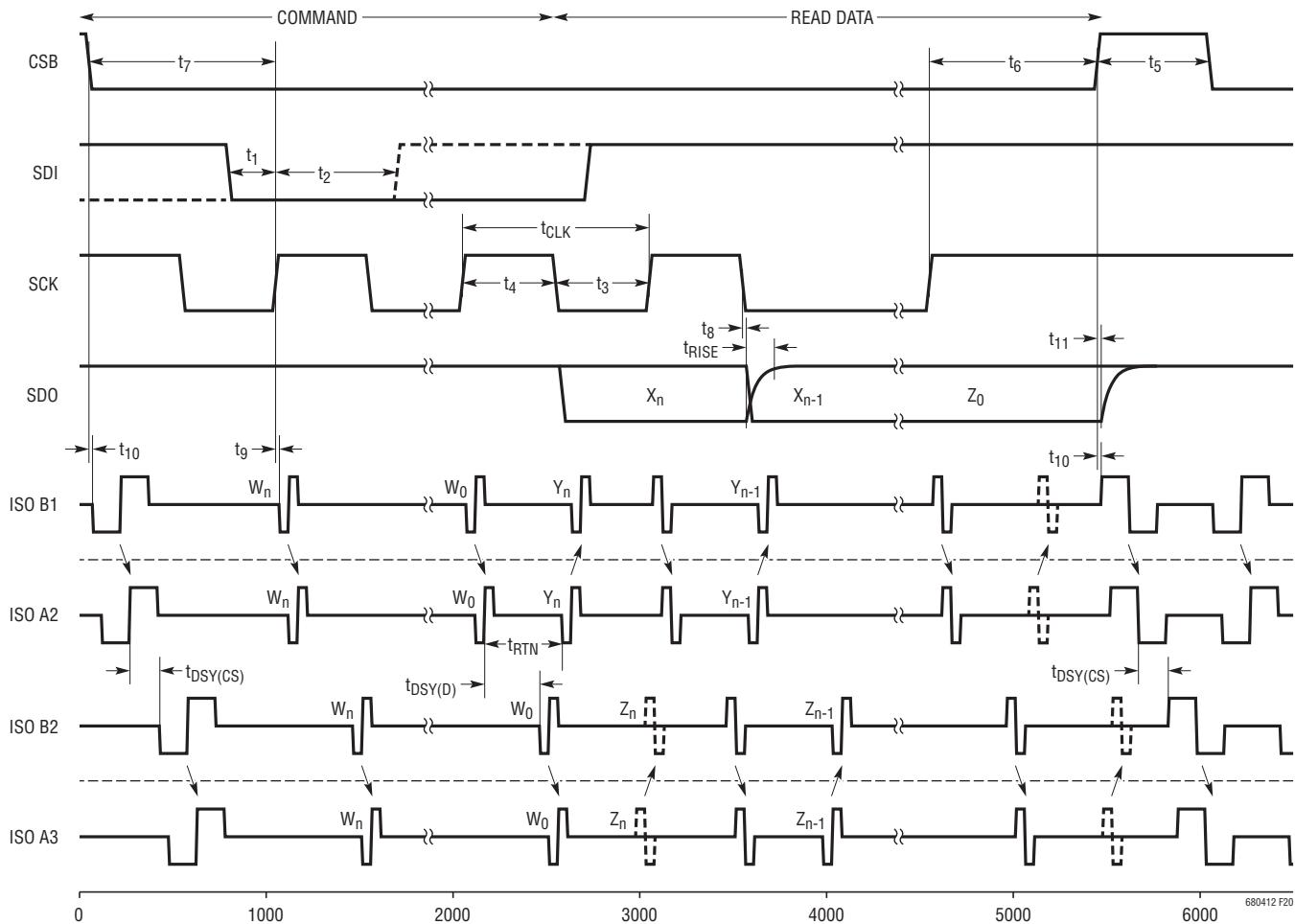

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

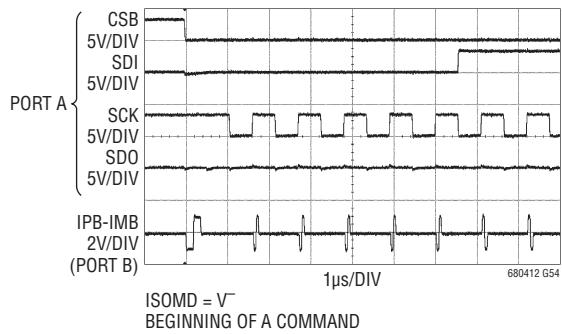

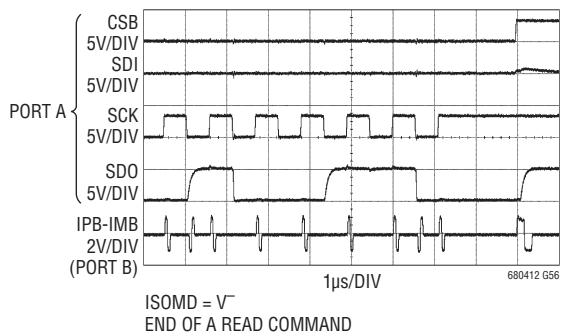

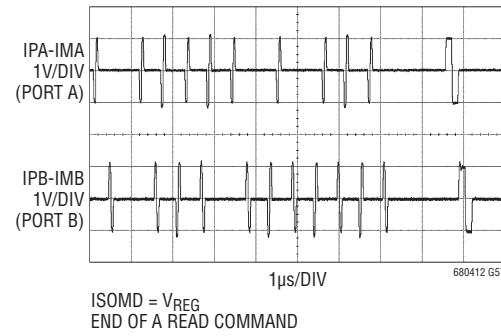

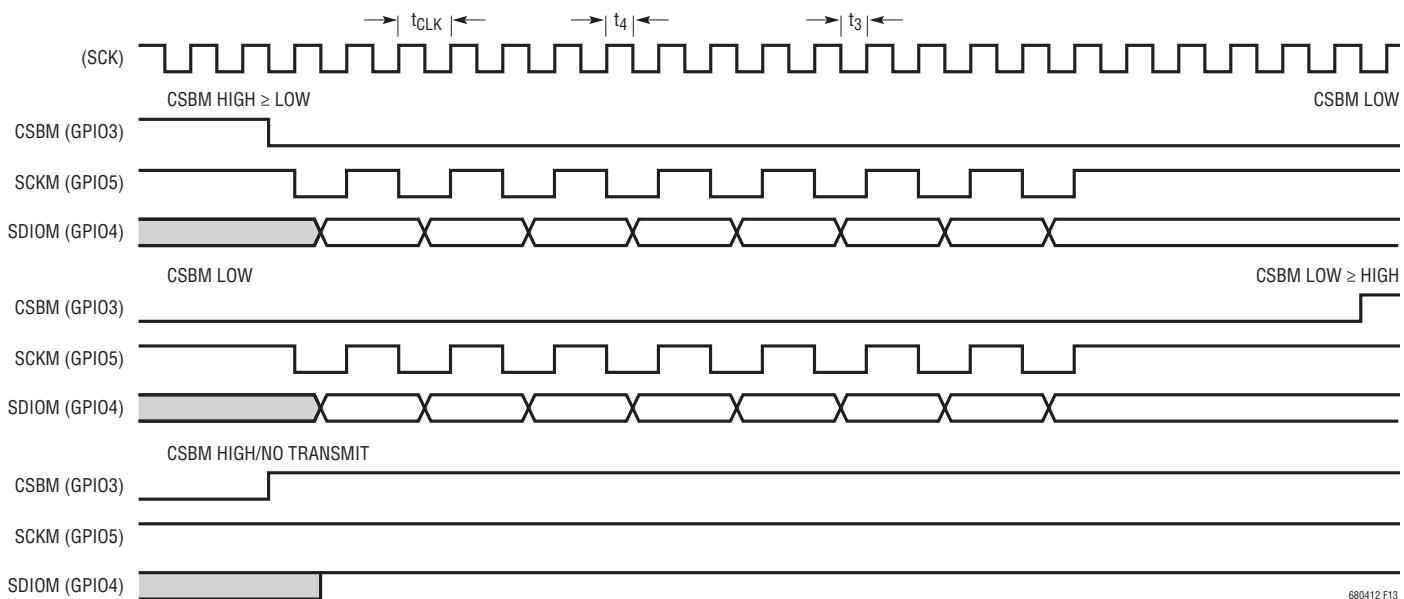

デイジーチェーン接続されたデバイス

へのコマンドの書き込み (ISOMD = 0)

デイジーチェーン接続されたデバイス

へのコマンドの書き込み (ISOMD = 1)

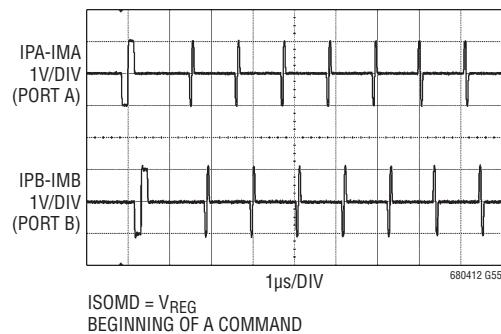

デイジーチェーン接続されたデバイス

からのデータ読み出し (ISOMD = 0)

デイジーチェーン接続されたデバイス

からのデータ読み出し (ISOMD = 1)

## ピン機能

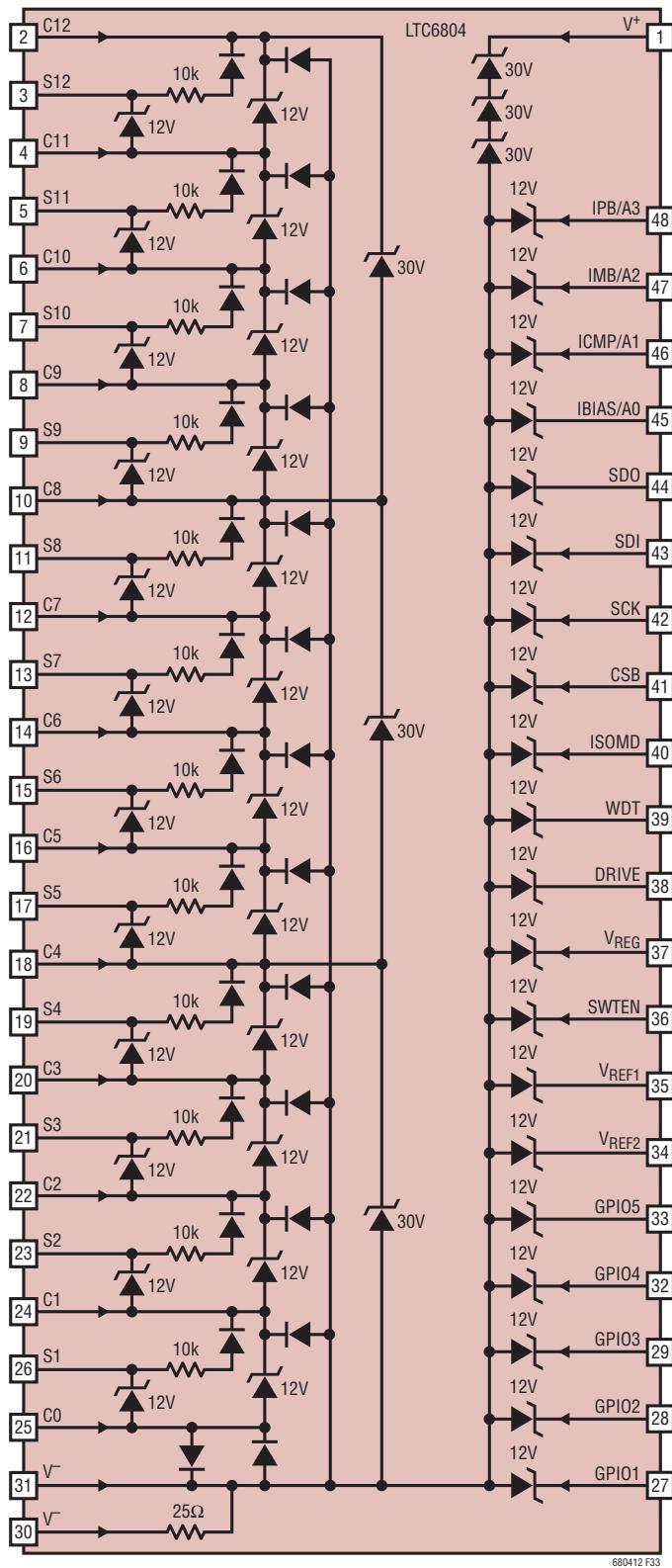

**C0～C12:** セルの入力。

**S1～S12:** 入力/出力均等化。S(n)とC(n - 1)の間に、12個のN-MOSFETを接続し各セルを放電します。

**V<sup>+</sup>:** 正電源ピン。

**V<sup>-</sup>:** 負電源ピン。デバイスの外部で、各V<sup>-</sup>ピンを互いに短絡させる必要があります。

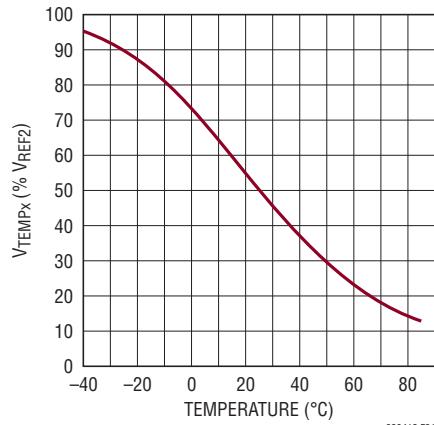

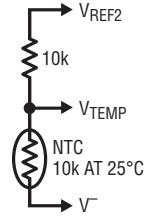

**V<sub>REF2</sub>:** 複数の10k サーミスタをドライブするためのバッファ付き2次リファレンス出力。外付けの1μFコンデンサでバイパスします。

**V<sub>REF1</sub>:** ADCリファレンス出力。外付けの1μFコンデンサでバイパスします。DC負荷を接続することはできません。

**GPIO[1～5]:** 汎用I/Oポート。デジタル入力またはデジタル出力として使用するか、V<sup>-</sup>～5Vの測定範囲でアナログ入力として使用できます。GPIO [3～5]を、I<sup>2</sup>CポートまたはSPIポートとして使用できます。

**SWTEN:** ソフトウェア・タイマ・イネーブル。ソフトウェア・タイマをイネーブルするには、このピンをV<sub>REG</sub>に接続します。

**DRIVE:** NPNのベースをこのピンに接続します。コレクタはV<sup>+</sup>に接続し、エミッタはV<sub>REG</sub>に接続します。

**V<sub>REG</sub>:** 5Vレギュレータ入力。外付けの1μFコンデンサでバイパスします。

**ISOMD:** シリアル・インターフェース・モード。2線絶縁型インターフェース(isoSPI)モードの場合、ISOMDをV<sub>REG</sub>に接続して LTC6804のピン41～44を設定します。ISOMDをV<sup>-</sup>に接続すると、LTC6804は4線SPIモードになります。

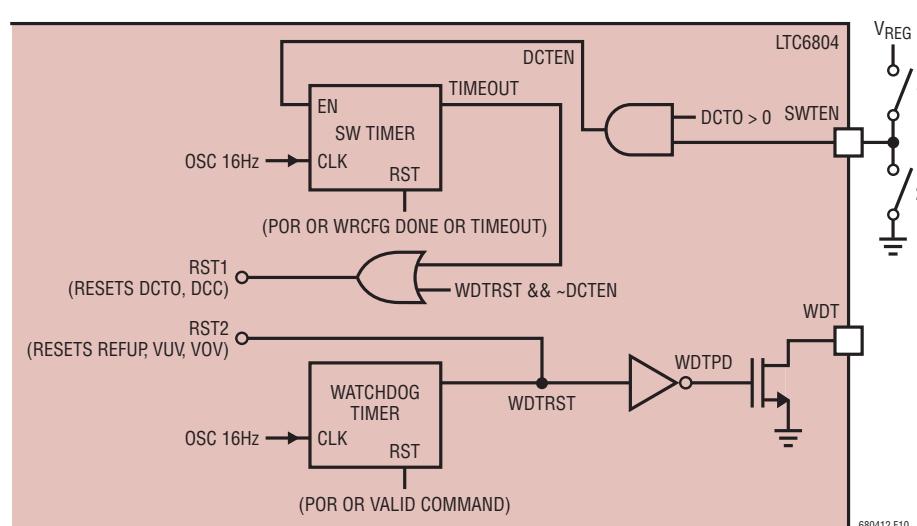

**WDT:** ウオッチドッグ・タイマ出力ピン。これはオープン・ドラインNMOSのデジタル出力です。このピンは未接続のままにするか、1Mの抵抗を介してV<sub>REG</sub>に接続することができます。LTC6804が2秒以内に有効なコマンドを受信しない場合は、ウォッチドッグ・タイマ回路がLTC6804をリセットし、WDTピンが高インピーダンスになります。

## シリアル・ポート・ピン

|                              | LTC6804-1<br>(デイジーチェーン可能) |                        | LTC6804-2<br>(アドレス指定可能)  |                        |

|------------------------------|---------------------------|------------------------|--------------------------|------------------------|

|                              | ISOMD = V <sub>REG</sub>  | ISOMD = V <sup>-</sup> | ISOMD = V <sub>REG</sub> | ISOMD = V <sup>-</sup> |

| PORT B<br>(Pins 45<br>to 48) | IPB                       | IPB                    | A3                       | A3                     |

|                              | IMB                       | IMB                    | A2                       | A2                     |

|                              | ICMP                      | ICMP                   | A1                       | A1                     |

|                              | IBIAS                     | IBIAS                  | A0                       | A0                     |

| PORT A<br>(Pins 41<br>to 44) | (NC)                      | SDO                    | IBIAS                    | SDO                    |

|                              | (NC)                      | SDI                    | ICMP                     | SDI                    |

|                              | IPA                       | SCK                    | IPA                      | SCK                    |

|                              | IMA                       | CSB                    | IMA                      | CSB                    |

**CSB、SCK、SDI、SDO:** 4線シリアル・ペリフェラル・インターフェース(SPI)。アクティブ“L”のチップ・セレクト(CSB)、シリアル・クロック(SCK)、およびシリアル・データ入力(SDI)はデジタル入力です。シリアル・データ出力(SDO)はオープン・ドラインNMOS出力ピンです。SDOには5Kのプルアップ抵抗が必要です。

**A0～A3:** アドレス・ピン。これらのデジタル入力は、アドレス指定可能なシリアル・コマンド用のチップ・アドレスを設定するために、V<sub>REG</sub>またはV<sup>-</sup>に接続されます。

**IPA、IMA:** 絶縁型2線シリアル・インターフェース・ポートA。IPA(プラス)とIMA(マイナス)は、差動入力/と出力の対です。

**IPB、IMB:** 絶縁型2線シリアル・インターフェース・ポートB。IPB(プラス)とIMB(マイナス)は、差動入力/と出力の対です。

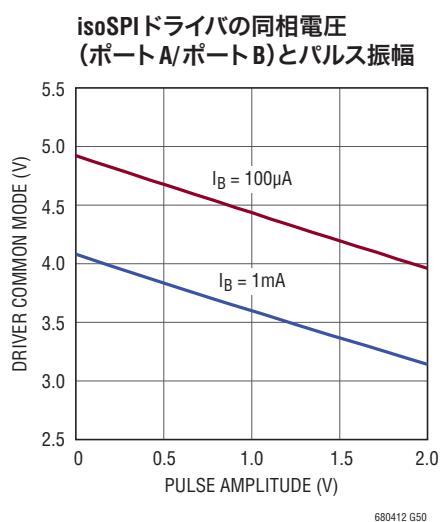

**IBIAS:** 絶縁型インターフェースの電流バイアス。抵抗分割器を介してIBIASをV<sup>-</sup>に接続し、インターフェースの出力電流レベルを設定します。isoSPIインターフェースがイネーブルされている場合、IBIASピンの電圧は2Vです。IPA/IMAまたはIPB/IMBの出力電流ドライブは、IBIASピンからソースされる電流(I<sub>B</sub>)の20倍に設定されます。

**ICMP:** 絶縁型インターフェースのコンパレータ電圧しきい値設定。このピンをIBIASとV<sup>-</sup>の間の抵抗分割器に接続し、isoSPIレシーバのコンパレータの電圧しきい値を設定します。コンパレータの電圧しきい値は、ICMPピン電圧の1/2に設定されます。

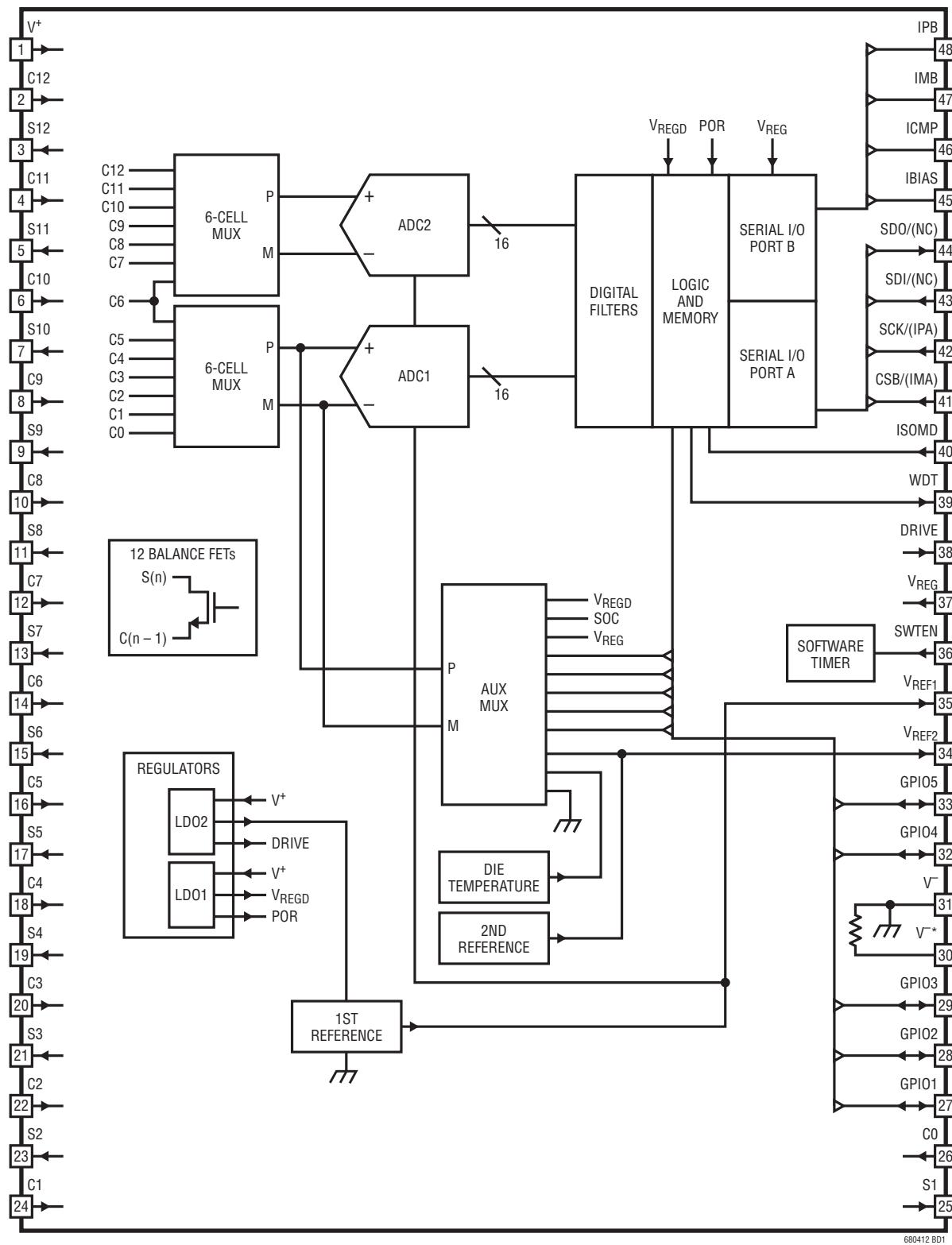

# LTC6804-1/LTC6804-2

## ブロック図

LTC6804-1

680412f

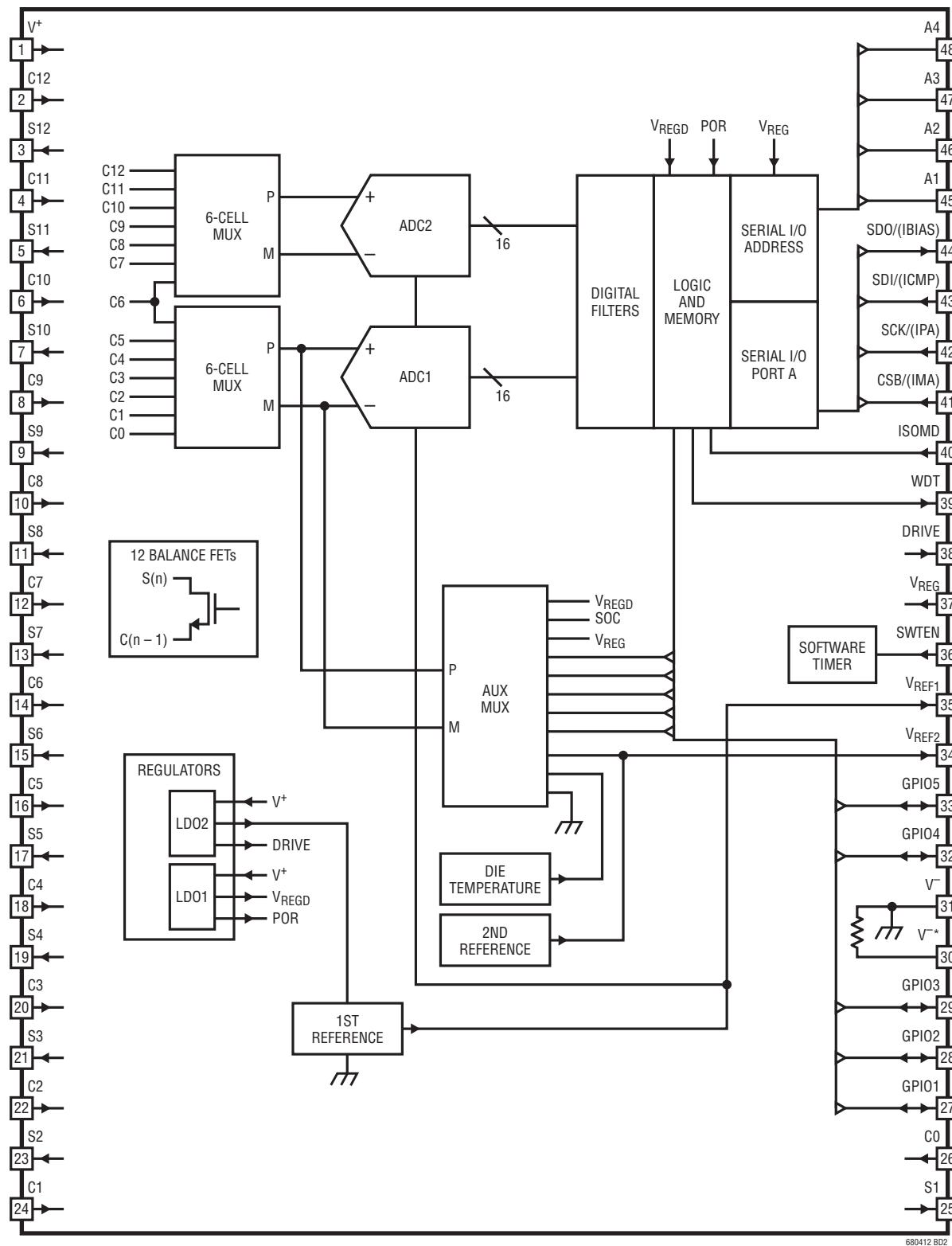

## ブロック図

LTC6804-2

# LTC6804-1/LTC6804-2

## 動作

### ステートチャート図

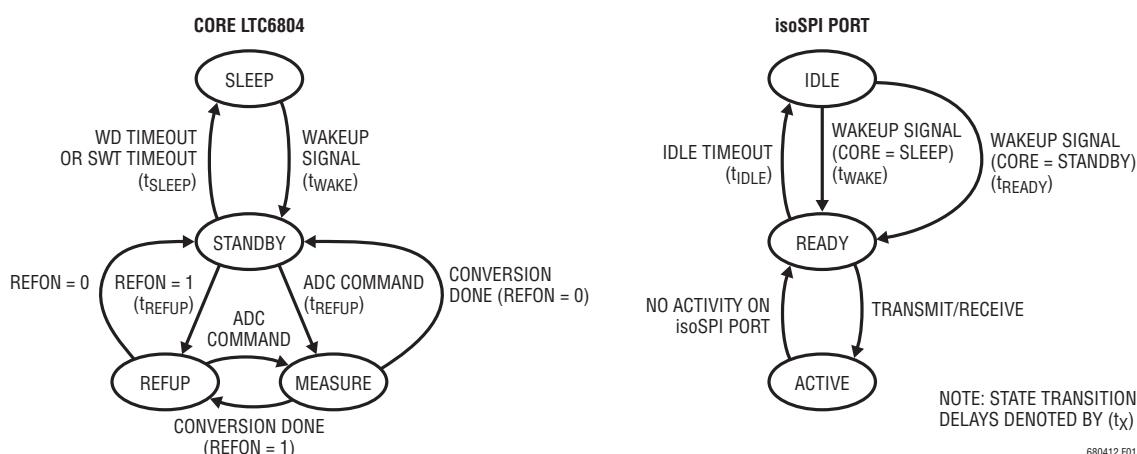

LTC6804の動作は、コア回路とisoSPI回路の2つの部分に分かれています。両方の部分は、独立した一連の動作ステートと、タイムアウトによるシャットダウンを備えています。

### LTC6804のコアのステートの説明

#### SLEEPステート

リファレンスとAD変換器がパワーダウンされます。ウォッチドッグ・タイマ（「ウォッチドッグとソフトウェア放電タイマ」を参照）はオーバーフローしています。また、ソフトウェア放電タイマも無効化またはオーバーフローしています。消費電流は、最小レベルに減少します。isoSPIポートは、IDLEステートになります。

ウェイクアップ信号を受信した場合（「シリアル・インターフェースのウェイクアップ」を参照）、LTC6804はSTANDBYステートに入ります。

#### STANDBYステート

リファレンスとAD変換器がオフになります。ウェイクアップ・タイマまたはソフトウェア放電タイマ（あるいは両方）は実行中です。DRIVEピンは、外付けトランジスタを経由してVREGピンに5Vの電力を供給します。（あるいは、外部電源からVREGに電力を供給できます。）

有効なADCコマンドを受け取るか、設定レジスタ・グループのREFONビットが1に設定された場合、デバイスはリファレンスをパワーアップできる状態になるまでtREFUPの間停止し、その後REFUPステートまたはMEASUREステートに移行します。

そうでない場合、LTC6804は、tSLEEPの経過後（ウォッチドッグとソフトウェア放電タイマの両方がオーバーフローしたとき）にSLEEPステートに戻ります。ソフトウェア放電タイマが無効化されている場合、ウォッチドッグ・タイマのみが関係します。

#### REFUPステート

このステートに達するには、設定レジスタ・グループのREFONビットを1に設定する必要があります（WRCFGコマンドを使用。表36を参照）。AD変換器はオフになります。LTC6804がSTANDBYステートから開始するよりも早くAD変換を開始できるようにするために、リファレンスがパワーアップされます。

有効なADCコマンドを受け取るとデバイスはMEASUREステートになり、変換を開始します。そうでない場合、手動（WRCFGコマンドを使用）でREFONビットを0に設定するか、ウォッチドッグ・タイマがオーバーフローしたときに自動的に、LTC6804はSTANDBYステートに戻ります。（その後、ウォッチドッグとソフトウェア放電タイマがオーバーフローすると、LTC6804は直接SLEEPステートに移行します。）

#### MEASUREステート

このステートでは、LTC6804はAD変換を実行します。リファレンスとAD変換器がパワーアップされます。

AD変換の完了後、REFONビットに応じて、LTC6804はREFUPステートまたはSTANDBYステートのいずれかに移行します。REFONを1に設定してREFUPステートを活用することによって、AD変換器の立上げ処理を短縮します。

図1.LTC6804動作状態図

680412f

## 動作

注記: ADCコマンド以外のコマンドは、コアのステートの移行を引き起こしません。ADCコマンドまたは診断コマンドのみが、コアをMEASUREステートに移行します。

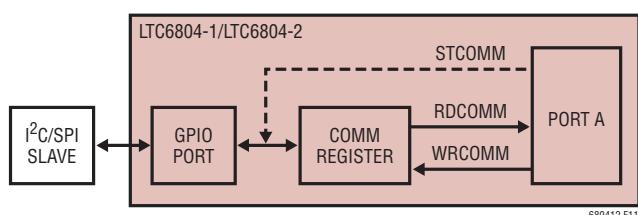

### isoSPIのステートの説明

注記:LTC6804-1は、デイジーチェーン通信用に2つのisoSPIポート(AおよびB)を備えています。LTC6804-2は、アドレス指定可能なパラレル通信用に1つのisoSPIポート(A)を備えています。

#### IDLEステート

isoSPIポートはパワーダウンされます。

isoSPIポートAがウェイクアップ信号を受信すると(「シリアル・インターフェースのウェイクアップ」を参照)、isoSPIはREADYステートに移行します。コアがSTANDBYステートにある場合、DRIVEピンとV<sub>REG</sub>ピンには既に電源供給があるため、素早く(t<sub>READY</sub>以内)READYステートに移行します。コアがSLEEPステートにある場合、isoSPIは、ウェイクアップ信号を受信してから、t<sub>WAKE</sub>以内でREADYステートに移行します。

#### READYステート

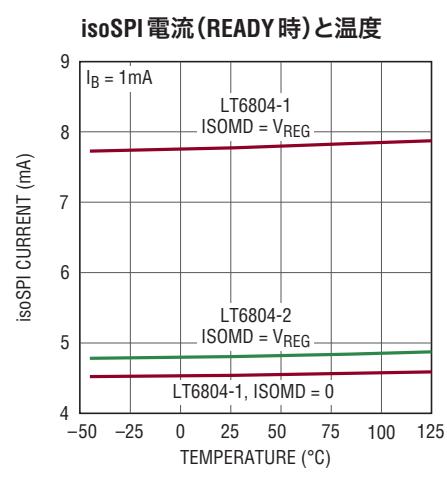

isoSPIポートは通信可能な状態にあります。ポートBは、LTC6804-1でのみイネーブルされ、LTC6804-2には存在しません。このステートでのシリアル・インターフェース電流はLTC6804-1とLTC6804-2で異なるほか、ISOMDピンの状態とR<sub>BIAS</sub> = R<sub>B1</sub> + R<sub>B2</sub>(IBIASピンに接続された外付け抵抗)によっても異なります。

t<sub>IDLE</sub> = 5.5msを超える間、ポートAで動作が発生しなかった場合(つまり、ウェイクアップ信号がなかった場合)、LTC6804はIDLEステートに移行します。シリアル・インターフェースがデータを送信または受信すると、LTC6804はACTIVEステートに移行します。

#### ACTIVEステート

LTC6804は、1つまたは2つ両方のisoSPIポートを用いてデータの送受信を行います。シリアル・インターフェースは、この状態で最も多くの電力を消費します。isoSPIパルスの密度が増えるに従って、クロック周波数と共に消費電流が増加します。

#### 消費電力

LTC6804には、V<sup>+</sup>ピンおよびV<sub>REG</sub>ピンを通して電力が供給されます。V<sup>+</sup>入力は、最上位セルの電圧以上の電圧を必要とし、コア回路の高電圧素子に電力を供給します。V<sup>+</sup>は、バッテリ・スタックの最上位セルに直接または外部電源に接続でき

ます。V<sub>REG</sub>入力は5Vを必要とし、残りのコア回路とisoSPI回路に電力を供給します。V<sub>REG</sub>入力は、安定化されたDRIVE出力ピンから、外付けトランジスタを経由して電力を供給され、ドライブできます。あるいは、外部電源からV<sub>REG</sub>に電力を供給できます。

消費電力は、動作ステートによって異なります。各ステートでの電源ピンの電流を近似する式を、表1と表2に示します。V<sup>+</sup>ピンの電流はコアのステートにのみ依存し、isoSPIのステートには依存しません。ただし、V<sub>REG</sub>ピンの電流は、コアのステートとisoSPIのステートの両方に依存するため、2つの成分に分けることができます。isoSPI回路にはV<sub>REG</sub>ピンからのみ電流を消費します。

$$I_{REG} = I_{REG(CORE)} + I_{REG(isoSPI)}$$

表1. コアの消費電流

| ステート    |                       | I <sub>V+</sub> | I <sub>REG(CORE)</sub> |

|---------|-----------------------|-----------------|------------------------|

| SLEEP   | V <sub>REG</sub> = 0V | 3.8μA           | 0μA                    |

|         | V <sub>REG</sub> = 5V | 1.6μA           | 2.2μA                  |

| STANDBY |                       | 32μA            | 35μA                   |

| REFUP   |                       | 550μA           | 450μA                  |

| MEASURE |                       | 550μA           | 11.5mA                 |

外部電源から電力が供給された場合、SLEEPステートでは、V<sub>REG</sub>ピンに約2.2μAが流れます。そうでない場合、V<sup>+</sup>ピンが必要な電流を供給します。

#### AD変換器の動作

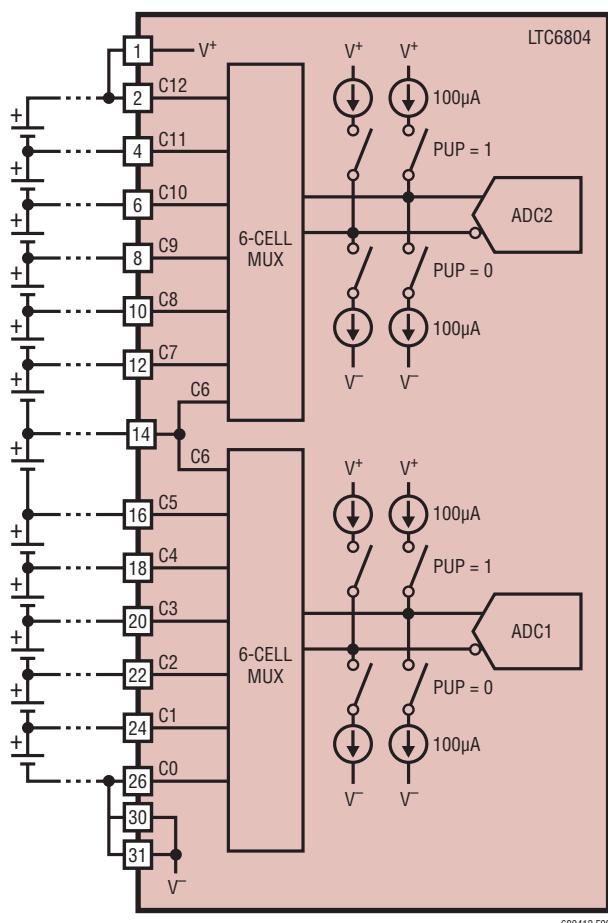

LTC6804には2つのAD変換器があります。これら2つのAD変換器は、12個のセルを測定する際に同時に動作します。汎用入力の測定に使われるAD変換器は1つだけです。以下の説明でADCと表記されている場合は、動作の内容に応じて1つまたは2つのAD変換器を表わします。また、例えばタイミング図でのように、2つの回路を区別する必要がある時はADC1、ADC2と表記します

#### ADCモード

設定レジスタ・グループのADCOPTビット(CFGRO[0])と変換コマンドのモード選択ビットMD[1:0]を組み合わせて、ADCの6つの動作モードが提供されます。これらのモードは、異なるオーバー・サンプリング率(OSR)に対応しています。これらのモードの精度を表3にまとめています。それぞれのモードにおいて、ADCは最初に入力を測定し、その次に各チャネルの較正を行います。各モードの名前は、ADC測定の-3dBの帯域幅に基づいています。

# LTC6804-1/LTC6804-2

## 動作

表2. isoSPIの消費電流の式

| isoSPIのステート | デバイス                | ISOMD接続          | I <sub>REG(isoSPI)</sub>                                                                                                                                                                  |

|-------------|---------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDLE        | LTC6804-1/LTC6804-2 | N/A              | 0mA                                                                                                                                                                                       |

| READY       | LTC6804-1           | V <sub>REG</sub> | 2.8mA + 5 • I <sub>B</sub>                                                                                                                                                                |

|             |                     | V <sup>-</sup>   | 1.6mA + 3 • I <sub>B</sub>                                                                                                                                                                |

|             | LTC6804-2           | V <sub>REG</sub> | 1.8mA + 3 • I <sub>B</sub>                                                                                                                                                                |

|             |                     | V <sup>-</sup>   | 0mA                                                                                                                                                                                       |

| ACTIVE      | LTC6804-1           | V <sub>REG</sub> | Write: 2.8mA + 5 • I <sub>B</sub> + (2 • I <sub>B</sub> + 0.4mA) • $\frac{1\mu s}{t_{CLK}}$<br>Read: 2.8mA + 5 • I <sub>B</sub> + (3 • I <sub>B</sub> + 0.5mA) • $\frac{1\mu s}{t_{CLK}}$ |

|             |                     | V <sup>-</sup>   | 1.6mA + 3 • I <sub>B</sub> + (2 • I <sub>B</sub> + 0.2mA) • $\frac{1\mu s}{t_{CLK}}$                                                                                                      |

|             |                     | V <sub>REG</sub> | Write: 1.8mA + 3 • I <sub>B</sub> + (0.3mA) • $\frac{1\mu s}{t_{CLK}}$<br>Read: 1.8mA + 3 • I <sub>B</sub> + (I <sub>B</sub> + 0.3mA) • $\frac{1\mu s}{t_{CLK}}$                          |

|             |                     | V <sup>-</sup>   | 0mA                                                                                                                                                                                       |

|             | LTC6804-2           | V <sub>REG</sub> |                                                                                                                                                                                           |

|             |                     | V <sup>-</sup>   |                                                                                                                                                                                           |

表3. ADC フィルタの帯域幅と精度

| モード                  | -3dB フィルタ帯域幅 | -40dB フィルタ帯域幅 | 3.3V、25°C での TME 仕様 | 3.3V、-40°C、85°C での TME 仕様 |

|----------------------|--------------|---------------|---------------------|---------------------------|

| 27kHz (Fast Mode)    | 27kHz        | 84kHz         | ±4.7mV              | ±4.7mV                    |

| 14kHz                | 13.5kHz      | 42kHz         | ±4.7mV              | ±4.7mV                    |

| 7kHz (Normal Mode)   | 6.8kHz       | 21kHz         | ±1.2mV              | ±2.2mV                    |

| 3kHz                 | 3.4kHz       | 10.5kHz       | ±1.2mV              | ±2.2mV                    |

| 2kHz                 | 1.7kHz       | 5.3kHz        | ±1.2mV              | ±2.2mV                    |

| 26Hz (Filtered Mode) | 26Hz         | 82Hz          | ±1.2mV              | ±2.2mV                    |

注記:TMEは全測定値誤差。

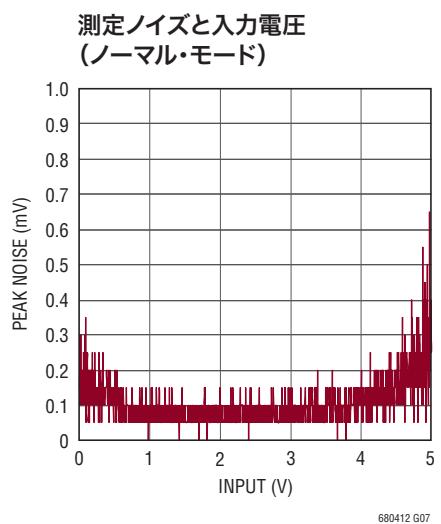

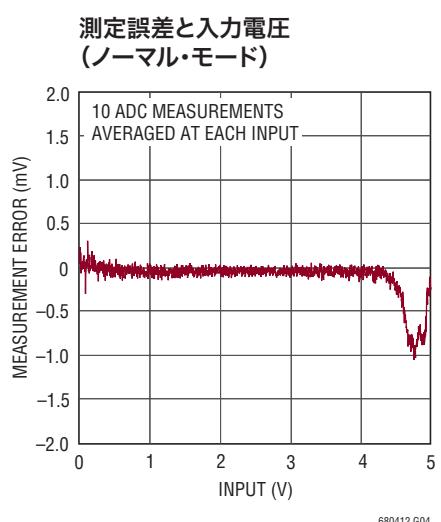

### 7kHzモード(ノーマル・モード)

このモードでは、ADCは高い分解能を持ち、TME(全測定誤差)が低く抑えられています。これは、速度と精度のバランスが最適になるように組み合わされていることから、ノーマル動作モードと見なされます。

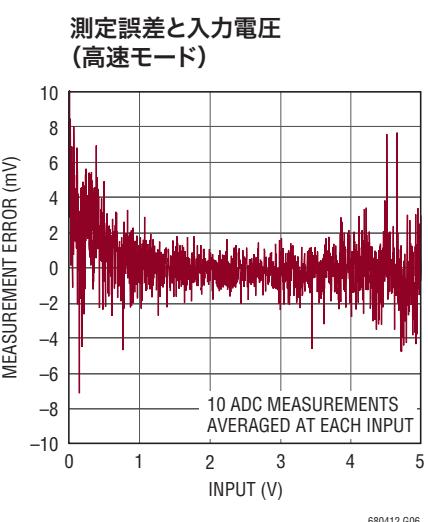

### 27kHzモード(高速モード)

このモードでは、ADCのスループットは最大になりますが、TME(全測定誤差)がある程度増加します。そのためこのモードは、高速モードとも呼ばれます。速度の向上は、オーバーサンプリング率を小さくすることによって実現されます。その結果、ノイズと平均測定誤差が増加します。

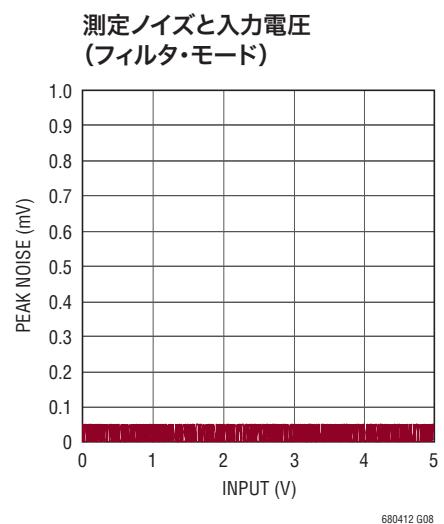

### 26Hzモード(フィルタ・モード)

このモードでは、OSRを増やすことによって、ADCのデジタル・フィルタの-3dB周波数を26Hzに低減します。このモードは、低い-3dB周波数のため、フィルタ・モードとも呼ばれます。精度は7kHzモード(ノーマル・モード)と同様ですが、ノイズが少なくなります。

### 14kHz、3kHz、および2kHzモード

14kHz、3kHz、および2kHzモードは、ADCデジタル・フィルタの-3dB周波数をそれぞれ13.5kHz、3.4kHz、および1.7kHzに設定する追加オプションを提供します。14kHzモードの精度は、27kHzモード(高速モード)と同様です。3kHzモードと2kHzモードの精度は、7kHzモード(ノーマル・モード)と同様です。

680412f

## 動作

これらのモードの変換時間を表5に示します。コアがSTANDBYステートにある場合、ADC変換を開始する前にリファレンスをパワーアップするために、さらにtREFUP時間が必要になります。設定レジスタ・グループのREFONビットを1に設定した場合、各AD変換の間でリファレンスをパワーアップしたままにできます。その場合、コアは、遅延tREFUPの後にREFUPステートになります。その後のADCコマンドでは、AD変換を開始する前にtREFUPの遅延は発生しません。

## ADCの範囲と分解能

C入力とGPIO入力の範囲と分解能は同じです。LTC6804内のADCの範囲は、およそ-0.82V～5.73Vです。負の読み取り値は0Vに丸められます。データのフォーマットは符号なし16ビット整数で、 LSBが100 $\mu$ Vを示します。したがって、0x80E8(10進数で33,000)は3.3Vの測定値を示します。

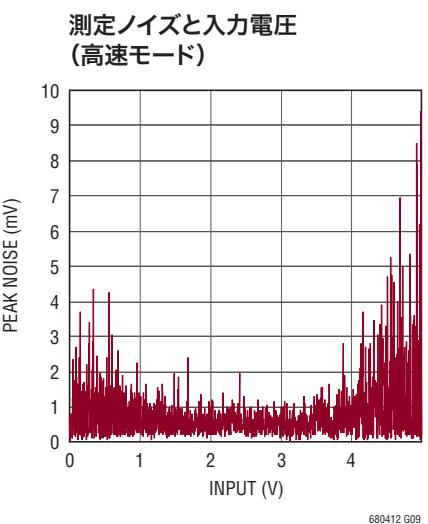

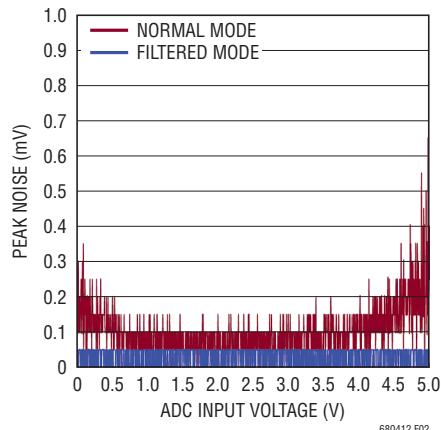

デルタシグマ型ADCでは、特に高速モードなどでオーバー・サンプリング率(OSR)が低い場合に、入力電圧に応じて量子化ノイズが発生します。ADCモードの一部では、量子化ノイズは、入力電圧がADC範囲の上限と下限に近付くに従って増加します。例として、図2に、ノーマル・モードとフィルタ・モードでの全測定ノイズと入力電圧を示します。

ADCの既定範囲は0V～5Vです。表4では、ADCの精度範囲は、0.5V～4.5Vの間で任意に定義されます。これは、より低いOSRモードでも量子化ノイズが相対的に一定になる範囲です(図2を参照)。ADCの6つの動作モードすべてについて、この範囲内の合計ノイズを表4にまとめます。ノイズのない分解能も示されています。例えば、ノーマル・モードでのノイズ

図2. 測定ノイズと入力電圧

のない14ビットの分解能とは、DC入力で上位14ビットにはノイズがないが、15番目と16番目の最下位ビット(LSB)が変動することを意味しています。

## ADC範囲と電圧リファレンス値

標準的なデルタシグマ型ADCの範囲は電圧リファレンスを正確に2倍した値で、ADCの測定誤差は電圧リファレンスの誤差に比例しますが、LTC6804のADCは標準的なものではありません。V<sub>REF1</sub>の絶対値は、ADCの利得誤差を補正するためにトリムアップ/ダウンされます。したがって、ADCの全測定誤差(TME)仕様はV<sub>REF1</sub>の仕様よりも優れています。例えば、7kHzモード(ノーマル・モード)での3.300V測定時の全測定誤差は25°C仕様で±1.2mVですが、V<sub>REF1</sub>の25°C仕様は3.200V±100mVです。

表4. ADCの範囲と分解能

| モード             | 全範囲 <sup>1</sup>    | 規定範囲     | 精度範囲 <sup>2</sup> | LSB         | 形式               | 最大ノイズ                       | ノイズのない分解能 <sup>3</sup> |

|-----------------|---------------------|----------|-------------------|-------------|------------------|-----------------------------|------------------------|

| 27kHz (Fast)    | -0.8192V to 5.7344V | 0V to 5V | 0.5V to 4.5V      | 100 $\mu$ V | Unsigned 16 Bits | ±4mV <sub>P-P</sub>         | 10 Bits                |

| 14kHz           |                     |          |                   |             |                  | ±1mV <sub>P-P</sub>         | 12 Bits                |

| 7kHz (Normal)   |                     |          |                   |             |                  | ±250 $\mu$ V <sub>P-P</sub> | 14 Bits                |

| 3kHz            |                     |          |                   |             |                  | ±150 $\mu$ V <sub>P-P</sub> | 14 Bits                |

| 2kHz            |                     |          |                   |             |                  | ±100 $\mu$ V <sub>P-P</sub> | 15 Bits                |

| 26Hz (Filtered) |                     |          |                   |             |                  | ±50 $\mu$ V <sub>P-P</sub>  | 16 Bits                |

1. 負の読み取り値は0Vに丸められます。

2. 精度範囲は、ノイズが最大ノイズより小さくなる範囲です。

3. ノイズのない分解能は、精度範囲内のノイズ・レベルの測定値です。

# LTC6804-1/LTC6804-2

## 動作

### セル電圧の測定(ADCVコマンド)

ADCVコマンドは、ピンC0からC12までのバッテリ・セル入力の測定を開始します。このコマンドには、測定チャネル数とADCモードを選択するためのオプションが複数あります。ADCVコマンドのフォーマットについては、「コマンド」のセクションを参照してください。

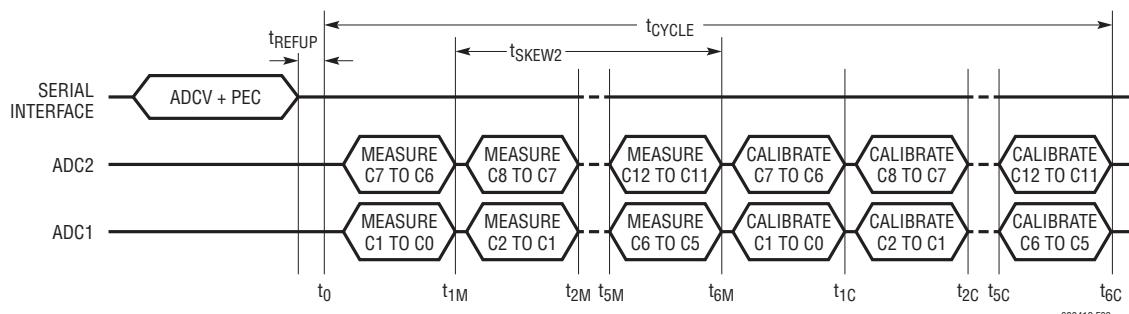

図3は、12個のセルすべてを測定するADCVコマンドのタイミングを示しています。12個のセルすべてを測定するためのADCVコマンドを受け取ると、ADC1がボトム側6個のセルを順に測定し、ADC2はトップ側6個のセルを順に測定します。セル測定が完了すると、オフセット誤差をなくすために各チャネルの較正が行われます。

12個のセルすべてを測定するADCVコマンドの変換時間を表5に示します。合計変換時間は、較正ステップの終了を示す $t_{6C}$ から得られます。

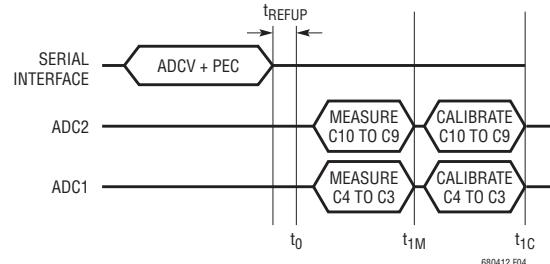

図4は、2つのセルのみを測定するADCVコマンドのタイミングを示しています。

2つのセルのみを測定するADCVコマンドの変換時間を、表6に示します。 $t_{1C}$ は、このコマンドの合計変換時間を示しています。

図4.2 セルを測定するADCVコマンドのタイミング

表6. さまざまなモードで2つのセルのみを測定するADCVコマンドの変換時間

| モード   | 変換時間(μs) |          |          |

|-------|----------|----------|----------|

|       | $t_0$    | $t_{1M}$ | $t_{1C}$ |

| 27kHz | 0        | 57       | 201      |

| 14kHz | 0        | 86       | 230      |

| 7kHz  | 0        | 144      | 405      |

| 3kHz  | 0        | 240      | 501      |

| 2kHz  | 0        | 493      | 754      |

| 26Hz  | 0        | 29,817   | 33,568   |

図3.12個のセルすべてを測定するADCVコマンドのタイミング

表5. さまざまなモードで12個のセルすべてを測定するADCVコマンドの変換時間

| モード   | 変換時間(μs) |          |          |          |          |          |          |          |          |

|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

|       | $t_0$    | $t_{1M}$ | $t_{2M}$ | $t_{5M}$ | $t_{6M}$ | $t_{1C}$ | $t_{2C}$ | $t_{5C}$ | $t_{6C}$ |

| 27kHz | 0        | 57       | 103      | 243      | 290      | 432      | 568      | 975      | 1,113    |

| 14kHz | 0        | 86       | 162      | 389      | 465      | 606      | 742      | 1,149    | 1,288    |

| 7kHz  | 0        | 144      | 278      | 680      | 814      | 1,072    | 1,324    | 2,080    | 2,335    |

| 3kHz  | 0        | 260      | 511      | 1,262    | 1,512    | 1,770    | 2,022    | 2,778    | 3,033    |

| 2kHz  | 0        | 493      | 976      | 2,425    | 2,908    | 3,166    | 3,418    | 4,175    | 4,430    |

| 26Hz  | 0        | 29,817   | 59,623   | 149,043  | 178,850  | 182,599  | 186,342  | 197,571  | 201,317  |

680412f

## 動作

### 低電圧/過電圧モニタ

セル電圧が測定された際、その結果は設定レジスタに保存された低電圧しきい値および過電圧しきい値と比較されます。セルの測定値が過電圧しきい値を超えている場合は、過電圧フラグのビットがセットされます。同様に、測定結果が低電圧しきい値を下回っている場合は低電圧フラグのビットがセットされます。過電圧しきい値と低電圧しきい値は、設定レジスタ・グループに格納されます。各フラグは、ステータス・レジスタ・グループBに格納されます。

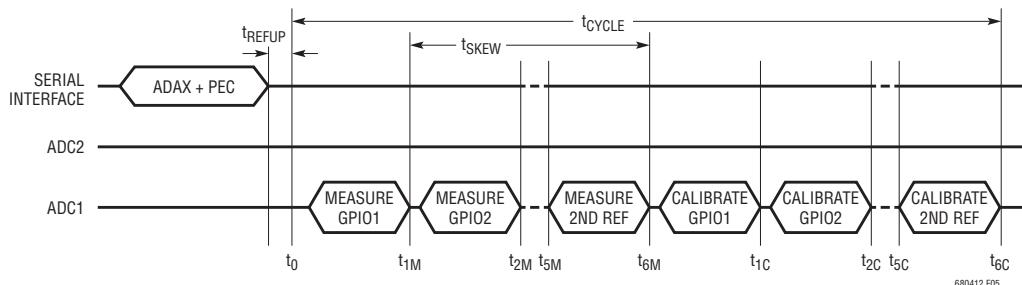

### 補助(GPIO)測定(ADAXコマンド)

ADAXコマンドによってGPIO入力の測定が開始されます。このコマンドには、測定するGPIO入力(GPIO1~5)とADCモードを選択するためのオプションがあります。ADAXコマンドは、2番目のリファレンスも測定します。ADAXコマンドには、各GPIOと2番目のリファレンスを個別に測定するためのオプションと、5つのGPIOすべてと2番目のリファレンスを1つのコマンドで測定するためのオプションがあります。ADAXコマンドのフォーマットについては、「コマンド」のセクションを参照してください。すべての補助測定はV<sup>-</sup>ピンの電圧を基準にしてください。

ます。GPIOに温度センサを接続すれば、このコマンドを使用して外部温度を測定することができます。これらのセンサの電源は2番目のリファレンスから取ることができ、このリファレンスもADAXコマンドによって測定されるので、正確な比率に基づいて測定を行うことができます。

図5は、すべてのGPIOと2番目のリファレンスを測定するADAXコマンドのタイミングを示しています。6つの測定がすべてADC1に対してのみ実行されるため、ADAXコマンドの変換時間はADCVコマンドと同様です。

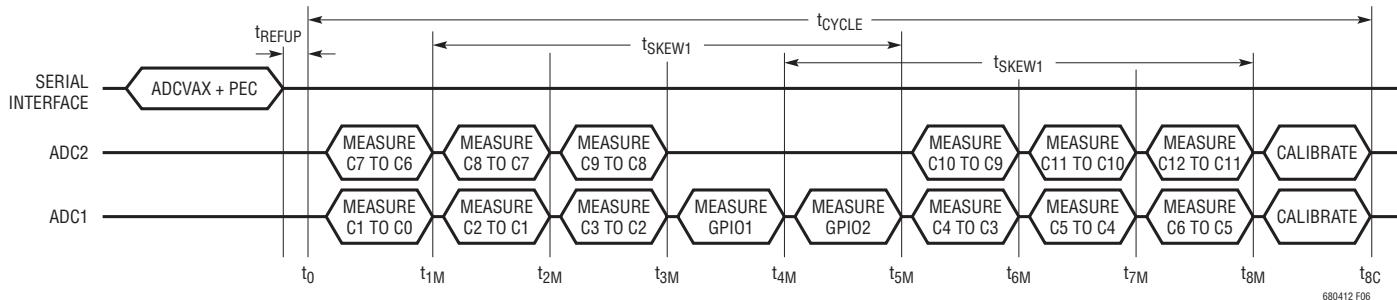

### セル電圧とGPIOの測定(ADCVAXコマンド)

ADCVAXコマンドは、12個のセルの測定値を2つのGPIO測定値(GPIO1およびGPIO2)と組み合わせます。このコマンドを使用すれば、電流センサをGPIO1入力またはGPIO2入力に接続した場合に、バッテリ・セル電圧測定値と電流測定値の同期が容易になります。ADCVAXコマンドのタイミングを図6に示します。ADCVAXコマンドのフォーマットについては、「コマンド」のセクションを参照してください。高速モードにおける電流測定値と電圧測定値の同期時間(t<sub>SKREW1</sub>)は、208μs以内です。

図5. すべてのGPIOと2番目のリファレンスを測定するADAXコマンドのタイミング

表7. さまざまなモードですべてのGPIOと2番目のリファレンスを測定するADAXコマンドの変換時間

| モード   | 変換時間(μs)       |                 |                 |                 |                 |                 |                 |                 |                 |

|-------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|       | t <sub>0</sub> | t <sub>1M</sub> | t <sub>2M</sub> | t <sub>5M</sub> | t <sub>6M</sub> | t <sub>1C</sub> | t <sub>2C</sub> | t <sub>5C</sub> | t <sub>6C</sub> |

| 27kHz | 0              | 57              | 103             | 243             | 290             | 432             | 568             | 975             | 1,113           |

| 14kHz | 0              | 86              | 162             | 389             | 465             | 606             | 742             | 1,149           | 1,288           |

| 7kHz  | 0              | 144             | 278             | 680             | 814             | 1,072           | 1,324           | 2,080           | 2,335           |

| 3kHz  | 0              | 260             | 511             | 1,262           | 1,512           | 1,770           | 2,022           | 2,778           | 3,033           |

| 2kHz  | 0              | 493             | 976             | 2,425           | 2,908           | 3,166           | 3,418           | 4,175           | 4,430           |

| 26Hz  | 0              | 29,817          | 59,623          | 149,043         | 178,850         | 182,599         | 186,342         | 197,571         | 201,317         |

# LTC6804-1/LTC6804-2

## 動作

図6.ADCVAXコマンドのタイミング

表8. さまざまなモードでのADCVAXコマンドの変換時間と同期時間

| モード   | 変換時間(μs)       |                 |                 |                 |                 |                 |                 |                 |                 | 同期時間(μs) |

|-------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------|

|       | t <sub>0</sub> | t <sub>1M</sub> | t <sub>2M</sub> | t <sub>3M</sub> | t <sub>4M</sub> | t <sub>5M</sub> | t <sub>6M</sub> | t <sub>7M</sub> | t <sub>8M</sub> |          |

| 27kHz | 0              | 57              | 106             | 155             | 216             | 265             | 326             | 375             | 424             | 1,564    |

| 14kHz | 0              | 86              | 161             | 237             | 320             | 396             | 479             | 555             | 630             | 1,736    |

| 7kHz  | 0              | 144             | 278             | 412             | 553             | 687             | 828             | 962             | 1,096           | 3,133    |

| 3kHz  | 0              | 260             | 511             | 761             | 1,018           | 1,269           | 1,526           | 1,777           | 2,027           | 4,064    |

| 2kHz  | 0              | 493             | 976             | 1,459           | 1,949           | 2,432           | 2,923           | 3,406           | 3,888           | 5,925    |

| 26Hz  | 0              | 29,817          | 59,623          | 89,430          | 119,244         | 149,051         | 178,864         | 208,671         | 238,478         | 268,442  |

|       |                |                 |                 |                 |                 |                 |                 |                 |                 | 119234   |

さまざまなモードでのADCVAXコマンドの変換時間と同期時間を表8に示します。このコマンドの合計変換時間は、t<sub>8C</sub>から得られます。

## データ収集システムの診断

バッテリ・モニタ・データ収集システムは、マルチプレクサ、ADC、1番目のリファレンス、デジタル・フィルタ、およびメモリで構成されます。信頼性の高い性能を長期間保証するために、診断コマンドがいくつかあります。これらのコマンドを使用して、各回路が正常に動作していることを確認できます。

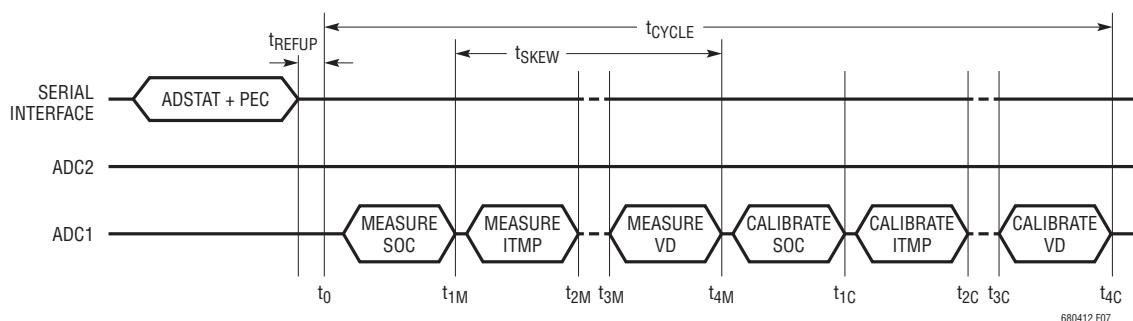

## 内部デバイス・パラメータの測定(ADSTATコマンド)

ADSTATコマンドは、次の内部デバイス・パラメータを測定する診断コマンドです：すべてのセルの合計(SOC)、内部ダイ温度(ITMP)、アナログ電源(VA)、およびデジタル電源(VD)。これらのパラメータについて、以降のセクションで説明します。6つのADCモードは、すべてこれらの変換で使用できます。ADSTATコマンドのフォーマットについては、「コマンド」のセクションを参照してください。図7は、4つの内部デバイス・パラメータすべてを測定するADSTATコマンドのタイミングを示しています。

図7.SOC、ITMP、VA、VDを測定するADSTATコマンドのタイミング

680412f

## 動作

4つの内部パラメータすべてを測定するADSTATコマンドの変換時間を表9に示します。 $t_{4C}$ は、ADSTATコマンドの合計変換時間を示しています。

**すべてのセルの合計測定：**すべてのセルの合計測定値は、減衰を20:1とした場合のC12とC0の間の電圧です。16ビットADCのセルの合計測定値(SOC)は、ステータス・レジスタ・グループAに格納されます。SOCの値から、すべてのセル電圧の合計測定値は、次の式によって得られます。

$$\text{すべてのセルの合計} = \text{SOC} \cdot 20 \cdot 100\mu\text{V}$$

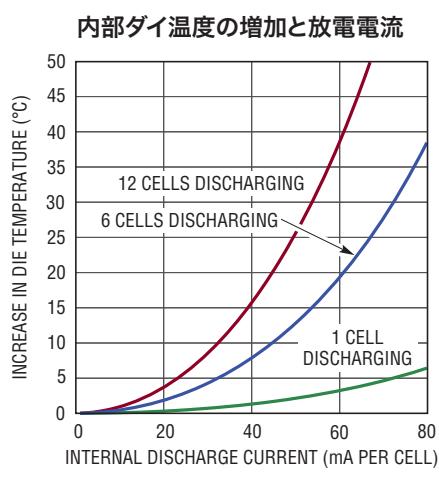

**内部ダイ温度：**ADSTATコマンドは、内部ダイ温度の測定にも使用できます。16ビットADCのダイ温度の測定値(ITMP)は、ステータス・レジスタ・グループAに格納されます。ITMPから、実際のダイ温度は次の式を用いて計算されます。

$$\text{内部ダイ温度} (\text{°C}) = (\text{ITMP}) \cdot 100\mu\text{V}/(7.5\text{mV})\text{°C} - 273\text{°C}$$

**電源測定値：**ADSTATコマンドは、アナログ電源( $V_{\text{REG}}$ )とデジタル電源( $V_{\text{REGD}}$ )の測定にも使われます。

16ビットADCのアナログ電源の測定値(VA)は、ステータス・レジスタ・グループAに格納されます。16ビットADCのデジタル電源の測定値(VD)は、ステータス・レジスタ・グループBに格納されます。VAとVDから、各電源の測定値は次の式によって得られます。

$$\text{アナログ電源の測定値} (V_{\text{REG}}) = V_A \cdot 100\mu\text{V}$$

$$\text{デジタル電源の測定値} (V_{\text{REGD}}) = V_D \cdot 100\mu\text{V}$$

$V_{\text{REG}}$ の公称範囲は4.5V～5.5Vです。 $V_{\text{REGD}}$ の公称範囲は2.7V～3.6Vです。

## 精度チェック

データ収集システムの精度を確認する最良の方法は、独立した電圧リファレンスを測定することです。LTC6804には、このために2番目のリファレンスが内蔵されています。ADAXコマンドは、この2番目のリファレンスの測定を開始します。測定結果は、補助レジスタ・グループBに配置されます。この結果の範囲は、ADC測定の精度と2番目のリファレンスの精度によって変わり、熱ヒステリシスと長期間ドリフトを含んでいます。読み取り値が2.980～3.020の範囲を外れる場合は、システムが指定された許容差に収まっていないことを示しています。

## MUXデコーダ・チェック

診断コマンドDIAGNによって、各マルチプレクサ・チャネルが正しく動作していることを確認できます。このコマンドはすべてのチャネルを巡回確認して、使われていないチャネル・デコーダがある場合はステータス・レジスタのグループBのMUXFAILビットを1に設定します。チャネル・デコーダがテストに合格した場合、MUXFAILビットは0に設定されます。MUXFAILビットは、パワーアップ時(POR)またはCLRSTATコマンドの実行後にも、1に設定されます。

コアがREFUPステートにある場合、DIAGNコマンドの実行には約400μsかかります。コアがSTANDBYステートにある場合、DIAGNコマンドの実行には約4.5msかかります。「ポーリング方法」のセクションに記載されたポーリング方法を使用して、DIAGNコマンドの完了を確認できます。

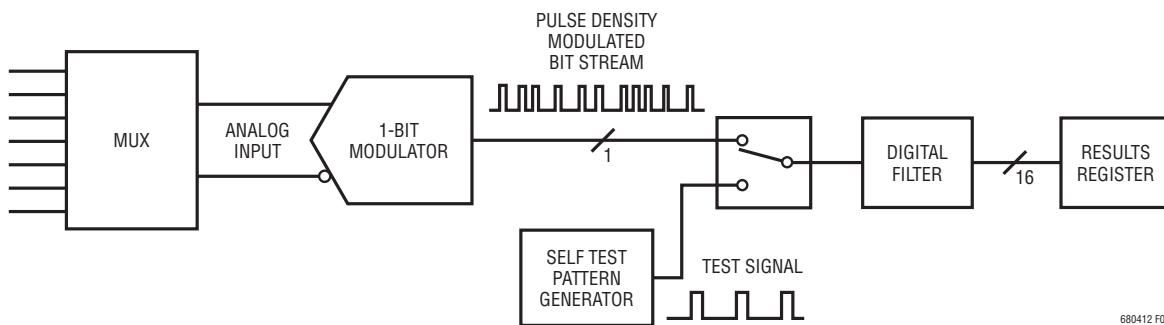

## デジタル・フィルタ・チェック

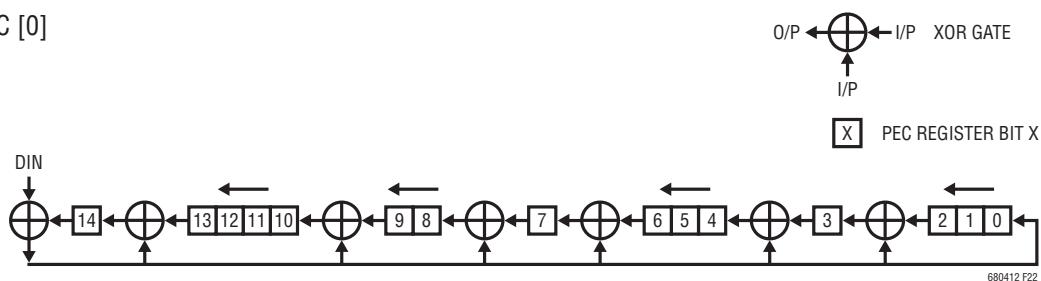

デルタシグマADCは、1ビット・パルス密度変調器とその後段に接続されたデジタル・フィルタで構成されています。アナログ入力電圧が高くなると、パルス密度変調ビット・ストリームにおける1の比率(%)が大きくなります。

表9. SOC、ITMP、VA、VDを測定するADSTATコマンドの変換時間

| モード   | 変換時間(μs) |          |          |          |          |          |          |          |          |  |

|-------|----------|----------|----------|----------|----------|----------|----------|----------|----------|--|

|       | $t_0$    | $t_{1M}$ | $t_{2M}$ | $t_{3M}$ | $t_{4M}$ | $t_{1C}$ | $t_{2C}$ | $t_{3C}$ | $t_{4C}$ |  |

| 27kHz | 0        | 57       | 103      | 150      | 197      | 338      | 474      | 610      | 748      |  |

| 14kHz | 0        | 86       | 162      | 237      | 313      | 455      | 591      | 726      | 865      |  |

| 7kHz  | 0        | 144      | 278      | 412      | 546      | 804      | 1,056    | 1,308    | 1,563    |  |

| 3kHz  | 0        | 260      | 511      | 761      | 1,011    | 1,269    | 1,522    | 1,774    | 2,028    |  |

| 2kHz  | 0        | 493      | 976      | 1,459    | 1,942    | 2,200    | 2,452    | 2,705    | 2,959    |  |

| 26Hz  | 0        | 29,817   | 59,623   | 89,430   | 119,237  | 122,986  | 126,729  | 130,472  | 134,218  |  |

680412f

# LTC6804-1/LTC6804-2

## 動作

デジタル・フィルタは、この頻度の高い1ビット・ストリームを1つの16ビット・ワードに変換します。デルタシグマ型ADCが、よくオーバーサンプリング・コンバータと呼ばれるのはこのためです。

デジタル・フィルタとメモリの動作は、自己テスト・コマンドによって確認できます。自己テスト中のADCの動作を図8に示します。1ビット・パルス密度変調器の出力は、1ビット・テスト信号に置き換えられます。このテスト信号はデジタル・フィルタを通過して16ビット値に変換されます。1ビット・テスト信号には、変調器からの通常の1ビット・パルスと同じデジタル変換が行われるので、自己テスト・コマンドによる変換時間は通常のADC変換コマンドによる変換時間とまったく同じです。16ビットADC値は、通常のADC変換コマンドと同じレジスタ・グループに保存されます。テスト信号は、1と0が交互に現れるパターンをレジスタ内に置くように設計されています。自己テスト・コマンドの一覧を表10に示します。デジタル・フィルタとメモリが正しく機能している場合は、表10に示す値がレジスタに格納されます。詳細については、「コマンド」のセクションを参照してください。

### ADCクリア・コマンド

LTC6804には、CLRCELL、CLRAUX、CLRSTATという3つのクリア・コマンドがあります。これらのコマンドは、すべてのADC変換結果の保存レジスタをクリアします。

CLRCELLコマンドは、セル電圧レジスタ・グループA、B、C、およびDをクリアします。これらのレジスタ内のすべてのバイトは、CLRCELLコマンドによって0xFFに設定されます。