## 特長

- 周波数範囲: 30MHz～1300MHz

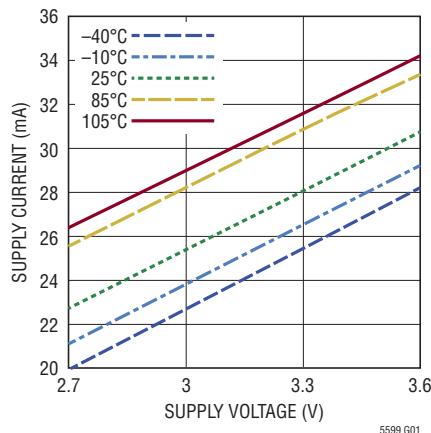

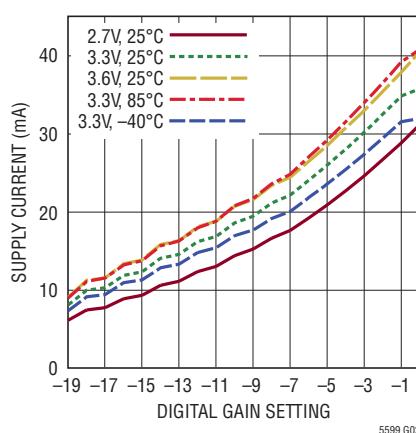

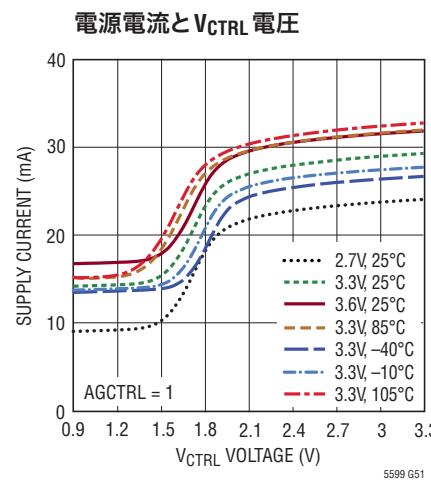

- 低消費電力: 2.7V～3.6V の電源電圧、28mA

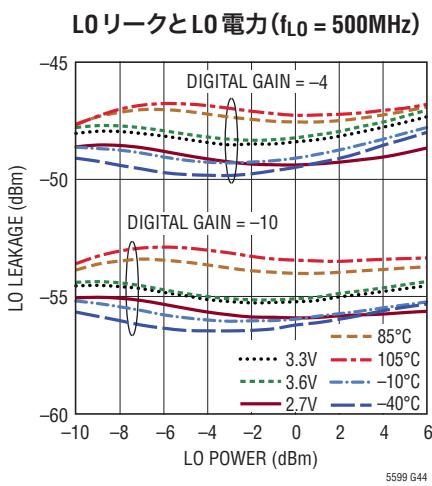

- LO搬送波の漏れが少ない: -51.5dBm (500MHz 時)

- 側波帯の抑圧比: -52.6dBc (500MHz 時)

- 出力IP3: 20.8dBm (500MHz 時)

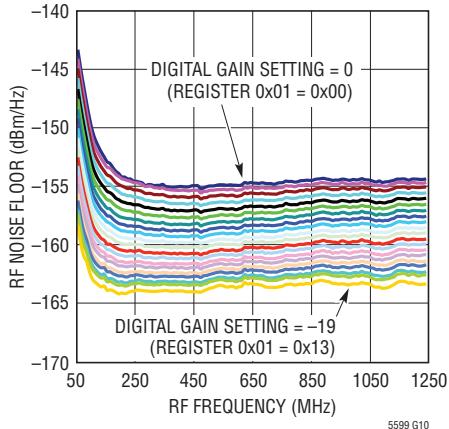

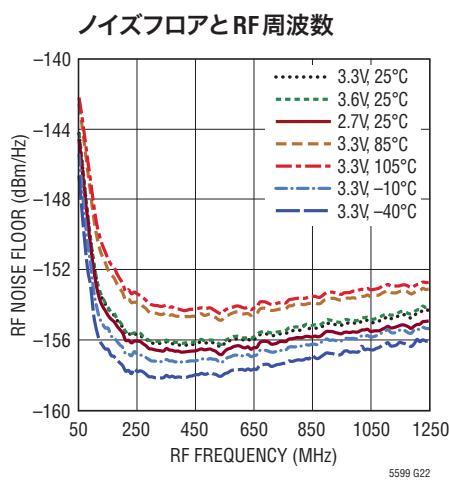

- RF出力ノイズフロアが低い:

-156dBm/Hz (オフセット 6MHz 時、 $P_{RF} = 3\text{dBm}$ )

- 正弦波または方形波によるLOの駆動

- SPI制御:

- 可変利得: -19dB～0dB/1dBステップ

- 電源電流が 8mA～35mA 变化

- I/Qオフセット調整: LO搬送波の漏れ: -65dBm

- I/Qの利得/位相調整: 側波帯の抑圧量が -60dBc

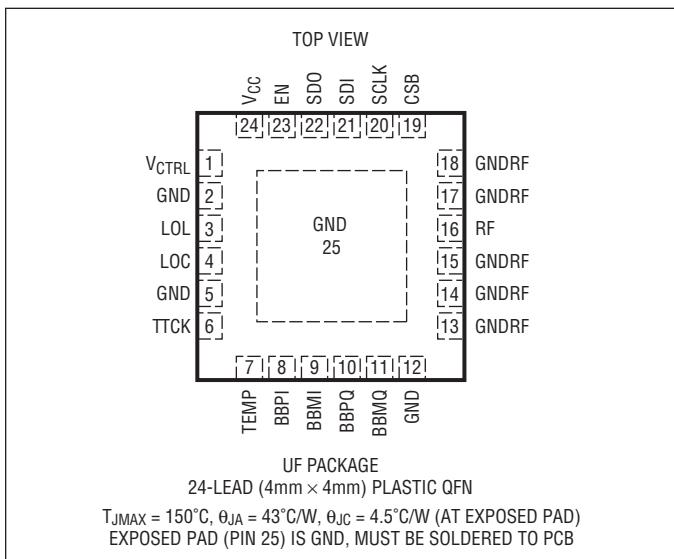

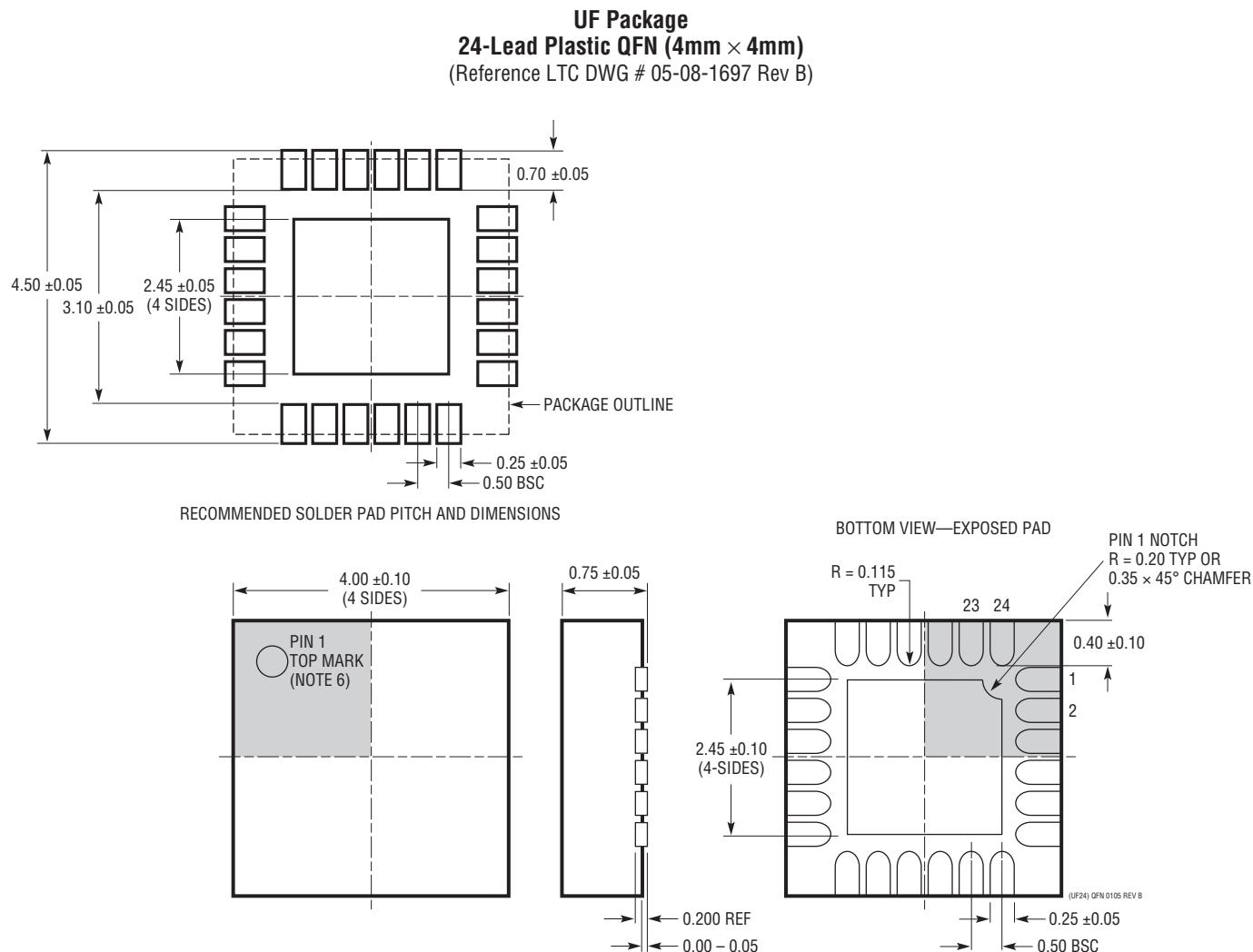

- 4mm×4mmの24ピンQFNパッケージ

## アプリケーション

- 無線マイクロホン

- バッテリ駆動の無線機器

- 臨時の無線インフラ・ネットワーク

- 「ホワイトスペース」トランスマッタ

- ソフトウェア無線(SDR)

- 軍用無線

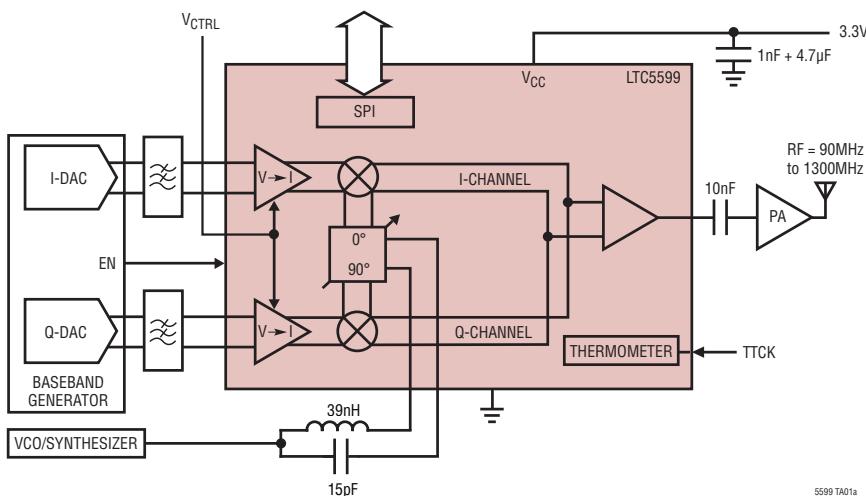

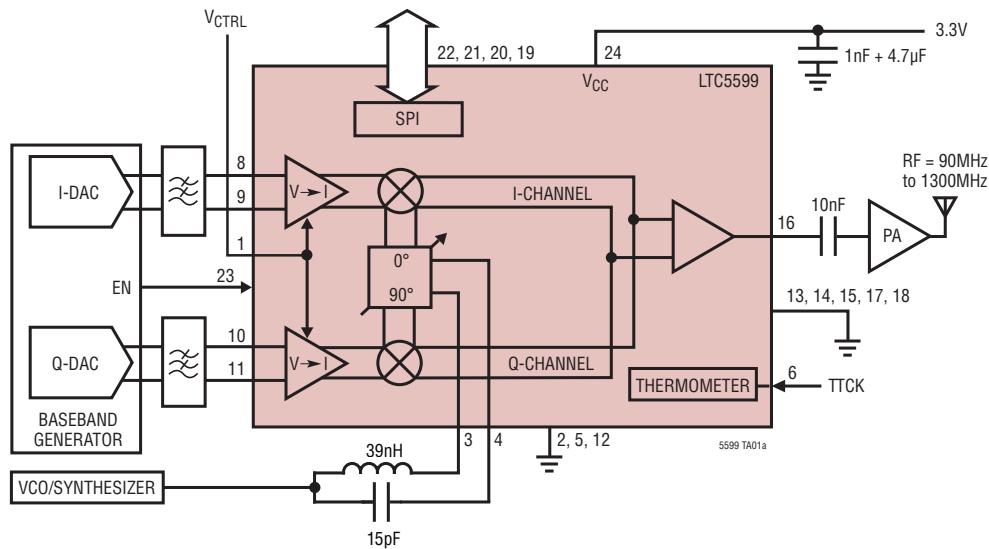

## 標準的応用例

90MHz～1300MHz 直接変換トランスマッタ・アプリケーション

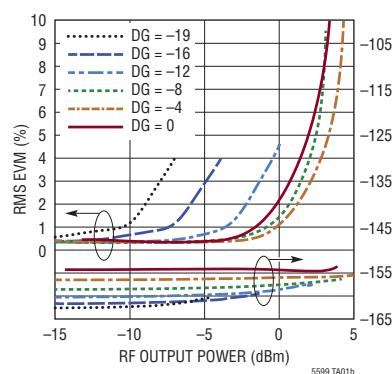

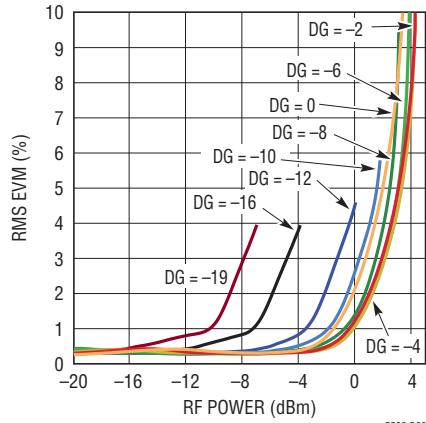

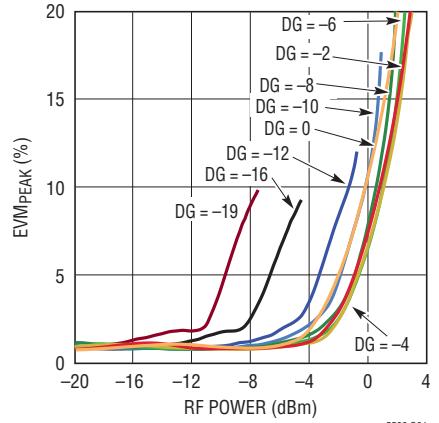

1Ms/s 16-QAM信号でのEVMおよび

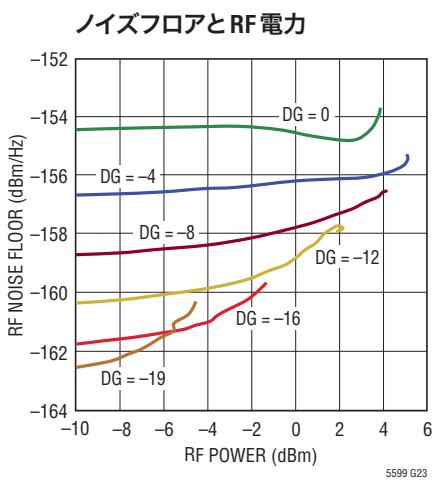

ノイズフロアとRF出力電力および

デジタル利得設定

## 概要

LTC<sup>®</sup>5599は、低消費電力のワイヤレス・アプリケーション向けに設計された直接変換I/Q変調器で、RF搬送波の差動ベースバンドI信号およびQ信号を直接変調できます。90°の位相シフト信号をI入力とQ入力に入力することにより、単側波帯変調または側波帯抑圧アップコンバージョンを実現できます。I/Qベースバンド入力ポートは、同相電圧レベルが約1.4Vの信号源にAC結合またはDC結合できます。SPIインターフェースは電源電流、変調器利得を制御し、LO搬送波のフィードスルーおよび側波帯抑圧の最適化が可能であり、正弦波または方形波のLO駆動回路を備えています。LOポートとRFポートの固定LC回路網は、90MHz～1300MHzでの連続動作をカバーしています。内蔵の温度計を作動して、利得の温度変動を補償できます。内蔵のダイオードを使用することにより、より正確な温度測定を行うことができます。さらに、連続アナログ利得制御(VCTRL)ピンを使用して、電力をすばやく制御できます。

LT、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。QuikEvalはリニアテクノロジー社の商標です。その他全ての商標の所有権は、それぞれの所有者に帰属します。

## 絶対最大定格

### (Note 1)

|                              |                            |

|------------------------------|----------------------------|

| 電源電圧                         | 3.8V                       |

| BBPI、BBMI、およびBBPQ、BBMQの同相レベル | 2V                         |

| LOL、LOCのDC電圧                 | $\pm 0.1V$                 |

| LOL、LOCの入力電力(Note 15)        | 20dBm                      |

| TEMP、SDOの電流シンク               | 10mA                       |

| 全てのピンの電圧(Note 16)            | $-0.3V \sim V_{CC} + 0.3V$ |

| T <sub>JMAX</sub>            | 150°C                      |

| ケース動作温度範囲                    | -40°C ~ 105°C              |

| 保存温度範囲                       | -65°C ~ 150°C              |

## ピン配置

## 発注情報

| 無鉛仕上げ          | テープ・アンド・リール      | 製品マーキング | パッケージ                         | ケース温度範囲        |

|----------------|------------------|---------|-------------------------------|----------------|

| LTC5599IUF#PBF | LTC5599IUF#TRPBF | 5599    | 24-Lead (4mm×4mm) Plastic QFN | -40°C to 105°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>をご覧ください。

テープ・アンド・リールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/>をご覧ください。

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>を参照してください。

**電気的特性** ●は全動作温度範囲での規格値を意味する。それ以外は  $T_C = 25^{\circ}\text{C}$  での値。注記がない限り、 $V_{CC} = 3.3\text{V}$ 、 $EN = 3.3\text{V}$ 、 $V_{CTRL} = 3.3\text{V}$ 、 $P_{LO} = 0\text{dBm}$ 、BBPI、BBMI、BBPQ、BBMQ の同相 DC 電圧  $V_{CMBB} = 1.4V_{DC}$ 、I および Q ベースバンド入力信号 = 2MHz、2.1MHz、1V<sub>P-P</sub>(DIFF, I or Q)、I および Q は 90°シフト、下側波帯選択、全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

| SYMBOL                                                                                                | PARAMETER                        | CONDITIONS                                                           | MIN | TYP            | MAX | UNITS      |

|-------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------|-----|----------------|-----|------------|

| $f_{LO} = 150\text{MHz}$ , $f_{RF1} = 147.9\text{MHz}$ , $f_{RF2} = 148\text{MHz}$ , レジスタ 0x00 = 0x62 |                                  |                                                                      |     |                |     |            |

| S <sub>22(ON)</sub>                                                                                   | RF Port Return Loss              |                                                                      |     | -26            |     | dB         |

| f <sub>LO(MATCH)</sub>                                                                                | LO Match Frequency Range         | S11 < -10dB                                                          |     | 116 to 272     |     | MHz        |

| Gain                                                                                                  | Conversion Voltage Gain          | $20 \cdot \log(V_{RF(OUT)}(50\Omega)/V_{IN(DIFF)}(I \text{ or } Q))$ |     | -7.5           |     | dB         |

| P <sub>OUT</sub>                                                                                      | Absolute Output Power            | 1V <sub>P-P(DIFF)</sub> CW Signal, I and Q                           |     | -3.5           |     | dBm        |

| OIP1dB                                                                                                | Output 1dB Compression           |                                                                      |     | 5              |     | dBm        |

| OIP2                                                                                                  | Output 2nd Order Intercept       | (Note 5)                                                             |     | 70.5           |     | dBm        |

| OIP3                                                                                                  | Output 3rd Order Intercept       | (Note 6)                                                             |     | 21.7           |     | dBm        |

| NFloor                                                                                                | RF Output Noise Floor            | No Baseband AC Input Signal (Note 3)                                 |     | -155.3         |     | dBm/Hz     |

| SB                                                                                                    | Side-Band Suppression            | (Note 7)                                                             |     | -61.4          |     | dBc        |

| LOFT                                                                                                  | Carrier Leakage (LO Feedthrough) | (Note 7)<br>EN = Low (Note 7)                                        |     | -52.8<br>-84.8 |     | dBm<br>dBm |

| 2LOFT                                                                                                 | LO Feedthrough at 2xLO           |                                                                      |     | -59            |     | dBm        |

**電気的特性**

●は全動作温度範囲での規格値を意味する。それ以外は $T_C = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = 3.3\text{V}$ 、 $EN = 3.3\text{V}$ 、 $V_{CTRL} = 3.3\text{V}$ 、 $P_{LO} = 0\text{dBm}$ 、BBPI、BBMI、BBPQ、BBMQの同相DC電圧 $V_{CMBB} = 1.4\text{V}_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1V<sub>P-P</sub>(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

| SYMBOL              | PARAMETER               | CONDITIONS                                                                                     | MIN | TYP   | MAX | UNITS |

|---------------------|-------------------------|------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| 2LO                 | Signal Powers at 2xLO   | Maximum of $2f_{LO} - 2f_{BB}$ ; $2f_{LO} - f_{BB}$ ; $2f_{LO} + f_{BB}$ , $2f_{LO} + 2f_{BB}$ |     | -51   |     | dBc   |

| 3LOFT               | LO Feedthrough at 3xLO  |                                                                                                |     | -57   |     | dBm   |

| 3LO                 | Signal Powers at 3xLO   | Maximum of $3f_{LO} - f_{BB}$ ; $3f_{LO} + f_{BB}$                                             |     | -10.7 |     | dBc   |

| BW1dB <sub>BB</sub> | -1dB Baseband Bandwidth | R <sub>SOURCE</sub> = 50Ω, Differential                                                        |     | 15    |     | MHz   |

| BW3dB <sub>BB</sub> | -3dB Baseband Bandwidth | R <sub>SOURCE</sub> = 50Ω, Differential                                                        |     | 28    |     | MHz   |

$f_{LO} = 500\text{MHz}$ 、 $f_{RF1} = 497.9\text{MHz}$ 、 $f_{RF2} = 498\text{MHz}$ 、レジスタ0x00 = 0x2D

|                        |                                  |                                                                                                |  |                  |  |                  |

|------------------------|----------------------------------|------------------------------------------------------------------------------------------------|--|------------------|--|------------------|

| S <sub>22(ON)</sub>    | RF Port Return Loss              |                                                                                                |  | -26              |  | dB               |

| f <sub>LO(MATCH)</sub> | LO Match Frequency Range         | S11 < -10dB                                                                                    |  | 180 to 1900      |  | MHz              |

| Gain                   | Conversion Voltage Gain          | $20 \cdot \log(V_{RF(OUT)}(50\Omega)/V_{IN(DIFF)(I or Q)})$                                    |  | -7.7             |  | dB               |

| P <sub>OUT</sub>       | Absolute Output Power            | 1V <sub>P-P(DIFF)</sub> CW Signal, I and Q                                                     |  | -3.7             |  | dBm              |

| OP1dB                  | Output 1dB Compression           |                                                                                                |  | 5.0              |  | dBm              |

| OIP2                   | Output 2nd Order Intercept       | (Note 5)                                                                                       |  | 63.6             |  | dBm              |

| OIP3                   | Output 3rd Order Intercept       | (Note 6)                                                                                       |  | 20.8             |  | dBm              |

| NFloor                 | RF Output Noise Floor            | No Baseband AC Input Signal (Note 3)<br>P <sub>OUT</sub> = 3dBm (Note 3)                       |  | -156.7<br>-156.0 |  | dBm/Hz<br>dBm/Hz |

| SB                     | Side-Band Suppression            | (Note 7)                                                                                       |  | -52.6            |  | dBc              |

| LOFT                   | Carrier Leakage (LO Feedthrough) | (Note 7)<br>EN = Low (Note 7)                                                                  |  | -51.5<br>-67.5   |  | dBm<br>dBm       |

| 2LOFT                  | LO Feedthrough at 2xLO           |                                                                                                |  | -61              |  | dBm              |

| 2LO                    | Signal Powers at 2xLO            | Maximum of $2f_{LO} - 2f_{BB}$ ; $2f_{LO} - f_{BB}$ ; $2f_{LO} + f_{BB}$ , $2f_{LO} + 2f_{BB}$ |  | -51              |  | dBc              |

| 3LOFT                  | LO Feedthrough at 3xLO           |                                                                                                |  | -62              |  | dBm              |

| 3LO                    | Signal Powers at 3xLO            | Maximum of $3f_{LO} - f_{BB}$ ; $3f_{LO} + f_{BB}$                                             |  | -11.8            |  | dBc              |

| BW1dB <sub>BB</sub>    | -1dB Baseband Bandwidth          | R <sub>SOURCE</sub> = 50Ω, Differential                                                        |  | 29               |  | MHz              |

| BW3dB <sub>BB</sub>    | -3dB Baseband Bandwidth          | R <sub>SOURCE</sub> = 50Ω, Differential                                                        |  | 57               |  | MHz              |

$f_{LO} = 900\text{MHz}$ 、 $f_{RF1} = 897.9\text{MHz}$ 、 $f_{RF2} = 898\text{MHz}$ 、レジスタ0x00 = 0x12

|                        |                                  |                                                                                                |  |                |  |            |

|------------------------|----------------------------------|------------------------------------------------------------------------------------------------|--|----------------|--|------------|

| S <sub>22(ON)</sub>    | RF Port Return Loss              |                                                                                                |  | -28            |  | dB         |

| f <sub>LO(MATCH)</sub> | LO Match Frequency Range         | S11 < -10dB                                                                                    |  | 223 to 1902    |  | MHz        |

| Gain                   | Conversion Voltage Gain          | $20 \cdot \log(V_{RF(OUT)}(50\Omega)/V_{IN(DIFF)(I or Q)})$                                    |  | -8.9           |  | dB         |

| P <sub>OUT</sub>       | Absolute Output Power            | 1V <sub>P-P(DIFF)</sub> CW Signal, I and Q                                                     |  | -4.9           |  | dBm        |

| OP1dB                  | Output 1dB Compression           |                                                                                                |  | 4.1            |  | dBm        |

| OIP2                   | Output 2nd Order Intercept       | (Note 5)                                                                                       |  | 63.5           |  | dBm        |

| OIP3                   | Output 3rd Order Intercept       | (Note 6)                                                                                       |  | 18.4           |  | dBm        |

| NFloor                 | RF Output Noise Floor            | No Baseband AC Input Signal (Note 3)                                                           |  | -155.6         |  | dBm/Hz     |

| SB                     | Side-Band Suppression            | (Note 7)                                                                                       |  | -61.3          |  | dBc        |

| LOFT                   | Carrier Leakage (LO Feedthrough) | (Note 7)<br>EN = Low (Note 7)                                                                  |  | -58.6<br>-62.3 |  | dBm<br>dBm |

| 2LOFT                  | LO Feedthrough at 2xLO           |                                                                                                |  | -59            |  | dBm        |

| 2LO                    | Signal Powers at 2xLO            | Maximum of $2f_{LO} - 2f_{BB}$ ; $2f_{LO} - f_{BB}$ ; $2f_{LO} + f_{BB}$ , $2f_{LO} + 2f_{BB}$ |  | -51            |  | dBc        |

5599f

**電気的特性** ●は全動作温度範囲での規格値を意味する。それ以外は  $T_C = 25^\circ\text{C}$  での値。注記がない限り、 $V_{CC} = 3.3\text{V}$ 、 $EN = 3.3\text{V}$ 、 $V_{CTRL} = 3.3\text{V}$ 、 $P_{LO} = 0\text{dBm}$ 、BBPI、BBMI、BBPQ、BBMQ の同相 DC 電圧  $V_{CMBB} = 1.4\text{V}_{DC}$ 、I および Q ベースバンド入力信号 = 2MHz、2.1MHz、1V<sub>P-P</sub>(DIFF, I or Q)、I および Q は 90°シフト、下側波帯選択、全てのレジスタはデフォルト値に設定。テスト回路を図 13 に示す。

| SYMBOL              | PARAMETER               | CONDITIONS                                         | MIN | TYP   | MAX | UNITS |

|---------------------|-------------------------|----------------------------------------------------|-----|-------|-----|-------|

| 3LOFT               | LO Feedthrough at 3xLO  |                                                    |     | -60   |     | dBm   |

| 3LO                 | Signal Powers at 3xLO   | Maximum of $3f_{LO} - f_{BB}$ ; $3f_{LO} + f_{BB}$ |     | -19.2 |     | dBc   |

| BW1dB <sub>BB</sub> | -1dB Baseband Bandwidth | $R_{SOURCE} = 50\Omega$ , Differential             |     | 37    |     | MHz   |

| BW3dB <sub>BB</sub> | -3dB Baseband Bandwidth | $R_{SOURCE} = 50\Omega$ , Differential             |     | 69    |     | MHz   |

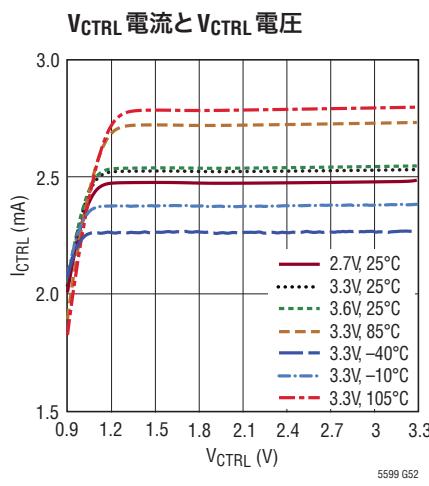

**可変利得制御( $V_{CTRL}$ )**

|             |                              |                                                            |  |            |  |          |

|-------------|------------------------------|------------------------------------------------------------|--|------------|--|----------|

| $V_{CTRLR}$ | Gain Control Voltage Range   | Set Bit 6 in Register 0x01                                 |  | 0.9 to 3.3 |  | V        |

| $t_{CTRL}$  | Gain Control Response Time   | Set Bit 6 in Register 0x01 (Note 8)                        |  | 20         |  | ns       |

| $Z_{CTRL}$  | Gain Control Input Impedance | Set Bit 6 in Register 0x01                                 |  | 10         |  | pF       |

| $I_{CTRL}$  | DC Input Current             | Set Bit 6 in Register 0x01<br>Clear Bit 6 in Register 0x01 |  | 2.58<br>0  |  | mA<br>mA |

**ベースバンド入力(BBPI、BBMI、BBPQ、BBMQ)**

|                |                              |                                                         |  |      |  |                  |

|----------------|------------------------------|---------------------------------------------------------|--|------|--|------------------|

| $V_{CMBB}$     | DC Common Mode Voltage       | Internally Generated                                    |  | 1.42 |  | V                |

| $R_{IN(DIFF)}$ | Input Resistance             | Differential                                            |  | 1.8  |  | kΩ               |

| $R_{IN(CM)}$   | Common Mode Input Resistance | Four Baseband Pins Shorted                              |  | 350  |  | Ω                |

| $I_{BB(OFF)}$  | Baseband Leakage Current     | Four Baseband Pins Shorted, EN = Low                    |  | 1.3  |  | nA               |

| $V_{SWING}$    | Amplitude Swing              | No Hard Clipping, Single-Ended, Digital Gain (DG) = -10 |  | 1.2  |  | V <sub>P-P</sub> |

**電源( $V_{CC}$ )**

|                 |                                |                                            |     |         |     |    |

|-----------------|--------------------------------|--------------------------------------------|-----|---------|-----|----|

| $V_{CC}$        | Supply Voltage                 |                                            | 2.7 | 3.3     | 3.6 | V  |

| $V_{RET(MIN)}$  | Minimum Data Retention Voltage | (Note 14)                                  | 1.6 | 1.3     |     | V  |

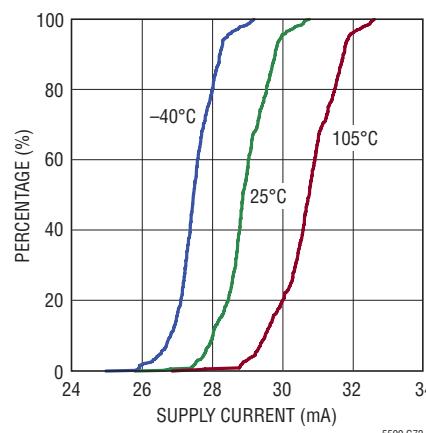

| $I_{CC(ON)}$    | Supply Current                 | EN = High                                  | 20  | 28      | 37  | mA |

| $I_{CC(RANGE)}$ | Supply Current Range           | EN = High, Register 0x01 from 0x00 to 0x13 |     | 8 to 36 |     | mA |

| $I_{CC(OFF)}$   | Supply Current, Sleep Mode     | EN = 0V                                    |     | 0.7     | 9   | μA |

| $t_{ON}$        | Turn-On Time                   | EN = Low to High (Notes 8, 12)             |     | 167     |     | ns |

| $t_{OFF}$       | Turn-Off Time                  | EN = High to Low (Notes 9, 12)             |     | 53      |     | ns |

| $t_{SB}$        | Side-Band Suppression Settling | Register 0x00 Change, <-50dBc (Note 12)    |     | 500     |     | ns |

| $t_{LO}$        | LO Suppression Settling        | Register 0x02 Change, <-60dBm (Note 12)    |     | 90      |     | ns |

**シリアル・ポート(CSB、SCLK、SDI、SDO)、イネーブル(EN)およびTTCK、SCLK = 20MHz**

|           |                             |                                   |   |                   |     |    |

|-----------|-----------------------------|-----------------------------------|---|-------------------|-----|----|

| $V_{IH}$  | Input High Voltage          |                                   | ● | 1.1               |     | V  |

| $V_{IL}$  | Input Low Voltage           |                                   | ● |                   | 0.2 | V  |

| $I_{IH}$  | Input High Current          |                                   |   | 0.02              |     | nA |

| $I_{IL}$  | Input Low Current           |                                   |   | -0.4              |     | nA |

| $V_{OH}$  | Output High Voltage         | (Note 13)                         | ● | $V_{CC\_L} - 0.2$ |     | V  |

| $V_{OL}$  | Output Low Voltage          | $I_{SINK} = 8\text{mA}$ (Note 10) | ● |                   | 0.7 | V  |

| $I_{OH}$  | SDO Leakage Current         | for SDO = High                    |   | 0.5               |     | nA |

| $V_{HYS}$ | Input Trip Point Hysteresis |                                   |   | 110               |     | mV |

| $t_{CKH}$ | SCLK High Time              |                                   | ● | 22.5              | 25  | ns |

**電気的特性**

●は全動作温度範囲での規格値を意味する。それ以外は $T_C = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = 3.3\text{V}$ 、 $EN = 3.3\text{V}$ 、 $V_{CTRL} = 3.3\text{V}$ 、 $P_{LO} = 0\text{dBm}$ 、BBPI、BBMI、BBPQ、BBMQの同相DC電圧 $V_{CMBB} = 1.4\text{V}_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、 $1V_{P-P}(DIFF, I \text{ or } Q)$ 、IおよびQは90°シフト、下側波帯選択、全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

| SYMBOL            | PARAMETER                 | CONDITIONS                          | MIN  | TYP | MAX | UNITS |

|-------------------|---------------------------|-------------------------------------|------|-----|-----|-------|

| t <sub>CS</sub> S | CSB Setup Time            |                                     | ● 20 |     |     | ns    |

| t <sub>CS</sub> H | CSB High Time             |                                     | ● 30 |     |     | ns    |

| t <sub>CS</sub>   | SDI to SCLK Setup Time    |                                     | ● 20 |     |     | ns    |

| t <sub>CH</sub>   | SDI to SCLK Hold Time     |                                     | ● 10 |     |     | ns    |

| t <sub>D0</sub>   | SCLK to SDO Time          |                                     | ● 45 |     |     | ns    |

| t <sub>C%</sub>   | SCLK Duty Cycle           |                                     | ● 45 | 50  | 55  | %     |

| f <sub>CLK</sub>  | Maximum SCLK Frequency    |                                     | ● 20 |     |     | MHz   |

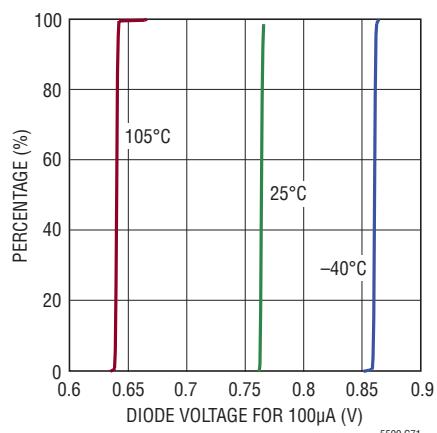

| V <sub>TEMP</sub> | Temperature Diode Voltage | <sub>I<sub>TEMP</sub> = 100μA</sub> |      | 763 |     | mV    |

|                   | Temperature Slope         | <sub>I<sub>TEMP</sub> = 100μA</sub> |      | 1.6 |     | mV/°C |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに回復不可能な損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** LTC5599は $-40^\circ\text{C} \sim 105^\circ\text{C}$ のケース動作温度範囲で動作することが保証されている。

**Note 3:** LO信号周波数からの6MHzのオフセットにおいて。BBPIおよびBBMI間に100nF、BBPQおよびBBMQ間に100nFを接続。

**Note 4:** デフォルトのレジスタ設定を表1に示す。

**Note 5:** IM2は $f_{LO} - 4.1\text{MHz}$ で測定される。

**Note 6:** IM3は $f_{LO} - 2.2\text{MHz}$ および $f_{LO} - 1.9\text{MHz}$ で測定される。OIP3は、 $(1.5 \cdot P[f_{LO} - 2.1\text{MHz}] - 0.5 \cdot P[f_{LO} - 2.2\text{MHz}])$ および $(1.5 \cdot P[f_{LO} - 2\text{MHz}] - 0.5 \cdot P[f_{LO} - 1.9\text{MHz}])$ のうちの低い方の値をとる。

**Note 7:** 側波帯またはLOのフィードスルーの除去はない(未調整)。

**Note 8:** RF電力は最終値の10%以内である。

**Note 9:** RF電力はそのオン状態より少なくとも30dB低い。

**Note 10:**  $V_{OL}$ 電圧は、電流シンクに対して線形に変化する。例えば、 $R_{PULL-UP} = 1\text{k}\Omega$ 、 $V_{CC\_L} = 3.3\text{V}$ の場合、SDOシンク電流は約 $(3.3 - 0.2)/1\text{k}\Omega = 3.1\text{mA}$ になる。最大 $V_{OL} = 0.7 \cdot 3.1/8 = 0.271\text{V}$ 。ここで、 $R_{PULL-UP}$ はSDOプルアップ抵抗、 $V_{CC\_L}$ は $R_{PULL-UP}$ が接続されるデジタル電源電圧。

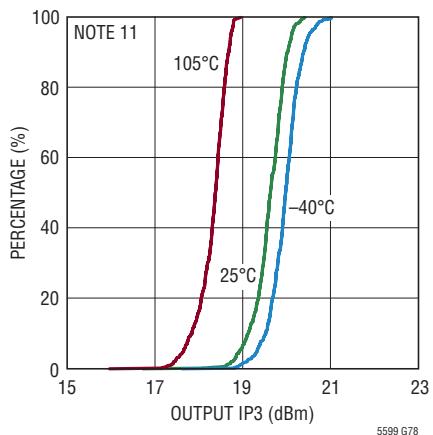

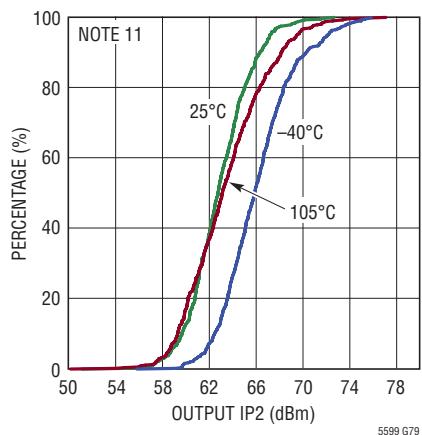

**Note 11:** IおよびQベースバンド入力信号は、それぞれ2MHz CW、 $0.8V_{P-P}$ 、 $\text{DIFF}$ 。IおよびQの位相シフトは0°。

**Note 12:**  $f_{LO} = 500\text{MHz}$ 、 $P_{LO} = 0\text{dBm}$ 、 $C4 = 1.5\text{nF}$

**Note 13:** 最大 $V_{OH}$ は、次式を用いて容量性負荷に対してディレイーティングされる。 $V_{CC\_L} \cdot \exp(-0.5 \cdot T_{CLK}/(R_{PULL-UP} \cdot C_{LOAD}))$ 。ここで、 $T_{CLK}$ は1 SCLKサイクルの時間、 $R_{PULL-UP}$ はSDOのプルアップ抵抗、 $V_{CC\_L}$ は $R_{PULL-UP}$ が接続されるデジタル電源電圧、 $C_{LOAD}$ はSDOピンでの容量性負荷。例えば、 $T_{CLK} = 100\text{ns}$ (10MHzのSCLK)、 $R_{PULL-UP} = 1\text{k}\Omega$ 、 $C_{LOAD} = 10\text{pF}$ 、 $V_{CC\_L} = 3.3\text{V}$ の場合、ディレイーティングが $3.3 \cdot \exp(-5) = 22.2\text{mV}$ になるため、最大 $V_{OH} = 3.3\text{V} - 0.1 - 0.0222 = 3.177\text{V}$ となる。

**Note 14:** レジスタのデータの内容を維持するための最大 $V_{CC}$ 。

**Note 15:** 設計および特性評価により保証されている。このパラメータに対するテストは実施されない。

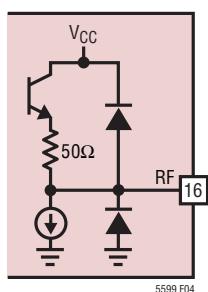

**Note 16:** RFピンは、10nFのカッピリング・コンデンサを使用して設計によって保証される。RFピンはテストされていない。

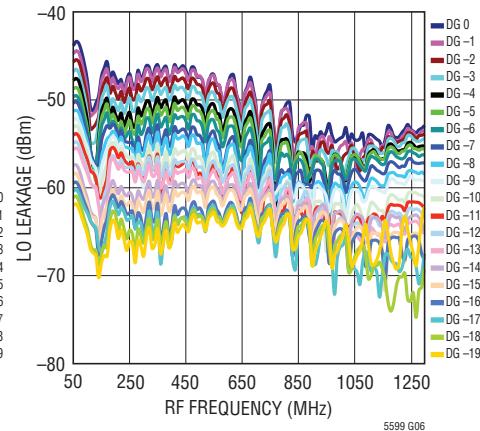

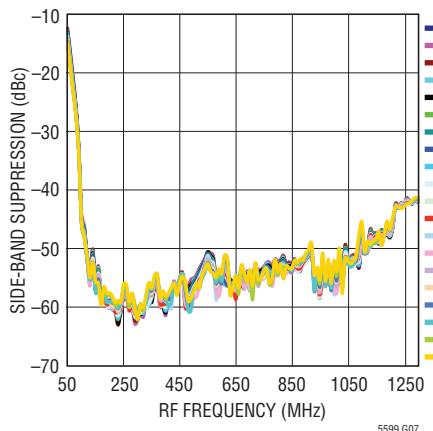

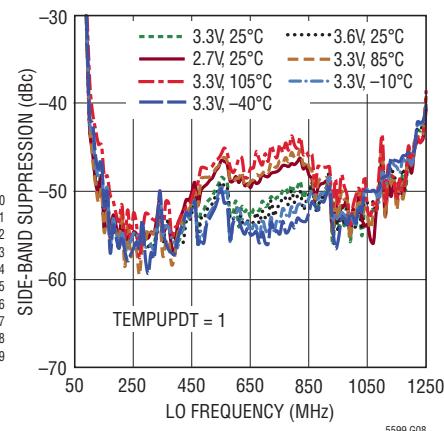

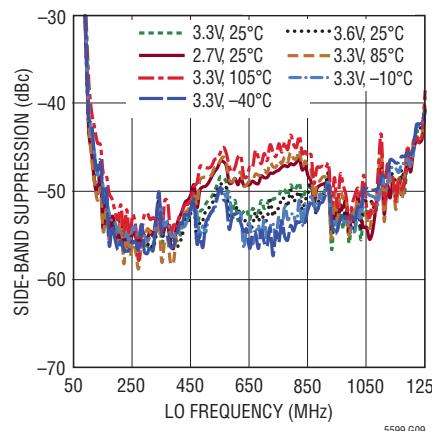

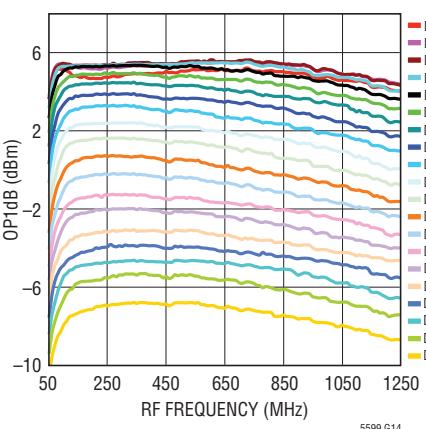

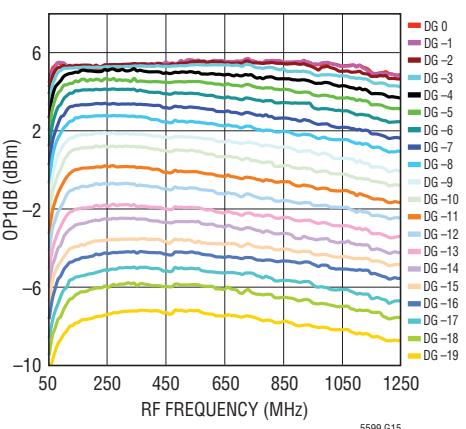

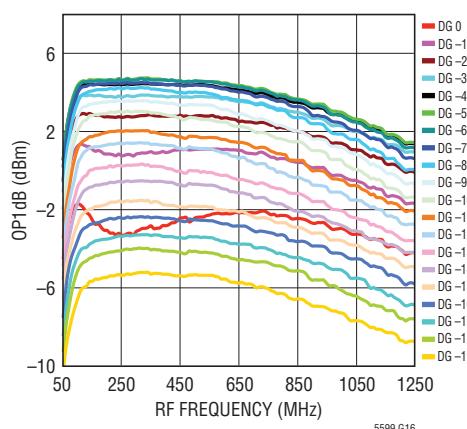

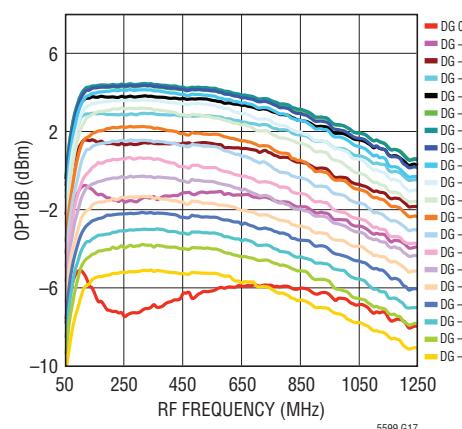

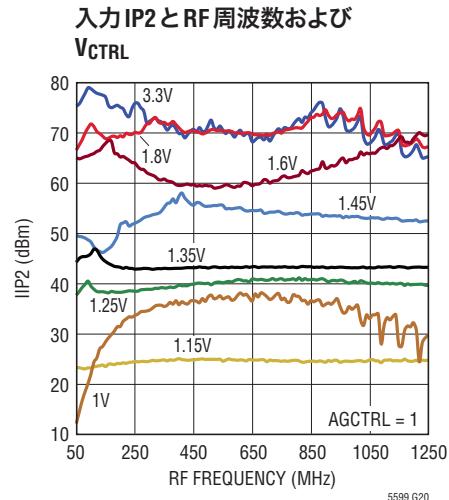

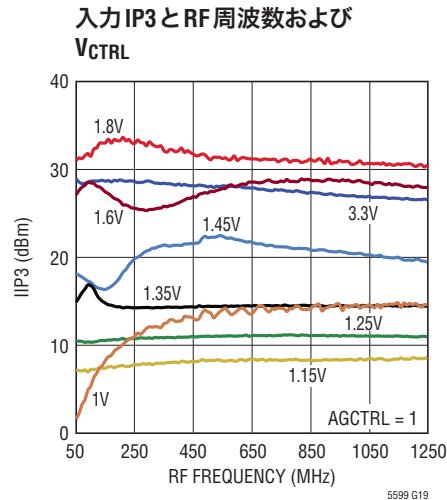

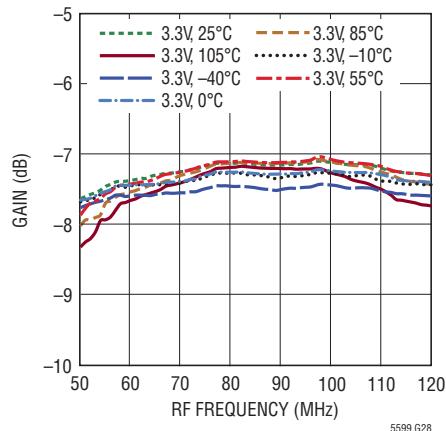

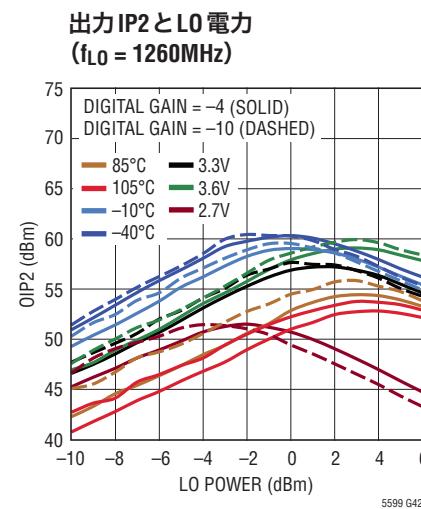

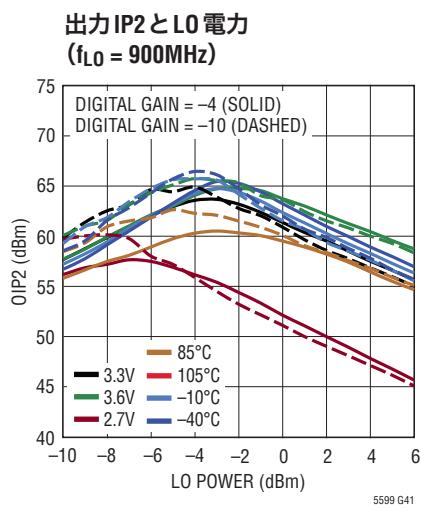

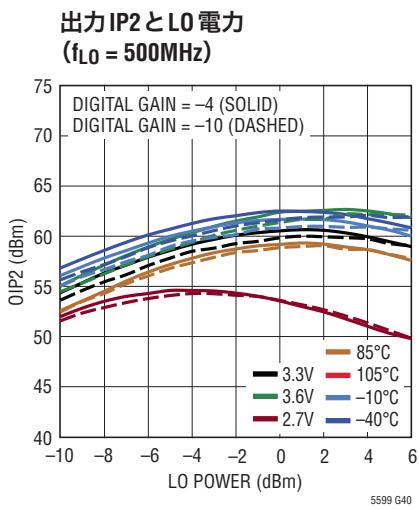

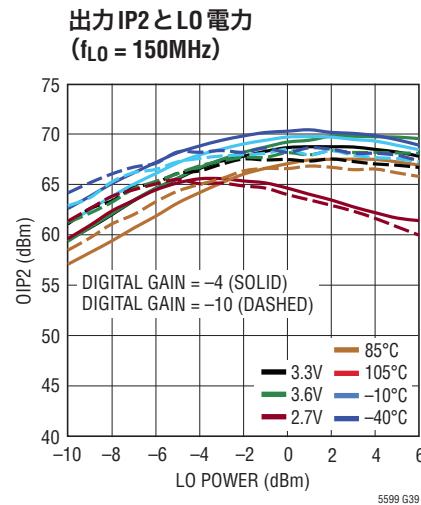

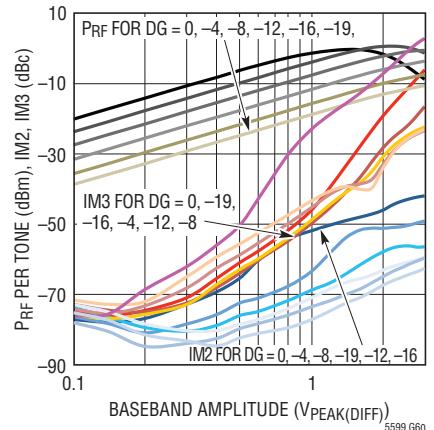

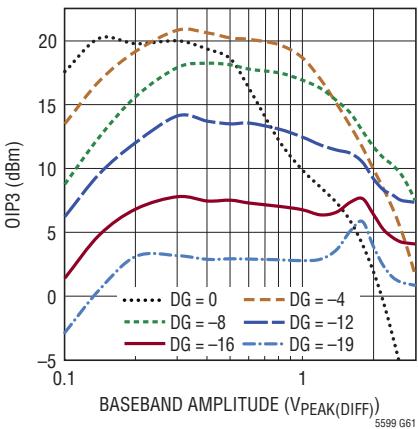

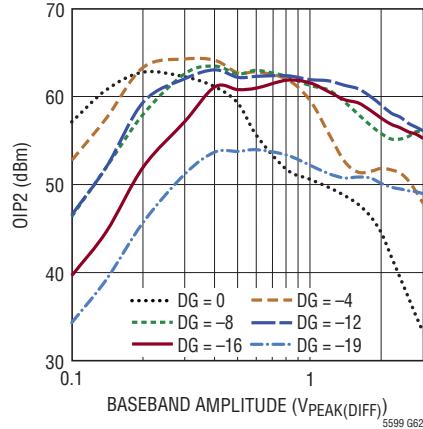

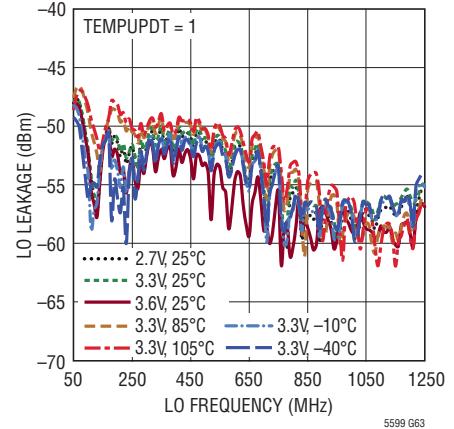

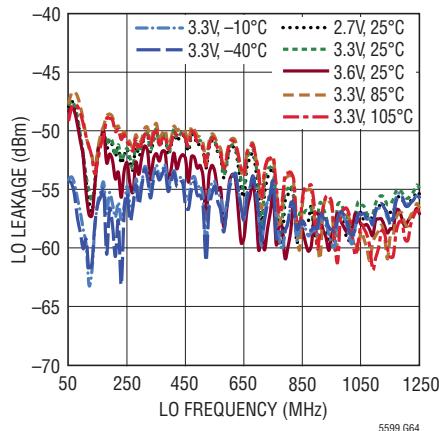

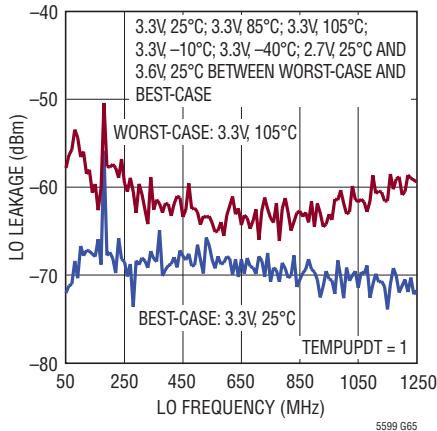

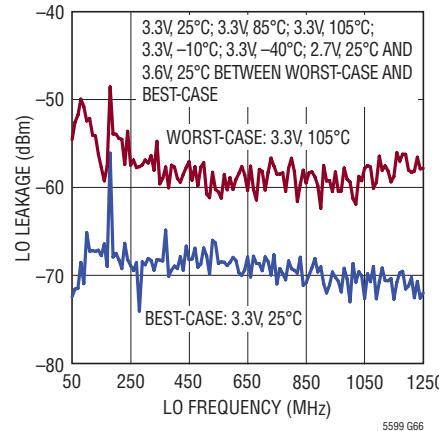

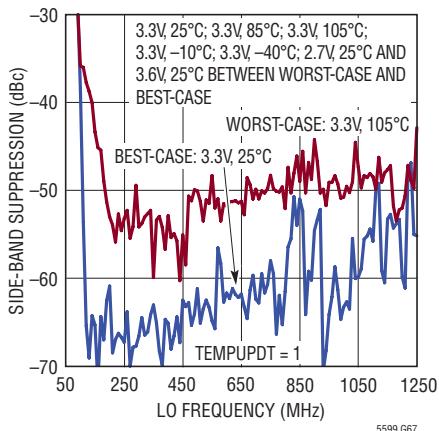

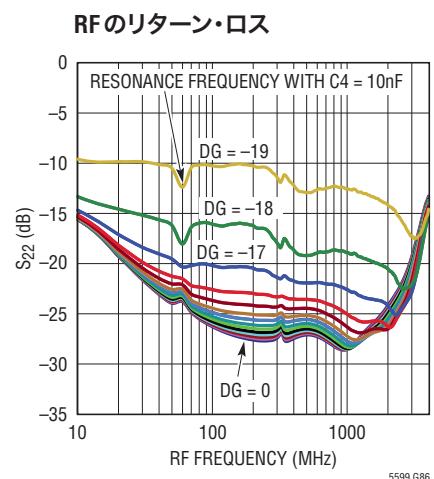

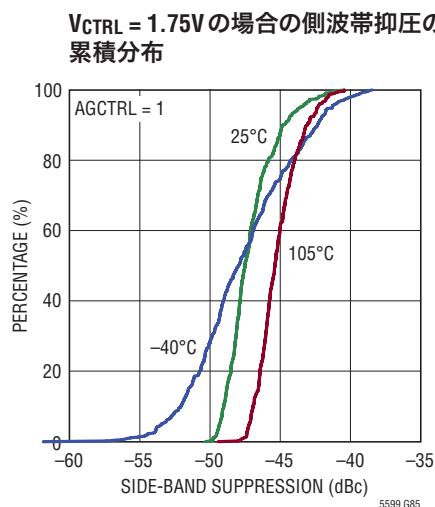

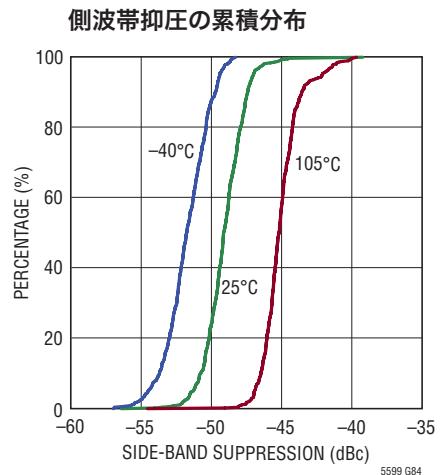

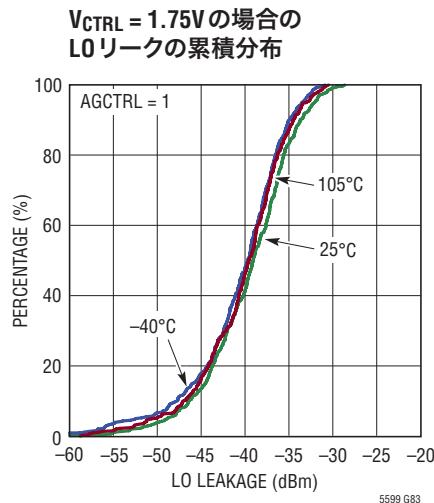

## 標準的性能特性

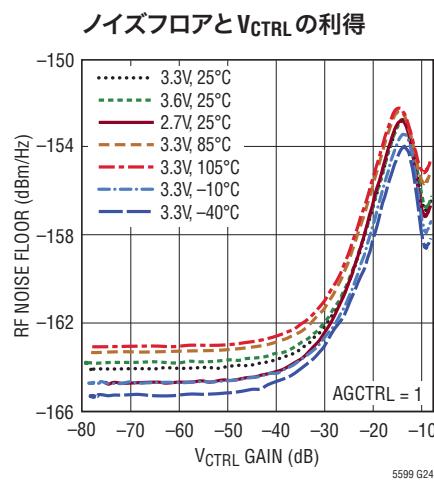

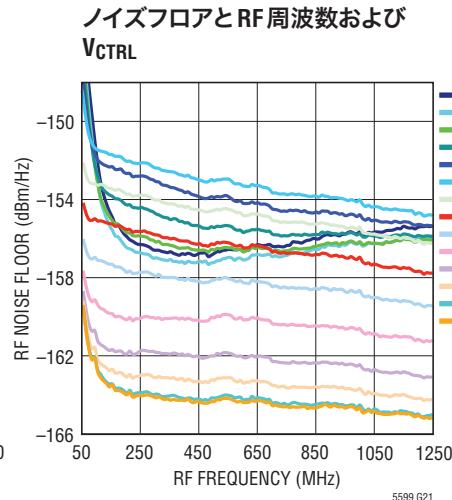

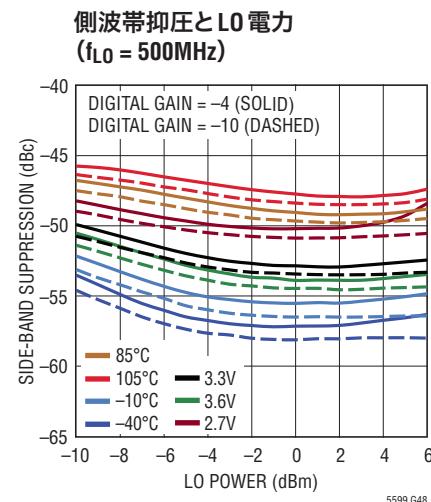

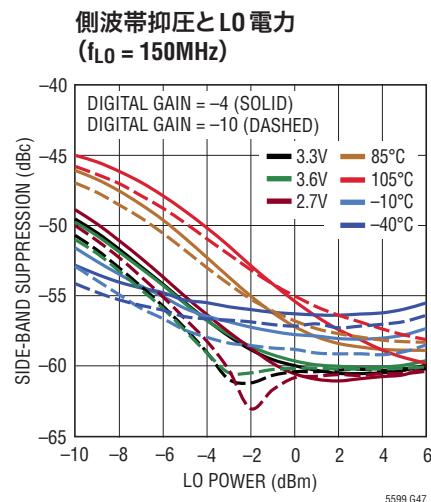

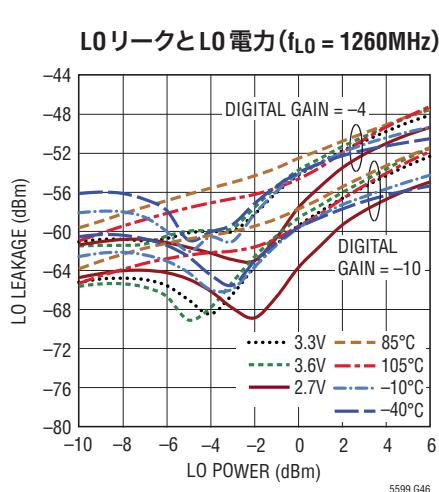

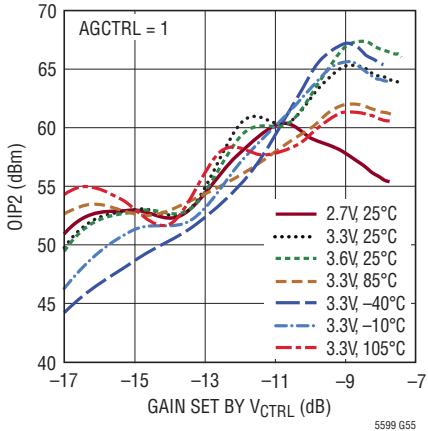

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、 $BBPI$ 、 $BBMI$ 、 $BBPQ$ 、 $BBMQ$ の同相DC電圧 $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1Vp-p(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、 $TEMPUPDT = 0$ 、レジスタ0x00の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

電源電流と電源電圧

電源電流と

デジタル利得設定

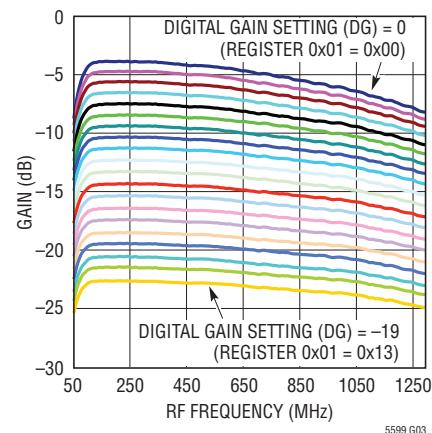

利得とRF周波数および

デジタル利得設定

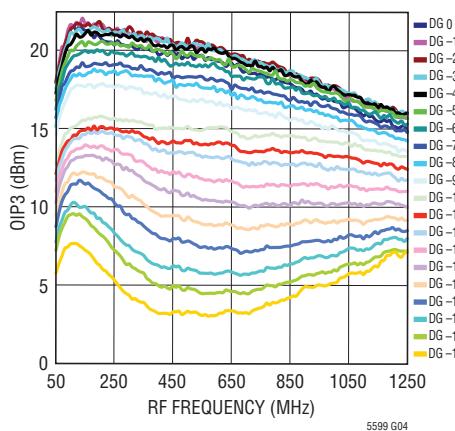

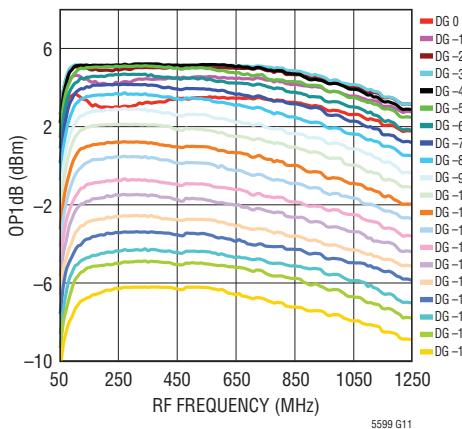

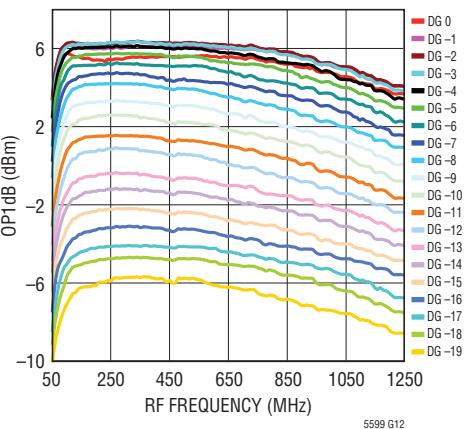

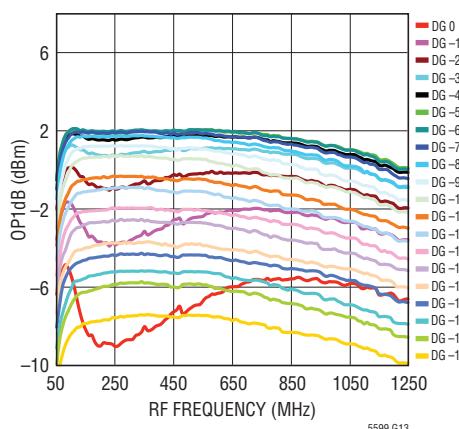

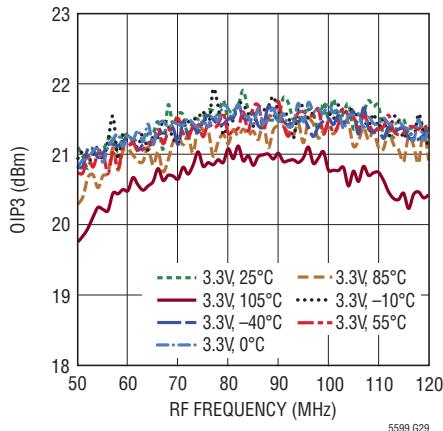

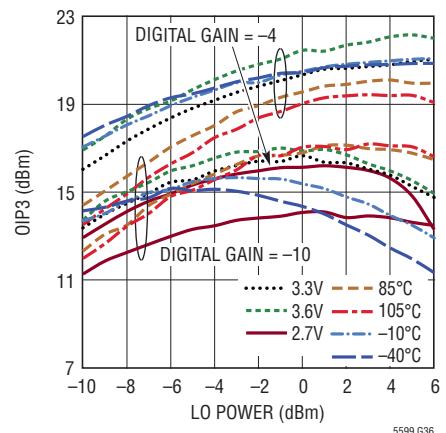

出力IP3とRF周波数および

デジタル利得設定

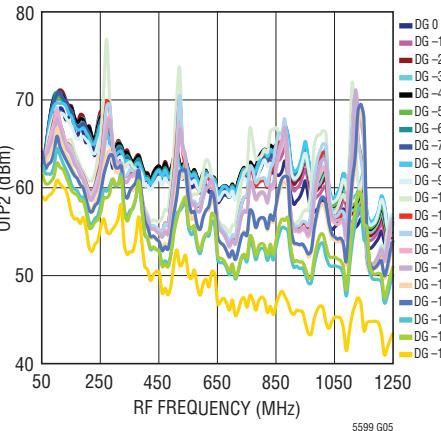

出力IP2とRF周波数および

デジタル利得設定

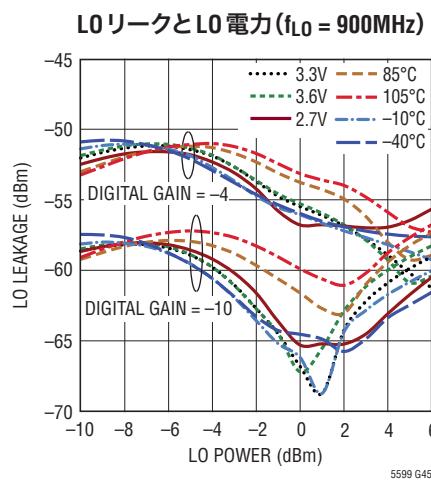

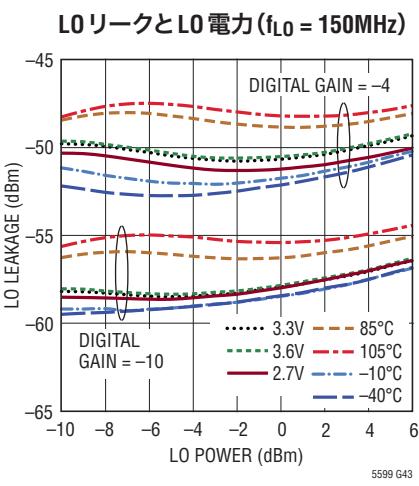

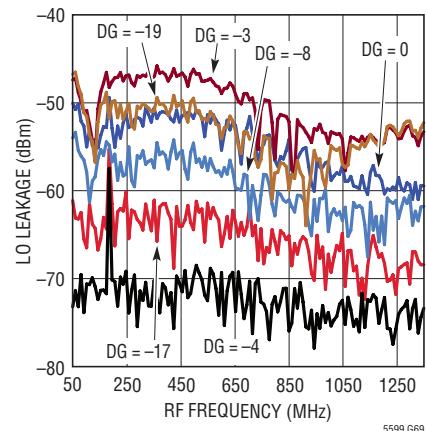

LOリークとRF周波数および

デジタル利得設定

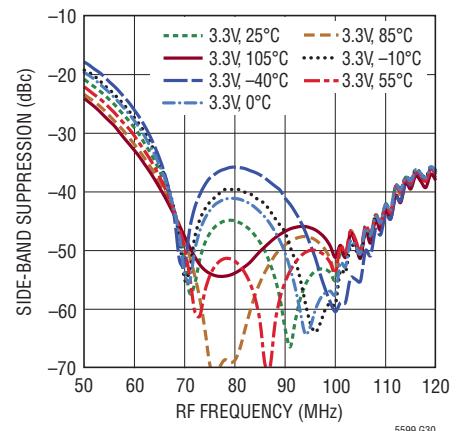

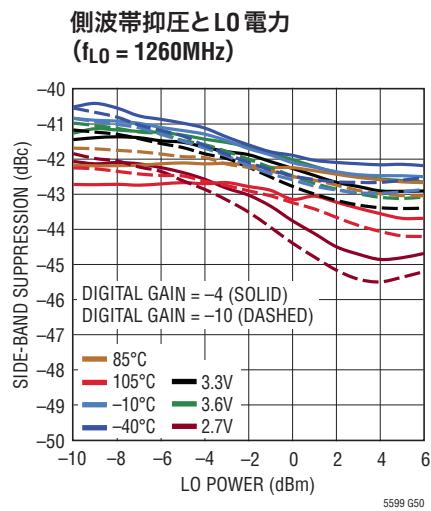

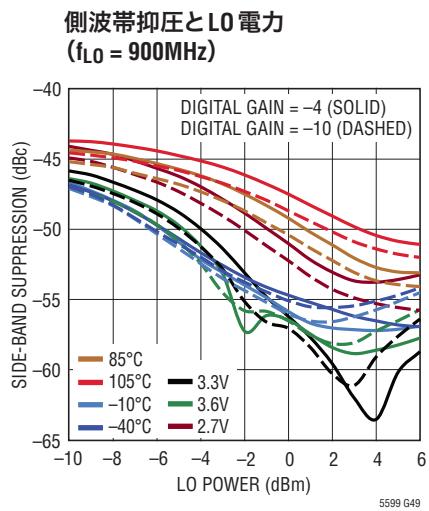

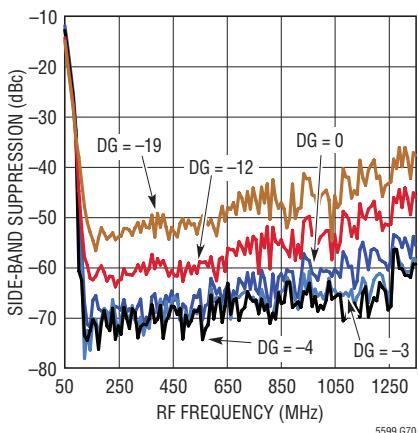

側波帯抑圧とRF周波数および

デジタル利得設定

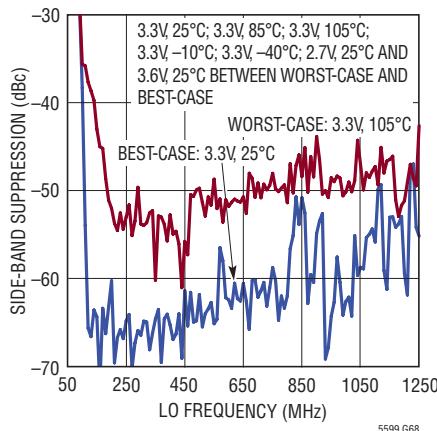

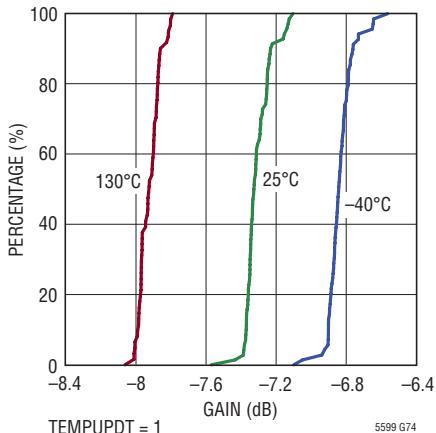

利得の温度比較オフの場合の

側波帯抑圧とLO周波数

利得の温度比較オンの場合の

側波帯抑圧とLO周波数

**標準的性能特性**

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、BBPI、BBMI、BBPQ、BBMQの同相DC電圧 $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1Vp-P (DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、TEMPUPDT = 0、レジスタ 0x00の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

ノイズフロアとRF周波数およびデジタル利得設定

出力1dB圧縮ポイントとRF周波数およびデジタル利得設定(3.3V電源)

出力1dB圧縮ポイントとRF周波数およびデジタル利得設定(3.6V電源)

出力1dB圧縮ポイントとRF周波数およびデジタル利得設定(2.7V電源)

出力1dB圧縮ポイントとRF周波数およびデジタル利得設定(-10°C)

出力1dB圧縮ポイントとRF周波数およびデジタル利得設定(-40°C)

出力1dB圧縮ポイントとRF周波数およびデジタル利得設定(85°C)

出力1dB圧縮ポイントとRF周波数およびデジタル利得設定(105°C)

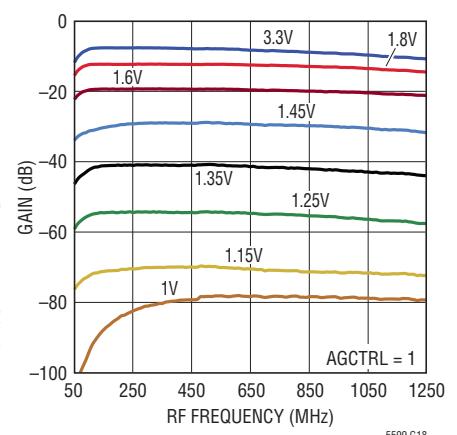

利得とRF周波数および $V_{CTRL}$

## 標準的性能特性

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、 $BBPI$ 、 $BBMI$ 、 $BBPQ$ 、 $BBMQ$ の同相DC電圧 $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1Vp-p(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、TEMPUPDT = 0、レジスタ0x00の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

## 標準的性能特性

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、BBPI、BBMI、BBPQ、BBMQの同相DC電圧 $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1V<sub>P-P</sub>(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、TEMPUPDT = 0、レジスタ0x00の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

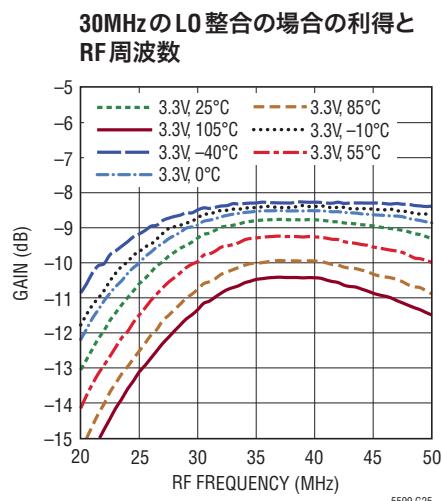

70MHzのLO整合の場合の利得とRF周波数

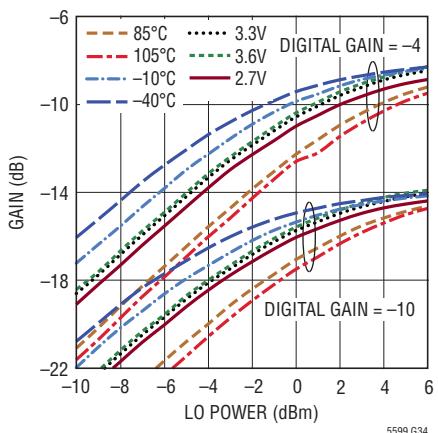

利得とLO電力( $f_{LO} = 150MHz$ )

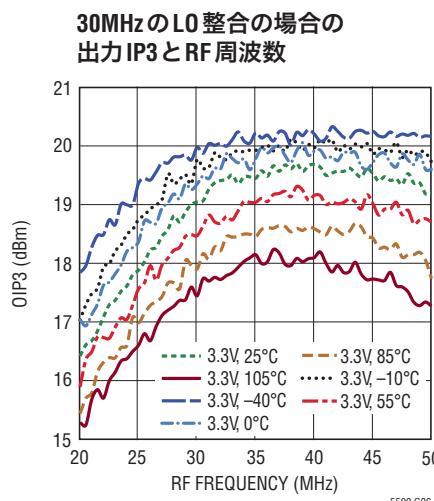

70MHzのLO整合の場合の出力IP3とRF周波数

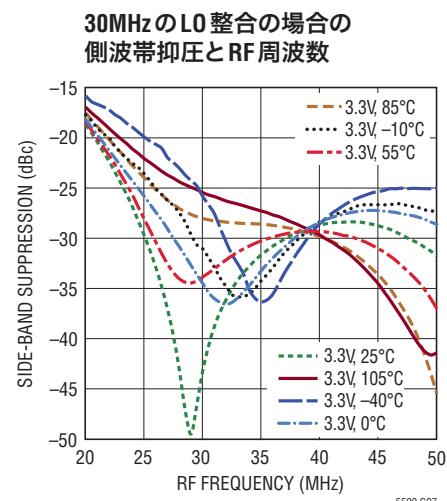

70MHzのLO整合の場合の側波帯抑圧とRF周波数

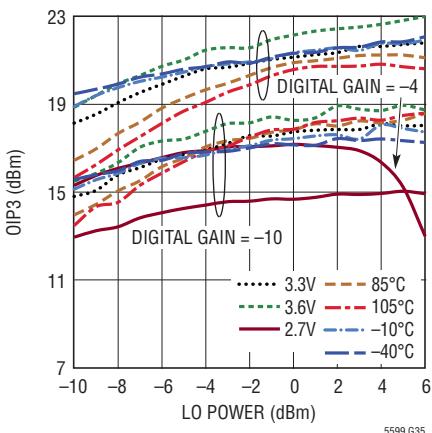

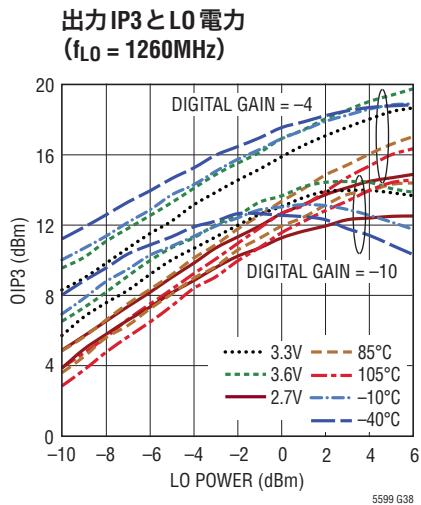

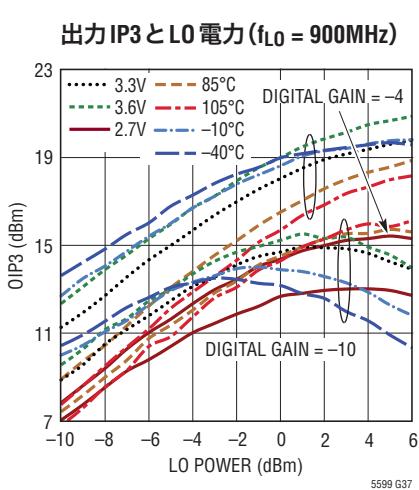

利得とLO電力( $f_{LO} = 1260MHz$ )出力IP3とLO電力( $f_{LO} = 150MHz$ )出力IP3とLO電力( $f_{LO} = 500MHz$ )

## 標準的性能特性

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、BBPI、BBMI、BBPQ、BBMQの同相DC電圧 $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1V\_P-P(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、TEMPUPDT = 0、レジスタ0x00の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

**標準的性能特性**

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、BBPI、BBMI、BBPQ、BBMQの同相DC電圧 $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1V\_P-P(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、TEMPUPDT = 0、レジスタ0x00の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

## 標準的性能特性

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、BBPI、BBMI、BBPQ、BBMQの同相DC電圧 $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1V\_P-P(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、TEMPUPDT = 0、レジスタ0x00の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

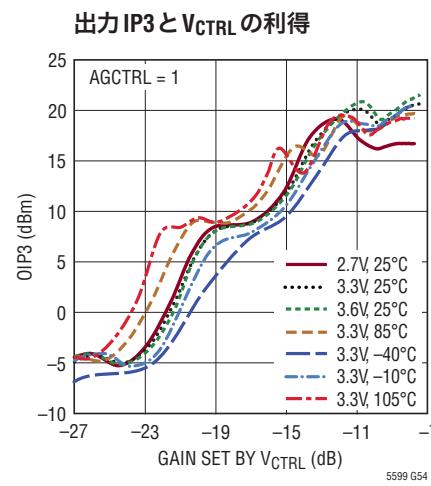

出力IP2と $V_{CTRL}$ の利得

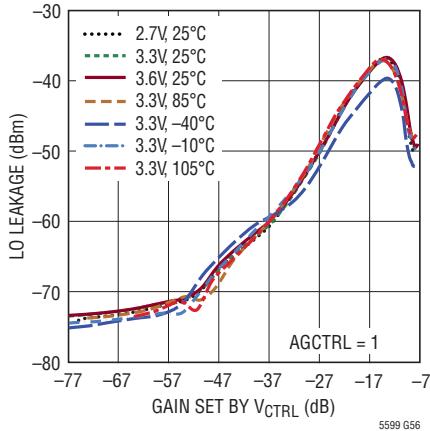

LOリークと $V_{CTRL}$ の利得

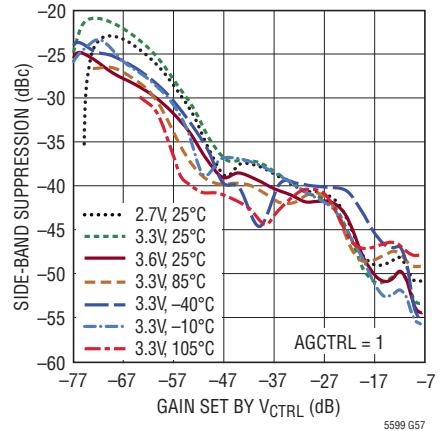

側波帯抑圧と $V_{CTRL}$ の利得

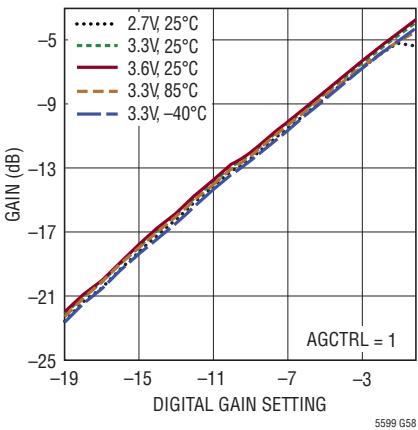

利得とデジタル利得設定

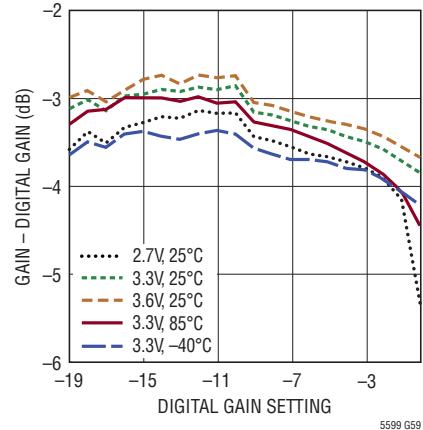

利得 - デジタル利得と

デジタル利得設定

PRF、IM2、IM3と

ベースバンド振幅

出力IP3とベースバンド振幅

出力IP2とベースバンド振幅

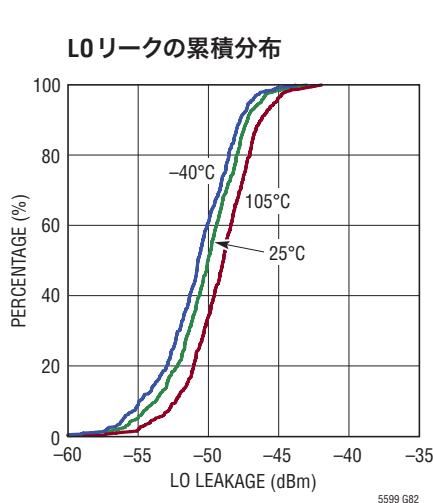

利得の温度比較オフの場合の

LOリークとLO周波数

## 標準的性能特性

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、 $BBPI$ 、 $BBMI$ 、 $BBPQ$ 、 $BBMQ$ の同相DC電圧 $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1V\_P-P(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、 $TEMPUPDT = 0$ 、レジスタ0x00の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

利得の温度比較オフの場合の

LOリークとLO周波数5個のデバイス上のワーストケースの

LOリークとLO周波数(利得の温度

比較オフの場合の $25^\circ C$ での較正後)5個のデバイス上のワーストケースの

LOリークとLO周波数(利得の温度

比較オフの場合の $25^\circ C$ での較正後)5個のデバイス上のワーストケースの

側波帯抑圧とLO周波数(利得の温度

比較オフの場合の $25^\circ C$ での較正後)5個のデバイス上のワーストケースの

側波帯抑圧とLO周波数(利得の温度

比較オフの場合の $25^\circ C$ での較正後)DG = -4での較正後のLOリークと

LO周波数およびデジタル利得設定DG = -4での較正後の

側波帯抑圧とLO周波数および

デジタル利得設定温度検出ダイオードの電圧の

累積分布

電源電流の累積分布

## 標準的性能特性

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、BBPI、BBMI、BBPQ、BBMQの同相DC電圧  $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1V<sub>P-P</sub>(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、TEMPUPDT = 0、レジスタ 0x00 の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

スリープ電流の累積分布

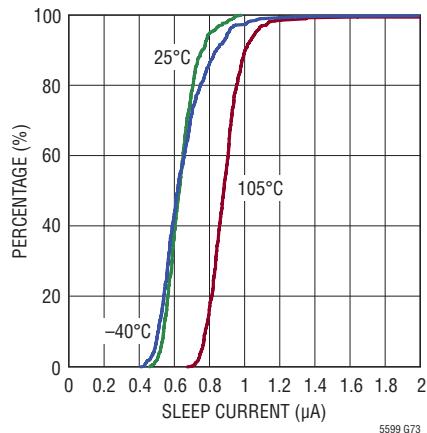

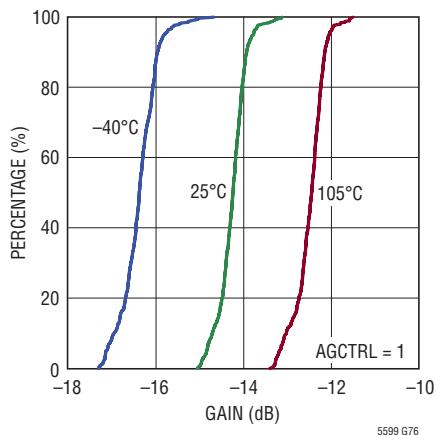

利得の温度比較オフの場合の

利得の累積分布

利得の温度比較オンの場合の

利得の累積分布

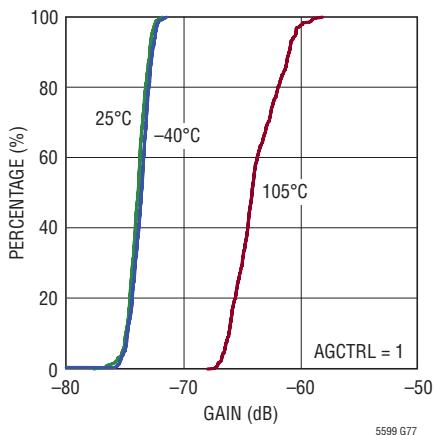

$V_{CTRL} = 1.75V$ の場合の利得の

累積分布

$V_{CTRL} = 1V$ の場合の利得の

累積分布

出力IP3の累積分布

出力IP2の累積分布

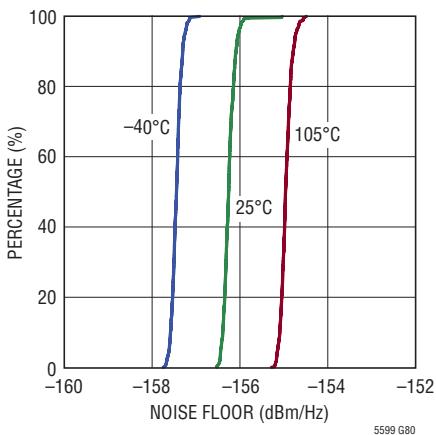

ノイズフロアの累積分布

フロート状態のベースバンド・ピンの

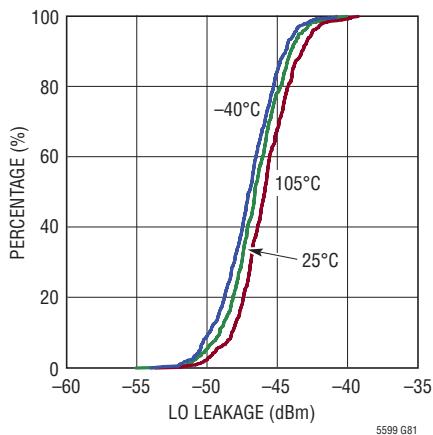

LOリークの累積分布

## 標準的性能特性

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、BBPI、BBMI、BBPQ、BBMQの同相DC電圧 $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1V\_P-P(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、TEMPUPDT = 0、レジスタ0x00の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

## 標準的性能特性

注記がない限り、 $V_{CC} = 3.3V$ 、 $EN = 3.3V$ 、 $V_{CTRL} = 3.3V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 0dBm$ 、 $f_{LO} = 500MHz$ 、BBPI、BBMI、BBPQ、BBMQの同相DC電圧 $V_{CMBB} = 1.4V_{DC}$ 、IおよびQベースバンド入力信号 = 2MHz、2.1MHz、1V<sub>P-P</sub>(DIFF, I or Q)、IおよびQは90°シフト、下側波帯選択、TEMPUPDT = 0、レジスタ0x00の値は表5に従う、他の全てのレジスタはデフォルト値に設定。テスト回路を図13に示す。

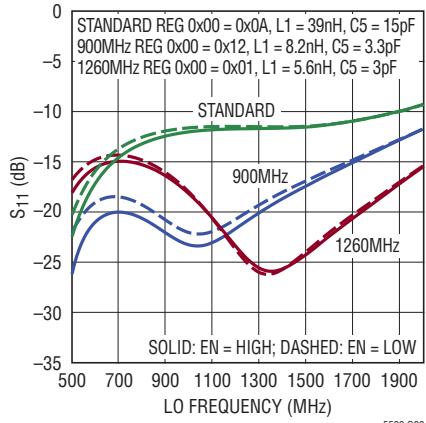

標準の900MHzおよび1260MHz整合の場合のLOのリターン・ロス

1Ms/s 16-QAM信号でのRMS EVMとRF出力電力

1Ms/s 16-QAM信号でのピークEVMとRF出力電力

5599 G89

5599 G90

5599 G91

5599f

## ピン機能

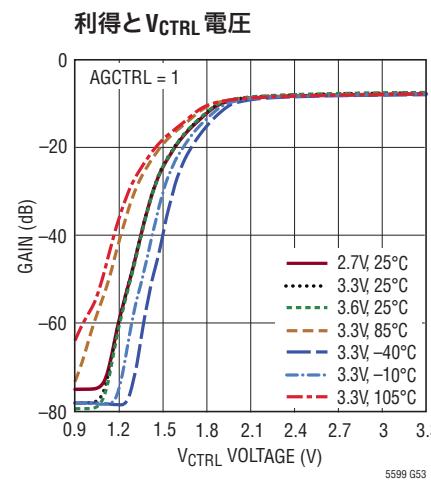

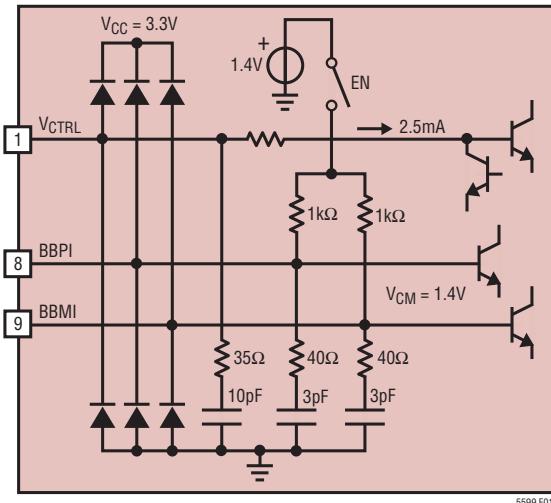

**V<sub>CTRL</sub>(ピン1)**: 可変利得制御入力。このアナログ制御ピンは、利得を設定します。このピンをアクティブにするには、レジスタ0x01のビット6に「1」(AGCTRL = 1)を書き込みます。その結果、2.58mAの電流が正電源から流れます。標準的なV<sub>CTRL</sub>電圧範囲は0.9V～3.3Vです。利得伝達関数は、dB単位で線形ではありません。使用しない場合は、V<sub>CC</sub>に接続します。

**GND(ピン2、5、12、露出パッド25)**: グランド。これらのピンは、全て内部で相互接続されています。RF性能を最適化するために、全てのグランド・ピンをRFグランドに接続してください。

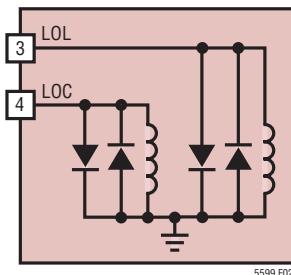

**LOL、LOC(ピン3、4)**: LO 入力。これらは差動入力ではありません。これらのピンは、50Ω入力です。これらのピンでLCデュプレクサを使用することを推奨します(図13を参照)。加えられるDCレベルが±100mVよりも高い場合は、これらのピンでACカップリング・コンデンサが必要です。

**TTCK(ピン6)**: 温度の更新。レジスタ0x01でTTCK温度更新モード(ビット7 = “H”、TEMPUPDT = 1)を選択した場合は、このピンでロジック“L”からロジック“H”に遷移することによって、温度の読み取りおよび温度に対するデジタル利得補償を更新できます。フロート状態にしないでください。

**TEMP(ピン7)**: 温度検出ダイオード。このピンは、ダイの温度を測定する目的で使用できるダイオードのアノードに接続されています。温度を測定するには、電流を強制的に流して電圧を測定します。このダイオードは、内蔵の温度計の一部ではありません。

**BBPI、BBMI(ピン8、9)**: Iチャネルのベースバンド入力。各入力の入力インピーダンスは、約1kΩです。これらのピンは、外部で1.4V同相レベルにバイアスするか、AC結合する必要があります。2V<sub>DC</sub>を超える同相電圧を加えないでください。

**BBPQ、BBMQ(ピン10、11)**: Qチャネルのベースバンド入力。各入力の入力インピーダンスは、約1kΩです。これらのピンは、外部で1.4V同相レベルにバイアスするか、AC結合する必要があります。2V<sub>DC</sub>を超える同相電圧を加えないでください。Qチャネルをディスエーブルする場合は、フロート状態にします。

**GNDRF(ピン13、14、15、17、18)**: RFグランド。これらのピンは、内部で相互接続されています。RF性能を最適化するために、全てのグランド・ピンをRFグランドに接続してください。

**RF(ピン16)**: RF出力。RF周波数での出力インピーダンスは、50Ωです。イネーブルされた場合、このピンのDC出力電圧は約1.7Vです。このピンでは、10nFの推奨値を持つACカップリング・コンデンサを使用してください。

**CSB(ピン19)**: シリアル・ポート・チップ・セレクト。このCMOS入力は、“L”にドライブするとシリアル・ポートのトランザクションを開始し、再度“H”にドライブするとトランザクションを終了します。フロート状態にしないでください。

**SCLK(ピン20)**: シリアル・ポート・クロック。このCMOS入力の立ち上がりエッジでシリアル・ポートの入力データをクロックします。フロート状態にしないでください。

**SDI(ピン21)**: シリアル・ポート・データ入力。シリアル・ポートはこのCMOS入力をデータに使います。フロート状態にしないでください。

**SDO(ピン22)**: シリアル・ポート・データ出力。このNMOSの出力は、読み出しトランザクションの間、シリアル・ポートのデータを出力します。“L”に引き下げられたときに電流が10mAを超えないようにするために、このピンを、十分に値の大きいプルアップ抵抗を介してデジタル電源電圧に接続します。

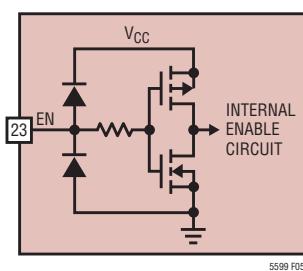

**EN(ピン23)**: イネーブル・ピン。ロジック“H”電圧がこのピンに加えられるとデバイスが完全にオンになり、ロジック“L”電圧が加えられると完全にオフになります。フロート状態にしないでください。

**V<sub>CC</sub>(ピン24)**: 電源。このピンでグランドにデカップリングする場合、1nFおよび4.7μFのコンデンサを使用することを推奨します。

# LTC5599

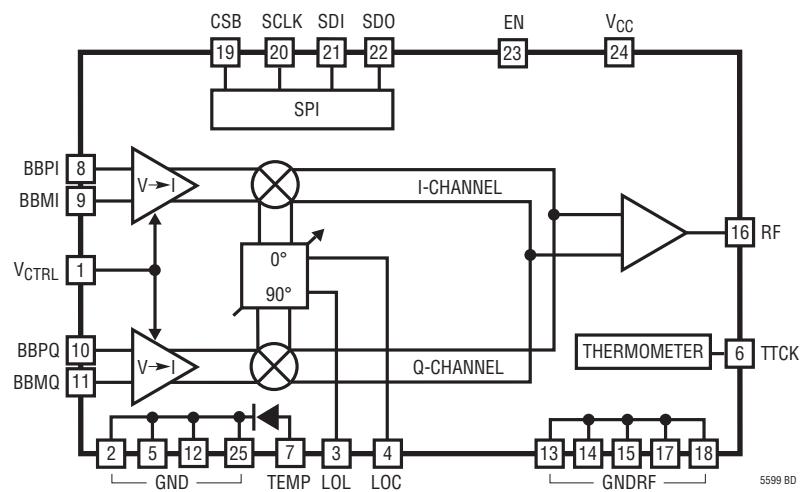

## ブロック図

## アプリケーション情報

LTC5599は、IおよびQ入力差動電圧-電流コンバータ、IおよびQアップコンバーティング・ミキサ、RF出力バッファ、およびLO直交位相ジェネレータで構成されています。SPIバスは、9個の制御レジスタのアドレスを指定し、側波帯抑圧、LOリーク、および変調器利得の調整の最適化を可能にします。書き込み可能レジスタおよびそれらのデフォルト値については、表1を参照してください。LTC5599の全てのレジスタの詳細なマップを、付録の表10および表11に示しています。

**表1. 書き込み可能なSPIレジスタとデフォルトのレジスタ値**

| アドレス | デフォルト値 | 設定      | レジスタの機能                         |

|------|--------|---------|---------------------------------|

| 0x00 | 0x2E   | 490MHz  | LO Frequency Tuning             |

| 0x01 | 0x84   | DG = -4 | Gain                            |

| 0x02 | 0x80   | 0mV     | Offset I-Channel                |

| 0x03 | 0x80   | 0mV     | Offset Q-Channel                |

| 0x04 | 0x80   | 0dB     | I/Q Gain Ratio                  |

| 0x05 | 0x10   | 0°      | I/Q Phase Balance               |

| 0x06 | 0x50   | OFF     | LO Port Matching Override       |

| 0x07 | 0x06   | OFF     | Temperature Correction Override |

| 0x08 | 0x00   | NORMAL  | Operating Mode                  |

SPIを使用しない場合、レジスタはデフォルト値を使用します。その場合、最適な側波帯抑圧(SB)が得られない可能性があります。例えば、LO周波数が約400MHz～約580MHzの場合、SBは約-45dBcになり、380MHz～400MHzおよび580MHz～630MHzの場合、SBは約-40dBcになり、350MHz～380MHzおよび630MHz～690MHzの場合、SBは約-35dBcになります。

LTC5599の起動とは別に、SRESET(レジスタ0x08のビット3)を1に設定することによって、レジスタをデフォルト値にリセットできます。約50nsの経過後、SRESETは自動的に再び0に設定されます。

外部のIおよびQベースバンド信号が、差動ベースバンド入力ピンBBPI、BBMIおよびBBPQ、BBMQに入力されます。これらの電圧信号は、電流に変換され、二重平衡アップコンバーティング・ミキサによってRF周波数に変換されます。これらのミキサの出力は、RF出力バッファの入力で結合されます。また、RF出力バッファは、出力インピーダンスを50Ωに変換します。生成されたRF信号の中心周波数は、LO信号周波数に等しくなります。LO入力は、位相シフタを駆動します。位相シフ

タはLO信号を同相信号と直交信号に分割し、これらの信号がアップコンバーティング・ミキサを駆動します。ほとんどのアプリケーションでは、LOL入力は39nHのインダクタを介してLOソースによって駆動され、LOC入力は15pFのコンデンサを介してLOソースによって駆動されます。このインダクタとコンデンサは、200MHzに調整されたデュプレクサ回路を形成します。RF出力はシングルエンドであり、0.6MHz～6GHzの広いRF周波数範囲に渡って、内部で50Ωに整合します。10nFのC4を使用すると、10dBよりも良好なリターン・ロスを実現できます。図13を参照してください。

## ベースバンド・インターフェース

ベースバンド入力(BBPI、BBMI、BBPQ、BBMQ)は、図1に示すように、約1.8kΩの差動入力インピーダンスを示します。ベースバンド帯域幅は、ソース・インピーダンスと周波数設定(レジスタ0x00)によって変わります。ベースバンド周波数に対する最高の利得平坦性を実現するために、ベースバンド・ローパスフィルタ設計で、ベースバンド入力インピーダンスを補償することを推奨します。さまざまなLO周波数と利得設定に関する各ベースバンド入力のSパラメータを、表2に示します。

**図1. ベースバンド入力インターフェースの簡略回路図

(1チャネルのみを示す)**

## アプリケーション情報

表2.EN = “H”および $V_{CMBB} = 1.4V$ の場合の

差動ベースバンド(BB)入力インピーダンスと周波数

| BB周波数<br>(MHz)                                        | 入力インピーダンス(Ω) |                 | REFL<br>係数 |      |

|-------------------------------------------------------|--------------|-----------------|------------|------|

|                                                       | 実数部*         | 虚数部*(容量)        | 振幅         | 位相   |

| <b>LO周波数 = 92MHz(レジスタ 0x00 = 0x79)、デジタル利得 = -4dB</b>  |              |                 |            |      |

| 1                                                     | 1.90k        | -7.17k (22.2pF) | 0.900      | -1.6 |

| 4                                                     | 1.76k        | -1.82k (21.9pF) | 0.893      | -6.3 |

| 10                                                    | 1.25k        | -751 (21.2pF)   | 0.854      | -15  |

| 20                                                    | 678          | -429 (18.6pF)   | 0.755      | -27  |

| 40                                                    | 342          | -308 (12.9pF)   | 0.585      | -39  |

| <b>LO周波数 = 150MHz(レジスタ 0x00 = 0x62)、デジタル利得 = -4dB</b> |              |                 |            |      |

| 1                                                     | 1.90k        | -9.11k (17.5pF) | 0.900      | -1.3 |

| 4                                                     | 1.82k        | -2.30k (17.3pF) | 0.896      | -5.0 |

| 10                                                    | 1.45k        | -935 (17.0pF)   | 0.872      | -12  |

| 20                                                    | 887          | -507 (15.7pF)   | 0.804      | -23  |

| 40                                                    | 441          | -325 (12.2pF)   | 0.658      | -36  |

| 100                                                   | 226          | -252 (6.3pF)    | 0.457      | -51  |

| <b>LO周波数 = 500MHz(レジスタ 0x00 = 0x2D)、デジタル利得 = -4dB</b> |              |                 |            |      |

| 1                                                     | 1.91k        | -14.7k (10.6pF) | 0.900      | -0.8 |

| 4                                                     | 1.89k        | -3.74k (10.7pF) | 0.899      | -3.0 |

| 10                                                    | 1.72k        | -1.50k (10.7pF) | 0.891      | -7.7 |

| 20                                                    | 1.35k        | -769 (10.4pF)   | 0.864      | -15  |

| 40                                                    | 786          | -426 (9.4pF)    | 0.785      | -27  |

| 100                                                   | 323          | -251 (6.4pF)    | 0.583      | -47  |

| 200                                                   | 212          | -190 (4.2pF)    | 0.478      | -65  |

| <b>LO周波数 = 500MHz(レジスタ 0x00 = 0x2D)、デジタル利得 = 0dB</b>  |              |                 |            |      |

| 1                                                     | 1.56k        | -15.0k (10.6pF) | 0.879      | -0.8 |

| 4                                                     | 1.56k        | -3.84k (10.4pF) | 0.880      | -3.0 |

| 10                                                    | 1.48k        | -1.52k (10.4pF) | 0.874      | -7.5 |

| 20                                                    | 1.21k        | -784 (10.2pF)   | 0.849      | -15  |

| 40                                                    | 753          | -432 (9.2pF)    | 0.776      | -27  |

| 100                                                   | 323          | -251 (6.3pF)    | 0.582      | -47  |

| 200                                                   | 213          | -190 (4.2pF)    | 0.478      | -65  |

| <b>LO周波数 = 900MHz(レジスタ 0x00 = 0x12)、デジタル利得 = -4dB</b> |              |                 |            |      |

| 1                                                     | 1.91k        | -17.0k (9.4pF)  | 0.901      | -0.7 |

| 2                                                     | 1.90k        | -4.3k (9.3pF)   | 0.900      | -2.7 |

| 10                                                    | 1.77k        | -1.72k (9.3pF)  | 0.893      | -6.7 |

表2.EN = “H”および $V_{CMBB} = 1.4V$ の場合の

差動ベースバンド(BB)入力インピーダンスと周波数 (続き)

| BB周波数<br>(MHz)                                    | 入力インピーダンス(Ω) |                | REFL<br>係数 |      |

|---------------------------------------------------|--------------|----------------|------------|------|

|                                                   | 実数部*         | 虚数部*(容量)       | 振幅         | 位相   |

| 20                                                | 1.46k        | -878 (9.1pF)   | 0.873      | -13  |

| 40                                                | 915          | -475 (8.4pF)   | 0.811      | -24  |

| 100                                               | 371          | -261 (6.1pF)   | 0.622      | -45  |

| 200                                               | 233          | -193 (4.1pF)   | 0.506      | -62  |

| <b>EN = “L”(デバイスはディスエーブルされる、レジスタ 0X00 = 0x2E)</b> |              |                |            |      |

| 1                                                 | 2.04k        | -18.2k (8.8pF) | 0.906      | -0.6 |

| 2                                                 | 2.02k        | -4.59k (8.7pF) | 0.906      | -2.5 |

| 10                                                | 1.91k        | -1.84k (8.7pF) | 0.901      | -6.3 |

| 20                                                | 1.59k        | -935 (8.5pF)   | 0.893      | -12  |

| 40                                                | 1.01k        | -502 (7.9pF)   | 0.826      | -23  |

| 100                                               | 402          | -269 (5.9pF)   | 0.644      | -43  |

| 200                                               | 246          | -197 (4.0pF)   | 0.522      | -60  |

\*並列等価

回路は、内部または外部で加えることのできる1.4Vの同相電圧に最適化されています。ベースバンド・ピンにAC結合する場合(内部で1.4Vのバイアスが生成される)、ハイパスフィルタ・コーナーがベースバンド信号の低周波数成分に影響しないことを確認してください。低ベースバンド周波数のわずかな誤差も、EVMを劣化させる可能性があります。

ベースバンド入力オフセット電圧は、ソース抵抗によって変わります。AC結合を行う場合、1シグマのオフセットは、約1.1mVであり、約-46.6dBmのLOリークを発生させます。短絡されたベースバンド・ピン(0Ωのソース抵抗)の場合、LOリークは約-50.1dBmに改善されます。AC結合の場合、LOリークを低減するには、抵抗をベースバンド入力と並列に接続します。これによって、ベースバンド入力のインピーダンスとオフセットが減少します。さらに、シャットダウン・モードで結合される1.3nAの低いベースバンド入力リーク電流によって、カップリング・コンデンサを超える電圧が維持されます。これは、デバイスが再びイネーブルされたときに素早く安定化するのに役立ちます。直線性を改善するために、ベースバンド入力を差動で駆動することを推奨します。D/Aコンバータを信号源として使用する場合、エイリアシングを防ぐために、再構成フィルタをD/Aコンバータの出力とLTC5599のベースバンド入力の間に配置してください。

## アプリケーション情報

### 内部利得調整D/Aコンバータ

4つ(ベースバンド・ピンごとに1つ)の内部利得調整D/Aコンバータは、それぞれ11ビットとして構成されています。使用できるD/Aコンバータの入力値の範囲は、64から2047までの連続的な整数値であり、シャットダウンの場合は0です。これらのD/Aコンバータは、ベースバンド信号生成ではなく、利得とオフセットの設定のみを目的としています。これは、D/Aコンバータとミキサ・コアの間に再構成フィルタが存在せず、D/Aコンバータの値と抵抗設定の間の間接的なアクセスのみが存在するためです。この方法で、以下の機能が実装されています。

- 1dBステップでの粗いデジタル利得制御

- 0.1dBステップでの微細なデジタル利得制御

- 利得-温度補正

- IチャネルでのDCオフセット調整

- QチャネルでのDCオフセット調整

- I/Q利得バランス制御

- Qチャネルのディスエーブル

- 連続的な可変利得制御

### 1dBステップ(レジスタ0x01)での粗いデジタル利得制御(DG)

1dBずつ離れた20個のデジタル利得位置は、4つ全てのD/Aコンバータに対して対応するDACコードをハードワイヤ接続することによって実装されています。粗いデジタル利得は、レジスタ0x01の最下位5ビットに書き込むことによって設定されます(表10および表11を参照)。利得は、コード00000(コード0 = 0dB, DG = 0)で最大になり、コード10011(コード19 = -19dB, DG = -19)で最小になります。デジタル利得制御によって設定された0dBの利得は、デバイスの電圧利得と同じではないので、注意してください。残りの12個のコード(10進数の20～31)は、予備です。

d B単位のデジタル利得は、利得レジスタの最下位5ビットに書き込まれる10進数値にマイナスを掛けた値になります。したがって、変調器の利得G(V/V単位)を最大変換利得に関連付ける式は、次のようになります。

$$G(V/V) = 10^{(DG/20)}$$

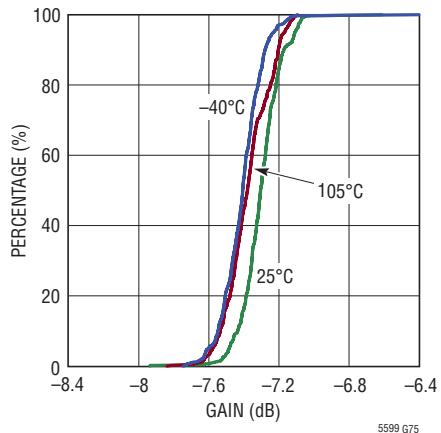

### 0.1dBステップでの微細なデジタル利得制御(FDG)と利得-温度補正(レジスタ0x07)

約0.1dBずつ離れた16個のデジタル利得位置を直接設定するには、レジスタ0x07の最下位4ビットを、レジスタ0x08のビット2 = 1 (TEMPCORR = 1)と組み合わせて使用します。粗

いデジタル利得設定の場合、コード9と、それよりもやや高い(つまり、微細なデジタル利得位置を加えた)コードは、11ビットD/Aコンバータの制限された分解能のため、同じになります。これらの0.1dB利得ステップの主な目的は、TEMPCORR = 1を設定することによってアクティブにできる自動利得/温度補正を実装することです。その場合、微細なデジタル利得制御の入力は、内蔵の温度計になります。この内蔵の温度計は、4ビットのデジタル・コードを生成します。コード0は-30°Cに対応し、コード15は120°Cに対応しており、各コード間は10°C離れています。内蔵の温度計の出力コードは、TEMPUPDT(レジスタ0x01のビット7、表10を参照)をクリアすることによって継続的に更新するか、外部でピンTTCKを“L”から“H”にする(かつ、TEMPUPDT = 1を設定する)ことによって更新できます。継続的に更新する場合、コードは、温度が特定のしきい値と交差するたびに非同期的に更新されます。データ・フレームの中間で利得更新が発生しないようにすることが必要になる場合があります。その場合、TTCKピンを使用して、例えばデータ・フレームの開始または終了に、利得/温度更新を同期させることができます。レジスタ0x1F(TEMP[3:0])を読み出すことによって、デバイス内部温度を読み取ることができます。TEMP[3:0]の10進数値は、次式で与えられます。

$$TEMP[3:0] = \text{round}(T/10) + 3$$

ここで、Tは実際のデバイス内部温度(°C)で、その精度は約±10°Cです。TEMPUPDTを1に設定し、ENが“L”から“H”に遷移した後に、TEMP[3:0]はデフォルトで7に設定されます。TEMPUPDT = 0からTEMPUPDT = 1に切り替えると、TEMP[3:0]はTTCKが最後に“L”から“H”に遷移したときの温度を示します。なお、TEMPCORRが1の場合、またはTEMPUPDTが1でTTCKが切り替わらない場合、実際のデバイス内部温度を読み取ることはできません。

### アナログ利得制御

LTC5599は、VCTRL(ピン1)に加えられる電圧による変換利得のアナログ制御をサポートしています。利得は、レジスタ0x01で設定されたデジタル利得設定(DG)の下方に制御できます。RF出力信号の歪みを最小限に抑えるために、AGCTRLビット(レジスタ0x01のビット6)を1に設定する必要があります。アナログ利得制御を使用しない場合は、VCTRLをVCCに接続し、AGCTRLを0に設定してください。これによって、約2.58mAの電源電流を節約できます。使用できる標準的な利得制御範囲は、0.9V～3.3Vです。VCTRLをVCCよりも低い電圧に設定し、AGCTRLを0に設定すると、RF出力信号の直線性が大きく損なわれ、VCTRLの応答時間が遅くなります。簡略回路図を図1に示します。

## アプリケーション情報

### I/QのDCオフセット調整(レジスタ0x02および0x03)とLOリーク

IチャネルとQチャネルのオフセットは、RFポートでのLOリークにつながります。このオフセットは、I/Q変調器によって発生するか、ベースバンド接続がDC結合され、外部で適用された場合に発生します。レジスタ0x02および0x03(IオフセットおよびQオフセット)を設定して、このオフセットをキャンセルし、LOリークを抑えることができます。Iチャネルのオフセットを調整するには、BBPI DACをBBMI DACとは(わずかに)異なる値に設定して、オフセットを導入します。これらの8ビット・レジスタのデフォルト値は128であり、0オフセットを表します。レジスタ値は、1~255の範囲で設定できます。値0は未サポートのコードを表しているため、使用しないでください。入力で参照されるオフセットは、利得によって変わります。そのため、入力オフセット値( $V_{os}$ )を次のように計算できます。

$$V_{os} = 1260 / ((3632 \cdot G) / (N_{os} - 128) - (N_{os} - 128) / (3632 \cdot G))$$

また、 $N_{os}=128$ の場合は、 $V_{os}=0$ です。Gは、表3の利得を表しています。

表3.粗いデジタル利得(DG)のレジスタ設定

| DG(dB) | G(V/V) | DEC | バイナリ  | 16進  |

|--------|--------|-----|-------|------|

| 0      | 1.000  | 0   | 00000 | 0x00 |

| -1     | 0.891  | 1   | 00001 | 0x01 |

| -2     | 0.794  | 2   | 00010 | 0x02 |

| -3     | 0.708  | 3   | 00011 | 0x03 |

| -4     | 0.631  | 4   | 00100 | 0x04 |

| -5     | 0.562  | 5   | 00101 | 0x05 |

| -6     | 0.501  | 6   | 00110 | 0x06 |

| -7     | 0.447  | 7   | 00111 | 0x07 |

| -8     | 0.398  | 8   | 01000 | 0x08 |

| -9     | 0.355  | 9   | 01001 | 0x09 |

| -10    | 0.316  | 10  | 01010 | 0x0A |

| -11    | 0.282  | 11  | 01011 | 0x0B |

| -12    | 0.251  | 12  | 01100 | 0x0C |

| -13    | 0.224  | 13  | 01101 | 0x0D |

| -14    | 0.200  | 14  | 01110 | 0x0E |

| -15    | 0.178  | 15  | 01111 | 0x0F |

| -16    | 0.158  | 16  | 10000 | 0x10 |

| -17    | 0.141  | 17  | 10001 | 0x11 |

| -18    | 0.126  | 18  | 10010 | 0x12 |

| -19    | 0.112  | 19  | 10011 | 0x13 |

正のオフセットは、正入力端子(BBPIまたはBBPQ)の電圧が負入力端子(BBMIまたはBBMQ)に対して増加していることを意味しています。

### I/Q利得比(レジスタ0x04)と側波帯抑圧

8ビットのI/Q利得比レジスタ0x04は、Iチャネル・ミキサ変換利得 $G_I$ とQチャネル・ミキサ変換利得 $G_Q$ の比率を制御します。直交位相不均衡レジスタ0x05と共にレジスタ0x04を使用して、変調器の側波帯抑圧をさらに最適化できます。

利得比 $G_I/G_Q$ を8ビット・レジスタ0x04の内容に関連付ける式を、10進数 $N_{IQ}$ と公称変換利得 $G$ で表すと、次のようにになります。

$$20 \log(G_I/G_Q) = 20 \log((3632 \cdot G - (N_{IQ} - 128)) / (3632 \cdot G + (N_{IQ} - 128))) \text{ (dB)}$$

$N_{IQ}$ に対する利得比調整のステップ・サイズ(dB単位)は、デジタル利得設定が同じである場合、ほぼ一定になります。例えば、デジタル利得設定が-4の場合、ステップ・サイズは約7.6dBになります。上の式から得られるデジタル利得設定ごとの利得ステップ・サイズを、表4に示します。

表4.I/Q利得比のステップ・サイズとデジタル利得設定

| DG(dB) | G(V/V) | $\Delta G_I/G_Q$ (m dB) |

|--------|--------|-------------------------|

| 0      | 1.000  | 4.8                     |

| -1     | 0.891  | 5.4                     |

| -2     | 0.794  | 6.0                     |

| -3     | 0.708  | 6.8                     |

| -4     | 0.631  | 7.6                     |

| -5     | 0.562  | 8.5                     |

| -6     | 0.501  | 9.6                     |

| -7     | 0.447  | 10.7                    |

| -8     | 0.398  | 12.0                    |

| -9     | 0.355  | 13.5                    |

| -10    | 0.316  | 15.1                    |

| -11    | 0.282  | 17.1                    |

| -12    | 0.251  | 19.2                    |

| -13    | 0.224  | 21.5                    |

| -14    | 0.200  | 24.2                    |

| -15    | 0.178  | 27.3                    |

| -16    | 0.158  | 30.7                    |

| -17    | 0.141  | 34.6                    |

| -18    | 0.126  | 39.0                    |

| -19    | 0.112  | 44.1                    |

## アプリケーション情報

$N_{IQ} = 128$  の場合、I チャネルと Q チャネルの変換利得は同じになります。 $N_{IQ} > 128$  の場合、I チャネルの利得は Q チャネルの利得よりも大きくなります。

### デジタル Q チャネル

レジスタ 0x01 (QDISABLE) のビット 5 を設定した場合、Q チャネルがオフに切り替わり、I/Q 変調器がアップコンバージョン・ミキサに変わります。このモードでは、BBPQ ピンと BBMQ ピンをフロート状態にすることを推奨します。Q チャネルがオン (QDISABLE = 0) であるのが、デフォルト・モードです。

### LO セクション (レジスタ 0x00)

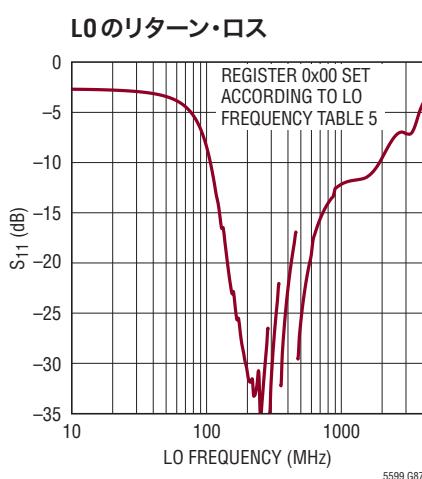

内部 LO チェーンは、画像排除二重平衡ミキサ用の I 信号と Q 信号を生成する PolyPhase フィルタで構成されています。PolyPhase フィルタの中心周波数は、レジスタ 0x00 の下位 7 ビットで設定されます。LO 周波数に対する推奨設定を表 5 に示します (QuikEval™ の GUI を参照)。

表 5. レジスタ 0x00 の設定と LO 周波数

| レジスタ値 |         |     | LO 周波数範囲 (MHz) |        |

|-------|---------|-----|----------------|--------|

| 10進   | バイナリ    | 16進 | 下限値            | 上限値    |

| 0     | 0000000 | 00  | N/A            | N/A    |

| 1     | 0000001 | 01  | 1249.1         | 1300.0 |

| 2     | 0000010 | 02  | 1248.6         | 1249.0 |

| 3     | 0000011 | 03  | 1238.1         | 1248.5 |

| 4     | 0000100 | 04  | 1214.1         | 1238.0 |

| 5     | 0000101 | 05  | 1191.2         | 1214.0 |

| 6     | 0000110 | 06  | 1165.6         | 1191.1 |

| 7     | 0000111 | 07  | 1141.0         | 1165.5 |

| 8     | 0001000 | 08  | 1120.6         | 1140.9 |

| 9     | 0001001 | 09  | 1100.5         | 1120.5 |

| 10    | 0001010 | 0A  | 1069.5         | 1100.4 |

| 11    | 0001011 | 0B  | 1039.6         | 1069.4 |

| 12    | 0001100 | 0C  | 1023.1         | 1039.5 |

| 13    | 0001101 | 0D  | 1007.1         | 1023.0 |

| 14    | 0001110 | 0E  | 988.3          | 1007.0 |

| 15    | 0001111 | 0F  | 961.8          | 988.2  |

| 16    | 0010000 | 10  | 941.3          | 961.7  |

| 17    | 0010001 | 11  | 921.5          | 941.2  |

| 18    | 0010010 | 12  | 895.2          | 921.4  |

| 19    | 0010011 | 13  | 877.6          | 895.1  |

| 20    | 0010100 | 14  | 863.6          | 877.5  |

| 21    | 0010101 | 15  | 843.2          | 863.5  |

表 5. レジスタ 0x00 の設定と LO 周波数 (続き)

| レジスタ値 |         |     | LO 周波数範囲 (MHz) |       |

|-------|---------|-----|----------------|-------|

| 10進   | バイナリ    | 16進 | 下限値            | 上限値   |

| 22    | 0010110 | 16  | 826.9          | 843.1 |

| 23    | 0010111 | 17  | 807.0          | 826.8 |

| 24    | 0011000 | 18  | 792.3          | 806.9 |

| 25    | 0011001 | 19  | 772.2          | 792.2 |

| 26    | 0011010 | 1A  | 752.7          | 772.1 |

| 27    | 0011011 | 1B  | 734.0          | 752.6 |

| 28    | 0011100 | 1C  | 724.2          | 739.9 |

| 29    | 0011101 | 1D  | 704.6          | 724.1 |

| 30    | 0011110 | 1E  | 688.7          | 704.5 |

| 31    | 0011111 | 1F  | 673.2          | 688.6 |

| 32    | 0100000 | 20  | 655.2          | 673.1 |

| 33    | 0100001 | 21  | 638.1          | 655.1 |

| 34    | 0100010 | 22  | 624.6          | 638.0 |

| 35    | 0100011 | 23  | 611.9          | 624.5 |

| 36    | 0100100 | 24  | 598.4          | 611.8 |

| 37    | 0100101 | 25  | 585.1          | 598.3 |

| 38    | 0100110 | 26  | 573.9          | 585.0 |

| 39    | 0100111 | 27  | 563.1          | 573.8 |

| 40    | 0101000 | 28  | 548.1          | 563.0 |

| 41    | 0101001 | 29  | 538.1          | 548.0 |

| 42    | 0101010 | 2A  | 529.1          | 538.0 |

| 43    | 0101011 | 2B  | 518.5          | 529.0 |

| 44    | 0101100 | 2C  | 507.0          | 518.4 |

| 45    | 0101101 | 2D  | 497.7          | 506.9 |

| 46    | 0101110 | 2E  | 488.0          | 497.6 |

| 47    | 0101111 | 2F  | 471.5          | 487.9 |

| 48    | 0110000 | 30  | 457.7          | 471.4 |

| 49    | 0110001 | 31  | 448.7          | 457.6 |

| 50    | 0110010 | 32  | 437.4          | 448.6 |

| 51    | 0110011 | 33  | 426.6          | 437.3 |

| 52    | 0110100 | 34  | 417.5          | 426.5 |

| 53    | 0110101 | 35  | 407.5          | 417.4 |

| 54    | 0110110 | 36  | 398.0          | 407.4 |

| 55    | 0110111 | 37  | 390.1          | 397.9 |

| 56    | 0111000 | 38  | 382.8          | 390.0 |

| 57    | 0111001 | 39  | 376.6          | 382.7 |

| 58    | 0111010 | 3A  | 369.8          | 376.5 |

| 59    | 0111011 | 3B  | 353.1          | 369.7 |

| 60    | 0111100 | 3C  | 339.0          | 353.0 |

## アプリケーション情報

表5. レジスタ 0x00 の設定と LO 周波数 (続き)

| レジスタ値 |         |     | LO 周波数範囲 (MHz) |       |

|-------|---------|-----|----------------|-------|

| 10進   | バイナリ    | 16進 | 下限値            | 上限値   |

| 61    | 0111101 | 3D  | 332.6          | 338.9 |

| 62    | 0111110 | 3E  | 327.2          | 332.5 |

| 63    | 0111111 | 3F  | 320.6          | 327.1 |

| 64    | 1000000 | 40  | 313.7          | 320.5 |

| 65    | 1000001 | 41  | 309.1          | 313.6 |

| 66    | 1000010 | 42  | 304.5          | 309.0 |

| 67    | 1000011 | 43  | 288.1          | 304.4 |

| 68    | 1000100 | 44  | 278.3          | 288.0 |

| 69    | 1000101 | 45  | 274.2          | 278.2 |

| 70    | 1000110 | 46  | 270.3          | 274.1 |

| 71    | 1000111 | 47  | 266.0          | 270.2 |

| 72    | 1001000 | 48  | 261.9          | 265.9 |

| 73    | 1001001 | 49  | 258.2          | 261.8 |

| 74    | 1001010 | 4A  | 254.1          | 258.1 |

| 75    | 1001011 | 4B  | 243.6          | 254.0 |

| 76    | 1001100 | 4C  | 233.8          | 243.5 |

| 77    | 1001101 | 4D  | 230.8          | 233.7 |

| 78    | 1001110 | 4E  | 228.0          | 230.7 |

| 79    | 1001111 | 4F  | 220.2          | 227.9 |

| 80    | 1010000 | 50  | 212.6          | 220.1 |

| 81    | 1010001 | 51  | 210.0          | 212.5 |

| 82    | 1010010 | 52  | 207.6          | 209.9 |

| 83    | 1010011 | 53  | 202.1          | 207.5 |

| 84    | 1010100 | 54  | 196.2          | 202.0 |

| 85    | 1010101 | 55  | 193.7          | 196.1 |

| 86    | 1010110 | 56  | 191.2          | 193.6 |

| 87    | 1010111 | 57  | 186.6          | 191.1 |

| 88    | 1011000 | 58  | 182.0          | 186.5 |

| 89    | 1011001 | 59  | 179.4          | 181.9 |

| 90    | 1011010 | 5A  | 176.0          | 179.3 |

| 91    | 1011011 | 5B  | 170.1          | 175.9 |

| 92    | 1011100 | 5C  | 165.0          | 170.0 |

| 93    | 1011101 | 5D  | 162.5          | 164.9 |

| 94    | 1011110 | 5E  | 160.0          | 162.4 |

| 95    | 1011111 | 5F  | 156.7          | 159.9 |

| 96    | 1100000 | 60  | 153.6          | 156.6 |

| 97    | 1100001 | 61  | 151.1          | 153.5 |

| 98    | 1100010 | 62  | 148.6          | 151.0 |

| 99    | 1100011 | 63  | 142.5          | 148.5 |

表5. レジスタ 0x00 の設定と LO 周波数 (続き)

| レジスタ値 |         |     | LO 周波数範囲 (MHz) |       |

|-------|---------|-----|----------------|-------|

| 10進   | バイナリ    | 16進 | 下限値            | 上限値   |

| 100   | 1100100 | 64  | 139.6          | 142.4 |

| 101   | 1100101 | 65  | 136.5          | 139.5 |

| 102   | 1100110 | 66  | 134.3          | 136.4 |

| 103   | 1100111 | 67  | 131.2          | 134.2 |

| 104   | 1101000 | 68  | 128.1          | 131.1 |

| 105   | 1101001 | 69  | 126.0          | 128.0 |

| 106   | 1101010 | 6A  | 123.8          | 125.9 |

| 107   | 1101011 | 6B  | 121.3          | 123.7 |

| 108   | 1101100 | 6C  | 118.3          | 121.2 |

| 109   | 1101101 | 6D  | 115.7          | 118.2 |

| 110   | 1101110 | 6E  | 113.5          | 115.6 |

| 111   | 1101111 | 6F  | 111.3          | 113.4 |

| 112   | 1110000 | 70  | 109.5          | 111.2 |

| 113   | 1110001 | 71  | 107.6          | 109.4 |

| 114   | 1110010 | 72  | 105.6          | 107.5 |

| 115   | 1110011 | 73  | 103.0          | 105.5 |

| 116   | 1110100 | 74  | 100.3          | 102.9 |

| 117   | 1110101 | 75  | 98.5           | 100.2 |

| 118   | 1110110 | 76  | 96.6           | 98.4  |

| 119   | 1110111 | 77  | 94.7           | 96.5  |

| 120   | 1111000 | 78  | 93.0           | 94.6  |

| 121   | 1111001 | 79  | 30.0           | 92.9  |

| 122   | 1111010 | 7A  | N/A            | N/A   |

| 123   | 1111011 | 7B  | N/A            | N/A   |

| 124   | 1111100 | 7C  | N/A            | N/A   |

| 125   | 1111101 | 7D  | N/A            | N/A   |

| 126   | 1111110 | 7E  | N/A            | N/A   |

| 127   | 1111111 | 7F  | N/A            | N/A   |

LOL および LOC インタフェースの簡略回路図を図2に示します。LOL 入力と LOC 入力は、差動 LO 入力ではありません。これらは、50Ω 入力であり、LOL 入力に接続されたインダクタおよび LOC 入力に接続されたコンデンサによって駆動されることを目的としています。コンデンサとインダクタを切り替えないでください。切り替えた場合、性能が著しく低下します。LO の範囲が広帯域である場合、これらのピンでは、39nH のインダクタ値と 15pF のコンデンサ値(標準的な LO 整合)を推奨します。これによって、200MHz の中心周波数を持つデュプレクサ回路が形成されます。このデュプレクサは、200MHz の周辺の較正されない側波带抑圧の大幅な改善に役立ちます。

## アプリケーション情報

200MHzから大きく離れたLO周波数の場合も、デュプレクサは、シングルエンドLO駆動や差動駆動よりも良好な性能を示します。PolyPhaseフィルタの製造時の較正により、標準的な側波帯抑圧は、100MHz～700MHzの周波数範囲で約50dBc、700MHz～1300MHzの周波数範囲で45dBcになります。帯域幅が200MHzよりも非常に狭いアプリケーションの場合、デュプレクサを別の周波数に調整すると、較正されない側波帯抑圧およびLO駆動レベルに対する利得の改善に役立つ場合があります。「標準的性能特性」セクションに、900MHz整合( $L_1 = 8.2\text{nH}$ ,  $C_5 = 3.3\text{pF}$ )および1260MHz整合( $L_1 = 5.6\text{nH}$ ,  $C_5 = 3\text{pF}$ )のリターン・ロスを示します。標準の200MHz整合で、900MHz整合および1260MHz整合に相当する性能を実現するには、LO電力をそれぞれ1.5dBおよび2dB増やす必要があります。標準の整合を使用しない場合、表5のレジスタ0x00の値も、調整が必要になる可能性があります。

図2. LOL入力およびLOC入力の簡略回路図

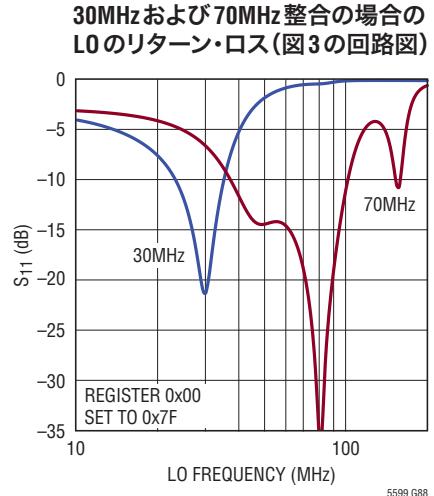

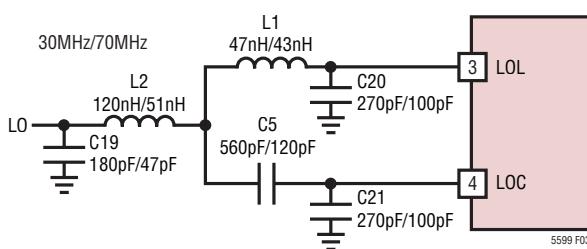

100MHz未満では、図3の整合ネットワークを使用できます。この場合の側波帯抑圧は、デュプレクサ $L_1$ 、 $C_5$ 、およびLOLとLOCの(温度に依存する)入力インピーダンスによって主に定義されます。「標準的性能特性」セクションの測定された性能を参照してください。

図3. 30MHz/70MHzで整合されるLOLおよびLOCインターフェースのインピーダンス整合ネットワーク

表6に、EN = “H”および $P_{LO} = 0\text{dBm}$ での周波数に対するLOLポートとLOCポートの入力インピーダンスを示します。その他のLOポート(LOCまたはLOL)は、 $50\Omega$ で終端されます。

表6. EN = “H”および $P_{LO} = 0\text{dBm}$ の場合のLOL、LOCポートの入力インピーダンスと周波数

(その他のLOポートは $50\Omega$ でグランドに終端される)

| 周波数<br>(MHz) | レジスタ<br>0x00 | LOL/LOCポートの<br>インピーダンス( $\Omega$ ) |                   | REFL係数 |     |

|--------------|--------------|------------------------------------|-------------------|--------|-----|

|              |              | 実数部*                               | 虚数部*<br>(インダクタンス) | 振幅     | 位相  |

| 20           | 79           | 7.9                                | 24.3 (194nH)      | 0.750  | 175 |

| 30           | 79           | 9.1                                | 19.0 (101nH)      | 0.743  | 172 |

| 40           | 79           | 10.8                               | 17.4 (69nH)       | 0.732  | 169 |

| 50           | 79           | 13.0                               | 17.6 (56nH)       | 0.716  | 165 |

| 60           | 79           | 15.7                               | 18.9 (50nH)       | 0.693  | 162 |

| 70           | 79           | 18.6                               | 21.4 (49nH)       | 0.661  | 158 |

| 80           | 79           | 21.6                               | 25.0 (50nH)       | 0.618  | 154 |

| 90           | 79           | 24.4                               | 30.3 (54nH)       | 0.564  | 151 |

| 100          | 75           | 27.0                               | 38.3 (61nH)       | 0.497  | 148 |

| 110          | 70           | 29.0                               | 51.4 (74nH)       | 0.419  | 146 |

| 120          | 60           | 30.3                               | 76.1 (101nH)      | 0.338  | 149 |

| 130          | 68           | 32.3                               | 109.3 (134nH)     | 0.276  | 150 |

| 140          | 64           | 34.3                               | 121.6 (138nH)     | 0.247  | 148 |

| 150          | 62           | 36.2                               | 119.4 (127nH)     | 0.234  | 142 |

| 160          | 5E           | 37.4                               | 149.1 (148nH)     | 0.201  | 143 |

| 170          | 5C           | 37.1                               | 357.5 (335nH)     | 0.160  | 162 |

| 180          | 59           | 39.6                               | 188.6 (167nH)     | 0.164  | 141 |

| 190          | 57           | 41.4                               | 192.0 (161nH)     | 0.150  | 135 |

| 200          | 54           | 40.7                               | 418.6 (333nH)     | 0.116  | 156 |

\*並列等価

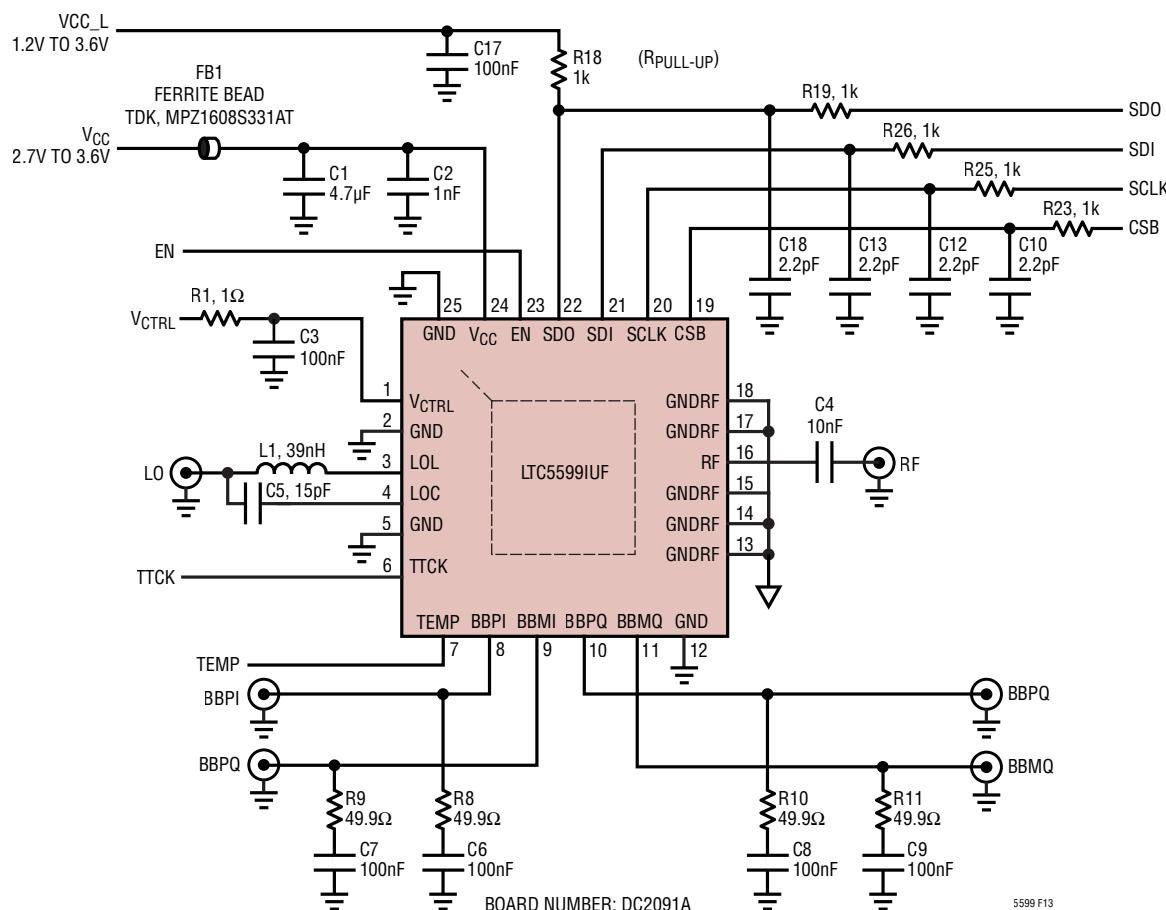

デモ・ボードの回路図を図13に示します。

## I/Q位相バランス調整レジスタ0x05と側波帯抑圧

理想的には、IチャネルのLO位相は、QチャネルのLO位相から正確に90°進んでいます。これを、直交と呼びます。ただし、実際には、I/Qの位相差は、わずかな誤差によって正確な直交とは異なっています。これは、部品パラメータの変動とLO信号に含まれる高調波成分に起因します(下記を参照)。

I/Q位相不均衡レジスタ(0x05)を使用してI/Qの位相シフトを調整し、このような誤差を補償できます。このレジスタを利得比レジスタ0x04と併用して、変調器の側波帯抑圧を最適化できます。

## アプリケーション情報

レジスタ0x05は、次の2つの部分(表11を参照)で構成されています。最下位5ビットのIQPHFは微細な位相調整を実現し、最上位3ビットのIQPHEは粗い調整に使用されます。IQPHFによって実現される微細な位相調整は、次のように近似できます。

$$\varphi_{IQ} = -((N_{ph} - 16)/15) \cdot \ln(f_{LO}/50) (\circ)$$

(30MHz < f<sub>LO</sub> < 1300MHzの場合)

ここで、N<sub>ph</sub>はIQPHFの10進数値、f<sub>LO</sub>はLO信号の周波数(MHz)です。φ<sub>IQ</sub>の正の値は、IチャネルのLO位相がQチャネルのLO位相よりも90°進んでいることを意味しています。式から、位相調整範囲と分解能が連動しており、LO周波数によって変化することがわかります。低いLO周波数では、最小の調整範囲と最高の分解能が達成されますが、高いLO周波数では、最大の調整範囲と最低の分解能が示されます。

拡張ビットIQPHEは、より大きな位相調整範囲を提供し、特に、低いLO周波数で役立ち、位相調整範囲とPolyPhaseフィルタの最大位中心周波数との間のトレードオフを解決します。このトレードオフは、PolyPhaseフィルタのIチャネルの容量(C<sub>ppI</sub>)とQチャネルの容量(C<sub>ppQ</sub>)がこれら両方のパラメータを制御することから生じます。これらの容量の差が位相シフトを設定し、合計がフィルタの中心周波数を決定します。

拡張ビットIQPHEは、IQPHFビットによって実現される微細な調整に加えて、より大きな位相オフセットを導入します。この大きなオフセットの符号は、負または正のいずれにもなり、IQPHSIGN(レジスタ0x00のビット7)によって制御されます。これらのビットを含めて、直交からの合計位相シフトを次のように表すことができます。

$$\varphi_{IQ} = -(M_{ph}/15) \cdot \ln(f_{LO}/50) (\circ)$$

$$M_{ph} = N_{COARSE} + N_{PH} - 16 \text{ および}$$

$$N_{COARSE} = 32 \cdot (-1)^{IQPHSIGN+1} \cdot N_{EXT}$$

ここで、N<sub>ext</sub>はIQPHEビットの10進数値です。(N<sub>ph</sub>-16)の値の有効な範囲は、{-16, -15, ..., +15}から{-240, -239, ..., +239}に拡張されます。付録の表9に、可能な全ての組み合わせを示します。IQPHSIGN=0およびIQPHSIGN=1のコードの範囲は、M<sub>ph</sub>=-16～M<sub>ph</sub>=+15の間で重なっているため、位相シフトが大きい場合、IQPHSIGNを変更するだけで済みます。

副作用として、新しいN<sub>COARSE</sub>値に向かって境界を交差した後に、拡張ビットによってPolyPhaseフィルタの中心周波数がわずかに劣化します。これは、実際の位相シフトでは、

大きなステップとして観察されます。これに対する解決策は、N<sub>COARSE</sub>値の境界での周波数レジスタ0x00の値を減らす(PolyPhaseフィルタの中心周波数を増やす)ことです。その結果、滑らかな位相調整が得られます。デモ・ボードのQuikEvalのGUIでは、このLO周波数レジスタの調整は自動的に行われます。

位相調整の滑らかさを改善するためにPolyPhaseフィルタの中心周波数を調整した場合、レジスタ0x06のCLOOビットを使用して、LOポートのインピーダンスの整合を手動で設定することを推奨します。デフォルトでは、フィルタの中心周波数を変更すると、LOポートの整合も自動的に調整されます(レジスタ0x06のCLOEN(ビット4)が設定されている場合)。ただし、LO搬送波周波数が変わらないため、この場合、LO整合の自動調整は望ましくありません。それによって、別の大きなステップが位相調整に追加される可能性があります。代わりに、LO整合を変えずに、フィルタの中心周波数を調整する必要があります。これは、次のようにして実現できます。まず、現在のLO整合の構成をレジスタ0x1DのCLOビットから読み出し、レジスタ0x06のCLOOオーバーライド・ビットに書き込みます。次に、CLOENビット(レジスタ0x06のビット4)をクリアして、自動LO整合調整をディスエーブルします。その結果、LO整合を変えることなく、レジスタ0x00で中心周波数を調整できます。

100MHzでは最大位相シフトは約±9.8°になり、1GHzでは約±3°になります。拡張ビットは、988.2MHzを超える場合は役立ちません。これは、PolyPhase中心周波数レジスタ0x00の値を、新しいN<sub>COARSE</sub>値に滑らかに遷移できるほど十分に低く調整できないためです。

### 方形波LO駆動

PolyPhaseフィルタを直交生成に使用するときに、LO信号の高調波成分は、直交位相の誤差と利得精度に必ず悪影響を与えます。LTC5599では、I/Q利得レジスタおよびI/Q位相レジスタに適切な値を設定することによって、LO搬送波(方形波など)の高調波成分に起因する位相と利得の誤差を修正できます。そのような調整は、通常、LO信号の第3次高調波が、望ましい側波帯抑圧から13dBを超えた場合に必要になります。PolyPhaseフィルタはLO搬送波の第2次高調波成分に敏感ではありませんが、それでも、第2次高調波成分の影響が大きくなる場合があります。I/Qの利得および位相の調整が行われなければ、-15dBcの第2次高調波成分の場合、側波帯抑圧は-45dBcに悪化する可能性があり、-20dBcの第2次高調波成分の場合、側波帯抑圧は-54dBcに悪化する可能があります。

## アプリケーション情報

### RF出力

アップコンバージョン後、IミキサとQミキサのRF出力は合成されます。内蔵バッファによって内部の差動からシングルエンジへの変換が行われ、図4に示すように、出力信号が $50\Omega$ に変換されます。

図4. RF出力ポートの簡略回路図

表7に、EN = “H”的場合の周波数とデジタル利得設定に対するRFポートの出力インピーダンスを示します。

表7. EN = “H”的場合のRFの出力インピーダンスと周波数およびデジタル利得設定(DG)

| 周波数(MHz) | DG(dB) | 出力インピーダンス(Ω) |                 | REFL係数 |     |

|----------|--------|--------------|-----------------|--------|-----|

|          |        | 実数部*         | 虚数部*(容量)        | 振幅     | 位相  |

| 30       | 0      | 59           | -413 (12.8pF)   | 0.104  | -43 |

| 30       | -12    | 61           | -465 (11.4pF)   | 0.114  | -35 |

| 30       | -16    | 64           | -529 (10.0pF)   | 0.133  | -27 |

| 30       | -18    | 69           | -623 (8.5pF)    | 0.166  | -19 |

| 30       | -19    | 83           | -902 (5.9pF)    | 0.249  | -10 |

| 50       | 0      | 56           | -671 (4.7pF)    | 0.068  | -38 |

| 50       | -12    | 58           | -762 (4.2pF)    | 0.082  | -27 |

| 50       | -16    | 61           | -859 (3.7pF)    | 0.107  | -19 |

| 50       | -18    | 67           | -972 (3.3pF)    | 0.146  | -13 |

| 50       | -19    | 81           | -1.21k (2.6pF)  | 0.239  | -8  |

| 100      | 0      | 55           | -1.08k (1.5pF)  | 0.050  | -30 |

| 100      | -12    | 57           | -1.32k (1.2pF)  | 0.066  | -19 |

| 100      | -16    | 60           | -1.55k (1.0pF)  | 0.096  | -12 |

| 100      | -18    | 66           | -1.75k (0.91pF) | 0.142  | -8  |

| 100      | -19    | 82           | -1.98k (0.80pF) | 0.246  | -5  |

| 600      | 0      | 54           | -1.35k (0.20pF) | 0.040  | -30 |

| 600      | -12    | 56           | -1.75k (0.15pF) | 0.057  | -16 |

| 600      | -16    | 58           | -1.77k (0.15pF) | 0.078  | -12 |

| 600      | -18    | 62           | -1.44k (0.18pF) | 0.109  | -11 |

| 600      | -19    | 77           | -680 (0.39pF)   | 0.217  | -14 |

表7. EN = “H”的場合のRFの出力インピーダンスと周波数およびデジタル利得設定(DG) (続き)

| 周波数(MHz) | DG(dB) | 出力インピーダンス(Ω) |               | REFL係数 |      |

|----------|--------|--------------|---------------|--------|------|

|          |        | 実数部*         | 虚数部*(容量)      | 振幅     | 位相   |

| 1300     | 0      | 48           | -802 (0.15pF) | 0.035  | -119 |

| 1300     | -12    | 51           | -807 (0.15pF) | 0.034  | -68  |

| 1300     | -16    | 55           | -709 (0.17pF) | 0.059  | -41  |

| 1300     | -18    | 59           | -526 (0.23pF) | 0.098  | -35  |

| 1300     | -19    | 73           | -280 (0.44pF) | 0.215  | -36  |

\*並列等価

EN = “L”的場合のRFポートの出力インピーダンスを表8に示します。

表8. EN = “L”的場合のRFの出力インピーダンスと周波数

| 周波数(MHz) | 出力インピーダンス(Ω) |                 | REFL係数 |      |

|----------|--------------|-----------------|--------|------|

|          | 実数部*         | 虚数部*(容量)        | 振幅     | 位相   |

| 30       | 16.1k        | -7.76k (0.68pF) | 0.994  | -0.7 |

| 40       | 16.2k        | -5.24k (0.76pF) | 0.994  | -1.1 |

| 50       | 15.7k        | -3.96k (0.80pF) | 0.994  | -1.4 |

| 60       | 16.5k        | -3.18k (0.83pF) | 0.994  | -1.8 |

| 70       | 16.8k        | -2.66k (0.86pF) | 0.994  | -2.2 |

| 80       | 16.4k        | -2.29k (0.87pF) | 0.994  | -2.5 |

| 90       | 17.1k        | -2.01k (0.88pF) | 0.994  | -2.9 |

| 100      | 17.9k        | -1.79k (0.89pF) | 0.994  | -3.2 |

| 200      | 14.7k        | -856 (0.93pF)   | 0.993  | -6.7 |

| 250      | 11.1k        | -679 (0.94pF)   | 0.991  | -8.4 |

| 300      | 8.55k        | -563 (0.94pF)   | 0.988  | -10  |

| 350      | 7.97k        | -481 (0.94pF)   | 0.988  | -12  |

| 400      | 6.42k        | -420 (0.95pF)   | 0.985  | -14  |

| 450      | 5.27k        | -373 (0.95pF)   | 0.982  | -15  |

| 500      | 4.26k        | -336 (0.95pF)   | 0.977  | -17  |

| 600      | 3.05k        | -281 (0.94pF)   | 0.969  | -20  |

| 700      | 2.32k        | -241 (0.94pF)   | 0.959  | -23  |

| 800      | 1.85k        | -211 (0.94pF)   | 0.950  | -27  |

| 900      | 1.54k        | -188 (0.94pF)   | 0.941  | -30  |

| 1000     | 1.30k        | -169 (0.94pF)   | 0.932  | -33  |

| 1100     | 1.12k        | -154 (0.94pF)   | 0.923  | -36  |

| 1200     | 991          | -141 (0.94pF)   | 0.914  | -39  |

| 1300     | 881          | -129 (0.95pF)   | 0.906  | -42  |

\*並列等価

## アプリケーション情報

$V_{CC} = 3.3V$  および  $EN = "H"$  の場合、RFピンの電圧は約1.68Vになります。 $V_{CC} = 3.3V$  および  $EN = "L"$  の場合、RFピンの電圧は約3.1Vになります。

## イネーブル・インターフェース

$EN$  ピンのインターフェースの簡略回路図を図5に示します。LTC5599をオンするのに必要な電圧は1.1Vです。デバイスをディスエーブルする(シャットダウンする)には、イネーブル電圧を0.2Vより低くする必要があります。

図5. ENインターフェースの簡略回路図

## シリアル・ポート

SPI互換のシリアル・ポートは、制御およびモニタ機能を備えています。

## 通信シーケンス

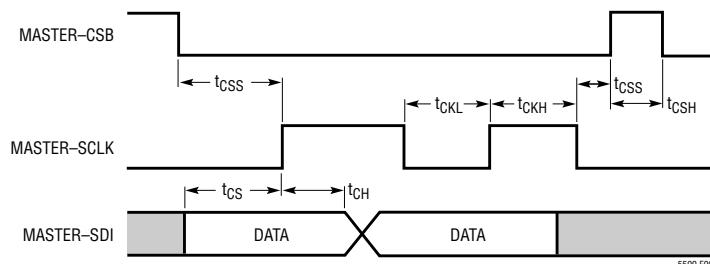

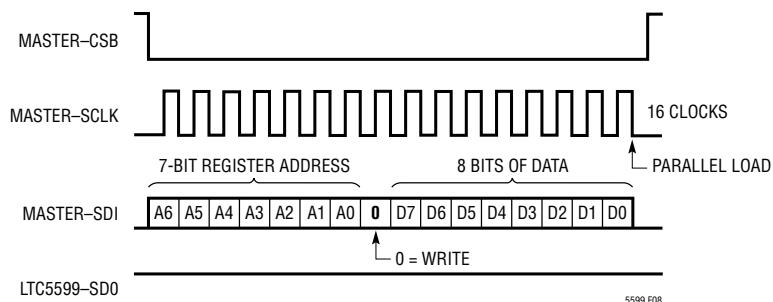

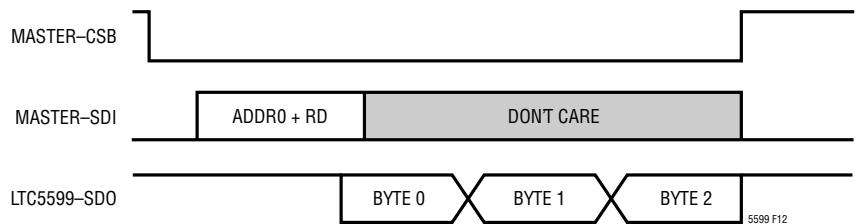

シリアル・バスは、CSB、SCLK、SDI、およびSDOで構成されています。デバイスへのデータ転送は、シリアル・バスのマスタ・デバイスが最初にCSBを“L”にしてLTC5599のポートをイネーブルすることにより、行われます。SDIに与えられた入力データはSCLKの立ち上がりエッジでクロックされます。データは常にMSBを先頭にして転送されます。通信バーストは、シリアル・バスのマスタがCSBを“H”に戻すと終了します。詳細については図6を参照してください。

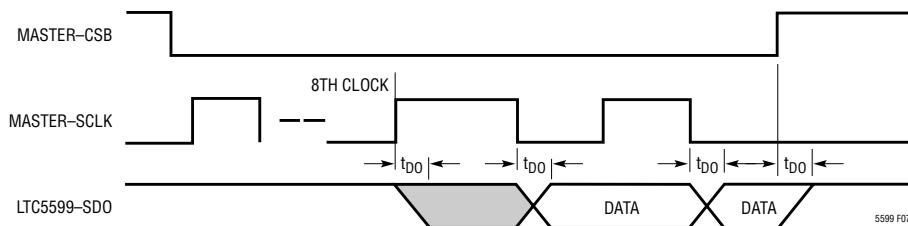

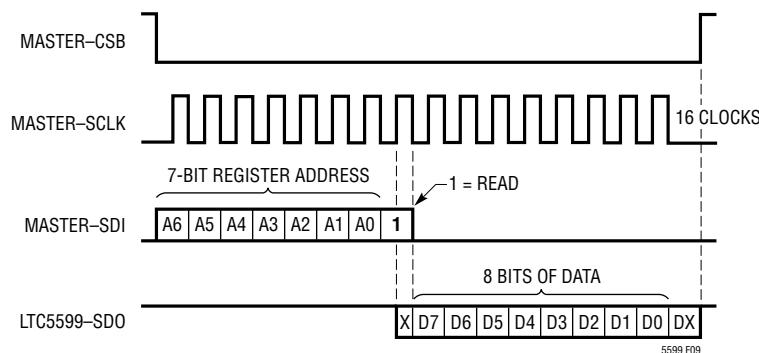

データは、通信バーストの間にSDOを使ってデバイスから読み出されます。CSB = 1のとき、またはデバイスからデータが読み出されていないとき、SDOは高インピーダンス(Hi-Z)になるので、読み出しをマルチドロップにする(シリアル・バスに複数のLTC5599を並列に接続する)ことができます。LTC5599をマルチドロップ構成で使用しない場合、またはシリアル・ポートのマスタが読み出しシーケンス間のSDOラインのレベルを設定できない場合は、SDOと $V_{CC\_L}$ の間に抵抗を接続して、Hi-Z状態のときにラインが確実に $V_{CC\_L}$ に戻るようにすることを推奨します。抵抗値は、SDO出力電流が確実に10mA以下になるように十分大きい値にする必要があります。詳細については図7を参照してください。

図6. シリアル・ポートの書き込みタイミング図

図7. シリアル・ポートの読み出しタイミング図

## アプリケーション情報

### 1バイトの転送

シリアル・ポートは簡単なメモリ・マップとして構成されており、9個の読み出し/書き込みバイト幅レジスタおよび23個の読み出し専用バイト幅レジスタにより、状態と制御のデータを利用できます。全てのデータ・バーストは少なくとも2バイトで構成されます。最初のバイトの最上位7ビットはレジスタのアドレスです。LSBが1であればデバイスからの読み出しを示し、LSBが0であればデバイスへの書き込みを示します。それに続く1バイト、または複数バイトは、指定されたアドレスからのデータ、または指定されたアドレスへのデータです。詳細な書き込みシーケンスの例については図8を、読み出しシーケンスについては図9を参照してください。

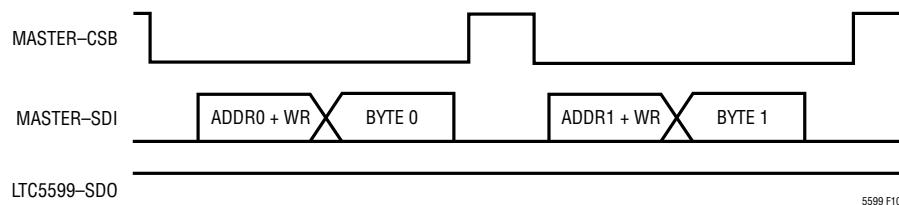

2つの書き込み通信バーストの例を図10に示します。シリアル・バスのマスターからSDIに送られる最初のバーストの最初のバイトには、宛先のレジスタ・アドレス(Addr0)および書き込みを示している0の LSBが含まれます。次のバイトはアドレスが Addr0 のレジスタ宛のデータです。続いて CSB が “H” になり、転送が終了します。2番目のバーストの最初のバイトには、宛先のレジスタ・アドレス(Addr1)および書き込みを示している LSB が含まれます。SDI の次のバイトはアドレスが Addr1 のレジスタ宛のデータです。続いて CSB が “H” になり、転送が終了します。

なお、書き込まれたデータは、16番目のクロック・サイクルの立ち下がりエッジで内部レジスタに転送されます(並列読み込み)。

図8. シリアル・ポートの書き込みシーケンス

図9. シリアル・ポートの読み出しシーケンス

図10. シリアル・ポートの1バイト書き込み

## アプリケーション情報

### 複数バイトの転送

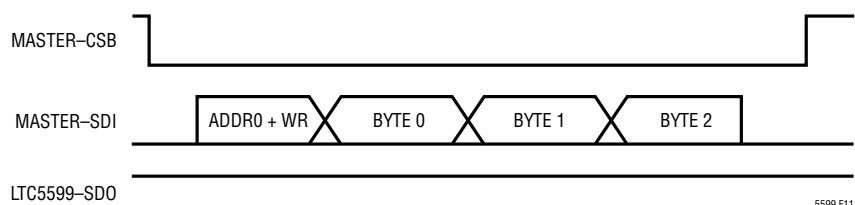

図11に示されているように、LTC5599のレジスタ・アドレス自動インクリメント機能を使って、複数バイトをもっと効率的にデータ転送することができます。前と同様、シリアル・ポートのマスターは、最初のバイトで宛先レジスタのアドレスを送り、2番目のバイトでそのレジスタ宛のデータを送りますが、引き続き後続のレジスタ宛のバイトを送ります。バイト1のアドレスはAddr0+1、バイト2のアドレスはAddr0+2、以下同様です。レジスタ・アドレス・ポインタは、31(0x1F)を過ぎてインクリメントしようとすると、自動的に0にリセットされます。

自動インクリメントによるデバイスからの読み出しの例を図12に示します。シリアル・バスのマスターからSDIに送られるバーストの最初のバイトには、宛先のレジスタ・アドレス(Address0)および読み出しを示す1のLSBが含まれます。LTC5599は、読み出しバーストを検出すると、SDOのHi-Z状態を終了し、レジスタAddress0のデータから開始してデータ・バイトを順に送り出します。デバイスは、バーストが終了するまで、SDIの他の全てのデータを無視します。

### マルチドロップ構成

複数のLTC5599がシリアル・バスを共有することができます。このマルチドロップ構成では、SCLK、SDI、およびSDOが全デバイスの間で共有されます。シリアル・バスのマスターはLTC5599ごとに別個のCSBを使って、必ず1個のデバイスのCSBだけがアサートされるようにする必要があります。値の大きな抵抗をSDOに接続して、Hi-Z状態のときにラインが既知のレベル( $V_{CC\_L}$ )に必ず戻るようにすることを推奨します。

### シリアル・ポート・レジスタ

LTC5599のメモリマップを付録の表10に示します。詳細なビットの説明を表11に示します。ADDRの列に16進数で示されているレジスタ・アドレスは、各レジスタを指定するのに使います。各レジスタは読み出し専用(R)または読み出し/書き込み(R/W)のどちらかとして示されています。デバイスの起動時またはリセット(レジスタ0x08のビット3、SRESET)後のレジスタの既定値が右側に示されています。

図11. シリアル・ポートの自動インクリメント書き込み

図12. シリアル・ポートの自動インクリメント読み出し

## アプリケーション情報

### SPI信号レベル

SPIバスでは、1.2V～3.6Vの範囲のデジタルV<sub>CC\_L</sub>の信号レベルをサポートしています。CSB = 1.2Vの条件によって、追加の0.2 $\mu$ Aの静的入力スリープ電流が生成されます。CSB = 1.8Vの場合、追加スリープ電流は無視できます。

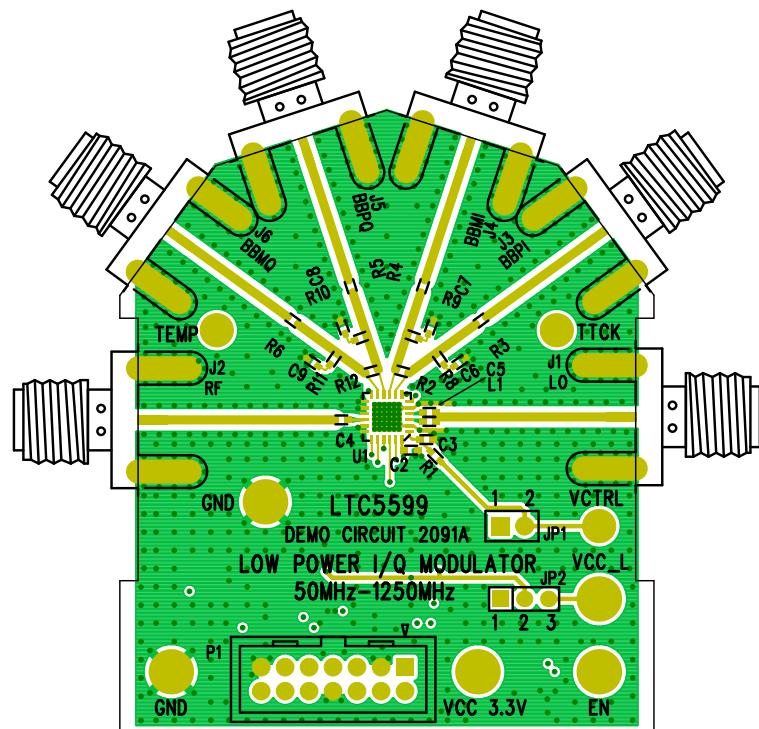

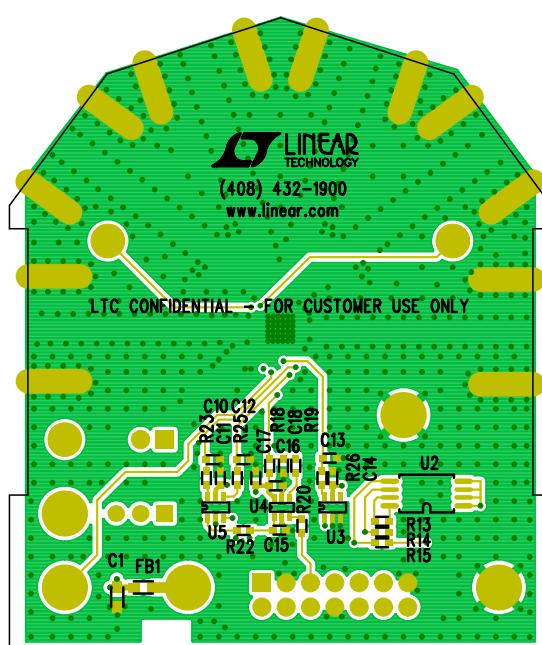

### 評価ボード

図13に、評価ボードの回路図を示します。露出パッドには適切なグランド接続が必要です。この接続が適切に行われないと、RF性能が低下します。図14および図15に、評価ボードの部品面および底面を示します。

フェライト・ビーズFB1は、V<sub>CC</sub>が急に電圧源に接続された場合に、電源電流の上昇速度を制限します。アプリケーションでは、V<sub>CC</sub>の上昇速度を最大1V/ $\mu$ sに制限します。

図13. 評価回路図

# LTC5599

## アプリケーション情報

図14. 評価ボードの部品面

図15. 評価ボードの底面

## 付録

### 位相シフト・レジスタ(0x05)マップ

この付録では、拡張ビットと符号ビット(レジスタ0x00のビット7)を含めて、位相シフト・レジスタへの詳細な値の割り当てをまとめます。

**表9. 拡張ビットと符号ビット(レジスタ0x00のビット7)を含むレジスタ0x05の位相シフト・レジスタ設定**

| M <sub>PH</sub> | N <sub>COARSE</sub> | N <sub>PH</sub> | B <sub>PH</sub> |

|-----------------|---------------------|-----------------|-----------------|

| -240            | -224                | 0               | 011100000       |

| -239            | -224                | 1               | 011100001       |

| -238            | -224                | 2               | 011100010       |

| -237            | -224                | 3               | 011100011       |

| -236            | -224                | 4               | 011100100       |

| -235            | -224                | 5               | 011100101       |

| -234            | -224                | 6               | 011100110       |

| -233            | -224                | 7               | 011100111       |

| -232            | -224                | 8               | 011101000       |

| -231            | -224                | 9               | 011101001       |

| -230            | -224                | 10              | 011101010       |

| -229            | -224                | 11              | 011101011       |

| -228            | -224                | 12              | 011101100       |

| -227            | -224                | 13              | 011101101       |

| -226            | -224                | 14              | 011101110       |

| -225            | -224                | 15              | 011101111       |

| -224            | -224                | 16              | 011110000       |

| -223            | -224                | 17              | 011110001       |

| -222            | -224                | 18              | 011110010       |

| -221            | -224                | 19              | 011110011       |

| -220            | -224                | 20              | 011110100       |

| -219            | -224                | 21              | 011110101       |

| -218            | -224                | 22              | 011110110       |

| -217            | -224                | 23              | 011110111       |

| -216            | -224                | 24              | 011111000       |

| -215            | -224                | 25              | 011111001       |

| -214            | -224                | 26              | 011111010       |

| -213            | -224                | 27              | 011111011       |

| -212            | -224                | 28              | 011111100       |

| -211            | -224                | 29              | 011111101       |

| -210            | -224                | 30              | 011111110       |

| -209            | -224                | 31              | 011111111       |

| -208            | -192                | 0               | 011000000       |

| -207            | -192                | 1               | 011000001       |

| -206            | -192                | 2               | 011000010       |

| -205            | -192                | 3               | 011000011       |

**表9. 拡張ビットと符号ビット(レジスタ0x00のビット7)を含むレジスタ0x05の位相シフト・レジスタ設定(続き)**

| M <sub>PH</sub> | N <sub>COARSE</sub> | N <sub>PH</sub> | B <sub>PH</sub> |

|-----------------|---------------------|-----------------|-----------------|

| -204            | -192                | 4               | 011000100       |

| -203            | -192                | 5               | 011000101       |

| -202            | -192                | 6               | 011000110       |

| -201            | -192                | 7               | 011000111       |

| -200            | -192                | 8               | 011001000       |

| -199            | -192                | 9               | 011001001       |

| -198            | -192                | 10              | 011001010       |

| -197            | -192                | 11              | 011001011       |

| -196            | -192                | 12              | 011001100       |

| -195            | -192                | 13              | 011001101       |

| -194            | -192                | 14              | 011001110       |

| -193            | -192                | 15              | 011001111       |

| -192            | -192                | 16              | 011010000       |

| -191            | -192                | 17              | 011010001       |

| -190            | -192                | 18              | 011010010       |

| -189            | -192                | 19              | 011010011       |

| -188            | -192                | 20              | 011010100       |

| -187            | -192                | 21              | 011010101       |

| -186            | -192                | 22              | 011010110       |

| -185            | -192                | 23              | 011010111       |

| -184            | -192                | 24              | 011011000       |

| -183            | -192                | 25              | 011011001       |

| -182            | -192                | 26              | 011011010       |

| -181            | -192                | 27              | 011011011       |

| -180            | -192                | 28              | 011011100       |

| -179            | -192                | 29              | 011011101       |

| -178            | -192                | 30              | 011011110       |

| -177            | -192                | 31              | 011011111       |

| -176            | -160                | 0               | 010100000       |

| -175            | -160                | 1               | 010100001       |

| -174            | -160                | 2               | 010100010       |

| -173            | -160                | 3               | 010100011       |

| -172            | -160                | 4               | 010100100       |

| -171            | -160                | 5               | 010100101       |

| -170            | -160                | 6               | 010100110       |

| -169            | -160                | 7               | 010100111       |

| -168            | -160                | 8               | 010101000       |

| -167            | -160                | 9               | 010101001       |

| -166            | -160                | 10              | 010101010       |

| -165            | -160                | 11              | 010101011       |

| -164            | -160                | 12              | 010101100       |

## 付録

表9. 拡張ビットと符号ビット(レジスタ0x00のビット7)を含むレジスタ0x05の位相シフト・レジスタ設定(続き)

| M <sub>PH</sub> | N <sub>COARSE</sub> | N <sub>PH</sub> | B <sub>PH</sub> |

|-----------------|---------------------|-----------------|-----------------|

| -163            | -160                | 13              | 010101101       |

| -162            | -160                | 14              | 010101110       |

| -161            | -160                | 15              | 010101111       |

| -160            | -160                | 16              | 010110000       |

| -159            | -160                | 17              | 010110001       |

| -158            | -160                | 18              | 010110010       |

| -157            | -160                | 19              | 010110011       |

| -156            | -160                | 20              | 010110100       |

| -155            | -160                | 21              | 010110101       |

| -154            | -160                | 22              | 010110110       |

| -153            | -160                | 23              | 010110111       |

| -152            | -160                | 24              | 010111000       |

| -151            | -160                | 25              | 010111001       |

| -150            | -160                | 26              | 010111010       |

| -149            | -160                | 27              | 010111011       |

| -148            | -160                | 28              | 010111100       |

| -147            | -160                | 29              | 010111101       |

| -146            | -160                | 30              | 010111110       |

| -145            | -160                | 31              | 010111111       |

| -144            | -128                | 0               | 010000000       |

| -143            | -128                | 1               | 010000001       |