## 特長

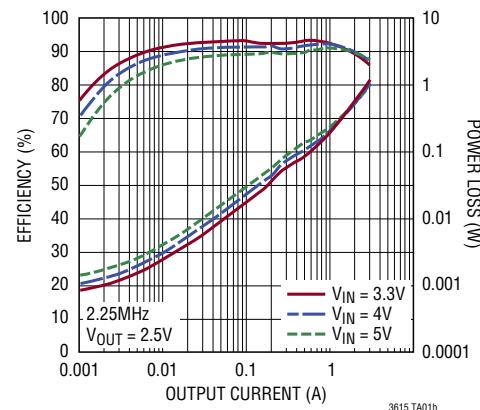

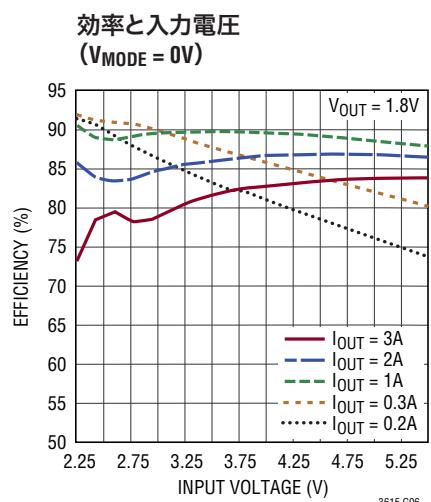

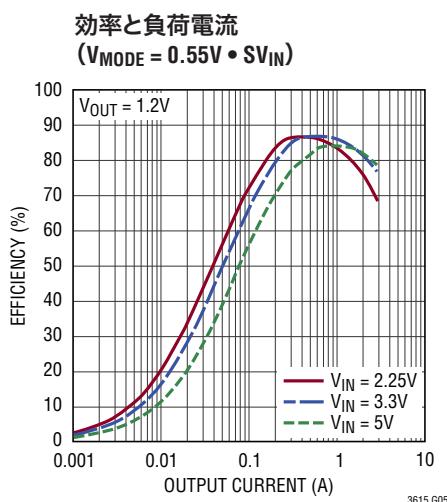

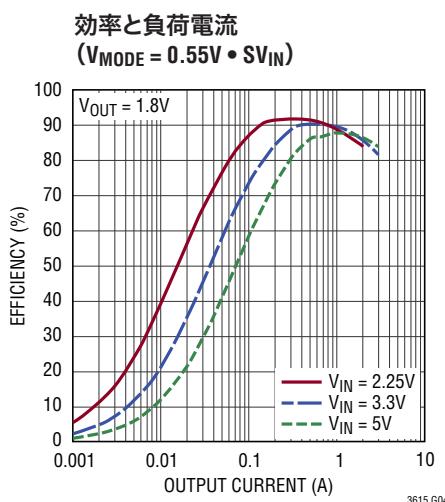

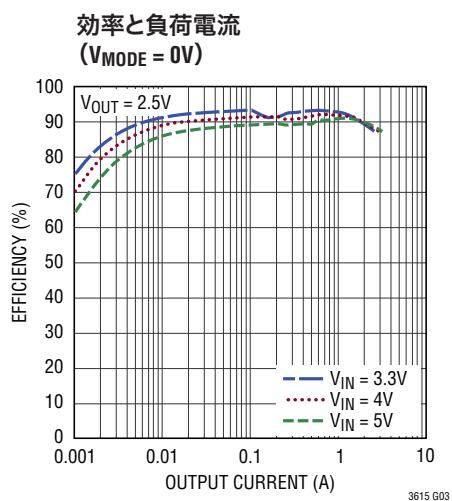

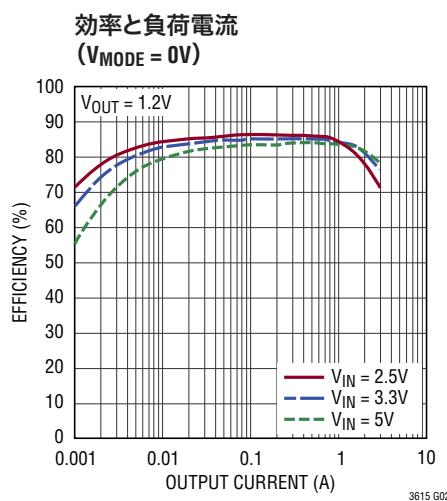

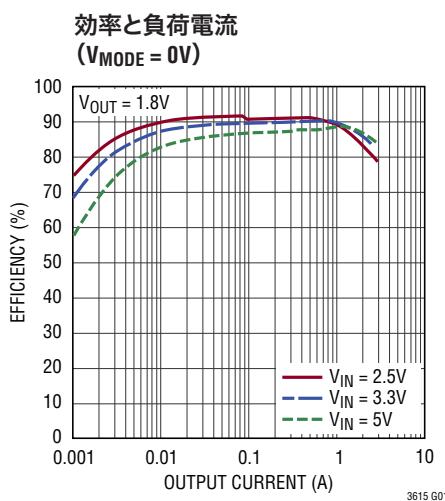

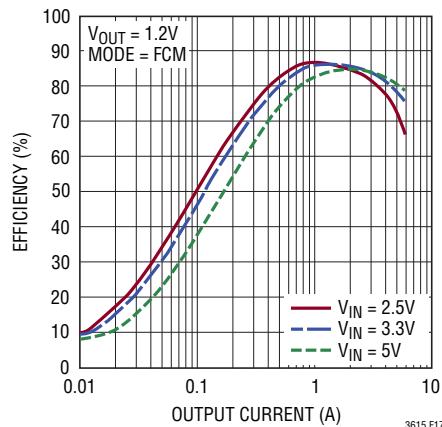

- 高効率: 最大94%

- 2x3Aの出力電流が可能なデュアル出力

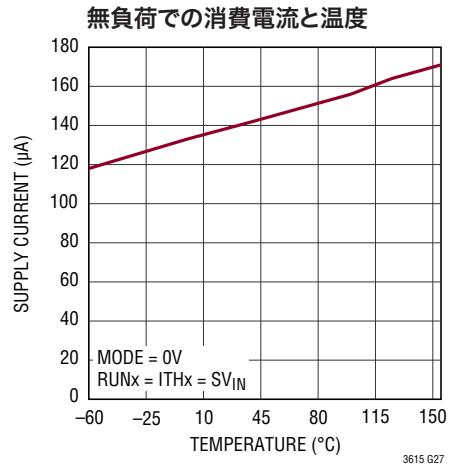

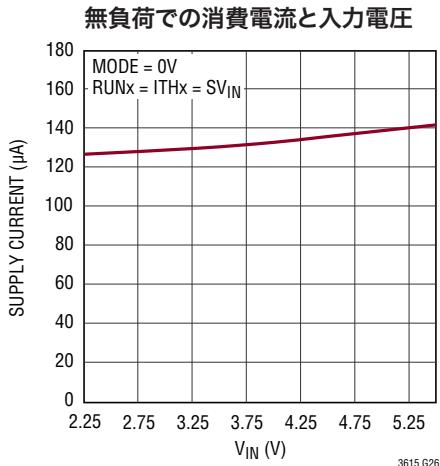

- 低出力リップルBurst Mode®動作:  $I_Q = 130\mu A$

- 入力電圧範囲: 2.25V~5.5V

- 出力電圧精度: ±1%

- 出力電圧: 最低0.6V

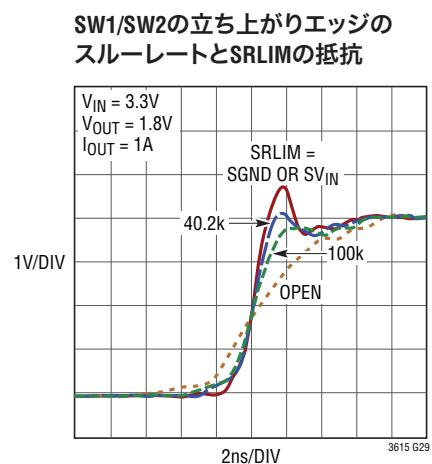

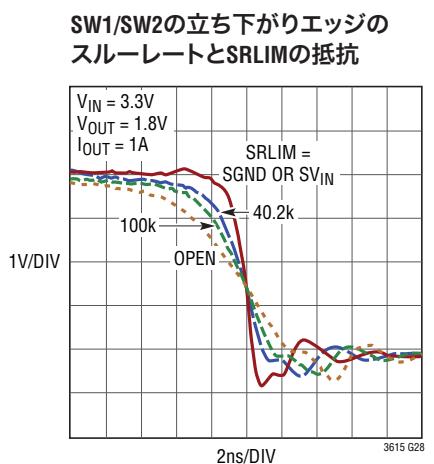

- スイッチ・ピンのスルーレートをプログラム可能

- 低損失動作: 100%デューティ・サイクル

- シャットダウン電流:  $\leq 1\mu A$

- 調整可能なスイッチング周波数: 最大4MHz

- 内部または外部補償

- パルススキップ動作、強制連続動作、バーストクランプを調整可能なBurst Mode動作のいずれかを選択可能

- オプションの内部補償付き

アクティブ電圧ポジショニング(AVP)

- チャネル間の位相差を選択可能: 0°/90°/180°(LTC3615)、

140°/180°(LTC3615-1)

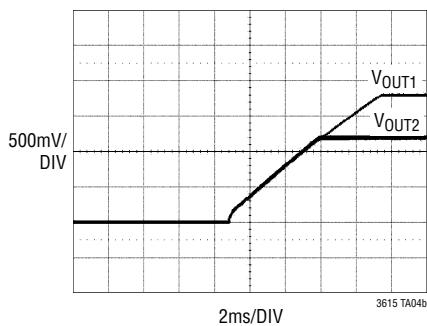

- 固定された内部ソフトスタートとプログラム可能な外部ソフトスタート

- 高精度の起動トラッキング機能

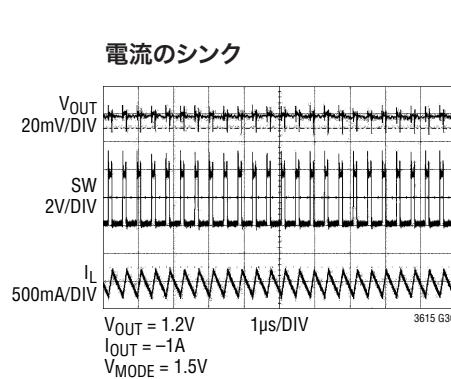

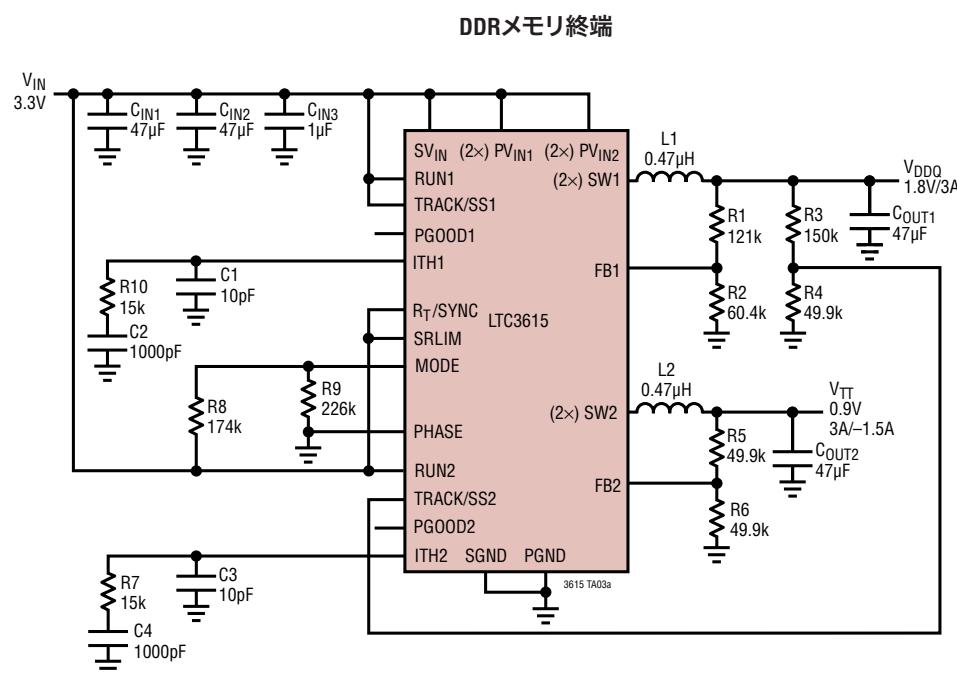

- DDRメモリ・モード、 $I_{QUT} = \pm 1.5A$

- 4mm×4mm QFN-24およびeTSSOP-24パッケージ

## アプリケーション

- ポイントオブロード電源

- 分配型電源

- 携帯型コンピュータ・システム

- DDRメモリの終端

- ハンドヘルド機器

## 概要

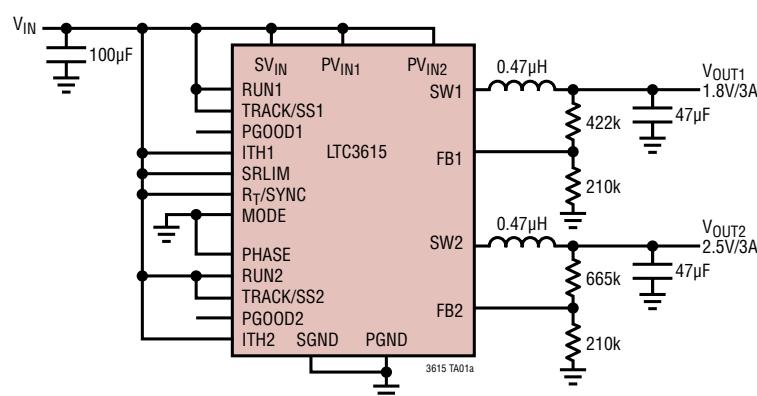

LTC®3615/LTC3615-1は、電流モード固定周波数アーキテクチャを採用したデュアル3A 同期整流式降圧レギュレータです。DC消費電流は、出力電圧を維持しながらわずか130μA (無負荷でのBurst Mode動作)で、シャットダウン時にはゼロ電流まで減少します。LTC3615/LTC3615-1は入力電源電圧範囲が2.25V~5.5Vなので、1セル・リチウムイオン・バッテリ・アプリケーションに最適です。100%デューティ・サイクルが可能なので、低損失動作を行い、バッテリ駆動システムの動作時間を延ばします。

動作周波数は最大4MHzまで外部設定可能なので、小型の表面実装インダクタを使用できます。2つのチャネル間の位相差を0°、90°、180°(LTC3615)または140°、180°(LTC3615-1)から選択できるので、デュアル3A出力構成またはシングル6A出力構成での入力電流リップルと出力電圧リップルを最小限に抑えます。また、プログラム可能なスルーレート制限によってEMIを低減し、外部同期は最大4MHzまで可能です。

内部同期スイッチによって効率が向上し、外付けのキャッチダイオードが不要になり、外付け部品とボードスペースを節減します。

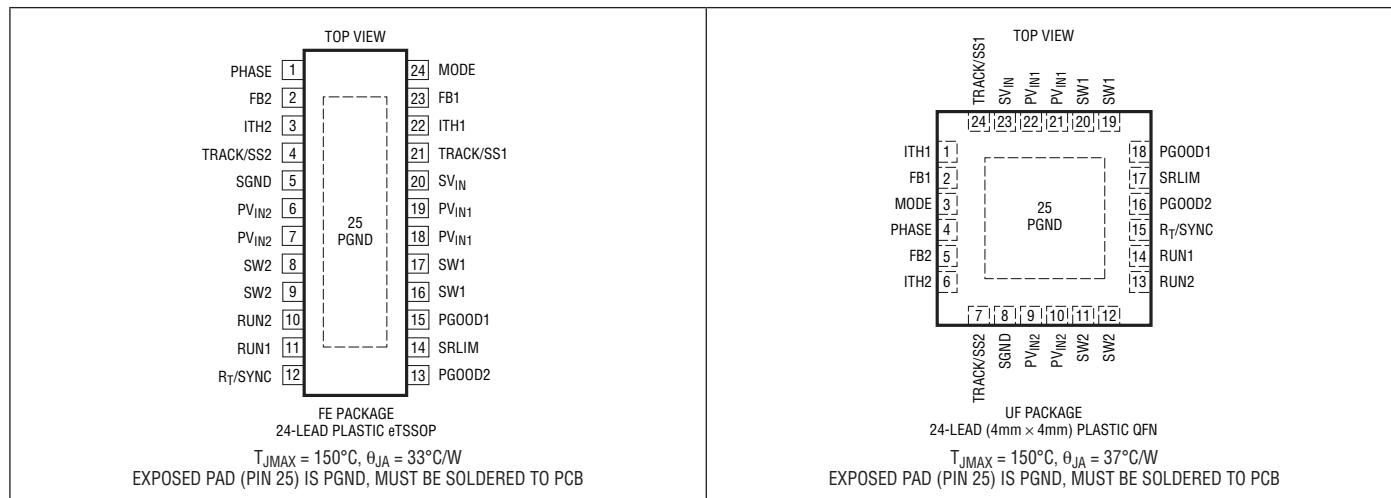

LTC3615/LTC3615-1はリードレス24ピン4mm×4mm QFNおよび熱特性が改善された24ピンeTSSOPパッケージで供給されます。

LT、LT、LTC、LTM、Linear Technology、Burst ModeおよびLinearのロゴはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。5481178、5994885、6304066、6498466、6580258、6611131を含む米国特許によって保護されています。

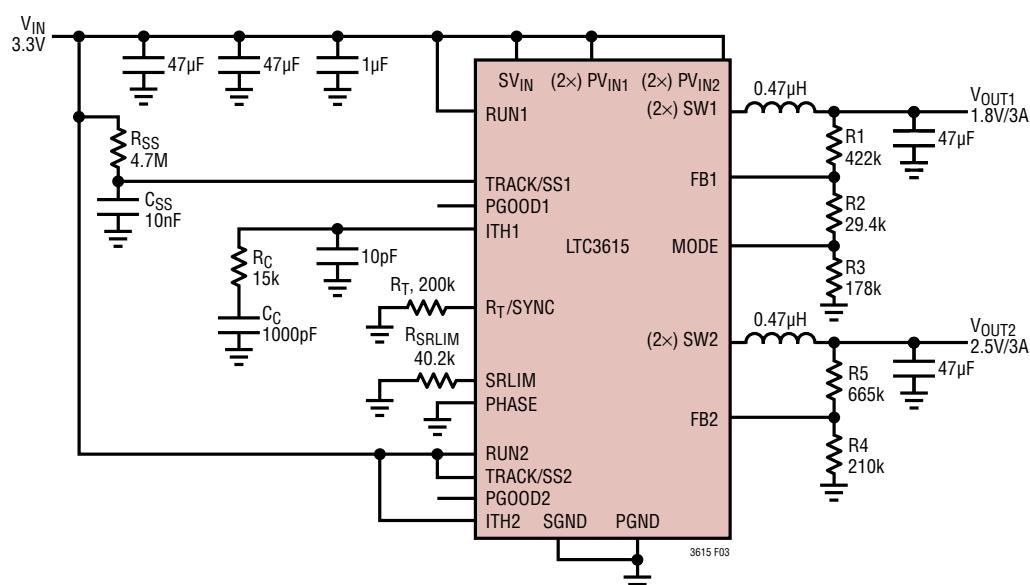

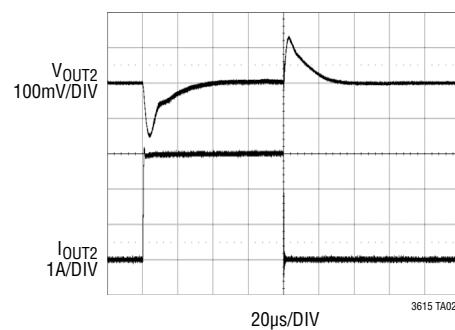

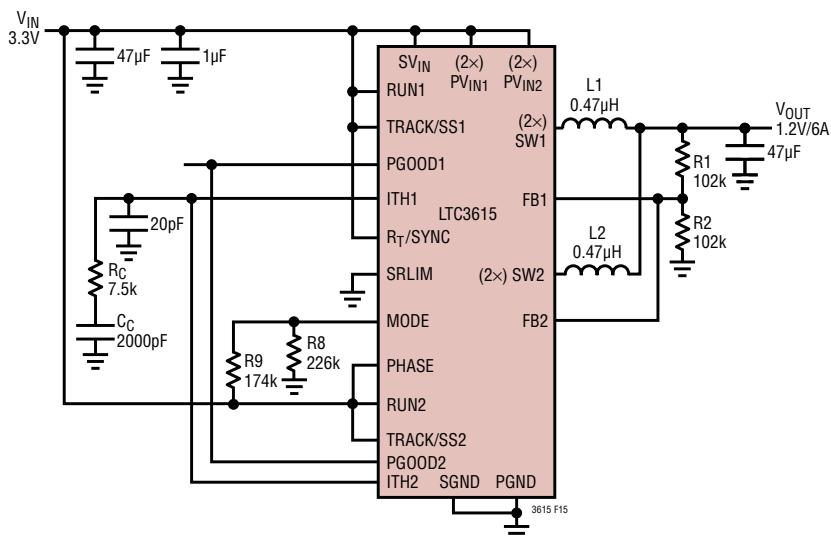

## 標準的応用例

### 効率および電力損失と負荷電流

3615fb

# LTC3615/LTC3615-1

## 絶対最大定格 (Note 1、11)

|                                          |                                 |                       |                                |

|------------------------------------------|---------------------------------|-----------------------|--------------------------------|

| PV <sub>IN1</sub> 、PV <sub>IN2</sub> の電圧 | -0.3V～(SV <sub>IN</sub> +0.3V)  | 他の他のすべてのピンの電圧         | -0.3V～(SV <sub>IN</sub> +0.3V) |

| SV <sub>IN</sub> の電圧                     | -0.3V～6V                        | 動作接合部温度範囲 (Note 2、11) | -55°C～150°C                    |

| SW1の電圧                                   | -0.3V～(PV <sub>IN1</sub> +0.3V) | 保存温度範囲                | -65°C～150°C                    |

| SW2の電圧                                   | -0.3V～(PV <sub>IN2</sub> +0.3V) | リード半田付け温度 (eTSSOP)    | 300°C                          |

| PGOOD1、PGOOD2の電圧                         | -0.3V～6V                        | リフロー・ピーク・ボディ温度 (QFN)  | 260°C                          |

## ピン配置

## 発注情報

| 無鉛仕上げ             | テープアンドリール           | 製品マーキング*    | パッケージ                           | 温度範囲           |

|-------------------|---------------------|-------------|---------------------------------|----------------|

| LTC3615EFE#PBF    | LTC3615EFE#TRPBF    | LTC3615FE   | 24-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3615IFE#PBF    | LTC3615IFE#TRPBF    | LTC3615FE   | 24-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3615HFE#PBF    | LTC3615HFE#TRPBF    | LTC3615FE   | 24-Lead Plastic TSSOP           | -40°C to 150°C |

| LTC3615MPFE#PBF   | LTC3615MPFE#TRPBF   | LTC3615FE   | 24-Lead Plastic TSSOP           | -55°C to 150°C |

| LTC3615EUF#PBF    | LTC3615EUF#TRPBF    | 3615        | 24-Lead (4mm x 4mm) Plastic QFN | -40°C to 125°C |

| LTC3615IUF#PBF    | LTC3615IUF#TRPBF    | 3615        | 24-Lead (4mm x 4mm) Plastic QFN | -40°C to 125°C |

| LTC3615HUF#PBF    | LTC3615HUF#TRPBF    | 3615        | 24-Lead (4mm x 4mm) Plastic QFN | -40°C to 150°C |

| LTC3615MPUF#PBF   | LTC3615MPUF#TRPBF   | 3615        | 24-Lead (4mm x 4mm) Plastic QFN | -55°C to 150°C |

| LTC3615EFE-1#PBF  | LTC3615EFE-1#TRPBF  | LTC3615FE-1 | 24-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3615IFE-1#PBF  | LTC3615IFE-1#TRPBF  | LTC3615FE-1 | 24-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3615HFE-1#PBF  | LTC3615HFE-1#TRPBF  | LTC3615FE-1 | 24-Lead Plastic TSSOP           | -40°C to 150°C |

| LTC3615MPFE-1#PBF | LTC3615MPFE-1#TRPBF | LTC3615FE-1 | 24-Lead Plastic TSSOP           | -55°C to 150°C |

| LTC3615EUF-1#PBF  | LTC3615EUF-1#TRPBF  | 36151       | 24-Lead (4mm x 4mm) Plastic QFN | -40°C to 125°C |

| LTC3615IUF-1#PBF  | LTC3615IUF-1#TRPBF  | 36151       | 24-Lead (4mm x 4mm) Plastic QFN | -40°C to 125°C |

| LTC3615HUF-1#PBF  | LTC3615HUF-1#TRPBF  | 36151       | 24-Lead (4mm x 4mm) Plastic QFN | -40°C to 150°C |

| LTC3615MPUF-1#PBF | LTC3615MPUF-1#TRPBF | 36151       | 24-Lead (4mm x 4mm) Plastic QFN | -55°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

3615fb

## 電気的特性

●は規定動作接合部温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 2)。注記がない限り、 $\text{SV}_{\text{IN}} = \text{PV}_{\text{INx}} = 3.3\text{V}$ 、 $R_T = 178\text{k}$ 、 $R_{\text{SRLIM}} = 40.2\text{k}$ 。

| SYMBOL                      | PARAMETER                                       | CONDITIONS                                                                                                                                                                                                                           | MIN        | TYP  | MAX   | UNITS |

|-----------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-------|-------|

| $V_{\text{IN}}$             | Operating Voltage Range                         |                                                                                                                                                                                                                                      | ● 2.25     | 5.5  |       | V     |

| $V_{\text{UVLO}}$           | Undervoltage Lockout Threshold                  | $\text{SV}_{\text{IN}}$ Ramping Down                                                                                                                                                                                                 | ● 1.7      |      |       | V     |

|                             |                                                 | $\text{SV}_{\text{IN}}$ Ramping Up                                                                                                                                                                                                   |            |      | 2.25  | V     |

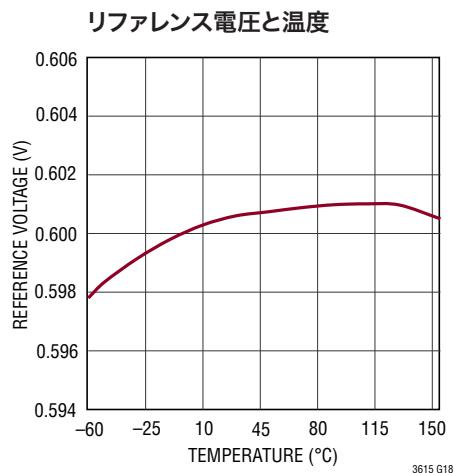

| $V_{\text{FB}}$             | Feedback Voltage Internal Reference             | (Note 3) $V_{\text{TRACK}} = \text{SV}_{\text{IN}}$ , $V_{\text{SRLIM}} = 0\text{V}$<br>$0^\circ\text{C} < T_J < 85^\circ\text{C}$<br>$-40^\circ\text{C} < T_J < 125^\circ\text{C}$<br>$-55^\circ\text{C} < T_J < 150^\circ\text{C}$ | ● 0.592    | 0.6  | 0.608 | V     |

|                             |                                                 |                                                                                                                                                                                                                                      | ● 0.590    |      | 0.610 | V     |

|                             |                                                 |                                                                                                                                                                                                                                      | ● 0.588    |      | 0.612 | V     |

|                             | Feedback Voltage External Reference<br>(Note 7) | (Note 3) $V_{\text{TRACK}} = 0.3\text{V}$ , $V_{\text{SRLIM}} = \text{SV}_{\text{IN}}$                                                                                                                                               | 0.289      | 0.3  | 0.311 | V     |

|                             |                                                 | (Note 3) $V_{\text{TRACK}} = 0.5\text{V}$ , $V_{\text{SRLIM}} = \text{SV}_{\text{IN}}$                                                                                                                                               | 0.489      | 0.5  | 0.511 | V     |

| $I_{\text{FB}}$             | Feedback Input Current                          | $V_{\text{FBx}} = 0.6\text{V}$                                                                                                                                                                                                       | ● 0        | ±30  |       | nA    |

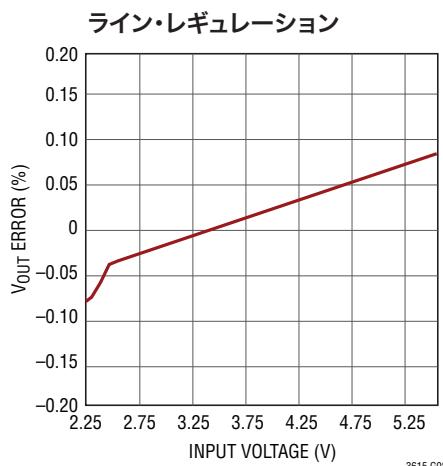

| $\Delta V_{\text{LINEREG}}$ | Line Regulation                                 | $\text{SV}_{\text{IN}} = \text{PV}_{\text{INx}} = 2.25\text{V}$ to $5.5\text{V}$ (Note 4)                                                                                                                                            | ● 0.2      |      |       | %/V   |

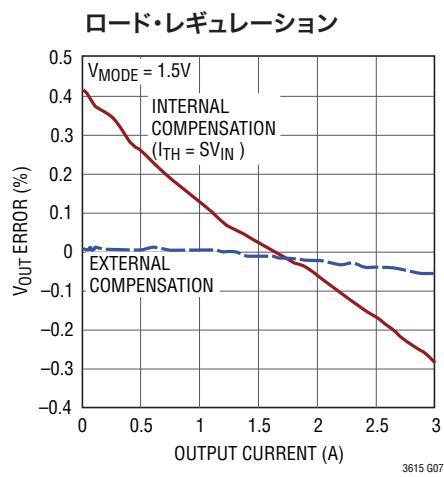

| $\Delta V_{\text{LOADREG}}$ | Load Regulation                                 | $V_{\text{ITHX}}$ from $0.5\text{V}$ to $0.9\text{V}$ (Note 4)<br>$V_{\text{ITHX}} = \text{SV}_{\text{IN}}$ , $V_{\text{FBx}} = 0.6\text{V}$ (Note 5)                                                                                |            | 0.2  |       | %     |

| $I_s$                       | Active Mode                                     | $V_{\text{FB1}} = 0.5\text{V}$ , $V_{\text{MODE}} = \text{SV}_{\text{IN}}$ , $V_{\text{RUN2}} = 0\text{V}$ (Note 6)                                                                                                                  |            | 1100 |       | μA    |

|                             |                                                 | $V_{\text{FBx}} = 0.5\text{V}$ , $V_{\text{MODE}} = \text{SV}_{\text{IN}}$ , $V_{\text{RUNx}} = \text{SV}_{\text{IN}}$ (Note 6)                                                                                                      |            | 1900 |       | μA    |

|                             | Sleep Mode                                      | $V_{\text{FB1}} = 0.7\text{V}$ , $V_{\text{RUN1}} = \text{SV}_{\text{IN}}$ , $V_{\text{RUN2}} = 0\text{V}$ ,<br>$V_{\text{MODE}} = 0\text{V}$ , $V_{\text{ITH1}} = \text{SV}_{\text{IN}}$ (Note 5)                                   |            | 95   | 130   | μA    |

|                             |                                                 | $V_{\text{FBx}} = 0.7\text{V}$ , $V_{\text{RUN1}} = \text{SV}_{\text{IN}}$ , $V_{\text{RUN2}} = 0\text{V}$ ,<br>$V_{\text{MODE}} = 0\text{V}$ (Note 4)                                                                               |            | 145  | 220   | μA    |

|                             |                                                 | $V_{\text{FBx}} = 0.7\text{V}$ , $V_{\text{RUNx}} = \text{SV}_{\text{IN}}$ , $V_{\text{MODE}} = 0\text{V}$ ,<br>$V_{\text{ITHx}} = \text{SV}_{\text{IN}}$ (Note 5)                                                                   |            | 130  | 200   | μA    |

|                             |                                                 | $V_{\text{FBx}} = 0.7\text{V}$ , $V_{\text{RUNx}} = \text{SV}_{\text{IN}}$ , $V_{\text{MODE}} = 0\text{V}$ ,<br>$I_{\text{TH}} = (\text{Note 4})$                                                                                    |            | 240  | 360   | μA    |

|                             | Shutdown                                        | $\text{SV}_{\text{IN}} = \text{PV}_{\text{IN}} = 5.5\text{V}$ , $V_{\text{RUNx}} = 0\text{V}$                                                                                                                                        |            | 0.1  | 1     | μA    |

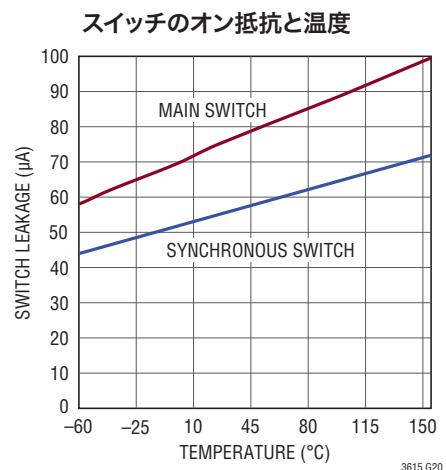

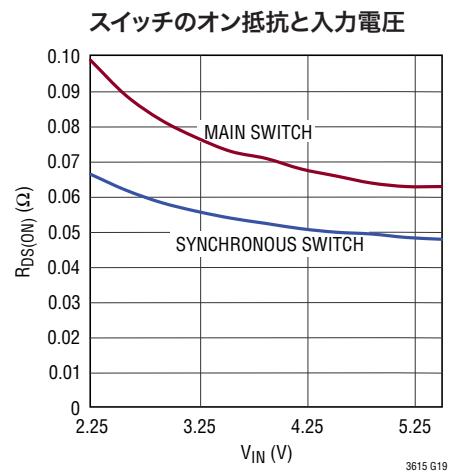

| $R_{\text{DS(ON)}}$         | Top Switch On-Resistance                        | $\text{PV}_{\text{INx}} = 3.3\text{V}$ (Note 10)                                                                                                                                                                                     |            | 75   |       | mΩ    |

|                             | Bottom Switch On-Resistance                     | $\text{PV}_{\text{INx}} = 3.3\text{V}$ (Note 10)                                                                                                                                                                                     |            | 55   |       | mΩ    |

| $I_{\text{LIM}}$            | Top Switch Current Limit                        | Sourcing (Note 8), $V_{\text{FB}} = 0.5\text{V}$<br>Duty Cycle < 35%<br>Duty Cycle = 100%                                                                                                                                            | 4.5<br>3.6 | 6    | 7.5   | A     |

|                             | Bottom Switch Current Limit                     | Sinking (Note 8), $V_{\text{FB}} = 0.7\text{V}$ ,<br>Forced Continuous Mode                                                                                                                                                          | -2.5       | -3.5 | -5    | A     |

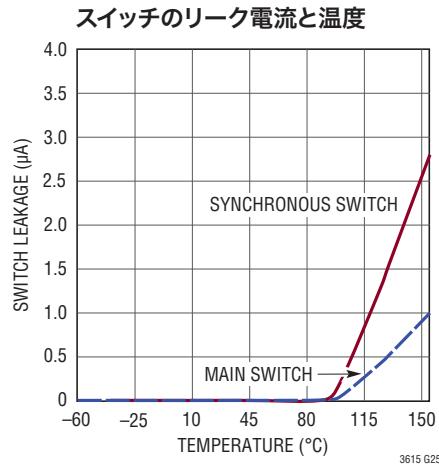

| $I_{\text{SW(LKG)}}$        | Switch Leakage Current                          | $\text{SV}_{\text{IN}} = \text{PV}_{\text{IN}} = 5.5\text{V}$ , $V_{\text{RUNx}} = 0\text{V}$                                                                                                                                        |            | 0.01 | 1     | μA    |

| $g_m(\text{EA})$            | Error Amplifier Transconductance                | $-5\mu\text{A} < I_{\text{TH}} < 5\mu\text{A}$                                                                                                                                                                                       |            | 240  |       | μmho  |

| $I_{\text{EA}}$             | Error Amplifier Output Current                  | (Note 4)                                                                                                                                                                                                                             |            | ±30  |       | μA    |

| $t_{\text{SOFT-START}}$     | Internal Soft-Start Time                        | $V_{\text{FBx}}$ from $0.06\text{V}$ to $0.54\text{V}$ , $\text{TRACK/SSx} = \text{SV}_{\text{IN}}$                                                                                                                                  | 0.65       | 1.1  | 1.7   | ms    |

| $R_{\text{DIS}}$            | TRACK/SS Pull-Down Resistance at Start-Up       |                                                                                                                                                                                                                                      |            |      | 200   | Ω     |

| $t_{\text{DIS}}$            | Soft-Start Discharge Time at Start-Up           |                                                                                                                                                                                                                                      |            | 70   |       | μs    |

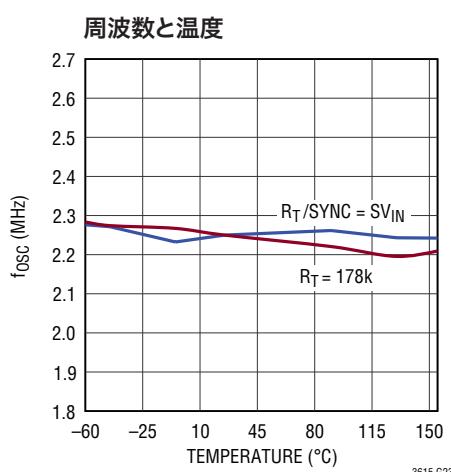

| $f_{\text{OSC}}$            | Internal Oscillator Frequency                   | $R_{\text{RT/SYNC}} = 178\text{k}$                                                                                                                                                                                                   | ● 1.85     | 2.25 | 2.65  | MHz   |

|                             |                                                 | $V_{\text{RT/SYNC}} = \text{SV}_{\text{IN}}$                                                                                                                                                                                         | ● 1.8      | 2.25 | 2.7   | MHz   |

| $f_{\text{SYNC}}$           | Synchronization Frequency                       | $t_{\text{LOW}}, t_{\text{HIGH}} > 30\text{ns}$                                                                                                                                                                                      | 0.4        | 4    |       | MHz   |

| $V_{\text{RT/SYNC}}$        | SYNC Level High                                 |                                                                                                                                                                                                                                      |            | 1.2  |       | V     |

|                             | SYNC Level Low                                  |                                                                                                                                                                                                                                      |            | 0.3  |       | V     |

## 電気的特性

●は規定動作接合部温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 2)。注記がない限り、 $\text{SV}_{\text{IN}} = \text{PV}_{\text{INx}} = 3.3\text{V}$ 、 $R_T = 178\text{k}\Omega$ 、 $V_{\text{SRLIM}} = 40.2\text{k}\Omega$ 。

| SYMBOL                        | PARAMETER                                          | CONDITIONS                                                                               | MIN                           | TYP                                | MAX | UNITS     |               |

|-------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------|------------------------------------|-----|-----------|---------------|

| $\varphi_{\text{SW1-SW2}}$    | Output Phase Shift Between SW1 and SW2 (LTC3615)   | $V_{\text{PHASE}} < 0.15 \cdot \text{SV}_{\text{IN}}$                                    |                               | 0                                  |     | Deg       |               |

|                               |                                                    | $0.35 \cdot \text{SV}_{\text{IN}} < V_{\text{PHASE}} < 0.65 \cdot \text{SV}_{\text{IN}}$ |                               | 90                                 |     | Deg       |               |

|                               |                                                    | $V_{\text{PHASE}} > 0.85 \cdot \text{SV}_{\text{IN}}$                                    |                               | 180                                |     | Deg       |               |

| $V_{\text{SRLIM}}$            | Output Phase Shift Between SW1 and SW2 (LTC3615-1) | $V_{\text{PHASE}} < 0.65 \cdot \text{SV}_{\text{IN}}$                                    |                               | 140                                |     | Deg       |               |

|                               |                                                    | $V_{\text{PHASE}} > 0.85 \cdot \text{SV}_{\text{IN}}$                                    |                               | 180                                |     | Deg       |               |

| $V_{\text{MODE}}$<br>(Note 9) | Voltage at SRLIM to Enable DDR Mode                | (Note 9)                                                                                 | $\text{SV}_{\text{IN}} - 0.3$ |                                    |     | V         |               |

| $V_{\text{FBx}}$              | Internal Burst Mode Operation                      |                                                                                          | 0.3                           |                                    |     | V         |               |

|                               | Pulse-Skipping Mode                                |                                                                                          | $\text{SV}_{\text{IN}} - 0.3$ |                                    |     | V         |               |

|                               | Forced Continuous Mode                             |                                                                                          | 1.1                           | $\text{SV}_{\text{IN}} \cdot 0.58$ |     | V         |               |

|                               | External Burst Mode Operation                      |                                                                                          | 0.5                           | 0.85                               |     | V         |               |

| PGOOD                         | Power Good Voltage Windows                         | TRACK/SSx = $\text{SV}_{\text{IN}}$ , Entering Window                                    |                               | -3.5                               | -6  | %         |               |

|                               |                                                    | $V_{\text{FBx}}$ Ramping Up                                                              | 3.5                           | 6                                  |     | %         |               |

|                               |                                                    | $V_{\text{FBx}}$ Ramping Down                                                            |                               | 9                                  | 11  | %         |               |

|                               |                                                    | TRACK/SSx = $\text{SV}_{\text{IN}}$ , Leaving Window                                     |                               | -9                                 | -11 | %         |               |

| $t_{\text{PGOOD}}$            | Power Good Blanking Time                           | $V_{\text{FBx}}$ Ramping Up                                                              |                               | 70                                 | 105 | 140       | $\mu\text{s}$ |

|                               |                                                    | $V_{\text{FBx}}$ Ramping Down                                                            |                               | 8                                  | 12  | 30        | $\Omega$      |

| $V_{\text{RUN}}$              | Enable Pin                                         | Input High                                                                               | ●                             | 1                                  |     | V         |               |

|                               |                                                    | Input Low                                                                                | ●                             | 0.4                                |     | V         |               |

|                               |                                                    | Pull-Down Resistance                                                                     |                               | 4                                  |     | $M\Omega$ |               |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:**LTC3615/LTC3615-1は $T_J$ が $T_A$ にほぼ等しいパルス負荷条件でテストされる。LTC3615E/LTC3615E-1は $0^\circ\text{C} \sim 85^\circ\text{C}$ の動作接合部温度範囲で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3615/LTC3615-1は $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲で仕様に適合することが保証されている。LTC3615H/LTC3615H-1は $-40^\circ\text{C} \sim 150^\circ\text{C}$ の動作温度範囲で性能仕様に適合することが保証されている。LTC3615MP/LTC3615MP-1は $-55^\circ\text{C} \sim 150^\circ\text{C}$ の全動作接合部温度範囲で性能仕様に適合することがテスト保証されている。高い接合部温度は動作寿命に悪影響を及ぼす。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命は短くなる。また、これらの仕様と調和する最大周囲温度は、基板レイアウト、パッケージの定格熱インピーダンスおよび他の環境要因と関連した特定の動作条件によって決まるに注意。接合部温度 $T_J$ (単位 $^\circ\text{C}$ )は、周囲温度 $T_A$ (単位 $^\circ\text{C}$ )および電力損失 $P_D$ (単位W)から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

ここで $\theta_{JA}$ (単位 $^\circ\text{C}/\text{W}$ )はパッケージの熱インピーダンス。

**Note 3:**このパラメータは、 $V_{\text{FB1}}/V_{\text{FB2}}$ をエラーアンプの中点( $V_{\text{ITH1}}/V_{\text{ITH2}} = 0.75\text{V}$ )にサーボ制御する帰還ループでテストされる。

**Note 4:**ITHピンの外部補償。

**Note 5:**ITHピンを $\text{SV}_{\text{IN}}$ に接続すると、選択されたチャネルに対して内部補償とAVPモードがイネーブルされる。

**Note 6:**スイッチング周波数で供給される内部のゲート電荷により、動作時消費電流は増加する。

**Note 7:**「ピン機能」セクションのTRACK/SSピンの説明を参照。

**Note 8:**電流ソース時、平均出力電流は SW ピンから流れ出すと定義されている。電流シンク時、平均出力電流は SW ピンに流れ込むと定義されている。電流をシンクする場合は強制連続モードを使用する必要がある。

**Note 9:**「ピン機能」セクションのMODEピンの説明を参照。

**Note 10:**QFNパッケージについては、設計およびウェハー・レベルの測定値との相関によって保証されている。

**Note 11:**このデバイスには短時間の過負荷状態のあいだデバイスを保護するための過温度保護が備わっている。過温度保護がアクティブなとき接合部温度は $150^\circ\text{C}$ を超える。規定された最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうか、またはデバイスに永続的損傷を与えるおそれがある。

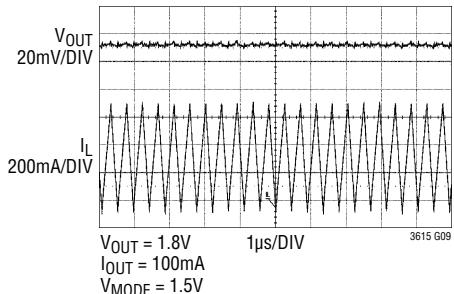

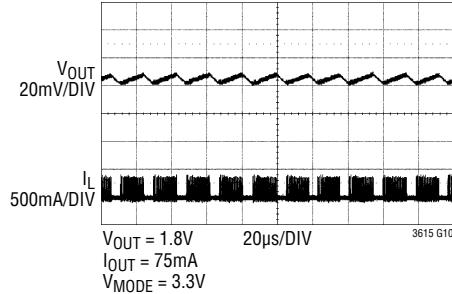

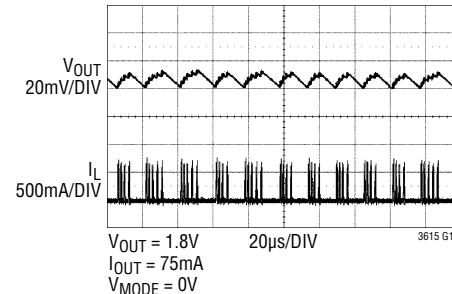

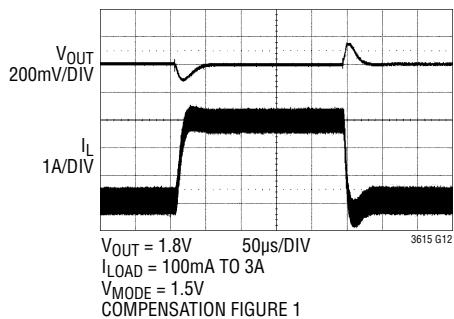

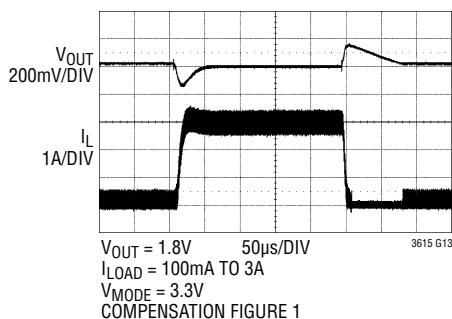

## 標準的性能特性

注記がない限り、 $V_{IN} = 3.3V$ 、 $R_T/SYNC = SV_{IN}$ 。

# LTC3615/LTC3615-1

標準的性能特性 注記がない限り、 $V_{IN} = 3.3V$ 、 $R_T/SYNC = SV_{IN}$ 。

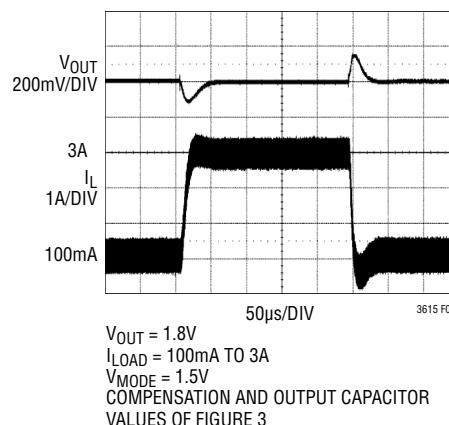

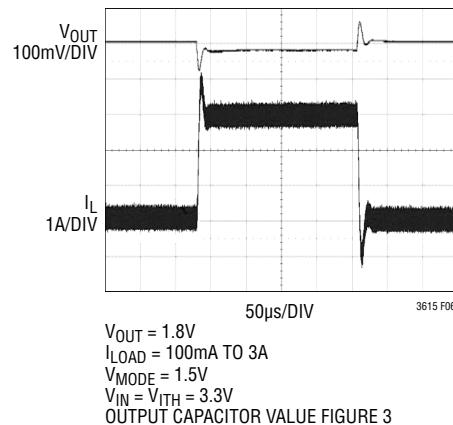

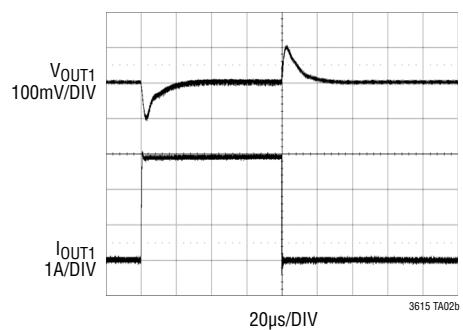

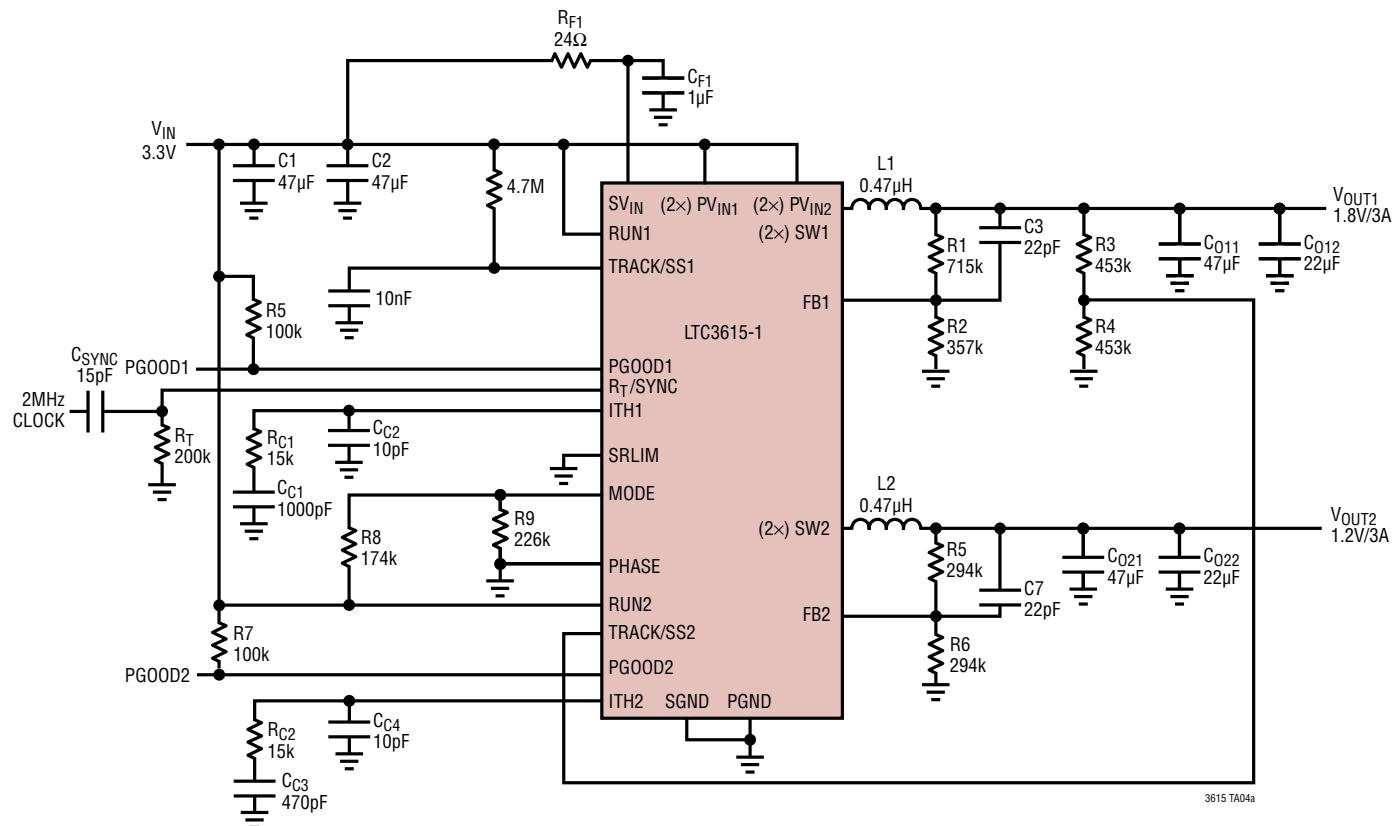

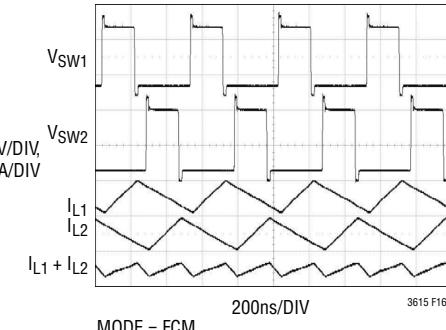

強制連続モードの動作(FCM)

パルス・スキップ・モードの動作

Burst Mode動作

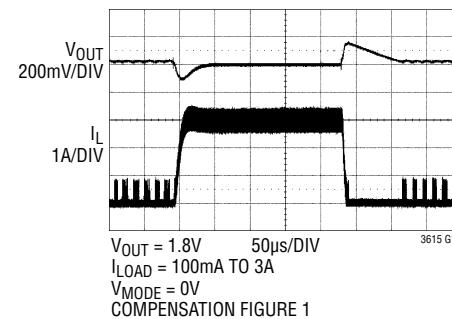

強制連続モード(FCM)の

外部補償の負荷ステップ過渡応答

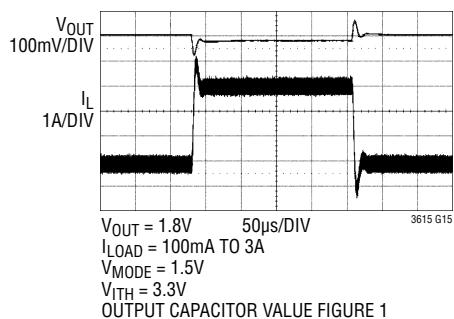

パルス・スキップ・モードの

負荷ステップ過渡応答

Burst Mode動作の

負荷ステップ過渡応答

AVPモードを使用した強制連続モード

(FCM)の負荷ステップ過渡応答

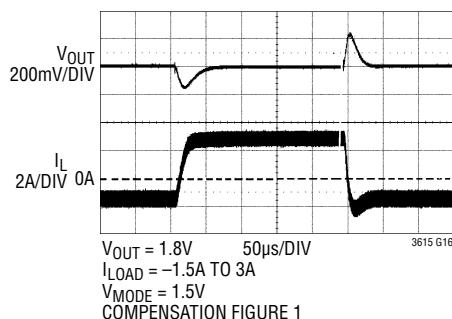

電流をソースおよびシンクする

強制連続モードの

負荷ステップ過渡応答

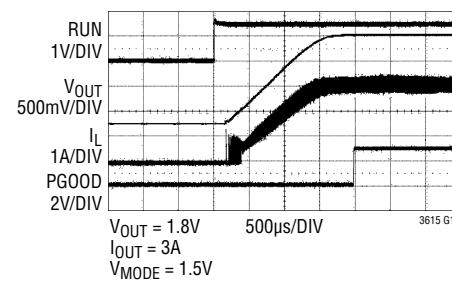

強制連続モードの内部起動

**標準的性能特性** 注記がない限り、 $V_{IN} = 3.3V$ 、 $R_T/SYNC = SV_{IN}$

# LTC3615/LTC3615-1

標準的性能特性 注記がない限り、 $V_{IN} = 3.3V$ 、 $R_T/SYNC = SV_{IN}$ 。

3615fb

## ピン機能 (FE/UF)

**PHASE(ピン1/ピン4)**:位相シフトの選択。PHASEピンをSGNDに接続すると、SW1とSW2間の位相は $0^\circ$ (LTC3615)または $140^\circ$ (LTC3615-1)になります。SV<sub>IN</sub>電圧の半分の電圧に接続すると、 $90^\circ$ (LTC3615)または $140^\circ$ (LTC3615-1)の位相シフトが選択されます。このピンをSV<sub>IN</sub>に接続すると $180^\circ$ (LTC3615とLTC3615-1)が選択されます。

**V<sub>FB2</sub>(ピン2/ピン5)**:チャネル2の電圧帰還入力ピン。V<sub>FB1</sub>を参照。

**ITH2(ピン3/ピン6)**:チャネル2のエラーアンプの補償。ITH1を参照。

**TRACK/SS2(ピン4/ピン7)**:チャネル2の内部ソフトスタート、外部ソフトスタート、外部リファレンス入力。TRACK/SS1を参照。

**SGND(ピン5/ピン8)**:信号グランド。小信号用部品と補償用部品はすべてこのグランドピンに接続し、このグランドは一点でPGNDに接続します。

**PV<sub>IN2</sub>(ピン6、7/ピン9、10)**:チャネル2の電源入力。PV<sub>IN1</sub>を参照。

**SW2(ピン8、9/ピン11、12)**:チャネル2のスイッチング・ノード。SW1を参照。

**RUN2(ピン10/ピン13)**:チャネル2のイネーブルピン。RUN1を参照。

**RUN1(ピン11/ピン14)**:チャネル1のイネーブルピン。RUN1を入力スレッショルドよりも高い値に強制すると、チャネル1の出力SW1がイネーブルされます。RUN1とRUN2の両方をグランドに強制すると、LTC3615はシャットダウンします。シャットダウン時は全機能がディスエーブルされ、LTC3615に流れる消費電流は $1\mu A$ 未満になります。

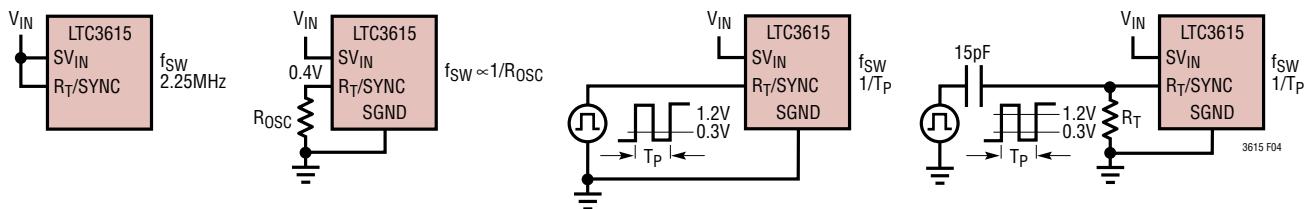

**R<sub>T</sub>/SYNC(ピン12/ピン15)**:発振器周波数。このピンは、3つのモードでスイッチング周波数を設定します。

1. R<sub>T</sub>/SYNCからグランドに抵抗を接続すると、その抵抗値に基づいてスイッチング周波数が設定されます。

2. R<sub>T</sub>/SYNCピンを外部クロック信号でドライブすると、スイッチは与えられた周波数に同期します。スロープ補償は自動的に外部クロック周波数に適応します。

3. このピンをSV<sub>IN</sub>に接続すると、内部発振器の周波数 $2.25\text{MHz}$ が有効になります。

**PGOOD2(ピン13/ピン16)**:チャネル2のパワーグッド出力。PGOOD1を参照してください。

**SRLIM(ピン14/ピン17)**:スルーレート制限。このピンによってスイッチ・ピンのスルーレートが以下のように設定されます。

1. このピンをSGNDに接続すると最大スルーレートが選択されます。

2. このピンをオープンにすると最小スルーレートが選択されます。

3. このピンからSGNDに抵抗を接続すると、スルーレートを連続的に調整できます。

4. このピンをSV<sub>IN</sub>に接続するとスルーレートが最大に設定され、DDRモードが有効になります(「アプリケーション情報」のセクションを参照)。

**PGOOD1(ピン15/ピン18)**:チャネル1のパワーグッド出力ピン。チャネルのFB1電圧がパワーグッド電圧ウインドウ内にないときは、オープンドレイン出力がグランドにプルダウンされます。このピンは、チャネルがRUN1ピンによってイネーブルされていない場合、またはSV<sub>IN</sub>で低電圧が検出された場合もプルダウンされます。DDRモード(SRLIM = SV<sub>IN</sub>)では、TRACK/SSピンの実際の電圧に応じてパワーグッド・ウインドウが移動します。

**SW1(ピン17、16/ピン19、20)**:チャネル1のスイッチング・ノード。外部インダクタへの接続。このピンは、内部同期パワーMOSFETスイッチのドレインに接続されています。

**PV<sub>IN1</sub>(ピン18、19/ピン21、22)**:チャネル1の電源入力。これらのピンは、チャネル1の内部Pチャネル・パワーMOSFETのソースに接続されています。PV<sub>IN1</sub>とPV<sub>IN2</sub>は互いに独立しています。これらは、SV<sub>IN</sub>と等しい電圧またはSV<sub>IN</sub>よりも低い電圧の電源に接続することができます。

**SV<sub>IN</sub>(ピン20/ピン23)**:信号入力電源。このピンは内部制御回路に電力を供給し、低電圧ロックアウト・コンパレータによってモニタされます。

# LTC3615/LTC3615-1

## ピン機能 (FE/U)

**TRACK/SS1(ピン21/ピン24)**: チャネル1の内部ソフトスタート、外部ソフトスタート、外部リファレンス入力の設定。このピンでチャネル1の起動時の動作を以下のように設定できます。

1. タイミングを固定した内部ソフトスタートは、TRACK/SS1を  $SV_{IN}$ に接続することによってプログラムできます。

2. 外部ソフトスタートは、グランドへのコンデンサと  $SV_{IN}$ への抵抗によりタイミングを設定してプログラムできます。

3. 別の電源の起動動作のトラッキングをプログラム可能です（「アプリケーション情報」のセクションを参照）。

4. このピンを外部リファレンス入力として使用できます。

**$I_{TH1}$ (ピン22/ピン1)**: エラーアンプの補償。 $I_{TH}$ からSGNDへ外部補償を接続します。電流コンパレータのスレッショルドはこの制御電圧に応じて増加します。このピンを  $SV_{IN}$ に接続すると、内部補償を伴うAVPモードがイネーブルされます。

**$V_{FB1}$ (ピン23/ピン2)**: チャネル1の電圧帰還入力ピン。出力の両端に接続された外部抵抗分割器から、チャネル1の帰還電圧を受け取ります。

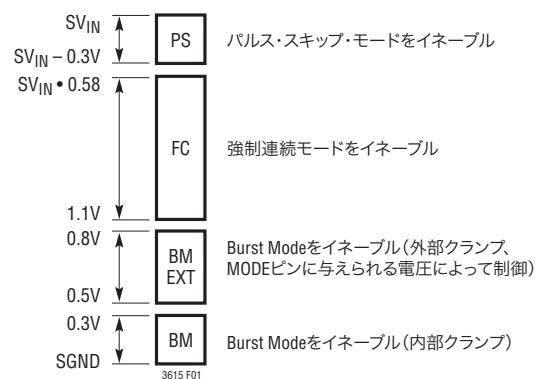

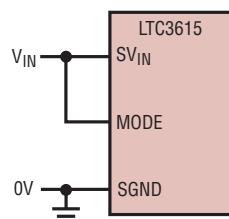

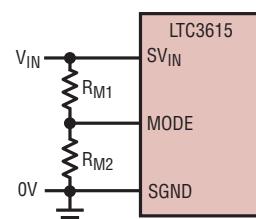

**MODE(ピン24/ピン3)**: モード選択。

1. このピンを  $SV_{IN}$ に接続するとパルス・スキップ・モードが、SGNDに接続するとBurst Mode動作（内部Burst Modeクラップ付き）がイネーブルされます。

2. このピンを  $SV_{IN}$ の半分よりわずか上に保つと、強制連続モードが選択されます。

3. このピンを外部電圧に接続するとBurst Mode動作が選択され、バースト・クラップがこのピンの電圧に設定されます。

**PGND(露出パッドピン25)**: 電源グランド。露出パッドは、パワーNチャネルMOSFETのソースに接続されています。PGNDピンは両チャネルで共通です。露出パッドはPCBに半田付けする必要があります。

電気的接続と定格熱性能の詳細については、「動作」と「アプリケーション情報」のセクションを参照してください。

3615fb

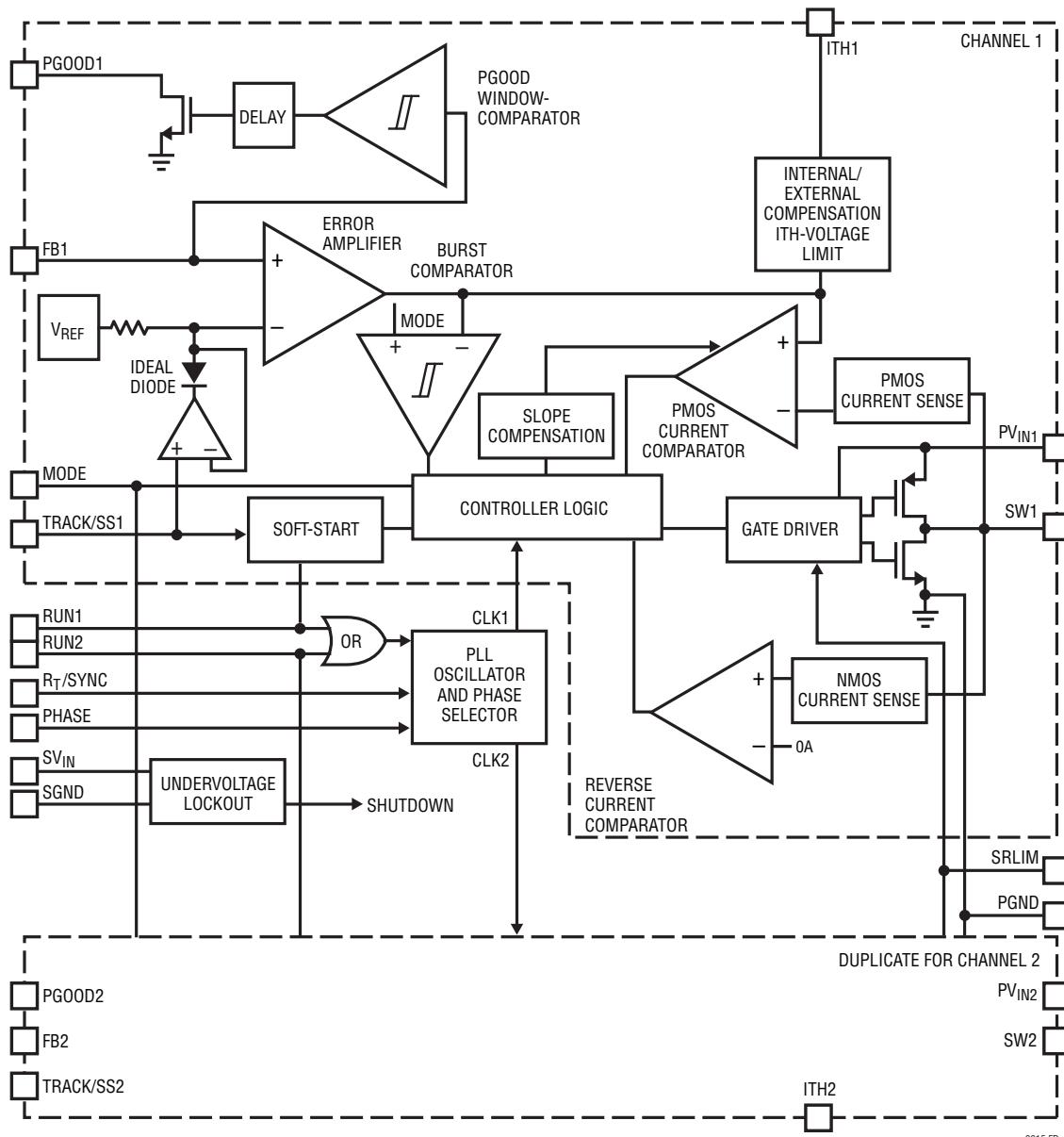

## 機能ブロック図

## 動作

### メイン制御ループ

LTC3615は、電流モードの固定周波数動作を特徴とするデュアル・モノリシック降圧DC/DCコンバータです。どちらのチャネルも同じ構成で、クロック回路とリファレンス回路を共有し、チャネル間の整合性を向上させています。

通常動作時は、各チャネルの内部トップ・パワースイッチ(PチャネルMOSFET)が各クロック・サイクルの始点でオンします。インダクタを流れる電流が、電流コンパレータがトリップしてトップ・パワーMOSFETがオフするまで増加します。電流コンパレータがオフするピーク・インダクタ電流は、ITHピンの電圧によって制御されます。エラーアンプは、 $V_{FBx}$ ピンの抵抗分割器から得られる帰還信号を0.6Vの内部リファレンスと比較して、ITHピンの電圧を調節します。負荷電流が増加すると、リファレンスに比べて帰還電圧が低下します。エラーアンプは平均インダクタ電流が新しい負荷電流に釣り合うまでITH電圧を上昇させます。ITHピンの標準電圧範囲は0.45V～1.05Vで、0.45Vがゼロ電流に対応します。

トップ・パワーMOSFETがオフすると、電流リミットに達するか、次のクロック・サイクルが開始されるまで同期パワースイッチ(NチャネルMOSFET)はオンします。ボトム電流リミットは強制連続モードでは標準で-4Aに設定され、Burst Mode動作およびパルス・スキップ・モードでは0Aに設定されます。

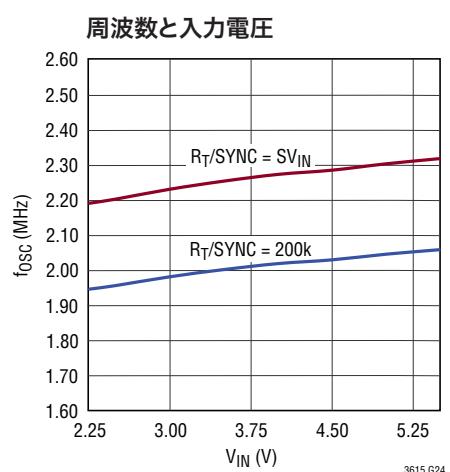

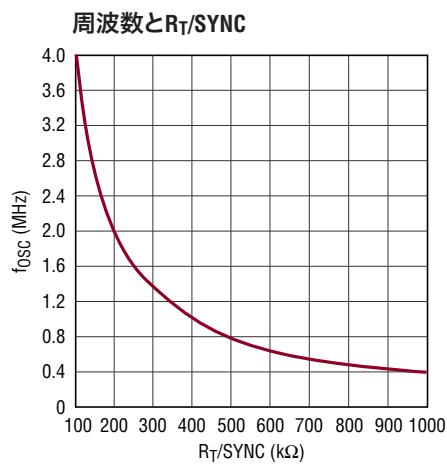

$R_T/SYNC$ が $SV_{IN}$ に接続されていると、動作周波数は既定で2.25MHzになります。また、 $R_T/SYNC$ ピンとグランドの間に接続された外部抵抗によって、あるいは $R_T/SYNC$ ピンに与えられるクロック信号によって動作周波数を設定することができます。スイッチング周波数は400kHz～4MHzに設定できます(「アプリケーション情報」のセクションを参照)。

過電圧コンパレータと低電圧コンパレータは、出力電圧が設定値から±7.5%以上変化するとPGOOD出力を“L”にします。

### モード選択

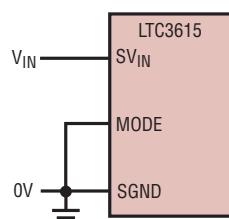

MODEピンは、両方のチャネルに対して同時に4種類の動作モードのいずれかを選択するのに使います(図1と図3を参照)。

図1. モード選択電圧

### Burst Mode動作(内部クランプ)

MODEピンをSGNDに接続するとBurst Mode動作がイネーブルされ、そのピーク電流は内部で設定されます。Burst Mode動作では、内部パワーMOSFETは軽負荷時、間欠的に動作します。このためスイッチング損失が最小限になり、効率が向上します。MOSFETがスイッチングを行わない間LTC3615はスリープ状態に入り、内部回路の多くがディスエーブルされ電力を節約します。Burst Mode動作中は、いつスリープ状態に入るか、またいつスリープ状態から再び出るかを決定するために、バースト・コンパレータによってITH電圧がモニタされます。平均インダクタ電流が負荷電流より大きいとITHピンの電圧が低下します。ITH電圧が内部スレッショルドを下回ると、LTC3615はスリープ状態になります。スリープ状態ではパワーMOSFETがオフに保たれ、負荷電流は出力コンデンサによってのみ供給されます。出力電圧が下がるとトップ・パワーMOSFETが再度オンし、内部回路が再度イネーブルされます。この過程が、負荷電流に依存した速度で繰り返されます。

## 動作

### Burst Mode動作(外部クランプ)

MODEピンを0.5V～0.8V範囲の電圧に接続すると、外部クランプを使うBurst Mode動作がイネーブルされます。この動作モードの間、ITHピンの最小電圧はMODEピンの電圧によって外部から設定されます。周囲温度が85°Cを超える場合は、内部クランプによるBurst Mode動作を使用することを推奨します。

### パルス・スキップ・モード動作

パルス・スキップ・モードはBurst Mode動作に似ていますが、スリープ・モードの間LTC3615は内部回路への電力をディスエーブルしません。これにより出力電圧リップルが改善されますが、消費電流が増え、軽負荷時の効率が下がります。

MODEピンをSV<sub>IN</sub>に接続すると、パルス・スキップ・モードがイネーブルされます。負荷電流が減少していく場合、ピーク・インダクタ電流は、ITH電圧が450mV(0Aに対応)を下回るまでITHピンの電圧によって決定されます。ITH電圧が450mVを下回ると、出力電圧を安定化状態に保つためにスイッチング・サイクルがスキップされます。

2a. 内部制御による

Burst Mode動作

### 強制連続モード動作

強制連続モードでは、インダクタ電流は一定のサイクルで流れ、全ての出力電流レベルで最小出力電圧リップルを生じます。

MODEピンを1.1V～SV<sub>IN</sub>・0.58の範囲の電圧に接続すると、強制連続モード動作が選択されます。

出力が電流をシンクする必要があれば、強制連続モードを使う必要があります。

### ドロップアウト動作

入力電源電圧が出力電圧に近づくと、デューティ・サイクルが最大オン時間に向かって増加します。電源電圧がさらに低下すると、メイン・スイッチは1サイクルを超えてオン状態に留まり、最終的に100%のデューティ・サイクルに達します。このときの出力電圧は、入力電圧から内部PチャネルMOSFETとインダクタの電圧降下を差し引いた電圧になります。

2b. 外部制御による

Burst Mode動作

2c. パルス・スキップ・モード

2d. 強制連続モード

図2. 動作モード

## 動作

### 低電源電圧動作

LTC3615は2.25Vの入力電源電圧まで動作するように設計されています。低い入力電源電圧で考慮すべきことは、PチャネルとNチャネルのパワースイッチのR<sub>D5(ON)</sub>が5V動作時に対して50%増加することです。LTC3615を低入力電圧、100%デューティ・サイクルで使用する時は、サーマル・リミットを超えないように電力損失を計算する必要があります。

### スロープ補償とインダクタのピーク電流

スロープ補償により50%を超えるデューティ・サイクルでの低調波発振が防止されるので、電流モード固定周波数アーキテクチャでは安定した動作が得られます。LTC3615では、インダクタ電流信号に補償ランプを追加することによってスロープ補償を実現しています。

### 短絡保護

電流コンバレータがトップ・パワースイッチをオフするピーク・インダクタ電流は、ITHピンの電圧によって制御されます。

出力電流が増加すると、エラーアンプは平均インダクタ電流が新しい負荷電流に釣り合うまでITHピンの電圧を上昇させます。通常動作では、LTC3615は最大ITHピン電圧を約1.05Vにクランプします。この電圧は約5Aのピーク・インダクタ電流に対応しています。

出力がグランドに短絡すると、インダクタ電流は1スイッチング・サイクルの間、非常にゆっくり減衰します。LTC3615は2つの手法を使って電流の暴走を防ぎます。

1. 出力電圧がその公称値の50%より低くなると、ITHピンのクランプ電圧が下がり、最大ピーク・インダクタ電流が出力電圧に伴って徐々に減少します。出力電圧が0Vに達すると、ITHピンのクランプ電圧は通常動作時のクランプ電圧の40%に低下します。短絡時のピーク・インダクタ電流は、LTC3615の最小オン時間、入力電圧およびインダクタの値によって決ります。このフォールドバック動作は、出力がグランドに短絡したときピーク・インダクタ電流を制限するのに役立ちます。これは、内部または外部のソフトスタートおよびトラッキングアップ/トラッキングダウン動作の間ディスエーブルされます（「アプリケーション情報」のセクションを参照）。

2. ボトムMOSFETのインダクタ電流が標準の6Aを超えて増加すると、トップ・パワーMOSFETがオフに保たれ、インダクタ電流が減少するまでスイッチング・サイクルがスキップされます。

## アプリケーション情報

### 動作周波数

動作周波数の選択には、効率と部品サイズの間のトレードオフが必要です。動作周波数を高くすると、小さい値のインダクタとコンデンサを使うことができます。

低い周波数で動作させると内部ゲート電荷による損失が減り、効率が改善されますが、出力リップル電圧を低く抑えるには、インダクタンスや容量の値を大きくする必要があります。

LTC3615の動作周波数は、 $R_T$ /SYNCとグランドの間に接続された外部抵抗によって決まります。この抵抗の値により、発振器内の内部タイミング・コンデンサを充放電するのに使われるランプ電流が設定されます。この抵抗の値は次式を使って計算することができます。

$$R_T = \frac{4 \cdot 10^{11} \Omega \text{Hz}}{f_{\text{OSC}}}$$

最高4MHzの周波数も可能ですが、LTC3615の最小オン時間により、動作デューティ・サイクルの最小値が制限されます。最小オン時間は標準60nsなので、最小デューティ・サイクルは  $60\text{ns} \cdot 100\% \cdot f_{\text{OSC}}(\text{Hz})$  に等しくなります。

$R_T$ /SYNCピンを $SV_{\text{IN}}$ に接続すると、内部動作周波数を既定の  $2.25\text{MHz} \pm 20\%$  に設定します。

### 周波数同期

LTC3615の内部発振器は、 $R_T$ /SYNCピンに方形波クロック信号を与えることによって外部周波数に同期させることができます。同期動作の間、チャネル1のトップMOSFETのオンするタイミングは、外部周波数ソースの立ち上がりエッジにロックされます。同期周波数範囲は400kHz～4MHzです。内部スロープ補償は自動的に外部クロック周波数に適応します。

$R_T$ /SYNCクロック入力からSW出力までの信号経路において、LTC3615は内部PLLによって外部クロック周波数を処理します。

$R_T$ /SYNCの最初の立ち上がりエッジで外部クロックを検出すると、PLLが  $2.25\text{MHz}$  の内部デフォルトで起動します。その後、SWの周波数が  $R_T$ /SYNCの周波数と位相に一致するまで、内部PLLはセトリングするのに一定数の周期を必要とします。

## アプリケーション情報

図4. スイッチング周波数の設定

外部クロック信号が取り去られた場合、LTC3615がこれを検出するのに約5μsかかります。この間PLLは、デフォルト周波数または選択された周波数(外部レジスタR<sub>T</sub>により設定)に戻るまでクロック・サイクルを継続します。

R<sub>T</sub>/SYNC入力をドライブする安全な方法として、15pFのコンデンサを介してクロック・ジェネレータにAC結合します。AC結合は、LTC3615の起動時、動作時、およびシャットダウン時に外部クロック・ジェネレータが連続してクロック信号を供給できない場合に問題が生じるのを防ぎます。

一般に、レギュレータのクロック周波数が突然変化するとSWピンのタイミングが影響を受け、出力電圧も同様に突然変化する恐れがあります。とりわけ外部クロック周波数が内部デフォルト値の2.25MHzと著しく異なる場合は、この点を考慮する必要があります。

### 位相の選択

LTC3615のチャネル2は、PHASEピンの状態、すなわち“L”、ミッドレール、“H”に応じ、チャネル1に対してそれぞれ同相、180°位相シフト(逆位相)、90°位相シフトで動作します。LTC3615-1のチャネル2はPHASEピンが“H”的ときに180°位相シフト(逆位相)で動作し、PHASEピンがミッドレールまたは“L”的場合140°位相シフトで動作します。一般に、逆位相の場合は入力の電圧と電流のリップルが減少します。スイッチ・ノードSW1、SW2と、FBx、ITHx、R<sub>T</sub>/SYNCまたはSRLIMに接続された部品や敏感なラインとの間のクロストークは、不安定なスイッチング波形や予期せず大きな入力と出力の電圧リップルを引き起こす可能性があります。

スイッチ・ノードの立ち上がりエッジと立ち下がりエッジが重ならないようにタイミングを取ることができればこの状況を改善することができます。2つのチャネルのデューティ・サイクルに応じ、エッジ同士が互いにできるだけ離れるようにチャネル間の位相差を選択してください。

たとえば、一方のチャネルのデューティ・サイクルが40%未満で他方のチャネルのデューティ・サイクルが60%を超える場合、位相シフトを0°または180°にすればSWノードのエッジが重なることはありません。両方のデューティ・サイクルが50%前後の場合は、90°の位相差がより望ましい選択です。デューティ・サイクルが25%前後および50%前後の場合は、140°の位相シフト(LTC3615-1のみ)が他の位相を選択するより望ましいと言えます。

### インダクタの選択

所定の入力電圧と出力電圧に対して、インダクタの値と動作周波数によってリップル電流が決まります。リップル電流ΔI<sub>L</sub>はV<sub>IN</sub>が高いほど増加し、インダクタンスが高いほど減少します。

$$\Delta I_L = \left( \frac{V_{OUT}}{f_{SW} \cdot L} \right) \cdot \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

リップル電流を小さくすると、インダクタのコア損失、出力コンデンサのESR損失、さらに出力電圧リップルが減少します。リップル電流を選択するための妥当な出発点はΔI<sub>L</sub> = 0.3 • I<sub>OUT(MAX)</sub>です。最大リップル電流は最大V<sub>IN</sub>で発生します。リップル電流が規定された最大値を超えないようにするには、次式に従ってインダクタンスを選択します。

$$L = \left( \frac{V_{OUT}}{f_{SW} \cdot \Delta I_{L(MAX)}} \right) \cdot \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

インダクタンス値はBurst Mode動作にも影響を与えます。ピーク・インダクタ電流がバースト・クランプによって設定されたレベルを下回ると、低電流動作への移行が開始されます。

## アプリケーション情報

インダクタンス値が小さいとリップル電流が大きくなるので、この移行がより低いDC負荷電流で起きるようになります。このため、低電流動作範囲の上の部分での効率が低下します。BurstMode動作では、インダクタンス値が小さいほどバースト周波数が高くなります。

### インダクタのコアの選択

$L$ の値が求まつたら、次にインダクタの種類を選択します。インダクタンス値が同じ場合、実際のコア損失はコア・サイズではなく、選択したインダクタンスによって大きく異なります。インダクタンスが大きいほどコア損失が減少します。残念ながら、インダクタンスを大きくするにはワイヤの巻数を増やす必要があるため銅損失が増加します。

フェライトを使ったタイプはコア損失が極めて低く、高いスイッチング周波数には最適なので、設計目標を銅損失と飽和を防ぐことに集中することができます。フェライト・コアの材質は「ハードに」飽和します。つまり、ピーク設計電流を超えるとインダクタンスが急に減少します。このため、インダクタのリップル電流が急増して、出力電圧リップルが増加します。フェライト・コアを飽和させないでください。そして、アプリケーションの温度範囲を基に外付けインダクタを選択してください！

コアの材質と形状が異なると、インダクタのサイズ/電流の関係および価格/電流の関係が変化します。フェライトやパーマロイを素材とするトロイド・コアやシールドされたポット型コアは小型で、エネルギー放射は大きくありませんが、類似の特性を有する鉄粉コアのインダクタより一般に高価です。使用するインダクタの種類の選択は、価格とサイズの条件や放射フィールド/EMIの条件に主に依存します。LTC3615のアプリケーションで適切に動作する標準的表面実装インダクタをいくつか表1に示します。

### 入力コンデンサ $C_{IN}$ の選択

連続モードでは、トップPチャネルMOSFETのソース電流はデューティ・サイクルが( $V_{OUT}/V_{IN}$ )の方形波になります。大きな入力過渡電圧を防止するには、最大RMS電流に対応できるサイズの低ESRコンデンサを $C_{IN}$ に使用する必要があります。

コンデンサの最大RMS電流は次式で与えられます。

$$I_{RMS} = I_{OUT(MAX)} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \sqrt{\left( \frac{V_{IN}}{V_{OUT}} - 1 \right)}$$

この式は $V_{IN} = 2V_{OUT}$ で最大値をとります。ここで、 $I_{RMS} = I_{OUT}/2$ です。大きく変化させてもそれほど状況が改善されないため、一般にはこの単純な最悪条件が設計に使用されます。コンデンサ・メーカーの規定するリップル電流定格は多くの場合2000時間だけの寿命試験に基づいているので、コンデンサをさらにディレーティングする、つまり必要とされるよりも高い温度定格のコンデンサを選択することを推奨します。一般に、アプリケーションの温度範囲を基にコンデンサを選択します。サイズまたは高さの設計条件を満たすため、複数のコンデンサを並列に接続することもできます。

表1. 標準的な表面実装インダクタ

| インダクタンス<br>( $\mu$ H)         | DCR<br>(mΩ) | 最大電流<br>(A) | 寸法<br>(mm)  | 高さ<br>(mm) |

|-------------------------------|-------------|-------------|-------------|------------|

| <b>Vishay IHLP-2020BZ-01</b>  |             |             |             |            |

| 0.33                          | 7.6         | 25          | 5.18 × 5.49 | 2          |

| 0.47                          | 8.9         | 21          | 5.18 × 5.49 | 2          |

| 0.68                          | 11.2        | 15          | 5.18 × 5.49 | 2          |

| 1                             | 18.9        | 16          | 5.18 × 5.49 | 2          |

| <b>東光 DE3518Cシリーズ</b>         |             |             |             |            |

| 0.22                          | 8           | 24          | 4.3 × 4.7   | 2          |

| <b>スミダ CDMC6D28シリーズ</b>       |             |             |             |            |

| 0.3                           | 3.2         | 15.4        | 6.7 × 7.25  | 3          |

| 0.47                          | 4.2         | 13.6        | 6.7 × 7.25  | 3          |

| 0.68                          | 5.4         | 11.3        | 6.7 × 7.25  | 3          |

| 1                             | 8.8         | 8.8         | 6.7 × 7.25  | 3          |

| <b>NEC/トーキン MPLC0730Lシリーズ</b> |             |             |             |            |

| 0.47                          | 4.5         | 16.6        | 6.9 × 7.7   | 3.0        |

| 0.75                          | 7.5         | 12.2        | 6.9 × 7.7   | 3.0        |

| 1.0                           | 9.0         | 10.6        | 6.9 × 7.7   | 3.0        |

| <b>Coilcraft D01813Hシリーズ</b>  |             |             |             |            |

| 0.33                          | 4           | 10          | 8.9 × 6.1   | 5          |

| 0.56                          | 10          | 7.7         | 8.9 × 6.1   | 5          |

| <b>Coilcraft SLC7530シリーズ</b>  |             |             |             |            |

| 0.27                          | 0.1         | 14          | 7.5 × 6.7   | 3          |

| 0.35                          | 0.1         | 11          | 7.5 × 6.7   | 3          |

| 0.4                           | 0.1         | 8           | 7.5 × 6.7   | 3          |

## アプリケーション情報

### 出力コンデンサC<sub>OUT</sub>の選択

C<sub>OUT</sub>の選択は、電圧リップルおよび負荷ステップに対する過渡応答を小さくするために必要なESRによって一般に決まります(低ESRセラミック・コンデンサについては次のセクションで説明します)。一般に、ESRの要件が満たされると、その容量はフィルタ機能にとって十分です。出力リップルΔV<sub>OUT</sub>は次式で求められます。

$$\Delta V_{OUT} \leq \Delta I_L \cdot \left( ESR + \frac{1}{8 \cdot f_{SW} \cdot C_{OUT}} \right)$$

ここで、f<sub>SW</sub>=動作周波数、C<sub>OUT</sub>=出力容量、ΔI<sub>L</sub>=インダクタのリップル電流です。ΔI<sub>L</sub>は入力電圧に応じて増加するので、出力リップルは入力電圧が最大のとき最大になります。

表面実装のアプリケーションでは、アプリケーションの要求する容量、ESRまたは実効電流の条件を満たすため、複数のコンデンサの並列接続が必要になることがあります。アルミ電解、特殊ポリマー、セラミック、および乾式タンタルの各コンデンサは全て表面実装パッケージで入手できます。

タンタル・コンデンサは最高の容量密度をもっていますが、ESRが大きいことがあります。スイッチング電源に使うためにサージテストされている必要があります。アルミ電解コンデンサのESRはかなり大きいのですが、リップル電流定格および長期信頼性に対して配慮すれば、コストに非常に敏感なアプリケーションに使うことができます。

### 入力と出力のセラミック・コンデンサ

セラミック・コンデンサは最もESRが小さく費用対効果が高いのですが、容量密度が低く、電圧係数と温度係数が高くて、可聴圧電効果を示します。さらに、寄生インダクタンスをともなったセラミック・コンデンサはQが高く、大きなリングングを引き起こすことがあります。

これらのコンデンサはESRが非常に小さいのでスイッチング・レギュレータに最適ですが、入力や出力に全てセラミック・コンデンサを使うときは細心の注意が必要です。

セラミック・コンデンサは温度の影響を受けやすいので、設計者は全動作温度範囲でループの安定性を確認する必要があります。大きな温度係数と電圧係数の影響を最小に抑えるため、X5RまたはX7Rのセラミック・コンデンサだけを使ってください。

セラミック・コンデンサを入力に使い、ACアダプタなど長いコードを通して電源を供給すると、出力の負荷ステップによってV<sub>IN</sub>ピンにリングングが誘起されることがあります。軽度であれば、このリングングが出力に結合して回路の不安定性と誤解されることがあるだけですが、最悪の場合この入力のリングングがデバイスに損傷を与えるほど大きくなることがあります。

セラミック・コンデンサのESRは非常に小さいので、入力コンデンサと出力コンデンサは代りに電荷保存の要件を満たす必要があります。負荷ステップ発生時には、帰還ループがスイッチ電流を十分増加させて負荷を支えるまで、出力コンデンサが即座に電流を供給して負荷を支える必要があります。帰還ループが応答するのに要する時間は補償部品と出力コンデンサのサイズに依存します。負荷ステップに応答するには標準で3~4サイクルを要しますが、最初のサイクルだけ出力が直線的に低下します。通常、出力の垂下(VDROOP)は最初のサイクルでの直線的低下の約2~3倍です。したがって、およそ以下の出力コンデンサのサイズから開始するのが良いでしょう。

$$C_{OUT} \approx \frac{2.5 \cdot \Delta I_{OUT}}{f_{SW} \cdot V_{DROOP}}$$

デューティ・サイクルや負荷ステップの要件によっては、さらに大きな容量が必要になることがあります。ほとんどのアプリケーションでは電源のインピーダンスは非常に小さいので、入力コンデンサは単に高周波をバイパスするためにだけ必要です。

## アプリケーション情報

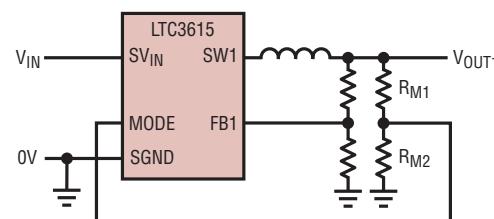

### 出力電圧のプログラミング

出力電圧は外部抵抗分割器によって設定されます。たとえば、V<sub>OUT2</sub>は次式に従って設定できます。

$$V_{\text{OUT2}} = 0.6V \cdot \left(1 + \frac{R_5}{R_4}\right)$$

図3に示すように、V<sub>FB</sub>ピンは出力電圧を抵抗分割器によって分圧した電圧を検出することができます。

### バースト・クランプのプログラミング

MODEピンの電圧が0.8Vより低いと、Burst Mode動作がイネーブルされます。MODEピンの電圧が0.3Vより低い場合は、内部の既定バースト・クランプ・レベルが選択されます。ITHピンの最小電圧は標準525mVです(内部クランプ)。

MODEピンの電圧が0.45V～0.8Vのとき、この電圧(V<sub>BURST</sub>)は、ITHピンの最小電圧(外部クランプ)に等しく、バースト・クランプ・レベルI<sub>BURST</sub>(標準1A～3.5A)を決定します。

ITH電圧が内部(または外部)クランプ電圧より低くなると、デバイスはスリープ状態になります。出力負荷電流が減少するとピーク・インダクタ電流が減少し、出力電圧を安定化された状態に保ちます。出力負荷電流がI<sub>BURST</sub>より小さなピーク・インダクタ電流しか必要としなくなると、負荷電流がさらに減少しても、ピーク・インダクタ電流はバースト・クランプによって強制的にI<sub>BURST</sub>に等しく保たれます。

平均インダクタ電流が出力負荷電流より大きいので、ITHピンの電圧は低下します。ITH電圧が低下するとスリープ・モードに入ります。このモードでは、ほとんどの回路および両方のパワースイッチがオフし、電力消費が最小に抑えられます。出力電圧が安定化状態から外れると、すべての回路が再度オンして、パワースイッチが動作を再開します。I<sub>BURST</sub>の値は望みの出力電圧リップルの大きさによって決まります。I<sub>BURST</sub>の値の増加に応じて、パルス間のスリープ期間と出力電圧リップルが増加します。周囲温度が85°Cを超える場合は、内部クランプによるBurst Mode動作を使用することを推奨します。

### パルス・スキップ・モード

低い出力電圧リップルと効率の間を妥協させたパルス・スキップ・モードは、MODEピンをS<sub>VIN</sub>に接続することによって実現することができます。これによりI<sub>BURST</sub>は0Aに設定されます。この条件では、ピーク・インダクタ電流は電流コンパレータの最小オン時間によって制限されます。不連続で動作しながら、最小の出力電圧リップルが達成されます。出力負荷が非常に軽いとき、パルス・スキップにより、出力電圧を安定化状態に保ったまま、スイッチングを数サイクルにわたってスキップすることができます。

### 内部補償と外部補償

レギュレータのループ応答は負荷電流過渡応答を観察すればチェックできます。スイッチング・レギュレータはDC負荷電流ステップに対して応答するのに数サイクルを要します。図5に示すような負荷ステップが生じると、V<sub>OUT</sub>はΔI<sub>LOAD</sub>・ESRに等しい量だけシフトします。ここで、ESRはC<sub>OUT</sub>の等価直列抵抗です。また、ΔI<sub>LOAD</sub>により、C<sub>OUT</sub>が充電または放電を開始して帰還誤差信号を生じ、レギュレータが電流変化に適応してV<sub>OUT</sub>をその定常状態の値に戻すように強制します。この回復期間に(安定性に問題があることを示す)過度のオーバーシュートやリングングが発生しないか、V<sub>OUT</sub>をモニタすることができます。ITHピンを利用可能なので、広い範囲の出力コンデンサに対して過渡応答の最適化を図ることができます。

図3に示されているITH1の外部部品(15kと100pF)は、ほとんどのアプリケーションで適切な補償を提供し、出発点として妥当なものです。これらの値は、PCBのレイアウトを完了し、特定の出力コンデンサの種類と容量値を決定したら、過渡応答を最適化するために多少は変更することができます。出力コンデンサのさまざまな種類と値によってループの利得と位相が決まるので、まず出力コンデンサを選択する必要があります。ループの利得はR<sub>C</sub>を大きくすると増加し、ループの帯域幅はC<sub>C</sub>を小さくすると拡大します。C<sub>C</sub>を減少させるのと同じ比率でR<sub>C</sub>を増加させるとゼロの周波数は変化しないので、帰還ループの最も重要な周波数範囲で位相シフトが一定に保たれます。出力電圧のセトリングの様子は閉ループ・システムの安定性に関係します。「標準的応用例」のセクションに示す外部補償の強制連続動作回路は、さらに高速な補償を採用することによって負荷ステップ応答を改善しています。

## アプリケーション情報

次に、大容量の( $>1\mu\text{F}$ )電源バイパス・コンデンサが接続されている負荷のスイッチが入れられると、さらに大きな過渡が発生します。放電しきったバイパス・コンデンサが実質的に $\text{C}_{\text{OUT}}$ と並列接続状態になるため、 $\text{V}_{\text{OUT}}$ が急速に降下します。負荷スイッチの抵抗が低く、しかも瞬間にドライブされると、どんなレギュレータでも出力電圧の急激なステップ変化を防止するほど素早く電流供給をえることはできません。デューティサイクルと負荷ステップの要件によっては、さらに大きな出力容量が必要になることがあります。

$\text{V}_{\text{ITH}}$ ピンが $\text{V}_{\text{IN}}$ に接続されると、アクティブ電圧ポジショニング(AVP)モードと内部補償が選択されます。

AVPモードでは意図的にロード・レギュレーション性能が抑制されるので、ある時点で得られる出力電圧は負荷電流に応じて変化します。負荷電流が突然増加した場合は出力電圧が公称値よりわずかに高いレベルからスタートするので、より大きく垂下しても規定電圧範囲内に留まることができます。

図5. 外部補償を用いた強制連続モードの負荷ステップ過渡電流

負荷電流が突然低下した場合は出力電圧が公称値より低いレベルからスタートするので、より大きくオーバーシュートしても規定電圧範囲内に留まることができます。この動作を図6に示します。

利点は、出力フィルタの容量を大きくしなくとも、一定の負荷ステップに対してピーク・トゥ・ピーク出力電圧変化が下がることです。あるいは、出力電圧フィルタの容量を減らしながら同じピーク・トゥ・ピーク過渡応答を維持することができます。この動作モードではループ利得が下がるので、外部補償は不要です。

### プログラム可能なスイッチ・ピンのスルーレート

スイッチング周波数が上がるに伴い、電力損失とスイッチが安定するためのブランディング時間を最小限にするために、スイッチング時に必要な遷移時間をできるだけ短くすることが望まれます。ただし、スイッチ・ノードのスルーリングが高速だと外部放射EMIが比較的高くなり、内蔵電源の過渡も高くなり、アプリケーションによっては問題を生じることがあります。

図6. AVPモードを用いた強制連続モードの負荷ステップ過渡電流

## アプリケーション情報

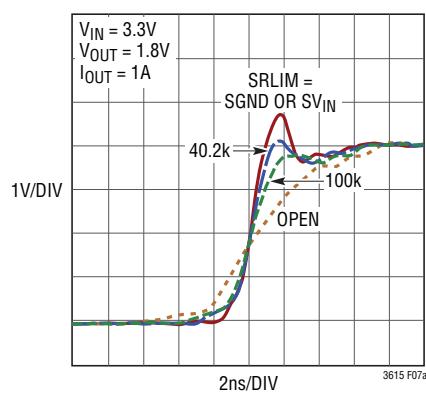

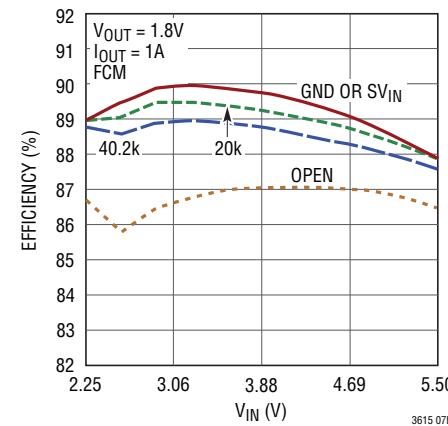

ユーザーは、LTC3615のSRLIMピンを使ってスイッチング・ノードSWのスルーレートを制御することができます。このピンをグランドに接続すると最速スルーレートが選択されます。ピンがオープンだと最も遅いスルーレートが選択されます。SRLIMピンからグランドに10k~100kの抵抗を接続すると、スルーレートが最大値と最小値の中間に調整されます。スイッチ・ノードのdV/dtを下げる、電源とグランドのリンクが大幅に減少し、放射EMIが低下します。例については、図7と「標準的性能特性」のセクションを参照してください。

スルーレートを小さくすると、効率と低EMIのトレードオフが必要になります(図7b参照)。

非常に高いスイッチング周波数では特に注意が必要です。最も遅いスルーレートを使うと(SRLIMをオープン)、最小デュエティ・サイクル能力が低下する可能性があります。

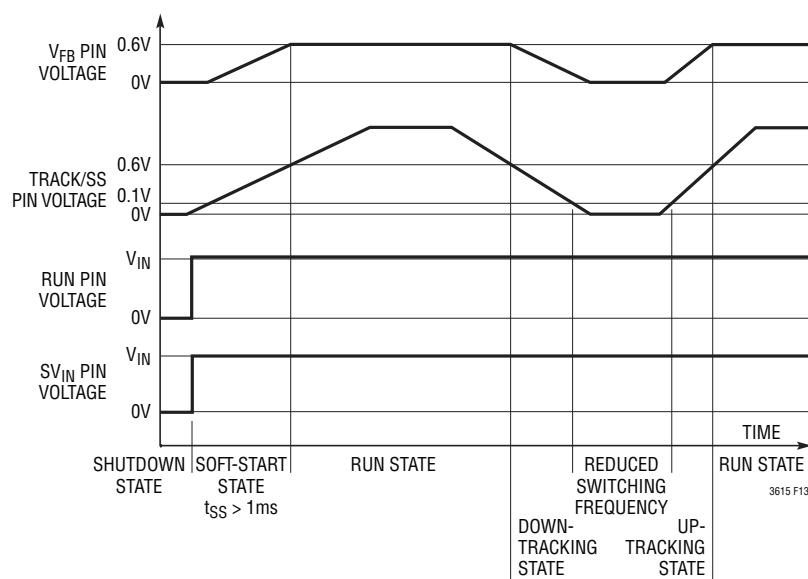

### ソフトスタート

RUNxピンを使うと、LTC3615の各チャネルをシャットダウンすることができます。両方のピンを0.3Vより低い電圧にすると、LTC3615は低消費電流のシャットダウン状態になります( $I_Q < 1\mu A$ )。

RUNxピンのどちらか一方または両方の電圧をスレッショルドよりも高い値にしてLTC3615をイネーブルすると、イネーブルされたチャネルはソフトスタート状態になります。ソフトスタート動作のタイプはTRACK/SSxピンによって設定されます。ソフトスタートサイクルは、初期化放電パルスによってTRACK/SSx

ピンをSGNDに引き下げ、外付けコンデンサ $C_{SS}$ を放電して開始されます(図3参照)。

最初の放電は、最大33nFのコンデンサを放電させる程度のものです。より大きなコンデンサが必要な場合は、RUNピンに外付けソフトスタート抵抗 $R_{SS}$ を接続して、コンデンサを完全に放電させてください。

1. このピンを $SV_{IN}$ に接続すると、内部ソフトスタート回路が選択されます。この回路は出力電圧を1ms以内に最終値までランプさせます。

2. ソフトスタート時間を延長したい場合は、図3に示すように、TRACK/SSxピンに抵抗とコンデンサを接続して外部的に設定することができます。TRACK/SSxピンに加えられた電圧は、TRACK/SSxが0.6Vを越えるまで $V_{FB}$ の内部リファレンスの値を設定します。外部ソフトスタートによる起動時間は次式を使って計算することができます。

$$t_{SS} = R_{SS} \cdot C_{SS} \cdot \ln \left( \frac{SV_{IN}}{SV_{IN} - 0.6V} \right)$$

3. TRACK/SSxピンは、別の電源の出力電圧トラッキングに使うことができます。

内部、外部どちらのソフトスタート状態かに関わらず、MODEピンは無視され、レギュレータはパルス・スキップ・モードがデフォルトになります。さらに、PGOODxピンは“L”に保たれ、周波数フォールドバック機能はディスエーブルされます。

(7a) SW1/2の立ち上がりエッジのスルーレートとSRLIMの抵抗

(7b) 効率とSRLIM抵抗のプログラミング

図7. スルーレートとSRLIM抵抗

# LTC3615/LTC3615-1

## アプリケーション情報

### 出力電圧トラッキング入力

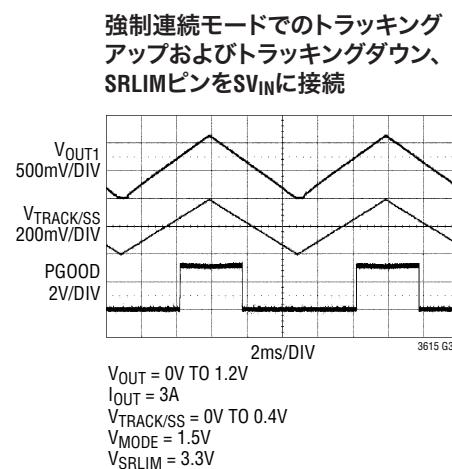

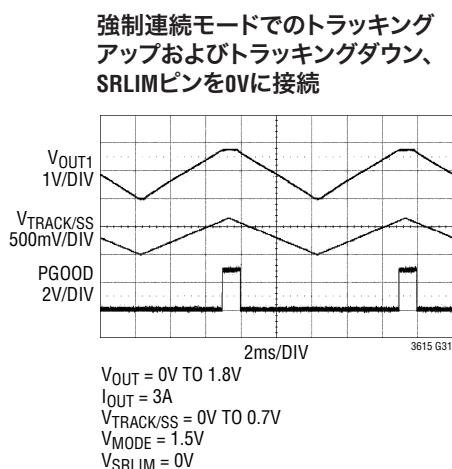

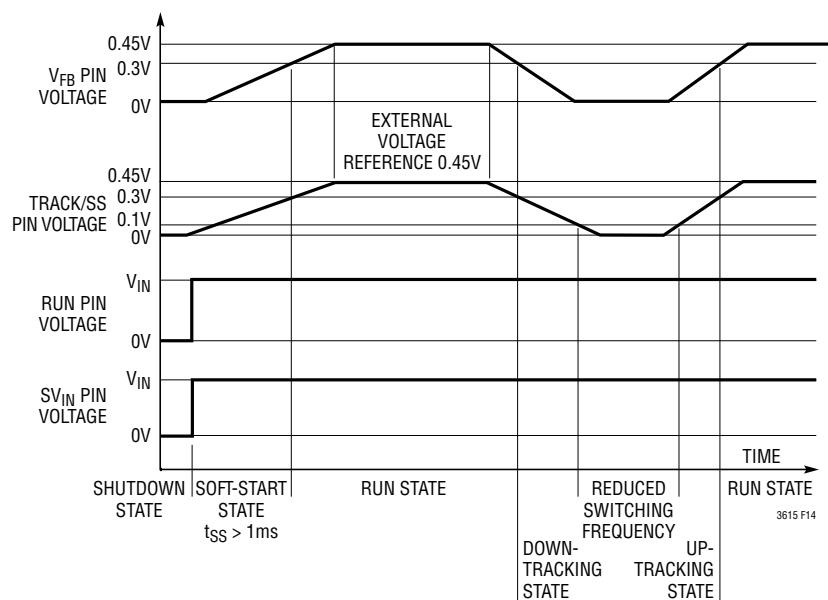

SRLIMが“L”の場合、 $V_{TRACK/SS}$ が0.6V以上になると動作状態に入り、MODE選択、パワーグッド、および電流フォールドバックの回路がイネーブルされます。

動作状態では、TRACK/SSピンを使って別の電源の出力電圧をトラックダウン/トラックアップすることができます。 $V_{TRACK/SS}$ が再び0.6Vより下になるとLTC3615はダウントラッキング状態に入り、TRACK/SS電圧が $V_{OUT}$ の基準になります。TRACK/SSピンが0.1Vになるとスイッチング周波数が1/4に下がり、最小デューティ・サイクルの制限のために出力がTRACK/SSピンに従うことが妨げられないようにします。 $V_{TRACK/SS}$ が再度0.6Vを超えると、再び動作状態になります。

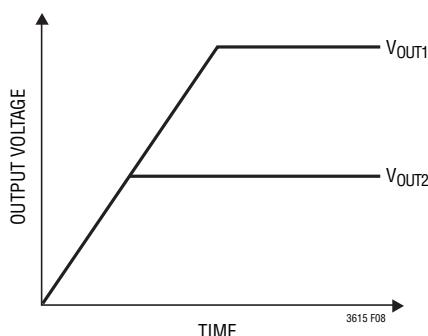

図8. 同時スタートアップ・トラッキング

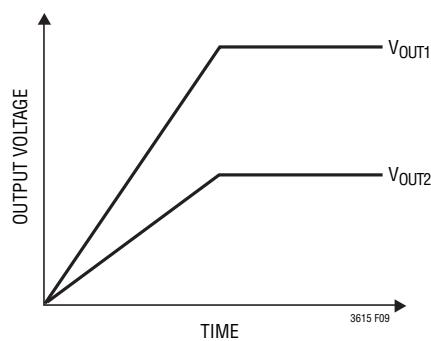

図8と図9に示すように、TRACK/SSピンを使って出力電圧を同時トラッキングまたは比例トラッキングに設定することができます。

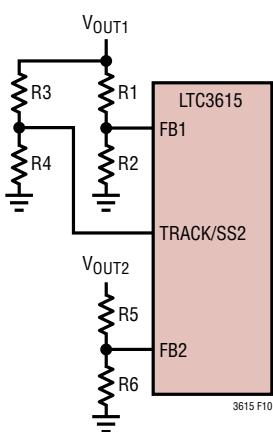

図8の同時トラッキング動作を実現するには、追加の抵抗分割器をマスタ・チャネルの出力に接続し、そのミッドポイントをスレーブ・チャネルのTRACK/SSピンに接続します。この分割器の比はスレーブ・チャネルの帰還分割器の比と同じにします(図10)。

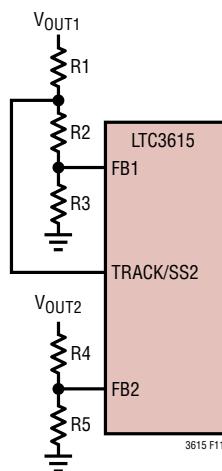

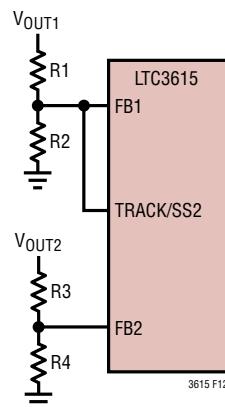

このトラッキング・モードでは、マスタ・チャネルの出力をスレーブ・チャネルの出力よりも高く設定する必要があります。図9の比例トラッキング動作を実現するには、分割器を追加する必要はなく、TRACK/SSピンをもう一方のチャネルの $V_{FB}$ ピンに接続するだけで済みます(図12)。

図9. 比例スタートアップ・トラッキング

図10. 同時トラッキングの設定

( $R3 = R5, R4 = R6$ )

図11. 同時スタートアップ・トラッキングの

もう1つのセットアップ ( $R1 = R3, R2 = R3 = R5$ )

図12. 比例トラッキングの

セットアップ

3615fb

## アプリケーション情報

### 外部リファレンス入力(DDRモード)

SRLIMをSVINに接続した場合は、必要に応じてTRACK/SSを0.3Vと0.5V間の外部リファレンス入力として使うことができます(図13参照)。

DDRモードでは最大スルーレートが選択されます。VTRACK/SSが0.3V~0.5Vの範囲内の場合は、PGOOD機能がイネーブルされます。VTRACK/SSが0.3Vよりも低い場合は、出力電流フォールドバックがディスエーブルされ、PGOODピンは常にプルダウンされます。

図13.  $V_{SRLIM}$ が“L”の場合のトラッキング

図14.  $V_{SRLIM}$ を $SV_{IN}$ に接続時のトラッキング

## アプリケーション情報

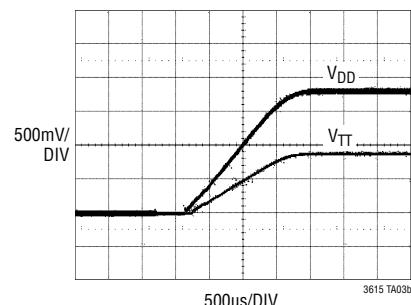

### DDRアプリケーション

LTC3615は、SRLIMピンをSV<sub>IN</sub>に接続することによって、DDRメモリ電源アプリケーションに使用することができます。DDRモードでは最大スルーレートが選択されます。出力は電流のソースとシンク両方が可能です。1MHzの周波数および1μHのインダクタでは、電流シンクは標準1.5Aに制限されますが、もっと高い周波数と低い出力電圧ではさらに下がることがあります。より高いリップル電流を許容できれば、より小さいインダクタ値を使ってシンク電流のリミットを上げることができます。詳細については「標準的性能特性」の曲線を参照してください。さらに、DDRモードでは、2つのチャネル間でより低い外部リファレンス電圧とトラッキング出力電圧を使用することができます。「出力電圧トラッキング入力」のセクションを参照してください。

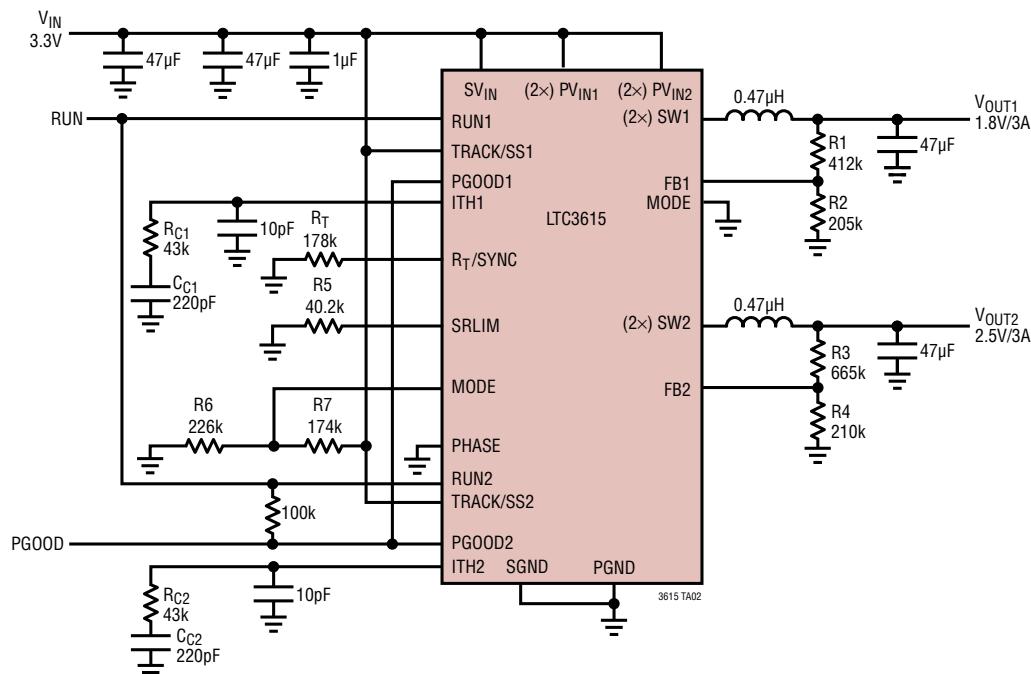

### 単一の低リップル6A出力アプリケーション

LTC3615は、2つのスイッチング・レギュレータの出力をいっしょに接続して1個の出力コンデンサを共有することで、単一の低リップル6A出力を生成することができます(データシート最終ページの図15を参照)。2つのレギュレータ間で均等に電流を分担するために、ピンFB1をFB2に、ITH1をITH2に接続して、MODEピンで強制連続モードを選択する必要があります。リップルを最小にするために、PHASEピンをミッドレールまたはSV<sub>IN</sub>に接続することによって、90°またはより望ましい180°(逆位相)の位相シフトを選択します。この2相降圧レギュレータにはいくつかの利点があります。入力と出力におけるリップル電流が小さくなつて電圧リップルも小さくなるので、より小型で安価なコンデンサを使用することができます。インダクタは2個必要ですが、いずれも単相レギュレータに必要なインダクタよりも小さいもので済みます。回路の高さが厳しく制限される場合、これは重要な要素となります。

### 効率に関する検討事項

スイッチング・レギュレータの効率は「出力電力÷入力電力×100%」で表されます。個々の損失を解析して、効率を制限する要素がどれであり、また何が変化すれば最も効率が改善されるかを判断できる場合がよくあります。効率は次式で表すことができます。

$$\text{効率} = 100\% - (L_1 + L_2 + L_3 + \dots)$$

ここで、L1、L2などは入力電力に対するパーセンテージで表した個々の損失です。

回路内の電力を消費する全ての要素で損失が生じますが、損失の大部分は2つの主な損失要因によって生じます。V<sub>IN</sub>の消費電流による損失とI<sup>2</sup>R損失です。非常に低い負荷電流ではV<sub>IN</sub>の消費電流による損失が効率の損失を支配するのに対して、中程度から高い負荷電流ではI<sup>2</sup>R損失が効率の損失を支配します。標準的な効率曲線では、非常に低い負荷電流での効率曲線は誤解を与えかねません。というのは、実際の電力損失は通常大したことはないからです。

1. V<sub>IN</sub>の消費電流は2つの要素からなります。「電気的特性」で与えられているDCバイアス電流および内部のメイン・スイッチと同期スイッチのゲート充電電流です。内部パワーMOSFETスイッチのゲート容量をスイッチングすると、ゲート充電電流が流れます。ゲートが“L”から“H”、そして再び“L”に切り替わるたびに、V<sub>IN</sub>からグランドに微小電荷dQが移動しますしたがって、dQ/dtはゲート電荷によりV<sub>IN</sub>から流出する電流であり、一般にDCバイアス電流より大きくなります。DCバイアス損失とゲート電荷損失は両方ともV<sub>IN</sub>に比例するので、それらの影響は電源電圧が高くなると顕著になります。

2. I<sup>2</sup>R損失は内部スイッチの抵抗R<sub>SW</sub>と外部インダクタの抵抗R<sub>L</sub>から計算されます。連続モードでは、インダクタLを流れる平均出力電流は、メイン・スイッチと同期スイッチの間に「こま切れ」にされます。したがって、SWピンを見たときの直列抵抗は、次式のとおり、トップMOSFETとボトムMOSFETの両方のR<sub>DS(ON)</sub>およびデューティサイクル(DC)の関数になります。

$$R_{SW} = (R_{DS(ON)\text{TOP}})(DC) + (R_{DS(ON)\text{BOT}})(1-DC)$$

トップMOSFETとボトムMOSFETの両方のR<sub>DS(ON)</sub>は、「標準的性能特性」の曲線から求めることができます。I<sup>2</sup>R損失を求めるには、単にR<sub>SW</sub>をR<sub>L</sub>に加え、その結果に平均出力電流の2乗を掛けます。

C<sub>IN</sub>やC<sub>OUT</sub>のESRによる損失やインダクタのコア損失など、その他の損失は一般に全損失の2%以下に過ぎません。

### 熱に関する検討事項

LTC3615は効率が高いので、ほとんどのアプリケーションで大きな発熱はありません。ただし、周囲温度が高く、(ドロップアウトの場合のように)低い電源電圧、高いデューティ・サイクルでLTC3615が動作するアプリケーションでは、発熱がデバイスの最大接合部温度を超えることがあります。

## アプリケーション情報

接合部温度が約170°Cに達すると、4個のパワースイッチすべてがオフし、SWノードが高インピーダンスになります。

LTC3615の接合部温度が最大値を超えないようにするには何らかの熱解析が必要です。デバイスの接合部温度が消費電力によって最大値を超えるかどうかを判断します。温度上昇は次式で与えられます。

$$T_{RISE} = P_D \cdot \theta_{JA}$$

ここで、 $P_D$ はレギュレータによって消費される電力で、 $\theta_{JA}$ はダイの接合部から周囲温度への熱抵抗です。接合部温度  $T_J$  は次式で与えられます。

$$T_J = T_A + T_{RISE}$$

ここで、 $T_A$  は周囲温度です。

例として次のようなケースを考えてみます。LT3615は、入力電圧が3.3V、各チャネルの負荷電流が2A、周囲温度が70°Cの条件でドロップアウト状態にあります。接合部温度が20°C上昇して90°Cになったとすると、 $R_{DS(ON)}$  は0.086mΩになります（「標準的性能特性」のセクションのグラフを参照）。したがって、デバイスが消費する電力は次の通りです。

$$P_D = (I_1^2 + I_2^2) \cdot R_{DS(ON)} = 0.69W$$

QFNパッケージの $\theta_{JA}$ は37°C/Wです。

したがって、70°Cの周囲温度で動作しているレギュレータの接合部温度は、およそ次の値となります。

$$T_J = 0.69W \cdot 37^\circ C/W + 70^\circ C = 95^\circ C$$

入力電圧が非常に低い場合はスイッチ抵抗 $R_{DS(ON)}$ が増大するので、接合部温度はさらに高くなることに注意してください。周囲温度が高く入力電圧が低い状態で最大負荷電流を使用することは推奨できません。

LTC3615の熱性能を最大限まで高めるには、露出パッドをグランド・プレーンに半田付けする必要があります。PCボード・レイアウトのチェックリストを参照してください。

### 設計例

設計例として、以下の仕様のアプリケーションにLTC3615を使う場合を考えます。

$$V_{IN} = 3.3V \sim 5.5V$$

$$V_{OUT1} = 2.5V$$

$$V_{OUT2} = 1.2V$$

$$I_{OUT1(MAX)} = 1A$$

$$I_{OUT2(MAX)} = 3A$$

$$I_{OUT(MIN)} = 100mA$$

$$f = 2.25MHz$$

高負荷電流と低負荷電流の両方で効率が重要なので、Burst Mode動作を利用します。

最初にタイミング抵抗を計算します。

$$R_{RT/SYNC} = \frac{4E11\Omega \cdot Hz}{2.25MHz} = 178k$$

次に、最大 $V_{IN}$ で約1Aのリップル電流になるようにインダクタ値を計算します。

$$L1 = \left( \frac{2.5V}{2.25MHz \cdot 1A} \right) \cdot \left( 1 - \frac{2.5V}{5.5V} \right) = 0.6\mu H$$

$$L2 = \left( \frac{1.2V}{2.25MHz \cdot 1A} \right) \cdot \left( 1 - \frac{1.2V}{5.5V} \right) = 0.42\mu H$$

標準値が0.56μHと0.47μHのインダクタを使うと、最大リップル電流は以下のようになります。

$$\Delta I_{L1} = \left( \frac{2.5V}{2.25MHz \cdot 0.56\mu H} \right) \cdot \left( 1 - \frac{2.5V}{5.5V} \right) = 1.08A$$

$$\Delta I_{L2} = \left( \frac{1.2V}{2.25MHz \cdot 0.47\mu H} \right) \cdot \left( 1 - \frac{1.2V}{5.5V} \right) = 0.89A$$

$C_{OUT}$ は、出力電圧リップルの要件を満たすESRと、ループの安定性に必要なバルク容量に基づいて選択します。このデザインでは、X5RまたはX7Rの誘電体を使用する47μFのセラミック・コンデンサを使います。

$C_{IN}$ は、次式で表される最大電流定格に合わせてサイズを決定します。

$$I_{RMS(MAX)} = \frac{|_{OUT1}|}{2} + \frac{|_{OUT2}|}{2} = 2A_{RMS}$$

# LTC3615/LTC3615-1

## アプリケーション情報

ほとんどのアプリケーションでは、 $P_{V_{IN}}$ を2個の47μFコンデンサでデカップリングすれば十分です。

最後に、TRACK/SSピンに接続するコンデンサと抵抗の適切な値を選択して、ソフトスタートの時間を定めることができます。最小T<sub>SS</sub> = 5msおよび4.7MΩの抵抗を設定すると、最大SV<sub>IN</sub> = 5.5Vで次式を解くことができます。

$$C_{SS} = \frac{5\text{ms}}{4.7\text{M} \cdot \ln\left(\frac{5.5\text{V}}{5.5\text{V} - 0.6\text{V}}\right)} = 9.2\text{nF}$$

10nFと4.7Mの標準値により、5msの最小ソフトスタート時間が保証されます。この設計例の回路を図3のチャネル1に示します。

### PCボード・レイアウトのチェックリスト

プリント回路基板をレイアウトする際は、以下のチェックリストを使用してLTC3615が正しく動作するようにします。

1. グランド・プレーンを推奨します。グランド・プレーン層が使われていなければ、信号グランドと電源グランドを分離し、小信号用部品は1点でSGNDピンに戻して、この1点を LTC3615の近くで露出パッドのPGNDノードに接続します。

2. 入力コンデンサC<sub>IN</sub>の(+)端子はPV<sub>INx</sub>ピンにできるだけ近づけ、(-)端子は露出パッドPGNDにできるだけ近づけて接続します。このコンデンサは内部パワーMOSFETにAC電流を供給します。

3. スイッチング・ノードSW<sub>x</sub>は、FB<sub>x</sub>、ITH<sub>x</sub>、RTSYNC、SRLIMなど、全ての敏感な小信号ノードから離します。

4. すべての層のすべての未使用領域を銅で覆います。銅で覆うと電力部品の温度上昇が小さくなります。最良の性能を得るため、銅領域をPGND(露出パッド)に接続します。

5. V<sub>FBx</sub>ピンは帰還抵抗に直接接続します。抵抗分割器はV<sub>OUTx</sub>とSGNDの間に接続する必要があります。

## 標準的応用例

比例スタートアップ

## 標準的應用例

外部補償、強制連続動作、同相スイッチング、スルーレート制限、共通PGOOD出力

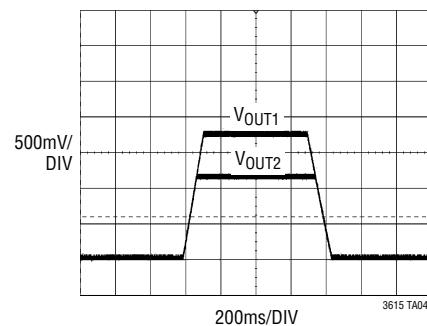

V<sub>OUT1</sub>波形V<sub>OUT2</sub>波形

# LTC3615/LTC3615-1

## 標準的応用例

2MHz外部クロックを使用した同時トラッキング出力のマスタとスレーブ

3615 TA04a

同時スタートアップ

同時トラッキングアップ/トラッキングダウン

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> をご覧ください。

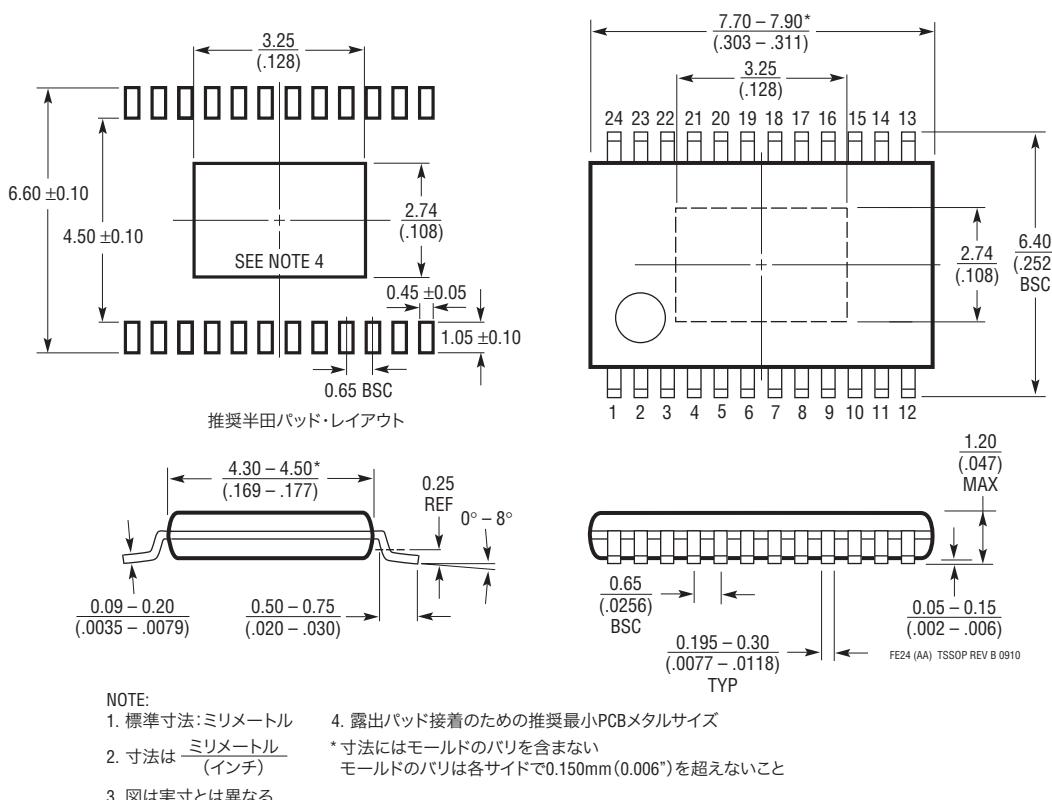

**FE Package

24-Lead Plastic TSSOP (4.4mm)**

(Reference LTC DWG # 05-08-1771 Rev B)

**Exposed Pad Variation AA**

# LTC3615/LTC3615-1

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/design-tools/packaging/> をご覧ください。

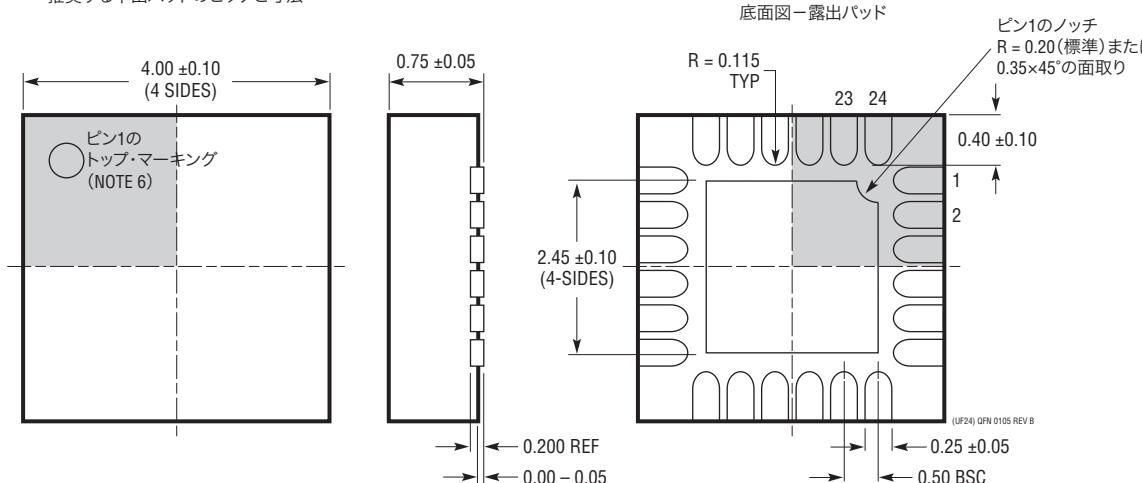

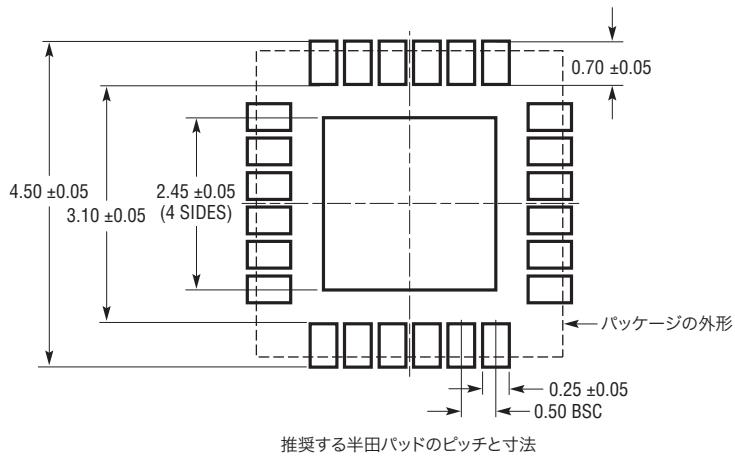

UF Package

24-Lead Plastic QFN (4mm × 4mm)

(Reference LTC DWG # 05-08-1697 Rev B)

### NOTE:

- 図はJEDEC/パッケージ外形MO-220のバリエーション(WGDD-X)にするよう提案されている(承認待ち)

- 図は実寸とは異なる

- すべての寸法はミリメートル

- パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

- 露出パッドは半田メッキとする

- 網掛けの部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

## 改訂履歴

| Rev | 日付   | 概要                                 | ページ番号 |

|-----|------|------------------------------------|-------|

| A   | 7/10 | LTC3615-1を追加。データシート全体に反映           | 1~32  |

| B   | 6/13 | 温度の最大定格を明確化。                       | 2     |

|     |      | 発注情報セクションを明確化。                     | 2     |

|     |      | 電気的特性セクションのV <sub>FB</sub> 仕様を明確化。 | 3     |

|     |      | Note 2とNote 11の温度仕様を明確化。           | 4     |

|     |      | 標準的性能特性のグラフを明確化。                   | 7、8   |

|     |      | インダクタと入力コンデンサの選択のセクションの文章を明確化。     | 17    |

|     |      | 熱に関する検討事項のセクションの最高接合部温度を明確化。       | 25    |

# LTC3615/LTC3615-1

## 標準的応用例

図15. 低リップルのシングル6A出力

図16. SW1とSW2間の180°位相シフトによるリップル電流(波形I<sub>L1</sub>+I<sub>L2</sub>)およびリップル電圧(図示されていない)の低減

図17. V<sub>OUT</sub> = 1.2VおよびI<sub>OUT</sub> = 最大6A時の効率と負荷電流

## 関連製品

| 製品番号       | 説明                                     | 注釈                                                                                                                               |

|------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| LTC3633    | 15V、デュアル3A、4MHz同期整流式降圧DC/DCコンバータ       | 効率:95%、V <sub>IN</sub> :3.60V~15V、V <sub>OUT(MIN)</sub> = 0.6V、消費電流:500µA、I <sub>SD</sub> < 13µA、4mm×5mm QFN-28およびTSSOP-28Eパッケージ |

| LTC3546    | 5.5V、デュアル3A/1A、4MHz同期整流式降圧DC/DCコンバータ   | 効率:95%、V <sub>IN</sub> :2.25V~5.5V、V <sub>OUT(MIN)</sub> = 0.6V、消費電流:160µA、I <sub>SD</sub> < 1µA、4mm×5mm QFN-28パッケージ             |

| LTC3417A-2 | 5.5V、デュアル1.5A/1A、4MHz同期整流式降圧DC/DCコンバータ | 効率:95%、V <sub>IN</sub> :2.25V~5.5V、V <sub>OUT(MIN)</sub> = 0.8V、消費電流:125µA、I <sub>SD</sub> < 1µA、TSSOP-16Eおよび3mm×5mm DFN-16パッケージ |

| LTC3612    | 5.5V、3A、4MHz同期整流式降圧DC/DCコンバータ          | 効率:95%、V <sub>IN</sub> :2.25V~5.5V、V <sub>OUT(MIN)</sub> = 0.6V、消費電流:75µA、I <sub>SD</sub> < 1µA、3mm×4mm QFN-20およびTSSOP-20Eパッケージ  |

| LTC3614    | 5.5V、4A、4MHz同期整流式降圧DC/DCコンバータ          | 効率:95%、V <sub>IN</sub> :2.25V~5.5V、V <sub>OUT(MIN)</sub> = 0.6V、消費電流:75µA、I <sub>SD</sub> < 1µA、3mm×4mm QFN-20 およびTSSOP-20Eパッケージ |

| LTC3616    | 5.5V、6A、4MHz同期整流式降圧DC/DCコンバータ          | 効率:95%、V <sub>IN</sub> :2.25V~5.5V、V <sub>OUT(MIN)</sub> = 0.6V、消費電流:75µA、I <sub>SD</sub> < 1µA、3mm×5mm QFN-24パッケージ              |

3615fb