## 正誤表

この製品のデータシートに間違いがありましたので、お詫びして訂正いたします。

この正誤表は、2021年8月11日現在、アナログ・デバイセズ株式会社で確認した誤りを記したものです。

なお、英語のデータシート改版時に、これらの誤りが訂正される場合があります。

正誤表作成年月日：2021年8月11日

製品名：LT3120

対象となるデータシートのリビジョン(Rev)：Rev.0

訂正箇所：24ページ

左の段、上から3行目

### 【誤】

「この例では、RHPZ 周波数の 1/6 のクロスオーバー周波数を使用します（式 28 を参照）。」

### 【正】

この例では、RHPZ 周波数の 1/7 のクロスオーバー周波数を使用します（式 28 を参照）。

アナログ・デバイセズ株式会社

本 社／〒105-6891 東京都港区海岸 1-16-1

ニューピア竹芝サウスタワービル

電話 03 (5402) 8200

大阪営業所／〒532-0003 大阪府大阪市淀川区富原 3-5-36

新大阪トラストタワー

電話 06 (6350) 6868

## 26V、9A、低 $I_Q$ のCC/CV モノリシック昇降圧コンバータ

### 特長

- 入力電圧範囲: 2.5V~26V

- 出力電圧範囲: 0.8V~24V

- 高出力電流

- 6.5A ( $V_{OUT} = 5V$ ,  $V_{IN} > 6V$ )

- 3A ( $V_{OUT} = 5V$ ,  $V_{IN} = 3V$ )

- 6.5A ( $V_{OUT} = 12V$ ,  $V_{IN} > 14V$ )

- 4A ( $V_{OUT} = 12V$ ,  $V_{IN} = 9V$ )

- 超低ノイズ昇降圧アーキテクチャ

- プログラマブルな出力電流制限

- プログラマブルな周波数範囲: 400kHz~2MHz

- 正確なイネーブル・コンパレータ閾値

- Burst Mode®動作、無負荷時の $I_Q = 35\mu A$

- 電流モード制御

- 外部クロック同期

- 最大電力点制御

- 28ピンLQFNパッケージ(4mm × 5mm)

### アプリケーション

- RF電源

- USB給電

- システム・バックアップ電源

- 1~5セルのリチウム・バッテリで駆動する製品

- 入力範囲が広い電源

- 鉛酸バッテリから12Vへのレギュレータ

### 概要

LT®3120は、高効率の26Vモノリシック昇降圧コンバータです。充実した機能を備え、非常に低い抵抗のパワー・スイッチを内蔵しているため、最も要求の厳しいアプリケーションにおいてもソリューション全体のフットプリントを最小限に抑えることができます。独自の4スイッチPWMアーキテクチャは、出力電圧に対して入力電圧が高い／低い／等しい場合のいずれにおいてもシームレスに低ノイズ動作を実現します。

外部からの周波数プログラミング、および内部PLLを使用した同期により、400kHz~2MHzの広いスイッチング周波数範囲で動作できます。2.5V~26Vの広い入力範囲は、バッテリ・スタックやバックアップ・コンデンサなど、レギュレーションされていない電源による動作に最適です。スタートアップ後、わずか500mVという低い入力電圧で動作可能です。

更に、出力短絡保護、熱過負荷保護、3μA未満のシャットダウン電流、パワー・グッド・インジケータ、Burst Mode動作、最大電力点制御などの機能を搭載しています。

LT3120は、熱強化型28ピンLQFNパッケージ(4mm × 5mm)で提供されます。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。

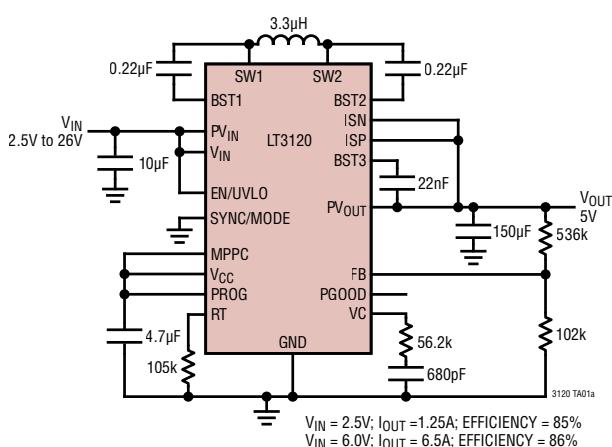

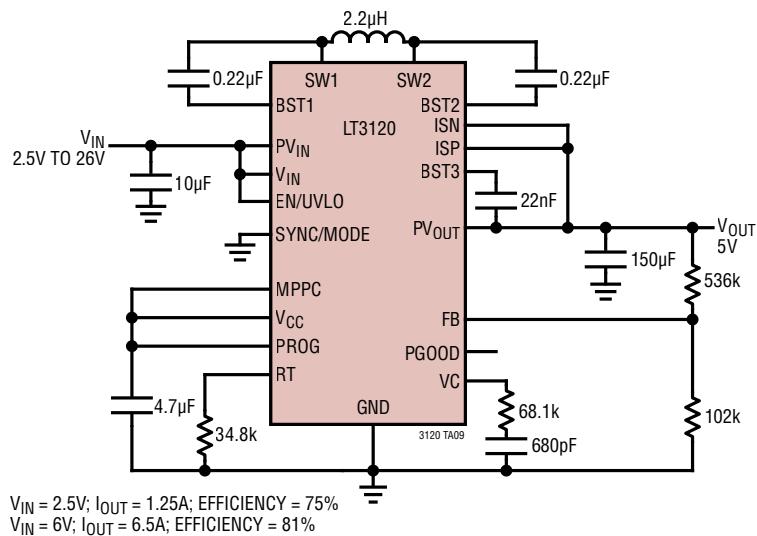

### 標準的応用例

#### 入力範囲の広い750kHz、5Vレギュレータ

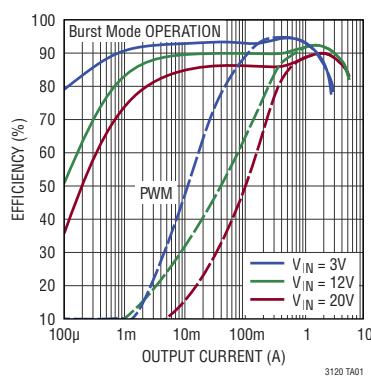

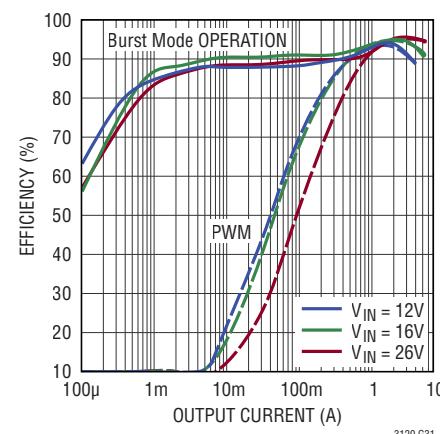

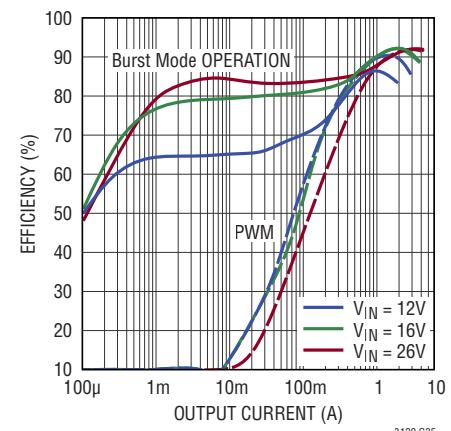

#### $V_{OUT} = 5V$ 、 $f_{SW} = 750\text{kHz}$ での効率

## 絶対最大定格 (Note 1)

|                                                  |                                                     |

|--------------------------------------------------|-----------------------------------------------------|

| $V_{IN}$ 、 $PV_{IN}$ 、 $PV_{OUT}$ 、EN/UVLO、PGOOD | -0.3V～27V                                           |

| FB、VC、RT、SYNC/MODE、MPPC、 $V_{CC}$                | -0.3V～6V                                            |

| BST1                                             | (SW1 - 0.3V)～(SW1 + 6V)                             |

| BST2                                             | (SW2 - 0.3V)～(SW2 + 6V)                             |

| BST3                                             | (PV <sub>OUT</sub> - 0.3V)～(PV <sub>OUT</sub> + 6V) |

| 動作ジャンクション温度 (Note 2)                             |                                                     |

| LT3120J                                          | -40°C～150°C                                         |

| 保存温度範囲                                           | -65°C～150°C                                         |

| 最大リフロー（パッケージ・ボディ）温度                              | 260°C                                               |

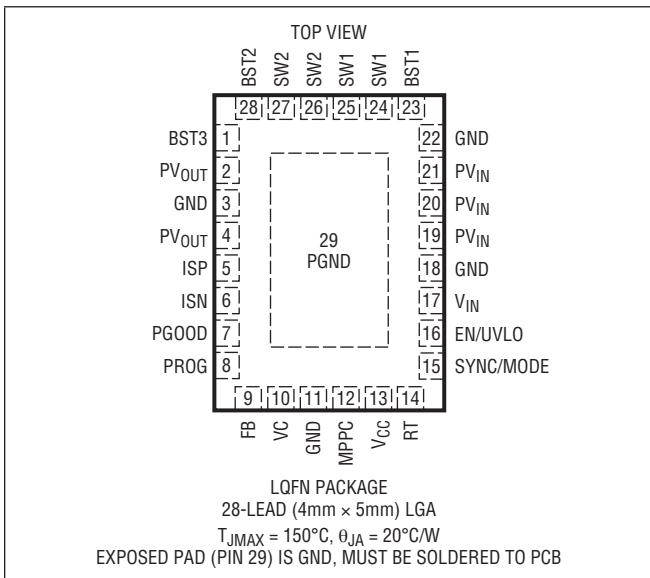

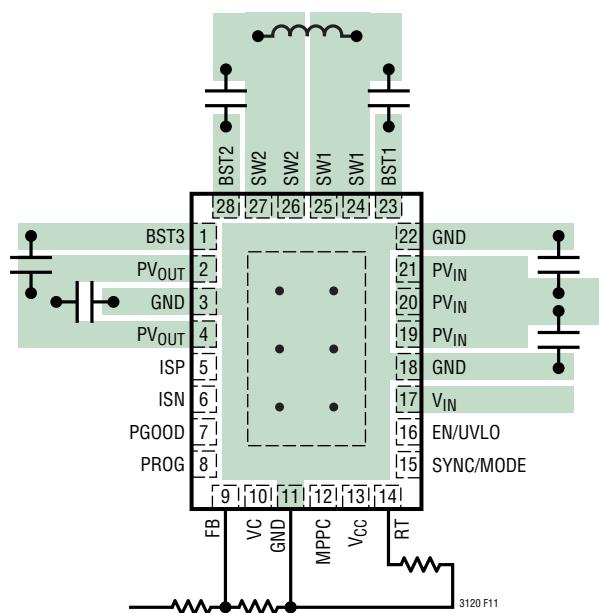

## ピン配置

発注情報

| 部品番号         | パッドまたはボール<br>仕上げ | 部品マーキング* |        | パッケージ<br>タイプ**                     | MSL<br>レーティング | 温度範囲(Note 2) |

|--------------|------------------|----------|--------|------------------------------------|---------------|--------------|

|              |                  | デバイス     | 仕上げコード |                                    |               |              |

| LT3120JV#PBF | Au (RoHS)        | 3120     | e4     | LQFN (QFN フット<br>プリントの積層<br>パッケージ) | 3             | -40°C~150°C  |

- 拡張動作温度範囲仕様の部品についてはアナログ・デバイセズまでお問い合わせください。

\*パッドまたはポールの仕上げコードはIPC/JEDEC J-STD-609によります。

- 推奨されるLGAおよびBGA PCBのアセンブリおよび製造手順

- LGAおよびBGAのパッケージ図面とトレーレイ面

## 電気的特性

●は、仕様規定されている動作温度範囲に適用される仕様であることを示します。それ以外の仕様は、特に指定のない限り  $T_A = 25^\circ\text{C}$ 、 $V_{IN} = PV_{IN} = 12\text{V}$ 、 $PV_{OUT} = 5\text{V}$  の値です。

| PARAMETER                                       | CONDITIONS                                                                         |        | MIN            | TYP            | MAX            | UNITS    |

|-------------------------------------------------|------------------------------------------------------------------------------------|--------|----------------|----------------|----------------|----------|

| Input Operating Voltage                         | After Start-Up (Note 4)                                                            | ●      | 2.5<br>0.5     | 26<br>26       | 26             | V<br>V   |

| Output Operating Range                          |                                                                                    | ●      | 0.8            | 24             |                | V        |

| V <sub>CC</sub> Undervoltage Lockout Threshold  | V <sub>CC</sub> Rising<br>V <sub>CC</sub> Falling                                  | ●<br>● |                | 2.35<br>2.2    | 2.4<br>2.25    | V<br>V   |

| V <sub>CC</sub> Undervoltage Lockout Hysteresis |                                                                                    |        |                | 100            |                | mV       |

| Input Current in Shutdown                       | EN/UVLO = 0V                                                                       |        |                |                | 3              | μA       |

| Input Current in Sleep                          | FB = 0.9V                                                                          |        |                | 30             |                | μA       |

| Oscillator Frequency                            | R <sub>T</sub> = 76.8kΩ                                                            | ●      | 900            | 1000           | 1100           | kHz      |

| Oscillator Frequency Range                      |                                                                                    | ●      | 400            | 2000           |                | kHz      |

| SYNC/MODE Frequency Range                       |                                                                                    | ●      | 400            | 2000           |                | kHz      |

| SYNC/MODE Logic Threshold                       |                                                                                    | ●      | 0.3            | 0.7            | 1.1            | V        |

| SYNC/MODE Minimum Pulse Width                   | Minimum Low or High Duration                                                       |        | 100            |                |                | ns       |

| Soft-Start Duration                             |                                                                                    |        |                | 6              |                | ms       |

| Feedback Voltage                                |                                                                                    | ●      | 787<br>779     | 795<br>795     | 803<br>811     | V<br>V   |

| FB Pin Input Current                            |                                                                                    |        |                | 1              | 50             | nA       |

| Error Amplifier Transconductance                |                                                                                    |        |                | 120            |                | μs       |

| EN/UVLO Pin Input Logic Threshold               |                                                                                    | ●      | 0.3            | 0.8            | 1.0            | V        |

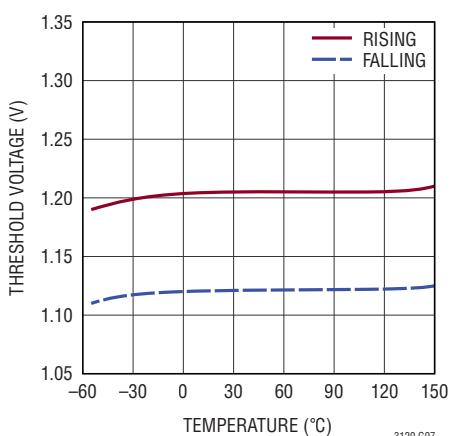

| EN/UVLO Pin Comparator Threshold                | Rising<br>Rising, $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$              | ●      | 1.169<br>1.169 | 1.205<br>1.241 | 1.258<br>1.241 | V<br>V   |

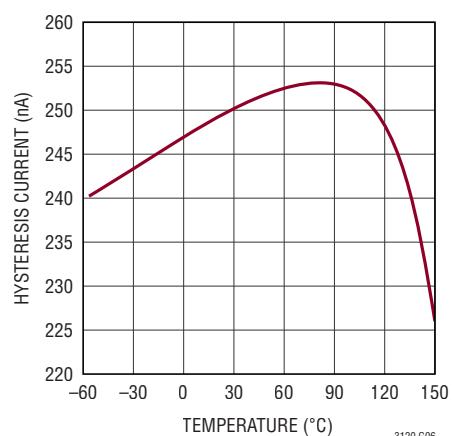

| EN/UVLO Pin Hysteresis Current                  |                                                                                    |        |                | 250            |                | nA       |

| EN/UVLO Pin Hysteresis Voltage                  |                                                                                    |        |                | 90             |                | mV       |

| PROG Pin Current                                | $V_{ISP} - V_{ISN} = 25\text{mV}$<br>$V_{ISP} - V_{ISN} = 10\text{mV}$             |        | 47.5<br>18     | 50<br>20       | 52.5<br>22     | μA<br>μA |

| PROG Pin Threshold                              |                                                                                    | ●      | 779            | 795            | 811            | V        |

| MPPC Pin Threshold                              |                                                                                    | ●      | 774            | 795            | 822            | V        |

| PGOOD Threshold                                 | Percent of FB Voltage Falling                                                      | ●      | -9.5           | -8             | -6.5           | %        |

| PGOOD Hysteresis                                | Percent of FB Voltage                                                              |        |                | 1.2            |                | %        |

| PGOOD Pull-Down Resistance                      |                                                                                    |        |                | 100            | 250            | Ω        |

| PGOOD Leakage                                   | $V_{PGOOD} = 24\text{V}$                                                           |        |                | 1              | 40             | nA       |

| Inductor Current Limit                          | Limit on Average (Not Peak) Inductor Current                                       | ●      | 8.25           | 9.5            |                | A        |

| Burst Mode Inductor Current Limit               | Limit on Average (Not Peak) Inductor Current                                       |        |                | 1              |                | A        |

| Maximum Duty Cycle                              | Percentage of Period SW2 is Low in Boost Mode, $R_T = 76.8\text{k}\Omega$ (Note 4) | ●      | 91             | 95             |                | %        |

| SW1, SW2 Minimum Low Time                       | (Note 4)                                                                           |        |                | 70             |                | ns       |

## 電気的特性

●は、仕様規定されている動作温度範囲に適用される仕様であることを示します。それ以外の仕様は、特に指定のない限り  $T_A = 25^\circ\text{C}$ 、 $V_{IN} = PV_{IN} = 12\text{V}$ 、 $PV_{OUT} = 5\text{V}$  の値です。

| PARAMETER                   | CONDITIONS                                                                                                        | MIN | TYP                  | MAX  | UNITS                                                                        |               |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------|-----|----------------------|------|------------------------------------------------------------------------------|---------------|

| N-Channel Switch Resistance | Switch A ( $PV_{IN}$ to SW1)<br>Switch B (SW1 to PGND)<br>Switch C (SW2 to PGND)<br>Switch D (SW2 to $PV_{OUT}$ ) |     | 25<br>23<br>23<br>25 |      | $\text{m}\Omega$<br>$\text{m}\Omega$<br>$\text{m}\Omega$<br>$\text{m}\Omega$ |               |

| N-Channel Switch Leakage    | $PV_{IN} = PV_{OUT} = 24\text{V}$ ; SW1 = SW2 = 0V                                                                |     | 1                    | 10   | $\mu\text{A}$                                                                |               |

| $V_{CC}$ Regulation Voltage |                                                                                                                   | ●   | 3.6                  | 3.73 | 3.86                                                                         | V             |

| $V_{CC}$ Dropout Voltage    | $I_{CC} = 50\text{mA}$ , $V_{IN} = 3.6\text{V}$                                                                   |     | 100                  |      |                                                                              | $\text{mV}$   |

| $V_{CC}$ Current Limit      |                                                                                                                   | 100 |                      |      |                                                                              | $\text{mA}$   |

| $V_{CC}$ Reverse Current    | $V_{CC} = 5\text{V}$ , $V_{IN} = 3\text{V}$                                                                       |     | 5                    |      |                                                                              | $\mu\text{A}$ |

**Note 1:** 上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えことがあります。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性と寿命に影響を与えることがあります。

**Note 2:** LT3120Jは、 $-40^\circ\text{C} \sim 150^\circ\text{C}$  の動作ジャンクション温度で性能仕様を満たすよう設計されています。ジャンクション温度が高い場合は動作寿命が低下し、 $125^\circ\text{C}$  を超えると動作寿命が定格値より短くなります。

**Note 3:** 最小入力電圧は  $V_{CC}$  のUVLO閾値で決まります。 $V_{CC}$  が外付けのブーストストラップを通じて維持される場合、このデバイスは出力に電力を伝送できなくなるまで動作し続けます。

**Note 4:** スイッチング時間はオープンループのテスト構成で測定しています。スイッチ・ピン電圧がインダクタ電流の大きさと方向の影響を受ける場合、オーバーラップしない時間においてスイッチ・ピン電圧が異なる値となり、アプリケーションでのタイミングはこれらの値から若干変化します。

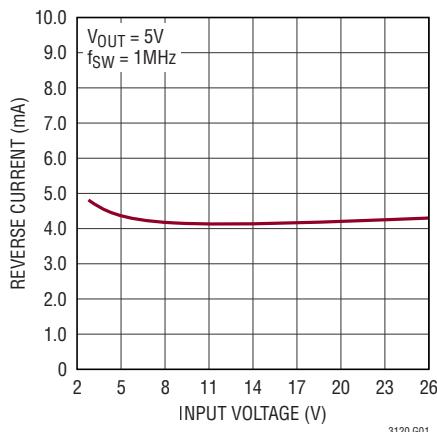

## 代表的な性能特性

MPPC制御の間の最大逆電流

( $V_{MPPC} < 0.83$ )

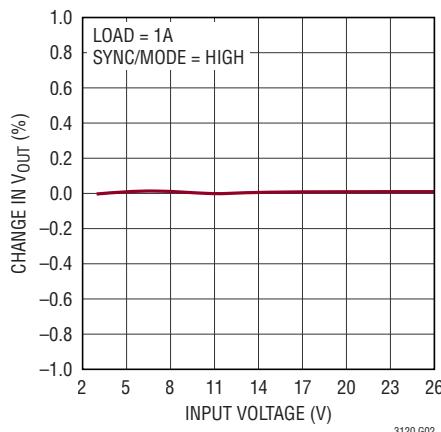

ライン・レギュレーション

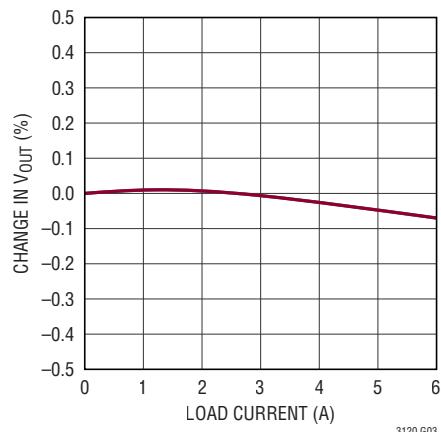

負荷レギュレーション

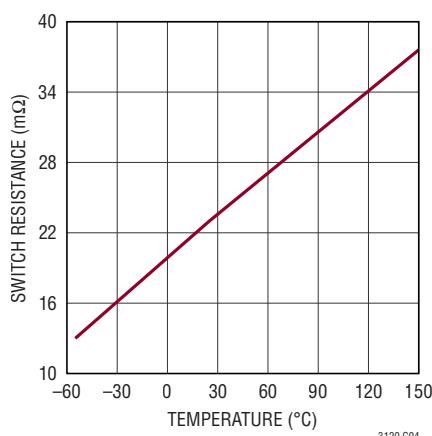

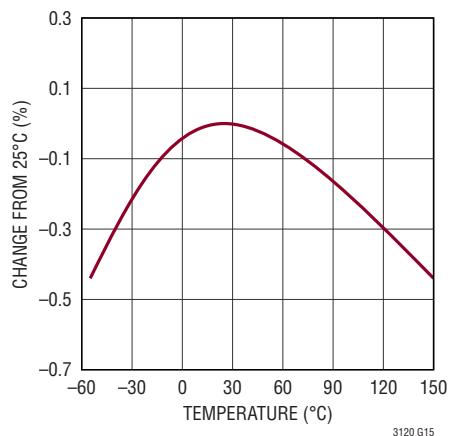

パワー・スイッチ抵抗の温度特性

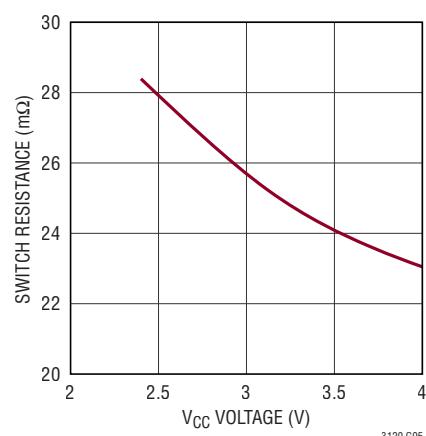

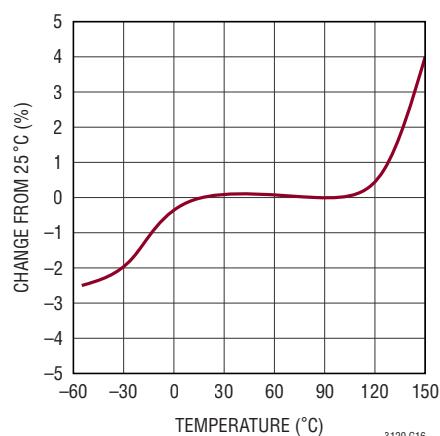

パワー・スイッチ抵抗と  $V_{CC}$  の関係

EN/UVLOピンのヒステリシス電流の温度特性

EN/UVLOピンの閾値精度の温度特性

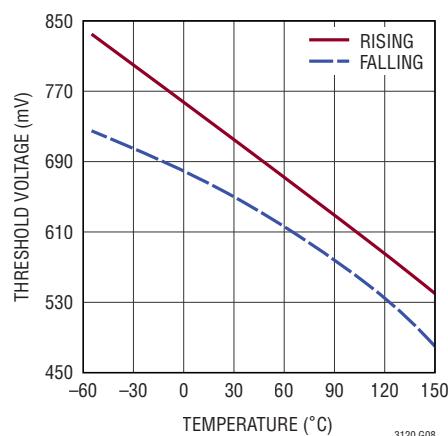

EN/UVLOピンのロジック閾値の温度特性

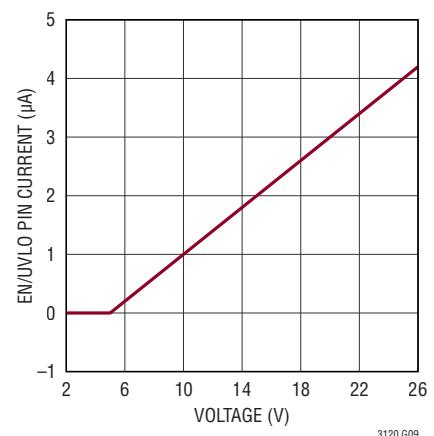

EN/UVLOピン電流とEN/UVLOピン電圧の関係

## 代表的な性能特性

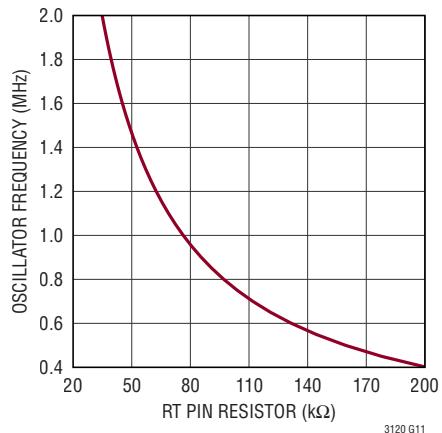

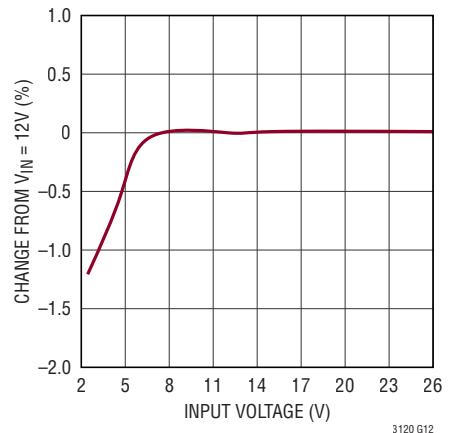

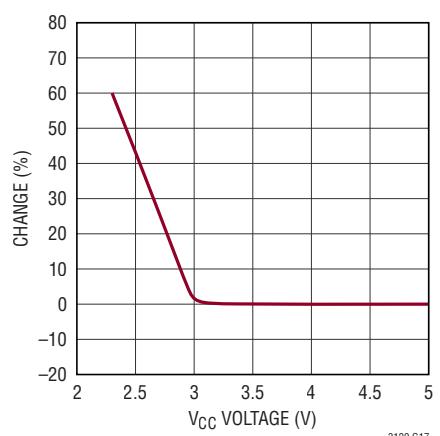

$V_{CC}$  UVLO 閾値の温度特性発振周波数と  $R_T$  の関係発振周波数と  $V_{IN}$  の関係

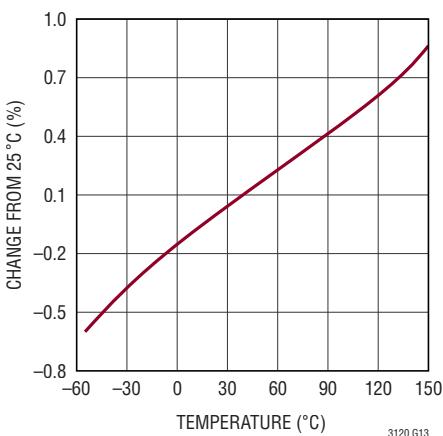

発振周波数の温度特性

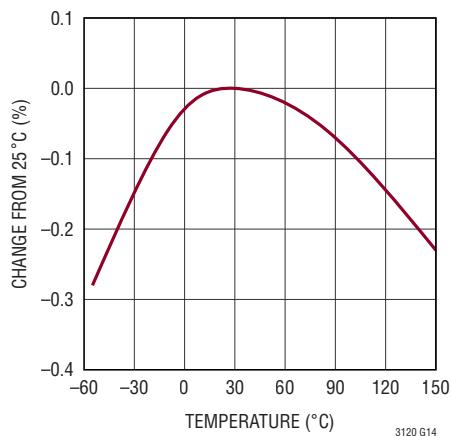

FB 電圧の温度特性

PROG ピン電圧の温度特性

MPPC ピン電圧の温度特性

SW1、SW2 の最小ロード時間と  $V_{CC}$  の関係

## 代表的な性能特性

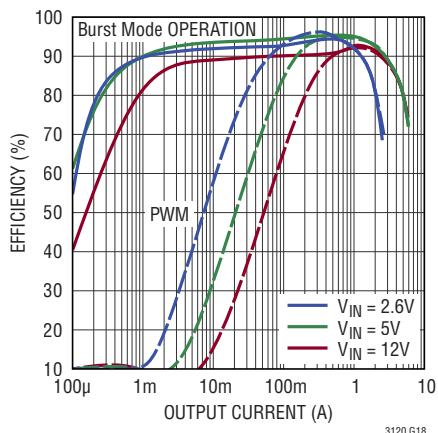

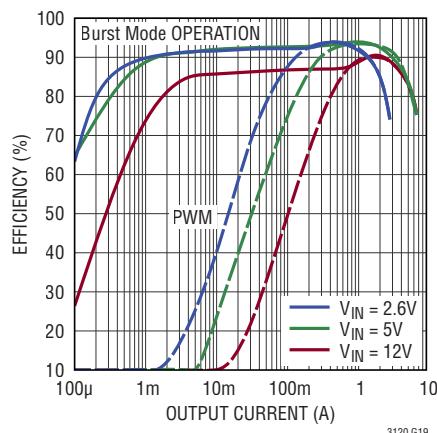

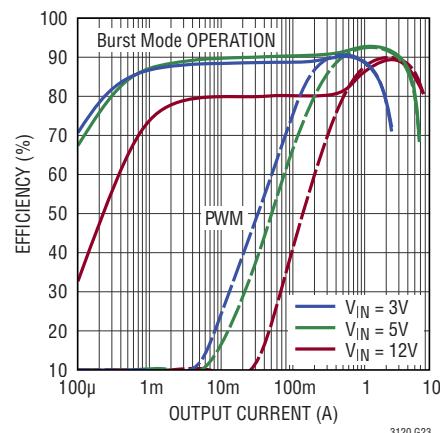

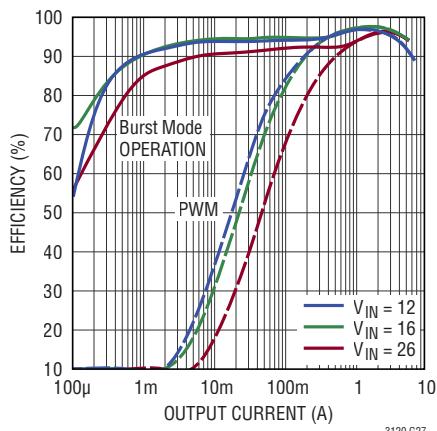

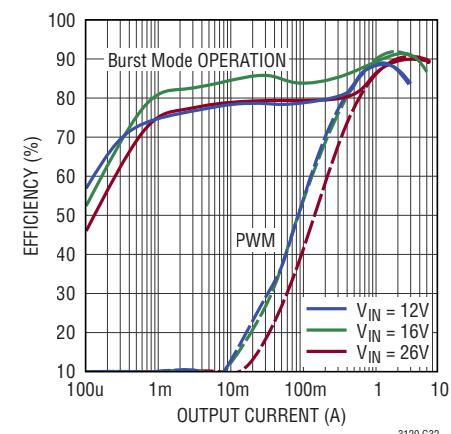

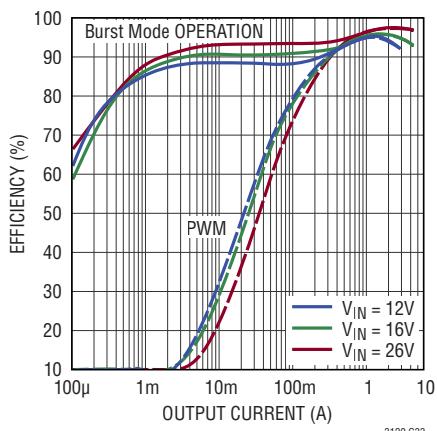

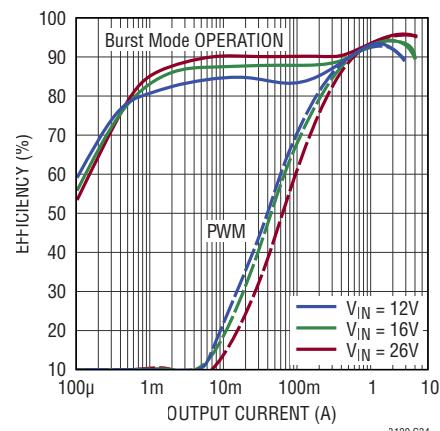

$V_{OUT} = 3.3V, f_{SW} = 500kHz$ での効率

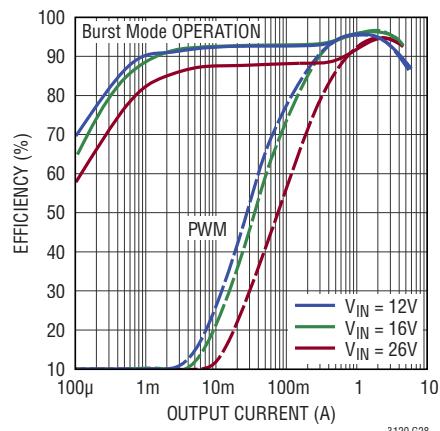

$V_{OUT} = 3.3V, f_{SW} = 1MHz$ での効率

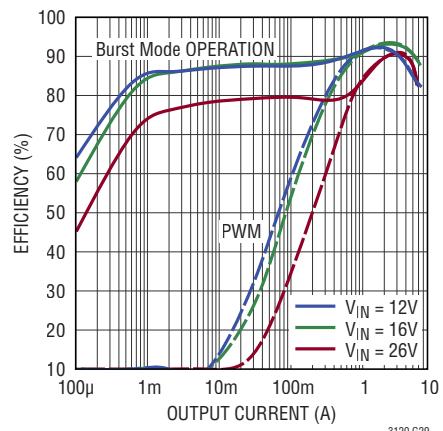

$V_{OUT} = 3.3V, f_{SW} = 2MHz$ での効率

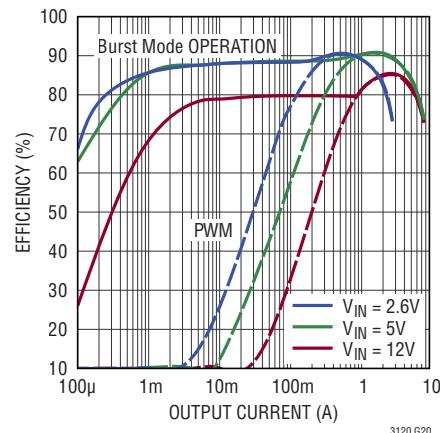

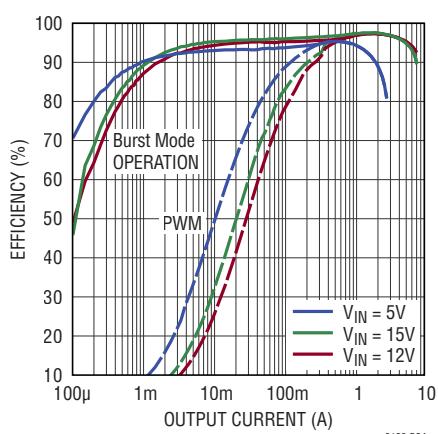

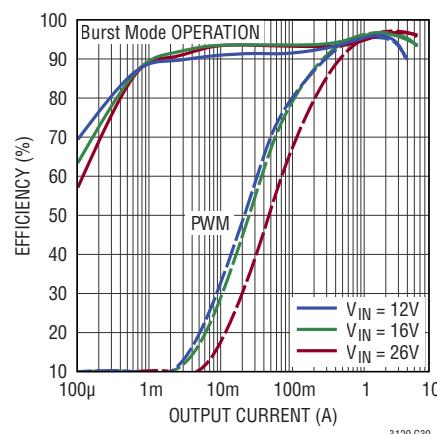

$V_{OUT} = 5V, f_{SW} = 500kHz$ での効率

$V_{OUT} = 5V, f_{SW} = 1MHz$ での効率

$V_{OUT} = 5V, f_{SW} = 2MHz$ での効率

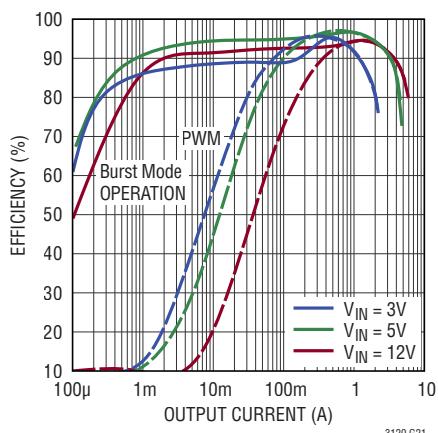

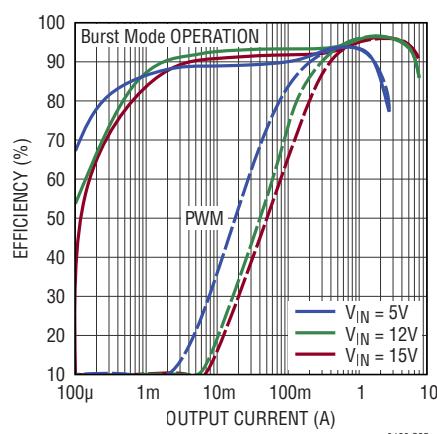

$V_{OUT} = 12V, f_{SW} = 500kHz$ での効率

$V_{OUT} = 12V, f_{SW} = 1MHz$ での効率

$V_{OUT} = 12V, f_{SW} = 2MHz$ での効率

## 代表的な性能特性

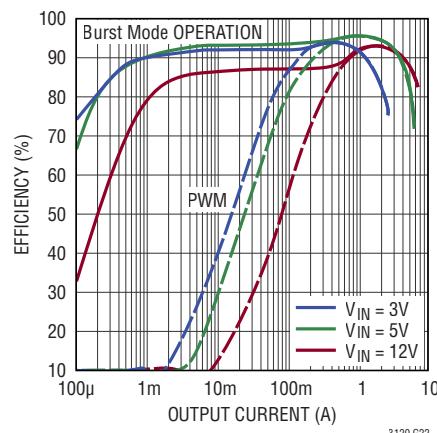

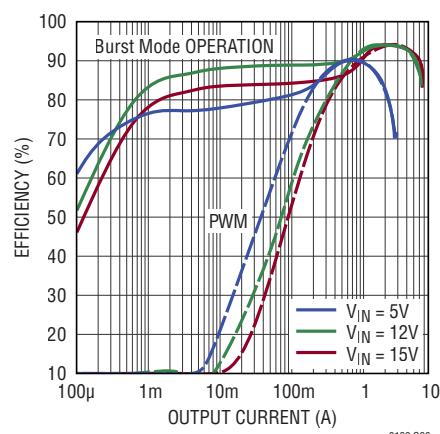

$V_{OUT} = 15V, f_{SW} = 500kHz$ での効率

$V_{OUT} = 15V, f_{SW} = 1MHz$ での効率

$V_{OUT} = 15V, f_{SW} = 2MHz$ での効率

$V_{OUT} = 20V, f_{SW} = 500kHz$ での効率

$V_{OUT} = 20V, f_{SW} = 1MHz$ での効率

$V_{OUT} = 20V, f_{SW} = 2MHz$ での効率

$V_{OUT} = 24V, f_{SW} = 500kHz$ での効率

$V_{OUT} = 24V, f_{SW} = 1MHz$ での効率

$V_{OUT} = 24V, f_{SW} = 2MHz$ での効率

## 代表的な性能特性

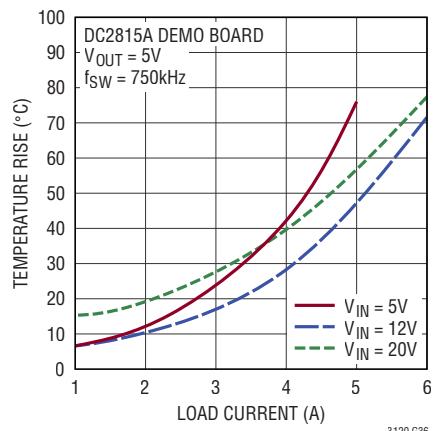

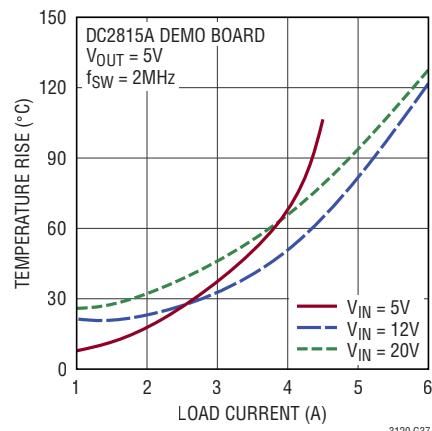

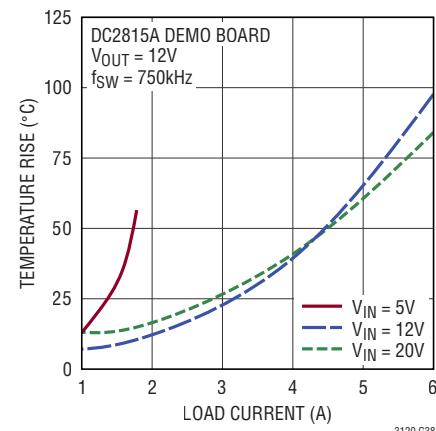

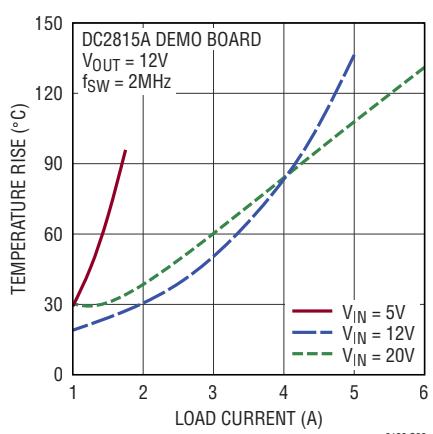

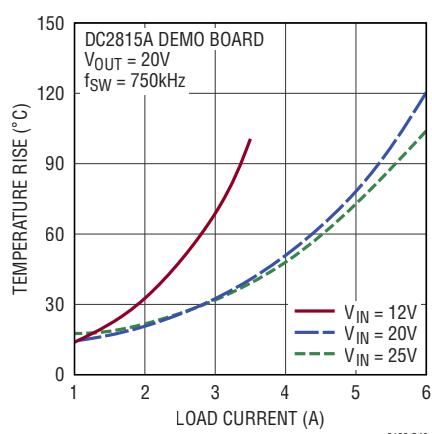

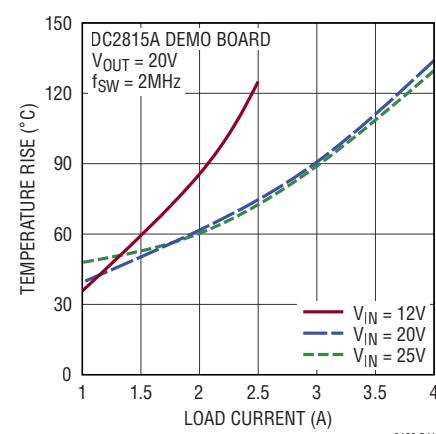

温度上昇と負荷電流の関係

温度上昇と負荷電流の関係

温度上昇と負荷電流の関係

温度上昇と負荷電流の関係

温度上昇と負荷電流の関係

温度上昇と負荷電流の関係

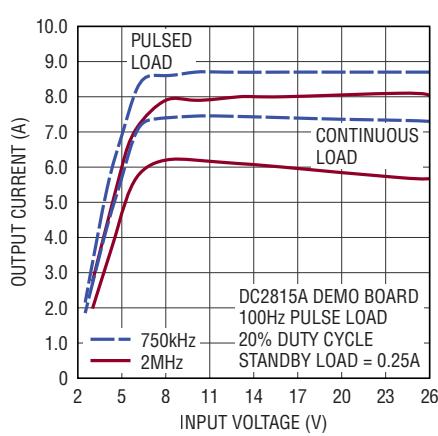

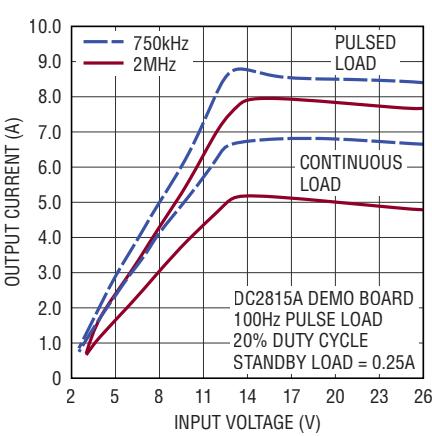

最大出力電流、V<sub>OUT</sub> = 5V

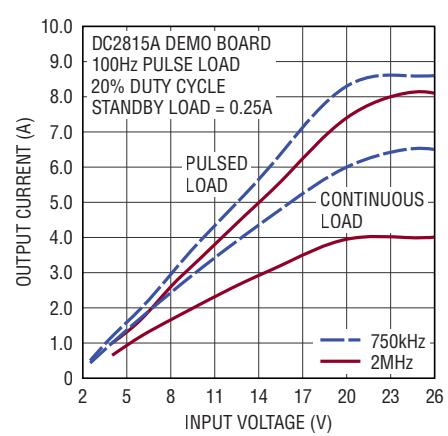

最大出力電流、V<sub>OUT</sub> = 12V

最大出力電流、V<sub>OUT</sub> = 20V

## 代表的な性能特性

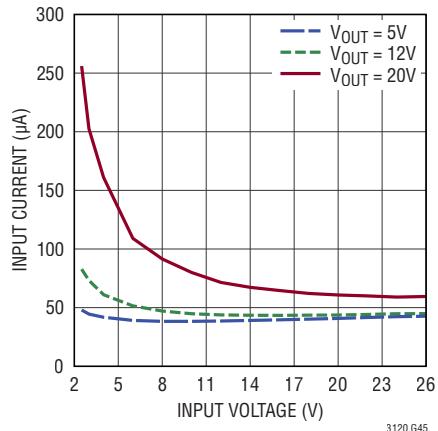

Burst Mode動作、無負荷時の入力電流

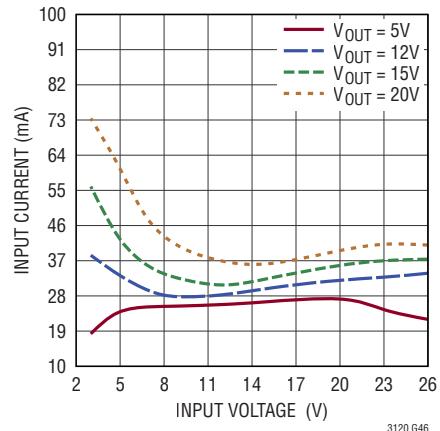

PWMモード、無負荷時の入力電流

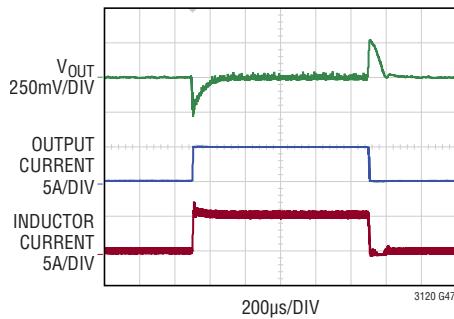

PWMモード動作、0.5A～5Aの負荷ステップ、 $V_{IN} = 12V$ 、 $V_{OUT} = 5V$

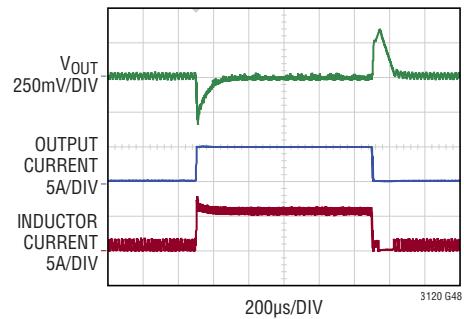

Burst Mode動作、0.5A～5Aの負荷ステップ、 $V_{IN} = 12V$ 、 $V_{OUT} = 5V$

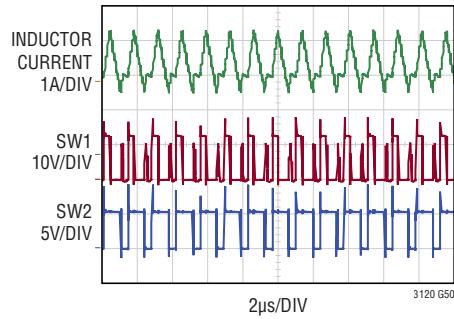

Burst Mode動作時の $V_{OUT}$ のリップル、 $V_{OUT} = 5V$

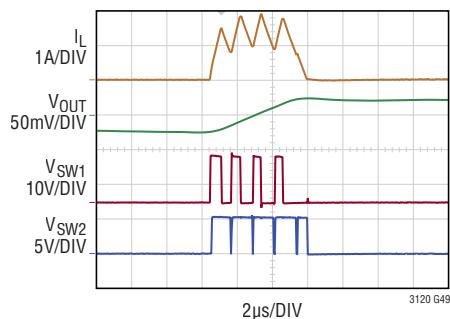

PWM軽負荷動作、 $V_{OUT} = 5V$

## ピン機能

**BST3(ピン1)**: 出力電流検出アンプのフライング・コンデンサ・ピン。このピンは、 $22\text{nF}$ のコンデンサを介してPVOUTに接続してください。

**PVOUT(ピン2、4)**: 出力電圧の電源接続。これらのピンは、昇降圧コンバータのスイッチDに接続されています。これらのピンとGNDの間には低ESRコンデンサを接続し、インピーダンス経路は最小限となるようにしてください。

**GND(ピン3、11、18、22、露出パッド・ピン29)**: グラウンド接続。これらのピンは、できるだけ短く幅の広いパターンを使用して基板のグラウンドに接続してください。露出パッド下のビアの密度を高くすることでデバイスの放熱を最大限に高めてください。

**ISP(ピン5)**: 電流検出の正入力。このピンは、出力電流検出抵抗のIC側に接続してください。電流検出を使用しない場合は、PVOUTに接続してください。

**ISN(ピン6)**: 電流検出の負入力。このピンは、出力電流検出抵抗のVOUT側に接続してください。電流検出を使用しない場合は、PVOUTに接続してください。

**PGOOD(ピン7)**: オープンドレイン出力インジケータ。FBがレギュレーション電圧を大幅に下回ると、この出力がグラウンドにプルダウンします。このピンと正側電源の間にプルアップ抵抗を接続してください。詳細については、[動作](#)のセクションを参照してください。

**PROG(ピン8)**: 平均出力電流の制限値の設定点。このピンとGNDの間に抵抗を接続して最大平均出力電流を設定します。このピンの出力電流は、アナログ出力電流インジケータとして使用することもできます。この機能を無効にするには、このピンをVCCに接続してください。

**FB(ピン9)**: 帰還電圧入力。このピンに抵抗分圧器を接続して昇降圧コンバータの出力電圧を設定します。FB電圧の公称値は $0.795\text{V}$ です。

**VC(ピン10)**: エラー・アンプ出力。このピンとGNDの間に周波数補償回路を接続して電圧制御ループを安定化させてください。

**MPPC(ピン12)**: 最大電力点制御ピンの設定点。VINとGNDの間に接続された抵抗分圧器にこのピンを接続して、入力レギュレーション電圧を設定します。MPPCピンを使用しないときはVCCに接続してください。

**Vcc(ピン13)**: 内部レギュレータ出力電圧。このピンは、制御回路に電源を供給する内部低電圧リニア・レギュレータの出力です。 $4.7\mu\text{F}$ のコンデンサを、このピンとGNDの間にできるだけ短いパターンを使用して接続してください。この出力

から、追加の外部負荷として最大 $10\text{mA}$ まで流すことができます。

**RT(ピン14)**: 発振周波数設定ピン。このピンとGNDの間に抵抗を接続して昇降圧コンバータのスイッチング周波数を設定します。

**SYNC/MODE(ピン15)**: Burst Mode動作／PWMモードの自動制御ピンおよび同期入力。このピンをハイにすると、RTピンで設定された周波数の内部発振器を使用して、デバイスはすべての負荷において固定周波数のPWMモードで動作します。このピンをローにすると、デバイスはBurst Mode動作を有効にして、軽負荷での効率を最大化します。このピンにクロック供給すると、RTピンで設定された周波数より高い周波数のクロックに同期します。このピンを同期入力として使用する場合は、最小 $100\text{ns}$ の入力パルス幅を使用してください。

**EN/UVLO(ピン16)**: デバイスのイネーブル／ディスエーブル入力、およびUVLO閾値のカスタマイズ入力。EN/UVLOピンを外部ロジック信号で駆動することにより、デバイスをイネーブル／ディスエーブルできます。また、このピンの電圧を、入力電圧に接続された抵抗分圧器で設定することにより、低電圧ロックアウト閾値を高精度で設定できます。EN/UVLOピンの電圧が公称 $1.215\text{V}$ を超えるとデバイスはイネーブルされます。

**VIN(ピン17)**: 内部VCCレギュレータの入力電圧ピン。

**PVIN(ピン19、20、21)**: 入力電圧の電源接続。これらのピンは、昇降圧コンバータのスイッチAに接続されています。これらのピンとGNDの間には $10\mu\text{F}$ 以上のコンデンサを接続し、インピーダンス経路は最小限となるようにしてください。

**BST1(ピン23)**: SW1のフライング・コンデンサ・ピン。このピンは、 $0.22\mu\text{F}$ のコンデンサを介してSW1に接続してください。このピンを使用して電源スイッチAのゲート駆動レールを生成します。

**SW1(ピン24、25)**: 昇降圧コンバータの電源スイッチ・ピン。これらのピンは、昇降圧インダクタの片側に接続してください。

**SW2(ピン26、27)**: 昇降圧コンバータの電源スイッチ・ピン。これらのピンは、昇降圧インダクタの片側に接続してください。

**BST2(ピン28)**: SW2のフライ・コンデンサ・ピン。このピンは、 $0.22\mu\text{F}$ のコンデンサを介してSW2に接続してください。このピンを使用して電源スイッチDのゲート駆動レールを生成します。このノードのコンデンサには、BST3とPVOUTの間で使用しているものより10倍大きいコンデンサを使用してください。

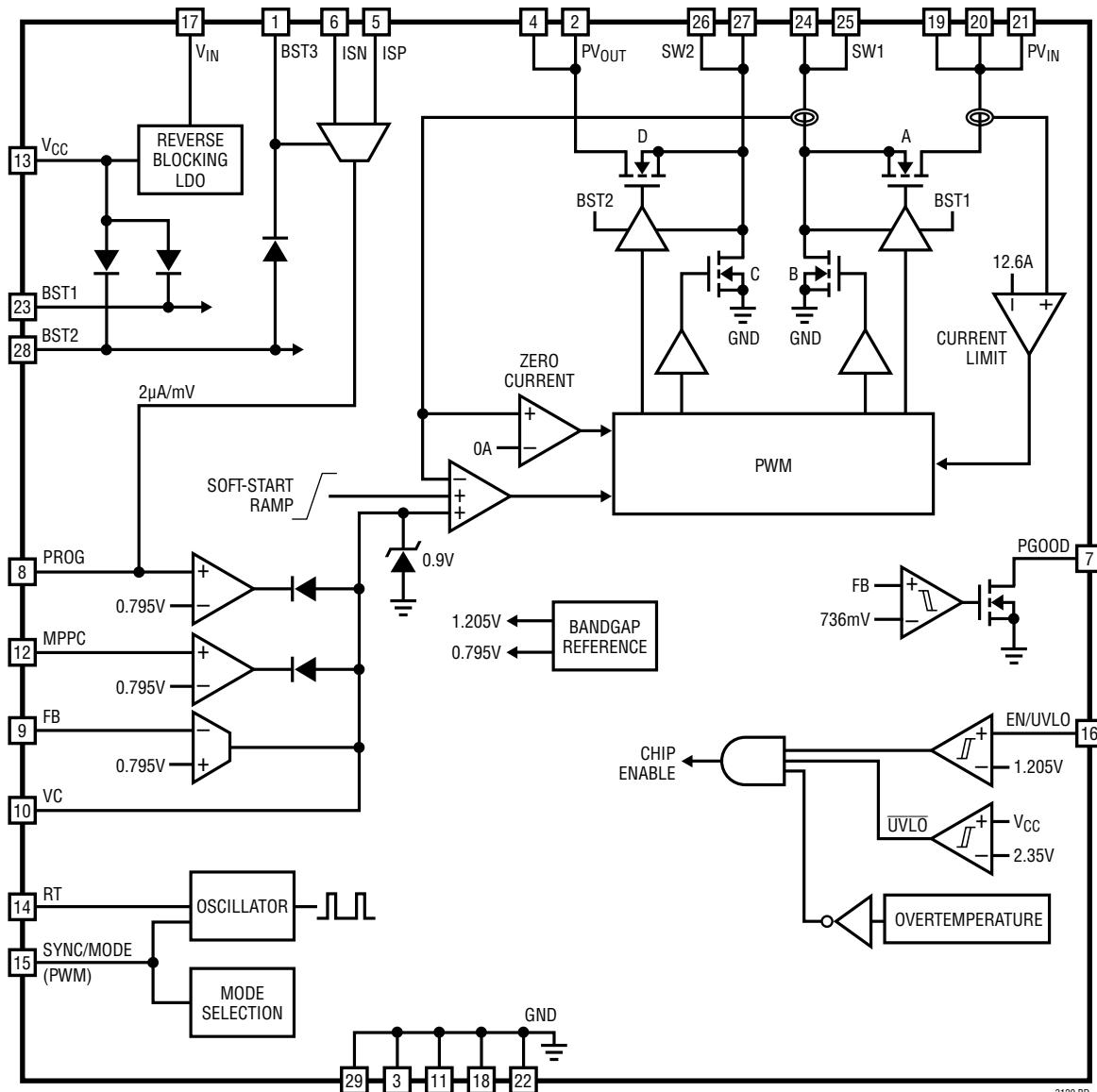

## ブロック図

3120 BD

## 動作

### はじめに

LT3120は、2.5V～26Vの入力電圧と0.8V～24Vの出力電圧範囲で動作するモノリシック昇降圧DC/DCコンバータです。低R<sub>DSON</sub> NチャンネルDMOS電源スイッチを内蔵しているため、ソリューションの複雑さを低減し、変換効率を最大化できます。内蔵のハイサイド電源スイッチ・ドライバには2つの小型コンデンサを外付けするだけでよいので、アプリケーション回路の設計を簡略化できます。LT3120には、高精度EN/UVLOピン・コンパレータ、400kHz～2MHzの広範な動作周波数範囲、外部クロック同期、パワー・グッド・インジケータ、入力電圧の最大電力点制御(MPPC、太陽光発電アレイなど電流の制限された電源での動作に使用)など、多くの機能が搭載されており、アプリケーションのソリューション設計において優れた柔軟性が得られます。

ハイサイド・ドライバと検出回路により、電流制御とスイッチ動作の同期を維持したまま0V出力まで動作させることができます。2.5Vを下回る入力電圧でも、V<sub>OUT</sub>からV<sub>CC</sub>ピンのブーストストラップを行なうか、代替源を使用することで動作できるため、スーパーキャパシタなどの蓄電デバイスから最大限にエネルギーを引き出すことができます。

独自の超低ノイズPWMスイッチング・アルゴリズムにより、出力電圧と比べて入力電圧が低い／等しい／高い場合のいずれにおいても出力のレギュレーションを維持します。降圧動作モードと昇圧動作モードの遷移は、トランジエントや低調波スイッチングを発生させることなくシームレスに行われます。LT3120は、幅広い動作周波数に設定できる発振器を内蔵しています。単一の設定抵抗で400kHz～2MHzの動作周波数を設定できるため、柔軟に基板面積と効率を最適化できます。ノイズに敏感なアプリケーションでは、SYNC/MODEピンに外部クロックを供給して内部発振器に同期させることもできます。

軽負荷時にはBurst Mode動作で高効率に動作することができますと共に、負荷が大きくなったときには自動的にPWMモードに遷移します。低出力電流時には、Burst Mode動作を有効にすることで電流をわずか30μA(代表値)にできます。シャットダウン時には、総電源電流を3μA(最大値)まで低減できます。

### PWMモードの動作

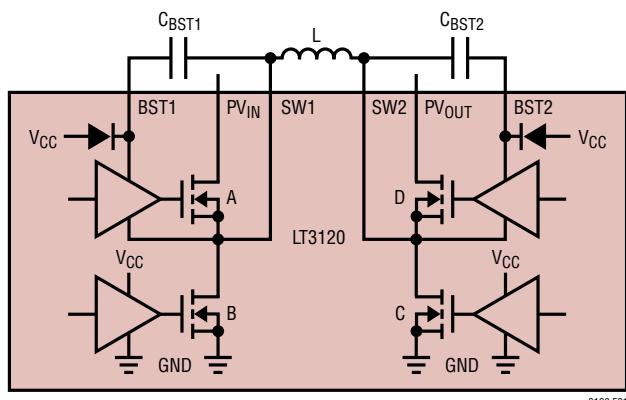

SYNC/MODEピンをハイにするか、SYNC/MODEピンがローの状態でPWMモード動作を有効にできるだけの負荷電流がデバイスに供給されると、LT3120は固定周波数のPWMモードで動作します。動作周波数は、本データシートの[アプリケーション情報](#)のセクションで説明するように、RTピンの抵抗で決まります。PWMモードは、出力電圧リップルを最小限に抑え、低ノイズのスイッチング周波数スペクトルが得られます。独自のスイッチング・アルゴリズムにより、動作モード間をシームレスに遷移することができ、すべての動作モードにおいて平均インダクタ電流、インダクタのリップル電流、ループ伝達関数の不連続性をなくすことができます。これらの利点により、従来の昇降圧コンバータと比較して、効率の向上、ループの安定性改善、および出力電圧リップルの低減を実現します。[図1](#)に、4つのNチャンネルDMOSスイッチとこれらを駆動するゲート・ドライバで構成されたLT3120のパワーワンのトポロジを示します。

3120.F01

図1. 出力段の回路図

PWMモードの動作では、入出力電圧には関係なく両方のスイッチ・ピンがサイクルごとに遷移します。内部の平均電流制御ループは、パルス幅変調器がスイッチのデューティ・サイクルを適切に生成し、出力電圧のレギュレーションを維持できるように動作します。

### 発振器とフェーズ・ロック・ループ(PLL)

LT3120は、内部発振器によって動作し、スイッチング周波数はRTピンとGNDの間に接続する1個の外付け抵抗で設定します。ノイズに敏感なアプリケーションでは、内部PLLを使用して、SYNC/MODEピンに供給された外部クロック信号と

## 動作

同期させることができます。PLLは、内部発振器の周波数を増加させることのみが可能で、これにより同期をとります。そのため、抵抗 $R_T$ は、SYNC/MODEピンに供給するクロック周波数より内部発振器の周波数が低くなるように選択する必要があります。外部同期クロックの周波数ばらつきと内部発振器周波数の最大ばらつきを考慮して、十分なマージンを持たせる必要があります。多くの場合、内部発振器の周波数は同期クロックより20%低く設定すれば十分です。内部発振器による動作でも、外部クロック信号と同期した動作でも、LT3120は400kHz～2MHzのスイッチング周波数で動作できますが、ソリューションの小型化と電力変換効率の最適化の間にトレードオフがあります。

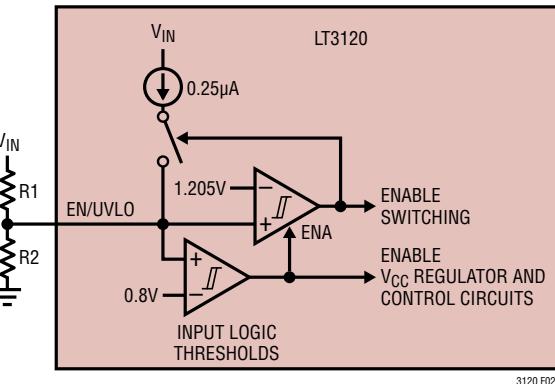

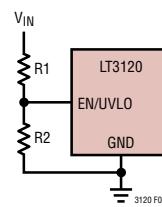

### EN/UVLOピン・コンパレータ

EN/UVLOピンには、デバイスをイネーブルするロジックレベル入力に加えて、高精度の内部コンパレータの機能があり、外付けの抵抗分圧器を使用することにより立上がり／立下がり入力の低電圧ロックアウト閾値をカスタムに設定することができます。EN/UVLOピンの駆動電圧がロジック閾値(通常0.8V)を超えると、 $V_{CC}$ レギュレータがイネーブルされてデバイスの内部制御回路に電源を供給します。そして高精度EN/UVLOピン・コンパレータがイネーブルされます。EN/UVLOピン電圧が更に高くなりEN/UVLOコンパレータ閾値(公称1.205V)を超えると、昇降圧コンバータがイネーブルされます。EN/UVLOピンがEN/UVLOコンパレータ閾値を下回ると、昇降圧コンバータはスイッチングを停止しますが、 $V_{CC}$ レギュレータと制御回路はEN/UVLOピンがロジック閾値を下回るまで電源オン状態を維持します。そのため、デバイスをシャットダウンして入力電流を最小レベル( $3\mu A$ )まで下げるには、EN/UVLOピンをロジック閾値の最低値(0.3V)を下回るまで低下させる必要があります。EN/UVLOピンは高電圧入力で $V_{IN}$ に直接接続できるため、入力電源が存在していればデバイスを常にイネーブルしておくことができます。EN/UVLOピンに5Vを超える電圧が印加された場合は、式1で与えられる小さな電流をシンクします。

$$I_{EN/UVLO} = \frac{(V_{EN/UVLO} - 5V)}{5M\Omega} \quad (1)$$

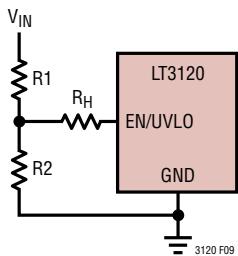

図2に示すように、外付けの抵抗分圧器を追加することにより、EN/UVLOピンを使用して低電圧ロックアウト閾値のカスタマイズが可能です。抵抗分圧器の比率によって立上がりUVLO閾値を設定できる値である1.205VにEN/UVLOピンが達すると、昇降圧コンバータがイネーブルされます。EN/UVLOピンがスレッショルド電圧に達すると、コンパレータがスイッチし、昇降圧コンバータがイネーブルされます。デバイスがイネーブルされると、 $0.25\mu A$ (代表値)の内部電流ソースがイネーブルされ、EN/UVLOピンから電流をソースし、EN/UVLOピン電圧を閾値より高くなります。

図2. 高精度EN/UVLOピン・コンパレータ

デバイスをディスエーブルするには、この電流によって発生するヒステリシスとEN/UVLOコンパレータが持つ90mVのヒステリシスを十分に下回るまで $V_{IN}$ を低下させる必要があります。両方の抵抗値を調整することにより、立上がりUVLO閾値に影響を与えるヒステリシスを独立に設定することができます。

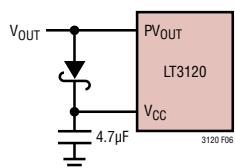

### $V_{CC}$ レギュレータ

内部の低ドロップアウト・レギュレータにより、 $V_{IN}$ から3.73V(公称値)の $V_{CC}$ レールを生成します。 $V_{CC}$ レールは、内部制御回路に電源を供給すると共に、LT3120のゲート・ドライバにも電源を供給します。 $V_{CC}$ レギュレータは、LT3120の内部回路への電源供給に加えて、10mAの外部負荷にも対応します。 $V_{CC}$ レギュレータは、EN/UVLOピンがロジック閾値を下回るとディスエーブルされ、EN/UVLOピンがロジック閾値を上回るとイネーブルされます。 $V_{CC}$ レギュレータには電流

## 動作

制限保護機能が搭載されており、短絡と過負荷状態から保護します。出力電圧を5Vに設定するアプリケーションでは、V<sub>CC</sub>をショットキー・ダイオードを介して出力レールから駆動することができます。この方法でブーストストラップすることにより、特に降圧比が大きい場合に効率を大きく改善することができます。また、より低い入力電圧で動作させることができます。V<sub>CC</sub>ピンの最大動作電圧は5.5Vです。外部からV<sub>CC</sub>を駆動する場合にはこの限界値に注意を払う必要があります。

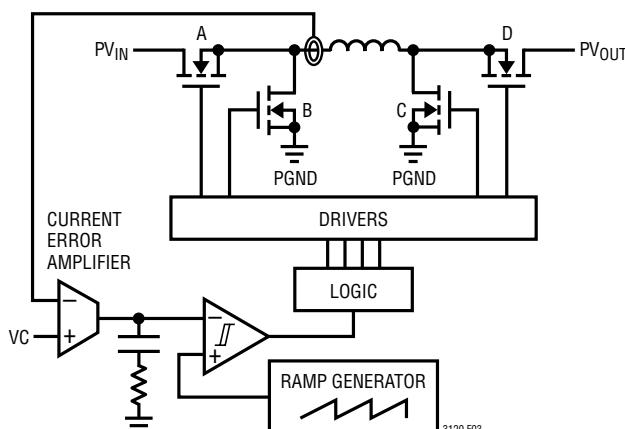

### 電流モード制御

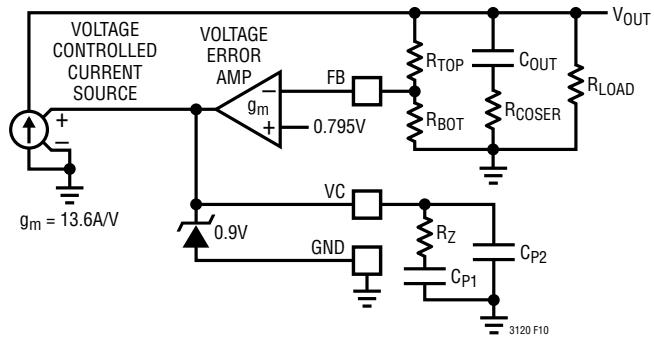

LT3120は、図3に示すように平均電流モード制御方式を使用しています。電流モード制御は、簡略化されたループ補償、負荷過渡応答への迅速な対応、および固有のライン電圧除去を実現します。VCピンの電圧が平均インダクタ電流レベルを決定し、エラー・アンプによってアクティブ制御ループ(FBまたはMPPC)のレギュレーションを維持するように調整されます。

図3. 内部平均電流ループ図

電流モード制御ループの内蔵エラー・アンプが、平均インダクタ電流の検出値と平均インダクタ電流レベルの制御値を比較して、サイクルごとにSW1ピンとSW2ピンを変調します。

平均電流モード制御方式は、平均電流アンプがその積分器としての構成を活かしてピーク電流の代わりに平均電流を制御する点を除いて、ピーク電流モード制御に近い方式です。この違いにより、ピーク電流モード制御で発生する

ピークto平均電流誤差がなく、同時にピーク電流モード制御が持つ利点のほとんどを保っています。内部電流ループの補償は、あらゆる動作条件において広帯域幅と低レギュレーション誤差を実現できるよう最適化された内部補償回路によって行われます。

### エラー・アンプ

LT3120には、3つの独立したエラー・アンプが内蔵されており、内部電流モード制御ループの入力を制御しています。この3つのアンプは、FBピン、PROGピン、MPPCピンの電圧をモニタします。3つのアンプの出力は加算され、内部電流モード制御ループの制御電流レベルとして使用されます。安定性を確保するため、補償回路はエラー・アンプの出力(VCピン)とGNDの間に接続する必要があります。コンバータの応答最適化と出力電圧のDC誤差低減に柔軟に対応できるため、図4に示すように、ほとんどのアプリケーションにはタイプIIの補償回路が推奨されます。

図4. FBおよびVCピン配置

FBのエラー・アンプのみ、設定された電流レベルを高くすることができますが、すべてのアンプは制御電流を低くすることによって、それぞれの制御ループのレギュレーションを維持します。(ブロック図参照)。常に1つの制御ループのみがアクティブになり、他の2つは非アクティブになります。PROGとMPPCの制御ループの優先度が高く、それぞれ電圧ループのオーバーライドと制御電流レベルの低減が可能です。MPPCまたはPROGのエラー・アンプによって制御されているときは、制御されているループの補償が優先され、VCピンの補償回路は無視されます。

## 動作

### 電流制限とゼロ電流検出

LT3120には、インダクタ電流の制限値があります。平均電流モード制御ループはインダクタの平均電流を9.5A(代表値)でクランプします。これは、電流制限にスムーズに遷移してデバイスの能力を超える電流レベルから保護します。

更に、12.6A(代表値)の最大ピーカ電流制限によってインダクタの瞬時電流を制限します。これは、ハード出力短絡において、平均電流ループが対応する前にすぐにトリガされます。

LT3120には、専用のゼロ電流検出コンパレータが内蔵されており、スイッチング時の逆電流を最小限に抑え、不連続モードの動作を可能にします。ゼロ電流検出の閾値は、動作条件に基づいて低調波スイッチングが生じないように調整しますが、いくつかの条件では負の電流値になります。デバイスがMPPC制御ループで制御されている場合には、ゼロ交差コンパレータの閾値を約150mAに設定して、蓄電素子の出力放電による逆電流を防止することができます。

### ソフトスタート

LT3120のソフトスタート回路は、最初のパワーアップ時に発生する入力電流のトランジエントと出力電圧のオーバーシュートを最小限に抑えます。ソフトスタートのタイミング生成に必要な部品はLT3120に内蔵されており、6ms(代表値)のソフトスタート時間を生成します。内部ソフトスタート回路は、電流モード制御ループへのコマンド信号(VCピン電圧)を緩やかにランプ・アップします。それによって、インダクタ電流もゼロからスタートしてゆっくりと増加します。ソフトスタートは、V<sub>CC</sub> UVLO、EN/UVLOピンの高精度イネーブル・コンパレータ、およびサーマル・シャットダウンによってリセットされます。

### 最大電力点制御(MPPC)

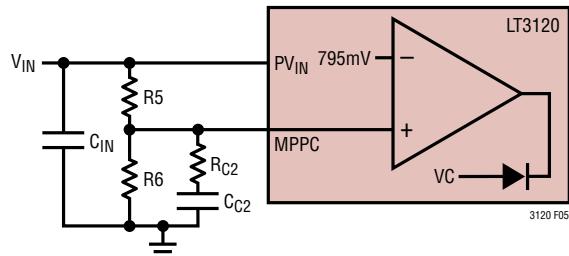

最小入力電圧を維持するため、LT3120のMPPC入力に外付けの分圧器を追加することで、インダクタ電流の設定値を動的に調整することができます。主に太陽電池パネルなどの抵抗性の電源を使用する場合に便利で、入力電力の伝送を最大化し、負荷に対してV<sub>IN</sub>が大幅に降下することを防ぎます。[図5](#)に示すように、MPPCピンは内部でトランスコンダ

クタンス・アンプの非反転入力に接続されています。MPPCピンの電圧がリファレンス電圧より低くなると、アンプの出力が平均インダクタ電流の設定値(VCピンの電圧)を下げて入力電流を減少させ、V<sub>IN</sub>を設定された最小電圧に調整します。

図5. MPPCピン配置

外部補償回路も必要で、一般的にはMPPCピンとGNDの間に直列に抵抗とコンデンサを接続することで得られます。この補償回路は、V<sub>IN</sub>の分圧回路の低い方の抵抗と並列に配置します。

### プログラマブルな出力電流

LT3120は、オプションでプログラマブルな電流制限機能を備えており、出力負荷に流す電流を制御することができます。電流制限回路には、ISPとISNの間に検出抵抗R<sub>SEN</sub>、およびPROGとグラウンドの間に設定抵抗を接続する必要があります。

電流検出アンプは、ISPピンとISNピンの間の電圧に比例した電流をPROGピンから出力します。PROGピンの電圧が795mVに達すると出力電流制限が始まります。

PROGピンからの電流出力は[式2](#)で得られます。

$$I_{PROG} = 2\mu A/mV \cdot R_{SEN} \cdot I_{OUT} \quad (2)$$

R<sub>SEN</sub>とR<sub>PROG</sub>の値を個別に選択することで、電流検出精度と検出部品の電力損失のトレードオフを考慮して設計することができます。出力電流は[式3](#)を使用して設定します。

$$I_{LIMIT} = 795V / (2 \cdot R_{SEN} \cdot R_{PROG}) \quad (3)$$

## 動作

$R_{SEN}$ の値は、ISPとISNの間の最大電圧が電流制限時に25mVになるように選定してください。

電流をモニタリングするアプリケーションでは、PROGピンの電圧が700mVを超えないように $R_{SEN}$ と $R_{PROG}$ の値を選定してください。

電流検出を使用しない場合は、ISPピンとISNピンは $V_{OUT}$ に、PROGピンは $V_{CC}$ に接続してください。

### Burst Mode動作

SYNC/MODEピンをローに維持するとLT3120はBurst Mode動作に設定されます。これにより、昇降圧DC/DCコンバータは、出力電流が省電力Burst Mode動作へ自動的に移行するレベルに低下するまでの間、連続PWMスイッチング動作を続けます。Burst Mode動作時には、出力電圧がレギュレーションの公称レベルに達するとLT3120はスリープ状態になります。スリープ状態では、PWMスイッチングを停止し、ICの不必要的機能をすべてオフにして、静止電流をわずか30μA(代表値)にまで低減します。これにより、軽負荷時の総電力変換効率を大幅に向上させます。コンバータはスリープ中にスイッチングしないため、出力電圧は、出力負荷抵抗と出力コンデンサ値によって決まる速度で、ゆっくりと減衰します。出力電圧がわずかに減衰すると、LT3120は復帰してPWMスイッチング動作を開始し、 $V_{OUT}$ の出力電圧が以前のレベルに戻るまで続けます。負荷が非常に軽い場合、 $V_{OUT}$ が戻るまでに数サイクルしか必要とせず、スリープ時間を長くできるため、効率が大幅に向上します。負荷がBurst Modeへの遷移閾値を急激に上回った場合、デバイスは自動的に連続PWM動作に入り、負荷が再び低下するまでこの動作を続けます。Burst Mode動作は、ソフトスタートが完了し、 $V_{OUT}$ が安定するまで停止しています。また、MPPCループが制御されている場合も動作しません。

### パワー・グッド・インジケータ

LT3120はオープンドレインのPGOOD出力を備えており、 $V_{OUT}$ が設定値より8%(代表値)以上低下するとローにプルダウンします。 $V_{OUT}$ が設定値の6.8%(代表値)以内まで上昇すると、内部のPGOODプルダウンはオフになり、外付けのプルアップ抵抗が接続されていればPGOODはハイになります。内部フィルタによって、 $V_{OUT}$ に発生する短いトランジントによるPGOODの誤作動を防止します。PGOODは、絶対最大定格の27Vを超えない限り、任意の電圧にプルアップすることができます。PGOOD機能は、EN/UVLOピン電圧が0.8V(代表値)のロジック閾値を超えると有効になります。EN/UVLOピン電圧が0.8V(代表値)を下回り、 $V_{CC}$ に電源が供給されている間は、PGOODプルダウンが有効になります。

### 熱に対する考慮事項

LT3120の電源スイッチは、電流が内部電流制限閾値に達するまで連続的に動作する設計になっています。高い電流レベルで動作させると、IC内部に大量の熱が発生することになります。また、多くのアプリケーションでは、 $V_{CC}$ レギュレータは入力電圧と出力電圧が大きく異なる状態で動作するため、通過する素子における消費電力が更に大きくなります。そのため、効率を最適化し、LT3120が定格どおりの出力電流を出せるよう、ICの熱環境に注意を払う必要があります。具体的には、LQFNのサーマル・パッドをプリント基板にハンダ付けする必要があります。プリント基板は、サーマル・パッドの接続部から大面積の銅プレーンにできるだけ多くのビアを設け、ICパッケージの放熱を最大化するように設計してください。より薄いプリント回路基板を使用し、サーマル・ビアを接続した内層数を多くすることにより、更に良い結果が得られます。これらによって、PCBの熱抵抗を最小限に抑え、幅広い温度範囲と大きな出力電流レベルでの動作が可能になります。ダイ温度が約165°Cを超えると、ICは過熱シャットダウンに入りすべてのスイッチングを停止します。ダイが約10°C低下するまでデバイスはディスエーブル状態を維持します。フォールト状態が解消されると、過熱シャットダウンからソフトスタート回路が再起動し、スムーズに復帰します。

## アプリケーション情報

### V<sub>CC</sub>コンデンサの選択

LT3120のV<sub>CC</sub>出力は、入力電圧から内部低ドロップアウト・レギュレータによって生成されます。V<sub>CC</sub>レギュレータは、幅広い出力コンデンサで安定して動作するように設計されています。4.7μFの低ESRセラミック・コンデンサは、ほとんどのアプリケーションに適しています。コンデンサは、できるだけ短いパターンでV<sub>CC</sub>ピンとグラウンドに接続する必要があります。

### V<sub>CC</sub>レギュレータのブートストラップ

4.5V～6Vの出力電圧では、V<sub>CC</sub>レギュレータは、図6に示すようにV<sub>OUT</sub>とV<sub>CC</sub>の間にダイオードを使用して電源供給されます。出力電圧が、ダイオードの順方向電圧より小さく、使用可能な外部駆動電圧の4.2V～5.5V以内になるよう、適切なダイオードを選定する必要があります。これは、ショットキー・ダイオードまたはシリコン・ダイオードを使用することで実現できます。どちらの場合も、V<sub>CC</sub>ピンを駆動するために十分な電流に対応できる能力が必要です。

図6. V<sub>OUT</sub>からのV<sub>CC</sub>のブートストラップ

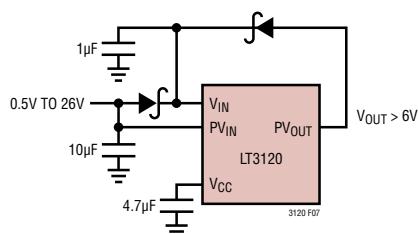

V<sub>CC</sub>ピンの最大定格を超える出力電圧(例えば、V<sub>OUT</sub> = 7V)を使用するアプリケーションでは、入力電圧と出力電圧の間にダイオードOR回路を使用して内部V<sub>CC</sub>レギュレータに電源供給することができます。これは、ダイオードORノードをV<sub>IN</sub>ピンに接続し、PV<sub>IN</sub>ピンを入力ソースに接続することで実現できます。この構成では、PV<sub>IN</sub>とGNDの間に配置するバイパス・コンデンサの他に、V<sub>IN</sub>ピンとGNDの間にバイパス・コンデンサを追加する必要があります。この構成を図7に示します。

図7. V<sub>CC</sub>レギュレータを駆動する入力電源とV<sub>OUT</sub>のダイオードOR

### V<sub>IN</sub>UVLO閾値の設定

図8に示すように、外付けの抵抗分圧器をV<sub>IN</sub>に接続することにより、EN/UVLOピンを使用してLT3120のイネーブル／ディスエーブルする入力電圧を設定することができます。

入力電圧の立上がりで、V<sub>IN</sub>が式4で与えられる閾値に達するとLT3120はイネーブルされます。ここで、R1とR2は抵抗分圧器の抵抗値です。

$$V_{TH(RISING)} = 1.205V \left( \frac{R1+R2}{R2} \right) \quad (4)$$

ノイズのある環境でも信頼性の高い動作を確保するため、EN/UVLOピンは2つのヒステリシスを備えています。EN/UVLOピン・コンパレータ内の90mVの固定ヒステリシスにより、抵抗分圧器の値に関係なく、入力ターンオン電圧の7.5%のヒステリシスが得られます。これに加えて、EN/UVLOピンから供給される内部ヒステリシス電流によってヒステリシスを追加することができます。このヒステリシスのレベルは、R1の値によって設定でき、必要なアプリケーション条件に適した総ヒステリシスになるまでヒステリシスを増加させることができます。

ICがイネーブルされると、入力電圧がコンパレータの閾値をヒステリシス電圧V<sub>HYST</sub>だけ下回るまでイネーブルが維持されます。このヒステリシス電圧は式5で与えられ、R1とR2は分圧器の抵抗値です。

$$V_{HYST} = R1 \cdot 0.25\mu A + \left( \frac{R1+R2}{R2} \right) \cdot 0.09V \quad (5)$$

図8. 入力UVLOとヒステリシスの設定

このように、立上がりUVLO閾値とヒステリシス量は、抵抗R1、R2を適切に選定することで独立に設定することができます。高いヒステリシス・レベルでは、R1の値が実用上望ましい値より大きくなることがあります。そのような場合は、図9に

## アプリケーション情報

示すように抵抗  $R_H$  を追加することでヒステリシス量を大きくすることができます。

$R_H$  抵抗を使用する場合、EN/UVLO ピンの立上がり閾値を求める式は元のままで、ヒステリシスは式 6 で与えられます。

$$V_{HYST} = \left( \frac{R_H R_2 + R_H R_1 + R_1 R_2}{R_2} \right) 0.25 \mu A + \left( \frac{R_1 + R_2}{R_2} \right) 0.09 V \quad (6)$$

図9. 入力UVLOヒステリシスの増加

ノイズへの耐性とUVLO閾値の精度を向上させるため、EN/UVLOとGNDの間に470pFのコンデンサを追加してEN/UVLOピンの入力にフィルタをかけることができます。これより容量の大きいコンデンサは、ヒステリシス動作に影響を与える可能性があるため使用しないでください。

## スイッチング周波数の選択

スイッチング周波数は、RTピンとグラウンドの間に接続する抵抗の値で設定します。スイッチング周波数と抵抗値の関係は式7で表され、ここで  $R_T$  は抵抗値です。

$$f_{SW} \cong \frac{100 \text{MHz}}{8 + (1.2 \cdot R_T / k\Omega)} \quad (7)$$

スイッチング周波数を高くすると小さなインダクタが使用しやすくなると共に入出力フィルタのコンデンサも小型化できるため、ソリューションの小型化と部品高さの低減を実現できます。ただし、スイッチング周波数を高くするとスイッチング損失が増加するため、一般的には変換効率が減少します。

## 出力コンデンサの選択

出力電圧のリップルを最小限に抑えるため、昇降圧コンバータの出力には低ESR出力コンデンサを使用します。低ESRでフットプリントが小さいため、多層セラミック・コンデンサが最適です。出力電圧リップルを受け入れ可能なレベルまで低減できる容量のコンデンサ値を選択してください。コンデンサのESRとESLを無視すると、ピークtoピークの出力電圧リップルは式8によって計算できます。ここで、 $f_{SW}$  はスイッチング周波数、 $C_{OUT}$  は出力コンデンサ、 $t_{LOW}$  はスイッチ・ピンの最小ロー時間、 $I_{LOAD}$  は出力電流です。スイッチング周波数および温度の関数として表した  $t_{LOW}$  の曲線は、[代表的な性能特性](#) のセクションを参照してください。

$$\Delta V_{P-P(BUCK)} \cong \frac{I_{LOAD} t_{LOW}}{C_{OUT}}$$

$$\Delta V_{P-P(BOOST)} \cong \frac{I_{LOAD}}{f_{SW} C_{OUT}} \left( \frac{V_{OUT} - V_{IN} + t_{LOW} f_{SW} V_{IN}}{V_{OUT}} \right) \quad (8)$$

出力電圧のリップルは負荷電流と共に増加し、一般的には降圧モードより昇圧モードにおいて大きくなります。これらの式は、出力電流が不連続になっているときに発生する出力電圧リップルのみを考慮しており、負荷電流が大きいときのリップルについては正しく近似できますが、負荷が非常に軽く、出力電圧リップルがインダクタの電流リップルに支配されるような場合、出力電圧リップルは過小に見積られます。

出力コンデンサの両端で生成される出力電圧リップルに加えて、出力コンデンサの内部抵抗によって発生するリップルもあります。このESRによって生成される出力電圧リップルは、出力コンデンサの直列抵抗に比例し、式9によって与えられます。ここで、 $R_{ESR}$  は出力コンデンサの直列抵抗で、その他は前述の定義と同様です。

$$\Delta V_{P-P(BUCK)} \cong \frac{I_{LOAD} \cdot R_{ESR}}{1 - t_{LOW} \cdot f_{SW}} \cong I_{LOAD} \cdot R_{ESR}$$

$$\Delta V_{P-P(BOOST)} \cong \frac{I_{LOAD} \cdot R_{ESR} \cdot V_{OUT}}{V_{IN}(1 - t_{LOW} \cdot f_{SW})} \cong I_{LOAD} \cdot R_{ESR} \left( \frac{V_{OUT}}{V_{IN}} \right) \quad (9)$$

## アプリケーション情報

### 入力コンデンサの選択

P<sub>VIN</sub>ピンはインダクタの総電流を伝送し、ICの内部制御回路に電源を供給します。入力電圧リップルを最小限に抑え、ICが正しく動作するように、10μF以上の低ESRバイパス・コンデンサをできるだけこのピンの近くに配置してください。このコンデンサとP<sub>VIN</sub>およびグランド・プレーンを接続するパターンは、できるだけ短くします。V<sub>IN</sub>ピンは、V<sub>CC</sub>レギュレータとその他の内部回路に電源を供給します。V<sub>IN</sub>とP<sub>VIN</sub>を接続するPCBパターンが長くなってしまう場合は、V<sub>IN</sub>ピンの近くに容量の小さなバイパス・コンデンサを追加しなければならないことがあります。

長いリード線を通じて電源供給する場合、または高ESRの電源を使用する場合は、より大きいバルクの入力コンデンサが必要になります。そのようなアプリケーションでは、47μF～100μFの電解コンデンサを1μFのセラミック・コンデンサと並列に接続することにより、一般的には高性能でロー・コストのソリューションが得られます。

長いケーブルのような誘導性の接続を通じて電源供給する場合、電源のインダクタンスと入力バイパス・コンデンサがQ値の高い共振LCフィルタを形成します。そのようなアプリケーションでは、電源にホット・プラグすると電圧に大きなオーバーシュートを発生させる可能性があり、入力電源の公称電圧の2倍にまで達することもあります。このような場合は、LT3120の入力電圧の絶対最大定格を超えないように注意してください。入力フィルタの減衰性能向上と電圧オーバーシュートの最小化に関するソリューションを記載したアナログ・デバイセズのアプリケーション・ノート88を参照してください。

### インダクタの選択

LT3120のアプリケーション回路で使用するインダクタの選定は、供給可能な最大出力電流、コンバータの帯域幅、インダクタ電流リップルの振幅、コンバータ全体の効率に影響を与えます。インダクタは、内部スイッチの抵抗(25mΩ)と比較して小さなDC直列抵抗のものを使用する必要があります。そうでないと、出力電流性能と効率が損なわれます。インダクタ値を大きくするとインダクタ電流のリップルは低減しますが、ピーク電流モード制御の場合のように、出力電流性能は向上しないことがあります。また、インダクタ値が大きい

と、所定のケース・サイズではDC直列抵抗が高くなる傾向があり、効率に悪影響を及ぼします。昇圧モード動作の場合、インダクタンスが大きいと右半平面ゼロ(RHPZ)周波数も低下するため、ループの安定性が損なわれます。LT3120のほとんどのアプリケーション回路では、1.5μH～15μHのインダクタ値を使用することで最適な性能が得られます。降圧モードのみを使用するアプリケーションでは、RHPZによる影響がないためこれより大きなインダクタを使用できますが、昇圧を使用することが多いアプリケーションでは、昇圧率に応じてこの範囲の低い方の値を使用する必要があります。インダクタ値に関わらず、飽和電流定格は、平均インダクタ電流の最も厳しい値にリップル電流の1/2を加えた値よりも大きくなるようにしてください。

それぞれの動作モードにおけるインダクタ電流リップルのピークtoピーク値は、式10を使用して計算できます。ここで、f<sub>SW</sub>はスイッチング周波数の設定値、Lはインダクタンス、t<sub>LOW</sub>はスイッチ・ピンの最小ロー時間で一般に70nsです。

$$\Delta I_{L(P-P)(BUCK)} \cong \frac{V_{OUT}}{L} \left( \frac{V_{IN} - V_{OUT}}{V_{IN}} \right) \left( \frac{1}{f_{SW}} - t_{LOW} \right)$$

$$\Delta I_{L(P-P)(BOOST)} \cong \frac{V_{IN}}{L} \left( \frac{V_{OUT} - V_{IN}}{V_{OUT}} \right) \left( \frac{1}{f_{SW}} - t_{LOW} \right) \quad (10)$$

インダクタ・リップル電流のピークtoピーク値が最大になるのは、降圧モードではデューティ・サイクルが最小(V<sub>IN</sub>が最大)のとき、昇圧モードではデューティ・サイクルが50%(V<sub>OUT</sub> ≈ 2 • V<sub>IN</sub>)のときです。

一例として、V<sub>IN</sub>(最小値)=2.5V、V<sub>IN</sub>(最大値)=15V、V<sub>OUT</sub>=5V、f<sub>SW</sub>=1MHz、L=4.7μHの場合の、インダクタ・リップルが最大になる電圧値(降圧モードで15V V<sub>IN</sub>、昇圧モードで2.5V V<sub>IN</sub>)でのピークtoピーク値を示します。(式11を参照。)

$$\Delta I_{L(P-P)(BUCK)} \cong \frac{5V}{4.7\mu H} \left( \frac{15V - 5V}{15V} \right) \cdot 930ns = 659mA$$

$$\Delta I_{L(P-P)(BOOST)} \cong \frac{2.5V}{4.7\mu H} \left( \frac{5V - 2.5V}{5V} \right) \cdot 930ns = 247mA \quad (11)$$

## アプリケーション情報

インダクタの飽和電流定格を適切に選択するため、予想最大平均インダクタ電流にこのインダクタ・リップル電流の1/2を加えてください。

### 出力電圧の設定

出力電圧は、図4に示すように、抵抗 $R_{TOP}$ および $R_{BOT}$ で構成された外付けの抵抗分圧器を使用して設定します。式12により、抵抗分圧器の値が出力レギュレーション電圧を決定します。

$$V_{OUT} = 0.795V \cdot \left( 1 + \frac{R_{TOP}}{R_{BOT}} \right) \quad (12)$$

### MPPC電圧の設定

LT3120には、電流が制限された入力電源を使用して動作する場合に性能を最適化できるMPPC機能が搭載されています。MPPC機能は、 $V_{IN}$ に接続された外付けの分圧器を使用して、ユーザが設定した最小入力電圧 $V_{MPPC}$ を維持するため、必要に応じて平均インダクタ電流を制御します。(図5を参照)。

$$V_{MPPC} = 0.795V \cdot \left( 1 + \frac{R_5}{R_6} \right) \quad (13)$$

太陽電池パネルはオープンサーキット電圧の約75%で動作するときに電力伝送点が最大になるため、コンバータが太陽電池から電力供給されるようなアプリケーションでMPPC機能は役に立ちます。例えば、オープンサーキット電圧が10Vの太陽電池パネルで動作している場合、電力伝送点は、パネルの出力電圧が約7.5Vになるように負荷をかけたときに最大になります。

MPPC機能を使用する場合、入力コンデンサは $100\mu F$ ～ $470\mu F$ のサイズのものを使用してください。抵抗 $R_6$ は $50k$ ～ $250k$ の値を選択してください。これより小さな値を使用すると、ライン過渡応答と負荷過渡応答の条件においてMPPCのトラッキング点のアンダーシュートを小さくすることができますが、入力電源からより大きな電流が流れます。このような場合は、 $100k\Omega$ を使用してください。次に、式14を使用して必要な入力MPPC電圧になるように $R_5$ の値を決定します。

$$\begin{aligned} R_5 &= \left( \frac{V_{MPPC}}{0.795V} - 1 \right) \cdot R_6 = \left( \frac{7.5V}{0.795V} - 1 \right) \cdot 100k\Omega \\ &= 843k\Omega \approx 845k\Omega \end{aligned} \quad (14)$$

これらの抵抗値を使用すると、最大入力電流を制御して $V_{IN}$ が7.56Vの最小値を維持するようにMPPC機能は設定されます。LT3120が流せる電力、または必要な負荷以上の電力を太陽電池パネルが供給できる場合、入力電圧は設定したMPPC点以上になります。入力電圧が高くなても、最大動作入力電圧を超えない限り問題はありません。太陽電池パネルに使用する場合は、十分な光が得られず $V_{IN}$ が大幅に低下したときにデバイスをディスエーブルできる、プログラマブルなEN/UVLO機能を使用することが望ましい場合があります。EN/UVLOピンを使用すると、入力電源が急激に低下したときにスイッチングを停止して出力の放電を防ぐことにより、適切に制御できます。この入力UVLO電圧は、MPPCのトラッキング電圧を十分に下回る値に設定することでトランジエント条件下にデバイスがディスエーブルされないようにします。

MPPCループには、入力電圧レギュレーション・ループの安定性を維持するための補償回路が必要となります。これは、図5に示すように、MPPCの低い方の抵抗 $R_6$ と並列に直列RC回路を形成し、MPPCピンにポールゼロ・ペアを構成することによって実現します。

低周波数ポールが約360Hz以下に、ゼロが入力コンデンサのサイズに基づいてスケールされた周波数になるように、ポールとゼロの位置を選択します。式15を使用して補償コンデンサ $C_{C2}$ とゼロ抵抗 $R_{C2}$ の値を決定します。

$$\begin{aligned} C_{C2} &= \frac{1}{2\pi \cdot R_6 \cdot 360Hz} \\ R_{C2} &= \frac{C_{IN}}{2\pi \cdot C_{C2}} \end{aligned} \quad (15)$$

前述の分圧器の値と $220\mu F$ の入力コンデンサを使用したときの補償回路の値は式16のように計算されます。

$$\begin{aligned} C_{C2} &= \frac{1}{2\pi \cdot 100k\Omega \cdot 360Hz} = 4.42nF \approx 4.3nF \\ R_{C2} &= \frac{220\mu F}{2\pi \cdot 4.3nF} = 8.14k\Omega \approx 8.25k\Omega \end{aligned} \quad (16)$$

## アプリケーション情報

### PROGの設定

電流検出アンプは、ISPピンとISNピンの間の電圧をモニタし、それに比例した電流をPROGピンから出力します。PROGピンの電圧と温度安定性に優れた0.795Vのリファレンス電圧を比較し、PROGピンの電圧がリファレンス値を超えた場合は、目的の出力電流レベルを維持するようにインダクタ電流を調整します。出力電流の制限値はPROGピンとGNDの間に接続する抵抗で設定します。この抵抗と並列に小さな容量のコンデンサを追加することもできます。RC回路の値は式17を使用して計算できます。

$$R_{PROG} = \frac{0.795V}{2mA/V \cdot R_{SEN} \cdot I_{OUT}}$$

$$C_{PROG} = \frac{3300nF \cdot \Omega}{R_{PROG}} \quad (17)$$

### 昇降圧コンバータの補償

LT3120は、2つの制御ループで構成された平均電流モード制御のアーキテクチャを採用しています。安定性を維持するには、内部の平均電流モード制御ループと外部の制御ループの両方を補償する必要があります。内部の電流モード制御ループは、広帯域で良好な過渡応答を維持できるように内部で補償します。多くのアプリケーションでは、内部電流ループは電圧制御された電流源(VCCS)として扱うことができます。この電流源は、電圧エラー・アンプによって制御され、主に負荷抵抗( $R_{LOAD}$ )と出力コンデンサ( $C_{OUT}$ )によって形成される出力負荷をレギュレーションします。これを簡略化した図を図10に示します。コンバータを補償する場合に考慮すべき重要な部品を示しています。

VCにフルスケールの制御電圧を使用することにより、LT3120昇降圧コンバータは9.5Aの平均インダクタ電流を生成します。200mV～900mVのVC電圧範囲を使用することにより、内部平均電流ループの電流ゲインは13.6A/Vになります。ピーク電流モード制御と同様、内部平均電流モード制御ループは、対象となる周波数範囲にわたりインダクタを等価的に電流源と見なし、電力段の周波数応答は単

極(-20dB/decade)のロールオフを示します。出力コンデンサ( $C_{OUT}$ )と負荷抵抗( $R_{LOAD}$ )が支配的な低周波数ポールを形成すると共に、出力コンデンサの等価直列抵抗と容量がゼロを形成し、通常、十分高い周波数では無視できます。LT3120を昇圧モードで動作させる場合には、問題を起こしやすい右半平面ゼロ(RHPZ)にも直面します。RHPZは、ゲインの増加(ゼロ点など)と位相の減少(ポールなど)を生じさせます。

図10. 制御ループ部品の簡略図

これは、最終的にLT3120で達成できる最大帯域幅を制限します。降圧モードで動作する場合にはRHPZは存在しません。DCでのオープンループ・ゲインの全体は式18から式20までの積で得られます。

電圧エラー・アンプのゲイン:

$$G_{EA} = g_m \cdot R_{EA} = 120\mu\text{s} \cdot 5M\Omega = 600 \quad (18)$$

分圧器のゲイン:

$$\frac{V_{FB}}{V_{OUT}} = \frac{0.795V}{V_{OUT}} \quad (19)$$

電流ループ・トランスコンダクタンス:

$$G_{CS} = \frac{9.5A}{0.7V} = 13.6A/V \quad (20)$$

$G_{CS}$ は、制御電圧VCとインダクタ電流レベル、すなわち降圧モードでの出力電流レベルの間のトランスコンダクタンス・ゲインであることに注意する必要があります。昇圧モードで

## アプリケーション情報

は、出力電流レベルは、昇圧率で除算された効率分だけ減少します(式21と式22を参照)。効率については、代表的な性能特性を参照してください。

$$G_{CS(OUT)} = 13.6A/V \text{ (Buck Mode)} \quad (21)$$

$$G_{CS(OUT)} = 13.6A/V \cdot \frac{V_{IN}}{2V_{OUT}} \cdot \text{Eff} \text{ (Boost Mode)} \quad (22)$$

ループ・ゲインに影響を与える周波数依存の特性は、式23から式26で与えられます。

出力負荷のポール(P1)

$$f_{P1} = \frac{2}{2\pi \cdot R_{LOAD} \cdot C_{OUT}} \quad (23)$$

エラー・アンプの補償(P2、Z1)

$$f_{P2} = \frac{1}{2\pi \cdot R_{EA} C_C} \text{ Hz (close to DC)} \quad (24)$$

$$f_{Z1} = \frac{1}{2\pi \cdot R_Z \cdot C_C} \text{ Hz} \quad (25)$$

右半平面ゼロ

$$f_{RHPZ} = \frac{V_{IN}^2 \cdot R_{LOAD}}{V_{OUT}^2 \cdot 2\pi \cdot L} \text{ Hz} \quad (26)$$

場合によっては、単純なRC回路をVCピンに接続しても十分なループ帯域幅と位相マージンが得られない可能性があります。このような場合は、追加の補償回路が必要です。これは、帰還分周器のトップ抵抗と並列にフィード・フォワードRC回路を追加することで実現できます。アプリケーションによつては、小さなフィード・フォワード・コンデンサを追加するだけで十分な場合もあります。

フィード・フォワード回路が必要となる一般的な状況は、コンバータが昇圧モードで動作し、クローズドループのクロスオーバー周波数( $f_{CC}$ )が右半平面に近い場合です。これは、ループ帯域幅を増加させ出力コンデンサの条件を軽減するために行います。RHPZにより位相損失が追加されるため、VCピンに単純なRC補償回路を追加しても十分に位相を増加することができずループを安定させられない場合があります。

## 補償回路の例

このセクションでは、補償部品の導出および選定方法を、最小3Vの入力電圧から5Vで3Aを出力する場合を例に説明します。補償回路は、一般的に安定性に関して最も厳しい条件となる昇圧モード動作の、最も厳しい条件に対して設計します。他のほとんどのアプリケーションにおいて、補償回路を設計する際には、この例の中で与えられる式に異なる値を代入し、得られたボード線図を調べ、必要に応じて調整するだけの問題で済みます。補償回路の設計手順ではLT3120の簡略化モデルを使用するため、結果は、時間軸ステップ応答のテストを使用して確認し、選んだ補償回路の有効性を検証する必要があります。コンデンサとインダクタの種類と値は、このデータシートの他のセクションに記載された内容に基づいて選択することを想定しています。入出力のバイパスに使用するコンデンサへの電圧バイアシングの影響には、特に注意を払う必要があります。同様に、インダクタ値と電流定格はアプリケーションの条件に基づいて選択することを想定しています。

動作条件の例:

$$V_{IN} = 3V \sim 20V$$

$$V_{OUT} = 5V$$

$$I_{LOAD(MAX)} = 3A$$

$$C_{OUT} = 150\mu F$$

$$L = 2.2\mu H$$

$$f_{SW} = 1MHz$$

最初に、RHPZの最小周波数を決める必要があります(式27を参照)。これは、昇圧モードで動作するコンバータを安全に構成できる最大帯域幅を決定します。

$$f_{RHPZ} = \frac{V_{IN}^2 \cdot R_{LOAD}}{V_{OUT}^2 \cdot 2\pi \cdot L} = 43.4kHz \quad (27)$$

安全性に関する十分なマージンを確保するため、ループ帯域幅は大きくできないかもしれません。IC内部の部品のばらつきとコンバータの応答に対する外部影響のばらつきを考慮して、クローズドループのクロスオーバー周波数( $f_{CC}$ )はRHPZ周波数より十分低くしてください。クロスオーバー周波数に十分な位相マージンがある場合は、安定性と

## アプリケーション情報

良好な過渡応答性を維持したままループ帯域幅を大きくすることも可能です。この例では、RHPZ周波数の1/6のクロスオーバー周波数を使用します(式28を参照)。

$$f_{CC} = \frac{f_{RHPZ}}{7} \approx 6.2 \text{kHz} \quad (28)$$

RHPZは、ループのクロスオーバーでゲインへの影響はほとんどありませんが、考慮すべき位相成分を持ってています(式29を参照)。

$$\varphi_{RHPZ} = -1 \cdot \tan^{-1} \left( \frac{f_{CC}}{f_{RHPZ}} \right) = -1 \cdot \tan^{-1} \left( \frac{1}{7} \right) = -8.1^\circ \quad (29)$$

コンバータは昇圧モードで動作するので、GCSは、制御された出力電流を表すようにスケーリングする必要があります。

代表的な性能特性のセクションを見ると、効率はほぼ80%であることが分かります。この情報を使用し、式30によって出力電流の実効ゲインが計算できます。

$$G_{CS(OUT)} = \left( G_{CS} \cdot \frac{V_{IN}}{2V_{OUT}} \cdot \text{Eff} \right) = 3.265 \text{A/V} \quad (30)$$

この結果を使用して、出力フィルタのゲイン成分と位相成分を式31で計算します。

$$G_{OUT} = G_{CS(OUT)} \cdot \sqrt{\frac{R_{LOAD}^2}{\left(\frac{f_{CC}}{f_{P1}}\right)^2 + 1}} = 1.098$$

$$\varphi_{P1} = -1 \cdot \tan^{-1} \left( \frac{f_{CC}}{f_{P1}} \right) = -1 \cdot \tan^{-1} \left( \frac{6200}{1273} \right) = -78.4^\circ \quad (31)$$

位相マージンを50度に選び、式31で計算した位相成分を合計することにより、補償回路によって増加させる位相値を決定します。P2には-90度の位相成分を想定しています。

$$\varphi_{Z1} = 50 - \varphi_{P2} - \varphi_{P1} - \varphi_{RHPZ} - 180 = 46.5^\circ \quad (32)$$

補償回路のゲインを使用して、目的の周波数でクロスオーバーするようにループ・ゲインを調整します。帰還分周器のゲインと出力ゲインを使用して、補償回路のゲインを式33によつて計算します。

$$G_{COMP} = \left( \frac{V_{REF}}{V_{OUT}} \cdot G_{OUT} \right)^{-1} = 5.727 \quad (33)$$

エラー・アンプ・トランスコンダクタンスと式33で得られた補償ゲインを使用して、補償回路の抵抗が得られます。

$$R_Z = \frac{G_{COMP}}{g_m} = \frac{5.727}{120\mu\text{s}} = 47.7 \text{k}\Omega \quad (34)$$

RZの値が分かったので、ゼロZ1が正しい位置になるように補償コンデンサを選択します。

$$C_{P1} = \frac{\tan(\varphi_{Z1})}{2\pi \cdot f_{CC} \cdot R_Z} = 565 \text{pF} \quad (35)$$

標準的な値を選択し、RZ = 47.5kΩとCP1 = 560pFの部品を使用します。

### PCBレイアウト時の考慮事項

LT3120昇降圧コンバータは、大きな電流を高い周波数でスイッチングします。安定でノイズのない高効率のアプリケーション回路を実現するため、基板レイアウトには特に注意を払う必要があります。図11にPCBの代表例を示し、主な考慮事項を説明します。重要なガイドラインを以下に示します。

1. 高電流が流れるバスの寄生インダクタンスと寄生抵抗は最小限に抑えます。これは、図11の太線で示したすべての部品までのパターンをできる限り短く太くすることで実現できます。コンデンサのグラウンド接続は、ビアを介してできる限り短いパターンを使用してグラウンド・プレーンに落としてください。PVIN、PVOUT、VCCのバイパス・コンデンサはできる限りデバイスの近くに配置し、できる限り短いパスでグラウンドに接続してください。

## アプリケーション情報

2. 露出パッドはLT3120の電気的なグラウンド接続です。複数のビアを使用して背面パッドとグランド・プレーンを直接接続してください。また、背面パッドと接続する金属面を最大化することで熱環境を改善し、デバイスの電力処理性能を向上させることができます。

3. 高周波電流ループの断面積が最小になるように、コンバータの下面全体に切れ目なくグランド・プレーンを配置してください。これによりEMIを最小限に抑制し、これらのループによる誘導性の電圧低下を減少できるため、SWピンのオーバーシュートとリンギングを抑えられます。

4. 太線で示した部品のすべての配線をできるだけ幅広くして、直列抵抗を減らしてください。これにより昇降圧コンバータの効率を向上させ、出力電流性能を最大化します。

5. グランド・プレーンに大電流が流れ LT3120 の動作を阻害しないように、すべての小信号のグラウンドは専用のケルビン配線を用いて直接 GND に戻してください。これは、図11 に示すように、RT ピン抵抗のグラウンド接続と帰還回路のグラウンド接続も含みます。

6. 高インピーダンスでノイズに敏感な入力 FB と RT の配線はできるだけ短くしてノイズの混入を減らしてください。

図11. PCBレイアウト

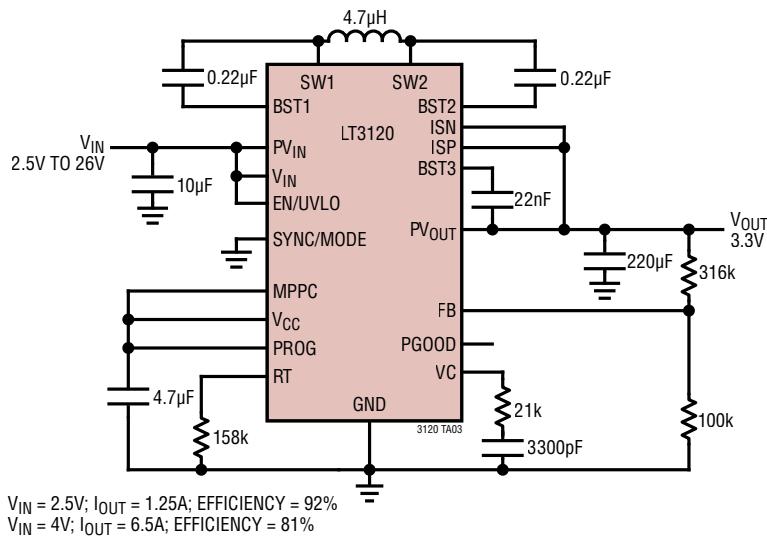

## 標準的応用例

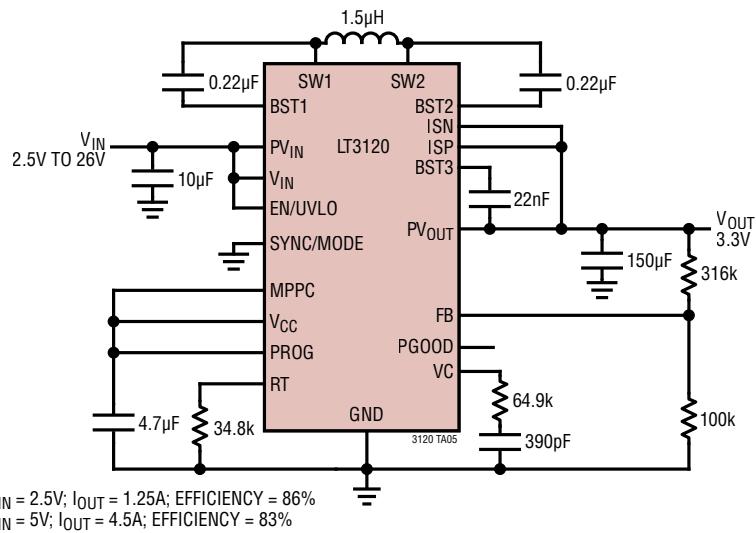

### 3.3Vのアプリケーション例

入力範囲の広い500kHzレギュレータ

入力範囲の広い1MHzレギュレータ

## 標準的応用例

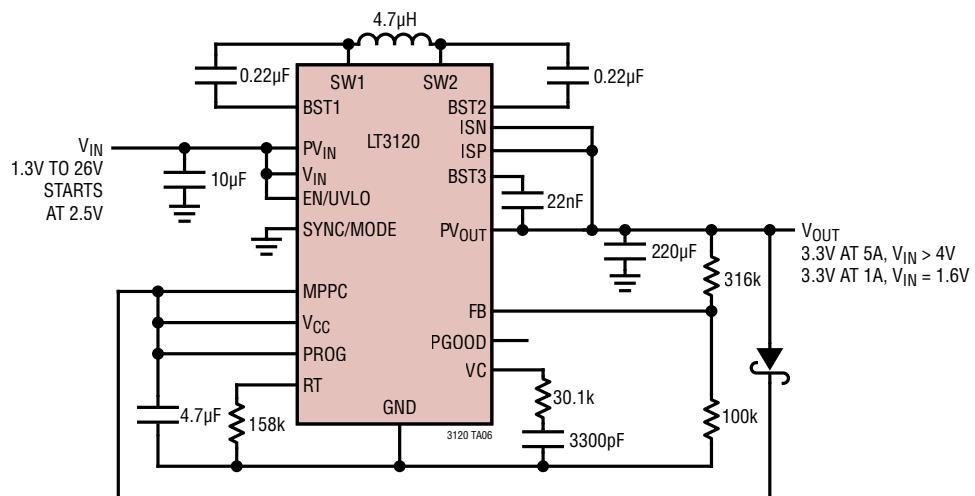

### 3.3Vのアプリケーション例

入力範囲の広い2MHzレギュレータ

$V_{CC}$ ブートストラップ・オプションを備えた入力範囲の広い500kHzレギュレータ

## 標準的応用例

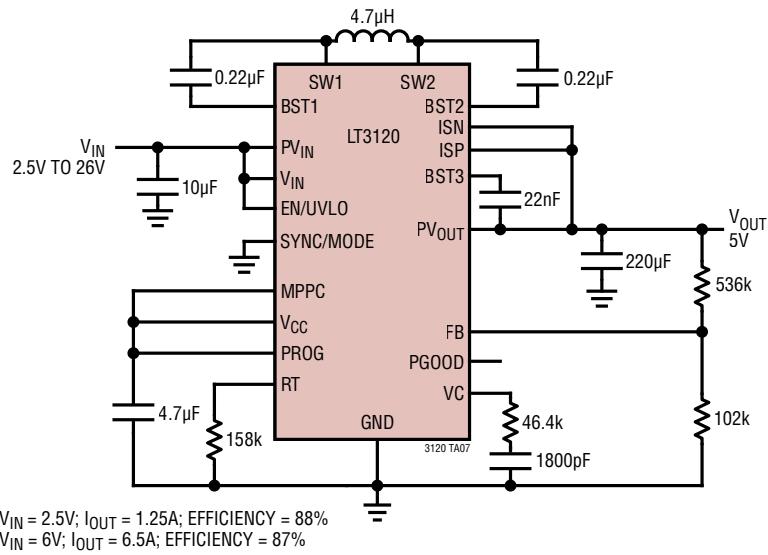

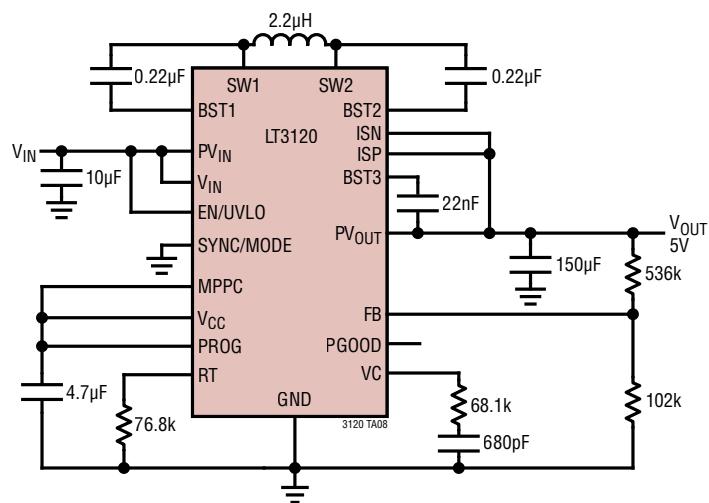

### 5Vのアプリケーション例

入力範囲の広い500kHzレギュレータ

入力範囲の広い1MHzレギュレータ

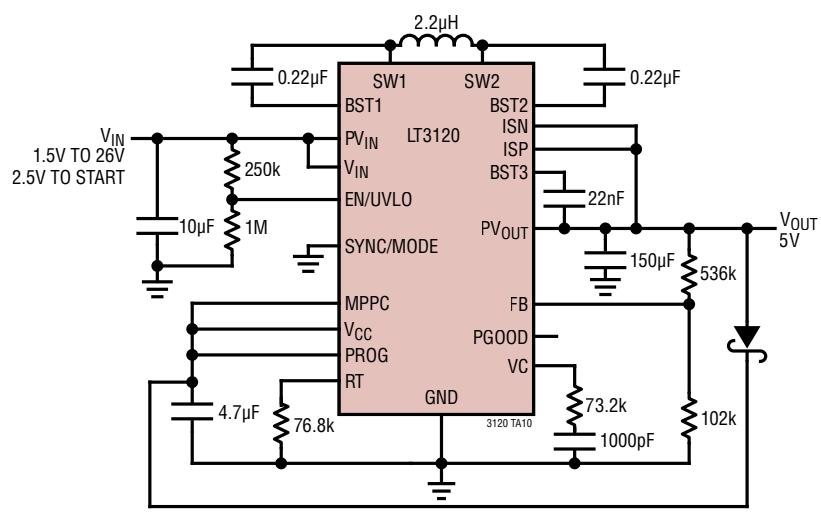

## 標準的応用例

## 5Vのアプリケーション例

入力範囲の広い2MHzレギュレータ

$V_{CC}$ ブーストストラップ・オプションを備えた入力範囲の広い1MHzレギュレータ

$V_{IN} = 1.6V; I_{OUT} = 1A; \text{EFFICIENCY} = 73\%$

$V_{IN} = 2.5V; I_{OUT} = 1.25A; \text{EFFICIENCY} = 88\%$

$V_{IN} = 6V; I_{OUT} = 6.5A; \text{EFFICIENCY} = 85\%$

## 標準的応用例

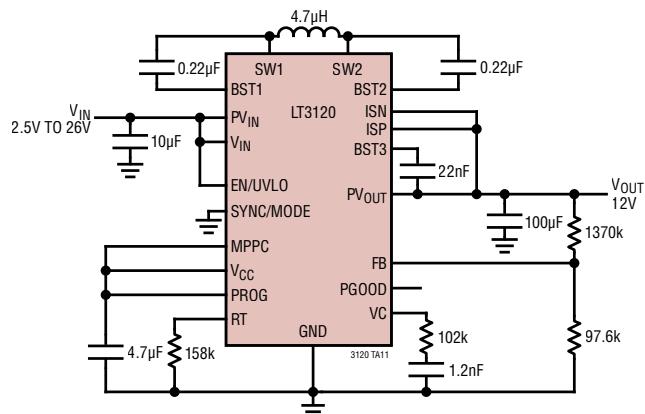

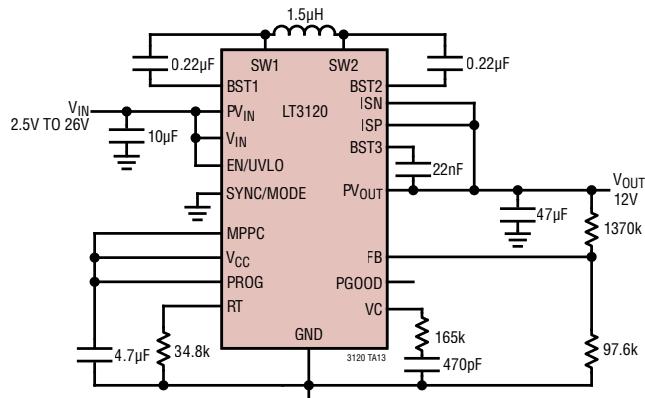

### 12Vのアプリケーション例

入力範囲の広い500kHzレギュレータ

$V_{IN} = 2.5V; I_{OUT} = 0.5A; \text{EFFICIENCY} = 82\%$

$V_{IN} = 13V; I_{OUT} = 6.5A; \text{EFFICIENCY} = 92\%$

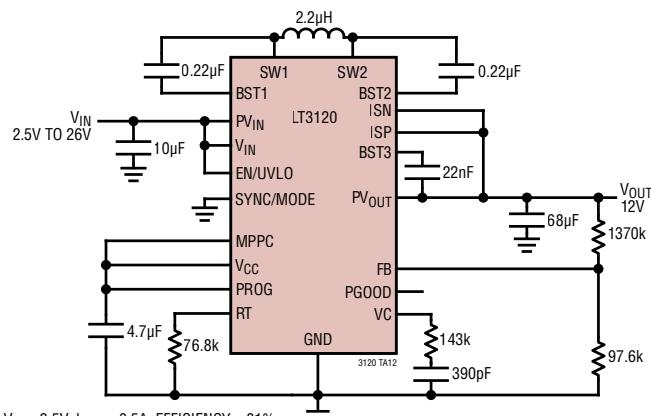

入力範囲の広い1MHzレギュレータ

$V_{IN} = 2.5V; I_{OUT} = 0.5A; \text{EFFICIENCY} = 81\%$

$V_{IN} = 13V; I_{OUT} = 6.5A; \text{EFFICIENCY} = 92\%$

入力範囲の広い2MHzレギュレータ

$V_{IN} = 2.5V; I_{OUT} = 0.25A; \text{EFFICIENCY} = 78\%$

$V_{IN} = 13V; I_{OUT} = 5A; \text{EFFICIENCY} = 89\%$

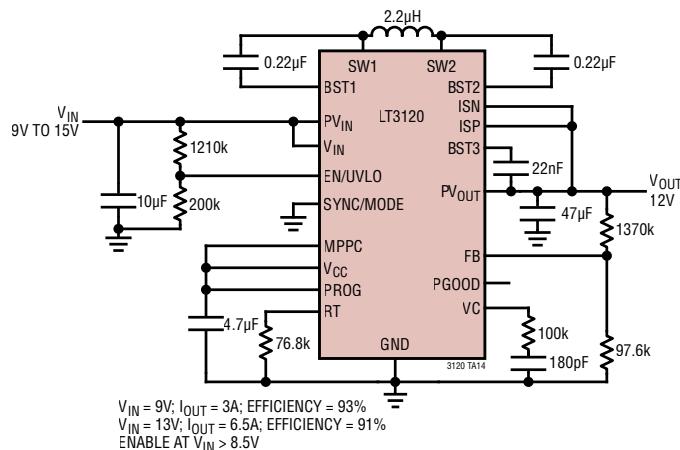

## 標準的応用例

### 12Vのアプリケーション例

入力範囲の狭い1MHzレギュレータ

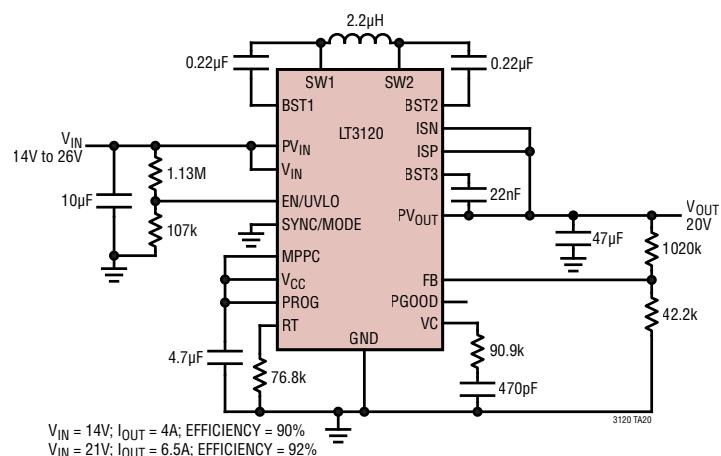

1MHz、12V ライン・コンディショナ

1MHz、20V ライン・コンディショナ

## 標準的応用例

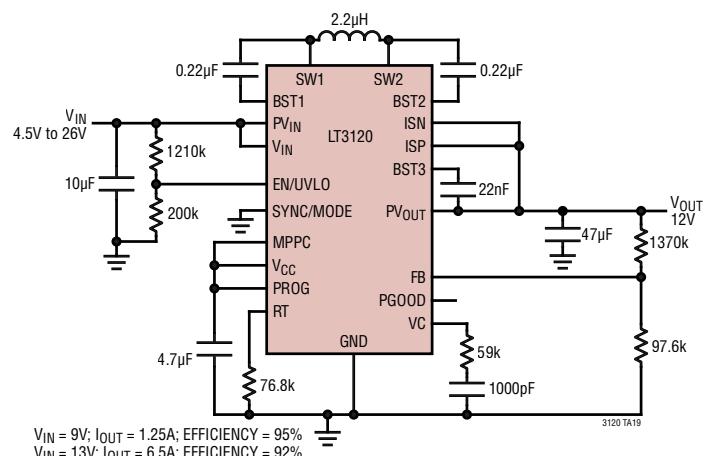

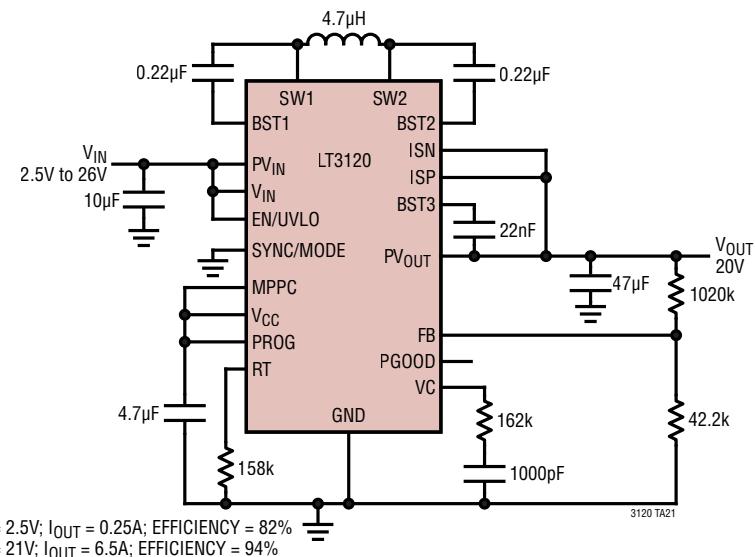

入力範囲の広い500kHz、20Vレギュレータ

入力電源ランダウを備えた750kHz、12Vレギュレータ

## 標準的応用例

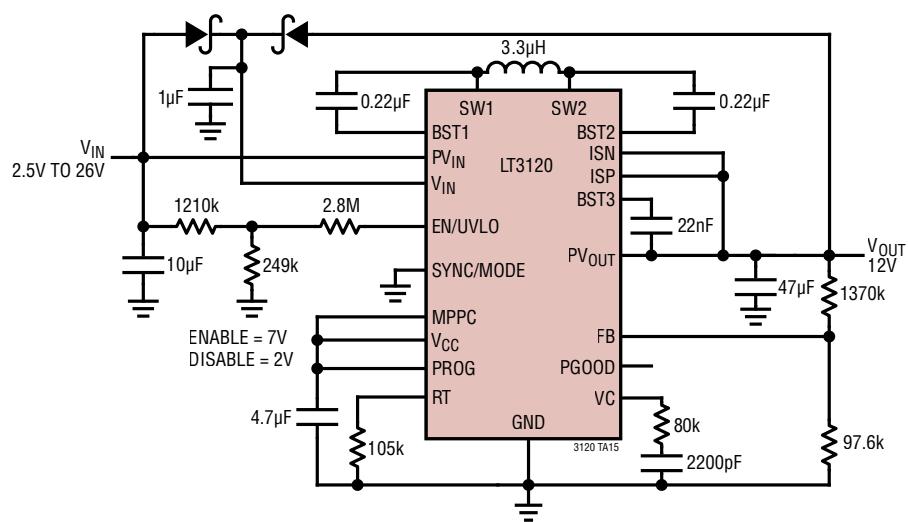

出力電流モニタリングを備えた15V、1MHzレギュレータ

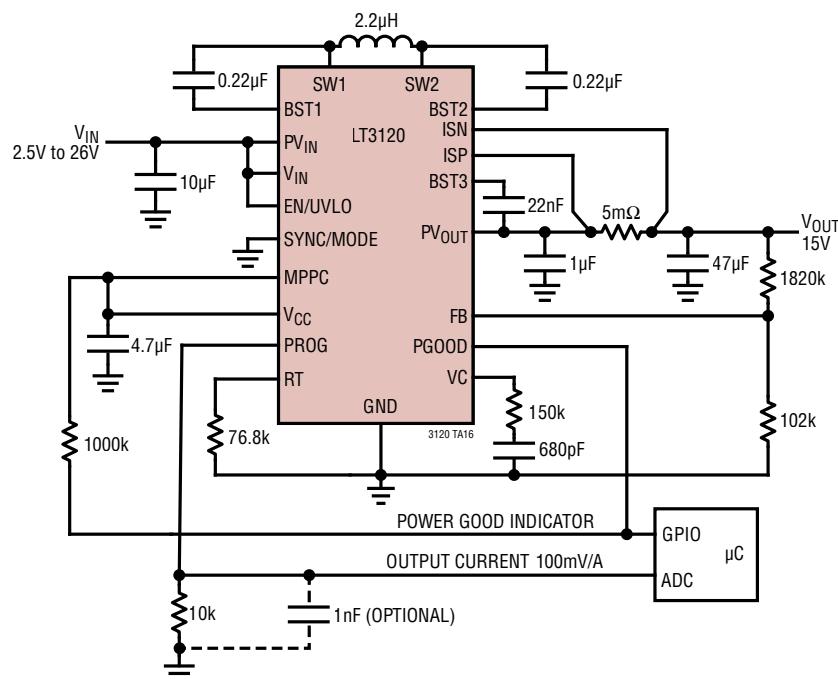

12Vと3.3Vを選択可能な出力レギュレータ

$V_{IN} = 5V; V_{OUT} = 3.3V; I_{OUT} = 1.25A; \text{EFFICIENCY} = 93\%$

$V_{IN} = 5V; V_{OUT} = 12V; I_{OUT} = 1.25A; \text{EFFICIENCY} = 90\%$

$V_{IN} = 13V; V_{OUT} = 12V; I_{OUT} = 6.5A; \text{EFFICIENCY} = 91\%$

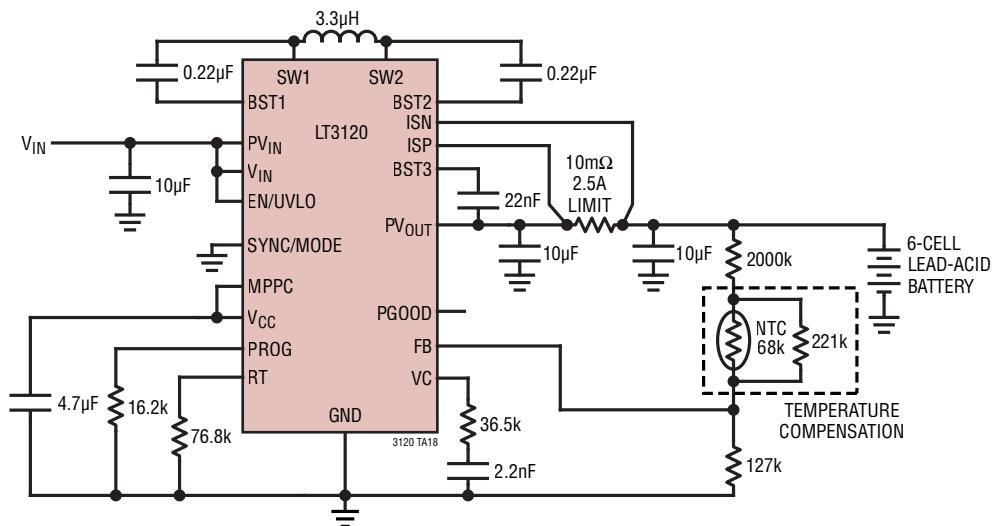

## 標準的応用例

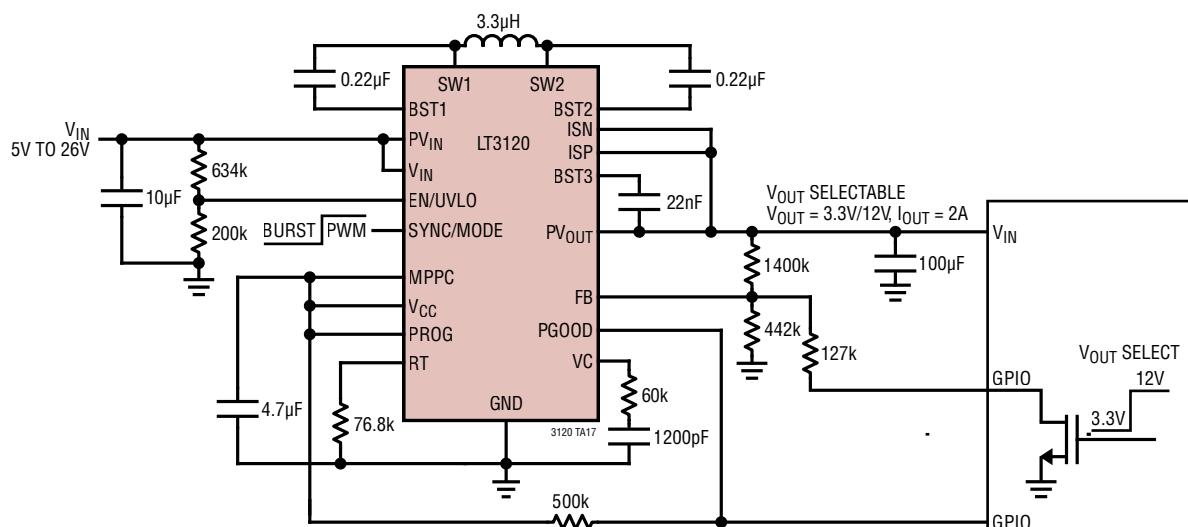

入力範囲の広い1MHz、2.5A鉛酸チャージャ

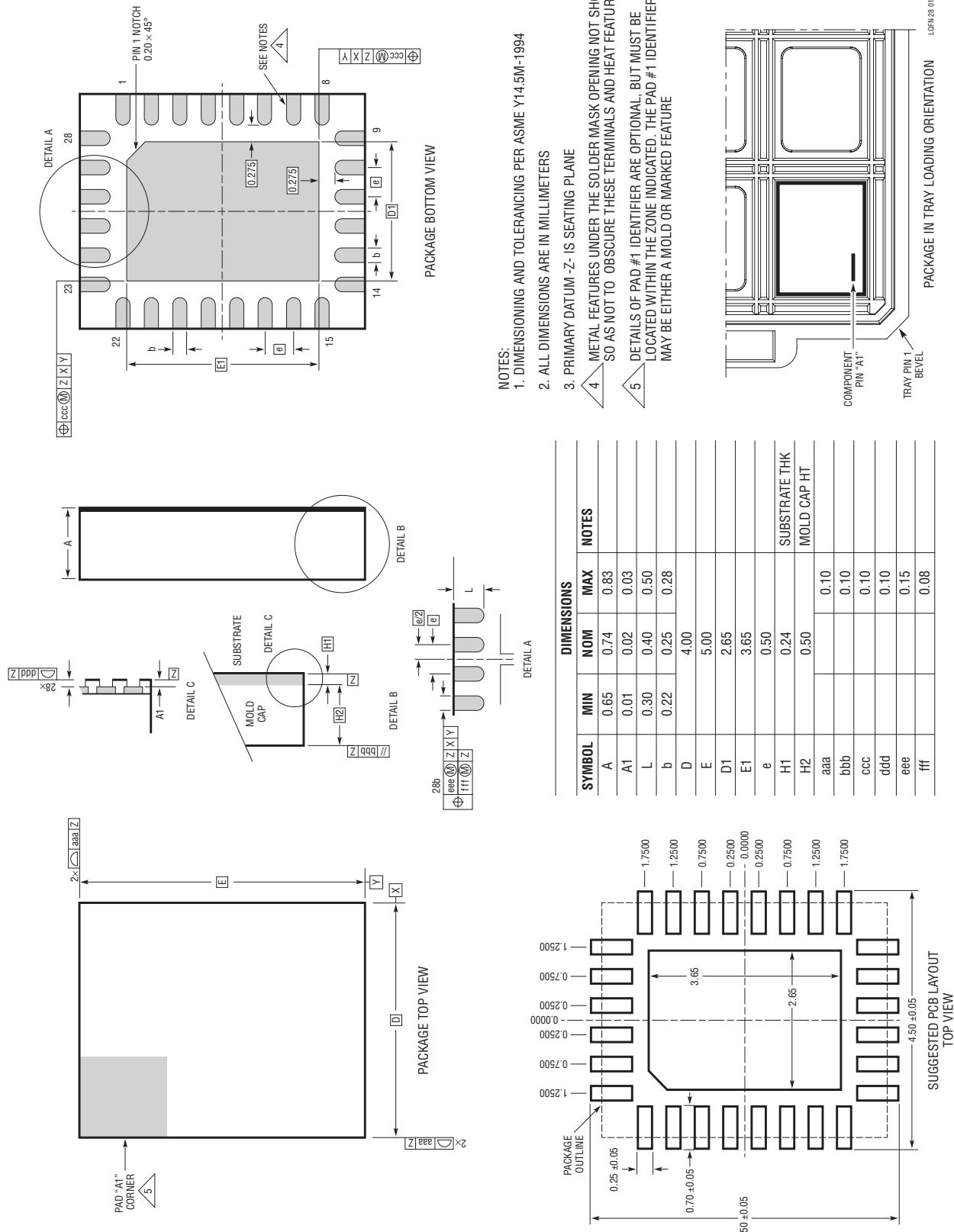

## パッケージの説明

**LQFN Package

28-Lead (5mm × 4mm × 0.74mm)**

(Reference LTC DWG # 05-08-1603 Rev 0)

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることに万全を期していますが、その利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。仕様は予告なく変更される場合があります。アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。

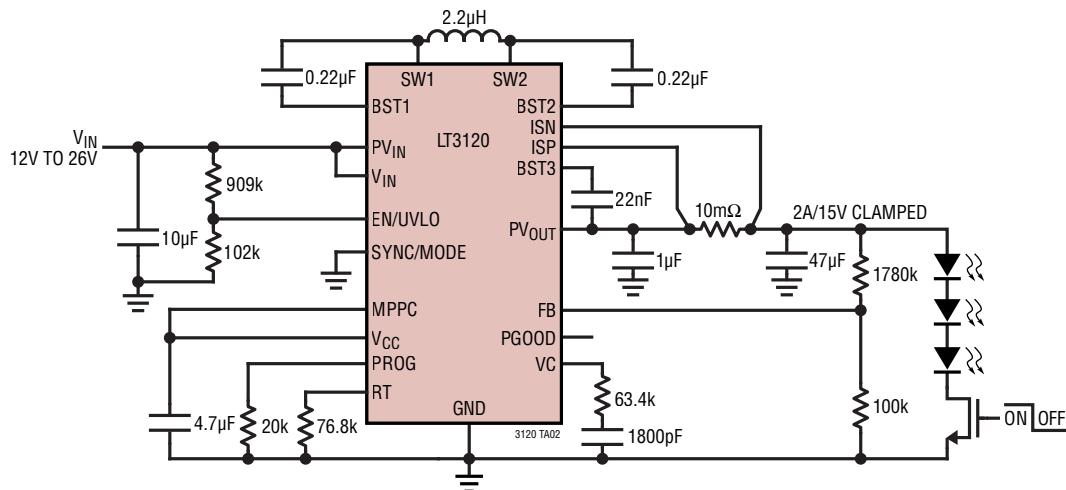

## 標準的応用例

1MHz、15Vのクランプ電圧を備えた2A LED出力

## 関連製品

| 製品番号                    | 概要                                                                  | 注釈                                                                                                            |

|-------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| LTC3112                 | 15V、2.5A同期整流式昇降圧DC/DCコンバータ                                          | $V_{IN} = 2.7V \sim 15V$ 、 $V_{OUT} = 2.5V \sim 14V$ 、 $I_Q = 40\mu A$ 、 $I_{SD} < 1\mu A$ 、DFNおよびTSSOPパッケージ  |

| LTC3122                 | 出力切断機能を備えた15V、2.5A同期整流式の昇圧DC/DCコンバータ                                | $V_{IN} = 1.8V \sim 5.5V$ 、 $V_{OUT} = 2.2V \sim 15V$ 、 $I_Q = 25\mu A$ 、 $I_{SD} < 1\mu A$ 、DFNおよびMSOPパッケージ  |

| LTC3124                 | 出力切断機能を備えた15V、5A、2相同期整流式昇圧DC/DCコンバータ                                | $V_{IN} = 1.8V \sim 5.5V$ 、 $V_{OUT} = 2.5V \sim 15V$ 、 $I_Q = 25\mu A$ 、 $I_{SD} < 1\mu A$ 、DFNおよびTSSOPパッケージ |

| LTC3119                 | 18V、5A同期整流式昇降圧DC/DCコンバータ                                            | $V_{IN} = 2.5V \sim 18V$ 、 $V_{OUT} = 0.8V \sim 18V$ 、 $I_Q = 35\mu A$ 、 $I_{SD} < 3\mu A$ 、QFNおよびTSSOPパッケージ  |

| LTC3115-1/<br>LTC3115-2 | 40V、2A同期整流式昇降圧DC/DCコンバータ                                            | $V_{IN} = 2.7V \sim 40V$ 、 $V_{OUT} = 2.7V \sim 40V$ 、 $I_Q = 30\mu A$ 、 $I_{SD} < 3\mu A$ 、DFNおよびTSSOPパッケージ  |

| LT3942                  | 42V/3.5A、効率96%、2.2MHzの同期整流式MicroPower降圧DC/DCコンバータ、 $I_Q = 2.5\mu A$ | $V_{IN} = 3V \sim 36V$ 、 $V_{OUT} = 0V \sim 36V$ 、4mm × 5mm QFN-28パッケージ                                       |

| LT8390/<br>LT8390A      | 高効率2MHz同期整流式4スイッチ昇降圧コントローラ                                          | $V_{IN} = 4V \sim 60V$ 、 $I_{SD} \leq 1\mu A$ 、TSSOP-28E、4mm × 5mm QFN-28パッケージ                                |