## 特長

- 広いバッテリ入力電圧範囲 : 4.5V ~ 30V

- 接地ランプまたはフローティング・ランプ構成

- オープン・ランプ保護

- 高精度100 $\mu$ AフルスケールDACプログラミング電流

- 2線式SMBusインターフェース

- 2つの選択可能なSMBusアドレス

- シャットダウン時にもDAC設定を保持

## アプリケーション

- ノートブックおよびパームトップ・コンピュータ

- 携帯用計測器

- パーソナル・デジタル・アシスタント

## 概要

LT®1786Fは、冷陰極蛍光管(CCFL)の制御機能を備えた固定周波数、電流モード・スイッチング・レギュレータです。このICには、効率的な高電流スイッチ、発振器、出力ドライバ・ロジック、制御回路、およびマイクロパワー6ビット100 $\mu$ Aフルスケール電流出力DACが内蔵されています。このDACは、単純な「ビット対ランプ電流制御」を提供し、2線式SMBusシリアル・インターフェースを使用して通信を行います。

ます。LT1786Fは、アドレス・ピンADRで設定される2つの選択可能なSMBusアドレスのうちの1つを使って、SMBusのスレーブ・デバイスとして動作します。

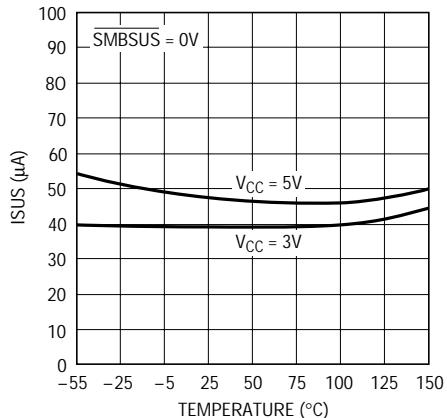

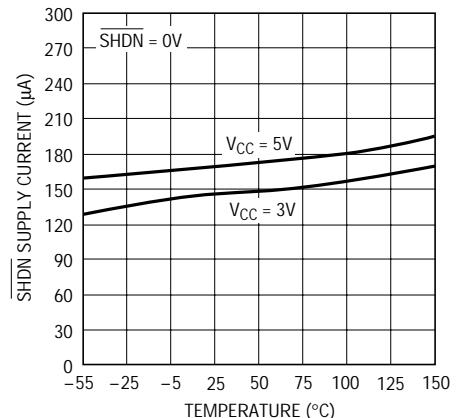

電源投入時には、DAC出力電流はADRピンのロジック状態に応じて、中間またはゼロ・スケールに設定されます。SMBUSピンを使用するかまたはSMBusコマンド・バイトでSHDNビット=1とセットすれば、IC全体をシャットダウンすることができます。DAC出力電流に対するデジタル・データは内部で保持され、電源電流は待機動作時には40 $\mu$ Aに低下します。アクティブ L のSHDNピンはCCFL制御回路をディスエーブルしますが、DACはアクティブのまま維持します。この動作モードでは電源電流は150 $\mu$ Aに低下します。

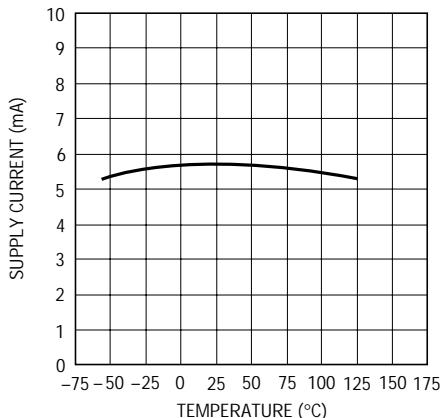

LT1786Fのコントロール回路は、3.3Vまたは5Vのロジック電源電圧で動作します。このICには、4.5V ~ 30Vで動作するバッテリ電源電圧ピンもあります。LT1786Fの消費電流は標準6mAです。200kHzのスイッチング周波数により、磁気部品のサイズが小さくてすみます。サイクル単位で制限を行う電流モード・スイッチング技術を使用して、高い信頼性とシンプルなループ周波数補償を実現しています。

LT1786Fは16ピン細型SOパッケージで供給されます。

**LTC**、LTC、LTはリニアテクノロジー社の登録商標です。

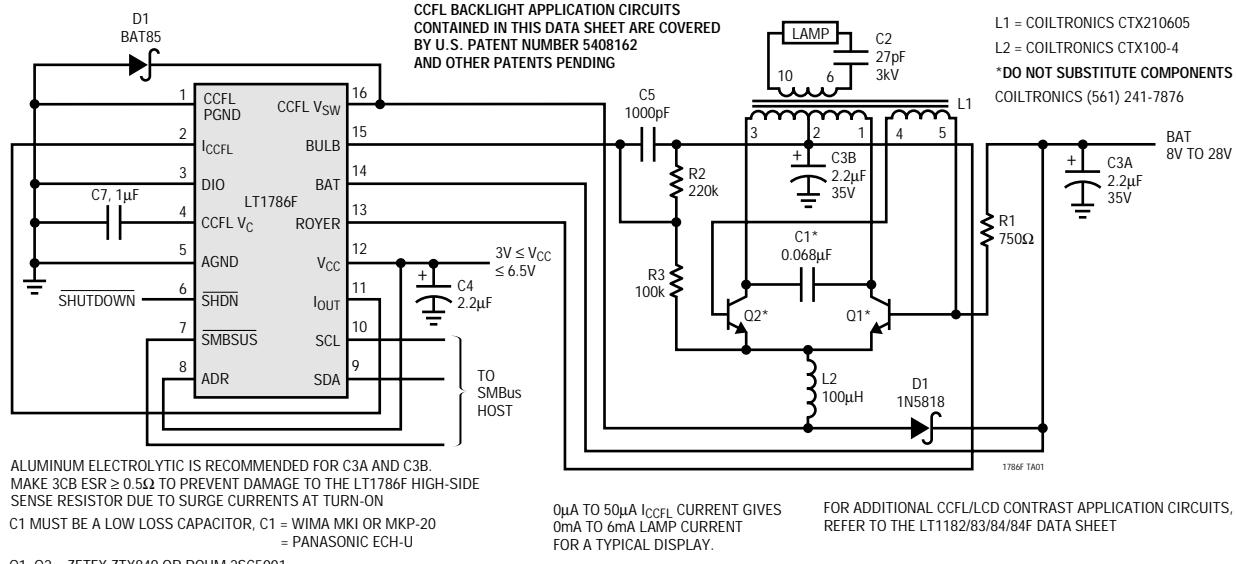

## 標準的応用例

### 2線式SMBusでランプ電流を制御する効率90%フローティングCCFL

**絶対最大定格**

|                      |                            |

|----------------------|----------------------------|

| $V_{CC}$             | 7V                         |

| BAT、Royer、BULB       | 30V                        |

| CCFL $V_{SW}$        | 60V                        |

| シャットダウン              | 6V                         |

| $I_{CCFL}$ 入力電流      | 10mA                       |

| DIO入力電流(ピーカ、100ms未満) | 100mA                      |

| デジタル入力               | -0.3V ~ ( $V_{CC}$ + 0.3V) |

| デジタル出力               | -0.3V ~ ( $V_{CC}$ + 0.3V) |

| DAC出力電圧              | -15V ~ ( $V_{CC}$ + 0.3V)  |

| 接合温度 (Note1)         | 100                        |

| 動作周囲温度範囲             | 0 ~ 70                     |

| 保存温度範囲               | -65 ~ 150                  |

| リード温度(半田付け、10秒)      | 300                        |

**パッケージ/発注情報**

| TOP VIEW                                                                                                                                                          |                                                                                                     | ORDER PART NUMBER |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------|

| CCFL PGND<br>1<br><br>I <sub>CCFL</sub><br>2<br><br>DIO<br>3<br><br>CCFL V <sub>C</sub><br>4<br><br>AGND<br>5<br><br>SHDN<br>6<br><br>SMBSUS<br>7<br><br>ADR<br>8 | 16 CCFL $V_{SW}$<br>15 BULB<br>14 BAT<br>13 ROYER<br>12 $V_{CC}$<br>11 $I_{OUT}$<br>10 SCL<br>9 SDA | LT1786FCS         |

S PACKAGE

16-LEAD PLASTIC SO

$T_{JMAX} = 100^{\circ}\text{C}$ ,  $\theta_{JA} = 100^{\circ}\text{C/W}$

インダストリアルおよびミリタリ・グレードに関してはお問い合わせください。

**電気的特性**

注記がない限り、 $T_A = 25^{\circ}\text{C}$ 、 $V_{CC} = \overline{\text{SHUTDOWN}} = \overline{\text{SMBSUS}} = \overline{\text{SCL}} = \overline{\text{SDA}} = 3.3\text{V}$ 、 $\text{BAT} = \text{Royer} = \text{BULB} = 12\text{V}$ 、 $I_{CCFL}$ および $\text{CCFL } V_{SW}$ はオープン、DIOおよび $I_{OUT}$ はグランド、 $\text{CCFL } V_C = 0.5\text{V}$

4

| SYMBOL     | PARAMETER                                                                        | CONDITIONS                                                                                                              | MIN | TYP            | MAX            | UNITS                          |                           |

|------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|----------------|----------------|--------------------------------|---------------------------|

| $I_0$      | Supply Current                                                                   | $3\text{V} \leq V_{CC} \leq 6.5\text{V}$ , $I_{OUT} = 0\mu\text{A}$                                                     | ●   | 6              | 9.5            | mA                             |                           |

| ISUS       | SMBSUS Supply Current                                                            | $\overline{\text{SMBSUS}} = 0\text{V}$ or Command Code Bit 7 = 1,<br>$\text{CCFL } V_C = \text{Open}$ (Note 2)          | ●   | 40             | 100            | $\mu\text{A}$                  |                           |

| $I_{SHDN}$ | SHUTDOWN Supply Current                                                          | SHUTDOWN = 0V, $\text{CCFL } V_C = \text{Open}$ (Note 2)                                                                | ●   | 150            | 300            | $\mu\text{A}$                  |                           |

|            | SHUTDOWN Input Bias Current                                                      | SHUTDOWN = 0V, $\text{CCFL } V_C = \text{Open}$                                                                         |     | 5              | 10             | $\mu\text{A}$                  |                           |

|            | SHUTDOWN Threshold Voltage                                                       |                                                                                                                         | ●   | 0.45           | 0.85           | 1.2                            | V                         |

| f          | Switching Frequency                                                              | Measured at CCFL $V_{SW}$ , $I_{SW} = 50\text{mA}$ ,<br>$I_{CCFL} = 100\mu\text{A}$ , $\text{CCFL } V_C = \text{Open}$  | ●   | 175<br>160     | 200<br>200     | 225<br>240                     | kHz<br>kHz                |

| DC(MAX)    | Maximum Switch Duty Cycle                                                        | Measured at CCFL $V_{SW}$                                                                                               | ●   | 80<br>75       | 85<br>85       | %<br>%                         |                           |

| BV         | Switch Breakdown Voltage                                                         | Measured at CCFL $V_{SW}$                                                                                               |     | 60             | 70             | V                              |                           |

|            | Switch Leakage Current                                                           | $V_{SW} = 12\text{V}$ , Measured at CCFL $V_{SW}$<br>$V_{SW} = 30\text{V}$ , Measured at CCFL $V_{SW}$                  |     |                | 20<br>40       | $\mu\text{A}$<br>$\mu\text{A}$ |                           |

|            | $I_{CCFL}$ Summing Voltage                                                       | $3\text{V} \leq V_{CC} \leq 6.5\text{V}$                                                                                | ●   | 0.425<br>0.385 | 0.465<br>0.465 | 0.505<br>0.555                 | V<br>V                    |

|            | $\Delta I_{CCFL}$ Summing Voltage for $\Delta I_{Input}$ Programming Current     | $I_{CCFL} = 0\mu\text{A}$ to $100\mu\text{A}$                                                                           |     |                | 5<br>15        | mV                             |                           |

|            | CCFL $V_C$ Offset Sink Current                                                   | $\text{CCFL } V_C = 1.5\text{V}$ , Positive Current Measured into Pin                                                   |     | -5             | 5              | 15                             | $\mu\text{A}$             |

|            | $\Delta I_{CCFL}$ $V_C$ Source Current for $\Delta I_{CCFL}$ Programming Current | $I_{CCFL} = 25\mu\text{A}$ , $50\mu\text{A}$ , $75\mu\text{A}$ , $100\mu\text{A}$ ,<br>$\text{CCFL } V_C = 1.5\text{V}$ | ●   | 4.70           | 4.95           | 5.20                           | $\mu\text{A}/\mu\text{A}$ |

|            | CCFL $V_C$ to DIO Current Servo Ratio                                            | DIO = 5mA out of Pin, Measure $I(V_C)$ at $\text{CCFL } V_C = 1.5\text{V}$                                              | ●   | 94             | 99             | 104                            | $\mu\text{A}/\text{mA}$   |

|            | CCFL $V_C$ Low Clamp Voltage                                                     | $V_{BAT} - V_{BULB} = \text{BULB Protect Servo Voltage}$                                                                | ●   |                | 0.1            | 0.3                            | V                         |

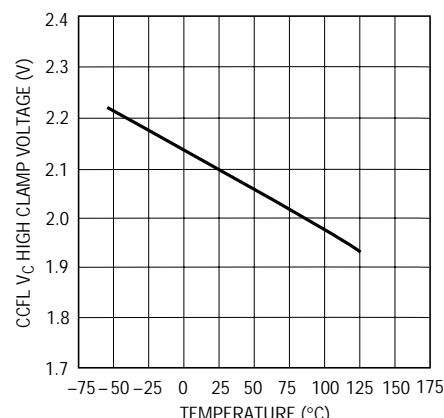

|            | CCFL $V_C$ High Clamp Voltage                                                    | $I_{CCFL} = 100\mu\text{A}$                                                                                             | ●   | 1.7            | 2.1            | 2.4                            | V                         |

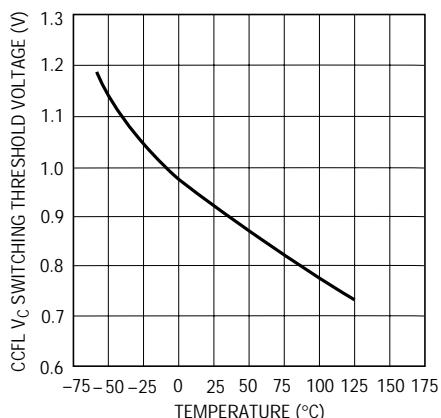

|            | CCFL $V_C$ Switching Threshold                                                   | $\text{CCFL } V_{SW}$ DC = 0%                                                                                           | ●   | 0.6            | 0.95           | 1.3                            | V                         |

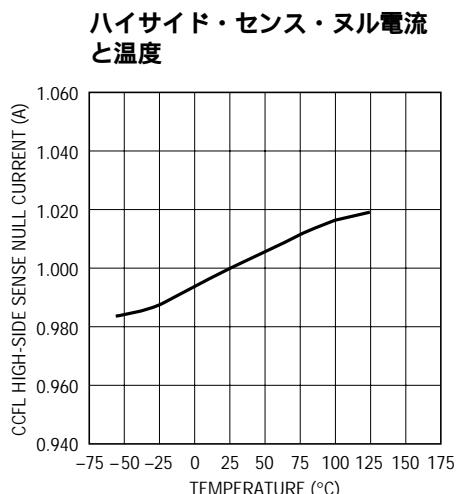

|            | CCFL High-Side Sense Servo Current                                               | $I_{CCFL} = 100\mu\text{A}$ , $I(V_C) = 0\mu\text{A}$ at $\text{CCFL } V_C = 1.5\text{V}$                               | ●   | 0.93           | 1.00           | 1.07                           | A                         |

## 電気的特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{CC} = \overline{\text{SHUTDOWN}} = \overline{\text{SMBSUS}} = \overline{\text{SCL}} = \overline{\text{SDA}} = 3.3\text{V}$ 、 $\text{BAT} = \text{Royer} = \text{BULB} = 12\text{V}$ 、 $I_{CCFL}$ および $\text{CCFL } V_{SW}$ はオーブン、DIOおよび $I_{OUT}$ はグランド、CCFL  $V_C = 0.5\text{V}$

| SYMBOL                             | PARAMETER                                          | CONDITIONS                                                                                                                           | MIN         | TYP                          | MAX        | UNIT                 |

|------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------|------------|----------------------|

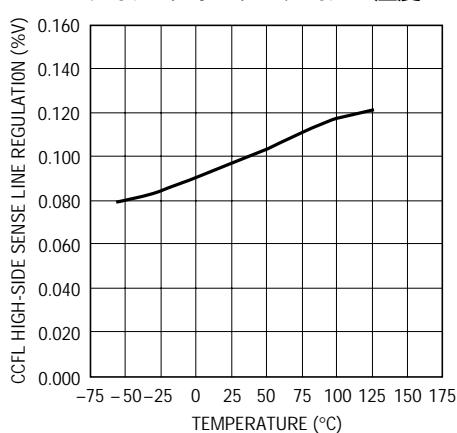

|                                    | CCFL High-Side Sense Servo Current Line Regulation | BAT = 5V to 30V, $I_{CCFL} = 100\mu\text{A}$ , $I(V_C) = 0\mu\text{A}$ at CCFL $V_C = 1.5\text{V}$                                   |             | 0.1                          | 0.16       | %/V                  |

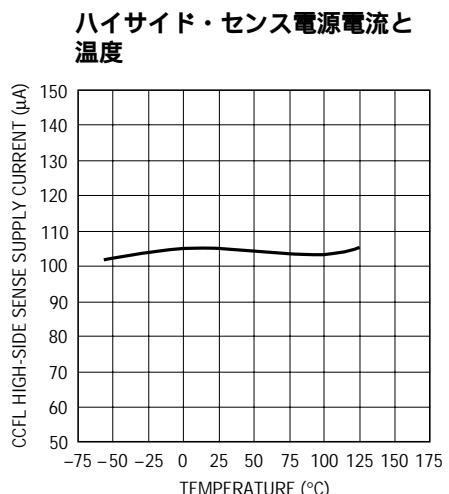

|                                    | CCFL High-Side Sense Supply Current                | Current Measured into BAT and Royer Pins                                                                                             | ●           | 50                           | 100        | 150                  |

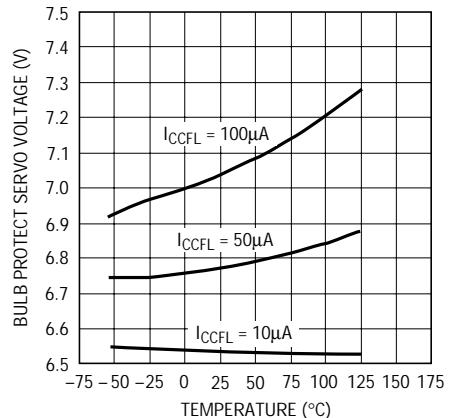

|                                    | BULB Protect Servo Voltage                         | $I_{CCFL} = 100\mu\text{A}$ , $I(V_C) = 0\mu\text{A}$ at CCFL $V_C = 1.5\text{V}$ , Servo Voltage Measured between BAT and BULB Pins | ●           | 6.5                          | 7.0        | 7.5                  |

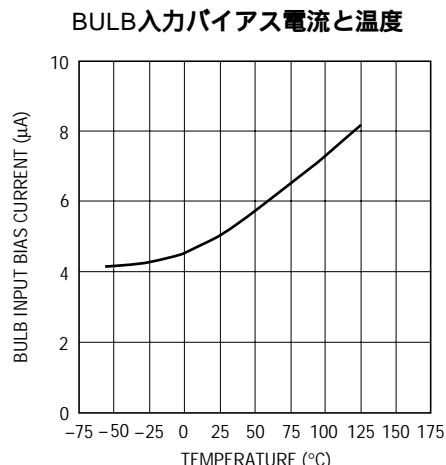

|                                    | BULB Input Bias Current                            | $I_{CCFL} = 100\mu\text{A}$ , $I(V_C) = 0\mu\text{A}$ at CCFL $V_C = 1.5\text{V}$                                                    |             | 5                            | 9          | $\mu\text{A}$        |

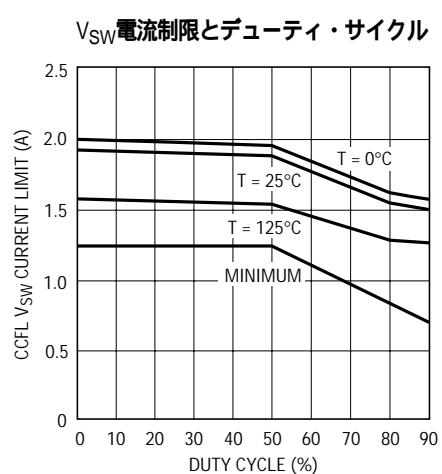

| $I_{LIM}$                          | CCFL Switch Current Limit                          | Duty Cycle = 50%<br>Duty Cycle = 75% (Note 3)                                                                                        | ●<br>●      | 1.25<br>0.9                  | 1.9<br>1.6 | A                    |

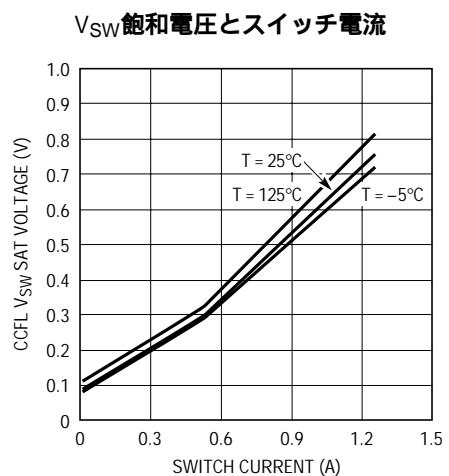

| $V_{SAT}$                          | CCFL Switch On Resistance                          | CCFL $I_{SW} = 1\text{A}$                                                                                                            | ●           | 0.6                          | 1.0        | $\Omega$             |

| $\frac{\Delta I_O}{\Delta I_{SW}}$ | Supply Current Increase During CCFL Switch On Time | CCFL $I_{SW} = 1\text{A}$                                                                                                            |             | 20                           | 30         | $\text{mA}/\text{A}$ |

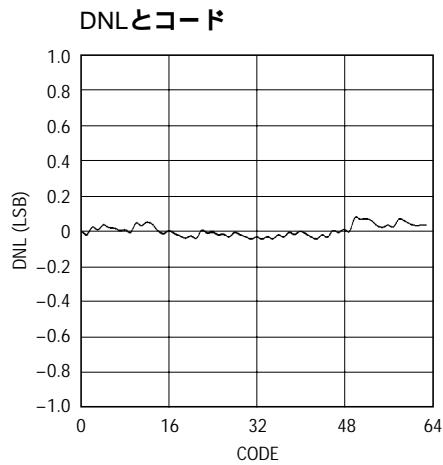

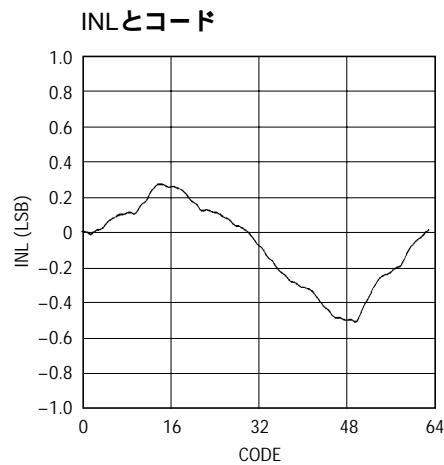

|                                    | DAC Resolution                                     |                                                                                                                                      |             | 6                            |            | Bits                 |

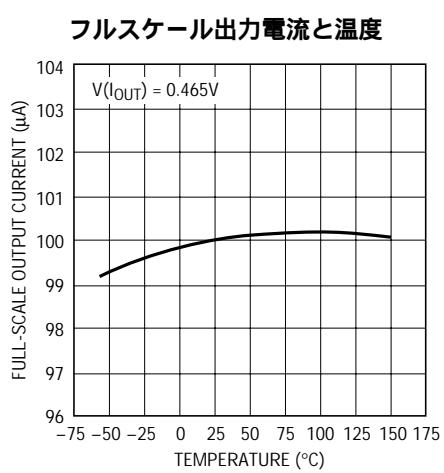

|                                    | DAC Full-Scale Current                             | $V(I_{OUT}) = 0.465\text{V}$                                                                                                         | ●<br>●      | 98<br>96                     | 100<br>100 | $\mu\text{A}$        |

|                                    | DAC Zero Scale Current                             | $V(I_{OUT}) = 0.465\text{V}$                                                                                                         | ●           |                              | $\pm 200$  | nA                   |

|                                    | DAC Differential Nonlinearity                      |                                                                                                                                      | ●           |                              | $\pm 0.1$  | $\pm 1$              |

|                                    | DAC Supply Voltage Rejection                       | $3\text{V} \leq V_{CC} \leq 6.5\text{V}$ , $I_{OUT}$ = Full Scale, $V(I_{OUT}) = 0.465\text{V}$                                      | ●           | 0.2                          | 2          | LSB                  |

| $I_{IN}$                           | Logic Input Current                                | $0\text{V} \leq V_{IN} \leq V_{CC}$                                                                                                  | ●           |                              | $\pm 1$    | $\mu\text{A}$        |

| $V_{IH}$                           | High Level Input Voltage                           | ADR<br>SMBSUS<br>SCL, SDA                                                                                                            | ●<br>●<br>● | $V_{CC} - 0.3$<br>2.4<br>1.4 |            | V                    |

| $V_{IL}$                           | Low Level Input Voltage                            | SMBSUS, ADR<br>SCL, SDA                                                                                                              | ●<br>●      |                              | 0.8<br>0.6 | V                    |

| $V_{OL}$                           | Low Level Output Voltage                           | $I_{OUT} = 3\text{mA}$ , <u>SDA Only</u><br>$I_{OUT} = 1.6\text{mA}$ , SMBSUS = 0V, Measured at SHDN Pin                             | ●<br>●      |                              | 0.4<br>0.4 | V                    |

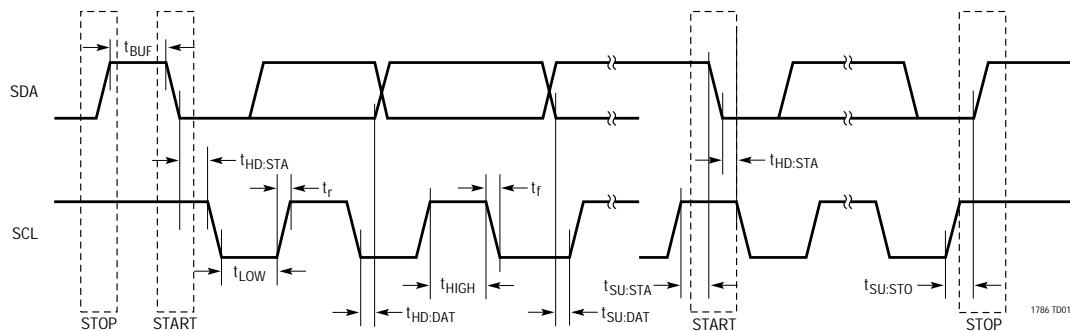

### SMBus Timing (Notes 4, 5)

|              |                                                |   |     |      |               |

|--------------|------------------------------------------------|---|-----|------|---------------|

| $f_{SMB}$    | SMB Operating Frequency                        | ● | 10  | 100  | kHz           |

| $t_{BUF}$    | Bus Free Time Between Stop and Start Condition | ● | 4.7 |      | $\mu\text{s}$ |

| $t_{HD:STA}$ | Hold Time After (Repeated) Start Condition     | ● | 4.0 |      | $\mu\text{s}$ |

| $t_{SU:STA}$ | Repeated Start Condition Setup Time            | ● | 4.7 |      | $\mu\text{s}$ |

| $t_{SU:STO}$ | Stop Condition Setup Time                      | ● | 4.0 |      | $\mu\text{s}$ |

| $t_{HD:DAT}$ | Data Hold Time                                 | ● | 300 |      | ns            |

| $t_{SU:DAT}$ | Data Setup Time                                | ● | 250 |      | ns            |

| $t_{LOW}$    | Clock Low Period                               | ● | 4.7 |      | $\mu\text{s}$ |

| $t_{HIGH}$   | Clock High Period                              | ● | 4.0 | 50   | $\mu\text{s}$ |

| $t_f$        | Clock/Data Fall Time                           | ● |     | 300  | ns            |

| $t_r$        | Clock/Data Rise Time                           | ● |     | 1000 | ns            |

●は全規定温度範囲の規格値を意味する。

Note 1 :  $T_J$ は周囲温度 $T_A$ と消費電力 $P_D$ から、次の式で計算される：

LT1786FCS :  $T_J = T_A + (P_D \times 100 \text{ mW})$

Note 2 : スイッチ・リーグは含まない。

Note 3: デューティ・サイクル(DC)が50%~80%の場合、LT1786Fの最小保証スイッチ電流は、内部スロープ補償回路により $I_{LIM} = 1.4(1.393 - DC)$ で与えられる。

Note 4: すべての信号のタイミングは、 $V_{IH}$ 信号および $V_{IL}$ 信号を基準とする。

Note 5: このパラメータは設計により保証されているが、製造工程でテストされていない。詳細は、タイミング図を参照のこと。

## 標準的性能特性

**電源電流と温度**

1786 G01

**ISUS電流と温度**

1786 G02

**SHDN電源電流と温度**

1786 G03

4

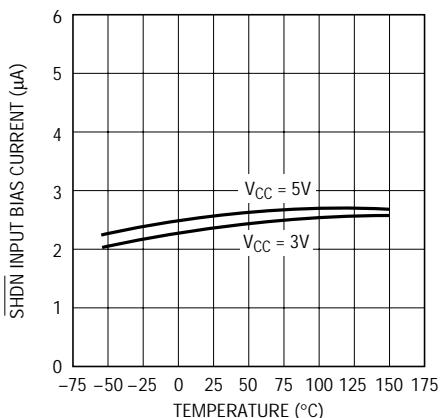

**SHDN入力バイアス電流と温度**

1786 G04

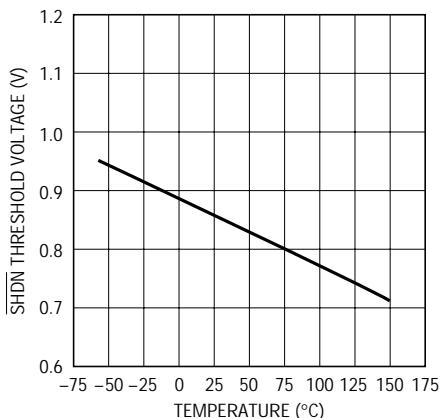

**SHDNスレッショルド電圧と温度**

1786 G05

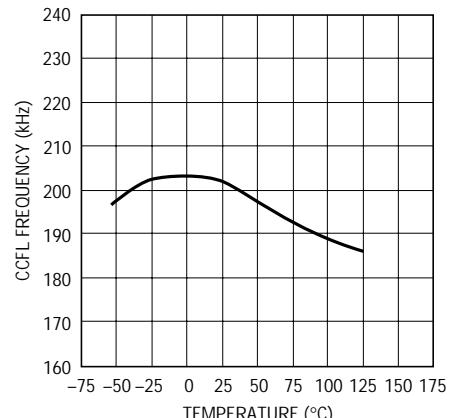

**周波数と温度**

1786 G06

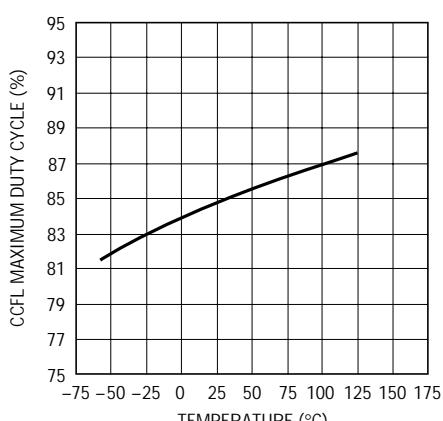

**最大デューティ・サイクルと温度**

1786 G07

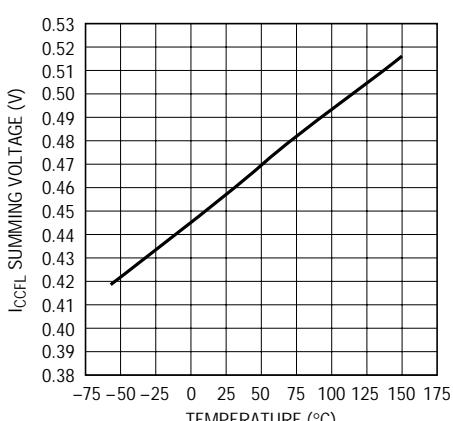

**I<sub>CCFL</sub>加算電圧と温度**

1786 G08

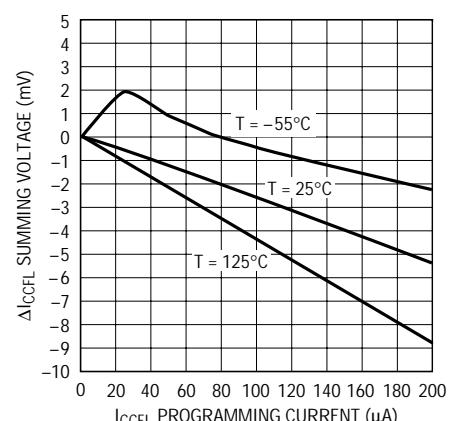

**I<sub>CCFL</sub>加算電圧とロード・レギュレーション**

1786 G09

## 標準的性能特性

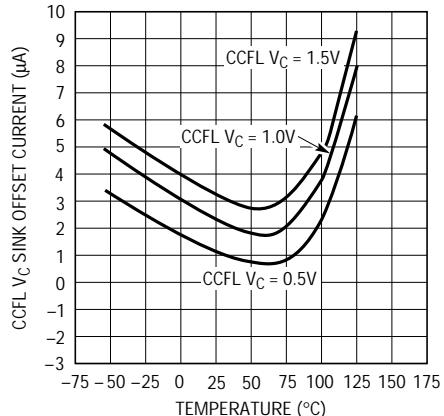

V<sub>C</sub>シンク・オフセット電流と

温度

1786 G10

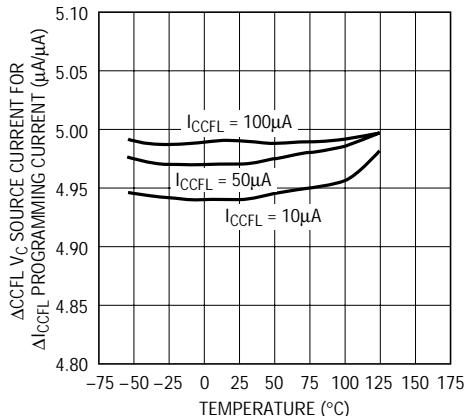

△I<sub>CCFL</sub>プログラミング電流に

対応する△CCFL V<sub>C</sub>ソース電流と

温度

1786 G11

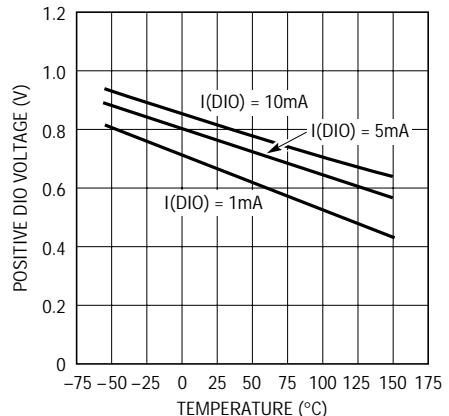

正DIO電圧と温度

1786 G12

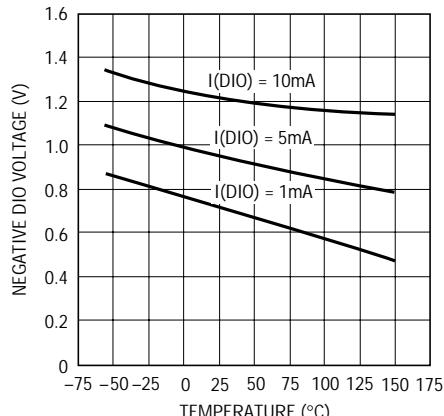

負DIO電圧と温度

1786 G13

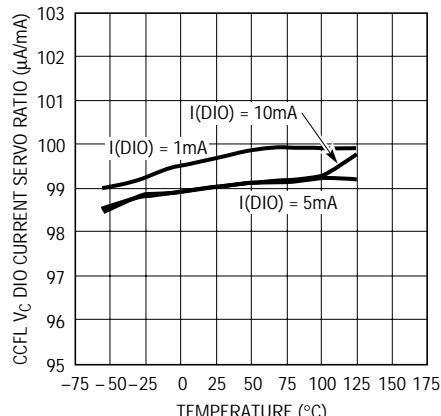

V<sub>C</sub>対DIOの電流サーボ比と温度

1786 G14

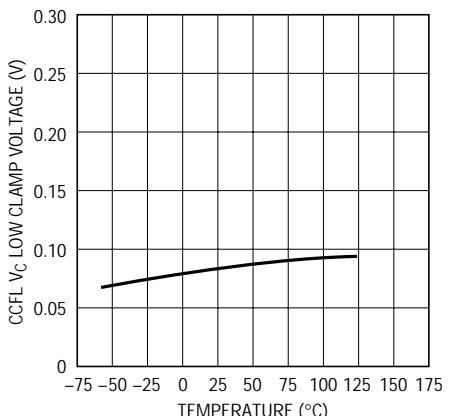

V<sub>C</sub>ロー・クランプ電圧と温度

1786 G15

V<sub>C</sub>ハイ・クランプ電圧と温度

1786 G16

V<sub>C</sub>スイッチング・スレッショルド

と温度

1786 G17

BULB保護サー保電圧と温度

1786 G18

## 標準的性能特性

1787 G19

1786 G20

1786 G21

1786 G22

1787 G23

1786 G24

1786 G25

1786 G26

## 標準的性能特性

1786 G27

1786 G28

## ピン機能

CCFL PGND( ピン1 ): このピンは内部NPNパワースイッチのエミッタです。CCFLスイッチ電流がこのピンを流れ、内部スイッチ電流を検知することができます。レギュレータは高電流グランド経路を低電流信号経路から分離するために、アナログ・グランドとパワー・グランドを別々に提供します。リニアテクノロジーは、星状グランド・レイアウト手法を推奨しています。

$I_{CCFL}$ ( ピン2 ): このピンはCCFLランプ電流プログラミング回路の入力です。このピンは内部で465mVに安定化します。また、DACから $0\mu A \sim 100\mu A$ のフルスケールのDC入力電流信号を受け入れます。この入力信号はCCFL  $V_C$ ピンで $0\mu A \sim 500\mu A$ のソース電流に変換されます。入力プログラミング電流が増加すると、安定化されたランプ電流が増加します。

DIO( ピン3 ): このピンは2個の内部ダイオードのカソードとアノード間の共通接続点です。2個のダイオードの残りの端子はグランドに接続します。接地ランプ構成では、DIOはランプの低電圧側に接続します。双方向ランプ電流がDIOピンを流れ、2個のダイオードが半サイクルごとに交互に導通します。ランプ電流は、平均ランプ電流の半分をモニタして制御されます。負の半サイクルで導通するダイオードが電流の1/10をCCFL  $V_C$ ピンに分流し、ランプ電流プログラマ回路から供給されるソース

電流をゼロにします。CCFL  $V_C$ ピンの1個のコンデンサは、安定したループ補償を行うだけでなく、半波整流された正弦波ランプ電流を平均化する機能も備えています。したがって、入力プログラミング電流は、平均ランプ電流の半分になります。この方式によりループ補償部品が削減され、以前に公表された回路と比較して、より高速なループ過渡応答を実現することができます。フローティング・ランプ構成を使用する場合、DIOピンはグランドに接続してください。

CCFL  $V_C$ ( ピン4 ): このピンはランプ電流プログラマ回路の出力であり、またCCFLレギュレータ用の電流コンバレータ入力でもあります。周波数補償、接地ランプ回路のためのランプ電流平均化、および電流制限に使用されます。CCFL  $V_C$ ピンの電圧でスイッチをターンオフするための電流トリップ・レベルが決まります。通常動作中は、このピンの電圧はアナログ・グランド(AGND)を基準にして、0.95V(スイッチ電流ゼロ)から2.1V(最大スイッチ電流)の範囲にあります。このピンはハイ・インピーダンス出力を備えており、電流制限を調整する外部電圧をクランプすることができます。1個のコンデンサをグランドに接続すれば、安定したループ補償を提供します。この簡略ループ補償方法により、CCFLレギュレータは単ポールの過渡特性動作が可能であり、実質上トランジスタ出力でオーバーシュートは発生しません。

## ピン機能

**AGND( ピン5 ):** これは低電流アナログ・グランドです。このピンは内部1.24Vリファレンスの負センス端子で、LT1786Fでは $I_{CCFL}$ の加算電圧となっています。最良のレギュレーションと性能を実現するには、グランドに終端される低電流信号経路と、グランドに終端される周波数補償部品をこのピンに直接接続してください。

**SHDN( ピン6 ):** このピンを“L”にするとレギュレータが完全にシャットダウンして、消費電流は標準で約150μAに減少します。この状態では、DAC回路はアクティブのままであり、DAC  $I_{OUT}$  レベルが維持されます。このピンを使用しない場合は、プルアップ抵抗を使用して強制的に“H”レベル( 最大6V )にしてください。このピンをフロート状態にすると、内部電流源がピンをロジック“H”レベルに引き上げます。ただし、PCBレイアウト手法に不備があると、スイッチング・ノイズがこのピンに入り、誤動作を引き起こすことがあります。そのため、リニアテクノロジーではプルアップ抵抗の使用を推奨しています。SMBUS<sub>S</sub>ピンを“L”にするとか、またはコマンド・バイトでビット7=1にすれば、ICは完全にシャットダウンします。内部オープン・ドレインNチャネル・デバイスはターンオンし、SHDNピンを“L”にします。このNチャネル・デバイスは最大1.6mAをシンク可能です。

**SMBUS<sub>S</sub>( ピン7 ):** このピンを“L”にすると、ICは完全にシャットダウンし、消費電流は標準40μAまで低下します。このSMBusサスPEND状態では、DACは直前の出力電流設定値を保持し、SMBUS<sub>S</sub>ピンの“L”信号がなくなると、そのレベルに復帰します。このピンを使用しない場合は、プルアップ抵抗を使用して強制的に“H”レベルにするか、直接 $V_{CC}$ に接続してください。PCBレイアウト手法に不備があると、スイッチング・ノイズがこのピンに入り、誤動作を引き起こすことがあります。このノイズをフィルタするために、小さな値のコンデンサが必要なこともあります。コマンド・バイトでビット7=1と設定しても、SMBusサスPEND状態がイネーブルされます。SMBusサスPEND状態をイネーブルすると、内部オープン・ドレインNチャネル・デバイスがターンオンし、SHDNピンを“L”にします。Nチャネル・デバイスは、SHDNピンで最大1.6mAをシンクします。

**ADR( ピン8 ):** これはSMBusアドレス選択ピンです。このピンを $V_{CC}$ またはGNDのどちらかに接続して、2つのSMBusアドレスからLT1786Fが応答するアドレスを1つ選択してください。ADRピンをGNDに接続すると、SMBusアドレスは

58 (HEX)に設定され、起動時にDAC  $I_{OUT}$  はゼロ・スケールになります。ADRピンを $V_{CC}$ に接続すると、SMBusアドレスは5A (HEX)に設定され、起動時にDAC  $I_{OUT}$  はハーフ・スケールになります。起動時のDAC  $I_{OUT}$  をその他の値にする必要がある場合は、SHDNピンを使用して、SMBusを通してDACに所要値がプログラムされるまでCCFLレギュレータをオフにしておいてください。

**SDA( ピン9 ):** これはSMBusの双方向データ入力およびデジタル出力ピンです。データはSDAピンにシフトされ、SDAピンによって認識応答されます。データがSDAピンにシフトされている間はハイ・インピーダンス状態になり、認識応答中はオープン・ドレインNチャネル出力になります。SDAには $V_{CC}$ へのプルアップ抵抗または電流源が必要です。

**SCL( ピン10 ):** これはSMBusクロック入力ピンです。データ転送中はSCLクロックの立上りエッジでデータがSDAピンにシフトされます。SCLはハイ・インピーダンス・ピンです。SCLには $V_{CC}$ へのプルアップ抵抗または電流源が必要です。

**$I_{OUT}$ ( ピン11 ):** このピンはDACの電流出力であり、全温度範囲にわたって $100\mu A \pm 4\mu A$ の出力電流を供給します。初期精度は $100\mu A \pm 2\mu A$ で、-10Vから( $V_{CC} - 1.3V$ )の範囲でバイアスすることができます。このピンは標準では $I_{CCFL}$ ピンに直接接続され、動作ランプ電流を設定するプログラミング電流を供給します。 $I_{CCFL}$ は安定化されているため、 $I_{OUT}$ ピンを $I_{CCFL}$ ピンに接続すれば、 $I_{OUT}$ ピンではほとんどバイアス電圧は変化しません。プログラミング電流は $I_{OUT}$ ピンから供給され、 $I_{CCFL}$ ピンでシンクされます。

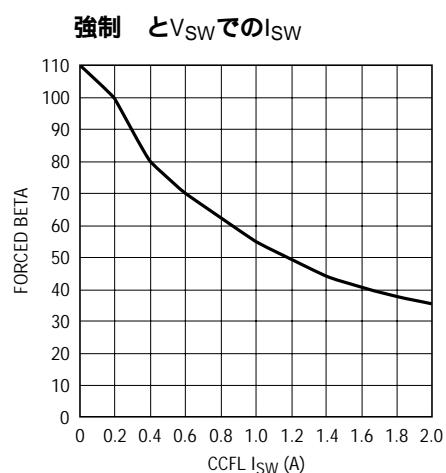

**$V_{CC}$ ( ピン12 ):** これはLT1786Fの電源ピンです。このICは3V(最小)から6.5V(最大)の入力電圧範囲の電圧を受け入れますが、静止動作電流(スイッチ電流ゼロ)はほとんど変化しません。低損失内部レギュレータが大部分の内部回路に2.4V電源を供給します。消費電流は、スイッチ電流の増加の約1/50の割合で増加します。これはパワー・スイッチの強制が50であるためです。このICはレギュレータ・ドロップアウトを検知すると、2.5V以下の入力電圧のスイッチングをロックアウトする低電圧ロックアウトを内蔵しています。入力電圧範囲を最大にするためにヒステリシスは使用されていません。標準入力電圧は3.3Vまたは5Vのロジック用電源です。

## ピン機能

ROYER( ピン13 ): このピンはRoyerコンバータの一次側センタタップに接続され、BATピンとともにフローティング・ランプ構成で使用されます。フローティング・ランプ構成では、ランプ電流はRoyerコンバータの一次側コンバータ電流を検知して制御されます。このピンはハイサイド電流センス・アンプの反転端子です。このピンには標準 $50\mu A$ の消費電流が流入します。CCFLレギュレータをフローティング・ランプ構成で使用していない場合は、RoyerピンとBATピンを連結してください。

BAT( ピン14 ): このピンは、CCFL Royerコンバータを動作させるバッテリ電圧またはACアダプタ電圧に接続します。この電圧は一般に $V_{CC}$ 電源電圧より高くなります。しかし、BAT電圧は内部2.4Vレギュレータ電圧より、最低でも2.1V高くしなければなりません(つまり4.5V以上)。このピンは、ランプ電流プログラミング・ブロックにバイアスを供給し、Royerピンとともにフローティング・ランプ構成に使用され、オープン・ランプ保護回路の1つの入力に接続します。フローティング・ランプ構成の場合、このピンはハイサイド電流センス・アンプの非反転端子です。このピンには標準 $50\mu A$ の消費電流が流入します。BATおよびRoyerピンは内部0.1Aのトップサイド電流センス抵抗を通して、一次側Royerコンバータ電流をモニタします。0A～1Aの一次側センタタップ・コンバータ電流は、0mV～100mVの入力信号範囲に変換され、電流センス・アンプに供給されます。この入力範囲はCCFL  $V_C$ ピンで $0\mu A$ から $500\mu A$ のシンク電流に変換され、プログラマ回路から供給されるソース電流をゼロ調整します。また、BATピンはBATピンとオープンランプ保護に使用されるBULBピンの間にある内部クランプのトップサイドにも接続されています。

BULB( ピン15 ): このピンはBATピンとBULBピンの間に接続された7Vスレッショルド・コンパレータの下側に接続されています。この回路は、全動作条件においてRoyerコンバータの一次側にかかる最大電圧レベルを設定し、起動時またはオープン・ランプ状態での最大二次側出力を制限します。これによって、トランスの電圧定格条件が緩和されます。ワーストケースでのランプ開始電圧および低温、システム動作条件でのランプの起動を保証するための電圧制限を設定してください。BULBピンは外部分割器の接合点に接続されます。この分割器はRoyerトランスのセンタタップまたは実際のバッテリ電源電圧から電流ソース「テール・インダクタ」のトップサイドに接続されています。分割器のトップに接続されたコンデンサは、スイッチング・リップルをフィルタし、クランプを起動する速度を決定する時定数を設定します。コンパレータが起動すると、シンク電流が生成されてCCFL  $V_C$ ピンをプルダウンします。これによって、レギュレータ・ループ全体が電流モード動作から電圧モード動作に切り替わります。

CCFL  $V_{SW}$ ( ピン16 ): このピンはCCFLレギュレータ用の内部NPNパワー・スイッチのコレクタです。パワー・スイッチは最小1.25Aを供給します。内部スロープ補償により50%以上のデューティ・サイクルでの安定動作が保証されているため、最大スイッチ電流はデューティ・サイクルによって決まります。スイッチを準飽和状態に保持するのに必要な最小値にベース・ドライバ電流を自動的に適合させるドライバ・ループを用いて、高速スイッチング時間と高効率動作を実現しています。スイッチ電流とドライバ電流の比は約50:1です。

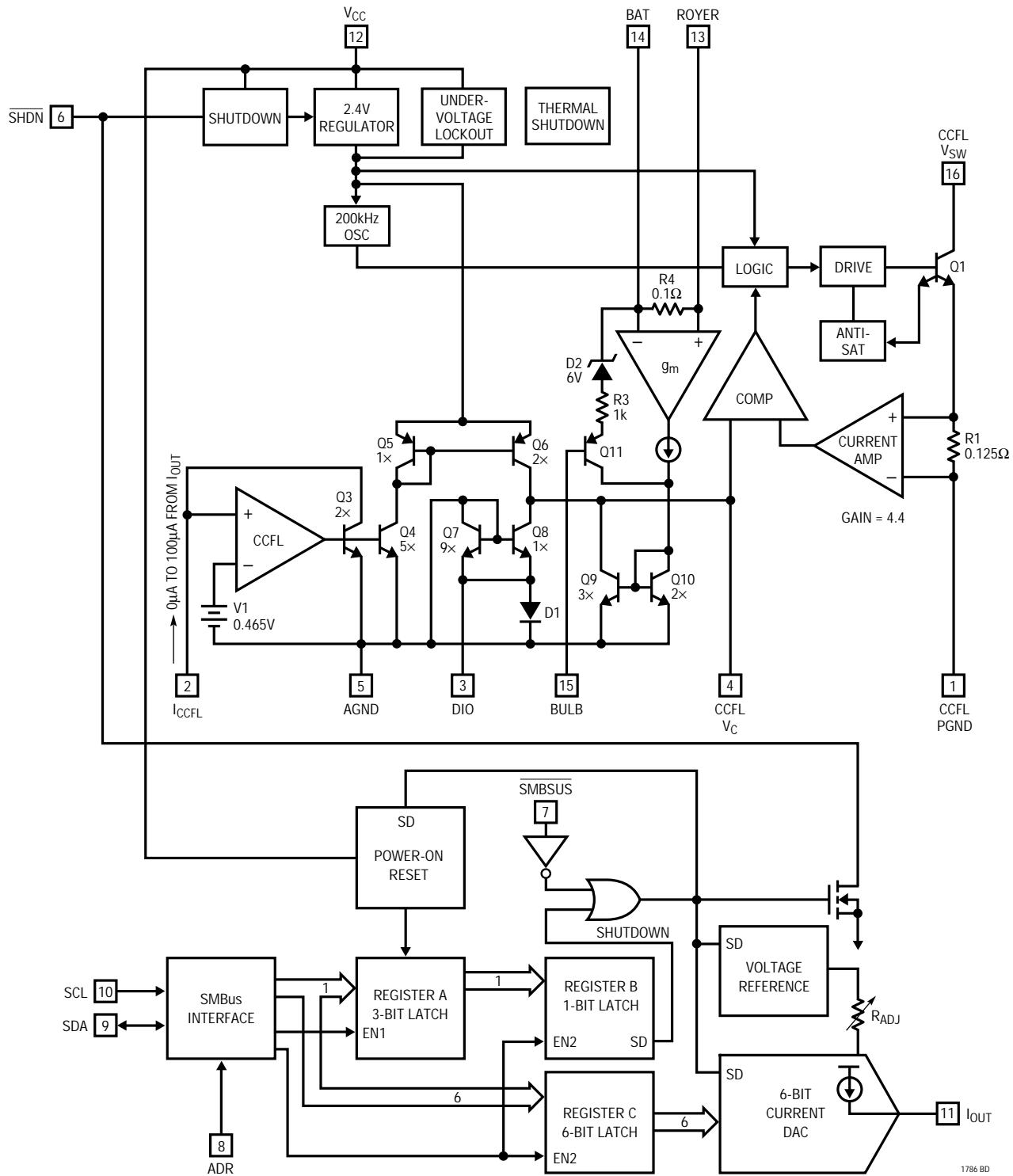

## プロック図

LT1786F、SMBusプログラマブルCCFLスイッチング・レギュレータ

## タイミング図

SMBusインターフェースのタイミング

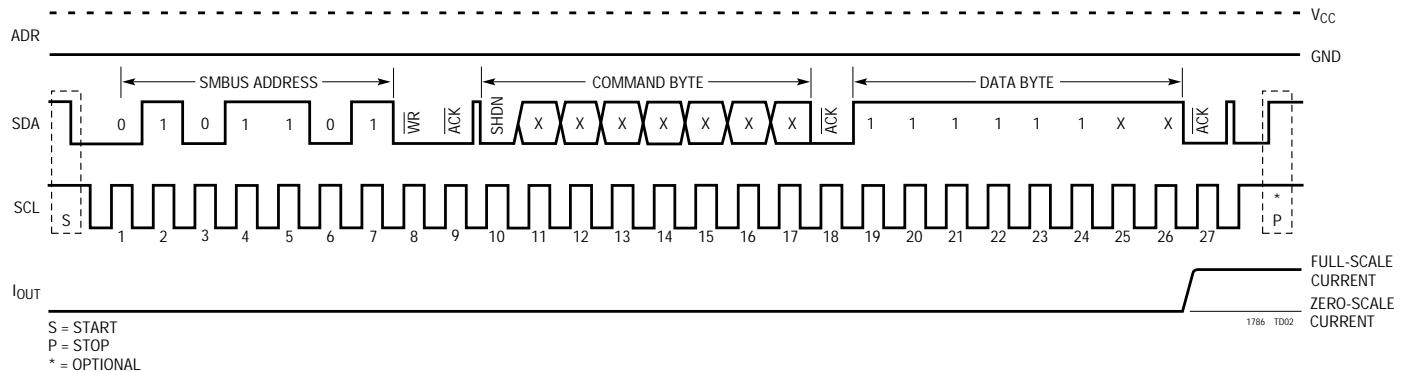

## 動作シーケンス

SMBusライト・バイト・プロトコル(SMBusアドレス = 0101101B、

コマンド・バイト = 0XXXXXXXXB、データ・バイト = 111111XXBの場合)

## アプリケーション情報

## はじめに

現世代のポータブル・コンピュータや携帯用機器では、バックライト式の液晶ディスプレイ(LCD)が使用されています。冷陰極蛍光管(CCFL)は、ディスプレイのバックライトに最高の効率を提供します。最重要目標は、最小限の入力電力で最大の明度を提供することです。これらのランプは動作時に高電圧ACが必要なため、高効率の高電圧DC/ACコンバータが不可欠です。ランプはDCでも動作しますが、マイグレーション効果によって損傷を受け寿命が短くなります。ランプ・ドライブには、DC成分が含まれてはなりません。コンバータは、高い効率に加えて、正弦波の形でランプ・ドライブを供給しなければなりません。これによって、EMIやRF放射

が抑えられます。このような放射が、他のデバイスに妨害を与えて、全体的な動作効率を低下させる可能性があります。正弦波CCFLドライブは、ランプでの電流 - 光変換を最大限に高めます。また、この回路はランプの輝度をヒステリシスや「ポップオン」なしで、ゼロから最大の明るさまで調整できなければなりません

LCDを備えた機器に必要な小型化やバッテリ駆動動作のために、これらの回路には部品点数の削減と高い効率が求められます。サイズの制約によって、回路アーキテクチャには厳しい制限が課され、またはバッテリ寿命を延長することも必要です。ラップトップ・コンピュータやハンドヘルド・ポータブル・コンピュータがその好例です。CCFLと

## アプリケーション情報

その電源がバッテリの消費電流のほぼ50%を占めることもあります。さらに、PCボードやハードウェアを含むすべての部品は、通常、高さが5mmから10mmに制限され、すべてLCDエンクロージャ内に収容できなければなりません。

CCFLレギュレータは、90%の高効率を達成する電流ドライブ型Royer級コンバータのスイッチト・モード電流ソースとなるインダクタをドライブします。制御ループはCCFL PWMに平均インダクタ電流を変調させて、ランプの電流を一定に維持します。この定電流値、つまりランプ輝度はプログラム可能です。このドライブ手法によって広範な輝度制御が実現します。また、独自のランプ電流プログラミング・ロックにより、接地またはフローティング・ランプ構成が可能です。接地ランプ回路は、実際のランプ電流の半分を直接検知します。フローティング・ランプ回路はRoyerコンバータの一次側電流を直接検知します。フローティング・ランプ回路はランプに対称的な差動ドライブを供給し、ランプ - フレーム間の浮遊容量による寄生損失を大幅に低減して、輝度範囲を拡大します。

### ブロック図の動作説明

LT1786Fは、固定周波数の電流モード・スイッチング・レギュレータです。固定周波数、電流モード・スイッチャは、スイッチのデューティ・サイクルを出力電圧ではなくスイッチ電流で直接制御します。LT1786Fのブロック図を参照すると、スイッチは発振器サイクルが開始するたびにターン“オン”し、スイッチ電流があらかじめ設定されたレベルに達するとターン“オフ”します。出力ランプ電流は、独自のプログラミング・ロックの出力を使用して、電流のトリップ・レベルを設定することによって制御されます。電流モード・スイッチング手法にはいくつかの利点があります。まず、入力電圧の変動に対する優れた除去を提供します。次にエネルギー蓄積インダクタでの中域周波数における90°の位相シフトが減少します。このため入力電圧または負荷条件が大きく変動する状態では、閉ループ周波数補償が簡素化されます。最後に、シンプルなパルス・バイ・パルス電流制限により、出力の過負荷または短絡回路条件下で最大のスイッチ保護を得ることができます。

LT1786Fは、大部分の内部回路に2.4V電源を供給する低損失内部レギュレータを内蔵しています。低損失設計により、入力電圧を3Vから6.5Vまで変化させても、消費電流はほとんど変化しません。アクティブ“L”のシャットダウン・ピンは、2.4Vレギュレータをシャットオフし

て全電源電流を標準150μAに低減し、スタンバイ動作のスイッチング動作をロックアウトします。このICには、レギュレータのドロップアウトを検知すると約2.5V以下のスイッチングをロックアウトする低電圧ロックアウトが内蔵されています。レギュレータは、接合部温度が過剰なときにスイッチングをロックアウトするサーマル・シャットダウン保護回路も備えています。

200kHz発振器はすべての内部タイミングの基本クロックです。発振器は専用のロジックおよびドライバ回路を介して、出力スイッチをターンオンします。適応型アンチSAT回路はパワースイッチが飽和したことを検出すると、ベース・ドライブ電流を調整して、瞬時にスイッチの飽和状態を制限します。したがって、ドライバの消費電力が最小限に抑えられ、スイッチは非常に高速でターンオフします。LT1786FではCCFLパワー・スイッチが最小1.25Aの電流を供給することが保証されています。アンチSAT回路は、約50:1のスイッチ電流対ドライバ電流の比率を提供します。

4

### デジタル・インターフェース

LT1786Fは、標準2線SMBusインターフェースを使用してSMBusホストと通信します。タイミング図にSMBusの信号を示します。このバスが使用されていないときには、SDAとSCLの2つのバス・ラインは“H”でなければなりません。これらのラインには外部プルアップ抵抗または電流源が必要です。

LT1786Fは受信専用(スレーブ)デバイスです。マスタは以下のライト・バイト・プロトコルを使用してLT1786Fと通信しなければなりません：

|   |               |    |   |              |   |           |   |   |

|---|---------------|----|---|--------------|---|-----------|---|---|

| 1 | 7             | 1  | 1 | 8            | 1 | 8         | 1 | 1 |

| S | Slave Address | WR | A | Command Byte | A | Data Byte | A | P |

S=スタート条件、WR=ライト・ビット、A=アクノレッジ・ビット、P=ストップ条件

マスタは、START条件でLT1786Fとの通信を開始し(SMBus動作シーケンスを参照)7ビット・アドレスの後にライト・ビット=0が続きます。LT1786Fから認識応答が返ると、マスタはコマンド・バイトを送ります。LT1786Fは認識応答し、認識応答・パルスの立下りエッジで、コマンド・バイトのアクティブ・ビットをレジスタA(ブロック図を参照)にラッチします。マスタはデータ・バイトを送り、LT1786Fはデータ・バイトを認識応答します。データ・バイトは最終アクノレッジ・パルスの立下りエッジでレジスタCにラッチされ、DAC電流出

## アプリケーション情報

力は新しい6ビット・データの値となります( ブロック図を参照 )。STOP条件はオプションです。コマンド・コードとデータ・バイトは、以下の形式で定義されます：

| コマンド・コード |   |   |   |   |   |   |   | データ・バイト |    |    |    |    |    |   |   |

|----------|---|---|---|---|---|---|---|---------|----|----|----|----|----|---|---|

| 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7       | 6  | 5  | 4  | 3  | 2  | 1 | 0 |

| SHDN     | X | X | X | X | X | X | X | D5      | D4 | D3 | D2 | D1 | D0 | X | X |

SHDN : 0 = 通常動作、1 = シャットダウン

D5 ~ D0 : DAC データ・バイト・ビット、D5 = 最上位ビット

### STARTおよびSTOP条件

SMBus通信の開始時点で、マスタはSCLが“ H ”の間にSDAを“ H ”から“ L ”に切り替えてSTART条件を送信しなければなりません。マスタがスレーブ・デバイスとの通信を終了したら、SCLが“ H ”の間にSDAを“ L ”から“ H ”に切り替えてSTOP条件を送出します。これで、SMBusが解放され別のSMBusデバイスとの通信が可能になります。

### 早期STOP条件

LT1786FはSMBus通信シーケンスのどの時点でも、STOP条件を認識します。ライト・バイト・プロトコルでデータ・バイトが認識応答される前に、早期にSTOPが発生した場合、DAC出力電流値は更新されません。そうでない場合は、内部レジスタCが新しいデータで更新され、それに応じてDAC出力電流が変化します。

### スレーブ・アドレス

LT1786Fは、2つの7ビット・アドレスのうち1つに応答します。初め5ビットは製造時に01011にプログラムされています。最後の2ビットのアドレス・ビットは、ADRピンをV<sub>CC</sub>またはGND( 機能表を参照 )に接続してユーザがプログラムします。

| ADR             | SMBus ADDRESS | DAC POWER-UP VALUE |

|-----------------|---------------|--------------------|

| GND             | 0101101       | Zero Scale         |

| V <sub>CC</sub> | 0101100       | Midscale           |

### 6ビット電流出力DAC

6ビット電流出力DACは単調性が保証されており、63の等ステップでデジタル的に調整可能です。電源投入時にADRがV<sub>CC</sub>に接続される場合、6ビット内部レジスタC( ブロック図参照 )は100000Bにリセットされ、DAC出力はレンジの中間にセットされます。電源投入時にADRがグランドに接続される場合、レジスタCは000000Bにリセットされ、DAC出力はゼロにセットされます。LT1786Fの場合、電流源出力( I<sub>OUT</sub> )は - 10Vから( V<sub>CC</sub> - 1.3V )にバイアスすることができます。フルスケール電流は、室温では ± 2%に、コマーシャル温度範囲では ± 4%に調整されています。

### シャットダウン

LT1786Fをシャット・ダウンする方法は3つあります( ブロック図を参照 )。

ロジック“ L ”レベルをSHDNピンに印加するか、SMBus通信シーケンスのコマンド・バイトのビット7をロジック“ H ”にすると、LT1786FはSMBusサスペンド・モードに入ります。SMBusサスペンド・モードでは、電源電流は標準40μAまで低下し、直前の出力電流設定値が内部で保持されます。DACは通常動作に復帰するところのレベルになります。SMBusサスペンド状態にしても、オープン・ドレインNチャネルMOSFETがターンオンされ、SHDNピンが“ L ”になります。Nチャネル・デバイスはSHDNピンで最大1.6mAをシンクし、ロジック“ L ”レベルが0.4V以下になることが保証されます。

SHDNピンにロジック“ L ”を印加すると、LT1786Fはシャットダウン・モードに入ります。シャットダウン・モードでは、電源電流は標準150μAまで低下し、スイッチング・レギュレータ回路がシャットダウンされ、DACはアクティブのままでです。DAC出力電流設定は維持されます。この機能は、CCFLレギュレータがターンオンする前に、DACを所要出力電流レベル( 選択されたSMBusアドレスで定義されるプリセット・ゼロスケールまたは中間スケール以外 )にプログラムするのに使用できます。

## アプリケーション情報

### LT1786F SMBusルックアップ・テーブル

#### SMBusアドレス・バイト・テーブル

| ADR             | DECIMAL | BINARY  | HEX | I <sub>OUT</sub> POWER-UP VALUE |

|-----------------|---------|---------|-----|---------------------------------|

| GND             | 91      | 0101101 | 5A  | Zero Scale                      |

| V <sub>CC</sub> | 88      | 0101100 | 58  | Midscale                        |

SMBusアドレスのビット0(LSB)はライト・ビット=0

#### SMBusコマンド・バイト・テーブル

| DECIMAL | BINARY   | HEX   | I <sub>OUT</sub> (μA) |

|---------|----------|-------|-----------------------|

| 0       | 000000XX | 00-03 | 0.000                 |

| 1       | 000001XX | 04-07 | 1.587                 |

| 2       | 000010XX | 08-0B | 3.175                 |

| 3       | 000011XX | 0C-0F | 4.762                 |

| 4       | 000100XX | 10-13 | 6.349                 |

| 5       | 000101XX | 14-17 | 7.937                 |

| 6       | 000110XX | 18-1B | 9.524                 |

| 7       | 000111XX | 1C-1F | 11.111                |

| 8       | 001000XX | 20-23 | 12.698                |

| 9       | 001001XX | 24-27 | 14.286                |

| 10      | 001010XX | 28-2B | 15.873                |

| 11      | 001011XX | 2C-2F | 17.460                |

| 12      | 001100XX | 30-33 | 19.048                |

| 13      | 001101XX | 34-37 | 20.635                |

| 14      | 001110XX | 38-3B | 22.222                |

| 15      | 001111XX | 3C-3F | 23.810                |

| 16      | 010000XX | 40-43 | 25.397                |

| 17      | 010001XX | 44-47 | 26.984                |

| 18      | 010010XX | 48-4B | 28.571                |

| 19      | 010011XX | 4C-4F | 30.159                |

| 20      | 010100XX | 50-53 | 31.746                |

| 21      | 010101XX | 54-57 | 33.333                |

| 22      | 010110XX | 58-5B | 34.921                |

| 23      | 010111XX | 5C-5F | 36.508                |

| 24      | 011000XX | 60-63 | 38.095                |

| 25      | 011001XX | 64-67 | 39.683                |

| 26      | 011010XX | 68-6B | 41.270                |

| 27      | 011011XX | 6C-6F | 42.857                |

| 28      | 011100XX | 70-73 | 44.444                |

| 29      | 011101XX | 74-77 | 46.032                |

| 30      | 011110XX | 78-7B | 47.619                |

| 31      | 011111XX | 7C-7F | 49.206                |

X = 不問、I<sub>OUT</sub> = 理想値

#### SMBusデータ・バイト・テーブル

| DECIMAL | BINARY   | HEX   | MODE     |

|---------|----------|-------|----------|

| 0-127   | 0XXXXXXX | 00-7F | Normal   |

| 128-255 | 1XXXXXXX | 80-FF | Shutdown |

X = 不問

| DECIMAL | BINARY   | HEX   | I <sub>OUT</sub> (μA) |

|---------|----------|-------|-----------------------|

| 32      | 100000XX | 80-83 | 50.794                |

| 33      | 100001XX | 84-87 | 52.381                |

| 34      | 100010XX | 88-8B | 53.968                |

| 35      | 100011XX | 8C-8F | 55.556                |

| 36      | 100100XX | 90-93 | 57.143                |

| 37      | 100101XX | 94-97 | 58.730                |

| 38      | 100110XX | 98-9B | 60.317                |

| 39      | 100111XX | 9C-9F | 61.905                |

| 40      | 101000XX | A0-A3 | 63.492                |

| 41      | 101001XX | A4-A7 | 65.079                |

| 42      | 101010XX | A8-AB | 66.667                |

| 43      | 101011XX | AC-AF | 68.254                |

| 44      | 101100XX | B0-B3 | 69.841                |

| 45      | 101101XX | B4-B7 | 71.429                |

| 46      | 101110XX | B8-BB | 73.016                |

| 47      | 101111XX | BC-BF | 74.603                |

| 48      | 110000XX | C0-C3 | 76.190                |

| 49      | 110001XX | C4-C7 | 77.778                |

| 50      | 110010XX | C8-CB | 79.365                |

| 51      | 110011XX | CC-CF | 80.952                |

| 52      | 110100XX | D0-D3 | 82.540                |

| 53      | 110101XX | D4-D7 | 84.127                |

| 54      | 110110XX | D8-DB | 85.714                |

| 55      | 110111XX | DC-DF | 87.302                |

| 56      | 111000XX | E0-E3 | 88.889                |

| 57      | 111001XX | E4-E7 | 90.476                |

| 58      | 111010XX | E8-EB | 92.063                |

| 59      | 111011XX | EC-EF | 93.651                |

| 60      | 111100XX | F0-F3 | 95.238                |

| 61      | 111101XX | F4-F7 | 96.825                |

| 62      | 111110XX | F8-FB | 98.413                |

| 63      | 111111XX | FC-FF | 100.000               |

## アプリケーション情報

### ランプ電流の簡略プログラミング

LT1786Fのプログラミング・ブロックはランプ電流を制御し、接地ランプまたはフローティング・ランプ構成を可能にします。接地構成では、実際のランプ電流の半分を直接制御し、それを帰還信号に変換して制御ループをクローズすることによりランプ電流を制御します。フローティング構成では、Royerの一次側コンバータ電流を直接制御し、帰還信号を生成して制御ループをクローズし、ランプ電流を制御します。

従来のバックライト方式では、制御ループ内で古典的な誤差アンプを使用して、ランプ電流を一定にしていました。このアプローチでは、RMS電流をDC電圧に変換して、誤差アンプの入力に印加します。また、安定したループ周波数補償を提供するために、いくつかの時定数を使用しています。この補償方法では、ループ速度がかなり低速でなければならず、また起動時あるいは過負荷状態での出力オーバーシュートを、トランジスタのストレスやブレーカダウン電圧条件の観点から慎重に評価しなければなりませんでした。

LT1786Fは誤差アンプの概念を完全になくして、それをランプ電流のプログラミング・ブロックに置き換えます。このブロックは、ランプ電流をプログラムするために使いやすいインターフェースを提供します。プログラマ回路は、誤差信号の変換方式と周波数補償を1つのコンデンサに集約することによって、制御ループ内の時定数の数も削減します。制御ループは、単ポール・システムの応答を示し、より高速なループ過渡応答を可能にし、起動時または過負荷条件でのオーバーシュートを実質的になくします。

ランプ電流はプログラマ・ブロック( $I_{CCFL}$ ピン)の入力でプログラムされます。このピンはシャント・レギュレータの入力であり、DACから $0\mu A \sim 100\mu A$ のDC入力電流信号を受け取ります。この入力信号はCCFL  $V_C$ ピンで $0\mu A \sim 500\mu A$ のソース電流に変換されます。プログラマ回路は、単に利得5を有する電流/電流コンバータです。

$I_{CCFL}$ ピンは容量性負荷に敏感で、 $10pF$ 以上の容量で発振します。たとえば、 $I_{CCFL}$ ピンに $1\times$ または $10\times$ スコープのプローブの負荷を接続すると、プローブの入力容量のためにCCFLレギュレータは発振したり誤動作しま

す。また、 $I_{CCFL}$ ピンと直列に電流メータを接続しても、シャント容量のために発振します。過剰なトレス浮遊容量が存在する場合は、 $I_{CCFL}$ ピンと $I_{OUT}$ ピンの間に数kΩのデカップリング抵抗を使用してください。通常、この抵抗は必要ありません。

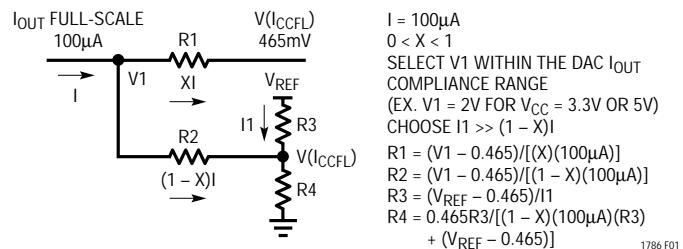

アプリケーションによっては、最大ランプ電流を得るために $I_{CCFL}$ ピンに必要な最大プログラミング電流は、DACのフルスケール出力電流である $100\mu A$ 以下になります。システム設計者は、システムに組み込まれたソフトウェアにより最大プログラミング電流を制限するか、あるいは $I_{CCFL}$ ピンからのフルスケール電流の一部をシャントする電流スプリッタを使用することができます。スプリッタ回路を図1に示します。分割器を使用してリファレンス電圧から、 $I_{CCFL}$ 加算電圧レベル( $465mV$ )に等しい電圧を設定します。分割器に流れる主電流は、分割器に流れ込むシャント電流の影響を受けないような値を選択しなければなりません。

図1.

### 接地ランプ構成

接地ランプ構成では、ランプの低電圧側をLT1786FのDIOピンに直接接続します。このピンは2個の内部ダイオードのカソードとアノード間の共通接続点です。従来の接地ランプ構成では、これらのダイオードはディスクリート・ユニットでしたが、現在はICに集積されており、コストとボード・スペースを節約できます。双方向ランプ電流がDIOピンを流れ、2個のダイオードが半サイクルごとに交互に導通します。ランプ電流は、平均ランプ電流の半分をモニタして制御されます。負の半サイクルで導通するダイオードが電流の1/10をCCFL  $V_C$ ピンに分流し、ランプ電流プログラマ回路で供給されるソ

## アプリケーション情報

ス電流をゼロにします。CCFL  $V_C$ ピンの補償コンデンサは安定したループ補償を行うだけでなく、整流された正弦波ランプ電流を平均化する機能も備えています。したがって、入力プログラミング電流は、平均ランプ電流の半分になります。

ランプ電流と入力プログラミング電流間の伝達関数は、経験に基づいて決定する必要があります。使用される特定のランプ/ディスプレイ・ハウジングの組合せによって異なります。ランプとディスプレイ・ハウジングは、寄生ランプ - フレーム容量のために、損失が分散される構造となっています。すなわち、ランプの高電圧側を流れる電流のほうがランプのDIOピン側を流れる電流より大きいということです。入力プログラミング電流は、帰還信号がランプ底部のランプ電流であっても、ランプの高電圧側でランプ電流を制御するように設定されます。これにより、ランプをオーバードライブしてランプの動作寿命を低下させないようにしています。したがって、DACのフルスケール電流は、必ずしも最大ランプ電流を設定するのに必要な電流と一致しません。

### フローティング・ランプ構成

フローティング・ランプ構成では、ランプは完全にフロート状態になりグランドへの電気的接続はありません。これによって、トランスはランプに対称的な差動ドライブを提供することができます。バランスのとれたドライブにより、寄生ランプ - フレーム間容量に付随するフィールドの不平衡をなくし、低ランプ電流時の「サーモメータリング」(ランプ長に沿って生じる不均等ランプ輝度)を低減します。

ランプの物理的レイアウト、ランプのリード、ディスプレイ・ハウジングの構造について、ディスプレイ・デザインを慎重に評価してください。任意の高電圧ポイントからDCまたはACグランドへの寄生容量によって、不要な電流フローの経路が形成されます。この寄生電流フローによって、電気的な効率が低下し、実際には最大25%の損失が観察されました。例として、Royer動作周波数が60kHz、浮遊容量1pFの場合は、2.65Mのインピーダンスになります。動作ランプ電圧が400V、動作ランプ電流が6mAの場合、寄生電流は150μAです。この余分な電流は、トランスの二次側から供給しなければなりません。寄生容量が増えてしまうレイアウト手法としては、

高電圧ランプのリードが長い、ランプ周囲に反射する金属箔がある、ディスプレイが金属エンクロージャに収容されている、などがあります。高品質のディスプレイの損失は5%未満であり、低品質のディスプレイの場合は損失が5% ~ 25%になります。損失が多いディスプレイの主な理由は、フローティング・ランプ構成を使用していることです。ランプに対称的な差動ドライブを供給すると、全寄生損失が半減します。

フローティング・ランプ構成で、ランプ電流の閉ループ制御を維持するには、Royerトランスの一次側から帰還信号を得る必要があります。従来の解決法では、外部高精度シャントとハイサイド・センス・アンプ構成を使用していました。この方式がLT1786Fに組み込まれ、設計が簡素化され使いやすくなりました。内部0.1Ω抵抗は、Royerコンバータ電流モニタし、ハイサイド・センス・アンプの入力端子間に接続されます。0~1AのRoyer一次側のセンタタップ電流は、CCFL  $V_C$ ピンで0μA ~ 500μAのシンク電流に変換され、ランプ電流プログラマ回路から供給されるソース電流をゼロ調整します。CCFL  $V_C$ ピンの補償コンデンサは、安定したループ補償と誤差シンク電流に対する平均化機能を提供します。したがって、入力プログラミング電流は、平均Royerコンバータ電流に関係します。フローティング・ランプ回路は、帰還信号の誘導を除いては、接地ランプ回路でも同様に動作します。

ランプ電流と入力プログラミング電流間の伝達関数は、経験に基づいて決定し、ランプ特性、ディスプレイ構造、トランスの巻線比率、およびRoyer発振器の同調など、多数の要素に依存します。前述したとおり、ランプ電流はランプの一端でわずかに高く、入力プログラミング電流は、ランプがオーバードライブされないように、より高いレベルに設定しなければなりません。

LT1786Fの内部0.1Ωハイサイド・センス抵抗は、最大DC電流1Aで定格が定められています。この抵抗は起動時に非常に高いサージ電流によって損傷を受ける可能性があります。Royerコンバータは、一般にトランスのセンタタップに数μFのバイパス・コンデンサを使用しています。このコンデンサは、システムが最初にバッテリ・パックまたはACアダプタから電力が供給されるときに充電されます。起動時に供給される電流は、この経路の全インピーダンスが小さく、電圧源が高い電流能力を有する場合には、非常に大きくなる可能性があります。

## アプリケーション情報

リニアテクノロジーは、トランスのセンタタップ用バイパス・コンデンサには、0.5 以上のESRを持つアルミニウム電解コンデンサを使用することを推奨しています。これによって、ピーク・サージ電流が許容レベルにまで低減されます。一般に、この経路の配線およびトレース・インダクタンスもサージ電流のdi/dtを低減するのに役立ちます。この問題は、接地ランプ回路ではハイサイド・センス抵抗を使用しないため、フローティング・ランプ回路にしか存在しません。

### 入力コンデンサの種類

スイッチング・レギュレータの入力コンデンサ・タイプを選択するには注意が必要です。アルミニウム電解コンデンサは、電気的に耐久性が高く低成本ですが、必要なリップル電流定格を満足させるには物理的形状が大きく、サイズの制約(特に高さ)のために使用できない場合があります。現在、大きな容量のセラミック・コンデンサが入手可能になりました。セラミック・コンデンサはリップル電流と電圧定格が高いため入力のバイパスには最適です。

固形タンタル・コンデンサも、起動時に大きなサージ電流が発生すると時に故障することを除いては、良い選択といえます。レギュレータの入力バイパス・コンデンサには、バッテリや大容量ソースが接続されていると、高サージが加わる可能性があります。一部のメーカーがサージ能力を特別に試験したタンタル・コンデンサ・ライン(AVX TPSシリーズなど)を開発しましたが、これらのユニットでも入力電圧サージがコンデンサの最大電圧定格に接近した場合は、故障する可能性があります。AVXは、高サージ・アプリケーションの場合はコンデンサ電圧を2:1にディレーティングすることを推奨しています。

### アプリケーション・サポート

リニアテクノロジーは、システム・デザインのためのバックライト/LCDコントラスト・ソリューションの検討、設計、および評価に、膨大な時間とリソース、および技術力を費やしています。効率が高くコンパクトな

LCDバックライト・システムの設計は、変換式電子システムにおいてどのように妥協を図るかを研究することです。設計のあらゆる局面に相互関係があり、いかなる設計変更も他の重要なすべてのデザイン・パラメータを完全に再評価する必要があります。リニアテクノロジーは、バックライト設計のための充実した試験および評価方式を開発し、コンパクトで効率的かつ経済的なソリューションを実現するための問題点とトレードオフを明確にしました。リニアテクノロジーは、お客さまと一緒に、バックライト/LCDコントラスト・システムを検討し、設計および評価、最適化する機会を歓迎致します。バックライト/LCDのコントラストの設計に関する詳細は、下記の参考文献を参照してください。

### 参考文献

1. Williams, Jim. August 1992. *Illumination Circuitry for Liquid Crystal Displays*. Linear Technology Corporation, Application Note 49.

2. Williams, Jim. August 1993. *Techniques for 92% Efficient LCD Illumination*. Linear Technology Corporation, Application Note 55.

3. Bonte, Anthony. March 1995. *LT1182 Floating CCFL with Dual Polarity Contrast*. Linear Technology Corporation, Design Note 99.

4. Williams, Jim. April 1995. *A Precision Wideband Current Probe for LCD Backlight Measurement*. Linear Technology Corporation, Design Note 101.

5. LT1182/LT1183/LT1184/LT1184F Data Sheet. *CCFL/LCD Contrast Switching Regulators*. April 1995. Linear Technology Corporation.

6. Williams, Jim. November 1995. *A Fourth Generation of LCD Backlight Technology*. Linear Technology Corporation, Application Note 65.

## 標準的応用例

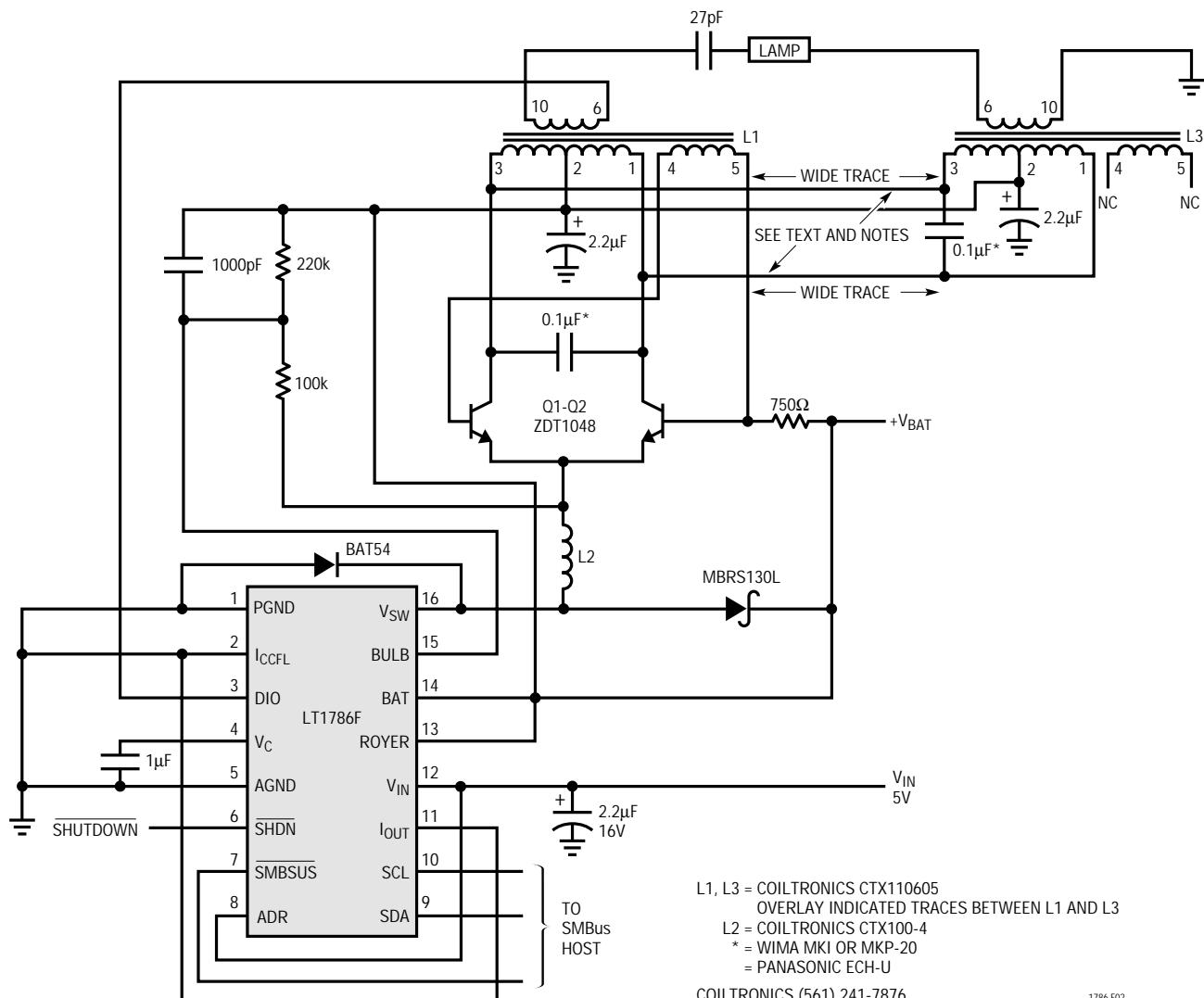

### デュアル・トランスCCFL電源

スペースの制約から、1個の大きなトランスではなく2個の小型トランスを使用しなければならないことがあります。この方法は多少費用がかかりますが、スペースの問題を解決することができ、他にも魅力的な利点があります。図2のアプローチは、基本的にはLT1786Fを使用した「接地ランプ」回路です。トランジスタは2つのトランスの一次側を並列にドライブします。トランスの二次側は直列に接続され出力を供給します。負荷電力を半分ずつ供給する比較的小さなトランスは、ランプ端子に直接配置することができます。この構成がスペース面で(特に高さ)優れているのは明らかですが、高い電圧のリード長をなくすことによって寄生配線損失も抑えることができます。

できます。さらに、ランプが差動ドライブを受けても寄生損失は低く、帰還信号はグランドを基準にしています。したがって、二次側を積み重ねることで、接地モードの電流精度とライン・レギュレーションを維持しながら、フローティング・ランプの動作効率を実現することができます。

L1は直接ドライブされ、巻線4-5は通常の方法で帰還を提供します。L1とL3相互接続の「スレーブ」であるL3は、波形の純度を維持するために、低いインダクタンスで配置しなければなりません。トレースの幅はできるだけ広く(例: 約0.32cm)し、重ね合わせて誘導性の影響をキャンセルしてください。

4

図2. 2個のトランスを使用して電流精度とライン・レギュレーションを維持しながら

スペースの節減と寄生損失の低減を実現。トレードオフはコストの増加

## 標準的応用例

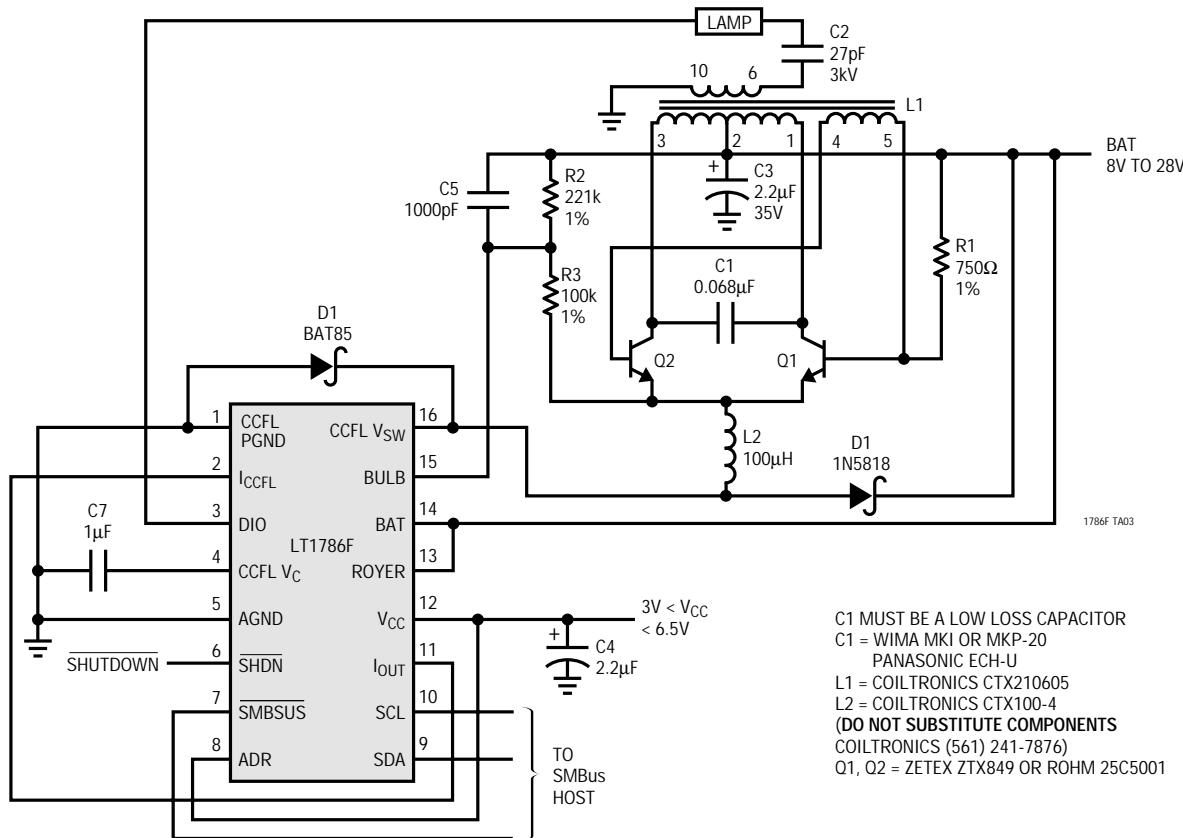

2線式SMBusでランプ電流を制御する効率90%フローティングCCFL

## 関連製品

| 製品番号    | 説明                                         | 注釈                          |

|---------|--------------------------------------------|-----------------------------|

| LT1172  | CCFLまたはLCDコントラスト調整用電流モード・スイッチング・レギュレータ     | 1.25A、100kHz                |

| LT1173  | LCDコントラスト調整用マイクロパワーDC/DCコンバータ              | 1A、24kHz、ヒステリシス有            |

| LT1182  | CCFLおよびLCDコントラスト調整用デュアル電流モード・スイッチング・レギュレータ | 1.25A、0.625A、200kHz         |

| LT1183  | CCFLおよびLCDコントラスト調整用デュアル電流モード・スイッチング・レギュレータ | 1.25A、0.625A、200kHz         |

| LT1184  | CCFL調整用電流モード・スイッチング・レギュレータ                 | 1.25A、200kHz                |

| LT1184F | CCFL調整用電流モード・スイッチング・レギュレータ                 | 1.25A、200kHz                |

| LT1186F | CCFL調整用DACプログラマブル電流モード・スイッチング・レギュレータ       | 1.25A、200kHz、SPI、またはパルス・モード |

| LT1316  | LCDコントラスト調整用マイクロパワーDC/DCコンバータ              | ピーク電流制限をプログラム可能             |

| LT1372  | CCFLまたはLCDコントラスト調整用電流モード・スイッチング・レギュレータ     | 1.5A、500kHz                 |