TNJ-006:LDO不安定性を抵抗とコンデンサの並直列変換で考える

2013年12月4日 公開

はじめに

アナログ・デバイセズの電源関連製品のご紹介のなかで「LDOの不安定性を検討するうえで、抵抗とコンデンサを並直列変換して考えてみると…??」という話題がありました。

このことをSPICEシミュレータ、NI Multisimで見ていきたいと思います。なお単にAC解析で解析するのではありません。NI Multisimに付属しているPost Processorという機能(この機能はかなり便利です!)を使って、解析していきたいと思います。

なおこの技術ノートはPost Processor機能を用いてみることが趣旨ですが、一部の計算式であればAC解析の中で直接、計算処理を指定できますので、そちらも活用いただければと思います。

LDO設計で注意が必要なこと

不安定領域のあるLDOを用いた電源回路設計では、バイパス・コンデンサにセラミック・コンデンサだけを用いた場合、不安定動作に注意が必要です。LDOが異常発振を引き起こしてしまうことがあるからです。

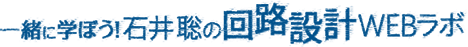

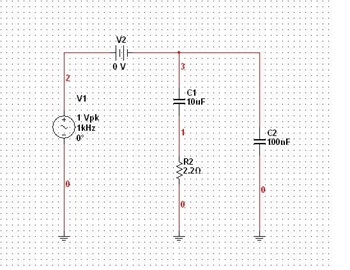

図1. ここで考えてみたい回路(負荷抵抗は表示していません)

自分の設計は並列に小容量のコンデンサを接続していた

自分のこれまでのLDOを用いた電源回路設計経験では、図1のように大きめの容量値の電源コンデンサC1には直列に抵抗R1を入れて、それと並列に小容量のコンデンサC2(100pF~1000pF)を複数つないで設計していました。これはアプリケーションが「動作周波数が高いシステム」であったために、このような小容量だったのでした…。

LDOによっては動作が不安定になることがある

LDOの種類にもよりけりですが、周波数が高い領域ではLDOの負荷となる容量により、位相回転が起きて、LDOが不安定になることがあります。そのため「大きめの容量値の電源コンデンサには直列に抵抗を入れて」、LDOの動作を安定化させる必要があります。LDOが不安定になると、異常発振を引き起こしてしまいます。

小容量のコンデンサには抵抗は入れていなかったが

小容量のコンデンサには、直列に抵抗を入れてはいませんでした。図1のように直列に挿入した抵抗R1(C1の容量が大きいので高い周波数ではC1はショートになる)と負荷回路の抵抗分、これとC2とでR//Cの並列回路になるので、その抵抗分をLDOのループが切れる周波数あたりで、R-Cの直列回路として並直列変換して考えてれば「まあ、大丈夫かなあ…」という感じで設計していました。このくらいの考察レベルでも、トラブルは発生なかったので、よかったなぁ…と、今では思っています。

図2. コンデンサと抵抗を並直列変換する

(C1/R1は同じ大きさにはなりません)

コンデンサと抵抗は並直列/直並列変換ができる

この「抵抗分とでR//Cの並列回路となるので……R-Cの直列回路として並直列変換して」というところですが、図2のように、抵抗とコンデンサの並列回路(図2左)は、その計算する周波数において、直列回路(図2右)に「計算式」により変換できます。逆に直列から並列に変換することもできます。

目的の周波数で成りたち、周波数が異なると結果も異なる

なお並直列(直並列)の計算では、計算する周波数が異なれば、直列に変換された(計算で得られる)RC定数も変わってきますので、注意してください。

あらためて図1に戻ります。これは「大きめの容量値の電源コンデンサには直列に抵抗を入れて」という、ここで考えてみたい回路に相当します(負荷抵抗は表示していません)。

C1が大きめのコンデンサ(たとえば10uF)、R1が安定化抵抗(たとえば1Ω)、C2が並列の小さいコンデンサ(たとえば100pF)です。

さきに示したように高域ではC1はショートになりますので、R1とC2(図2ではC1に相当)の並列接続と考えられるわけです。

並列から直列の変換をシミュレーションで計算してみる

図2ように、並列回路を直列回路とすると、周波数に応じてどのように変化していくかを、式計算でやるのも大変(簡易計算する方法もあるが)ですから、NI Multisimを使って見ていこうと思います(Post Processorという機能のご紹介でもあります)。

シミュレーションでやってみること

図1において、LDOが動作する周波数帯域(一番重要なのはLDOの内部ループが切れる周波数)で抵抗R1が支配的であればいいのですが、並列接続の小さいコンデンサC2(図2ではC1に相当)が支配的だと、LDOが不安定になってしまいます。そこで抵抗成分R1がこの帯域で支配的であるかを確認する、というのが目論見であります。

これをNI Multisimを用いて、LDOが動作する周波数帯域において、小さめのコンデンサC2を並列に入れた状態で抵抗R1がどのように見えてくるか、安定性が確保できるのかを(簡易計算もできますが…)シミュレーションで考えてみたいと思います。

図3. シミュレーションしてみる回路

シミュレーションしてみる回路図

図3をご参照ください。さきほどはR1は(たとえば)1Ωの直列抵抗と説明しましたが、ここではR2として2.2Ωにしてあります。シミュレーションのデモなので、抵抗の大きさはいくつでもいいのですが…。並列のコンデンサC2は100pFだと面白いところが見えづらいことと、実際に自分が設計していた回路としては、100pF(100pFと小さい理由は動作周波数の関係です)が並列に複数接続されていましたから、それらを考慮して1nF(=1000pF)としてみました。

タンタル・コンデンサ使用時の注意点

過去の設計ではLDO出力にタンタル・コンデンサC1を大容量コンデンサとして使用していました。そのため寄生抵抗は低いものとし、2.2Ωを外部抵抗R1として挿入、というところでした。

ところでタンタル・コンデンサは、故障モードがショート・モードで生じますから(フューズがありオープンになるものもある)、電源回路に使用するには十分な注意が必要です。

電源インピーダンスが低いと、突入電流により故障の原因になりますし(ここではLDO出力なので、ある程度インピーダンスがあると想定もできるが)、定格電圧に近いところで使うと、これまた故障率が上昇します。私は定格の1/3程度で使用していました。そうすることでFIT表示での故障率が、ICなどと同じ程度まで低下します。

この技術ノートの流れ

この技術ノートの流れとしては以下の4点です。

1) アナログ・デバイセズのLDO「anyCAP(R)」以外の一般的LDOでは負荷容量に抵抗成分がないと不安定になる

2) そこで大容量コンデンサに抵抗を挿入したが、並列につながっている1000pFによりあらためて不安定にならないか?

3) これをNI Multsimを使って、並列⇒直列変換のイメージで計算して

4) これらのようすをPost Processorという機能で解析する

というところです。

回路のうごきを目利きしてみる

シミュレーションで精査する前に、この回路のうごきを「目利き」してみましょう。

図3のC1 10μFに対してRの抵抗2.2Ωが直列ですので、低い周波数領域では、すぐにこの2.2ΩのR1が支配的になってきます。

一方で、C2 1000pF(1nF)が2.2Ωになるのは72MHz、この1/10としてみても、7.2MHzですから、この条件であればLDOのループ帯域外でしょうから、「問題ないだろう」ということがわかります。

逆にC2に104(0.1uF)などのコンデンサを使う場合は、要注意ですね!このようすは後半で示してみます。

ゼロVの電圧源で電流量をモニタできる

SPICE使用時の技ですが、図3で電圧源V2をゼロVとして挿入してあります。こうするとネットを分離することもできますし、この電圧源V2を流れる電流量を(V2を電流センサとして)シミュレーション結果でモニタリングできます。

この図3ではV2はV1に対して直列ですから、単にV1を測定すればいいことなんですが、この説明をしたいがために、入れておきました(笑)。このような方法での電流量のモニタリングは、分岐電流計測などに便利です。

一つポイントは「電流の向きを考えてV2を挿入する向きを決める」ということです。

シミュレーションしてみる

まずはACシミュレーションを実施する

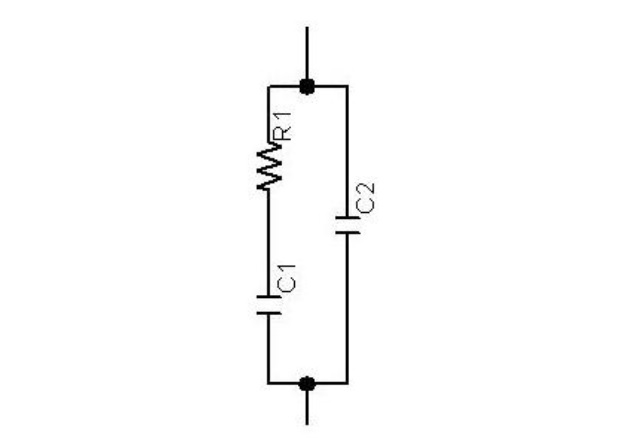

Post Processorで(3)端子から見たインピーダンスを測定したいので、前処理として、まずACシミュレーションを実施します。

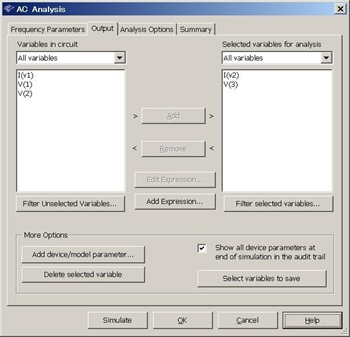

図4のように、計算・表示するパラメータとしては、V(3)とI(v2)とします。それでACシミュレーションをかけてみると、図5のような答えが得られます。

図4. シミュレーション(AC解析)の設定

図5. シミュレーション結果

計算のところをPost Processorで!

こうすればZ = V(3)/I(v2)としてCR回路のインピーダンスが求められます。図6のようにメニューからPost Processorを選択します。

Post Processorは、ポストプロセス = 後処理のとおり、補助的(というより強力)な演算機能を提供してくれます。

なおACシミュレーションでも、計算式を設定すれば(この程度の計算なら)結果を得ることができます。

図6. Post Processorを起動する

Post Processorで用意されている関数群

用意されている関数群をまずご紹介しておきましょう。これはPost ProcessorのHelpで詳細を見ることができます。

ここでは詳細情報ではないため、十分な情報になっていないことをおことわりしておきます。「こんなに関数があるの!」と思っていただければと思います。

[Algebraic Functions]

+ ― plus

- ― minus

* ― times

/ ― divided by

^ ― to the power of

% ― modulus

, ― complex 3,4 = 3 + j (4)

abs(X) ― absolute value

sqrt(X) ― square root

[Trigonometric Functions]

sgn(X) ― 1(if x>0), 0(if x=0), -1(if x<0)

sin(X) ― trigonometric sine (argument in radians)

cos(X) ― trigonometric cosine (argument in radians)

tan(X) ― trigonometric tangent (argument in radians)

atan(X) ― trigonometric inverse tangent

[Relational Functions]

gt ― greater than

lt ― less than

ge ― greater than or equal to

le ― less than or equal to

ne ― not equal to

eq ― equal to

[Logical Functions]

and ― and

or ― or

not ― not

[Exponential Functions]

db(X) ― decibels 20 log10(mag(X))

log(X) ― logarithm (base 10)

ln(X) ― natural logarithm (base e)

exp(X) ― exponential e to the vector power

[Complex Functions]

j(X) ― complex i (sqrt(-1)) times X

real(X) ― complex real component of X

imag(X) ― complex imaginary part of X

vi(X) ― complex vi(X) = image (v(X))

vr(X) ― complex vr(X) = real (v(X))

[Vector Functions]

avg(X) ― running average of the vector X where

avgx(X, d) ― running average of the vector X over d where

deriv(X) ― vector derivative of X

envmax(X, n) ― upper envelope of the vector X

envmin(X, n) ― lower envelope of the vector X

grpdelay(X) ― group delay of vector X in seconds

integral(X) ― running integral of vector X

mag(X) ― vector magnitude

ph(X) ― vector phase

norm(X) ― vector X normalized to 1

rms(X) ― running RMS average of vector X where

rnd(X) ― vector random

mean(X) ― vector results in a scalar

Vector(n) ― vector results in a vector

length(X) ― vector length of vector X

max(X) ― vector maximum value from X

min(X) ― vector minimum value from X

vm(X) ― vector vm(x) = mag(v(X))

vp(X) ― vector vp(x) = ph(v(X))

[Constant Functions]

yes ― yes

true ― true

no ― no

false ― false

pi ― pi

e ― natural logarithm base

c ― speed of light in vacuum

i ― square root of -1

kelvin ― absolute zero in Celsius

echarge ― fundamental charge

boltz ― Boltzman’s constant

planck ― Planck’s constant

実際にPost Processorで計算してみる

AC Simulationは電圧量と電流量を求めることが基本です(計算機能もありますが)。

ここで最初にやりたかったこととしては、RC回路を並列直変換と考えて、R-C並列回路をR-C直列回路として表し、その回路の抵抗分、リアクタンス分がどれだけになるか?というところです。

そこでAC Simulationの結果を、Post ProcessorでZ = V/Iとして計算させ、その実数部(real)と虚数部(imag)をとります。実数部が抵抗成分、虚数部がリアクタンス成分に相当し、直列回路のそれぞれの成分が計算できることになります。

Frequencyという変数もある

なおVariableではAC Simulationで求めたV3とI(v2)だけではなく、Frequencyという変数も利用できます。いろいろ活用できそうです。

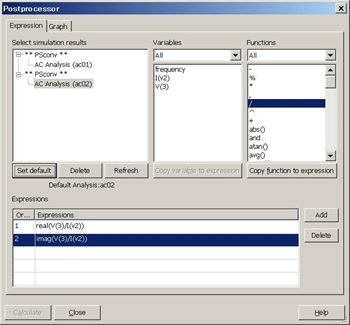

Post Processorの計算設定のスナップショットをつけてみました。図7をご覧ください。

図7. Post Processor計算設定画面

Graphタブに切り替えると数式が見える

つづいてExpressionタブからGraphタブに切り替えます。切り替えたようすが図8です。

左下の「Expressions available」にさきほど示した数式が表示されていますので、希望するものをクリックしてハイライトさせ、「>」矢印を押します。そうすると、それらの数式が右側の「Expressions selected」に移動してきます(これが図8の状態)。

これで左下のCalculateボタンを押すと計算してくれます!

図8. Post Processor計算設定画面

Post Processorで計算

Post Processorで計算して、図9のように抵抗成分(real)、リアクタンス成分(imag)をそれぞれ表示してみました。何が言いたいかというと、「こんなに簡単に計算できるんです!」ということです。

図9を見ていただいて分かるように(赤の四角で囲んで、ハイライトさせてみた)、72MHz程度で抵抗成分が2.2Ωから半分の1.1Ω程度に低下してきます。

72MHzがLDOの内部ループ周波数帯域であるはずもありませんので、この電源回路設計はほぼ問題ない(安定に動作する)だろうと想定できます。

図9. Post Processorでの計算結果

コンデンサを替えてシミュレーションしてみる

つづいてC2を0.1uFにしてシミュレーションをしてみましょう。低周波回路ですとありがちな(というか間違いなくある)定数でしょう。

回路図を図10に示します。これでまずAC解析を行います。

図10. コンデンサを0.1uFに変更してみる

2回目の解析情報活用には儀式が必要

この2回目のAC解析結果を、Post Processorで活用させるためには、ちょっと儀式が必要です。図11の画面のように、Select simulation resultsの部分を開いて、AC Analysis (ac02)をクリックし、さらにSet Defaultのボタンを押します。

そうすると、Post Processorでの計算に用いられる数値データが、この2回目のシミュレーション結果になるというわけです。

図11. 2回目の解析情報活用には儀式が必要

0.1uFを用いてPost Processorで計算

この条件でAC解析をして、さらにPost Processorで計算させて表示した結果を示します。

2.2MHz程度で抵抗成分が1/10(0.22Ω程度)になっていますね。十分にLDO内部ループ周波数帯域に入り込んでいる(動作が不安定になる)可能性があるということもわかります。

図12. 0.1uFのコンデンサでPost Processorで計算

最後に

SPICEシミュレーションをうまく活用することで、このようにいろいろな解析ができます。SPICEシミュレータは自分の知識とアイディアを具現化してくれる「スーパー電卓」なわけですね。

※ NI Multisim Analog Devices Editionの提供は終了しております。この資料ではNI Multisimを用いていますが、本内容はADIsimPEなど他のSPICEシミュレータでも同様にご活用いただけます。

著者について

デジタル回路(FPGAやASIC)からアナログ、高周波回路まで多...