# DC/DC コンバータ内蔵 4 チャンネル・アイソレータ

## データシート

**ADuM6410/ADuM6411/ADuM6412**

### 特長

isoPower 内蔵の絶縁型 DC/DC コンバータ

最大出力 150 mW

4 本の DC ~ 150 Mbps 信号絶縁チャンネル

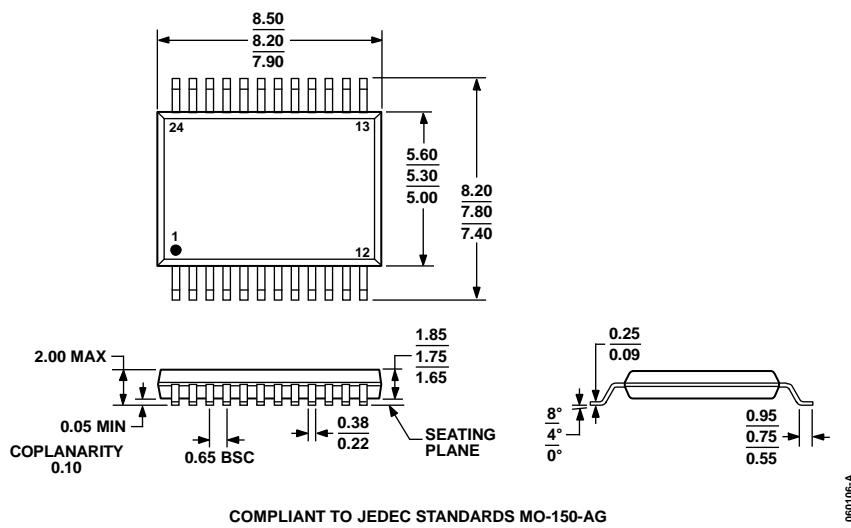

沿面距離 5.3 mm の 24 ピン SSOP パッケージ

高温動作: 105 °C

高いコモンモード過渡耐性: 100 kV/μs

安全性と規制に対する認定

UL 認定 (申請中) :

1 分間にわたる 3750 V rms の UL 1577 規格に準拠

CSA Component Acceptance Notice 5A (申請中)

VDE 適合性認定 (申請中)

DIN V VDE V 0884-10 (VDE V 0884-10) : 2006-12

$V_{IORM} = 565 \text{ V}$  (peak)

### アプリケーション

RS-232 トランシーバ

電源スタートアップ・バイアスとゲート・ドライブ

絶縁センサー・インターフェース

工業用 PLC

### 概要

ADuM6410/ADuM6411/ADuM6412<sup>1</sup> は、isoPower® 内蔵の DC/DC コンバータを組み込んだ 4 チャンネル・デジタル・アイソレータです。アナログ・デバイセズの iCoupler® 技術を採用したこの DC/DC コンバータは、3.15 V ~ 5.25 V の範囲で調整可能な安定化された絶縁電源を提供します。よく使われる電圧の組み合わせと、それらに対応するパワー・レベルを表 1 に示します。

ADuM6410/ADuM6411/ADuM6412 を使用した低消費電力の絶縁設計では、絶縁型 DC/DC コンバータを個別に用意する必要はありません。また、iCoupler チップ・スケール・トランス技術をロジック信号の絶縁と DC/DC コンバータの磁気部品の両方に採用し、小型サイズのトータル絶縁ソリューションとなっています。

ADuM6410/ADuM6411/ADuM6412 アイソレータは、さまざまなチャンネル構成とデータ・レートが可能な 4 つの独立した絶縁チャンネルを備えています（詳細についてはオーダー・ガイドを参照）。

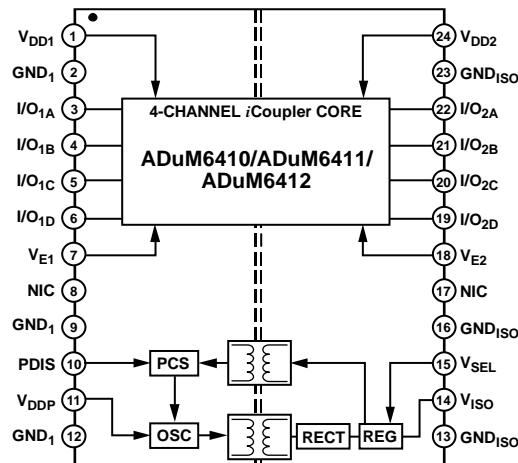

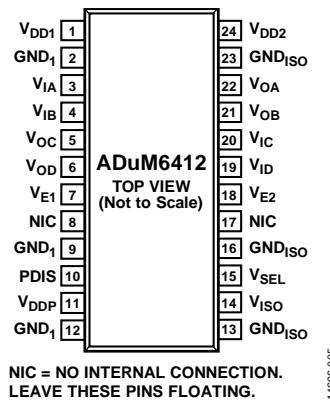

### 機能ブロック図

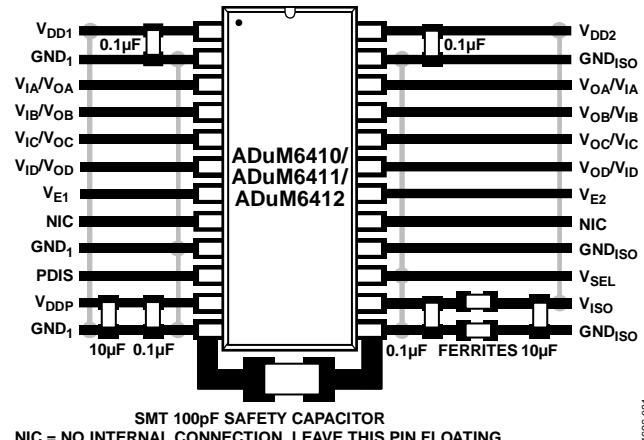

NIC = NO INTERNAL CONNECTION. LEAVE THIS PIN FLOATING.

14986-001

図 1

表 1. パワー・レベル

| Input Voltage (V) | Output Voltage (V) | Output Power (mW) |

|-------------------|--------------------|-------------------|

| 5                 | 5                  | 150               |

| 5                 | 3.3                | 100               |

| 3.3               | 3.3                | 66                |

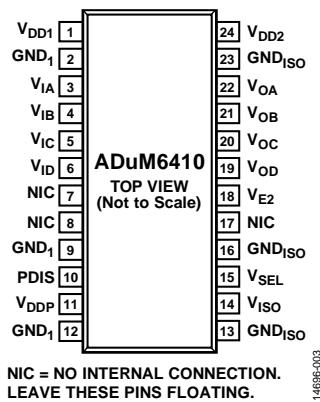

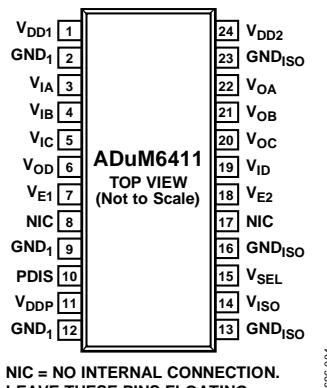

表 2. データ入力／出力ポートの割り当て

| Ch.               | Pin No. | ADuM6410        | ADuM6411        | ADuM6412        |

|-------------------|---------|-----------------|-----------------|-----------------|

| I/O <sub>1A</sub> | 3       | V <sub>IA</sub> | V <sub>IA</sub> | V <sub>IA</sub> |

| I/O <sub>1B</sub> | 4       | V <sub>IB</sub> | V <sub>IB</sub> | V <sub>IB</sub> |

| I/O <sub>1C</sub> | 5       | V <sub>IC</sub> | V <sub>IC</sub> | V <sub>OC</sub> |

| I/O <sub>1D</sub> | 6       | V <sub>ID</sub> | V <sub>OD</sub> | V <sub>OD</sub> |

| I/O <sub>2A</sub> | 22      | V <sub>OA</sub> | V <sub>OA</sub> | V <sub>OA</sub> |

| I/O <sub>2B</sub> | 21      | V <sub>OB</sub> | V <sub>OB</sub> | V <sub>OB</sub> |

| I/O <sub>2C</sub> | 20      | V <sub>OC</sub> | V <sub>OC</sub> | V <sub>IC</sub> |

| I/O <sub>2D</sub> | 19      | V <sub>OD</sub> | V <sub>ID</sub> | V <sub>ID</sub> |

<sup>1</sup> 米国特許 5,952,849; 6,873,065; 6,903,578; 7,075,329 により保護されています。その他の特許は申請中です。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                                      |    |

|--------------------------------------|----|

| 特長                                   | 1  |

| アプリケーション                             | 1  |

| 機能ブロック図                              | 1  |

| 概要                                   | 1  |

| 改訂履歴                                 | 2  |

| 仕様                                   | 3  |

| 電気的特性 — 5 V 主入力電源／5 V 二次絶縁電源         | 3  |

| 電気的特性 — 3.3 V 主入力電源／3.3 V 二次絶縁電源     | 5  |

| 電気的特性 — 5 V 主入力電源／3.3 V 二次絶縁電源       | 7  |

| 電気的特性 — 2.5 V 動作のデジタル・アイソレータ・チャンネルのみ | 9  |

| 電気的特性 — 1.8 V 動作のデジタル・アイソレータ・チャンネルのみ | 11 |

| パッケージ特性                              | 13 |

| 規制に対する認定                             | 13 |

| 絶縁および安全性関連の仕様                        | 13 |

|                                          |    |

|------------------------------------------|----|

| DIN V VDE V 0884-10 (VDE V 0884-10) 絶縁特性 | 14 |

| 推奨動作条件                                   | 14 |

| 絶対最大定格                                   | 15 |

| ESD に関する注意                               | 15 |

| ピン配置およびピン機能の説明                           | 16 |

| 真理値表                                     | 19 |

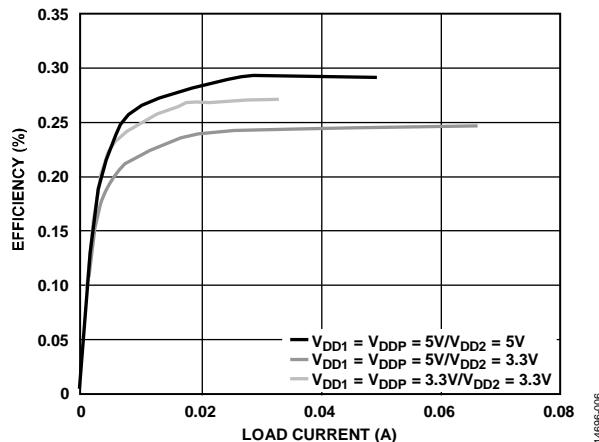

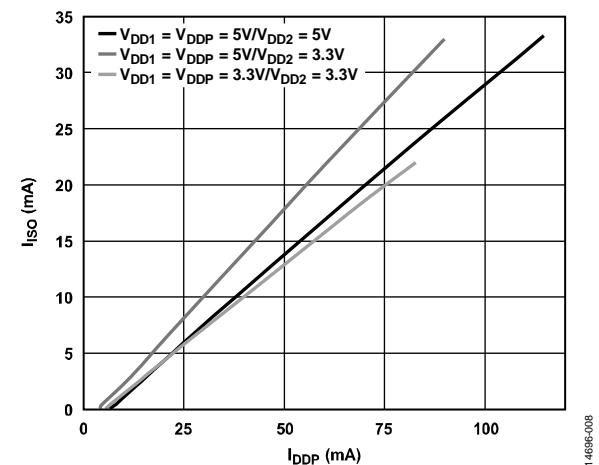

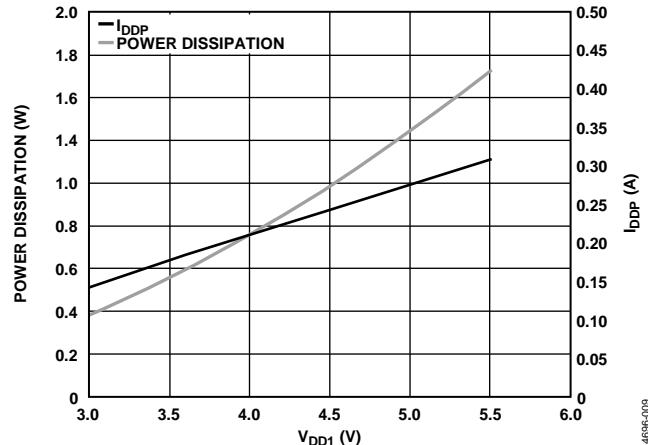

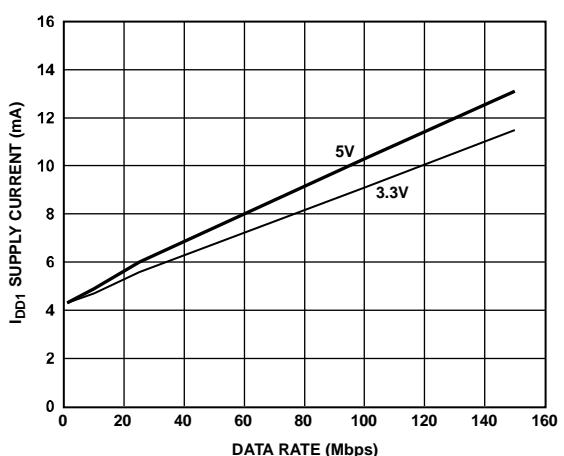

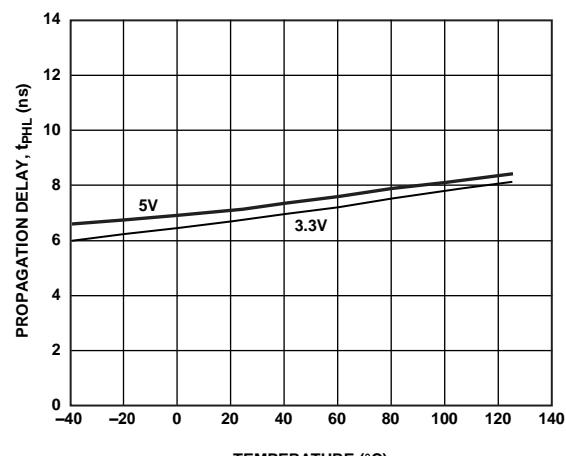

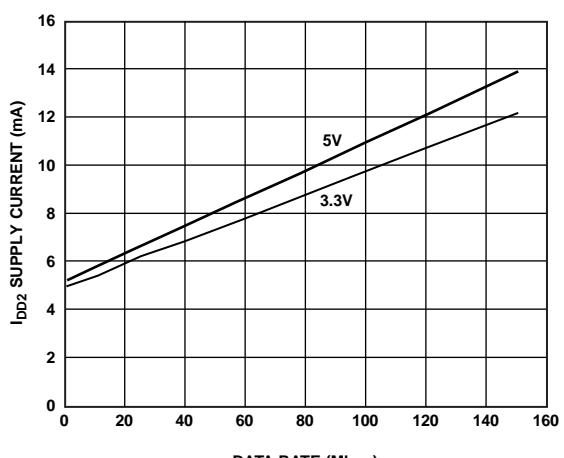

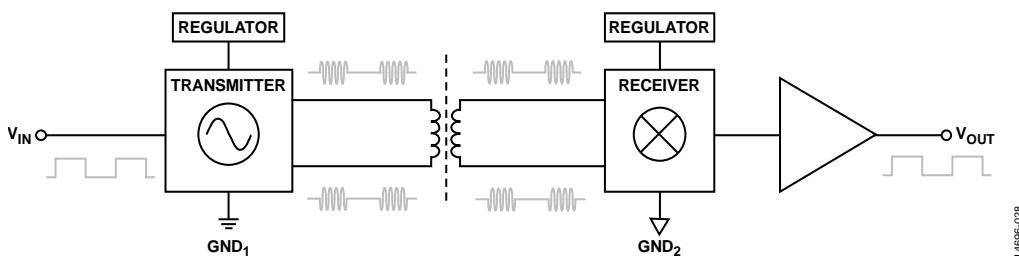

| 代表的な性能特性                                 | 20 |

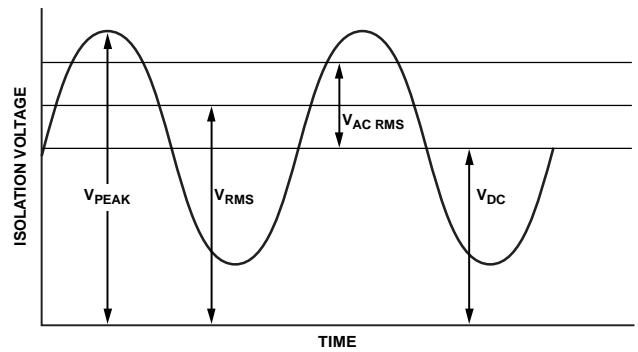

| 用語の定義                                    | 24 |

| 動作原理                                     | 25 |

| アプリケーション情報                               | 26 |

| PCB レイアウト                                | 26 |

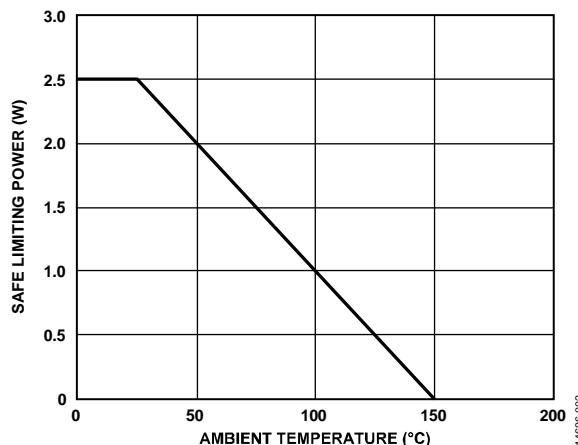

| 熱解析                                      | 27 |

| 伝搬遅延に関するパラメータ                            | 27 |

| EMI に関する考慮事項                             | 27 |

| 消費電力                                     | 27 |

| 絶縁寿命                                     | 27 |

| 外形寸法                                     | 29 |

| オーダー・ガイド                                 | 29 |

## 改訂履歴

7/2016—Revision 0: Initial Version

## 仕様

### 電気的特性 — 5 V 主入力電源／5 V 二次絶縁電源

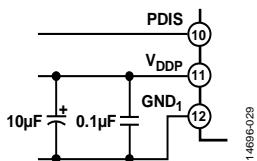

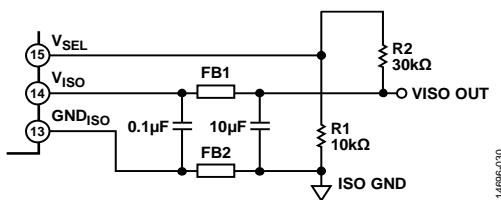

仕様に規定するすべての代表値は、 $T_A = 25^\circ\text{C}$ 、 $V_{DD1} = V_{DDP} = V_{ISO} = 5\text{ V}$  の時に、 $V_{SEL}$  抵抗回路を使用した場合の値です。抵抗回路は  $R1 = 10\text{ k}\Omega \pm 1\%$ 、 $R2 = 30.9\text{ k}\Omega \pm 1\%$  で、 $V_{ISO}$  と  $\text{GND}_{ISO}$  の間に接続（図 31 参照）。最大／最小仕様は、特に指定のない限り  $4.5\text{ V} \leq V_{DD1}$ 、 $V_{DDP}$ 、 $V_{ISO} \leq 5.5\text{ V}$ 、および  $-40^\circ\text{C} \leq T_A \leq +105^\circ\text{C}$  の全推奨動作範囲に適用されます。特に指定がない限り、スイッチング仕様は、 $CL = 15\text{ pF}$ 、CMOS 信号レベルで試験されます。

表 3. DC/DC コンバータの静的仕様

| Parameter                           | Symbol                  | Min | Typ | Max | Unit   | Test Conditions/Comments                                                                                  |

|-------------------------------------|-------------------------|-----|-----|-----|--------|-----------------------------------------------------------------------------------------------------------|

| DC-TO-DC CONVERTERS SUPPLY          |                         |     |     |     |        |                                                                                                           |

| Setpoint                            | $V_{ISO}$               | 4.7 | 5.0 | 5.4 | V      | $I_{ISO} = 15\text{ mA}$ , $R1 = 10\text{ k}\Omega$ , $R2 = 30.9\text{ k}\Omega$                          |

| Line Regulation                     | $V_{ISO}(\text{LINE})$  |     | 20  |     | mV/V   | $I_{ISO} = 15\text{ mA}$ , $V_{DDP} = 4.5\text{ V}$ to $5.5\text{ V}$                                     |

| Load Regulation                     | $V_{ISO}(\text{LOAD})$  | 1   | 5   |     | %      | $I_{ISO} = 3\text{ mA}$ to $27\text{ mA}$                                                                 |

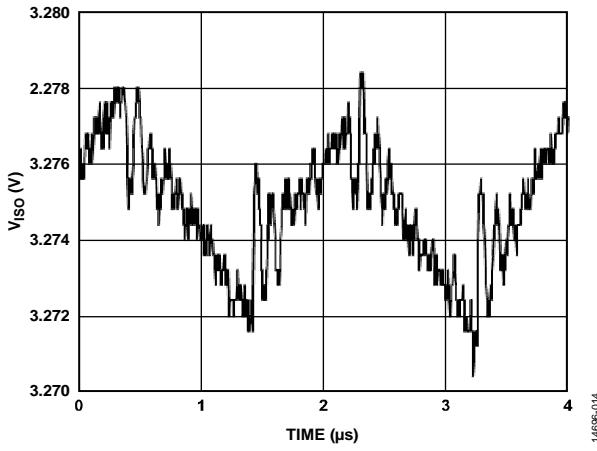

| Output Ripple                       | $V_{ISO}(\text{RIP})$   | 75  |     |     | mV p-p | 20 MHz bandwidth, $C_{BO} = 0.1\text{ }\mu\text{F}$    $10\text{ }\mu\text{F}$ , $I_{ISO} = 27\text{ mA}$ |

| Output Noise                        | $V_{ISO}(\text{NOISE})$ | 200 |     |     | mV p-p | $C_{BO} = 0.1\text{ }\mu\text{F}$    $10\text{ }\mu\text{F}$ , $I_{ISO} = 27\text{ mA}$                   |

| Switching Frequency                 | $f_{OSC}$               | 125 |     |     | MHz    |                                                                                                           |

| Pulse-Width Modulation Frequency    | $f_{PWM}$               | 600 |     |     | kHz    |                                                                                                           |

| Output Supply                       | $I_{ISO}(\text{MAX})$   | 30  |     |     | mA     | $V_{ISO} > 4.5\text{ V}$                                                                                  |

| Efficiency at $I_{ISO}(\text{MAX})$ |                         | 29  |     |     | %      | $I_{ISO} = 27\text{ mA}$                                                                                  |

| $V_{DDP}$ Supply Current            |                         |     |     |     |        |                                                                                                           |

| No $V_{ISO}$ Load                   | $I_{DDP}(\text{Q})$     | 14  | 20  |     | mA     |                                                                                                           |

| Full $V_{ISO}$ Load                 | $I_{DDP}(\text{MAX})$   | 104 | 140 |     | mA     |                                                                                                           |

| Thermal Shutdown                    |                         |     | 154 |     | °C     |                                                                                                           |

| Shutdown Temperature                |                         |     | 10  |     | °C     |                                                                                                           |

| Thermal Hysteresis                  |                         |     |     |     |        |                                                                                                           |

表 4. データ・チャンネルの電源電流仕様

| Parameter      | Symbol    | 1 Mbps |      |     | 25 Mbps |      |     | 100 Mbps |      |     | Unit | Test Conditions/Comments |

|----------------|-----------|--------|------|-----|---------|------|-----|----------|------|-----|------|--------------------------|

|                |           | Min    | Typ  | Max | Min     | Typ  | Max | Min      | Typ  | Max |      |                          |

| SUPPLY CURRENT |           |        |      |     |         |      |     |          |      |     |      |                          |

| ADuM6410       | $I_{DD1}$ | 6.8    | 10   |     | 7.8     | 12   |     | 11.8     | 17.4 |     | mA   |                          |

|                | $I_{DD2}$ | 2.1    | 3.7  |     | 3.9     | 5.7  |     | 9.2      | 13   |     | mA   |                          |

| ADuM6411       | $I_{DD1}$ | 5.8    | 10.3 |     | 7.0     | 10.9 |     | 11.4     | 15.9 |     | mA   |                          |

|                | $I_{DD2}$ | 4.0    | 6.85 |     | 5.5     | 8.5  |     | 10.3     | 14.0 |     | mA   |                          |

| ADuM6412       | $I_{DD1}$ | 4.3    | 7.7  |     | 6.0     | 9.3  |     | 10.3     | 14.2 |     | mA   |                          |

|                | $I_{DD2}$ | 5.3    | 8.7  |     | 6.7     | 10.1 |     | 11.0     | 14.9 |     | mA   |                          |

表 5. スイッチング仕様

| Parameter                | Symbol             | Min | Typ | Max | Unit   | Test Conditions/Comments                                         |

|--------------------------|--------------------|-----|-----|-----|--------|------------------------------------------------------------------|

| SWITCHING SPECIFICATIONS |                    |     |     |     |        |                                                                  |

| Pulse Width              | $PW$               | 6.6 |     |     | ns     | Within pulse width distortion (PWD) limit                        |

| Data Rate                |                    |     |     | 150 | Mbps   | Within PWD limit                                                 |

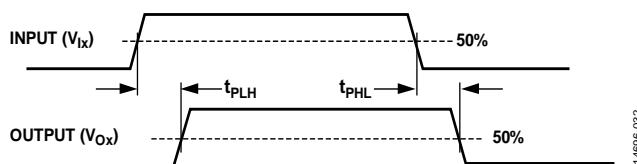

| Propagation Delay        | $t_{PHL}, t_{PLH}$ | 4.8 | 7.2 | 13  | ns     | 50% input to 50% output                                          |

| Pulse Width Distortion   | $PWD$              | 0.5 | 3   |     | ns     | $ t_{PLH} - t_{PHL} $                                            |

| Change vs. Temperature   |                    | 1.5 |     |     | ps/°C  |                                                                  |

| Propagation Delay Skew   | $t_{PSK}$          |     | 6.1 |     | ns     | Between any two units at the same temperature, voltage, and load |

| Channel Matching         |                    |     |     |     |        |                                                                  |

| Codirectional            | $t_{PSKCD}$        | 0.5 | 3.0 |     | ns     |                                                                  |

| Opposing Direction       | $t_{PSKOD}$        | 0.5 | 3.0 |     | ns     |                                                                  |

| Jitter                   |                    | 490 |     |     | ps p-p |                                                                  |

|                          |                    | 70  |     |     | ps rms |                                                                  |

表 6. 入力特性と出力特性

| Parameter                                   | Symbol                       | Min                                              | Typ                                              | Max                                              | Unit    | Test Conditions/ Comments                                                                                                             |

|---------------------------------------------|------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| DC SPECIFICATIONS                           |                              |                                                  |                                                  |                                                  |         |                                                                                                                                       |

| Input Threshold                             |                              |                                                  |                                                  |                                                  |         |                                                                                                                                       |

| Logic High                                  | V <sub>IH</sub>              | 0.7 × V <sub>ISO</sub> or 0.7 × V <sub>DD1</sub> |                                                  |                                                  | V       |                                                                                                                                       |

| Logic Low                                   | V <sub>IL</sub>              |                                                  |                                                  | 0.3 × V <sub>ISO</sub> or 0.3 × V <sub>DD1</sub> | V       |                                                                                                                                       |

| Output Voltage                              |                              |                                                  |                                                  |                                                  |         |                                                                                                                                       |

| Logic High                                  | V <sub>OH</sub>              | V <sub>DD1</sub> - 0.2 or V <sub>DD2</sub> - 0.2 | V <sub>DD1</sub> or V <sub>DD2</sub>             |                                                  | V       | I <sub>Ox</sub> <sup>1</sup> = -20 μA, V <sub>Ix</sub> = V <sub>IxH</sub> <sup>2</sup>                                                |

|                                             |                              | V <sub>DD1</sub> - 0.5 or V <sub>DD2</sub> - 0.5 | V <sub>DD1</sub> - 0.2 or V <sub>DD2</sub> - 0.2 |                                                  | V       | I <sub>Ox</sub> = -4 mA, V <sub>Ix</sub> = V <sub>IxH</sub>                                                                           |

| Logic Low                                   | V <sub>OL</sub>              |                                                  | 0.0                                              | 0.1                                              | V       | I <sub>Ox</sub> = 20 μA, V <sub>Ix</sub> = V <sub>IxL</sub> <sup>3</sup>                                                              |

|                                             |                              |                                                  | 0.0                                              | 0.4                                              | V       | I <sub>Ox</sub> = 4 mA, V <sub>Ix</sub> = V <sub>IxL</sub>                                                                            |

| Undervoltage Lockout                        | UVLO                         |                                                  |                                                  |                                                  |         | V <sub>DD1</sub> , V <sub>DD2</sub> , and V <sub>DDP</sub> supply                                                                     |

| Positive Going Threshold                    | V <sub>UV+</sub>             |                                                  | 1.6                                              |                                                  | V       |                                                                                                                                       |

| Negative Going Threshold                    | V <sub>UV-</sub>             |                                                  | 1.5                                              |                                                  | V       |                                                                                                                                       |

| Hysteresis                                  | V <sub>UVH</sub>             |                                                  | 0.1                                              |                                                  | V       |                                                                                                                                       |

| Input Currents per Channel                  | I <sub>I</sub>               | -10                                              | +0.01                                            | +10                                              | μA      | 0 V ≤ V <sub>Ix</sub> ≤ V <sub>DDx</sub>                                                                                              |

| Quiescent Supply Current                    |                              |                                                  |                                                  |                                                  |         |                                                                                                                                       |

| ADuM6410                                    | I <sub>DD1 (Q)</sub>         |                                                  | 1.2                                              | 2.2                                              | mA      | V <sub>Ix</sub> = Logic 0                                                                                                             |

|                                             | I <sub>DD2 (Q)</sub>         |                                                  | 2.0                                              | 2.72                                             | mA      | V <sub>Ix</sub> = Logic 0                                                                                                             |

|                                             | I <sub>DD1 (Q)</sub>         |                                                  | 12.0                                             | 20.0                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                                             |

|                                             | I <sub>DD2 (Q)</sub>         |                                                  | 2.0                                              | 2.92                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                                             |

| ADuM6411                                    | I <sub>DD1 (Q)</sub>         |                                                  | 1.6                                              | 2.46                                             | mA      | V <sub>Ix</sub> = Logic 0                                                                                                             |

|                                             | I <sub>DD2 (Q)</sub>         |                                                  | 1.9                                              | 2.62                                             | mA      | V <sub>Ix</sub> = Logic 0                                                                                                             |

|                                             | I <sub>DD1 (Q)</sub>         |                                                  | 10.0                                             | 17.0                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                                             |

|                                             | I <sub>DD2 (Q)</sub>         |                                                  | 6.0                                              | 10.0                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                                             |

| ADuM6412                                    | I <sub>DD1 (Q)</sub>         |                                                  | 1.6                                              | 2.46                                             | mA      | V <sub>Ix</sub> = Logic 0                                                                                                             |

|                                             | I <sub>DD2 (Q)</sub>         |                                                  | 1.6                                              | 2.46                                             | mA      | V <sub>Ix</sub> = Logic 0                                                                                                             |

|                                             | I <sub>DD1 (Q)</sub>         |                                                  | 7.2                                              | 11.5                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                                             |

|                                             | I <sub>DD2 (Q)</sub>         |                                                  | 8.4                                              | 11.5                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                                             |

| Dynamic Supply Current                      |                              |                                                  |                                                  |                                                  |         |                                                                                                                                       |

| Input                                       | I <sub>DD1 (D)</sub>         |                                                  | 0.01                                             |                                                  | mA/Mbps | Inputs switching, 50% duty cycle                                                                                                      |

| Output                                      | I <sub>DDO (D)</sub>         |                                                  | 0.01                                             |                                                  | mA/Mbps | Inputs switching, 50% duty cycle                                                                                                      |

| AC SPECIFICATIONS                           |                              |                                                  |                                                  |                                                  |         |                                                                                                                                       |

| Output Rise/Fall Time                       | t <sub>R/t<sub>F</sub></sub> |                                                  | 2.5                                              |                                                  | ns      | 10% to 90%                                                                                                                            |

| Common-Mode Transient Immunity <sup>4</sup> | CM <sub>H</sub>              | 75                                               | 100                                              |                                                  | kV/μs   | V <sub>Ix</sub> = V <sub>DD1</sub> or V <sub>ISO</sub> , common-mode voltage (V <sub>CM</sub> ) = 1000 V, transient magnitude = 800 V |

|                                             | CM <sub>L</sub>              | 75                                               | 100                                              |                                                  | kV/μs   | V <sub>Ix</sub> = 0 V, V <sub>CM</sub> = 1000 V, transient magnitude = 800 V                                                          |

<sup>1</sup> I<sub>Ox</sub> はチャンネル x の出力電流で、x = A、B、C、または D。<sup>2</sup> V<sub>IxH</sub> は入力側ロジック・ハイ・レベル。<sup>3</sup> V<sub>IxL</sub> は、入力側ロジック・ロー・レベル。<sup>4</sup> |CM<sub>H</sub>| は、電圧出力 (V<sub>O</sub>) > 0.8 V<sub>DDx</sub> を維持しながら持続できるコモンモード電圧の最大スループートです。|CM<sub>L</sub>| は VO > 0.8 V を維持しながら持続できるコモンモード電圧の最大スループートです。コモンモード電圧スループートは、立ち上がりと立ち下がり両方のコモンモード電圧エッジに適用されます。

## 電気的特性 — 3.3 V 主入力電源／3.3 V 二次絶縁電源

仕様に規定するすべての代表値は、 $T_A = 25^\circ\text{C}$ 、 $V_{DD1} = V_{DDP} = V_{ISO} = 3.3\text{ V}$  の時に、 $V_{SEL}$  抵抗回路を使用した場合の値です。抵抗回路は  $R1 = 10\text{ k}\Omega \pm 1\%$ 、 $R2 = 16.9\text{ k}\Omega \pm 1\%$  で、 $V_{ISO}$  と GND<sub>ISO</sub> の間に接続（図 31 参照）。最大／最小仕様は、特に指定のない限り  $3.0\text{ V} \leq V_{DD1}$ 、 $V_{DDP}$ 、 $V_{ISO} \leq 3.6\text{ V}$ 、および  $-40^\circ\text{C} \leq T_A \leq +105^\circ\text{C}$  の全推奨動作範囲に適用されます。特に指定がない限り、スイッチング仕様は、 $CL = 15\text{ pF}$ 、CMOS 信号レベルで試験されます。

表 7. DC/DC コンバータの静的仕様

| Parameter                           | Symbol                  | Min | Typ | Max | Unit   | Test Conditions/Comments                                                                              |

|-------------------------------------|-------------------------|-----|-----|-----|--------|-------------------------------------------------------------------------------------------------------|

| DC-TO-DC CONVERTER SUPPLY           |                         |     |     |     |        |                                                                                                       |

| Setpoint                            | $V_{ISO}$               | 3.0 | 3.3 | 3.6 | V      | $I_{ISO} = 10\text{ mA}$ , $R1 = 10\text{ k}\Omega$ , $R2 = 16.9\text{ k}\Omega$                      |

| Line Regulation                     | $V_{ISO}(\text{LINE})$  |     | 20  |     | mV/V   | $I_{ISO} = 10\text{ mA}$ , $V_{DD1} = 3.0\text{ V}$ to $3.6\text{ V}$                                 |

| Load Regulation                     | $V_{ISO}(\text{LOAD})$  | 1   | 5   |     | %      | $I_{ISO} = 2\text{ mA}$ to $18\text{ mA}$                                                             |

| Output Ripple                       | $V_{ISO}(\text{RIP})$   | 50  |     |     | mV p-p | 20 MHz bandwidth, $C_{BO} = 0.1\text{ }\mu\text{F}  10\text{ }\mu\text{F}$ , $I_{ISO} = 18\text{ mA}$ |

| Output Noise                        | $V_{ISO}(\text{NOISE})$ | 130 |     |     | mV p-p | $C_{BO} = 0.1\text{ }\mu\text{F}  10\text{ }\mu\text{F}$ , $I_{ISO} = 18\text{ mA}$                   |

| Switching Frequency                 | $f_{OSC}$               | 125 |     |     | MHz    |                                                                                                       |

| Pulse-Width Modulation Frequency    | $f_{PWM}$               | 600 |     |     | kHz    |                                                                                                       |

| Output Supply                       | $I_{ISO}(\text{MAX})$   | 20  |     |     | mA     | $3.6\text{ V} > V_{ISO} > 3\text{ V}$                                                                 |

| Efficiency at $I_{ISO}(\text{MAX})$ |                         | 27  |     |     | %      | $I_{ISO} = 18\text{ mA}$                                                                              |

| $V_{DDP}$ Supply Current            |                         |     |     |     |        |                                                                                                       |

| No $V_{ISO}$ Load                   | $I_{DDP}(\text{Q})$     | 14  | 20  |     | mA     |                                                                                                       |

| Full $V_{ISO}$ Load                 | $I_{DDP}(\text{MAX})$   | 77  | 115 |     | mA     |                                                                                                       |

| Thermal Shutdown                    |                         |     | 154 |     | °C     |                                                                                                       |

| Shutdown Temperature                |                         |     | 10  |     | °C     |                                                                                                       |

| Thermal Hysteresis                  |                         |     |     |     |        |                                                                                                       |

表 8. データ・チャンネルの電源電流仕様

| Parameter      | Symbol    | 1 Mbps |      |     | 25 Mbps |      |     | 100 Mbps |      |     | Unit | Test Conditions/Comments |

|----------------|-----------|--------|------|-----|---------|------|-----|----------|------|-----|------|--------------------------|

|                |           | Min    | Typ  | Max | Min     | Typ  | Max | Min      | Typ  | Max |      |                          |

| SUPPLY CURRENT |           |        |      |     |         |      |     |          |      |     |      |                          |

| ADuM6410       | $I_{DD1}$ | 6.6    | 9.8  |     | 7.4     | 11.2 |     | 10.7     | 15.9 |     | mA   |                          |

|                | $I_{DD2}$ | 2.0    | 3.7  |     | 3.5     | 5.5  |     | 8.2      | 11.6 |     | mA   |                          |

| ADuM6411       | $I_{DD1}$ | 5.65   | 10.1 |     | 6.65    | 10.5 |     | 10.4     | 14.9 |     | mA   |                          |

|                | $I_{DD2}$ | 3.9    | 6.65 |     | 5.2     | 8.0  |     | 9.4      | 12.8 |     | mA   |                          |

| ADuM6412       | $I_{DD1}$ | 4.3    | 7.7  |     | 5.6     | 9.0  |     | 9.1      | 13   |     | mA   |                          |

|                | $I_{DD2}$ | 5.0    | 8.4  |     | 6.2     | 9.6  |     | 9.8      | 13.7 |     | mA   |                          |

表 9. スイッチング仕様

| Parameter                | Symbol             | Min | Typ | Max | Unit   | Test Conditions/Comments                                         |

|--------------------------|--------------------|-----|-----|-----|--------|------------------------------------------------------------------|

| SWITCHING SPECIFICATIONS |                    |     |     |     |        |                                                                  |

| Pulse Width              | $PW$               | 6.7 |     |     | ns     | Within PWD limit                                                 |

| Data Rate                |                    |     | 150 |     | Mbps   | Within PWD limit                                                 |

| Propagation Delay        | $t_{PHL}, t_{PLH}$ | 6.8 | 14  |     | ns     | 50% input to 50% output                                          |

| Pulse Width Distortion   | $PWD$              | 0.7 | 3.0 |     | ns     | $ t_{PLH} - t_{PHL} $                                            |

| Change vs. Temperature   |                    | 1.5 |     |     | ps/°C  |                                                                  |

| Propagation Delay Skew   | $t_{PSK}$          |     | 7.5 |     | ns     | Between any two units at the same temperature, voltage, and load |

| Channel Matching         |                    |     |     |     |        |                                                                  |

| Codirectional            | $t_{PSKCD}$        | 0.7 | 3.0 |     | ns     |                                                                  |

| Opposing Direction       | $t_{PSKOD}$        | 0.7 | 3.0 |     | ns     |                                                                  |

| Jitter                   |                    | 640 |     |     | ps p-p |                                                                  |

|                          |                    | 75  |     |     | ns rms |                                                                  |

表 10. 入力特性と出力特性

| Parameter                                   | Symbol               | Min                                              | Typ                                              | Max                                              | Unit    | Test Conditions/ Comments                                                                                      |

|---------------------------------------------|----------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------|

| DC SPECIFICATIONS                           |                      |                                                  |                                                  |                                                  |         |                                                                                                                |

| Input Threshold                             |                      |                                                  |                                                  |                                                  |         |                                                                                                                |

| Logic High                                  | V <sub>IH</sub>      | 0.7 × V <sub>ISO</sub> or 0.7 × V <sub>DD1</sub> |                                                  |                                                  | V       |                                                                                                                |

| Logic Low                                   | V <sub>IL</sub>      |                                                  |                                                  | 0.3 × V <sub>ISO</sub> or 0.3 × V <sub>DD1</sub> | V       |                                                                                                                |

| Output Voltage                              |                      |                                                  |                                                  |                                                  |         |                                                                                                                |

| Logic High                                  | V <sub>OH</sub>      | V <sub>DD1</sub> − 0.2 or V <sub>DD2</sub> − 0.2 | V <sub>DD1</sub> or V <sub>DD2</sub>             |                                                  | V       | I <sub>Ox</sub> = −20 μA, V <sub>Ix</sub> = V <sub>IxH</sub>                                                   |

|                                             |                      | V <sub>DD1</sub> − 0.5 or V <sub>DD2</sub> − 0.5 | V <sub>DD1</sub> − 0.2 or V <sub>DD2</sub> − 0.2 |                                                  | V       | I <sub>Ox</sub> = −4 mA, V <sub>Ix</sub> = V <sub>IxH</sub>                                                    |

| Logic Low                                   | V <sub>OL</sub>      |                                                  | 0.0                                              | 0.1                                              | V       | I <sub>Ox</sub> = 20 μA, V <sub>Ix</sub> = V <sub>IxL</sub>                                                    |

|                                             |                      |                                                  | 0.0                                              | 0.4                                              | V       | I <sub>Ox</sub> = 4 mA, V <sub>Ix</sub> = V <sub>IxL</sub>                                                     |

| Undervoltage Lockout                        | UVLO                 |                                                  |                                                  |                                                  |         | V <sub>DD1</sub> , V <sub>DD2</sub> , and V <sub>DDP</sub> supply                                              |

| Positive Going Threshold                    | V <sub>UV+</sub>     |                                                  | 1.6                                              |                                                  | V       |                                                                                                                |

| Negative Going Threshold                    | V <sub>UV-</sub>     |                                                  | 1.5                                              |                                                  | V       |                                                                                                                |

| Hysteresis                                  | V <sub>UVH</sub>     |                                                  | 0.1                                              |                                                  | V       |                                                                                                                |

| Input Currents per Channel                  | I <sub>I</sub>       | −10                                              | +0.01                                            | +10                                              | μA      | 0 V ≤ V <sub>Ix</sub> ≤ V <sub>DDx</sub>                                                                       |

| Quiescent Supply Current                    |                      |                                                  |                                                  |                                                  |         |                                                                                                                |

| ADuM6410                                    | I <sub>DD1 (Q)</sub> |                                                  | 1.2                                              | 2.12                                             | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 2.0                                              | 2.68                                             | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD1 (Q)</sub> |                                                  | 12.0                                             | 19.6                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 2.0                                              | 2.8                                              | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

| ADuM6411                                    | I <sub>DD1 (Q)</sub> |                                                  | 1.5                                              | 2.36                                             | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 1.8                                              | 2.52                                             | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD1 (Q)</sub> |                                                  | 9.8                                              | 16.7                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 5.7                                              | 9.7                                              | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

| ADuM6412                                    | I <sub>DD1 (Q)</sub> |                                                  | 1.6                                              | 2.4                                              | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 1.6                                              | 2.4                                              | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD1 (Q)</sub> |                                                  | 7.2                                              | 11.2                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 8.4                                              | 11.2                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

| Dynamic Supply Current                      |                      |                                                  |                                                  |                                                  |         |                                                                                                                |

| Input                                       | I <sub>DD1 (D)</sub> |                                                  | 0.01                                             |                                                  | mA/Mbps | Inputs switching, 50% duty cycle                                                                               |

| Output                                      | I <sub>DDO (D)</sub> |                                                  | 0.01                                             |                                                  | mA/Mbps | Inputs switching, 50% duty cycle                                                                               |

| AC SPECIFICATIONS                           |                      |                                                  |                                                  |                                                  |         |                                                                                                                |

| Output Rise/Fall Time                       | t <sub>R/F</sub>     |                                                  | 2.5                                              |                                                  | ns      | 10% to 90%                                                                                                     |

| Common-Mode Transient Immunity <sup>1</sup> | CM <sub>H</sub>      | 75                                               | 100                                              |                                                  | kV/μs   | V <sub>Ix</sub> = V <sub>DD1</sub> or V <sub>ISO</sub> , V <sub>CM</sub> = 1000 V, transient magnitude = 800 V |

|                                             | CM <sub>L</sub>      | 75                                               | 100                                              |                                                  | kV/μs   | V <sub>Ix</sub> = 0 V, V <sub>CM</sub> = 1000 V, transient magnitude = 800 V                                   |

<sup>1</sup> |CM<sub>H</sub>| は、電圧出力 (V<sub>O</sub>) > 0.8 V<sub>DDx</sub> を維持しながら持続できるコモンモード電圧の最大スループートレートです。|CM<sub>L</sub>| は VO > 0.8 V を維持しながら持続できるコモンモード電圧の最大スループートレートです。コモンモード電圧スループートレートは、立ち上がりと立ち下がり両方のコモンモード電圧エッジに適用されます。

## 電気的特性—5 V 主入力電源／3.3 V 二次絶縁電源

仕様に定めるすべての代表値は、 $T_A = 25^\circ\text{C}$ 、 $V_{DD1} = V_{DDP} = 5.0\text{ V}$ 、 $V_{ISO} = 3.3\text{ V}$  で、 $V_{SEL}$  抵抗回路を使用した場合の値です。抵抗回路は  $R1 = 10\text{ k}\Omega \pm 1\%$ 、 $R2 = 16.9\text{ k}\Omega \pm 1\%$  で、 $V_{ISO}$  と  $\text{GND}_{ISO}$  の間に接続（図 31 参照）。最大／最小仕様は、特に指定のない限り、 $4.5\text{ V} \leq V_{DD1} = V_{DDP} \leq 5.5\text{ V}$ 、 $3.0\text{ V} \leq V_{ISO} \leq 3.6\text{ V}$ 、および  $-40^\circ\text{C} \leq T_A \leq +105^\circ\text{C}$  の全推奨動作範囲に適用されます。スイッチング仕様は、特に指定がない限り  $C_L = 15\text{ pF}$ 、CMOS 信号レベルで試験されます。

表 11. DC/DC コンバータの静的仕様

| Parameter                           | Symbol                  | Min | Typ | Max | Unit   | Test Conditions/Comments                                                                                  |

|-------------------------------------|-------------------------|-----|-----|-----|--------|-----------------------------------------------------------------------------------------------------------|

| DC-TO-DC CONVERTER SUPPLY           |                         |     |     |     |        |                                                                                                           |

| Setpoint                            | $V_{ISO}$               | 3.0 | 3.3 | 3.6 | V      | $I_{ISO} = 15\text{ mA}$ , $R1 = 10\text{ k}\Omega$ , $R2 = 16.9\text{ k}\Omega$                          |

| Line Regulation                     | $V_{ISO}(\text{LINE})$  | 20  |     |     | mV/V   | $I_{ISO} = 15\text{ mA}$ , $V_{DD1} = 3.0\text{ V}$ to $3.6\text{ V}$                                     |

| Load Regulation                     | $V_{ISO}(\text{LOAD})$  | 1   | 5   |     | %      | $I_{ISO} = 3\text{ mA}$ to $27\text{ mA}$                                                                 |

| Output Ripple                       | $V_{ISO}(\text{RIP})$   | 50  |     |     | mV p-p | 20 MHz bandwidth, $C_{BO} = 0.1\text{ }\mu\text{F}$    $10\text{ }\mu\text{F}$ , $I_{ISO} = 27\text{ mA}$ |

| Output Noise                        | $V_{ISO}(\text{NOISE})$ | 130 |     |     | mV p-p | $C_{BO} = 0.1\text{ }\mu\text{F}$    $10\text{ }\mu\text{F}$ , $I_{ISO} = 27\text{ mA}$                   |

| Switching Frequency                 | $f_{OSC}$               | 125 |     |     | MHz    |                                                                                                           |

| Pulse-Width Modulation Frequency    | $f_{PWM}$               | 600 |     |     | kHz    |                                                                                                           |

| Output Supply                       | $I_{ISO}(\text{MAX})$   | 30  |     |     | mA     |                                                                                                           |

| Efficiency at $I_{ISO}(\text{MAX})$ |                         | 24  |     |     | %      |                                                                                                           |

| $V_{DDP}$ Supply Current            |                         |     |     |     |        | $3.6\text{ V} > V_{ISO} > 3\text{ V}$                                                                     |

| No $V_{ISO}$ Load                   | $I_{DDP}(\text{Q})$     | 14  | 20  |     | mA     |                                                                                                           |

| Full $V_{ISO}$ Load                 | $I_{DDP}(\text{MAX})$   | 85  | 115 |     | mA     |                                                                                                           |

| Thermal Shutdown                    |                         | 154 |     |     | °C     |                                                                                                           |

| Shutdown Temperature                |                         | 10  |     |     | °C     |                                                                                                           |

| Thermal Hysteresis                  |                         |     |     |     |        |                                                                                                           |

表 12. データ・チャンネルの電源電流仕様

| Parameter      | Symbol    | 1 Mbps |      |     | 25 Mbps |      |     | 100 Mbps |      |     | Unit | Test Conditions/Comments |

|----------------|-----------|--------|------|-----|---------|------|-----|----------|------|-----|------|--------------------------|

|                |           | Min    | Typ  | Max | Min     | Typ  | Max | Min      | Typ  | Max |      |                          |

| SUPPLY CURRENT |           |        |      |     |         |      |     |          |      |     |      |                          |

| ADuM6410       | $I_{DD1}$ | 6.8    | 10   |     | 7.8     | 12   |     | 11.8     | 17.4 |     | mA   |                          |

|                | $I_{DD2}$ | 2.0    | 3.7  |     | 3.5     | 5.5  |     | 8.2      | 11.6 |     | mA   |                          |

| ADuM6411       | $I_{DD1}$ | 5.8    | 10.3 |     | 7.0     | 10.9 |     | 11.4     | 15.9 |     | mA   |                          |

|                | $I_{DD2}$ | 3.9    | 6.65 |     | 5.2     | 8.0  |     | 9.4      | 12.8 |     | mA   |                          |

| ADuM6412       | $I_{DD1}$ | 4.3    | 7.7  |     | 6.0     | 9.3  |     | 10.3     | 14.2 |     | mA   |                          |

|                | $I_{DD2}$ | 5.0    | 8.4  |     | 6.2     | 9.6  |     | 9.8      | 13.7 |     | mA   |                          |

表 13. スイッチング仕様

| Parameter                | Symbol             | Min | Typ | Max | Unit   | Test Conditions/Comments                                         |

|--------------------------|--------------------|-----|-----|-----|--------|------------------------------------------------------------------|

| SWITCHING SPECIFICATIONS |                    |     |     |     |        |                                                                  |

| Data Rate                |                    |     |     | 150 | Mbps   | Within PWD limit                                                 |

| Propagation Delay        | $t_{PHL}, t_{PLH}$ | 6.8 | 14  |     | ns     | 50% input to 50% output                                          |

| Pulse Width Distortion   | PWD                | 0.7 | 3.0 |     | ns     | $ t_{PLH} - t_{PHL} $                                            |

| Pulse Width              | PW                 | 6.7 |     |     | ns     | Within PWD limit                                                 |

| Propagation Delay Skew   | $t_{PSK}$          |     | 7.5 |     | ns     | Between any two units at the same temperature, voltage, and load |

| Channel Matching         |                    |     |     |     |        |                                                                  |

| Codirectional            | $t_{PSKCD}$        | 0.7 | 3.0 |     | ns     |                                                                  |

| Opposing Direction       | $t_{PSKOD}$        | 0.7 | 3.0 |     | ns     |                                                                  |

| Jitter                   |                    | 640 |     |     | ps p-p |                                                                  |

|                          |                    | 75  |     |     | ns rms |                                                                  |

表 14. 入力特性と出力特性

| Parameter                                   | Symbol               | Min                                              | Typ                                              | Max                                          | Unit    | Test Conditions/ Comments                                                                                      |

|---------------------------------------------|----------------------|--------------------------------------------------|--------------------------------------------------|----------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------|

| DC SPECIFICATIONS                           |                      |                                                  |                                                  |                                              |         |                                                                                                                |

| Input Threshold                             |                      |                                                  |                                                  |                                              |         |                                                                                                                |

| Logic High                                  | V <sub>IH</sub>      | 0.7×V <sub>ISO</sub> or 0.7×V <sub>DD1</sub>     |                                                  |                                              | V       |                                                                                                                |

| Logic Low                                   | V <sub>IL</sub>      |                                                  |                                                  | 0.3×V <sub>ISO</sub> or 0.3×V <sub>DD1</sub> | V       |                                                                                                                |

| Output Voltage                              |                      |                                                  |                                                  |                                              |         |                                                                                                                |

| Logic High                                  | V <sub>OH</sub>      | V <sub>DD1</sub> - 0.2 or V <sub>DD2</sub> - 0.2 | V <sub>DD1</sub> or V <sub>DD2</sub>             |                                              | V       | I <sub>Ox</sub> = -20 μA, V <sub>Ix</sub> = V <sub>IxH</sub>                                                   |

|                                             |                      | V <sub>DD1</sub> - 0.5 or V <sub>DD2</sub> - 0.5 | V <sub>DD1</sub> - 0.2 or V <sub>DD2</sub> - 0.2 |                                              | V       | I <sub>Ox</sub> = -4 mA, V <sub>Ix</sub> = V <sub>IxH</sub>                                                    |

| Logic Low                                   | V <sub>OL</sub>      |                                                  | 0.0                                              | 0.1                                          | V       | I <sub>Ox</sub> = 20 μA, V <sub>Ix</sub> = V <sub>IxL</sub>                                                    |

|                                             |                      |                                                  | 0.0                                              | 0.4                                          | V       | I <sub>Ox</sub> = 4 mA, V <sub>Ix</sub> = V <sub>IxL</sub>                                                     |

| Undervoltage Lockout                        | UVLO                 |                                                  |                                                  |                                              |         | V <sub>DD1</sub> , V <sub>DD2</sub> , and V <sub>DDP</sub> supply                                              |

| Positive Going Threshold                    | V <sub>UV+</sub>     |                                                  | 1.6                                              |                                              | V       |                                                                                                                |

| Negative Going Threshold                    | V <sub>UV-</sub>     |                                                  | 1.5                                              |                                              | V       |                                                                                                                |

| Hysteresis                                  | V <sub>UVH</sub>     |                                                  | 0.1                                              |                                              | V       |                                                                                                                |

| Input Currents per Channel                  | I <sub>I</sub>       | -10                                              | +0.01                                            | +10                                          | μA      | 0 V ≤ V <sub>Ix</sub> ≤ V <sub>DDx</sub>                                                                       |

| Quiescent Supply Current                    |                      |                                                  |                                                  |                                              |         |                                                                                                                |

| ADuM6410                                    | I <sub>DD1 (Q)</sub> |                                                  | 1.2                                              | 2.2                                          | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 2.0                                              | 2.68                                         | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD1 (Q)</sub> |                                                  | 12.0                                             | 20.0                                         | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 2.0                                              | 2.8                                          | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

| ADuM6411                                    | I <sub>DD1 (Q)</sub> |                                                  | 1.6                                              | 2.46                                         | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 1.8                                              | 2.52                                         | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD1 (Q)</sub> |                                                  | 10.0                                             | 17.0                                         | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 5.7                                              | 9.7                                          | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

| ADuM6412                                    | I <sub>DD1 (Q)</sub> |                                                  | 1.6                                              | 2.46                                         | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 1.6                                              | 2.4                                          | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD1 (Q)</sub> |                                                  | 7.2                                              | 11.5                                         | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 8.4                                              | 11.2                                         | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

| Dynamic Supply Current                      |                      |                                                  |                                                  |                                              |         |                                                                                                                |

| Input                                       | I <sub>DD1 (D)</sub> |                                                  | 0.01                                             |                                              | mA/Mbps | Inputs switching, 50% duty cycle                                                                               |

| Output                                      | I <sub>DDO (D)</sub> |                                                  | 0.01                                             |                                              | mA/Mbps | Inputs switching, 50% duty cycle                                                                               |

| AC SPECIFICATIONS                           |                      |                                                  |                                                  |                                              |         |                                                                                                                |

| Output Rise/Fall Time                       | t <sub>R/F</sub>     |                                                  | 2.5                                              |                                              | ns      | 10% to 90%                                                                                                     |

| Common-Mode Transient Immunity <sup>1</sup> | CM <sub>H</sub>      | 75                                               | 100                                              |                                              | kV/μs   | V <sub>Ix</sub> = V <sub>DD1</sub> or V <sub>ISO</sub> , V <sub>CM</sub> = 1000 V, transient magnitude = 800 V |

|                                             | CM <sub>L</sub>      | 75                                               | 100                                              |                                              | kV/μs   | V <sub>Ix</sub> = 0 V, V <sub>CM</sub> = 1000 V, transient magnitude = 800 V                                   |

<sup>1</sup> |CM<sub>H</sub>| は、電圧出力 (V<sub>O</sub>) > 0.8 V<sub>DDx</sub> を維持しながら持続できるコモンモード電圧の最大スルーレートです。|CM<sub>L</sub>| は V<sub>O</sub> > 0.8 V を維持しながら持続できるコモンモード電圧の最大スルーレートです。コモンモード電圧スルーレートは、立ち上がりと立ち下がり両方のコモンモード電圧エッジに適用されます。

## 電気的特性 — 2.5 V 動作のデジタル・アイソレータ・チャンネルのみ

すべての代表的な仕様は、 $T_A = 25^\circ\text{C}$ 、 $V_{DD1} = V_{DD2} = 2.5\text{ V}$  時の値です。最小／最大仕様は、特に指定のない限り、 $2.25\text{ V} \leq V_{DD1} \leq 2.75\text{ V}$ 、 $2.25\text{ V} \leq V_{DD2} \leq 2.75\text{ V}$ 、および $-40^\circ\text{C} \leq T_A \leq +105^\circ\text{C}$  の全推奨動作範囲に適用されます。特に指定がない限り、スイッチング仕様は、 $CL = 15\text{ pF}$ 、CMOS 信号レベルで試験されます。電源電流の仕様は 50% デューティ・サイクルで指定されています。

表 15. データ・チャンネルの電源電流仕様

| Parameter             | Symbol    | 1 Mbps |      |     | 25 Mbps |      |     | 100 Mbps |      |     | Unit | Test Conditions/Comments |

|-----------------------|-----------|--------|------|-----|---------|------|-----|----------|------|-----|------|--------------------------|

|                       |           | Min    | Typ  | Max | Min     | Typ  | Max | Min      | Typ  | Max |      |                          |

| <b>SUPPLY CURRENT</b> |           |        |      |     |         |      |     |          |      |     |      |                          |

| ADuM6410              | $I_{DD1}$ | 6.5    | 9.8  |     | 7.3     | 11.1 |     | 10.4     | 15.5 |     | mA   |                          |

|                       | $I_{DD2}$ | 2.0    | 3.6  |     | 3.3     | 5.2  |     | 7.3      | 10.2 |     | mA   |                          |

| ADuM6411              | $I_{DD1}$ | 5.6    | 10.0 |     | 6.4     | 10.4 |     | 9.7      | 14.5 |     | mA   |                          |

|                       | $I_{DD2}$ | 3.8    | 6.55 |     | 4.8     | 7.7  |     | 8.3      | 11.5 |     | mA   |                          |

| ADuM6412              | $I_{DD1}$ | 4.3    | 7.7  |     | 5.4     | 8.8  |     | 8.8      | 12.7 |     | mA   |                          |

|                       | $I_{DD2}$ | 5.0    | 8.4  |     | 6.1     | 9.5  |     | 9.5      | 13.4 |     | mA   |                          |

表 16. スイッチング仕様

| Parameter                       | Symbol             | Min | Typ | Max | Unit                 | Test Conditions/Comments                                         |

|---------------------------------|--------------------|-----|-----|-----|----------------------|------------------------------------------------------------------|

| <b>SWITCHING SPECIFICATIONS</b> |                    |     |     |     |                      |                                                                  |

| Pulse Width                     | PW                 | 6.6 |     |     | ns                   | Within PWD limit                                                 |

| Data Rate                       |                    |     |     | 150 | Mbps                 | Within PWD limit                                                 |

| Propagation Delay               | $t_{PHL}, t_{PLH}$ | 5.0 | 7.0 | 14  | ns                   | 50% input to 50% output                                          |

| Pulse Width Distortion          | PWD                |     | 0.7 | 3   | ns                   | $ t_{PLH} - t_{PHL} $                                            |

| Change vs. Temperature          |                    |     |     | 1.5 | ps/ $^\circ\text{C}$ |                                                                  |

| Propagation Delay Skew          | $t_{PSK}$          |     |     | 6.8 | ns                   | Between any two units at the same temperature, voltage, and load |

| Channel Matching                |                    |     |     |     |                      |                                                                  |

| Codirectional                   | $t_{PSKCD}$        |     | 0.7 | 3.0 | ns                   |                                                                  |

| Opposing Direction              | $t_{PSKOD}$        |     | 0.7 | 3.0 | ns                   |                                                                  |

| Jitter                          |                    | 800 |     |     | ps p-p               |                                                                  |

|                                 |                    | 190 |     |     | ps rms               |                                                                  |

表 17. 入力特性と出力特性

| Parameter                                   | Symbol               | Min                                              | Typ                                              | Max                                              | Unit    | Test Conditions/ Comments                                                                                      |

|---------------------------------------------|----------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------|

| DC SPECIFICATIONS                           |                      |                                                  |                                                  |                                                  |         |                                                                                                                |

| Input Threshold                             |                      |                                                  |                                                  |                                                  |         |                                                                                                                |

| Logic High                                  | V <sub>IH</sub>      | 0.7 × V <sub>ISO</sub> or 0.7 × V <sub>DD1</sub> |                                                  |                                                  | V       |                                                                                                                |

| Logic Low                                   | V <sub>IL</sub>      |                                                  |                                                  | 0.3 × V <sub>ISO</sub> or 0.3 × V <sub>DD1</sub> | V       |                                                                                                                |

| Output Voltage                              |                      |                                                  |                                                  |                                                  |         |                                                                                                                |

| Logic High                                  | V <sub>OH</sub>      | V <sub>DD1</sub> − 0.2 or V <sub>DD2</sub> − 0.2 | V <sub>DD1</sub> or V <sub>DD2</sub>             |                                                  | V       | I <sub>Ox</sub> = −20 μA, V <sub>Ix</sub> = V <sub>IxH</sub>                                                   |

|                                             |                      | V <sub>DD1</sub> − 0.5 or V <sub>DD2</sub> − 0.5 | V <sub>DD1</sub> − 0.2 or V <sub>DD2</sub> − 0.2 |                                                  | V       | I <sub>Ox</sub> = −4 mA, V <sub>Ix</sub> = V <sub>IxH</sub>                                                    |

| Logic Low                                   | V <sub>OL</sub>      |                                                  | 0.0                                              | 0.1                                              | V       | I <sub>Ox</sub> = 20 μA, V <sub>Ix</sub> = V <sub>IxL</sub>                                                    |

|                                             |                      |                                                  | 0.0                                              | 0.4                                              | V       | I <sub>Ox</sub> = 4 mA, V <sub>Ix</sub> = V <sub>IxL</sub>                                                     |

| Undervoltage Lockout                        | UVLO                 |                                                  |                                                  |                                                  |         | V <sub>DD1</sub> , V <sub>DD2</sub> , and V <sub>DDP</sub> supply                                              |

| Positive Going Threshold                    | V <sub>UV+</sub>     |                                                  | 1.6                                              |                                                  | V       |                                                                                                                |

| Negative Going Threshold                    | V <sub>UV-</sub>     |                                                  | 1.5                                              |                                                  | V       |                                                                                                                |

| Hysteresis                                  | V <sub>UVH</sub>     |                                                  | 0.1                                              |                                                  | V       |                                                                                                                |

| Input Currents per Channel                  | I <sub>I</sub>       | −10                                              | +0.01                                            | +10                                              | μA      | 0 V ≤ V <sub>Ix</sub> ≤ V <sub>DDx</sub>                                                                       |

| Quiescent Supply Current                    |                      |                                                  |                                                  |                                                  |         |                                                                                                                |

| ADuM6410                                    | I <sub>DD1 (Q)</sub> |                                                  | 1.2                                              | 2.0                                              | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 2.0                                              | 2.64                                             | mA      | V <sub>Ix</sub> = Logic 0                                                                                      |

|                                             | I <sub>DD1 (Q)</sub> |                                                  | 1.2                                              | 19.6                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |

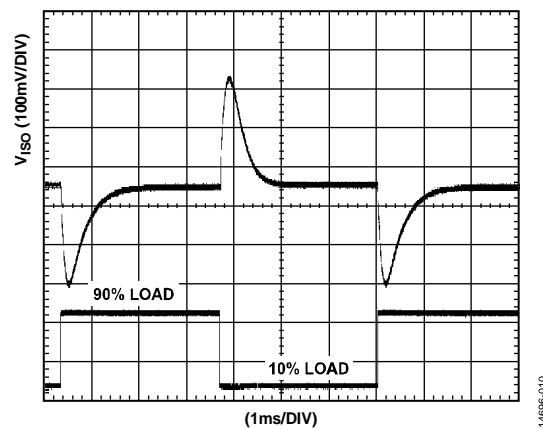

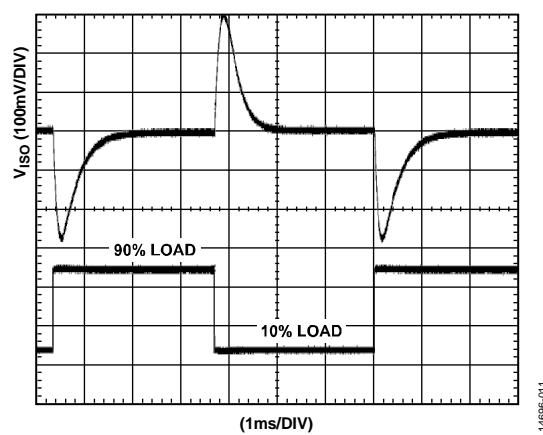

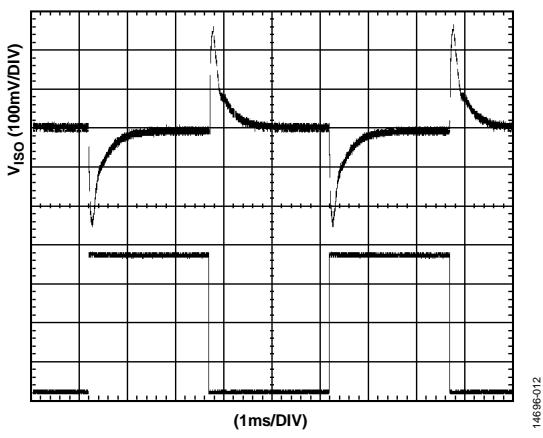

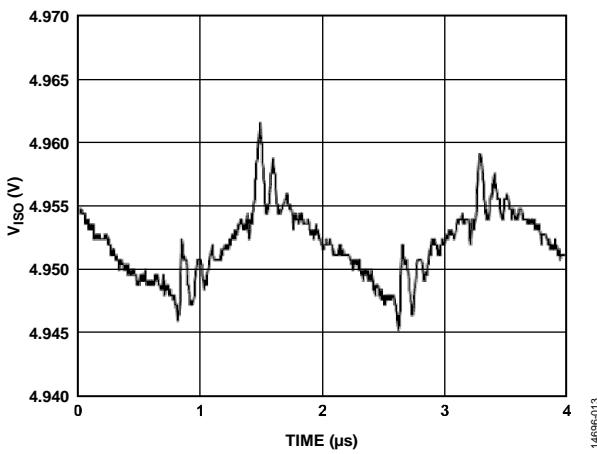

|                                             | I <sub>DD2 (Q)</sub> |                                                  | 2.0                                              | 2.76                                             | mA      | V <sub>Ix</sub> = Logic 1                                                                                      |