# MPPT と充電管理機能付き超低消費電力のエネルギー・ハーベスター PMU

## データシート

## ADP5091/ADP5092

### 特長

動的センシングまたは非センシング・モードによる最大電力点追従 (MPPT) 機能付き昇圧レギュレータ

超軽負荷時に最大効率を実現するためのヒステリシス・モード

動作時の SYS ピンにおける静止電流 ( $V_{IN} > V_{CBP} \geq V_{MINOP}$ ) : 510 nA

スリープ時の SYS ピンにおける静止電流 ( $V_{CBP} < V_{MINOP}$ ) : 390 nA

入力の動作電圧範囲: 0.08 V ~ 3.3 V

チャージ・ポンプ使用時の 380 mV (typ) からの高速コールド・スタート

MINOP ピンのシャットダウンは入力のオープン・サーキット電圧 (OCV) に基づいて設定可能

1.5 V ~ 3.6 V の範囲で 150 mA のレギュレーション出力

蓄電素子の充電をサポートするバッテリ充電終了の閾値 (2.2 V ~ 5.2 V)

オプションの BACK\_UP 電力経路の管理機能

マイクロコントローラ・ユニット (MCU) 通信を介してスイッチを一時的にシャットダウンすることで、RF (無線周波数) 伝送の性能を向上

### アプリケーション

PV セル (太陽電池) によるエネルギー・ハーベスティング

TEG (熱電発電) エネルギー・ハーベスティング

工業用モニタリング

電源内蔵ワイヤレス・センサー・デバイス

エネルギー・ハーベスティングによるポータブル機器とウェアラブル機器

### 概要

ADP5091/ADP5092 は、インテリジェントな統合型エネルギー・ハーベスティング向けの超低消費電力パワー・マネージメント・ユニット (PMU) ソリューションであり、PV セルや TEG からの DC 電力を変換します。これらのデバイスは、充電式リチウムイオン電池、薄膜電池、スーパー・キャパシタ、従来型のコンデンサなどの蓄電素子を充電し、小型の電子機器やバッテリ不要システムを起動させます。

ADP5091/ADP5092 は 6  $\mu$ W ~ 600 mW の範囲で収集した限られた電力を効率よく変換し、損失を抑えます。内蔵のコールド・スタート回路とレギュレータを使用することで、最小 380 mV の入力電圧で動作を開始できます。コールド・スタートアップの後、レギュレータは 0.08 V ~ 3.3 V の入力電圧範囲で動作します。外部抵抗分圧器または VID ピンを使用して、150 mA のレギュレーション出力を追加することもできます。

MPPT 制御機能を備えているので、固定範囲内に入力電圧リップルを抑えることができます。これにより、DC/DC 昇圧変換が安定します。動的センシング・モードと非センシング・モードの両方で、入力電圧の調整値を設定できるので、ハーベスターから可能な限り最大の電力を取り出すことができます。動作の最小閾値を設定できるので、入力値の低い状態で昇圧をシャットダウンでき

ます。ADP5091 の LLD ピンは MINOP のコンバレータ出力であり、マイクロプロセッサに対する低光量インジケータとして機能します。一方、ADP5092 の REG\_GOOD フラグは REG\_OUT 電圧を監視します。さらに、DIS\_SW ピンを使用すると、一時的に昇圧レギュレータをシャットダウンできるので、RF 伝送が容易になります。

ADP5091/ADP5092 は充電制御機能を備えているので、充電式バッテリを保護できます。この機能は、充電終了時の電圧とシャットダウン放電電圧を設定してバッテリの電圧をモニタすることで実現されます。さらに、PGOOD 出力を設定することで、SYS 電圧を監視できます。

オプションのバックアップ・バッテリを接続して、内蔵の電力経路の制御回路から管理できます。この電力経路の制御回路は、エネルギー・ハーベスター、充電式バッテリ、バックアップ・バッテリの間で電源を自動的に切り替えます。

ADP5091/ADP5092 は 24 ピン LFCSP パッケージに収納されています。温度範囲の定格値は -40 °C ~ +125 °C です。

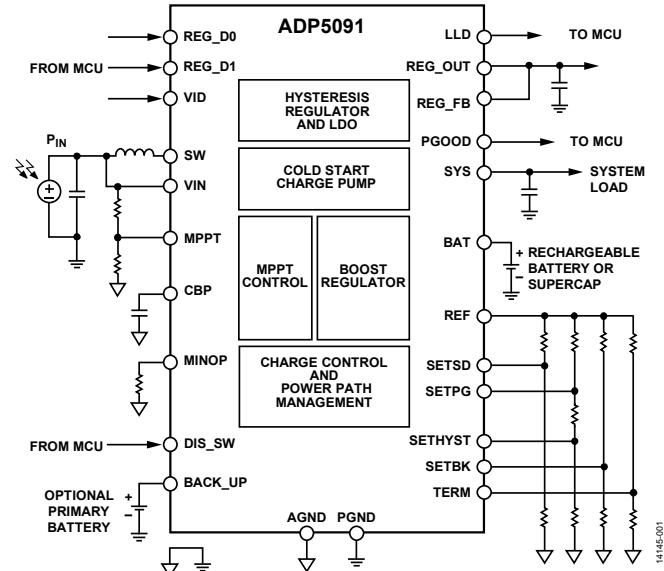

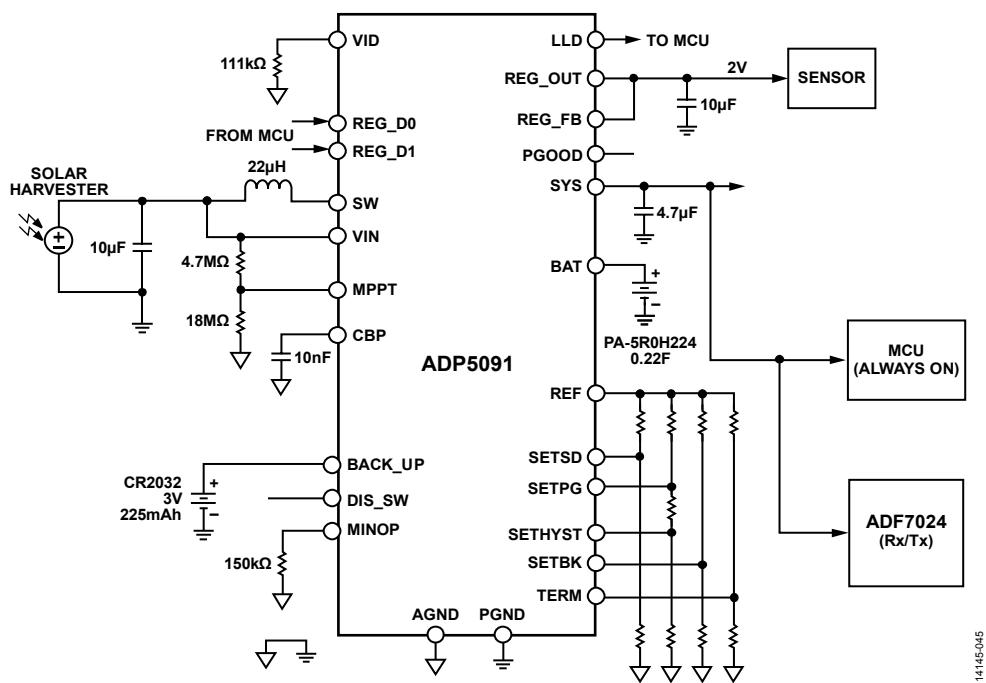

### 代表的なアプリケーション回路

図 1.

## 目次

|                                                                  |    |                      |    |

|------------------------------------------------------------------|----|----------------------|----|

| 特長                                                               | 1  | レギュレーション出力の構成        | 17 |

| アプリケーション                                                         | 1  | REG_GOOD (ADP5092のみ) | 18 |

| 代表的なアプリケーション回路                                                   | 1  | バッテリの充電管理            | 18 |

| 概要                                                               | 1  | バックアップの蓄電経路          | 18 |

| 改訂履歴                                                             | 2  | バックアップと BAT の選択閾値    | 19 |

| 詳細な機能ブロック図                                                       | 3  | バッテリの過放電防止の機能        | 19 |

| 仕様                                                               | 4  | バッテリ過放電防止の機能         | 19 |

| レギュレーションされた出力仕様                                                  | 6  | パワーグッド (PGOOD)       | 20 |

| 絶対最大定格                                                           | 7  | 電力経路の動作フロー           | 20 |

| 熱抵抗                                                              | 7  | 電流制限機能と短絡保護の機能       | 20 |

| ESD に関する注意                                                       | 7  | サーマル・シャットダウン         | 21 |

| ピン配置およびピン機能の説明                                                   | 8  | アプリケーション情報           | 23 |

| 代表的な性能特性                                                         | 10 | エネルギー・ハーベ스타の選択       | 23 |

| 動作原理                                                             | 16 | 蓄電素子の選択              | 23 |

| 高速コールド・スタートアップ回路 ( $V_{SYS} < V_{SYS\_TH}, V_I > V_{IN\_COLD}$ ) | 16 | インダクタの選択             | 23 |

| メイン昇圧レギュレータ ( $V_{BAT\_TERM} > V_{SYS} > V_{SYS\_TH}$ )          | 16 | コンデンサの選択             | 24 |

| VIN オープン・サーキットと MPPT                                             | 16 | レイアウトと組み立てについての考慮事項  | 24 |

| 最小動作閾値の機能                                                        | 17 | 代表的なアプリケーション回路       | 25 |

| 昇圧動作のディスエーブル機能                                                   | 17 | 出荷時にプログラム可能なオプション    | 27 |

| レギュレーション出力の動作モード                                                 | 17 | 外形寸法                 | 28 |

| REG_D0 と REG_D1                                                  | 17 | オーダー・ガイド             | 28 |

## 改訂履歴

7/2016-Revision 0: Initial Version

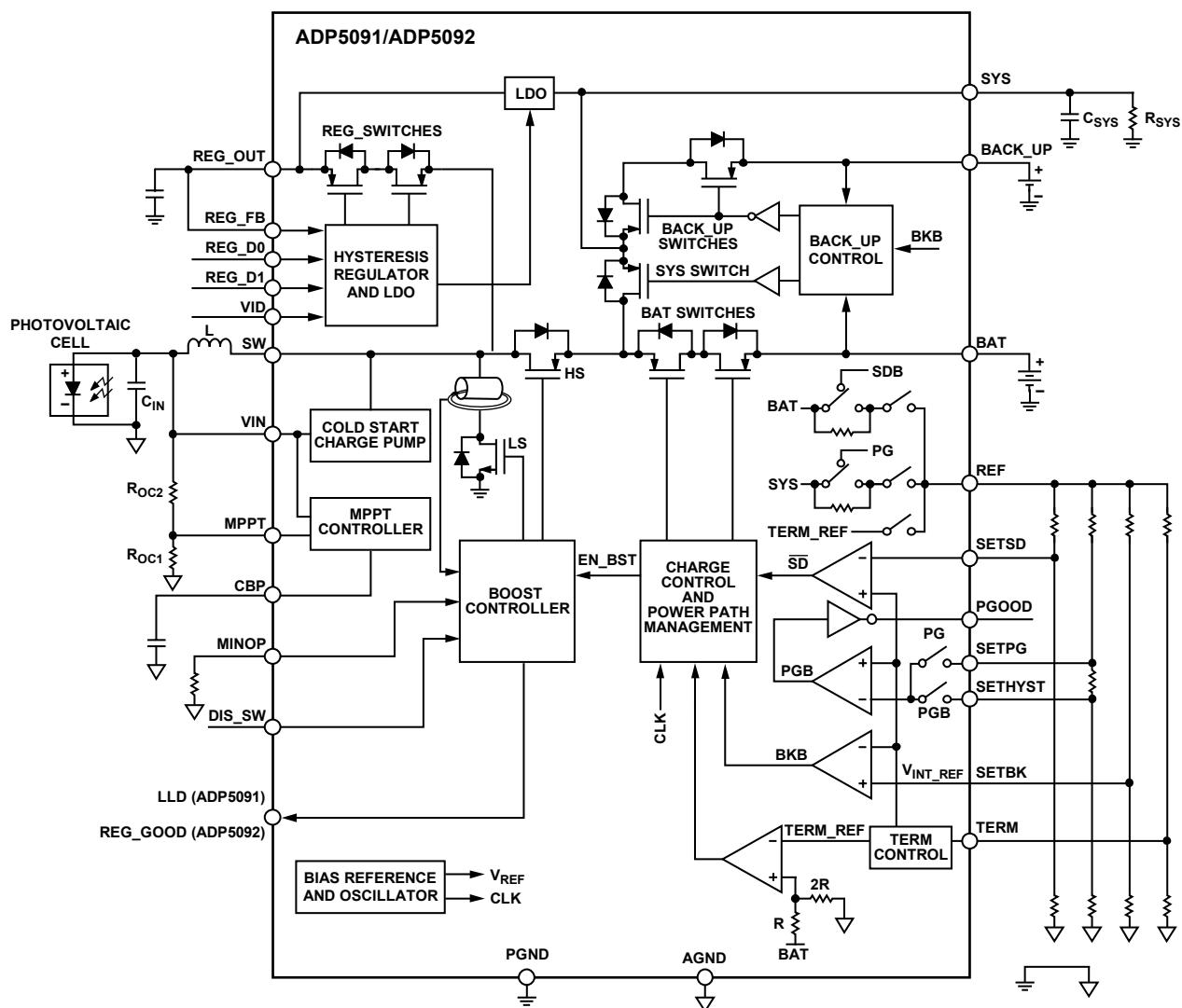

## 詳細な機能ブロック図

14145-040

図 2. 詳細な機能ブロック図

## 仕様

特に指定がない限り、電圧入力 ( $V_{IN}$ ) = 1.2 V、 $V_{SYS} = V_{BAT} = 3$  V、ジャンクション温度の最小／最大仕様は  $T_J = -40$  °C ~ +125 °C、周囲温度の代表仕様は  $T_A = 25$  °C。外付け部品およびインダクタ (L) = 22 μH、入力容量 ( $C_{IN}$ ) = 4.7 μF、 $C_{SYS} = 4.7$  μF。

表 1.

| Parameter                                                                    | Symbol               | Test Conditions/Comments                                                                                                                               | Min  | Typ                             | Max                                 | Unit                       |

|------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------|-------------------------------------|----------------------------|

| QUIESCENT CURRENT                                                            |                      |                                                                                                                                                        |      |                                 |                                     |                            |

| Operating Quiescent Current of SYS Pin ( $V_{IN} > V_{CBP} \geq V_{MINOP}$ ) | $I_{Q\_SYS}$         | REG_D0 = low, REG_D1 = low<br>REG_D0 = high, REG_D1 = low<br>REG_D0 = low, REG_D1 = high<br>REG_D0 = high, REG_D1 = high<br>REG_D0 = low, REG_D1 = low |      | 510<br>650<br>750<br>760<br>390 | 1000<br>1150<br>1290<br>1300<br>880 | nA<br>nA<br>nA<br>nA<br>nA |

| Sleeping Quiescent Current of SYS Pin ( $V_{CBP} < V_{MINOP}$ )              | $I_{Q\_SLEEP\_SYS}$  |                                                                                                                                                        |      |                                 |                                     |                            |

| COLD START CIRCUIT                                                           |                      |                                                                                                                                                        |      |                                 |                                     |                            |

| Minimum Input Voltage for Cold Start                                         | $V_{IN\_COLD}$       | $V_{SYS} = 0$ V, $0^\circ\text{C} < T_A < 85^\circ\text{C}$                                                                                            |      | 380                             | 500                                 | mV                         |

| Minimum Input Power for Cold Start                                           | $P_{IN\_COLD}$       |                                                                                                                                                        |      | 6                               |                                     | μW                         |

| End of Cold Start Operation                                                  |                      |                                                                                                                                                        |      |                                 |                                     |                            |

| Threshold                                                                    | $V_{SYS\_TH}$        |                                                                                                                                                        | 1.73 | 1.87                            | 2.00                                | V                          |

| Hysteresis                                                                   | $V_{SYS\_HYS}$       |                                                                                                                                                        |      | 95                              |                                     | mV                         |

| BOOST REGULATOR                                                              |                      |                                                                                                                                                        |      |                                 |                                     |                            |

| Input Voltage Operating Range                                                | $V_{IN}$             | Cold start completed                                                                                                                                   | 0.08 | 3.3                             |                                     | V                          |

| Input Power Operating Range                                                  | $P_{IN}$             | Cold start completed, $V_{IN} = 3$ V                                                                                                                   |      | 600                             |                                     | mW                         |

| Start Charging BAT Threshold on SYS                                          | $V_{SYS\_CHG}$       |                                                                                                                                                        | 2.00 | 2.19                            | 2.35                                | V                          |

| Start Charging BAT Hysteresis on SYS                                         | $V_{SYS\_CHG\_HYS}$  |                                                                                                                                                        |      | 150                             |                                     | mV                         |

| Input Peak Current                                                           | $I_{IN\_PEAK}$       | Factory trim, 1 bit, Option 0<br>Option 1                                                                                                              |      | 200<br>300                      | 250                                 | mA                         |

| Low-Side Switch On Resistance                                                | $R_{LS\_DS\_ON}$     | Pin to pin measurement                                                                                                                                 |      | 0.44                            | 0.6                                 | Ω                          |

| High-Side Switch On Resistance                                               | $R_{HS\_DS\_ON}$     | Pin to pin measurement                                                                                                                                 |      | 0.85                            | 1.2                                 | Ω                          |

| SYS Switch On Resistance                                                     | $R_{SYS\_DS\_ON}$    |                                                                                                                                                        |      | 0.32                            | 0.70                                | Ω                          |

| DIS_SW Voltage                                                               |                      |                                                                                                                                                        |      |                                 |                                     |                            |

| High                                                                         | $V_{DIS\_SW\_HIGH}$  |                                                                                                                                                        | 1    |                                 |                                     | V                          |

| Low                                                                          | $V_{DIS\_SW\_LOW}$   |                                                                                                                                                        |      |                                 | 0.5                                 | V                          |

| DIS_SW Delay                                                                 | $t_{DIS\_SW\_DELAY}$ |                                                                                                                                                        |      | 1                               |                                     | μs                         |

| VIN CONTROL AND MINOP                                                        |                      |                                                                                                                                                        |      |                                 |                                     |                            |

| VIN Open Circuit Voltage                                                     |                      |                                                                                                                                                        |      |                                 |                                     |                            |

| Default Sampling Cycle                                                       | $t_{OCV\_CYCLE}$     | Factory trim, 2 bit (4 sec, 8 sec, 16 sec, 32 sec)                                                                                                     |      | 16                              |                                     | sec                        |

| Sampling Time                                                                | $t_{OCV\_SAMPL}$     |                                                                                                                                                        |      | 256                             |                                     | ms                         |

| MINOP Bias Current                                                           | $I_{MINOP}$          |                                                                                                                                                        | 1.58 | 2.00                            | 2.45                                | μA                         |

| MINOP Operation Voltage Threshold of Dynamic MPPT Sensing Mode               | $V_{MINOP\_DSM}$     |                                                                                                                                                        |      |                                 | 1.5                                 | V                          |

| MPPT Bias Current of MPPT No Sensing Mode                                    | $I_{MPPT}$           |                                                                                                                                                        | 1.7  | 2.0                             | 2.3                                 | μA                         |

| LLD (ADP5091 Only)                                                           |                      |                                                                                                                                                        |      |                                 |                                     |                            |

| Pull-Up Resistor                                                             |                      |                                                                                                                                                        |      | 12                              | 17                                  | kΩ                         |

| Pull-Down Resistor                                                           |                      |                                                                                                                                                        |      | 12                              | 17                                  | kΩ                         |

| High Voltage                                                                 | $V_{LLD\_IH}$        |                                                                                                                                                        |      | $V_{REG\_OUT}$                  |                                     | V                          |

| Leakage Current at CBP Pin                                                   | $I_{CBP\_LEAK}$      |                                                                                                                                                        |      | 10                              | 2000                                | pA                         |

| Parameter                                   | Symbol                    | Test Conditions/Comments                                                                                                                                   | Min                | Typ                   | Max                   | Unit |

|---------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-----------------------|------|

| ENERGY STORAGE MANAGEMENT                   |                           |                                                                                                                                                            |                    |                       |                       |      |

| Internal Reference Voltage                  | V <sub>INT_REF</sub>      |                                                                                                                                                            | 0.955              | 1.011                 | 1.067                 | V    |

| Battery Stop Discharging Threshold          | V <sub>SETSD</sub>        |                                                                                                                                                            | 2.0                |                       | V <sub>BAT_TERM</sub> | V    |

| Hysteresis Resistor                         | R <sub>SETSD_HYS</sub>    |                                                                                                                                                            | 80                 | 115                   | 160                   | kΩ   |

| Battery Terminal Charging Threshold         | V <sub>BAT_TERM</sub>     |                                                                                                                                                            | 2.2                |                       | 5.2                   | V    |

| Hysteresis                                  | V <sub>BAT_TERM_HYS</sub> |                                                                                                                                                            |                    | 3                     | 3.1                   | %    |

| PGOOD Rising Threshold at SYS Pin           | V <sub>SYS_PG</sub>       |                                                                                                                                                            | V <sub>SETSD</sub> | V <sub>BAT_TERM</sub> | V                     |      |

| PGOOD Pull-Up Resistor                      |                           |                                                                                                                                                            |                    | 11.6                  | 17.0                  | kΩ   |

| PGOOD Pull-Down Resistor                    |                           |                                                                                                                                                            |                    | 11.6                  | 17.0                  | kΩ   |

| PGOOD High Voltage                          | V <sub>PGOOD_HIGH</sub>   |                                                                                                                                                            | V <sub>SYS</sub>   |                       | V                     |      |

| Battery Switches On Resistance              | R <sub>BAT_SW_ON</sub>    | Pin to pin measurement                                                                                                                                     | 0.59               | 0.85                  |                       | Ω    |

| Battery Source Current                      | I <sub>BAT</sub>          |                                                                                                                                                            |                    |                       | 1                     | A    |

| Leakage Current at BAT Pin                  | I <sub>BAT_LEAK</sub>     | V <sub>BAT</sub> = 2 V, V <sub>SETSD</sub> = 2.2 V, V <sub>SYS</sub> = 2 V<br>V <sub>BAT</sub> = 3.3 V, V <sub>SETSD</sub> = 2.2 V, V <sub>SYS</sub> = 0 V |                    | 22                    | 50                    | nA   |

|                                             |                           |                                                                                                                                                            |                    | 3.5                   | 35                    | nA   |

| BACK_UP POWER PATH                          |                           |                                                                                                                                                            |                    |                       |                       |      |

| Turning Off BACK_UP Switch Threshold on BAT | V <sub>SETBK</sub>        |                                                                                                                                                            | 2.0                |                       | V <sub>BAT_TERM</sub> | V    |

| Hysteresis Resistor                         | R <sub>SETBK_HYS</sub>    |                                                                                                                                                            | 80                 | 115                   | 160                   | kΩ   |

| BACK_UP Switches On Resistance              |                           |                                                                                                                                                            |                    | 0.85                  | 1.20                  | Ω    |

| BACK_UP and BAT Comparator Offset           | V <sub>BKP_OFFSET</sub>   | V <sub>SYS</sub> ≥ V <sub>SYS_TH</sub>                                                                                                                     | 158                | 190                   | 271                   | mV   |

| Hysteresis                                  | V <sub>BAT_HYS</sub>      |                                                                                                                                                            | 68                 | 75                    | 108                   | mV   |

| BACK_UP Current Capability                  | I <sub>BKP</sub>          | V <sub>SYS</sub> < V <sub>SYS_TH</sub>                                                                                                                     |                    | 250                   |                       | μA   |

| Leakage Current at BACK_UP Pin              | I <sub>BKP_LEAK</sub>     | V <sub>BACK_UP</sub> = V <sub>SYS</sub> = V <sub>BAT</sub> = 3 V                                                                                           |                    | 16                    | 40                    | nA   |

| THERMAL SHUTDOWN                            |                           |                                                                                                                                                            |                    |                       |                       |      |

| Threshold                                   | T <sub>SHDN</sub>         | V <sub>SYS</sub> ≥ V <sub>SYS_TH</sub>                                                                                                                     |                    | 142                   |                       | °C   |

| Hysteresis                                  | T <sub>HYS</sub>          |                                                                                                                                                            |                    | 15                    |                       | °C   |

## レギュレーションされた出力仕様

特に指定がない限り、 $V_{IN} = 1.2\text{ V}$ 、 $V_{SYS} = V_{BAT} = 3\text{ V}$ 、 $V_{REG\_OUT} = 2\text{ V}$ 、 $L = 22\text{ }\mu\text{H}$ 、 $C_{IN} = 4.7\text{ }\mu\text{F}$ 、 $C_{SYS} = 4.7\text{ }\mu\text{F}$ 、 $C_{REG\_OUT} = 4.7\text{ }\mu\text{F}$ 、ジャンクション温度の最小／最大仕様は、 $T_J = -40\text{ }^{\circ}\text{C} \sim +125\text{ }^{\circ}\text{C}$ 。周囲温度の代表仕様は  $T_A = 25\text{ }^{\circ}\text{C}$ 。

表 2.

| Parameter                             | Symbol                | Test Conditions/Comments                                                                     | Min                         | Typ                         | Max                         | Unit              |

|---------------------------------------|-----------------------|----------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------|

| REGULATED OUTPUT                      |                       |                                                                                              |                             |                             |                             |                   |

| Output Options by VID Control         | $V_{REG\_OUT}$        |                                                                                              | 1.5                         |                             | 3.6                         | V                 |

| Rating Current                        | $I_{REG\_OUT}$        |                                                                                              |                             | 150                         |                             | mA                |

| REG_OUT Pull-Down Resistance          | $R_{REG\_OUT}$        |                                                                                              |                             | 235                         |                             | $\Omega$          |

| REG_OUT IN BOOST MODE                 |                       |                                                                                              |                             |                             |                             |                   |

| REG_OUT Wake Threshold                | $V_{REG\_WAKE}$       |                                                                                              | $1.008 \times V_{REG\_OUT}$ | $1.027 \times V_{REG\_OUT}$ | $1.048 \times V_{REG\_OUT}$ | V                 |

| REG_OUT Wake Threshold Hysteresis     | $V_{REG\_WAKE\_HYS}$  |                                                                                              | 1                           |                             |                             | %                 |

| Adjustable REG_OUT Wake Threshold     | $V_{ADJ\_REG\_WAKE}$  |                                                                                              | 1.008                       | 1.028                       | 1.048                       | V                 |

| Adjustable REG_OUT Sleep Threshold    | $V_{ADJ\_REG\_SLEEP}$ |                                                                                              | 1.018                       | 1.038                       | 1.058                       | V                 |

| High-Side Switches On Resistance      | $R_{BST\_DS\_ON}$     |                                                                                              |                             | 1.63                        | 2.15                        | $\Omega$          |

| Current-Limit Threshold of Boost Mode | $I_{REG\_BST\_LIM}$   |                                                                                              |                             | 100                         | 155                         | mA                |

| REG_OUT IN LOW DROPOUT (LDO) MODE     |                       |                                                                                              |                             |                             |                             |                   |

| REG_OUT Accuracy                      | $V_{REG\_LDO}$        | $0\text{ }\mu\text{A} < I_{OUT} < 150\text{ mA}$ , $V_{SYS} = (V_{REG\_OUT} + 0.5\text{ V})$ | -3.5                        |                             | +3.5                        | %                 |

| Adjustable REG_OUT Accuracy           | $V_{REG\_LDO\_ADJ}$   | $I_{OUT} = 1\text{ mA}$                                                                      | 0.999                       | 1.015                       | 1.028                       | V                 |

| REG_OUT Dropout                       | $V_{REG\_DROP}$       | $0\text{ }\mu\text{A} < I_{OUT} < 150\text{ mA}$ , $V_{SYS} = (V_{REG\_OUT} + 0.5\text{ V})$ | 0.985                       | 1.015                       | 1.045                       | V                 |

| Current-Limit Threshold of LDO Mode   | $I_{REG\_LIM}$        | $I_{OUT} = 150\text{ mA}$                                                                    |                             | 200                         |                             | mV                |

| Output Noise                          | $OUT_{NOISE}$         | $V_{SYS} \geq V_{SYS\_TH}$                                                                   | 200                         | 260                         |                             | mA                |

| Power Supply Rejection Ratio          | PSRR                  | 10 Hz to 100 kHz                                                                             |                             | 700                         |                             | $\mu\text{V rms}$ |

|                                       |                       | 100 Hz                                                                                       |                             | 60                          |                             | dB                |

|                                       |                       | 1 kHz                                                                                        |                             | 40                          |                             | dB                |

| REG_D0 and REG_D1                     |                       |                                                                                              |                             |                             |                             |                   |

| Input Logic                           |                       |                                                                                              |                             |                             |                             |                   |

| High                                  | $V_{REG\_DX\_IH}$     |                                                                                              | 1.2                         |                             |                             | V                 |

| Low                                   | $V_{REG\_DX\_IL}$     |                                                                                              |                             | 0.4                         |                             | V                 |

| Input Leakage Current                 | $I_{REG\_DX\_LEAK}$   |                                                                                              |                             | 20                          |                             | nA                |

| REG_GOOD (ADP5092 ONLY)               |                       |                                                                                              |                             |                             |                             |                   |

| Rising Threshold                      | $V_{REG\_GOOD}$       |                                                                                              | 89.5                        | 92.5                        | 95.7                        | %                 |

| Hysteresis                            | $V_{REG\_GOOD\_HYS}$  |                                                                                              | 2                           |                             |                             | %                 |

| Pull-Up Resistor                      |                       |                                                                                              |                             | 11.6                        | 17                          | k $\Omega$        |

| Pull-Down Resistor                    |                       |                                                                                              |                             | 11.6                        | 17                          | k $\Omega$        |

| High Voltage                          | $V_{REG\_GOOD\_IH}$   |                                                                                              |                             |                             | $V_{REG\_OUT}$              | V                 |

## 絶対最大定格

表 3.

| Parameter                                                                                                | Rating           |

|----------------------------------------------------------------------------------------------------------|------------------|

| VIN, MPPT, CBP, MINOP                                                                                    | -0.3 V to +3.6 V |

| DIS_SW, TERM, SETPG, SETSD, SETBK,<br>PGOOD, SETHYST, REF, REG_D0, VID,<br>REG_D1, LLD, REG_GOOD to AGND | -0.3 V to +6.0 V |

| SW, SYS, BAT, BACK_UP, REG_OUT, REG_FB<br>to PGND                                                        | -0.3 V to +6.0 V |

| PGND to AGND                                                                                             | -0.3 V to +0.3 V |

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。製品を長時間にわたり絶対最大定格状態に置くと、製品の信頼性に影響を与えることがあります。

### 熱抵抗

$\theta_{JA}$  は最も厳しい条件、すなわち、回路基板に表面実装パッケージをハンダ付けした状態で仕様規定されています。

表 4.

| Package Type  | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|---------------|---------------|---------------|------|

| 24-Lead LFCSP | 58.7          | 36            | °C/W |

### ESDに関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

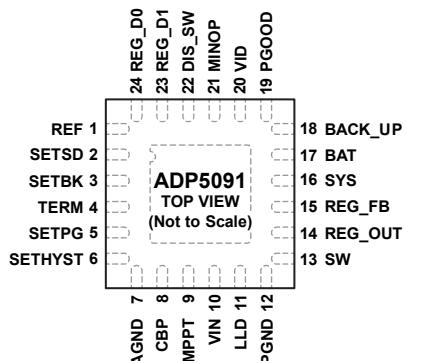

## ピン配置およびピン機能の説明

## NOTES

1. THE EXPOSED PAD MUST BE CONNECTED TO AGND.

14145-002

図 3. ADP5091 ピン配置

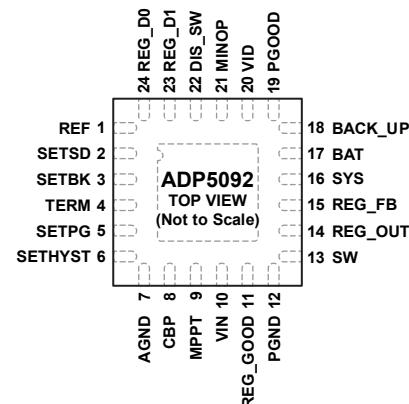

## NOTES

1. THE EXPOSED PAD MUST BE CONNECTED TO AGND.

14145-003

図 4. ADP5092 ピン配置

表 5. ピン機能の説明

| ピン番号 <sup>1</sup> |         | 記号       | 説明                                                                                                                                 |

|-------------------|---------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| ADP5091           | ADP5092 |          |                                                                                                                                    |

| 1                 | 1       | REF      | SETSD、SETPG、SETBK、TERM 各ピンの内部電圧リファレンス監視ノード。                                                                                        |

| 2                 | 2       | SETSD    | シャットダウン設定。このピンは、BAT ピン電圧の放電シャットダウン電圧を設定します。                                                                                        |

| 3                 | 3       | SETBK    | BACK_UP ディスエーブル閾値を監視する BAT 電圧の設定。BACK_UP 蓄電素子なしで、SETBK ピンを AGND ピンに接続します。                                                          |

| 4                 | 4       | TERM     | 充電終了時の電圧。このピンは、BAT ピンの電圧値に応じて充電終了時の電圧を設定します。                                                                                       |

| 5                 | 5       | SETPG    | SYS ノード電圧値の設定を監視する Power Good 立上がり閾値。                                                                                              |

| 6                 | 6       | SETHYST  | PGOOD の立下がりヒステリシス設定。PGOOD 立下がりヒステリシスを設定するには、SETPG と SETHYST の間に抵抗を接続します。                                                           |

| 7                 | 7       | AGND     | アナログ・グラウンド。                                                                                                                        |

| 8                 | 8       | CBP      | コンデンサ・バイパス。最大電力点の電圧をサンプル&ホールドします。CBP ピンと AGND ピンの間に 10 nF のコンデンサを接続します。MPPT ピンがディスエーブルになっている場合は、CBP ピンを VIN ピンよりも低い外部リファレンスに接続します。 |

| 9                 | 9       | MPPT     | 最大電力点追従の設定。このピンは抵抗分圧器を使用し、様々なエネルギー・ハーベスタ向けの最大電力点比を設定します。非センシング・モードの場合、AGND を経由して抵抗を接続し、MPPT 電圧を設定します。電流の代表値は 2.0 μA です。            |

| 10                | 10      | VIN      | エネルギー・ハーベスタ・ソースからの入力電源。VIN と PGND の間に、最小 10 μF のコンデンサをできるだけ近づけて接続してください。                                                           |

| 11                | N/A     | LLD      | ADP5091 では、マイクロコントローラに対する低光密度インジケータ。LLD は、CBP 電圧より高い MINOP 電圧にプルアップします。                                                            |

| N/A               | 11      | REG_GOOD | ADP5092 では、レギュレーション出力のパワーグッド。                                                                                                      |

| 12                | 12      | PGND     | 電源グラウンド。                                                                                                                           |

| 13                | 13      | SW       | 誘導性の昇圧レギュレータの場合、外部インダクタに接続するスイッチング・ノード。SW と VIN の間に 22 μH のインダクタを接続します。                                                            |

| 14                | 14      | REG_OUT  | レギュレーション出力。REG_OUT と PGND の間に、最小 4.7 μF のコンデンサをできるだけ近づけて接続します。                                                                     |

| 15                | 15      | REG_FB   | 帰還電圧の検出入力のレギュレーション出力。固定出力の場合、このピンを REG_OUT に接続します。調整可能な出力の場合、このピンを REG_OUT からの抵抗分圧器に接続します。                                         |

| 16                | 16      | SYS      | システム負荷に供給する出力電圧。このピンと PGND の間に、最小 4.7 μF のコンデンサをできるだけ近づけて接続します。                                                                    |

| 17                | 17      | BAT      | SYS 出力電源用のバッテリ。SYS 出力電源用のバッテリとして、充電式バッテリまたはスーパー・キャパシタを接続します。                                                                       |

| 18                | 18      | BACK_UP  | バックアップ・バッテリの入力電源。                                                                                                                  |

| ピン番号 <sup>1</sup> |         | 記号     | 説明                                                                                                                                                                    |

|-------------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADP5091           | ADP5092 |        |                                                                                                                                                                       |

| 19                | 19      | PGOOD  | マイクロコントローラへのパワーグッド出力信号。SYS電圧がSETPG閾値よりも高い場合、このピンはロジック・ハイ・レベルを維持します。                                                                                                   |

| 20                | 20      | VID    | REG_OUTの電圧設定ピン。このピンは、AGNDに接続された抵抗を介して、最高で8つの異なるレギュレーション出力をローに設定します。出力構成の詳細を表7に示します。                                                                                   |

| 21                | 21      | MINOP  | 最小動作電圧の設定。このピンに抵抗を接続して、最小の動作入力電圧を設定します。CBP電圧がMINOP電圧を超えると、昇圧レギュレータがスイッチングを開始します。MINOPピンがフロート状態の場合、ICは非センシング・モードの固定MPPTレベルで動作します。MINOP機能をディスエーブルにするには、このピンをAGNDに接続します。 |

| 22                | 22      | DIS_SW | マイクロコントローラまたはRFトランシーバーからのコントロール信号で、スイッチング昇圧チャージャを停止させることができます。                                                                                                        |

| 23                | 23      | REG_D1 | レギュレーション出力の動作モード設定D1。このピンをハイにプルアップすると、LDOモードが有効になります。                                                                                                                 |

| 24                | 24      | REG_D0 | レギュレーション出力の動作モード設定D0。このピンをハイにプルアップすると、昇圧モードが有効になります。                                                                                                                  |

|                   |         | EPAD   | エクスポート・パッド。エクスポート・パッドはAGNDに接続する必要があります。                                                                                                                               |

<sup>1</sup> N/Aは該当なしを表します。

## 代表的な性能特性

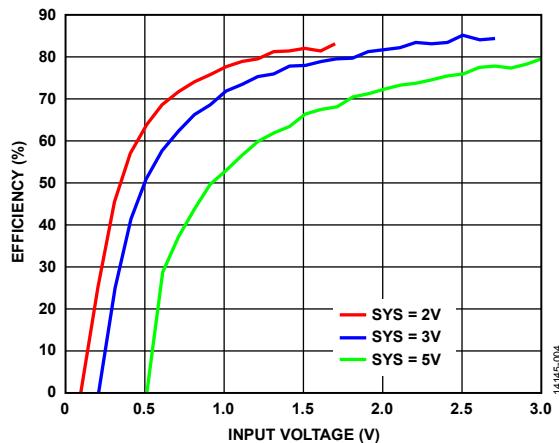

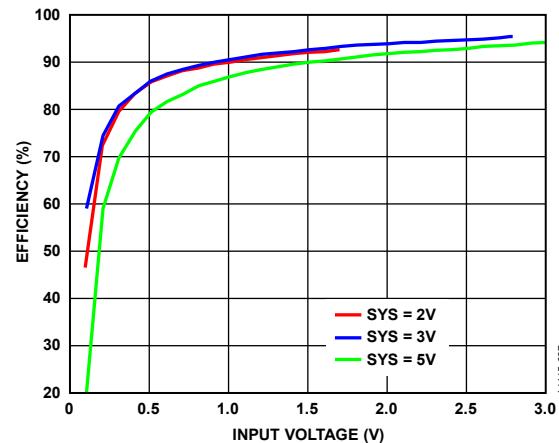

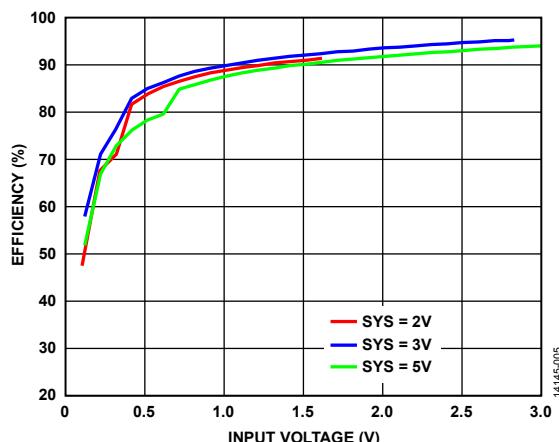

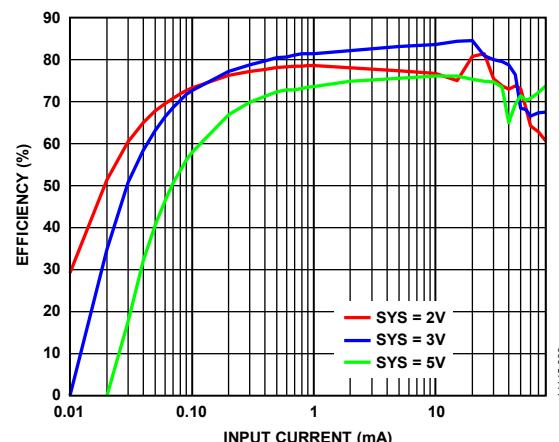

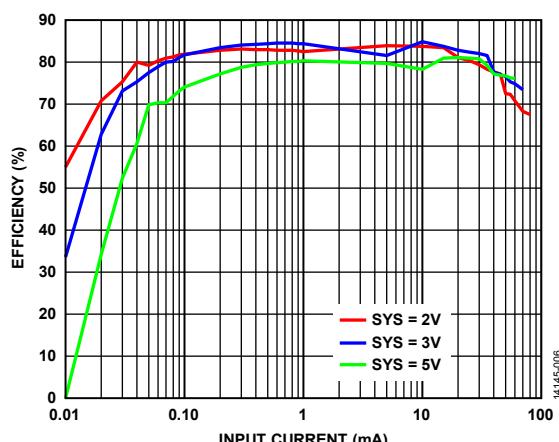

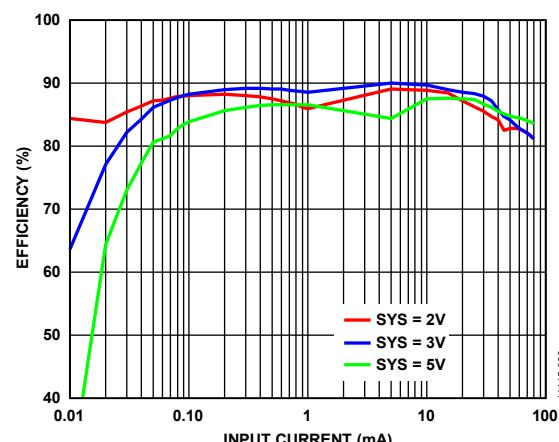

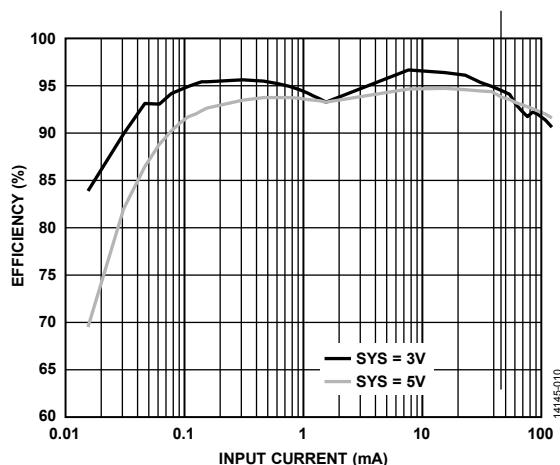

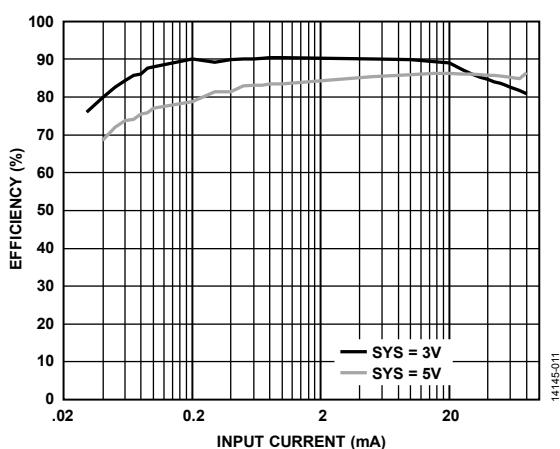

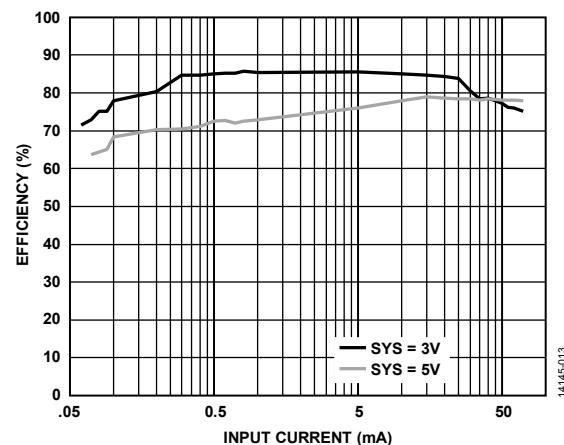

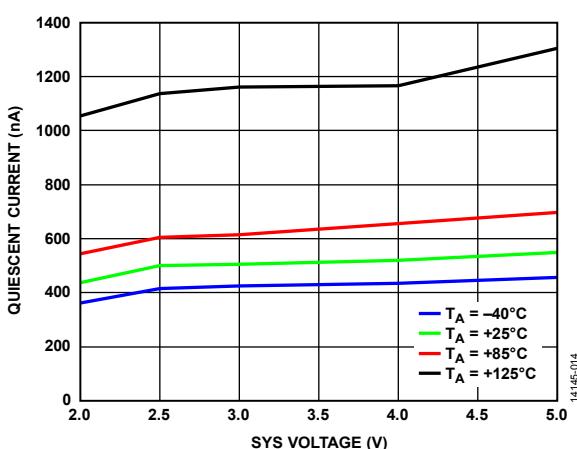

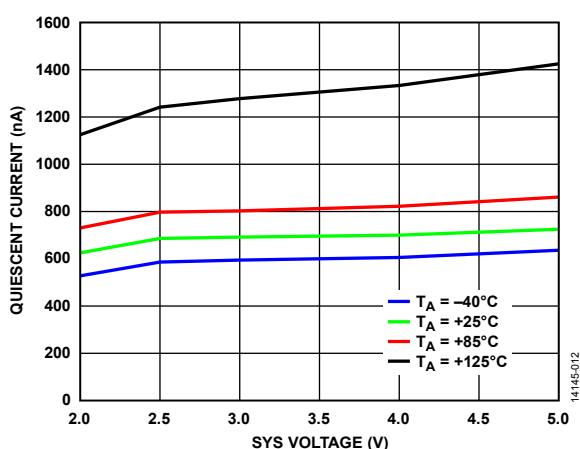

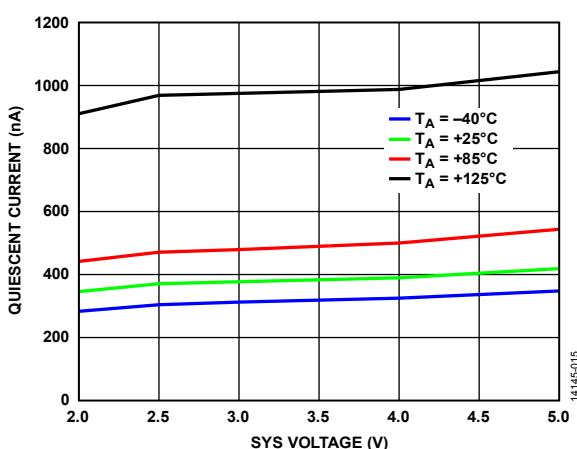

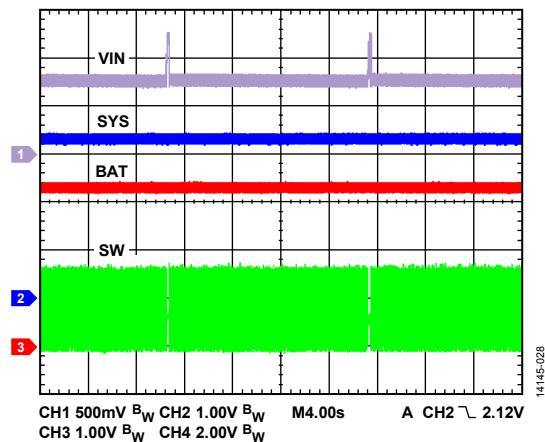

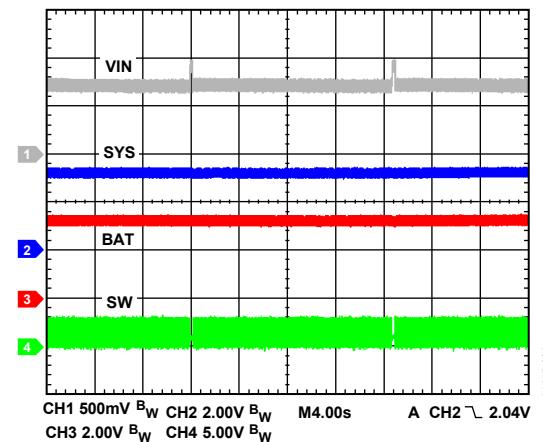

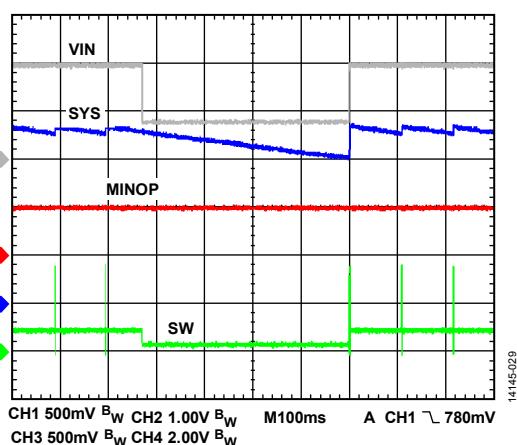

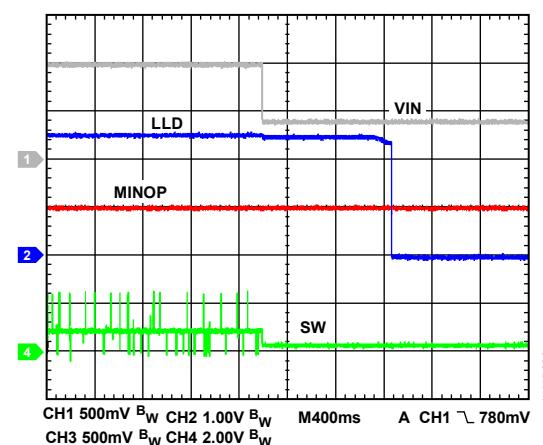

$V_{BAT\_TERM} = 3.5\text{ V}$ 、 $V_{SYS\_PG} = 2.8\text{ V}$ 、 $V_{SETSD} = 2.4\text{ V}$ 、MPPT (OCV) = 80%、 $L = 22\text{ }\mu\text{H}$ 、 $C_{IN} = 10\text{ }\mu\text{F}$ 、 $C_{SYS} = 4.7\text{ }\mu\text{F}$ 、 $C_{REG\_OUT} = 10\text{ }\mu\text{F}$ 、 $C_{CBP} = 10\text{ nF}$ 。

図 5. 効率と入力電圧の関係、 $I_{IN} = 10\text{ }\mu\text{A}$

図 8. 効率と入力電圧の関係、 $I_{IN} = 100\text{ }\mu\text{A}$

図 6. 効率と入力電圧の関係、 $I_{IN} = 10\text{ mA}$

図 9. 効率と入力電流の関係、 $V_{IN} = 0.2\text{ V}$

図 7. 効率と入力電流の関係、 $V_{IN} = 0.5\text{ V}$

図 10. 効率と入力電流の関係、 $V_{IN} = 1\text{ V}$

図 11. 効率と入力電流の関係、 $V_{IN} = 2\text{ V}$ 図 12. 効率と入力電流の関係、 $V_{IN} = 1\text{ V}$ 、 $V_{REG\_OUT} = 2\text{ V}$ 、

$I_{REG\_OUT} = 10\text{ }\mu\text{A}$ 図 15. 静止電流と SYS 電圧の関係、 $V_{MINOP} \leq V_{CBP}$ 図 13. 静止電流と SYS 電圧の関係、 $V_{REG\_D0} = V_{REG\_D1} = V_{SYS}$ 、

$V_{MINOP} \leq V_{CBP}$ 図 16. 静止電流と SYS 電圧の関係、 $V_{MINOP} > V_{CBP}$

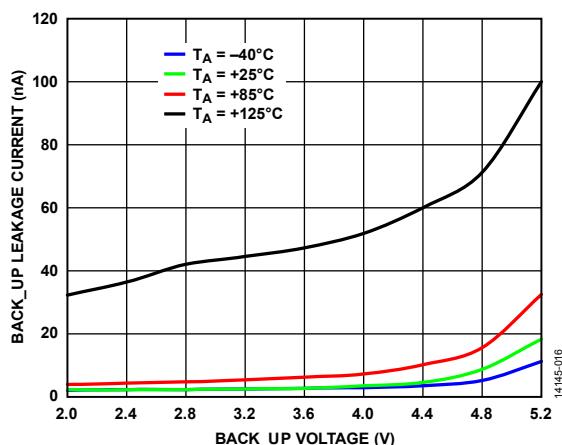

図 17. BACK\_UP リーク電流と BACK\_UP 電圧の関係

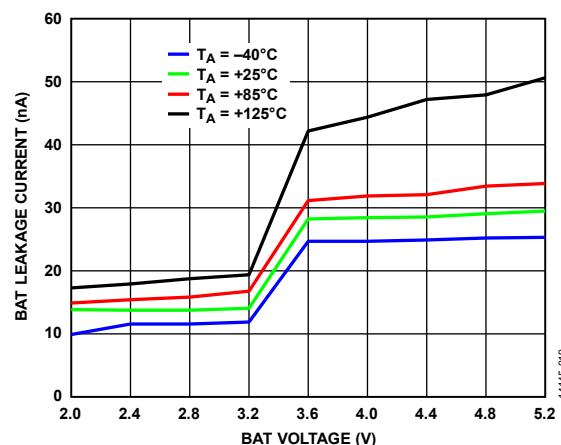

図 20. BAT リーク電流と BAT 電圧の関係

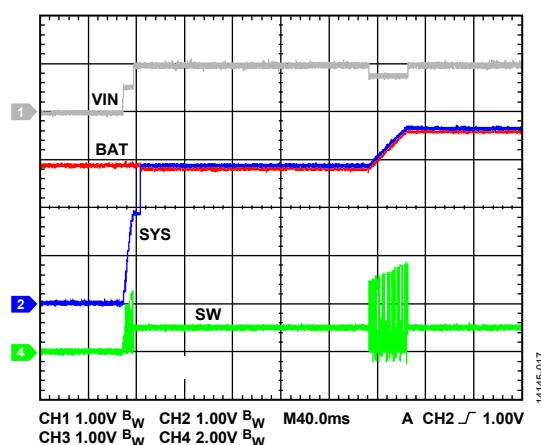

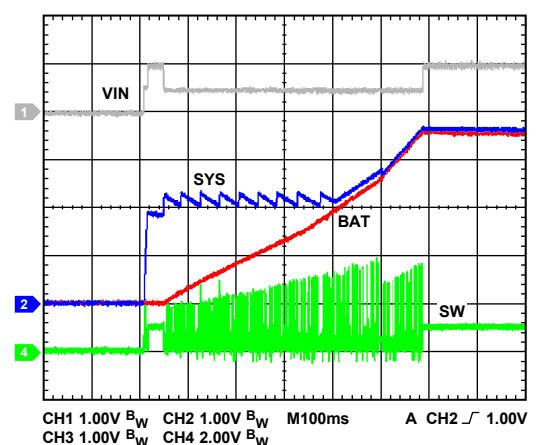

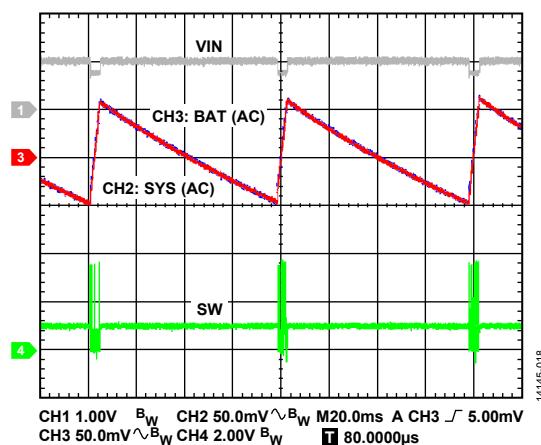

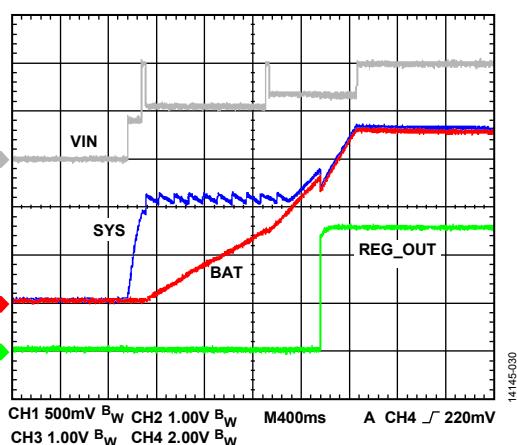

図 18. 100  $\mu\text{F}$  バッテリでの起動、 $V_{\text{BAT}} > V_{\text{SETSD}}$ 図 21. 空の 100  $\mu\text{F}$  コンデンサでの起動図 19. TERM 機能の出力リップル、100  $\mu\text{A}$  負荷

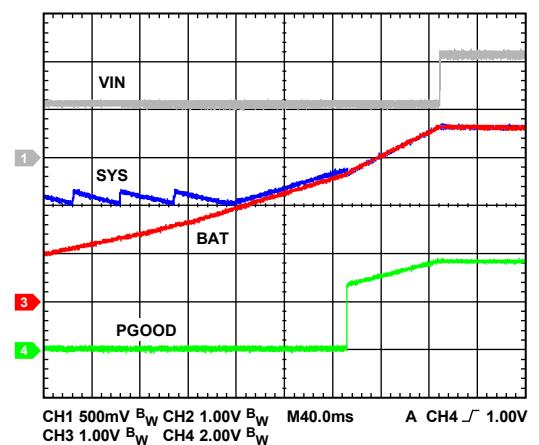

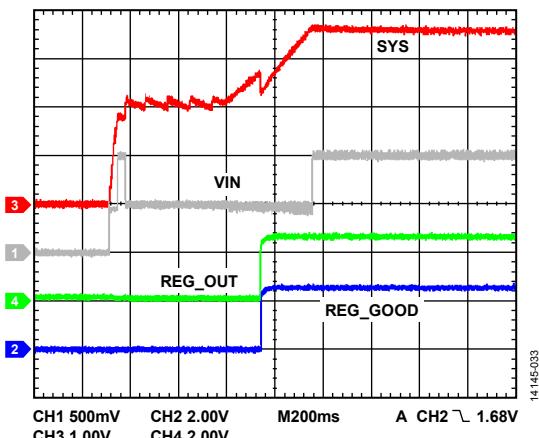

図 22. PGOOD 機能の波形

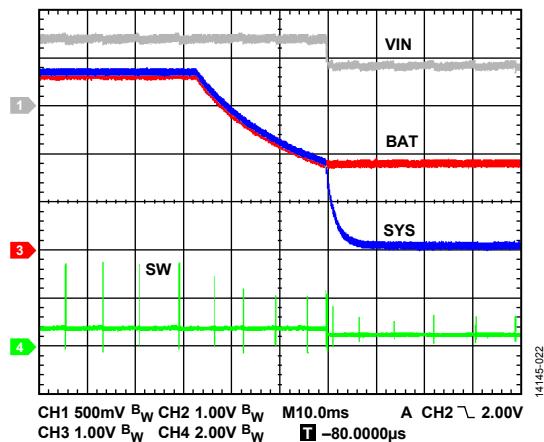

図 23. バッテリ保護機能の波形

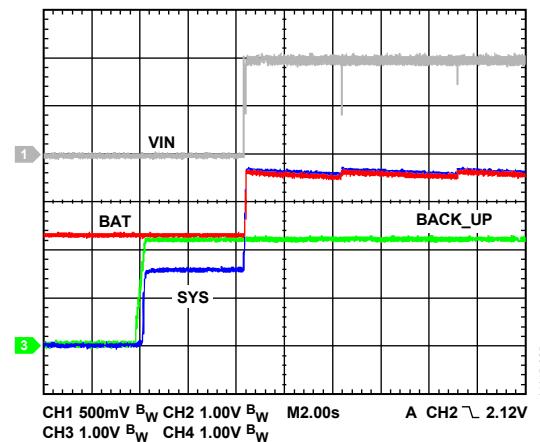

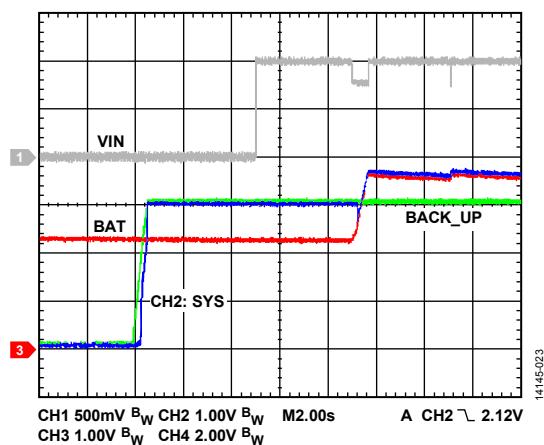

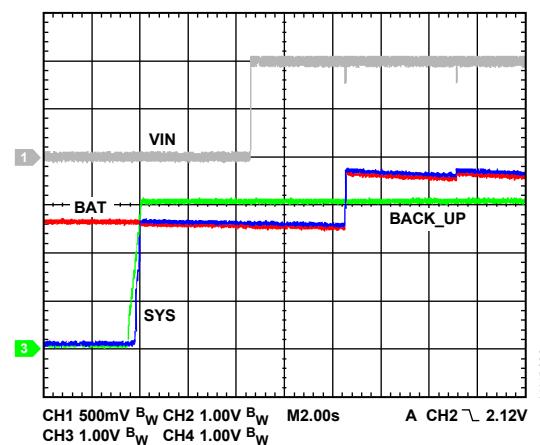

図 26. BACK\_UP 機能、 $V_{BAT} < V_{SETBK}$ 、 $V_{BACK\_UP} < V_{BAT}$ 図 24. バックアップ機能、 $V_{BAT} < V_{SETBK}$ 、 $V_{BACK\_UP} > V_{BAT}$ 図 27. BACK\_UP 機能、 $V_{BAT} > V_{SETBK}$ 、 $V_{BACK\_UP} > V_{BAT}$

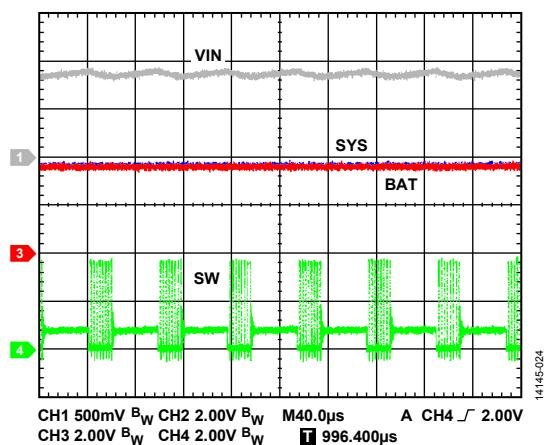

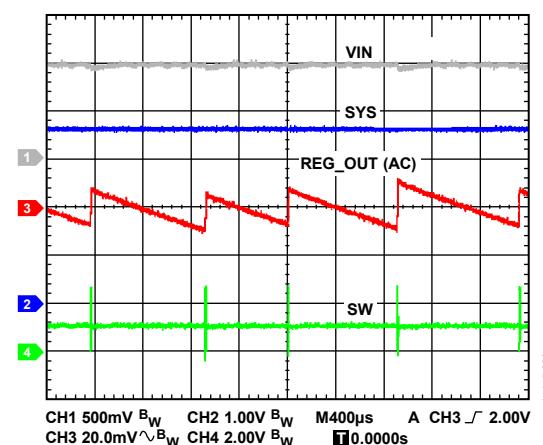

図 25. メイン昇圧 PFM (パルス周波数変調) 波形、200 μA 負荷

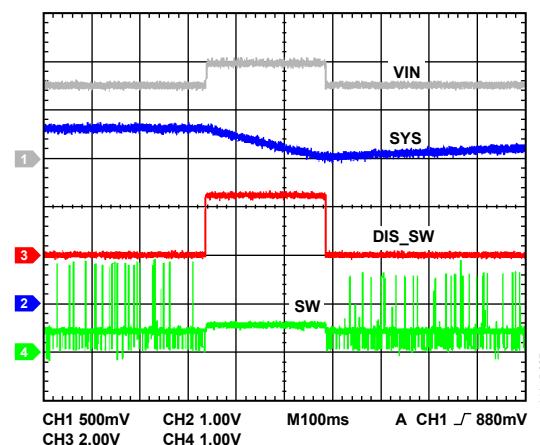

図 28. DIS\_SW 機能の波形

図 29. MPPT 非センシング・モード、 $R_{MPPT} = 400 \text{ k}\Omega$

図 32. MPPT 動的センシング・モード

図 30. MINOP 機能

図 33. LLD 機能

図 31. REG\_OUT 起動 (ハイブリッド・モード)

図 34. REG\_OUT リップル (昇圧モード)

図 35. REG\_GOOD 機能

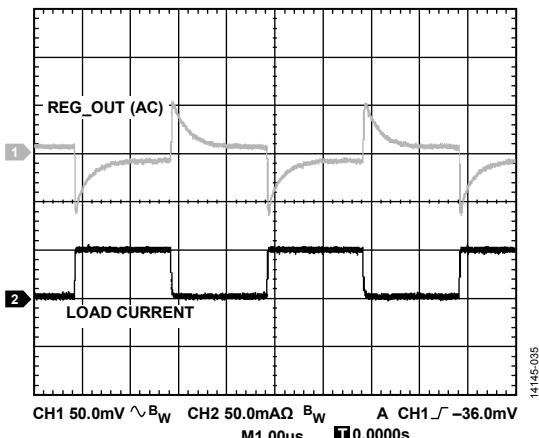

図 38. REG\_OUT 負荷過渡（ハイブリッド）、

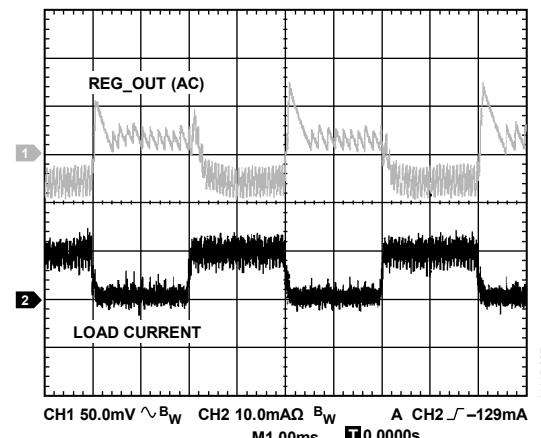

$I_{REG\_OUT}$  は  $10 \mu\text{A} \sim 10 \text{ mA}$ 図 36. REG\_OUT 負荷過渡（LDO）、 $I_{REG\_OUT}$  は  $10 \mu\text{A} \sim 50 \text{ mA}$

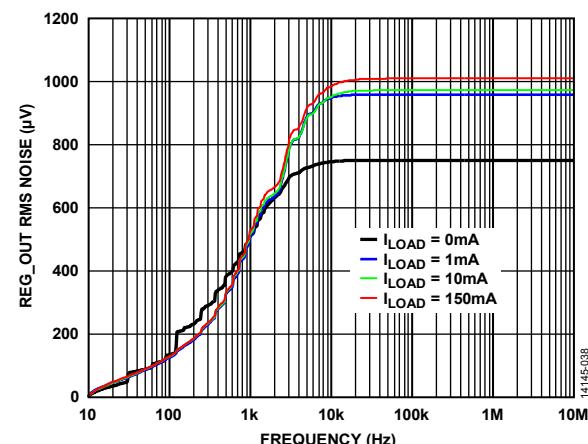

図 39. REG\_OUT RMS ノイズと周波数の関係

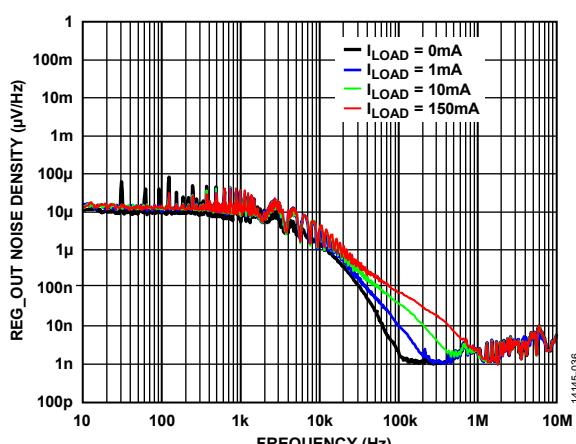

図 37. 各種の電流負荷 ( $I_{LOAD}$ ) に対する REG\_OUT ノイズ密度

と周波数の関係

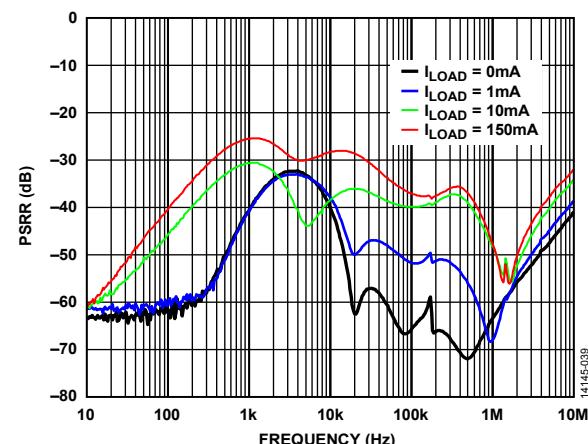

図 40. 電源電圧変動除去比（PSRR）と周波数の関係

## 動作原理

ADP5091/ADP5092は、インテリジェントな統合型のエネルギー・ハーベスティング用の超低消費電力管理ソリューションで、コールド・スタートアップ回路、同期メイン昇圧コントローラ1個、スイッチ付きのレギュレーション出力ハイブリッド・コントローラ1個、スイッチ付きの充電コントローラ1個、バックアップ電力経路スイッチを組み合わせたものです。メイン昇圧コントローラは、PVセル、TEG、圧電モジュールのような低電圧高インピーダンスDC電源からの電力を変換し、バッテリ保護機能付きの充電式バッテリまたはコンデンサに電力を保存し、負荷に電力を供給します。自動的なヒステリシス昇圧/LDOモード、または純粹なLDOモードを搭載したもう1つのレギュレーション出力は、低出力電流(10 μA、図41参照)から200 mAの高電流にわたる範囲で高い効率を実現するように最適化されています。ADP5091/ADP5092は、メイン・バッテリを使用した、追加の電力経路を制御することもできます。外部信号を使用すれば、2個の昇圧回路を一時的に停止させて、RF伝送との干渉を防止することができます。

### 高速コールド・スタートアップ回路

( $V_{SYS} < V_{SYS\_TH}$ ,  $V_I > V_{IN\_COLD}$ )

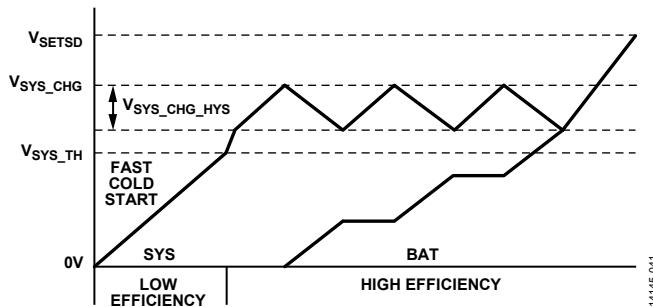

高速コールド・スタートアップ回路は、VINピンに存在する電を取り出して、SYSピンのコンデンサを $V_{SYS\_TH}$ の電圧まで充電します。この閾値を上回ると、メイン昇圧レギュレータと充電コントローラが動作を開始します。SYS電圧が内部のBAT充電閾値( $V_{SYS\_CHG}$ )よりも高い場合、効率的な昇圧レギュレータがBATピンに接続された蓄電素子を充電します。SYS電圧が内部のBAT充電閾値とヒステリシスよりも低い場合、BATピンへの充電が停止し、SYSピンの充電が再開します。こうすることで、コールド・スタートアップへの移行を防止できます。図41に、高速コールド・スタートアップのシーケンスを示します。

VINピンがコールド・スタートの最小入力電圧( $V_{IN\_COLD}$ )よりも高く、SYSピンに接続されたバッテリの電圧がコールド・スタート動作終了時の閾値( $V_{SYS\_TH}$ )よりも低い場合、コールド・スタートアップ回路が必要です。コールド・スタートアップを完了させるには、エネルギー・ハーベスタが十分な電力を供給する必要があります(エネルギー・ハーベスタの選択セクションを参照)。コールド・スタートアップは、メイン昇圧レギュレータに比べて効率がかなり低いですが、スタートアップ時間を短縮し、PGOOD信号によってイネーブルになったシステム負荷から流れるシャットダウン電流が低くなります。コールド・スタートアップをバイパスするには、BACK\_UPピンにメイン・バッテリを接続します(バックアップの蓄電経路セクションを参照)。

図41. 高速コールド・スタートアップのシーケンス

### メイン昇圧レギュレータ

( $V_{BAT\_TERM} > V_{SYS} > V_{SYS\_TH}$ )

VINピンとSWピンの間に外付けインダクタを接続したスイッチング・モードの同期昇圧レギュレータは、パルス周波数モード(PFM)で動作し、入力コンデンサに保存された電力をBATピンに接続されたバッテリへ転送します。CBPピンとAGNDピンに接続されたコンデンサは、MPPTピンでサンプルしたレベルに充電され、MPPT制御ループはVIN電圧をこのレベルに調整します。広い入力電力範囲でレギュレータの効率を維持するため、電流検出回路は内部ディザのピーク電流制限値によって、インダクタ電流を制御します。

BATピンの電圧が、SETSDピンで設定されたバッテリ充電終了時の閾値を下回る場合、メイン昇圧レギュレータの動作はバッテリ・コントローラを通じて非同期モードに達します。あるいは、BATピンの電圧が、TERMピンで設定されたバッテリ過充電の閾値を上回る場合、スイッチングが停止します。CBPピンの電圧がMINOPピンの抵抗で設定された閾値まで低下すると、昇圧レギュレータがディスエーブルになります。さらに、オープン電圧サンプル回路により昇圧が周期的に停止されます。また、DIS\_SWピンをハイ・レベルにして、一時的にディスエーブルにすることもできます。

### VINオープン・サーキットとMPPT

MINOPピンをフロート状態にすると、MPPT非センシング・モードを固定されたMPPT電圧で動作することができます。MPPTピンに対して抵抗経由で2.0 μA(typ)のバイアス電流を流すと、MPPT電圧は昇圧入力レギュレーションのリファレンス電圧と同じ値に設定されます。

AGNDに接続した抵抗を通じて、MINOPピンの電圧を $V_{MINOP\_DSM}$ 未満に設定すると、ADP5091/ADP5092はMPPT動的センシング・モードで動作します。昇圧入力レギュレーションのリファレンス電圧は、MPPTピンの抵抗分圧器によって設定される比でスケーリングされるVINピンのオープン電圧になります。ADP5091/ADP5092の入力でエネルギー・ハーベスタから得られる最大電力点の電圧で動作するようにVIN電圧を維持する目的で、MPPT電圧は周期的にサンプルされて、CBPピンに接続されたコンデンサに保持されます。BAT電圧がSETSDの立上がり閾値を上回る場合、定期的に昇圧レギュレータを256 msディスエーブルにし、オープン・サーキットの電圧比をサンプリングしてリファレンス電圧を16秒ごとに再取得します。ファクトリー・ビットでサンプル・サイクルを設定できます。リファレンス電圧は次式で設定されます。

$$V_{MPPT} = V_{IN} (\text{Open Circuit}) \left( \frac{R_{OC1}}{R_{OC1} + R_{OC2}} \right) \quad (1)$$

ここで

$V_{IN}$ (オープン・サーキット)は、入力のオープン・サーキット電圧( $V_{IN\_OCV}$ )。

$R_{OC1}$ と $R_{OC2}$ については、図2を参照してください。

MPPT 比 (typ) は、ハーベスタのタイプに依存します。例えば、PV セルの場合は 0.7 ~ 0.85 になり、TEG の場合は約 0.5 になります。OCV サンプル・レートは、以前にサンプルした OCV のレベルに基づいて調整できます。MPPT 機能をディスエーブルにするには、MPPT ピンをフロート状態にし、CBP ピンを VIN 電圧よりも低い外部リファレンス電圧に設定します。

## 最小動作閾値の機能

AGND に接続した抵抗を通じて MINOP ピンの電圧を、動的 MPPT センシング・モードの MINOP 動作電圧範囲 ( $V_{MINOP\_DSM}$ ) を下回る値に設定する場合、ハーベスタで生成される電力がシステムの消費電力を下回ると、最小動作閾値の機能によってメイン昇圧レギュレータをディスエーブルにして蓄電素子の放電を防止できます。CBP ピンの電圧が、MINOP ピンの抵抗で設定された閾値まで低下すると、昇圧レギュレータがスイッチングを停止します。MINOP バイアス電流の代表値は 2.00  $\mu$ A です。最小動作閾値の機能は MPPT 機能をディスエーブルにし、390 nA (typ) というスリープ静止電流を実現します。この機能をディスエーブルにするには、MINOP ピンを AGND ピンに接続します。

LLD (Low Light Density: 低い光密度) インジケータ (ADP5091 のみ) は、MINOP コンバレータの出力で、特定の期間内で入力電力が不十分であるサイクルを計算するよう、マイクロプロセッサに信号を送信します。

## 昇圧動作のディスエーブル機能

ノイズまたは EMI に敏感なアプリケーションの場合、DIS\_SW ピンをロジック・ハイにして、昇圧動作を一時的に停止させて RF 回路との干渉を防止できます。DIS\_SW ピンをロジック・ローにすると、昇圧スイッチングが再開されます。移行遅延は 1  $\mu$ s (typ) 以下です。

## レギュレーション出力の動作モード

ADP5091/ADP5092 の 150 mA レギュレーション出力は、ヒステリシス昇圧モードまたは LDO モードで動作するだけでなく、レギュレータが自動的にこれら 2 つのモード間で円滑に遷移できるハイブリッド・モードでも動作します。BAT 電圧が SETSD 閾値を上回るか、または SYS 電圧が SETPG 閾値を上回ると、レギュレータがイネーブルになります。

ヒステリシス昇圧モードでは、ADP5091/ADP5092 の昇圧レギュレータは、出力電圧を自らのプリセット出力電圧よりわずかに高い値まで充電します。出力検知信号がヒステリシス・コンバレータの上側閾値 (スリープ閾値) を上回るまで出力電圧が上昇した場合、レギュレータはスリープ・モードに移行します。スリープ・モードでは、低静止電流と高い効率性能を実現できるように、下側スイッチと上側スイッチ、さらに回路の大部分がディスエーブルになります。

スリープ・モードの間、出力コンデンサは電力を負荷に供給し、出力電圧はヒステリシス・コンバレータの下側閾値 (ウェイク閾値) を下回るまで低下します。その時点で昇圧レギュレータがウェイクアップし、PWM (パルス幅変調) パルスを生成して出力を再度充電します。ヒステリシス・モードでは、レギュレータがキープ・アライブ電源として動作します。

LDO モードでは、少なくとも 4.7  $\mu$ F の小容量セラミック・コンデンサを使用して SYS ピンから電力を出力します。新しい革新的な設計手法を採用することで、デジタル・アプリケーションと RF アプリケーションにおいて LDO が超低静止電流と優れた過渡特性を実現し、ノイズに敏感なアプリケーションをサポートします。

ハイブリッド・モードでは、VIN ピンと SYS ピンの両方を使用して REG\_OUT ピンに電力を出力します。荷電力が入力電力を下回る場合、レギュレータは LDO モードを終了し、入力側のみから電力を取得します。

## REG\_D0 と REG\_D1

REG\_D0 ピンと REG\_D1 ピンを使用して、レギュレーション出力の動作モードを柔軟に設定できます。表 6 に、これら 2 本のピンで設定する動作モードの詳細を示します。

表 6. レギュレーション出力の動作モードの設定

| Working Mode  | REG_D0         | REG_D1         |

|---------------|----------------|----------------|

| Boost Disable | Low            | Not applicable |

| Boost Enable  | High           | Not applicable |

| LDO Disable   | Not applicable | Low            |

| LDO Enable    | Not applicable | High           |

## レギュレーション出力の構成

VID ピンから AGND ピンに 1 本の抵抗を接続することで、ADP5091/ADP5092 の 150 mA レギュレーション出力として、1.5 V ~ 3.6 V の範囲にある 8 つの固定出力電圧オプションのいずれかを利用できます。表 7 に、VID ピンで設定される出力電圧オプションを示します。

表 7. VID ピンで設定される出力電圧のオプション

| VID Configuration                | Output Voltage Set by the VID Pin  |

|----------------------------------|------------------------------------|

| Short to Ground                  | Programmed with external resistors |

| Floating                         | $V_{OUT} = 2.5$ V                  |

| $R_{VID} = 7 \text{ k}\Omega$    | $V_{OUT} = 1.5$ V                  |

| $R_{VID} = 14 \text{ k}\Omega$   | $V_{OUT} = 1.8$ V                  |

| $R_{VID} = 27.7 \text{ k}\Omega$ | $V_{OUT} = 3.6$ V                  |

| $R_{VID} = 55.6 \text{ k}\Omega$ | $V_{OUT} = 3.3$ V                  |

| $R_{VID} = 111 \text{ k}\Omega$  | $V_{OUT} = 2.0$ V                  |

| $R_{VID} = 221 \text{ k}\Omega$  | $V_{OUT} = 3.0$ V                  |

| $R_{VID} = 442 \text{ k}\Omega$  | $V_{OUT} = 2.8$ V                  |

外部抵抗分圧器または VID ピンで、レギュレーション出力を設定できます。2 本の外部抵抗の比により、図 47 に示すように、1.5 V ~ 3.6 V の範囲で出力電圧を調整できます。このデバイスは出力に対するサーボとして機能し、グラウンドを基準とした 1.0 V のリファレンス電圧に REG\_FB ピンの電圧を維持します。その後、R1 を流れる電流は  $1.0 \text{ V}/R2$  の値に等しくなり、R1 を流れる電流は、R2 を流れる電流に REG\_FB ピンのバイアス電流を加えた値に等しくなります。出力電圧は以下の式で計算します。

$$V_{OUT} = 1.02 \text{ V} \times (1 + R1/R2) \quad (2)$$

ここで

$$V_{OUT} = V_{REG\_OUT}$$

$R1$  と  $R2$  については、図 47 を参照してください。

静止電流を最小化するため、R1 と R2 で大きい抵抗値を使用することが推奨されます。

## REG\_GOOD (ADP5092 のみ)

REG\_GOOD ピンのロジック・ハイは、約 2 ms よりも長い遅延時間にわたって REG\_OUT 電圧がその公称出力の 92.5 % (typ) を上回っていることを表します。REG\_GOOD のロジック・ハイ・レベルは REG\_OUT 電圧に等しく、ロジック・ロー・レベルはグラウンドと同じ値です。REG\_OUT 電圧が立上がり閾値の 2 % ヒステリシス (typ) を下回ると、REG\_GOOD ピンはローに遷移します。電流を制限するため、ロジック・ハイ・レベルは内部で約 11.6 kΩ の抵抗に直列接続されています。

## バッテリの充電管理

BAT ピンにバッテリを接続します。蓄電素子は、充電式バッテリ、スーパー・キャパシタ、または 100 μF 以上のコンデンサに接続できます。蓄電コントローラは充放電の動作を管理し、SYS ピン電圧を監視します。この電圧が SETPG ピンで設定された閾値を超えると、PGOOD ピンがロジック・ハイ信号を出力します。

BAT ピン電圧が TERM ピンで設定したバッテリ充電終了時の閾値を超えると、昇圧動作が停止して、バッテリの過充電が防止されます。バッテリ充電終了時の閾値は、2.2 V ~ 5.2 V の範囲に設定できます。BAT 電圧が SETSD ピンで設定されたバッテリ充電終了時の閾値を下回ると、BAT ピンと SYS ピンの間のスイッチがオフになるので、バッテリの損傷につながる過放電を防止できます。この際、昇圧動作は非同期モードになります。SYS ピンと BAT ピンには電流制限値はありませんが、システム負荷電流を最大 1000 mA に制限することが推奨されます。システム負荷電流が大きくなると、SYS スイッチ、BAT スイッチ、接続された充電式バッテリの内部抵抗により、SYS ピンと BAT ピンに接続したバッテリとの間に電圧降下が発生します。

入力ソースが接続されていない場合、BAT ピンに蓄電素子を接続する前に SYS ピンをグラウンドへ放電させてください。充電済みの蓄電素子を接続した後に、SYS ピンを解放してください。これは、SYS 電圧がコールド・スタート動作終了時の閾値 ( $V_{SYS\_TH}$ ) を下回る場合、BAT スイッチがオープン状態を保持し、SYS 電圧が  $V_{SYS\_TH}$  に到達するまで蓄電素子を保護するためです。この保存モードは、BAT ピンに接続された蓄電素子を放電させることなく、長時間にわたり電力を保存できる最小リーク（代表値 3.5 nA）の状態にあります。

## バックアップの蓄電経路

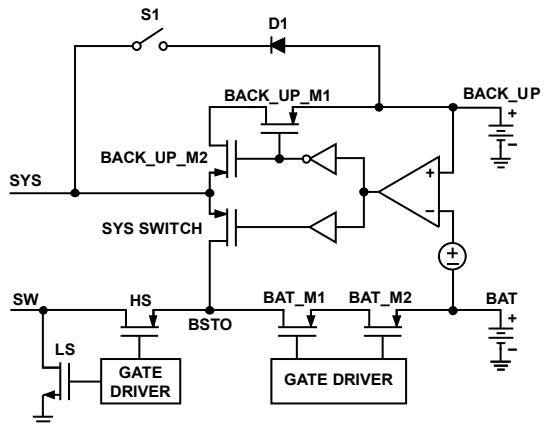

ADP5091/ADP5092 には、バックアップの蓄電経路とバックアップ・コントローラ、BACK\_UP ピンと SYS ピンの間にある背面合わせの 2 個のパワー・スイッチが内蔵されています。収集／保存した電力が定期的に不足する状態でシステムが動作する場合、バックアップの蓄電素子を BACK\_UP ピンに接続できます。

SYS 電圧が、コールド・スタート動作終了時の閾値 ( $V_{SYS\_TH}$ ) を超えると、バックアップ・コントローラがイネーブルになります。BAT 電圧が SETBK 閾値を下回る前に、バックアップ・バッテリのスイッチがオフになります。BAT 電圧が SETBK 閾値を下回っている間、これらのスイッチの状態は BACK\_UP ピンと BAT ピンの電圧レベルによって異なります。BACK\_UP\_Mx と BACK\_UP の内部制御回路は、BACK\_UP スイッチ (BACK\_UP\_M1 と BACK\_UP\_M2) のオン／オフ状態を自動的に判断し、SYS の電力ソースとして、電圧の高い端子を選択します。BAT ピンのコンパレータ入力オフセットである 190 mV (typ) により、入力ソースと BAT ピンによる BACK\_UP ピンの充電が回避されます（図 44 を参照）。

さらに、バックアップの蓄電素子は、突入電流の保護回路により、コールド・スタートアップをバイパスできます。ただし、コールド・スタートが完了する前にバックアップ・バッテリを接続した場合、電流能力はわずか 250 μA (typ) に制限されます。電力経路が確実に通常動作の状態に移行するように、SYS ピンからのシステム負荷電流を制限することが推奨されます。表 9 で、電力経路の動作状態を説明します。保存モードが長時間にわたる場合、バックアップの蓄電素子を接続解除してから、SYS をグラウンドに放電してください。

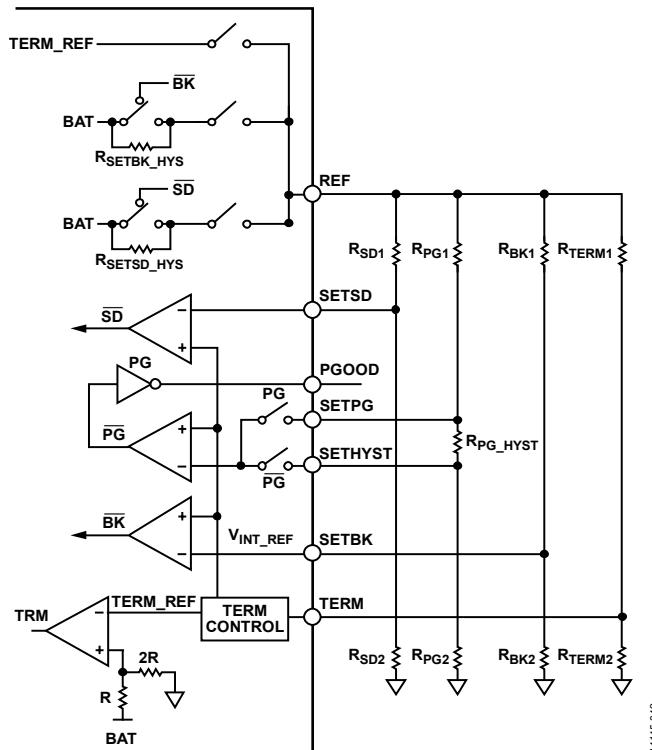

## バックアップと BAT の選択閾値

BACK\_UP 機能をイネーブルにするタイミングを判断するため、SETBK ピンの外部抵抗を使用して BAT ピンのスイッチ閾値を設定する必要があります。BAT 電圧が SETBK 閾値を下回っている場合、BACK\_UP\_Mx の内部制御回路は SYS の電力ソースとして、電圧の高い端子を選択します。図 42 に、式 3 で与えられる  $V_{SETBK}$  立下がり閾値電圧を示します。

$$V_{SETBK} = V_{INT\_REF} \left( 1 + \frac{R_{BK1}}{R_{BK2}} \right) \quad (3)$$

ADP5091/ADP5092 には  $R_{SETBK\_HYS} = 115 \text{ k}\Omega$  (typ) の内部抵抗があり、式 4 で与えられるヒステリシスを設定します。

$$V_{SETBK\_HYS} = V_{SETBK} \times \frac{R_{SETBK\_HYS}}{R_E} \quad (4)$$

ここで、 $R_E$  は、外部設定の抵抗分圧器 4 個の等価抵抗です。

静止電流を考慮すると、抵抗分圧器を構成する抵抗 ( $R_{SETBK\_HYS}$ 、 $R_{BK1}$ 、 $R_{BK2}$ ) の合計は  $6 \text{ M}\Omega$  を上回る必要があります。すなわち、

$$R_{SETBK\_HYS} + R_{BK1} + R_{BK2} > 6 \text{ M}\Omega \quad (5)$$

外部設定の抵抗分圧器 4 個の等価抵抗 ( $R_E$ ) は、3 本の抵抗分圧器の並列接続値に等しくなります。

図 42. ADP5091/ADP5092 プログラム・パラメータの設定方法

## バッテリの過放電防止の機能

充電式バッテリが過放電して損傷するのを防止するため、外付け抵抗を使ってバッテリ充電終了時の閾値 ( $V_{BAT\_TERM}$ ) を設定する必要があります。図 42 に、式 6 で与えられる  $V_{BAT\_TERM}$  の立上がり閾値電圧を示します。

$$V_{BAT\_TERM} = \frac{3}{2} \times V_{INT\_REF} \times \left( 1 + \frac{R_{TERM1}}{R_{TERM2}} \right) \quad (6)$$

静止電流を考慮すると、抵抗の合計は  $6 \text{ M}\Omega$  を上回る必要があります。すなわち、

$$R_{TERM1} + R_{TERM2} \geq 6 \text{ M}\Omega \quad (7)$$

バッテリ充電終了時の閾値は、 $V_{BAT\_TERM\_HYS}$  で与えられます。これは、バッテリ充電終了時の閾値から、 $V_{BAT\_TERM\_HYS}$  で表記される内部ヒステリシス電圧を引いた値に設定されます。バッテリの電圧が  $V_{BAT\_TERM}$  の閾値を上回っている場合、メイン昇圧レギュレータがディスエーブルになります。バッテリの電圧が  $V_{BAT\_TERM\_HYS}$  のレベルを下回ると、メイン昇圧動作が再開されます。入力エネルギーが大きい場合、VBAT ピンの電圧は  $V_{BAT\_TERM}$  電圧と  $V_{BAT\_TERM\_HYS}$  電圧の間で変動します。

## バッテリ過放電防止の機能

充電式バッテリが過放電して損傷するのを防止するため、外付け抵抗を使用してバッテリ放電停止の閾値 ( $V_{SETSD}$ ) を設定する必要があります。図 42 に、式 8 で与えられる立下がり閾値電圧を示します。

$$V_{SETSD} = V_{INT\_REF} \left( 1 + \frac{R_{SD1}}{R_{SD2}} \right) \quad (8)$$

ADP5091/ADP5092 は、式 9 で与えられるヒステリシスを設定する抵抗  $R_{SETSD\_HYS} = 115 \text{ k}\Omega$  (typ) を内蔵しています。

$$V_{SETSD\_HYS} = V_{SETSD} \times \frac{R_{SETSD\_HYS}}{R_E} \quad (9)$$

静止電流を考慮すると、抵抗分圧器を構成する抵抗 ( $R_{SETSD\_HYS}$ 、 $R_{SD1}$ 、 $R_{SD2}$ ) の合計が  $6 \text{ M}\Omega$  を超える必要があります。すなわち、

$$R_{SETSD\_HYS} + R_{SD1} + R_{SD2} \geq 6 \text{ M}\Omega \quad (10)$$

外付けの抵抗分圧器 3 個の等価抵抗 ( $R_E$ ) は、3 個の抵抗分圧器の並列接続と等価です。

## パワーグッド (PGOOD)

ADP5091/ADP5092 では、SYS 電圧が許容レベルにあることを表示する PGOOD 電圧の閾値をユーザーが設定できます。外付け抵抗を使用する必要があります。図 42 に、式 11 で与えられる  $V_{SETPG}$  立下がり閾値電圧を示します。

$$V_{SETPG\_FALLING} = V_{INT\_REF} \left( 1 + \frac{R_{PG1}}{R_{PG2} + R_{PG\_HYST}} \right) \quad (11)$$

SETHYST ピンで、式 12 で与えられる外部抵抗 ( $R_{PG\_HYST}$ ) を使用してヒステリシスを設定できます。

$$V_{SETPG\_RISING} = V_{INT\_REF} \left( 1 + \frac{R_{PG1} + R_{PG\_HYST}}{R_{PG2}} \right) \quad (12)$$

静止電流を考慮すると、パワーグッド抵抗分圧器を構成する抵抗 ( $R_{PG\_HYST}$ 、 $R_{PG1}$ 、 $R_{PG2}$ ) の合計は  $6 \text{ M}\Omega$  を超える必要があります。すなわち、

$$R_{PG\_HYST} + R_{PG1} + R_{PG2} \geq 6 \text{ M}\Omega$$

PGOOD のロジック・ハイ・レベルは SYS 電圧に等しく、ロジック・ロー・レベルはグラウンドに等しい値になります。利用可能な電流を制限するため、ロジック・ハイ・レベルは内部で約  $11.6 \text{ k}\Omega$  (typ) の抵抗に直列接続されています。 $V_{SETPG\_FALLING}$  閾値は、 $V_{SETSD}$  閾値を超える必要があります。

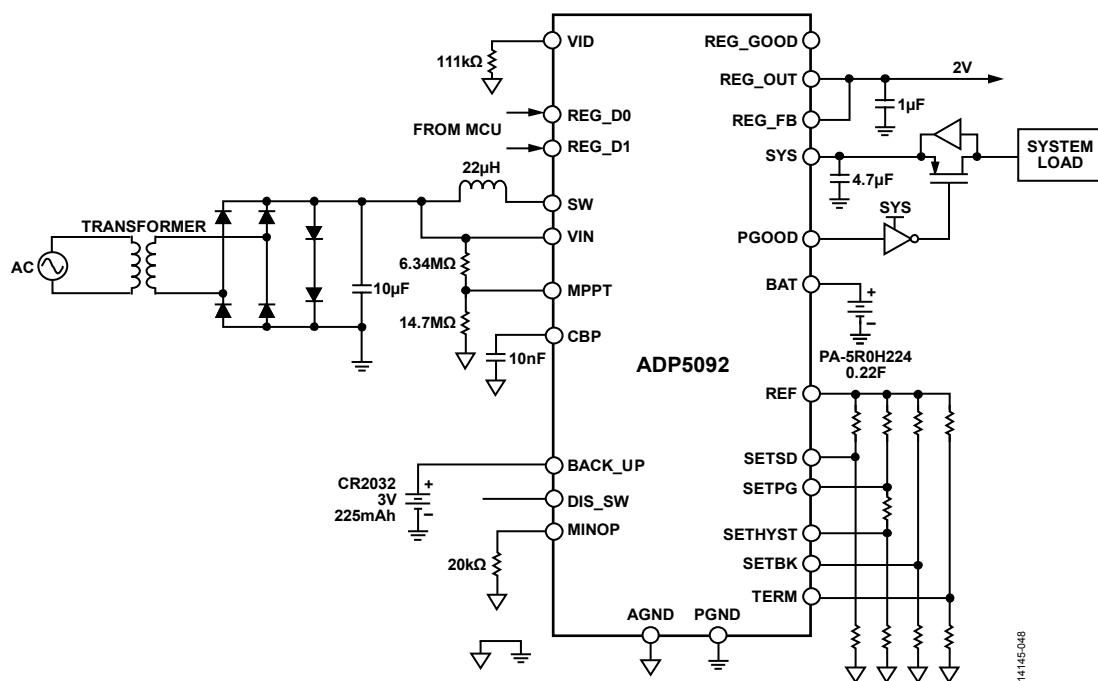

最高のシステム動作性能を引き出すには、PGOOD を設定してシステム負荷をイネーブルにするか、超低電力負荷スイッチをイネーブルにするか、SYS とシステム負荷の間でインバータを介して外付け p 型電界効果トランジスタ (PFET) を駆動して、負荷の接続/切り離しのタイミングを決める必要があります(図 48 参照)。

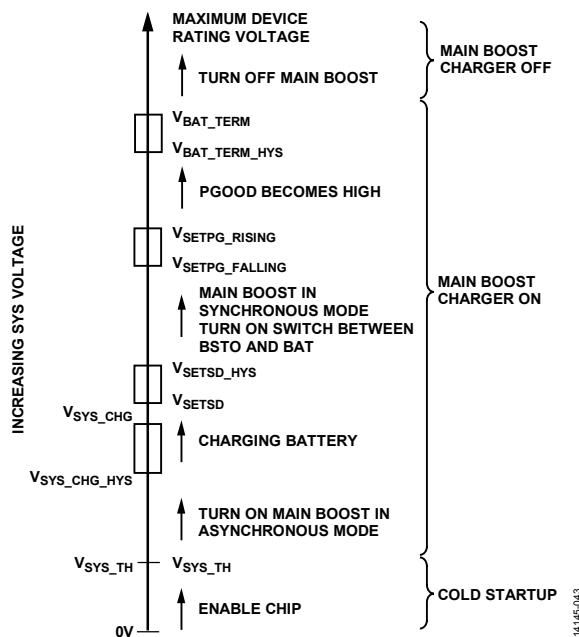

表 8 に、 $10 \text{ M}\Omega$  抵抗分圧器による種々の電圧に対応する、閾値抵抗の設定例を示します。図 43 に、各閾値電圧の状態を示します。

図 43. ADP5091/ADP5092 の様々な閾値電圧の状態

(式 8 と式 9 を参照)

## 電力経路の動作フロー

図 44 に、バックアップ用メイン・バッテリを使用する場合のパワー・スイッチ構造を示します。コールド・スタートの実行中、メイン・バッテリが BACK\_UP ピンに接続されている場合、S1 スイッチがオンになります。メイン・バッテリから、ダイオード D1 の順方向電圧降下を差し引いて、SYS の電力ソースとして使用できます。

コールド・スタートの完了後、BAT 電圧が SETBK 立下がり閾値を上回っている場合、BACK\_UP スイッチはオフのままになります。BAT 電圧が SETBK 立下がり閾値を下回ると、SYS 電圧が  $V_{SYS\_CHG}$  を上回っている限り、バックアップ制御回路は SYS の電力ソースとして、電圧の高い端子を選択します。また、バックアップ制御回路は BAT ピンから BACK\_UP メイン・バッテリへの充電を防止します。その間、コンパレータの BAT オフセットにより、入力ソースから BACK\_UP メイン・バッテリへの充電が防止されます。表 9 に、動作状態の電力経路を示します。

図 44. ADP5091/ADP5092 の電力スイッチ構造

## 電流制限機能と短絡保護の機能

ヒステリシス昇圧モードで動作する ADP5091/ADP5092 の昇圧レギュレータとレギュレーション出力には、ローサイド昇圧スイッチを流れる正電流を制限する電流制限の保護回路が内蔵されています。昇圧レギュレータの電流制限回路はサイクルごとに 3 レベルでピーク電流を制限する保護機能を備えています。3 番目のレベルは  $200 \text{ mA}$  (typ) で、レギュレーション出力の電流制限機能は  $100 \text{ mA}$  (typ) です。LDO モードでは、負荷が  $260 \text{ mA}$  (typ) に達した時点で電流を制限するように、電流制限の保護機能が設計されています。出力負荷が  $260 \text{ mA}$  を超えると、出力電圧を下げて一定の電流限界値が維持されます。

SYS ピンと AT ピンには電流制限値はありませんが、システム負荷電流を  $1000 \text{ mA}$  に制限することが推奨されます。SYS スイッチと BAT スイッチ ( $1.03 \Omega$ , typ) の合計抵抗により、システム負荷に BAT から大きな電流が流れると、電圧降下が生じます。BAT ピンに接続される蓄電素子の内部抵抗を考慮する必要があります。

## サーマル・シャットダウン

ADP5091/ADP5092 のジャンクション温度が 142 °C を超えると、サーマル・シャットダウン (TSD) 回路が BAT ピンと SYS ピンの間のスイッチをオフにして、高い周囲温度での蓄電素子の損傷を

防止します。さらに、昇圧動作も停止します。15 °C のヒステリシスがあるため、内部温度が 127°C. を下回ると、ADP5091/ADP5092 は動作を再開できます。サーマル・シャットダウンが終了すると、昇圧レギュレータと蓄電コントローラは動作を再開します。

表 8. 閾値抵抗の設定 (図 42 参照)

| Voltage Threshold (V) | R <sub>BK1</sub> , R <sub>SD1</sub> , and R <sub>PG1</sub> (MΩ) | R <sub>BK2</sub> , R <sub>SD2</sub> , and R <sub>PG2</sub> (MΩ) | R <sub>TERM1</sub> (MΩ) | R <sub>TERM2</sub> (MΩ) |

|-----------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|-------------------------|-------------------------|

| 2                     | 5                                                               | 5                                                               | Not applicable          | Not applicable          |

| 2.1                   | 5.23                                                            | 4.75                                                            | Not applicable          | Not applicable          |

| 2.2                   | 5.49                                                            | 4.53                                                            | 3.2                     | 6.81                    |

| 2.3                   | 5.62                                                            | 4.32                                                            | 3.48                    | 6.49                    |

| 2.4                   | 5.9                                                             | 4.12                                                            | 3.74                    | 6.2                     |

| 2.5                   | 6.04                                                            | 4                                                               | 4                       | 6.04                    |

| 2.6                   | 6.19                                                            | 3.83                                                            | 4.22                    | 5.76                    |

| 2.7                   | 6.34                                                            | 3.74                                                            | 4.42                    | 5.6                     |

| 2.8                   | 6.49                                                            | 3.57                                                            | 4.64                    | 5.36                    |

| 2.9                   | 6.6                                                             | 3.48                                                            | 4.87                    | 5.23                    |

| 3                     | 6.65                                                            | 3.32                                                            | 5                       | 5                       |

| 3.1                   | 6.8                                                             | 3.24                                                            | 5.11                    | 4.87                    |

| 3.2                   | 6.81                                                            | 3.09                                                            | 5.36                    | 4.7                     |

| 3.3                   | 6.98                                                            | 3.01                                                            | 5.49                    | 4.53                    |

| 3.4                   | 6.98                                                            | 2.94                                                            | 5.6                     | 4.42                    |

| 3.5                   | 7.15                                                            | 2.87                                                            | 5.76                    | 4.3                     |

| 3.6                   | 7.15                                                            | 2.8                                                             | 5.9                     | 4.12                    |

| 3.7                   | 7.32                                                            | 2.7                                                             | 5.9                     | 4.02                    |

| 3.8                   | 7.32                                                            | 2.61                                                            | 6.04                    | 3.92                    |

| 3.9                   | 7.5                                                             | 2.55                                                            | 6.19                    | 3.83                    |

| 4                     | 7.5                                                             | 2.5                                                             | 6.2                     | 3.74                    |

| 4.1                   | 7.5                                                             | 2.43                                                            | 6.34                    | 3.65                    |

| 4.2                   | 7.68                                                            | 2.37                                                            | 6.49                    | 3.57                    |

| 4.3                   | 7.68                                                            | 2.32                                                            | 6.49                    | 3.48                    |

| 4.4                   | 7.68                                                            | 2.26                                                            | 6.6                     | 3.4                     |

| 4.5                   | 7.87                                                            | 2.21                                                            | 6.65                    | 3.32                    |

| 4.6                   | 7.87                                                            | 2.15                                                            | 6.8                     | 3.24                    |

| 4.7                   | 7.87                                                            | 2.15                                                            | 6.81                    | 3.2                     |

| 4.8                   | 7.87                                                            | 2.1                                                             | 6.81                    | 3.09                    |

| 4.9                   | 7.87                                                            | 2.05                                                            | 6.98                    | 3.09                    |

| 5                     | 8.06                                                            | 2                                                               | 6.98                    | 3                       |

| 5.1                   | 8.06                                                            | 1.96                                                            | 6.98                    | 2.94                    |

| 5.2                   | 8.06                                                            | 1.91                                                            | 7.15                    | 2.87                    |

表 9. 電力経路の動作状態（図 44 参照）

| <b>Backup Battery</b> | <b>Power Condition<sup>1</sup></b>                                                                    | <b>Main Boost</b> | <b>BAT_M1</b> | <b>BAT_M2</b> | <b>SYS Switch</b> | <b>BACK_UP_M1</b> | <b>BACK_UP_M2</b> |

|-----------------------|-------------------------------------------------------------------------------------------------------|-------------------|---------------|---------------|-------------------|-------------------|-------------------|

| Without               | $V_{SYS\_CHG} > V_{SYS} > V_{SYS\_TH}$ ,<br>$V_{SETSD} > V_{BAT}$                                     | Asynchronous      | Off           | Off           | On                | Off               | Off               |

|                       | $V_{SYS} > V_{SYS\_CHG}$ , $V_{SETSD} > V_{BAT}$                                                      | Asynchronous      | On            | Off           | On                | Off               | Off               |

|                       | $V_{BAT\_TERM} > V_{BAT} = V_{SYS} > V_{SETSD}$                                                       | Synchronous       | On            | On            | On                | Off               | Off               |

|                       | $V_{SYS} > V_{SYS\_TH}$ , $V_{BAT} > V_{BAT\_TERM}$                                                   | Disabled          | On            | On            | On                | Off               | Off               |

| With                  | $V_{SYS\_CHG} > V_{SYS} > V_{SYS\_TH}$ ,<br>$V_{SETSD} > V_{BAT}$                                     | Asynchronous      | Off           | Off           | On                | Off               | Off               |

|                       | $V_{SYS} > V_{SYS\_CHG}$ , $V_{SETSD} > V_{BAT}$ , $V_{BACK\_UP} > V_{BAT}$                           | Asynchronous      | On            | Off           | Off               | On                | On                |

|                       | $V_{SYS} > V_{SYS\_TH}$ , $V_{BAT} > V_{SETSD}$ ,<br>$V_{BAT} > V_{SETBK}$                            | Synchronous       | On            | On            | On                | Off               | Off               |

|                       | $V_{SYS} > V_{SYS\_TH}$ , $V_{BAT} > V_{SETSD}$ ,<br>$V_{BAT} < V_{SETBK}$ , $V_{BACK\_UP} > V_{BAT}$ | Synchronous       | On            | On            | Off               | On                | On                |

|                       | $V_{SYS} < V_{SYS\_TH}$                                                                               | Disabled          | Off           | Off           | On                | Off               | Off               |

<sup>1</sup>  $V_{BACK\_UP}$  は BACK\_UP ピンの電圧、 $V_{SETBK}$  は SETBK ピンの閾値です。

## アプリケーション情報

ADP5091/ADP5092 は、VIN ピンからエネルギーを取り出して SYS ピンと BAT ピンを充電します。これは、コールド・スタート、非同期昇圧、同期昇圧の 3 段階で行われます。ここでは、エネルギー伝導システムを保守するための外付け部品の選択手順、レイアウトと組み立ての考慮事項について説明します。

### エネルギー・ハーベスタの選択

エネルギー・ハーベスタの入力ソースは、コールド・スタート、非同期昇圧、同期昇圧に対して最小レベルの電力を供給する必要があります。コールド・スタートを完了するために必要な最小入力電力は、次式で計算できます。

$$V_{IN} \times I_{IN} \times \eta_{COLD} > V_{SYS\_TH} \times I_{SYS\_LOAD} \quad (13)$$

ここで

$V_{IN}$  は  $V_{IN\_COLD} = 380 \text{ mV} (\text{typ})$  にクランプされ、コールド・スタートの最小入力電圧を表します。

$I_{IN}$  は入力電流。

$\eta_{COLD}$  はコールド・スタート効率で、約 5 % ~ 7 % です。

( $V_{SYS\_TH}$  はコールド・スタート動作終了時の値です)

$I_{SYS\_LOAD}$  は SYS ピンでのシステム負荷電流。システム負荷を小さくすると、コールド・スタートが加速されます。PGOOD 閾値を設定してシステム負荷電流をイネーブルにすることが推奨されます。

ADP5091/ADP5092 がコールド・スタートを完了した後、MPPT 機能がイネーブルになります。平均のシステム負荷電流を満たすため、入力ソースは昇圧レギュレータに十分な電力を供給して、蓄電素子をフル充電すると同時に、システムは低消費電力の状態(すなわちスリープ・モード)に移行する必要があります。システムに必要とされる電力は、次式で計算できます。

$$V_{IN} \times I_{IN} \times \eta_{BOOST} > V_{BAT\_TERM} \times (I_{STR\_LEAK} + I_{SYS\_LOAD}) \quad (14)$$

ここで

$V_{IN}$  は MPPT ピン電圧 (MPPT 比 × OCV) にレギュレーションされます。

$I_{IN}$  は入力電流。

$\eta_{BOOST}$  は昇圧レギュレータの効率。詳細については、代表的な性能特性セクションの図 5 ~ 図 12 を参照してください。

$V_{BAT\_TERM}$  はバッテリ充電終了時の閾値です (表 1 参照)。

$I_{STR\_LEAK}$  は BAT ピンでの蓄電素子のリーク電流。

$I_{SYS\_LOAD}$  は SYS ピンの平均システム負荷電流。

表 10. 推奨される太陽電池

| Vendor       | Device Type               |

|--------------|---------------------------|

| Alta Devices | GaAs                      |

| Fujikura     | Dye sensitized solar cell |

| Gcell        | Dye sensitized solar cell |

| ElectricFilm | Dye sensitized solar cell |

### 蓄電素子の選択

過充電または過放電から蓄電素子を保護するため、BAT ピンに蓄電素子を接続し、SYS ピンにシステム負荷を接続する必要があります。ADP5091/ADP5092 では、充電式バッテリ、スーパー・キャパシタ、従来型コンデンサのような、多くのタイプの蓄電素子をサポートしています。PFM スイッチング・コンバータのパルス電流をフィルタリングするため、100  $\mu\text{F}$  の等価容量を持つ蓄電素子が必要です。入力ソースが発電を停止した場合、蓄電素子の容量が全システム負荷になります。

パルス電流が大きい場合、または蓄電素子のインピーダンスが大きい場合、SYS コンデンサの容量を最小の 4.7  $\mu\text{F}$  よりも大きくするか、BAT ピンにコンデンサを追加して、SYS 電圧の低下を防止する必要があります。SYS コンデンサの容量を大きくすると、昇圧レギュレータはスタートアップ時に、コールド・スタートの効率が低くなり、この段階で動作する時間が長くなることに注意してください。アプリケーションにおいてコールド・スタート時間が長くなることを許容できない場合は、蓄電素子と並列にコンデンサを追加してください。詳細については、コンデンサの選択のセクションを参照してください。

### インダクタの選択

昇圧レギュレータを正常に動作させるには、適切なインダクタが必要です。インダクタの飽和電流は、予想されるピーク・インダクタ電流を少なくとも 30 % 上回る必要があります。また、直列抵抗値(DCR)を小さくして高い効率を維持する必要があります。昇圧レギュレータの内部制御回路は、効率を最適化し、22  $\mu\text{H} \pm 20\%$  の公称インダクタンスでスイッチング動作を制御するように設計されています。表 11 に、推奨インダクタを示します。

表 11. 推奨インダクタ

| Vendor           | Device No.   | L ( $\mu\text{H}$ ) | I <sub>SAT</sub> (A) <sup>1</sup> | I <sub>RMS</sub> (A) <sup>2</sup> | DCR (mΩ) |

|------------------|--------------|---------------------|-----------------------------------|-----------------------------------|----------|

| Würth Elektronik | 74437324220  | 22                  | 2                                 | 1                                 | 470      |

|                  | 744042220    | 22                  | 0.6                               | 0.88                              | 255      |

| Coilcraft        | LPS4018-223M | 22                  | 0.8                               | 0.65                              | 360      |

<sup>1</sup> I<sub>SAT</sub> は、電流が流れていないときの値からインダクタンス値を 20 % 低下する DC 電流。

<sup>2</sup> I<sub>RMS</sub> は、周囲温度 25 °C のときに 20 °C の温度上昇をもたらす電流。

## コンデンサの選択

リーク電流に敏感な超低消費電力アプリケーションには、低リーク・コンデンサが必要です。コンデンサからのリークがあると効率は低下し、静止電流が増加し、MPPT の効果が低下します。

## 入力コンデンサ

VIN ピンと PGND ピンに接続するコンデンサ ( $C_{IN}$ ) が入力ソースからのエネルギーを保存します。エネルギー・ハーベスタのソース・インピーダンスでは、容量性動作が支配的になります。エネルギー・ハーベスタの出力容量に従い、入力コンデンサの容量を決めてください。最小  $10\ \mu F$  が推奨されます。

メイン・バッテリを使用するアプリケーションの場合、容量が大きいほど、入力電圧リップルが小さくなり、電池寿命を長くするためのソース電流の安定化に役立ちます。

## SYS コンデンサ

ADP5091/ADP5092 では、SYS ピンと PGND ピンの間に 2 個のコンデンサを接続する必要があります。最小  $4.7\ \mu F$  の低 ESR セラミック・コンデンサと  $0.1\ \mu F$  の高周波バイパス・コンデンサを並列接続してください。バイパス・コンデンサは、SYS と PGND の間に、できるだけ近づけて接続してください。

## REG\_OUT コンデンサ

ADP5091/ADP5092 のレギュレーション出力は、スペース節約型の小型セラミック・コンデンサで動作するように設計されています。ただし、ESR（等価直列抵抗）に注意すれば、一般的に使用されるほとんどのコンデンサで動作します。出力コンデンサのESRは、LDO 制御ループの安定性に影響を与えます。レギュレーション出力を安定させるには、ESR が  $1\ \Omega$  以下で最小  $4.7\ \mu F$  のコンデンサを使用するよう推奨します。負荷電流の変化に対する過渡応答も、出力コンデンサの影響を受けます。出力容量を大きくすると、負荷電流の大きな変化に対するレギュレーション出力の過渡応答を改善できます。

## CBP コンデンサ

MPPT ピンの動作は、OCV のサンプル値に依存します。VIN ピンは、CBP コンデンサに保存された電圧に調整されます。このコンデンサは、出力保持時間が約 16 秒であるため、リークに敏感です。コンデンサ電圧がリークのために低下すると、VIN のレギュレーション電圧も低下して、MPPT の効果に影響を与えます。IC

ジャンクション温度が  $85^\circ C$  を超えると、CBP ピンのリーク電流が大幅に上昇するため、容量が大きいほど MPPT の効果に有利です。図 45 の代表的なアプリケーション回路と同じ MPPT 抵抗と CBP コンデンサ（最大  $22\ \mu F$ ）を使用する RC 時定数を維持することが推奨されます。MPPT 抵抗分圧器と CBP コンデンサの時定数を考慮すると、低リーク X7R または C0G  $10\ nF$  セラミック・コンデンサが推奨されます。

## レイアウトと組み立てについての考慮事項

スイッチング電源を設計する際、特に高ピーク電流と高スイッチング周波数を想定して、プリント回路ボード(PCB) のレイアウトを注意深く行う必要があります。このため、メインの電源経路と電源グラウンド経路には、短く、幅の広いパターンを使用することが推奨されます。入力コンデンサ、出力コンデンサ、インダクタ、蓄電素子は、IC のできるだけ近くに配置します。出力からグラウンドまでの電力経路を短くすることが昇圧レギュレータにとって最も重要です。このため、出力コンデンサは SYS ピンと PGND ピンの間に、できるだけ近づけて配置してください。入力コンデンサからインダクタまで、VIN ピンから PGND ピンまでの電力経路をできる限り短くしてください。入力コンデンサは VIN ピンと PGND ピンの間にできるだけ近づけて配置し、インダクタは VIN ピンと SW ピンの近くに配置します。該当するピンにインダクタを接続するときは、ビアと裏面パターンを使用するのが最適です。高インピーダンスの閾値設定ノード (REF、TERM、SETSD、SETPG) からのノイズ混入を抑えるため、IC の近くにパターンの短い外付け抵抗を接続してください。

CBP コンデンサは MPPT 電圧を 16 秒間保持するため、リークがあると MPPT の効率が損なわれます。ボードの組み立てと洗浄中、ハンダ溶剤や残留物のような汚染があると、空気流量と湿度が高い環境では特に、グラウンドに対する寄生抵抗が形成されることがあります。このため、電圧調整の性能が大幅に低下し、外付け抵抗で設定される閾値電圧が変化します。したがって、CBP コンデンサまたは閾値設定抵抗の近くにグラウンド・プレーンを設けないことが推奨されます。さらに、ボードを注意深く洗浄する必要があります。可能な場合、CBP コンデンサと閾値設定抵抗は、脱イオン水でイオン汚染を洗浄してください。

## 代表的なアプリケーション回路

図 45. ADP5091 採用のエネルギー・ハーベスター・ワイヤレス・センサー・アプリケーション、

PV セルをハーベスティング・エネルギー・ソース (Trony 0.7 V, 60 µA, Alta Devices 0.72 V, 42 µA, cell 1.1 V, 100 µA)

として使用、Cooper Bussmann 社のスーパー・キャパシタ PA-5R0H224 を収集済みエネルギーの保存に使用、

Panasonic 社の 1 次リチウムイオン・コイン型セル CR2032 をバックアップ・バッテリとして使用

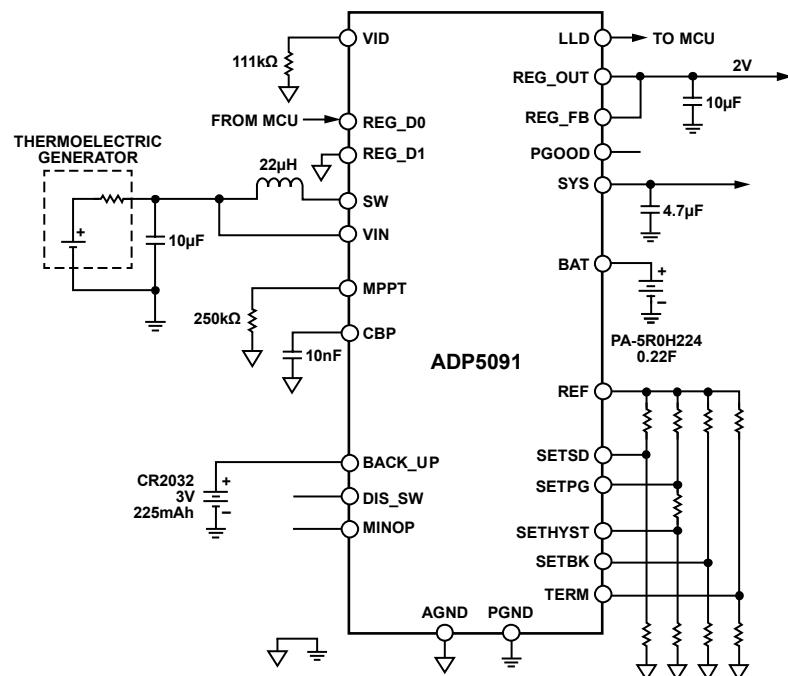

図 46. ADP5091 採用のエネルギー・ハーベスター回路、熱電発電をハーベスティング・エネルギー・ソースとして使用、

Cooper Bussmann 社のスーパー・キャパシタ PA-5R0H224 を収集済みエネルギーの保存に使用、

パナソニック社の 1 次リチウムイオン・コイン型セル CR2032 をバックアップ・バッテリとして使用

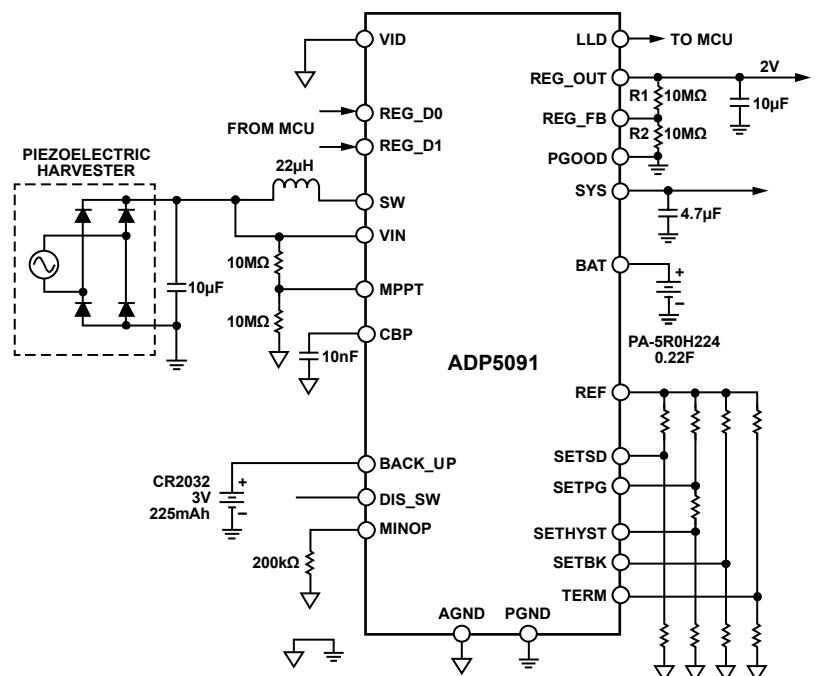

図 47. ADP5091 採用のエネルギー・ハーベスター回路、圧電発電をハーベスティング・エネルギー・ソースとして使用、Cooper Bussmann 社のスーパー・キャパシタ PA-5R0H224 を収集済みエネルギーの保存に使用、パナソニック社の 1 次リチウムイオン・コイン型セル CR2032 をバックアップ・バッテリとして使用

図 48. ADP5092 AC 入力ソースと PGOOD 機能により、システム負荷を有効にするタイミングを決定

## 出荷時にプログラム可能なオプション

デフォルト以外のオプションでデバイスを注文される場合は、アナログ・デバイセズの担当営業または代理店までお問い合わせください。

表 12. 入力電流制限オプション

| Option   | Description      |

|----------|------------------|

| Option 0 | 200 mA (default) |

| Option 1 | 300 mA           |

表 13. VIN オープン・サーキット電圧のサンプル・サイクル・オプション

| Option   | Description      |

|----------|------------------|

| Option 0 | 4 sec            |

| Option 1 | 8 sec            |

| Option 2 | 16 sec (default) |

| Option 3 | 32 sec           |

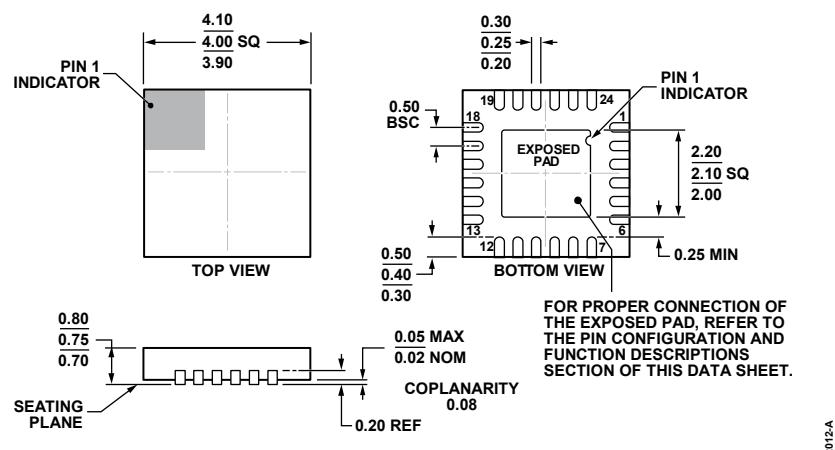

## 外形寸法

図 49. 24 ピン・リードフレーム・チップスケール・パッケージ [LFCSP]

4 mm × 4 mm ボディ、0.75 mm パッケージ高 (CP-24-10)

寸法: mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                                       | Package Option |

|--------------------|-------------------|-----------------------------------------------------------|----------------|

| ADP5091ACPZ-1-R7   | -40°C to + 125°C  | 24-Lead Lead Frame Chip Scale Package [LFCSP]             | CP-24-10       |

| ADP5092ACPZ-1-R7   | -40°C to + 125°C  | 24-Lead Lead Frame Chip Scale Package [LFCSP]             | CP-24-10       |

| ADP5091-1-EVALZ    |                   | Evaluation Board                                          |                |

| ADP5091-2-EVALZ    |                   | Evaluation Board with Solar Harvester and Super Capacitor |                |

| ADP5092-1-EVALZ    |                   | Evaluation Board                                          |                |

<sup>1</sup> Z = RoHS 準拠製品。