## 特長

- ・SONETのジッター基準（ジッター伝達、ジッター発生、ジッター耐性）をクリア

- ・量子化回路感度：4 mV (Typ)

- スライス・レベル： $\pm 100\text{mV}$

- 最小帯域幅：1.9GHz

- ・特有のクロック再生構造（特許取得）

- ・LOSの検出範囲：3mV ~15mV

- ・ネイティブSONETおよび15/14(7%)の両ラッパー・レートに

対して1つのリファレンス・クロックの周波数を使用

- ・19.44MHz、38.88MHz、77.76MHz、155.52MHzのREFCLK

- LVPECL/LVDS/LVCMOS/LVTTLとして選択可能

- ・外付け水晶発振器を用いれば、オンチップの19.44MHz発

振器が使用可能

- ・LOSの表示

- ・高速テスト・データ用のループバック・モード

- ・出力スケルチ機能およびバイパス機能を装備

- ・単電源動作：3.3V

- ・低消費電力：540mW (Typ値)

- ・パッケージ：48ピンLFCSP (7mm角)

## アプリケーション

SONET OC-48、SDH STM-16、15/14 FEC

WDMのトランスポンダ

信号再生/リピーター

テスト装置

バックプレーン・アプリケーション

## 製品説明

ADN2811は、量子化回路からの受信機能、信号レベル検出機能、OC-48およびOC-48FECレートでのクロックおよびデータの再生機能を提供します。すべてのSONETジッター条件（ジッター伝達、ジッター発生、ジッター耐性）を満たしています。特に指定がない限りすべての仕様は-40°C ~ +85°Cの周囲温度で規定されています。

ADN2811は外部リファレンスクロック、または水晶振動子を使用したオンチップの発振器で動作することができます。ADN2811は2.48Gb/sおよび2.66Gb/sの両デジタル・ラッパー・レートを、リファレンス・クロックの変更なしでサポートします。

PIN・フォトダイオード、およびTIAプリアンプと組み合わせて使用することで、高集積度、低消費電流の光ファイバー受信器を構成することができます。

入力信号が、ユーザーの設定したしきい値を下回った場合、LOSによって検知が可能です。信号検出回路は、出力のチャタリングを防止するようなヒステリシスになっています。

ADN2811は、48ピンLFCSP (7mm角) を採用しています。

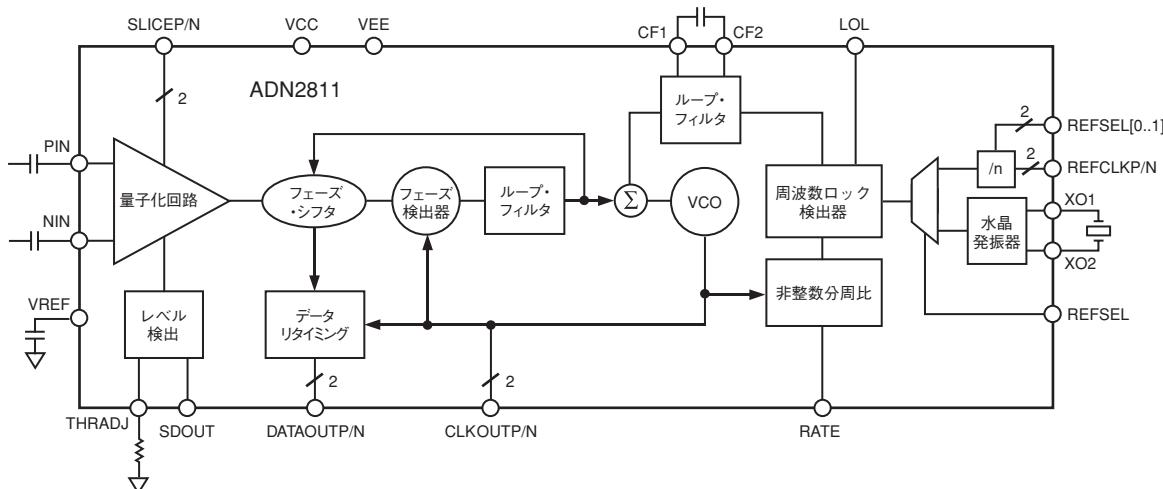

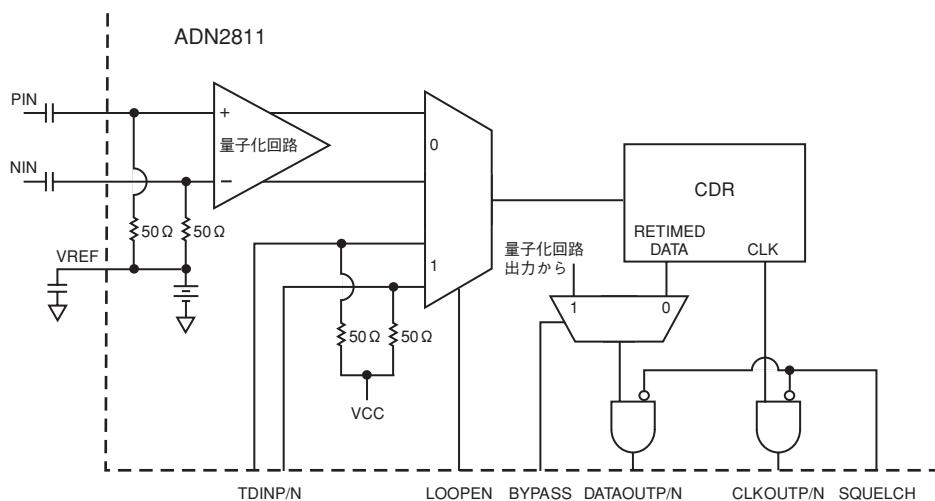

ブロック図

アナログ・デバイセズ社が提供する情報は正確で信頼できるものを期していますが、その情報の利用または利

用了ことにより引き起こされる第3者の特許または権利の侵害に関して、当社はいっさいの責任を負いません。

さらに、アナログ・デバイセズ社の特許または特許の権利の使用を許諾するものではありません。

\*日本語データシートは、REVISIONが古い場合があります。最新の内容については英語版をご参照ください。

# ADN2811—仕様

(特に指定のない限り、 $T_A = T_{MIN} \sim T_{MAX}$ 、 $V_{CC} = V_{MIN} \sim V_{MAX}$ 、 $V_{EE} = 0V$ 、 $C_F = 4.7 \mu F$ 、 $SLICEP = SLICEN = VCC$ )

| パラメータ                            | 条件                                                    | Min              | Typ       | Max                | 単位                |

|----------------------------------|-------------------------------------------------------|------------------|-----------|--------------------|-------------------|

| 量子化回路—DC特性                       |                                                       |                  |           |                    |                   |

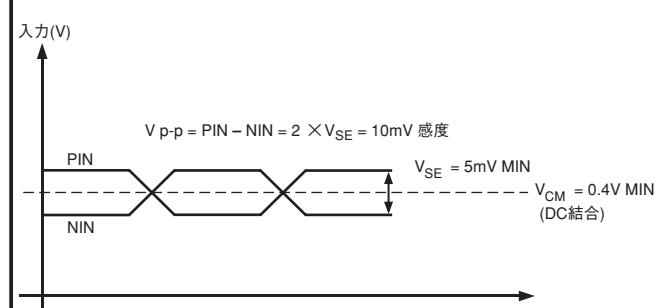

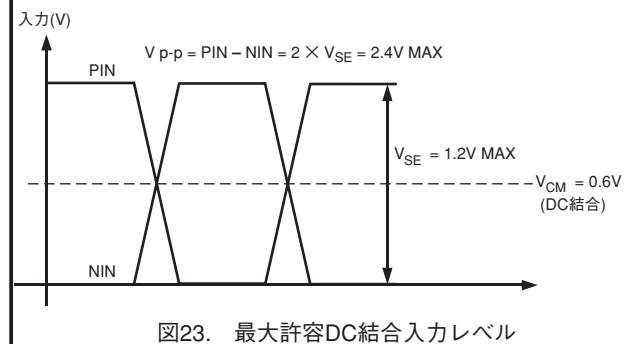

| 入力電圧レンジ                          | PINまたはNINでの値、DC結合                                     | 0                |           | 1.2                | V                 |

| Peak-to-Peak差動入力                 |                                                       |                  |           | 2.4                | V                 |

| 入力コモン・モード・レベル                    | DC結合。図22参照。                                           | 0.4              |           |                    | V                 |

| 差動入力感度                           | PIN-NIN間、AC結合 <sup>1</sup> 、BER = $1 \times 10^{-10}$ |                  | 4         | 10                 | mV <sub>p-p</sub> |

| 入力オーバードライブ                       | 図4                                                    |                  | 2         | 5                  | mV <sub>p-p</sub> |

| 入力オフセット                          |                                                       |                  | 500       |                    | $\mu$ V           |

| 入力RMSノイズ                         | BER = $1 \times 10^{-10}$                             |                  | 244       |                    | $\mu$ V rms       |

| 量子化回路-AC特性                       |                                                       |                  |           |                    |                   |

| 上側-3dB帯域幅                        |                                                       |                  | 1.9       |                    | GHz               |

| 小信号ゲイン                           | 差動                                                    |                  | 54        |                    | dB                |

| S11                              | @ 2.5GHz                                              |                  | -15       |                    | dB                |

| 入力抵抗                             | 差動                                                    |                  | 100       |                    | $\Omega$          |

| 入力容量                             |                                                       |                  | 0.65      |                    | pF                |

| パルス幅歪み <sup>2</sup>              |                                                       |                  | 10        |                    | ps                |

| 量子化回路スライス調整                      |                                                       |                  |           |                    |                   |

| ゲイン                              | SLICEP-SLICEN = $\pm 0.5V$                            | 0.115            | 0.200     | 0.300              | V/V               |

| 制御電圧レンジ                          | SLICEP-SLICEN                                         | -0.8             |           | +0.8               | V                 |

| 制御電圧レンジ                          | @ SLICEPまたはSLICEN                                     | 1.3              |           | VCC                | V                 |

| スライス・レベル・オフセット                   |                                                       |                  | $\pm 1.0$ |                    | mV                |

| レベル信号検出(SDOUT)                   |                                                       |                  |           |                    |                   |

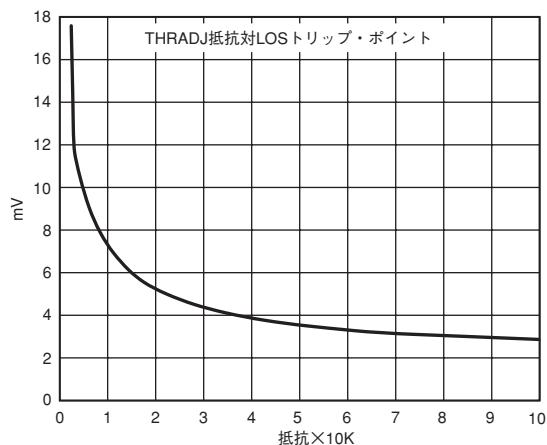

| レベル検出レンジ(図2参照)                   | $R_{Thresh} = 2k\Omega$                               | 9.4              | 13.3      | 18.0               | mV                |

|                                  | $R_{Thresh} = 20k\Omega$                              | 2.5              | 5.3       | 7.6                | mV                |

|                                  | $R_{Thresh} = 90k\Omega$                              | 0.7              | 3.0       | 5.2                | mV                |

| 応答時間                             | DC結合                                                  | 0.1              | 0.3       | 5                  | $\mu$ s           |

| ヒステリシス(電気的)、PRBS 2 <sup>23</sup> | $R_{Thresh} = 2k\Omega$                               | 5.6              | 6.6       | 7.8                | dB                |

|                                  | $R_{Thresh} = 20k\Omega$                              | 3.9              | 6.1       | 8.5                | dB                |

|                                  | $R_{Thresh} = 90k\Omega$                              | 3.2              | 6.7       | 9.9                | dB                |

| 非ロック状態検出(LOL)                    |                                                       |                  |           |                    |                   |

| LOL応答時間                          | $f_{VCO}$ エラー > 1000ppmから                             |                  | 60        |                    | $\mu$ s           |

| 電源電圧                             |                                                       | 3.0              | 3.3       | 3.6                | V                 |

| 電源電流                             |                                                       | 150              | 164       | 215                | mA                |

| PLL特性                            | PIN-NIN = 10mV <sub>p-p</sub>                         |                  |           |                    |                   |

| ジッタ伝達帯域幅                         | OC-48                                                 |                  | 590       | 880                | kHz               |

| ジッタ・ピーク                          | OC-48                                                 |                  | 0.025     |                    | dB                |

| ジッタ発生                            | OC-48、12kHz～20MHz                                     |                  |           | 0.003 <sup>3</sup> | UI <sub>rms</sub> |

| ジッタ耐性                            | OC-48(図9参照)                                           |                  | 0.05      | 0.09               | UI <sub>p-p</sub> |

|                                  | 600Hz                                                 | 92 <sup>3</sup>  |           |                    | UI <sub>p-p</sub> |

|                                  | 6kHz                                                  | 20 <sup>3</sup>  |           |                    | UI <sub>p-p</sub> |

|                                  | 100kHz                                                | 5.5              |           |                    | UI <sub>p-p</sub> |

|                                  | 1MHz                                                  | 1.0 <sup>3</sup> |           |                    | UI <sub>p-p</sub> |

| パラメータ                                | 条件                                              | Min      | Typ   | Max      | 単位 |

|--------------------------------------|-------------------------------------------------|----------|-------|----------|----|

| CML出力(CLKOUTP/N、DATAOUTP/N)          |                                                 |          |       |          |    |

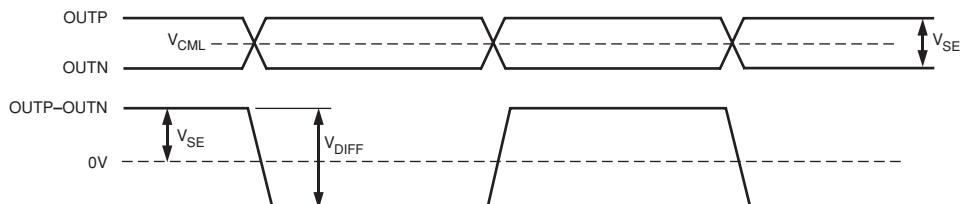

| シングル・エンド出力振幅                         | V <sub>SE</sub> 、図3参照                           | 300      | 455   | 600      | mV |

| 差動出力振幅                               | V <sub>DIFF</sub> 、図3参照                         | 600      | 910   | 1200     | mV |

| 出力ハイレベル電圧                            | V <sub>OH</sub>                                 |          | VCC   |          | V  |

| 出力ローレベル電圧                            | V <sub>OL</sub>                                 | VCC -0.6 |       | VCC -0.3 | V  |

| 立ち上がり時間                              | 20%~80%                                         |          | 84    | 150      | ps |

| 立ち下がり時間                              | 80%~20%                                         |          | 84    | 150      | ps |

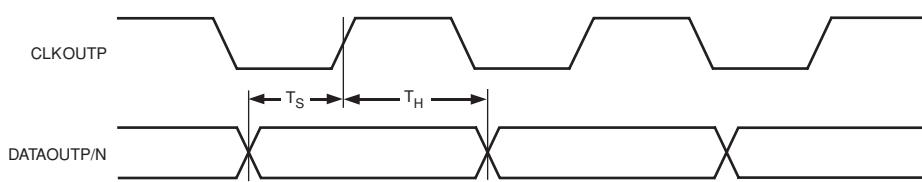

| セットアップ時間                             | T <sub>S</sub> 、図1参照                            |          |       |          |    |

| OC-48                                |                                                 | 140      |       |          | ps |

| ホールド時間                               | T <sub>H</sub> 、図1参照                            |          |       |          |    |

|                                      | OC-48                                           | 150      |       |          | ps |

| REFCLK DC入力特性                        |                                                 |          |       |          |    |

| 入力電圧レンジ                              | @ REFCLKPまたはREFCLKN                             | 0        | VCC   |          | V  |

| Peak-to-Peak差動入力                     |                                                 | 100      |       |          | mV |

| コモン・モード・レベル                          | DC結合、シングル・エンド                                   |          | VCC/2 |          | V  |

| テスト・データDC入力特性 <sup>4</sup> (TDINP/N) | CML入力                                           |          | 0.8   |          | V  |

| Peak-to-Peak差動入力電圧                   |                                                 |          |       |          |    |

| LVTTL DC入力特性                         |                                                 |          |       |          |    |

| 入力ハイ電圧                               | V <sub>IH</sub>                                 | 2.0      |       |          | V  |

| 入力ロー電圧                               | V <sub>IL</sub>                                 |          | 0.8   |          | V  |

| 入力電流                                 | V <sub>IN</sub> = 0.4VまたはV <sub>IN</sub> = 2.4V | -5       |       | +5       |    |

| LVTTL DC出力特性                         |                                                 |          |       |          |    |

| 出力ハイ電圧                               | V <sub>OH</sub> 、I <sub>OH</sub> = -2.0mA       | 2.4      |       |          | V  |

| 出力ロー電圧                               | V <sub>OL</sub> 、I <sub>OL</sub> = +2.0mA       |          | 0.4   |          | V  |

## 注

- 1 PINとNINは差動駆動、AC結合時に最適感度。

- 2 PWDの計測はBYPASSモードで量子化回路出力で実施。

- 3 計測は装置により制限されます。

- 4 TDINP/NはCML入力。TDINP/N入力に対するドライバがCML以外の場合には、AC結合にする必要があります。

仕様は予告なく変更されることがあります。

# ADN2811

## 絶対最大定格\*

|                      |                |

|----------------------|----------------|

| 電源電圧(VCC) .....      | 5.5V           |

| 最小入力電圧(全入力) .....    | VEE - 0.4V     |

| 最大入力電圧(全入力) .....    | VCC +0.4V      |

| 最大接合温度 .....         | 165°C          |

| 保存温度 .....           | -65°C ~ +150°C |

| ピン温度(ハンダ処理10秒) ..... | 300°C          |

\*上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作の節に記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## 熱特性

### 熱抵抗

48ピンLFCSP、4層ボード、露出パドルをVCCにハンダ付け

$\theta_{JA} = 25°C/W$

## オーダー・ガイド

| 製品モデル             | 温度レンジ         | パッケージ                       | オプション |

|-------------------|---------------|-----------------------------|-------|

| ADN2811ACP-CML    | -40°C ~ +85°C | 48ピンLFCSP                   | CP-48 |

| ADN2811ACP-CML-RL | -40°C ~ +85°C | 48ピンLFCSP、テープ/リール、<br>2500個 | CP-48 |

## 注意

ESD（静電気放電）の影響を受けやすいデバイスです。4000Vにおよぶ高圧の静電気が人体やテスト装置に容易に帯電し、検知されることなく放電されることがあります。本製品には当社独自のESD保護回路を備えていますが、高エネルギーの静電放電を受けたデバイスには回復不可能な損傷が発生することがあります。このため、性能低下や機能喪失を回避するために、適切なESD防止措置をとるようお奨めします。

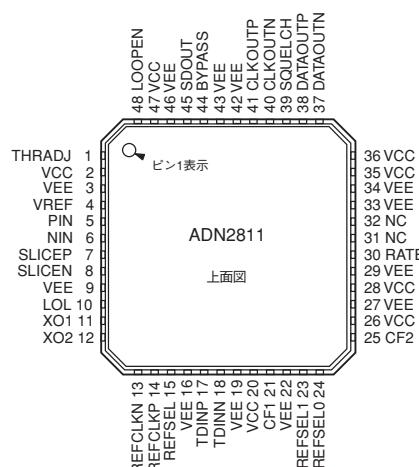

## ピン配置

## ピン機能の説明

| ピン番号                              | 記号       | タイプ | 説明                                                               |

|-----------------------------------|----------|-----|------------------------------------------------------------------|

| 1                                 | THRADJ   | AI  | LOSしきい値設定抵抗                                                      |

| 2、26、28、Pad                       | VCC      | P   | アナログ電源                                                           |

| 3、9、16、19、22、27、29、33、34、42、43、46 | VEE      | P   | GND                                                              |

| 4                                 | VREF     | AO  | 内部V <sub>REF</sub> 電圧。0.1 μFのコンデンサでGNDへデカップリング。                  |

| 5                                 | PIN      | AI  | 差動データ入力。(CML)                                                    |

| 6                                 | NIN      | AI  | 差動データ入力。(CML)                                                    |

| 7                                 | SLICEP   | AI  | 差動スライス・レベル調整入力                                                   |

| 8                                 | SLICEN   | AI  | 差動スライス・レベル調整入力                                                   |

| 10                                | LOL      | DO  | 非ロック状態の表示。LVTTLアクトライブ・ハイ。                                        |

| 11                                | XO1      | AO  | 水晶振動子                                                            |

| 12                                | XO2      | AO  | 水晶振動子                                                            |

| 13                                | REFCLKN  | DI  | 差動REFCLK入力。LVTTL、LVCMS、LVPECL、LVDS (LVPECL、LVDSは155.52MHzの場合のみ)。 |

| 14                                | REFCLKP  | DI  | 差動REFCLK入力。LVTTL、LVCMS、LVPECL、LVDS (LVPECL、LVDSは155.52MHzの場合のみ)。 |

| 15                                | REFSEL   | DI  | リファレンス・クロックの選択。"0" = 外付け水晶振動子によるオンチップ発振器； "1" = 外部クロック入力。(LVTTL) |

| 17                                | TDINP    | AI  | 差動テスト・データ入力                                                      |

| 18                                | TDINN    | AI  | 差動テスト・データ入力                                                      |

| 20、47                             | VCC      | P   | デジタル電源                                                           |

| 21                                | CF1      | AO  | 周波数ループ・コンデンサ                                                     |

| 23                                | REFSEL1  | DI  | リファレンス周波数の選択、表II参照。(LVTTL)                                       |

| 24                                | REFSEL0  | DI  | リファレンス周波数の選択、表II参照。(LVTTL)                                       |

| 25                                | CF2      | AO  | 周波数ループ・コンデンサ                                                     |

| 30                                | RATE     | DI  | データ・レートの選択、表I参照。(LVTTL)                                          |

| 31                                | NC       | DI  | 未接続                                                              |

| 32                                | NC       | DI  | 未接続                                                              |

| 35、36                             | VCC      | P   | 出力ドライバ電源                                                         |

| 37                                | DATAOUTN | DO  | 差動タイミング補正済みデータ出力。(CML)                                           |

| 38                                | DATAOUTP | DO  | 差動タイミング補正済みデータ出力。(CML)                                           |

| 39                                | SQUELCH  | DI  | クロックおよびデータ出力のディスエーブル。アクトライブ・ハイ。(LVTTL)                           |

| 40                                | CLKOUTN  | DO  | 差動再生済みクロック出力。(CML)                                               |

| 41                                | CLKOUTP  | DO  | 差動再生済みクロック出力。(CML)                                               |

| 44                                | BYPASS   | DI  | CDRモードをバイパス。アクトライブ・ハイ。(LVTTL)                                    |

| 45                                | SDOUT    | DO  | LOS出力。アクトライブ・ハイ。(LVTTL)                                          |

| 48                                | LOOPEN   | DI  | テスト・データ入力をイネーブル。アクトライブ・ハイ。(LVTTL)                                |

タイプ : P = 電源、AI = アナログ入力、AO = アナログ出力、DI = デジタル入力、DO = デジタル出力

# ADN2811

図1. 出力タイミング

図2. LOSコンパレータ・トリップ・ポイントの設定

図3. シングル・エンド出力対差動出力の比較

## 用語の定義

### Max値、Min値、Typ値の仕様

各パラメータの仕様は、複数のウェハ・ロットからの複数のデバイスについて取得したデータを統計的に解析して導出します。Typ値仕様は、そのパラメータに対するデータ分布の平均値を意味します。パラメータがMax値(またはMin値)を持つ場合、値は分布の標準偏差の6倍を平均値に加算(または減算)して計算されます。この手順は、製造時のバラツキに対応することを目的にしています。平均値が標準偏差の1.5倍だけシフトしても、標準偏差値の4.5倍のマージンが残るため、3.4ppmのエラー・レートを維持することができます。データシート仕様を満たさないデバイスを出荷しないように、パラメータすべてについて、テストのバラツキも考慮してテスト規定値にマージンを持たせてあります。

### 入力感度と入力オーバードライブ

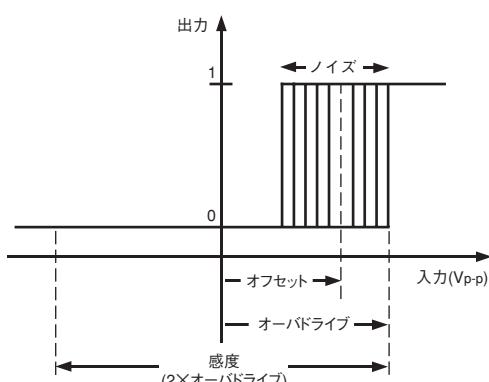

量子化回路の感度仕様とオーバードライブ仕様には、オフセット電圧、ゲイン、ノイズが含まれます。量子化回路のロジック出力とアナログ電圧入力との関係を図4に示します。十分大きな正の入力に対しては、ロジック出力は常にレベル1になります。同様に負の入力が十分大きければ、ロジック出力は常にレベル0になります。しかし、ロジックレベル0.1の判断は、定められた入力電圧レベルに厳密に判断されるのではなく、一定の幅があります。この、ある入力電圧レベルの幅域においては、出力レベルは1または0、または不定となります。この領域の幅は、量子化回路の入力電圧ノイズによって決定されます。この曖昧領域の中心は、量子化回路の入力オフセット電圧になります。入力オーバードライブは、 $1 \times 10^{-10}$ の確度で正確なロジック・レベルを保証するために必要な信号の振幅を意味します。

図4. 入力感度と入力オーバードライブ

### シングル・エンド対差動

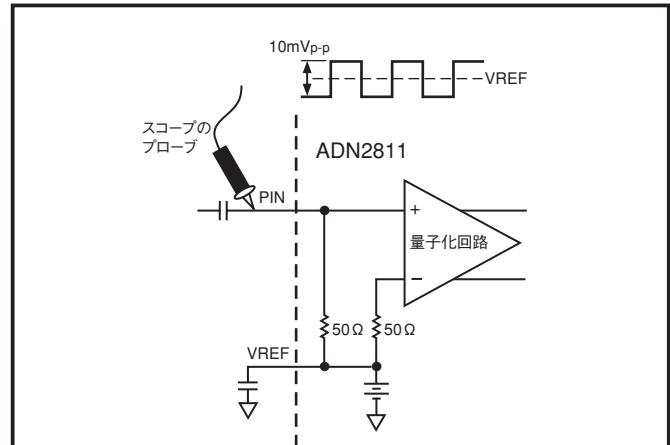

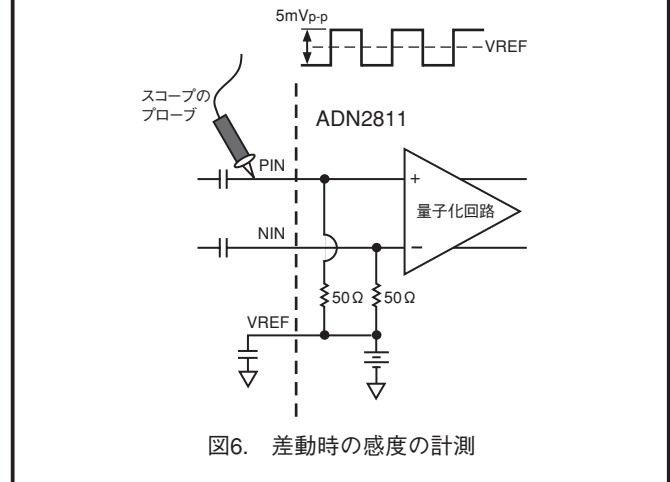

量子化回路入力の駆動には、通常AC結合が使用されます。入力は内部でコモン・モード電位約0.6VにDCバイアスされます。シングル・エンドでADN2811を駆動し、図5に示すポイントにオシロスコープのプローブを接続して量子化回路入力を観測すると、コモン・モード電位に等しい平均値を持ち、かつ平均値の上と下に瞬時値を持つバイナリ信号が観測されます。この信号のpeak-to-peak振幅を測定して、量子化回路感度の最小所要値を容易に求められます。図4では、正と負の両オフセットに対応できることが望ましいため、感度はオーバードライブの2倍になります。

図5. シングル・エンド時の感度の計測

図6. 差動時の感度の計測

ADN2811を差動で駆動すると(図6)、感度はオシロスコープのプローブを使った量子化回路入力の観測により改善されるように見えます。シングル・エンド・プローブを使用するので、このように見えてしまいますが、5mVp-p信号が、ADN2811の量子化回路を駆動しているように見えますが、シングル・エンド・プローブは信号の半分しか測定ていません。他方の量子化回路入力には観測している信号の相補信号が入力されているため、真の量子化回路入力信号はこの値の2倍になります。

### LOS応答時間

LOS応答時間の定義は、入力信号が無くなつてからSDOUTに信号喪失表示(LOS)が表示されるまでの遅延時間です。入力がDC結合の場合、ADN2811のLOS応答時間は300ns (typ)です。実際には、量子化回路入力のAC結合部分の時定数がLOS応答時間を決定します。

# ADN2811

## ジッタ仕様

ADN2811 CDRは最良のビット・エラー・レート(BER)性能を得るよう設計されているため、Telcordia Technologiesで規定されたSONET/SDH装置に対するジッタの発生、伝達、耐性の仕様より優れています。

ジッタはデジタル信号エッジの長時間平均位置からの動的な変位を意味し、UI (Unit Interval)単位で表されます。(ここで、1 UI = 1ビット周期です) 入力データのジッタは、再生されたクロックのサンプリング・エッジの動的な位相誤差から発生することがあります。再生クロックのジッタにより、タイミング調整済みデータにジッタが発生します。

以下に、装置レベルでの光インターフェースに対するTelcordia仕様(2000年9月のGR-253-CORE、Issue 3)に基づく、ジッタの発生、伝達、耐性の仕様と、これらの仕様に関するADN2811の性能について簡単にまとめます。

## ジッタの発生 (Jitter Generation)

ジッタ発生仕様は、入力にジッタと変動が入力されていないデバイスによって発生されるジッタの大きさを規定します。OC-48デバイスに対するバンドパス・フィルタは、12kHzのハイパス・カットオフ周波数、20dB/ディケードのロールオフ、最低でも20MHzのローパス・カットオフ周波数を持ちます。発生するジッタは0.01 UI rms未満、かつ0.1 UI p-p未満でなければなりません。

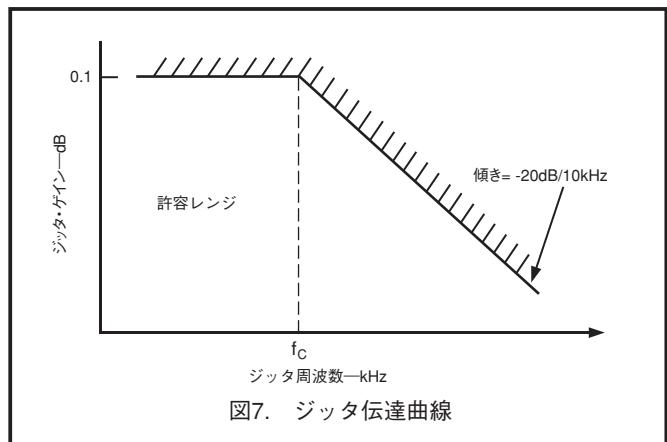

## ジッタ伝達 (Jitter Transfer)

ジッタの伝達関数は、各周波数について、入力信号に加えられたジッタに対する出力信号のジッタの比で表されます。このパラメータは、入力信号から出力信号へ伝達されるジッタの大きさを表します(図7参照)。

図7. ジッタ伝達曲線

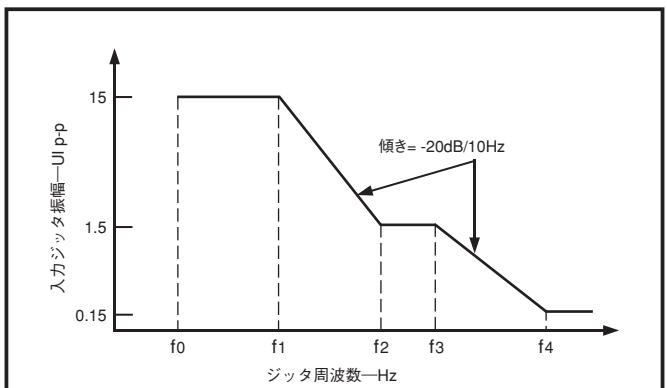

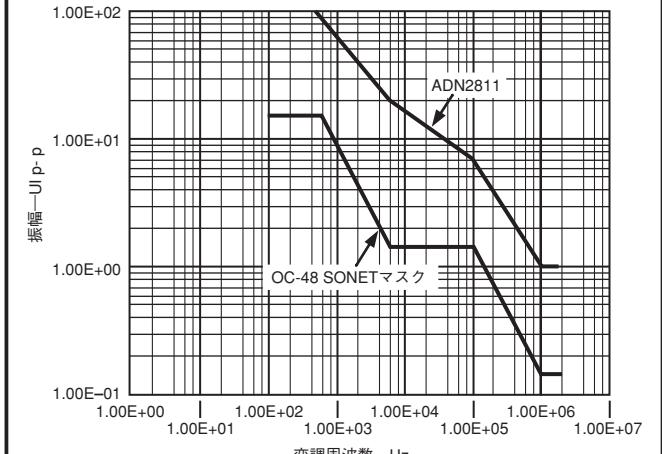

## ジッタ耐性 (Jitter Tolerance)

ジッタ耐性は、パワーが1dB不利になるように入力信号に加えられる、発生させる正弦波ジッタの振幅(p-p)として規定されます。これは、動作条件下でさらにペナルティが追加されないことを確認することを目的としたストレステストです(図8参照)。図9に、ADN2811の主なOC-48ジッタ耐性性能を示します。

図8. SONETのジッタ耐性マスク

図9. OC-48のジッタ耐性曲線

## 動作原理

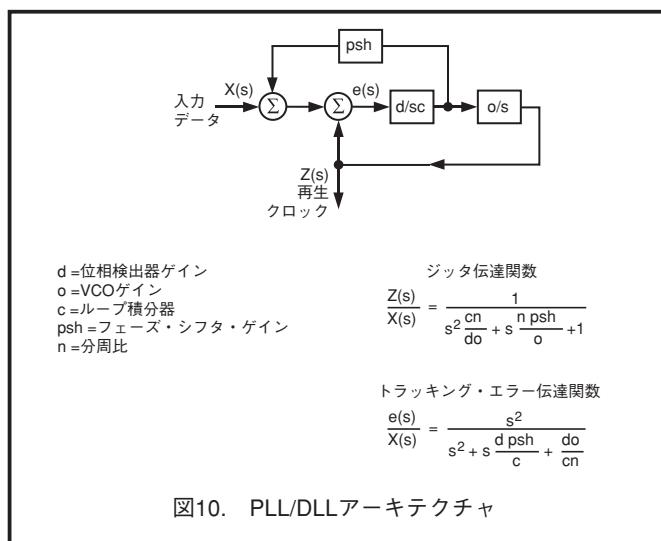

ADN2811は、NRZ符号データ・ストリームから取り出したデータに対してクロックの再生とタイミング調整を行うためのDLL(Delay Locked Loop)およびPLL(Phase Locked Loop)回路です。共通の制御電圧を使用する2つの独立した帰還ループにより入力データ信号の位相を追跡します。高速なDLLパスは電圧制御フェーズ・シフタを使って入力ジッタの高周波数成分を追跡します。VCOで構成される各フェーズ制御ループは、入力ジッタの低周波数成分に追従します。VCOの初期周波数は、3番目のループによって設定されます。このループはVCO周波数とリファレンス周波数を比較して、大ざっぱにチューニング電圧を設定します。ジッタ追跡用のPLLは、チューニングの微調整により、VCOを制御します。

DLLおよびPLLはともに、入力データ信号の位相に追従します。例えば、クロックが入力データに遅れている場合は、位相検出器がVCOを高い周波数に駆動し、フェーズ・シフタを使って遅延を大きくします。この2つの動作により、クロックとデータの間の位相誤差が小さくなります。クロックが高速になると位相が進みますが、データが遅延すると位相が遅れます。ループ・フィルタは積分器なので、静的な位相差ではなくゼロに駆動されます。

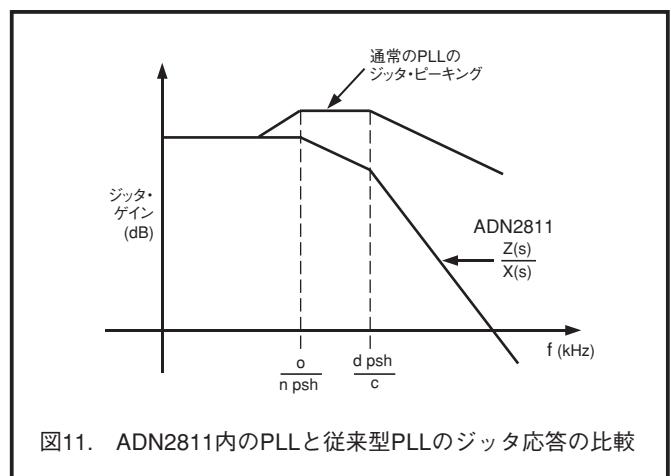

フェーズ・シフタは2次PLLの周波数補償に必要とされるゼロ点を構成する回路と見ることもでき、ゼロ点は帰還バス内に配置されるため、クローズ・ループ伝達関数内には現れません。従来型の2次PLLにおけるジッタ・ピーキングは、クローズ・ループ伝達関数内のゼロ点が原因で発生します。この回路はクローズ・ループ伝達関数内にゼロ点を持たないため、ジッタ・ピーキングは最小になります。

DLLおよびPLLを組み合わせると、広帯域のジッタ耐性と狭帯域ジッタ・フィルタリング機能を同時に提供できます。このジッタ伝達関数 $Z(s)/X(s)$ が優れたフィルタ機能を持つ、2次ローパスであることを、図10に示します。通常の2次PLLとは異なり、このジッタ伝達関数にはゼロ点がないことに注意してください。これは、メインPLLループのジッタ・ピーキングが小さいことを意味します(図11参照)。つまりADN2811は、ジェネレータに直列に接続されたジッタ・ピーキングにより致命的なジッタ累積が発生してしまうような信号再生アプリケーションに最適です。

図10. PLL/DLLアーキテクチャ

エラー伝達関数 $e(s)/X(s)$ は、通常のPLLと同じハイパス特性を持っています。ジッタ伝達関数 $Z(s)/X(s)$ が狭帯域ジッタ・フィルタ機能を持っているため、この伝達関数は優れた広帯域ジッタ許容量を持つように自由に最適化することができます。

DLLおよびPLLは、全体のジッタ許容量に寄与します。ループ・フィルタ内の積分器は、データ信号上の入力ジッタの低周波成分に対して高いゲインを持ち、小さい位相誤差で大きなジッタ振幅に追跡します。この場合、VCOが周波数変調され、ジッタは通常のPLLと同じように追跡されます。追跡可能な低周波ジッタの大きさは、VCOチューニング範囲の関数になります。チューニング範囲を広げると、低周波ジッタ許容量は大きくなります。小さいフェーズ・エラーの内部ループ制御電圧は小さいため、フェーズ・シフタはチューニング範囲の中央付近に留まるので、低周波ジッタ許容量にはほとんど寄与しません。

中周波のジッタ周波数では、VCOのゲインとチューニング範囲は入力ジッタを追跡できるほど大きくありません。この場合、VCO制御電圧は大きくなりやがて飽和するので、VCO周波数はチューニング範囲の上限または下限に留まります。したがって、VCOチューニング範囲の大きさは、ジッタ許容量に対してほとんど影響しません。ここではDLLの制御電圧が大きいので、フェーズ・シフタ側が入力ジッタの追跡を担うことになります。UIで表したフェーズ・シフタ範囲は、ジッタ許容量曲線上で広い平坦部として表されます。フェーズ・シフタのチューニング範囲は、すべてのデータ・レートで最低2 UIです。

ループ積分器のゲインは高いジッタ周波数に対しては小さくなるため、フェーズ・シフタの範囲を調節するのに十分大きいループ制御電圧を得るには、大きな位相差が必要になります。高いジッタ周波数で位相エラーは致命的です。この領域では、積分器のゲインがジッタ許容量を決定します。ループ積分器のゲインは周波数に比例して小さくなるため、高いジッタ周波数に対してジッタ許容量が小さくなります。最も高い周波数では、ループ・ゲインが非常に小さくなるため、フェーズ・シフタのチューニング効果はほとんど期待できません。この場合、ジッタ許容量は入力データのアイ・パターン、静的な位相誤差、残留ループ・ジッタ生成によって決定されます。この領域でのジッタ許容量は約0.5 UIです。負の傾きと平坦領域との間の境界の周波数は、DLLの閉ループ帯域幅を表し、約5MHzになります。

# ADN2811

## 機能説明

### クロックおよびデータの再生

ADN2811は、OC-48および15/14 FECのレートを持つシリアル・ビット・ストリームからクロックとデータを再生します。データ・レートはRATE入力を使って選択します(表I参照)。

表I. データ・レートの選択

| RATE | データ・レート   | 周波数(MHz) |

|------|-----------|----------|

| 0    | OC-48     | 2488.32  |

| 1    | OC-48 FEC | 2666.06  |

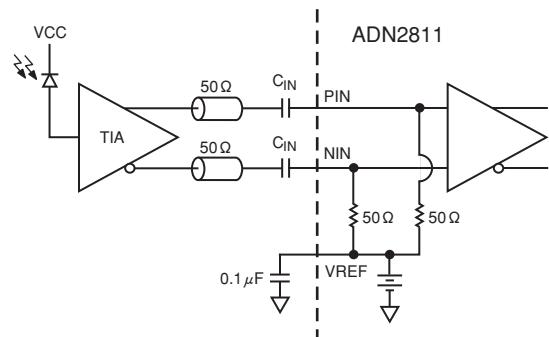

### リミッティング・アンプ

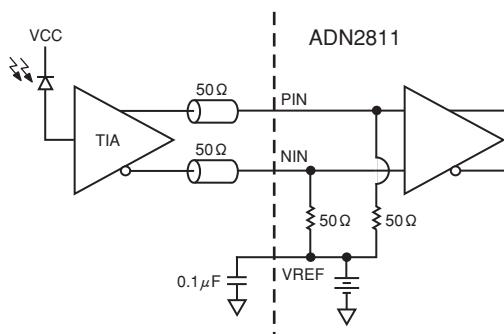

リミッティング・アンプは差動入力(PIN/NIN)を持っており、 $50\Omega$ で内蔵電圧リファレンスに内部終端されています( $VREF = 0.6V$  typ)。入力コンモン・モード電圧が $0.4V$ より大きい場合にはDC結合も可能ですが、一般にはAC結合されます(図20～図22)。入力オフセットは、最小ドリフトで $4mV$  (typ)以上の感度を持つように出荷時に調整されています。制限アンプは差動またはシングル・エンドで駆動することができます。

### スライス調整

SLICEP/N入力に $\pm 0.8V$ の差動電圧入力を加えることにより、量子化回路のスライス・レベルに $\pm 100mV$ のオフセットを与えて、自己放射(ASE)ノイズ増幅の影響を緩和することができます。スライス・レベルの調整が不要な場合は、SLICEP/NをVCCに接続する必要があります。

### LOS(Loss of Signal)の検出

レシーバのフロントエンド・レベル信号検出回路を使うと、入力信号レベルがユーザーが設定するしきい値を下回ったこと(LOS)を表示できます。しきい値は、ピン1(THRADJ)とGNDの間に1本の外部抵抗を接続して設定します。LOSコンパレータのトリップ・ポイントと抵抗値の関係を図2に示します(SLICEP = SLICEN = VCCの場合にのみ有効)。ADN2811への入力レベルが設定されたLOSしきい値を下回ると、SDOUT(ピン45)にロジック1が出力されて、信号喪失状態が表示されます。LOS応答時間は約300nsに設計されていますが、AC結合アプリケーションでのRC時定数によって支配されます。

LOS検出回路を使用するときは、両方の量子化回路スライス調整ピンをVCCに接続します。これは、LOSしきい値レベルとの干渉を防止するためです。

注)LOSとスライス調整を同時に使用することは想定されておりません。すなわち、光アンプを使うシステムではASEを回避するためにスライス調整が必要になりますが、光アンプを使う光リンクでLOSが発生すると、光アンプ出力がフルスケール・ノイズになってしまいます。この条件下では、LOSは故障を検出できません。この場合、CDR回路がフルスケール・ノイズの信号にロックできないため、LOLで故障を表示することができます。

### リファレンス・クロック

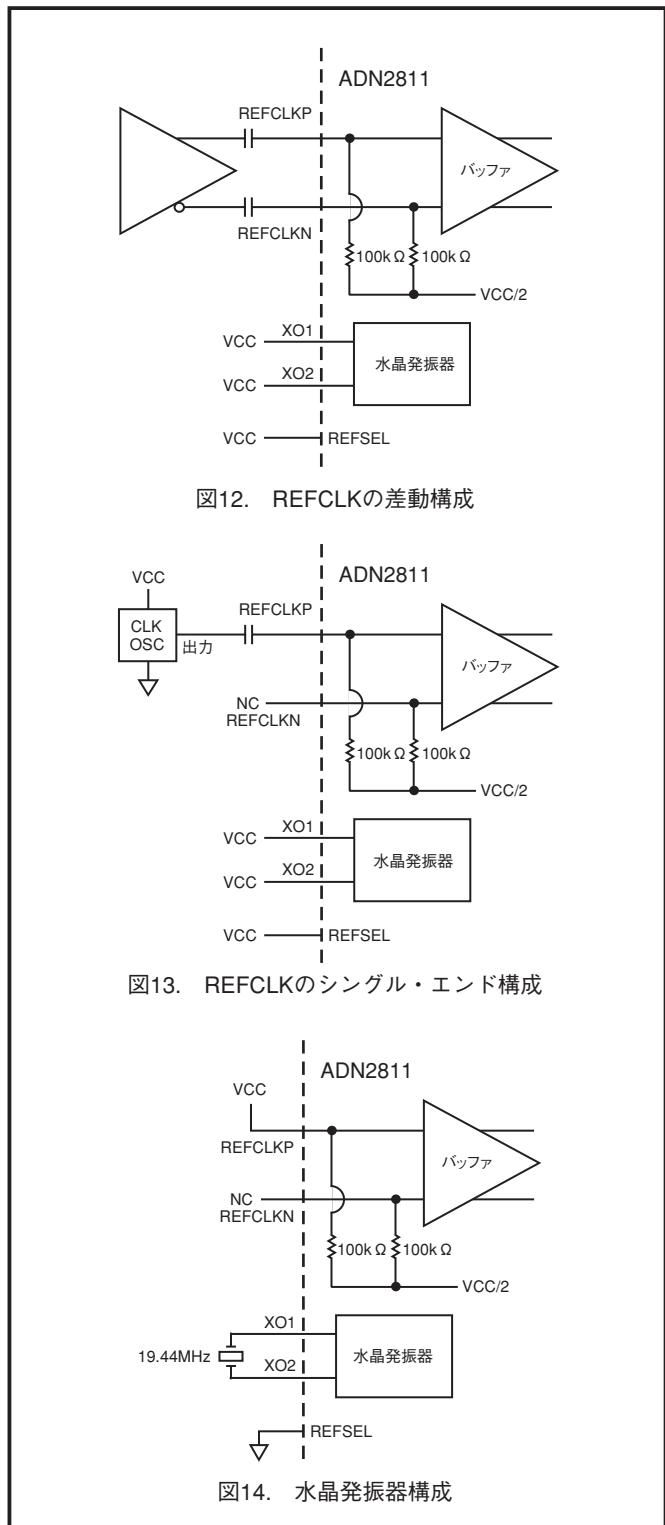

ADN2811にリファレンス周波数を提供する方法としては、差動クロック、シングル・エンド・クロック、クリスタル・オシレータの3つのオプションがあります。図12～図14に、構成例を示します。

ADN2811には、リファレンス・クロック周波数として、LVTTL/LVCMS/LVPECL/LVDSレベルでは $19.44MHz$ 、 $38.88MHz$ 、

$77.76MHz$ を、LVPECL/ LVDSレベルでは $155.52MHz$ を、それぞれデータ・レートに無関係にREFCLKN/P経由で入力できます。入力バッファには、 $100mV$ 以上のpeak-to-peak差動振幅を持つ任意の差動信号(例えば、LVPECL/LVDS)または標準のシングル・エンド低電圧TTLを入力することができるので、システムの柔軟性が最大になります。表IIに従い、REFSEL0/1ピンを使って該当する分周比を選択することができます。リファレンス・クロックのフェーズ・ノイズとデューティ・サイクルはクリティカルではなく、 $100ppm$ の精度で十分です。

REFCLKN/P入力の代わりに、外付けの水晶発振器と組み合わせて使用する発振器も内蔵されています。水晶発振器の推奨仕様の詳細を表IIIに示します。

表II. リファレンス周波数の選択

| REFSEL | REFSEL[1..0] | 入力リファレンス周波数 (MHz)                                                           |

|--------|--------------|-----------------------------------------------------------------------------|

| 1      | 00           | 19.44                                                                       |

| 1      | 01           | 38.88                                                                       |

| 1      | 10           | 77.76                                                                       |

| 1      | 11           | 155.52                                                                      |

| 0      | XX           | REFCLKP/Nは非アクティブ。<br>ピンXO1、XO2に19.44MHz<br>のXTAL発振器を接続<br>(REFCLKPはVCCに接続)。 |

表III. 必要な水晶発振器仕様

| パラメータ      | 部品定数                 |

|------------|----------------------|

| モード        | 直列共振                 |

| 周波数／全体の安定性 | 19.44MHz $\pm$ 50ppm |

| 周波数精度      | $\pm$ 50ppm          |

| 温度安定性      | $\pm$ 50ppm          |

| エージング      | $\pm$ 50ppm          |

| ESR        | 20Ω max              |

推奨メーカー：

Raltron (305) 593-6033

製品番号：H10S-19.440-S-EXT-AD1

REFCLKN/P入力がアクティブのときは、必ずREFSELをVCCに接続します。また、発振器を使用するときは、必ずREFSELをVEEに接続します。XO端子とREFCLK入力の接続は不要です(図12～図14参照)。水晶発振器は外部寄生容量に強い直列共振モードで動作する必要があることに注意してください。トリマー・コンデンサは不要です。

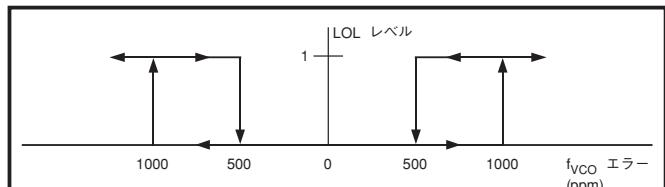

#### ロック検出器の動作

ロック検出器はVCOとリファレンス・クロックとの間の周波数差を監視して、VCOが中心周波数からのエラーが500ppm以内に入ると、LOLのアサートを解除します(図15参照)。この動作により、フェーズ・ループがイネーブルされ、VCO周波数が残りの分だけ引き込まれ、フェーズ・ロックも開始されます。ロックした後に、入力周波数誤差が1000ppm (0.1%)を超えると、LOLが再アサートされて、周波数ループに制御が戻されます。この動作により、フェーズが再度ロックされて出力では安定したクロック信号が維持されます。

図15. LOLの伝達関数

この周波数ループは、CF1とCF2の間に外付けコンデンサが1つ必要です。コンデンサの仕様を表IVに示します。

表IV. 推奨C<sub>f</sub>コンデンサ仕様

| パラメータ | 部品定数          |

|-------|---------------|

| 温度範囲  | -40°C ~ +85°C |

| 容量    | >3.0 μF       |

| リーカー  | <80nA         |

| 定格    | >6.3V         |

推奨メーカー：

Murata Electronics (770) 436-1300

製品番号：GRM32RR71C475LC01

#### スケルチ・モード

スケルチ入力にTTLハイレベル状態を入力すると、クロック出力とデータ出力がゼロ状態に設定されて、それより下流の処理を停止させます。必要に応じて、このピンに直接LOS検出器出力SDOUTを入力することができます。スケルチ機能が不要な場合は、このピンをVEEに接続しておきます。

#### テスト・モード：バイパスとループバック

バイパス入力にTTLハイレベル状態を入力すると、量子化回路出力がデータ出力ピンを駆動するバッファに直接接続されるため、CDR回路がバイパスされます(図16)。この機能は、非標準のビット・レートを扱うシステムに便利です。

LOOPENピンにTTLハイレベル状態を入力するとループバック・モードが開始されるので、システム診断テストに使うことができます。この動作により、テスト入力(TDINP/N)がCDR回路に接続されます(図16)。テスト入力には内蔵の50Ωの終端抵抗が接続されており、未使用時にフロー状態にしておくことができます。TDINP/NはCML入力であるため、CML出力から駆動する場合はAC結合はできません。TDINP/N入力をCML出力以外から駆動する場合はAC結合にならなければなりません。バイパス・モードとループバック・モードは互いに排他的で、1度にどちらか1つのモードしか使用できません。BYPASSピンとLOOPENピンが同時にロジック1に設定されると、ADN2811は不定状態になります。

# ADN2811

図16. テスト・モード

## アプリケーション情報

### PCBデザインのガイドライン

最適性能を得るには、正しいRF PCBデザイン技術の使用が必要です。

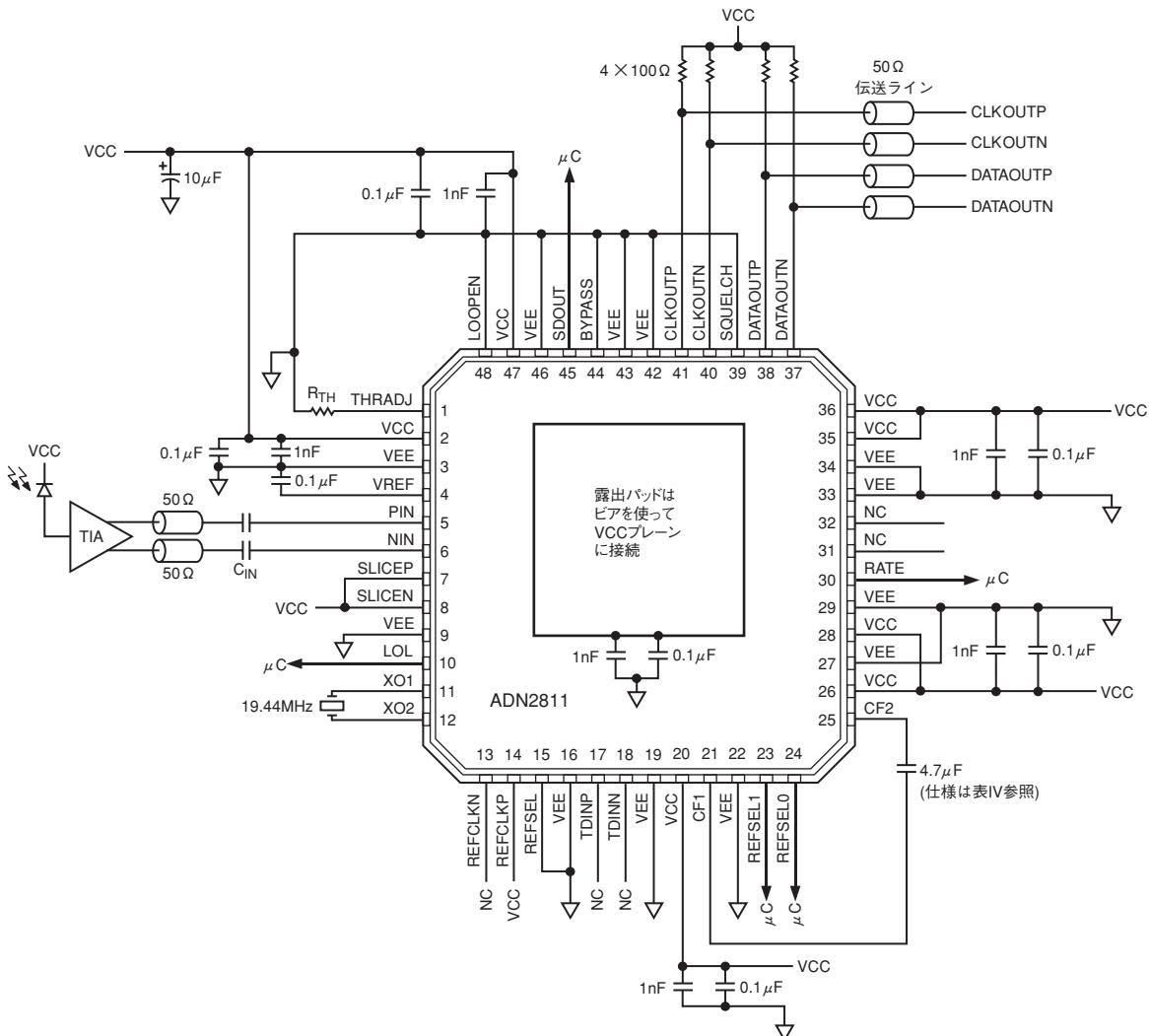

### 電源接続とグラウンド・プレーン

アナログ・グラウンドとデジタル・グラウンドのどちらにも、低インピーダンスのグラウンド・プレーンが推奨されます。VEEピンはグラウンド・プレーンに直接ハンダ付けして、直列インダクタンスを減らす必要があります。グラウンド・プレーンが内部プレーンで、かつグラウンド・プレーンへの接続をビアを使って行う場合は、複数のビアを並列に使用して直列インダクタンスを減らす必要があります(特に、出力バッファへのグラウンド・リターンを構成する33番端子と34番端子)。

3.3V電源がPCBへ入力される場所に、VCCとGNDの間に $10\mu F$ の電解コンデンサを接続することを推奨いたします。ADN2811のVCC端子のできるだけ近くの、IC電源VCCとGNDの間には、 $0.1\mu F$ と $1nF$ のセラミック・チップ・コンデンサを接続する必要があります。ここでも、電源とグラウンドへの接続をビアを介して行う場合は、複数のビアを並列に使用すると、直列インダクタンスの減少に役立ちます(特に、高速なCLKOUTP/NとDATAOUTP/N出力バッファに電源を供給する35番端子と36番端子)。推奨接続については、図17の回路図を参照してください。

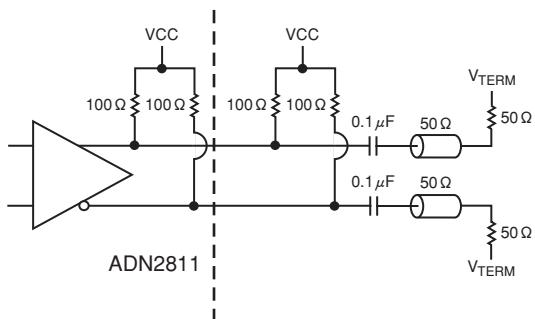

### 送信ライン

PIN、NIN、CLKOUTP、CLKOUTN、DATAOUTP、DATAOUTN(155.2MHzのREFCLKに対するREFCLKPとREFCLKN)など、すべての高周波入力および出力信号には、反射を削減するため $50\Omega$ の伝送ラインを使用しなくてはなりません。PIN/NIN入力のパターン

長さは一致している必要があります。また、CLKOUTP/NとDATAOUTP/N出力のパターン長さも一致していなくてはなりません。すべての高速CML出力(CLKOUTP/NとDATAOUTP/N)に対しても、出力端子とVCCの間に $100\Omega$ のバック・ターミネーションチップ抵抗を接続する必要があります。これらの抵抗はできるだけ出力端子の近くに配置する必要があります。これらの $100\Omega$ 抵抗はオンチップの $100\Omega$ 終端抵抗と並列に接続して、 $50\Omega$ バック・ターミネーションを構成します(図18)。

高速入力(PINとNIN)は、 $50\Omega$ で内部リファレンス電圧に内部終端されています(図19)。VREF(ピン4)とGNDの間に $0.1\mu F$ のコンデンサを接続して、入力に対するACグラウンドを用意することが推奨されます。

すべての高速ミックス・シグナル・デザインと同様に、すべての高速デジタル・パターンは敏感なアナログ・ノードから遠ざけるように注意する必要があります。

### チップスケール・パッケージに対するハンダ付けのガイドライン

48ピンLFCSPのランドは長方形です。これに対するプリント基板のパッドは、パッケージのランド長より $0.1mm$ 長く、かつパッケージのランド幅より $0.05mm$ 広くし、ランドの中心はパッドの中心にある必要があります。これは、ハンダ接続部のサイズを最大にするために必要です。チップスケール・パッケージの底部には、中央に露出パッドがあります。プリント回路ボード上のパッドは、少なくともこの露出パッドと同じ大きさが必要です。この露出パッドはアナログVCCに接続する必要があります。ビアを使用する場合は、 $1.2mm$ ピッチ・グリッドのパッドに使用する必要があります。ビアの直径は $0.3mm \sim 0.33mm$ で、ビア・パレルは $1 oz.$ の銅でメッキして、ビアを構成する必要があります。

図18. AC結合の出力構成

図19. AC結合の入力構成

# ADN2811

## AC結合コンデンサの選択

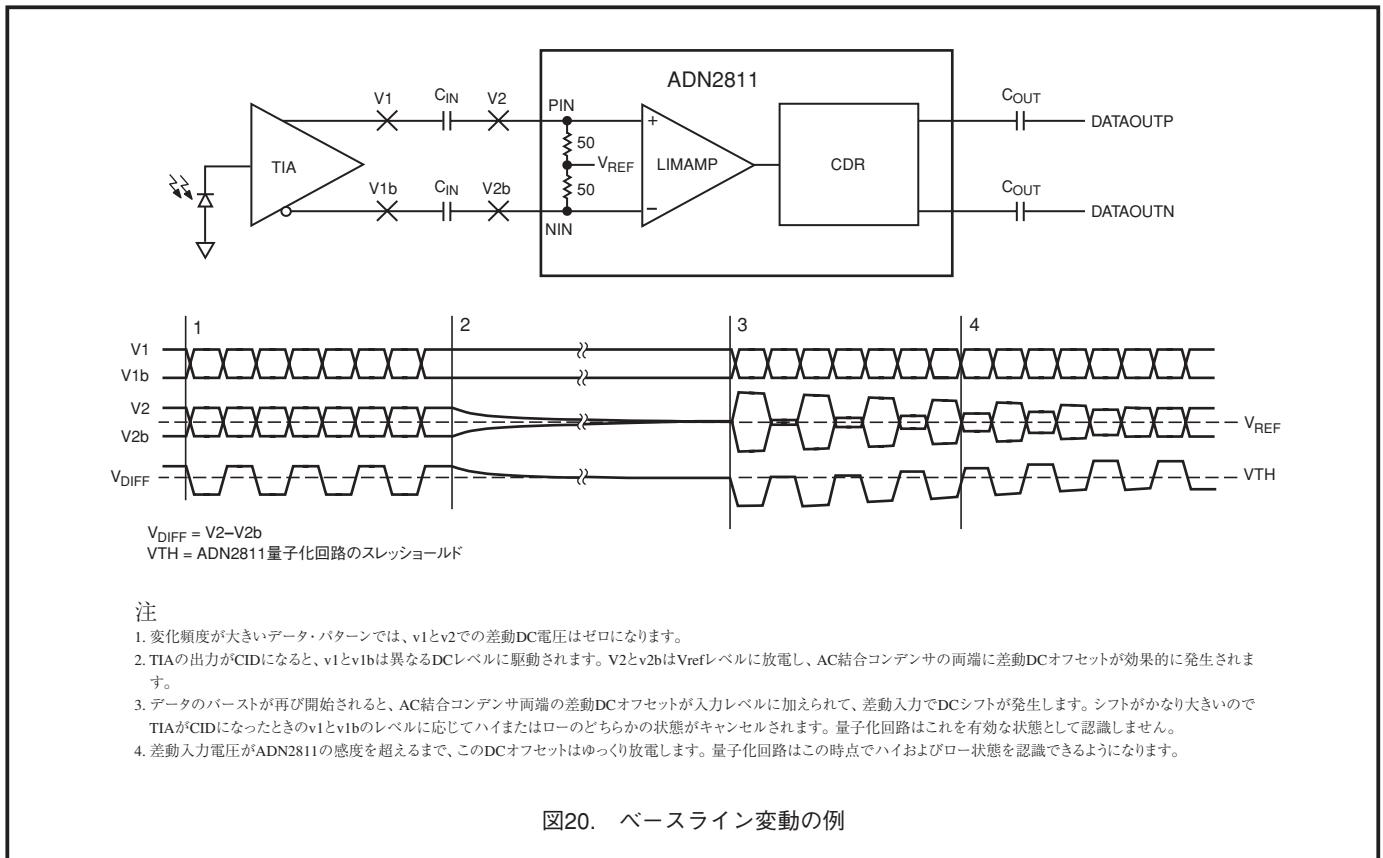

ADN2811の入力(PIN、NIN)と出力(DATAOUTP、DATAOUTN)のAC結合コンデンサの選択は、慎重に行う必要があります。コンデンサを選択するときは、信号バス内に2個の50Ω抵抗で構成される時定数を考慮する必要があります。多くの連続するCID(Consecutive Identical Digits)が入力されると、コンデンサ電圧はベースライン変動に起因して低下するため(図20)、パターンに依存するジッタ(PDJ)が発生します。

OC-48の速度でADN2811が安定して動作するには、PIN/NINに最小0.1μFのコンデンサを、またDATAOUTP/ DATAOUTNに0.1μFを使う必要があります。これは、1000CIDに耐え、かつPDJを0.01 UI p-pに抑えるという仮定から算出されています。

## DC結合アプリケーション

ADN2811の入力をDC結合することもできます。CIDの期間が長くベースライン変動が許容できないバースト・モード・アプリケーションでは、DC結合が必要になります。ADN2811の入力をDC結合する際は、ADN2811の入力範囲条件とコモンモード・レベル条件を満たすように注意する必要があります(図21~図23)。DC結合で、かつTIAの出力レベルが図22と図23に示すレベルを満たさない場合は、TIA出力とADN2811入力との間にレベル・シフトおよび/または減衰器が必要になります。

図21. DC結合入力構成

### 入力データ喪失時のLOLのトグル

光リンクの切断(あるいは何らかの理由)により入力データ・ストリームが喪失した場合、ADN2811のクロック出力は、有効なリファレンス・クロックが存在する限り、VCO中心周波数の1000ppm以内に留まります。LOL端子は、数kHzのレートでトグルします。これは、LOL端子がロジック1とロジック0の間でトグルすると同時に、周波数ループとフェーズ・ループとの間でVCO制御がやり取りされるためです。次に以下の動作が続きます。

- ・ADN2811が入力データ・ストリームにロックされます。LOL = 0。

- ・リンクの断線で入力データ・ストリームが喪失します。周波数誤差が1000ppmより大きくなるまでVCO周波数のドリフトが続けます。VCOの制御が周波数ループに戻されたとき、LOLがロジック1にアサートされます。

- ・周波数ループが中心周波数の500ppm以内にVCOを戻します。VCOの制御がフェーズ・ループに戻されて、LOLはロジック0に設定されます。

- ・フェーズ・ループはロックしようとしていますが、入力データが存在しないのでVCO周波数がドリフトします。

- ・周波数誤差が1000ppmを超えるまで、VCO周波数がドリフトします。VCOの制御が周波数ループに戻されたとき、LOLがロジック1にアサートされます。有効な入力データ・ストリームが再入力されるまで、この動作が繰り返されます。

図22. 最小許容DC結合入力レベル

図23. 最大許容DC結合入力レベル

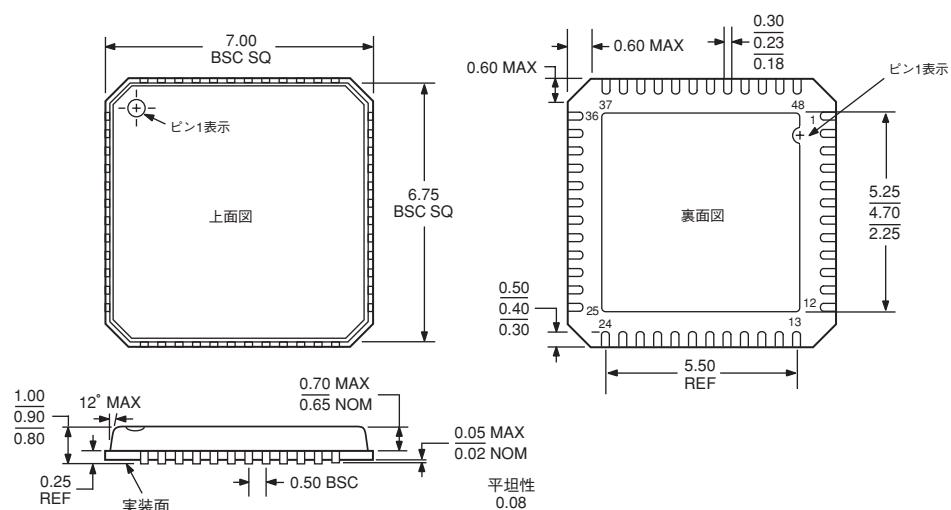

## 外形寸法

48ピン・フレーム・チップ・スケール・パッケージ[LFCSP]

7mm×7mmボディ

(CP-48)

寸法表示：mm

JEDEC標準MO-220-VKKD-2に準拠