ADES1754/ADES1755/ADES1756

## 14 チャンネル高電圧 データ・アクイジション・システム

### 概要

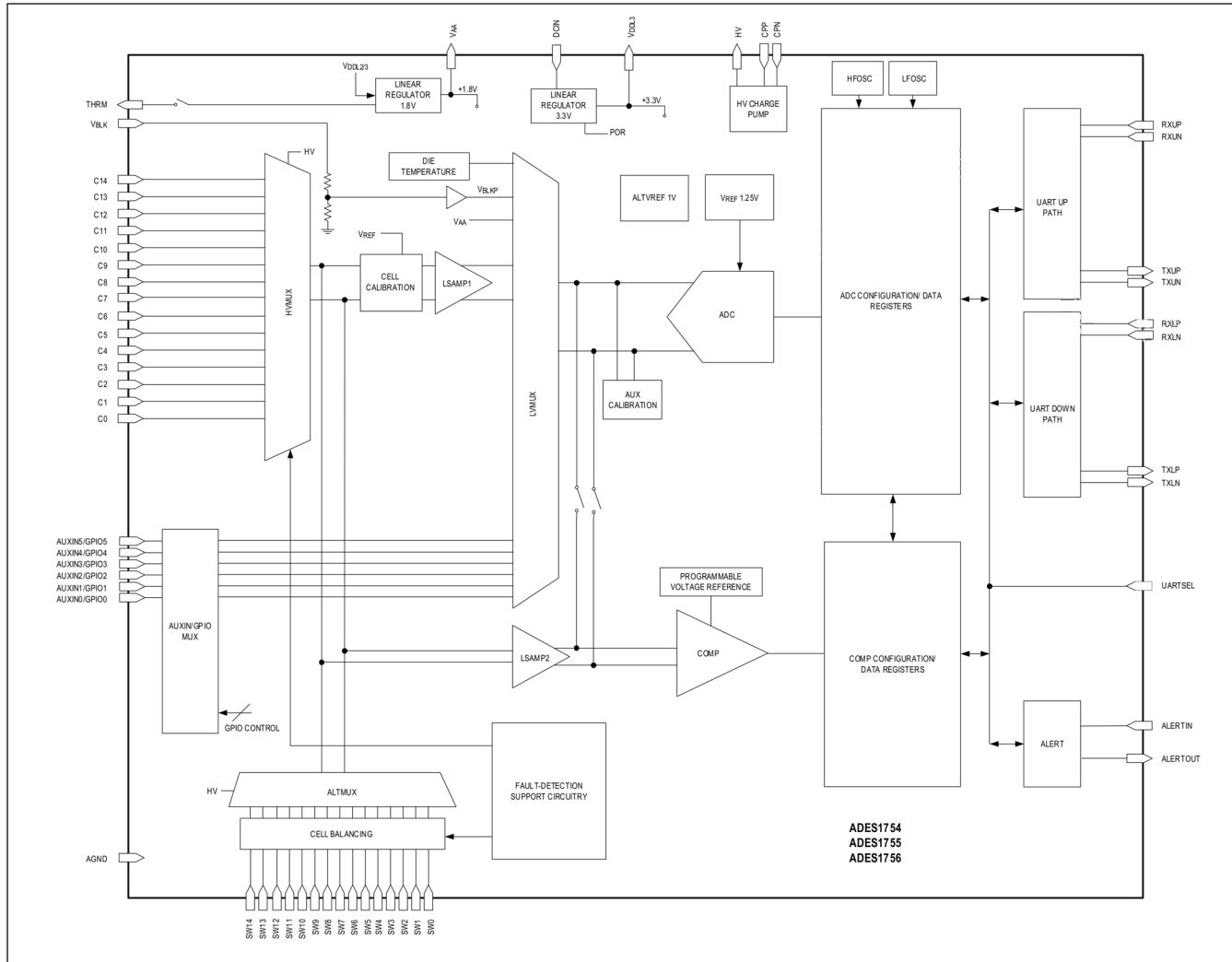

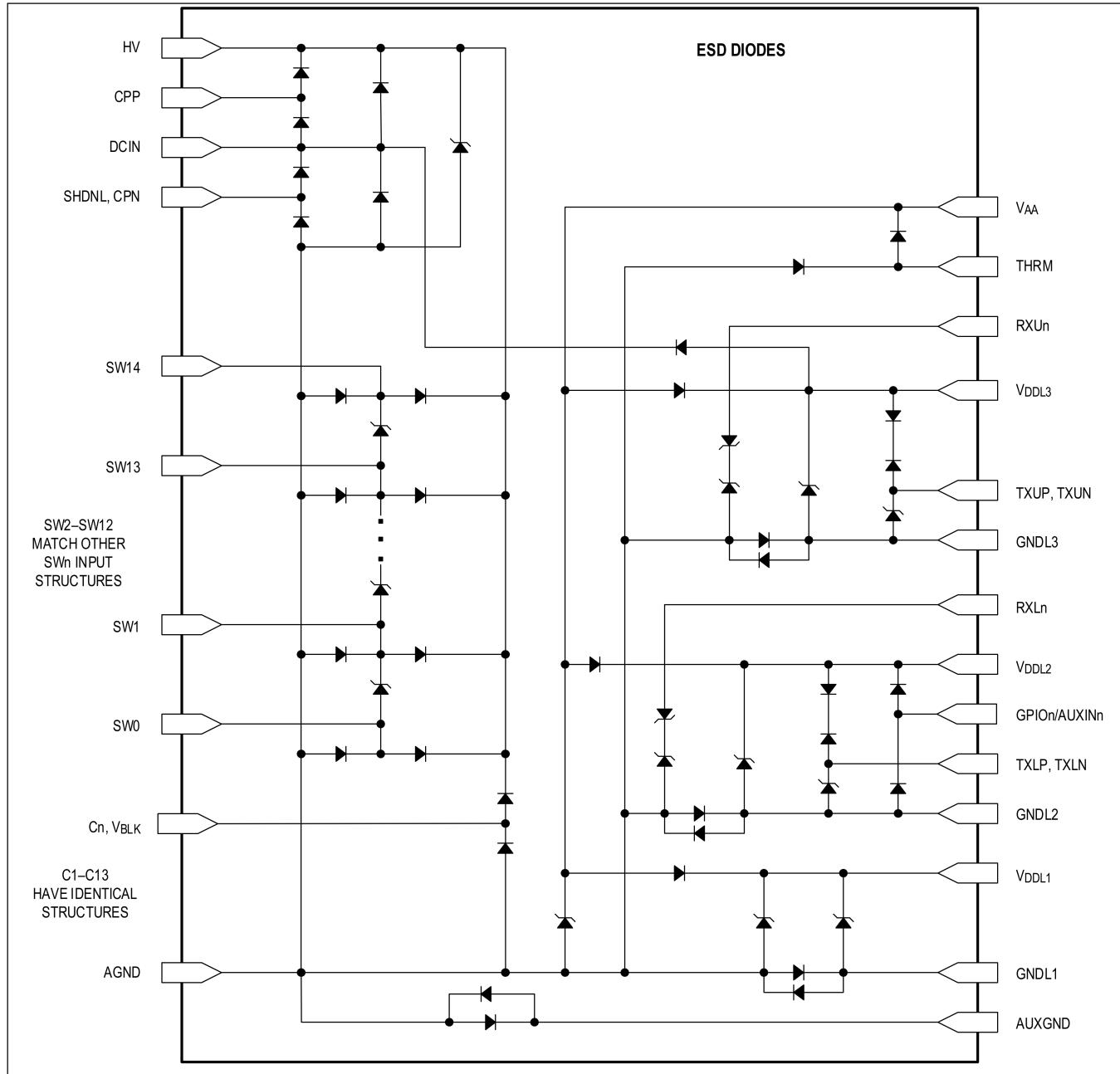

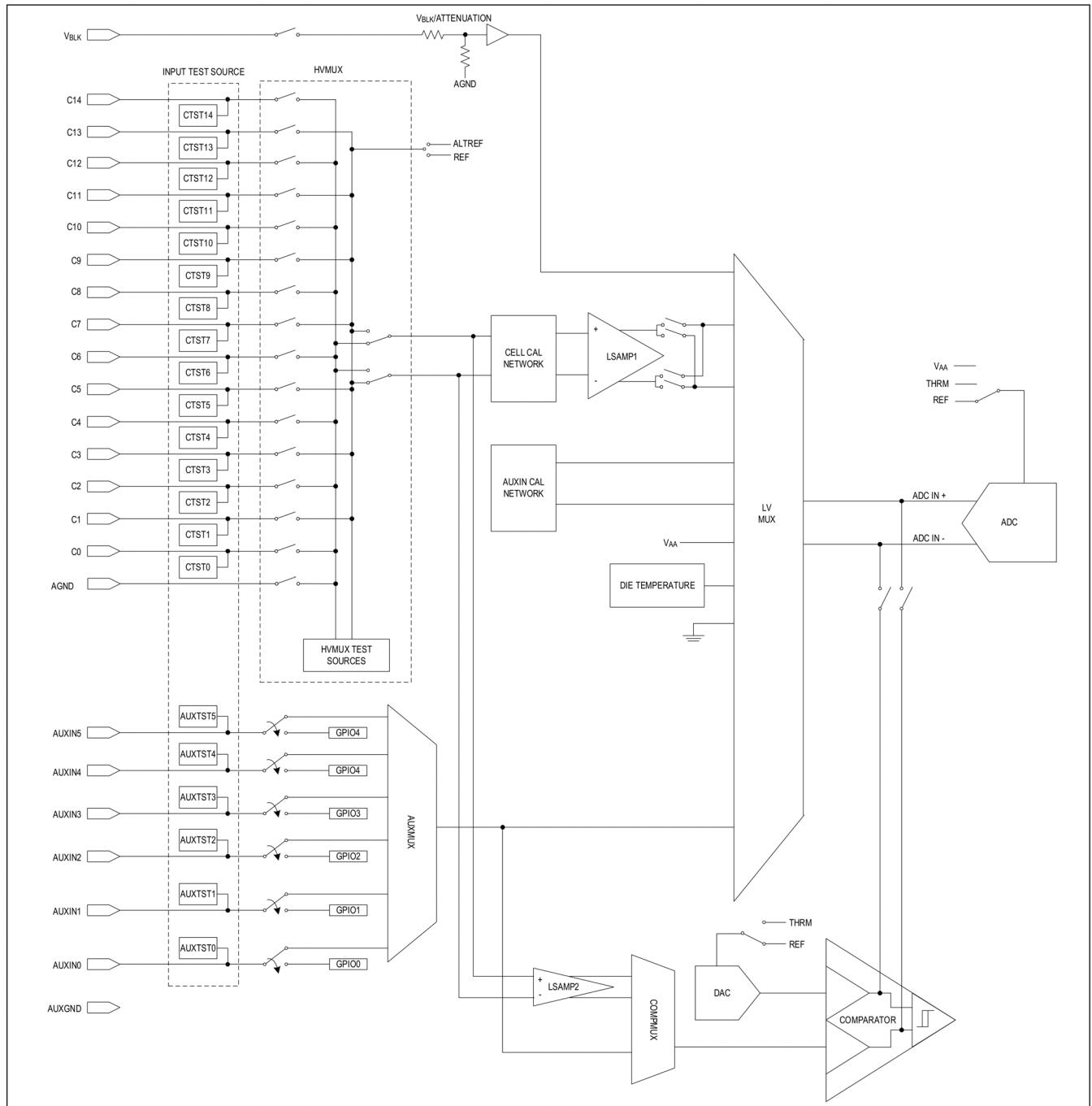

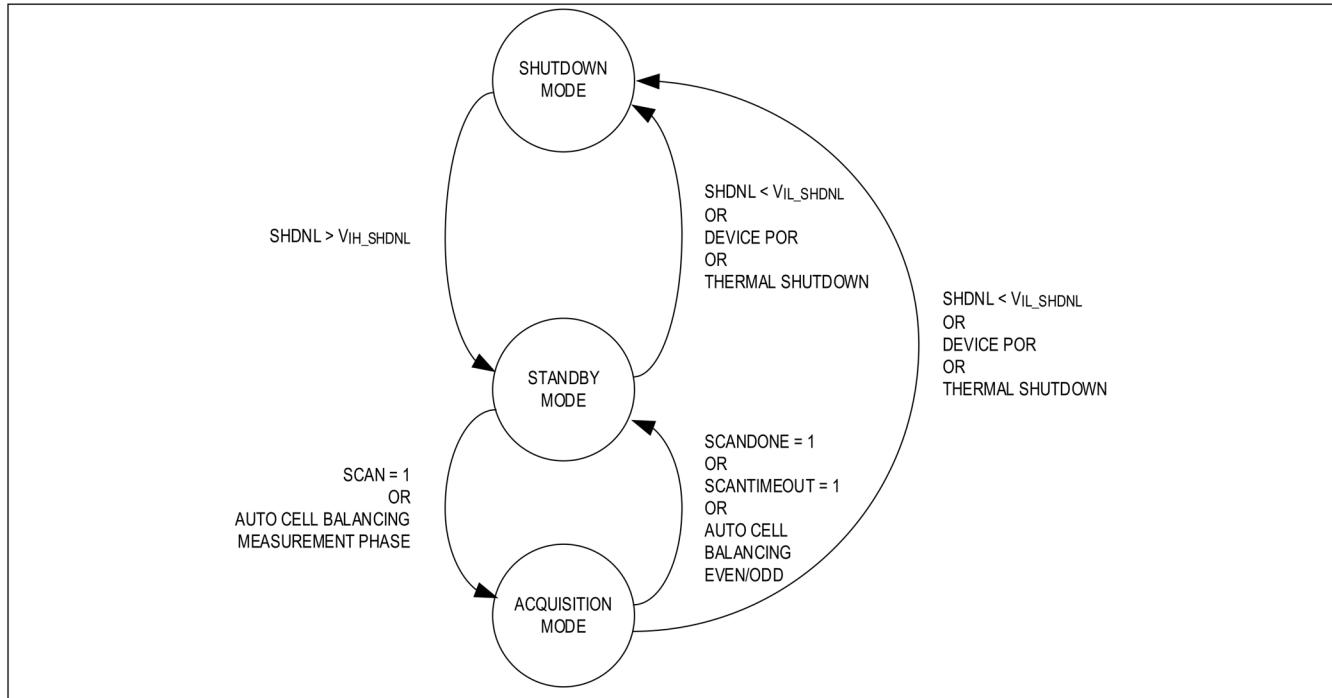

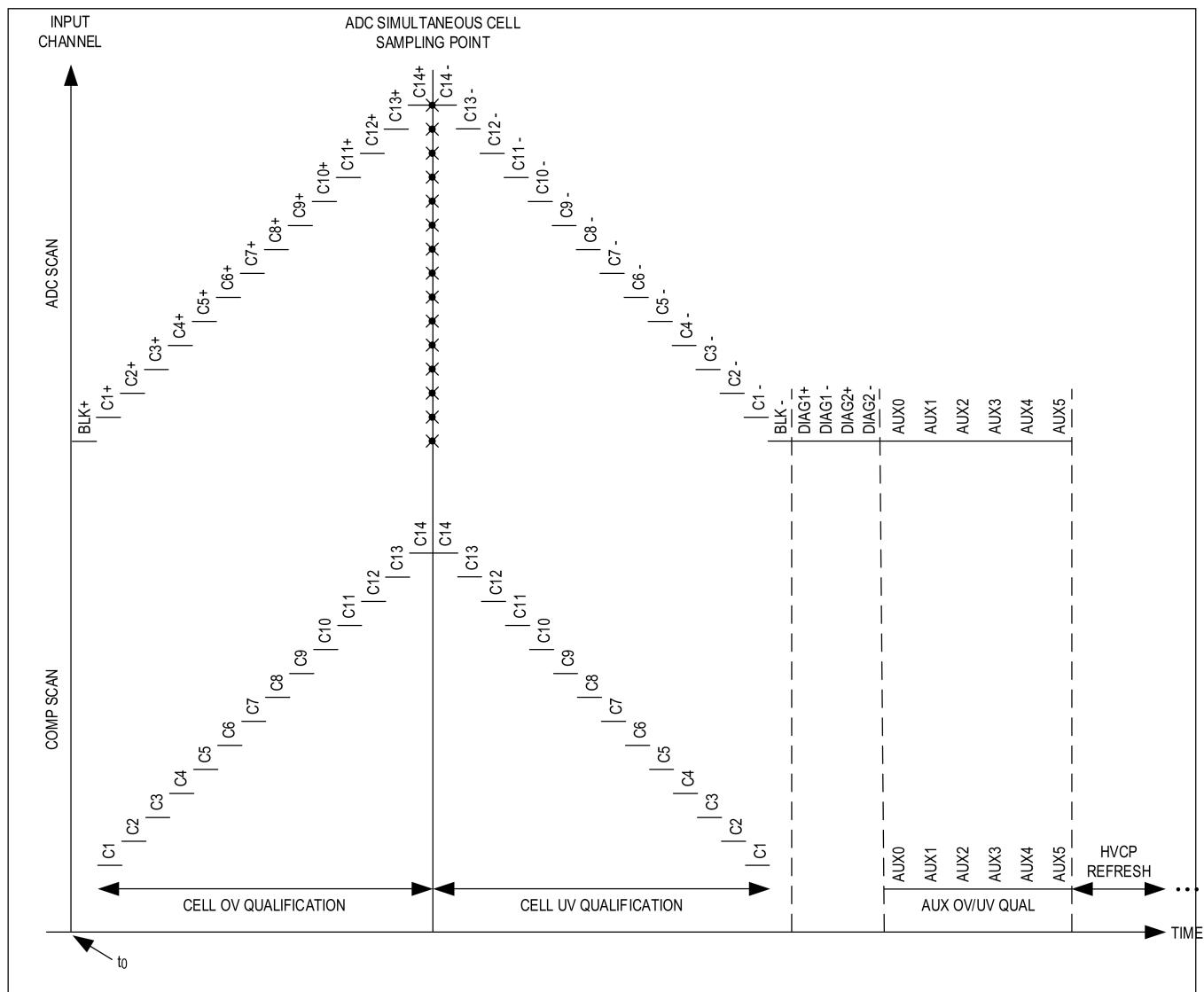

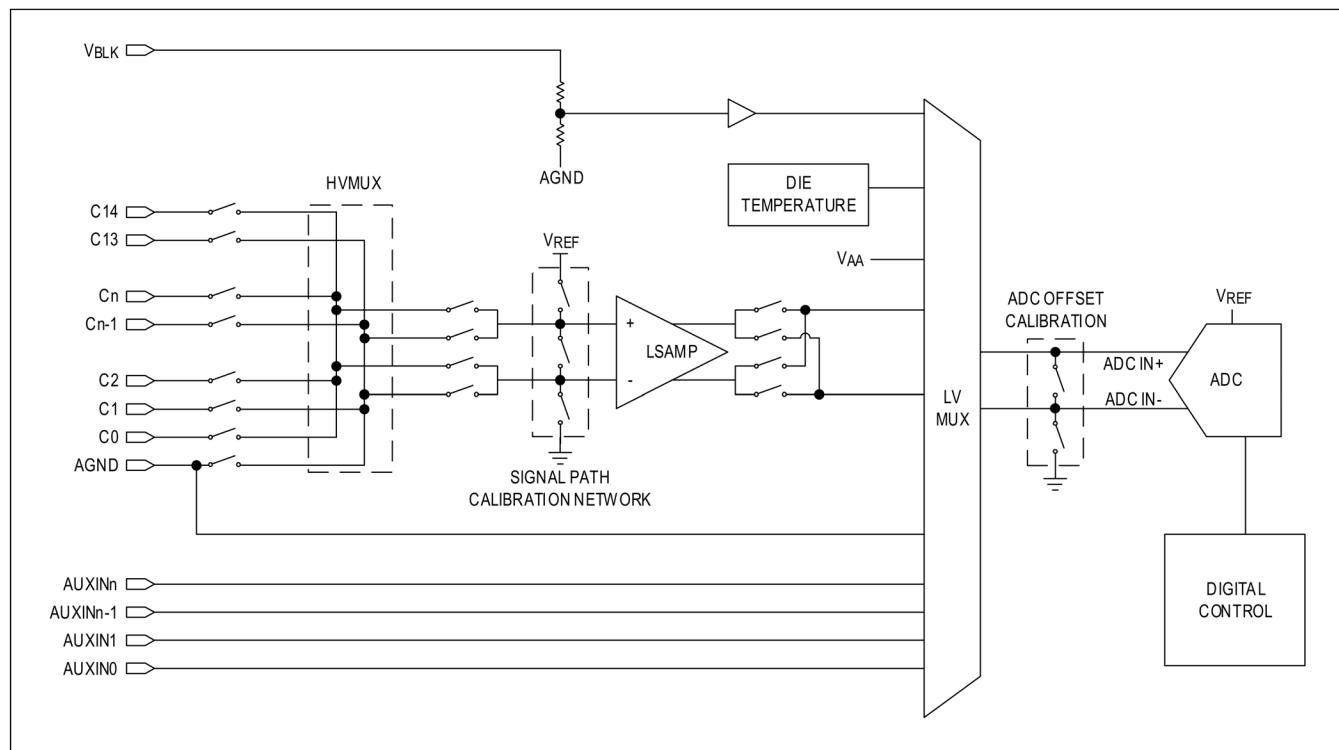

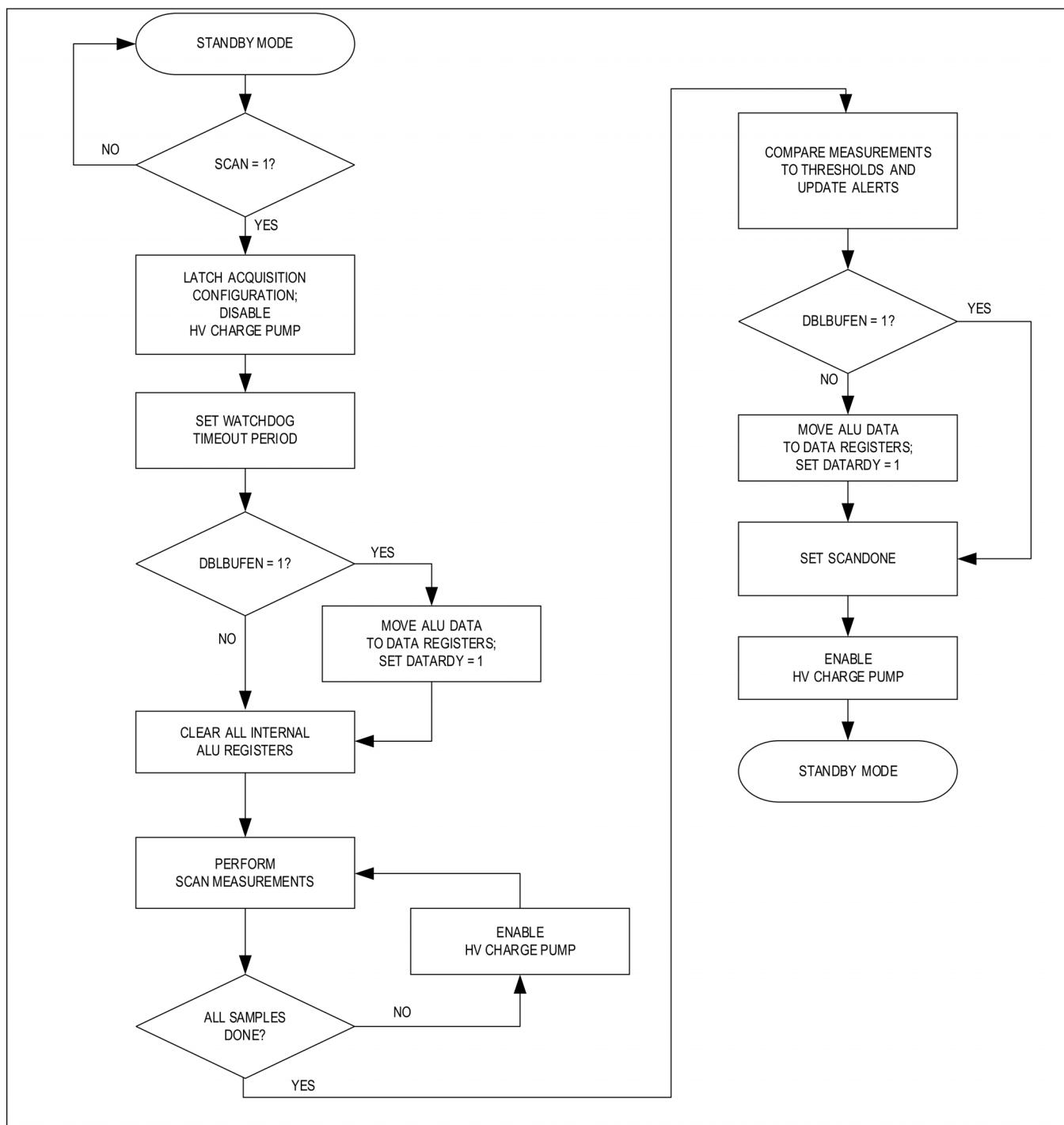

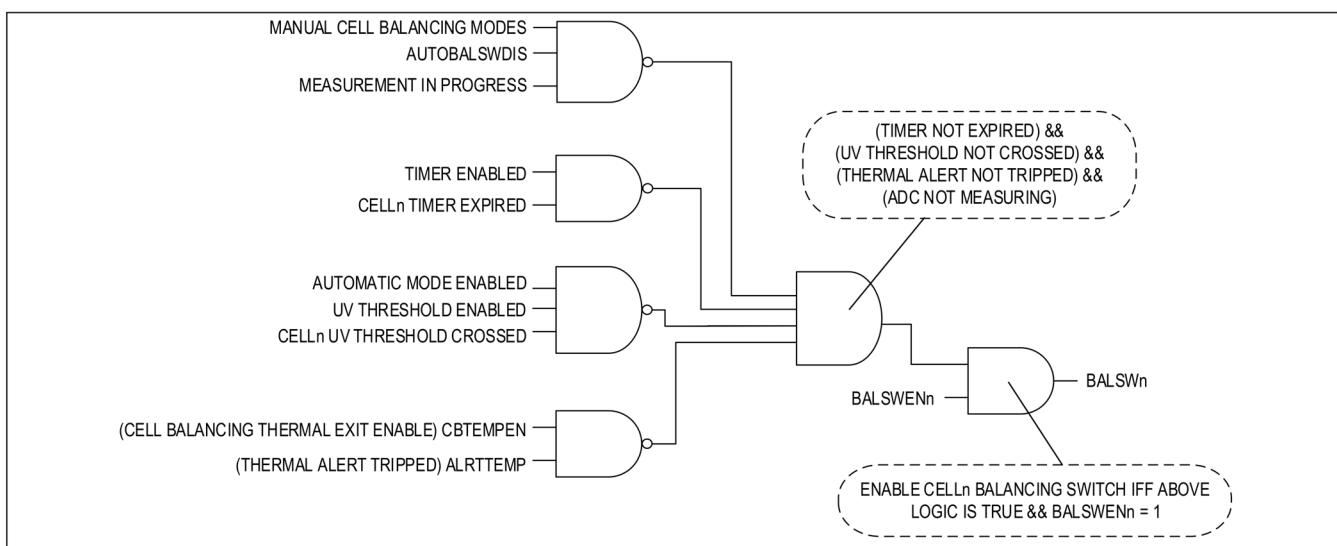

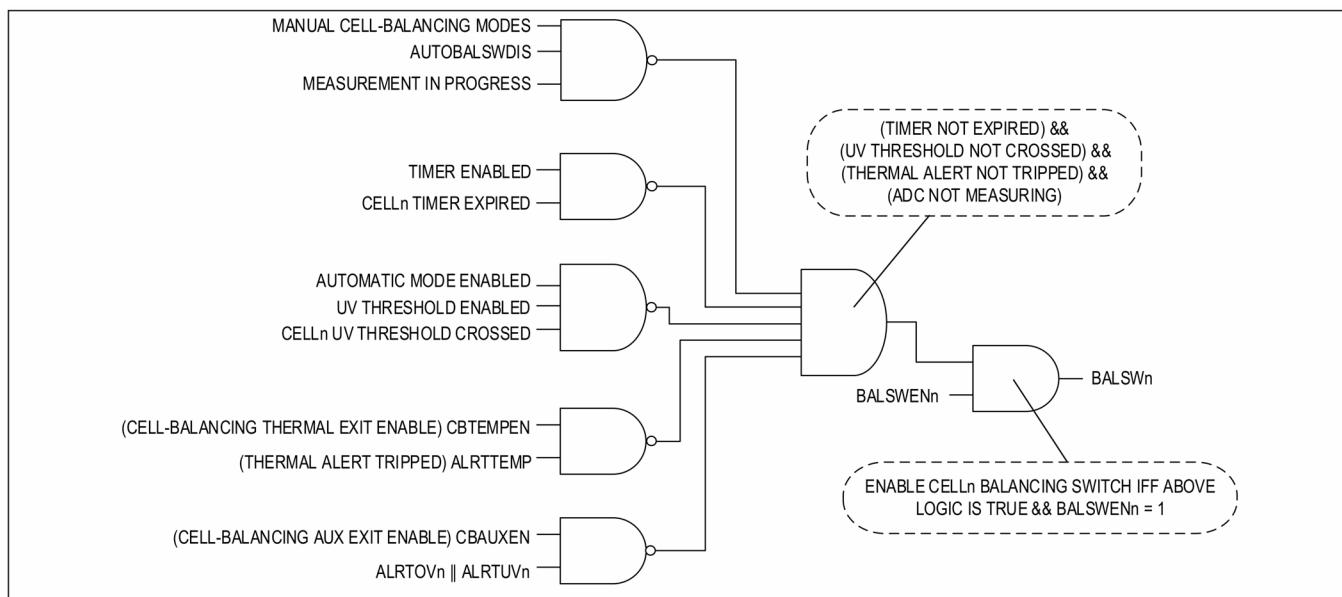

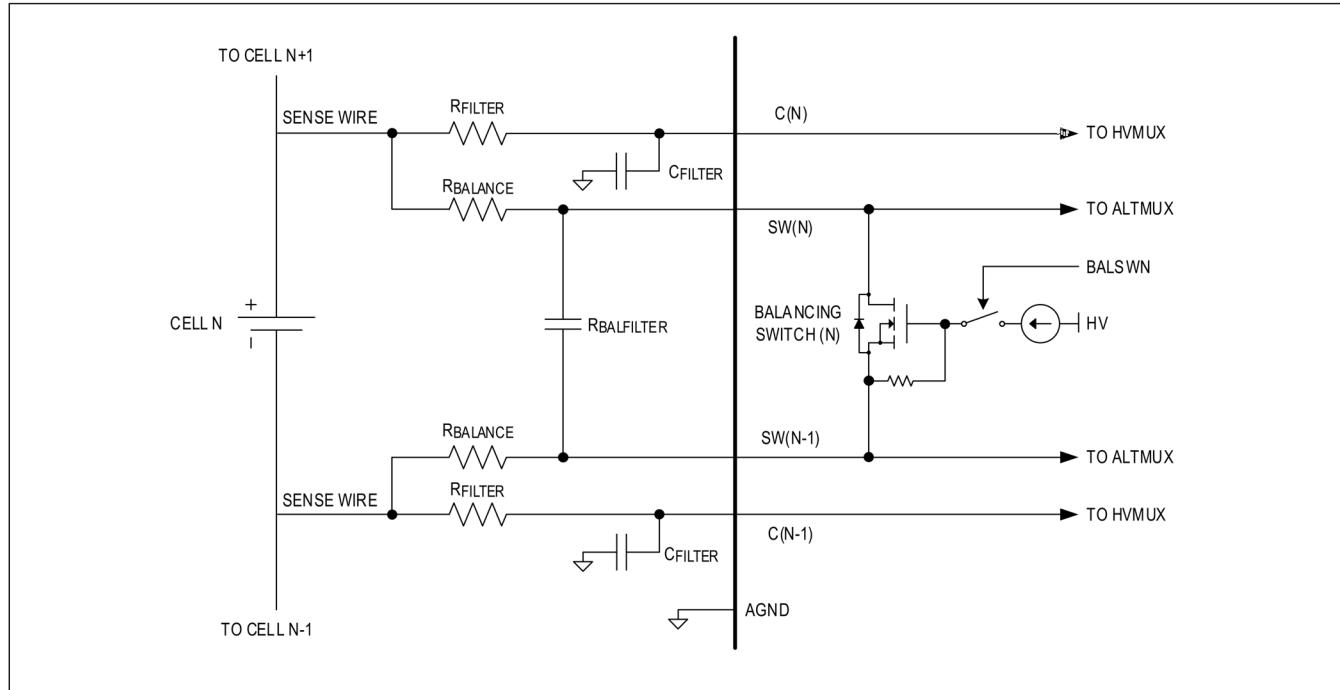

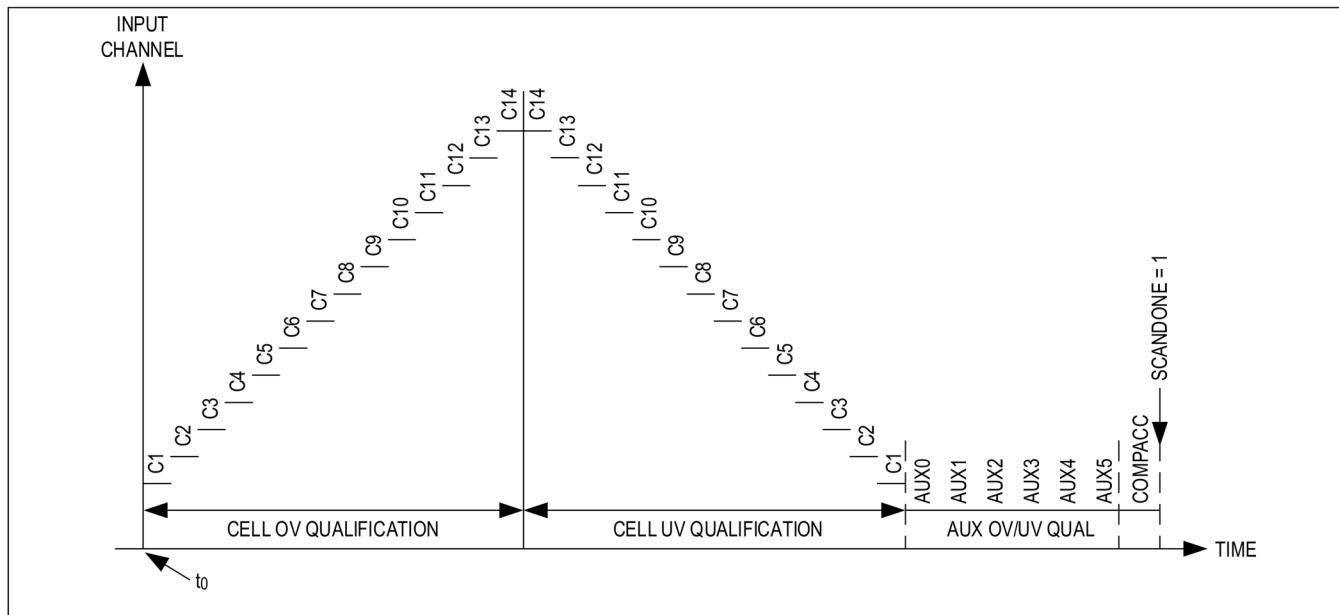

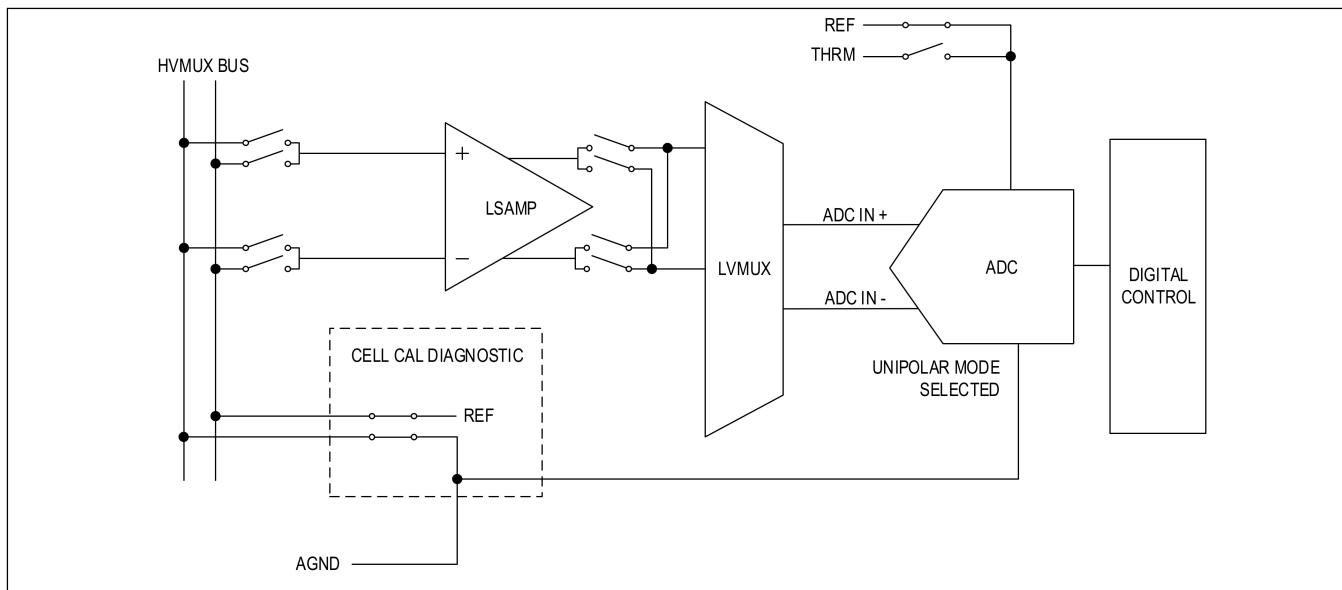

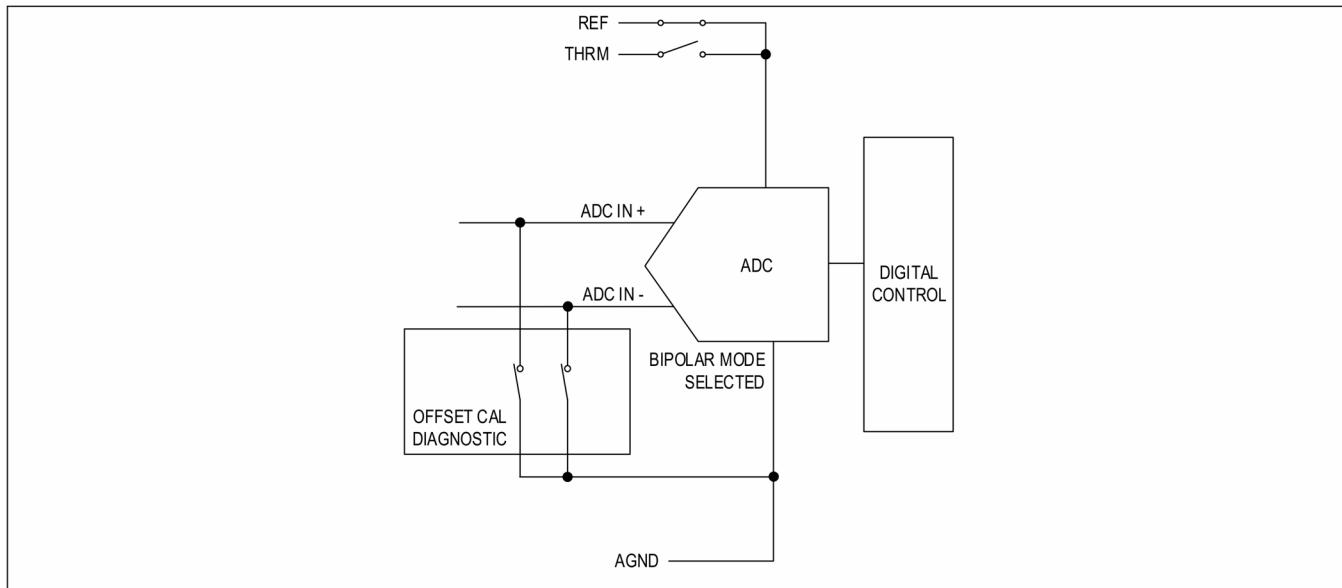

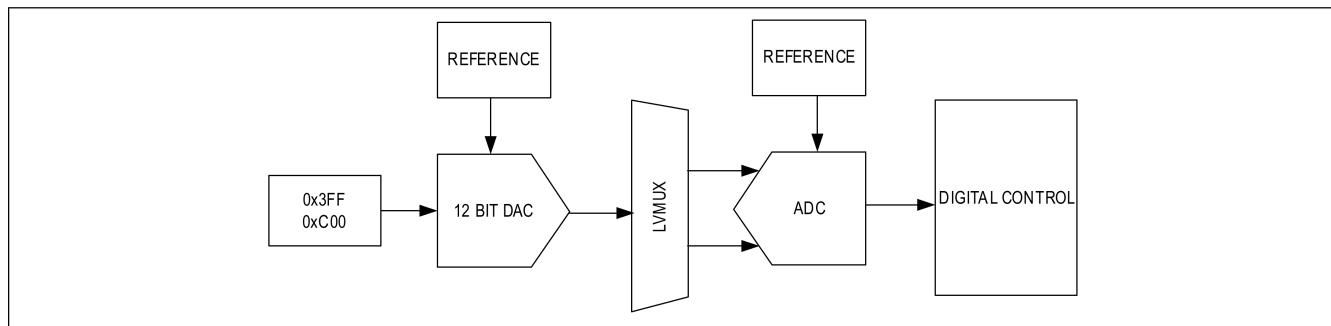

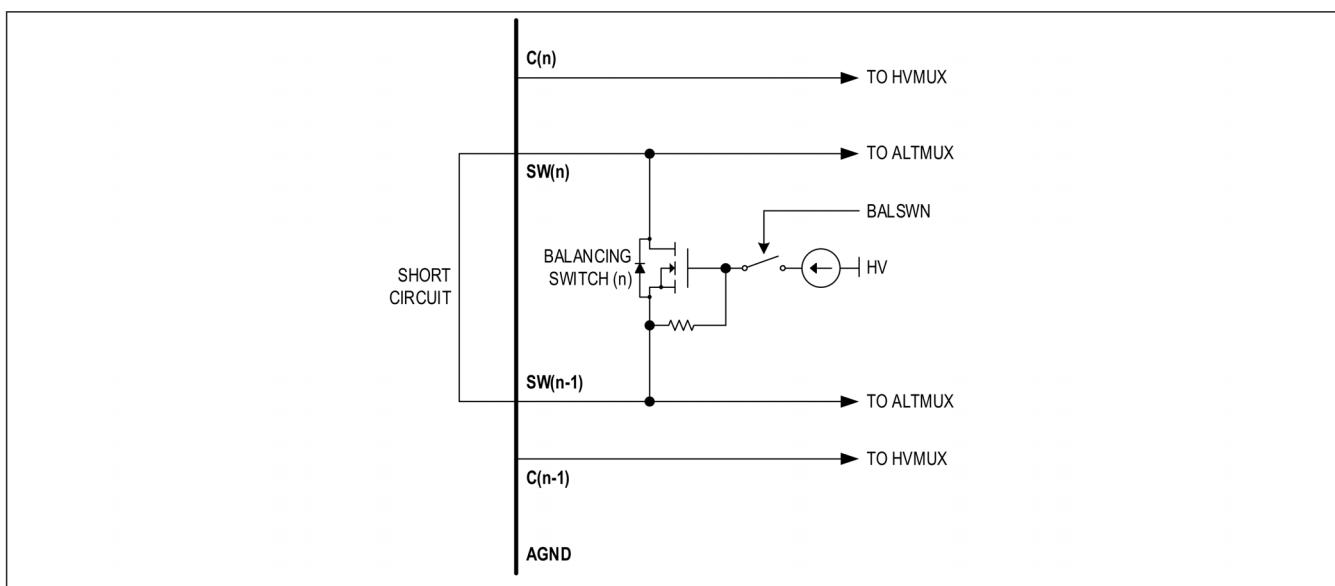

ADES1754/ADES1755/ADES1756 は、高電圧および低電圧のバッテリ・モジュールを管理するための柔軟なデータ・アクイジション・システムです。このシステムは完全に冗長化された測定エンジンを使用して、14 個のセル電圧、および 6 個の温度／システム電圧測定の組み合わせを  $162\mu\text{s}$  で測定したり、ADC 測定エンジンのみですべての入力を  $99\mu\text{s}$  で実行したりすることができます。300mA を超えるセル・バランスング電流に対応できるよう定格が定められた 14 個の内部バランスング・スイッチは、広範な診断機能を内蔵しています。最大 32 台のデバイスをデイジーチェーン接続して 448 個のセルを管理し、192 個の温度値をモニタすることができます。

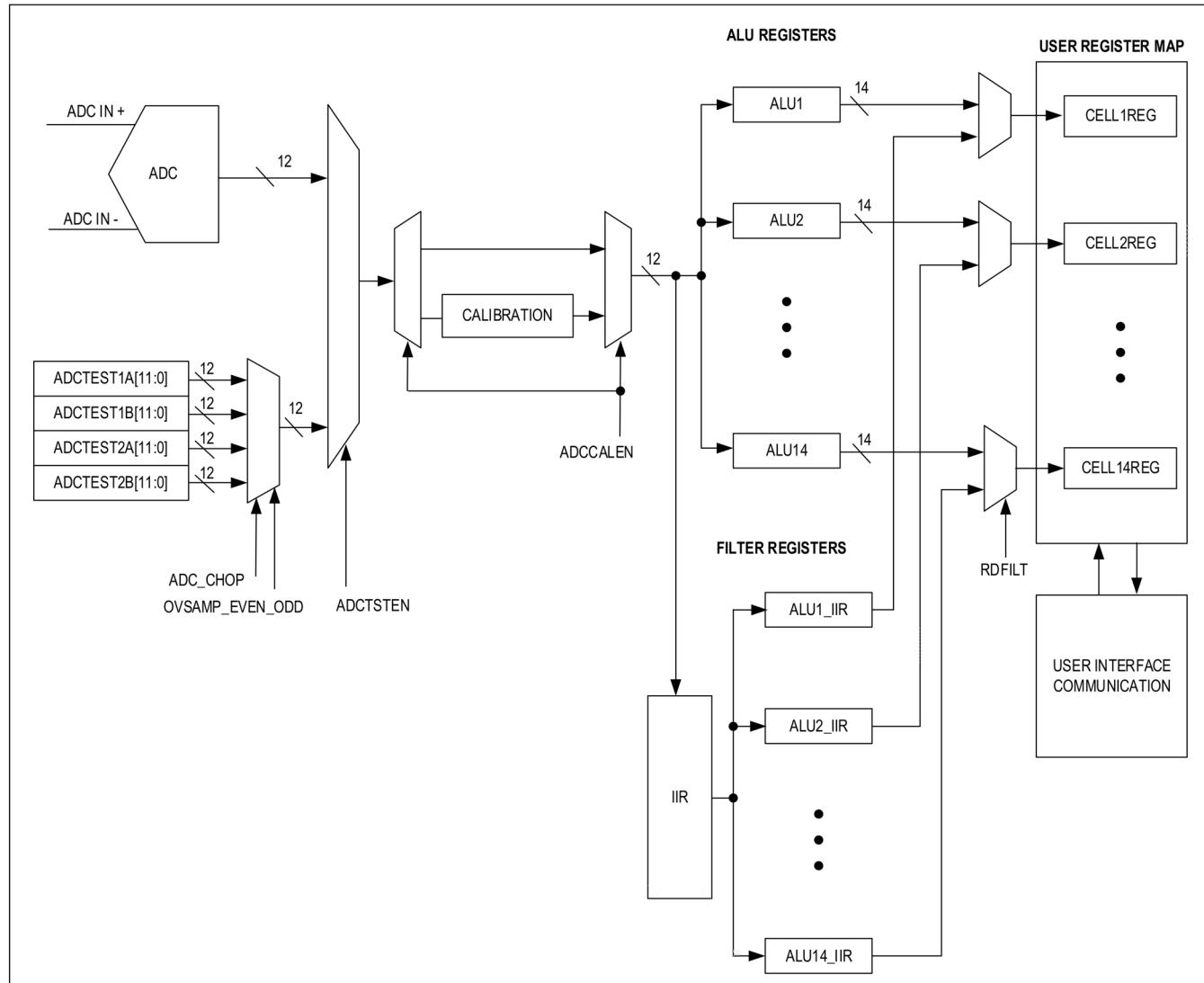

$-2.5\text{V} \sim +5\text{V}$  のセル電圧とバスバー電圧が、 $65\text{V}$  の同相電圧範囲で差動で測定されます。測定精度は  $100\mu\text{V}$ （代表値）です。オーバーサンプリングをイネーブルした場合は、14 ビットの分解能で 1 チャンネルあたり最大 128 個の測定値を内部的に平均し、デジタル・ポストプロセス IIR フィルタリングと組み合せることでノイズ耐性を向上させることができます。

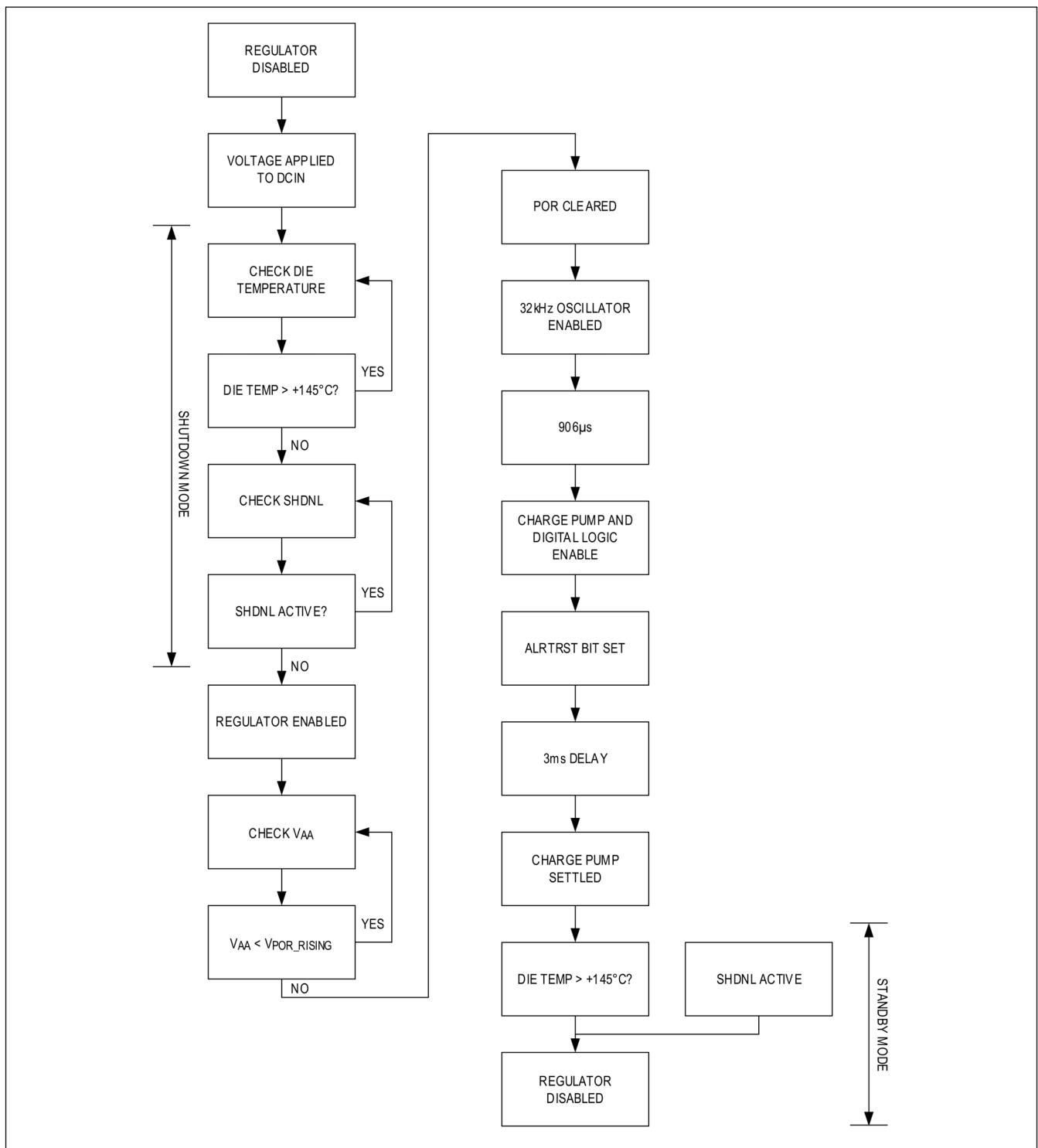

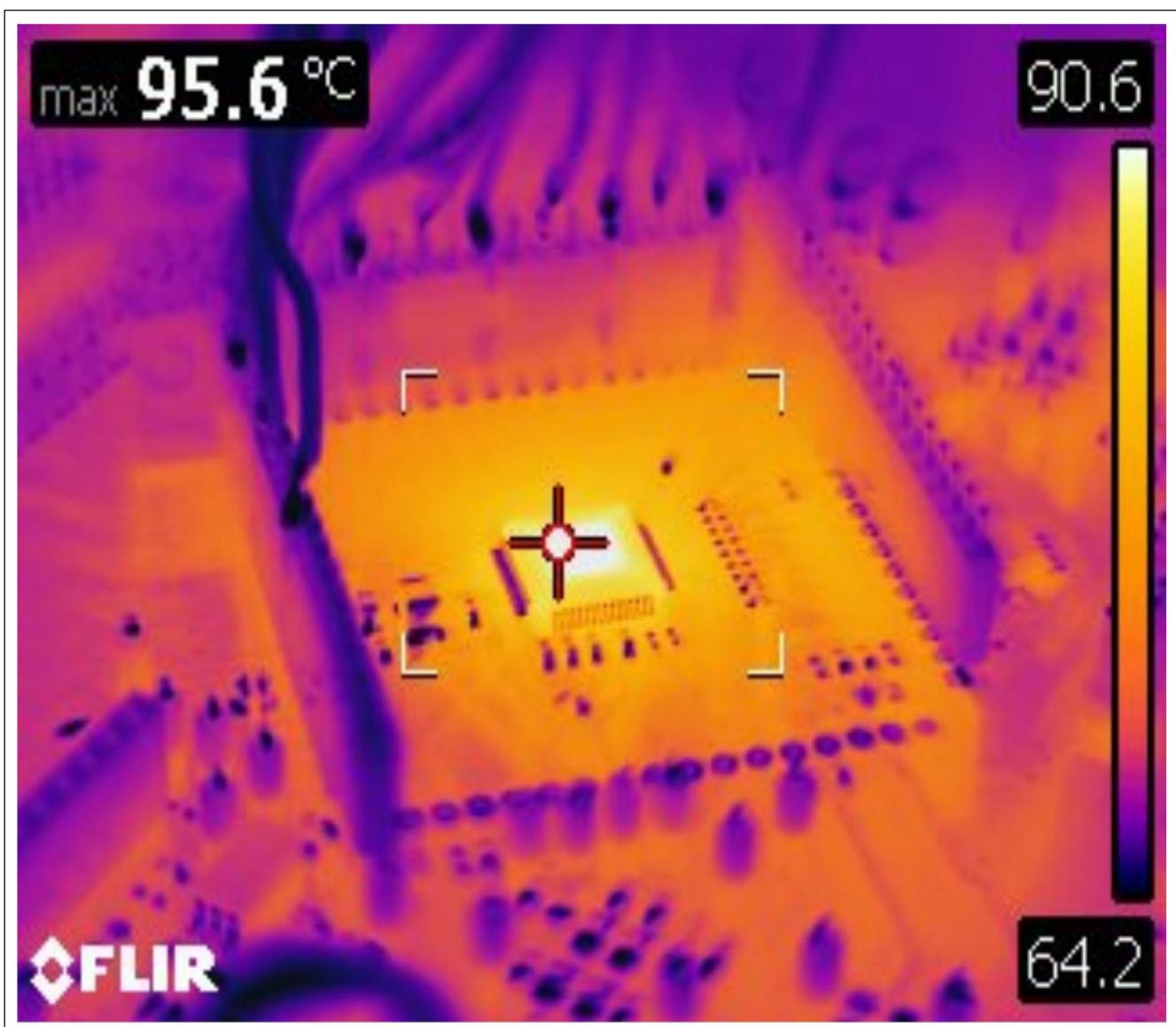

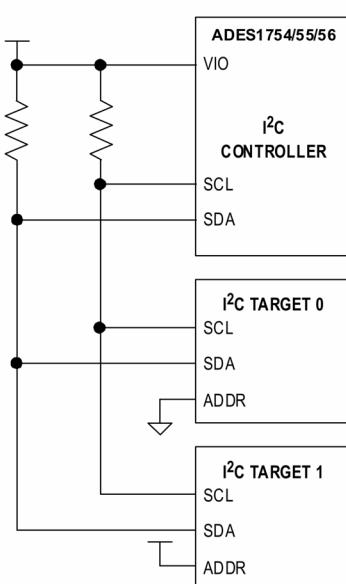

このシステムはダイ温度を測定して、熱過負荷が発生した場合は自動的にシステムをシャットダウンすることができます。このシステムはアナログ・デバイスのバッテリ管理 UART プロトコルを使用して信頼性の高い通信を実現すると共に、外部デバイス制御用に I<sup>2</sup>C コントローラ・インターフェイスをサポートしています。また、組込みの通信インターフェイスとハードウェア・アラート・インターフェイスを通じて、内部診断と迅速なアラート通信に限定された機能セットをサポートするよう最適化されています。

### 主なアプリケーション

- 住宅用バッテリ・ストレージ・システム

- 高電圧バッテリ・スタック

- バッテリ・バックアップ・システム (UPS)

- スーパー・キャパシタ・システム

- バッテリ駆動ツール

- EV 充電

### 特長と利点

- 動作電圧 :  $65\text{V}$

- 超低消費電力動作

- シャットダウン・モード :  $2\mu\text{A}$

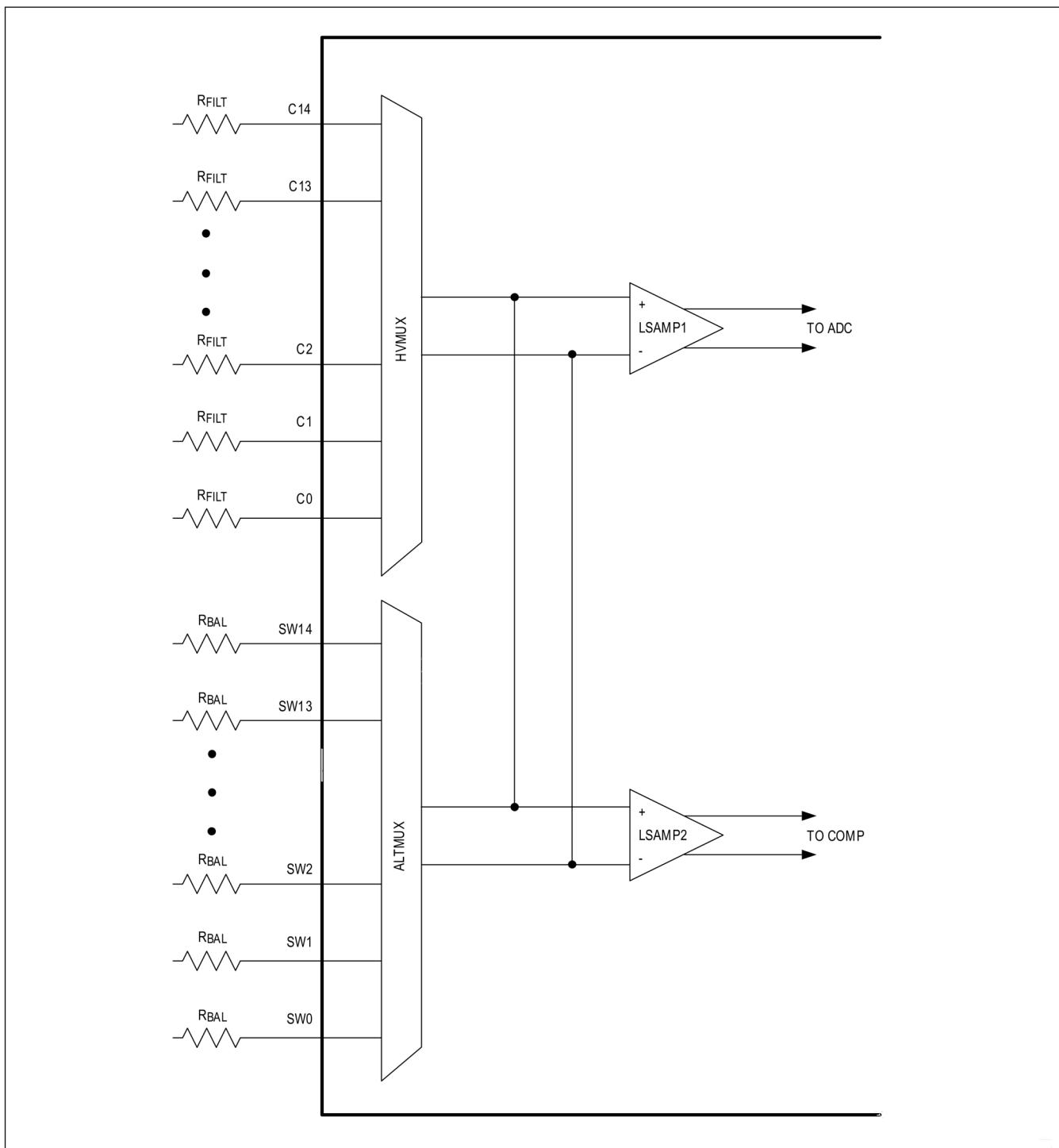

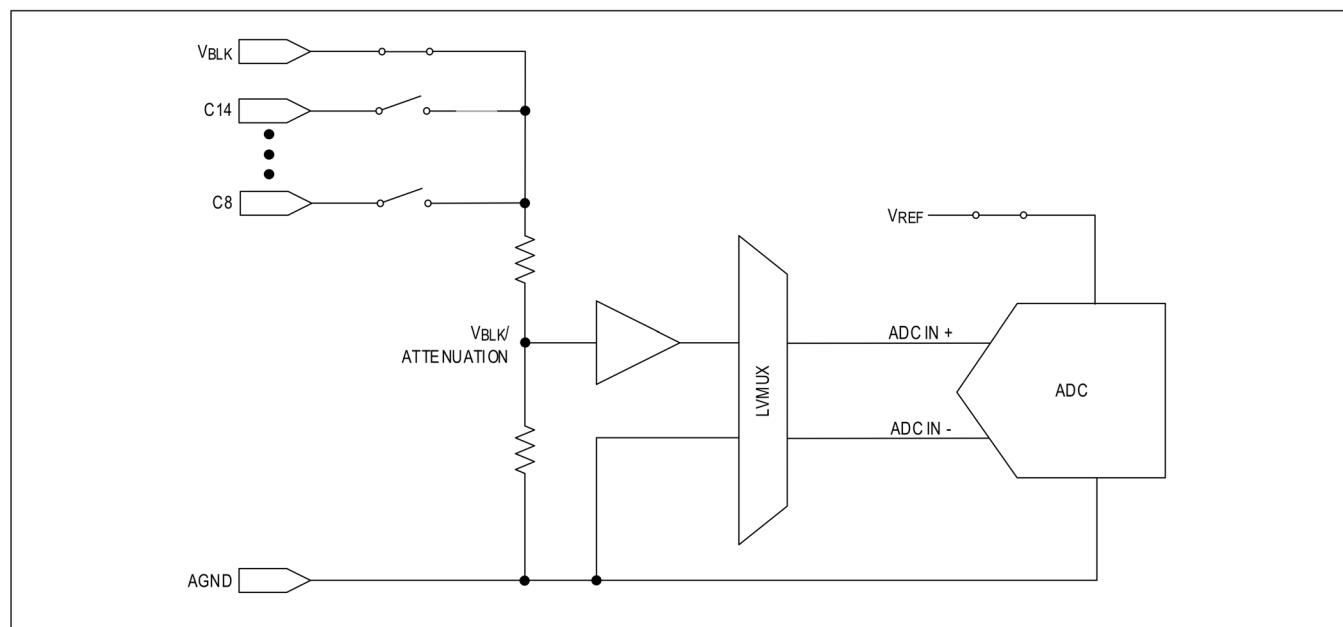

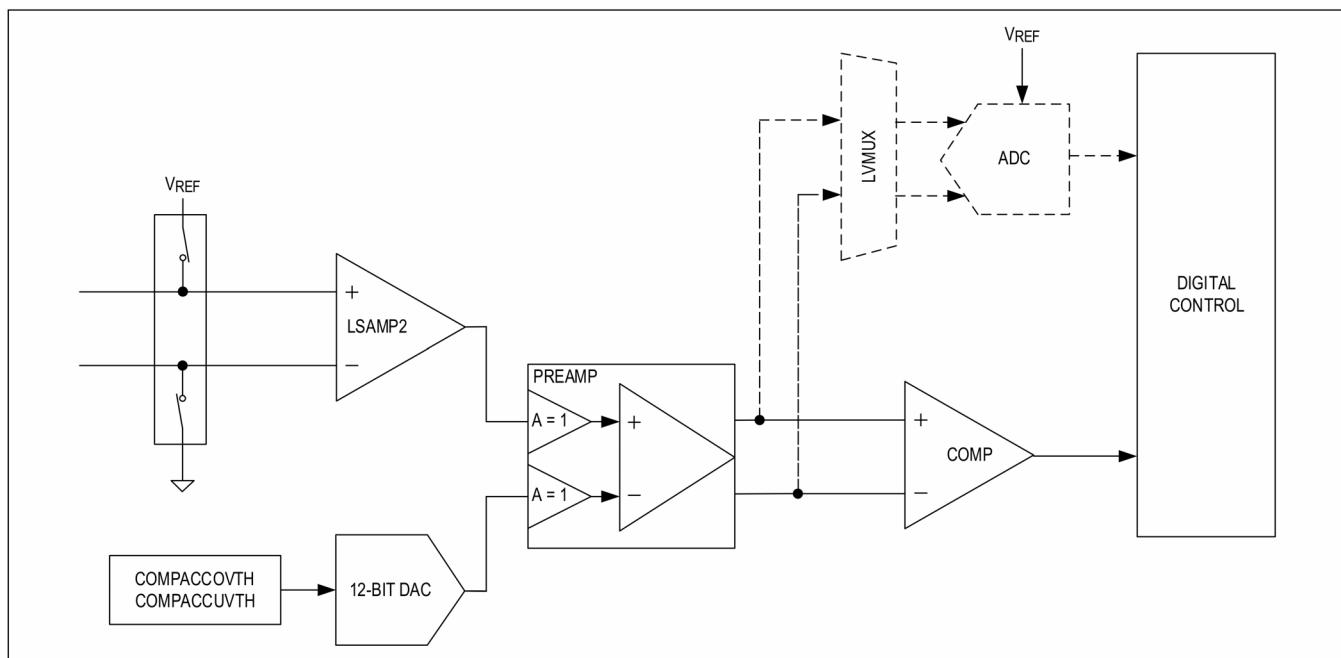

- 冗長 ADC とコンパレータ (COMP) によるデータ・アクイジション

- セル電圧とバスバー電圧の同時アクイジション

- 14 個のセル電圧測定チャンネル

- 精度 :  $2.2\text{mV}/5\text{mV}/10\text{mV}$  ( $-40^\circ\text{C} \sim +105^\circ\text{C}$ )

- 精度 :  $1.8\text{mV}$  ( $+5^\circ\text{C} \sim +65^\circ\text{C}$ )

- 14 個のセル・バランスング・スイッチ

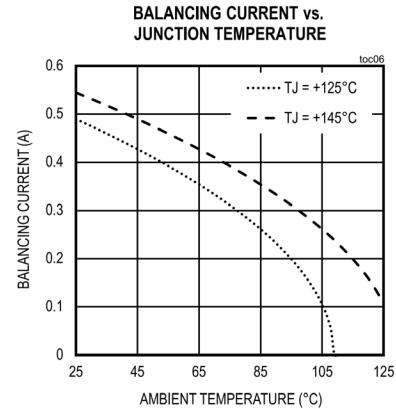

- ソフトウェアで設定可能なバランスング電流 :  $>300\text{mA}$

- 個別セル・タイマーによる自動バランスング

- セル電圧による自動バランスング

- 緊急放電モード

- 温度、電圧、GPIO 用の設定可能な 6 つの補助入力

- ダイ温度測定機能を内蔵

- 自動過熱保護機能

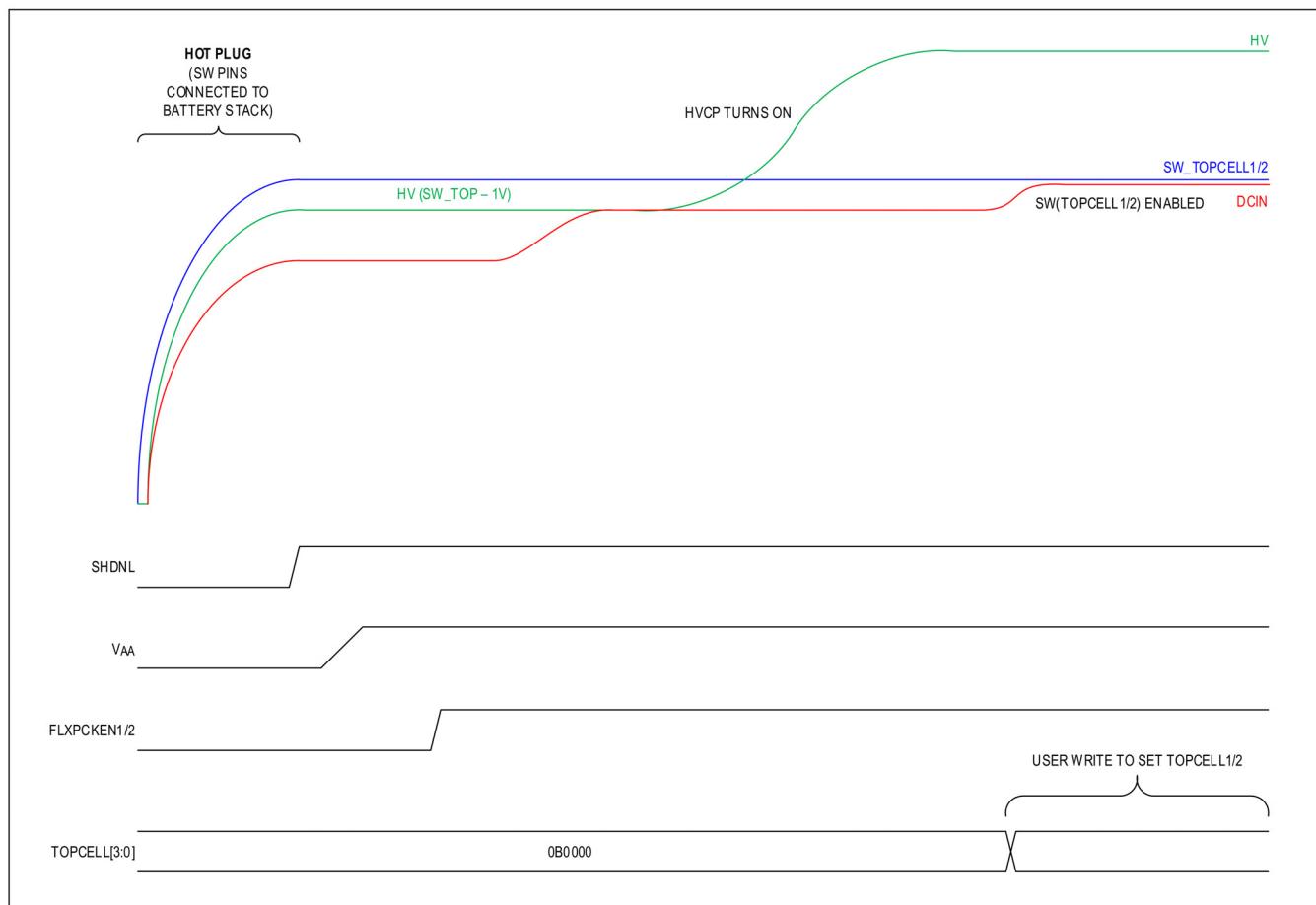

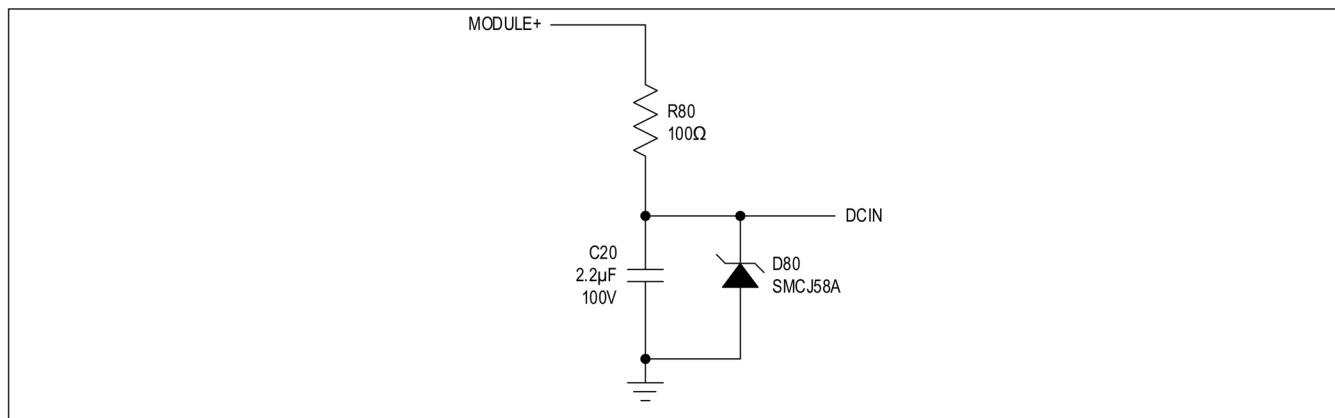

- 外部保護機能によらないホットプラグ耐性

- 個別に設定可能なセーフティ・アラート

- 過電圧／低温フォルト

- 低電圧／過熱フォルト

- 1 セル・ミスマッチ・アラート

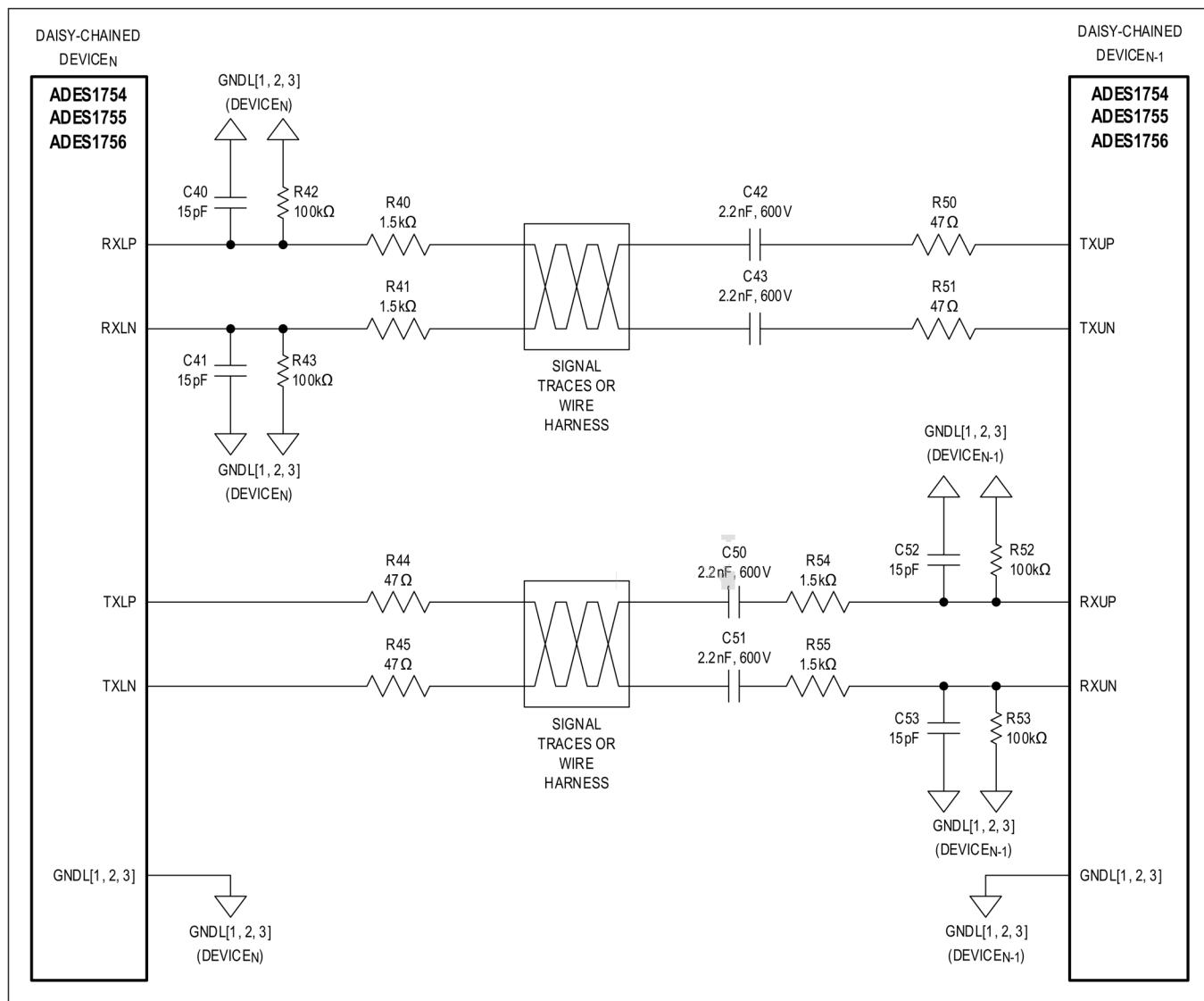

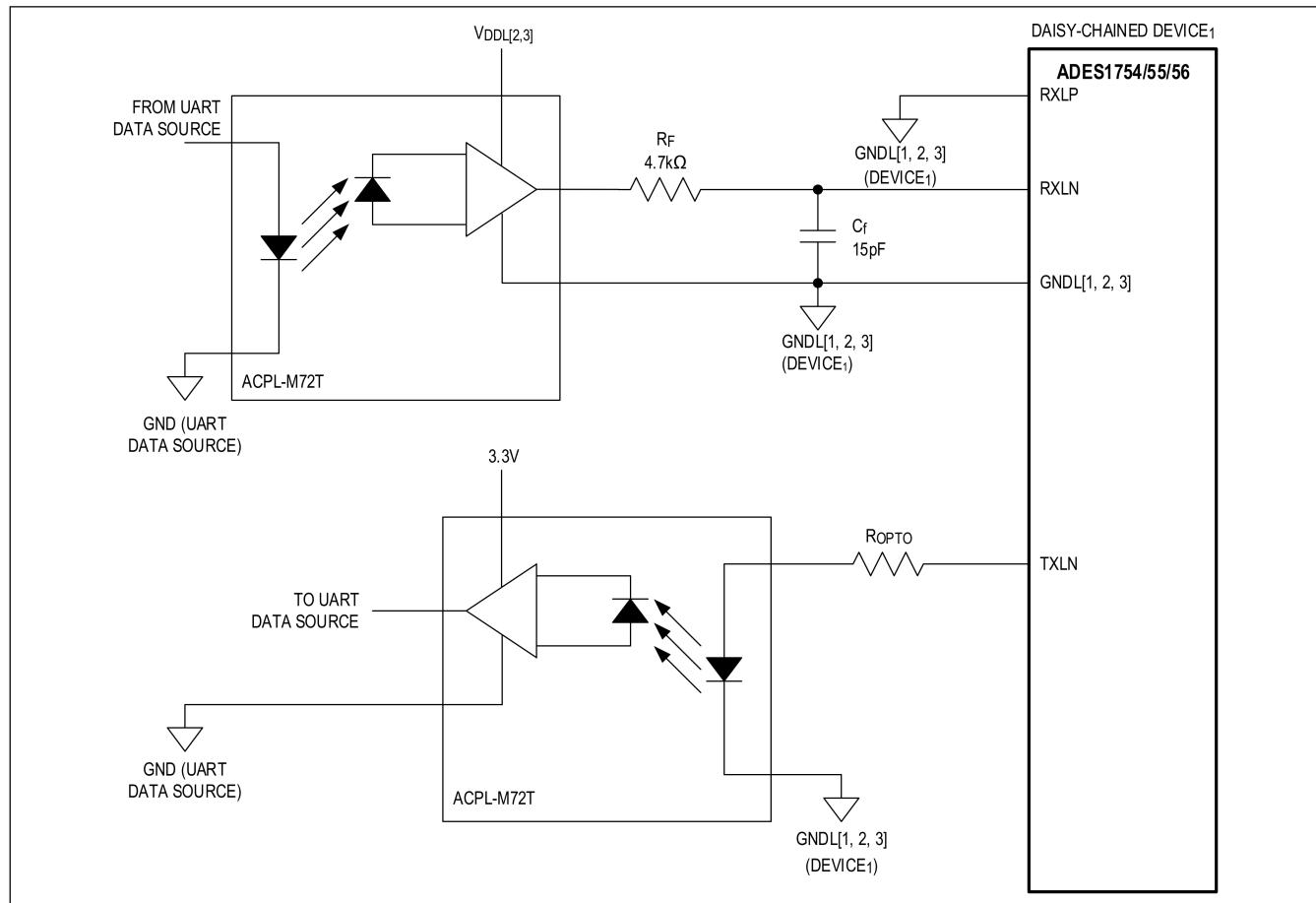

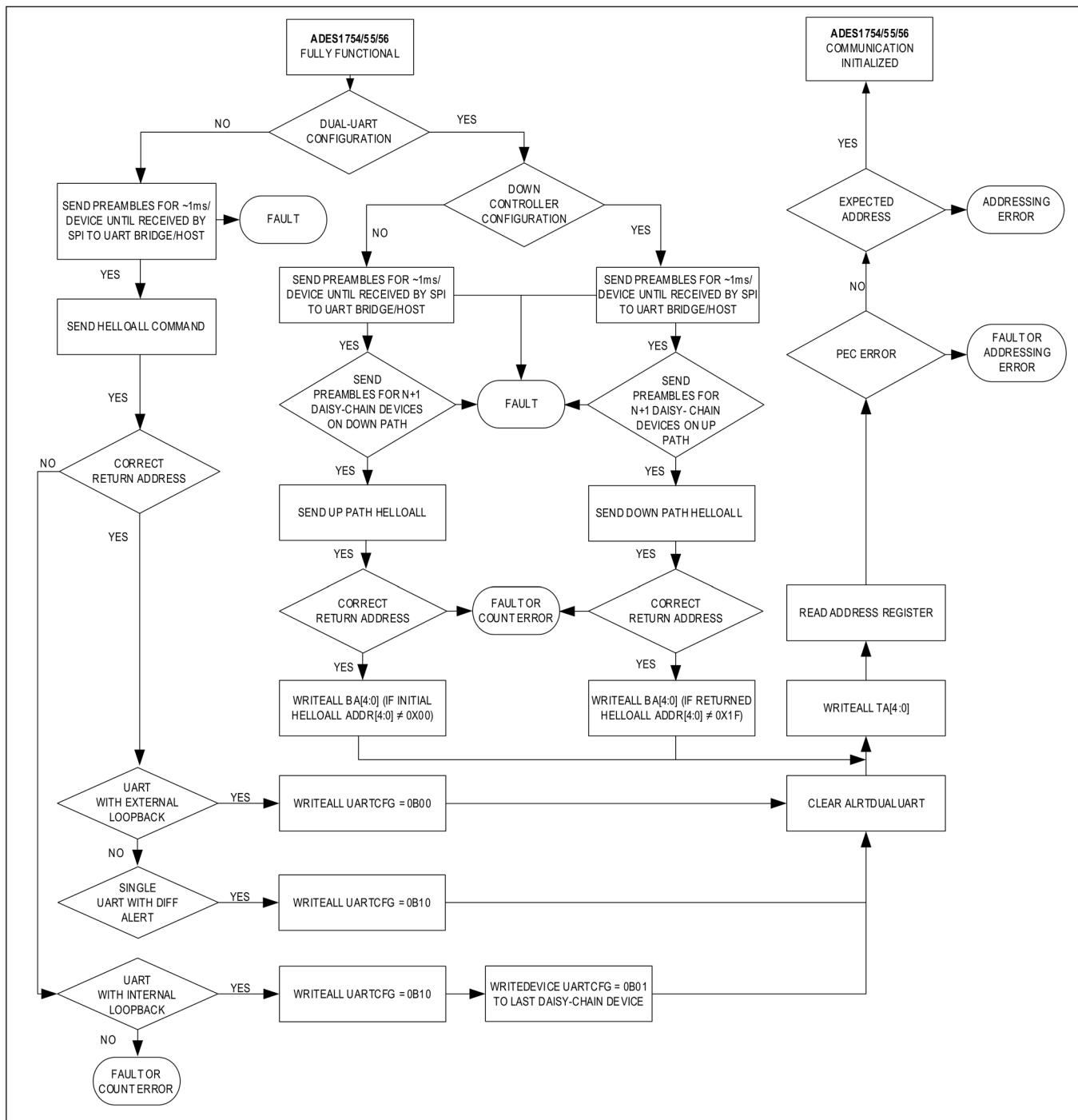

- UART、デュアル UART インターフェイス

- バッテリ管理 UART プロトコル

- 最大 32 個のデバイスをデイジーチェーン接続可能

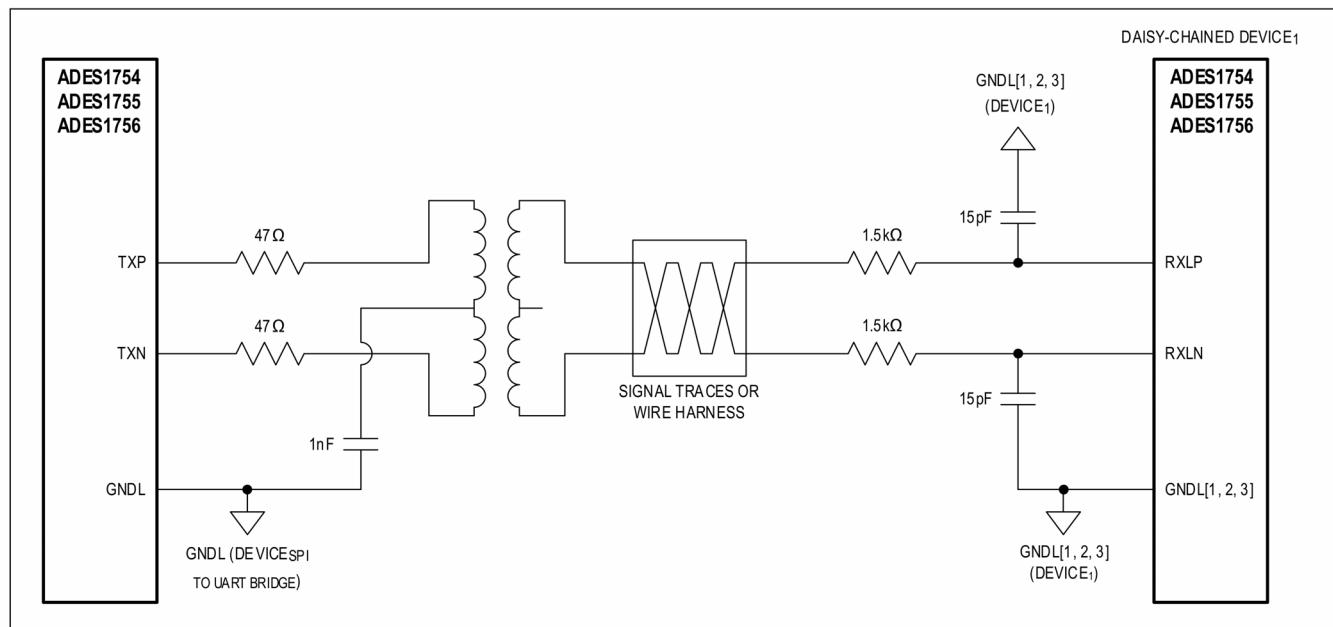

- より確実なガルバニック絶縁を実現する誘導方式

- 最大ボーリート :  $2\text{Mbps}$  (自動検出)

- デバイスあたりの伝搬遅延 :  $1.5\mu\text{s}$

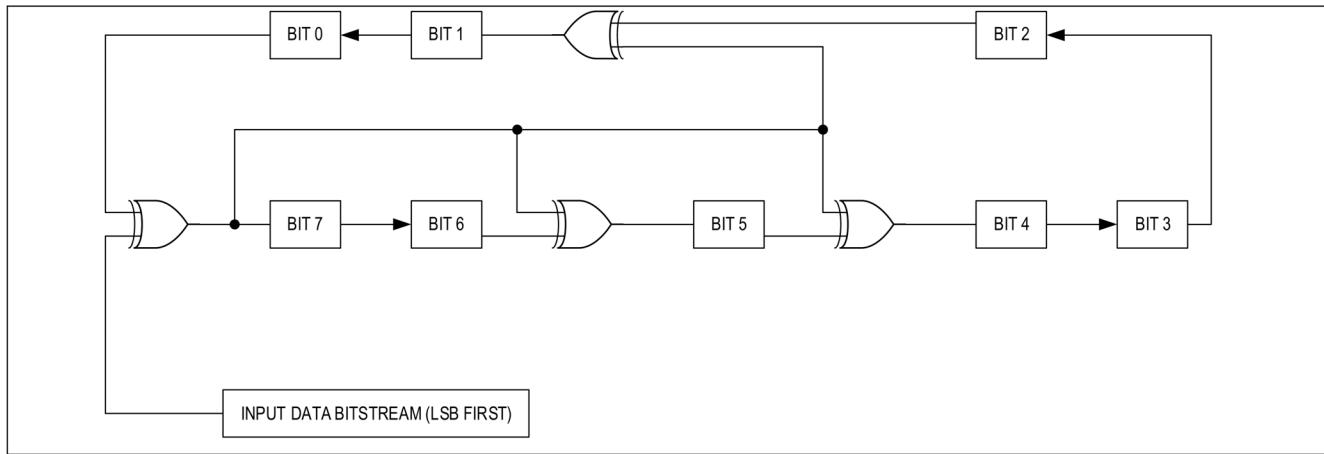

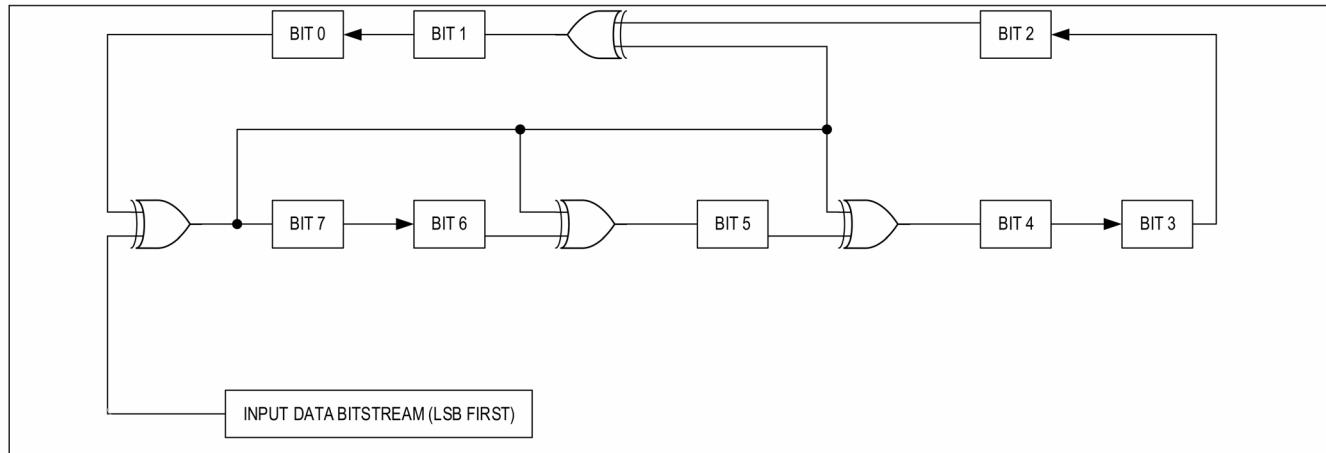

- パケット・エラー・チェック (PEC)

- I<sup>2</sup>C コントローラ

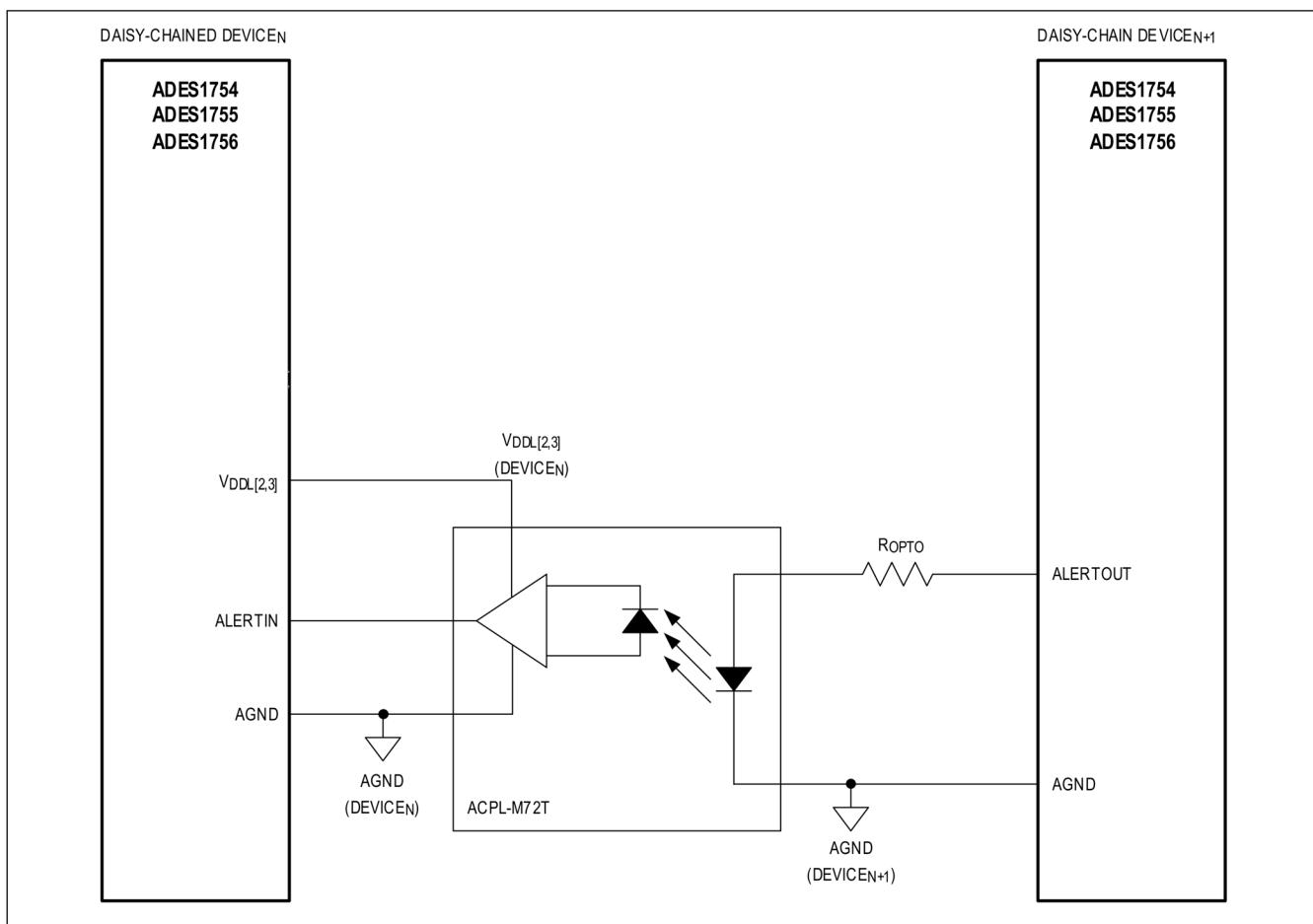

- 設定可能なハードウェア・アラート・インターフェイス

- 32 ビットの固有デバイス ID

型番はデータシート末尾に記載されています。

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

©2023 Analog Devices, Inc. All rights reserved. 商標および登録商標は各社の所有に属します。

本社 / 〒105-7323 東京都港区東新橋 1-9-1 東京汐留ビルディング 23F

大阪営業所 / 〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー 10F

名古屋営業所 / 〒451-6038 愛知県名古屋市西区牛島町 6-1 名古屋ルーセントタワー 38F

19-101802; Rev 0; 11/23

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

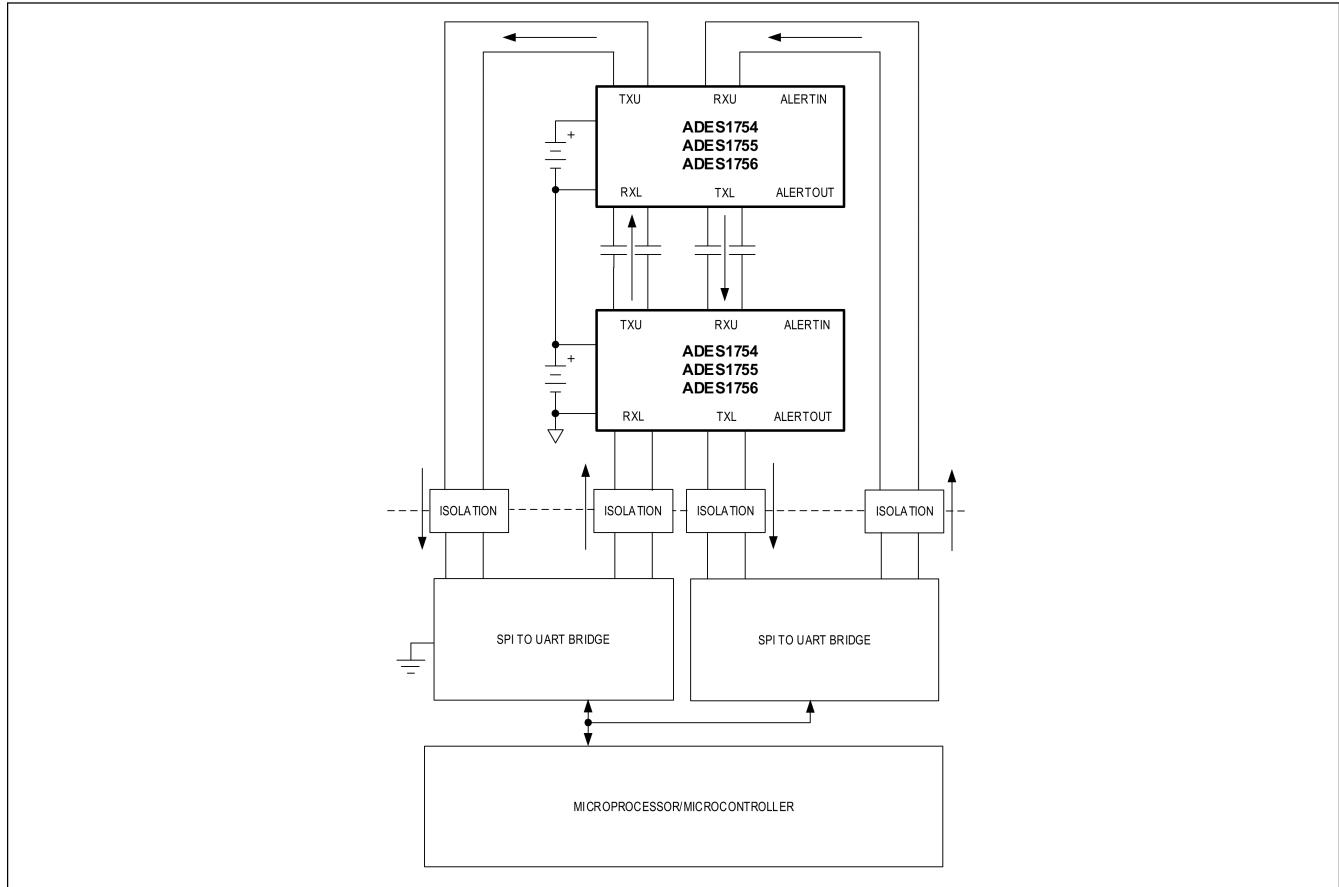

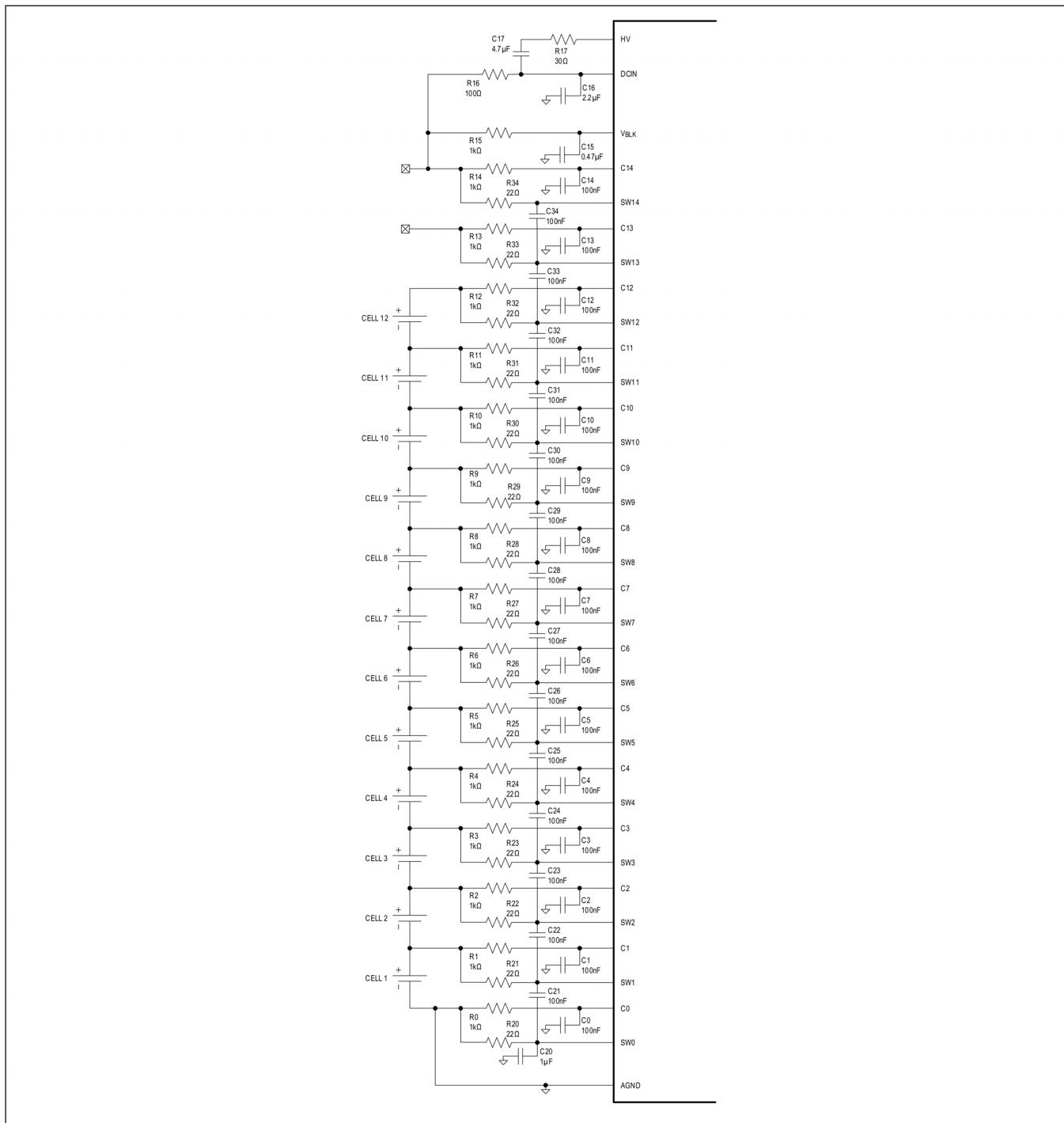

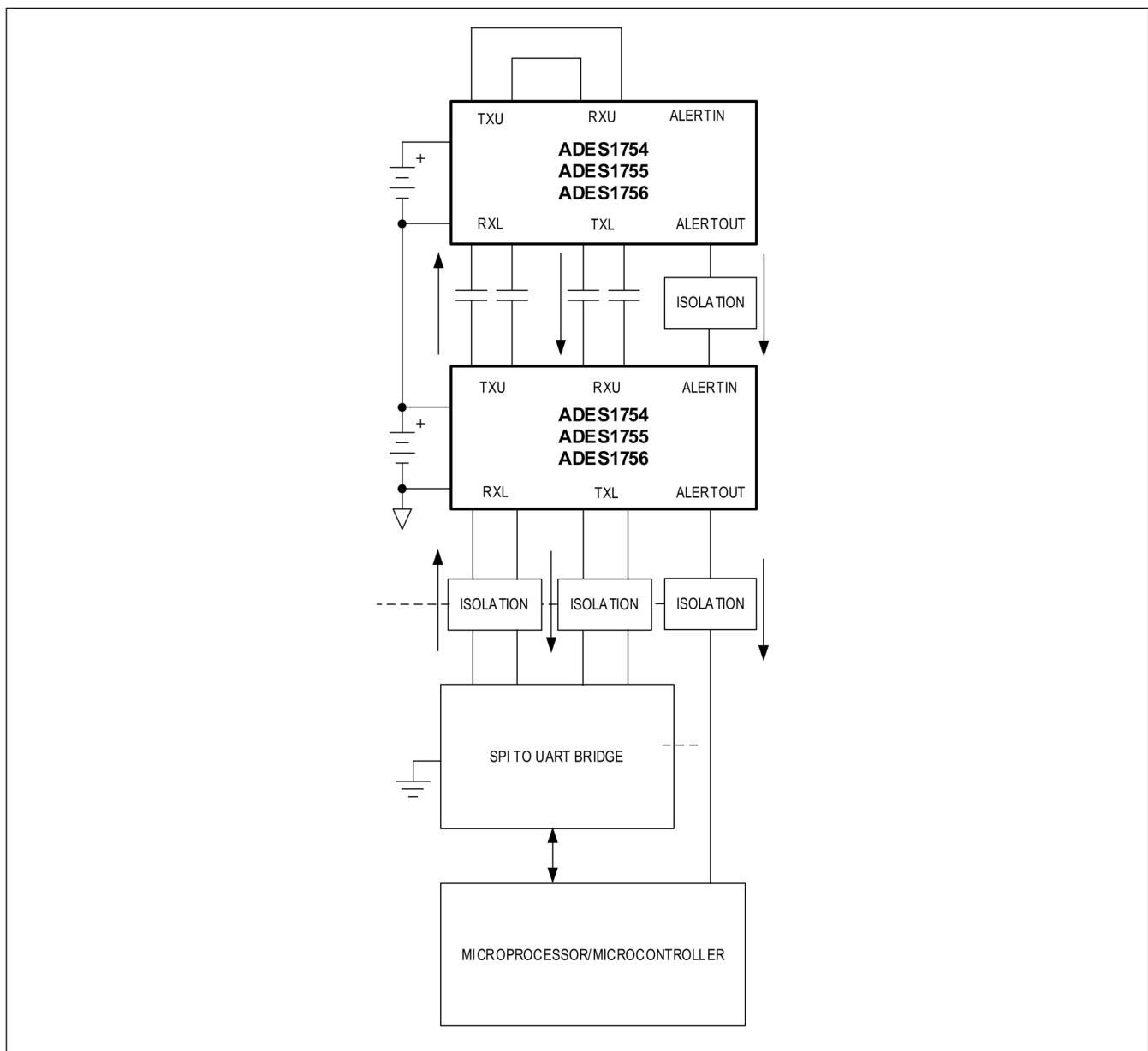

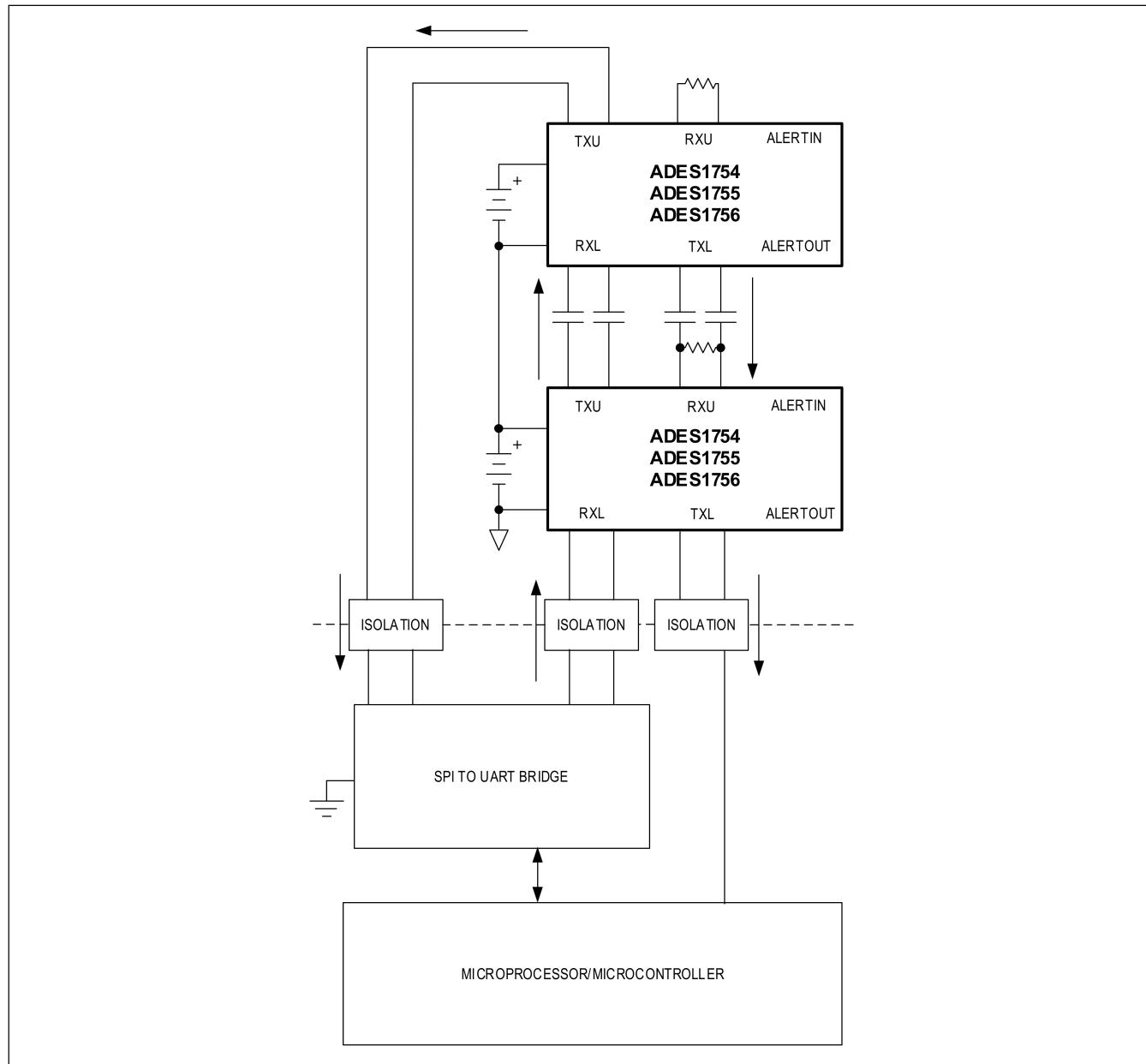

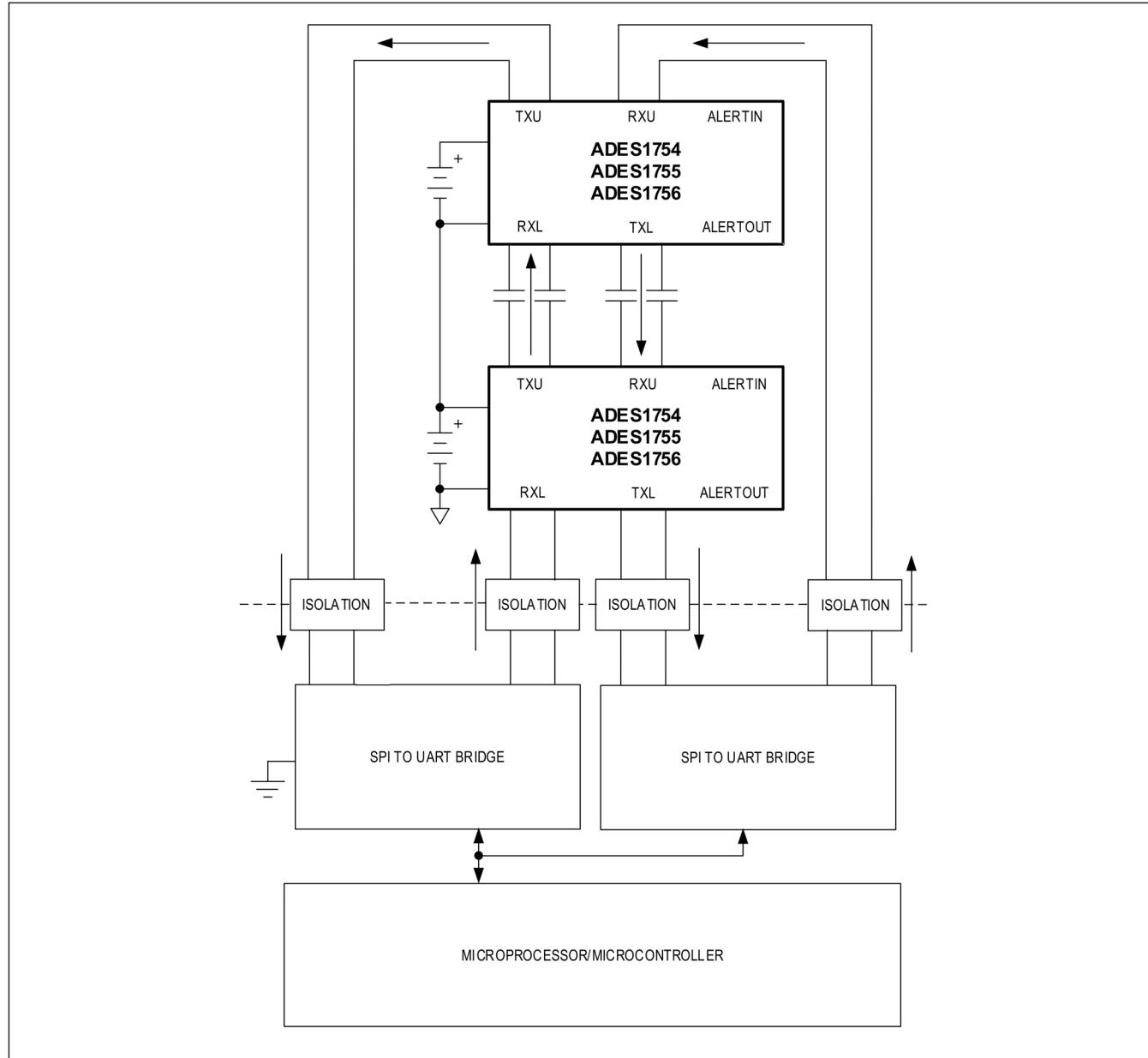

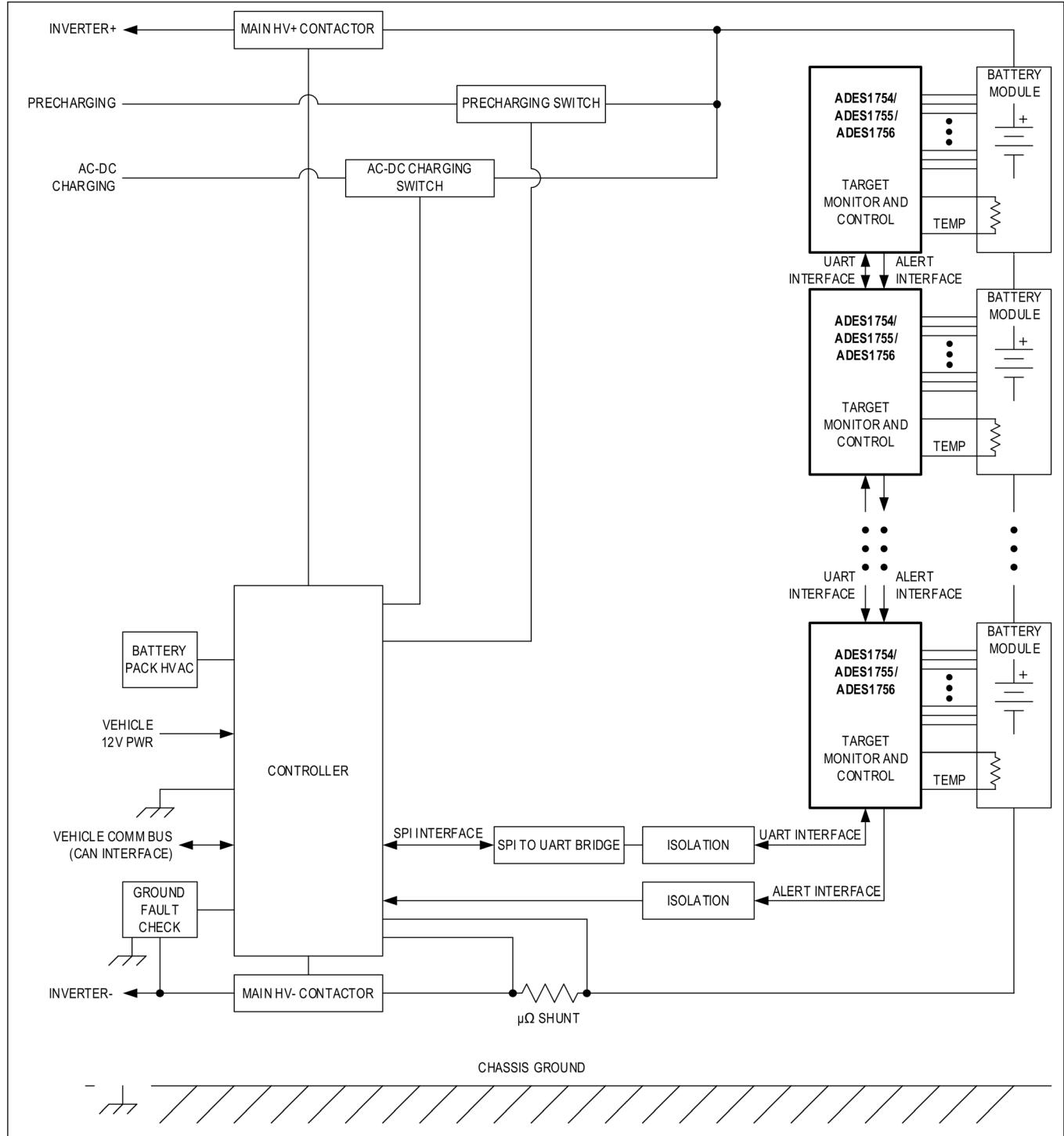

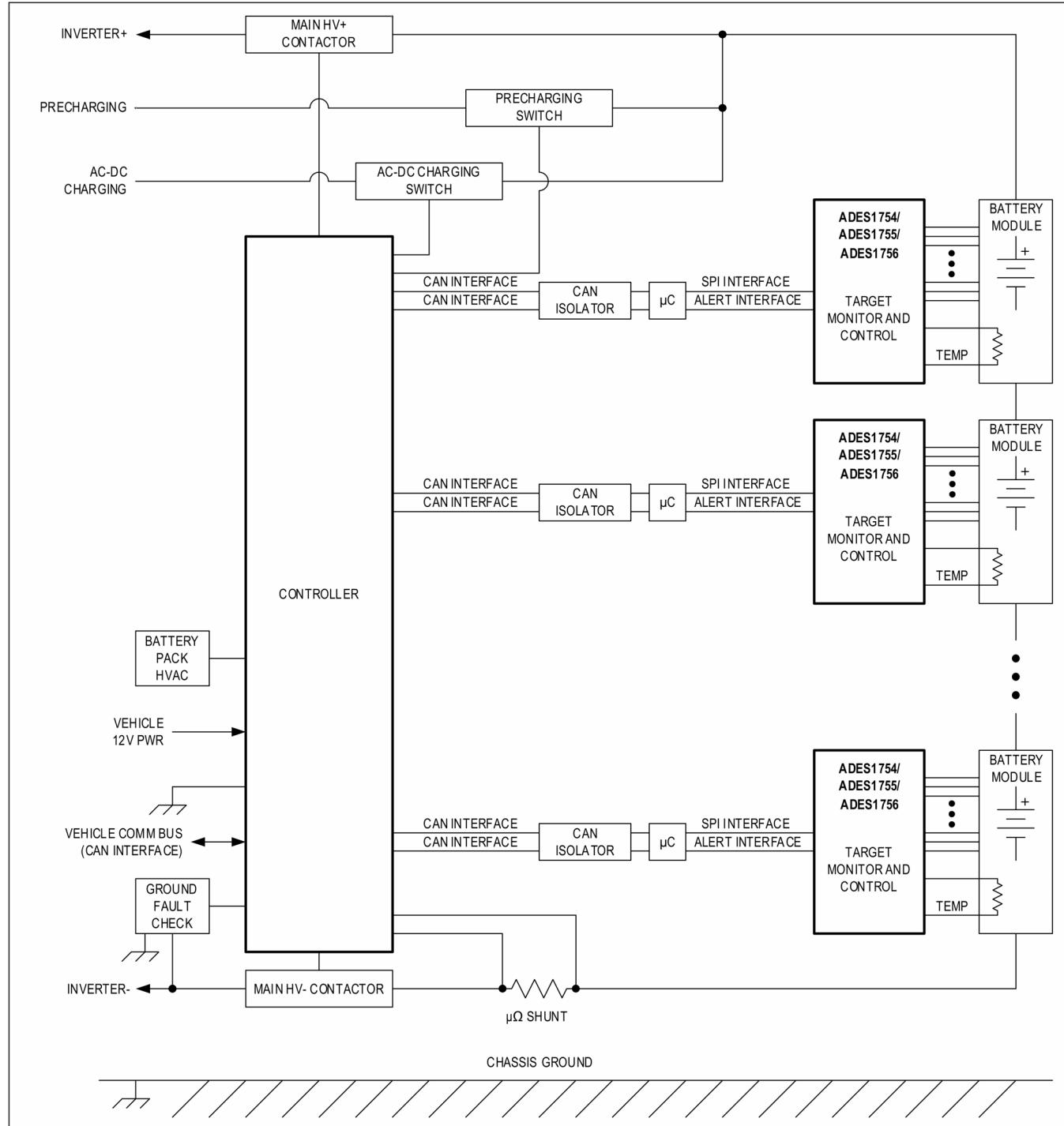

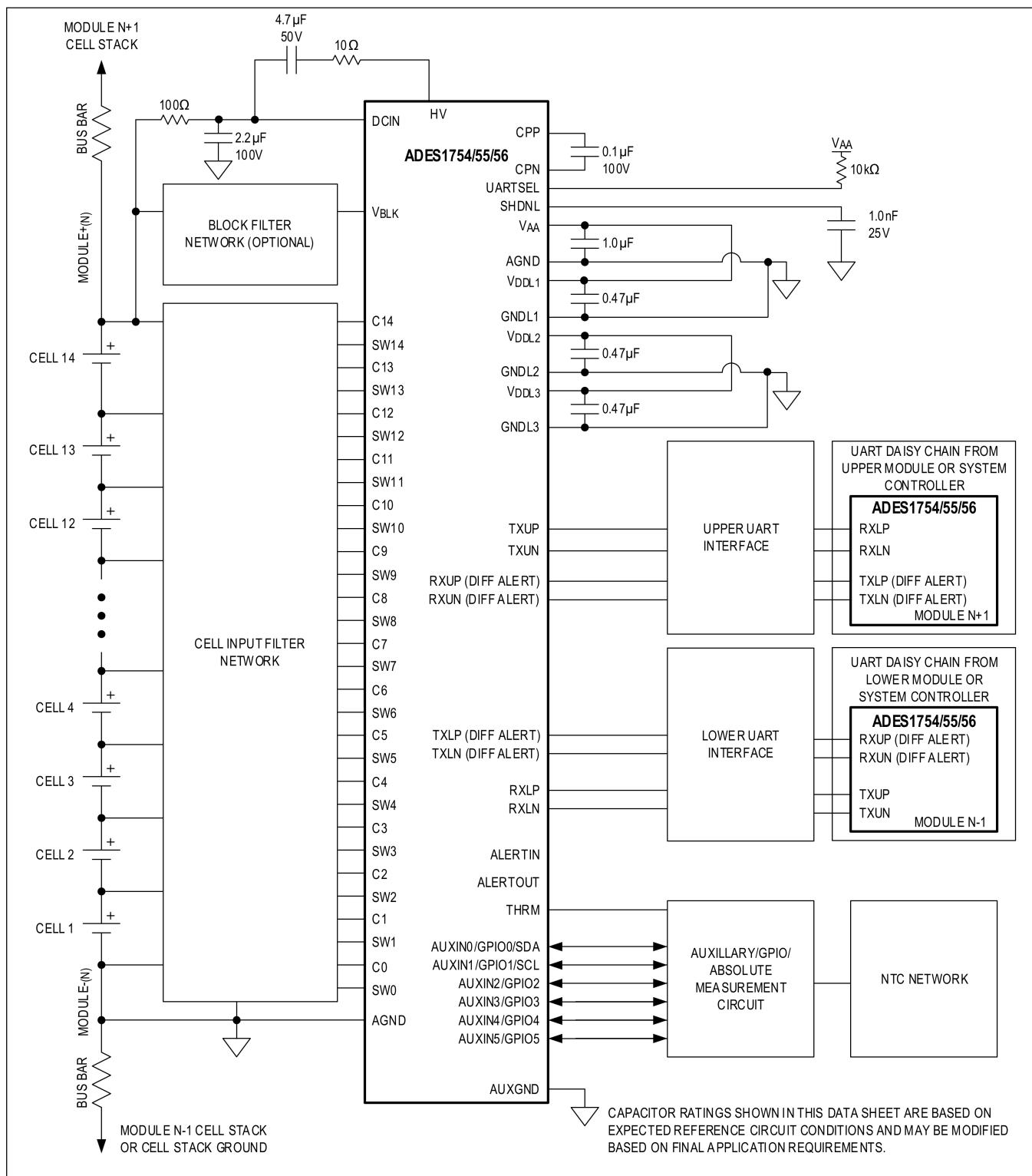

## 代表的なアプリケーションの図

### 絶対最大定格

|                                                         |                                         |

|---------------------------------------------------------|-----------------------------------------|

| HV～AGND .....                                           | -0.3V～+80V                              |

| DCIN、SWn、V <sub>BLK</sub> 、Cn～AGND .....                | -0.3V～min(V <sub>HV</sub> + 0.3 or 72)V |

| Cn～Cn-1 .....                                           | -72V～+72V                               |

| SWn～SWn-1 .....                                         | -0.3V～+52V                              |

| V <sub>AA</sub> ～AGND .....                             | -0.3V～+2.2V                             |

| V <sub>DDL1</sub> ～GNDL1 .....                          | -0.3V～+2.2V                             |

| V <sub>AA</sub> ～V <sub>DDL1</sub> .....                | -0.3V～+0.3V                             |

| V <sub>DDL2</sub> 、V <sub>DDL3</sub> ～GNDL2、GNDL3 ..... | -0.3V～6.0V                              |

| AGND～GNDL1、GNDL2、GNDL3 .....                            | -0.3V～0.3V                              |

| AGND～AUXGND .....                                       | -0.3V                                   |

| GPIOn/AUXINn .....                                      | -0.3V～V <sub>DDL2</sub> + 0.3V          |

| THRM～AGND .....                                         | -0.3V～V <sub>AA</sub> + 0.3V            |

| SHDNL～AGND .....                                        | -0.3V～V <sub>DCIN</sub> + 0.3V          |

|                                 |                                                |

|---------------------------------|------------------------------------------------|

| RXLP、RXLN、RXUP、RXUN、            |                                                |

| ALERTIN～AGND .....              | -30V～+30V                                      |

| TXLP、TXLN、ALERTOUT～GNDL2 .....  | -0.3V～+6V                                      |

| TXUP、TXUN～GNDL3 .....           | -0.3V～+6V                                      |

| CPP～AGND .....                  | V <sub>DCIN</sub> - 1V to V <sub>HV</sub> + 1V |

| CPN～AGND .....                  | -0.3V～V <sub>DCIN</sub> + 0.3V                 |

| 任意のピンへの最大連続電流 (Note 1) .....    |                                                |

| SWn ピンへの最大連続電流 (Note 2) .....   | -50mA～+50mA                                    |

| ESD ダイオードの最大平均電力 (Note 3) ..... | -650mA～+650mA                                  |

| パッケージの連続電力 (Note 4) .....       | 14.4W / √t                                     |

| 動作温度範囲 .....                    | 2000mW                                         |

| 保存温度範囲 .....                    | -40°C～+105°C                                   |

| ジャンクション温度 (連続) .....            | -55°C～+150°C                                   |

| 半田処理温度 (最大 10 秒) .....          | +150°C                                         |

|                                 | +300°C                                         |

Note 1 : バランシング・スイッチングはディスエーブル。

Note 2 : 1つのバランシング・スイッチを最大 60 秒間イネーブル。

Note 3 : 時間長 t における平均電力で、t はホットプラグ時に流れるトランジエント・ダイオード電流の時定数 (μs)。例えば、t が 330μs の場合の最大平均電力は 0.793W です。ピーク電流が 2A を超えないようにしてください。アプリケーション回路のダイオード電流波形からホットプラグ時の実際の平均電力を計算して、最大定格値と比較する必要があります。

Note 4 : 多層ボード。T<sub>A</sub> > +70°C では 25mW/°C にディレーティングしてください。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらの規定はストレス定格のみを定めたものであり、この仕様の動作セクションに記載する規定値以上でデバイスが正常に動作することを意味するものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### パッケージ情報

#### LQFP

|                                              |         |

|----------------------------------------------|---------|

| Package Code                                 | C64+13C |

| Outline Number                               | 21-0083 |

| Land Pattern Number                          | 90-0141 |

| <b>Thermal Resistance, Four Layer Board:</b> |         |

| Junction to Ambient (θ <sub>JA</sub> )       | 40°C/W  |

| Junction to Case (θ <sub>JC</sub> )          | 8°C/W   |

最新のパッケージ外形図とランド・パターン（フットプリント）に関しては、[パッケージ・インデックス](#)で確認してください。パッケージ・コードの「+」、「#」、「-」は RoHS 対応状況のみを示します。パッケージ図面は異なる末尾記号が示されている場合がありますが、図面は RoHS 状況に関わらず該当のパッケージについて図示しています。

パッケージの熱抵抗は、JEDEC 規格 JESD51-7 に記載の方法で 4 層基板を使用して求めたものです。パッケージの熱に対する考慮事項の詳細については、[IC パッケージの熱的特性評価](#)を参照してください。

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

## 電気的特性

(特に指定のない限り、 $V_{DCIN} = +56V$ 、 $T_A = T_{MIN} \sim T_{MAX}$ 。ここで、 $T_{MIN} = -40^{\circ}C$ 、 $T_{MAX} = +105^{\circ}C$ 。代表値は  $T_A = +25^{\circ}C$  における値。動作は推奨アプリケーション回路による (Note 5)。)

| PARAMETER                                                   | SYMBOL                                     | CONDITIONS                                                                                                                                             | MIN               | TYP                 | MAX               | UNITS    |

|-------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|-------------------|----------|

| <b>POWER REQUIREMENTS</b>                                   |                                            |                                                                                                                                                        |                   |                     |                   |          |

| Supply Voltage, DCIN                                        | $V_{DCIN}$                                 |                                                                                                                                                        | 9                 |                     | 65                | V        |

| Supply Voltage VDDL2,<br>VDDL3                              | $V_{DDL2}$ ,<br>$V_{DDL3}$ ,<br>$V_{DDIO}$ | $V_{DDL2} = V_{DDL3}$<br>External overdrive ( $>V_{DDL2/3\_REG}$ ) allowed.<br>Also used as $V_{DDIO}$ in I <sup>2</sup> C applications.               | $V_{DDL2/3\_REG}$ | 3.3                 | 5.5               | V        |

| DCIN Current,<br>Shutdown Mode                              | $I_{DCSHDN}$                               | $V_{SHDNL} = 0V$                                                                                                                                       |                   | 0.1                 |                   | $\mu A$  |

| DCIN Current, Standby<br>Mode                               | $I_{DCSTBY}$                               | $V_{SHDNL} > 1.8V$ , UART in idle mode; not in acquisition mode; balance switches, test current sources, and alert interface disabled; Note 6          |                   | 2.2                 | 3.1               | mA       |

| DCIN Current, ADC<br>Acquisition Mode                       | $I_{DC\_ADC}$                              | All cell and auxiliary measurements enabled, OVSAMPL[2:0] = 000b; Note 6                                                                               |                   | 4.2                 | 5                 | mA       |

| DCIN Current, COMP<br>Acquisition Mode                      | $I_{DC\_COMP}$                             | All cell and auxiliary measurements enabled, OVSAMPL[2:0] = 000b; Note 6                                                                               |                   | 4.6                 | 5.5               | mA       |

| DCIN Current, ADC +<br>COMP Acquisition Mode                | $I_{DC\_ADCCOMP}$                          | All cell and auxiliary measurements enabled; Note 6                                                                                                    |                   | 5.4                 | 6.4               | mA       |

| DCIN Incremental<br>Current, UART<br>Communication          | $I_{DCCOMM\_UART}$                         | Baud rate = 2Mbps (0% idle time preambles mode), 200pF load on TXUP and TXUN, TXL not active, not in acquisition mode, BALSWEN, CTSTEN = 0000h; Note 6 |                   | 160                 | 230               | $\mu A$  |

| HV Current, ADC<br>Acquisition Mode                         | $I_{HVMEAS}$                               | ADC-only acquisition, all cells and auxiliary channels enabled, $V_{HV} = V_{DCIN} + 5.5V$                                                             | 0.7               | 0.9                 | 1.1               | mA       |

| HV Current, Comparator<br>Scan Mode                         | $I_{HVCOMP}$                               | COMP only acquisition, all cells and auxiliary channels enabled, $V_{HV} = V_{DCIN} + 5.5V$                                                            | 0.7               | 0.9                 | 1.1               | mA       |

| Incremental HV Current,<br>Cell-Balancing Mode              | $I_{HVBAL}$                                | $V_{HV} = V_{DCIN} + 5.5V$ , n balancing switches enabled                                                                                              | $(n+1) \times 5$  | $(n+1) \times 15.5$ | $(n+1) \times 26$ | $\mu A$  |

| <b>CELL VOLTAGE INPUTS (C<sub>n</sub>, V<sub>BLK</sub>)</b> |                                            |                                                                                                                                                        |                   |                     |                   |          |

| Differential Input Range                                    | $V_{CELLn}$                                | Unipolar mode, Note 7                                                                                                                                  | 0                 |                     | 5                 | V        |

|                                                             |                                            | Bipolar mode, Note 7                                                                                                                                   |                   | -2.5                | 2.5               |          |

| Common-Mode Input<br>Range                                  | $V_{CnCM}$                                 | Not connected to SW <sub>n</sub> inputs                                                                                                                | 0                 |                     | 65                | V        |

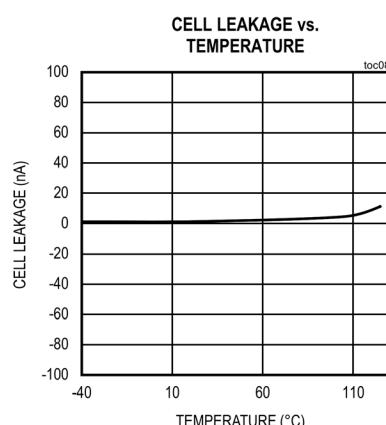

| Input Leakage Current                                       | $I_{LKG\_Cn}$                              | Not in acquisition mode, $V_{Cn} = 65V$                                                                                                                | -100              | $\pm 10$            | 100               | nA       |

| $V_{BLK}$ Input Resistance                                  | $R_{VBLK}$                                 | $V_{BLK} = V_{DCIN} = 57.6V$                                                                                                                           | 4.5               | 10                  | 20                | MΩ       |

| HVMUX Switch<br>Resistance                                  | $R_{HVMUX}$                                | CTSTDAC[3:0] = Fh                                                                                                                                      | 1.7               | 3.3                 | 5                 | kΩ       |

| <b>CELL-BALANCING INPUTS (SW<sub>n</sub>)</b>               |                                            |                                                                                                                                                        |                   |                     |                   |          |

| Leakage Current                                             | $I_{LKG\_SW}$                              | $V_{SW0} = 0V$ , $V_{SWn} = 5V$ , $V_{SWn-1} = 0V$                                                                                                     | -1.0              |                     | +1.0              | $\mu A$  |

| Resistance, SW <sub>n</sub> to<br>SW <sub>n-1</sub>         | $R_{SW}$                                   | $BALSWEN[n-1] = 1$ , $I_{SWn} = 100mA$                                                                                                                 | 0.5               | 1.25                | 2.25              | $\Omega$ |

|                                                             |                                            | $BALSWEN[n-1] = 1$ , $I_{SWn} = 300mA$ ; Note 8                                                                                                        |                   |                     | 1.3               |          |

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

(特に指定のない限り、 $V_{DCIN} = +56V$ 、 $T_A = T_{MIN} \sim T_{MAX}$ 。ここで、 $T_{MIN} = -40^\circ C$ 、 $T_{MAX} = +105^\circ C$ 。代表値は  $T_A = +25^\circ C$  における値。動作は推奨アプリケーション回路による (Note 5)。)

| PARAMETER                            | SYMBOL           | CONDITIONS                                                                                                                             | MIN  | TYP          | MAX  | UNITS    |

|--------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|--------------|------|----------|

| Maximum Allowed Balancing Current    | $I_{BAL\_MAX}$   | $T_J = +105^\circ C$ , CBMEASEN = 0x00, FLXPCKEN1/2 = 0, all even or all odd channels enabled. Note 9                                  |      | 650          |      | mA       |

| <b>AUXILIARY INPUTS (AUXINn)</b>     |                  |                                                                                                                                        |      |              |      |          |

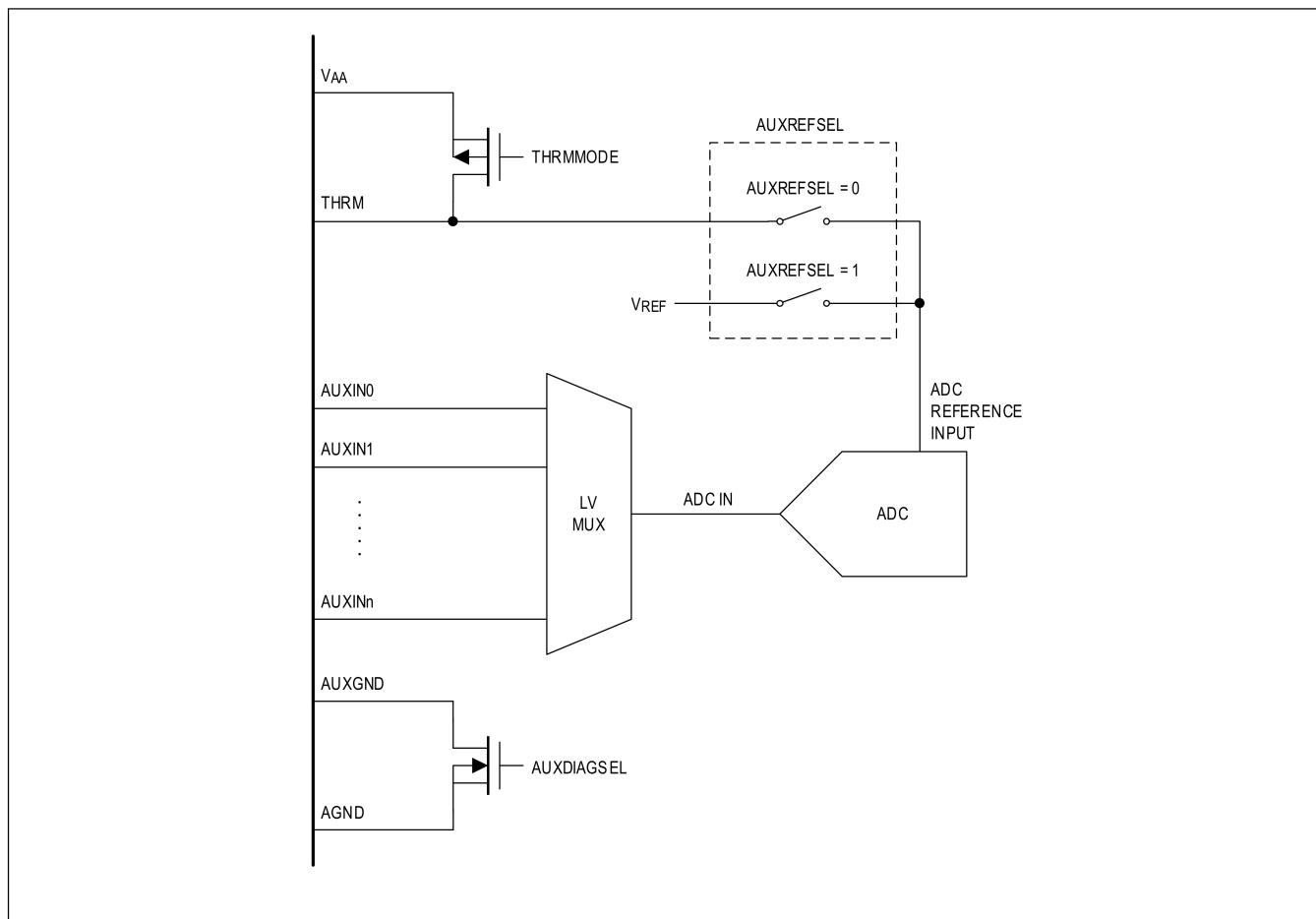

| Input Voltage Range                  | $V_{AUXIN}$      | $V_{ADCREF} = V_{THRIM}$ or $V_{REF}$ based on AUXREFSEL                                                                               | 0    | $V_{ADCREF}$ |      | V        |

| Input Leakage Current                | $I_{LKG\_AUX}$   | Not in acquisition mode, $V_{AUXINn} = 1.65V$                                                                                          | -400 | +10          | +400 | nA       |

| <b>THRIM OUTPUT</b>                  |                  |                                                                                                                                        |      |              |      |          |

| Switch Resistance, $V_{AA}$ to THRIM | $R_{THRIM}$      |                                                                                                                                        |      | 25           | 70   | $\Omega$ |

| Leakage Current                      | $I_{LKG\_THRIM}$ | $V_{THRIM} = V_{AA}$                                                                                                                   | -1   |              | +1   | $\mu A$  |

| <b>MEASUREMENT ACCURACY</b>          |                  |                                                                                                                                        |      |              |      |          |

| ADC Measurement Error, HVMUX Inputs  | $V_{CELLnERR}$   | Unipolar mode; $V_{CELLn} = 3.6V$ ; SCANMODE = 0x0, 0x1; Note 10                                                                       |      | $\pm 200$    |      | $\mu V$  |

|                                      |                  | Unipolar mode; $0.2V \leq V_{CELLn} \leq 4.8V$ ; $+5^\circ C < \text{temp} < +65^\circ C$ ; SCANMODE = 0x0, 0x1; Note 10               | -1.8 |              | +1.8 | mV       |

|                                      |                  | Unipolar mode; $0.2V \leq V_{CELLn} \leq 4.8V$ ; $-40^\circ C < \text{temp} < +105^\circ C$ ; SCANMODE = 0x0, 0x1; Note 10 (ADES1754)  | -2.2 |              | +2.2 |          |

|                                      |                  | Unipolar mode; $0.2V \leq V_{CELLn} \leq 4.8V$ ; $-40^\circ C < \text{temp} < +105^\circ C$ ; SCANMODE = 0x0, 0x1; Note 10 (ADES1755)  | -5   |              | +5   |          |

|                                      |                  | Unipolar mode; $0.2V \leq V_{CELLn} \leq 4.8V$ ; $-40^\circ C < \text{temp} < +105^\circ C$ ; SCANMODE = 0x0, 0x1; Note 10 (ADES1756)  | -10  |              | +10  |          |

|                                      |                  | Bipolar mode; $V_{CELLn} = 1.1V$ ; SCANMODE = 0x0, 0x1; Note 10                                                                        |      | $\pm 200$    |      | $\mu V$  |

|                                      |                  | Bipolar mode; $-2.3V \leq V_{CELLn} \leq +2.3V$ ; $+5^\circ C < \text{temp} < +65^\circ C$ ; SCANMODE = 0x0, 0x1; Note 10              | -1.8 |              | +1.8 | mV       |

|                                      |                  | Bipolar mode; $-2.3V \leq V_{CELLn} \leq +2.3V$ ; $-40^\circ C < \text{temp} < +105^\circ C$ ; SCANMODE = 0x0, 0x1; Note 10 (ADES1754) | -2.2 |              | +2.2 |          |

|                                      |                  | Bipolar mode; $-2.3V \leq V_{CELLn} \leq +2.3V$ ; $-40^\circ C < \text{temp} < +105^\circ C$ ; SCANMODE = 0x0, 0x1; Note 10 (ADES1755) | -5   |              | +5   |          |

|                                      |                  | Bipolar mode; $-2.3V \leq V_{CELLn} \leq +2.3V$ ; $-40^\circ C < \text{temp} < +105^\circ C$ ; SCANMODE = 0x0, 0x1; Note 10 (ADES1756) | -10  |              | +10  |          |

| ADC Measurement Error, ALTMUX Inputs | $V_{SWnERR}$     | Unipolar mode; $V_{CELL} = 3.6V$ ; SCANMODE = 0x0, 0x1; Note 10                                                                        |      | $\pm 200$    |      | $\mu V$  |

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

(特に指定のない限り、 $V_{DCIN} = +56V$ 、 $T_A = T_{MIN} \sim T_{MAX}$ 。ここで、 $T_{MIN} = -40^\circ C$ 、 $T_{MAX} = +105^\circ C$ 。代表値は  $T_A = +25^\circ C$  における値。動作は推奨アプリケーション回路による (Note 5)。)

| PARAMETER                                       | SYMBOL                 | CONDITIONS                                                                               | MIN  | TYP       | MAX  | UNITS         |

|-------------------------------------------------|------------------------|------------------------------------------------------------------------------------------|------|-----------|------|---------------|

|                                                 |                        | Unipolar mode; $0.2V \leq V_{CELLn} \leq 4.8V$ ; SCANMODE = 0x0, 0x1; Note 10 (ADES1754) | -2.2 |           | +2.2 | mV            |

|                                                 |                        | Unipolar mode; $0.2V \leq V_{CELLn} \leq 4.8V$ ; SCANMODE = 0x0, 0x1; Note 10 (ADES1755) | -5   |           | +5   |               |

|                                                 |                        | Unipolar mode; $0.2V \leq V_{CELLn} \leq 4.8V$ ; SCANMODE = 0x0, 0x1; Note 10 (ADES1756) | -10  |           | +10  |               |

|                                                 |                        | Bipolar mode; $V_{CELLn} = 1.1V$ ; SCANMODE = 0x0, 0x1; Note 10                          |      | $\pm 200$ |      | $\mu V$       |

|                                                 |                        | Bipolar mode; $0 \leq V_{CELLn} \leq 2.3V$ ; SCANMODE = 0x0, 0x1 (ADES1754)              | -2.2 |           | +2.2 | mV            |

|                                                 |                        | Bipolar mode; $0 \leq V_{CELLn} \leq 2.3V$ ; SCANMODE = 0x0, 0x1 (ADES1755)              | -5   |           | +5   |               |

|                                                 |                        | Bipolar mode; $0 \leq V_{CELLn} \leq 2.3V$ ; SCANMODE = 0x0, 0x1 (ADES1756)              | -10  |           | +10  |               |

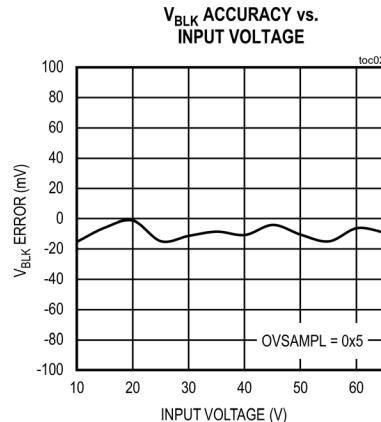

| ADC Measurement Error, $V_{BLK}$ Input          | $V_{BLKERR}$           | $9V \leq V_{BLK} \leq 64.4V$ ; $V_{DCIN} = 64.4V$ ; SCANMODE = 0x0, 0x1; Note 11         | -160 |           | +160 | mV            |

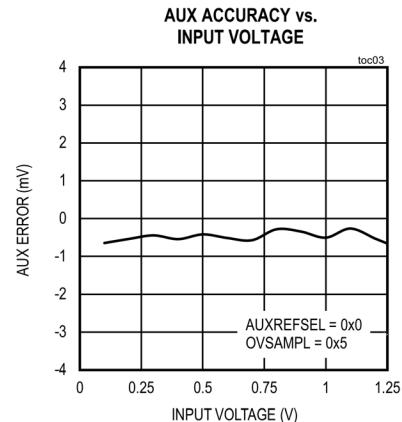

| ADC Measurement Error, Ratiometric AUXIN Inputs | $V_{OS\_AUX\_RAT\_IO}$ | AUXREF[n] = 0b; SCANMODE = 0x0, 0x1; OVSAMPL != 0x0; Note 11                             | -3.5 |           | +3.5 | mV            |

| ADC Measurement Error, Absolute AUXIN Inputs    | $V_{OS\_AUX\_ABS}$     | AUXREF[n] = 1b; SCANMODE = 0x0, 0x1; Note 11                                             | -4   |           | +4   | mV            |

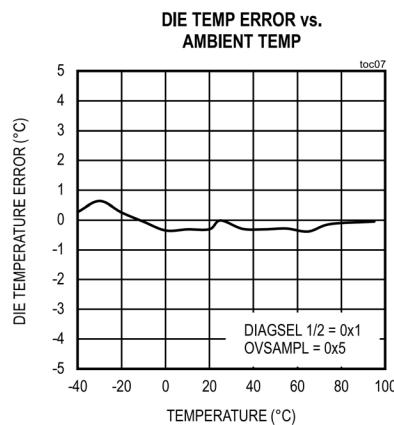

| Total Measurement Error, Die Temperature        | $T_{DIE\_ERR}$         | $T_J = -40^\circ C$ to $+105^\circ C$ ; OVSAMPL[2:0] = 000b; Note 8                      | -5   | 0         | +5   | $^\circ C$    |

| Cell Input Referred Noise                       | $V_{CELLNOISE}$        | OVSAMPL[2:0] = 0x3h; Note 8                                                              |      | 250       |      | $\mu V_{RMS}$ |

| Auxiliary Input Referred Noise                  | $V_{AUXNOISE}$         | OVSAMPL[2:0] = 0x3h; Note 8                                                              |      | 50        |      | $\mu V_{RMS}$ |

| Differential Nonlinearity (Any Conversion)      | DNL                    |                                                                                          |      | $\pm 1.0$ |      | LSb           |

| ADC Resolution                                  |                        |                                                                                          |      | 12        |      | bits          |

| Level-Shifting Amplifier Offset                 | $V_{OS\_LSAMP}$        | DIAGSEL[2:0] = 011b; Note 12                                                             | -2   | +0.1      | +2   | mV            |

| <b>COMPARATOR</b>                               |                        |                                                                                          |      |           |      |               |

| Input Common-Mode Range                         | $V_{CM\_COMP}$         |                                                                                          | 0    |           | 65   | V             |

| Input Differential Mode Range                   | $V_{DM\_COMP}$         |                                                                                          | 0    |           | 5    | V             |

| Comparator Accuracy CELL                        | $V_{OS\_COMP\_CELL}$   | $0.2V \leq V_{CELLn} \leq 4.8V$                                                          | -20  |           | +20  | mV            |

| Comparator Accuracy AUX                         | $V_{OS\_COMP\_AUX}$    | $0V \leq V_{AUXn} \leq V_{AA}$                                                           | -20  |           | +20  | mV            |

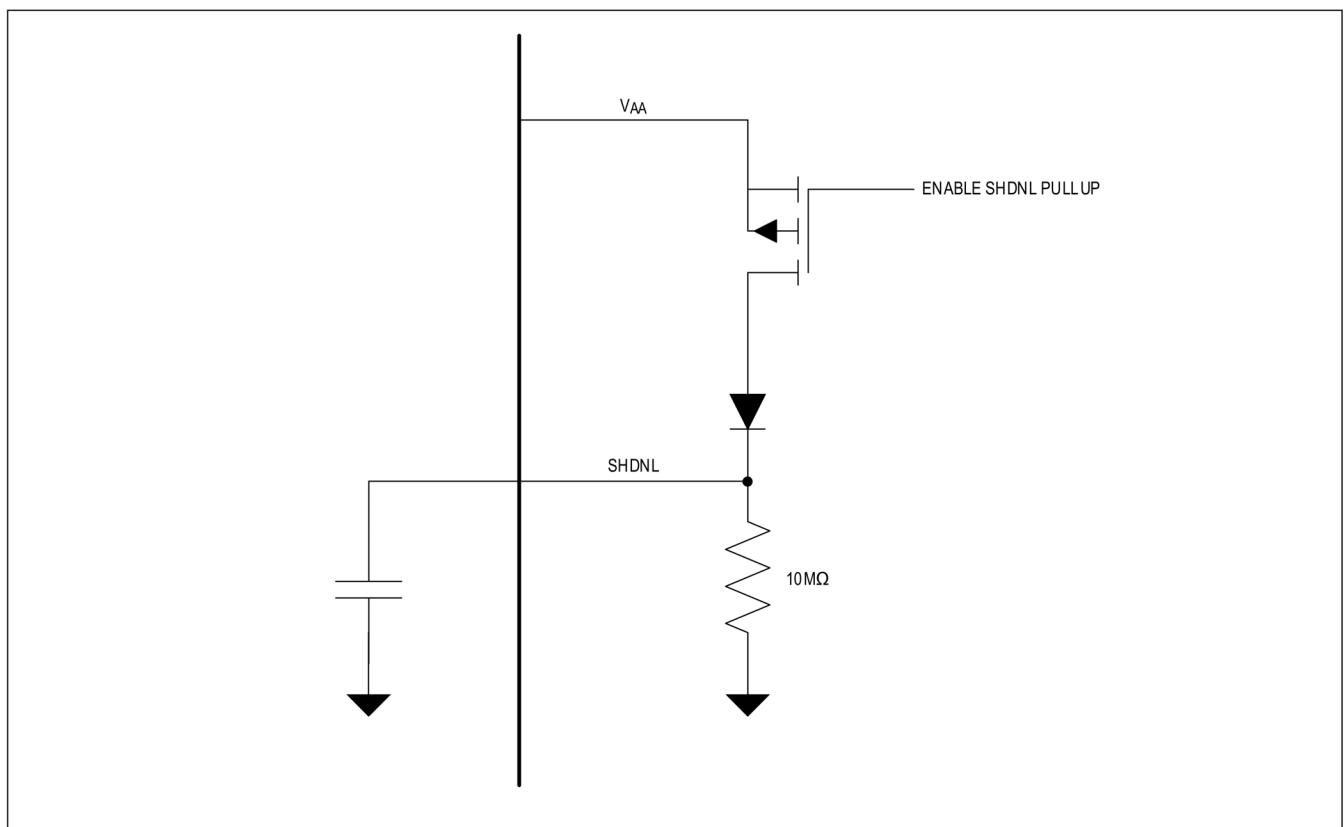

| <b>SHDNL INPUT AND CHARGE PUMP</b>              |                        |                                                                                          |      |           |      |               |

| Input Low Voltage                               | $V_{IL\_SHDNL}$        |                                                                                          |      |           | 0.6  | V             |

| Input High Voltage                              | $V_{IH\_SHDNL}$        |                                                                                          | 1.8  |           |      | V             |

| Regulated Voltage                               | $V_{SHDNLIMIT}$        | $V_{DCIN} \geq 12V$                                                                      | 7    | 10.8      | 14   | V             |

|                                                 |                        | $V_{DCIN} = 9V$                                                                          |      |           | 8.5  |               |

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

(特に指定のない限り、 $V_{DCIN} = +56V$ 、 $T_A = T_{MIN} \sim T_{MAX}$ 。ここで、 $T_{MIN} = -40^\circ C$ 、 $T_{MAX} = +105^\circ C$ 。代表値は  $T_A = +25^\circ C$  における値。動作は推奨アプリケーション回路による (Note 5)。)

| PARAMETER                                                            | SYMBOL                 | CONDITIONS                                               | MIN                    | TYP                   | MAX                    | UNITS            |

|----------------------------------------------------------------------|------------------------|----------------------------------------------------------|------------------------|-----------------------|------------------------|------------------|

| Pull-down Resistance                                                 | $R_{FORCEPOR}$         | $FORCEPOR = 1$                                           | 200                    | 500                   | 800                    | $\Omega$         |

| Input Leakage Current                                                | $I_{LKG\_SHDNL}$       | $V_{SHDNL} = 3.3V$                                       |                        |                       | 1                      | $\mu A$          |

|                                                                      |                        | $V_{SHDNL} = 65V$                                        |                        | 40                    | 75                     |                  |

| Charge Pump Current - UARTL/UARTU                                    | $I_{SHDNL}$            | $V_{SHDNL} < V_{SHDNLIMIT}$ ; baud rate = 2Mbps; Note 13 | 15                     | 117                   | 350                    | $\mu A$          |

| <b>UARTSEL</b>                                                       |                        |                                                          |                        |                       |                        |                  |

| UARTSEL Input High Voltage                                           | $V_{IH\_UARTSEL}$      |                                                          | $0.7 \times V_{AA}$    |                       |                        | V                |

| <b>GENERAL-PURPOSE I/O (GPIOn)</b>                                   |                        |                                                          |                        |                       |                        |                  |

| Input Low Voltage                                                    | $V_{IL\_GPIO}$         |                                                          |                        | $0.3 \times V_{DDL2}$ |                        | V                |

| Input High Voltage                                                   | $V_{IH\_GPIO}$         |                                                          | $0.7 \times V_{DDL2}$  |                       |                        | V                |

| Pull-down Resistance                                                 | $R_{GPIO}$             | AUXINn/GPIOn configured as GPIO input                    | 0.5                    | 2                     | 7.5                    | $M\Omega$        |

| Output Low Voltage                                                   | $V_{OL\_GPIO}$         | $I_{SINK} = 4mA$                                         |                        |                       | 0.4                    | V                |

| Output High Voltage                                                  | $V_{OH\_GPIO}$         | $I_{SOURCE} = 4mA$                                       | $V_{DDL2} - 0.4$       |                       |                        | V                |

| <b>ALERTIN</b>                                                       |                        |                                                          |                        |                       |                        |                  |

| ALERTIN Comparator Threshold                                         | $V_{CL}$               |                                                          | $V_{DDL2/3} / 2 - 0.4$ | $V_{DDL2/3} / 2$      | $V_{DDL2/3} / 2 + 0.4$ | V                |

| ALERTIN Comparator Hysteresis                                        | $V_{HYS\_ALERTIN}$     |                                                          |                        | 75                    |                        | mV               |

| ALERTIN Common-Mode Voltage Bias                                     | $V_{CM}$               |                                                          | $V_{DDL2/3} / 2$       |                       |                        | V                |

| Leakage Current                                                      | $I_{LKG\_ALERTIN}$     | $V_{ALERTIN} = 1.5V$                                     |                        | $\pm 1.0$             |                        | $\mu A$          |

| Input Capacitance                                                    | $C_{ALERTIN}$          |                                                          |                        | 2                     |                        | pF               |

| Bit Period                                                           | $t_{BIT}$              | Note 14                                                  |                        | 8                     |                        | $1/f_{OSC\_16M}$ |

| ALERTIN Fall Time                                                    | $t_{ALERTIN\_FALL}$    | Note 8, Note 15                                          |                        |                       | 0.5                    | $t_{BIT}$        |

| ALERTIN Rise Time                                                    | $t_{ALERTIN\_RISE}$    | Note 8, Note 15                                          |                        |                       | 0.5                    | $t_{BIT}$        |

| ALERTIN Qualification Time                                           | $t_{ALERTIN\_QUAL}$    |                                                          |                        | 25                    |                        | $\mu s$          |

| Propagation Delay (ALERTIN Port to ALERTOUT Port)                    | $t_{ALERT\_PROP}$      |                                                          |                        | 2.5                   | 3                      | $t_{BIT}$        |

| Start-Up Time from SHNDL High and $V_{AA} = 0V$ to ALERTIN Valid     | $t_{ALERTIN\_STARTUP}$ |                                                          |                        | 1                     |                        | ms               |

| <b>ALERTOUT</b>                                                      |                        |                                                          |                        |                       |                        |                  |

| Output Low Voltage                                                   | $V_{OL\_ALERTOUT}$     | $I_{SINK} = 20mA$                                        |                        |                       | 0.4                    | V                |

| Output High Voltage                                                  | $V_{OH\_ALERTOUT}$     | $I_{SOURCE} = 20mA$                                      | $V_{DDL2} - 0.4$       |                       |                        | V                |

| Leakage Current                                                      | $I_{LKG\_ALERTOUT}$    | $V_{ALERTOUT} = 1.5V$                                    | -1                     |                       | +1                     | $\mu A$          |

| <b>3.3V REGULATOR (<math>V_{DDL2}</math>, <math>V_{DDL3}</math>)</b> |                        |                                                          |                        |                       |                        |                  |

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

(特に指定のない限り、 $V_{DCIN} = +56V$ 、 $T_A = T_{MIN} \sim T_{MAX}$ 。ここで、 $T_{MIN} = -40^\circ C$ 、 $T_{MAX} = +105^\circ C$ 。代表値は  $T_A = +25^\circ C$  における値。動作は推奨アプリケーション回路による (Note 5)。)

| PARAMETER                                                | SYMBOL                  | CONDITIONS                                                                   | MIN   | TYP    | MAX   | UNITS   |

|----------------------------------------------------------|-------------------------|------------------------------------------------------------------------------|-------|--------|-------|---------|

| 3.3V Regulator Output Voltage                            | $V_{DDL2/3\_REG}$       | $0 \leq I_{DDL2/3} < 30mA$                                                   | 3.2   | 3.3    | 3.4   | V       |

| Short-Circuit Current                                    | $I_{DDL2/3\_SC}$        | $V_{DDL2/3}$ shorted to AGND                                                 | 30    |        |       | mA      |

| <b>1.8V REGULATOR (V<sub>AA</sub>)</b>                   |                         |                                                                              |       |        |       |         |

| 1.8V Regulator Output Voltage                            | $V_{AA}$                | $0 \leq I_{AA} < 3mA$                                                        | 1.71  | 1.8    | 1.89  | V       |

| Short-Circuit Current                                    | $I_{AA\_SC}$            | $V_{AA}$ shorted to AGND                                                     | 10    |        |       | mA      |

| POR Threshold                                            | $V_{1.8REG\_POR\_RISE}$ | $V_{AA}$ rising                                                              | 1.3   | 1.5    | 1.65  | V       |

|                                                          | $V_{1.8REG\_POR\_HYS}$  |                                                                              |       | 50     |       | mV      |

| <b>THERMAL SHUTDOWN</b>                                  |                         |                                                                              |       |        |       |         |

| Thermal Shutdown Temperature                             | $T_{SHDN}$              | Temperature rising; Note 8                                                   |       | +145   |       | °C      |

| Thermal Shutdown Hysteresis                              | $T_{HYS}$               | Note 8                                                                       |       | 15     |       | °C      |

| <b>HV CHARGE PUMP</b>                                    |                         |                                                                              |       |        |       |         |

| Output Voltage (V <sub>HV</sub> - V <sub>DCIN</sub> )    | $V_{HV-DCIN}$           | $9V \leq V_{DCIN} \leq 12V$ , $I_{LOAD} = 1.5mA$                             | 6.5   | 6.9    | 7.4   | V       |

|                                                          |                         | $12V \leq V_{DCIN} \leq 65V$ , $I_{LOAD} = 3mA$                              | 6.5   | 6.9    | 7.4   |         |

| Output Voltage (V <sub>HV</sub> - V <sub>TOPCELL</sub> ) | $V_{HV-DCIN\_FLEX}$     | $14V \leq V_{DCIN} \leq 65V$ , $I_{LOAD} = 3mA$ , FLXPCKEN1/2 = 1b           | 8.0   | 8.5    | 9.0   | V       |

| Charge Pump Efficiency                                   | $Eff_{HVCP}$            | $V_{DCIN} = 57.6V$ ; Note 16                                                 |       | 38     |       | %       |

| <b>OSCILLATORS</b>                                       |                         |                                                                              |       |        |       |         |

| LFOSC Frequency                                          | $f_{LFOSC}$             |                                                                              | 32.11 | 32.768 | 33.42 | kHz     |

| HFOSC Frequency                                          | $f_{HFOSC}$             |                                                                              | 15.68 | 16     | 16.32 | MHz     |

| <b>DIAGNOSTIC TEST SOURCES</b>                           |                         |                                                                              |       |        |       |         |

| Cell Test Source Current                                 | $I_{TSTCn}$             | $CTSTDAC[3:0] = 9h$ , $V_{C0} < V_{DDL2/3} - 1.4V$ , $V_{DDL2/3} = 3.3V$     | 50    | 62.5   | 75    | $\mu A$ |

|                                                          |                         | $CTSTDAC[3:0] = 6h$ , $V_{C0} < V_{DDL2/3} - 1.4V$ , $V_{DDL2/3} = 3.3V$     | 36    | 45     | 54    |         |

|                                                          |                         | $CTSTDAC[3:0] = 6h$ , $V_{C1-C14} > V_{AGND} + 1.4V$                         | -54   | -45    | -36   |         |

|                                                          |                         | $CTSTDAC[3:0] = 9Fh$ , $V_{C1-C14} > V_{AGND} + 1.4V$                        | -75   | -62.5  | -50   |         |

| HVMUX Test Source Current                                | $I_{TSTHVMUX}$          | $CTSTDAC[3:0] = 9h$ , $V_{Cn} < V_{HV} - 1.4V$ , $V_{HV} = 53.5V$            | 25    | 31.25  | 37.5  | $\mu A$ |

|                                                          |                         | $CTSTDAC[3:0] = 6h$ , $V_{Cn} < V_{HV} - 1.4V$ , $V_{HV} = 53.5V$            | 18    | 22.5   | 27    |         |

| AUXIN Test Source Current                                | $I_{TSTAUXIN}$          | $CTSTDAC[3:0] = 9h$ , $V_{AUXINn} < V_{DDL2/3} - 1.4V$ , $V_{DDL2/3} = 3.3V$ | 50    | 62.5   | 75    | $\mu A$ |

|                                                          |                         | $CTSTDAC[3:0] = 6h$ , $V_{AUXINn} < V_{DDL2/3} - 1.4V$ , $V_{DDL2/3} = 3.3V$ | 36    | 45     | 54    |         |

|                                                          |                         | $CTSTDAC[3:0] = 6h$ , $V_{AUXINn} > V_{AGND} + 1.4V$                         | -54   | -45    | -36   |         |

|                                                          |                         | $CTSTDAC[3:0] = 9h$ , $V_{AUXINn} > V_{AGND} + 1.4V$                         | -75   | -62.5  | -50   |         |

| <b>DIAGNOSTIC REFERENCES</b>                             |                         |                                                                              |       |        |       |         |

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

(特に指定のない限り、 $V_{DCIN} = +56V$ 、 $T_A = T_{MIN} \sim T_{MAX}$ 。ここで、 $T_{MIN} = -40^\circ C$ 、 $T_{MAX} = +105^\circ C$ 。代表値は  $T_A = +25^\circ C$  における値。動作は推奨アプリケーション回路による (Note 5)。)

| PARAMETER                                                       | SYMBOL              | CONDITIONS                                                             | MIN               | TYP         | MAX               | UNITS           |

|-----------------------------------------------------------------|---------------------|------------------------------------------------------------------------|-------------------|-------------|-------------------|-----------------|

| ALTREF Voltage                                                  | $V_{ALTREF}$        | DIAGSEL[2:0] = 001b; Note 12                                           | 0.99              | 1.00        | 1.01              | V               |

|                                                                 |                     | DIAGSEL[2:0] = 001b; $5^\circ C < \text{temp} < +65^\circ C$ ; Note 12 | 0.995             | 1.00        | 1.005             |                 |

| ALTREF Temperature Coefficient ( $\Delta V_{ALTREF}/\Delta T$ ) | $A_{ALTREF}$        | Note 8                                                                 |                   | $\pm 25$    |                   | ppm/ $^\circ C$ |

| PTAT Output Voltage                                             | $V_{PTAT}$          | $T_J = +120^\circ C$ ; Note 8                                          |                   | 1.14        |                   | V               |

| PTAT Temperature Coefficient ( $\Delta V_{PTAT}/\Delta T$ )     | $A_{V\_PTAT}$       | Note 8                                                                 |                   | 2.87        |                   | mV/ $^\circ C$  |

| PTAT Temperature Offset                                         | $T_{OS\_PTAT}$      | Note 8                                                                 |                   | -4.4        |                   | $^\circ C$      |

| <b>ALERTS</b>                                                   |                     |                                                                        |                   |             |                   |                 |

| ALRTVDDL1 Threshold                                             | $V_{VDDL1\_OC}$     | $V_{AA} = 1.8V$                                                        | 1.62              | 1.65        | 1.68              | V               |

| ALRTVDDL2/3 Threshold                                           | $V_{VDDL2/3\_OC}$   | $V_{DDL2/3} = 3.3V$                                                    | 2.9               | 3.0         | 3.1               | V               |

| ALRTGNDL <sub>n</sub> Threshold                                 | $V_{GNDL\_OC}$      | $AGND = 0V$                                                            | 0.05              | 0.15        | 0.3               | V               |

| ALRTHVUV Threshold                                              | $V_{HVUV}$          | $V_{HV} - V_{DCIN}$ falling, $FLXPCKEN1/2 = 0$                         | 1.8               | 2           | 2.2               | V               |

| ALRTHVOV Threshold                                              | $V_{HVOV}$          | $V_{HV} - V_{DCIN}$ rising                                             | 9.0               | 9.5         | 9.9               | V               |

| ALRTHVHDRM Threshold                                            | $V_{HVHDRM}$        | ALRTHVHDRM = 0                                                         |                   | 3.0         |                   | V               |

| ALRTTEMP Threshold                                              | $T_{ALRTTEMP}$      | Note 8                                                                 | 115               | 120         | 125               | $^\circ C$      |

| ALRTTEMP Hysteresis                                             | $T_{ALRTTEMPHY\_S}$ | Note 8                                                                 |                   | 2           |                   | $^\circ C$      |

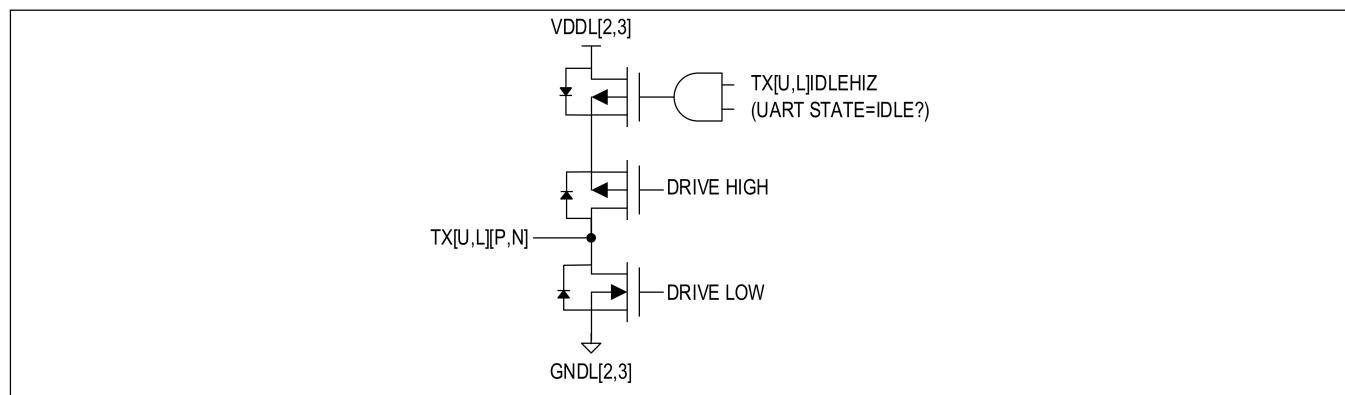

| <b>UART OUTPUTS (TXLP, TXLN, TXUP, TXUN)</b>                    |                     |                                                                        |                   |             |                   |                 |

| Output Low Voltage                                              | $V_{OL}$            | $I_{SINK} = 20mA$                                                      |                   |             | 0.4               | V               |

| Output High Voltage (TXLP, TXLN)                                | $V_{OH}$            | $I_{SOURCE} = 20mA$                                                    | $V_{DDL2} - 0.4$  |             |                   | V               |

| Output High Voltage (TXUP, TXUN)                                | $V_{OH}$            | $I_{SOURCE} = 20mA$                                                    | $V_{DDL3} - 0.4$  |             |                   | V               |

| Leakage Current                                                 | $I_{LKG\_TX}$       | $V_{TX} = 1.5V$                                                        | -1                |             | +1                | $\mu A$         |

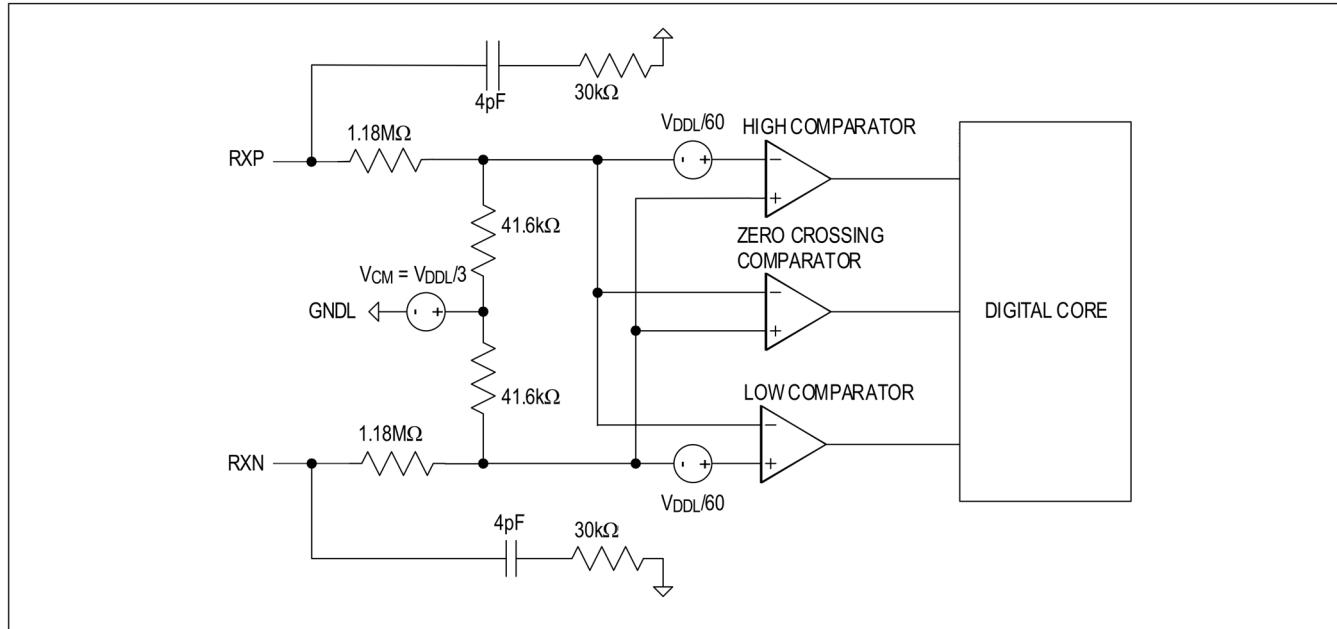

| <b>UART INPUTS (RXLP, RXLN, RXUP, RXUN)</b>                     |                     |                                                                        |                   |             |                   |                 |

| Input Voltage Range                                             | $V_{RX}$            |                                                                        | -25               |             | +25               | V               |

| Receiver High Comparator Threshold                              | $V_{CH}$            | Note 17                                                                | $V_{AA}/2 - 0.4$  | $V_{AA}/2$  | $V_{AA}/2 + 0.4$  | V               |

| Receiver Zero-Crossing Comparator Threshold                     | $V_{ZC}$            | Note 17                                                                | -0.4              | 0           | +0.4              | V               |

| Receiver Low Comparator Threshold                               | $V_{CL}$            | Note 17                                                                | $-V_{AA}/2 - 0.4$ | $-V_{AA}/2$ | $-V_{AA}/2 + 0.4$ | V               |

| Receiver Comparator Hysteresis                                  | $V_{HYS\_RX}$       | Note 17                                                                |                   | 75          |                   | mV              |

| Receiver Common-Mode Voltage Bias                               | $V_{CM}$            | Note 17                                                                |                   | $V_{AA}/2$  |                   | V               |

| Leakage Current                                                 | $I_{LKG\_RX}$       | $V_{RX} = 0.9V$                                                        |                   | $\pm 1.0$   |                   | $\mu A$         |

| Input Capacitance (RXLP, RXLN)                                  | $C_{RXL}$           |                                                                        |                   | 4           |                   | pF              |

| Input Capacitance (RXUP, RXUN)                                  | $C_{RXU}$           |                                                                        |                   | 4           |                   | pF              |

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

(特に指定のない限り、 $V_{DCIN} = +56V$ 、 $T_A = T_{MIN} \sim T_{MAX}$ 。ここで、 $T_{MIN} = -40^\circ C$ 、 $T_{MAX} = +105^\circ C$ 。代表値は  $T_A = +25^\circ C$  における値。動作は推奨アプリケーション回路による (Note 5)。)

| PARAMETER                                                          | SYMBOL                  | CONDITIONS                                                                 | MIN  | TYP  | MAX                      | UNITS                      |

|--------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------|------|------|--------------------------|----------------------------|

| <b>UART TIMING</b>                                                 |                         |                                                                            |      |      |                          |                            |

| Bit Period                                                         | t <sub>BIT</sub>        | Baud rate = 2Mbps; Note 14                                                 | 8    |      |                          | 1/f <sub>OSC_1</sub><br>6M |

|                                                                    |                         | Baud rate = 1Mbps; Note 14                                                 | 16   |      |                          |                            |

|                                                                    |                         | Baud rate = 0.5Mbps; Note 14                                               | 32   |      |                          |                            |

| Rx Idle to START Setup Time                                        | t <sub>RXSTSU</sub>     | Note 8                                                                     | 0    | 1    |                          | t <sub>BIT</sub>           |

| STOP Hold Time to Idle                                             | t <sub>SPHD</sub>       | Note 8                                                                     |      |      | 0.5                      | t <sub>BIT</sub>           |

| Rx Minimum Idle Time (STOP Bit to START Bit)                       | t <sub>RXIDLESPST</sub> | Note 8                                                                     |      | 1    |                          | t <sub>BIT</sub>           |

| Rx Fall Time                                                       | t <sub>FALL</sub>       | Note 8, Note 15                                                            |      |      | 0.5                      | t <sub>BIT</sub>           |

| Rx Rise Time                                                       | t <sub>RISE</sub>       | Note 8, Note 15                                                            |      |      | 0.5                      | t <sub>BIT</sub>           |

| Propagation Delay (Rx Port to Tx Port)                             | t <sub>PROP</sub>       |                                                                            | 2.5  | 3    |                          | t <sub>BIT</sub>           |

| Start-Up Time from SHNDL High and $V_{AA} = 0V$ to RXUP/RXUN Valid | t <sub>STARTUP</sub>    |                                                                            |      | 1    |                          | ms                         |

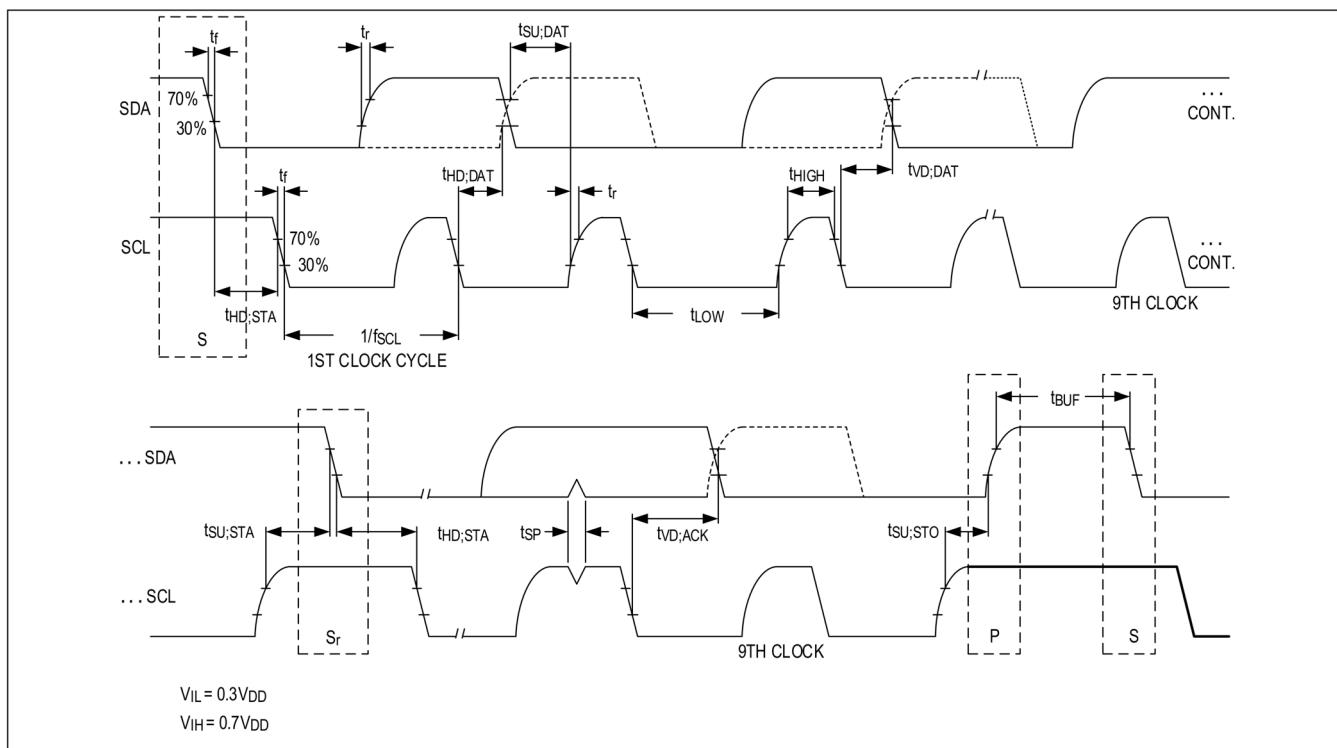

| <b>I<sup>2</sup>C</b>                                              |                         |                                                                            |      |      |                          |                            |

| Input Voltage Low                                                  | V <sub>IL</sub>         | $V_{DDL2/3} \leq V_{DDIO} \leq 5.5V$                                       |      |      | 0.3V <sub>DDI</sub><br>O | V                          |

| Input Voltage High                                                 | V <sub>IH</sub>         | $V_{DDL2/3} \leq V_{DDIO} \leq 5.5V$                                       |      |      | 0.7V <sub>DDI</sub><br>O | V                          |

| Input Voltage Hysteresis                                           | V <sub>HYST</sub>       |                                                                            |      | 0.15 |                          | V                          |

| Input Leakage Current                                              | I <sub>IN</sub>         |                                                                            | -1.0 | +0.1 | +1.0                     | µA                         |

| Input Capacitance                                                  | C <sub>IN</sub>         |                                                                            |      | 10   |                          | pF                         |

| Output Voltage Low                                                 | V <sub>OL</sub>         | I <sub>SINK</sub> = 3mA                                                    |      |      | 0.4                      | V                          |

| SCL Clock Frequency                                                | f <sub>SCL</sub>        | 400kHz mode (I2CFSCL = 1)                                                  | 0    | 400  |                          | kHz                        |

|                                                                    |                         | 100kHz mode (I2CFSCL = 0)                                                  | 0    | 100  |                          |                            |

| Hold Time for a (Repeated) START Condition                         | t <sub>HD;STA</sub>     | 400kHz mode (I2CFSCL = 1)                                                  | 0.6  |      |                          | µs                         |

|                                                                    |                         | 100kHz mode (I2CFSCL = 0)                                                  | 4.0  |      |                          |                            |

| SCL Pulse Width Low                                                | t <sub>LOW</sub>        | 400kHz mode (I2CFSCL = 1)                                                  | 1.3  |      |                          | µs                         |

|                                                                    |                         | 100kHz mode (I2CFSCL = 0)                                                  | 4.7  |      |                          |                            |

| SCL Pulse Width High                                               | t <sub>HIGH</sub>       | 400kHz mode (I2CFSCL = 1)                                                  | 0.6  |      |                          | µs                         |

|                                                                    |                         | 100kHz mode (I2CFSCL = 0)                                                  | 4.0  |      |                          |                            |

| Set-up Time for a Repeated START Condition                         | t <sub>SU;STA</sub>     | 400kHz mode (I2CFSCL = 1)                                                  | 0.6  |      |                          | µs                         |

|                                                                    |                         | 100kHz mode (I2CFSCL = 0)                                                  | 4.7  |      |                          |                            |

| Data Hold Time                                                     | t <sub>HD;DAT</sub>     | Note 18                                                                    | 0    |      |                          | ns                         |

|                                                                    |                         | Controller transmitting data                                               | 300  |      |                          |                            |

| Data Setup Time                                                    | t <sub>SU;DAT</sub>     | Controller receiving data, and 400kHz mode (I2CFSCL = 1) bus monitor check | 100  |      |                          | ns                         |

|                                                                    |                         | Controller receiving data, and 100kHz mode (I2CFSCL = 0) bus monitor check | 250  |      |                          |                            |

|                                                                    |                         | Controller transmitting data                                               | 300  |      |                          |                            |

## 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

(特に指定のない限り、 $V_{DCIN} = +56V$ 、 $T_A = T_{MIN} \sim T_{MAX}$ 。ここで、 $T_{MIN} = -40^{\circ}C$ 、 $T_{MAX} = +105^{\circ}C$ 。代表値は  $T_A = +25^{\circ}C$  における値。動作は推奨アプリケーション回路による (Note 5)。)

| PARAMETER                                        | SYMBOL       | CONDITIONS                                                                              | MIN            | TYP | MAX | UNITS   |

|--------------------------------------------------|--------------|-----------------------------------------------------------------------------------------|----------------|-----|-----|---------|

| Rise Time of SDA and SCL                         | $t_r$        |                                                                                         |                |     | 300 | ns      |

| Fall Time of SDA and SCL                         | $t_f$        |                                                                                         |                |     | 300 | ns      |

| Setup Time for STOP Condition                    | $t_{SU;STO}$ | 400kHz mode ( $I2CFSCL = 1$ )                                                           | 0.6            |     |     | $\mu s$ |

|                                                  |              | 100kHz mode ( $I2CFSCL = 0$ )                                                           | 4.0            |     |     |         |

| Bus Free Time Between a STOP and START Condition | $t_{BUF}$    | 400kHz mode ( $I2CFSCL = 1$ )                                                           | 1.3            |     |     | $\mu s$ |

|                                                  |              | 100kHz mode ( $I2CFSCL = 0$ )                                                           | 4.7            |     |     |         |

| Bus Capacitance Allowed                          | $C_b$        |                                                                                         |                |     | 400 | pF      |

| Suppressed Spike Pulse Width                     | $t_{sp}$     | Width of spikes that must be suppressed by the input filter of both SDA and SCL signals |                | 50  |     | ns      |

| Noise Margin at LOW Level                        | $V_{nL}$     | For each connected device (including hysteresis)                                        | 0.1 $V_{DDIO}$ |     |     | V       |

| Noise Margin at HIGH Level                       | $V_{nL}$     | For each connected device (including hysteresis)                                        | 0.2 $V_{DDIO}$ |     |     | V       |

Note 5 : 特に指定のない限り、制限値は  $T_A = +25^{\circ}C$  で 100% 製品テストされています。全動作温度範囲および関連電源電圧範囲での制限値は、設計と特性評価によって確認されています。

Note 6 : SCAN ビットがセットされるとアクイジション・モード (ADC 変換) になり、SCANDONE がセットされると終了します。アクイジション・デューティサイクルの代表値が非常に低いので、平均電流  $I_{DCIN}$  は  $I_{DCMEAS}$  よりはるかに小さくなります。通信中の合計電源電流は、 $I_{DCIN} = I_{DCCOMM} + I_{DCSTBY}$  です。

Note 7 : 保証測定精度範囲は、 $V_{CELLn\_min} + 0.2V$  から  $V_{CELLn\_max} - 0.2V$  までです。

Note 8 : 設計により性能は確認されていますが、出荷テストは行っていません。

Note 9 : 出荷テストは行っていません。最大許容バランス電流の詳細については、セル・バランスのセクションを参照してください。デューティサイクルは 10 年間のデバイス寿命で計算されています。

Note 10 :  $V_{CELLn} = V_{Cn} - V_{Cn-1}$ 、 $V_{CELLn} = V_{CELLn-1}$ 、および  $V_{DCIN} = 14 \times |V_{CELLn}|$  ( $V_{DCIN} = 9V$ 、最小値)。測定精度は、1LSB 未満で入力ノイズをオーバーサンプリングした場合の初期合計測定誤差を表します。

Note 11 : 測定精度は、1LSB 未満で入力ノイズをオーバーサンプリングした場合の初期合計測定誤差を表します。

Note 12 : 指定された診断モードでの測定値。

Note 13 :  $V_{SHDNL} = 0.3V$ 、STOP キャラクタ、ゼロ・アイドル時間、 $V_{RX\_PEAK} = 3.3V$  で測定した  $I_{SHDNL}$ 。

Note 14 : ディジーチェーン・アプリケーションでは、デバイス間のクロック・レート変動とサンプリング誤差を考慮して、2 つ目のストップ・ビットのビット時間を指定値未満とすることができます。

Note 15 : 立下がり時間は 90% ~ 10% で測定し、立上がり時間は 10% ~ 90% で測定。

Note 16 : チャージ・ポンプ効率 =  $\Delta I_{LOAD} / \Delta I_{SUPPLY}$  で、 $I_{LOAD}$  は HV と AGND の間に置かれ、 $\Delta I_{LOAD} = 5mA$ 、 $\Delta I_{SUPPLY} = I_{DCIN}$  (for  $I_{LOAD} = 5mA$ ) -  $I_{DCIN}$  (for  $I_{LOAD} = 0$ ) です。

Note 17 : 差動信号 ( $V_{UARTP} - V_{UARTN}$ ) で、 $V_{UARTP}$  と  $V_{UARTN}$  が  $\pm 40V$  の同相電圧範囲を超えることはありません。

Note 18 : SCL の立下がりエッジの不定領域を越えるには、デバイス内部での SDA 信号のホールド時間を 300ns 以上とする必要があります (SCL 信号の  $V_{IH\_min}$  基準)。

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

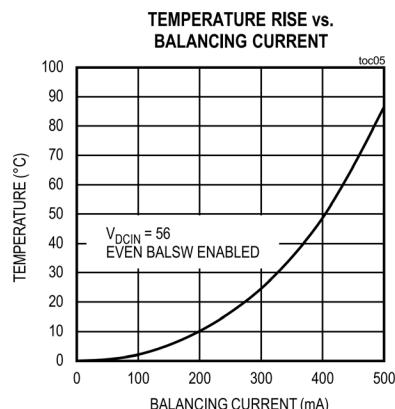

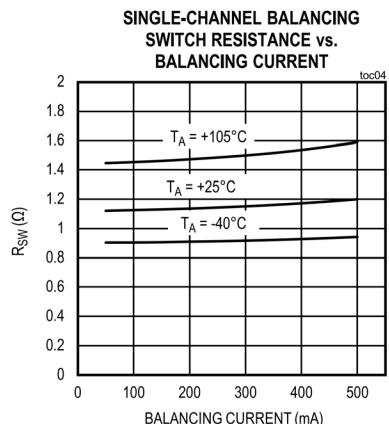

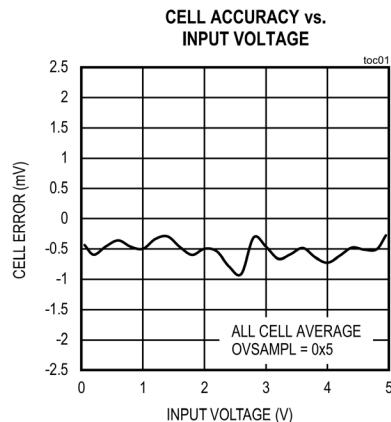

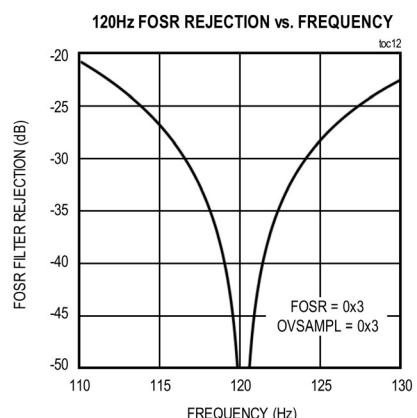

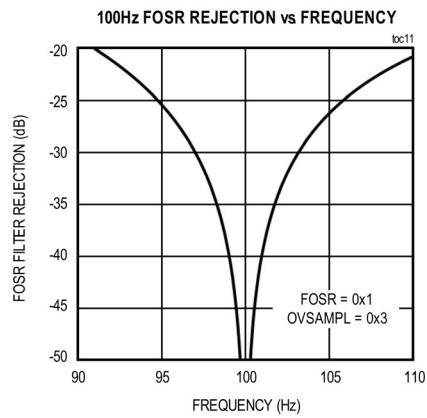

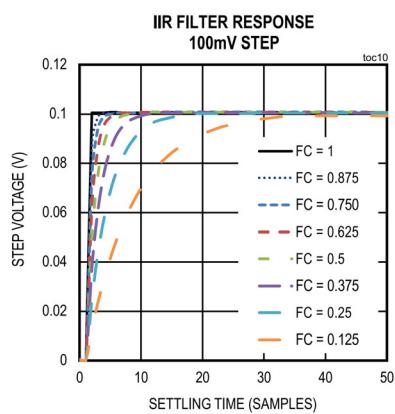

## 標準動作特性

(特に指定のない限り、DCIN = 56V、V<sub>DDL2/3</sub> = 3.3V、T<sub>A</sub> = +25°C)

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

(特に指定のない限り、DCIN = 56V、V<sub>DDL2/3</sub> = 3.3V、T<sub>A</sub> = +25°C)

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

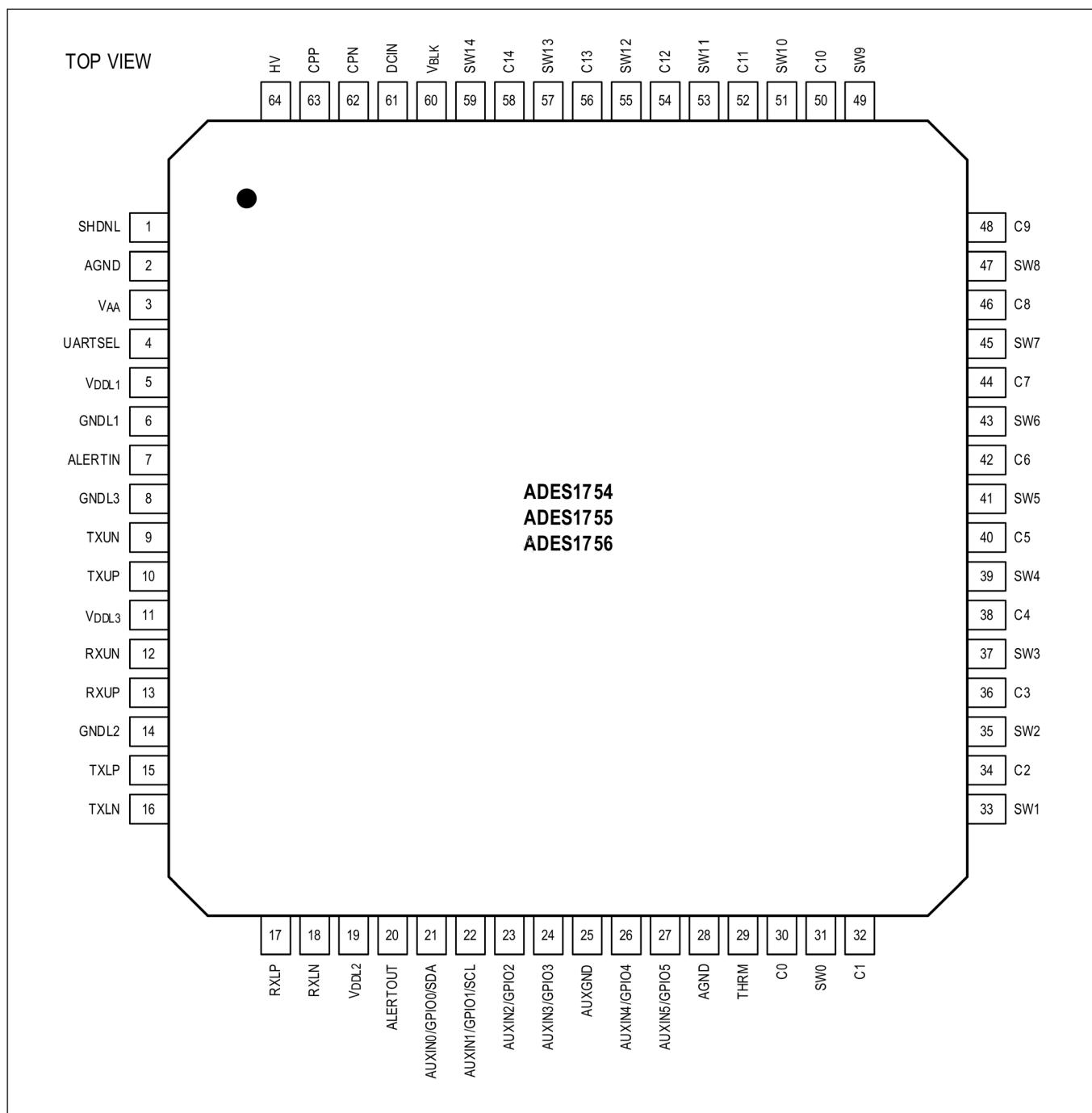

## ピン配置

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

## 端子説明

| ピン | 名称                   | 説明                                                                                                                                                                                                                                                                                                                                | リファレンス電源          | タイプ              |

|----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|

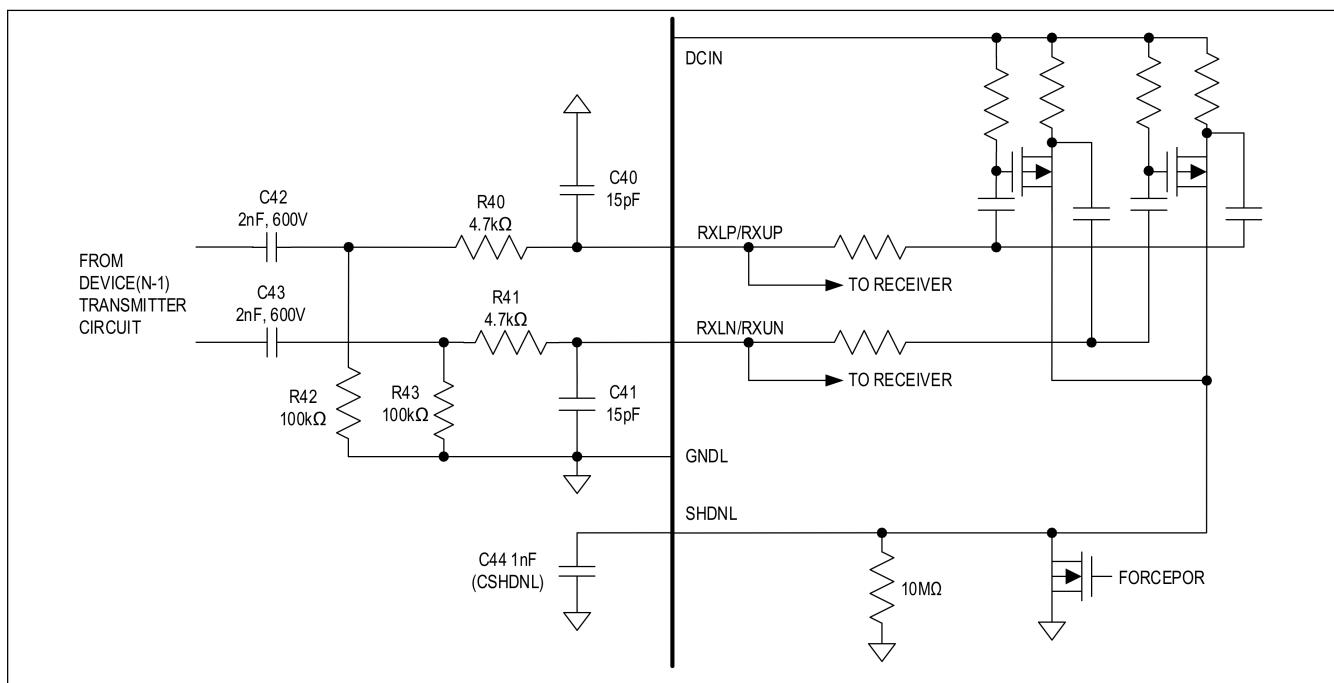

| 1  | SHDNL                | シャットダウンのアクティブ・ロー入力で、許容される電圧は+72V。1nFのコンデンサでAGNDへバイパスした場合、この入力はUART通信とソフトウェア制御のみを通じて制御されます。このピンには受動部品だけを接続してください。シングルエンドUARTの場合はSHDNLを外部的に駆動する必要があります。                                                                                                                                                                             | AGND              | Input            |

| 2  | AGND                 | アナログ・グラウンド。セル1の負端子とグランド・プレーンに接続します。                                                                                                                                                                                                                                                                                               | DCIN              | Ground           |

| 3  | V <sub>AA</sub>      | V <sub>DDL1</sub> 電源に使用する V <sub>AA</sub> (1.8V) レギュレータ出力。1μF のコンデンサで AGND にバイパスします。                                                                                                                                                                                                                                              | AGND              | Power            |

| 4  | UARTSEL              | V <sub>AA</sub> に接続します。                                                                                                                                                                                                                                                                                                           | V <sub>DDL1</sub> | Input            |

| 5  | V <sub>DDL1</sub>    | 1.8V デジタル電源。外部で V <sub>AA</sub> に接続して、0.47μF のコンデンサで GNDL1 にバイパスします。                                                                                                                                                                                                                                                              | GNDL1             | Power            |

| 6  | GNDL1                | デジタル・グラウンド。グランド・プレーンに接続します。                                                                                                                                                                                                                                                                                                       | V <sub>DDL1</sub> | Ground           |

| 7  | ALERTIN              | フォルト・アラート入力。上側デイジーチェーン接続デバイスに接続します。                                                                                                                                                                                                                                                                                               | V <sub>AA</sub>   | Input            |

| 8  | GNDL3                | 上側ポート・トランスマッタ用のグラウンド。グランド・プレーンに接続します。                                                                                                                                                                                                                                                                                             | V <sub>DDL3</sub> | Ground           |

| 9  | TXUN                 | 上側 UART トランスマッタ用の負出力。V <sub>DDL3</sub> ～GNDL3 の範囲に駆動されます。                                                                                                                                                                                                                                                                         | V <sub>DDL3</sub> | Output/<br>Input |

| 10 | TXUP                 | 上側UART トランスマッタ用の正出力。V <sub>DDL3</sub> ～GNDL3の範囲に駆動されます。                                                                                                                                                                                                                                                                           | V <sub>DDL3</sub> | Output/<br>Input |

| 11 | V <sub>DDL3</sub>    | 3.3V レギュレータ出力。上側 UART トランシーバーと ALERT ピン用の電源です。外部で V <sub>DDL2</sub> に接続して、0.47μF のコンデンサで GNDL3 にバイパスします。外部オーバードライブが可能 : V <sub>DDL3</sub> ≥ V <sub>DDL2/3_REG</sub> でなければなりません。                                                                                                                                                   | GNDL3             | Power            |

| 12 | RXUN                 | 上側 UART ポート・レシーバ用の負入力。このピンを使用しない場合は、未接続のままにするか GNDL3 に接続してください。許容される電圧は±30V です。                                                                                                                                                                                                                                                   | V <sub>AA</sub>   | Input            |

| 13 | RXUP                 | 上側 UART ポート・レシーバ用の正入力。このピンを使用しない場合は、未接続のままにするか GNDL3 に接続してください。許容される電圧は±30V です。シングルエンド UART 用に設定する場合は、GNDL3 に接続します。                                                                                                                                                                                                               | V <sub>AA</sub>   | Input            |

| 14 | GNDL2                | 下側ポート・トランスマッタ用のグラウンド。グランド・プレーンに接続します。                                                                                                                                                                                                                                                                                             | V <sub>DDL2</sub> | Ground           |

| 15 | TXLP                 | 下側 UART トランスマッタ用の正出力。V <sub>DDL2</sub> ～GNDL2 の範囲に駆動されます。                                                                                                                                                                                                                                                                         | V <sub>DDL2</sub> | Output           |

| 16 | TXLN                 | 下側 UART トランスマッタ用の負出力。UARTSEL の選択に依存し、V <sub>DDL2</sub> ～GNDL2 の範囲に駆動されます。                                                                                                                                                                                                                                                         | V <sub>DDL2</sub> | Output           |

| 17 | RXLP                 | 下側 UART ポート・レシーバ用の正入力。このピンを使用しない場合は、未接続のままにするか GNDL3 に接続してください。許容される電圧は±30V です。シングルエンド UART 用に設定する場合は、GNDL3 に接続します。                                                                                                                                                                                                               | V <sub>AA</sub>   | Input            |

| 18 | RXLN                 | 下側 UART ポート・レシーバ用の負入力。このピンを使用しない場合は、未接続のままにするか GNDL2 に接続してください。許容される電圧は±30V です。                                                                                                                                                                                                                                                   | V <sub>AA</sub>   | Input            |

| 19 | V <sub>DDL2</sub>    | 3.3V レギュレータ出力。下側 UART トランシーバーと ALERT ピン用の電源。外部で V <sub>DDL3</sub> に接続して、0.47μF のコンデンサで GNDL3 にバイパスします。外部オーバードライブが可能 : V <sub>DDL2</sub> ≥ V <sub>DDL2/3_REG</sub> でなければなりません。                                                                                                                                                     | GNDL2             | Power            |

| 20 | ALERTOUT             | アラート出力インターフェイス。SPIDRVINT を使ってデイジーチェーン接続の CMOS 出力として設定するか (ALERTIN に接続) 、オープン・ドレイン出力として設定します (V <sub>DDL2</sub> 、V <sub>DDL3</sub> との間の外部 10kΩ プルアップ抵抗に接続) 。                                                                                                                                                                       | V <sub>DDL2</sub> | Output           |

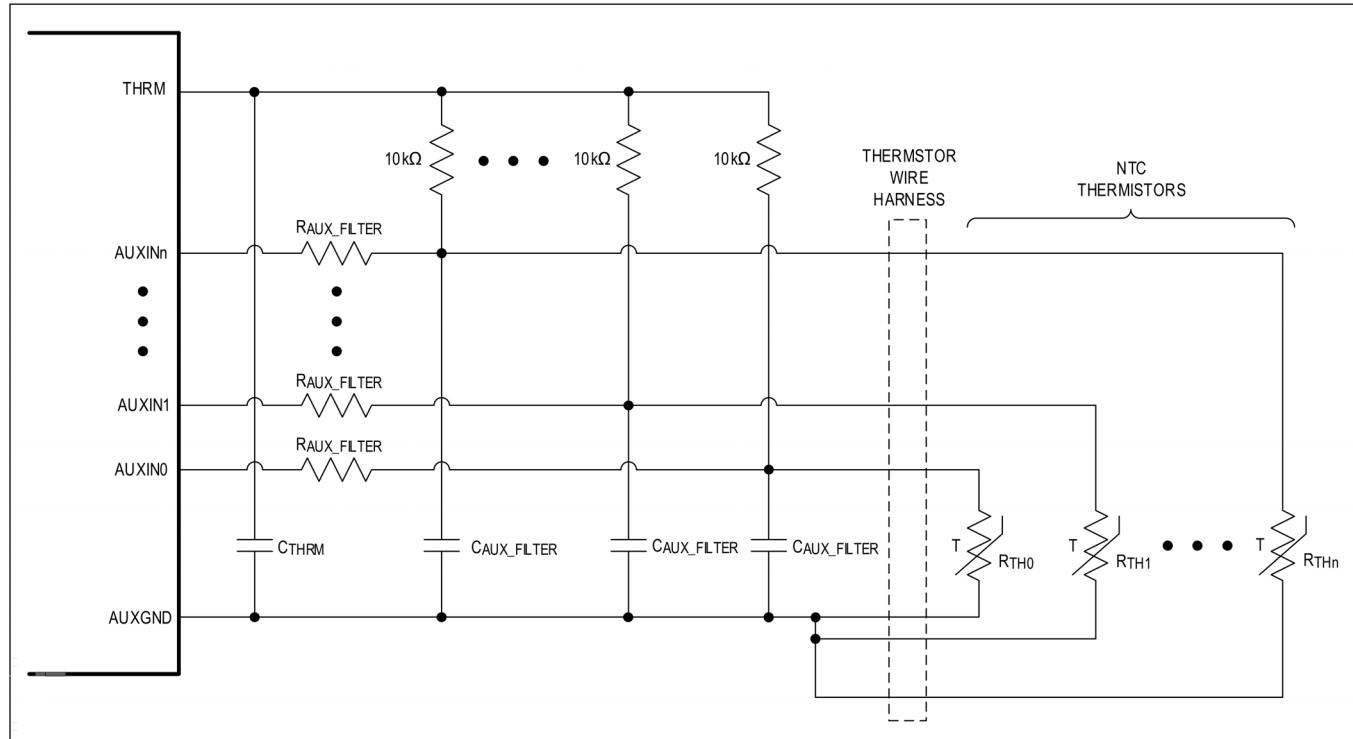

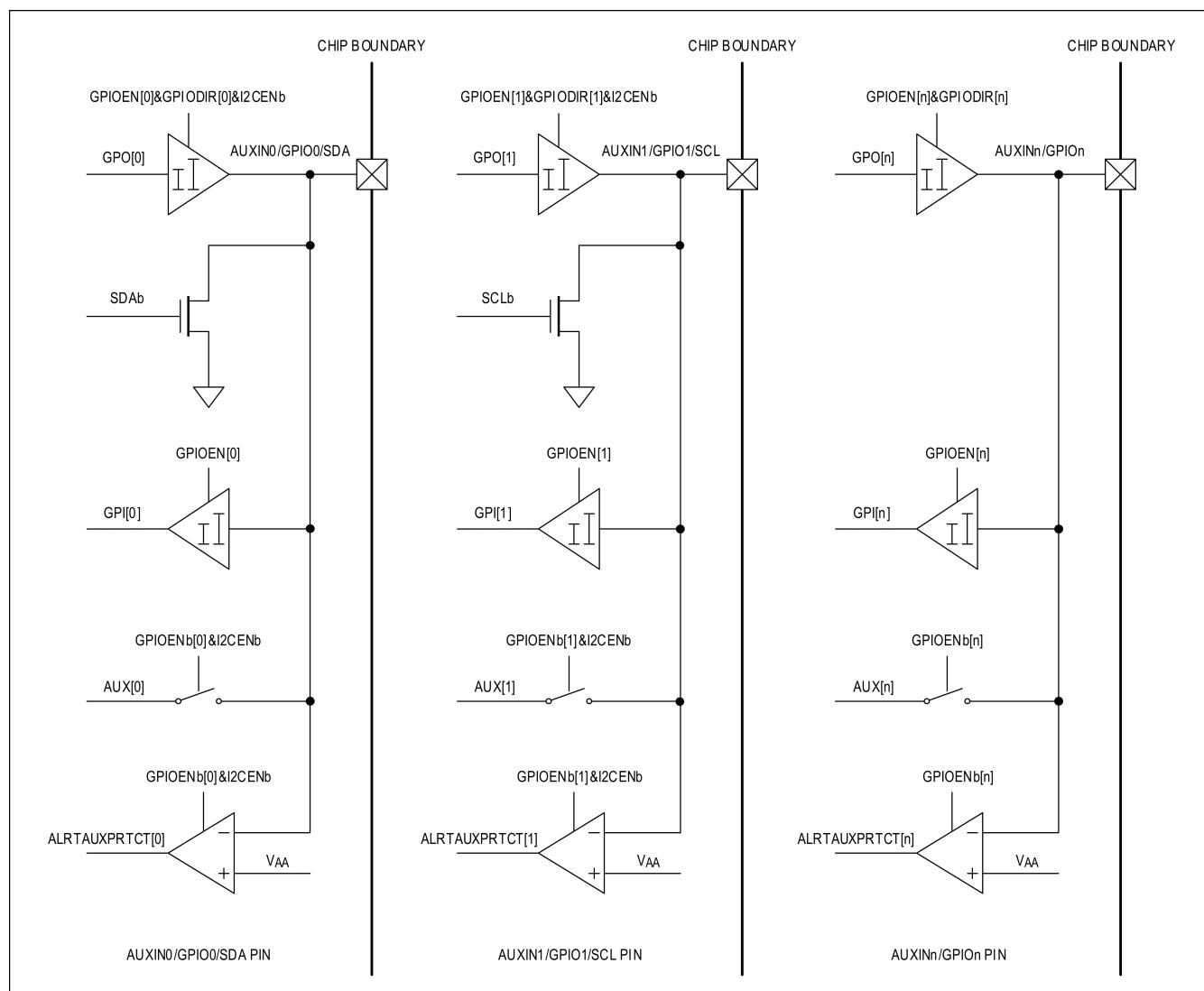

| 21 | AUXIN0/<br>GPIO0/SDA | 補助入力、GPIO、またはSDAとして設定できます。<br>温度測定用のレシオメトリック補助入力として設定する場合は、THRMへの 10kΩ プルアップとAGNDへの10kΩ NTC サーミスタで構成された分圧器に接続します。使用しない場合はプルアップ抵抗にだけ接続してください。<br>GPIOとして設定した場合は、V <sub>DDL2</sub> ～GNDL2の範囲に駆動されます。このピンを入力として設定する場合は、2MΩの内部プルダウン抵抗が必要です。I <sup>2</sup> C SDA I/Oとして設定する場合は、外部プルアップ抵抗が必要です。このピンはV <sub>DDL2</sub> ～GNDL2の範囲に駆動されます。 | V <sub>DDL2</sub> | Input/<br>Output |

# 14 チャンネル高電圧 データ・アクイジション・システム

ADES1754/ADES1755/ADES1756

|    |                      |                                                                                                                                                                                                                                                                                                 |        |                  |

|----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|

| 22 | AUXIN1/<br>GPIO1/SCL | 補助入力、GPIO、またはSCLとして設定できます。<br>温度測定用のレシオメトリック補助入力として設定する場合は、THRMへの10kΩプルアップとAGNDへの10kΩ NTCサーミスタで構成された分圧器に接続します。使用しない場合はプルアップ抵抗にだけ接続してください。<br>GPIOとして設定した場合は、V <sub>DDL2</sub> ～GNDL2の範囲に駆動されます。このピンを入力として設定する場合は、2MΩの内部プルダウン抵抗が必要です。I <sup>2</sup> C SCLとして設定した場合はI <sup>2</sup> Cのクロック出力となります。 | VDDL2  | Input/<br>Output |

| 23 | AUXIN2/<br>GPIO2     | 補助入力またはGPIOとして設定できます。<br>温度測定用のレシオメトリック補助入力として設定する場合は、THRMへの10kΩプルアップとAGNDへの10kΩ NTCサーミスタで構成された分圧器に接続します。使用しない場合はプルアップ抵抗にだけ接続してください。<br>GPIOとして設定した場合は、V <sub>DDL2</sub> ～GNDL2の範囲に駆動されます。このピンを入力として設定する場合は、2MΩの内部プルダウン抵抗が必要です。                                                                 | VDDL2  | Input/<br>Output |

| 24 | AUXIN3/<br>GPIO3     | 補助入力またはGPIOとして設定できます。<br>温度測定用のレシオメトリック補助入力として設定する場合は、THRMへの10kΩプルアップとAGNDへの10kΩ NTCサーミスタで構成された分圧器に接続します。使用しない場合はプルアップ抵抗にだけ接続してください。<br>GPIOとして設定した場合は、V <sub>DDL2</sub> ～GNDL2の範囲に駆動されます。このピンを入力として設定する場合は、2MΩの内部プルダウン抵抗が必要です。                                                                 | VDDL2  | Input/<br>Output |

| 25 | AUXGND               | AGND グランド・プレーンに接続します。                                                                                                                                                                                                                                                                           | VAA    | Power            |

| 26 | AUXIN4/<br>GPIO4     | 補助入力またはGPIOとして設定できます。<br>温度測定用のレシオメトリック補助入力として設定する場合は、THRMへの10kΩプルアップとAGNDへの10kΩ NTCサーミスタで構成された分圧器に接続します。使用しない場合はプルアップ抵抗にだけ接続してください。<br>GPIOとして設定した場合は、V <sub>DDL2</sub> ～GNDL2の範囲に駆動されます。このピンを入力として設定する場合は、2MΩの内部プルダウン抵抗が必要です。                                                                 | VDDL2  | Input/<br>Output |

| 27 | AUXIN5/<br>GPIO5     | 補助入力またはGPIOとして設定できます。<br>温度測定用のレシオメトリック補助入力として設定する場合は、THRMへの10kΩプルアップとAGNDへの10kΩ NTCサーミスタで構成された分圧器に接続します。使用しない場合はプルアップ抵抗にだけ接続してください。<br>GPIOとして設定した場合は、V <sub>DDL2</sub> ～GNDL2の範囲に駆動されます。このピンを入力として設定する場合は、2MΩの内部プルダウン抵抗が必要です。                                                                 | VDDL2  | Input/<br>Output |

| 28 | AGND                 | アナログ・グラウンド。セル1の負端子とグランド・プレーンに接続します。                                                                                                                                                                                                                                                             | DCIN   | Ground           |

| 29 | THRM                 | 内部でV <sub>AA</sub> に接続されたスイッチ出力。THRMは、補助入力用外部NTC分圧器の駆動に使われます。この出力は、測定時、またはTHRMMODE[1:0]によって設定された場合のみイネーブルされます。この出力は最大2mAをソースできます。                                                                                                                                                               | AUXGND | Power            |

| 30 | C0                   | セル1 負端子用電圧入力。AGNDに接続してください。                                                                                                                                                                                                                                                                     |        | Input            |

| 31 | SW0                  | セル1 負端子用バランス入力。                                                                                                                                                                                                                                                                                 |        | Input            |

| 32 | C1                   | セル1 正端子（セル2 負端子）用電圧入力。                                                                                                                                                                                                                                                                          |        | Input            |

| 33 | SW1                  | セル1 正端子（セル2 負端子）用バランス入力。                                                                                                                                                                                                                                                                        |        | Input            |

| 34 | C2                   | セル2 正端子（セル3 負端子）用電圧入力。                                                                                                                                                                                                                                                                          |        | Input            |

| 35 | SW2                  | セル2 正端子（セル3 負端子）用バランス入力。                                                                                                                                                                                                                                                                        |        | Input            |

| 36 | C3                   | セル3 正端子（セル4 負端子）用電圧入力。                                                                                                                                                                                                                                                                          |        | Input            |

| 37 | SW3                  | セル3 正端子（セル4 負端子）用バランス入力。                                                                                                                                                                                                                                                                        |        | Input            |

## 14 チャンネル高電圧 データ・アクイジション・システム

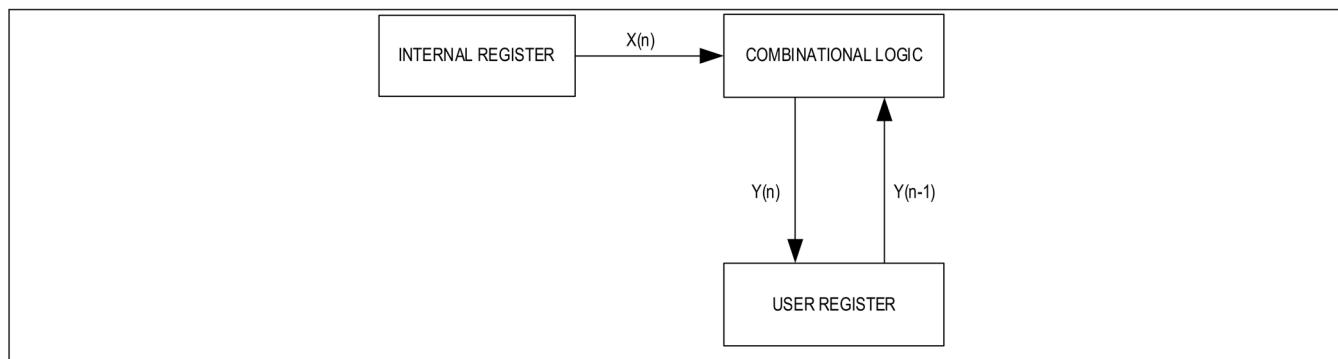

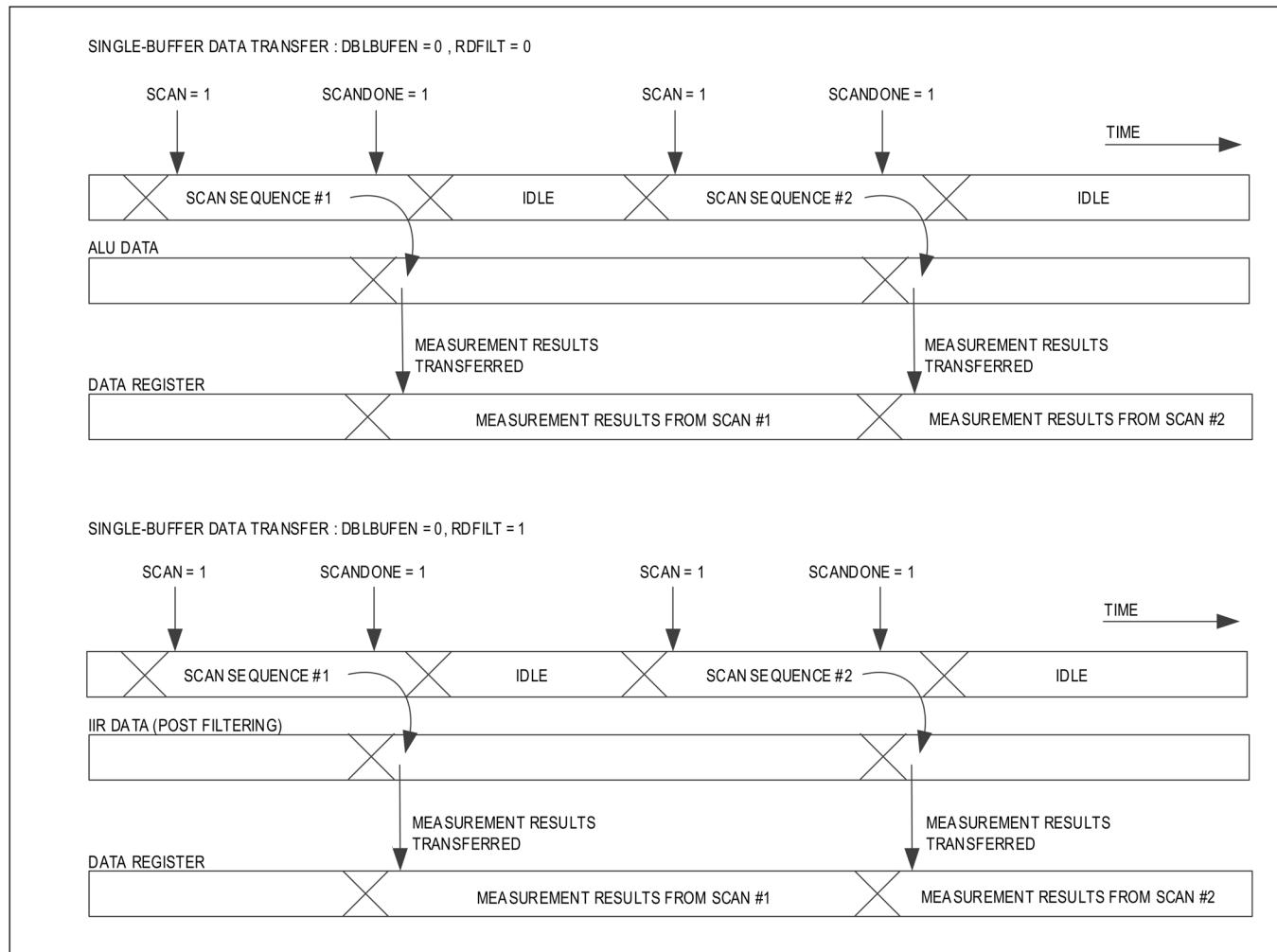

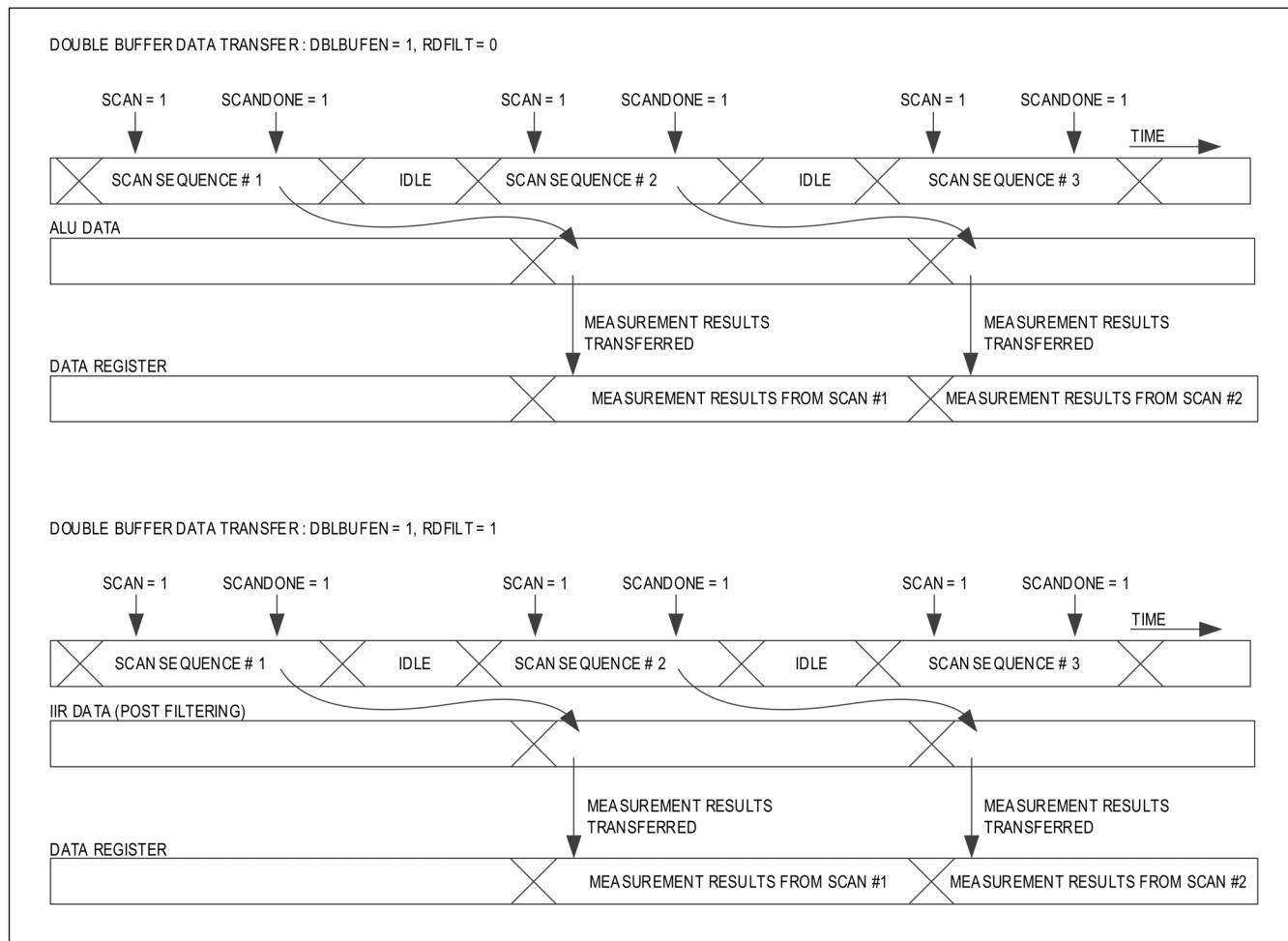

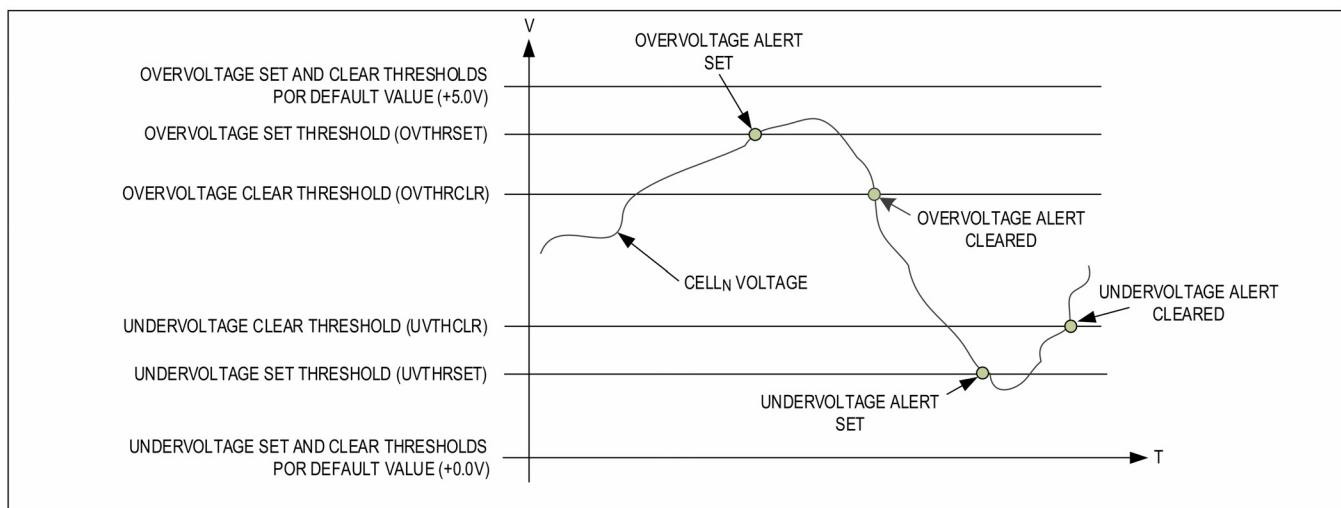

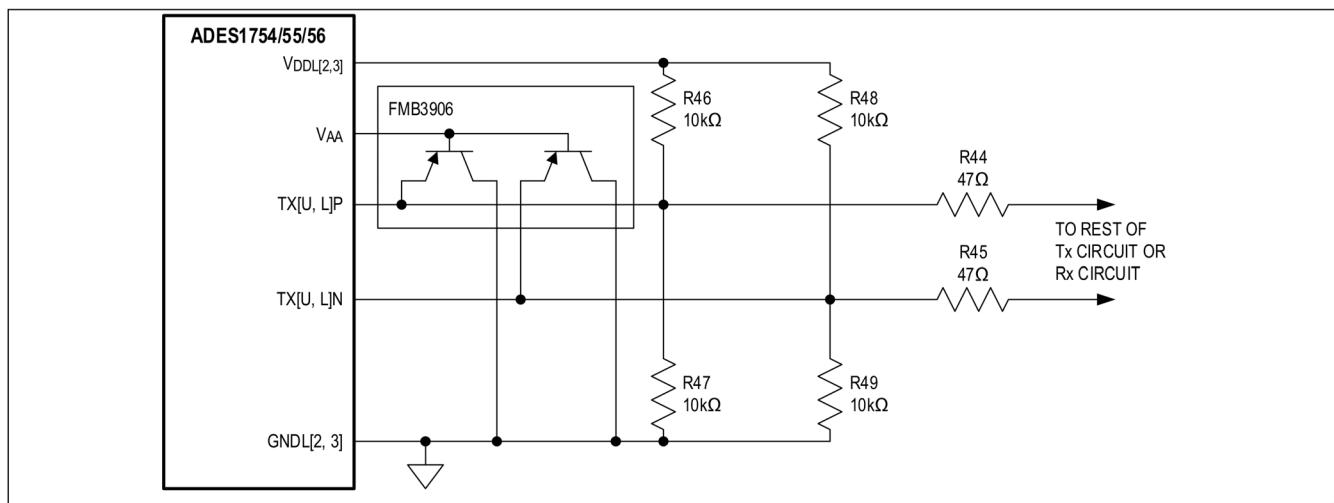

ADES1754/ADES1755/ADES1756