# 高入力インピーダンス、プログラマブル・ゲイン、24ビット、1MSPS、エイリアス・フリーのμModule® DAQ ソリューション

## 特長

- ▶ 高集積データ・アクイジション・ソリューション

- ▶ 広い入力コモンモード電圧範囲

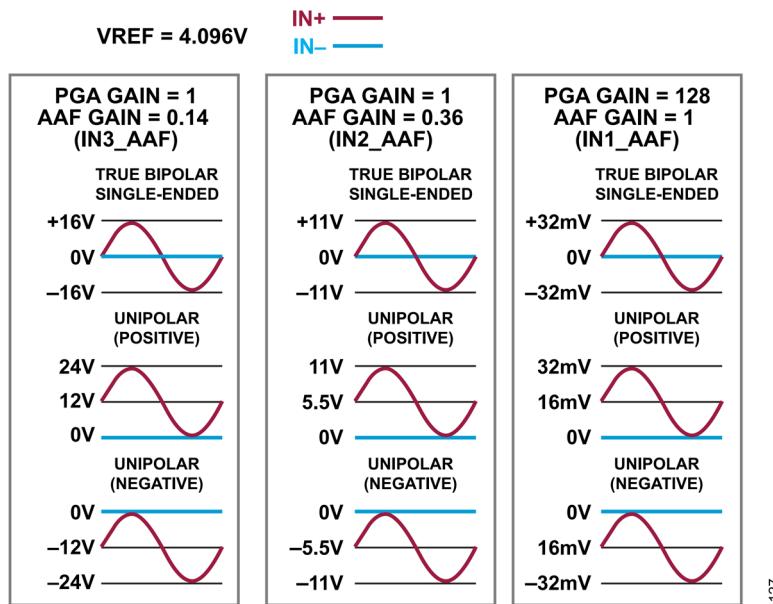

- ▶ 最大ユニポーラ入力範囲: +24V または -24V

- ▶ 設定可能な 8 つのバイナリ・ゲイン・オプション: 1V/V ~ 128V/V

- ▶ 3 つのピンで選択可能なアンチエイリアシング・フィルタ (AAF) ゲイン・オプション

- ▶ G = 1V/V, 0.364V/V, 0.143V/V

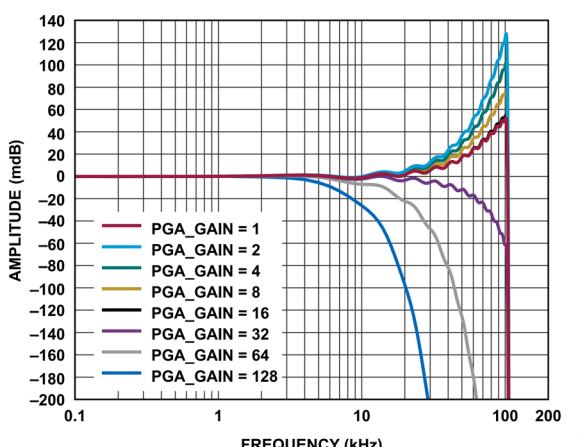

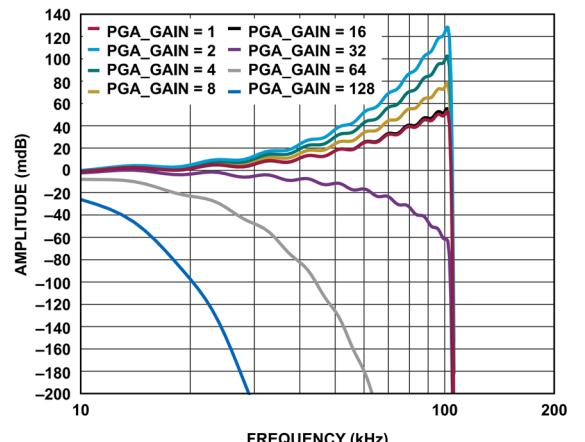

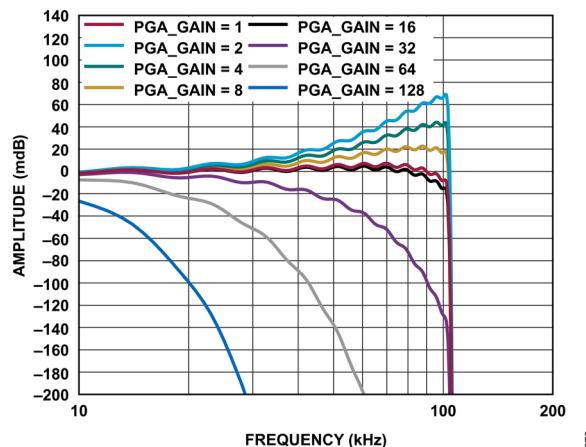

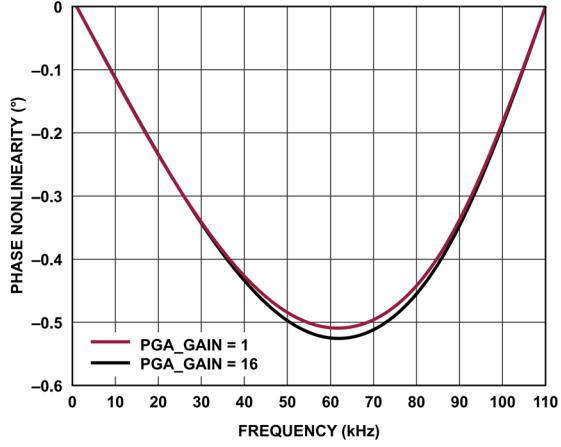

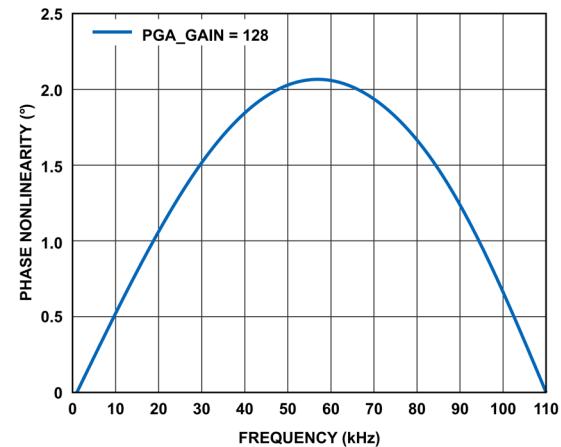

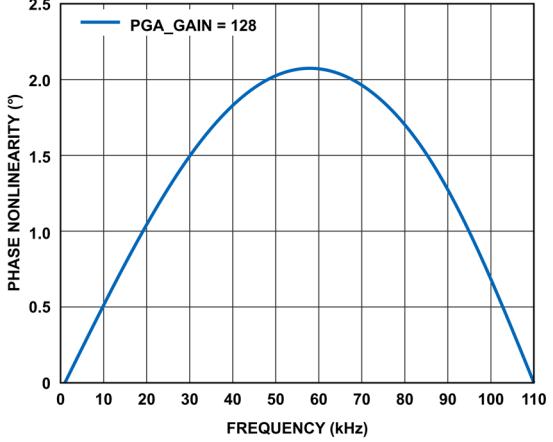

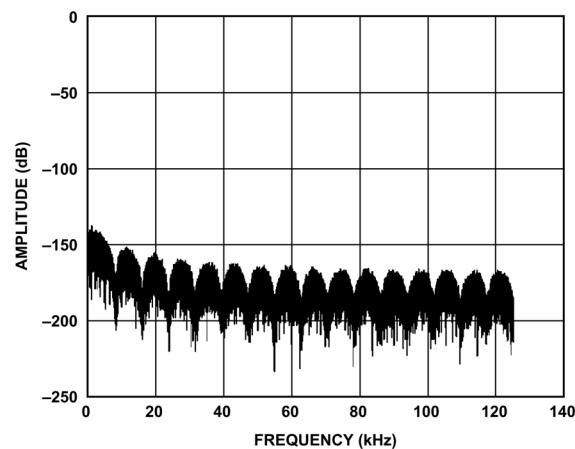

- ▶ 最大の平坦度と直線的な位相特性を持つ 4 次 AAF

- ▶ 90dB (代表値) の除去によるエイリアシングからの完全な保護

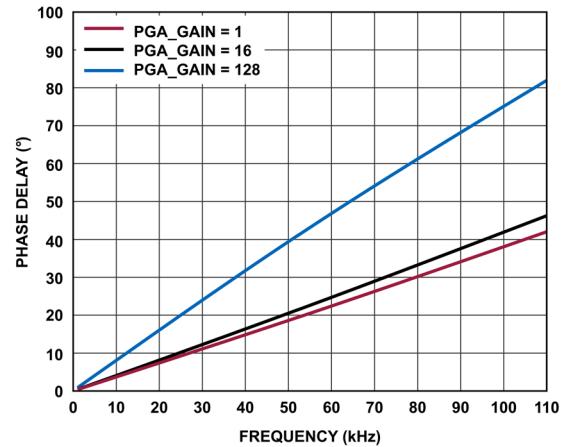

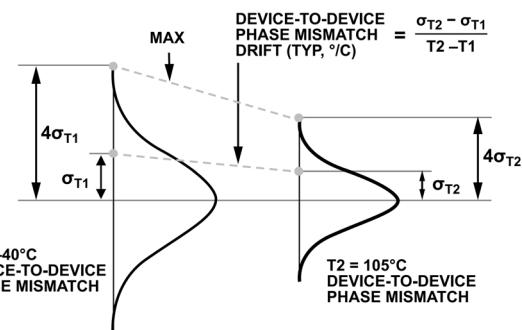

- ▶ デバイス間の優れた位相整合とドリフト

- ▶ 高精度の AC 性能と DC 性能を両立

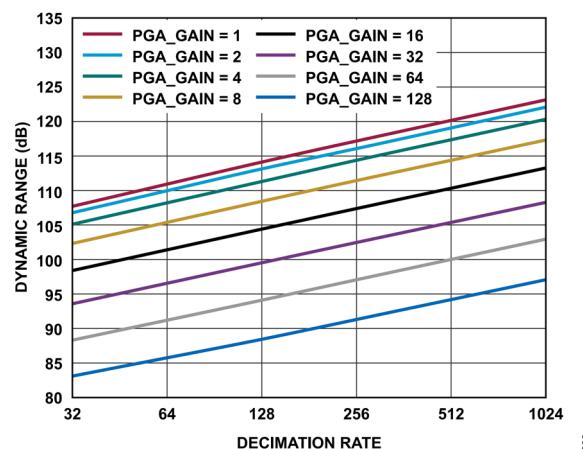

- ▶ システム全体のダイナミック・レンジ: 最大 136dB

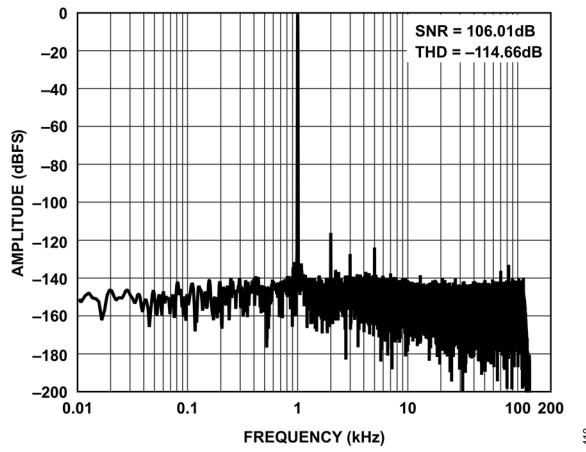

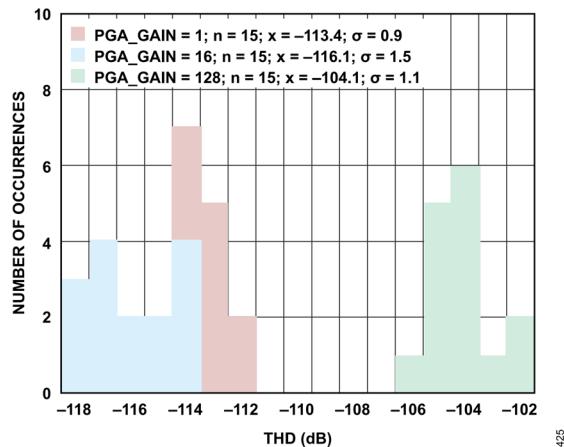

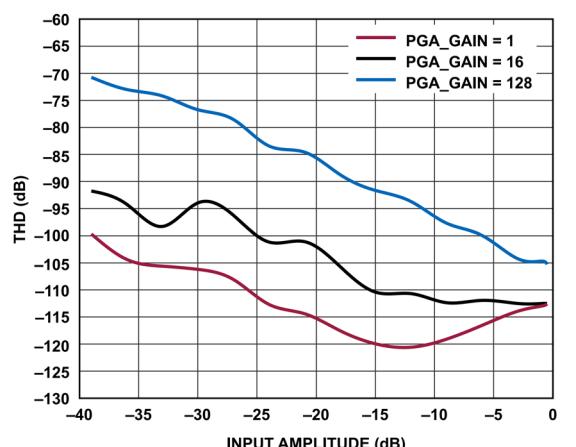

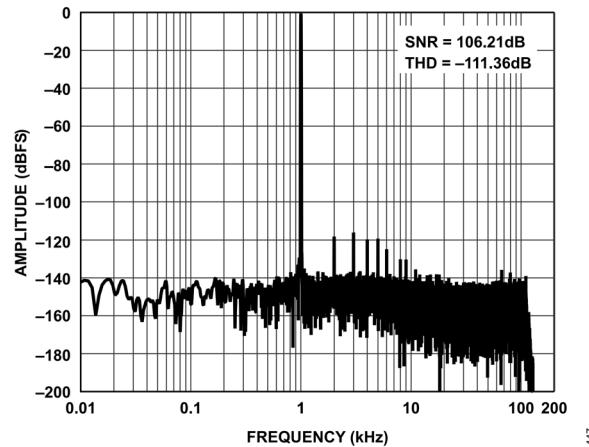

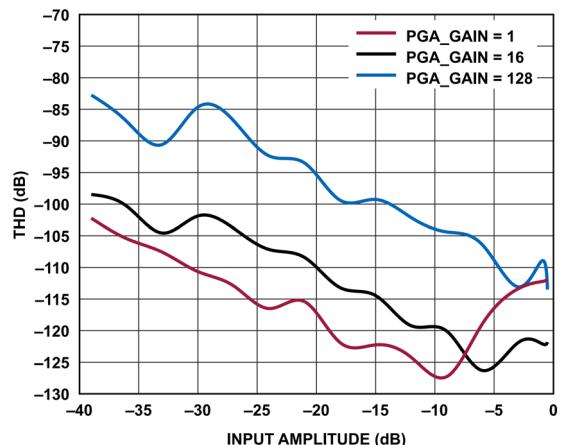

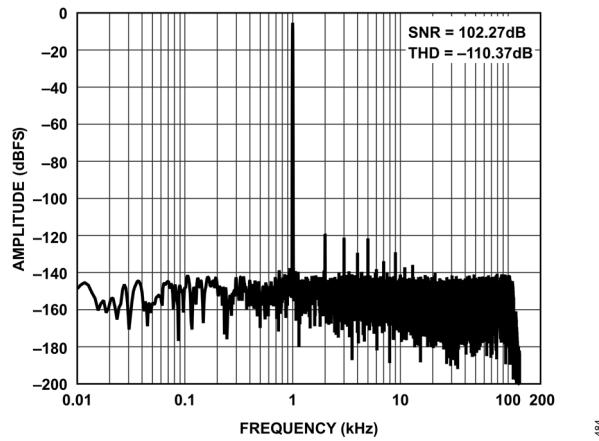

- ▶ THD: -113dB (代表値、入力トーン 1kHz、総ゲイン = 1 の場合)

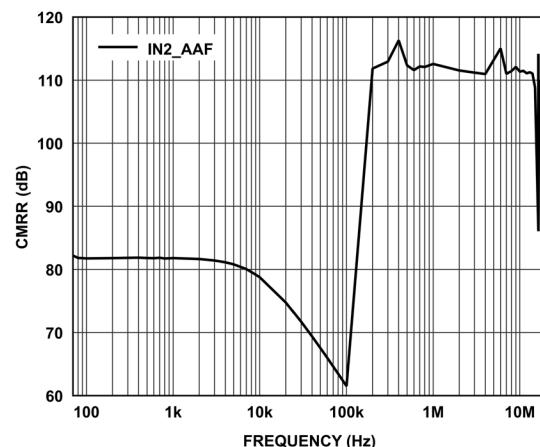

- ▶ DC CMRR: 81dB (代表値、総ゲイン = 1 の場合)

- ▶ 入力バイアス電流: 1pA (代表値、25°C 時)

- ▶ INL: ±3.3ppm (代表値)

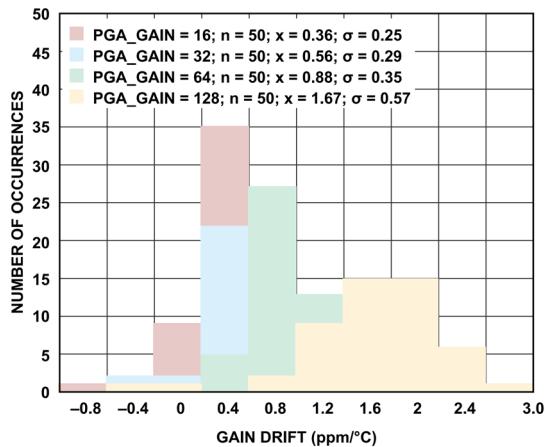

- ▶ ゲイン誤差ドリフト: 5ppm/°C (最大値)

- ▶ デバイス間の位相不整合: ±0.5° (最大値、20kHz 時)

- ▶ プログラマブルな出力データ・レート、フィルタ・タイプ、レイテンシ

- ▶ リニア位相デジタル・フィルタ・オプション:

- ▶ 広帯域低リップル FIR フィルタ (256kSPS、最大入力帯域幅 110kHz)

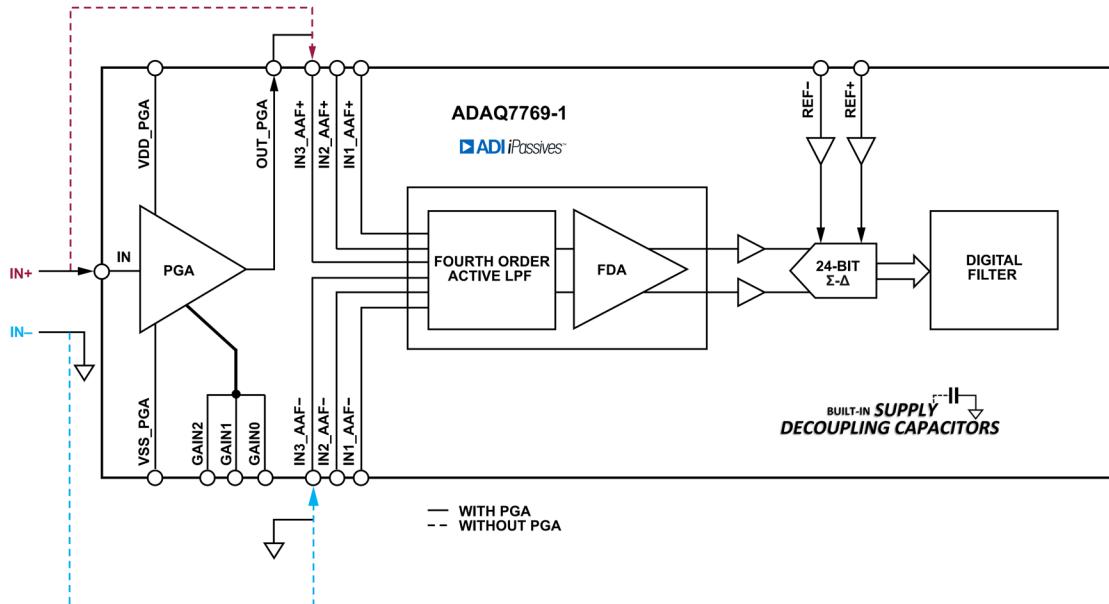

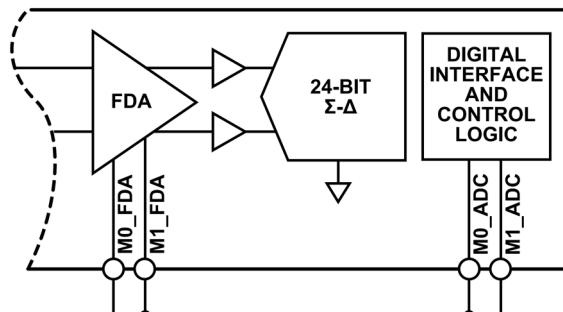

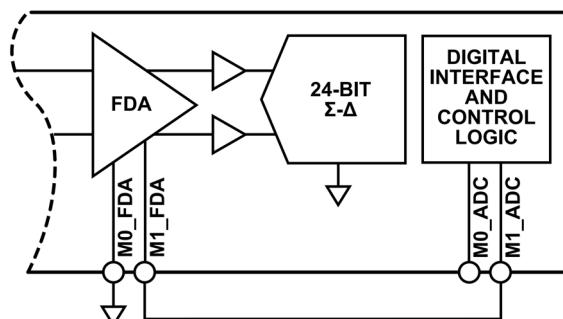

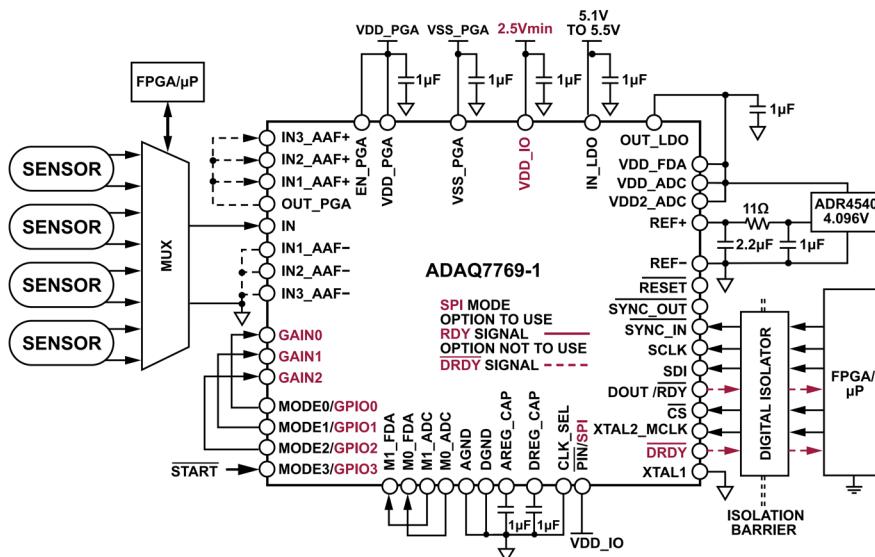

## 機能ブロック図

図 1. 機能ブロック図

## 目次

|                        |    |                                  |     |

|------------------------|----|----------------------------------|-----|

| 特長                     | 1  | ノイズ性能                            | 92  |

| アプリケーション               | 1  | デジタル・インターフェース                    | 96  |

| 機能ブロック図                | 1  | SPI での読み出しと書き込み                  | 97  |

| 概要                     | 4  | SPI 制御インターフェースのエラー処理             | 98  |

| 仕様                     | 6  | シリアル・インターフェースでの CRC チェック         | 98  |

| AAF_GAIN = IN1_AAF     | 6  | 変換読み出しモード                        | 100 |

| AAF_GAIN = IN2_AAF     | 12 | データ変換モード                         | 103 |

| AAF_GAIN = IN3_AAF     | 18 | 連続変換モード                          | 103 |

| 一般仕様                   | 24 | ワンショット変換モード                      | 103 |

| タイミング仕様                | 27 | シングル変換モード                        | 104 |

| 1.8V タイミング仕様           | 28 | デューティサイクル変換モード                   | 104 |

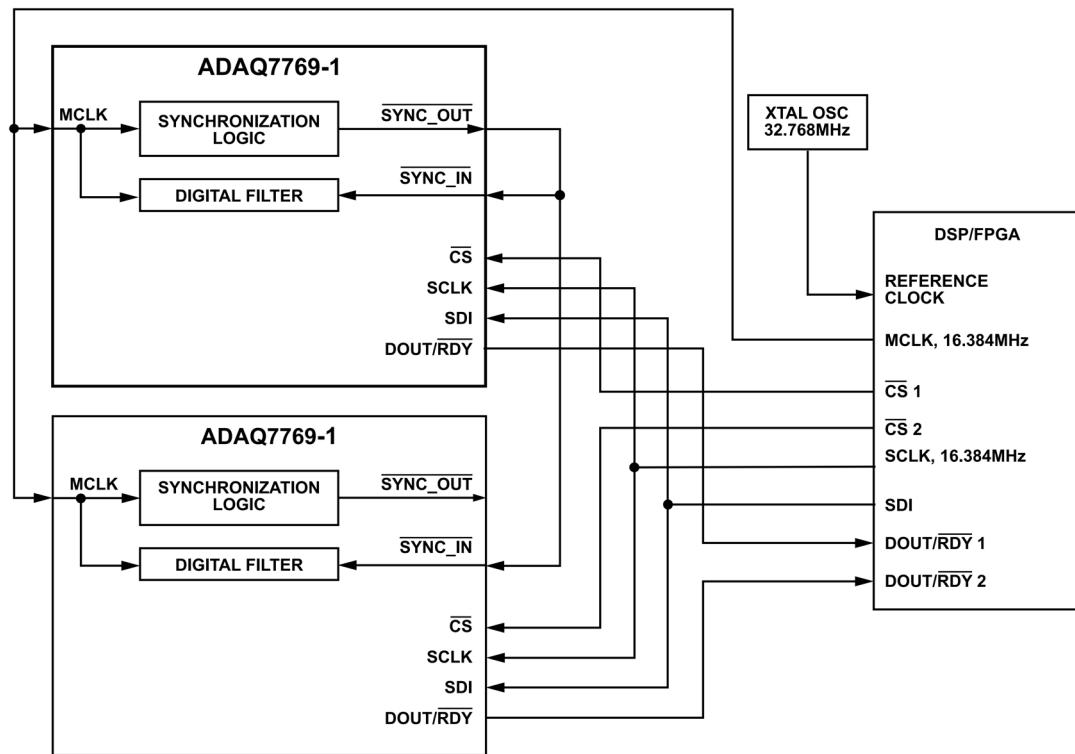

| 絶対最大定格                 | 32 | 複数の ADAQ7769-1 デバイスの同期           | 105 |

| 熱抵抗                    | 32 | ADAQ7769-1 のその他の機能               | 106 |

| 静電放電 (ESD) 定格          | 32 | リセット                             | 106 |

| ピン配置およびピン機能の説明         | 33 | ステータス・ヘッダ                        | 106 |

| 代表的な性能特性               | 36 | 診断機能                             | 106 |

| AAF_GAIN = IN1_AAF     | 36 | アプリケーション情報                       | 107 |

| AAF_GAIN = IN2_AAF     | 43 | 状態基準保全 (CBM) アプリケーション            | 107 |

| AAF_GAIN = IN3_AAF     | 50 | アナログ入力                           | 107 |

| 用語の定義                  | 57 | センサーとのインターフェース                   | 110 |

| 動作原理                   | 59 | PIN 制御モードと SPI 制御モード             | 111 |

| アナログ入力                 | 59 | 電源                               | 111 |

| アンチエイリアシング・フィルタ (AAF)  | 65 | リファレンス、リファレンス・バッファ、<br>直線性向上バッファ | 111 |

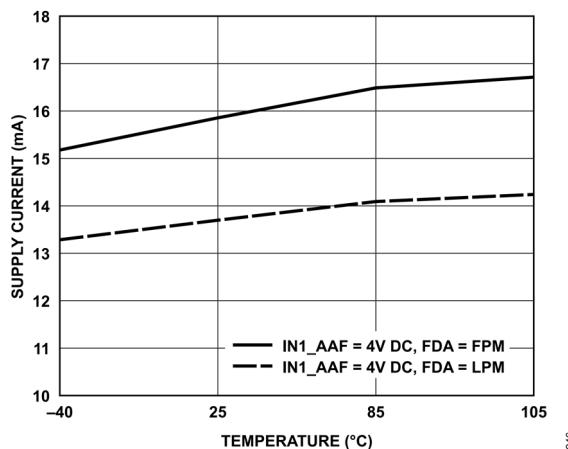

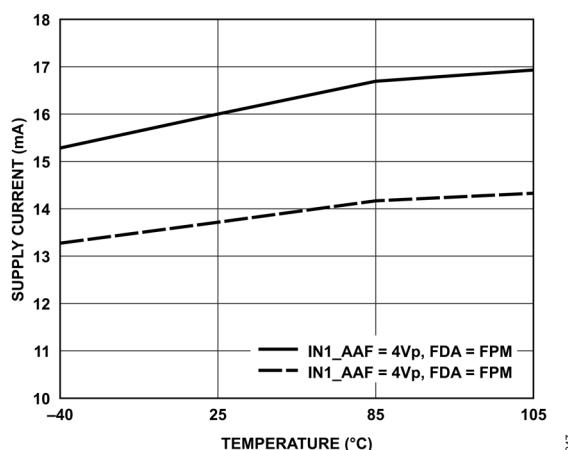

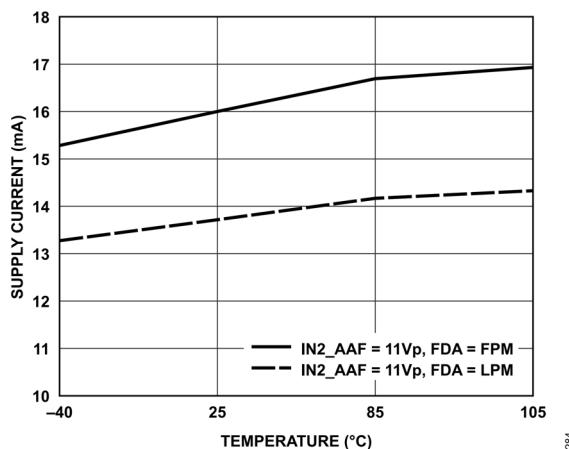

| 完全差動アンプ (FDA) の消費電力モード | 68 | 推奨インターフェース                       | 111 |

| 直線性向上バッファ              | 68 | プログラマブル・デジタル・フィルタ                | 113 |

| リファレンス入力とバッファリング       | 68 | レイアウトのガイドライン                     | 116 |

| コア・コンバータ               | 69 | レジスタの一覧                          | 117 |

| 電源                     | 70 | レジスタの詳細                          | 119 |

| 電源のデカッピング              | 70 | コンポーネント・タイプ・レジスタ                 | 119 |

| 電源スタンバイ                | 70 | 製品固有 ID レジスタ                     | 119 |

| クロック供給とサンプリング・ツリー      | 70 | デバイス・グレードおよびリビジョン・レジスタ           | 119 |

| クロッキングとクロックの選択         | 71 | ユーザ・スクラッチ・パッド・レジスタ               | 119 |

| デジタル・フィルタ処理            | 72 | デバイス・ベンダ ID レジスタ                 | 120 |

| 合計群遅延                  | 79 | インターフェース・フォーマット制御レジスタ            | 120 |

| ADC の速度と性能             | 79 | 電力およびクロック制御レジスタ                  | 121 |

| デバイスの設定方法              | 79 | アナログ・バッファ制御レジスタ                  | 121 |

| PIN 制御モードの概要           | 80 | 変換ソース選択およびモード制御レジスタ              | 122 |

| SPI 制御の概要              | 83 | デジタル・フィルタおよびデシメーション制御レジスタ        | 122 |

| SPI 制御モード              | 84 | sinc3 デシメーション・レート (MSB) レジスタ     | 123 |

| クイック・スタートアップ・ガイド       | 88 | sinc3 デシメーション・レート (LSB) レジスタ     | 123 |

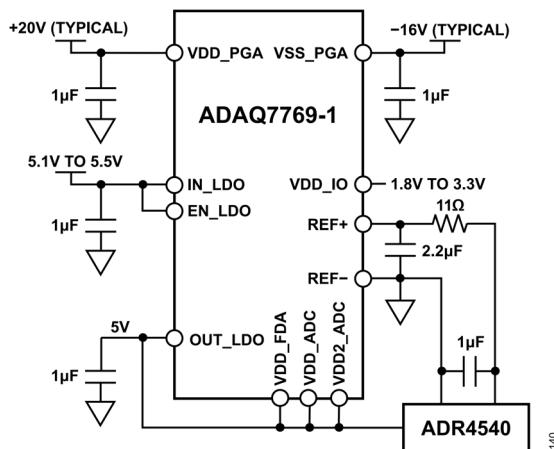

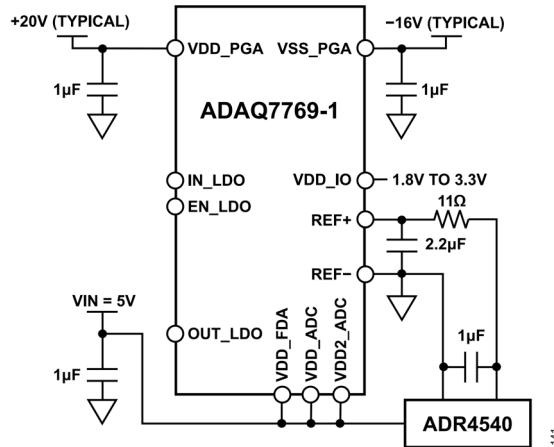

| 電源の接続                  | 88 | 周期的変換レート制御レジスタ                   | 123 |

| デバイスの制御モード             | 89 | 同期モードおよびリセット・トリガリング・レジスタ         | 124 |

| 入力範囲の選択                | 89 | GPIO ポート制御レジスタ                   | 124 |

| MCLK の分周器とソースの選択       | 89 |                                  |     |

| デジタル・フィルタの設定           | 90 |                                  |     |

| ADC の消費電力モード           | 90 |                                  |     |

| 基本的なレジスタ・セットアップ        | 90 |                                  |     |

| クイック・スタートの例            | 91 |                                  |     |

## 目次

|                                |     |

|--------------------------------|-----|

| GPIO 出力制御レジスタ .....            | 124 |

| GPIO 入力読出しレジスタ .....           | 125 |

| オフセット・キャリブレーション MSB レジスタ ..... | 125 |

| オフセット・キャリブレーション MID レジスタ ..... | 125 |

| オフセット・キャリブレーション LSB レジスタ ..... | 125 |

| ゲイン・キャリブレーション MSB レジスタ .....   | 126 |

| ゲイン・キャリブレーション MID レジスタ .....   | 126 |

| ゲイン・キャリブレーション LSB レジスタ .....   | 126 |

| SPI 診断制御レジスタ .....             | 126 |

| ADC 診断機能制御レジスタ .....           | 127 |

| デジタル診断機能制御レジスタ .....           | 127 |

| 変換結果レジスタ .....                 | 127 |

|                             |     |

|-----------------------------|-----|

| デバイス・エラー・フラグ・メイン・レジスタ ..... | 127 |

| SPI エラー・レジスタ .....          | 128 |

| ADC 診断出力レジスタ .....          | 128 |

| デジタル診断出力レジスタ .....          | 128 |

| MCLK 診断出力レジスタ .....         | 128 |

| 係数制御レジスタ .....              | 129 |

| 係数データ・レジスタ .....            | 129 |

| アクセス・キー・レジスタ .....          | 129 |

| 外形寸法 .....                  | 130 |

| オーダー・ガイド .....              | 130 |

| 評価用ボード .....                | 130 |

## 改訂履歴

7/2025—Revision 0: Initial Version

## 概要

ADAQ7769-1 は、シグナル・コンディショニング、変換、および処理ブロックを 1 つのシステム・イン・パッケージ (SiP) 設計に組み込んだ、24 ビットの高精度データ・アクイジション (DAQ)  $\mu$ Module<sup>®</sup> システムです。このシステムは、超小型、高性能、高精度の DAQ システムを短時間で開発することを可能にします。

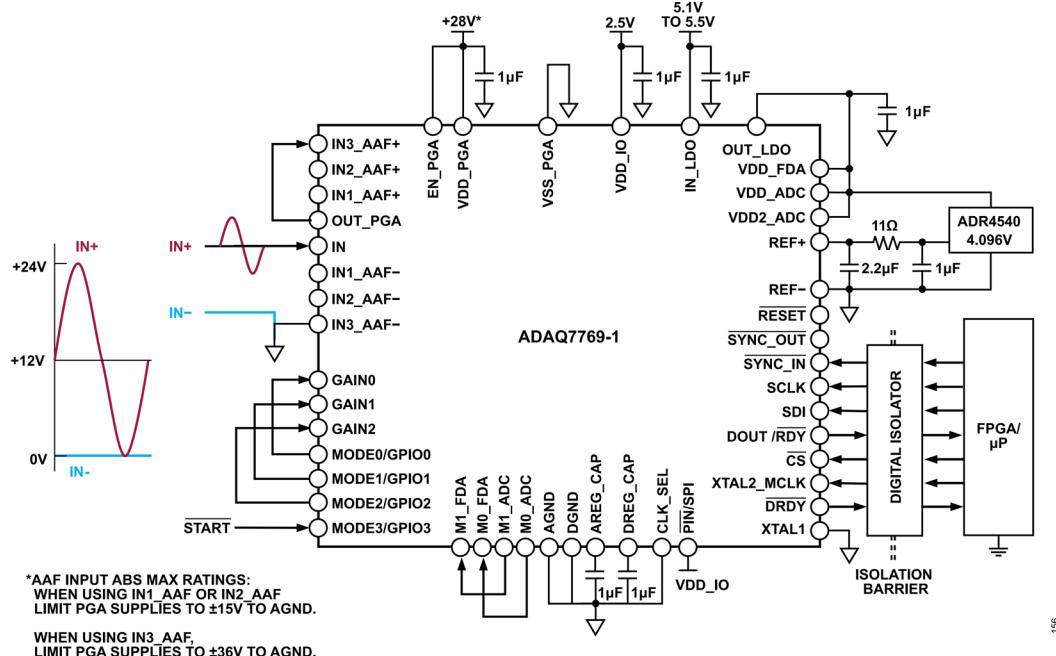

ADAQ7769-1 の構成要素は次のとおりです。

- ▶ 1~128 のバイナリ・ゲインで動作するように設定可能な、低ノイズ、低バイアス電流、高帯域幅のプログラマブル・ゲイン・アンプ (PGA)

- ▶ 低ノイズ、直線的位相の 4 次アンチエイリアシング・フィルタ (AAF)

- ▶ 低ノイズ、低歪み、広帯域幅、ゲイン選択可能な ADC ドライバ、およびオプションの直線性向上バッファ

- ▶ プログラマブル・デジタル・フィルタを備えた高性能、中帯域幅の 24 ビット・シグマ・デルタ ADC

- ▶ 低ノイズ、低ドロップアウトのリニア・レギュレータ

- ▶ リファレンス・バッファ

- ▶ シグナル・チェーンに必要な重要受動部品

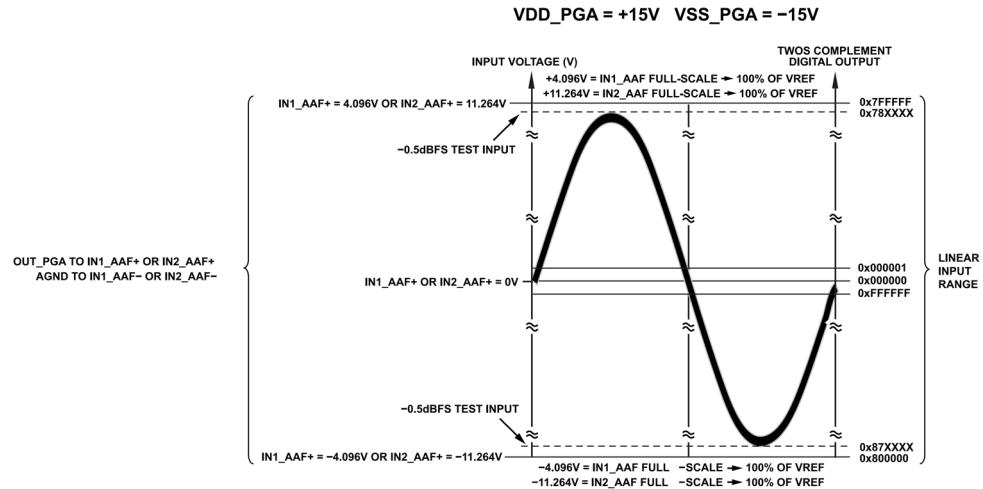

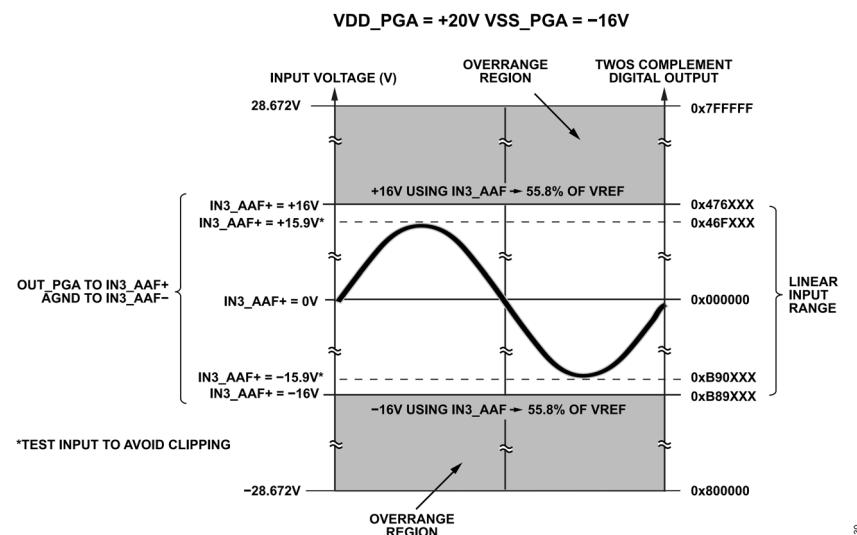

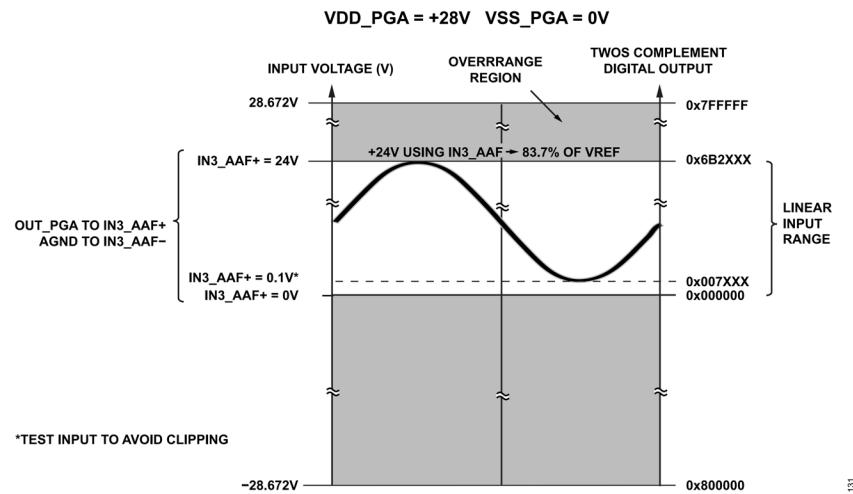

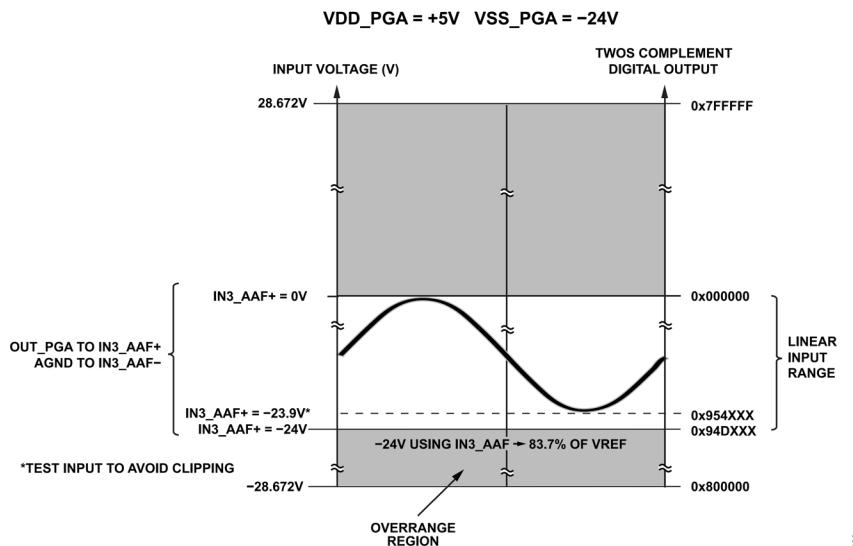

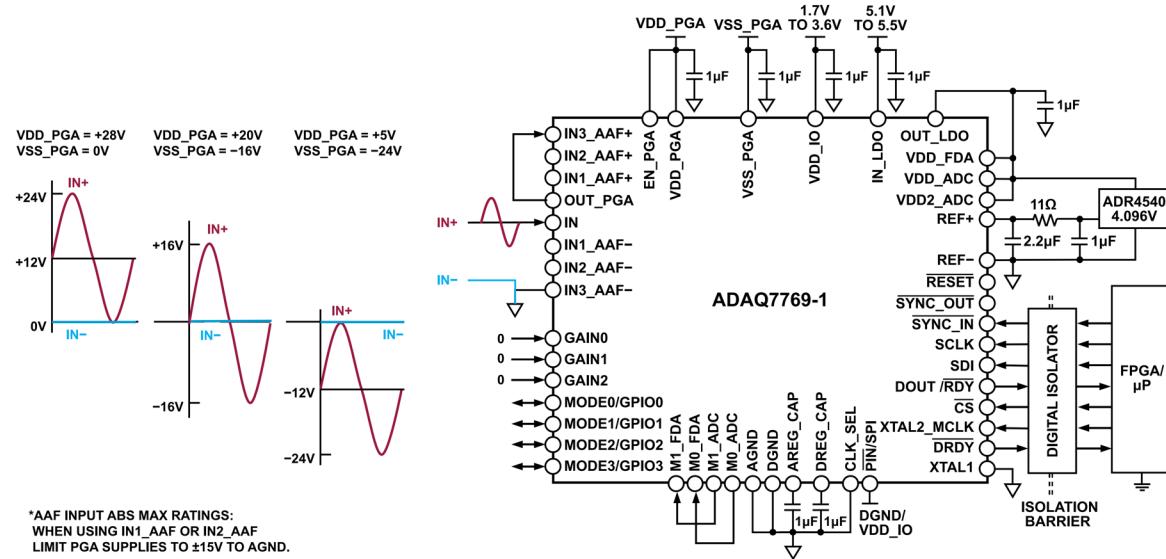

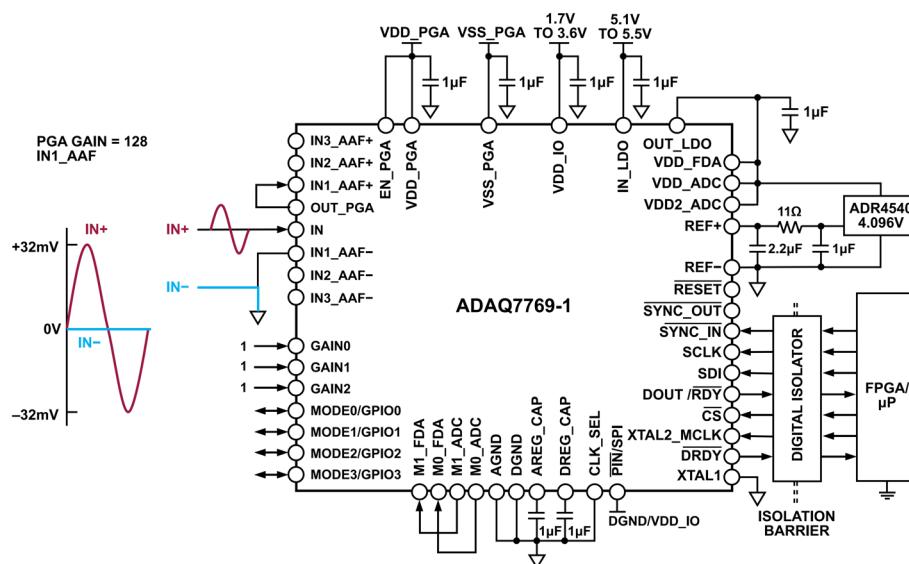

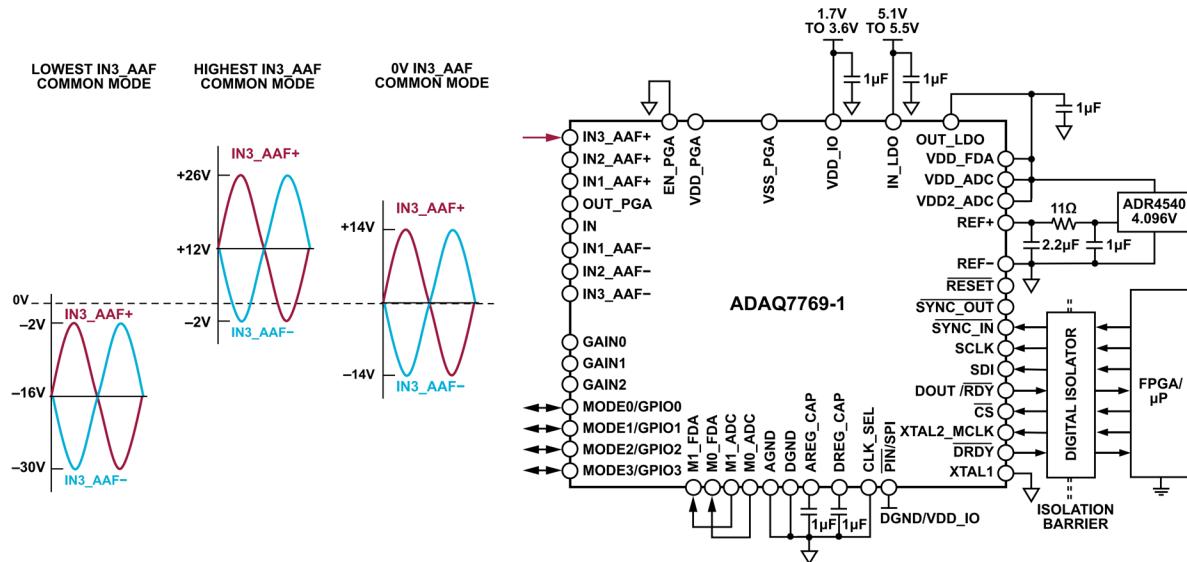

ADAQ7769-1 は PGA の電源電圧に応じた柔軟性を備え、最大で 0V~+24V/0V~-24V のユニポーラ範囲、または  $\pm 16V$  のバイポーラ範囲にわたる幅広いシングルエンド入力振幅をサポートします。8 つのバイナリ PGA ゲイン設定とピン選択による 3 つの AAF ゲイン設定が可能な ADAQ7769-1 は、システムのダイナミック・レンジを拡張し、より低振幅の入力信号に対するシグナル・チェーンのノイズ性能を向上させます。入力信号は 1pA (代表値) という極めて低い入力バイアス電流で完全にバッファリングされます。これにより入力インピーダンスの整合が容易になり、高い出力インピーダンスを持つセンサーに ADAQ7769-1 を直接インターフェース接続できます。

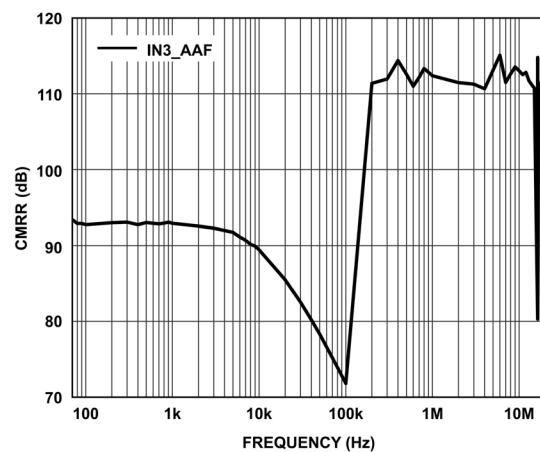

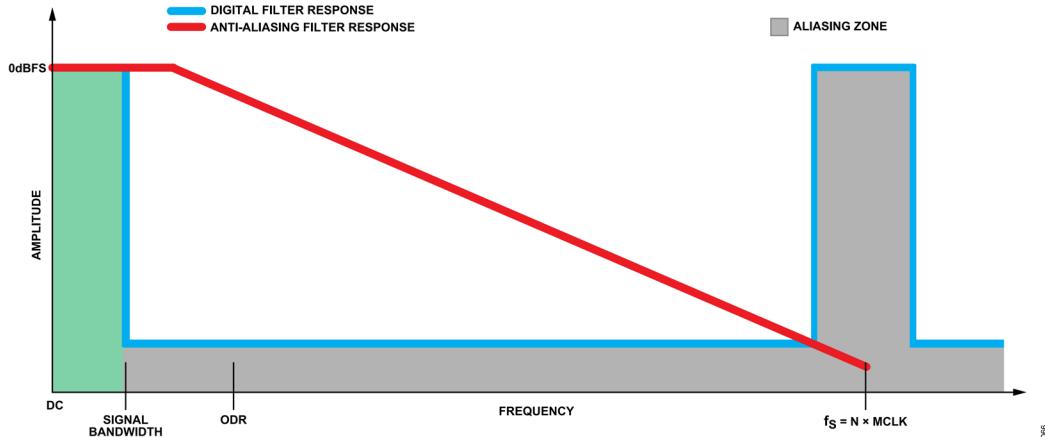

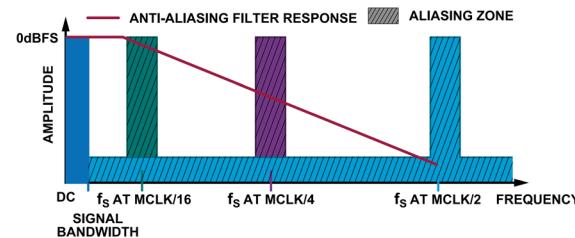

4 次ローパス・アナログ・フィルタとユーザ設定可能なデジタル・フィルタを組み合わせることにより、入力ノードで発生する高周波ノイズと帯域外トーンがエイリアシングによって対象帯域に混ざるのを防ぎ、シグナル・チェーンを完全に保護します。アナログ・ローパス・フィルタは、位相直線性を高め、帯域内振幅応答を最大限に平坦化できるよう綿密に設計されています。アナログ・ローパス・フィルタ内で使用される抵抗ネットワークは iPassives<sup>TM</sup> 技術を用いて構築されており、絶対値においても温度範囲全体においても優れた抵抗整合特性を備えています。結果として、温度変化によるドリフトを最小限に抑えながらシグナル・チェーンの性能が維持されます。また ADAQ7769-1 は、デバイス間での位相不整合がほとんどありません。

高性能 ADC ドライバ・アンプによって、最大サンプリング・レートにおける ADC 入力の完全なセトリングが確保されます。ドライバ回路は、安定性を維持しながら、付加ノイズ、誤差、歪みを最小限に抑えるように設計されています。完全差動アーキテクチャは、シグナル・チェーンのダイナミック・レンジを最大限に引き出します。

ADAQ7769-1 内の A/D コンバータ (ADC) は、高性能、24 ビット精度、シングル・チャンネルのシグマ・デルタ・コンバータで、優れた AC 性能と DC 精度を備え、16.384MHz の MCLK から 256kSPS のスループット・レートを実現しています。このデバイスは、シグナル・チェーンの直線性を更に向上できる直線性向上バッファをオプションで備えています。

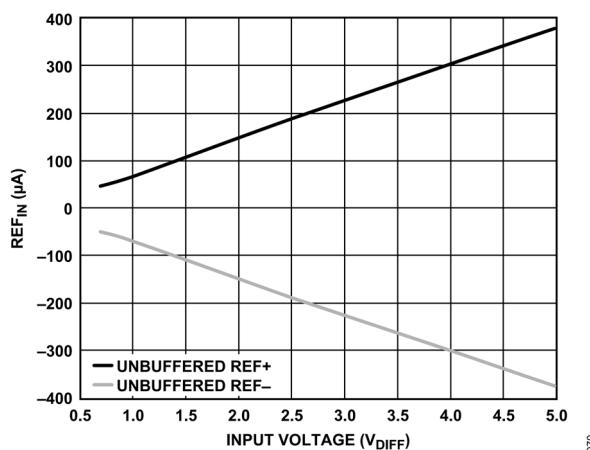

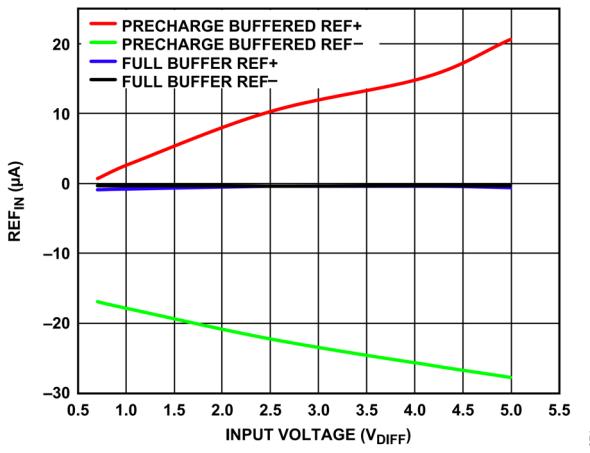

ADAQ7769-1 は入力リファレンス電圧 4.096V で仕様規定されていますが、このデバイスは VDD\_ADC から 1V までのリファレンス電圧に対応できます。

ADAQ7769-1 には 2 種類のリファレンス・バッファがあります。1 つはリファレンス入力の駆動条件を緩和するプリチャージ・リファレンス・バッファ、もう 1 つは高インピーダンスのリファレンス入力を提供するフル・リファレンス・バッファです。どちらのバッファもオプションであり、レジスタ設定でオフにすることができます。

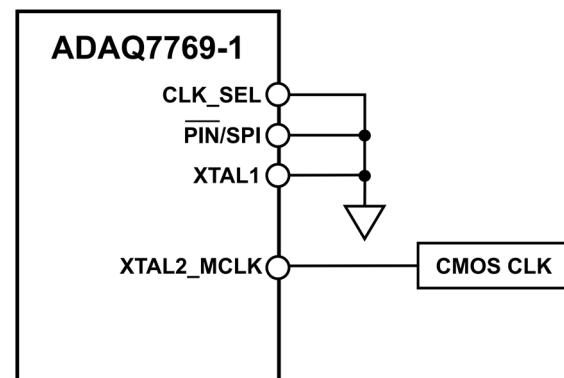

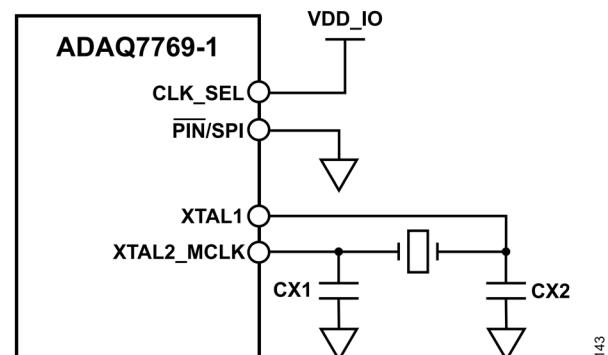

ADAQ7769-1 は、水晶、CMOS、または LVDS の 3 種類のクロック入力に対応しています。

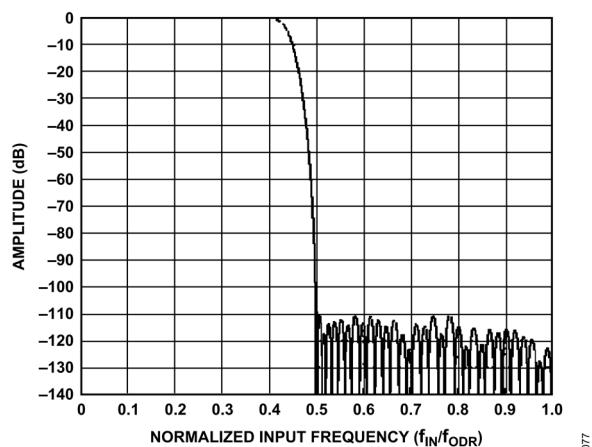

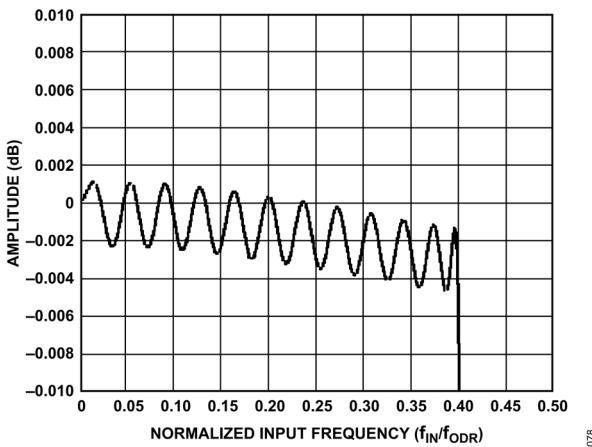

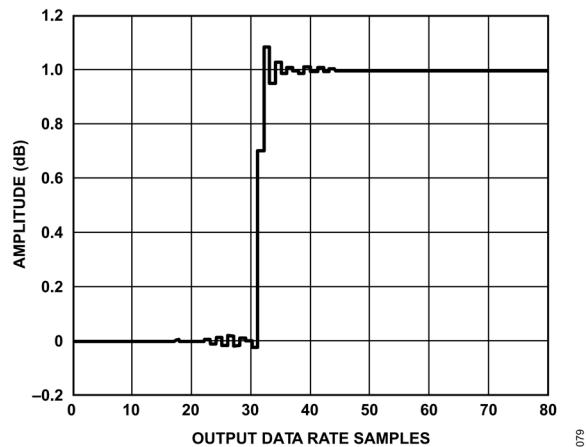

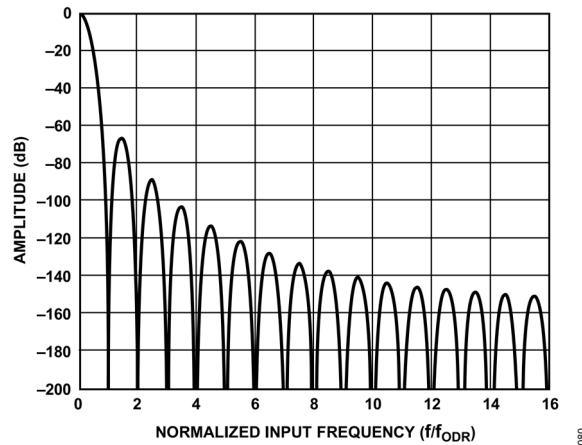

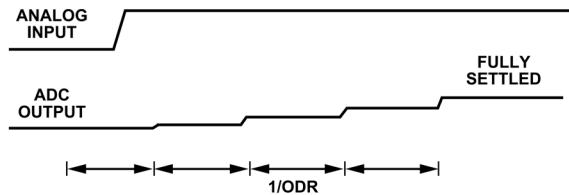

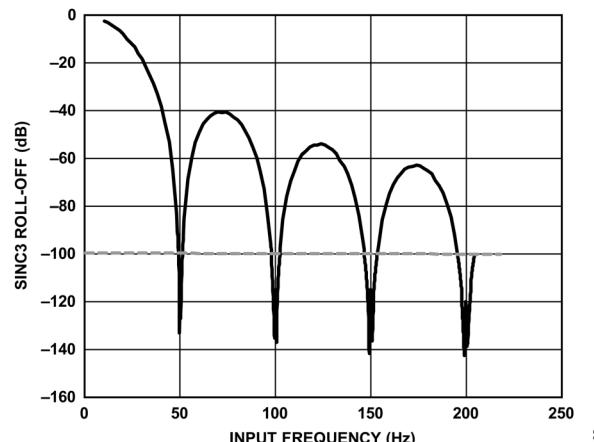

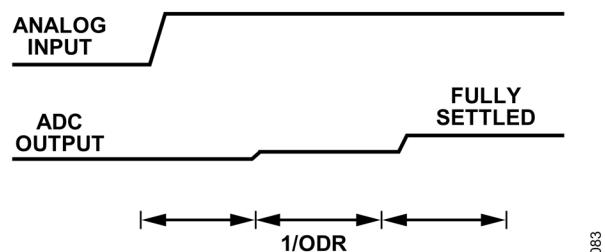

ADAQ7769-1 には 3 種類のデジタル・ローパス・フィルタがあります。広帯域低リップル FIR フィルタは理想的なブリック・ウォール・フィルタと同様のフィルタ・プロファイルを備えているので、周波数分析に最適です。sinc5 フィルタは、良好なエイリアシング除去レベルを維持しながら、低レイテンシの経路とスムーズなステップ応答を実現します。また、16.384MHz の MCLK で最大 1.024MSPS の出力データ・レートをサポートしていることから、sinc5 フィルタは低レイテンシのデータ収集と時間領域分析に最適なものとなっています。sinc3 フィルタは幅広いデシメーション・レシオをサポートし、16.384MHz の MCLK で最小 50SPS までの出力データ・レートを生成できます。そのため、50Hz/60Hz の同時除去ポスト・フィルタと組み合わせた場合、sinc3 フィルタは高精度の DC 測定に特に有効です。ADAQ7769-1 の 3 つのデジタル・フィルタは、いずれも直線的な位相応答を持つ FIR フィルタです。フィルタの帯域幅は DAQ シグナル・チェーンの帯域幅に直接対応しており、全てレジスタを使用して設定できます。

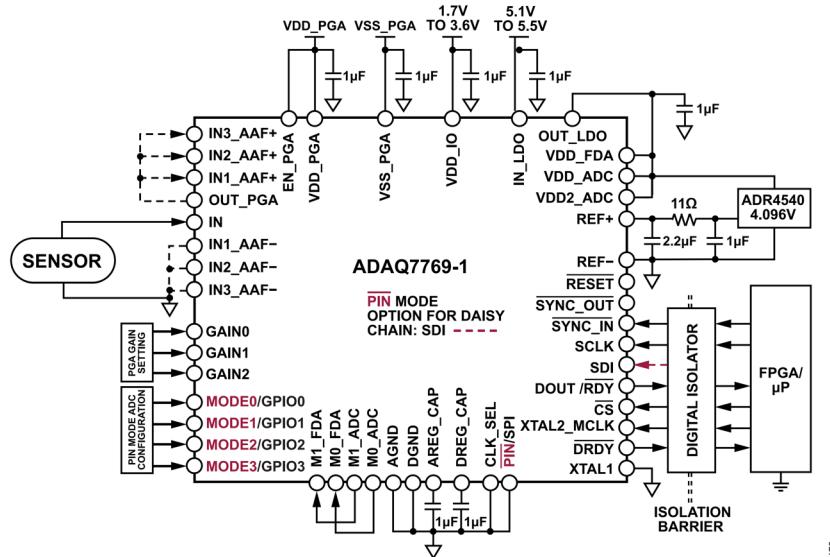

ADAQ7769-1 は、2 つのデバイス設定方法をサポートしています。SPI インターフェースを通じたレジスタ書き込みを介してデバイスを設定する方法と、単純なハードウェア・ピン・ストラッピングを通じ、事前定義された複数のモードのいずれかで動作するようにデバイスを設定する方法です。

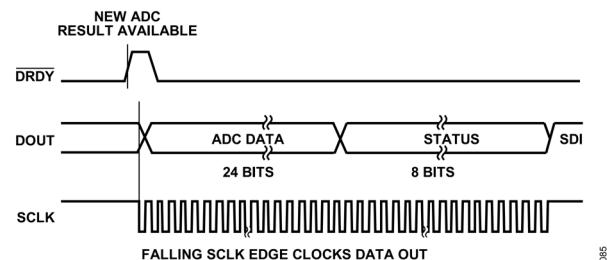

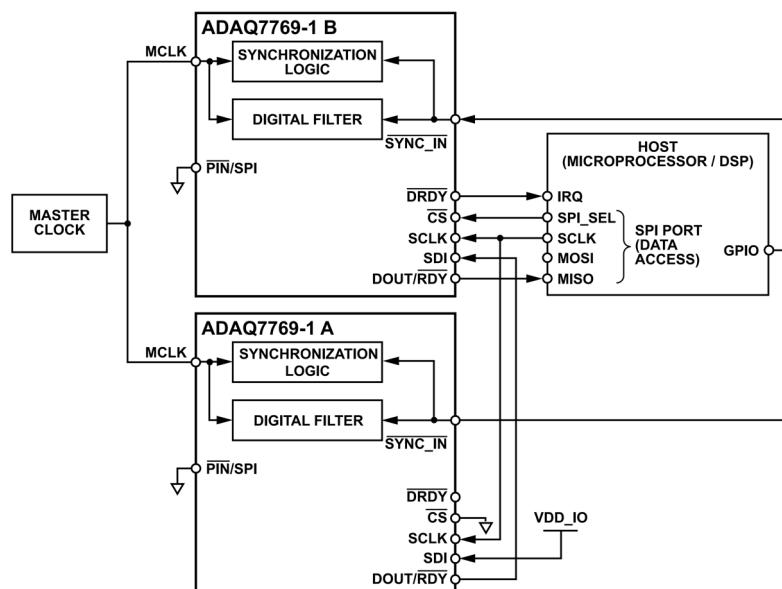

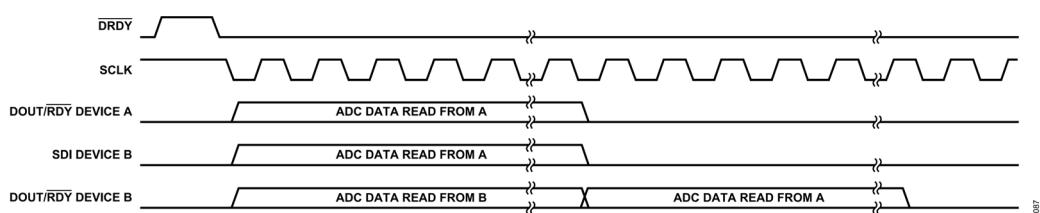

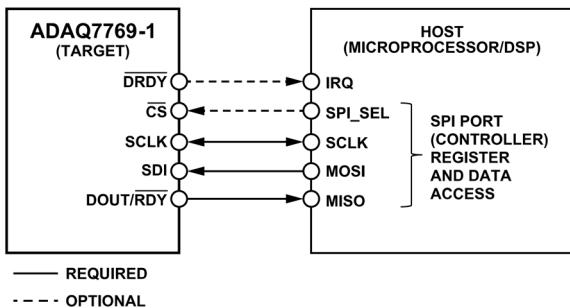

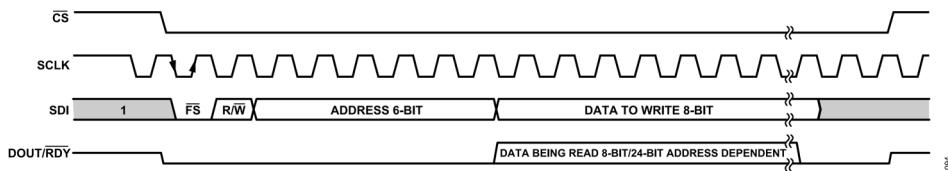

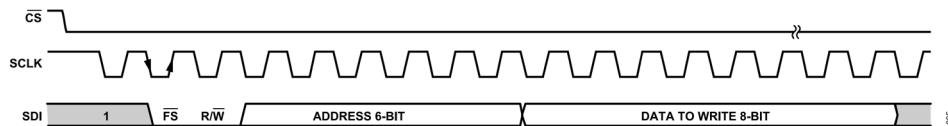

レジスタ・アクセスとサンプル・データ・リードバックの両方の機能が、单一の SPI インターフェースでサポートされています。ADAQ7769-1 は常に SPI ターゲットとして機能します。デバイスとの通信に 3 つ以上の IO チャンネルを用いれば、複数のインターフェース・モードに対応できます。

システムの信頼性向上を助けるために、ADAQ7769-1 には動作中の多様なエラーを検出する一連の内部診断機能が組み込まれています。

ADAQ7769-1 の電源接続は、内蔵 LDO を使用することで大幅に簡素化できます。なお、ディスクリート部品の数を更に削減するために、0.1 $\mu$ F のデカッピング・コンデンサも内蔵されています。

電源スタンバイ時はデバイスの各機能ブロックをスタンバイ・モードにすることができる、これによりデバイスの合計消費電力を 0.65mW 未満にすることが可能です。

## 概要

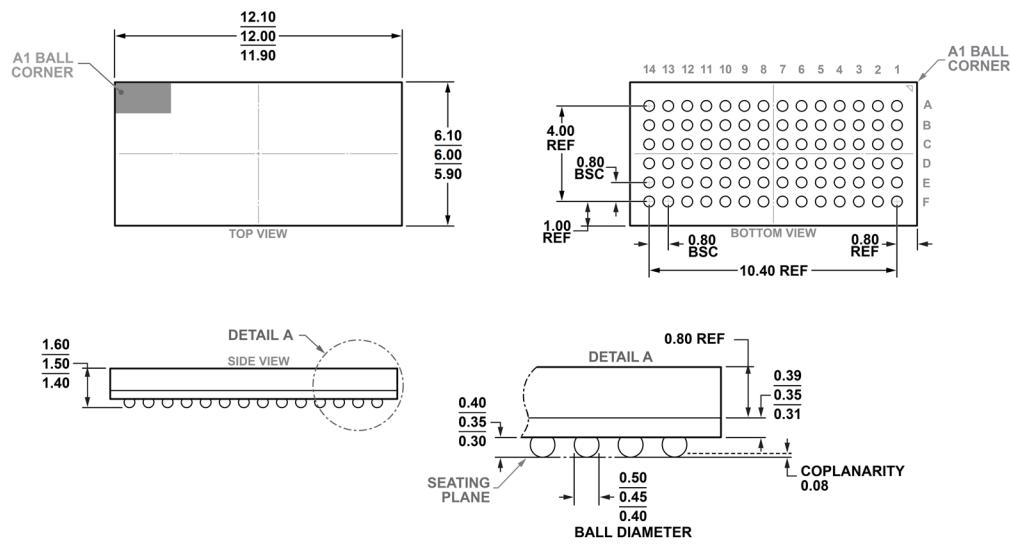

ADAQ7769-1 デバイスの動作温度範囲は-40°C～+105°C で、

12mm × 6mm、84 ポール、ポール・ピッチ 0.8mm の BGA パッケージを採用しており、マルチチャンネル・アプリケーションに適しています。デバイスのフットプリントは、ディスクリート部品を使用した同じソリューションのフットプリントと比較して 1/8 のサイズです。

## 仕様

## AAF\_GAIN = IN1\_AAF

特に指定のない限り、IN1\_AAF+ = OUT\_PGA、IN1\_AAF- = AGND、VDD\_PGA = 15V、VSS\_PGA = -15V、AGND = DGND = 0V、IN\_LDO = EN\_LDO = 5.1V～5.5V、OUT\_LDO = VDD\_FDA = VDD\_ADC、VDD2\_ADC = 2V～5.5V、VDD\_IO = 1.7V～3.6V、REF+ = 4.096V、REF- = 0V、MCLK = SCLK = 16.384MHz、デューティサイクル 50:50、f<sub>MOD</sub> = MCLK/2、フィルタ = 広帯域低リップル、デシメーション = 32、ODR = 256kSPS、直線性向上バッファ・オン、リファレンス・プリチャージ・バッファ・オン、FDA = 通常消費電力モード、T<sub>A</sub> = -40°C～105°C。代表値は T<sub>A</sub> = 25°C での値です。

表 1. AAF\_GAIN = IN1\_AAF 使用時の仕様

| Parameter                                | Test Conditions/Comments                                                                | Min     | Typ                | Max         | Unit                      |

|------------------------------------------|-----------------------------------------------------------------------------------------|---------|--------------------|-------------|---------------------------|

| ANALOG INPUT CHARACTERISTICS             |                                                                                         |         |                    |             |                           |

| Programmable Gain Amplifier (PGA) Input  | IN pin                                                                                  |         |                    |             |                           |

| Input Bias Current                       | -40°C < T <sub>A</sub> < 85°C                                                           |         | 1                  | 150         | pA                        |

|                                          | -40°C < T <sub>A</sub> < 105°C                                                          |         |                    | 600         | pA                        |

| PGA Common-Mode Input Range              |                                                                                         | VSS_PGA |                    | VDD_PGA - 4 | V                         |

| PGA Gain Range                           | PGA_GAIN = 1, 2, 4, 8, 16, 32, 64, 128                                                  | 1       |                    | 128         | V/V                       |

| Linear Input Range                       | PGA_GAIN = 1                                                                            |         | ±4.096             |             | V                         |

| Anti-Aliasing Filter (AAF) Input         | IN1_AAF+/- pins                                                                         |         |                    |             |                           |

| AAF Gain                                 | AAF_GAIN = 1                                                                            |         | 1                  |             | V/V                       |

| AAF Differential Input Range             | ±V <sub>REF</sub> /AAF_GAIN                                                             |         | ±4.096             |             | V                         |

| AAF Common-Mode Input Range              |                                                                                         | -2.1    |                    | +4.5        | V                         |

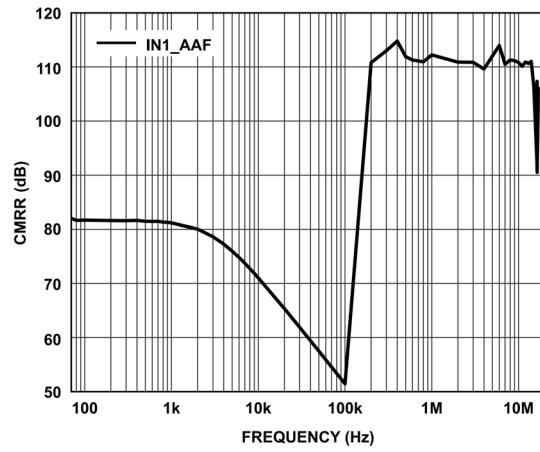

| AAF Common-Mode Rejection DC             | DC to 60Hz, referred to IN1_AAF input                                                   |         | 81.8               |             | dB                        |

| AAF Common-Mode Rejection AC             | f = 10kHz, referred to IN1_AAF input                                                    |         | 71.0               |             | dB                        |

| AAF Input Resistance, R <sub>IN</sub>    | Fully-differential configuration (IN1_AAF+ = positive input, IN1_AAF- = negative input) |         | 4                  |             | kΩ                        |

|                                          | Single-ended to differential configuration (IN1_AAF+ = input, IN1_AAF- = AGND)          |         | 2.67               |             | kΩ                        |

| OVERALL SYSTEM DC ACCURACY               |                                                                                         |         |                    |             |                           |

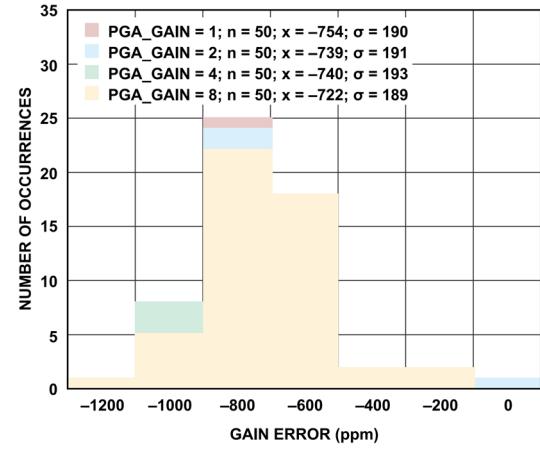

| Gain Error <sup>1</sup>                  | All PGA_GAIN, RTI                                                                       | -0.16   | -0.07              | +0.06       | %                         |

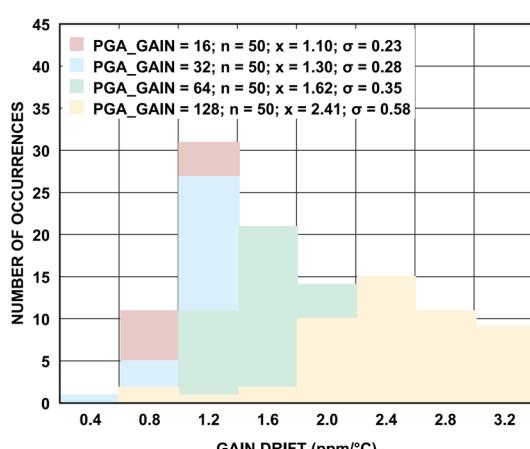

| Gain Error Drift <sup>1, 2</sup>         | Endpoint Method                                                                         |         |                    |             |                           |

|                                          | PGA_GAIN = 1 to 64                                                                      | 0.0     | 1.6                | 3.0         | ppm/°C                    |

|                                          | PGA_GAIN = 128                                                                          | 0.1     | 2.4                | 4.8         | ppm/°C                    |

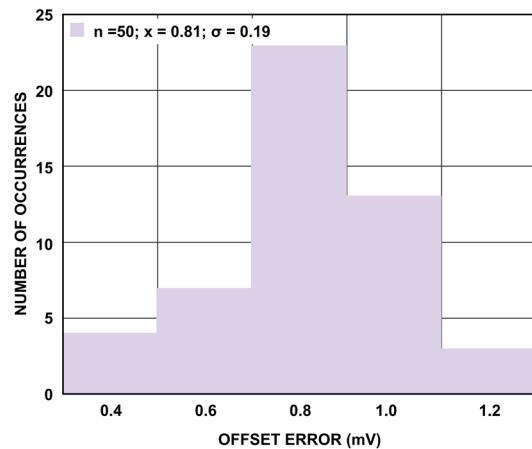

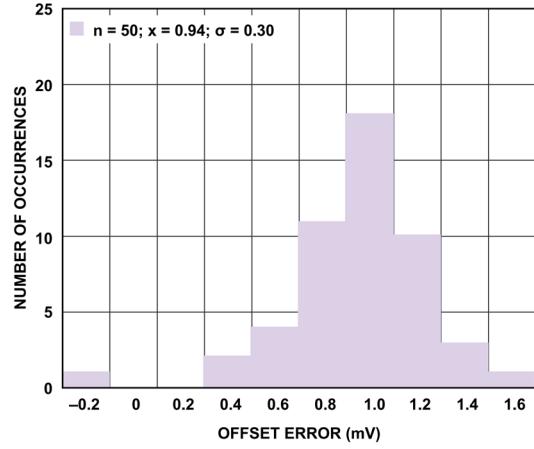

| Offset Error <sup>1</sup>                | RTI, T <sub>A</sub> = 25°C                                                              |         |                    |             |                           |

|                                          | PGA_GAIN = 1                                                                            |         | ±(10+390/PGA_GAIN) | ±1100       | μV                        |

|                                          | PGA_GAIN = 2 to 128                                                                     |         | ±(10+390/PGA_GAIN) |             | μV                        |

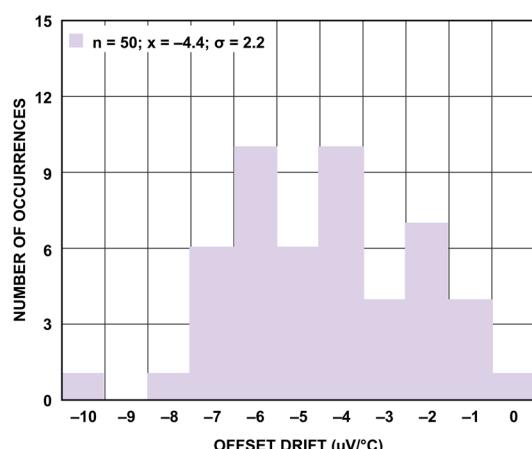

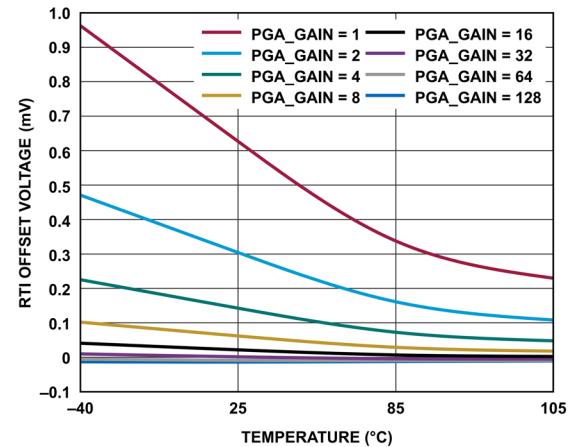

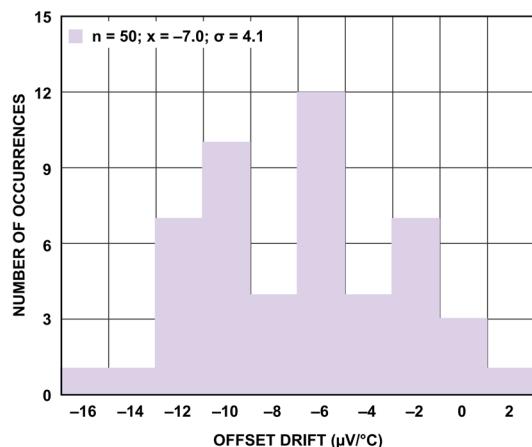

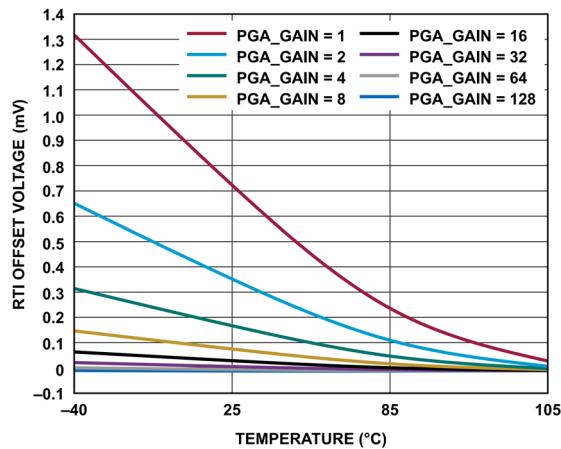

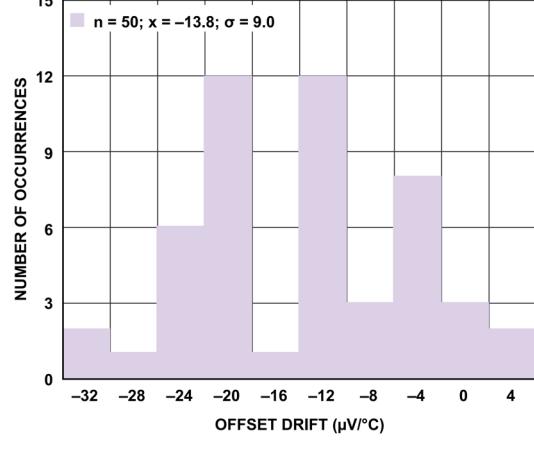

| Offset Error Drift <sup>1, 2</sup>       | RTI, Endpoint Method                                                                    |         |                    |             |                           |

|                                          | PGA_GAIN = 1                                                                            | -13.1   | 0.1-(3.1/PGA_GAIN) | 4.2         | μV/°C                     |

|                                          | PGA_GAIN = 2 to 128                                                                     |         | 0.1-(3.1/PGA_GAIN) |             | μV/°C                     |

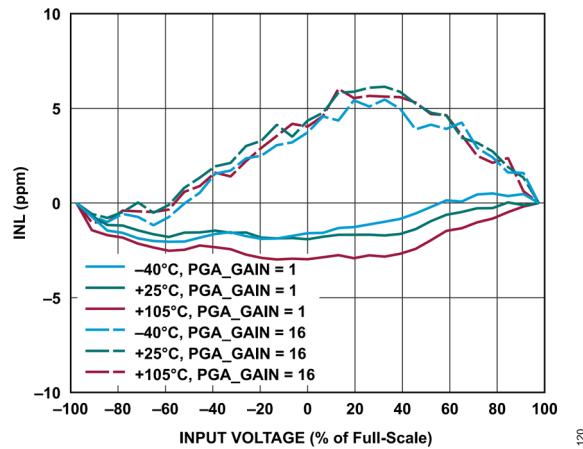

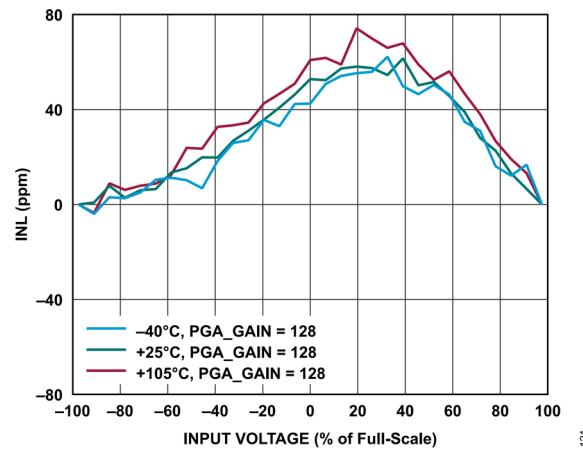

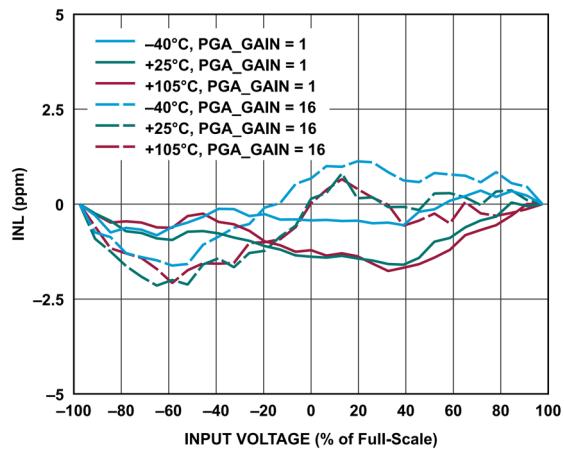

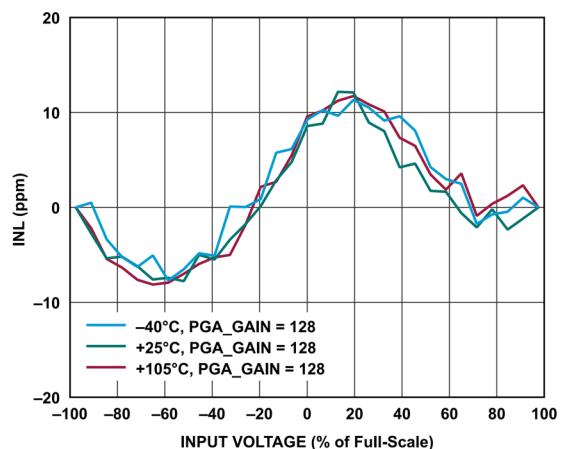

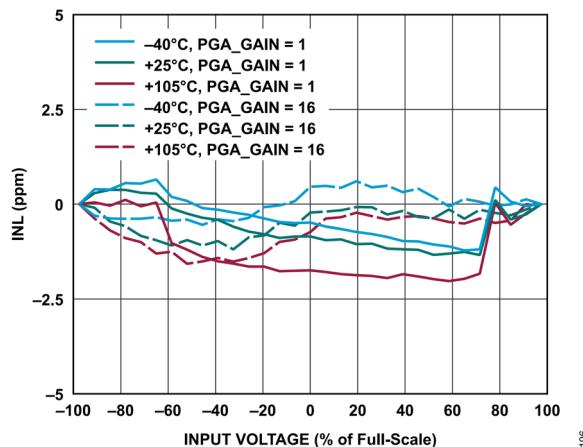

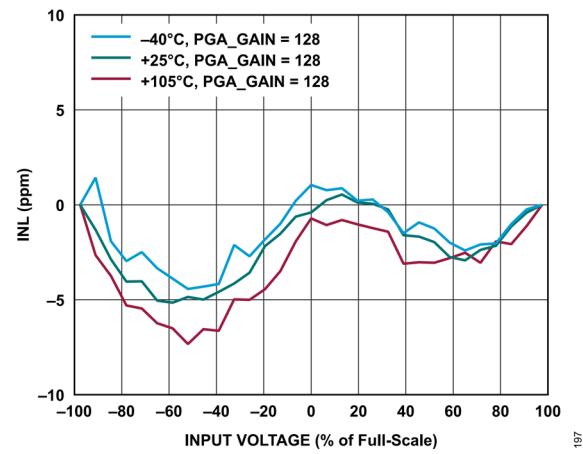

| Integral Nonlinearity (INL) <sup>3</sup> | Endpoint Method                                                                         |         |                    |             |                           |

|                                          | PGA_GAIN = 1                                                                            |         | ±3.3               |             | ppm of linear input range |

|                                          | PGA_GAIN = 16                                                                           |         | ±7.6               |             | ppm of linear input range |

|                                          | PGA_GAIN = 128                                                                          |         | ±75.0              |             | ppm of linear input range |

| Low-Frequency Noise                      | Sinc3 filter, ODR = 50SPS, BW = 15Hz, shorted input, RTI                                |         |                    |             |                           |

|                                          | PGA_GAIN = 1                                                                            |         | 0.37               |             | μV rms                    |

|                                          | PGA_GAIN = 2                                                                            |         | 0.22               |             | μV rms                    |

## 仕様

表 1. AAF\_GAIN = IN1\_AAF 使用時の仕様 (続き)

| Parameter                            | Test Conditions/Comments                                                                                                                                                                                                                                                                           | Min   | Typ                                                                       | Max | Unit                                                     |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------|-----|----------------------------------------------------------|

| Peak-to-Peak Resolution <sup>4</sup> | PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128<br>Sinc3 filter, ODR = 50SPS, BW = 15Hz, shorted input, RTI<br>PGA_GAIN = 1<br>PGA_GAIN = 2<br>PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128 |       | 0.12<br>0.08<br>0.05<br>0.05<br>0.04<br>0.04                              |     | µV rms<br>µV rms<br>µV rms<br>µV rms<br>µV rms<br>µV rms |

| OVERALL SYSTEM AC PERFORMANCE        | Wideband low-ripple FIR filter, ODR = 256kSPS, DEC_RATE = 32, BW = 110.8kHz<br>Shorted input                                                                                                                                                                                                       |       |                                                                           |     |                                                          |

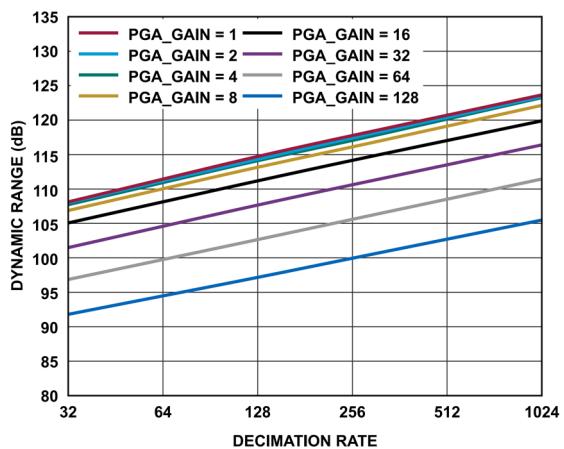

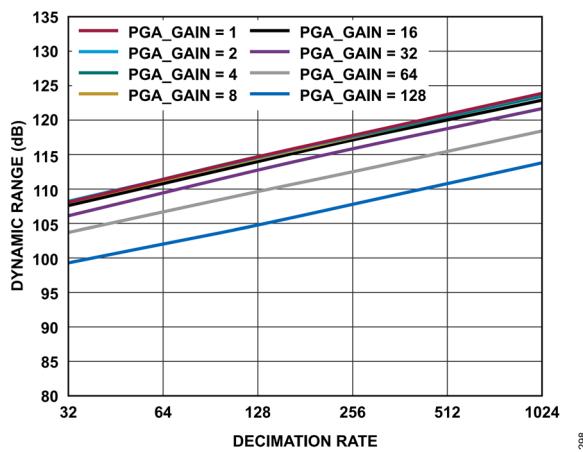

| Dynamic Range (DR) <sup>5</sup>      | PGA_GAIN = 1<br>PGA_GAIN = 2<br>PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128<br>Total system DR                                                                                                                                               | 105.5 | 107.6<br>106.7<br>105.1<br>102.3<br>98.4<br>93.6<br>88.3<br>83.2<br>125.5 |     | dB                                                       |

| Noise Spectral Density               | RTI, shorted input, at 1kHz<br>PGA_GAIN = 1<br>PGA_GAIN = 2<br>PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128                                                                                                                                   |       | 36<br>20<br>12<br>8.4<br>6.6<br>5.7<br>5.1<br>4.8                         |     | nV/√Hz                                                   |

| Total RMS Noise                      | RTI, shorted input<br>PGA_GAIN = 1<br>PGA_GAIN = 2<br>PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128                                                                                                                                            |       | 12.0<br>6.7<br>4.1<br>2.8<br>2.2<br>1.9<br>1.7<br>1.6                     |     | µV rms                                                   |

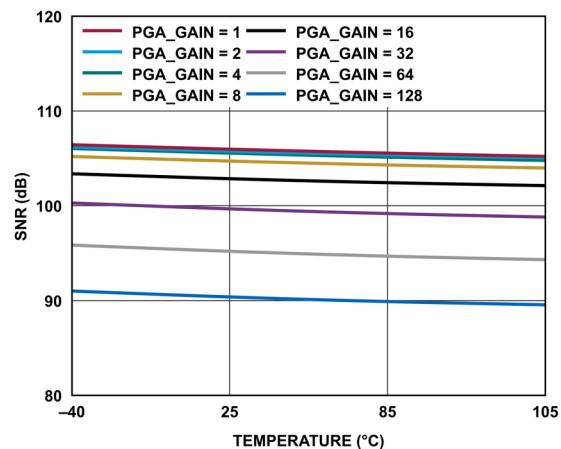

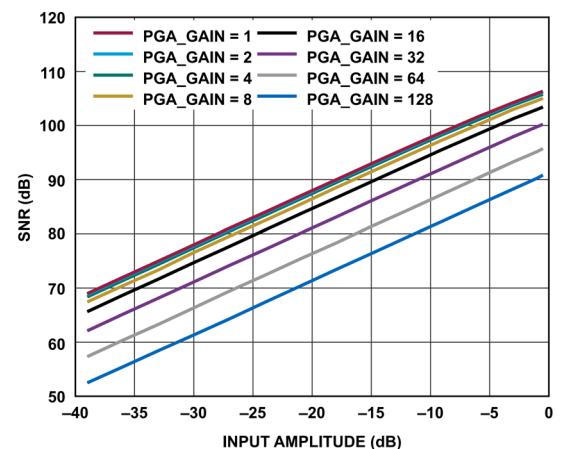

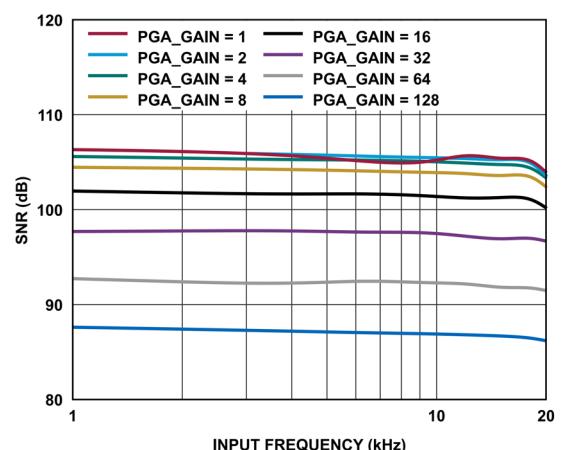

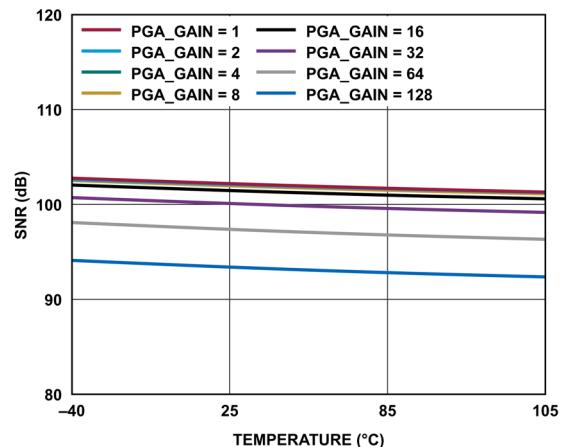

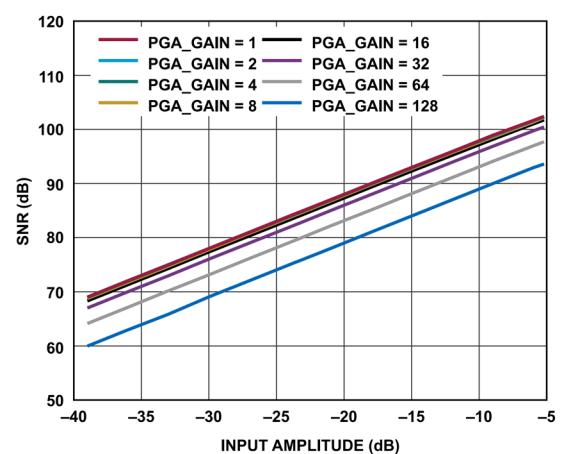

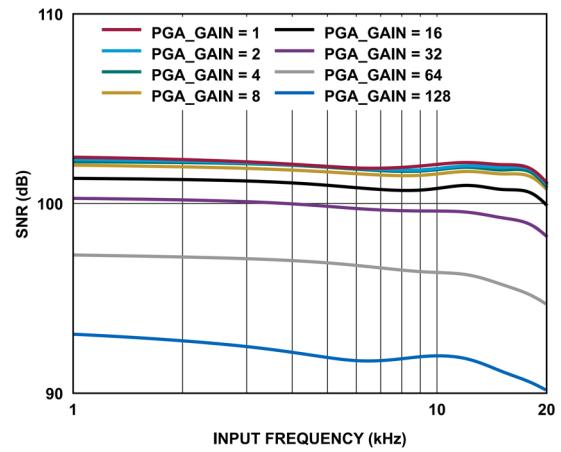

| Signal-to-Noise Ratio (SNR)          | ~0.5dBFS, sine input, 1kHz tone<br>PGA_GAIN = 1, 3.87Vp<br>PGA_GAIN = 2, 1.93Vp                                                                                                                                                                                                                    |       | 105.8<br>105.0                                                            |     | dB<br>dB                                                 |

## 仕様

表 1. AAF\_GAIN = IN1\_AAF 使用時の仕様 (続き)

| Parameter                                    | Test Conditions/Comments                            | Min | Typ    | Max | Unit |

|----------------------------------------------|-----------------------------------------------------|-----|--------|-----|------|

| Total Harmonic Distortion (THD)              | PGA_GAIN = 4, 0.97Vp                                |     | 103.4  |     | dB   |

|                                              | PGA_GAIN = 8, 0.48Vp                                |     | 100.8  |     | dB   |

|                                              | PGA_GAIN = 16, 0.24Vp                               |     | 97.0   |     | dB   |

|                                              | PGA_GAIN = 32, 0.12Vp                               |     | 92.0   |     | dB   |

|                                              | PGA_GAIN = 64, 0.060Vp                              |     | 86.9   |     | dB   |

|                                              | PGA_GAIN = 128, 0.030Vp                             |     | 81.9   |     | dB   |

|                                              | -0.5dBFS, sine input, 1kHz tone                     |     |        |     |      |

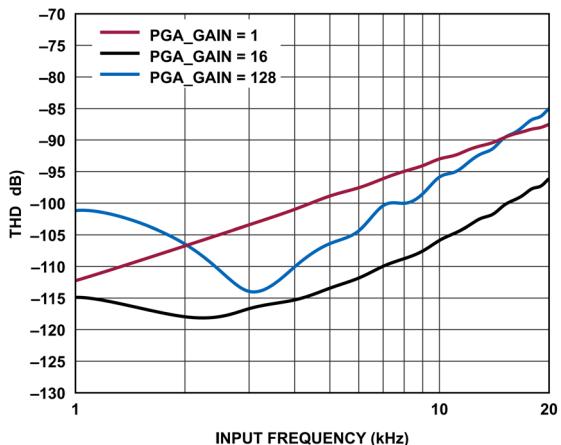

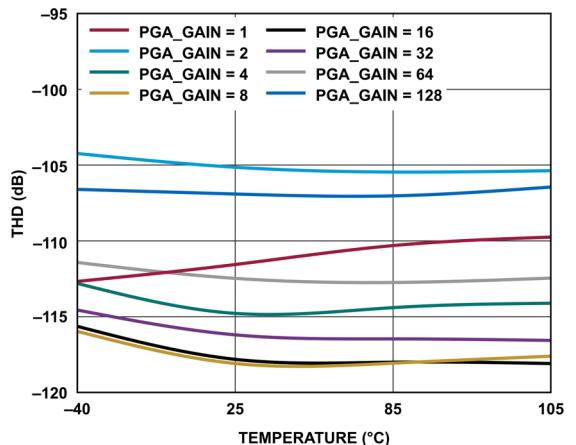

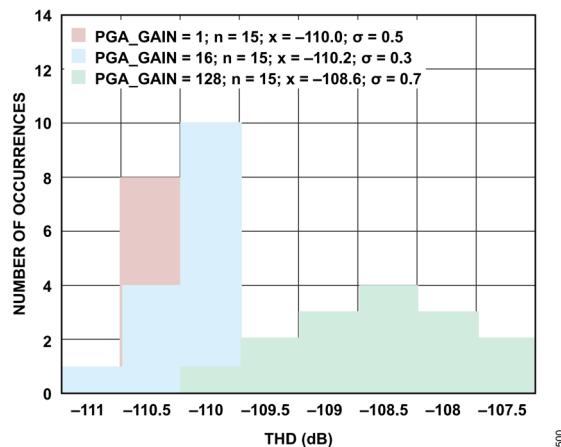

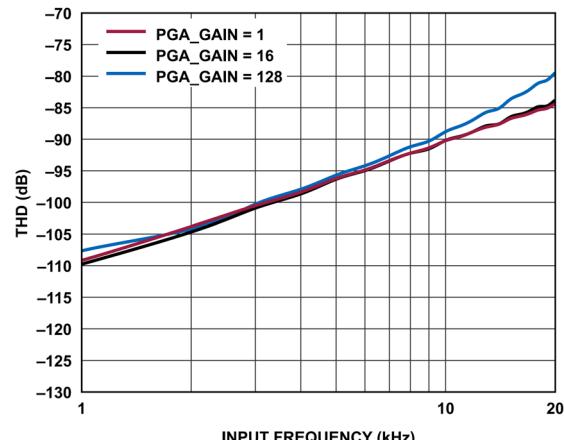

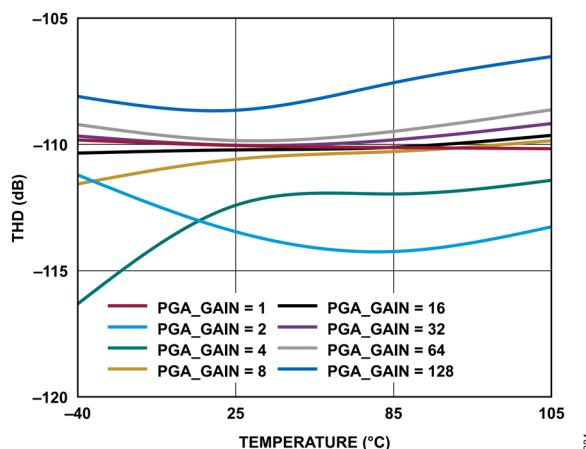

|                                              | PGA_GAIN = 1, 3.87Vp                                |     | -113.4 |     | dB   |

|                                              | PGA_GAIN = 2, 1.93Vp                                |     | -112.1 |     | dB   |

|                                              | PGA_GAIN = 4, 0.97Vp                                |     | -113.8 |     | dB   |

|                                              | PGA_GAIN = 8, 0.48Vp                                |     | -114.6 |     | dB   |

|                                              | PGA_GAIN = 16, 0.24Vp                               |     | -116.1 |     | dB   |

|                                              | PGA_GAIN = 32, 0.12Vp                               |     | -116.1 |     | dB   |

|                                              | PGA_GAIN = 64, 0.060Vp                              |     | -111.6 |     | dB   |

|                                              | PGA_GAIN = 128, 0.030Vp                             |     | -104.1 |     | dB   |

| Signal-to-Noise and Distortion Ratio (SINAD) | -0.5dBFS, sine input, 1kHz tone                     |     |        |     |      |

|                                              | PGA_GAIN = 1, 3.87Vp                                |     | 105.1  |     | dB   |

|                                              | PGA_GAIN = 2, 1.93Vp                                |     | 104.2  |     | dB   |

|                                              | PGA_GAIN = 4, 0.97Vp                                |     | 103.0  |     | dB   |

|                                              | PGA_GAIN = 8, 0.48Vp                                |     | 100.6  |     | dB   |

|                                              | PGA_GAIN = 16, 0.24Vp                               |     | 97.0   |     | dB   |

|                                              | PGA_GAIN = 32, 0.12Vp                               |     | 92.0   |     | dB   |

|                                              | PGA_GAIN = 64, 0.060Vp                              |     | 86.9   |     | dB   |

|                                              | PGA_GAIN = 128, 0.030Vp                             |     | 81.9   |     | dB   |

|                                              | -0.5dBFS, sine input, 1kHz tone                     |     |        |     |      |

|                                              | PGA_GAIN = 1, 3.87Vp                                |     | -114.6 |     | dBc  |

|                                              | PGA_GAIN = 2, 1.93Vp                                |     | -112.6 |     | dBc  |

|                                              | PGA_GAIN = 4, 0.97Vp                                |     | -115.1 |     | dBc  |

|                                              | PGA_GAIN = 8, 0.48Vp                                |     | -116.9 |     | dBc  |

| Spurious-Free Dynamic Range (SFDR)           | PGA_GAIN = 16, 0.24Vp                               |     | -118.9 |     | dBc  |

|                                              | PGA_GAIN = 32, 0.12Vp                               |     | -121.8 |     | dBc  |

|                                              | PGA_GAIN = 64, 0.060Vp                              |     | -113.7 |     | dBc  |

|                                              | PGA_GAIN = 128, 0.030Vp                             |     | -105.6 |     | dBc  |

|                                              | -0.5dBFS, sine input, 1kHz tone                     |     |        |     |      |

|                                              | PGA_GAIN = 1, 3.87Vp                                |     | -114.6 |     | dBc  |

|                                              | PGA_GAIN = 2, 1.93Vp                                |     | -112.6 |     | dBc  |

|                                              | PGA_GAIN = 4, 0.97Vp                                |     | -115.1 |     | dBc  |

|                                              | PGA_GAIN = 8, 0.48Vp                                |     | -116.9 |     | dBc  |

|                                              | PGA_GAIN = 16, 0.24Vp                               |     | -118.9 |     | dBc  |

|                                              | PGA_GAIN = 32, 0.12Vp                               |     | -121.8 |     | dBc  |

|                                              | PGA_GAIN = 64, 0.060Vp                              |     | -113.7 |     | dBc  |

|                                              | PGA_GAIN = 128, 0.030Vp                             |     | -105.6 |     | dBc  |

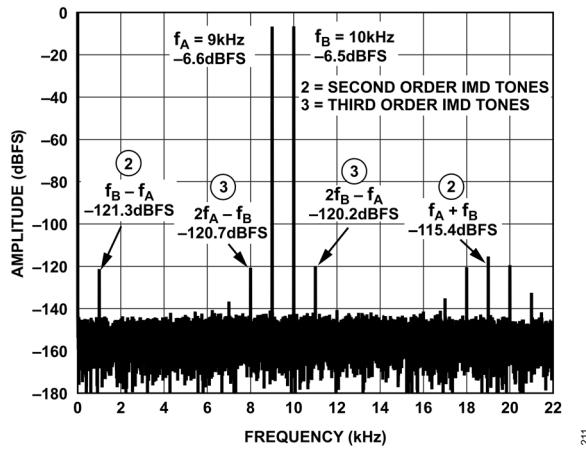

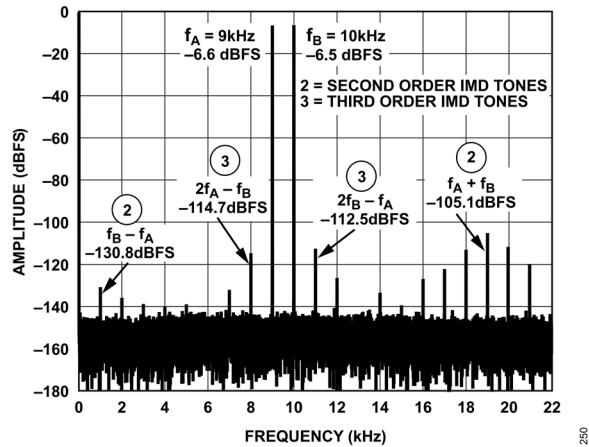

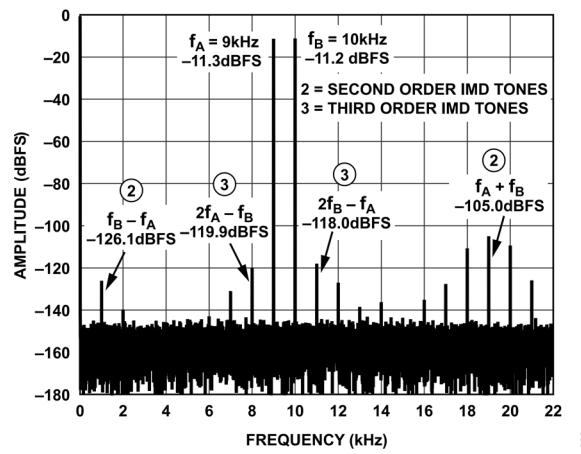

| Intermodulation Distortion (IMD)             | $f_{IN\_A} = 9\text{kHz}, f_{IN\_B} = 10\text{kHz}$ |     |        |     |      |

|                                              | Second-order                                        |     |        |     |      |

|                                              | PGA_GAIN = 1                                        |     | -115   |     | dBc  |

|                                              | PGA_GAIN = 2                                        |     | -106   |     | dBc  |

|                                              | PGA_GAIN = 4                                        |     | -115   |     | dBc  |

|                                              | PGA_GAIN = 8                                        |     | -117   |     | dBc  |

|                                              | PGA_GAIN = 16                                       |     | -113   |     | dBc  |

|                                              | PGA_GAIN = 32                                       |     | -109   |     | dBc  |

|                                              | PGA_GAIN = 64                                       |     | -104   |     | dBc  |

|                                              | PGA_GAIN = 128                                      |     | -98    |     | dBc  |

|                                              | Third-order                                         |     |        |     |      |

|                                              | PGA_GAIN = 1 to 16                                  |     | -120   |     | dBc  |

|                                              | PGA_GAIN = 32                                       |     | -118   |     | dBc  |

|                                              | PGA_GAIN = 64                                       |     | -115   |     | dBc  |

|                                              | PGA_GAIN = 128                                      |     | -110   |     | dBc  |

## 仕様

表 1. AAF\_GAIN = IN1\_AAF 使用時の仕様 (続き)

| Parameter                                                           | Test Conditions/Comments                                                                    | Min    | Typ         | Max    | Unit        |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------|-------------|--------|-------------|

| ANALOG FRONT-END (AFE) MAGNITUDE AND PHASE PERFORMANCE <sup>6</sup> |                                                                                             |        |             |        |             |

| AFE Bandwidth                                                       | -3dB relative to signal amplitude at DC                                                     |        |             |        |             |

|                                                                     | PGA_GAIN = 1                                                                                | 358.2  |             |        | kHz         |

|                                                                     | PGA_GAIN = 2                                                                                | 382.7  |             |        | kHz         |

|                                                                     | PGA_GAIN = 4                                                                                | 375.1  |             |        | kHz         |

|                                                                     | PGA_GAIN = 8                                                                                | 366.9  |             |        | kHz         |

|                                                                     | PGA_GAIN = 16                                                                               | 351.3  |             |        | kHz         |

|                                                                     | PGA_GAIN = 32                                                                               | 309.1  |             |        | kHz         |

|                                                                     | PGA_GAIN = 64                                                                               | 224.8  |             |        | kHz         |

|                                                                     | PGA_GAIN = 128                                                                              | 117.2  |             |        | kHz         |

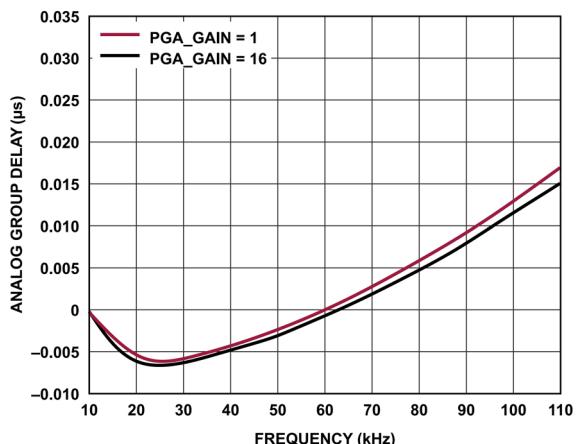

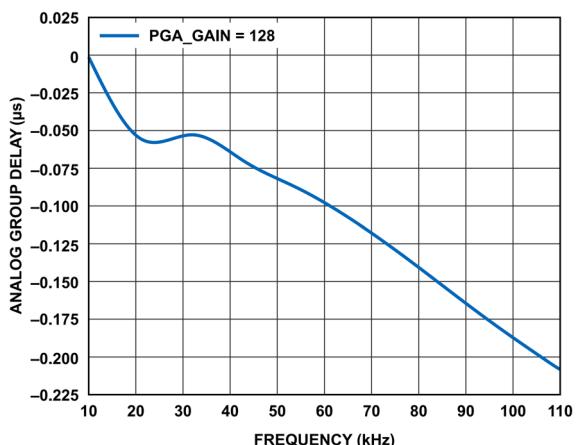

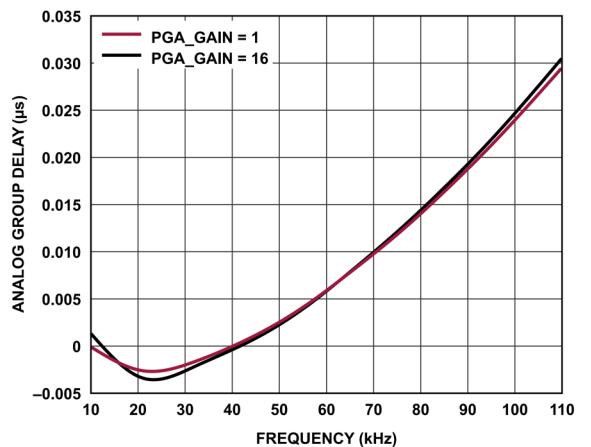

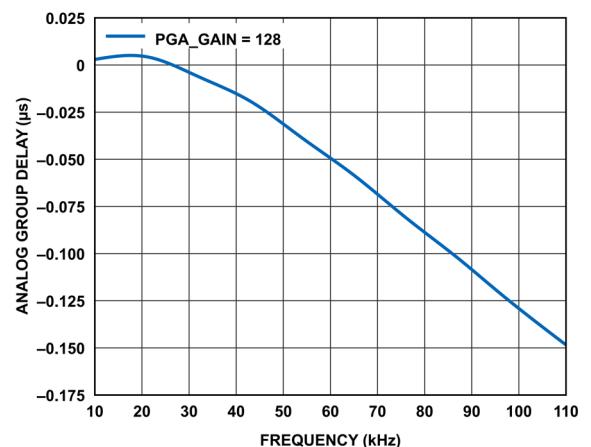

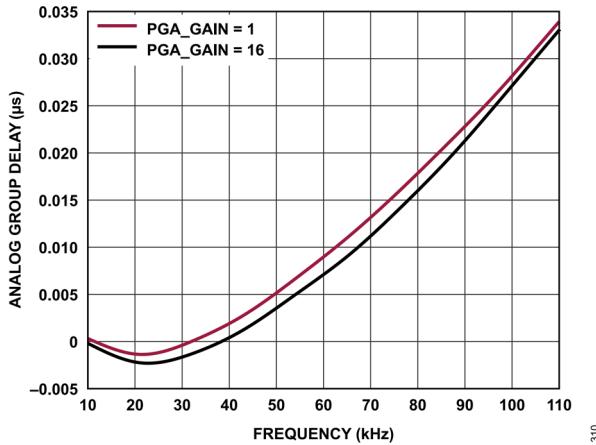

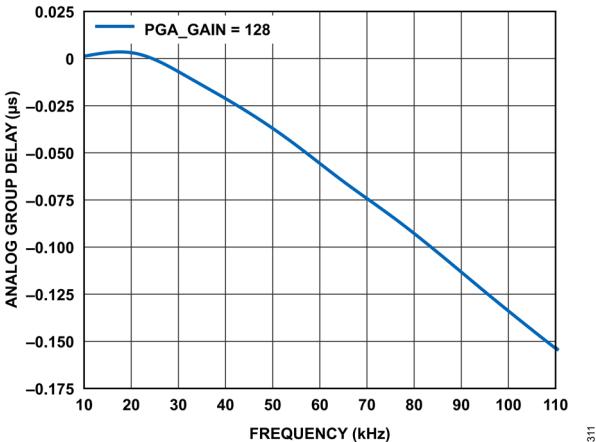

| Analog Group Delay                                                  | $f_{IN} = 20$ kHz                                                                           |        |             |        |             |

|                                                                     | PGA_GAIN = 1                                                                                | 0.81   |             |        | μs          |

|                                                                     | PGA_GAIN = 2                                                                                | 0.69   |             |        | μs          |

|                                                                     | PGA_GAIN = 4                                                                                | 0.73   |             |        | μs          |

|                                                                     | PGA_GAIN = 8                                                                                | 0.81   |             |        | μs          |

|                                                                     | PGA_GAIN = 16                                                                               | 0.92   |             |        | μs          |

|                                                                     | PGA_GAIN = 32                                                                               | 1.11   |             |        | μs          |

|                                                                     | PGA_GAIN = 64                                                                               | 1.44   |             |        | μs          |

|                                                                     | PGA_GAIN = 128                                                                              | 2.10   |             |        | μs          |

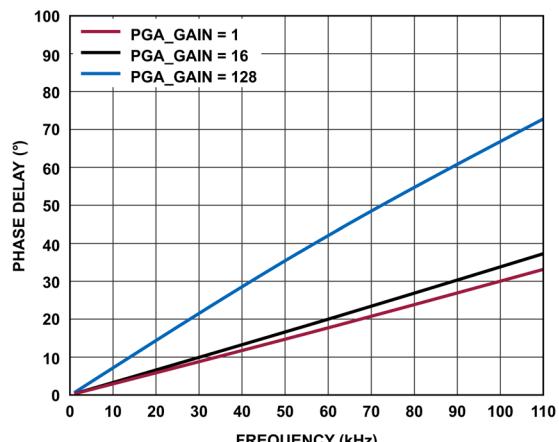

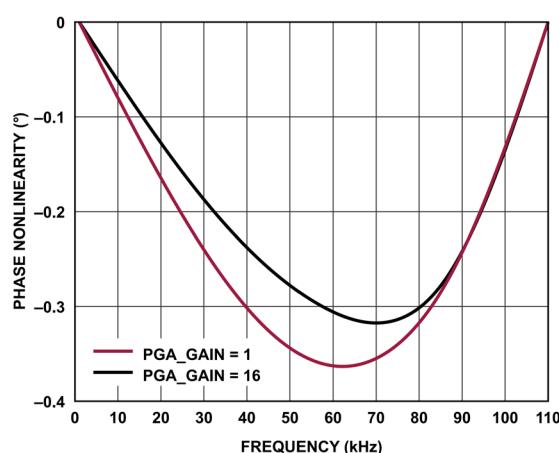

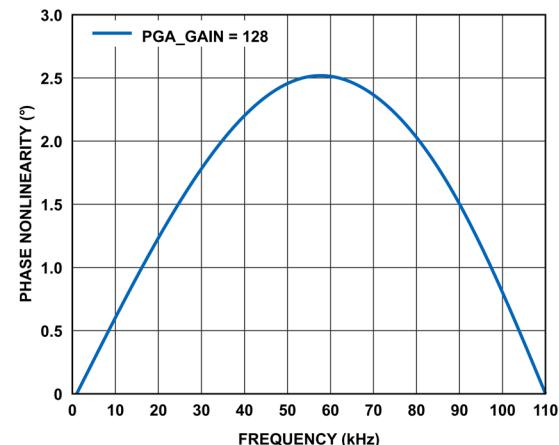

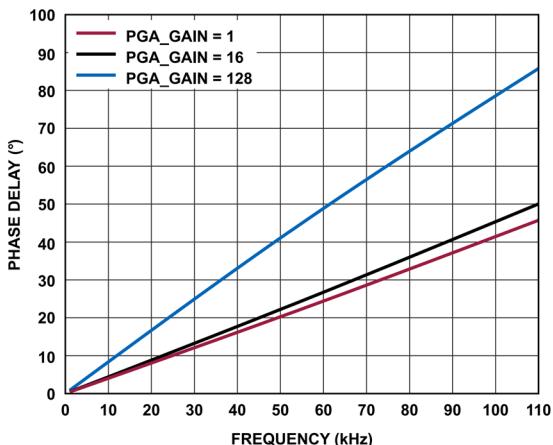

| Phase Angle Mismatch over Gain <sup>2, 3, 6</sup>                   | Sine wave, $f_{IN} = 20$ kHz, single device, normalized to PGA_GAIN = 1, $T_A = 25^\circ C$ |        |             |        |             |

|                                                                     | PGA_GAIN = 2                                                                                | -0.936 | -0.865      | -0.793 | Degrees     |

|                                                                     | PGA_GAIN = 4                                                                                | -0.595 | -0.531      | -0.467 | Degrees     |

|                                                                     | PGA_GAIN = 8                                                                                | 0.006  | 0.063       | 0.119  | Degrees     |

|                                                                     | PGA_GAIN = 16                                                                               | 0.774  | 0.842       | 0.910  | Degrees     |

|                                                                     | PGA_GAIN = 32                                                                               | 2.036  | 2.155       | 2.273  | Degrees     |

|                                                                     | PGA_GAIN = 64                                                                               | 4.360  | 4.594       | 4.829  | Degrees     |

|                                                                     | PGA_GAIN = 128                                                                              | 8.868  | 9.336       | 9.804  | Degrees     |

| Phase Angle Drift <sup>2, 3, 6</sup>                                | $f_{IN} = 20$ kHz                                                                           |        |             |        |             |

|                                                                     | PGA_GAIN = 1                                                                                | 0.13   | 0.20        | 0.26   | $m^\circ/C$ |

|                                                                     | PGA_GAIN = 2                                                                                | -0.01  | 0.05        | 0.12   | $m^\circ/C$ |

|                                                                     | PGA_GAIN = 4                                                                                | 0.25   | 0.32        | 0.39   | $m^\circ/C$ |

|                                                                     | PGA_GAIN = 8                                                                                | 0.61   | 0.82        | 1.03   | $m^\circ/C$ |

|                                                                     | PGA_GAIN = 16                                                                               | 1.24   | 1.72        | 2.20   | $m^\circ/C$ |

|                                                                     | PGA_GAIN = 32                                                                               | 2.46   | 3.47        | 4.47   | $m^\circ/C$ |

|                                                                     | PGA_GAIN = 64                                                                               | 4.88   | 6.89        | 8.90   | $m^\circ/C$ |

|                                                                     | PGA_GAIN = 128                                                                              | 9.52   | 13.47       | 17.42  | $m^\circ/C$ |

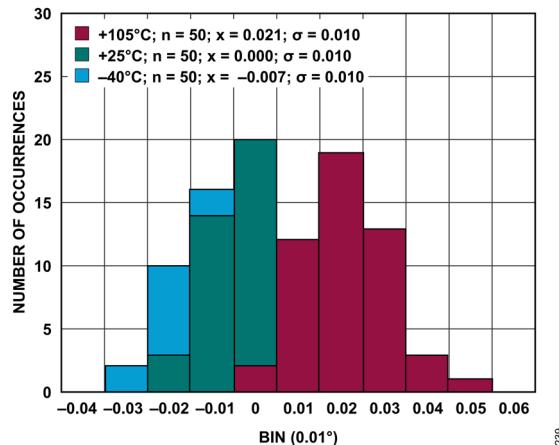

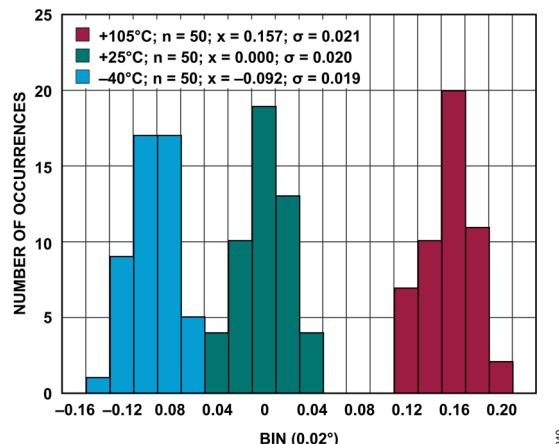

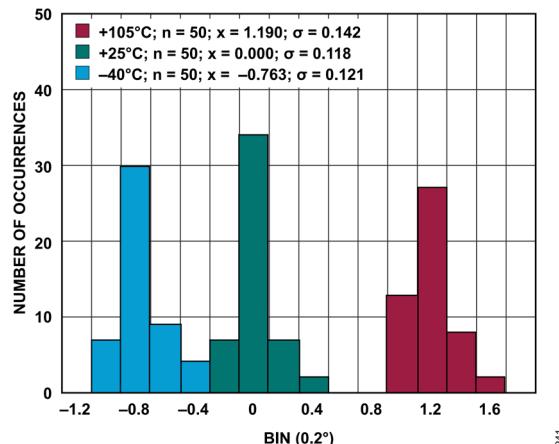

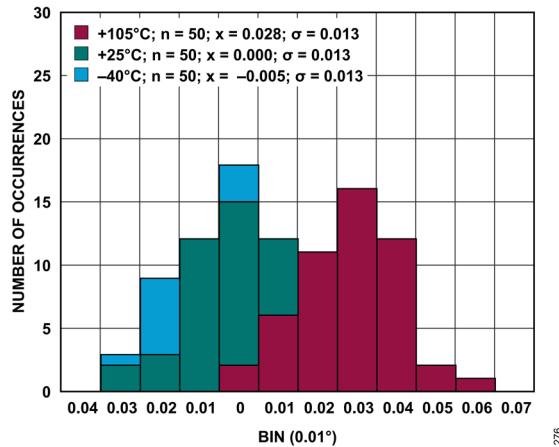

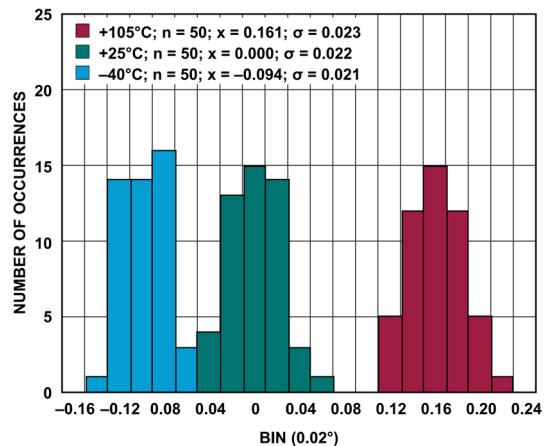

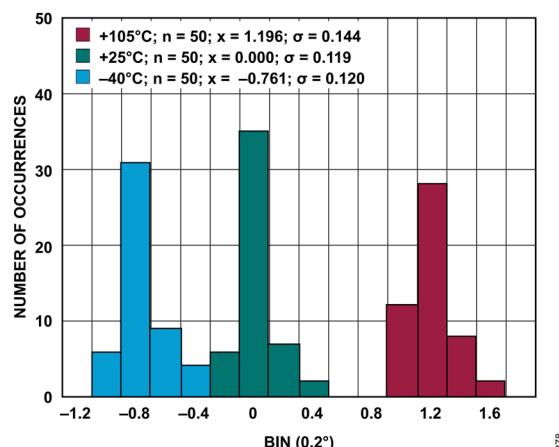

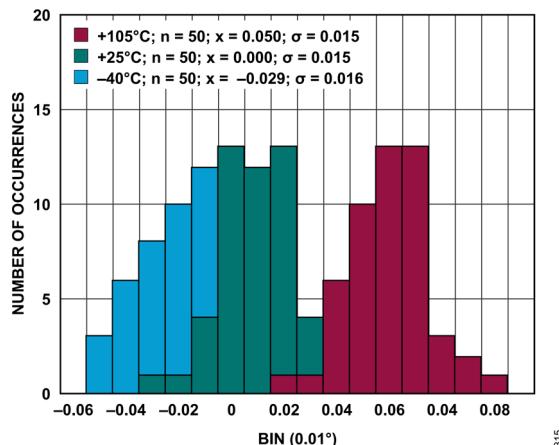

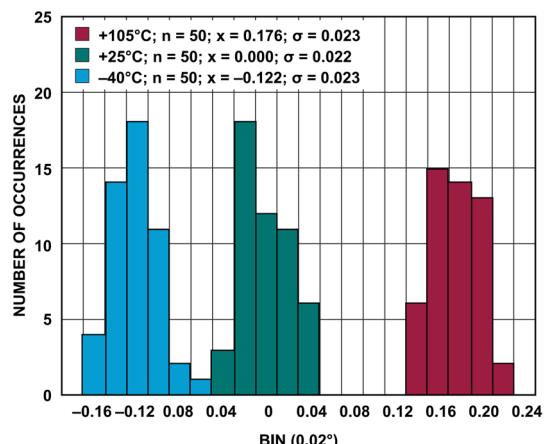

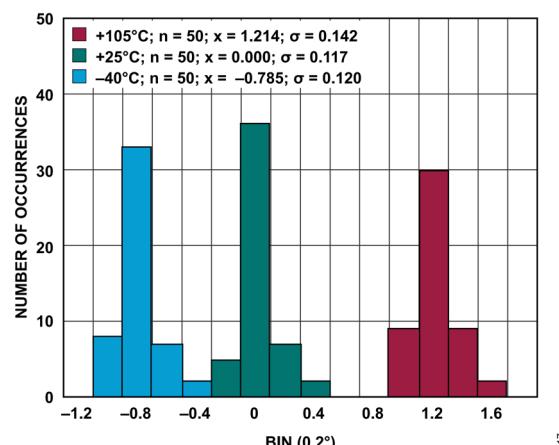

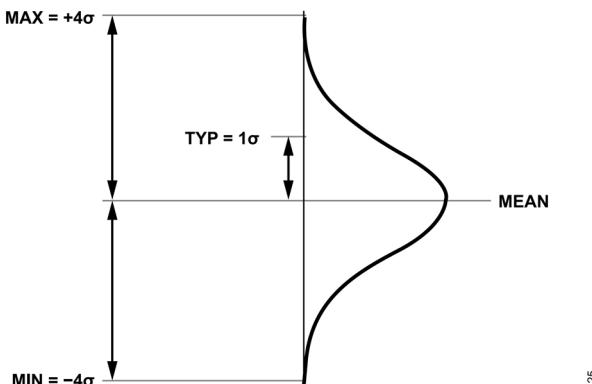

| Device-to-Device Phase Angle Mismatch <sup>2, 3, 6</sup>            | $f_{IN} = 20$ kHz, typical = $\pm 1\sigma$ , $T_A = 25^\circ C$                             |        |             |        |             |

|                                                                     | PGA_GAIN = 1                                                                                | -0.038 | $\pm 0.013$ | 0.038  | Degrees     |

|                                                                     | PGA_GAIN = 2                                                                                | -0.079 | $\pm 0.020$ | 0.079  | Degrees     |

|                                                                     | PGA_GAIN = 4                                                                                | -0.073 | $\pm 0.018$ | 0.073  | Degrees     |

|                                                                     | PGA_GAIN = 8                                                                                | -0.067 | $\pm 0.017$ | 0.067  | Degrees     |

|                                                                     | PGA_GAIN = 16                                                                               | -0.078 | $\pm 0.020$ | 0.078  | Degrees     |

|                                                                     | PGA_GAIN = 32                                                                               | -0.126 | $\pm 0.032$ | 0.126  | Degrees     |

|                                                                     | PGA_GAIN = 64                                                                               | -0.240 | $\pm 0.060$ | 0.240  | Degrees     |

|                                                                     | PGA_GAIN = 128                                                                              | -0.471 | $\pm 0.118$ | 0.471  | Degrees     |

## 仕様

表 1. AAF\_GAIN = IN1\_AAF 使用時の仕様 (続き)

| Parameter                                                      | Test Conditions/Comments                                               | Min         | Typ   | Max | Unit                           |

|----------------------------------------------------------------|------------------------------------------------------------------------|-------------|-------|-----|--------------------------------|

| Device-to-Device Phase Angle Mismatch Drift <sup>2, 3, 6</sup> | $f_{IN} = 20\text{kHz}$ , typical = $ 1\sigma $ per $^{\circ}\text{C}$ |             |       |     |                                |

|                                                                | PGA_GAIN = 1                                                           | 0.2         | 1.0   |     | $\mu^{\circ}/^{\circ}\text{C}$ |

|                                                                | PGA_GAIN = 2                                                           | -2.7        | -11.0 |     | $\mu^{\circ}/^{\circ}\text{C}$ |

|                                                                | PGA_GAIN = 4                                                           | -2.6        | -10.4 |     | $\mu^{\circ}/^{\circ}\text{C}$ |

|                                                                | PGA_GAIN = 8                                                           | 0.1         | 0.4   |     | $\mu^{\circ}/^{\circ}\text{C}$ |

|                                                                | PGA_GAIN = 16                                                          | 9.1         | 36.6  |     | $\mu^{\circ}/^{\circ}\text{C}$ |

|                                                                | PGA_GAIN = 32                                                          | 32.1        | 128.3 |     | $\mu^{\circ}/^{\circ}\text{C}$ |

|                                                                | PGA_GAIN = 64                                                          | 72.4        | 289.6 |     | $\mu^{\circ}/^{\circ}\text{C}$ |

|                                                                | PGA_GAIN = 128                                                         | 141.5       | 565.9 |     | $\mu^{\circ}/^{\circ}\text{C}$ |

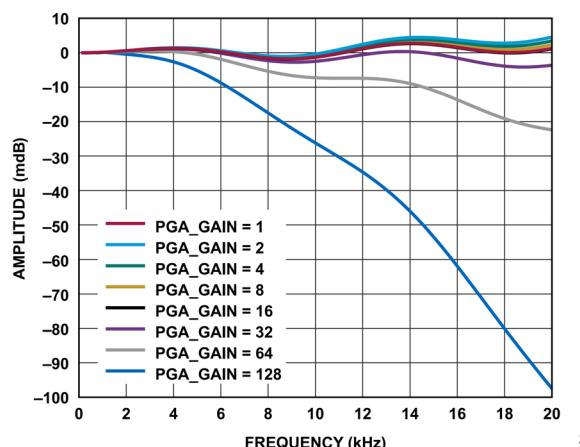

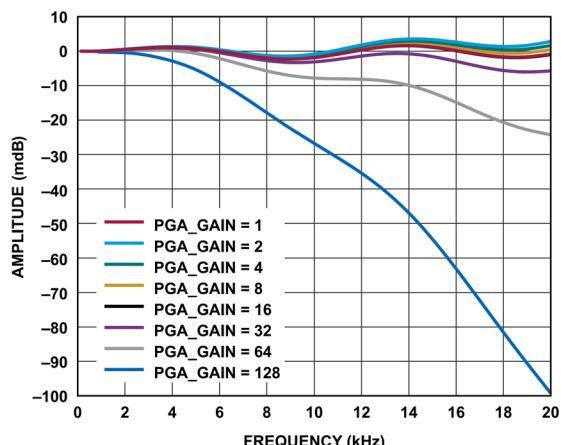

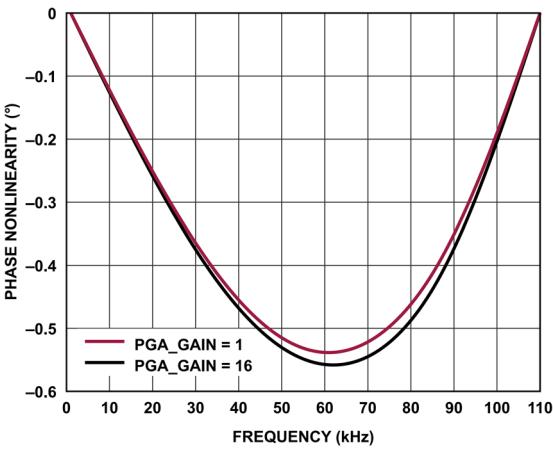

| Magnitude Flatness                                             | $f_{IN} = 20\text{kHz}$                                                |             |       |     |                                |

|                                                                | PGA_GAIN = 1 to 16                                                     | $\pm 0.005$ |       |     | dB                             |

|                                                                | PGA_GAIN = 32                                                          | -0.010      |       |     | dB                             |

|                                                                | PGA_GAIN = 64                                                          | -0.030      |       |     | dB                             |

|                                                                | PGA_GAIN = 128                                                         | -0.100      |       |     | dB                             |

|                                                                | $f_{IN} = 100\text{kHz}$                                               |             |       |     |                                |

|                                                                | PGA_GAIN = 1 to 16                                                     | $\pm 0.10$  |       |     | dB                             |

|                                                                | PGA_GAIN = 32                                                          | -0.10       |       |     | dB                             |

|                                                                | PGA_GAIN = 64                                                          | -0.50       |       |     | dB                             |

|                                                                | PGA_GAIN = 128                                                         | -2.00       |       |     | dB                             |

| Alias Rejection                                                | All PGA_GAIN, -6.0dBFS input signal at MCLK = 16.384MHz                | 90          |       |     | dB                             |

| POWER SUPPLY CURRENT                                           |                                                                        |             |       |     |                                |

| VDD_PGA                                                        | IN = AGND                                                              | 1.3         |       |     | mA                             |

|                                                                | Full-scale 1kHz sine input with common mode = AGND, any PGA_GAIN       | 1.35        |       |     | mA rms                         |

|                                                                | Full-scale DC input with common mode = AGND, any PGA_GAIN              | 2.4         |       |     | mA                             |

| VSS_PGA                                                        | IN = AGND                                                              | -2.0        |       |     | mA                             |

|                                                                | Full-scale 1kHz sine input with common mode = AGND, any PGA_GAIN       | -2.1        |       |     | mA rms                         |

|                                                                | Full-scale DC input with common mode = AGND, any PGA_GAIN              | -1.3        |       |     | mA                             |

| VDD_FDA                                                        | IN1_AAF+ = IN1_AAF- = AGND                                             | 4.9         |       |     | mA                             |

|                                                                | Full-scale 1kHz sine input with common mode = AGND, any PGA_GAIN       | 5.0         |       |     | mA rms                         |

|                                                                | Full-scale DC input with common mode = AGND, any PGA_GAIN              | 4.8         |       |     | mA                             |

| VDD_ADC                                                        | Standby                                                                | 120         |       |     | $\mu\text{A}$                  |

|                                                                | Linearity boost buffer on, reference precharge buffer on               | 6.3         |       |     | mA                             |

|                                                                | Linearity boost buffer off, reference precharge buffers off            | 2.4         |       |     | mA                             |

| VDD2_ADC                                                       | Standby                                                                | 205         |       |     | $\mu\text{A}$                  |

|                                                                |                                                                        | 4.7         |       |     | mA                             |

| VDD_IO                                                         | Standby                                                                | 30          |       |     | $\mu\text{A}$                  |

| Sinc3 Filter                                                   |                                                                        | 3.5         |       |     | mA                             |

| Sinc5 Filter                                                   |                                                                        | 3.7         |       |     | mA                             |

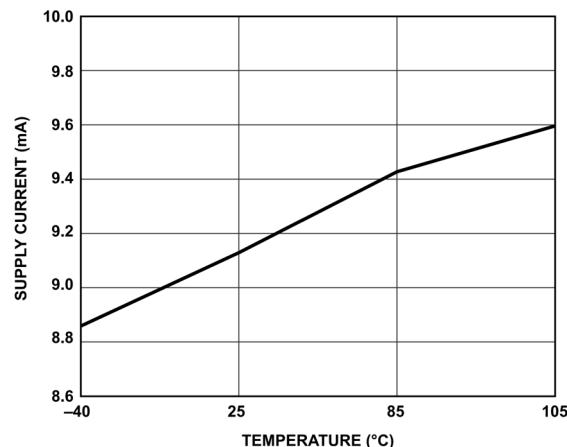

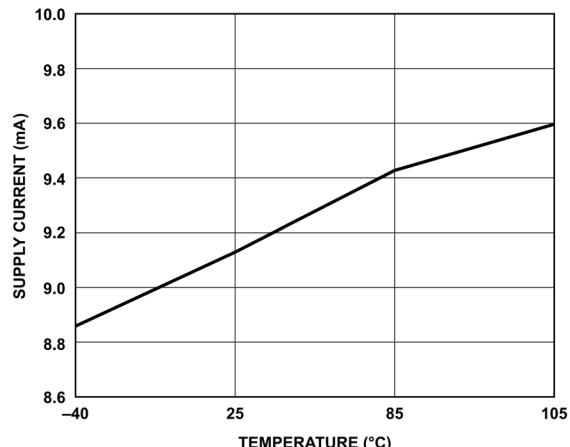

| Wideband Low-Ripple FIR Filter                                 |                                                                        | 9.1         |       |     | mA                             |

## 仕様

表 1. AAF\_GAIN = IN1\_AAF 使用時の仕様（続き）

| Parameter                      | Test Conditions/Comments                                                                                                                                                                     | Min        | Typ | Max | Unit |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|------|

| Standby                        |                                                                                                                                                                                              | 380        |     |     | μA   |

| POWER DISSIPATION              | VDD_PGA = 15V, VSS_PGA = -15V, IN_LDO = EN_LDO = 5.3 V, OUT_LDO = VDD_FDA = VDD_ADC = VDD2_ADC, VDD_IO = 3.3 V, linearity boost buffer on, reference precharge buffer on, external CMOS MCLK |            |     |     |      |

| Full Operating Mode            |                                                                                                                                                                                              |            |     |     |      |

| Sinc3 Filter                   | IN = AGND, any PGA_GAIN                                                                                                                                                                      | 145        |     |     | mW   |

| Sinc5 Filter                   | IN = AGND, any PGA_GAIN                                                                                                                                                                      | 146        |     |     | mW   |

| Wideband Low-Ripple FIR Filter | IN = AGND, any PGA_GAIN<br>Full-scale 1kHz sine input with common mode = AGND, any PGA_GAIN                                                                                                  | 164<br>167 |     |     | mW   |

|                                | Full-scale DC input with common mode = AGND, any PGA_GAIN                                                                                                                                    | 169        |     |     | mW   |

| Standby Mode                   | FDA in standby mode, and ADC in standby mode                                                                                                                                                 | 3.14       |     |     | mW   |

| ADC Power-Down                 | FDA in standby mode, and ADC in power-down mode                                                                                                                                              | 0.65       |     |     | mW   |

<sup>1</sup> テスターの繰り返し性と再現性のガード・バンドは含まれていません。

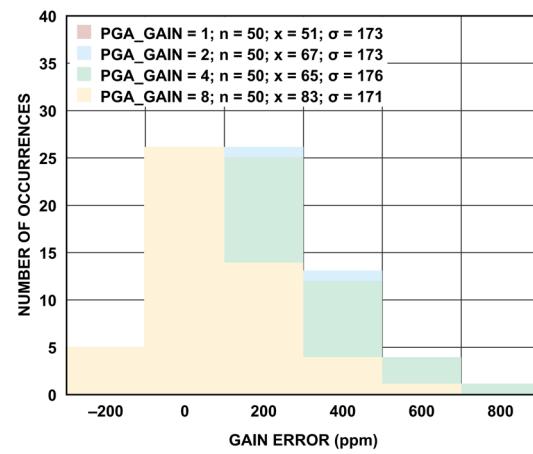

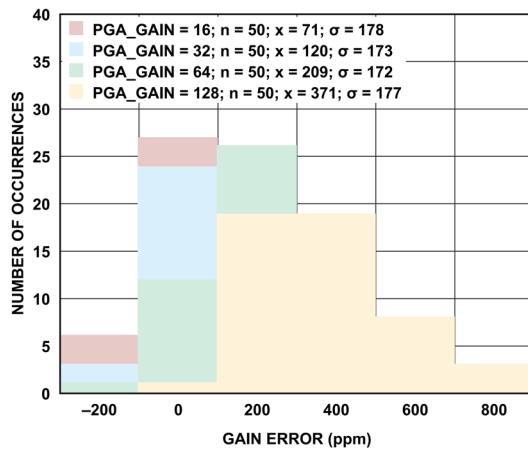

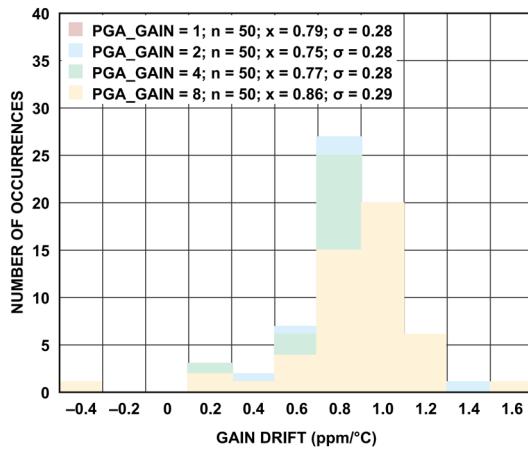

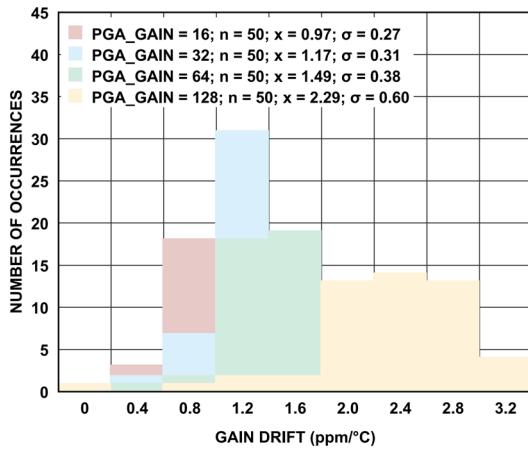

<sup>2</sup> 手順に従って IC を作製した 1 枚のウェハから抽出した 50 個のサンプルを用い、-40°C～+105°C の温度範囲で行った特性評価のデータに基づき計算した制限値。

<sup>3</sup> これらの値に対する製品テストは行われていませんが、量産開始時の特性評価データで裏付けられています。

<sup>4</sup> ピーク to ピーク分解能については、[用語の定義](#)のセクションを参照してください。計算に用いたノイズは、「Low-Frequency Noise」の仕様に記載されています。

<sup>5</sup> 異なるゲインおよびフィルタ設定におけるダイナミック・レンジとノイズの詳細については、[ノイズ性能](#)のセクションを参照してください。

<sup>6</sup> AFE 性能、用語の定義、計算については、[AFE の位相性能の計算](#)のセクションを参照してください。

## 仕様

## AAF\_GAIN = IN2\_AAF

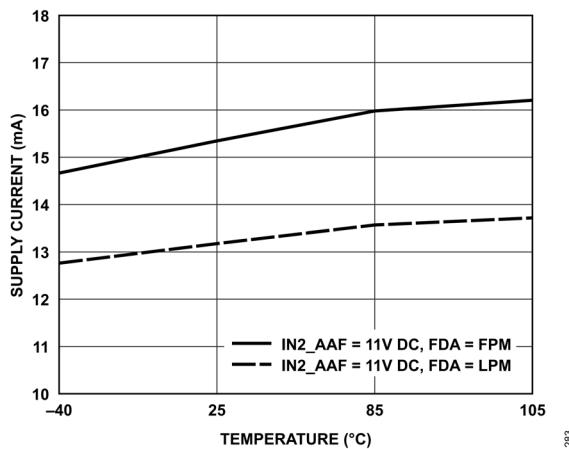

特に指定のない限り、IN2\_AAF+ = OUT\_PGA、IN2\_AAF- = AGND、VDD\_PGA = 15V、VSS\_PGA = -15V、AGND = DGND = 0V、IN\_LDO = EN\_LDO = 5.1V～5.5V、OUT\_LDO = VDD\_FDA = VDD\_ADC、VDD2\_ADC = 2V～5.5V、VDD\_IO = 1.7V～3.6V、REF+ = 4.096V、REF- = 0V、MCLK = SCLK = 16.384MHz、デューティサイクル 50:50、f<sub>MOD</sub> = MCLK/2、フィルタ = 広帯域低リップル、デシメーション = 32、ODR = 256kSPS、直線性向上バッファ・オン、リファレンス・プリチャージ・バッファ・オン、FDA = 通常消費電力モード、T<sub>A</sub> = -40°C～105°C。代表値は T<sub>A</sub> = 25°C での値です。

表 2. AAF\_GAIN = IN2\_AAF 使用時の仕様

| Parameter                             | Test Conditions/Comments                                                                | Min   | Typ                | Max   | Unit                      |

|---------------------------------------|-----------------------------------------------------------------------------------------|-------|--------------------|-------|---------------------------|

| ANALOG INPUT CHARACTERISTICS          |                                                                                         |       |                    |       |                           |

| PGA Input                             | IN pin                                                                                  |       |                    |       |                           |

| Input Bias Current                    | -40°C < T <sub>A</sub> < 85°C                                                           | 1     | 150                |       | pA                        |

|                                       | -40°C < T <sub>A</sub> < 105°C                                                          |       | 600                |       | pA                        |

| PGA Common-Mode Input Range           | VSS_PGA                                                                                 |       | VDD_PGA - 4        |       | V                         |

| PGA Gain Range                        | 1                                                                                       |       | 128                |       | V/V                       |

| Linear Input Range                    | PGA_GAIN = 1                                                                            |       | ±11.264            |       | V                         |

| AAF Input                             | IN2_AAF+/- pins                                                                         |       |                    |       |                           |

| AAF Gain                              | AAF_GAIN = 0.364                                                                        |       | 4/11               |       | V/V                       |

| AAF Differential Input Range          | ±V <sub>REF</sub> /AAF_GAIN                                                             |       | ±11.264            |       | V                         |

| AAF Common-Mode Input Range           | DC to 60Hz, referred to IN2_AAF input                                                   | -6.1  |                    | +6.2  | V                         |

| AAF Common-Mode Rejection DC          | f = 10kHz, referred to IN2_AAF input                                                    |       | 81.9               |       | dB                        |

| AAF Common-Mode Rejection AC          | Fully-differential configuration (IN2_AAF+ = positive input, IN2_AAF- = negative input) |       | 78.8               |       | dB                        |

| AAF Input Resistance, R <sub>IN</sub> | Single-ended to differential configuration (IN2_AAF+ = input, IN2_AAF- = AGND)          |       | 11                 |       | kΩ                        |

|                                       |                                                                                         |       | 6.35               |       | kΩ                        |

| OVERALL SYSTEM DC ACCURACY            |                                                                                         |       |                    |       |                           |

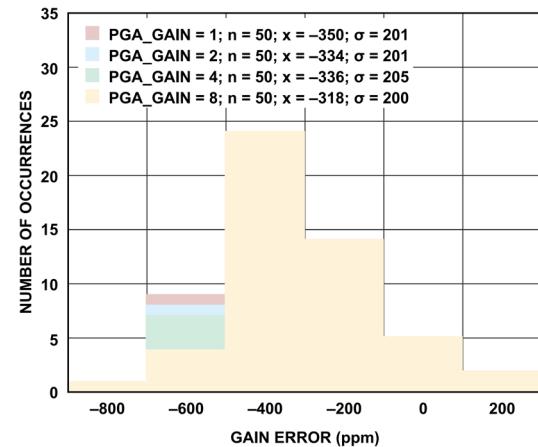

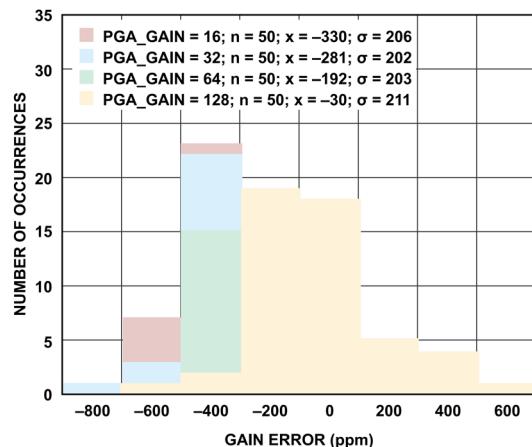

| Gain Error <sup>1</sup>               | All PGA_GAIN, RTI                                                                       | -0.12 | -0.02              | +0.10 | %                         |

| Gain Error Drift <sup>1, 2</sup>      | Endpoint Method                                                                         |       |                    |       |                           |

|                                       | PGA_GAIN = 1 to 64                                                                      | -0.9  | +0.9               | +2.3  | ppm/°C                    |

|                                       | PGA_GAIN = 128                                                                          | -0.6  | +1.7               | +4.0  | ppm/°C                    |

| Offset Error <sup>1</sup>             | RTI, T <sub>A</sub> = 25°C                                                              |       |                    |       |                           |

|                                       | PGA_GAIN = 1                                                                            |       | ±(10+620/PGA_GAIN) | ±1600 | μV                        |

|                                       | PGA_GAIN = 2 to 128                                                                     |       | ±(10+620/PGA_GAIN) |       | μV                        |

| Offset Error Drift <sup>1, 2</sup>    | RTI, Endpoint Method                                                                    |       |                    |       |                           |

|                                       | PGA_GAIN = 1                                                                            | -23.4 | 0.1-(5.1/PGA_GAIN) | 9.4   | μV/°C                     |

|                                       | PGA_GAIN = 2 to 128                                                                     |       | 0.1-(5.1/PGA_GAIN) |       | μV/°C                     |

| INL <sup>3</sup>                      | Endpoint Method                                                                         |       |                    |       |                           |

|                                       | PGA_GAIN = 1                                                                            |       | ±2.0               |       | ppm of linear input range |

|                                       | PGA_GAIN = 16                                                                           |       | ±2.6               |       | ppm of linear input range |

|                                       | PGA_GAIN = 128                                                                          |       | ±19.9              |       | ppm of linear input range |

| Low-Frequency Noise                   | Sinc3 filter, ODR = 50SPS, BW = 15Hz, shorted input, RTI                                |       |                    |       |                           |

|                                       | PGA_GAIN = 1                                                                            |       | 1.08               |       | μV rms                    |

|                                       | PGA_GAIN = 2                                                                            |       | 0.73               |       | μV rms                    |

## 仕様

表 2. AAF\_GAIN = IN2\_AAF 使用時の仕様 (続き)

| Parameter                            | Test Conditions/Comments                                                                                                                                                                                                                                                                           | Min   | Typ                                                                | Max                                                                | Unit                                                                         |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------|

| Peak-to-Peak Resolution <sup>4</sup> | PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128<br>Sinc3 filter, ODR = 50SPS, BW = 15Hz, shorted input, RTI<br>PGA_GAIN = 1<br>PGA_GAIN = 2<br>PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128 |       | 0.25<br>0.12<br>0.08<br>0.08<br>0.06<br>0.07                       |                                                                    | μV rms<br>μV rms<br>μV rms<br>μV rms<br>μV rms<br>μV rms                     |

| OVERALL SYSTEM AC PERFORMANCE        | Wideband low-ripple FIR filter, ODR = 256kSPS, DEC_RATE = 32, BW = 110.8kHz<br>Shorted input<br>PGA_GAIN = 1<br>PGA_GAIN = 2<br>PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128<br>Total system DR                                               |       |                                                                    |                                                                    |                                                                              |

| DR <sup>5</sup>                      | RTI, shorted input, at 1kHz<br>PGA_GAIN = 1<br>PGA_GAIN = 2<br>PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128                                                                                                                                   | 105.5 | 108.1<br>108.0<br>107.6<br>106.8<br>104.9<br>101.4<br>96.9<br>91.9 | 108.1<br>108.0<br>107.6<br>106.8<br>104.9<br>101.4<br>96.9<br>91.9 | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB                                 |

| Noise Spectral Density               | RTI, shorted input, at 1kHz<br>PGA_GAIN = 1<br>PGA_GAIN = 2<br>PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128                                                                                                                                   |       | 95<br>48<br>25<br>14<br>8.4<br>6.3<br>5.4<br>4.8                   |                                                                    | nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz<br>nV/√Hz |

| Total RMS Noise                      | RTI, shorted input<br>PGA_GAIN = 1<br>PGA_GAIN = 2<br>PGA_GAIN = 4<br>PGA_GAIN = 8<br>PGA_GAIN = 16<br>PGA_GAIN = 32<br>PGA_GAIN = 64<br>PGA_GAIN = 128                                                                                                                                            |       | 31.5<br>15.8<br>8.3<br>4.6<br>2.8<br>2.1<br>1.8<br>1.6             |                                                                    | μV rms<br>μV rms<br>μV rms<br>μV rms<br>μV rms<br>μV rms<br>μV rms<br>μV rms |

| SNR                                  | -0.5dBFS, sine input, 1kHz tone<br>PGA_GAIN = 1, 10.6Vp<br>PGA_GAIN = 2, 5.32Vp                                                                                                                                                                                                                    |       | 106.0<br>105.8                                                     |                                                                    | dB<br>dB                                                                     |

## 仕様

表 2. AAF\_GAIN = IN2\_AAF 使用時の仕様 (続き)

| Parameter | Test Conditions/Comments                               | Min | Typ    | Max | Unit |

|-----------|--------------------------------------------------------|-----|--------|-----|------|

| THD       | PGA_GAIN = 4, 2.66Vp                                   |     | 105.6  |     | dB   |

|           | PGA_GAIN = 8, 1.33Vp                                   |     | 104.7  |     | dB   |

|           | PGA_GAIN = 16, 0.67Vp                                  |     | 102.9  |     | dB   |

|           | PGA_GAIN = 32, 0.33Vp                                  |     | 99.7   |     | dB   |

|           | PGA_GAIN = 64, 0.16Vp                                  |     | 95.2   |     | dB   |

|           | PGA_GAIN = 128, 0.083Vp                                |     | 90.3   |     | dB   |

|           | -0.5dBFS, sine input, 1kHz tone                        |     |        |     |      |

|           | PGA_GAIN = 1, 10.6Vp                                   |     | -111.6 |     | dB   |

|           | PGA_GAIN = 2, 5.32Vp                                   |     | -105.2 |     | dB   |

|           | PGA_GAIN = 4, 2.66Vp                                   |     | -114.8 |     | dB   |

| SINAD     | PGA_GAIN = 8, 1.33Vp                                   |     | -118.1 |     | dB   |

|           | PGA_GAIN = 16, 0.67Vp                                  |     | -117.8 |     | dB   |

|           | PGA_GAIN = 32, 0.33Vp                                  |     | -116.2 |     | dB   |

|           | PGA_GAIN = 64, 0.16Vp                                  |     | -112.5 |     | dB   |

|           | PGA_GAIN = 128, 0.083Vp                                |     | -106.9 |     | dB   |

|           | -0.5dBFS, sine input, 1kHz tone                        |     |        |     |      |

|           | PGA_GAIN = 1, 10.6Vp                                   |     | 104.9  |     | dB   |

|           | PGA_GAIN = 2, 5.32Vp                                   |     | 102.4  |     | dB   |

|           | PGA_GAIN = 4, 2.66Vp                                   |     | 105.1  |     | dB   |

|           | PGA_GAIN = 8, 1.33Vp                                   |     | 104.5  |     | dB   |

| SFDR      | PGA_GAIN = 16, 0.67Vp                                  |     | 102.7  |     | dB   |

|           | PGA_GAIN = 32, 0.33Vp                                  |     | 99.5   |     | dB   |

|           | PGA_GAIN = 64, 0.16Vp                                  |     | 95.1   |     | dB   |

|           | PGA_GAIN = 128, 0.083Vp                                |     | 90.2   |     | dB   |

|           | -0.5dBFS, sine input, 1kHz tone                        |     |        |     |      |

|           | PGA_GAIN = 1, 10.6Vp                                   |     | -116.6 |     | dBc  |

|           | PGA_GAIN = 2, 5.32Vp                                   |     | -104.3 |     | dBc  |

|           | PGA_GAIN = 4, 2.66Vp                                   |     | -115.4 |     | dBc  |

|           | PGA_GAIN = 8, 1.33Vp                                   |     | -124.1 |     | dBc  |

|           | PGA_GAIN = 16, 0.67Vp                                  |     | -129.4 |     | dBc  |

| IMD       | PGA_GAIN = 32, 0.33Vp                                  |     | -126.0 |     | dBc  |

|           | PGA_GAIN = 64, 0.16Vp                                  |     | -115.3 |     | dBc  |

|           | PGA_GAIN = 128, 0.083Vp                                |     | -109.3 |     | dBc  |

|           | $f_{IN\_A} = 9\text{kHz}$ , $f_{IN\_B} = 10\text{kHz}$ |     |        |     |      |

|           | Second-order                                           |     |        |     |      |

|           | PGA_GAIN = 1                                           |     | -105   |     | dBc  |

|           | PGA_GAIN = 2                                           |     | -93    |     | dBc  |

|           | PGA_GAIN = 4                                           |     | -107   |     | dBc  |

|           | PGA_GAIN = 8                                           |     | -116   |     | dBc  |

|           | PGA_GAIN = 16                                          |     | -110   |     | dBc  |

| IMD       | PGA_GAIN = 32                                          |     | -107   |     | dBc  |

|           | PGA_GAIN = 64                                          |     | -104   |     | dBc  |

|           | PGA_GAIN = 128                                         |     | -100   |     | dBc  |

|           | Third-order                                            |     |        |     |      |

|           | PGA_GAIN = 1                                           |     | -113   |     | dBc  |

|           | PGA_GAIN = 2                                           |     | -117   |     | dBc  |

|           | PGA_GAIN = 4                                           |     | -119   |     | dBc  |

|           | PGA_GAIN = 8                                           |     | -118   |     | dBc  |

|           | PGA_GAIN = 16                                          |     | -116   |     | dBc  |

## 仕様

表 2. AAF\_GAIN = IN2\_AAF 使用時の仕様 (続き)

| Parameter                                                | Test Conditions/Comments                                                                                 | Min    | Typ         | Max    | Unit                      |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------|-------------|--------|---------------------------|

|                                                          | PGA_GAIN = 32                                                                                            |        | -115        |        | dBc                       |

|                                                          | PGA_GAIN = 64                                                                                            |        | -112        |        | dBc                       |

|                                                          | PGA_GAIN = 128                                                                                           |        | -108        |        | dBc                       |

| AFE MAGNITUDE AND PHASE PERFORMANCE <sup>6</sup>         |                                                                                                          |        |             |        |                           |

| AFE Bandwidth                                            | -3dB relative to signal amplitude at DC                                                                  |        |             |        |                           |

|                                                          | PGA_GAIN = 1                                                                                             |        | 299.3       |        | kHz                       |

|                                                          | PGA_GAIN = 2                                                                                             |        | 312.6       |        | kHz                       |

|                                                          | PGA_GAIN = 4                                                                                             |        | 308.7       |        | kHz                       |

|                                                          | PGA_GAIN = 8                                                                                             |        | 303.1       |        | kHz                       |

|                                                          | PGA_GAIN = 16                                                                                            |        | 293.5       |        | kHz                       |

|                                                          | PGA_GAIN = 32                                                                                            |        | 265.4       |        | kHz                       |

|                                                          | PGA_GAIN = 64                                                                                            |        | 202.6       |        | kHz                       |

|                                                          | PGA_GAIN = 128                                                                                           |        | 116.1       |        | kHz                       |

| Analog Group Delay                                       | $f_{IN} = 20\text{kHz}$                                                                                  |        |             |        |                           |

|                                                          | PGA_GAIN = 1                                                                                             |        | 1.05        |        | $\mu\text{s}$             |

|                                                          | PGA_GAIN = 2                                                                                             |        | 0.93        |        | $\mu\text{s}$             |

|                                                          | PGA_GAIN = 4                                                                                             |        | 0.98        |        | $\mu\text{s}$             |

|                                                          | PGA_GAIN = 8                                                                                             |        | 1.06        |        | $\mu\text{s}$             |

|                                                          | PGA_GAIN = 16                                                                                            |        | 1.17        |        | $\mu\text{s}$             |

|                                                          | PGA_GAIN = 32                                                                                            |        | 1.35        |        | $\mu\text{s}$             |

|                                                          | PGA_GAIN = 64                                                                                            |        | 1.68        |        | $\mu\text{s}$             |

|                                                          | PGA_GAIN = 128                                                                                           |        | 2.34        |        | $\mu\text{s}$             |

| Phase Angle Mismatch over Gain <sup>2, 3, 6</sup>        | Sine wave, $f_{IN} = 20\text{kHz}$ , single device, normalized to PGA_GAIN = 1, $T_A = 25^\circ\text{C}$ |        |             |        |                           |

|                                                          | PGA_GAIN = 2                                                                                             | -0.936 | -0.863      | -0.791 | Degrees                   |

|                                                          | PGA_GAIN = 4                                                                                             | -0.595 | -0.531      | -0.466 | Degrees                   |

|                                                          | PGA_GAIN = 8                                                                                             | -0.003 | 0.054       | 0.122  | Degrees                   |

|                                                          | PGA_GAIN = 16                                                                                            | 0.779  | 0.847       | 0.914  | Degrees                   |

|                                                          | PGA_GAIN = 32                                                                                            | 2.036  | 2.155       | 2.273  | Degrees                   |

|                                                          | PGA_GAIN = 64                                                                                            | 4.335  | 4.570       | 4.805  | Degrees                   |

|                                                          | PGA_GAIN = 128                                                                                           | 8.807  | 9.275       | 9.743  | Degrees                   |

| Phase Angle Drift <sup>2, 3, 6</sup>                     | $f_{IN} = 20\text{kHz}$                                                                                  |        |             |        |                           |

|                                                          | PGA_GAIN = 1                                                                                             | 0.11   | 0.23        | 0.35   | $\text{m}^\circ/\text{C}$ |

|                                                          | PGA_GAIN = 2                                                                                             | -0.03  | 0.09        | 0.20   | $\text{m}^\circ/\text{C}$ |

|                                                          | PGA_GAIN = 4                                                                                             | 0.24   | 0.35        | 0.47   | $\text{m}^\circ/\text{C}$ |

|                                                          | PGA_GAIN = 8                                                                                             | 0.63   | 0.86        | 1.08   | $\text{m}^\circ/\text{C}$ |

|                                                          | PGA_GAIN = 16                                                                                            | 1.25   | 1.76        | 2.27   | $\text{m}^\circ/\text{C}$ |

|                                                          | PGA_GAIN = 32                                                                                            | 2.49   | 3.50        | 4.51   | $\text{m}^\circ/\text{C}$ |

|                                                          | PGA_GAIN = 64                                                                                            | 4.90   | 6.92        | 8.94   | $\text{m}^\circ/\text{C}$ |

|                                                          | PGA_GAIN = 128                                                                                           | 9.59   | 13.50       | 17.40  | $\text{m}^\circ/\text{C}$ |

| Device-to-Device Phase Angle Mismatch <sup>2, 3, 6</sup> | $f_{IN} = 20\text{kHz}$ , typical = $\pm 1\sigma$ , $T_A = 25^\circ\text{C}$                             |        |             |        |                           |

|                                                          | PGA_GAIN = 1                                                                                             | -0.051 | $\pm 0.015$ | 0.051  | Degrees                   |

|                                                          | PGA_GAIN = 2                                                                                             | -0.088 | $\pm 0.022$ | 0.088  | Degrees                   |

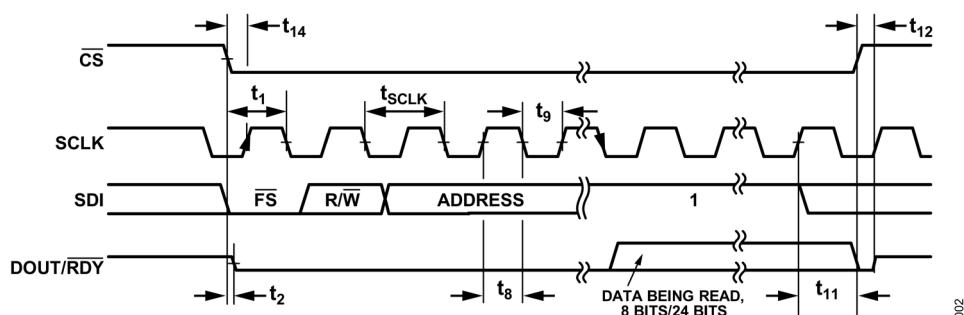

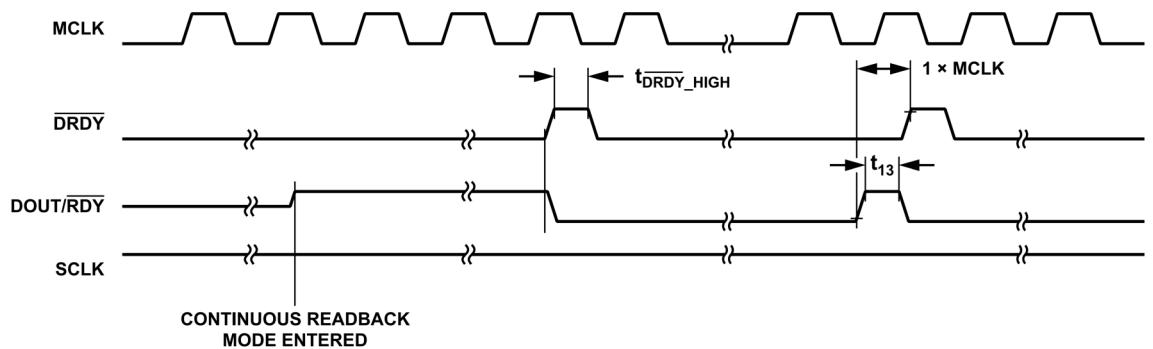

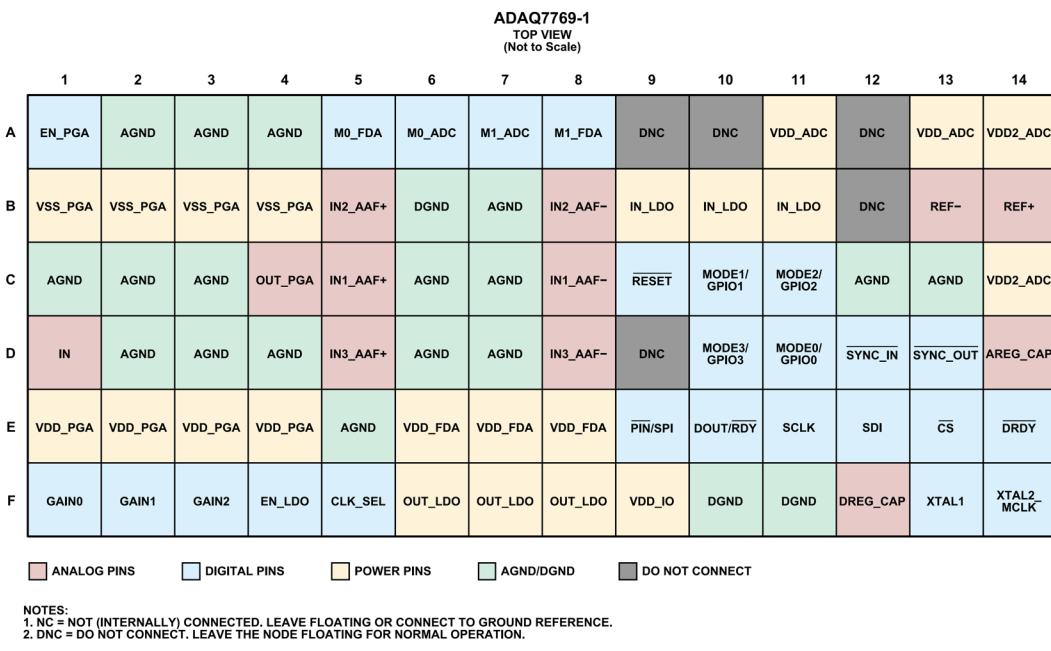

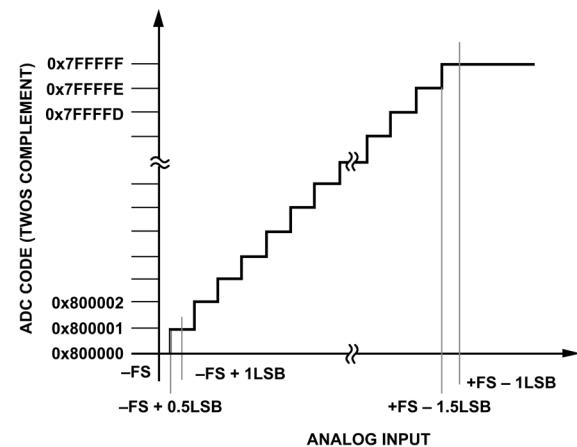

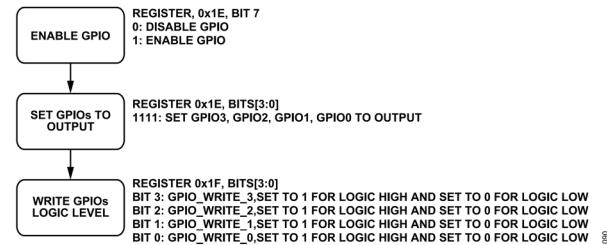

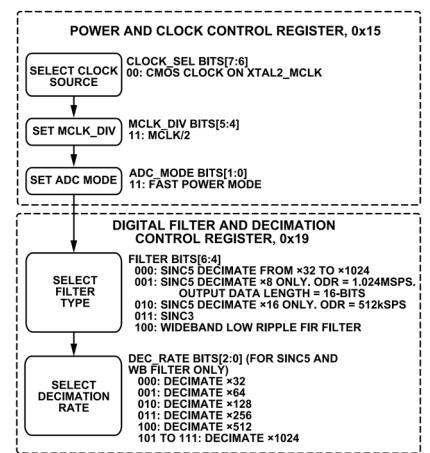

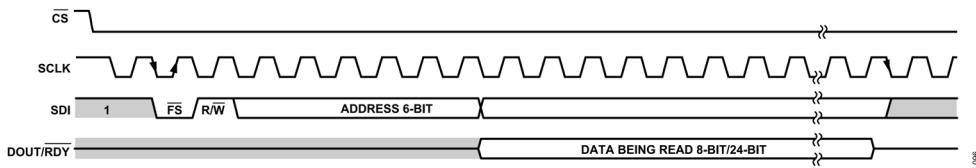

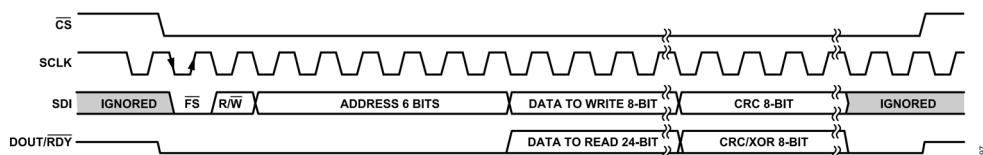

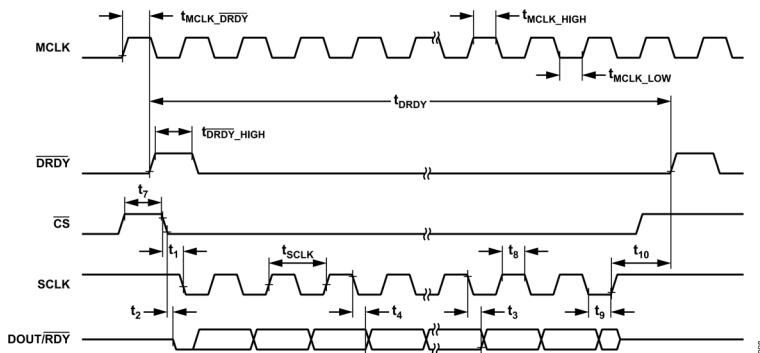

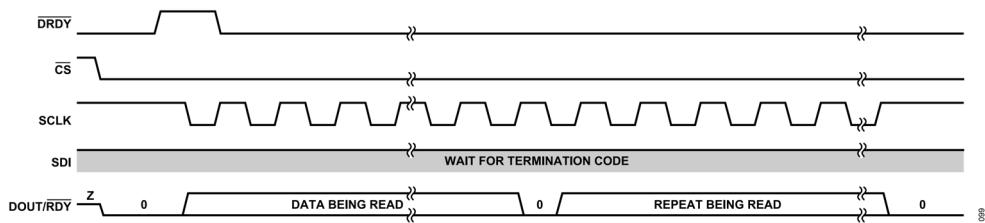

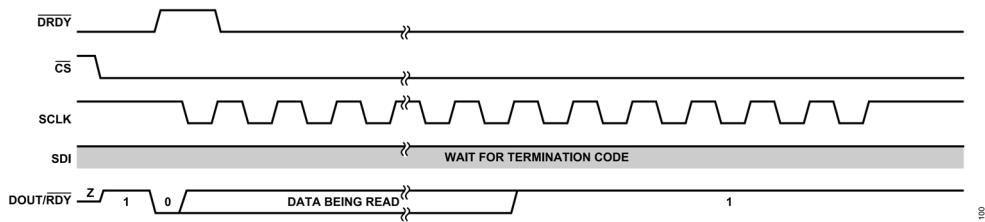

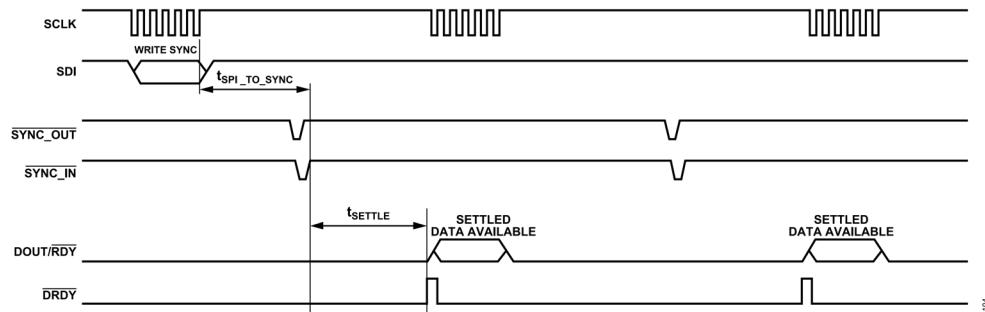

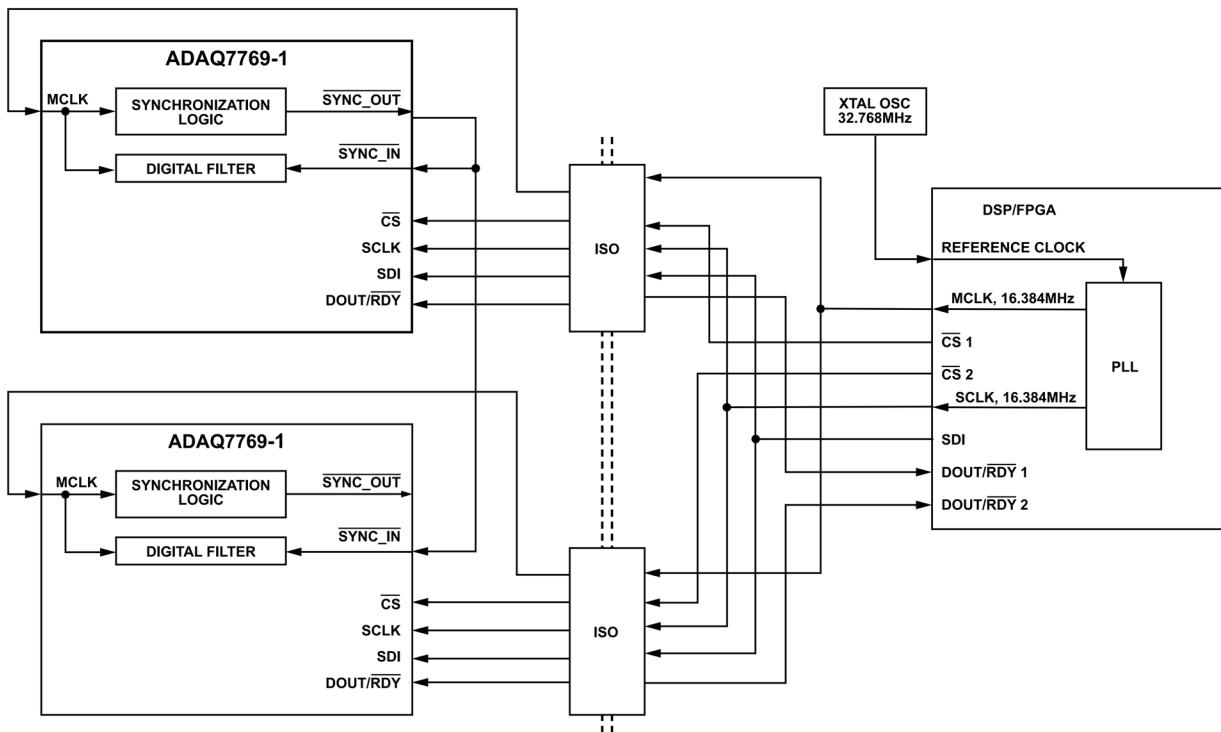

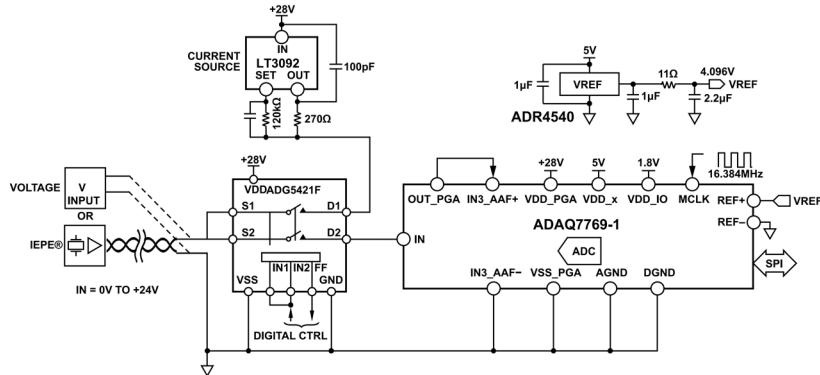

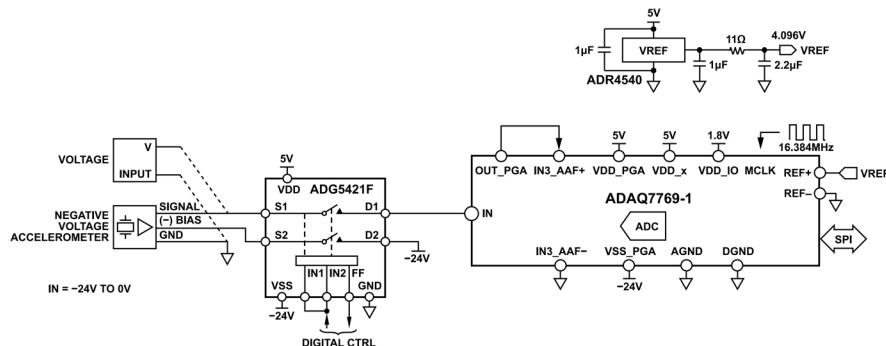

|                                                          | PGA_GAIN = 4                                                                                             | -0.082 | $\pm 0.021$ | 0.082  | Degrees                   |