# 24 ビット、2MSPS の μModule データ・アクイジション・ソリューション

## 特長

- ▶ 高性能

- ▶ スループット : 2MSPS、無遅延

- ▶ INL :  $\pm 1\text{ppm}$  (最大値) (-40°C~105°C)

- ▶ システム・ダイナミック・レンジ : 128dB (代表値)

- ▶ S/N 比 : 106.5dB (代表値)、THD : -122dB (代表値)

- ▶ オフセット誤差ドリフト :  $+4.1\mu\text{V}/^\circ\text{C}$  (最大値)

- ▶ ゲイン誤差ドリフト :  $+1.50\text{ppm}/^\circ\text{C}$  (最大値)

- ▶ 使いやすい機能でシステムの複雑さを軽減

- ▶ 270kHz の 2 次アンチエイリアス・フィルタ

- ▶ 高インピーダンス PGIA ゲイン・オプション : 1/3, 5/9, 20/9, 20/3

- ▶ 柔軟な外部リファレンス電圧 : 4.096V または 5V

- ▶ 差動入力電圧範囲、 $\pm\text{REFIN}/\text{ゲイン}$  :  $\pm 15\text{V}$ ,  $\pm 9\text{V}$ ,  $\pm 2.25\text{V}$ ,  $\pm 0.75\text{V}$

- ▶ 広い入力コモンモード電圧範囲 : -8V~+10V

- ▶ 低入力バイアス電流 : -30pA (代表値)

- ▶ システム・フットプリントの削減を実現する高密度ソリューション

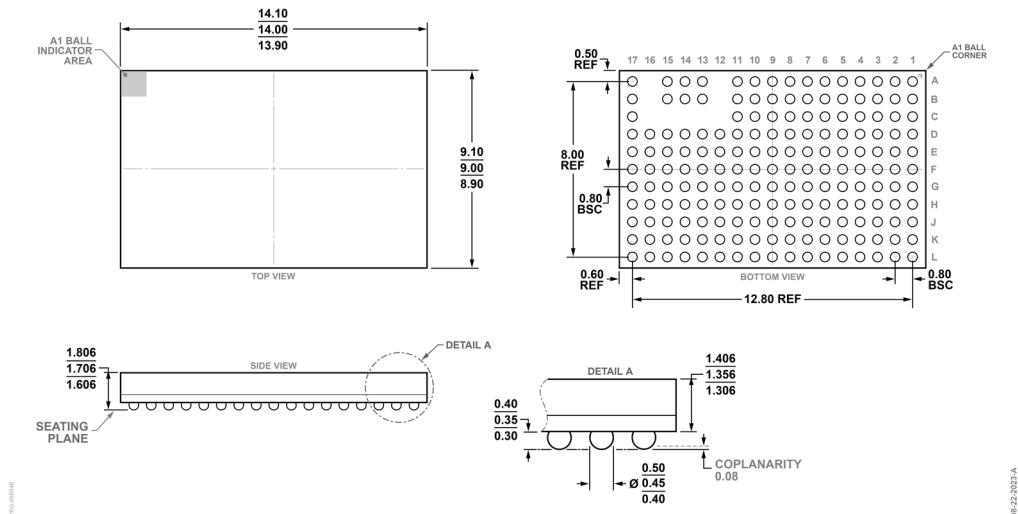

- ▶ 14mm × 9mm、0.8 mm ピッチ、178 ポール CSP BGA

- ▶ フットプリントを同等のディスクリート・ソリューションの 1/4 に削減

- ▶ 内部 VCM 生成機能を備えたリファレンス・バッファを内蔵

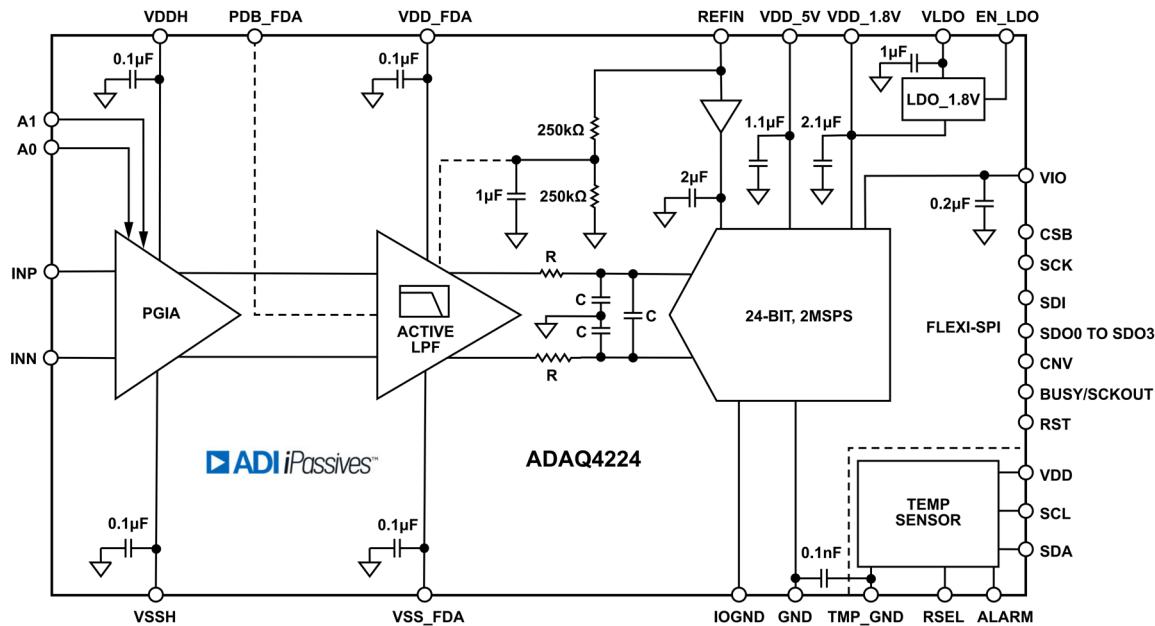

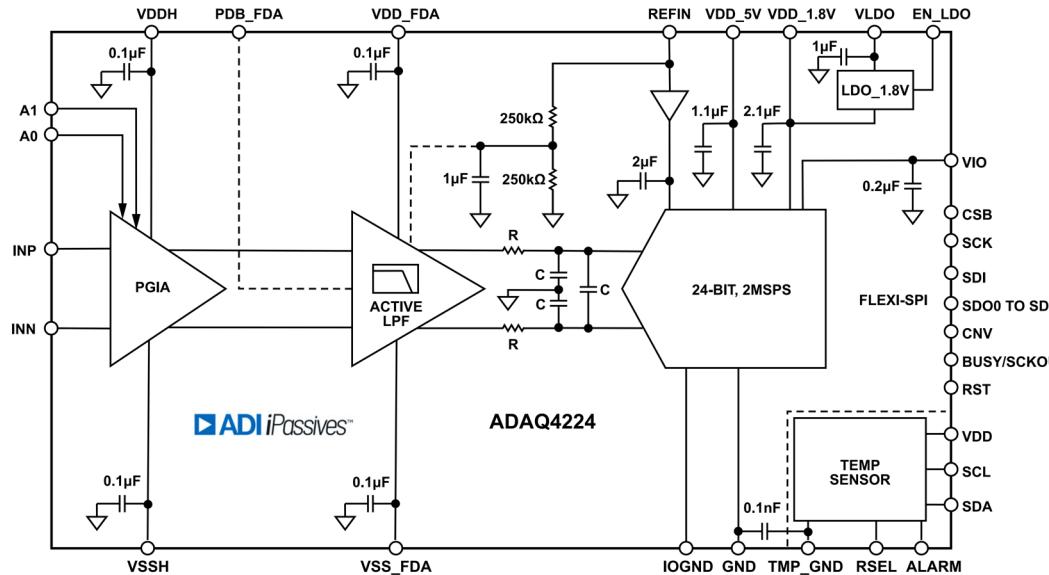

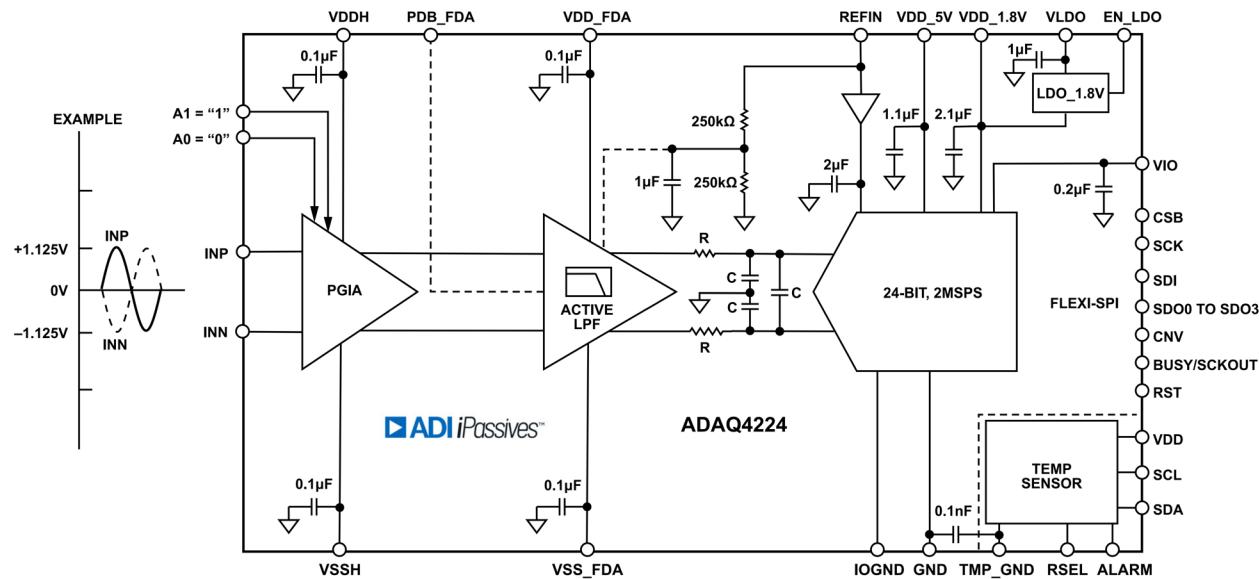

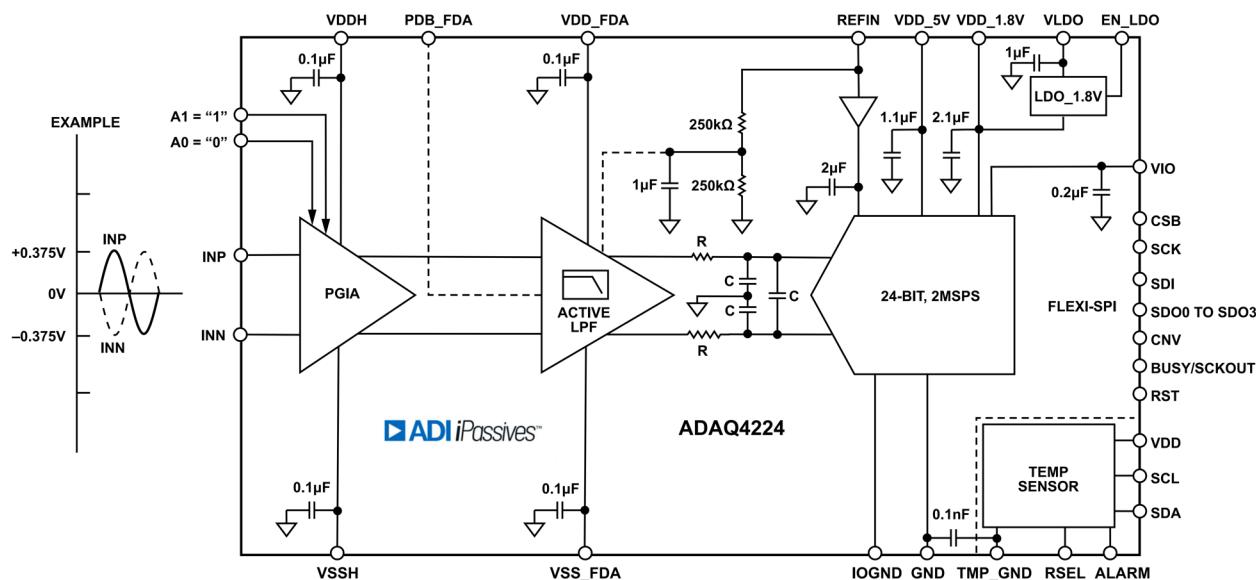

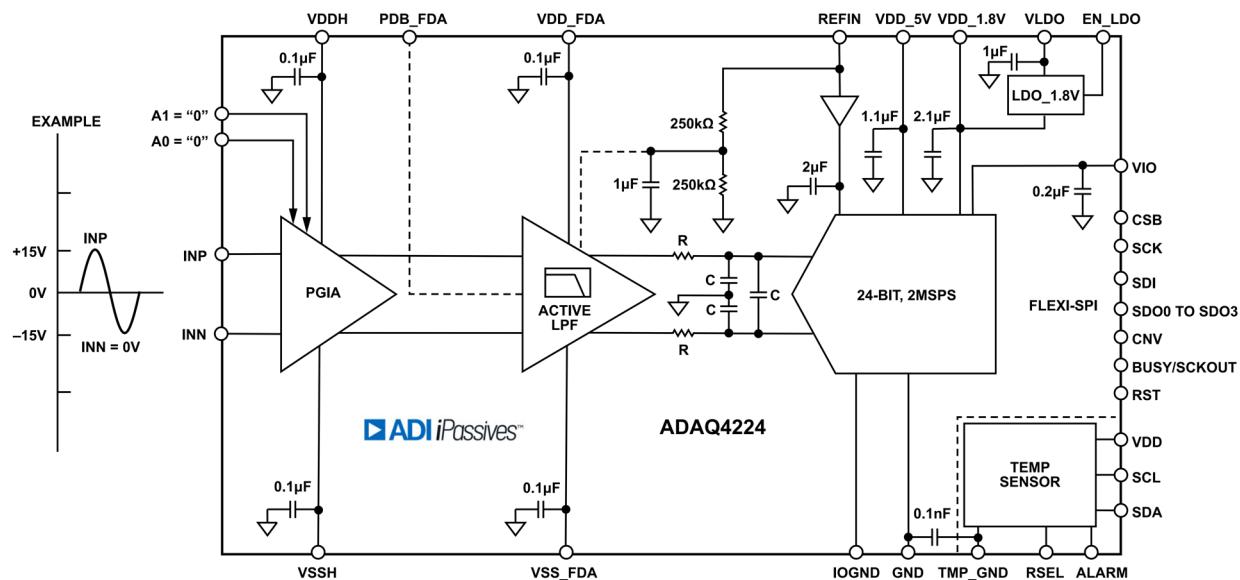

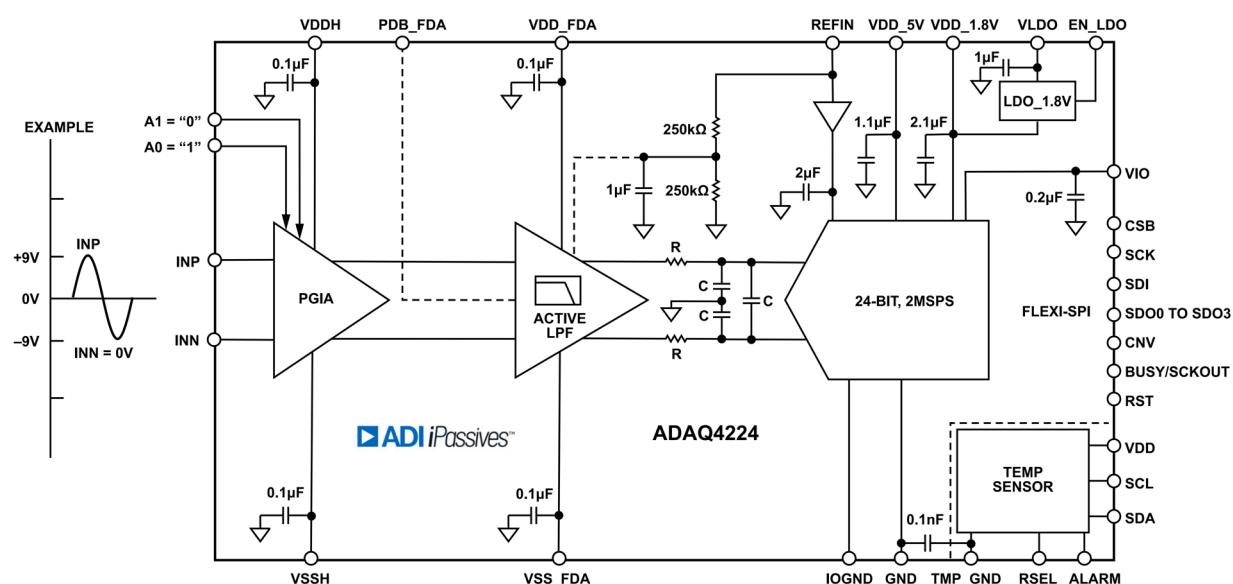

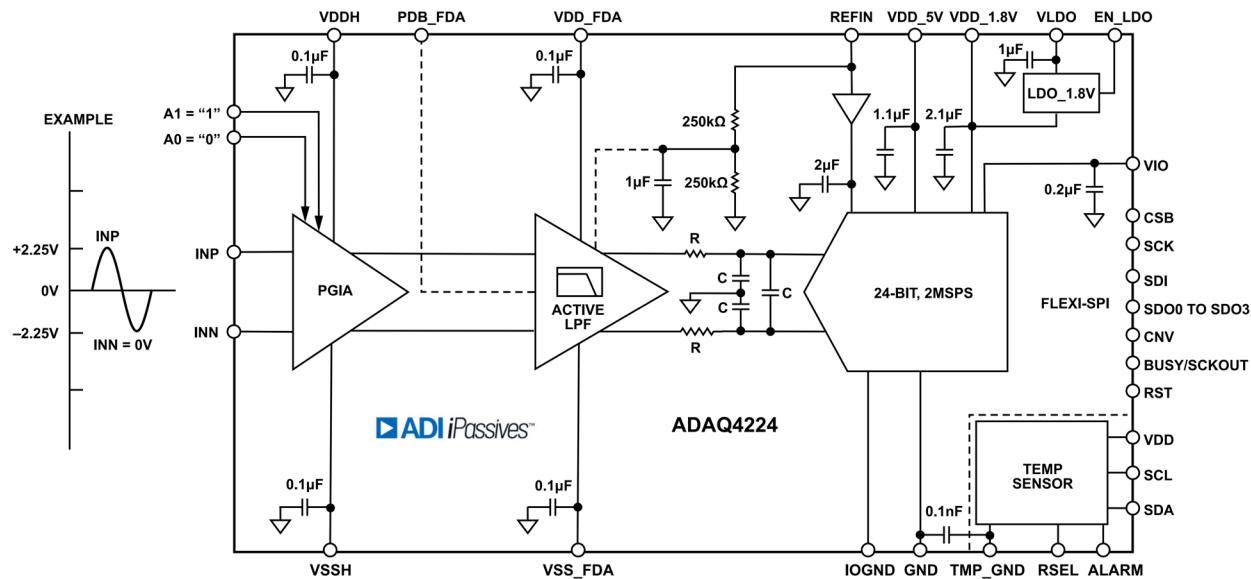

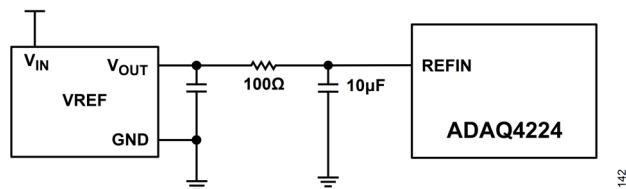

## 機能ブロック図

図 1. ADAQ4224 の機能ブロック図

## 目次

|                   |    |                       |    |

|-------------------|----|-----------------------|----|

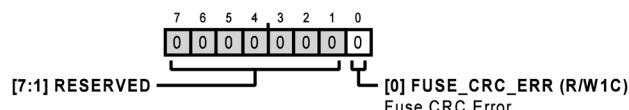

| 特長                | 1  | レジスタ                  | 55 |

| アプリケーション          | 1  | レジスタの詳細               | 56 |

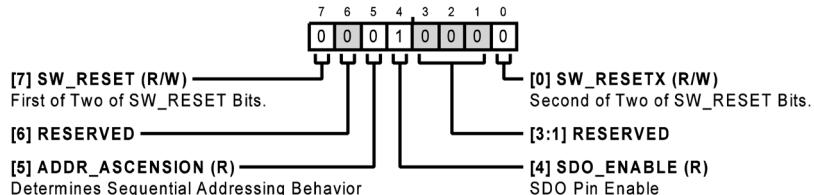

| 機能ブロック図           | 1  | インターフェース設定 A レジスタ     | 56 |

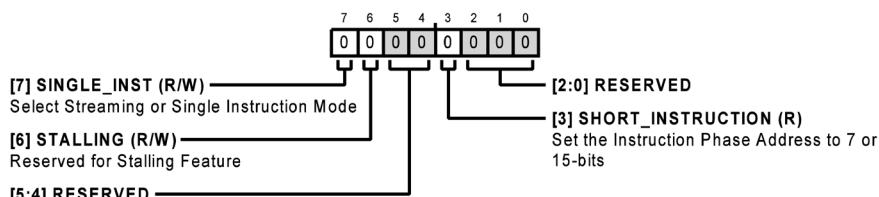

| 概要                | 3  | インターフェース設定 B レジスタ     | 56 |

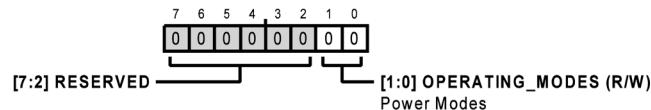

| 仕様                | 4  | デバイス設定レジスタ            | 57 |

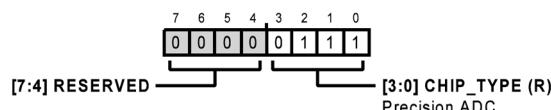

| タイミング仕様           | 8  | チップ・タイプ・レジスタ          | 57 |

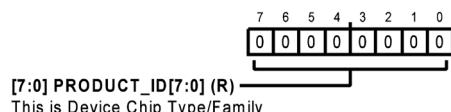

| 絶対最大定格            | 13 | 製品 ID ロー・レジスタ         | 57 |

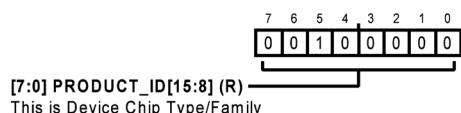

| 熱抵抗               | 13 | 製品 ID ハイ・レジスタ         | 57 |

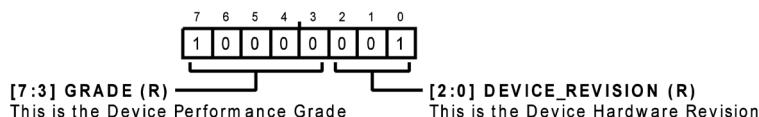

| 静電放電定格            | 13 | チップ・グレード・レジスタ         | 58 |

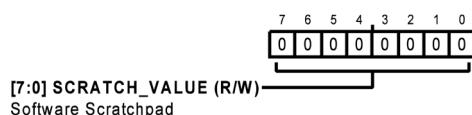

| ESD に関する注意        | 13 | スクラッチ・パッド・レジスタ        | 58 |

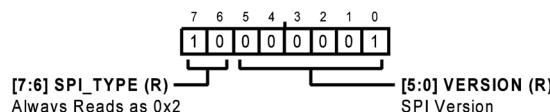

| ピン配置およびピン機能の説明    | 14 | SPI リビジョン・レジスタ        | 58 |

| 代表的な性能特性          | 16 | ベンダ ID ロー・レジスタ        | 59 |

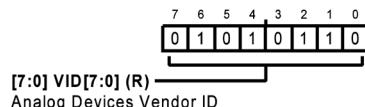

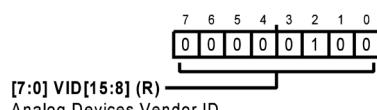

| 用語の定義             | 28 | ベンダ ID ハイ・レジスタ        | 59 |

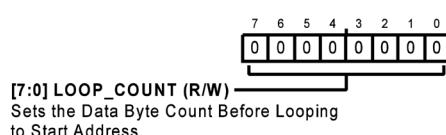

| 動作原理              | 29 | ストリーム・モード・レジスタ        | 59 |

| 概要                | 29 | インターフェース・ステータス A レジスタ | 59 |

| 伝達関数              | 29 | 設定モード終了レジスタ           | 60 |

| シグナル・チェーンの動作      | 30 | 平均化モード・レジスタ           | 60 |

| デジタル・サンプリング処理機能   | 30 | オフセット・レジスタ            | 60 |

| 温度センサーの動作         | 31 | ゲイン・レジスタ              | 61 |

| アプリケーション情報        | 35 | モード・レジスタ              | 62 |

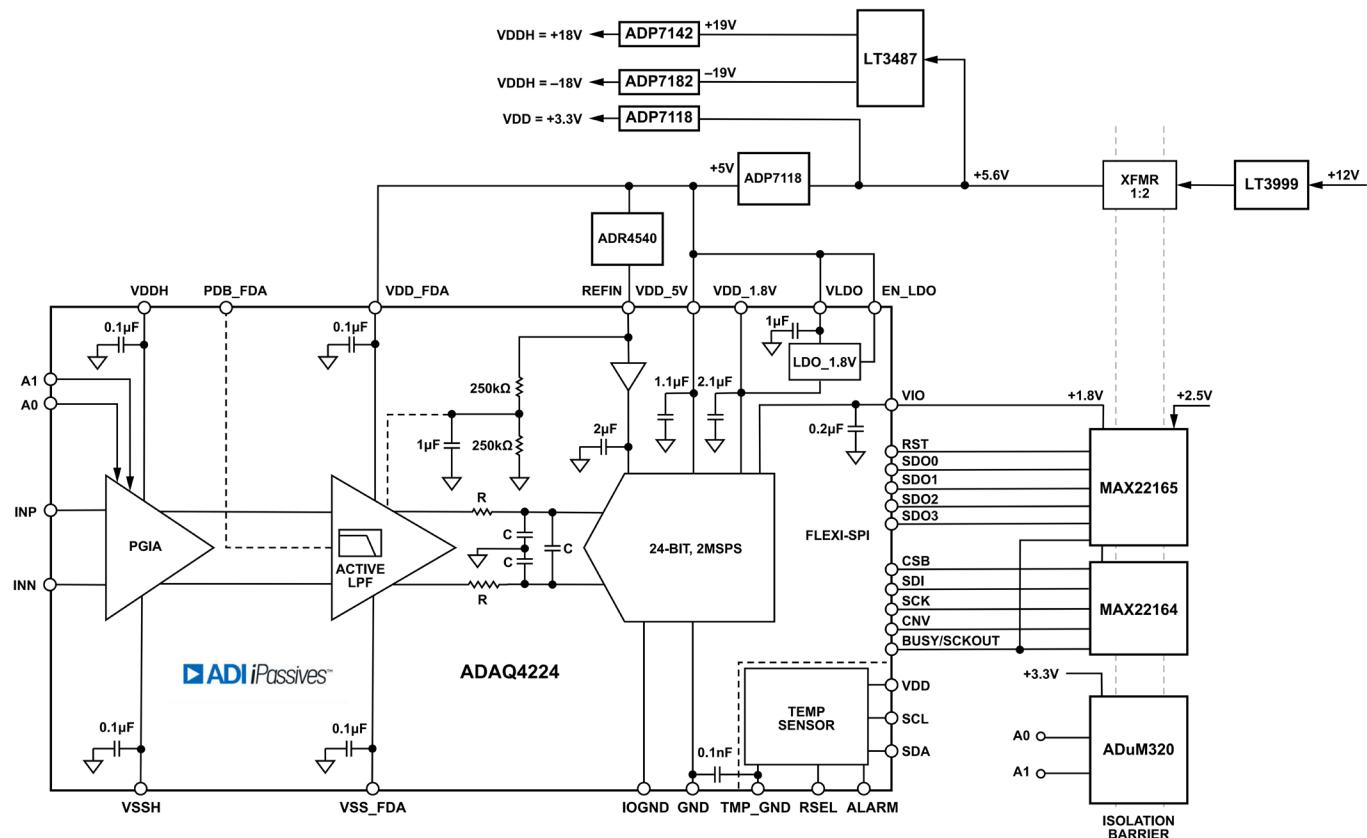

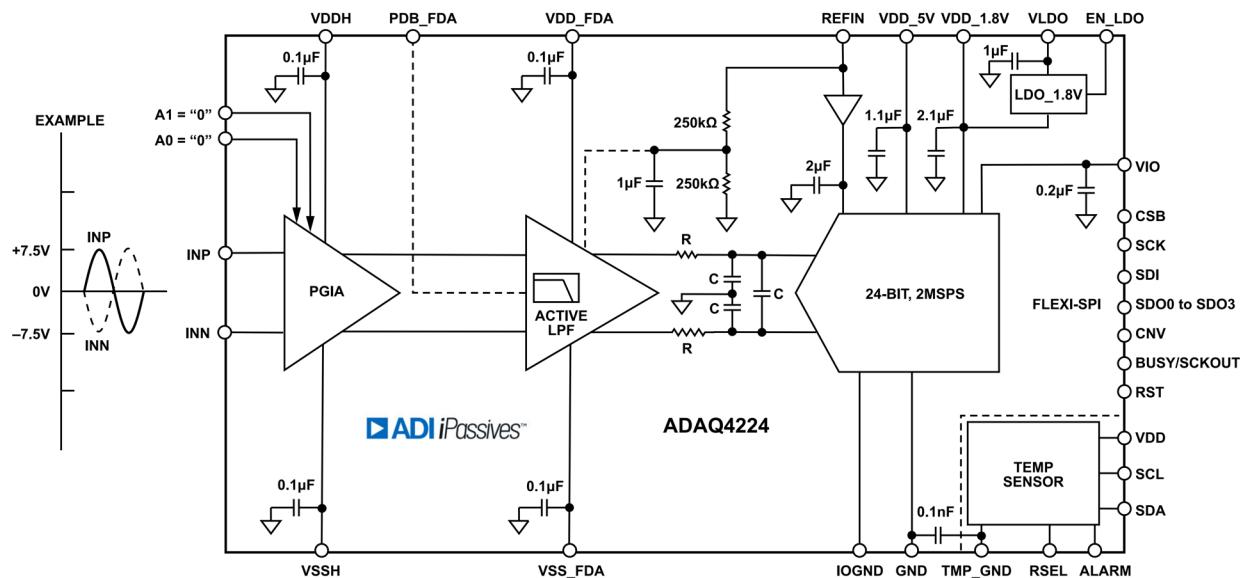

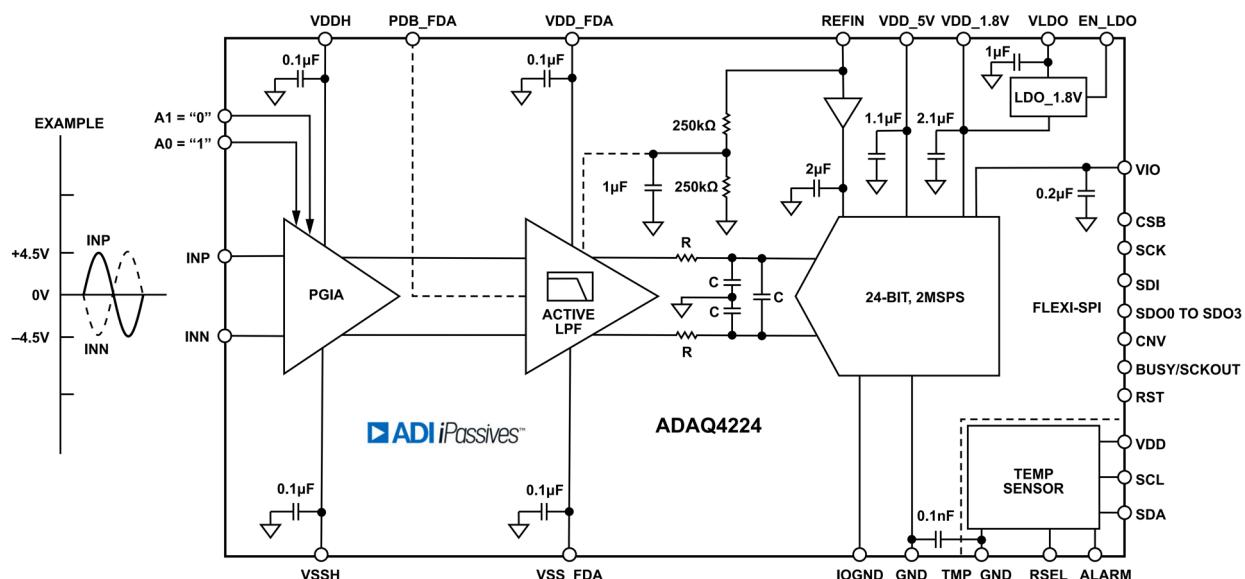

| 代表的なアプリケーション図     | 35 | 内部発振器レジスタ             | 62 |

| リファレンス回路の設計       | 40 | 出力ドライバ・レジスタ           | 63 |

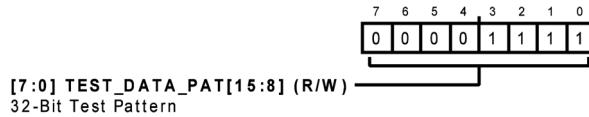

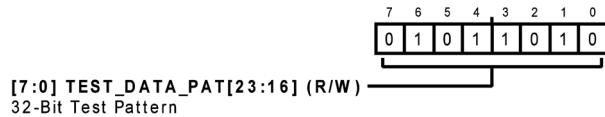

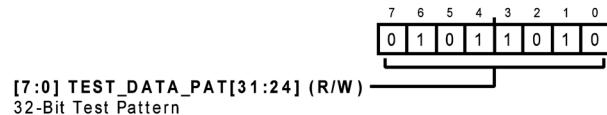

| ADC リセット          | 41 | テスト・パターン・レジスタ         | 63 |

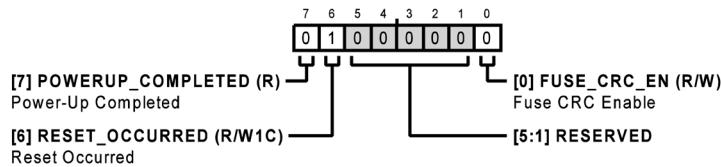

| 電源                | 41 | デジタル診断レジスタ            | 64 |

| シリアル・インターフェース     | 43 | デジタル・エラー・レジスタ         | 64 |

| SPI 信号            | 43 | 温度センサー・レジスタ           | 65 |

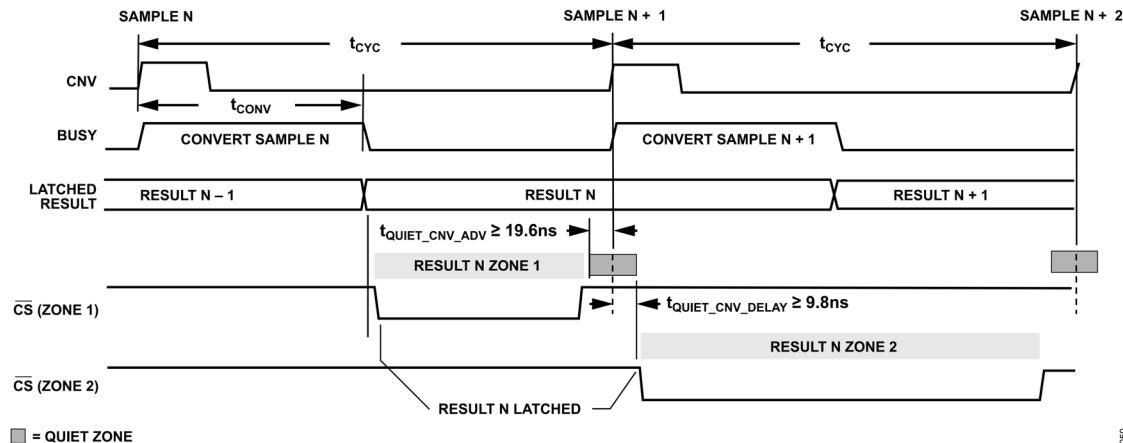

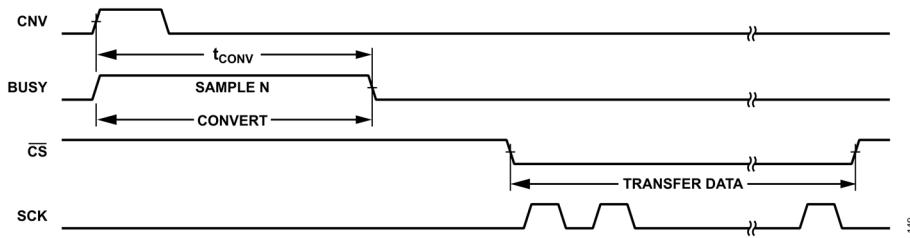

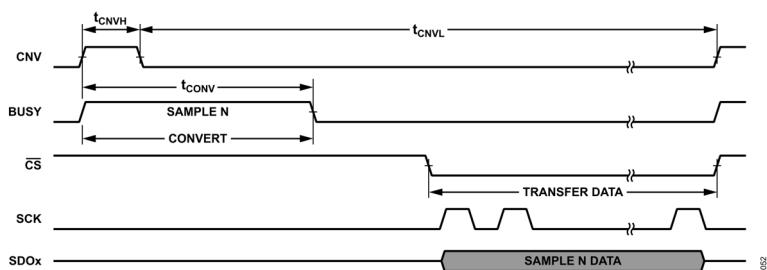

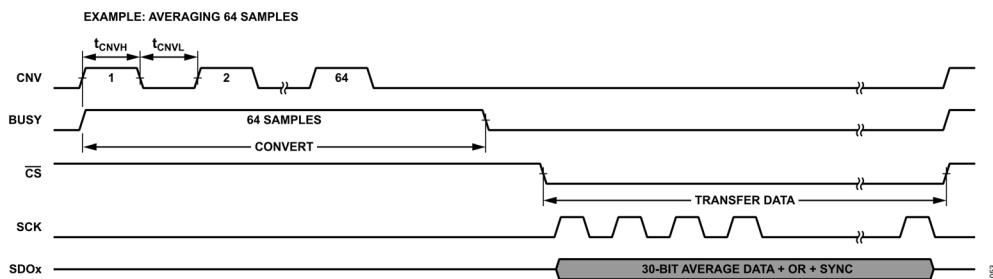

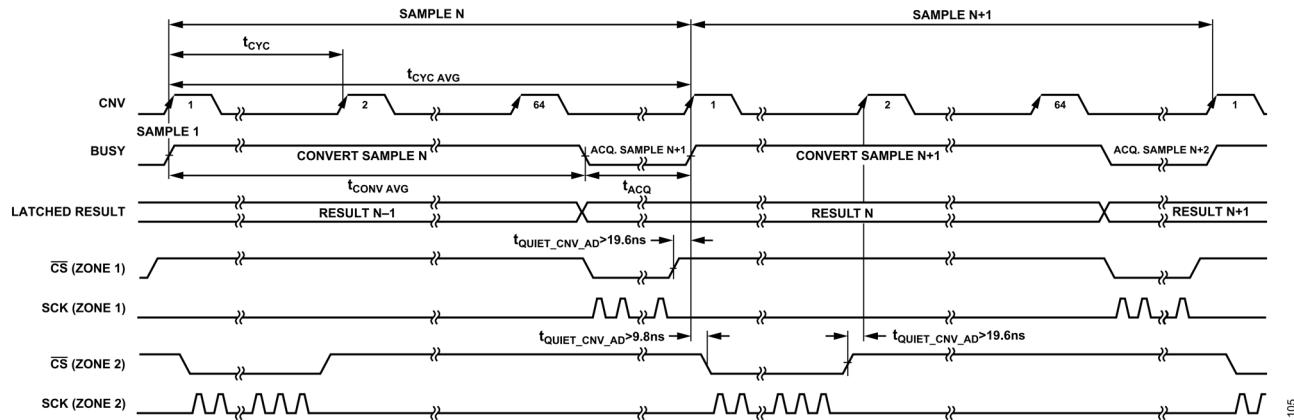

| サンプル変換タイミングとデータ転送 | 45 | 設定およびステータス・レジスタ       | 66 |

| クロック・モード          | 46 | 外形寸法                  | 67 |

| データ・クロック条件とタイミング  | 49 | オーダー・ガイド              | 67 |

| レイアウトのガイドライン      | 54 | 評価用ボード                | 67 |

## 改訂履歴

9/2024—Revision 0: Initial Version

## 概要

ADAQ4224 は、部品の選択、最適化、およびレイアウトに関するシグナル・チェーン設計上の課題を設計者からデバイスへ移転することによって、高精度測定システムの開発サイクルを短縮できる  $\mu$ Module<sup>®</sup>高精度データ・アクイジション (DAQ) シグナル・チェーン・ソリューションです。24 ビット時に最大  $\pm 1.0\text{ppm}$  の INL とノード・ミス・コードが確保された ADAQ4224 は、 $-40^\circ\text{C} \sim +105^\circ\text{C}$  の範囲で比類のない精度を実現します。

ADAQ4224 はシステム・イン・パッケージ (SIP) 技術を採用し、データ・アクイジション・ソリューションで必須とされる一般的な信号処理ブロックを低フットプリントの 178 ボール CSP\_BGA パッケージ (14mm × 9mm、0.8mm ピッチ) にまとめた搭載しています。

ADAQ4224 は以下のコンポーネントを内蔵しています。

- ▶ 低ノイズの広帯域幅プログラマブル・ゲイン計装アンプ (PGIA)

- ▶ 2 次アンチエイリアス・フィルタ

- ▶ 低ノイズ、低歪み、広帯域幅の ADC ドライバ

- ▶ 高精度、24 ビット、2MSPS の逐次比較レジスタ (SAR) ADC

- ▶ 最大  $\pm 1^\circ\text{C}$  の優れた精度を備え、電気的に絶縁された I<sup>2</sup>C 対応温度センサー

- ▶ 1.8V の低ドロップアウト (LDO) レギュレータ

- ▶ 性能重視の受動部品

ADAQ4224 は、アナログ・デバイスの iPassive<sup>®</sup>技術を使用して、優れたマッチング特性とドリフト特性を備えた性能重視の受動部品を内蔵することにより、温度依存性のある誤差源を最小限に抑えて最適な性能を実現します。重要な電源とリファレンス・バイパス・コンデンサを内蔵することで、システムレベルのボード・レイアウトによる影響を受けにくくなります。

また、ソリューションのフットプリントを削減することでシステムに搭載する機能を増やすことが可能になり、性能を犠牲にすることなく計測器を小型化することができます。

このシステム統合によって設計上の多くの課題が解決されると同時に、 $\mu$ Module で PGIA を柔軟に構成できるため、ゲインや減衰の調整が可能になり、シングルエンド入力信号や差動入力信号の収集をサポートできます。PGIA および ADC ドライバ段の高速セトリングと遅延のない SAR ADC により、多数のチャンネルのマルチプレクス・シグナル・チェーン・アーキテクチャおよび制御ループ・アプリケーション向けに比類のないソリューションを提供します。

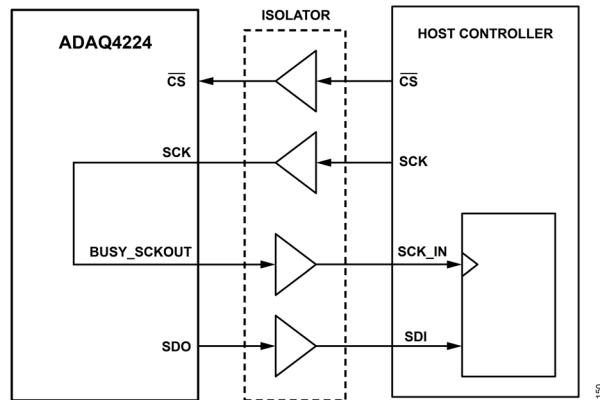

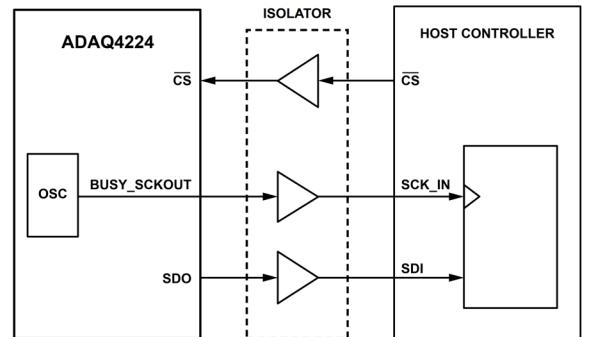

デジタル機能には Flexi-SPI シリアル・ペリフェラル・インターフェース (SPI) が含まれ、これにより、複数の SPI モードによるデータ・アクセスの他、オフセット補正、ゲイン調整、平均化が可能になります。これらのデジタル機能はホスト・プロセッサの負担を軽減します。広いデータ・クロック・ウィンドウ、複数の SDO レーン、オプションの DDR (デュアル・データ・レート) データ・クロックにより、最高速の 2MSPS で動作させながらシリアル・クロック周波数を下げることができます。また、DAQ ソリューションを容易に絶縁できるため、消費電力と EMI も抑えられます。ADAQ4224 のエコー・クロック・モードとホスト・クロック・モードではタイミング条件が緩和されるので、デジタル・アイソレータの使用が容易になります。

Flexi-SPI、PGIA ゲイン制御、および I<sup>2</sup>C 対応温度センサー・シリアル・ユーザ・インターフェースは、独立した VIO 電源を採用することで、1.2V～1.8V、2.5V、3V、5V のロジックに対応しています。ADAQ4224 の動作は  $-40^\circ\text{C} \sim +105^\circ\text{C}$  の温度範囲で仕様規定されています。

## 仕様

特に指定のない限り、 $V_{DDH} = 18V$ 、 $V_{SSH} = -18V$ 、 $V_{DD\_FDA} = 5.4V$ 、 $V_{SS\_FDA} = 0V$ 、 $V_{DD\_5V} = 5.4V$ 、 $V_{LDO} = 5.4V$ 、 $V_{IO} = 1.8V$ 、 $V_{DD} = 3.3V$ 、 $REFIN = 5V$ 、サンプリング周波数 ( $f_S$ ) = 2MSPS、すべてのゲインと仕様は  $T_{MIN} \sim T_{MAX}$  での値。

表 1. 仕様

| Parameter                                  | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                     | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Typ                                                                                                                                                                     | Max                                                                                                                                                                                                                                                                                                              | Unit                                                                                                                                                            |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESOLUTION                                 |                                                                                                                                                                                                                                                                                                                                                              | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                  | Bits                                                                                                                                                            |

| DIFFERENTIAL INPUT VOLTAGE RANGE, $V_{IN}$ | $V_{IN} = \pm REFIN/Gain$<br>Gain = 1/3<br>Gain = 5/9<br>Gain = 20/9<br>Gain = 20/3<br>Analog Front-End Gain (G)<br>A0 = low, A1 = low<br>A0 = high, A1 = low<br>A0 = low, A1 = high<br>A0 = high, A1 = high<br>Input Common-Mode Voltage Range<br>Common-Mode Rejection Ratio (CMRR)<br>Input Current <sup>1</sup><br>Input Resistance<br>Input Capacitance | -15<br>-9<br>-2.25<br>-0.75<br>1/3<br>5/9<br>20/9<br>20/3<br>-8<br>95<br>-130<br>10 <sup>12</sup><br>22                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                         | +15<br>+9<br>+2.25<br>+0.75<br>V/V<br>V/V<br>V/V<br>V/V<br>V<br>dB<br>pA<br>$\Omega$<br>pF                                                                                                                                                                                                                       | V<br>V<br>V<br>V<br>V/V<br>V/V<br>V/V<br>V/V<br>V<br>dB<br>pA<br>$\Omega$<br>pF                                                                                 |

| THROUGHPUT                                 |                                                                                                                                                                                                                                                                                                                                                              | 500<br>264<br>244<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 282<br>260                                                                                                                                                              | 300<br>275<br>2                                                                                                                                                                                                                                                                                                  | ns<br>ns<br>ns<br>MSPS                                                                                                                                          |

| DC ACCURACY                                | No Missing Codes<br>Integral Nonlinearity Error (INL) <sup>1</sup><br>Differential Nonlinearity Error (DNL) <sup>1</sup><br>Transition Noise<br>Offset Error<br>Offset Error Drift<br>Gain Error<br>Gain Error Drift<br>Power-Supply Rejection Ratio (PSRR)<br>Low Frequency Noise <sup>3</sup>                                                              | 24<br>All gains. $V_{SS\_FDA} = 0V$<br>All gains<br>G = 1/3<br>G = 5/9<br>G = 20/9<br>G = 20/3<br>G = 1/3<br>G = 5/9<br>G = 20/9<br>G = 20/3<br>T = -40°C to +105°C, End point method<br>G = 1/3, 5/9, 20/9<br>G = 20/3<br>REFIN = 5 V<br>T = -40°C to +105°C, End point method<br>All gains<br>$V_{DDH} = +15V$ to +18 V step<br>$V_{SSH} = -15V$ to -18 V step<br>$V_{DD\_FDA} = +4.5V$ to +5.5 V step<br>$V_{SS\_FDA} = 0V$ to -1 V step<br>$V_{DD\_5V} = +5.3V$ to +5.5 V step<br>$V_{LDO} = +5.3V$ to +5.5 V step<br>Referred to input, bandwidth = 0.1 Hz to 10 Hz, all gains | -1<br>±0.4<br>±0.5<br>73.33<br>45.02<br>13.37<br>6.67<br>-0.8<br>-0.8<br>-0.95<br>-1.4<br>-7.1<br>-9.2<br>-0.06<br>-1.25<br>122<br>129<br>109<br>104<br>109<br>113<br>6 | ±0.4<br>±0.5<br>73.33<br>45.02<br>13.37<br>6.67<br>±0.10<br>±0.11<br>±0.13<br>±0.23<br>±1.7<br>±1.2<br>±0.006<br>0.1<br>+4.1<br>+6.8<br>+0.06<br>1.50<br>ppm<br>LSB<br>LSBrms<br>LSBrms<br>LSBrms<br>mV<br>mV<br>mV<br>mV<br>μV/°C<br>μV/°C<br>%FS<br>ppm/°C<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>μV-p-p | Bits<br>ppm<br>LSB<br>LSBrms<br>LSBrms<br>LSBrms<br>mV<br>mV<br>mV<br>mV<br>μV/°C<br>μV/°C<br>%FS<br>ppm/°C<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>μV-p-p |

## 仕様

表 1. 仕様 (続き)

| Parameter                                    | Test Conditions/Comments                                 | Min    | Typ   | Max   | Unit   |

|----------------------------------------------|----------------------------------------------------------|--------|-------|-------|--------|

| AC ACCURACY                                  |                                                          |        |       |       |        |

| Dynamic Range                                | G = 1/3                                                  | 107.7  |       |       | dB     |

|                                              | G = 5/9                                                  | 107.5  |       |       | dB     |

|                                              | G = 20/9                                                 | 106    |       |       | dB     |

|                                              | G = 20/3                                                 | 102.5  |       |       | dB     |

| Total-System Dynamic Range                   |                                                          | 128    |       |       | dB     |

| Noise Spectral Density (NSD)                 | $f_{IN} = 10 \text{ kHz}$                                |        |       |       |        |

|                                              | G = 1/3                                                  | 67.12  |       |       | nV/√Hz |

|                                              | G = 5/9                                                  | 41.21  |       |       | nV/√Hz |

|                                              | G = 20/9                                                 | 12.72  |       |       | nV/√Hz |

|                                              | G = 20/3                                                 | 6.69   |       |       | nV/√Hz |

| Total RMS Noise, RTI                         | $f_{IN} = 10 \text{ kHz}$                                |        |       |       |        |

|                                              | G = 1/3                                                  | 43.7   |       |       | μV RMS |

|                                              | G = 5/9                                                  | 26.8   |       |       | μV RMS |

|                                              | G = 20/9                                                 | 8      |       |       | μV RMS |

|                                              | G = 20/3                                                 | 4      |       |       | μV RMS |

| Signal-to-Noise Ratio (SNR)                  | $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dBFS}$              |        |       |       |        |

|                                              | G = 1/3                                                  | 105    | 106.5 |       | dB     |

|                                              | G = 5/9                                                  | 104    | 106   |       | dB     |

|                                              | G = 20/9                                                 | 103.2  | 105   |       | dB     |

|                                              | G = 20/3                                                 | 98.8   | 101   |       | dB     |

| Spurious-Free Dynamic Range (SFDR)           | $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dBFS}$              |        |       |       |        |

|                                              | G = 1/3                                                  | 122    |       |       | dB     |

|                                              | G = 5/9                                                  | 118    |       |       | dB     |

|                                              | G = 20/9                                                 | 122    |       |       | dB     |

|                                              | G = 20/3                                                 | 122    |       |       | dB     |

| Total Harmonic Distortion (THD)              | $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dBFS}$              |        |       |       |        |

|                                              | G = 1/3                                                  | -114.5 | -122  |       | dB     |

|                                              | G = 5/9                                                  | -106   | -118  |       | dB     |

|                                              | G = 20/9                                                 | -116   | -122  |       | dB     |

|                                              | G = 20/3                                                 | -116   | -122  |       | dB     |

| Signal-to-Noise-and-Distortion (SINAD) Ratio | $f_{IN} = 1 \text{ kHz}, -0.5 \text{ dBFS}$              |        |       |       |        |

|                                              | G = 1/3                                                  | 104.7  | 106.4 |       | dB     |

|                                              | G = 5/9                                                  | 103.7  | 105.9 |       | dB     |

|                                              | G = 20/9                                                 | 103    | 104.9 |       | dB     |

|                                              | G = 20/3                                                 | 98.6   | 100.9 |       | dB     |

| Oversampled Dynamic Range                    | OSR = 2                                                  |        | 108   |       | dB     |

|                                              | OSR = 1024                                               |        | 134   |       | dB     |

| -3 dB Input Bandwidth                        | $V_{OUTDIFF} = 2 \text{ V p-p}$                          |        |       |       |        |

|                                              | G = 1/3                                                  | 270    |       |       | kHz    |

|                                              | G = 5/9                                                  | 270    |       |       | kHz    |

|                                              | G = 20/9                                                 | 250    |       |       | kHz    |

|                                              | G = 20/3                                                 | 225    |       |       | kHz    |

| Aperture Delay                               |                                                          |        | 0.7   |       | ns     |

| Aperture Jitter                              |                                                          |        | 1.4   |       | ps RMS |

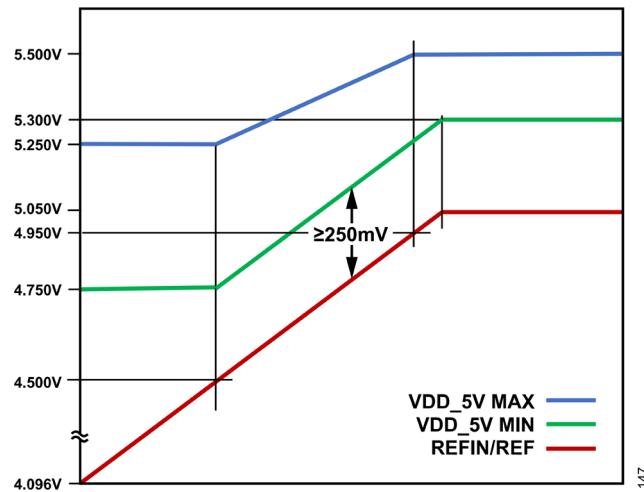

| INTERNAL REFERENCE BUFFER                    | External reference drives REFIN                          |        |       |       |        |

| REFIN Voltage Range                          | $5.3 \text{ V} \leq VDD\_5\text{V} \leq 5.5 \text{ V}$   | 4.95   | 5     | 5.05  | V      |

|                                              | $4.75 \text{ V} \leq VDD\_5\text{V} \leq 5.25 \text{ V}$ | 4.046  | 4.096 | 4.146 | V      |

| REFIN Bias Current                           | REFIN = 5 V                                              |        | 10    | 13.5  | μA     |

| REFIN Input Impedance                        |                                                          |        | 500   |       | kΩ     |

## 仕様

表 1. 仕様 (続き)

| Parameter                                        | Test Conditions/Comments                               | Min                  | Typ         | Max                   | Unit                         |

|--------------------------------------------------|--------------------------------------------------------|----------------------|-------------|-----------------------|------------------------------|

| REFIN Input Capacitance                          |                                                        |                      | 40          |                       | pF                           |

| Reference Buffer Offset-Error                    | REFIN = 5 V or 4.096 V, $T_A = 25^\circ\text{C}$       | -150                 | $\pm 20$    | +150                  | $\mu\text{V}$                |

| Reference Buffer Offset-Drift                    |                                                        |                      | $\pm 0.3$   |                       | $\mu\text{V}/^\circ\text{C}$ |

| Power-On Settling Time                           |                                                        |                      | 3           |                       | ms                           |

| DIGITAL INPUTS, ADC                              | $1.14 \text{ V} \leq V_{IO} \leq 1.89 \text{ V}$       |                      |             |                       |                              |

| Logic Levels                                     |                                                        |                      |             |                       |                              |

| Input Voltage Low ( $V_{IL}$ )                   |                                                        | -0.3                 |             | $+0.35 \times V_{IO}$ | V                            |

| Input Voltage High ( $V_{IH}$ )                  |                                                        | $0.65 \times V_{IO}$ |             | $V_{IO} + 0.3$        | V                            |

| Input Current Low ( $I_{IL}$ )                   |                                                        | -10                  |             | +10                   | $\mu\text{A}$                |

| Input Current High ( $I_{IH}$ )                  |                                                        | -10                  |             | +10                   | $\mu\text{A}$                |

| Input Pin Capacitance                            |                                                        |                      | 2           |                       | pF                           |

| DIGITAL INPUTS, A0 and A1                        |                                                        |                      |             |                       |                              |

| Logic Levels                                     |                                                        | 2                    |             | 0.8                   | V                            |

| Input Voltage Low ( $V_{IL}$ )                   |                                                        |                      |             | 0.002                 | V                            |

| Input Voltage High ( $V_{IH}$ )                  |                                                        |                      |             | 2                     | $\mu\text{A}$                |

| Input Current ( $I_{IL}$ or $I_{IH}$ )           |                                                        |                      |             |                       | pF                           |

| Input Pin Capacitance                            |                                                        |                      |             |                       |                              |

| DIGITAL INPUTS, FDA                              |                                                        |                      |             |                       |                              |

| PDB_FDA Input Current                            | PDB_FDA = VDD_FDA or 0 V                               |                      | 50          |                       | $\mu\text{A}$                |

| DIGITAL INPUTS, TEMPERATURE SENSOR (SDA AND SCL) |                                                        |                      |             |                       |                              |

| Logic Levels                                     |                                                        |                      |             |                       |                              |

| Input Voltage Low ( $V_{IL}$ )                   |                                                        | -0.5                 |             | $V_{DD} \times 0.3$   | V                            |

| Input Voltage High ( $V_{IH}$ )                  | $V_{DD} = 3.3 \text{ V}$                               | $V_{DD} \times 0.7$  |             | 3.6                   | V                            |

| Input High-Leakage Current                       |                                                        |                      |             | +1                    | $\mu\text{A}$                |

| Input Low-Leakage Current                        |                                                        | -1                   | $\pm 0.005$ | +1                    | $\mu\text{A}$                |

| Input Capacitance                                |                                                        |                      |             | 5                     | pF                           |

| DIGITAL OUTPUTS                                  | $1.14 \text{ V} \leq V_{IO} \leq 1.89 \text{ V}$       |                      |             |                       |                              |

| Pipeline Delay                                   |                                                        |                      |             |                       |                              |

| Output Voltage Low ( $V_{OL}$ )                  |                                                        |                      |             | $0.25 \times V_{IO}$  | V                            |

| Output Voltage High ( $V_{OH}$ )                 | Sink current ( $I_{SINK}$ ) = 2 mA                     | 0.75 $\times V_{IO}$ |             |                       | V                            |

| Source current ( $I_{SOURCE}$ ) = 2 mA           |                                                        |                      |             |                       |                              |

| LDO CHARACTERISTICS                              |                                                        |                      |             |                       |                              |

| VDD_1.8V Output Voltage                          |                                                        | 1.71                 | 1.8         | 1.89                  | V                            |

| Load Regulation                                  |                                                        |                      | 0.003       |                       | %/mA                         |

| Dropout Voltage <sup>4</sup>                     | $I_{OUT} = 1 \text{ mA to } 100 \text{ mA}$            |                      | 45          |                       | mV                           |

| Start-up Time <sup>5</sup>                       | $I_{OUT} = 100 \text{ mA}$                             |                      | 200         |                       | $\mu\text{s}$                |

| Current Limit Threshold                          |                                                        |                      | 260         |                       | $\text{mA}$                  |

| EN_LDO Input Current                             | $EN\_LDO = V_{LDO}$                                    |                      | 0.001       | 1                     | $\mu\text{A}$                |

| Thermal Shutdown Threshold                       |                                                        |                      |             | 150                   | $^\circ\text{C}$             |

| Thermal Shutdown Hysteresis                      |                                                        |                      |             | 15                    | $^\circ\text{C}$             |

| TEMPERATURE SENSOR CHARACTERISTICS               |                                                        |                      |             |                       |                              |

| Temperature Measurement Error                    | $T = -40^\circ\text{C} \text{ to } +105^\circ\text{C}$ | -1                   | $\pm 0.3$   | +1                    | $^\circ\text{C}$             |

| Conversion Time                                  | 10-bit resolution, $T = 25^\circ\text{C}$              |                      | 35          | 150                   | ms                           |

| Temperature Resolution                           | 12-bit (Configuration Bits[D6:D5] = 11)                |                      |             | 0.0625                | $^\circ\text{C}$             |

|                                                  | 10-bit (Configuration Bits[D6:D5] = 10)                |                      |             | 0.25                  | $^\circ\text{C}$             |

## 仕様

表 1. 仕様 (続き)

| Parameter                  | Test Conditions/Comments                                                                                         | Min               | Typ              | Max              | Unit           |

|----------------------------|------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|----------------|

| First Conversion Completed | 9-bit (Configuration Bits[D6:D5] = 01)<br>8-bit (Configuration Bits[D6:D5] = 00)<br>After $V_{DD}$ exceeds 1.6 V | 0.5<br>1.0<br>500 | 0.5<br>1.0<br>ms | 0.5<br>1.0<br>ms | °C<br>°C<br>ms |

| ISOLATION LEAKAGE CURRENT  | $\pm 250$ V between GND and TMP_GND planes                                                                       | 1                 | 1                | 1                | nA             |

| POWER SUPPLIES             |                                                                                                                  |                   |                  |                  |                |

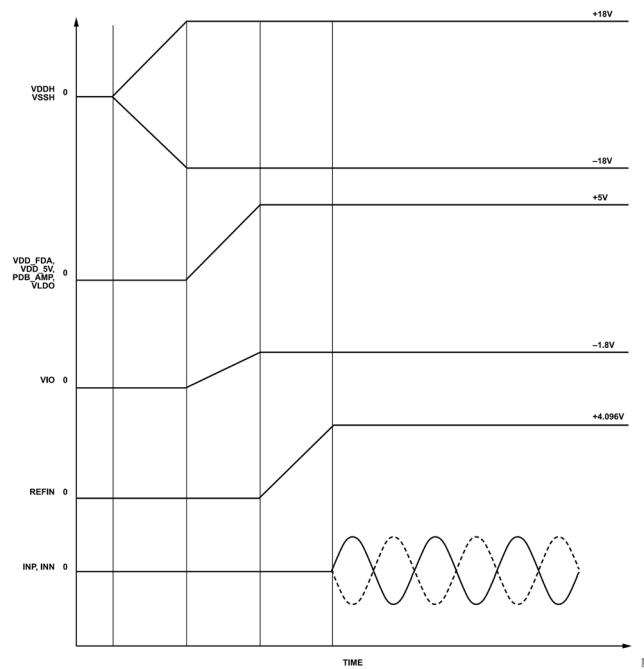

| $V_{DDH}$                  |                                                                                                                  |                   | 18               |                  | V              |

| $V_{SSH}$                  |                                                                                                                  |                   | -18              |                  | V              |

| $VDD\_FDA$                 |                                                                                                                  | 3                 | 5.4              | $VSS\_FDA + 10$  | V              |

| $VSS\_FDA$                 |                                                                                                                  |                   | $VDD\_FDA - 10$  | 0                | V              |

| $VDD\_5V$                  | REF = 5 V                                                                                                        | 5.3               | 5.4              | 5.5              | V              |

|                            | REF = 4.096 V                                                                                                    | 4.75              | 5                | 5.25             | V              |

| $VDD\_1.8V$                |                                                                                                                  | 1.71              | 1.8              | 1.89             | V              |

| $V_{IO}^6$                 |                                                                                                                  | 1.14              |                  | 1.89             | V              |

| $VDD$                      |                                                                                                                  | 3.0               | 3.3              | 3.6              | V              |

| $V_{LDO}$                  |                                                                                                                  | 2.2               | 5.4              | 5.5              | V              |

| Standby Current            | Inputs grounded                                                                                                  |                   |                  |                  |                |

| $V_{DDH}$                  |                                                                                                                  |                   | 8                |                  | mA             |

| $V_{SSH}$                  |                                                                                                                  |                   | -9               |                  | mA             |

| $VDD\_FDA$                 |                                                                                                                  |                   | 4.8              |                  | mA             |

| $VSS\_FDA$                 |                                                                                                                  |                   | -3.5             |                  | mA             |

| $VDD\_5V$                  |                                                                                                                  |                   | 525              |                  | μA             |

| $V_{IO}$                   |                                                                                                                  |                   | <1               |                  | μA             |

| $V_{DD}$                   |                                                                                                                  |                   | 1.5              | 4.5              | μA             |

| $V_{LDO}$                  |                                                                                                                  |                   | 108              |                  | μA             |

| Shutdown Current           | Inputs grounded                                                                                                  |                   |                  |                  |                |

| $VDD\_FDA$                 | $PDB\_FDA = 0$ V                                                                                                 |                   | 32               |                  | μA             |

| $VSS\_FDA$                 | $PDB\_FDA = 0$ V                                                                                                 |                   | 25.5             |                  | μA             |

| $VDD\_5V$                  | ADC in Shutdown Mode                                                                                             |                   | 5                |                  | μA             |

| $V_{IO}$                   |                                                                                                                  |                   | <1               |                  | μA             |

| $V_{LDO}$                  | $EN\_LDO = 0$ V, ADC in shutdown mode                                                                            |                   | 0.8              |                  | μA             |

| Operating Current          | 2 MSPS, Input = -0.5 dBFS                                                                                        |                   |                  |                  |                |

| $V_{DDH}$                  | $V_{DDH} = +18$ V                                                                                                |                   | 10               |                  | mA             |

| $V_{SSH}$                  | $V_{SSH} = -18$ V                                                                                                |                   | -9.8             |                  | mA             |

| $VDD\_5V$                  | $VDD\_5V = 5.4$ V                                                                                                |                   | 2.5              | 3.2              | mA             |

| $VDD\_FDA$                 | $VDD\_FDA = 5$ V                                                                                                 |                   | 5.6              | 7.5              | mA             |

| $VSS\_FDA$                 | $VSS\_FDA = 0$ V                                                                                                 | -7.5              | -5.6             |                  | mA             |

| $V_{IO}$                   | $V_{IO} = 1.8$ V, 1-lane SDO                                                                                     |                   | 1.3              |                  | mA             |

| $V_{LDO}$                  | $V_{LDO} = 5.4$ V                                                                                                |                   | 8.2              | 10.5             | mA             |

| $V_{DD}$                   | $V_{DD} = 3.3$ V                                                                                                 |                   | 80               | 150              | μA             |

| Power Dissipation          | 2 MSPS                                                                                                           |                   | 446              |                  | mW             |

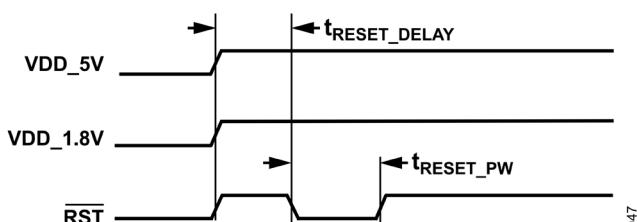

| $t_{RESET\_DELAY}$         | After power-on, delay from $VDD\_5V$ and $VDD\_1.8V$ valid to $\overline{RST}$ assertion                         | 3                 |                  |                  | ms             |

| $t_{RESET\_PW}$            | $\overline{RST}$ pulse width                                                                                     | 50                |                  |                  | ns             |

| TEMPERATURE RANGE          |                                                                                                                  |                   |                  |                  |                |

| Specified Performance      | $T_{MIN}$ to $T_{MAX}$                                                                                           | -40               |                  | +105             | °C             |

<sup>1</sup> これらの仕様は製品テストを受けたものではありませんが、製品の初期リリース時に特性評価データで裏付けられています。

## 仕様

<sup>2</sup> アクイジション・フェーズとは、入力サンプリング・コンデンサが、2MSPS のスループット・レートで動作する ADC で新しい入力を取得するために使用できる時間です。

<sup>3</sup> 図 61 の低周波数ノイズ・プロットを参照してください。1/f ノイズは、オートゼロ機能により内部で打ち消されます。ノイズ・スペクトル密度は、DC~ $f_s/2$  の範囲で実質的に一定です。

<sup>4</sup> ドロップアウト電圧は、入力電圧を公称出力電圧に設定したときの入力電圧と出力電圧間の電圧差として定義されます。

<sup>5</sup> スタートアップ時間は、EN\_LDO の立上がりエッジから VDD\_1.8V が公称値の 90% になるまでの時間として定義されます。

<sup>6</sup>  $V_{IO} < 1.4V$  の場合はビット IO2X を 1 に設定する必要があります。詳細については出力ドライバ・レジスタのセクションを参照してください。

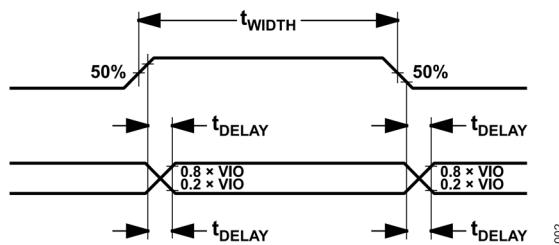

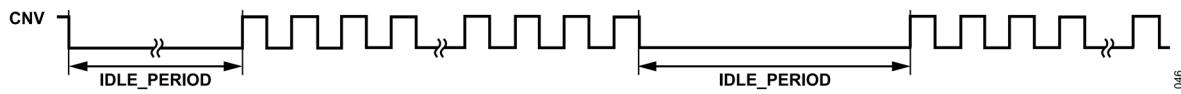

## タイミング仕様

特に指定のない限り、 $V_{DDH} = 18V$ 、 $V_{SSH} = -18V$ 、 $VDD\_FDA = 5.4V$ 、 $VSS\_FDA = 0V$ 、 $VDD\_5V = 5.4V$ 、 $V_{LDO} = 5.4V$ 、 $V_{IO} = 1.8V$ 、 $REFIN = 5V$ 、 $V_{DD} = 3.3V$ 、 $f_s = 2MSPS$ 、すべての仕様は  $T_{MIN} \sim T_{MAX}$  における値。タイミング電圧レベルについては図 2 を参照してください。 $V_{IO} < 1.4V$  の場合はビット IO2X を 1 に設定する必要があります。

表 2. デジタル・タイミング・インターフェース

| Parameter <sup>1</sup>                             | Symbol     | Min  | Typ | Max  | Unit |

|----------------------------------------------------|------------|------|-----|------|------|

| Conversion Time: CNV Rising Edge to Data Available | $t_{CONV}$ | 264  | 282 | 300  | ns   |

| Acquisition Phase <sup>2</sup>                     | $t_{ACQ}$  | 244  | 260 | 275  | ns   |

| Time Between Conversions                           | $t_{CYC}$  | 500  |     |      | ns   |

| CNV High Time                                      | $t_{CNVH}$ | 10   |     |      | ns   |

| CNV Low Time                                       | $t_{CNVL}$ | 20   |     |      | ns   |

| Internal Oscillator Frequency                      | $f_{OSC}$  | 75.1 | 80  | 84.7 | MHz  |

<sup>1</sup> タイミング仕様は、デジタル出力ピンでの負荷容量が 5pF であると仮定しています。 $t_{CONV}$ 、 $t_{CYC}$ 、 $t_{SCK}$ 、 $t_{SCKOUT}$  は出荷テスト済みです。それ以外のタイミング仕様は特性評価および設計により確保されています。

<sup>2</sup> アクイジション・フェーズとは、入力サンプリング・コンデンサが、2MSPS のスループット・レートで動作する ADC で新しい入力を取得するために使用できる時間です。

図 2. タイミングの電圧レベル

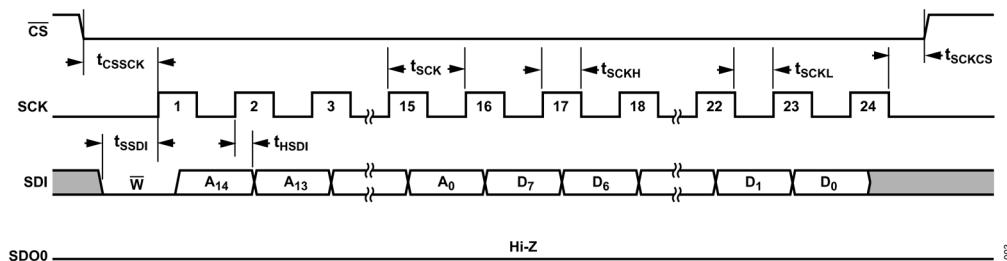

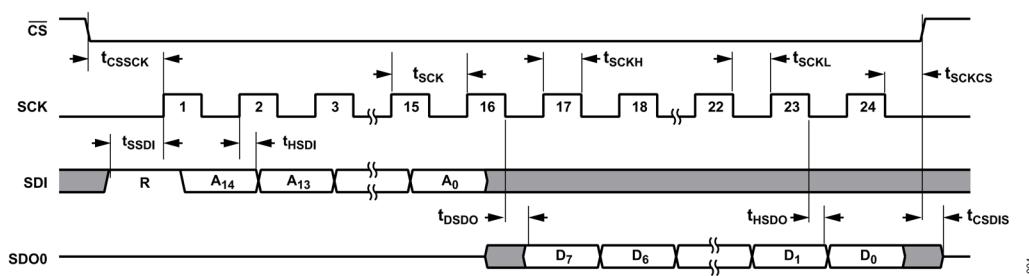

表 3. レジスタ読出し/書き込みのタイミング

| Parameter                                | Symbol      | Min  | Typ | Max  | Unit |

|------------------------------------------|-------------|------|-----|------|------|

| CS Pulse Width                           | $t_{CSPW}$  | 10   |     |      | ns   |

| SCK Period                               | $t_{SCK}$   | 11.6 |     |      | ns   |

| $V_{IO} > 1.71V$                         |             | 12.3 |     |      | ns   |

| $V_{IO} > 1.14V$                         |             |      |     |      | ns   |

| SCK Low Time                             | $t_{SCKL}$  | 5.2  |     |      | ns   |

| SCK High Time                            | $t_{SCKH}$  | 5.2  |     |      | ns   |

| SCK Falling Edge to Data Remains Valid   | $t_{HSDO}$  | 2.1  |     |      | ns   |

| SCK Falling Edge to Data Valid Delay     | $t_{DSDO}$  |      |     | 9.4  | ns   |

| $V_{IO} > 1.71V$                         |             |      |     | 11.8 | ns   |

| $V_{IO} > 1.14V$                         |             |      |     |      | ns   |

| CS Rising Edge to SDO High Impedance     | $t_{CSDIS}$ |      |     | 9    | ns   |

| SDI Valid Setup Time to SCK Rising Edge  | $t_{SSDI}$  | 1.5  |     |      | ns   |

| SDI Valid Hold Time from SCK Rising Edge | $t_{HSDI}$  | 1.5  |     |      | ns   |

| CS Falling Edge to First SCK Rising Edge | $t_{CSSCK}$ |      |     |      | ns   |

## 仕様

表3. レジスタ読出し／書込みのタイミング (続き)

| Parameter                                           | Symbol      | Min  | Typ | Max | Unit |

|-----------------------------------------------------|-------------|------|-----|-----|------|

| $V_{IO} > 1.71 \text{ V}$                           |             | 11.6 |     |     | ns   |

| $V_{IO} > 1.14 \text{ V}$                           |             | 12.3 |     |     | ns   |

| Last SCK Edge to $\overline{\text{CS}}$ Rising Edge | $t_{SCKCS}$ | 5.2  |     |     | ns   |

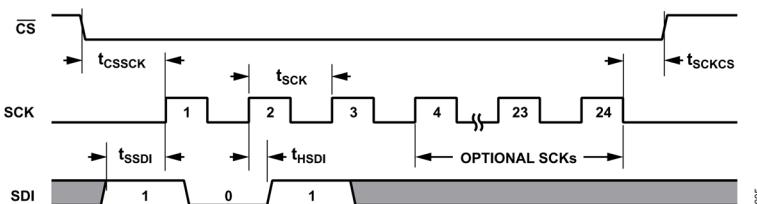

図3. レジスタ設定モードの書き込みタイミング

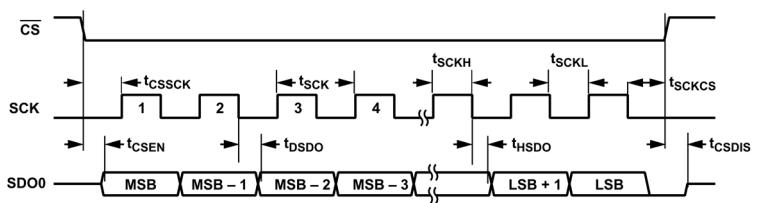

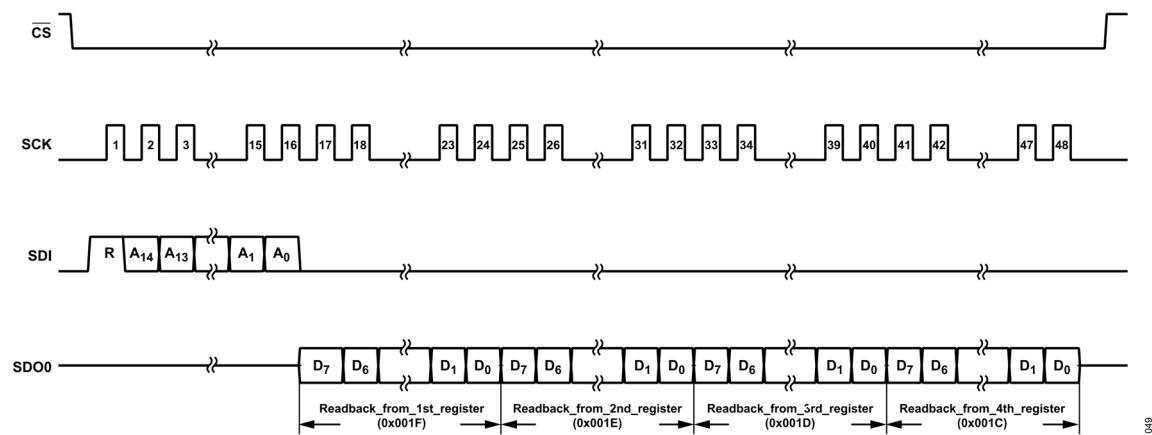

図4. レジスタ設定モードの読み出しタイミング

図5. レジスタ設定モードのコマンド・タイミング

表4. SPI互換モードのタイミング

| Parameter                              | Symbol     | Min  | Typ | Max | Unit |

|----------------------------------------|------------|------|-----|-----|------|

| SCK Period                             |            |      |     |     |      |

| $V_{IO} > 1.71 \text{ V}$              | $t_{SCK}$  | 9.8  |     |     | ns   |

| $V_{IO} > 1.14 \text{ V}$              |            | 12.3 |     |     | ns   |

| SCK Low Time                           | $t_{SCKL}$ |      |     |     |      |

| $V_{IO} > 1.71 \text{ V}$              |            | 4.2  |     |     | ns   |

| $V_{IO} > 1.14 \text{ V}$              |            | 5.2  |     |     | ns   |

| SCK High Time                          | $t_{SCKH}$ |      |     |     |      |

| $V_{IO} > 1.71 \text{ V}$              |            | 4.2  |     |     | ns   |

| $V_{IO} > 1.14 \text{ V}$              |            | 5.2  |     |     | ns   |

| SCK Falling Edge to Data Remains Valid | $t_{HSDO}$ |      |     |     |      |

| SCK Falling Edge to Data Valid Delay   | $t_{DSDO}$ | 1.4  |     |     | ns   |

| $V_{IO} > 1.71 \text{ V}$              |            |      | 5.6 |     | ns   |

| $V_{IO} > 1.14 \text{ V}$              |            |      | 8.1 |     | ns   |

## 仕様

表 4. SPI 互換モードのタイミング (続き)

| Parameter                                | Symbol       | Min  | Typ | Max | Unit |

|------------------------------------------|--------------|------|-----|-----|------|

| CS Falling Edge to SDO Valid             | $t_{CSEN}$   |      |     |     | ns   |

| $V_{IO} > 1.71 \text{ V}$                |              |      |     | 6.8 | ns   |

| $V_{IO} > 1.14 \text{ V}$                |              |      |     | 9.3 | ns   |

| CS Falling Edge to First SCK Rising Edge | $t_{CSSCK}$  |      |     |     | ns   |

| $V_{IO} > 1.71 \text{ V}$                |              | 9.8  |     |     | ns   |

| $V_{IO} > 1.14 \text{ V}$                |              | 12.3 |     |     | ns   |

| Last SCK Edge to CS Rising Edge          | $t_{SCKCS}$  |      | 4.2 |     | ns   |

| CS Rising Edge to SDO High Impedance     | $t_{CSDIS}$  |      |     | 9   | ns   |

| CS Falling Edge to BUSY Rising Edge      | $t_{CSBUSY}$ | 6    |     |     | ns   |

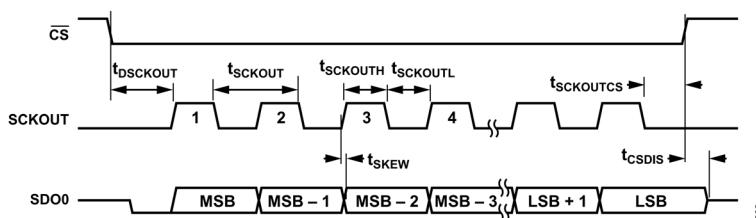

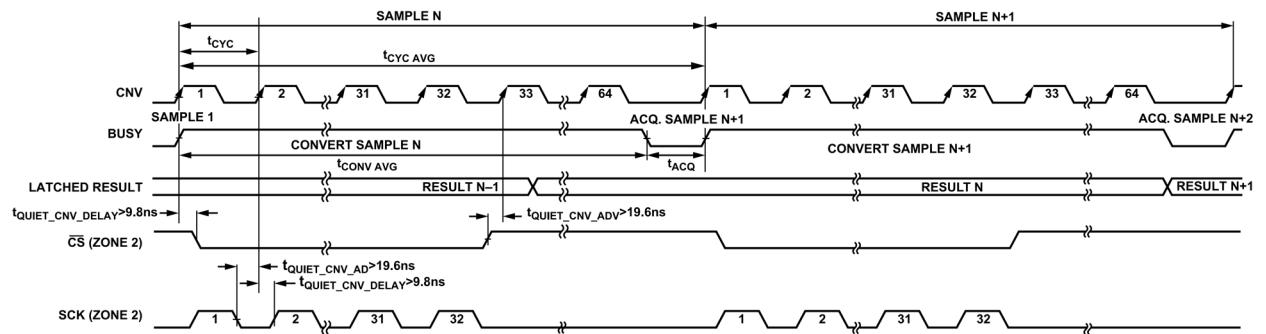

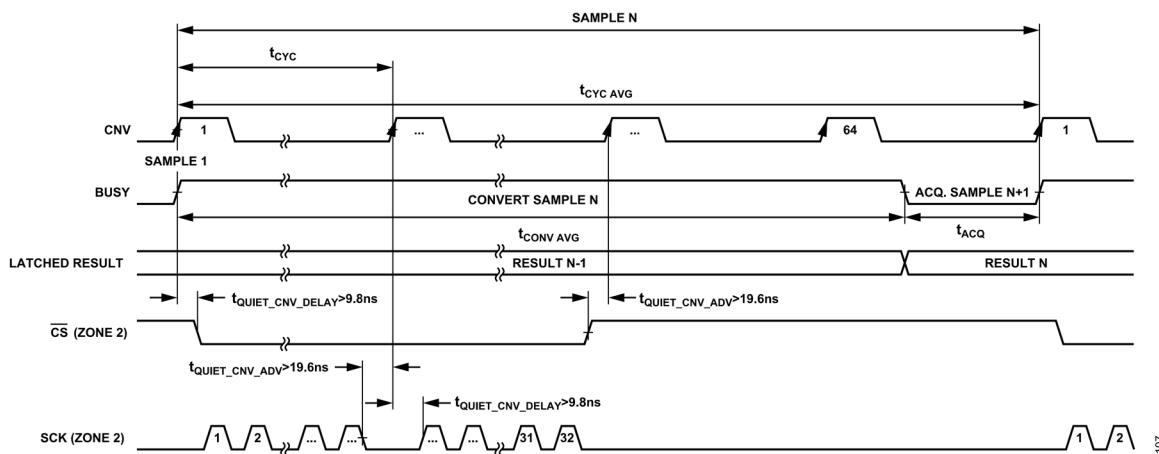

図 6. SPI クロック・モードの 1 レーン SDR のタイミング

表 5. エコー・クロック・モードのタイミング、SDR、1 レーン

| Parameter                                    | Symbol               | Min  | Typ | Max  | Unit |

|----------------------------------------------|----------------------|------|-----|------|------|

| SCK Period                                   | $t_{SCK}$            |      |     |      | ns   |

| $V_{IO} > 1.71 \text{ V}$                    |                      | 9.8  |     |      | ns   |

| $V_{IO} > 1.14 \text{ V}$                    |                      | 12.3 |     |      | ns   |

| SCK Low Time, SCK High Time                  | $t_{SCKL}, t_{SCKH}$ |      |     |      | ns   |

| $V_{IO} > 1.71 \text{ V}$                    |                      | 4.2  |     |      | ns   |

| $V_{IO} > 1.14 \text{ V}$                    |                      | 5.2  |     |      | ns   |

| SCK Rising Edge to Data/SCKOUT Remains Valid | $t_{HSDO}$           |      | 1.1 |      | ns   |

| SCK Rising Edge to Data/SCKOUT Valid Delay   | $t_{DSDO}$           |      |     | 5.6  | ns   |

| $V_{IO} > 1.71 \text{ V}$                    |                      |      |     | 8.1  | ns   |

| $V_{IO} > 1.14 \text{ V}$                    |                      |      |     |      | ns   |

| CS Falling Edge to First SCK Rising Edge     | $t_{CSSCK}$          |      |     |      | ns   |

| $V_{IO} > 1.71 \text{ V}$                    |                      | 9.8  |     |      | ns   |

| $V_{IO} > 1.14 \text{ V}$                    |                      | 12.3 |     |      | ns   |

| Skew Between Data and SCKOUT                 | $t_{SKEW}$           | -0.4 | 0   | +0.4 | ns   |

| Last SCK Edge to CS Rising Edge              | $t_{SCKCS}$          |      | 4.2 |      | ns   |

| CS Rising Edge to SDO High Impedance         | $t_{CSDIS}$          |      |     | 9    | ns   |

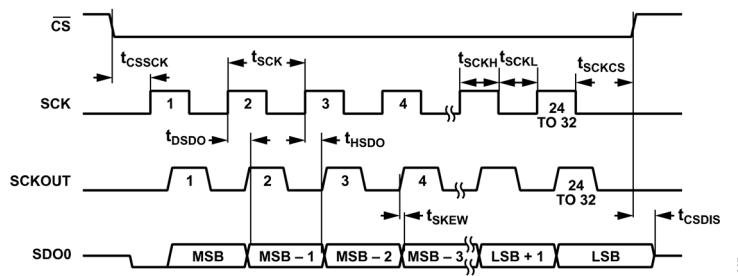

図 7. エコー・クロック・モードのタイミング、SDR、1 レーン

## 仕様

表 6. エコー・クロック・モードのタイミング、DDR、1 レーン

| Parameter                                             | Symbol               | Min  | Typ | Max  | Unit |

|-------------------------------------------------------|----------------------|------|-----|------|------|

| SCK Period                                            | $t_{SCK}$            | 12.3 |     |      | ns   |

| SCK Low Time, SCK High Time                           | $t_{SCKL}, t_{SCKH}$ | 5.2  |     |      | ns   |

| SCK Edge to Data/SCKOUT Remains Valid                 | $t_{HSDO}$           | 1.1  |     |      | ns   |

| SCK Edge to Data/SCKOUT Valid Delay                   | $t_{DSDO}$           |      |     |      |      |

| $V_{IO} > 1.71 \text{ V}$                             |                      |      |     | 6.2  | ns   |

| $V_{IO} > 1.14 \text{ V}$                             |                      |      |     | 8.7  | ns   |

| $\overline{CS}$ Falling Edge to First SCK Rising Edge | $t_{CSSCK}$          | 12.3 |     |      | ns   |

| Skew Between Data and SCKOUT                          | $t_{SKEW}$           | -0.4 | 0   | +0.4 | ns   |

| Last SCK Edge to $\overline{CS}$ Rising Edge          | $t_{SCKCS}$          | 9    |     |      | ns   |

| $\overline{CS}$ Rising Edge to SDO High Impedance     | $t_{CSDIS}$          |      |     | 9    | ns   |

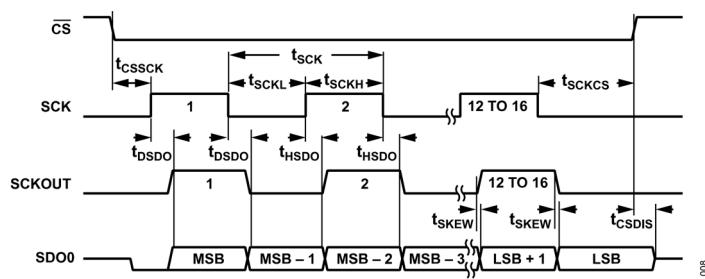

図 8. エコー・クロック・モードのタイミング、DDR、1 レーン

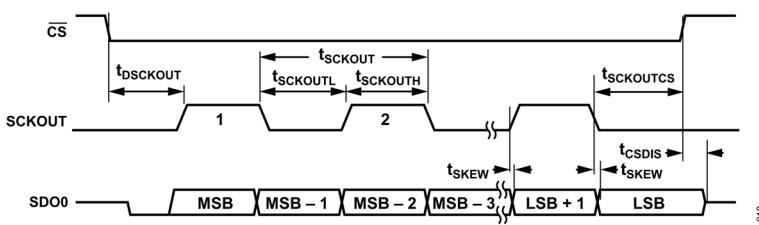

表 7. ホスト・クロック・モードのタイミング

| Parameter                                                | Symbol         | Min                      | Typ  | Max                      | Unit |

|----------------------------------------------------------|----------------|--------------------------|------|--------------------------|------|

| SCK Period                                               | $t_{SCKOUT}$   |                          |      |                          |      |

| OSC_DIV = No Divide                                      |                | 11.8                     | 12.5 | 13.3                     | ns   |

| OSC_DIV = Divide by 2                                    |                | 23.6                     | 25   | 26.6                     | ns   |

| OSC_DIV = Divide by 4                                    |                | 47.4                     | 50   | 53.2                     | ns   |

| SCK Low Time                                             | $t_{SCKOUTL}$  | $0.45 \times t_{SCKOUT}$ |      | $0.55 \times t_{SCKOUT}$ | ns   |

| SCK High Time                                            | $t_{SCKOUTH}$  | $0.45 \times t_{SCKOUT}$ |      | $0.55 \times t_{SCKOUT}$ | ns   |

| $\overline{CS}$ Falling Edge to First SCKOUT Rising Edge | $t_{DSCKOUT}$  |                          |      |                          |      |

| $V_{IO} > 1.71 \text{ V}$                                |                | 10                       | 13.6 | 19                       | ns   |

| $V_{IO} > 1.14 \text{ V}$                                |                | 10                       | 15   | 21                       | ns   |

| Skew Between Data and SCKOUT                             | $t_{SKEW}$     | -0.4                     | 0    | +0.4                     | ns   |

| Last SCKOUT Edge to $\overline{CS}$ Rising Edge          | $t_{SCKOUTCS}$ | 5.2                      |      |                          | ns   |

| $\overline{CS}$ Rising Edge to SDO High Impedance        | $t_{CSDIS}$    |                          |      | 9                        | ns   |

図 9. ホスト・クロック・モードのタイミング、SDR、1 レーン

## 仕様

図 10. ホスト・クロック・モードのタイミング、DDR、1 レーン

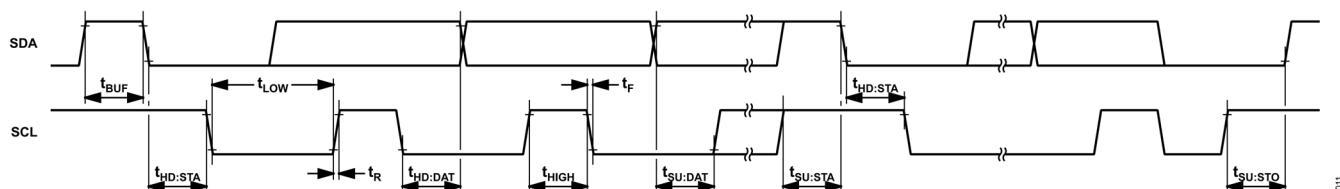

表 8. 温度センサーの I<sup>2</sup>C タイミング

| Parameter                                               | Symbol        | Min                           | Typ | Max | Unit |

|---------------------------------------------------------|---------------|-------------------------------|-----|-----|------|

| Serial Clock Frequency                                  | $f_{SCL}$     | 20                            |     | 1M  | Hz   |

| Bus Free Time Between Start and Stop Conditions         | $t_{BUF}$     | 0.5                           |     |     | μs   |

| START Condition Hold Time                               | $t_{HD:STA}$  | 0.26                          |     |     | μs   |

| STOP Condition Setup Time <sup>1</sup>                  | $t_{SU:STO}$  | 0.26                          |     |     | μs   |

| Clock Low Period                                        | $t_{LOW}$     | 0.5                           |     |     | μs   |

| Clock High Period                                       | $t_{HIGH}$    | 0.26                          |     |     | μs   |

| Start Condition Setup Time <sup>2</sup>                 | $t_{SU:STA}$  | 0.26                          |     |     | μs   |

| Data Setup Time <sup>3</sup>                            | $t_{SU:DAT}$  | 50                            |     |     | ns   |

| Data In Hold Time <sup>4</sup>                          | $t_{HD:DAT}$  | 0                             |     |     | μs   |

| SCL/SDA Rise Time                                       | $t_R$         |                               |     | 120 | ns   |

| SCL/SDA Fall Time <sup>5</sup>                          | $t_F$         | 20 × (V <sub>DD</sub> /5.5 V) |     | 120 | ns   |

| SCL Time Low for Reset of Serial Interface <sup>6</sup> | $t_{TIMEOUT}$ | 10                            |     | 85  | ms   |

<sup>1</sup> 90% SCL～10% SDA。<sup>2</sup> 90% SCL～90% SDA。<sup>3</sup> 10% SDA～10% SCL。<sup>4</sup> 10% SCL～10% SDA。<sup>5</sup>  $C_B = 1$  つのバス・ラインの合計容量 (pF)。 $C_B = 400$  pF でテスト。<sup>6</sup> SCL ラインをローに保持している時間が  $t_{TIMEOUT}$  を超えると、このデバイスは SDA をリセットしてシリアル・バス通信をアイドル状態にします (SDA が解放されます)。図 11. 温度センサーの I<sup>2</sup>C タイミング図

## 絶対最大定格

表 9. 絶対最大定格

| Parameter                               | Rating                                                 |

|-----------------------------------------|--------------------------------------------------------|

| Analog Inputs                           |                                                        |

| Input Voltage, INP, INN                 | $V_{SSH} - 0.2 \text{ V}$ to $V_{DDH} + 0.2 \text{ V}$ |

| REFIN to GND                            | -0.3 V to $V_{DD\_5V} + 0.3 \text{ V}$                 |

| Input Current <sup>1</sup>              | $\pm 20 \text{ mA}$                                    |

| Supply Voltage                          |                                                        |

| $V_{DDH}$ to $V_{SSH}$                  | 40 V                                                   |

| $V_{DD\_FDA}$ to GND                    | 11 V                                                   |

| $V_{DD\_5V}$ to GND                     | -0.3 V to +6.0 V                                       |

| $V_{IO}$ to GND                         | -0.3 V to +2.1 V                                       |

| $V_{LDO}$ to GND                        | -0.3 V to +6.5 V                                       |

| $V_{DD}$ to $V_{TMP\_GND}$              | -0.3 V to +4 V                                         |

| Digital Inputs to GND                   | -0.3 V to $V_{IO} + 0.3 \text{ V}$                     |

| CNV to GND                              | -0.3 V to $V_{IO} + 0.3 \text{ V}$                     |

| RSEL, ALARM, SCL, SDA to $V_{TMP\_GND}$ | -0.3 V to +4 V                                         |

| Digital Outputs to GND                  | -0.3 V to $V_{IO} + 0.3 \text{ V}$                     |

| Temperature                             |                                                        |

| Storage Range                           | -55°C to +150°C                                        |

| Operating Junction Range                | -40°C to +105°C                                        |

| Maximum Reflow (Package Body)           | 260°C                                                  |

<sup>1</sup> 入力ピンには電源ピンへのクランプ・ダイオードが接続されています。入力信号が電源レールを 0.3V 超える場合は、常に入力電流を 20mA 未満に制限します。

上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

## 熱抵抗

熱性能は、プリント回路基板 (PCB) の設計と動作環境に直接関連しています。PCB の熱設計には細心の注意を払う必要があります。 $\theta_{JA}$  は、1 立方フィートの密封容器内で測定された、自然対流でのジャンクションから周囲への熱抵抗です。 $\theta_{JC}$  は、ジャンクションからケースへの熱抵抗です。

表 10. 热抵抗

| Package Type | $\theta_{JA}$ | $\theta_{JC\_TOP}$ | $\theta_{JC\_BOT}$ | $\Psi_{JT}$ | Unit |

|--------------|---------------|--------------------|--------------------|-------------|------|

| BC-178-2     | 28.96         | 22.60              | 14.09              | 14.03       | °C/W |

## 静電放電定格

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。

ANSI/ESDA/JEDEC JS-001 準拠の人体モデル (HBM)。

ANSI/ESDA/JEDEC JS-002 準拠の電界誘起帶電デバイス・モデル (FICDM)。

## ADAQ4224 の ESD 定格

表 11. ADAQ4224、178 ボール CSP\_BGA

| ESD Model | Withstand Threshold (kV) | Class |

|-----------|--------------------------|-------|

| HBM       | $\pm 4$                  | 3A    |

| FICDM     | $\pm 1$                  | C3    |

## ESD に関する注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

## ピン配置およびピン機能の説明

|   | 1   | 2   | 3    | 4    | 5    | 6       | 7       | 8      | 9    | 10   | 11       | 12       | 13      | 14    | 15    | 16    | 17          |

|---|-----|-----|------|------|------|---------|---------|--------|------|------|----------|----------|---------|-------|-------|-------|-------------|

| A | GND | GND | GND  | GND  | VDDH | VDDH    | GND     | GND    | GND  | GND  | GND      |          | TMP_GND | VDD   | ALARM |       | GND         |

| B | GND | GND | GND  | GND  | GND  | GND     | GND     | GND    | GND  | GND  | GND      |          | RSEL    | SCL   | SDA   |       | GND         |

| C | INP | GND | VSSH | VSSH | GND  | INN     | INN     | GND    | GND  | GND  | GND      |          |         |       |       |       | GND         |

| D | INP | GND | GND  | GND  | GND  | GND     | GND     | GND    | GND  | GND  | REFIN    | VDD_5V   | GND     | GND   | CNV   | RSTB  | VIO         |

| E | GND | GND | A1   | A0   | GND  | VDD_FDA | GND     | GND    | OUTP | ADCP | GND      | VDD_5V   | GND     | GND   | IOGND | IOGND | VIO         |

| F | GND | GND | GND  | GND  | GND  | VDD_FDA | GND     | GND    | OUTN | ADCN | GND      | GND      | GND     | GND   | IOGND | SDO3  | SDO1        |

| G | GND | GND | VSSH | VSSH | GND  | GND     | GND     | GND    | GND  | DNC  | DNC      | GND      | GND     | GND   | IOGND | SDO2  | SDO0        |

| H | GND | GND | GND  | GND  | GND  | GND     | PDB_FDA | GND    | GND  | DNC  | DNC      | GND      | GND     | GND   | IOGND | IOGND | BUSY_SCKOUT |

| J | GND | GND | VDDH | VDDH | GND  | VSS_FDA | GND     | GND    | NIC  | GND  | GND      | GND      | GND     | GND   | IOGND | DNC   | DNC         |

| K | GND | GND | GND  | GND  | GND  | VSS_FDA | GND     | GND    | NIC  | GND  | VDD_1P8V | GND      | GND     | IOGND | DNC   | DNC   |             |

| L | GND | GND | GND  | GND  | GND  | GND     | GND     | EN_LDO | GND  | GND  | GND      | VDD_1P8V | GND     | CSB   | SDI   | SCK   | IOGND       |

図 12. ピン配置

表 12. ピン機能の説明

| ピン番号                                                                                                                                                                                                                                                                                                                                                                       | 記号                   | タイプ <sup>1</sup> | 説明                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 to A4, A7 to A11, A17, B1 to B11, B17, C2, C5, C8 to C11, C17, D2 to D10, D13 to D14, E1 to E2, E5, E7 to E8, E11, E13 to E14, F1 to F5, F7 to F8, F11 to F14, G1 to G2, G5 to G6, G8 to G10, G13 to G14, H1 to H6, H8 to H10, H13 to H14, J1 to J2, J5, J7 to J9, J11 to J14, K1 to K5, K7 to K9, K11, K13 to K14, L1 to L6, L9 to L11, L13 A5 to A6, J3 to J4 A13 A14 | GND VDDH TMP_GND VDD | P P P P          | 電源グラウンド。<br>PGIA の正電源。このピンは、パッケージ内に 0.1μF のバイパス・コンデンサを内蔵しています。<br>温度センサーのグラウンド・リターン・バス。<br>温度センサーの電源。電源を 1.6V~3.6V の範囲とするか VIO に接続すれば、電源レール数を少なくできます。このピンは、パッケージ内部で 0.1μF のバイパス・コンデンサを介して TMP_GND に接続されています。 |

| A15                                                                                                                                                                                                                                                                                                                                                                        | ALARM                | DO               | 温度センサー・アラーム出力。測定温度が TH 閾値を超えるか TL 閾値を下回るとアクティブになり、アクティブ・ハイまたはアクティブ・ローに設定できます。これはオープン・ドレイン出力で、動作させるにはブルアップ抵抗が必要です。                                                                                            |

| B13                                                                                                                                                                                                                                                                                                                                                                        | RSEL                 | DI               | このピンと TMP_GND の間には抵抗を接続してください。同じ温度センサーの I <sup>2</sup> C バスに接続された最大 32 個のターゲット・デバイスを個々に識別するために使われます。1 個のデバイスのみを使用する場合は、TMP_GND に接続します。                                                                       |

| B14<br>B15<br>C1, D1                                                                                                                                                                                                                                                                                                                                                       | SCL<br>SDA<br>INP    | DI<br>DI<br>AI   | 温度センサーの I <sup>2</sup> C クロック。<br>温度センサーの I <sup>2</sup> C バス・データ・ライン。<br>正のアナログ入力。INP ピンはフロート状態のままにしないでください。INP ピンをフロート状態のままにすると、VDDH および VSSH 電源から PGIA へ流れる電流が大きくなります。                                    |

| C3 to C4, G3 to G4<br>C6 to C7                                                                                                                                                                                                                                                                                                                                             | VSSH<br>INN          | P<br>AI          | PGIA の負電源。このピンは、パッケージ内に 0.1μF のバイパス・コンデンサを内蔵しています。<br>負のアナログ入力。INN ピンはフロート状態のままにしないでください。INN ピンをフロート状態のままにすると、VDDH および VSSH 電源から PGIA へ流れる電流が大きくなります。                                                        |

## ピン配置およびピン機能の説明

表 12. ピン機能の説明 (続き)

| ピン番号                                            | 記号          | タイプ <sup>1</sup> | 説明                                                                                                                                                                            |

|-------------------------------------------------|-------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

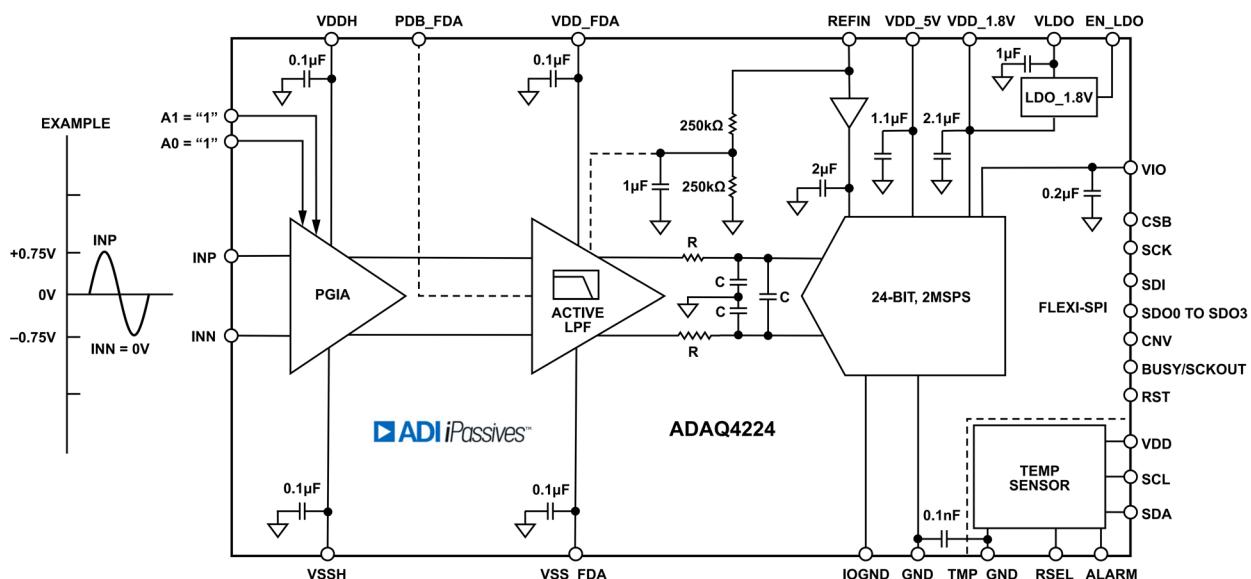

| D11                                             | REFIN       | AI               | リファレンス入力。REFINは4.096V~5V (グラウンド基準) で駆動します。このピンには内部リファレンス・バッファへの入力があり、内部の 2μF バイパス・コンデンサを介してバッファの出力に接続されています。                                                                  |

| D12, E12                                        | VDD_5V      | P                | 5V 電源。VDD_5V の範囲はリファレンスの値によって異なり、5V のリファレンスの場合は 5.3V~5.5V、4.096V のリファレンスの場合は 4.75V~5.25V です。このピンはパッケージ内に 1μF と 0.1μF のバイパス・コンデンサを内蔵しています。                                     |

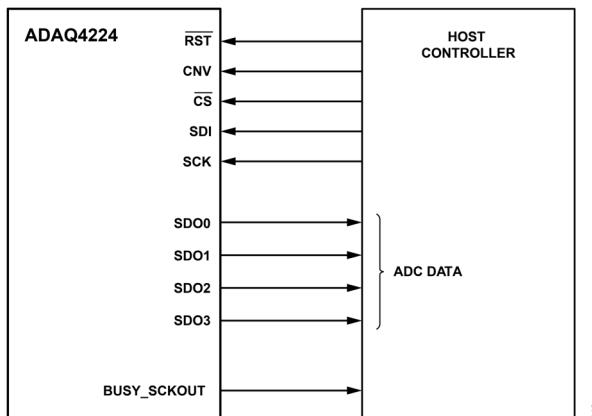

| D15                                             | CNV         | DI               | 変換入力。この入力の立上がりエッジによってデバイスがパワー・アップし、新たな変換が開始されます。ADC の仕様規定された性能を実現するには、この信号が低ジッタであることが必要です。ロジック・レベルは VIO ピンによって決まります。                                                          |

| D16                                             | RSTB        | DI               | リセット入力 (アクティブ・ロー)。非同期 ADC リセット。                                                                                                                                               |

| D17, E17                                        | VIO         | P                | 入出力インターフェースのデジタル電源。このピンの公称電圧はホスト・インターフェースと同じ (1.8V, 1.5V、または 1.2V) です。このピンにはパッケージ内に 0.2μF のバイパス・コンデンサがあります。VIO < 1.4V の場合、出力ドライバ・レジスタのビット IO2X を 1 に設定する必要があります。              |

| E3                                              | A1          | DI               | PGIA ゲイン制御ロジック入力 1。                                                                                                                                                           |

| E4                                              | A0          | DI               | PGIA ゲイン制御ロジック入力 0。                                                                                                                                                           |

| E6, F6                                          | VDD_FDA     | P                | FDA の正電源。このピンは、パッケージ内に 0.1μF のバイパス・コンデンサを内蔵しています。このピンは、2.2μF 以上の (0402, X5R) セラミック・コンデンサを使って GND へバイパスします。                                                                    |

| E9                                              | OUTP        | AO               | 正の FDA 出力。                                                                                                                                                                    |

| E10                                             | ADCP        | AI               | 正の ADC 入力。                                                                                                                                                                    |

| E15 to E16, F15, G15, H15 to H16, J15, K15, L17 | IOGND       | P                | VIO グラウンド。すべての GND ピンと同じグランド・プレーンに接続します。                                                                                                                                      |

| F9                                              | OUTN        | AO               | 負の FDA 出力。                                                                                                                                                                    |

| F10                                             | ADCN        | AI               | 負の ADC 入力。                                                                                                                                                                    |

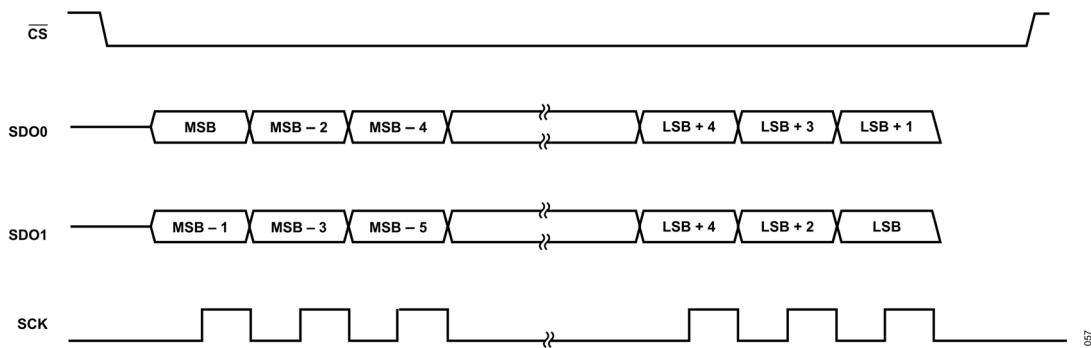

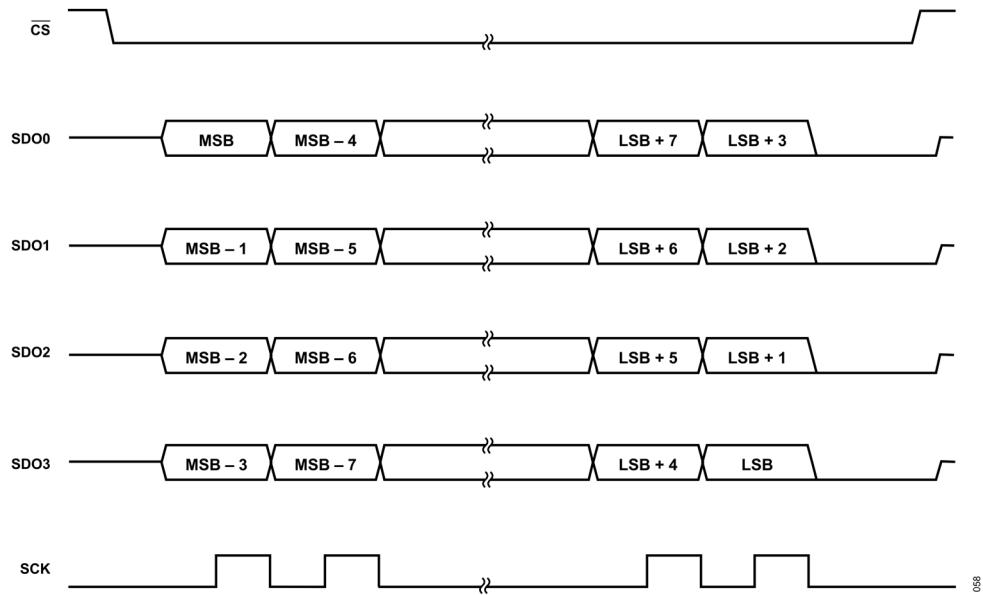

| F16                                             | SDO3        | DO               | シリアル・データ出力。変換結果はこのピンに出力されます。SCK に同期されます。                                                                                                                                      |

| F17                                             | SDO1        | DO               | シリアル・データ出力。変換結果はこのピンに出力されます。SCK に同期されます。                                                                                                                                      |

| G7, G11 to G12, H11 to H12                      | DNC         |                  | 接続なし。                                                                                                                                                                         |

| G16                                             | SDO2        | DO               | シリアル・データ出力。変換結果はこのピンに出力されます。SCK に同期されます。                                                                                                                                      |

| G17                                             | SDO0        | DO               | シリアル・データ出力。変換結果はこのピンに出力されます。SCK に同期されます。                                                                                                                                      |

| H7                                              | PDB_FDA     | DI               | FDA をパワーダウン・アクティブ・ロー。FDA をパワーダウンするには PDB_FDA ピンを GND に接続します。もしくは、PDB_FDA ピンを VDD_FDA ロジック・ハイ電源に接続します。                                                                         |

| H17                                             | BUSY_SCKOUT | DO               | SPI クロック・モードのビジー・インジケータ。このピンは、新たな変換の開始時にハイとなり、変換が終了するとローになります。ロジック・レベルは VIO ピンによって決まります。SCKOUT がイネーブルされている場合、このピン機能は、ホスト・コントローラから入力される SCK のエコー、または内部発振器から送られるクロックのどちらかになります。 |

| J6, K6                                          | VSS_FDA     | P                | FDA の負電源。このピンは、パッケージ内に 0.1μF のバイパス・コンデンサを内蔵しています。このピンは、2.2μF 以上の (0402, X5R) セラミック・コンデンサを使って GND へバイパスします。電源レール数を少なくするには GND に接続します。                                          |

| J10, K10                                        | NIC         |                  | 内部では未接続。これらのピンは、内部では接続されていません。                                                                                                                                                |

| J16 to J17, K16 to K17                          | DNC         |                  | 接続なし。高インピーダンス・モードの場合、これらのピンは内部でデジタル出力ドライバに接続されます。                                                                                                                             |

| K12, L12                                        | VDD_1.8V    | P                | LDO の電圧出力。出力は 1.8V (代表値) です。このピンは、パッケージ内に 1μF と 0.1μF のバイパス・コンデンサを内蔵しています。                                                                                                    |

| L7                                              | EN_LDO      | DI               | LDO イネーブル ピン。自動スタートアップの場合は、EN_LDO を VLDO に接続します。                                                                                                                              |

| L8                                              | VLDO        | P                | 内部 LDO 入力電源。このピンにはパッケージ内に 1μF のバイパス・コンデンサがあります。VLDO の入力範囲は 2.2V~5.5V です。                                                                                                      |

| L14                                             | CSB         | DI               | チップ・セレクト入力 (アクティブ・ロー)。                                                                                                                                                        |

| L15                                             | SDI         | DI               | シリアル・データ入力。                                                                                                                                                                   |

| L16                                             | SCK         | DI               | シリアル・データ・クロック入力。デバイスを選択すると (CSB = ロー)、変換結果はこのクロックによってシフト出力されます。                                                                                                               |

<sup>1</sup> AI はアナログ入力、AO はアナログ出力、P は電源、DI はデジタル入力、DO はデジタル出力です。

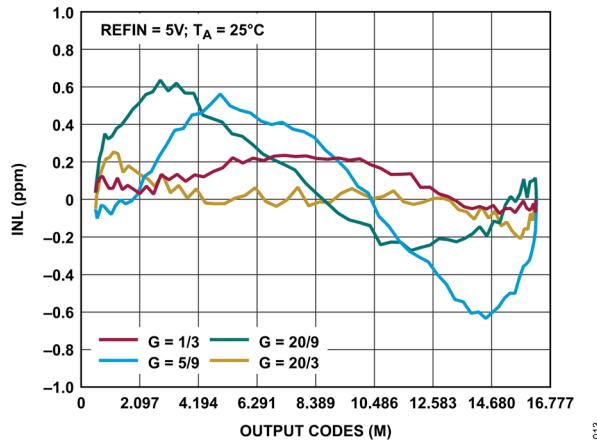

## 代表的な性能特性

特に指定のない限り、 $V_{DDH} = 18V$ 、 $V_{SSH} = -18V$ 、 $VDD\_FDA = 5.4V$ 、 $VSS\_FDA = 0V$ 、 $VDD\_5V = 5.4V$ 、 $V_{LDO} = 5.4V$ 、 $VDD\_1.8V = 1.8V$ 、 $V_{IO} = 1.8V$ 、 $REFIN = 5V$ 、 $f_s = 2MSPS$ 、すべての仕様は  $T_{MIN} \sim T_{MAX}$  における値。

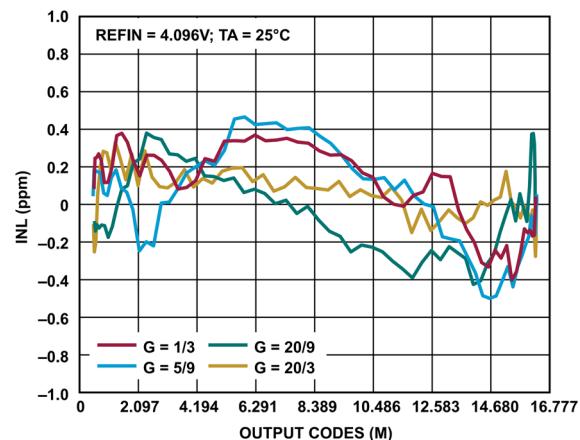

図 13. INL 誤差と出力コードの関係 (差動入力、REFIN = 5V)

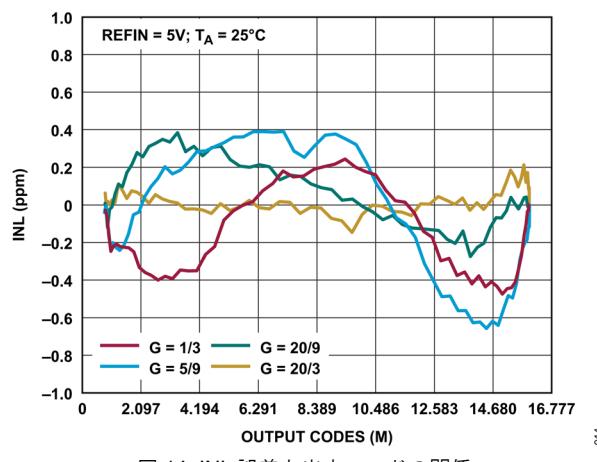

図 16. INL 誤差と出力コードの関係 (差動入力、REFIN = 4.096V)

図 14. INL 誤差と出力コードの関係 (シングルエンド入力、REFIN = 5V)

図 17. INL 誤差と出力コードの関係 (シングルエンド入力、REFIN = 4.096V)

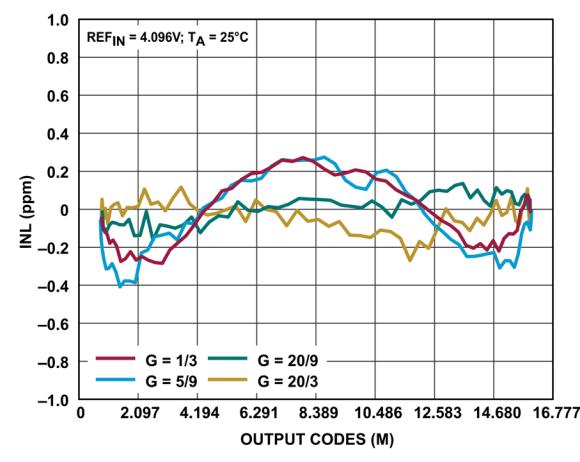

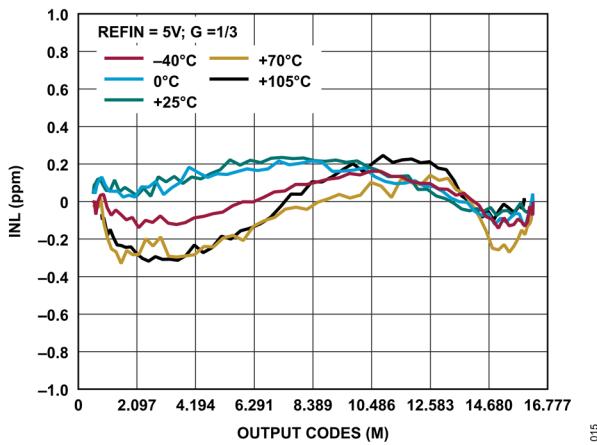

図 15. 異なる温度での INL 誤差と出力コードの関係 ( $G = 1/3$ )

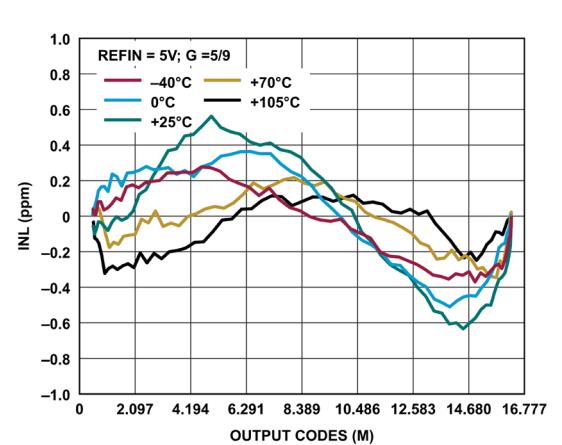

図 18. 異なる温度での INL 誤差と出力コードの関係 ( $G = 5/9$ )

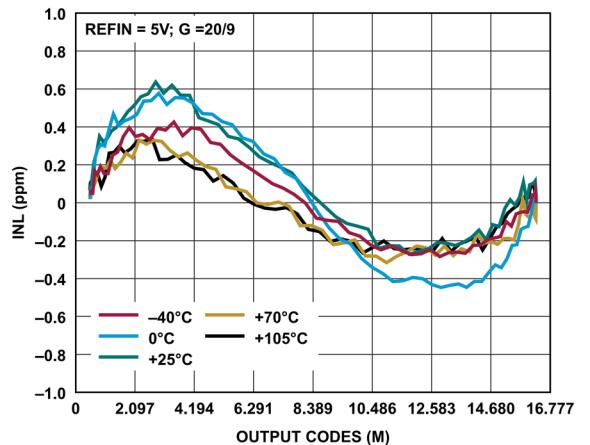

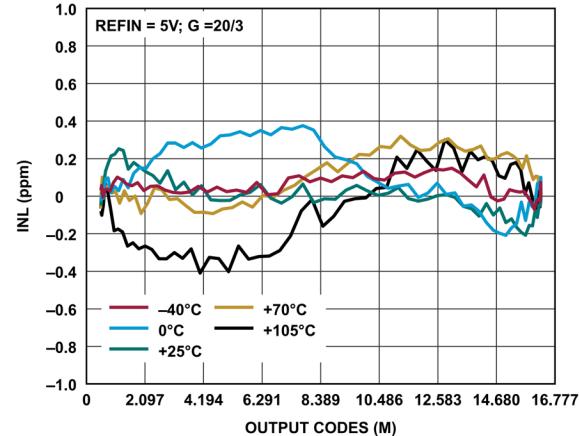

## 代表的な性能特性

図 19. 異なる温度での INL 誤差と出力コードの関係 (G = 20/9)

図 22. 異なる温度での INL 誤差と出力コードの関係 (G = 20/3)

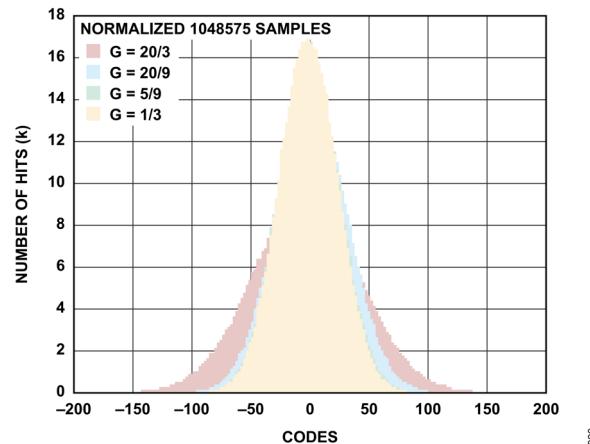

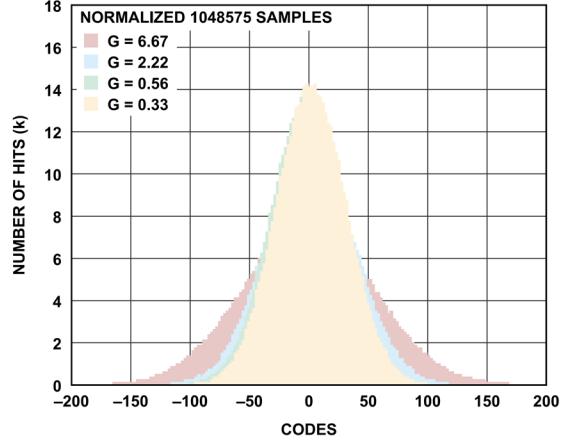

図 20. 入力短絡時のコード・ヒストグラム (REFIN = 5V)

図 23. 入力短絡時のコード・ヒストグラム (REFIN = 4.096V)

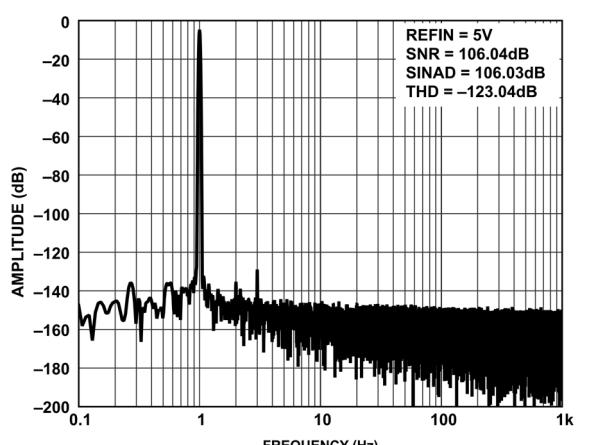

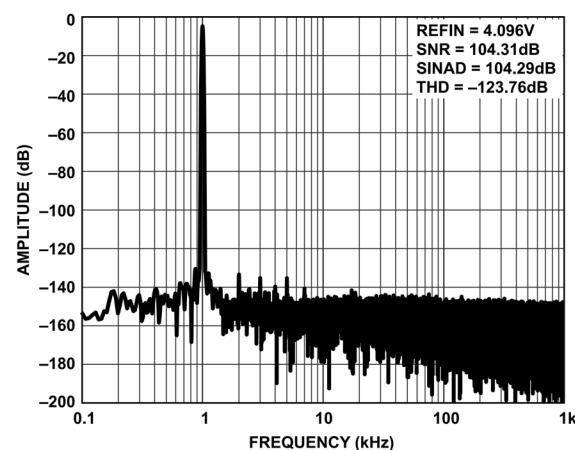

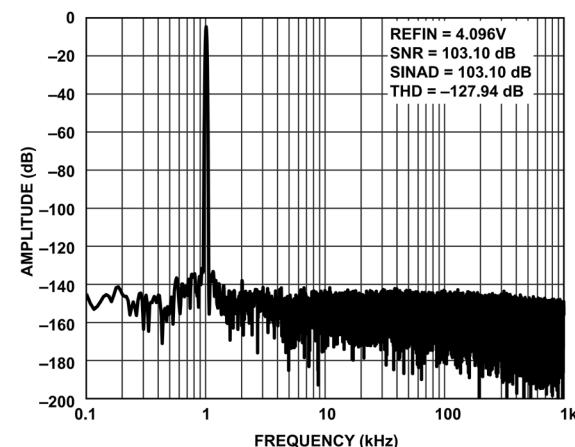

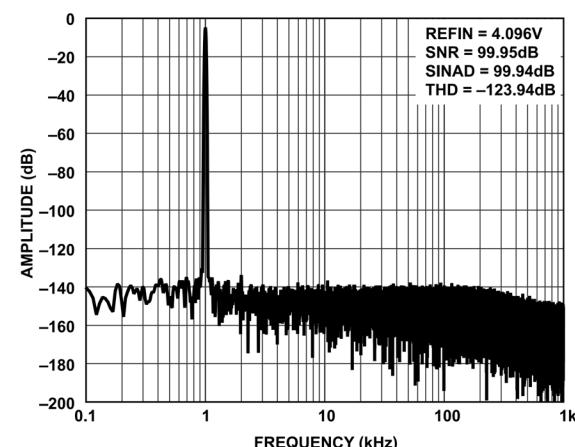

図 21. FFT

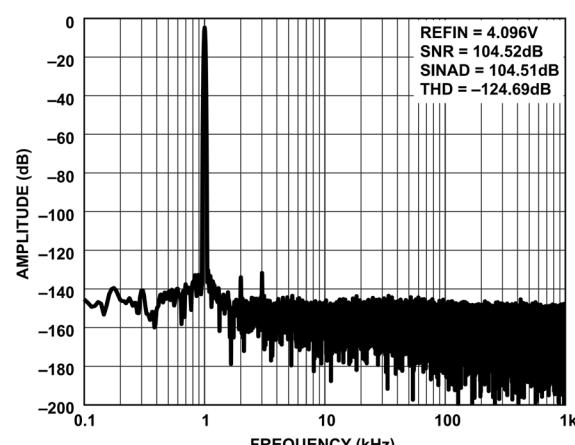

(2MSPS、 $f_{IN}$  = 1kHz、差動入力 = -0.5dBFS、G = 1/3)図 24. FFT

(2MSPS、 $f_{IN}$  = 1kHz、差動入力 = -0.5dBFS、G = 1/3)

## 代表的な性能特性

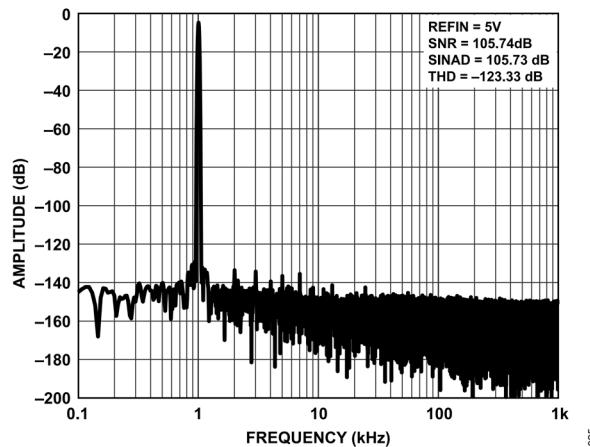

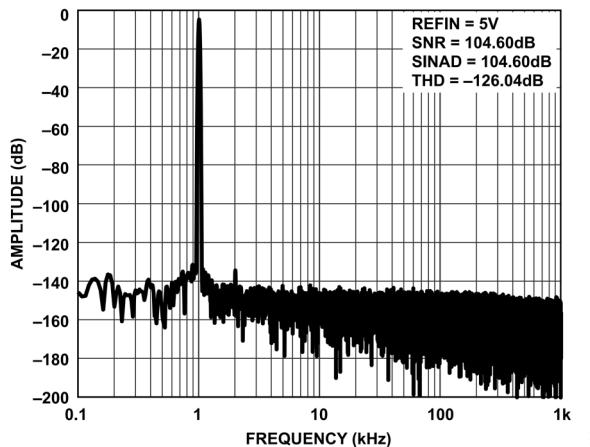

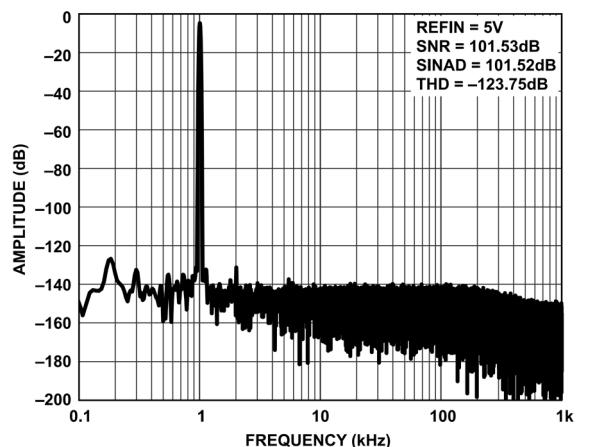

図 25. FFT

(2MSPS、 $f_{IN}$  = 1kHz、差動入力 = -0.5dBFS、G = 5/9)

図 28. FFT

(2MSPS、 $f_{IN}$  = 1kHz、差動入力 = -0.5dBFS、G = 5/9)

図 26. FFT

(2MSPS、 $f_{IN}$  = 1kHz、差動入力 = -0.5dBFS、G = 20/9)

図 29. FFT

(2MSPS、 $f_{IN}$  = 1kHz、差動入力 = -0.5dBFS、G = 20/9)

図 27. FFT

(2MSPS、 $f_{IN}$  = 1kHz、差動入力 = -0.5dBFS、G = 20/3)

図 30. FFT

(2MSPS、 $f_{IN}$  = 1kHz、差動入力 = -0.5dBFS、G = 20/3)

## 代表的な性能特性

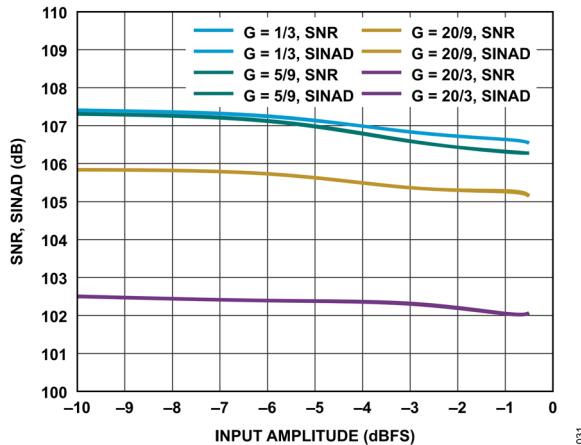

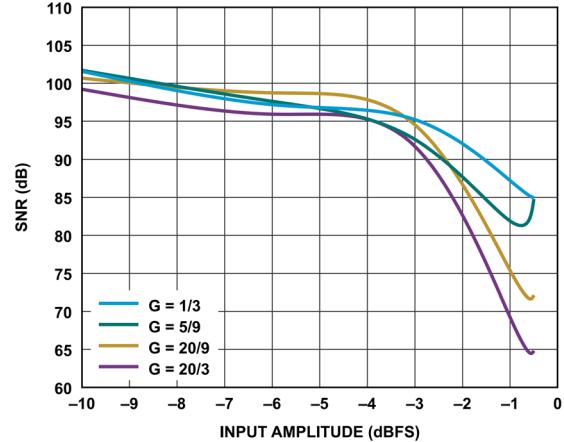

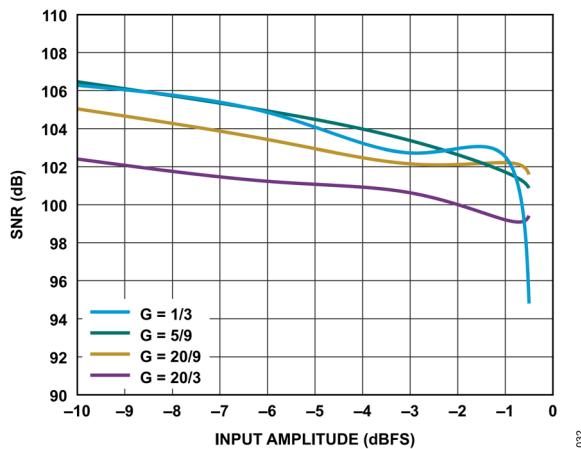

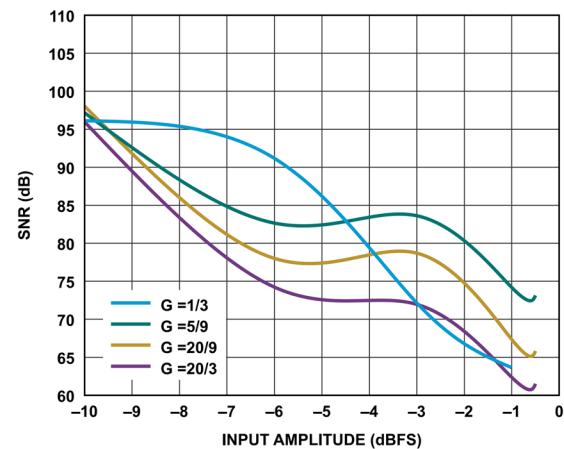

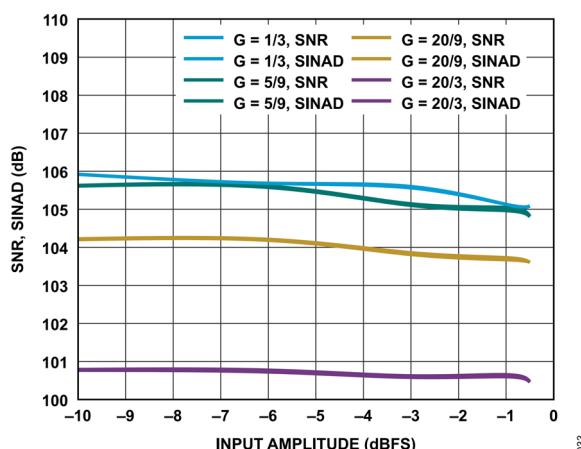

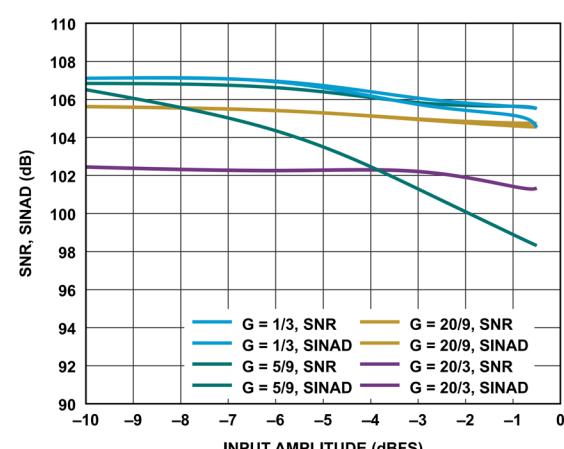

図 31. S/N 比および SINAD と入力振幅の関係 ( $f_{IN} = 1\text{kHz}$ )図 34. S/N 比と入力振幅の関係 ( $f_{IN} = 50\text{kHz}$ )図 32. S/N 比と入力振幅の関係 ( $f_{IN} = 20\text{kHz}$ )図 35. S/N 比と入力振幅の関係 ( $f_{IN} = 100\text{kHz}$ )図 33. S/N 比および SINAD と入力振幅の関係 ( $f_{IN} = 1\text{kHz}$ 、 $REFIN = 4.096\text{V}$ )図 36. S/N 比および SINAD と入力振幅の関係 ( $f_{IN} = 1\text{kHz}$ 、シングルエンド)

## 代表的な性能特性

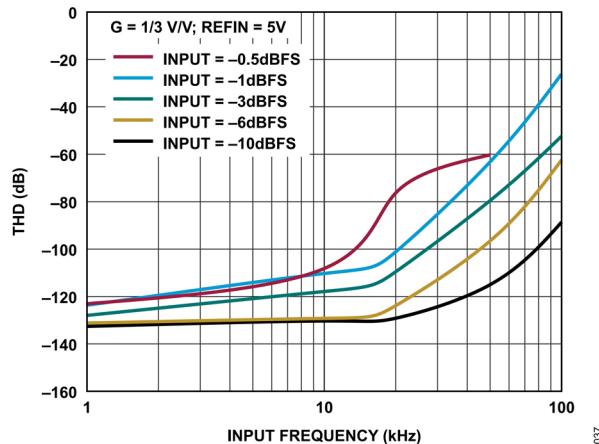

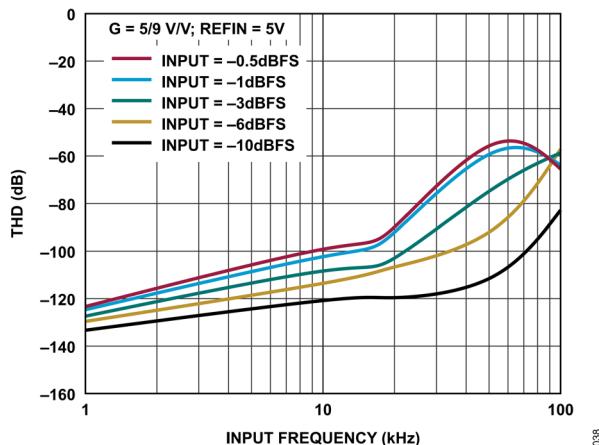

図 37. 異なる振幅での THD と入力周波数の関係 ( $G = 1/3$ )図 40. 異なる振幅での THD と入力周波数の関係 ( $G = 20/9$ )図 38. 異なる振幅での THD と入力周波数の関係 ( $G = 5/9$ )図 41. 異なる振幅での THD と入力周波数の関係 ( $G = 20/3$ )

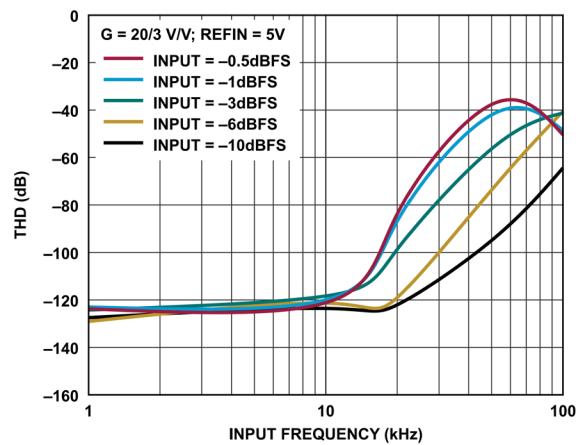

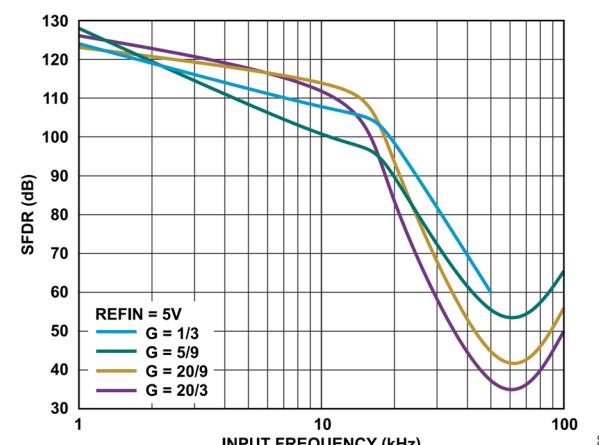

図 39. SFDR と入力周波数の関係 (-0.5dBFS, REFIN = 5V)

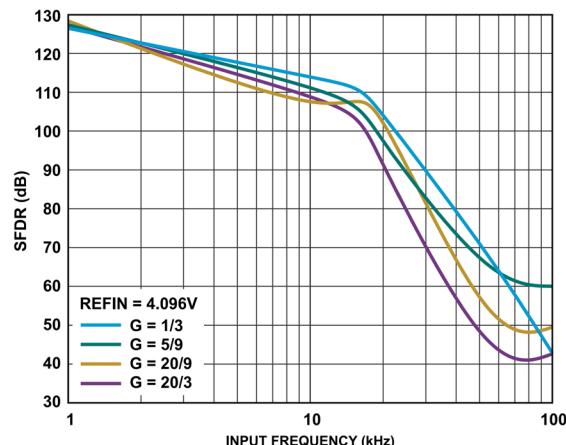

図 42. SFDR と入力周波数の関係 (-0.5dBFS, REFIN = 4.096V)

## 代表的な性能特性

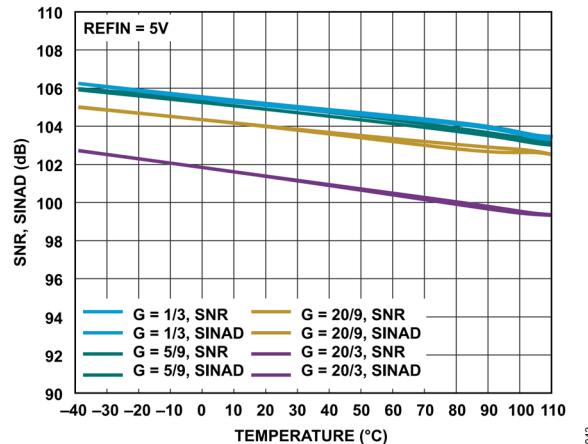

図 43. S/N 比および SINAD と温度の関係

( $f_{IN} = 1\text{kHz}$ 、差動入力、REFIN = 5V)

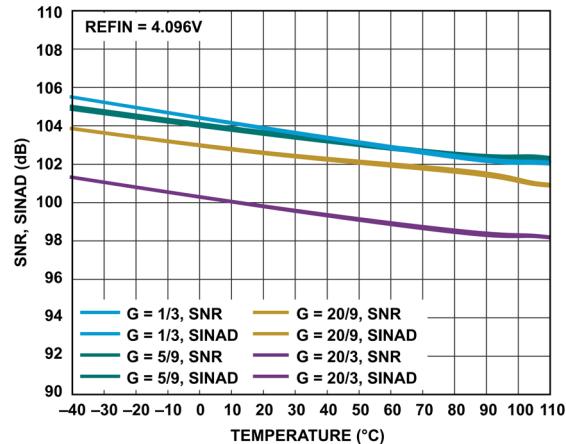

図 46. S/N 比および SINAD と温度の関係

( $f_{IN} = 1\text{kHz}$ 、差動入力、REFIN = 4.096V)

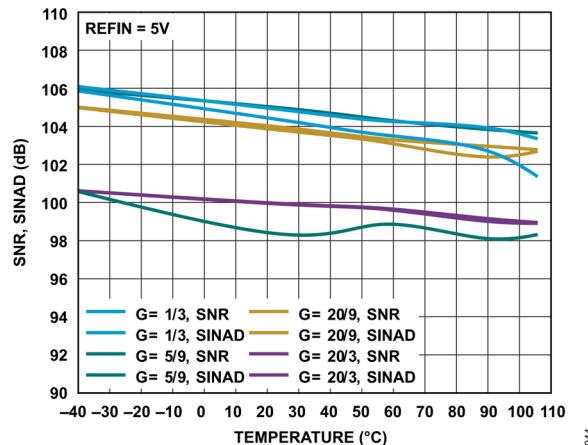

図 44. S/N 比および SINAD と温度の関係

( $f_{IN} = 1\text{kHz}$ 、シングルエンド入力、REFIN = 5V)

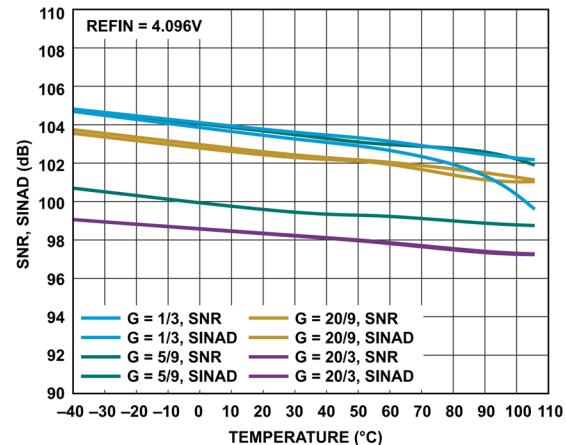

図 47. S/N 比および SINAD と温度の関係

( $f_{IN} = 1\text{kHz}$ 、シングルエンド入力、REFIN = 4.096V)

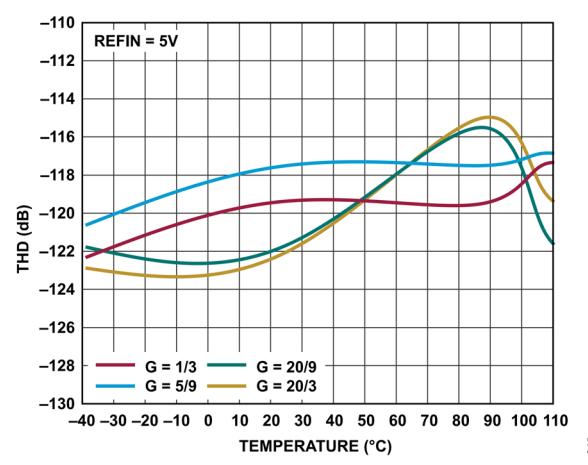

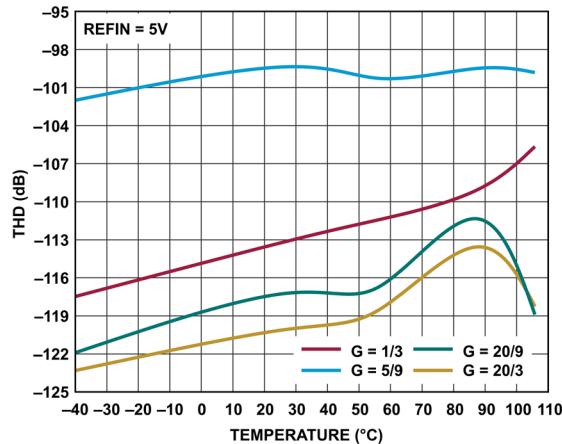

図 45. THD と温度の関係 ( $f_{IN} = 1\text{kHz}$ 、差動入力、REFIN = 5V)

図 48. THD と温度の関係

( $f_{IN} = 1\text{kHz}$ 、差動入力、REFIN = 4.096V)

## 代表的な性能特性

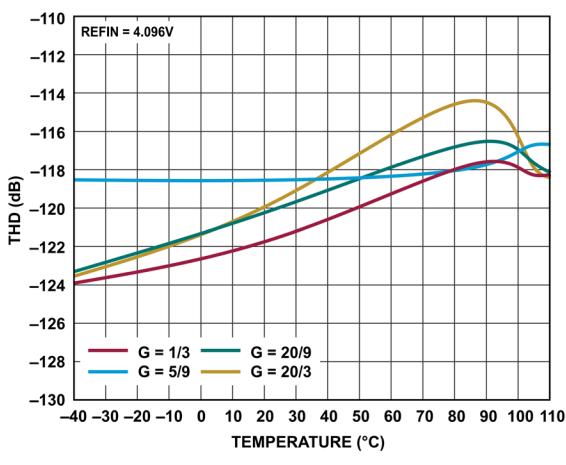

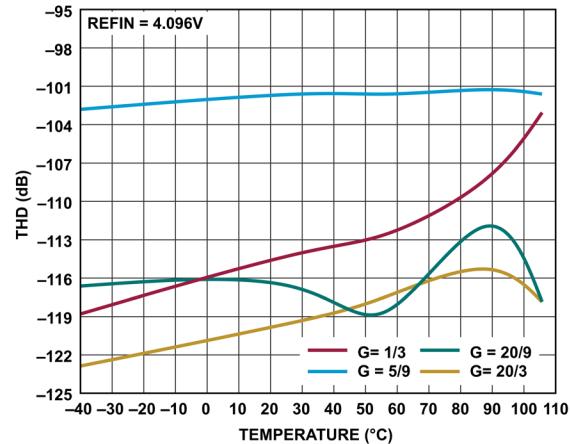

図 49. THD と温度の関係

( $f_{IN} = 1\text{kHz}$ 、シングルエンド入力、REFIN = 5V)

049

図 52. THD と温度の関係

( $f_{IN} = 1\text{kHz}$ 、シングルエンド入力、REFIN = 4.096V)

052

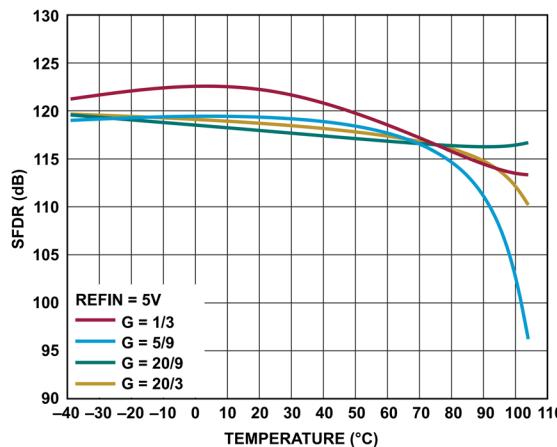

図 50. SFDR と温度の関係 ( $f_{IN} = 1\text{kHz}$ 、REFIN = 5V)

050

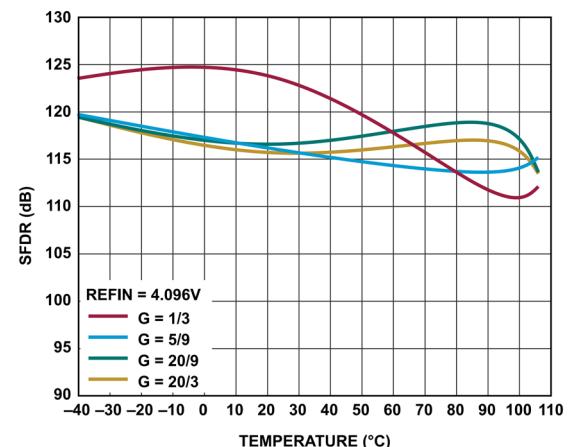

図 53. SFDR と温度の関係 ( $f_{IN} = 1\text{kHz}$ 、REFIN = 4.096V)

053

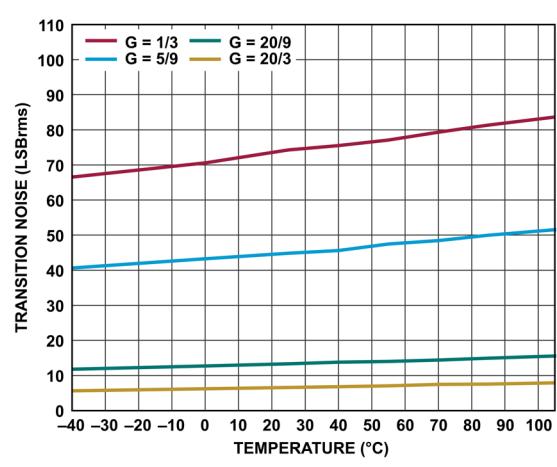

図 51. 遷移ノイズと温度の関係 (REFIN = 5V)

051

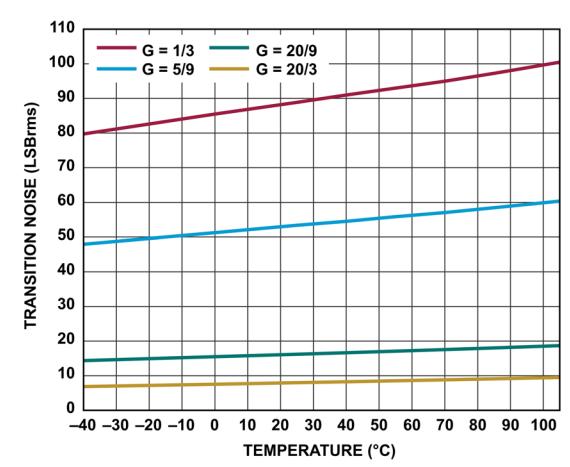

図 54. 遷移ノイズと温度の関係 (REFIN = 4.096V)

054

## 代表的な性能特性

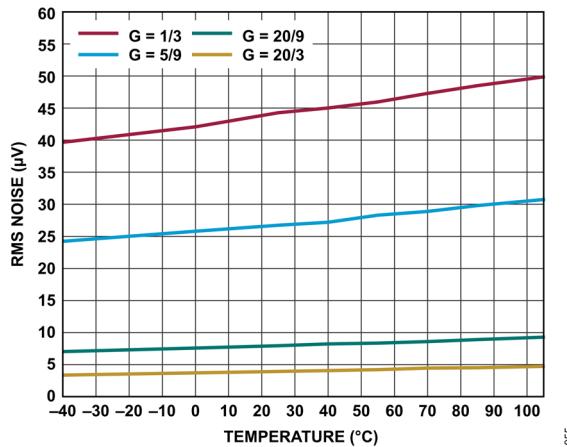

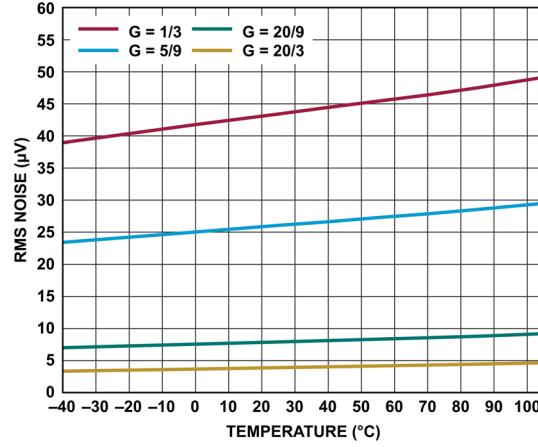

図 55. 実効値ノイズと温度の関係 (REFIN = 5V)

図 58. 実効値ノイズと温度の関係 (REFIN = 4.096V)

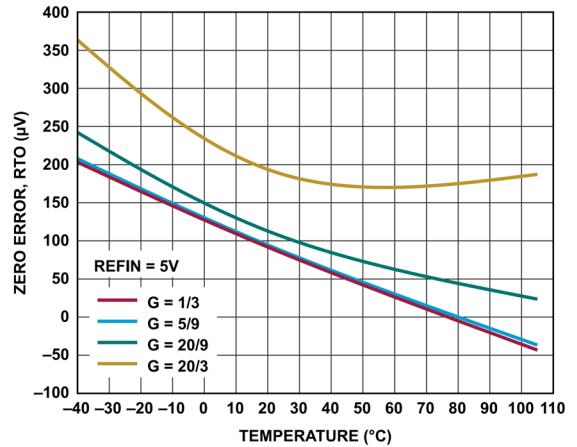

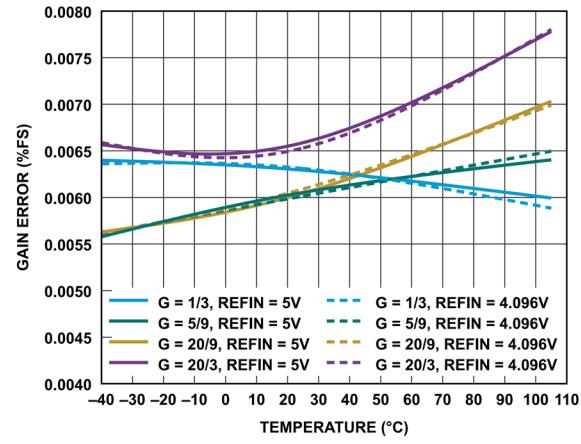

図 56. ゼロ誤差と温度の関係

図 59. ゲイン誤差と温度の関係

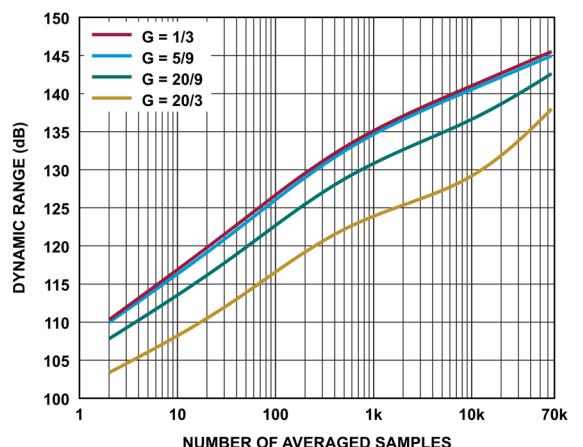

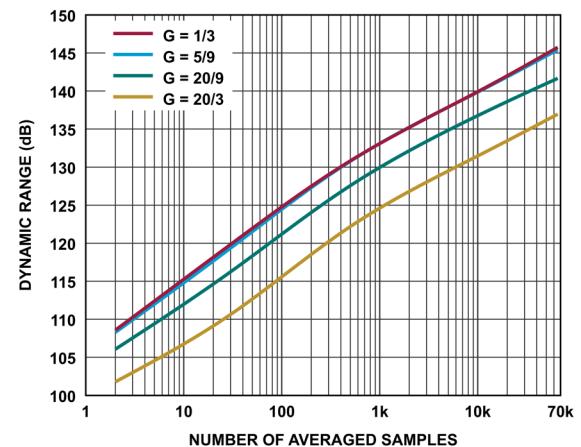

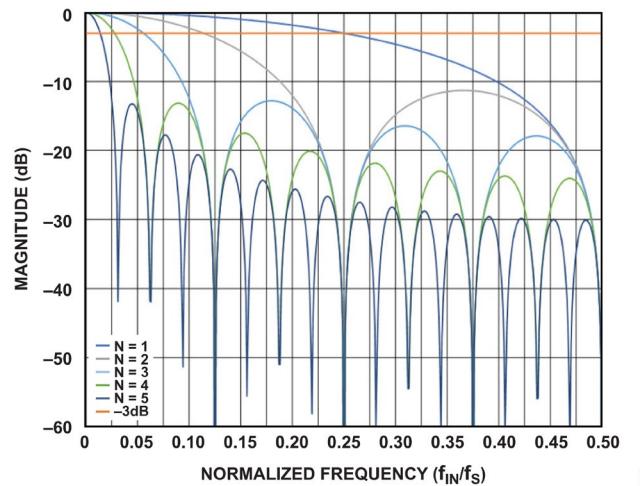

図 57. ダイナミック・レンジと平均数の関係

(入力 = -60dBFS、REFIN = 5V)図 60. ダイナミック・レンジと平均数の関係

(入力 = -60dBFS、REFIN = 4.096V)

## 代表的な性能特性

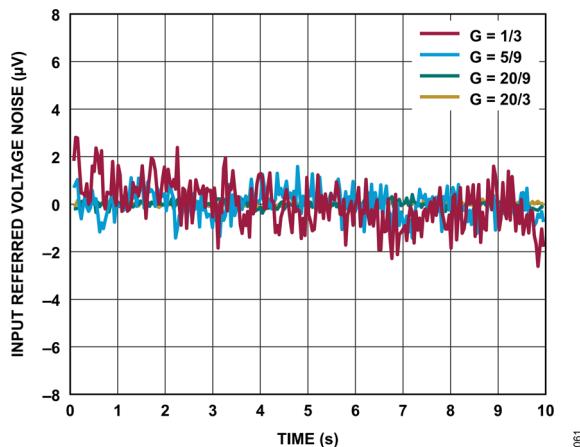

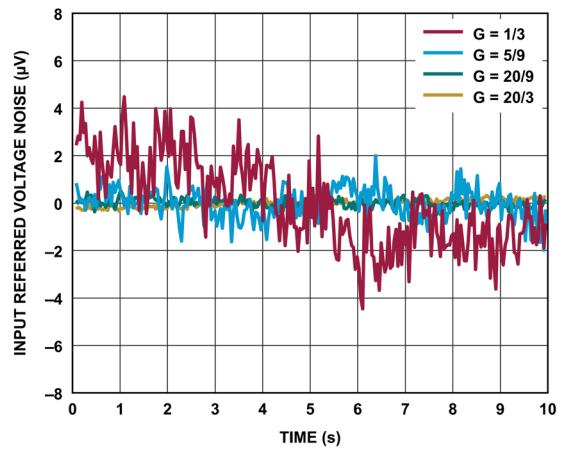

図 61. 低周波数ノイズ（出力データ・レート = 19.5SPS、2048 サンプルのブロックを平均後、REFIN = 5V）

図 64. 低周波数ノイズ（出力データ・レート = 19.5SPS、2048 サンプルのブロックを平均後、REFIN = 4.096V）

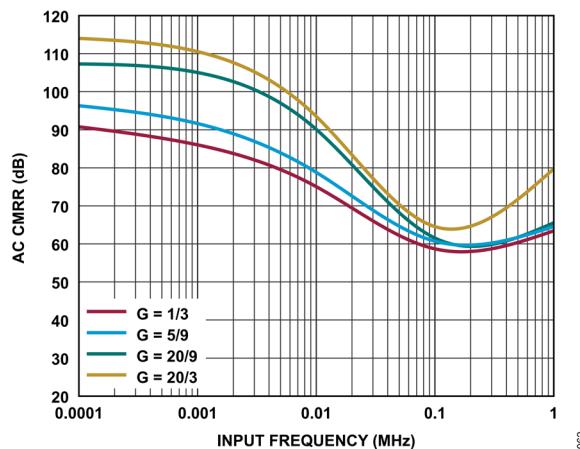

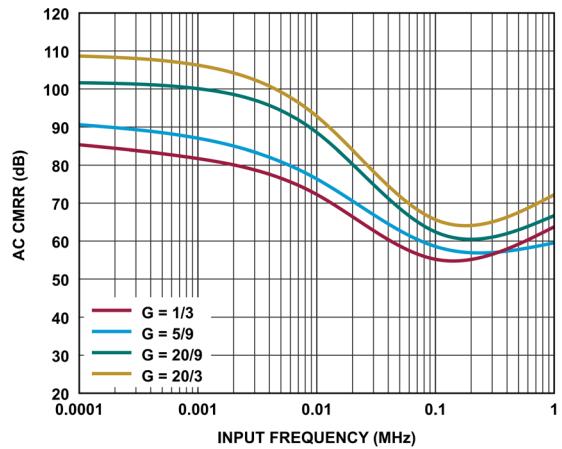

図 62. AC CMRR と入力周波数の関係 (REFIN = 5V)

図 65. AC CMRR と入力周波数の関係 (REFIN = 4.096V)

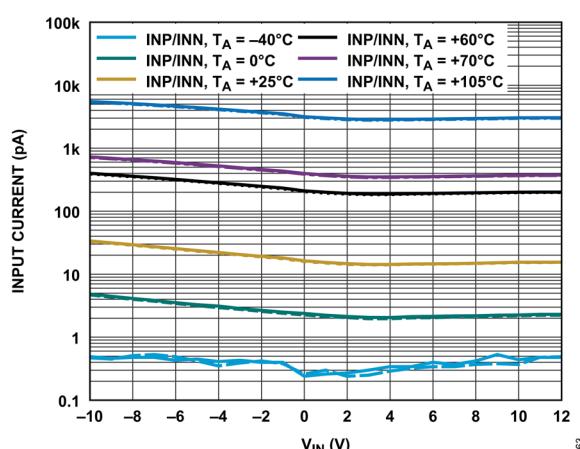

図 63. 異なる温度での入力電流と入力電圧の関係

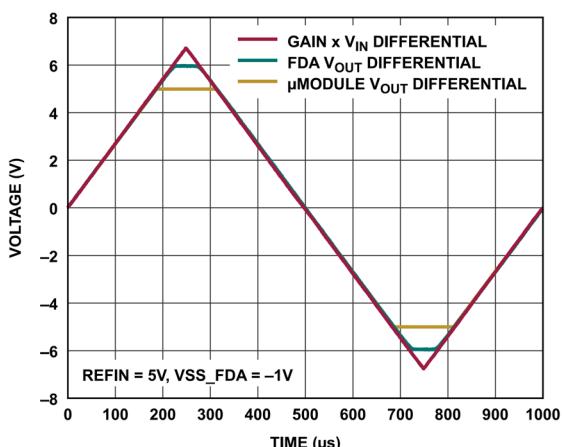

図 66. 出力オーバードライブ回復特性 (IN = 1kHz)

## 代表的な性能特性

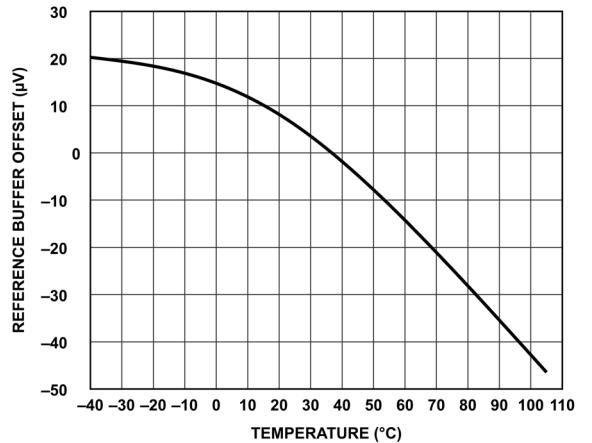

図 67. リファレンス・バッファ・オフセットと温度の関係

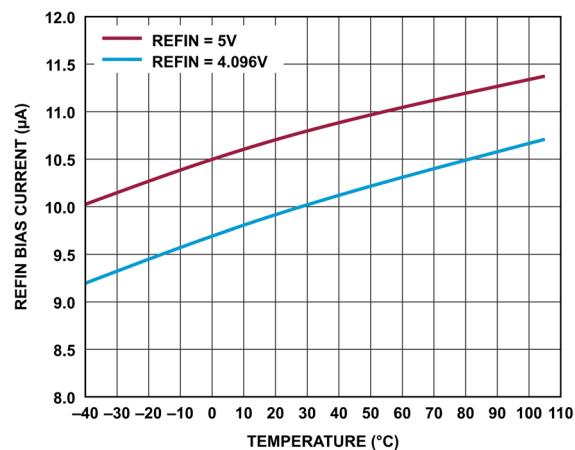

図 70. 通常動作時の REFIN 電流と温度の関係

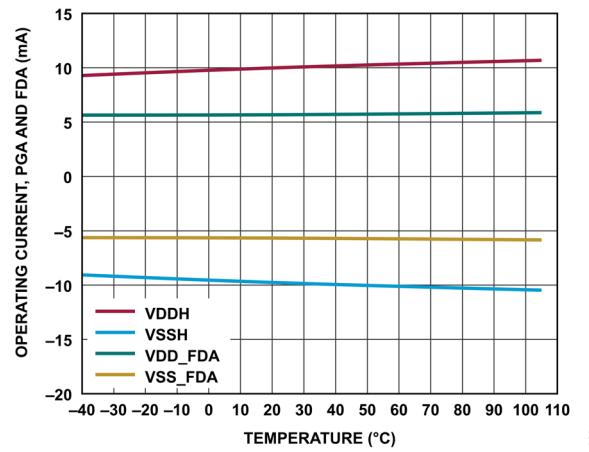

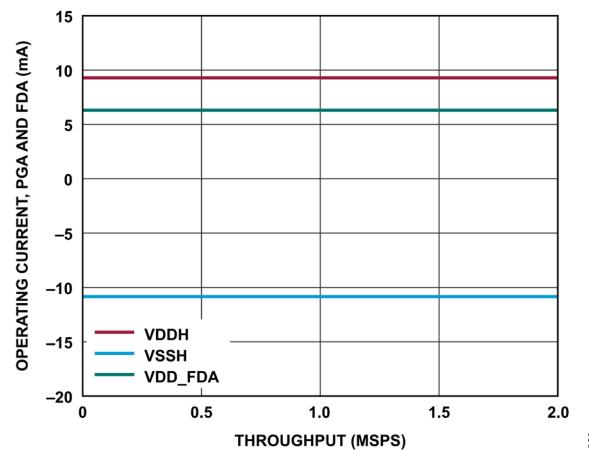

図 68. PGA および FDA の動作電流と温度の関係

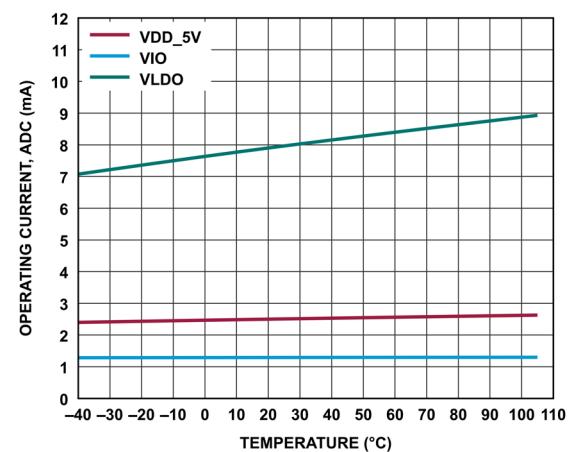

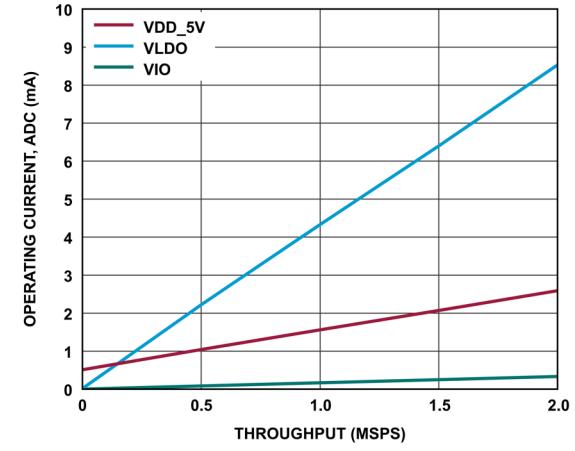

図 71. ADC 動作電流と温度の関係

図 69. PGA および FDA の動作電流とサンプル・レートの関係

図 72. ADC 動作電流とサンプル・レートの関係

## 代表的な性能特性

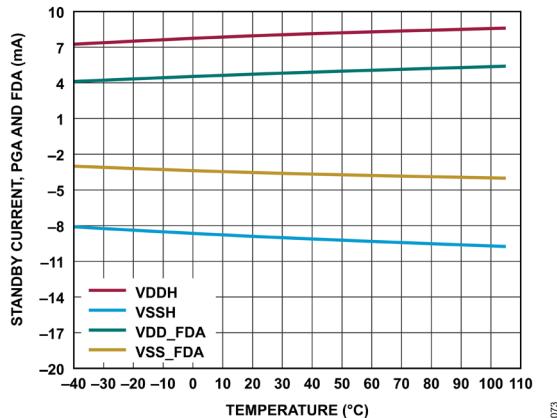

図 73. PGA および FDA のスタンバイ電流と温度の関係

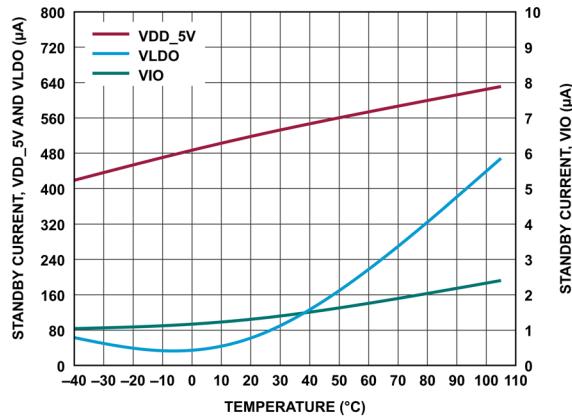

図 76. ADC スタンバイ電流と温度の関係

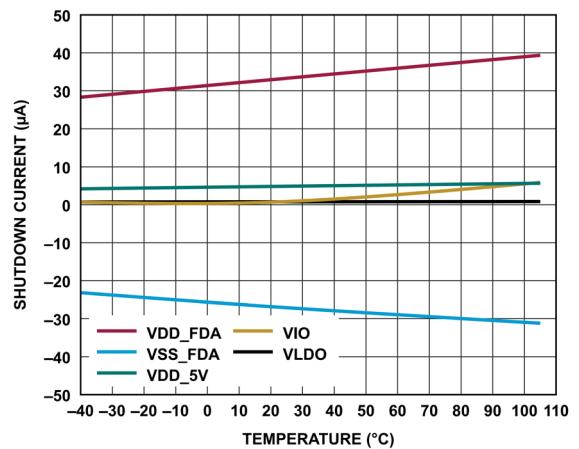

図 74. シャットダウン電流と温度の関係

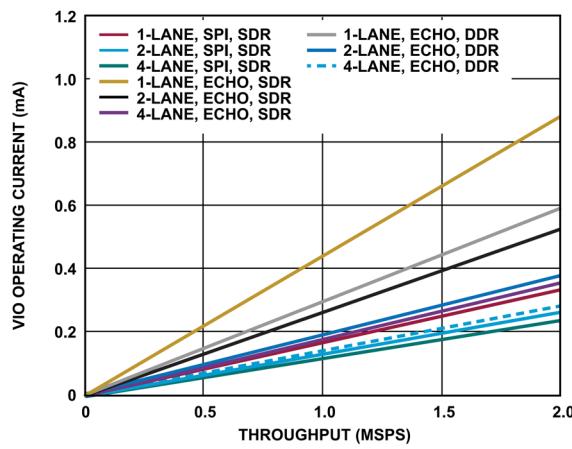

図 77. VIO 動作電流とサンプル・レートの関係

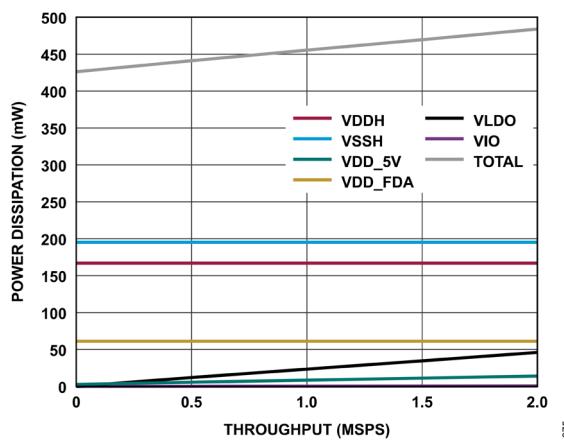

図 75. 消費電力とスループットの関係

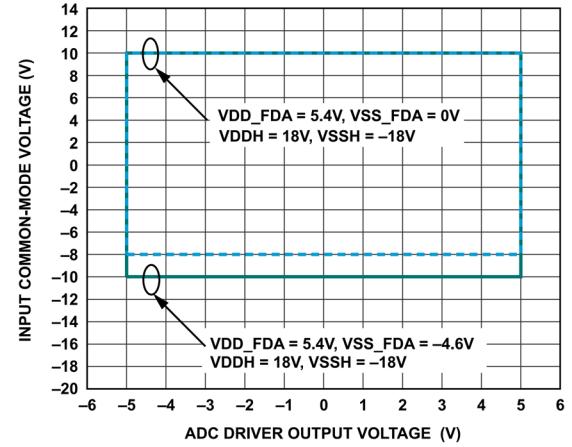

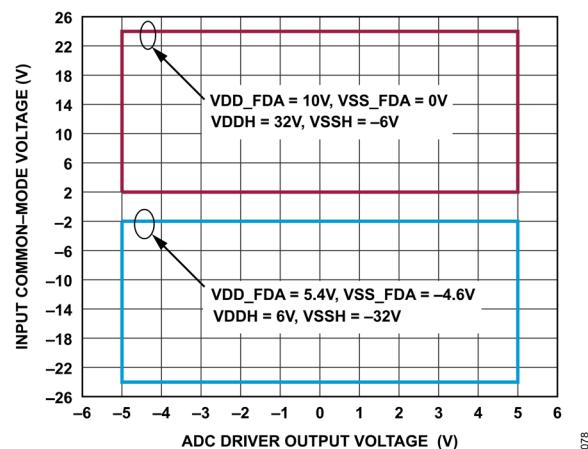

図 78. 入力コモンモード電圧と ADC ドライバ出力電圧の関係 (すべてのゲイン)

## 代表的な性能特性

図 79. 入力コモンモード電圧と ADC ドライバ出力電圧の関係

(すべてのゲイン)

## 用語の定義

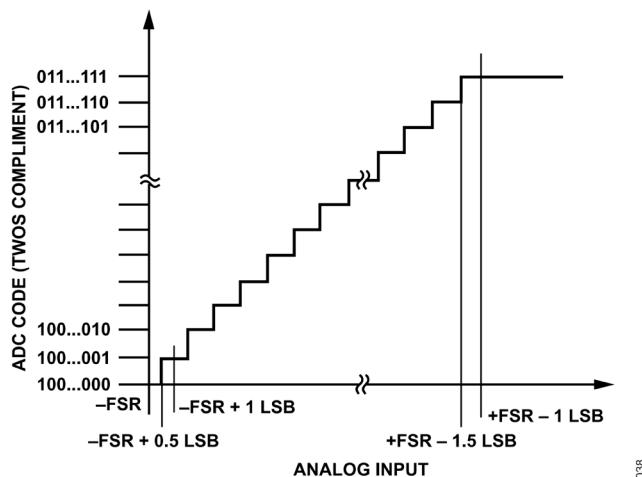

### 積分非直線性誤差 (INL)

INL は、負のフルスケールと正のフルスケールを結ぶ直線と個々のコードとの偏差です。最初のコード遷移より  $\frac{1}{2}$ LSB だけ手前の点を負のフルスケールとして使います。正のフルスケールは、最後のコード遷移を  $1\frac{1}{2}$ LSB 上回ったレベルとして定義されます。偏差は各コードの中央から真の直線までの距離として測定されます (図 81 参照)。

### 微分非直線性誤差 (DNL)

理想的な ADC では、コード遷移は 1LSB ごとに生じます。DNL とは、この理想値からの最大偏差のことです。ノー・ミス・コードの分解能で仕様規定されます。

### オフセット誤差

オフセット誤差は、理想的なミッドスケール電圧 (0V) とミッドスケール出力コード (0LSB) を生成する実際の電圧との差です。

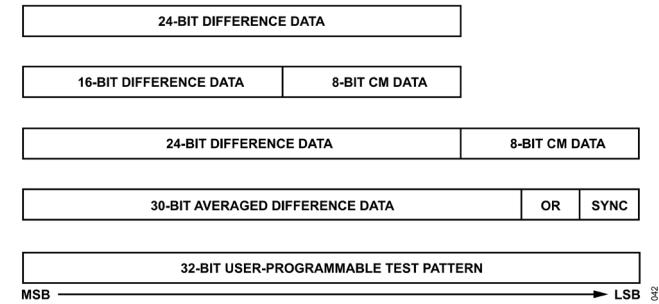

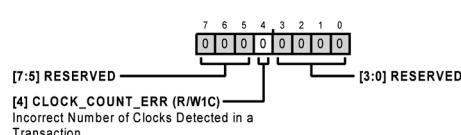

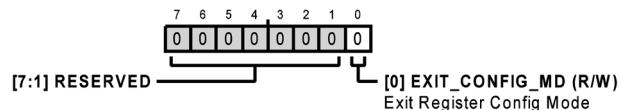

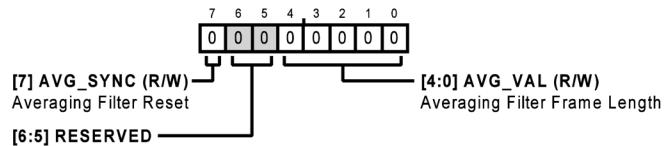

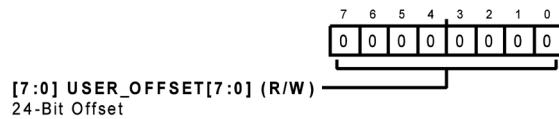

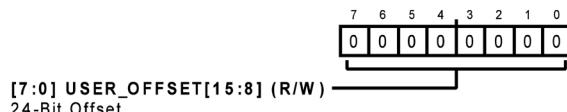

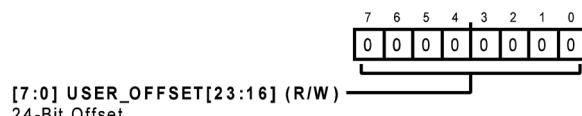

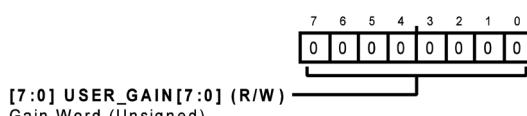

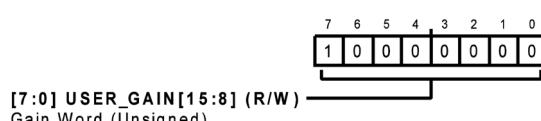

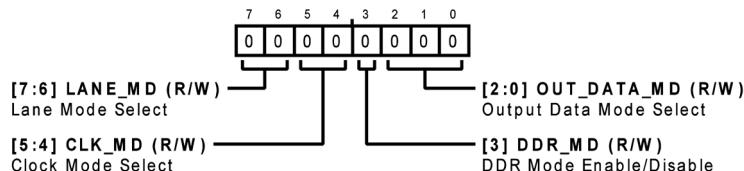

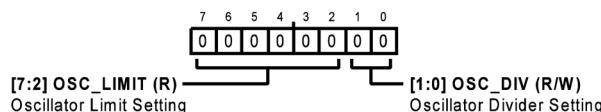

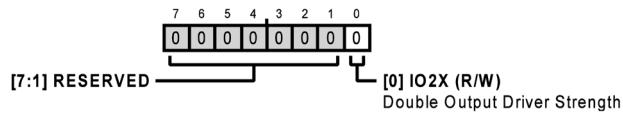

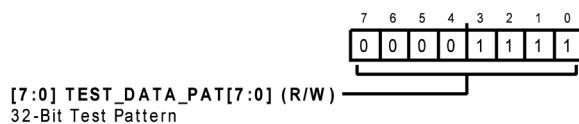

### ゲイン誤差