## 特長

内部クロック速度: 1 GSPS (最大 400 MHz のアナログ出力)

1 GSPS、14 ビットの DAC を内蔵

周波数分解能: 0.23 Hz 以下

位相ノイズ: 1 kHz オフセットで -125 dBc/Hz 以下 (400 MHz キャリア)

優れたダイナミック性能: 狹帯域 SFDR 80 dB 以上

シリアル入力/出力(I/O)制御

自動リニアまたは任意の周波数、位相、振幅スイープ機能

8 種類の周波数および位相オフセット・プロファイル

$\text{Sin}(x)/(x)$ 補正(逆 sinc フィルタ)

電源: 1.8 V および 3.3 V

ソフトウェアおよびハードウェア制御によるパワーダウン

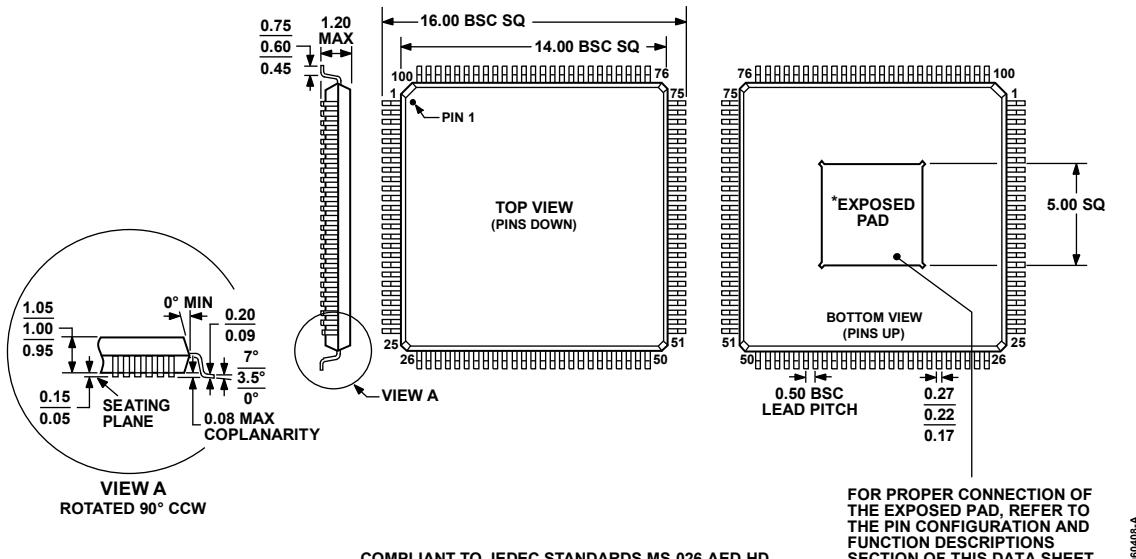

100 ピン TQFP\_EP パッケージを採用

1024 ワード × 32 ビット RAM を内蔵

PLL REFCLK 遅倍器

パラレル・データパス・インターフェース

1 個の水晶から内蔵発振器を駆動可能

位相変調機能

振幅変調機能

複数チップの同期が可能

## アプリケーション

即応性に優れたローカル発振器(LO)周波数シンセシス

プログラマブルなクロック・ジェネレータ

レーダ・システムおよびスキャン・システム用の FM チャープ・ソース

テスト装置および計測装置

音響光学デバイス・ドライバ

ポーラ変調器

高速周波数ホッピング

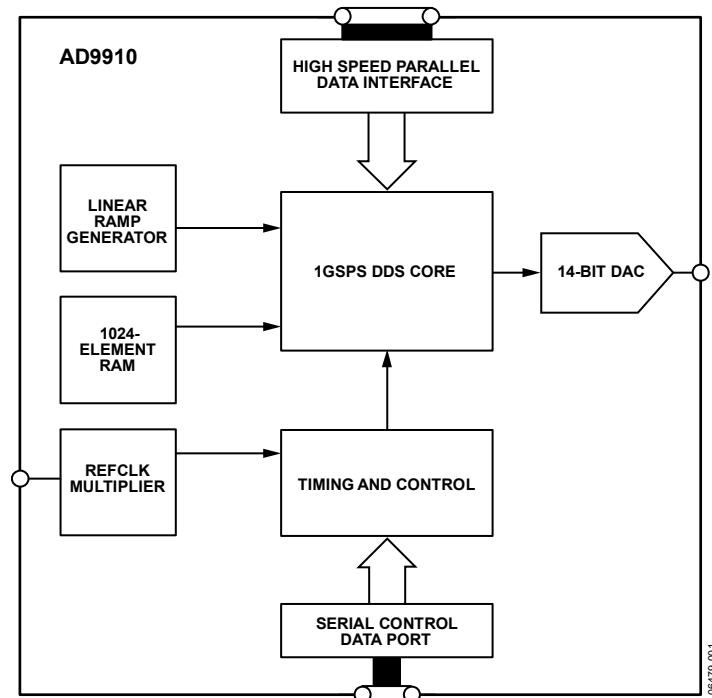

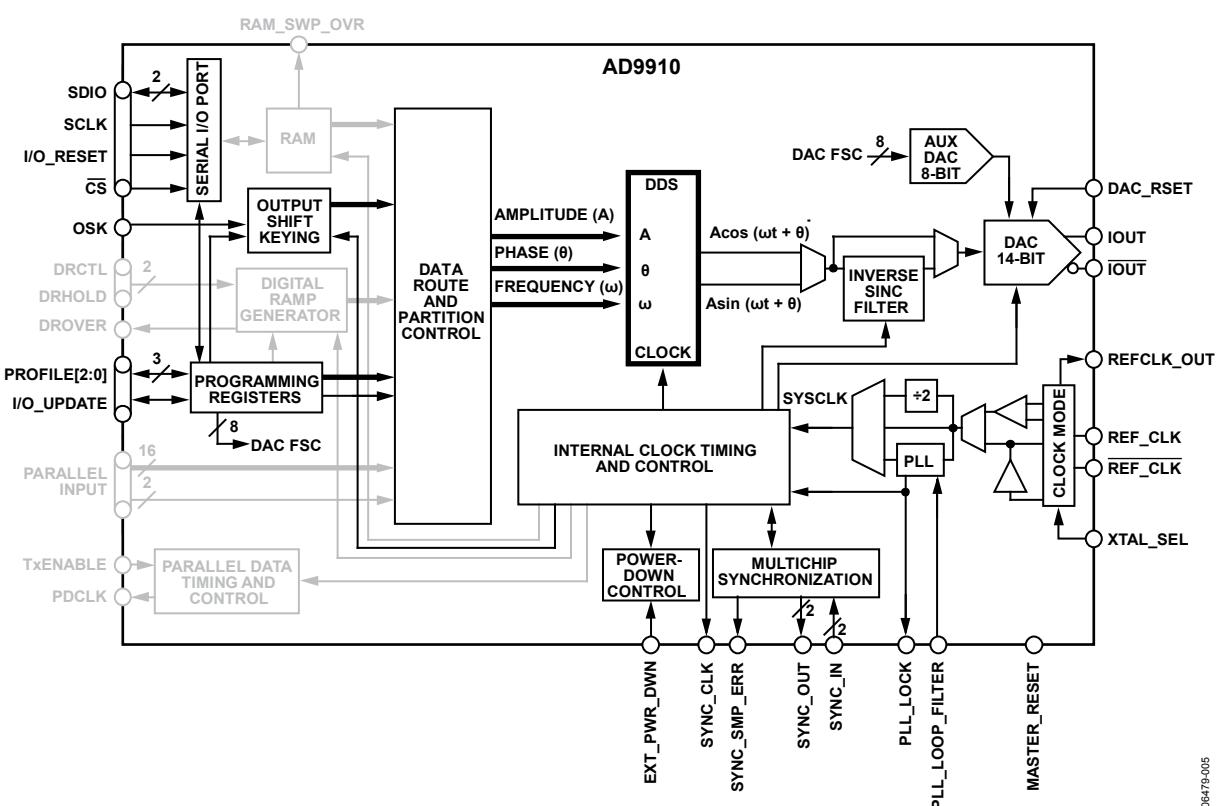

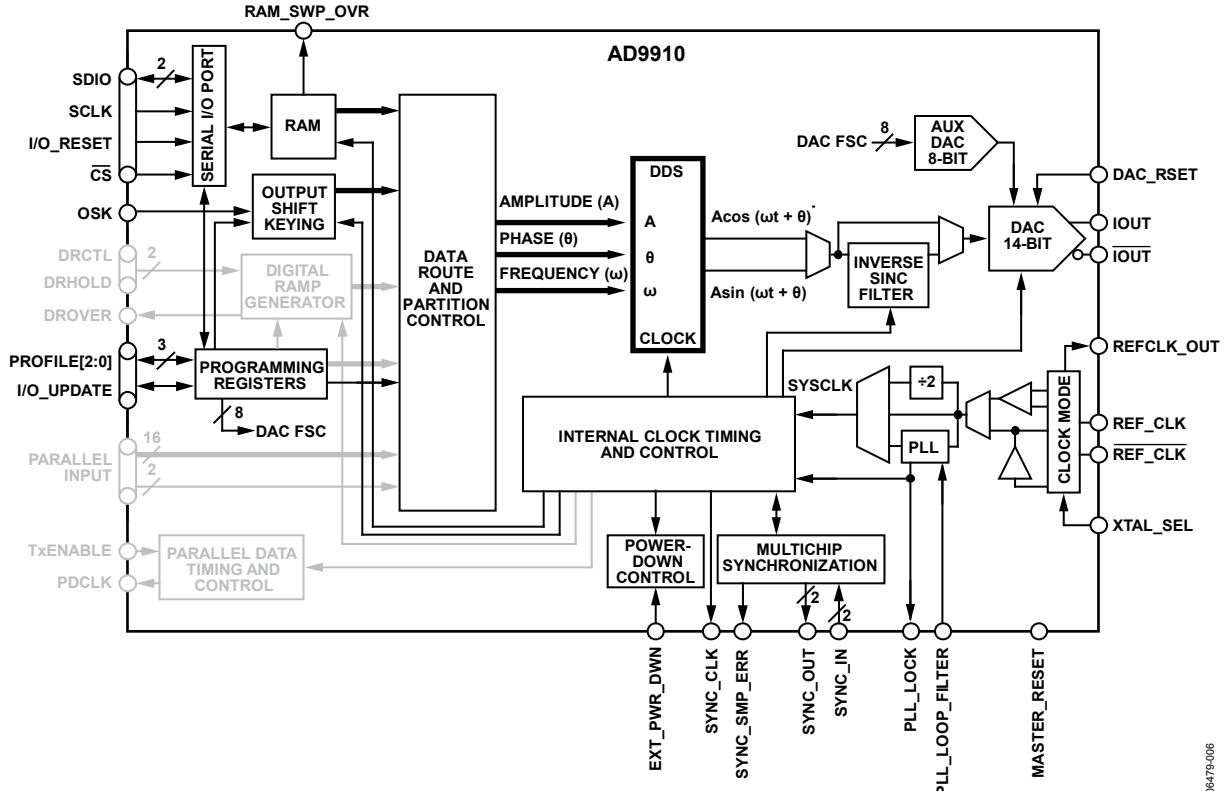

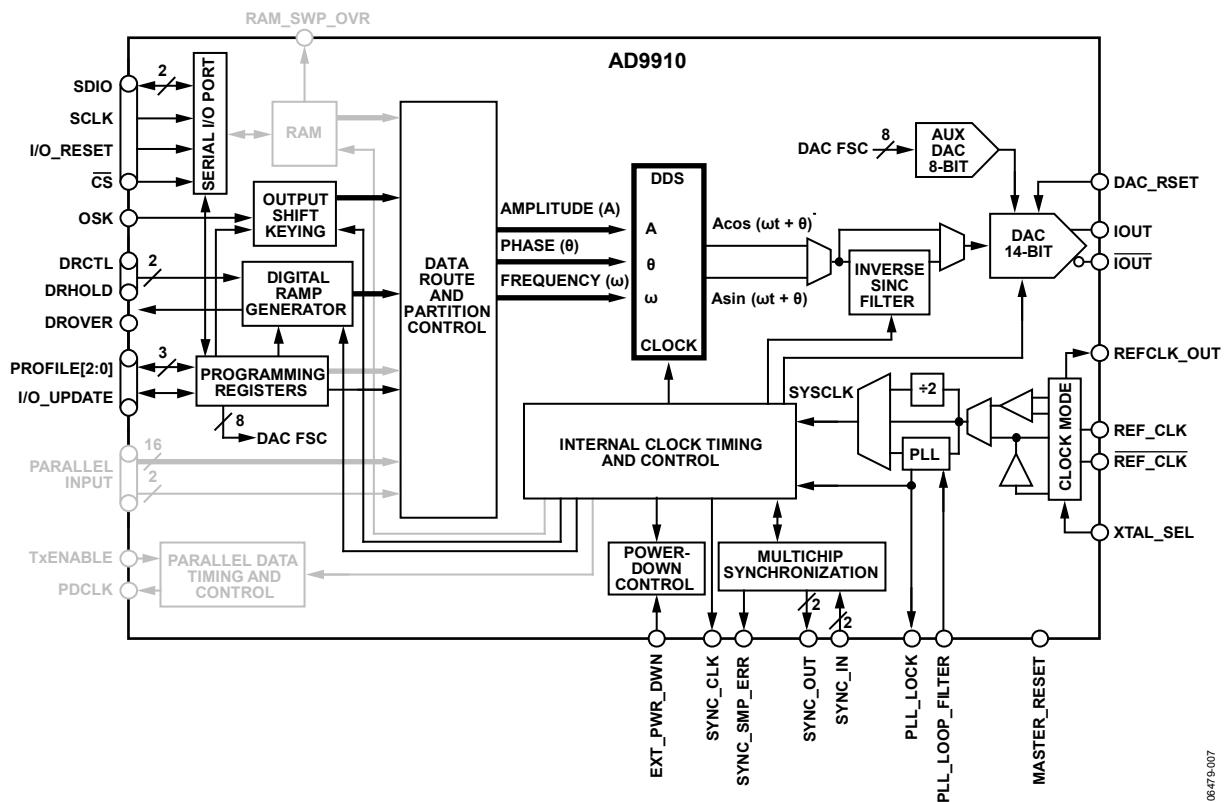

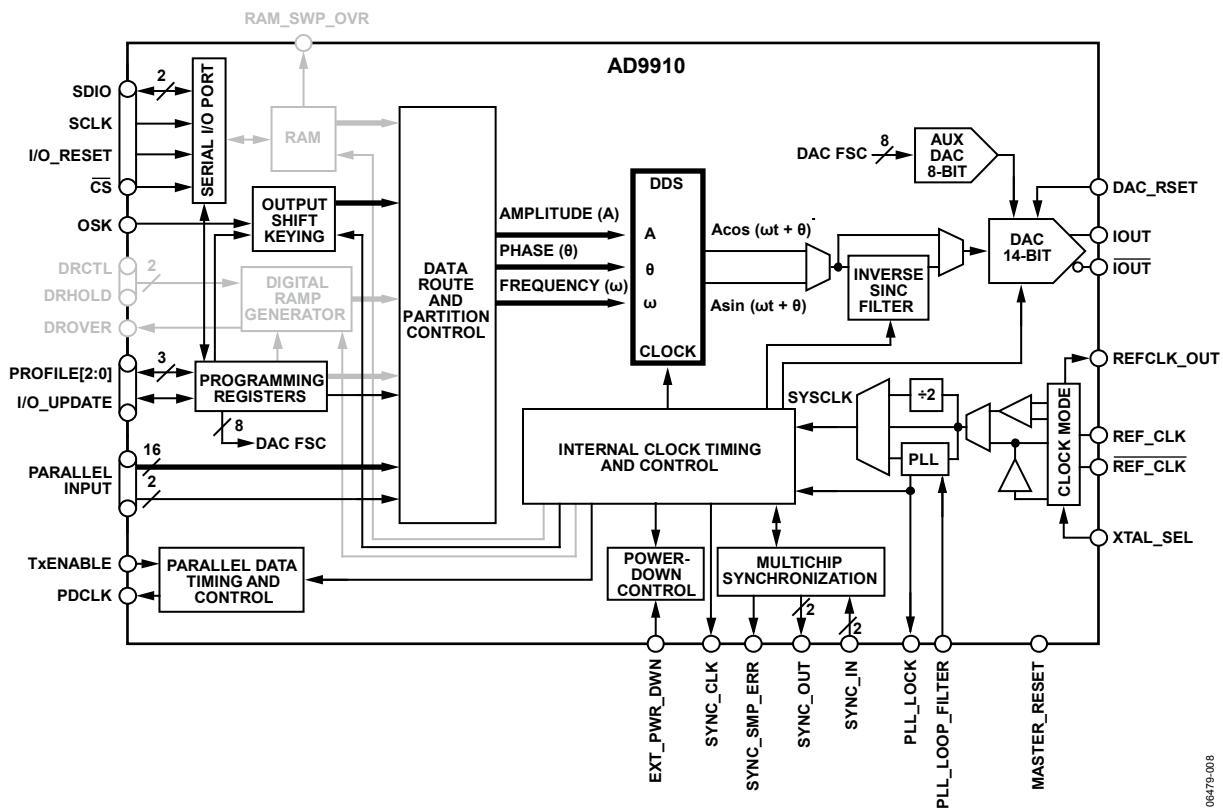

## 機能ブロック図

図1.

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関する、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。

©2007–2008 Analog Devices, Inc. All rights reserved.

# 目次

|                                  |    |

|----------------------------------|----|

| 特長                               | 1  |

| アプリケーション                         | 1  |

| 機能ブロック図                          | 1  |

| 改訂履歴                             | 4  |

| 概要                               | 5  |

| 仕様                               | 6  |

| 電気的仕様                            | 6  |

| 絶対最大定格                           | 9  |

| 等価回路                             | 9  |

| ESDの注意                           | 9  |

| ピン配置およびピン機能説明                    | 10 |

| 代表的な性能特性                         | 13 |

| アプリケーション回路                       | 16 |

| 動作原理                             | 17 |

| シングル・トーン・モード                     | 17 |

| RAM変調モード                         | 18 |

| デジタル・ランプ変調モード                    | 19 |

| パラレル・データ・ポート変調モード                | 20 |

| パラレル・データ・クロック(PDCLK)             | 20 |

| 送信イネーブル(TxENABLE)                | 21 |

| モードの優先順位                         | 22 |

| 機能ブロック図の詳細                       | 23 |

| DDSコア                            | 23 |

| 14 ビットDAC出力                      | 23 |

| 補助DAC                            | 24 |

| 逆sincフィルタ                        | 24 |

| クロック入力(REF_CLK/ <u>REF_CLK</u> ) | 24 |

| REF_CLK/ <u>REF_CLK</u> の概要      | 24 |

| REF_CLK/ <u>REF_CLK</u> の水晶駆動    | 25 |

| REF_CLK/ <u>REF_CLK</u> の直接駆動    | 25 |

| 位相ロック・ループ(PLL)倍増器                | 25 |

| PLLチャージ・ポンプ                      | 26 |

| 外付けPLLループ・フィルタ部品                 | 27 |

| PLLロック表示                         | 27 |

| 出力シフト・キーイング(OSK)                 | 27 |

| 手動OSK                            | 27 |

| 自動OSK                            | 28 |

| デジタル・ランプ・ジェネレータ(DRG)             | 28 |

| DRGの概要                           | 28 |

| DRGスロープの制御                       | 30 |

| DRG限界値の制御                        | 30 |

| DRGアキュムレータのクリア                   | 30 |

| 通常ランプの生成                         | 30 |

| ノードウェル・ランプの生成                    | 32 |

| DROVERピン                         | 32 |

|                                                             |    |

|-------------------------------------------------------------|----|

| RAMコントロール                                                   | 33 |

| RAMの概要                                                      | 33 |

| RAMのロード/読み出し動作                                              | 33 |

| RAM再生動作(波形生成)                                               | 33 |

| RAM_SWP_OVR (RAMスイープ・オーバー)ピン                                | 34 |

| RAM再生モードの概要                                                 | 34 |

| RAMダイレクト・スイッチ・モード                                           | 34 |

| ゼロ交差機能によるRAMダイレクト・スイッチ・モード                                  | 35 |

| RAMランプアップ・モード                                               | 35 |

| RAMランプアップ内部プロファイル制御モード                                      | 36 |

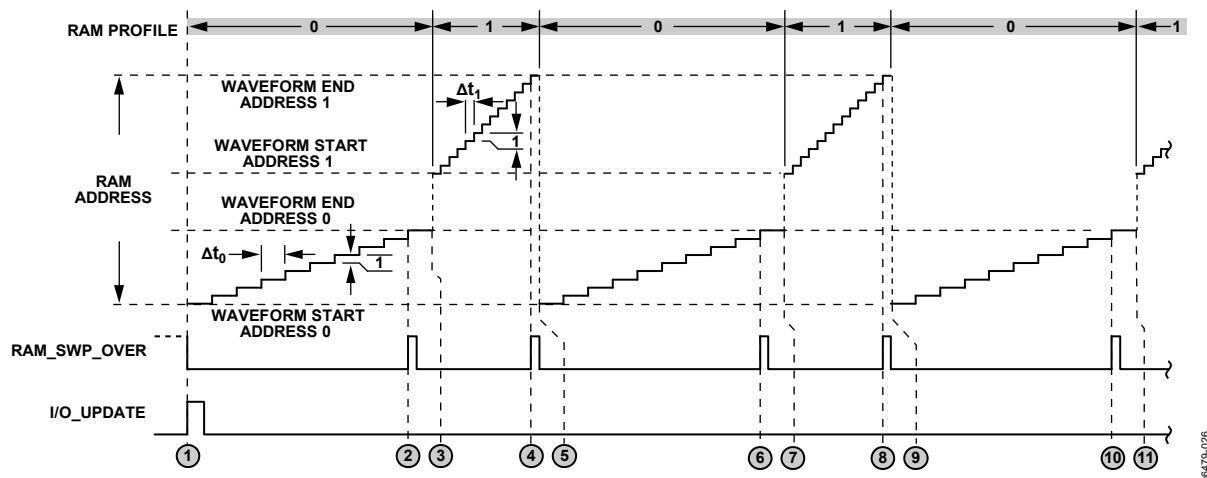

| 内部プロファイル制御連続波形のタイミング図                                       | 38 |

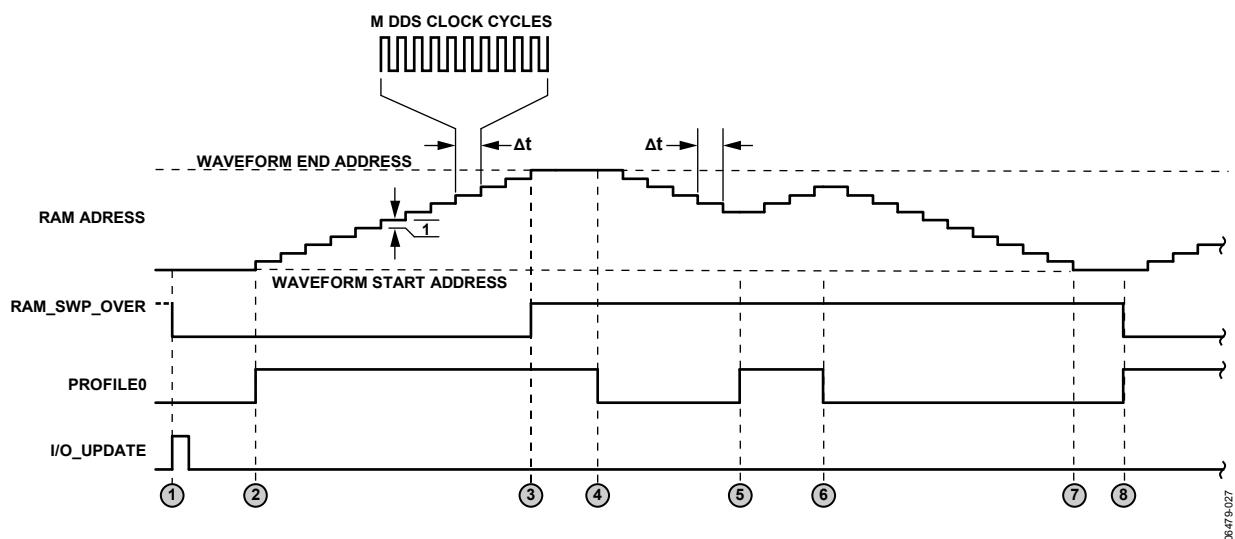

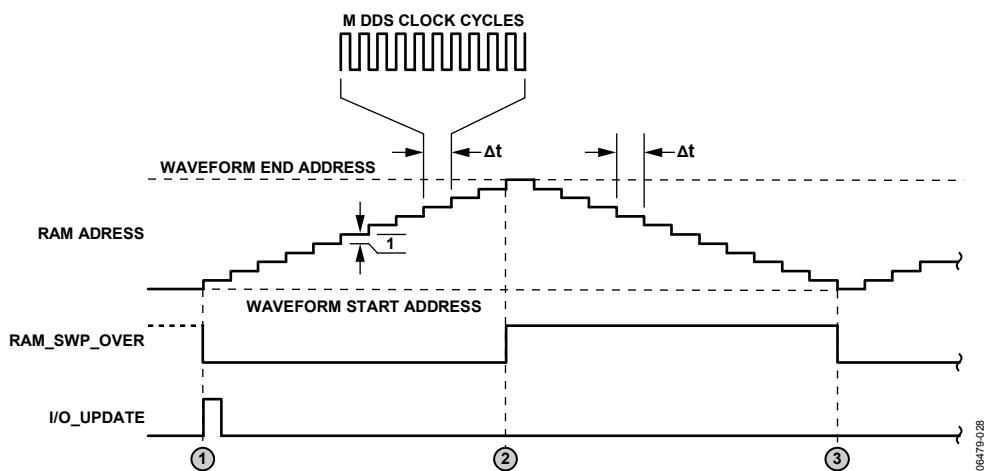

| RAM双方向ランプ・モード                                               | 38 |

| RAM連続双方向ランプ・モード                                             | 39 |

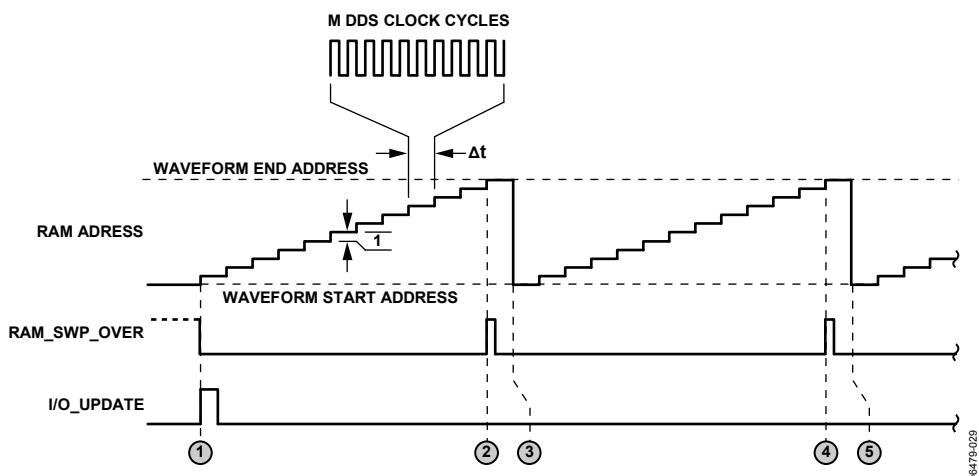

| RAM連続巡回モード                                                  | 41 |

| その他の機能                                                      | 42 |

| プロファイル                                                      | 42 |

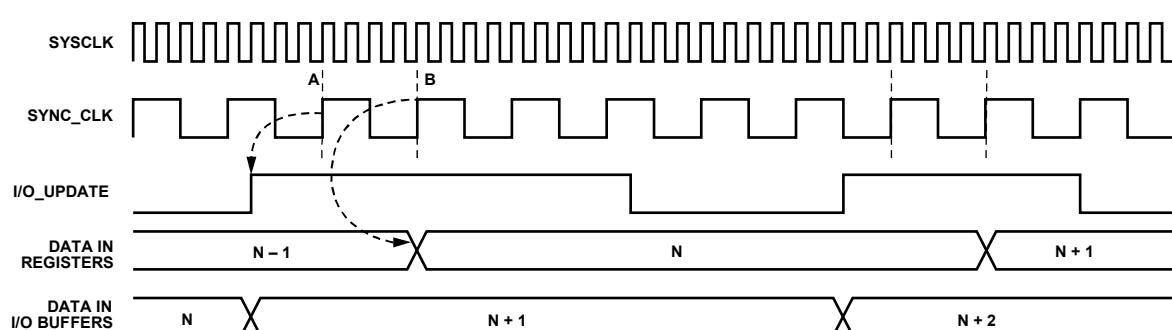

| I/O_UPDATE、SYNC_CLK、システム・クロックの関係                            | 42 |

| 自動I/O更新                                                     | 43 |

| パワーダウンのコントロール                                               | 43 |

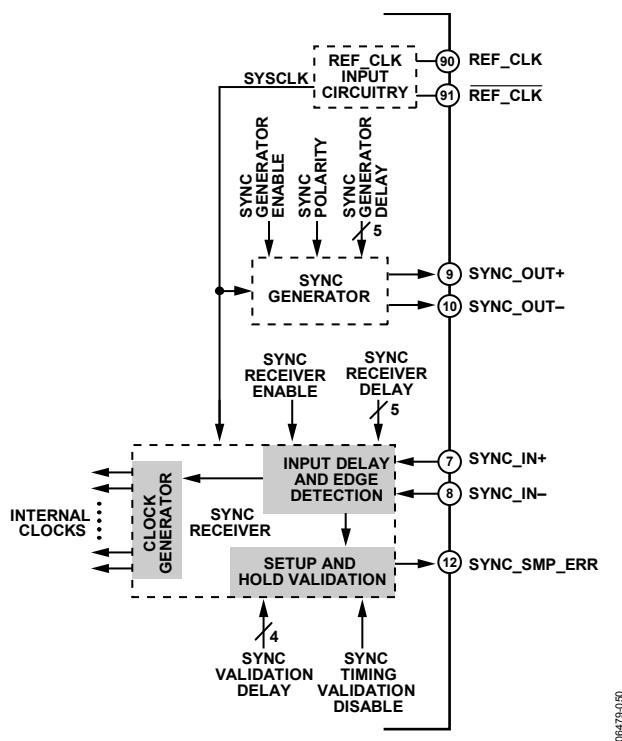

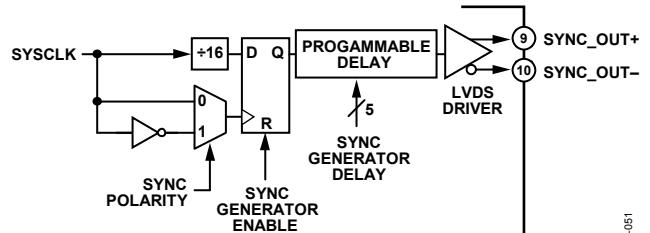

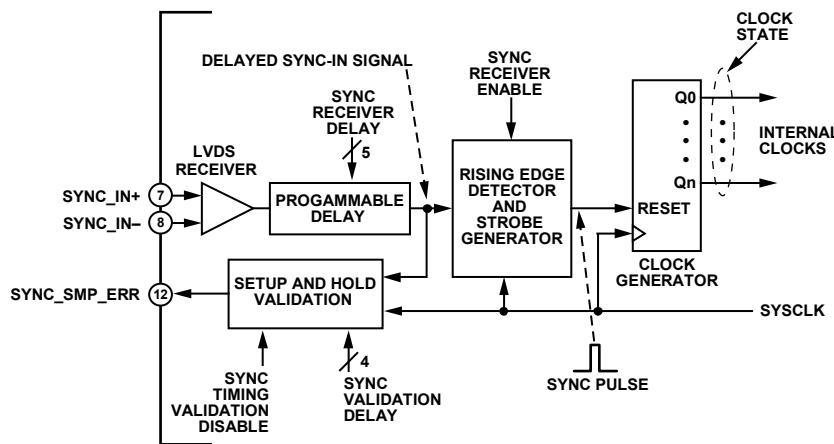

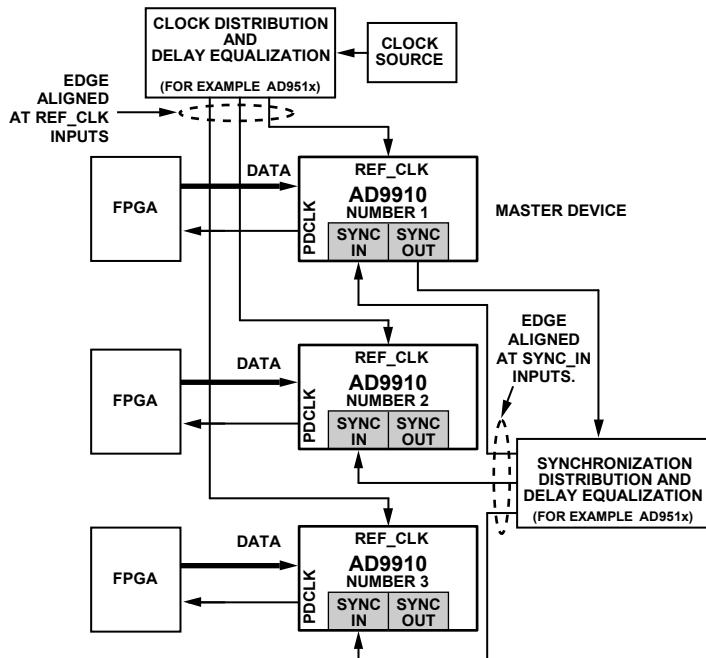

| 複数デバイスの同期                                                   | 44 |

| 電源の分割                                                       | 47 |

| 3.3 V電源                                                     | 47 |

| DVDD_I/O (3.3V) (ピン 11、ピン 15、ピン 21、ピン 28、ピン 45、ピン 56、ピン 66) | 47 |

| AVDD (3.3V) (ピン 74～ピン 77、ピン 83)                             | 47 |

| 1.8 V電源                                                     | 47 |

| DVDD (1.8V) (ピン 17、ピン 23、ピン 30、ピン 47、ピン 57、ピン 64)           | 47 |

| AVDD (1.8V) (ピン 3)                                          | 47 |

| AVDD (1.8V) (ピン 6)                                          | 47 |

| AVDD (1.8V) (ピン 89 と ピン 92)                                 | 47 |

| シリアルの設定                                                     | 48 |

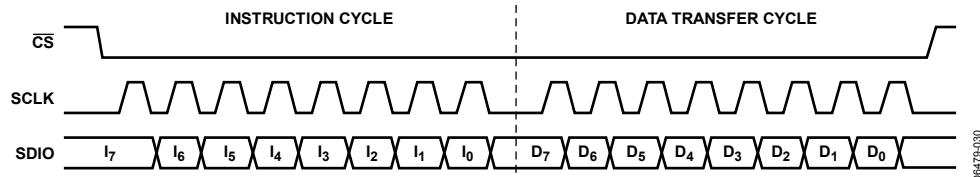

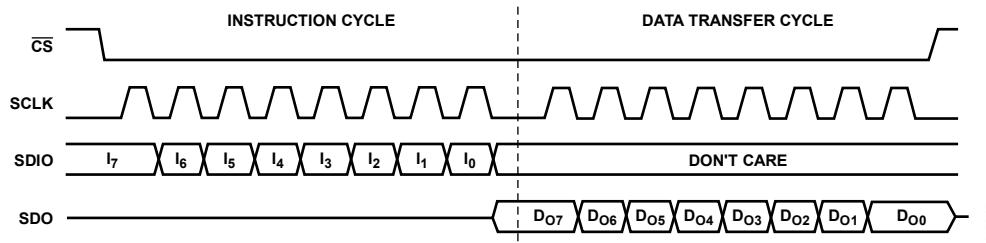

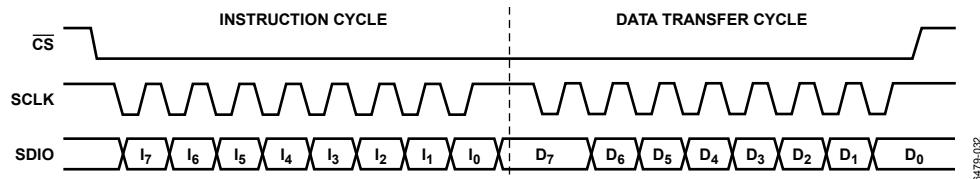

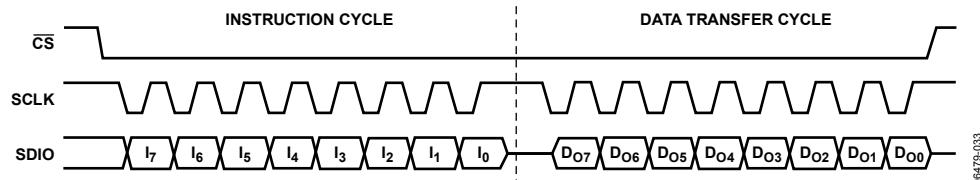

| コントロール・インターフェース—シリアルI/O                                     | 48 |

| シリアルI/Oの動作概要                                                | 48 |

| 命令バイト                                                       | 48 |

| 命令バイト情報のビット・マップ                                             | 48 |

| シリアルI/Oポート・ピンの説明                                            | 48 |

| SCLK—シリアル・クロック                                              | 48 |

| <u>CS</u> —チップ・セレクト・バー                                      | 48 |

| SDIO—シリアル・データ入力/出力                                          | 48 |

| SDO—シリアル・データ出力                                              | 48 |

| I/O_RESET—入力/出力リセット                                         | 49 |

| I/O_UPDATE—入力/出力更新                                          | 49 |

| シリアルI/Oのタイミング図                                              | 49 |

| MSB/LSBの転送                                                  | 49 |

|                                               |    |

|-----------------------------------------------|----|

| レジスタ・マップとビット説明 .....                          | 50 |

| レジスタ・ビットの説明 .....                             | 55 |

| コントロール・ファンクション・レジスタ 1 (CFR1)——アドレス 0x00 ..... | 55 |

| コントロール・ファンクション・レジスタ 2 (CFR2)——アドレス 0x01 ..... | 57 |

| コントロール・ファンクション・レジスタ 3 (CFR3)——アドレス 0x02 ..... | 58 |

| 補助DACコントロール・レジスター——アドレス 0x03 .....            | 58 |

| I/O更新レート・レジスター——アドレス 0x04 .....               | 59 |

| 周波数チューニング・ワード・レジスタ(FTW)——アドレス 0x07 .....      | 59 |

|                                          |    |

|------------------------------------------|----|

| フェーズオフセット・ワード・レジスタ(POW)——アドレス 0x08 ..... | 59 |

| 振幅スケール・ファクタ・レジスタ(AFS)——アドレス 0x09 .....   | 59 |

| マルチチップ同期レジスター——アドレス 0x0A .....           | 60 |

| デジタル・ランプ限界値レジスター——アドレス 0x0B .....        | 60 |

| デジタル・ランプ・ステップ・サイズ・レジスター——アドレス 0x0C ..... | 60 |

| デジタル・ランプ・レート・レジスター——アドレス 0x0D .....      | 60 |

| プロファイル・レジスタ .....                        | 61 |

| 外形寸法 .....                               | 62 |

| オーダー・ガイド .....                           | 62 |

## 改訂履歷

### 12/08—Rev. A to Rev. B

|                                                                                                          |    |

|----------------------------------------------------------------------------------------------------------|----|

| Changes to Figure 2 .....                                                                                | 5  |

| Changes to I/O_UPDATE Pulse Width Parameter and Minimum Profile Toggle Period Parameter in Table 1 ..... | 7  |

| Added XTAL_SEL Input Parameter in Table 1 .....                                                          | 8  |

| Changes to Table 3 .....                                                                                 | 11 |

| Changes to Figure 20 .....                                                                               | 16 |

| Changes to Figure 22 .....                                                                               | 17 |

| Changes to Figure 23 .....                                                                               | 18 |

| Changes to Figure 24 .....                                                                               | 19 |

| Changes to Figure 25 .....                                                                               | 20 |

| Changes to REF_CLK/REF_CLK Overview Section .....                                                        | 24 |

| Changes to Crystal Driven REF_CLK/REF_CLK Section .....                                                  | 25 |

| Changes to PLL Lock Indication Section and Output Shift Keying (OSK) Section .....                       | 27 |

| Changes to DRG Slope Control Section and Normal Ramp Generation Section .....                            | 30 |

| Changes to Drovver Pin Section .....                                                                     | 32 |

| Changes to Figure 43 .....                                                                               | 35 |

| Changes to Figure 45 and Internal Profile Control Continuous Waveform Timing Diagram Section .....       | 38 |

| Changes to Figure 47 .....                                                                               | 40 |

| Changes to Figure 48 .....                                                                               | 41 |

| Deleted I/O_UPDATE Pin Section .....                                                                     | 41 |

| Changes to Profiles Section .....                                                                        | 42 |

| Added I/O_UPDATE, SYNC_CLK, and System Clock Relationships Section .....                                 | 42 |

| Added Figure 49; Renumbered Sequentially .....                                                           | 42 |

| Changes to Synchronization of Multiple Devices Section .....                                             | 44 |

|                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Changes to DVDD (1.8V) (Pin 17, Pin 23, Pin 30, Pin 47, Pin 57, and Pin 64) Section and AVDD (1.8V) (Pin 89 and Pin 92) Section ..... | 47 |

| Changes to Control Interface—Serial I/O Section .....                                                                                 | 48 |

| Changes to Table 17 .....                                                                                                             | 50 |

| Changes to Table 19 .....                                                                                                             | 57 |

| Changes to Table 20 and Table 21 .....                                                                                                | 58 |

### 2/08—Rev. 0 to Rev. A

|                                                                                             |    |

|---------------------------------------------------------------------------------------------|----|

| Changes to Features .....                                                                   | 1  |

| Changes to REFCLK Multiplier Specification in Table 1 .....                                 | 5  |

| Changes to Minimum Setup Time to SYNC_CLK .....                                             | 6  |

| Changes to I/O Update/Profile[2:0] Timing Characteristics .....                             | 6  |

| Changes to TxENABLE/Data Setup Time (to PDCLK) and TxENABLE/Data Hold Time (to PDCLK) ..... | 6  |

| Changes to Miscellaneous Timing Characteristics .....                                       | 6  |

| Changes to Table 3 .....                                                                    | 10 |

| Changes to Figure 9, Figure 10, Figure 11, Figure 12, Figure 13, and Figure 14 .....        | 12 |

| Changes to Figure 30 and Table 7 .....                                                      | 24 |

| Changes to Automatic I/O Update Section .....                                               | 41 |

| Added Table 16, Renumbered Sequentially .....                                               | 41 |

| Changes to Figure 49 to Figure 53 .....                                                     | 43 |

| Added Power Supply Partitioning Section .....                                               | 46 |

| Changes to General Serial I/O Operation Section .....                                       | 47 |

| Changes to Table 17 .....                                                                   | 49 |

| Changes to Table 19 .....                                                                   | 56 |

| Changes to Table 20 .....                                                                   | 57 |

| Added Table 32 .....                                                                        | 60 |

### 5/07—Revision 0: Initial Version

## 概要

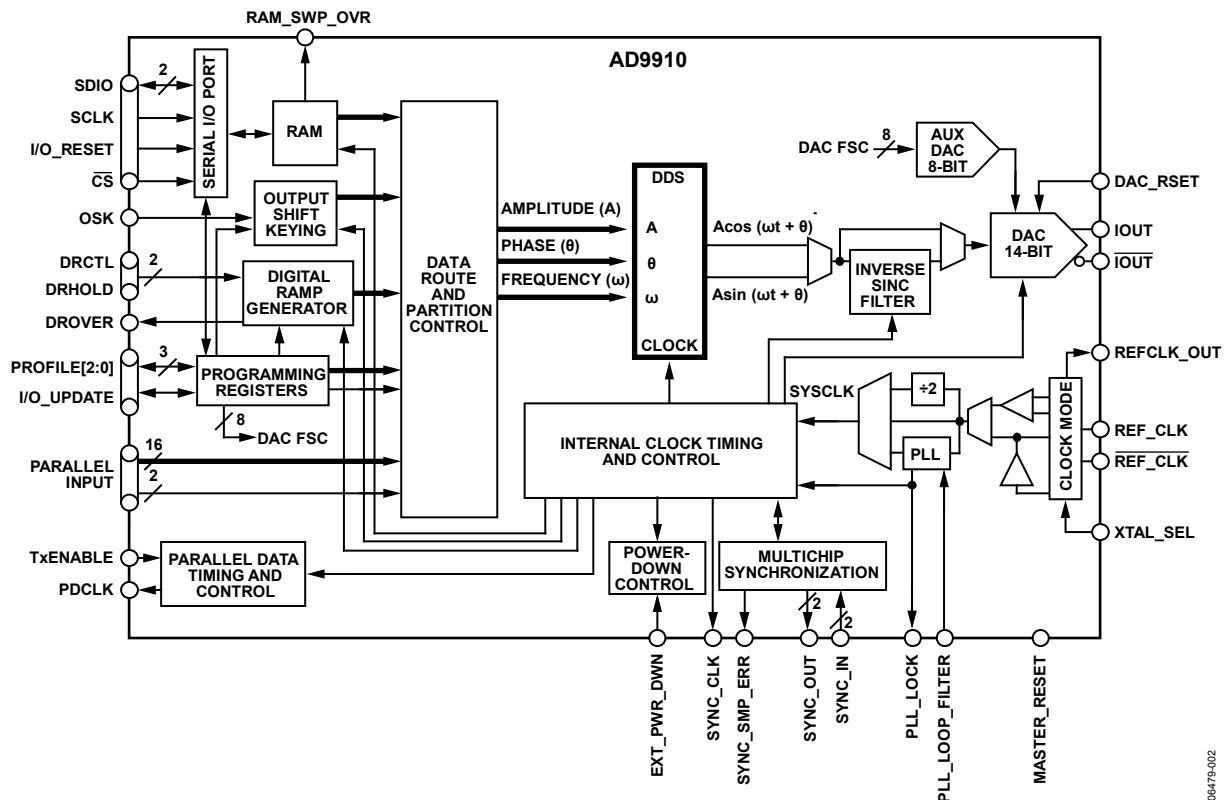

AD9910 は、14 ビット DAC を内蔵し、最大 1 GSPS のサンプル・レートをサポートするダイレクト・デジタル・シンセサイザ(DDS)です。AD9910 は、性能の犠牲なしで消費電力を大幅に削減する当社独自の最新 DDS 技術を採用しています。DDS と DAC の組み合わせにより、最大 400 MHz の周波数即応性に優れた正弦波波形を発生することができ、デジタル的に設定可能な高周波アナログ出力シンセサイザを構成しています。

ユーザは、DDS を制御する 3 個の信号コントロール・パラメータ(周波数、位相、振幅)をアクセスすることができます。この DDS は、高速な周波数ホッピングと 32 ビット・アキュムレータによる周波数チューニング分解能を提供します。1 GSPS のサンプル・レートで、チューニング分解能は約 0.23 Hz です。また、この DDS は位相と振幅の高速なスイッチング機能も可能になります。

AD9910 は、シリアル I/O ポートを介して内部コントロール・レジスタを設定することにより制御されます。AD9910 は、周波数変調、位相変調、および/または振幅変調の種々の組み合わせをサポートするスタティック RAM を内蔵しています。AD9910 は、デジタル的に制御されるユーザ定義のデジタル・ランプ動作モードもサポートしています。このモードでは、周波数、位相、または振幅を時間に対してリニアに変えることができます。さらに高度な変調機能のために、高速パラレル・データ入力ポートを内蔵して、ダイレクトな周波数変調、位相変調、振幅変調、またはポーラ変調を可能にしています。

AD9910 の動作は、拡張工業温度範囲で規定されています(詳細については、絶対最大定格のセクション参照)。

図2. 詳細ブロック図

# 仕様

## 電気的仕様

特に指定がない限り、AVDD (1.8V)およびDVDD (1.8V) = 1.8 V ± 5%、AVDD (3.3V) = 3.3 V ± 5%、DVDD\_I/O (3.3V) = 3.3 V ± 5%、T = 25°C、 $R_{SET}$  = 10 kΩ、 $I_{OUT}$  = 20 mA、外部リファレンス・クロック周波数= 1000 MHz、リファレンス・クロック(REFCLK)倍増器をディスエーブル。

表1.

| Parameter                              | Conditions/Comments                                 | Min  | Typ  | Max  | Unit   |

|----------------------------------------|-----------------------------------------------------|------|------|------|--------|

| REFCLK INPUT CHARACTERISTICS           |                                                     |      |      |      |        |

| Frequency Range                        |                                                     |      |      |      |        |

| REFCLK Multiplier                      | Disabled                                            | 60   | 1000 |      | MHz    |

|                                        | Enabled                                             | 3.2  | 60   |      | MHz    |

| Maximum REFCLK Input Divider Frequency | Full temperature range                              | 1500 | 1900 |      | MHz    |

| Minimum REFCLK Input Divider Frequency | Full temperature range                              | 25   | 35   |      | MHz    |

| External Crystal                       |                                                     | 25   |      |      | MHz    |

| Input Capacitance                      |                                                     | 3    |      |      | pF     |

| Input Impedance                        | Differential                                        | 2.8  |      |      | kΩ     |

|                                        | Single-ended                                        | 1.4  |      |      | kΩ     |

| Duty Cycle                             | REFCLK multiplier disabled                          | 45   | 55   |      | %      |

|                                        | REFCLK multiplier enabled                           | 40   | 60   |      | %      |

| REFCLK Input Level                     | Single-ended                                        | 50   | 1000 |      | mV p-p |

|                                        | Differential                                        | 100  | 2000 |      | mV p-p |

| REFCLK MULTIPLIER VCO CHARACTERISTICS  |                                                     |      |      |      |        |

| VCO Gain ( $K_V$ ) @ Center Frequency  | VCO range Setting 0                                 | 429  |      |      | MHz/V  |

|                                        | VCO range Setting 1                                 | 500  |      |      | MHz/V  |

|                                        | VCO range Setting 2                                 | 555  |      |      | MHz/V  |

|                                        | VCO range Setting 3                                 | 750  |      |      | MHz/V  |

|                                        | VCO range Setting 4                                 | 789  |      |      | MHz/V  |

|                                        | VCO range Setting 5 <sup>1</sup>                    | 850  |      |      | MHz/V  |

| REFCLK_OUT CHARACTERISTICS             |                                                     |      |      |      |        |

| Maximum Capacitive Load                |                                                     | 20   |      |      | pF     |

| Maximum Frequency                      |                                                     | 25   |      |      | MHz    |

| DAC OUTPUT CHARACTERISTICS             |                                                     |      |      |      |        |

| Full-Scale Output Current              |                                                     | 8.6  | 20   | 31.6 | mA     |

| Gain Error                             |                                                     | -10  |      | +10  | % FS   |

| Output Offset                          |                                                     |      |      | 2.3  | μA     |

| Differential Nonlinearity              |                                                     |      | 0.8  |      | LSB    |

| Integral Nonlinearity                  |                                                     |      | 1.5  |      | LSB    |

| Output Capacitance                     |                                                     |      | 5    |      | pF     |

| Residual Phase Noise                   | @ 1 kHz offset, 20 MHz $A_{OUT}$                    |      |      |      |        |

| REFCLK Multiplier                      | Disabled                                            |      | -152 |      | dBc/Hz |

|                                        | Enabled @ 20×                                       |      | -140 |      | dBc/Hz |

|                                        | Enabled @ 100×                                      |      | -140 |      | dBc/Hz |

| Voltage Compliance Range               |                                                     | -0.5 |      | +0.5 | V      |

| Wideband SFDR                          | See the Typical Performance Characteristics section |      |      |      |        |

| Narrow-Band SFDR                       |                                                     |      |      |      |        |

| 50.1 MHz Analog Output                 | ±500 kHz                                            |      | -87  |      | dBc    |

|                                        | ±125 kHz                                            |      | -87  |      | dBc    |

|                                        | ±12.5 kHz                                           |      | -96  |      | dBc    |

| 101.3 MHz Analog Output                | ±500 kHz                                            |      | -87  |      | dBc    |

|                                        | ±125 kHz                                            |      | -87  |      | dBc    |

|                                        | ±12.5 kHz                                           |      | -95  |      | dBc    |

| Parameter                                      | Conditions/Comments                              | Min  | Typ               | Max | Unit                      |

|------------------------------------------------|--------------------------------------------------|------|-------------------|-----|---------------------------|

| 201.1 MHz Analog Output                        | $\pm 500$ kHz<br>$\pm 125$ kHz<br>$\pm 12.5$ kHz |      | -87               |     | dBc                       |

| 301.1 MHz Analog Output                        | $\pm 500$ kHz<br>$\pm 125$ kHz<br>$\pm 12.5$ kHz |      | -87<br>-91        | -86 | dBc                       |

| 401.3 MHz Analog Output                        | $\pm 500$ kHz<br>$\pm 125$ kHz<br>$\pm 12.5$ kHz |      | -88<br>-84<br>-84 | -85 | dBc                       |

| SERIAL PORT TIMING CHARACTERISTICS             |                                                  |      |                   |     |                           |

| Maximum SCLK Frequency                         |                                                  |      | 70                |     | Mbps                      |

| Minimum SCLK Clock Pulse Width                 | Low                                              | 4    |                   |     | ns                        |

| Maximum SCLK Rise/Fall Time                    | High                                             | 4    | 2                 |     | ns                        |

| Minimum Data Setup Time to SCLK                |                                                  | 5    |                   |     | ns                        |

| Minimum Data Hold Time to SCLK                 |                                                  | 0    |                   |     | ns                        |

| Maximum Data Valid Time in Read Mode           |                                                  |      | 11                |     | ns                        |

| I/O_UPDATE/PROFILE[2:0] TIMING CHARACTERISTICS |                                                  |      |                   |     |                           |

| Minimum Setup Time to SYNC_CLK                 |                                                  | 1.75 |                   |     | ns                        |

| Minimum Hold Time to SYNC_CLK                  |                                                  | 0    |                   |     | ns                        |

| I/O_UPDATE Pulse Width                         | High                                             | >1   |                   |     | SYNC_CLK cycle            |

| Minimum Profile Toggle Period                  |                                                  | 2    |                   |     | SYNC_CLK cycles           |

| TxENABLE and 16-BIT PARALLEL (DATA) BUS TIMING |                                                  |      |                   |     |                           |

| Maximum PDCLK Frequency                        |                                                  | 250  |                   |     | MHz                       |

| TxENABLE/Data Setup Time (to PDCLK)            |                                                  | 1.75 |                   |     | ns                        |

| TxENABLE/Data Hold Time (to PDCLK)             |                                                  | 0    |                   |     | ns                        |

| MISCELLANEOUS TIMING CHARACTERISTICS           |                                                  |      |                   |     |                           |

| Wake-Up Time <sup>2</sup>                      |                                                  |      |                   |     |                           |

| Fast Recovery                                  |                                                  | 8    |                   |     | SYCLK cycles <sup>3</sup> |

| Full Sleep Mode                                | REFCLK multiplier enabled                        | 1    |                   |     | ms                        |

| Minimum Reset Pulse Width High                 | REFCLK multiplier disabled                       |      | 150               |     | $\mu$ s                   |

| 5                                              |                                                  |      |                   |     | SYCLK cycles <sup>3</sup> |

| DATA LATENCY (PIPELINE DELAY)                  |                                                  |      |                   |     |                           |

| Data Latency, Single Tone or Using Profiles    |                                                  |      |                   |     |                           |

| Frequency, Phase, Amplitude-to-DAC Output      | Matched latency enabled and OSK enabled          | 91   |                   |     | SYCLK cycles <sup>3</sup> |

| Frequency, Phase-to-DAC Output                 | Matched latency enabled and OSK disabled         | 79   |                   |     | SYCLK cycles <sup>3</sup> |

| Amplitude-to-DAC Output                        | Matched latency disabled                         | 79   |                   |     | SYCLK cycles <sup>3</sup> |

| Data Latency Using RAM Mode                    | Matched latency disabled                         | 47   |                   |     | SYCLK cycles <sup>3</sup> |

| Frequency, Phase-to-DAC Output                 | Matched latency enabled/disabled                 | 94   |                   |     | SYCLK cycles <sup>3</sup> |

| Amplitude-to-DAC Output                        | Matched latency enabled                          | 106  |                   |     | SYCLK cycles <sup>3</sup> |

| Matched latency disabled                       |                                                  | 58   |                   |     | SYCLK cycles <sup>3</sup> |

| Data Latency, Sweep Mode                       |                                                  |      |                   |     |                           |

| Frequency, Phase-to-DAC Output                 | Matched latency enabled/disabled                 | 91   |                   |     | SYCLK cycles <sup>3</sup> |

| Amplitude-to-DAC Output                        | Matched latency enabled                          | 91   |                   |     | SYCLK cycles <sup>3</sup> |

| Matched latency disabled                       |                                                  | 47   |                   |     | SYCLK cycles <sup>3</sup> |

| Data Latency, 16-Bit Input Modulation Mode     |                                                  |      |                   |     |                           |

| Frequency, Phase-to-DAC Output                 | Matched latency enabled                          | 103  |                   |     | SYCLK cycles <sup>3</sup> |

| Matched latency disabled                       |                                                  | 91   |                   |     | SYCLK cycles <sup>3</sup> |

| Parameter                 | Conditions/Comments | Min | Typ | Max | Unit |

|---------------------------|---------------------|-----|-----|-----|------|

| CMOS LOGIC INPUTS         |                     |     |     |     |      |

| Logic 1 Voltage           |                     | 2.0 |     |     | V    |

| Logic 0 Voltage           |                     |     | 0.8 |     | V    |

| Logic 1 Current           |                     | 90  | 120 |     | μA   |

| Logic 0 Current           |                     | 38  | 50  |     | μA   |

| Input Capacitance         |                     | 2   |     |     | pF   |

| XTAL_SEL INPUT            |                     | 2.0 |     |     | V    |

| Logic 1 Voltage           |                     |     | 0.8 |     | V    |

| Logic 0 Voltage           |                     | 90  | 120 |     | μA   |

| Logic 1 Current           |                     | 38  | 50  |     | μA   |

| Logic 0 Current           |                     | 2   |     |     | pF   |

| CMOS LOGIC OUTPUTS        | 1 mA load           | 2.8 |     |     | V    |

| Logic 1 Voltage           |                     |     | 0.4 |     | V    |

| Logic 0 Voltage           |                     |     |     |     |      |

| POWER SUPPLY CURRENT      |                     |     |     |     |      |

| I <sub>AVDD</sub> (1.8 V) |                     | 110 |     |     | mA   |

| I <sub>AVDD</sub> (3.3 V) |                     | 29  |     |     | mA   |

| I <sub>DVDD</sub> (1.8 V) |                     | 222 |     |     | mA   |

| I <sub>DVDD</sub> (3.3 V) |                     | 11  |     |     | mA   |

| TOTAL POWER CONSUMPTION   |                     |     |     |     |      |

| Single Tone Mode          |                     | 715 | 850 |     | mW   |

| Rapid Power-Down Mode     |                     | 330 | 400 |     | mW   |

| Full Sleep Mode           |                     | 19  | 25  |     | mW   |

<sup>1</sup> VCO 範囲設定値 5 のゲイン値は 1000 MHz で測定。<sup>2</sup> ウェイクアップ・タイムとは、パワーダウン状態からの回復時間を意味します。リファレンス・クロック倍増器の PLL がリファレンスに再ロックするときは最長の時間が必要です。ウェイクアップ・タイムは、推奨 PLL ループ・フィルタ値を使用した場合です。<sup>3</sup> SYSCLK サイクルは、DDS がチップ内で使用する実際のクロック周波数を意味します。リファレンス・クロック倍増器を使って外部リファレンス・クロック周波数を倍増する場合、SYSCLK 周波数は外部周波数にリファレンス・クロック倍率を乗算した値になります。リファレンス・クロック倍増器を使わない場合は、SYSCLK 周波数は外部リファレンス・クロック周波数に一致します。

## 絶対最大定格

表2.

| Parameter                             | Rating          |

|---------------------------------------|-----------------|

| AVDD (1.8V), DVDD (1.8V) Supplies     | 2 V             |

| AVDD (3.3V), DVDD_I/O (3.3V) Supplies | 4 V             |

| Digital Input Voltage                 | -0.7 V to +4 V  |

| Digital Output Current                | 5 mA            |

| Storage Temperature Range             | -65°C to +150°C |

| Operating Temperature Range           | -40°C to +85°C  |

| $\theta_{JA}$                         | 22°C/W          |

| $\theta_{JC}$                         | 2.8°C/W         |

| Maximum Junction Temperature          | 150°C           |

| Lead Temperature (10 sec Soldering)   | 300°C           |

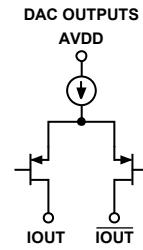

### 等価回路

MUST TERMINATE OUTPUTS TO AGND

FOR CURRENT FLOW. DO NOT EXCEED

THE OUTPUT VOLTAGE COMPLIANCE

RATING.

06479-003

図3.等価入力回路

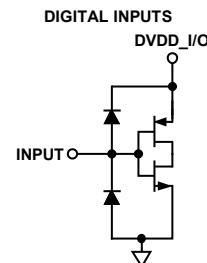

AVOID OVERDRIVING DIGITAL INPUTS.

FORWARD BIASING ESD DIODES MAY

COUPLE DIGITAL NOISE ONTO POWER

PINS.

06479-005

図4.等価出力回路

### ESDの注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

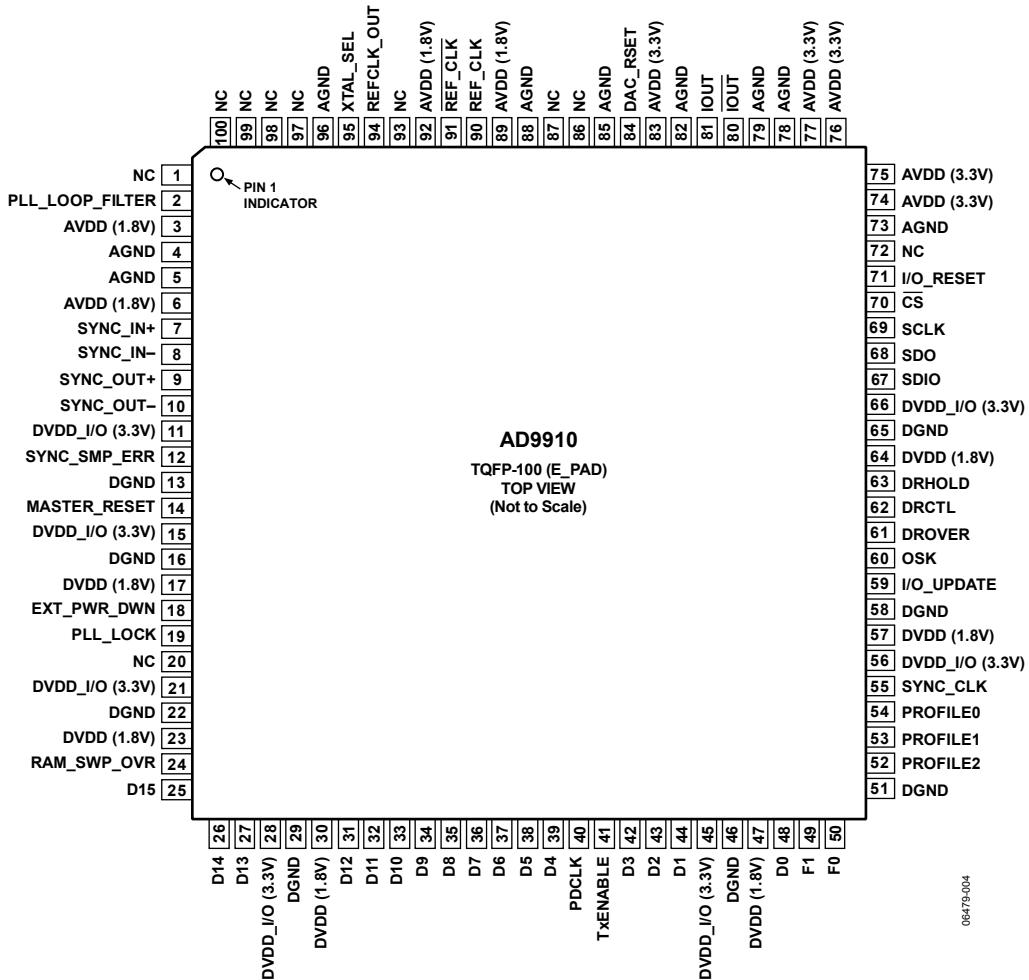

## ピン配置およびピン機能説明

06479-004

図5. ピン配置

表3.ピン機能の説明

| ピン番号                       | 記号              | I/O <sup>1</sup> | 説明                                                                                                                                                               |

|----------------------------|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1、20、72、86、87、93、97 to 100 | NC              |                  | 未接続。これらのデバイス・ピンはフローティングのままにすることができます。                                                                                                                            |

| 2                          | PLL_LOOP_FILTER | I                | PLLループ・フィルタ補償ピン。詳細については、外付けPLLループ・フィルタ部品のセクションを参照してください。                                                                                                         |

| 3、6、89、92                  | AVDD (1.8V)     | I                | アナログ・コア VDD 用 1.8 V アナログ電源。                                                                                                                                      |

| 74 to 77、83                | AVDD (3.3V)     | I                | アナログ DAC VDD 用 3.3 V アナログ電源。                                                                                                                                     |

| 17、23、30、47、57、64          | DVDD (1.8V)     | I                | デジタル・コア VDD 用 1.8 V デジタル電源。                                                                                                                                      |

| 11、15、21、28、45、56、66       | DVDD_I/O (3.3V) | I                | デジタル入力/出力 VDD 用 3.3 V デジタル電源。                                                                                                                                    |

| 4、5、73、78、79、82、85、88、96   | AGND            | I                | アナログ・グラウンド。                                                                                                                                                      |

| 13、16、22、29、46、51、58、65    | DGND            | I                | デジタル・グラウンド。                                                                                                                                                      |

| 7                          | SYNC_IN+        | I                | 同期信号(LVDS)、デジタル入力(立上がりアクティブ)。内部サブクロックを同期化する、外部マスターからの同期信号。詳細については、複数デバイスの同期のセクションを参照してください。                                                                      |

| 8                          | SYNC_IN-        | I                | 同期信号(LVDS)、デジタル入力。内部サブクロックを同期化する、外部マスターからの同期信号。詳細については、複数デバイスの同期のセクションを参照してください。                                                                                 |

| 9                          | SYNC_OUT+       | O                | 同期信号(LVDS)、デジタル出力(立上がりアクティブ)。外部スレーブ・デバイスを同期化する、内部デバイス・サブクロックからの同期信号。詳細については、複数デバイスの同期のセクションを参照してください。                                                            |

| 10                         | SYNC_OUT-       | O                | 同期信号(LVDS)、デジタル出力。外部スレーブ・デバイスを同期化する、内部デバイス・サブクロックからの同期信号。詳細については、複数デバイスの同期のセクションを参照してください。                                                                       |

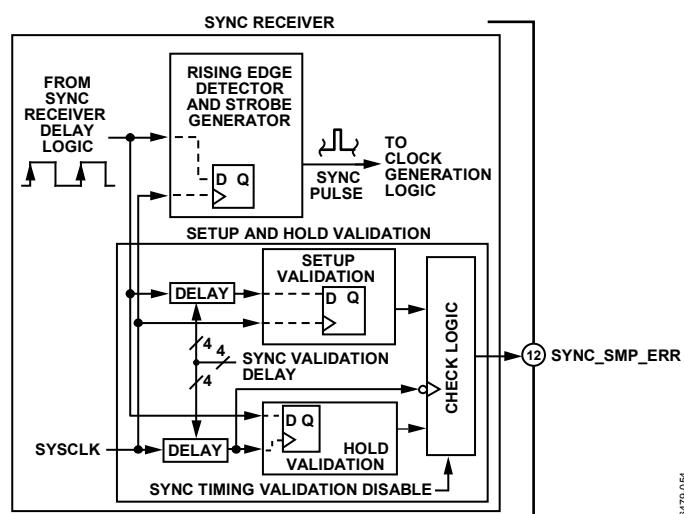

| 12                         | SYNC_SMP_ERR    | O                | 同期サンプル誤差、デジタル出力(アクティブ・ハイ)。同期サンプル誤差。このピンがハイ・レベルの場合、AD9910 が SYNC_IN+/SYNC_IN-上で有効な同期信号を受信しなかったことを表します。                                                            |

| 14                         | MASTER_RESET    | I                | マスター・リセット、デジタル入力(アクティブ・ハイ)。マスター・リセット。すべてのメモリ・エレメントをクリアし、レジスタにデフォルト値を設定します。                                                                                       |

| 18                         | EXT_PWR_DWN     | I                | 外部パワーダウン、デジタル入力(アクティブ・ハイ)。このピンをハイ・レベルにすると、現在設定されているパワーダウン・モードが開始されます。詳細については、パワーダウンのコントロールのセクションを参照してください。未使用時はグラウンドに接続してください。                                   |

| 19                         | PLL_LOCK        | O                | クロック倍増器 PLL ロック、デジタル出力(アクティブ・ハイ)。このピンがハイ・レベルの場合、クロック倍増器 PLL がリファレンス・クロック入力にロックしたことを表します。                                                                         |

| 24                         | RAM_SWP_OVR     | O                | RAM スイープ・オーバー、デジタル出力(アクティブ・ハイ)。このピンがハイ・レベルの場合、RAM スイープ・プロファイルが完了したことを表します。                                                                                       |

| 25~27、31~39、42~44、48       | D[15:0]         | I                | パラレル入力バス(アクティブ・ハイ)。                                                                                                                                              |

| 49、50                      | F[1:0]          | I                | 変調フォーマット・ピン。変調フォーマットを指定するデジタル入力。                                                                                                                                 |

| 40                         | PDCLK           | O                | パラレル・データ・クロック。このピンはデジタル出力(クロック)。パラレル・データ・クロックは、パラレル入力でデータを整列させるタイミング信号を提供します。                                                                                    |

| 41                         | TxENABLE        | I                | 送信イネーブル。デジタル入力(アクティブ・ハイ)。バースト・モード通信で、このピンがハイ・レベルのとき、新しいデータが送信されます。連続モードでは、このピンはハイ・レベルを維持します。                                                                     |

| 52~54                      | PROFILE[2:0]    | I                | プロファイル・セレクト・ピン。デジタル入力(アクティブ・ハイ)。これらのピンを使って、DDS 用の 8 種類の位相/周波数プロファイルを選択します。これらのピンの状態の 1 つを変えると、すべての I/O バッファの現在の値が対応するレジスタへ転送されます。状態の変更は、SYNC_CLK ピンで設定する必要があります。 |

| 55                         | SYNC_CLK        | O                | 出力クロック 4 分周。デジタル出力(クロック)。チップ上の多くのデジタル入力(例えば I/O_UPDATE や PROFILE[2:0])は、この信号の立上がりエッジで設定される必要があります。                                                               |

| ピン番号      | 記号               | I/O <sup>1</sup> | 説明                                                                                                                                                                                                           |

|-----------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 59        | I/O_UPDATE       | I/O              | 入力/出力更新。デジタル入力(アクティブ・ハイ)。このピンがハイ・レベルの場合、I/O バッファの値が対応する内部レジスタへ転送されます。                                                                                                                                        |

| 60        | OSK              | I                | 出力シフト・キーイング。デジタル入力(アクティブ・ハイ)。OSK 機能が手動モードまたは自動モードにされると、このピンが OSK 機能を制御します。手動モードでは、このピンにより通倍器が 0(ロー・レベル)と設定済みの振幅スケール・ファクタ(ハイ・レベル)の間でトグルされます。自動モードでは、ロー・レベルで振幅をゼロに向かってスイープし、ハイ・レベルで振幅を振幅スケール・ファクタに向かってスイープします。 |

| 61        | DROVER           | O                | デジタル・ランプ・オーバー。デジタル出力(アクティブ・ハイ)。このピンは、デジタル・ランプ・ジェネレータが設定済みの上限または下限に到達するごとにロジック 1 に切り替わります。                                                                                                                    |

| 62        | DRCTL            | I                | デジタル・ランプ制御。デジタル入力(アクティブ・ハイ)。このピンは、デジタル・ランプ・ジェネレータのスロープ極性を制御します。詳細については、デジタル・ランプ・ジェネレータ(DRG)のセクションを参照してください。デジタル・ランプ・ジェネレータを使用しない場合は、このピンをロジック 0 に接続してください。                                                   |

| 63        | DRHOLD           | I                | デジタル・ランプ・ホールド。デジタル入力(アクティブ・ハイ)。このピンは、デジタル・ランプ・ジェネレータを現在の状態で停止させます。詳細については、デジタル・ランプ・ジェネレータ(DRG)のセクションを参照してください。デジタル・ランプ・ジェネレータを使用しない場合は、このピンをロジック 0 に接続してください。                                                |

| 67        | SDIO             | I/O              | シリアル・データ入力/出力。デジタル入力/出力(アクティブ・ハイ)。このピンは、設定値に応じて单方向または双方向(デフォルト)になります。双方向シリアル・ポート・モードでは、このピンは、シリアル・データ入力/出力として機能します。单方向モードでは、入力専用になります。                                                                       |

| 68        | SDO              | O                | シリアル・データ出力。デジタル出力(アクティブ・ハイ)。このピンは、单方向シリアル・データ・モードでのみアクティブになります。このモードでは、出力として機能します。双方向モードでは、このピンは動作しないたるフローティングのままにしておく必要があります。                                                                               |

| 69        | SCLK             | I                | シリアル・データ・クロック。デジタル・クロック(立上がりエッジで書込み、立下がりエッジで読出し)。このピンは、コントロール・データ・パスのシリアル・データ・クロックを提供します。AD9910への書込み動作は立上がりエッジを使います。AD9910からのリードバック動作は立下がりエッジを使います。                                                          |

| 70        | CS               | I                | チップ・セレクト。デジタル入力(アクティブ・ロー)。このピンにより、AD9910 はデータ・バスを制御する共通シリアル・バス上で動作できるようになります。このピンをロー・レベルにすると、AD9910 がシリアル・クロックの立上がり/立下がりエッジを検出するようになります。このピンをハイ・レベルにすると、AD9910 はシリアル・データ・ピンの入力を無視します。                        |

| 71        | I/O_RESET        | I                | 入力/出力リセット。デジタル入力(アクティブ・ハイ)。シリアル I/O 通信サイクルが失敗したときにこのピンを使うことができます(詳細については、I/O_RESET—入力/出力リセットのセクション参照)。使用しないときは、このピンはグラウンドに接続しておきます。                                                                          |

| 80        | IOUT             | O                | オープン・ドレインの DAC 相補出力ソース。アナログ出力(電流モード)。50 Ω 抵抗を介して AGND へ接続してください。                                                                                                                                             |

| 81        | IOUT             | O                | オープン・ドレインの DAC 出力ソース。アナログ出力(電流モード)。50 Ω 抵抗を介して AGND へ接続してください。                                                                                                                                               |

| 84        | DAC_RSET         | O                | アナログ・リファレンス電圧ピン。DAC 出力のフルスケール・リファレンス電流を調整。このピンと AGNDとの間に 10 kΩ の抵抗を接続してください。                                                                                                                                 |

| 90        | REF_CLK          | I                | リファレンス・クロック入力。アナログ入力。内部発振器を使用する場合、このピンを外部発振器または水晶から駆動することができます。詳細については、REF_CLK/の概要のセクションを参照してください。                                                                                                           |

| 91        | REF_CLK          | I                | リファレンス・クロック入力。アナログ入力。詳細については、REF_CLK/の概要のセクションを参照してください。                                                                                                                                                     |

| 94        | REFCLK_OUT       | O                | 水晶出力。アナログ出力。詳細については、REF_CLK/の概要のセクションを参照してください。                                                                                                                                                              |

| 95        | XTAL_SEL         | I                | 水晶の選択(1.8 V ロジック)。アナログ入力(アクティブ・ハイ)。XTAL_SEL ピンをハイ・レベルにすると、AVDD (1.8V) ピンにより、水晶共振子を使用した内部発振器の使用が可能になります。未使用時は AGND に接続してください。                                                                                 |

| 96 (EPAD) | エクスポート・パドル(EPAD) |                  | EPAD はグラウンドへハンダ付けする必要があります。                                                                                                                                                                                  |

<sup>1</sup> I = 入力、O = 出力。

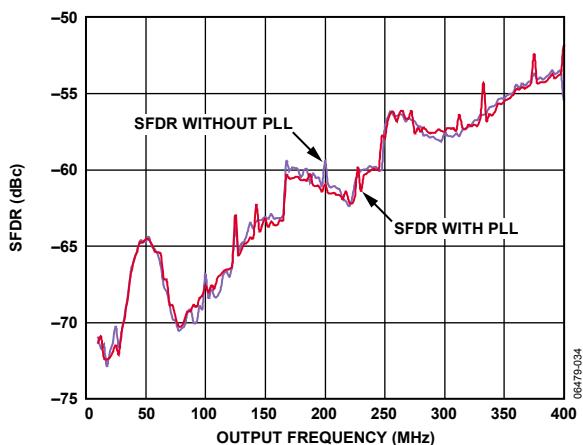

## 代表的な性能特性

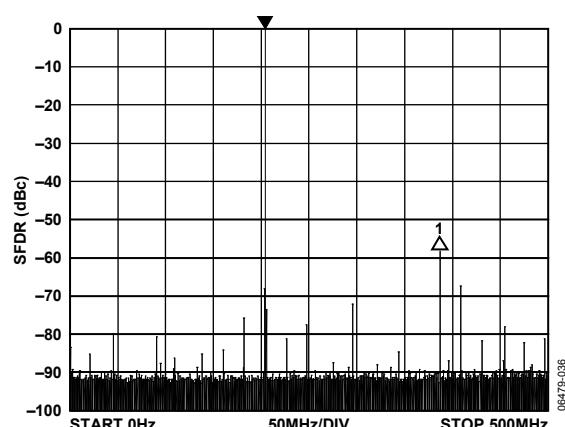

図6.出力周波数対広帯域 SFDR

(PLL リファレンス・クロック = 15.625 MHz × 64)

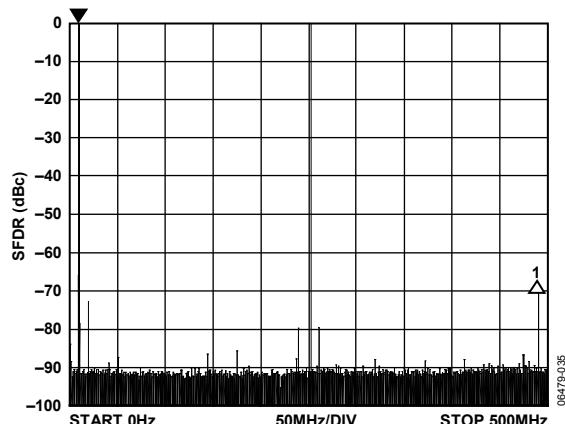

図9.広帯域 SFDR、10 MHz、REFCLK = 1 GHz

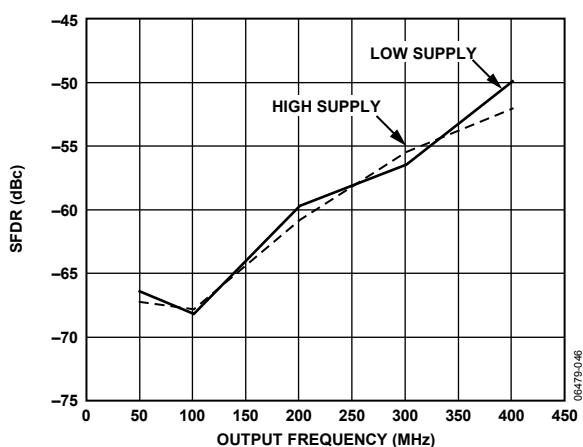

図7.出力周波数および電源(±5%)対広帯域 SFDR

REFCLK = 1 GHz

図10.広帯域 SFDR、204 MHz、REFCLK = 1 GHz

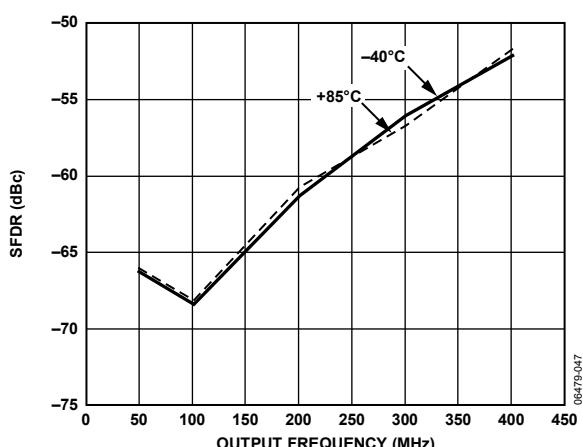

図8.出力周波数および温度対広帯域 SFDR

REFCLK = 1 GHz

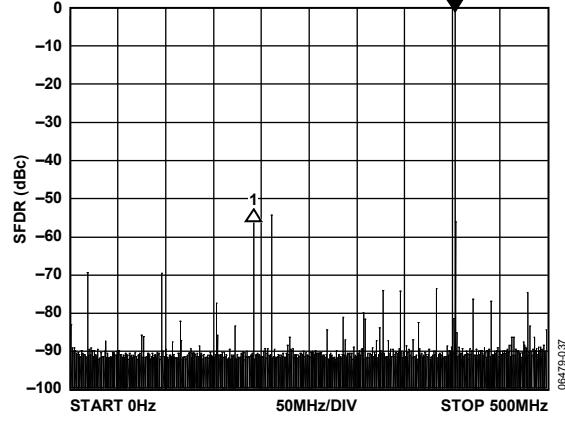

図11.広帯域 SFDR、403 MHz、REFCLK = 1 GHz

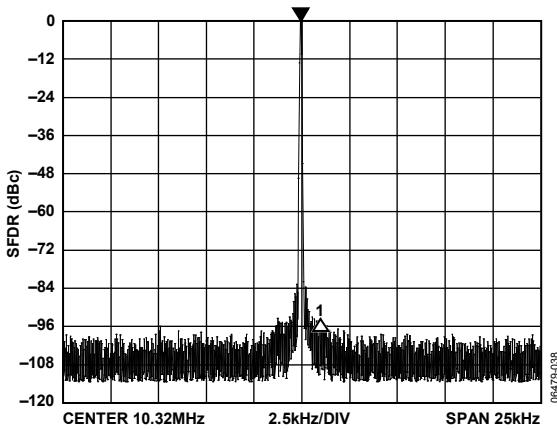

図12.狭帯域 SFDR、10.32 MHz、REFCLK = 1 GHz

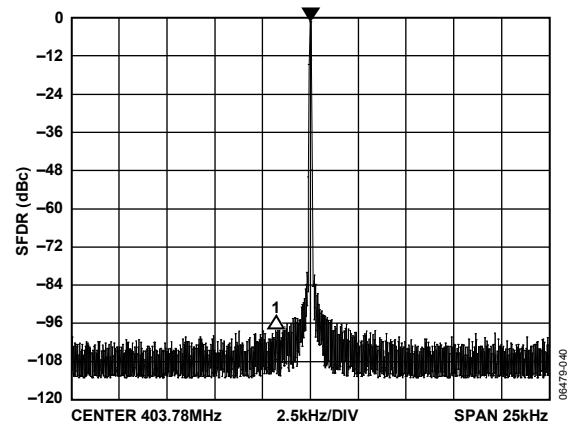

図14.狭帯域 SFDR、403.78 MHz、REFCLK = 1 GHz

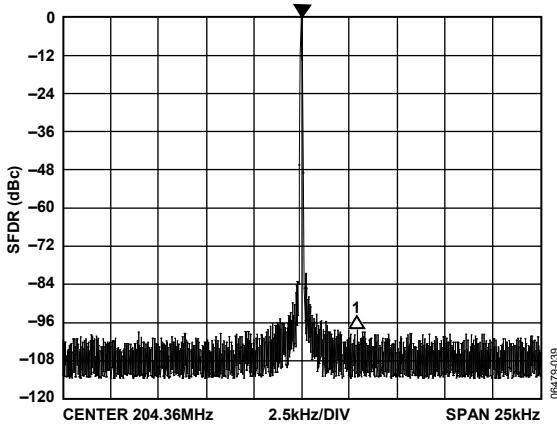

図13.狭帯域 SFDR、204.36 MHz、REFCLK = 1 GHz

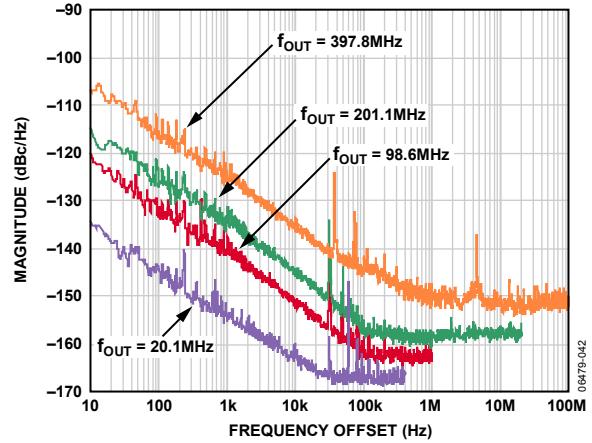

図15.残留位相ノイズのプロット、1 GHz 動作

PLL をディスエーブル

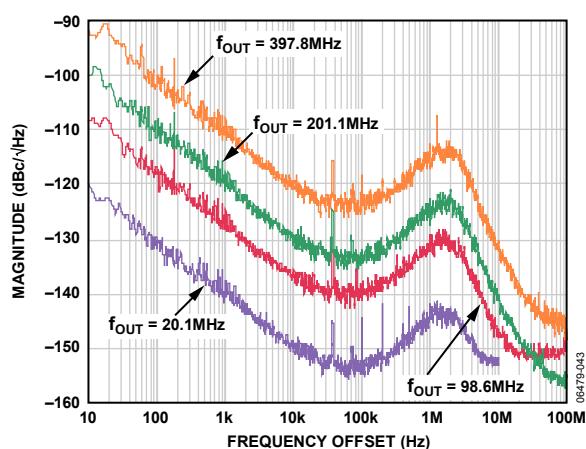

図16. 残留位相ノイズ、1 GHz動作

50 MHz リファレンス・クロック、20× PLL 過倍器

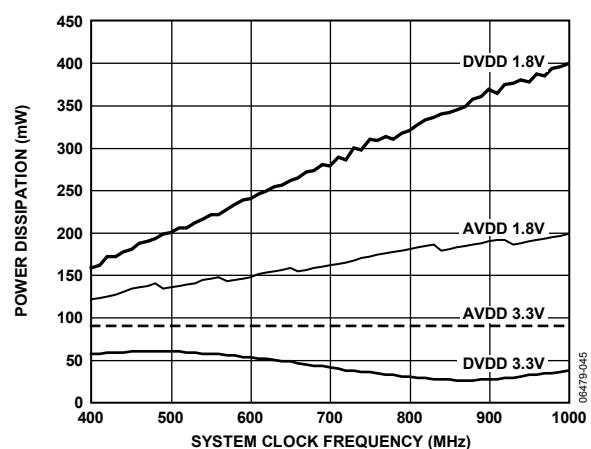

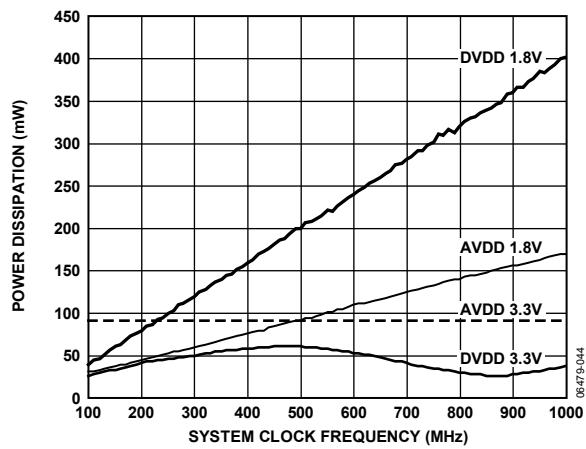

図18. システム・クロック周波数対消費電力

(PLL をイネーブル)

図17. システム・クロック周波数対消費電力

(PLL をディスエーブル)

## アプリケーション回路

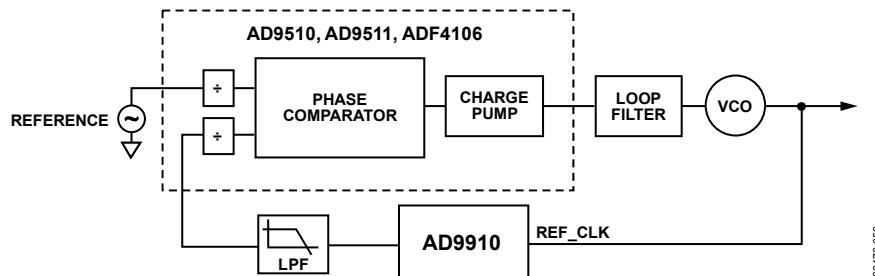

図19.リファレンスにロックするPLL帰還パス内のDDS、周波数と遅延の細かいチューニングが可能

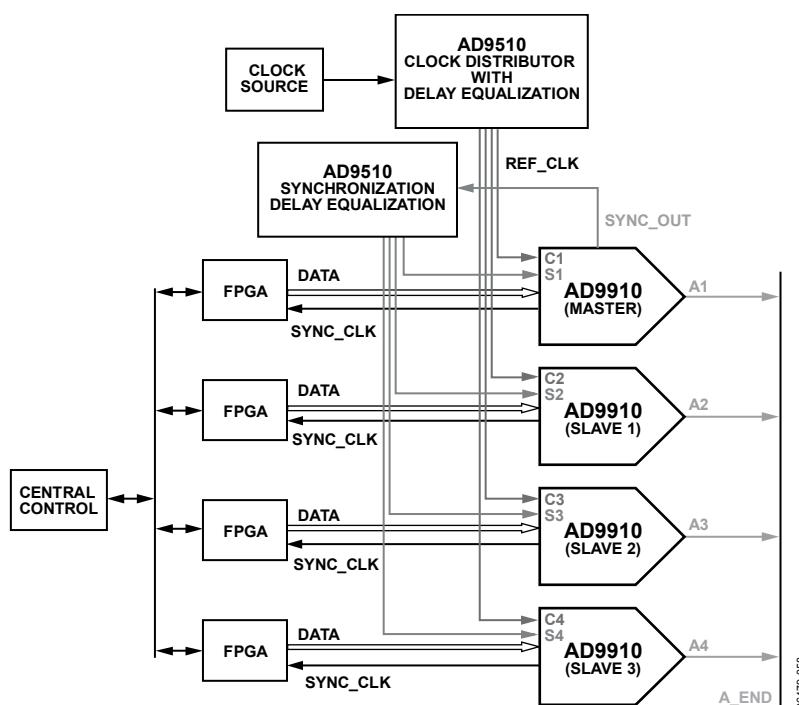

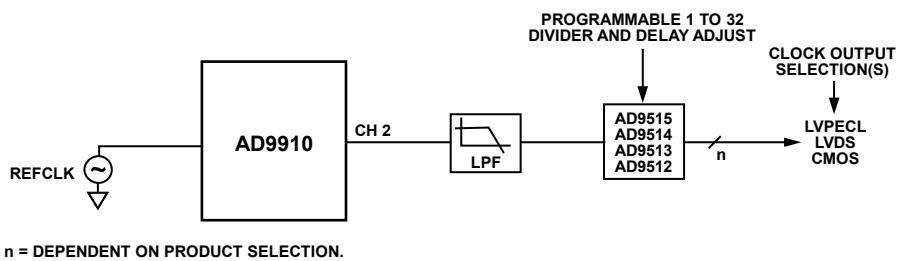

図20.チャンネル容量を増やすための複数デバイスの同期化、リファレンス・クロックと同期クロックの分配にAD9510を使用

n = DEPENDENT ON PRODUCT SELECTION.

図21.AD9512/AD9513/AD9514/AD9515 シリーズのクロック分配チップを使ったクロック発生回路

## 動作原理

AD9910は次の4種類の動作モードを持っています。

- ・ シングル・トーン

- ・ RAM変調

- ・ デジタル・ランプ変調

- ・ パラレル・データ・ポート変調

各モードは、周波数、位相、または振幅の信号コントロール・パラメータを DDS へ入力する際に使われるデータ・ソースに関係しています。データを周波数、位相、振幅の種々の組み合わせに分割する処理は、モード・コントロール・ビットおよび/または特定のコントロール・ビットに基づいて自動的に行われます。

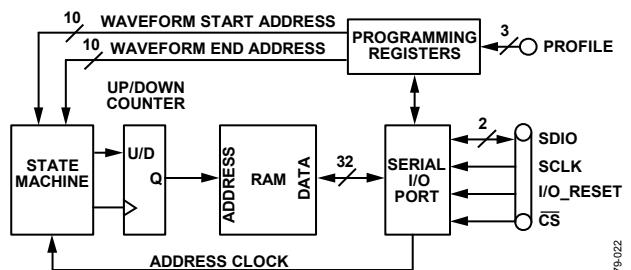

シングル・トーン・モードでは、DDS 信号コントロール・パラメータはシリアル I/O ポートに対応するプログラミング・レジスタから直接取得されます。RAM 変調モードでは、DDS 信号コントロール・パラメータは内部 RAM に格納され、コマンド実行時に読み出されます。デジタル・ランプ変調モードでは、DDS 信号コントロール・パラメータはデジタル・ランプ・ジェネレータから直接取得されます。パラレル・データ・ポート変調モードでは、DDS 信号コントロール・パラメータは直接パラレル・ポートへ入力されます。

これらの種々の変調モードは、一般に1つの DDS 信号コントロール・パラメータでのみ動作します(ポーラ変調フォーマットの場合は2つ使用)。非変調の DDS 信号コントロール・パラメータは該当するプログラミング・レジスタに格納され、選択されたモードに応じて自動的に DDS へ渡されます。

さらに、別の出力シフト・キーイング(OSK)機能も使用することができます。この機能では、DDS の振幅パラメータのみに影響を与える別のデジタル・リニア・ランプ・ジェネレータを使用しています。この OSK 機能は、DDS 振幅パラメータを駆動できるその他のデータ・ソースより高い優先順位を持っています。したがって、この OSK 機能がイネーブルされている場合、他のデータ・ソースは DDS 振幅を駆動することはできません。

種々のモード(このOSK機能も含む)は独立に説明しますが、これらは同時にイネーブルすることができます。これにより、複数変調方式の構成にこれまでにないレベルの柔軟性が提供されますが、複数のデータ・ソースが同じ DDS 信号コントロール・パラメータを駆動しないように、デバイスは優先順位規約を持っています(モードの優先順位のセクションの表5参照)。

### シングル・トーン・モード

シングル・トーン・モードでは、DDS 信号コントロール・パラメータはプログラミング・レジスタから直接供給されます。プロファイルとは、DDS 信号コントロール・パラメータを格納する独立なレジスタを意味します。8個のプロファイル・レジスタがあります。

各プロファイルは独立にアクセスすることができます。3本の外部プロファイル・ピン(PROFILE[2:0])を使って、プロファイルを選択します。プロファイル・ピンの状態が変化すると、SYNC\_CLK の次の立ち上がりエッジで、選択したプロファイルで指定されたパラメータにより DDS が更新されます。

06479-005

図22. シングル・トーン・モード

## RAM変調モード

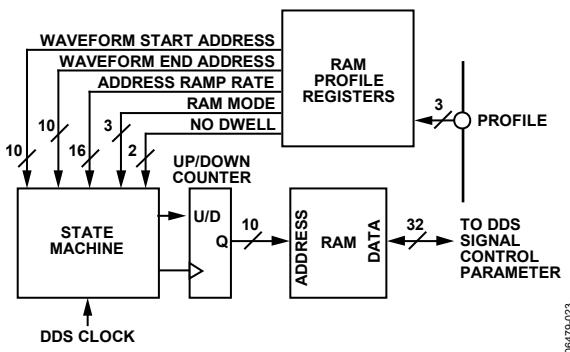

RAM変調モード(図 23 参照)は、RAMイネーブル・ビットと I/O\_UPDATE ピンのアーサーション(すなわちプロファイルの変更)により開始されます。このモードでは、変調される DDS 信号コントロール・パラメータは直接 RAM から供給されます。

RAM の構成は、32 ビット・ワード×1024 ワードです。高度な内部ステート・マシンと RAM の組み合わせにより、時間依存の任意の波形を発生する非常に柔軟な方法を提供します。プログラマブル・タイマは、ワードを DDS へ渡すために RAM からワードを読出す際の読み出レートを制御します。したがって、プログラマブル・タイマは、DDS へ 32 ビット・サンプルを供給するサンプル・レートを設定することになります。

RAM サンプルのディステネーションとして機能する特定の DDS 信号コントロール・パラメータの選択も、8 個の独立な RAM プロファイル・レジスタを使って設定することができます。特定のプロファイルは、3 本の外部プロファイル・ピン(PROFILE[2:0])を使って選択します。プロファイル・ピンの状態が変化すると、SYNC\_CLK の次の立上がりエッジで、選択したプロファイルがアクティブになります。

RAM 変調モードでは、時間依存の振幅、位相、または周波数信号を発生する機能により、DDS キャリア信号を制御するパラメータの 1 つを変調することができます。さらに、ポーラ変調フォーマットを使用することができます。このフォーマットは各 RAM サンプルを 1 つの振幅と位相成分に分割します。16 ビットは位相に、14 ビットは振幅に、それぞれ割り当てられます。

図23.RAM 変調モード

## デジタル・ランプ変調モード

デジタル・ランプ変調モード(図 24参照)では、変調DDS信号コントロール・パラメータは直接デジタル・ランプ・ジェネレータ(DRG)から供給されます。ランプ発生パラメータは、シリアルI/Oポートを介して制御されます。

ランプ発生パラメータを使うと、ランプの立上がりと立下がりスロープを制御することができます。ランプの上限と下限、ランプの立上がり部分のステップ・サイズとステップ・レート、ランプの立下がり部分のステップ・サイズとステップ・レートはすべて、設定することができます。

ランプは、32ビットの出力分解能でデジタル的に発生されます。DRGの32ビット出力は、周波数、位相、または振幅を表すように設定することができます。周波数を表すように設定する場合は、32ビットすべてを使いますが、位相または振幅を表すように設定する場合は、それぞれ上位16ビットまたは上位14ビットのみを使います。

ランプ方向(立上がりまたは立下がり)は、DRCTLピンを使って外部から制御します。もう1本のピン(DRHOLD)を使うと、ランプ・ジェネレータをプリセット状態に停止させることができます。

図24.デジタル・ランプ変調モード

## パラレル・データ・ポート変調モード

パラレル・データ・ポート変調モード(図 25参照)では、変調 DDS信号コントロール・パラメータは直接 18 ビット・パラレル・データ・ポートから供給されます。

データ・ポートは 2 つのセクションに分割されます。上位 16 ビットは 16 ビット・データ・ワード(D[15:0]ピン)に、下位 2 ビットは 2 ビット・ディステネーション・ワード(F[1:0]ピン)に、それぞれなります。ディステネーション・ワードは、16 ビット・データ・ワードを DDS 信号コントロール・パラメータに使用する方法を指定します。表 4 に、ディステネーション・ビット、16 ビット・データ・ワードの分割、データのディステネーション(DDS 信号コントロール・パラメータの意味で)との間の関係を示します。16 ビット・データ・ワードのフォーマットは、ディステネーションに無関係に符号なしバイナリです。

データ・ワードが DDS 周波数パラメータとして使用されることが、ディステネーション・ビットにより指定されている場合、16 ビット・データ・ワードは、FTW レジスタ内の 32 ビット周波数チューニング・ワードに対するオフセットとして機能します。これは、16 ビット・データ・ワードを何らかの方法で FTW レジスタ内で 32 ビット・ワードに整列させる必要があることを意味します。これは、プログラミング・レジスタ内の 4 ビット FM ゲイン・ワードを使って実現されます。FM ゲイン・ワード

を使うと、16 ビット・データ・ワードの重み係数を使用することができます。デフォルト状態(0)では、FTW レジスタ内の 16 ビット・データ・ワードと 32 ビット・ワードは LSB に揃えられます。FM ゲイン・ワード値の各インクリメントにより、16 ビット・データ・ワードが FTW レジスタ内の 32 ビット・ワードに対して左ヘシフトされるため、FTW レジスタで指定される周波数に対する 16 ビット・データ・ワードの効果が 2 倍になります。FM ゲイン・ワードは、データ・ワードにより決定される周波数範囲を有效地に制御します。

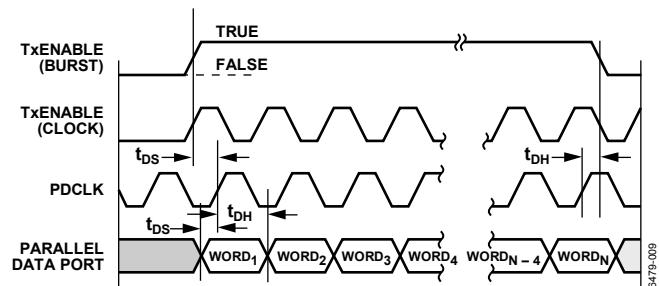

## パラレル・データ・クロック(PDCLK)

AD9910 は、PDCLK ピンにクロック信号を発生します。このクロック信号は DAC サンプル・レートの 1/4 で動作します(パラレル・データ・ポートのサンプル・レート)。PDCLK は、パラレル・ポートのデータ・クロックとして機能します。デフォルトで、PDCLK の各立上がりエッジは、データ・ポートへのユーザ入力データの 18 ビットをラッチする際に使われます。エッジの極性は、PDCLK 反転ビットを使って変更することができます。さらに、PDCLK 出力信号は PDCLK イネーブル・ビットを使ってオフにすることができますが、出力信号がオフにされた場合でも、パラレル・ポートのデータを取り込む内部 PDCLK タイミングを使って内部で動作を続けています。ディスエーブル時に、PDCLK はロジック 0 になることに注意してください。

図25.パラレル・データ・ポート変調モード

表4.パラレル・ポート・ディステネーション・ビット

| F[1:0] | D[15:0] | Parameter(s)                                     | Comments                                                                                                                                                                                                                                                                   |

|--------|---------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00     | D[15:2] | 14-bit amplitude parameter<br>(unsigned integer) | Amplitude scales from 0 to $1 - 2^{-14}$ . D[1:0] are not used.                                                                                                                                                                                                            |

| 01     | D[15:0] | 16-bit phase parameter<br>(unsigned integer)     | Phase offset ranges from 0 to $2\pi(1 - 2^{-16})$ radians.                                                                                                                                                                                                                 |

| 10     | D[15:0] | 32-bit frequency parameter<br>(unsigned integer) | The alignment of the 16-bit data-word with the 32-bit frequency parameter is controlled by a 4-bit FM gain word in the programming registers.                                                                                                                              |

| 11     | D[15:8] | 8-bit amplitude (unsigned integer)               | The MSB of the data-word amplitude aligns with the MSB of the DDS 14-bit amplitude parameter. The six LSBs of the DDS amplitude parameter are assigned from Bit [5:0] of the ASF register. The resulting 14-bit word scales the amplitude from 0 to $1 - 2^{-14}$ .        |

|        | D[7:0]  | 8-bit phase (unsigned integer)                   | The MSB of the data-word phase aligns with the MSB of the 16-bit phase parameter of the DDS. The eight LSBs of the DDS phase parameter are assigned from Bit [7:0] of the POW register. The resulting 16-bit word offsets the phase from 0 to $2\pi(1 - 2^{-16})$ radians. |

### 送信イネーブル(TxENABLE)

AD9910 は、ユーザ入力データに対してゲートとして機能する TxENABLE ピンに入力されるユーザ発生の信号も受け付けます。デフォルトでは、TxENABLE でのロジック 1 を真と、ロジック 0 を偽と、それぞれ見なしますが、このピンの論理動作を TxENABLE 反転ビットを使って逆にすることができます。TxENABLE が真のとき、デバイスは PDCLK の指定されたエッジ(PDCLK 反転ビットによる指定)でデータをデバイスにラッチします。TxENABLE が偽の場合、PDCLK は動作を続けますが、デバイスはポートに入力されたデータを無視します。さらに、TxENABLE ピンを偽にすると、デバイスは内部で 18 ビット・データ・ワードをクリアするか、または TxENABLE が偽状態に切り替わる前にデータ・ポートに入力された直前の値を維持します(これはデータ・アセンブラー・ホールド・ラスト・バリュービットの設定値に応じた動作になります)。

あるいは、TxENABLE ピンをゲートとして動作させる代わりに、パラレル・ポート・データレートで動作するクロック信号で TxENABLE ピンを駆動することができます。クロック信号で駆動する場合、偽状態から真状態の変化は、正常動作を保証するため、必要とされるセットアップとホールド・タイムを各サイクルで満たす必要があります。TxENABLE と PDCLK のタイミングを図 26 に示します。

図26.PDCLK と TxENABLE のタイミング図

## モードの優先順位

3種類の変調モードを使って、DDS信号コントロール・パラメータとして使用する周波数、位相、および/または振幅データを発生します。さらに、OSK機能によりDDSで使用する振幅データを発生します。これらの各機能は、シリアルI/Oポートを介して該当するコントロール・ビットを使用して独立に起動されます。

これらの各機能を独立に起動する機能により、複数のデータ・ソースで同じDDS信号コントロール・パラメータを駆動してしま

う可能性が生じます。AD9910は競合を回避するため優先順位システムを採用しています。表5に、各DDS信号コントロール・パラメータの優先順位を示します。表5の各行には、DDS信号コントロール・パラメータのデータ・ソースを優先順位の降順で示します。例えば、RAMとパラレル・ポートが共にイネーブルされ、かつ両方ともディステネーションに対して周波数が設定される場合、DDS周波数パラメータはパラレル・データ・ポートではなくRAMから駆動されます。

表5.データ・ソースの優先順位

| Priority         | DDS Signal Control Parameters              |                                                                               |                                                            |                                                                           |                                                            |                                                                     |

|------------------|--------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|

|                  | Frequency                                  |                                                                               | Phase                                                      |                                                                           | Amplitude                                                  |                                                                     |

|                  | Data Source                                | Conditions                                                                    | Data Source                                                | Conditions                                                                | Data Source                                                | Conditions                                                          |

| Highest Priority | RAM                                        | RAM enabled and data destination is frequency                                 | RAM                                                        | RAM enabled and data destination is phase or polar                        | OSK generator                                              | OSK enabled (auto mode)                                             |

|                  | DRG                                        | DRG enabled and data destination is frequency                                 | DRG                                                        | DRG enabled and data destination is phase                                 | ASF register                                               | OSK enabled (manual mode)                                           |

|                  | Parallel data port and FTW register        | Parallel data port enabled and data destination is frequency                  | Parallel data port                                         | Parallel data port enabled and data destination is phase                  | RAM                                                        | RAM enabled and data destination is amplitude or polar              |

|                  | FTW register                               | RAM enabled and data destination is phase, amplitude, or polar                | Parallel data port concatenated with the POW register LSBs | Parallel data port enabled and data destination is polar                  | DRG                                                        | DRG enabled and data destination is amplitude                       |

|                  | FTW in active single tone profile register | DRG enabled and data destination is phase or amplitude                        | POW register                                               | RAM enabled and destination is frequency or amplitude                     | Parallel data port                                         | Parallel data port enabled and data destination is amplitude        |

|                  | FTW in active single tone profile register | Parallel data port enabled and data destination is phase, amplitude, or polar | POW in active single tone profile register                 | DRG enabled and data destination is frequency or amplitude                | Parallel data port concatenated with the ASF register LSBs | Parallel data port enabled and data destination is polar            |

|                  | FTW in active single tone profile register | None                                                                          | POW in active single tone profile register                 | Parallel data port enabled and data destination is frequency or amplitude | ASF in active single tone profile register                 | Enable amplitude scale from single tone profiles bit (CFR2[24]) set |

|                  |                                            |                                                                               | POW in active single tone profile register                 | None                                                                      | No amplitude scaling                                       | None                                                                |

| Lowest Priority  |                                            |                                                                               |                                                            |                                                                           |                                                            |                                                                     |

## 機能ブロック図の詳細

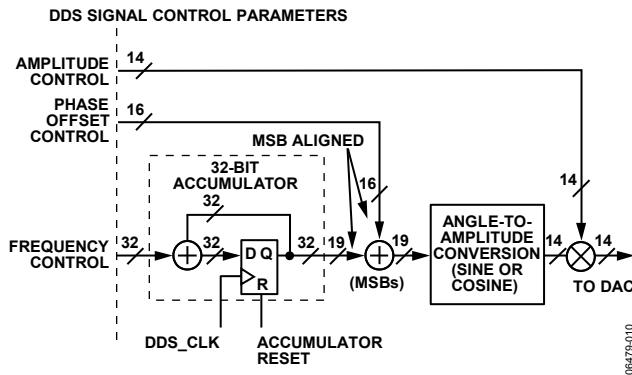

### DDSコア

ダイレクト・デジタル・シンセサイザ(DDS)ブロックは、リファレンス信号を発生します(セレクト DDS 正弦波出力ビット CFR1[16]に応じて正弦波または余弦波を発生)。リファレンス信号のパラメータ(周波数、位相、振幅)は、DDS の周波数入力、位相オフセット入力、振幅コントロール入力に入力されます(図 27 参照)。

図27.DDS のブロック図

AD9910 の出力周波数( $f_{OUT}$ )は、DDS への周波数コントロール入力である周波数チューニング・ワード(FTW)により制御されます。 $f_{OUT}$ 、FTW、 $f_{SYSCLK}$  の間の関係は次式で与えられます。

$$f_{OUT} = \left( \frac{FTW}{2^{32}} \right) f_{SYSCLK} \quad (1)$$

ここで、FTWは0~2,147,483,647 ( $2^{31} - 1$ )の範囲の32ビット整数で、フル32ビット範囲の下半分を表します。この範囲が、DC~ナイキスト( $\frac{1}{2} f_{SYSCLK}$ )周波数を構成します。

所望の値 $f_{OUT}$ を発生するため必要なFTWは、式1をFTWについて解くことにより式2のように求めます。

$$FTW = \text{round}\left( 2^{32} \left( \frac{f_{OUT}}{f_{SYSCLK}} \right) \right) \quad (2)$$

ここで、 $\text{round}(x)$ 関数は、引数(xの値)に対する最寄りの整数を返します。これは、FTWが整数値に制約されているために必要です。例えば、 $f_{OUT} = 41 \text{ MHz}$ かつ $f_{SYSCLK} = 122.88 \text{ MHz}$ の場合、 $FTW = 1,433,053,867 (0x556AAAAB)$ となります。

FTWを $2^{31}$ より大きく設定すると、次式で表される周波数に、折り返しされたイメージが現れます。

$$f_{OUT} = \left( 1 - \frac{FTW}{2^{32}} \right) f_{SYSCLK} \quad (FTW \geq 2^{31})$$

16 ビット位相オフセット・ワード(POW)を使うと、DDS 信号の相対位相をデジタル的に制御することができます。この位相オフセットは、DDS コア内部の角度/振幅変換ブロック内部の前で加えられます。相対位相オフセット( $\Delta\theta$ )は次式で与えられます。

$$\Delta\theta = \begin{cases} 2\pi \left( \frac{POW}{2^{16}} \right) \\ 360 \left( \frac{POW}{2^{16}} \right) \end{cases}$$

ここで、位相オフセットの上の値はラジアン単位で表され、下の値は度単位で表されます。任意の  $\Delta\theta$  を表すために必要な POW 値を求めるときは、前式を POW について解き結果をまるめ処理します(任意の FTW を求めた前述の方法と同じ方法を使用)。

14 ビット振幅スケール・ファクタ(ASF)を使うと、DDS 信号の相対振幅(フルスケール基準)をデジタル的にスケールすることができます。振幅スケール値は、DDS コア内の角度/振幅変換ブロック出力に適用されます。振幅スケールは次式で与えられます。

$$Amplitude Scale = \begin{cases} \frac{ASF}{2^{14}} \\ 20 \log \left( \frac{ASF}{2^{14}} \right) \end{cases} \quad (3)$$

ここで、上の値はフルスケールに対する比として表された振幅で、下の値はフルスケールに対するデシベル値です。特定のスケール・ファクタに必要な ASF 値を求めるときは、ASF について式 3 を解き結果をまるめ処理します(任意の FTW を求めるために説明した前の方法と同じ方法を使用)。

AD9910 を DDS 信号コントロール・パラメータを変調するように設定する場合、最大変調サンプル・レートは  $1/4 f_{SYSCLK}$  になります。これは、変調信号が  $1/4 f_{SYSCLK}$  の整数倍にイメージを持つことを意味します。これらのイメージの影響は、デバイスを変調器として使用する際に考慮する必要があります。

### 14 ビットDAC出力

AD9910 は 14 ビットの電流出力DACを内蔵しています。出力電流は、2 つの出力を使う平衡信号として出力されます。平衡出力を使うと、DAC出力に現れる同相モード・ノイズの電位が小さくなるので、信号対ノイズ比が大きくなる利点があります。DAC\_RSETピンとAGNDとの間に外付け抵抗( $R_{SET}$ )を接続する限りリファレンス電流が設定されます。DACのフルスケール出力電流( $I_{OUT}$ )は、リファレンス電流のスケール済み電流として発生されます(補助DACのセクション参照)。 $R_{SET}$ の推奨値は  $10 \text{ k}\Omega$ です。

出力電圧が規定のコンプライアンス・レンジ内に収まるように負荷終端に注意してください。電圧がこの範囲を超えると、歪みが大きくなり、DAC 出力回路に損傷を与えることがあります。

### 補助DAC

8ビット補助DACは、メインDAC( $I_{OUT}$ )のフルスケール出力電流を制御します。該当するレジスタ・マップ・ロケーションに格納されている8ビット・コード・ワードにより、次式に従って $I_{OUT}$ が設定されます。

$$I_{OUT} = \frac{86.4}{R_{SET}} \left( 1 + \frac{CODE}{96} \right)$$

ここで、

$R_{SET}$ は $R_{SET}$ 抵抗値( $\Omega$ )。

$CODE$ は補助DACに入力する8ビット値(デフォルトは127)。例えば、 $R_{SET} = 10,000\Omega$ かつ $CODE = 127$ の場合、 $I_{OUT} = 20.07\text{ mA}$ となります。

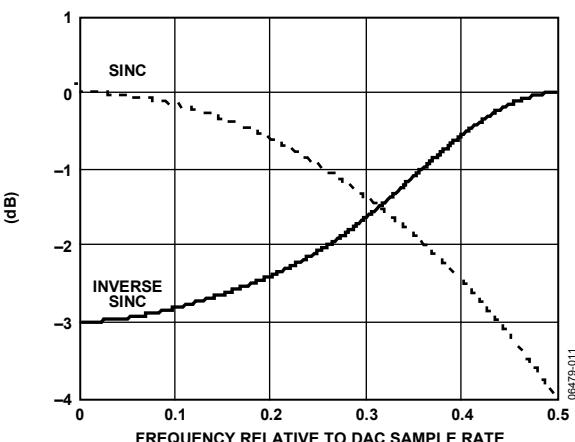

図28.sinc 応答と逆 sinc 応答

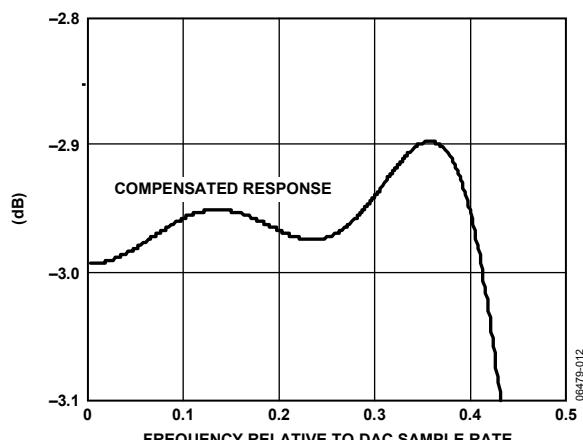

### 逆sincフィルタ

サンプルされたキャリア・データ・ストリームは、AD9910 内蔵のD/Aコンバータ(DAC)に入力されます。DAC出力スペクトルは、DACで発生される信号に固有なゼロ次ホールドの影響を持つため、 $\sin(x)/x$  (すなわちsinc)特性エンベロープにより整形されます。sincエンベロープの形状は、既知であるため補償が可能です。このエンベロープ補正機能は、DACの前に接続される逆sincフィルタにより提供されます。逆sincフィルタは、デジタルFIRフィルタとして実現されます。このデジタル・フィルタの応答特性は、sincエンベロープの逆数に良く一致します。逆sincフィルタの応答を 図 28に示します(比較のためにsincエンベロープも示します)。

逆sincフィルタは、CFR1[22]を使ってイネーブルします。表 6に、フィルタ・タップ係数を示します。データをDACに入力する前にフィルタを使って、スペクトル歪の原因となっているsincエンベロープを相殺させる歪みが加えられます。

逆 sinc フィルタをイネーブルすると、約 3.0 dB の挿入損失が発生します。逆 sinc 補償は、DAC サンプル・レートの約 40%までの出力周波数で有効です。

表6.逆 sinc フィルタのタップ係数

| Tap No. | Tap Value |

|---------|-----------|

| 1, 7    | -35       |

| 2, 6    | +134      |

| 3, 5    | -562      |

| 4       | +6729     |

図 28に示すように、sincエンベロープにより周波数に依存する減衰が生じます。この減衰はナイキスト周波数(DACサンプル・レートの 1/2)で 4 dBにもなります。逆sincフィルタがない場合、DAC出力はsincエンベロープの周波数に依存して減衰させられます。逆sincフィルタは、図 29に示すように、この減衰を±0.05 dB以内で平坦にします。この図には、逆sincフィルタをイネーブルした補正後のsinc応答が示してあります。

図29.逆 sinc 補償を行った DAC 応答

### クロック入力(REF\_CLK/REF\_CLK)

#### REF\_CLK/REF\_CLKの概要

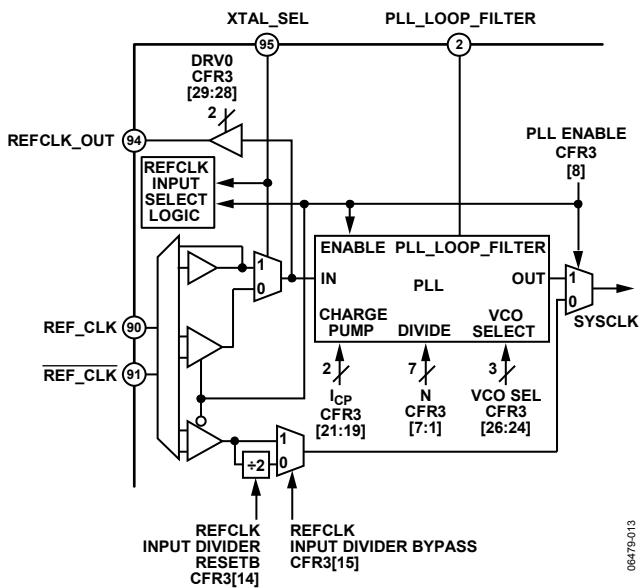

AD9910 では、REF\_CLK/REF\_CLK 入力ピンを使って内部SYSCLK信号(すなわちDACサンプル・クロック)を発生する多くのオプションをサポートしています。REF\_CLK入力を差動またはシングルエンドのソースから直接駆動するか、または 2 本の入力ピン間に水晶を接続することができます。また、独立にイネーブルできる内部位相ロック・ループ(PLL)通倍器もあります。REF\_CLKの機能を 図 30に示します。種々の入力設定は、XTAL\_SELピンとCFR3 レジスタのコントロール・ビットを使って制御されます。図 30 に、CFR3 コントロール・ビットと機能ブロックとの対応も示してあります。

図30.REF\_CLKのブロック図

PLL イネーブル・ビットは、PLL パスまたは直接入力パスを選択する際に使います。直接入力パスを選択するときは、REF\_CLK/REF\_CLK ピンを外部信号ソース(シングルエンドまたは差動)から駆動する必要があります。最大 2 GHz 入力周波数をサポートしています。1 GHz 以上の入力周波数の場合、デバイスが正常動作するためには、入力分周器をイネーブルする必要があります。

PLLをイネーブルすると、バッファされたクロック信号がREFCLK\_OUTピンに出力されます。このクロック信号は、REF\_CLK入力と同じ周波数です。この機能は、特に水晶を接続するときに便利です。これは、他の外部デバイスを駆動する際に、このクロックを水晶クロックの複製として使えるためです。REFCLK\_OUTにはプログラマブルな駆動機能があります。この機能は、表7に示す2ビットにより制御されます。

表7.REFCLK\_OUT のバッファ制御

| <b>DRV0 Bits (CFR3[29:28])</b> | <b>REFCLK_OUT Buffer</b> |

|--------------------------------|--------------------------|

| 00                             | Disabled (tristate)      |

| 01                             | Low output current       |

| 10                             | Medium output current    |

| 11                             | High output current      |

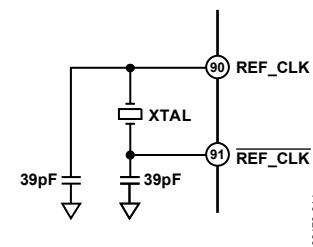

#### REF CLK/REF CLKの水晶駆動

REF\_CLK/REF\_CLK入力に水晶を使う場合、共振周波数は約 25 MHzが必要があります。図 31に推奨回路構成を示します。内蔵発振器は基本波モード水晶でのみ動作します。水晶動作は、XTAL\_SELピンのロジック 1 (1.8 Vロジックが必要)でイネーブルされます。

図31.水晶接続図

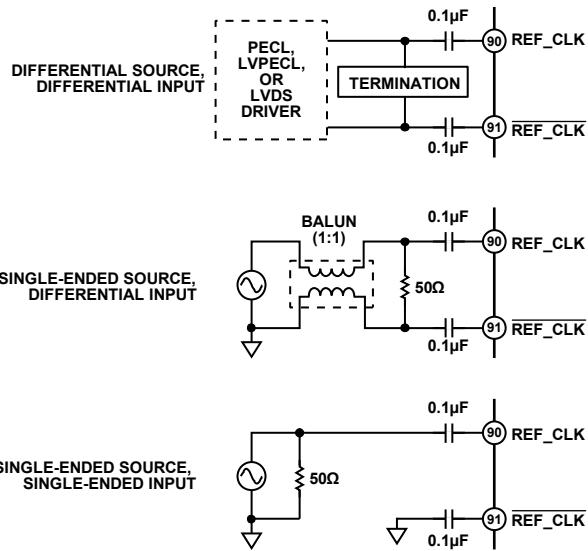

### REF\_CLK/REF\_CLKの直接駆動

信号ソースからREF\_CLK/REF\_CLK入力を直接駆動する場合は、シングルエンドまたは差動の信号を使うことができます。差動信号ソースを使う場合、REF\_CLK/REF\_CLKピンを相補信号で駆動し、 $0.1\ \mu\text{F}$ のコンデンサでAC結合します。シングルエンド信号ソースを使う場合は、シングルエンド/差動変換を使うか、またはREF\_CLK入力をシングルエンドで直接駆動することができます。いずれの場合も、 $0.1\ \mu\text{F}$ のコンデンサを使って、両REF\_CLK/REF\_CLKピンをAC結合して、約 $1.35\ \text{V}$ の内部DCバイアス電圧に影響を与えないようにする必要があります。詳細については、図32を参照してください。

REF\_CLK/REF\_CLK入力抵抗は差動で約 2.5 k $\Omega$ です(シングルエンドでは約 1.2 k $\Omega$ )。大部分の信号ソースは比較的低い出力インピーダンスを持っています。REF\_CLK/REF\_CLKの入力抵抗は比較的高いため、終端インピーダンスへの影響は無視できるので、信号ソースの出力インピーダンスと同じ値を使うことができます。図 32の 2つの例では、50  $\Omega$ 出力インピーダンスの信号ソースを使っています。

図32.直接接続

## 位相ロック・ループ(PLL)倍増器

内部位相ロック・ループ(PLL)は、システム・クロック周波数より非常に低い周波数のリファレンス・クロックを使うオプションを提供します。この PLL は、広い範囲のプログラマブルな周波数倍率(12×～127×)、プログラマブルなチャージ・ポンプ電流、外部ループ・フィルタ部品(PLL\_LOOP\_FILTER ピンを使って接続)をサポートしています。これらの機能は PLL の柔軟性をさらに強化して、位相ノイズ性能の最適化と周波数プラン制

定の柔軟性を可能にします。この PLL には PLL\_LOCK ピンもあります。

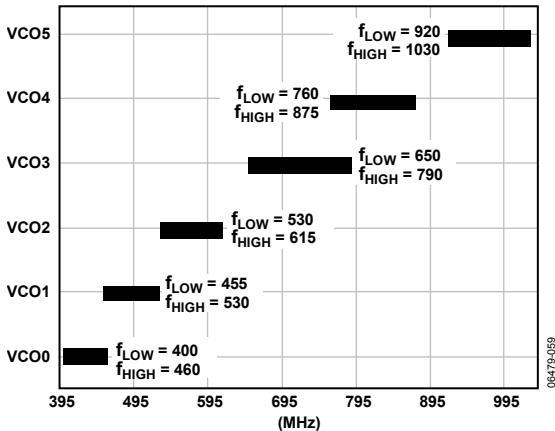

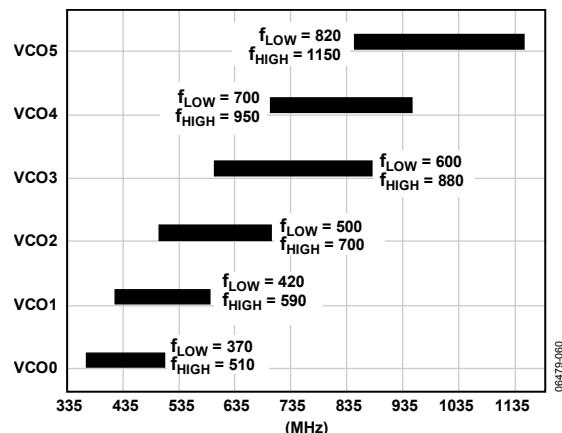

PLL出力周波数範囲( $f_{SYSCLK}$ )は、内蔵VCOの 420 MHz  $\leq f_{SYSCLK} \leq$  1 GHzの範囲に制限されます。さらに、 $f_{SYSCLK}$ が規定範囲内になるように 6 種類の動作範囲から 1 つを選んでVCOを設定する必要があります。図 33と 図 34に、これらのVCO範囲をまとめます。

図 33 に、母集団に属するすべてのデバイスの全温度範囲と電源電圧変動に対するVCO周波数範囲の境界を示します。この図は、複数のデバイスを母集団からランダムに選択して、広く変化する条件で動作させる場合、同じ周波数で動作させるためには CFR3[26:24]に異なる値を設定する必要があることを意味しています。例えば、母集団からランダムに選択し、周囲温度 -10°C で動作させ、システム・クロック周波数= 900 MHzとするデバイスAの場合、CFR3[26:24]に 100bを設定する必要があります。これに対して、母集団からランダムに選択し、周囲温度 90°Cで動作させ、システム・クロック周波数= 900 MHzとするデバイスBの場合には、CFR3[26:24]に 101bを設定する必要があります。システム・クロック周波数が 1 セットの境界内で動作するように周波数プランを選択する場合(図 33参照)、CFR3[26:24]に必要とされる値は、デバイス間で一致します。

図 34 に、母集団から選択されたある 1 個のデバイスの全温度範囲と電源電圧変動に対するVCO周波数範囲の境界を示します。図 34 は、条件の全範囲で動作させる場合、1 個のデバイスの VCO周波数範囲は、常に重複することを示します。

CFR3[26:24]に対して 1 つのデフォルト値を使用したい場合は、図 33に示す複数の範囲内の 1 つに入る周波数を選択する必要があります。さらに、与えられたいずれのデバイスでも、VCO周波数範囲が重なります。これは、与えられたデバイスが条件の全範囲で、VCO範囲に周波数カバレッジのギャップを持つてないことを意味しています。

図33.代表的なウェハー・プロセス歪みを含む各 VCO 範囲

図34.代表的な各 VCO 範囲

表8.VCO 範囲ビットの設定

| VCO SEL Bits (CFR3[26:24]) | VCO Range    |

|----------------------------|--------------|

| 000                        | VCO0         |

| 001                        | VCO1         |

| 010                        | VCO2         |

| 011                        | VCO3         |

| 100                        | VCO4         |

| 101                        | VCO5         |

| 110                        | PLL bypassed |

| 111                        | PLL bypassed |

#### PLLチャージ・ポンプ

PLL性能の最適化で柔軟性を強化するため、チャージ・ポンプ電流( $I_{CP}$ )は設定可能になっています。表 9に、ビット設定値対公称チャージ・ポンプ電流を示します。

表9.PLL チャージ・ポンプ電流

| I <sub>CP</sub> Bits (CFR3[21:19]) | Charge Pump Current, I <sub>CP</sub> (μA) |

|------------------------------------|-------------------------------------------|

| 000                                | 212                                       |

| 001                                | 237                                       |

| 010                                | 262                                       |

| 011                                | 287                                       |

| 100                                | 312                                       |

| 101                                | 337                                       |

| 110                                | 363                                       |

| 111                                | 387                                       |

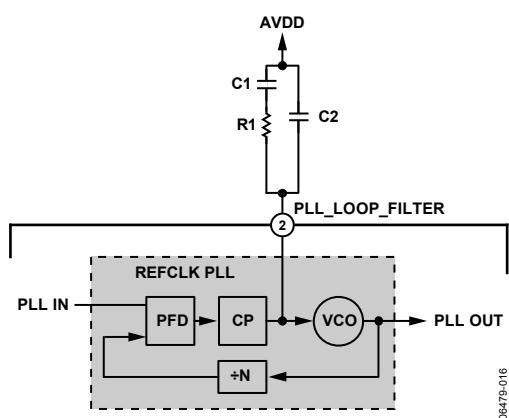

## 外付けPLLループ・フィルタ部品

PLL\_LOOP\_FILTER ピンは、外付けループ・フィルタ部品を接続する接続インターフェースを提供します。カスタム・ループ・フィルタ部品を使用するこの機能により、PLL性能の最適化が柔軟に行えるようになります。PLLと外付けループ・フィルタ部品を図 35に示します。

図35.REFCLK PLL の外付けループ・フィルタ

一般的な文献では、この構成は 3 次のタイプII PLLになります。ループ・フィルタ部品値を計算するときは、VCO SEL ビットの設定値に基づいて、帰還分周値(N)、位相検出ゲイン( $K_D$ )、VCO ゲイン( $K_V$ )から始めます( $K_V$ については表 1参照)。ループ・フィルタ部品値は、次のように、必要とされるオープン・ループ帯域幅( $f_{OL}$ )と位相マージン( $\phi$ )に依存します。

$$R1 = \frac{\pi N f_{OL}}{K_D K_V} \left( 1 + \frac{1}{\sin(\phi)} \right) \quad (4)$$

$$C1 = \frac{K_D K_V \tan(\phi)}{2N(\pi f_{OL})^2} \quad (5)$$

$$C2 = \frac{K_D K_V}{N(2\pi f_{OL})^2} \left( \frac{1 - \sin(\phi)}{\cos(\phi)} \right) \quad (6)$$

ここで、

$K_D$ は $I_{CP}$ の設定値に一致。

$K_V$ は表 1から取得。

式 4～式 6 の変数には正しい単位を使用してください。 $I_{CP}$ はAである必要があります(表 9の $\mu$ Aとは異なります)。 $K_V$ はHz/Vである必要があります(表 1のMHz/Vとは異なります)。ループ帯域幅( $f_{OL}$ )はHzで、位相マージン( $\phi$ )はラジアンである必要があります。

例えば、PLL の設定を  $I_{CP} = 287 \mu$ A、 $K_V = 625 \text{ MHz/V}$ 、 $N = 25$  とします。必要とされるループ帯域幅と位相マージンはそれぞれ 50 kHz と 45°である場合、ループ・フィルタ部品値は、 $R1 = 52.85 \Omega$ 、 $C1 = 145.4 \text{ nF}$ 、 $C2 = 30.11 \text{ nF}$  になります。

## PLLロック表示

PLL を使用する場合、PLL\_LOCK ピンがアクティブ・ハイ表示を提供し、PLL が REFCLK 入力信号にロックしたことを表示します。PLL\_LOCK ピンはラッ奇された出力であることに注意してください。PLL がバイパスされると、このピンはロジック 1 のままになります。PFD リセット・ビットをセットすることにより PLL\_LOCK ピンをクリアすることができます。通常の動作では、PFD リセット・ビットをクリアする必要があります。

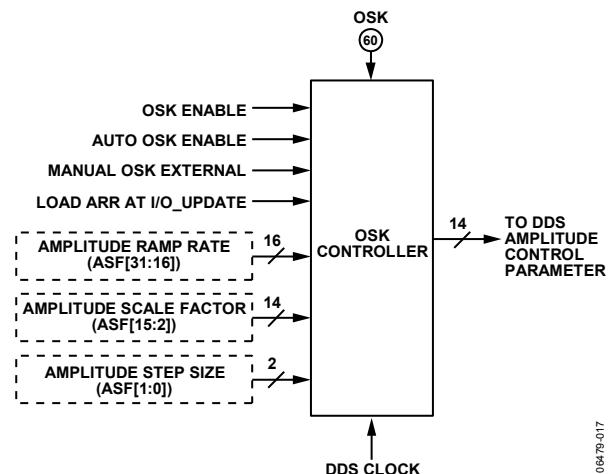

## 出力シフト・キーイング(OSK)

OSK機能(図 36を使うと)、DDSの出力信号振幅を制御することができます。プログラム制御下で、手動モードと自動モードを使用することができます。OSKブロックで発生される振幅データは、振幅データをDDSへ出力するように設定された他の機能ブロックより高い優先順位を持ちます。したがって、OSKデータ・ソースがイネーブルされると、他のすべての振幅データ・ソースより優先されます。

図36.OSK のブロック図

OSK機能の動作は、CFR1 レジスタの 2 ビット(OSKイネーブルとセレクト自動OSK)、外部OSKピン、ASFレジスタの全 32 ビットにより制御されます。OSKブロックのプライマリ制御は、OSKイネーブル・ビットです。OSK機能をディスエーブルすると、OSK入力の制御が無視され、内部クロックが停止します。

OSK 機能をイネーブルする場合、セレクト自動 OSK ビットを使って、自動動作または手動動作が選択されます。ロジック 0 が手動モード(デフォルト)を指定します。

## 手動OSK

手動モードでは、ASF レジスタの振幅スケール・ファクタ部分に対する連続書き込み動作により、出力振幅が変更されます。振幅変化を出力信号に適用できるレートは、シリアル I/O ポートの速度により制限されます。手動モードでは、OSK ピン機能は手動 OSK 外部コントロール・ビットの状態で決定されます。OSK ピンがロジック 0 のとき、出力振幅が 0 になります。その他の場合は、振幅スケール・ファクタ値により出力振幅が設定されます。

## 自動OSK

自動モードでは、リニア振幅対時間のプロファイル(すなわち振幅ランプ)を OSK 機能が自動的に発生します。振幅ランプは、最大振幅スケール・ファクタ、振幅ステップ・サイズ、ステップ間の時間間隔の 3 つのパラメータにより制御されます。振幅ランプ・パラメータは、32 ビット ASF レジスタに格納されており、シリアル I/O ポートを介して設定されます。振幅ステップ間の時間間隔は、ASF レジスタ(Bit [31:16])の 16 ビット振幅ランプ・レート部分を使って設定されます。最大振幅スケール・ファクタは、ASF レジスタ(Bit [15:2])の 14 ビット振幅スケール・ファクタを使って設定されます。振幅ステップ・サイズは、ASF レジスタ(Bit [1:0])の 2 ビット振幅ステップ・サイズ部分を使って設定されます。さらに、ランプの方向(正または負のスロープ)は外部 OSK ピンにより制御されます。

ステップ間隔は、 $f_{SYSCLK}$  の 1/4 レートで駆動される 16 ビット・プログラマブル・タイマにより制御されます。タイマ周期は、振幅ステップ間の時間間隔を設定します。ステップ時間間隔( $\Delta t$ )は次式で与えられます。

$$\Delta t = \frac{4M}{f_{SYSCLK}}$$

ここで、

$M$  は ASF レジスタの振幅ランプ・レート(ARR)部分に格納されている 16 ビット数値。例えば、 $f_{SYSCLK} = 750 \text{ MHz}$ かつ  $M = 23218 (0x5AB2)$ の場合、 $\Delta t \approx 123.8293 \mu\text{s}$ となります。

OSK 機能の出力は、14 ビット符号なしデータ・バスです。このデータ・バスは、DDS の振幅パラメータを制御します(OSK イネーブル・ビットがセットされている場合)。OSK ピンがセットされると、OSK 出力値は 0 (ゼロ)から開始し、設定された振幅ステップ・サイズでインクリメントし、設定された最大振幅値に到達します。OSK ピンがクリアされると、OSK 出力は設定済みの値から開始し、0 (ゼロ)に到達するまで、設定済みの振幅ステップ・サイズでデクリメントします。

OSK ピンを最大値に到達する前にロジック 0 に切り替える場合、OSK 出力は最大振幅値に到達しません。同様に、OSK ピンを 0 に到達する前にロジック 1 に切り替える場合、OSK 出力は 0 に到達しません。

OSK 出力はパワーアップ時に 0 (ゼロ)に初期化され、OSK イネーブル・ビットまたはセレクト自動 OSK ビットがクリアされるごとにリセットされます。

OSK 出力の振幅ステップ・サイズは、表 10 に従い ASF レジスタの振幅ステップ・サイズ・ビットにより設定されます。ステップ・サイズは、14 ビット OSK 出力の LSB 数で表します。設定されるステップ・サイズに無関係に、OSK 出力は ASF レジスタに設定された最大振幅値を超えることはありません。

表10.OSK の振幅ステップ・サイズ

| Amplitude Step Size Bits (ASF[1:0]) | Amplitude Step Size |

|-------------------------------------|---------------------|

| 00                                  | 1                   |

| 01                                  | 2                   |

| 10                                  | 4                   |

| 11                                  | 8                   |

前述のように、16 ビット・プログラマブル・タイマがステップ間隔を制御します。通常、タイマが経過するごとにこのタイマには設定済みのタイミング値がロードされて、新しいタイミング・サイクルが開始されます。ただし、タイマの経過前にタイマにタイミング値の再ロードを発生させる 3 つのイベントがあります。この内の 1 つのイベントは、セレクト自動 OSK ビットがクリア状態からセット状態に変化し、その後に I/O 更新が続く場合に発生します。2 つ目のイベントは、OSK ピンの状態変化です。3 つ目は、I/O 更新時のロード ARR ビットの状態に依存します。このビットがクリアされる場合は、アクションはありません。その他の場合、I/O\_UPDATE ピンがアサートされると(プロファイル変化が発生)、タイマは初期スタート・ポイントにリセットされます。

## デジタル・ランプ・ジェネレータ(DRG)

### DRG の概要

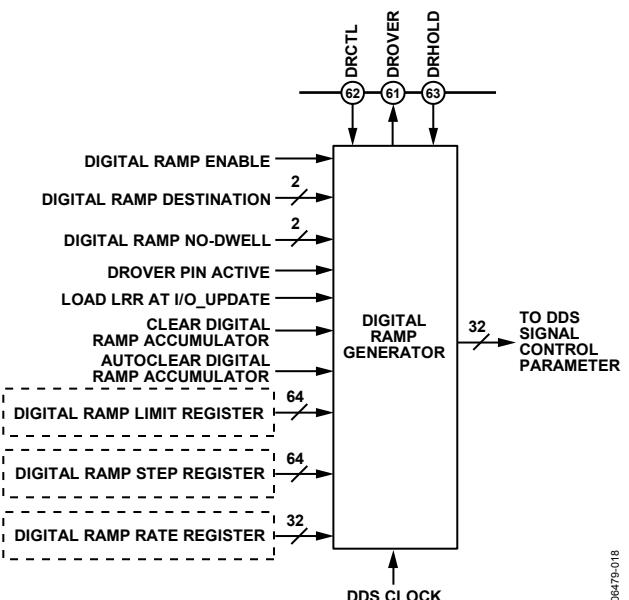

指定されたスタート・ポイントから指定されたエンドポイントまで位相、周波数、または振幅をスイープするために、完全にデジタル化されたデジタル・ランプ・ジェネレータが AD9910 に内蔵されています。DRG は、9 ビットのコントロール・レジスタ・ビット、3 本の外部 PIN、2 個の 64 ビット・レジスタ、1 個の 32 ビット・レジスタを使っています(図 37 参照)。

06479-018

図37.デジタル・ランプのブロック図

DRGのプライマリ制御は、デジタル・ランプ・イネーブル・ビットです。この機能をディスエーブルすると、他のDRG入力制御は無視されて、消費電力を削減するために内部クロックが停止します。

DRGの出力は、32 ビット符号なしデータ・バスです。このバスは表 11 に従いコントロール・ファンクション・レジスタ 2 の 2 ビットのデジタル・ランプ・ディステネーション・ビットから制御されて、3 種類のDDS信号コントロール・パラメータの内の 1 つに接続することができます。32 ビット出力バスは、ディステネーション・ビットの指定に従い、32 ビット周波数パラメータ、16 ビット位相パラメータ、または 14 ビット振幅パラメータのMSBに整列されます。ディステネーションが位相または振幅の場合、未使用 LSB は無視されます。

表11.デジタル・ランプのディステネーション

| Digital Ramp Destination Bits (CFR2[21:20]) | DDS Signal Control Parameter | Bits Assigned to DDS Parameter |

|---------------------------------------------|------------------------------|--------------------------------|

| 00                                          | Frequency                    | 31:0                           |

| 01                                          | Phase                        | 31:16                          |

| 1x <sup>1</sup>                             | Amplitude                    | 31:18                          |

<sup>1</sup> x = Don't care.

DRGのランプ特性はすべて設定可能です。これには、ランプの上限と下限、およびランプの正と負スロープ特性に対するステップ・サイズとステップ・レートの独立な制御が含まれます。DRG の詳しいブロック図を図 38 に示します。

ランプ機能の方向は、DRCTL ピンから制御されます。このピンがロジック 0 になると、負スロープで DRG がランプし、ロジック 1 になると、正スロープで DRG がランプします。

また、DRG は DRHOLD ピンから制御されるホールド機能もサポートします。このピンがロジック 1 に設定されると、DRG は直前の状態で停止し、その他の場合、DRG は通常動作を行います。

DRG のディステネーションではない DDS 信号コントロール・パラメータは、アクティブ・プロファイルから取得されます。

06479-019

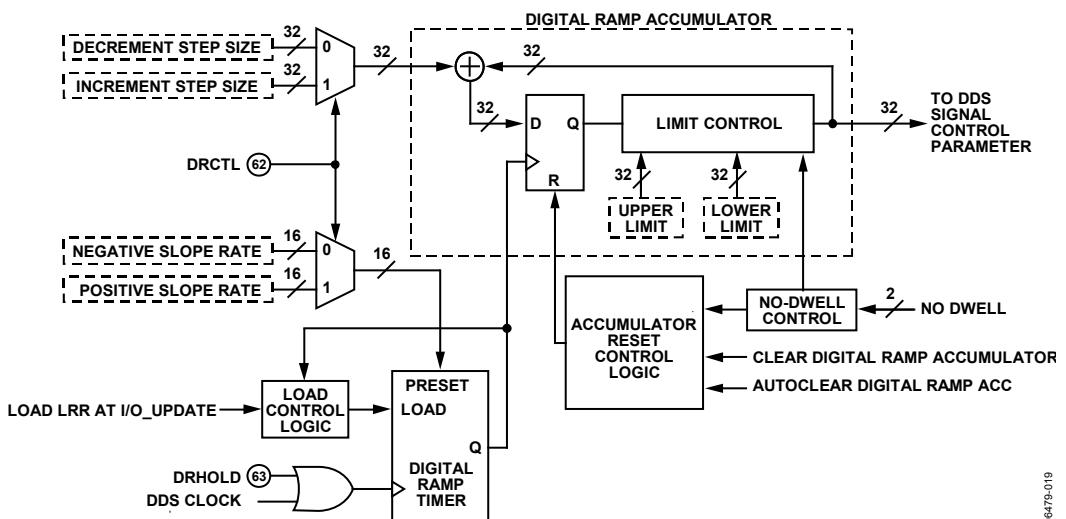

図38.デジタル・ランプ・ジェネレータの詳細

## DRGスロープの制御

DRG のコアは、プログラマブル・タイマからクロック駆動される 32 ビット・アキュムレータです。タイマのタイム・ベースは、 $1/4 f_{SYSCLK}$  で動作する DDS クロックです。このタイマは、アキュムレータ連続更新の間の間隔を設定します。正( $+Δt$ )と負( $-Δt$ )スロープのステップ間隔は、次式のように独立に設定可能です。

$$+Δt = \frac{4P}{f_{SYSCLK}}$$

$$-Δt = \frac{4N}{f_{SYSCLK}}$$

ここで、

$P$  と  $N$  は 32 ビット・デジタル・ランプ・レート・レジスタに格納されている 2 つの 16 ビット値で、ステップ間隔を制御します。

$N$  は、ランプの負スロープ部分のステップ間隔を指定します。

$P$  は、ランプの正スロープ部分のステップ間隔を指定します。

ランプの正( $STEP_P$ )と負( $STEP_N$ )スロープ部分のステップ・サイズは、64 ビット・デジタル・ランプ・ステップ・サイズ・レジスタに設定される 32 ビット値です。各ステップ・サイズは符号なし整数で設定します(ハードウェアが自動的に  $STEP_N$  を負値と解釈します)。32 ビットのステップ・サイズ値と、周波数、位相、または振幅の実際の単位との間の関係は、デジタル・ランプ・ディステネーション・ビットに依存します。必要に応じて、次式の  $M$  に  $STEP_N$  または  $STEP_P$  を代入して、実際の周波数、位相、または振幅ステップ・サイズを計算してください。

$$Frequency Step = \left( \frac{M}{2^{32}} \right) f_{SYSCLK}$$

$$Phase Step = \frac{\pi M}{2^{31}} \quad (\text{ラジアン})$$

$$Phase Step = \frac{45M}{2^{29}} \quad (\text{度})$$

$$Amplitude Step = \left( \frac{M}{2^{32}} \right) I_{FS}$$

周波数の単位は、 $f_{SYSCLK}$  で使った単位(たとえば MHz)と同じであることに注意してください。振幅の単位は、DAC のフルスケール出力電流  $I_{FS}$  に使った単位(たとえば mA)と同じです。

位相と振幅ステップ・サイズの式は、平均ステップ・サイズを与えます。ステップ・サイズは 32 ビット精度で累積されますが、位相または振幅ディステネーションは、それぞれ 16 ビットまたは 14 ビットです。したがって、ディステネーションでは、実際

の位相または振幅ステップは累積された 32 ビット値をそれぞれ 16 ビットまたは 14 ビットに切り詰めた値になります。

前述のように、ステップ間隔は 16 ビットのプログラマブル・タイマから制御されます。このタイマの経過前に再ロードを発生させるイベントは 3 つあります。この内の 1 つのイベントは、デジタル・ランプ・イネーブル・ビットがクリア状態からセット状態に変化し、その後に I/O 更新が続く場合に発生します。2 つ目のイベントは、DRCTL ピンの状態変化です。3 つ目のイベントは、I/O 更新時の LRR ロード・ビットを使ってイネーブルされます(詳細については、レジスタ・マップとビット説明のセクション参照)。

## DRG限界値の制御

ランプ・アキュムレータは、ランプ・ジェネレータ出力の上限と下限を決定する限界値制御ロジックから制御されます。いかなる状況でも、DRG がイネーブルされているとき、DRG 出力は設定済みの限界値を超えることはありません。限界値は、64 ビット・デジタル・ランプ限界値レジスタを使って設定します。正常動作のためには上限値は下限値より大きい必要があることに注意してください。

## DRGアキュムレータのクリア

ランプ・アキュムレータはプログラム制御の下でクリア(すなはち 0 ヘリセット)することができます。ランプ・アキュムレータがクリアされると、DRG 出力がデジタル・ランプ限界値レジスタに設定された下限値になります。

アキュムレータの帰還パスに組込まれている限界値制御ブロックにとって、アキュムレータをリセットすることは下限値にプリセットすることと同じです。

## 通常ランプの生成

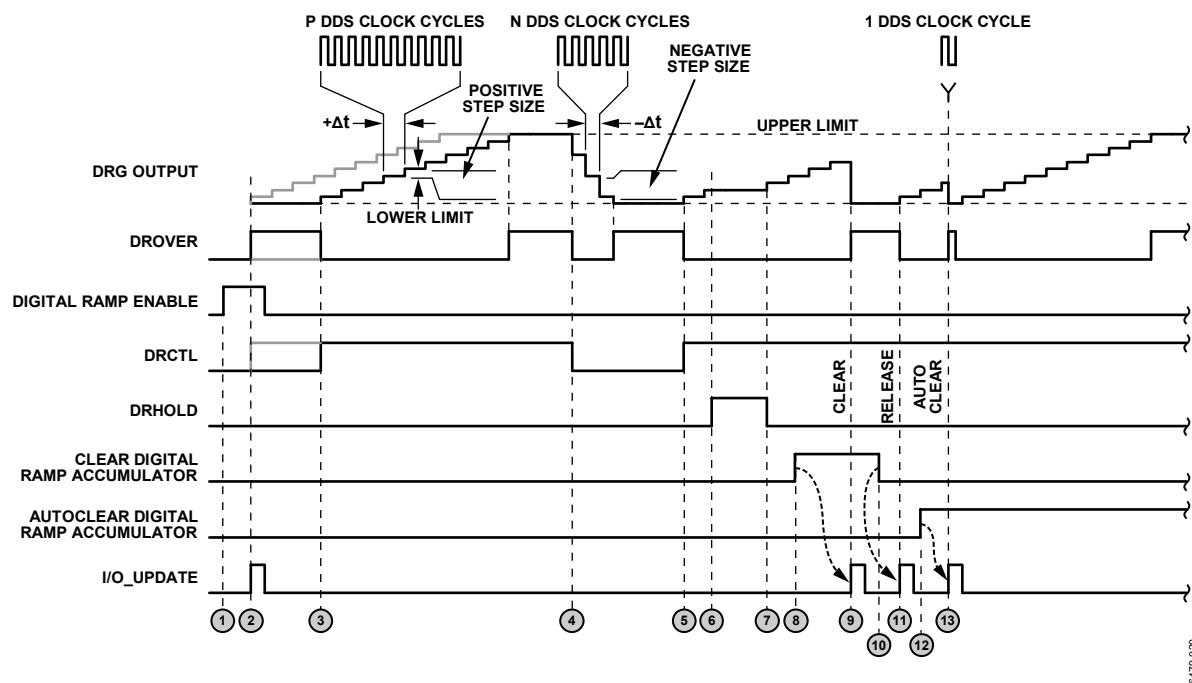

通常ランプの生成は、両ノード・ドゥエル・ビットがクリアされることを意味します(詳細については、ノード・ドゥエル・ランプの生成のセクション参照)。図 39 に、ランプ波形例を必要とするコントロール信号と一緒に示します。上のトレースは DRG 出力です。下のトレースは DROVER 出力ピンのステータスです(DROVER ピン・アクティブ・ビットがセットされている場合)。残りのトレースはコントロール・ビットとコントロール・ピンです。関連するランプ・パラメータも示しています(上限、下限、ステップ・サイズ、正と負スロープの  $Δt$ )。下のトレースで、丸で囲んだ番号は特定のイベントを示しています。これらのイベントは、次の節では番号で参照します(イベント 1 など)。

この特定例では、ランプの正と負スロープは、DRG の柔軟性を示すために異なっています。両スロープのパラメータは、正と負スロープを同じ値するように設定することができます。

図39.通常ランプの生成

イベント 1—デジタル・ランプ・イネーブル・ビットがセットされます。このビットは I/O の更新まで有効にならないので、DRG 出力に影響を与えません。

イベント 2—I/O 更新がイネーブル・ビットを保持します。DRCTL = 1 がこの時点で有効な場合(DRCTL トレースのグレイ部分)、DRG 出力が直ちに正スロープを開始します(DRG 出力トレースのグレイ部分)。その他の場合、DRCTL = 0 のとき、DRG 出力は下限に初期化されます。

イベント 3—DRCTL がロジック 1 へ変化すると、DRG 出力で正スロープが開始されます。この例では、DRCTL ピンが十分長く維持されて、DRG が設定済みの上限値に到達します。DRG は上限値を維持して、ランプ・アキュムレータがクリアされるまで(DRCTL = 0)、または上限値が大きな値に再設定されるまで続けます。後者の場合は、DRG は直ちに前の正スロープ・プロファイルを再開します。

イベント 4—DRCTL がロジック 0 へ変化すると、DRG 出力で負スロープが開始されます。この例では、DRCTL ピンが十分長く維持されて、DRG が設定済みの下限値に到達します。DRG は下限値を維持して、DRCTL = 1 まで、または下限が小さい値に再設定されるまで続けます。後者の場合は、DRG は直ちに前の負スロープ・プロファイルを再開します。

イベント 5—2 回目に DRCTL がロジック 1 へ変化すると、2 回目の正スロープが開始されます。

イベント 6—正スロープ・プロファイルが DRHOLD のロジック 1 への変化により中断されます。これにより、ランプ・アキュムレータが停止し、DRG 出力が直前の値に固定されます。

イベント 7—DRHOLD がロジック 0 へ変化すると、ランプ・アキュムレータがリリースされて、前の正スロープ・プロファイルが再開されます。

イベント 8—クリア・デジタル・ランプ・アキュムレータ・ビットがセットされます。このビットは I/O 更新が発行されるまで有効にならないので、DRG に影響を与えません。

イベント 9—クリア・デジタル・ランプ・アキュムレータ・ビットがセットされ、ランプ・アキュムレータがリセットされ、DRG 出力が設定済みの下限になることを I/O 更新が登録します。DRG 出力は下限を維持し、クリア条件がなくなるまで続きます。

イベント 10—クリア・デジタル・ランプ・アキュムレータ・ビットがクリアされます。このビットは I/O 更新が発行されるまで有効にならないので、DRG 出力に影響を与えません。

イベント 11—I/O 更新が、クリア・デジタル・ランプ・アキュムレータ・ビットがクリアされ、ランプ・アキュムレータがリリースされ、前の正スロープ・プロファイルが再開されたことを登録します。

イベント 12—自動クリア・デジタル・ランプ・アキュムレータ・ビットがセットされます。このビットは I/O 更新が発行されるまで有効にならないので、DRG 出力に影響を与えません。

イベント 13—I/O 更新が、自動クリア・デジタル・ランプ・アキュムレータ・ビットがセットされ、ランプ・アキュムレータがリセットされたことを登録します。ただし、自動クリアにより、ランプ・アキュムレータは DDS クロックの 1 サイクル間だけリセットを維持します。これにより DRG 出力が下限値になりますが、ランプ・アキュムレータは、直ちに通常動作可能になります。この例では、DRCTL ピンはロジック 1 を維持するため、DRG 出力は前の正ランプ・プロファイルを再開します。

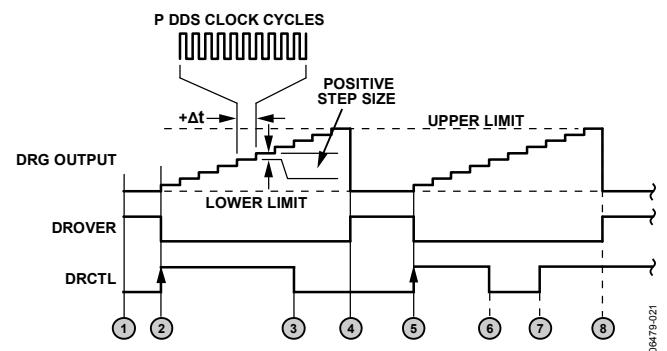

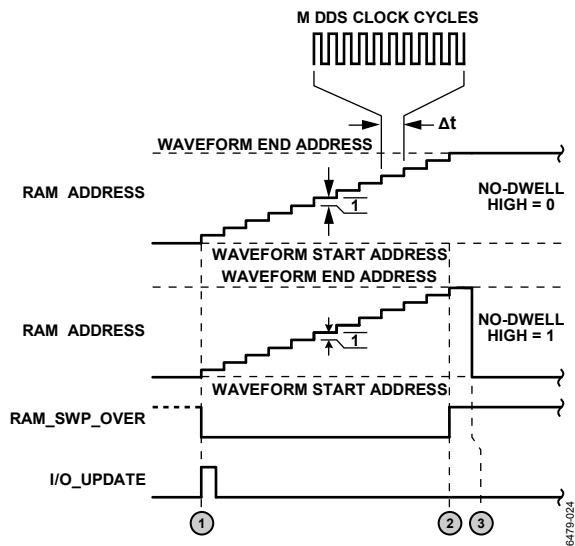

## ノー・ドウエル・ランプの生成

コントロール・ファンクション・レジスタ 2 内の 2 ビットのノー・ドウエル・ビットにより、DRG機能の柔軟性が増えます。通常ランプの発生時に、DRG出力が設定済みの上限または下限に到達すると、限界値を維持し、動作パラメータが他の指示を行うまで続きますが、ノー・ドウエル動作時には、DRG出力は限界値を維持するとは限りません。例えば、DRGが上限値に到達したとき、デジタル・ランプ・ノー・ドウエル・ハイ・ビットがセットされて、DRGは自動的に(そして直ちに)下限に切り替わります(すなわち、ランプ動作で下限に戻るのではなく、下限へジャンプします)。同様に、デジタル・ランプ・ノー・ドウエル・ロー・ビットがセットされて、DRGは自動的に(そして直ちに)上限に切り替わります。

ノー・ドウエル動作時、DRCTLピンの状態変化のみがモニタされます。すなわち、スタティック・ロジック・レベルは無視されます。

ノー・ドウエル・ハイ動作時、DRCTLピンが立上がり変化すると、正スロープ・ランプが開始され、中断せずに(DRCTLピンにさらに動作があっても無視されます)上限値に到達するまで続きます。

ノー・ドウエル・ロー動作時、DRCTLピンが立下がり変化すると、負スロープ・ランプが開始され、中断せずに(DRCTLピンにさらに動作があっても無視されます)下限値に到達するまで続きます。

両ノー・ドウエル・ビットをセットすると、連続ランプ動作モードが開始されます。すなわち、DRG 出力が設定済みのスロープ・パラメータを使って 2 つの限界値の間で自動的に発振します。さらに、DRCTL ピンの機能が少し異なります。このピンはランプ・シーケンスの開始を制御する代わりに、ランプ方向の変更だけを行います。すなわち、DRG 出力が正スロープの中央にあり、かつ DRCTL ピンがロジック 1 からロジック 0 へ変化すると、DRG は直ちに負スロープ・パラメータに切り替えて限界値の間での発振を再開します。同様に、DRG 出力が負スロープの中央にあり、かつ DRCTL ピンがロジック 0 からロジック 1 へ変化すると、DRG は直ちに正スロープ・パラメータに切り替えて限界値の間での発振を再開します。

両ノー・ドウエル・ビットがセットされると、DRG出力がいざれかの設定済みの限界値に到達するごとに、DROVER信号は正パルス(DDSクロックの 2 サイクル)を発生します(ただし、DROVERピン・アクティブ・ビットがセットされている場合)。

ノー・ドウエル・ハイ DRG出力波形を 図 40 に示します。波形図は、デジタル・ランプ・ノー・ドウエル・ハイ・ビットがセットされていて、かつI/O 更新により登録されている場合です。DROVERピン・アクティブ・ビットがセットされているものとして、DROVERピンのステータスも示しております。

図40.ノー・ドウエル・ハイ・ランプの発生

図 40 の丸で囲んだ番号は、次に説明する特定のイベントを表します。

イベント 1—デジタル・ランプ・イネーブル・ビットがセットされいることを I/O 更新レジスタが登録したタイミングを示します。

イベント 2—DRCTLがロジック 1 へ変化すると、DRG出力で正スロープが開始されます。

イベント 3—DRCTLがロジック 0 へ変化しそうが、DRG出力には影響しません。

イベント 4—デジタル・ランプ・ノー・ドウエル・ハイ・ビットがセットされているため、DRG出力が上限値に到達すると、直ちに下限へ切り替わり、DRCTLの次のロジック 0 からロジック 1 への変化が発生するまでこれを維持します。

イベント 5—DRCTLがロジック 0 からロジック 1 へ変化して、正スロープ・ランプが再開されます。

イベント 6 およびイベント 7—DRG出力が設定済みの上限値に到達するまで、DRCTLの変化は無視されます。

イベント 8—デジタル・ランプ・ノー・ドウエル・ハイ・ビットがセットされているため、DRG出力が上限値に到達すると、直ちに下限へ切り替わり、DRCTLの次のロジック 0 からロジック 1 への変化が発生するまでこれを維持します。

デジタル・ランプ・ノー・ドウエル・ロー・ビット(デジタル・ランプ・ノー・ドウエル・ハイ・ビットではなく)がセットされたときの動作は同じですが、DRCTLのロジック 1 からロジック 0 への変化でDRG出力が負方向へランプし、下限に到達したときに上限値へジャンプする点が異なります。

## DROVERピン

DROVERピンは、DRGのステータスを表示する外部信号を出力します。特に、DRG出力が設定済みの限界値のいずれかにあるとき、DROVERピンがロジック 1 となり、その他の場合はロジック 0 になります。両ノー・ドウエル・ビットがセットされる特別なケースでは、DRG出力が設定済みのいずれかの限界値に到達するごとに、DROVERピンは DDSクロックで 2 サイクル幅の正パルスを発生します。

## RAMコントロール

### RAMの概要

AD9910は、 $1024 \times 32$ ビットのRAMを使用しています。RAMには、データ・ロード/読み出しモードと再生モードの2つの基本動作モードがあります。シリアルI/Oポートを介してRAMデータをロードまたはリードバックするとき、データ・ロード/読み出しモードがアクティブになります。RAMイネーブル値が内部データ・ディステネーションの1つに接続されたときに、再生モードがアクティブになります。

特定の再生モードに応じて、RAMを最大8個の独立な時間領域波形で分割することができます。これらの波形はDDS信号コントロール・パラメータを駆動して、周波数変調、位相変調、振幅変調、またはポーラ変調された信号を発生できるようにします。

コントロール・ファンクション・レジスタ1のRAMイネーブル・ビットをセットすると、RAM動作がイネーブルされます。このビットの状態に対する変更を行うためには、I/O更新(プロファイル変更)が必要です。

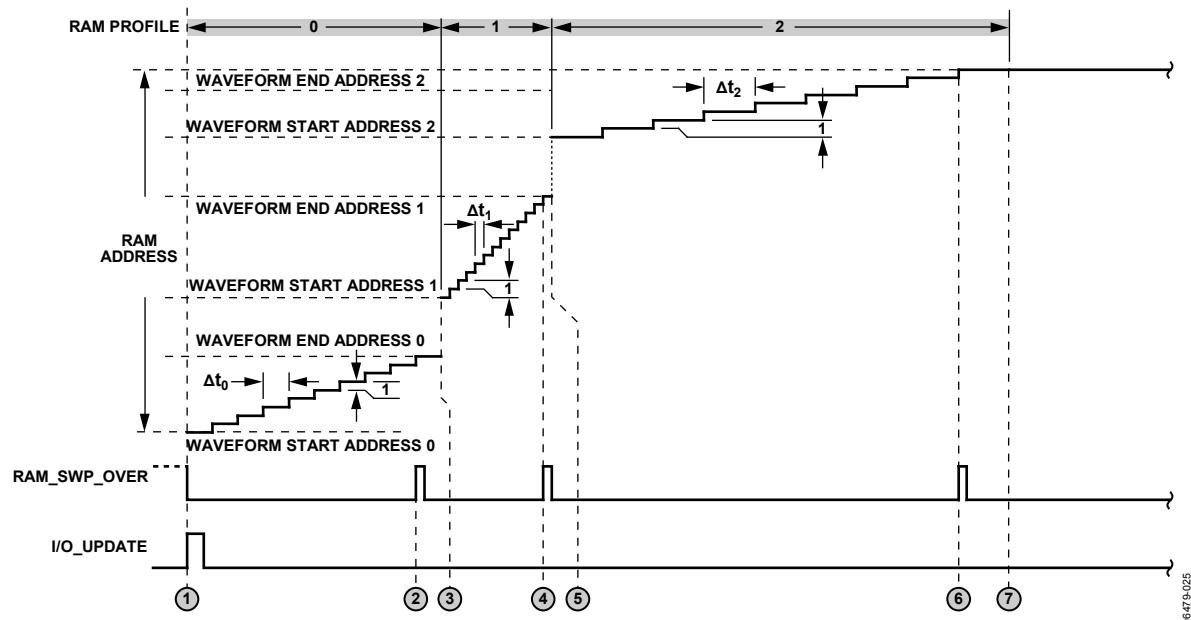

波形は、3本のプロファイル・ピンからアクセスされる8個のRAMプロファイル・コントロール・レジスタを使って発生されます。各プロファイルには次の内容が含まれます。

- 10ビット波形開始アドレス・ワード

- 10ビット波形終了アドレス・ワード