### 特長

- コンポジット・ビデオ出力：NTSCとPALとともにサポート

- クロミナンスと輝度の出力(Sビデオ出力)

- クロスカラー・アーティファクトを除去する輝度トラップ・ポート

- TTLロジック・レベル

- 遅延ラインと自動調整フィルタ組み込み

- 75°の逆終端負荷を駆動

- 低消費電力設計、+5 Vで動作

- パワーダウン時は1 μA未満に

- 非常に低価格

### アプリケーション

- RGB/VGAからNTSC/PALへのエンコード

- パーソナル・コンピュータ/ネットワーク・コンピュータ

- テレビゲーム

- テレビ会議用カメラ

- ディジタル・スチル・カメラ

### 概要

AD725は、非常に低価格の汎用RGB NTSC/PALエンコーダで、レッド、グリーンおよびブルーの3原色信号を対応するNTSCあるいはPAL標準に応じた輝度(ベースバンド振幅)信号とクロミナンス(サブキャリア振幅および位相)信号に変換します。また、オンチップでこれら2つの出力を合成してコンポジット・ビデオ出力も生成します。3つの出力はすべて、逆終端された75°のケーブルをドライブするために必要な標準信号レベルの2倍の電圧で個別に扱うことができます。

AD725の特長として、輝度信号内に見られるサブキャリア周波数によって生成されるクロスカラーの除去を提供する輝度トラップ(YTRAP)ピンを備えていることが挙げられます。またパワーダウン時には消費電流が1 μA未満になるので、ポータブル製品等の消費電力が重要な要素となる製品にも適しています。すべてのロジック・レベルはTTL互換で、3 V CMOSシステムで求められるロジック条件をサポートしています。

AD725は、低価格の16ピンSOICパッケージに実装され、+5 Vの電源で動作します。

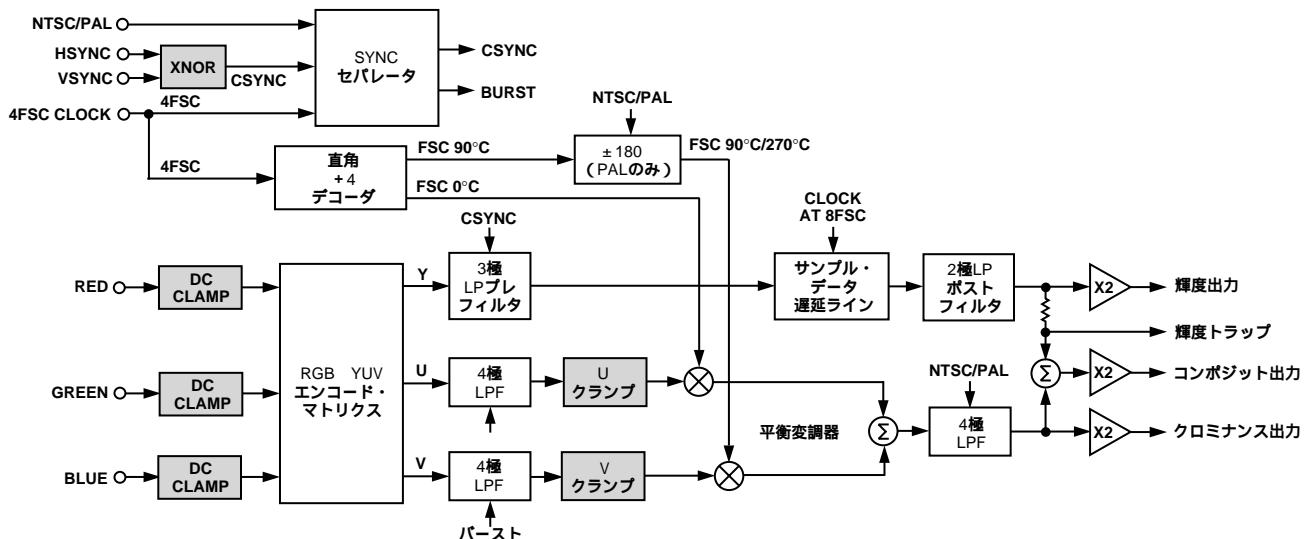

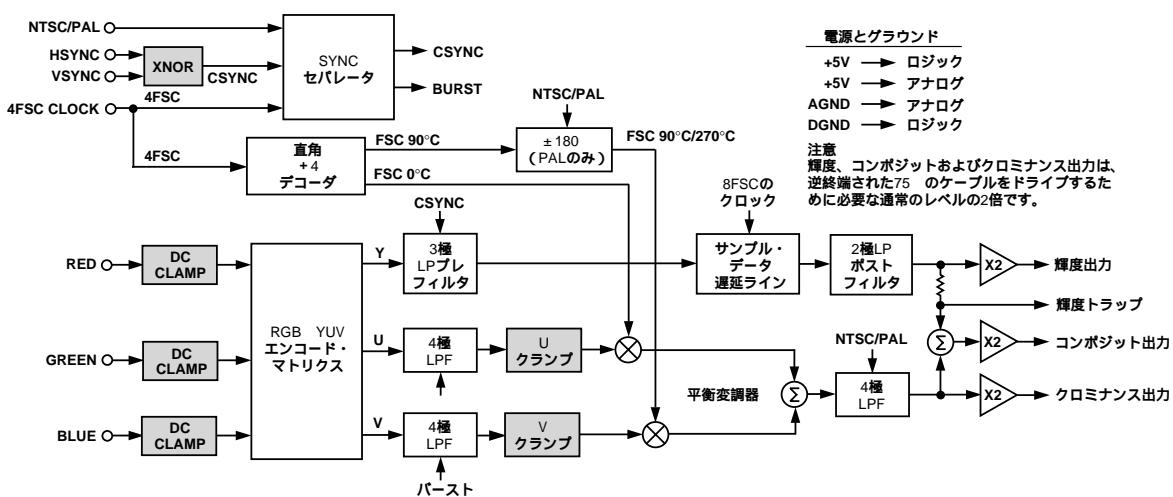

### 機能ブロック図

# AD725 仕様

(特に指定のない限り、 $V_S = +5$ 、 $T_A = +25$  、4FSC同期クロックを使用。すべての負荷は、ICピンにおいて $150 \pm 5\%$ 。出力は75 の逆終端負荷で測定)

| パラメータ                                | 条件            | Min     | Typ | Max   | 単位      |

|--------------------------------------|---------------|---------|-----|-------|---------|

| 信号入力(RIN, GIN, BIN)                  |               |         |     |       |         |

| 入力振幅                                 | フルスケール        |         |     | 714   | mV p-p  |

| 黒レベル <sup>1</sup>                    |               | 0.8     |     |       | V       |

| 入力抵抗 <sup>2</sup>                    | RIN, GIN, BIN | 1       |     |       | M       |

| 入力容量 <sup>3</sup>                    |               | 5       |     |       | pF      |

| ロジック入力(HSYNC, VSYNC, 4FSC, CE, STND) | TTLロジック・レベル   |         |     |       |         |

| ロジック・ロー入力電圧                          |               | 1       |     |       | V       |

| ロジック・ハイ入力電圧                          |               | 2       |     |       | V       |

| ロジック・ロー入力電流(DC)                      |               | 1       |     |       | $\mu A$ |

| ロジック・ハイ入力電流(DC)                      |               | 1       |     |       | $\mu A$ |

| ビデオ出力 <sup>3</sup>                   |               |         |     |       |         |

| 輝度(LUMA)                             |               |         |     |       |         |

| 帯域幅、-3 dB                            | NTSC          | 4.4     |     |       | MHz     |

|                                      | PAL           | 5.2     |     |       | MHz     |

| ゲイン誤差                                |               | -7      | -2  | +7    | %       |

| 非直線性                                 | max p-p       | 0.3     |     |       | %       |

| 同期レベル                                | NTSC          | 252     | 279 | 310   | mV      |

|                                      | PAL           | 264     | 291 | 325   | mV      |

| DC黒レベル                               |               | 1.3     |     |       | V       |

| 輝度トラップ(YTRAP)                        |               | 1.0     |     |       | k       |

| 出力抵抗                                 |               | 1.0     |     |       | V       |

| DC黒レベル                               |               | 1.0     |     |       | V       |

| クロミナンス(CRMA)                         |               |         |     |       |         |

| 帯域幅、-3 dB                            | NTSC          | 1.2     |     |       | MHz     |

|                                      | PAL           | 1.5     |     |       | MHz     |

| カラー・バースト振幅                           | NTSC          | 206     | 255 | 305   | mV p-p  |

|                                      | PAL           | 221     | 291 | 362   | mV p-p  |

| カラー・バースト幅                            | NTSC          | 2.51    |     |       | $\mu s$ |

|                                      | PAL           | 2.28    |     |       | $\mu s$ |

| 彩度レベル誤差 <sup>4</sup>                 |               | -4      |     |       | %       |

| 彩度位相誤差 <sup>5</sup>                  |               | $\pm 3$ |     |       | 度       |

| DC黒レベル                               |               | 2.0     |     |       | V       |

| 彩度フィードスルー                            | R、G、B = 0     | 15      | 40  |       | mV p-p  |

| コンポジット(COMP)                         |               |         |     |       |         |

| 絶対ゲイン誤差                              | 輝度に関するもの      | -5      | -1  | +3    | %       |

| 微分誤差                                 | 彩度に関するもの      |         | 0.5 |       | %       |

| 微分位相                                 | 彩度に関するもの      |         | 1.5 |       | 度       |

| DC黒レベル                               |               | 1.4     |     |       | V       |

| 彩度 / 輝度時間アライメント                      | Sビデオ          | 20      |     |       | ns      |

| 電源                                   |               |         |     |       |         |

| 推奨電源範囲                               | 単電源           | +4.75   |     | +5.25 | V       |

| 無負荷時電源電流 エンコード・モード                   |               | 30      | 36  |       | mA      |

| 無負荷時電源電流 パワーダウン・モード                  |               | <1      |     |       | $\mu A$ |

注

<sup>1</sup> R、G、B信号は、外付けの結合キャバシタを経由して入力します。

<sup>2</sup> dc復帰時間(バック・ポーチ・クランプ)を除きます。

<sup>3</sup> すべて75 の逆終端負荷で測定した出力；IC出力ピンのac電圧はここに示した値の2倍になります。

<sup>4</sup> カラーバー・サブキャリア振幅における理想と実際の差を表します。

<sup>5</sup> カラーバー・サブキャリア位相における理想と実際の差を表します。

仕様は予告なしに変更されることがあります。

**絶対最大定格\***

|                   |       |                             |

|-------------------|-------|-----------------------------|

| 電源電圧、APOSとAGNDの間  | ..... | + 6 V                       |

| 電源電圧、DPOSとDGNDの間  | ..... | + 6 V                       |

| AGNDとDGNDの間       | ..... | - 0.3 V ~ + 0.3 V           |

| 入力                | ..... | DGND - 0.3 V ~ DPOS + 0.3 V |

| 内部消費電力            | ..... | 800 mW                      |

| 動作温度範囲            | ..... | - 40 ~ + 85                 |

| 保管温度範囲            | ..... | - 65 ~ + 125                |

| リード温度範囲(ハンダ付け30秒) | ..... | + 230                       |

\* 上記の絶対最大定格を超えるストレスは、デバイスの永久的なダメージを招くおそれがあります。このリストはストレス定格を示すことだけを目的とし、これらの条件もしくは本仕様書の動作に関するセクションに示した以外の条件におけるこのデバイスの機能的な動作を意味するものではありません。長時間にわたって絶対最大定格条件で使用すると、デバイスの信頼性に影響が現れることがあります。

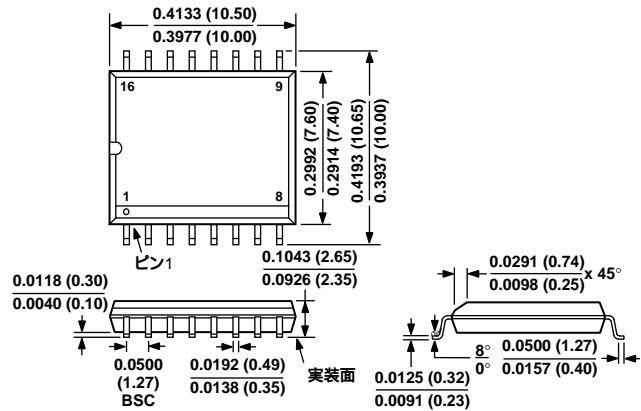

温度特性 : 16ビンSOIC/パッケージ :  $J_A = 100 \text{ } /W$

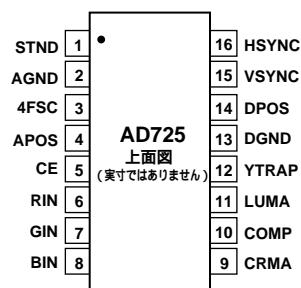

**ピン配置**

16ピン・ワイド・ボディ(SOIC)

(R-16)

**オーダー・ガイド**

| モデル           | 温度範囲        | パッケージ区分  | パッケージ・オプション |

|---------------|-------------|----------|-------------|

| AD725AR       | - 40 ~ + 85 | 16ビンSOIC | R-16        |

| AD725AR-Reel  | - 40 ~ + 85 | 16ビンSOIC | R-16        |

| AD725AR-Reel7 | - 40 ~ + 85 | 16ビンSOIC | R-16        |

| AD725-EB      |             | 評価ボード    |             |

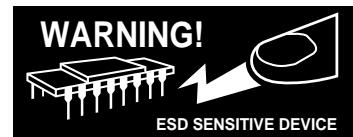

**注意**

ESD(静電放電)の影響を受けやすいデバイスです。人体やテスト装置には4000 Vもの高圧の静電気が容易に蓄積され、検知されることなくそれが放電されることがあります。このAD725は当社独自のESD保護回路を備えていますが、高エネルギーの静電放電さらされたデバイスに回復不能な損傷が残ることもあります。したがって、性能低下や機能喪失を避けるために、適切なESD予防措置を行うようお奨めします。

# AD725

## ピンの説明

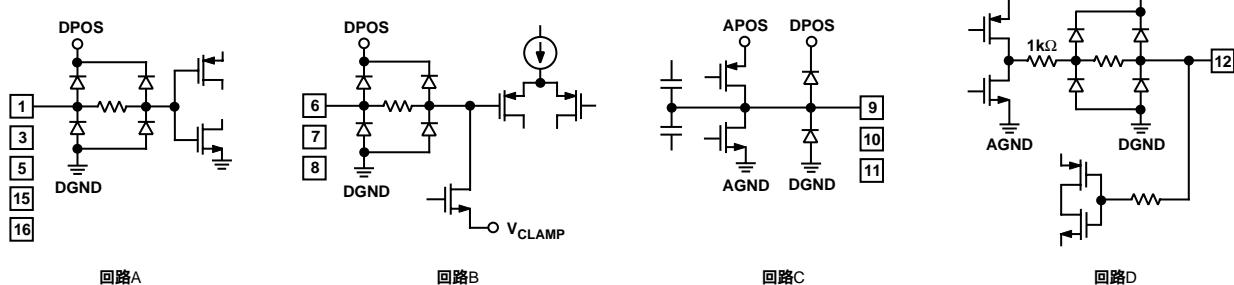

| ピン | 名称    | 説明                                                                                         | 等価回路 |

|----|-------|--------------------------------------------------------------------------------------------|------|

| 1  | STND  | エンコード標準ピン。ロジック・ハイ入力で、NTSCエンコードが選択されます。<br>ロジック・ロー入力でPALエンコードが選択されます。<br>TTLロジック・レベル。       | 回路A  |

| 2  | AGND  | アナログ・グラウンド接続。                                                                              |      |

| 3  | 4FSC  | 4FSCクロック入力。<br>NTSCの場合: 14.318 180 MHz<br>PALの場合: 17.734 475 MHz<br>TTLロジック・レベル。           | 回路A  |

| 4  | APOS  | 正のアナログ電源( +5 V ±5% )。                                                                      |      |

| 5  | CE    | チップ・イネーブル。ロジック・ハイ入力でエンコード機能がイネーブルになります。<br>未使用時は、ロジック・ロー入力でチップがパワーダウンされます。<br>TTLロジック・レベル。 | 回路A  |

| 6  | RIN   | レッド成分のビデオ入力。<br>0 mVから714 mVのAC結合された入力です。                                                  | 回路B  |

| 7  | GIN   | グリーン成分のビデオ入力。<br>0 mVから714 mVのAC結合された入力です。                                                 | 回路B  |

| 8  | BIN   | ブルー成分のビデオ入力。<br>0 mVから714 mVのAC結合された入力です。                                                  | 回路B  |

| 9  | CRMA  | クロミナンス出力。<br>NTSC、PALともに約1.8 V p-p。                                                        | 回路C  |

| 10 | COMP  | コンポジット・ビデオ出力。<br>NTSC、PALともに約2.5 V p-p。                                                    | 回路C  |

| 11 | LUMA  | 輝度とCSYNCの合成出力。<br>NTSC、PALともに約2 V p-p。                                                     | 回路C  |

| 12 | YTRAP | 輝度トラップ・フィルタのタップ。LC共振回路を接続することによってクロスカラー・アーティファクトが低減されます。                                   | 回路D  |

| 13 | DGND  | デジタル・グラウンド接続。                                                                              |      |

| 14 | DPOS  | 正のデジタル電源( +5 V ±5% )。                                                                      |      |

| 15 | VSYNC | 垂直同期信号( +2 V 超にセットされた外部CSYNCを使用する場合 )。TTLロジック・レベル。                                         | 回路A  |

| 16 | HSYNC | 水平同期信号( またはCSYNC信号 )。TTLロジック・レベル。                                                          | 回路A  |

\* 輝度、クロミナンス、およびコンポジット出力は、逆終端された75 Ω のケーブルをドライブするために必要な通常のレベルの2倍です。

図1 . 等価回路

# 代表的な特性 AD725

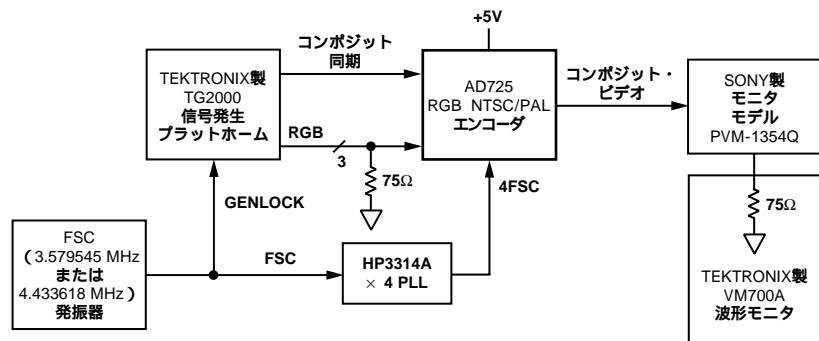

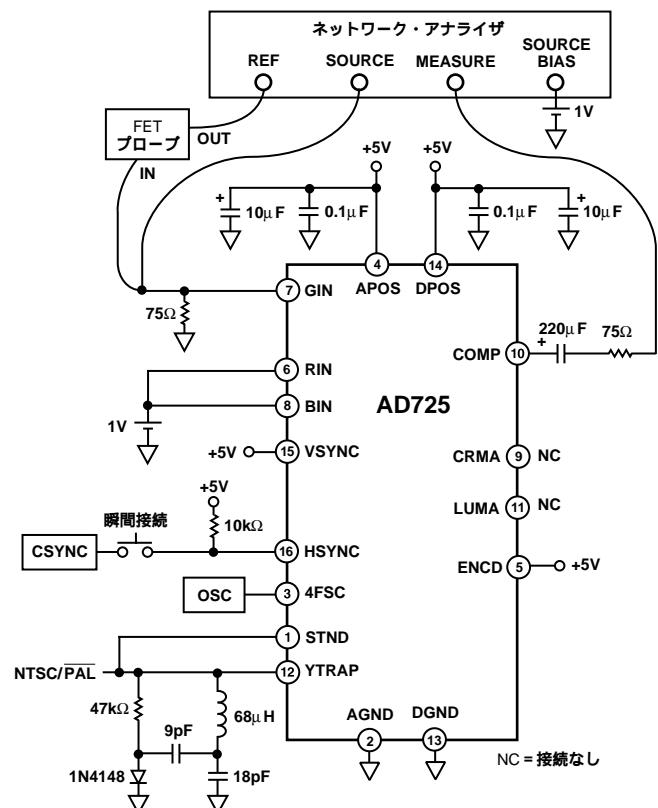

図2. 評価セットアップ

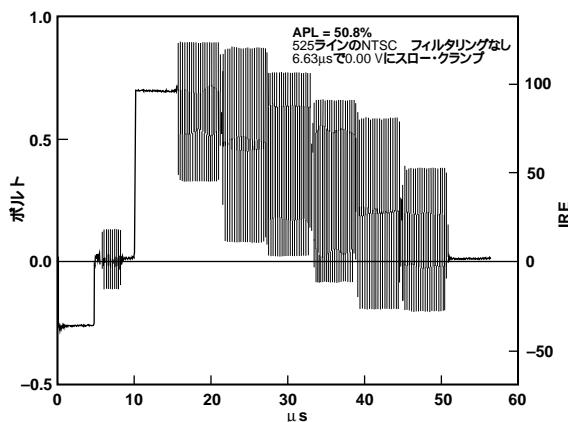

図3. 100%カラーバー NTSC

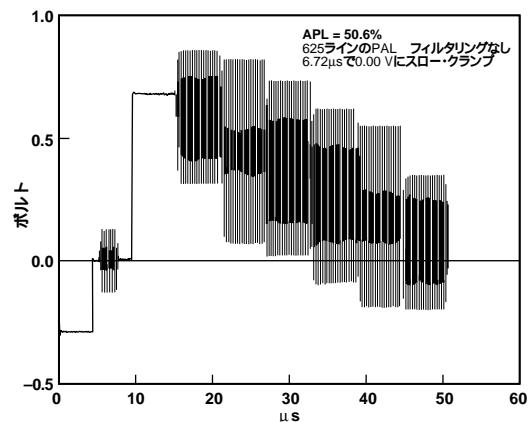

図5. 100%カラーバー PAL

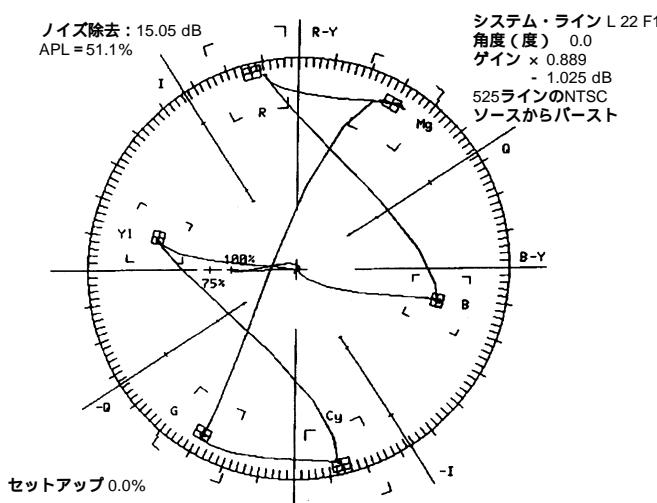

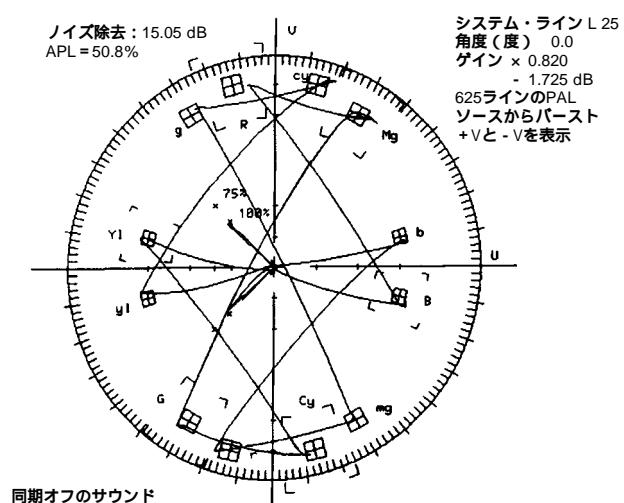

図4. ベクトル・スコープ上での100%カラーバー NTSC

図6. ベクトル・スコープ上での100%カラーバー PAL

# AD725 代表的な特性

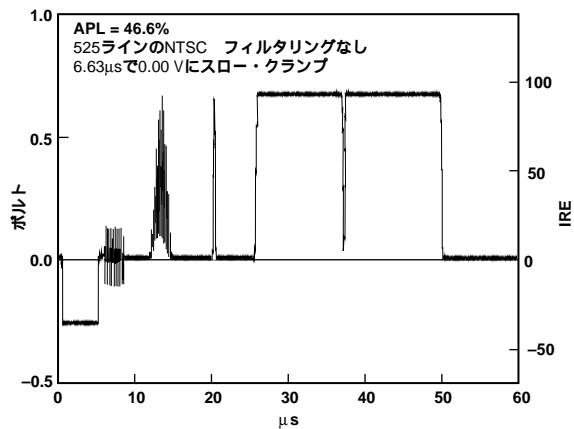

図7. 変調後のパルスとバー NTSC

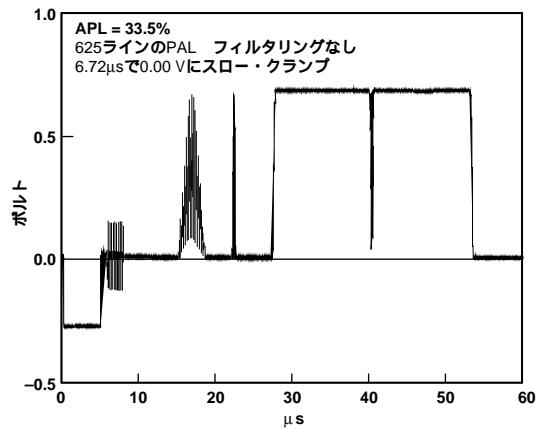

図9. 変調後のパルスとバー PAL

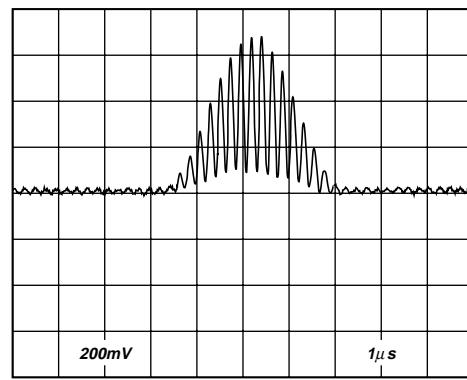

図8. 拡大した変調後のパルス NTSC

図10. 拡大した変調後のパルス PAL

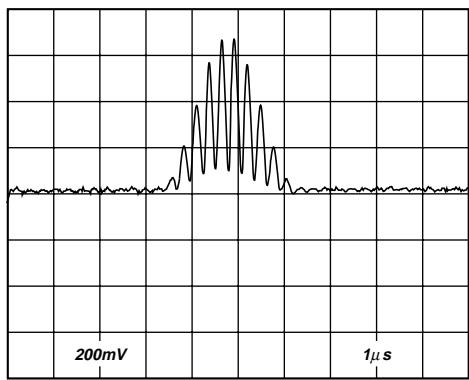

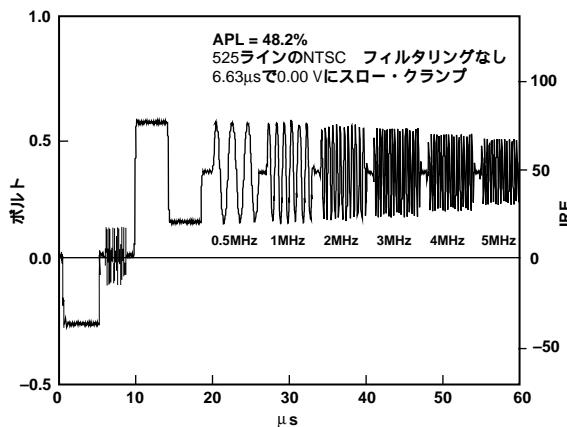

図11. マルチバースト NTSC

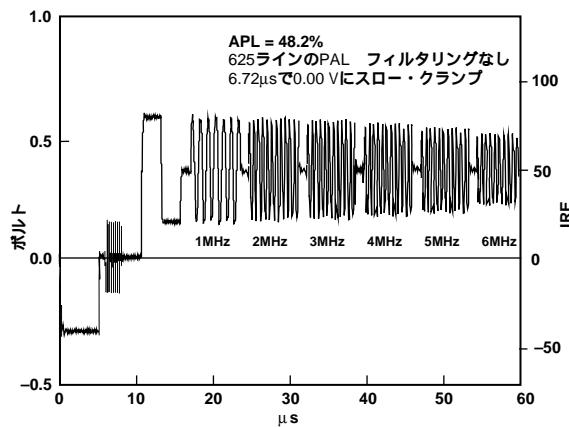

図14. マルチバースト PAL

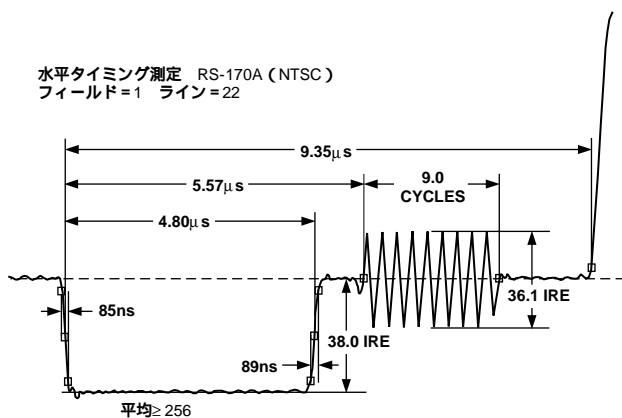

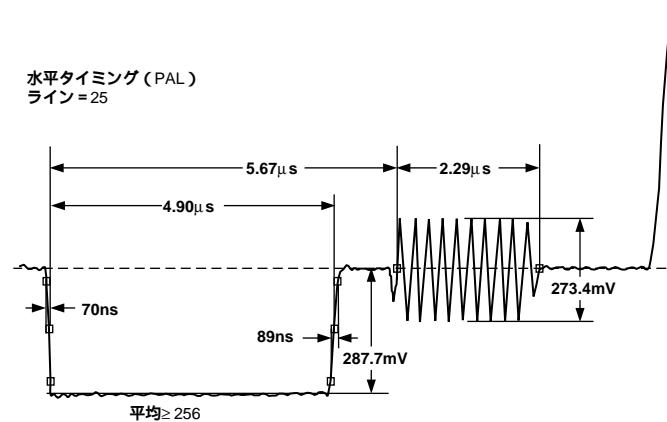

図12. 水平タイミング NTSC

図15. 水平タイミング PAL

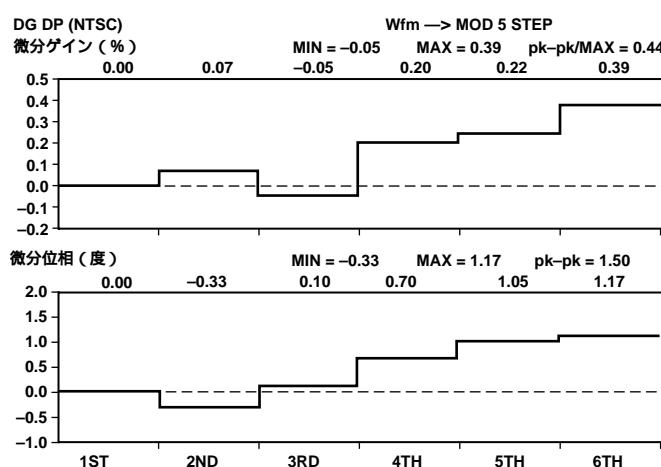

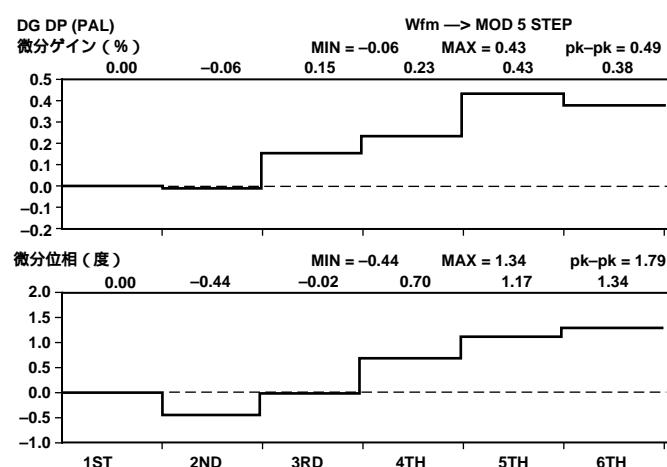

図13. コンポジット出力の微分位相、微分ゲイン NTSC

図16. コンポジット出力の微分位相、微分ゲイン PAL

# AD725

## 動作原理

AD725は、ディジタル・ロジックでタイミングをコントロールできる卓越したアナログ設計です。このタイミング・ロジックは、AD725の4FSCピンに外部から基準周波数を入力することによりカラー・サブキャリア周波数の4倍で動作します。この周波数は、NTSC方式でエンコードする場合には14.318 180 MHz、PAL方式でエンコードする場合には17.734 475 MHzです。4FSCには、標準のTTLロジック・レベルを入力することができます。この入力クロックのデューティ・サイクルは、それほど決定的ではありませんが、エッジの鋭いクロックを使用すれば、タイミングに発生する不必要的ジッターを防げます。

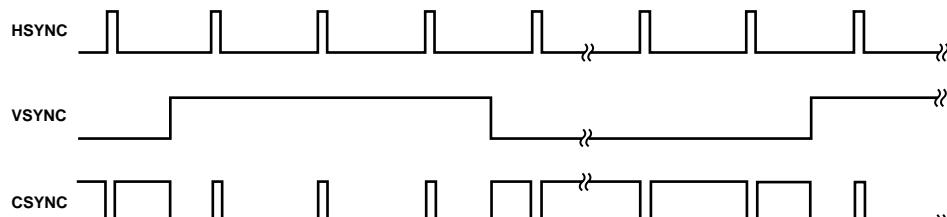

AD725では、よく使用される2つの同期標準、つまりコンポジット同期と、分離垂直水平同期を使用することができます。外部のコンポジット同期を使用するときは、VSYNCピンにロジック・ハイの信号を印加し、HSYNCピンにコンポジット同期を入力します。分離垂直水平同期が使用できるときは、水平同期をHSYNCピンに、垂直同期をVSYNCピンにそれぞれ入力します。このデバイスは、内部で2つの同期入力のXNOR(排他的否定論理和)を行って合成し、負のパルスを持ったコンポジット同期を生成します。

AD725は、同期パルスの立下りエッジを検出し、その幅を時間測定します。標準水平幅の同期パルスであれば、適切なタイミングで彩度変調回路にカラー・バースト・ペクトルが挿入されます。同期パルスが検出レンジ外であると、カラー・バーストが抑圧され、デバイスは垂直帰線消去モードに入ります。このモードの間、入力基準周波数を使用してオンチップRCの時定数の検証が行われ、また必要に応じてフィルタのカットオフ周波数が返されます。

原色入力RIN、GIN、およびBINには、希望するアクティブ・ビデオ出力に対応するアナログ信号を入力します。これらの入力のフルスケール・レンジは、(NTSC動作、PAL動作ともに)0.714 mVです。外部黒レベルは、これらの入力が外側で終端された後、AD725とac結合されることから重要ではありません。

AD725は、オンチップのRGB入力クランプを備え、オンチップでdcレベルを再生して単電源の信号バスに整合させます。このdc再生タイミングは、同期信号の立下りから約5.5 μs後に開始され、2.5 μs継続されるバースト・フラグに一致します。この期間は、デバイスを黒入力でドライブすることになります。dcクランプに続いてRGB入力がバッファされ、輝度とクロミナンスの出力を形成するための2つの信号バスに分離されます。

図17. 機能ブロック図

## 輝度信号バス

輝度バスは、輝度(Y)マトリクスで始まります。このマトリクスは、RGB入力の組み合わせから出力ビデオの明度情報を生成します。これらの入力の変換には、次に示す標準変換式が用いられます。

$$Y = 0.299 \times R + 0.587 \times G + 0.114 \times B$$

この式は、それぞれの原色に対する人間の視覚感度から得られたもので、明度を表す1つの値を導きます。この式は、フルスケールのRGB入力からフルスケールのY出力が導かれるように調和されています。輝度マトリクスに続いて、コンポジット同期が追加されます。(HSYNC入力とVSYNC入力から)ユーザが供給した同期信号は、マスター・クロック・レートの1/2のレートでAD725にラッチされ、輝度信号の同期パルスになります。クロック・エッジの遷移を除けば、出力同期タイミングは、入力同期タイミングと同じフォーマットになります。また出力同期レベルは、エンコード標準に応じて、NTSC方式では286 mV(40 IRE)、PAL方式では300 mVになります(ピンの電圧はその2倍のレベルになります)。

フィルタリング後の彩度信号バスと時間的に整列させるため、出力に先立って輝度信号を遅延させる必要があります。AD725では、サンプル遅延ラインを用いてこの遅延を行っています。

輝度マトリクスとこの遅延ラインの間では、サンプル遅延によるエイリアシングを防止するために、プレフィルタによって輝度信号から高い周波数成分が取り除かれます。この3極ベッセル・ローパス・フィルタの-3 dB周波数は、NTSC方式で4.85 MHz、PAL方式で6 MHzとなっています。

輝度プレフィルタによって帯域制限された輝度信号は、マスター・リファレンス・クロック・レートの2倍のレートで一連のキャッシュ上にサンプリングされます。適切な遅延の後、データが遅延ライン上に読み出されて輝度信号が再生されます。この遅延ラインで行われる8FSCのオーバーサンプリングは、再生同期出力に発生するジッターの量を抑えます。遅延ラインを駆動するクロックは、バースト・フラグの間に、ビデオ・ラインごとに1回のリセットが行われます。輝度バスの出力は、この間に変更されることなく、またRGB入力の変化にも応答しません。

再生された輝度信号は、2極ベッセル・ローパス・フィルタによってスムージングされます。このフィルタの -3 dB帯域幅は、NTSC 方式で 5.25 MHz、PAL 方式で 6.5 MHz です。最終段のバッファは、LUMA 出力ピン用の電流ドライブとして機能します。

#### クロミナンス信号バス

クロミナンス・バスの始まりは、U と V の差分マトリクスです。AD725 では、NTSC と PAL に U および V の変調ベクトル (+U は位相 0 度として定義されます) を使用しているので、設計が I および Q を用いる設計に比べて簡素化されます。U と V のマトリクスは、次に示す標準変換式を用いて RGB 入力を変換します。

$$U = 0.493 \times (B - Y)$$

$$V = 0.877 \times (R - Y)$$

これらの変換式で使用されている Y 信号は、輝度マトリクスから与えられます。

U 信号と V 信号は、エイリアシングを防止するために、変調の前にプレフィルタによる前処理が行われます。これらの 4 極修正ベッセル・ローパス・フィルタの -3 dB 帯域幅は、NTSC 方式で 1.2 MHz、PAL 方式で 1.5 MHz となっています。

プレフィルタと変調回路の間では、U 信号と V 信号にカラー・ペースト・ベクトルが追加されます。カラー・ペーストのレベルは、コード化の標準に従って決定されます。NTSC 方式の場合は、-U 方向 (V 成分はありません) で、合成振幅 286 mV (40 IRE)、位相 180 度のカラー・ペーストになります。PAL 方式の場合のカラー・ペーストは、-U と ±V のベクトルが等分に含まれ (ラインごとに V 位相を変更) 合成振幅 300 mV、位相が 135 度と 225 度となります (ピンの電圧はこれらのレベルの 2 倍です)。

ペースト・ゲートのタイミングは、同期信号の立下りエッジからのリファレンス・クロックが所定の数になると生成されます。同期パルスの水平方向の幅が標準外であれば、デバイスが  $h/2$  期間 (垂直帰線消去期間) 内にあるとみなされて、ペーストが抑圧されます。

U 信号と V 信号は、1/4 のリファレンス周波数入力 (NTSC 方式では 3.579 545 MHz、PAL 方式では 4.433 618 MHz) でペアとなる直交クロック (サインとコサイン) を変調します。PAL 方式の場合は、同期信号の立下りの検出後にコサイン (V) クロックの位相が変更されます。これにより、PAL モードの V ベクトルの位相が水平ラインごとに変化します。フィールドごとに奇数番号の同期エッジで AD725 を駆動すれば、標準で求められているように、各フィールドのそれぞれのラインで位相が反転するようになります。

クロミナンス信号内のキャリアを抑圧するために U と V には平衡変調回路が用いられています。RGB 入力が等しいときは、変調回路における水平ライン 1 本当たりのオフセットが相殺されるので残留サブキャリアが最小になります。このオフセットの相殺は、U 信号と V 信号バスの dc 復元も行うので、この間、RGB 入力が黒レベルに

保持されていることが重要です。オフセットの相殺は、同期信号の各立下りエッジから約 350 ns 後に始まり、140 ns 間持続します。この間に入力が不平衡になると (たとえばグリーン同期 RGB 入力が使用されると) カラー・ペーストも含めて、残りの水平ラインでこの入力のクロミナンス応答にオフセットが生じてしまいます。

U 信号はサイン・クロックによって、V 信号はコサイン・クロックによって、それぞれ変調回路内でサンプリングされ、その後、加算されてクロミナンス (C) 信号になります。

その後このクロミナンス信号は、最後に 4 極修正ベッセル・ローパス・フィルタを通り、スイッチング変調により生じた高調波がそこで除去されます。このフィルタの -3 dB 周波数は、NTSC 方式で 4.4 MHz、PAL 方式で 5.9 MHz です。最終段のバッファは、CRMA 出力ピン用の電流ドライブとして機能します。

#### コンポジット出力

コンポジット・ビデオ信号を提供するため、分離している (S ビデオ) 輝度とクロミナンスの信号バスが加算されます。しかし、この加算に先立って受信機内のクロスカラー・アーティファクトを除去する必要があるため、フィルタ・トラップが備わっています。

輝度バスには、コンポジット加算回路の手前に抵抗、出力ピン (YTRAP) およびバッファが備わっています。このピンにインダクタとキャパシタを接続することによって、R-L-C 直列共振回路が構成され、クロミナンスのサブキャリア周波数 (NTSC 方式では 3.579 545 MHz、PAL 方式では 4.433 618 MHz) での輝度周波数応答を除去することができます。このフィルタの中心周波数 ( $f_c$ ) は、外付けのインダクタとキャパシタに応じて、次式により決定されます。

$$f_c = \frac{1}{2\sqrt{LC}}$$

この式から、このトラップの中心周波数が外付けのコンポーネントのみによって決定されることがわかります。

ノッチの帯域幅に対する中心周波数の比は ( $Q = f_c/BW$ ) は、次の式で表されます。

$$Q = \frac{1}{1000} \sqrt{\frac{L}{C}}$$

フィルタの Q を選択するときは、サブキャリア周波数に絞込むためにノッチをシャープにするほど、外付けのコンポーネントの許容誤差を厳密にしなければならないという点に注意する必要があります。さらに、Q ノッチが高いほど、輝度ステップ後にリンギングを伴った過渡応答が生じます。Q 値が 1.5 より大きくなると、このリンギングは、シャドウが肉眼で確認できるほどの大きさになります。

# AD725

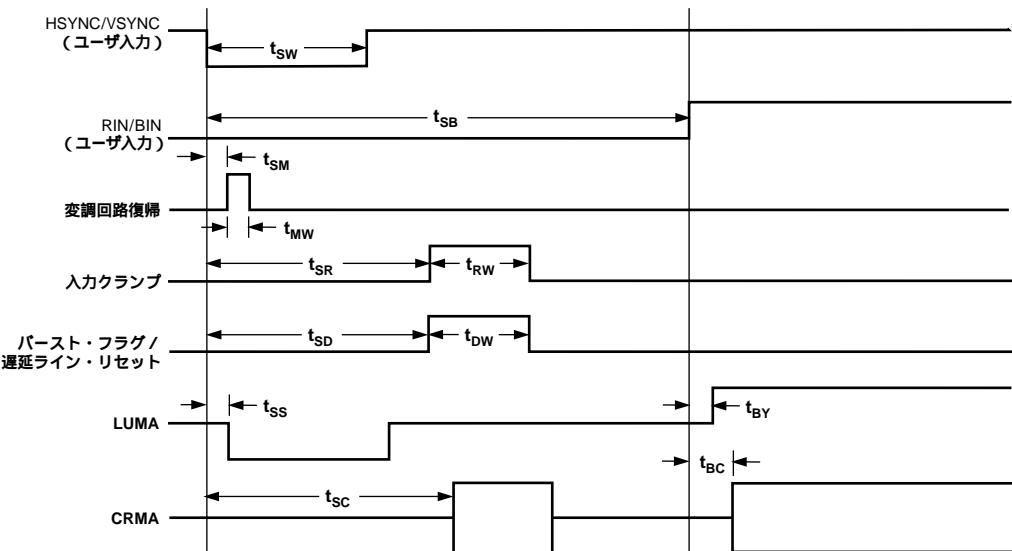

図18 . タイミング図(実際の時間軸を示すものではありません)

表I . タイミング説明(図18を参照してください)

| 記号       | 名称               | 説明                                                | NTSC <sup>1</sup> |        | PAL <sup>2</sup> |        |

|----------|------------------|---------------------------------------------------|-------------------|--------|------------------|--------|

| $t_{SW}$ | 同期幅              | バースト挿入のための入力有効同期幅(ユーザ・コントロール)                     | Min               | 2.8 μs | Min              | 3.3 μs |

| $t_{SB}$ | 同期から帰線消去終了まで     | 同期からカラーまでの最小遅延時間(ユーザ・コントロール)                      | Max               | 5.3 μs | Max              | 5.4 μs |

| $t_{SM}$ | 同期から変調回路復帰まで     | 変調回路のクランプ開始までの遅延時間。                               | Min               | 8.2 μs | Min              | 8.1 μs |

| $t_{MW}$ | 変調回路復帰の幅         | 変調回路オフセット・クランプの長さ(この間彩度信号はありません)                  |                   | 392 ns |                  | 298 ns |

| $t_{SR}$ | 同期からRGBのDC復元まで   | 入力クランプ開始までの遅延時間。                                  |                   | 140 ns |                  | 113 ns |

| $t_{RW}$ | DC復元の幅           | 入力クランプの長さ(この間RGB応答はありません)                         |                   | 5.4 μs |                  | 5.6 μs |

| $t_{SD}$ | 同期から遅延ラインのリセットまで | 遅延ラインのクロックのリセット開始までの遅延時間。                         |                   | 2.5 μs |                  | 2.3 μs |

| $t_{DW}$ | 遅延ラインのリセット幅      | 遅延ラインのクロックのリセットの長さ(この間輝度応答はありません)。バースト・ゲートにもなります。 |                   | 5.7 μs |                  | 5.8 μs |

| $t_{ss}$ | 同期入力から輝度同期出力まで   | 同期入力のアサートからLUMAの出力が同期するまでの遅延時間。                   | typ               | 2.5 μs |                  | 2.3 μs |

| $t_{BY}$ | 帰線消去終了からLUMA開始まで | RGB入力のアサートからLUMA出力応答までの遅延時間。                      | typ               | 310 ns | typ              | 265 ns |

| $t_{sc}$ | 同期からカラー・バーストまで   | 有効な水平同期の開始からCRMAカラー・バーストが開始するまでの遅延時間。             | typ               | 340 ns | typ              | 280 ns |

| $t_{BC}$ | 帰線消去終了からCRMA開始まで | RGB入力のアサートからCRMA出力応答までの遅延時間。                      | typ               | 5.8 μs | typ              | 5.9 μs |

|          |                  |                                                   | typ               | 360 ns | typ              | 300 ns |

注

<sup>1</sup> 入力ロック = 14.318180 MHz、STNDピン = ロジック・ハイ

<sup>2</sup> 入力ロック = 17.734475 MHz、STNDピン = ロジック・ロー

## AD725の適用

### 入力

RIN, BIN, GINは、アナログ入力で、ICに近接した位置で75°でグラウンドに終端します。適切に終端されていれば、最大入力レベルのピーク・トゥ・ピーク電圧は、714 mV p-pになります。水平帰線消去期間は、各信号のもっとも負側になる部分になります。

水平帰線消去期間の入力は、入力信号の黒レベルに保持します。内蔵dcクランプは、カラー・バーストの間、このレベルを内部的に黒レベルとして使用する基準値にクランプします。この間にRIN, GIN, BINまたはAGNDピンにあるノイズは、入力キャパシタにサンプリングされます。この結果、すべての出力において、あるいは不平衡の場合はCOMPとCRMAの出力におけるサブキャリアのフィードスルーに、ライン間のdcレベル変動が生じます。

ノイズ除去を向上させるためには、容量の大きい入力キャパシタを使用します。通常は、 $0.1\mu F$ のキャパシタで充分です。

同様に、CSYNCの立下り直後の間に、UとVのクランプが変調回路を平衡させます。この期間内にノイズが存在すると、変調回路に取込まれ、COMPとCRMAの出力に残留サブキャリアが生じます。

HSYNCとVSYNCはロジック・レベルの入力で、これら2つの入力は内部で合成されてコンポジット同期信号になります。コンポジット信号を直接使用する場合は、VSYNCをロジック・ハイ(> +2 V)に引上げた状態で信号をHSYNCに印加します。

入力同期信号のフォームは、コンポジット・ビデオ(COMP)出力と輝度(LUMA)出力のコンポジット同期のフォームを決定します。等化パルスまたは鋸歯状パルスをHSYNC入力に印加しなくても出力には影響ありません。等化パルスまたは鋸歯状パルスのない同期信号は技術的にビデオ標準の仕様と適合しませんが、多くのモニタでは、これらのパルスがなくても良好な画像が表示できます。これらの信号を含めるか否かは、コストと複雑性およびビデオ標準の厳守といった面でのシステム的な検討事項となります。

HSYNCとVSYNCのロジック入力は、わずかなヒステリシスを有し、これによりノイズを原因とする入力エッジと複数同期信号のエッジを区別します。このことは、同期パルスを時間的基準にして垂直帰線消去期間の検出が行われることから非常に重要です。

ロジック入力は、動作温度と電源電圧の全範囲にわたってVIL < 1.0 V, VIH > 2.0 Vに設計されています。これによりAD725は、TTLまたは3 VのCMOS互換出力だけでなくVOLが1.0 V未満となる5 VのCMOS出力と直接的にインターフェースすることができます。

NTSC仕様では、3.579545 MHzの定格サブキャリア周波数に対して±10 Hzの精度が求められます。放送局のスタジオでこの精度を維持することはそれほど難しくありませんが、それを低価格のコンシューマ製品で実現することには価格面で困難が伴います。

AD725は、TV標準で求められるものとはかなり隔たったサブキャリア周波数でも動作します。しかしながら、モニタは通常それほど許容範囲が広くありません。ほとんどのモニタで画像の劣化を招くことなく許容されるサブキャリア周波数は、定格値から数百へ

ルツまでの範囲です。このことは、サブキャリア周波数の精度はシステムの仕様であって、AD725自体の仕様ではないことを示唆しています。

STNDピンは、NTSC動作とPAL動作の選択に使用されます。AD725内部の各種のブロックでは、この入力を使用してそれぞれの動作をプログラムします。AD725では、NTSCとPALの一般的なパリアントのほとんどをサポートしています。しかし、よく知られた標準の中に標準のAD725がサポートしていないものが2つあります。それはNTSC 4.43とM-PALです。

これら2つの標準では、基本的にその名称が対応する標準のほとんどの機能を使用しますが、サブキャリア周波数については、他方の周波数もしくはそれに近い周波数を使用します。これらの標準をサポートするためには、クロミナンス・バスのフィルタの自動プログラミングとその他のタイミングの問題から、工場でプログラムされた特別バージョンのAD725が必要になります。

### レイアウトに関する考察

AD725は、すべてCMOSを使用したミックスド・シグナル部品です。これには、アナログ用とディジタル用の+5 V電源とグラウンドが個別に備わっています。アナログとディジタルのグラウンド・ピンは、どちらも長さの短いインダクタンスの低いパスでグラウンド面に接続する必要があります。各電源ピンは、インダクタンスの低い $0.1\mu F$ のキャパシタとそれより大きな約 $10\mu F$ のタンタル・キャパシタによってグラウンドにバイパスします。

3つのアナログ入力(RIN, GIN, BIN)は、それぞれのピンに近い位置において75°で終端します。しかしながらこれらは、高インピーダンス入力であることから、構成上のループ内に置くことができます。このテクニックは、適当に離隔された高い周波数信号を伴う2つもしくはそれ以上のデバイスに使用されます。その場合、局部的に終端していないAD725に対して接続を行い、信号用に終端されている他方の離れたデバイスに信号を供給します。

AD725の出力振幅は、AD725が駆動するデバイスで必要とされるレベルの2倍になっています。これは、回路で必要になるターミネータによって1/2になるレベルを補償します。AD725の各出力の近傍には、75°の直列抵抗が必要ですが、グラウンドに対する75°の終端は、各ラインの遠端で行います。

出力にはdcバイアスが含まれ、適正に動作させるためにはac結合が必要です。COMPとLUMAでは、低い周波数の情報、NTSCの場合であれば30 Hz(PALの場合であれば25 Hz)までの情報を出力して伝送しなければなりません。それぞれの出力には、これらの低い周波数を通過させるために75°の抵抗と直列に接続した $220\mu F$ のキャパシタが必要になります。CRMA信号は、ほぼ彩度周波数に近い周波数の情報を有しています。したがって容量の小さいキャパシタが好ましい場合には、それを使用できますが、 $220\mu F$ のキャパシタを使用すれば、設計に使用される各種コンポーネントの数をもっとも少なくすることができます。

# AD725

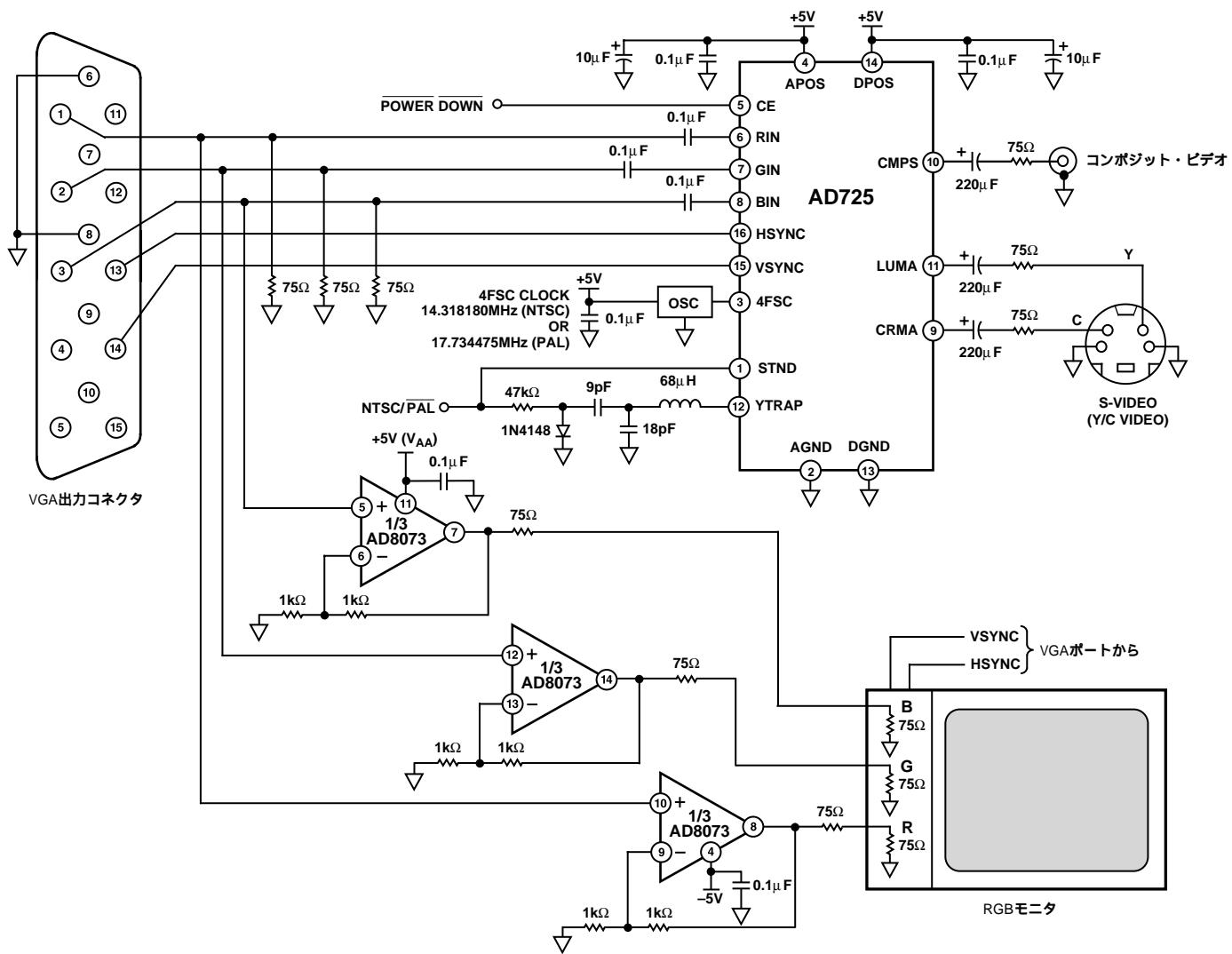

## TV上でのVGA出力の表示

AD725を使用して、パーソナル・コンピュータのVGAカードから出力されたアナログRGBをNTSC方式またはPAL方式のテレビジョン標準に変換することができます。これを行うためには、これらのテレビジョン標準に適合したインターレースRGBビデオとクロック・レートがAD725でも必要になることを理解することが重要です。ほとんどのコンピュータでは、デフォルト出力がインターレースなしのRGB信号で、フレーム・レートはNTSC方式やPAL方式で使用されるものより高くなっています。

多くのVGAコントローラでは、各種の出力モードがサポートされており、内蔵レジスタの内容を変更することによってそのコントロールができます。60 Hz(PALの場合は50 Hz)のインターレース出力を得るために必要な正しい構成については、VGAコントローラのメーカーに問い合わせるのが最善策でしょう。

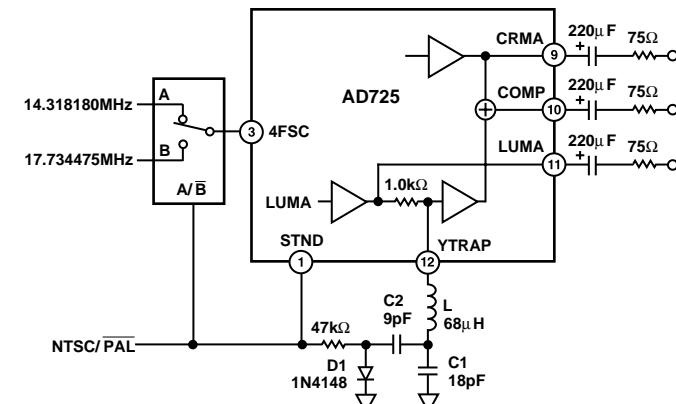

図19は、PCのVGAポートとの接続のための回路を示しています。RGB出力は、AD725の対応する入力にac結合されます。これらの信号は、それぞれ $75\Omega$ でグラウンドに終端されます。

標準の15ピンVGAコネクタは、ピン13がHSYNCに、ピン14がVSYNCになっています。これらの信号は、AD725上の対応する名称の入力に直接接続します。同期NTSCシステムの場合は、VGAコン

トローラをドライブする内部の4FSC(14.318 180 MHz)クロックをAD725の4FSC用に使用することができます。コンピュータの外側からこの信号に直接アクセスすることはできませんが、VGAカード上にあります。(1FSC入力用のエンコーダAD724も用意されています。)

別のRGBモニタも使用する場合は、R、G、B信号と単純に接続することはできません。モニタにはターミネータが備わっており、これらの信号が二重に終端されてしまいます。R、G、B信号は、入力インピーダンスの高い3つのアンプを用いてそれぞれバッファしなければなりません。これらを2倍のゲインで構成すれば、RGBモニタに使用されている二重終端スキームによって正規化されます。

AD8073は、この場合の適用に必要となるバッファリングを提供することができる低価格のトリプル・ビデオ・アンプです。しかし、水平同期の間にR、G、B信号がすべてグラウンドに落ちることから、AD8073では -5 Vの電源がないとこれらの信号を扱うことができません。単電源を使用してR、G、B信号のバッファを可能にするためには、レール・トゥ・レールのアンプが必要になります。この場合の適用では、AD8051(シングル)とAD8052(デュアル)を使用して必要な3つのチャンネルが提供できます。なおこれらのデバイスは、3 Vから5 Vの単電源で動作することができます。

図19 . AD725とPCの(インターレース)VGAポートとのインターフェース

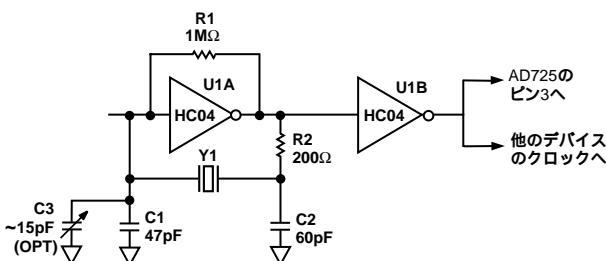

## 低価格水晶発振器

AD725の4FSCおよびこの周波数のクロックを必要とするシステム内の他のデバイスの駆動に使用できるCWクロックは、低価格の発振器で供給することができます。図20に、74HC04パッケージに含まれるインバータを2つ使用した発振器を示します。ここでは一方のインバータが水晶発振回路の構成に、他方のインバータが他の負荷を駆動するための発振回路のバッファに使用されています。ロジック・ファミリは動作周波数をサポートできるCMOSタイプとし、シュミット・トリガ・タイプのインバータは使用できません。U1Aの入力と出力の間をつなぐ抵抗R1は、インバータのゲインを直線化し、発振器をドライブするための有効なゲインと180度の位相シフトをもたらします。

図20. 低価格水晶発振器

水晶発振子は、適切な周波数(NTSC/PAL, 4FSC)の並列共振タイプとします。C1とC2の直列合成容量は、水晶発振子を指定の周波数で動作させるために必要な並列容量についてメーカー側から指定された値と概略で等しくします。この場合、インバータの寄生容量から、一般的にはC1にいく分小さめの値のキャパシタが使われる傾向があります。高い精度で周波数を調整することが望ましい場合は、C1を小さめにしたまま、可変容量キャパシタを並列に接続し、これにより必要な周波数に微調整します。

抵抗R2は、回路が発振を維持するために必要な追加の位相シフトを提供します。この値は、 $R2 = 1/(2 \times \pi \times f \times C2)$ で与えられます。R2の別の機能は、水晶発振子の高調波で発振を抑圧し、インバータ出力を水晶発振器回路がもたらす共振負荷から分離するローパス・フィルタの機能です。

上記の基本的な発振器は、U1Bによってバッファされ、AD725の4FSCピンおよびそのほかのシステム内のデバイスをドライブします。NTSCとPAL用の発振器をともに必要とするシステムでは、同じパッケージに備わるインバータをもう1組使用して、同様な回路を構成することができます。

## ドット・クロール

TVモニタ上にコンポジット信号を表示させると、多くの歪みが現れます。これらの影響の程度は、モニタで使用している信号処理のための回路と、表示する画像の特性によって異なります。コンポジット・モニタを用いて、標準品質のRGB、VGAモニタと同じ程度の高い品質の画像を得ることは一般に不可能です。

コンポジット・ビデオ画像でよく知られている歪みに、ドット・クロールと呼ばれるものがあります。これが生じると、異なる色の2つのエリア間の境界でドット・パターンの移動が現れます。これは、モニタの回路が輝度信号とクロミナンス信号を適切に分離できないために起こるものです。

ドット・クロールを回避する1つの方法は、輝度とクロミナンスが分離されたビデオ信号を使用することです。この種の信号は、SビデオあるいはY/Cビデオと呼ばれています。輝度とクロミナンスがすでに分離されているので、モニタ側でこの機能を実行する必要

がありません。モニタ側にSビデオ入力が備わっている場合には、AD725のSビデオ出力を使用してより質の高い画像を生成することができます。

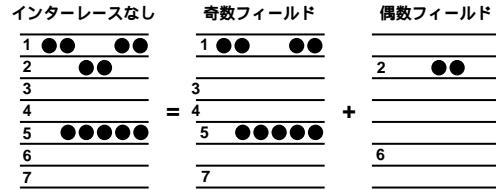

## フリッカ

ソフトウェア・コントロールによりレジスタが適切に設定されるVGA変換アプリケーションで、VGAコントローラ・メーカーがインターレース信号の生成によく使用するテクニックが2つあります。それぞれのテクニックは、AD725が生成する表示に独特な特徴をもたらします。後述するアーティファクトは、どのようなエンコーダを使用してもこれらの入力で同一の表示となることから、エンコーダもしくはコード化のアルゴリズムを原因とするものではありません。これは、コントローラのディスプレイ・チップでインターレースされていない出力をインターレース信号に変換するために使用している方法に原因があります。

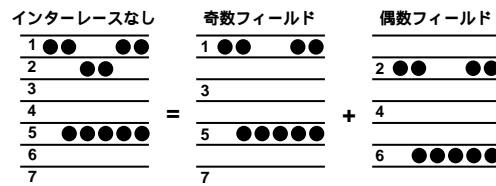

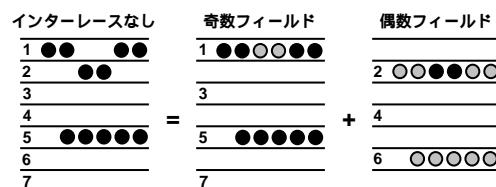

最初のインターレース・テクニックでは、奇数フィールドと偶数フィールドで真のインターレース信号を出力します(図21aの各フレーム)。この方法は、写真、CDビデオ、および動画(ゲーム等)を最良の品質で表示することができます。しかしこの方法は、一般にディスプレイのフリッカと呼ばれている障害を招きます。フリッカは、インターレースされた表示では本質的なもので、フィールドを交番するインターレース・テクニックの特性から惹き起こされます。ここで、白いスクリーン上を水平に横切る1ピクセルの高さを持った黒いラインについて考えます。このラインは、一方のフィールドだけにあり、30 Hz(PAL方式では25 Hz)でリフレッシュされます。他方のフィールドが表示されている間は表示されません。人間の目には、この違いを感じられ、黒いラインが脈動しあるいはちらついているように見えます。この効果は、表示内容に敏感で、文字や細い水平ラインがあるアプリケーションでもっとも顕著になります。CDビデオや写真、動画といったアプリケーションでは、オブジェクトの部分が奇数フィールドと偶数フィールドの両方に自然に現れるので、フリッカ効果が感じられなくなります。

一般的に使用されている2つめのテクニックは、奇数フィールドと偶数フィールドをまったく同じにして出力する方法です(図21b)。この方法では、いずれか一方のフィールドにもともと存在したデータが無視されます。この場合、上記の1ピクセルの高さを持った黒いラインは、2ピクセルの高さを持った黒いラインとして現れるか(奇数フィールドと偶数フィールドの両方に1ピクセルの高さを持った黒いラインがあります)、それがコントローラが無視する側のデータである場合にはまったく現れません。これらのはずれになるかは、スクリーン上のラインの配置によります。このテクニックにより、すべてのアプリケーションで安定した(つまりフリッカのない)表示が得られますが、小さい文字は読みづらくなり、図(またはスプレッドシート)のラインが消えてしまうこともあります。なお、上記の場合と同様にグラフィックや動画は、特別これによって影響を受けることはありませんが、解像度がある程度失われます。

フリッカを劇的に抑えて高い解像度を維持する方法があります。もっとも一般的なものは、表示データが1本のラインに単独で存在しないようにする方法です。これは、真のインターレース出力を生成する前に、連続するか複数に別れたインターレースのないラインを平均または重み付けすることによって実現することができます(図21c)。ある意味でこれは、上記の2つの極端な方法を折衷した出力を提供します。重み、つまり1本のラインが他方に現れるパーセンテージ、および使用するラインの本数は、このタイプのシステムを開発するときの検討事項となります。このタイプの信号処理を実行する場合は、AD725にデータを渡してエンコードする前に処理を完了しておかなければなりません。

# AD725

## 垂直スケーリング

NTSCまたはPALに適合させるためには、コンピュータが生成した画像をインターレースのない状態からインターレース済みのフォーマットに変換することに加えて、画像を縮尺する必要があります。VGAディスプレイでもっとも一般的な1スクリーン当たりの垂直ライン数は、480本と600本です。NTSC方式では、1フレーム当たり約400本(1フィールド当たり200本)PAL方式では1フレーム当たり576本(1フィールド当たり288本)の可視ラインしか扱うことができません。したがってスケーリングを行わないと、オリジナル画像の一部がテレビ用のディスプレイから失われてしまいます。

ライン数の少数化は、単純にN番目(480本でNTSC方式用に間引くときは6番目、600本でPAL方式用に間引くときは25番目)のラインを取り除くことによって行われます。この結果、エッジの滑らかさが失われたり、動きが不自然になったりするおそれがあります。有効なデータがスケーリングのプロセスによって機械的に破棄されないようにするために、スケーリングと前述した補間/平均テクニックを組み合わせることが最善の策です。前述のフリック除去のテクニックと同様に、ラインの少数化もAD725によるコード化のオペレーションの前に完了しなければなりません。

これらのテクニックを使用して、文字に指向されたアプリケーションとグラフィックに指向されたアプリケーションの両方に鮮明で安定した表示を提供するための、特別に設計された新世代のVGAコントローラが市販されています。さらにこれらのチップは、コンピュータからの出力をスケーリングしてテレビのスクリーンに適合させます。発表済みのデバイスのリストは、アナログ・デバイセズ社のアプリケーション・グループから入手可能ですが、もっとも完全な最新の情報については、グラフィック・コントローラICのメーカーに問い合わせてください。

## 同期動作と非同期動作

システムによっては、AD725の入力として使用するRGBビデオと同期信号のソースが、AD725のサブキャリア入力(4FSC)に使用するものと同じクロック信号から導かれます。このようなシステムは、同期動作システムと呼ばれます。これに対し、これらの信号に2つの異なるクロック・ソースが使用されるシステムは、非同期動作システムと呼ばれます。

AD725は、同期動作と非同期動作とともにサポートしますが、これらの間のわずかな違いに気付かれるかもしれません。これらは、AD725の内蔵回路のある種の詳細から生じます。

サブキャリア信号とまったく非同期ですべてのビデオ信号と同期信号を処理しようとする試みがあります。これは、輝度チャンネルでの輝度とクロミナンスの時間的な整列のために用いられるサンプル遅延ラインを除くすべての場所で成功しています。この遅延ラインは、そのクロックとして、サブキャリア周波数の8倍の信号を使用します。

遅延ラインのクロックと輝度信号(およびそれに挿入されたコンポジット同期信号)の間の位相差は、同期動作の間は一定になりますが、非同期動作の間は、周期的に変動します。この周期的な位相変動があることから、非同期ビデオ出力のジマーは、わずかに大きくなります。

a. インターレースされていない信号からインターレース信号への変換

b. ラインを複製する変換テクニック

c. ラインを平均するテクニック

図21.

## 輝度トラップの理論

画像のタイプによっては、輝度トラップ(またはYトラップ)をエンコーダ回路に組み込むことによって、AD725のコンポジット・ビデオ出力を改善することができます。この種の回路の基本構成は、中心周波数をサブキャリア周波数に一致させたノッチ、つまり帯域除去フィルタです。この輝度トラップは、AD725のコンポジット・ビデオ出力だけに機能します。Sビデオ(またはY/Cビデオ)出力には、まったく影響ありません。

輝度トラップの必要性は、ビデオ信号の色部品(クロミナンスまたは彩度)をコード化するためにコンポジット・ビデオが使用する方法からもたらされます。これは、サブキャリアの振幅変調と位相変調によって行われます。サブキャリアの振幅変調で飽和(または白による色の希釈の欠如)が起こる一方、サブキャリアの位相変調に色相(つまり虹の構成色と考えられている色)情報が含まれられます。変調されたこのサブキャリアは、ビデオ標準に応じて、1 MHzよりやや広い帯域を占有します。

コンポジット信号の場合、輝度(または明度)に彩度が直線的に加算され、さらに同期信号が加えられてすべての画像情報を持った单一のコンポジット信号が生成されます。この加算が実行された後は、どの要素がコンポジット信号のどの部分に寄与しているかを突き止めることは不可能になります。

受信機では、適正に処理するために、この単一のコンポジット信号を各要素に分離しなければなりません。具体的には、彩度を分離し、さらにそれをUとVの直交成分に復調しなければなりません。その後、輝度信号とともにU、V信号から、モニタの3つの電子銃をコントロールするRGB信号を生成します。

基本的な問題は、輝度信号(カラー情報をまったく含んでいません)が彩度周波数帯域内に落ちる周波数成分を含んでいるときに生じます。彩度処理回路では、これらの信号がどこで生成されたかを

知ることができないため、この帯域内のすべての信号を、彩度情報として処理します。つまり、彩度帯域内の輝度信号から偽性色が生成されます。この効果は、クロス・クロミナンスと呼ばれています。

クロス・クロミナンス効果は、背景を黒くして白い文字を表示すると、文字の周囲を虹色のパターンが移動することから明らかになります。黒から白へ(またはその逆)の急激な変化では、すべてのビデオ帯域にわたる周波数要素と彩度帯域にわたる周波数要素が含まれ、これがクロス・クロミナンスを惹き起こします。これは特に、文字の生成に使用するドット・クロックが彩度サブキャリア周波数の整数倍になっているとき、はっきりと現れます。

これとは別の例として、衣服におけるある種の縞模様パターンが放映されるときにクロス・クロミナンス効果を惹き起こすこともよく知られています。特定のズームにより、垂直の縞模様パターンの空間周波数が彩度帯域に含まれる輝度周波数を発生します。この周波数要素は、最終的にビデオ・モニタにおいて色に変わります。これらの信号の位相がサブキャリアとコヒーレントでないことから、クロス・クロミナンス効果はランダムな色として現れます。テレビ・カメラのズームが変更されるか、帯状パターンの移動があると、偽性色が激しく変化し、きわめて不快な“ムービング・レインボー”効果を招きます。テレビ放送に精通した人の多くは、これを知っているので、特定のパターンの服の着用を避けています。

すべてのクロス・クロミナンス効果を実質的に除去する優れた方法は、Sビデオを使用することです。輝度と彩度が2つの分離された回路で搬送されるので、どちらの回路がどの信号を処理するかといったことについての混乱がありません。残念ながら、現存するすべてのテレビがSビデオ入力を備えているわけではなく、おそらくは販売済み総数の半分にも達しないでしょう。

現存する多数派のテレビの入力機能との互換性を確保するため、コンポジット・ビデオの提供は欠かせません。カメラやVCRとの接続のためのポートとして、Sビデオ・ポートを備えているテレビよりコンポジット・ベースバンド・ビデオ入力ポートを備えているテレビの方が圧倒的に多いのです。

しかし、ほとんどすべてのテレビは、唯一の共通分母とも言えるRF入力を備えています。この場合、一般に3チャンネルまたは4チャンネル(NTSC方式の場合)に同調されるRF搬送波にベースバンドを変調する必要があります。単一の出力だけを備えたテレビゲームの大半は、汎用性からRFインターフェースを使用しています。このチャンネルでは、サウンドも搬送することができます。

クロス・クロミナンスの除去による画像品質の改善をSビデオだけに頼ることは実際的でないことから、コンポジット・ビデオを使用するシステムで輝度トラップを使用してこの効果を最小化する工夫が生まれました。輝度トラップは、輝度と彩度を加算する前に、輝度信号に含まれる有害な周波数をノッチ、つまり“トラップ”します。したがって、これらの周波数によって惹き起こされるクロス・クロミナンスが著しく減衰されます。

結果として起こる唯一の犠牲は、輝度応答に彩度周波数の“穴”があくことです。これは、空間周波数が彩度帯域内に周波数要素を発生させる輝度ディテールの分解能より低くなります。しかし、画像品質におけるクロス・クロミナンスの減衰の方がはるかに重要です。なおSビデオでは、クロス・クロミナンスが除去されるだけでなく、輝度応答におけるこのノッチもありません。

### 輝度トラップの具体化

AD725では、オンチップの抵抗と外付けのインダクタおよびキャパシタを使用してRLCノッチフィルタを構成し、輝度トラップを具体化しています。このフィルタは、AD725から出力されるビデオ標準の中心周波数に同調させなければなりません。NTSC方式ではそれが3.58 MHzに、PAL方式では4.43 MHzになります。

図22にこの回路を示します。AD725のコンポジット・ビデオの輝度バス内にある1 kΩの直列抵抗は、外付けの直列LCのインピーダンスに対して作用し、ノッチ・フィルタを形成します。このフィルタの周波数は、次の式で与えられます。

$$f = \frac{1}{2\sqrt{LC}}$$

図22 . NTSCおよびPALビデオ用の輝度トラップ回路

### 2つの標準に適合する輝度トラップ

PAL方式とNTSC方式で機能するフィルタを構成する場合は、2つのサブキャリア周波数の間で同調を切換える手段が必要になります。PAL標準では、NTSC標準より高い周波数が要求されます。そこでPAL方式のサブキャリアに同調させたフィルタを基本的な構成として、同調周波数をNTSC動作用の周波数に下げるキャパシタをそれに並列接続し、この接続を単純なダイオード回路で切換えます。

図22には、STND(ピン1)をドライブするロジック信号を利用して輝度トラップ回路の同調周波数を切換える方法が示されています。STND(ピン1)に印加される信号がロー(グラウンド)のときは、PALモードが選択されます。これは、D1の両端を0 Vでバイアスすることになるので、ダイオードがオフになります。この結果、C2がフィルタ回路から外れてC1のみとなり、PAL方式のサブキャリア周波数、4.43 MHzにフィルタが同調されます。

これとは逆に、STNDがハイ(+5 V)のときは、NTSCモードが選択され、D1が順方向にバイアスされます。これによりダイオードがオンになり、C1と並列にC2が接続されます。この結果、NTSCサブキャリア周波数、3.58 MHzにフィルタが同調されます。

# AD725

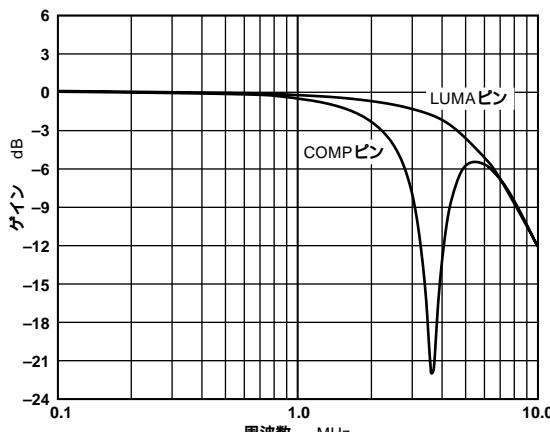

## 輝度トラップの周波数応答の測定

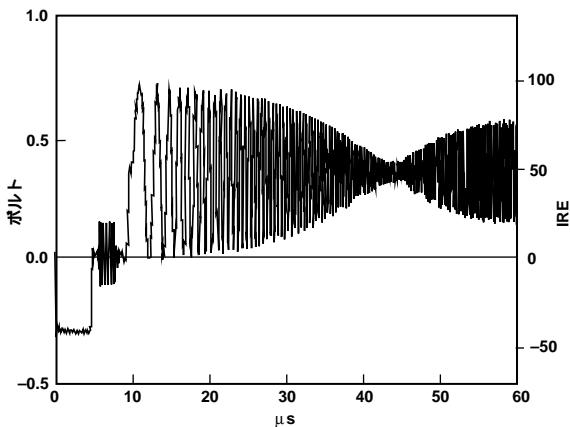

輝度トラップの周波数応答は、2種類の方法で測定することができます。最初の方法は、RGBの周波数掃引パターンをAD725に入力してTVモニタ、TV波形モニタあるいはオシロスコープ上でコンポジット出力を観察します。

TVモニタ上のこのコンポジット・ビデオ表示は、左端で間隔がもっとも粗く(周波数が低く)右に行くに従って間隔が細かい(周波数が高い)垂直の白黒のしま模様となります。このパターンの右側中央よりの位置に、不明瞭なグレーの垂直領域が現れます。これは輝度トラップによるもので、その周波数帯の輝度ディテールがフィルタアウトされた結果です。

ディスプレイの下端には、水平位置と周波数の関係を表すマークがメガヘルツごとに表示されます。周波数マークのスケールに沿って、グレー領域の中心位置からフィルタアウトされる周波数レンジを測定します。グレー領域は、NTSC方式の場合には3 MHzと4 MHzのほぼ中間、PAL方式の場合には4 MHzと5 MHzのほぼ中間でなければなりません。

水平ラインをオシロスコープまたはビデオ波形モニタで観察すると、応答のノッチが明らかになります。周波数は、Hラインに沿ってノッチの位置から補間する必要があります。

図23 . トラップ時の輝度掃引、COMPピン出力

第2の方法では、ネットワーク・アナライザを使用してコンポジット信号の周波数応答を測定します。この測定を成功させるためには、AD725に適切な信号を与えてビデオ信号がそれを通過するようにしなければなりません。図24に、この測定に使用されるセットアップを示します。

ここではまず、部品にサブキャリア・クロックを受信させる必要があります。これにより内蔵遅延ラインにクロックが与えられて、ビデオ信号を通過させることができます。サブキャリア・クロックは、NTSC方式、PAL方式のいずれの場合も4FSC周波数とします。

次に、直線動作用にRGB入力を正しくバイアスし、タイミング・ロジックを適正にリセットします。この場合、RGB入力をac結合し、HSYNC信号を瞬間に印加してタイミングをリセットし、dc復元を実行することができます。入力インピーダンスが高いことか

ら、テスト間のドリープは最小限に抑えられます。ただし、HSYNC入力への継続的なパルスの印加は、これらのパルスのスペクトルが出力応答に現れることから好ましくありません。

ノイズの低く、より安定した方法を図23に示します。この場合、電源とネットワーク・アナライザのソース・ポート・バイアス入力を使用してRGB入力をバイアスします。ここでもデバイスの内部タイミングをリセットするために瞬間的な同期信号を使用しますが、テストの間のドリープはなくなります。

最大出力応答が得られるようにGIN入力に信号ソースを印加します。この入力は、適切な終端抵抗(ネットワーク・アナライザの出力インピーダンスと整合する終端抵抗)を用いて終端する必要があります。必要な場合には、FETプローブを用いて入力リファレンスを読みれば、キャリブレーション誤差を平坦にすることができます。

図24 . 輝度トラップ周波数を決定するための測定セットアップ

コンポジット出力は、50 または75 の抵抗で逆終端されて、ネットワーク・アナライザの測定チャンネルに入力されます。

グリーン入力だけがドライブされることから、この方法によりコンポジット信号レベルの絶対的な測定値を得ることができないのでですが、コンポジット出力のノッチを簡単に見分けることができます。この後、輝度ノッチ・フィルタ(輝度トラップ)の周波数の精密測定に、ネットワーク・アナライザの周波数測定機能を使用することができます。

図25 . NTSC ト ラップ の ある 漢 度 周 波 数 応 答

### 同期信号

AD725は、適正な動作を確保するために明確に区分できる垂直と水平の同期信号を必要とします。この情報は、RGB信号のいずれとも組み合わせることも不可能であり、またそれを行ってはなりません。しかし同期情報は、水平(HSYNC)と垂直(VSYNC)を分離した信号とすることもできれば、コンポジット同期(CSYNC)信号とすることもできます。

AD725は、ほとんどはハイで、水平同期期間にローとなるコンポジット同期ロジック信号を内部的に必要とします。垂直同期期間

は、この信号を反転した信号になります。この信号が、AD725に組み込まれたXNOR(排他的否定論理)ゲートの出力で得られる必要があります、その入力はそれぞれHSYNC(ピン16)とVSYNC(ピン15)になります。この条件を満たすための選択肢は、いくつがあります。

第1は、HSYNCとVSYNC用の分離された信号を使用することです。それぞれは、ローがベースで、対応する期間をアサートする場合にハイになります。これは、ほとんどのPC用のRGBモニタで使用される変換方法です。これらの入力を使用すれば、オンチップのXNORゲート出力で適正なコンポジット同期信号が得られます。

コンポジット同期信号がすでにある場合は、それをHSYNC(ピン16)に印加し、VSYNC(ピン15)を使用して極性変換を行うことができます(実際は、HSYNCとVSYNCが2入力ゲートに対して対称であることから、互いを交換することができます)。

ほとんどの部分でコンポジット同期入力がハイであり、HSYNCがアクティブになるときローとなつていれば(VSYNCの場合はこれを反転した状態になります)すでに正しい極性になっています。その場合、VSYNCをハイに引上げてコンポジット同期信号をHSYNCに印加すれば、信号が反転されずにXNORゲートを通過します。

これに対し、コンポジット信号が上記と逆の極性になっているときは、VSYNCをローに引込めばXNORゲートによって信号が反転されます。こうすることにより、AD725内部で使用する正しい極性が得られます。図26は、これらのロジック条件を示しています。

図26 . 同期ロジック・レベル(等化パルスと鋸歯パルスは示していません)

# AD725

外形寸法

サイズはインチと(mm)で示します。

16ピン・ワイド・ボディSOIC

(R-16)

「この取扱説明書はエコマーク認定の再生紙を使用しています。」 - 20 -