## 高精度なインピーダンス測定および 電気化学測定フロント・エンド

### 特長

- ▶ アナログ入力

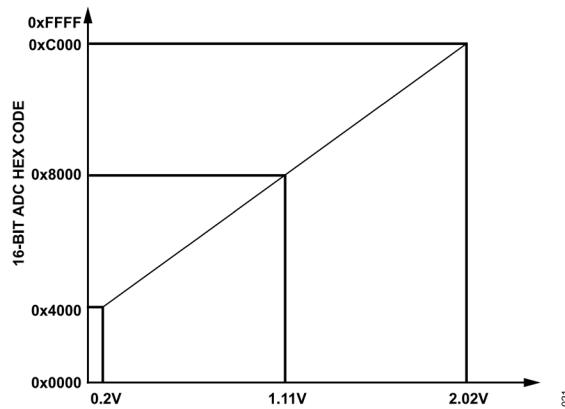

- ▶ 800kSPS と 1.6MSPS の両方のオプションを備えた 16 ビット ADC

- ▶ 電圧、電流、インピーダンスの測定が可能

- ▶ 内部および外部の電流チャンネルおよび電圧チャンネル

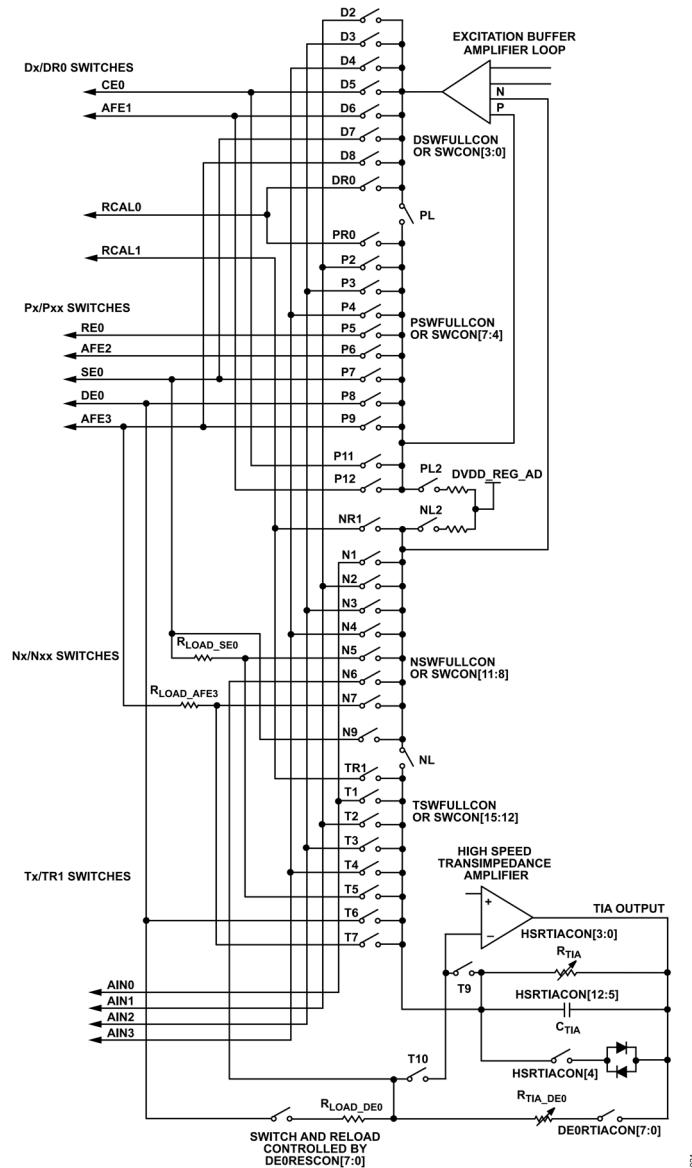

- ▶ 超低リーケのスイッチ・マトリクスおよび入力マルチブレカ

- ▶ 入力バッファおよびプログラマブル・ゲイン・アンプ

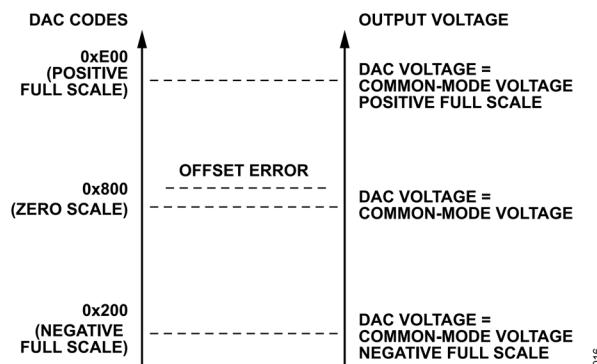

- ▶ 電圧 DAC

- ▶ 0.2V～2.4V の出力範囲を持つデュアル出力電圧 DAC

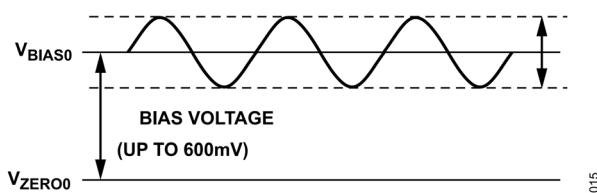

- ▶ ポテンショスタットをバイアスするための 12 ビット  $V_{BIAS0}$  出力

- ▶ TIA をバイアスするための 6 ビット  $V_{ZERO0}$  出力

- ▶ 超低消費電力 : 1 $\mu$ A

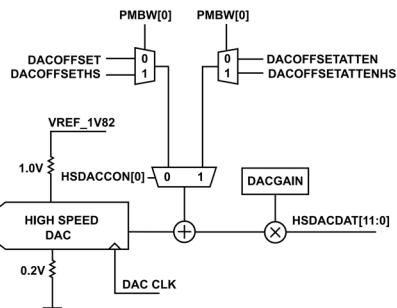

- ▶ 1 個の高速 12 ビット DAC

- ▶ 高速 DAC (HSDAC) からの出力範囲 :  $\pm 607\text{mV}$

- ▶ プログラマブル・ゲイン・アンプの HSDAC 出力時のゲイン設定 : 2 および 0.05

- ▶ アンプ、アクセラレータ、およびリファレンス

- ▶ 電気化学センシングにおけるポテンショスタット・バイアスに適した低消費電力および低ノイズのポテンショスタット・アンプ : 1 個

- ▶ センサー電流出力の測定に適した低ノイズおよび低消費電力の TIA : 1 個

- ▶ 範囲 : 50pA～3mA

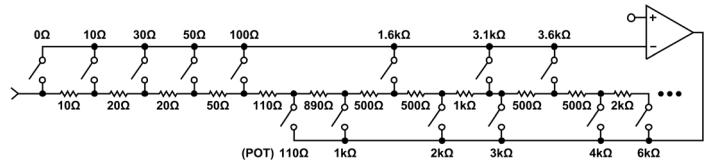

- ▶ センサー出力用のプログラマブルな負荷抵抗およびゲイン抵抗

- ▶ アナログ・ハードウェア・アクセラレータ

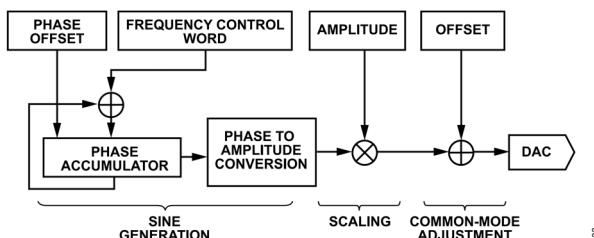

- ▶ デジタル波形発生器

- ▶ 受信フィルタ

- ▶ 複素インピーダンス測定 (DFT) エンジン

- ▶ 0.015Hz～200kHz の広帯域幅入力信号を処理する高速 TIA : 1 個

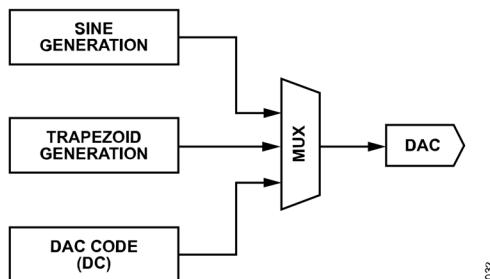

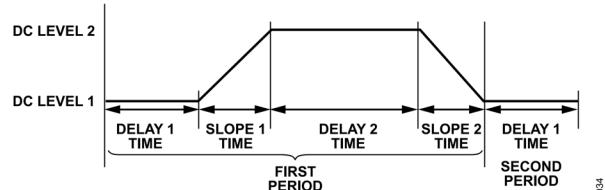

- ▶ 正弦波形および台形波形を発生するデジタル波形発生器

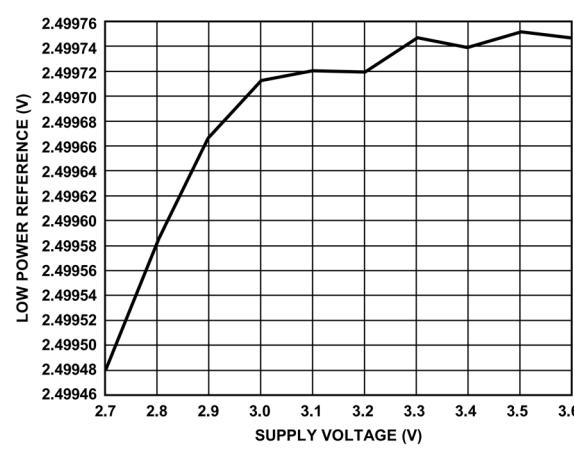

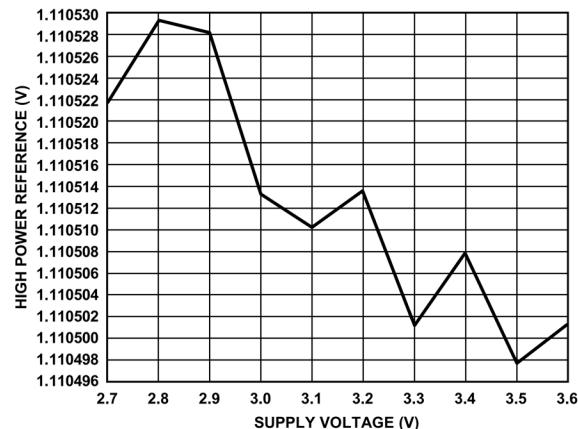

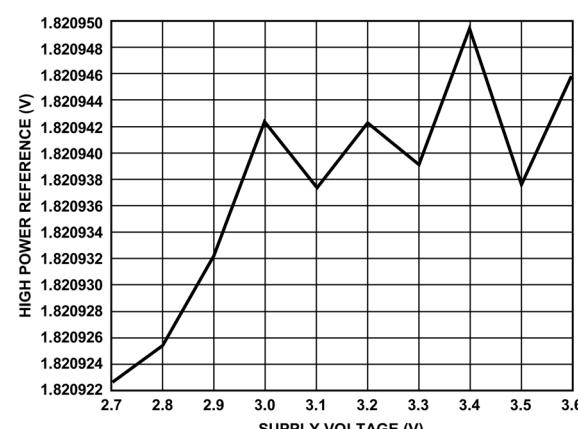

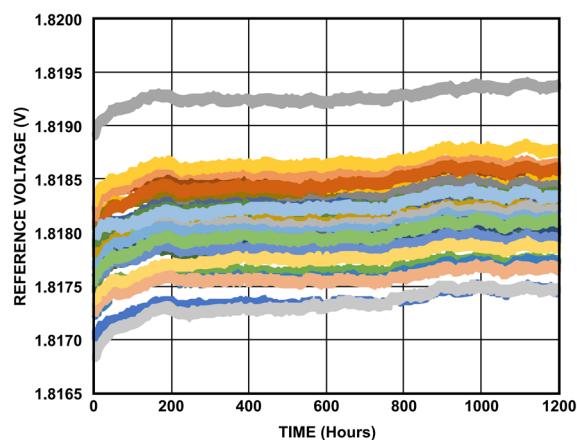

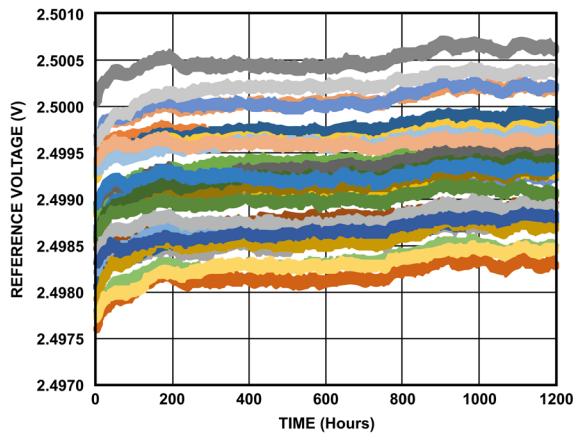

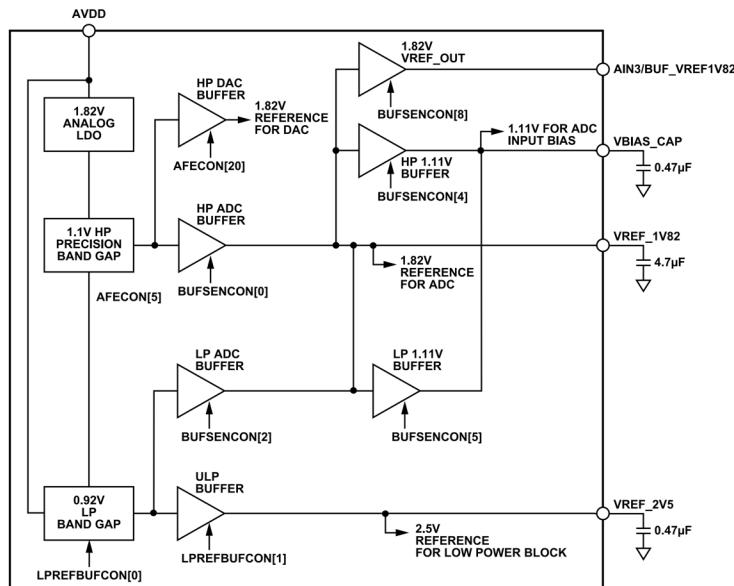

- ▶ 2.5V および 1.82V の内部リファレンス電圧源

- ▶ システム・レベルの節電

- ▶ デューティ・サイクル動作のためのアナログ・ブロックの高速パワーアップおよびパワーダウン

- ▶ ホスト・コントローラにかかるワーカロードを最小化するプログラマブル AFE シーケンサ

- ▶ AFE シーケンスを事前にプログラムするための 6kB SRAM

- ▶ 超低消費電力ポテンショスタット・チャンネルの消費電流 : 6.5 $\mu$ A (電源投入され、他の全ブロックが休止モードの場合)

- ▶ スマート・センサーの同期およびデータ収集

- ▶ センサー計測のサイクル精度の制御

- ▶ シーケンサ制御の GPIO

- ▶ オンチップ・ペリフェラル

- ▶ SPI シリアル入出力

- ▶ ウェイクアップ・タイマー

- ▶ 割込みコントローラ

- ▶ 電源

- ▶ 2.8V～3.6V の電源

- ▶ 1.82V 入出力に対応

- ▶ パワー・オン・リセット

- ▶ 低電力 DAC およびポテンショスタット・アンプの電源をオンにした状態でセンサー・バイアスを維持する休止状態モード

- ▶ パッケージおよび温度範囲

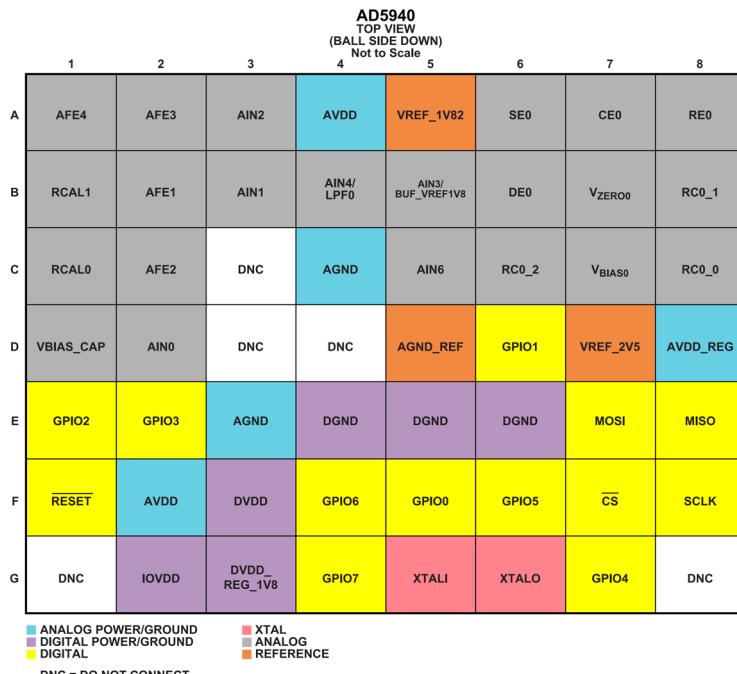

- ▶ AD5940 : 3.6 mm × 4.2 mm、56 ポール WLCSP

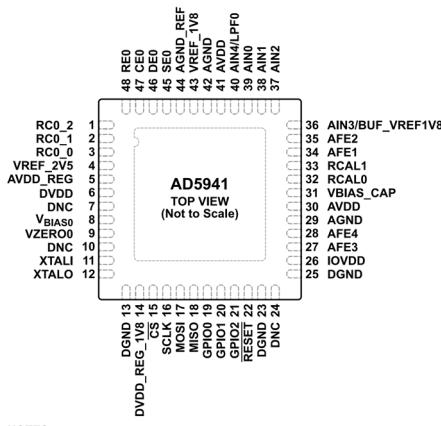

- ▶ AD5941 : 7mm × 7mm、48 ピン LFCSP

- ▶ AD5940 および AD5941 は、-40°C～+85°C の動作温度範囲に対して完全仕様化

- ▶ AD5941W は、-40°C～+105°C の動作温度範囲に対して完全仕様化

- ▶ オートモーティブ・アプリケーション向けの AEC-Q100 に適合

### アプリケーション

- ▶ 電気化学測定

- ▶ 電気化学ガス・センサー測定

- ▶ ポテンショスタット／アンペロメトリ (電流滴定) / ボルタメトリ / サイクリック・ボルタンメトリ

- ▶ 生体インピーダンス・アプリケーション

- ▶ 皮膚インピーダンス

- ▶ 人体インピーダンス

- ▶ 持続血糖値測定

- ▶ バッテリ・インピーダンス

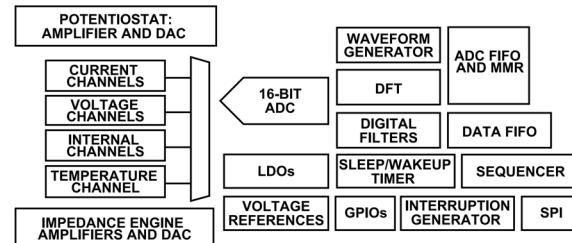

### 簡略ブロック図

図 1.

※こちらのデータシートには正誤表が付属しています。当該資料の最終ページ以降をご参照ください。

Rev. E

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|                               |    |                               |     |

|-------------------------------|----|-------------------------------|-----|

| 特長                            | 1  | 高性能 ADC 回路                    | 54  |

| アプリケーション                      | 1  | ADC 回路の概要                     | 54  |

| 簡略ブロック図                       | 1  | ADC の回路図                      | 54  |

| 機能ブロック図                       | 5  | ADC 回路の特徴                     | 55  |

| 概要                            | 6  | ADC 回路の動作                     | 55  |

| 仕様                            | 7  | ADC の伝達関数                     | 55  |

| ADC の実効値ノイズ仕様                 | 16 | ADC の低電力電流入力チャンネル             | 56  |

| SPI のタイミング仕様                  | 17 | ADC マルチプレクサへの入力の選択            | 56  |

| 絶対最大定格                        | 18 | ADC のポストプロセス                  | 57  |

| 熱抵抗                           | 18 | 内部温度センサー・チャンネル                | 57  |

| ESD に関する注意                    | 18 | 50Hz/60Hz のメイン除去フィルタ          | 57  |

| ピン配置およびピン機能の説明                | 19 | ADC のキャリブレーション                | 57  |

| 代表的な性能特性                      | 22 | ADC 回路のレジスタ                   | 58  |

| リファレンス・テスト回路                  | 24 | ADC キャリブレーション・レジスタ            | 64  |

| 動作原理                          | 25 | ADC デジタル・ポストプロセス・レジスタ (オプション) | 71  |

| 設定レジスタ                        | 25 | ADC 統計レジスタ                    | 72  |

| シリコン ID                       | 28 | プログラマブルなスイッチ・マトリクス            | 74  |

| 識別レジスタ                        | 28 | SWITCH の説明                    | 74  |

| システムの初期化                      | 29 | 休止モード時の推奨設定                   | 74  |

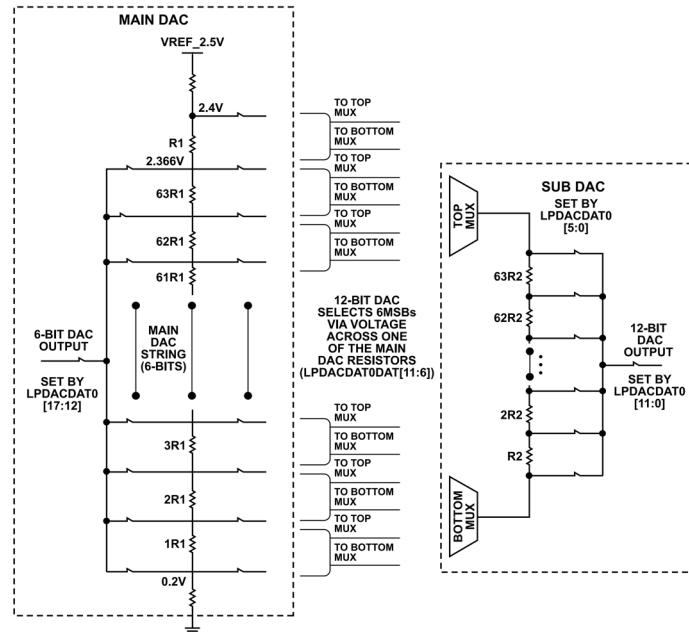

| 低電力 DAC                       | 30 | 全スイッチを制御するためのオプション            | 74  |

| 低電力 DAC のスイッチ・オプション           | 30 | プログラマブル・スイッチ・レジスタ             | 76  |

| 12 ビット出力と 6 ビット出力の関係          | 31 | 高精度電圧リファレンス                   | 87  |

| 低電力 DAC の使用事例                 | 31 | 大電力および低電力バッファ制御レジスタ—BUFSENCON | 87  |

| 低電力 DAC 回路のレジスタ               | 32 | シーケンサ                         | 89  |

| 低電力ポテンショスタット                  | 36 | シーケンサ機能                       | 89  |

| 低電力 TIA                       | 37 | シーケンサの概要                      | 89  |

| 低電力 TIA 保護ダイオード               | 37 | シーケンサのコマンド                    | 89  |

| 外部 RTIA の使用                   | 37 | シーケンサの動作                      | 91  |

| 様々な動作モードのための推奨スイッチ設定          | 37 | シーケンサおよび FIFO のレジスタ           | 93  |

| 低電力 TIA 回路のレジスタ               | 39 | 波形発生器                         | 99  |

| 高速 DAC 回路                     | 43 | 波形発生器の機能                      | 99  |

| 高速 DAC 出力信号の発生                | 43 | 波形発生器の動作                      | 99  |

| 高速 DAC コアの電力モード               | 43 | 波形発生器と低電力 DAC の使用             | 99  |

| 高速 DAC のフィルタ・オプション            | 43 | 波形発生器のレジスタ                    | 99  |

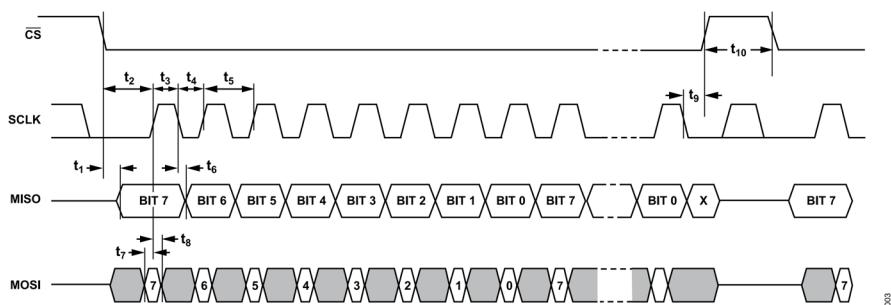

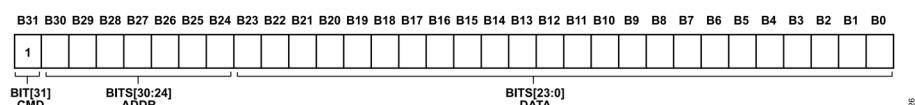

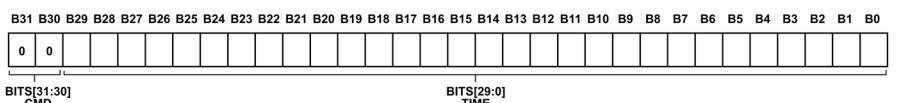

| 高速 DAC 出力の減衰オプション             | 45 | SPI インターフェース                  | 104 |

| 高速 DAC 励起アンプ                  | 45 | 概要                            | 104 |

| 高速 DAC の AC 信号を低電力 DAC で設定された |    | SPI ピン                        | 104 |

| DC レベルに結合する方法                 | 45 | SPI 動作                        | 104 |

| インピーダンス測定時の励起周波数と測定周波数の間の     |    | コマンド・バイト                      | 104 |

| インコヒーレントな誤差を回避する方法            | 45 | レジスタとの間の読み書き                  | 104 |

| 高速 DAC のキャリブレーション・オプション       | 46 | データ FIFO からのデータの読み出し          | 104 |

| 高速 DAC 回路のレジスタ                | 47 | データ FIFO 用 ECC                | 106 |

| 高速 TIA 回路                     | 50 | ECC のアルゴリズム                   | 106 |

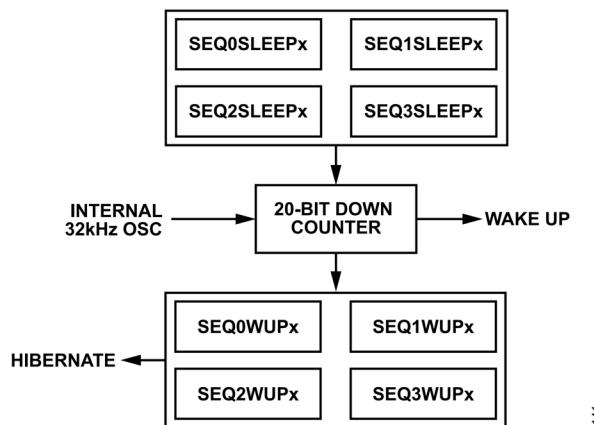

| 高速 TIA の設定                    | 50 | スリープおよびウェイクアップ・タイマー           | 107 |

| 高速 TIA 回路のレジスタ                | 52 | スリープおよびウェイクアップ・タイマー機能         | 107 |

## 目次

|                                                          |     |

|----------------------------------------------------------|-----|

| スリープおよびウェイクアップ・タイマーの概要                                   | 107 |

| 定義されたシーケンスの順序の設定                                         | 107 |

| スリープおよびウェイクアップ・タイマーの推奨動作                                 | 107 |

| スリープおよびウェイクアップ・タイマーのレジスタ                                 | 108 |

| 割込み                                                      | 112 |

| 割込みコントローラの割込み                                            | 112 |

| 割込みの設定                                                   | 112 |

| カスタム割込み                                                  | 112 |

| 外部割込み設定                                                  | 112 |

| 割込みレジスタ                                                  | 113 |

| 外部割込み設定レジスタ                                              | 118 |

| デジタル入出力                                                  | 122 |

| デジタル入出力の機能                                               | 122 |

| デジタル入出力の動作                                               | 122 |

| GPIO レジスタ                                                | 123 |

| システム・リセット                                                | 127 |

| アナログ・ダイ・リセット・レジスタ                                        | 127 |

| 電力モード                                                    | 129 |

| アクティブ大電力モード (>80kHz)                                     | 129 |

| アクティブ低電力モード (<80kHz)                                     | 129 |

| 休止モード                                                    | 129 |

| シャットダウン・モード                                              | 129 |

| 低電力モード                                                   | 129 |

| 電力モード・レジスタ                                               | 129 |

| クロック・アーキテクチャ                                             | 132 |

| クロック機能                                                   | 132 |

| クロック・アーキテクチャ・レジスタ                                        | 132 |

| アプリケーション情報                                               | 137 |

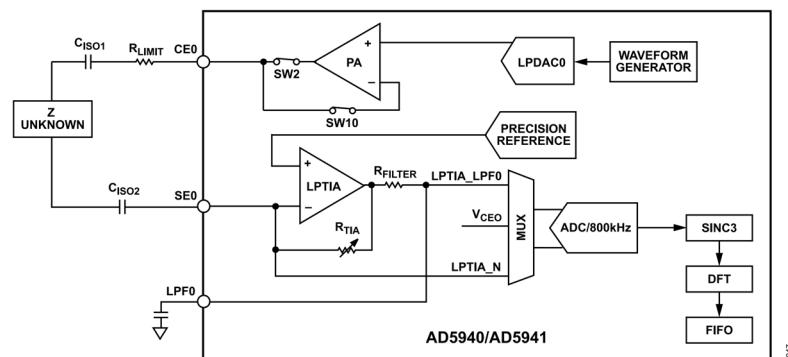

| 狭帯域幅ループを用いたEDAバイオインピーダンス測定                               | 137 |

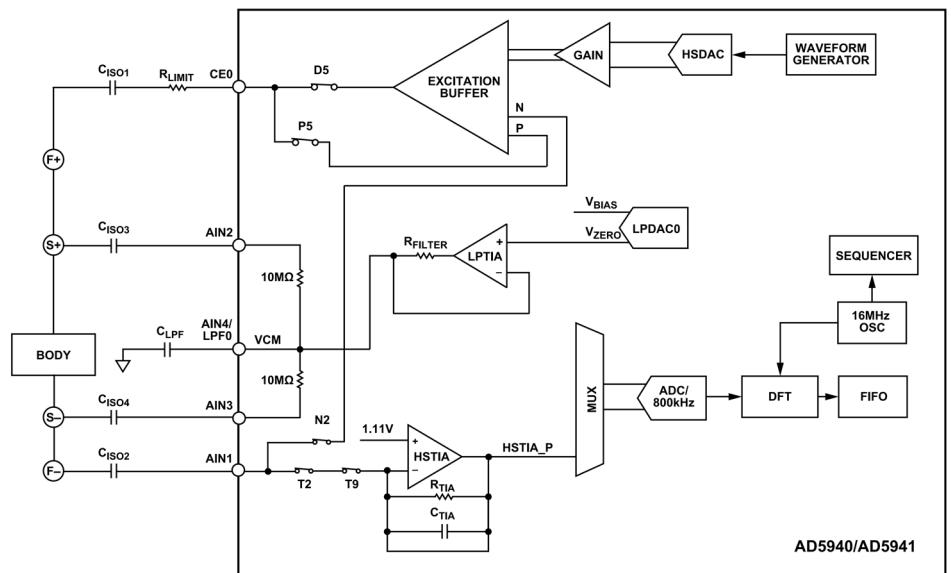

| 広帯域幅ループを用いた人体インピーダンス解析 (BIA) 測定                          | 138 |

| 高精度ポテンショスタット設定                                           | 139 |

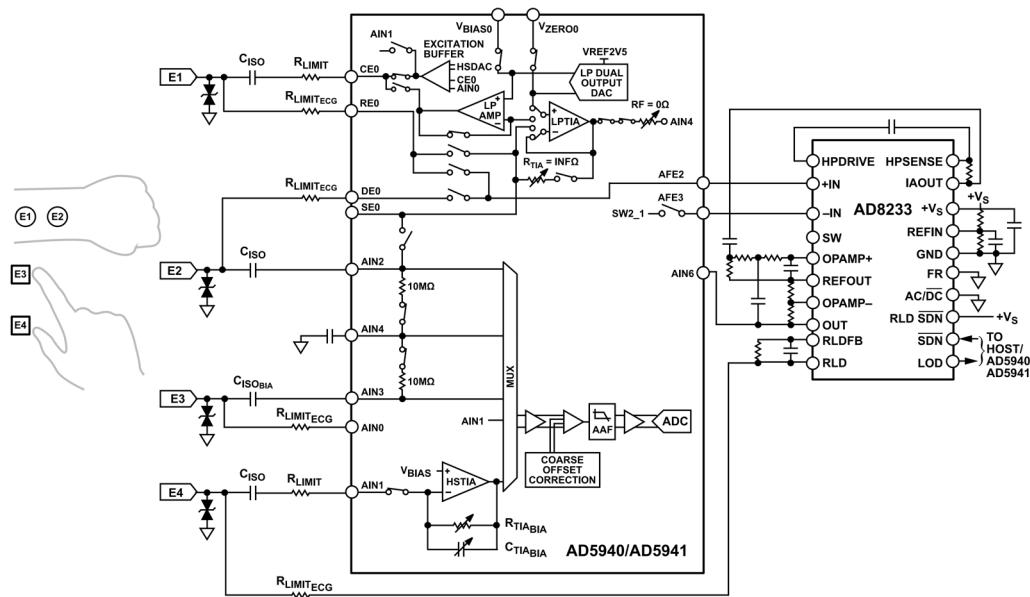

| AD5940/AD5941、AD8232、AD8233を用いた、生体インピーダンスおよび心電図 (ECG) 測定 | 140 |

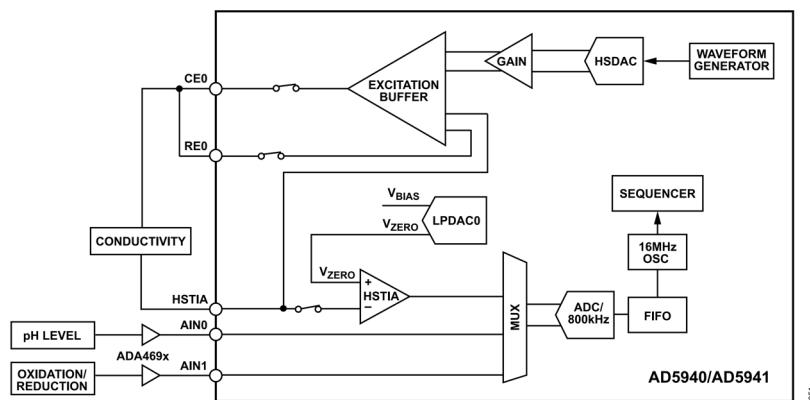

| スマート水質／液質AFE                                             | 141 |

| 外形寸法                                                     | 142 |

| オーダー・ガイド                                                 | 142 |

| 評価用ボード                                                   | 142 |

| オートモーティブ製品                                               | 142 |

## 改訂履歴

## 12/2024—Rev. D to Rev. E

|                    |    |

|--------------------|----|

| Changes to Table 9 | 25 |

|--------------------|----|

## 1/2024—Rev. C to Rev. D

|                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------|----|

| Changed Master to Initiator and Slave to Target (Throughout)                                          | 1  |

| Changes to Features Section                                                                           | 1  |

| Change to Applications Section                                                                        | 1  |

| Changes to Figure 2                                                                                   | 5  |

| Deleted Figure 3; Renumbered Sequentially                                                             | 5  |

| Changes to ADC RMS Noise Specifications Section                                                       | 16 |

| Change to Table 9                                                                                     | 25 |

| Change to Low Power DAC Section                                                                       | 30 |

| Changes to Equation 6 and Equation 7                                                                  | 31 |

| Changes to High Speed DAC Output Attenuation Options Section                                          | 45 |

| Changes to Figure 29                                                                                  | 50 |

| Change to Table 38                                                                                    | 52 |

| Changes to ADC Circuit Features Section                                                               | 55 |

| Changes to ADC Postprocessing Section                                                                 | 57 |

| Changed Sinc2 Filter (50 Hz/60 Hz Mains Filter) Section to 50 Hz/60 Hz Mains Rejection Filter Section | 57 |

| Added 50 Hz/60 Hz Notch Filter Section                                                                | 57 |

| Change to Table 43                                                                                    | 58 |

| Changes to Table 45                                                                                   | 60 |

| Changes to Table 46                                                                                   | 60 |

| Changes to Table 51                                                                                   | 62 |

## 目次

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| Changes to AFEx Switches Section.....                                             | 74  |

| Changes to Figure 35.....                                                         | 75  |

| Change to Sinusoid Generator Section.....                                         | 99  |

| Change to Table 122 .....                                                         | 102 |

| Change to SCLK Section.....                                                       | 104 |

| Added ECC for DATA FIFO Section and Table 127; Renumbered Sequentially.....       | 106 |

| Added ECC Algorithm Section, Table 128, and Table 129.....                        | 106 |

| Changes to Active High Power Mode (>80 KHz) Section.....                          | 129 |

| Changes to Clock Features Section and Figure 52.....                              | 132 |

| Changes to Table 171.....                                                         | 132 |

| Deleted Key Protection Register for the CLKCON0 Register—CLKCON0KEY Section ..... | 132 |

| Changes to Table 172.....                                                         | 133 |

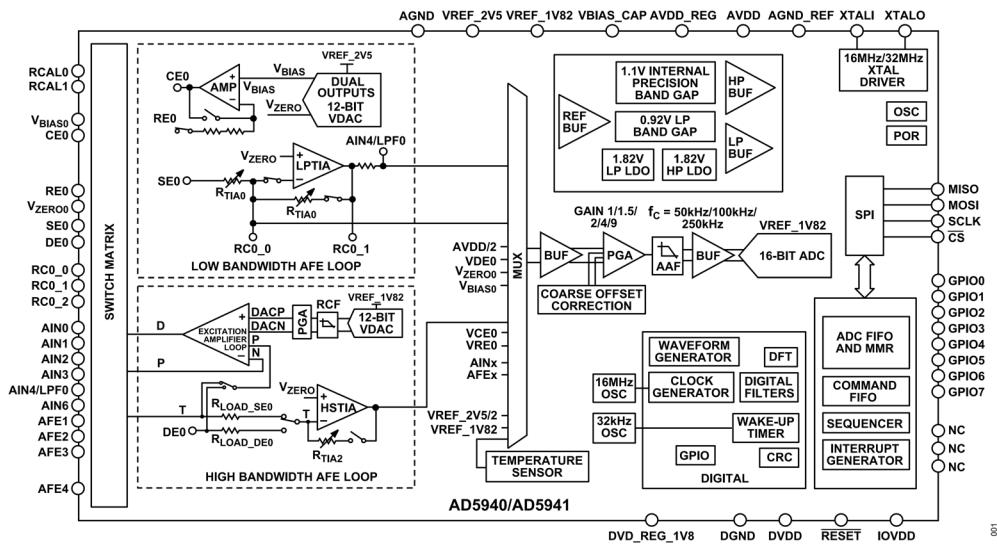

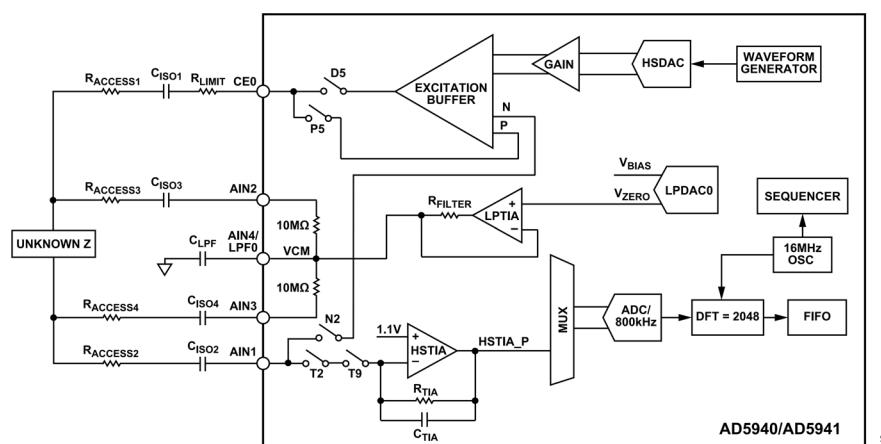

## 機能ブロック図

図 2. AD5940/AD5941 の機能ブロック図

## 概要

AD5940 および AD5941 は、アンペロメトリ、ボルタンメトリ、またはインピーダンス測定などの電気化学ベースの高精度の測定技術を必要とするポータブル・アプリケーション向けに設計された、高精度および低消費電力のアナログ・フロント・エンド (AFE) です。AD5940/AD5941 は、皮膚インピーダンスや人体インピーダンスの測定用に設計されており、フル機能の生体電気／生体電位測定システムにおいて [AD8233](#) AFE と連動するように設計されています。AD5940/AD5941 は、電気化学式有毒ガス・センシング用に設計されています。

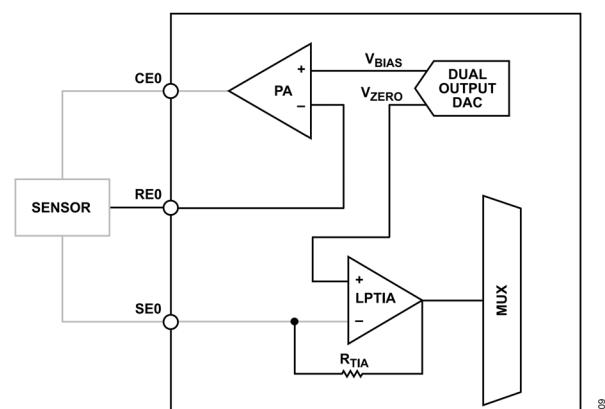

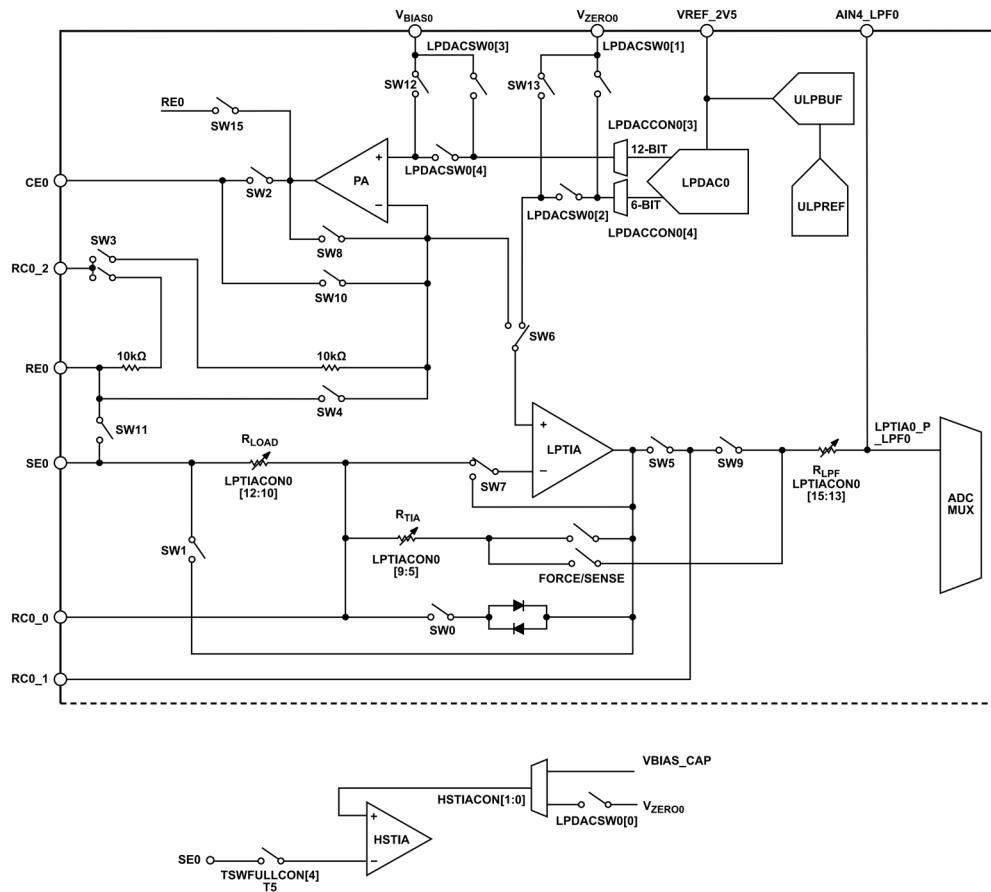

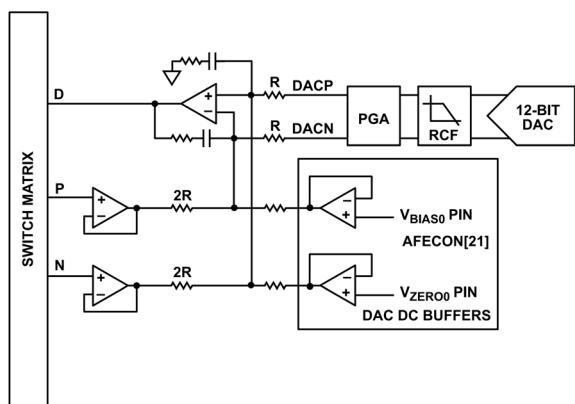

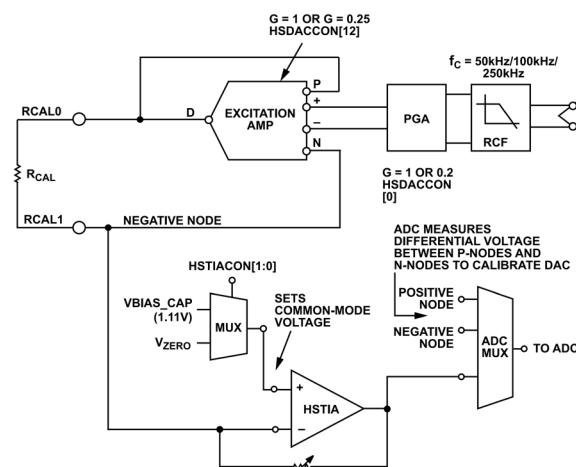

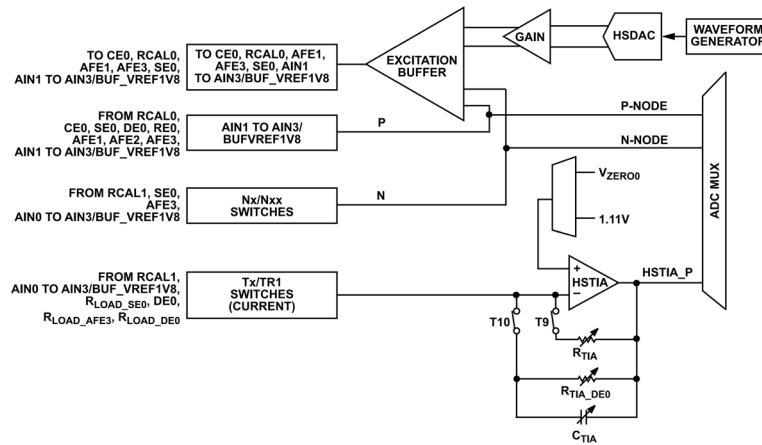

AD5940/AD5941 は、2 つの高精度励起ループと 1 つの共通の測定チャンネルで構成されており、テスト対象のセンサーを幅広く測定できます。1 つ目の励起ループは、超低電力デュアル出力ストリング D/A コンバータ (DAC) と低消費電力低ノイズのポテンショスタットで構成されています。DAC の一方の出力でポテンショスタットの非反転入力を制御し、他方の出力でトランスインピーダンス・アンプ (TIA) の非反転入力を制御します。この低電力励起ループは、DC~200Hz の信号を生成できます。

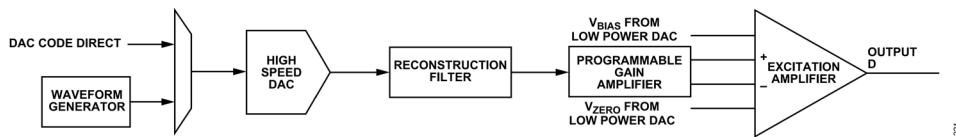

2 つ目の励起ループは、高速 DAC と呼ばれる 12 ビット DAC で構成されています。この DAC は、最大 200kHz の高周波励起信号を生成できます。

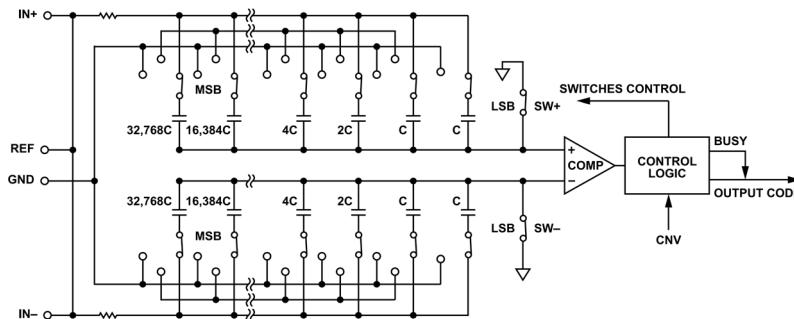

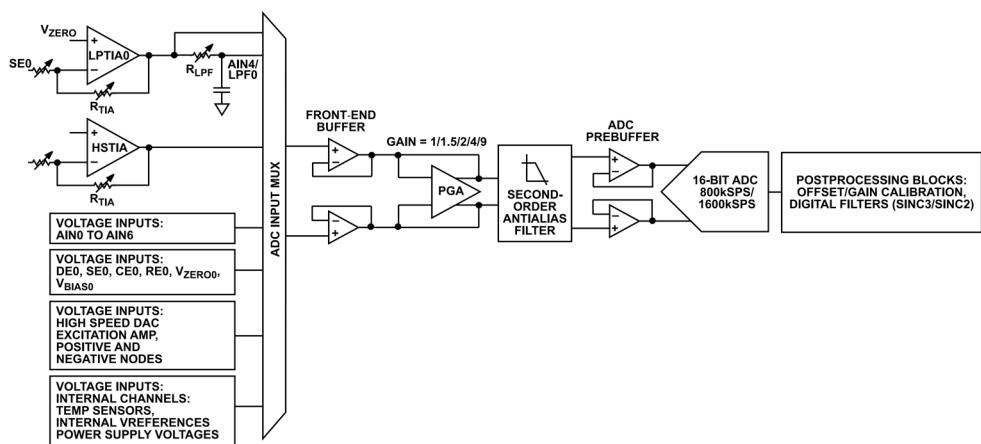

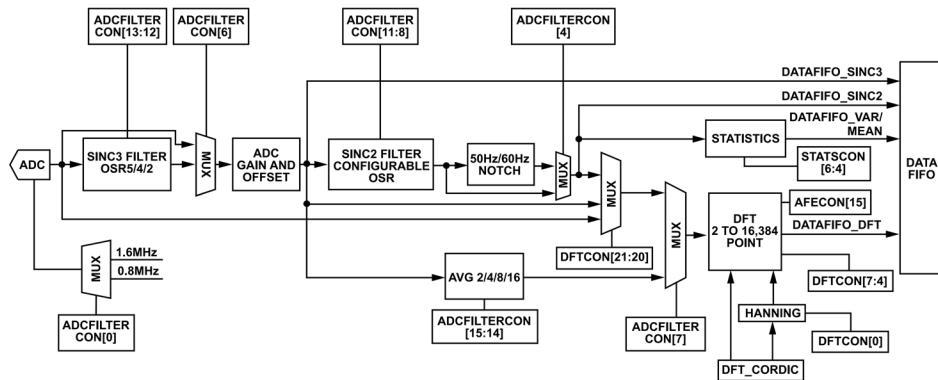

AD5940/AD5941 測定チャンネルには、入力バッファ、内蔵アンチエイリアス・フィルタ、およびプログラマブル・ゲイン・アンプ (PGA) を備えた 16 ビット 800kSPS マルチチャンネル逐次比較レジスタ (SAR) A/D コンバータ (ADC) が使用されています。ADC の前段の入力マルチプレクサ (mux) により、ユーザは測定する入力チャンネルを選択できます。これらの入力チャンネルには、複数の外部電流入力、外部電圧入力、内部チャンネルなどがあります。内部チャンネルでは、内部の電源電圧、ダイ温度、リファレンス電圧の診断測定ができます。

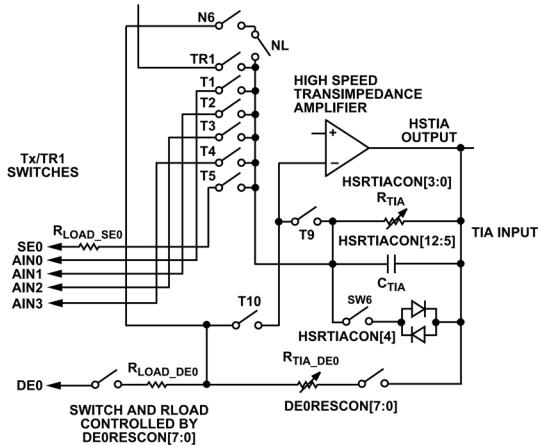

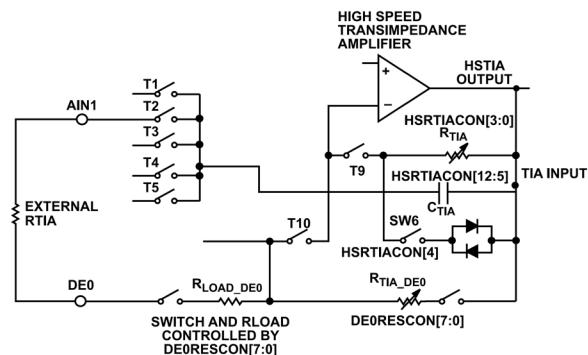

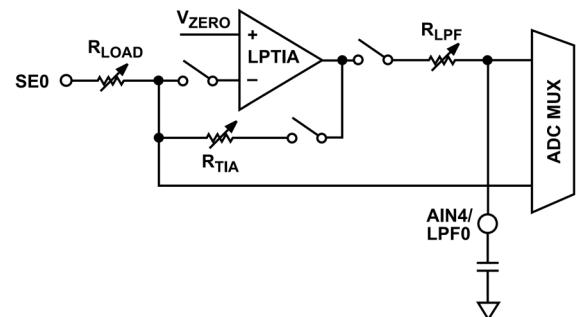

電流入力には、様々なタイプのセンサーを測定するためのプログラマブルなゲイン抵抗と負荷抵抗を備えた 2 つの TIA が含まれています。1 つ目の TIA は、低電力 TIA と呼ばれ、狭帯域幅

の信号を測定します。2 つ目の TIA は、高速 TIA と呼ばれ、200kHz までの広帯域幅の信号を測定します。

超低リークのプログラマブル・スイッチ・マトリクスにより、センサーが内部アナログ励起ブロックと測定ブロックに接続されます。このマトリクスは外付けのトランス・インピーダンス・アンプ抵抗 ( $R_{TIA}$ ) およびキャリブレーション抵抗を接続するためのインターフェースとして機能します。このマトリクスを使用して、複数の電子測定デバイスを同じウェアラブル電極にマルチプレクスすることもできます。

高精度の 1.82V および 2.5V 内蔵リファレンス・ソースが使用可能です。内部の ADC 回路および DAC 回路は、この内蔵リファレンス・ソースを使用して、1.82V および 2.5V の周辺機器に対して低ドリフト性能を実現します。

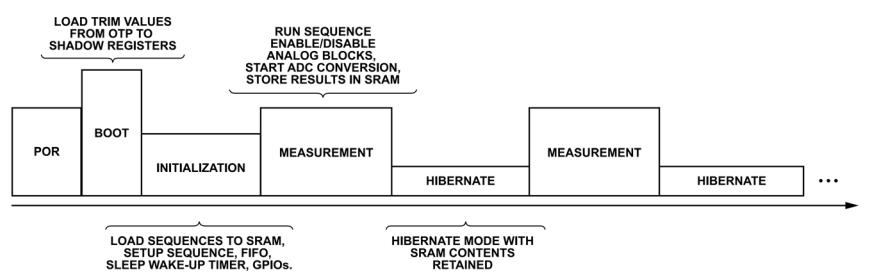

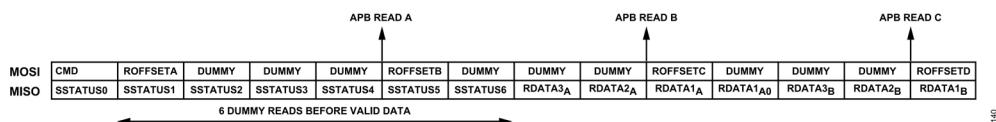

AD5940/AD5941 測定ブロックは、シリアル・ペリフェラル・インターフェース (SPI) インターフェースから直接レジスタに書き込むことで制御するか、または AFE チップの自律的な制御を可能にするプログラマブル・シーケンサを使用して制御することができます。6kB のスタティック・ランダム・アクセス・メモリ (SRAM) は、ディープ・データ FIFO (先入れ先出し) とコマンド FIFO 用に分割されています。測定コマンドはコマンド FIFO に保存され、測定結果はデータ FIFO に保存されます。FIFO が満杯の状態を示すために、FIFO に関する多くの割込みが用意されています。

多数の汎用入出力 (GPIO) が使用可能で、これらは AFE シーケンサを用いて制御できます。AFE シーケンサは複数の外部センサー・デバイスをサイクル精度で制御できます。

AD5940/AD5941 は 2.8V~3.6V の電源で動作し、-40°C~+85°C の温度範囲向けに仕様規定されています。AD5940 は、3.6mm × 4.2mm の 56 ピン WLCSP にパッケージされています。AD5941 は 48 ピン LFCSP にパッケージされています。

## 仕様

AVDD = DVDD = 2.8V~3.6V、電源間の最大電圧差 = 0.3V、IOVDD = 1.8V  $\pm$  10%および2.8V~3.6V、ADC リファレンス、励起、DAC、アンプ = 1.82V、内部リファレンス、低電力 DAC リファレンス = 2.5V、内部リファレンス、特に指定のない限り、AD5940 およびAD5941 の場合、 $T_A = -40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ 。特に指定のない限り、AD5941W の場合、 $T_A = -40^{\circ}\text{C} \sim 105^{\circ}\text{C}$ 。

表 1.

| Parameter                                | Symbol              | Min   | Typ       | Max                           | Unit                           | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------|---------------------|-------|-----------|-------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BASIC ADC SPECIFICATIONS                 |                     |       |           |                               |                                | Pseudo differential mode measured relative to ADC bias voltage (voltage on VBIAS_CAP <sup>1</sup> pin, 1.11 V), unless otherwise noted; specifications based on high speed mode, unless otherwise noted; ADC voltage channel calibrated in production with PGA gain = 1.5; AFE die clock for the analog domain (ACLK) = 32 MHz or 16 MHz, unless otherwise noted |

| Data Rate <sup>2</sup>                   | $f_{\text{SAMPLE}}$ |       |           | 400<br>200                    | kSPS                           | High speed mode; decimation factor = 4                                                                                                                                                                                                                                                                                                                           |

| Resolution <sup>2</sup>                  |                     | 16    |           |                               | Bits                           | Normal mode; decimation factor = 4                                                                                                                                                                                                                                                                                                                               |

| Integral Nonlinearity <sup>2</sup>       | INL                 |       |           |                               |                                | Number of data bits                                                                                                                                                                                                                                                                                                                                              |

| Normal Mode                              |                     | -4    | $\pm 2.0$ | +4                            | LSB                            | PGA gain = 1.5, 1.82 V internal reference, 1 LSB = 1.82 V $\div$ $2^{15} \div$ PGA gain                                                                                                                                                                                                                                                                          |

| Differential Nonlinearity <sup>2</sup>   | DNL                 |       |           | -5.6<br>-0.99                 | LSB                            | PGA gain = 9, 1.82 V internal reference                                                                                                                                                                                                                                                                                                                          |

| Normal Mode                              |                     | -0.99 | $\pm 0.9$ | +2.5                          | LSB                            | PGA gain = 1.5, 1.82 V internal reference; 1 LSB = 1.82 V $\div$ $2^{15} \div$ PGA gain, no missing codes                                                                                                                                                                                                                                                        |

| DC Code Distribution <sup>3</sup>        |                     |       |           | $\pm 6$<br>$\pm 6$<br>$\pm 6$ | LSB                            | PGA gain = 1.5, low power mode, ADC input = 0.9 V; ADC output data rate = 200 kSPS; 1 LSB = 1.82 V $\div$ $2^{15}$                                                                                                                                                                                                                                               |

|                                          |                     |       |           |                               |                                | Input channel is low power TIA = 1 $\mu\text{A}$ , $R_{\text{TIA}} = 512 \text{ k}\Omega$ , $R_{\text{LOAD}} = 10 \Omega$ , ADC output data rate = 200 kSPS                                                                                                                                                                                                      |

|                                          |                     |       |           |                               |                                | Input channel is high speed TIA = 1 $\mu\text{A}$ , $R_{\text{TIA}} = 10 \text{ k}\Omega$ , $R_{\text{LOAD}} = 100 \Omega$ , ADC output data rate = 200 kSPS                                                                                                                                                                                                     |

| ADC ENDPOINT ERRORS                      |                     |       |           |                               |                                |                                                                                                                                                                                                                                                                                                                                                                  |

| Offset Error                             |                     |       |           |                               |                                |                                                                                                                                                                                                                                                                                                                                                                  |

| Low Power Mode                           |                     | -600  | $\pm 200$ | +600                          | $\mu\text{V}$                  | PGA gain = 1.5, low power mode, all channels except AIN3                                                                                                                                                                                                                                                                                                         |

| High Power Mode <sup>2, 4</sup>          |                     | -620  | $\pm 200$ | +880                          | $\mu\text{V}$                  | PGA gain = 1.5, AIN3 only                                                                                                                                                                                                                                                                                                                                        |

| Drift over Temperature <sup>2</sup>      |                     | -1.1  | $\pm 0.5$ | +1.4                          | $\text{mV}$                    | PGA gain = 1.5                                                                                                                                                                                                                                                                                                                                                   |

| Offset Matching                          |                     |       | $\pm 3$   |                               | $\mu\text{V}/^{\circ}\text{C}$ | Using 1.82 V internal reference                                                                                                                                                                                                                                                                                                                                  |

| Full-Scale Error                         |                     |       | $\pm 2$   |                               | LSB                            | Matching compared to AIN3                                                                                                                                                                                                                                                                                                                                        |

| High Power Mode <sup>2, 4</sup>          |                     | -1000 | $\pm 400$ | +800                          | $\mu\text{V}$                  | PGA gain = 1.5, excluding internal channels and AIN3; both negative and positive full scale; error at both endpoints                                                                                                                                                                                                                                             |

| Internal Channels <sup>2</sup>           |                     | -1000 |           | +1000                         | $\mu\text{V}$                  | PGA gain = 1.5, AIN3 only                                                                                                                                                                                                                                                                                                                                        |

| Gain Drift over Temperature <sup>2</sup> |                     | -2.2  | $\pm 0.9$ | +1.82                         | $\text{mV}$                    | PGA gain = 1.5                                                                                                                                                                                                                                                                                                                                                   |

| Gain Error Matching                      |                     | 0.2   |           | 0.75                          | % FS                           | AVDD/2, DVDD/2, VBIAS_CAP, VREF_2V5, VREF_1V82, AVDD_REG                                                                                                                                                                                                                                                                                                         |

| PGA Mismatch Error <sup>2</sup>          |                     | -3    | $\pm 1$   | +3                            | $\mu\text{V}/^{\circ}\text{C}$ | Full-scale error drift minus offset error drift                                                                                                                                                                                                                                                                                                                  |

| PGA Gain = 1 to 1.5                      |                     |       | $\pm 3$   |                               | LSB                            | Mismatch from channel to channel                                                                                                                                                                                                                                                                                                                                 |

| PGA Gain = 1.5 to 2                      |                     | -0.2  | $\pm 0.1$ | +0.3                          | %                              | ADC offset and gain calibration <sup>5, 6, 7, 8</sup> with a gain value of 1.5                                                                                                                                                                                                                                                                                   |

| PGA Gain = 2 to 4                        |                     | -0.2  | $\pm 0.1$ | +0.3                          | %                              |                                                                                                                                                                                                                                                                                                                                                                  |

| PGA Gain = 4 to 9                        |                     | -0.65 | $\pm 0.2$ | +0.65                         | %                              |                                                                                                                                                                                                                                                                                                                                                                  |

| PGA Gain = 4 to 9                        |                     | -0.65 | $\pm 0.2$ | +0.65                         | %                              |                                                                                                                                                                                                                                                                                                                                                                  |

| ADC DYNAMIC PERFORMANCE                  |                     |       |           |                               |                                | $f_{\text{IN}} = 20 \text{ kHz}$ sine wave, $f_{\text{SAMPLE}} = 200 \text{ kSPS}$ ; using AINx voltage input channels; PGA gain = 1.5                                                                                                                                                                                                                           |

| Signal-to-Noise Ratio                    | SNR                 |       |           |                               |                                | Includes distortion and noise components                                                                                                                                                                                                                                                                                                                         |

## 仕様

表 1. (続き)

| Parameter                                                                                                                                                       | Symbol | Min                                      | Typ    | Max  | Unit   | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------|--------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Total Harmonic Distortion <sup>2</sup><br>Peak Harmonic or Spurious Noise <sup>2</sup><br>Channel to Channel Crosstalk <sup>2</sup><br>Noise (RMS) <sup>9</sup> | THD    | 80<br>76 <sup>2</sup><br>70 <sup>2</sup> | -84    | -86  | dB     | PGA gain = 1, 1.5, and 2                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                 |        |                                          |        |      |        | PGA gain = 4                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                 |        |                                          |        |      |        | PGA gain = 9                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                 |        | -86                                      | -86    | -86  | dB     | Measured on adjacent channels                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                 |        | 800                                      | 800    | 400  | nV/√Hz | Chop on                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                 |        |                                          |        |      | nV/√Hz | Chop off                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ADC INPUT                                                                                                                                                       |        |                                          |        |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Input Voltage Ranges <sup>2</sup>                                                                                                                               |        | 0.2                                      | 2.1    |      | V      | Input to ADC mux                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                 |        |                                          |        |      | V      | Voltage applied to any input pin                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                 |        |                                          |        |      |        | Pseudo differential voltage between VBIAS_CAP pin and analog input from ADC mux                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                 |        | -0.9                                     | +0.9   |      | V      | Gain = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                 |        | -0.9                                     | +0.9   |      | V      | Gain = 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                 |        | -0.6                                     | +0.6   |      | V      | Gain = 2                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                 |        | -0.3                                     | +0.3   |      | V      | Gain = 4                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                 |        | -0.133                                   | +0.133 |      | V      | Gain = 9                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Input Current Range <sup>2</sup>                                                                                                                                |        | 0.00005                                  | 3000   |      | μA     | Low power TIA and high speed TIA current input channel ranges                                                                                                                                                                                                                                                                                                                                                                                                   |

| Common Mode Range <sup>2</sup>                                                                                                                                  |        | 0.2                                      | 1.1    | 2.1  | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Leakage Current                                                                                                                                                 |        | -1.5                                     | ±0.5   | +1.5 | nA     | AIN0, AIN1, AIN2, AIN3/BUF_VREF1V82, AIN4/LPF0, AIN6 (TA = -40°C to +85°C)                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                 |        | -6                                       |        | +6   | nA     | CE0, RE0, SE0 and DE0 (TA = -40°C to 85°C)                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                 |        | -3.5                                     | ±0.5   | +3.5 | nA     | AIN0, AIN1, AIN2, AIN3/BUF_VREF1V82, AIN4/LPF0, AIN6 (TA = -40°C to +105°C)                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                 |        | -8                                       |        | +8   | nA     | CE0, RE0, SE0 and DE0 (TA = -40°C to +105°C)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Input Current <sup>2</sup>                                                                                                                                      |        | -8                                       | ±2     | +8   | nA     | AIN0, AIN1, AIN2, AIN3, AIN4, AIN6, CE0, RE0, SE0, and DE0                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input Capacitance <sup>2</sup>                                                                                                                                  |        |                                          | 40     |      | pF     | During ADC acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Antialias Filter 3 dB Frequency Range <sup>2</sup>                                                                                                              |        |                                          |        |      |        | Three programmable settings                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Mode 0                                                                                                                                                          |        |                                          | 50     |      | kHz    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Mode 1                                                                                                                                                          |        |                                          | 100    |      | kHz    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Mode 2                                                                                                                                                          |        |                                          | 250    |      | kHz    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ADC Channel Switch Settling Time                                                                                                                                |        |                                          |        |      |        | Time delay required after switching ADC input channel; excludes sinc3 settling time                                                                                                                                                                                                                                                                                                                                                                             |

| Antialias Filter -3 dB Cutoff Frequency <sup>2</sup>                                                                                                            |        |                                          |        |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 250 kHz                                                                                                                                                         |        | 20                                       |        |      | μs     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 100 kHz                                                                                                                                                         |        | 40                                       |        |      | μs     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 50 kHz                                                                                                                                                          |        | 60                                       |        |      | μs     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DISCRETE FOURIER TRANSFORM (DFT)-BASED IMPEDANCE MEASUREMENTS <sup>2</sup>                                                                                      |        |                                          |        |      |        | For impedance (Z) of 1000 Ω (0.1% tolerant resistor), excitation frequency = 0.1 Hz to 200 kHz, sine amplitude = 10 mV rms, R <sub>TIA</sub> = 5 kΩ; R <sub>CAL</sub> = 200 Ω; 1% accurate temperature coefficient 5 ppm/°C; single DFT measurement; DFT using 8192 ADC samples; Hanning on; HSDACCON Bits[8:1] = 0x1B for low power mode and impedance measurements ≤ 80 kHz; HSDACCON Bits[8:1] = 0x7 for high power mode and impedance measurements ≥ 80 kHz |

| With High Bandwidth Loop                                                                                                                                        |        |                                          |        |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## 仕様

表 1. (続き)

| Parameter                                         | Symbol | Min   | Typ       | Max     | Unit                         | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------|--------|-------|-----------|---------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Accuracy                                          |        |       |           |         |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Magnitude                                         |        | -1.25 | $\pm 0.2$ | +1.25   | %                            | 20 kHz to 200 kHz                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                   |        |       | $\pm 0.2$ |         | %                            | 10 Hz to 20 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                   |        |       | $\pm 1$   |         | %                            | 1 Hz to <10 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Phase                                             |        | -0.3  | $\pm 0.1$ | +0.3    | Degrees                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

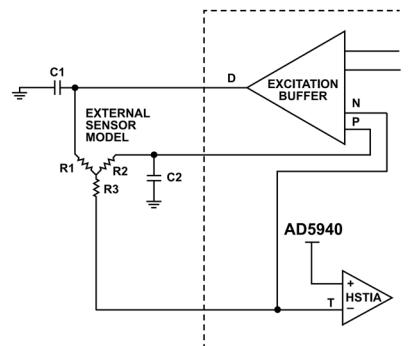

| Three-Resistor Star Cell                          |        |       |           |         |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Accuracy                                          |        |       |           |         |                              | $R_1 = R_2 = R_3 = 2.2 \Omega$ (see Figure 17); 0.1 Hz to 200 kHz                                                                                                                                                                                                                                                                                                                                                                               |

| Magnitude                                         |        |       | $\pm 0.5$ |         | %                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Phase                                             |        |       | $\pm 0.5$ |         | Degrees                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Accuracy                                          |        |       |           |         |                              | $R_1 = R_2 = R_3 = 100 \Omega$ connected (see Figure 17); 0.1 kHz to 200 kHz                                                                                                                                                                                                                                                                                                                                                                    |

| Magnitude                                         |        |       | $\pm 0.2$ |         | %                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Phase                                             |        |       | $\pm 0.2$ |         | Degrees                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| With High Bandwidth Loop, 50 kHz, 4-Wire Isolated |        |       |           |         |                              | For $Z = 1 \text{ k}\Omega$ (0.1% tolerant resistor); excitation frequency = 50 kHz; sine amplitude = 0.6 V p-p; $R_{TIA} = 1 \text{ k}\Omega$ ; $C_{TIA} = 32 \text{ pF}$ ; Isolation Capacitor 1 ( $C_{ISO1} = 15 \text{ nF}$ ); Isolation Capacitor 2 ( $C_{ISO2} = \text{Isolation Capacitor 3}$ ( $C_{ISO3} = \text{Isolation Capacitor 4}$ ( $C_{ISO4} = 470 \text{ nF}$ ); current-limiting resistor ( $R_{LIMIT} = 1 \text{ k}\Omega$ ) |

| Accuracy                                          |        |       |           |         |                              | Device to device repeatability for three devices at 50 kHz                                                                                                                                                                                                                                                                                                                                                                                      |

| Magnitude                                         |        |       | 0.26      |         | %                            | Percentage error                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Phase                                             |        |       | 1         |         | Degrees                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

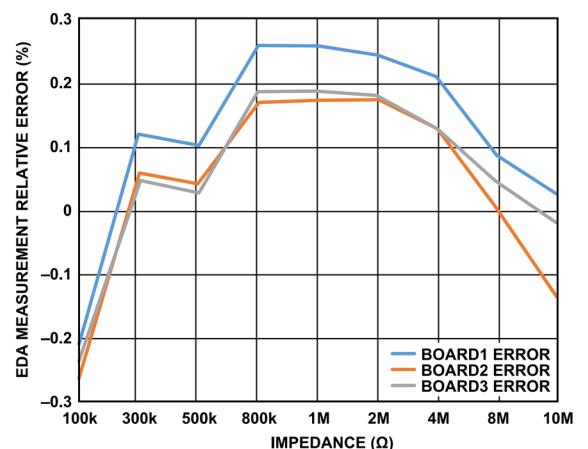

| With Low Bandwidth Loop                           |        |       |           |         |                              | For $Z = 100 \text{ k}\Omega$ ; excitation frequency = 100 Hz; sine amplitude = 1.1 V p-p; $R_{TIA} = 100 \text{ k}\Omega$ ; $C_{TIA} = 100 \text{ nF}$ ; $C_{ISO1} = 15 \text{ nF}$ ; $C_{ISO2} = 470 \text{ nF}$ ; $R_{LIMIT} = 1000 \Omega$                                                                                                                                                                                                  |

| Frequency Range                                   |        | 1     |           | 300     | Hz                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Accuracy <sup>2</sup>                             |        |       |           |         |                              | Device to device repeatability for three devices at 100 Hz                                                                                                                                                                                                                                                                                                                                                                                      |

| Magnitude                                         |        |       | $\pm 0.3$ |         | %                            | Percentage error                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Precision <sup>2</sup>                            |        |       |           | 450     | $\Omega$                     | Standard deviation                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Magnitude                                         |        |       |           |         |                              | See Figure 17; valid for impedance spectroscopy, voltammetry, and pulse tests                                                                                                                                                                                                                                                                                                                                                                   |

| High Speed Loop                                   |        |       |           |         |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Allowed External Load Capacitance <sup>2</sup>    |        |       |           | 100     | pF                           | $R_2 + R_3 \leq 100 \Omega$ ; $R_1 \leq 100 \Omega$                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   |        |       |           | 50      | pF                           | $R_2 + R_3 \leq 500 \Omega$ ; $R_1 \leq 100 \Omega$                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                   |        |       |           | 40      | pF                           | $R_2 + R_3 \leq 1600 \Omega$ ; $R_1 \leq 800 \Omega$ ; frequency $\geq 1 \text{ kHz}$                                                                                                                                                                                                                                                                                                                                                           |

| Excitation Amplifier Bandwidth <sup>2</sup>       |        |       | 3         |         | MHz                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Impedance Frequency Range <sup>2</sup>            |        | 0.015 |           | 200,000 | Hz                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

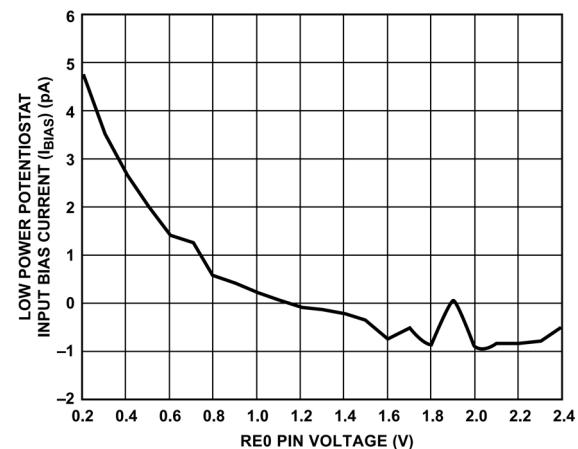

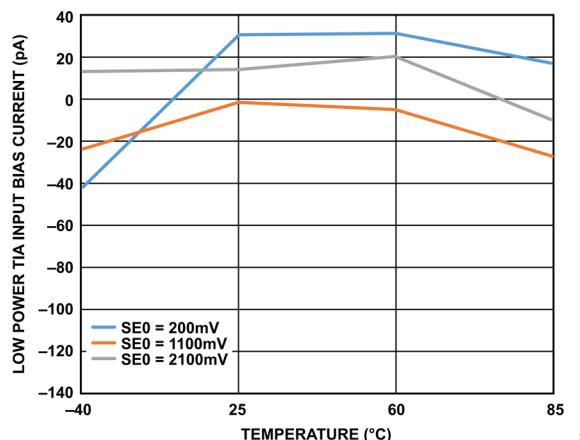

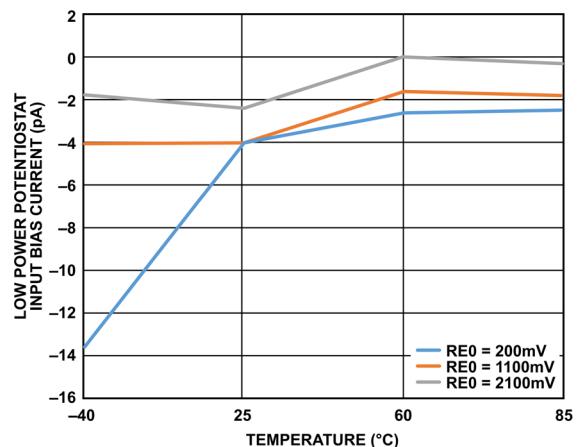

| LOW POWER TIA AND POTENTIOSTAT                    |        |       |           |         |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Input Bias Current <sup>2</sup>                   |        |       |           |         |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TIA Amplifier, SE0 Pin                            |        |       | 80        | 200     | pA                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Potentiostat Amplifier                            |        |       | 20        | 150     | pA                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Offset Voltage <sup>2</sup>                       |        |       | 50        | 150     | $\mu\text{V}$                |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Offset Voltage Drift vs. Temperature              |        |       | 1         |         | $\mu\text{V}/^\circ\text{C}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Noise <sup>2</sup>                                |        |       |           |         |                              | Unity-gain mode; V p-p in 0.1 Hz to 10 Hz range                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                   |        |       | 1.6       |         | $\mu\text{V}$                | Normal mode (LPTIACON0 Bit 2 = 0)                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                   |        |       | 2         |         | $\mu\text{V}$                | Half power mode (LPTIACON0 Bit 2 = 1)                                                                                                                                                                                                                                                                                                                                                                                                           |

| Potentiostat Source/Sink Current <sup>2</sup>     |        | -750  |           | +750    | $\mu\text{A}$                | Normal mode (LPTIACON0 Bits[4:3] = 00); from CE0                                                                                                                                                                                                                                                                                                                                                                                                |

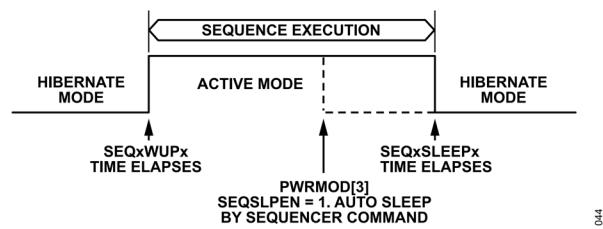

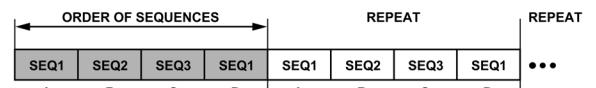

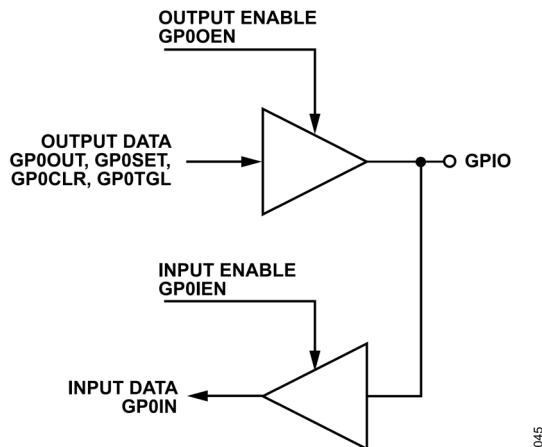

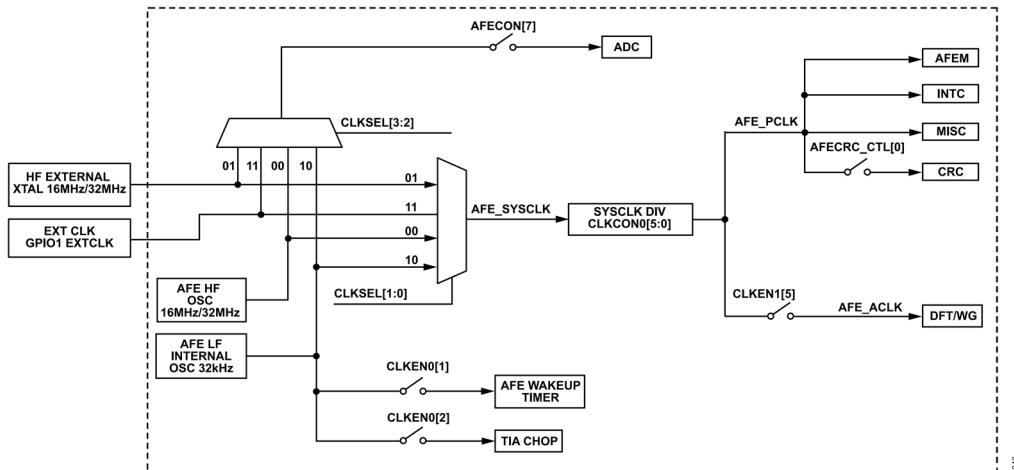

|                                                   |        | -3    |           | +3      | mA                           | High current mode (LPTIACON0 Bits[4:3] = 01 or 11 from CE0)                                                                                                                                                                                                                                                                                                                                                                                     |