## PGA内蔵、24ビット、DC~50kHz入力帯域幅、マルチチャンネルの低ノイズ高精度シグマデルタ型ADC

### 特長

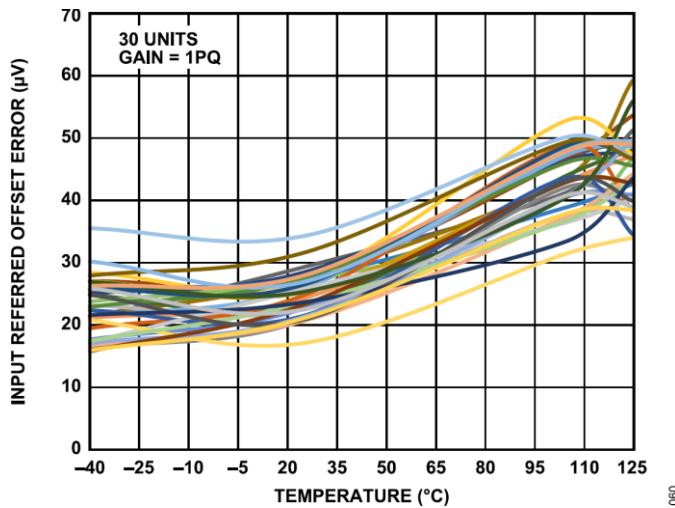

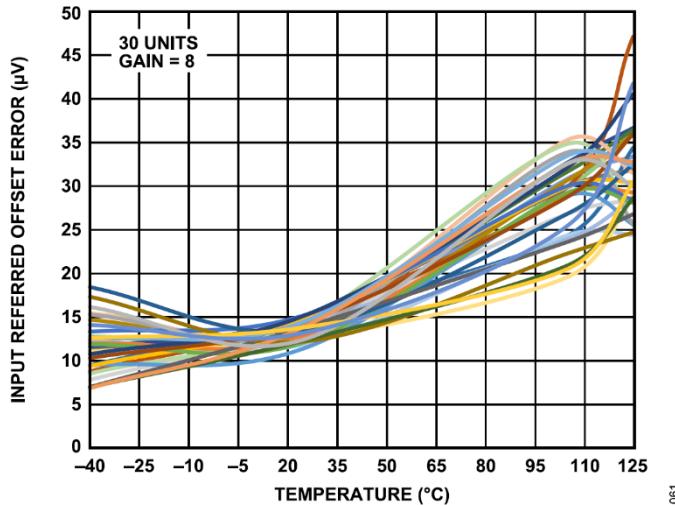

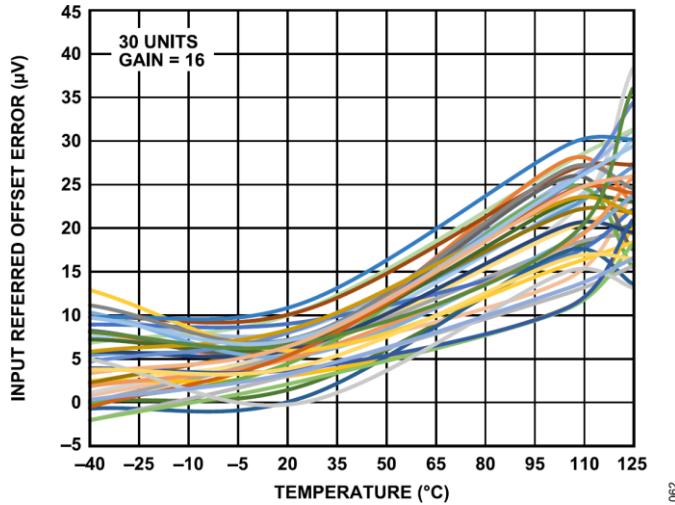

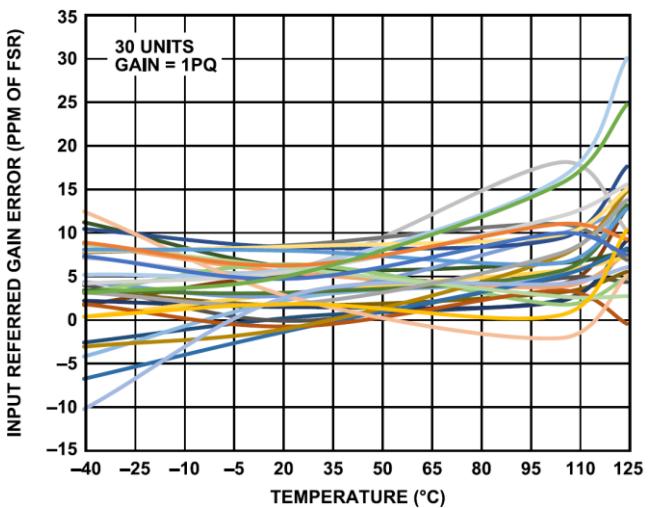

- ▶ 高精度のACおよびDC性能

- ▶ 入力換算 (RTI) ノイズ : 5.5nV/ $\sqrt{\text{Hz}}$  (ゲイン = 128)

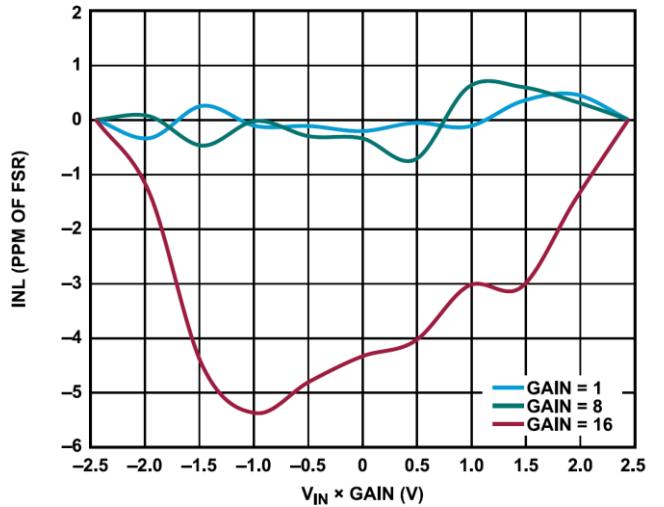

- ▶ INL : FSRの±0.5ppm

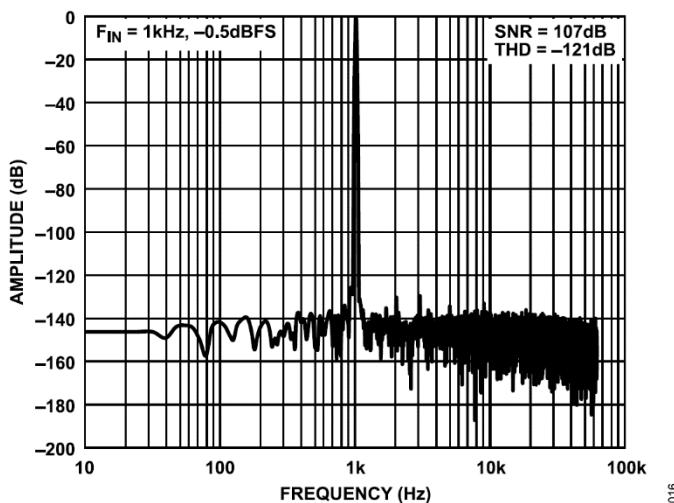

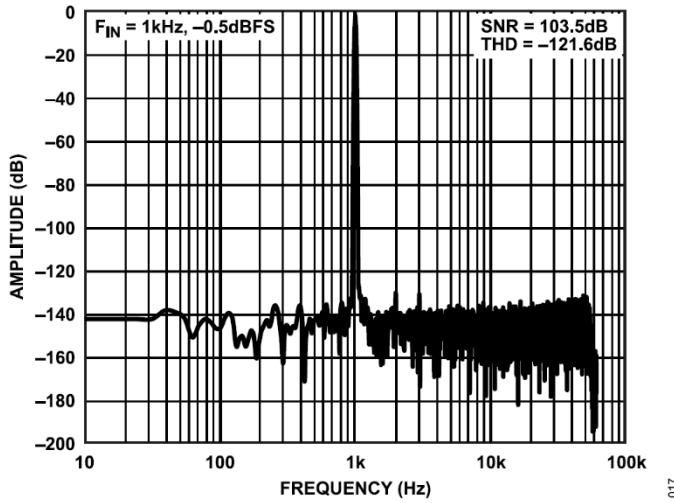

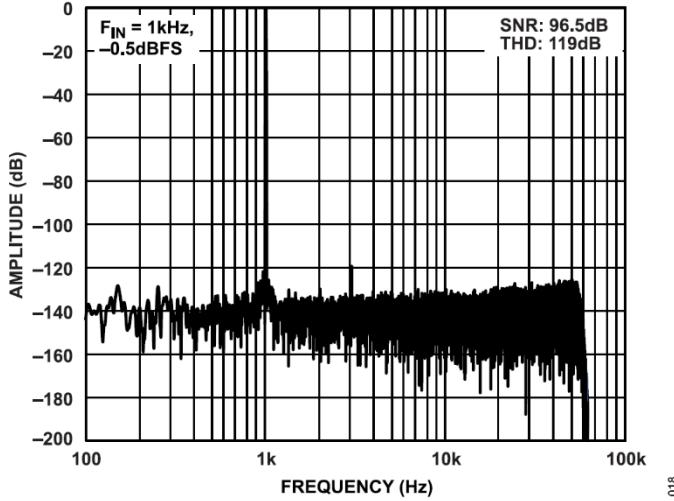

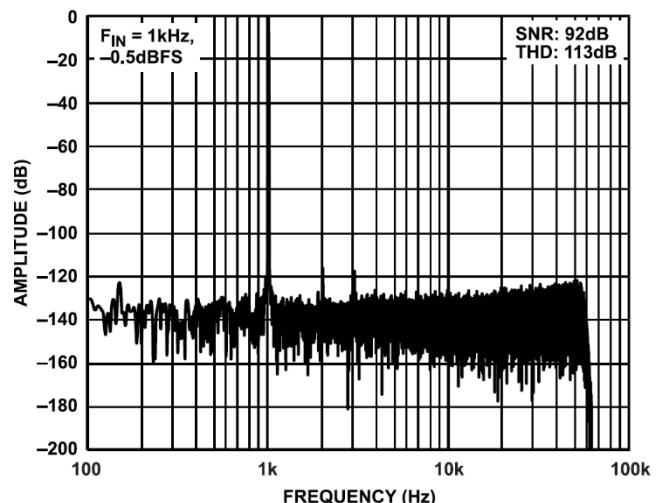

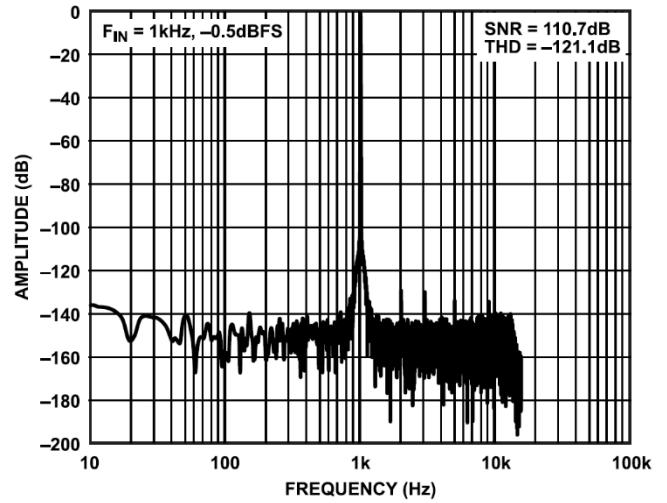

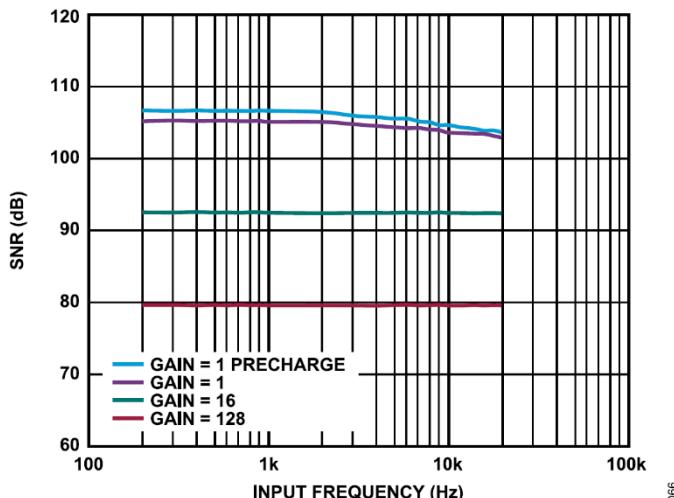

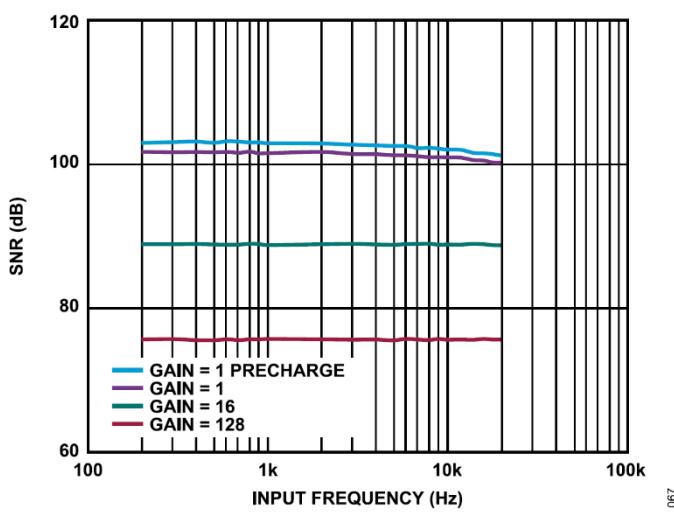

- ▶ S/N比 : 110dB (代表値、 $V_{\text{REF}} = 4.096\text{V}$ 、ゲイン = 1プリチャージ、 $\text{sinc}^5$ フィルタ)

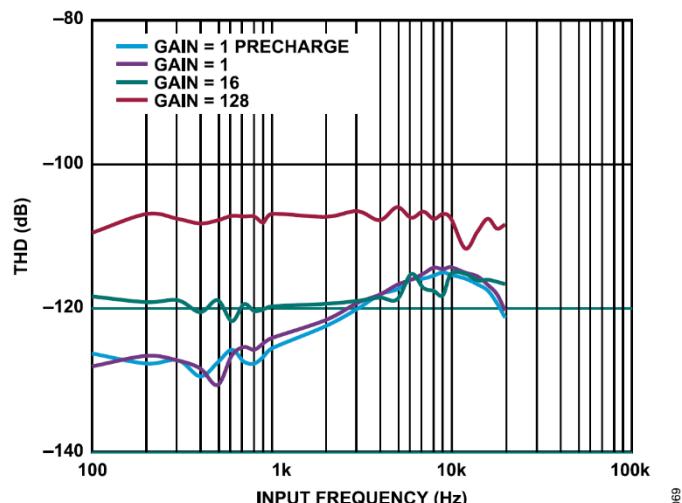

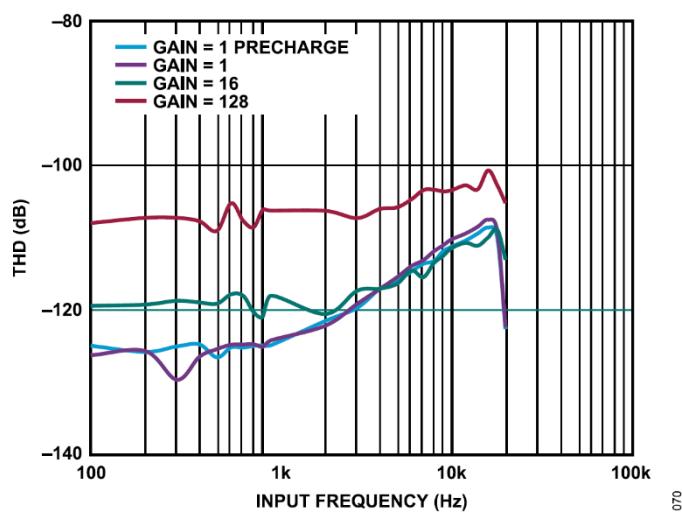

- ▶ THD : -120dB (代表値)

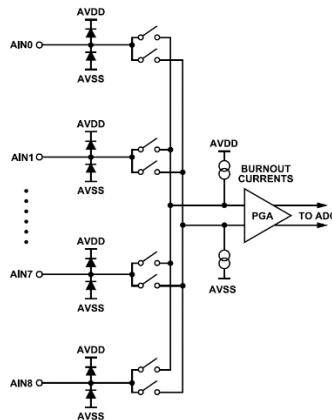

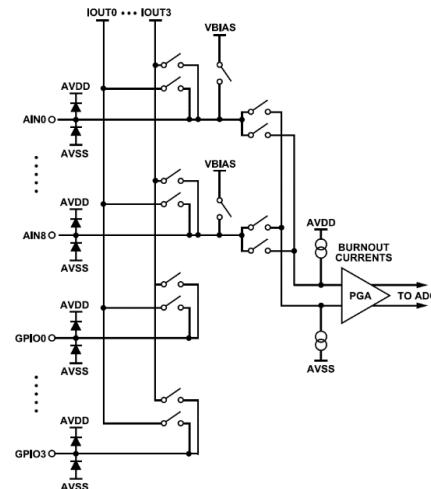

- ▶ クロスポイント・マルチプレクサ・アナログ入力

- ▶ 4個の差動入力／8個の疑似差動入力

- ▶ 非アクティブなアナログ入力での過電圧／低電圧耐性

- ▶ チャンネル・スキャン・データ・レート : 71.4kSPS／チャンネル (セトリング時間14 $\mu\text{s}$ )

- ▶ 超低ノイズの内蔵PGA (ゲイン : 0.5~128)

- ▶ 出力データ・レート : 7.6SPS~500kSPS

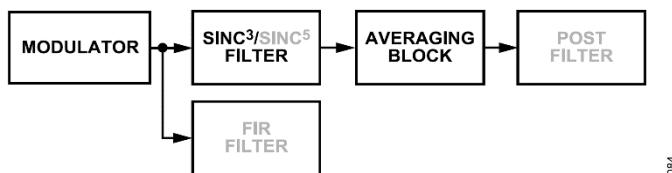

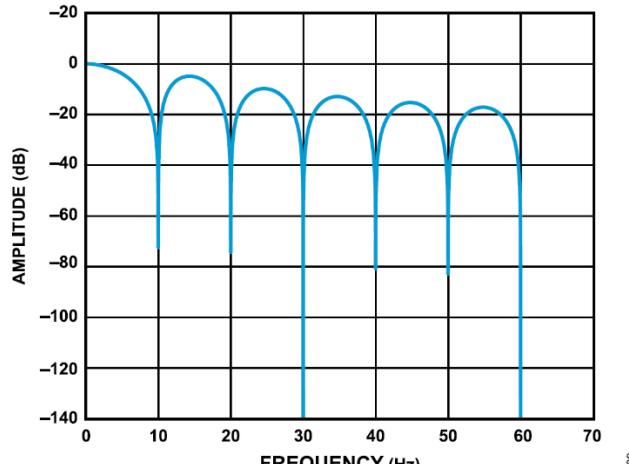

- ▶ 柔軟なデジタル・フィルタ

- ▶ 低リップルFIR : ±0.005dBの最大通過帯域リップル

- ▶ ユーザ・プログラマブルなFIRフィルタ・オプション

- ▶ 低遅延sincフィルタ

- ▶ 50Hz/60Hzを同時に除去

- ▶ ドリフト5ppm/ $^{\circ}\text{C}$  (代表値) のバンド・ギャップ・リファレンス

- ▶ 内部発振器および温度センサー

- ▶ アナログ電源 : 4.75V~5.25Vまたは±2.5V

- ▶ デジタル電源 : 1.7V~5.25V

- ▶ マッチングがとれたプログラマブル励起電流源

- ▶ ローサイド・パワー・スイッチ

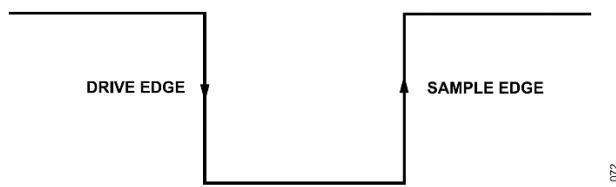

- ▶ AC励起

- ▶ 内蔵バイアス電圧発生器

- ▶ 4つの汎用入出力

- ▶ 内部およびシステム・キャリブレーション

- ▶ センサー・バーンアウト検出

- ▶ 診断機能

- ▶ チャンネルごとの設定

- ▶ 柔軟なチャンネル・シーケンサ

- ▶ 3線式または4線式シリアル・インターフェース

- ▶ SCLKにシュミット・トリガ内蔵

- ▶ SPI、QSPI、MICROWIRE、DSP互換

- ▶ データ・ストリーミング用のTDM対応インターフェース

- ▶ 性能温度範囲 : -40°C~+105°C

- ▶ 動作温度範囲 : -40°C~+125°C

- ▶ 32ピン、4mm × 6mmのLFCSP

### アプリケーション

- ▶ 工業用プロセス制御 : PLC/DCSモジュール

- ▶ 温度計測および圧力計測

- ▶ 高精度の医療用および科学用計測器

- ▶ クロマトグラフィ

- ▶ 地震探査およびエネルギー探査

- ▶ 電子テストおよび計測

- ▶ 音響解析

- ▶ 計測器

- ▶ 重量計

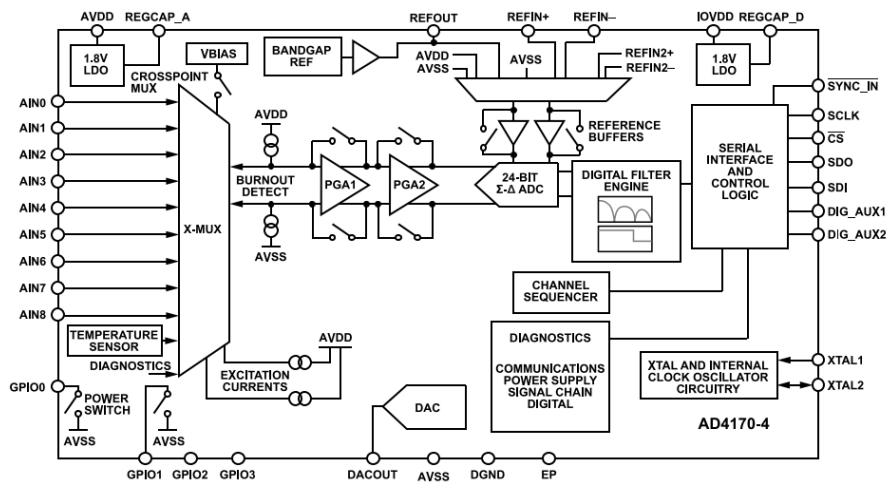

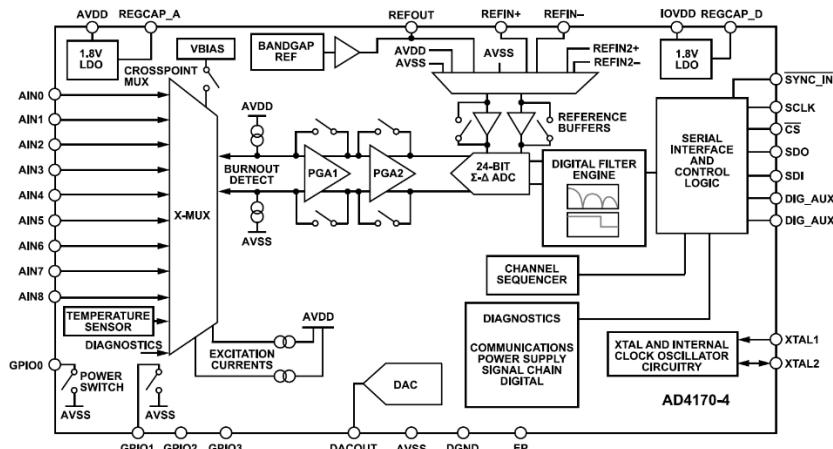

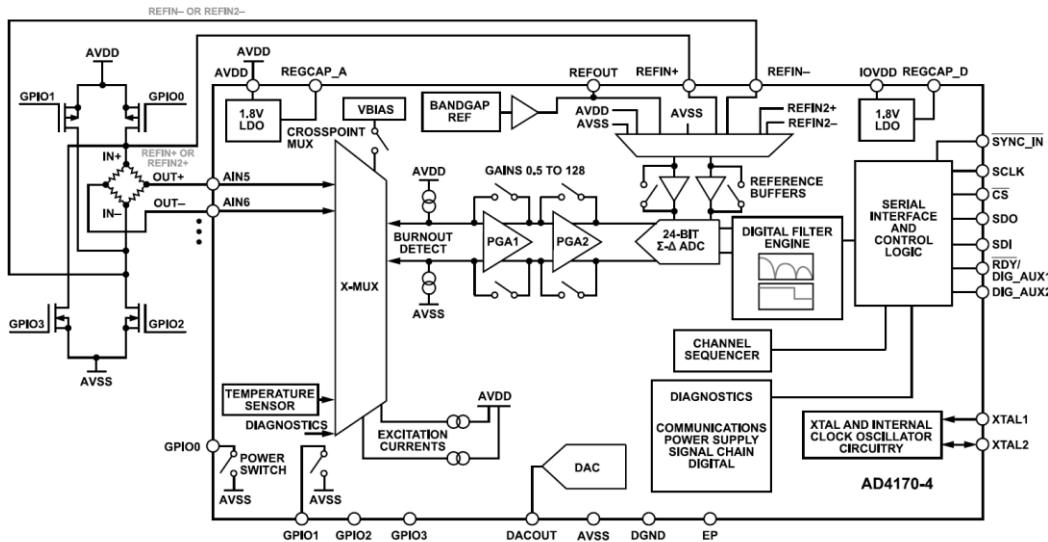

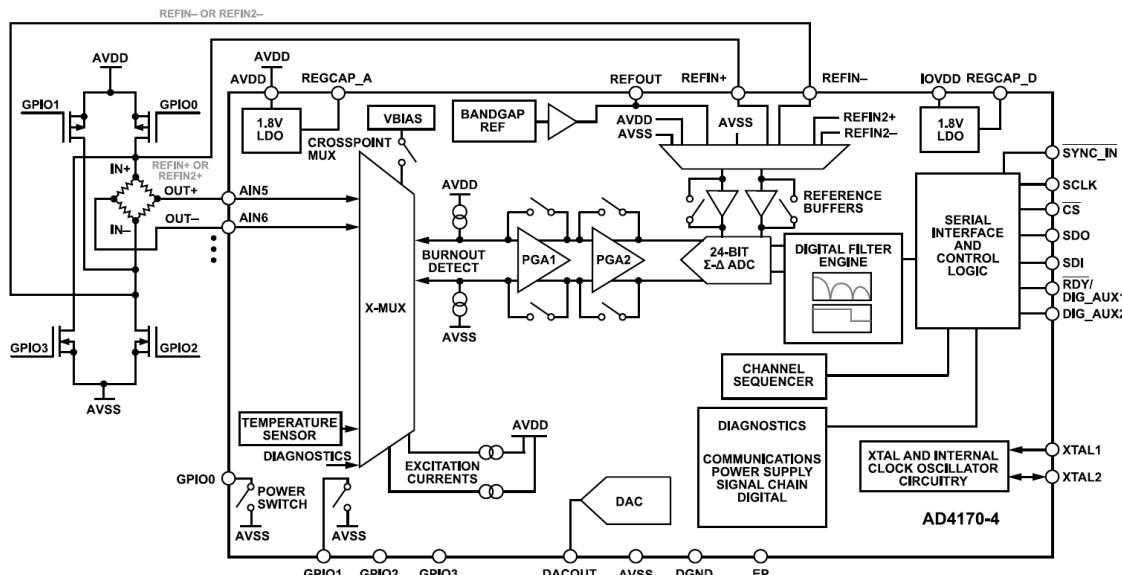

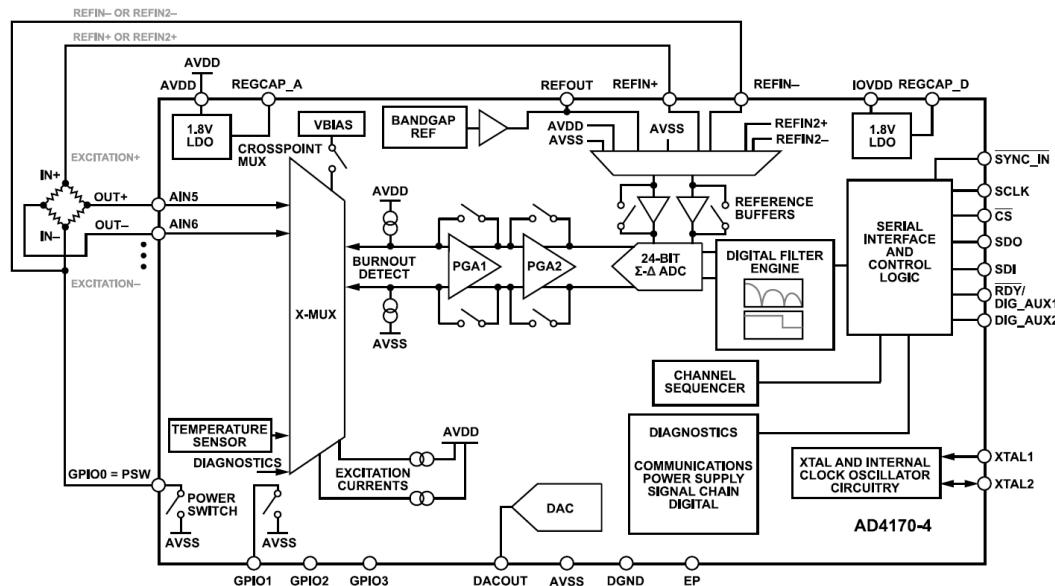

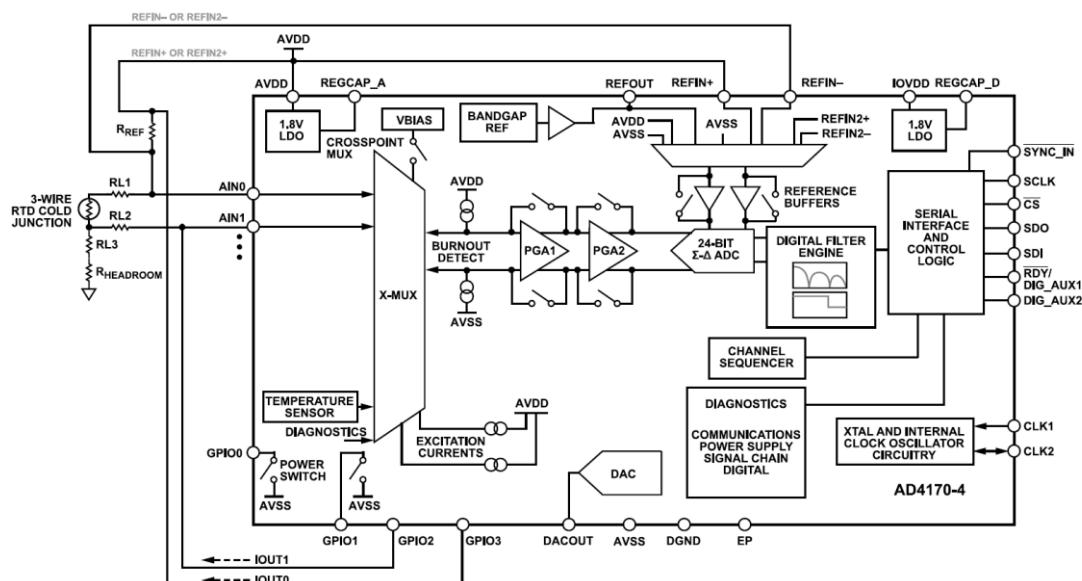

### 機能ブロック図

図1.

## 目次

|                             |    |                                 |    |

|-----------------------------|----|---------------------------------|----|

| 特長                          | 1  | sinc <sup>3</sup> フィルタ          | 56 |

| アプリケーション                    | 1  | sinc <sup>3</sup> の50Hzと60Hzの除去 | 57 |

| 機能ブロック図                     | 1  | ポスト・フィルタ                        | 57 |

| 概要                          | 4  | FIRフィルタ                         | 58 |

| 仕様                          | 5  | アンチエイリアシング・フィルタ処理               | 60 |

| タイミング特性                     | 11 | デジタル・インターフェース                   | 62 |

| 絶対最大定格                      | 15 | ADCの変換モードと変換へのアクセス方法            | 62 |

| 熱抵抗                         | 15 | 連続読み出し                          | 62 |

| ESDに関する注意                   | 15 | 連続送信                            | 63 |

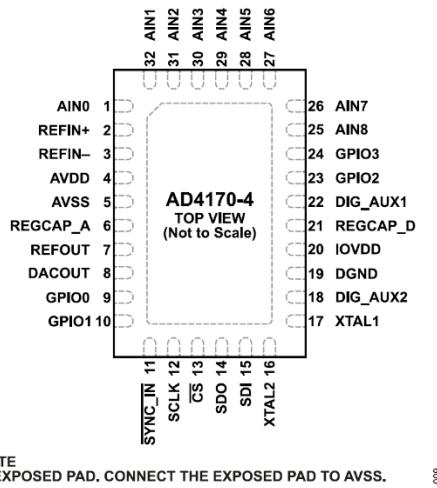

| ピン配置およびピン機能の説明              | 16 | SPIフレーム同期                       | 64 |

| 代表的な性能特性                    | 19 | ADCの同期                          | 67 |

| 実効値ノイズと分解能                  | 29 | 標準同期                            | 67 |

| SINC <sup>5</sup> + AVG     | 29 | オルタネート同期                        | 67 |

| SINC <sup>3</sup>           | 30 | 複数のAD4170-4デバイスの同期              | 67 |

| SINC <sup>5</sup>           | 31 | 診断機能                            | 68 |

| ポスト・フィルタ                    | 31 | デバイス・エラー                        | 68 |

| 16平均ポスト・フィルタ                | 32 | シグナル・チェーンのチェック                  | 68 |

| FIRフィルタ                     | 32 | リファレンス検出                        | 68 |

| S/N比およびTHD                  | 34 | リファレンス過電圧／低電圧の検出                | 68 |

| 動作原理                        | 35 | 変換エラー                           | 68 |

| 概要                          | 35 | アナログ入力過電圧／低電圧検出                 | 68 |

| 電源                          | 36 | 励起電流コンプライアンス                    | 68 |

| デジタル・コミュニケーション              | 37 | 電源モニタ                           | 68 |

| 設定の概要                       | 37 | LDOモニタリング                       | 69 |

| ADC回路情報                     | 45 | SPI SCLKカウンタ                    | 69 |

| アナログ入力チャンネル                 | 45 | SPI読み出し／書き込みエラー                 | 69 |

| プログラマブル・ゲイン・アンプ (PGA)       | 45 | ノット・レディ・エラー                     | 69 |

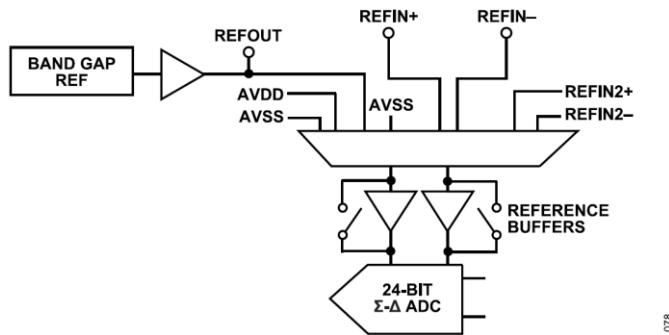

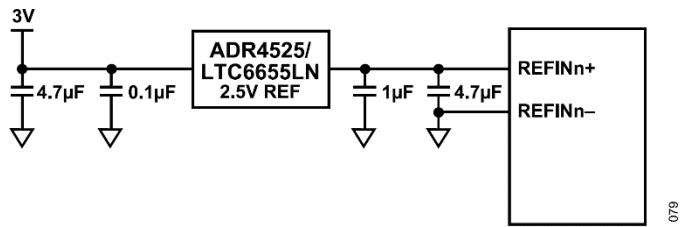

| リファレンス                      | 45 | チェックサム保護                        | 69 |

| バイポーラ／ユニポーラ設定               | 46 | メモリ・マップ・チェックサム保護                | 72 |

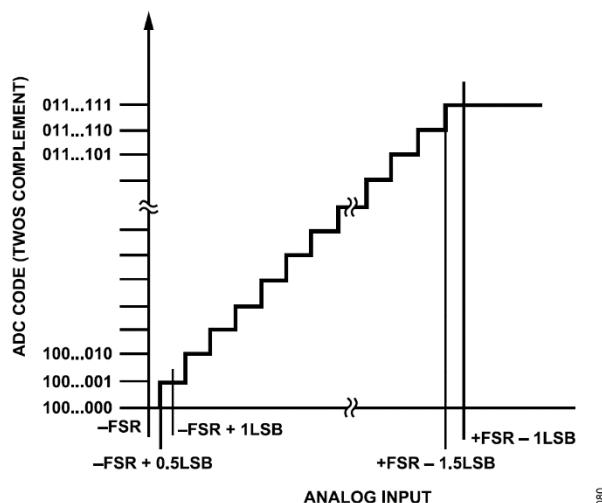

| データ出力コーディング                 | 46 | ROMチャックサム保護                     | 72 |

| 励起電流                        | 47 | バーンアウト電流                        | 72 |

| ブリッジ・パワーダウン・スイッチ            | 47 | ブルアップ電流                         | 72 |

| 汎用入出力 (GPIO0~GPIO3)         | 48 | 温度センサー                          | 72 |

| バイアス電圧発生器                   | 48 | グラウンドディングとレイアウト                 | 73 |

| DAC                         | 48 | アプリケーション情報                      | 74 |

| マルチブレクサ・ショッピング              | 48 | 重量計 (AC励起)                      | 74 |

| AC励起                        | 49 | 重量計 (DC励起)                      | 75 |

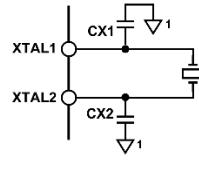

| クロック                        | 50 | RTDを使用した温度計測                    | 76 |

| スタンバイ・モードとパワーダウン・モード        | 50 | 内蔵レジスタ・マップ                      | 78 |

| キャリブレーション                   | 51 | INTERFACE_CONFIG_Aレジスタ          | 82 |

| スパンとオフセットの限界値               | 51 | INTERFACE_CONFIG_Bレジスタ          | 82 |

| デジタル・フィルタ                   | 53 | DEVICE_CONFIGレジスタ               | 83 |

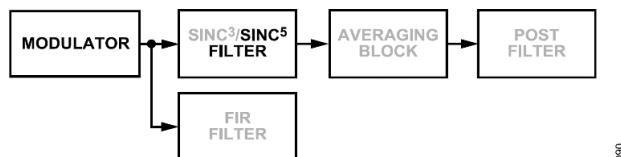

| sinc <sup>5</sup> + 平均化フィルタ | 53 | CHIP_TYPEレジスタ                   | 83 |

| sinc <sup>5</sup> フィルタ      | 55 | PRODUCT_ID Lレジスタ                | 83 |

## 目次

|                                 |     |                             |     |

|---------------------------------|-----|-----------------------------|-----|

| PRODUCT_ID_Hレジスタ .....          | 83  | OFFSETレジスタ .....            | 102 |

| CHIP_GRADEレジスタ .....            | 84  | ゲイン・レジスタ .....              | 102 |

| SCRATCH_PADレジスタ .....           | 84  | REF_CONTROLレジスタ .....       | 102 |

| SPI_REVISIONレジスタ .....          | 84  | V_BIASレジスタ .....            | 103 |

| VENDOR_Lレジスタ .....              | 85  | I_PULL_UPレジスタ .....         | 103 |

| VENDOR_Hレジスタ .....              | 85  | CURRENT_SOURCEレジスタ .....    | 104 |

| INTERFACE_CONFIG_Cレジスタ .....    | 85  | FIR_CONTROLレジスタ .....       | 105 |

| INTERFACE_STATUS_Aレジスタ .....    | 86  | COEFF_WRITE_DATAレジスタ .....  | 106 |

| STATUSレジスタ .....                | 86  | COEFF_READ_DATAレジスタ .....   | 106 |

| DATA_16Bレジスタ .....              | 87  | COEFF_ADDRESSレジスタ .....     | 106 |

| DATA_16B_STATUSレジスタ .....       | 87  | COEFF_WR_RD_STBレジスタ .....   | 107 |

| DATA_24Bレジスタ .....              | 87  | DAC_SPANレジスタ .....          | 107 |

| DATA_24B_STATUSレジスタ .....       | 88  | DAC_ENABLEレジスタ .....        | 107 |

| DATA_PER_CHANNELレジスタ .....      | 88  | HW_TOGGLE_MASKレジスタ .....    | 108 |

| PIN_MUXINGレジスタ .....            | 88  | HW_LDAC_MASKレジスタ .....      | 108 |

| CLOCK_CTRLレジスタ .....            | 90  | DAC_DATAレジスタ .....          | 108 |

| STANDBY_CTRLレジスタ .....          | 90  | SW_TOGGLE_TRIGGERレジスタ ..... | 109 |

| POWER_DOWN_SWレジスタ .....         | 91  | SW_LDACレジスタ .....           | 109 |

| ADC_CTRLレジスタ .....              | 91  | DAC_INPUT_Aレジスタ .....       | 109 |

| ERROR_ENレジスタ .....              | 93  | DAC_INPUT_Bレジスタ .....       | 110 |

| ERRORレジスタ .....                 | 94  | GPIO_MODEレジスタ .....         | 110 |

| CHANNEL_ENレジスタ .....            | 95  | GPIO_OUTPUT_DATAレジスタ .....  | 111 |

| CHANNEL_SETUPレジスタ .....         | 96  | GPIO_INPUT_DATAレジスタ .....   | 111 |

| CHANNEL_MAPレジスタ .....           | 97  | 外形寸法 .....                  | 112 |

| MISCELLANEOUS (MISC) レジスタ ..... | 98  | オーダー・ガイド .....              | 112 |

| AFEレジスタ .....                   | 99  | 評価用ボード .....                | 112 |

| FILTERレジスタ .....                | 100 |                             |     |

| FILTER_FSレジスタ .....             | 101 |                             |     |

## 改訂履歴

5/2024—Revision 0: Initial Version

## 概要

AD4170-4は、高精度計測アプリケーションに適した、入力帯域幅DC～50kHz、低ノイズ、高速の全機能内蔵型アナログ・フロント・エンドです。このデバイスは、7.6SPSから最大500kSPSまでの出力データ・レートが可能です。低ノイズ、24ビットΣ-Δ型のA/Dコンバータ（ADC）を内蔵しており、4個の差動入力または8個のシングルエンド入力または疑似差動入力を使用するように構成できます。内蔵の低ノイズ・ゲイン段により、小さな振幅の信号を直接AD4170-4に入力できます。

AD4170-4により、最高レベルのシグナル・チェーン集積化を実現できます。このデバイスは内部リファレンスを備えています。また、2つの外部差動リファレンスにも対応し、これらは内部でバッファ処理が可能です。その他の主要な内蔵機能は次のとおりです。

- ▶ プログラマブル・ゲイン・アンプ（PGA）。ゲインがプログラマブル（0.5～128）であることから、このPGAは、抵抗ブリッジ、熱電対、測温抵抗体（RTD）など低出力振幅のトランスジューサに直接インターフェースできます。

- ▶ PGAは広いコモンモード入力範囲を備えているため、広い範囲で変化する入力コモンモードに対しマージンを大きくとることができます。

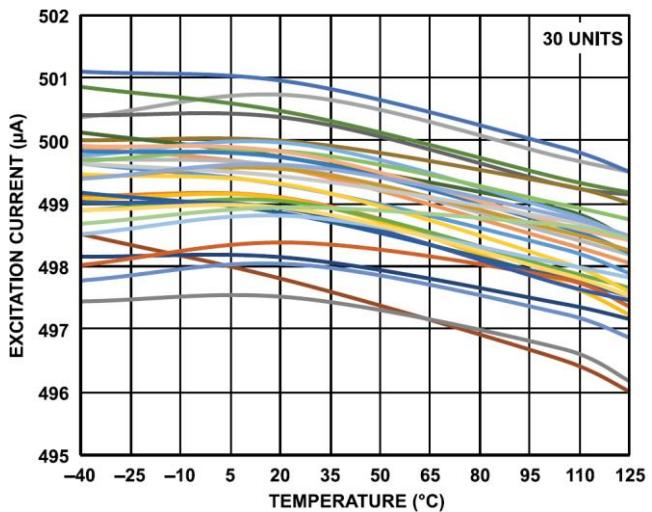

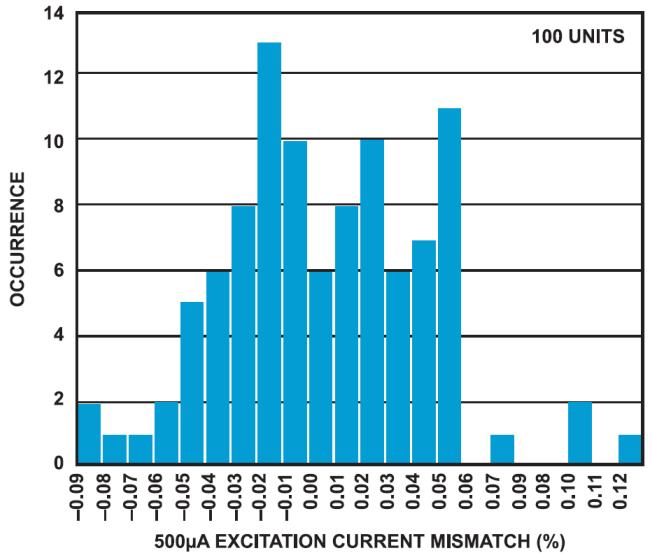

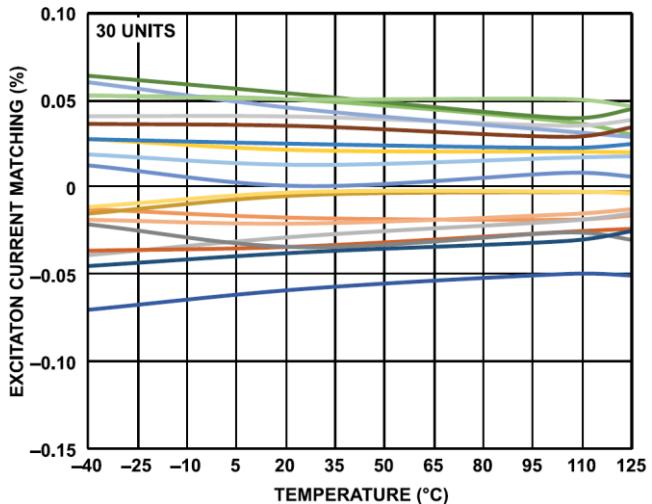

- ▶ 低ドリフトでマッチングの十分にとれた高精度電流源。励起電流源を使用して、2線式、3線式、4線式RTDまたはブリッジ型センサーを励起できます。励起電流出力オプションには、10µA、50µA、100µA、250µA、500µA、1mA、1.5mAがあります。より大きな電流が必要な場合は、電流を追加することもできます。電流は2つのペアで構成され、ペアはマッチングとドリフト・マッチングに関し最適化されています。

- ▶ ローサイド・パワー・スイッチ（PDSW）を使用して、変換と変換の間にブリッジ・センサーをパワーダウンできます。

- ▶ 熱電対用電圧バイアス（VBIASソースがチャンネルのコモンモード電圧を $(AVDD + AVSS)/2$ に設定）。

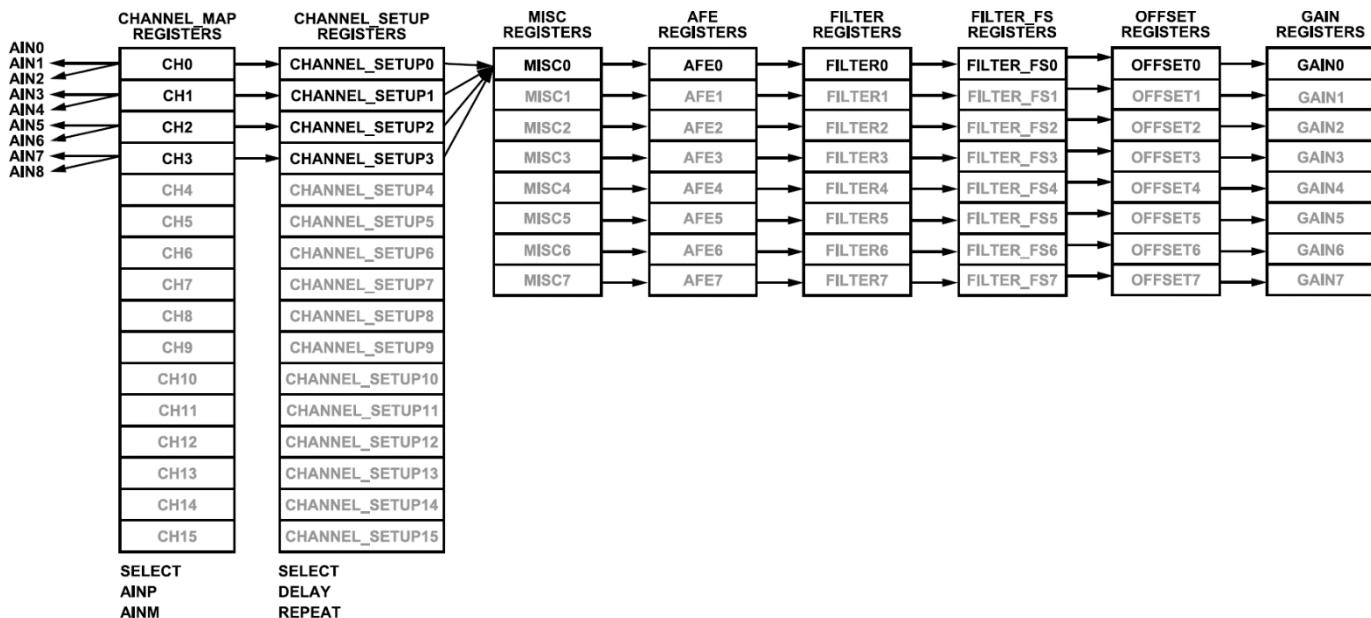

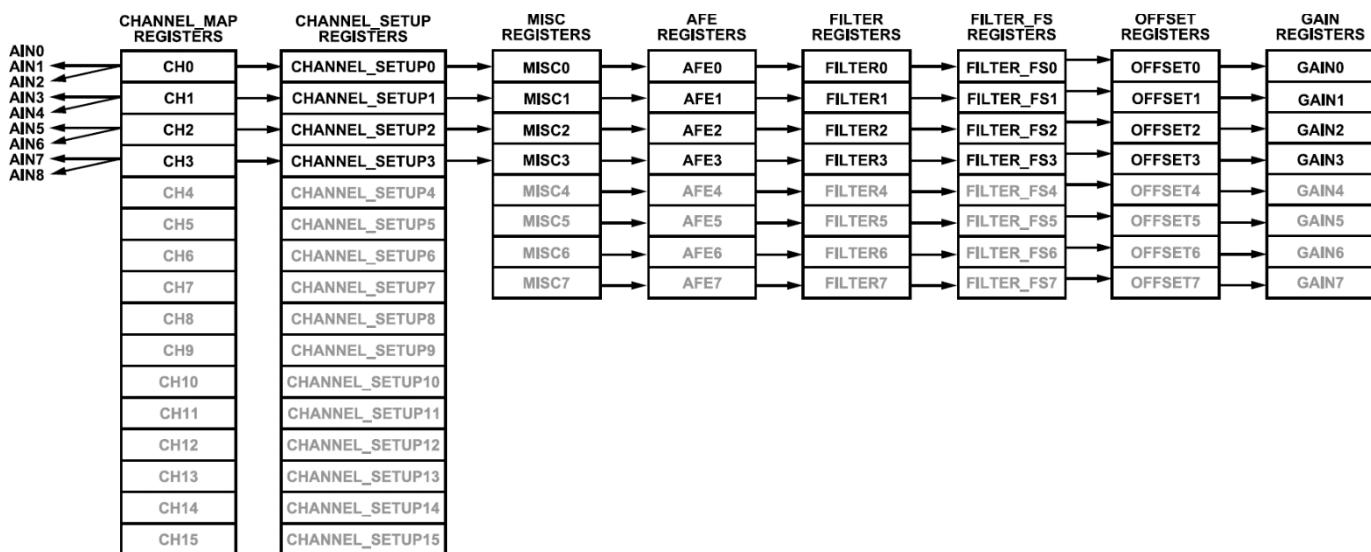

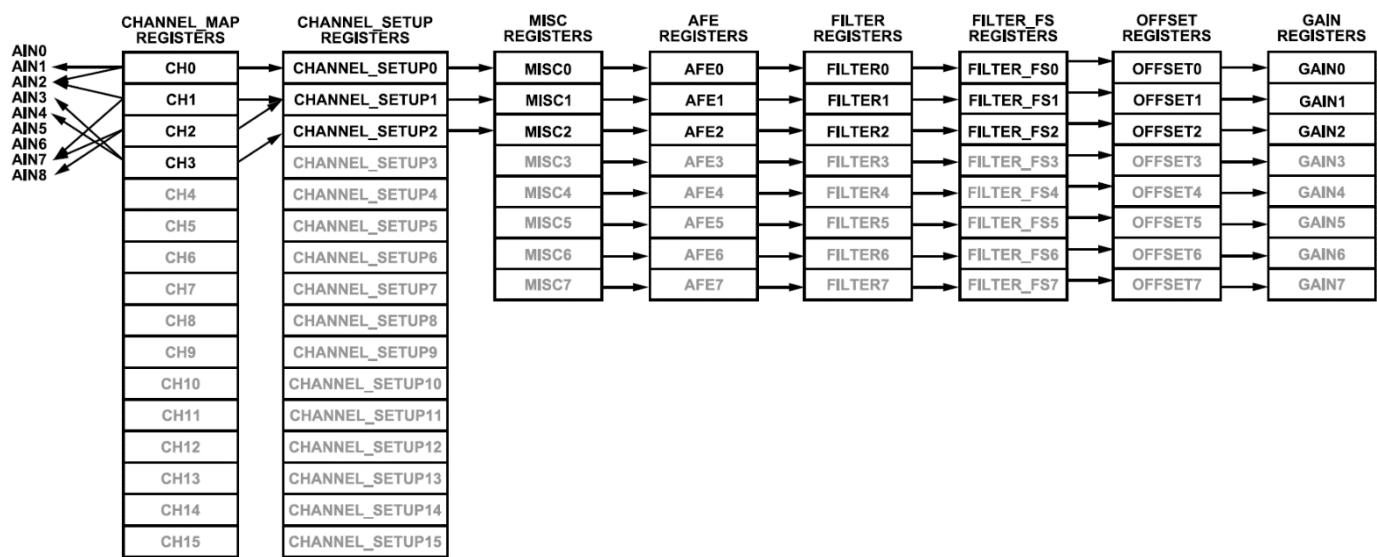

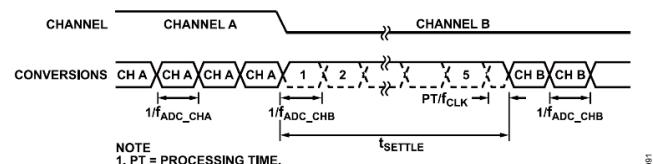

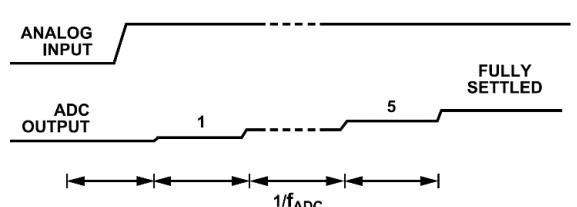

- ▶ スマート・シーケンサにより、イネーブルされた各事前設定チャンネルをあらかじめ定めた順序で変換できるので、トランス

ジューサ、システム・チェック、診断計測を組み合わせてインターリープできます。このシーケンサにより、設定を変更するのにデバイスとのシリアル・インターフェース通信を繰り返し行う必要がなくなります。このシーケンスでは16個のチャンネルを設定できます。これらのチャンネルはそれぞれ、ゲイン、フィルタ・タイプ、出力データ・レート、バッファリング、およびリファレンス源を選択できる8つのユーザ定義のADCセットアップから選択します。

AD4170-4は、充実した機能セットの一部として広範な診断機能も備えています。これらの診断機能には、巡回冗長性チェック（CRC）、シグナル・チェーン・チェック、シリアル・インターフェース・チェックが含まれ、より信頼性の高いソリューションになっています。

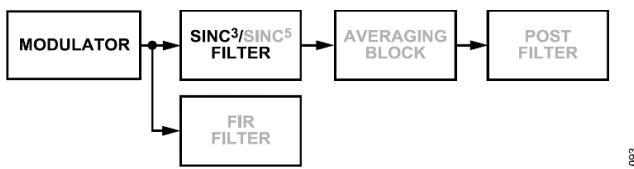

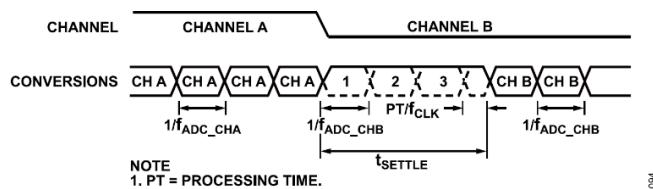

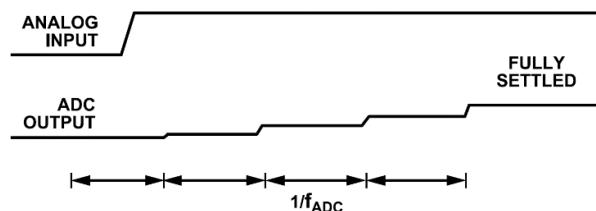

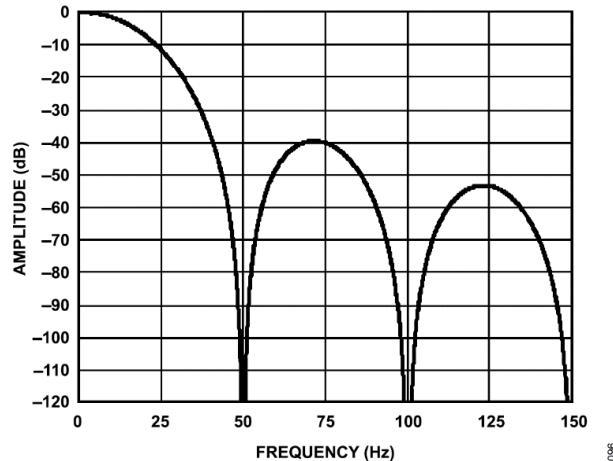

また、このデバイスは複数のデジタル・フィルタ・オプションを備えており、最高レベルの柔軟性をユーザーに提供します。デバイスには有限インパルス応答（FIR）フィルタが備わっており、DC～最大50kHzまでのアナログ入力に対する低い通過帯域リップル、迅速なロールオフ、優れたストップバンド除去が可能です。また、最大72個のユーザ係数に対応できるプログラマブルFIRフィルタも使用可能です。更に、多重化されたアプリケーションにより高速のセトリングを可能にするsincフィルタを内蔵するほか、50Hzと60Hzを同時に除去するための複数のオプションを備えています。

AD4170-4には過電圧／低電圧に対する耐性もあります。あるチャンネルの信号がAVDDまたはAVSSをわずかに超える場合でも、隣接するチャンネルは引き続き機能し、正しく変換できます。組み込み機能、診断機能、インテリジェンスにより、シグナル・チェーンの設計時に必要な部品数が最小限に抑えられ、必要なボード・スペース、設計サイクル時間、コストを節約できます。

このデバイスは、4.75V～5.25Vのアナログ単電源または+2.5Vのバイポーラ電源で動作します。デジタル電源の範囲は1.7V～5.25Vです。このデバイスは-40°C～+105°Cの温度範囲で仕様規定されています。AD4170-4は32ピンLFCSPパッケージに収められています。

## 仕様

特に指定のない限り、AVDD = 4.75V～5.25V、IOVDD = 1.7V～5.25V、AVSS = DGND = 0V、2.5Vの外部リファレンスを使用しREFIN+ = 2.5VおよびREFIN- = AVSS、MCLK = 16MHz。

表1.

| パラメータ <sup>1</sup>                              | テスト条件/コメント                                                                                                                                                                                         | 最小値                                                    | 代表値                                         | 最大値                                 | 単位                                   |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------|-------------------------------------|--------------------------------------|

| ADC SPEED, CODING AND PERFORMANCE               |                                                                                                                                                                                                    |                                                        |                                             |                                     |                                      |

| Output Data Rate (ODR)                          |                                                                                                                                                                                                    |                                                        |                                             |                                     |                                      |

| Sinc <sup>5</sup>                               |                                                                                                                                                                                                    | 1,953                                                  |                                             | 500,000                             | SPS                                  |

| Sinc <sup>5</sup> + Avg                         |                                                                                                                                                                                                    | 7.6                                                    |                                             | 125,000                             | SPS                                  |

| Sinc <sup>3</sup>                               |                                                                                                                                                                                                    | 7.6                                                    |                                             | 125,000                             | SPS                                  |

| FIR                                             | デフォルトおよびユーザ設定                                                                                                                                                                                      | 3,906                                                  |                                             | 125,000                             | SPS                                  |

| 50 Hz/60 Hz Post Filters                        |                                                                                                                                                                                                    | 16.67                                                  | 20                                          | 25                                  | SPS                                  |

| No Missing Codes <sup>2</sup>                   | sinc <sup>5</sup> フィルタ : ODR < 500kSPS、sinc <sup>3</sup> フィルタ : ODR < 125kSPS                                                                                                                      | 24                                                     |                                             |                                     | Bits                                 |

| Data Output Coding                              | バイポーラ・モード<br>ユニポーラ・モード                                                                                                                                                                             |                                                        | Twos complement<br>Straight binary          |                                     |                                      |

| Resolution                                      |                                                                                                                                                                                                    |                                                        | See the RMS Noise and Resolution section    |                                     |                                      |

| Noise                                           |                                                                                                                                                                                                    |                                                        | See the RMS Noise and Resolution section    |                                     |                                      |

| ACCURACY                                        |                                                                                                                                                                                                    |                                                        |                                             |                                     |                                      |

| Gains                                           |                                                                                                                                                                                                    | 0.5, 1<br>precharge,<br>1, 2, 4, 8, 16,<br>32, 64, 128 |                                             |                                     |                                      |

| Integral Nonlinearity (INL)                     |                                                                                                                                                                                                    |                                                        |                                             |                                     |                                      |

| Offset Error <sup>3</sup>                       | ゲイン = 1、ゲイン = 1プリチャージ<br>ゲイン = 1またはゲイン = 0.5<br>ゲイン = 1プリチャージ<br>ゲイン < 16<br>ゲイン ≥ 16                                                                                                              | -2.5<br>-10<br>-60<br>-40 -<br>-32                     | ±0.5<br>±2<br>±25<br>±10 +<br>±15           | +2.5<br>+10<br>+60<br>+40 +<br>+32  | ppm of FSR<br>ppm of FSR<br>μV<br>μV |

| Offset Error Drift vs. Temperature <sup>2</sup> | ゲイン = 1プリチャージ<br>ゲイン < 16<br>ゲイン = 32<br>ゲイン = 64<br>ゲイン = 128                                                                                                                                     | -50<br>-20 -<br>-70<br>-140<br>-100                    | ±20<br>±15 +<br>±30<br>±75<br>±50           | +50<br>+20 +<br>+70<br>+140<br>+100 | nV/°C<br>nV/°C<br>nV/°C<br>nV/°C     |

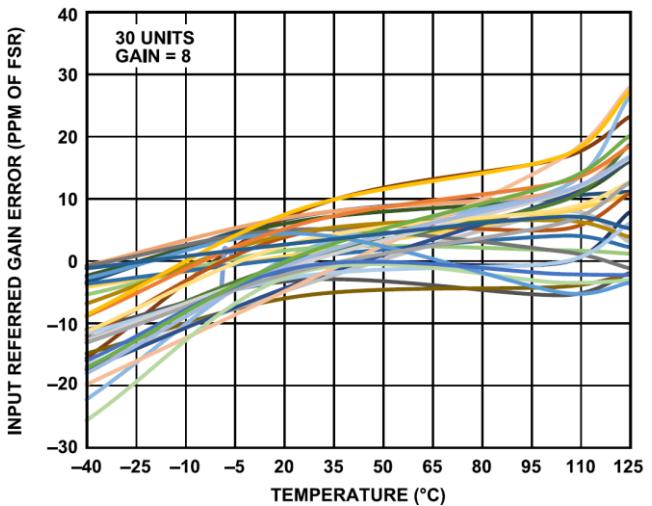

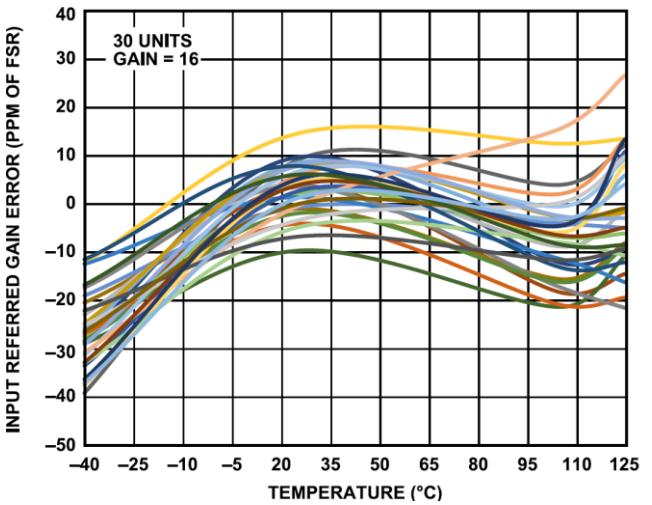

| Gain Error <sup>3</sup>                         | ゲイン = 1プリチャージ、TA = 25°C<br>その他全てのゲイン、TA = 25°C                                                                                                                                                     | -50<br>-250                                            | ±10<br>±50                                  | +50<br>+250                         | ppm of FSR<br>ppm of FSR             |

| Gain Error Drift vs. Temperature <sup>2</sup>   | 全てのゲイン                                                                                                                                                                                             | -0.75                                                  | ±0.25                                       | +0.75                               | ppm/°C                               |

| DYNAMIC PERFORMANCE                             |                                                                                                                                                                                                    |                                                        |                                             |                                     |                                      |

| Signal-to-Noise Ratio (SNR)                     | 外部16MHz MCLK、4.096Vの外部リファレンス<br>1kHz、-0.5dBFS、サイン波入力<br>sinc <sup>5</sup> フィルタ、ゲイン = 1プリチャージ<br>sinc <sup>5</sup> フィルタ、その他全てのゲイン<br>FIRフィルタ、ゲイン = 1およびゲイン = 1プリチャージ<br>FIRフィルタ、ゲイン = 0.5およびゲイン > 1 | 108<br>102.5                                           | 110<br>See the SNR and THD section<br>105.5 |                                     | dBFS                                 |

| Signal-to-Noise-and-Distortion (SINAD)          | 1kHz、-0.5dBFS、サイン波入力<br>sinc <sup>5</sup> フィルタ、ゲイン = 1プリチャージ<br>FIRフィルタ、ゲイン = 1プリチャージおよび<br>ゲイン = 1                                                                                                | 107.5<br>102                                           | 109.5<br>105                                |                                     | dBFS                                 |

| Total Harmonic Distortion (THD)                 | 1kHz、-0.5dBFS、サイン波入力<br>ゲイン = 1およびゲイン = 1プリチャージ<br>ゲイン = 0.5およびゲイン > 1                                                                                                                             |                                                        | -120<br>-112                                |                                     | dBFS                                 |

|                                                 |                                                                                                                                                                                                    |                                                        | See the SNR and THD section                 |                                     |                                      |

## 仕様

表1. (続き)

| パラメータ <sup>1</sup>                                                     | テスト条件/コメント                                                                                              | 最小値                          | 代表値                                               | 最大値                                               | 単位                      |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------|---------------------------------------------------|-------------------------|

| Spurious-Free Dynamic Range (SFDR)<br>INTERMODULATION DISTORTION (IMD) | ゲイン = 1およびゲイン = 1プリチャージ<br>外部16MHz MCLK、fa = 9.7kHz、fb = 10.3kHz、全ゲイン<br>2次<br>3次                       | 125<br><br>-125<br><br>-125  | 125                                               | -125                                              | dBc<br><br>dB<br><br>dB |

| REJECTION                                                              |                                                                                                         |                              |                                                   |                                                   |                         |

| DC Power Supply Rejection                                              | V <sub>IN</sub> = 1V/ゲイン、全電源<br>ゲイン = 0.5<br>ゲイン = 1プリチャージ、および1~8<br>ゲイン ≥ 16                           | 98<br>89<br>102              | 98<br>104<br>122                                  | 104                                               | dB                      |

| Common-Mode Rejection <sup>4</sup>                                     | V <sub>IN</sub> = 1V/ゲイン<br>At DC<br>ゲイン = 0.5<br>ゲイン = 1プリチャージ、および1~8<br>ゲイン ≥ 16                      | 106<br>98<br>107             | 106<br>108<br>127                                 | 108                                               | dB<br>dB<br>dB          |

| At 50 Hz, 60 Hz                                                        | 20Hz ODR (ポスト・フィルタ使用)、50Hz ± 1Hz および 60Hz ± 1Hz                                                         | 120                          | 120                                               | 120                                               | dB                      |

| Normal Mode Rejection <sup>2</sup>                                     | 50Hz ± 1Hz および 60Hz ± 1Hz<br>内部クロック、セトリング時間50msのポスト・フィルタ使用<br>外部クロック、セトリング時間50msのポスト・フィルタ使用             | 74<br>85                     | 74                                                | 85                                                | dB<br>dB                |

| ANALOG INPUTS                                                          |                                                                                                         |                              |                                                   |                                                   |                         |

| Differential Input Voltage Range <sup>5</sup>                          | V <sub>REF</sub> = (REF+ - REF-)または内部リファレンス                                                             | -V <sub>REF</sub> /gain<br>0 | +V <sub>REF</sub> /gain<br>V <sub>REF</sub> /gain | +V <sub>REF</sub> /gain<br>V <sub>REF</sub> /gain | V<br>V                  |

| Single-Ended Input Voltage Range                                       |                                                                                                         | AVSS                         | AVDD                                              | AVDD                                              | V                       |

| Absolute AIN Voltage Limits <sup>2</sup>                               |                                                                                                         | 8                            | 8                                                 | 8                                                 | pF                      |

| Input Capacitance                                                      |                                                                                                         |                              |                                                   |                                                   |                         |

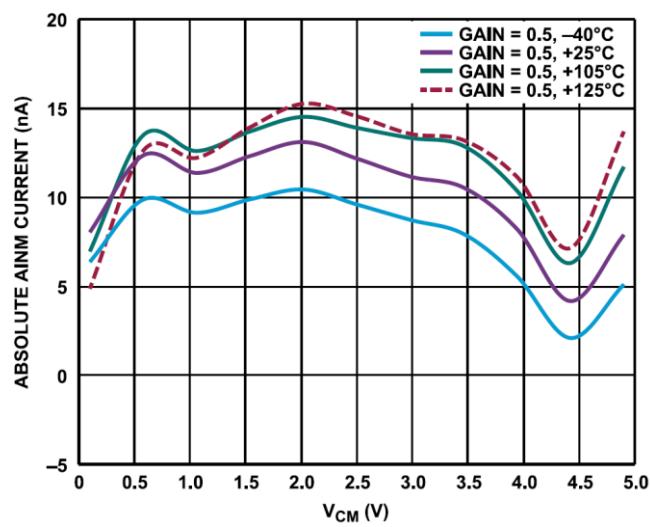

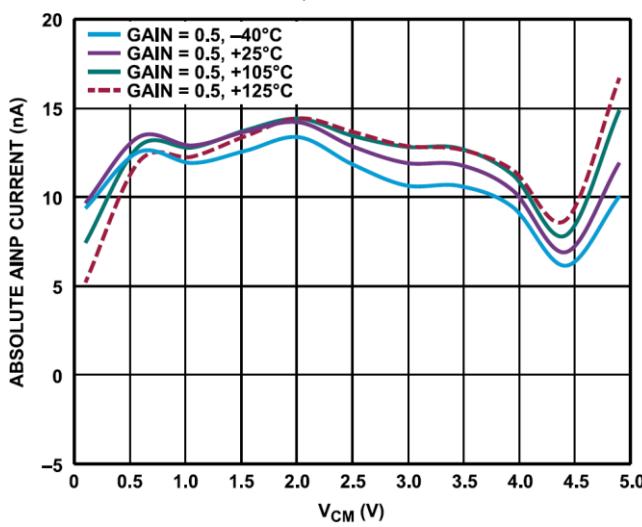

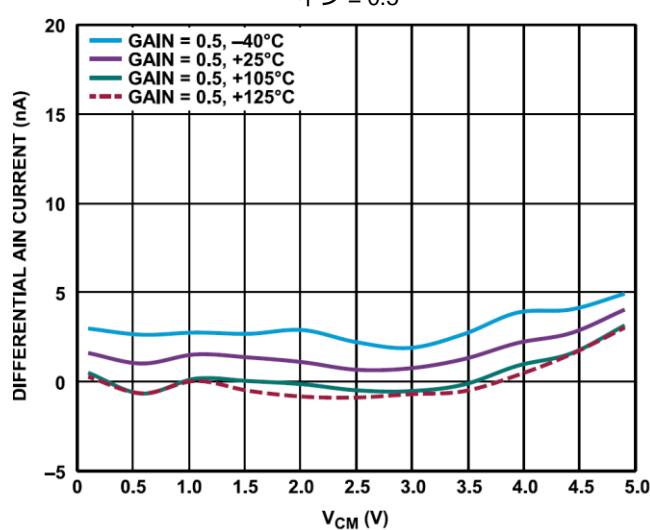

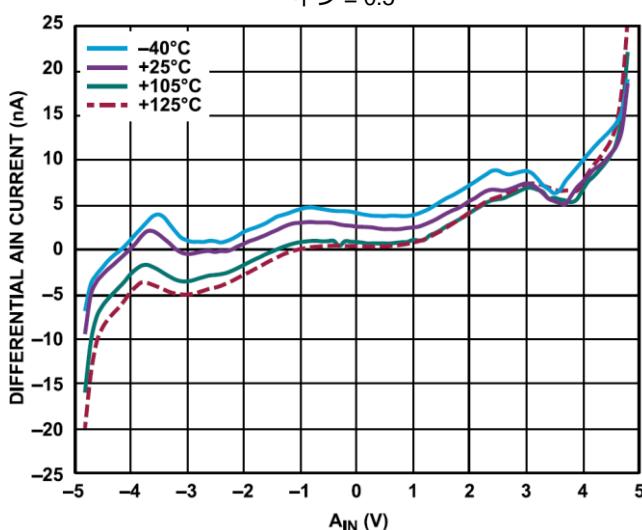

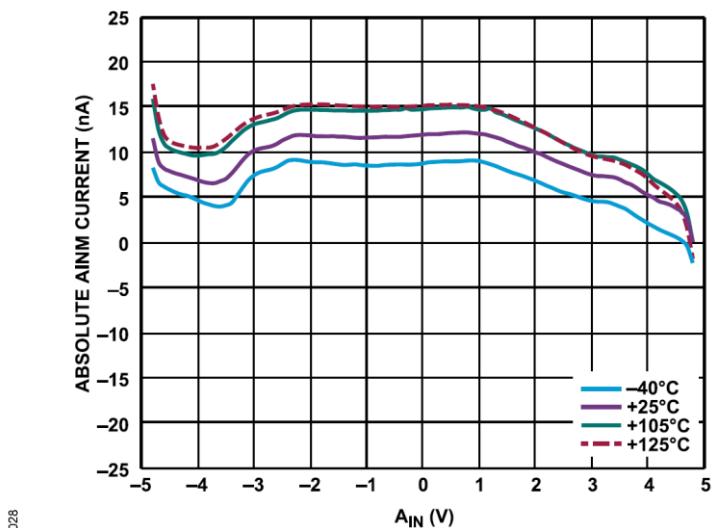

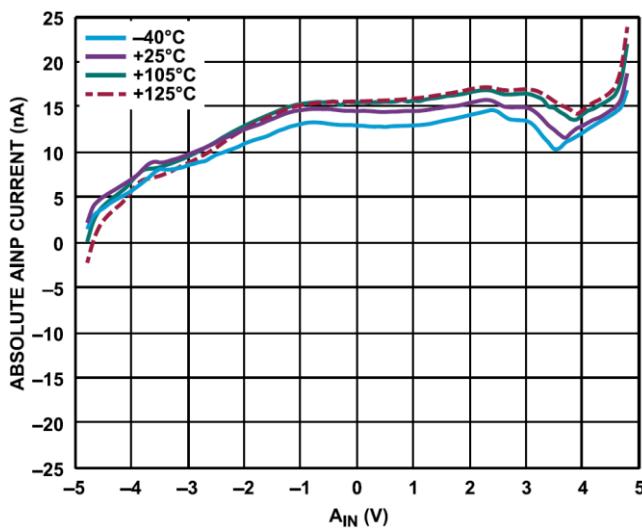

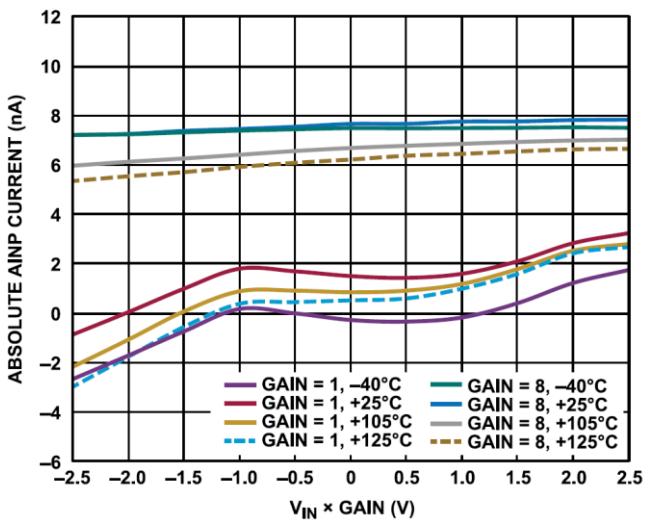

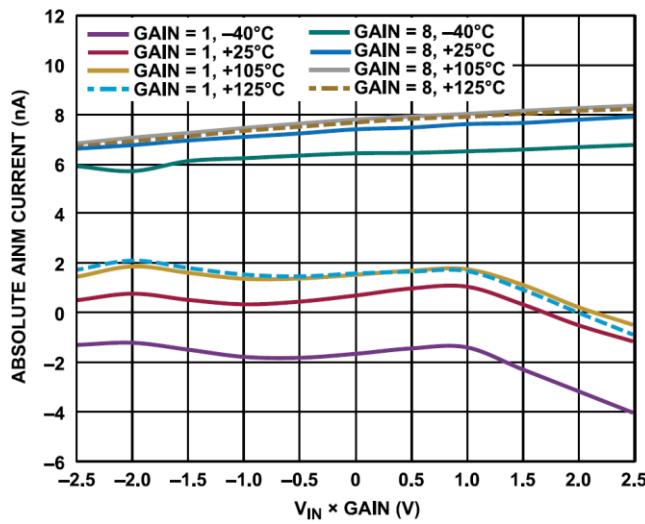

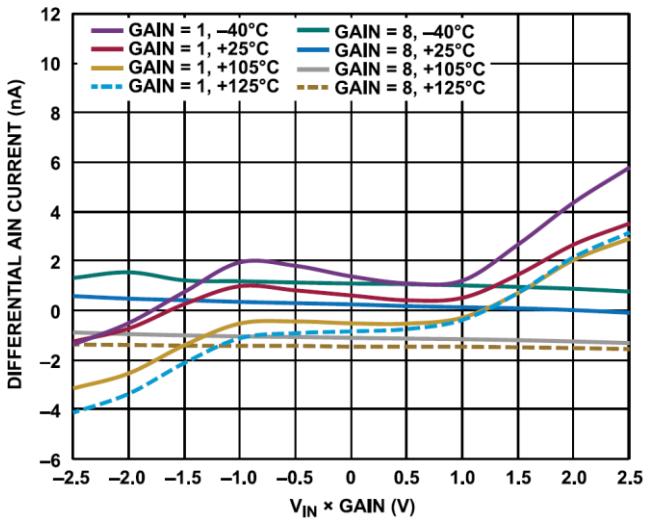

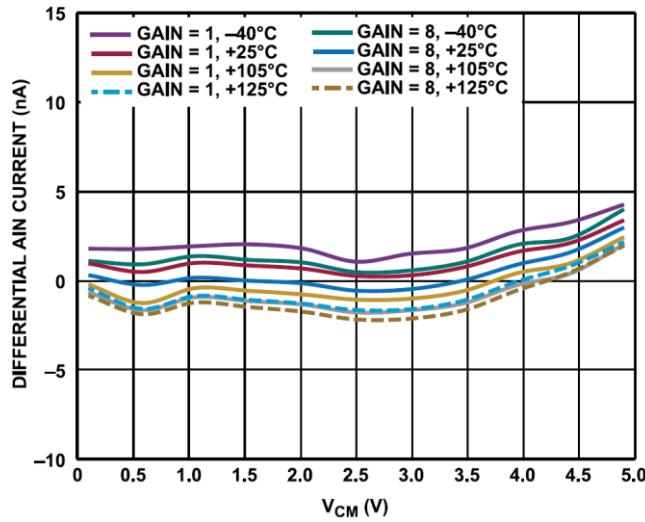

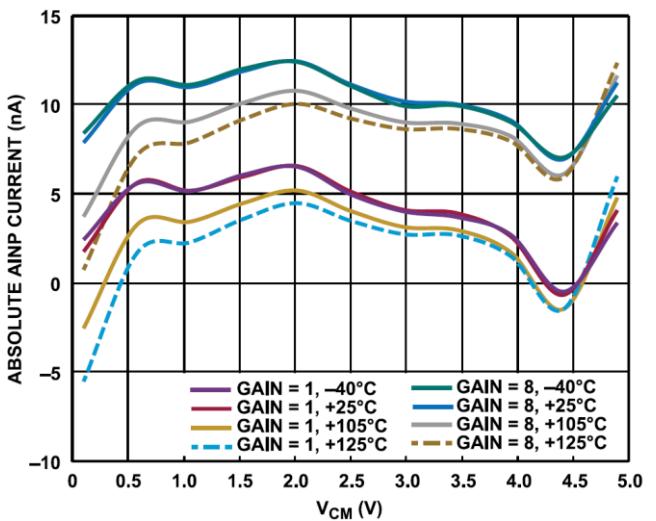

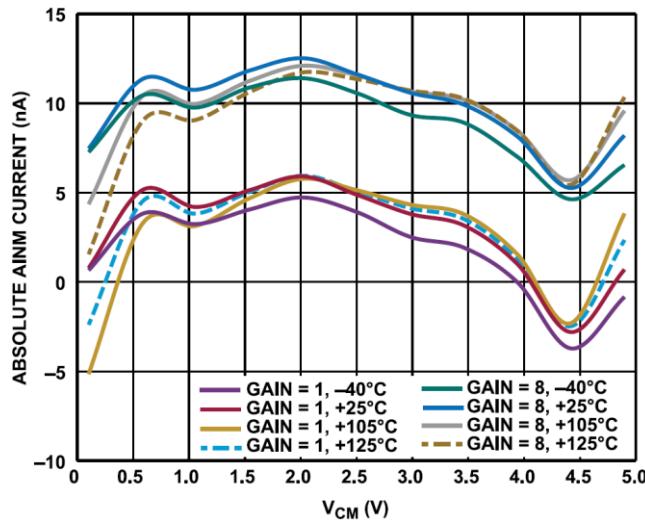

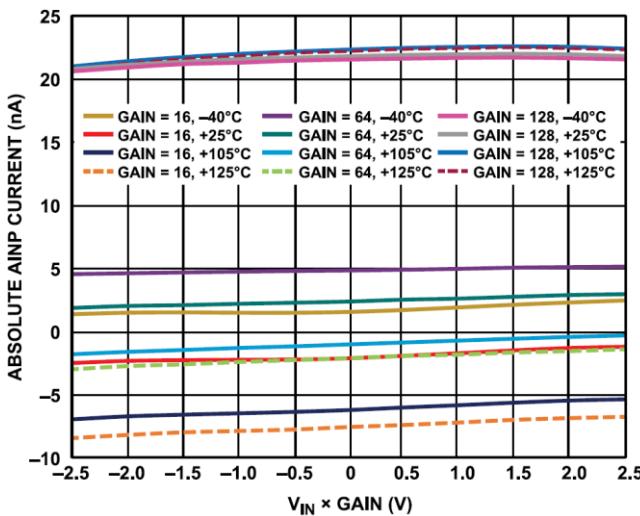

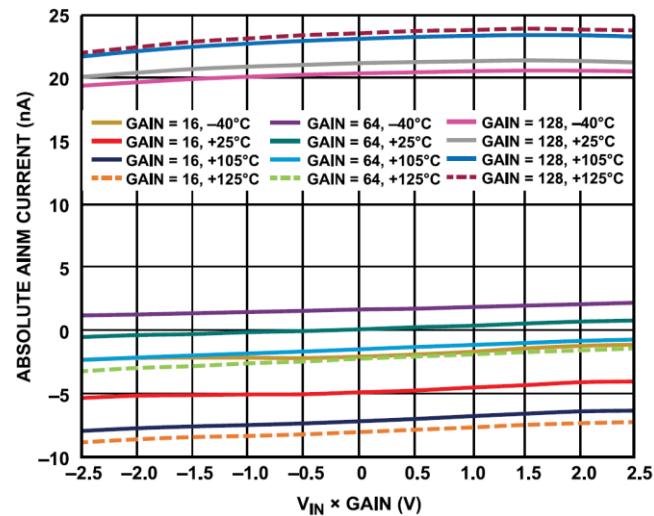

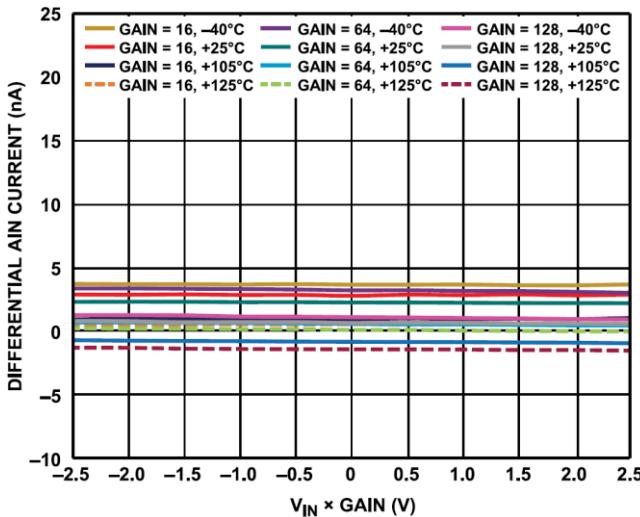

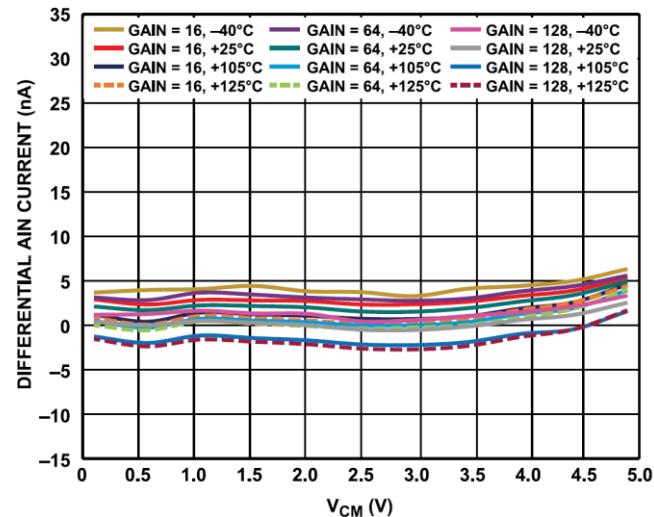

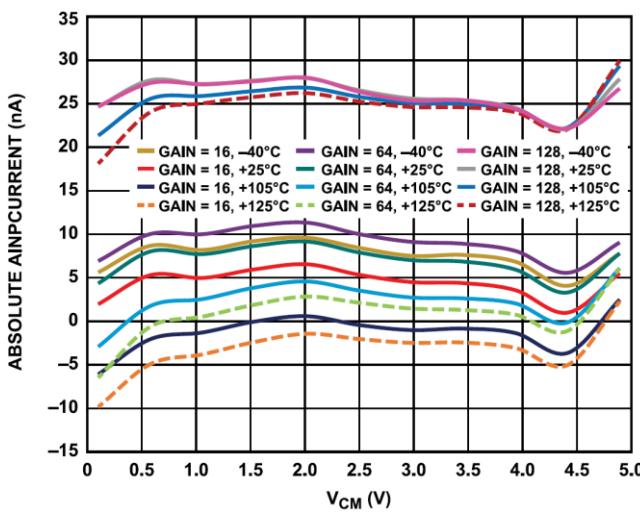

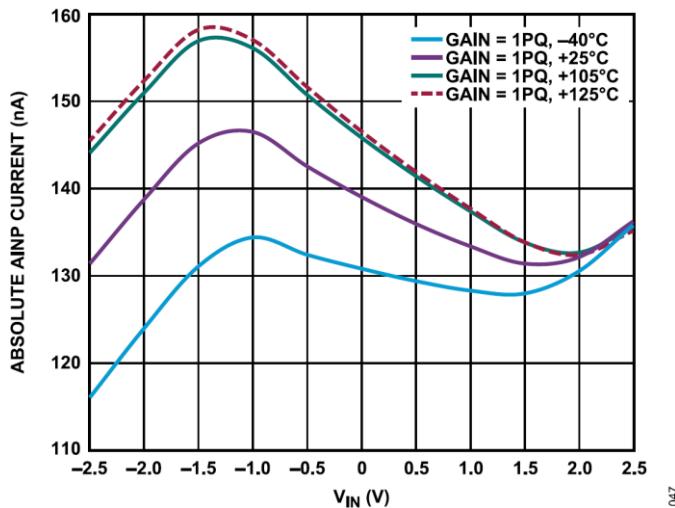

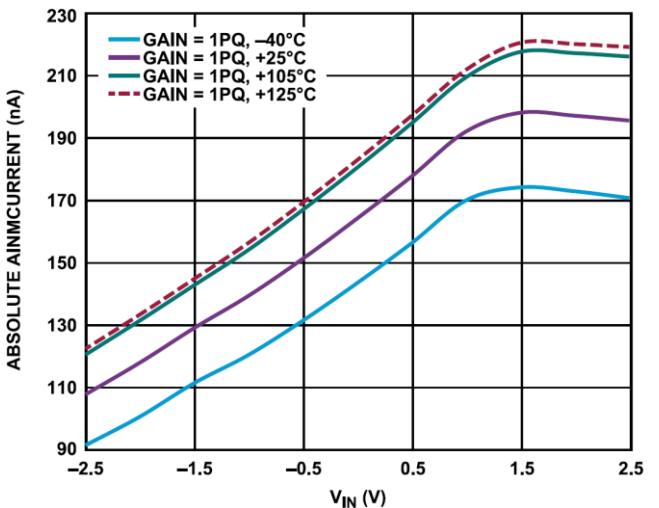

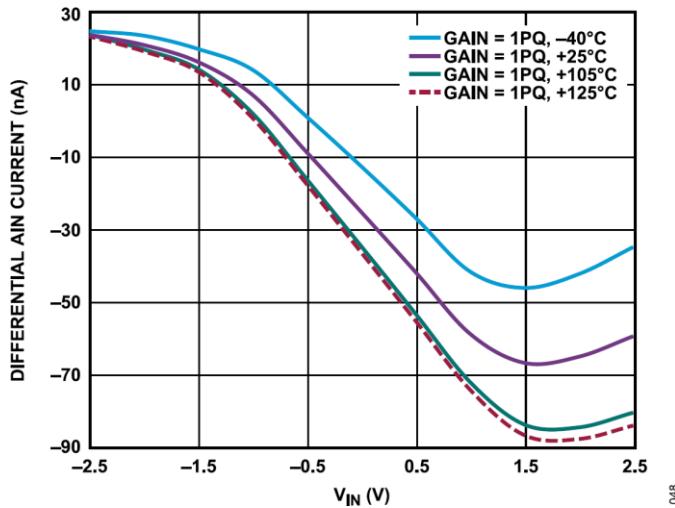

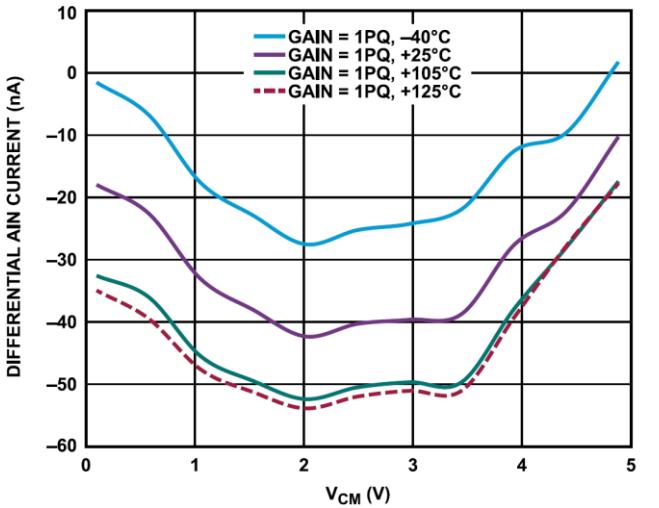

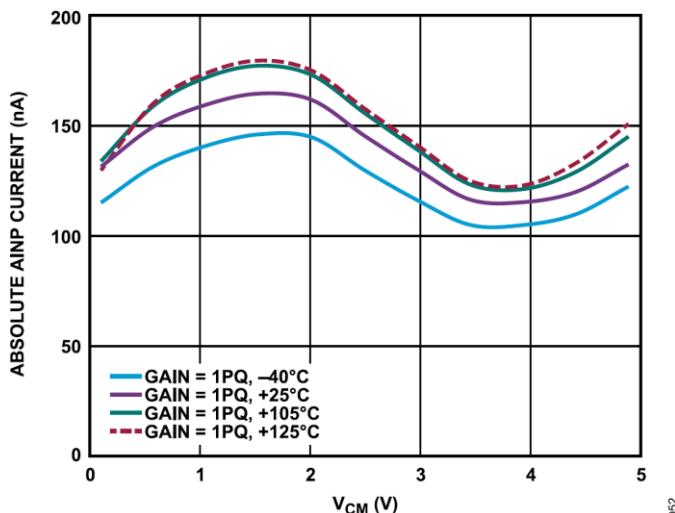

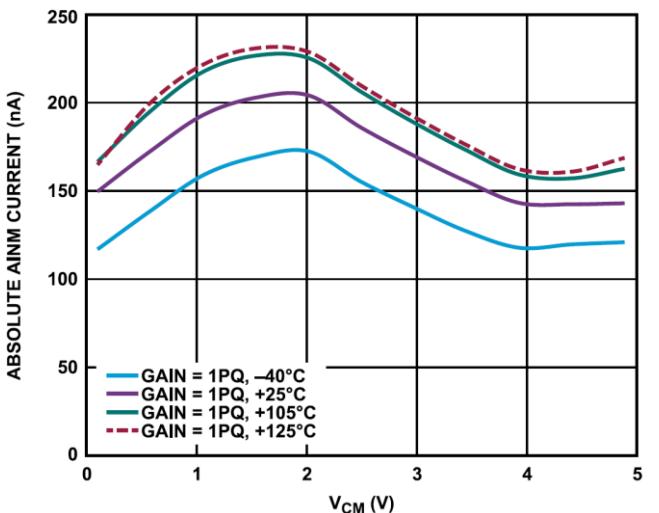

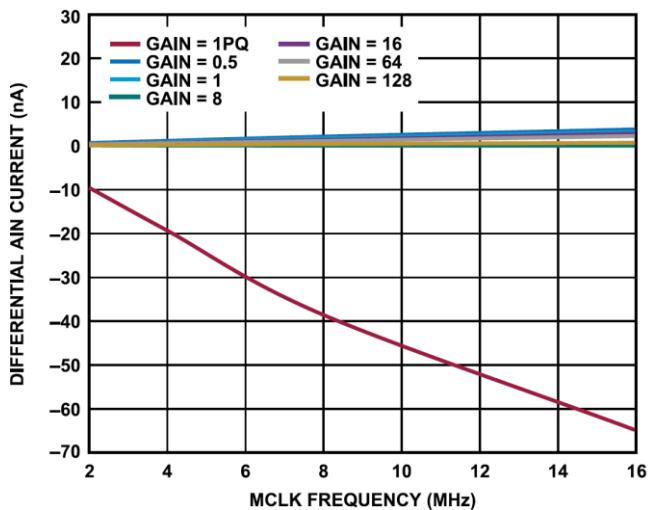

| Analog Input Current                                                   | AVSS + 0.1 V ~ AVDD - 0.1 V の範囲のAINで測定した絶対入力電流<br>フルスケール入力、V <sub>CM</sub> = (AVDD - AVSS)/2で測定した差動入力電流 |                              |                                                   |                                                   |                         |

| Gain = 1 precharge                                                     |                                                                                                         |                              |                                                   |                                                   |                         |

| Absolute Input Current                                                 |                                                                                                         | -450                         | ±200                                              | +450                                              | nA                      |

| Differential Input Current                                             |                                                                                                         | -120                         | ±40                                               | +120                                              | nA                      |

| Absolute Input Current Drift <sup>2</sup>                              |                                                                                                         | -550                         | ±280                                              | +550                                              | pA/°C                   |

| Gain = 1                                                               |                                                                                                         |                              |                                                   |                                                   |                         |

| Absolute Input Current                                                 |                                                                                                         | -40                          | ±5                                                | +40                                               | nA                      |

| Differential Input Current                                             |                                                                                                         | -20                          | ±5                                                | +20                                               | nA                      |

| Absolute Input Current Drift <sup>2</sup>                              |                                                                                                         | -44                          | ±12                                               | +44                                               | pA/°C                   |

| Gain = 0.5                                                             |                                                                                                         |                              |                                                   |                                                   |                         |

| Absolute Input Current                                                 |                                                                                                         | -60                          | ±20                                               | +60                                               | nA                      |

| Differential Input Current                                             |                                                                                                         | -35                          | ±15                                               | +35                                               | nA                      |

| Absolute Input Current Drift <sup>2</sup>                              |                                                                                                         | -75                          | ±30                                               | +75                                               | pA/°C                   |

| Gain = 128                                                             |                                                                                                         |                              |                                                   |                                                   |                         |

| Absolute Input Current                                                 |                                                                                                         | -50                          | ±25                                               | +50                                               | nA                      |

| Differential Input Current                                             |                                                                                                         | -10                          | ±3                                                | +10                                               | nA                      |

| Absolute Input Current Drift <sup>2</sup>                              |                                                                                                         | -90                          | ±40                                               | +90                                               | pA/°C                   |

| All other gains                                                        |                                                                                                         |                              |                                                   |                                                   |                         |

| Absolute Input Current                                                 |                                                                                                         | -35                          | ±5                                                | +35                                               | nA                      |

| Differential Input Current                                             |                                                                                                         | -10                          | ±3                                                | +10                                               | nA                      |

## 仕様

表1. (続き)

| パラメータ <sup>1</sup>                               | テスト条件／コメント                                                      | 最小値             | 代表値                            | 最大値         | 単位      |

|--------------------------------------------------|-----------------------------------------------------------------|-----------------|--------------------------------|-------------|---------|

| Absolute Input Current Drift <sup>2</sup>        |                                                                 | -150            | ±70                            | +150        | pA/°C   |

| Crosstalk                                        | 1kHz入力                                                          |                 | -120                           |             | dB      |

| AC                                               | AVDDまたはAVSSから300mV範囲外となった隣接アナログ入力                               |                 | -100                           |             | dB      |

| DC                                               |                                                                 |                 |                                |             |         |

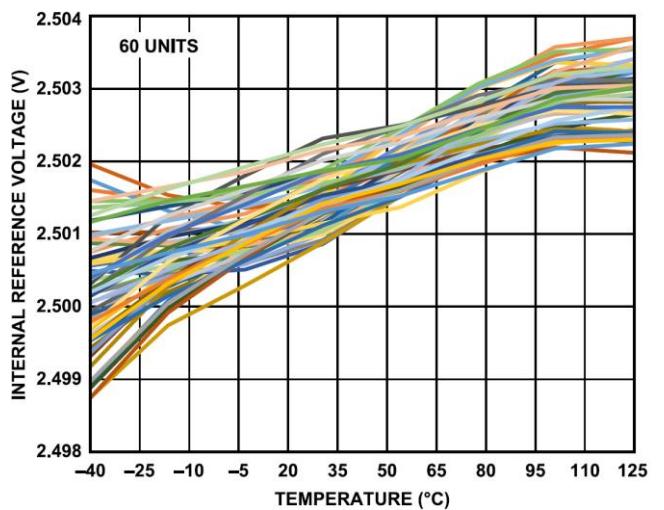

| INTERNAL REFERENCE                               | 100nFのコンデンサをAVSSに外付け<br>AVSS基準のREFOUT、 $T_A = 25^\circ\text{C}$ | 2.495           | 2.5                            | 2.505       | V       |

| Initial Accuracy <sup>6</sup>                    |                                                                 | ±5              | +15                            |             | ppm/°C  |

| Temperature Coefficient                          |                                                                 | -10             | +10                            |             | mA      |

| Reference Load Current, $I_{LOAD}$               |                                                                 |                 |                                |             |         |

| Thermal Hysteresis                               | 25°C、+75°C、-25°C、+25°Cのサイクル                                     | 44              |                                |             | ppm     |

| Power Supply Rejection                           | AVDD (ライン・レギュレーション)                                             | 100             |                                |             | dB      |

| Load Regulation                                  | $\Delta V_{OUT}/\Delta I_{LOAD}$                                | 12              |                                |             | ppm/mA  |

| Voltage Noise                                    | $e_N$ 、0.1Hz～10Hz、2.5Vリファレンス                                    | 4.5             |                                |             | μV rms  |

| Voltage Noise Density                            | $e_N$ 、1kHz、2.5Vリファレンス                                          | 215             |                                |             | nV/√Hz  |

| Turn-On Settling Time                            | 100nFのREFOUTコンデンサ                                               | 200             |                                |             | μs      |

| Short-Circuit Current, $I_{SC}$                  |                                                                 | 28              |                                |             | mA      |

| EXTERNAL REFERENCE INPUTS                        |                                                                 |                 |                                |             |         |

| Differential Input Range <sup>2</sup>            | $V_{REF} = \text{REF}^+ - \text{REF}^-$                         | 1               | 2.5                            | AVDD        | V       |

| Absolute Voltage Limits <sup>2</sup>             |                                                                 | AVSS - 0.05     |                                | AVDD + 0.05 | V       |

| Reference Buffers Disabled                       | リファレンス・バッファまたはプリチャージ・バッファ                                       | AVSS            |                                | AVDD        | V       |

| Reference Buffers Enabled                        |                                                                 |                 |                                |             |         |

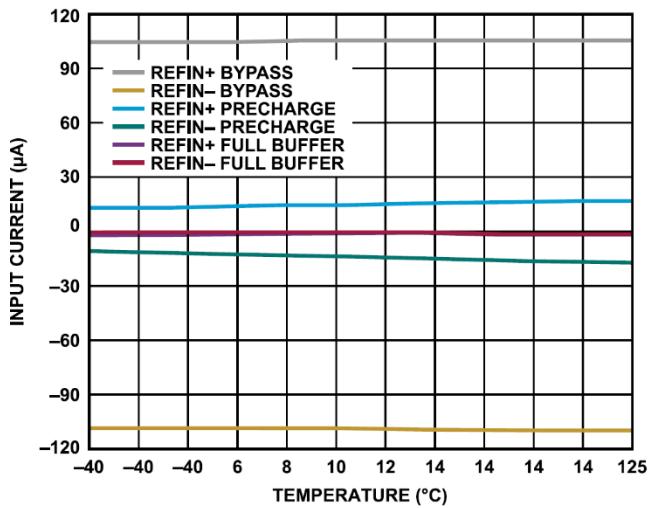

| REFIN Input Current (Reference Buffers Disabled) |                                                                 |                 | ±44                            |             | μA/V    |

| Reference Input Current                          | 外部クロック                                                          |                 | ±1.2                           |             | nA/V/°C |

| Reference Input Current Drift                    | 内部クロック                                                          |                 | ±6                             |             | nA/V/°C |

| Reference Buffers Enabled                        |                                                                 |                 |                                |             |         |

| Reference Input Current                          | プリチャージ・バッファ                                                     | ±18             |                                |             | μA      |

| Reference Input Current Drift                    | フル・バッファ                                                         | ±200            |                                |             | nA      |

| Normal Mode Rejection                            | プリチャージ・バッファ                                                     | 40              |                                |             | nA/°C   |

| Normal Mode Rejection                            | フル・バッファ                                                         | 1.25            |                                |             | nA/°C   |

| Normal Mode Rejection                            | 除去のパラメータを参照                                                     |                 |                                |             |         |

| DIGITAL FILTER RESPONSE                          |                                                                 |                 |                                |             |         |

| FIR Filter                                       |                                                                 |                 |                                |             |         |

| Decimation Rate                                  |                                                                 | 32              |                                | 1024        |         |

| Group Delay                                      | 遅延                                                              |                 | 34/ODR                         |             | seconds |

| Settling Time                                    |                                                                 |                 | 68/ODR                         |             | seconds |

| Pass-Band Ripple                                 | DC～50kHz (125kSPS)                                              |                 |                                | ±0.005      | dB      |

| Pass Band                                        | ±0.005dBの帯域幅                                                    |                 | 0.4 × ODR                      |             | Hz      |

|                                                  | -0.1dBの帯域幅                                                      |                 | 0.409 × ODR                    |             | Hz      |

|                                                  | -3dBの帯域幅                                                        |                 | 0.433 × ODR                    |             | Hz      |

| Stop-Band Frequency                              | 減衰 > 105dB                                                      |                 | 0.499 × ODR                    |             | Hz      |

| Stop-Band Attenuation                            | アンチエイリアシング・フィルタ処理のセクションを参照                                      | 105             |                                |             | dB      |

| Sinc Filters, Sinc <sup>5</sup> + Avg Filter     |                                                                 |                 | See the Digital Filter section |             |         |

| VBIAS                                            |                                                                 |                 |                                |             |         |

| Output Voltage Setting                           |                                                                 | (AVDD + AVSS)/2 |                                |             | V       |

| Output Impedance                                 |                                                                 | 1               |                                |             | kΩ      |

| Start-Up Time                                    | AINnに接続された容量に依存。                                                | 9               |                                |             | μs/nF   |

## 仕様

表1. (続き)

| パラメータ <sup>1</sup>                                | テスト条件／コメント                                                                                     | 最小値                                     | 代表値                              | 最大値        | 単位                         |

|---------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------|------------|----------------------------|

| EXCITATION CURRENTS                               |                                                                                                |                                         |                                  |            |                            |

| Current Settings                                  |                                                                                                | 10, 50, 100,<br>250, 500,<br>1000, 1500 |                                  |            | μA                         |

| Output Compliance <sup>2</sup>                    | 10μA、50μA、100μA、1%精度<br><br>250μA/500μA/1mA/1.5mA、1%精度                                         |                                         | AVDD -<br>1.25<br>AVDD -<br>1.45 |            | V                          |

| Initial Accuracy                                  | T <sub>A</sub> = 25°C、10μA<br>T <sub>A</sub> = 25°C、50μA、100μA<br>T <sub>A</sub> = 25°C、>100μA | ±3<br>-1<br>-2                          | ±0.1<br>+1<br>±0.2               | +2         | %                          |

| Drift <sup>2</sup>                                | 10μA<br>50μA、100μA<br>> 100μA                                                                  | ±20<br>-30<br>-80                       | ±5<br>±0.1                       | +30<br>+80 | ppm/°C<br>ppm/°C<br>ppm/°C |

| Current Mismatch                                  | ABまたはCDのペアを使用                                                                                  |                                         |                                  |            |                            |

| Same Current Matching <sup>2</sup>                | 10μA<br>250μA、1mA<br>50μA/100μA/500μA/1.5mA                                                    | ±1.3<br>-1.2<br>-0.7                    | ±0.1<br>+1.2                     | +0.7       | %                          |

| Different Current Matching                        |                                                                                                | ±1                                      |                                  |            | %                          |

| Drift Matching <sup>2</sup>                       | ABまたはCDのペアを使用。同じ値の電流源。<br>10μA<br>50μA、100μA、250μA<br>> 250μA                                  | 3<br>-7<br>-4                           | ±2<br>±1                         | +7<br>+4   | ppm/°C<br>ppm/°C<br>ppm/°C |

| Line Regulation (AVDD)                            | AVDD = 5V ± 5%                                                                                 | 150                                     |                                  |            | ppm/V                      |

| Load Regulation                                   | > 10μA                                                                                         | 40                                      |                                  |            | ppm/V                      |

| Start-Up time                                     | R <sub>LOAD</sub> = 1kΩ、C <sub>LOAD</sub> = 0pF<br>AINxに接続された負荷に依存                             | 7                                       |                                  |            | μs                         |

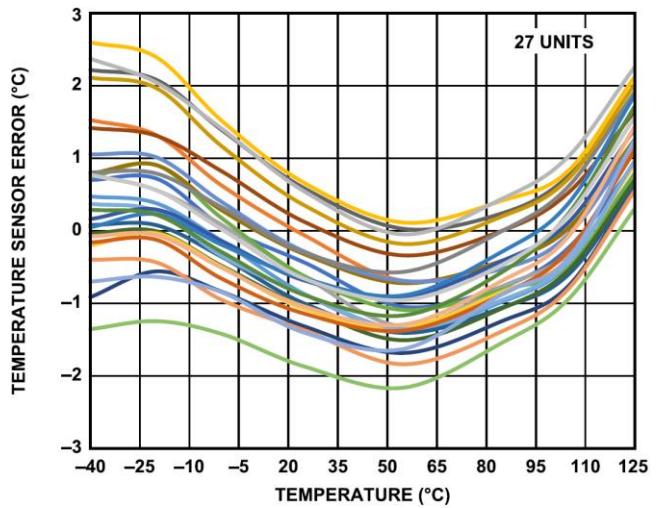

| TEMPERATURE SENSOR                                |                                                                                                |                                         |                                  |            |                            |

| Accuracy                                          | 25°Cでのユーザ・キャリブレーション後                                                                           | ±2                                      |                                  |            | °C                         |

| Sensitivity                                       |                                                                                                | 477                                     |                                  |            | μV/K                       |

| LOW-SIDE POWER SWITCH                             |                                                                                                |                                         |                                  |            |                            |

| R <sub>ON</sub>                                   |                                                                                                | 10                                      | 14                               |            | Ω                          |

| Current Through Switch <sup>2</sup>               | 連続電流                                                                                           |                                         | 30                               |            | mA                         |

| BURNOUT CURRENTS                                  |                                                                                                |                                         |                                  |            |                            |

| Source/Sink Current                               |                                                                                                | ±0.1, ±2, ±10                           |                                  |            | μA                         |

| Accuracy                                          | シンキング／ソーシング                                                                                    | 10                                      |                                  |            | %                          |

| PULL-UP CURRENTS                                  |                                                                                                |                                         |                                  |            |                            |

| Source Current                                    |                                                                                                | 100                                     |                                  |            | nA                         |

| GENERAL-PURPOSE I/O (GPIO0 to GPIO3) <sup>2</sup> | AVSS基準                                                                                         |                                         |                                  |            |                            |

| Input Mode Leakage Current                        |                                                                                                | -1                                      | +1                               |            | μA                         |

| Floating State Output Capacitance                 |                                                                                                | 5                                       |                                  |            | pF                         |

| Output High Voltage, V <sub>OH</sub>              | I <sub>SOURCE</sub> = 200μA                                                                    | AVSS + 4                                |                                  |            | V                          |

| Output Low Voltage, V <sub>OL</sub>               | I <sub>SINK</sub> = 800μA                                                                      |                                         | AVSS + 0.4                       |            | V                          |

| Input High Voltage, V <sub>IH</sub>               |                                                                                                | AVSS + 3                                |                                  |            | V                          |

| Input Low Voltage, V <sub>IL</sub>                |                                                                                                |                                         | AVSS + 0.7                       |            | V                          |

| DAC                                               |                                                                                                |                                         |                                  |            |                            |

| Resolution                                        |                                                                                                | 12                                      |                                  |            | Bits                       |

| Range                                             | ゲイン = 1                                                                                        | 0                                       | V <sub>REF</sub>                 |            | V                          |

|                                                   | ゲイン = 2                                                                                        | 0                                       | 2 × V <sub>REF</sub>             |            | V                          |

| INL                                               |                                                                                                | -2                                      | +2                               |            | LSB                        |

## 仕様

表1. (続き)

| パラメータ <sup>1</sup>                     | テスト条件/コメント                                         | 最小値          | 代表値          | 最大値         | 単位       |

|----------------------------------------|----------------------------------------------------|--------------|--------------|-------------|----------|

| DNL                                    |                                                    | -0.5         | ±0.2         | +0.5        | LSB      |

| Offset Error                           |                                                    |              | ±2           |             | mV       |

| Offset Error Drift                     |                                                    |              | ±10          |             | µV/°C    |

| Full-Scale Error                       |                                                    |              | ±0.1         |             | % of FSR |

| Full-Scale Error Drift                 |                                                    |              | ±10          |             | µV/°C    |

| Output Swing                           |                                                    | AVSS + 0.06  |              | AVDD - 0.25 | V        |

| Capacitive Load                        | R <sub>LOAD</sub> = 無限大<br>R <sub>LOAD</sub> = 2kΩ |              | 100          | 2           | nF       |

| Resistive Load                         |                                                    | 1            |              |             | kΩ       |

| Settling Time                          | 0.25 × FS~0.75 × FS                                |              | 6            |             | µs       |

| Slew Rate                              | R <sub>LOAD</sub> = 2kΩ、C <sub>LOAD</sub> = 200pF  |              | 1            |             | V/µs     |

| Noise Density                          | ミッドスケール・コード、1kHz                                   |              | 200          |             | nV/√Hz   |

| RMS Noise                              | 0.1Hz~10Hz                                         |              | 8            |             | µV rms   |

| Short-Circuit Current, I <sub>SC</sub> |                                                    |              | 15           |             | mA       |

| DIAGNOSTIC TRIP POINTS                 |                                                    |              |              |             |          |

| Reference Detect Level                 |                                                    | 0.6          |              | 0.85        | V        |

| Reference/AIN OV/UV Trip Level         |                                                    |              |              |             |          |

| Overvoltage                            |                                                    | AVDD + 0.065 |              |             | V        |

| Undervoltage                           |                                                    |              | AVSS - 0.065 |             | V        |

| Reference/AIN OV/UV Clear Level        |                                                    |              |              |             |          |

| Overvoltage                            |                                                    | AVDD + 0.015 |              |             | V        |

| Undervoltage                           |                                                    |              | AVSS - 0.01  |             | V        |

| Excitation Current Source Compliance   | 10µA、50µA、100µA<br>250µA、500µA、1000µA、1500µA       | AVDD - 1.3   |              | AVDD - 0.8  | V        |

| ALDO Trip Level                        |                                                    | AVDD - 1.6   |              | AVDD - 1    | V        |

| DLDO Trip Level                        |                                                    |              | 1.5          |             | V        |

|                                        |                                                    |              | 1.6          |             | V        |

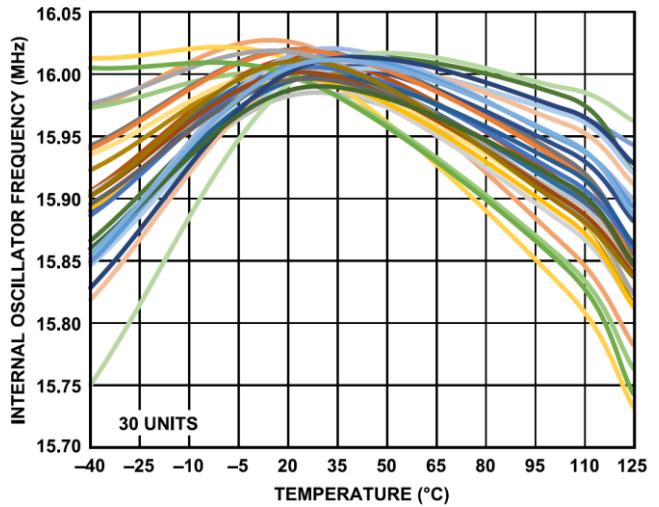

| CLOCK                                  |                                                    |              |              |             |          |

| Internal Clock                         |                                                    |              |              |             |          |

| Frequency                              |                                                    | 16           |              |             | MHz      |

| Accuracy                               |                                                    | -2.5%        |              | +2.5%       | %        |

| Duty Cycle                             |                                                    | 50:50        |              |             | %        |

| Crystal                                |                                                    |              |              |             |          |

| Frequency                              | 8                                                  | 16           | 17           |             | MHz      |

| Start-Up Time                          |                                                    | 10           |              |             | µs       |

| External Clock                         | 1                                                  | 16           | 17           |             | MHz      |

| Minimum Low Time                       |                                                    | 27.6         |              |             | ns       |

| Minimum High Time                      |                                                    | 27.6         |              |             | ns       |

| LOGIC INPUTS <sup>2</sup>              |                                                    |              |              |             |          |

| Input High Voltage, V <sub>INH</sub>   |                                                    | 0.8 × IOVDD  |              |             | V        |

| Input Low Voltage, V <sub>INL</sub>    |                                                    |              | 0.2 × IOVDD  |             | V        |

| Hysteresis                             |                                                    | 0.04         |              |             | V        |

| Leakage Currents                       | SYNC_INピン<br>その他全てのピン                              |              | +15          |             | µA       |

| Input Capacitance                      | 全てのデジタル入力                                          | -1           | 1            |             | µA       |

|                                        |                                                    |              | 10           |             | pF       |

# 仕様

表1. (続き)

| パラメータ <sup>1</sup>                                           | テスト条件/コメント                                                              | 最小値                        | 代表値 | 最大値                     | 単位            |

|--------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------|-----|-------------------------|---------------|

| LOGIC OUTPUT <sup>2</sup> (XTAL2,<br>DIG_AUX1,DIG_AUX2, SDO) |                                                                         |                            |     |                         |               |

| Output High Voltage, $V_{OH}^2$                              | $I_{SOURCE} = 1\text{mA}$                                               | $0.8 \times \text{IOVDD}$  |     |                         | V             |

| Output Low Voltage, $V_{OL}^2$                               | $I_{SINK} = 2\text{mA}$                                                 |                            | 0.4 |                         | V             |

| Leakage Current                                              | フロート状態                                                                  | -1                         |     | +1                      | $\mu\text{A}$ |

| Output Capacitance                                           | フロート状態                                                                  |                            | 10  |                         | pF            |

| SYSTEM CALIBRATION <sup>2</sup>                              |                                                                         |                            |     |                         |               |

| Full-Scale (FS) Calibration Limit                            |                                                                         |                            |     | $1.05 \times \text{FS}$ | V             |

| Zero-Scale Calibration Limit                                 |                                                                         | $-1.05 \times \text{FS}$   |     |                         | V             |

| Input Span                                                   |                                                                         | $0.8 \times \text{FS}$     |     | $2.1 \times \text{FS}$  | V             |

| POWER REQUIREMENTS                                           |                                                                         |                            |     |                         |               |

| Power Supply Voltage                                         |                                                                         |                            |     |                         |               |

| AVDD to AVSS                                                 |                                                                         | 4.75                       |     | 5.25                    | V             |

| AVSS to DGND                                                 |                                                                         | -2.625                     |     | 0                       | V             |

| IOVDD to DGND                                                |                                                                         | 1.7                        |     | 5.25                    | V             |

| IOVDD to AVSS                                                |                                                                         |                            |     | 6.35                    | V             |

| POWER SUPPLY CURRENTS <sup>7</sup>                           |                                                                         |                            |     |                         |               |

| AVDD Current                                                 |                                                                         |                            |     |                         |               |

| Gain =1 Precharge                                            |                                                                         | 6.7                        |     | 7.7                     | mA            |

| Gain < 16 except Gain =1                                     |                                                                         | 9.5                        |     | 11                      | mA            |

| Precharge                                                    |                                                                         |                            |     |                         |               |

| Gain $\geq 16$                                               |                                                                         | 12.5                       |     | 14.7                    | mA            |

| AVDD Increase due to                                         |                                                                         |                            |     |                         |               |

| Both Reference Buffers                                       |                                                                         |                            |     |                         |               |

| Precharge                                                    |                                                                         | 1.2                        |     | 1.5                     | mA            |

| Full Buffer                                                  |                                                                         | 3.3                        |     | 4.1                     | mA            |

| Internal Reference                                           |                                                                         | 0.5                        |     | 0.6                     | mA            |

| DAC                                                          |                                                                         | 0.1                        |     | 0.15                    | mA            |

| Diagnostics                                                  |                                                                         | 0.1                        |     |                         | mA            |

| VBIAS                                                        |                                                                         | 0.05                       |     |                         | mA            |

| Excitation Currents                                          |                                                                         | 0.06                       |     |                         | mA            |

| AVDD Standby Mode                                            | LDOオンのみ                                                                 | 70                         |     | 110                     | $\mu\text{A}$ |

| AVDD Power-Down Mode                                         |                                                                         | 0.2                        |     | 1                       | $\mu\text{A}$ |

| IOVDD Current                                                |                                                                         | 2                          |     | 2.3                     | mA            |

|                                                              | 外部クロック                                                                  | 2.3                        |     | 2.6                     | mA            |

|                                                              | 内部クロック                                                                  |                            |     |                         | mA            |

|                                                              | 外部水晶振動子 (16.384MHz)                                                     | 2.4                        |     |                         | mA            |

| IOVDD Increase due to                                        |                                                                         |                            |     |                         |               |

| Default FIR Filter                                           |                                                                         | 2.4                        |     | 2.7                     | mA            |

| Programmable FIR Filter                                      |                                                                         | 1.1 + (0.025 × FIR_LENGTH) |     |                         | mA            |

| IOVDD Standby Mode                                           | LDOオンのみ                                                                 | 15                         |     | 180                     | $\mu\text{A}$ |

| IOVDD Power-Down Mode                                        |                                                                         | 0.8                        |     | 1.5                     | $\mu\text{A}$ |

| POWER DISSIPATION <sup>2</sup>                               |                                                                         |                            |     |                         |               |

| Full Operating Mode                                          | AVDD = 5.25V、IOVDD = 5.25V<br>ゲイン = 1、リファレンス・バッファがディスエーブル、外部クロック、リファレンス | 60.4                       |     | 70                      | mW            |

|                                                              | ゲイン > 16、リファレンス・バッファがイネーブル、内部クロック、リファレンス                                | 115                        |     | 137                     | mW            |

| Standby Mode                                                 | LDOオンのみ                                                                 | 447                        |     | 1,530                   | $\mu\text{W}$ |

| Power-Down Mode                                              |                                                                         | 5.25                       |     | 13.2                    | $\mu\text{W}$ |

1 温度範囲は-40°C～+105°Cです。

これらは、これらの仕様については製品テストを行っていませんが製品発売開始時の特性評価データでサポートされています。

3 オフセット誤差は、システム・キャリブレーションまたは内部ゼロスケール・キャリブレーションに従って選択されたプログラム済みODRのノイズの程度です。システム・フルスケール・キャリブレーションにより、プログラム済みODRのノイズと同等レベルにまでゲイン誤差が減少します。

4 AINPおよびAINMの最小および最大電圧は、AVSS + 0.1VおよびAVDD - 0.1Vです。

5 差動アナログ入力の最大許容範囲は、 $\pm(\text{AVDD} - 0.65\text{ V})/\text{ゲイン}$ です。一方、シングルエンド・アナログ入力の最大許容範囲は、 $0\sim(\text{AVDD} - 0.65\text{V})/\text{ゲイン}$ で、これは高リザーブアンプ電圧を用いた場合に該当します。

6 この仕様には、湿度感度レベル（MSL）プリコンディショニングの影響が含まれています。

7 これは、REFOUT、DAC、励起電流、デジタル出力ピンに負荷が接続されていないときの仕様です。デジタル入力はIOVDDまたはDGNDに接続します。

## 仕様

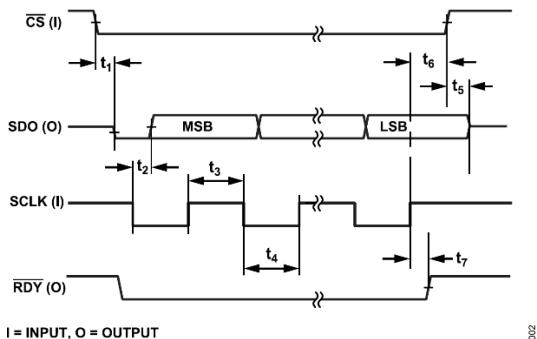

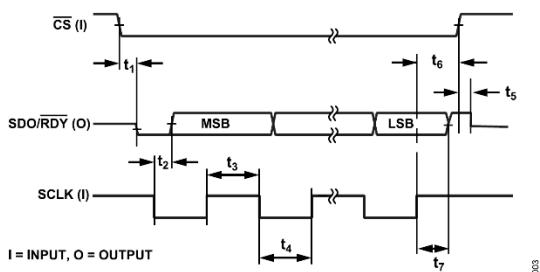

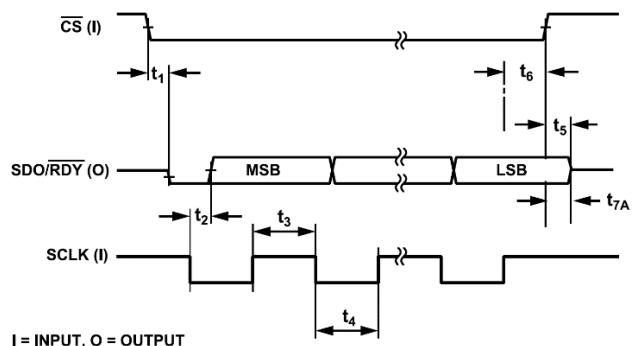

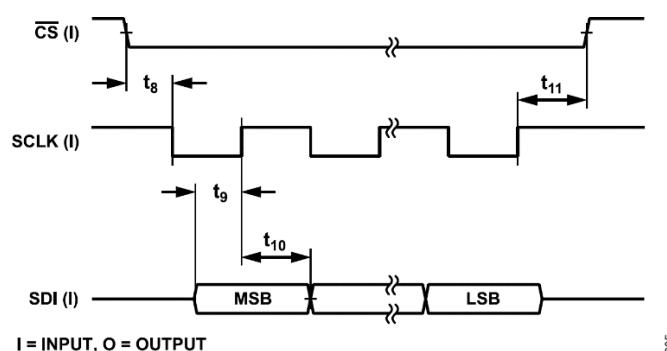

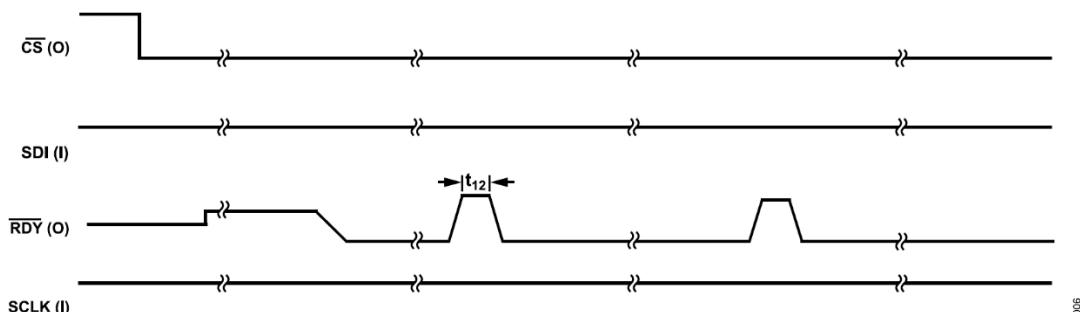

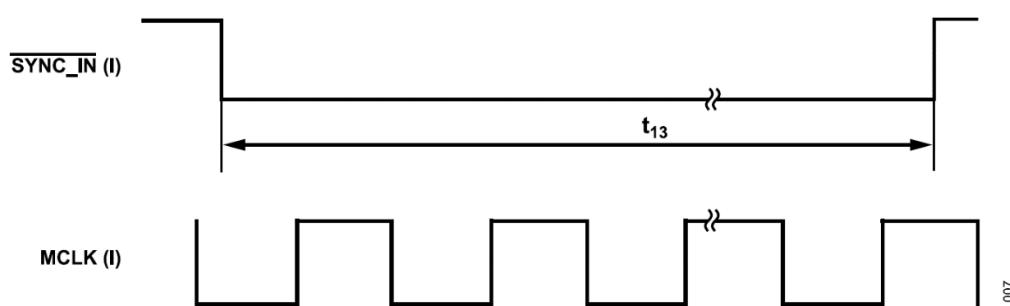

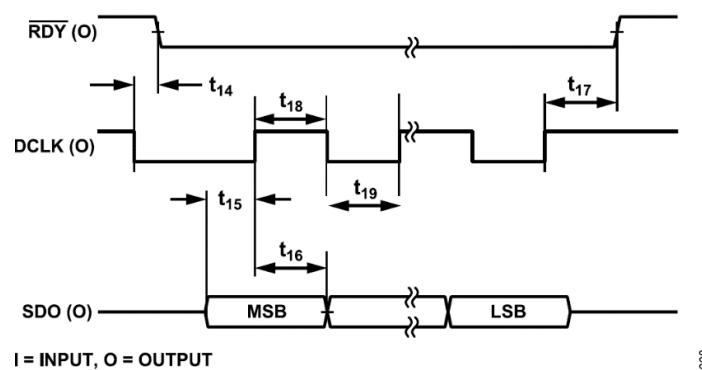

## タイミング特性

特に指定のない限り、 $\text{IOVDD} = 1.7\text{V} \sim 5.25\text{V}$  ( $\text{IOVDD} < 3\text{ V}$  の場合は  $\text{DIG\_OUT\_STR}$  ビットをセット)、 $\text{DGND} = 0\text{V}$ 、入力ロジック 0 =  $0\text{V}$ 、入力ロジック 1 =  $\text{IOVDD}$ 、 $C_{\text{LOAD}} = 20\text{pF}$ 。

表2.

| パラメータ                               | $T_{\text{MIN}}, T_{\text{MAX}}$ の限界値                                                                                                               |                              | 単位 | テスト条件/コメント <sup>1, 2</sup>                                                                                                                                                                                                                |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | 最小値                                                                                                                                                 | 最大値                          |    |                                                                                                                                                                                                                                           |

| SCLK                                |                                                                                                                                                     |                              |    |                                                                                                                                                                                                                                           |

| $t_3$                               | 25                                                                                                                                                  |                              | ns | SCLKハイのパルス幅                                                                                                                                                                                                                               |

| $t_4$                               | 25                                                                                                                                                  |                              | ns | SCLKローのパルス幅                                                                                                                                                                                                                               |

| $t_{12}$                            |                                                                                                                                                     |                              |    | $\overline{\text{RDY}}$ がローでかつ次の変換が可能である場合 ( $f_{\text{MOD}} = \text{MCLK}/4$ ) の $\overline{\text{RDY}}$ のハイの時間                                                                                                                          |

| $t_{13}$                            | 2.25/ $f_{\text{MOD}}$<br>4.25/ $f_{\text{MOD}}$<br>8.25/ $f_{\text{MOD}}$<br>8.25/ $f_{\text{MOD}}$ to<br>16/ $f_{\text{MOD}}$<br>2/ $\text{MCLK}$ |                              |    | sinc <sup>5</sup> 、FILTER_FS = 1<br>sinc <sup>5</sup> 、FILTER_FS = 2<br>他の全てのsincオプション<br>FIR、FILTER_FS = 4~FILTER_FS = 128<br><br>$\overline{\text{SYNC\_IN}}$ ローのパルス幅                                                                   |

| READ OPERATION                      |                                                                                                                                                     |                              |    |                                                                                                                                                                                                                                           |

| $t_1$                               | 0                                                                                                                                                   |                              | ns | $\overline{\text{CS}}$ の立下がりエッジから SDO のアクティブ化までの時間                                                                                                                                                                                        |

|                                     |                                                                                                                                                     | 12.5                         | ns | $4.75\text{V} < \text{IOVDD} \leq 5.25\text{V}$                                                                                                                                                                                           |

|                                     |                                                                                                                                                     | 17.5                         | ns | $3\text{V} \leq \text{IOVDD} \leq 4.75\text{V}$                                                                                                                                                                                           |

|                                     |                                                                                                                                                     | 25                           | ns | $1.7\text{V} \leq \text{IOVDD} < 3\text{V}$                                                                                                                                                                                               |

| $t_2^3$                             | 5                                                                                                                                                   |                              | ns | SCLK のアクティブ・エッジからデータ有効化までの遅延                                                                                                                                                                                                              |

|                                     |                                                                                                                                                     | 12.5                         | ns | $4.75\text{V} < \text{IOVDD} \leq 5.25\text{V}$                                                                                                                                                                                           |

|                                     |                                                                                                                                                     | 17.5                         | ns | $3\text{V} \leq \text{IOVDD} \leq 4.75\text{V}$                                                                                                                                                                                           |

|                                     |                                                                                                                                                     | 25                           | ns | $1.7\text{V} \leq \text{IOVDD} < 3\text{V}$                                                                                                                                                                                               |

| $t_5^5$                             | 2.5                                                                                                                                                 |                              | ns | $\overline{\text{CS}}$ の非アクティブ・エッジ後のバス放棄時間                                                                                                                                                                                                |

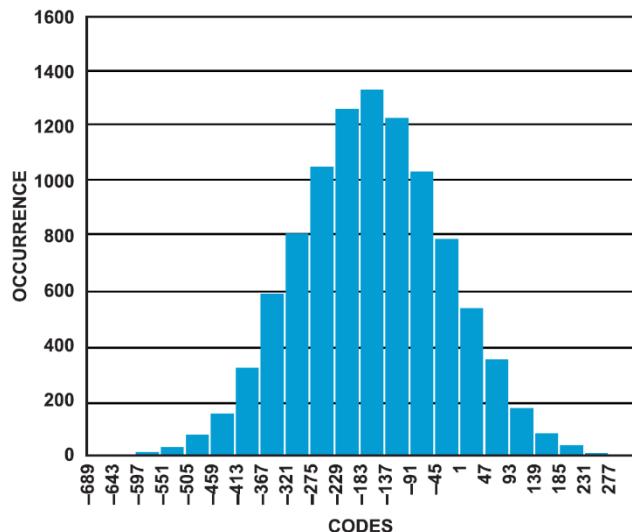

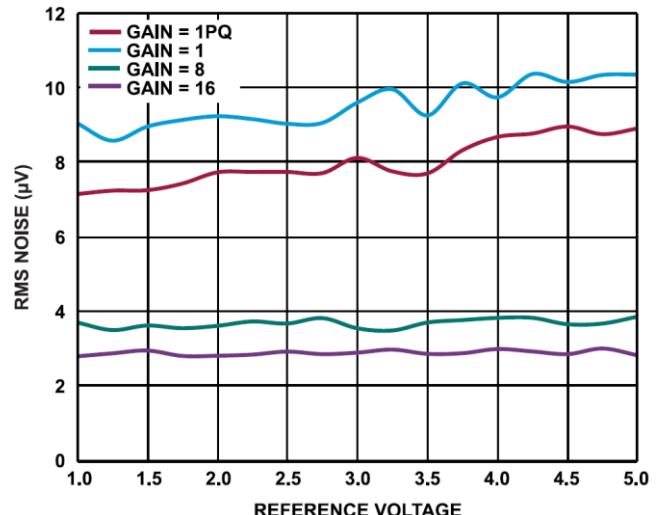

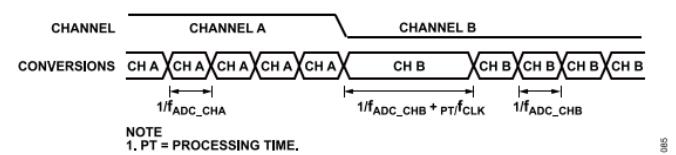

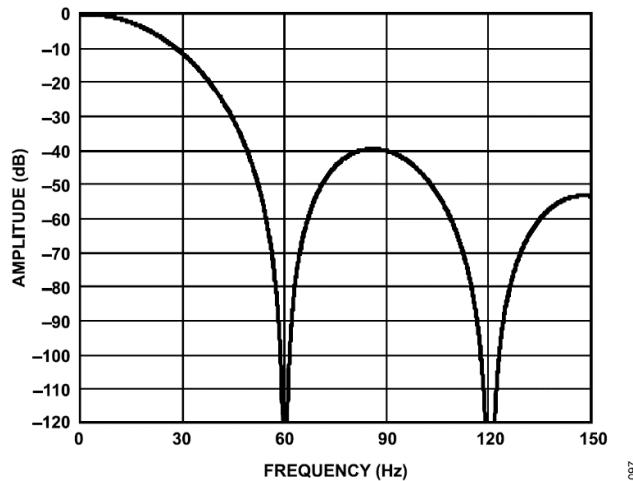

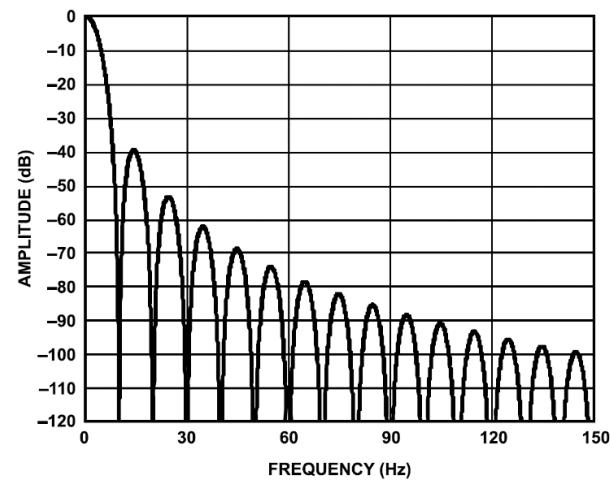

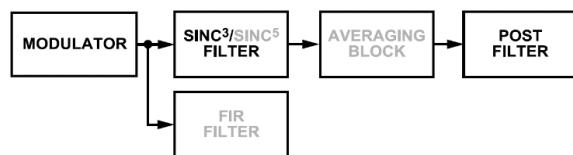

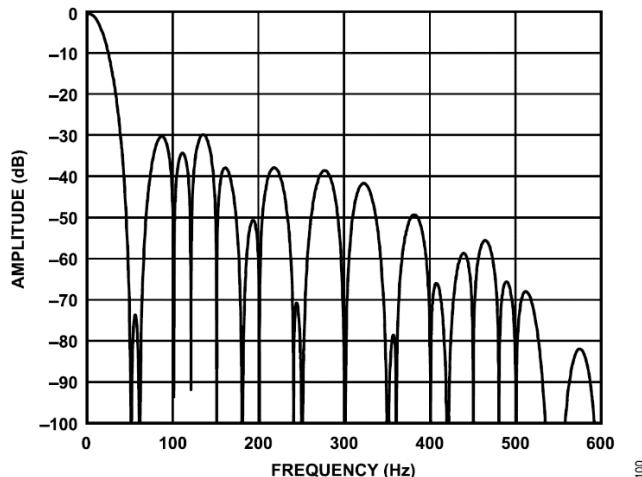

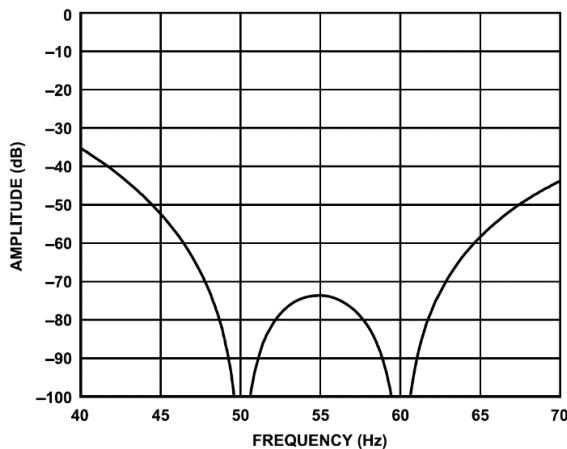

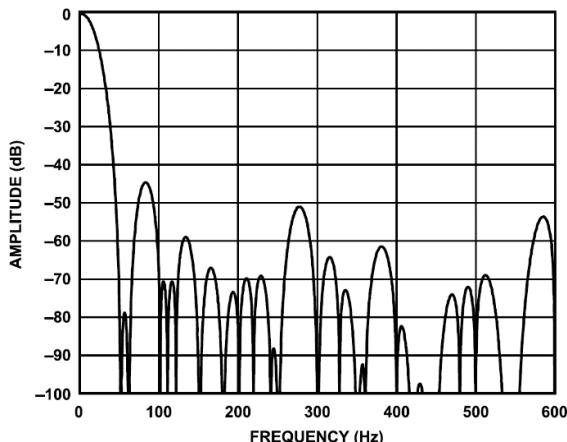

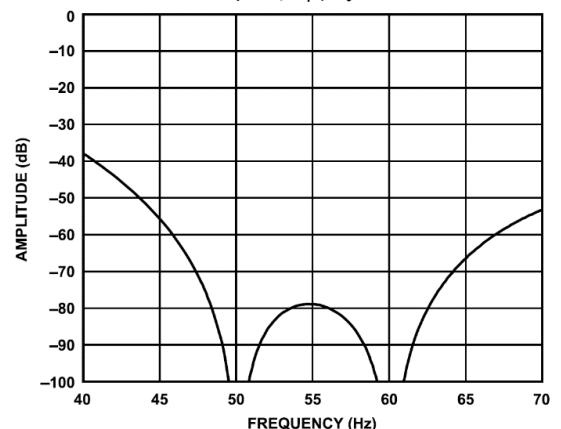

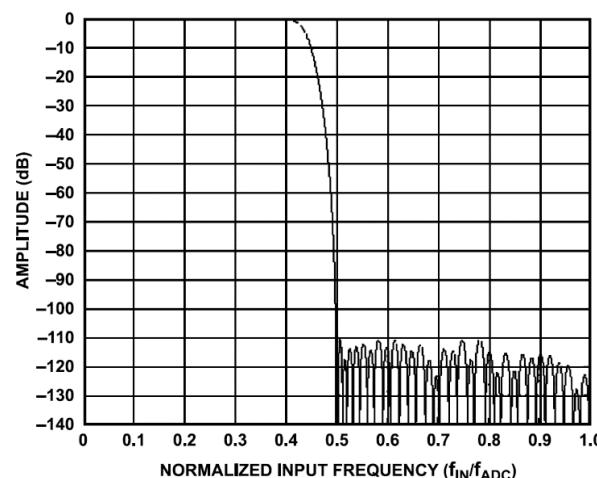

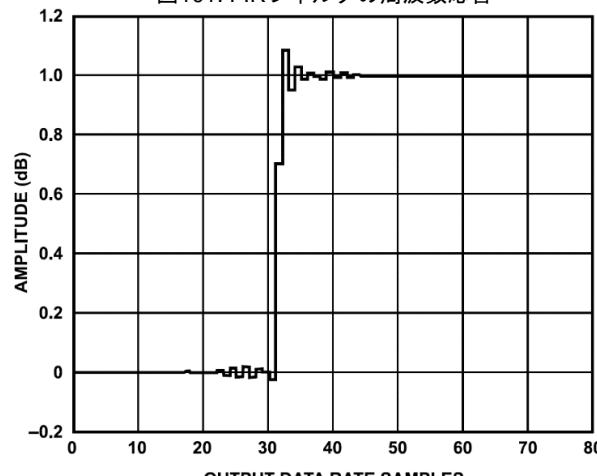

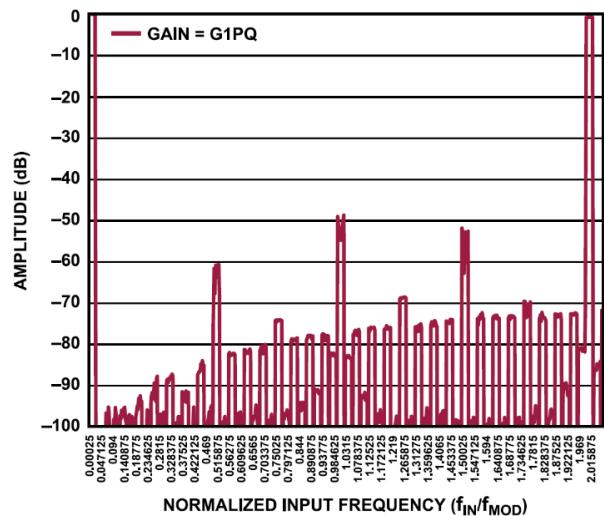

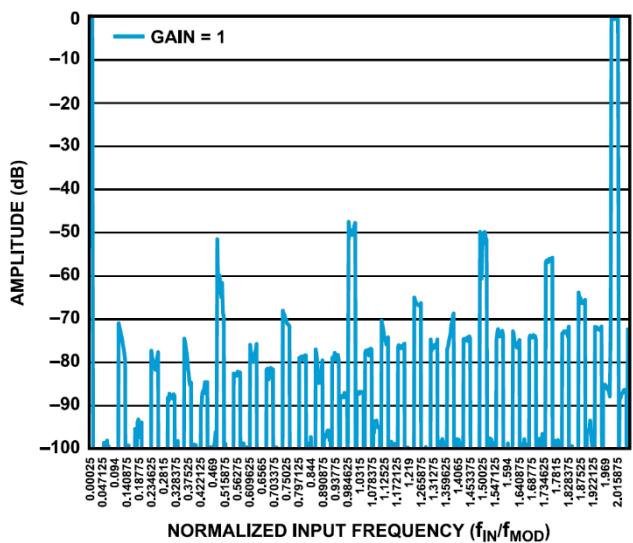

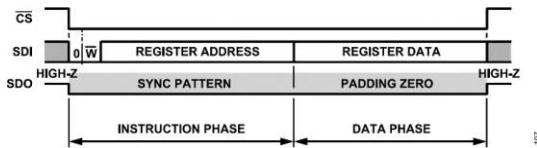

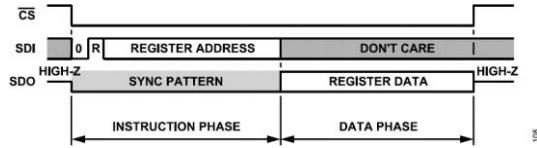

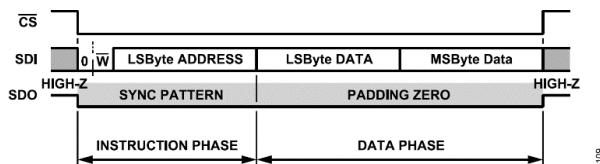

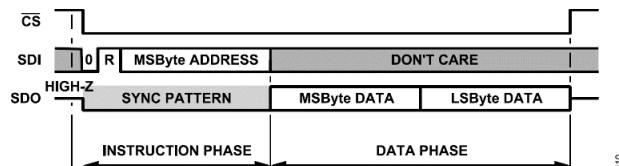

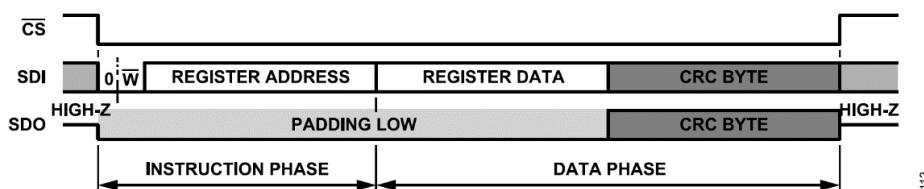

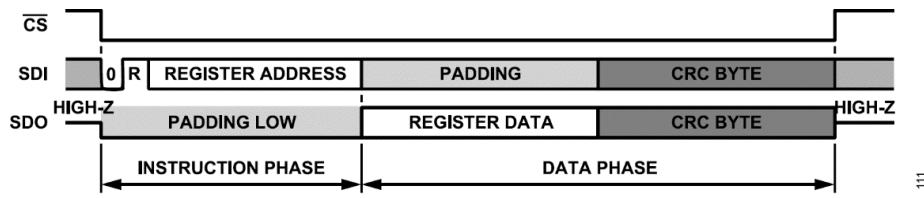

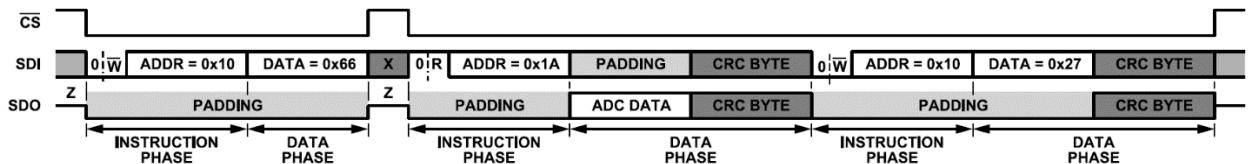

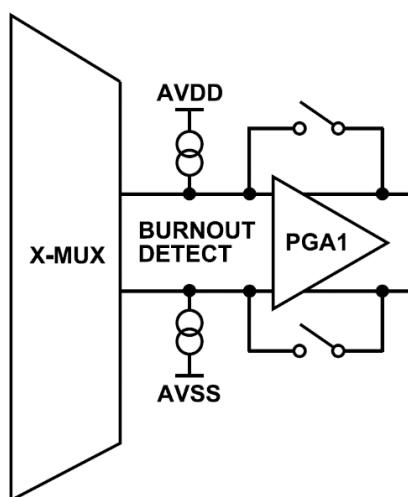

|                                     |                                                                                                                                                     | 20                           | ns |                                                                                                                                                                                                                                           |