## 32 $\mu$ A、超低消費電力、24ビット・シグマデルタADC (PGAとFIFOを統合)

### 特長

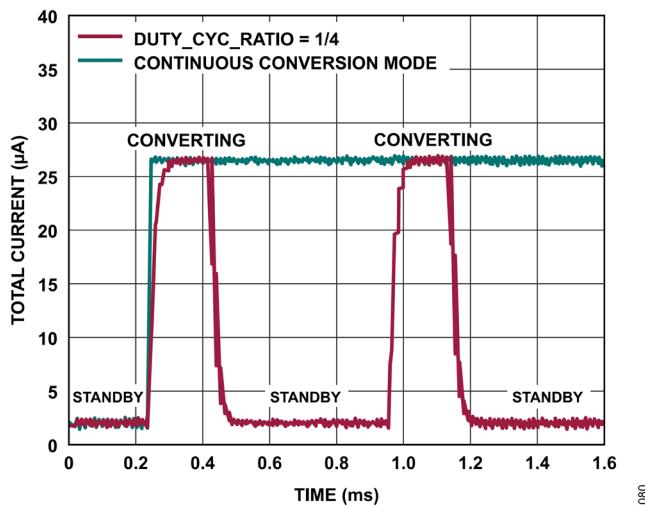

- ▶ 超低消費電流（代表値）

- ▶ 32 $\mu$ A：連続変換モード（ゲイン = 128）

- ▶ 5 $\mu$ A：デューティ・サイクル・モード（デューティ比 = 1/16）

- ▶ 0.5 $\mu$ A：スタンバイ・モード

- ▶ 0.1 $\mu$ A：パワーダウン・モード

- ▶ システム・レベルの節電を実現する組込み機能

- ▶ 電流節減デューティ・サイクル比：1/4 または 1/16

- ▶ スマート・シーケンサとチャンネル単位の構成によりホスト・プロセッサの負荷を最小限に抑制

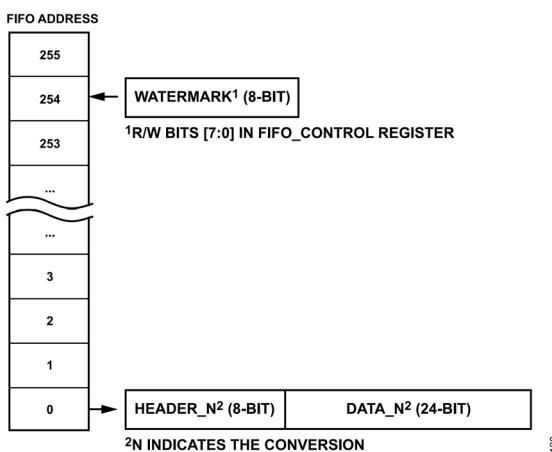

- ▶ 内蔵のディープ FIFO によりホスト・プロセッサの負荷を最小限に抑制（256サンプルの深度）

- ▶ 自律型 FIFO 割込み機能、閾値検出

- ▶ わずか 1.71V の低電圧单電源によりバッテリ寿命を延長

- ▶ 実効値ノイズ：1.17SPS（ゲイン = 128）で 25nV rms - 48nV/ $\sqrt{\text{Hz}}$

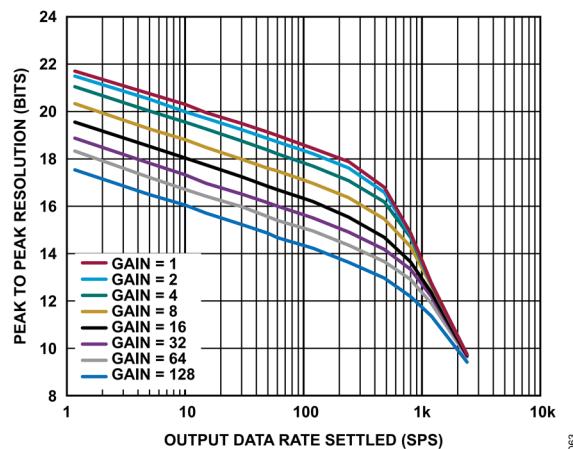

- ▶ ノイズ・フリー・ビット：最大 22（ゲイン = 1）

- ▶ 出力データレート：1.17SPS~2.4kSPS

- ▶ 1.71V~3.6V の单電源または $\pm 1.8V$  の分離電源で動作

- ▶ 最大ドリフトが 15ppm/ $^{\circ}\text{C}$  のバンド・ギャップ・リファレンス

- ▶ レール to レールのアナログ入力を備えた PGA

- ▶ 適応性の高いセンサー・インターフェース機能

- ▶ RTD 用にマッチングの取れたプログラマブルな励起電流

- ▶ チップ内蔵のバイアス電圧発生器（熱電対用）

▶ ローサイド・パワー・スイッチ（ブリッジ型トランジスタ用）

- ▶ センサー断線検出

- ▶ 内部温度センサーおよび発振器

- ▶ 自己校正とシステム校正に対応

- ▶ 柔軟性の高いフィルタ・オプション

- ▶ 50Hz/60Hz の同時除去（特定のフィルタ・オプションを選択した場合）

- ▶ 汎用出力

- ▶ 診断機能

- ▶ クロスポイントでマルチプレックスされた入力

- ▶ 4 個の差動入力／8 個の疑似差動入力

- ▶ 5MHz の SPI（3 線式または 4 線式）

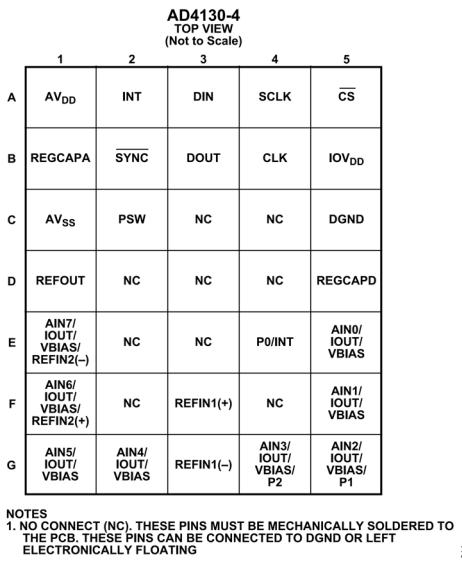

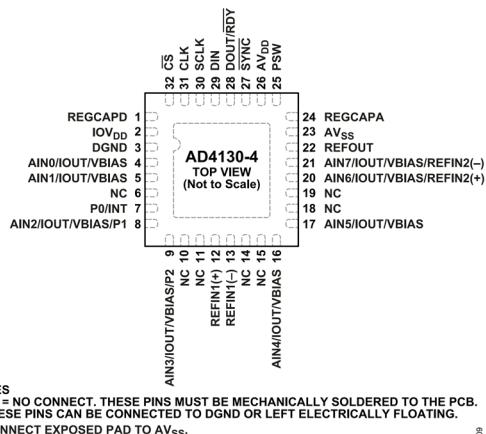

- ▶ 35 ポール、2.7mm × 3.56mm WLCSP および 32 ピン、5mm × 5mm LFCSP を採用

- ▶ 温度範囲：-40°C~+105°C (WLCSP)、-40°C~+125°C (LFCSP)

- ▶ AD4130-4 LFCSP は [AD7124-4](#) LFCSP とピン互換

### アプリケーション

- ▶ スマート・トランスマッタ

- ▶ バッテリおよび環境エネルギーで動作するワイヤレス・センサー・ノード

- ▶ 携帯型計測器

- ▶ 温度計測：熱電対、RTD、サーミスター

- ▶ 圧力計測：ブリッジ型トランジスタ

- ▶ ヘルスケアおよびウェアラブル

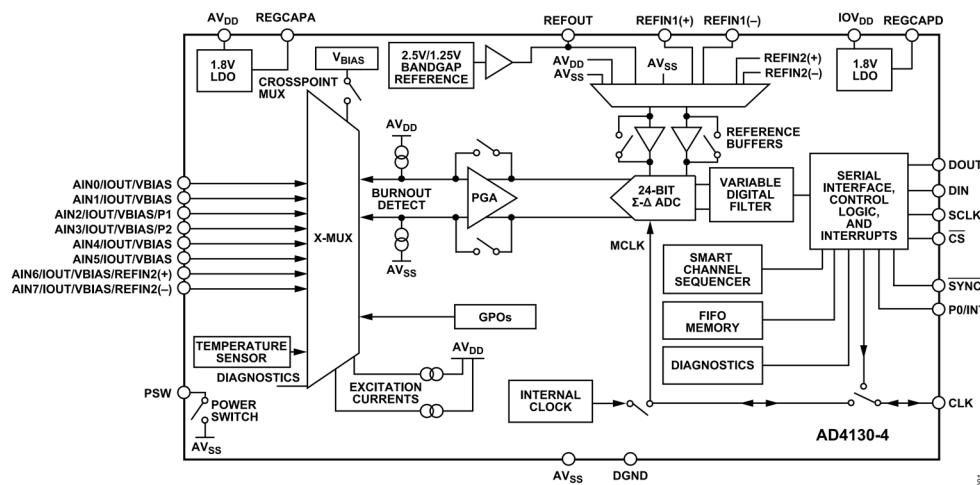

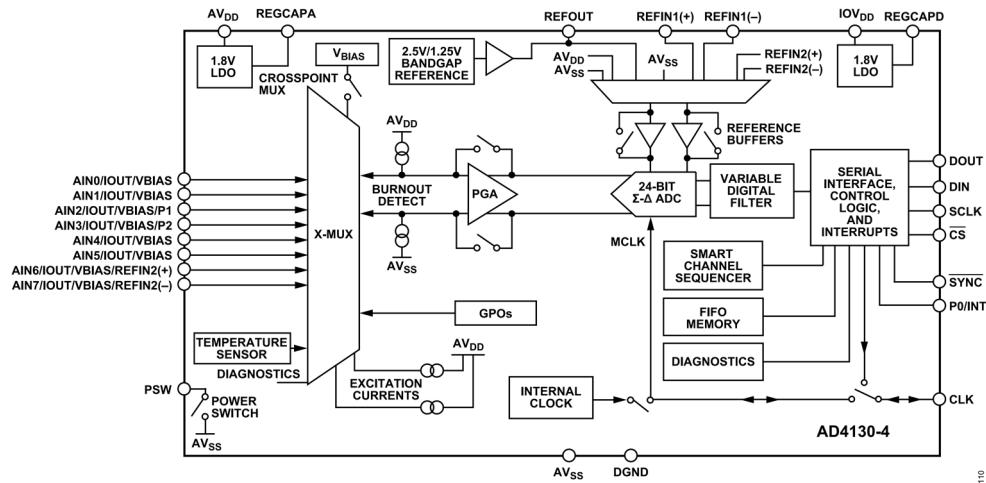

### 機能ブロック図

図 1. 機能ブロック図

## 目次

|                   |    |                                                  |     |

|-------------------|----|--------------------------------------------------|-----|

| 特長                | 1  | ADC の設定と動作                                       | 50  |

| アプリケーション          | 1  | バイポーラ／ユニポーラ設定                                    | 50  |

| 機能ブロック図           | 1  | ステータス・ビット                                        | 50  |

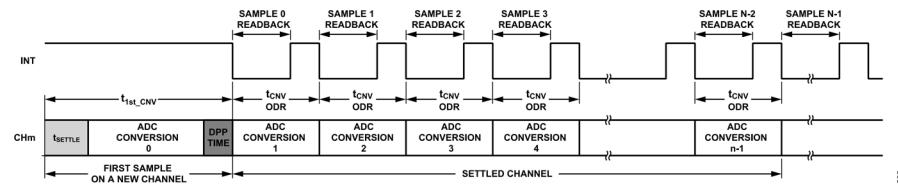

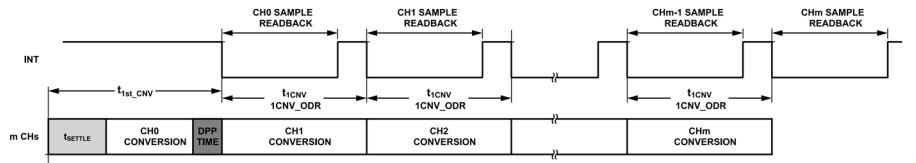

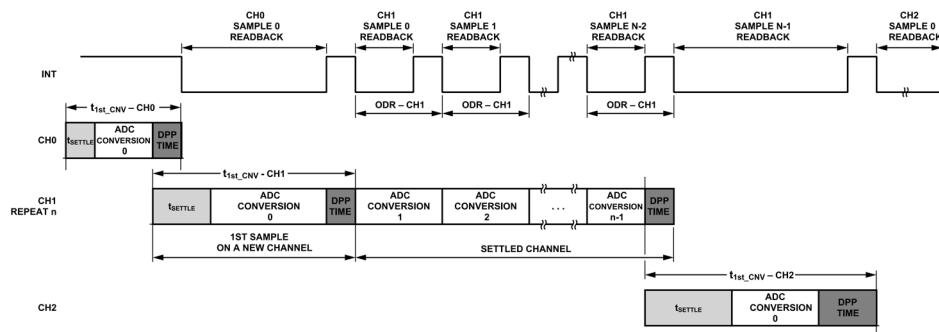

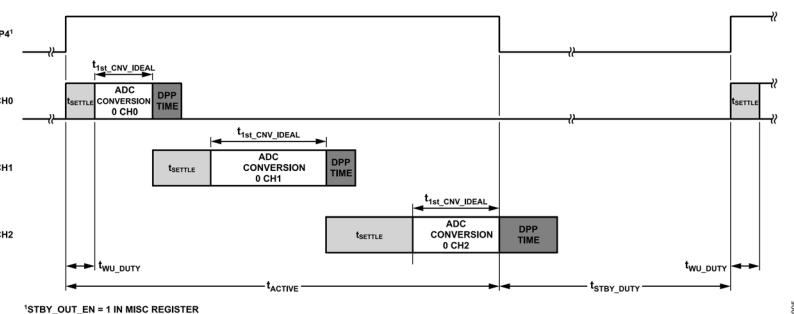

| 概要                | 4  | スマート・チャンネル・シーケンサ                                 | 51  |

| 関連製品              | 4  | ADC の変換モード                                       | 52  |

| 仕様                | 5  | データ・レディ信号                                        | 54  |

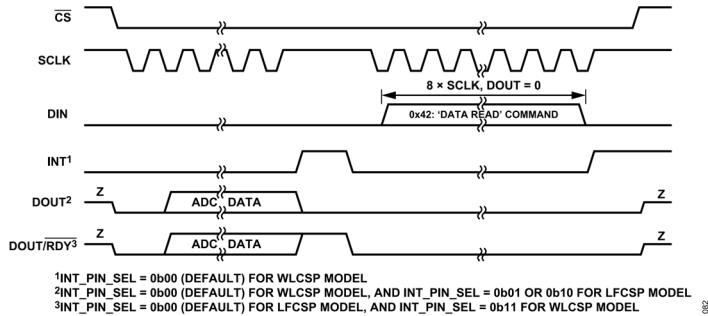

| ADC 仕様および AFE 仕様  | 5  | 連続読み出しモード                                        | 54  |

| アナログ入力仕様          | 6  | システム同期                                           | 56  |

| リファレンス仕様          | 6  | ADC の校正                                          | 56  |

| センサーのバイアス設定仕様     | 7  | デジタル・フィルタ                                        | 59  |

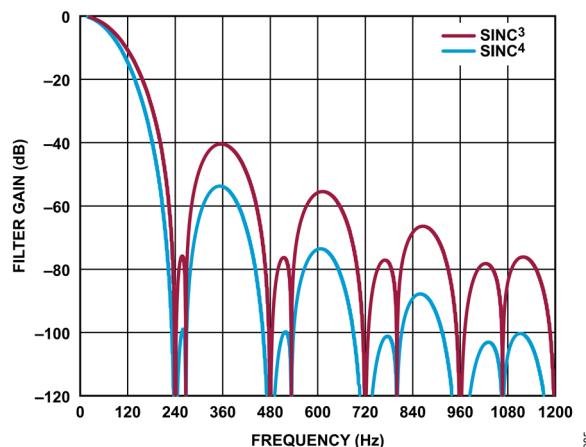

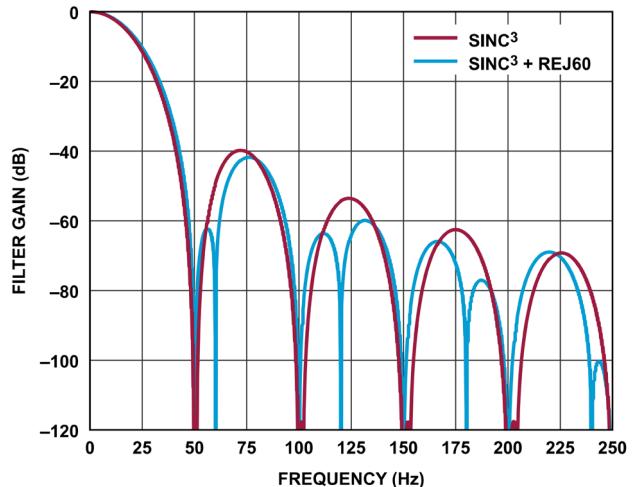

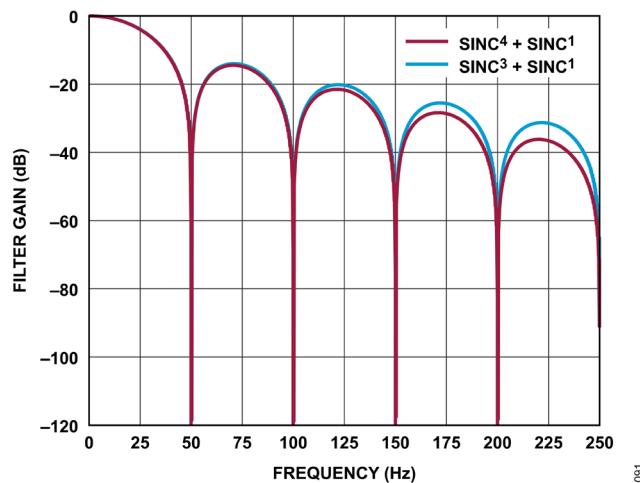

| 診断仕様              | 8  | sinc <sup>3</sup> フィルタおよび sinc <sup>4</sup> フィルタ | 59  |

| 除去仕様              | 8  | 平均化フィルタ                                          | 59  |

| ロジック入出力仕様         | 10 | ポスト・フィルタ                                         | 59  |

| 電源仕様              | 10 | 出力データレート                                         | 60  |

| タイミング仕様           | 12 | 50Hz および 60Hz の除去                                | 61  |

| 絶対最大定格            | 17 | シーケンサ                                            | 62  |

| 熱特性               | 17 | 診断機能                                             | 66  |

| 静電放電 (ESD) 定格     | 17 | シグナル・チェーンのチェック                                   | 66  |

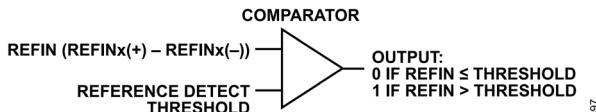

| ESD に関する注意        | 17 | リファレンス検出                                         | 66  |

| ピン配置およびピン機能の説明    | 18 | ADC エラー                                          | 66  |

| 代表的な性能特性          | 23 | 過電圧／低電圧の検出                                       | 66  |

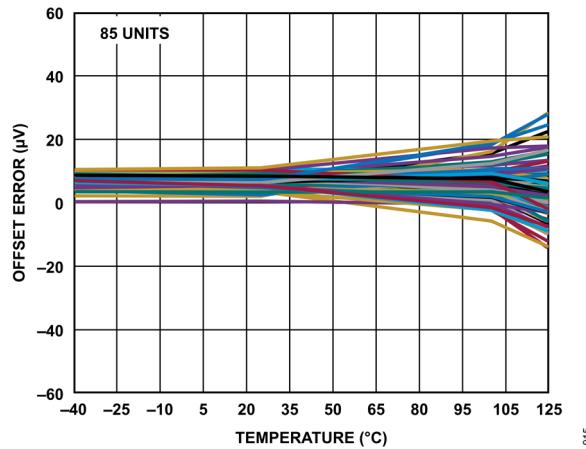

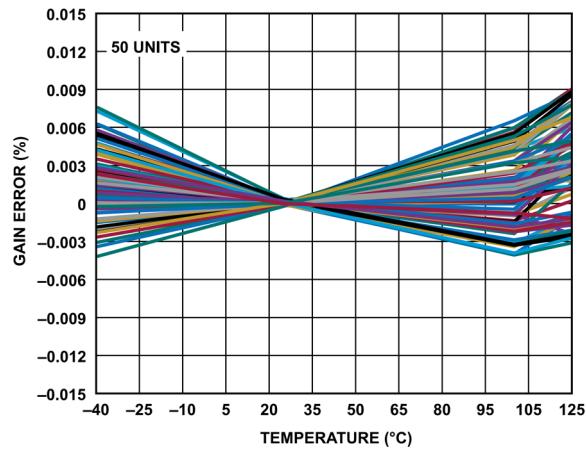

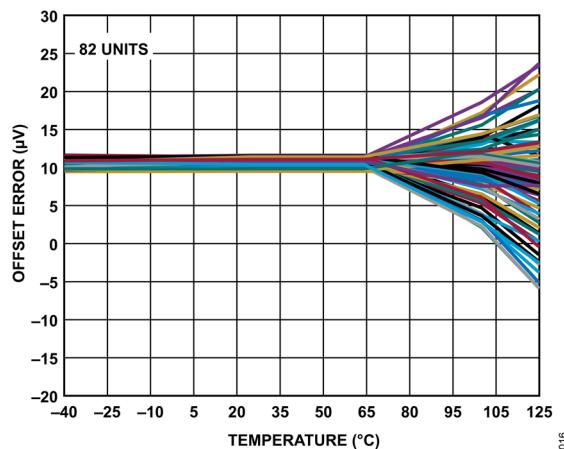

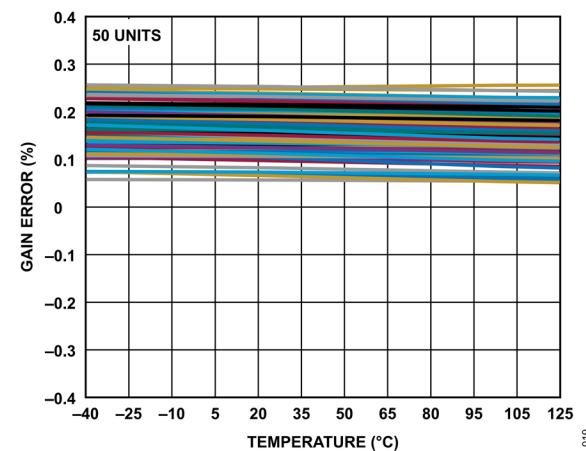

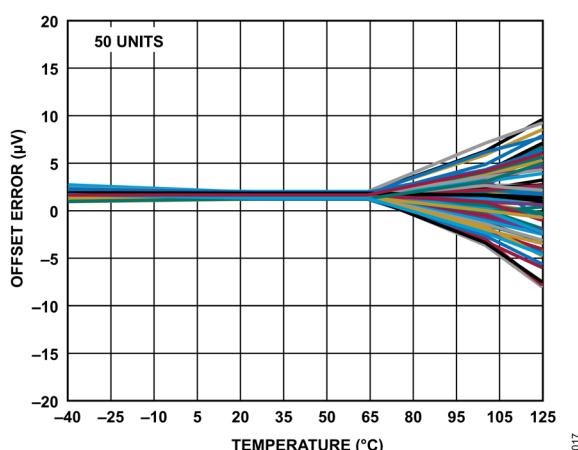

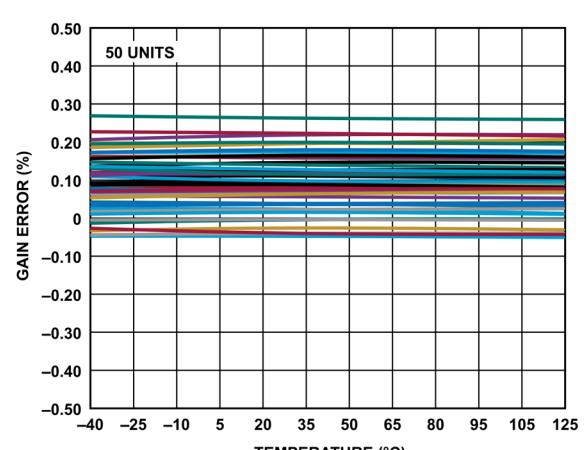

| オフセット誤差およびゲイン誤差   | 23 | 電源モニタ                                            | 67  |

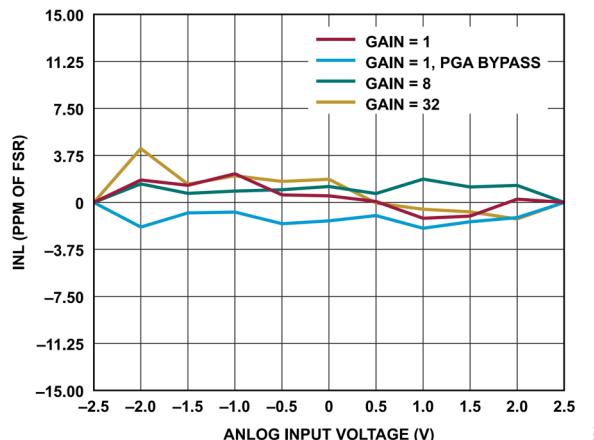

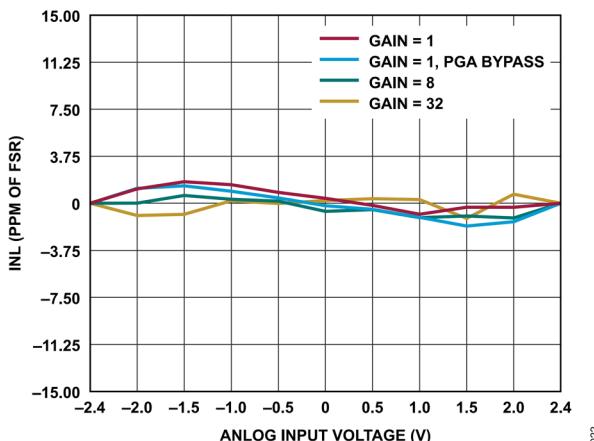

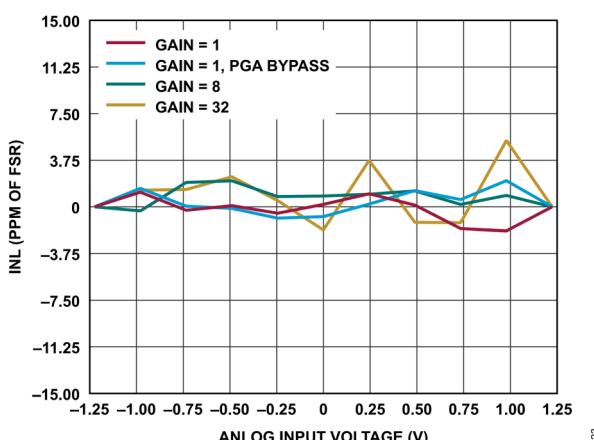

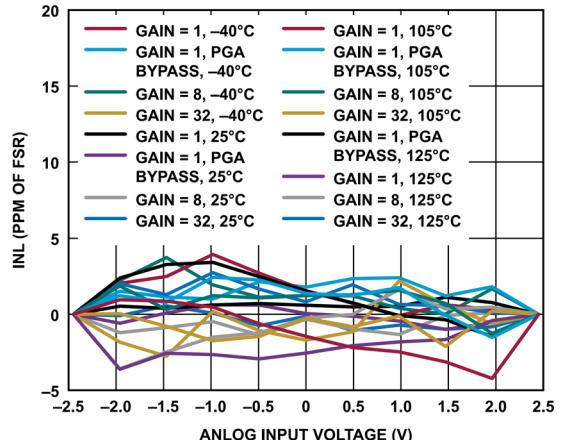

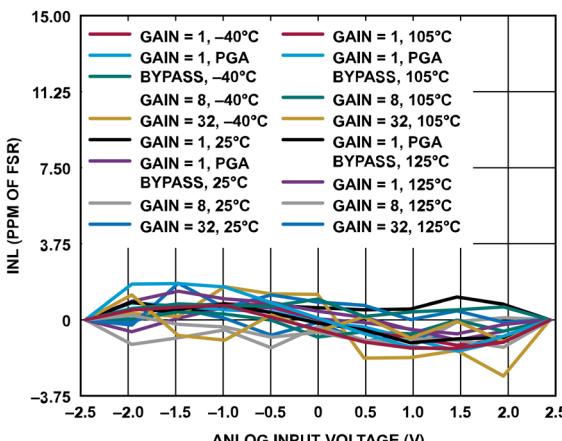

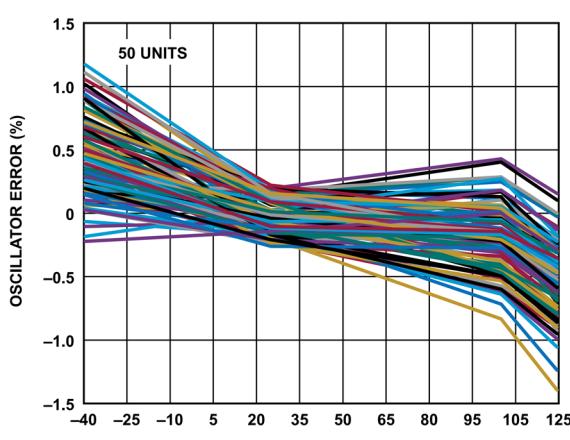

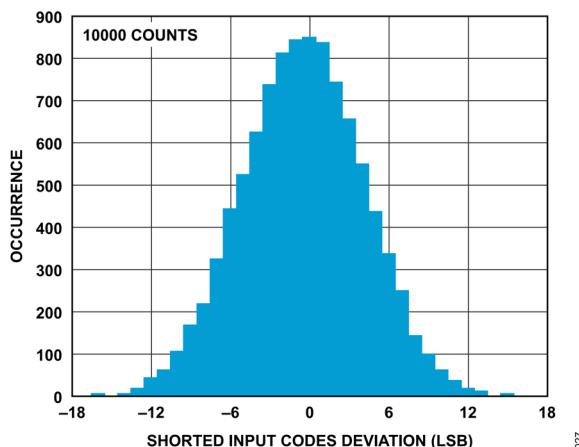

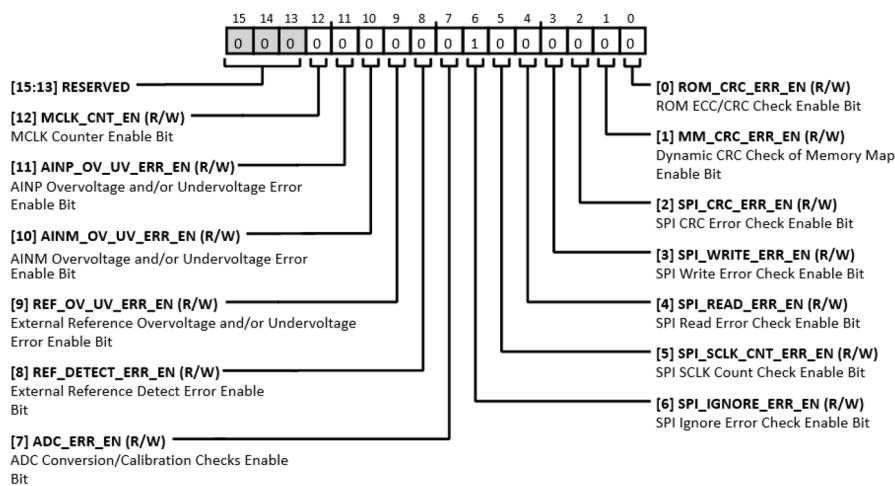

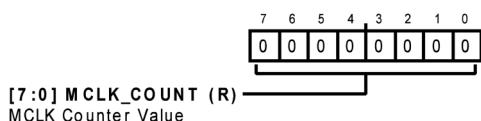

| INL 誤差および発振器      | 24 | メイン・クロックのカウンタ                                    | 67  |

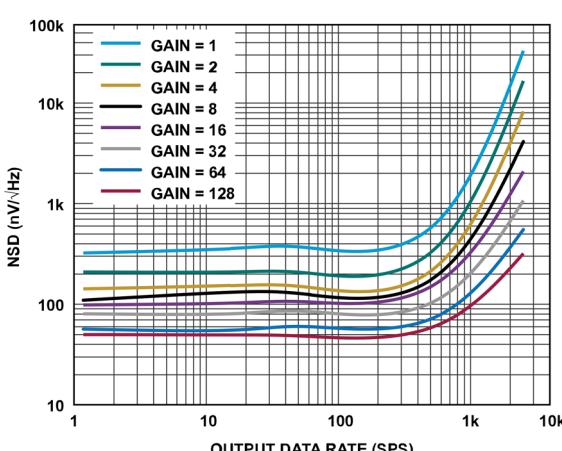

| ノイズ               | 25 | SPI 診断機能                                         | 67  |

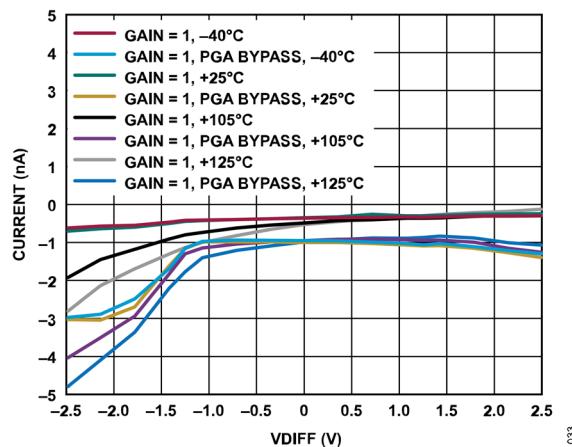

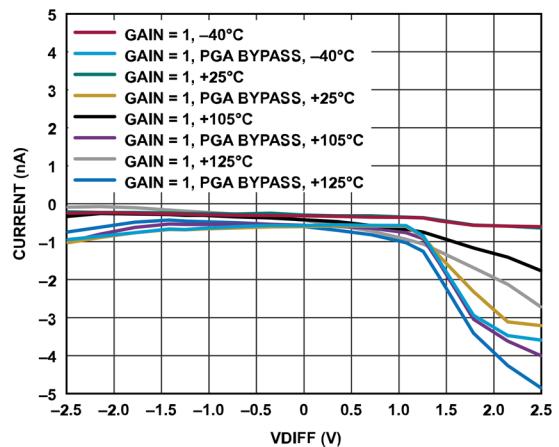

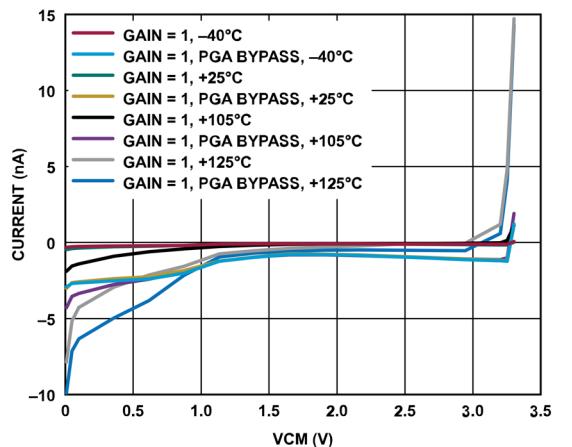

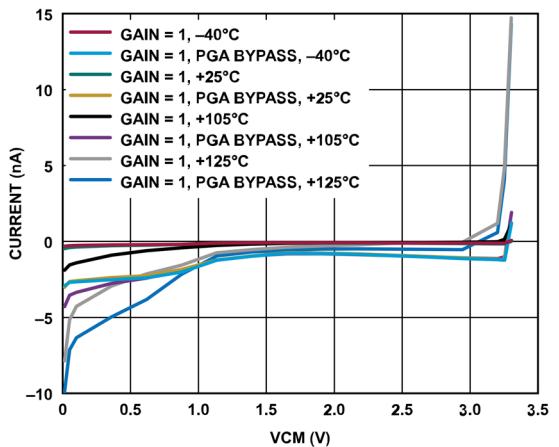

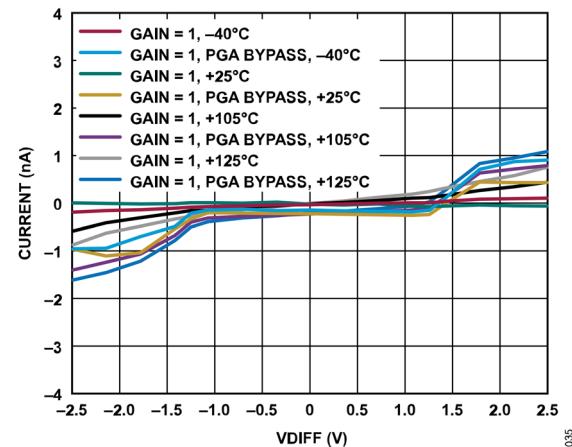

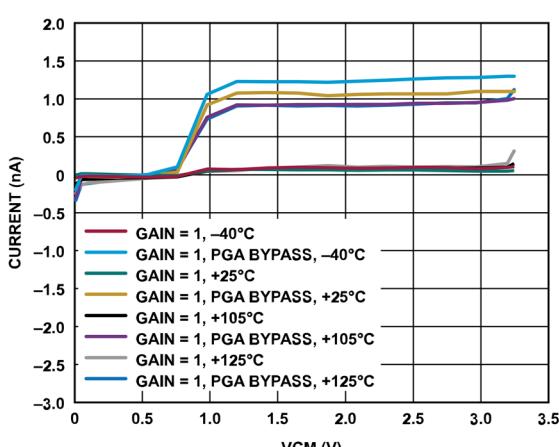

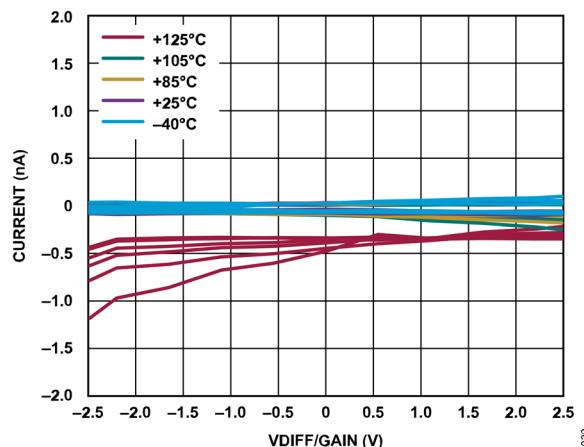

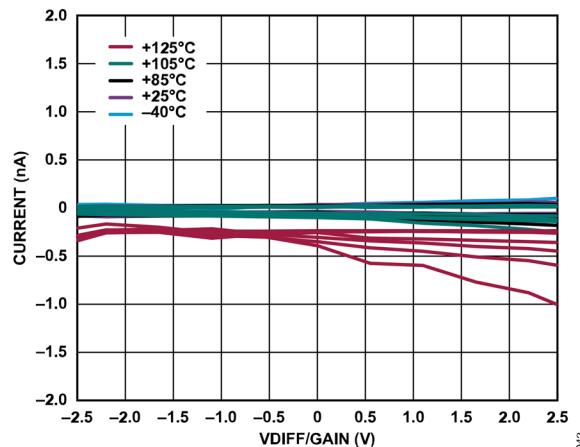

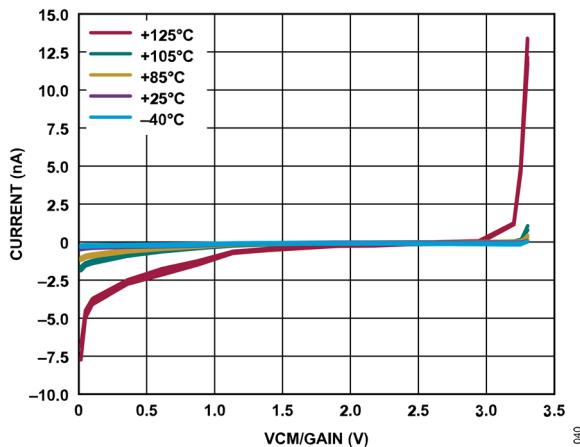

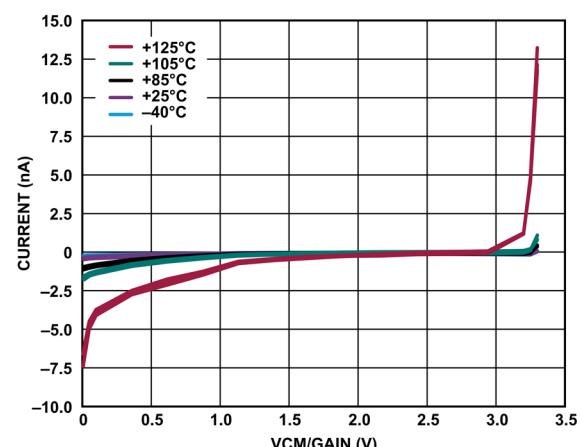

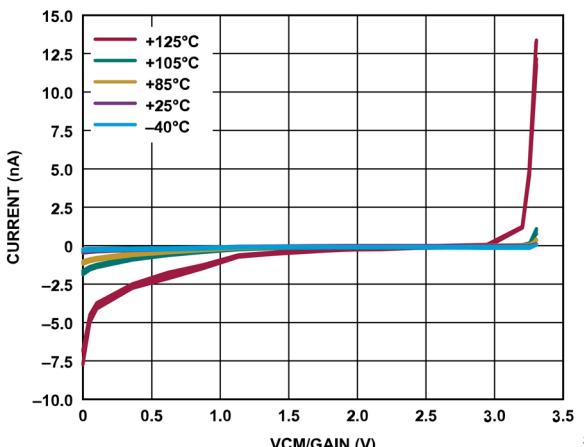

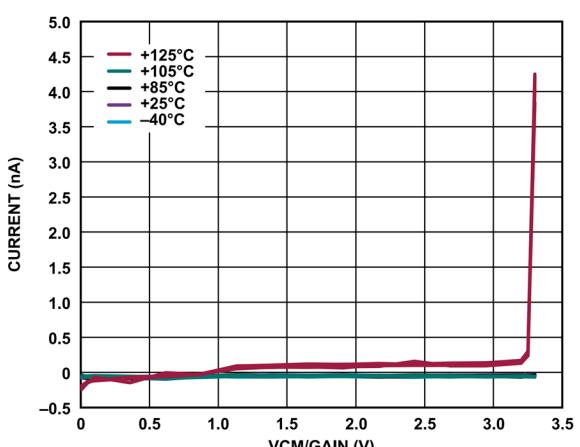

| アナログ入力電流          | 26 | CRC 保護                                           | 67  |

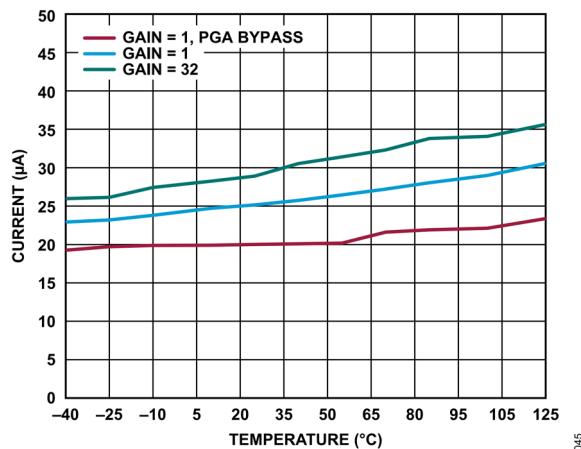

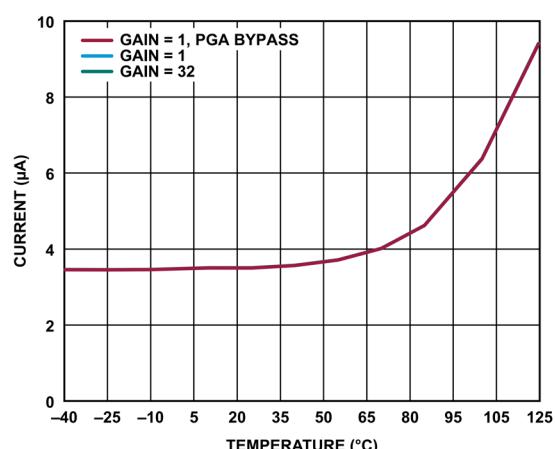

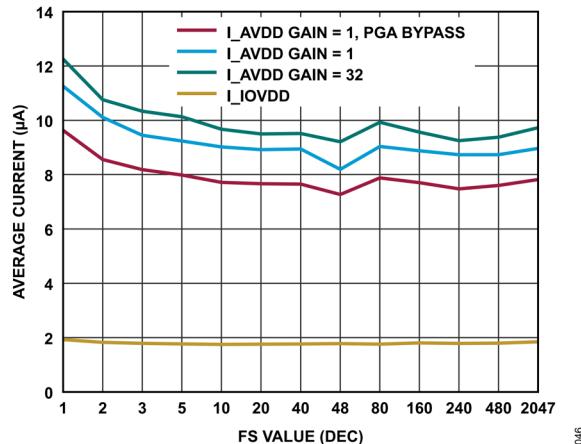

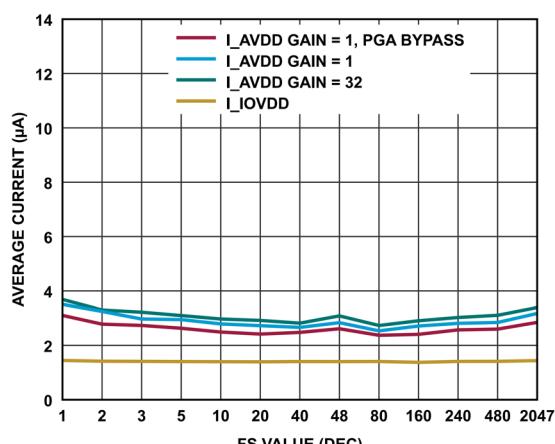

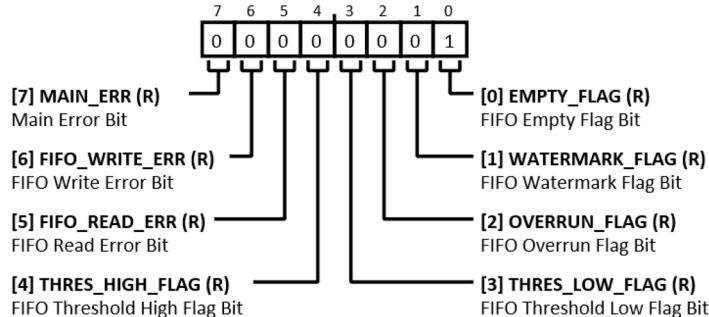

| 電源電流              | 28 | FIFO 診断機能                                        | 68  |

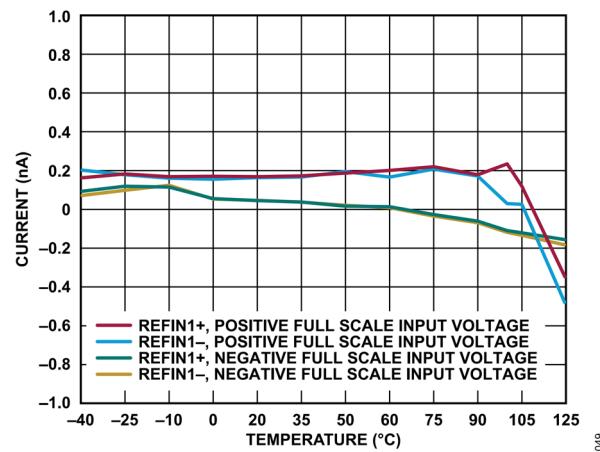

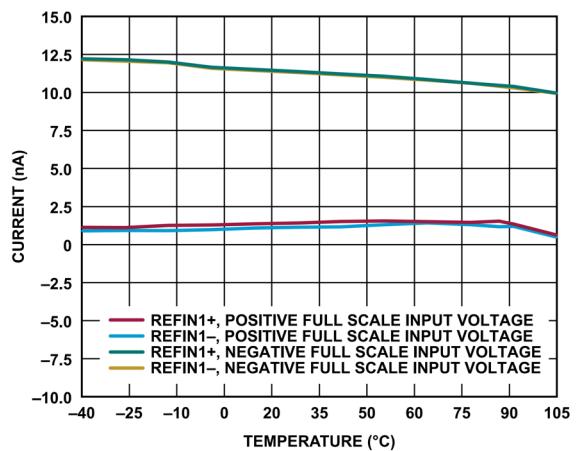

| リファレンス入力電流        | 29 | バーンアウト電流                                         | 68  |

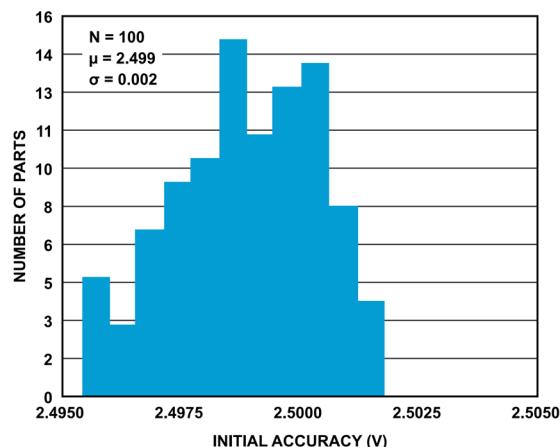

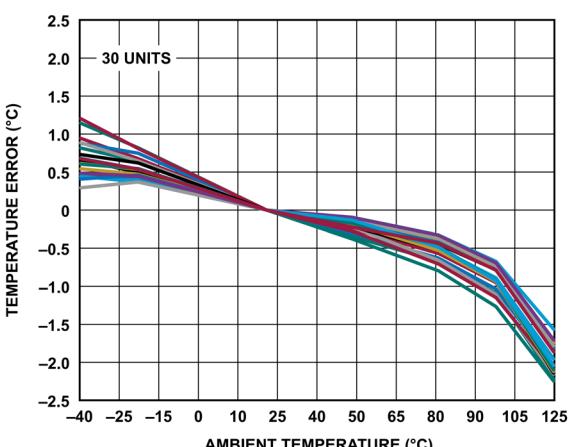

| 内部リファレンスおよび温度センサー | 30 | 温度センサー                                           | 69  |

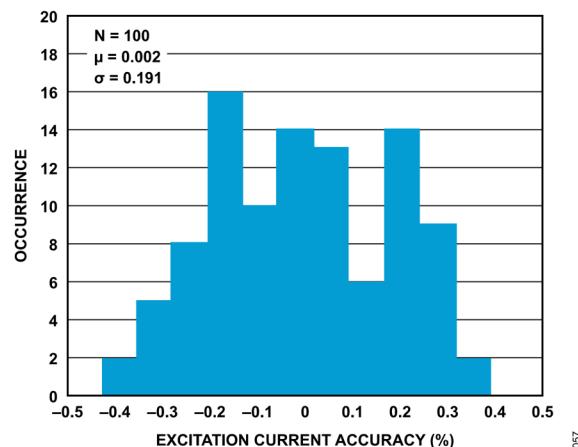

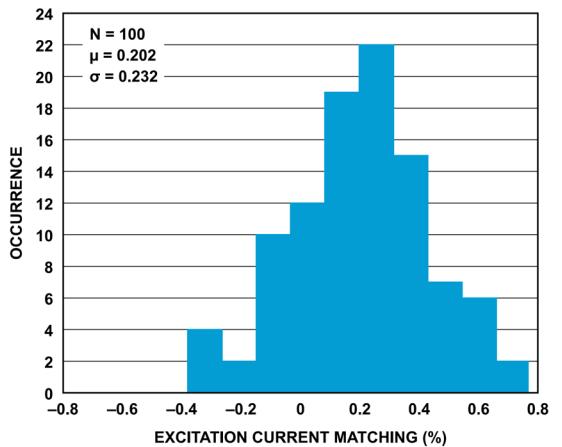

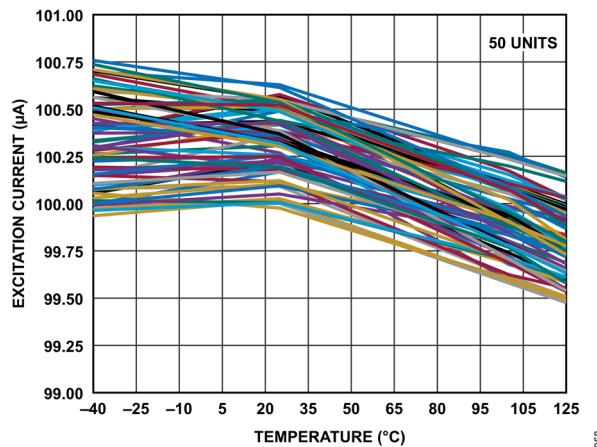

| 励起電流              | 31 | 診断機能とスタンバイ・モード                                   | 69  |

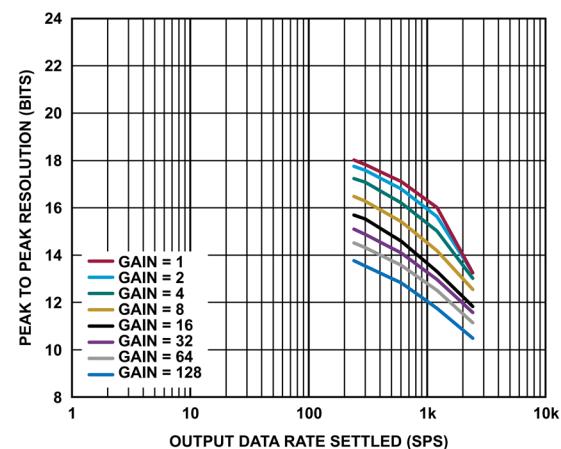

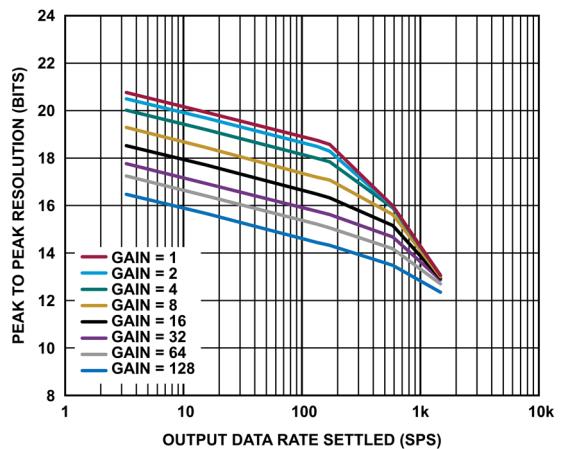

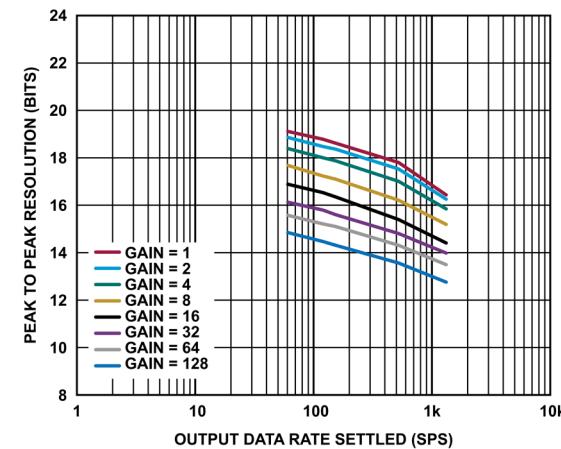

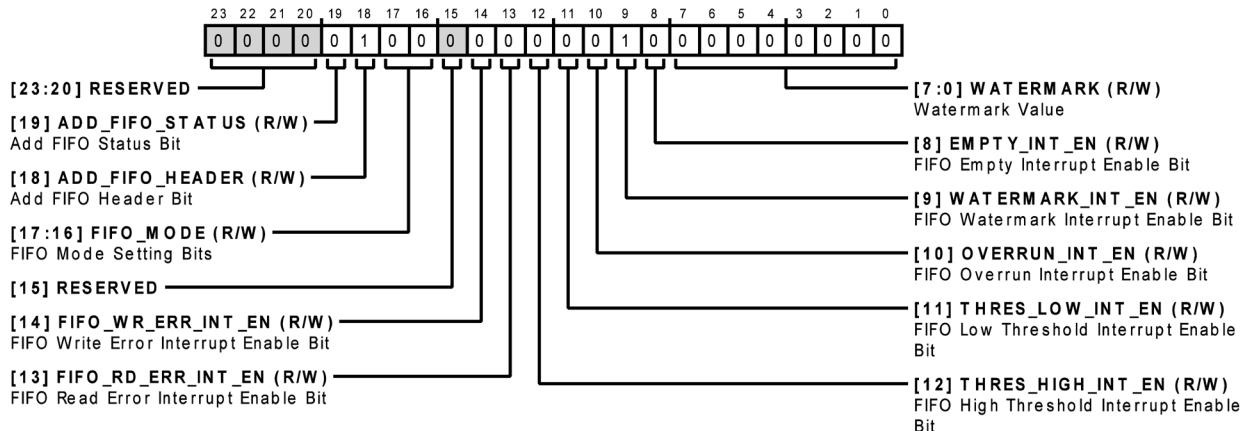

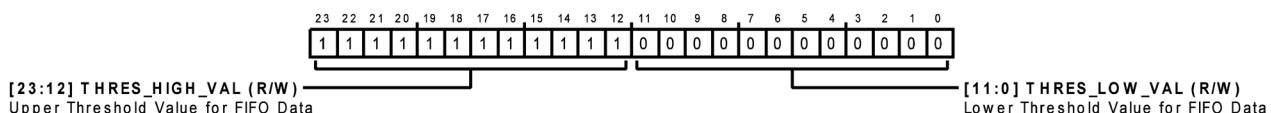

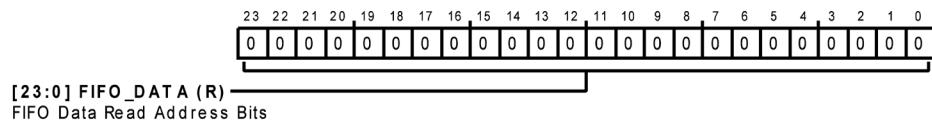

| 分解能               | 32 | FIFO                                             | 70  |

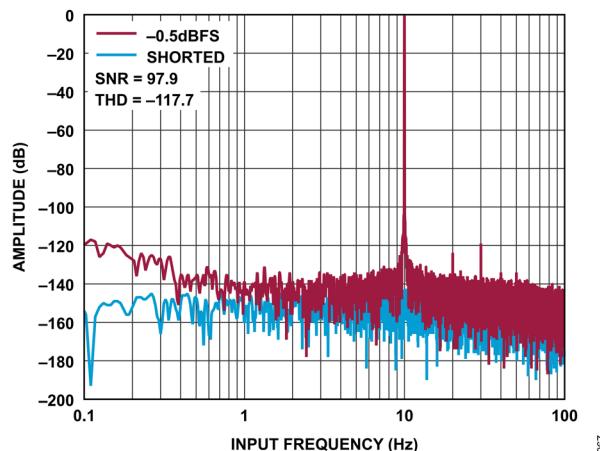

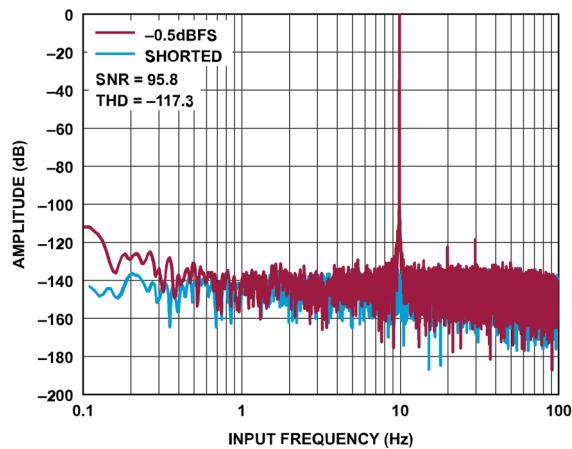

| FFT               | 33 | FIFO モード                                         | 70  |

| 用語の定義             | 34 | FIFO のリードバック                                     | 71  |

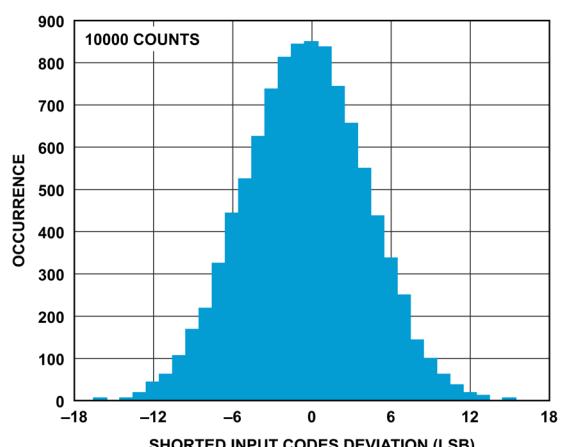

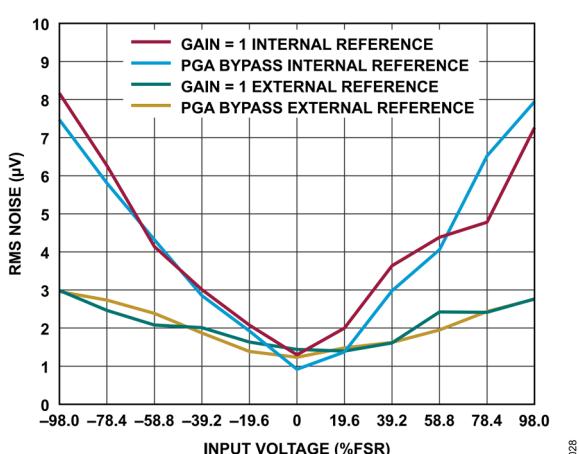

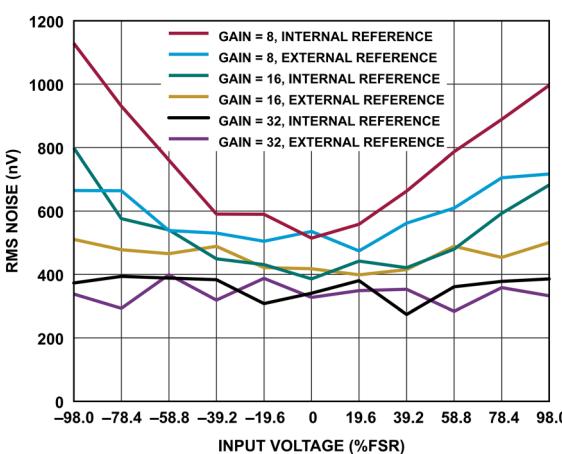

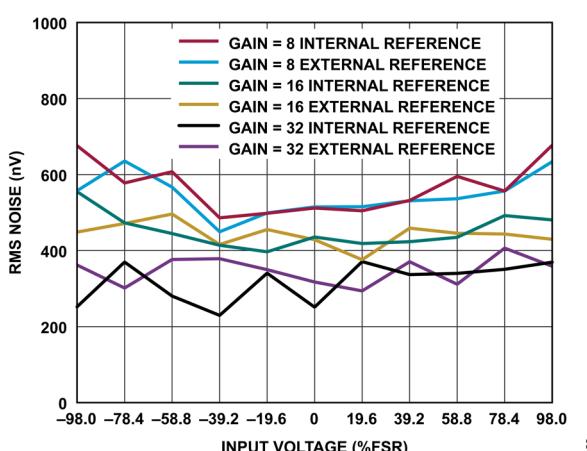

| ノイズおよび分解能         | 36 | FIFO 割込み                                         | 74  |

| 2.5V リファレンス       | 36 | FIFO のクリア                                        | 75  |

| 1.25V リファレンス      | 38 | アプリケーション情報                                       | 76  |

| ノイズのスペクトル密度       | 41 | 電源供給方式                                           | 76  |

| 動作原理              | 42 | 推奨デカップリング方法                                      | 76  |

| 概要                | 42 | 入力フィルタ                                           | 76  |

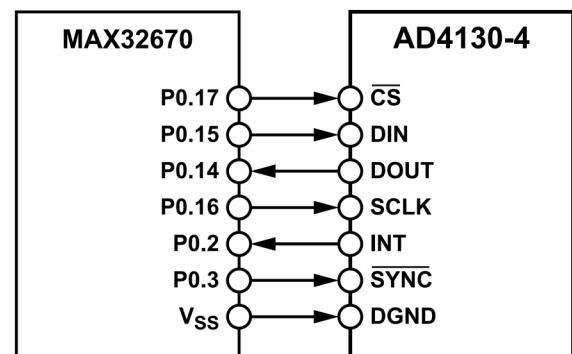

| ADC のコア           | 42 | マイクロプロセッサのインターフェース                               | 76  |

| ADC メイン・クロック      | 43 | 不使用ピン                                            | 76  |

| ADC リファレンス        | 43 | パワーアップと初期化                                       | 77  |

| アナログ・フロント・エンド     | 44 | レイアウトと接地                                         | 77  |

| プログラマブル・ゲイン・アンプ   | 45 | アセンブリのガイドライン                                     | 77  |

| その他の機能            | 46 | AD4130-4 のレジスタ                                   | 78  |

| 電源                | 46 | AD4130-4 のレジスタの概要                                | 78  |

| パワーダウン・モード        | 47 | レジスタの詳細                                          | 80  |

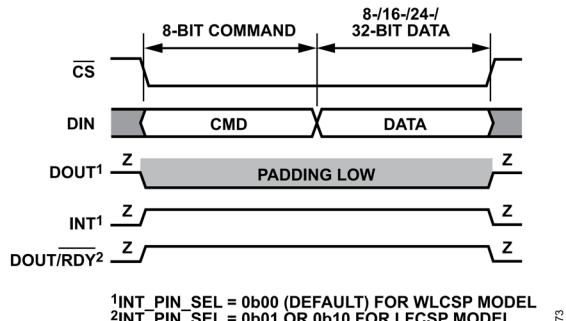

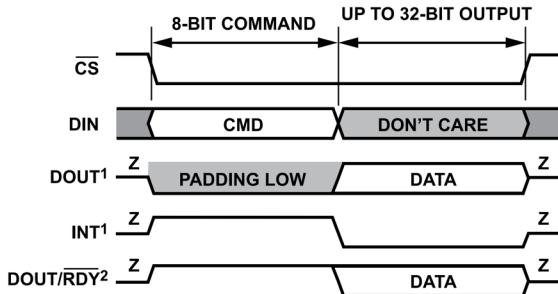

| デジタル・インターフェース     | 48 | 外形寸法                                             | 108 |

| レジスタ・マップへのアクセス    | 48 | オーダー・ガイド                                         | 108 |

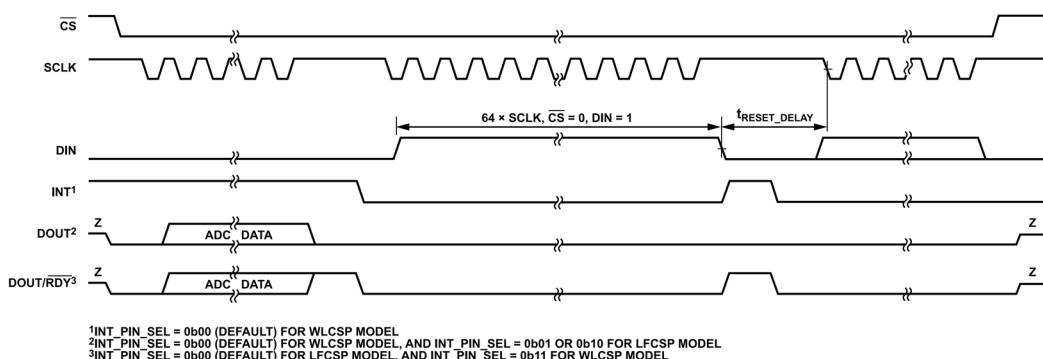

| デバイスのリセット         | 49 | 評価用ボード                                           | 108 |

**改訂履歴****1/2025—Rev. 0 to Rev. A**

|                                                                                                                                                                                                                                                                     |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Changed Master and Controller to Main (Throughout) .....                                                                                                                                                                                                            | 1   |

| Added 35-Ball WLCSP (Universal) .....                                                                                                                                                                                                                               | 1   |

| Changes to Features Section.....                                                                                                                                                                                                                                    | 1   |

| Changes to Functional Block Diagram Section .....                                                                                                                                                                                                                   | 1   |

| Changes to TMAX Parameter, Table 8 .....                                                                                                                                                                                                                            | 10  |

| Changes to Last SCLK Rising for SW Reset Serial Peripheral Interface (SPI) Transaction to First SCLK Falling for Next SPI Transaction Parameter and CS Rising Edge for SW Reset SPI Transaction to CS Falling Edge for Next SPI Transaction Parameter, Table 9..... | 12  |

| Changes to Thermal Characteristics Section and Table 12 .....                                                                                                                                                                                                       | 17  |

| Added Table 13; Renumbered Sequentially .....                                                                                                                                                                                                                       | 17  |

| Added Figure 14 and Table 15; Renumbered Sequentially.....                                                                                                                                                                                                          | 18  |

| Changes to Data Ready Signal Section and Table 55 .....                                                                                                                                                                                                             | 54  |

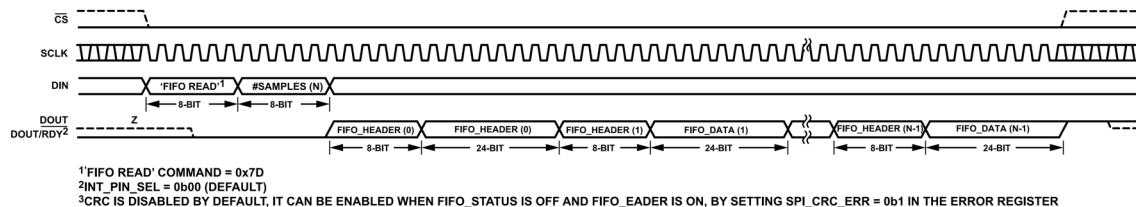

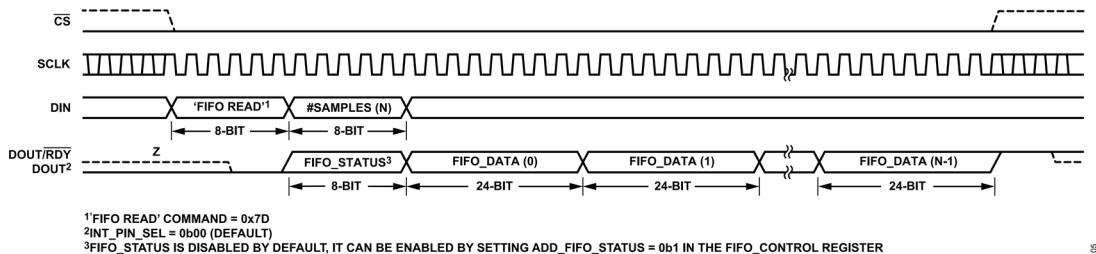

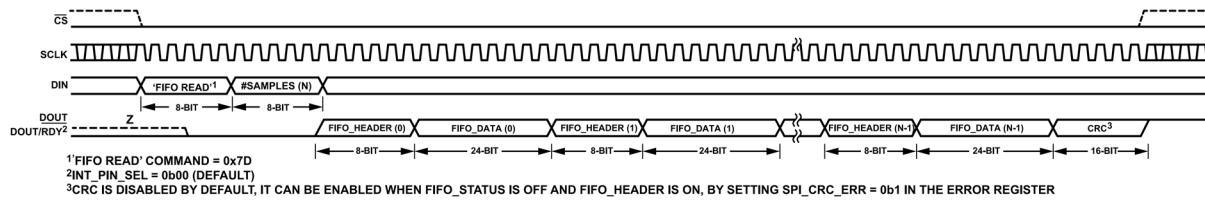

| Changes to FIFO Readback Section .....                                                                                                                                                                                                                              | 71  |

| Changes to FIFO Ready Signal Section.....                                                                                                                                                                                                                           | 71  |

| Changes to Table 72 .....                                                                                                                                                                                                                                           | 74  |

| Changes to Assembly Guidelines Section .....                                                                                                                                                                                                                        | 77  |

| Changes to Table 77 .....                                                                                                                                                                                                                                           | 82  |

| Changes to Table 79 .....                                                                                                                                                                                                                                           | 84  |

| Updated Outline Dimensions.....                                                                                                                                                                                                                                     | 108 |

| Changes to Ordering Guide .....                                                                                                                                                                                                                                     | 108 |

| Changes to Evaluation Boards.....                                                                                                                                                                                                                                   | 108 |

**2/2024—Revision 0: Initial Version**

## 概要

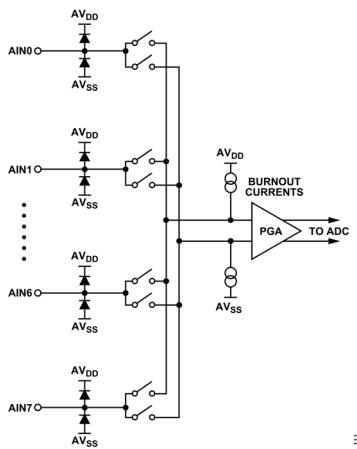

AD4130-4 は、狭帯域幅のバッテリ駆動アプリケーションに適した超低消費電力で高精度の計測ソリューションです。全機能を内蔵したアナログ・フロント・エンド (AFE) には、最大 8 個のシングルエンド入力または最大 4 個の差動入力を扱うマルチプレクサ、プログラマブル・ゲイン・アンプ (PGA)、24 ビットのシグマデルタ ( $\Sigma-\Delta$ ) A/D コンバータ (ADC)、内蔵リファレンスおよび発振器、選択可能なフィルタ・オプション、スマート・シーケンサ、センサーのバイアス設定および励起オプション、診断機能などが備わっている他、バッテリ駆動時の寿命を延ばす（コイン電池で 5 年以上）ために新たな機能、すなわち先入れ先出し (FIFO) バッファおよびデューティ・サイクル機能が追加されています。

AD4130-4 を用いることで、連続変換を行なながら、 $28.5\mu\text{A}$ （ゲイン = 1）や  $32.5\mu\text{A}$ （ゲイン = 128）の消費電流で低周波数信号を測定できます。また、いずれかのデューティ・サイクル・オプションを使用した場合、平均電流を更に下げることができます。AD4130-4 では、4 個の差動入力または 8 個のシングルエンドあるいは疑似差動入力として構成し、これらの入力をクロスポイント・マルチプレクサに接続できます。この場合、任意の入力ペアを PGA および ADC への測定チャンネル入力とすることができます。

AD4130-4 は、1.71V～3.6V のアナログ単電源で動作できるよう設計されています。バッテリ・アプリケーションの場合、1.71V という低電圧での動作により、バッテリ電圧が低下した場合でも AFE は動作を続行できるため、システム寿命を延長できます。デジタル電源を別個に設けることができ、その範囲は 1.65V～3.6V です。

消費電流の低減と相まって、オン・チップ FIFO バッファをスマート・シーケンサと併用することで、AD4130-4 を自律型計測システムとすることができます。これにより、マイクロコントローラをより長時間にわたってスリープ状態にできます。

インテリジェントな割込み機能があるため、エラー検出と安全の両方においてより大きな信頼を置くことができます。ユーザは、FIFO のサンプルが事前に設定した値に達した場合、または、ユーザ設定可能な閾値を超えた場合に、割込み信号をトリガできます。

AD4130-4 は、以下に示す主要なアナログ機能を備えているため、温度、負荷、圧力を計測するのに用いるトランジシューサに簡単かつ効果的に接続できます。

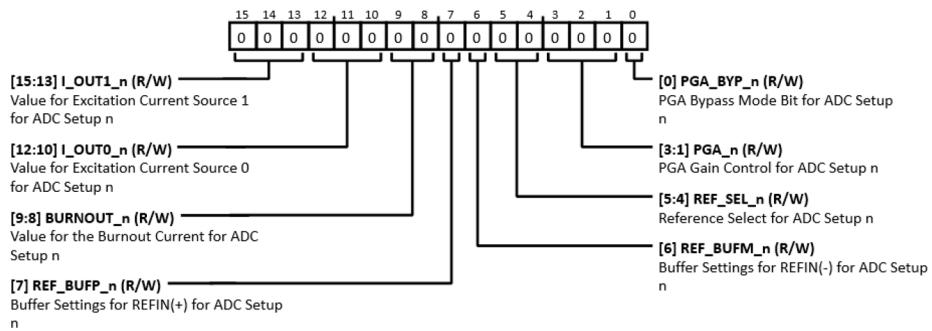

- ▶ PGA : PGA は、プログラマブルなゲイン（1～128）と高入力インピーダンス低入力電流により、抵抗ブリッジ、熱電対、測温抵抗体 (RTD) など低出力振幅のトランジシューサに直接インターフェース接続できます。

- ▶ 容量性 PGA は全コモンモード入力範囲に対応可能であり、大きく変化する入力コモンモードに対して設計マージンを広げることができます。コモンモード入力範囲が広いため、全体的な分解能が向上し、レシオメトリック計測に非常に効果的です。

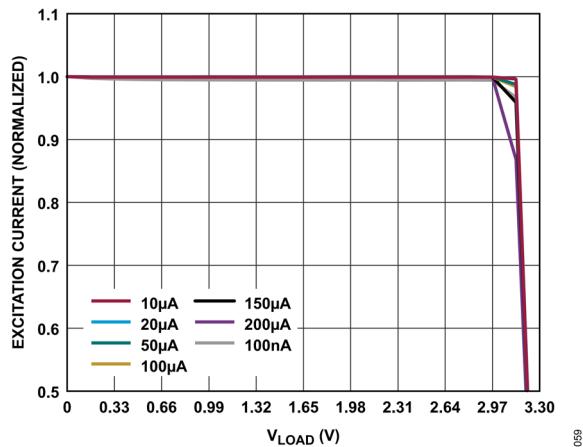

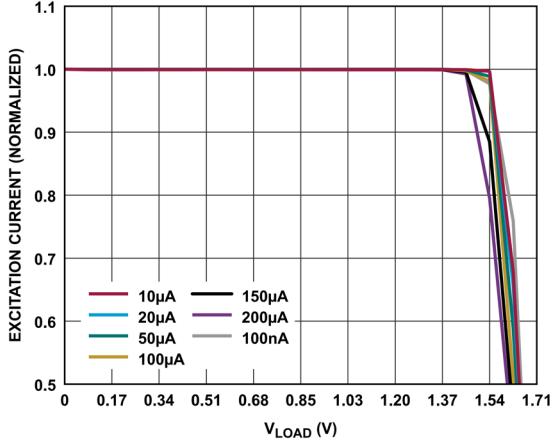

- ▶ 低ドリフトの高精度電流源。IEXC0 および IEXC1 の電流源は、2 線式、3 線式、4 線式の RTD を励起するのに使用できます。励起電流出力オプションには、100nA、10μA、20μA、50μA、100μA、150μA、200μA があります。

- ▶ ローサイド・パワー・スイッチ (PDSW) を使用して、変換と変換の間にブリッジ・センサーをパワーダウンできます。この PDSW は、シーケンサ内ではチャンネル単位で制御できるため、システム全体での最適なタイミングとエネルギー節約が可能です。PDSW を使用することで、消費電力が高いアナログ・センサーを低消費電力システムで用いることも可能となります。

- ▶ 热電対用の電圧バイアス (VBIAS ソースがチャンネルのコモンモード電圧を  $\text{AV}_{\text{DD}}/2$  に設定)。

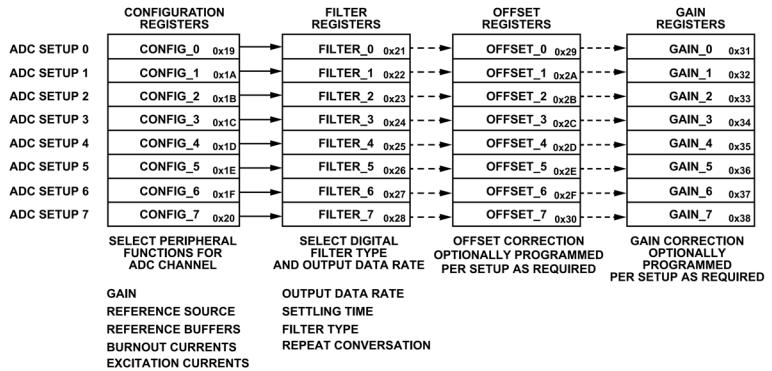

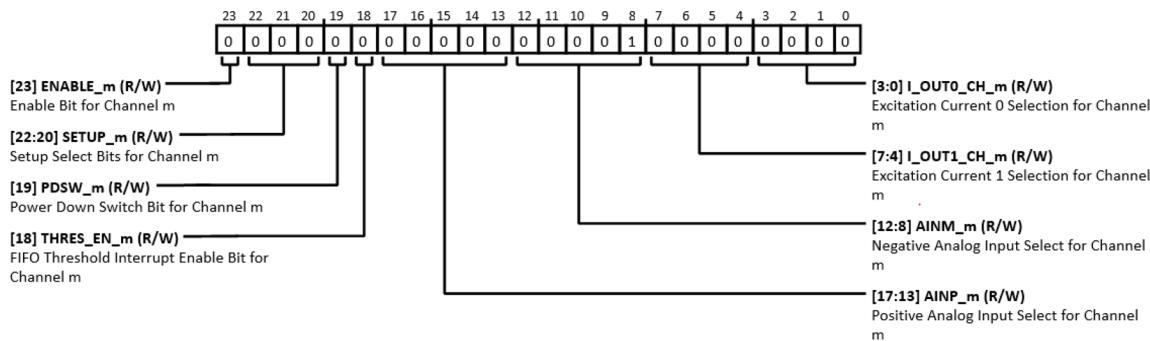

- ▶ スマート・シーケンサにより、イネーブル済みの事前に設定されたチャンネルのそれぞれを予め定められた順序で変換できるため、トランジシューサ、システム・チェック、診断測定を混在させて順に実施できます。このシーケンサにより、デバイスとのシリアル・インターフェース通信を繰り返す必要がなくなります。シーケンスには 16 個のチャンネルを構成でき、各チャンネルは、事前に定められた 8 個の ADC セットアップから選択できます。この設定により、ゲイン、フィルタ・タイプ、出力データレート、バッファリング、タイミング、リファレンス・ソースの選択が可能となります。

高度に集積されたフロント・エンド機能が小型のパッケージ・オプションと組み合わざり、エンド・ソリューションの小型化を可能にします。例えば、AD4130-4 は、低温度ドリフトのバンド・ギャップ・リファレンスを内蔵している他に、外部の差動リファレンスを受け付けることができ、これは内部でバッファリング可能です。

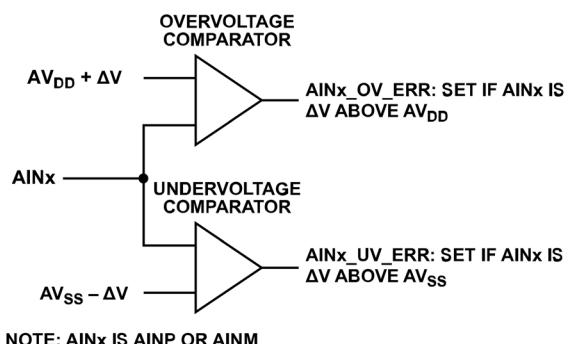

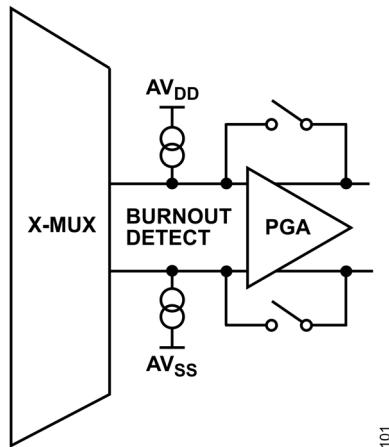

安全性が重視されるアプリケーションに対して、AD4130-4 は診断機能を備えています。例えば、バーンアウト電流による断線検出、内部温度センサー、リファレンス電圧の検出、アナログ入力の過電圧／低電圧検出などがかかるうです。デジタル・インターフェースには、巡回冗長検査 (CRC) およびシリアル・インターフェース・チェックなどの診断機能が追加されているため、堅牢な通信リンクを実現できます。

## 関連製品

- ▶ 低ノイズ、低ドロップアウトのレギュレータ : [ADP150ACBZ-3.3](#) および [ADP150ACBZ-1.8](#)

- ▶ 安定化チャージポンプ・インバータ : [LTC1983ES6-3](#) および [ADP7182AUJZ-1.8](#)

- ▶ 電圧リファレンス : [ADR391](#) または [ADR3625](#)

- ▶ 低消費電力マイクロコントローラ : [MAX32670](#) (高精度) 、[MAX32655](#) (BLE) 、[MAX32663A](#) (ECG)

## 仕様

特に指定のない限り、AV<sub>DD</sub> = 1.71V～3.6V、IOV<sub>DD</sub> = 1.65V～3.6V、AV<sub>SS</sub> = DGND = 0V、REFIN1(+) = 2.5V (AV<sub>DD</sub> - AV<sub>SS</sub> ≥ 2.7V の場合)、REFIN1(+) = 1.25V (AV<sub>DD</sub> - AV<sub>SS</sub> < 2.7V の場合)、REFIN1(-) = AV<sub>SS</sub>、内部メイン・クロック (MCLK) (MCLK 周波数 (f<sub>MCLK</sub>) = 76.8kHz)、PGA イネーブル (デフォルト)、リファレンス・バッファ・バイパス (デフォルト)、温度範囲 = T<sub>MIN</sub>～T<sub>MAX</sub>、[推奨デカッピング方法](#)のセクションに従いデカッピング。

## ADC 仕様およびAFE 仕様

表 1. ADC 仕様およびAFE 仕様

| Parameter <sup>1</sup>                          | Min      | Typ               | Max    | Unit                    | Test Conditions/Comments                             |

|-------------------------------------------------|----------|-------------------|--------|-------------------------|------------------------------------------------------|

| <b>SAMPLING DYNAMICS</b>                        |          |                   |        |                         |                                                      |

| Output Data Rate (ODR)                          | 1.17     |                   | 2400   | SPS                     | See the <a href="#">Output Data Rate</a> section     |

| Active Time <sup>2</sup>                        |          | 100%              |        |                         | Continuous conversion mode                           |

|                                                 |          | 25%               |        |                         | DUTY_CYC_RATIO = 1/4 <sup>3</sup>                    |

|                                                 |          | 6.25%             |        |                         | DUTY_CYC_RATIO = 1/16 <sup>3</sup>                   |

| <b>STATIC PERFORMANCE</b>                       |          |                   |        |                         |                                                      |

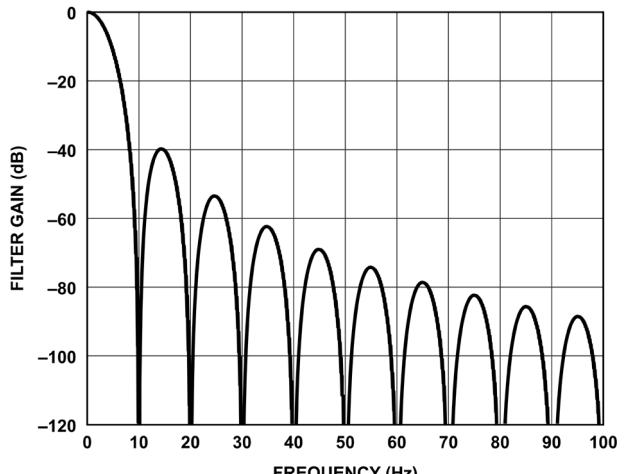

| No Missing Codes <sup>2</sup>                   | 24       |                   |        | Bits                    | FS <sup>4</sup> > 2, sinc <sup>4</sup> filter        |

|                                                 | 24       |                   |        | Bits                    | FS <sup>4</sup> > 8, sinc <sup>3</sup> filter        |

| Resolution and Update Rate <sup>2</sup>         |          |                   |        |                         | See the <a href="#">Noise and Resolution</a> section |

| RMS Noise and Update Rate <sup>2</sup>          |          |                   |        |                         | See the <a href="#">Noise and Resolution</a> section |

| Noise Spectral Density <sup>2</sup>             |          |                   |        |                         | See the <a href="#">Noise and Resolution</a> section |

| Integral Nonlinearity (INL) <sup>2</sup>        | -5       | ±2                | +5     | ppm of FSR <sup>1</sup> | Gain = 1                                             |

|                                                 | -15      | ±4                | +15    | ppm of FSR <sup>1</sup> | Gain > 1 <sup>5</sup>                                |

| Offset Error <sup>6</sup>                       |          |                   |        |                         |                                                      |

| Before Calibration                              |          | ±2                |        | µV                      | Gain = 1, PGA bypass <sup>7</sup>                    |

|                                                 |          | ±10               |        | µV                      | Gain = 1 to 16                                       |

|                                                 |          | ±2                |        | µV                      | Gain = 32 to 128                                     |

| After Internal and System Calibration           |          | In order of noise |        |                         |                                                      |

| Offset Error Drift vs. Temperature <sup>8</sup> | 3        | 30                |        | nV/°C                   | Gain = 1, PGA bypass <sup>7</sup>                    |

|                                                 | 120/gain | (140/gain) + 90   |        | nV/°C                   | Gain = 1 to 128                                      |

| Gain Error <sup>6,9</sup>                       |          |                   |        |                         |                                                      |

| Before Calibration                              | -0.015   |                   | +0.015 | %                       | Gain = 1 <sup>10</sup> , T <sub>A</sub> = 25°C       |

|                                                 | 0.5      |                   |        | %                       | Gain = 1, PGA bypass <sup>7</sup>                    |

|                                                 | 0.5      |                   |        | %                       | Gain > 1                                             |

| After Internal Calibration <sup>11</sup>        | -0.12    | +0.01             | +0.12  | %                       |                                                      |

| After System Calibration <sup>11</sup>          |          | In order of noise |        |                         |                                                      |

| Gain Error Drift vs. Temperature                | 0.1      | 1                 |        | ppm/°C                  | Gain = 1, PGA bypass <sup>7</sup>                    |

|                                                 | 0.1      | 2                 |        | ppm/°C                  | Gain = 1 to 16, T <sub>A</sub> = -40°C to +105°C     |

|                                                 | 0.1      | 3                 |        | ppm/°C                  | T <sub>A</sub> = -40°C to +125°C (LFCSP only)        |

|                                                 | 0.1      | 3                 |        | ppm/°C                  | Gain = 32 to 128, T <sub>A</sub> = -40°C to +105°C   |

|                                                 | 0.1      | 4                 |        | ppm/°C                  | T <sub>A</sub> = -40°C to +125°C (LFCSP only)        |

<sup>1</sup> 用語の定義のセクションを参照してください。<sup>2</sup> これらの仕様については出荷テストを行っていませんが量産開始時の特性評価データで確認されています。<sup>3</sup> デューティ・サイクル・モードを有効にするには、ADC\_CONTROL レジスタにおいて MODE = 0b1001 に設定します。DUTY\_CYC\_RATIO ビットは同じレジスタ内にあります。[デューティ・サイクル・モードとデューティ・サイクル・モードのタイミング](#)の各セクションを参照してください。<sup>4</sup> FS は、フィルタ・レジスタの FS ビット[10:0]を10進数に変換した値です。<sup>5</sup> ゲインが 1 より大きい場合の非直線性は、ゲイン = 32 および電圧リファレンス (V<sub>REF</sub>) = 2.5V の条件で製品テストを行っています。その他の条件については、この仕様は製品の初期リリース時に特性評価データで裏付けられています。<sup>6</sup> システム校正または内部のゼロ・スケール校正を行った後、オフセット誤差は、選択されたプログラム済みのゲインおよび出力データレートにおけるノイズの範囲内に収まります。システムのフルスケール校正を行うと、ゲイン誤差は、プログラム済みのゲインおよび出力データレートにおけるノイズの範囲内まで低下します。<sup>7</sup> PGA\_BYP\_n = 1。PGA\_BYP\_n ビットは、対応する CONFIG\_n レジスタ内にあります。詳細については[プログラマブル・ゲイン・アンプ](#)のセクションを参照してください。

## 仕様

<sup>8</sup> これらの誤差は、どの温度でも再校正を行えば除去されます。

<sup>9</sup> ゲイン誤差は、正および負のフルスケールに適用されます。工場校正は、ゲイン=1 および  $T_A = 25^\circ\text{C}$  ( $\text{PGA\_BYP\_n} = 0$ ) で実施されています。

<sup>10</sup> このゲイン誤差は、ゲインが 1 ( $\text{PGA\_BYP\_n} = 0$ ) で周囲温度において工場校正されています。

<sup>11</sup>  $\text{CAL\_RANGE\_X2} = 1$  ( $V_{\text{REF}} > 2\text{V}$ )。 $\text{CAL\_RANGE\_X2}$  ビットは MISC レジスタ内にあります。詳細については[内部ゲイン校正](#)のセクションを参照してください。

## アナログ入力仕様

表 2. アナログ入力仕様

| Parameter <sup>1</sup>                                                                        | Min                                       | Typ       | Max                                                         | Unit                 | Test Conditions/Comments <sup>2</sup>                                                                 |

|-----------------------------------------------------------------------------------------------|-------------------------------------------|-----------|-------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------|

| ANALOG INPUT VOLTAGE <sup>3</sup>                                                             |                                           |           |                                                             |                      | $V_{\text{REF}} = \text{REFIN1}(+) - \text{REFIN1}(-)$ , or internal reference<br>PGA on <sup>4</sup> |

| Differential Input Voltage Ranges<br>Absolute Analog Input ( $A_{\text{IN}}$ ) Voltage Limits | $AV_{\text{SS}} - 0.05$                   |           | $\pm V_{\text{REF}}/\text{gain}$<br>$AV_{\text{DD}} + 0.05$ | V<br>V               |                                                                                                       |

| ANALOG INPUT CURRENT <sup>3</sup>                                                             |                                           |           |                                                             |                      |                                                                                                       |

| Absolute Input Current                                                                        |                                           |           |                                                             |                      |                                                                                                       |

| Gain = 1                                                                                      | -3                                        | $\pm 0.5$ | +3                                                          | nA                   |                                                                                                       |

| Gain = 1                                                                                      |                                           | $\pm 2.5$ |                                                             | nA                   | PGA bypass <sup>5</sup>                                                                               |

| Gain > 1                                                                                      | -1                                        | $\pm 0.5$ | +1                                                          | nA                   |                                                                                                       |

| Differential Input Current                                                                    |                                           |           |                                                             |                      |                                                                                                       |

| Gain = 1                                                                                      | -3                                        | $\pm 0.5$ | +3                                                          | nA                   |                                                                                                       |

| Gain = 1                                                                                      |                                           | $\pm 1.5$ |                                                             | nA                   | PGA bypass <sup>5</sup>                                                                               |

| Gain > 1                                                                                      | -1                                        | $\pm 0.5$ | +1                                                          | nA                   |                                                                                                       |

| Analog Input Current Drift                                                                    |                                           |           |                                                             |                      |                                                                                                       |

| Gain = 1, Gain > 1                                                                            |                                           | 2         | 15                                                          | pA/ $^\circ\text{C}$ |                                                                                                       |

| Gain = 1                                                                                      |                                           | 2         |                                                             | pA/ $^\circ\text{C}$ | PGA bypass <sup>5</sup>                                                                               |

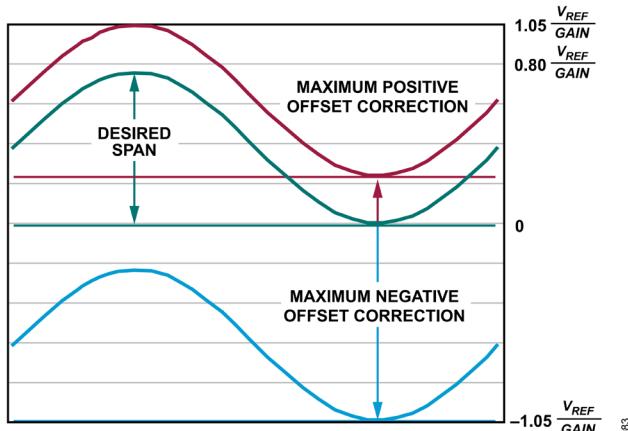

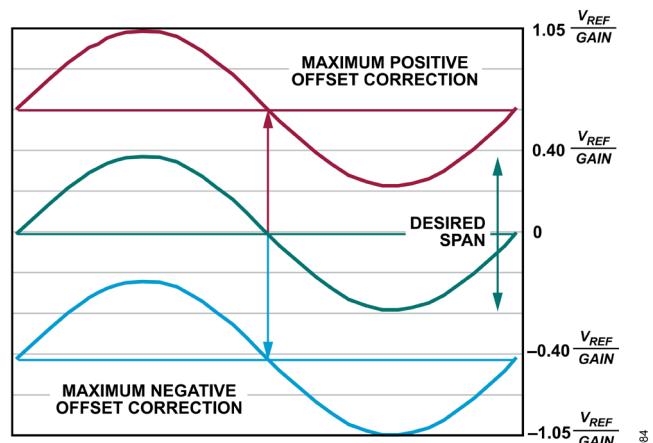

| SYSTEM CALIBRATION <sup>3</sup>                                                               |                                           |           |                                                             |                      |                                                                                                       |

| Calibration Limits                                                                            |                                           |           |                                                             |                      |                                                                                                       |

| Full Code                                                                                     |                                           |           | $1.05 \times V_{\text{REF}}/\text{gain}$                    | V                    | DATA = 0xFFFFFFF                                                                                      |

| Zero Code                                                                                     | $-1.05 \times V_{\text{REF}}/\text{gain}$ |           |                                                             | V                    | DATA = 0x000000                                                                                       |

| Input Span                                                                                    | $0.8 \times V_{\text{REF}}/\text{gain}$   |           | $2.1 \times V_{\text{REF}}/\text{gain}$                     | V                    |                                                                                                       |

<sup>1</sup> 用語の定義のセクションを参照してください。

<sup>2</sup>  $T_A = -40^\circ\text{C} \sim +105^\circ\text{C}$ 。

<sup>3</sup> これらの仕様は、製品テストを受けたものではありませんが、製品の初期リリース時に特性評価データで裏付けられています。

<sup>4</sup>  $\text{PGA\_BYP\_n} = 0$ 。 $V_{\text{REF}} > (AV_{\text{DD}} - AV_{\text{SS}} - 200\text{mV})$  の場合、入力差動範囲は  $(AV_{\text{DD}} - AV_{\text{SS}} - 200\text{mV})/\text{ゲイン}$  を超えることはできません。

<sup>5</sup>  $\text{PGA\_BYP\_n} = 1$ 。 $\text{PGA\_BYP\_n}$  ビットは、対応する CONFIG\_n レジスタ内にあります。詳細については[プログラマブル・ゲイン・アンプ](#)のセクションを参照してください。

## リファレンス仕様

表 3. リファレンス仕様

| Parameter <sup>1</sup>                            | Min          | Typ     | Max          | Unit                    | Test Conditions/Comments <sup>2</sup>                                                                      |

|---------------------------------------------------|--------------|---------|--------------|-------------------------|------------------------------------------------------------------------------------------------------------|

| REFERENCE OUTPUT                                  |              |         |              |                         | Internal reference enabled, load capacitance ( $C_L$ ) = 1 nF                                              |

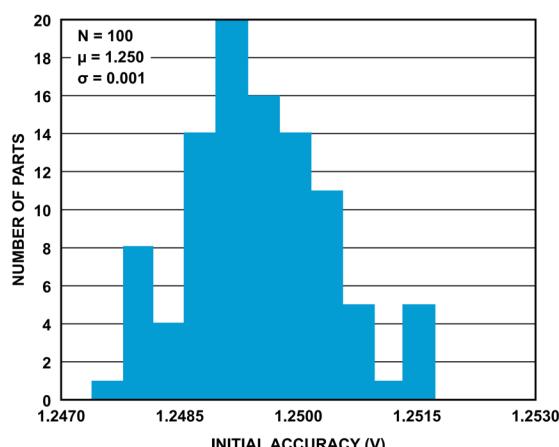

| Initial Accuracy                                  | 2.5 – 0.2%   | 2.5     | 2.5 + 0.2%   | V                       | $T_A = 25^\circ\text{C}$                                                                                   |

|                                                   | 1.25 – 0.45% | 1.25    | 1.25 + 0.45% | V                       | $T_A = 25^\circ\text{C}$                                                                                   |

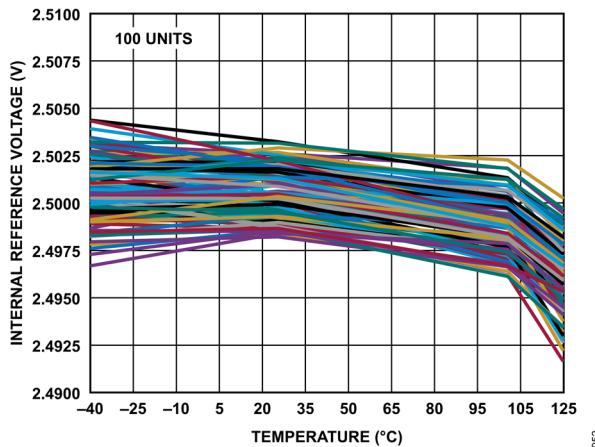

| Temperature Coefficient (TC) (Drift) <sup>3</sup> |              | 2       | 15           | ppm/ $^\circ\text{C}$   | $T_A = -40^\circ\text{C} \text{ to } +105^\circ\text{C}$ , $V_{\text{REF}} = 2.5\text{ V}$                 |

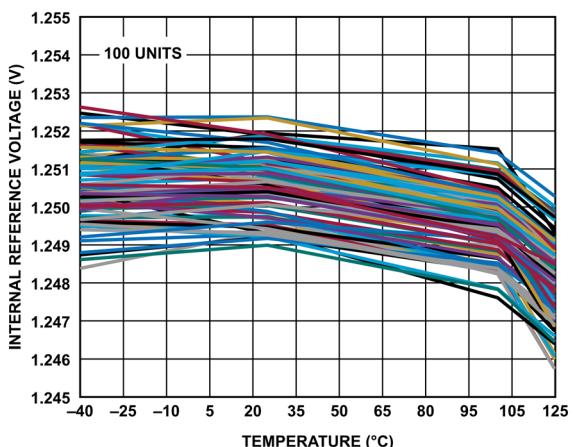

|                                                   |              | 2       | 15           | ppm/ $^\circ\text{C}$   | $T_A = -40^\circ\text{C} \text{ to } +105^\circ\text{C}$ , $V_{\text{REF}} = 1.25\text{ V}$                |

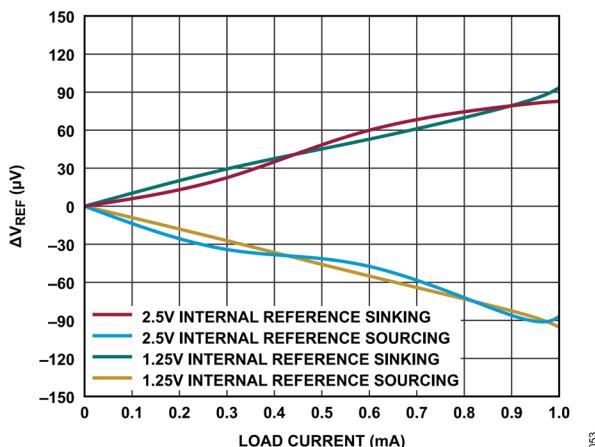

| Output Current Load Capability                    |              | $\pm 1$ |              | mA                      |                                                                                                            |

| Load Regulation Sourcing and Sinking              |              | 90      |              | $\mu\text{V}/\text{mA}$ | Change in output voltage ( $\Delta V_{\text{OUT}}$ )/change in output current ( $\Delta I_{\text{LOAD}}$ ) |

| Power Supply Rejection                            |              | 95      |              | dB                      |                                                                                                            |

## 仕様

表3. リファレンス仕様（続き）

| Parameter <sup>1</sup>                           | Min                     | Typ  | Max                                 | Unit   | Test Conditions/Comments <sup>2</sup>           |

|--------------------------------------------------|-------------------------|------|-------------------------------------|--------|-------------------------------------------------|

| Output Voltage Noise (0.1 Hz to 10 Hz)           |                         | 40   |                                     | μV p-p | T <sub>A</sub> = 25°C                           |

| Output Voltage Noise Density                     |                         | 800  |                                     | nV/√Hz | T <sub>A</sub> = 25°C                           |

| Turn On Settling Time                            |                         | 280  |                                     | μs     | T <sub>A</sub> = 25°C                           |

| REFERENCE INPUTS                                 |                         |      |                                     |        |                                                 |

| External REFIN Voltage <sup>3</sup>              | 0.5                     |      | AV <sub>DD</sub> - AV <sub>SS</sub> | V      | Reference input (REFIN) = REFIN1(+) - REFIN1(-) |

| Absolute REFINx pins Voltage Limits <sup>3</sup> | AV <sub>SS</sub> - 0.05 |      | AV <sub>DD</sub> + 0.05             | V      | Reference buffers disabled <sup>4</sup>         |

|                                                  | AV <sub>SS</sub> + 0.1  |      | AV <sub>DD</sub> - 0.1              | V      | Reference buffers enabled <sup>4</sup>          |

| Reference Input Current                          |                         |      |                                     |        |                                                 |

| Absolute Input Current                           | -11                     | ±7   | +11                                 | nA     | Reference buffers disabled <sup>4</sup>         |

|                                                  | -4                      | ±0.2 | +4                                  | nA     | Reference buffers enabled <sup>4</sup>          |

| Reference Input Current Drift <sup>3</sup>       |                         | 10   | 21                                  | pA/°C  | Reference buffers disabled <sup>4</sup>         |

|                                                  |                         | 1.6  | 20                                  | pA/°C  | Reference buffers enabled <sup>4</sup>          |

| Normal Mode Rejection                            |                         |      |                                     |        | Same as for analog inputs                       |

| Common-Mode Rejection                            |                         | 90   |                                     | dB     |                                                 |

<sup>1</sup>用語の定義のセクションを参照してください。<sup>2</sup>T<sub>A</sub> = -40°C～+105°C。<sup>3</sup>これらの仕様は、製品テストを受けたものではありませんが、製品の初期リリース時に特性評価データで裏付けられています。<sup>4</sup>REF\_BUFP\_n ビットおよびREF\_BUFM\_n ビットは対応する CONFIG\_n レジスタ内にあります。詳細については、リファレンス・バッファのセクションを参照してください。

## センサーのバイアス設定仕様

表4. センサーのバイアス設定仕様

| Parameter <sup>1</sup>                       | Min                     | Typ                                      | Max                     | Unit   | Test Conditions/Comments                                                                               |

|----------------------------------------------|-------------------------|------------------------------------------|-------------------------|--------|--------------------------------------------------------------------------------------------------------|

| EXCITATION CURRENT SOURCES (IEXC0 and IEXC1) |                         |                                          |                         |        |                                                                                                        |

| Output Current                               |                         | 10/20/50/100/<br>150/200/0.1             |                         | μA     | Selectable on a per channel basis                                                                      |

| Initial Tolerance                            |                         | ±1                                       |                         | %      | T <sub>A</sub> = 25°C                                                                                  |

| Current Drift <sup>2</sup>                   |                         | 50                                       |                         | ppm/°C |                                                                                                        |

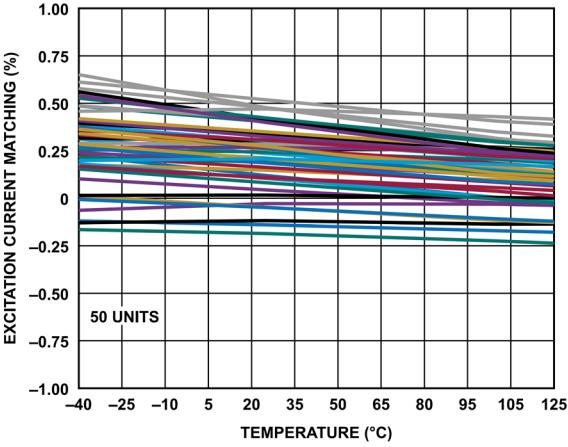

| Current Matching <sup>2,3</sup>              | -1.6                    | ±0.5                                     | +1.6                    | %      | 10 μA/20 μA/50 μA/100 μA/150 μA/200 μA                                                                 |

|                                              | -3.2                    | ±1                                       | +3.2                    | %      | 100 nA                                                                                                 |

| Current Drift Matching <sup>2</sup>          |                         | 3                                        | 25                      | ppm/°C | 10 μA/20 μA/50 μA/100 μA/150 μA/200 μA,<br>T <sub>A</sub> = -40°C to +105°C                            |

|                                              |                         | 32                                       |                         |        | T <sub>A</sub> = -40°C to +125°C (LFCSP only)                                                          |

|                                              |                         | 5                                        | 60                      | ppm/°C | 100 nA, T <sub>A</sub> = -40°C to +105°C                                                               |

|                                              |                         |                                          | 78                      |        | T <sub>A</sub> = -40°C to +125°C (LFCSP only)                                                          |

| Line Regulation                              |                         | 0.1                                      |                         | %/V    | 10 μA/20 μA/50 μA/100 μA/150 μA/200 μA                                                                 |

|                                              |                         | 0.3                                      |                         | %/V    | 100 nA                                                                                                 |

| Load Regulation                              |                         | 0.1                                      |                         | %/V    | 10 μA/20 μA/50 μA/100 μA/150 μA/200 μA                                                                 |

|                                              |                         | 2.5                                      |                         | %/V    | 100 nA                                                                                                 |

| Output Compliance                            | AV <sub>SS</sub> + 0.05 |                                          | AV <sub>DD</sub> - 0.27 | V      | 2% accuracy                                                                                            |

| BIAS VOLTAGE (V <sub>BIAS</sub> ) GENERATOR  |                         |                                          |                         |        |                                                                                                        |

| V <sub>BIAS</sub>                            |                         | (AV <sub>DD</sub> + AV <sub>SS</sub> )/2 |                         | V      | Available on any analog input pin                                                                      |

| Start-Up Time                                |                         | 3.7                                      |                         | μs/nF  | Dependent on the capacitance connected to AI <sub>Nx</sub>                                             |

|                                              |                         | 6.7                                      |                         | μs/nF  | AV <sub>DD</sub> = 3.3 V, AV <sub>SS</sub> = DGND<br>AV <sub>DD</sub> = 1.8 V, AV <sub>SS</sub> = DGND |

| LOW-SIDE POWER SWITCH <sup>2</sup>           |                         |                                          |                         |        |                                                                                                        |

| On Resistance (R <sub>ON</sub> )             | 10                      | 15                                       |                         | Ω      |                                                                                                        |

## 仕様

表 4. センサーのバイアス設定仕様（続き）

| Parameter <sup>1</sup> | Min | Typ | Max | Unit | Test Conditions/Comments |

|------------------------|-----|-----|-----|------|--------------------------|

| Allowable Current      |     |     | 30  | mA   | Continuous current       |

<sup>1</sup> 用語の定義のセクションを参照してください。<sup>2</sup> これらの仕様については出荷テストを行っていませんが量産開始時の特性評価データで確認されています。<sup>3</sup> IOUT0 と IOUT1 の間のマッチング、V<sub>OUT</sub> = 0V。

## 診断仕様

表 5. 診断仕様

| Parameter <sup>1, 2</sup>                              | Min                     | Typ                     | Max | Unit | Test Conditions/Comments                                        |

|--------------------------------------------------------|-------------------------|-------------------------|-----|------|-----------------------------------------------------------------|

| TEMPERATURE SENSOR                                     |                         |                         |     |      | 2.5 V external reference, gain = 1<br>After calibration at 25°C |

| Accuracy                                               |                         | ±1                      |     | °C   |                                                                 |

| Nominal Sensitivity <sup>3</sup>                       |                         | 860.66                  |     | µV/K |                                                                 |

| Reading at 25°C                                        |                         | 258                     |     | mV   |                                                                 |

| REFERENCE                                              |                         |                         |     |      | REFIN = REFIN1(+) – REFIN1(-)                                   |

| Reference Detect Threshold                             | 0.7                     | 1                       |     | V    |                                                                 |

| REFIN1(+) Overvoltage Detect Level                     | AV <sub>DD</sub> + 0.13 | AV <sub>DD</sub> + 0.03 |     | V    |                                                                 |

| REFIN1(–) Undervoltage Detect Level                    | AV <sub>SS</sub> – 0.03 | AV <sub>SS</sub> – 0.13 |     | V    |                                                                 |

| A <sub>IN</sub> OVERVOLTAGE (OV) AND UNDERVOLTAGE (UV) |                         |                         |     |      |                                                                 |

| A <sub>IN</sub> OV Detect Level                        | AV <sub>DD</sub> + 0.13 | AV <sub>DD</sub> + 0.03 |     | V    |                                                                 |

| A <sub>IN</sub> UV Detect Level                        | AV <sub>SS</sub> – 0.03 | AV <sub>SS</sub> – 0.13 |     | V    |                                                                 |

| BURNOUT CURRENTS                                       |                         |                         |     |      |                                                                 |

| A <sub>IN</sub> Current                                |                         | 0.5, 2, 4               |     | µA   |                                                                 |

<sup>1</sup> 用語の定義のセクションを参照してください。<sup>2</sup> これらの仕様については出荷テストを行っていませんが量産開始時の特性評価データで確認されています。<sup>3</sup> 設計により裏付けられています。

## 除去仕様

表 6. 除去仕様

| Parameter <sup>1</sup>                     | Min                               | Typ              | Max | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------|-----------------------------------|------------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY REJECTION (AV <sub>DD</sub> ) | 96<br>79<br>94<br>90<br>102<br>96 |                  |     | dB   | External MCLK, f <sub>MCLK</sub> = 76.8 kHz, A <sub>IN</sub> = 1 V/gain<br>Gain = 1, gain = 1 and PGA bypass <sup>2</sup> , T <sub>A</sub> = -40°C to +105°C<br>T <sub>A</sub> = -40°C to +125°C (LFCSP only)<br>Gain = 2 to 16, T <sub>A</sub> = -40°C to +105°C<br>T <sub>A</sub> = -40°C to +125°C (LFCSP only)<br>Gain = 32 to 128, T <sub>A</sub> = -40°C to +105°C<br>T <sub>A</sub> = -40°C to +125°C (LFCSP only) |

| COMMON-MODE REJECTION <sup>3, 4, 5</sup>   |                                   |                  |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                           |

| At DC                                      | 86<br>85<br>112<br>108            | 90<br>135<br>122 |     | dB   | A <sub>IN</sub> = 1 V, gain = 1, T <sub>A</sub> = -40°C to +105°C<br>T <sub>A</sub> = -40°C to +125°C (LFCSP only)<br>A <sub>IN</sub> = 1 V/gain, gain = 2 to 16<br>A <sub>IN</sub> = 1 V/gain, gain = 32 to 128                                                                                                                                                                                                          |

| Sinc <sup>3</sup> Filter                   |                                   |                  |     |      | Input frequency (f <sub>IN</sub> ) = notch frequency (f <sub>NOTCH</sub> ) ± 1 Hz                                                                                                                                                                                                                                                                                                                                         |

| At 50 Hz and 60 Hz                         | 115                               |                  |     | dB   | 10 SPS (FS = 240)                                                                                                                                                                                                                                                                                                                                                                                                         |

| At 50 Hz                                   | 115                               |                  |     | dB   | 50 SPS (FS = 48)                                                                                                                                                                                                                                                                                                                                                                                                          |

| At 60 Hz                                   | 115                               |                  |     | dB   | 60 SPS (FS = 40)                                                                                                                                                                                                                                                                                                                                                                                                          |

| Sinc <sup>3</sup> + REJ60 Filter           |                                   |                  |     |      | f <sub>IN</sub> = f <sub>NOTCH</sub> ± 1 Hz                                                                                                                                                                                                                                                                                                                                                                               |

## 仕様

表 6. 除去仕様（続き）

| Parameter <sup>1</sup>                                                       | Min | Typ | Max | Unit | Test Conditions/Comments                                  |

|------------------------------------------------------------------------------|-----|-----|-----|------|-----------------------------------------------------------|

| At 50 Hz and 60 Hz<br>Sinc <sup>3</sup> + Sinc <sup>1</sup> Averaging Filter | 115 |     |     | dB   | 50 SPS (FS = 48)<br>$f_{IN} = f_{NOTCH} \pm 1 \text{ Hz}$ |

| At 50 Hz                                                                     | 120 |     |     | dB   | 40 SPS (FS = 6, first notch at 50 Hz)                     |

| At 60 Hz                                                                     | 120 |     |     | dB   | 48 SPS (FS = 5, first notch at 60 Hz)                     |

| Sinc <sup>4</sup> + Sinc <sup>1</sup> Averaging Filter                       |     |     |     |      | $f_{IN} = f_{NOTCH} \pm 1 \text{ Hz}$                     |

| At 50 Hz                                                                     | 115 |     |     | dB   | 36.36 SPS (FS = 6, first notch at 60 Hz)                  |

| At 60 Hz                                                                     | 115 |     |     | dB   | 43.63 SPS (FS = 5, first notch at 50 Hz)                  |

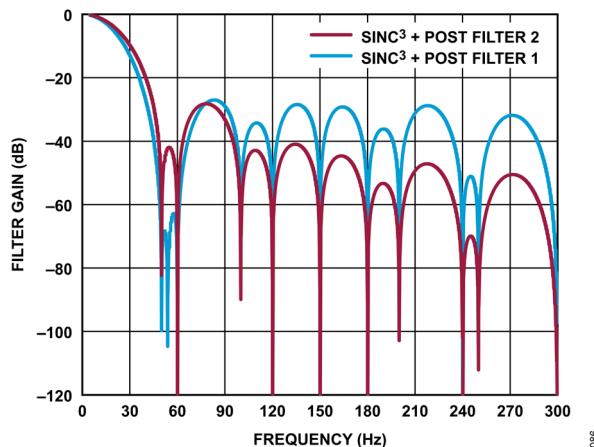

| Post Filters                                                                 |     |     |     |      | $f_{IN} = f_{NOTCH} \pm 1 \text{ Hz}$                     |

| At 50 Hz and 60 Hz                                                           | 125 |     |     | dB   | Post Filter 1, ODR = 26.087 SPS                           |

|                                                                              | 125 |     |     | dB   | Post Filter 2, ODR = 24 SPS                               |

|                                                                              | 125 |     |     | dB   | Post Filter 3, ODR = 19.355 SPS                           |

|                                                                              | 120 |     |     | dB   | Post Filter 4, ODR = 16.21 SPS                            |

| <b>NORMAL MODE REJECTION<sup>3, 4</sup></b>                                  |     |     |     |      |                                                           |

| Sinc <sup>3</sup> Filter                                                     |     |     |     |      | $f_{IN} = f_{NOTCH} \pm 1 \text{ Hz}$                     |

| External Clock                                                               |     |     |     |      |                                                           |

| At 50 Hz and 60 Hz                                                           | 100 |     |     | dB   | 10 SPS (FS = 240)                                         |

|                                                                              | 65  |     |     | dB   | 50 SPS (FS = 48), Sinc <sup>3</sup> + REJ60 filter        |

| At 50 Hz                                                                     | 95  |     |     | dB   | 50 SPS (FS = 48)                                          |

| At 60 Hz                                                                     | 98  |     |     | dB   | 60 SPS (FS = 40)                                          |

| Internal Clock                                                               |     |     |     |      |                                                           |

| At 50 Hz and 60 Hz                                                           | 84  |     |     | dB   | 10 SPS (FS = 240)                                         |

|                                                                              | 58  |     |     | dB   | 50 SPS (FS = 48), Sinc <sup>3</sup> + REJ60 filter        |

| At 50 Hz                                                                     | 79  |     |     | dB   | 50 SPS (FS = 48)                                          |

| At 60 Hz                                                                     | 81  |     |     | dB   | 60 SPS (FS = 40)                                          |

| Averaging Filters                                                            |     |     |     |      | $f_{IN} = f_{NOTCH} \pm 0.5 \text{ Hz}$                   |

| External Clock                                                               |     |     |     |      |                                                           |

| At 50 Hz                                                                     | 40  |     |     | dB   | FS = 6                                                    |

| At 60 Hz                                                                     | 42  |     |     | dB   | FS = 5                                                    |

| Internal Clock                                                               |     |     |     |      |                                                           |

| At 50 Hz                                                                     | 30  |     |     | dB   |                                                           |

| At 60 Hz                                                                     | 31  |     |     | dB   |                                                           |

| Post Filters                                                                 |     |     |     |      | $f_{IN} = f_{NOTCH} \pm 1 \text{ Hz}$                     |

| External Clock                                                               |     |     |     |      |                                                           |

| At 50 Hz and 60 Hz                                                           | 46  |     |     | dB   | Post Filter 1, ODR = 26.087 SPS                           |

|                                                                              | 62  |     |     | dB   | Post Filter 2, ODR = 24 SPS                               |

|                                                                              | 86  |     |     | dB   | Post Filter 3, ODR = 19.355 SPS                           |

|                                                                              | 91  |     |     | dB   | Post Filter 4, ODR = 16.21 SPS                            |

| Internal Clock                                                               |     |     |     |      |                                                           |

| At 50 Hz and 60 Hz                                                           | 40  |     |     | dB   | Post Filter 1, ODR = 26.087 SPS                           |

|                                                                              | 54  |     |     | dB   | Post Filter 2, ODR = 24 SPS                               |

|                                                                              | 73  |     |     | dB   | Post Filter 3, ODR = 19.355 SPS                           |

|                                                                              | 77  |     |     | dB   | Post Filter 4, ODR = 16.21 SPS                            |

<sup>1</sup> 用語の定義のセクションを参照してください。<sup>2</sup> PGA\_BYP\_n = 1。PGA\_BYP\_n ビットは、対応する CONFIG\_n レジスタ内にあります。詳細についてはプログラマブル・ゲイン・アンプのセクションを参照してください。<sup>3</sup> これらの仕様については出荷テストを行っていませんが量産開始時の特性評価データで確認されています。<sup>4</sup> FS は、フィルタ・レジスタの FS ビット[10:0]を 10 進数に変換した値です。<sup>5</sup> ゲイン > 1 の場合、コモンモード電圧は  $(AV_{SS} + 0.1 + 0.5/\text{ゲイン}) \sim (AV_{DD} - 0.1 - 0.5/\text{ゲイン})$  です。

## 仕様

## ロジック入出力仕様

表 7. ロジック入出力仕様

| Parameter                                     | Min                   | Typ                              | Max                   | Unit    | Test Conditions/Comments                                |

|-----------------------------------------------|-----------------------|----------------------------------|-----------------------|---------|---------------------------------------------------------|

| LOGIC INPUTS <sup>1, 2</sup>                  |                       |                                  |                       |         |                                                         |

| Input Low Voltage ( $V_{INL}$ )               | 0                     |                                  | $0.3 \times IOV_{DD}$ | V       | $1.65 V \leq IOV_{DD} < 3.6 V$                          |

| Input High Voltage ( $V_{INH}$ )              | $0.7 \times IOV_{DD}$ |                                  | $IOV_{DD}$            | V       | $1.65 V \leq IOV_{DD} < 3.6 V$                          |

| Voltage Hysteresis                            |                       | 0.5                              |                       | V       | $1.65 V \leq IOV_{DD} < 3.6 V$                          |

| Current                                       | -1                    |                                  | +1                    | $\mu A$ | Input voltage ( $V_{IN}$ ) = $IOV_{DD}$ or DGND         |

| Pin Capacitance                               |                       | 10                               |                       | pF      | Per digital pin                                         |

| LOGIC OUTPUTS <sup>1, 2</sup> (INCLUDING CLK) |                       |                                  |                       |         |                                                         |

| Output Low Voltage ( $V_{OL}$ )               | 0                     |                                  | 0.4                   | V       | Sink current ( $I_{SINK}$ ) = 100 $\mu A$               |

| Output High Voltage ( $V_{OH}$ )              | $IOV_{DD} - 0.35$     |                                  | $IOV_{DD}$            | V       | Source current ( $I_{SOURCE}$ ) = 100 $\mu A$           |

| Floating State Leakage Current                | -1                    |                                  | +1                    | $\mu A$ |                                                         |

| Floating State Output Capacitance             |                       | 10                               |                       | pF      |                                                         |

| Data Output Coding <sup>3</sup>               |                       | Offset binary<br>Straight binary |                       |         | Bipolar bit = 0b1, default setting<br>Bipolar bit = 0b0 |

| CLOCK                                         |                       |                                  |                       |         |                                                         |

| Internal Clock                                |                       |                                  |                       |         |                                                         |

| Frequency                                     | 76.8 - 2%             | 76.8                             | 76.8 + 2%             | kHz     |                                                         |

| Duty Cycle <sup>2</sup>                       |                       | 50:50                            |                       | %       |                                                         |

| Wake-Up Time <sup>2, 4</sup>                  |                       | 850                              |                       | $\mu s$ |                                                         |

| External Clock <sup>2</sup>                   |                       |                                  |                       |         |                                                         |

| Frequency                                     |                       | 76.8                             |                       | kHz     |                                                         |

| Duty Cycle                                    |                       | 45:55 to 55:45                   |                       | %       |                                                         |

| DIGITAL OUTPUTS (P1 to P4) <sup>5</sup>       |                       |                                  |                       |         |                                                         |

| Output Low Voltage ( $V_{OL}$ ) <sup>2</sup>  | 0                     |                                  | 0.4                   | V       | $I_{SINK} = 100 \mu A$                                  |

| Output High Voltage ( $V_{OH}$ ) <sup>2</sup> | $AV_{DD} - 0.6$       |                                  | $AV_{DD}$             | V       | $I_{SOURCE} = 100 \mu A$                                |

<sup>1</sup> ピン配置およびピン機能の説明のセクションを参照してください。<sup>2</sup> これらの仕様については出荷テストを行っていませんが量産開始時の特性評価データで確認されています。<sup>3</sup> バイポーラ・ビットは ADC\_CONTROL レジスタ内にあります。詳細についてはデータ出力コーディングのセクションを参照してください。<sup>4</sup> 詳細についてはスタンバイ・モードからの復帰タイミングのセクションも参照してください。<sup>5</sup> デジタル・ピンとして使用される汎用出力ピンでは、 $AV_{SS} = DGND$ かつ $AV_{DD} = IOV_{DD}$ とする必要があります。汎用出力のセクションを参照してください。

## 電源仕様

表 8. 電源仕様

| Parameter                          | Min  | Typ | Max     | Unit                               | Test Conditions/Comments    |

|------------------------------------|------|-----|---------|------------------------------------|-----------------------------|

| POWER SUPPLY VOLTAGE               |      |     |         |                                    |                             |

| $AV_{DD}$ to $AV_{SS}$             | 1.71 |     | 3.6     | V                                  |                             |

| $IOV_{DD}$ to DGND                 | 1.65 |     | 3.6     | V                                  |                             |

| $AV_{SS}$ to DGND                  | -1.8 |     | 0       | V                                  |                             |

| $AV_{DD}$ to DGND                  | 0.9  |     |         | V                                  |                             |

| $IOV_{DD}$ to $AV_{SS}$            |      |     | 5.4     | V                                  |                             |

| POWER SUPPLY CURRENTS <sup>1</sup> |      |     |         |                                    |                             |

| $AV_{DD}$ Current                  |      |     |         |                                    | Internal oscillator enabled |

| External Reference                 |      |     |         |                                    |                             |

| Gain = 1                           | 20   | 23  | $\mu A$ | PGA bypass <sup>2</sup>            |                             |

|                                    |      | 24  | $\mu A$ | $T_{MAX} = 125^\circ C$            |                             |

| Gain = 1 to 16                     | 25   | 30  | $\mu A$ | Continuous conversion mode current |                             |

## 仕様

表 8. 電源仕様（続き）

| Parameter                                          | Min  | Typ  | Max | Unit | Test Conditions/Comments               |

|----------------------------------------------------|------|------|-----|------|----------------------------------------|

| Gain = 32 to 128                                   |      |      | 32  | µA   | T <sub>MAX</sub> = 125°C               |

|                                                    | 7.5  |      |     | µA   | DUTY_CYC_RATIO = 1/4 <sup>3</sup>      |

|                                                    | 2.5  |      |     | µA   | DUTY_CYC_RATIO = 1/16 <sup>3</sup>     |

|                                                    | 29   | 35   |     | µA   | Continuous conversion mode current     |

|                                                    |      | 38   |     | µA   | T <sub>MAX</sub> = 125°C               |

|                                                    | 8.5  |      |     | µA   | DUTY_CYC_RATIO = 1/4 <sup>3</sup>      |

|                                                    | 3    |      |     | µA   | DUTY_CYC_RATIO = 1/16 <sup>3</sup>     |

| Increase due to Reference Buffer <sup>4</sup>      | 0.25 |      |     | µA   | Per reference buffer                   |

| Increase due to Internal Reference <sup>4</sup>    | 6.5  | 8    |     | µA   | Continuous conversion mode current     |

|                                                    | 1.75 |      |     | µA   | DUTY_CYC_RATIO = 1/4 <sup>3</sup>      |

|                                                    | 0.45 |      |     | µA   | DUTY_CYC_RATIO = 1/16 <sup>3</sup>     |

| Increase due to V <sub>BIA</sub> S on <sup>4</sup> | 1    | 1.2  |     | µA   |                                        |

| IOV <sub>DD</sub> Current                          | 3.5  | 6.9  |     | µA   | Continuous conversion mode current     |

|                                                    |      | 12.5 |     | µA   | T <sub>MAX</sub> = 125°C               |

|                                                    | 1.8  |      |     | µA   | DUTY_CYC_RATIO = 1/4 <sup>3</sup>      |

|                                                    | 1.4  |      |     | µA   | DUTY_CYC_RATIO = 1/16 <sup>3</sup>     |

| Increase due to FIFO                               | 50   |      |     | nA   |                                        |

| POWER-DOWN CURRENTS <sup>1</sup>                   |      |      |     |      |                                        |

| Standby Mode Current                               |      |      |     |      |                                        |

| AV <sub>DD</sub>                                   | 0.2  | 1.3  |     | µA   | Analog low dropout (LDO) regulator on  |

|                                                    |      | 2.5  |     | µA   | T <sub>MAX</sub> = 125°C               |

| IOV <sub>DD</sub>                                  | 0.35 | 3.5  |     | µA   | Digital LDO regulator on               |

|                                                    |      | 11   |     | µA   | T <sub>MAX</sub> = 125°C               |

| Power-Down Mode Current                            |      |      |     |      |                                        |

| AV <sub>DD</sub>                                   | 0.01 | 1    |     | µA   | Analog LDO regulator off               |

|                                                    |      | 1.2  |     | µA   | T <sub>MAX</sub> = 125°C               |

| IOV <sub>DD</sub>                                  | 0.13 | 1    |     | µA   | Digital LDO regulator off              |

| OPERATING TEMPERATURE RANGE                        |      |      |     |      |                                        |

| T <sub>MIN</sub>                                   | -40  |      |     | °C   |                                        |

| T <sub>MAX</sub>                                   |      | 105  |     | °C   | Wafer level chip scale package (WLCSP) |

|                                                    |      | 125  |     | °C   | Lead frame chip scale package (LFCSP)  |

<sup>1</sup> 励起電流がディスエーブルになっている場合、デジタル入力は IOV<sub>DD</sub> または DGND と等しくなります。

<sup>2</sup> PGA\_BYP\_n = 1。PGA\_BYP\_n ビットは、対応する CONFIG\_n レジスタ内にあります。詳細については [プログラマブル・ゲイン・アンプ](#) のセクションを参照してください。

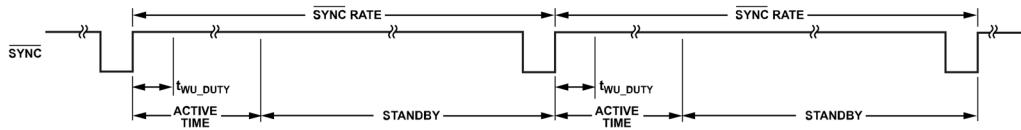

<sup>3</sup> デューティ・サイクル・モードを有効にするには、ADC\_CONTROL レジスタにおいて MODE = 0b1001 に設定します。DUTY\_CYC\_RATIO ビットは同じレジスタ内にあります。[デューティ・サイクル・モードとデューティ・サイクル・モードのタイミング](#) の各セクションを参照してください。

<sup>4</sup> これらの仕様については出荷テストを行っていませんが量産開始時の特性評価データで確認されています。

## 仕様

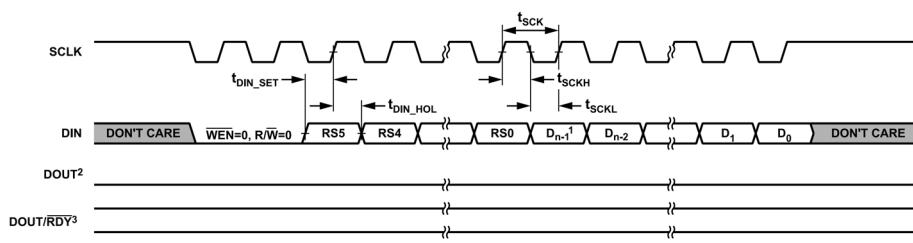

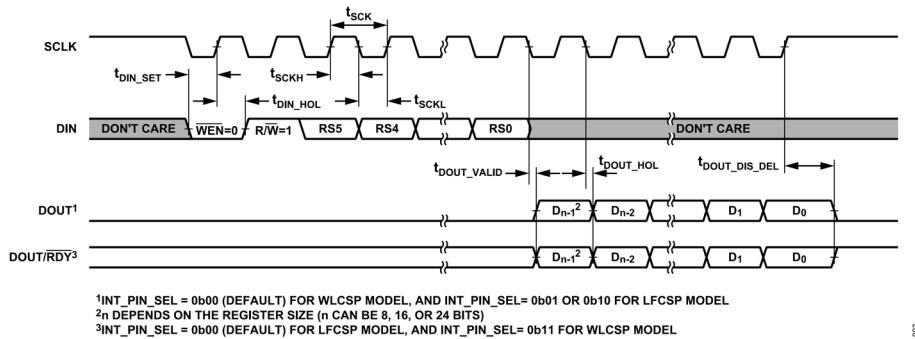

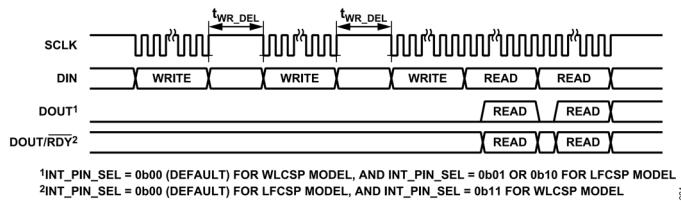

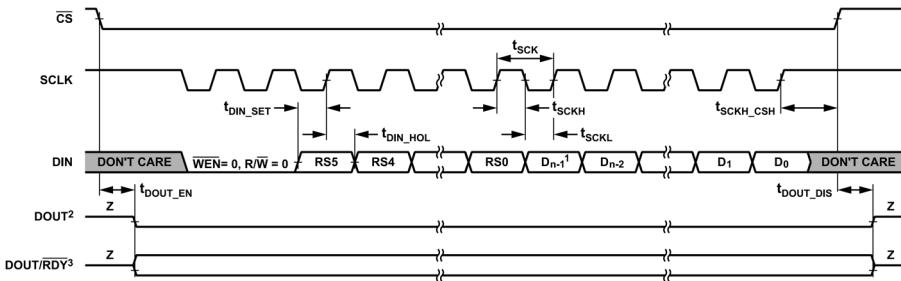

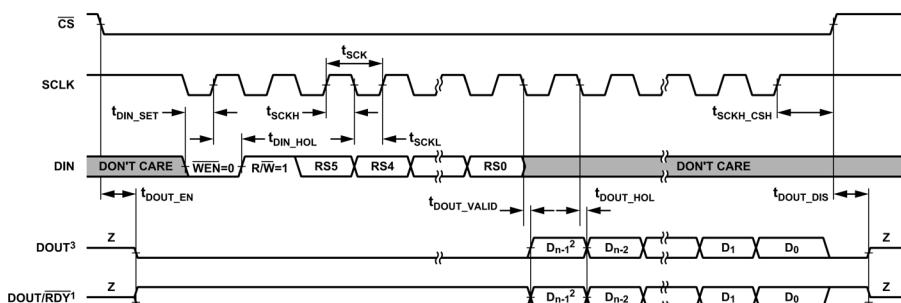

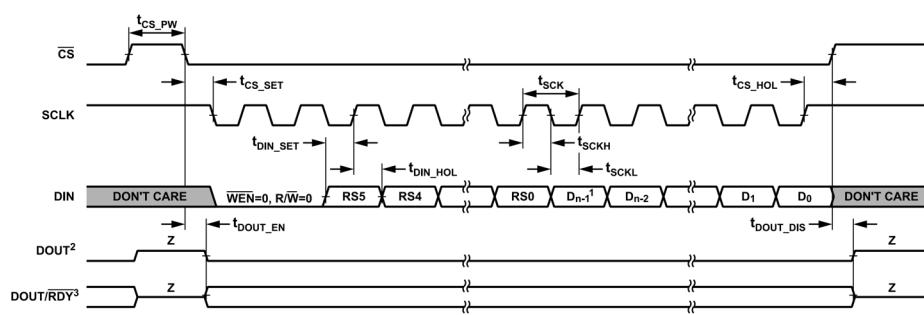

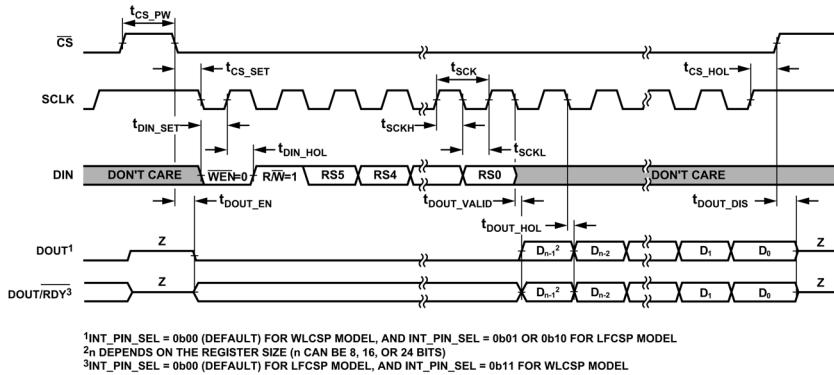

## タイミング仕様

特に指定のない限り、AV<sub>DD</sub> = 1.71V~3.6V、IOV<sub>DD</sub> = 1.65V~3.6V、AV<sub>SS</sub> = DGND = 0V、入力ロジック 0 = DGND = 0V、入力ロジック 1 = IOV<sub>DD</sub>、内部 MCLK (f<sub>MCLK</sub> = 76.8kHz)、温度範囲 = T<sub>MIN</sub>~T<sub>MAX</sub>、[推奨デカップリング方法](#)のセクションに従いデカップリング。全てのデジタル入力信号は、立上がり時間 (t<sub>R</sub>) = 立下がり時間 (t<sub>F</sub>) = 5ns に規定されています (IOV<sub>DD</sub> の 10%~90%で、IOV<sub>DD</sub>/2 の電圧レベルから時間を計測)。

表 9. タイミング仕様

| Parameter <sup>1</sup>                                                                                                     | Symbol                                                                                                    | Min                    | Max                  | Unit |

|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------|----------------------|------|

| REGISTER ACCESS IN 3-WIRE MODE <sup>2, 3, 4</sup>                                                                          |                                                                                                           |                        |                      |      |

| SCLK Cycle Time                                                                                                            | t <sub>SCK</sub>                                                                                          | 200                    |                      | ns   |

| SCLK High Pulse Width                                                                                                      | t <sub>SCKH</sub>                                                                                         | 90                     |                      | ns   |

| SCLK Low Pulse Width                                                                                                       | t <sub>SCKL</sub>                                                                                         | 90                     |                      | ns   |

| DIN Data Setup Time                                                                                                        | t <sub>DIN_SET</sub>                                                                                      | 10                     |                      | ns   |

| DIN Data Hold Time                                                                                                         | t <sub>DIN_HOL</sub>                                                                                      | 10                     |                      | ns   |

| SCLK Falling Edge to DOUT Becomes Available                                                                                | t <sub>DOUT_VALID</sub>                                                                                   |                        | 80                   | ns   |

| SCLK Falling Edge to DOUT Remains Available                                                                                | t <sub>DOUT_HOL</sub>                                                                                     | 10                     |                      | ns   |

| SCLK Rising Edge to DOUT Disable Delay <sup>5</sup>                                                                        | t <sub>DOUT_DIS_DEL</sub>                                                                                 |                        |                      |      |

| DOUT_DIS_DEL = 0 <sup>6</sup>                                                                                              |                                                                                                           | 10                     |                      | ns   |

| DOUT_DIS_DEL = 1 <sup>6</sup>                                                                                              |                                                                                                           | 100                    |                      | ns   |

| Delay Between Consecutive Write Operations <sup>7</sup> (Last SCLK Rising to First SCLK Falling)                           | t <sub>WR_DEL</sub>                                                                                       | 3/f <sub>MCLK</sub>    | 4/f <sub>MCLK</sub>  | sec  |

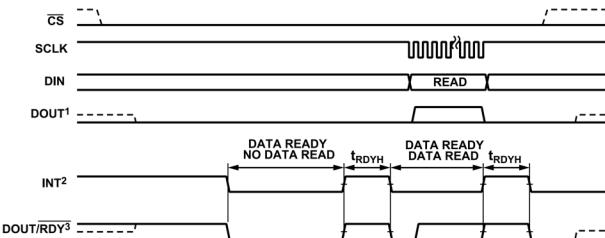

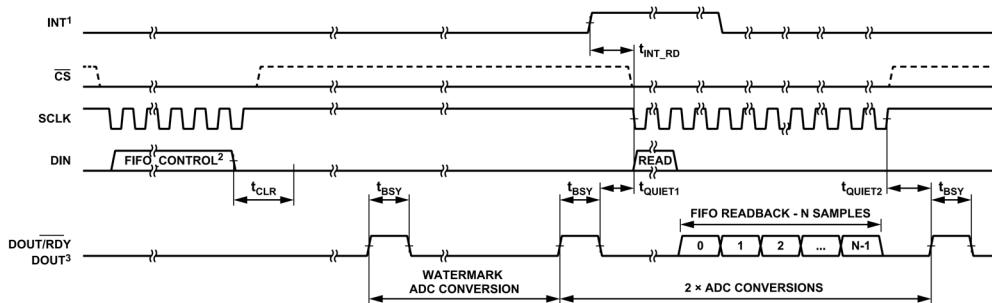

| Data Ready <sup>8</sup> High Time if Data Ready is Low and the Next Conversion is Available                                | t <sub>RDYH</sub>                                                                                         | 4/f <sub>MCLK</sub>    |                      | sec  |

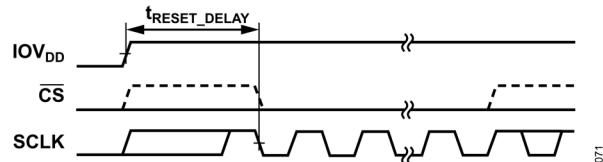

| Last SCLK Rising for SW Reset Serial Peripheral Interface (SPI) Transaction to First SCLK Falling for Next SPI Transaction | t <sub>RESET_DELAY</sub><br>IOV <sub>DD</sub> = 1.8 V<br>to 3.6 V<br>IOV <sub>DD</sub> = 1.65 V to 1.79 V | 1920/f <sub>MCLK</sub> |                      | sec  |

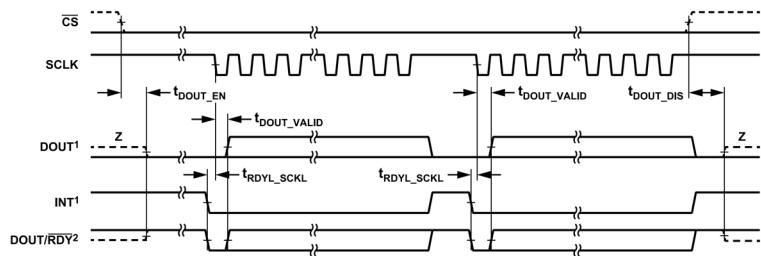

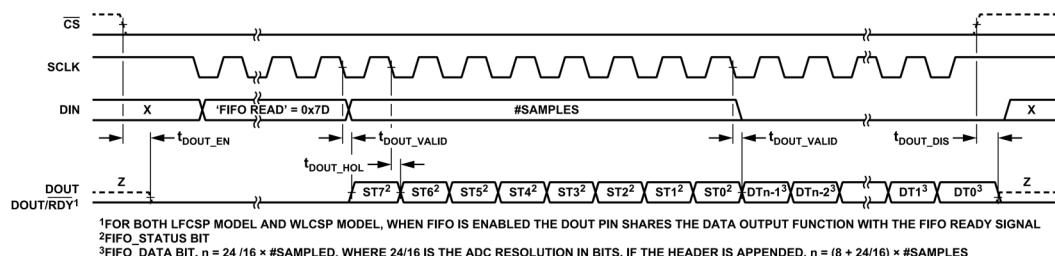

| REGISTER ACCESS IN 4-WIRE MODE <sup>2, 3, 9</sup>                                                                          |                                                                                                           |                        |                      |      |

| CS Falling Edge to DOUT Enable Time <sup>10</sup>                                                                          | t <sub>DOUT_EN</sub>                                                                                      |                        | 80                   | ns   |

| CS Setup Time: CS Falling Edge to First SCLK Falling Edge                                                                  | t <sub>CS_SET</sub>                                                                                       | 0                      |                      | ns   |

| CS Hold Time: Last SCK Rising Edge to CS Rising Edge Delay                                                                 | t <sub>CS_HOL</sub>                                                                                       | 0                      |                      | ns   |

| CS Rising Edge to DOUT Disable Time <sup>10</sup>                                                                          | t <sub>DOUT_DIS</sub>                                                                                     |                        | 80                   | ns   |

| CS High Pulse Width (Between Read/Write Operations)                                                                        | t <sub>CS_PW</sub>                                                                                        | 20                     |                      | ns   |

| CS Rising Edge for SW Reset SPI Transaction to CS Falling Edge for Next SPI Transaction                                    | t <sub>RESET_DELAY</sub><br>IOV <sub>DD</sub> = 1.8 V<br>to 3.6 V<br>IOV <sub>DD</sub> = 1.65 V to 1.79 V | 1920/f <sub>MCLK</sub> |                      | sec  |

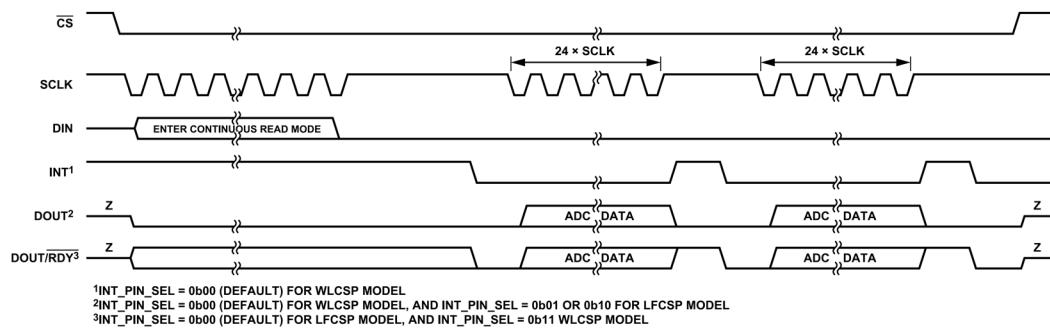

| CONTINUOUS READ MODE <sup>11</sup>                                                                                         |                                                                                                           |                        |                      |      |

| Data Ready <sup>8</sup> Falling Edge to First SCLK Falling Edge                                                            | t <sub>RDYL_SCKL</sub>                                                                                    | 20                     |                      | ns   |

| SCLK Falling Edge to New DOUT Becomes Available                                                                            | t <sub>DOUT_VALID</sub>                                                                                   |                        | 80                   | ns   |

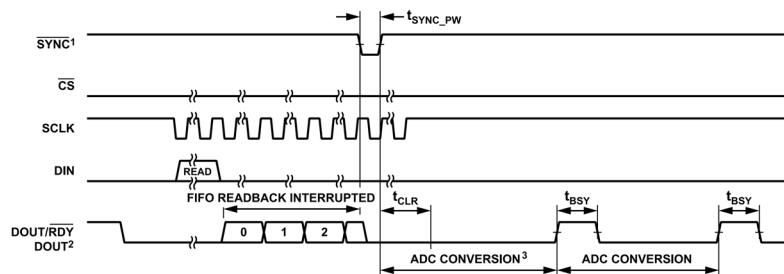

| SYNCHRONIZATION MODE <sup>12</sup>                                                                                         |                                                                                                           |                        |                      |      |

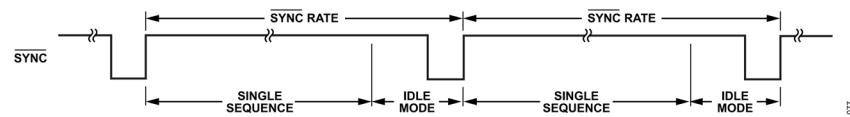

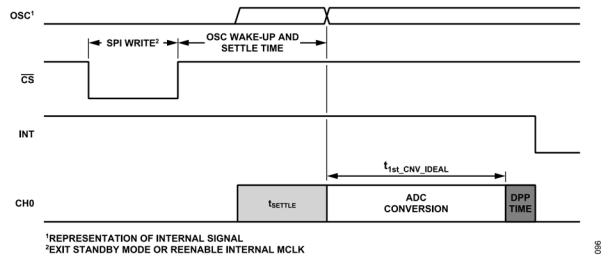

| SYNC Low Pulse Width                                                                                                       | t <sub>SYNC_PW</sub>                                                                                      | 4/f <sub>MCLK</sub>    |                      | sec  |