## High Power Positive Hot Swap Controller with Power Monitor

### FEATURES

- ▶ Drives two gates for high power applications

- ▶ Wide input supply voltage range: 6.5 V to 80 V

- ▶ Optimizes MOSFET SOA with multimode start-up sequencing and operation

- ▶ Monitors currents, voltages, power, and energy with the ADC

- ▶ Limits MOSFET temperature for overstress protection

- ▶ Adjustable, 6.6% accurate (5 mV) current limit with foldback

- ▶ BlackBox capturing and configuration using an optional external EEPROM

- ▶ SMBus 3.1 interface and PMBus-compliant command structure

- ▶ Parallelable controllers for high current levels

- ▶ Minimum and maximum ADC measurements logging with alerts

- ▶ Available in 48(39)-lead plastic QFN (7 mm × 7 mm) package

- ▶ Available in 48-lead side-wettable plastic QFN (7 mm × 7 mm) package

- ▶ Configurable current foldback

### APPLICATIONS

- ▶ High availability server backplane systems

- ▶ 12 V/24 V/48 V/54 V distributed power systems

- ▶ Industrial

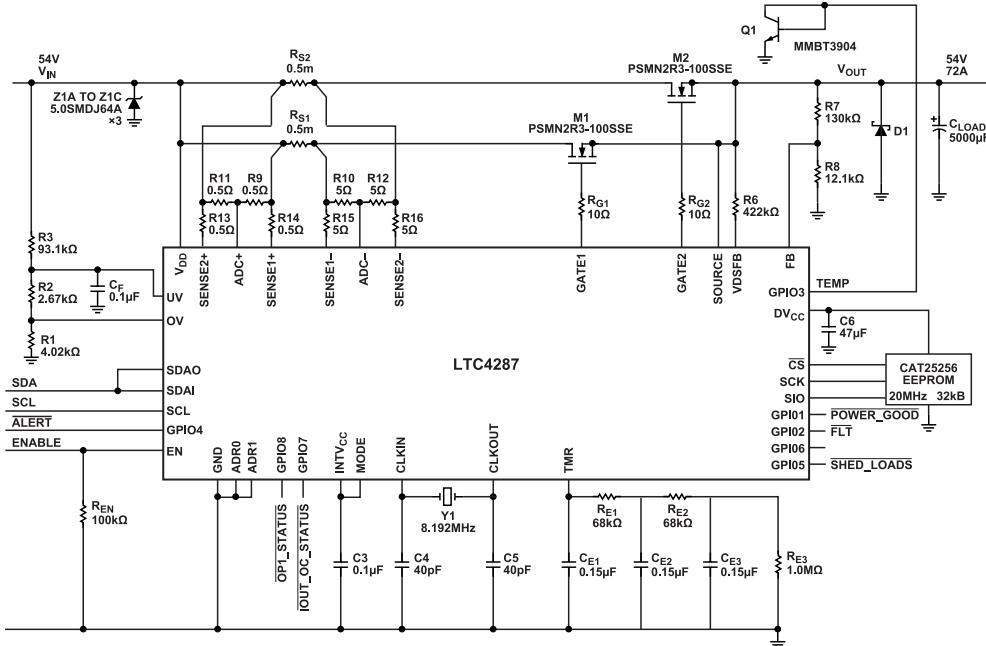

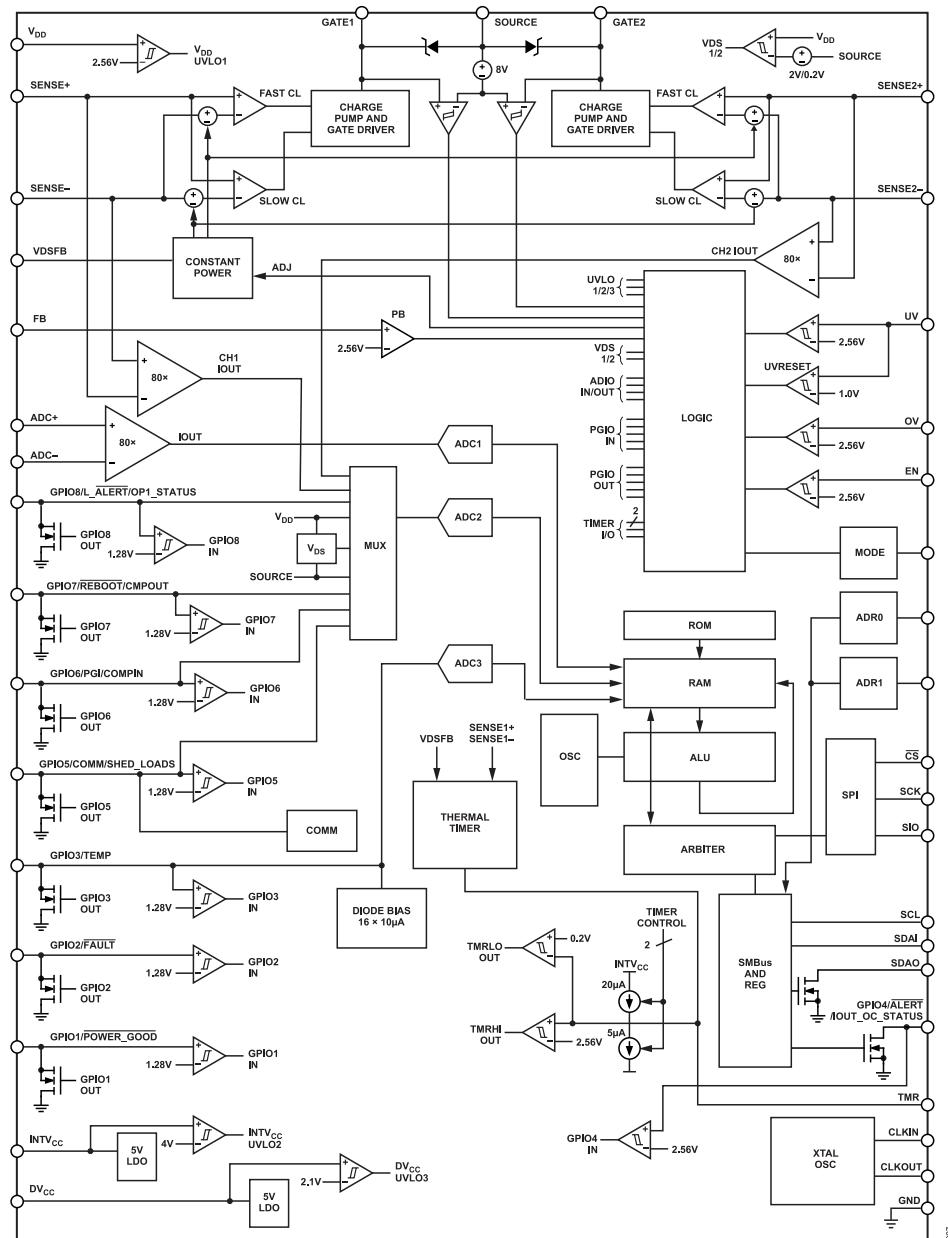

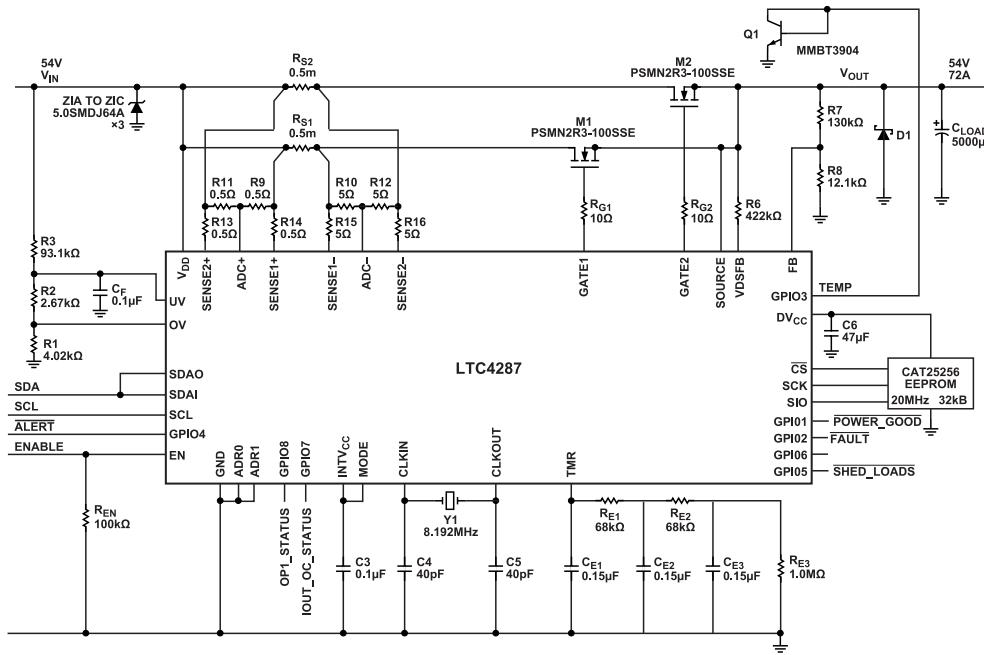

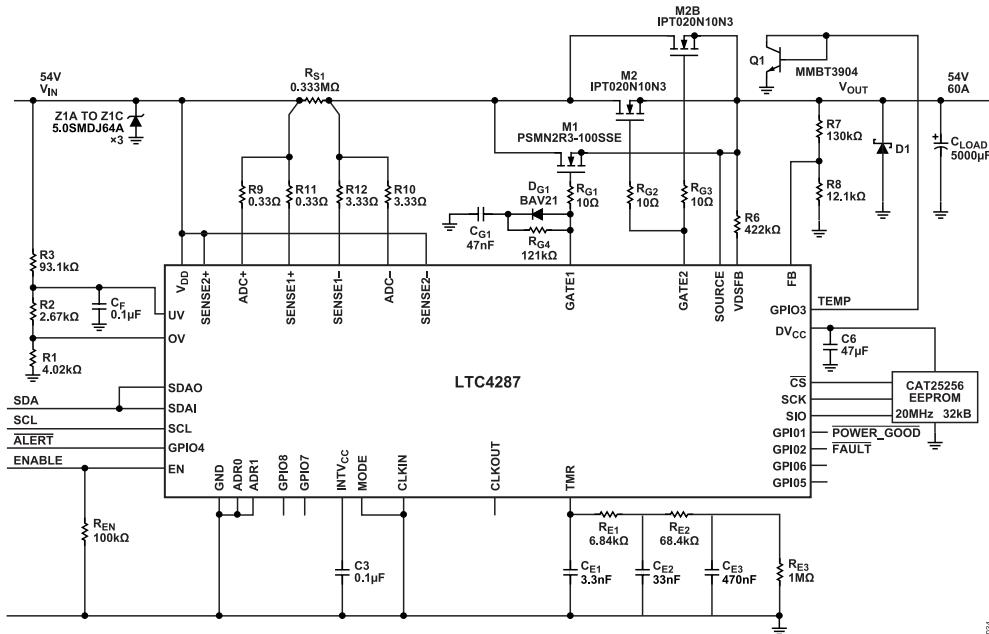

### TYPICAL APPLICATION

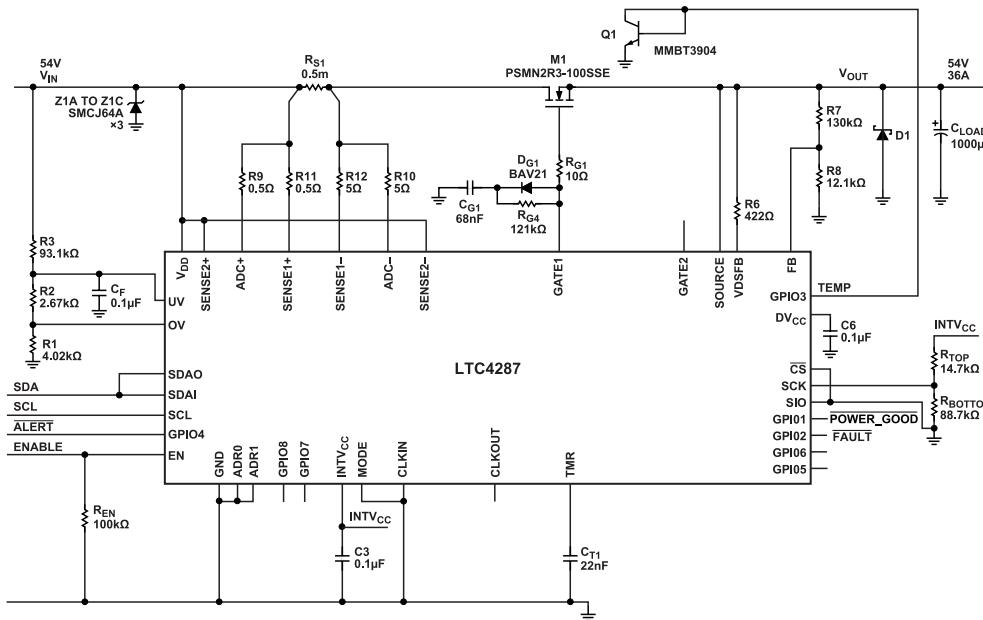

Figure 1. 54 V, 3900 W Hot-Swap Controller (Parallel Mode)

Rev. A

#### DOCUMENT FEEDBACK

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. All Analog Devices products contained herein are subject to release and availability.

#### TECHNICAL SUPPORT

## TABLE OF CONTENTS

|                                                                |    |                                                                         |    |

|----------------------------------------------------------------|----|-------------------------------------------------------------------------|----|

| Features.....                                                  | 1  | Data Converters.....                                                    | 34 |

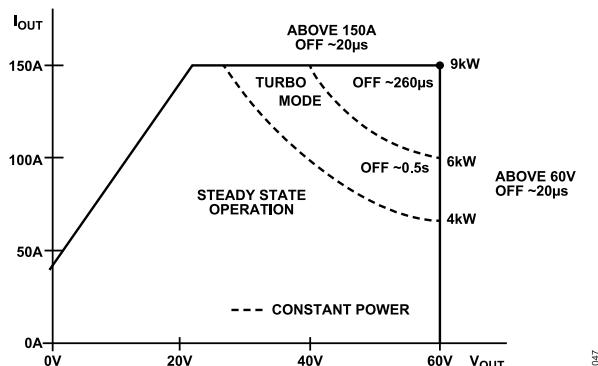

| Applications.....                                              | 1  | Overpower Faults and Turbo Mode.....                                    | 35 |

| General Description.....                                       | 1  | Configuration Without EEPROM.....                                       | 36 |

| Typical Application.....                                       | 1  | Design Examples.....                                                    | 38 |

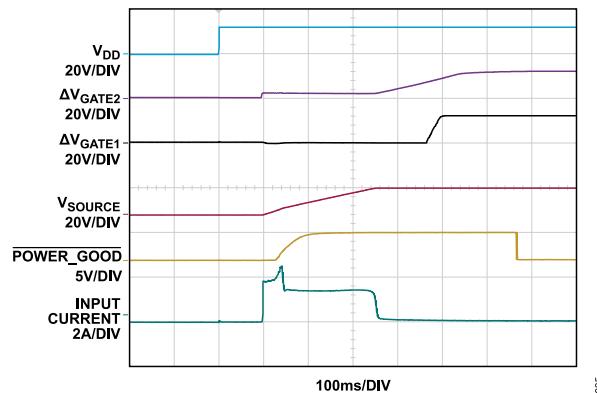

| Electrical Characteristics.....                                | 4  | Example 1: Parallel Mode With Current Limit Start-Up and SOA Timer..... | 38 |

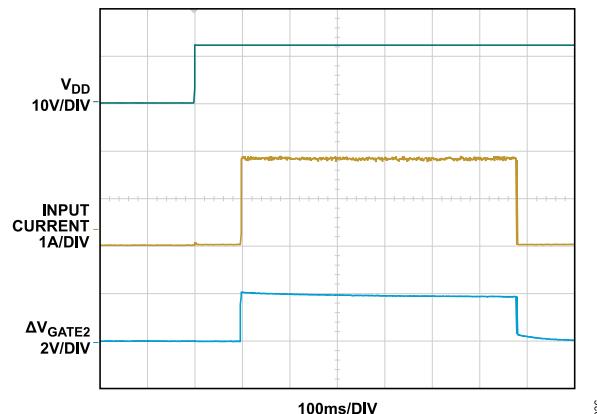

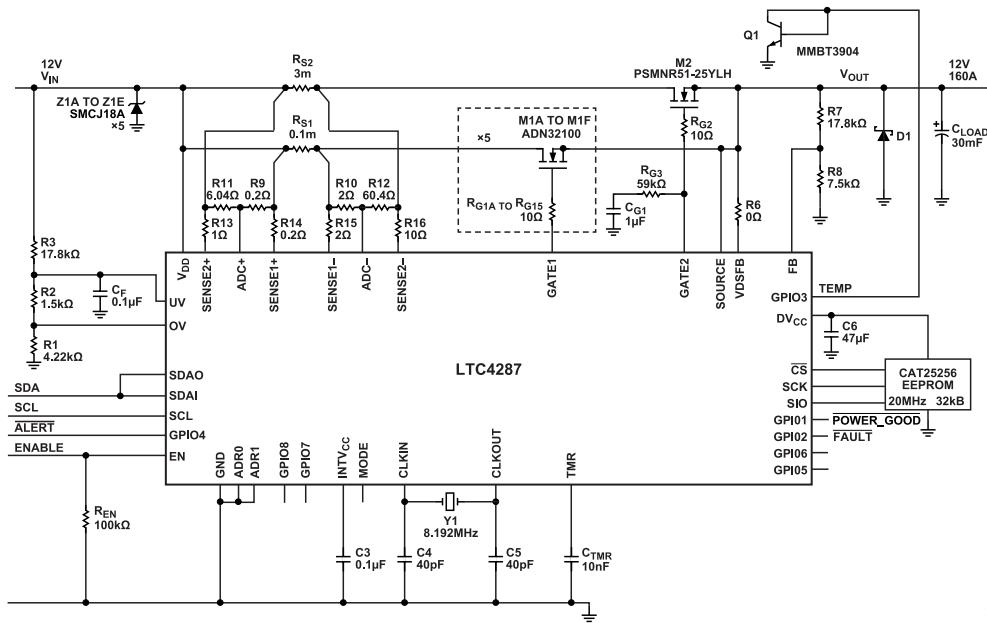

| Absolute Maximum Ratings.....                                  | 10 | Example 2: LSSS Mode with a Basic Timer.....                            | 39 |

| Thermal Resistance.....                                        | 10 | Layout Considerations.....                                              | 41 |

| ESD Caution.....                                               | 10 | Chip Tick Timer and ADC Timing.....                                     | 42 |

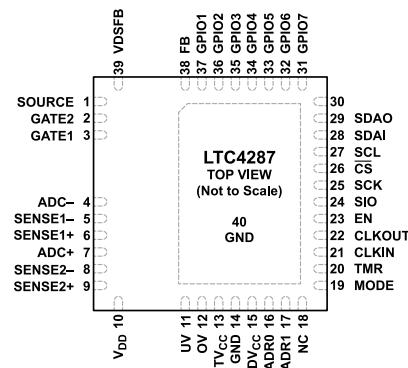

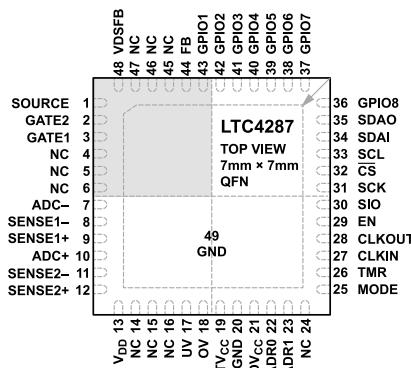

| Pin Configuration and Function Description.....                | 11 | Latched Status and Mask Commands.....                                   | 43 |

| Typical Performance Characteristics.....                       | 15 | Overview.....                                                           | 43 |

| Theory of Operation.....                                       | 19 | External EEPROM.....                                                    | 44 |

| Applications Information.....                                  | 21 | Overview.....                                                           | 44 |

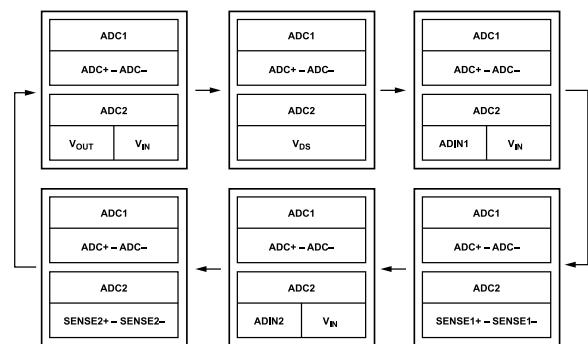

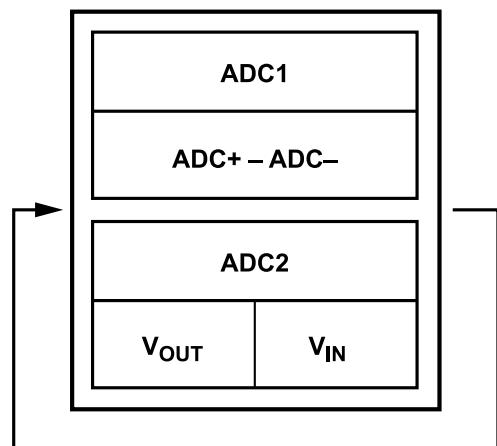

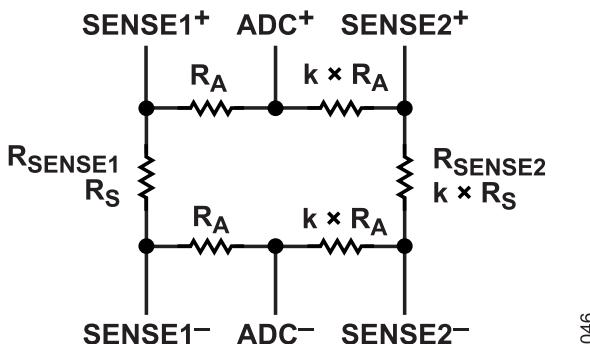

| Application 1: Parallel Mode.....                              | 21 | EEPROM Data Usage.....                                                  | 44 |

| Application 2: HSSS Mode.....                                  | 26 | Data Access Methods.....                                                | 44 |

| Application 3: LSSS Mode.....                                  | 28 | Logging.....                                                            | 45 |

| Single Driver Mode.....                                        | 30 | Digital Interface.....                                                  | 46 |

| FET_BAD Fault and Auto-Retry.....                              | 31 | PMBus Serial Digital Interface.....                                     | 46 |

| Overvoltage Fault.....                                         | 32 | PMBus.....                                                              | 46 |

| Undervoltage Fault.....                                        | 32 | PMBus Command Summary.....                                              | 47 |

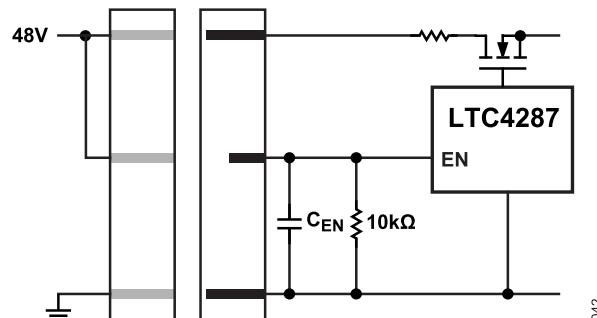

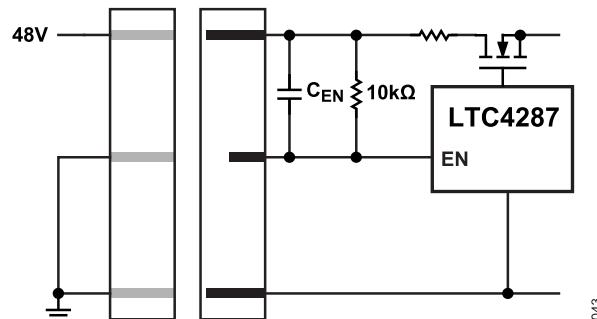

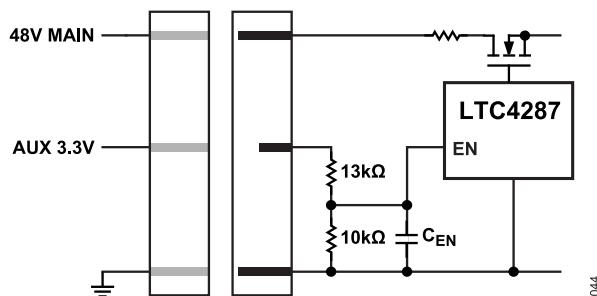

| On and Off Control with the EN Pin.....                        | 32 | Command Details.....                                                    | 54 |

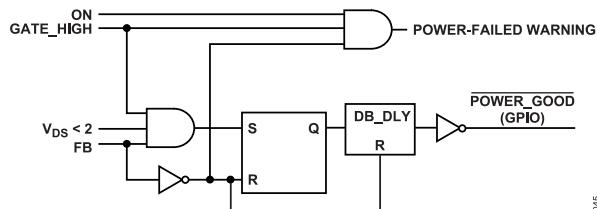

| Power Good and Power Failed.....                               | 33 | Related Parts.....                                                      | 77 |

| PGI Fault.....                                                 | 33 | Outline Dimensions.....                                                 | 78 |

| FET Short Fault.....                                           | 33 | Ordering Guide.....                                                     | 78 |

| Parallel Controllers Using the COMM Function of the GPIO5..... | 34 | Evaluation Boards.....                                                  | 78 |

| REBOOT Bit.....                                                | 34 |                                                                         |    |

## REVISION HISTORY

## 7/2025—Rev. 0 to Rev. A

|                                                                                                                            |    |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Added 48-Lead QFN (Universal).....                                                                                         | 1  |

| Changes to Features Section.....                                                                                           | 1  |

| Changes to OV Threshold Voltage, FB Threshold Voltage Parameter, and Refresh Rate in Continuous Mode Section; Table 1..... | 4  |

| Added Figure 3; Renumbered Sequentially.....                                                                               | 11 |

| Changes to Table 4.....                                                                                                    | 11 |

| Changes to Overpower Faults and Turbo Mode Section.....                                                                    | 35 |

| Change to Configuration Without EEPROM Section.....                                                                        | 36 |

| Changes to Example 1: Parallel Mode With Current Limit Start-Up and SOA Timer Section.....                                 | 38 |

| Changes to Example 2: LSSS Mode with a Basic Timer Section.....                                                            | 39 |

| Changes to Chip Tick Timer and ADC Timing Section.....                                                                     | 42 |

| Changes to EEPROM Data Usage Section.....                                                                                  | 44 |

| Changes to Data Access Methods Section.....                                                                                | 44 |

| Changes to Logging Section.....                                                                                            | 45 |

| Changes to Table 15.....                                                                                                   | 48 |

| Changes to Command Details Section.....                                                                                    | 54 |

| Changes to Table 46.....                                                                                                   | 67 |

| Updated Outline Dimensions.....                                                                                            | 78 |

| Changes to Ordering Guide .....                                                                                            | 78 |

---

**TABLE OF CONTENTS**

**10/2023—Revision 0: Initial Version**

## ELECTRICAL CHARACTERISTICS

Specifications apply over the full operating temperature range, unless otherwise noted. All currents into pins are positive, and all voltages are referenced to GND, unless otherwise specified.

Table 1. Electrical Characteristics

| Parameter                                                                                    | Symbol                              | Test Conditions/Comments                                                                                                                           | Min | Typ | Max | Unit    |

|----------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------|

| POWER SUPPLY                                                                                 |                                     |                                                                                                                                                    |     |     |     |         |

| Input Supply Range                                                                           | $V_{DD}$                            |                                                                                                                                                    | 6.5 | 80  |     | V       |

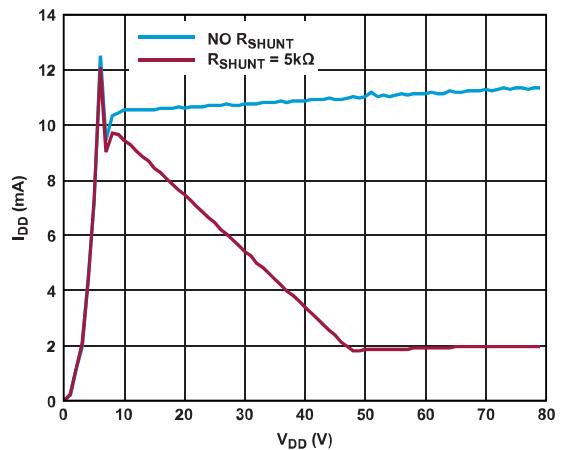

| Input Supply Current                                                                         | $I_{DD}$                            | No external resistor, input voltage ( $V_{IN}$ ) to $INTV_{CC}$ , no load on $DV_{CC}$<br>5 k $\Omega$ pull-up on $INTV_{CC}$ from $V_{DD}$ , 48 V |     | 12  | 18  | mA      |

| Input Supply Undervoltage Lockout                                                            | $V_{DD}$ (UVLO)                     | $V_{DD}$ rising<br>$V_{DD}$ falling                                                                                                                | 5   | 6   | 7   | V       |

| Input Supply Undervoltage Lockout Hysteresis                                                 | $\Delta V_{DD}$ (HYST)              |                                                                                                                                                    |     | 0.5 |     | V       |

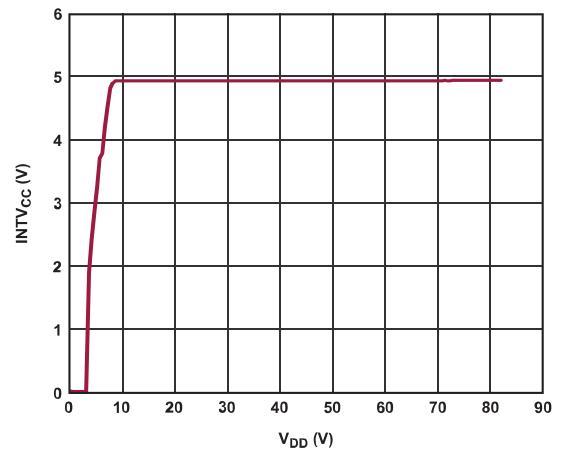

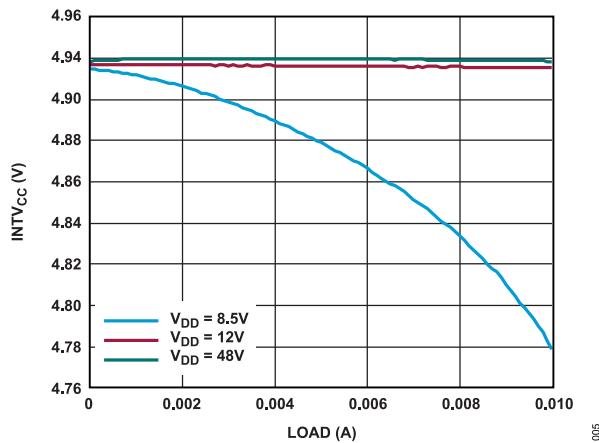

| $INTV_{CC}$ Output Voltage                                                                   | $INTV_{CC}$                         | $V_{DD} = 8.5$ V and 80 V, load current ( $I_{LOAD}$ ) = 0 mA and $\sim$ 4 mA                                                                      | 4.5 | 5   | 5.5 | V       |

| $INTV_{CC}$ Undervoltage Lockout                                                             | $INTV_{CC}$ (UVLO)                  | $INTV_{CC}$ rising<br>$INTV_{CC}$ falling                                                                                                          | 3.6 | 4   | 4.5 | V       |

| $INTV_{CC}$ Undervoltage Lockout Hysteresis                                                  | $\Delta INTV_{CC}$ (UVLO)           |                                                                                                                                                    |     | 115 |     | mV      |

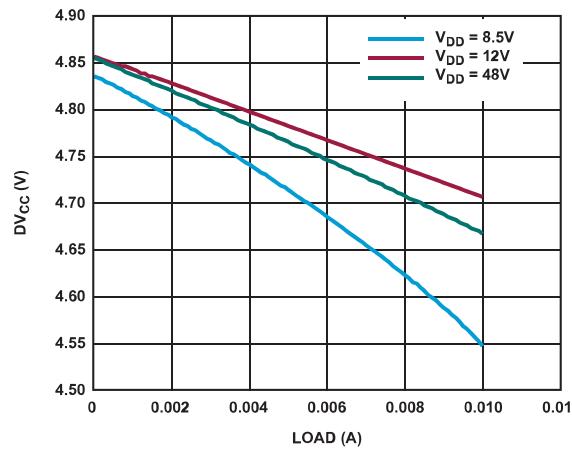

| $DV_{CC}$ Output Voltage                                                                     | $DV_{CC}$                           | $V_{DD} = 8.5$ V and 80 V, $I_{LOAD} = 0$ mA                                                                                                       | 4.5 | 5   | 5.5 | V       |

| $DV_{CC}$ Undervoltage Lockout                                                               | $DV_{CC}$ (UVLO)                    | $DV_{CC}$ rising<br>$DV_{CC}$ falling                                                                                                              | 1.9 | 2.2 | 2.5 | V       |

| Lockout Hysteresis                                                                           |                                     |                                                                                                                                                    | 1.7 | 2.0 | 2.3 | V       |

|                                                                                              |                                     |                                                                                                                                                    |     | 150 |     | mV      |

| GATE DRIVE                                                                                   |                                     |                                                                                                                                                    |     |     |     |         |

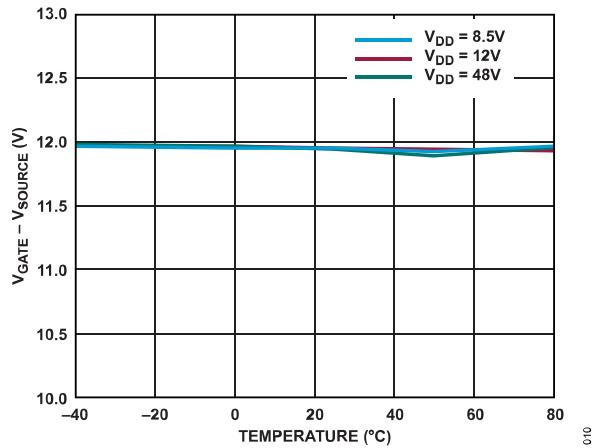

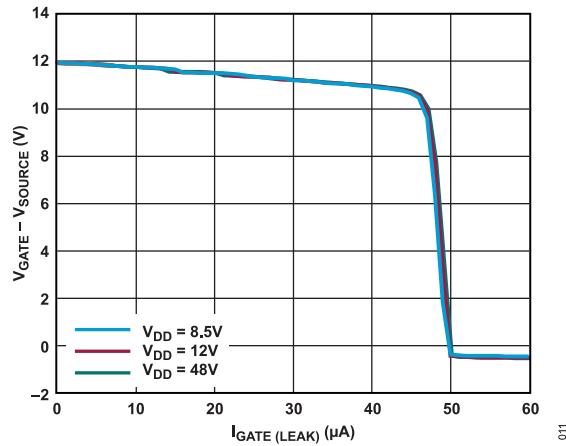

| External N-Channel Gate Drive at GATE1 and GATE2 ( $V_{GATE} - V_{SOURCE}$ ) <sup>1</sup>    | $\Delta V_{GATE1}/\Delta V_{GATE2}$ | $V_{DD} = 8.5$ V to 80 V, gate current ( $I_{GATE}$ ) = 0 $\mu$ A and $\sim$ 10 $\mu$ A                                                            | 10  | 12  | 14  | V       |

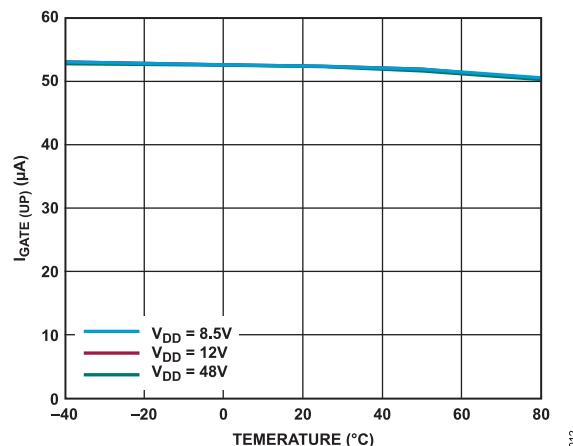

| GATE1 and GATE2 Pull-Up Current                                                              | $I_{GATE}$ (UP)                     | Gate drive on, gate voltage ( $V_{GATE}$ ) = source voltage ( $V_{SOURCE}$ ) = 0 V                                                                 | -35 | -50 | -70 | $\mu$ A |

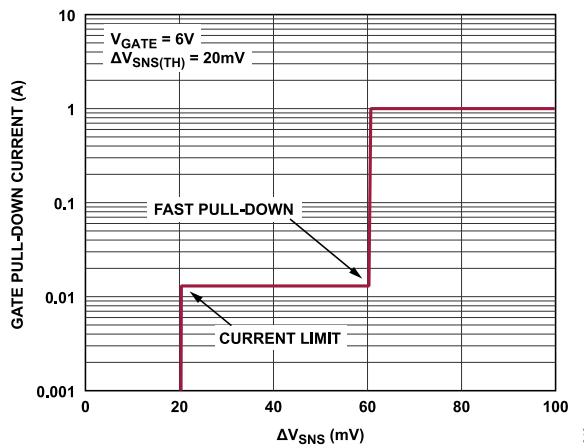

| GATE1 and GATE2 Pull-Down Current                                                            | $I_{GATE}$ (DN)                     | Gate drive off, $V_{GATE} = 58$ V, $V_{SOURCE} = 48$ V                                                                                             | 6   | 10  | 15  | mA      |

| GATE1 and GATE2 Fast Pull-Down Current                                                       | $I_{GATE}$ (FST)                    | Fast turn off, $V_{GATE} = 58$ V, $V_{SOURCE} = 48$ V                                                                                              |     | 1   |     | A       |

| Gate Source Voltage for FET Bad and Power-Failed Faults and Turning on Low Stress FET        | $V_{TH}$ (GS)                       |                                                                                                                                                    | 6   | 8   | 10  | V       |

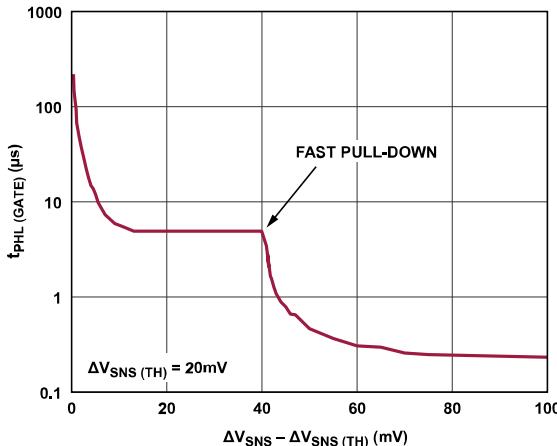

| $\Delta SENSE1/\Delta SENSE2$ High to GATE1 and GATE2 Low Propagation Delay                  | $t_{PHL(SENSE)}$                    | ILIM = 0000, $\Delta V_{SNS} = 0$ mV step to 100 mV step, $\Delta V_{GATE} = 6$ V, gate capacitance ( $C_{GATE}$ ) = 10 nF                         |     | 0.5 | 1   | $\mu$ s |

| GATE1 and GATE2 Propagation Delay—OV                                                         | $t_{PHL(GATE) OV}$                  |                                                                                                                                                    |     |     |     |         |

| Off                                                                                          |                                     | OV = high, $\Delta V_{GATE} = 6$ V                                                                                                                 |     | 1   | 2   | $\mu$ s |

| On                                                                                           |                                     | OV = low                                                                                                                                           | 0   | 5   | 10  | $\mu$ s |

| GATE1 and GATE2 Off Propagation Delay—UV                                                     | $t_{PHL(GATE) UV}$                  | UV = low, $\Delta V_{GATE} = 6$ V gate open                                                                                                        | 0.3 | 2   | 3   | $\mu$ s |

| GATE1 and GATE2 Off Propagation Delay—EN                                                     | $t_{PHL(GATE) EN}$                  | EN = low, $\Delta V_{GATE} = 6$ V gate open                                                                                                        | 15  | 40  | 70  | $\mu$ s |

| $V_{DD}$ to Source Threshold Voltage for Turning on Low Stress FET Gate and Power Bad Faults | $V_{DS}$ (LOW-STRESS FET)           | $V_{DD}$ to source falling                                                                                                                         | 1.6 | 2.0 | 2.4 | V       |

| Propagation Delay for Turning Off Low Stress FET                                             | $t_{PHL(LOW-STRESS FET)}$           |                                                                                                                                                    |     | 13  | 30  | $\mu$ s |

| FET_BAD Fault Threshold ( $V_{DD} - SOURCE$ ) to Start FET_BAD Timer                         | $V_{TH, FET\_BAD}$                  | $V_{DD}$ to source rising<br>$VDTH = 00$<br>$VDTH = 01$<br>$VDTH = 10$<br>$VDTH = 11$                                                              | 35  | 50  | 65  | mV      |

|                                                                                              |                                     |                                                                                                                                                    | 70  | 100 | 130 | mV      |

|                                                                                              |                                     |                                                                                                                                                    | 105 | 150 | 195 | mV      |

|                                                                                              |                                     |                                                                                                                                                    | 140 | 200 | 260 | mV      |

## ELECTRICAL CHARACTERISTICS

Table 1. Electrical Characteristics (Continued)

| Parameter                                                                                     | Symbol                            | Test Conditions/Comments                                                                                                                                                       | Min                                                                  | Typ                                                                  | Max                                                                  | Unit                                                          |     |

|-----------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------|-----|

| TIMING                                                                                        |                                   |                                                                                                                                                                                |                                                                      |                                                                      |                                                                      |                                                               |     |

| Power-Good Delay                                                                              | $t_{DL}(PG)$                      | DB_DL = 0<br>DB_DL = 1                                                                                                                                                         | 21.5<br>172                                                          | 22.7<br>181                                                          | 23.8<br>190                                                          | ms                                                            |     |

| Power-Good Watchdog Timer                                                                     | $t_{DL}(PGIWD)$                   |                                                                                                                                                                                | 551                                                                  | 580                                                                  | 609                                                                  | ms                                                            |     |

| Debounce Delay, Auto-Retry Delay Following Undervoltage Fault                                 | $t_{DL}(DB)$                      | DB_DL = 0<br>DB_DL = 1                                                                                                                                                         | 10.8<br>86.1                                                         | 11.3<br>90.6                                                         | 11.9<br>95.2                                                         | ms                                                            |     |

| Auto-Retry Delay Following PGI Fault                                                          | $t_{DL}(PGI\_RTRY)$               |                                                                                                                                                                                | 0.551                                                                | 0.580                                                                | 0.609                                                                | Sec                                                           |     |

| FET_BAD Delay                                                                                 | $t_{DL}(FET\_BAD)$                | FETBD_FLT_DL = 000<br>FETBD_FLT_DL = 001<br>FETBD_FLT_DL = 010<br>FETBD_FLT_DL = 011<br>FETBD_FLT_DL = 100<br>FETBD_FLT_DL = 101<br>FETBD_FLT_DL = 110<br>COOLING_DL = 000     | 0.069<br>0.138<br>0.276<br>0.551<br>1.102<br>2.204<br>4.408<br>0.551 | 0.073<br>0.145<br>0.290<br>0.580<br>1.160<br>2.230<br>4.640<br>0.580 | 0.076<br>0.152<br>0.305<br>0.609<br>1.218<br>2.436<br>4.872<br>0.609 | Sec                                                           |     |

| Auto-Retry Delay Following Overcurrent Fault (PIN_OP1_FAULT, PIN_OP2_FAULT, or FET_BAD_FAULT) | $t_{DL}(RTRY)$                    | COOLING_DL = 001<br>COOLING_DL = 010<br>COOLING_DL = 011<br>COOLING_DL = 100<br>COOLING_DL = 101<br>COOLING_DL = 110<br>COOLING_DL = 111                                       | 1.10<br>2.20<br>4.41<br>8.82<br>17.6<br>35.3<br>70.5                 | 1.16<br>2.32<br>4.64<br>9.28<br>18.6<br>37.1<br>74.2                 | 1.22<br>2.44<br>4.87<br>9.74<br>19.5<br>39.0<br>78.0                 | Sec                                                           |     |

| Auto-Retry Counter Reset Delay                                                                | $t_{DL}(RTCRST)$                  | VIN_UV_FAULT_RETRY,<br>VIN_OV_FAULT_RETRY,<br>OC_FAULT_RETRY, FET_BAD_RETRY,<br>OT_FAULT_RETRY, PGI_RETRY,<br>OP_FAULT_RETRY = 001 to 110                                      | 88.2                                                                 | 92.8                                                                 | 97.4                                                                 | Sec                                                           |     |

| OP1 Fault Unit Delay                                                                          | $t_{DL}(OP1-UNIT)$                | Delay = OP_TIMER (Value) × Unit Delay                                                                                                                                          | 1.08                                                                 | 1.13                                                                 | 1.19                                                                 | ms                                                            |     |

| Power Off Unit Delay                                                                          | $t_{DL}(PWROFF UNIT)$             | Delay = POWER_OFF_DELAY (Value) × Unit Delay                                                                                                                                   | 135                                                                  | 142                                                                  | 149                                                                  | μs                                                            |     |

| Auto-Reboot Delay                                                                             | $t_{DL}(RBT)$                     | After REBOOT is set to 1 via the PMBus command<br>RBT_DL = 000<br>RBT_DL = 001<br>RBT_DL = 010<br>RBT_DL = 011<br>RBT_DL = 100<br>RBT_DL = 101<br>RBT_DL = 110<br>RBT_DL = 111 |                                                                      | 0.551<br>1.10<br>2.20<br>4.41<br>8.82<br>17.6<br>35.3<br>70.5        | 0.580<br>1.16<br>2.32<br>4.64<br>9.28<br>18.6<br>37.1<br>74.2        | 0.609<br>1.22<br>2.44<br>4.87<br>9.74<br>19.5<br>39.0<br>78.0 | Sec |

| CURRENT LIMIT                                                                                 |                                   |                                                                                                                                                                                |                                                                      |                                                                      |                                                                      |                                                               |     |

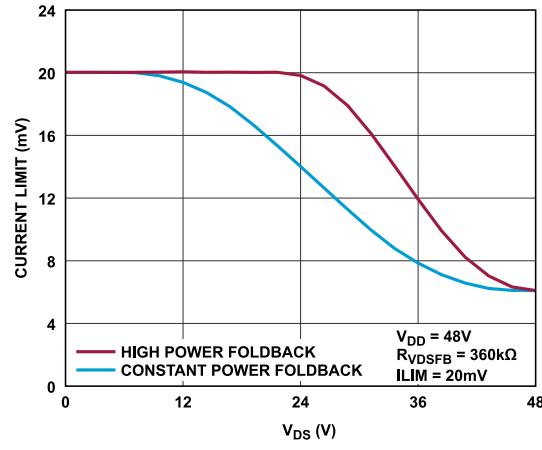

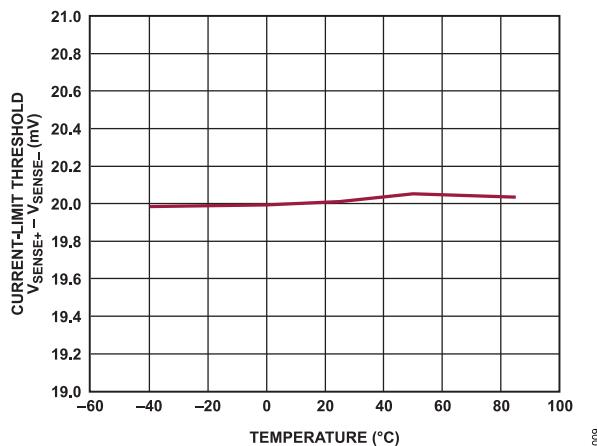

| Current-Limit Sense Voltage Threshold ( $V_{SENSE+} - V_{SENSE-}$ )                           | $\Delta V_{SNS}$                  | ILIM = 0000<br>ILIM = 1111                                                                                                                                                     | 4.67<br>18.55                                                        | 5<br>20                                                              | 5.33<br>21.45                                                        | mV                                                            |     |

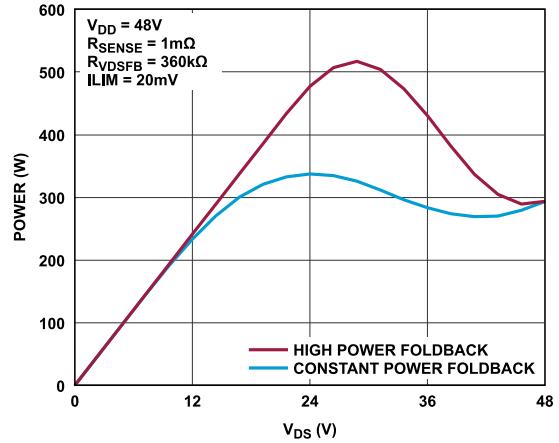

| Foldback Factor                                                                               | $\alpha$                          | 10%<br>30%                                                                                                                                                                     | 5<br>15                                                              | 10<br>30                                                             | 15<br>45                                                             | %                                                             |     |

| Current-Limit Sense Voltage Linearity                                                         | $V_{(TH)FPD}$                     |                                                                                                                                                                                |                                                                      | 0                                                                    | ±100                                                                 | μV                                                            |     |

| Fast Pull-Down Threshold Multiplier                                                           | $I_{SENSE1+(IN)}/I_{SENSE2+(IN)}$ |                                                                                                                                                                                |                                                                      | 3                                                                    |                                                                      | Ratio                                                         |     |

| SENSE1+ and SENSE2+ Input Current                                                             |                                   | SENSE1+ = SENSE2+ = SENSE1- = SENSE2- = 48 V                                                                                                                                   | 0                                                                    | 120                                                                  | 250                                                                  | μA                                                            |     |

## ELECTRICAL CHARACTERISTICS

Table 1. Electrical Characteristics (Continued)

| Parameter                                     | Symbol                      | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                    | Min                                | Typ                                  | Max                              | Unit                 |   |

|-----------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------------------------|----------------------------------|----------------------|---|

| SENSE1- Input Current                         | $I_{SENSE1- (IN)}$          | SENSE1- = SENSE1+ = 48 V, all other modes<br>SENSE1- = SENSE1+ = 48 V, high stress staged start (HSSS) mode, Channel 2 off                                                                                                                                                                                                                                  | 0                                  | $\pm 1$                              |                                  | $\mu A$              |   |

| SENSE2- Input Current                         | $I_{SENSE2- (IN)}$          | SENSE2- = SENSE2+ = 48 V                                                                                                                                                                                                                                                                                                                                    | 0                                  | $\pm 1$                              |                                  | $\mu A$              |   |

| OVERCURRENT TIMER                             |                             |                                                                                                                                                                                                                                                                                                                                                             |                                    |                                      |                                  |                      |   |

| TMR Fault Threshold                           | $V_{TMR (H)}$               | $V_{TMR}$ rising                                                                                                                                                                                                                                                                                                                                            | 2.5                                | 2.56                                 | 2.62                             | V                    |   |

| TMR Low Threshold                             | $V_{TMR (L)}$               | $V_{TMR}$ falling                                                                                                                                                                                                                                                                                                                                           | 0.18                               | 0.2                                  | 0.22                             | V                    |   |

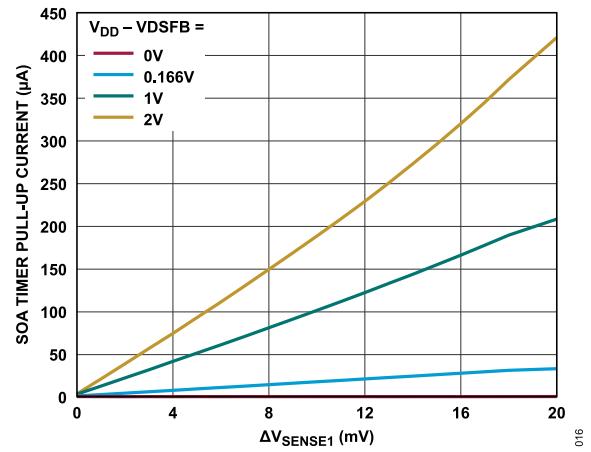

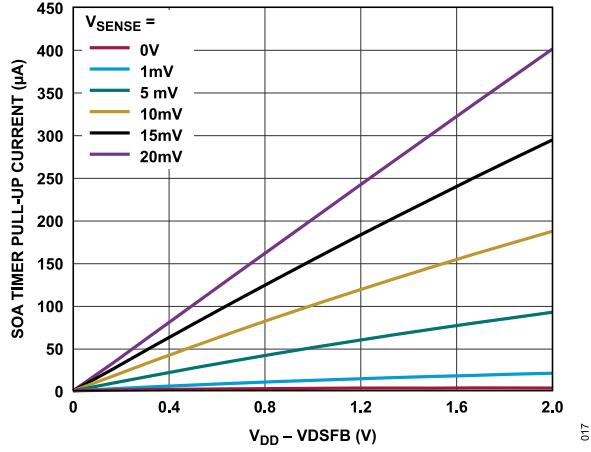

| TMR Thermal Pull-Up Current                   | $I_{TMR, THERM (UP)}$       | $V_{TMR} = 0 V$ , SENSE2+ - SENSE2- ( $\Delta V_{SNS2}$ ) = 10 mV, $V_{DD}$ - VDSFB voltage ( $V_{VDSFB}$ ) = 6 V<br>$V_{TMR} = 0 V$ , $\Delta V_{SNS2} = 0$ mV, $V_{DD}$ - $V_{VDSFB} = 0$ V<br>$V_{TMR} = 0 V$ , $\Delta V_{SNS2} = 1.6$ mV, $V_{DD}$ - $V_{VDSFB} = 12$ V<br>$V_{TMR} = 0 V$ , $\Delta V_{SNS2} = 20$ mV, $V_{DD}$ - $V_{VDSFB} = 50$ mV | -120                               | -100                                 | -80                              | $\mu A$              |   |

| TMR Pull-Up Current                           | $I_{TMR (UP)}$              | $V_{TMR} = 0 V$                                                                                                                                                                                                                                                                                                                                             | -5                                 | 0                                    | +1                               | $\mu A$              |   |

| TMR Pull-Down Current                         | $I_{TMR (DN)}$              | $V_{TMR} = 2.56$ V                                                                                                                                                                                                                                                                                                                                          | 3                                  | 5                                    | 7                                | $\mu A$              |   |

| INPUT PINS                                    |                             |                                                                                                                                                                                                                                                                                                                                                             |                                    |                                      |                                  |                      |   |

| UV, OV, and FB Threshold Voltage              | $V_{(TH) UV/OV/FB}$         | $V_{UV}/V_{OV}/V_{FB}$ rising                                                                                                                                                                                                                                                                                                                               | 2.51                               | 2.56                                 | 2.61                             | V                    |   |

| OV Threshold Voltage                          | $V_{(TH) OV-F}$             | OV voltage ( $V_{OV}$ ) falling                                                                                                                                                                                                                                                                                                                             | 2.4                                | 2.5                                  | 2.58                             | V                    |   |

| OV Hysteresis                                 | $\Delta V_{(HYST) OV}$      |                                                                                                                                                                                                                                                                                                                                                             |                                    | 55                                   |                                  | mV                   |   |

| FB Threshold Voltage                          | $V_{(TH) FBF}$              | FB voltage ( $V_{FB}$ ) falling                                                                                                                                                                                                                                                                                                                             | 2.4                                | 2.5                                  | 2.58                             | V                    |   |

| FB Hysteresis                                 | $\Delta V_{(HYST) FB}$      |                                                                                                                                                                                                                                                                                                                                                             |                                    | 79                                   |                                  | mV                   |   |

| UV Threshold Voltage                          | $V_{(TH) UVF}$              | UV voltage ( $V_{UV}$ ) falling                                                                                                                                                                                                                                                                                                                             | 2.15                               | 2.2                                  | 2.25                             | V                    |   |

| UV Hysteresis                                 | $\Delta V_{(HYST) UV}$      |                                                                                                                                                                                                                                                                                                                                                             |                                    | 360                                  |                                  | mV                   |   |

| UV Retry Threshold Voltage                    | $V_{(TH) UVR}$              | $V_{UV}$ falling<br>$V_{UV}$ rising                                                                                                                                                                                                                                                                                                                         | 0.95<br>1                          | 1.0<br>1.1                           | 1.05<br>1.2                      | V                    |   |

| UV Retry Threshold Hysteresis                 | $\Delta V_{(HYST) UVR}$     |                                                                                                                                                                                                                                                                                                                                                             |                                    | 100                                  |                                  | mV                   |   |

| ADR0, ADR1, and MODE Input High Threshold     | $V_{ADR, MODE (H)}$         |                                                                                                                                                                                                                                                                                                                                                             |                                    | $INTV_{CC}$<br>- 0.8                 | $INTV_{CC}$<br>- 0.5             | $INTV_{CC}$<br>- 0.2 | V |

| ADR0, ADR1, and MODE Input Low Threshold      | $V_{ADR, MODE (L)}$         |                                                                                                                                                                                                                                                                                                                                                             | 0.2                                | 0.5                                  | 0.8                              | V                    |   |

| ADR0, ADR1, and MODE Input Current            | $I_{ADR, MODE (IN)}$        | $V_{ADR, MODE} = 1$ V, $V_{PIN} = INTV_{CC} - 0.85$ V                                                                                                                                                                                                                                                                                                       |                                    |                                      | $\pm 10$                         | $\mu A$              |   |

| EN and GPIO1 to GPIO8 Input Threshold Voltage | $V_{EN/GPIO (TH)}$          | $V_{EN/GPIO}$ rising                                                                                                                                                                                                                                                                                                                                        | 1.25                               | 1.28                                 | 1.31                             | V                    |   |

| EN and GPIO1 to GPIO8 Hysteresis              | $\Delta V_{EN/GPIO (HYST)}$ |                                                                                                                                                                                                                                                                                                                                                             |                                    | 20                                   |                                  | mV                   |   |

| VDSFB Internal Resistor                       | $R_{VDSFB}$                 |                                                                                                                                                                                                                                                                                                                                                             | 75                                 | 120                                  | 150                              | $k\Omega$            |   |

| VDSFB Leakage Current                         | $I_{LEAK, VDSFB}$           | $V_{DSFB} = 0$ V, $V_{DD} = 80$ V, FET off                                                                                                                                                                                                                                                                                                                  | 0                                  | $\pm 1$                              |                                  | $\mu A$              |   |

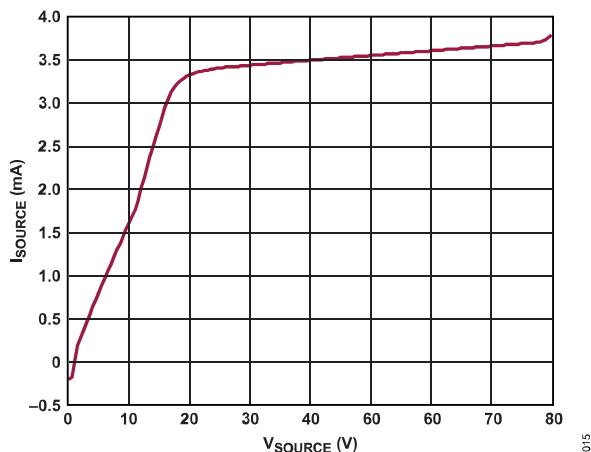

| SOURCE Input Current                          | $I_{SOURCE}$                | $V_{SOURCE} = 48$ V, FET on<br>$V_{SOURCE} = 0$ V, FET off<br>$V_{SOURCE} = 2$ V, FET off                                                                                                                                                                                                                                                                   |                                    |                                      | 300<br>-200<br>500               | $\mu A$              |   |

| GPIO5 (COMM) Pin Threshold Voltage            | $V_{GPIO5 (TH)}$            | Low 1, low stress staged start mode (LSSS) on<br>Low 2, global on<br>High, global electronic current limit (ECL) engaged                                                                                                                                                                                                                                    | 0.18<br>1.05<br>$INTV_{CC}$<br>- 2 | 0.25<br>1.55<br>$INTV_{CC}$<br>- 1.5 | 0.3<br>1.9<br>$INTV_{CC}$<br>- 1 | V                    |   |

| GPIO5 (COMM) Pin Clamp Voltage                | $V_{GPIO5 (CLAMP)}$         | Low<br>Mid                                                                                                                                                                                                                                                                                                                                                  | 0.35<br>2.3                        | 0.75<br>2.56                         | 1.0<br>2.7                       | V                    |   |

## ELECTRICAL CHARACTERISTICS

Table 1. Electrical Characteristics (Continued)

| Parameter                                             | Symbol                     | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Min                                                                                                   | Typ      | Max           | Unit                                                                                                                                                                           |

|-------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO5 (COMM) Pin,<br>OV, UV, EN, and FB Input Current | $I_{GPIO5}$<br>$I_{INPUT}$ | Source current<br>Sink current<br>OV, UV, EN, and FB = 3 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -4<br>3                                                                                               | -5<br>0  | -6<br>$\pm 1$ | $\mu A$<br>$mA$<br>$\mu A$                                                                                                                                                     |

| OUTPUT PINS                                           |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |          |               |                                                                                                                                                                                |

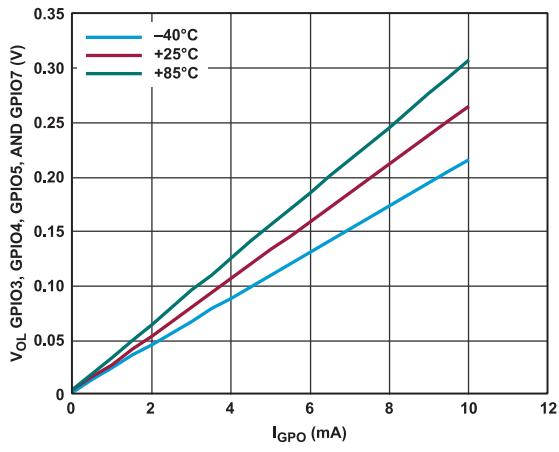

| GPIO1 to GPIO8 Output Low Voltage                     | $V_{OL, GPIO}$             | GPIO1 to GPIO8 current ( $I_{GPIO1 \text{ to } GPIO8}$ ) = 3 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       | 0.2      | 0.5           | V                                                                                                                                                                              |

| GPIO1 to GPIO8 Leakage Current                        | $I_{LEAK, GPIO}$           | GPIO4 and GPIO8 = 6 V, GPIO1, GPIO2, and GPIO6 = 80 V, GPIO3, GPIO5, GPIO7 = $INTV_{CC}$                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       | 0        | $\pm 1$       | $\mu A$                                                                                                                                                                        |

| GPIO3 Pull-Up Current                                 | $I_{PU\_GPIO3}$            | GPIO3 configured as GPO or $I_{OUT\_OC\_STATUS}$ output                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -8                                                                                                    | -10      | -12           | $\mu A$                                                                                                                                                                        |

| GPIO5 Pull-Up Current                                 | $I_{PU\_GPIO5}$            | GPIO5 configured as GPO or $SHED\_LOADS$ output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -4                                                                                                    | -5       | -6            | $\mu A$                                                                                                                                                                        |

| ADC                                                   |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |          |               |                                                                                                                                                                                |

| Resolution (No Missing Codes) <sup>2</sup>            |                            | All channels<br>15BIT = 0<br>15BIT = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12<br>15                                                                                              |          |               | Bits<br>Bits                                                                                                                                                                   |

| Full-Scale Voltage                                    | $V_{FS}$                   | ( $ADC^+ - ADC^-$ ), ( $SENSE1^+ / SENSE2^+ - SENSE1^- / SENSE2^-$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       | 32       |               | mV                                                                                                                                                                             |

| LSB Step Voltage                                      | LSB                        | $V_{DS}$<br>ADIN1 to ADIN2<br>$V_{IN}(V_{DD}) / V_{OUT}$ (SOURCE), 25 V range<br>$V_{IN}(V_{DD}) / V_{OUT}$ (SOURCE), 100 V range<br>( $ADC^+ - ADC^-$ ), ( $SENSE1^+ / SENSE2^+ - SENSE1^- / SENSE2^-$ )<br>15_BIT_MODE = 0<br>15_BIT_MODE = 1<br>$V_{DS}$<br>15_BIT_MODE = 0<br>15_BIT_MODE = 1<br>ADIN1 to ADIN2<br>15_BIT_MODE = 0<br>15_BIT_MODE = 1<br>$V_{IN}(V_{DD}) / V_{OUT}$ (SOURCE), 25 V range<br>15_BIT_MODE = 0<br>15_BIT_MODE = 1<br>$V_{IN}(V_{DD}) / V_{OUT}$ (SOURCE), 100 V range<br>15 bit = 0<br>15 bit = 1 | 320<br>2.56<br>25.6<br>102.4<br>7.8<br>0.98<br>78<br>9.8<br>0.625<br>78<br>6.25<br>0.78<br>25<br>3.13 |          |               | mV<br>mV<br>mV<br>mV<br>$\mu V$<br>$\mu V$ |

| Offset Error, 15BIT = 0                               | $V_{OS}$                   | $ADC^+ - ADC^-$ , $SENSE1^+ / SENSE2^+ - SENSE1^- / SENSE2^-$<br>$V_{DD}$ /SOURCE, ADIN1 to ADIN2<br>$V_{DS}$                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                       | $\pm 20$ |               | LSB                                                                                                                                                                            |

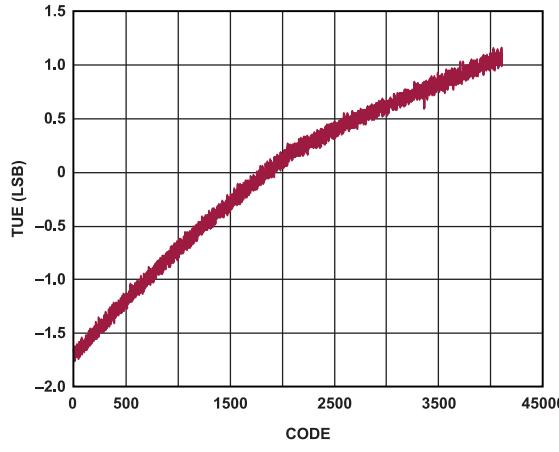

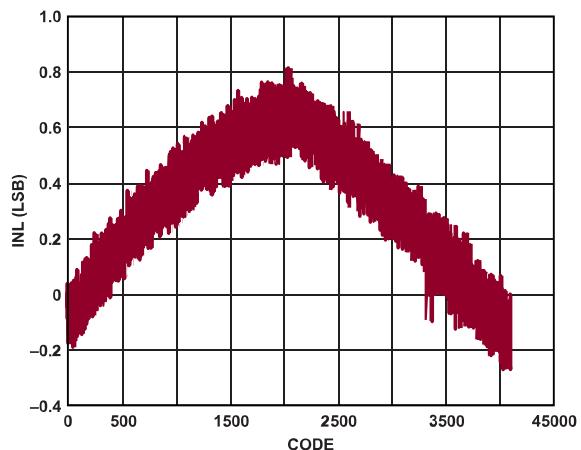

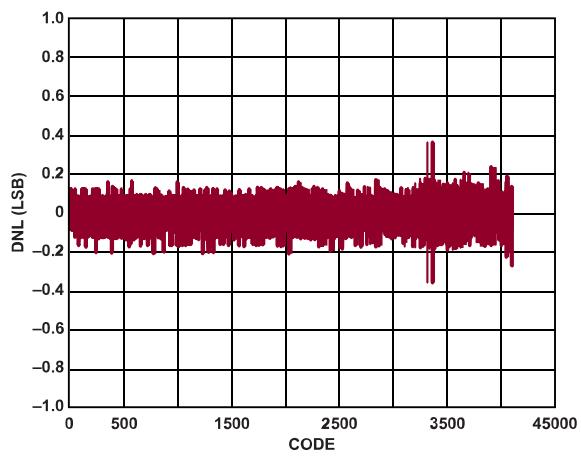

| Integral Nonlinearity, 15BIT = 0                      | INL                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       | $\pm 1$  |               | LSB                                                                                                                                                                            |

| Full-Scale Error, 15BIT = 0                           | FSE                        | ( $ADC^+ - ADC^-$ ), $V_{DD}$ /SOURCE, ADIN1 to ADIN2<br>( $SENSE1^+ / SENSE2^+ - SENSE1^- / SENSE2^-$ ), $V_{DS}$                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       | $\pm 1$  | $\pm 1$       | %                                                                                                                                                                              |

|                                                       |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -3                                                                                                    |          | $\pm 1$       | %                                                                                                                                                                              |

## ELECTRICAL CHARACTERISTICS

Table 1. Electrical Characteristics (Continued)

| Parameter                                                                  | Symbol     | Test Conditions/Comments                                     | Min  | Typ  | Max  | Unit |  |

|----------------------------------------------------------------------------|------------|--------------------------------------------------------------|------|------|------|------|--|

| Refresh Rate in Continuous Mode, Internal Oscillator                       | $f_{CONV}$ | (ADC+ – ADC-), $V_{DD}$ /SOURCE, ADIN1-2, POWER              |      |      |      |      |  |

|                                                                            |            | 15_BIT_MODE = 0                                              | 3.36 | 3.53 | 3.71 | kHz  |  |

|                                                                            |            | 15_BIT_MODE = 1                                              | 421  | 442  | 465  | Hz   |  |

|                                                                            |            | (SENSE1+/SENSE2+ – SENSE1-/SENSE2-), $V_{DS}$                |      |      |      |      |  |

|                                                                            |            | 15_BIT_MODE = 0                                              | 1.68 | 1.77 | 1.86 | kHz  |  |

|                                                                            |            | 15_BIT_MODE = 1                                              | 210  | 221  | 232  | Hz   |  |

|                                                                            |            | (ADC+ – ADC-), (SENSE1+/SENSE2+ – SENSE1-/SENSE2-), $V_{DS}$ |      |      |      |      |  |

|                                                                            |            | 15_BIT_MODE = 0                                              | 269  | 283  | 310  | μs   |  |

|                                                                            |            | 15_BIT_MODE = 1                                              | 2.15 | 2.26 | 2.37 | ms   |  |

|                                                                            |            | $V_{DD}$ /SOURCE, ADIN1-2                                    |      |      |      |      |  |

| Individual Channel Conversion Time, Internal Oscillator                    | $t_{CONV}$ | 15_BIT_MODE = 0                                              | 269  | 283  | 310  | μs   |  |

|                                                                            |            | 15_BIT_MODE = 1                                              | 2.15 | 2.26 | 2.37 | ms   |  |

|                                                                            |            | $V_{DD}$ /SOURCE, ADIN1-2                                    |      |      |      |      |  |

|                                                                            |            | 15_BIT_MODE = 0                                              | 269  | 283  | 310  | μs   |  |

|                                                                            |            | 15_BIT_MODE = 1                                              | 2.15 | 2.26 | 2.37 | ms   |  |

|                                                                            |            | ADC+ = $V_{DD}$ = 48 V, ADC- = $V_{DD}$ – 21.3 mV            |      | 73   | 132  | μA   |  |

|                                                                            |            | ADC+ = $V_{DD}$ = 48 V, ADC- = $V_{DD}$ – 21.3 mV            |      | 0    | ±1   | μA   |  |

|                                                                            |            | ADIN1 to ADIN2 = 2 V                                         | 2    | 10   |      | MΩ   |  |

|                                                                            |            | ADIN1 to ADIN2 = 2 V                                         | 0    | ±1   |      | μA   |  |

|                                                                            |            |                                                              |      |      |      |      |  |

| TEMPERATURE MEASUREMENT                                                    |            |                                                              |      |      |      |      |  |

| Resolution (No Missing Codes) <sup>2</sup>                                 |            |                                                              |      |      |      |      |  |

| Refresh Rate in Continuous Mode                                            |            |                                                              |      |      |      |      |  |

| $f_{TCONV}$                                                                |            |                                                              |      |      |      |      |  |

| $R_{TFS}$                                                                  |            |                                                              |      |      |      |      |  |

| $R_{TOP}$                                                                  |            |                                                              |      |      |      |      |  |

| $T_{RMT}$                                                                  |            |                                                              |      |      |      |      |  |

| -40°C to +125°C <sup>3</sup>                                               |            |                                                              |      |      |      |      |  |

| Remote Temperature Error, $\eta$ = 1.004                                   |            |                                                              |      |      |      |      |  |

| Temperature LSB Step                                                       |            |                                                              |      |      |      |      |  |

| $LSB_{TEMP}$                                                               |            |                                                              |      |      |      |      |  |

| TEMP Current                                                               |            |                                                              |      |      |      |      |  |

| SMBus INTERFACE <sup>4</sup>                                               | $I_{TEMP}$ | Low level                                                    |      | 10   |      | μA   |  |

|                                                                            |            | Midlevel                                                     |      | 80   |      | μA   |  |

|                                                                            |            | High level                                                   |      | 150  |      | μA   |  |

|                                                                            |            |                                                              |      |      |      |      |  |

|                                                                            |            |                                                              |      |      |      |      |  |

| SMBus INTERFACE TIMING <sup>24</sup>                                       |            |                                                              |      |      |      |      |  |

| SCL Clock Frequency                                                        |            |                                                              |      |      |      |      |  |

| $f_{SCL}$                                                                  |            |                                                              |      |      |      |      |  |

| SCL Low Period                                                             |            |                                                              |      |      |      |      |  |

| $t_{LOW}$                                                                  |            |                                                              |      |      |      |      |  |

| SCL High Period                                                            |            |                                                              |      |      |      |      |  |

| $t_{HIGH}$                                                                 |            |                                                              |      |      |      |      |  |

| Data Setup Time                                                            |            |                                                              |      |      |      |      |  |

| $t_{SU, DAT}$                                                              |            |                                                              |      |      |      |      |  |

| Data Hold Time                                                             |            |                                                              |      |      |      |      |  |

| $t_{HD, DAT}$                                                              |            |                                                              |      |      |      |      |  |

| Hold Time Start Bit                                                        |            |                                                              |      |      |      |      |  |

| $t_{HD, STA}$                                                              |            |                                                              |      |      |      |      |  |

| Setup Time for Repeated Start                                              |            |                                                              |      |      |      |      |  |

| $t_{SU, STA}$                                                              |            |                                                              |      |      |      |      |  |

| Setup Time for Stop Bit                                                    |            |                                                              |      |      |      |      |  |

| $t_{SU, STO}$                                                              |            |                                                              |      |      |      |      |  |

| SDAO Delay                                                                 |            |                                                              |      |      |      |      |  |

| SDAO delay from SCL ↓ for maximum load capacitance ( $C_{LOAD}$ ) = 550 pF |            |                                                              |      |      |      |      |  |

| SEL_1M = 0                                                                 |            |                                                              |      |      |      |      |  |

| 100                                                                        |            |                                                              |      |      |      |      |  |

| SEL_1M = 1                                                                 |            |                                                              |      |      |      |      |  |

| 75                                                                         |            |                                                              |      |      |      |      |  |

| 125                                                                        |            |                                                              |      |      |      |      |  |

| 220                                                                        |            |                                                              |      |      |      |      |  |

## ELECTRICAL CHARACTERISTICS

Table 1. Electrical Characteristics (Continued)

| Parameter                                                    | Symbol             | Test Conditions/Comments                                                                                       | Min                  | Typ                  | Max               | Unit    |

|--------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------|----------------------|----------------------|-------------------|---------|

| SCL or SDAI Pulse Spike Rejection <sup>2</sup>               | $t_{PW}$           |                                                                                                                | 55                   | 75                   | 110               | ns      |

| PMBus Stuck Bus Timeout                                      | $t_D$ (STUCK)      |                                                                                                                | 25                   | 30                   | 35                | ms      |

| SCL and SDA Input Capacitance                                | $C_X$              | SDAI tied to SDAO                                                                                              | 5                    | 10                   |                   | pF      |

| SERIAL PERIPHERAL INTERFACE (SPI)                            |                    |                                                                                                                |                      |                      |                   |         |

| SIO Input Low Voltage                                        | $V_{IL}$           |                                                                                                                | -0.3                 | $0.3 \times DV_{CC}$ |                   | V       |

| SIO Input High Voltage                                       | $V_{IH}$           |                                                                                                                | $0.7 \times DV_{CC}$ | $DV_{CC} + 0.3$      |                   | V       |

| $\overline{CS}$ , SCK, and SIO Output Threshold Low Voltage  | $V_{OL}$           | Output low threshold current ( $I_{OL}$ ) = 3 mA                                                               |                      | 0.4                  |                   | V       |

| $\overline{CS}$ , SCK, and SIO Output Threshold High Voltage | $V_{OH}$           | Output high threshold current ( $I_{OH}$ ) = -1.6 mA                                                           | $DV_{CC} - 0.8$      |                      |                   | V       |

| $\overline{CS}$ , SCK, and SIO Tristate Input Current        | $I_{CS, SCK, SIO}$ | CS, SCK, and SIO = 5 V                                                                                         | 0                    | $\pm 1$              |                   | $\mu A$ |

| SIO, SCK, and $\overline{CS}$ Rise Time                      | $t_{RISE}$         | $C_{LOAD} = 50 \text{ pF}$                                                                                     |                      | 100                  |                   | ns      |

| SIO, SCK, and $\overline{CS}$ Fall Time                      | $t_{FALL}$         | $C_{LOAD} = 50 \text{ pF}$                                                                                     |                      | 40                   |                   | ns      |

| CONFIGURATION WITHOUT EEPROM                                 |                    |                                                                                                                |                      |                      |                   |         |

| SIO Input High Threshold Voltage                             | $V_{SIO-SU(H)}$    | Only during device configuration at startup                                                                    | $INTV_{CC} - 0.8$    | $INTV_{CC} - 0.5$    | $INTV_{CC} - 0.2$ | V       |

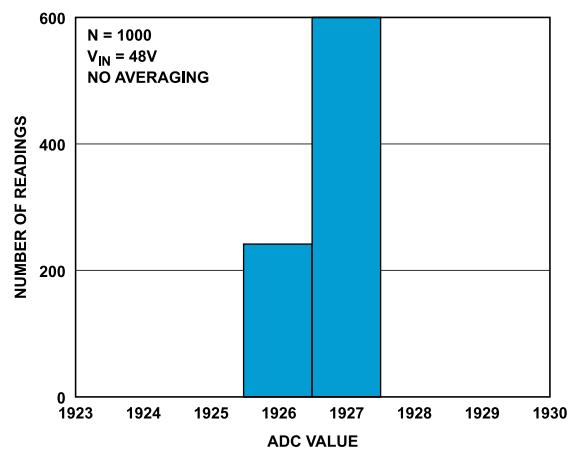

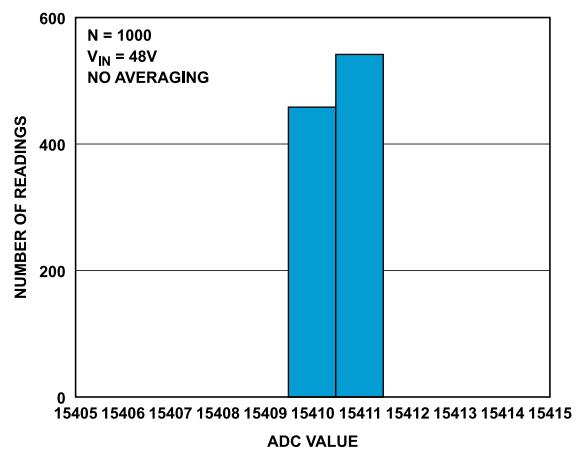

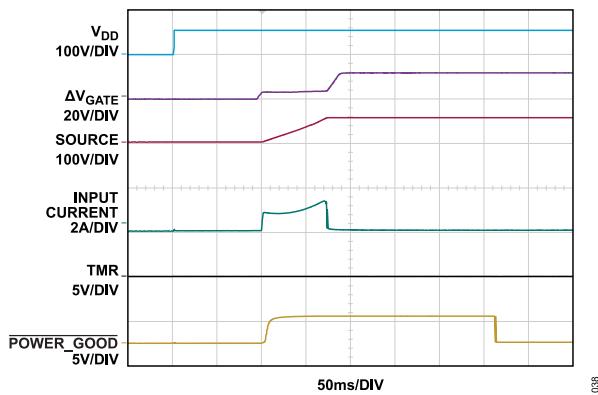

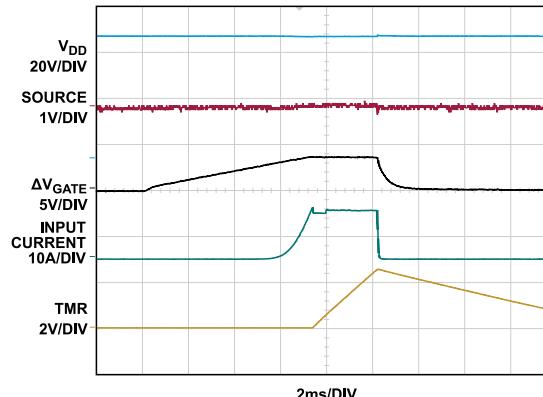

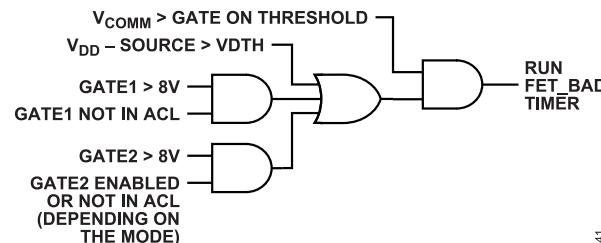

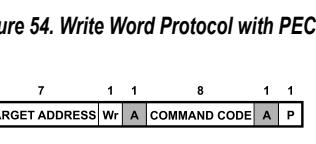

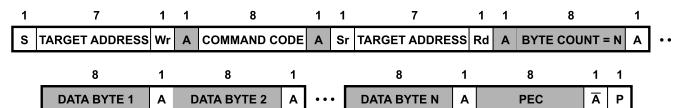

| SIO Input Low Threshold Voltage                              | $V_{SIO-SU(L)}$    | Only during device configuration at startup                                                                    | 0.2                  | 0.5                  | 0.8               | V       |