## MAX77542

# 16V<sub>IN</sub>/16A, Quad-Phase High-Efficiency Buck Converter

### General Description

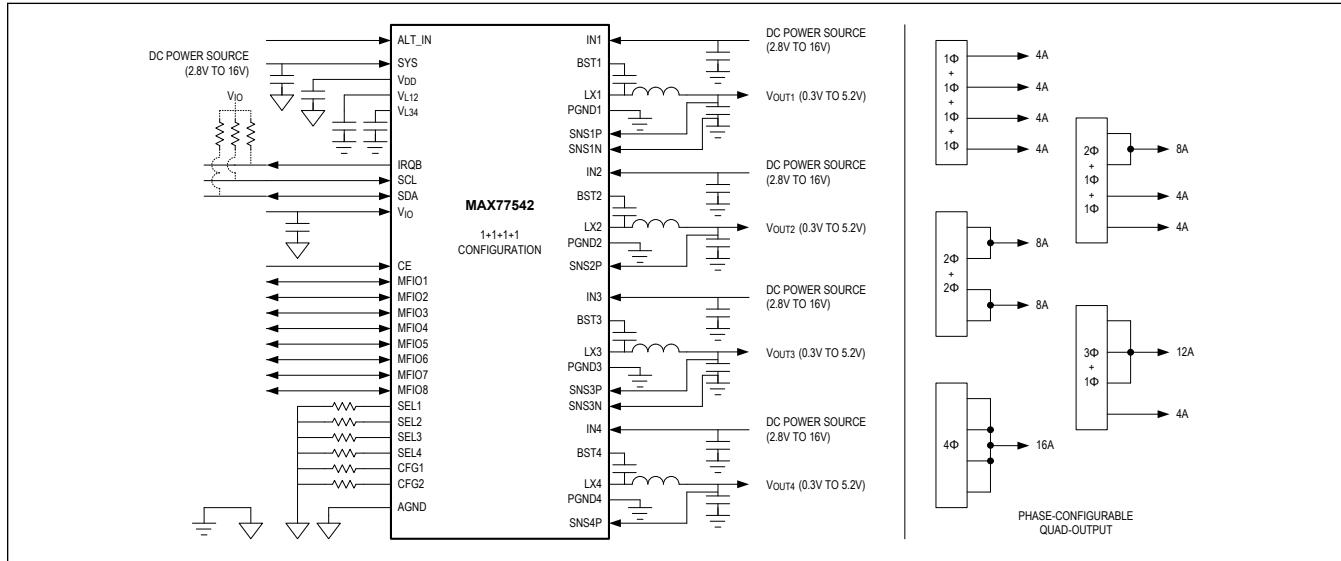

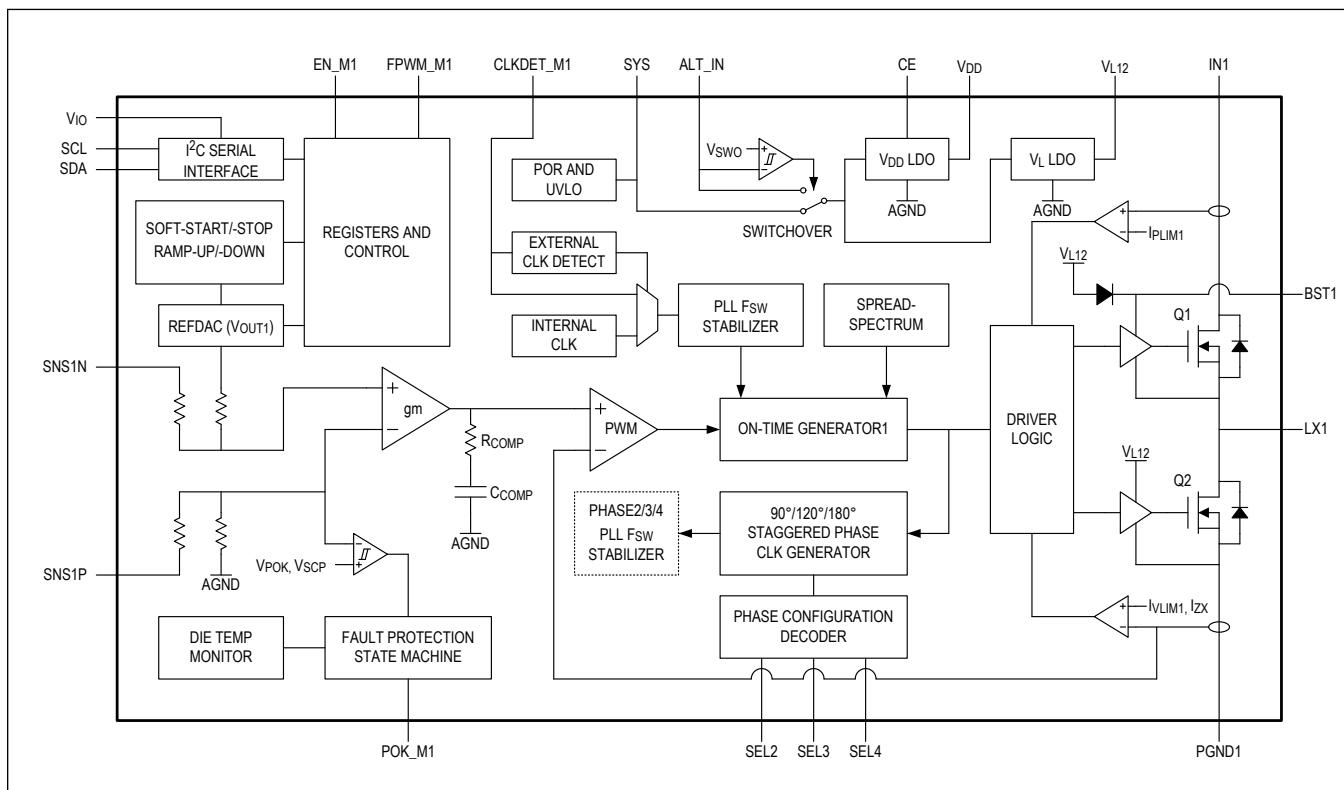

The MAX77542 is a high-efficiency step-down converter with four 4A switching phases. It uses an adaptive constant on-time (COT) current-mode control scheme and its flexible architecture supports five phase configurations. Its wide input-voltage range enables a direct conversion for less than 1V outputs from 1 to 3-cell Li<sup>+</sup> batteries and USB power delivery (PD) supply rails. The output voltages are preset with resistors and are further adjustable through an I<sup>2</sup>C-compatible interface.

Flexible sequencer and programmable soft-start/soft-stop slew rates provide controlled transitions between operating states. Programmable switching frequency, frequency tracking, and spread-spectrum features allow easier system optimization for noise-sensitive applications. Multifunction I/Os allow for flexible control of each output for EN, LPM, FPWM, POK, RSTINB, and RSTOB status. An array of built-in protections ensures safe operation under abnormal operating conditions.

### Applications

- 1 to 3-Cell Li<sup>+</sup> and USB-C Power Delivery Systems

- Audio/Video Equipment and PCIe/RAID Cards

- Application Processors, FPGAs, DSPs, and ASICs

### Benefits and Features

- 2.8V to 16V Input-Voltage Range

- 0.3V to 5.2V Output-Voltage Range

- Max 16A (4A/Φ) with Five Phase Configurations

- $\pm 0.5\%$  V<sub>OUT</sub> Accuracy (Default V<sub>OUT</sub> at +25°C)

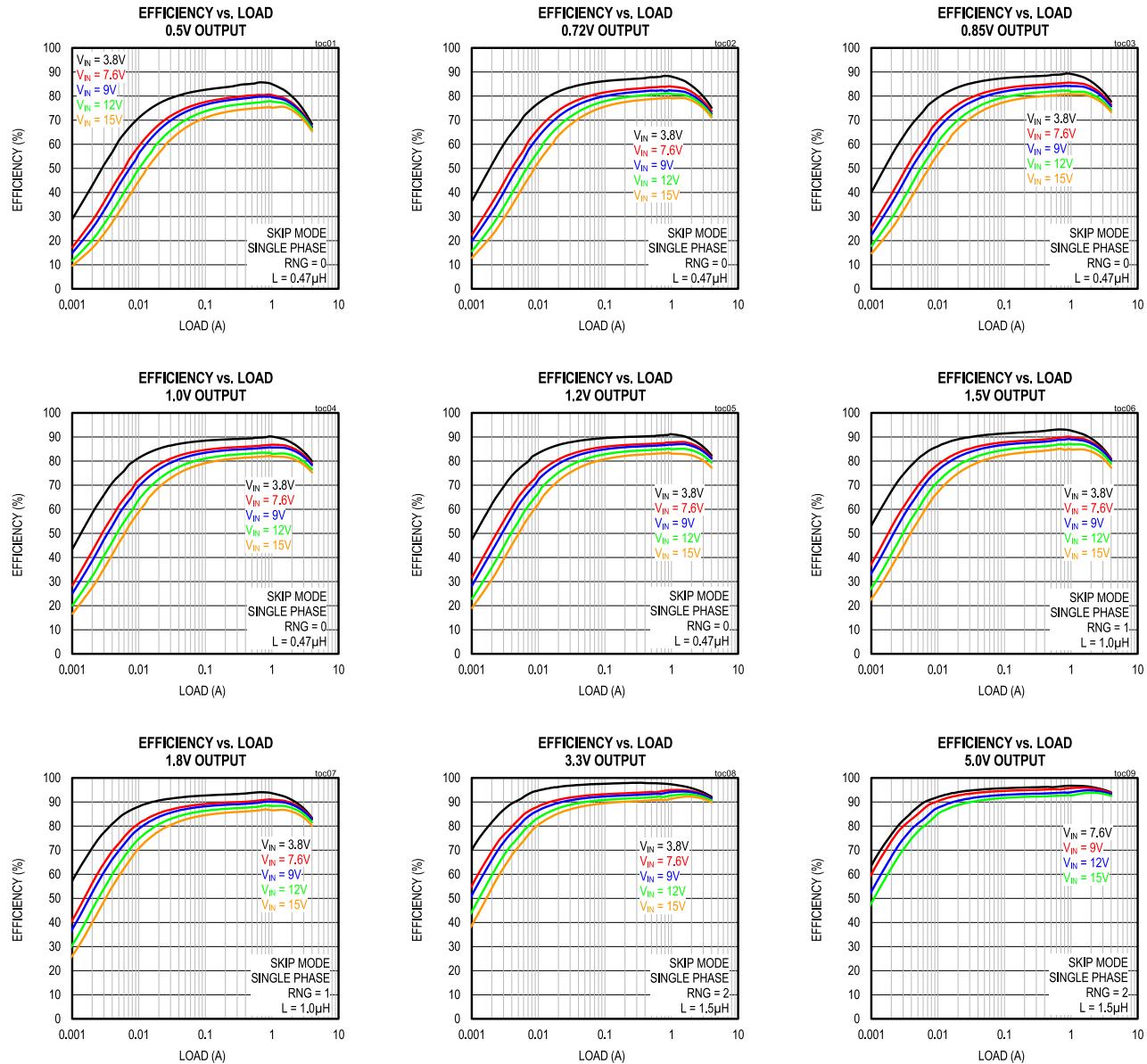

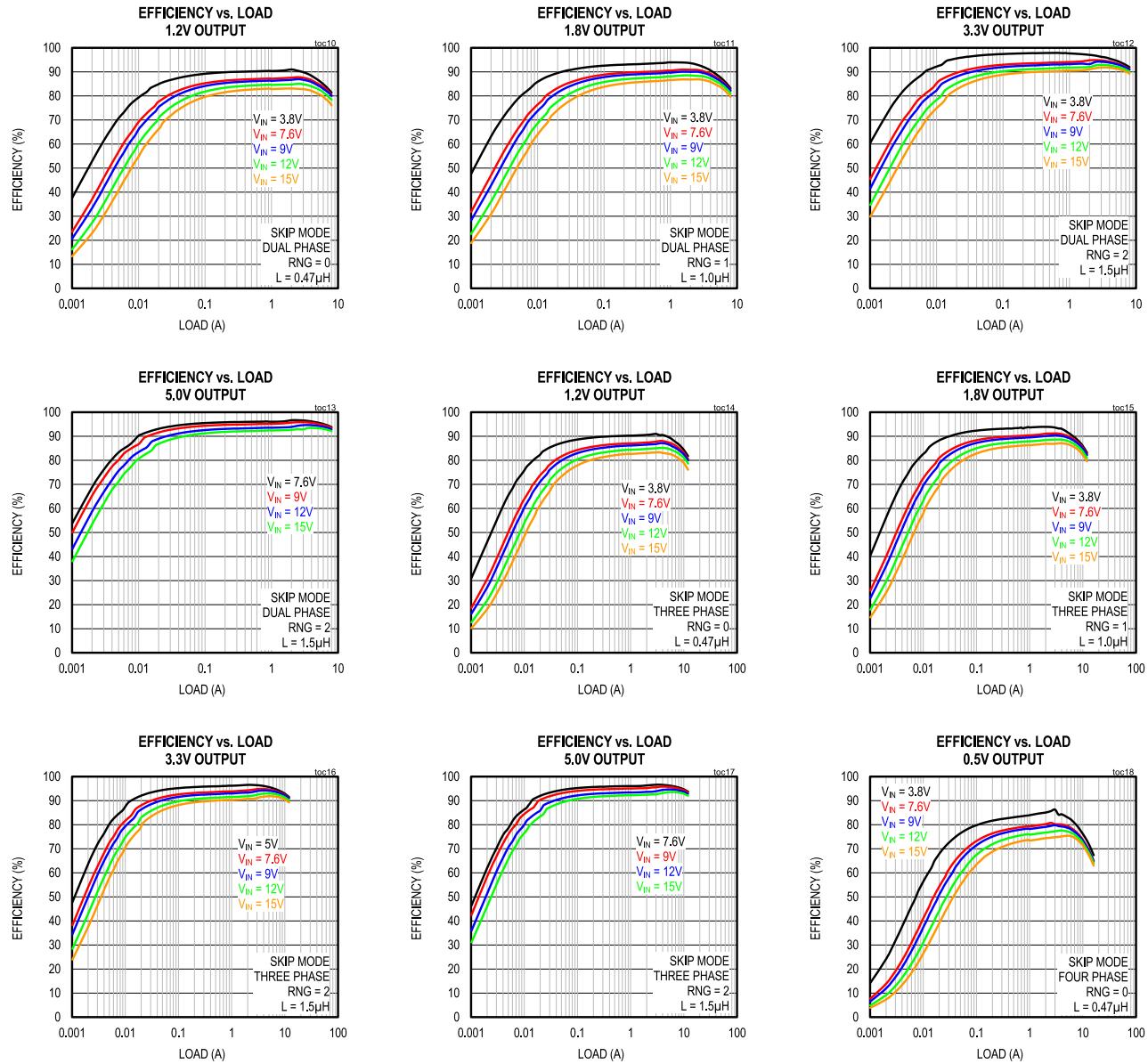

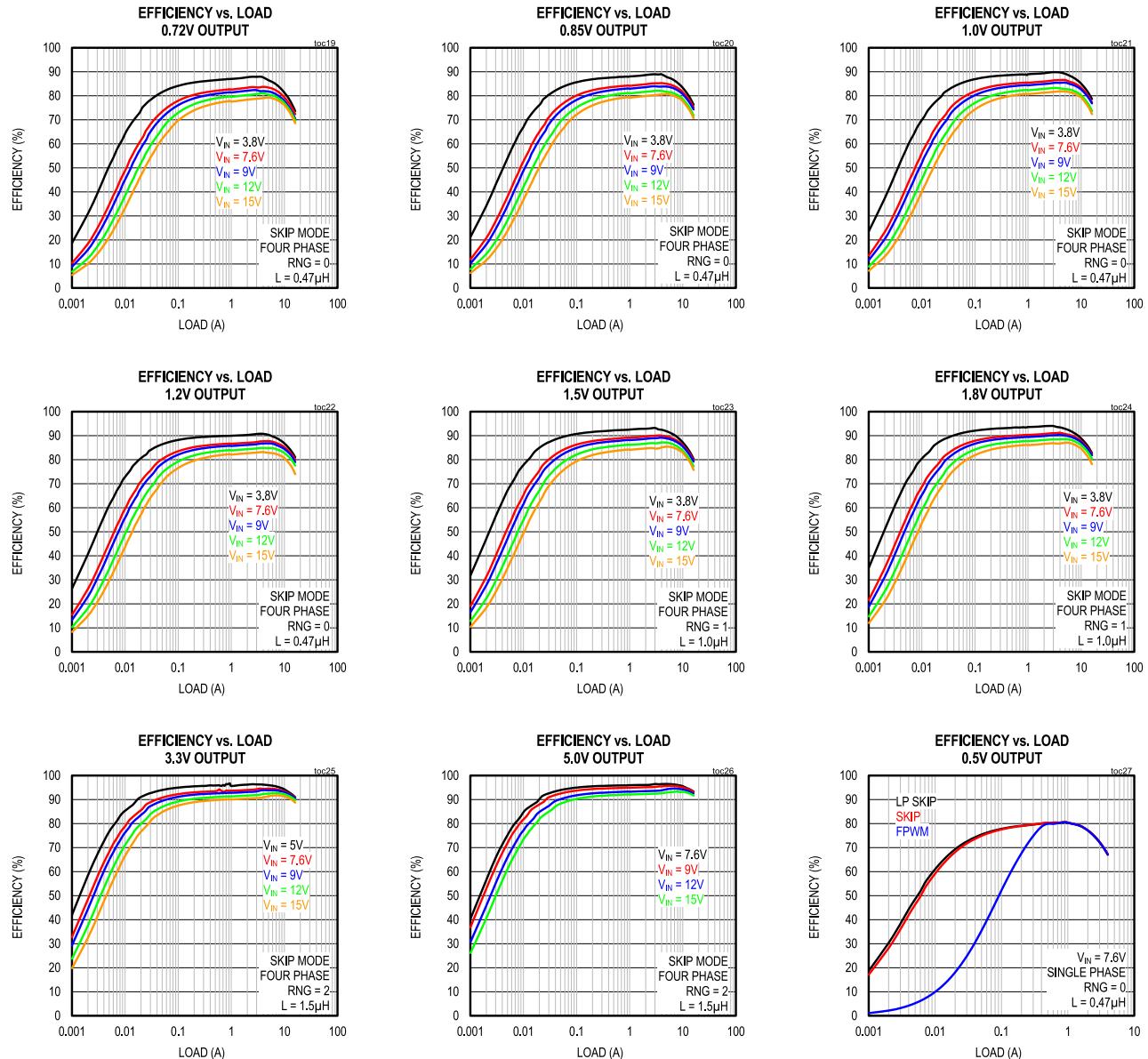

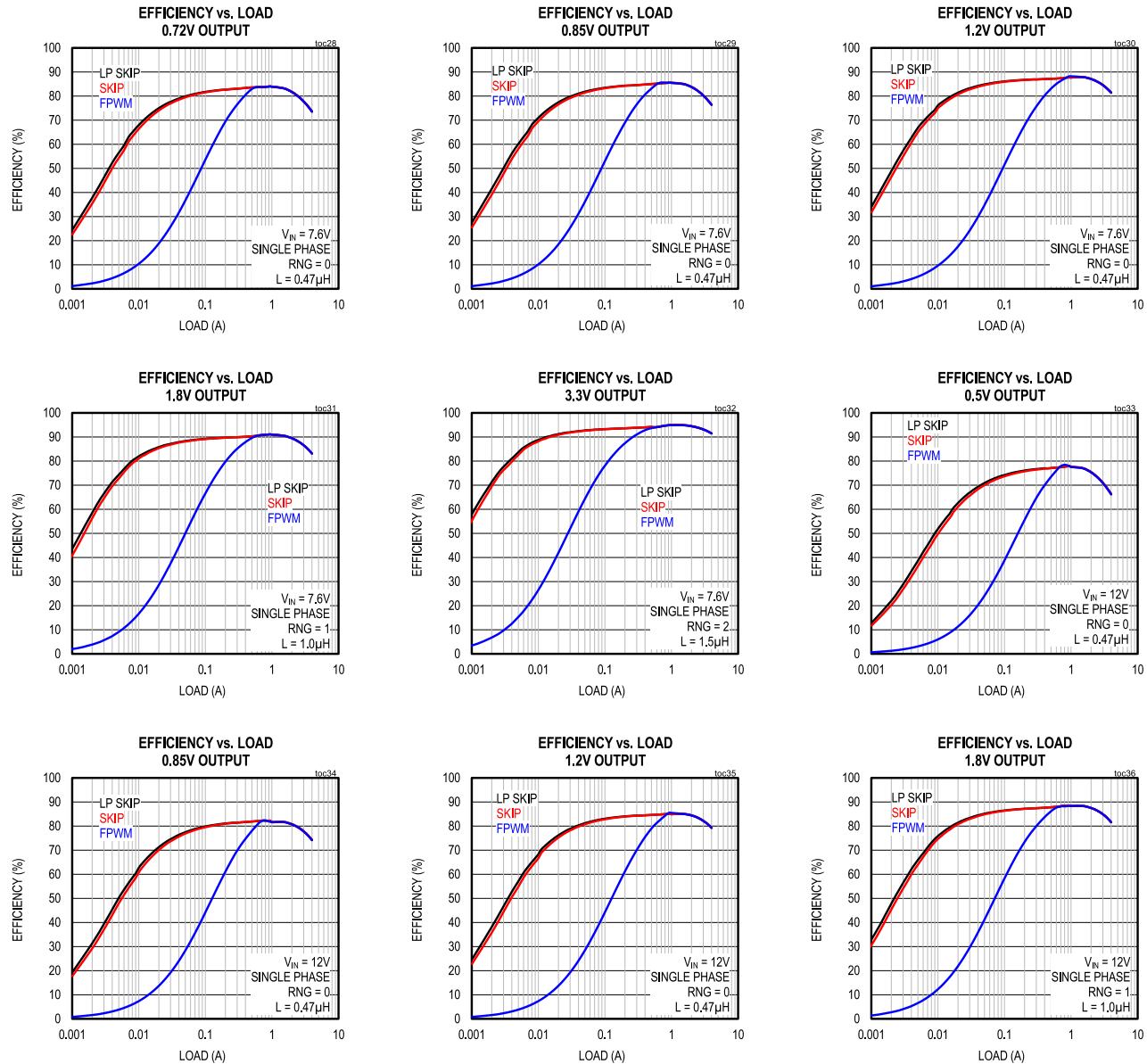

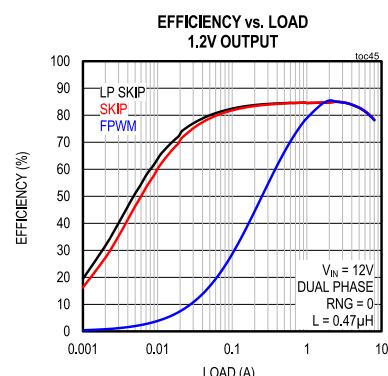

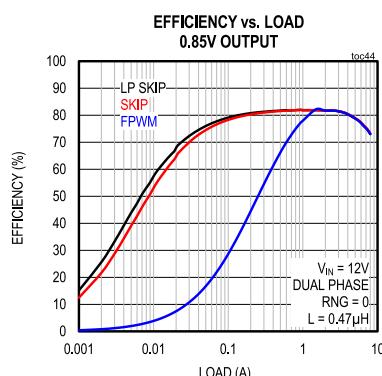

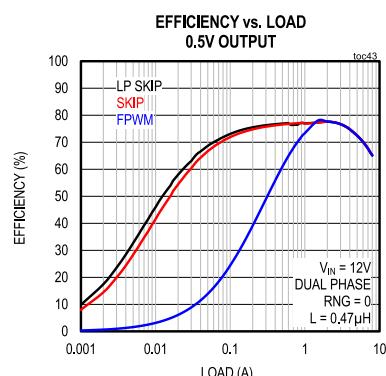

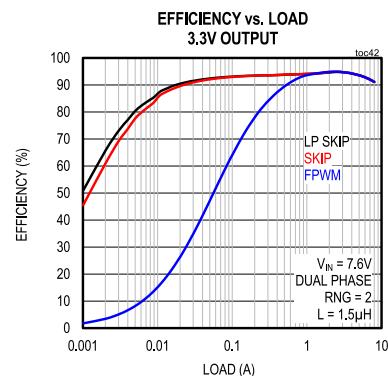

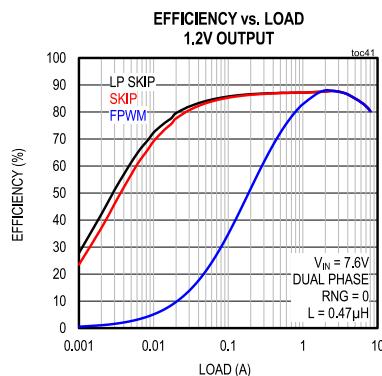

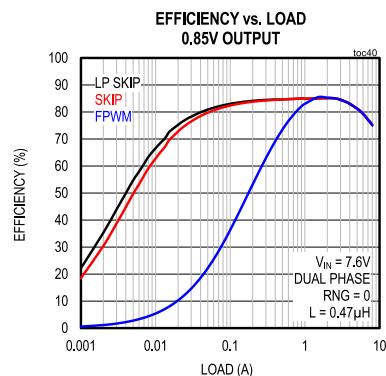

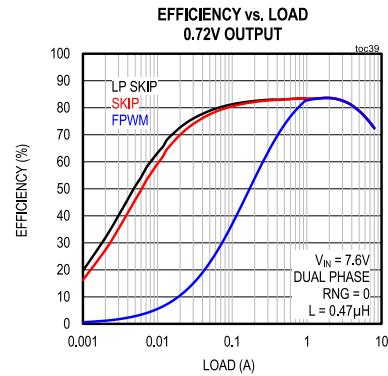

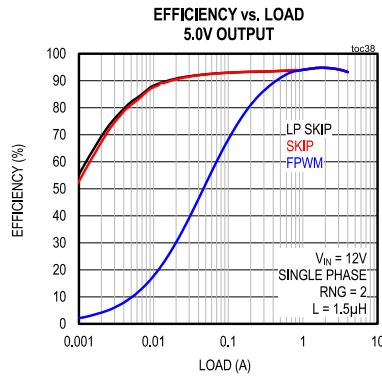

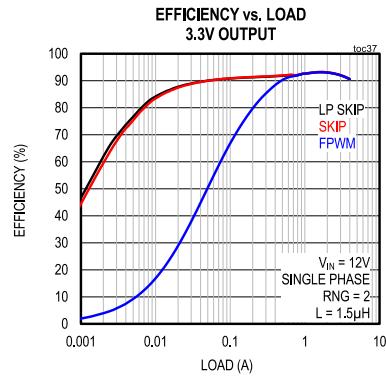

- 94% Peak Efficiency (7.6V<sub>IN</sub>, 3.3V<sub>OUT</sub>, 1MHz)

- Auto Skip/PWM Transition and Low-Power Mode

- Drop-Out Operation with 98% of Max Duty Cycle

- Differential Output-Voltage Sensing

- Flexible Sequencer with Soft-Start/Soft-Stop Slew Rates

- Prebiased Startup and Active Output Discharge

- 0.5MHz/1.0MHz/1.5MHz Nominal Switching Frequency

- Spread-Spectrum Modulation for EMI Reduction

- Internal/External Frequency Tracking

- Default V<sub>OUT</sub> and Phase Configuration Setting by R<sub>SELx</sub>

- Multifunction I/Os for EN, LPM, FPWM, and POK

- UVLO, Thermal-Shutdown, and Short-Circuit Protection

- High-Speed, I<sup>2</sup>C Serial Interface

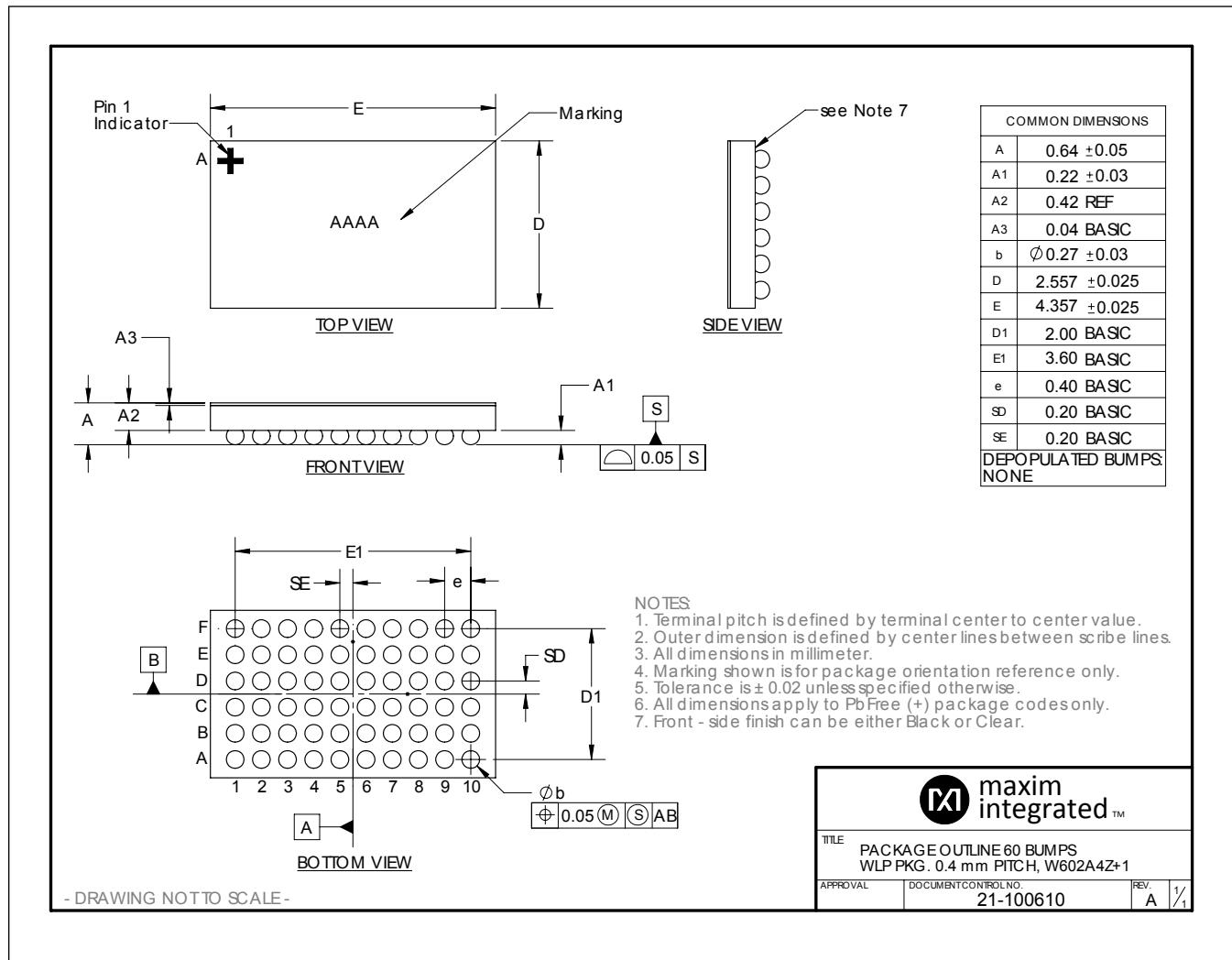

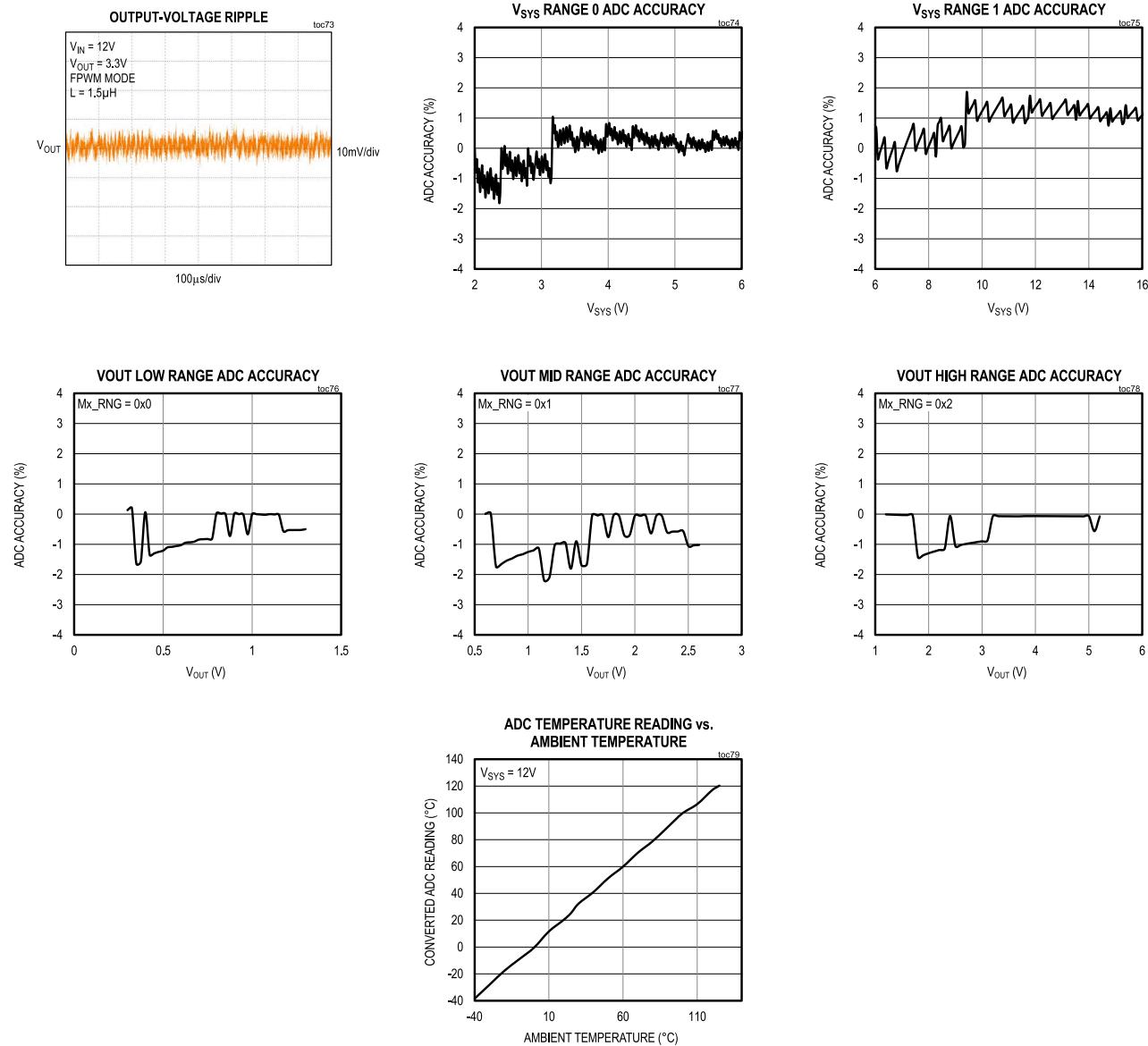

- Available in 60-Bump WLP (4.36mm x 2.56mm x 0.65mm)

- Less than 115mm<sup>2</sup> Total Solution Size with 2520 Inductors

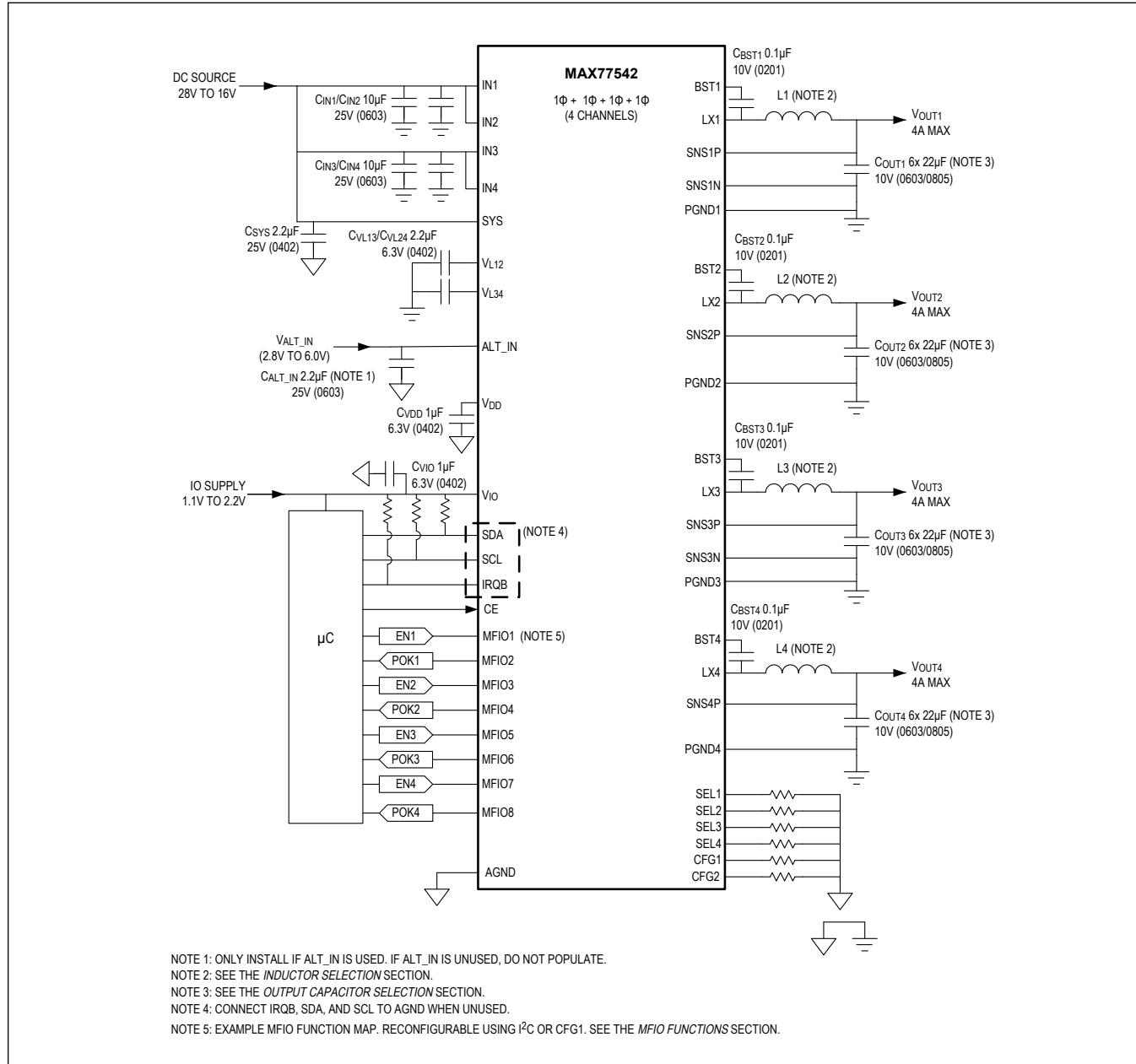

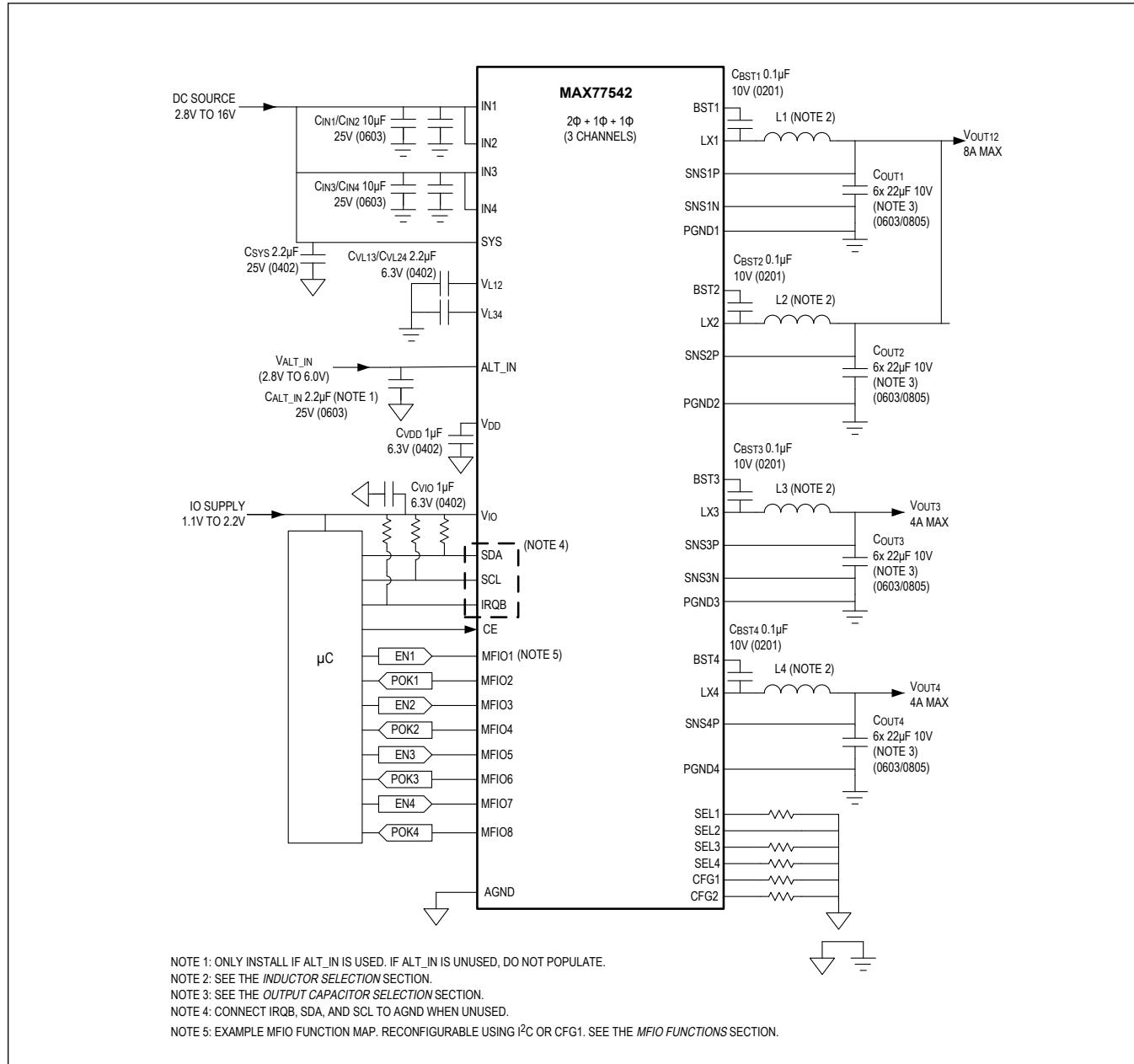

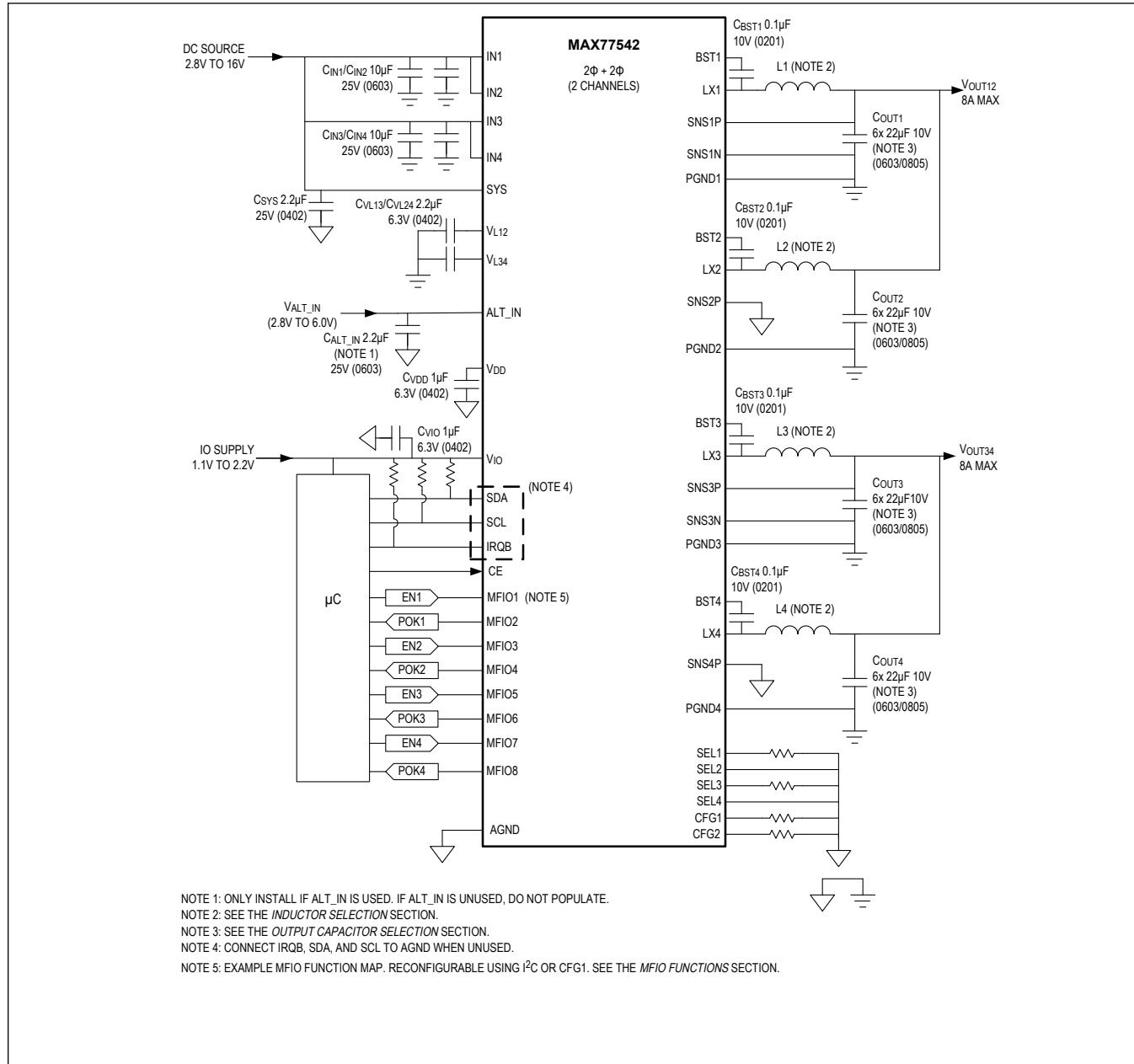

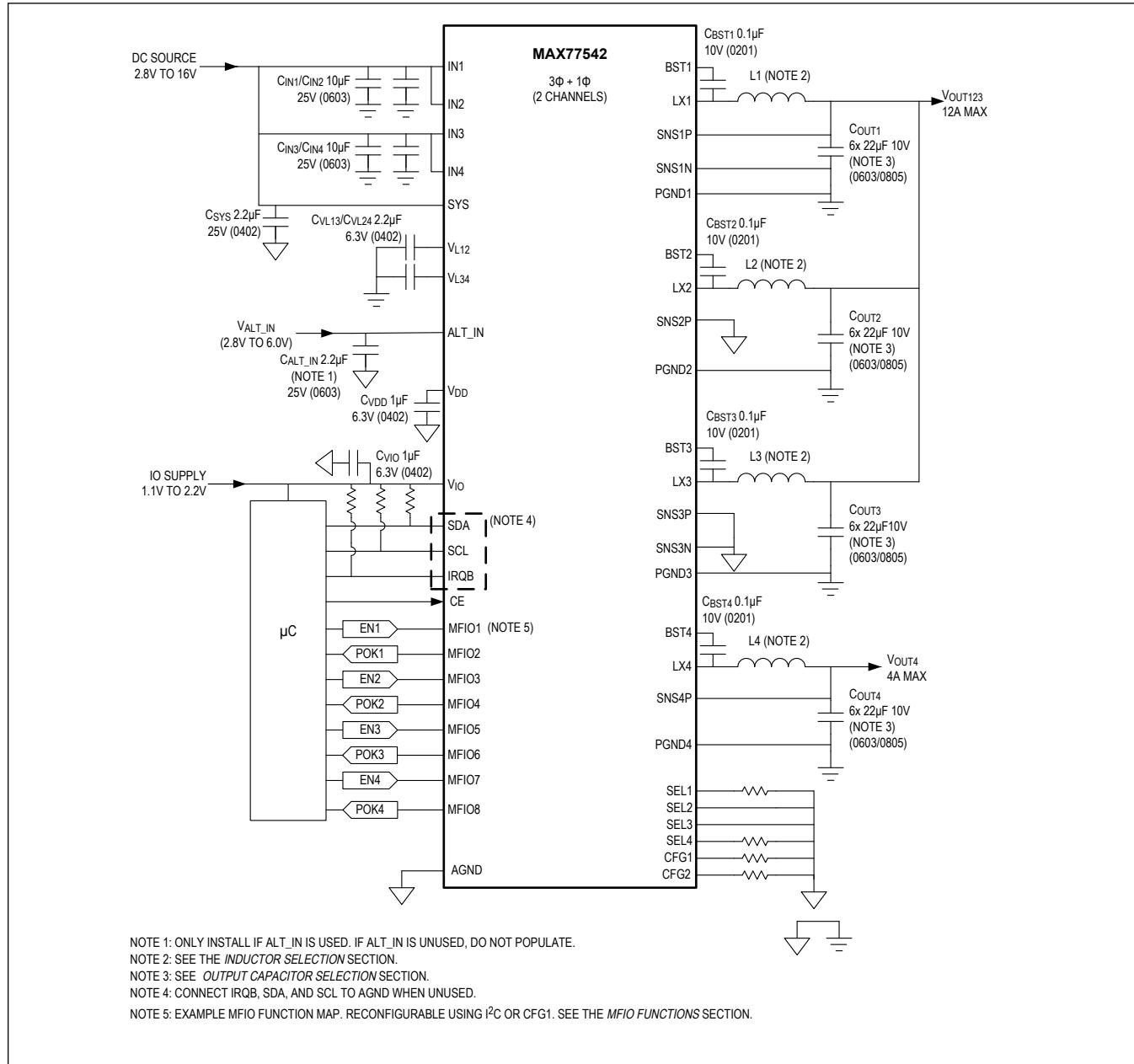

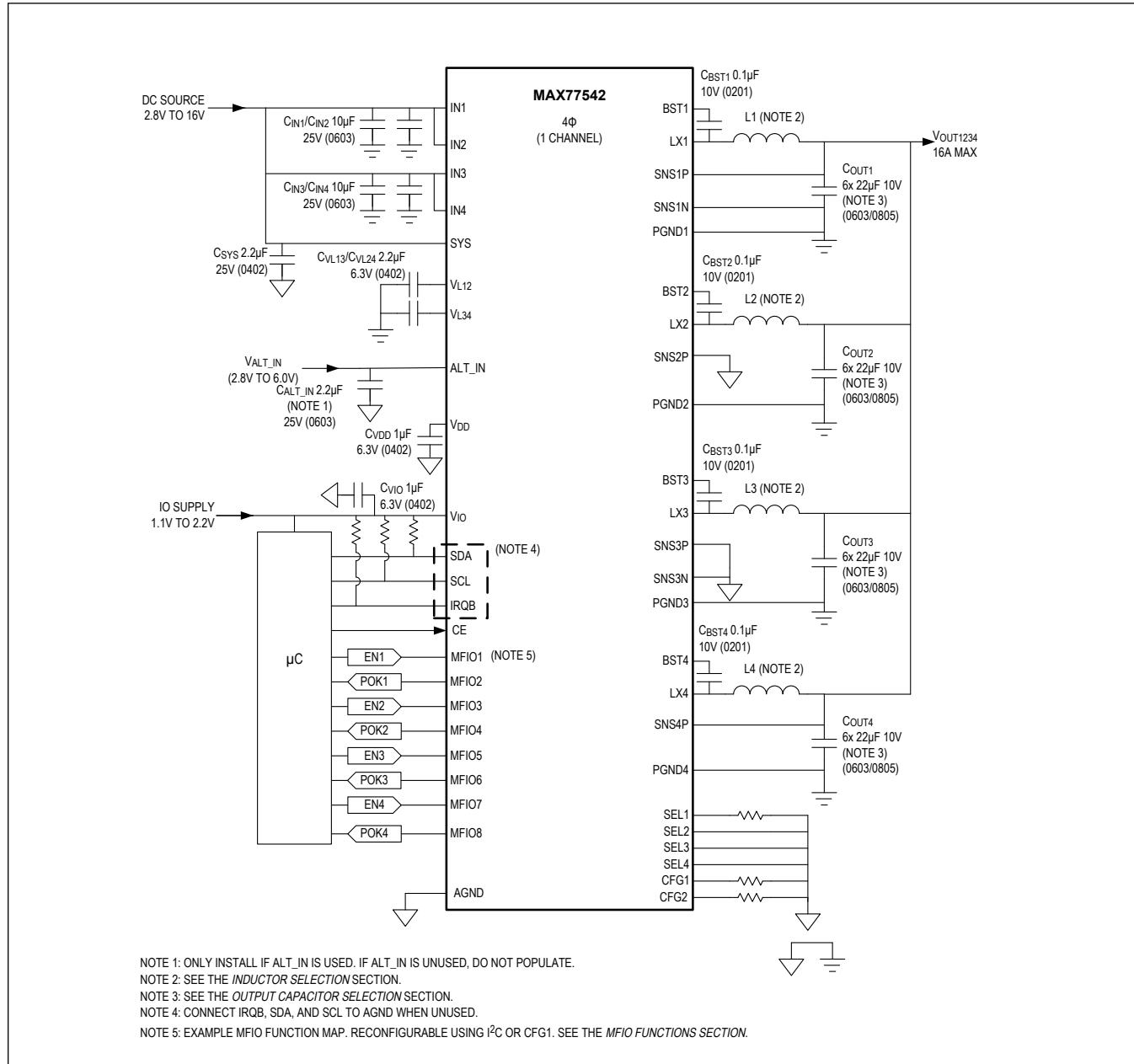

### Typical Applications Circuit

*Typical Application Circuits* continued at end of data sheet.

*Ordering Information* appears at end of data sheet.

19-101947; Rev 1; 7/25

**TABLE OF CONTENTS**

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| General Description . . . . .                                               | 1  |

| Applications . . . . .                                                      | 1  |

| Benefits and Features . . . . .                                             | 1  |

| Typical Applications Circuit                                                | 1  |

| Absolute Maximum Ratings . . . . .                                          | 7  |

| Recommended Operating Conditions . . . . .                                  | 7  |

| Package Information . . . . .                                               | 7  |

| 60 WLP (Thick UBM) . . . . .                                                | 7  |

| Electrical Characteristics—Top-Level . . . . .                              | 9  |

| Electrical Characteristics—Quad-Phase Configurable Buck Converter . . . . . | 11 |

| Electrical Characteristics—Multifunction I/Os . . . . .                     | 15 |

| Electrical Characteristics—ADC . . . . .                                    | 16 |

| Electrical Characteristics—I <sup>2</sup> C Serial Interface . . . . .      | 16 |

| Typical Operating Characteristics . . . . .                                 | 19 |

| Pin Configuration . . . . .                                                 | 28 |

| MAX77542 . . . . .                                                          | 28 |

| Pin Description . . . . .                                                   | 28 |

| Detailed Description—Top-Level . . . . .                                    | 31 |

| Chip Enable (CE) and Internal Bias Supplies . . . . .                       | 31 |

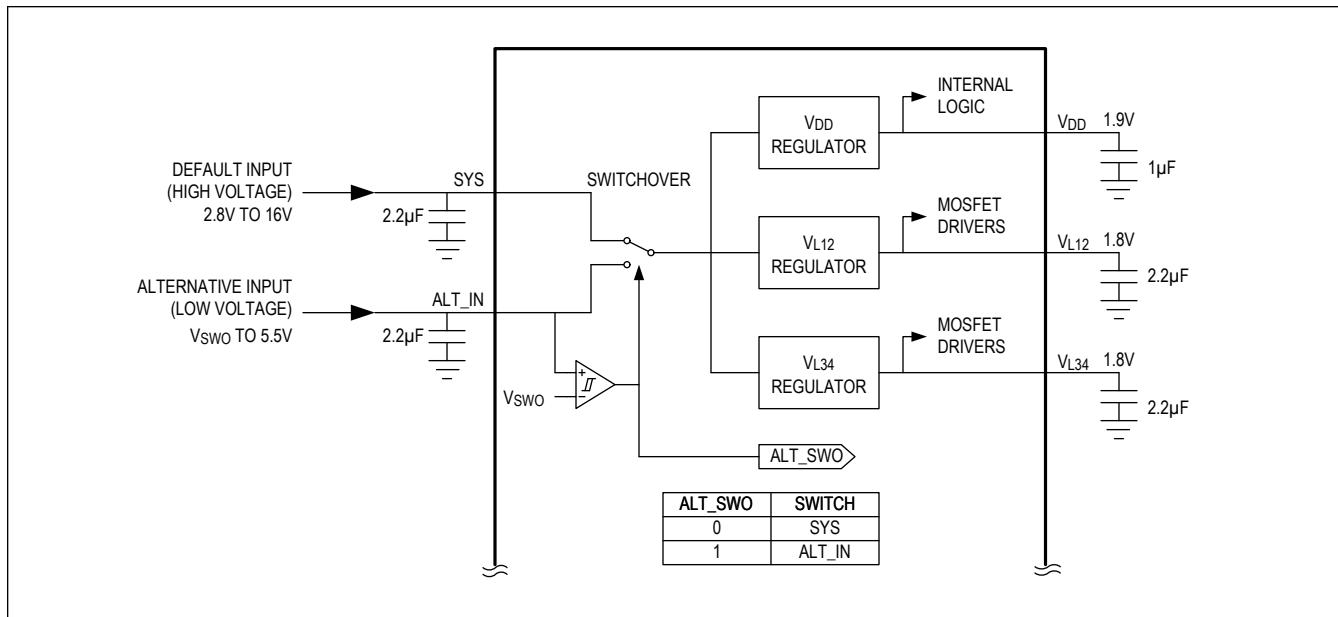

| Alternative Low-Voltage Input (ALT_IN) . . . . .                            | 31 |

| Device Configuration (CFGx) . . . . .                                       | 32 |

| Output Enable Control . . . . .                                             | 35 |

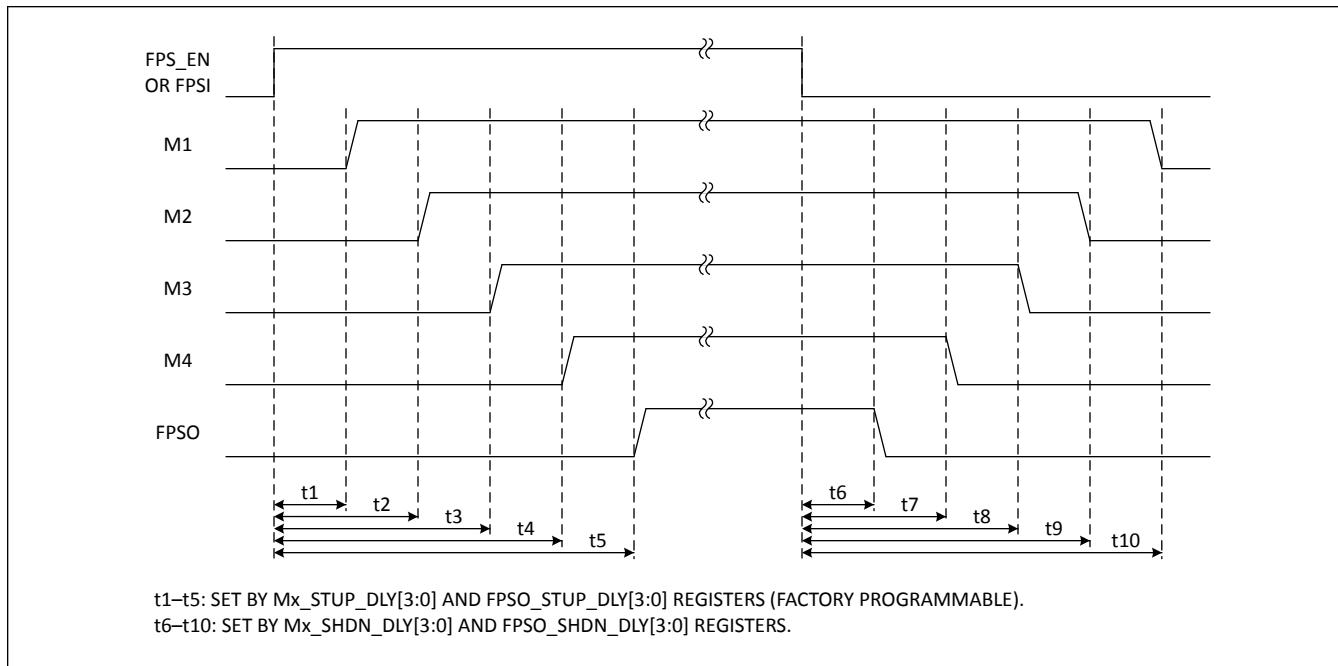

| Flexible Power Sequencer (FPS) . . . . .                                    | 35 |

| Undervoltage Lock-Out (UVLO) . . . . .                                      | 36 |

| V <sub>IO</sub> Fault . . . . .                                             | 36 |

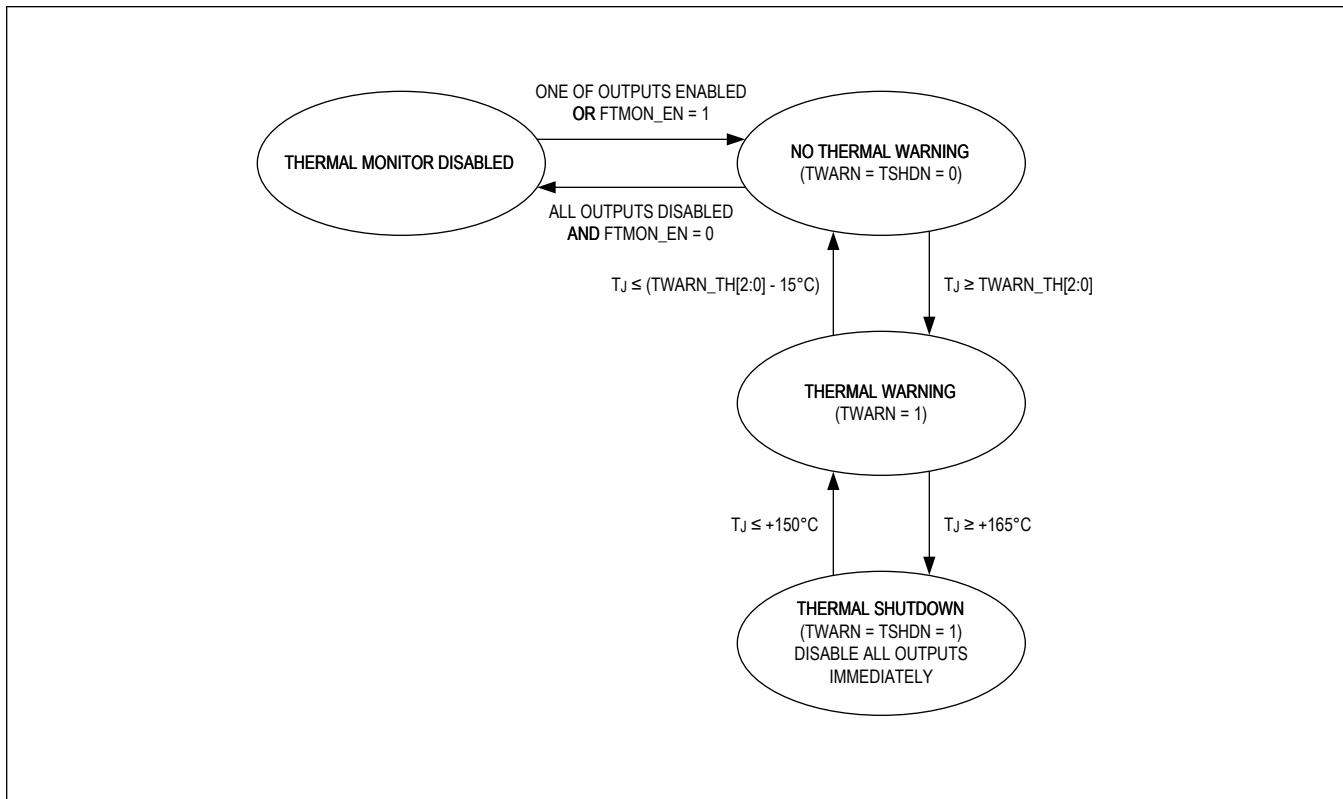

| Thermal Warning and Thermal Shutdown (TSHDN) . . . . .                      | 36 |

| Reset Input and Output . . . . .                                            | 37 |

| Interrupt (IRQB), Mask and Status . . . . .                                 | 37 |

| Register Reset Conditions . . . . .                                         | 38 |

| Factory Options . . . . .                                                   | 38 |

| Detailed Description—Quad-Phase Configurable Buck Converter . . . . .       | 39 |

| Buck Converter Control Scheme . . . . .                                     | 39 |

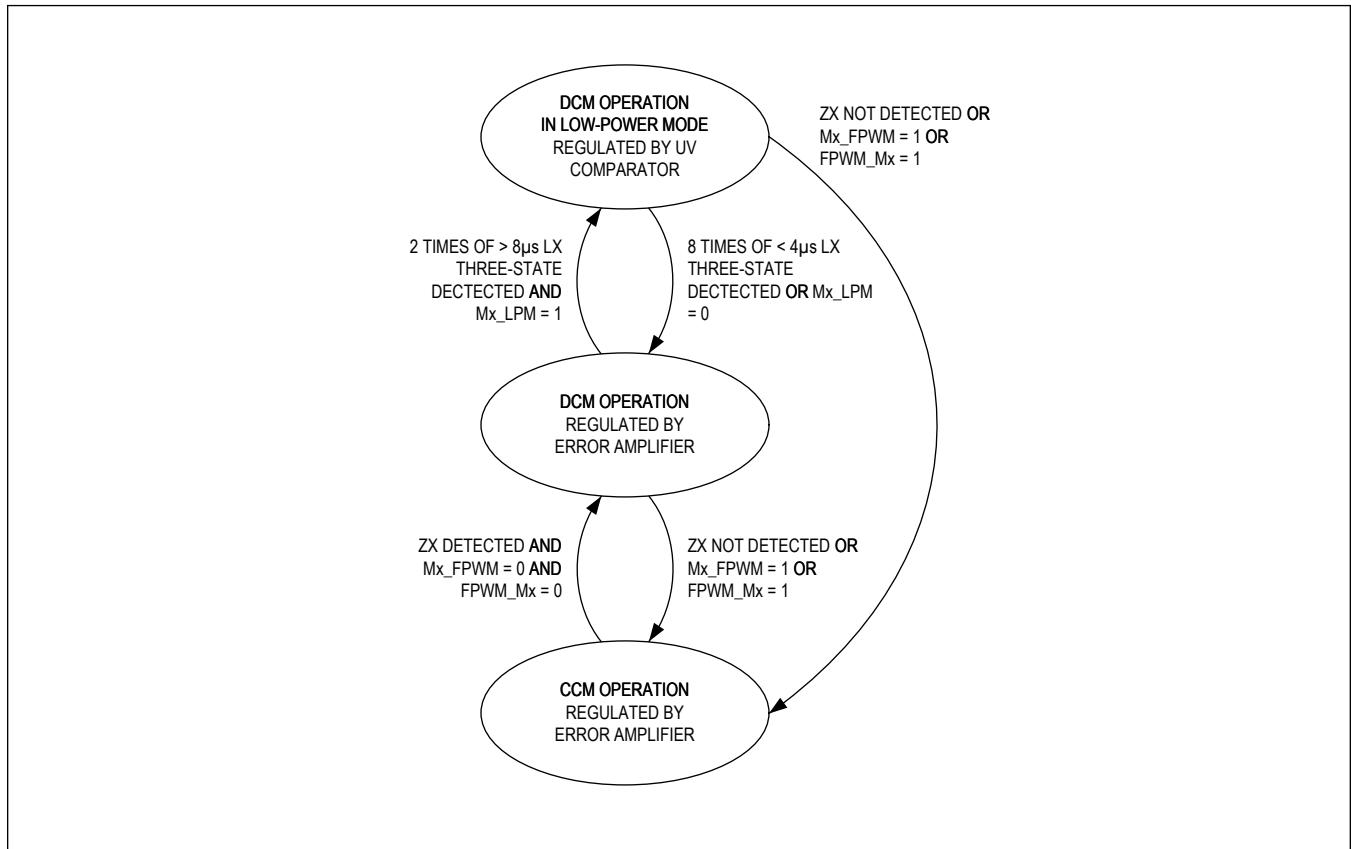

| Buck Operating Modes . . . . .                                              | 40 |

| Skip Mode . . . . .                                                         | 40 |

| Low-Power Skip (LP-Skip) Mode . . . . .                                     | 41 |

| Forced-PWM (FPWM) Mode . . . . .                                            | 41 |

| Drop-Out Mode . . . . .                                                     | 41 |

| Switching Frequency . . . . .                                               | 41 |

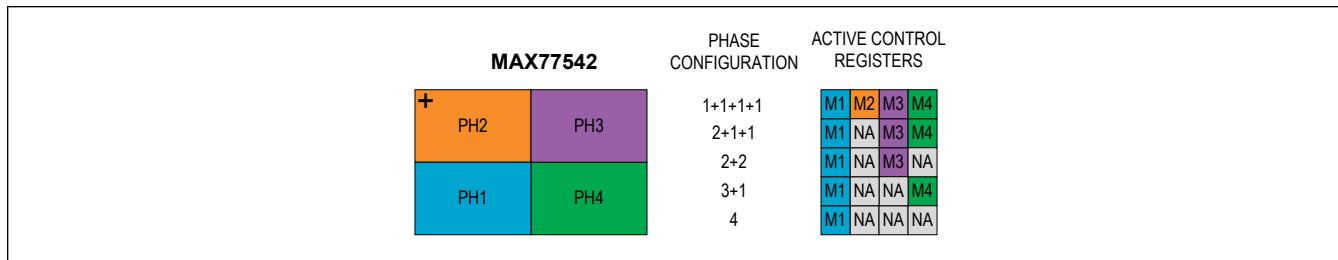

| Phase and Output Configuration . . . . .                                    | 42 |

**TABLE OF CONTENTS (CONTINUED)**

|                                                        |    |

|--------------------------------------------------------|----|

| Default Output-Voltage Selection (SELx) . . . . .      | 43 |

| Output-Voltage Setting . . . . .                       | 45 |

| Soft-Start and Soft-Stop . . . . .                     | 45 |

| Dynamic Output-Voltage Scaling . . . . .               | 46 |

| Output-Voltage Active Discharge . . . . .              | 46 |

| Bootstrap Refresh . . . . .                            | 46 |

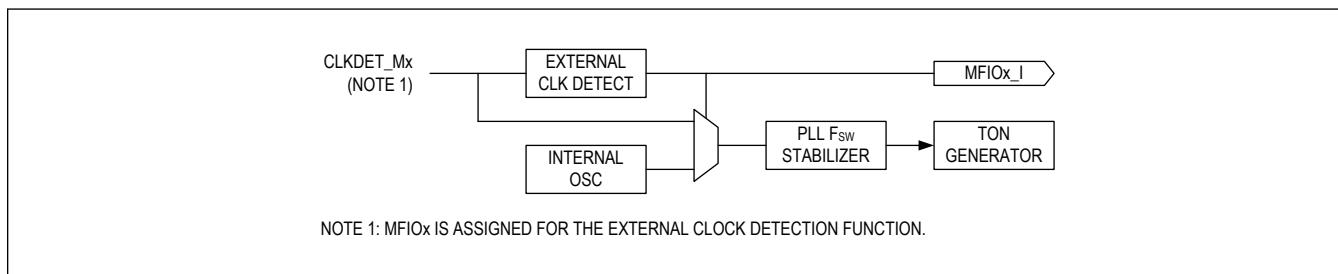

| Frequency Tracking (FTRAK) . . . . .                   | 47 |

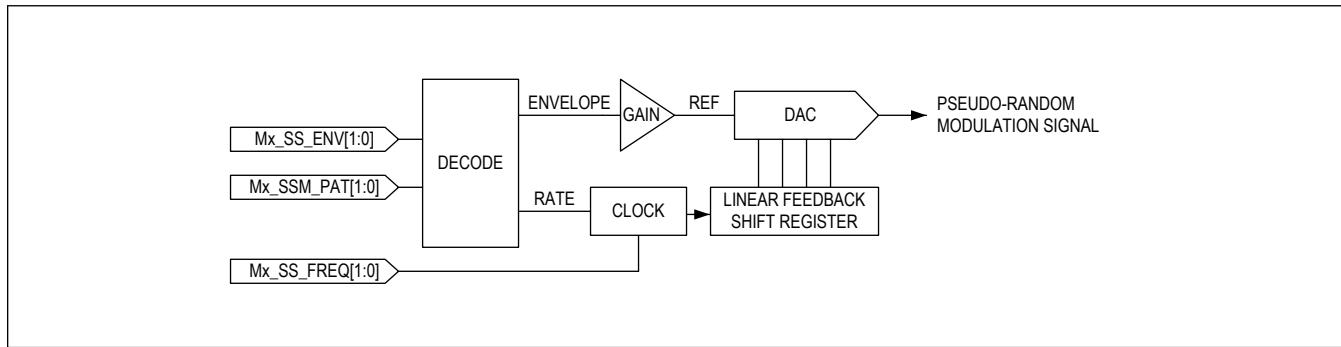

| Spread-Spectrum Modulation . . . . .                   | 48 |

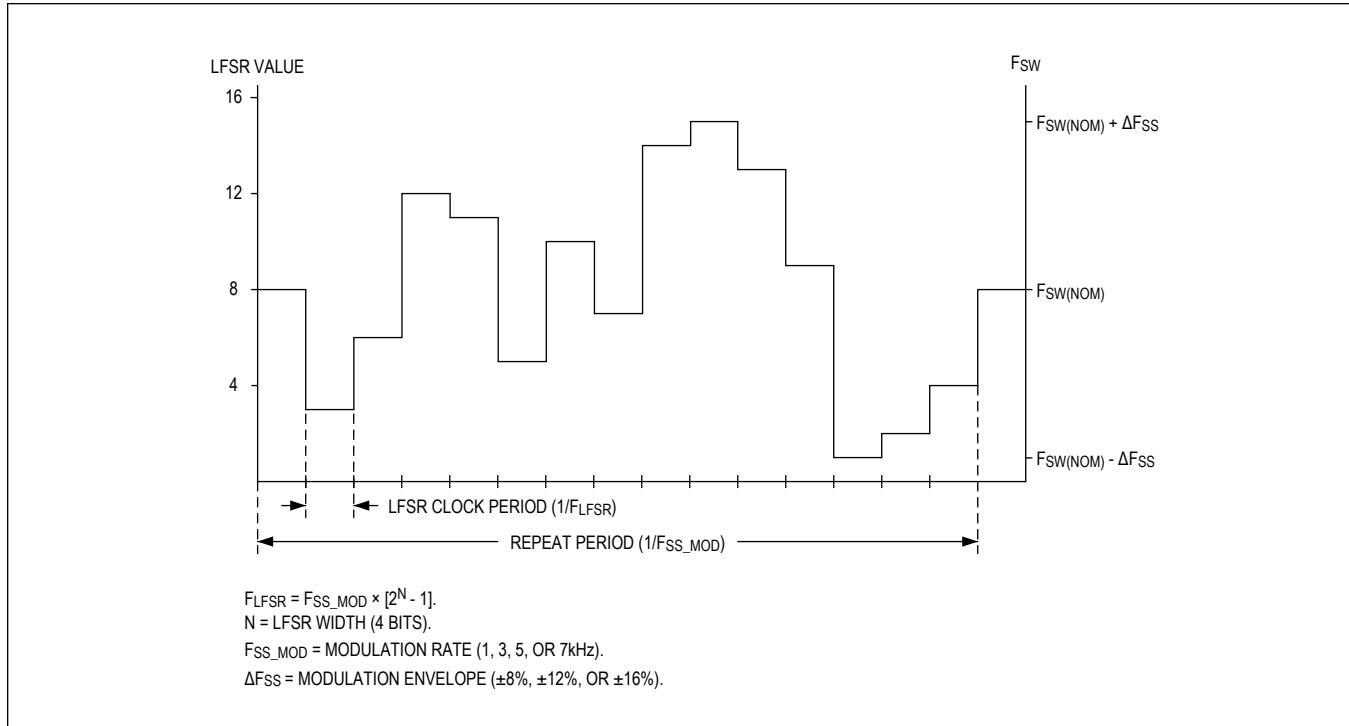

| Pseudo-Random Pattern . . . . .                        | 48 |

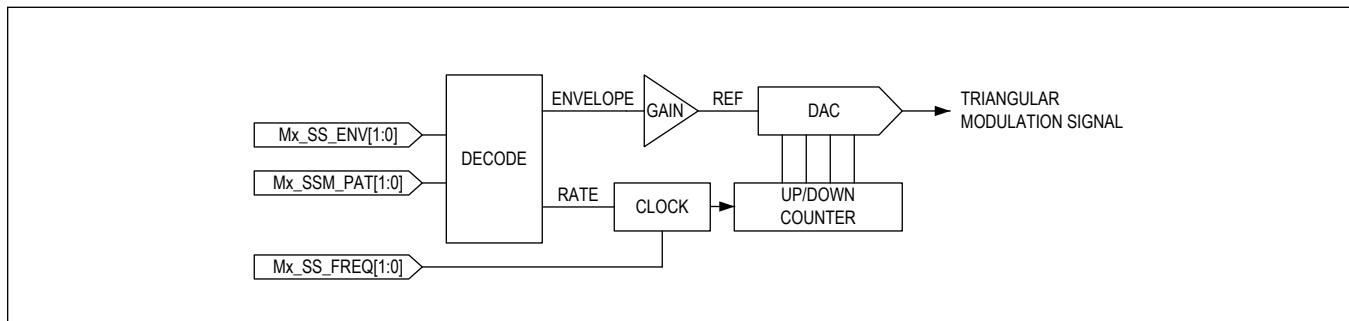

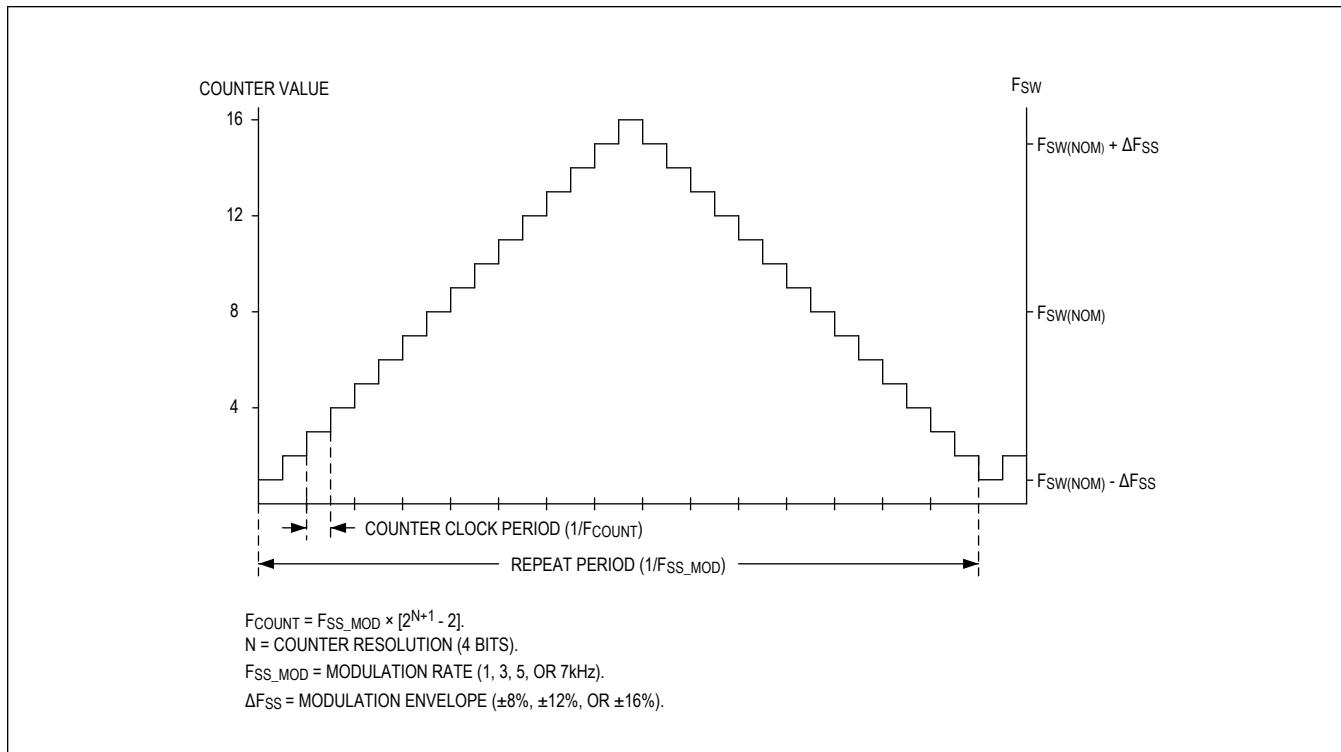

| Triangular Pattern . . . . .                           | 49 |

| Inductor Current Limits . . . . .                      | 50 |

| Power-OK (POK) . . . . .                               | 50 |

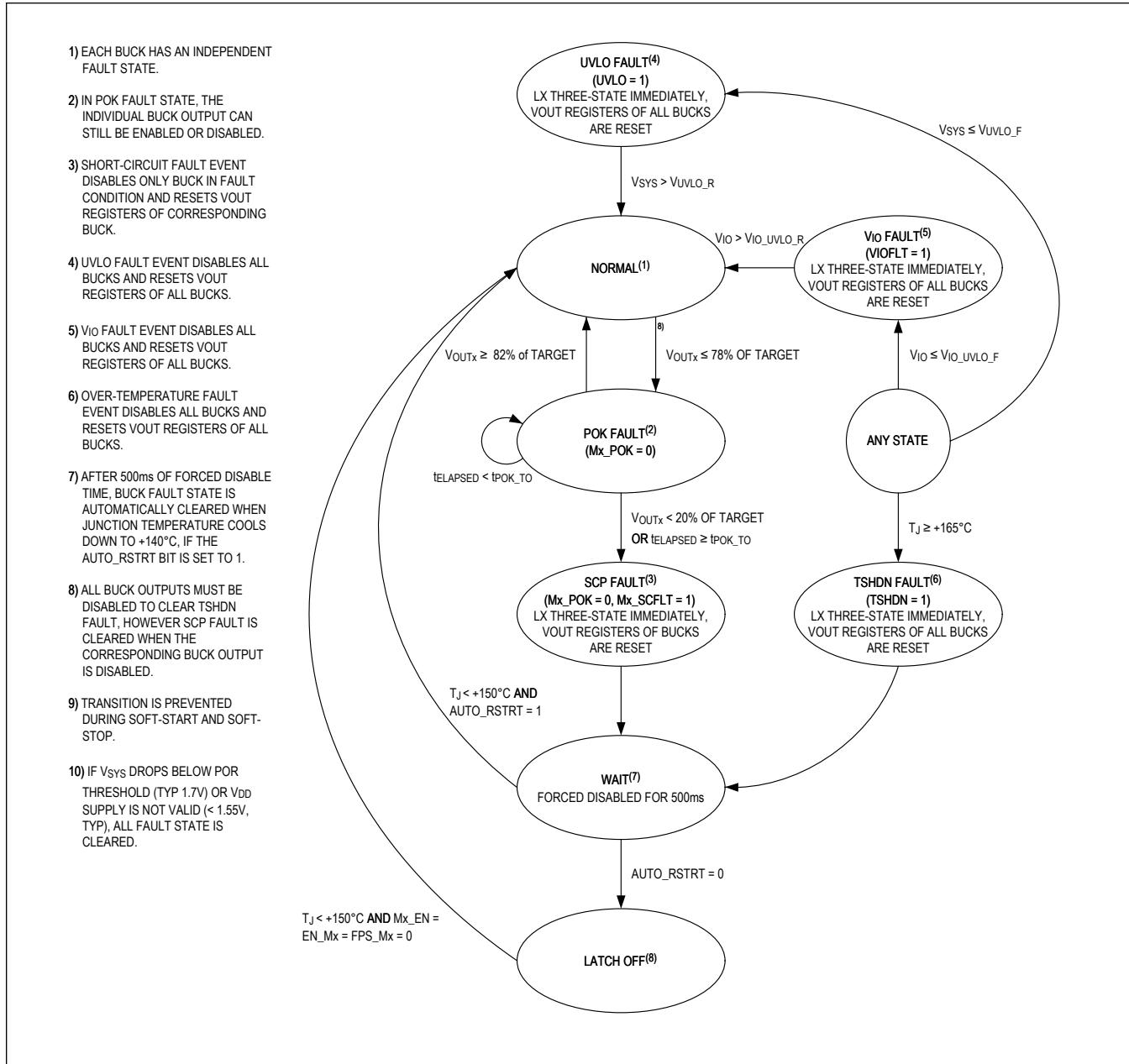

| Fault Protection . . . . .                             | 51 |

| Detailed Description—Multifunction I/Os . . . . .      | 53 |

| MFIO Functions . . . . .                               | 53 |

| Output Enable (EN) . . . . .                           | 54 |

| Low-Power Mode (LPM) . . . . .                         | 54 |

| FPWM Mode (FPWM) . . . . .                             | 54 |

| External Clock Detection (CLKDET) . . . . .            | 54 |

| Clock Output (CLKOUT) . . . . .                        | 54 |

| Output-Voltage Selection (VSEL) . . . . .              | 54 |

| Boot (Default) Output-Voltage Selection (VB) . . . . . | 55 |

| Power-OK (POK) Output . . . . .                        | 55 |

| FPS Input (FPSI) . . . . .                             | 55 |

| FPS Output (FPSO) . . . . .                            | 55 |

| System Reset Input (RSTINB) . . . . .                  | 55 |

| System Reset Output (RSTOB) . . . . .                  | 55 |

| Thermal Warning Output (TWARNB) . . . . .              | 55 |

| General-Purpose Input (GPI) . . . . .                  | 56 |

| General-Purpose Output (GPO) . . . . .                 | 56 |

| ADC Mux Input (ADCMUX) . . . . .                       | 56 |

| Debounce Timer . . . . .                               | 56 |

| Internal Pull-Down and Pull-Up Resistor . . . . .      | 57 |

| Output Driver Mode . . . . .                           | 57 |

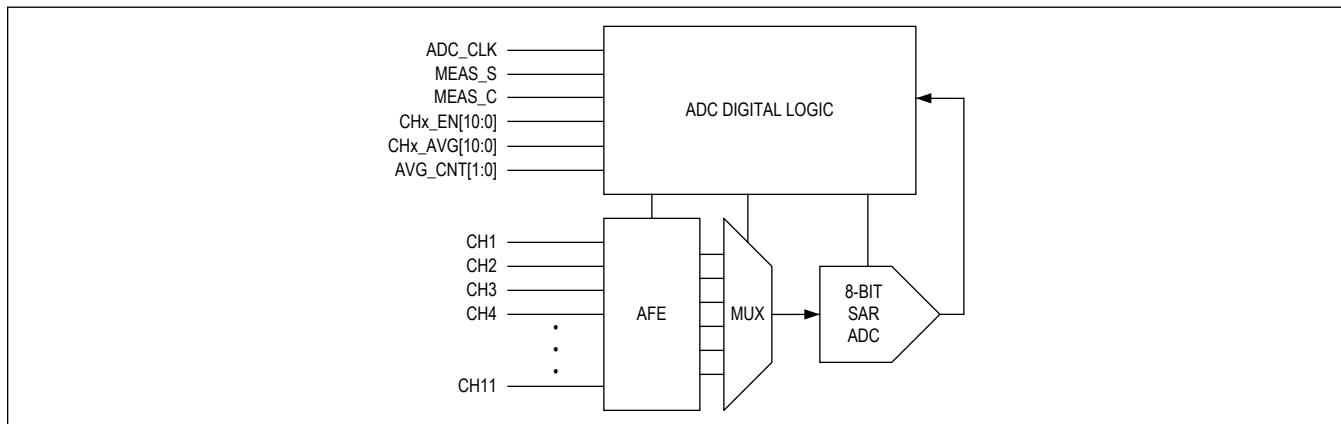

| Detailed Description—ADC . . . . .                     | 57 |

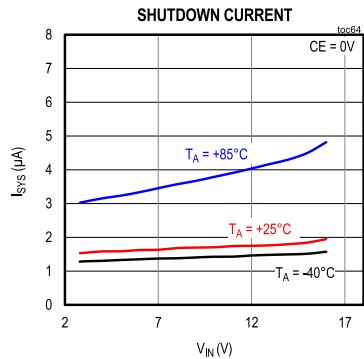

| ADC Enable and Measurement Options . . . . .           | 58 |

| Output-Current Measurement . . . . .                   | 58 |

| Output-Voltage Measurement . . . . .                   | 58 |

| SYS-Voltage Measurement . . . . .                      | 59 |

**TABLE OF CONTENTS (CONTINUED)**

|                                                                           |     |

|---------------------------------------------------------------------------|-----|

| Junction-Temperature Measurement . . . . .                                | 59  |

| External-Voltage Measurement . . . . .                                    | 59  |

| Detailed Description—I <sup>2</sup> C Serial Interface . . . . .          | 59  |

| Slave Address . . . . .                                                   | 59  |

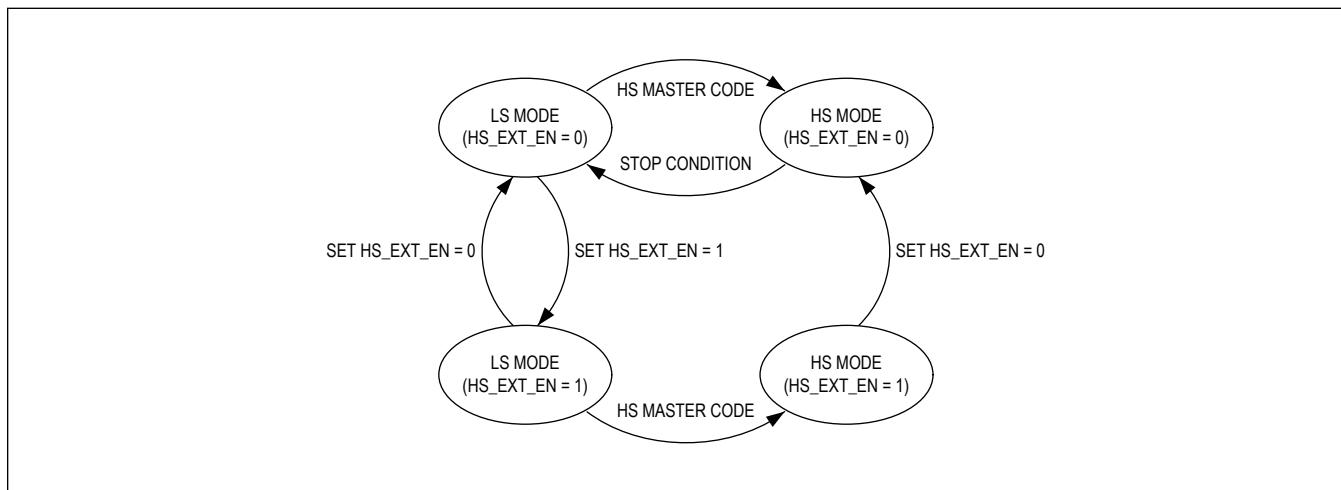

| HS Extension Mode . . . . .                                               | 60  |

| I <sup>2</sup> C Watchdog Timer . . . . .                                 | 60  |

| Register Map . . . . .                                                    | 61  |

| MAX77542 . . . . .                                                        | 61  |

| Register Details . . . . .                                                | 64  |

| Applications Information—Quad-Phase Configurable Buck Converter . . . . . | 115 |

| Inductor Selection . . . . .                                              | 115 |

| Input-Capacitor Selection . . . . .                                       | 115 |

| Output-Capacitor Selection . . . . .                                      | 115 |

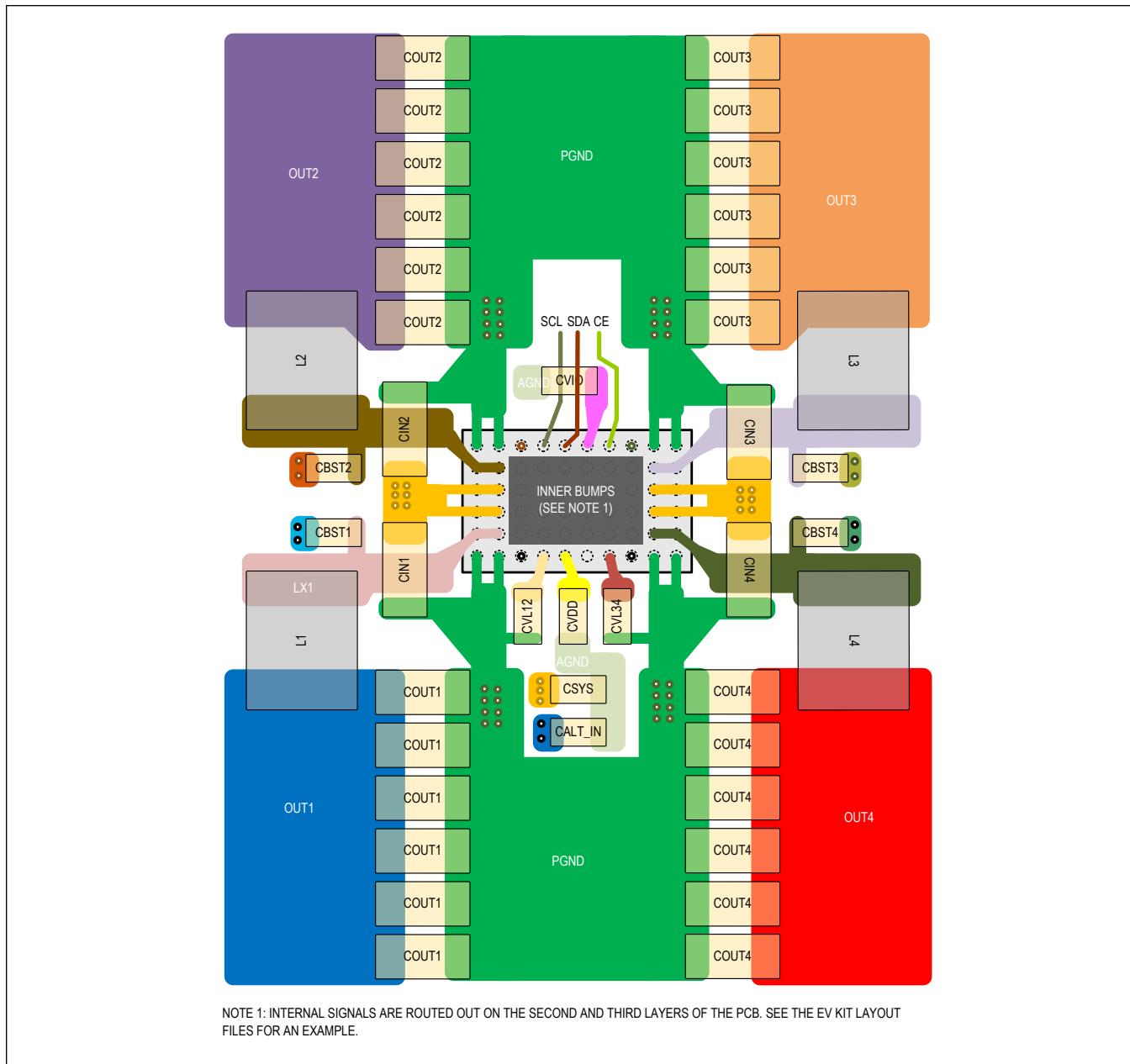

| General PCB Layout Guidelines . . . . .                                   | 116 |

| Unused Outputs . . . . .                                                  | 117 |

| Typical Application Circuits . . . . .                                    | 118 |

| 1+1+1+1 Phase Configuration . . . . .                                     | 118 |

| 2+1+1 Phase Configuration . . . . .                                       | 119 |

| 2+2 Phase Configuration . . . . .                                         | 120 |

| 3+1 Phase Configuration . . . . .                                         | 121 |

| 4 Phase Configuration . . . . .                                           | 122 |

| Ordering Information . . . . .                                            | 123 |

| Revision History . . . . .                                                | 124 |

---

**LIST OF FIGURES**

---

|                                                                    |     |

|--------------------------------------------------------------------|-----|

| Figure 1. Alternative Input Switchover Circuit . . . . .           | 32  |

| Figure 2. Typical Startup and Shutdown Sequence . . . . .          | 36  |

| Figure 3. Thermal Warning and Thermal Shutdown . . . . .           | 37  |

| Figure 4. Functional Block Diagram . . . . .                       | 39  |

| Figure 5. Buck Operating Modes. . . . .                            | 40  |

| Figure 6. Active Control Registers. . . . .                        | 43  |

| Figure 7. Frequency Tracking . . . . .                             | 47  |

| Figure 8. Pseudo-Random Modulator Engine . . . . .                 | 48  |

| Figure 9. 4-Bit Pseudo-Random Modulation Signal Example . . . . .  | 49  |

| Figure 10. Triangular Modulator Engine . . . . .                   | 49  |

| Figure 11. 4-Bit Triangular Modulation Signal Example . . . . .    | 50  |

| Figure 12. Fault-Protection State Diagram . . . . .                | 52  |

| Figure 13. ADC Block Diagram . . . . .                             | 57  |

| Figure 14. I <sup>2</sup> C Operating Mode State Diagram . . . . . | 60  |

| Figure 15. PCB Layout Example . . . . .                            | 117 |

---

**LIST OF TABLES**

---

|                                                                        |     |

|------------------------------------------------------------------------|-----|

| Table 1. V <sub>DD</sub> and I <sup>2</sup> C Enable Truth Table ..... | 31  |

| Table 2. Device Configuration by RCFG1 .....                           | 32  |

| Table 3. Device Configuration by RCFG2 .....                           | 34  |

| Table 4. MAX77542 Factory-Programmed Defaults (OTP Options) .....      | 38  |

| Table 5. Phase-Configuration Selection .....                           | 42  |

| Table 6. Buck Output-Voltage Sensing Assignment .....                  | 42  |

| Table 7. Default V <sub>OUT1</sub> Selection .....                     | 43  |

| Table 8. Default V <sub>OUT2/3/4</sub> Selection .....                 | 44  |

| Table 9. Buck Output-Voltage Range .....                               | 45  |

| Table 10. Mx_FSRREN Effect on Buck Behavior .....                      | 46  |

| Table 11. Bootstrap-Refresh Interval Selection .....                   | 46  |

| Table 12. Mx_FTRAK Enable Truth Table .....                            | 47  |

| Table 13. Phase Sequence .....                                         | 47  |

| Table 14. MFIO Functions .....                                         | 53  |

| Table 15. MFIO I/O Selection .....                                     | 54  |

| Table 16. Debounce Timer Setting .....                                 | 56  |

| Table 17. Internal Resistor Setting .....                              | 57  |

| Table 18. ADC Functions and Measurement Ranges .....                   | 57  |

| Table 19. Recommended Inductors .....                                  | 115 |

| Table 20. Recommended Minimum Effective Output Capacitance .....       | 115 |

---

**Absolute Maximum Ratings**

|                                                         |                                               |                                                                                                                |                                             |

|---------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| SYS to AGND .....                                       | -0.3V to +17.6V                               | SNSxN to AGND .....                                                                                            | -0.3V to +0.3V                              |

| ALT_IN to AGND .....                                    | -0.3V to +6.0V                                | PGNDx to AGND .....                                                                                            | -0.3V to +0.3V                              |

| V <sub>DD</sub> to AGND .....                           | -0.3V to +2.2V                                | V <sub>IO</sub> to AGND .....                                                                                  | -0.3V to +2.2V                              |

| V <sub>L12</sub> , V <sub>L34</sub> to AGND, PGND ..... | -0.3V to +2.2V                                | SCL to AGND .....                                                                                              | -0.3V to +2.2V                              |

| CE to AGND .....                                        | -0.3V to min (V <sub>SYS</sub> + 0.3, +17.6)V | SDA to AGND .....                                                                                              | -0.3V to +2.2V                              |

| CFGx to AGND .....                                      | -0.3V to min (V <sub>DD</sub> + 0.3, +2.2)V   | IRQB to AGND .....                                                                                             | -0.3V to +2.2V                              |

| SELx to AGND .....                                      | -0.3V to min (V <sub>DD</sub> + 0.3, +2.2)V   | MFIOx to AGND .....                                                                                            | -0.3V to min (V <sub>IO</sub> + 0.3, +2.2)V |

| INx to PGNDx, AGND .....                                | -0.3V to +17.6V                               | Continuous Power Dissipation (JESD51-7, T <sub>A</sub> = +70°C)<br>60 WLP (derate 25.4mW/°C above +70°C) ..... | 2037mW                                      |

| Lxx to PGNDx .....                                      | -0.3V to +17.6V                               | Junction Temperature .....                                                                                     | +150°C                                      |

| Lxx to PGNDx (less than 10ns) .....                     | (V <sub>IN</sub> - 22)V to +22V               | Storage Temperature Range .....                                                                                | -65°C to +150°C                             |

| BSTx to Lxx .....                                       | -0.3V to +2.2V                                | Soldering Temperature (reflow) .....                                                                           | +260°C                                      |

| SNSxP to AGND .....                                     | -0.3V to +12.0V                               |                                                                                                                |                                             |

**Note 1:** LXx has internal clamp diodes to its corresponding PGNDx and INx. Applications that forward bias these diodes should take care not to exceed the IC's package power dissipation limits.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Recommended Operating Conditions**

| PARAMETER                  | SYMBOL           | CONDITION                                                                                                                                                                                                       | TYPICAL RANGE | UNIT |

|----------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|

| Input Voltage Range        | V <sub>IN</sub>  |                                                                                                                                                                                                                 | 2.8 to 16     | V    |

| Output Current Range       | I <sub>OUT</sub> | For continuous operation at 4A, the junction temperature (T <sub>J</sub> ) is limited to +120°C; if the junction temperature is higher than +120°C, the expected lifetime at 4A continuous operation is derated | 0 to 4        | A    |

| Junction Temperature Range | T <sub>J</sub>   |                                                                                                                                                                                                                 | -40 to +125   | °C   |

**Note:** These limits are not guaranteed.

**Package Information****60 WLP (Thick UBM)**

|                                        |                                       |

|----------------------------------------|---------------------------------------|

| Packkage Code                          | W602A4Z+1                             |

| Outline Number                         | <a href="#">21-100610</a>             |

| Land Pattern Number                    | <a href="#">Application Note 1891</a> |

| Thermal Resistance, Four-Layer Board:  |                                       |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 39.27°C/W                             |

For the latest package outline information and land patterns (footprints), go to [www.maximintegrated.com/packages](http://www.maximintegrated.com/packages). Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to [www.maximintegrated.com/thermal-tutorial](http://www.maximintegrated.com/thermal-tutorial).

**Electrical Characteristics—Top-Level**

( $V_{SYS} = V_{INx} = 12V$ ,  $V_{OUT1} = 0.8V$  ( $M1\_RNG = 0x0$ ),  $V_{OUT2} = 1.1V$  ( $M2\_RNG = 0x1$ ),  $V_{OUT3} = 1.8V$  ( $M3\_RNG = 0x1$ ),  $V_{OUT4} = 3.3V$  ( $M4\_RNG = 0x2$ ), single-phase configuration,  $V_{CE} = 1.8V$ ,  $V_{IO} = 1.8V$ ,  $T_A = T_J = -40^\circ C$  to  $+125^\circ C$ , typical values are at  $T_A = T_J = +25^\circ C$ , unless otherwise noted. [Note 2](#).)

| PARAMETER                                                           | SYMBOL                | CONDITIONS                                                                                                        | MIN                            | TYP  | MAX | UNITS   |

|---------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------|------|-----|---------|

| <b>INPUT VOLTAGE AND SUPPLY CURRENT</b>                             |                       |                                                                                                                   |                                |      |     |         |

| SYS and INx Voltage Range                                           | $V_{SYS}$ , $V_{INx}$ |                                                                                                                   | 2.8                            | 16   |     | V       |

| SYS Undervoltage Lock-Out (UVLO)                                    | $V_{UVLO\_R}$         | $V_{SYS}$ rising                                                                                                  | 2.8                            | 2.9  | 3.0 | V       |

|                                                                     | $V_{UVLO\_F}$         | $V_{SYS}$ falling with 200mV of hysteresis                                                                        | 2.6                            | 2.7  | 2.8 |         |

| Power-On Reset (POR) Threshold ( <a href="#">Note 7</a> )           | $V_{POR}$             | $V_{SYS}$ falling                                                                                                 |                                | 1.7  |     | V       |

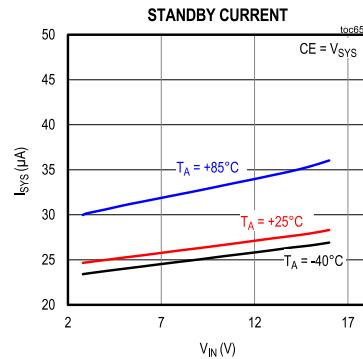

| Shutdown Supply Current ( <a href="#">Note 3</a> )                  | $I_{SHDN}$            | $V_{CE} = 0V$ , $T_J = -40^\circ C$ to $+85^\circ C$                                                              |                                | 1.5  | 15  | $\mu A$ |

| Standby Supply Current ( <a href="#">Note 3</a> )                   | $I_{STBY}$            | FTMON_EN = 0, all bucks are disabled, $T_J = -40^\circ C$ to $+85^\circ C$                                        |                                | 25   | 60  | $\mu A$ |

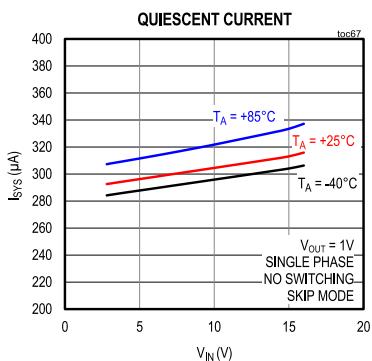

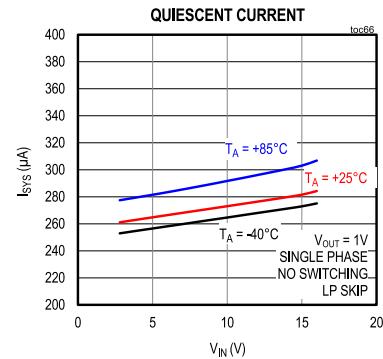

| Quiescent Supply Current in LP-Skip Mode ( <a href="#">Note 3</a> ) | $I_{Q\_LP-SKIP}$      | $V_{ALT\_IN} = 0V$ , $V_{OUT} > V_{OUT(TARGET)}$ , no load                                                        | Only one buck phase is enabled | 270  | 370 | $\mu A$ |

|                                                                     |                       |                                                                                                                   | Two buck phases are enabled    | 380  | 480 |         |

|                                                                     |                       |                                                                                                                   | Three buck phases are enabled  | 505  | 635 |         |

|                                                                     |                       |                                                                                                                   | All buck phases are enabled    | 625  | 755 |         |

| Quiescent Supply Current in Skip Mode ( <a href="#">Note 3</a> )    | $I_{Q\_SKIP}$         | $V_{ALT\_IN} = 0V$ , $V_{OUT} > V_{OUT(TARGET)}$ , no load                                                        | Only one buck phase is enabled | 300  | 405 | $\mu A$ |

|                                                                     |                       |                                                                                                                   | Two buck phases are enabled    | 450  | 555 |         |

|                                                                     |                       |                                                                                                                   | Three buck phases are enabled  | 620  | 750 |         |

|                                                                     |                       |                                                                                                                   | All buck phases are enabled    | 780  | 910 |         |

| <b>INTERNAL BIAS SUPPLY</b>                                         |                       |                                                                                                                   |                                |      |     |         |

| $V_{DD}$ Regulator Voltage                                          | $V_{DD}$              |                                                                                                                   |                                | 1.9  |     | V       |

| $V_{DD}$ Undervoltage Lock-Out (UVLO)                               | $V_{DD\_UVLO\_F}$     |                                                                                                                   |                                | 1.55 |     | V       |

| $V_{L12}$ , $V_{L34}$ Regulator Voltage                             | $V_{Lx}$              |                                                                                                                   |                                | 1.8  |     | V       |

| $V_{L12}$ , $V_{L34}$ Undervoltage Lock-Out (UVLO)                  | $V_{L\_UVLO\_F}$      |                                                                                                                   |                                | 1.55 |     | V       |

| ALT_IN Switchover Threshold                                         | $V_{SWO}$             | $V_{ALT\_IN}$ rising, 100mV hysteresis, $V_L$ and $V_{DD}$ input switches from SYS to ALT_IN above this threshold | 2.7                            | 2.8  | 2.9 | V       |

| ALT_IN Valid Voltage Range                                          | $V_{ALT\_IN}$         |                                                                                                                   | $V_{SWO}$                      | 5.5  |     | V       |

| ALT_IN Shutdown Supply Current                                      | $I_{ALT\_IN\_SHDN}$   | $V_{CE} = 0V$ , $V_{ALT\_IN} = 3.3V$                                                                              |                                | 0.2  |     | $\mu A$ |

**Electrical Characteristics—Top-Level (continued)**

( $V_{SYS} = V_{INx} = 12V$ ,  $V_{OUT1} = 0.8V$  ( $M1\_RNG = 0x0$ ),  $V_{OUT2} = 1.1V$  ( $M2\_RNG = 0x1$ ),  $V_{OUT3} = 1.8V$  ( $M3\_RNG = 0x1$ ),  $V_{OUT4} = 3.3V$  ( $M4\_RNG = 0x2$ ), single-phase configuration,  $V_{CE} = 1.8V$ ,  $V_{IO} = 1.8V$ ,  $T_A = T_J = -40^\circ C$  to  $+125^\circ C$ , typical values are at  $T_A = T_J = +25^\circ C$ , unless otherwise noted. [Note 2](#).)

| PARAMETER                             | SYMBOL                | CONDITIONS                                                                                          | MIN                                               | TYP  | MAX  | UNITS |    |

|---------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|-------|----|

| <b>THERMAL PROTECTION</b>             |                       |                                                                                                     |                                                   |      |      |       |    |

| Thermal Warning                       | T <sub>WARN</sub>     | T <sub>J</sub> rising, 15°C hysteresis                                                              | TWARN_TH[2:0] = 0x0                               | +95  |      | °C    |    |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x1                               | +100 |      |       |    |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x2                               | +105 |      |       |    |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x3                               | +110 |      |       |    |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x4                               | +115 |      |       |    |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x5 (default)                     | +120 |      |       |    |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x6                               | +125 |      |       |    |

|                                       |                       |                                                                                                     | TWARN_TH[2:0] = 0x7                               | +130 |      |       |    |

| Thermal Shutdown (TSHDN)              | T <sub>SHDN</sub>     | T <sub>J</sub> rising, 15°C hysteresis                                                              | +165                                              |      |      | °C    |    |

| <b>FLEXIBLE POWER SEQUENCER (FPS)</b> |                       |                                                                                                     |                                                   |      |      |       |    |

| Sequence Start Delay                  | t <sub>DLY_SEQ</sub>  | Delay from rising edge of FPS_EN signal to V <sub>OUTx</sub> ramping start-off in the 1st time slot | V <sub>Lx</sub> is enabled                        | 100  |      | μs    |    |

| Time Slot Delay Step                  | t <sub>DLY_STEP</sub> | DLY_STEP[1:0] = 0x0                                                                                 |                                                   | 0.5  |      | ms    |    |

|                                       |                       | DLY_STEP[1:0] = 0x1                                                                                 |                                                   | 1.0  |      |       |    |

|                                       |                       | DLY_STEP[1:0] = 0x2                                                                                 |                                                   | 2.0  |      |       |    |

|                                       |                       | DLY_STEP[1:0] = 0x3                                                                                 |                                                   | 4.0  |      |       |    |

| Time Slot Accuracy                    | f <sub>OSC_ACC</sub>  | Root oscillator accuracy                                                                            | -5                                                | +5   |      | %     |    |

| <b>LOGIC INPUT AND OUTPUT</b>         |                       |                                                                                                     |                                                   |      |      |       |    |

| CE Input Logic High Threshold         | V <sub>IH_CE</sub>    | CE_PD_EN = 0                                                                                        |                                                   | 1.1  |      | V     |    |

|                                       |                       | CE_PD_EN = 1                                                                                        |                                                   | 1.5  |      |       |    |

| CE Input Logic Low Threshold          | V <sub>IL_CE</sub>    |                                                                                                     |                                                   | 0.4  |      | V     |    |

| IRQB Output Logic Low Threshold       | V <sub>OL_IRQB</sub>  | Sinking 2mA                                                                                         |                                                   | 0.2  |      | V     |    |

| CE Pull-Down Current                  | I <sub>PD_CE</sub>    | CE_PD_EN = 1                                                                                        | 1.1V ≤ V <sub>CE</sub> ≤ 16V                      | 0.5  | 1.7  | 4.0   | μA |

|                                       |                       |                                                                                                     | V <sub>CE</sub> ≤ 0.4V                            | 100  | 200  |       | nA |

| CE Leakage Current                    | I <sub>LKG_CE</sub>   | V <sub>SYS</sub> = 16V, V <sub>CE</sub> = 0V and 16V, CE_PD_EN = 0                                  | T <sub>J</sub> = +25°C                            |      | ±0.1 |       | μA |

|                                       |                       |                                                                                                     | T <sub>J</sub> = +85°C ( <a href="#">Note 5</a> ) |      | ±0.5 |       |    |

**Electrical Characteristics—Top-Level (continued)**

( $V_{SYS} = V_{INx} = 12V$ ,  $V_{OUT1} = 0.8V$  ( $M1\_RNG = 0x0$ ),  $V_{OUT2} = 1.1V$  ( $M2\_RNG = 0x1$ ),  $V_{OUT3} = 1.8V$  ( $M3\_RNG = 0x1$ ),  $V_{OUT4} = 3.3V$  ( $M4\_RNG = 0x2$ ), single-phase configuration,  $V_{CE} = 1.8V$ ,  $V_{IO} = 1.8V$ ,  $T_A = T_J = -40^\circ C$  to  $+125^\circ C$ , typical values are at  $T_A = T_J = +25^\circ C$ , unless otherwise noted. [Note 2.](#).)

| PARAMETER            | SYMBOL          | CONDITIONS                                                                          | MIN | TYP | MAX | UNITS   |

|----------------------|-----------------|-------------------------------------------------------------------------------------|-----|-----|-----|---------|

| IRQB Leakage Current | $I_{LKG\_IRQB}$ | IRQB set to high impedance (i.e., no interrupt pending), $V_{IRQB} = 0V$ and $2.0V$ | -1  |     | +1  | $\mu A$ |

**Electrical Characteristics—Quad-Phase Configurable Buck Converter**

( $V_{SYS} = V_{INx} = 12V$ ,  $V_{OUT1} = 0.8V$  ( $M1\_RNG = 0x0$ ),  $V_{OUT2} = 1.1V$  ( $M2\_RNG = 0x1$ ),  $V_{OUT3} = 1.8V$  ( $M3\_RNG = 0x1$ ),  $V_{OUT4} = 3.3V$  ( $M4\_RNG = 0x2$ ), single-phase configuration,  $V_{CE} = 1.8V$ ,  $V_{IO} = 1.8V$ ,  $T_A = T_J = -40^\circ C$  to  $+125^\circ C$ , typical values are at  $T_A = T_J = +25^\circ C$ , unless otherwise noted. Note 2.)

| PARAMETER                             | SYMBOL         | CONDITIONS                                                                             | MIN  | TYP | MAX  | UNITS |

|---------------------------------------|----------------|----------------------------------------------------------------------------------------|------|-----|------|-------|

| <b>INPUT SUPPLY</b>                   |                |                                                                                        |      |     |      |       |

| Input-Voltage Range                   | $V_{INx}$      |                                                                                        | 2.8  |     | 16   | V     |

| <b>DC OUTPUT VOLTAGE AND ACCURACY</b> |                |                                                                                        |      |     |      |       |

| Output-Voltage Range                  | $V_{OUT\_RNG}$ | Low range ( $Mx\_RNG[1:0] = 0x0$ )                                                     | 0.3  | 1.3 | 5.2  | V     |

|                                       |                | Mid range ( $Mx\_RNG[1:0] = 0x1$ )                                                     | 0.6  | 2.6 |      |       |

|                                       |                | High range ( $Mx\_RNG[1:0] = 0x2$ )                                                    | 1.2  |     |      |       |

| Line Regulation                       |                | 1Φ, FPWM mode, $V_{INx} = 2.8V$ to $16V$ , $V_{OUT} = \text{default}$ , $I_{OUT} = 0A$ | -0.1 |     | +0.1 | %/V   |

| Load Regulation                       |                | 1Φ, FPWM mode, $I_{OUT} = 0A$ to $4A$ ( <a href="#">Note 2</a> )                       |      | 0.1 |      | %/A   |

**Electrical Characteristics—Quad-Phase Configurable Buck Converter (continued)**

( $V_{SYS} = V_{INx} = 12V$ ,  $V_{OUT1} = 0.8V$  ( $M1\_RNG = 0x0$ ),  $V_{OUT2} = 1.1V$  ( $M2\_RNG = 0x1$ ),  $V_{OUT3} = 1.8V$  ( $M3\_RNG = 0x1$ ),  $V_{OUT4} = 3.3V$  ( $M4\_RNG = 0x2$ ), single-phase configuration,  $V_{CE} = 1.8V$ ,  $V_{IO} = 1.8V$ ,  $T_A = T_J = -40^\circ C$  to  $+125^\circ C$ , typical values are at  $T_A = T_J = +25^\circ C$ , unless otherwise noted. Note 2.)

| PARAMETER                                       | SYMBOL               | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MIN                                                     | TYP                   | MAX  | UNITS |

|-------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------|------|-------|

| DC Output-Voltage Accuracy                      | V <sub>OUT_ACC</sub> | 0.3V ≤ V <sub>OUT</sub> < 0.5V ( $Mx\_RNG = 0x0$ )<br>0.5V ≤ V <sub>OUT</sub> < 0.8V ( $Mx\_RNG = 0x0$ )<br>0.8V ≤ V <sub>OUT</sub> ≤ 1.3V ( $Mx\_RNG = 0x0$ )<br>0.6V ≤ V <sub>OUT</sub> < 1.2V ( $Mx\_RNG = 0x1$ )<br>1.2V ≤ V <sub>OUT</sub> < 1.9V ( $Mx\_RNG = 0x1$ )<br>1.9V ≤ V <sub>OUT</sub> ≤ 2.6V ( $Mx\_RNG = 0x1$ )<br>1.2V ≤ V <sub>OUT</sub> < 2.2V ( $Mx\_RNG = 0x2$ )<br>2.2V ≤ V <sub>OUT</sub> < 3.6V ( $Mx\_RNG = 0x2$ )<br>3.6V ≤ V <sub>OUT</sub> ≤ 5.2V ( $Mx\_RNG = 0x2$ ) | -3.0                                                    |                       | +3.0 | %     |

|                                                 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -2.0                                                    |                       | +2.0 |       |

|                                                 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -1.0                                                    |                       | +1.0 |       |

|                                                 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -3.0                                                    |                       | +3.0 |       |

|                                                 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -1.5                                                    |                       | +1.5 |       |

|                                                 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -1.0                                                    |                       | +1.0 |       |

|                                                 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -3.0                                                    |                       | +3.0 |       |

|                                                 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -1.5                                                    |                       | +1.5 |       |

|                                                 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -1.0                                                    |                       | +1.0 |       |

|                                                 |                      | 1Φ, FPWM mode, $V_{INx} = 2.8V$ to $16V$ , $I_{OUT} = 0A$ , $T_A = T_J = 0^\circ C$ to $+85^\circ C$                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>OUT</sub> = factory default, $T_J = +25^\circ C$ | -0.5                  |      | +0.5  |

| POWER STAGE                                     |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                         |                       |      |       |

| High-Side MOSFET Peak Current Limit             | I <sub>PLIM</sub>    | M <sub>x</sub> _ILIM[1:0] = 0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.1                                                     | 3.5                   | 3.9  | A     |

|                                                 |                      | M <sub>x</sub> _ILIM[1:0] = 0x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.0                                                     | 4.5                   | 5.0  |       |

|                                                 |                      | M <sub>x</sub> _ILIM[1:0] = 0x2                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4.9                                                     | 5.5                   | 6.1  |       |

|                                                 |                      | M <sub>x</sub> _ILIM[1:0] = 0x3                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.4                                                     | 6.0                   | 6.6  |       |

| Low-Side MOSFET Valley Current Limit            | I <sub>VLIM</sub>    | Tracks I <sub>PLIM</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                         | I <sub>PLIM</sub> - 1 |      | A     |

| Low-Side MOSFET Negative Current Limit          | I <sub>NLIM</sub>    | FPWM mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -3.6                                                    | -3.0                  | -2.4 | A     |

| Low-Side MOSFET Zero-Crossing Current Threshold | I <sub>ZX</sub>      | Skip or LP-skip mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         | 150                   |      | mA    |

| High-Side MOSFET On-Resistance                  | R <sub>ON_HS</sub>   | 1Φ, I <sub>Lxx</sub> = 190mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         | 35                    | 70   | mΩ    |

**Electrical Characteristics—Quad-Phase Configurable Buck Converter (continued)**

( $V_{SYS} = V_{INx} = 12V$ ,  $V_{OUT1} = 0.8V$  ( $M1\_RNG = 0x0$ ),  $V_{OUT2} = 1.1V$  ( $M2\_RNG = 0x1$ ),  $V_{OUT3} = 1.8V$  ( $M3\_RNG = 0x1$ ),  $V_{OUT4} = 3.3V$  ( $M4\_RNG = 0x2$ ), single-phase configuration,  $V_{CE} = 1.8V$ ,  $V_{IO} = 1.8V$ ,  $T_A = T_J = -40^\circ C$  to  $+125^\circ C$ , typical values are at  $T_A = T_J = +25^\circ C$ , unless otherwise noted. Note 2.)

| PARAMETER                      | SYMBOL        | CONDITIONS                                                                                                                 |                                                                 | MIN | TYP | MAX | UNITS     |

|--------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|-----|-----|-----------|

| Low-Side MOSFET On-Resistance  | $R_{ON\_LS}$  | 1Φ, $I_{LXx} = -190mA$                                                                                                     |                                                                 |     | 18  | 40  | $m\Omega$ |

| Nominal Switching Frequency    | $F_{SW}$      | FPWM mode, no load, no external clock, $T_J = +25^\circ C$<br>( <a href="#">Note 4</a> )                                   | $Mx\_FREQ[1:0] = 0x0$                                           | 0.5 |     |     | MHz       |

|                                |               |                                                                                                                            | $Mx\_FREQ[1:0] = 0x1$                                           | 1   |     |     |           |

|                                |               |                                                                                                                            | $Mx\_FREQ[1:0] = 0x2$                                           | 1.5 |     |     |           |

| Maximum Duty Cycle             | $D_{MAX}$     | Drop-out region ( $V_{OUT}$ falls below its regulation target)                                                             |                                                                 | 97  | 98  |     | %         |

| LX Active Discharge Resistance | $R_{AD1}$     | 1Φ, buck output disabled, active discharge enabled ( $Mx\_ADIS1 = 1$ ), resistance from corresponding $LX_x$ to $PGND_x$   |                                                                 |     | 1   |     | $\Omega$  |

|                                | $R_{AD100}$   | 1Φ, buck output disabled, active discharge enabled ( $Mx\_ADIS100 = 1$ ), resistance from corresponding $LX_x$ to $PGND_x$ |                                                                 |     | 100 |     |           |

| LX Leakage Current             | $I_{LX\_LKG}$ | $1\Phi, V_{LXx} = 0V$ or $16V, Mx\_ADIS100 = 0$                                                                            | $T_J = +25^\circ C$                                             | 1   | 15  |     | $\mu A$   |

|                                |               |                                                                                                                            | $T_J = -40^\circ C$ to $+85^\circ C$ ( <a href="#">Note 5</a> ) |     | 1   |     |           |

**SLEW RATE AND TIMING**

|                                                    |                           |                            |        |            |

|----------------------------------------------------|---------------------------|----------------------------|--------|------------|

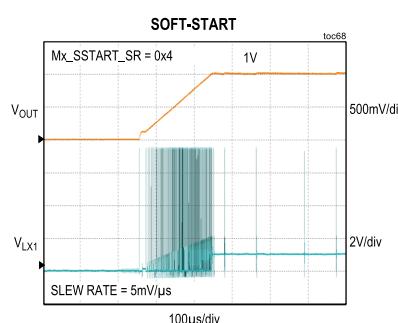

| Soft-Start Slew Rate<br>( <a href="#">Note 6</a> ) | $\Delta V_{OUT}/\Delta t$ | $Mx\_SSTRT\_SR[2:0] = 0x0$ | 0.15   | $mV/\mu s$ |

|                                                    |                           | $Mx\_SSTRT\_SR[2:0] = 0x1$ | 0.625  |            |

|                                                    |                           | $Mx\_SSTRT\_SR[2:0] = 0x2$ | 1.25   |            |

|                                                    |                           | $Mx\_SSTRT\_SR[2:0] = 0x3$ | 2.5    |            |

|                                                    |                           | $Mx\_SSTRT\_SR[2:0] = 0x4$ | 5      |            |

|                                                    |                           | $Mx\_SSTRT\_SR[2:0] = 0x5$ | 10     |            |

|                                                    |                           | $Mx\_SSTRT\_SR[2:0] = 0x6$ | 20     |            |

|                                                    |                           | $Mx\_SSTRT\_SR[2:0] = 0x7$ | 40     |            |

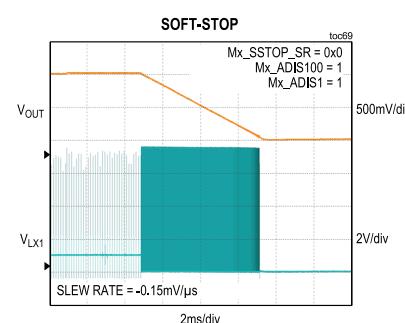

| Soft-Stop Slew Rate<br>( <a href="#">Note 6</a> )  | $\Delta V_{OUT}/\Delta t$ | $Mx\_SSTOP\_SR[2:0] = 0x0$ | -0.15  | $mV/\mu s$ |

|                                                    |                           | $Mx\_SSTOP\_SR[2:0] = 0x1$ | -0.625 |            |

|                                                    |                           | $Mx\_SSTOP\_SR[2:0] = 0x2$ | -1.25  |            |

|                                                    |                           | $Mx\_SSTOP\_SR[2:0] = 0x3$ | -2.5   |            |

|                                                    |                           | $Mx\_SSTOP\_SR[2:0] = 0x4$ | -5     |            |

|                                                    |                           | $Mx\_SSTOP\_SR[2:0] = 0x5$ | -10    |            |

|                                                    |                           | $Mx\_SSTOP\_SR[2:0] = 0x6$ | -20    |            |

|                                                    |                           | $Mx\_SSTOP\_SR[2:0] = 0x7$ | -40    |            |

**Electrical Characteristics—Quad-Phase Configurable Buck Converter (continued)**

( $V_{SYS} = V_{INx} = 12V$ ,  $V_{OUT1} = 0.8V$  ( $M1\_RNG = 0x0$ ),  $V_{OUT2} = 1.1V$  ( $M2\_RNG = 0x1$ ),  $V_{OUT3} = 1.8V$  ( $M3\_RNG = 0x1$ ),  $V_{OUT4} = 3.3V$  ( $M4\_RNG = 0x2$ ), single-phase configuration,  $V_{CE} = 1.8V$ ,  $V_{IO} = 1.8V$ ,  $T_A = T_J = -40^\circ C$  to  $+125^\circ C$ , typical values are at  $T_A = T_J = +25^\circ C$ , unless otherwise noted. Note 2.)

| PARAMETER                                                                | SYMBOL                    | CONDITIONS                                                                     |                             | MIN      | TYP | MAX | UNITS       |

|--------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------|-----------------------------|----------|-----|-----|-------------|

| Ramp-Up Slew Rate<br>( <a href="#">Note 6</a> )                          | $\Delta V_{OUT}/\Delta t$ | Mx_RU_SR[2:0] = 0x0                                                            |                             | 0.15     |     |     | mV/ $\mu$ s |

|                                                                          |                           | Mx_RU_SR[2:0] = 0x1                                                            |                             | 0.625    |     |     |             |

|                                                                          |                           | Mx_RU_SR[2:0] = 0x2                                                            |                             | 1.25     |     |     |             |

|                                                                          |                           | Mx_RU_SR[2:0] = 0x3                                                            |                             | 2.5      |     |     |             |

|                                                                          |                           | Mx_RU_SR[2:0] = 0x4                                                            |                             | 5        |     |     |             |

|                                                                          |                           | Mx_RU_SR[2:0] = 0x5                                                            |                             | 10       |     |     |             |

|                                                                          |                           | Mx_RU_SR[2:0] = 0x6                                                            |                             | 20       |     |     |             |

|                                                                          |                           | Mx_RU_SR[2:0] = 0x7                                                            |                             | 40       |     |     |             |

| Ramp-Down Slew Rate<br>( <a href="#">Note 6</a> )                        | $\Delta V_{OUT}/\Delta t$ | Mx_RD_SR[2:0] = 0x0                                                            |                             | -0.15    |     |     | mV/ $\mu$ s |

|                                                                          |                           | Mx_RD_SR[2:0] = 0x1                                                            |                             | -0.625   |     |     |             |

|                                                                          |                           | Mx_RD_SR[2:0] = 0x2                                                            |                             | -1.25    |     |     |             |

|                                                                          |                           | Mx_RD_SR[2:0] = 0x3                                                            |                             | -2.5     |     |     |             |

|                                                                          |                           | Mx_RD_SR[2:0] = 0x4                                                            |                             | -5       |     |     |             |

|                                                                          |                           | Mx_RD_SR[2:0] = 0x5                                                            |                             | -10      |     |     |             |

|                                                                          |                           | Mx_RD_SR[2:0] = 0x6                                                            |                             | -20      |     |     |             |

|                                                                          |                           | Mx_RD_SR[2:0] = 0x7                                                            |                             | -40      |     |     |             |

| Slew-Rate Accuracy                                                       |                           | REFDAC slew-rate accuracy                                                      |                             | -5       |     | +5  | %           |

| Turn-On Delay                                                            | $t_{DLY}$                 | Delay from rising edge of EN_Mx (MFIOx) signal to $V_{OUTx}$ ramping start-off | $V_{Lx}$ is pre-enabled     | 90       | 110 |     | $\mu$ s     |

|                                                                          |                           |                                                                                | $V_{Lx}$ is not pre-enabled | 110      | 150 |     |             |

| <b>FREQUENCY TRACKING</b>                                                |                           |                                                                                |                             |          |     |     |             |

| External Frequency Tracking Lockable Range<br>( <a href="#">Note 6</a> ) | $F_{FTRAK}$               | Expressed as a percentage of the nominal frequency set by Mx_FREQ[1:0]         |                             | 95       | 105 |     | %           |

| <b>SPREAD-SPECTRUM</b>                                                   |                           |                                                                                |                             |          |     |     |             |

| Modulation Frequency<br>( <a href="#">Note 6</a> )                       | $F_{SS\_MOD}$             | Mx_SS_FREQ[1:0] = 0x0                                                          |                             | 1        |     |     | kHz         |

|                                                                          |                           | Mx_SS_FREQ[1:0] = 0x1                                                          |                             | 3        |     |     |             |

|                                                                          |                           | Mx_SS_FREQ[1:0] = 0x2                                                          |                             | 5        |     |     |             |

|                                                                          |                           | Mx_SS_FREQ[1:0] = 0x3                                                          |                             | 7        |     |     |             |

| Modulation Envelope                                                      | $\Delta F_{SS}$           | Mx_SS_ENV[1:0] = 0x1                                                           |                             | $\pm 8$  |     |     | %           |

|                                                                          |                           | Mx_SS_ENV[1:0] = 0x2                                                           |                             | $\pm 12$ |     |     |             |

|                                                                          |                           | Mx_SS_ENV[1:0] = 0x3                                                           |                             | $\pm 16$ |     |     |             |

| <b>POWER-OK AND SHORT-CIRCUIT PROTECTION</b>                             |                           |                                                                                |                             |          |     |     |             |

| Power-OK Rising Threshold                                                | $V_{POK\_R}$              | Expressed as a percentage of $V_{OUT}$                                         |                             | 77       | 82  | 87  | %           |

| Power-OK Falling Threshold                                               | $V_{POK\_F}$              | Expressed as a percentage of $V_{OUT}$                                         |                             | 73       | 78  | 83  | %           |

**Electrical Characteristics—Quad-Phase Configurable Buck Converter (continued)**

( $V_{SYS} = V_{INx} = 12V$ ,  $V_{OUT1} = 0.8V$  ( $M1\_RNG = 0x0$ ),  $V_{OUT2} = 1.1V$  ( $M2\_RNG = 0x1$ ),  $V_{OUT3} = 1.8V$  ( $M3\_RNG = 0x1$ ),  $V_{OUT4} = 3.3V$  ( $M4\_RNG = 0x2$ ), single-phase configuration,  $V_{CE} = 1.8V$ ,  $V_{IO} = 1.8V$ ,  $T_A = T_J = -40^\circ C$  to  $+125^\circ C$ , typical values are at  $T_A = T_J = +25^\circ C$ , unless otherwise noted. Note 2.)

| PARAMETER                                          | SYMBOL              | CONDITIONS                                                       | MIN | TYP | MAX | UNITS |

|----------------------------------------------------|---------------------|------------------------------------------------------------------|-----|-----|-----|-------|

| Power-OK Fault Time-Out ( <a href="#">Note 6</a> ) | t <sub>POK_TO</sub> | POK_TO[1:0] = 0x1                                                |     | 1   |     | ms    |

|                                                    |                     | POK_TO[1:0] = 0x2                                                |     | 5   |     |       |

|                                                    |                     | POK_TO[1:0] = 0x3                                                |     | 10  |     |       |

| Short-Circuit Detection Threshold                  | V <sub>SCP</sub>    | $V_{OUT}$ falling, expressed as a percentage of target $V_{OUT}$ |     | 20  |     | %     |

**Electrical Characteristics—Multifunction I/Os**

( $V_{SYS} = 12V$ ,  $V_{CE} = 1.8V$ ,  $V_{IO} = 1.8V$ ,  $T_A = T_J = -40^\circ C$  to  $+125^\circ C$ , typical values are at  $T_A = T_J = +25^\circ C$ , unless otherwise noted. Note 2.)

| PARAMETER                       | SYMBOL               | CONDITIONS                                            | MIN                                               | TYP                    | MAX  | UNITS |    |

|---------------------------------|----------------------|-------------------------------------------------------|---------------------------------------------------|------------------------|------|-------|----|

| <b>MULTIFUNCTION I/O (MFIO)</b> |                      |                                                       |                                                   |                        |      |       |    |

| MFIO Input Logic High Threshold | V <sub>IH</sub>      |                                                       | 0.75 x V <sub>IO</sub>                            |                        |      | V     |    |

| MFIO Input Logic Low Threshold  | V <sub>IL</sub>      |                                                       |                                                   | 0.25 x V <sub>IO</sub> |      | V     |    |

| MFIO Output High Voltage        | V <sub>OH_MFIO</sub> | Push-pull output mode, sourcing 2mA                   | 0.8 x V <sub>IO</sub>                             |                        |      | V     |    |

| MFIO Output Low Voltage         | V <sub>OL_MFIO</sub> | Sinking 2mA                                           |                                                   | 0.2                    |      | V     |    |

| MFIO Input Debounce Time        | t <sub>DB_MFIO</sub> | MFIOx_DEB[2:0] = 0x0                                  | 0                                                 |                        |      | μs    |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x1                                  | 0.5                                               |                        |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x2                                  | 1                                                 |                        |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x3                                  | 2                                                 |                        |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x4                                  | 4                                                 |                        |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x5                                  | 8                                                 |                        |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x6                                  | 16                                                |                        |      |       |    |

|                                 |                      | MFIOx_DEB[2:0] = 0x7                                  | 32                                                |                        |      |       |    |

| MFIO Pull-Down Resistance       | R <sub>PD_MFIO</sub> | Input mode, MFIOx_PDPU = 0x0                          | 400                                               | 800                    | 1600 | kΩ    |    |

|                                 |                      | Input mode, MFIOx_PDPU = 0x1                          | 50                                                | 100                    | 200  |       |    |

| MFIO Pull-Up Resistance         | R <sub>PU_MFIO</sub> | Input mode, MFIOx_PDPU = 0x2                          | 50                                                | 100                    | 200  | kΩ    |    |

| MFIO Leakage Current            | I <sub>LK_MFIO</sub> | V <sub>MFIOx</sub> = 0V and 2.0V,<br>MFIOx_PDPU = 0x3 | T <sub>J</sub> = +25°C                            | -1.5                   | 0.01 | 1.5   | μA |

|                                 |                      |                                                       | T <sub>J</sub> = +85°C ( <a href="#">Note 5</a> ) |                        | 0.1  |       |    |

**Electrical Characteristics—ADC**

( $V_{SYS} = 12V$ ,  $V_{CE} = 1.8V$ ,  $V_{IO} = 1.8V$ ,  $T_A = T_J = -40^\circ C$  to  $+125^\circ C$ , typical values are at  $T_A = T_J = +25^\circ C$ , unless otherwise noted. Note 2.)

| PARAMETER                                          | SYMBOL                | CONDITIONS                                                                           |                                                              | MIN | TYP | MAX | UNITS |  |  |

|----------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|-----|-----|-------|--|--|

| <b>READBACK ACCURACY (Note 7)</b>                  |                       |                                                                                      |                                                              |     |     |     |       |  |  |

| Output-Current<br>Readback Accuracy                | I <sub>OUT_ADC</sub>  | 1Φ, I <sub>OUT</sub> =<br>I <sub>OUT(MAX)</sub>                                      | T <sub>J</sub> = -40°C to<br>+85°C                           | 5   |     | %   |       |  |  |

|                                                    |                       |                                                                                      | T <sub>J</sub> = +125°C                                      | 7.5 |     |     |       |  |  |

| Output-Voltage<br>Readback Accuracy                | V <sub>OUT_ADC</sub>  | T <sub>J</sub> = -40°C to +85°C                                                      | 3                                                            |     | %   |     |       |  |  |

|                                                    |                       |                                                                                      | T <sub>J</sub> = +125°C                                      | 5   |     |     |       |  |  |

| SYS Input-Voltage<br>Readback Accuracy             | V <sub>SYS_ADC</sub>  | 3.0V ≤ V <sub>SYS</sub> ≤ 16V                                                        | T <sub>J</sub> = -40°C to<br>+85°C                           | 3   |     | %   |       |  |  |

|                                                    |                       |                                                                                      | T <sub>J</sub> = +125°C                                      | 5   |     |     |       |  |  |

| Junction Temperature<br>Readback Accuracy          | T <sub>J_ADC</sub>    | T <sub>J</sub> = +85°C to +125°C                                                     |                                                              | 5   |     | %   |       |  |  |

| MFIO Voltage Readback<br>Accuracy                  | V <sub>MFIO_ADC</sub> | T <sub>J</sub> = -40°C to +85°C                                                      | 3                                                            |     | %   |     |       |  |  |

|                                                    |                       |                                                                                      | T <sub>J</sub> = +125°C                                      | 5   |     |     |       |  |  |