PPG Optimized Buck-Boost Converter with 500mA Output Current and Ultra-Fast DVS Capability

#### **FEATURES**

- Extend System Runtime

- ► Ultra-fast dynamic voltage scaling with direct AFE control

- Low, 2.5μA (typical) quiescent current

- ▶ 96% peak efficiency

- ► Low, Continuous Noise Profile

- ▶ No post-filtering LDO required in PPG systems

- No discontinuities across operating voltage

- ► Adaptable Load Transient Response

- ► Fast load transient response minimizes AFE settling time

- ► FAST mode pre-triggers load response and improves load transient

### **APPLICATIONS**

► Biometric Optical Sensing (example, PPG)

# **GENERAL DESCRIPTION**

The MAX20363 is an ultra-low guiescent current, noninverting buck-boost converter with 500mA output current capability. The MAX20363 is intended for applications that require long run times while also demanding bursts of high current. The device employs a proprietary control algorithm that seamlessly transitions between buck, buck-boost, and boost modes, minimizing discontinuities and subharmonics in the output voltage ripple. The low 1.8V input voltage allows the device to be powered from a variety of sources such as lithium ion rechargeable and lithium primary batteries. The MAX20363 is designed to minimize inductance and capacitance requirements to keep the overall solution size as small as possible.

The MAX20363 is optimized for powering optical photoplethysmogram (PPG) systems. The ultra-fast dynamic voltage scaling (DVS) capability allows the device to transition quickly between output voltages and enable in-frame scaling of LED supply voltage. Additionally, the low output ripple and fast, predictable transient response maximizes the signal-to-noise ratio (SNR) of high-performance optical PPG analog-frontend (AFE).

The MAX20363 is available in an 18-bump, 2.43mm x 1.25mm WLP package, with 0.4mm pitch.

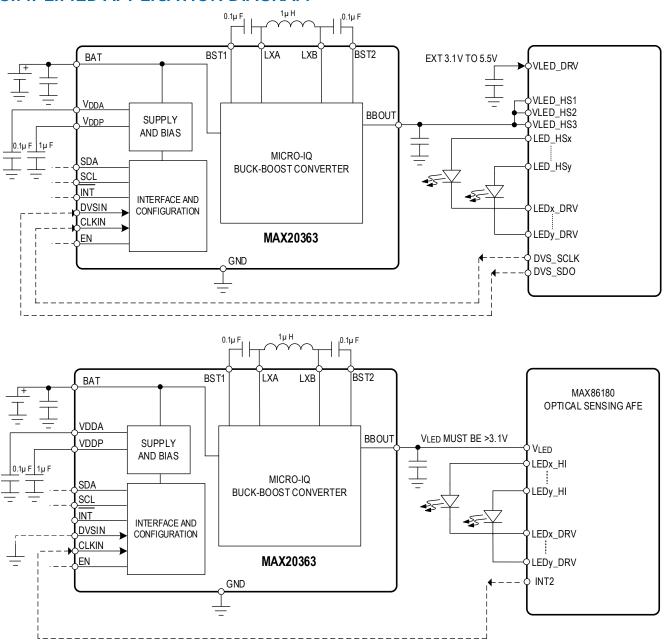

# SIMPLIFIED APPLICATION DIAGRAM

analog.com Rev 1 | 2 of 51

# **SPECIFICATIONS**

#### **Table 1. Electrical Characteristics**

$(V_{BAT} = +1.8V \text{ to } +5.5V, C_{BAT\_EFF} = 5\mu\text{F}, C_{BBOUT\_EFF} = \text{See } \textit{Figure } 34$ ,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ ,  $V_{BAT} = +3.7V$ ,  $L = 1\mu\text{H}$ , limits are 100% tested at  $T_A = +25^{\circ}\text{C}$ .) (Note 1))

| PARAMETER                 | SYMBOL                                                        | CONDITIONS/COMMENTS                                                                                                                                                                                          |                                                                                                                                                                                                              |     | TYP | MAX | UNITS |

|---------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Input Voltage Range       | $V_{BAT}$                                                     |                                                                                                                                                                                                              | 1.8                                                                                                                                                                                                          |     | 5.5 | V   |       |

|                           | IQ                                                            | No load, V <sub>BBOUT</sub> = 5°<br>2)                                                                                                                                                                       |                                                                                                                                                                                                              | 2.5 |     |     |       |

|                           | I <sub>Q_ROOM</sub>                                           | No load, $V_{BBOUT} = 5^{\circ}$<br>2), $T_A = 25^{\circ}$ C                                                                                                                                                 | No load, $V_{BBOUT} = 5V$ , $V_{BAT} = 3.7V$ (Note 2), $T_A = 25^{\circ}C$                                                                                                                                   |     |     | 6   | μΑ    |

| Quiescent Supply Current  | I <sub>Q_FAST</sub>                                           | No load, $V_{BBOUT} = 5V$ , $V_{BAT} = 3.7V$ (Note 2)                                                                                                                                                        | FAST = 1                                                                                                                                                                                                     |     | 75  |     |       |

|                           | $I_{Q_{\_FPWM}}$ No load, $V_{BBOUT} = 5V$ , $V_{BAT} = 3.7V$ | FPWM = 1, L =<br>1µH<br>(DFE201210U1R0<br>M)                                                                                                                                                                 |                                                                                                                                                                                                              | 11  |     | mA  |       |

| Shutdown Supply           | 1                                                             | EN = 1, Disabled by                                                                                                                                                                                          |                                                                                                                                                                                                              | 1.2 |     | μA  |       |

| Current                   | I <sub>SHDN</sub>                                             | EN = 0                                                                                                                                                                                                       |                                                                                                                                                                                                              | 0.1 |     | μΛ  |       |

| Maximum Output<br>Current | I <sub>BBOUT_MAX</sub>                                        | $V_{BAT} \ge 2.5V, 1.5V \le V_{BBOUT} \le 5.0V$                                                                                                                                                              | BBFetScale = 00,<br>$L = 1\mu H$<br>(DFE201210U-<br>1R0M),<br>BBL2P2Sel = 0,<br>$C_{BBOUT\_EFF}$ = refer<br>to <i>Figure 34</i> , $I_{PSET1}$<br>= default, $I_{PSET2}$ =<br>300mA, Load Reg<br>$\geq$ -7.5% | 500 |     |     | mA    |

|                           | V <sub>BBOUT</sub> ≤ 5.0V                                     | BBFetScale = 01<br>or 10, L = $1\mu$ H<br>(DFE201210U-<br>1R0M),<br>BBL2P2Sel = 0,<br>C <sub>BBOUT_EFF</sub> = $1/2$ of<br>that shown in<br>Figure 34, I <sub>PSET1</sub> =<br>default, I <sub>PSET2</sub> = | 250                                                                                                                                                                                                          |     |     |     |       |

analog.com Rev 1 3 of 51

$(V_{BAT} = +1.8 \text{V to } +5.5 \text{V}, C_{BAT\_EFF} = 5 \mu \text{F}, C_{BBOUT\_EFF} = \text{See } \textit{Figure 34}, T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ}\text{C}, V_{BAT} = +3.7 \text{V}, L = 1 \mu \text{H}, \text{ limits are } 100\% \text{ tested at } T_A = +25 ^{\circ}\text{C}.) \text{ (Note 1))}$

| PARAMETER                   | SYMBOL          | CONDITIONS                                                                                                                                              | S/COMMENTS                                                                                                                                                                                                         | MIN  | TYP           | MAX  | UNITS |

|-----------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|------|-------|

|                             |                 |                                                                                                                                                         | 300mA, Load Reg ≥ -7.5%                                                                                                                                                                                            |      |               |      |       |

|                             |                 |                                                                                                                                                         | BBFetScale = 11,<br>$L = 1\mu H$<br>(DFE201210U-<br>1R0M),<br>BBL2P2Sel = 0<br>$C_{BBOUT\_EFF} = 1/4$ of<br>that shown in<br>Figure 34, $I_{PSET1} =$<br>default, $I_{PSET2} =$<br>300mA, Load Reg<br>$\geq$ -7.5% | 125  |               |      |       |

|                             |                 | $V_{BAT} \ge 2.0V, 1.5V \le V_{BBOUT} \le 5.0V$                                                                                                         | BBFetScale = 00,<br>L = $1\mu$ H<br>(DFE201210U-<br>1R0M),<br>BBL2P2Sel = 0,<br>$C_{BBOUT\_EFF}$ = refer<br>to <i>Figure 34</i> , $I_{PSET1}$<br>= default, $I_{PSET2}$ = 300mA, Load Reg<br>$\geq$ -7.5%          | 350  |               |      |       |

| Output Voltage Set<br>Range | $V_{BBOUT}$     | 50mV step resolut                                                                                                                                       | ion                                                                                                                                                                                                                |      | 1.5 to<br>5.5 |      | V     |

| Average Output-Voltage      | ACC_OUT         | $I_{BBOUT} = 10$ mA, FAS<br>$0, L = 1\mu H$ (DFE201<br>$= default, I_{PSET2} = 36$<br>$20\mu F$                                                         | .210U-1R0M), I <sub>PSET1</sub>                                                                                                                                                                                    | -1   |               | +2.5 | %     |

| Accuracy                    | , nee_001       | $I_{BBOUT}$ = 10mA, FAST = 0, BBL2P2Sel = 0, L = 1 $\mu$ H (DFE201210U-1R0M), $I_{PSET1}$ = default, $I_{PSET2}$ = 300mA, $C_{BBOUT\_EFF}$ = 20 $\mu$ F |                                                                                                                                                                                                                    | -0.5 |               | +3   | 76    |

| Line Regulation Error       | $V_{LINE\_REG}$ | $I_{BBOUT} = 50 \text{mA}, C_{BBO}$                                                                                                                     | <sub>UT_EFF</sub> = 20μF                                                                                                                                                                                           | -1   |               | +1   | %/V   |

| Load Regulation Error       | $V_{LOAD\_REG}$ | $V_{BAT} = 3.7V, V_{BBOUT} = BBFetScale = 00, C$ Figure 34, $I_{PSET1} = d$                                                                             |                                                                                                                                                                                                                    |      | -2.5          |      | %     |

analog.com Rev 1 | 4 of 51

$(V_{BAT} = +1.8 \text{V to } +5.5 \text{V}, C_{BAT\_EFF} = 5 \mu \text{F}, C_{BBOUT\_EFF} = \text{See } \textit{Figure } 34$ ,  $T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ}\text{C}$ ,  $V_{BAT} = +3.7 \text{V}$ ,  $L = 1 \mu \text{H}$ , limits are 100 % tested at  $T_A = +25 ^{\circ}\text{C}$ .) (Note 1))

| PARAMETER                                                       | SYMBOL                                        | CONDITIONS/COMMENTS                                                                                                                                                                                                                          | MIN      | TYP          | MAX | UNITS |

|-----------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|-----|-------|

|                                                                 |                                               | 300mA, BBL2P2Sel = 0, L = 1μH<br>(DFE201210U-1R0M)                                                                                                                                                                                           |          |              |     |       |

|                                                                 |                                               | $V_{BAT}$ = 3.7V, $V_{BBOUT}$ = 5V, $I_{BBOUT}$ = 250mA,<br>BBFetScale = 01 or 10, $C_{BBOUT}$ = 1/2 of<br>that shown in <i>Figure 34</i> , $I_{PSET1}$ =<br>default, $I_{PSET2}$ = 300mA, BBL2P2Sel =<br>0, L = 1 $\mu$ H (DFE201210U-1R0M) |          | -2.0         |     |       |

|                                                                 |                                               | $V_{BAT}$ = 3.7V, $V_{BBOUT}$ = 5V, $I_{BBOUT}$ = 125mA,<br>BBFetScale = 11, $C_{BBOUT}$ = ½ of that<br>shown in <i>Figure 34</i> , $I_{PSET1}$ = default,<br>$I_{PSET2}$ = 300mA, BBL2P2Sel = 0, L =<br>1 $\mu$ H (DFE201210U-1R0M)         |          | -2.0         |     |       |

| Line Transient Response                                         | $V_{LINE\_TRAN}$                              | $V_{BBOUT}$ = 3.4V, $V_{BAT}$ from 3.4V to 2.9V,<br>1 $\mu$ s fall time, $I_{LOAD}$ = 1 $\mu$ mA, $C_{BBOUT}$ = refer to <i>Figure 34</i>                                                                                                    |          | 20           |     | mV    |

| Load Transient<br>Response                                      | $V_{LOAD\_TRAN}$                              | $V_{BBOUT}$ = 5V, $V_{BAT}$ = 3.7V, $I_{LOAD}$ = 10 $\mu$ A to 300mA, $I_{PSET1}$ = default, $I_{PSET2}$ = 300mA, BBL2P2Sel = 0, L = 1 $\mu$ H (DFE201210U-1R0M), $C_{BBOUT}$ = refer to <i>Figure 34</i>                                    |          | 80           |     | mV    |

| Programmable Inductor<br>Valley Current Limit<br>During Startup | I <sub>IVLY_STUP</sub>                        | BBIPwpMaxP<br>50mA steps                                                                                                                                                                                                                     |          | 0 to 750     |     | mA    |

| Maximum Output Load<br>Current during Start Up                  | I <sub>PWR_MAX_STUP</sub>                     | V <sub>BAT</sub> > 2.5V, I <sub>PSET1</sub> = default, I <sub>PSET2</sub> = 300mA, I <sub>VLY_STUP</sub> min setting (BBIPwpMaxP = 0)                                                                                                        |          | 40           |     | mA    |

| Startup Time                                                    | Time from enable (B<br>goes high) to final va |                                                                                                                                                                                                                                              |          | 10           |     | ms    |

| Nominal Valley Inductor                                         |                                               | BBFetScale = 00, 50mA steps                                                                                                                                                                                                                  |          | 0 to<br>1600 |     |       |

| Current Limit Range                                             | I <sub>VLY_LIM</sub>                          | BBFetScale = 01 or 10, 25mA steps                                                                                                                                                                                                            | 0 to 800 |              |     | mA    |

|                                                                 |                                               | BBFetScale = 11, 12.5mA steps                                                                                                                                                                                                                |          | 0 to 400     |     |       |

analog.com Rev 1 | 5 of 51

$(V_{BAT} = +1.8 \text{V to } +5.5 \text{V}, C_{BAT\_EFF} = 5 \mu \text{F}, C_{BBOUT\_EFF} = \text{See } \textit{Figure } 34$ ,  $T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25 ^{\circ}\text{C}$ ,  $V_{BAT} = +3.7 \text{V}$ ,  $L = 1 \mu \text{H}$ , limits are 100 % tested at  $T_A = +25 ^{\circ}\text{C}$ .) (Note 1))

| PARAMETER                                                         | SYMBOL                    | CONDITIONS/COMMENTS                                             | MIN | TYP              | MAX  | UNITS |  |

|-------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------|-----|------------------|------|-------|--|

| Nominal Falling                                                   |                           | BBFetScale = 00, 50mA steps                                     |     | -200 to<br>-1800 |      |       |  |

| Dynamic Voltage Scaling<br>Valley Inductor Current<br>Limit Range | $I_{DVSF}$                | BBFetScale = 01 or 10, 25mA steps                               |     | -200 to<br>-1000 |      | mA    |  |

| Limit Kange                                                       |                           | BBFetScale = 11, 12.5mA steps                                   |     | -100 to<br>-500  |      |       |  |

| Active Discharge Current                                          | I <sub>ACTD</sub>         | Applied on BBOUT for 50ms after shutdown if BBstActDsc = 1      |     | 20               |      | mA    |  |

| Passive Discharge<br>Resistance                                   | $R_{PSVD}$                | Applied on BBOUT after shutdown, if BBstPsvDsc = 1 or EN is low |     | 1.3              |      | kΩ    |  |

| Output UVLO                                                       | $V_{\text{OUT\_UVLO\_F}}$ | V <sub>BBOUT</sub> falling                                      | 1   | 1.1              |      | V     |  |

| output oveo                                                       | $V_{\text{OUT\_UVLO\_R}}$ | V <sub>BBOUT</sub> rising                                       |     | 1.13             | 1.25 | V     |  |

| VDDA UVLO                                                         | $V_{VDDA\_UVLO\_R}$       | V <sub>VDDA</sub> rising                                        |     | 1.658            | 1.7  | V     |  |

|                                                                   | $V_{VDDA\_UVLO\_F}$       | V <sub>VDDA</sub> falling                                       | 1.6 | 1.642            |      |       |  |

| LXA, LXB Leakage                                                  | I <sub>LX_LKG</sub>       | EN is low                                                       |     |                  | 2.5  | μΑ    |  |

| BST1, BST2 Leakage                                                | I <sub>BST_LKG</sub>      | EN is low                                                       |     |                  | 4.5  | μΑ    |  |

| BBOUT Leakage                                                     | I <sub>BBOUT_LKG</sub>    | EN is high and BBstEna = 0                                      |     |                  | 1    | μΑ    |  |

| DIGITAL                                                           |                           |                                                                 |     |                  |      |       |  |

| SDA, SCL, EN, INT,<br>DVSIN, CLKIN Input<br>Leakage Current       | I <sub>LK_IO</sub>        |                                                                 | -1  |                  | +1   | μΑ    |  |

| SDA, SCL, EN, DVSIN,<br>CLKIN Input Logic<br>High                 | $V_{\text{IO\_IH}}$       |                                                                 | 1.4 |                  |      | V     |  |

| SDA, SCL, EN, DVSIN,<br>CLKIN Input Logic Low                     | $V_{IO_{IL}}$             |                                                                 |     |                  | 0.4  | V     |  |

| INT Output Logic Low                                              | V <sub>IO_OL_INT</sub>    | I <sub>OL</sub> = 4mA                                           |     |                  | 0.4  | V     |  |

| SDA Output Logic Low                                              | $V_{IO\_OL\_SDA}$         | I <sub>OL</sub> = 20mA                                          |     |                  | 0.4  | V     |  |

| SCL Clock Frequency                                               | f <sub>SCL</sub>          |                                                                 | 0   |                  | 1    | MHz   |  |

analog.com Rev 1 6 of 51

$(V_{BAT} = +1.8V \text{ to } +5.5V, C_{BAT\_EFF} = 5\mu\text{F}, C_{BBOUT\_EFF} = \text{See } \textit{Figure 34}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C}, V_{BAT} = +3.7V, L = 1\mu\text{H}, \text{ limits are } 100\% \text{ tested at } T_A = +25^{\circ}\text{C}.) \text{ (Note 1))}$

| PARAMETER                                            | SYMBOL                | CONDITIONS/COMMENTS | MIN  | TYP | MAX | UNITS |

|------------------------------------------------------|-----------------------|---------------------|------|-----|-----|-------|

| Bus Free Time<br>Between STOP and<br>START Condition | t <sub>BUF</sub>      |                     | 0.5  |     |     | μs    |

| START Condition<br>(Repeated) Hold Time              | t <sub>HD_STA</sub>   |                     | 0.26 |     |     | μs    |

| Low Period of SCL<br>Clock                           | t <sub>LOW</sub>      |                     | 0.5  |     |     | μs    |

| High Period of SCL<br>Clock                          | t <sub>HIGH</sub>     |                     | 0.26 |     |     | μs    |

| Setup Time for a<br>Repeated START<br>Condition      | t <sub>su_sta</sub>   |                     | 0.26 |     |     | μs    |

| Data Hold Time                                       | t <sub>HD_DAT</sub>   |                     | 0    |     |     | μs    |

| Data Setup Time                                      | t <sub>SU_DAT</sub>   |                     | 50   |     |     | ns    |

| Setup Time for STOP<br>Condition                     | t <sub>su_sto</sub>   |                     | 0.26 |     |     | μs    |

| Spike Pulse Widths<br>Suppressed by Input<br>Filter  | t <sub>sp</sub>       |                     |      | 50  |     | ns    |

| DATA Valid Time                                      | t <sub>VD_DAT</sub>   |                     |      |     | 450 | ns    |

| DATA Valid Ack Time                                  | t <sub>VD_ACK</sub>   |                     |      |     | 450 | ns    |

| SPI                                                  |                       |                     | l .  |     |     |       |

| CLKIN Frequency                                      | f <sub>CLKIN</sub>    |                     |      |     | 20  | MHz   |

| DVSIN Setup Time                                     | $t_{	extsf{DS}}$      |                     | 10   |     |     | ns    |

| DVSIN Hold Time                                      | t <sub>DH</sub>       |                     | 20   |     |     | ns    |

| CLKIN Pulse Width Low                                | t <sub>LOW_SPI</sub>  |                     | 20   |     |     | ns    |

| CLKIN Pulse Width High                               | t <sub>HIGH_SPI</sub> |                     | 20   |     |     | ns    |

All devices are 100% production tested at  $T_A$  = +25°C. Limits over the operating temperature range are guaranteed by design.

analog.com Rev 1 7 of 51

<sup>&</sup>lt;sup>2</sup> Quiescent current specification is guaranteed only down to 1.9V

# **ABSOLUTE MAXIMUM RATINGS**

Table 2. Absolute Maximum Ratings

| PARAMETER                                                                                               | RATING                                                                                                             |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| BAT, BBOUT, SDA, SCL, EN, CLKIN, DVSIN                                                                  | -0.3V to +6.0V                                                                                                     |

| INT                                                                                                     | -0.3V to 12V                                                                                                       |

| LXA                                                                                                     | -0.3V to Min (V <sub>BAT</sub> + 0.3V, +6.0V)                                                                      |

| LXB                                                                                                     | -0.3V to Min (V <sub>BBOUT</sub> + 0.3V, +6.0V)                                                                    |

| VDDP                                                                                                    | -0.3V to 2.2V                                                                                                      |

| VDDA                                                                                                    | Max (-0.3V, $V_{DDP}$ = 0.1V) to Min (2.2V, $V_{DDP}$ + 0.1V)                                                      |

| BST1                                                                                                    | Max (V <sub>DDP</sub> = 0.3V, V <sub>LXA</sub> = 0.3V) to Min<br>(V <sub>LXA</sub> +2.2V, V <sub>DDP</sub> +7.5V)  |

| BST2                                                                                                    | Max (V <sub>DDP</sub> = 0.3V,V <sub>LXB</sub> = 0.3V) to Min<br>(V <sub>LXB</sub> + 2.2V, V <sub>DDP</sub> + 7.5V) |

| Current into BAT, LXA, LXB (10% utilization for 100k hours)                                             | ±1.6A                                                                                                              |

| Current into BBOUT (10% utilization for 100k hours)                                                     | ±600mA                                                                                                             |

| Continuous Current into Any Other Terminal                                                              | ±100mA                                                                                                             |

| Continuous Power Dissipation (Multilayer Board, T <sub>A</sub> = +70°C) (derate 17.63mW/°C above +70°C) | 1410.72mW                                                                                                          |

| Junction Temperature                                                                                    | +150°C                                                                                                             |

| Storage Temperature Range                                                                               | -40°C to +150°C                                                                                                    |

| Soldering Temperature (reflow)                                                                          | +260°C                                                                                                             |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **Thermal Resistance**

Thermal performance is directly linked to PCB design and operating environment. Close attention to PCB thermal design is required.

| Package Type | θ <sub>JA</sub> | Unit |

|--------------|-----------------|------|

| W181A2+1     | 56.71           | °C/W |

analog.com Rev 1 8 of 51

MAX20363

### **Electrostatic Discharge (ESD)**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only Human body model (HBM) per ANSI/ESDA/JEDEC JS-001 Field induced charged device model (FICDM) and charged device model (CDM) per ANSI/ESDA/JEDEC JS-002. International Electrotechnical Commission (IEC) electromagnetic compatibility: Part 4-2 (IEC) per IEC 61000-4-2. Machine model (MM) per ANSI/ESD STM5.2. MM voltage values are for characterization only.

# **ESD Ratings**

#### Table 3. MAX20363

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| НВМ       | ±2500                   | 2     |

### **ESD Caution**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev 1 | 9 of 51

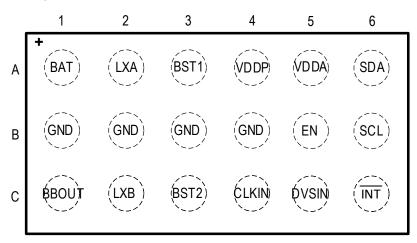

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

TOP VIEW (BUMP SIDE DOWN)

18-bump, 0.4mm WLP (1.25mm x 2.43mm)

Table 4. Pin Descriptions

| PIN               | NAME             | DESCRIPTION                                                                                                                                                                                                                     |

|-------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

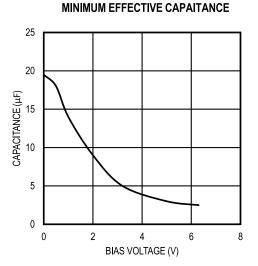

| A1                | BAT              | Input Supply. Bypass to GND with effective capacitance at least the maximum between $5\mu F$ and the value of the derating curve ( <i>Figure 34</i> ) for a bias voltage $V_{BAT}$ , placed as close to the device as possible. |

| A2                | LXA              | Switching Node A. Connect through 1µH or 2.2µH inductor to LXB.                                                                                                                                                                 |

| A3                | BST1             | Boostrap Cap 1. Connect through 100nF capacitor to LXA, placed as close to the device as possible.                                                                                                                              |

| A4                | V <sub>DDP</sub> | 1.8V regulator output voltage. Bypass with $1\mu F$ capacitor to GND, placed as close to the device as possible. Do not externally load the VDDP pin.                                                                           |

| A5                | $V_{DDA}$        | 1.8V analog output supply. Internally connected to VDDP through 20 ohm resistance. Bypass with 100nF capacitor to GND, placed as close to the device as possible. Do not externally load the VDDA pin.                          |

| A6                | SDA              | I <sup>2</sup> C Serial Data Input/Open-Drain Output. Connect to GND when not in use.                                                                                                                                           |

| B1, B2,<br>B3, B4 | GND              | Ground                                                                                                                                                                                                                          |

| B5                | EN               | Enable. Active-high.                                                                                                                                                                                                            |

| B6                | SCL              | I <sup>2</sup> C Serial Clock Input. Connect to GND when not in use.                                                                                                                                                            |

| C1                | BBOUT            | Buck Boost Output. Bypass to ground with effective capacitance shown in <i>Figure 34</i> , place as close to the device as possible. Refer to Input and Output Capacitance section for detail.                                  |

| C2                | LXB              | Switching Node B. Connect through 1µH or 2.2µH inductor to LXA.                                                                                                                                                                 |

analog.com Rev 1 | 10 of 51

MAX20363

# **Data Sheet**

| C3 | BST2  | Boostrap Cap 2. Connect through 100nF capacitor to LXB, placed as close to the device as possible.          |

|----|-------|-------------------------------------------------------------------------------------------------------------|

| C4 | CLKIN | Dedicated SPI Clock Input. Connect to GND when not in use.                                                  |

| C5 | DVSIN | Dedicated SPI DVS Input. Connect to GND when not in use.                                                    |

| C6 | ĪNT   | Interrupt Open-Drain Output. Active low. Externally connect through pullup resistor to system logic supply. |

analog.com Rev 1 | 11 of 51

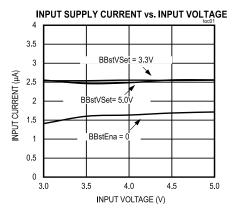

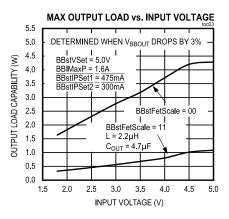

### TYPICAL PERFORMANCE CHARACTERISTICS

$(V_{BAT} = +3.7V, C_{BAT} = C_{BBOUT} = 22\mu F$ , refer to *Figure 34* single capacitor derating, L = 1 $\mu$ H, BBstLowEMIB = 1, BBstIpPadPEnb = 0, BBFetScale = 0,  $T_A = +25$ °C, unless otherwise noted.)

Figure 1. Input Supply Current vs. Input Voltage

Figure 3. Max Output Load vs. Input Voltage

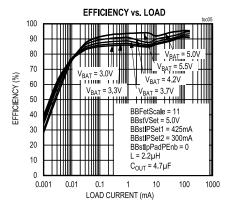

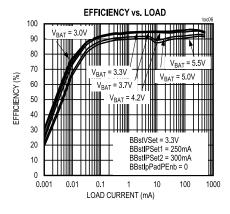

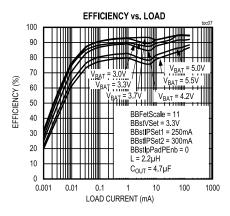

Figure 5. Efficiency vs. Load

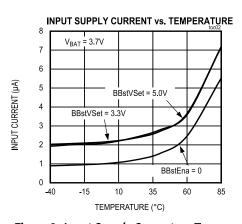

Figure 2. Input Supply Current vs. Temperature

Figure 4. Efficiency vs. Load

Figure 6. Efficiency vs. Load

analog.com Rev 1 | 12 of 51

$(V_{BAT} = +3.7V, C_{BAT} = C_{BBOUT} = 22\mu F$ , refer to *Figure 34* single capacitor derating, L = 1 $\mu$ H, BBstLowEMIB = 1, BBstIpPadPEnb = 0, BBFetScale = 0,  $T_A = +25$ °C, unless otherwise noted.)

Figure 7. Efficiency vs. Load

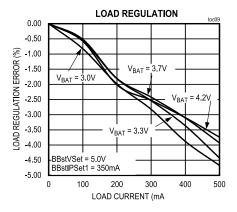

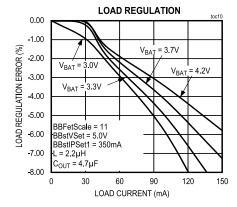

Figure 9. Load Regulation

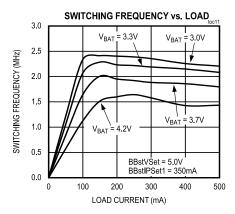

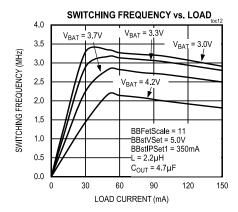

Figure 11. Switching Frequency vs. Load

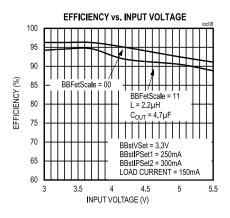

Figure 8. Efficiency vs. Input Voltage

Figure 10. Load Regulation

Figure 12. Switching Frequency vs. Load

analog.com Rev 1 | 13 of 51

$(V_{BAT} = +3.7V, C_{BAT} = C_{BBOUT} = 22\mu F$ , refer to *Figure 34* single capacitor derating, L = 1 $\mu$ H, BBstLowEMIB = 1, BBstlpPadPEnb = 0, BBFetScale = 0,  $T_A = +25$ °C, unless otherwise noted.)

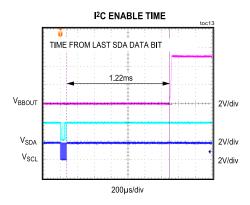

Figure 13. PC Enable Time

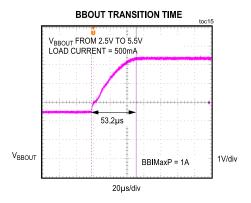

Figure 15. BBOUT Transition Time

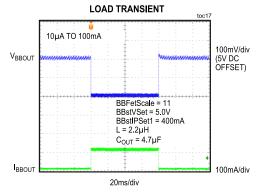

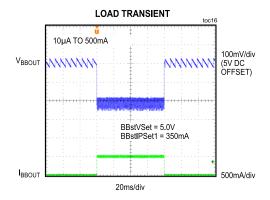

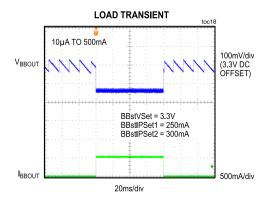

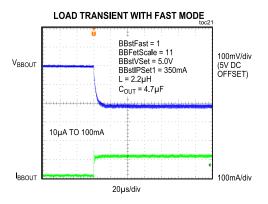

Figure 17. Load Transient

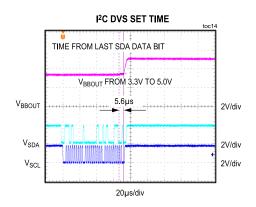

Figure 14. f<sup>2</sup>C DVS Set Time

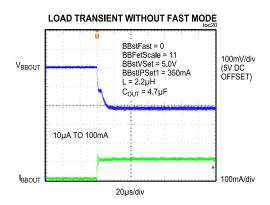

Figure 16. Load Transient

Figure 18. Load Transient

analog.com Rev 1 | 14 of 51

$(V_{BAT} = +3.7V, C_{BAT} = C_{BBOUT} = 22\mu F$ , refer to *Figure 34* single capacitor derating, L = 1 $\mu$ H, BBstLowEMIB = 1, BBstIpPadPEnb = 0, BBFetScale = 0,  $T_A = +25$ °C, unless otherwise noted.)

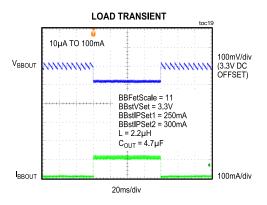

Figure 19. Load Transient

Figure 21. Load Transient with Fast Mode

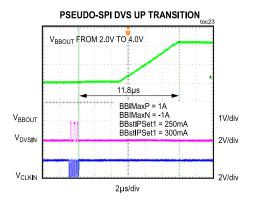

Figure 23. Pseudo-SPI DVS Up Transition

Figure 20. Load Transient without Fast Mode

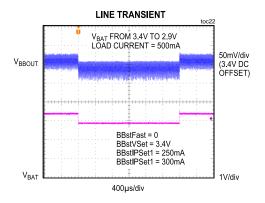

Figure 22. Line Transient

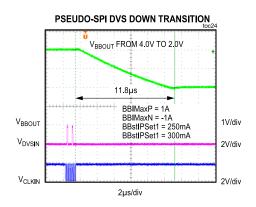

Figure 24. Pseudo-SPI DVS Down Transition

analog.com Rev 1 | 15 of 51

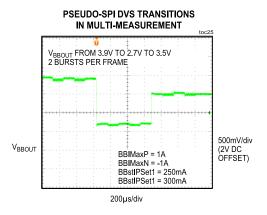

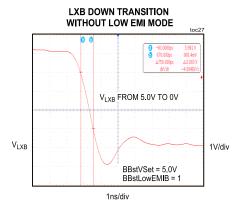

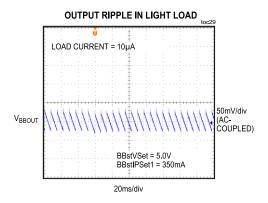

$(V_{BAT} = +3.7V, C_{BAT} = C_{BBOUT} = 22\mu F$ , refer to *Figure 34* single capacitor derating, L = 1 $\mu$ H, BBstLowEMIB = 1, BBstIpPadPEnb = 0, BBFetScale = 0,  $T_A = +25$ °C, unless otherwise noted.)

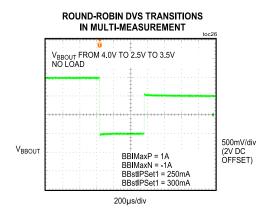

Figure 25. Pseudo-SPI DVS Transitions in Multi-Measurement

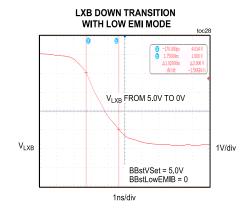

Figure 27. LXB Down Transition without Low EMI Mode

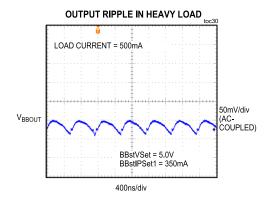

Figure 29. Output Ripple in Light Load

Figure 26. Round-Robin DVS Transitions in Multi-Measurement

Figure 28. LXB Down Transition with Low EMI Mode

Figure 30. Output Ripple in Heavy Load

analog.com Rev 1 | 16 of 51

#### THEORY OF OPERATION

The MAX20363 is an ultra-low quiescent current, non-inverting buck-boost converter with 500mA output current capability. The MAX20363 is intended for applications that require long run times while also demanding bursts of high current. The device employs a proprietary control algorithm that seamlessly transitions between buck, buck-boost, and boost modes, minimizing discontinuities and subharmonics in the output voltage ripple. The low 1.8V input voltage allows the device to be powered from a variety of sources such as lithium ion rechargeable and lithium primary batteries. The MAX20363 is designed to minimize inductance and capacitance requirements to keep the overall solution size as small as possible.

The MAX20363 is optimized for powering optical PPG systems. The ultra-fast dynamic voltage scaling (DVS) capability allows the device to transition quickly between output voltages and enable in-frame scaling of LED supply voltage. Additionally, the low output ripple and fast, predictable transient response maximizes the SNR of high-performance optical PPG AFEs.

### **Architectural Description**

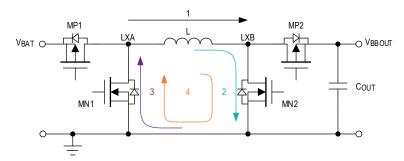

*Figure 31* illustrates the basic structure of the MAX20363 switching regulator with arrows depicting the inductor current flow in each switching phase.

Figure 31. The Buck-Boost Regulator and Switching Phases

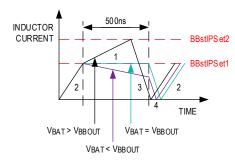

Figure 32. Buck-Boost Inductor Current in Buck-Boost Mode

#### **Switching Phases**

Depending on the buck-boost configurations, the topology enters different sequences of phases to generate the desired output voltage. Only two switches are on in each phase.

- Phase 1: MP1 on, MP2 on. Inductor charges.

- ▶ Phase 2: MP1 on, MN2 on. Inductor charges.

analog.com Rev 1 | 17 of 51

- ▶ Phase 3: MN1 on, MP2 on. Inductor discharges.

- ▶ Phase 4: MN1 on, MN2 on. Freewheeling.

#### **Buck-Boost Mode**

The regulator operates in buck-boost mode. The inductor charges in Phase 2 up to BBstIPSet1. The buck-boost then transitions to Phase 1. If  $V_{BAT} > V_{BBOUT}$ , BBstIPSet1 is gradually reduced to 0 and the inductor charges until either the current reaches BBstIPSet2 or after a 500ns delay. If  $V_{BAT} \le V_{BBOUT}$ , the buck-boost waits for the 500ns timeout to elapse or until the current drops to the valley limit. Next, the regulator enters Phase 3 to discharge the inductor current to the valley limit. When the inductor current reaches the valley-current crossing threshold or falls below 0, the regulator freewheels in Phase 4 until the next charge phase. When operating in continuous conduction mode (CCM), the buck-boost enters Phase 4 for approximately 30ns. *Figure 32* shows the inductor current in buck-boost mode.

#### **Inductor Peak and Valley Current Limits**

The buck-boost regulator monitors the maximum and minimum values of the inductor current. If BBstIpPadPEnb = 1, the peak currents are fixed to the values in BBstISet and the valley current is fixed to 0mA. If BBstIpPadPEnb = 0, the peak and valley currents are allowed to change based on load requirements.

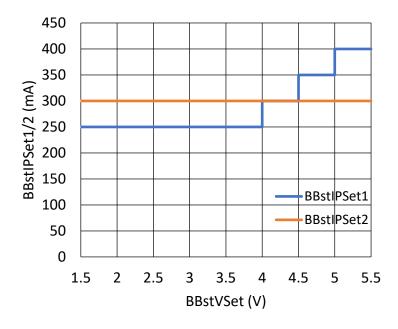

Peak currents are set in the BBstlSet register. BBstlPSet1 controls the peak current when  $V_{BAT} < V_{BBOUT}$  and begins the timeout period for Phase 1. BBstlPSet2 sets a secondary current limit in buck-boost mode when  $V_{BAT} > V_{BBOUT}$ . The buck-boost regulator transitions from Phase 1 to Phase 3 if the inductor current reaches BBstlPSet2 or if the 500ns timeout has elapsed. The MAX20363 gradually reduce BBstlPSet1 in such a way that when BBstlPSet2 is reached, the BBstlPSet1 is 0. Minimizing the settings of BBstlPSet1 and BBstlPSet2 reduces the output ripple but decreases efficiency. Care must be taken to optimize the peak current settings to keep a low output ripple while maximizing efficiency. Minimum BBstlPSet2 should never be lower than 200mA to avoid unwanted behavior. *Figure 33* is a graphical guide to selecting combinations of BBstlPSet1 and BBstlPSet2 to balance efficiency for specific BBstVSet values.

Figure 33. Recommended BBstlPSet1 and BBstlPSet2 Settings

analog.com Rev 1 | 18 of 51

MAX20363

To control inrush current during start-up, the MAX20363 startup valley current is limited through BBIPwpMaxP. The peak current is BBIPwpMaxP + max(BBstIPSet1,BBstIPSet2) settings. Once the output reaches its final voltage, the BBIMaxP setting is restored. See BBIPwpMaxP (*Table 5*) for device-specific values.

The MAX20363 behavior when BBstIPAdptDis = 0 can be further defined with a zero current comparator. The device transitions to Phase 4 when its control loop detects a zero current crossing.

### **Dynamic Voltage Scaling**

The MAX20363 utilizes dynamic voltage scaling (DVS) to rapidly change the output voltage on demand. DVS can significantly reduce the power consumption of PPG systems using LEDs with highly variable forward voltage drops.

DVS voltage transitions can be positive or negative going and the slew-rate of the output voltage is programmable through the positive and negative valley current limits (see I<sup>2</sup>C register descriptions.) The programmed valley current should account for the current source/sink capability of the input supply.

# **Dynamic Voltage Scaling (DVS) Modes**

The MAX20363 features three different DVS control modes:

- ▶ I<sup>2</sup>C: In I<sup>2</sup>C mode, a dedicated register (BBstVset, register 0x02) in the regmap can be written with the voltage value required.

- ▶ Pseudo-SPI: Two dedicated pins (CLKIN, DVSIN) are used to implement a serial digital interface used to pass the DVS voltages and additional information; this mode requires the use of a compatible analog front end (AFE) device that features the DVS capability and pseudo-SPI controller, such as the Analog Devices MAX86181.

- ▶ Round-Robin: Up to 20 FPWM and voltage values are preprogrammed through the I<sup>2</sup>C interface. These values are cycled through in succession at each rising/falling edge of the CLKIN pin. This control mode can be utilized with Analog Devices AFEs that feature multiple interrupt output pins, such as the MAX86180, and the ability to set the interrupt to trigger on changes in the 'FIFO Data Ready' status bit.

#### I<sup>2</sup>C Based DVS Control

If the RREna and DVSSource bits are set to zero, the DVS output voltage is set directly through  $I^2C$  using bits 6 to 0 of register 0x02, BBstVset, and can be used to dynamically program the output voltage value. Use bits 6 to 0 of register 0x1E to read back BBstVset value. Bit 7 of register 0x02, BBstFpwm enables the FPWM feature, whereas bit 4 of register 0x01, BBstFast enables the FAST feature. Note that  $I^2C$  is the only mode where both these features can be enabled together. Bit FpwmFast of register 0x6E selects the feature for status check (0 = Fast, 1 = FPWM) and bit 7 of register 0x1E, BB\_LOWBP reads back the feature status (0 = disabled, 1 = enabled). For example, if FpwmFast = 1 and BBstFpwm = 1, then BB\_LOWBP reads back 1 regardless of BBstFast value. On the other hand, if FpwmFast = 1, BBstFpwm = 0 and BBstFast = 1, then BB\_LOWBP reads back 0 even the FAST feature is enabled. Note that bit FpwmFast has no effect in setting high performance feature in  $I^2C$  mode.

In Round-Robin and in pseudo-SPI, only FPWM or FAST can be enabled. To choose which one, use read-write bit FpwmFast (register 0x06E, bit 0) (0 = Fast, 1 = FPWM). BB\_LOWBP reads back 1 if either of the high performance features is enabled. In Round-Robin mode, use each RRLowPBxx bit to disable/enable high performance feature for that cycle. If RRLowPBxx = 0, neither FPWM nor FAST is enabled. If RRLowPBxx = 1, FPWM or FAST is enabled according to FpwmFast bit and BB\_LOWPB reads back 1. In pseudo-SPI mode, the serial communication protocol includes a bit (example, bit DVS\_MODE\_SEL in MAX86181) that has the same function as RRLowPBxx. If

analog.com Rev 1 | 19 of 51

MAX20363

DVS\_MODE\_SEL in MAX86181 is low, neither FPWM nor FAST is enabled. If DVS\_MODE\_SEL in MAX86181 is high, FPWM or FAST is enabled according to FpwmFast bit.

The BBstVSet register (0x02) features write protection that can be enabled or disabled by writing 0xAA or 0x55 to register LockUnlock (0x51). For this write operation to take effect, the bit BBLck on register 0x50 must be 0, otherwise the operation on LockUnlock is ignored. The BBstVSet register (0x02) is locked by default.

#### **DVS Target Mode/Pseudo-SPI**

When used with a compatible Analog Devices AFE, such as the MAX86181, the MAX20363 output voltage is controlled by a proprietary serial digital interface on the CLKIN and DVSIN pins. To enable this mode, the register bit DVSSource should be set to 1. Once enabled,  $300\mu s$  is required until the device is ready to receive a new DVS command from the AFE controller. The default  $V_{BBOUT}$  in pseudo-SPI mode is 1.5 V.

In DVS target mode, the MAX20363 acts as a target only. All DVS values are programmed in the corresponding controller AFE. Register 0x13 contains the relevant status bits for DVS target mode, indicating controller requests complete, interface timeout expiration, and parity error.

For additional information on the operation of DVS target mode, reference the data sheet of the relevant DVS controller AFE device, such as MAX86181.

#### **DVS Round-Robin Interface**

The DVS round-robin mode provides allows to preprogram multiple DVS output voltages cycled through on the rising/falling edge of the CLKIN signal (see RRClkPolarity). This mode enables fast DVS output capability on Analog Devices AFEs that do not feature the DVS controller function.

To utilize round-robin mode:

First program up to 20 DVS voltage values into registers 0x20 to 0x33.

If fewer than 20 registers are utilized, write register 0x55, RRSize to define which register location is the last one utilized.

Configure RRWrap bit, in register 0x54, RRWrap, to determine if the round-robin pointer either remains on the final voltage register or returns to location zero after reaching the final voltage value.

Configure the RRTimeoutRes bit, register 0x55 to determine the device behavior after a timeout.

Configure the RRClkPolarity bit for high/low-going edge triggering.

Finally, enable the round-robin mode by writing 1 on the bit RREna (register 0x54, bit 1).

### APPLICATIONS INFORMATION

### **Input and Output Capacitance**

The MAX20363 is designed to be compatible with small case-size ceramic capacitors. As such, the device has low-input and low-output capacitance requirements to accommodate the steep voltage derating of 0603 and 0402 (imperial) capacitors. *Figure 34* presents the minimum capacitance required at BAT and BBOUT. To ensure stability and low noise, the capacitance value under bias on BAT should be at least the maximum between  $5\mu F$  and the value of *Figure 34* at the lowest expected  $V_{BAT}$ . The minimum capacitance value under bias on BBOUT should be equal to the value of *Figure 34* at the lowest expected  $V_{BBOUT}$  for BBFetScale = 00, 1/2 of that value for BBFetScale = 01 or 10, and 1/4 of that value for BBFetScale = 11.

analog.com Rev 1 | 20 of 51

Figure 34. Buck-Boost Required Minimum Input/Output Capacitance

#### **Inductor Selection**

Inductor selection for the MAX20363 should be optimized for the intended application. A  $1\mu H$  is recommended, and a  $2.2~\mu H$  can be used but can result in worse accuracy, load regulation, and load step response. Aside from the inductor value physical size, DC resistance (DCR), maximum average current, and saturation current are the primary factors to consider. The maximum average inductor current is obtained using the following equation:

$$I_{L MAX} = BBIMaxP + (0.5 \times BBstIPSet1)$$

The average inductor current calculated above dictates the required maximum average current for temperature rise on the inductor. To determine the required inductor saturation current, the peak current must be calculated. The peak current for this converter can be calculated as:

$$I_{\text{L.PEAK}} = BBIMaxP + BBstIPSet1$$

where BBstIPSet1 is the peak current setting described in register 0x03. When selecting an inductor, one primary factor in achieving high efficiency is the DCR of the inductor. For maximum efficiency, select an inductor with the lowest DCR possible in the required package size. Another factor to consider is magnetic losses. Generally magnetic losses are lower in inductors with larger physical size and/or higher saturation current ratings. In most cases, ferrite inductors should be avoided as they tend to exhibit poor AC characteristics, especially in discontinuous conduction mode (DCM).

#### Soft-Start

Current at start-up is programmable through the start-up inductor current limit register (BBstIPwpMaxP). It can be programmed up to 750mA.

# I<sup>2</sup>C Interface

The MAX20363 contains an I<sup>2</sup>C-compatible interface for data communication with a host controller (SCL and SDA). The MAX20363 can support I<sup>2</sup>C frequencies up to 1MHz. SCL and SDA require pullup resistors connected to a positive supply.

analog.com Rev 1 | 21 of 51

MAX20363

#### **Peripheral Address**

In the MAX20363, the peripheral address is configured at the factory by the i2c\_2nd\_sid OTP bit to be either 0b1101000 (0x68) plus the Read/Write bit or 0b1101100 (0x6C) plus the Read/Write bit. For versions with the 7-bit peripheral address 0x68, set the Read/Write bit high to configure the MAX20363 to read mode (0xD1) or set the Read/Write bit low to configure the MAX20363 to write mode (0xD0). For versions with the 7-bit peripheral address 0x6C, set the Read/Write bit high to configure the MAX20363 to read mode (0xD8) or set the Read/Write bit low to configure the MAX20363 to write mode (0xD9). See i2c\_2nd\_sid in *Table 5* for the peripheral address for a given part number. The address is the first byte of information sent to the MAX20363 after the START condition.

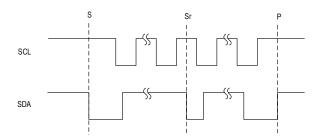

#### Start, Stop, and Repeated Start Conditions

When writing to the MAX20363 using I<sup>2</sup>C, the controller sends a START condition (S) followed by the MAX20363 I<sup>2</sup>C write address. After the address, the controller sends the register address of the register to be programmed. The controller then ends communication by issuing a STOP condition (P) to relinquish control of the bus, or a REPEATED START condition (Sr) to communicate to another I<sup>2</sup>C peripheral. See *Figure 35*.

Figure 35. PC START, STOP, and REPEATED START Conditions

#### **Bit Transfer**

One data bit is transferred on the rising edge of each SCL clock cycle. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high and stable are considered control signals (see the *Start, Stop, and Repeated Start Conditions* section). Both SDA and SCL remain high when the bus is not active.

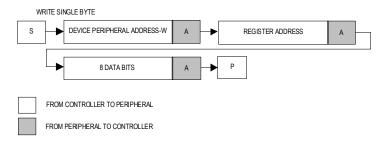

#### Single-Byte Write

In this operation, the controller sends an address and two data bytes to the peripheral device (*Figure 36*). The following procedure describes the single byte write operation:

- 1. The controller sends a START condition.

- 2. The controller sends the 7-bit peripheral address plus a write bit (low).

- 3. The addressed peripheral asserts an ACK on the data line.

- 4. The controller sends the 8-bit register address.

- 5. The peripheral asserts an ACK on the data line.

- 6. The controller sends 8 data bits.

- 7. The peripheral asserts an ACK on the data line.

- 8. The controller generates a STOP condition.

analog.com Rev 1 | 22 of 51

Figure 36. Write Byte Sequence

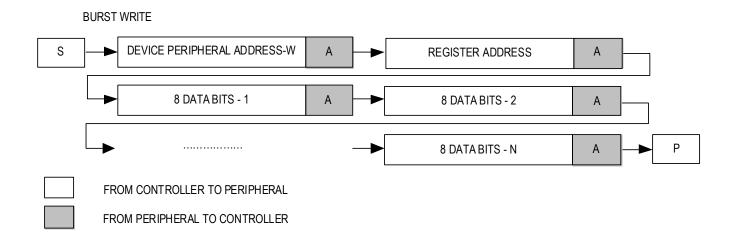

#### **Burst Write**

In this operation, the controller sends an address and multiple data bytes to the peripheral device (*Figure 37*). The peripheral device automatically increments the register address after each data byte is sent, unless the register being accessed reaches 0xFF, in which case the register address remains the same. The following procedure describes the burst write operation:

- 1. The controller sends a START condition.

- 2. The controller sends the 7-bit peripheral address plus a write bit (low).

- 3. The addressed peripheral asserts an ACK on the data line.

- 4. The controller sends the 8-bit register address.

- 5. The peripheral asserts an ACK on the data line.

- 6. The controller sends 8 data bits.

- 7. The peripheral asserts an ACK on the data line.

- 8. Repeat 6 and 7 N-1 times.

- 9. The controller generates a STOP condition.

Figure 37. Burst Write Sequence

analog.com Rev 1 | 23 of 51

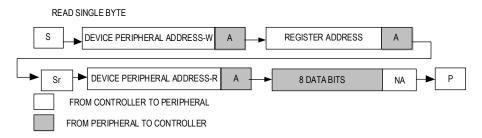

#### Single Byte Read

In this operation, the controller sends an address plus two data bytes and receives one data byte from the peripheral device (*Figure 38*). The following procedure describes the single byte read operation:

- 1. The controller sends a START condition.

- 2. The controller sends the 7-bit peripheral address plus a write bit (low).

- 3. The addressed peripheral asserts an ACK on the data line.

- 4. The controller sends the 8-bit register address.

- 5. The peripheral asserts an ACK on the data line.

- 6. The controller sends a REPEATED START condition.

- 7. The controller sends the 7-bit peripheral address plus a read bit (high).

- 8. The addressed peripheral asserts an ACK on the data line.

- 9. The peripheral sends 8 data bits.

- 10. The controller asserts a NACK on the data line.

- 11. The controller generates a STOP condition.

Figure 38. Read Byte Sequence

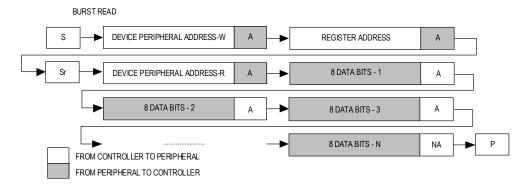

#### **Burst Read**

In this operation, the controller sends an address plus two data bytes and receives multiple data bytes from the peripheral device (*Figure 39*). The following procedure describes the burst byte read operation:

- 1. The controller sends a START condition.

- 2. The controller sends the 7-bit peripheral address plus a write bit (low).

- 3. The addressed peripheral asserts an ACK on the data line.

- 4. The controller sends the 8-bit register address.

- The peripheral asserts an ACK on the data line.

- 6. The controller sends a REPEATED START condition.

- 7. The controller sends the 7-bit peripheral address plus a read bit (high).

- 8. The peripheral asserts an ACK on the data line.

analog.com Rev 1 | 24 of 51

- 9. The peripheral sends 8 data bits.

- 10. The controller asserts an ACK on the data line.

- 11. Repeat 9 and 10 N-2 times.

- 12. The peripheral sends the last 8 data bits.

- 13. The controller asserts a NACK on the data line.

- 14. The controller generates a STOP condition.

Figure 39. Burst Read Sequence

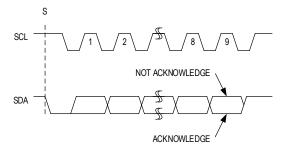

#### **Acknowledge Bits**

Data transfers are acknowledged with an acknowledge bit (ACK) or a not-acknowledge bit (NACK). Both the controller and the MAX20363 generate ACK bits. To generate an ACK, pull SDA low before the rising edge of the ninth clock pulse and hold it low during the high period of the ninth clock pulse (*Figure 40*). To generate a NACK, leave SDA high before the rising edge of the ninth clock pulse and leave it high for the duration of the ninth clock pulse. Monitoring for NACK bits allows detection of unsuccessful data transfers.

Figure 40. Acknowledge Bits

analog.com Rev 1 25 of 51

# **REGISTER MAP**

# MAX20363

| ADDRE<br>SS | NAME                  | MSB           |           |                   |                  |              |                   |                   | LSB              |

|-------------|-----------------------|---------------|-----------|-------------------|------------------|--------------|-------------------|-------------------|------------------|

| USER        |                       |               |           |                   |                  |              |                   |                   |                  |

| 0x00        | ChipID[7:0]           |               |           |                   | Chi              | pID[7:0]     |                   |                   |                  |

| 0x01        | BBstCfg0[7:0]         | BBstLow       | EMIB[1:0] | BBstEna           | BBstFast         | _            | BBFHighSh         | BBstActDsc        | BBstPsvDsc       |

| 0x02        | BBstVSet[7:0]         | BBstFpw<br>m  |           |                   |                  | BBstVSet[6:0 | ]                 |                   |                  |

| 0x03        | BBstlSet[7:0]         |               | BBstl     | PSet2[3:0]        |                  |              | BBstIPS           | et1[3:0]          |                  |

| 0x04        | BBstIMaxN[7:0]        | ı             | ı         |                   |                  | BBIMa        | xN[5:0]           |                   |                  |

| 0x05        | BBstIMaxP[7:0]        | -             | -         |                   |                  | BBIMa        | xP[5:0]           |                   |                  |

| 0x06        | BBstlPwpMaxP<br>[7:0] | -             | -         |                   |                  | BBIPwpl      | MaxP[5:0]         |                   |                  |

| 0x08        | BBstCfg1[7:0]         | _             | -         | _                 | -                | BBL2P2Sel    | BBstlpPadPE<br>nb | BBFetS            | cale[1:0]        |

| 0x10        | Status[7:0]           | -             | -         | BBstOnSts         | BBstOffSts       | VddUvloSts   | BBOutUvloSts      | BstSts            | ThmFltSts        |

| 0x11        | Int[7:0]              | -             | -         | BBstOnInt         | BBstOffInt       | VddUvloInt   | BBOutUvloInt      | BstFltInt         | ThmFltInt        |

| 0x12        | Mask[7:0]             | -             | -         | BBstOnMsk         | BBstOffMsk       | VddUvloMsk   | BBoutUvloMsk      | BstFltMsk         | ThmFltMsk        |

| 0x13        | CommInt[7:0]          | -             | -         | ChgModDone        | RRTimeout        | RRInc        | SPIDone           | SPITimeout        | SPIParErr        |

| 0x14        | CommMsk[7:0]          | -             | _         | ChgModDone<br>Msk | RRTimeout<br>Msk | RRIncMsk     | SPIDoneMsk        | SPITimeout<br>Msk | SPIParErrM<br>sk |

| 0x15        | BBFsmState[7: 0]      | _             | -         |                   |                  | BBCtrlS      | state[5:0]        |                   |                  |

| 0x1E        | BBVset[7:0]           | BB_LOW<br>PB  |           |                   |                  | BB_VSET[6:0  | ]                 |                   |                  |

| 0x1F        | RRpoint[7:0]          | -             | -         | -                 |                  |              | RRPointer[4:0]    |                   |                  |

| 0x20        | RRVset00[7:0]         | RRLowPB<br>00 |           |                   |                  | RRVset00[6:0 | )]                |                   |                  |

| 0x21        | RRVset01[7:0]         | RRLowPB<br>01 |           | RRVset01[6:0]     |                  |              |                   |                   |                  |

| 0x22        | RRVset02[7:0]         | RRLowPB<br>02 |           | RRVset02[6:0]     |                  |              |                   |                   |                  |

| 0x23        | RRVset03[7:0]         | RRLowPB<br>03 |           | RRVset03[6:0]     |                  |              |                   |                   |                  |

| 0x24        | RRVset04[7:0]         | RRLowPB<br>04 |           |                   |                  | RRVset04[6:0 | ]                 |                   |                  |

analog.com Rev 1 | 26 of 51

| ADDRE<br>SS | NAME            | MSB           |                   |                  |             |              |        |                | LSB               |

|-------------|-----------------|---------------|-------------------|------------------|-------------|--------------|--------|----------------|-------------------|

| 0x25        | RRVset05[7:0]   | RRLowPB<br>05 |                   | RRVset05[6:0]    |             |              |        |                |                   |

| 0x26        | RRVset06[7:0]   | RRLowPB<br>06 |                   |                  |             | RRVset06[6:0 | ]      |                |                   |

| 0x27        | RRVset07[7:0]   | RRLowPB<br>07 |                   |                  |             | RRVset07[6:0 | 1]     |                |                   |

| 0x28        | RRVset08[7:0]   | RRLowPB<br>08 |                   |                  |             | RRVset08[6:0 | ]      |                |                   |

| 0x29        | RRVset09[7:0]   | RRLowPB<br>09 |                   |                  |             | RRVset09[6:0 | )]     |                |                   |

| 0x2A        | RRVset0A[7:0]   | RRLowPB<br>0A |                   |                  |             | RRVset0A[6:0 | )]     |                |                   |

| 0x2B        | RRVset0B[7:0]   | RRLowPB<br>0B |                   |                  |             | RRVset0B[6:0 | )]     |                |                   |

| 0x2C        | RRVset0C[7:0]   | RRLowPB<br>0C |                   |                  |             | RRVset0C[6:0 | )]     |                |                   |

| 0x2D        | RRVset0D[7:0]   | RRLowPB<br>0D |                   | RRVset0D[6:0]    |             |              |        |                |                   |

| 0x2E        | RRVset0E[7:0]   | RRLowPB<br>0E |                   |                  |             | RRVset0E[6:0 | )]     |                |                   |

| 0x2F        | RRVset0F[7:0]   | RRLowPB<br>0F |                   |                  |             | RRVset0F[6:0 | )]     |                |                   |

| 0x30        | RRVset10[7:0]   | RRLowPB<br>10 |                   |                  |             | RRVset10[6:0 | ]      |                |                   |

| 0x31        | RRVset11[7:0]   | RRLowPB<br>11 |                   |                  |             | RRVset11[6:0 | ]      |                |                   |

| 0x32        | RRVset12[7:0]   | RRLowPB<br>12 |                   |                  |             | RRVset12[6:0 | ]      |                |                   |

| 0x33        | RRVset13[7:0]   | RRLowPB<br>13 |                   |                  |             | RRVset13[6:0 | ]      |                |                   |

| 0x50        | LockMsk[7:0]    | -             | _                 | -                | -           | -            | -      | _              | BBLck             |

| 0x51        | LockUnlock[7:0] |               |                   |                  | PAS         | SWD[7:0]     |        |                |                   |

| 0x54        | DVSCfg[7:0]     | -             | -                 | -                | _           | I2CLkptDis   | RRWrap | RREna          | DVSSource         |

| 0x55        | RRCfg1[7:0]     | _             | RRClkPola<br>rity | RRTimeoutRe<br>s | RRSIZEI4'UI |              |        |                |                   |

| 0x56        | RRCfg2[7:0]     | _             | -                 | -                | _           | -            | RRT    | imeoutLength[2 | ::0]              |

| 0x57        | SPICfg[7:0]     | -             | -                 | -                | -           | -            | -      | _              | SPITimeout<br>Ena |

analog.com Rev 1 | 27 of 51

| ADDRE<br>SS | NAME         | MSB |   |   |   |                    |                      |            | LSB        |

|-------------|--------------|-----|---|---|---|--------------------|----------------------|------------|------------|

| 0x6E        | ConfOtp[7:0] | -   | - | - | - | -                  | -                    | -          | FpwmFast   |

| 0x6F        | FuncDef[7:0] | -   | - | - | - | LtchOffVdd<br>Uvlo | LtchOffBBOut<br>Uvlo | LtchOffBst | LtchOffThm |

# **Register Details**

# ChipID (0x0)

| ВІТ         | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------------|---|-------------|---|---|---|---|---|---|--|

| Field       |   | ChipID[7:0] |   |   |   |   |   |   |  |

| Reset       |   | 0x00        |   |   |   |   |   |   |  |

| Access Type |   | Read Only   |   |   |   |   |   |   |  |

| BITFIELD | BITS | DESCRIPTION                                             |

|----------|------|---------------------------------------------------------|

| ChipID   | 7:0  | ChipID[7:0] indicates the version of the device in use. |

# BBstCfg0 (0x1)

| BIT         | 7                | 6    | 5           | 4           | 3 | 2           | 1           | 0           |

|-------------|------------------|------|-------------|-------------|---|-------------|-------------|-------------|

| Field       | BBstLowEMIB[1:0] |      | BBstEna     | BBstFast    | - | BBFHighSh   | BBstActDsc  | BBstPsvDsc  |

| Reset       |                  |      |             |             | - |             |             |             |

| Access Type | Write,           | Read | Write, Read | Write, Read | ı | Write, Read | Write, Read | Write, Read |

| BITFIELD    | BITS | DESCRIPTION                                                                                                                                                                                                    | DECODE                                                                  |

|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| BBstLowEMIB | 7:6  | Buck-Boost Low EMI Mode Disable Increases the rise/fall time of LXA/LXB to reduce EMI, at the cost of efficiency. It can be changed only when BBstEna = 0. 10,11 = Reserved not to be used                     | 0x0: Increase rise/fall time on LXA/LXB by 4x 0x1: Nominal Slopes       |

| BBstEna     | 5    | Buck-Boost Enable                                                                                                                                                                                              | 0x0: Buck-boost disabled 0x1: Buck-boost enabled                        |

| BBstFast    | 4    | Buck-Boost Fast Feature Enable Increases the quiescent current of the buck-boost to improve output regulation during load transients. If 1, I <sub>Q_FAST</sub> increased to 75µA (typical).                   | 0x0: Fast response disabled<br>0x1: Fast response enabled               |

| BBFHighSh   | 2    | Buck-Boost $f_{HIGH}$ Thresholds<br>Selects the switching frequency threshold $f_{HIGH}$ . If<br>the buck-boost switching frequency exceeds the<br>$f_{HIGH}$ rising threshold, all the blocks are kept ON (Iq | 0x0: 50kHz rising / 25kHz falling<br>0x1: 100kHz rising / 50kHz falling |

analog.com Rev 1 | 28 of 51

| BITFIELD   | BITS | DESCRIPTION                                                                                                                                                                                                    | DECODE                                                                                      |

|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|            |      | is higher) until the frequency reaches the f <sub>HIGH</sub> falling threshold. A small glitch on V <sub>OUT</sub> can be present at the f <sub>HIGH</sub> crossover. It can be changed only when BBstEna = 0. |                                                                                             |

| BBstActDsc | 1    | Buck-Boost Active Discharge Control                                                                                                                                                                            | 0x0: Buck-boost not actively discharged 0x1: Buck-boost actively discharged when disabled   |

| BBstPsvDsc | 0    | Buck-Boost Passive Discharge Control                                                                                                                                                                           | 0x0: Buck-boost not passively discharged 0x1: Buck-boost passively discharged when disabled |

# BBstVSet (0x2)

| BIT         | 7           | 6 | 5             | 4 | 3 | 2 | 1 | 0 |

|-------------|-------------|---|---------------|---|---|---|---|---|

| Field       | BBstFpwm    |   | BBstVSet[6:0] |   |   |   |   |   |

| Reset       |             |   |               |   |   |   |   |   |

| Access Type | Write, Read |   | Write, Read   |   |   |   |   |   |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                             | DECODE                                        |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| BBstFpwm | 7    | Buck-Boost Fpwm Feature Enable With FPWM best load regulation/ripple but high quiescent and poor efficiency at light loads. Use it only for ≥70mA loads | 0x0: FPWM is disabled<br>0x1: FPWM is enabled |

| BBstVSet | 6:0  | Buck-Boost Output Voltage Setting<br>1.5V to 5.5V, linear scale, 50mV increments                                                                        | 0x0: 1.50V<br>0x1: 1.55V<br><br>≥0x50: 5.50V  |

### BBstlSet (0x3)

| BIT         | 7 | 6           | 5         | 4 | 3               | 2      | 1    | 0 |  |

|-------------|---|-------------|-----------|---|-----------------|--------|------|---|--|

| Field       |   | BBstIPS     | Set2[3:0] |   | BBstlPSet1[3:0] |        |      |   |  |

| Reset       |   |             |           |   |                 |        |      |   |  |

| Access Type |   | Write, Read |           |   |                 | Write, | Read |   |  |

| BITFIELD   | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                    | DECODE                                  |

|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| BBstlPSet2 | 7:4  | Buck-Boost Nominal Maximum Peak Current Setting 2. Sets the extra peak current on top of IPSET1 when VBAT>VBBOUT. See buck-boost operation section for a description of the peak current settings.  From 0 to 375mA, 25mA step. Suggested value 300mA  Note1: The values are increased by about 30% when BBL2P2Sel = 0 is set. | 0x0: 0mA<br>0x1: 25mA<br><br>0xF: 375mA |

analog.com Rev 1 | 29 of 51

| BITFIELD   | вітѕ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DECODE                                     |

|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|            |      | Note2 : Actual peak current in the inductor is larger because of the delay of peak comparator and power stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                            |

| BBstlPSet1 | 3:0  | Buck-boost Nominal Maximum Peak Current Setting 1 Nominal peak current when charging inductor between V <sub>BAT</sub> and GND. See buck-boost operation section for a description of the peak current settings.  From 100mA to 475mA, 25mA step. Optimal values are set according to look-up table which is set by OTP register settings of bits IPm50, IPm60M50, IPm70M60 and IPM70. Suggested values to get optimal efficiency: BBstVSet≤4V: IPSET1 = 250mA 4V <bbstvset≤4.5v: 4.5v<bbstvset≤5v:="" bbstvset="" ipset1="350mA">5V: IPSET1 = 400mA  Note1: The values are increased by about 30% when BBL2P2Sel = 0 is set. Note 2: Real IPSET1 is gradually reduced to 0 when V<sub>BAT</sub>&gt;V<sub>BBOUT</sub>.</bbstvset≤4.5v:> | 0x0: 100mA<br>0x1: 125mA<br><br>0xF: 475mA |

# BBstlMaxN (0x4)