# ADuM3165/ADuM3166

# 3.75 kV RMS Digital Isolators for Isolated USB 2.0 High, Full, and Low Speed

## **FEATURES**

- ▶ USB 2.0 signaling with automatic detection of low, full, and high speed connections

- ▶ 1.5 Mbps, 12 Mbps, and 480 Mbps data rates

- ▶ Bidirectional USB isolator for upstream and downstream ports

- ▶ Redriving and high speed data retiming for input jitter removal and an open eye

- ▶ Flexible clock input options

- ▶ 4.5 V to 5.5 V V<sub>BUSx</sub> or 3 V to 3.6V operation on each side

- ▶ 21 mA typical idle, low or full speed mode supply current

- ▶ 48 mA typical idle, high speed mode supply current

- ▶ Ultra low power standby in USB 2.0 suspend (L2) or disconnect

- ▶ 1.7 mA typical low power standby, upstream supply current

- ▶ 20 µA typical low power standby, downstream supply current

- ±6000 V IEC 61000-4-2 ESD protection across the isolation barrier

- ▶ Passed CISPR32/EN55032 Class B emissions

- ▶ High common-mode transient immunity: 50 kV/µs typical

- ► Safety and regulatory approvals

- ▶ UL 1577

- ▶ VISO = 3750 V rms for 1 minute

- ▶ IEC/EN/CSA 62368-1

- ▶ IEC/CSA 60601-1

- ▶ IEC/CSA 61010-1

- ► CQC GB 4943.1

- ▶ DIN EN IEC 60747-17 (VDE 0884-17)

- ► V<sub>IORM</sub> = 849 V<sub>PEAK</sub> (working voltage)

- ▶ Operating temperature range: -55°C to +125°C

- ▶ Compact 20-lead SSOP with 5.3 mm creepage and clearance

#### **APPLICATIONS**

- ▶ USB peripheral, USB host, and USB hub isolation

- ▶ Electronic test and measurement equipment

- Medical devices and integrated PCs

- ▶ Industrial PCs and isolated USB ports for debug or upgrade

- ▶ USB isolator modules and USB cable isolators

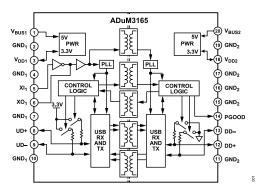

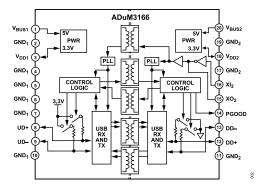

## **FUNCTIONAL BLOCK DIAGRAMS**

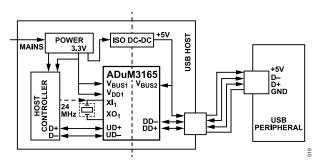

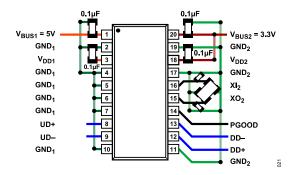

Figure 1. ADuM3165 (Clock Input from Host Side)

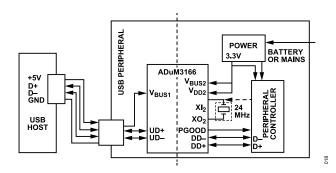

Figure 2. ADuM3166 (Clock Input from Peripheral Side)

#### **GENERAL DESCRIPTION**

The ADuM3165/ADuM3166<sup>1</sup> are USB 2.0 port isolators, utilizing Analog Devices, Inc., *i*Coupler<sup>®</sup> technology to dynamically support all USB 2.0 data rates: low (1.5 Mbps), full (12 Mbps), or high (480 Mbps), as required. The devices support host isolation with automatic speed negotiation as well as peripheral isolation.

High speed data is retimed for jitter reduction, requiring an external clock signal or crystal input. The ADuM3165 supports the clock or crystal input on the upstream side, and the ADuM3166 supports the clock or crystal input on the downstream side, offering two options to best suit the system design.

The low power standby mode for downstream (Side 2) supports applications with limited available power, such as battery-operated peripherals. The upstream (Side 1) standby current meets USB 2.0 requirements for suspended operation.

The isolators are specified over an extended industrial temperature range of -55°C to +125°C and are available in a compact 20-lead shrink small outline package (SSOP) with 5.3 mm creepage and clearance.

<sup>&</sup>lt;sup>1</sup> Protected by U.S. Patents 5,952,849; 6,873,065; 6,903,578; and 7,075,329. Other patents are pending.

## **TABLE OF CONTENTS**

| Features 1                                          | Typical Performance Characteristics    | 16 |

|-----------------------------------------------------|----------------------------------------|----|

| Applications1                                       | Terminology                            | 18 |

| Functional Block Diagrams1                          | Theory of Operation                    | 20 |

| General Description1                                | Automatic Data Transfer and Modes      |    |

| Specifications3                                     | Retimer and Other Features             | 20 |

| Timing Specifications5                              | Isolator Characteristics and Low Power |    |

| Insulation and Safety Related Specifications 6      | Modes                                  | 21 |

| Package Characteristics6                            | Applications Information               | 22 |

| Regulatory Information6                             | Power Supply Options                   |    |

| DIN EN IEC 60747-17 (VDE 0884-17)                   | Clock Options                          |    |

| Insulation Characteristics7                         | PGOOD, Clock, and Power Sequencing     |    |

| Recommended Operating Conditions9                   | Isolated USB Implementations           |    |

| Absolute Maximum Ratings10                          | PCB Layout and Electromagnetic         |    |

| Thermal Resistance10                                | Interference (EMI)                     | 25 |

| Electrostatic Discharge (ESD) Ratings11             | Insulation Lifetime                    |    |

| ESD Caution11                                       | Outline Dimensions                     |    |

| Pin Configurations and Function Descriptions12      | Ordering Guide                         | 27 |

| Truth Tables13                                      | Evaluation Boards                      |    |

| REVISION HISTORY                                    |                                        |    |

| 9/2025—Rev. A to Rev. B                             |                                        |    |

| Changes to Features Section                         |                                        | 1  |

| Changes to Table 5                                  |                                        |    |

| Changes to Table 6                                  |                                        | 7  |

| 12/2024—Rev. 0 to Rev. A                            |                                        |    |

| Changes to Features Section                         |                                        | 1  |

| Changes to Table 3                                  |                                        |    |

| Changes to Regulatory Information Section and Table |                                        |    |

| Changes to Table 6 and Figure 3 Caption             |                                        |    |

| Changes to Table 10                                 |                                        |    |

|                                                     |                                        |    |

5/2022—Revision 0: Initial Version

$4.5 \text{ V} \le \text{V}_{\text{BUS1}} \le 5.5 \text{ V}, 4.5 \text{ V} \le \text{V}_{\text{BUS2}} \le 5.5 \text{ V}, 3.0 \text{ V} \le \text{V}_{\text{DD1}} \le 3.6 \text{ V}, \text{ and } 3.0 \text{ V} \le \text{V}_{\text{DD2}} \le 3.6 \text{ V}.$  All minimum and maximum specifications are applied over the entire recommended operation range, unless otherwise noted. All typical specifications are at  $\text{T}_{\text{A}} = 25^{\circ}\text{C}$  and  $\text{V}_{\text{DD1}} = \text{V}_{\text{DD2}} = 3.3 \text{ V}$ , unless otherwise noted. Each voltage is relative to its respective ground.

Table 1. Specifications

| Table 1. Specifications                                                              | 1                                              |      |      |      |      |                                                                                                                                                                    |

|--------------------------------------------------------------------------------------|------------------------------------------------|------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                            | Symbol                                         | Min  | Тур  | Max  | Unit | Test Conditions/Comments                                                                                                                                           |

| POWER SUPPLY                                                                         |                                                |      |      |      |      |                                                                                                                                                                    |

| Supply Current                                                                       |                                                |      |      |      |      |                                                                                                                                                                    |

| Idle $(V_{DD1}, V_{DD2}, V_{BUS1}, or V_{BUS2})^1$                                   |                                                |      |      |      |      | UD+, UD-, DD+, and DD- idle                                                                                                                                        |

| Low or Full Speed Mode                                                               | I <sub>DD1(LFI)</sub> ,                        |      | 21   | 27   | mA   |                                                                                                                                                                    |

|                                                                                      | I <sub>DD2(LFI)</sub>                          |      |      |      |      |                                                                                                                                                                    |

| High Speed Mode                                                                      | I <sub>DD1(HI)</sub> ,<br>I <sub>DD2(HI)</sub> |      | 48   | 60   | mA   |                                                                                                                                                                    |

| Busy $(V_{DD1}, V_{DD2}, V_{BUS1}, or V_{BUS2})^2$                                   |                                                |      |      |      |      |                                                                                                                                                                    |

| Low Speed Mode                                                                       | I <sub>DD1(L)</sub> ,<br>I <sub>DD2(L)</sub>   |      | 29   | 45   | mA   | Input frequency ( $f_{IN}$ ) = 750 kHz, load capacitance ( $C_L$ ) = 450 pF                                                                                        |

| Full Speed Mode                                                                      | I <sub>DD1(F)</sub> ,<br>I <sub>DD2(F)</sub>   |      | 31   | 45   | mA   | $f_{IN}$ = 6 MHz, $C_L$ = 50 pF                                                                                                                                    |

| High Speed Mode                                                                      | I <sub>DD1(H)</sub> ,<br>I <sub>DD2(H)</sub>   |      | 59   | 69   | mA   | $f_{IN} = 240 \text{ MHz}, C_L = 10 \text{ pF}$                                                                                                                    |

| Low Power Standby                                                                    | DDZ(II)                                        |      |      |      |      | USB suspended or disconnected                                                                                                                                      |

| Upstream (V <sub>DD1</sub> or V <sub>BUS1</sub> )                                    | I <sub>DD1(S)</sub>                            |      | 1.7  | 2.5  | mA   | Side 2 not powered                                                                                                                                                 |

| . (                                                                                  | (-/                                            |      | 1.7  |      | mA   | Side 2 powered (average)                                                                                                                                           |

| Downstream (V <sub>DD2</sub> and V <sub>BUS2</sub> )                                 | I <sub>DD2(S)</sub>                            |      | 20   | 40   | μA   | $V_{BUS2} = V_{DD2} = 3 \text{ V to } 3.6 \text{ V, Side 1 not powered}$                                                                                           |

| , 332 3002,                                                                          | 332(0)                                         |      | 40   | 100  | μA   | V <sub>BUS2</sub> = 4.5 V to 5.5 V, Side 1 not powered                                                                                                             |

|                                                                                      |                                                |      | 40   |      | μA   | Side 1 powered (average)                                                                                                                                           |

| V <sub>DD2</sub> Maximum Voltage Until After<br>Side 1 Start-Up                      | V <sub>START</sub>                             |      |      | 3.5  | V    | See the PGOOD, Clock, and Power Sequencing section                                                                                                                 |

| Side 1 Start-Up Time                                                                 | t <sub>START</sub>                             |      | 3    |      | ms   | Time after V <sub>DD1</sub> rises above V <sub>UVLO3+</sub> <sup>3</sup> before V <sub>DD2</sub> can be >3.5 V, see the PGOOD, Clock, and Power Sequencing section |

| V <sub>BUS1</sub> or V <sub>BUS2</sub> Undervoltage Lockout (UVLO)                   |                                                |      |      |      |      |                                                                                                                                                                    |

| UVLO Threshold, V <sub>BUS1</sub> or V <sub>BUS2</sub><br>Rising                     | V <sub>UVLO5+</sub>                            | 3.5  | 4.16 | 4.35 | V    |                                                                                                                                                                    |

| UVLO Threshold, $V_{BUS1}$ or $V_{BUS2}$ Falling                                     | V <sub>UVLO5</sub> -                           | 3.0  | 3.77 | 3.95 | V    |                                                                                                                                                                    |

| $V_{BUS1}$ or $V_{BUS2}$ UVLO Hysteresis $V_{DD1}$ or $V_{DD2}$ Undervoltage Lockout | V <sub>UVLO5HST</sub>                          |      | 0.44 |      | V    |                                                                                                                                                                    |

| UVLO Threshold, V <sub>DD1</sub> or V <sub>DD2</sub> Rising                          | V <sub>UVLO3+</sub>                            | 2.4  | 2.77 | 2.95 | V    |                                                                                                                                                                    |

| UVLO Threshold, $V_{DD1}$ or $V_{DD2}$ Falling                                       | V <sub>UVLO3</sub> -                           | 2.2  | 2.60 | 2.90 | V    |                                                                                                                                                                    |

| V <sub>DD1</sub> or V <sub>DD2</sub> UVLO Hysteresis                                 | V <sub>UVLO3HST</sub>                          |      | 0.18 |      | V    |                                                                                                                                                                    |

| LOGIC INPUTS                                                                         |                                                |      |      |      |      |                                                                                                                                                                    |

| Input Current                                                                        | I <sub>IN</sub>                                |      |      |      |      | 0 V ≤ input voltage (V <sub>IN</sub> ) ≤ 3.6 V                                                                                                                     |

| UD+ and UD-                                                                          |                                                | -20  | +0.1 | +20  | μA   |                                                                                                                                                                    |

| DD+ and DD-                                                                          |                                                | -250 | +0.1 | +250 | μA   |                                                                                                                                                                    |

| XI <sub>1</sub> and XI <sub>2</sub>                                                  |                                                | -30  | +0.1 | +30  | μA   |                                                                                                                                                                    |

| Single-Ended Inputs                                                                  |                                                |      |      |      |      |                                                                                                                                                                    |

| Input Logic High Threshold                                                           | V <sub>IH</sub>                                | 2.0  |      |      | V    |                                                                                                                                                                    |

| Input Logic Low Threshold                                                            | V <sub>IL</sub>                                |      |      | 0.8  | V    |                                                                                                                                                                    |

| Input Hysteresis                                                                     | V <sub>HYS</sub>                               |      | 0.4  |      | V    |                                                                                                                                                                    |

|                                                                                      |                                                | 1    |      |      |      | 1                                                                                                                                                                  |

analog.com Rev. B | 3 of 27

Table 1. Specifications (Continued)

| Parameter                                                      | Symbol            | Min                  | Тур  | Max  | Unit  | Test Conditions/Comments                                                                                                           |

|----------------------------------------------------------------|-------------------|----------------------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| High Speed Input Differential<br>Threshold <sup>4</sup>        | V <sub>TH</sub>   |                      | 0.09 |      | V     | (DD+) – (DD-)  or  (UD+) – (UD-)                                                                                                   |

| Low and Full Speed Differential Input Sensitivity <sup>4</sup> | V <sub>DI</sub>   | 0.2                  |      |      | V     | (DD+) – (DD-)  or  (UD+) – (UD-)                                                                                                   |

| OUTPUTS (DRIVERS)                                              |                   |                      |      |      |       |                                                                                                                                    |

| Low or Full Speed Output Voltages                              |                   |                      |      |      |       | UD+, UD-, DD+, and DD-                                                                                                             |

| Logic High                                                     | V <sub>OH</sub>   | 0.8 V <sub>DDx</sub> |      | 3.6  | V     | Load resistance ( $R_L$ ) = 15 k $\Omega$ , load voltage ( $V_L$ ) = 0 V                                                           |

| Logic Low                                                      | V <sub>OL</sub>   | 0                    |      | 0.3  | V     | $R_L = 1.5 \text{ k}\Omega, V_L = 3.6 \text{ V}$                                                                                   |

| Transceiver Capacitance                                        | C <sub>IN</sub>   |                      | 14   |      | pF    | $C_{IN, UD+}$ or $C_{IN, UD-}$ (UD+ or UD- to $GND_1$ ), $C_{IN, DD+}$ or $C_{IN, DD-}$ (DD+ or DD- to $GND_2$ ), $f_{IN}$ = 6 MHz |

|                                                                |                   |                      | 19   |      | pF    | $C_{IN, UD+}$ , $C_{IN, UD-}$ , $C_{IN, DD+}$ or $C_{IN, DD-}$ , $f_{IN} = 240 \text{ MHz}$                                        |

| Capacitance Matching                                           |                   |                      | 1    |      | %     | 1 - C <sub>IN, UD+</sub> /C <sub>IN, UD-</sub>                                                                                     |

|                                                                |                   |                      | 3    |      | %     | 1- C <sub>IN, DD+</sub> /C <sub>IN, DD-</sub>                                                                                      |

| Full Speed Driver Impedance                                    | Z <sub>OUTH</sub> | 40.5                 | 45   | 49.5 | Ω     |                                                                                                                                    |

| Impedance Matching                                             |                   |                      | 10   |      | %     | UD+ and UD- or DD+ and DD-                                                                                                         |

| COMMON-MODE TRANSIENT IMMUNITY <sup>4</sup>                    |                   |                      |      |      |       | Common-mode voltage ( $V_{CM}$ ) = 1000 V, transient magnitude = 800 $V^5$                                                         |

| At Logic High Output <sup>6</sup>                              | CMTI <sub>H</sub> | 40                   | 50   |      | kV/µs | $V_{IN}$ = $V_{DD1}$ for UD+ or UD- (other input = 0 V), $V_{IN}$ = $V_{DD2}$ for DD+ or DD- (other input = 0 V)                   |

| At Logic Low Output <sup>7</sup>                               | CMTI <sub>L</sub> | 40                   | 50   |      | kV/µs | UD+ and UD- = 0 V, or DD+ and DD- = 0 V                                                                                            |

Measured when the device is powered, connected to a USB host, and connected to a USB peripheral using the specified communication speed. However, the USB is idle without being suspended, meaning there has been no USB activity for a frame interval (1 ms for low or full speed, or 0.125 ms for high speed), but short keep alive packets may be occurring within each frame to keep the USB from suspending.

analog.com Rev. B | 4 of 27

<sup>&</sup>lt;sup>2</sup> The busy USB supply current values are for the device running at a fixed continuous data rate at 50% duty cycle, alternating J and K states. Supply current values are specified with a USB-compliant load present.

$<sup>^3~\</sup>rm V_{UVLO3+}$  is the UVLO threshold,  $\rm V_{DD1}$  or  $\rm V_{DD2}$  rising.

<sup>&</sup>lt;sup>4</sup> These specifications are guaranteed by design and characterization.

<sup>&</sup>lt;sup>5</sup> CMTI is the maximum common-mode voltage slew rate that can be sustained while maintaining specification compliant operation. V<sub>CM</sub> is the common-mode potential difference between Side 1 and Side 2. The transient magnitude is the range over which the common mode is slewed. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.

<sup>6</sup> Output voltage for UD+ or UD− > 0.8 V<sub>DD1</sub> (other output ≤ 0.3 V), and output voltage for DD+ or DD− > 0.8 V<sub>DD2</sub> (other output ≤ 0.3 V).

<sup>&</sup>lt;sup>7</sup> UD+ and UD-  $\leq$  0.3 V or DD+ and DD-  $\leq$  0.3 V.

#### **TIMING SPECIFICATIONS**

$4.5 \text{ V} \le \text{V}_{\text{BUS1}} \le 5.5 \text{ V}$ ,  $4.5 \text{ V} \le \text{V}_{\text{BUS2}} \le 5.5 \text{ V}$ ,  $3.0 \text{ V} \le \text{V}_{\text{DD1}} \le 3.6 \text{ V}$ , and  $3.0 \text{ V} \le \text{V}_{\text{DD2}} \le 3.6 \text{ V}$ . All minimum and maximum specifications were applied over the entire recommended operation range, unless otherwise noted. All typical specifications are at  $T_A = 25^{\circ}\text{C}$  and  $V_{\text{DD1}} = V_{\text{DD2}} = 3.3 \text{ V}$ , unless otherwise noted. Each voltage is relative to its respective ground.

Table 2. Timing Specifications

| Parameter                                           | Symbol                                | Min | Тур | Max | Unit   | Test Conditions/Comments                              |

|-----------------------------------------------------|---------------------------------------|-----|-----|-----|--------|-------------------------------------------------------|

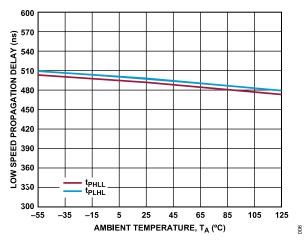

| USB INPUT AND OUTPUT PINS LOW                       |                                       |     |     |     |        | UD+, UD-, DD+, and DD- and $C_L$ = 450 pF             |

| SPEED MODE                                          |                                       |     |     |     |        |                                                       |

| Data Rate                                           |                                       |     | 1.5 |     | Mbps   |                                                       |

| Propagation Delay <sup>1</sup>                      | t <sub>PHLL</sub> , t <sub>PLHL</sub> | 300 | 500 | 600 | ns     | $T_A = 25$ °C and $V_{DD1} = V_{DD2} = 3.3 \text{ V}$ |

|                                                     |                                       | 300 | 500 | 650 | ns     |                                                       |

| Output Rise and Fall Time (10% to 90%)              | t <sub>RL</sub> /t <sub>FL</sub>      | 75  |     | 300 | ns     | $T_A = 25$ °C and $V_{DD1} = V_{DD2} = 3.3 \text{ V}$ |

|                                                     |                                       | 75  |     | 350 | ns     |                                                       |

| Differential Jitter                                 |                                       |     |     |     |        |                                                       |

| Next Transition                                     | t <sub>LJN</sub>                      |     | 5   |     | ns     |                                                       |

| Paired J to K Transition                            | t <sub>LJPJK</sub>                    |     | 2   |     | ns     |                                                       |

| Paired K to J Transition                            | t <sub>LJPKJ</sub>                    |     | 3   |     | ns     |                                                       |

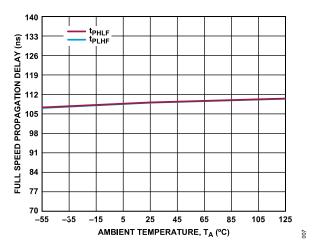

| USB INPUT AND OUTPUT PINS FULL<br>SPEED MODE        |                                       |     |     |     |        | UD+, UD-, DD+, and DD-, and $C_L = 50 \text{ pF}$     |

| Data Rate                                           |                                       |     | 12  |     | Mbps   |                                                       |

| Propagation Delay <sup>1</sup>                      | t <sub>PHLF</sub> , t <sub>PLHF</sub> | 70  | 110 | 140 | ns     |                                                       |

| Output Rise/Fall Time (10% to 90%)                  | t <sub>RF</sub> /t <sub>FF</sub>      | 4   |     | 20  | ns     | $T_A = 25$ °C and $V_{DD1} = V_{DD2} = 3.3 \text{ V}$ |

|                                                     |                                       | 4   |     | 32  | ns     |                                                       |

| Differential Jitter                                 |                                       |     |     |     |        |                                                       |

| Next Transition                                     | t <sub>FJN</sub>                      |     | 450 |     | ps     |                                                       |

| Paired J to K Transition                            | t <sub>FJPJK</sub>                    |     | 300 |     | ps     |                                                       |

| Paired K to J Transition                            | t <sub>FJPKJ</sub>                    |     | 500 |     | ps     |                                                       |

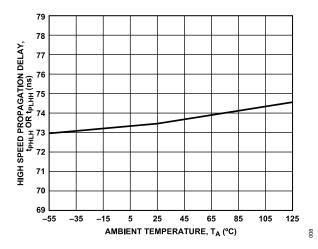

| USB INPUT AND OUTPUT PINS HIGH<br>SPEED MODE        |                                       |     |     |     |        | UD+, UD-, DD+, and DD-, and $C_L = 10 \text{ pF}$     |

| Data Rate                                           |                                       |     | 480 |     | Mbps   |                                                       |

| Propagation Delay <sup>2, 3</sup>                   | t <sub>PHLH</sub> , t <sub>PLHH</sub> | 71  | 73  | 77  | ns     |                                                       |

| Output Rise and Fall Time (10% to 90%) <sup>3</sup> | t <sub>RH</sub> , t <sub>FH</sub>     | 675 |     |     | ps     |                                                       |

| Differential Jitter (rms)                           |                                       |     |     |     |        |                                                       |

| Next Transition                                     | t <sub>HJN(R)</sub>                   |     | 40  |     | ps rms |                                                       |

| Paired J to K Transition                            | t <sub>HJPJK(R)</sub>                 |     | 11  |     | ps rms |                                                       |

| Paired K to J Transition                            | t <sub>HJPKJ(R)</sub>                 |     | 14  |     | ps rms |                                                       |

| Differential Jitter (peak)                          |                                       |     |     |     |        |                                                       |

| Next Transition                                     | t <sub>HJN(P)</sub>                   |     | 90  |     | ps     |                                                       |

| Paired J to K Transition                            | t <sub>HJPJK(P)</sub>                 |     | 30  |     | ps     |                                                       |

| Paired K to J Transition                            | t <sub>HJPKJ(P)</sub>                 |     | 40  |     | ps     |                                                       |

Propagation delay of the low or full speed USB signals in either direction is measured from the 50% level of the input signal rising or falling edge to the 50% level of the rising or falling edge of the corresponding output signal. This delay is between one and two hub differential data delays as defined in USB 2.0 specification, Table 7-11 (T<sub>HDD1</sub> and T<sub>LHDD</sub> parameters).

analog.com Rev. B | 5 of 27

Propagation delay of the high speed USB signals in either direction is measured from the 50% level of the input signal rising or falling edge to the 50% level of the rising or falling edge of the corresponding output signal. This delay is specified to be less than one hub data delay (without cable) as defined in USB 2.0 specification, Table 7-11 (T<sub>HSHDD</sub> parameter).

<sup>&</sup>lt;sup>3</sup> These specifications are guaranteed by design and characterization.

#### **INSULATION AND SAFETY RELATED SPECIFICATIONS**

For additional information, see www.analog.com/icouplersafety.

Table 3. Insulation and Safety Related Specifications

| Parameter                                                                   | Symbol  | Value | Unit  | Test Conditions/Comments                                                                                                   |

|-----------------------------------------------------------------------------|---------|-------|-------|----------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage                                         |         | 3750  | V rms | 1 minute duration                                                                                                          |

| Minimum External Air Gap (Clearance) <sup>1</sup>                           | L (I01) | 5.3   | mm    | Measured from input terminals to output terminals, shortest distance through air                                           |

| Minimum External Tracking (Creepage) <sup>1</sup>                           | L (102) | 5.3   | mm    | Measured from input terminals to output terminals, shortest distance path along body <sup>2</sup>                          |

| Minimum Clearance in the Plane of the Printed Circuit Board (PCB Clearance) | L (PCB) | 5.3   | mm    | Measured from input terminals to output terminals, shortest distance through air, line of sight, in the PCB mounting plane |

| Minimum Internal Gap (Internal Clearance)                                   |         | 29    | μm    | Insulation distance through insulation                                                                                     |

| Tracking Resistance (Comparative Tracking Index) <sup>3</sup>               | CTI     | >600  | V     | Tested in accordance to IEC 60112                                                                                          |

| Material Group                                                              |         | 1     |       | Material Group per IEC 60664-1                                                                                             |

<sup>1</sup> In accordance with IEC 62368-1/IEC 60601-1 guidelines for the measurement of creepage and clearance distances for a pollution degree of 2 and altitudes ≤2000 m.

## PACKAGE CHARACTERISTICS

Table 4. Package Characteristics

| Parameter                                  | Symbol           | bol Min Typ Max l |                  | Unit | Test Conditions/Comments |                                                          |

|--------------------------------------------|------------------|-------------------|------------------|------|--------------------------|----------------------------------------------------------|

| Resistance (Input to Output) <sup>1</sup>  | R <sub>I-O</sub> |                   | 10 <sup>12</sup> |      | Ω                        | Voltage (input to output) (V <sub>I-O</sub> ) = 500 V dc |

| Capacitance (Input to Output) <sup>1</sup> | C <sub>I-O</sub> |                   | 2.2              |      | pF                       | Frequency = 1 MHz                                        |

<sup>1</sup> Device is considered a 2-terminal device; Pin 1 through Pin 10 are shorted together, and Pin 11 through Pin 20 are shorted together.

## REGULATORY INFORMATION

The ADuM3165/ADuM3166 certification approvals are listed in Table 5.

See Table 10 for details regarding the recommended maximum working voltages for specific cross-isolation waveforms and insulation levels.

Table 5. Regulatory Information

| Regulatory Agency | Standard Certification/Approval                | File           |

|-------------------|------------------------------------------------|----------------|

| CSA               | UL 1577 <sup>1</sup>                           | 205078         |

|                   | Single protection, 3750 V rms                  |                |

|                   | IEC/EN/CSA 62368-1                             |                |

|                   | Basic insulation, 530 V rms                    |                |

|                   | Reinforced insulation, 265 V rms               |                |

|                   | IEC/CSA 61010-1                                |                |

|                   | Basic insulation, 300 V rms                    |                |

|                   | Reinforced insulation, 150 V rms               |                |

|                   | IEC/CSA 60601-1                                |                |

|                   | Basic insulation (1 MOPP), 347 V rms           |                |

|                   | Reinforced insulation (2MOPP), 50 V rms        |                |

| VDE               | DIN EN IEC 60747-17 (VDE 0884-17) <sup>2</sup> | 40051926       |

|                   | Reinforced insulation, 849 V <sub>PEAK</sub>   |                |

| CQC               | CQC GB 4943.1                                  | CQC25001466586 |

analog.com Rev. B | 6 of 27

Consideration must be given to pad layout to ensure the minimum required distance for clearance is maintained.

<sup>&</sup>lt;sup>3</sup> CTI rating for the ADUM4165/ADUM4166 is >600 V and a Material Group I isolation group.

## Table 5. Regulatory Information (Continued)

| Regulatory Agency | Standard Certification/Approval  | File |

|-------------------|----------------------------------|------|

|                   | Basic insulation, 530 V rms      |      |

|                   | Reinforced insulation, 265 V rms |      |

<sup>&</sup>lt;sup>1</sup> In accordance with UL 1577, each ADuM3165/ADuM3166 is proof tested by applying an insulation test voltage ≥4500 V rms for 1 sec

## DIN EN IEC 60747-17 (VDE 0884-17) INSULATION CHARACTERISTICS

This isolator is suitable for reinforced electrical isolation only within the safety limit data. Protective circuits ensure the maintenance of the safety data.

Table 6. DIN EN IEC 60747-17 (VDE 0884-17) Insulation Characteristics

| Description                                          | Test Conditions/Comments <sup>1</sup>                                                                          | Symbol              | Characteristic   | Unit              |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|------------------|-------------------|

| Installation Classification per DIN VDE 0110         |                                                                                                                |                     |                  |                   |

| For Rated Mains Voltage ≤ 150 V rms                  |                                                                                                                |                     | I to IV          |                   |

| For Rated Mains Voltage ≤ 300 V rms                  |                                                                                                                |                     | I to IV          |                   |

| For Rated Mains Voltage ≤ 600 V rms                  |                                                                                                                |                     | I to III         |                   |

| Climatic Classification                              |                                                                                                                |                     | 55/125/21        |                   |

| Pollution Degree per DIN VDE 0110, Table 1           |                                                                                                                |                     | 2                |                   |

| Maximum Repetitive Insulation Voltage                |                                                                                                                | V <sub>IORM</sub>   | 849              | V <sub>PEAK</sub> |

| Maximum Working Insulation Voltage                   |                                                                                                                | V <sub>IOWM</sub>   | 600              | V <sub>RMS</sub>  |

| Input to Output Test Voltage, Method B1              | $V_{IORM} \times 1.875 = V_{PD (M)}$ , 100% production test, $t_{INI} = t_M = 1$ sec, partial discharge < 5 pC | V <sub>PD (m)</sub> | 1592             | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method A               |                                                                                                                | V <sub>PD (m)</sub> |                  |                   |

| After Environmental Tests Subgroup 1                 | $V_{IORM} \times 1.6 = V_{PD (M)}$ , $t_{INI} = 60$ sec, $t_M = 10$ sec, partial discharge < 5 pC              |                     | 1358             | V <sub>PEAK</sub> |

| After Input or Safety Test Subgroup 2 and Subgroup 3 | $V_{IORM} \times 1.2 = V_{PD (M)}$ , $t_{INI} = 60$ sec, $t_M = 10$ sec, partial discharge < 5 pC              |                     | 1019             | V <sub>PEAK</sub> |

| Maximum Transient Isolation Voltage                  |                                                                                                                | V <sub>IOTM</sub>   | 6000             | V <sub>PEAK</sub> |

| Maximum Impulse Voltage                              | Tested in air, 1.2 µs/50 µs waveform per IEC 61000-4-5                                                         | V <sub>IMP</sub>    | 6000             | V <sub>PEAK</sub> |

| Maximum Surge Isolation Voltage                      | $V_{TEST} \ge 1.3 \times V_{IMP}$ (Sample Test), tested in oil, 1.2 µs/50 µs waveform per IEC 61000-4-5        | V <sub>IOSM</sub>   | 10,000           | V <sub>PEAK</sub> |

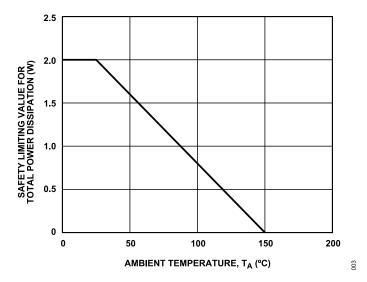

| Safety Limiting Values                               | Maximum value allowed in the event of a failure (see Figure 3)                                                 |                     |                  |                   |

| Maximum Junction Temperature                         |                                                                                                                | T <sub>S</sub>      | 150              | °C                |

| Total Power Dissipation at 25°C                      |                                                                                                                | Ps                  | 2                | W                 |

| Insulation Resistance at T <sub>S</sub>              | V <sub>IO</sub> = 500 V                                                                                        | R <sub>S</sub>      | >10 <sup>9</sup> | Ω                 |

$<sup>^{\</sup>rm 1}~$  For information about  $t_{\rm M},\,t_{\rm INI},$  and  $V_{\rm IO},$  see VDE 0884-17.

analog.com Rev. B | 7 of 27

In accordance with DIN EN IEC 60747-17, each ADuM3165/ADuM3166 is proof tested by applying an insulation test voltage ≥1592 V<sub>PEAK</sub> for 1 sec (partial discharge detection limit = 5 pC).

Figure 3. Thermal Derating Curve, Dependence of Safety Limiting Values with Ambient Temperature per VDE 0884-17

analog.com Rev. B | 8 of 27

## **RECOMMENDED OPERATING CONDITIONS**

## **Table 7. Recommended Operating Conditions**

| Parameter                                                | Symbol                                | Rating          |  |

|----------------------------------------------------------|---------------------------------------|-----------------|--|

| Supply Voltages                                          | V <sub>BUS1</sub> , V <sub>BUS2</sub> | 3.0 V to 5.5 V  |  |

|                                                          | $V_{DD1}, V_{DD2}$                    | 3.0 V to 3.6 V  |  |

| Operating Temperature (See Power Supply Options Section) | T <sub>A</sub>                        |                 |  |

| T <sub>J</sub> ≤ 150°C (See Thermal Resistance Section)  |                                       | -55°C to +125°C |  |

| Low or Full Speed                                        |                                       | -55°C to +125°C |  |

| High Speed                                               |                                       |                 |  |

| Side 1 and Side 2 LDO Not Used                           |                                       | -55°C to +120°C |  |

| Side 1 or Side 2 LDO Used                                |                                       | −55°C to +110°C |  |

| Side 1 and Side 2 LDO Used                               |                                       | −55°C to +100°C |  |

analog.com Rev. B | 9 of 27

## **ABSOLUTE MAXIMUM RATINGS**

Table 8.

| 14410 01                                                                                               |                                                            |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Parameter                                                                                              | Rating                                                     |

| Supply (V <sub>BUS1</sub> , V <sub>DD1</sub> ) to GND <sub>1</sub>                                     | -0.5 V to +6.5 V                                           |

| Supply (V <sub>BUS2</sub> , V <sub>DD2</sub> ) to GND <sub>2</sub>                                     | -0.5 V to +6.5 V                                           |

| Upstream Input Voltage (UD-, UD+, $XI_1$ , and $XO_1$ ) to $GND_1$                                     | -0.5 V to V <sub>DD1</sub> + 0.5 V                         |

| Downstream Input Voltage (DD-, DD+, XI <sub>2</sub> , XO <sub>2</sub> , and PGOOD) to GND <sub>2</sub> | -0.5 V to V <sub>DD2</sub> + 0.5 V                         |

| Common-Mode Transients <sup>1</sup>                                                                    | -100 kV/µs to +100 kV/µs                                   |

| Temperature                                                                                            |                                                            |

| Operating Range                                                                                        | -55°C to +125°C                                            |

| Storage Range                                                                                          | -65°C to +150°C                                            |

| Junction (T <sub>J</sub> Maximum)                                                                      | 150°C                                                      |

| Power Dissipation <sup>2</sup>                                                                         | (T <sub>J</sub> maximum - T <sub>A</sub> )/θ <sub>JA</sub> |

Refers to common-mode transients across the insulation barrier. Common-mode transients exceeding the absolute maximum ratings may cause latch-up or permanent damage.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operation environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\Psi_{JT}$  is the junction to top thermal characterization parameter.

Table 9. Thermal Resistance

| Package Type <sup>1</sup> | $\theta_{JA}$ | $\Psi_{JT}$ | Unit |

|---------------------------|---------------|-------------|------|

| RS-20                     | 62.5          | 2.2         | °C/W |

Test Condition 1: thermal impedance simulated with 4-layer standard JEDEC PCB.

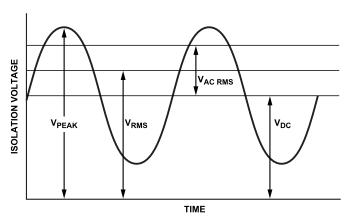

Table 10. Maximum Continuous Working Voltage<sup>1</sup>

| Parameter             | Rating                 | Constraint                                                                                                      |

|-----------------------|------------------------|-----------------------------------------------------------------------------------------------------------------|

| AC Voltage            |                        |                                                                                                                 |

| Bipolar Waveform      |                        |                                                                                                                 |

| Basic Insulation      | 650 V rms              | Basic insulation rating per IEC60747-17. Accumulative failure rate over lifetime (FROL) ≤ 1000 ppm at 24 years. |

| Reinforced Insulation | 600 V rms              | Reinforced insulation rating per IEC60747-17. Accumulative FROL ≤ 1 ppm at 30 years.                            |

| Unipolar Waveform     |                        |                                                                                                                 |

| Basic Insulation      | 1726 V <sub>PEAK</sub> | Rating limited by package creepage per IEC 60664-1 in Pollution Degree 2 environment.                           |

| Reinforced Insulation | 860 V <sub>PEAK</sub>  | Rating limited by package creepage per IEC 60664-1 in Pollution Degree 2 environment.                           |

| DC Voltage            |                        |                                                                                                                 |

| Basic Insulation      | 1057 V dc              | Rating limited by package creepage per IEC 60664-1 in Pollution Degree 2 environment.                           |

| Reinforced Insulation | 527 V dc               | Rating limited by package creepage per IEC 60664-1 in Pollution Degree 2 environment.                           |

<sup>1</sup> Maximum continuous working voltage refers to the continuous voltage magnitude imposed across the isolation barrier in a Pollution Degree 2 environment. See the Insulation Lifetime section for more details.

analog.com Rev. B | 10 of 27

<sup>&</sup>lt;sup>2</sup> See Figure 3 for the maximum power dissipation for various temperatures.

## **ABSOLUTE MAXIMUM RATINGS**

## **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

International electrotechnical commission (IEC) electromagnetic compatibility: Part 4-2 (IEC) per IEC 61000-4-2.

## ESD Ratings for ADuM3165/ADuM3166

Table 11. ADuM3165/ADuM3166, 20-Lead SSOP

| ESD Model        | Withstand Threshold (V)   | Class   |

|------------------|---------------------------|---------|

| HBM <sup>1</sup> | ±4000                     | 3A      |

| IEC <sup>2</sup> | ±6000 (contact discharge) | Level 3 |

$<sup>^{1}~</sup>$  All pins to respective GNDx, 1.5 k $\!\Omega,$  100 pF.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. B | 11 of 27

$<sup>^2~{\</sup>rm GND_1}$  to  ${\rm GND_2}$  or  ${\rm GND_2}$  to  ${\rm GND_1}$  across isolation barrier.

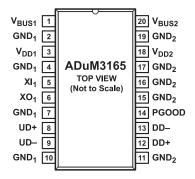

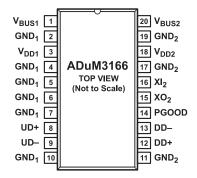

#### NOTES:

1. PIN 2 AND PIN 10 ARE INTERNALLY CONNECTED, AND CONNECTING BOTH TO SIDE 1 PCB GROUND IS RECOMMENDED.

2. PIN 11 AND PIN 19 ARE INTERNALLY CONNECTED, AND CONNECTING BOTH TO SIDE 2 PCB GROUND IS RECOMMENDED.

Figure 4. ADuM3165 Pin Configuration

Table 12. ADuM3165 Pin Function Descriptions

| Pin No.    | Mnemonic          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1          | V <sub>BUS1</sub> | Optional 5 V Power Supply/Low Dropout (LDO) Input for Side 1. Connect V <sub>BUS1</sub> to 4.5 V to 5.5 V and bypass to GND <sub>1</sub> using a 0.1 μF capacitor to power Side 1 from a 5 V supply (an integrated LDO regulator generates the 3.3 V required internally). Alternatively, if powering Isolator Side 1 directly from an external 3.3 V power supply, connect both V <sub>BUS1</sub> and V <sub>DD1</sub> together to 3.3 V. (Bypass to GND <sub>1</sub> is still required.)                  |  |  |  |  |

| 2, 10      | GND₁              | Ground, Side 1. Ground reference for Isolator Side 1, connect to Side 1 PCB ground.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 3          | V <sub>DD1</sub>  | $3.3 \text{ V}$ Power Supply/LDO Output for Side 1. Bypass to $\text{GND}_1$ with a required capacitor value of $0.1 \mu\text{F}$ for correct operation of the internal $3.3 \text{ V}$ regulator (used when connecting 5 V to $\text{V}_{\text{BUS}1}$ ). Alternatively, if powering Isolator Side 1 directly from an external $3.3 \text{ V}$ power supply, connect both $\text{V}_{\text{BUS}1}$ and $\text{V}_{\text{DD}1}$ together to $3.3 \text{ V}$ . (Bypass to $\text{GND}_1$ is still required.) |  |  |  |  |

| 4, 7       | GND <sub>1</sub>  | Ground, Side 1. These pins must be connected to Side 1 PCB ground for proper operation. These pins are not suitable for connection of bypass capacitance.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 5          | XI <sub>1</sub>   | Crystal Input or External Clock Input, Isolator Side 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 6          | XO <sub>1</sub>   | Crystal Output Driver, Isolator Side 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 8          | UD+               | USB D+ Signal, Upstream (Isolator Side 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 9          | UD-               | USB D- Signal, Upstream (Isolator Side 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 11, 19     | GND <sub>2</sub>  | Ground 2. Ground reference for Isolator Side 2, connect to Side 2 PCB ground.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 12         | DD+               | USB D+ Signal, Downstream (Isolator Side 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 13         | DD-               | USB D- Signal, Downstream (Isolator Side 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 14         | PGOOD             | Power Good. High output indicates that the voltages at V <sub>BUS1</sub> /V <sub>DD1</sub> and V <sub>BUS2</sub> /V <sub>DD2</sub> are greater than UVLO thresholds, and low output indicates V <sub>BUS1</sub> /V <sub>DD1</sub> or V <sub>BUS2</sub> /V <sub>DD2</sub> are less than UVLO thresholds. When PGOOD is low, Side 2 reverts to low power standby mode.                                                                                                                                        |  |  |  |  |

| 15, 16, 17 | GND <sub>2</sub>  | Ground 2. These pins must be connected to Side 2 PCB ground for proper operation. These pins are not suitable for connection of bypass capacitance.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 18         | V <sub>DD2</sub>  | $3.3 \text{ V}$ Power Supply/LDO Output for Side 2. Bypass to $\text{GND}_2$ with a required capacitor value of $0.1 \mu\text{F}$ for correct operation of the internal $3.3 \text{ V}$ regulator (used when connecting 5 V to $\text{V}_{\text{BUS}2}$ ). Alternatively, if powering Isolator Side 2 directly from an external $3.3 \text{ V}$ power supply, connect both $\text{V}_{\text{BUS}2}$ and $\text{V}_{\text{DD}2}$ together to $3.3 \text{V}$ . (Bypass to $\text{GND}_2$ is still required.)  |  |  |  |  |

| 20         | V <sub>BUS2</sub> | Optional 5 V Power Supply/LDO Input for Side 2. Connect $V_{BUS2}$ to 4.5 V to 5.5 V and bypass to $GND_2$ using a 0.1 $\mu$ F capacitor to power Side 2 from a 5 V supply (an integrated LDO regulator generates the 3.3 V required internally). Alternatively, if powering Isolator Side 2 directly from an external 3.3 V power supply, connect both $V_{BUS2}$ and $V_{DD2}$ together to 3.3 V. (Bypass to $GND_2$ is still required.)                                                                  |  |  |  |  |

analog.com Rev. B | 12 of 27

#### NOTES:

1. PIN 2 AND PIN 10 ARE INTERNALLY CONNECTED, AND CONNECTING BOTH TO SIDE 1 PCB GROUND IS RECOMMENDED.

2. PIN 11 AND PIN 19 ARE INTERNALLY CONNECTED, AND CONNECTING BOTH TO SIDE 2 PCB GROUND IS RECOMMENDED.

Figure 5. ADuM3166 Pin Configuration

Table 13. ADuM3166 Pin Function Descriptions

| Pin No.    | Mnemonic          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | V <sub>BUS1</sub> | Optional 5 V Power Supply/LDO Input for Side 1. Connect $V_{BUS1}$ to 4.5 V to 5.5 V and bypass to $GND_1$ using a 0.1 $\mu$ F capacitor to power Side 1 from a 5 V supply (an integrated LDO regulator generates the 3.3 V required internally). Alternatively, if powering Isolator Side 1 directly from an external 3.3 V power supply, connect both $V_{BUS1}$ and $V_{DD1}$ together to 3.3 V. (Bypass to $GND_1$ is still required.)                              |  |

| 2, 10      | GND <sub>1</sub>  | Ground, Side 1. Ground reference for Isolator Side 1, connect to Side 1 PCB ground.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 3          | V <sub>DD1</sub>  | $3.3 \text{ V}$ Power Supply/LDO Output for Side 1. Bypass to GND <sub>1</sub> with a required capacitor value of $0.1 \mu\text{F}$ for correct operation of internal $3.3 \text{V}$ regulator (used when connecting $5 \text{V}$ to $V_{BUS1}$ ). Alternatively, if powering Isolator Side 1 directly from an external $3.3 \text{V}$ power supply, connect both $V_{BUS1}$ and $V_{DD1}$ together to $3.3 \text{V}$ . (Bypass to GND <sub>1</sub> is still required.) |  |

| 4, 5, 6, 7 | GND <sub>1</sub>  | Ground, Side 1. These pins must be connected to Side 1 PCB ground for proper operation. These pins are not suitable for connection of bypass capacitance.                                                                                                                                                                                                                                                                                                               |  |

| 8          | UD+               | USB D+ Signal, Upstream (Isolator Side 1).                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 9          | UD-               | USB D- Signal, Upstream (Isolator Side 1).                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 11, 19     | GND <sub>2</sub>  | Ground 2. Ground reference for isolator side 2, connect to side 2 PCB ground.                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 12         | DD+               | USB D+ Signal, Downstream (Isolator Side 2).                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 13         | DD-               | USB D- Signal, Downstream (Isolator Side 2).                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 14         | PGOOD             | Power Good. High output indicates that the voltages at V <sub>BUS1</sub> /V <sub>DD1</sub> and V <sub>BUS2</sub> /V <sub>DD2</sub> are greater than UVLO thresholds, and low output indicates V <sub>BUS1</sub> /V <sub>DD1</sub> or V <sub>BUS2</sub> /V <sub>DD2</sub> are less than UVLO thresholds. When PGOOD is low, Side 2 reverts to low power standby mode.                                                                                                    |  |

| 15         | XO <sub>2</sub>   | Crystal Output Driver, Isolator Side 2.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 16         | XI <sub>2</sub>   | Crystal Input or External Clock Input, Isolator Side 2.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 17         | GND <sub>2</sub>  | Ground 2. This pin must be connected to Side 2 PCB ground for proper operation. This pin is not suitable for connection of bypass capacitance.                                                                                                                                                                                                                                                                                                                          |  |

| 18         | V <sub>DD2</sub>  | $3.3 \text{ V}$ Power Supply/LDO Output for Side 2. Bypass to $GND_2$ with a required capacitor value of $0.1 \mu\text{F}$ for correct operation of internal $3.3 \text{V}$ regulator (used when connecting $5 \text{V}$ to $V_{BUS2}$ ). Alternatively, if powering Isolator Side 2 directly from an external $3.3 \text{V}$ power supply, connect both $V_{BUS2}$ and $V_{DD2}$ together to $3.3 \text{V}$ . (Bypass to $GND_2$ is still required).                   |  |

| 20         | V <sub>BUS2</sub> | Optional 5 V Power Supply/LDO Input for Side 2. Connect $V_{BUS2}$ to 4.5 V to 5.5 V and bypass to $GND_2$ using a 0.1 $\mu$ F capacitor to power Side 2 from a 5 V supply (an integrated LDO regulator generates the 3.3 V required internally). Alternatively, if powering Isolator Side 2 directly from an external 3.3 V power supply, connect both $V_{BUS2}$ and $V_{DD2}$ together to 3.3 V. (Bypass to $GND_2$ is still required).                              |  |

#### **TRUTH TABLES**

Table 14. USB Signals, All Modes

| Table 14. USB Signals, All Modes |                      |                      |                       |                       |  |  |

|----------------------------------|----------------------|----------------------|-----------------------|-----------------------|--|--|

| State                            | UD+                  | UD-                  | DD+                   | DD-                   |  |  |

| Downstream Disconnected          | Low (host pull-down) | Low (host pull-down) | Low (15 kΩ pull-down) | Low (15 kΩ pull-down) |  |  |

| No Host or Peripheral            | High-Z               | High-Z               | Low (15 kΩ pull-down) | Low (15 kΩ pull-down) |  |  |

analog.com Rev. B | 13 of 27

Table 15. USB Signals, High Speed

| State                        | UD+                                | UD-                               | DD+                                    | DD-                                   |

|------------------------------|------------------------------------|-----------------------------------|----------------------------------------|---------------------------------------|

| Idle and Reset               | Low <sup>1</sup>                   | Low <sup>1</sup>                  | Low <sup>1</sup>                       | Low <sup>1</sup>                      |

| Initiate Suspend (<3.125 ms) | Low (host pull-down) <sup>2</sup>  | Low (host pull-down) <sup>2</sup> | Low (15 kΩ pull-down) <sup>2</sup>     | Low (15 kΩ pull-down) <sup>2</sup>    |

| Suspend (>3.125 ms)          | High (1.5 kΩ pull-pp) <sup>3</sup> | Low (host pull-down)              | High (peripheral pull-up) <sup>3</sup> | Low (15 kΩ pull-down)                 |

| Upstream Disconnected        | High (1.5 kΩ pull-up)              | High-Z                            | High (peripheral pull-up) 4            | Low (15 kΩ pull-pown)                 |

| J to Downstream              | ~0.4 V due to host <sup>1</sup>    | Low <sup>1</sup>                  | ~0.4 V per UD+1                        | Low <sup>1</sup>                      |

| J to Upstream                | ~0.4 V per DD+1                    | Low <sup>1</sup>                  | ~0.4 V due to peripheral <sup>1</sup>  | Low <sup>1</sup>                      |

| K to Downstream              | Low <sup>1</sup>                   | ~0.4 V due to Host <sup>1</sup>   | Low <sup>1</sup>                       | ~0.4 V per UD-1                       |

| K to Upstream                | Low <sup>1</sup>                   | ~0.4 V per DD-1                   | Low <sup>1</sup>                       | ~0.4 V due to peripheral <sup>1</sup> |

After high speed handshake, host and peripheral terminate to local GND with 45 Ω. The isolator also terminates UD+, UD-, DD+, and DD- to local GND with its own 45 Ω resistors. During high speed transmission, the host or peripheral and the isolator drive 17.8 mA on the appropriate D+ or D- signals, giving a voltage of ~0.4 V across the parallel 45 Ω terminations.

Table 16. USB Signals, Full Speed

| State                 | UD+1                  | UD-                   | DD+ <sup>1, 2</sup>       | DD-2                  |

|-----------------------|-----------------------|-----------------------|---------------------------|-----------------------|

| Idle and Reset        | High (pull-up)        | Low (host pull-down)  | High (peripheral pull-up) | Low (pull-pown)       |

| Upstream Disconnected | High (pull-up)        | High-Z                | High (peripheral pull-up) | Low (pull-pown)       |

| J to Downstream       | High (host)           | Low (host)            | High (driven per UD+)     | Low (driven per UD-)  |

| J to Upstream         | High (driven per DD+) | Low (driven per DD-)  | High (peripheral)         | Low (peripheral)      |

| K to Downstream       | Low (host)            | High (host)           | Low (driven per UD+)      | High (driven per UD-) |

| K to Upstream         | Low (driven per DD+)  | High (driven per DD-) | Low (peripheral)          | High (peripheral)     |

| SE0 to Downstream     | Low (host)            | Low (host)            | Low (driven per UD+)      | Low (driven per UD-)  |

| SE0 to Upstream       | Low (driven per DD+)  | Low (driven per DD-)  | Low (peripheral)          | Low (peripheral)      |

$<sup>^{1}</sup>$  A 1.5 kΩ pull-up is connected on UD+ by the isolator, per peripheral 1.5 kΩ pull-up on DD+.

Table 17. USB Signals, Low Speed

| State                 | UD+                   | UD-1                  | DD+ <sup>2</sup>      | DD- <sup>1, 2</sup>       |

|-----------------------|-----------------------|-----------------------|-----------------------|---------------------------|

| Idle and Reset        | Low (host pull-down)  | High (pull-up)        | Low (pull-down)       | High (peripheral pull-up) |

| Upstream Disconnected | High-Z                | High (pull-up)        | Low (pull-down)       | High (peripheral pull-up) |

| J to Downstream       | Low (host)            | High (host)           | Low (driven per UD+)  | High (driven per UD-)     |

| J to Upstream         | Low (driven per DD+)  | High (driven per DD-) | Low (peripheral)      | High (peripheral)         |

| K to Downstream       | High (host)           | Low (host)            | High (driven per UD+) | Low (driven per UD-)      |

| K to Upstream         | High (driven per DD+) | Low (driven per DD-)  | High (peripheral)     | Low (peripheral)          |

| SE0 to Downstream     | Low (host)            | Low (host)            | Low (driven per UD+)  | Low (driven per UD-)      |

| SE0 to Upstream       | Low (driven per DD+)  | Low (driven per DD-)  | Low (peripheral)      | Low (peripheral)          |

<sup>&</sup>lt;sup>1</sup> A 1.5 kΩ pull-up connected on UD– by the isolator, per peripheral 1.5 kΩ pull-up on DD–.

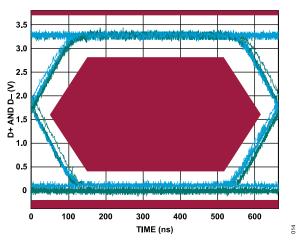

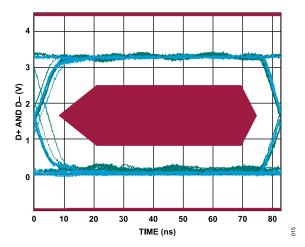

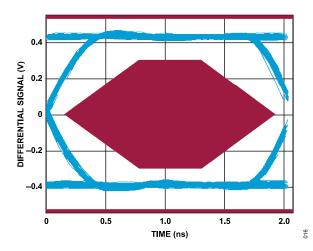

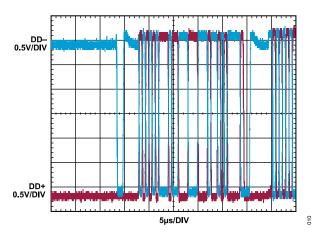

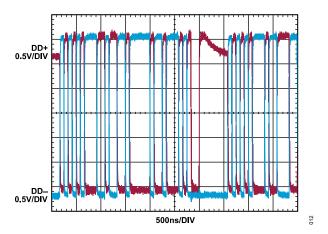

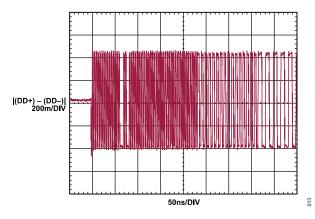

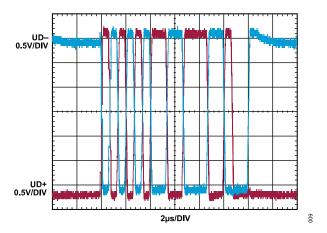

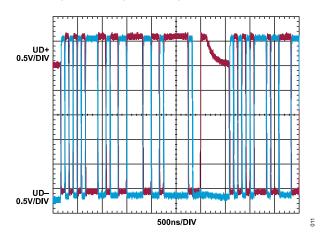

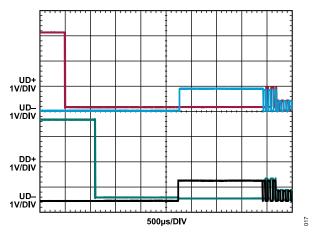

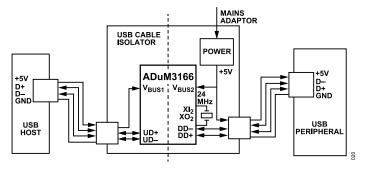

analog.com Rev. B | 14 of 27