# Hot-Swap Controller and Digital Power and Energy Monitor with PMBus Interface

## **FEATURES**

- ▶ Drop-in replacement to ADM1278

- ▶ ±0.3% accurate, 12-bit ADC for I<sub>OUT</sub>, V<sub>IN</sub>, V<sub>OUT</sub>, and temperature

- ▶ 290 ns response time to short-circuit

- Shutdown on detection of FET health fault

- ► Constant power foldback for tighter FET SOA protection

- Remote temperature sensing with programmable warning and shutdown thresholds

- ▶ Resistor-programmable 5 mV to 25 mV V<sub>SENSE</sub> current limit

- ▶ Programmable start-up current limit

- ▶ 1% accurate UV, OV, and PWRGD thresholds

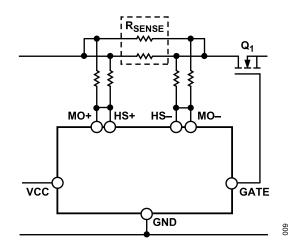

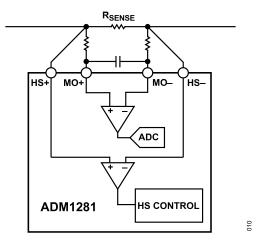

- Split hot-swap and power monitor inputs to allow additional external ADC filtering

- ▶ Reports power and energy consumption over time

- ▶ Peak detect registers for current, voltage, and power

- PROCHOT power throttling capability

- ▶ PMBus fast mode compliant interface

- ▶ Available in 5 mm × 5 mm, 32-lead LFCSP package

### **APPLICATIONS**

- Servers

- Power monitoring and control/power budgeting

- ▶ Telecommunication and data communication equipment

### **GENERAL DESCRIPTION**

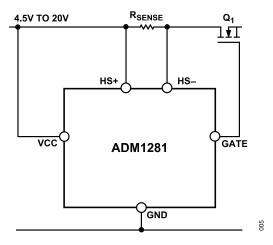

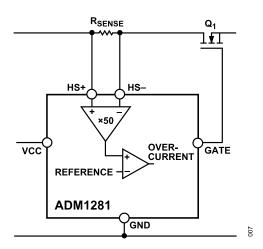

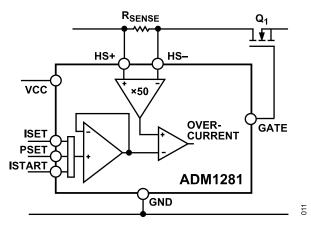

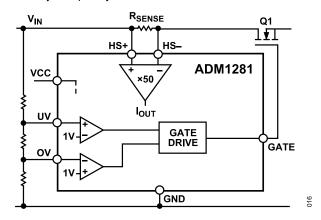

The ADM1281 is a hot-swap controller that allows a circuit board to be removed from or inserted into a live backplane. It also features current, voltage, power, and temperature readback through an integrated 12-bit analog-to-digital converter (ADC), accessed using a PMBus™ interface. The load current is measured using an internal current sense amplifier that measures the voltage across a sense resistor in the power path through the HS+ and HS− pins. A default current limit of 20 mV is set, but this limit can be adjusted, if required.

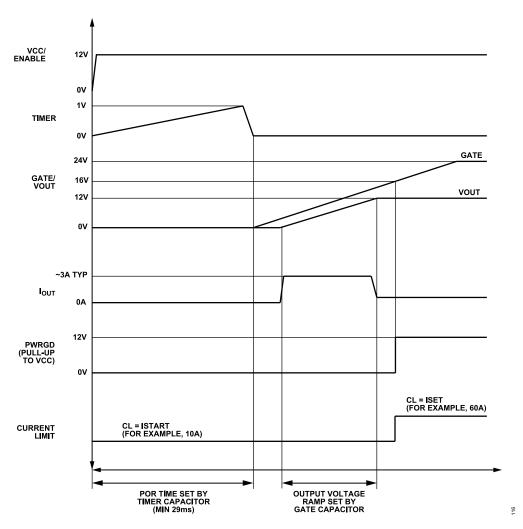

The ADM1281 limits the current through the sense resistor by controlling the gate voltage of an external N-channel FET in the power path, through the GATE pin. The sense voltage, and therefore the load current, is maintained below the preset maximum. The ADM1281 protects the external FET by limiting the time that the FET remains on while the current is at its maximum value. This current-limit time is set by the choice of capacitor connected to the TIMER pin. In addition, a constant power foldback scheme is used to control the power dissipation in the MOSFET during power-up and fault conditions. The level of this power, along with the TIMER

regulation time, can be set to ensure that the MOSFET remains within safe operating area (SOA) limits.

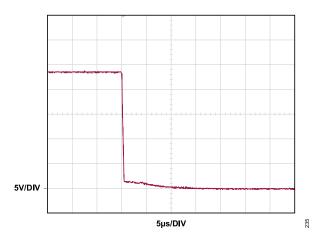

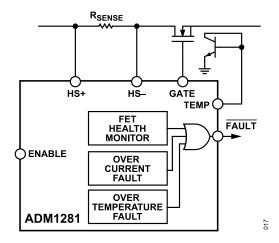

In case of a short-circuit event, a fast internal overcurrent detector responds within 290 ns and signals the gate to shut down. A 2400 mA pull-down device ensures a fast FET response.

The ADM1281 features overvoltage (OV) and undervoltage (UV) protection, programmed using external resistor dividers on the UV and OV pins. A PWRGD signal can be used to detect when the output supply is valid, using the PWGIN pin to accurately monitor the output.

The ADM1281 is available in a 32-lead LFCSP with a RETRY pin that can be configured for automatic retry or latch-off when an overcurrent fault occurs.

Table 1. Model Options

| Model       | ADC Accuracy | Serial-Peripheral<br>Interface (SPI) | Enable Pin <sup>1</sup> |

|-------------|--------------|--------------------------------------|-------------------------|

| ADM1281-1AA | ±0.3%        | No                                   | Active high             |

| ADM1281-1A  | ±0.7%        | No                                   | Active high             |

| ADM1281-2A  | ±0.7%        | Yes                                  | Active high             |

| ADM1281-3A  | ±0.7%        | No                                   | Active low              |

Active high relates to the ENABLE pin, and active low relates to the ENABLE pin.

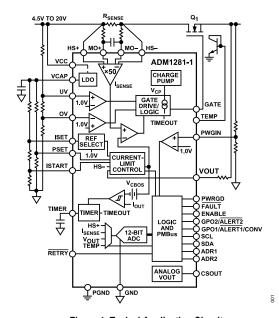

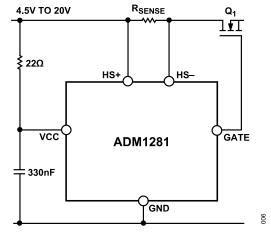

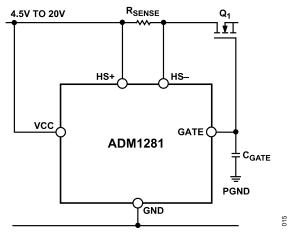

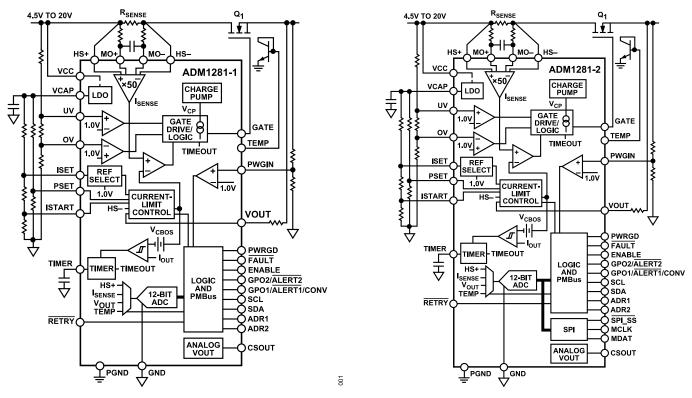

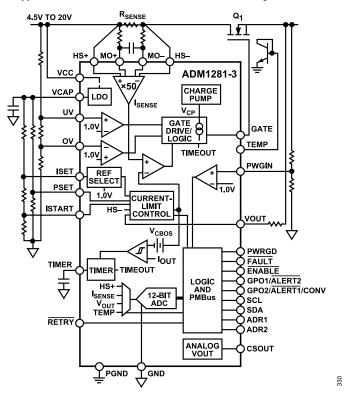

### TYPICAL APPLICATION CIRCUIT

Figure 1. Typical Application Circuit

## **TABLE OF CONTENTS**

| Features                                     | 1    | GPO and Alert Pin Setup Commands           | 39 |

|----------------------------------------------|------|--------------------------------------------|----|

| Applications                                 | 1    | Power Monitor Commands                     | 39 |

| General Description                          | 1    | Warning Limit Setup Commands               | 40 |

| Typical Application Circuit                  | 1    | PMBus Direct Format Conversion             | 41 |

| Specifications                               | 4    | Voltage and Current Conversion Using LS    | В  |

| Power Monitoring Accuracy Specification      | s 8  | Values                                     |    |

| Serial Bus Timing Characteristics            | 8    | Alert Pin Behavior                         | 43 |

| SPI Timing Characteristics (ADM1281-2)       | 9    | Faults and Warnings                        | 43 |

| Absolute Maximum Ratings                     | 10   | Generating an Alert                        |    |

| Thermal Resistance                           | 10   | Handling/Clearing an Alert                 | 43 |

| ESD Caution                                  | 10   | SMBus ARA                                  | 44 |

| Pin Configurations and Function Descriptio   | ns11 | Example Use of SMBus ARA                   | 44 |

| Typical Performance Characteristics          |      | Digital Comparator Mode                    | 44 |

| Theory of Operation                          |      | Typical Application Circuits               | 45 |

| Differences from ADM1278                     | 23   | PMBus Command Reference                    | 46 |

| Powering the ADM1281                         | 23   | Register Details                           | 47 |

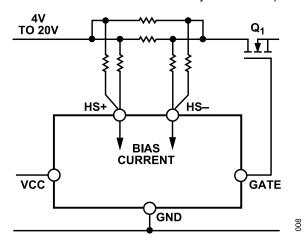

| Hot-Swap Current Sense Inputs                | 23   | Operation Register                         | 47 |

| Power Monitor Current Sense Inputs           |      | Clear Faults Register                      | 47 |

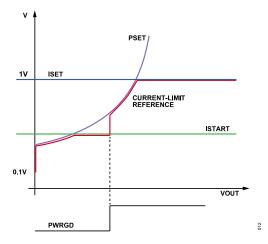

| Current-Limit Reference                      | 24   | PMBus Capability Register                  | 47 |

| Setting the Current Limit (ISET)             | 25   | V <sub>OUT</sub> OV Warning Limit Register | 47 |

| Setting a Linear Output Voltage Ramp at      |      | V <sub>OUT</sub> UV Warning Limit Register |    |

| Power-Up                                     |      | I <sub>OUT</sub> OC Warning Limit Register |    |

| Start-Up Current Limit                       |      | OT Fault Limit Register                    |    |

| Constant Power Foldback                      | 28   | OT Warning Limit Register                  | 48 |

| Timer                                        |      | V <sub>IN</sub> OV Warning Limit Register  |    |

| Hot-Swap Retry                               |      | V <sub>IN</sub> UV Warning Limit Register  |    |

| FET Gate Drive Clamps                        |      | P <sub>IN</sub> OP Warning Limit Register  |    |

| Fast Response to Severe Overcurrent          |      | Status Byte Register                       |    |

| Undervoltage and Overvoltage                 |      | Status Word Register                       |    |

| Power Good                                   |      | V <sub>OUT</sub> Status Register           |    |

| FAULT Pin                                    |      | I <sub>OUT</sub> Status Register           |    |

| ENABLE/ENABLE Input                          |      | Input Status Register                      |    |

| Current Sense Output (CSOUT)                 |      | Temperature Status Register                | 52 |

| Remote Temperature Sensing                   |      | Communication/Memory/Logic Fault           |    |

| Serial-Peripheral Interface (SPI)            |      | Register                                   |    |

| V <sub>OUT</sub> Measurement                 |      | Manufacturer Specific Status Register      |    |

| FET Health                                   |      | Read E <sub>IN</sub> Register              |    |

| Power Throttling                             |      | Read V <sub>IN</sub> Register              |    |

| Power Monitor                                |      | Read V <sub>OUT</sub> Register             |    |

| PMBus Interface                              |      | Read I <sub>OUT</sub> Register             |    |

| Device Addressing                            |      | Read Temperature 1 Register                |    |

| SMBus Protocol Usage                         |      | Read P <sub>IN</sub> Register              |    |

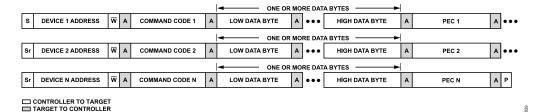

| Packet Error Checking (PEC)                  |      | PMBus Revision Register                    |    |

| Partial Transactions on I <sup>2</sup> C Bus |      | Manufacturer ID Register                   |    |

| SMBus Message Formats                        |      | Manufacturer Model Register                |    |

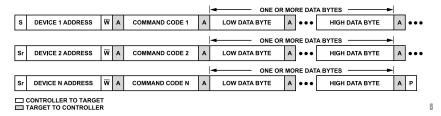

| Group Commands                               |      | Manufacturer Revision Register             |    |

| Hot-Swap Control Commands                    |      | Manufacturer Date Register                 |    |

| ADM1281 Information Commands                 |      | Peak I <sub>OUT</sub> Register             |    |

| Status Commands                              | 38   | Peak V <sub>IN</sub> Register              | 57 |

## **TABLE OF CONTENTS**

| Peak V <sub>OUT</sub> Register                                                                         | Read P <sub>IN</sub> (Extended) Register | 61<br>61<br>62 |

|--------------------------------------------------------------------------------------------------------|------------------------------------------|----------------|

| Peak Temperature Register59                                                                            | Start-Up I <sub>OUT</sub> Limit Register |                |

| Device Configuration Register60                                                                        | Outline Dimensions                       |                |

| Power Cycle Register61                                                                                 | Ordering Guide                           | 63             |

| Peak P <sub>IN</sub> Register61                                                                        | Evaluation Boards                        | 63             |

| REVISION HISTORY                                                                                       |                                          |                |

| 4/2025—Rev. 0 to Rev. A Changes to Figure 40 and Figure 41 Changes to Differences from ADM1278 Section |                                          |                |

| Changes to Ordering Guide                                                                              |                                          |                |

| 3/2024—Revision 0: Initial Version                                                                     |                                          |                |

analog.com Rev. A | 3 of 63

## **SPECIFICATIONS**

$V_{CC} = 4.5 \text{ V to } 20 \text{ V}, V_{CC} \\ \ge V_{HS+} \text{ and } V_{MO+}, V_{HS+} \\ = 4 \text{ V to } 20 \text{ V}, V_{SENSE\_HS} \\ = (V_{HS+} - V_{HS-}) \\ = 0 \text{ V}, T_A \\ = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$

Table 2. Electrical Specifications

| Parameter <sup>1</sup>               | Symbol                   | Min   | Тур  | Max   | Unit | Test Conditions/Comments                                                                               |

|--------------------------------------|--------------------------|-------|------|-------|------|--------------------------------------------------------------------------------------------------------|

| POWER SUPPLY                         |                          |       |      |       |      |                                                                                                        |

| Operating Voltage Range              | V <sub>CC</sub>          | 4.5   |      | 20    | V    |                                                                                                        |

| Undervoltage Lockout                 | UVLO                     | 2.4   |      | 2.7   | ٧    | V <sub>CC</sub> rising                                                                                 |

| Undervoltage Hysteresis              |                          |       | 100  | 120   | mV   |                                                                                                        |

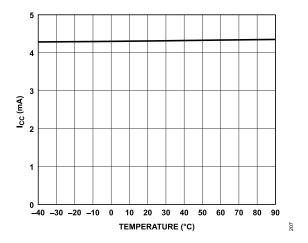

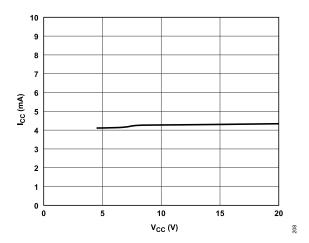

| Quiescent Current                    | I <sub>CC</sub>          |       |      | 5.5   | mA   | GATE on and power monitor running                                                                      |

| UV PIN                               |                          |       |      |       |      |                                                                                                        |

| Input Current                        | I <sub>UV</sub>          |       |      | 50    | nA   | UV ≤ 2.7 V                                                                                             |

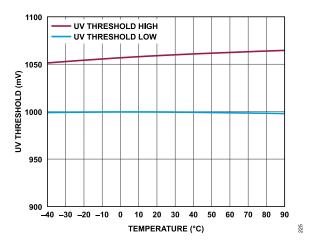

| UV Threshold                         | UV <sub>TH</sub>         | 0.99  | 1.0  | 1.01  | V    | UV falling                                                                                             |

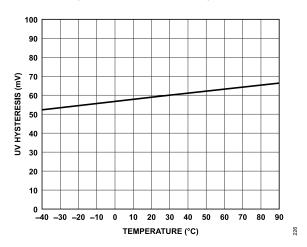

| UV Threshold Hysteresis              | UV <sub>HYST</sub>       | 40    | 60   | 75    | mV   |                                                                                                        |

| UV Glitch Filter                     | UV <sub>GF</sub>         | 2     |      | 7     | μs   | 50 mV overdrive                                                                                        |

| UV Propagation Delay                 | UV <sub>PD</sub>         |       | 5    | 8     | μs   | UV low to GATE pull-down active                                                                        |

| OV PIN                               |                          |       |      |       |      |                                                                                                        |

| Input Current                        | I <sub>OV</sub>          |       |      | 50    | nA   | OV ≤ 2.7 V                                                                                             |

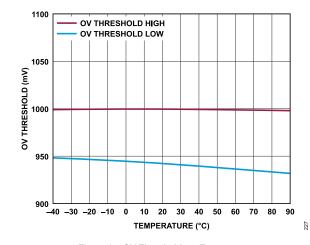

| OV Threshold                         | OV <sub>TH</sub>         | 0.99  | 1.0  | 1.01  | V    | OV rising                                                                                              |

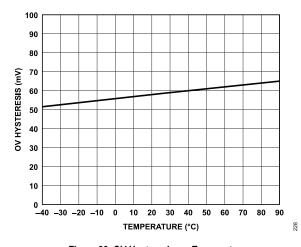

| OV Threshold Hysteresis              | OV <sub>HYST</sub>       | 40    | 60   | 75    | mV   |                                                                                                        |

| OV Glitch Filter                     | OV <sub>GF</sub>         | 1.5   |      | 3.5   | μs   | 50 mV overdrive                                                                                        |

| OV Propagation Delay                 | OV <sub>PD</sub>         |       | 3.0  | 4.0   | μs   | OV high to GATE pull-down active                                                                       |

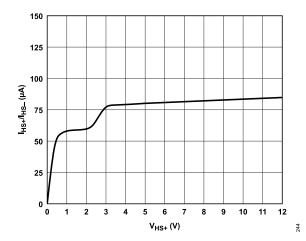

| HS+ AND HS- PINS                     |                          |       |      |       |      |                                                                                                        |

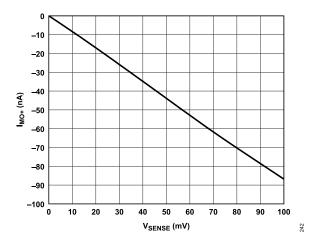

| Input Current                        | I <sub>SENSEx</sub>      |       |      | 150   | μA   | Per individual pin; V <sub>HS+</sub> , V <sub>HS-</sub> = 20 V                                         |

| Input Imbalance                      | I <sub>ΔSENSE</sub>      |       |      | 8     | μA   | $I_{\Delta SENSE} = (I_+ - I)$                                                                         |

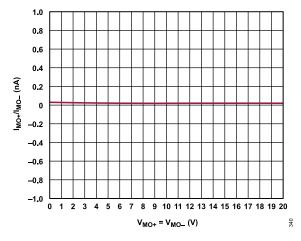

| MO+ AND MO- PINS                     |                          |       |      |       |      |                                                                                                        |

| Input Current                        | I <sub>MO±</sub>         |       |      | 60    | nA   | Per individual pin; V <sub>MO+</sub> , V <sub>MO</sub> - = 19.6 V                                      |

| VCAP PIN                             |                          |       |      |       |      |                                                                                                        |

| Internally Regulated Voltage         | V <sub>VCAP</sub>        | 2.68  | 2.7  | 2.72  | V    | $0$ μA ≤ $I_{VCAP}$ ≤ 100 μA; $C_{VCAP}$ = 1 μF                                                        |

| ISET PIN                             |                          |       |      |       |      |                                                                                                        |

| Reference Select Threshold           | V <sub>ISETRSTH</sub>    | 1.45  | 1.5  | 1.55  | V    | If V <sub>ISET</sub> > V <sub>ISETRSTH</sub> , an internal 1 V reference (V <sub>CLREF</sub> ) is used |

| Internal Reference                   | V <sub>CLREF</sub>       |       | 1    |       | V    | Accuracies included in total sense voltage accuracies                                                  |

| Gain of Current Sense Amplifier      | AV <sub>CSAMP</sub>      |       | 50   |       | V/V  | Accuracies included in total sense voltage accuracies                                                  |

| Recommended Maximum Operating Range  | V <sub>ISET</sub>        | 0.25  |      | 1.25  | V    | 5 mV to 25 mV V <sub>SENSE</sub> current limit                                                         |

| Input Current                        | I <sub>ISET</sub>        |       |      | 100   | nA   | $V_{ISET} \le V_{VCAP}$                                                                                |

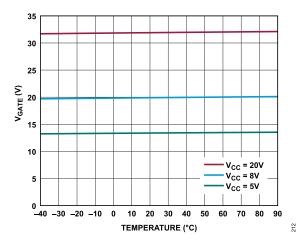

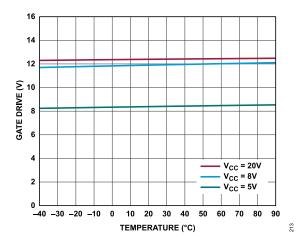

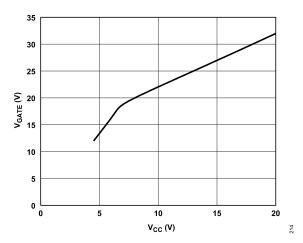

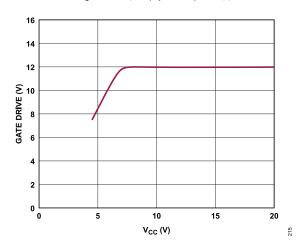

| GATE PIN                             |                          |       |      |       |      | Maximum voltage on the gate is always clamped to ≤31 V                                                 |

| GATE Drive Voltage                   | $\Delta V_{GATE}$        |       |      |       |      | $\Delta V_{GATE} = V_{GATE} - V_{OUT}$                                                                 |

|                                      |                          | 10    | 12   | 14    | V    | 20 V ≥ V <sub>CC</sub> ≥ 8 V; I <sub>GATE</sub> ≤ 5 μA                                                 |

|                                      |                          | 8     |      | 10    | V    | $V_{HS+} = V_{CC} = 5 \text{ V}; I_{GATE} \le 5 \mu\text{A}$                                           |

|                                      |                          | 7     |      | 9     | V    | $V_{HS+} = V_{CC} = 4.5 \text{ V}; I_{GATE} \le 1  \mu\text{A}$                                        |

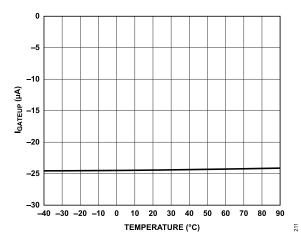

| GATE Pull-Up Current                 | I <sub>GATEUP</sub>      | -20   |      | -30   | μA   | V <sub>GATE</sub> = 0 V                                                                                |

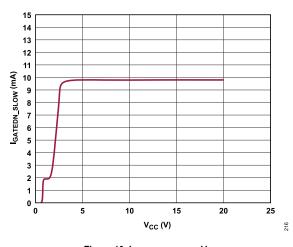

| GATE Pull-Down Current               | I <sub>GATEDN</sub>      |       |      |       |      |                                                                                                        |

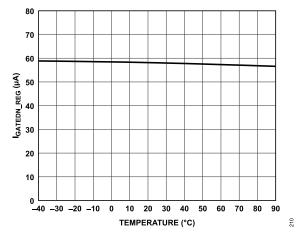

| Regulation                           | I <sub>GATEDN_REG</sub>  | 45    | 60   | 75    | μA   | $V_{GATE} \ge 2 \text{ V}; V_{ISET} = 1.0 \text{ V}; (V_{HS+} - V_{HS-}) = 30 \text{ mV}$              |

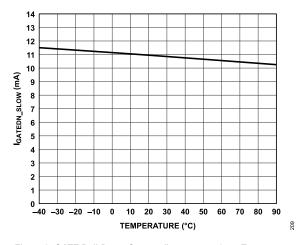

| Slow                                 | I <sub>GATEDN_SLOW</sub> | 5     | 10   | 15    | mA   | V <sub>GATE</sub> ≥ 2 V                                                                                |

| Fast                                 | I <sub>GATEDN_FAST</sub> | 1500  | 2400 | 3000  | mA   | V <sub>GATE</sub> ≥ 12 V; V <sub>CC</sub> ≥ 12 V                                                       |

| GATE Holdoff Resistance              |                          |       | 20   |       | Ω    | $V_{CC} = 0 \text{ V}, V_{GATE} = 2 \text{ V}$                                                         |

| HOT-SWAP SENSE VOLTAGE               |                          |       |      |       |      |                                                                                                        |

| Hot-Swap Sense Voltage Current Limit | V <sub>SENSECL</sub>     |       |      |       |      |                                                                                                        |

|                                      |                          | 19.75 | 20   | 20.25 | mV   | $V_{ISET} > 1.65 \text{ V}; V_{GATE} = (V_{HS+} + 3 \text{ V}); I_{GATE} = 0 \mu\text{A}$              |

| Constant Power Inactive              |                          |       |      |       |      | $V_{GATE} = (V_{HS+} + 3 V); I_{GATE} = 0 \mu A; V_{DS} = (HS-) - V_{OUT}$                             |

|                                      |                          | 24.75 | 25   | 25.25 | mV   | V <sub>ISET</sub> = 1.25 V; V <sub>DS</sub> < 2 V                                                      |

analog.com Rev. A | 4 of 63

# **SPECIFICATIONS**

Table 2. Electrical Specifications (Continued)

| Parameter <sup>1</sup>                | Symbol                      | Min   | Тур  | Max   | Unit | Test Conditions/Comments                                                                                                          |

|---------------------------------------|-----------------------------|-------|------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                       |                             | 19.75 | 20   | 20.25 | mV   | V <sub>ISET</sub> = 1.0 V; V <sub>DS</sub> < 2 V                                                                                  |

|                                       |                             | 14.75 | 15   | 15.25 | mV   | V <sub>ISET</sub> = 0.75 V; V <sub>DS</sub> < 2 V                                                                                 |

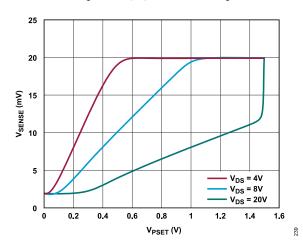

| Constant Power Active                 |                             |       |      |       |      | FET power limit = $(V_{PSET} \times 8)/(50 \times R_{SENSE})$ ; constant power active when $V_{DS} > (V_{PSET} \times 8)/I_{SET}$ |

|                                       |                             | 9.25  | 10   | 10.75 | mV   | V <sub>ISET</sub> > 1.65 V; V <sub>PSET</sub> = 0.25 V; V <sub>DS</sub> = 4 V                                                     |

|                                       |                             | 4.65  | 5    | 5.35  | mV   | V <sub>ISET</sub> > 1.65 V; V <sub>PSET</sub> = 0.25 V; V <sub>DS</sub> = 8 V                                                     |

|                                       |                             | 1.7   | 2    | 2.3   | mV   | V <sub>ISET</sub> > 1.65 V; V <sub>PSET</sub> = 0.25 V; V <sub>DS</sub> = 20 V                                                    |

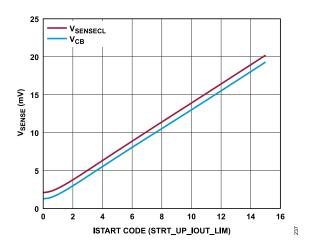

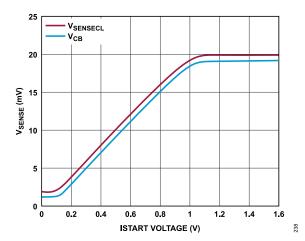

| Start-Up Current Limit                | V <sub>ISTARTCL</sub>       |       |      |       |      | IOET / FOET / BO                                                                                                                  |

| •                                     | IOTATIOE                    | 4.7   | 5    | 5.3   | mV   | STRT_UP_IOUT_LIM = 3; V <sub>ISET</sub> > 1.65 V                                                                                  |

|                                       |                             | 3.7   | 4    | 4.3   | mV   | V <sub>ISTART</sub> = 0.2 V                                                                                                       |

| Start-Up Current-Limit Clamp          | V <sub>ISTARTCL_CLAMP</sub> | 1.6   | 2    | 2.4   | mV   | V <sub>ISTART</sub> = 0 V or STRT_UP_IOUT_LIM = 0                                                                                 |

| Circuit Breaker Offset                | V <sub>CBOS</sub>           | 0.5   | 0.88 | 1.12  | mV   | Circuit breaker trip voltage, V <sub>CB</sub> = V <sub>SENSECL</sub> - V <sub>CBOS</sub>                                          |

| SEVERE OVERCURRENT                    | - 0003                      |       |      |       |      |                                                                                                                                   |

| Voltage Threshold                     | V <sub>SENSEOC</sub>        |       |      |       |      |                                                                                                                                   |

| rollago miloshola                     | SENSEUC                     | 23    | 25   | 27    | mV   | V <sub>ISET</sub> > 1.65 V; V <sub>PSET</sub> > 1.1 V; optional select PMBus (125%)                                               |

|                                       |                             | 28    | 30   | 32    | mV   | V <sub>ISET</sub> > 1.65 V; V <sub>PSET</sub> > 1.1 V; optional select PMBus (150%)                                               |

|                                       |                             | 38    | 40   | 42    | mV   | V <sub>ISET</sub> > 1.65 V; V <sub>PSET</sub> > 1.1 V; optional select PMBus (200%)                                               |

|                                       |                             | 43    | 45   | 47    | mV   | V <sub>ISET</sub> > 1.65 V; V <sub>PSET</sub> > 1.1 V; default at power-up (225%)                                                 |

| Short Glitch Filter Duration          |                             | 170   | 40   | 280   | ns   | V <sub>SENSE</sub> H <sub>S</sub> step = 18 mV to (2 mV above V <sub>SENSEOC</sub> MAX)                                           |

| Long Glitch Filter Duration (Default) |                             | 530   |      | 900   | ns   | V <sub>SENSE HS</sub> step = 18 mV to (2 mV above v <sub>SENSEOC_MAX</sub> )                                                      |

| Response Time                         |                             | 330   |      | 300   | 113  | V SENSE_HS SUCP = 10 HIV to (2 HIV above V SENSEOC_MAX)                                                                           |

| Short Glitch Filter                   |                             | 160   |      | 290   | ns   | V <sub>SENSE HS</sub> step = 18 mV to (2 mV above V <sub>SENSEOC MAX</sub> )                                                      |

| Long Glitch Filter                    |                             | 500   |      | 1000  | ns   | V <sub>SENSE HS</sub> step = 18 mV to (2 mV above V <sub>SENSEOC MAX</sub> )                                                      |

| ISTART PIN                            |                             | 300   |      | 1000  | 113  | V SENSE_HS SIEP - TO THIV TO (2 THIV ADOVE V SENSEOC_MAX)                                                                         |

|                                       |                             | 0.1   |      | 1.05  | /    | Tie ISTART to VCAR to discable start up aurrent limit                                                                             |

| Active Range                          | A) /                        | 0.1   | F0   | 1.25  | V    | Tie ISTART to VCAP to disable start-up current limit                                                                              |

| Gain of Current Sense Amplifier       | AV <sub>CSAMP</sub>         |       | 50   | 100   | V/V  | Accuracies included in total sense voltage accuracies                                                                             |

| Input Current                         | I <sub>ISTART</sub>         |       |      | 100   | nA   | V <sub>ISTART</sub> ≤ V <sub>VCAP</sub>                                                                                           |

| TIMER PIN                             |                             |       |      |       |      |                                                                                                                                   |

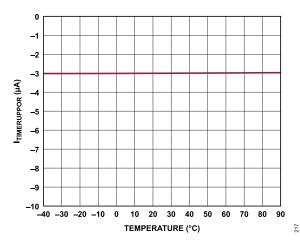

| TIMER Pull-Up Current                 |                             |       | •    |       |      | 177.1                                                                                                                             |

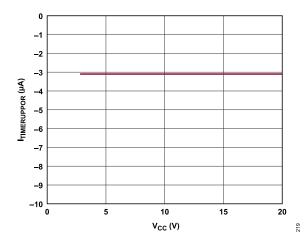

| Power-On Reset (POR)                  | ITIMERUPPOR                 | -2    | -3   | -4    | μA   | Initial power-on reset; V <sub>TIMER</sub> = 0.5 V                                                                                |

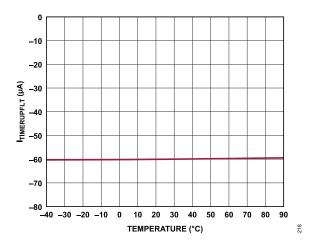

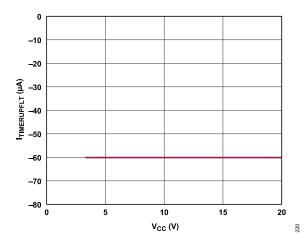

| Overcurrent (OC) Fault                | ITIMERUPFLT                 | -57   | -60  | -63   | μA   | Overcurrent fault; 0.2 V ≤ V <sub>TIMER</sub> ≤ 1 V                                                                               |

| TIMER Pull-Down Current               |                             | 4 -   | •    | 0.0   |      | A6 6 K L 0ATE: 6 W                                                                                                                |

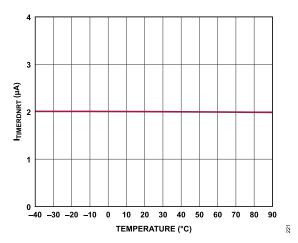

| Retry                                 | ITIMERDNRT                  | 1.7   | 2    | 2.3   | μA   | After fault when GATE is off; V <sub>TIMER</sub> = 0.5 V                                                                          |

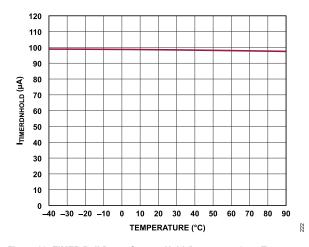

| Hold                                  | ITIMERDNHOLD                |       | 100  | 4.00  | μA   | Holds TIMER at 0 V when inactive; V <sub>TIMER</sub> = 0.5 V                                                                      |

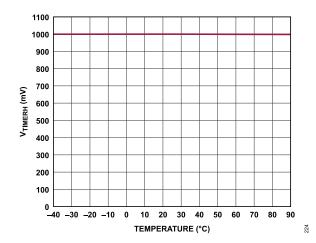

| TIMER High Threshold                  | V <sub>TIMERH</sub>         | 0.98  | 1.0  | 1.02  | V    |                                                                                                                                   |

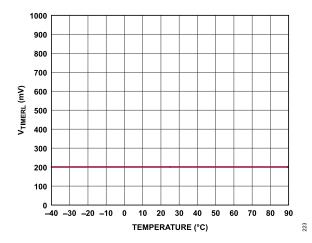

| TIMER Low Threshold                   | V <sub>TIMERL</sub>         | 0.18  | 0.2  | 0.22  | V    |                                                                                                                                   |

| TIMER Glitch Filter                   | TIMER <sub>GF</sub>         |       | 10   |       | μs   |                                                                                                                                   |

| Minimum POR Duration                  |                             |       | 29   |       | ms   | Minimum initial insertion delay regardless of C <sub>TIMER</sub> value                                                            |

| PSET PIN                              |                             |       |      |       |      | FET power limit = (V <sub>PSET</sub> × 8)/(50 × R <sub>SENSE</sub> )                                                              |

| Reference Select Threshold            | V <sub>PSETRSTH</sub>       | 1.45  | 1.5  | 1.55  | V    | If V <sub>PSET</sub> > V <sub>PSETRSTH</sub> , constant power is disabled                                                         |

| Gain of Current Sense Amplifier       | AV <sub>CSAMP</sub>         |       | 50   |       | V/V  | Accuracies included in total sense voltage accuracies                                                                             |

| Input Current                         | I <sub>PSET</sub>           |       |      | 100   | nA   | V <sub>PSET</sub> ≤ V <sub>VCAP</sub>                                                                                             |

| VOUT PIN                              |                             |       |      |       |      |                                                                                                                                   |

| Input Current                         |                             |       |      | 40    | μA   | V <sub>OUT</sub> = 20 V                                                                                                           |

| FAULT PIN                             |                             |       |      |       |      |                                                                                                                                   |

| Output Low Voltage                    | V <sub>OL_LATCH</sub>       |       |      | 0.4   | V    | I <sub>FAULT</sub> = 1 mA                                                                                                         |

| •                                     |                             |       |      | 1.5   | V    | I <sub>FAULT</sub> = 5 mA                                                                                                         |

analog.com Rev. A | 5 of 63

# **SPECIFICATIONS**

Table 2. Electrical Specifications (Continued)

| Parameter <sup>1</sup>           | Symbol                | Min  | Тур      | Max      | Unit     | Test Conditions/Comments                                                            |

|----------------------------------|-----------------------|------|----------|----------|----------|-------------------------------------------------------------------------------------|

| Leakage Current                  |                       |      |          | 100      | nA       | V <sub>FAULT</sub> ≤ 2 V; <del>FAULT</del> output high-Z                            |

|                                  |                       |      |          | 1        | μA       | V <sub>FAULT</sub> = 20 V; <del>FAULT</del> output high-Z                           |

| ENABLE PIN                       |                       |      |          |          |          |                                                                                     |

| Input High Voltage               | V <sub>IH</sub>       | 1.1  |          |          | V        |                                                                                     |

| Input Low Voltage                | V <sub>IL</sub>       |      |          | 0.8      | V        |                                                                                     |

| Glitch Filter                    |                       |      | 1        |          | μs       |                                                                                     |

| RETRY PIN                        |                       |      |          |          |          |                                                                                     |

| Input High Voltage               | V <sub>IH</sub>       | 1.1  |          |          | V        | Latch off when high; internal pull-up sets this as default                          |

| Input Low Voltage                | V <sub>IL</sub>       |      |          | 0.8      | V        | 10 second automatic retry when pin pulled low                                       |

| Glitch Filter                    |                       |      | 1        |          | μs       |                                                                                     |

| Internal Pull-Up Current         |                       |      | 8        |          | μA       |                                                                                     |

| CSOUT PIN                        |                       |      |          |          |          |                                                                                     |

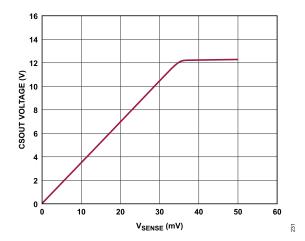

| CSOUT Gain                       |                       |      | 350      |          | V/V      | CSOUT = V <sub>SENSE HS</sub> × 350; VCC > CSOUT + 2 V                              |

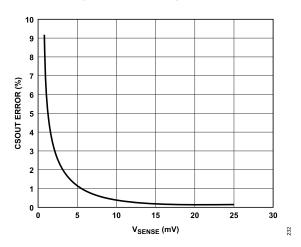

| Total Output Error               |                       | -1.6 |          | +1.6     | %        | V <sub>SENSE HS</sub> = 20 mV; I <sub>CSOUT</sub> ≤ 1 mA; C <sub>CSOUT</sub> = 1 nF |

|                                  |                       | -3.0 |          | +3.0     | %        | V <sub>SENSE HS</sub> = 10 mV; I <sub>CSOUT</sub> ≤ 1 mA; C <sub>CSOUT</sub> = 1 nF |

| Output Swing to GND              |                       |      | 40       |          | mV       | 1000                                                                                |

| Current Limiting                 |                       |      | 5        |          | mA       | CSOUT short-circuit current                                                         |

| GPO1/ALERT1/CONV PIN             |                       |      |          |          |          |                                                                                     |

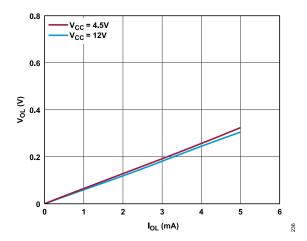

| Output Low Voltage               | V <sub>OL_GPO1</sub>  |      |          | 0.4      | V        | I <sub>GPO1</sub> = 1 mA                                                            |

|                                  | 02_01 01              |      |          | 1.5      | V        | I <sub>GPO1</sub> = 5 mA                                                            |

| Leakage Current                  |                       |      |          | 100      | nA       | V <sub>GPO1</sub> ≤ 2 V; GPO1 output high-Z                                         |

| ŭ                                |                       |      |          | 1        | μA       | $V_{GPO1} = 20 \text{ V}$ ; GPO1 output high-Z                                      |

| Input High Voltage               | V <sub>IH</sub>       | 1.1  |          |          | V        | Configured as CONV                                                                  |

| Input Low Voltage                | V <sub>IL</sub>       |      |          | 0.8      | V        | Configured as CONV                                                                  |

| Glitch Filter                    | - 12                  |      | 1        |          | μs       | Configured as CONV                                                                  |

| GPO2/ALERT2 PIN                  |                       |      |          |          | <u>'</u> |                                                                                     |

| Output Low Voltage               | V <sub>OL_GPO2</sub>  |      |          | 0.4      | V        | I <sub>GPO2</sub> = 1 mA                                                            |

| 3                                | OL_OI OZ              |      |          | 1.5      | V        | $I_{GPO2} = 5 \text{ mA}$                                                           |

| Leakage Current                  |                       |      |          | 100      | nA       | V <sub>GPO2</sub> ≤ 2 V; GPO2 output high-Z                                         |

|                                  |                       |      |          | 1        | μA       | $V_{\text{GPO2}} = 20 \text{ V}$ ; GPO2 output high-Z                               |

| PWRGD PIN                        |                       |      |          |          | <u>'</u> | 0102 - 7 - 1 3                                                                      |

| Output Low Voltage               | V <sub>OL PWRGD</sub> |      |          | 0.4      | V        | I <sub>PWRGD</sub> = 1 mA                                                           |

| 2 mp m 2 m 1 m 2 m               | - OL_FWRGD            |      |          | 1.5      | V        | I <sub>PWRGD</sub> = 5 mA                                                           |

| VCC That Guarantees Valid Output |                       | 1    |          |          | V        | I <sub>SINK</sub> = 100 µA; V <sub>OL PWRGD</sub> = 0.4 V                           |

| Leakage Current                  |                       | '    |          | 100      | nA       | V <sub>PWRGD</sub> ≤ 2 V; PWRGD output high-Z                                       |

| Louinage Garrotti                |                       |      |          | 1        | μA       | V <sub>PWRGD</sub> = 20 V; PWRGD output high-Z                                      |

| PWGIN PIN                        |                       |      |          | •        | ۳,,      | - FWAGD 2017, 111100 output light 2                                                 |

| Input Current                    | IDMOIN                |      |          | 50       | nA       | PWGIN ≤ 3.6 V                                                                       |

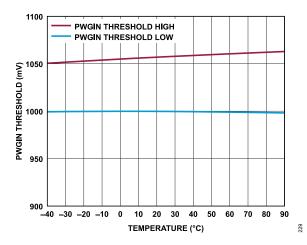

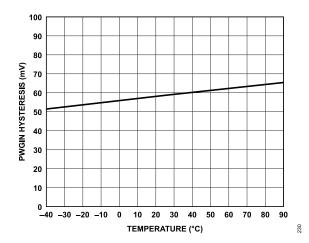

| PWGIN Threshold                  | PWGINTH               | 0.99 | 1.0      | 1.01     | V        | PWGIN sliing                                                                        |

| PWGIN Threshold Hysteresis       | PWGIN <sub>HYST</sub> | 40   | 60       | 75       | mV       | 1 Tront luming                                                                      |

| Glitch Filter                    | HYST                  | ٠,٠  | 1        | 10       | μs       | Asserting and deasserting of PWRGD pin                                              |

| CURRENT AND VOLTAGE MONITORING   |                       |      | 1        |          | μο       | For power monitor accuracy specifications, see Table 3                              |

| ADC Conversion Time              |                       |      |          |          |          | Includes time for power multiplication                                              |

| ADO CONVENSION TIME              |                       |      | 111      | 165      | 110      | ·                                                                                   |

|                                  |                       |      | 144      | 165      | μs       | One sample of I <sub>OUT</sub> ; from command received to valid data in register    |

|                                  |                       |      | 64<br>64 | 73<br>72 | μs       | One sample of V <sub>IN</sub> ; from command received to valid data in register     |

| ADD, DINC                        |                       |      | 64       | 73       | μs       | One sample of V <sub>OUT</sub> ; from command received to valid data in register    |

| ADRX PINS                        |                       |      |          | 0.0      |          | Connect to CND                                                                      |

| Address Set to 00                |                       | 0    |          | 0.8      | V        | Connect to GND                                                                      |

analog.com Rev. A | 6 of 63

## **SPECIFICATIONS**

Table 2. Electrical Specifications (Continued)

| Parameter <sup>1</sup>                                       | Symbol                | Min | Тур  | Max  | Unit | Test Conditions/Comments                                                                                |

|--------------------------------------------------------------|-----------------------|-----|------|------|------|---------------------------------------------------------------------------------------------------------|

| Input Current for Address Set to 00                          |                       | -40 | -22  |      | μA   | V <sub>ADRx</sub> = 0 V to 0.8 V                                                                        |

| Address Set to 01                                            |                       | 135 | 150  | 165  | kΩ   | Resistor to GND                                                                                         |

| Address Set to 10                                            |                       | -1  |      | +1   | μA   | No connect state; maximum leakage current allowed                                                       |

| Address Set to 11                                            |                       | 2   |      |      | V    | Connect to VCAP                                                                                         |

| Input Current for Address Set to 11                          |                       |     | 3    | 10   | μA   | V <sub>ADRx</sub> = 2.0 V to VCAP; must not exceed the maximum allowable current draw from VCAP         |

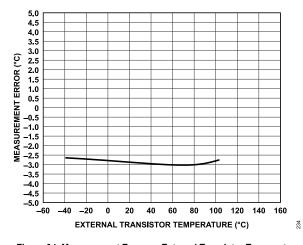

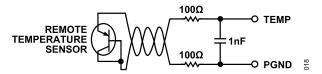

| TEMP PIN                                                     |                       |     |      |      |      | External transistor is 2N3904                                                                           |

| Operating Range                                              |                       | -55 |      | +150 | °C   | Limited by external diode                                                                               |

| Accuracy                                                     |                       |     | ±1   | ±10  | °C   | $T_A = T_{DIODE} = -40$ °C to +85°C                                                                     |

| Resolution                                                   |                       |     | 0.25 |      | °C   | LSB size                                                                                                |

| Output Current Source <sup>2</sup>                           |                       |     |      |      |      |                                                                                                         |

| Low Level                                                    |                       |     | 5    |      | μA   |                                                                                                         |

| Medium Level                                                 |                       |     | 30   |      | μA   |                                                                                                         |

| High Level                                                   |                       |     | 105  |      | μA   |                                                                                                         |

| Maximum Series Resistance for External Diode <sup>2</sup>    | R <sub>S</sub>        |     |      | 100  | Ω    | For <±0.5°C additional error, C <sub>P</sub> = 0 F                                                      |

| Maximum Parallel Capacitance for External Diode <sup>2</sup> | C <sub>P</sub>        |     |      | 1    | nF   | $R_S = 0 \Omega$                                                                                        |

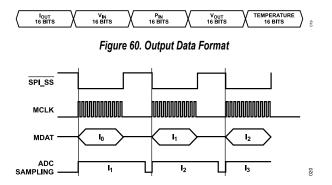

| SPI DIGITAL INPUTS (SPI_SS, MCLK, MDAT)                      |                       |     |      |      |      | Compatible with SPI Mode 0; MDAT is the output data pin; output is high impedance when not transmitting |

| Input High Voltage                                           | V <sub>IH</sub>       | 2.0 |      |      | V    |                                                                                                         |

| Input Low Voltage                                            | V <sub>IL</sub>       |     |      | 0.8  | V    |                                                                                                         |

| Output Low Voltage                                           | V <sub>OL</sub>       |     |      | 0.4  | V    | I <sub>OL</sub> = 4 mA                                                                                  |

| Leakage Current                                              |                       |     |      | 1    | μA   |                                                                                                         |

| Data Rate                                                    |                       |     |      | 1    | MHz  |                                                                                                         |

| SERIAL BUS DIGITAL INPUTS (SDA, SCL)                         |                       |     |      |      |      |                                                                                                         |

| Input High Voltage                                           | V <sub>IH</sub>       | 1.1 |      |      | V    |                                                                                                         |

| Input Low Voltage                                            | V <sub>IL</sub>       |     |      | 8.0  | V    |                                                                                                         |

| Output Low Voltage                                           | V <sub>OL</sub>       |     |      | 0.4  | V    | I <sub>OL</sub> = 4 mA                                                                                  |

| Input Leakage                                                | I <sub>LEAK-PIN</sub> | -10 |      | +10  | μA   |                                                                                                         |

|                                                              |                       | -5  |      | +5   | μA   | Device is not powered                                                                                   |

| Nominal Bus Voltage                                          | $V_{DD}$              | 2.7 |      | 5.5  | V    | 3 V to 5 V ± 10%                                                                                        |

| Capacitance for SDA, SCL Pins                                | C <sub>PIN</sub>      |     | 5    |      | pF   |                                                                                                         |

| Input Glitch Filter                                          | t <sub>SP</sub>       | 0   |      | 50   | ns   |                                                                                                         |

Dual function pin names are referenced by the relevant function only (for full pin mnemonics and descriptions, see the Pin Configurations and Function Descriptions section).

analog.com Rev. A | 7 of 63

<sup>&</sup>lt;sup>2</sup> Sampled during initial release to ensure compliance, but not subject to production testing.

## **SPECIFICATIONS**

## POWER MONITORING ACCURACY SPECIFICATIONS

**Table 3. Power Monitoring Accuracy Specifications**

|                                   |     | AA Grade |       |     | A Grad | е    |      |                                                                                                  |

|-----------------------------------|-----|----------|-------|-----|--------|------|------|--------------------------------------------------------------------------------------------------|

| Parameter                         | Min | Тур      | Max   | Min | Тур    | Max  | Unit | Test Conditions/Comments                                                                         |

| CURRENT AND VOLTAGE<br>MONITORING |     |          |       |     |        |      |      |                                                                                                  |

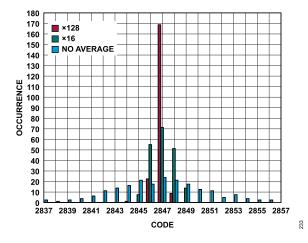

| Current Sense Absolute<br>Error   |     |          |       |     |        |      |      | $V_{CC}$ = 4.5 V to 15 V; $V_{MO+}$ = 4 V to 15 V, 128-sample averaging (unless otherwise noted) |

|                                   |     |          | ±0.25 |     |        | ±0.7 | %    | V <sub>SENSE_MO</sub> = 25 mV                                                                    |

|                                   |     | ±0.04    | ±0.3  |     | ±0.04  | ±0.7 | %    | V <sub>SENSE_MO</sub> = 20 mV                                                                    |

|                                   |     |          | ±0.5  |     |        | ±1.0 | %    | V <sub>SENSE_MO</sub> = 20 mV; 16-sample averaging                                               |

|                                   |     |          | ±1.5  |     |        | ±2.8 | %    | V <sub>SENSE_MO</sub> = 20 mV; one-sample averaging                                              |

|                                   |     |          | ±0.3  |     |        | ±0.8 | %    | V <sub>SENSE_MO</sub> = 15 mV                                                                    |

|                                   |     |          | ±0.4  |     |        | ±1.1 | %    | V <sub>SENSE_MO</sub> = 10 mV                                                                    |

|                                   |     |          | ±0.75 |     |        | ±2.0 | %    | V <sub>SENSE_MO</sub> = 5 mV                                                                     |

|                                   |     |          | ±1.6  |     |        | ±4.3 | %    | $V_{SENSE\_MO} = 2.5 \text{ mV}$                                                                 |

| HS+/VOUT Absolute Error           |     |          | ±0.35 |     |        | ±1.0 | %    | $V_{HS+}$ , $V_{OUT}$ = 10 V to 20 V                                                             |

|                                   |     |          | ±0.5  |     |        | ±1.0 | %    | $V_{HS+}, V_{OUT} = 5 V$                                                                         |

| Power Absolute Error              |     |          | ±0.65 |     |        | ±1.7 | %    | V <sub>SENSE MO</sub> = 20 mV, V <sub>HS+</sub> = 12 V                                           |

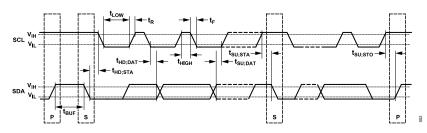

## **SERIAL BUS TIMING CHARACTERISTICS**

Table 4. Serial Bus Timing Characteristics

| Parameter           | Description        | Min | Тур | Max | Unit |

|---------------------|--------------------|-----|-----|-----|------|

| f <sub>SCLK</sub>   | Clock frequency    |     |     | 400 | kHz  |

| t <sub>BUF</sub>    | Bus free time      | 1.3 |     |     | μs   |

| t <sub>HD;STA</sub> | Start hold time    | 0.6 |     |     | μs   |

| t <sub>SU;STA</sub> | Start setup time   | 0.6 |     |     | μs   |

| t <sub>su;sto</sub> | Stop setup time    | 0.6 |     |     | μs   |

| t <sub>HD;DAT</sub> | SDA hold time      | 300 |     | 900 | ns   |

| t <sub>su;dat</sub> | SDA setup time     | 100 |     |     | ns   |

| $t_{LOW}$           | SCL low time       | 1.3 |     |     | μs   |

| t <sub>HIGH</sub>   | SCL high time      | 0.6 |     |     | μs   |

| t <sub>R</sub> 1    | SCL, SDA rise time | 20  |     | 300 | ns   |

| t <sub>F</sub> 1    | SCL, SDA fall time | 20  |     | 300 | ns   |

$<sup>^{1}</sup>$   $t_{R} = (V_{IL(MAX)} - 0.15)$  to  $(V_{IH3V3} + 0.15)$  and  $t_{F} = 0.9 V_{DD}$  to  $(V_{IL(MAX)} - 0.15)$ ; where  $V_{IH3V3} = 2.1 V$ , and  $V_{DD} = 3.3 V$ .  $V_{IH3V3}$  is the input high voltage when  $V_{DD} = 3.3 V$ .

Figure 2. Serial Bus Timing Diagram

analog.com Rev. A | 8 of 63

## **SPECIFICATIONS**

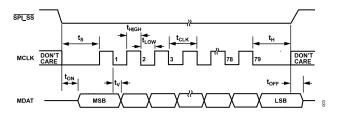

# **SPI TIMING CHARACTERISTICS (ADM1281-2)**

Table 5. SPI Timing Characteristics (ADM1281-2)

| Parameter           | Description                          | Min | Тур | Max | Unit | Test Conditions/Comments                           |

|---------------------|--------------------------------------|-----|-----|-----|------|----------------------------------------------------|

| $t_S^1$             | SPI_SS falling edge to MCLK rising   | 50  |     |     | ns   |                                                    |

|                     | edge setup time                      |     |     |     |      |                                                    |

| t <sub>HIGH</sub> 1 | MCLK high time                       | 180 |     |     | ns   |                                                    |

| $t_{LOW}^{1}$       | MCLK low time                        | 180 |     |     | ns   |                                                    |

| t <sub>CLK</sub> 1  | MCLK cycle time                      | 1   |     |     | μs   |                                                    |

| $t_H^1$             | Hold time between SPI_SS and         | 1   |     |     | μs   |                                                    |

|                     | MCLK                                 |     |     |     |      |                                                    |

| $t_V$               | Hold time between new data valid and | 110 |     | 260 | ns   | Track capacitance = 120 pF; I <sub>OL</sub> = 4 mA |

|                     | MCLK falling edge                    |     |     |     |      |                                                    |

| $t_{ON}$            | SPI_SS falling edge to MDAT active   | 130 |     | 240 | ns   | Track capacitance = 120 pF; I <sub>OL</sub> = 4 mA |

|                     | time                                 |     |     |     |      |                                                    |

| t <sub>OFF</sub>    | Bus relinquish time after SPI_SS     | 130 |     | 280 | ns   | Track capacitance = 120 pF; I <sub>OL</sub> = 4 mA |

|                     | rising edge                          |     |     |     |      |                                                    |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design, but not production tested.

Figure 3. SPI Timing Diagram

analog.com Rev. A | 9 of 63

## **ABSOLUTE MAXIMUM RATINGS**

Table 6. Absolute Maximum Ratings

| Parameter                                                    | Rating                 |

|--------------------------------------------------------------|------------------------|

| VCC Pin                                                      | -0.3 V to +25 V        |

| UV Pin                                                       | -0.3 V to +4 V         |

| OV Pin                                                       | -0.3 V to +4 V         |

| ISTART Pin                                                   | -0.3 V to +4 V         |

| TIMER Pin                                                    | -0.3 V to VCAP + 0.3 V |

| TEMP Pin                                                     | -0.3 V to VCAP + 0.3 V |

| VCAP Pin                                                     | -0.3 V to +4 V         |

| ISET Pin                                                     | -0.3 V to +4 V         |

| PSET Pin                                                     | -0.3 V to +4 V         |

| FAULT Pin                                                    | -0.3 V to +25 V        |

| RETRY Pin                                                    | -0.3 V to +4 V         |

| PWGIN Pin                                                    | -0.3 V to +4 V         |

| SCL Pin                                                      | -0.3 V to +6.5 V       |

| SDA Pin                                                      | -0.3 V to +6.5 V       |

| SPI_SS Pin                                                   | -0.3 V to +4 V         |

| MCLK Pin                                                     | -0.3 V to +4 V         |

| MDAT Pin                                                     | -0.3 V to +4 V         |

| ADR1 Pin                                                     | -0.3 V to +6.5 V       |

| ADR2 Pin                                                     | -0.3 V to +6.5 V       |

| ENABLE Pin                                                   | -0.3 V to +25 V        |

| GPO1/ALERT1/CONV Pin                                         | -0.3 V to +25 V        |

| GPO2/ALERT2 Pin                                              | -0.3 V to +25 V        |

| PWRGD Pin                                                    | -0.3 V to +25 V        |

| VOUT Pin                                                     | -0.3 V to +25 V        |

| GATE Pin (Internal Supply Only) <sup>1</sup>                 | -0.3 V to +36 V        |

| HS+ Pin                                                      | -0.3 V to +25 V        |

| HS- Pin                                                      | -0.3 V to +25 V        |

| MO+ Pin                                                      | -0.3 V to +25 V        |

| MO- Pin                                                      | -0.3 V to +25 V        |

| PGND                                                         | ±0.3 V                 |

| V <sub>SENSE HS</sub> (V <sub>HS+</sub> - V <sub>HS-</sub> ) | ±0.3 V                 |

| V <sub>SENSE MO</sub> (V <sub>MO+</sub> - V <sub>MO-</sub> ) | ±0.3 V                 |

| CSOUT Short-Circuit Duration                                 | Indefinite             |

| Continuous Current into Any Pin                              | ±10 mA                 |

| Temperature                                                  |                        |

| Storage Range                                                | -65°C to +125°C        |

| Operating Range                                              | -40°C to +85°C         |

| Lead, Soldering (10 sec)                                     | 300°C                  |

| Junction                                                     | 105°C                  |

The GATE pin has internal clamping circuits to prevent the GATE pin voltage from exceeding the maximum ratings of a MOSFET with gate to source voltage, V<sub>GSMAX</sub> = 20 V, and internal process limits. Applying a voltage source to this pin externally may cause irreversible damage.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{\text{JA}}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure.

Table 7. Thermal Resistance

| Package Type | $\theta_{JA}$ | Unit |

|--------------|---------------|------|

| CP-32-20     | 32.5          | °C/W |

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. A | 10 of 63

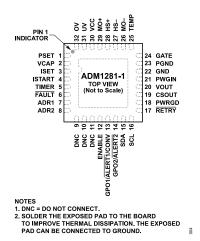

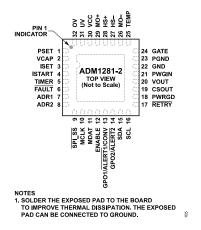

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 4. ADM1281-1 Pin Configuration

NOTES

1. DNC = DO NOT CONNECT.

2. SOLDER THE EXPOSED PAD TO THE BOARD TO IMPROVE THERMAL DISSIPATION. THE EXPOSED PAD CAN BE CONNECTED TO GROUND.

Figure 5. ADM1281-3 Pin Configuration

## Table 8. ADM1281-1 and ADM1281-3 Pin Function Descriptions

| Mnemonic  |              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin No.   | ADM1281-1    | ADM1281-3    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1         | PSET         | PSET         | Power Limit. This pin allows the constant power limit to be programmed. The current limit is dynamically adjusted to ensure that the maximum power dissipation in the FET never exceeds this limit during any operating condition. The power limit can be adjusted to a user-defined value using a resistor-divider from VCAP. An external reference can also be used. The FET power is limited to $(V_{PSET} \times 8)/(50 \times R_{SENSE})$ .                                                                                                                                                                                                                            |  |

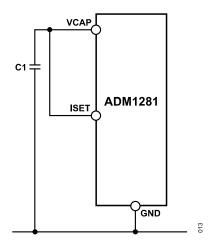

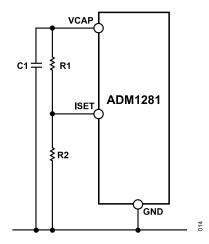

| 2         | VCAP         | VCAP         | Internal Regulated Supply. Place a capacitor with a value of 1 $\mu$ F or greater on this pin to maintain accuracy. This pin can be used as a reference to program the ISET pin voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 3         | ISET         | ISET         | Current Limit. This pin allows the current-limit threshold to be programmed. The default limit is set when this pin is connected directly to VCAP. To achieve a user-defined sense voltage, the current limit can be adjusted using a resistor-divider from VCAP. An external reference can also be used.                                                                                                                                                                                                                                                                                                                                                                   |  |

| 4         | ISTART       | ISTART       | Start-Up Current Limit. This pin allows a separate start-up current limit to be set for dv/dt power-up mode. When powering up in dv/dt mode, the current charging the capacitor is constant and is typically much smaller than the normal load current. The ISTART pin sets the start-up current limit in a similar manner as ISET is used to set the normal current limit. The start-up current limit is only active while PWRGD is low. The start-up current limit can also be set over PMBus with the STRT_UP_IOUT_LIM register. Start-up current limit = V <sub>ISET</sub> × (STRT_UP_IOUT_LIM/ 16). The lowest of all the active current limits always takes priority. |  |

| 5         | TIMER        | TIMER        | Timer. An external capacitor, C <sub>TIMER</sub> , sets an initial timing cycle delay and a fault delay. The GATE pin is pulled low when the voltage on the TIMER pin exceeds the upper threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 6         | FAULT        | FAULT        | Fault. This pin asserts low and latches after a fault has occurred. The faults that can trigger this pin include an overcurrent fault resulting in the TIMER pin voltage exceeding the upper threshold, an overtemperature fault, and a FET health fault. This is an open-drain output pin.                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 7, 8      | ADR1, ADR2   | ADR1, ADR2   | PMBus Address. These pins can be connected to GND, connected to VCAP, left floating, or connected low through a resistor for a total of 16 unique PMBus device addresses (for more details, see the Device Addressing section).                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 9, 10, 11 | DNC          | DNC          | Do Not Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 12        | ENABLE       | ENABLE       | Enable. On the ADM1281-1, the ENABLE pin is an active high digital input pin. This input must be high to allow the ADM1281-1 hot-swap controller to begin a power-up sequence. If the ENABLE pin is held low, the ADM1281-1 is prevented from initiating a hot-swap attempt.  On the ADM1281-3, the ENABLE pin is an active low digital input pin. This input must be low to allow the ADM1281-3 hot-swap controller to begin a power-up sequence. If the ENABLE pin is held high, the ADM1281-3 is                                                                                                                                                                         |  |

|           |              |              | prevented from initiating a hot-swap attempt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 13        | GPO1/ALERT1/ | GPO1/ALERT1/ | General-Purpose Digital Output (GPO1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|           | CONV         | CONV         | Alert (ALERT1). This pin can be configured to generate an alert signal when one or more fault or warning conditions are detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|           |              |              | Conversion (CONV). This pin can be used as an input signal to control when a power monitor ADC sampling cycle begins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|           |              |              | The GPO1/ALERT1/CONV pin defaults to an alert output at power-up. This is an open-drain output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 14        | GPO2/ALERT2  | GPO2/ALERT2  | General-Purpose Digital Output (GPO2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

Rev. A | 11 of 63 analog.com

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Table 8. ADM1281-1 and ADM1281-3 Pin Function Descriptions (Continued)

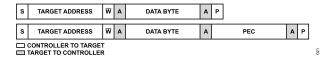

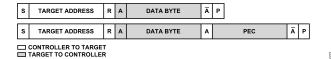

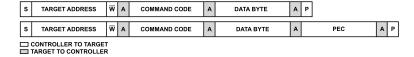

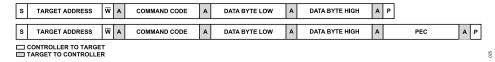

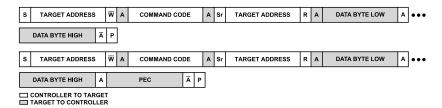

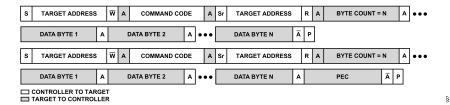

| Mnemonic  Pin No ADM/004 4 - ADM/004 4 - ADM/004 5 |           |           | Book Selbor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |