# Microwave Wideband Synthesizer with Integrated VCO

#### **FEATURES**

- ▶ RFOUT frequency range: 7300MHz to 14,600MHz

- ▶ PDIV\_OUT and NDIV\_OUT frequency range: 57MHz to 14.600MHz

- ▶ Fractional-N synthesizer and integer-N synthesizer modes

- ▶ Typical PFD spurious: <-105dBc

- ▶ Integrated RMS jitter at 1kHz to 100MHz integration bandwidth: <40fs</p>

- Normalized inband phase noise floor FOM

- ► Integer mode: -232dBc/Hz

- ► Fractional mode: -229dBc/Hz

- ► Maintains frequency lock over -40°C to +85°C (lock and leave)

- ▶ Low phase noise VCO

- ▶ -115dBc/Hz typical at 100kHz (7.3GHz)

- ► -114dBc/Hz typical at 100kHz (10GHz)

- ► -109dBc/Hz typical at 100kHz (14.6GHz)

- ► RFOUT power (typical): 6dBm

- ▶ Programmable divide by 1, 2, 4, 8, 16, 32, 64, or 128 output

- Programmable output power level

- ▶ Typical power dissipation: 1W

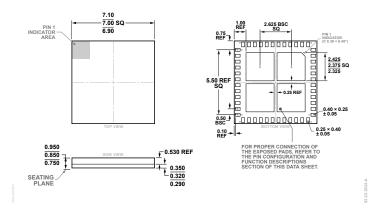

- ▶ 48-terminal, 7 mm × 7 mm LGA package: 49 mm<sup>2</sup>

#### **APPLICATIONS**

- Military and defense

- Test equipment

- Clock generation

- ▶ Wireless infrastructure

- Satellite and very small aperture terminals (VSATs)

- Microwave radios

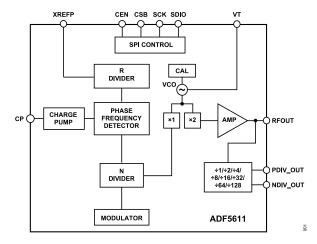

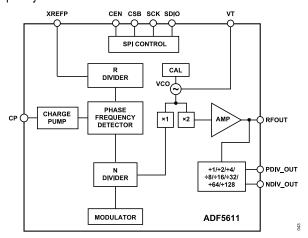

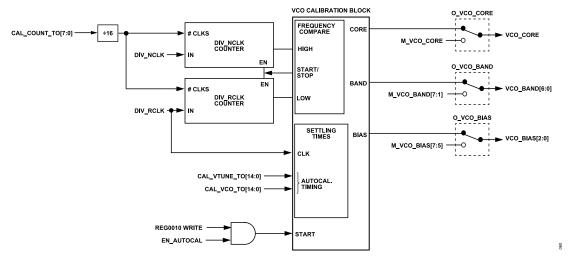

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

### **GENERAL DESCRIPTION**

The ADF5611 allows implementation of fractional-N or integer-N phase-locked loop (PLL) frequency synthesizers when used with an external loop filter and an external reference source. The wideband microwave voltage controlled oscillator (VCO) design permits frequency operation from 7300MHz to 14,600MHz at a single RF output. A series of frequency dividers with a differential frequency output allows operation from 57MHz to 14,600MHz. Analog and digital power supplies for the PLL circuitry range from 3.15V to 3.45V, and the VCO supplies are between 4.75V and 5.25V.

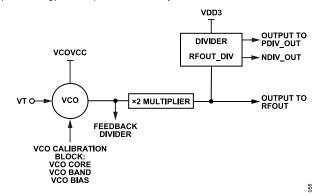

The ADF5611 has an integrated VCO with a fundamental frequency of 3650MHz to 7300MHz. These frequencies are internally doubled and routed to the RFOUT pin. An additional differential output allows the doubled VCO frequency to be divided by 1, 2, 4, 8, 16, 32, 64, or 128, allowing the user to generate RF output frequencies as low as 57MHz. A simple 3- or 4-wire serial port interface (SPI) provides control of all on-chip registers. To conserve power, this divider block can be disabled when not needed through the SPI. Likewise, the output power for both the single-ended output and the differential output are programmable.

The integrated phase detector and  $\Delta$ - $\Sigma$  modulator, capable of operating at up to 100MHz, permit wide loop bandwidths and fast frequency tuning with a typical spurious level of -105dBc.

With a VCO open-loop phase noise at an 100kHz offset from -115dBc/Hz at a 7.3GHz RFOUT to -109dBc/Hz at a 14.6GHz RFOUT, the ADF5611 is equipped to minimize blocker effects and to improve receiver sensitivity and transmitter spectral purity. The low phase noise floor eliminates any contribution to modulator and mixer noise floor in transmitter applications.

## **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| Functional Block Diagram                    | 1  |

| General Description                         | 1  |

| Specifications                              | 3  |

| SPI Timing Characteristics                  |    |

| Absolute Maximum Ratings                    | 8  |

| Thermal Resistance                          |    |

| Transistor Count                            | 8  |

| Electrostatic Discharge (ESD) Ratings       |    |

| ESD Caution                                 |    |

| Pin Configuration and Function Descriptions | 9  |

| Typical Performance Characteristics         | 11 |

| Theory of Operation                         |    |

| ,                                           |    |

| Introduction                         | 18 |

|--------------------------------------|----|

| Output Frequency                     | 18 |

| Circuit Description                  | 19 |

| Applications Information             | 25 |

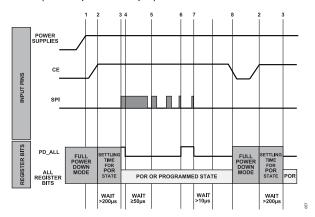

| Power-Up and Initialization Sequence | 25 |

| Loop Filter Design                   | 26 |

| VCO                                  | 27 |

| VCO Calibration                      | 27 |

| Register Map                         | 29 |

| Register Details                     | 31 |

| Outline Dimensions                   | 48 |

| Ordering Guide                       | 48 |

| Evaluation Boards                    | 48 |

# **REVISION HISTORY**

2/2025—Revision 0: Initial Version

analog.com Rev. 0 | 2 of 48

## **SPECIFICATIONS**

AVDD = DVDD =  $3.3V \pm 5\%$ , VDDLS, VPPCP, RVDD, VCCPD, VCCPS, and VCCHF =  $3.3V \pm 5\%$ , VDD1, VDD2, and VDD3 =  $3.3V \pm 5\%$ , VCOVCC =  $5.0V \pm 5\%$ , and GND = 0V for the minimum and maximum specifications across the -40°C to +85°C temperature range, unless otherwise noted.

Table 1. Specifications

| Parameter                                | Symbol               | Min  | Тур        | Max    | Unit    | Test Conditions/Comments                        |

|------------------------------------------|----------------------|------|------------|--------|---------|-------------------------------------------------|

| RF OUTPUT CHARACTERISTICS                |                      |      |            |        |         |                                                 |

| RFOUT Frequency                          | f <sub>OUT</sub>     | 7300 |            | 14,600 | MHz     |                                                 |

| VCO Frequency at PLL Input               | f <sub>VCO</sub>     | 3650 |            | 7300   | MHz     |                                                 |

| PDIV_OUT and NDIV_OUT                    | f <sub>OUT_DIV</sub> | 57   |            | 14,600 | MHz     |                                                 |

| Frequency Range                          | 1001_01              |      |            | ,      |         |                                                 |

| OUTPUT POWER                             |                      |      |            |        |         |                                                 |

| RFOUT Power                              | P <sub>RFOUT</sub>   |      | 6          |        | dBm     | 7,300MHz to 10,500MHz, RFOUT PWR = 3            |

|                                          | 141 001              |      | 2          |        | dBm     | 10,500MHz to 14,600MHz, RFOUT_PWR = 0           |

| RFOUT Power Control Range                |                      |      | 3          |        | dB      | Power range from RFOUT PWR = 0 to 3             |

| RFOUT Power Variation vs.                |                      |      | ±1         |        | dB      |                                                 |

| Temperature                              |                      |      |            |        |         |                                                 |

| RFOUT Power Variation vs.                |                      |      | ±2         |        | dB      |                                                 |

| Frequency                                |                      |      |            |        |         |                                                 |

| PDIV_OUT and NDIV_OUT Power              | P <sub>O_DIV</sub>   |      | 3          |        | dBm     | Single-ended, DIV_PWR = 3                       |

|                                          | 0_5                  |      | 6          |        | dBm     | Differential, DIV_PWR = 3                       |

| PDIV OUT and NDIV OUT Control            |                      |      | 9          |        | dB      | Single-ended, power range from DIV PWR = 0 to 3 |

| Range                                    |                      |      |            |        |         | g                                               |

|                                          |                      |      | 9          |        | dB      | Differential, power range from DIV_PWR = 0 to 3 |

| HARMONICS (RFOUT)                        |                      |      |            |        |         |                                                 |

| ½ Harmonic                               |                      |      | -25        |        | dBc     |                                                 |

| 1.5 Harmonic                             |                      |      | -30        |        | dBc     |                                                 |

| Second Harmonic                          |                      |      | -30        |        | dBc     |                                                 |

| 2.5 Harmonic                             |                      |      | -45        |        | dBc     |                                                 |

| Third Harmonic                           |                      |      | -30        |        | dBc     |                                                 |

| HARMONICS (PDIV_OUT and NDIV_OUT)        |                      |      |            |        |         |                                                 |

| Single-Ended                             |                      |      |            |        |         |                                                 |

| ½ Harmonic                               |                      |      | -25        |        | dBc     | Fundamental feed through                        |

| Second Harmonic                          |                      |      | -26        |        | dBc     | Push-push feed through                          |

| Third Harmonic                           |                      |      | -24        |        | dBc     | i usii pusii ieeu uiiougii                      |

| Differential                             |                      |      | 47         |        | QDC     |                                                 |

| ½ Harmonic                               |                      |      | -25        |        | dBc     | Fundamental feed through                        |

| /2 Haimonic                              |                      |      | -90        |        | dBc     | Push-push feed through                          |

| Second Harmonic                          |                      |      | -90<br>-31 |        | dBc     | rusii-pusii leed tiilougii                      |

| Third Harmonic                           |                      |      | -31<br>-24 |        | dBc     |                                                 |

|                                          |                      |      | -24<br>67  |        |         | DECLIT (V.T. = 4.05\V)                          |

| VCO Supply Pushing (VDD1) <sup>1</sup>   |                      |      |            |        | MHz/V   | RFOUT (VT = 1.65V)                              |

| VCO Supply Pushing (VCOVCC) <sup>1</sup> |                      |      | 1.0        |        | MHz/V   | RFOUT (VT = 1.65V)                              |

| VCO Load Pulling (2.0:1) <sup>2</sup>    |                      |      | 1.0        |        | MHz p-p | RFOUT (VT = 1.65V)                              |

| VCO Frequency Drift                      |                      |      | 0.54       |        |         | RFOUT (VT = 1.65V)                              |

|                                          |                      |      | 0.54       |        | MHz/°C  | Operating at 7.3GHz                             |

|                                          |                      |      | 1.09       |        | MHz/°C  | Operating at 14.6GHz                            |

| REFERENCE INPUT<br>CHARACTERISTICS       |                      |      |            |        |         |                                                 |

| XREFP Input Frequency                    | f <sub>REF</sub>     | 10   | 50         | 350    | MHz     | Refer to the Reference Input section            |

| XREFP Input Level                        |                      | 0.4  |            | 3.5    | V p-p   | Refer to the Reference Input section            |

| XREFP Input Capacitance                  |                      |      | 6.9        |        | pF      |                                                 |

analog.com Rev. 0 | 3 of 48

# **SPECIFICATIONS**

Table 1. Specifications (Continued)

| Parameter                         | Symbol                                 | Min                     | Тур        | Max       | Unit | Test Conditions/Comments                                                                                           |

|-----------------------------------|----------------------------------------|-------------------------|------------|-----------|------|--------------------------------------------------------------------------------------------------------------------|

| 14-Bit R Divider Range            | R <sub>DIV</sub>                       | 1                       |            | 16,383    |      | All integers included                                                                                              |

| Input Current                     |                                        |                         | 150        |           | μA   |                                                                                                                    |

| PHASE DETECTOR                    |                                        |                         |            |           |      |                                                                                                                    |

| Input Frequency                   | f <sub>PFD</sub>                       |                         |            |           |      |                                                                                                                    |

| Fractional Mode <sup>3</sup>      |                                        |                         |            | 100       | MHz  |                                                                                                                    |

| Integer Mode                      |                                        |                         |            | 100       | MHz  |                                                                                                                    |

| CHARGE PUMP                       |                                        |                         |            |           |      |                                                                                                                    |

| Output Current                    | I <sub>CP</sub>                        |                         | 0.2 to 3.2 |           | mA   | Set by the CP_I bit fields, see Table 50                                                                           |

| Charge Pump Gain Step Size        |                                        |                         | 200        |           | μA   |                                                                                                                    |

| LOGIC INPUTS (CSB, SCK, AND SDIO) |                                        |                         |            |           |      |                                                                                                                    |

| Input High Voltage                | V <sub>INH</sub>                       | 1.2                     |            |           | V    |                                                                                                                    |

| Input Low Voltage                 | VINL                                   | 1.2                     |            | 0.6       | V    |                                                                                                                    |

| Input Current                     | I <sub>IH</sub> /I <sub>IL</sub>       |                         |            | ±1        | μA   |                                                                                                                    |

| Input Capacitance                 | C <sub>IN</sub>                        |                         | 2          | ±1        | pF   |                                                                                                                    |

| LOGIC INPUT (CE)                  | OIN                                    |                         |            |           | Pi   |                                                                                                                    |

| Input High Voltage                | V <sub>INH-3V</sub>                    | 1.8                     |            |           | V    |                                                                                                                    |

| Input Low Voltage                 | V <sub>INL-3V</sub>                    | 1.0                     |            | 0.8       | V    |                                                                                                                    |

| Input Current                     | I <sub>IH-3V</sub> /I <sub>IL-3V</sub> |                         |            | 0.6<br>±1 | μA   |                                                                                                                    |

| Input Capacitance                 | C <sub>IN-3V</sub>                     |                         | 1          | ±1        | pF   |                                                                                                                    |

| LOGIC OUTPUT (SDO AND SDIO)       | OIN-3V                                 |                         | -          |           | bi   |                                                                                                                    |

| Output High Voltage (1.8V Mode)   | V.                                     | 1.5                     | 1.8        |           | V    | Output high current (I <sub>OH</sub> ) = 500µA, 1.8V output                                                        |

| Output riigii voitage (1.5v Mode) | V <sub>OH</sub>                        | 1.5                     | 1.0        |           | V    | selected (default setting)                                                                                         |

| Output High Voltage (3.3V Mode)   | V <sub>OH-3V</sub>                     | V <sub>3.3V</sub> - 0.4 |            |           | V    | I <sub>OH</sub> = 500μA, 3.3V output selected, Set by voltage on DVDD pin                                          |

| Output Low Voltage                | V <sub>OL</sub>                        |                         |            | 0.4       | V    | Output low current (I <sub>OL</sub> ) = 500µA                                                                      |

| SDO High-Z Leakage                | I <sub>ZH</sub> /I <sub>ZL</sub>       |                         |            | ±1        | μA   | ( OL)                                                                                                              |

| POWER SUPPLY VOLTAGES             | ZII ZE                                 |                         |            |           | '    |                                                                                                                    |

| 3.3 V Supplies                    |                                        | 3.15                    | 3.3        | 3.45      | V    | AVDD, VCCHF, VCCPS, VCCPD, RVDD, DVDD, VPPCP, VDDLS, VDD1, VDD2, and VDD3                                          |

| 5.0 V Supplies                    |                                        | 4.75                    | 5.0        | 5.25      | V    | vcovcc                                                                                                             |

| POWER DISSIPATION                 |                                        |                         |            |           |      |                                                                                                                    |

| Typical Power Dissipation         | P <sub>DIS</sub>                       |                         | 1          |           | W    | $f_{REF}$ = $f_{PFD}$ = 100MHz, R_DIV = 1, $I_{CP}$ = 3.2mA, RFOUT_PWR = 3, DIV_PWR = 3, RFOUT_DIV = divide by 128 |

| POWER SUPPLY CURRENTS             |                                        |                         |            |           |      | $f_{REF} = f_{PFD} = 100MHz$ , $R_DIV = 1$ , $I_{CP} = 3.2mA$ , $RFOUT_PWR = 3$ , $DIV_PWR = 0$                    |

| AVDD                              |                                        |                         | 1          |           | μA   | 3.3V                                                                                                               |

| RVDD                              |                                        |                         | 3          |           | mA   | 3.3V                                                                                                               |

| VCCHF                             |                                        |                         | <1         |           | μA   | 3.3V                                                                                                               |

| VCCPS                             |                                        |                         | 27         |           | mA   | 3.3V                                                                                                               |

| VCCPD                             |                                        |                         | 4          |           | mA   | 3.3V                                                                                                               |

| DVDD                              |                                        |                         | 3          |           | mA   | 3.3V                                                                                                               |

| VPPCP and VDDLS                   |                                        |                         | 3          |           | mA   | 3.3V, grouped supply current for VPPCP and VDDLS                                                                   |

| VDD1                              |                                        |                         | 6          |           | mA   | 3.3V                                                                                                               |

| VDD2                              |                                        |                         | 1          |           | mA   | 3.3V                                                                                                               |

analog.com Rev. 0 | 4 of 48

# **SPECIFICATIONS**

Table 1. Specifications (Continued)

| Parameter                               | Symbol | Min Typ | Max | Unit   | Test Conditions/Comments                                                                                               |

|-----------------------------------------|--------|---------|-----|--------|------------------------------------------------------------------------------------------------------------------------|

| VDD3                                    |        | 58      |     | mA     | Divide by 1                                                                                                            |

|                                         |        | 71      |     | mA     | Divide by 2                                                                                                            |

|                                         |        | 77      |     | mA     | Divide by 4                                                                                                            |

|                                         |        | 81      |     | mA     | Divide by 8                                                                                                            |

|                                         |        | 86      |     | mA     | Divide by 16                                                                                                           |

|                                         |        | 88      |     | mA     | Divide by 32                                                                                                           |

|                                         |        | 90      |     | mA     | Divide by 64                                                                                                           |

|                                         |        | 92      |     | mA     | Divide by 128                                                                                                          |

| VCOVCC                                  |        | 92      |     | mA     | 5.0V                                                                                                                   |

| Power-Down                              |        |         |     |        |                                                                                                                        |

| PLL <sup>4</sup>                        |        | 2.3     |     | μA     | Power down via the SPI and the PD_RDIV,<br>PD_NDIV, PD_LD, PD_PFDCP, and PD_PFDNCLK<br>bits, see Table 56 and Table 57 |

| VCOVCC <sup>5</sup>                     |        | 13      |     | mA     | Power down via the SPI and the PD_VCO and PD_ADC bits, see Table 56                                                    |

| Divider <sup>5</sup>                    |        | 202     |     | μΑ     | Power down via the SPI and the PD_ODIV bit, see Table 57                                                               |

| /CO OPEN-LOOP PHASE NOISE               |        |         |     |        |                                                                                                                        |

| RFOUT at 7.3GHz                         |        |         |     |        |                                                                                                                        |

| 10kHz Offset                            |        | -92     |     | dBc/Hz |                                                                                                                        |

| 100kHz Offset                           |        | -115    |     | dBc/Hz |                                                                                                                        |

| 1MHz Offset                             |        | -135    |     | dBc/Hz |                                                                                                                        |

| 10MHz Offset                            |        | -155    |     | dBc/Hz |                                                                                                                        |

| 100MHz Offset                           |        | -168    |     | dBc/Hz |                                                                                                                        |

| RFOUT at 10GHz                          |        |         |     |        |                                                                                                                        |

| 10kHz Offset                            |        | -90     |     | dBc/Hz |                                                                                                                        |

| 100kHz Offset                           |        | -114    |     | dBc/Hz |                                                                                                                        |

| 1MHz Offset                             |        | -135    |     | dBc/Hz |                                                                                                                        |

| 10MHz Offset                            |        | -155    |     | dBc/Hz |                                                                                                                        |

| 100MHz Offset                           |        | -164    |     | dBc/Hz |                                                                                                                        |

| RFOUT at 11GHz                          |        |         |     |        |                                                                                                                        |

| 10kHz Offset                            |        | -89     |     | dBc/Hz |                                                                                                                        |

| 100kHz Offset                           |        | -112    |     | dBc/Hz |                                                                                                                        |

| 1MHz Offset                             |        | -132    |     | dBc/Hz |                                                                                                                        |

| 10MHz Offset                            |        | -152    |     | dBc/Hz |                                                                                                                        |

| 100MHz Offset                           |        | -164    |     | dBc/Hz |                                                                                                                        |

| RFOUT at 14.6GHz                        |        |         |     |        |                                                                                                                        |

| 10kHz Offset                            |        | -86     |     | dBc/Hz |                                                                                                                        |

| 100kHz Offset                           |        | -109    |     | dBc/Hz |                                                                                                                        |

| 1MHz Offset                             |        | -130    |     | dBc/Hz |                                                                                                                        |

| 10MHz Offset                            |        | -150    |     | dBc/Hz |                                                                                                                        |

| 100MHz Offset                           |        | -165    |     | dBc/Hz |                                                                                                                        |

| PLL                                     |        |         |     |        |                                                                                                                        |

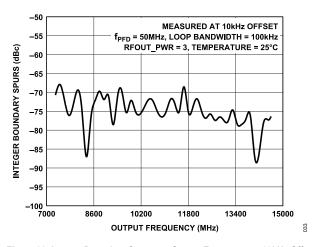

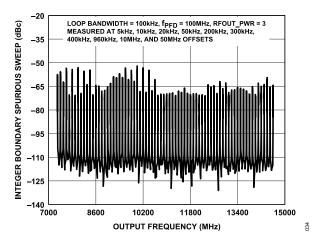

| Integer Boundary Spurs                  |        | -55     |     | dBc    | LOCKED bit = 1, f <sub>REF</sub> = f <sub>PFD</sub> = 100MHz, R <sub>DIV</sub> = 1, se<br>Figure 34                    |

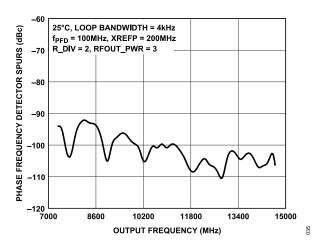

| Phase Frequency Detector (PFD)<br>Spurs |        | -105    |     | dBc    | LOCKED bit = 1, $f_{REF}$ = 200MHz, $f_{PFD}$ = 100MHz , $R_{DIV}$ = 2, see Figure 35                                  |

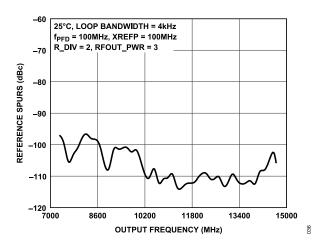

| Reference Spurs                         |        | -100    |     | dBc    | LOCKED bit = 1, f <sub>REF</sub> = f <sub>PFD</sub> = 100MHz, R <sub>DIV</sub> = 1, set<br>Figure 36                   |

analog.com Rev. 0 | 5 of 48

## **SPECIFICATIONS**

Table 1. Specifications (Continued)

| Parameter                                                          | Symbol                 | Min | Тур       | Max | Unit   | Test Conditions/Comments                        |

|--------------------------------------------------------------------|------------------------|-----|-----------|-----|--------|-------------------------------------------------|

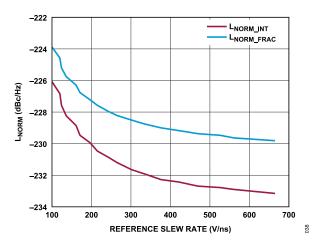

| Normalized Inband Phase Noise<br>Floor Figure of Merit (FOM)       | L <sub>NORM</sub>      |     |           |     |        | Normalized to 1Hz                               |

| Floor Integer Mode                                                 | L <sub>NORM_INT</sub>  |     | -232      |     | dBc/Hz |                                                 |

| Floor Fractional Mode                                              | L <sub>NORM FRAC</sub> |     | -229      |     | dBc/Hz |                                                 |

| Normalized 1/f Phase Noise Floor (Integer and Fractional Mode)     | L <sub>1/f</sub>       |     | -268      |     | dBc/Hz |                                                 |

| Integrated RMS Jitter                                              |                        |     | <40       |     | fs     | Integration bandwidth from 1kHz to 100MHz       |

| VCO CHARACTERISTICS                                                |                        |     |           |     |        |                                                 |

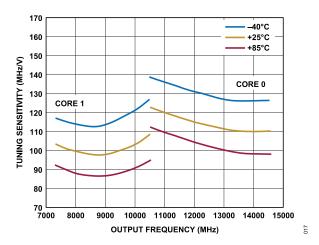

| Tuning Sensitivity (RFOUT)                                         | K <sub>VCO</sub>       |     | 95 to 125 |     | MHz/V  | 7300MHz to 14,600MHz                            |

| Tune Port Capacitance                                              |                        |     | 155       |     | pF     |                                                 |

| Auto Calibration Time                                              |                        |     | 100       |     | μs     | Refer to the Total Autocalibration Time section |

| VCO OUTPUT DIVIDER                                                 |                        |     |           |     |        |                                                 |

| VCO RF Divider Range                                               |                        | 1   |           | 128 |        | 1, 2, 4, 6, 8, 16, 32, 64, or 128               |

| VCO Supply Pushing (VCOVCC) <sup>1</sup>                           |                        |     | 0.7       |     | MHz/V  | PDIV_OUT and NDIV_OUT, divide by 1, VT = 1.65V  |

| VCO Supply Pushing (VDD1) <sup>5</sup>                             |                        |     | 67        |     | MHz/V  | PDIV_OUT and NDIV_OUT, divide by 1, VT = 1.65V  |

| Divided Reference Clock<br>(DIV_RCLK) VCO Calibration<br>Frequency |                        |     |           | 50  | MHz    |                                                 |

| TEMPERATURE SENSOR                                                 |                        |     |           |     |        |                                                 |

| ADC Clock Frequency                                                |                        |     | 400       |     | kHz    |                                                 |

| RETURN LOSS                                                        |                        |     |           |     |        |                                                 |

| RFOUT                                                              |                        |     | 5         |     | dB     |                                                 |

| PDIV_OUT (N > 1)                                                   |                        |     | 14        |     | dB     |                                                 |

| NDIV_OUT (N > 1)                                                   |                        |     | 14        |     | dB     |                                                 |

<sup>1</sup> Pushing refers to a change in VCO frequency due to a change in the power supply voltage. To derive pushing at other divide ratios, divide the nominal pushing value by the divide ratio

## **SPI TIMING CHARACTERISTICS**

AVDD = DVDD =  $3.3V \pm 5\%$ , VCOVCC =  $5V \pm 5\%$ , all voltages are with respect to GND, and  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. EPAD = 0V.

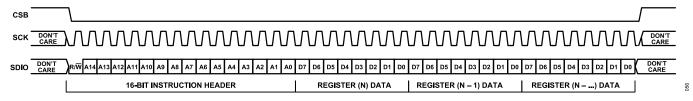

Table 2. SPI Timing Characteristics

| Parameter                                  | Symbol                   | Min | Тур | Max | Unit | Test Conditions/Comments              |

|--------------------------------------------|--------------------------|-----|-----|-----|------|---------------------------------------|

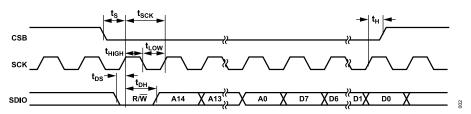

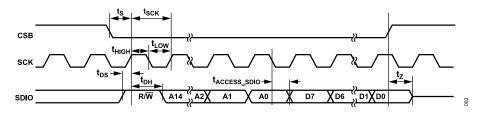

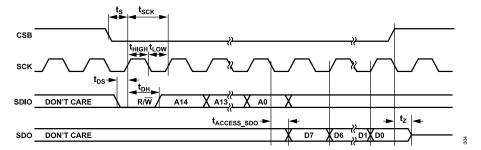

| SERIAL INTERFACE (CSB, SCK, SDIO, AND SDO) |                          |     |     |     |      | See Figure 2, Figure 3, and Figure 4  |

| SCK Frequency                              | f <sub>SCK</sub>         |     |     | 65  | MHz  | f <sub>SCK</sub> = 1/t <sub>SCK</sub> |

| SCK Pulse Width High                       | t <sub>HIGH</sub>        | 7.6 |     |     | ns   |                                       |

| SCK Pulse Width Low                        | t <sub>LOW</sub>         | 7.6 |     |     | ns   |                                       |

| SDIO Setup Time                            | t <sub>DS</sub>          | 3   |     |     | ns   |                                       |

| SDIO Hold Time                             | t <sub>DH</sub>          | 3   |     |     | ns   |                                       |

| SCK Fall Edge to SDIO Valid Prop Delay     | t <sub>ACCESS_SDIO</sub> | 7.6 |     |     | ns   |                                       |

| SCK Fall Edge to SDO Valid Prop Delay      | t <sub>ACCESS_SDO</sub>  | 7.6 |     |     | ns   |                                       |

| CSB Rising Edge to SDIO High-Z             | t <sub>Z</sub>           | 7.6 |     |     | ns   |                                       |

| CSB Falling Edge to SCLK Rise Setup Time   | t <sub>S</sub>           | 3   |     |     | ns   |                                       |

analog.com Rev. 0 | 6 of 48

<sup>&</sup>lt;sup>2</sup> Pulling refers to a change in VCO frequency due to a change in the load impedance.

This maximum phase detector frequency can only be achieved if the minimum N value is respected. For example, in the case of fractional mode, the maximum phase detector frequency = f<sub>VCO</sub>/20 or 100MHz, whichever is less.

<sup>&</sup>lt;sup>4</sup> Reference disconnected.

<sup>&</sup>lt;sup>5</sup> Some circuits remain on.

## **SPECIFICATIONS**

Table 2. SPI Timing Characteristics (Continued)

| Parameter                             | Symbol         | Min | Тур | Max | Unit | Test Conditions/Comments |

|---------------------------------------|----------------|-----|-----|-----|------|--------------------------|

| SCK Rising Edge to CSB Rise Hold Time | t <sub>H</sub> | 3   |     |     | ns   |                          |

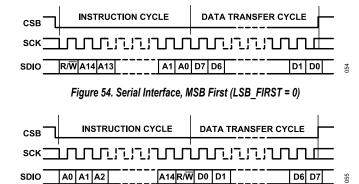

# **SPI Timing Diagrams**

Figure 2. Write Timing Diagram

Figure 3. 3-Wire Read Timing Diagram (SDO\_ACTIVE = 0)

Figure 4. 4-Wire Read Timing Diagram (SDO\_ACTIVE = 1)

analog.com Rev. 0 | 7 of 48

#### **ABSOLUTE MAXIMUM RATINGS**

Table 3. Absolute Maximum Ratings

| Parameter                                                                                            | Rating                       |

|------------------------------------------------------------------------------------------------------|------------------------------|

| V <sub>3.3V</sub> (AVDD, RVDD, VCCHF, VCCPS, VCCPD, DVDD, VPPCP, VDDLS, VDD1, VDD2, and VDD3) to GND | -0.3V to +3.6V               |

| VCOVCC                                                                                               | -0.3V to +5.5V               |

| XREFP                                                                                                | -0.3V to AVDD + 0.3V         |

| Voltage on All Other Pins                                                                            | $-0.3V$ to $V_{3.3V} + 0.3V$ |

| Digital Outputs (SDO and SDIO)                                                                       | 5mA                          |

| Temperature                                                                                          |                              |

| Operating Range                                                                                      | -40°C to +85°C               |

| Storage Range                                                                                        | -55°C to +150°C              |

| Maximum Junction                                                                                     | 150°C                        |

| Reflow Soldering                                                                                     |                              |

| Peak                                                                                                 | 260°C                        |

| Time at Peak                                                                                         | 30sec                        |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.  $\theta_{JC\text{-}TOP}$  and  $\theta_{JC\text{-}BOTTOM}$  are the junction-to-case thermal resistance top and bottom.

Table 4. Thermal Resistance

| Package Type <sup>1</sup> | $\theta_{JA}$ | θ <sub>JC-TOP</sub> | θ <sub>JC-BOTTOM</sub> | Unit |

|---------------------------|---------------|---------------------|------------------------|------|

| CC-48-14                  | 27.17         | 13.32               | 6.67                   | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on use of a 4-layer PCB with the thermal impedance paddle soldered to a ground plane.

#### TRANSISTOR COUNT

The transistor count for the ADF5611 is 2,300 (bipolar) and 140,270 (complementary metal-oxide semiconductor (CMOS)).

## **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

## **ESD Ratings for ADF5611**

Table 5. ADF5611, 48-Terminal LGA

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | 1500                    | 1C    |

| CDM       | 1000                    | C3    |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 8 of 48

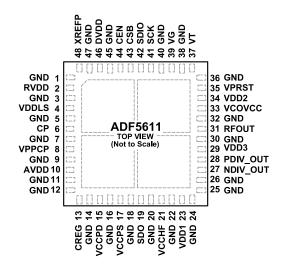

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### NOTES

1. EXPOSED PAD. THE EXPOSED PAD OR GROUND PADDLE ON THE BACKSIDE OF THE PACKAGE MUST BE TIED TO DC GROUND FOR ELECTRICAL, MECHANICAL, AND THERMAL REASONS. NOTE THAT RF GROUND AND DC GROUND ARE THE SAME IN THIS CASE.

Figure 5. Pin Configuration

900

Table 6. Pin Function Descriptions

| Pin No.                                                                         | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5, 7, 9, 11, 12, 14, 16, 18, 20, 22, 24 to 26, 30, 32, 36, 38, 40, 45, 47 | GND      | Negative Power Supply (Ground). Tie the GND pins directly to the ground pad.                                                                                                                                                                                                                                                                                                                                                                                                |

| 2                                                                               | RVDD     | 3.3V ± 5% Positive Power Supply for the Reference Circuitry. Short the RVDD pin to the other pins in the 3.3V power supply group.                                                                                                                                                                                                                                                                                                                                           |

| 4                                                                               | VDDLS    | 3.3V ± 5% Typical Power Supply for the Charge Pump Digital Section. VDDLS must be equal to VPPCP.                                                                                                                                                                                                                                                                                                                                                                           |

| 6                                                                               | СР       | Charge Pump Output. When enabled, this output provides the positive and negative output current magnitude (±l <sub>CP</sub> ) to the external loop filter. The output of the loop filter is connected to the VT pin to drive the internal VCO. Place first pole of low-pass loop filter close to this pin if loop filter path is electrically long.                                                                                                                         |

| 8                                                                               | VPPCP    | 3.3V ± 5% Typical Power Supply for Charge Pump. VPPCP must be equal to VDDLS.                                                                                                                                                                                                                                                                                                                                                                                               |

| 10                                                                              | AVDD     | 3.3V ± 5% Analog Supply. AVDD must be equal to DVDD.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13                                                                              | CREG     | Output of the On-Chip Regulator. Connect an external bypass decoupling capacitor of 220nF.                                                                                                                                                                                                                                                                                                                                                                                  |

| 15                                                                              | VCCPD    | 3.3V ± 5% Phase Detector Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17                                                                              | VCCPS    | 3.3V ± 5% Prescaler Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19                                                                              | SDO      | Serial Data Output. Various other functions are available via an internal mulitplexer. In 3-wire mode (default mode), this three-state CMOS pin remains in a high impedance state. In 4-wire readback mode, the SDO pin presents data from the SPI during a read communication burst. When the CSB is de-asserted, SDO returns to a high impedance. Optionally, attach a resistor of $>1$ k $\Omega$ to prevent a floating output. See the MUXOUT section for more details. |

| 21                                                                              | VCCHF    | 3.3V ± 5% Power Supply for PLL RF Section. Place a decoupling capacitor as close as possible to this pin.                                                                                                                                                                                                                                                                                                                                                                   |

| 23                                                                              | VDD1     | 3.3V ± 5% Bias for VCO Digital Logic.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 27                                                                              | NDIV_OUT | Complementary Output of Differential Frequency Divider. N = 1, 2, 4, 8, 16, 32, 64, or 128. A DC block is required, and a broadband 100nF capacitor is recommended. Pin disabled upon power-up.                                                                                                                                                                                                                                                                             |

| 28                                                                              | PDIV_OUT | Primary Output of Differential Frequency Divider. N = 1, 2, 4, 8, 16, 32, 64, or 128. A DC block is required, and a broadband 100nF capacitor is recommended. Pin disabled upon power-up.                                                                                                                                                                                                                                                                                   |

| 29                                                                              | VDD3     | 3.3V ± 5% Differential Output Divider Supply.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 31                                                                              | RFOUT    | RF Output (7300MHz to 14,600MHz). RFOUT has an internal DC block, and an external DC block with a 100nF capacitor is required.                                                                                                                                                                                                                                                                                                                                              |

| 33                                                                              | VCOVCC   | 5.0V ± 5% VCO Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 34                                                                              | VDD2     | 3.3V ± 5% VCO Calibration DAC Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 35                                                                              | VPRST    | Temperature Dependent, Calibration Preset. Decouple VPRST with a 470nF capacitor.                                                                                                                                                                                                                                                                                                                                                                                           |

analog.com Rev. 0 | 9 of 48

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 6. Pin Function Descriptions (Continued)

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                   |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37      | VT       | VCO Tuning Port. Place last pole of low-pass filtered charge pump output close to the VT pin if loop filter path is electrically long.                                                                                        |

| 39      | VG       | Gate Voltage Bypassing. Decouple VG to GND with a low effective series resistance (ESR), 10µF capacitor.                                                                                                                      |

| 41      | SCK      | Serial Port Clock. This CMOS input clocks the serial port input data on its rising edge.                                                                                                                                      |

| 42      | SDIO     | Serial Data Input/Output; CMOS Input and Output. When configured as an input, the SPI uses this CMOS input for data. In 3-wire mode (default mode), the SDIO pin outputs data from the SPI during a read communication burst. |

| 43      | CSB      | Serial Port Chip Select. This CMOS input initiates a SPI communication burst when driven low, ending the burst when driven back high.                                                                                         |

| 44      | CEN      | Chip Enable. This CMOS input enables the device when driven high. A logic low disables the device, putting the device in a full power-down state causing the register to reset.                                               |

| 46      | DVDD     | 3.3V ± 5% Digital Power Supply. Retain bias to hold the PLL register contents when powering down the PLL.                                                                                                                     |

| 48      | XREFP    | External Reference Input. For $50\Omega$ match, AC-couple to the XREFP pin using a low reactant capacitor value and add a $50\Omega$ resistor to ground.                                                                      |

|         | EPAD     | Exposed Pad. The exposed pad or ground paddle on the backside of the package must be tied to DC ground for electrical, mechanical, and thermal reasons. Note that RF ground and DC ground are the same in this case.          |

analog.com Rev. 0 | 10 of 48

## TYPICAL PERFORMANCE CHARACTERISTICS

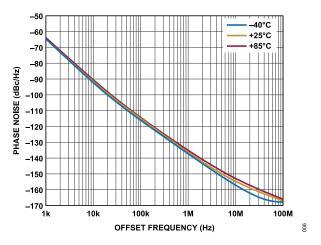

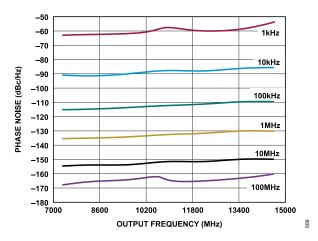

Figure 6. Open-Loop VCO Phase Noise at 8GHz RFOUT vs. Offset Frequency Across Various Temperatures

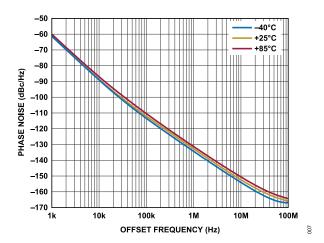

Figure 7. Open-Loop VCO Phase Noise at 12GHz RFOUT vs. Offset Frequency Across Various Temperatures

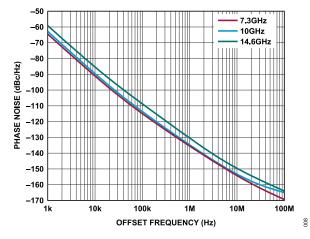

Figure 8. Open-Loop VCO Phase Noise vs. Offset Frequency at Various

Output Frequencies

Figure 9. Open-Loop VCO Phase Noise vs. Output Frequency Across Various

Offset Frequency

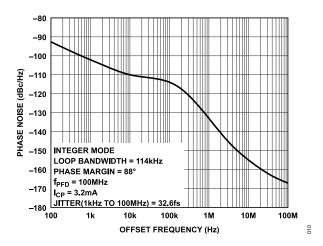

Figure 10. Closed-Loop Phase Noise vs. Offset Frequency at 8GHz RFOUT

Figure 11. Closed-Loop Phase Noise vs. Offset Frequency at 14.4GHz RFOUT

analog.com Rev. 0 | 11 of 48

## TYPICAL PERFORMANCE CHARACTERISTICS

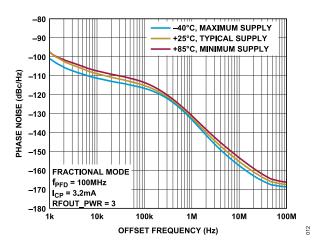

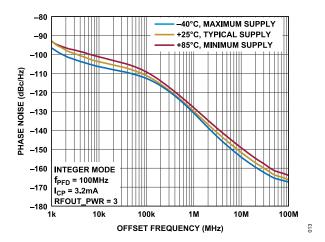

Figure 12. Closed-Loop Phase Noise at 7.3GHz RFOUT vs. Output Frequency Across Various Temperatures and Supplies

Figure 13. Closed-Loop Phase Noise at 12GHz RFOUT vs. Output Frequency Across Various Temperatures and Supplies

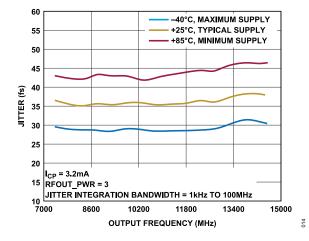

Figure 14. Jitter vs. Output Frequency Across Various Temperatures and Supplies, Integer Mode

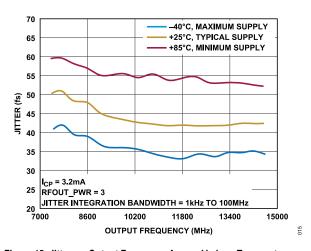

Figure 15. Jitter vs. Output Frequency Across Various Temperatures and Supplies, Fractional Mode

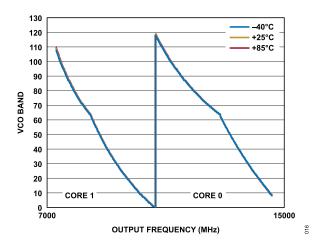

Figure 16. VCO Band vs. Output Frequency Across Various Temperatures, EN\_AUTOCAL Enabled

Figure 17. Tuning Sensitivity vs. Output Frequency Across Various Temperatures

analog.com Rev. 0 | 12 of 48

## TYPICAL PERFORMANCE CHARACTERISTICS

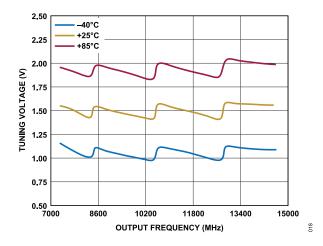

Figure 18. Tuning Voltage vs. Output Frequency after Calibration Across Various Temperatures

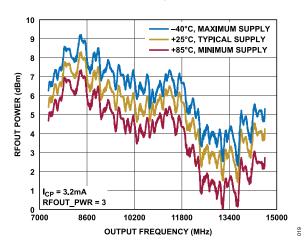

Figure 19. RFOUT Power vs. Output Frequency Across Various Temperatures and Supplies

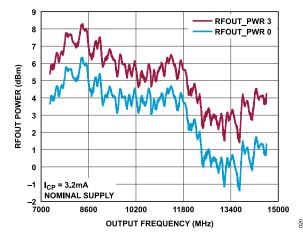

Figure 20. RFOUT Power vs. Output Frequency Across Various Power Settings, 25°C

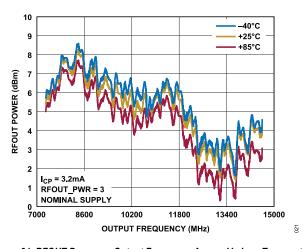

Figure 21. RFOUT Power vs. Output Frequency Across Various Temperatures

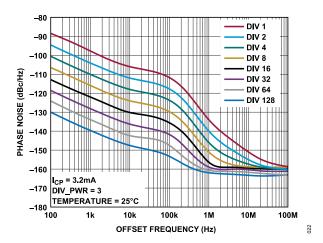

Figure 22. Closed Loop Phase Noise vs. Offset Frequency Across Various Output Divider Settings at 7.3GHz Fundamental Frequency

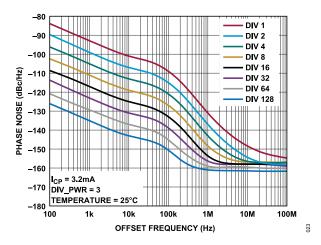

Figure 23. Closed Loop Phase Noise vs. Offset Frequency Across Various Output Divider Settings at 12GHz Fundamental Frequency

analog.com Rev. 0 | 13 of 48

## TYPICAL PERFORMANCE CHARACTERISTICS

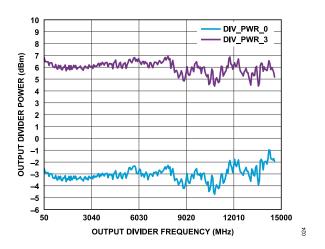

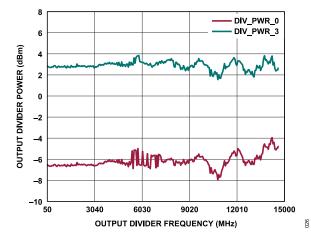

Figure 24. Differential Output Divider Power vs. Output Divider Frequency Across Various Power Settings, 25°C

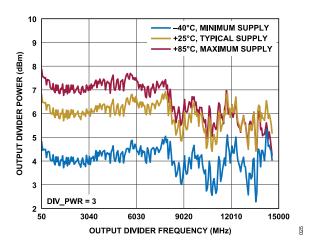

Figure 25. Differential Output Divider Power vs. Output Divider Frequency Across Various Temperatures and Supplies

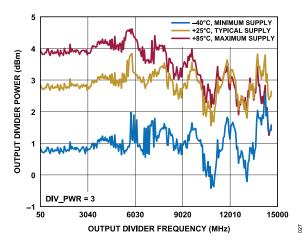

Figure 26. Single-Ended Output Divider Power vs. Output Divider Frequency Across Various Power Settings, 25°C

Figure 27. Single-Ended Output Divider Power vs. Output Divider Frequency Across Various Temperatures and Supplies

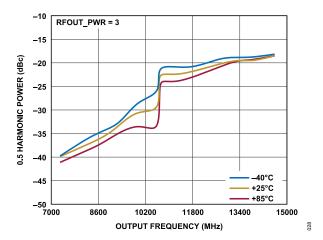

Figure 28. 0.5 Harmonic Power vs. Output Frequency Across Various Temperatures

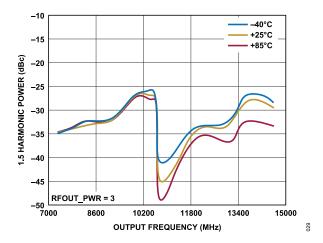

Figure 29. 1.5 Harmonic Power vs. Output Frequency Across Various

Temperatures

analog.com Rev. 0 | 14 of 48

## TYPICAL PERFORMANCE CHARACTERISTICS

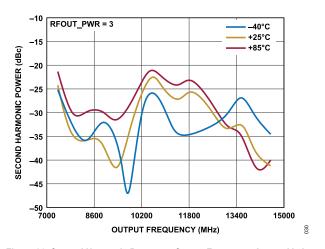

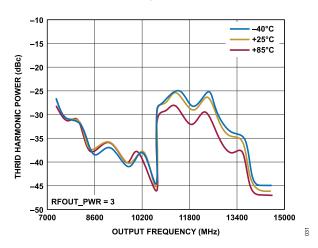

Figure 30. Second Harmonic Power vs. Output Frequency Across Various Temperatures

Figure 31. Third Harmonic Power vs. Output Frequency Across Various

Temperatures

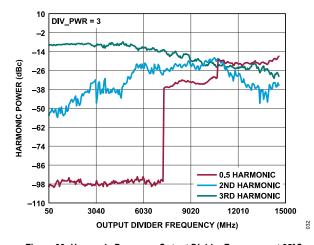

Figure 32. Harmonic Power vs. Output Divider Frequency at 25°C

Figure 33. Integer Boundary Spurs vs. Output Frequency at 10kHz Offset

Figure 34. Worst Case Integer Boundary Spurious Sweep vs. Output Frequency at 25°C

Figure 35. Phase Frequency Detector Spurs vs. Output Frequency

analog.com Rev. 0 | 15 of 48

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 36. Reference Spurs vs. Output Frequency

Figure 37. L<sub>NORM</sub> vs. Reference Slew Rate at 25°C

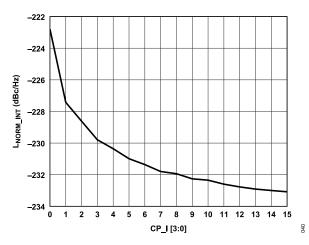

Figure 38. L<sub>NORM INT</sub> vs. CP\_I[3:0] Settings, 25°C

Figure 39. L<sub>1/f</sub> vs. Reference Slew Rate, 25°C

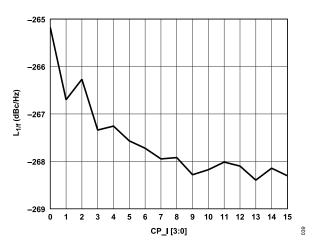

Figure 40. L<sub>1/f</sub> vs. CP\_I[3:0] Settings, 25°C

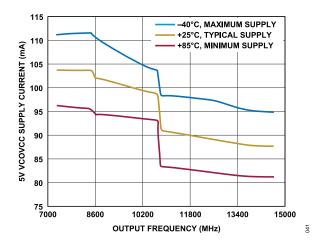

Figure 41. 5V VCOVCC Supply Current vs. Output Frequency Across Various

Temperatures and Supplies

analog.com Rev. 0 | 16 of 48

## **TYPICAL PERFORMANCE CHARACTERISTICS**

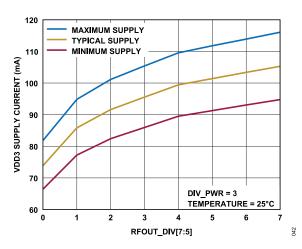

Figure 42. 3V VDD3 Supply Current vs. Output Divider Settings (RFOUT\_DIV[7:5]) Across Various Supplies

analog.com Rev. 0 | 17 of 48

#### THEORY OF OPERATION

#### INTRODUCTION

A PLL is a complex feedback system that can conceptually be considered a frequency multiplier. The system multiplies the reference frequency input at XREFP and outputs a higher frequency at RFOUT (single-ended output) or at PDIV\_OUT or NDIV\_OUT (differential output). The PFD, charge pump, output divider, feedback divider, VCO, and external loop filter form a feedback loop to accurately control the output frequency (see Figure 43). When operating in integer mode, the reference divider sets the frequency resolution. When operating in fractional mode, the fractional-N divider sets the frequency resolution.

Figure 43. PLL Loop Diagram

## **OUTPUT FREQUENCY**

When the loop is locked, the  $f_{VCO}$  (in Hz) produced at the output of the VCO is determined by the reference frequency ( $f_{REF}$ ), reference division factor (R\_DIV), and the N values given by the following equation:

$$f_{VCO} = f_{PFD} \times N \tag{1}$$

where the Feedback Counter N is given by the following:

$$N = N_{INT} + \left(\frac{FRAC1WORD + \frac{FRAC2WORD}{MOD1WORD}}{MOD1WORD}\right)$$

(2)

where:

INT is a 20-bit integer value.

FRAC1WORD is the numerator of the primary modulus (0 to 33554431).

FRAC2WORD is the numerator of the 24-bit auxiliary modulus (0 to 16777215).

MOD2WORD is the programmable, 24-bit auxiliary fractional modulus (2 to 16777215).

MOD1WORD is a 25-bit primary modulus with a fixed value of  $2^{25}$  = 33554432

The f<sub>PFD</sub> is expressed by the following:

$$f_{PFD} = \frac{f_{REF}}{R_{DIV}} \tag{3}$$

The output frequency, f<sub>RFOUT</sub>, produced at the output channel RFOUT is given by the following:

$$f_{RFOUT} = 2 \times f_{VCO} \tag{4}$$

While the differential output frequency,  $f_{\text{DIVOUT}}$ , produced at PDIV OUT and NDIV OUT

is expressed by the following:

$$f_{DIVOUT} = \frac{2 \times f_{VCO}}{2^{RFOUT\_DIV}}$$

(5)

RFOUT\_DIV refers to the clock output divider, which can divide the RFOUT from 1 to 128, following a power of 2 progression, see the RF Output Divider section.

## **Output Frequency Calculation Procedure**

The following is a worked example for a fractional mode f<sub>RFOUT</sub> using the formulas in the Output Frequency section.

For  $f_{RFOUT}$  = 12.1234GHz and a channel spacing ( $f_{CHSP}$ ) of 1Hz, where  $f_{REF}$  =  $f_{PFD}$  = 100MHz and the reference divider is set to divide by 1 (R\_DIV = 1), the output frequency is within the fundamental VCO frequency range ( $f_{VCO}$ ).

The steps to calculate all N-divider component values are outlined as follows:

Calculate the overall N value required based on the f<sub>RFOUT</sub> and f<sub>PFD</sub> provided as follows:

$$N = \frac{f_{RFOUT}}{2 \times f_{PFD}} \tag{6}$$

$$N = \frac{12.1234 \text{GHz}}{2 \times 100 \text{MHz}} = 60.617 \tag{7}$$

2. Separate the N<sub>INT</sub> and N<sub>FRAC</sub> components as follows:

$$N_{INT} = INT(N) = 60 \tag{8}$$

$$N_{FRAC} = N - N_{INT} = 0.617$$

(9)

3. Calculate the FRAC1WORD as follows:

$$N_{FRAC1WORD} = N_{FRAC} \times MOD1WORD \tag{10}$$

Where MOD1WORD is a fixed value of  $2^{25}$  = 33554432.

$$N_{\text{FRAC1WORD}} = 0.617 \times 33554432 = 20703084.544$$

(11)

FRAC1WORD=

$$INT(N_{FRAC1WORD}) = 20703084$$

(12)

FRAC2WORD and MOD2WORD are only required if N<sub>FRAC1WORD</sub> is not an integer number. If N<sub>FRAC1WORD</sub> is

analog.com Rev. 0 | 18 of 48

Data Sheet ADF561'

## THEORY OF OPERATION

an integer, no further calculation is required. In this case, VAR\_MOD\_EN is set to 0 to disable FRAC2WORD and MOD2WORD.

- 4. Calculate the MOD2WORD as follows:

- **a.** Determine the remainder of the fractional word.

$$N_{REMAINDER} = N_{FRAC1WORD} - FRAC1WORD$$

$$N_{REMAINDER} = 20703084.544$$

$-20703084 = 0.544$

**b.** Find the greatest common divisor (GCD) between  $f_{\text{FPD}}$  and MOD1WORD ×  $f_{\text{CHSP}}$ .

$$GCD(MOD1WORD \times f_{CHSP}, f_{PFD})$$

$$GCD(2^{25} \times 1, 100MHz) = 256$$

c. Calculate the initial MOD2WORD calculation as follows:

$$\begin{aligned} & \text{MOD2WORD}_{\text{INITIAL}} = \\ & \frac{f_{\text{PFD}}}{GCD(\text{MOD1WORD} \times f_{\text{CHSP}}, f_{\text{PFD}})} \end{aligned}$$

$$MOD2WORD_{INITIAL} = \frac{100MHz}{256} = 390625$$

d. Calculate the final MOD2WORD.

To maximize frequency resolution, the final value of MOD2WORD is calculated by obtaining the highest integer multiple of the initial MOD2WORD, that is less than or equal to the  $MOD2WORD_{MAX}$  as follows.

$$\begin{array}{l} \text{MOD2WORD} = \\ \text{INT} \Big( \frac{\text{MOD2WORD}_{\text{MAX}}}{\text{MO2WORD}_{\text{INITIAL}}} \Big) \times \\ \text{MOD2WORD}_{\text{INITIAL}} \end{array}$$

Where MOD2WORD<sub>MAX</sub> is a fixed value of  $2^{24} - 1 = 16777215$

$$MOD2WORD = INT(\frac{16777215}{390625}) \times 390625$$

(20)

$$MOD2WORD = 42 \times 390625 = 16406250$$

(21)

5. Calculate FRAC2WORD as follows:

$$FRAC2WORD = INT(N_{REMAINDER} \times MOD2WORD)$$

(22)

$$FRAC2WORD = INT(0.544 \times 16406250)$$

(23)

$$FRAC2WORD = 8925000 \tag{24}$$

**6.** Calculate the total N value using the original formula as follows:

$$N = N_{INT} + \frac{FRAC1WORD + \frac{FRAC2WORD}{MOD2WORD}}{MOD1WORD}$$

(25)

$$N = 60 + \frac{20703084 + \frac{8925000}{16406250}}{33554432} = 60.617$$

(26)

7. Calculate the f<sub>RFOUT</sub> frequency as follows:

$$f_{VCO} = f_{PFD} \times N \tag{27}$$

$$f_{RFOUT} = 2 \times f_{VCO} \tag{28}$$

$$f_{RFOUT} = 2 \times (f_{PFD} \times N) \tag{29}$$

(14)

$$f_{RFOUT} = 2 \times (100 MHz \times 60.617) = 12.1234 GHz$$

(30)

#### CIRCUIT DESCRIPTION

(15) RF Output Divider

- (16) The RFOUT\_DIV (Register 0x022, Bits[7:5]) is a 3-bit divider used to divide the frequency seen at the output buffer. The divide ratio can be set from 1, 2, 4, 8, 16, 32, 64, or 128, offering a frequency range from 57MHz to 14,600MHz. The divider output

- power can be set via the DIV\_PWR bits (Register 0x022, Bits[2:0]).

The RFOUT\_DIV and output divider channels,NDIV\_OUT and

PDIV\_OUT, can be disabled when not in use via the PD\_ODIV

(18) PDIV\_OUT, can be disabled when not in use via the PD\_ODIV bit (Register 0x028, Bit 1).

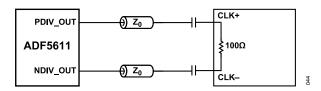

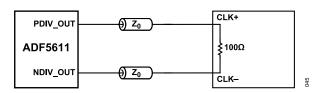

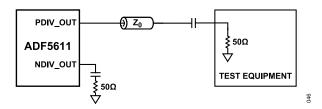

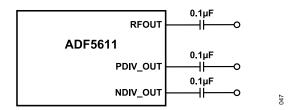

The RF output divider channels, NDIV\_OUT and PDIV\_OUT, can be either AC- or DC-coupled and terminated with a  $100\Omega$  resistor differentially as shown in Figure 44 and Figure 45. If a single-ended output is desired, each side of the output must be individually AC-coupled and terminated with a  $50\Omega$  resistor, see Figure 46. For AC-coupled applications, a series of  $0.1\mu\text{F}$  capacitors must be connected to the RFOUT, PDIV\_OUT, and NDIV\_OUT pins as

19) shown in Figure 47.

Figure 44. Common Clock Interface: Differential Clock with End Termination  $(Z_{\Omega} = 50 \ \Omega)$ , AC-Coupled

Figure 45. Common Clock Interface: Differential Clock with End Termination  $(Z_O = 50 \ \Omega)$ , DC-Coupled

analog.com Rev. 0 | 19 of 48

#### THEORY OF OPERATION

Figure 46. Common Clock Interface: Single-Ended Clock with End Termination ( $Z_{\Omega}$  = 50  $\Omega$ )

Figure 47. Output Interface Schematic

## Feedback Divider (N)

The feedback divider provides a division ratio in the PLL feedback path. The division ratio consists of a 20-bit N\_INT (Register 0x010 to Register 0x012), a 25-bit FRAC1WORD (Register 0x012 to Register 0x015), a 24-bit FRAC2WORD (Register 0x017 to Register 0x019), and a 24-bit MOD2WORD (Register 0x01A to Register 0x01C) bit field values that this divider comprises together with the fixed modulus MOD1WORD ( $2^{25}$ ).

## Reference Input

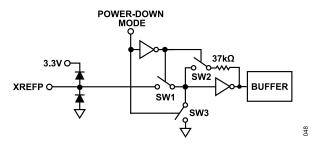

The reference signal of the PLL is input through XREFP, which operates as a single-ended input. This high impedance input is self biased and requires AC-coupling (refer to Figure 48 for a simplified schematic of the reference input stage). The reference signal input on the XREFP is enabled by configuring the PD\_RDIV bit (Register 0x027, Bit 6) to 0. In this case, SW1 and SW2 are closed, and SW3 is open.

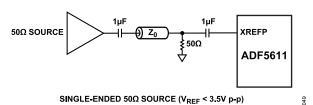

The slew rate of the input reference signal significantly affects the performance. The device is functional with signals as low as 0.4V p-p amplitude. However, to achieve optimal performance and the in-band phase noise performance of the ADF5611, apply a continuous sine-wave signal or a square-wave signal with a slew rate of at least 500V/µs. Achieving this slew rate with sinusoidal waves requires high amplitudes and may not be possible at low frequencies. For a frequency input of 10MHz, a square wave is required. A high performance square wave signal with a high slew rate is recommended as the reference input signal to achieve the best performance. See Figure 49 for reference input signal requirements and interfacing.

Figure 48. Reference Input Stage

Figure 49. Reference Input Source

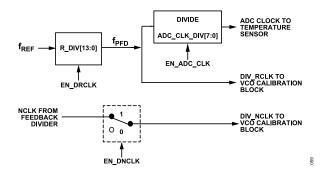

#### Reference Divider

The reference path R divider, R\_DIV (Register 0x01F, Bits[7:0] and Register 0x20, Bits[5:0], respectively), is based on a 14-bit counter. This divider is used to reduce the frequency seen at the PFD, and its divide ratio (R) can be set to any integer from 1 to 16,383, inclusive. Use the R DIV bits to directly program the R divide ratio.

## **Phase and Frequency Detector (PFD)**

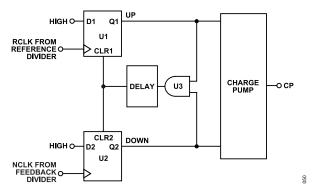

The PFD, in conjunction with the charge pump, produces source and sink current pulses proportional to the phase difference between the outputs of the reference divider or reference doubler and feedback divider. These source and sink pulses are required to phase lock the loop, forcing a phase alignment at the inputs of the PFD. The PFD includes a fixed delay element that sets the width of the antibacklash pulse. This pulse ensures that there is no dead zone in the PFD transfer function and provides a consistent reference spur level. Set the phase detector polarity to positive on this device because of the positive tuning of the VCO. See Figure 50 for a simplified schematic of the PFD.

Figure 50. Simplified PFD Schematic

analog.com Rev. 0 | 20 of 48

#### THEORY OF OPERATION

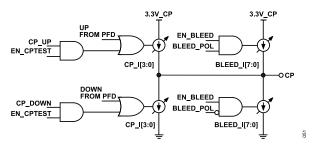

## **Charge Pump**

The charge pump, controlled by the PFD, forces sink (down) or source (up) current pulses onto the CP pin, which must be connected to an appropriate loop filter. See Figure 51 for a simplified schematic of the charge pump.

Figure 51. Simplified Charge Pump Schematic

The output current magnitude,  $I_{CP}$ , can be set from 0.2mA to 3.2mA using the CP\_I bits (Register 0x021, Bits[3:0]). A larger  $I_{CP}$  can result in lower in-band noise due to the lower impedance of the loop filter components, while a smaller  $I_{CP}$  can result in better spurious performance. See Table 7 for the charge pump programming values.

Table 7. CP Programming

| CP_I, Bits[3:0] | I <sub>CP</sub> (mA) |  |

|-----------------|----------------------|--|

| 0               | 0.2                  |  |

| 1               | 0.4                  |  |

| 2               | 0.6                  |  |

| 3               | 0.8                  |  |

| 4               | 1                    |  |

| 5               | 1.2                  |  |

| 6               | 1.4                  |  |

| 7               | 1.6                  |  |

| 8               | 1.8                  |  |

| 9               | 2                    |  |

| 10              | 2.2                  |  |

| 11              | 2.4                  |  |

| 12              | 2.6                  |  |

| 13              | 2.8                  |  |

| 14              | 3                    |  |

| 15              | 3.2                  |  |

## **Charge Pump Test Mode**

When the charge pump test mode EN\_CPTEST bit (Register 0x02B, Bit 2) is set to 1, it allows the CP\_UP and CP\_DOWN bits (Register 0x02B, Bit 0 and Bit 1, respectively) to enforce a constant I<sub>CP</sub> source or sink current, respectively, on the CP pin. These bits can be used as an aid to debug issues related to PLL during the hardware and software development phase of a project. For normal operation, set EN\_CPTEST, CP\_UP, and CP\_DOWN to 0. See Table 8 for applicable charge pump test mode.

Table 8. Charge Pump Test Mode

| EN_CPTEST | CP_UP | CP_DOWN | CP Pin State          | Debug Test                              |

|-----------|-------|---------|-----------------------|-----------------------------------------|

| 1         | 0     | 0       | High-Z                | VCO open loop                           |

| 1         | 1     | 0       | ~V <sub>3.3V_CP</sub> | Charge pump output voltage verification |

| 1         | 0     | 1       | ~GND                  | Charge pump output voltage verification |

| 0         | 0     | 0       | Normal operation      | Not applicable                          |

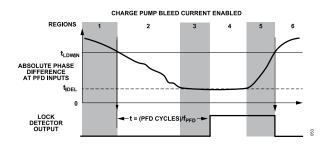

## **Charge Pump Bleed Current Optimization**

A small programmable constant charge pump current, known as bleed current, can be used to optimize the phase noise and fractional spurious signals in fractional mode, which also changes the propagation delay from the XREFP input pin to the RFOUT, PDIV OUT, and NDIV OUT output pins.

Configure the EN\_BLEED bit (Register 0x01E, Bit 6) to 1 to enable the bleed current. If the BLEED\_POL bit (Register 0x01E, Bit 0) is set to 1, a constant source current is applied to the CP pin. Conversely, if the BLEED\_POL bit is adjusted to 0, a constant sink current is applied to the CP pin.

The 8-bit BLEED\_I bits (Register 0x01D, Bits[7:0]) are used to optimize the spurious performance of the ADF5611. The bleed current, BLEED\_I, is calculated and configured based on the required bleed time ( $t_{BLEED}$ ) at a given VCO frequency,  $I_{CP}$ , and  $f_{PFD}$  as shown in the following equations:

$$\begin{split} t_{BLEED} &= \quad \frac{4}{2 \times \textit{VCO}} \\ I_{BLEED} &= t_{BLEED} \times f_{PFD} \times I_{CP} \\ BLEED\_I &= \frac{I_{BLEED}}{3.125 \mu A} \end{split}$$

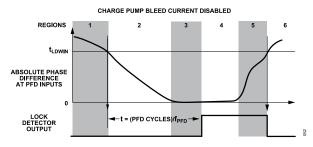

#### **Lock Detector**

The lock detector uses internal signals from the PFD to measure the phase difference between the output signal of the reference divider (RCLK) and the output signal of the feedback divider (NCLK) in Figure 50. This detector is enabled by configuring the PD\_LD bit (Register 0x027, Bit 3) to 0, and both the EN\_LOL and EN\_LDWIN bits (Register 0x02A, Bit 5 and Bit 4, respectively) to 1. The output of the lock detector can be accessed either through the LOCKED bit (Register 0x048, Bit 0), or via the SDO pin (Pin 19) by setting the EN\_MUXOUT bits (Register 0x02B, Bits 3) to 1 and programming the MUXOUT bits (Register 0x02B, Bits [7:4]) to 1 (LKDET).

The PFD RCLK and NCLK phase difference must be less than the phase difference lock window time, t<sub>LDWIN</sub>, for a set number of PFD cycles before the lock detector output indicates the PLL has locked. The desired number of PFD cycles varies depending on whether the lock detect accuracy or speed is prioritized. See Table 9 to set

analog.com Rev. 0 | 21 of 48

Data Sheet ADF561'

#### THEORY OF OPERATION