# Energy Management DSP with PEN Fault Detection

#### **FEATURES**

- Metrology chip for use with any combination of the following AFEs

- ► ADE9113 (3-channel, isolated, Σ-Δ ADC)

- ► ADE9112 (2-channel, isolated, Σ-Δ ADC)

- ► ADE9103 (3-channel, non-isolated, Σ-Δ ADC)

- Can support up to four ADE9113/ADE9112/ADE9103 daisychained ADCs through 4-wire SPI

- Supports up to a total of 12 ADC channels of data

- ▶ 4-wire SPI for Host MCU communications up to 25 MHz

- ► Total active energy calculation

- ► Class C accuracy (0.5%), supports the following

- ▶ MID 2014/32/EU Annex V

- ► EN 50470-1:2006

- ► EN 50470-3:2006

- ► EN 50470-3:2022

- ▶ IEC 62052-11:2020

- ▶ IEC 62053-21:2020

- ▶ OIML G 22:2022

- ▶ NIST Handbook 44:2023

- ▶ Total apparent energy calculation using filtered RMS

- Energy accumulation, import and export for reverse power/vehicle to grid (V2G) applications

- Basic power quality features

- Short-duration undervoltage or overvoltage (dip/swell) detection

- Short-duration undercurrent or overcurrent (dip/swell) detection

- ▶ Line frequency calculation with 10 mHz accuracy

- Angles between phase voltages and currents

- ▶ Power-factor calculation

- Configurable phase, gain and offset calibration registers for all ADC channels

- ▶ Two configurable calibration frequency (CF) pulse outputs

- ▶ Configurable: no load detection

- ▶ Phase-sequence detection

- RMS on full cycle, half cycle and filtered RMS on all ADC channels

- ▶ Supported frequency range: 45 Hz to 65 Hz

- ▶ Four user-programmable interrupt outputs (IRQs)

- ▶ PEN open fault detection (BS 7671:2018 Amendment 1:2020)

- Waveform streaming through UART transmit pin

- Datapath multiplexing to allow any ADC data to be used for any data processing path

- ► Temperature range: -40°C to +105°C

- ► Available in 5 mm × 5 mm, 40-lead LFCSP package

#### **APPLICATIONS**

- ▶ Electric vehicle supply equipment

- ▶ Shunt-based polyphase meters

- Solar inverters

- Energy and power monitoring

#### **GENERAL DESCRIPTION**

The ADE9178 is a metrology digital signal processor (DSP) for use with a combination of ADE9113/ADE9112/ADE9103 sigma delta analog-to-digital converters (ADCs). The ADE9178 is a high accuracy, 3-phase electrical energy measurement IC primarily for the electric vehicle supply equipment (EVSE) market with serial peripheral interface (SPI) and two flexible pulse outputs. The ADE9178 can interface with up to four daisy-chained ADE9113/ADE9112/ADE9103 devices through SPI protocol. The ADE9178 incorporates all the signal processing required to perform total active energy, apparent energy measurements, and root mean square (RMS) calculations. A fixed function DSP executes this signal processing.

The ADE9178 is well-suited for the EVSE market due to its broad feature set such as protective earth and neutral (PEN) open fault detection without the need for any additional hardware, overcurrent, and overvoltage detection using RMS of half cycle/one cycle and vehicle to grid/home (V2X) capabilities.

The ADE9178 measures active and apparent energy in various 3-phase configurations, such as wye or delta services, with both three and four wires, single phase, and split phase while supporting both 50 Hz and 60 Hz line frequencies. The ADE9178 provides gain, offset, and phase calibration features for each ADC channel. The CF1 and CF2 logic outputs provide power information that is proportional to the measured accumulated energy.

The ADE9178 incorporates some basic power quality measurement features, such as short-duration undervoltage/undercurrent or overvoltage/overcurrent detection, line voltage period measurements, and angles between phase voltages and currents. A Host microcontroller unit (MCU) can be used to communicate with the ADE9178 through 4-wire SPI. Waveform streaming can be accessed by the Host MCU through the WAVEFORM\_TX pin of the ADE9178. The ADE9178 also has four user-programmable interrupt pins,  $\overline{IRQ0}$ ,  $\overline{IRQ1}$ ,  $\overline{IRQ2}$ , and  $\overline{IRQ3}$ , to indicate that an enabled interrupt event has occurred. The ADE9178 is available in a 40-lead, LFCSP package.

For more details on how to setup the ADE9178 in an EVSE application, refer to the application note Using ADE9178 for EV Charger Metrology Solution.

19-101907; Rev A; 3/25

DOCUMENT FEEDBACK

TECHNICAL SUPPORT

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. All Analog Devices products contained herein are subject to release and availability.

# **TABLE OF CONTENTS**

| Features 1                                     | Theory of Operation                     | 22    |

|------------------------------------------------|-----------------------------------------|-------|

| Applications1                                  | ADC and Host SPI                        |       |

| General Description1                           | Full-Scale Codes And Conversion Equatio | ns 31 |

| Typical Applications Circuit3                  | ADE9178 Data Processing Flow            | 35    |

| Functional Block Diagram4                      | Power and Energy Measurements           |       |

| Specifications5                                | All Channel Measurements                | 42    |

| System Specifications for ADE9178,             | Measurements Only for Voltage Channels. | 46    |

| ADE9103, ADE9112, and ADE91135                 | Measurements Only for Current Channels. |       |

| ADE9178 Specifications7                        | PEN Fault Detection                     |       |

| SPI Timing Parameters8                         | Waveform Streaming                      | 48    |

| Absolute Maximum Ratings9                      | Output Register Update Rates            | 49    |

| Thermal Resistance9                            | Interrupts and Status Outputs           |       |

| ESD Caution9                                   | Power Management                        | 54    |

| Pin Configurations and Function Descriptions10 | Applications Information                |       |

| Typical Performance Characteristics            | Calibration Method                      |       |

| Energy Linearity Over Supply and               | Quick Start                             | 57    |

| Temperature12                                  | Layout Guidelines                       |       |

| Energy Error Over Frequency and Power          | Silicon Anomaly                         |       |

| Factor                                         | Functionality Issues                    |       |

| Energy Linearity Repeatability14               | Register Number Format                  |       |

| RMS Linearity Over Temperature and RMS         | Register Summary: ADE9178               | 62    |

| Error Over Frequency15                         | Register Details: ADE9178               |       |

| CF vs. Energy Register Correlation and CF      | Outline Dimensions                      | 122   |

| Jitter18                                       | Ordering Guide                          | 122   |

| Test Circuit20                                 | Evaluation Boards                       | 122   |

| Terminology21                                  | Licenses                                | 122   |

| REVISION HISTORY                               |                                         |       |

| 3/2025—Rev. 0 to Rev. A                        |                                         |       |

| Change to Features Section                     |                                         |       |

| Change to General Description Section          |                                         |       |

| Change to Table 4                              |                                         |       |

| Changes to Table 6                             |                                         |       |

| Changes to Figure 29                           |                                         |       |

| Changes to Figure 30 and Figure 31             |                                         |       |

| Changes to Hardware Reset Section              |                                         |       |

| Changes to Quick Start Section                 |                                         | 57    |

|                                                |                                         |       |

7/2024—Revision 0: Initial release

# **TYPICAL APPLICATIONS CIRCUIT**

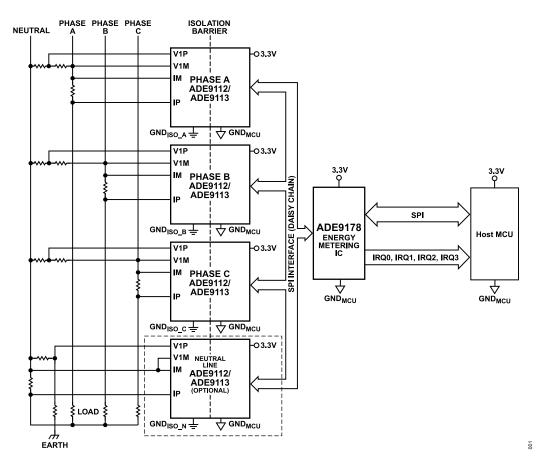

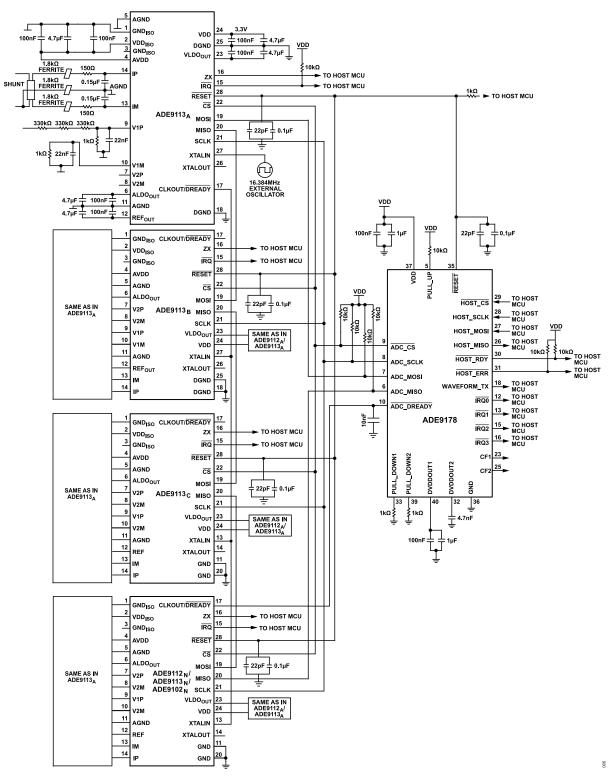

Figure 1. Typical Applications Circuit

analog.com Rev. A | 3 of 122

## **FUNCTIONAL BLOCK DIAGRAM**

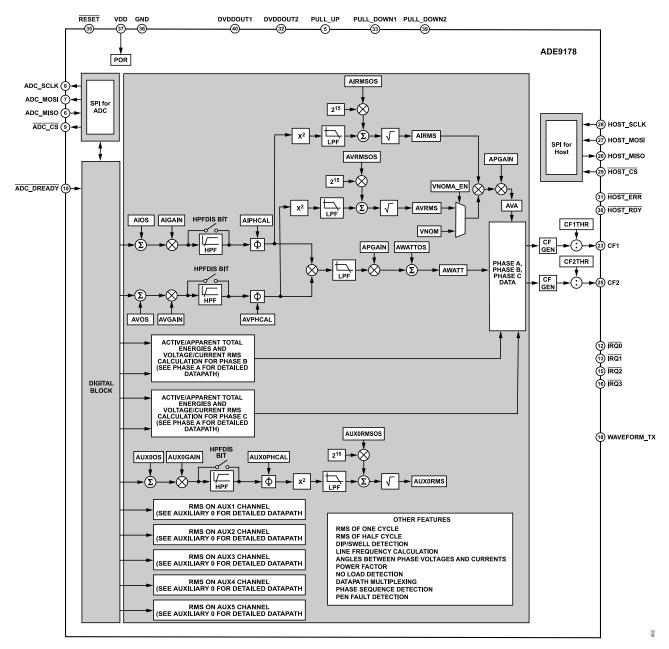

Figure 2. Functional Block Diagram

analog.com Rev. A | 4 of 122

# **SPECIFICATIONS**

# SYSTEM SPECIFICATIONS FOR ADE9178, ADE9103, ADE9112, AND ADE9113

$V_{DD}$  = 3.3 V ± 10%, GND = DGND = 0 V,  $T_{MIN}$  to  $T_{MAX}$  = -40°C to +105°C,  $T_{TYP}$  = +25°C, and high-pass filter (HPF) on, unless otherwise noted.

Table 1. System Specifications

| Parameter                     | Min | Тур   | Max | Unit    | Test Conditions/Comments                                                                                              |

|-------------------------------|-----|-------|-----|---------|-----------------------------------------------------------------------------------------------------------------------|

| TOTAL ACTIVE ENERGY           |     |       |     |         |                                                                                                                       |

| Measurement Error (3-Phases)  |     |       |     |         |                                                                                                                       |

| Total Active Energy           |     | 0.1   |     | %       | Over a dynamic range of 2000 to 1, power factor (PF) = 1, 10 second accumulation, power offset calibration applied    |

|                               |     | 0.2   |     | %       | Over a dynamic range of 2000 to 1, power factor (PF) = 1, 10 second accumulation, no power offset calibration applied |

| Total Active Energy Bandwidth |     | 1.65  |     | kHz     | ADE91xx LPF_BW = 0                                                                                                    |

| TOTAL APPARENT ENERGY         |     |       |     |         |                                                                                                                       |

| Measurement Error (3-Phases)  |     |       |     |         |                                                                                                                       |

| Total Apparent Energy         |     | 0.1   |     | %       | Over a dynamic range of 2000 to 1, power factor (PF) = 1, 10 second accumulation, RMS offset calibration applied      |

|                               |     | 0.6   |     | %       | Over a dynamic range of 2000 to 1, power factor (PF) = 1, 10 second accumulation, no RMS offset calibration applied   |

| RMS MEASUREMENTS              |     |       |     |         |                                                                                                                       |

| Filtered IRMS                 |     | 0.4   |     | %       | Over a dynamic range of 2000 to 1, average of 1 sample pe line cycle for 1 second, RMS offset calibration applied     |

|                               |     | 0.65  |     | %       | Over a dynamic range of 2000 to 1, average of 1 sample pe line cycle for 1 second, no RMS offset calibration applied  |

| Filtered VRMS                 |     | 0.2   |     | %       | Over a dynamic range of 2000 to 1, average of 1 sample pe line cycle for 1 second, RMS offset calibration applied     |

|                               |     | 0.2   |     | %       | Over a dynamic range of 2000 to 1, average of 1 sample pe line cycle for 1 second, no RMS offset calibration applied  |

| IRMS of Half Cycle            |     | 2.5   |     | %       | Over a dynamic range of 1000 to 1, based on a single result RMS offset calibration applied                            |

|                               |     | 2.5   |     | %       | Over a dynamic range of 1000 to 1, based on a single result no RMS offset calibration applied                         |

| VRMS of Half Cycle            |     | 1     |     | %       | Over a dynamic range of 1000 to 1, based on a single result RMS offset calibration applied                            |

|                               |     | 1     |     | %       | Over a dynamic range of 1000 to 1, based on a single result no RMS offset calibration applied                         |

| IRMS of Full Cycle            |     | 2     |     | %       | Over a dynamic range of 1000 to 1, based on a single result RMS offset calibration applied                            |

|                               |     | 2     |     | %       | Over a dynamic range of 1000 to 1, based on a single result no RMS offset calibration applied                         |

| VRMS of Full Cycle            |     | 0.5   |     | %       | Over a dynamic range of 1000 to 1, based on a single result RMS offset calibration applied                            |

|                               |     | 0.5   |     | %       | Over a dynamic range of 1000 to 1, based on a single result no RMS offset calibration applied                         |

| METROLOGY MESUREMENTS         |     |       |     |         |                                                                                                                       |

| Phase Angle                   |     |       |     |         |                                                                                                                       |

| Measurement Error             |     | 0.5   |     | Degrees | Over a dynamic range of 100 to 1, line frequency = 45 Hz to 65 Hz, phase angle = 0° to 360°, HPF on                   |

| Power Factor                  |     |       |     |         |                                                                                                                       |

| Measurement Error             |     | 0.005 |     | PF      | Over a dynamic range of 2000 to 1, power factor (PF)= -1 to                                                           |

analog.com Rev. A | 5 of 122

# **SPECIFICATIONS**

Table 1. System Specifications (Continued)

| Parameter              | Min | Тур    | Max  | Unit | Test Conditions/Comments                                                                                                              |

|------------------------|-----|--------|------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| Period                 |     |        |      |      |                                                                                                                                       |

| Measurement Error      |     | 5      |      | mHz  | Line frequency = 45 Hz to 65 Hz,<br>CONFIGO:PERIOD_AVG_CFG[4:3] = 0x0 (no period<br>averaging)                                        |

| CF1, CF2 PULSE OUTPUTS |     |        |      |      |                                                                                                                                       |

| Output Frequency       |     |        | 500  | Hz   | CF saturates at 1 kHz but performance specification is up to 500 Hz                                                                   |

| Active-Low Pulse Width | 0.2 |        |      | ms   |                                                                                                                                       |

| CF1 Jitter             |     | 0.1    |      | %    | Voltage = 50% of full scale, current over dynamic range of 2000 to 1, CF1_THR = d1341078 = 500 Hz at current full scale, CF2 disabled |

|                        |     | 0.1    |      | %    | Voltage = 50% of full scale, current over dynamic range of 2000 to 1, CF1_THR = d22351312 = 30 Hz at current full scale, CF2 disabled |

| CF2 Jitter             |     | 0.5    |      | %    | Voltage = 50% of full scale, current over dynamic range of 2000 to 1, CF1_THR = d1341078 = 500 Hz at current full scale, CF1 enabled  |

|                        |     | 0.1    |      | %    | Voltage = 50% of full scale, current over dynamic range of 2000 to 1, CF1_THR = d22351312 = 30 Hz at current full scale, CF1 enabled  |

| BOOT TIME              |     |        |      |      |                                                                                                                                       |

| System-Level Boot Time |     | 16     |      | ms   | From RSTN pin toggle to RSTDONE flag being set, $V_{DD} \ge 2.97 \text{ V}$                                                           |

| ADE91xx CLOCK          |     |        |      |      |                                                                                                                                       |

| Input Clock Frequency  |     | 16.384 |      | MHz  |                                                                                                                                       |

| Tolerance              |     |        | 1000 | ppm  |                                                                                                                                       |

analog.com Rev. A | 6 of 122

# **SPECIFICATIONS**

# **ADE9178 SPECIFICATIONS**

Table 2. ADE9178 Specifications

| Parameter                               | Min  | Тур | Max  | Unit | Test Conditions/Comments                                       |

|-----------------------------------------|------|-----|------|------|----------------------------------------------------------------|

| POWER SUPPLY                            |      |     |      |      |                                                                |

| $V_{DD}$                                | 2.97 | 3.3 | 3.63 | V    |                                                                |

| I <sub>DD</sub> Startup                 |      | 55  |      | mA   | During POR, there is a spike in current                        |

| I <sub>DD</sub> Operating               |      | 13  |      | mA   | Typical I <sub>DD</sub> during normal operation                |

| LOGIC INPUTS                            |      |     |      |      | ADC_MISO, HOST_MOSI, HOST_SCLK, HOST_CS, ADC_DREADY, and RESET |

| Input High Voltage (V <sub>INH</sub> )  | 2.31 |     |      | V    |                                                                |

| Input Low Voltage (V <sub>INL</sub> )   |      |     | 0.99 | V    |                                                                |

| Internal Capacitance (C <sub>IN</sub> ) |      | 4   |      | pF   |                                                                |

| LOGIC OUTPUTS                           |      |     |      |      | ADC_MOSI, ADC_SCLK, ADC_CS                                     |

| Output High Voltage (V <sub>OH</sub> )  | 2.9  |     |      | V    |                                                                |

| Source Current (I <sub>SOURCE</sub> )   |      | 8   |      | mA   |                                                                |

| Output Low Voltage (V <sub>OL</sub> )   |      | 0.2 | 0.4  | V    |                                                                |

| Sink Current (I <sub>SINK</sub> )       |      | 8   |      | mA   |                                                                |

| LOGIC OUTPUTS                           |      |     |      |      | IRQ0, IRQ1, IRQ2, IRQ3, HOST_MISO, and CF1                     |

| Output High Voltage (V <sub>OH</sub> )  | 2.9  |     |      | V    |                                                                |

| Source Current (I <sub>SOURCE</sub> )   |      | 12  |      | mA   |                                                                |

| Output Low Voltage (V <sub>OL</sub> )   |      | 0.2 | 0.4  | V    |                                                                |

| Sink Current (I <sub>SINK</sub> )       |      | 12  |      | mA   |                                                                |

| LOGIC OUTPUTS                           |      |     |      |      | CF2, HOST_RDY, and HOST_ERR                                    |

| Output High Voltage (V <sub>OH</sub> )  | 2.9  |     |      | V    |                                                                |

| I <sub>SOURCE</sub>                     |      | 20  |      | mA   |                                                                |

| Output Low Voltage (V <sub>OL</sub> )   |      | 0.2 | 0.4  | V    |                                                                |

| I <sub>SINK</sub>                       |      | 20  |      | mA   |                                                                |

analog.com Rev. A | 7 of 122

# **SPECIFICATIONS**

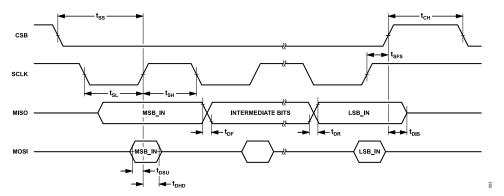

# **SPI TIMING PARAMETERS**

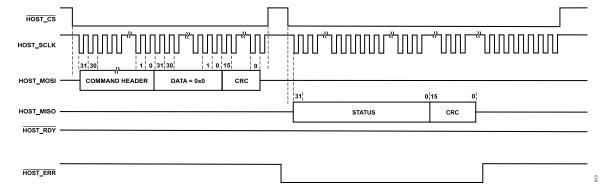

Table 3. SPI Timing Parameters

| Parameter                              | Symbol            | Min | Тур                  | Max | Unit |

|----------------------------------------|-------------------|-----|----------------------|-----|------|

| CS to SCLK Positive Edge               | t <sub>SS</sub>   |     | 10                   |     | ns   |

| SCLK Frequency                         | f <sub>SCLK</sub> |     |                      | 25  | MHz  |

| SCLK Period                            | t <sub>SCLK</sub> |     | 1/f <sub>SCLK</sub>  |     | ns   |

| SCLK Low-Pulse Width                   | t <sub>SL</sub>   |     | t <sub>SCLK</sub> /2 |     | ns   |

| SCLK High-Pulse Width                  | t <sub>SH</sub>   |     | t <sub>SCLK</sub> /2 |     | ns   |

| Data-Input Setup Time Before SCLK Edge | t <sub>DSU</sub>  |     | 5                    |     | ns   |

| Data-Input Hold Time After SCLK Edge   | t <sub>DHD</sub>  |     | 1                    |     | ns   |

| MISO Disable After CS Rising Edge      | t <sub>DIS</sub>  |     | 10                   |     | ns   |

| CS High After SCLK Edge                | t <sub>SFS</sub>  |     | 10                   |     | ns   |

| CS High-Pulse Width                    | t <sub>CH</sub>   |     | 1/f <sub>SCLK</sub>  |     | ns   |

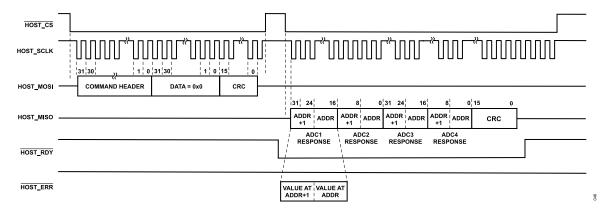

# **Timing Diagram**

Figure 3. SPI Timing Diagram

analog.com Rev. A | 8 of 122

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 4. Absolute Maximum Ratings

| Parameter                                                                                                                     | Rating                |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| VDD to GND                                                                                                                    | -0.3 V to +3.63 V     |

| RESET, GPIO's to GND                                                                                                          | -0.3 V to VDD + 0.3 V |

| Total Current into ALL GPIO Combined                                                                                          | 100 mA                |

| GND                                                                                                                           | 100 mA                |

| Output Current (sink) by Any GPIO Pin                                                                                         | 25 mA                 |

| Output Current (source) by Any GPIO Pin                                                                                       | −25 mA                |

| Continuous Package Power Dissipation 40-Lead LFCSP (multilayer board), T <sub>A</sub> = +70°C (derate 35.7 mW/°C above +70°C) | 2857.10 mW            |

| Temperature                                                                                                                   |                       |

| Operating Range                                                                                                               | -40°C to +105°C       |

| Storage Range                                                                                                                 | -65°C to +125°C       |

| Soldering (reflow)                                                                                                            | +260°C                |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure, and  $\theta_{JC}$  is the junction-to-case thermal resistance.

Table 5. Thermal Resistance

| Package Type | $\theta_{JA}$ | θ <sub>JC</sub> | Unit |

|--------------|---------------|-----------------|------|

| CP-40-33     | 45.0          | 2.0             | °C/W |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. A | 9 of 122

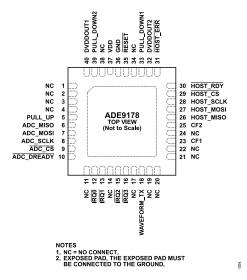

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

Table 6. Pin Function Descriptions

| Pin Number                                               | Mnemonic                  | Input/Output     | Active Low/High  | Description                                                                                                                                                                                                                                               |

|----------------------------------------------------------|---------------------------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3, 4, 11, 14, 17,<br>19, 20, 21, 22, 24,<br>34, 38 | NC                        | N/A <sup>1</sup> | N/A <sup>1</sup> | No Connect.                                                                                                                                                                                                                                               |

| 5                                                        | PULL_UP                   | N/A <sup>1</sup> | N/A <sup>1</sup> | 10 kΩ Pull-Up to VDD.                                                                                                                                                                                                                                     |

| 6                                                        | ADC_MISO                  | Input            | Active High      | Data Input for the ADC SPI Port to the supported Analog Front End (AFEs).                                                                                                                                                                                 |

| 7                                                        | ADC_MOSI                  | Output           | Active High      | Data Output for the ADC SPI Port from the supported AFEs.                                                                                                                                                                                                 |

| 8                                                        | ADC_SCLK                  | Output           | Active High      | Serial-Clock Output for the ADC SPI Port.                                                                                                                                                                                                                 |

| 9                                                        | ADC_CS                    | Output           | Active Low       | Chip Select for ADC SPI Port.                                                                                                                                                                                                                             |

| 10                                                       | ADC_DREADY                | Input            | Active Low       | DREADY Input, Signal to let ADE9178 know that ADC samples are ready. 0.01 $\mu\text{F}$ capacitor to GND.                                                                                                                                                 |

| 12, 13, 15, 16                                           | IRQ0, IRQ1, IRQ2,<br>IRQ3 | Output           | Active Low       | User-Programmable Interrupt Request Output.                                                                                                                                                                                                               |

| 18                                                       | WAVEFORM_TX               | Output           | Active High      | Waveform Streaming through a UART transmit pin.                                                                                                                                                                                                           |

| 23, 25                                                   | CF1, CF2                  | Output           | Active High      | Calibration Frequency (CF) Logic Output. This output provides power information and is used for operational and calibration purposes.                                                                                                                     |

| 26                                                       | HOST_MISO                 | Output           | Active High      | Data Output for the SPI Port to the Host MCU.                                                                                                                                                                                                             |

| 27                                                       | HOST_MOSI                 | Input            | Active High      | Data Input for the SPI Port from the Host MCU.                                                                                                                                                                                                            |

| 28                                                       | HOST_SCLK                 | Input            | Active High      | Serial-Clock Input from the Host MCU.                                                                                                                                                                                                                     |

| 29                                                       | HOST_CS                   | Input            | Active Low       | Chip-Select Input for Host SPI Port.                                                                                                                                                                                                                      |

| 30                                                       | HOST_RDY                  | Output           | Active Low       | Flag to let the Host MCU know that response from the Host Command is ready. 10 k $\Omega$ pull-up to VDD.                                                                                                                                                 |

| 31                                                       | HOST_ERR                  | Output           | Active Low       | Flag to let the Host MCU know that there is an error during the Command processing. 10 k $\Omega$ pull-up to VDD.                                                                                                                                         |

| 32                                                       | DVDDOUT2                  | N/A <sup>1</sup> | N/A <sup>1</sup> | Bypass with 4.7 nF to GND.                                                                                                                                                                                                                                |

| 33, 39                                                   | PULL_DOWN1,<br>PULL_DOWN2 | N/A <sup>1</sup> | N/A <sup>1</sup> | 1 kΩ Pull-Down to GND.                                                                                                                                                                                                                                    |

| 35                                                       | RESET                     | Input            | Active Low       | External System Reset Input. The device remains in reset while this pin is in its active state. When the pin transitions to its inactive state, the device performs a POR reset (resetting all logic) and begins execution. 22 pF and 0.1 $\mu$ F to GND. |

| 36                                                       | GND                       | N/A <sup>1</sup> | N/A <sup>1</sup> | Ground Reference for the Input Circuitry.                                                                                                                                                                                                                 |

| 37                                                       | VDD                       | Input            | N/A <sup>1</sup> | Supply Voltage. This pin provides the supply voltage. For specified operation, maintain the supply voltage at 3.3 V $\pm$ 10%. Bypass with 100 nF to GND and 1 $\mu F$ with 10 m $\Omega$ to 150 m $\Omega$ equivalent series resistance (ESR) to GND.    |

analog.com Rev. A | 10 of 122

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

# Table 6. Pin Function Descriptions (Continued)

| Pin Number | Mnemonic | Input/Output     | Active Low/High  | Description                                                                              |

|------------|----------|------------------|------------------|------------------------------------------------------------------------------------------|

| 40         | DVDDOUT1 | N/A <sup>1</sup> | N/A <sup>1</sup> | Bypass with 100 nF to GND and 1 $\mu$ F with 10 m $\Omega$ to 150 m $\Omega$ ESR to GND. |

| EP         | EPAD     | N/A <sup>1</sup> | N/A <sup>1</sup> | Exposed pad. The exposed pad must be connected to the ground.                            |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

analog.com Rev. A | 11 of 122

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

# **ENERGY LINEARITY OVER SUPPLY AND TEMPERATURE**

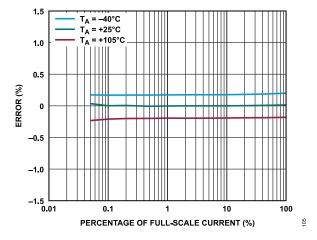

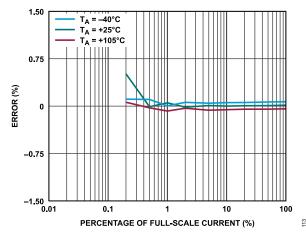

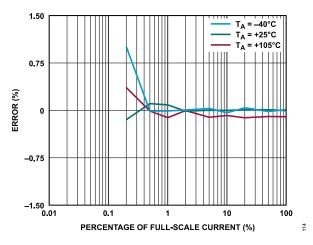

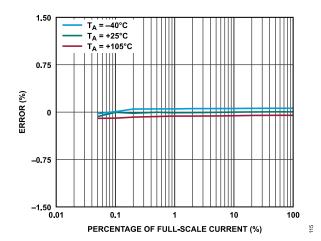

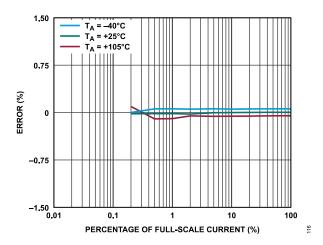

Total energies obtained from a sinusoidal voltage with an amplitude of 50% of full scale, a sinusoidal current with variable amplitude from 100% of full scale down to 0.05% of full scale. Frequency = 50 Hz and PF = 1.

Figure 5. Total Active Energy as a Percentage of Reading Over Temperature

Figure 6. Total Apparent Energy Error as a Percentage of Reading Over Temperature

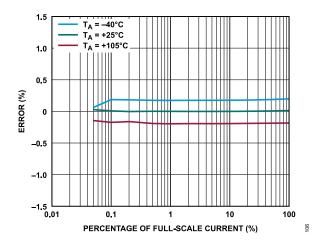

Figure 7. Total Active Energy as a Percentage of Reading Over Supply,  $T_{\Delta} = 25^{\circ}\text{C}$

Figure 8. Total Apparent Energy as a Percentage of Reading Over Supply,  $T_A = 25^{\circ}\text{C}$

analog.com Rev. A | 12 of 122

## TYPICAL PERFORMANCE CHARACTERISTICS

## **ENERGY ERROR OVER FREQUENCY AND POWER FACTOR**

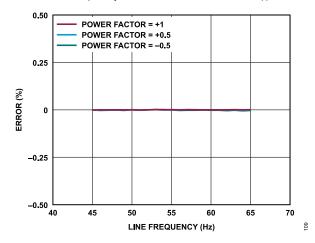

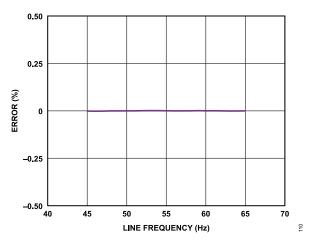

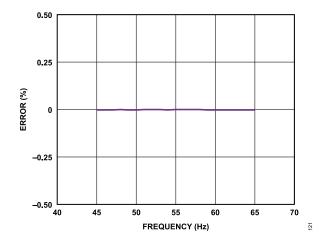

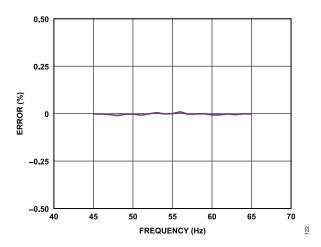

Total energies obtained from a sinusoidal voltage with an amplitude of 50% of full scale, a sinusoidal current with an amplitude of 10% of full scale. Variable frequency between 45 Hz and 65 Hz.  $T_A = 25$ °C,  $V_{DD} = 3.3$  V.

Figure 9. Total Active Energy Error as a Percentage of Reading Over Frequency, PF = +1, +0.5, -0.5

Figure 10. Total Apparent Energy Error as a Percentage of Reading Over Frequency, PF = +1

analog.com Rev. A | 13 of 122

## TYPICAL PERFORMANCE CHARACTERISTICS

## **ENERGY LINEARITY REPEATABILITY**

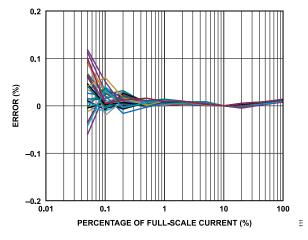

Total energies obtained from a sinusoidal voltage with an amplitude of 50% of full scale, a sinusoidal current with variable amplitude from 100% of full scale down to 0.05% of full scale. Frequency = 50 Hz, PF = 1,  $T_A = 25^{\circ}C$  and  $V_{DD} = 3.3$  V. Measurement repeated 30 times.

Figure 11. Total Active Energy Error as a Percentage of Full-Scale Current

analog.com Rev. A | 14 of 122

## TYPICAL PERFORMANCE CHARACTERISTICS

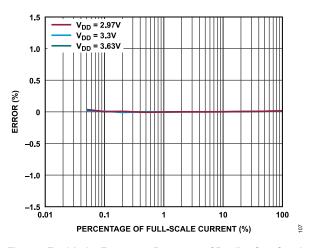

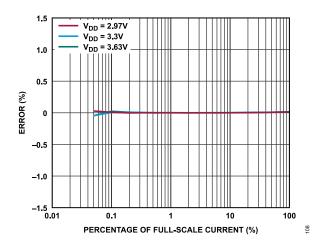

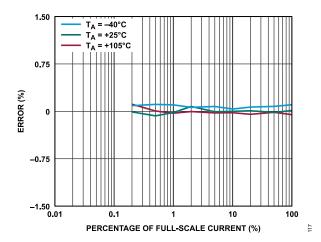

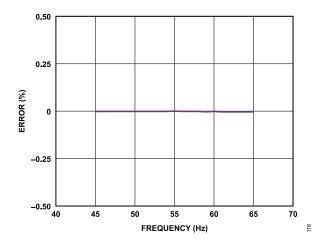

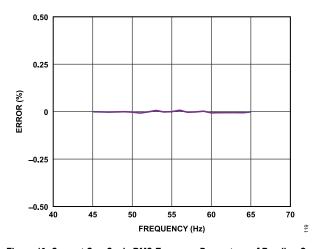

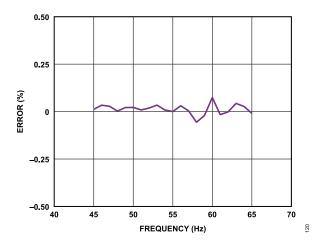

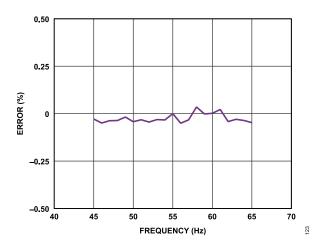

## RMS LINEARITY OVER TEMPERATURE AND RMS ERROR OVER FREQUENCY

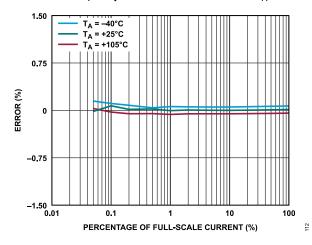

RMS linearity obtained from a variable sinusoidal voltage and current from 100% of full scale down to 0.05% of full scale. Frequency = 50 Hz, PF = 1,  $V_{DD} = 3.3$  V and HPF on.

RMS error obtained from a sinusoidal voltage with an amplitude of 50% of full scale and a sinusoidal current with an amplitude of 50% of full scale. Variable frequency between 45 Hz and 65 Hz.  $T_A = 25^{\circ}$ C,  $V_{DD} = 3.3$  V and HPF on.

Figure 12. Current Filtered RMS Error as a Percentage of Reading Over Temperature

Figure 13. Current One Cycle RMS Error as a Percentage of Reading Over Temperature

Figure 14. Current Half Cycle RMS Error as a Percentage of Reading Over Temperature

Figure 15. Voltage Filtered RMS Error as a Percentage of Reading Over Temperature

analog.com Rev. A | 15 of 122

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 16. Voltage One Cycle RMS Error as a Percentage of Reading Over Temperature

Figure 17. Voltage Half Cycle RMS Error as a Percentage of Reading Over Temperature

Figure 18. Current Filtered RMS Error as a Percentage of Reading Over Frequency

Figure 19. Current One Cycle RMS Error as a Percentage of Reading Over Frequency

Figure 20. Current Half Cycle RMS Error as a Percentage of Reading Over Frequency

Figure 21. Voltage Filtered RMS Error as a Percentage of Reading Over Frequency

analog.com Rev. A | 16 of 122

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 22. Voltage One Cycle RMS Error as a Percentage of Reading Over Frequency

Figure 23. Voltage Half Cycle RMS Error as a Percentage of Reading Over Frequency

analog.com Rev. A | 17 of 122

## TYPICAL PERFORMANCE CHARACTERISTICS

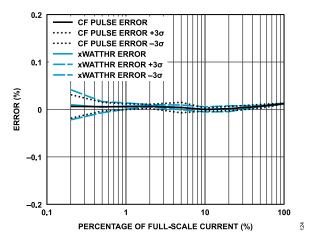

#### CF VS. ENERGY REGISTER CORRELATION AND CF JITTER

CF vs. energy register correlation obtained from a sinusoidal voltage with an amplitude of 50% of full scale, a sinusoidal current with variable amplitude from 100% of full scale down to 0.05% of full scale. Frequency = 50 Hz, PF = 1,  $T_A = 25^{\circ}C$  and  $V_{DD} = 3.3 \text{ V}$ .

CF jitter obtained from a sinusoidal voltage with an amplitude of 50% of full scale, a sinusoidal current with variable amplitude from 100% of full scale down to 0.05% of full scale. Frequency = 50 Hz, PF = 1,  $T_A$  = 25°C and  $V_{DD}$  = 3.3 V. CFx\_THR set to d1341078, which equates to 500 Hz CF output at full-scale current and CFx\_THR set to d22351312, which equates to 30 Hz at full-scale current.

Figure 24. Correlation Between CF Pulse and Registers for Total Active Energy Accumulation

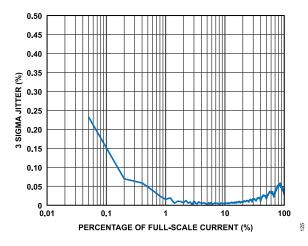

Figure 25. CF1 Jitter Over Current Full Scale, CF1\_THR = d1341078, CF2 Disabled

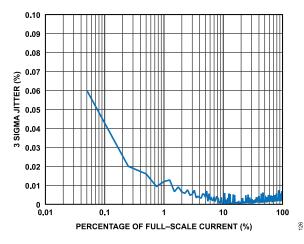

Figure 26. CF1 Jitter Over Current Full Scale, CF1\_THR = d22351312, CF2 Disabled

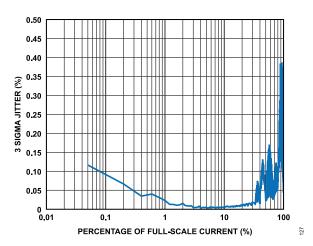

Figure 27. CF2 Jitter Over Current Full Scale, CF2\_THR = d1341078, CF1 Enabled

analog.com Rev. A | 18 of 122

# **TYPICAL PERFORMANCE CHARACTERISTICS**

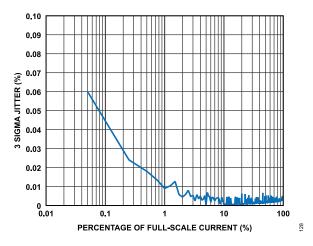

Figure 28. CF2 Jitter Over Current Full Scale, CF2\_THR = d22351312, CF1 Enabled

analog.com Rev. A | 19 of 122

## **TEST CIRCUIT**

Figure 29. ADE9178 + ADE91xx Test Circuit

analog.com Rev. A | 20 of 122

# **TERMINOLOGY**

For the common terminology, refer to the Analog Wiki.

analog.com Rev. A | 21 of 122

#### THEORY OF OPERATION

#### **ADC AND HOST SPI**

#### **ADC SPI**

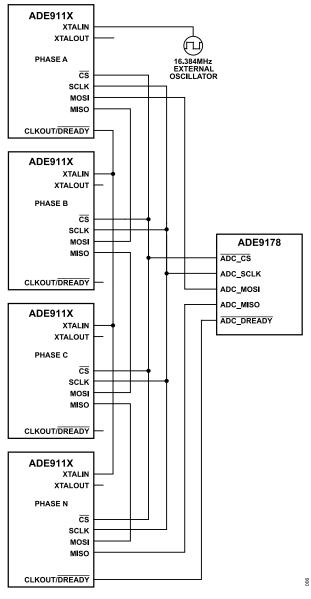

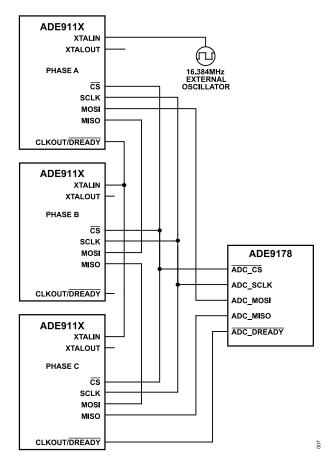

The ADE9178 receives ADC samples through ADC SPI. The application should connect the ADC in daisy-chain mode as explained in ADE9113 data sheet. The ADC clock should be provided by crystal to phase A ADC. Clock for phase B, phase C, and phase N ADC's can be connected to DREADY/CLKOUT of phase A as shown in Figure 30. The DREADY of last ADC in the chain should be connected to DREADY input pin of the ADE9178. Figure 30 and Figure 31 show the required connections when four ADCs and three ADCs are connected to ADE9178, respectively. Single and two ADC configurations are also supported.

Figure 30. Four ADCs Connection Diagram to ADE9178

Figure 31. Three ADCs Connection Diagram to ADE9178

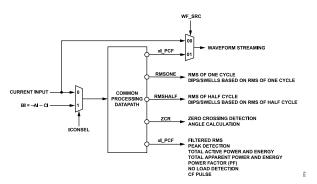

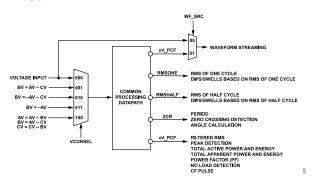

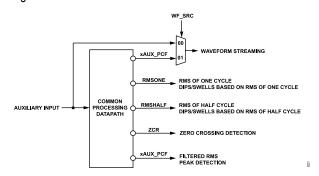

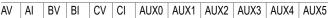

The ADE9178 supports three voltage (referred as AV, BV, and CV) and three current channels (referred as AI, BI, and CI) for metrology measurements and six auxiliary channels (AUX0, AUX1, ..., AUX5) for other measurements. The ADE9178 provides a multiplexer option that allows any ADC output to be redirected to any processing datapath by writing appropriate slot number to ADC\_REDIRECT0 and ADC\_REDIRECT1 register.

In the connections shown in Figure 30 and Figure 31, ADC SPI frames contain the data in the following sequence as shown in Table 7 (with last ADC data comes first). This position in SPI frames is referred as slots in this document where SLOT0 is the I channel of the ADC, which has its MISO connected directly to ADE9178.

analog.com Rev. A | 22 of 122

#### THEORY OF OPERATION

Table 7. ADC Channel to ADE9178 SLOT Mapping for Four and Three ADC Configurations

|       |             | ADE9113/ADE9103s Connected Three ADE9113/ADE9103s Connected Four ADE 0C_CONFIG:NUM_ADC = 0x4) (ADC_CONFIG:NUM_ADC = 0x3) |             |                  |              |                  | Connected (ADC_<br>= 0x4) | CONFIG:NUM_ADC |

|-------|-------------|--------------------------------------------------------------------------------------------------------------------------|-------------|------------------|--------------|------------------|---------------------------|----------------|

| Phase | ADC Channel | ADE9178 SLOT                                                                                                             | Phase       | ADC Channel      | ADE9178 SLOT | Phase            | ADC Channel               | ADE9178 SLOT   |

| N     | I           | SLOT0                                                                                                                    | С           | I                | SLOT0        | N                | I                         | SLOT0          |

| N     | V1          | SLOT1                                                                                                                    | С           | V1               | SLOT1        | N                | V1                        | SLOT1          |

| N     | V2          | SLOT2                                                                                                                    | С           | V2               | SLOT2        | N/A <sup>1</sup> | N/A <sup>1</sup>          | SLOT2          |

| С     | I           | SLOT3                                                                                                                    | В           | 1                | SLOT3        | С                | 1                         | SLOT3          |

| С     | V1          | SLOT4                                                                                                                    | В           | V1               | SLOT4        | С                | V1                        | SLOT4          |

| С     | V2          | SLOT5                                                                                                                    | В           | V2               | SLOT5        | N/A <sup>1</sup> | N/A <sup>1</sup>          | SLOT5          |

| В     | I           | SLOT6                                                                                                                    | Α           | 1                | SLOT6        | В                | 1                         | SLOT6          |

| В     | V1          | SLOT7                                                                                                                    | Α           | V1               | SLOT7        | В                | V1                        | SLOT7          |

| В     | V2          | SLOT8                                                                                                                    | Α           | V2               | SLOT8        | N/A <sup>1</sup> | N/A <sup>1</sup>          | SLOT8          |

| Α     | I           | SLOT9                                                                                                                    | Not present | N/A <sup>1</sup> | SLOT9        | Α                | 1                         | SLOT9          |

| Α     | V1          | SLOT10                                                                                                                   | Not present | N/A <sup>1</sup> | SLOT10       | Α                | V1                        | SLOT10         |

| Α     | V2          | SLOT11                                                                                                                   | Not present | N/A <sup>1</sup> | SLOT11       | N/A <sup>1</sup> | N/A <sup>1</sup>          | SLOT11         |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

Note that this means for a change in NUM\_ADC value away from default (0x4) the ADC\_REDIRECT0 and ADC\_REDIRECT1 registers must be updated. For example, with a three ADE91xx configuration shown in Figure 31, SLOT0 is now mapped to the current channel of phase C rather than the current channel of phase N.

For two channel ADCs (ADE9112), the V2 input is not present therefore the V2 data is 0 in the data packet. For the four ADE9112 example shown in Table 7, the ADC\_REDIRECT0 and ADC\_REDIRECT1 values stay the same as the four ADE9113/ADE9103 example except the data in SLOT2, SLOT5, SLOT8, and SLOT11 is 0.

Table 8 shows the default values to write to ADC\_REDIRECTO and ADC\_REDIRECT1 for different NUM\_ADC values assuming that the phase sequence matches the examples shown in Table 7 (ADE9178 MOSI connected to the first ADE91xx in the chain and ADE9178 MISO connected to the last ADE91xx in the chain).

For channels that are not present, a slot number of 0x1F should be written to corresponding bitfields of the ADC\_REDIRECT0 and ADC\_REDIRECT1.

Table 8. Default ADC REDIRECTx Values

| NUM_ADC Value | ADC_REDIRECT0 Value | ADC_REDIRECT1 Value |

|---------------|---------------------|---------------------|

| 0x4           | 0x6431D2A           | 0x410150B           |

| 0x3           | 0x1190C7            | 0x3FFF88A8          |

| 0x2           | 0x3FF00464          | 0x3FFFFC45          |

| 0x1           | 0x3FFFFC01          | 0x3FFFFFE2          |

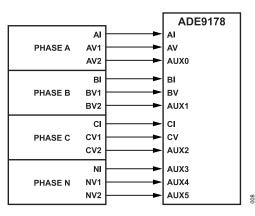

By default, for above connection, following mapping is done where AV1, BV1, and CV1 are mapped to AV, BV, and CV and AV2, BV2, CV2, NI, NV1, and NV2 are mapped to auxiliary channels as shown in Figure 32.

Figure 32. ADC to ADE9178 Channel Mapping

Note that setting ADC\_CONTROL RUN bit to 1 sets the sampling rate of the ADCs to 4 kHz.

# **Multiple ADC Synchronization**

If multiple ADCs are connected to ADE9178, the application can periodically issue synchronization of these ADCs through the ADC\_CONTROL register. This ensures that all ADCs sample at the same time. The ADC\_CONTROL register can be used to synchronize all ADCs periodically. To ensure correct operation, it is recommended to synchronize ADCs by writing ADC\_CONTROL = 0x5 (ADC\_SYNC = 1, ADC\_RUN = 1) once every day. The ADE9178 performs a synchronization sequence if the ADCs are out of synchronization. Note that energy calculation can be disrupted for ~1 ms during synchronization if it is required.

#### **ADC SPI Protocol CRC**

The ADE9178 checks whether there are any CRC errors in the data transmitted by ADC over SPI. If there is a CRC error in the data frame transmitted by an ADC, previous correct sample is used for

analog.com Rev. A | 23 of 122

#### THEORY OF OPERATION

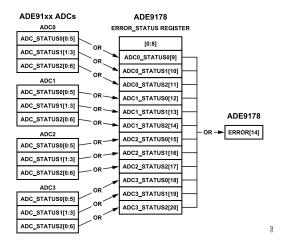

all calculations for all channels in that ADC. The ADE9178 also raises an error interrupt (ERROR\_STATUS:ADC\_CRC\_ERROR[6]) when this CRC error is detected. It is recommended to check ADC SPI connections if this error persists or raised frequently during development/design time of the application.

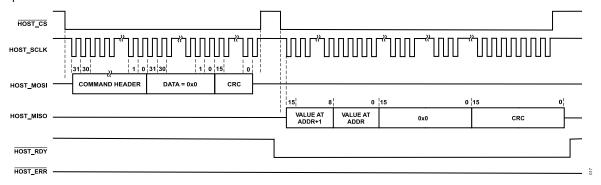

#### **Host SPI**

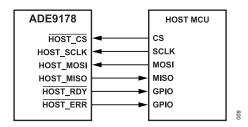

The SPI of the ADE9178 always acts as the subordinate and consists of six pins. These pins are shown with prefix HOST in Figure 33. Apart from standard SPI pins, HOST\_RDY or HOST\_ERR signal is used to indicate response is ready or error has occurred.

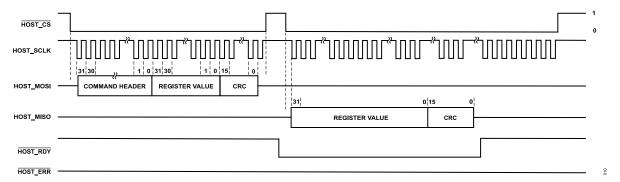

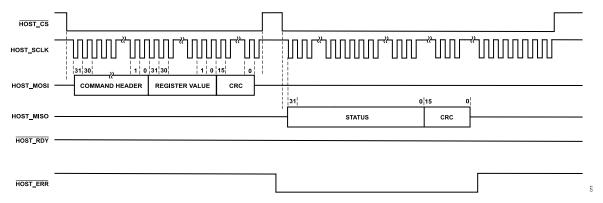

Data shifts into the device at the MOSI logic input on the falling edge of SCLK, and the device samples the input data on the rising edge of SCLK. Data shifts out of the ADE9178 at the MISO logic output on the falling edge of SCLK and must be sampled by the main device on the rising edge of SCLK. The least significant byte of the word is shifted in and out first. The most significant bit of each byte is sent first.

The ADE9178 is compatible with the following micro controller SPI port clock polarity and phase settings:

CPOL = 1 and CPHA = 1 (typically Mode 3).

The minimum and maximum serial clock frequency supported is 500 kHz and 25 MHz, respectively.

The ADE9178 takes time to a process read or write command. The ADE9178 raises HOST\_RDY when the command is successful. The host program must initiate the SPI read only after this IRQ is raised.

Figure 33. ADE9178 to Host MCU SPI Connection

#### Table 9. HOST SPI Pin Description

| Pins                                     | Description                                   |

|------------------------------------------|-----------------------------------------------|

| HOST_CS, HOST_SCLK, HOST_MOSI, HOST_MISO | Standard 4-wire SPI pins.                     |

| HOST_ERR                                 | Indicates last command has thrown error.      |

| HOST_RDY                                 | Indicates response for last command is ready. |

The HOST\_CS input must stay low for the whole SPI transaction. Bringing HOST\_CS high during a data transfer operation aborts the transfer. A new transfer can be initiated by returning the HOST\_CS logic input low. Therefore, if the application does not need to read back the register value (success case) or the status bits (error case) after a write command the application MCU can toggle HOST\_CS to ignore the returned value.

It is not recommended to connect HOST\_CS to ground because the high-to-low transition on HOST\_CS starts the ADE9178 SPI transaction.

analog.com Rev. A | 24 of 122

## THEORY OF OPERATION

Figure 34. Register Write SPI Protocol - Success Case

Figure 35. Register Write SPI Protocol - Error Case

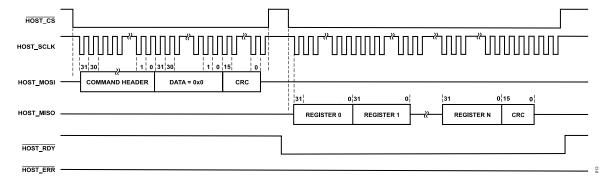

Figure 36. Register Read SPI Protocol - Success Case

Figure 37. Register Read SPI Protocol - Error Case

analog.com Rev. A | 25 of 122

#### THEORY OF OPERATION

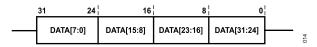

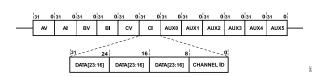

Note that all data including register values for write, read response, and status are 32-bit values and sent over the SPI as least significant byte (LSByte) first as shown in Figure 38.

Figure 38. ADE9178 Data/Response SPI Frame Format

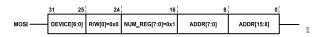

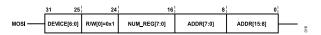

The command header is also a 32-bit field with 24<sup>th</sup> bit indicates if the command is read or write. The format for the write and read command header is shown in Figure 39 and Figure 40, respectively.

Figure 39. Write Command Header

Figure 40. Read Command Header

Table 10. Command Header Details

| Field         | Description                                                                                                                                                                                                                                                                                                                                                   |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR          | Address of registers, which need to be accessed.                                                                                                                                                                                                                                                                                                              |

| R/W           | 1: Read.<br>0: Write.                                                                                                                                                                                                                                                                                                                                         |

| Device        | 0: ADE9178. 1: ADC0 - ADC connected to ADC_MISO pin of the ADE9178. 2: ADC1 - ADC connected to ADC_MOSI pin of ADC1. 3: ADC2 - ADC connected to ADC_MOSI pin of ADC2. 4: ADC3 - ADC connected to ADC_MOSI pin of ADC3. 5: All ADCs.                                                                                                                           |

| NUM Registers | Number of registers to be read. The ADE9178 sends those many registers starting from the address in the command header. Note that this must be 1 for write commands. If the device field of the command is not ADE9178 (0), NUM_REGISTER field is ignored and always two 8-bit registers are returned as response. For more details, see the ADC SPI section. |

In case of error, 4 bytes status code is sent as response for read and write command.

Table 11 shows the status codes that return.

analog.com Rev. A | 26 of 122

# **THEORY OF OPERATION**

Table 11. Status Code Description

| Error Code                    | Failure Reason                                                                                                                                       | Relevant Commands           | Command Purpose          | ERROR_STATUS Bit                                                    | Solution                                                                                                                                                                                                                  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x1                           | Register address not present.                                                                                                                        | Read/Write ADE9178 Register |                          | N/A <sup>1</sup>                                                    | For more details on the register, see the Register Summary: ADE9178 section. Use macros in ade9178.h for address.                                                                                                         |

| 0x2                           | Invalid device.                                                                                                                                      | Read/Write AD               | DE9178/ADC Register      | N/A <sup>1</sup>                                                    | Verify that the device field is correct.                                                                                                                                                                                  |

| 0x3                           | Write to more than one register at a time is not supported.                                                                                          | Write AD                    | E9178 Register           | N/A <sup>1</sup>                                                    | Make NUM_REGISTERS = 1 for write command.                                                                                                                                                                                 |

| 0x4                           | Register is a read only register. Note that this error is applicable only when device field is ADE9178. Read only check is not done for ADC devices. | Write ADE9178 Register      |                          | N/A <sup>1</sup>                                                    | For more details on the registers read/write access, see the Register Summary: ADE9178 section.                                                                                                                           |

| 0x5                           | Provided BAUD_RATE field of WFS_CONFIG register is not sufficient to stream all channels that are enabled in WFS_CONFIG.                             | Write ADE9178 Register      |                          | N/A <sup>1</sup>                                                    | Update BAUD_RATE. For more details on minimum baud rate, see the Waveform Streaming section.                                                                                                                              |

| 0x6                           | Configuration Lock is enabled.                                                                                                                       | Write ADE9178 Register      |                          | N/A <sup>1</sup>                                                    | Unlock configuration registers by writing 0 to CONFIG_LOCK register.                                                                                                                                                      |

| 0x7                           | Slots configured in the ADC_REDIRECTx register is not supported.                                                                                     | ADC_REDIRECTx               | ADC Datapath Redirection | N/A <sup>1</sup>                                                    | Verify that the value written to the register is correct.                                                                                                                                                                 |

| 0x8                           | Command failed to execute.                                                                                                                           | ADC_CONTROL = 0x2           | Initialize ADC           | ADC_INIT_ERROR                                                      | Retry the command.                                                                                                                                                                                                        |

|                               |                                                                                                                                                      | Read/Write ADC Register     |                          | N/A <sup>1</sup>                                                    | If ADE9178 is reset while ADC_RUN = 1, then subsequent ADC read/ writes may return the COMMAND_FAILED code even though the ADC read/ write is successful. It is recommended to reinitialize the ADCs after ADE9178 reset. |

|                               | Number of ADCs configured is incorrect.                                                                                                              | ADC_CONFIG                  | Configure number of ADCs | N/A <sup>1</sup>                                                    | Check if the number of ADCs being configured is between 1 and 4.                                                                                                                                                          |

| 0x9 ADCs are not initialized. | ADC_CONTROL = 0x1                                                                                                                                    | Start ADC data capture      | N/A <sup>1</sup>         | Verify that ADC initialization is done by writing 2 to ADC_CONTROL. |                                                                                                                                                                                                                           |

|                               |                                                                                                                                                      | ADC_CONTROL = 0x5           | Synchronize ADC          | N/A <sup>1</sup>                                                    | Verify that ADC initialization is done by writing 2 to ADC_CONTROL.                                                                                                                                                       |

| 0xA                           | Issue in SPI communication between Host MCU and ADE9178.                                                                                             | Read/Write ADE9178 Register |                          | N/A <sup>1</sup>                                                    | Check CRC header values. Reset ADE9178 if error persists.                                                                                                                                                                 |

| 0xB                           | Synchronization already in progress and has not yet                                                                                                  | ADC_CONTROL = 0x5           | Synchronize ADCs         | N/A <sup>1</sup>                                                    | Synchronization is already issued. Wait for it to complete.                                                                                                                                                               |

|                               | complete.                                                                                                                                            | Read/Write ADC Register     |                          | N/A <sup>1</sup>                                                    | Synchronization is already issued. Wait for it to complete.                                                                                                                                                               |

analog.com Rev. A | 27 of 122

# **THEORY OF OPERATION**

Table 11. Status Code Description (Continued)

| Error Code       | Failure Reason                  | Relevant Commands | Command Purpose  | ERROR_STATUS Bit           | Solution                                                |

|------------------|---------------------------------|-------------------|------------------|----------------------------|---------------------------------------------------------|

| N/A <sup>1</sup> | Issue in SPI data transmission. | Read/Write        | ADE9178 Register | HOST_SPI_RUNTIME_ERR<br>OR | Retry the command. Reset ADE9178 if the error persists. |

| N/A <sup>1</sup> | Issue in UART communication.    |                   | WFS              | UART_RUNTIME_ERROR         | Reset ADE9178 if the error persists.                    |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

analog.com Rev. A | 28 of 122

#### THEORY OF OPERATION

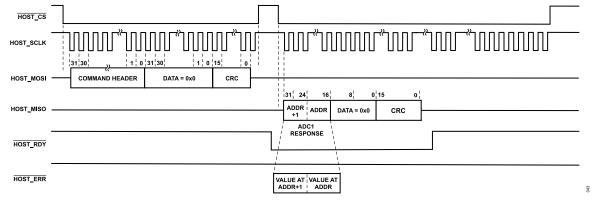

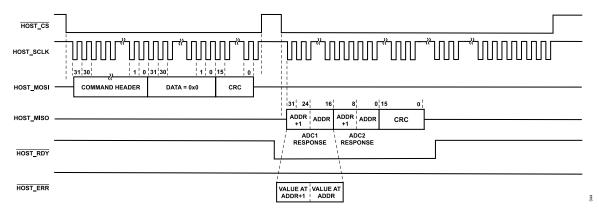

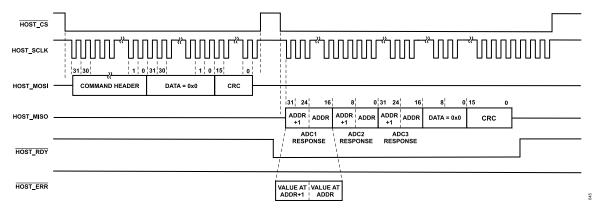

# Support for Reading and Writing ADC Registers

The ADE9178 provides support for reading and writing ADC registers by configuring the device field of the command. If the device is a nonzero value less than 5, the read or write command is sent to corresponding ADC. If the device field is 5, the same command is sent to all ADCs in the daisy chain. ADC reads return two 8-bit values, the value at the address in the command header and the value at the consecutive address.

See Table 10 to relate ADC number to physical ADC channel, for example, ADC1 relates to the ADC that is connected to the ADC MISO pin of the ADE9178.

For single ADC write, the protocol is the same as shown in Figure 34 except the register value in the Command Header and the Register Value is stored in the lower 8 bits of the 32-bit register (upper 24 bits are 0 padded). For multiple ADC write, it is important to note that the same register value is written to all ADCs and depending on how many ADCs are connected to ADE9178 the response size changes.

Figure 41. Protocol to Read ADC Registers Individually

Figure 42. Protocol to Read ADC Registers Simultaneously (NUM ADC = 0x1)

analog.com Rev. A | 29 of 122

#### THEORY OF OPERATION

Figure 43. Protocol to Read ADC Registers Simultaneously (NUM\_ADC = 0x2)

Figure 44. Protocol to Read ADC Registers Simultaneously (NUM\_ADC = 0x3)

Figure 45. Protocol to Read ADC Registers Simultaneously (NUM\_ADC = 0x4)

analog.com Rev. A | 30 of 122

#### THEORY OF OPERATION

#### **Host SPI Protocol CRC**

The ADE9178 SPI port uses CRC to verify the integrity of the data received and sent over the SPI. CRC-16-CCITT algorithm with initial value 0xFFFF is used for this purpose.

The CRC of the command field (COMMAND\_HEADER + DATA) is calculated and compared against the CRC field of the command. If there is a CRC mismatch, command is not executed, HOST\_ERR pin is raised, and status code 0xA (for more details, see Table 11) is returned. By default the CRC check is enabled and can be disabled by writing CRC\_DIS bit of CONFIG0. For that purpose, use the following command fields:

- Command Header = 0x0001AE00

- ▶ Register Value = 0x20000180

- ► CRC = 0x26BE

Note that the SPI command frame size is fixed and application should send 2 dummy bytes as CRC even if CRC check is disabled for the command. The 16-bit CRC of the response is appended at the end of every response. There is no option to disable this but application can ignore the CRC if there is no need to verify the integrity of the response.

## **CRC of Configuration Registers**

The configuration register CRC feature monitors many register values. It also optionally includes 15 register sets that are individually selectable in the CRC\_OPTEN register. The result is stored in the CRC\_RSLT register. If any of the monitored registers change value, the CRC\_RSLT changes as well, and the CRC\_CHG bit in the STATUS1 register is set; this can also be configured to generate an interrupt on  $\overline{IRQ1}$ . For more details, see CRC\_OPTEN in the Register Details: ADE9178 section.

## **Configuration Lock**

To prevent accidental overwriting of configuration registers, a provision to lock writing of configuration registers is provided. The user can write 0x1 to the CONFIG\_LOCK register to lock the ability to write to the configuration registers. When the lock is enabled, all writes to configuration registers other than CONFIG\_LOCK throw an error. The configuration register write can be unlocked by writing 0x0 to the CONFIG\_LOCK register.

#### **Burst Register Read**

The ADE9178 supports burst reading of up to 256 registers by using the NUM\_REGISTERS field in the SPI write command header (for more details, see the Host SPI section). There are five address ranges supported by the ADE9178, which are shown in Table 12.

Table 12. Burst Read Address Ranges

| Name                                 | Address Range (Inclusive) |

|--------------------------------------|---------------------------|

| Config registers                     | 0x0 to 0xDD               |

| Output registers                     | 0x200 to 0x295            |

| Status registers                     | 0x400 to 0x40B            |

| Output registers grouped by function | 0x600 to 0x630            |

| Output registers grouped by phase    | 0x631 to 0x661            |

For each address space, wrap-around happens if start address and NUM\_REGISTERS combination gives an address greater than last address in that range. For example, if application issues a read with 0x290 as ADDRESS and NUM\_REGISTERS as 10, then the returned registers are 0x290, 0x291, 0x292, 0x293, 0x294, 0x295, 0x200, 0x201, 0x202, and 0x203.

There are some address gaps in the register map, which are not documented and untested. Burst read works as if it is a normal register but the value is undefined.

## Clear-on-Read Registers

The energy registers can be configured to be clear-on-read (for more details, see the Energy Calculation section) and peak registers are always clear-on-read. If burst access is issued for such registers, registers are cleared just before initiating the SPI traction for response. For example, addresses of IPEAK, VPEAK, and AUXPEAK are 0x285, 0x286, and 0x287, respectively. If a read is issued with ADDRESS 0x284 and NUM\_REGISTERS as 4, all three peak registers are cleared before sending the values of registers from 0x284 to 0x287.

Note that the exact time of clearing the register is not defined. It can vary between the time the command reaches the ADE9178 and the HOST\_RDY pin is asserted. Even if the transaction is aborted or the response is corrupted for clear-on-register register reads, the register is cleared and there is no way to retrieve the data.

# FULL-SCALE CODES AND CONVERSION EQUATIONS

The ADE9178 calculates various parameters on the input channels and provides output as 32-bit registers in fixed point format. It can be easily converted to physical units such as amperes, volts, and watt. It is required to have knowledge of what is the input voltage and current that gives full-scale ADC input and what are the output registers given by the ADE9178 for such input. Signals corresponding to full-scale input in physical units are referred as  $X_{FS}$ , where,  $X_{FS}$  can be either  $I_{FS}$ ,  $V_{FS}$ \_T, or AUX<sub>FS</sub> based on whether channels are current, voltage, or auxiliary, respectively. These parameters are choices made during system design and it is assumed that the application developers are already aware of it. Table 13 summarizes the ADE9178 register values when full-scale inputs are provided at ADC inputs. These are referred as  $X_{FS}$  CODES, where X can vary based on type of the register.

analog.com Rev. A | 31 of 122

# THEORY OF OPERATION

Table 13. Terminology and Full-Scale Codes

| Notation                | Description                                                                                                                                                                                                                                                                                                                        | Value                                                                                                                 | Applicable Registers                         |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| I <sub>FS</sub>         | RMS Current in amperes (A <sub>RMS</sub> ), which gives full-scale signal at ADC input. This is the current that gives full scale at the ADC current (IP) inputs of ±31.25 mV peak to peak.                                                                                                                                        | Depends on system parameters. For more details, see the example system configuration. Depends on shunt resistor size. |                                              |

| V <sub>FS_T</sub>       | Theoretical full-scale RMS voltage in volts (V <sub>RMS</sub> ), which gives full-scale input at ADC input. This is the voltage that gives full scale at the ADC voltage (V1P) inputs of ±1 V peak to peak.                                                                                                                        | Depends on system parameters. Depends on resistor-divider ratio.                                                      |                                              |

| AUX <sub>FS</sub>       | Signal value (RMS) in appropriate units, which gives full-scale value at ADC input. The units can be either voltage or current. This is the voltage/current that gives full scale at the auxiliary ADC input. ±1 V peak to peak for V1P/V2P inputs and ±31.25 mV peak to peak for IP input, which depends on the ADC Mux settings. | Depends on system parameters.                                                                                         |                                              |

| $RMS_{FS\_CODES}$       | RMS output register value when full-scale input is applied to the ADC input.                                                                                                                                                                                                                                                       | 107310840                                                                                                             | xRMS, xRMSONE, xRMSHALF, xDIP, xSWELL, xPEAK |

| POW <sub>FS_CODES</sub> | Power output register value when full-scale voltage and current of same phase is applied at the ADC input.                                                                                                                                                                                                                         | 85829040                                                                                                              | xWATT, xVA                                   |

| PCF <sub>FS_CODES</sub> | Phase compensation filter (PCF) output for waveform streaming.                                                                                                                                                                                                                                                                     | 6706531                                                                                                               |                                              |

| M                       | Meter constant (impls/kWHr), which defines the frequency of the CF pulse output.                                                                                                                                                                                                                                                   | System Configuration. Supported between 100 and 10000.                                                                |                                              |

The format for configuration registers for each feature are given along with description of appropriate features are shown in the

following sections. To convert output registers to physical quantities, use the following equations shown in Table 14.

Table 14. Conversion Equations

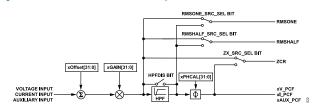

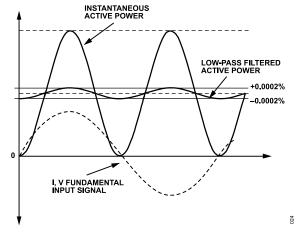

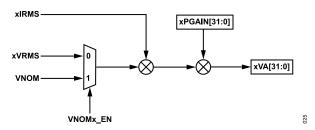

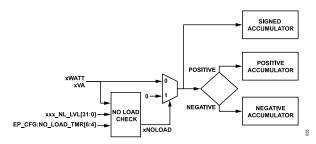

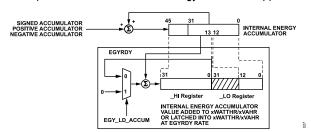

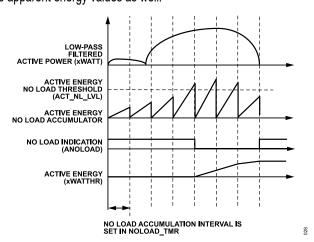

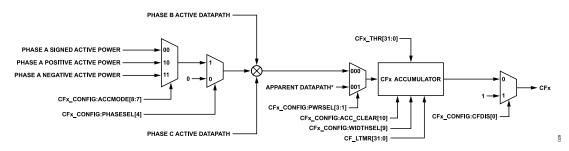

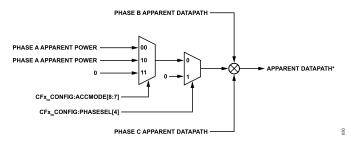

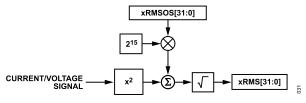

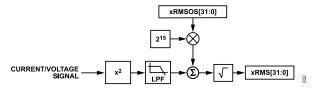

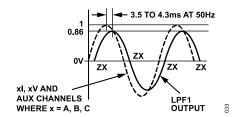

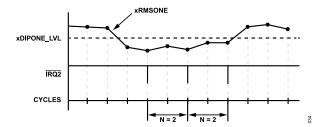

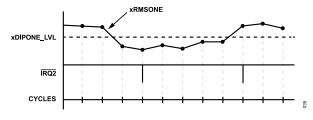

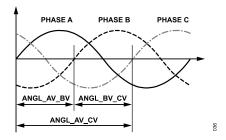

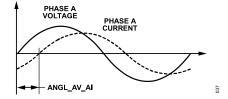

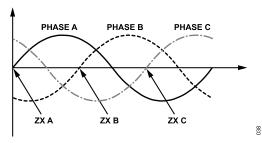

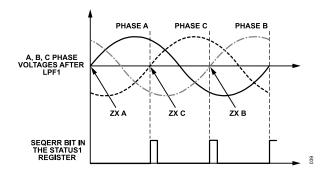

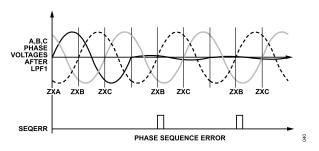

| Purpose                        | Equation                                                                                                                 | Unit                 | Applicable registers                                                                          |