# 24-Bit, DC to 50 kHz Input Bandwidth, Multichannel, Low Noise Precision Sigma-Delta ADC with PGA

#### **FEATURES**

- ▶ Precision AC and DC performance

- Noise RTI 5.5 nV/√Hz (gain = 128)

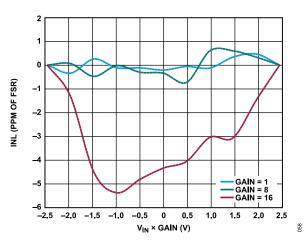

- ▶ INL: ±0.5 ppm of FSR

- SNR 110 dB typical (V<sub>REF</sub> = 4.096 V, gain = 1 precharge, sinc<sup>5</sup> filter)

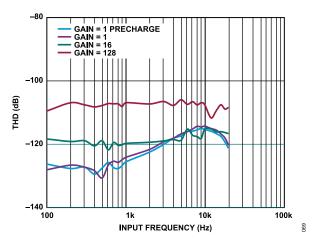

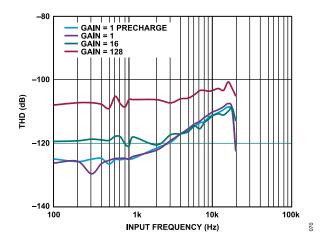

- ► THD: -120 dB typical

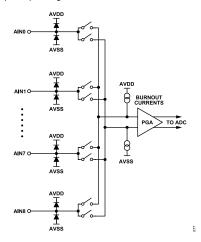

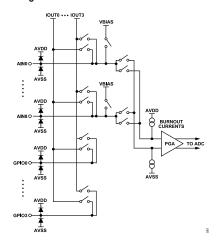

- ▶ Crosspoint multiplexed analog inputs

- ▶ 4 differential/8 pseudodifferential inputs

- Overvoltage/undervoltage tolerant on inactive analog inputs

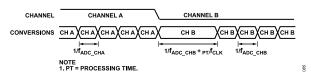

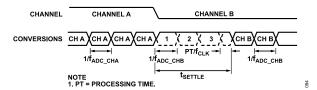

- ► Channel scan data rate of 71.4 kSPS/channel (14 µs settling)

- ▶ Ultra-low noise integrated PGA, gains of 0.5 to 128

- Output data rate: 7.6 SPS to 500 kSPS

- ▶ Flexible digital filters

- ▶ Low ripple FIR: ±0.005 dB maximum pass-band ripple

- User programmable FIR filter options

- Low latency sinc filters

- ▶ Simultaneous 50 Hz/60 Hz rejection

- ▶ Band gap reference with 5 ppm/°C drift typical

- Internal oscillator and temperature sensor

- ▶ Analog power supply: 4.75 V to 5.25 V or ±2.5 V

- Digital power supply: 1.7 V to 5.25 V

- Matched programmable excitation current sources

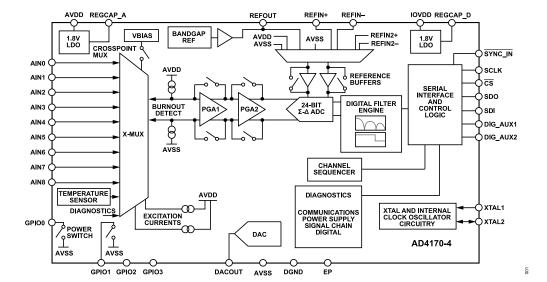

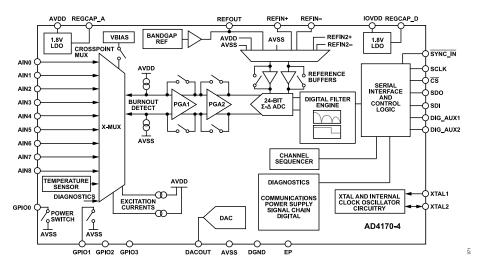

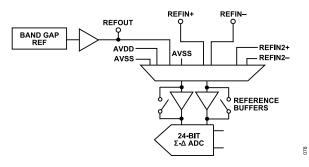

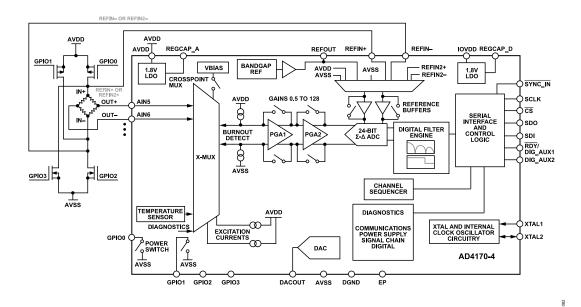

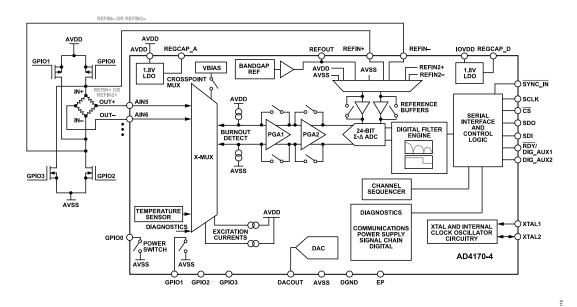

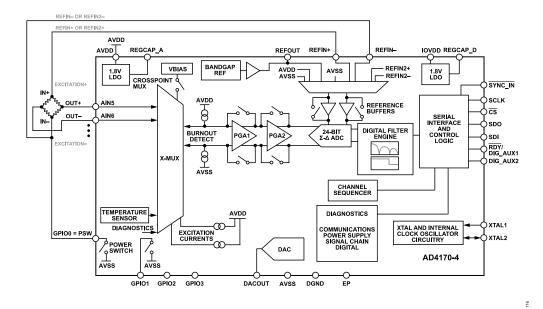

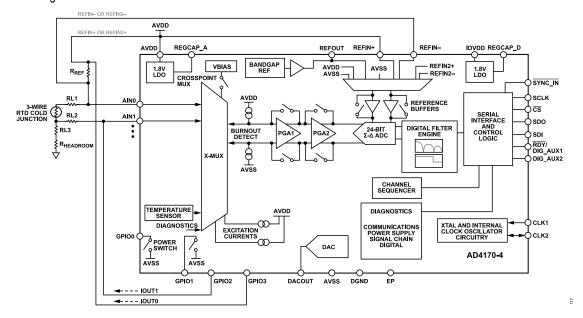

**FUNCTIONAL BLOCK DIAGRAM**

- ► Low-side power switches

- ▶ AC excitation

- On-chip bias voltage generator

- ▶ 4 general-purpose inputs/outputs

- ▶ Internal and system calibration

- Sensor burnout detection

- Diagnostic functions

- ▶ Per channel configuration

- Flexible channel sequencer

- ▶ 3- or 4-wire serial interface

- Schmitt trigger on SCLK

- ▶ SPI, QSPI, MICROWIRE, and DSP compatible

- ▶ TDM compatible interface for data streaming

- ▶ Performance temperature range: -40°C to +105°C

- ► Functional temperature range: -40°C to +125°C

- ▶ 32-lead 4 mm × 6 mm LFCSP

#### **APPLICATIONS**

- ▶ Industrial process control: PLC/DCS modules

- ▶ Temperature and pressure measurement

- High accuracy medical and scientific instrumentation

- Chromatography

- Seismic and energy exploration

- ▶ Electrical test and measurement

- Acoustic analysis

- Instrumentation

- Weigh scale

Figure 1.

# **TABLE OF CONTENTS**

| Features                                    | 1  | Digital Interface                       | 62 |

|---------------------------------------------|----|-----------------------------------------|----|

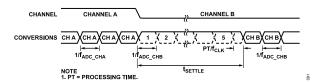

| Applications                                | 1  | ADC Conversion Modes and Accessing      |    |

| Functional Block Diagram                    | 1  | Conversions                             | 62 |

| General Description                         | 4  | Continuous Read                         | 62 |

| Specifications                              | 5  | Continuous Transmit                     | 63 |

| Timing Characteristics                      | 11 | SPI Frame Synchronization               | 64 |

| Absolute Maximum Ratings                    | 15 | ADC Synchronization                     |    |

| Thermal Resistance                          |    | Standard Synchronization                | 67 |

| ESD Caution                                 | 15 | Alternate Synchronization               |    |

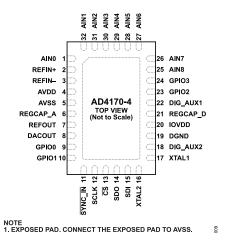

| Pin Configuration and Functions Description | 16 | Synchronizing Multiple AD4170-4 Devices |    |

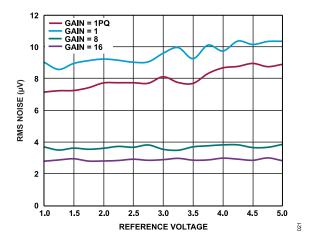

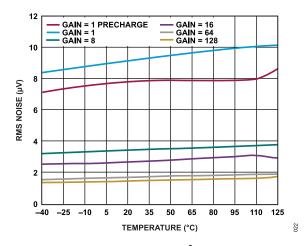

| Typical Performance Characteristics         |    | Diagnostics                             |    |

| RMS Noise and Resolution                    |    | Device Error                            |    |

| Sinc <sup>5</sup> + Avg                     |    | Signal Chain Check                      |    |

| Sinc <sup>3</sup>                           |    | Reference Detect                        |    |

| Sinc <sup>5</sup>                           |    | Reference Overvoltage/Undervoltage      |    |

| Post Filters                                |    | Detection                               | 68 |

| Average by 16 Post Filter                   |    | Conversion Errors                       |    |

| FIR Filter                                  |    | Analog Input Overvoltage/Undervoltage   |    |

| SNR and THD                                 |    | Detection                               | 68 |

| Theory of Operation                         |    | Excitation Current Compliance           |    |

| Overview                                    |    | Power Supply Monitors                   |    |

| Power Supplies                              |    | LDO Monitoring                          |    |

| Digital Communication                       |    | SPI SCLK Counter                        |    |

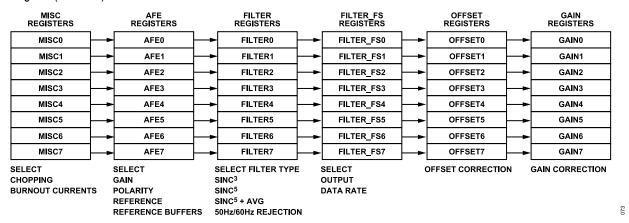

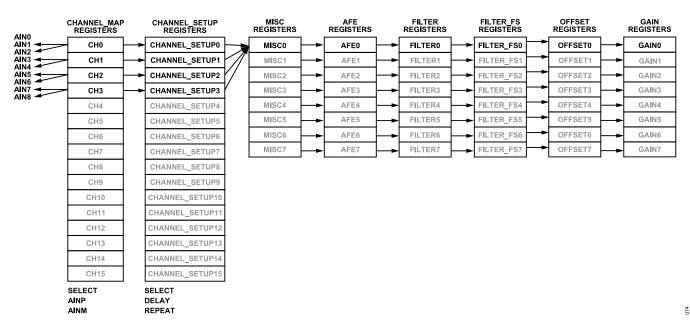

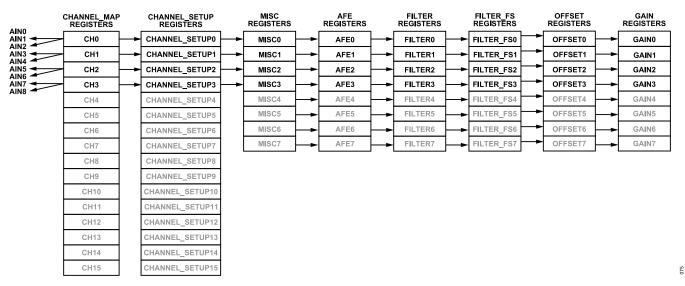

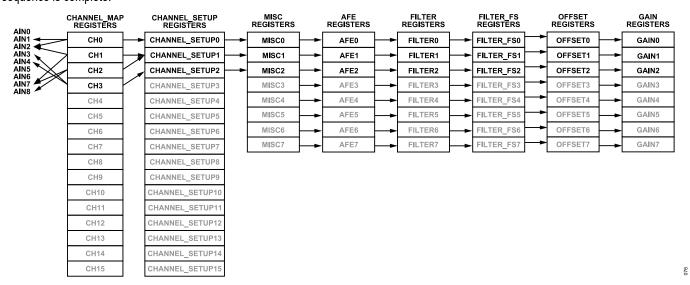

| Configuration Overview                      |    | SPI Read/Write Errors                   |    |

| ADC Circuit Information                     |    | Not Ready Error                         |    |

| Analog Input Channel                        |    | Checksum Protection                     |    |

| Programmable Gain Amplifier (PGA)           |    | Memory Map Checksum Protection          |    |

| Reference                                   |    | ROM Checksum Protection                 |    |

| Bipolar/Unipolar Configuration              |    | Burnout Currents                        |    |

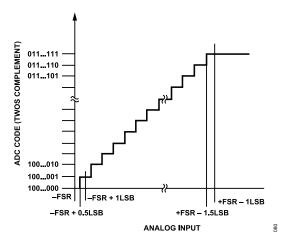

| Data Output Coding                          |    | Pull-up Currents                        |    |

| Excitation Currents                         |    | Temperature Sensor                      |    |

| Bridge Power-Down Switch                    |    | Grounding and Layout                    |    |

| General-Purpose Inputs/Outputs (GPIO0 to    |    | Applications Information                |    |

| GPIO3)                                      |    | Weigh Scale (AC Excitation)             |    |

| Bias Voltage Generator                      | 48 | Weigh Scale (DC Excitation)             |    |

| DAC                                         |    | Temperature Measurement Using an RTD    |    |

| Multiplexer Chopping                        |    | On-chip Register Map                    |    |

| AC Excitation                               |    | INTERFACE CONFIG A Register             |    |

| Clock                                       |    | INTERFACE_CONFIG_B Register             |    |

| Standby and Power-Down Modes                |    | DEVICE_CONFIG Register                  |    |

| Calibration                                 |    | CHIP TYPE Register                      |    |

| Span and Offset Limits                      |    | Product_ID L Register                   |    |

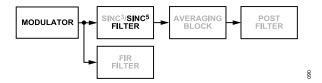

| Digital Filter                              |    | Product_ID_H Register                   |    |

| Sinc <sup>5</sup> + Avg Filter              |    | CHIP GRADE Register                     |    |

| Sinc <sup>5</sup> Filter                    |    | SCRATCH _PAD Register                   |    |

| Sinc <sup>3</sup> Filter                    |    | SPI REVISION Register                   |    |

| Post Filters                                |    | VENDOR_L Register                       |    |

| FIR Filter                                  |    | VENDOR_H Register                       |    |

| Anti-Aliasing Filtering                     |    | INTERFACE CONFIG C Register             |    |

| , with a wild string in the tring           |    | TATE IN AGE_GOINT TO_G TREGISTER        | 00 |

# **TABLE OF CONTENTS**

| INTERFACE_STATUS_A Register           | 86      | V BIAS Register             | 103 |

|---------------------------------------|---------|-----------------------------|-----|

| STATUS Register                       |         | I_PULL_UP Register          | 103 |

| DATA_16B Register                     | 87      | CURRENT SOURCE Registers    |     |

| DATA 16B STATUS Register              |         | FIR CONTROL Register        | 105 |

| DATA 24B Register                     | 87      | COEFF WRITE DATA Register   | 106 |

| DATA_24B_STATUS Register              | 88      | COEFF_READ_DATA Register    | 106 |

| DATA_PER_CHANNEL Registers            | 88      | COEFF_ADDRESS Register      | 106 |

| PIN_MUXING Register                   |         | COEFF_WR_RD_STB Register    | 107 |

| CLOCK_CTRL Register                   | 90      | DAC_SPAN Register           | 107 |

| STANDBY_CTRL Register                 | 90      | DAC_ENABLE Register         | 107 |

| POWER_DOWN_SW Register                | 91      | HW_TOGGLE_MASK Register     | 108 |

| ADC_CTRL Register                     | 91      | HW_LDAC_MASK Register       | 108 |

| ERROR_EN Register                     | 93      | DAC_DATA Register           |     |

| ERROR Register                        | 94      | SW_TOGGLE_TRIGGERS Register | 109 |

| CHANNEL_EN Register                   | 95      | SW_LDAC Register            | 109 |

| CHANNEL_SETUP Registers               | 96      | DAC_INPUT_A Register        | 109 |

| CHANNEL_MAP Registers                 |         | DAC_INPUT_B Register        | 110 |

| Miscellaneous (MISC) Registers        | 98      | GPIO_MODE Register          | 110 |

| AFE Registers                         | 99      | GPIO_OUTPUT_DATA Register   | 111 |

| FILTER Registers                      | 100     | GPIO_INPUT_DATA Register    |     |

| FILTER_FS Registers                   | 101     | Outline Dimensions          | 112 |

| OFFSET Registers                      | 102     | Ordering Guide              | 112 |

| GAIN Registers                        |         | Evaluation Boards           | 112 |

| REF_CONTROL Register                  | 102     |                             |     |

| REVISION HISTORY                      |         |                             |     |

| 10/2025—Rev. 0 to Rev. A              |         |                             |     |

|                                       |         |                             | 30  |

|                                       |         |                             |     |

| •                                     |         |                             |     |

| Change to Weigh Scale (AC Excitation) | Section |                             | 74  |

|                                       |         | e 58                        |     |

| _                                     |         |                             |     |

5/2024—Revision 0: Initial Version

analog.com Rev. A | 3 of 112

#### **GENERAL DESCRIPTION**

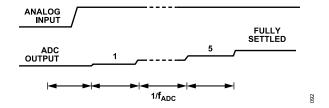

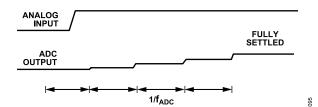

The AD4170-4 is a DC to 50 kHz input bandwidth, low noise, high speed, completely integrated analog front end for high precision measurement applications. The AD4170-4 offers output data rates from 7.6 SPS up to 500 kSPS. The device contains a low noise, 24-bit  $\Sigma$ - $\Delta$  analog-to-digital converter (ADC), and can be configured to have four differential inputs or eight single-ended or pseudodifferential inputs. The on-chip low noise gain stage ensures that signals of small amplitude can be interfaced directly to the AD4170-4.

The AD4170-4 offers the highest degree of signal chain integration. The device contains an internal reference and accepts two external differential references, which can be internally buffered. Other key integrated features include the following:

- ▶ Programmable gain amplifier (PGA). Due to the programmable gain (0.5 to 128), the PGA allows direct interfacing to transducers with low output amplitudes such as resistive bridges, thermocouples, and resistance temperature detectors (RTDs).

- ► The PGA has a wide common-mode input range, giving designers greater margin for widely varying input common modes.

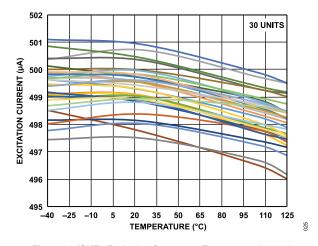

- Low drift, well matched precision current sources. Excitation current sources can be used to excite 2-, 3-, and 4-wire RTDs or bridge type sensors. Excitation current output options include 10 μA, 50 μA, 100 μA, 250 μA, 500 μA, 1 mA, and 1.5 mA. The currents can also be added if higher currents are needed. The currents are made up of two pairs with the pairs optimized for matching and drift matching.

- ► The low-side power switch (PDSW) can be used to power down bridge sensors between conversions.

- ▶ Voltage bias for thermocouples (the VBIAS source sets the common-mode voltage of a channel to (AVDD + AVSS)/2.

- ➤ The smart sequencer allows the conversion of each enabled preconfigured channel in a predetermined order, allowing a mix of transducer, system checks, and diagnostic measurements to

be interleaved. The sequencer eliminates the need for repetitive serial interface communication with the device to change configuration. Sixteen channels can be configured in the sequence. Each of these channels selects from eight user-defined ADC setups that allow selection of gain, filter type, output data rate, buffering, and reference source.

The AD4170-4 also has extensive diagnostic functionality integrated as part of its comprehensive feature set. These diagnostics include a cyclic redundancy check (CRC), signal chain checks, and serial interface checks, which lead to a more robust solution.

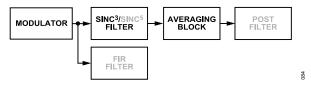

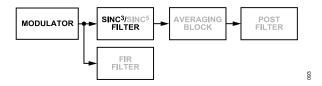

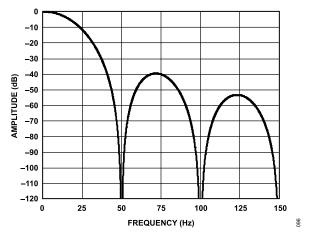

The device also offers a multitude of digital filter options, ensuring that the user has the highest degree of flexibility. The device contains a finite impulse response (FIR) filter which offers low pass-band ripple for analog inputs from DC up to 50 kHz, quick roll-off and excellent stop-band rejection. Also available in this device is a programmable FIR filter that can accept up to 72 user coefficients. The part contains sinc filters which allow faster settling in multiplexed applications. In addition, the AD4170-4 offers multiple options for simultaneous 50 Hz and 60 Hz rejection.

The AD4170-4 also has overvoltage/undervoltage tolerance. If a channel has a signal which is slightly beyond AVDD or AVSS, adjacent channels can continue to function and convert correctly. The embedded features, diagnostics, and intelligence minimize the component count when designing a signal chain, resulting in reduced board space needs, reduced design cycle times, and cost savings.

The device operates with a single analog power supply from 4.75 V to 5.25 V or a bipolar +2.5 V power supply. The digital supply has a range of 1.7 V to 5.25 V. The device is specified for a temperature range of  $-40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ . The AD4170-4 is housed in a 32-lead LFCSP package.

analog.com Rev. A | 4 of 112

# **SPECIFICATIONS**

AVDD = 4.75 V to 5.25 V, IOVDD = 1.7 V to 5.25 V, AVSS = DGND = 0 V, external 2.5 V reference with REFIN+ = 2.5 V and REFIN- = AVSS, MCLK = 16 MHz, unless otherwise noted.

Table 1.

| Parameter <sup>1</sup>                          | Test Conditions/Comments                                                           | Min             | Тур                 | Max             | Unit       |

|-------------------------------------------------|------------------------------------------------------------------------------------|-----------------|---------------------|-----------------|------------|

| ADC SPEED, CODING AND                           |                                                                                    |                 |                     |                 |            |

| PERFORMANCE                                     |                                                                                    |                 |                     |                 |            |

| Output Data Rate (ODR)                          |                                                                                    |                 |                     |                 |            |

| Sinc <sup>5</sup>                               |                                                                                    | 1,953           |                     | 500,000         | SPS        |

| Sinc <sup>5</sup> + Avg                         |                                                                                    | 7.6             |                     | 125,000         | SPS        |

| Sinc <sup>3</sup>                               |                                                                                    | 7.6             |                     | 125,000         | SPS        |

| FIR                                             | Default and user-configured                                                        | 3,906           |                     | 125,000         | SPS        |

| 50 Hz/60 Hz Post Filters                        |                                                                                    | 16.67           | 20                  | 25              | SPS        |

| No Missing Codes <sup>2</sup>                   | Sinc <sup>5</sup> filter: ODR < 500 kSPS, sinc <sup>3</sup> filter: ODR < 125 kSPS | 24              |                     |                 | Bits       |

| Data Output Coding                              | Bipolar mode                                                                       |                 | Twos complement     |                 |            |

|                                                 | Unipolar mode                                                                      |                 | Straight binary     |                 |            |

| Resolution                                      |                                                                                    | See the RI      | MS Noise and Resolu | ution section   |            |

| Noise                                           |                                                                                    | See the RI      | MS Noise and Resolu | ution section   |            |

| ACCURACY                                        |                                                                                    |                 |                     |                 |            |

| Gains                                           |                                                                                    |                 | 0.5, 1 precharge,   |                 |            |

|                                                 |                                                                                    |                 | 1, 2, 4, 8, 16, 32, |                 |            |

|                                                 |                                                                                    |                 | 64, 128             |                 |            |

| Integral Nonlinearity (INL)                     |                                                                                    |                 |                     |                 |            |

|                                                 | Gain = 1, gain = 1 precharge                                                       | -2.5            | ±0.5                | +2.5            | ppm of FSF |

| -m 2                                            | Gain > 1 or gain = 0.5                                                             | -10             | ±2                  | +10             | ppm of FSF |

| Offset Error <sup>3</sup>                       | Gain = 1 precharge                                                                 | -60             | ±25                 | +60             | μV         |

|                                                 | Gain < 16                                                                          |                 | ±10 + (±40/gain)    | +40 + (40/gain) | μV         |

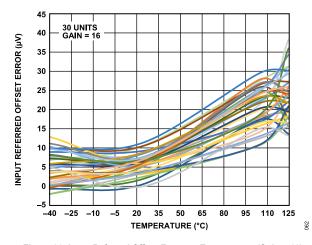

|                                                 | Gain ≥ 16                                                                          | -32             | ±15                 | +32             | μV         |

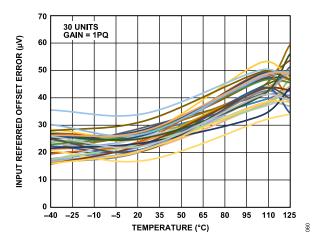

| Offset Error Drift vs. Temperature <sup>2</sup> | Gain = 1 precharge                                                                 | -50             | ±20                 | +50             | nV/°C      |

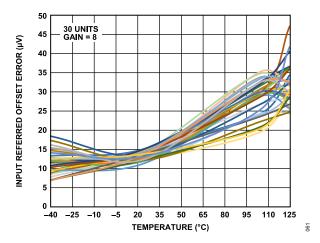

|                                                 | Gain < 16                                                                          | -20 - (80/gain) |                     | +20 + (80/gain) | nV/°C      |

|                                                 | Gain = 32                                                                          | <del>-7</del> 0 | ±30                 | +70             | nV/°C      |

|                                                 | Gain = 64                                                                          | -140            | ±75                 | +140            | nV/°C      |

|                                                 | Gain = 128                                                                         | -100            | ±50                 | +100            | nV/°C      |

| Gain Error <sup>3</sup>                         | Gain = 1 precharge, T <sub>A</sub> = 25°C                                          | -50             | ±10                 | +50             | ppm of FSF |

|                                                 | All other gains, T <sub>A</sub> = 25°C                                             | -250            | ±50                 | +250            | ppm of FSF |

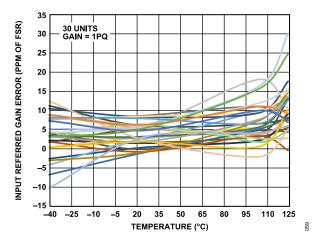

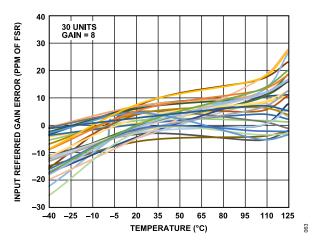

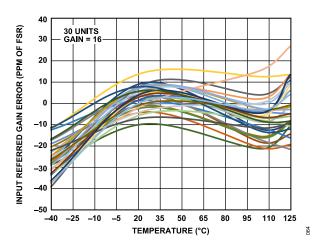

| Gain Error Drift vs. Temperature <sup>2</sup>   | All gains                                                                          | -0.75           | ±0.25               | +0.75           | ppm/°C     |

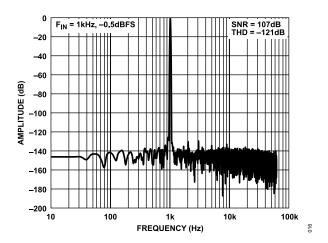

| DYNAMIC PERFORMANCE                             | External 16 MHz MCLK, 4.096 V external reference                                   |                 |                     |                 |            |

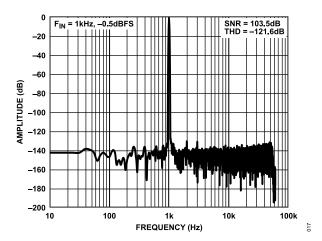

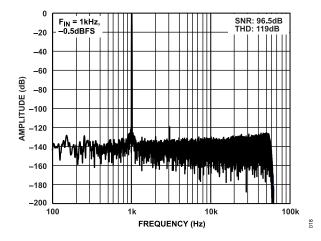

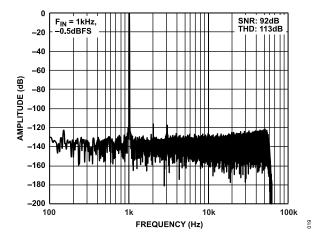

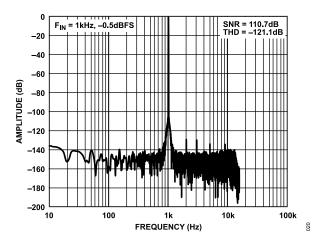

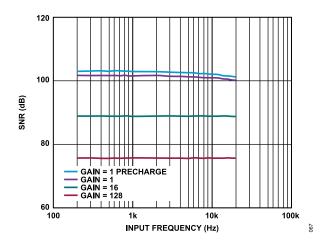

| Signal-to-Noise Ratio (SNR)                     | 1 kHz, −0.5 dBFS, sine wave input                                                  |                 |                     |                 |            |

|                                                 | Sinc <sup>5</sup> filter, gain = 1 precharge                                       | 108             | 110                 |                 | dBFS       |

|                                                 | Sinc <sup>5</sup> filter, all other gains                                          | See             | the SNR and THD se  | ection          |            |

|                                                 | FIR filter, gain = 1 and gain = 1 precharge                                        | 102.5           | 105.5               |                 | dBFS       |

|                                                 | FIR filter, gain = 0.5 and gain > 1                                                | See             | the SNR and THD se  | ection          |            |

| Signal-to-Noise-and-Distortion (SINAD)          | 1 kHz, −0.5 dBFS, sine wave input                                                  |                 |                     |                 |            |

|                                                 | Sinc <sup>5</sup> filter, gain = 1 precharge                                       | 107.5           | 109.5               |                 | dBFS       |

|                                                 | FIR filter, gain = 1 precharge and gain = 1                                        | 102             | 105                 |                 |            |

| Total Harmonic Distortion (THD)                 | 1 kHz, -0.5 dBFS, sine wave input                                                  |                 |                     |                 |            |

|                                                 | Gain = 1 and gain = 1 precharge                                                    |                 | -120                | -112            | dBFS       |

|                                                 | Gain = 0.5 and gain > 1                                                            | See             | the SNR and THD se  | ection          |            |

| Spurious-Free Dynamic Range (SFDR)              | Gain = 1 and gain = 1 precharge                                                    |                 | 125                 |                 | dBc        |

analog.com Rev. A | 5 of 112

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter <sup>1</sup>                        | Test Conditions/Comments                                                                     | Min                     | Тур              | Max                     | Unit  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------|------------------|-------------------------|-------|

| INTERMODULATION DISTORTION (IMD)              | External 16 MHz MCLK, fa = 9.7 kHz, fb = 10.3 kHz, all                                       |                         |                  |                         |       |

|                                               | gains                                                                                        |                         | 405              |                         | 4D    |

|                                               | 2nd order                                                                                    |                         | -125             |                         | dB    |

|                                               | 3rd order                                                                                    |                         | -125             |                         | dB    |

| REJECTION                                     |                                                                                              |                         |                  |                         |       |

| DC Power Supply Rejection                     | V <sub>IN</sub> = 1 V/gain, all supplies                                                     |                         |                  |                         |       |

|                                               | Gain = 0.5                                                                                   |                         | 98               |                         | dB    |

|                                               | Gains of 1 precharge and 1 to 8                                                              | 89                      | 104              |                         |       |

|                                               | Gain ≥ 16                                                                                    | 102                     | 122              |                         | dB    |

| Common-Mode Rejection <sup>4</sup>            | V <sub>IN</sub> = 1 V/gain                                                                   |                         |                  |                         |       |

| At DC                                         | Gain = 0.5                                                                                   |                         | 106              |                         | dB    |

|                                               | Gains of 1 precharge and 1 to 8                                                              | 98                      | 108              |                         | dB    |

|                                               | Gain ≥ 16                                                                                    | 107                     | 127              |                         | dB    |

| At 50 Hz, 60 Hz                               | 20 Hz ODR (post filter), 50 Hz ± 1 Hz and 60 Hz ± 1 Hz                                       | 120                     |                  |                         | dB    |

| Normal Mode Rejection <sup>2</sup>            | 50 Hz ± 1 Hz and 60 Hz ± 1 Hz                                                                |                         |                  |                         |       |

|                                               | Internal clock, 50 ms settling post filter                                                   | 74                      |                  |                         | dB    |

|                                               | External clock, 50 ms settling post filter                                                   | 85                      |                  |                         | dB    |

| ANALOG INPUTS                                 |                                                                                              |                         |                  |                         |       |

| Differential Input Voltage Range <sup>5</sup> | V <sub>REF</sub> = (REF+ - REF-) or internal reference                                       | -V <sub>REF</sub> /gain |                  | +V <sub>REF</sub> /gain | V     |

| Single-Ended Input Voltage Range              | ,                                                                                            | 0                       |                  | V <sub>REF</sub> /gain  | V     |

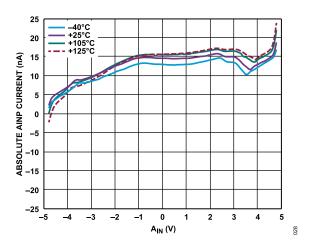

| Absolute AIN Voltage Limits <sup>2</sup>      |                                                                                              | AVSS                    |                  | AVDD                    | V     |

| Input Capacitance                             |                                                                                              |                         | 8                |                         | pF    |

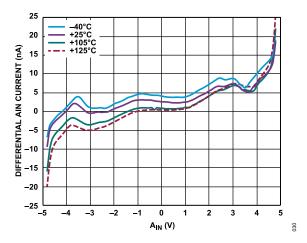

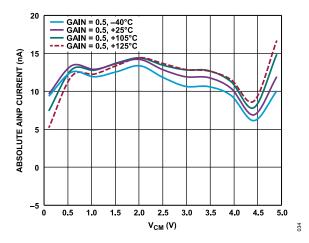

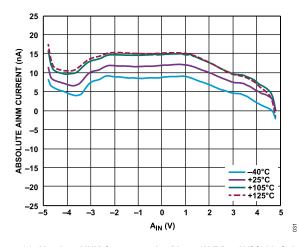

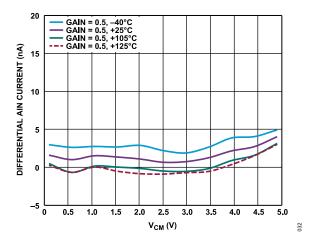

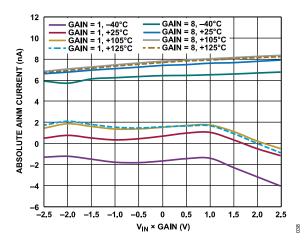

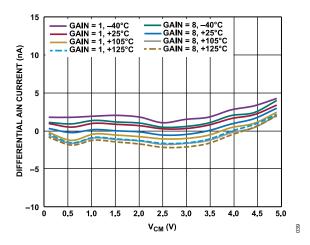

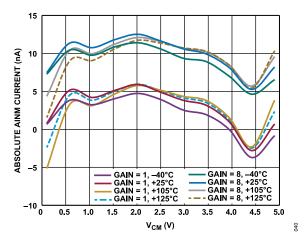

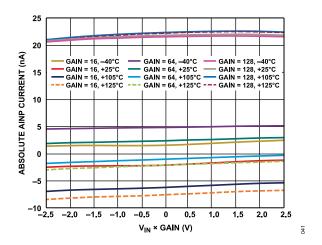

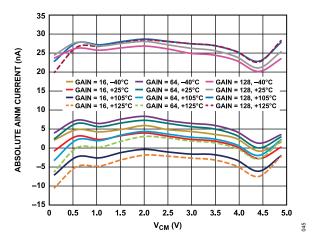

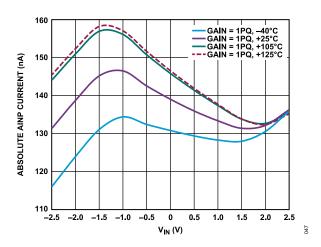

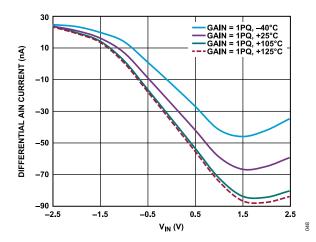

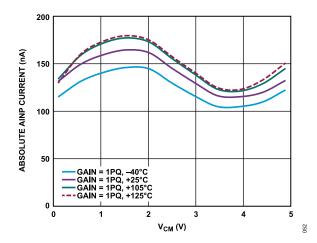

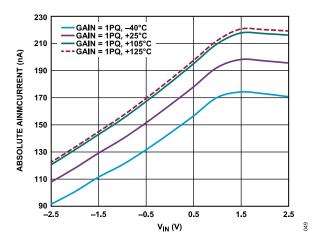

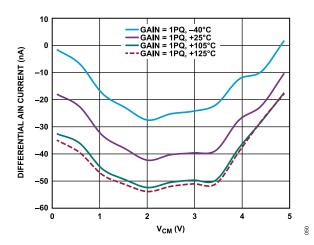

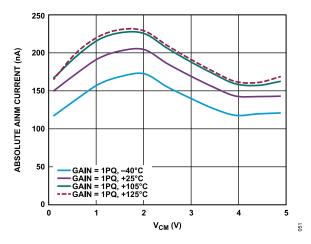

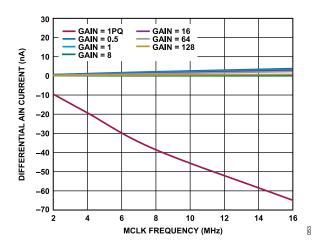

| Analog Input Current                          | Absolute input current measured with AIN between AVSS                                        |                         |                  |                         |       |

| , manag mpan damam                            | + 0.1 V and AVDD – 0.1 V                                                                     |                         |                  |                         |       |

|                                               | Differential input current measured with full-scale input, V <sub>CM</sub> = (AVDD – AVSS)/2 |                         |                  |                         |       |

| Gain = 1 precharge                            | Siii (                                                                                       |                         |                  |                         |       |

| Absolute Input Current                        |                                                                                              | -450                    | ±200             | +450                    | nA    |

| Differential Input Current                    |                                                                                              | -120                    | ±40              | +120                    | nA    |

| Absolute Input Current Drift <sup>2</sup>     |                                                                                              | -550                    | ±280             | +550                    | pA/°C |

| Gain = 1                                      |                                                                                              |                         |                  |                         |       |

| Absolute Input Current                        |                                                                                              | -40                     | ±5               | +40                     | nA    |

| Differential Input Current                    |                                                                                              | -20                     | ±5               | +20                     | nA    |

| Absolute Input Current Drift <sup>2</sup>     |                                                                                              | -44                     | ±12              | +44                     | pA/°C |

| Gain = 0.5                                    |                                                                                              |                         |                  |                         |       |

| Absolute Input Current                        |                                                                                              | -60                     | ±20              | +60                     | nA    |

| Differential Input Current                    |                                                                                              | -35                     | ±15              | +35                     | nA    |

| Absolute Input Current Drift <sup>2</sup>     |                                                                                              | -75                     | ±30              | +75                     | pA/°C |

| Gain = 128                                    |                                                                                              | 10                      | ±00              | 110                     | pA C  |

| Absolute Input Current                        |                                                                                              | -50                     | ±25              | +50                     | nA    |

| Differential Input Current                    |                                                                                              | -50<br>-10              | ±25<br>±3        | +50                     | nA    |

| Absolute Input Current Drift <sup>2</sup>     |                                                                                              | -10<br>-90              | ±3<br>±40        | +10                     | pA/°C |

| •                                             |                                                                                              | -90                     | ± <del>4</del> 0 | T⊎U                     | pA/ C |

| All other gains                               |                                                                                              | 25                      | ıE               | .05                     | μ. A  |

| Absolute Input Current                        |                                                                                              | -35                     | ±5               | +35                     | nA    |

| Differential Input Current                    |                                                                                              | -10                     | ±3               | +10                     | nA    |

| Absolute Input Current Drift <sup>2</sup>     |                                                                                              | -150                    | ±70              | +150                    | pA/°C |

| Crosstalk                                     | l                                                                                            |                         | 100              |                         |       |

| AC                                            | 1 kHz input                                                                                  |                         | -120             |                         | dB    |

| DC                                            | Adjacent analog input 300 mV outside AVDD or AVSS                                            |                         | -100             |                         | dB    |

analog.com Rev. A | 6 of 112

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter <sup>1</sup>                              | Test Conditions/Comments                                                    | Min         | Тур                      | Max                        | Unit    |

|-----------------------------------------------------|-----------------------------------------------------------------------------|-------------|--------------------------|----------------------------|---------|

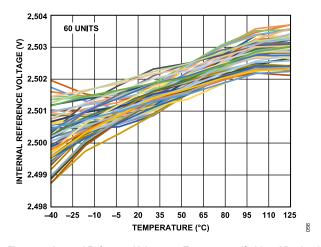

| INTERNAL REFERENCE                                  | 100 nF external capacitor to AVSS                                           |             |                          |                            |         |

| Initial Accuracy <sup>6</sup>                       | REFOUT with respect to AVSS, T <sub>A</sub> = 25°C                          | 2.495       | 2.5                      | 2.505                      | V       |

| Temperature Coefficient                             |                                                                             |             | ±5                       | +15                        | ppm/°C  |

| Reference Load Current, I <sub>LOAD</sub>           |                                                                             | -10         |                          | +10                        | mA      |

| Thermal Hysteresis                                  | Cycle of 25°C, +75°C, -25°C, +25°C                                          |             | 44                       |                            | ppm     |

| Power Supply Rejection                              | AVDD (line regulation)                                                      |             | 100                      |                            | dB      |

| Load Regulation                                     | $\Delta V_{OUT}/\Delta I_{LOAD}$                                            |             | 12                       |                            | ppm/mA  |

| Voltage Noise                                       | e <sub>N</sub> , 0.1 Hz to 10 Hz, 2.5 V reference                           |             | 4.5                      |                            | μV rms  |

| Voltage Noise Density                               | e <sub>N</sub> , 1 kHz, 2.5 V reference                                     |             | 215                      |                            | nV/√Hz  |

| Turn-On Settling Time                               | 100 nF REFOUT capacitor                                                     |             | 200                      |                            | μs      |

| Short-Circuit Current, I <sub>SC</sub>              |                                                                             |             | 28                       |                            | mA      |

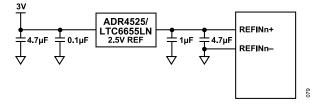

| EXTERNAL REFERENCE INPUTS                           |                                                                             |             |                          |                            |         |

| Differential Input Range <sup>2</sup>               | V <sub>REF</sub> = REF+ - REF-                                              | 1           | 2.5                      | AVDD                       | V       |

| Absolute Voltage Limits <sup>2</sup>                |                                                                             |             |                          |                            |         |

| Reference Buffers Disabled                          |                                                                             | AVSS - 0.05 |                          | AVDD + 0.05                | V       |

| Reference Buffers Enabled                           | Full buffer or precharge buffer                                             | AVSS        |                          | AVDD                       | V       |

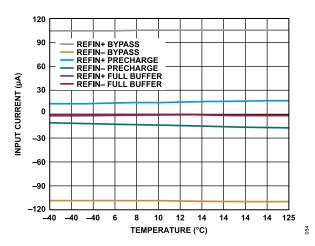

| REFIN Input Current (Reference<br>Buffers Disabled) |                                                                             |             |                          |                            |         |

| Reference Input Current                             |                                                                             |             | ±44                      |                            | μΑ/V    |

| Reference Input Current Drift                       | External clock                                                              |             | ±1.2                     |                            | nA/V/°C |

| ·                                                   | Internal clock                                                              |             | ±6                       |                            | nA/V/°C |

| Reference Buffers Enabled                           |                                                                             |             |                          |                            |         |

| Reference Input Current                             | Precharge buffer                                                            |             | ±18                      |                            | μA      |

| ·                                                   | Full buffer                                                                 |             | ±200                     |                            | nA      |

| Reference Input Current Drift                       | Precharge buffer                                                            |             | 40                       |                            | nA/°C   |

| •                                                   | Full buffer                                                                 |             | 1.25                     |                            | nA/°C   |

| Normal Mode Rejection                               | See the rejection parameter                                                 |             |                          |                            |         |

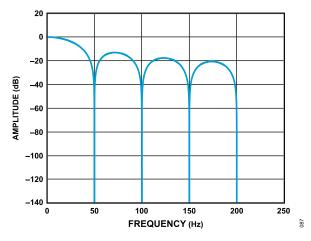

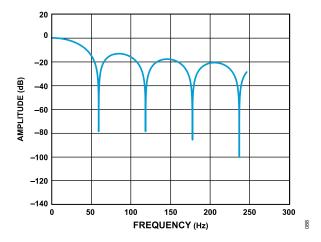

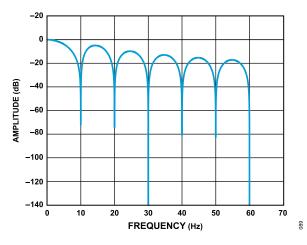

| DIGITAL FILTER RESPONSE                             | , .                                                                         |             |                          |                            |         |

| FIR Filter                                          |                                                                             |             |                          |                            |         |

| Decimation Rate                                     |                                                                             | 32          |                          | 1024                       |         |

| Group Delay                                         | Latency                                                                     |             | 34/ODR                   |                            | seconds |

| Settling Time                                       | ,                                                                           |             | 68/ODR                   |                            | seconds |

| Pass-Band Ripple                                    | From DC to 50 kHz at 125 kSPS                                               |             |                          | ±0.005                     | dB      |

| Pass Band                                           | ±0.005 dB bandwidth                                                         |             | 0.4 × ODR                |                            | Hz      |

|                                                     | −0.1 dB bandwidth                                                           |             | 0.409 × ODR              |                            | Hz      |

|                                                     | -3 dB bandwidth                                                             |             | 0.433 × ODR              |                            | Hz      |

| Stop-Band Frequency                                 | Attenuation > 105 dB                                                        |             | 0.499 × ODR              |                            | Hz      |

| Stop-Band Attenuation                               | See the Anti-Aliasing Filtering section                                     |             | 105                      |                            | dB      |

| Sinc Filters, Sinc <sup>5</sup> + Avg Filter        | Soo the final financing financing section                                   | Se          | ee the Digital Filter se | ection                     |         |

| /BIAS                                               |                                                                             |             | or the Bightan I more    | 7041011                    |         |

| Output Voltage Setting                              |                                                                             |             | (AVDD + AVSS)/2          |                            | V       |

| Output Impedance                                    |                                                                             |             | 1                        |                            | kΩ      |

| Start-Up Time                                       | Dependent on the capacitance connected to AINn.                             |             | 9                        |                            | µs/nF   |

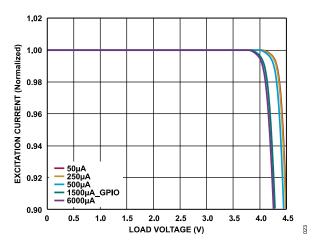

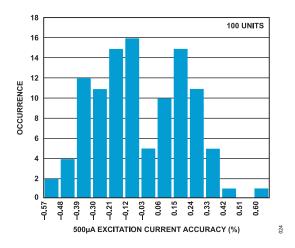

| EXCITATION CURRENTS                                 | Depondent on the supusitance confidence to Alivin.                          |             | •                        |                            | μοπι    |

| Current Settings                                    |                                                                             |             | 10, 50, 100, 250,        |                            | 11Δ     |

| ountil Sellings                                     |                                                                             |             | 500, 1000, 1500          |                            | μA      |

|                                                     |                                                                             | I           | 555, 1555, 1566          |                            | ,,      |

| Output Compliance <sup>2</sup>                      | 10 uA 50 uA 100 uA 1% accuracy                                              |             |                          | AVDD - 1 25                | V       |

| Output Compliance <sup>2</sup>                      | 10 μA, 50 μA, 100 μA, 1% accuracy<br>250 μA/500 μA/1 mA/1.5 mA, 1% accuracy |             |                          | AVDD - 1.25<br>AVDD - 1.45 | V       |

analog.com Rev. A | 7 of 112

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter <sup>1</sup>               | Test Conditions/Comments                                | Min         | Тур           | Max                  | Unit       |  |

|--------------------------------------|---------------------------------------------------------|-------------|---------------|----------------------|------------|--|

|                                      | T <sub>A</sub> = 25°C, 50 μA, 100 μA                    | -1          | ±0.1          | +1                   | %          |  |

|                                      | T <sub>A</sub> = 25°C, >100 μA                          | -2          | ±0.2          | +2                   | %          |  |

| Drift <sup>2</sup>                   | 10 μΑ                                                   |             | ±20           |                      | ppm/°C     |  |

|                                      | 50 μΑ, 100 μΑ                                           | -30         | ±5            | +30                  | ppm/°C     |  |

|                                      | >100 µA                                                 | -80         | ±25           | +80                  | ppm/°C     |  |

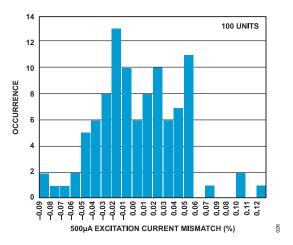

| Current Mismatch                     | Using pair AB or CD                                     |             |               |                      | ' '        |  |

| Same Current Matching <sup>2</sup>   | 10 µA                                                   |             | ±1.3          |                      | %          |  |

| ŭ                                    | 250 μA, 1 mA                                            | -1.2        | ±0.1          | +1.2                 | %          |  |

|                                      | 50 μA/100 μA/500 μA/1.5 mA                              | -0.7        | ±0.1          | +0.7                 | %          |  |

| Different Current Matching           |                                                         |             | ±1            |                      | %          |  |

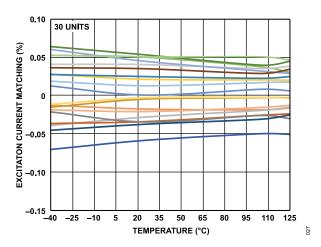

| Drift Matching <sup>2</sup>          | Using pair AB or CD. Current sources at the same value. |             |               |                      |            |  |

| g                                    | 10 µA                                                   |             | 3             |                      | ppm/°C     |  |

|                                      | 50 μΑ, 100 μΑ, 250 μΑ                                   | -7          | ±2            | +7                   | ppm/°C     |  |

|                                      | >250 µA                                                 | <i>-</i> 4  | ±1            | +4                   | ppm/°C     |  |

| Line Regulation (AVDD)               | AVDD = 5 V ± 5%                                         | -           | 150           | .4                   | ppm/V      |  |

| Load Regulation                      | >10 µA                                                  |             | 40            |                      | ppm/V      |  |

| Start-Up time                        | $R_{LOAD} = 1 \text{ k}\Omega, C_{LOAD} = 0 \text{ pF}$ |             | 7             |                      | 1          |  |

| Start-Op time                        | Dependent on the load connected to AlNn                 |             | 1             |                      | μs         |  |

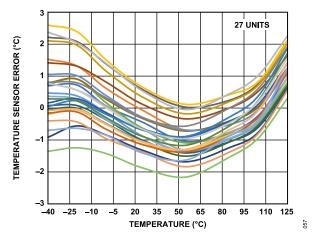

| TEMPERATURE SENSOR                   |                                                         |             |               |                      |            |  |

| Accuracy                             | After user calibration at 25°C                          |             | ±2            |                      | °C         |  |

| Sensitivity                          |                                                         |             | 477           |                      | μV/K       |  |

| OW-SIDE POWER SWITCH                 |                                                         |             |               |                      |            |  |

| Ron                                  |                                                         |             | 10            | 14                   | Ω          |  |

| Current Through Switch <sup>2</sup>  | Continuous current                                      |             |               | 30                   | mA         |  |

| BURNOUT CURRENTS                     |                                                         |             |               |                      |            |  |

| Source/Sink Current                  |                                                         |             | ±0.1, ±2, ±10 |                      | μA         |  |

| Accuracy                             | Sinking/sourcing                                        |             | 10            |                      | %          |  |

| PULL-UP CURRENTS                     |                                                         |             |               |                      |            |  |

| Source Current                       |                                                         |             | 100           |                      | nA         |  |

| GENERAL-PURPOSE I/O (GPIO0 to        | With respect to AVSS                                    |             |               |                      |            |  |

| GPIO3) <sup>2</sup>                  | ·                                                       |             |               |                      |            |  |

| Input Mode Leakage Current           |                                                         | -1          |               | +1                   | μA         |  |

| Floating State Output Capacitance    |                                                         |             | 5             |                      | pF         |  |

| Output High Voltage, V <sub>OH</sub> | I <sub>SOURCE</sub> = 200 μA                            | AVSS + 4    |               |                      | V          |  |

| Output Low Voltage, V <sub>OL</sub>  | I <sub>SINK</sub> = 800 μA                              |             |               | AVSS + 0.4           | V          |  |

| Input High Voltage, V <sub>IH</sub>  |                                                         | AVSS + 3    |               |                      | V          |  |

| Input Low Voltage, V <sub>IL</sub>   |                                                         |             |               | AVSS + 0.7           | V          |  |

| DAC                                  |                                                         |             |               |                      |            |  |

| Resolution                           |                                                         |             | 12            |                      | Bits       |  |

| Range                                | Gain = 1                                                | 0           |               | $V_{REF}$            | V          |  |

| <del>3</del> -                       | Gain = 2                                                | 0           |               | 2 × V <sub>REF</sub> | V          |  |

| INL                                  |                                                         | -2          |               | +2                   | LSB        |  |

| DNL                                  |                                                         | -0.5        | ±0.2          | +0.5                 | LSB        |  |

| Offset Error                         |                                                         | 0.0         | ±2            | . 0.0                | mV         |  |

| Offset Error Drift                   |                                                         |             | ±10           |                      | μV/°C      |  |

| Full-Scale Error                     |                                                         |             | ±0.1          |                      | % of FSF   |  |

| Full-Scale Error Drift               |                                                         |             | ±0.1<br>±10   |                      | μV/°C      |  |

|                                      |                                                         | V/66 + 0 06 | ±10           | V/DD 0.05            | μν/ C<br>V |  |

| Output Swing                         | D = infinity                                            | AVSS + 0.06 |               | AVDD – 0.25          |            |  |

| Capacitive Load                      | $R_{LOAD}$ = infinity                                   |             |               | 2                    | nF         |  |

analog.com Rev. A | 8 of 112

# **SPECIFICATIONS**

Table 1. (Continued)

| arameter <sup>1</sup>                                                                                    | Test Conditions/Comments                     | Min                    | Тур   | Max                   | Unit   |  |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------|-------|-----------------------|--------|--|

|                                                                                                          | $R_{LOAD} = 2 k\Omega$                       |                        | 100   |                       | nF     |  |

| Resistive Load                                                                                           |                                              | 1                      |       |                       | kΩ     |  |

| Settling Time                                                                                            | 0.25 × FS to 0.75 × FS                       |                        | 6     |                       | μs     |  |

| Slew Rate                                                                                                | $R_{LOAD} = 2 k\Omega$ , $C_{LOAD} = 200 pF$ |                        | 1     |                       | V/µs   |  |

| Noise Density                                                                                            | Midscale code, 1 kHz                         |                        | 200   |                       | nV/√Hz |  |

| RMS Noise                                                                                                | 0.1 Hz to 10 Hz                              |                        | 8     |                       | μV rms |  |

| Short-Circuit Current, I <sub>SC</sub>                                                                   |                                              |                        | 15    |                       | mA     |  |

| IAGNOSTIC TRIP POINTS                                                                                    |                                              |                        |       |                       |        |  |

| Reference Detect Level                                                                                   |                                              | 0.6                    |       | 0.85                  | V      |  |

| Reference/AIN OV/UV Trip Level                                                                           |                                              |                        |       |                       |        |  |

| Overvoltage                                                                                              |                                              | AVDD + 0.0             | 65    |                       | V      |  |

| Undervoltage                                                                                             |                                              | 7.1.22 3.0             |       | AVSS - 0.065          | V      |  |

| Reference/AIN OV/UV Clear Level                                                                          |                                              |                        |       | 7.1.00                |        |  |

| Overvoltage                                                                                              |                                              | AVDD + 0.0             | 115   |                       | V      |  |

| Undervoltage                                                                                             |                                              | 7.000                  |       | AVSS - 0.01           | V      |  |

| Excitation Current Source Compliance                                                                     | 10 μΑ, 50 μΑ, 100 μΑ                         | AVDD - 1.3             |       | AVDD - 0.8            | V      |  |

| Excitation outrent oddice compliance                                                                     | 250 μΑ, 500 μΑ, 1000 μΑ, 1500 μΑ             | AVDD - 1.6             |       | AVDD - 1              | V      |  |

| ALDO Trip Level                                                                                          | 250 μλ, 500 μλ, 1000 μλ, 1500 μλ             | AVDD 1.0               | 1.5   | AVDD                  | V      |  |

| DLDO Trip Level                                                                                          |                                              |                        | 1.6   |                       | V      |  |

| LOCK                                                                                                     |                                              |                        | 1.0   |                       | V      |  |

|                                                                                                          |                                              |                        |       |                       |        |  |

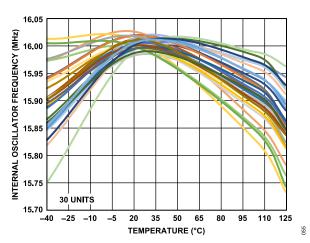

| Internal Clock                                                                                           |                                              |                        | 40    |                       | N41.1- |  |

| Frequency                                                                                                |                                              | 0.50/                  | 16    | .0.50/                | MHz    |  |

| Accuracy                                                                                                 |                                              | -2.5%                  | 50.50 | +2.5%                 | %      |  |

| Duty Cycle                                                                                               |                                              |                        | 50:50 |                       | %      |  |

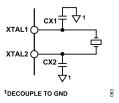

| Crystal                                                                                                  |                                              |                        |       |                       |        |  |

| Frequency                                                                                                |                                              | 8                      | 16    | 17                    | MHz    |  |

| Start-Up Time                                                                                            |                                              |                        | 10    |                       | μs     |  |

| External Clock                                                                                           |                                              | 1                      | 16    | 17                    | MHz    |  |

| Minimum Low Time                                                                                         |                                              | 27.6                   |       |                       | ns     |  |

| Minimum High Time                                                                                        |                                              | 27.6                   |       |                       | ns     |  |

| OGIC INPUTS <sup>2</sup>                                                                                 |                                              |                        |       |                       |        |  |

| Input High Voltage, V <sub>INH</sub>                                                                     |                                              | 0.8 × IOVDI            | D     |                       | V      |  |

| Input Low Voltage, V <sub>INL</sub>                                                                      |                                              |                        |       | 0.2 × IOVDD           | V      |  |

| Hysteresis                                                                                               |                                              |                        | 0.04  |                       | V      |  |

| Leakage Currents                                                                                         | SYNC_IN Pin                                  |                        |       | +15                   | μA     |  |

|                                                                                                          | All other pins                               | -1                     |       | 1                     | μA     |  |

| Input Capacitance                                                                                        | All digital inputs                           |                        | 10    |                       | pF     |  |

| DGIC OUTPUT <sup>2</sup> (XTAL2, DIG_AUX1, IG_AUX2, SDO)                                                 |                                              |                        |       |                       |        |  |

| Output High Voltage, V <sub>OH</sub> <sup>2</sup>                                                        | I <sub>SOURCE</sub> = 1 mA                   | 0.8 × IOVDI            | D     |                       | V      |  |

| Output Low Voltage, V <sub>OL</sub> <sup>2</sup>                                                         | I <sub>SINK</sub> = 2 mA                     |                        |       | 0.4                   | V      |  |

| Leakage Current                                                                                          | Floating state                               | -1                     |       | +1                    | μA     |  |

| Output Capacitance                                                                                       | Floating state                               |                        | 10    | •                     | pF     |  |

|                                                                                                          |                                              |                        |       |                       | L.     |  |

|                                                                                                          |                                              |                        |       | 1 05 x FS             | V      |  |

| , ,                                                                                                      |                                              | _1 05 v E9             |       | 1.00 ~ 1 0            | V      |  |

|                                                                                                          |                                              |                        |       | 21 4 50               | V      |  |

| YSTEM CALIBRATION <sup>2</sup> Full-Scale (FS) Calibration Limit Zero-Scale Calibration Limit Input Span | Floating state                               | -1.05 × FS<br>0.8 × FS | 10    | 1.05 × FS<br>2.1 × FS |        |  |

analog.com Rev. A | 9 of 112

## **SPECIFICATIONS**

Table 1. (Continued)

| Parameter <sup>1</sup>             | Test Conditions/Comments                                            | Min    | Тур            | Max   | Unit |

|------------------------------------|---------------------------------------------------------------------|--------|----------------|-------|------|

| POWER REQUIREMENTS                 |                                                                     |        |                |       |      |

| Power Supply Voltage               |                                                                     |        |                |       |      |

| AVDD to AVSS                       |                                                                     | 4.75   |                | 5.25  | V    |

| AVSS to DGND                       |                                                                     | -2.625 |                | 0     | V    |

| IOVDD to DGND                      |                                                                     | 1.7    |                | 5.25  | V    |

| IOVDD to AVSS                      | For AVSS < DGND                                                     |        |                | 6.35  | V    |

| POWER SUPPLY CURRENTS <sup>7</sup> |                                                                     |        |                |       |      |

| AVDD Current                       |                                                                     |        |                |       |      |

| Gain =1 Precharge                  |                                                                     |        | 6.7            | 7.7   | mA   |

| Gain < 16 except Gain =1 Precharge |                                                                     |        | 9.5            | 11    | mA   |

| Gain ≥ 16                          |                                                                     |        | 12.5           | 14.7  | mA   |

| AVDD Increase due to               |                                                                     |        |                |       |      |

| Both Reference Buffers             |                                                                     |        |                |       |      |

| Precharge                          |                                                                     |        | 1.2            | 1.5   | mA   |

| Full Buffer                        |                                                                     |        | 3.3            | 4.1   | mA   |

| Internal Reference                 |                                                                     |        | 0.5            | 0.6   | mA   |

| DAC                                |                                                                     |        | 0.1            | 0.15  | mA   |

| Diagnostics                        |                                                                     |        | 0.1            |       | mA   |

| $V_{BIAS}$                         |                                                                     |        | 0.05           |       | mA   |

| Excitation Currents                |                                                                     |        | 0.06           |       | mA   |

| AVDD Standby Mode                  | LDOs on only                                                        |        | 70             | 110   | μA   |

| AVDD Power-Down Mode               |                                                                     |        | 0.2            | 1     | μA   |

| IOVDD Current                      | External clock                                                      |        | 2              | 2.3   | mA   |

|                                    | Internal clock                                                      |        | 2.3            | 2.6   | mA   |

|                                    | External crystal (16.384 MHz)                                       |        | 2.4            |       | mA   |

| IOVDD Increase due to              |                                                                     |        |                |       |      |

| Default FIR Filter                 |                                                                     |        | 2.4            | 2.7   | mA   |

| Programmable FIR Filter            |                                                                     |        | 1.1 + (0.025 × |       | mA   |

|                                    |                                                                     |        | FIR_LENGTH)    |       |      |

| IOVDD Standby Mode                 | LDOs on only                                                        |        | 15             | 180   | μA   |

| IOVDD Power-Down Mode              |                                                                     |        | 0.8            | 1.5   | μA   |

| POWER DISSIPATION <sup>2</sup>     | AVDD = 5.25 V, IOVDD = 5.25 V                                       |        |                |       |      |

| Full Operating Mode                | Gain = 1, reference buffers disabled, external clock, and reference |        | 60.4           | 70    | mW   |

|                                    | Gain > 16, reference buffers enabled, internal clock, and reference |        | 115            | 137   | mW   |

| Standby Mode                       | LDOs on only                                                        |        | 447            | 1,530 | μW   |

| Power-Down Mode                    |                                                                     |        | 5.25           | 13.2  | μW   |

<sup>&</sup>lt;sup>1</sup> Temperature range is −40°C to +105°C.

analog.com Rev. A | 10 of 112

<sup>&</sup>lt;sup>2</sup> These specifications are not production tested but are supported by characterization data at the initial product release.

<sup>&</sup>lt;sup>3</sup> The offset error is in the order of the noise for the programmed ODR selected following a system or internal zero-scale calibration. A system full-scale calibration reduces the gain error to the order of the noise for the programmed ODR.

$<sup>^4</sup>$  The minimum and maximum voltages on AINP and AINM are AVSS + 0.1 V and AVDD – 0.1 V.

The maximum allowed differential analog input range is ±(AVDD – 0.65 V)/gain while the maximum allowed single-ended analog input range is 0 to (AVDD – 0.65 V)/gain which applies when higher reference voltages are used.

<sup>&</sup>lt;sup>6</sup> This specification includes moisture sensitivity level (MSL) preconditioning effects.

<sup>&</sup>lt;sup>7</sup> This specification is with no load on the REFOUT, DAC, excitation currents, and digital output pins. Digital inputs are connected to IOVDD or DGND.

# **SPECIFICATIONS**

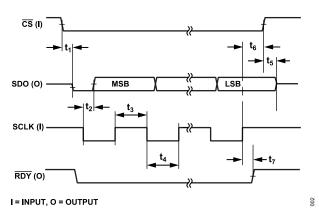

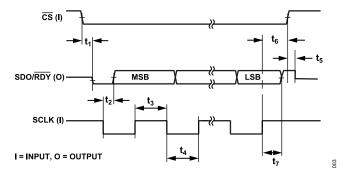

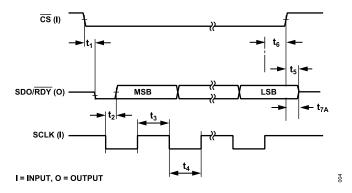

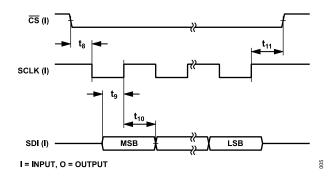

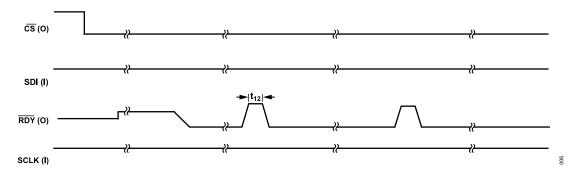

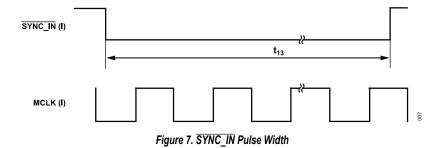

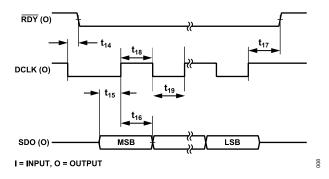

# **TIMING CHARACTERISTICS**

IOVDD = 1.7 V to 5.25 V with Bit DIG\_OUT\_STR set when IOVDD < 3 V, DGND = 0 V, Input Logic 0 = 0 V, Input Logic 1 = IOVDD,  $C_{LOAD}$  = 20 pF, unless otherwise noted.

Table 2.

|                                     | Limit                    | at T <sub>MIN</sub> , T <sub>MAX</sub>                      |          |                                                                                                                                                                                                                        |

|-------------------------------------|--------------------------|-------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                           | Min                      | Max                                                         | Unit     | Test Conditions/Comments <sup>1, 2</sup>                                                                                                                                                                               |

| SCLK                                |                          |                                                             |          |                                                                                                                                                                                                                        |

| $t_3$                               | 25                       |                                                             | ns       | SCLK high pulse width                                                                                                                                                                                                  |

| $t_4$                               | 25                       |                                                             | ns       | SCLK low pulse width                                                                                                                                                                                                   |

| t <sub>12</sub>                     |                          |                                                             |          | $\overline{RDY}$ high time if $\overline{RDY}$ is low and the next conversion is available ( $f_{MOD} = MCLK/4$ )                                                                                                      |

|                                     | 2.25/f <sub>MOD</sub>    |                                                             |          | Sinc <sup>5</sup> , FILTER_FS = 1                                                                                                                                                                                      |

|                                     | 4.25/f <sub>MOD</sub>    |                                                             |          | Sinc <sup>5</sup> , FILTER_FS = 2                                                                                                                                                                                      |

|                                     | 8.25/f <sub>MOD</sub>    |                                                             |          | All other sinc options                                                                                                                                                                                                 |

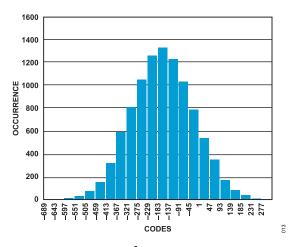

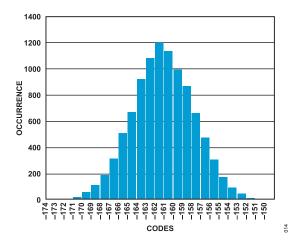

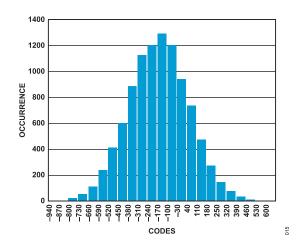

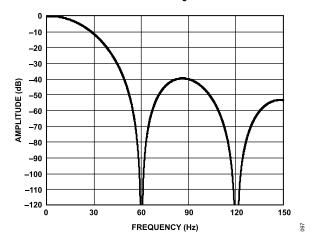

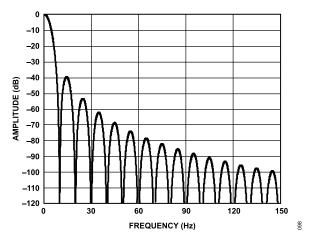

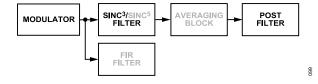

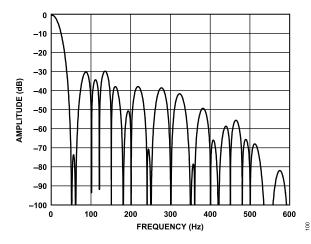

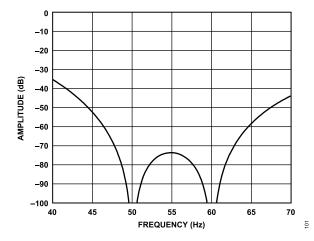

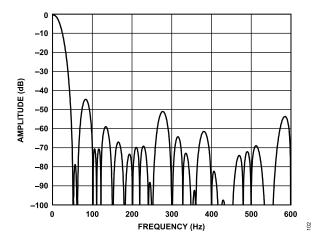

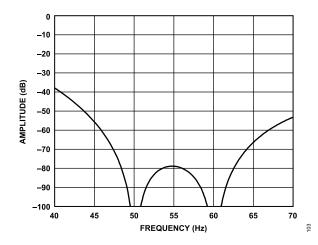

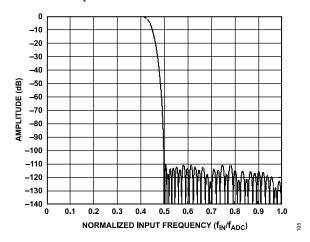

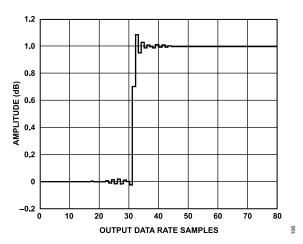

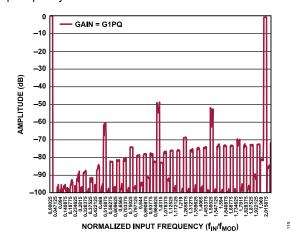

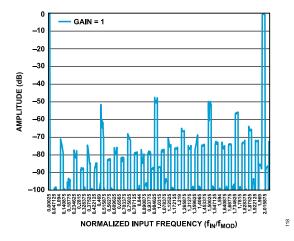

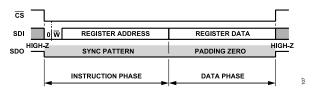

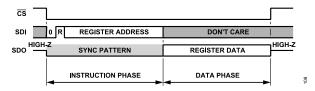

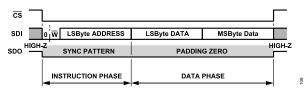

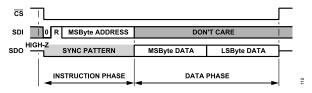

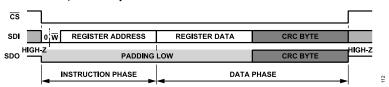

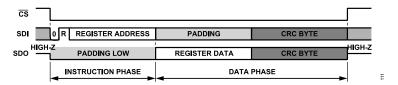

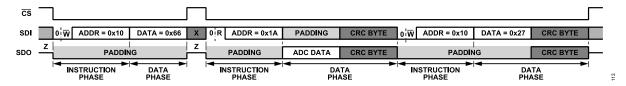

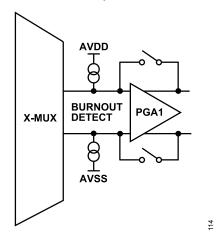

|                                     | 8.25/f <sub>MOD</sub> to |                                                             |          | FIR, FILTER_FS = 4 to FILTER_FS = 128                                                                                                                                                                                  |