时钟与定时

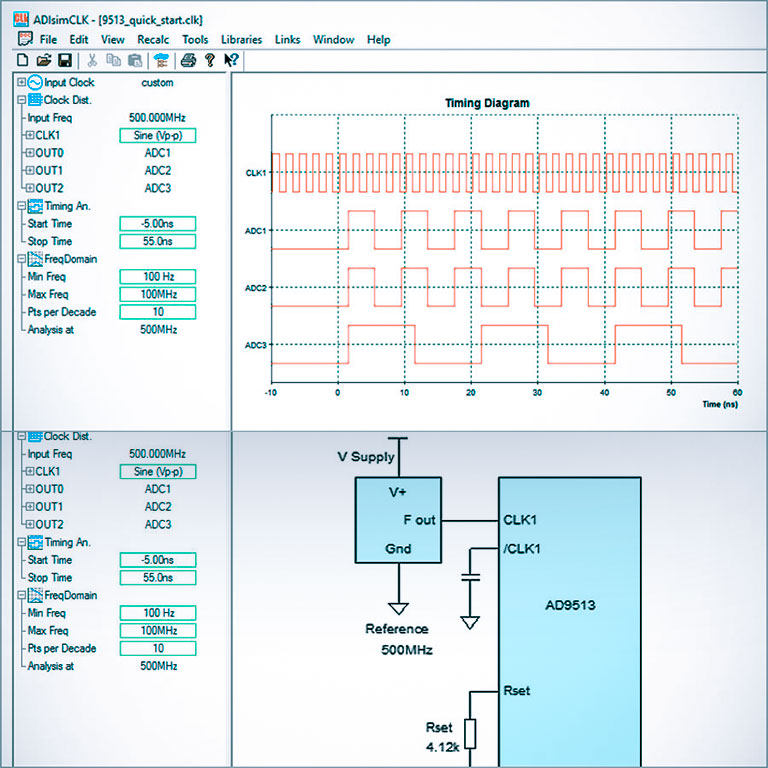

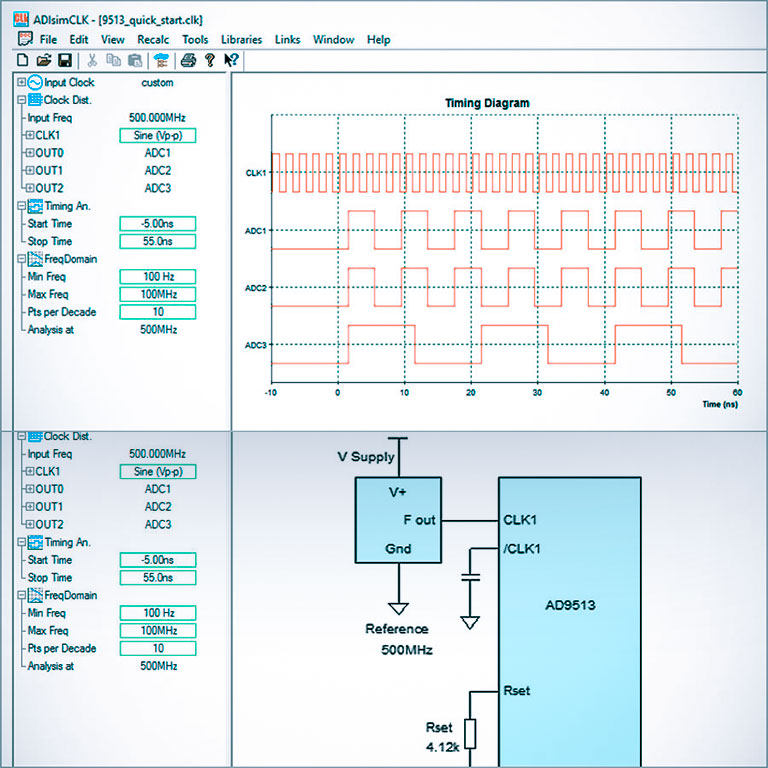

Analog Design Tool: ADIsimCLK™

ADIsimCLK is the design tool developed specifically for Analog Devices' range of ultra-low jitter clock distribution and clock generation products. Whether your application is in wireless infrastructure, instrumentation, networking, broadband, ATE or other areas demanding predictable clock performance, ADIsimCLK will enable you to rapidly develop, evaluate and optimize your design. It is a highly successful tool for predicting phase noise and jitter for ADI clock products.

Analog Design Tool: ADIsimCLK™

ADIsimCLK is the design tool developed specifically for Analog Devices' range of ultra-low jitter clock distribution and clock generation products. Whether your application is in wireless infrastructure, instrumentation, networking, broadband, ATE or other areas demanding predictable clock performance, ADIsimCLK will enable you to rapidly develop, evaluate and optimize your design. It is a highly successful tool for predicting phase noise and jitter for ADI clock products.

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}