# 電圧トラッキング機能と同期機能を備えた同期降圧DC/DCコントローラ

## データシート

## ADP1853

### 特長

入力電圧範囲 : 2.75~20 V

出力電圧範囲 : 0.6 V~90%  $V_{IN}$

最大出力電流 > 25 A

電流検出入力による電流モード・アーキテクチャ

電圧モードの設定が可能

電圧精度は全温度範囲で±1%

電圧トラッキング入力

プログラム可能な周波数 : 200 kHz~1.5 MHz

同期入力

内部クロック出力

軽負荷時節電モード

高精度のインエーブル入力

内部プルアップ抵抗を備えたパワーグッド

調整可能なソフトスタート機能

プログラム可能な電流検出ゲイン

内部ブートストラップ・ダイオード

プレチャージ負荷でのスタートアップ

外部調整可能なスロープ補償

あらゆる出力コンデンサに適合

過電圧および過電流制限保護

過熱保護

入力低電圧ロックアウト (UVLO)

20 ピンの 4 mm × 4 mm LFCSP パッケージ

ADIsimPower™ 設計ツールに対応

### アプリケーション

シーケンシングとトラッキングを必要とする中間バスおよび POL システム (以下を含む)

電気通信用基地局およびネットワーキング

工業／計測用途

医療／ヘルスケア用途

### 概要

ADP1853 は広範な入力範囲を持つ DC/DC 同期整流降圧コントローラです。一般的な 3.3~12 V (最大 20 V) の電圧入力で使用することができます。通常は、バレー電流検出による電流モードで動作し、デジタル負荷に対して最速のステップ応答を実現します。また、高感度負荷に対するノイズとクロストークの小さい電圧モード・コントローラの設定にも対応します。

ADP1853 は、パワー・システム用のマスター同期クロックや、コントローラ間の便利な同期装置として使用することができます。CLKOUT 信号によってマスターに対してスレーブ・デバイスを位相シフトさせ、ADP185x ファミリーのほかのデバイスと同期させることができます。入力リップル電流の低減、EMI

の改善、入力バルク・コンデンサの小型化などが実現します。また、ADP1853 は、電流共有用のスレーブ・デバイスとして設定することも可能です。さらに、ADP1853 は、シーケンシングのためのトラッキング機能、高精度インエーブル機能、およびパワーグッド機能を備えています。ADP1853 は、エネルギー効率の優れた電力変換を可能にする高速の高ピーク電流ゲート・ドライブ機能を備えています。このデバイスは、パルス・スキッピングによって節電モードの動作を設定することができ、スイッチング損失を低減し、軽負荷時やスタンバイ状態での効率を向上します。

さらに、高精度の電流制限機能によって狭い許容誤差範囲での設計も可能になり、コンバータ全体のサイズとコストを低減することができます。ADP1853 は、-40°C~125°C の温度範囲で、誤差が±1%の高精度リファレンスを使用して最小 0.6 V まで出力を安定化することができます。

広範な入力電圧範囲に対応する ADP1853 は、さまざまなシステム構成で使用できる最大限の設計の柔軟性を提供します。ループ補償、ソフトスタート、周波数設定、節電モード、電流制限値、電流検出ゲインなどは、すべて外付け部品を使って設定することができます。さらに、外付けの RAMP 抵抗を使用すれば、電流モードと電圧モードの両方で最適なスロープと  $V_{IN}$  フィードフォワードを選ぶことができ、優れたライン・ノイズ除去比を実現できます。また、ハイサイド・ドライバ用のリニア・レギュレータとブートストラップ・ダイオードを内蔵しています。

保護機能としては、低電圧ロックアウト、過電圧保護、過電流／短絡保護、過熱保護を提供します。

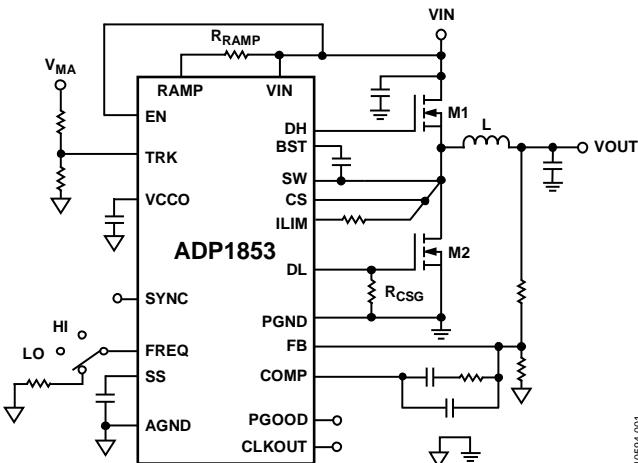

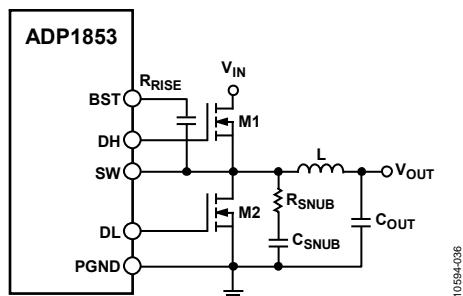

図 1. 代表的な動作回路

10594-01

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

©2012 Analog Devices, Inc. All rights reserved.

Rev. 0

アナログ・デバイセズ株式会社

本社／〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワー

電話 03 (5402) 8200

大阪営業所／〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー

電話 06 (6350) 6868

## 目次

|                        |    |                        |    |

|------------------------|----|------------------------|----|

| 特長                     | 1  | 過熱保護                   | 16 |

| アプリケーション               | 1  | インターリーブ・デュアルフェーズ動作     | 16 |

| 概要                     | 1  | アプリケーション情報             | 17 |

| 改訂履歴                   | 2  | ADIsimPower 設計ツール      | 17 |

| 仕様                     | 3  | 出力電圧の設定                | 17 |

| 絶対最大定格                 | 6  | ソフトスタート                | 17 |

| ESD に関する注意             | 6  | 電流制限の設定                | 17 |

| 簡略ブロック図                | 7  | 高精度の電流制限検出             | 17 |

| ピン配置と機能の説明             | 8  | 入力コンデンサの選択             | 17 |

| 代表的な性能特性               | 10 | VIN ピン・フィルタ            | 18 |

| 動作原理                   | 12 | 昇圧コンデンサの選択             | 18 |

| 制御アーキテクチャ              | 12 | インダクタの選択               | 18 |

| 発振器周波数                 | 12 | 出力コンデンサの選択             | 18 |

| 同期                     | 13 | MOSFET の選択             | 19 |

| PWM あるいはパルス・スキップ・モード動作 | 13 | ループ補償 - 電圧モード          | 20 |

| CLKOUT 信号              | 13 | ループ補償 - 電流モード          | 21 |

| 同期整流器とデッドタイム           | 14 | スイッチング・ノイズとオーバーシュートの低減 | 23 |

| 入力低電圧ロックアウト            | 14 | 電圧トラッキング               | 23 |

| 内部リニア・レギュレータ           | 14 | PCB レイアウトのガイドライン       | 24 |

| 過電圧保護                  | 14 | 代表的な動作回路               | 25 |

| パワーゲッド                 | 14 | 外形寸法                   | 27 |

| 短絡および電流制限保護            | 15 | オーダー・ガイド               | 27 |

| イネーブル/ディスエーブル制御        | 15 |                        |    |

## 改訂履歴

5/12—Revision 0: Initial Version

## 仕様

温度限界におけるすべての規定値は、標準の統計的品質管理手法 (SQC) を使う相関により保証しています。 $V_{IN} = 12\text{ V}$ 。特に指定のない限り、仕様の有効温度範囲は  $T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$  です。代表値 (typ) は  $T_A = 25^\circ\text{C}$  における値です。

表 1.

| Parameter                                          | Symbol                          | Test Conditions/Comments                                                                                                                                                                                                                                                                 | Min                                            | Typ                                           | Max                                            | Unit                                         |

|----------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------|------------------------------------------------|----------------------------------------------|

| POWER SUPPLY                                       |                                 |                                                                                                                                                                                                                                                                                          |                                                |                                               |                                                |                                              |

| Input Voltage                                      | $V_{IN}$                        |                                                                                                                                                                                                                                                                                          | 2.75                                           | 20                                            |                                                | V                                            |

| Undervoltage Lockout Threshold                     | $UVLO_{TRSH}$                   | $V_{IN}$ rising<br>$V_{IN}$ falling                                                                                                                                                                                                                                                      | 2.55<br>2.35                                   | 2.65<br>2.45                                  | 2.75<br>2.50                                   | V                                            |

| Undervoltage Lockout Hysteresis                    | $UVLO_{HYST}$                   |                                                                                                                                                                                                                                                                                          |                                                | 0.2                                           |                                                | V                                            |

| Quiescent Current                                  | $I_{IN}$                        | $EN = V_{IN} = 12\text{ V}$ , $V_{FB} = V_{CCO}$ in forced pulse width modulation (PWM) mode (no switching)<br>$EN = V_{IN} = 12\text{ V}$ , $V_{FB} = V_{CCO}$ in PSM mode                                                                                                              |                                                | 4.2                                           | 5.7                                            | mA                                           |

| Shutdown Current                                   | $I_{IN\_SD}$                    | $EN = GND$ , $V_{IN} = 5.5\text{ V}$ or $20\text{ V}$                                                                                                                                                                                                                                    |                                                | 2.5<br>100                                    | 200                                            | mA<br>$\mu\text{A}$                          |

| ERROR AMPLIFIER                                    |                                 |                                                                                                                                                                                                                                                                                          |                                                |                                               |                                                |                                              |

| FB Input Bias Current                              | $I_{FB}$                        |                                                                                                                                                                                                                                                                                          | -100                                           | +1                                            | +100                                           | nA                                           |

| Open-Loop Gain <sup>1</sup>                        |                                 |                                                                                                                                                                                                                                                                                          |                                                | 80                                            |                                                | dB                                           |

| Gain-Bandwidth Product <sup>1</sup>                |                                 |                                                                                                                                                                                                                                                                                          |                                                | 20                                            |                                                | MHz                                          |

| TRK Input Bias Current                             | $I_{TRK}$                       | $0\text{ V} \leq V_{TRK} \leq 5\text{ V}$                                                                                                                                                                                                                                                | -100                                           | +1                                            | +100                                           | nA                                           |

| CURRENT SENSE AMPLIFIER GAIN                       | $A_{CS}$                        | Gain resistor connected to DL,<br>$R_{CSG} = 47\text{ k}\Omega \pm 5\%$<br>Gain resistor connected to DL,<br>$R_{CSG} = 22\text{ k}\Omega \pm 5\%$<br>Default setting, $R_{CSG} = \text{open}$<br>Voltage mode operation, resistor DL to PGND,<br>$R_{CSG} = 100\text{ k}\Omega \pm 5\%$ | 2.6<br>5.2<br>10.5                             | 3<br>6<br>12                                  | 3.4<br>6.8<br>13.5                             | V/V<br>V/V<br>V/V                            |

| OUTPUT CHARACTERISTICS                             |                                 |                                                                                                                                                                                                                                                                                          |                                                |                                               |                                                |                                              |

| Feedback Accuracy Voltage                          | $V_{FB}$                        | $T_J = -40^\circ\text{C} \text{ to } +85^\circ\text{C}$<br>$T_J = -40^\circ\text{C} \text{ to } +125^\circ\text{C}$                                                                                                                                                                      | 597<br>594                                     | 600<br>600                                    | 603<br>606                                     | mV<br>mV                                     |

| Line Regulation of PWM                             | $\Delta V_{FB}/\Delta V_{IN}$   |                                                                                                                                                                                                                                                                                          |                                                |                                               | $\pm 0.015$                                    | %/V                                          |

| Load Regulation of PWM <sup>1</sup>                | $\Delta V_{FB}/\Delta V_{COMP}$ | $V_{COMP}$ range = $0.9\text{ V}$ to $2.2\text{ V}$                                                                                                                                                                                                                                      |                                                |                                               | $\pm 0.3$                                      | %                                            |

| OSCILLATOR                                         |                                 |                                                                                                                                                                                                                                                                                          |                                                |                                               |                                                |                                              |

| Frequency                                          | $f_{OSC}$                       | $R_{FREQ} = 332\text{ k}\Omega$ to AGND<br>$R_{FREQ} = 78.7\text{ k}\Omega$ to AGND<br>$R_{FREQ} = 40.2\text{ k}\Omega$ to AGND<br>FREQ to AGND<br>FREQ to $V_{CCO}$<br>$R_{FREQ}$ range from $332\text{ k}\Omega$ to $40.2\text{ k}\Omega$                                              | 170<br>720<br>1275<br>240<br>480<br>170<br>100 | 200<br>800<br>1500<br>300<br>600<br>1725<br>5 | 230<br>880<br>1725<br>360<br>720<br>1725<br>ns | kHz<br>kHz<br>kHz<br>kHz<br>kHz<br>kHz<br>ns |

| SYNC Input Frequency Range <sup>1</sup>            | $f_{SYNC}$                      |                                                                                                                                                                                                                                                                                          |                                                |                                               |                                                |                                              |

| SYNC Input Pulse Width <sup>1</sup>                | $t_{SYNCPW}$                    |                                                                                                                                                                                                                                                                                          |                                                |                                               |                                                |                                              |

| SYNC Pin Capacitance to GND                        | $C_{SYNC}$                      |                                                                                                                                                                                                                                                                                          |                                                |                                               |                                                |                                              |

| CLKOUT Frequency Range <sup>1</sup>                | $f_{CLKOUT}$                    | $f_{OSC}$ range from $170\text{ kHz}$ to $1725\text{ kHz}$                                                                                                                                                                                                                               | 170                                            |                                               | 1725                                           | kHz                                          |

| CLKOUT Pulse Duty Cycle                            | $D_{CLKOUT}$                    |                                                                                                                                                                                                                                                                                          |                                                |                                               | 50                                             | %                                            |

| CLKOUT Rise and Fall Time                          |                                 | $C_{CLKOUT} = 47\text{ pF}$                                                                                                                                                                                                                                                              |                                                |                                               | 10                                             | ns                                           |

| LINEAR REGULATOR                                   |                                 |                                                                                                                                                                                                                                                                                          |                                                |                                               |                                                |                                              |

| $V_{CCO}$ Output Voltage                           |                                 | $I_{VCCO} = 100\text{ mA}$                                                                                                                                                                                                                                                               | 4.7                                            | 5.0                                           | 5.3                                            | V                                            |

| $V_{CCO}$ Load Regulation                          |                                 | $I_{VCCO} = 0\text{ mA}$ to $100\text{ mA}$                                                                                                                                                                                                                                              |                                                | 35                                            |                                                | mV                                           |

| $V_{CCO}$ Line Regulation                          |                                 | $V_{IN} = 5.5\text{ V}$ to $20\text{ V}$ , $I_{VCCO} = 20\text{ mA}$                                                                                                                                                                                                                     |                                                | 10                                            |                                                | mV                                           |

| $V_{CCO}$ Current Limit <sup>1</sup>               |                                 | $V_{CCO}$ drops to $4\text{ V}$ from $5\text{ V}$                                                                                                                                                                                                                                        |                                                | 350                                           |                                                | mA                                           |

| $V_{CCO}$ Short-Circuit Current <sup>1</sup>       |                                 | $V_{CCO} < 0.5\text{ V}$                                                                                                                                                                                                                                                                 |                                                | 370                                           | 400                                            | mA                                           |

| $V_{IN}$ to $V_{CCO}$ Dropout Voltage <sup>2</sup> | $V_{DROPOUT}$                   | $I_{VCCO} = 100\text{ mA}$ , $V_{IN} \leq 5\text{ V}$                                                                                                                                                                                                                                    |                                                | 0.33                                          |                                                | V                                            |

| Parameter                                                       | Symbol                                                 | Test Conditions/Comments                                                     | Min   | Typ  | Max   | Unit |

|-----------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------|-------|------|-------|------|

| LOGIC INPUTS                                                    | I <sub>EN</sub>                                        | EN rising                                                                    | 0.57  | 0.63 | 0.68  | V    |

| EN Hysteresis                                                   |                                                        |                                                                              |       | 0.03 |       | V    |

| EN Input Leakage Current                                        |                                                        | V <sub>IN</sub> = 2.75 V to 20 V                                             | 1     | 200  | 200   | nA   |

| SYNC Logic Input Low                                            |                                                        |                                                                              |       |      | 1.3   | V    |

| SYNC Logic Input High                                           |                                                        |                                                                              | 1.9   |      | 1.3   | V    |

| SYNC Input Pull-Down Resistance                                 | R <sub>SYNC</sub>                                      |                                                                              |       | 1    |       | MΩ   |

| GATE DRIVERS                                                    | R <sub>ON_SOURCE</sub>                                 | C <sub>DH</sub> = 3 nF, V <sub>BST</sub> – V <sub>SW</sub> = 5 V             |       | 16   |       | ns   |

| DH Rise Time                                                    |                                                        | C <sub>DH</sub> = 3 nF, V <sub>BST</sub> – V <sub>SW</sub> = 5 V             |       | 14   |       | ns   |

| DH Fall Time                                                    |                                                        | C <sub>DL</sub> = 3 nF                                                       |       | 16   |       | ns   |

| DL Rise Time                                                    |                                                        | C <sub>DL</sub> = 3 nF                                                       |       | 14   |       | ns   |

| DL Fall Time                                                    |                                                        | External 3 nF is connected to DH and DL                                      |       | 25   |       | ns   |

| DH to DL Dead Time                                              |                                                        | Sourcing 2 A with a 100 ns pulse                                             |       | 2    |       | Ω    |

| DH or DL Driver R <sub>ON</sub> , Sourcing Current <sup>1</sup> |                                                        | Sourcing 1 A with a 100 ns pulse, V <sub>IN</sub> = 3 V                      |       | 2.3  |       | Ω    |

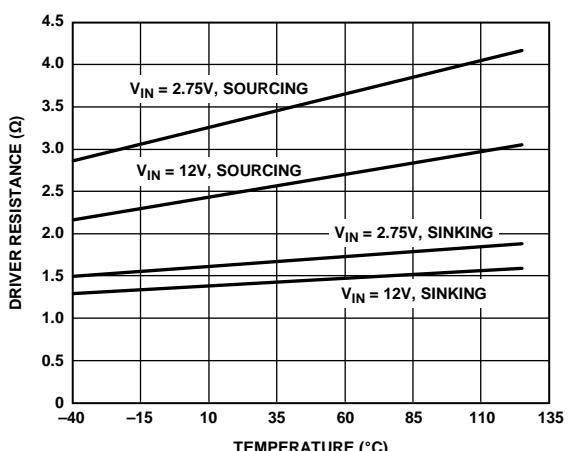

| DH or DL Driver R <sub>ON</sub> , Tempco                        | T <sub>C<sub>RON</sub></sub>                           | V <sub>IN</sub> = 3 V or 12 V                                                |       | 0.3  |       | %/°C |

| DH or DL Driver R <sub>ON</sub> , Sinking Current <sup>1</sup>  | R <sub>ON_SINK</sub>                                   | Sinking 2 A with a 100 ns pulse                                              |       | 1.5  |       | Ω    |

| DH Maximum Duty Cycle <sup>1</sup>                              | Sinking 1 A with a 100 ns pulse, V <sub>IN</sub> = 3 V |                                                                              | 2     |      | Ω     |      |

| DH Maximum Duty Cycle <sup>1</sup>                              | f <sub>OSC</sub> = 300 kHz                             | 90                                                                           |       |      | %     |      |

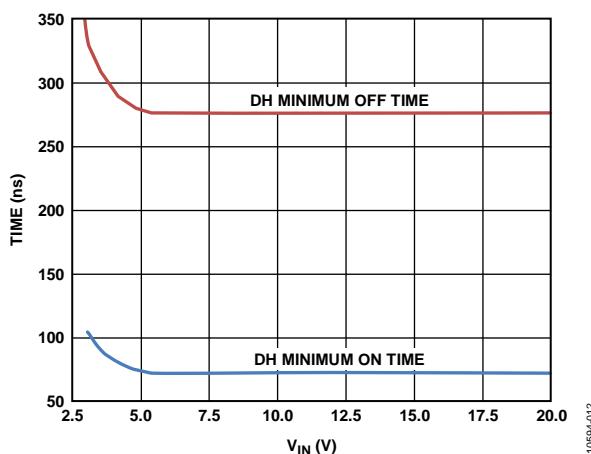

| Minimum DH On Time                                              | f <sub>OSC</sub> = 1500 kHz                            | 50                                                                           |       |      | %     |      |

| Minimum DH Off Time                                             | f <sub>OSC</sub> = 200 kHz to 1500 kHz                 |                                                                              | 85    |      | ns    |      |

| Minimum DL On Time                                              | f <sub>OSC</sub> = 200 kHz to 1500 kHz                 |                                                                              | 345   |      | ns    |      |

|                                                                 | f <sub>OSC</sub> = 200 kHz to 1500 kHz                 |                                                                              | 295   |      | ns    |      |

| COMP VOLTAGE RANGE                                              |                                                        |                                                                              |       |      |       |      |

| COMP Pulse Skip Threshold                                       | V <sub>COMP,THRES</sub>                                | In pulse skip mode (PSM)                                                     |       | 0.9  |       | V    |

| COMP Clamp High Voltage                                         | V <sub>COMP,HIGH</sub>                                 |                                                                              | 2.2   |      |       | V    |

| THERMAL SHUTDOWN                                                |                                                        |                                                                              |       |      |       |      |

| Thermal Shutdown Threshold                                      | T <sub>TMSD</sub>                                      |                                                                              |       | 155  |       | °C   |

| Thermal Shutdown Hysteresis                                     |                                                        |                                                                              |       | 20   |       | °C   |

| OVERVOLTAGE AND POWER GOOD THRESHOLDS                           |                                                        |                                                                              |       |      |       |      |

| FB Overvoltage Threshold                                        | V <sub>OV</sub>                                        | V <sub>FB</sub> rising                                                       | 0.630 | 0.65 | 0.670 | V    |

| FB Overvoltage Hysteresis                                       |                                                        |                                                                              |       | 18   |       | mV   |

| FB Undervoltage Threshold                                       | V <sub>UV</sub>                                        | V <sub>FB</sub> falling                                                      | 0.525 | 0.55 | 0.575 | V    |

| FB Undervoltage Hysteresis                                      |                                                        |                                                                              |       | 15   |       | mV   |

| TRK INPUT VOLTAGE RANGE <sup>1</sup>                            |                                                        |                                                                              | 0     | 5    |       | V    |

| FB TO TRK OFFSET VOLTAGE                                        |                                                        | TRK = 0.1 V to 0.57 V; offset = V <sub>FB</sub> – V <sub>TRK</sub>           | -10   | 0    | +10   | mV   |

| SOFT START                                                      |                                                        |                                                                              |       |      |       |      |

| SS Output Current                                               | I <sub>SS</sub>                                        | During startup                                                               | 4.6   | 6.5  | 8.4   | μA   |

| SS Pull-Down Resistor                                           |                                                        | During a fault condition                                                     |       | 3    |       | kΩ   |

| FB to SS offset                                                 |                                                        | V <sub>SS</sub> = 0.1 V to 0.6 V; offset = V <sub>FB</sub> – V <sub>SS</sub> | -10   |      | +10   | mV   |

| Parameter                                           | Symbol      | Test Conditions/Comments                                           | Min | Typ  | Max | Unit      |

|-----------------------------------------------------|-------------|--------------------------------------------------------------------|-----|------|-----|-----------|

| PGOOD                                               |             |                                                                    |     |      |     |           |

| PGOOD Pull-Up Resistor                              | $R_{PGOOD}$ | Internal pull-up resistor to VCCO                                  |     | 12.5 |     | $k\Omega$ |

| PGOOD Delay                                         |             |                                                                    |     | 12   |     | $\mu s$   |

| Overvoltage or Undervoltage Minimum Duration        |             | This is the minimum duration required to trip the PGOOD signal     |     | 10   |     | $\mu s$   |

| ILIM Threshold Voltage <sup>1</sup>                 |             | Relative to PGND                                                   | -5  | 0    | +5  | $mV$      |

| ILIM Output Current                                 |             | ILIM = PGND                                                        | 45  | 50   | 55  | $\mu A$   |

| Current Sense Blanking Period                       |             | After DL goes high, current limit is not sensed during this period |     | 100  |     | ns        |

| INTEGRATED RECTIFIER (BOOST DIODE) RESISTANCE       |             | At 20 mA forward current                                           |     | 16   |     | $\Omega$  |

| ZERO CURRENT CROSS OFFSET (SW TO PGND) <sup>1</sup> |             | In pulse skip mode only; $f_{osc} = 300$ kHz                       | 0   | 2    | 4   | $mV$      |

<sup>1</sup> 設計により保証しています。

<sup>2</sup>  $V_{IN} < 5.5$  V のときは  $V_{IN}$  を VCCO に接続してください。

## 絶対最大定格

表 2.

| Parameter                                          | Rating                 |

|----------------------------------------------------|------------------------|

| VIN, EN, RAMP                                      | 21 V                   |

| FB, COMP, SS, TRK, FREQ, SYNC, VCCO, PGOOD, CLKOUT | -0.3 V to +6 V         |

| ILIM, SW, CS to PGND                               | -0.3 V to +21 V        |

| BST, DH to PGND                                    | -0.3 V to +28 V        |

| DL to PGND                                         | -0.3 V to VCCO + 0.3 V |

| BST to SW                                          | -0.3 V to +6 V         |

| BST to PGND to PGND 20 ns Transients               | 32 V                   |

| SW, CS to PGND 20 ns Transients                    | 25 V                   |

| DL, SW, CS, ILIM to PGND 20 ns Negative Transients | -8 V                   |

| PGND to AGND                                       | -0.3 V to +0.3 V       |

| PGND to AGND 20 ns Transients                      | -8 V to +4 V           |

| $\theta_{JA}$ (Natural Convection) <sup>1,2</sup>  | 40°C/W                 |

| Operating Junction Temperature Range <sup>3</sup>  | -40°C to +125°C        |

| Storage Temperature Range                          | -65°C to +150°C        |

| Maximum Soldering Lead Temperature                 | 260°C                  |

左記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

絶対最大定格は、これらの値の組み合わせではなく個別に適用されます。特に指定のない限り、他のすべての電圧は GND を基準としています。

### ESD に関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

<sup>1</sup> 露出パッドを PC ボードに接続した状態で測定した値です。

<sup>2</sup> パッケージのジャンクション／周囲間熱抵抗 ( $\theta_{JA}$ ) は、多層 PC ボードを前提として計算またはシミュレートした値です。

<sup>3</sup> デバイスのジャンクション温度 ( $T_J$ ) は、周囲温度 ( $T_A$ ) 、デバイスの消費電力 ( $P_D$ ) 、およびパッケージのジャンクション／周囲間熱抵抗 ( $\theta_{JA}$ ) によって異なります。最大ジャンクション温度は、式  $T_J = T_A + P_D \times \theta_{JA}$  を使用して周囲温度と消費電力から計算した値です。

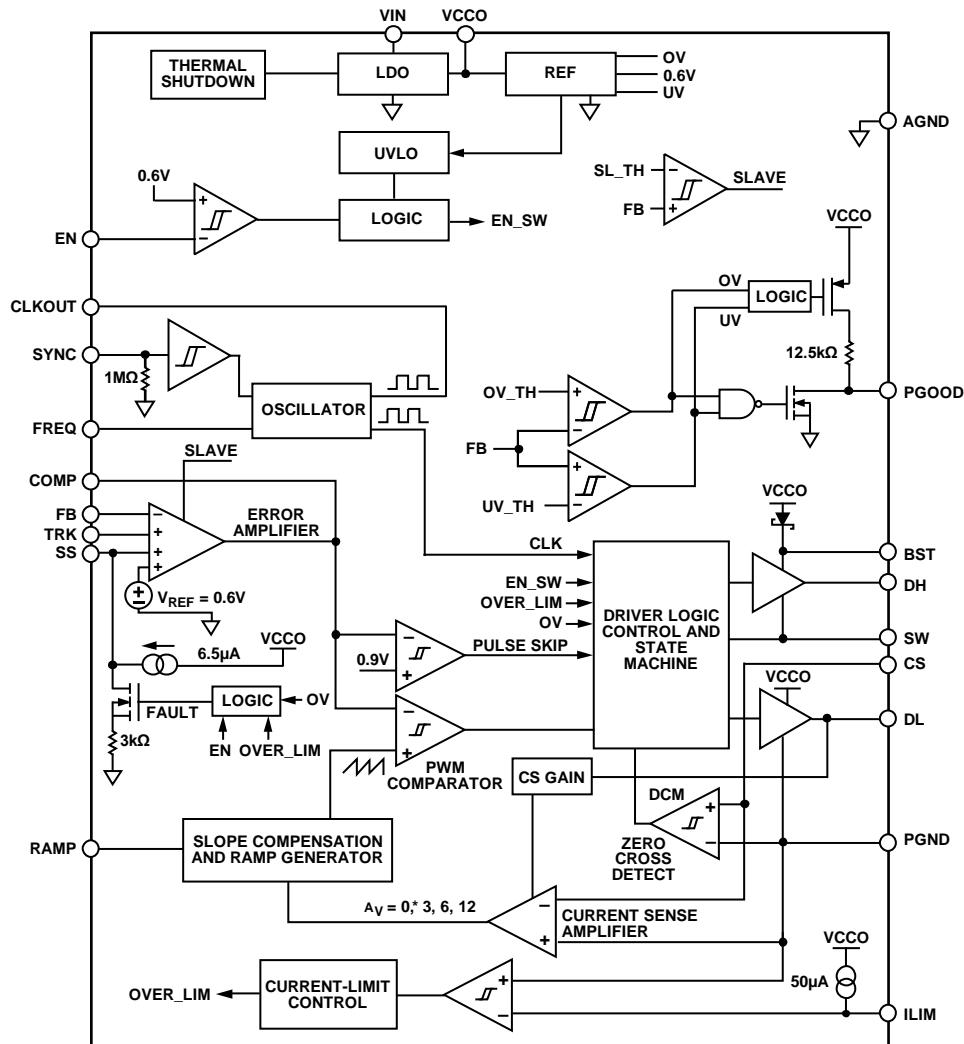

## 簡略ブロック図

\*0 (ZERO) GAIN IS FOR VOLTAGE MODE WITH RAMP FROM 0.7V TO 2.2V.

10594-002

図 2.

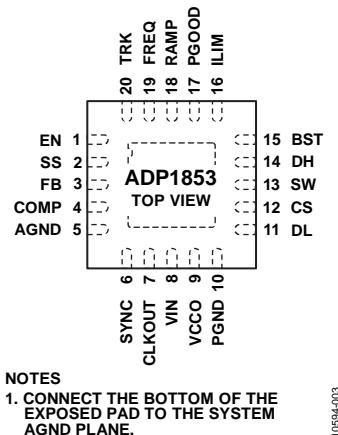

## ピン配置と機能の説明

図 3. ピン配置

表 3. ピン機能の説明

| ピン番号 | 記号     | 説明                                                                                                                                                                                                                                                   |

|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | EN     | イネーブル入力。コントローラをオンにするには EN をハイレベルにし、オフにするにはローレベルにします。自動スタートアップとするには EN を $V_{IN}$ に接続します。高精度の UVLO を行うには、 $V_{IN}$ と AGND の間に適切なサイズの抵抗分圧器を配置して、中間点をこのピンに接続します。                                                                                        |

| 2    | SS     | ソフトスタート入力。ソフトスタート時間設定するには、SS と AGND の間にコンデンサを接続します。このノードは、 $6.5\mu A$ 電流源を通じて VCCO に内部でプルアップされます。                                                                                                                                                    |

| 3    | FB     | 出力電圧帰還。このピンは抵抗分圧器を介して出力に接続します。インターリーブ・デュアルフェーズ構成でスレーブ・モード動作をさせるには、FB を VCCO に接続します。                                                                                                                                                                  |

| 4    | COMP   | 補償ノード。誤差アンプの出力。レギュレーション制御ループを補償するには、COMP と FB の間に抵抗／コンデンサ・ネットワークを接続します。インターリーブ・デュアルフェーズ構成では、このピンをもう一方の COMP ピンに接続します。                                                                                                                                |

| 5    | AGND   | アナログ・グラウンド。システムの AGND プレーンに接続します。                                                                                                                                                                                                                    |

| 6    | SYNC   | 周波数同期入力。このピンは、FREQ ピンによって設定する内部発振器周波数 $f_{osc}$ の等倍に近い周波数の外部クロック信号を受け入れます。コントローラは、SYNC で周期的なクロック信号が検出されるか SYNC がハイレベルになると、強制 PWM で動作します。この場合のスイッチング周波数は SYNC 周波数の等倍です。SYNC がローレベルかフロート状態の場合、コントローラはパルス・スキップ・モードで動作します。                               |

| 7    | CLKOUT | 内部クロック出力。CLKOUT は内部発振器周波数または入力 SYNC 信号周波数の等倍で、 $180^\circ$ 位相シフトされています。このピンは、別の ADP1853 かほかのコントローラを同期させるために使用できます。                                                                                                                                   |

| 8    | VIN    | 主電源に接続します。このピンと AGND にできるだけ近い位置に接続した $1\mu F$ 以上のセラミック・コンデンサでバイパスしてください。                                                                                                                                                                             |

| 9    | VCCO   | 内部低ドロップアウト・レギュレータ (LDO) の出力。内部回路とゲート・ドライバの電源は VCCO から供給されます。VCCO は、 $1\mu F$ 以上のセラミック・コンデンサを使って AGND にバイパスしてください。VCCO は、EN がローレベルになってもアクティブのままでです。 $5V$ 未満の $V_{IN}$ で動作させる場合は、 $V_{IN}$ を VCCO にジャンプさせることができます。LDO は、ほかの補助システム負荷への電源供給には使用しないでください。 |

| 10   | PGND   | 電源グラウンド。内部ドライバ用電源。差動電流です。                                                                                                                                                                                                                            |

| 11   | DL     | ローサイド同期整流器ゲート・ドライバ出力。電流モードの電流検出アンプのゲインを設定したり、電圧モード制御を設定したりするには、DL と PGND の間に抵抗を接続します。このピンは、合計入力容量 $20\text{ nF}$ までの MOSFET をドライブすることができます。                                                                                                          |

| 12   | CS     | 電流検出アンプ入力。差動電流は CS と PGND の間で検出されます。電流を検出するには、このピンを電流検出抵抗か SW ピンに接続します。電圧モード動作とするには、このピンを PGND に接続します。                                                                                                                                               |

| 13   | SW     | パワー・スイッチ・ノード。このピンは、ハイサイド N チャンネル MOSFET のソースと、ローサイド N チャンネル MOSFET のドレインに接続してください。                                                                                                                                                                   |

| 14   | DH     | ハイサイド・スイッチ・ゲート・ドライバ出力。このピンは、合計入力容量 $20\text{ nF}$ までの MOSFET をドライブすることができます。                                                                                                                                                                         |

| 15   | BST    | ハイサイド内部ドライバのブートストラップ・アッパー・レール。BST と SW の間に $0.1\sim0.22\mu F$ の多層セラミック・コンデンサ (MLCC) を接続してください。VCCO と BST の間には、内部昇圧ダイオード整流器が接続されています。                                                                                                                 |

| 16   | ILIM   | 電流制限検出コンパレータ反転入力。電流制限オフセットを設定するには、ILIM と SW の間に抵抗を接続します。高精度の電流制限検出を行うには、ILIM をローサイド MOSFET のソースにある電流検出抵抗に接続します。                                                                                                                                      |

| ピン番号 | 記号          | 説明                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17   | PGOOD       | パワーグッド。オーブンドレイン・パワーグッド・インジケータ・ロジック出力で、PGOOD と VCCO の間には $12.5\text{ k}\Omega$ の内部抵抗が組み込まれています。出力がレギュレーション領域を外れると、PGOOD はグラウンドにプルダウンされます。外付けのプルアップ抵抗は必要ありません。インターリーブ・デュアルフェーズ・アプリケーションにおいて、ハイレベルの FB ピンを VCCO に接続することによってコントローラがスレーブとして構成されている場合で、マスターが軽負荷状態のパルス・スキップ・モードにある場合は、PGOOD ピンを外部からローレベルにドライブすることでパルス・スキップ・モードがイネーブルになります。それ以外で、マスターが強制 PWM動作に設定されている場合は、スレーブ・コントローラの PGOOD をマスターの PGOOD に接続する必要があります。 |

| 18   | RAMP        | スロープ補償のためのプログラム可能な電流設定。RAMP から $V_{IN}$ の間に抵抗を接続します。動作中の RAMP の電圧は $0.2\text{ V}$ です。チャンネルがディスエーブルになっている場合、このピンは高インピーダンスです。                                                                                                                                                                                                                                                                                     |

| 19   | FREQ        | 内部発振器周波数 $f_{osc}$ 。FREQ と AGND の間に抵抗を 1つ入れることによって、 $200\text{ kHz}$ ~ $1.5\text{ MHz}$ の範囲で必要な動作周波数を設定します。動作周波数をあらかじめ $300\text{ kHz}$ に設定するには FREQ を AGND に接続し、 $600\text{ kHz}$ とするには FREQ を VCCO に接続します。                                                                                                                                                                                                    |

| 20   | TRK<br>EPAD | トランкиング入力。トランкиングを使わない場合は TRK を VCCO に接続します。<br>露出パッド。露出パッドの底面をシステムの AGND プレーンに接続します。                                                                                                                                                                                                                                                                                                                           |

## 代表的な性能特性

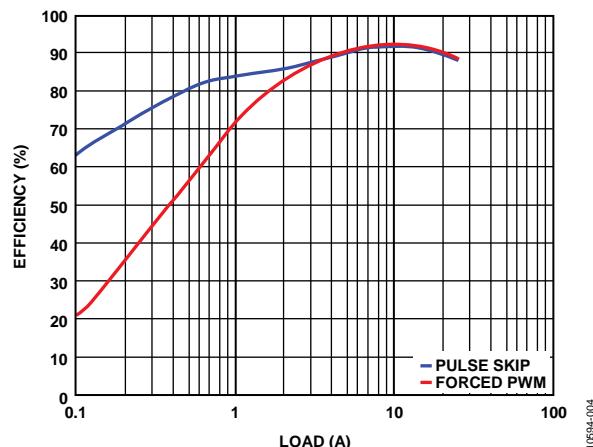

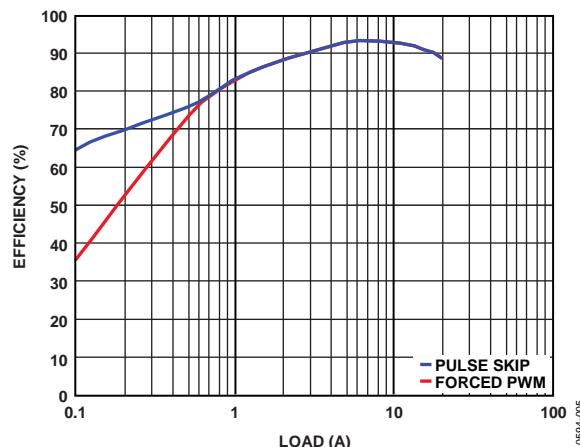

図 4. 効率プロット

(12 V<sub>IN</sub>、3.3 V<sub>OUT</sub>、300 kHz、回路は図 36 を参照)

図 7. 効率プロット

(15 V<sub>IN</sub>、5 V<sub>OUT</sub>、600 kHz、回路は図 35 を参照)

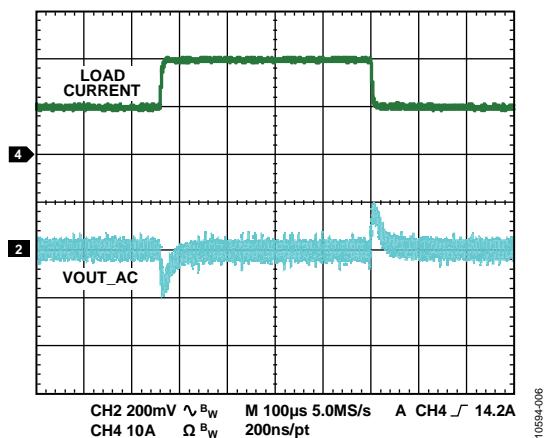

図 5. 10~20 A 負荷ステップ

(12 V<sub>IN</sub>、3.3 V<sub>OUT</sub>、300 kHz、電流モード)

図 8. 10~20 A 負荷ステップ

(12 V<sub>IN</sub>、3.3 V<sub>OUT</sub>、300 kHz、電圧モード)

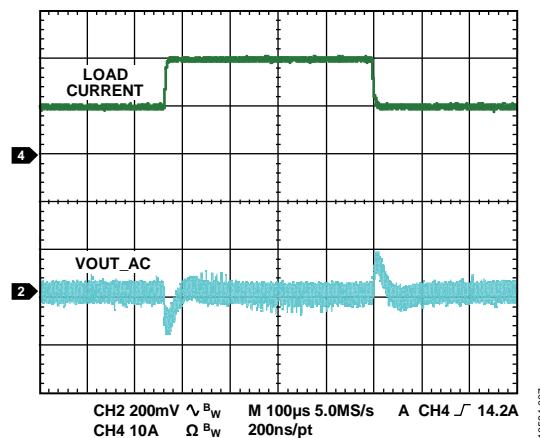

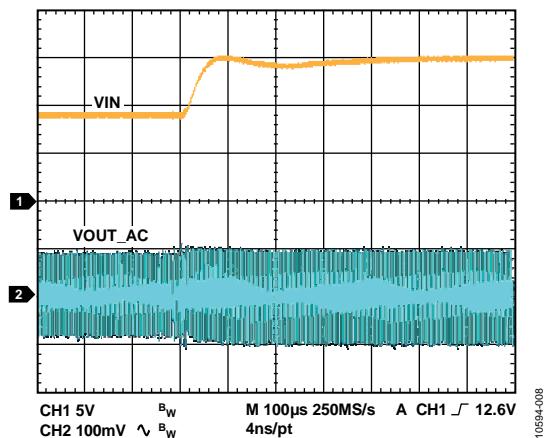

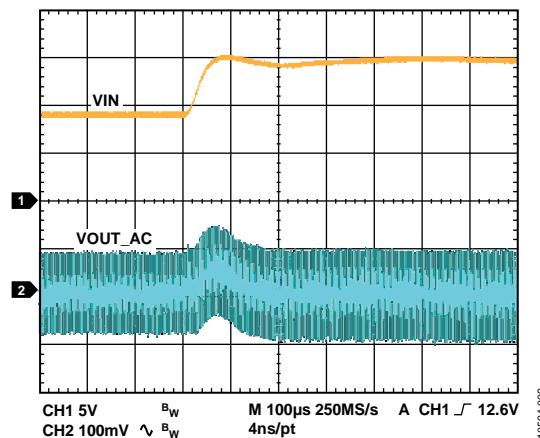

図 6. 9~15 V ライン・ステップ

(3.3 V<sub>OUT</sub>、15 A 負荷、電流モード)

図 9. 9~15 V ライン・ステップ

(3.3 V<sub>OUT</sub>、15 A 負荷、電圧モード)

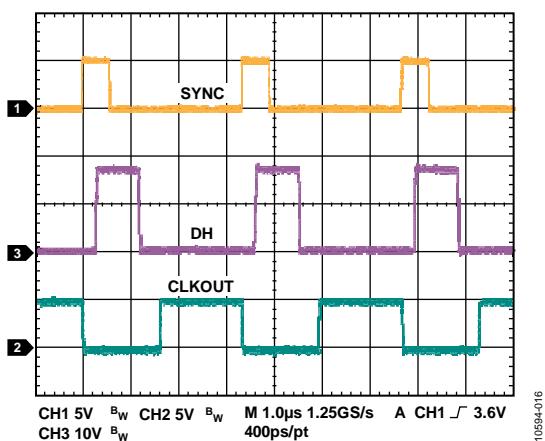

図 10. 同期と CLKOUT ( $f_{SYNC} = 300$  kHz)図 13. プレチャージ出力によるソフトスタート

(3.3 V<sub>OUT</sub> 強制 PWM)

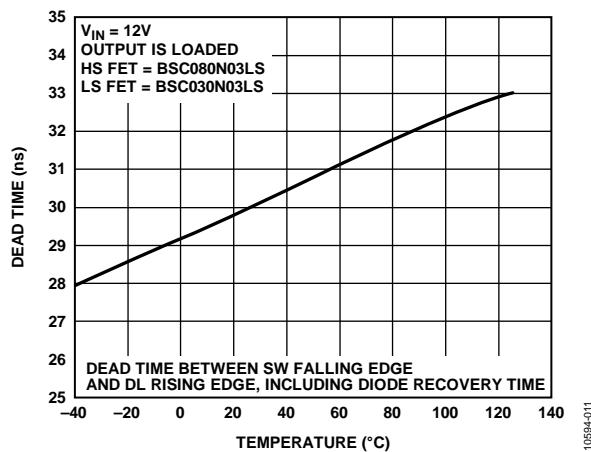

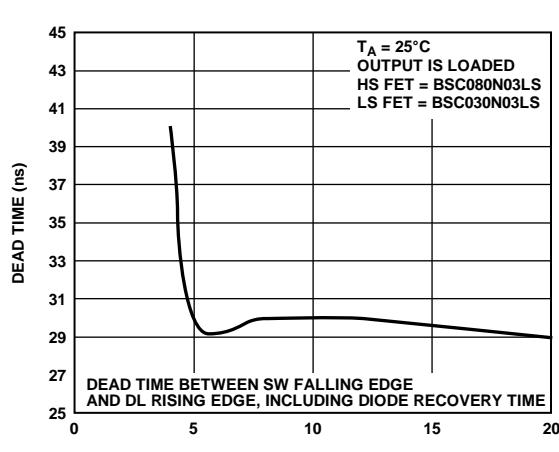

図 11. デッドタイムの温度特性

図 14. V<sub>IN</sub> 対 デッドタイム

図 12. 代表的な DH 最小オン時間とオフ時間

図 15. ドライバ抵抗の温度特性

## 動作原理

ADP1853 は固定周波数の降圧同期整流スイッチング・コントローラです。内部ドライバと、外付け N チャンネル・パワー MOSFET 用のブートストラップ回路を備えています。電流モード制御ループは電圧モードに変更することができます。また、コントローラは、軽負荷時や強制 PWM 時の消費電力を低減するために、パルス・スキップ・モードの動作も設定できます。ADP1853 は、プログラマブル・ソフトスタート、出力過電圧保護、プログラマブル電流制限、パワーグッド、トラッキングなどの機能を備えています。コントローラは 200 kHz~1.5 MHz の周波数で動作しますが、この周波数は抵抗によって設定するか、外部クロックに同期させます。また、内部クロックアウト信号もあり、ほかのデバイスを同期させるために使用できます。

## 制御アーキテクチャ

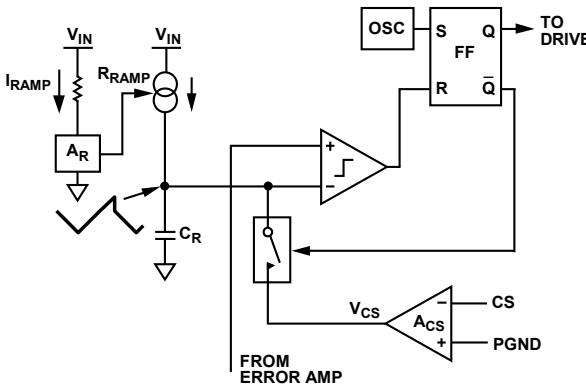

ADP1853 は、固定周波数、エミュレート・ピーク電流モードの PWM 制御アーキテクチャを採用しています。インダクタ電流は、外付けのローサイド MOSFET ( $R_{DSON}$ ) 両端、またはローサイド MOSFET のソースと電源グラウンドの間に直列に配置された検出抵抗両端の電圧降下を測定することによって検出されます。電流はスイッチング・サイクルのオフ時間内に検出され、内部電流検出アンプによって処理されます。電流検出アンプのゲインは 3 V/V、6 V/V、または 12 V/V に設定可能で、デバイスがスイッチングを開始する前、コントローラのパワーアップ時の初期化中に設定されます。DL と PGND 間の抵抗を 47 kΩ にするとゲインは 3 V/V に設定され、22 kΩ にすると 6 V/V に設定されます。抵抗なしの場合、ゲインは 12 V/V になります。電流検出アンプの出力信号は保持され、図 16 に示すように、次のスイッチング・サイクルの DH オン時間中にエミュレート電流ランプに加算され、PWM コンパレータに送られます。この信号と誤差アンプからの COMP 信号とを比較して、PWM パルスを発生させるフリップ・フロップをリセットします。DL と PGND の間に 100 kΩ の抵抗を配置して電圧モード制御を選択した場合、エミュレート・ランプはそのまま PWM コンパレータに送られ、電流検出信号は加算されません。

図 16. 制御アーキテクチャの簡略図

図 16 に示すように、エミュレート電流ランプは IC 内部で生成されますが、RAMP ピンから設定することができます。 $V_{IN}$  と RAMP ピンの間に適切な値の抵抗を配置すれば、必要なスロープ補償値を得ることができますとともに、 $V_{IN}$  のフィードフォワード機能も利用できます。制御ロジックは強制的にアンチシュートスルーモードを行い、内部ドライバと外付け MOSFET 間のクロス導通を制限します。

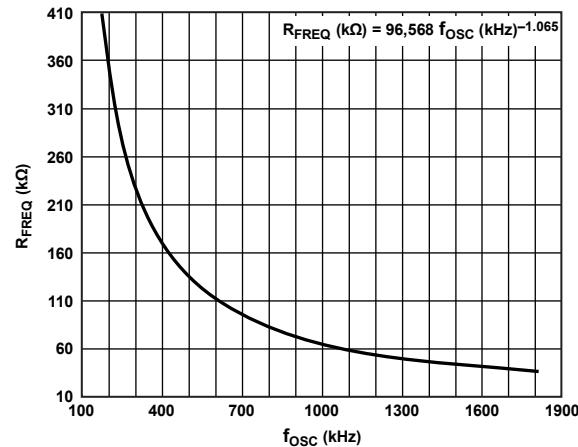

## 発振器周波数

内部発振器の周波数範囲は 200 kHz~1.5 MHz で、その値は FREQ ピンに外付け抵抗  $R_{FREQ}$  を接続して設定します。一般的な  $f_{osc}$  の値の例を表 4 に、両者の関係を図 17 に示します。たとえば、抵抗値を 78.7 kΩ にすると発振器周波数は 800 kHz になります。さらに、FREQ を AGND に接続すると発振器周波数は 300 kHz に、FREQ を VCCO に接続すると 600 kHz になります。表 4 に含まれていない周波数における  $R_{FREQ}$  と  $f_{osc}$  の値は、図 17 から求めることができます。

$$R_{FREQ}(\text{k}\Omega) = 96,568 \times f_{osc}(\text{kHz})^{-1.065}$$

表 4. 発振器周波数の設定

| $R_{FREQ}$   | $f_{osc}$ (Typical) |

|--------------|---------------------|

| 332 kΩ       | 200 kHz             |

| 78.7 kΩ      | 800 kHz             |

| 60.4 kΩ      | 1000 kHz            |

| 51 kΩ        | 1200 kHz            |

| 40.2 kΩ      | 1500 kHz            |

| FREQ to AGND | 300 kHz             |

| FREQ to VCCO | 600 kHz             |

図 17.  $f_{osc}$  対  $R_{FREQ}$

## 外部周波数同期

ADP1853 のスイッチング周波数は、外部クロック信号を SYNC ピンに接続することによって、その信号に同期させることができます。FREQ ピンの抵抗で設定する内部発振器の周波数は、外部クロック周波数に近い値に設定する必要があります。したがって、外部クロック周波数は、内部クロック設定の 0.85 倍～1.3 倍とすることができます。この場合のスイッチング周波数は、外部 SYNC 周波数の等倍です。同期後の ADP1853 は PWM で動作します。

最初の SYNC エッジで外部クロックが検出されると、内部発振器がリセットされてクロック制御が SYNC にシフトし、その後は SYNC エッジが PWM 出力のクロッキングをトリガします。DH の立ち上がりエッジは対応する SYNC エッジの約 100 ns 後に発生し、周波数が外部信号にロックされます。動作中に外部 SYNC 信号が途切れた場合、ADP1853 は内部発振器による動作に戻ります。SYNC 機能使用時は、SYNC 信号が失われた場合でも ADP1853 が PWM で動作を継続するように、SYNC と VCCO の間にプルアップ抵抗を接続することを推奨します。

## PWM あるいはパルス・スキップ・モード動作

SYNC ピンは多機能ピンです。SYNC が VCCO に接続するかハイ・ロジックになると、PWM モードがイネーブルになります。SYNC をグラウンドに接続するかフロート状態にすると、パルス・スキップ・モードがイネーブルになります。動作中に SYNC をローレベルからハイレベルに切り替えると、コントローラは 2 クロック・サイクルで強制 PWM モードからパルス・スキップ・モードに遷移し、ハイレベルからローレベルに切り替えると、パルス・スキップ・モードから強制 PWM モードに遷移します。

表 5. 動作モード

| SYNC Pin     | Mode of Operation |

|--------------|-------------------|

| Low          | Pulse skip mode   |

| High         | Forced PWM        |

| No Connect   | Pulse skip mode   |

| Clock Signal | Forced PWM        |

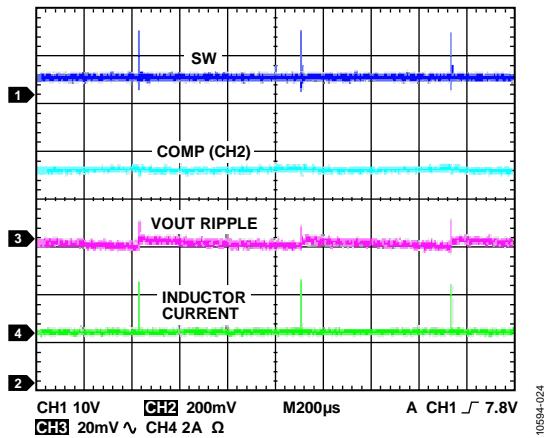

ADP1853 には、PWM パルスをスキップできるようにパルス・スキップ検出回路が組み込まれており、軽負荷時にはスイッチング周波数を低下させることによって優れた効率を維持します。この場合の出力リップルは、固定周波数の強制 PWM における値よりも大きくなります。図 18 に、軽負荷時における ADP1853 の PSM 動作を示します。軽負荷時のパルス・スキップ周波数は、インダクタ、出力容量、出力負荷、入力電圧、出力電圧によって異なります。

図 18. 軽負荷時のパルス・スキップ・モードの例

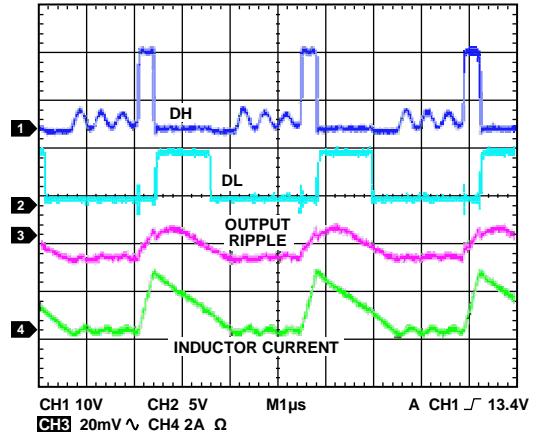

出力負荷がパルス・スキップ閾値電流より大きくなると、つまり、 $V_{COMP}$  が 0.9 V の閾値に達すると、ADP1853 はパルス・スキップ・モード動作を終了して、図 19 に示すように固定周波数の電流不連続モード (DCM) に入ります。さらに負荷が大きくなると、ADP1853 は電流連続モード (CCM) に入ります。

図 19. 電流不連続モード (DCM) 波形の例

強制 PWM では、ADP1853 は負荷に関わらずつねに CCM で動作するため、インダクタ電流はつねに連続です。

## CLKOUT 信号

ADP1853 は、ほかの ADP1853 コントローラの同期に使用できるクロック出力 CLKOUT を備えているため、外部クロック源は不要です。CLKOUT の周波数は内部発振器周波数  $f_{osc}$  の等倍で、位相が 180° 異なります。

## 同期整流器とデッドタイム

ADP1853 では、アンチシートスルー回路が DH/SW 間および DL/PGND 間の電圧を監視し、ローサイド・ドライバとハイサイド・ドライバを調整して、ハイサイド MOSFET とローサイド MOSFET 間のクロス導通やシートスルーを防ぐブレーカ・ビフォア・マーク・スイッチングが行われるようにします。ブレーカ・ビフォア・マーク・スイッチングはデッドタイムと呼ばれます。この値は固定ではなく、MOSFET のオン／オフの速度によって異なります。中サイズの MOSFET と約 3 nF の入力コンデンサを使用する標準的なアプリケーション回路の場合、デッドタイムの代表値は約 25 ns です。ダイオード回復時間の短い小型の高速 MOSFET を使用する場合は、デッドタイムを 13 ns 程度に短縮できます。

## 入力低電圧ロックアウト

VIN ピンのバイアス入力電圧が、2.6 V (typ) の低電圧ロックアウト (UVLO) 閾値よりも低い場合、スイッチ・ドライバは非アクティブのままになります。EN がハイレベルになるとコントローラはスイッチングを開始し、VIN ピンの電圧が UVLO 閾値を超えます。

## 内部リニア・レギュレータ

内部リニア・レギュレータは低ドロップアウト (LDO) VCCO です。VCCO は内部制御回路をパワーアップして、ゲート・ドライバに電力を供給します。出力電流能力は 200 mA 以上が保証されていますが、これは、最大 1.5 MHz で駆動される標準的ロジック閾値の MOSFET に関するゲート・ドライバ要件を十分に満たすことのできる値です。VCCO はつねにアクティブで、EN 信号によってシャットダウンすることはできませんが、過熱保護イベントが発生すると、LDO はコントローラとともにディスエーブルになります。VCCO は、1  $\mu$ F 以上のコンデンサを使って AGND にバイパスしてください。

LDO はゲート・ドライバ電流を供給するため、それぞれのスイッチング・サイクルでドライバがスイッチングを行い、昇圧コンデンサが充電される際に、VCCO の出力に急激な過渡電流が発生します。LDO は、過負荷フォルトを発生させることなくこれらの過渡状態に対応できるように最適化されています。ゲート駆動負荷への対応上、ほかの外付け補助システムの負荷のために VCCO 出力を使用することは推奨できません。

LDO には電流制限がありますが、予想される最大ゲート駆動負荷に対して十分な余裕が取られています。この電流制限には、短絡フォルト発生時にさらに VCCO 電流を制限するための短絡フォールドバック機能も含まれています。

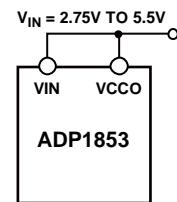

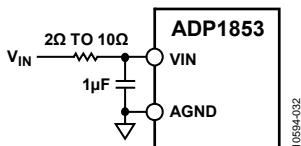

入力電圧が 5.5 V より低い場合は、図 20 に示すように VIN を VCCO に接続することによって LDO をバイパスして、ドロップアウト電圧をなくすことを推奨します。ただし、入力範囲が 4~7 V の場合、VIN を VCCO に短絡することによって LDO をバイパスすることはできません。これは、入力が 7 V の場合は VCCO ピンの最大電圧定格を超てしまうためです。この場合は LDO を使用して内部ドライバを駆動しますが、VIN が 5 V 未満の場合はドロップアウトがあるという点に留意してください。

図 20.  $V_{IN} < 5.5$  V の場合の構成

## 過電圧保護

ADP1853 には、FB ノードの出力過電圧を検出するための回路が組み込まれています。FB 電圧  $V_{FB}$  が過電圧閾値を超えた場合はハイサイド N チャンネル MOSFET (NMOSFET) がオフになります。 $V_{FB}$  が低電圧閾値を下回るまでローサイド NMOSFET がオンになります。この動作はクロロバー過電圧保護と呼ばれます。過電圧状態が解消されない場合、コントローラは過電圧閾値と低電圧閾値の間でフィードバック電圧を維持し、出力はレギュレーション電圧の  $\pm 8\%$  (typ) 以内に安定化します。過電圧イベントの場合、SS ノードは  $3\text{k}\Omega$  の内部プルダウン抵抗を通じてゼロまで放電されます。FB の電圧が低電圧閾値を下回ると、ソフトスタート・シーケンスが再開します。PSM動作中の過電圧保護方式を図 21 に示します。

図 21. PSM における過電圧保護

## パワーグッド

PGOOD ピンは、PGOOD と VCCO の間に  $12.5\text{k}\Omega$  の内部プルアップ抵抗を接続したオープンドレイン NMOSFET です。PGOOD は通常動作時に内部的にプルアップされ、トリップするとアクティブ・ローになります。フィードバック電圧  $V_{FB}$  が過電圧閾値を上回るか低電圧閾値を下回ると、PGOOD 出力は  $12\text{\mu s}$  の遅延後にグラウンドまでプルダウンされます。PGOOD がアクティブになるには、過電圧状態または低電圧状態の持続時間が  $10\text{\mu s}$  を超えなければなりません。PGOOD 出力は、過熱状態が検出された場合もアクティブになります。

## 短絡および電流制限保護

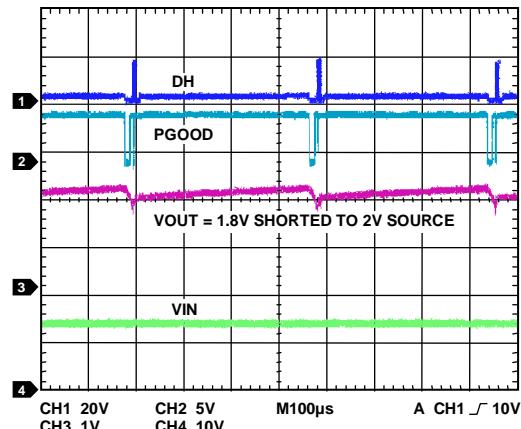

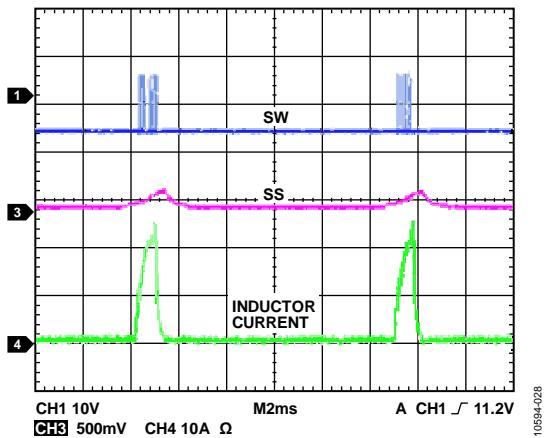

出力が短絡するか、出力電流が電流制限設定抵抗 (ILIM と CS の間) によって設定された電流制限を連続 8 サイクルにわたって超えると、ADP1853 はハイサイドとローサイド両方のドライバをシャットオフして、10 ms ごとにソフトスタート・シーケンスを再開します。これはヒップ・モード (しゃっくりモード) と呼ばれます。過電流または短絡イベントが発生すると、SS ノードは 3 kΩ の内部抵抗を通じてゼロまで放電します。図 22 は、大電流アプリケーション回路に組み込まれた ADP1853 が、出力短絡時に電流制限ヒップ・モードを維持するようすを示したもの

図 22. 電流制限ヒップ・モード、20 A 電流制限

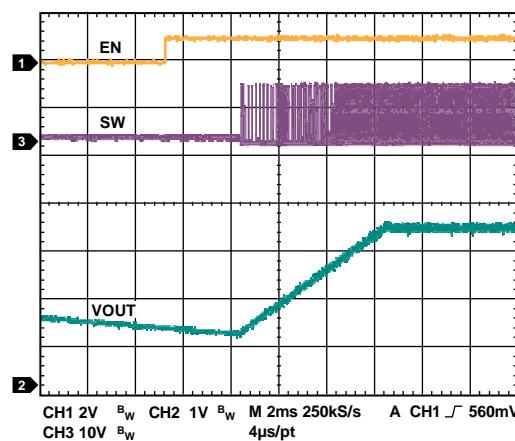

## イネーブル/ディスエーブル制御

EN ピンは、ADP1853 コントローラをイネーブルまたはディスエーブルするために使われます。高精度イネーブル閾値は 0.63 V (typ) です。EN の電圧が閾値電圧を超えるとコントローラがイネーブルされ、内部発振器、リファレンス、各種設定、およびソフトスタート期間の初期化後に通常動作を開始します。EN の電圧が閾値電圧を 30 mV (typ, ヒステリシス) 下回ると、ADP1853 のドライバと内部制御回路はオフになります。さらに、EN 信号は VCCO の LDO をシャットダウンしません。V<sub>IN</sub> が UVLO 閾値を上回っている間は、LDO はつねにアクティブです。

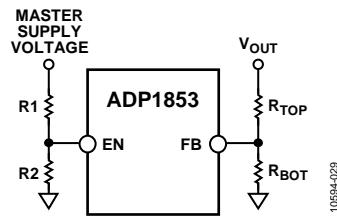

ADP1853 は、図 23 に示すように、主電源から EN ピンに適切な抵抗分圧器を接続することによってスタートアップ時の電源シーケンシングを設定することができます。たとえば、必要な主電源電圧が 10 V の場合、R1 と R2 はそれぞれ 156 kΩ と 10 kΩ に設定することができます。

図 23. オプションのパワーアップ・シーケンシング回路

## 過熱保護

ADP1853 には、チップのジャンクション温度を検出するための内部温度センサーが組み込まれています。ADP1853 のジャンクション温度が約 155°C に達すると、ADP1853 はサーマル・シャットダウン状態になってコンバータがオフになり、SS が 3 kΩ の内部抵抗を通じてゼロまで放電します。同時に、VCCO がゼロまで放電します。ジャンクション温度が 135°C を下回ると、ADP1853 はソフトスタート・シーケンスを経て通常動作を再開します。

## インターリープ・デュアルフェーズ動作

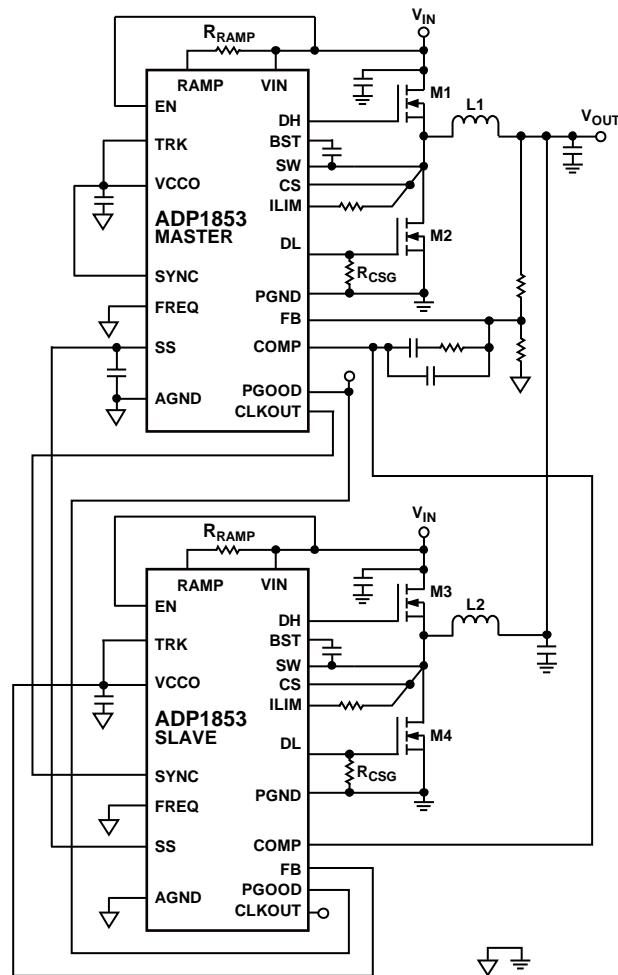

2 個の ADP1853 コントローラを組み合わせることにより、デュアルフェーズのインターリープ降圧スイッチング DC/DC レギュレータを設計することができます。デュアルフェーズ動作では、スイッチング・レギュレータの 2 つの出力を組み合わせて、電源部品の選択に応じて 50 A 以上の出力電流を供給することができます。標準的なデュアルフェーズ・アプリケーション回路については、図 24 を参照してください。誤差アンプは、マスター ADP1853 のものだけが機能します。スレーブ ADP1853 出力の誤差アンプは、FB を VCCO に接続することによってスリーステートになります。マスターの CLKOUT 信号はスレーブ・コントローラの SYNC 入力に接続します。マスターとスレーブの SS 信号は互いに接続し、スレーブの COMP はマスターの COMP に、スレーブの PGOOD もマスターの PGOOD に接続する必要があります。

図 24. デュアルフェーズ・アプリケーション

10594-030

## アプリケーション情報

### ADIsimPower 設計ツール

ADP1853 には、ADIsimPower 設計ツールセットを使用できます。ADIsimPower は、特定の設計目標に合わせて最適化されたパワー設計を実現するツールの集合で、すべての要素を含む回路図と部品表を作成して、詳細な性能を計算することができます。ADIsimPower を使用すれば、IC およびすべての外付け部品の動作条件や制限事項を考慮に入れながら、コスト、面積、効率、部品数などについて設計を最適化することができます。ADIsimPower ツールは [www.analog.com/jp/ADIsimPower](http://www.analog.com/jp/ADIsimPower) から入手することができます。ご要望により未実装ボードもご利用いただけます。

### 出力電圧の設定

出力電圧は、出力から FB の間に接続した抵抗分圧器を使用して設定します。R<sub>BOT</sub>には 1~20 kΩ の抵抗を使用します。出力電圧を設定するための R<sub>TOP</sub>は、次の式を使って設定します。

$$R_{TOP} = R_{BOT} \left( \frac{V_{OUT} - V_{FB}}{V_{FB}} \right)$$

ここで、

R<sub>TOP</sub>はハイサイドの分圧器抵抗、

R<sub>BOT</sub>はローサイドの分圧器抵抗、

V<sub>OUT</sub>は安定化出力電圧、

V<sub>FB</sub>は帰還レギュレーション閾値 (0.6 V) です。

### ソフトスタート

ソフトスタート期間は、SS と AGND の間の外付けコンデンサによって設定します。ソフトスタート機能は、入力突入電流を制限して出力のオーバーシュートを防止します。EN がイネーブルになると 6.5 μA の電流源がコンデンサの充電を開始し、SS の電圧が 0.6 V になるとレギュレーション電圧に達します。ソフトスタート時間は次式で近似することができます。

$$t_{SS} = \frac{0.6 \text{ V}}{6.5 \mu\text{A}} C_{SS}$$

SS ピンの最終的な電圧は VCCO と同じ電圧です。

たとえばコントローラがディスエーブルの時は、EN がローレベルになった場合や過電流制限状態になった場合に、3 kΩ のプルダウン抵抗を通じてソフトスタート・コンデンサが放電されます。

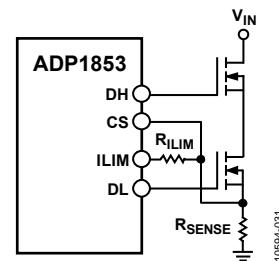

### 電流制限の設定

電流制限コンパレータは、負過電流を調べるためにローサイド MOSFET 両端の電圧を測定します。

電流制限は、ILIM と CS の間の外付け電流制限抵抗 R<sub>ILIM</sub>によって設定します。電流検出ピン ILIM は、この外付け抵抗に公称 50 μA の電流を流します。これによって、R<sub>ILIM</sub>に 50 μA を掛けた値に等しいオフセット電圧が発生します。電流検出素子 R<sub>CS</sub> (検出抵抗またはローサイド MOSFET、R<sub>DSON</sub>) 両端での電圧降下がこのオフセット電圧以上の場合、ADP1853 は電流制限イベントをフラグします。

$$R_{ILIM} = \frac{1.06 \times I_{LPK} \times R_{CS}}{50 \mu\text{A}}$$

ここで、

I<sub>LPK</sub>はインダクタのピーク電流です。

### 高精度の電流制限検出

MOSFET の R<sub>DSON</sub>は、使用温度範囲に応じて 50%以上変化することがあります。高精度の電流制限検出は、ローサイド MOSFET のソースから PGND の間に電流検出抵抗を追加することによって実現できます。電流検出抵抗の電力定格は、用途に合ったものを選択してください。高精度電流制限の実装を図 25 に示します。

図 25. 高精度電流制限検出

### 入力コンデンサの選択

ハイサイド・スイッチ MOSFET のドレインの近くに、2 つのコンデンサを並列に取り付けます(十分に大きな電流定格を持つバルク・コンデンサと 10 μF のセラミック・デカップリング・コンデンサ)。

入力バルク・コンデンサは、そのリップル電流定格に基づいて選択します。特定の負荷に対して必要な最小入力容量は、次式で得られます。

$$C_{IN,MIN} = \frac{I_O \times D(1-D)}{(V_{PP} - I_O \times DR_{ESR})f_{SW}}$$

ここで、

I<sub>O</sub>は出力電流、

Dはデューティ・サイクル、

V<sub>PP</sub>は必要な入力リップル電圧、

R<sub>ESR</sub>はコンデンサの等価直列抵抗です。

## VIN ピン・フィルタ

VIN ピンにはローパス・フィルタの使用を推奨します。2~10 Ω の抵抗を VIN と直列に接続し、VIN と AGND の間に 1 μF のセラミック・コンデンサを接続すると、スイッチング・レギュレータによって生じる不要なグリッチを効果的に除去する、ローパス・フィルタが形成されます。大きな MOSFET を駆動する場合は、入力電流が 100 mA を超えることがあります。10 Ω の抵抗に 100 mA の電流が流れると 1 V の電圧降下が生じますが、これは VCCO における電圧降下と同じです。この場合は抵抗値を低くするとよいでしょう。

図 26. 入力フィルタの構成

## 昇圧コンデンサの選択

SW ピンと BST ピンの間には、スイッチング時にハイサイド・ドライバへの電流を供給するために昇圧コンデンサを接続します。容量が 0.1~0.22 μF のセラミック・コンデンサを選択してください。

## インダクタの選択

大部分のアプリケーションでは、インダクタのリップル電流が最大 DC 出力負荷電流の 20~40%となるように、インダクタ値を選択します。

インダクタ値は次式に従って選択してください。

$$L = \frac{V_{IN} - V_{OUT}}{f_{SW} \times \Delta I_L} \times \frac{V_{OUT}}{V_{IN}}$$

ここで、

$L$  はインダクタ値、

$f_{SW}$  はスイッチング周波数、

$V_{OUT}$  は出力電圧、

$V_{IN}$  は入力電圧、

$\Delta I_L$  はピーク to ピークのインダクタのリップル電流です。

インダクタのデータシートを参照して、インダクタの飽和電流が、設計に使用するインダクタのピーク電流よりも十分に高い値であることを確認してください。

## 出力コンデンサの選択

出力における最大許容スイッチング・リップルに対し、次式の値よりも大きい出力コンデンサを選択します。

$$C_{OUT} \cong \frac{\Delta I_L}{8f_{SW}} \times \frac{1}{\sqrt{\Delta V_{OUT}^2 - \Delta I_L^2 \times (R_{ESR}^2 - (4f_{SW} \times L_{ESL})^2)}}$$

ここで、

$\Delta V_{OUT}$  は目標最大出力リップル電圧、

$\Delta I_L$  はインダクタのリップル電流、

$R_{ESR}$  は出力コンデンサの等価直列抵抗（またはすべての出力コンデンサの ESR を並列に組み合わせた値）、

$L_{ESL}$  は出力コンデンサの等価直列インダクタンス（またはすべての出力コンデンサの ESL を並列に組み合わせた値）です。

スイッチング周波数における出力コンデンサのインピーダンスにリップル電流の値を掛けると、出力電圧リップルが得られます。インピーダンスは、容量性インピーダンスと非理想寄生特性、等価直列抵抗（ESR）、および等価直列インダクタンス（ESL）で構成されます。

通常、コンデンサの主なインピーダンスは ESR によるものです。電解コンデンサや高分子コンデンサなどの最大 ESR 定格は、メーカーのデータシートに記載されています。したがって、出力リップル電流は次式で表される値まで減少します。

$$\Delta V_{OUT} \cong \Delta I_L \times R_{ESR}$$

電解コンデンサも ESL が 5~20 nH 程度と大きく、その値はタイプやサイズ、形状によって異なります。PC ボードのパターンも、ESR や ESL に一定程度影響します。しかし、コンデンサのデータシートに記載されている最大 ESR 定格値にはある程度のマージンが含まれているのが普通で、これらの値を使用すれば、通常 ESL を測定する必要はありません。

たとえば、出力コンデンサが並列の MLCC コンデンサ・バンクなどのように、スイッチング周波数における ESR や ESL のインピーダンスが小さい場合は、容量性インピーダンスが支配的となるため、出力コンデンサを次式の値より大きくしなければなりません。

$$C_{OUT} \cong \frac{\Delta I_L}{8 \Delta V_{OUT} \times f_{SW}}$$

出力コンデンサのリップル電流定格は、インダクタの最大リップル電流より大きくなるようにしてください。

負荷除去時における出力電圧オーバーシュートの条件を満たすには、出力容量を次式の値より大きくしなければなりません。

$$C_{OUT} \cong \frac{\Delta I_{STEP}^2 L}{(V_{OUT} + \Delta V_{OVERSHOOT})^2 - V_{OUT}^2}$$

ここで、

$\Delta V_{OVERSHOOT}$  は最大許容オーバーシュートです。

上記 2 つの式のうち、大きい方の出力容量を選択してください。

## MOSFET の選択

MOSFET の選択は、DC/DC コンバータの性能に直接影響します。MOSFET のオン抵抗が小さければ  $I^2R$  損失が減少し、ゲート電荷が小さければ遷移損失が減少します。MOSFET では、消費された電力によってダイが過熱しないようにするために、熱抵抗を小さくする必要があります。

ハイサイド MOSFET にはオン時間中に負過電流が流れ、通常は、コンバータにおける遷移損失のほとんどがハイサイド MOSFET によって生じます。普通、MOSFET のオン抵抗が小さいほどゲート電荷は大きくなり、オン抵抗が大きいほどゲート電荷は小さくなります。したがって、これら 2 つのバランスが取れたハイサイド MOSFET を選ぶことが重要です。ハイサイド MOSFET の導通損失は、次式で求めることができます。

$$P_C = (I_{LOAD(RMS)})^2 \times R_{DSON}$$

ここで、

$R_{DSON}$  は MOSFET のオン抵抗です。

ゲート電荷損失は次式で近似することができます。

$$P_G \approx V_{PV} \times Q_G \times f_{SW}$$

ここで、

$V_{PV}$  ゲート・ドライバの電源電圧、

$Q_G$  は MOSFET の合計ゲート電荷です。

ゲート電荷損失は、MOSFET 内よりも、むしろ ADP1853 の内部ドライバで発生します。全体的な電力効率を計算するときは、この電力損失を考慮する必要があります。

ハイサイド MOSFET の遷移損失は、次式で近似することができます。

$$P_T \approx \frac{V_{IN} \times I_{LOAD} \times (t_R + t_F) \times f_{SW}}{2}$$

ここで、

$P_T$  はハイサイド MOSFET のスイッチング損失電力、

$t_R$  はハイサイド MOSFET の充電立上がり時間、

$t_F$  はハイサイド MOSFET の放電立下がり時間です。

$t_R$  と  $t_F$  は次式で計算することができます。

$$t_R \approx \frac{Q_{GSW}}{I_{DRIVER\_RISE}}$$

$$t_F \approx \frac{Q_{GSW}}{I_{DRIVER\_FALL}}$$

ここで、

$Q_{GSW}$  はスイッチング時の MOSFET のゲート電荷で、この値は MOSFET のデータシートに示されています。

$I_{DRIVER\_RISE}$  と  $I_{DRIVER\_FALL}$  は、ADP1853 の内部ゲート・ドライバからのドライバ電流出力です。

$Q_{GSW}$  がデータシートに示されていない場合は、次式で近似することができます。

$$Q_{GSW} \approx Q_{GD} + \frac{Q_{GS}}{2}$$

ここで、

$Q_{GD}$  と  $Q_{GS}$  は、MOSFET のデータシートに記載されているゲート／ドレイン間電荷とゲート／ソース間電荷です。

$I_{DRIVER\_RISE}$  と  $I_{DRIVER\_FALL}$  は次式で計算することができます。

$$I_{DRIVER\_RISE} \approx \frac{V_{DD} - V_{SP}}{R_{ON\_SOURCE} + R_{GATE}}$$

$$I_{DRIVER\_FALL} \approx \frac{V_{SP}}{R_{ON\_SINK} + R_{GATE}}$$

ここで、

$V_{DD}$  はドライバへの入力電源電圧で、これは入力電圧に応じて 2.75~5 V です。

$V_{SP}$  は、MOSFET が完全導通するスイッチング・ポイントです。この電圧は、MOSFET のデータシートに記載されているゲート電荷グラフから推定することができます。

$R_{ON\_SOURCE}$  は、MOSFET を充電する際の ADP1853 内部ドライバのオン抵抗で、表 1 に示されています。

$R_{ON\_SINK}$  は、MOSFET を放電させる際の ADP1853 内部ドライバのオン抵抗で、これも表 1 に示されています。

$R_{GATE}$  は、MOSFET のデータシートに記載されているゲートのオン抵抗です。外付けのゲート抵抗を追加する場合は、その外付け抵抗を  $R_{GATE}$  に加算してください。

ハイサイド MOSFET の合計消費電力は、導通損失と遷移損失を足した値です。

$$P_{HS} = P_C + P_T$$

ハイサイド MOSFET がオフになると、同期整流器、つまりローサイド MOSFET にインダクタ電流が流れます。ローサイド MOSFET の遷移損失は小さく、計算では無視することができます。入力電圧が高く出力電圧が低い場合、ローサイド MOSFET には、ほとんどの時間電流が流れる状態になります。したがって、高効率を実現するには、ローサイド MOSFET を最適化してオン抵抗を小さくすることが不可欠です。電力損失が MOSFET の定格を超える場合や、1 つの MOSFET で実現できないほど抵抗を小さくする必要がある場合は、複数のローサイド MOSFET を並列に接続します。ローサイド MOSFET の導通電力損失は次式で得られます。

$$P_{CLS} = (I_{LOAD(RMS)})^2 \times R_{DSON}$$

このほかにもデッドタイムと呼ばれる損失があります。これは、ハイサイド・スイッチのターンオフとローサイド・スイッチのターンオンの間にローサイド MOSFET のボディ・ダイオードに出力電流が流れ生じる電力損失です。ボディ・ダイオードの電力損失は次式で求めることができます。

$$P_{BODYDIODE} = V_F \times t_D \times f_{SW} \times I_O$$

ここで、

$V_F$  はボディ・ダイオードの順方向電圧降下で、代表値は 0.7 V、 $t_D$  は ADP1853 のデッドタイムで、約 3 nF の入力コンデンサ  $C_{iss}$  を使用して中サイズの MOSFET を駆動しているときの代表値は 30 ns です。デッドタイムは変化します。その有効値はゲート駆動抵抗および  $C_{iss}$  によって変化し、大負過電流設計や低電圧設計では  $P_{BODYDIODE}$  が増加します。

ローサイド MOSFET の電力損失は次式で得られます。

$$P_{LS} = P_{CLS} + P_{BODYDIODE}$$

MOSFET のオン抵抗  $R_{DS(ON)}$  は温度の上昇とともに増大し、このときの温度係数は 0.4%/ $^{\circ}\text{C}$  (typ) です。周囲温度に対する MOSFET のジャンクション温度 ( $T_J$ ) の上昇値は次式で表すことができます。

$$T_J = T_A + \theta_{JA} \times P_D$$

ここで、

$\theta_{JA}$  は MOSFET パッケージの熱抵抗、

$T_A$  は周囲温度、

$P_D$  は MOSFET の合計消費電力です。

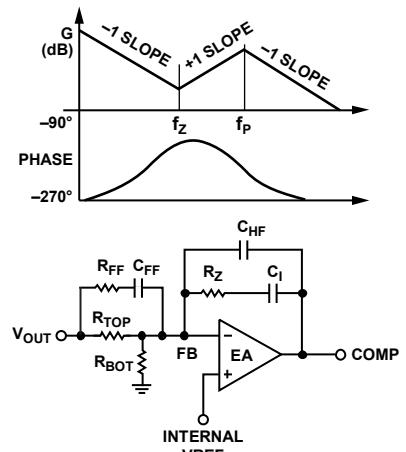

## ループ補償 - 電圧モード

コントローラを電圧モード動作に設定するには、DL と PGND の間に 100 k $\Omega$  の抵抗を接続します。1.5 V 未満の電圧モードでは、できるだけ大きいランプ値を選択してください。ランプ電圧は、 $V_{IN}$  と RAMP ピンの間の抵抗値によって設定します。

$$R_{RAMP} = \frac{V_{IN} - 0.2 \text{ V}}{100 \text{ pF} \times f_{SW} \times V_{RAMP}}$$

RAMP ピンの電圧は 0.2 V に固定されており、RAMP に流れる電流は 10~160  $\mu\text{A}$  とする必要があります。次の条件が満たされていることを確認してください。

$$10 \mu\text{A} \leq \frac{V_{IN} - 0.2 \text{ V}}{R_{RAMP}} \leq 160 \mu\text{A} \quad (1)$$

たとえば、入力電圧が 12 V の場合は、 $R_{RAMP}$  を 73.8 k $\Omega$  よりも小さくする必要があります。

LC フィルタの設計に問題がなければ、帰還制御システムを補償することができます。一般に、アルミ電解コンデンサの ESR は大きな値を取りますが、複数のアルミ電解コンデンサを並列に接続すれば、ESR を効果的に減らすことができます。この場合に必要な補償はタイプ III です。さらに、セラミック・コンデンサの ESR は非常に低いので（わずか数ミリオーム）、タイプ III 補償が最適です。

## タイプ III 補償

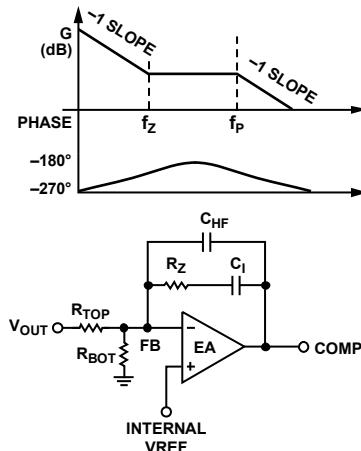

105944033

図 27. タイプ III 補償

出力コンデンサの ESR ゼロ周波数がクロスオーバー周波数の 1/2 より大きい場合は、図 27 に示すタイプ III コンペニセータを使用します。

出力 LC フィルタの共振周波数は次式で計算します。

$$f_{LC} = \frac{1}{2\pi\sqrt{LC}} \quad (2)$$

クロスオーバー周波数はスイッチング周波数の 1/10 となるように選択します。

$$f_{CO} = \frac{f_{SW}}{10} \quad (3)$$

極とゼロは次のように設定します。

$$f_{P1} = f_{P2} = \frac{1}{2} f_{SW} \quad (4)$$

$$f_{Z1} = f_{Z2} = \frac{f_{CO}}{4} = \frac{f_{SW}}{40} = \frac{1}{2\pi R_Z C_I} \quad (5)$$

または

$$f_{Z1} = f_{Z2} = \frac{f_{LC}}{2} = \frac{1}{2\pi R_Z C_I} \quad (6)$$

ゼロ周波数は、式 5 または式 6 で求めた値のどちらか低い方を使用します。コンペニセータの抵抗  $R_Z$  は次式で求めます。

$$R_Z = \frac{R_{TOP} V_{RAMP} f_{Z1} f_{CO}}{V_{IN} f_{LC}^2} \quad (7)$$

次に、 $C_I$  を計算します。

$$C_I = \frac{1}{2\pi R_Z f_{Z1}} \quad (8)$$

誤差アンプの出力電流駆動は有限であるため、 $C_I$  は 10 nF 未満とする必要があります。このコンデンサが 10 nF 以上の場合は  $R_{TOP}$  の値を大きくして、 $C_I$  が 10 nF 未満になるまで  $R_Z$  と  $C_I$  を計算します。

$C_{HF} \ll C_I$  であるため、 $C_{HF}$  は次式で計算します。

$$C_{HF} = \frac{1}{\pi f_{SW} R_Z} \quad (9)$$

次に、 $R_{FF} \ll R_{TOP}$  として、フィードフォワード・コンデンサ  $C_{FF}$  の値を計算します。

$$R_{FF} = \frac{1}{\pi C_{FF} f_{SW}} \quad (10)$$

計算で求めた各部品の値が適切なものであるかどうかを確認します。たとえば、10 pFよりも小さいコンデンサは避けたほうがよいでしょう。また、 $R_Z$  の値は 3 kΩ より小さくならないようにし、 $C_I$  の値は 10 nF より大きくならないようにしてください。必要な場合は、 $R_{TOP}$  の初期値を異なる値にして補償ネットワークを計算し直してください。 $R_Z$  が小さ過ぎたり  $C_I$  が大き過ぎたりする場合は、 $R_{TOP}$  の値を大きくしてから計算します。この補償方法を取れば、良好な結果を得ることができます。

精密な補償が必要な場合は、[ADIsimPower](#) 設計ツールを使用します。

## ループ補償 – 電流モード

電流モードにおける ADP1853 の誤差電圧ループには、タイプ II 補償を使用します。

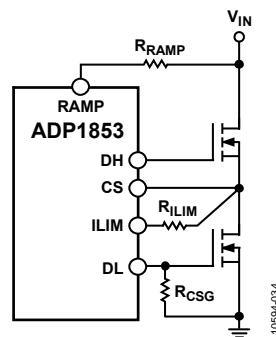

### スロープ補償の設定

電流モード制御の設計では、インダクタ電流の分数調波振動を防いで安定した出力を保つために、スロープ補償を行う必要があります。外部スロープ補償は、増幅した検出信号と RAMP ピンにおける換算電圧を合計することによって行います。効果的なスロープ補償を設定するには、RAMP ピンと入力電圧 ( $V_{IN}$ ) の間に抵抗 ( $R_{RAMP}$ ) を接続します。 $R_{RAMP}$  は次式で計算します。

$$R_{RAMP} = \frac{7 \times 10^6 \times L}{A_{CS} \times R_{CS}}$$

ここで、

$L$  はインダクタの値 (単位:  $\mu$ H) 、

$R_{CS}$  (mΩ) は CS と PGND 間の電流検出素子の抵抗です (たとえば、 $R_{DS0N\_MAX}$  はローサイド MOSFET の最大オン抵抗)。

$A_{CS}$  は電流検出アンプのゲインで、3 V/V、6 V/V、または 12 V/V です。

したがって、電圧ランプの大きさ  $V_{RAMP}$  は次のようにになります。

$$V_{RAMP} = \frac{V_{IN} - 0.2 \text{ V}}{100 \text{ pF} \times f_{SW} \times R_{RAMP}}$$

ここで、100 pF は内蔵ランプ・コンデンサ  $C_{RAMP}$  の有効容量で、温度および  $V_{IN}$  の範囲に対する誤差は ±4% です。RAMP ピンの電圧は 0.2 V に固定されており、RAMP に流れる電流は 10~160 μA とする必要があります。次の条件が満たされていることを確認してください。

$$10 \mu\text{A} \leq \frac{V_{IN} - 0.2 \text{ V}}{R_{RAMP}} \leq 160 \mu\text{A}$$

たとえば、入力電圧が 12 V の場合は  $R_{RAMP}$  が 1.1 MΩ を超えないようにする必要があります。算出した  $R_{RAMP}$  に基づく電流が 10 μA 未満の場合は、電流値が 10~15 μA となる  $R_{RAMP}$  を選択してください。

図 28 に、スロープ補償抵抗  $R_{RAMP}$  と電流検出ゲイン抵抗  $R_{CSG}$  の接続方法を示します。

図 28. スロープ補償と CS ゲインの接続

## 電流検出ゲインの設定

外付けのローサイド MOSFET 両端での電圧降下は、電流検出アンプを使用し、インダクタのピーク電流と MOSFET の  $R_{DS0N}$  を掛けることによって検出します。結果はゲイン係数 3 V/V、6 V/V、または 12 V/V によって増幅しますが、この係数は、DL ピンに接続した外付け抵抗  $R_{CSG}$  によって設定します。このゲインはパワーアップ時のみ検出され、通常動作時には検出されません。増幅された電圧をスロープ補償ランプ電圧と合計し、PWM コントローラへ送って、レギュレーション電圧を安定させます。

内部ノード  $V_{CS}$  の電圧範囲は 0.4~2.2 V です。電流検出ゲインは、内部最小増幅電圧 ( $V_{CSMIN}$ ) が 0.4 V よりも大きく、最大増幅電圧 ( $V_{CSMAX}$ ) が 2.1V となるように選択します。 $V_{CSMIN}$  または  $V_{CSMAX}$  と  $V_{COMP}$  は同じではなく、後者の範囲は 0.85~2.2 V です。温度や個体差による変動にも対応できるように、最大  $V_{COMP}$  ( $V_{COMP MAX}$ ) は 2.2 V を超えないようにしてください。 $V_{CSMIN}$ 、 $V_{CSMAX}$ 、および  $V_{COMP MAX}$  については以下の式を参照してください。

$$V_{CSMIN} = 0.75 \text{ V} - \frac{1}{2} I_L \times R_{DS0N\_MIN} \times A_{CS}$$

$$V_{CSMAX} = 0.75 \text{ V} + (I_{LOADMAX} - \frac{1}{2} I_L) \times R_{DS0N\_MAX} \times A_{CS}$$

$$V_{COMP MAX} = \frac{(V_{IN} - 0.2 \text{ V}) \times t_{ON}}{100 \text{ pF} \times R_{RAMP}} + V_{CSMAX}$$

ここで、

$V_{CSMIN}$  はゼロ出力電流における内蔵電流検出アンプの最小増幅電圧、

$I_L$  はインダクタのピーク to ピーク・リップル電流、

$R_{DS0N\_MIN}$  はローサイド MOSFET の最小オン抵抗で、電流検出アンプのゼロ電流レベル電圧は 0.75 V です。

$V_{CSMAX}$  は、最大出力電流時の内蔵電流検出アンプの最大増幅電圧、 $I_{LOADMAX}$  は最大出力 DC 負荷電流、

$V_{COMP MAX}$  は COMP ピンの最大電圧、

$t_{ON}$  はハイサイド・ドライバ (DH) のオン時間です。

電流検出素子  $R_{CS}$  を使用する場合は、 $R_{DS0N}$  をこの値に置き換えてください。

## タイプ II 補償

105944235

図 29. タイプ II 補償

この場合は、図 29 に示す回路を使用します。補償抵抗  $R_Z$  は次式で計算します。

$$R_Z = R_{TOP} \times R_S \times 2\pi \times C_{OUT} f_{CO} \quad (11)$$

ここで、

$f_{CO}$  は  $f_{SW}$  の 1/10 となるように選択します。

$$R_S = A_{CS} \times R_{DS0N\_MIN}$$

$A_{CS}$  は 3 V/V、6 V/V、または 12 V/V の電流検出ゲインで、DL と PGND 間のゲイン設定抵抗によって設定します。

$R_{DS0N\_MIN}$  はローサイド MOSFET の最小オン抵抗です。

電流検出抵抗  $R_{CS}$  で電流を検出する場合、 $R_{CS}$  は次のようにになります。

$$R_S = A_{CS} \times R_{CS}$$

次に、補償ゼロ  $f_{ZI}$  を、クロスオーバー周波数の 1/5 か、LC 共振周波数の 1/2 に設定する補償コンデンサを選択します。

$$f_{ZI} = \frac{f_{CO}}{5} = \frac{f_{SW}}{50} = \frac{1}{2\pi R_Z C_I} \quad (12)$$

または

$$f_{ZI} = \frac{f_{LC}}{2} = \frac{1}{2\pi R_Z C_I} \quad (13)$$

式 12 を  $C_I$  について解くと次のようにになります。

$$C_I = \frac{25}{\pi R_Z f_{SW}} \quad (14)$$

式 13 を  $C_I$  について解くと次のようにになります。

$$C_I = \frac{1}{\pi R_Z f_{LC}} \quad (15)$$

$C_1$ には、式 14 または式 15 で得られる値のどちらか大きい方を使用します。誤差アンプの出力電流駆動は有限であるため、 $C_1$ は 10 nF 未満とする必要があります。このコンデンサが 10 nF 以上の場合には  $R_{TOP}$  の値を大きくして、 $C_1$  が 10 nF 未満になるまで  $R_Z$  と  $C_1$  を計算し直してください。

次に、 $f_{SW}$  の 1/2 となるような高周波極  $f_{PI}$  を選択します。

$$f_{PI} = \frac{1}{2} f_{SW} \quad (16)$$

$C_{HF} \ll C_1$  であるため、

$$f_{PI} = \frac{1}{2\pi R_Z C_{HF}} \quad (17)$$

式 16 と 17 を組み合わせた式を  $C_{HF}$  について解きます。

$$C_{HF} = \frac{1}{\pi f_{SW} R_Z} \quad (18)$$

できるだけ精密な補償を行いたい場合は、**ADIsimPower** 設計ツールを使用してください。

## スイッチング・ノイズとオーバーシュートの低減

大電流アプリケーションで電圧のリングングとノイズを低減するには、図 30 に示すように SW と PGND の間に RC スナバを追加することを推奨します。

大部分のアプリケーションでは、通常、 $R_{SNUB}$  は 2~4 Ω で、 $C_{SNUB}$  は 1.2~3 nF です。

RC スナバのコンポーネントは、消費電力に対応できるだけの適切なサイズのものを選ぶ必要があります。 $R_{SNUB}$  で消費される電力は次式で表すことができます。

$$P_{SNUB} = V_{IN}^2 \times C_{SNUB} \times f_{SW}$$

大部分のアプリケーションでは、0805 を  $R_{SNUB}$  に使用すればサイズ的には十分です。RC スナバを使用しても電圧のオーバーシュートは改善されません。図 30 に  $R_{RISE}$  と記載されている BST ピンの抵抗はオーバーシュートの低減に効果的であり、通常は 2~4 Ω の値を取ります。また、一般に 2~4 Ω の並列抵抗とゲート・ドライバを追加することもオーバーシュートの低減に有効です。ゲート抵抗を追加する場合、 $R_{RISE}$  は不要です。

図 30. スナバを用いたアプリケーション回路

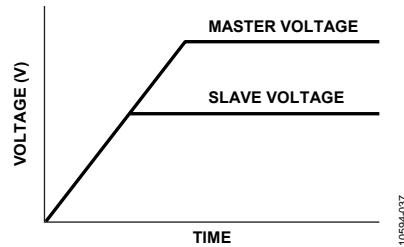

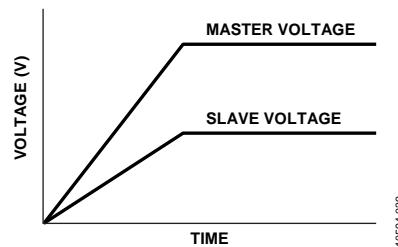

## 電圧トラッキング

ADP1853 は、マスター電圧を追跡するトラッキング機能を備えています。出力は、すべてのトラッキング条件において、所定の動作条件に対し最小 0.6 V まで設定することができます。マスター電圧のソフトスタート時間設定は、スレーブ電圧のソフトスタートよりも長くする必要があります。これによって、マスター電圧の立上がり時間がスレーブ電圧にも強制的に適用されます。スレーブ電圧のソフトスタート設定の方が長いとスレーブの立上がりの方が遅くなり、出力のトラッキング関係が成立しません。

ADP1853 では 2 つのトラッキング設定を使用できます。同時トラッキングと比例トラッキングです。

### 同時トラッキング

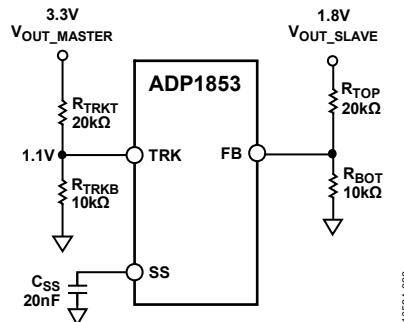

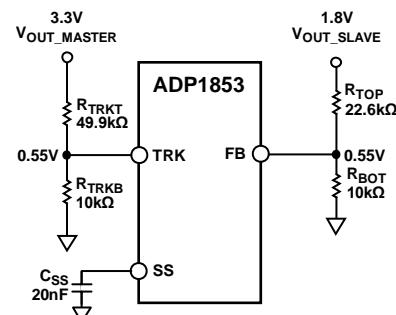

最も一般的に使用されているのが同時トラッキングで、コア電圧対 I/O 電圧のシーケンシングや、これと同様のアプリケーションで利用します。同時トラッキングでは、スレーブ出力が安定するまで、マスターとスレーブの出力電圧のランプ・レートが強制的に同じ値に設定されます。スレーブの TRK 入力はマスター電圧からの抵抗分圧器に接続しますが、この分圧器はスレーブの FB ピンに使われているものと同じです。これによって、スレーブ電圧は強制的にマスター電圧と同じ値になります。同時トラッキングでは、図 32 に示すように、 $R_{TRKT} = R_{TOP}$  および  $R_{TRKB} = R_{BOT}$  とします。

図 31. 同時トラッキング

図 32. 同時トラッキング回路の例

スレーブ出力電圧とマスター電圧の比は、2 つの抵抗分圧器の関数です。

$$\frac{V_{OUT\_SLAVE}}{V_{OUT\_MASTER}} = \frac{\left(1 + \frac{R_{TOP}}{R_{BOT}}\right)}{\left(1 + \frac{R_{TRKT}}{R_{TRKB}}\right)}$$

マスター電圧が上昇すると、スレーブ電圧も同様に上昇します。最終的にはスレーブ電圧がレギュレーション電圧に達し、そこで内部リファレンスにレギュレーションが渡されますが、TRK 入力は引き続き増加するので除外され、出力電圧には影響しなくなります。

TRK ピンの電圧がリファレンス電圧 ( $V_{FB}$ , typ 値: 0.6 V) に近くなくなり過ぎて出力電圧精度に悪影響が出ないように、スレーブ・チャンネルの TRK 電圧の最終値は、少なくとも  $V_{FB}$  より 30 mV 高い値となるようにしてください。

### 比例トラッキング

比例トラッキングは、図 33 と図 34 に示すように、出力電圧をマスター電圧の一定の比率に制限します。スレーブ・チャンネルの最終的な TRK 電圧は、マスター・チャンネルの FB 電圧より少なくとも 30 mV 低い値に設定する必要があります。スレーブ・チャンネルの TRK 電圧が最小オン時間条件より低いレベルまで低下した場合、スレーブ・チャンネルはパルス・スキップ・モードで動作しますが、出力はマスター・チャンネルに合わせて安定化され、トラッキングも維持されます。さらに、TRK または FB が PGOOD 低電圧閾値を下回ると、PGOOD 信号がトリップされアクティブ・ローになります。

図 33. 比例トラッキング

図 34. 比例トラッキング回路の例

### PCB レイアウトのガイドライン

同期降圧コントローラの推奨ボード・レイアウト方法は、[アプリケーション・ノート AN-1119](#) に記載されています。

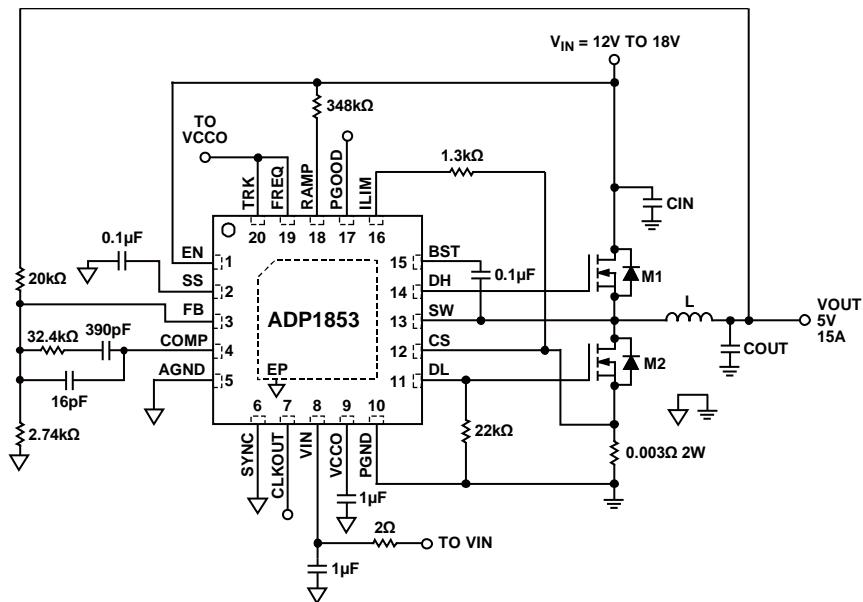

## 代表的な動作回路

10594-04a

図 35. 電流モードで動作する 15 A 回路

$f_{SW} = 300\text{kHz}$

$C_{IN}$ : OS-CON 150 $\mu\text{F}$ /20V, 20SEP150M, SANYO + CAP CER 10 $\mu\text{F}$  25V X7R 1210, MURATA GRM32DR71E106KA12

L: 1 $\mu\text{H}$  COILCRAFT SER1412-102ME

M1: INFINEON BSC052N03LS

M2: INFINEON BSC0902NS

$C_{OUT}$ : POSCAP 330 $\mu\text{F}$ /6.3V SANYO 6TPE330MFL + CAP CER 22 $\mu\text{F}$  10V X5R 1210 MURATA GRM32ER61A226KE20L

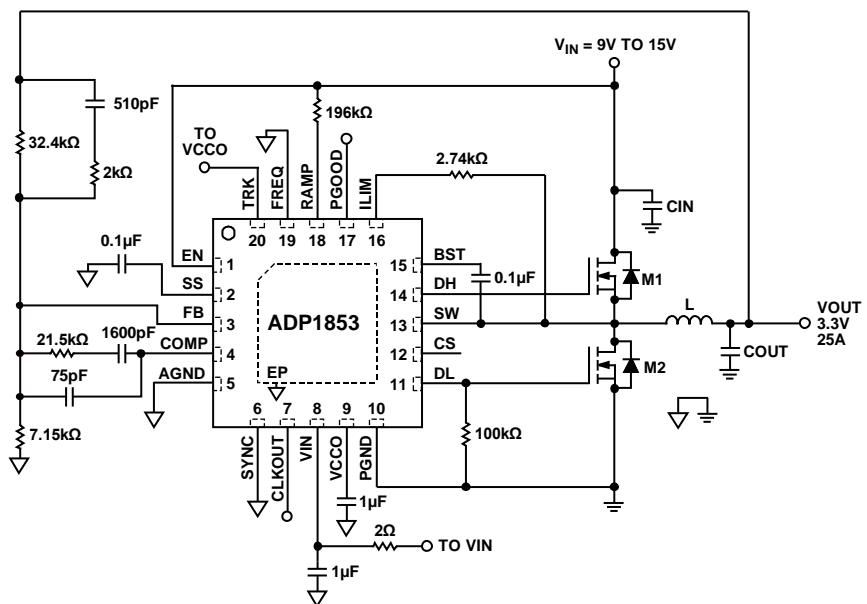

10594-042

図 36. 電圧モードで動作する 25 A 回路

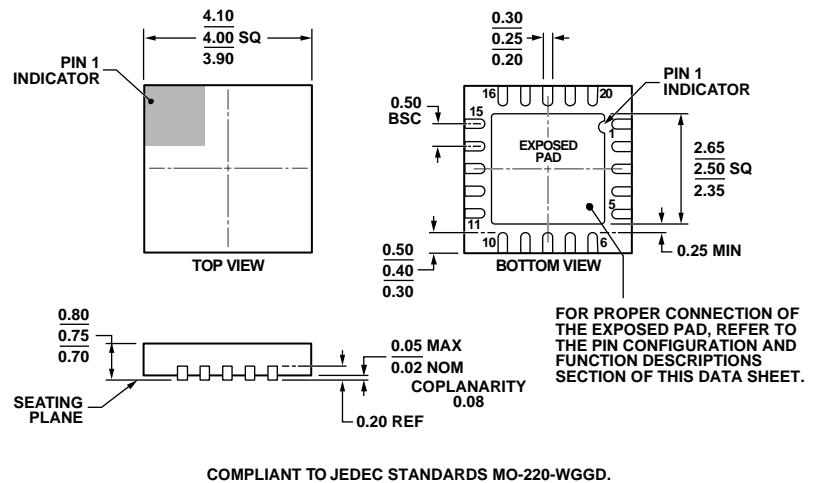

## 外形寸法

図 37. 20 ピン・リード・フレーム・チップ・スケール・パッケージ [LFCSP\_WQ]

4 mm x 4 mm ボディ、超薄型クワッド

(CP-20-10)

寸法単位: mm

## オーダー・ガイド

| Model <sup>1</sup> | Temperature Range | Package Description                              | Package Option |

|--------------------|-------------------|--------------------------------------------------|----------------|

| ADP1853ACPZ-R7     | -40°C to +125°C   | 20-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-20-10       |

<sup>1</sup> Z = RoHS 準拠製品