## ADM13305

### 特長

デュアル監視回路

電源電圧範囲: 2.7 V~5.5 V

調整済みレッショールド・オプション: 1.8 V、2.5 V、3.3 V、5 V

調整可能な 0.6 V リファレンス電圧

最大電源電流: 40  $\mu$ A

最小リセット・タイムアウト: 140 ms

タイムアウト 1.6 sec (typ 値) のウォッチドッグ・タイマー

$V_{DD} \geq 1.1$  V で RESET 有効

RESET 出力と  $\overline{\text{RESET}}$  出力はプッシュプル

8 ピンのナロウ・ボディ SOIC パッケージを採用

温度範囲: -40°C~+85°C

### アプリケーション

DSP/マイクロコントローラの監視

工業用装置および携帯型装置

ワイヤレス・システム

ノートブック/デスクトップ・コンピュータ

### 概要

ADM13305 は、2 つの電源を監視して DSP およびマイクロプロセッサを採用したシステムへリセット信号を出力するようにデザインされたデュアル電圧監視回路です。

5 種類のモデルを提供しており、全モデルが 1.8 V、2.5 V、3.3 V、5 V の各電源監視用の内部調整済み低電圧レッショールド・オプションの組み合わせを持っています。また、低電圧レッショールド電圧 0.6 V の調整可能な入力オプションもあります。

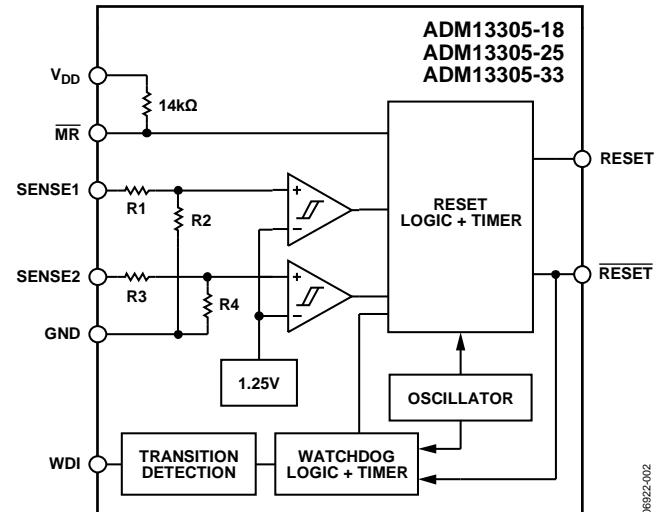

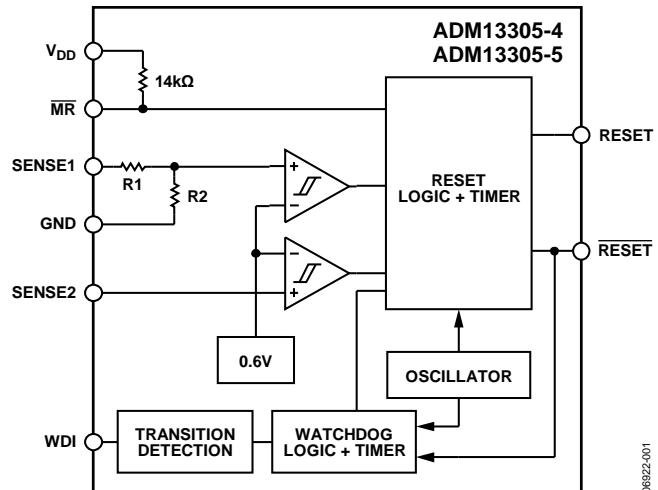

ADM13305-18、ADM13305-25、ADM13305-33 の各モデルは内部固定レッショールドを 2 個持っています。ADM13305-4 と ADM13305-5 は、内部固定のレッショールド 1 個と抵抗ストリングを使って外部から設定可能なレッショールド 1 個を持っています。提供中のすべてのオプションについては、[オーダー・ガイド](#)を参照してください。

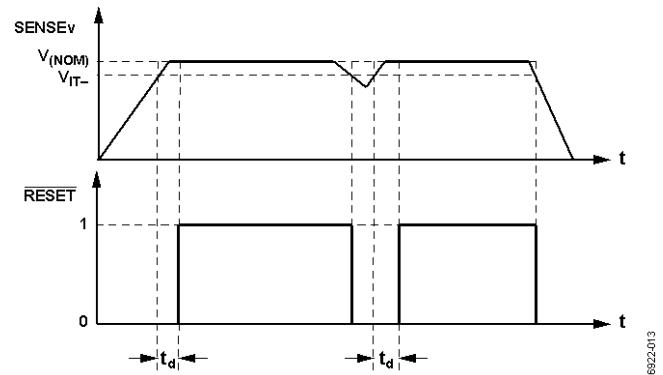

パワーアップ時、電源電圧が 1.1 V を超えると、RESET がアサートされます。次に、デバイスは SENSEv 入力ピンを監視し、いずれかの SENSEv 入力が立ち上がりレッショールド電圧  $V_{IT+}$  を下回っている間 RESET 出力をロー・レベルに維持します。SENSEv 入力で監視している電源電圧が該当するレッショールドを超えると、リセット信号のアサートはリセット・タイムアウト周期だけロー・レベルを維持した後に解除されます。

次に、SENSEv ピンで監視している電圧が該当する立ち下がりレッショールド  $V_{IT-}$  を下回ると、RESET 出力がアサートされます。ADM13305 は、アクティブ・ハイの RESET 出力とアクティブ・ローの  $\overline{\text{RESET}}$  出力を持っています。

### 機能ブロック図

図 1.

図 2..

パワーオン・リセット信号を提供する他に、内蔵ウォッチドッグ・タイマーは、マイクロプロセッサが予め設定されているタイムアウト期間内にウォッチドッグ・タイマーをリセットできない場合にマイクロプロセッサをリセットします。また、マニュアル・リセット入力ピンを使用して外部プッシュ・ボタンにより、リセット信号をアサートすることもできます。

ADM13305 は 8 ピンのナロウ・ボディ SOIC パッケージを採用しています。このデバイスは拡張工業用温度範囲-40°C~+85°Cで動作します。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関する、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものではありません。仕様は、予告なく変更される場合があります。本記載の商標および登録商標は、各社の所有に属します。

©2007 Analog Devices, Inc. All rights reserved.

# 目次

|          |   |                               |    |

|----------|---|-------------------------------|----|

| 特長       | 1 | ESD の注意                       | 7  |

| アプリケーション | 1 | ピン配置およびピン機能説明                 | 8  |

| 概要       | 1 | 代表的な性能特性                      | 9  |

| 機能ブロック図  | 1 | 動作原理                          | 11 |

| 改訂履歴     | 2 | 入力の構成                         | 11 |

| 仕様       | 3 | リセット出力                        | 11 |

| タイミング条件  | 5 | ウォッチドッグ・タイマー                  | 11 |

| スイッチング特性 | 5 | マニュアル・リセット( $\overline{MR}$ ) | 12 |

| 真理値表     | 6 | 外形寸法                          | 13 |

| 絶対最大定格   | 7 | オーダー・ガイド                      | 13 |

| 熱抵抗      | 7 |                               |    |

## 改訂履歴

8/07—Revision 0: Initial Version

# 仕様

特に指定のない限り、 $V_{DD} = 2.7 \text{ V} \sim 5.5 \text{ V}$ 、 $-40^\circ\text{C} \leq T_A \leq +85^\circ\text{C}$ 。

表 1. ADM13305-18、ADM13305-25、ADM13305-33

| Parameter                                     | Min                 | Typ                 | Max  | Unit          | Test Conditions/Comments                                |

|-----------------------------------------------|---------------------|---------------------|------|---------------|---------------------------------------------------------|

| OPERATING VOLTAGE RANGE, $V_{DD}$             | 2.7                 |                     | 5.5  | V             |                                                         |

| SUPPLY CURRENT, $I_{DD}$                      |                     |                     | 40   | $\mu\text{A}$ |                                                         |

| INPUT CAPACITANCE, $C_I$                      |                     | 10                  |      | pF            | $V_I = 0 \text{ V}$ to $V_{DD}$                         |

| RESET, $\overline{\text{RESET}}$ OUTPUT       |                     |                     |      |               |                                                         |

| High Level Output Voltage, $V_{OH}$           | $V_{DD} - 0.2$      |                     |      | V             | $I_{OH} = -20 \mu\text{A}$                              |

|                                               | $V_{DD} - 0.4$      |                     |      | V             | $I_{OH} = -2 \text{ mA}$ , $V_{DD} = 3.3 \text{ V}$     |

|                                               | $V_{DD} - 0.4$      |                     |      | V             | $I_{OH} = -3 \text{ mA}$ , $V_{DD} = 5.5 \text{ V}$     |

| Low Level Output Voltage, $V_{OL}$            |                     | 0.2                 |      | V             | $I_{OL} = 20 \mu\text{A}$                               |

|                                               |                     | 0.4                 |      | V             | $I_{OL} = 2 \text{ mA}$ , $V_{DD} = 3.3 \text{ V}$      |

|                                               |                     | 0.4                 |      | V             | $I_{OL} = 3 \text{ mA}$ , $V_{DD} = 5.5 \text{ V}$      |

| Power-Up Reset Voltage <sup>1</sup>           |                     | 0.4                 |      | V             | $I_{OL} = 20 \mu\text{A}$ , $V_{DD} \geq 1.1 \text{ V}$ |

| SENSE INPUTS                                  |                     |                     |      |               |                                                         |

| Falling Threshold Voltage, $V_{IT-}$          | 1.64                | 1.68                | 1.72 | V             | $T_A = 0^\circ\text{C}$ to $85^\circ\text{C}$           |

|                                               | 2.20                | 2.25                | 2.30 | V             | $T_A = 0^\circ\text{C}$ to $85^\circ\text{C}$           |

|                                               | 2.86                | 2.93                | 3.00 | V             | $T_A = 0^\circ\text{C}$ to $85^\circ\text{C}$           |

|                                               | 4.46                | 4.55                | 4.64 | V             | $T_A = 0^\circ\text{C}$ to $85^\circ\text{C}$           |

|                                               | 1.64                | 1.68                | 1.73 | V             | $T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$        |

|                                               | 2.20                | 2.25                | 2.32 | V             | $T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$        |

|                                               | 2.86                | 2.93                | 3.02 | V             | $T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$        |

|                                               | 4.46                | 4.55                | 4.67 | V             | $T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$        |

| Hysteresis at SENSEv Inputs, $V_{HYS}$        |                     | 15                  |      | mV            | $V_{IT-} = 1.68 \text{ V}$                              |

|                                               |                     | 20                  |      | mV            | $V_{IT-} = 2.25 \text{ V}$                              |

|                                               |                     | 30                  |      | mV            | $V_{IT-} = 2.93 \text{ V}$                              |

|                                               |                     | 40                  |      | mV            | $V_{IT-} = 4.55 \text{ V}$                              |

| WDI                                           |                     |                     |      |               |                                                         |

| Average High Level Input Current, $I_{H(AV)}$ |                     | 100                 | 150  | $\mu\text{A}$ | $WDI = V_{DD} = 5.5 \text{ V}$                          |

| Average Low Level Input Current, $I_{L(AV)}$  |                     | -15                 | -20  | $\mu\text{A}$ | $WDI = 0 \text{ V}$ , $V_{DD} = 5.5 \text{ V}$          |

| INPUT VOLTAGE AT MR AND WDI                   |                     |                     |      |               |                                                         |

| High Level, $V_{IH}$                          | 0.7 $\times V_{DD}$ |                     |      | V             |                                                         |

| Low Level, $V_{IL}$                           |                     | 0.3 $\times V_{DD}$ |      | V             |                                                         |

| INPUT TRANSITION RISE AND FALL RATE AT MR     |                     | 50                  |      | ns/V          |                                                         |

| HIGH LEVEL INPUT CURRENT, $I_H$               |                     |                     |      |               |                                                         |

| WDI                                           |                     | 120                 | 170  | $\mu\text{A}$ | $WDI = V_{DD} = 5.5 \text{ V}$                          |

| MR                                            |                     | -130                | -180 | $\mu\text{A}$ | $MR = 0.7 \times V_{DD}$ , $V_{DD} = 5.5 \text{ V}$     |

| SENSE1                                        |                     | 5                   | 8    | $\mu\text{A}$ | $SENSE1 = V_{DD} = 5.5 \text{ V}$                       |

| SENSE2                                        |                     | 6                   | 9    | $\mu\text{A}$ | $SENSE2 = V_{DD} = 5.5 \text{ V}$                       |

| LOW LEVEL INPUT CURRENT, $I_L$                |                     |                     |      |               |                                                         |

| WDI                                           |                     | -120                | -170 | $\mu\text{A}$ | $WDI = 0 \text{ V}$ , $V_{DD} = 5.5 \text{ V}$          |

| MR                                            |                     | -430                | -600 | $\mu\text{A}$ | $MR = 0 \text{ V}$ , $V_{DD} = 5.5 \text{ V}$           |

| SENSEv                                        |                     | -1                  | +1   | $\mu\text{A}$ | $SENSE1, SENSE2 = 0 \text{ V}$                          |

<sup>1</sup>  $\overline{\text{RESET}}$ がアクティブになる最小電圧、 $t_r$ ,  $V_{DD} \geq 15 \mu\text{s}/\text{V}$ 。

特に指定のない限り、 $V_{DD} = 2.7 \text{ V} \sim 5.5 \text{ V}$ 、 $-40^\circ\text{C} \leq T_A \leq +85^\circ\text{C}$ 。

表 2.ADM13305-4、ADM13305-5

| Parameter                                     | Min                 | Typ                 | Max    | Unit          | Test Conditions/Comments                                |

|-----------------------------------------------|---------------------|---------------------|--------|---------------|---------------------------------------------------------|

| OPERATING VOLTAGE RANGE, $V_{DD}$             | 2.7                 | 5.5                 |        | V             |                                                         |

| SUPPLY CURRENT, $I_{DD}$                      |                     | 40                  |        | $\mu\text{A}$ |                                                         |

| INPUT CAPACITANCE, $C_I$                      |                     | 10                  |        | pF            | $V_I = 0 \text{ V}$ to $V_{DD}$                         |

| RESET, RESET OUTPUT                           |                     |                     |        |               |                                                         |

| High-Level Output Voltage, $V_{OH}$           | $V_{DD} - 0.2$      |                     |        | V             | $I_{OH} = -20 \mu\text{A}$                              |

|                                               | $V_{DD} - 0.4$      |                     |        | V             | $I_{OH} = -2 \text{ mA}$ , $V_{DD} = 3.3 \text{ V}$     |

|                                               | $V_{DD} - 0.4$      |                     |        | V             | $I_{OH} = -3 \text{ mA}$ , $V_{DD} = 5.5 \text{ V}$     |

| Low-Level Output Voltage, $V_{OL}$            |                     | 0.2                 |        | V             | $I_{OH} = 20 \mu\text{A}$                               |

|                                               |                     | 0.4                 |        | V             | $I_{OH} = 2 \text{ mA}$ , $V_{DD} = 3.3 \text{ V}$      |

|                                               |                     | 0.4                 |        | V             | $I_{OH} = 3 \text{ mA}$ , $V_{DD} = 5.5 \text{ V}$      |

| Power-Up Reset Voltage <sup>1</sup>           |                     | 0.4                 |        | V             | $I_{OH} = 20 \mu\text{A}$ , $V_{DD} \geq 1.1 \text{ V}$ |

| SENSEv INPUTS                                 |                     |                     |        |               |                                                         |

| Falling Input Threshold Voltage, $V_{IT-}$    | 0.5952              | 0.6                 | 0.6048 | V             | $T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$        |

|                                               | 2.23                | 2.25                | 2.29   | V             | $T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$        |

|                                               | 2.90                | 2.93                | 2.98   | V             | $T_A = -40^\circ\text{C}$ to $+85^\circ\text{C}$        |

| Hysteresis at SENSEv Inputs, $V_{HYS}$        |                     | 0                   |        | mV            | $V_{IT-} = 0.6 \text{ V}$                               |

|                                               |                     | 20                  |        | mV            | $V_{IT-} = 2.25 \text{ V}$                              |

|                                               |                     | 30                  |        | mV            | $V_{IT-} = 2.93 \text{ V}$                              |

| WDI                                           |                     |                     |        |               |                                                         |

| Average High Level Input Current, $I_{H(AV)}$ | 100                 | 150                 |        | $\mu\text{A}$ | $WDI = V_{DD} = 5.5 \text{ V}$                          |

| Average Low Level Input Current, $I_{L(AV)}$  | -15                 | -20                 |        | $\mu\text{A}$ | $WDI = 0 \text{ V}$ , $V_{DD} = 5.5 \text{ V}$          |

| INPUT VOLTAGE AT MR AND WDI                   |                     |                     |        |               |                                                         |

| High Level, $V_{IH}$                          | $0.7 \times V_{DD}$ |                     |        | V             |                                                         |

| Low Level, $V_{IL}$                           |                     | $0.3 \times V_{DD}$ |        | V             |                                                         |

| INPUT TRANSITION RISE AND FALL RATE AT MR     |                     | 50                  |        | ns/V          |                                                         |

| HIGH LEVEL INPUT CURRENT, $I_H$               |                     |                     |        |               |                                                         |

| WDI                                           | 120                 | 170                 |        | $\mu\text{A}$ | $WDI = V_{DD} = 5.5 \text{ V}$                          |

| MR                                            | -130                | -180                |        | $\mu\text{A}$ | $MR = 0.7 \times V_{DD}$ , $V_{DD} = 5.5 \text{ V}$     |

| SENSE1                                        | 5                   | 8                   |        | $\mu\text{A}$ | $SENSE1 = V_{DD} = 5.5 \text{ V}$                       |

| SENSE2                                        | -50                 | +50                 |        | nA            | $SENSE2 = V_{DD} = 5.5 \text{ V}$                       |

| LOW LEVEL INPUT CURRENT, $I_L$                |                     |                     |        |               |                                                         |

| WDI                                           | -120                | -170                |        | $\mu\text{A}$ | $WDI = 0 \text{ V}$ , $V_{DD} = 5.5 \text{ V}$          |

| MR                                            | -430                | -600                |        | $\mu\text{A}$ | $MR = 0 \text{ V}$ , $V_{DD} = 5.5 \text{ V}$           |

| SENSEv                                        | -1                  | +1                  |        | $\mu\text{A}$ | $SENSE1, SENSE2 = 0 \text{ V}$                          |

<sup>1</sup> RESETがアクティブになる最小電圧、 $t_r$ 、 $V_{DD} \geq 15 \mu\text{s}/\text{V}$ 。

## タイミング条件

$V_{DD} = 2.7 \text{ V} \sim 5.5 \text{ V}$ 、 $R_L = 1 \text{ M}\Omega$ 、 $C_L = 50 \text{ pF}$ 、 $T_A = 25^\circ\text{C}$ 。

表 3. ADM13305-18、ADM13305-25、ADM13305-33

| Parameter             | Min | Typ | Max | Unit | Test Conditions/Comments                                                            |

|-----------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------|

| PULSE WIDTH ( $t_w$ ) |     |     |     |      |                                                                                     |

| SENSEv                | 6   |     |     | μs   | $V_{SENSEvL} = V_{IT^-} - 0.3 \text{ V}$ , $V_{SENSEvH} = V_{IT^+} + 0.3 \text{ V}$ |

| MR                    | 100 |     |     | ns   | $V_{IH} = 0.7 \times V_{DD}$ , $V_{IL} = 0.3 \times V_{DD}$                         |

| WDI                   | 100 |     |     | ns   | $V_{IH} = 0.7 \times V_{DD}$ , $V_{IL} = 0.3 \times V_{DD}$                         |

表 4 ADM13305-4、ADM13305-5

| Parameter             | Min | Typ | Max | Unit | Test Conditions/Comments                                                            |

|-----------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------|

| PULSE WIDTH ( $t_w$ ) |     |     |     |      |                                                                                     |

| SENSEv                |     | 30  |     | μs   | $V_{SENSEvL} = V_{IT^-} - 0.3 \text{ V}$ , $V_{SENSEvH} = V_{IT^+} + 0.3 \text{ V}$ |

| MR                    | 100 |     |     | ns   | $V_{IH} = 0.7 \times V_{DD}$ , $V_{IL} = 0.3 \times V_{DD}$                         |

| WDI                   | 100 |     |     | ns   | $V_{IH} = 0.7 \times V_{DD}$ , $V_{IL} = 0.3 \times V_{DD}$                         |

## スイッチング特性

$V_{DD} = 2.7 \text{ V} \sim 5.5 \text{ V}$ 、 $R_L = 1 \text{ M}\Omega$ 、 $C_L = 50 \text{ pF}$ 、 $T_A = 25^\circ\text{C}$ 。

表 5. ADM13305-18、ADM13305-25、ADM13305-33

| Parameter                                                                                        | Mi<br>n | Typ | Max | Unit | Test Conditions/Comments                                                                                           |

|--------------------------------------------------------------------------------------------------|---------|-----|-----|------|--------------------------------------------------------------------------------------------------------------------|

| Watchdog Timeout ( $t_{t(OUT)}$ )                                                                | 1.1     | 1.6 | 2.3 | sec  | $V_{I(SENSEv)} \geq V_{IT^+} + 0.2 \text{ V}$ , $\overline{MR} \geq 0.7 \times V_{DD}$                             |

| Delay Time ( $t_d$ )                                                                             | 140     | 200 | 280 | ms   | $V_{I(SENSEv)} \geq V_{IT^+} + 0.2 \text{ V}$ , $\overline{MR} \geq 0.7 \times V_{DD}$                             |

| Propagation Delay, High-to-Low, $\overline{MR}$ to RESET <sup>1</sup> /RESET (t <sub>PHL</sub> ) |         | 200 | 500 | ns   | $V_{I(SENSEv)} \geq V_{IT^+} + 0.2 \text{ V}$ , $V_{IH} \geq 0.7 \times V_{DD}$ , $V_{IL} \geq 0.3 \times V_{DD}$  |

| Propagation Delay, Low-to-High, $\overline{MR}$ to RESET/RESET <sup>1</sup> (t <sub>PLH</sub> )  |         | 200 | 500 | ns   | $V_{I(SENSEv)} \geq V_{IT^+} + 0.2 \text{ V}$ , $V_{IH} \geq 0.7 \times V_{DD}$ , $V_{IL} \geq 0.3 \times V_{DD}$  |

| Propagation Delay, High-to-Low, SENSEv to RESET <sup>1</sup> /RESET (t <sub>PHL</sub> )          | 1       | 5   |     | μs   | $V_{IH} = V_{IT^+} + 0.3 \text{ V}$ , $V_{IL} = V_{IT^-} - 0.3 \text{ V}$ , $\overline{MR} \geq 0.7 \times V_{DD}$ |

| Propagation Delay, Low-to-High, SENSEv to RESET/RESET <sup>1</sup> (t <sub>PLH</sub> )           | 1       | 5   |     | μs   | $V_{IH} = V_{IT^+} + 0.3 \text{ V}$ , $V_{IL} = V_{IT^-} - 0.3 \text{ V}$ , $\overline{MR} \geq 0.7 \times V_{DD}$ |

<sup>1</sup> 200 ms のリセット・タイムアウト遅延により伝搬遅延がマスクされます。

表 6. ADM13305-4、ADM13305-5

| Parameter                                                                                        | Min | Typ | Max | Unit | Test Conditions/Comments                                                                                           |

|--------------------------------------------------------------------------------------------------|-----|-----|-----|------|--------------------------------------------------------------------------------------------------------------------|

| Watchdog Timeout ( $t_{t(out)}$ )                                                                | 1.1 | 1.6 | 2.3 | sec  | $V_{I(SENSEv)} \geq V_{IT^+} + 0.2 \text{ V}$ , $\overline{MR} \geq 0.7 \times V_{DD}$                             |

| Delay Time ( $t_d$ )                                                                             | 140 | 200 | 280 | ms   | $V_{I(SENSEv)} \geq V_{IT^+} + 0.2 \text{ V}$ , $\overline{MR} \geq 0.7 \times V_{DD}$                             |

| Propagation Delay, High-to-Low, $\overline{MR}$ to RESET <sup>1</sup> /RESET (t <sub>PHL</sub> ) |     | 200 | 500 | ns   | $V_{I(SENSEv)} \geq V_{IT^+} + 0.2 \text{ V}$ , $V_{IH} \geq 0.7 \times V_{DD}$ , $V_{IL} \geq 0.3 \times V_{DD}$  |

| Propagation Delay, Low-to-High, $\overline{MR}$ to RESET/RESET <sup>1</sup> (t <sub>PLH</sub> )  |     | 200 | 500 | ns   | $V_{I(SENSEv)} \geq V_{IT^+} + 0.2 \text{ V}$ , $V_{IH} \geq 0.7 \times V_{DD}$ , $V_{IL} \geq 0.3 \times V_{DD}$  |

| Propagation Delay, High-to-Low, SENSEv to RESET <sup>1</sup> /RESET (t <sub>PHL</sub> )          |     | 30  |     | μs   | $V_{IH} = V_{IT^+} + 0.3 \text{ V}$ , $V_{IL} = V_{IT^-} - 0.3 \text{ V}$ , $\overline{MR} \geq 0.7 \times V_{DD}$ |

| Propagation Delay, Low-to-High, SENSEv to RESET/RESET <sup>1</sup> (t <sub>PLH</sub> )           |     | 30  |     | μs   | $V_{IH} = V_{IT^+} + 0.3 \text{ V}$ , $V_{IL} = V_{IT^-} - 0.3 \text{ V}$ , $\overline{MR} \geq 0.7 \times V_{DD}$ |

<sup>1</sup> 200 ms のリセット・タイムアウト遅延により伝搬遅延がマスクされます。

**真理值表**

表 7.

| MR | SENSE1 > V <sub>IT1</sub> | SENSE2 > V <sub>IT2</sub> | RESET | RESET |

|----|---------------------------|---------------------------|-------|-------|

| L  | X <sup>1</sup>            | X <sup>1</sup>            | L     | H     |

| H  | 0                         | 0                         | L     | H     |

| H  | 0                         | 1                         | L     | H     |

| H  | 1                         | 0                         | L     | H     |

| H  | 1                         | 1                         | H     | L     |

<sup>1</sup> X = don't care.

## 絶対最大定格

表 8.

| Parameter                                            | Rating                                             |

|------------------------------------------------------|----------------------------------------------------|

| Supply Voltage Range, $V_{DD}$                       | -0.3 V to +6 V                                     |

| $\overline{MR}$ , $\overline{WDI}$                   | -0.3 V to $V_{DD} + 0.3$ V                         |

| SENSE1, SENSE2                                       | $(V_{DD} + 0.3)$ V <sub>IT</sub> /V <sub>REF</sub> |

| RESET, $\overline{RESET}$                            | -0.3 V to +6 V                                     |

| Maximum Low Output Current                           | 5 mA                                               |

| Maximum High Output Current                          | -5 mA                                              |

| Input Clamp Current ( $V_I < 0$ V, $V_I > V_{DD}$ )  | $\pm 20$ mA                                        |

| Output Clamp Current ( $V_O < 0$ V, $V_O > V_{DD}$ ) | $\pm 20$ mA                                        |

| Operating Temperature Range                          | -40°C to +85°C                                     |

| Storage Temperature Range                            | -65°C to +150°C                                    |

| Lead Temperature                                     |                                                    |

| Soldering (10 sec)                                   | 300°C                                              |

| Vapor Phase (60 sec)                                 | 215°C                                              |

| Infrared (15 sec)                                    | 220°C                                              |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作の節に記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

## 熱抵抗

表 9.

| Package Type        | $\theta_{JA}$ | Unit |

|---------------------|---------------|------|

| 8-Lead SOIC_N (R-8) | 206           | °C/W |

## ESD の注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

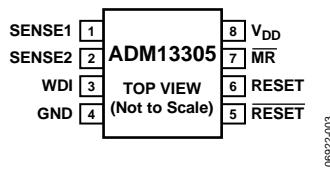

## ピン配置およびピン機能説明

図 3. ピン配置

表 10. ピンの機能説明

| ピン番号 | 記号     | 説明               |

|------|--------|------------------|

| 1    | SENSE1 | 入力電圧 1 の検出。      |

| 2    | SENSE2 | 入力電圧 2 の検出。      |

| 3    | WDI    | ウォッチドッグ・タイマー入力。  |

| 4    | GND    | グランド。            |

| 5    | RESET  | アクティブ・ローのリセット出力。 |

| 6    | RESET  | アクティブ・ハイのリセット出力。 |

| 7    | MR     | マニュアル・リセット入力。    |

| 8    | VDD    | 電源電圧             |

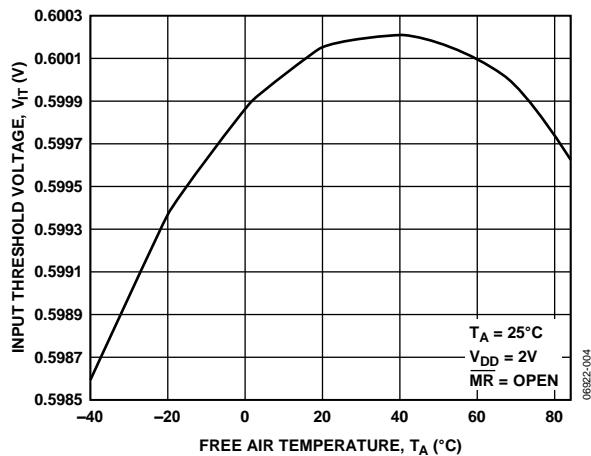

## 代表的な性能特性

図 4.検出スレッショルド電圧対  $V_{DD}$  での自然空冷温度

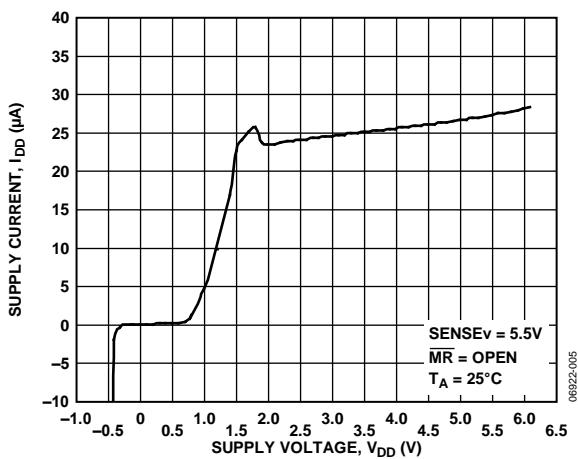

図 5.電源電流対電源電圧

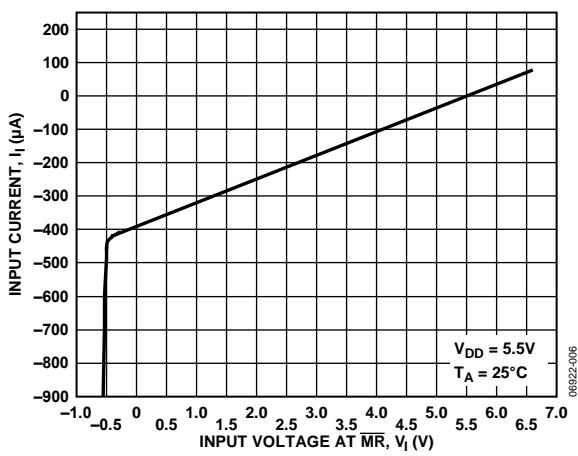

図 6.  $\overline{\text{MR}}$ の入力電流対入力電圧

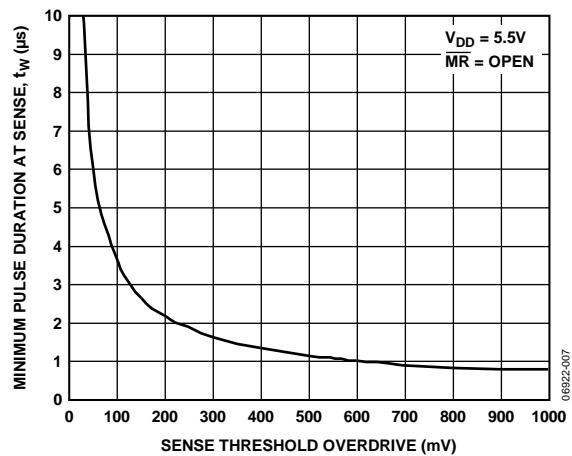

図 7.ADM13305-18、ADM13305-25、ADM13305-33 の SENSE 最小パルス幅対検出スレッショルド・オーバードライブ

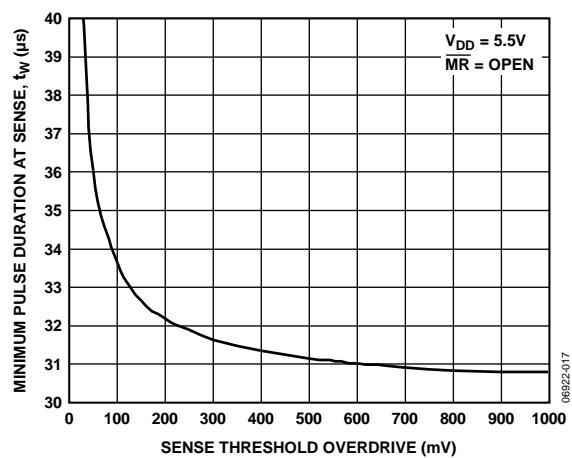

図 8.ADM13305-4、ADM13305-5 の SENSE 最小パルス幅対検出スレッショルド・オーバードライブ

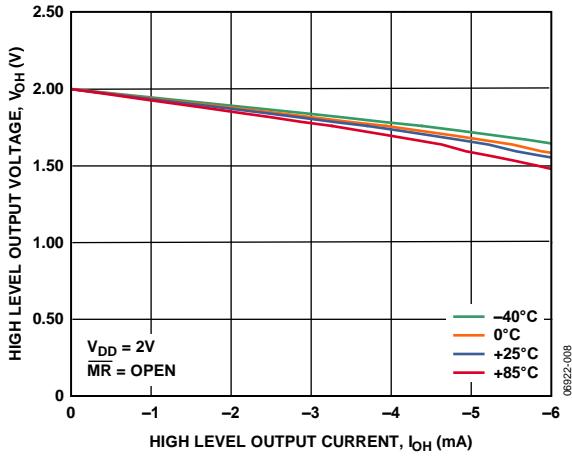

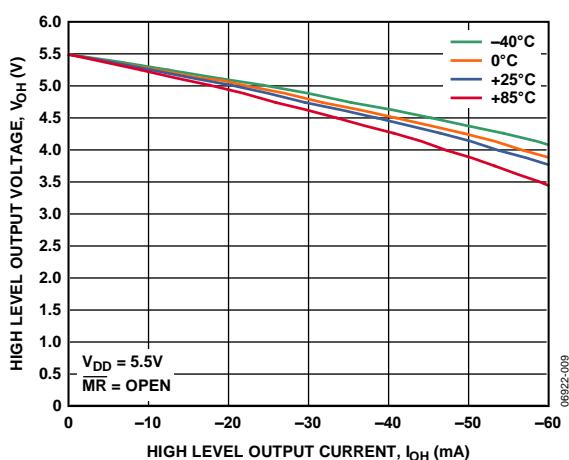

図 9.ハイ・レベル出力電圧対ハイ・レベル出力電流

図 10.ハイ・レベル出力電圧対ハイ・レベル出力電流

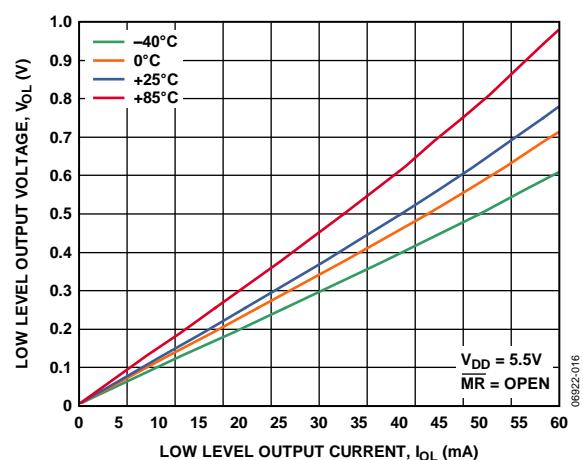

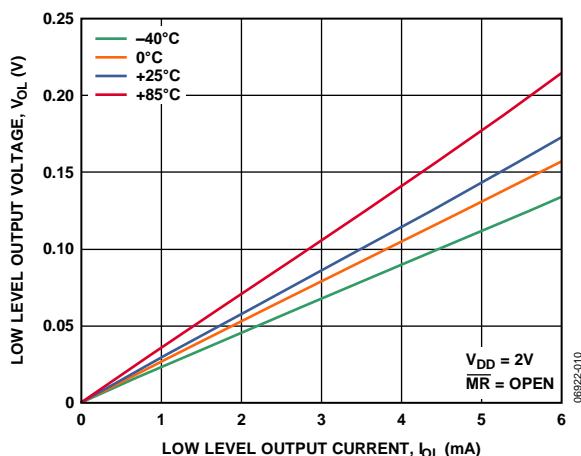

図 12.ロー・レベル出力電圧対ロー・レベル出力電流

図 11.ロー・レベル出力電圧対ロー・レベル出力電流

## 動作原理

ADM13305 は、2 つの電源を監視して DSP およびマイクロプロセッサを採用したシステムへリセット信号を出力するようにデザインされたデュアル電圧監視回路です。

5 種類のモデルを提供しており、全モデルが 1.8 V、2.5 V、3.3 V、5 V の各電源監視用の内部調整済み低電圧スレッショルド・オプションの組み合わせを持っています。また、低電圧スレッショルド電圧が 0.6 V の調整可能な入力オプションもあります。

ADM13305-18、ADM13305-25、ADM13305-33 は内部固定スレッショルドを 2 個持ち、ADM13305-4 と ADM13305-5 は内部固定スレッショルド 1 個と抵抗ストリングを使って外部設定可能なスレッショルド 1 個を持っています。提供中のすべてのオプションについては、オーダー・ガイドを参照してください。

## 入力の構成

ADM13305 の電源は  $V_{DD}$  から供給されます。ノイズの多いアプリケーションでノイズ耐性を向上させるためには、 $V_{DD}$  入力とグラウンドとの間に  $0.1 \mu F$  のコンデンサを接続してください。

SENSEv 入力は、狭い電源グリッチに対して耐性を持っています。未使用 SENSEv 入力をフローティングまたはグラウンド接続にしないでください。これらのピンに規定されたスレッショルド電圧より高い電源電圧に接続してください。

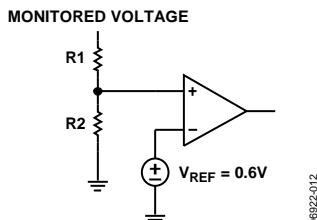

一般に、調整可能な各 SENSEv 入力のスレッショルド電圧は 0.6 V です。0.6 V より高い電圧を監視するときは、図 13 に示すように抵抗分圧回路をデバイスに接続してください。ここで、

$$V_{MONITORED} = 0.6 V \left( \frac{R1 + R2}{R2} \right)$$

図 13. 調整可能な監視回路の設定

## リセット出力

リセット出力は、 $V_{DD}$  が 1.1 V まで低下しても正しい状態が保証されています。パワーアップ時に、電源電圧が 1.1 V を上回ると、RESETがアサートされます。

図 14. リセットのタイミング図

SENSEv 入力で監視している電源が該当するスレッショルドを超えると、RESET信号のアサートはリセット・タイムアウト周期だけロー・レベルを維持した後に解除されます。次に、SENSEv ピンで監視しているいずれかの電圧が該当する立ち下がりスレッショルドを下回ると、RESET出力が再アサートされます。

ADM13305 は、アクティブ・ローのプッシュプル RESET 出力とアクティブ・ハイのプッシュプル RESET 出力を持っています。

## ウォッチドッグ・タイマー

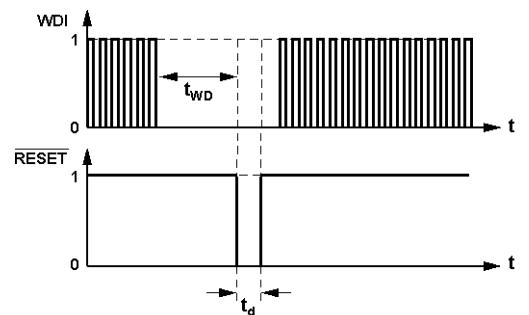

ADM13305 は、マイクロプロセッサの動作を監視するウォッチドッグ・タイマーを内蔵しています。タイマー回路は、ウォッチドッグ入力ピン(WDI)上の各ローからハイ・レベルへのロジック変化ごとまたは各ハイからロー・レベルへのロジック変化ごとにクリアされます。タイマーは予め設定されているウォッチドッグ・タイムアウト周期 1.6 sec までカウントすると、図 15 に示すように、RESETがアサートされます。

マイクロプロセッサは、WDI ピンをトグルしてリセットが発生することを防止する必要があります。マイクロプロセッサがタイムアウト周期以内に WDI をトグルできない場合には、コード実行エラーと見なされ、リセット・パルスが発生されて、マイクロプロセッサは既知の状態から再起動されます。ウォッチドッグ・タイマーは、WDI をフローティングにしておくことにより、ディスエーブルすることができます。

図 15. ウォッチドッグのタイミング図

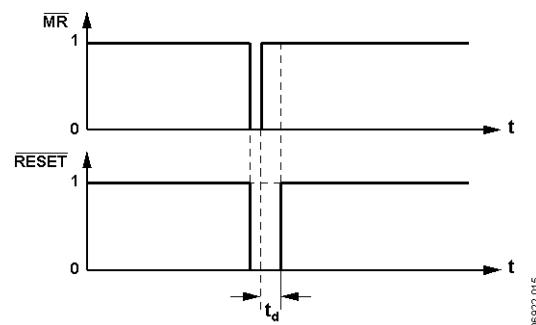

## マニュアル・リセット( $\overline{MR}$ )

ADM13305 にはマニュアル・リセット入力があります。この入力をロー・レベルに駆動すると、図 16 に示すように、リセット出力がアサートされます。 $\overline{MR}$ がローからハイ・レベルへ変化すると、リセットはリセット・アクティブ・タイムアウト周期だけアサート状態を維持した後にアサート状態が解除されます。 $\overline{MR}$ とグラウンドとの間に外付けプッシュ・ボタン・スイッチを接続すると、これを使ってリセットを発生させることができます。

図 16.マニュアル・リセットのタイミング図

06/02/05

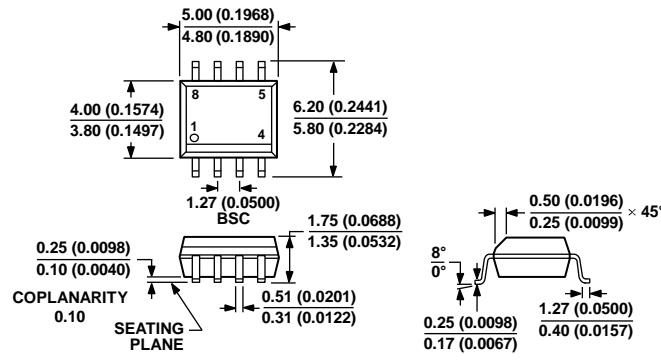

## 外形寸法

COMPLIANT TO JEDEC STANDARDS MS-012-A-A

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

012407A

図 17.8 ピン標準スモール・アウトライン・パッケージ[SOIC\_N]

ナロウ・ボディ

(R-8)

寸法: mm (インチ)

## オーダー・ガイド

| Model                           | Nominal Supervised Voltage |                         | Threshold Voltage (Typical) |        | Temperature Range | Package Description | Package Option |

|---------------------------------|----------------------------|-------------------------|-----------------------------|--------|-------------------|---------------------|----------------|

|                                 | SENSE1                     | SENSE2                  | SENSE1                      | SENSE2 |                   |                     |                |

| ADM13305-18ARZ <sup>1</sup>     | 3.3 V                      | 1.8 V                   | 2.93 V                      | 1.68 V | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| ADM13305-18ARZ-RL7 <sup>1</sup> | 3.3 V                      | 1.8 V                   | 2.93 V                      | 1.68 V | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| ADM13305-25ARZ <sup>1</sup>     | 3.3 V                      | 2.5 V                   | 2.93 V                      | 2.25 V | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| ADM13305-25ARZ-RL7 <sup>1</sup> | 3.3 V                      | 2.5 V                   | 2.93 V                      | 2.25 V | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| ADM13305-33ARZ <sup>1</sup>     | 5 V                        | 3.3 V                   | 4.55 V                      | 2.93 V | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| ADM13305-33ARZ-RL7 <sup>1</sup> | 5 V                        | 3.3 V                   | 4.55 V                      | 2.93 V | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| ADM13305-4ARZ <sup>1</sup>      | 3.3 V                      | Adjustable <sup>2</sup> | 2.93 V                      | 0.6 V  | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| ADM13305-4ARZ-RL7 <sup>1</sup>  | 3.3 V                      | Adjustable <sup>2</sup> | 2.93 V                      | 0.6 V  | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| ADM13305-5ARZ <sup>1</sup>      | 2.5 V                      | Adjustable <sup>2</sup> | 2.25 V                      | 0.6 V  | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

| ADM13305-5ARZ-RL7 <sup>1</sup>  | 2.5 V                      | Adjustable <sup>2</sup> | 2.25 V                      | 0.6 V  | -40°C to +85°C    | 8-Lead SOIC_N       | R-8            |

<sup>1</sup>Z = RoHS 準拠製品<sup>2</sup>0.6 V 調整可能。外付け抵抗分圧器で実際の検出電圧を決めます。