**ADCMP608****特長**

$V_{CC}=2.5\sim 5.5V$ で完全に仕様規定されたレールtoレール動作

$-0.2V\sim V_{CC}+0.2V$ 範囲の入力同相電圧

低グリッチのCMOS/TTL互換出力段

伝播遅延: 40ns

低消費電力: 1 mW @ 2.5V

シャットダウン・ピン

電源電圧変動除去比: >60dB

動作温度範囲:  $-40\sim +125^{\circ}C$

**アプリケーション**

高速計測機器

クロックおよびデータ信号の再生

ロジック・レベルのシフトおよび変換

高速ライン・レシーバ

スレッショールド検出

ピークおよびゼロクロス検出器

高速トリガ回路

パルス幅変調器

電流/電圧制御発振器

**概要**

ADCMP608は、アナログ・デバイセズ独自のXFCB2プロセスで製造された高速コンパレータで、融通性が非常に高く使いやすい製品です。 $V_{EE}-0.2V$ から $V_{CC}+0.2V$ までの入力範囲、低ノイズ、TTL/CMOS互換出力ドライバ、シャットダウン入力などの機能を持っています。ADCMP608は、電源電流500 $\mu$ A (typ)、オーバードライブ10mVで、15pF負荷駆動時の伝播遅延が40nsです。

柔軟性の高い電源方式を採用しているため、+2.5V单電源では $-0.2\sim +2.7V$ の入力信号範囲で、+5.5Vまでの单電源では $-0.2\sim +5.7V$ の入力信号範囲で、それぞれ動作することができます。

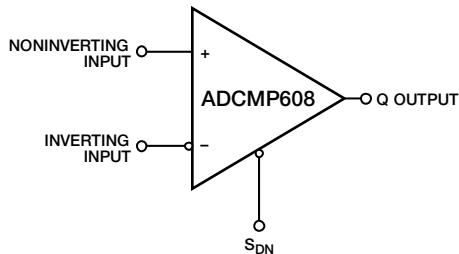

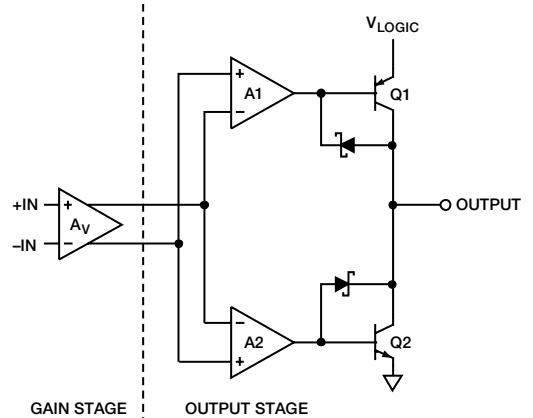

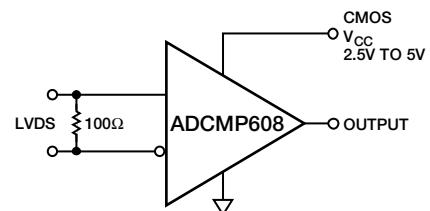

**機能ブロック図**

図1

TTL/CMOS互換の出力段は、定格タイミング仕様で最大15pFの容量負荷を駆動し、容量が増えた場合でも、駆動能力が比例して低下するようにデザインされています。コンパレータ入力段は大きい入力オーバードライブに対して確実に保護されており、入力信号が有効な入力範囲を超えて、出力は位相反転しません。

ADCMP608は、シングルエンド出力とシャットダウン・ピンを持つ6pinの小型SC70パッケージを採用しています。

# ADCMP608

## 目次

|              |   |                       |    |

|--------------|---|-----------------------|----|

| 特長           | 1 | アプリケーション情報            | 7  |

| アプリケーション     | 1 | 電源／グラウンドのレイアウトおよびバイパス | 7  |

| 機能ブロック図      | 1 | TTL/CMOS互換出力段         | 7  |

| 概要           | 1 | 性能の最適化                | 7  |

| 改訂履歴         | 2 | コンパレータの伝播遅延のバラツキ      | 7  |

| 仕様           | 3 | クロスオーバ・バイアス・ポイント      | 8  |

| 電気特性         | 3 | 最小入力スルーレート条件          | 8  |

| 絶対最大定格       | 4 | 代表的なアプリケーション回路        | 9  |

| 熱抵抗          | 4 | 外形寸法                  | 10 |

| ESDに関する注意    | 4 | オーダー・ガイド              | 10 |

| ピン配置とピン機能の説明 | 5 |                       |    |

| 代表的な性能特性     | 6 |                       |    |

## 改訂履歴

4/07—Revision 0: Initial Version

# 仕様

## 電気特性

特に指定のない限り、 $V_{CC}=2.5V$ 、 $T_A=-40\sim+125^{\circ}C$ 、 $T_A$  (typ) = $25^{\circ}C$ 。

表1

| Parameter                                           | Symbol     | Conditions                                                         | Min  | Typ            | Max      | Unit       |

|-----------------------------------------------------|------------|--------------------------------------------------------------------|------|----------------|----------|------------|

| DC INPUT CHARACTERISTICS                            |            |                                                                    |      |                |          |            |

| Voltage Range                                       | $V_P, V_N$ | $V_{CC} = 2.5V$ to $5.5V$                                          | -0.2 |                | $V_{CC}$ | V          |

| Common-Mode Range                                   |            | $V_{CC} = 2.5V$ to $5.5V$                                          | -0.2 |                | $V_{CC}$ | V          |

| Differential Voltage                                |            | $V_{CC} = 2.5V$ to $5.5V$                                          |      |                | $V_{CC}$ | V          |

| Offset Voltage                                      | $V_{OS}$   |                                                                    | -5.0 | $\pm 3$        | +5.0     | mV         |

| Bias Current                                        | $I_P, I_N$ |                                                                    | -0.4 |                | +0.4     | $\mu A$    |

| Offset Current                                      |            |                                                                    | -1.0 |                | +1.0     | $\mu A$    |

| Capacitance                                         | $C_P, C_N$ |                                                                    |      | 1              |          | pF         |

| Resistance, Differential Mode                       |            | -0.5 V to $V_{CC} + 0.5V$                                          | 200  |                | 7000     | k $\Omega$ |

| Resistance, Common Mode                             |            | -0.5 V to $V_{CC} + 0.5V$                                          | 100  |                | 4000     | k $\Omega$ |

| Active Gain                                         | $A_V$      |                                                                    |      | 80             |          | dB         |

| Common-Mode Rejection                               | CMRR       | $V_{CC} = 2.5V$ ,<br>$V_{CM} = -0.2V$ to $2.7V$<br>$V_{CC} = 5.5V$ | 45   |                |          | dB         |

|                                                     |            |                                                                    | 45   |                |          | dB         |

| SHUTDOWN PIN CHARACTERISTICS <sup>1</sup>           |            |                                                                    |      |                |          |            |

| $V_{IH}$                                            |            | Comparator is operating                                            | 2.0  |                | $V_{CC}$ | V          |

| $V_{IL}$                                            |            | Shutdown guaranteed                                                | -0.2 | +0.4           | +0.4     | V          |

| $I_{IH}$                                            |            | $V_{IH} = V_{CC}$                                                  | -6   |                | +6       | $\mu A$    |

| Sleep Time                                          | $t_{SD}$   | $I_{CC} < 100\mu A$                                                |      | 300            |          | ns         |

| Wake-Up Time                                        | $t_H$      | $V_{PP} = 10mV$ , output valid                                     |      | 150            |          | ns         |

| DC OUTPUT CHARACTERISTICS                           |            | $V_{CC} = 2.5V$ to $5.5V$                                          |      |                |          |            |

| Output Voltage High Level                           | $V_{OH}$   | $I_{OH} = 0.8mA$ , $V_{CC} = 2.5V$                                 |      | $V_{CC} - 0.4$ |          | V          |

| Output Voltage Low Level                            | $V_{OL}$   | $I_{OL} = 0.8mA$ , $V_{CC} = 2.5V$                                 |      |                | 0.4      | V          |

| AC PERFORMANCE <sup>2</sup>                         |            | $V_{CC} = 2.5V$ to $5.5V$                                          |      |                |          |            |

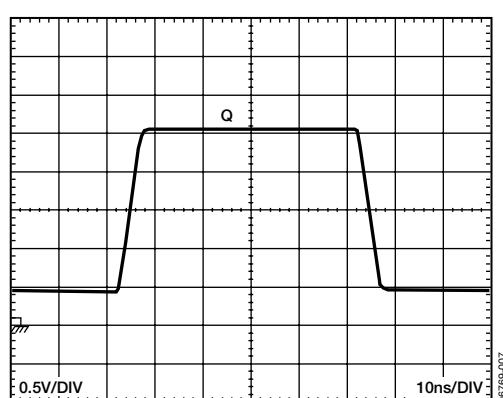

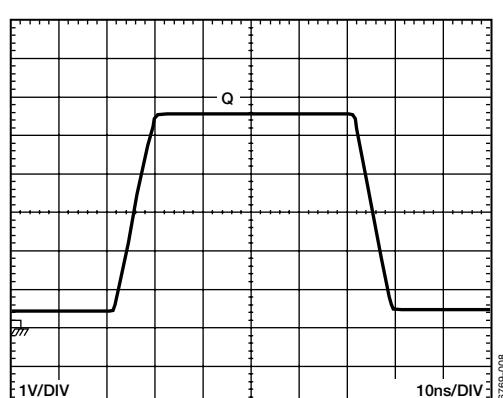

| Rise Time/Fall Time                                 | $t_R, t_F$ | 10% to 90%, $V_{CC} = 2.5V$                                        |      | 25 to 50       |          | ns         |

|                                                     |            | 10% to 90%, $V_{CC} = 5.5V$                                        |      | 45 to 75       |          | ns         |

| Propagation Delay                                   | $t_{PD}$   | $V_{OD} = 10mV$ , $V_{CC} = 2.5V$                                  |      | 30 to 50       |          | ns         |

|                                                     |            | $V_{OD} = 50mV$ , $V_{CC} = 5.5V$                                  |      | 35 to 60       |          | ns         |

| Propagation Delay Skew—Rising to Falling Transition |            | $V_{CC} = 2.5V$                                                    |      | 4.5            |          | ns         |

|                                                     |            | $V_{CC} = 5.5V$                                                    |      | 8              |          | ns         |

| Overdrive Dispersion                                |            | $10mV < V_{OD} < 125mV$                                            |      | 12             |          | ns         |

| Common-Mode Dispersion                              |            | $-0.2V < V_{CM} < V_{CC} + 0.2V$                                   |      | 1.5            |          | ns         |

| POWER SUPPLY                                        |            |                                                                    |      |                |          |            |

| Supply Voltage Range                                | $V_{CC}$   |                                                                    | 2.5  |                | 5.5      | V          |

| Positive Supply Current                             | $I_{VCC}$  | $V_{CC} = 2.5V$                                                    |      | 550            | 800      | $\mu A$    |

|                                                     |            | $V_{CC} = 5.5V$                                                    |      | 800            | 1300     | $\mu A$    |

| Power Dissipation                                   | $P_D$      | $V_{CC} = 2.5V$                                                    |      | 1.375          | 2.0      | mW         |

|                                                     |            | $V_{CC} = 5.5V$                                                    |      | 4.95           | 7.15     | mW         |

| Power Supply Rejection Ratio                        | PSRR       | $V_{CC} = 2.5V$ to $5.5V$                                          | -50  |                |          | dB         |

| Shutdown Current                                    | $I_{SD}$   | $V_{CC} = 2.5V$ to $5.5V$                                          |      | 250            | 350      | $\mu A$    |

<sup>1</sup> デバイスがシャットダウン・モードのとき、出力は高インピーダンス・モードになります。イネーブル／ディスエーブル時間は真のスリーステート出力の場合よりかなり長いため、この機能を使用するときは注意が必要です。

<sup>2</sup> 特に指定のない限り、 $V_{IN}=100mV$ 矩形入力 (1MHz時)、 $V_{CM}=0V$ 、 $CL=15pF$ 、 $V_{CCI}=2.5V$ 。

## 絶対最大定格

表2

| Parameter                            | Rating                     |

|--------------------------------------|----------------------------|

| Supply Voltages                      |                            |

| Supply Voltage<br>( $V_{CC}$ to GND) | -0.5 V to +6.0 V           |

| Supply Differential                  | -6.0 V to +6.0 V           |

| Input Voltages                       |                            |

| Input Voltage                        | -0.5 V to $V_{CC} + 0.5$ V |

| Differential Input Voltage           | $\pm(V_{CC} + 0.5$ V)      |

| Maximum Input/Output Current         | $\pm 50$ mA                |

| Shutdown Control Pin                 |                            |

| Applied Voltage ( $S_{DN}$ to GND)   | -0.5 V to $V_{CC} + 0.5$ V |

| Maximum Input/Output Current         | $\pm 50$ mA                |

| Output Current                       | $\pm 50$ mA                |

| Temperature                          |                            |

| Operating Temperature, Ambient       | -40°C to +125°C            |

| Operating Temperature, Junction      | 150°C                      |

左記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作セクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

### 熱抵抗

$\theta_{JA}$ は最悪の条件、すなわち回路ボードに表面実装パッケージをハンダ付けした状態で規定しています。

表3. 热抵抗

| Package Type         | $\theta_{JA}$ <sup>1</sup> | Unit |

|----------------------|----------------------------|------|

| ADCMP608 6-Lead SC70 | 426                        | °C/W |

<sup>1</sup> 自然空冷で測定

### ESDに関する注意

ESD（静電放電）の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

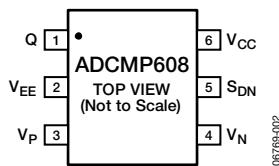

## ピン配置とピン機能の説明

図2. ピン配置

表4. ADCMP608のピン機能の説明

| ピン番号 | 記号       | 説明                                                                          |

|------|----------|-----------------------------------------------------------------------------|

| 1    | Q        | 非反転出力。非反転入力 ( $V_P$ ) のアナログ電圧が反転入力 ( $V_N$ ) のアナログ電圧より大きい場合、Qはロジック・ハイとなります。 |

| 2    | $V_{EE}$ | 負の電源電圧                                                                      |

| 3    | $V_P$    | 非反転アナログ入力                                                                   |

| 4    | $V_N$    | 反転アナログ入力                                                                    |

| 5    | $S_{DN}$ | シャットダウン。ピンをローレベルに駆動してデバイスをシャットダウンします。                                       |

| 6    | $V_{CC}$ | $V_{CC}$ 電源                                                                 |

## 代表的な性能特性

特に指定のない限り、 $V_{CC}=2.5V$ 、 $T_A=25^{\circ}C$ 。

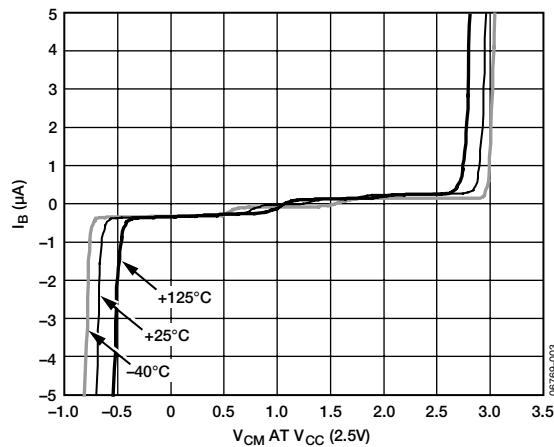

図3. 入力同相電圧 対 入力バイアス電流

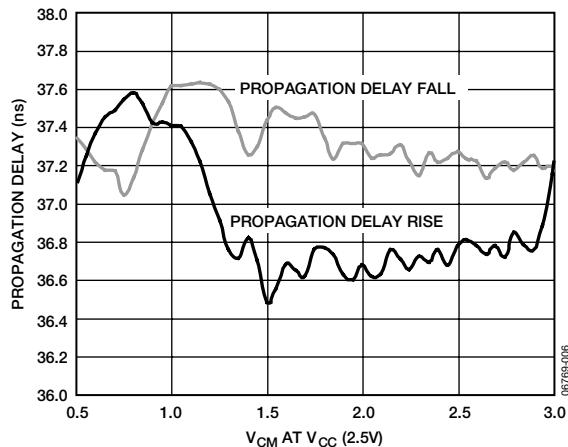

図6. 入力同相電圧 対 伝播遅延

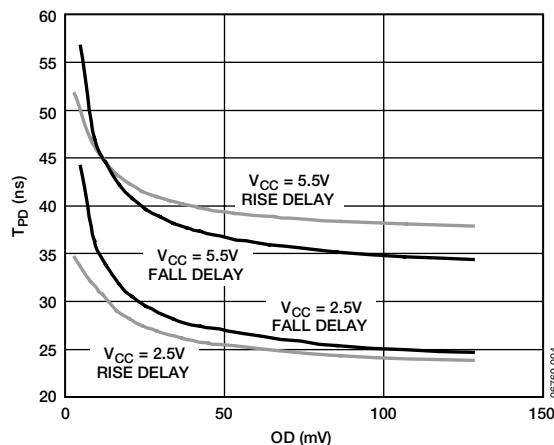

図4.  $V_{CC}=2.5V$ 、 $5.5V$ 時の入力オーバードライブ 対 伝播遅延

図7. 1MHzの出力電圧波形、 $V_{CC}=2.5V$

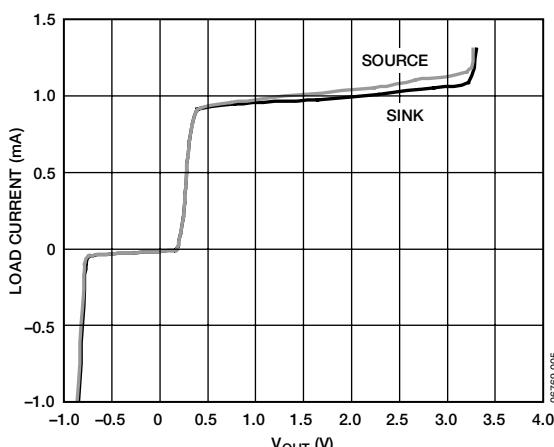

図5.  $V_{OH}/V_{OL}$  対 負荷電流 (mA)

図8. 1MHzの出力電圧波形、 $V_{CC}=5.5V$

## アプリケーション情報

**電源／グラウンドのレイアウトおよびバイパス**

ADCMP608コンパレータは高速のデバイスです。低ノイズの出力段の場合でも、仕様性能を達成するには、適正な高速デザイン技術を採用する必要があります。コンパレータは補償を行っていないアンプであるため、いかなる位相関係でも帰還によって発振や好ましくないヒステリシスが生じる可能性があります。とりわけ重要なのは、低インピーダンスの電源プレーン、特に出力電源プレーン ( $V_{CC}$ ) およびグラウンド・プレーン (GND) を使用することです。各電源プレーンは、多層ボード内に設けることが推奨されます。特定のアプリケーションで最適な性能を可能にするには、電流スイッチング用に最小インダクタンスのリターン・パスを設ける必要があります。

入出力電源を適正にバイパスすることも重要であり、 $0.1\mu F$ のバイパス・コンデンサを  $V_{CC}$  電源ピンのできるだけ近くに配置します。コンデンサをGNDプレーンに接続し、冗長ビアを設けてリターン・パスを物理的に短くし、出力電流がグラウンドから  $V_{CC}$  ピンに戻れるようにします。高周波のバイパス・コンデンサは注意して選択し、寄生インダクタンスとESRを最小限に抑えます。高周波において最大のバイパス効率を達成するには、レイアウトでの寄生インダクタンスを厳しく管理する必要があります。

### TTL/CMOS互換出力段

仕様で規定された伝搬遅延性能は、容量負荷を規定の最小値以下に抑えるだけで達成できます。ADCMP608の出力は、1個のショットキTTLまたは3個の低消費電力ショットキTTL負荷（または、これらと同等の負荷）を直接駆動します。大きなファンアウト、バス、伝送ラインに対しては、適正なバッファを使ってコンパレータの優れた速度性や安定性を維持する必要があります。

定格 $15pF$ の負荷容量を使用する場合、出力段のスルーライフタイムはデバイスの全伝搬遅延の $1/2$ より大きな値となります。このため、 $V_{CC}$ の低下に伴って全伝搬遅延も減少し、電源の不安定性が大きな遅延のバラツキとして現れる場合があります。

遅延は、使用する電源によらず $50\%$ ポイントまで測定されます。したがって、最速時間は $2.5V$ の  $V_{CC}$  電源で得られ、また別の電圧レベルでスイッチングする負荷を駆動するときには速度が低下します。

オーバードライブと入力スルーレートのバラツキは、出力負荷や  $V_{CC}$  変動の影響をあまり受けません。

TTL/CMOS互換の出力段を簡略回路図に示します（図9を参照）。この出力段は、固有な対称性を持ち、全体として動作が優れているため、さまざまなフィルタや特殊な負荷を駆動できます。

図9. TTL/CMOS互換出力段の簡略回路図

### 性能の最適化

他の高速コンパレータと同様に、仕様性能を実現するためには、正しいデザインとレイアウト技術を採用する必要があります。浮遊容量、インダクタンス、コモン電源／グラウンドのインピーダンスなど、レイアウト上の問題があると、性能は著しく制限され、発振が生じる場合もよくあります。信号源インピーダンスはできる限り最小限に抑える必要があります。コンパレータの寄生入力容量と高い信号源インピーダンスとが組み合わさると、入力の帯域幅が低下して、全体の応答が劣化します。高インピーダンスは、不要なカッピングを助長することになります。

### コンパレータの伝播遅延のバラツキ

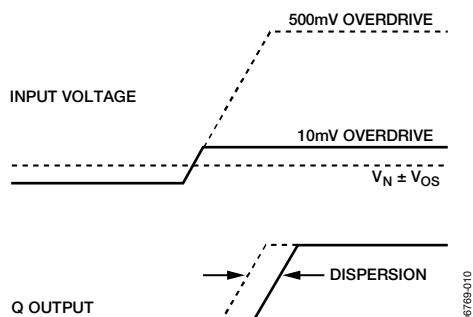

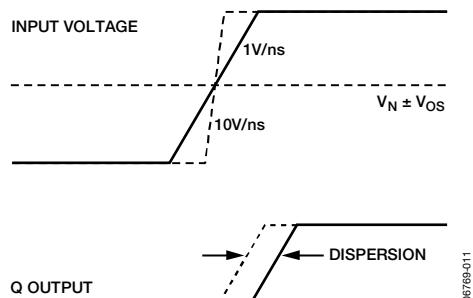

ADCMP608は、 $10mV \sim V_{CC} - 1V$  の広い入力オーバードライブ電圧範囲で伝搬遅延バラツキを減らすようにデザインされています。伝搬遅延バラツキとは、オーバードライブまたはスルーレートの変化（入力信号がスイッチング・スレッショルドを超える際の程度と速度）から生じる伝搬遅延の変化を意味します。

伝搬遅延のバラツキは、データ通信、自動試験／測定、計測などのタイミングが重視されるアプリケーションや、パルス分光法、原子力計測、医療用画像処理などのイベント駆動型アプリケーションにとって重要な仕様です。バラツキとは、入力オーバードライブ条件が変化するときの伝搬遅延の変動をいいます（図10と図11を参照）。

ADCMP608の場合は、オーバードライブが $10mV$ から $125mV$ まで変化する条件下で、バラツキは $12ns$ 未満（typ値）です。このコンパレータでは正方向と負方向で入力の遅延時間がほぼ等しく、出力スキーが非常に小さいため、この仕様を正と負の両方の信号に適用できます。バラツキの繰り返し測定では、実際のデバイス・オフセットをオーバードライブに加算してください。

# ADCMP608

図10. 伝播遅延（オーバードライブのバラツキ）

図11. 伝播遅延（スルーレートのバラツキ）

## クロスオーバ・バイアス・ポイント

オペアンプもコンパレータもこの種のレールtoレール入力は、デュアル・フロントエンド・デザインを採用しています。一部のデバイスは $V_{CC}$ レールの近くでアクティブになります。ほかのデバイスは $V_{EE}$ レールの近くでアクティブになります。クロスオーバは、同相電圧範囲内の事前に指定されたポイントで発生します。このポイント（通常は $V_{CC}/2$ ）で、バイアス電流の方向が逆になります。オフセット電圧と電流の測定値は変化します。

この図は、ADCMP608について説明しています。クロスオーバ・ポイントは、約0.8Vと約1.6Vの位置にあります。

## 最小入力スルーレート条件

「性能の最適化」でも示したように、定格の負荷容量や通常の優れたボードデザイン法を採用して、これらのコンパレータがヒステリシスなしですべての入力スルーレートに対して安定性を保つようにします。入力段では広帯域ノイズは発生しますが、ほかの大部分の高速コンパレータにみられるような激しいチャタリングは発生しません。容量負荷の増加や不適切なバイパスを行うと、発振が生じことがあります。この発振は、コンパレータの高いゲイン帯域幅と、パッケージおよびPCボード上の寄生成分を通しての帰還との組み合せが原因となって発生します。多くのアプリケーションでは、チャタリングは有害ではありません。

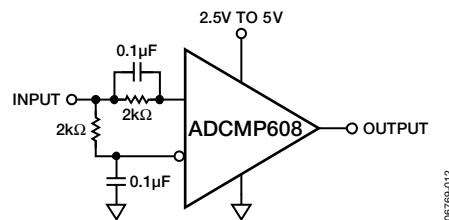

## 代表的なアプリケーション回路

図12. 自己バイアスの50%スライサ

図13. LVDS—CMOSレシーバ間接続

# ADCMP608

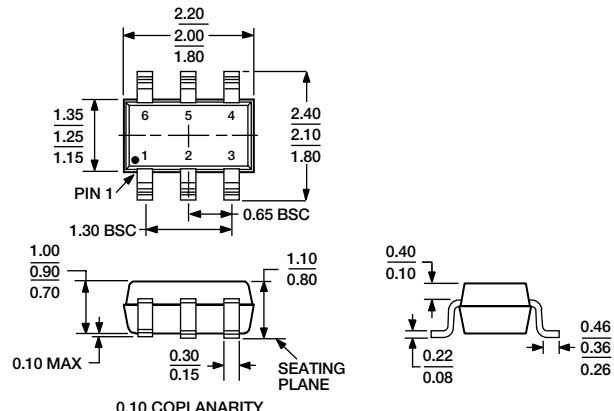

## 外形寸法

図14. 6ピン・プラスチック表面実装パッケージ [SC70]

(KS-6)

寸法単位 : mm

## オーダー・ガイド

| Model                          | Temperature Range | Package Description                                        | Package Option | Branding |

|--------------------------------|-------------------|------------------------------------------------------------|----------------|----------|

| ADCMP608BKSZ-R2 <sup>1</sup>   | -40°C to +125°C   | 6-Lead Thin Shrink Small Outline Transistor Package (SC70) | KS-6           | G0U      |

| ADCMP608BKSZ-RL <sup>1</sup>   | -40°C to +125°C   | 6-Lead Thin Shrink Small Outline Transistor Package (SC70) | KS-6           | G0U      |

| ADCMP608BKSZ-REEL <sup>7</sup> | -40°C to +125°C   | 6-Lead Thin Shrink Small Outline Transistor Package (SC70) | KS-6           | G0U      |

<sup>1</sup> Z=RoHS準拠製品