# 125 MSPS、シリアル LVDS、1.8 V の オクタル 14 ビット A/D コンバータ

## データシート

AD9681

### 特長

低消費電力

8 チャンネルの ADC を 1 パッケージに内蔵

125 MSPS でのチャンネルあたりの消費電力 110 mW、消費電力調整オプション付き

SNR = 74 dBFS (ナイキスト・レートまで)、SFDR = 90 dBc (ナイキスト・レートまで)

DNL =  $\pm 0.8$  LSB (typ)、INL =  $\pm 1.2$  LSB (typ)

最悪隣接チャンネル、70 MHz、-1 dBFS でのクロストーク: -83 dB (typ)

シリアル LVDS (ANSI-644、デフォルト)

低消費電力、縮小信号オプション (IEEE 1596.3 と同じ)

データ・クロック出力とフレーム・クロック出力を装備

フル・パワー・アナログ帯域幅: 650 MHz

入力電圧範囲: 2 V p-p

電源動作: 1.8 V

シリアル・ポート制御

柔軟なビット指向

組込みおよびカスタムのデジタル・テスト・パターン生成

プログラマブルなクロックとデータのアライメント

パワーダウン・モードとスタンバイ・モード

### アプリケーション

医用画像処理

通信器レシーバ

多チャンネル・データ・アクイジョン

### 概要

AD9681 はサンプル・アンド・ホールド回路内蔵の 8ch、14 ビット 125 MSPS A/D コンバータ(ADC)であり、低価格、低消費電力、小型、使い易さを追求してデザインされています。このデバイスは、最大 125 MSPS の変換レートで動作し、小型パッケージが重要なアプリケーションで優れたダイナミック性能と低消費電力をを持つように最適化されています。

この ADC は、フル性能動作のために 1.8 V の单電源と LVPECL/CMOS/LVDS 互換のサンプル・レート・クロックを必要とします。多くのアプリケーションに対して、外付けのリファレンス電圧またはドライバなしで済みます。

この AD9681 は適切な LVDS シリアル・データレートを得るために、サンプル・レート・クロックを自動的に遙倍します。出力上有るデータをキャプチャするためのデータ・クロック出力 (DCO $\pm 1$ 、DCO $\pm 2$ ) と、新しい出力バイトの有効を通知するフレーム・クロック出力 (FCO $\pm 1$ 、FCO $\pm 2$ ) を備えています。個別チャンネル・パワーダウンをサポートしており、すべてのチャンネルをディスエーブルしたときのデバイス消費電力は 2 mW 以下です。

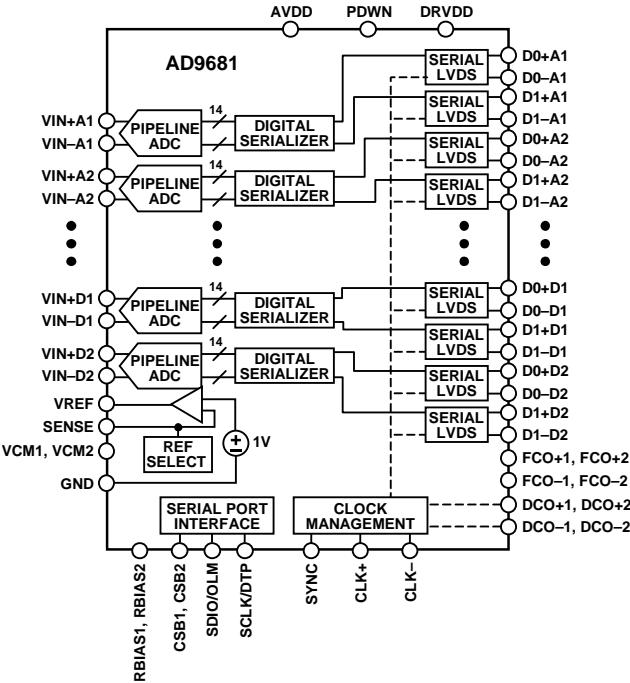

### 簡略化した機能ブロック図

11557-200

図 1.

この ADC は、柔軟性を高め、システム・コストを下げるためにデザインされた、プログラマブルなクロック、データ・アライメント、プログラマブルなデジタル・テスト・パターンの生成などの複数の機能を内蔵しています。使用可能なデジタル・テスト・パターンとしては、決定論的パターン、疑似ランダム・パターン、ユーザー定義のテスト・パターン(シリアル・ポート・インターフェース(SPI)を介して入力)などがあります。

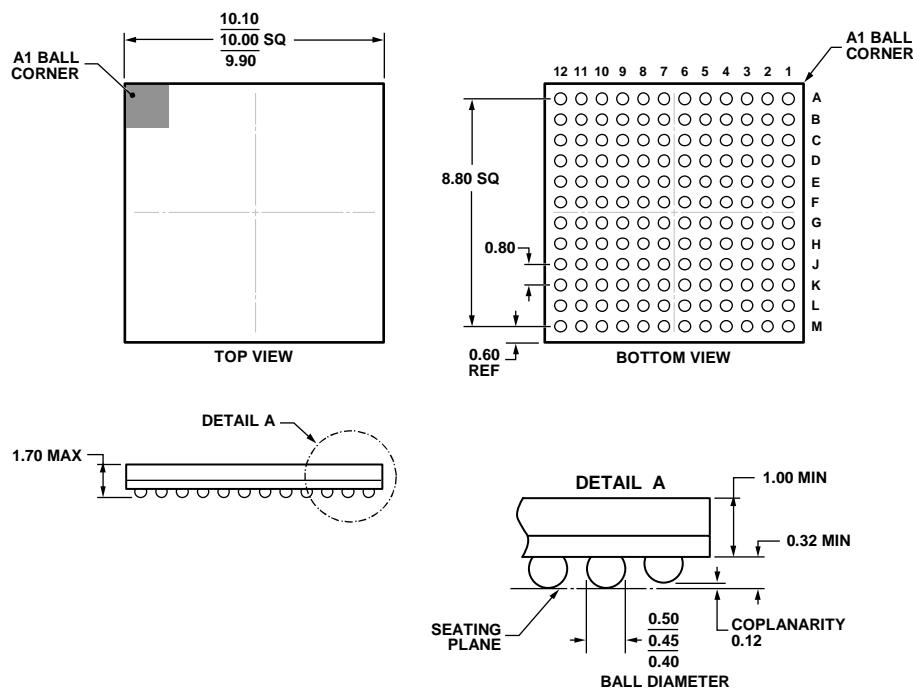

AD9681 は、RoHS 準拠の 144 ポール CSP-BGA パッケージを採用しています。仕様は -40°C ~ +85°C の工業用温度範囲で規定されています。このデバイスは、米国特許により保護されています。

### 製品のハイライト

- 小型フットプリント。8 個の ADC が小型 10 mm × 10 mm のパッケージに内蔵されています。

- 低消費電力。125 MSPS でのチャンネルあたりの消費電力は 110 mW で、消費電力調整オプション付き

- 使い易い。データ・クロック出力 (DCO $\pm 1$ 、DCO $\pm 2$ ) は最大周波数 500 MHz で動作し、ダブル・データ・レート (DDR) 動作をサポートします。

- 柔軟性。SPI 制御は、特定のシステム条件を満たすように広範囲で柔軟な機能を提供します。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、それぞれの所有者の財産です。※日本語版資料は REVISION が古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|               |    |

|---------------|----|

| 特長            | 1  |

| アプリケーション      | 1  |

| 概要            | 1  |

| 簡略化した機能ブロック図  | 1  |

| 製品のハイライト      | 1  |

| 改訂履歴          | 2  |

| 機能ブロック図       | 3  |

| 仕様            | 4  |

| DC 仕様         | 4  |

| AC 仕様         | 5  |

| デジタル仕様        | 6  |

| スイッチング仕様      | 7  |

| タイミング仕様       | 8  |

| 絶対最大定格        | 12 |

| 熱特性           | 12 |

| ESD の注意       | 12 |

| ピン配置およびピン機能説明 | 13 |

| 代表的な性能特性      | 15 |

| 等価回路          | 18 |

| 動作原理          | 19 |

| アナログ入力に対する考慮  | 19 |

| リファレンス電圧      | 20 |

| クロック入力の考慮事項   | 21 |

|                        |    |

|------------------------|----|

| 消費電力とパワーダウン・モード        | 23 |

| デジタル出力とタイミング           | 24 |

| 出力テスト・モード              | 27 |

| シリアル・ポート・インターフェース(SPI) | 28 |

| SPI を使う設定              | 28 |

| ハードウェア・インターフェース        | 29 |

| SPI を使わない設定            | 29 |

| SPI からアクセス可能な機能        | 29 |

| メモリ・マップ                | 30 |

| メモリ・マップ・レジスタ・テーブルの読み出し | 30 |

| メモリ・マップ                | 31 |

| メモリ・マップ・レジスタの説明        | 34 |

| アプリケーション情報             | 37 |

| デザイン・ガイドライン            | 37 |

| 電源とグラウンドの推奨事項          | 37 |

| ボード・レイアウト時の考慮事項        | 37 |

| クロック安定性の考慮事項           | 38 |

| VCM                    | 38 |

| リファレンス電圧のデカップリング       | 38 |

| SPI ポート                | 38 |

| 外形寸法                   | 39 |

| オーダー・ガイド               | 39 |

## 改訂履歴

### 12/13—Rev. 0 to Rev. A

Changes to Ordering Guide ..... 39

### 11/13—Revision 0: Initial Version

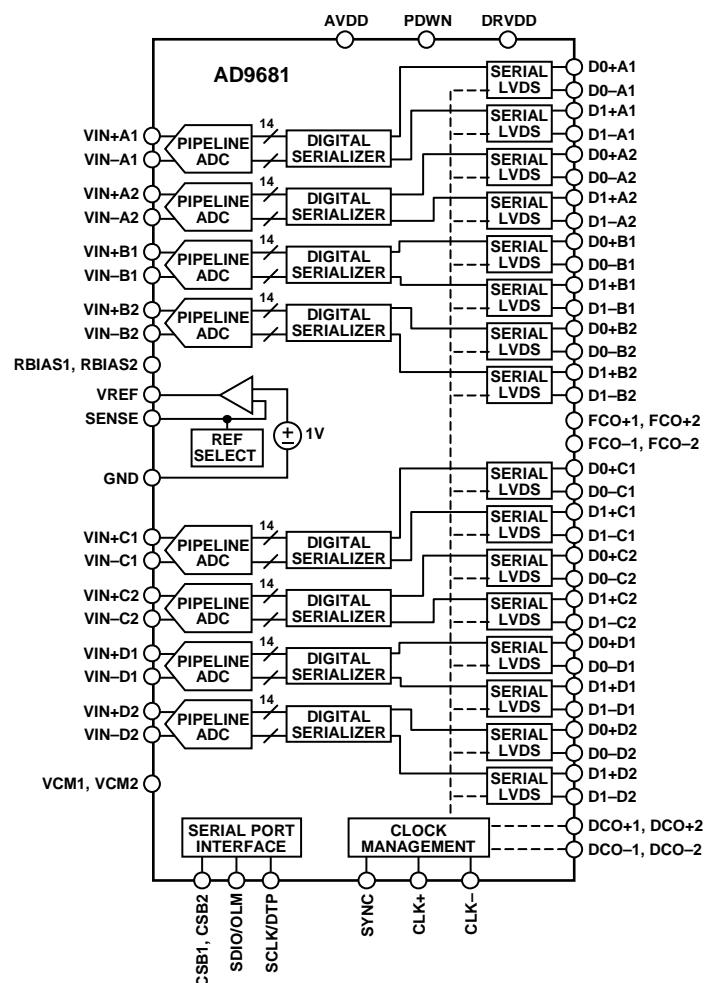

## 機能ブロック図

11537-201

図 2.

## 仕様

## DC 仕様

特に指定がない限り、AVDD = 1.8 V、DRVDD = 1.8 V、2 V p-p 差動入力、1.0 V 内蔵リファレンス電圧、 $A_{IN} = -1.0$  dBFS。

表 1.

| Parameter <sup>1</sup>                                                                | Temp | Min   | Typ        | Max   | Unit    |

|---------------------------------------------------------------------------------------|------|-------|------------|-------|---------|

| RESOLUTION                                                                            |      | 14    |            |       | Bits    |

| ACCURACY                                                                              |      |       |            |       |         |

| No Missing Codes                                                                      | Full |       | Guaranteed |       |         |

| Offset Error                                                                          | Full | -0.23 | +0.21      | +0.62 | % FSR   |

| Offset Matching                                                                       | Full | 0     | 0.24       | 0.7   | % FSR   |

| Gain Error                                                                            | Full | -8.0  | -3.1       | +1.7  | % FSR   |

| Gain Matching                                                                         | Full | 0     | 1.8        | 6.0   | % FSR   |

| Differential Nonlinearity (DNL)                                                       | Full | -0.92 | $\pm 0.8$  | +1.75 | LSB     |

| Integral Nonlinearity (INL)                                                           | Full | -4.0  | $\pm 1.2$  | +4.0  | LSB     |

| TEMPERATURE DRIFT                                                                     |      |       |            |       |         |

| Offset Error                                                                          | Full |       | -4         |       | ppm/°C  |

| Gain Error                                                                            | Full |       | 38         |       | ppm/°C  |

| INTERNAL VOLTAGE REFERENCE                                                            |      |       |            |       |         |

| Output Voltage (1 V Mode)                                                             | Full | 0.98  | 1.0        | 1.02  | V       |

| Load Regulation at 1.0 mA ( $V_{REF} = 1$ V)                                          | 25°C |       | 3          |       | mV      |

| Input Resistance                                                                      | Full |       | 7.5        |       | kΩ      |

| INPUT-REFERRED NOISE                                                                  |      |       |            |       |         |

| $V_{REF} = 1.0$ V                                                                     | 25°C |       | 0.99       |       | LSB rms |

| ANALOG INPUTS                                                                         |      |       |            |       |         |

| Differential Input Voltage ( $V_{REF} = 1$ V)                                         | Full |       | 2          |       | V p-p   |

| Common-Mode Voltage                                                                   | Full | 0.5   | 0.9        | 1.3   | V       |

| Differential Input Resistance                                                         | Full |       | 5.2        |       | kΩ      |

| Differential Input Capacitance                                                        | Full |       | 3.5        |       | pF      |

| POWER SUPPLY                                                                          |      |       |            |       |         |

| AVDD                                                                                  | Full | 1.7   | 1.8        | 1.9   | V       |

| DRVDD                                                                                 | Full | 1.7   | 1.8        | 1.9   | V       |

| $I_{AVDD}$                                                                            | Full |       | 368        | 423   | mA      |

| $I_{DRVDD}$ (ANSI-644 Mode)                                                           | Full |       | 120        | 126   | mA      |

| $I_{DRVDD}$ (Reduced Range Mode)                                                      | 25°C |       | 90         |       | mA      |

| TOTAL POWER CONSUMPTION                                                               |      |       |            |       |         |

| Total Power Dissipation (Eight Channels, Including Output Drivers ANSI-644 Mode)      | Full |       | 879        | 988   | mW      |

| Total Power Dissipation (Eight Channels, Including Output Drivers Reduced Range Mode) | 25°C |       | 825        |       | mW      |

| Power-Down Dissipation                                                                | 25°C |       | 2          |       | mW      |

| Standby Dissipation <sup>2</sup>                                                      | 25°C |       | 485        |       | mW      |

<sup>1</sup> 完全な定義とこれらのテストの実施方法については [AN-835](#) アプリケーション・ノート「Understanding High Speed ADC Testing and Evaluation」を参照してください。

<sup>2</sup> SPI 経由で制御。

## AC 仕様

特に指定がない限り、AVDD = 1.8 V、DRVDD = 1.8 V、2 V p-p 差動入力、1.0 V 内蔵リファレンス電圧、A<sub>IN</sub> = -1.0 dBFS。

表 2.

| Parameter <sup>1</sup>                                              | Temp | Min  | Typ  | Max | Unit |

|---------------------------------------------------------------------|------|------|------|-----|------|

| SIGNAL-TO-NOISE RATIO (SNR)                                         |      |      |      |     |      |

| f <sub>IN</sub> = 9.7 MHz                                           | 25°C |      | 74.8 |     | dBFS |

| f <sub>IN</sub> = 19.7 MHz                                          | 25°C |      | 74.7 |     | dBFS |

| f <sub>IN</sub> = 69.5 MHz                                          | Full | 72.6 | 73.9 |     | dBFS |

| f <sub>IN</sub> = 139.5 MHz                                         | 25°C |      | 71.5 |     | dBFS |

| f <sub>IN</sub> = 201 MHz                                           | 25°C |      | 69.6 |     | dBFS |

| f <sub>IN</sub> = 301 MHz                                           | 25°C |      | 66.6 |     | dBFS |

| SIGNAL-TO-NOISE AND DISTORTION RATIO (SINAD)                        |      |      |      |     |      |

| f <sub>IN</sub> = 9.7 MHz                                           | 25°C |      | 74.7 |     | dBFS |

| f <sub>IN</sub> = 19.7 MHz                                          | 25°C |      | 74.7 |     | dBFS |

| f <sub>IN</sub> = 69.5 MHz                                          | Full | 72.3 | 73.8 |     | dBFS |

| f <sub>IN</sub> = 139.5 MHz                                         | 25°C |      | 71.4 |     | dBFS |

| f <sub>IN</sub> = 201 MHz                                           | 25°C |      | 69.3 |     | dBFS |

| f <sub>IN</sub> = 301 MHz                                           | 25°C |      | 65.8 |     | dBFS |

| EFFECTIVE NUMBER OF BITS (ENOB)                                     |      |      |      |     |      |

| f <sub>IN</sub> = 9.7 MHz                                           | 25°C |      | 12.1 |     | Bits |

| f <sub>IN</sub> = 19.7 MHz                                          | 25°C |      | 12.1 |     | Bits |

| f <sub>IN</sub> = 69.5 MHz                                          | Full | 11.7 | 12.0 |     | Bits |

| f <sub>IN</sub> = 139.5 MHz                                         | 25°C |      | 11.6 |     | Bits |

| f <sub>IN</sub> = 201 MHz                                           | 25°C |      | 11.2 |     | Bits |

| f <sub>IN</sub> = 301 MHz                                           | 25°C |      | 10.6 |     | Bits |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)                                  |      |      |      |     |      |

| f <sub>IN</sub> = 9.7 MHz                                           | 25°C |      | 94   |     | dBc  |

| f <sub>IN</sub> = 19.7 MHz                                          | 25°C |      | 94   |     | dBc  |

| f <sub>IN</sub> = 69.5 MHz                                          | Full | 81   | 90   |     | dBc  |

| f <sub>IN</sub> = 139.5 MHz                                         | 25°C |      | 87   |     | dBc  |

| f <sub>IN</sub> = 201 MHz                                           | 25°C |      | 83   |     | dBc  |

| f <sub>IN</sub> = 301 MHz                                           | 25°C |      | 73   |     | dBc  |

| WORST HARMONIC (SECOND OR THIRD)                                    |      |      |      |     |      |

| f <sub>IN</sub> = 9.7 MHz                                           | 25°C |      | -94  |     | dBc  |

| f <sub>IN</sub> = 19.7 MHz                                          | 25°C |      | -94  |     | dBc  |

| f <sub>IN</sub> = 69.5 MHz                                          | Full |      | -90  | -81 | dBc  |

| f <sub>IN</sub> = 139.5 MHz                                         | 25°C |      | -87  |     | dBc  |

| f <sub>IN</sub> = 201 MHz                                           | 25°C |      | -83  |     | dBc  |

| f <sub>IN</sub> = 301 MHz                                           | 25°C |      | -73  |     | dBc  |

| WORST OTHER (EXCLUDING SECOND OR THIRD)                             |      |      |      |     |      |

| f <sub>IN</sub> = 9.7 MHz                                           | 25°C |      | -98  |     | dBc  |

| f <sub>IN</sub> = 19.7 MHz                                          | 25°C |      | -94  |     | dBc  |

| f <sub>IN</sub> = 69.5 MHz                                          | Full |      | -96  | -84 | dBc  |

| f <sub>IN</sub> = 139.5 MHz                                         | 25°C |      | -90  |     | dBc  |

| f <sub>IN</sub> = 201 MHz                                           | 25°C |      | -85  |     | dBc  |

| f <sub>IN</sub> = 301 MHz                                           | 25°C |      | -75  |     | dBc  |

| TWO-TONE INTERMODULATION DISTORTION (IMD)—AIN1 AND AIN2 = -7.0 dBFS |      |      |      |     |      |

| f <sub>IN1</sub> = 70 MHz, f <sub>IN2</sub> = 72.5 MHz              | 25°C |      | 94   |     | dBc  |

| CROSSTALK, WORST ADJACENT CHANNEL <sup>2</sup>                      | 25°C |      | -83  |     | dB   |

| Crosstalk, Worst Adjacent Channel Overrange Condition <sup>3</sup>  | 25°C |      | -79  |     | dB   |

| ANALOG INPUT BANDWIDTH, FULL POWER                                  | 25°C |      | 650  |     | MHz  |

<sup>1</sup> 完全な定義とこれらのテストの実施方法についてはアプリケーション・ノート AN-835 「Understanding High Speed ADC Testing and Evaluation」を参照してください。

<sup>2</sup> クロストークは、片方のアナログ・チャンネルに-1.0 dBFS を入力し、隣接チャンネルは入力なしで、70 MHz で測定。

<sup>3</sup> オーバーレンジ状態は、入力がフルスケールより 3 dB 上にある状態と定義します。

## デジタル仕様

特に指定がない限り、AVDD = 1.8 V、DRVDD = 1.8 V、2 V p-p 差動入力、1.0 V 内蔵リファレンス電圧、 $A_{IN} = -1.0$  dBFS。

表 3.

| Parameter <sup>1</sup>                                           | Temp | Min       | Typ              | Max        | Unit  |

|------------------------------------------------------------------|------|-----------|------------------|------------|-------|

| CLOCK INPUTS (CLK+, CLK-)                                        |      |           | CMOS/LVDS/LVPECL |            |       |

| Logic Compliance                                                 | Full | 0.2       |                  | 3.6        | V p-p |

| Differential Input Voltage <sup>2</sup>                          | Full | GND - 0.2 |                  | AVDD + 0.2 | V     |

| Input Voltage Range                                              | Full |           | 0.9              |            | V     |

| Input Common-Mode Voltage                                        | 25°C |           | 15               |            | kΩ    |

| Input Resistance (Differential)                                  | 25°C |           | 4                |            | pF    |

| Input Capacitance                                                | 25°C |           |                  |            |       |

| LOGIC INPUTS (PDWN, SYNC, SCLK)                                  |      |           |                  |            |       |

| Logic 1 Voltage                                                  | Full | 1.2       |                  | AVDD + 0.2 | V     |

| Logic 0 Voltage                                                  | Full | 0         |                  | 0.8        | V     |

| Input Resistance                                                 | 25°C |           | 30               |            | kΩ    |

| Input Capacitance                                                | 25°C |           | 2                |            | pF    |

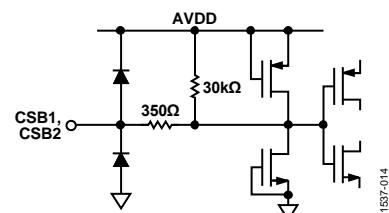

| LOGIC INPUTS (CSB1, CSB2)                                        |      |           |                  |            |       |

| Logic 1 Voltage                                                  | Full | 1.2       |                  | AVDD + 0.2 | V     |

| Logic 0 Voltage                                                  | Full | 0         |                  | 0.8        | V     |

| Input Resistance                                                 | 25°C |           | 26               |            | kΩ    |

| Input Capacitance                                                | 25°C |           | 2                |            | pF    |

| LOGIC INPUT (SDIO)                                               |      |           |                  |            |       |

| Logic 1 Voltage                                                  | Full | 1.2       |                  | AVDD + 0.2 | V     |

| Logic 0 Voltage                                                  | Full | 0         |                  | 0.8        | V     |

| Input Resistance                                                 | 25°C |           | 26               |            | kΩ    |

| Input Capacitance                                                | 25°C |           | 5                |            | pF    |

| LOGIC OUTPUT (SDIO) <sup>3</sup>                                 |      |           |                  |            |       |

| Logic 1 Voltage ( $I_{OH} = 800$ μA)                             | Full |           | 1.79             |            | V     |

| Logic 0 Voltage ( $I_{OL} = 50$ μA)                              | Full |           |                  | 0.05       | V     |

| DIGITAL OUTPUTS (D0±xx, D1±xx), ANSI-644                         |      |           | LVDS             |            |       |

| Logic Compliance                                                 | Full | 290       | 345              | 400        | mV    |

| Differential Output Voltage ( $V_{OD}$ )                         | Full | 1.15      | 1.25             | 1.35       | V     |

| Output Offset Voltage ( $V_{OS}$ )                               |      |           |                  |            |       |

| Output Coding (Default)                                          |      |           | Twos complement  |            |       |

| DIGITAL OUTPUTS (D0±xx, D1±xx), LOW POWER, REDUCED SIGNAL OPTION |      |           | LVDS             |            |       |

| Logic Compliance                                                 | Full | 160       | 200              | 230        | mV    |

| Differential Output Voltage ( $V_{OD}$ )                         | Full | 1.15      | 1.25             | 1.35       | V     |

| Output Offset Voltage ( $V_{OS}$ )                               |      |           |                  |            |       |

| Output Coding (Default)                                          |      |           | Twos complement  |            |       |

<sup>1</sup> 完全な定義とこれらのテストの実施方法についてはアプリケーション・ノート AN-835 「Understanding High Speed ADC Testing and Evaluation」を参照してください。

<sup>2</sup> LVDS と LVPECL に対してのみ規定。

<sup>3</sup> これは、同じ接続を共用する 13 本の SDIO/OLM ピンに対して規定。

## スイッティング仕様

特に指定がない限り、AVDD = 1.8 V、DRVDD = 1.8 V、2 V p-p 差動入力、1.0 V 内蔵リファレンス電圧、A<sub>IN</sub> = -1.0 dBFS。

表 4.

| Parameter <sup>1, 2</sup>                       | Symbol                                        | Temp | Min                             | Typ                                          | Max                             | Unit         |

|-------------------------------------------------|-----------------------------------------------|------|---------------------------------|----------------------------------------------|---------------------------------|--------------|

| CLOCK <sup>3</sup>                              |                                               |      |                                 |                                              |                                 |              |

| Input Clock Rate                                |                                               | Full | 10                              |                                              | 1000                            | MHz          |

| Conversion Rate                                 |                                               | Full | 10                              |                                              | 125                             | MSPS         |

| Clock Pulse Width High                          | t <sub>EH</sub>                               | Full |                                 | 4.00                                         |                                 | ns           |

| Clock Pulse Width Low                           | t <sub>EL</sub>                               | Full |                                 | 4.00                                         |                                 | ns           |

| OUTPUT PARAMETERS <sup>3</sup>                  |                                               |      |                                 |                                              |                                 |              |

| Propagation Delay                               | t <sub>PD</sub>                               | Full | 1.5                             | 2.3                                          | 3.1                             | ns           |

| Rise Time (20% to 80%)                          | t <sub>R</sub>                                | Full |                                 | 300                                          |                                 | ps           |

| Fall Time (20% to 80%)                          | t <sub>F</sub>                                | Full |                                 | 300                                          |                                 | ps           |

| FCO±1, FCO±2 Propagation Delay                  | t <sub>FCO</sub>                              | Full | 1.5                             | 2.3                                          | 3.1                             | ns           |

| DCO±1, DCO±2 Propagation Delay <sup>4</sup>     | t <sub>CPD</sub>                              | Full |                                 | t <sub>FCO</sub> + (t <sub>SAMPLE</sub> /16) |                                 | ns           |

| DCO±1, DCO±2 to Data Delay <sup>4</sup>         | t <sub>DATA</sub>                             | Full | (t <sub>SAMPLE</sub> /16) - 300 | (t <sub>SAMPLE</sub> /16)                    | (t <sub>SAMPLE</sub> /16) + 300 | ps           |

| DCO±1, DCO±2 to FCO±1, FCO±2 Delay <sup>4</sup> | t <sub>FRAME</sub>                            | Full | (t <sub>SAMPLE</sub> /16) - 300 | (t <sub>SAMPLE</sub> /16)                    | (t <sub>SAMPLE</sub> /16) + 300 | ps           |

| Lane Delay                                      | t <sub>LD</sub>                               |      |                                 | 90                                           |                                 | ps           |

| Data to Data Skew                               | t <sub>DATA-MAX</sub> - t <sub>DATA-MIN</sub> | Full |                                 | ±50                                          | ±200                            | ps           |

| Wake-Up Time (Standby)                          |                                               | 25°C |                                 | 250                                          |                                 | ns           |

| Wake-Up Time (Power-Down) <sup>5</sup>          |                                               | 25°C |                                 | 375                                          |                                 | μs           |

| Pipeline Latency                                |                                               | Full |                                 | 16                                           |                                 | Clock cycles |

| APERTURE                                        |                                               |      |                                 |                                              |                                 |              |

| Aperture Delay                                  | t <sub>A</sub>                                | 25°C |                                 | 1                                            |                                 | ns           |

| Aperture Uncertainty (Jitter)                   | t <sub>J</sub>                                | 25°C |                                 | 135                                          |                                 | fs rms       |

| Out-of-Range Recovery Time                      |                                               | 25°C |                                 | 1                                            |                                 | Clock cycles |

<sup>1</sup> 完全な定義とこれらのテストの実施方法についてはアプリケーション・ノート AN-835 「Understanding High Speed ADC Testing and Evaluation」を参照してください。

<sup>2</sup> 標準 FR-4 材上で測定。

<sup>3</sup> SPI を使って調整。変換レートは分周後のクロック・レートです。

<sup>4</sup> t<sub>SAMPLE</sub>/16 は 2 つの LVDS データ・レーン内のビット数に基づきます。t<sub>SAMPLE</sub> = 1/f<sub>SAMPLE</sub>。

<sup>5</sup> ウェイクアップ時間は、パワーダウン・モードから通常動作へ戻るために要する時間として定義されます。

## タイミング仕様

表 5.

| Parameter                | Description                                                                                                                    | Limit | Unit   |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| SYNC TIMING REQUIREMENTS |                                                                                                                                |       |        |

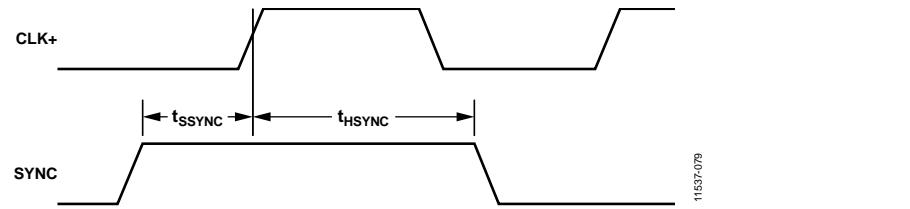

| $t_{SSYNC}$              | SYNC to rising edge of CLK+ setup time                                                                                         | 0.24  | ns typ |

| $t_{HSYNC}$              | SYNC to rising edge of CLK+ hold time                                                                                          | 0.40  | ns typ |

| SPI TIMING REQUIREMENTS  |                                                                                                                                |       |        |

| $t_{DS}$                 | Setup time between the data and the rising edge of SCLK                                                                        | 2     | ns min |

| $t_{DH}$                 | Hold time between the data and the rising edge of SCLK                                                                         | 2     | ns min |

| $t_{CLK}$                | Period of the SCLK                                                                                                             | 40    | ns min |

| $t_s$                    | Setup time between CSB1/CSB2 and SCLK                                                                                          | 2     | ns min |

| $t_h$                    | Hold time between CSB1/CSB2 and SCLK                                                                                           | 2     | ns min |

| $t_{HIGH}$               | SCLK pulse width high                                                                                                          | 10    | ns min |

| $t_{LOW}$                | SCLK pulse width low                                                                                                           | 10    | ns min |

| $t_{EN\_SDIO}$           | Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge (not shown in Figure 53) | 10    | ns min |

| $t_{DIS\_SDIO}$          | Time required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge (not shown in Figure 53)  | 10    | ns min |

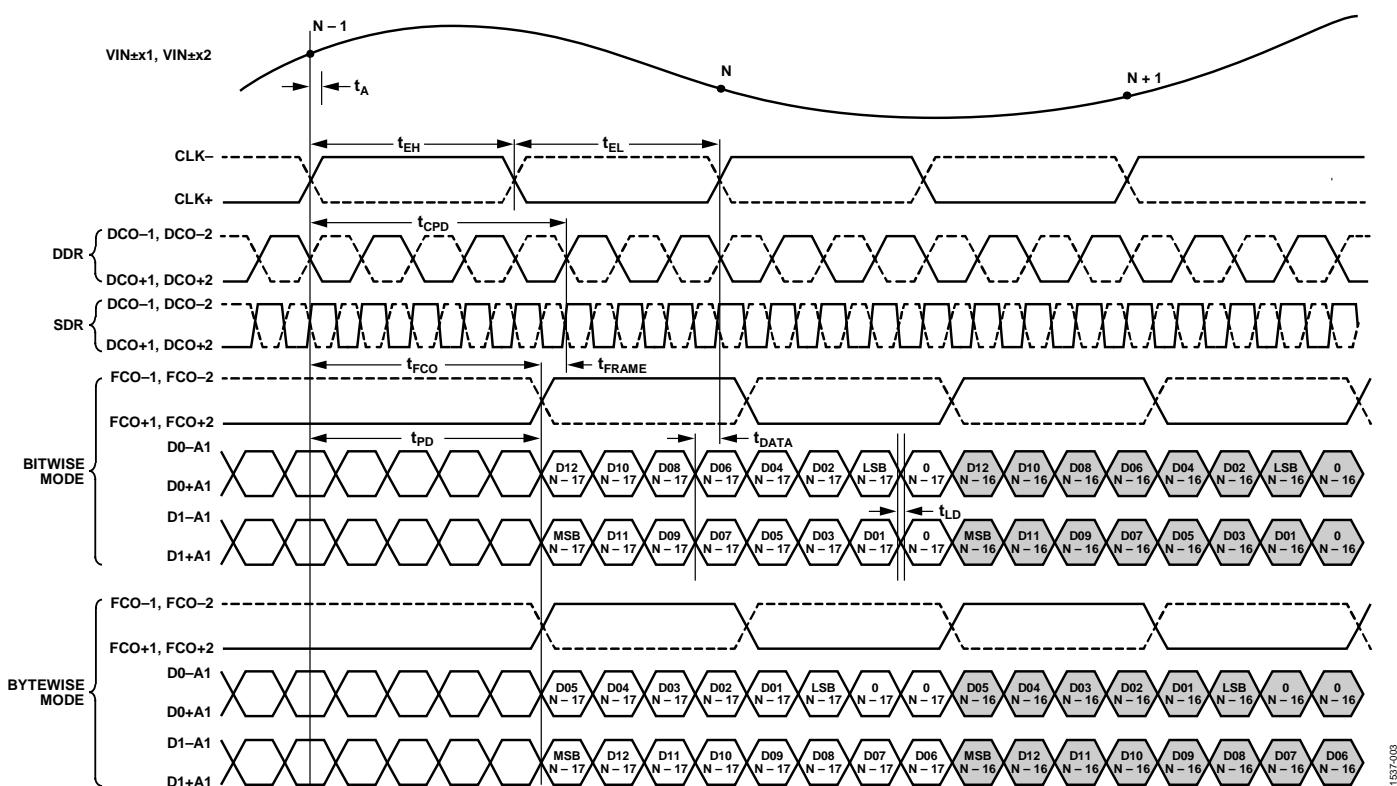

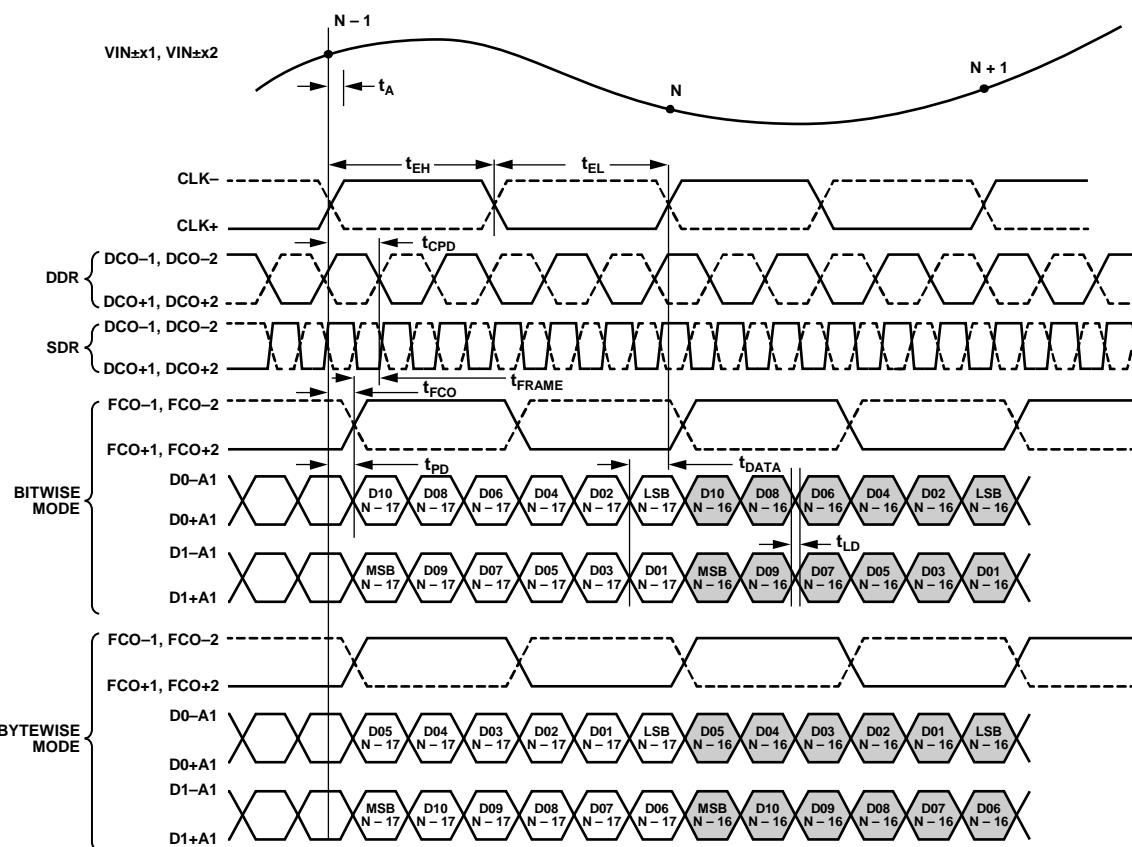

## タイミング図

出力モードの SPI レジスタ設定値については、メモリ・マップ・レジスタの説明のセクションと表 21 を参照してください。

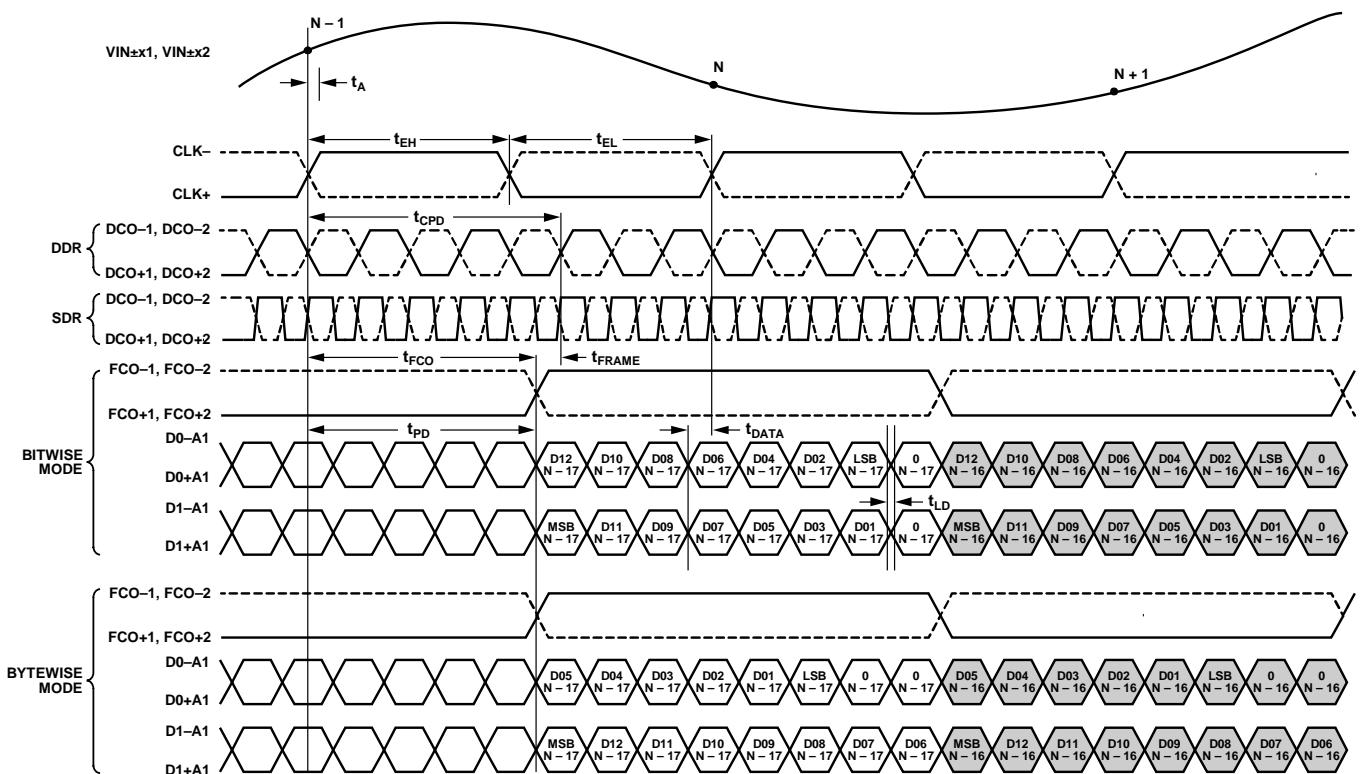

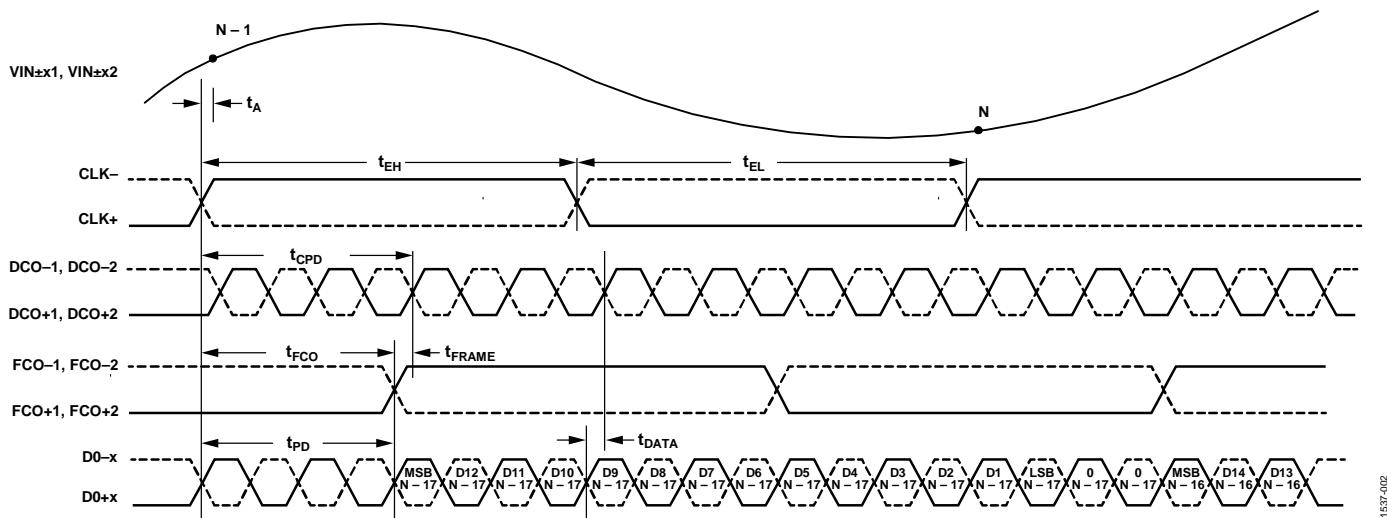

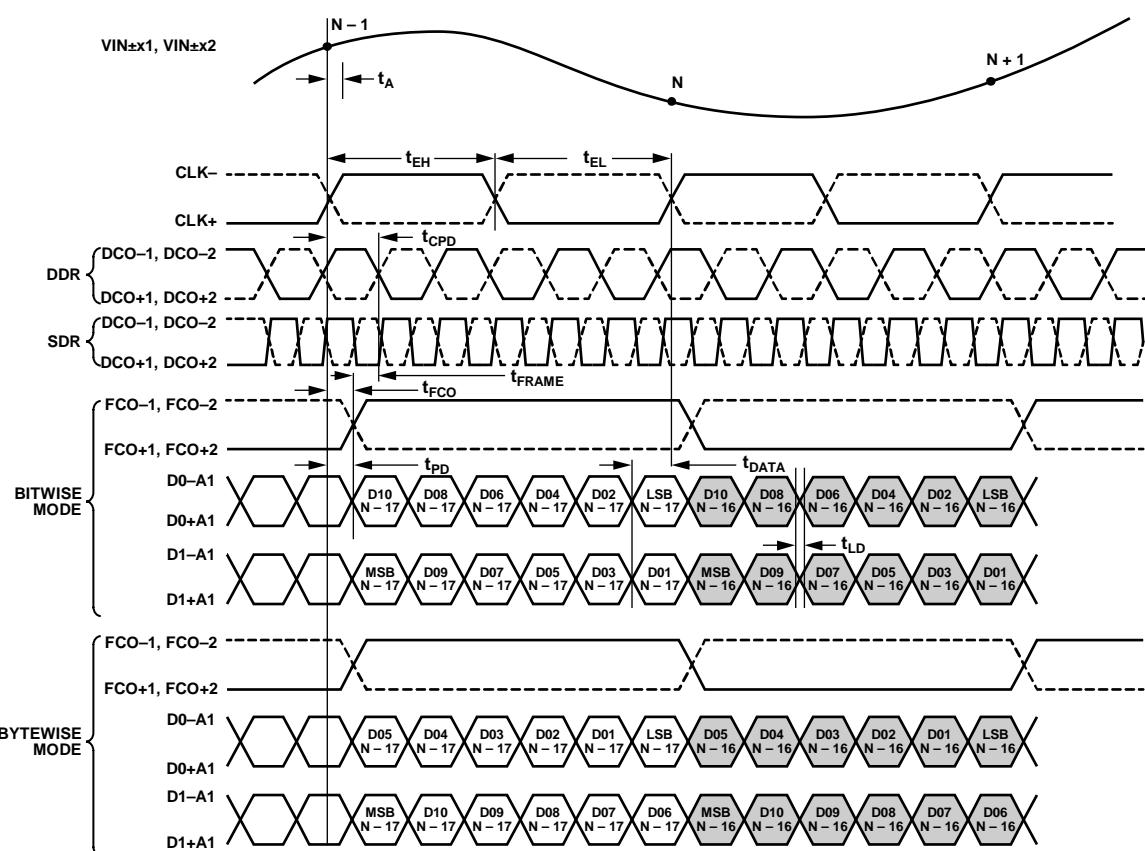

図 3.16 ビット DDR/SDR、2 レーン、1x フレーム・モード(デフォルト)

11537-003

図 4.12 ビット DDR/SDR、2 レーン、1x フレーム・モード

図 5.16 ビット DDR/SDR、2 レーン、2x フレーム・モード

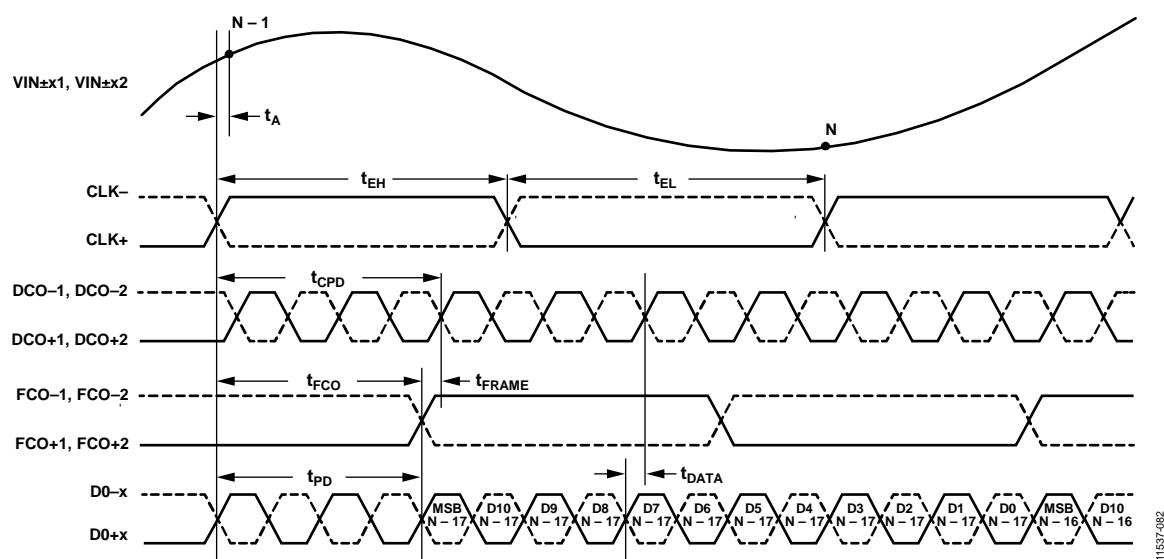

図 8. ワード幅 DDR、1 レーン、1x フレーム、12 ビット出力モード

図 9. SYNC の入力タイミング条件

## 絶対最大定格

表 6.

| Parameter                                                                                             | Rating           |

|-------------------------------------------------------------------------------------------------------|------------------|

| Electrical                                                                                            |                  |

| AVDD to GND                                                                                           | -0.3 V to +2.0 V |

| DRVDD to GND                                                                                          | -0.3 V to +2.0 V |

| Digital Outputs (D0 $\pm$ xx, D1 $\pm$ xx, DCO $\pm$ 1, DCO $\pm$ 2, FCO $\pm$ 1, FCO $\pm$ 2) to GND | -0.3 V to +2.0 V |

| CLK+, CLK- to GND                                                                                     | -0.3 V to +2.0 V |

| VIN $\pm$ x1, VIN $\pm$ x2 to GND                                                                     | -0.3 V to +2.0 V |

| SCLK/DTP, SDIO/OLM, CSB1, CSB2 to GND                                                                 | -0.3 V to +2.0 V |

| SYNC, PDWN to GND                                                                                     | -0.3 V to +2.0 V |

| RBIAS1, RBIAS2 to GND                                                                                 | -0.3 V to +2.0 V |

| VREF, VCM1, VCM2, SENSE to GND                                                                        | -0.3 V to +2.0 V |

| Environmental                                                                                         |                  |

| Operating Temperature Range (Ambient)                                                                 | -40°C to +85°C   |

| Maximum Junction Temperature                                                                          | 150°C            |

| Lead Temperature (Soldering, 10 sec)                                                                  | 300°C            |

| Storage Temperature Range (Ambient)                                                                   | -65°C to +150°C  |

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。この規定はストレス定格の規定のみを目的とするものであり、この仕様の動作のセクションに記載する規定値以上でのデバイス動作を定めたものではありません。デバイスを長時間絶対最大定格状態に置くとデバイスの信頼性に影響を与えます。

### 熱特性

$\theta_{JA}$  (typ)は、厚いグラウンド・プレーンを持つ4層PCBに対して規定します。空気流があると放熱効果が良くなるため、 $\theta_{JA}$ が小さくなります。また、メタル・パターン、スルー・ホール、グラウンド・プレーン、電源プレーンとパッケージ・ピンが直接接触する場合も、これらのメタルによっても $\theta_{JA}$ が小さくなります。

表 7. 热抵抗 (シミュレーション結果)

| Package Type                    | Airflow Velocity (m/sec) | $\theta_{JA}$ <sup>1,2</sup> | $\Psi_{JT}$ <sup>1,2</sup> | Unit |

|---------------------------------|--------------------------|------------------------------|----------------------------|------|

| 144-Ball, 10 mm × 10 mm CSP-BGA | 0                        | 30.2                         | 0.13                       | °C/W |

<sup>1</sup> JEDEC 51-7 と JEDEC 51-5 2S2P テスト・ボードに準拠。

<sup>2</sup> JEDEC JESD51-2 (自然空冷)または JEDEC JESD51-6 (強制空冷)に準拠。

### ESD の注意

ESD (静電放電) の影響を受けやすいデバイスです。電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術であるESD保護回路を内蔵していますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

## ピン配置およびピン機能説明

| AD9681<br>TOP VIEW<br>(Not to Scale) |        |        |       |        |       |        |       |        |        |       |          |          |

|--------------------------------------|--------|--------|-------|--------|-------|--------|-------|--------|--------|-------|----------|----------|

|                                      | 1      | 2      | 3     | 4      | 5     | 6      | 7     | 8      | 9      | 10    | 11       | 12       |

| A                                    | VIN-D1 | VIN+D1 | NC    | VIN-C2 | NC    | VIN-C1 | NC    | NC     | VIN-B2 | NC    | VIN+B1   | VIN-B1   |

| B                                    | NC     | NC     | NC    | VIN+C2 | NC    | VIN+C1 | NC    | NC     | VIN+B2 | NC    | NC       | NC       |

| C                                    | VIN-D2 | VIN+D2 | SYNC  | VCM1   | VCM2  | VREF   | SENSE | RBIAS1 | RBIAS2 | GND   | VIN+A2   | VIN-A2   |

| D                                    | GND    | GND    | GND   | AVDD   | AVDD  | AVDD   | AVDD  | AVDD   | AVDD   | GND   | NC       | NC       |

| E                                    | CLK-   | CLK+   | GND   | AVDD   | GND   | GND    | GND   | GND    | AVDD   | CSB1  | VIN+A1   | VIN-A1   |

| F                                    | GND    | GND    | GND   | AVDD   | GND   | GND    | GND   | GND    | AVDD   | CSB2  | SDIO/OLM | SCLK/DTP |

| G                                    | D1-D2  | D1+D2  | GND   | AVDD   | GND   | GND    | GND   | GND    | AVDD   | PDWN  | D0+A1    | D0-A1    |

| H                                    | D0-D2  | D0+D2  | GND   | AVDD   | GND   | GND    | GND   | GND    | AVDD   | GND   | D1+A1    | D1-A1    |

| J                                    | D1-D1  | D1+D1  | GND   | AVDD   | AVDD  | AVDD   | AVDD  | AVDD   | AVDD   | GND   | D0+A2    | D0-A2    |

| K                                    | D0-D1  | D0+D1  | DRVDD | DRVDD  | GND   | GND    | GND   | GND    | DRVDD  | DRVDD | D1+A2    | D1-A2    |

| L                                    | D1-C2  | D1+C2  | D1+C1 | D0+C1  | FCO+1 | DCO+1  | DCO+2 | FCO+2  | D1+B2  | D0+B2 | D0+B1    | D0-B1    |

| M                                    | D0-C2  | D0+C2  | D1-C1 | D0-C1  | FCO-1 | DCO-1  | DCO-2 | FCO-2  | D1-B2  | D0-B2 | D1+B1    | D1-B1    |

## NOTES

1. NC = NO CONNECT. THESE PINS ARE NOT ELECTRICALLY CONNECTED TO THE DEVICE. HOWEVER, CONNECT THESE PINS TO BOARD GROUND WHERE POSSIBLE.

11537-009

図 10. ピン配置

表 8. ピン機能の説明

| ピン番号                                                                                      | 記号                 | 説明                                                       |

|-------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------|

| A3、A5、A7、A8、<br>A10、B1～B3、B5、<br>B7、B8、B10～B12、<br>D11、D12                                | NC                 | 未接続。これらのピンは電気的にデバイスに接続されていませんが、可能な場合、ボードのグラウンドへ接続してください。 |

| C10、D1～D3、D10、<br>E3、E5～E8、F1～<br>F3、F5～F8、G3、G5<br>～G8、H3、H5～H8、<br>H10、J3、J10、K5～<br>K8 | GND                | グラウンド。                                                   |

| D4～D9、E4、E9、<br>F4、F9、G4、G9、<br>H4、H9、J4～J9                                               | AVDD               | 1.8 V のアナログ電源。                                           |

| K3、K4、K9、K10<br>E1、E2                                                                     | DRVDD<br>CLK-、CLK+ | 1.8 V デジタル出力ドライバ電源。<br>入力クロック—相補、入力クロック—真。               |

| ピン番号            | 記号                          | 説明                                                                                                                                                          |

|-----------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G12、G11         | D0-A1、D0+A1                 | レーン0 バンク1 デジタル出力—相補、レーン0 バンク1 デジタル出力—真。                                                                                                                     |

| H12、H11         | D1-A1、D1+A1                 | レーン1 バンク1 デジタル出力—相補、レーン1 バンク1 デジタル出力—真。                                                                                                                     |

| J12、J11         | D0-A2、D0+A2                 | レーン0 バンク2 デジタル出力—相補、レーン0 バンク2 デジタル出力—真。                                                                                                                     |

| K12、K11         | D1-A2、D1+A2                 | レーン1 バンク2 デジタル出力—相補、レーン1 バンク2 デジタル出力—真。                                                                                                                     |

| L12、L11         | D0-B1、D0+B1                 | レーン0 バンク1 デジタル出力—相補、レーン0 バンク1 デジタル出力—真。                                                                                                                     |

| M12、M11         | D1-B1、D1+B1                 | レーン1 バンク1 デジタル出力—相補、レーン1 バンク1 デジタル出力—真。                                                                                                                     |

| M10、L10         | D0-B2、D0+B2                 | レーン0 バンク2 デジタル出力—相補、レーン0 バンク2 デジタル出力—真。                                                                                                                     |

| M9、L9           | D1-B2、D1+B2                 | レーン1 バンク2 デジタル出力—相補、レーン1 バンク2 デジタル出力—真。                                                                                                                     |

| M4、L4           | D0-C1、D0+C1                 | レーン0 バンク1 デジタル出力—相補、レーン0 バンク1 デジタル出力—真。                                                                                                                     |

| M3、L3           | D1-C1、D1+C1                 | レーン1 バンク1 デジタル出力—相補、レーン1 バンク1 デジタル出力—真。                                                                                                                     |

| M1、M2           | D0-C2、D0+C2                 | レーン0 バンク2 デジタル出力—相補、レーン0 バンク2 デジタル出力—真。                                                                                                                     |

| L1、L2           | D1-C2、D1+C2                 | レーン1 バンク2 デジタル出力—相補、レーン1 バンク2 デジタル出力—真。                                                                                                                     |

| K1、K2           | D0-D1、D0+D1                 | レーン0 バンク1 デジタル出力—相補、レーン0 バンク1 デジタル出力—真。                                                                                                                     |

| J1、J2           | D1-D1、D1+D1                 | レーン1 バンク1 デジタル出力—相補、レーン1 バンク1 デジタル出力—真。                                                                                                                     |

| H1、H2           | D0-D2、D0+D2                 | レーン0 バンク2 デジタル出力—相補、レーン0 バンク2 デジタル出力—真。                                                                                                                     |

| G1、G2           | D1-D2、D1+D2                 | レーン1 バンク2 デジタル出力—相補、レーン1 バンク2 デジタル出力—真。                                                                                                                     |

| M6、L6;<br>M7、L7 | DCO-1、DCO+1;<br>DCO-2、DCO+2 | データ・クロック・デジタル出力—相補、データ・クロック・デジタル出力—真。DCO $\pm$ 1はD0 $\pm$ x1/D1 $\pm$ x1 デジタル出力データのキャプチャに使用されます。DCO $\pm$ 2はD0 $\pm$ x2/D1 $\pm$ x2 デジタル出力データのキャプチャに使用されます。 |

| M5、L5;<br>M8、L8 | FCO-1、FCO+1;<br>FCO-2、FCO+2 | フレーム・クロック・デジタル出力—相補、フレーム・クロック・デジタル出力—真。FCO $\pm$ 1はD0 $\pm$ x1/D1 $\pm$ x1 デジタル出力データをフレーム化し、FCO $\pm$ 2はD0 $\pm$ x2/D1 $\pm$ x2 デジタル出力データをフレーム化します。         |

| F12             | SCLK/DTP                    | シリアル・クロック/デジタル・テスト・パターン。                                                                                                                                    |

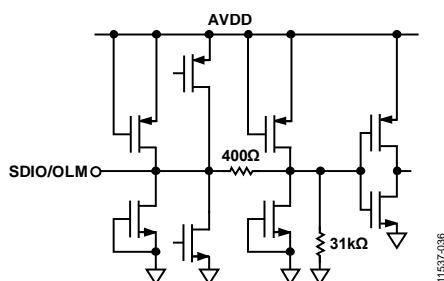

| F11             | SDIO/OLM                    | シリアル・データ入力/出力/出力レーン・モード。                                                                                                                                    |

| E10、F10         | CSB1、CSB2                   | チップ・セレクト・バー。CSB1はバンク1の4チャンネルに対してSPIをイネーブル/ディスエーブルし、CSB2はバンク2の4チャンネルに対してSPIをイネーブル/ディスエーブルします。                                                                |

| G10             | PDWN                        | パワーダウン。                                                                                                                                                     |

| E12、E11         | VIN-A1、VIN+A1               | アナログ入力—相補、アナログ入力—真。                                                                                                                                         |

| C12、C11         | VIN-A2、VIN+A2               | アナログ入力—相補、アナログ入力—真。                                                                                                                                         |

| A12、A11         | VIN-B1、VIN+B1               | アナログ入力—相補、アナログ入力—真。                                                                                                                                         |

| A9、B9           | VIN-B2、VIN+B2               | アナログ入力—相補、アナログ入力—真。                                                                                                                                         |

| A6、B6           | VIN-C1、VIN+C1               | アナログ入力—相補、アナログ入力—真。                                                                                                                                         |

| A4、B4           | VIN-C2、VIN+C2               | アナログ入力—相補、アナログ入力—真。                                                                                                                                         |

| A1、A2           | VIN-D1、VIN+D1               | アナログ入力—相補、アナログ入力—真。                                                                                                                                         |

| C1、C2           | VIN-D2、VIN+D2               | アナログ入力—相補、アナログ入力—真。                                                                                                                                         |

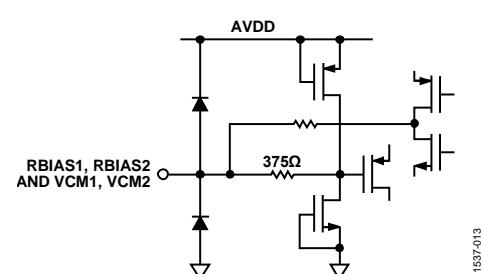

| C8、C9           | RBIAS1、RBIAS2               | アナログ電流バイアスの設定。各 RBIAS $x$ ピンとグラウンドの間に10 k $\Omega$ の抵抗(1%許容誤差)を接続してください。                                                                                    |

| C7              | SENSE                       | リファレンス電圧モード選択。                                                                                                                                              |

| C6              | VREF                        | リファレンス電圧入力/出力。                                                                                                                                              |

| C4、C5           | VCM1、VCM2                   | 電源中央値のアナログ出力電圧。ADC外部でアナログ入力の同相モードを設定します(図38と図39参照)。                                                                                                         |

| C3              | SYNC                        | デジタル入力。クロック分周器への同期入力。このピンは、内部で30 k $\Omega$ の抵抗でグランドにプルダウンされています。                                                                                           |

## 代表的な性能特性

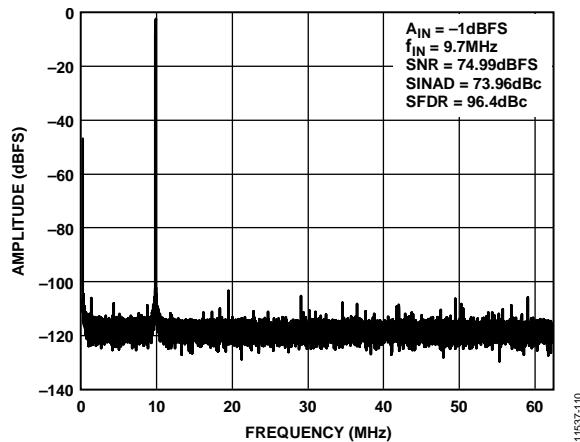

図 11. シングル・トーン 32k FFT

$f_{IN} = 9.7\text{ MHz}$ ;  $f_{SAMPLE} = 125\text{ MSPS}$

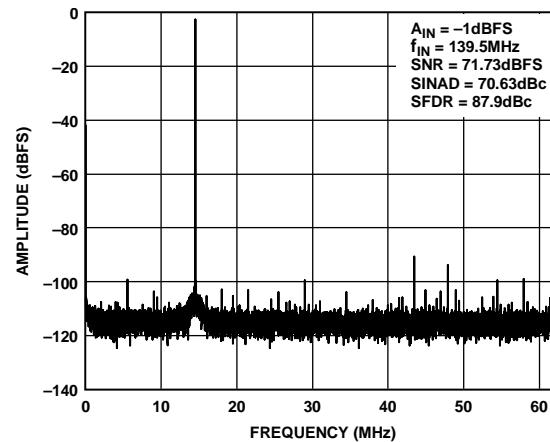

図 14. シングル・トーン 32k FFT

$f_{IN} = 139.5\text{ MHz}$ ;  $f_{SAMPLE} = 125\text{ MSPS}$

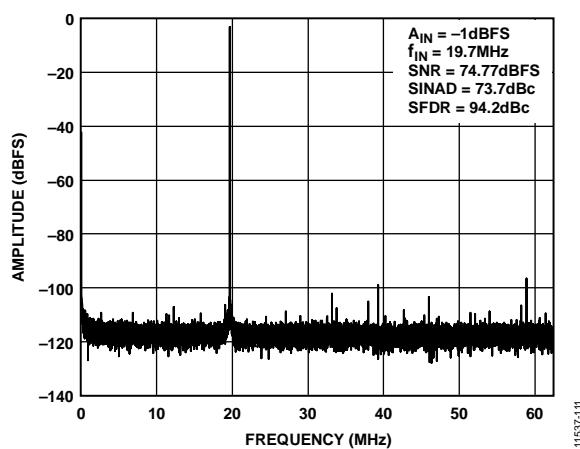

図 12. シングル・トーン 32k FFT

$f_{IN} = 19.7\text{ MHz}$ ;  $f_{SAMPLE} = 125\text{ MSPS}$

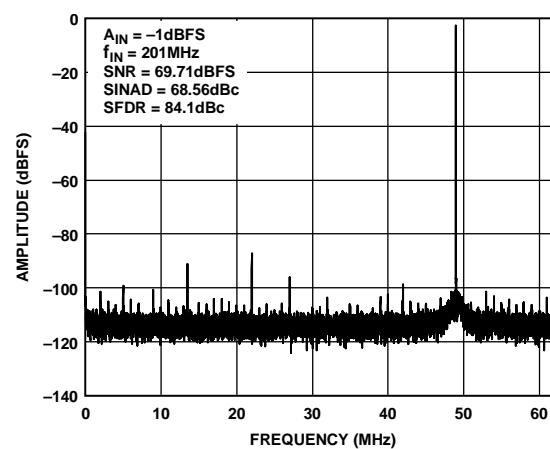

図 15. シングル・トーン 32k FFT

$f_{IN} = 201\text{ MHz}$ ;  $f_{SAMPLE} = 125\text{ MSPS}$

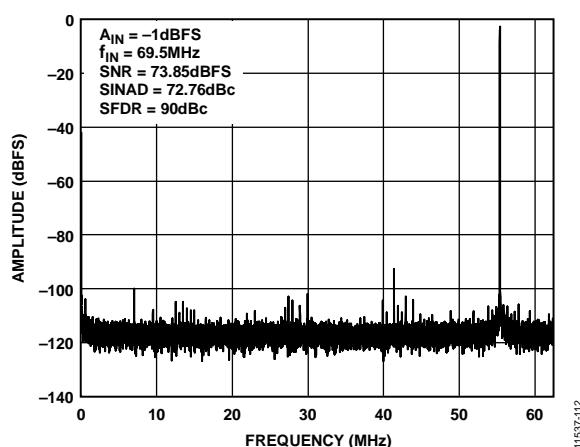

図 13. シングル・トーン 32k FFT

$f_{IN} = 69.5\text{ MHz}$ ;  $f_{SAMPLE} = 125\text{ MSPS}$

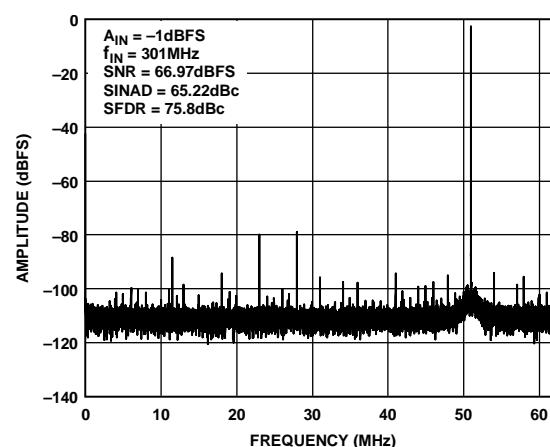

図 16. シングル・トーン 32k FFT

$f_{IN} = 301\text{ MHz}$ ;  $f_{SAMPLE} = 125\text{ MSPS}$

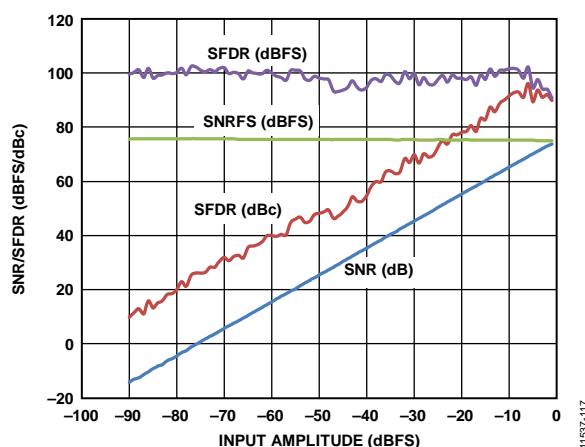

図 17. 入力振幅 ( $A_{IN}$ ) 対 SNR/SFDR

$f_{IN} = 9.7$  MHz;  $f_{SAMPLE} = 125$  MSPS

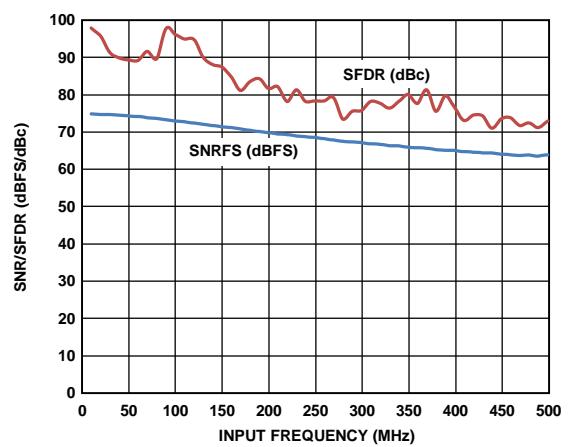

図 20.  $f_{IN}$  対 SNR/SFDR

$f_{SAMPLE} = 125$  MSPS

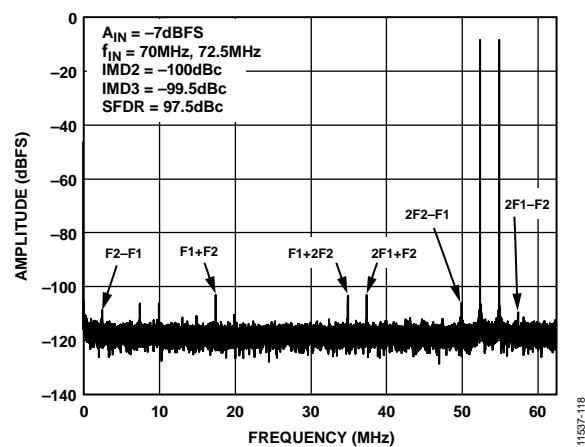

図 18.2 トーン 32k FFT

$f_{IN1} = 70.5$  MHz,  $f_{IN2} = 72.5$  MHz;  $f_{SAMPLE} = 125$  MSPS

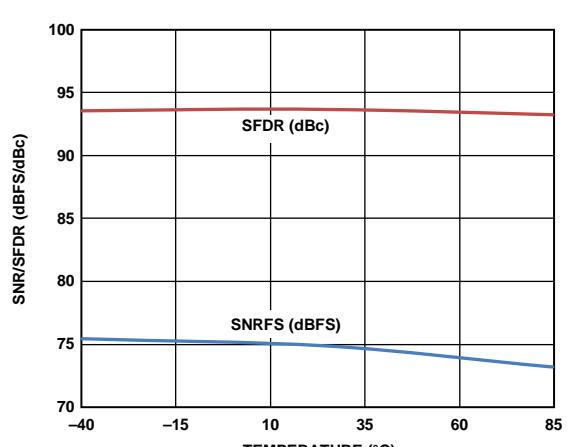

図 21. SNR/SFDR の温度特性

$f_{IN} = 9.7$  MHz,  $f_{SAMPLE} = 125$  MSPS

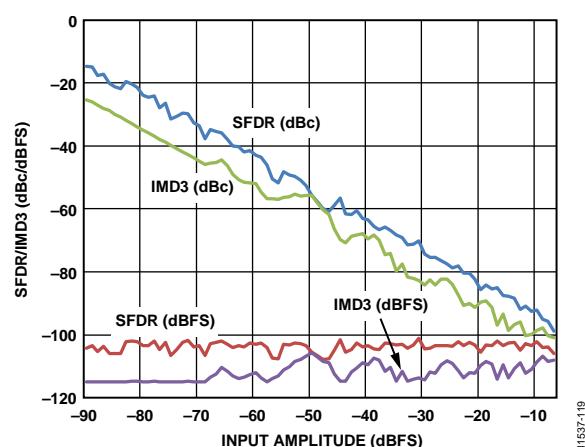

図 19. 入力振幅 ( $A_{IN}$ ) 対 2 トーン SFDR/IMD3

$f_{IN1} = 70.0$  MHz,  $f_{IN2} = 72.5$  MHz;  $f_{SAMPLE} = 125$  MSPS

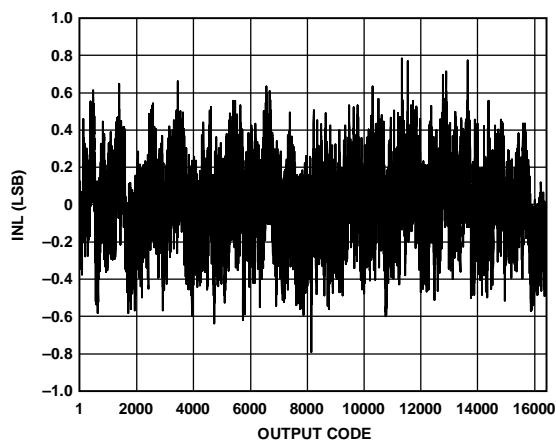

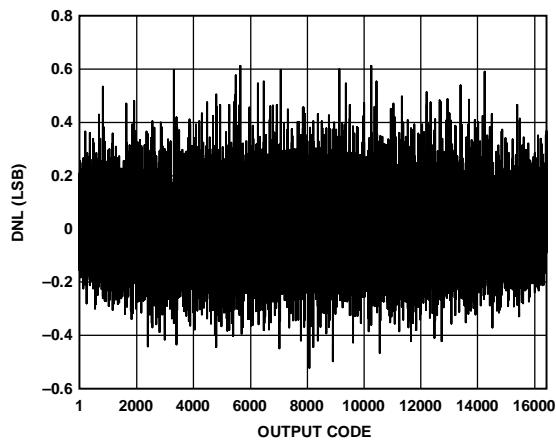

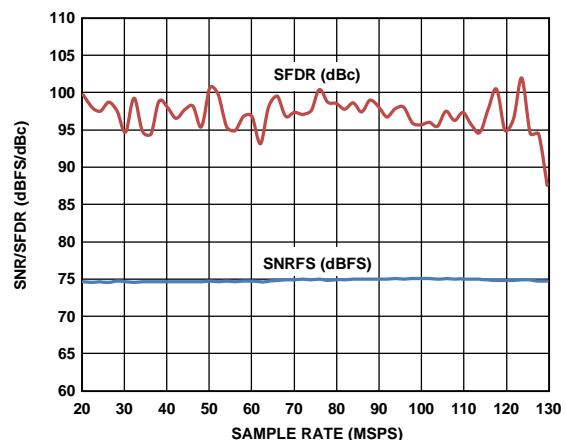

図 22.INL、 $f_{IN} = 9.7$  MHz、 $f_{SAMPLE} = 125$  MSPS図 23.DNL、 $f_{IN} = 9.7$  MHz、 $f_{SAMPLE} = 125$  MSPS図 25.サンプル・レート対 SNR/SFDR

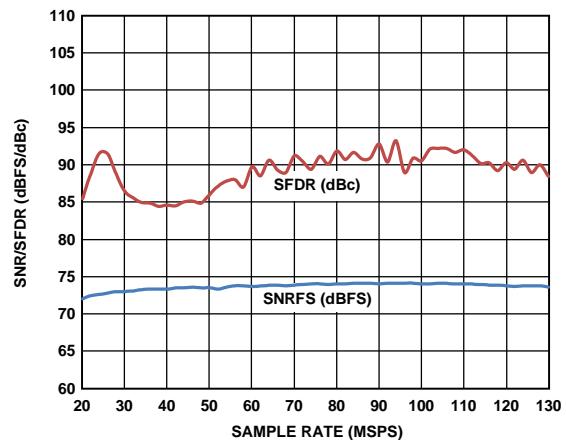

$f_{IN} = 9.7$  MHz、 $f_{SAMPLE} = 125$  MSPS図 26.サンプル・レート対 SNR/SFDR

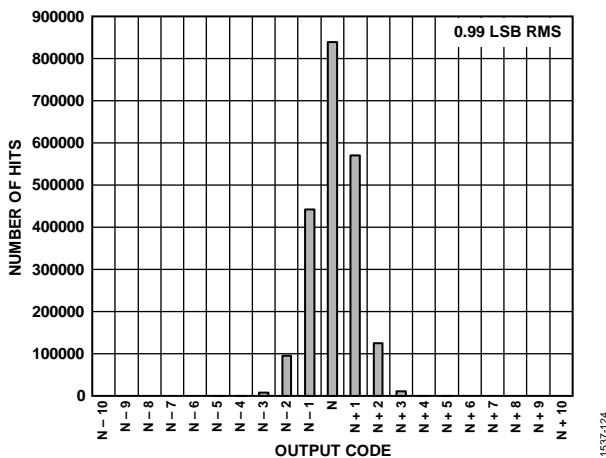

$f_{IN} = 70$  MHz、 $f_{SAMPLE} = 125$  MSPS図 24.入力換算ノイズ・ヒストグラム

$f_{SAMPLE} = 125$  MSPS

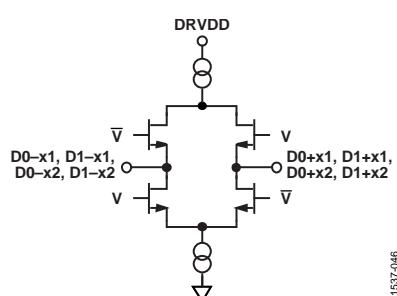

## 等価回路

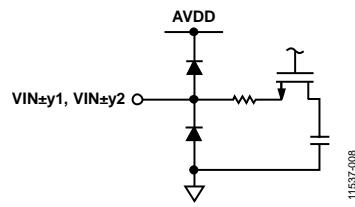

図 27. アナログ入力の等価回路

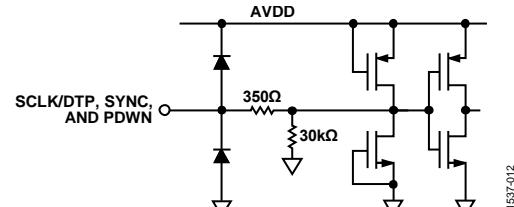

図 31. SCLK/DTP、SYNC、PDWN 入力の等価回路

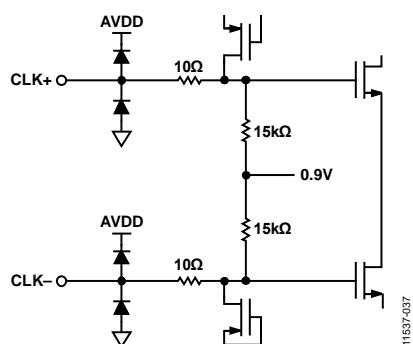

図 28. クロック入力の等価回路

図 32. Rbias<sub>x</sub> と Vcm<sub>x</sub> の等価回路

図 29. SDIO/OLM 入力の等価回路

図 33. CSB<sub>x</sub> 入力の等価回路

図 30. デジタル出力の等価回路

図 34. VREF の等価回路

## 動作原理

AD9681 は、マルチステージのパイプライン化 ADC です。各ステージは、前ステージのフラッシュ誤差を訂正するように十分オーバーラップするようになっています。各ステージからの量子化された出力は、デジタル補正ロジックで結合されて最終的に 14 ビットになります。シリアルライザは、この変換したデータを 16 ビット出力で送信します。パイプライン化されたアーキテクチャにより、新しい入力サンプルに対して最初のステージが動作すると同時に、残りのステージは先行しているサンプルに對して動作することができます。サンプリングはクロックの立ち上がりエッジで行われます。

最終ステージ以外のパイプラインの各ステージは、スイッチド・キャパシタ DAC に接続された低分解能のフラッシュ ADC とステージ間残差アンプ(例えば乗算 D/A コンバータ(MDAC))により構成されています。この残差アンプは、再生された DAC 出力とパイプライン内の次のステージに対するフラッシュ入力の差を増幅します。各ステージ内で冗長な 1 ビットを使って、フラッシュ誤差のデジタル補正を可能にしています。最終ステージはフラッシュ ADC のみで構成されています。

出力ステージのブロックで、データの整列、誤差補正、出力バッファへの出力が行われます。その後、データはシリアル化され、フレーム・クロックとデータ・クロックに整列されます。

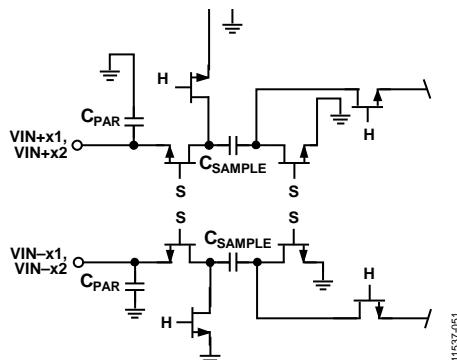

## アナログ入力に対する考慮

AD9681 のアナログ入力は、差動入力信号処理用にデザインされた差動のスイッチド・キャパシタ回路になっています。この回路は広い同相モード範囲をサポートすると同時に、優れた性能を維持することができます。電源電圧の 1/2 での入力同相モード電圧は信号依存誤差を最小化するため、最適性能を提供します。

図 35.スイッチド・キャパシタ入力回路

クロック信号により、入力回路がサンプル・モードとホールド・モードの間で交互に切り替えられます(図 35 参照)。入力回路がサンプル・モードになったとき、信号源はサンプル・コンデンサを充電して、クロック・サイクルの 1/2 以内に安定する必要があります。各入力に小さい抵抗を直列に接続すると、駆動源側の出力ステージから発生するピーク過渡電流を減少させることに役立ちます。

さらに、Q の小さいインダクタまたはフェライト・ビーズを各入力に接続して、アナログ入力の大きな差動容量を小さくすることにより、ADC の最大帯域幅を実現することができます。このような低 Q インダクタまたはフェライト・ビーズの使用は、コンバータのフロントエンドを高い IF 周波数で駆動する際に必要となります。差動コンデンサまたは 2 個のシングルエンド・コンデンサを入力に接続して、受動整合回路を設けることができます。この構成により入力に最終的にローパス・フィルタが形成されて、不要な広帯域幅ノイズが制限されます。詳細については、[AN-742 アプリケーション・ノート「Frequency Domain Response of Switched-Capacitor ADCs」](#)、[AN-827 アプリケーション・ノート「A Resonant Approach to Interfacing Amplifiers to Switched-Capacitor ADCs」](#)、アナログ・ダイアログ資料「[Transformer-Coupled Front-End for Wideband A/D Converters](#)」(Volume 39, April 2005)を参照してください。一般に、正確な値はアプリケーションによって変わります。

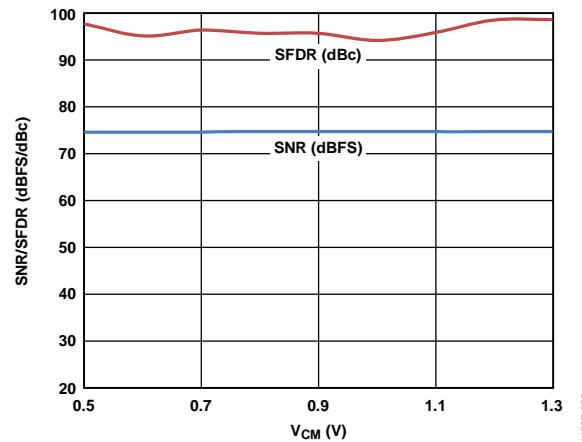

## 入力同相モード

AD9681 のアナログ入力は内部で DC バイアスされていません。そのため、AC 結合のアプリケーションでは、ユーザーが外部からこのバイアスを与える必要があります。最適性能を得るために  $V_{CM} = AVDD/2$  となるようにデバイスを設定することが推奨されますが、デバイスは広い範囲で適切な性能で機能します(図 36 参照)。

AD9681 は同相モード・リファレンス電圧が内蔵されており、 $V_{CMX}$  ピンに出力されています。 $V_{CMX}$  ピンは、0.1  $\mu$ F のコンデンサでグラウンドにデカップリングする必要があります(アプリケーション情報のセクション参照)。

最大 SNR 性能は、ADC を差動構成で最大スパンに設定したときに得られます。AD9681 の場合、最大有効入力振幅は 2 V p-p です。

図 36.同相モード電圧対 SNR/SFDR

$f_{IN} = 9.7$  MHz,  $f_{SAMPLE} = 125$  MSPS

## 差動入力構成

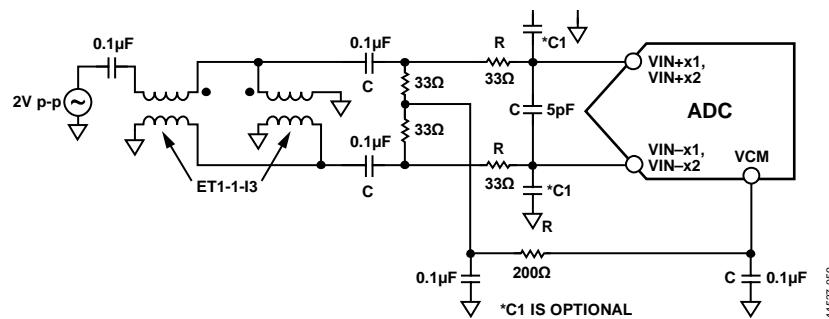

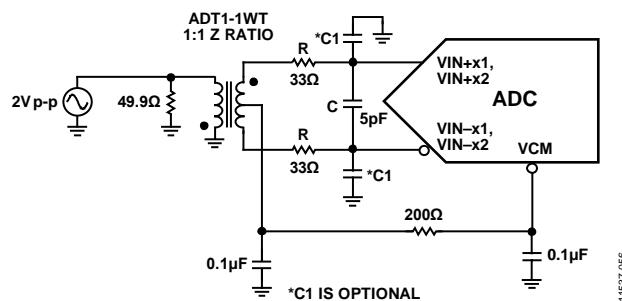

AD9681 を能動的または受動的に駆動する方法は複数ありますが、最適性能は、アナログ入力を差動で駆動したときに得られます。差動ダブル・バラン構成で AD9681 を駆動すると、優れた性能とベースバンド・アプリケーションで ADC に対する柔軟なインターフェースが実現できます(図 38 参照)。同様に、差動トランス結合も優れた性能を提供します(図 39 参照)。AD9681 の真の性能を引き出すためには、大部分のアンプのノイズ性能は不十分であるため、可能な場合にはこれらの能動構成の使用が推奨されます。

どの構成でも、シャント・コンデンサ C の値は入力周波数に依存するため、小さくするか、削除する必要があります。

AD9681入力をシングルエンドで駆動しないことを推奨します。

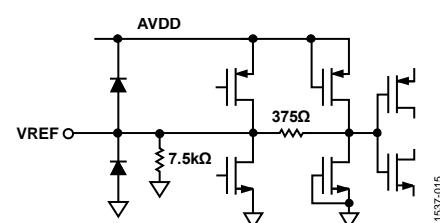

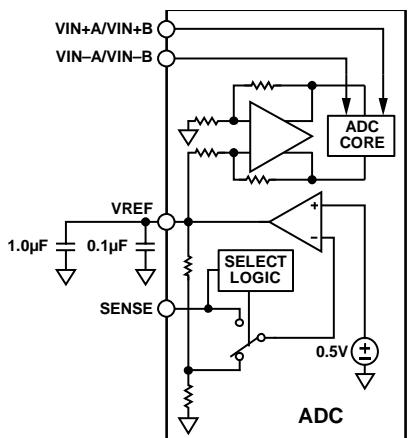

## リファレンス電圧

AD9681には、安定かつ正確な 1.0 V のリファレンス電圧が内蔵されています。VREF は 1.0 V の内蔵リファレンス出力として、または 1.0 V の外付けリファレンス電圧の入力として使うことができます。種々のリファレンス・モードを内蔵リファレンス電圧の接続のセクションと外付けリファレンス電圧による動作のセクションにまとめます。VREF ピンは、ESR の小さい 1.0  $\mu$ F のコンデンサと ESR の小さい 0.1  $\mu$ F のセラミック・コンデンサとの並列接続により外部でグラウンドへバイパスしてください。

## 内蔵リファレンス電圧の接続

AD9681 内部のコンパレータが SENSE ピンの電位を検出して、リファレンスを表 9 に示す 2 つの状態のいずれかに設定します。SENSE をグラウンドに接続すると、リファレンス電圧アンプ・スイッチは内部抵抗分圧器に接続され(図 37)、VREF が 1.0 V に設定されます。

表 9.リファレンス構成の一覧

| Selected Mode            | SENSE Voltage (V) | Resulting VREF (V)               | Resulting Differential Span (V p-p) |

|--------------------------|-------------------|----------------------------------|-------------------------------------|

| Fixed Internal Reference | GND to 0.2        | 1.0 internal                     | 2.0                                 |

| Fixed External Reference | AVDD              | 1.0 applied to external VREF pin | 2.0                                 |

図 37.内蔵リファレンス電圧の構成

図 38.ベースバンド・アプリケーション向けの差動ダブル・バランス入力構成

図 39.ベースバンド・アプリケーション向けの差動トランス結合構成

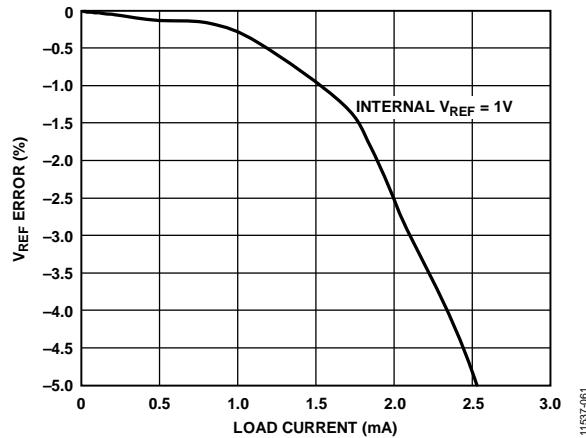

ゲイン・マッチングを改善するために、AD9681 の内蔵リファレンス電圧を使って複数のコンバータを駆動する場合、他のコンバータによるリファレンス電圧への負荷を考慮する必要があります。図 40 に内蔵リファレンス電圧が負荷から受ける影響を示します。

図 40. 負荷電流対  $V_{REF}$  誤差

#### 外付けリファレンス電圧による動作

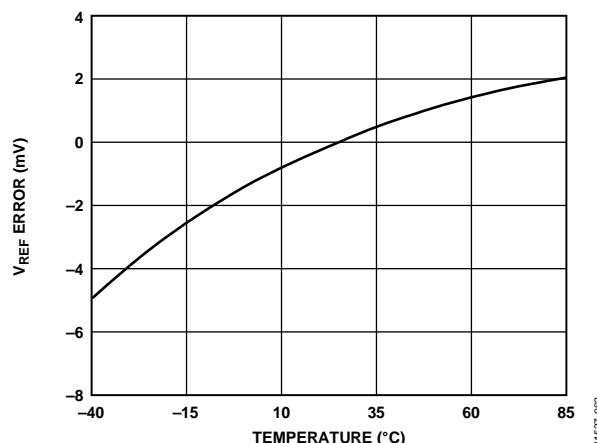

ADC のゲイン精度を向上させる場合または温度ドリフト特性を改善する場合、外付けリファレンス電圧の使用が必要となることがあります。図 41 に、1.0 V モードについて、代表的な内蔵リファレンスのドリフト特性を示します。

図 41. 代表的な  $V_{REF}$  ドリフト

SENSE ピンを AVDD に接続すると、内蔵リファレンス電圧がディスエーブルされて、外付けリファレンス電圧の使用が可能になります。内蔵リファレンス・バッファに対して、等価 7.5 k $\Omega$  を持つ外付けリファレンスが負荷になります(図 34 参照)。この内蔵バッファは、ADC コアに対して正側と負側のフルスケール・リファレンスを発生します。したがって、外付けリファレンス電圧は最大 1.0 V に制限する必要があります。

SENSE ピンはフローティングのままにしないでください。

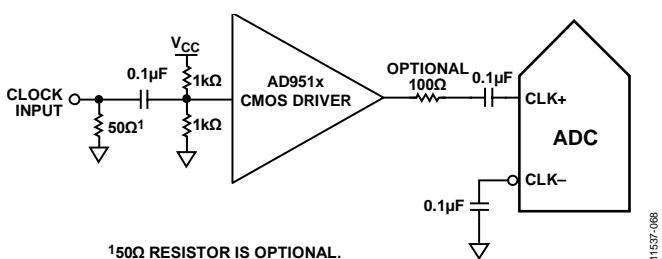

#### クロック入力の考慮事項

最適性能を得るために、AD9681 のサンプル・クロック入力 CLK+ と CLK- を差動信号で駆動する必要があります。信号は、一般にトランスまたはコンデンサを介して CLK+ ピンと CLK- ピンに AC 結合されます。これらのピンは内部でバイアスされるため(図 28 参照)、外付けバイアスは不要です。

#### クロック入力オプション

AD9681 は柔軟なクロック入力構造を持っています。クロック入力としては、CMOS、LVDS、LVPECL、または正弦波信号が可能です。使用する信号タイプによらず、クロック・ソース・ジッタは、ジッタについての考慮事項のセクションで説明するように、最も大きな問題です。

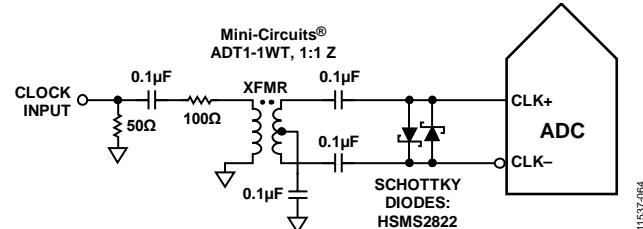

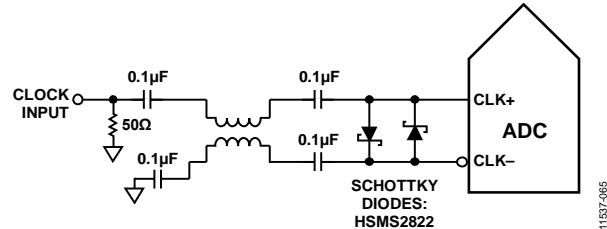

図 42 と図 43 に、AD9681 をクロック駆動する 2 つの望ましい方法を示します(内蔵クロック分周器の前で最大 1 GHz のクロック・レート)。ジッタの少ないクロック・ソースは、RF バランまたは RF トランスを使ってシングルエンド信号から差動信号に変換されます。

RF バラン構成は 125 MHz~1 GHz のクロック周波数に、RF トランス構成は 10 MHz~200 MHz のクロック周波数に、それぞれ推奨されます。トランス/バランの 2 次側に互いに逆向きに接続されたショットキ・ダイオードが、AD9681 に入力されるクロックを約 0.8 Vp-p 差動に制限します。

この機能は、クロックの大きな電圧振幅が AD9681 の別の部分に混入することを防止すると同時に、低ジッタ性能にとって重要な、信号の高速な立上がり時間と立下がり時間を維持します。ただし、ダイオード容量は 500 MHz より上の周波数で効いてきます。適切な信号制限ダイオードの選択には注意が必要です。

図 42. トランス結合の差動クロック(最大 200 MHz)

図 43. バラン結合の差動クロック(最大 1 GHz)

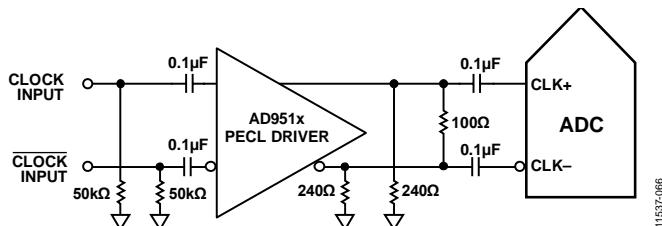

低ジッタ・クロックが使用できない場合、もう1つのオプションは差動 PECL 信号をサンプル・クロック入力ピンへ AC 結合することです(図 44 参照)。AD9510/AD9511/AD9512/AD9513/AD9514/AD9515-x/AD9516-x/AD9517-x クロック・ドライバは、優れたジッタ性能を提供します。

図 44. 差動 PECL サンプル・クロック

(最大 1 GHz)

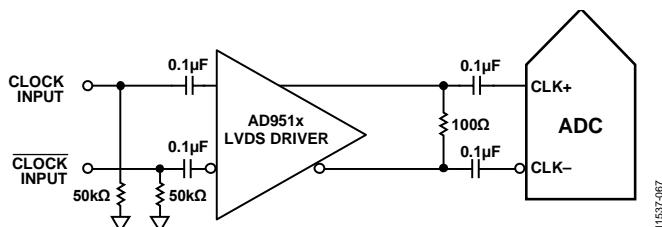

3 つ目のオプションは、差動 LVDS 信号をサンプル・クロック入力ピンへ AC 結合する方法です(図 45 参照)。AD9510/AD9511/AD9512/AD9513/AD9514/AD9515-x/AD9516-x/AD9517-x クロック・ドライバは、優れたジッタ性能を提供します。

図 45. 差動 LVDS サンプル・クロック

(最大 1 GHz)

アプリケーションによっては、サンプル・クロック入力をシングルエンド 1.8 V CMOS 信号で駆動できる場合があります。このようなアプリケーションでは、CLK+ピンを CMOS ゲートで直接駆動し、CLK-ピンは 0.1 μF のコンデンサによりグラウンドへバイパスします(図 46 参照)。

図 46. シングルエンド 1.8 V CMOS 入力クロック

(最大 200 MHz)

## 入力クロック・ドライバ

AD9681 は、入力クロックを 1~8 分周できる入力クロック分周器を内蔵しています。

AD9681 のクロック分周器は外部 SYNC 入力を使って同期させることができます。レジスタ 0x109 のビット 0 とビット 1 を使うと、各 SYNC 信号で、またはレジスタが書込まれた後の最初の SYNC 信号で、クロック分周器を再同期することができます。有効な SYNC により、クロック分周器は初期状態にリセットされます。この同期機能を使うと、複数のデバイスのクロック分周器の位相を一致させることができますので、入力の同時サンプリングが保証されます。

## クロック・デューティ・サイクル

代表的な高速 ADC では両クロック・エッジを使って、様々な内部タイミング信号を発生しているため、クロックのデューティ・サイクルの影響を大きく受けます。一般に、動的性能特性を維持するためにはクロック・デューティ・サイクルの許容誤差は±5%以内である必要があります。

AD9681 は、非サンプリング・エッジ(立下がり)の再タイミングを行って、公称 50% のデューティ・サイクルを持つ内部クロック信号を発生するデューティ・サイクル・スタビライザ(DCS)を内蔵しています。この回路により、AD9681 の性能に影響を与える広範囲なクロック入力のデューティ・サイクルを許容することができます。DCS をオンにすると、ノイズ性能と歪み性能はデューティ・サイクルの広い範囲でほぼ平坦になります。それでも、入力での立上がりエッジのジッタは問題であり、内部安定化回路で容易に減少させることはできません。デューティ・サイクル制御ループは、公称 20 MHz 以下のクロック・レートでは機能しません。このループは時定数を持っているため、クロック・レートがダイナミックに変わるとときは、これをアプリケーションで考慮する必要があります。ダイナミックにクロック周波数が増減した後に、DCS ループが入力信号に再ロックするまで、1.5 μs~5 μs の待ち時間が必要です。

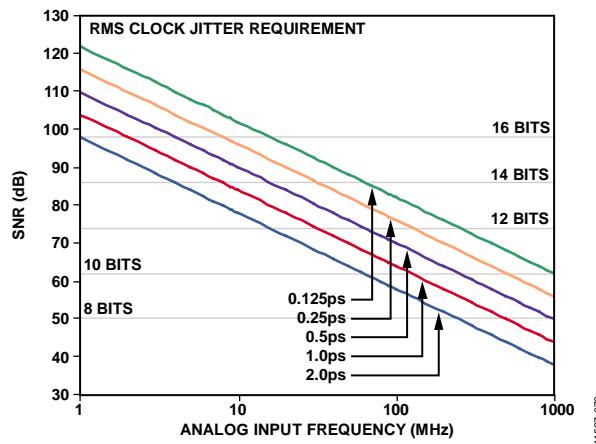

### ジッタについての考慮事項

高速な高分解能 ADC は、クロック入力の品質に敏感です。与えられた入力周波数( $f_A$ )でジッタ( $t_J$ )のみにより発生する SNR 性能の低下は次式で表されます。

$$SNR \text{ の低下} = 20 \log_{10} \left( \frac{1}{2\pi \times f_A \times t_J} \right)$$

この式で、rms アパー・チャ・ジッタは、クロック入力、アナログ入力信号、ADC アパー・チャ・ジッタの規定値を含む全ジッタ・ソースの 2 乗和平方根を表します。IF アンダーサンプリング・アプリケーションは、特にジッタに敏感です(図 47)。

図 47. 入力周波数およびジッタ対理論 SNR

アパー・チャ・ジッタが AD9681 のダイナミックレンジに影響を与えるケースでは、クロック入力はアナログ信号として扱う必要があります。クロック・ドライバの電源は ADC 出力ドライバの電源から分離して、クロック信号がデジタル・ノイズから変調を受けないようにする必要があります。低ジッタの水晶制御オシレータは優れたクロック源です。クロックが別のタイプのソース(ゲーティング、分周、または別の方)から発生される場合、最終ステップで元のクロックを使って再タイミングする必要があります。

ADC に関するジッタ性能の詳細については、[AN-501](#) アプリケーション・ノート「Aperture Uncertainty and ADC System Performance」と [AN-756](#) アプリケーション・ノート「Sampled Systems and the Effects of Clock Phase Noise and Jitter」を参照してください。

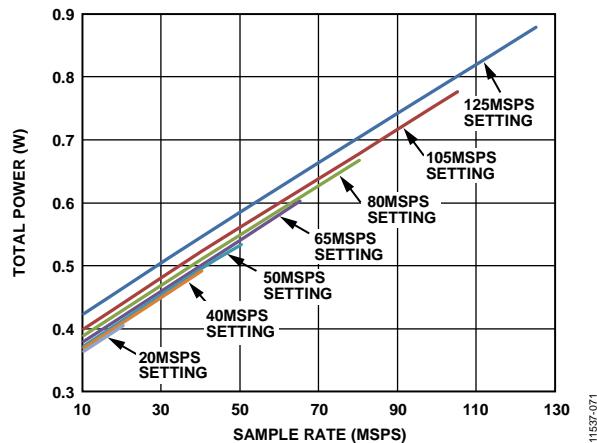

### 消費電力とパワーダウン・モード

図 48 に示すように、AD9681 で消費される電力はサンプル・レートに比例するため、レジスタ 0x100 のビット[2:0]を使って複数の省電力モードを設定することができます。

図 48.  $f_{\text{SAMPLE}}$  対総合消費電力、 $f_{\text{IN}} = 9.7 \text{ MHz}$

SPI ポートを用いるか、または PDWN ピンをハイ・レベルにすると、AD9681 はパワーダウン・モードになります。この状態で、ADC の消費電力は 2 mW (typ) になります。パワーダウン時は、出力ドライバはハイ・インピーダンス状態になります。PDWN ピンをロー・レベルにすると、AD9681 は通常動作モードに戻ります。PDWN はデジタル出力ドライバ電源(DRVDD)を基準にしているため、この電源電圧を超えることはできません。

パワーダウン・モードでの低消費電力は、リファレンス電圧、リファレンス・バッファ、バイアス回路、クロックをシャットダウンすることにより、実現されています。パワーダウン・モードに入ると、内蔵コンデンサは放電するため、通常動作に戻るときには再充電する必要があります。このため、ウェイクアップ時間はパワーダウン・モードに留まる時間に関係し、パワーダウン・サイクルが短いほど、ウェイクアップ時間も短くなります。SPI ポートを使うとき、ADC をパワーダウン・モードまたはスタンバイ・モードにすることができます。スタンバイ・モードにすると、高速なウェイクアップ時間が必要な場合に内蔵リファレンス回路を動作させたままにしておくことができます。これらの機能の詳細については、メモリ・マップのセクションを参照してください。

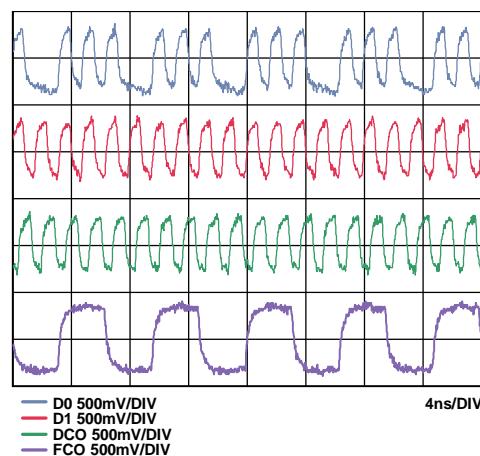

## デジタル出力とタイミング

AD9681 の差動出力は、デフォルトのパワーアップ時に ANSI-644 LVDS 規格に準拠します。この機能は、SPI を介して低消費電力(IEEE 1596.3 規格と同様の縮小信号オプション)に変更することができます。LVDS ドライバの電流は内部で生成され、各出力での出力電流公称値は 3.5 mA に設定されます。LVDS レシーバ入力に接続される 100 Ω の差動終端抵抗は、レシーバ側で公称 350 mV (差動 700 mV p-p) の振幅を発生させます。

縮小レンジ・モードで動作する場合、出力電流は 2 mA に減少します。これにより、レシーバの 100 Ω 終端での振幅は 200 mV (差動 400 mV p-p) になります。

AD9681 の LVDS 出力によりカスタム ASIC や FPGA 内にある LVDS レシーバとのインターフェースが可能になり、ノイズの多い環境で優れたスイッチング性能を得ることができます。100 Ω の終端抵抗をできるだけレシーバの近くに接続した 1 対 1 回路の使用が推奨されます。遠端でレシーバ終端がない場合、または差動パターン配線が良くない場合には、タイミング誤差が発生します。このようなタイミング誤差を防止するため、パターン長を 24 インチ以下に抑え、すべてのパターンを同じ長さにすることが推奨されます。差動出力パターンは、できるだけ互いに近づけて配置してください。適切なパターン長と配置の FCO とデータ・ストリームの例を図 49 に示します。図 50 に縮小レンジ・モードでの LVDS 出力タイミング例を示します。

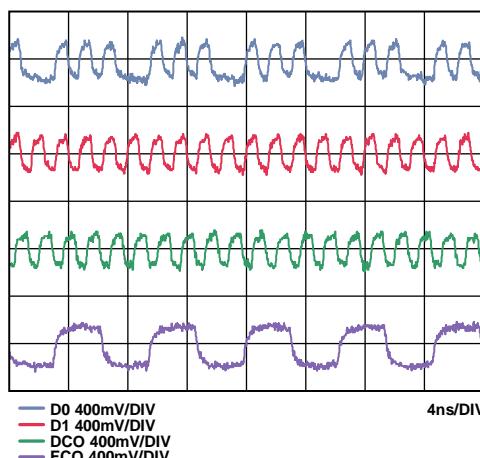

図 49. ANSI-644 モード(デフォルト)での LVDS 出力タイミング例

図 50. 縮小レンジ・モードでの LVDS 出力タイミング例

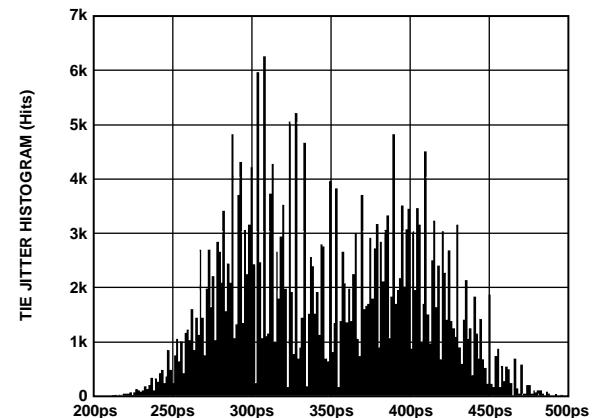

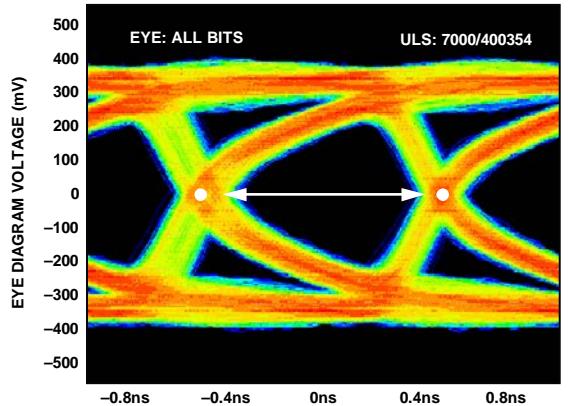

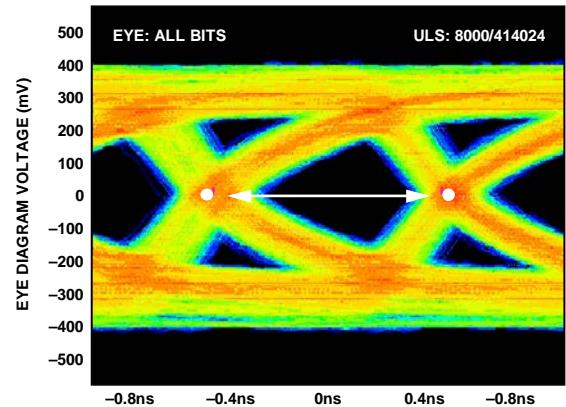

図 51 に ANSI-644 規格(デフォルト)データ・アイを使用した LVDS 出力例と、標準 FR-4 材上でパターン長を 24 インチ以下とした場合のタイム・インターバル誤差(TIE)ジッタのヒストグラム例を示します。

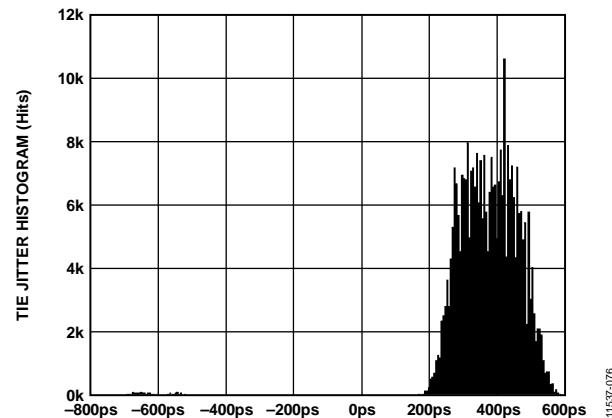

図 52 には、標準 FR-4 材上でパターン長を 24 インチ以上にした場合の例を示します。TIE ジッタ・ヒストグラムに、エッジが理想位置からはずれることによるデータ・アイ開口の減少が反映されていることに注意してください。

図 51. 標準 FR-4 材料上でパターン長を 24 インチ以下にした ANSI-644 モードの LVDS 出力のデータ・アイ、外付け  $100\Omega$  遠端終端のみ

パターン長が 24 インチを超える場合に、波形がデザイン上のタイミング条件を満たすか否かはユーザーの判断によります。追加の SPI オプションを使うと、8 個の出力すべての内部終端を大きくして(電流を増やして)、長いパターンを駆動することができます。これはレジスタ 0x15 の設定で実現することができます。これにより、データ・エッジの立上がり時間と立下がり時間がシャープになり、ビット・エラーが少なくなりますが、このオプションを使うと DRVDD 電源の消費電力が大きくなります。

図 52. 標準 FR-4 材料上でパターン長を 24 インチ以上にした ANSI-644 モードの LVDS 出力のデータ・アイ、外付け  $100\Omega$  遠端終端のみ

出力データのデフォルト・フォーマットは 2 の補数です。表 10 に、出力コーディング・フォーマットの例を示します。出力データ・フォーマットをオフセット・バイナリへ変更するときは、メモリ・マップのセクションのレジスタ 0x14 のビット[0]を参照してください。

表 10. デジタル出力コーディング

| Input (V)           | Condition (V)                | Offset Binary Output Mode | Twos Complement Mode |

|---------------------|------------------------------|---------------------------|----------------------|

| $V_{IN+} - V_{IN-}$ | $<-V_{REF} - 0.5\text{ LSB}$ | 0000 0000 0000 0000       | 1000 0000 0000 0000  |

| $V_{IN+} - V_{IN-}$ | $-V_{REF}$                   | 0000 0000 0000 0000       | 1000 0000 0000 0000  |

| $V_{IN+} - V_{IN-}$ | 0 V                          | 1000 0000 0000 0000       | 0000 0000 0000 0000  |

| $V_{IN+} - V_{IN-}$ | $+V_{REF} - 1.0\text{ LSB}$  | 1111 1111 1111 1100       | 0111 1111 1111 1100  |

| $V_{IN+} - V_{IN-}$ | $>+V_{REF} - 0.5\text{ LSB}$ | 1111 1111 1111 1100       | 0111 1111 1111 1100  |

各 ADC からのデータはシリアル化されて、DDR モードで 2 レーンの別々のチャンネルから出力されます。各シリアル・ストリームのデータレートは等しく 16 ビット×サンプル・クロック・レートで、最大 500 Mbps/レーン[(16 ビット×125 MSPS)/(2 × 2) = 500 Mbps/レーン]です。最小変換レートは 10 MSPS(typ) です。この機能のイネーブルについては、メモリ・マップのセクションを参照してください。

AD9681 からのデータのキャプチャに役立てるため、2 個の出力クロック・タイプが用意されています。DCO±1 と DCO±2 は出力データのクロックとして使われ、周波数はデフォルトの動作モードに対してサンプリング・クロック(CLK±)レートの 4 倍です。データはクロックで駆動されて AD9681 から出力され、ダブル・データレート(DDR)でのキャプチャをサポートする DCO の立上がりエッジと立下がりエッジでキャプチャすることができます。DCO±1 は D0±x1/D1±x1(バンク 1)データのキャプチャに使用され、DCO±2 は D0±x2/D1±x2(バンク 2)データのキャプチャに使用されます。FCO±1 と FCO±2 は新しい出力バイトの開始を知らせるために使い、1×フレーム・モードではサンプル・クロック・レートに一致します。FCO±1 は D0±x1/D1±x1(バンク 1)データをフレーム化し、FCO±2 は D0±x2/D1±x2 (バンク 2)データをフレーム化します。詳細については、タイミング図のセクションを参照してください。

SPI を使用する場合、DCO の位相は 1 データ・サイクルに対して 60°単位で増加させることができます(1 DCO サイクルに対しては 30°)。この機能を使うと、必要に応じてシステムのタイミング・マージンを調整することができます。

表 11.柔軟な出力テスト・モード

| Output Test Mode Bit Sequence (Reg. 0x0D) | Pattern Name                   | Digital Output Word 1 <sup>1</sup>                      | Digital Output Word 2 <sup>1</sup>                      | Subject to Data Format Select <sup>1</sup> | Notes                                      |

|-------------------------------------------|--------------------------------|---------------------------------------------------------|---------------------------------------------------------|--------------------------------------------|--------------------------------------------|

| 0000                                      | Off (default)                  | N/A                                                     | N/A                                                     | N/A                                        |                                            |

| 0001                                      | Midscale short                 | 1000 0000 0000 (12-bit)<br>1000 0000 0000 0000 (16-bit) | N/A                                                     | Yes                                        | Offset binary code shown                   |

| 0010                                      | +Full-scale short              | 1111 1111 1111 (12-bit)<br>0000 0000 0000 0000 (16-bit) | N/A                                                     | Yes                                        | Offset binary code shown                   |

| 0011                                      | -Full-scale short              | 0000 0000 0000 (12-bit)<br>0000 0000 0000 0000 (16-bit) | N/A                                                     | Yes                                        | Offset binary code shown                   |

| 0100                                      | Checkerboard                   | 1010 1010 1010 (12-bit)<br>1010 1010 1010 1010 (16-bit) | 0101 0101 0101 (12-bit)<br>0101 0101 0101 0100 (16-bit) | No                                         |                                            |

| 0101                                      | PN sequence long <sup>2</sup>  | N/A                                                     | N/A                                                     | Yes                                        | PN23<br>ITU 0.150<br>$X^{23} + X^{18} + 1$ |

| 0110                                      | PN sequence short <sup>2</sup> | N/A                                                     | N/A                                                     | Yes                                        | PN9<br>ITU 0.150<br>$X^9 + X^5 + 1$        |

| 0111                                      | One-/zero-word toggle          | 1111 1111 1111 (12-bit)<br>111 1111 1111 1100 (16-bit)  | 0000 0000 0000 (12-bit)<br>0000 0000 0000 0000 (16-bit) | No                                         |                                            |

| 1000                                      | User input                     | Register 0x19 to Register 0x1A                          | Register 0x1B to Register 0x1C                          | No                                         |                                            |

| 1001                                      | 1-/0-bit toggle                | 1010 1010 1010 (12-bit)<br>1010 1010 1010 1000 (16-bit) | N/A                                                     | No                                         |                                            |

| 1010                                      | 1× sync                        | 0000 0011 1111 (12-bit)<br>0000 0001 1111 1100 (16-bit) | N/A                                                     | No                                         |                                            |

| 1011                                      | One bit high                   | 1000 0000 0000 (12-bit)<br>1000 0000 0000 0000 (16-bit) | N/A                                                     | No                                         | Pattern associated with the external pin   |

| 1100                                      | Mixed bit frequency            | 1010 0011 0011 (12-bit)<br>1010 0001 1001 1100 (16-bit) | N/A                                                     | No                                         |                                            |

<sup>1</sup> N/A は該当なし。

<sup>2</sup> PN シーケンス・ショートと PN シーケンス・ロングを除くすべてのテスト・モード・オプションでは、レシーバのデータ・キャプチャを確認するために 12 ビット～16 ビットのワード長をサポートすることができます。

図 3 に示す DCO±1 と DCO±2 のデフォルト出力データ・エッジ・タイミングは、1 データ・サイクルに対して 180°です(1 DCO サイクルに対しては 90°)。

また、SPI から 12 ビットのシリアル・ストリームを開始することができます。この機能を使うと、低分解能のシステムに対する互換性を実現してテストすることができます。分解能を 12 ビット・シリアル・ストリームに変更すると、データ・ストリームは短くなります。12 ビットの例については、図 4 を参照してください。ただし、シリアル出力ビット数が 16 のデフォルト・オプションでは、データ・ストリームの 14 ビット・シリアル・データの後に 2 個の 0 が詰め込まれます。

図 3 に示すデフォルト・モードでは、データ出力シリアル・ストリーム内で MSB が先頭です。データ出力シリアル・ストリーム内で LSB が先頭になるように SPI を使って変更することができます。

12 種類のデジタル出力テスト・パターン・オプションがあり、これらは SPI を使って開始させることができます。この機能は、レシーバ・キャプチャとタイミングを確認する際に便利です(使用可能な出力ビット・シーケンス・オプションについては表 11 を参照してください)。幾つかのテスト・パターンは、2 種類のシリアル・シーケンシャル・ワードを持っているため、選択したテスト・パターンに応じて種々の方法で切り替えることができます。幾つかのパターンはデータ・フォーマット選択オプションに準拠していないことに注意してください。さらに、カスタムのユーザー定義テスト・パターンを 0x19、0x1A、0x1B、0x1C の各レジスタへ割り当てることができます。

PN シーケンス・ショート・パターンは、各  $2^9 - 1$  すなわち 511 ビットごとに繰り返す擬似ランダム・ビット・シーケンスを発生します。PN シーケンスの説明と発生方法については、ITU-T 0.150 (05/96) 規格のセクション 5.1 を参照してください。シード値は全ビット 1 です(初期値については表 12 を参照)。出力は、MSB ファースト・フォーマットのシリアル PN9 シーケンスをパラレル表現したものです。先頭の出力ワードは、MSB に位置合わせした PN9 シーケンスの先頭 14 ビットです。

表 12.PN シーケンス

| Sequence          | Initial Value | Next Three Output Samples (MSB First) Twos Complement |

|-------------------|---------------|-------------------------------------------------------|

| PN Sequence Short | 0x7F80        | 0x77C4, 0xF320, 0xA538                                |

| PN Sequence Long  | 0x7FFC        | 0x7F80, 0x8004, 0x7000                                |

PN シーケンス・ロング・パターンは、各  $2^{23} - 1$  すなわち 8,388,607 ビットごとに繰り返す擬似ランダム・ビット・シーケンスを発生します。PN シーケンスの説明と発生方法については、ITU-T 0.150 (05/96) 規格のセクション 5.6 を参照してください。シード値は全ビット 1 であり(初期値については表 12 を参照)、AD9681 では ITU 規格に対してビット・ストリームを逆にしています。出力は、MSB ファースト・フォーマットのシリアル PN23 シーケンスをパラレル表現したものです。先頭の出力ワードは、MSB に位置合わせした PN23 シーケンスの先頭 14 ビットです。

これらの追加デジタル出力タイミング機能の、SPI を介する変更方法については、メモリ・マップのセクションを参照してください。

### SDIO/OLM ピン

SPI 動作モードが不要なアプリケーションでは、CSB1 ピンと CSB2 ピンを AVDD に接続し、SDIO/OLM ピンにより表 13 に従って出力レーン・モードを制御します。

SDIO/OLM ピンを使用しないアプリケーションでは、CSB1 と CSB2 を AVDD へ接続してください。1 レーン・モードを使用する場合、変換レートを 62.5 MSPS 以下にして、1 Gbps の最大出力レートを満たすようにしてください。

表 13.出力レーン・モードのピン設定

| Output Lane Mode Voltage (SDIO/OLM Pin) | Output Mode                               |

|-----------------------------------------|-------------------------------------------|

| AVDD (Default)                          | Two-lane, 1× frame, 16-bit serial output. |

| GND                                     | One-lane, 1× frame, 16-bit serial output. |

### SCLK/DTP ピン

デバイスのパワーアップ時に、SCLK/DTP ピンと CSB1 ピンおよび CSB2 ピンをハイ・レベルにすると、シングル・デジタル・テスト・パターンをイネーブルすることができます。SCLK/DTP を AVDD に接続すると、ADC チャンネルはパターン 1000 0000 0000 0000 をシフト出力します。FCO $\pm$ 1、FCO $\pm$ 2、DCO $\pm$ 1、DCO $\pm$ 2 の各ピンは通常通りに動作しますが、すべてのチャンネルは繰り返しテスト・パターンをシフト出力します。このパターンを使うと、FCO $\pm$ 1、FCO $\pm$ 2、DCO $\pm$ 1、DCO $\pm$ 2、出

力データの間のタイミング・アライメント調整を行うことができます。SCLK/DTP ピンには GND へ接続した 30 k $\Omega$  の抵抗が内蔵されているため、通常動作では未接続のままにすることができます。

表 14.デジタル・テスト・パターンのピン設定

| Selected Digital Test Pattern | DTP Voltage | Resulting D0 $\pm$ xx and D1 $\pm$ xx |

|-------------------------------|-------------|---------------------------------------|

| Normal Operation              | No connect  | Normal operation                      |

| DTP                           | AVDD        | 1000 0000 0000 0000                   |

SPI ポートからコマンドを与えると、その他およびカスタムのテスト・パターンも観測することができます。オプションの詳細については、メモリ・マップのセクションを参照してください。

### CSB1 ピンと CSB2 ピン

SPI 動作モードが不要なアプリケーションでは、CSB1 ピンと CSB2 ピンを AVDD へ接続する必要があります。CSB1 と CSB2 をハイ・レベルに接続すると、SCLK と SDIO のすべての SPI 通信情報が無視されます。

CSB1 は、D0 $\pm$ x1/D1 $\pm$ x1 出力(バンク 1)に影響する SPI 回路を選択／非選択します。CSB2 は、D0 $\pm$ x2/D1 $\pm$ x2(バンク 2)出力に影響する SPI 回路を選択／非選択します。

CSB1 と CSB2 は同じ信号(両信号を接続)で制御することが推奨されます。この方法では、両信号を AVDD に接続するか、または SPI 機能を選択するかによらず、ADC の両バンクは同じ制御を受け、常に同じ状態になります。

### RBIAS1 ピンと RBIAS2 ピン

ADC の内部コア・バイアス電流を設定するときは、グラウンドと RBIAS1 ピンおよび RBIAS2 ピンとの間に 1%許容誤差の 10.0 k $\Omega$  抵抗を接続してください。

### 出力テスト・モード

AD9681 は、各データ出力チャンネルのテストとボード・レベルのデバッグを可能にするテスト機能を内蔵しています。AD9681 の出力に予測可能な値を出力させるための様々な出力テスト・オプションも用意されています。

出力テスト・モードを表 11 に示します。これらは、アドレス 0x0D の出力テスト・モード・ビットから制御されます。出力テスト・モードをイネーブルすると、ADC のアナログ・セクションが後段のデジタル・ブロックから切り離され、テスト・パターンが出力フォーマッティング・ブロックで実行されます。テスト・パターンには出力フォーマッティングが行われるものと、行われないものもあります。レジスタ 0x0D のビット 4 またはビット 5 をセットすることにより、PN シーケンス・テストの PN ジェネレータをリセットすることができます。これらのテストはアナログ信号の有無によらず(有りの場合、アナログ信号は無視されます)実行することができますが、エンコード・クロックは必要です。詳細については、アプリケーション・ノート AN877 「Interfacing to High Speed ADCs via SPI」を参照してください。

## シリアル・ポート・インターフェース(SPI)

AD9681 シリアル・ポート・インターフェース(SPI)を使うと、ADC 内部に用意されている構造化されたレジスタ・スペースを介してコンバータの特定の機能または動作を設定することができます。SPI を使うと、アプリケーションに応じて、柔軟性とカスタマイズ性が向上します。シリアル・ポートを介してアドレスがアクセスされ、ポートを介して読み書きすることができます。メモリは、バイトで構成されており、さらにフィールドに分割できます。これについてはメモリ・マップのセクションに記載してあります。詳細については、AN-877 アプリケーション・ノート「*Interfacing to High Speed ADCs via SPI*」を参照してください。AD9681 に固有な SPI 情報は AD9681 データシートに記載されており、この情報の方が AN-877 アプリケーション・ノートに記載されている一般情報より優先されます。

### SPI を使う設定

この ADC の SPI は、SCLK/DTP ピン(SCLK 機能)、SDIO/OLM ピン(SDIO 機能)、CSB1 ピン、CSB2 ピンの 4 本のピンにより定義されます(表 15 参照)。SCLK(シリアル・クロック)ピンは、ADC に対する読み出し/書き込みデータの同期に使用されます。SDIO(シリアル・データ入力/出力)ピンは 2 つの機能で共用されるピンであり、内部 ADC メモリ・マップ・レジスタに対するデータの送受信に使われます。CSB1 と CSB2(チップ・セレクト・バー)はアクティブ・ローのコントロール信号であり、読み出しサイクルと書き込みサイクルをイネーブル/ディスエーブルします。

表 15.シリアル・ポート・インターフェース・ピン

| Pin             | Function                                                                                                                                                                                           |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK (SCLK/DTP) | Serial clock. The serial shift clock input, which is used to synchronize serial interface reads and writes.                                                                                        |

| SDIO (SDIO/OLM) | Serial data input/output. A dual-purpose pin that serves as an input or an output, depending on the instruction being sent and the relative position in the timing frame.                          |

| CSB1, CSB2      | Chip select bar. An active low control that gates the read and write cycles. CSB1 enables/disables the SPI for four channels in Bank 1; CSB2 enables/disables the SPI for four channels in Bank 2. |

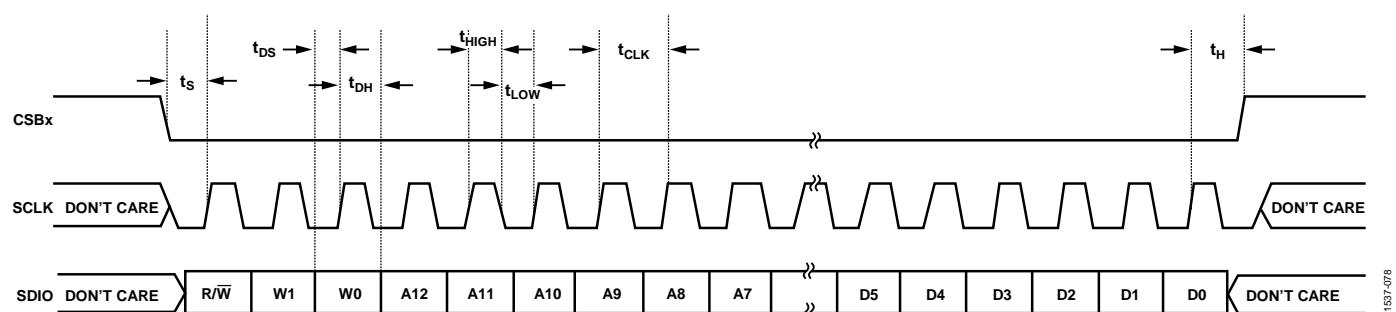

CSB1 および/または CSB2 の立下がりエッジと SCLK の立上がりエッジの組み合わせにより、フレームの開始が指定されます。シリアル・タイミングの例とその定義を図 53 と表 5 に示します。

CSB1 ピンと CSB2 ピンを使用するその他のモードもあります。デバイスをイネーブル固定にするときは、CSB1 と CSB2 をロー・レベルに固定します。これはストリーミングと呼ばれます。CSB1 と CSB2 をバイト間でハイ・レベルに維持して外部タイミングを延ばすことができます。CSB1 と CSB2 をハイ・レベルに固定すると、SPI 機能はハイ・インピーダンス・モードになります。このモードではすべての SPI ピンは 2 つ目の機能になります。

CSB1 と CSB2 は同じ信号で制御することが推奨されます(両信号を接続します)。この方法では、両信号を AVDD に接続するか、または SPI 機能を選択するかによらず、ADC の両バンクは同じ制御を受け、常に同じ状態になります。

命令フェーズでは、16 ビット命令が送信されます。命令フェーズの後ろにはデータが続き、長さは W0 ビットと W1 ビットにより指定されます。

命令フェーズでは、ワード長の他に、シリアル・フレームが読み出し動作または書き込み動作のいずれであるかを指定します。これにより、シリアル・ポートをチップの設定と内蔵メモリ値の読み出しに使うことができます。マルチバイト・シリアル・データの先頭バイトの先頭ビットは、読み出しコマンドまたは書き込みコマンドのいずれが発行されているかを表示します。命令がリードバック動作の場合、リードバックを実行すると、シリアル・データ入力/出力(SDIO)ピンの方向がシリアル・フレーム内の該当するポイントで入力から出力へ変わります。

入力データは、SCLK の立上がりエッジでレジスタにロードされ、出力データは立下がりエッジで送信されます。読み出しを要求しているコンバータヘアドレス情報が渡されると、SDIO ラインがクロック・サイクルの 1/2 以内に入力から出力へ変化します。このタイミングにより、次のクロック・サイクルの立下がりエッジまでに、データが安全にこのシリアル・ラインに出力されてコントローラから読み出せるようになります。

すべてのデータは 8 ビット・ワードで構成されます。データは、MSB ファースト・モードまたは LSB ファースト・モードで送信することができます。MSB ファースト・モードはパワーアップ時のデフォルトであり、SPI ポート設定レジスタを使って変えることができます。この機能およびその他の詳細については、AN-877 アプリケーション・ノート「*Interfacing to High Speed ADCs via SPI*」を参照してください。

図 53.シリアル・ポート・インターフェースのタイミング図

## ハードウェア・インターフェース

表 15 に示すピンにより、ユーザー書込みデバイスと AD9681 のシリアル・ポートとの間の物理インターフェースが構成されています。SPI インターフェースを使用するときは、SCLK/DTP ピン(SCLK 機能)、CSB1 ピン、CSB2 ピンは入力として機能します。SDIO/OLM ピン(SDIO 機能)は双方向で、書込みフェーズでは入力として、リードバック時は出力として、それぞれ機能します。

SPI インターフェースは、FPGA またはマイクロコントローラから制御できるように十分な柔軟性を持っています。SPI 設定の一方法は、AN-812 アプリケーション・ノート「*Microcontroller-Based Serial Port Interface (SPI) Boot Circuit*」に記載してあります。

コンバータのフル・ダイナミック性能が必要な区間では、SPI ポートをアクティブにしないようにしておく必要があります。SCLK 信号、CSB1 信号、CSB2 信号、SDIO 信号は一般に ADC クロックに非同期であるため、これらの信号からのノイズがコンバータ性能を低下させることができます。内蔵 SPI バスを他のデバイスに対して使う場合には、このバスと AD9681 との間にバッファを設けて、クリティカルなサンプリング区間にコンバータ入力でこれらの信号が変化することを防止することが必要になります。

SPI インターフェースを使用しない場合には、幾つかのピンは共用ピンとして機能します。デバイス・パワーオン時にピンをDRVDD またはグラウンドに接続すると、それらのピンは特定の機能として使われます。表 13 と表 14 に、AD9681 でサポートしているストラップ接続可能な機能を示します。

## SPI を使わない設定

SPI コントロール・レジスタにインターフェースしないアプリケーションでは、SDIO/OLM ピン、SCLK/DTP ピン、PDWN ピンは、独立した CMOS 互換のコントロール・ピンとして機能します。デバイスがパワーアップすると、これらのピンは出力レーン・モード制御、デジタル・テスト・パターン制御、パワーダウン機能制御のスタティック・コントロール・ラインとして使用されるものと見なされます。このモードでは、CSB1 ピンおよび CSB2 ピンを AVDD に接続する必要があります。この接続により、シリアル・ポート・インターフェースがディスエーブルされます。

デバイスが SPI モードの場合、PDWN ピン(イネーブル時)はアクティブのままになります。パワーダウンの SPI 制御の場合、PDWN ピンは非アクティブ状態(ロー・レベル)に設定してください。

## SPI からアクセス可能な機能

表 16 に、SPI からアクセスできる一般的な機能の簡単な説明を示します。これらの機能は、AN-877 アプリケーション・ノート「*Interfacing to High Speed ADCs via SPI*」で詳しく説明しています。AD9681 デバイスに固有な機能は表 17 外部メモリ・マップ・レジスタ・テーブルの後のメモリ・マップ・レジスタの説明のセクションに説明します。

表 16. SPI を使ってアクセスできる機能

| Feature Name   | Description                                                                                                         |

|----------------|---------------------------------------------------------------------------------------------------------------------|

| Power Mode     | Allows the user to set either power-down mode or standby mode                                                       |

| Clock          | Allows the user to access the DCS, set the clock divider, set the clock divider phase, and enable the sync function |

| Offset         | Allows the user to digitally adjust the converter offset                                                            |

| Test I/O       | Allows the user to set test modes to have known data on output bits                                                 |

| Output Mode    | Allows the user to set the output mode                                                                              |

| Output Phase   | Allows the user to set the output clock polarity                                                                    |

| ADC Resolution | Allows scalable power consumption options with respect to the sample rate                                           |

## メモリ・マップ

### メモリ・マップ・レジスタ・テーブルの読出し

メモリ・マップ・レジスタ・テーブル内の各行には 8 ビットのロケーションがあります。メモリ・マップは大まかに、チップ設定レジスタ(アドレス 0x00～アドレス 0x02)、デバイス・インデックス・レジスタと転送レジスタ(アドレス 0x05 とアドレス 0xFF)、セットアップ、コントロール、テストなどのグローバル ADC ファンクション・レジスタ(アドレス 0x08～アドレス 0x109)の 3 つのセクションに分かれています。

メモリ・マップ・レジスタ・テーブル(表 17 参照)には、各 16 進アドレスに対するデフォルトの 16 進値が記載してあります。先頭ビット 7 (MSB) の列は、デフォルト 16 進値の開始になります。例えば、アドレス 0x05 のデバイス・インデックス・レジスタは、16 進デフォルト値 0x3F を持ります。これは、アドレス 0x05 で、ビット [7:6] = 0 かつ残りのビット [5:0] = 1 を意味します。この設定値は、デフォルトのチャンネル・インデックス設定値です。デフォルト値により、全 ADC チャンネルは次の書き込みコマンド受信になります。この機能およびその他の詳細については、AN-877 アプリケーション・ノート「*Interfacing to High Speed ADCs via SPI*」を参照してください。このアプリケーション・ノートでは、レジスタ 0x00～0xFF により制御される機能を詳しく説明しています。残りのレジスタは、メモリ・マップ・レジスタの説明のセクションに記載してあります。

### 未使用ロケーション

表 17 に記載されていないすべてのアドレスとビット・ロケーションは、このデバイスでは現在サポートされていません。有効アドレス・ロケーションの未使用ビットには 0 を書込んでください。アドレス・ロケーションの一部が有効な場合にのみ、これらのロケーションへの書き込みが必要です(例えばアドレス 0x05)。アドレス・ロケーション全体が未使用、またはアドレスが表 17 に記載されていない場合(例えばアドレス 0x13)、このアドレス・ロケーションに対しては書き込みを行わないでください。

### デフォルト値

AD9681 をリセットした後(アドレス 0x00 のビット 5 とビット 2 を使用)、レジスタにはデフォルト値がロードされます。レジス

タのデフォルト値は、表 17 メモリ・マップ・レジスタ表のデフォルト値(16 進)の列に記載してあります。

### ロジック・レベル

ロジック・レベルは次のように定義します。

- 「ビットをセットする」は、「ビットをロジック 1 に設定する」または「ビットにロジック 1 を書込む」と同じ意味です。

- 「ビットをクリアする」は、「ビットをロジック 0 に設定する」または「ビットにロジック 0 を書込む」と同じ意味です。

### チャンネル固有のレジスタ

幾つかのチャンネル・セットアップ機能は、各チャンネルごとに独立に設定することができます。これらの場合、チャンネル・アドレス・ロケーションは、内部で各チャンネルにコピーされます。すなわち、各チャンネルには固有のレジスタ・セットがあります。これらのレジスタとビットは、表 17 でローカルと表示されています。これらのローカル・レジスタとビットをアクセスするときは、レジスタ 0x05 の該当するデータ・チャンネル・ビット(A1、A2 から D1、D2 まで)とクロック・チャンネル(DCO $\pm$ 1、DCO $\pm$ 2、FCO $\pm$ 1、FCO $\pm$ 2) をセットします。レジスタ 0x05 のすべての有効ビットがセットされると、あるローカル・レジスタに対する後続の書き込みが、すべてのデータ・チャンネルのレジスタと DCO $\pm$ x/FCO $\pm$ x クロック・チャンネルに対して有効になります。読み出しサイクルでは、1 つのチャンネル(A1、A2 から D1、D2 まで)のみをセットして、1 つローカル・レジスタを読み出してください。SPI 読出しサイクルで全ビットがセットされると、デバイスはチャンネル A1 の値を返します。

表 17 でグローバルと指定されたレジスタとビットは、独立した設定が許されていないチャンネル機能に対して適用されるため、デバイス全体に有効です。レジスタ 0x05 内の設定は、グローバルなレジスタとビットに影響を与えません。

## メモリ・マップ

AD9681 では、3 線式 (双方向 SDIO) インターフェースと 16 ビット・アドレッシングを採用しています。このためレジスタ 0x00 のビット 0 とビット 7 は 0 に、ビット 3 とビット 4 は 1 に、それぞれ設定されます。レジスタ 0x00 のビット 5 がハイ・レベルに設定されると、SPI はソフト・リセットを開始し、すべてのユーザー・レジスタがデフォルト値に戻され、ビット 2 は自動的にクリアされます。

表 17.メモリ・マップ・レジスタ・テーブル

| Reg. Addr. (Hex)                    | Register Name          | Bit 7 (MSB)     | Bit 6     | Bit 5                                                               | Bit 4                       | Bit 3                | Bit 2                | Bit 1                                                                                                   | Bit 0 (LSB)          | Default Value (Hex)                                 | Comments                                                                                                                                                         |

|-------------------------------------|------------------------|-----------------|-----------|---------------------------------------------------------------------|-----------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip Configuration Registers        |                        |                 |           |                                                                     |                             |                      |                      |                                                                                                         |                      |                                                     |                                                                                                                                                                  |

| 0x00                                | SPI port configuration | 0 = SDIO active | LSB first | Soft reset                                                          | 1 = 16-bit address          | 1 = 16-bit address   | Soft reset           | LSB first                                                                                               | 0 = SDIO active      | 0x18                                                | Nibbles are mirrored such that a given register value yields the same function for either LSB-first mode or MSB-first mode. The default for ADCs is 16-bit mode. |

| Device Index and Transfer Registers |                        |                 |           |                                                                     |                             |                      |                      |                                                                                                         |                      |                                                     |                                                                                                                                                                  |

| 0x05                                | Device index           | Open            | Open      | DCO±1, DCO±2 clock channels                                         | FCO±1, FCO±2 clock channels | D1, D2 data channels | C1, C2 data channels | B1, B2 data channels                                                                                    | A1, A2 data channels | 0x3F                                                | Bits are set to determine which device on chip receives the next write command. The default is all devices on chip.                                              |

| 0xFF                                | Transfer               | Open            | Open      | Open                                                                | Open                        | Open                 | Open                 | Open                                                                                                    | Initiate override    | 0x00                                                | Sets resolution/ sample rate override.                                                                                                                           |