## シンプル・シーケンサ ADM108x を使った パワーアップ・シーケンスとパワーダウン・シーケンス

著者: Naiqian Ren

### 概要

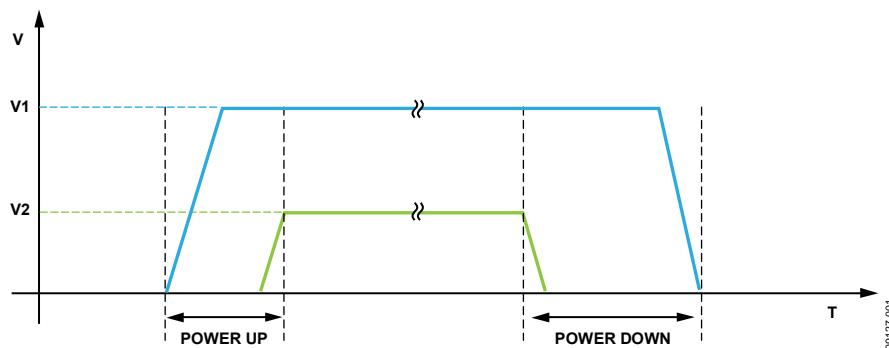

シンプル・シーケンサADM108xを使うと、コンデンサで設定可能な時間遅延により、パワーアップ時に2つの電圧レールに対する簡単なシーケンシングを行うことができます。同じファミリーのもう1つのデバイスを追加使用すると、別々の設定可能な時間遅延を使って、2つの電圧レールに対してパワーアップとパワーダウンのシーケンシングを行うことができます(図1参照)。このアプリケーション・ノートでは、このような回路のデザイン方法を説明します。

図1.パワーアップとパワーダウンの代表的なシーケンス条件

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属します。※日本語資料はREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

## 目次

|        |   |        |   |

|--------|---|--------|---|

| 概要     | 1 | タイミング図 | 4 |

| 改訂履歴   | 2 | 検証     | 5 |

| 実装     | 3 | 回路図    | 5 |

| 回路デザイン | 3 | テスト結果  | 6 |

## 改訂履歴

6/10—Revision 0: Initial Version

## 実装

### 回路デザイン

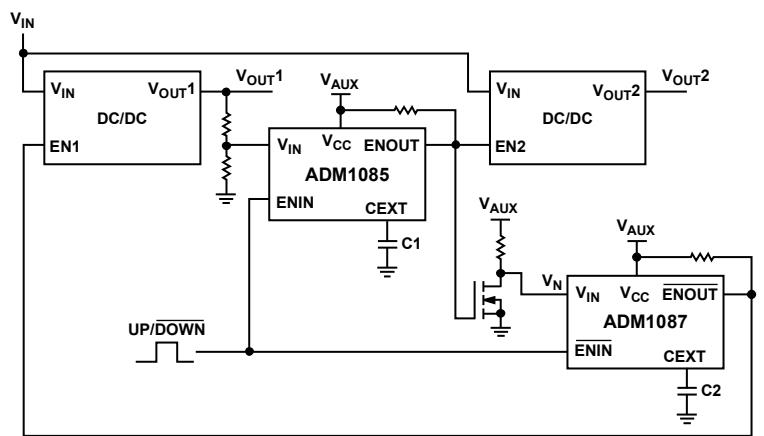

図 2 に、回路のブロック図を示します。回路の主な部品は、2 個の電源レギュレータ、Nch MOSFET、ADM1085、ADM1087 です。この回路は、イネーブル入力を持つ大部分のDC/DC レギュレータをサポートします。

ADM1085 入力の抵抗分圧器を使って、1 つ目の電源出力  $V_{OUT1}$  を正確にモニタします。この機能により、2 つ目電源出力  $V_{OUT2}$  がイネーブルされる前に、1 つ目電源がパワーオンすることが保証されます。あるいは、ADM1085 の  $V_{IN}$  ピンを 1 つ目のレギュレータの電源正常(パワーグッド)出力(存在する場合)へ直接接続することもできます。

パワーアップ時には、C1 が  $V_{OUT1}$  と  $V_{OUT2}$  との間の時間遅延を制御し、パワーダウン時には、C2 が  $V_{OUT2}$  と  $V_{OUT1}$  との間の時間遅延を制御します。

シーケンシング回路に別々に電源を供給するために補助電源  $V_{AUX}$  が使われます。この  $V_{AUX}$  は  $V_{IN}$  で置換えることができ、その影響の詳細については、タイミング図のセクションで説明します。

パワーアップ・シーケンスとパワーダウン・シーケンスの起動は、UP/DOWN ロジック信号から制御されます。

図 2.回路ブロック図

## タイミング図

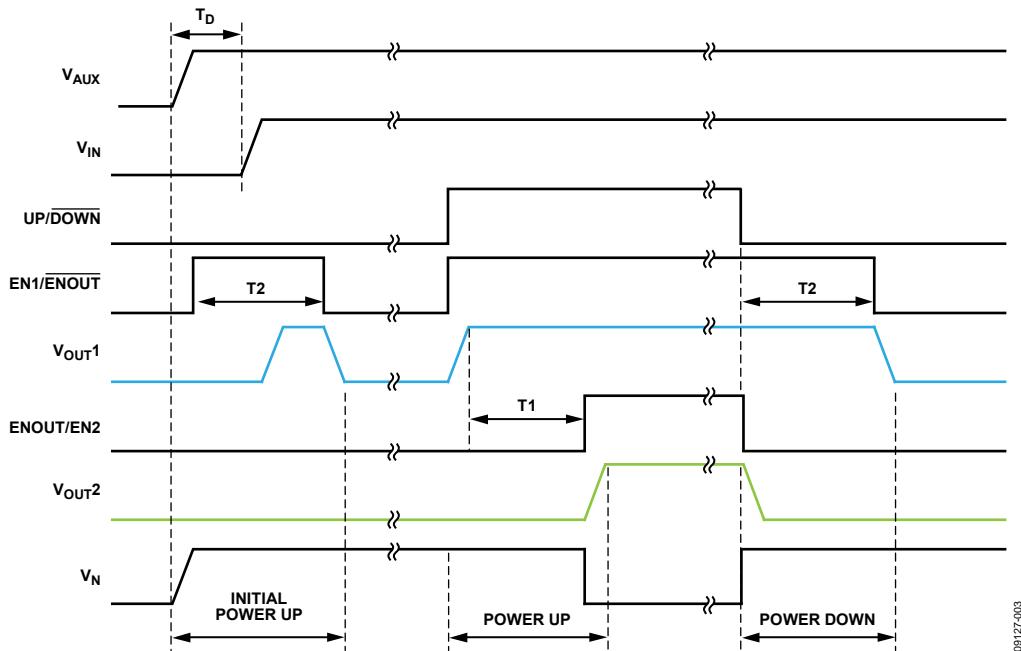

図 3.回路のタイミング図

09127/003

09126

図 3 に、回路タイミング図の概要を示します。このタイミングは、初期パワーアップ、パワーアップ・シーケンス、パワーダウン・シーケンスの 3 つのフェーズから構成されています。

初期パワーアップ・フェーズでは、UP/DOWN信号がロー・レベルに維持されます。V<sub>AUX</sub>がハイ・レベルになると、ADM1087のENOUT出力がT<sub>2</sub> 時間(これはC2により制御されます)後にハイ・レベルになります、その後ロー・レベルになります。この区間に、1つ目のレギュレータは、EN1がENOUTに接続されているため短時間イネーブルされることがあります。初期パワーアップ・フェーズで 1 つ目のレギュレータがイネーブルされている間、T<sub>ON</sub>はV<sub>AUX</sub>とV<sub>IN</sub>の間のパワーアップ遅延T<sub>D</sub>に依存します。T<sub>2</sub>はT<sub>ON</sub> = T<sub>2</sub> - T<sub>D</sub>の関係を満たします。

T<sub>D</sub> > T<sub>2</sub> の場合、例えばV<sub>AUX</sub>がV<sub>IN</sub>より T<sub>2</sub> sec 以上前にパワーアップする場合、1つ目のレギュレータは初期パワーアップ・フェーズの間イネーブルされません。V<sub>AUX</sub>をV<sub>IN</sub>で置換える場合は、T<sub>D</sub>がゼロであるため、レギュレータは初期パワーアップ・フェーズで T<sub>2</sub> 時間の間イネーブルされます。

初期パワーアップ時に 1 つ目の電源の狭いパルスで問題を生じないシステムでは、V<sub>IN</sub>を回路電源にのみ使用することが推奨されます。

もう 1 つのオプションは、UP/DOWN信号とV<sub>IN</sub>を接続する方法です。この場合、V<sub>IN</sub>が立ち上ると、1つ目のレギュレータが自動的にターンオンし、1つ目のレギュレータ出力が正常になってからT<sub>2</sub> sec 後に 2 つ目のレギュレータがイネーブルされます。

パワーアップ・シーケンス・フェーズでは、UP/DOWNをハイ・レベルにするとシーケンスが開始され、これによりADM1087のENOUTがハイ・レベルになるため、1つ目のレギュレータがイネーブルされます。1つ目のレギュレータ出力がADM1085のV<sub>IN</sub>ピンで検出されると、T<sub>1</sub> sec 後にENOUTピンがハイ・レベルになって、2つ目のレギュレータがイネーブルされます。T<sub>1</sub>はC1により制御され、パワーアップ時の出力電圧V<sub>OUT1</sub>と出力電圧V<sub>OUT2</sub>の間のプログラマブルな遅延が発生されます。このフェーズでのシーケンス方法は、シンプル・シーケンサADM108xの標準的な使用によります。

パワーダウン・シーケンス・フェーズでのシーケンスは、UP/DOWN信号をロー・レベルにすることにより開始されます。この直接的な影響は、ADM1085のENINピンがロー・レベルになるため、ENOUTピンもロー・レベルになることです。このために、EN2ピンを介して2つ目のレギュレータがディスエーブルされ、さらにNch-MOSFETのゲートがロー・レベルに駆動されるためN-ch-MOSFETもターンオフします。FETがオフすると、ADM1087のV<sub>IN</sub>ピンがハイ・レベルになり、ENINが既にロー・レベルであるため、T<sub>2</sub> sec 後にそのENOUT出力がロー・レベルになって、EN1を介して1つ目のレギュレータがターンオフします。C2によりT<sub>2</sub>が制御されて、パワーダウン時の出力電圧V<sub>OUT2</sub>と出力電圧V<sub>OUT1</sub>の間のプログラマブルな遅延が発生されます。

## 検証

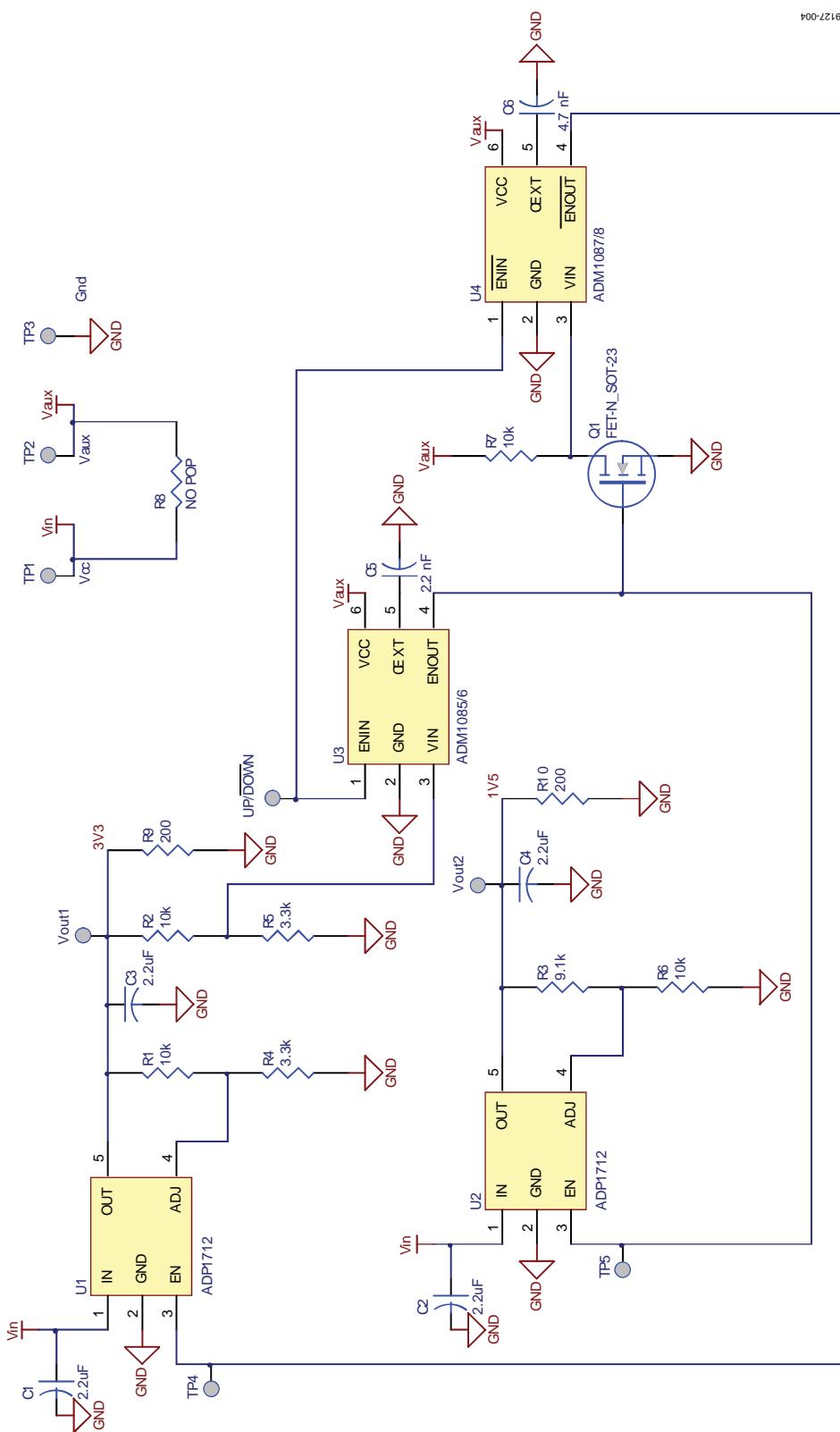

## 回路図

図 4. 検証回路図

## テスト結果

チャンネル 1: V<sub>OUT1</sub> (金色)、チャンネル 2: V<sub>OUT2</sub> (ピンク色)、チャンネル 3: UP/DOWN (青色)、チャンネル 4: V<sub>IN</sub> (緑色)。

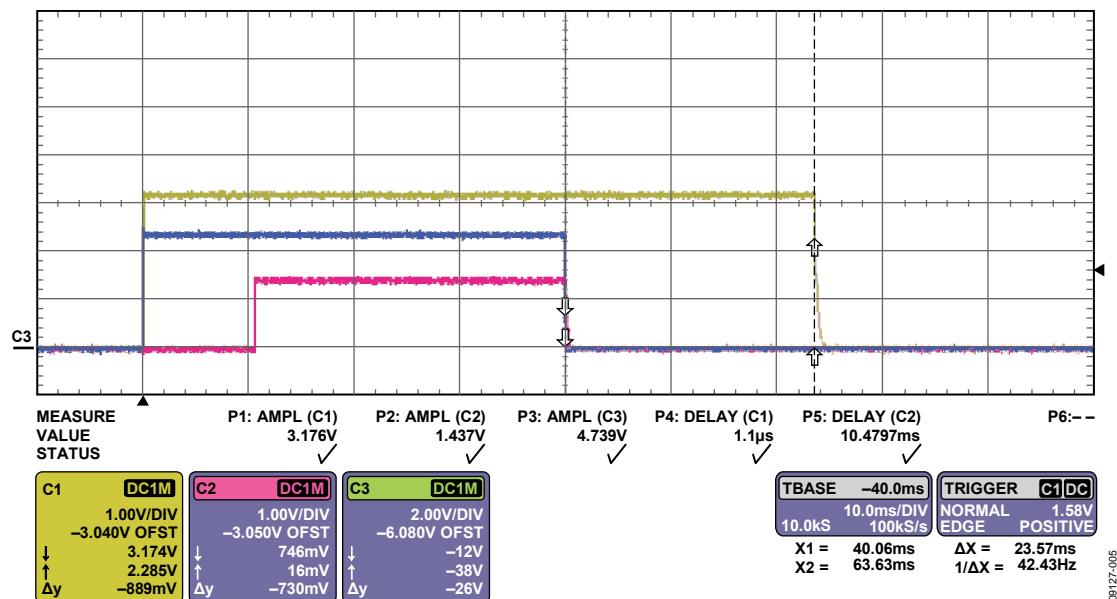

図 5. テスト・プロットの概要

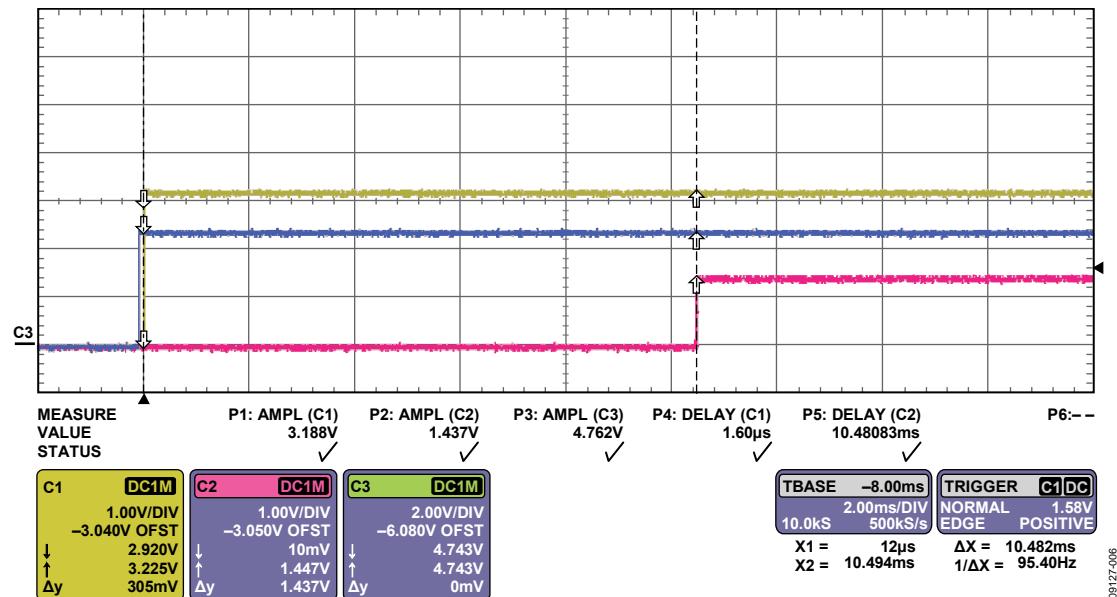

図 6. パワーダウン・フェーズの拡大

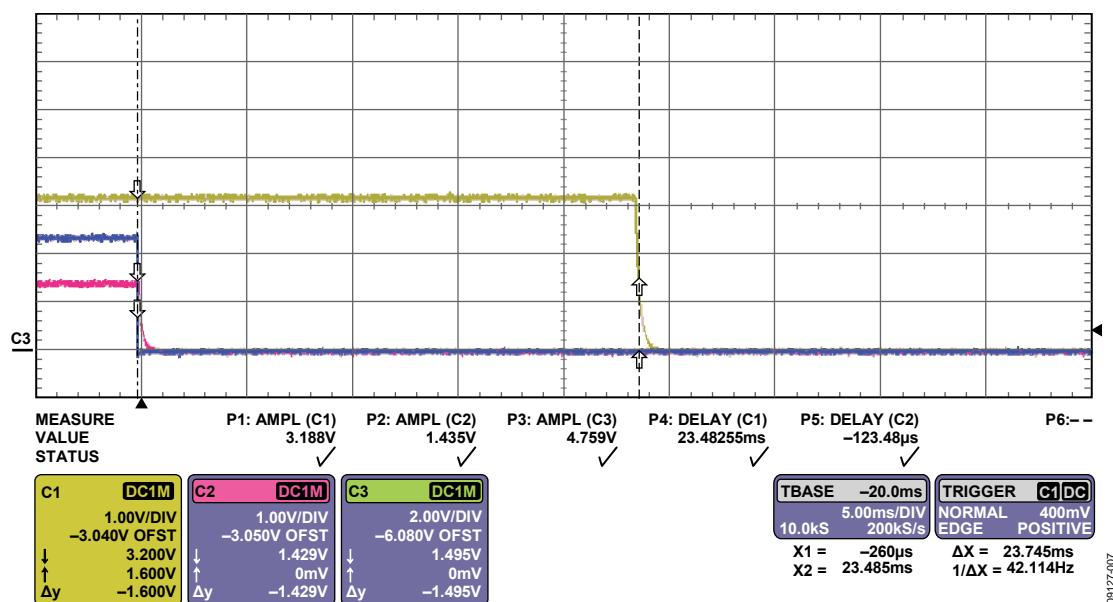

図 7.パワーアップ・フェーズの拡大

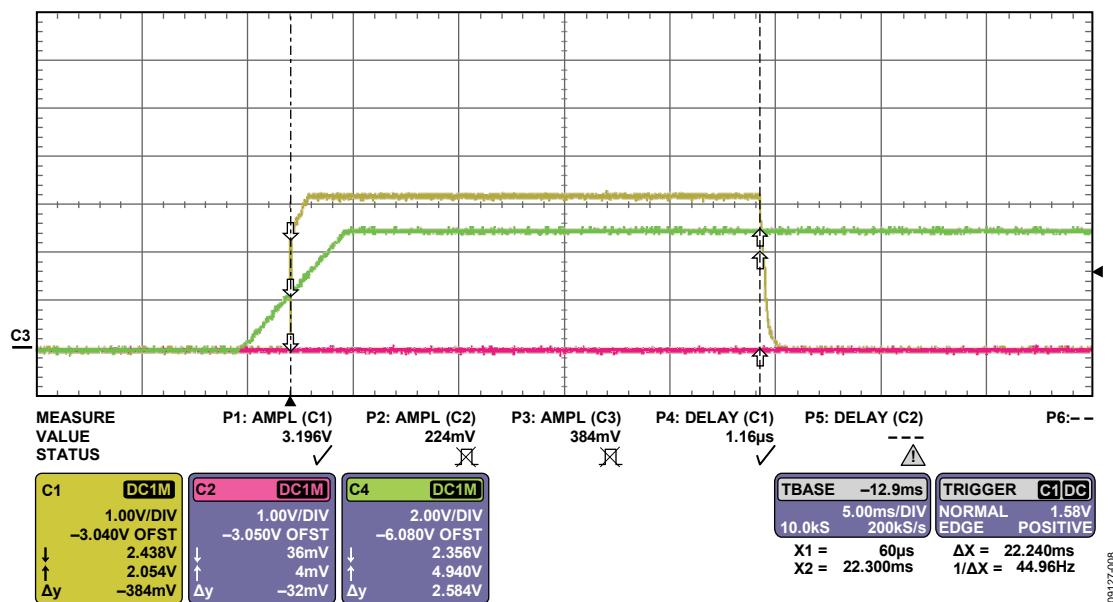

図 8.初期パワーアップ・フェーズ