# 14ビット・ ダイレクトコンバージョン・ レシーバ・サブシステム

## 特長

- デュアル14ビット高速ADC、ローパス・フィルタ、差動利得段、I/Q復調器を内蔵

- ADCチャネルごとのローパス・フィルタ

- 1.92MHz(LTM9004-AA)

- 4.42MHz(LTM9004-AB)

- 9.42MHz(LTM9004-AC)

- 20MHz(LTM9004-AD)

- RF入力周波数範囲: 0.7GHz～2.7GHz

- 50ΩのシングルエンドRFおよびLOポート

- I/Q利得ミスマッチ: 標準0.2dB

- I/Q位相ミスマッチ: 標準1.5°

- 復調器のDCオフセットを電圧で調整可能

- SNR: 76dB/1.92MHz(LTM9004-AA)

- SFDR: 63.5dB(LTM9004-AA)

- クロック・デューティ・サイクル・スタビライザ

- 低消費電力: 1.83W

- シャットダウン・モードとナップ・モード

- 15mm×22mm LGAパッケージ

## アプリケーション

- 通信機器

- ダイレクトコンバージョン・レシーバ

- セルラー基地局

## 概要

LTM®9004は14ビット、ダイレクトコンバージョン・レシーバ・サブシステムです。μModule®レシーバであるLTM9004は、集積化システム・イン・パッケージ(SiP)技術を利用し、デュアル高速14ビットA/Dコンバータ、ローパス・フィルタ、差動利得段、直交復調器を内蔵しています。カスタム対応については、弊社にお問い合わせください。

LTM9004はゼロIFの通信アプリケーションに最適で、SNRが76dB、SFDRが63.5dBという優れたAC特性を備えています。シグナル・チェーン全体がDC結合されており、DCオフセットを調整する機能を搭載しています。RF入力とLO入力には広帯域トランスを搭載し、50Ωのシングルエンド・インターフェースを提供します。

5V電源がミキサと第1アンプに電力を供給するので、歪みを最小限に抑えることができます。また、3V電源が低消費電力のADC動作を可能にします。独立した電源により、出力が0.5V～3.3Vのロジックをドライブできます。オプションのマルチプレクサにより、2つのチャネルが1つのデジタル出力バスを共用できます。また、オプションのクロック・デューティ・サイクル・スタビライザにより、広範なクロック・デューティ・サイクルにわたって最高速度で高性能を発揮できます。

**△**、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。μModuleはリニアテクノロジー社の登録商標です。他の全ての商標はそれぞれの所有者に所有権があります。

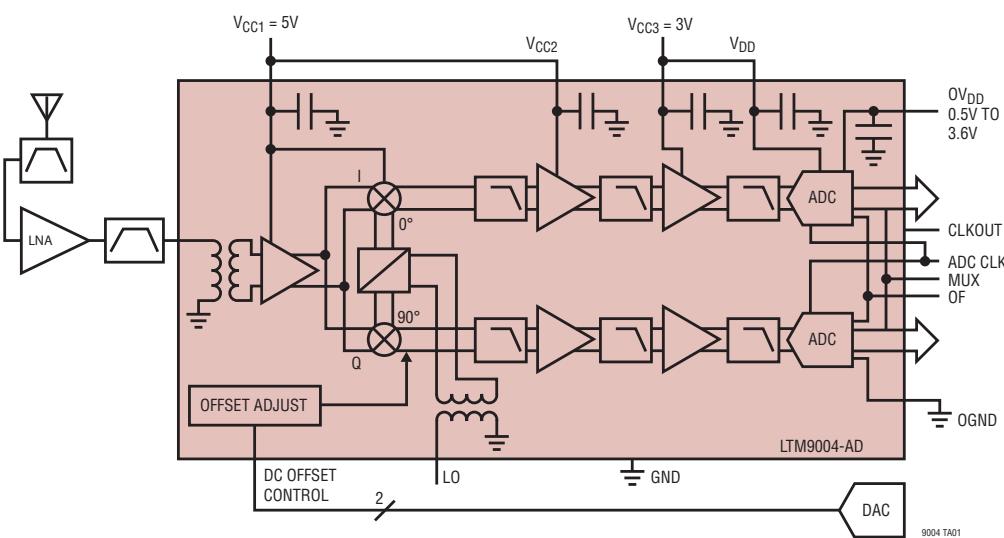

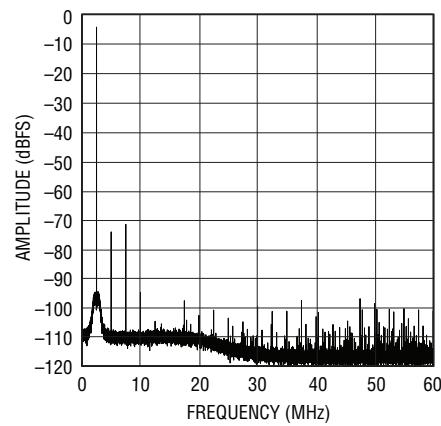

## 標準的応用例

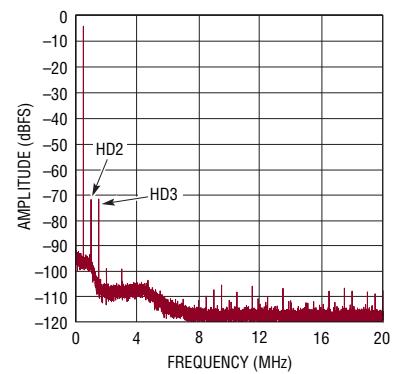

**LTM9004-AA:64kポイントのFFT**

**fIN = 1950.5MHz, -1dBFS**

**SENSE=VDD**

9004fa

# LTM9004

## 絶対最大定格

(Note 1, 2)

|                                             |                               |

|---------------------------------------------|-------------------------------|

| 電源電圧 ( $V_{CC1}$ 、 $V_{CC2}$ )              | -0.3V ~ 5.5V                  |

| 電源電圧<br>( $V_{CC3}$ 、LTM9004-AA、LTM9004-AB) | -0.3V ~ 5.5V                  |

| 電源電圧<br>( $V_{CC3}$ 、LTM9004-AC、LTM9004-AD) | -0.3V ~ 3.5V                  |

| 電源電圧 ( $V_{DD}$ 、 $OV_{DD}$ )               | -0.3V ~ 4.0V                  |

| デジタル出力のグランド電圧 (OGND)                        | -0.3V ~ 1V                    |

| LO入力電力                                      | 10dBm                         |

| RF入力電力                                      | 20dBm                         |

| RF入力のDC電圧                                   | $\pm 0.1V$                    |

| LO入力のDC電圧                                   | $\pm 0.1V$                    |

| $x_{ADJ}$ の入力電圧                             | -0.3V ~ $V_{CC1}$ 、 $V_{CC2}$ |

| SENSE入力の電圧                                  | -0.3V ~ $V_{DD}$              |

| デジタル入力電圧 (MIXENABLE)                        | -0.3V ~ ( $V_{CC1} + 0.3V$ )  |

| デジタル入力電圧 (AMP1ENABLE)                       | -0.3V ~ ( $V_{CC2} + 0.3V$ )  |

| デジタル入力電圧 (AMP2ENABLE)                       | -0.3V ~ ( $V_{CC3} + 0.3V$ )  |

| デジタル入力電圧<br>(MIXENABLEとAMPxENABLEを除く)       | -0.3V ~ ( $V_{DD} + 0.3V$ )   |

| デジタル出力電圧                                    | -0.3V ~ ( $OV_{DD} + 0.3V$ )  |

| 動作温度範囲                                      |                               |

| LTM9004C                                    | 0°C ~ 70°C                    |

| LTM9004I                                    | -40°C ~ 85°C                  |

| 保存温度範囲                                      | -65°C ~ 125°C                 |

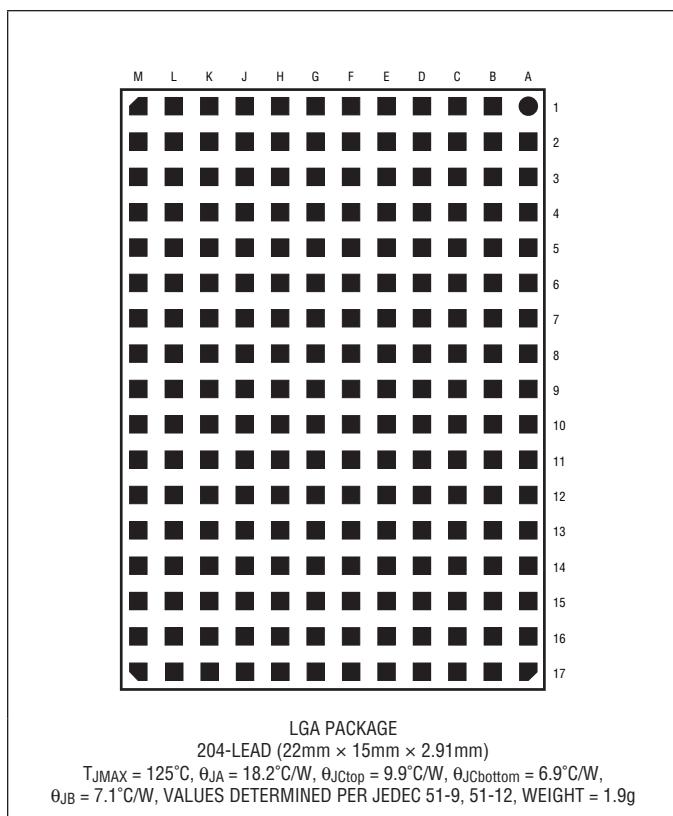

## ピン配置

LGA PACKAGE

204-LEAD (22mm × 15mm × 2.91mm)

$T_{JMAX} = 125^{\circ}\text{C}$ ,  $\theta_{JA} = 18.2^{\circ}\text{C/W}$ ,  $\theta_{JCtop} = 9.9^{\circ}\text{C/W}$ ,  $\theta_{JCbottom} = 6.9^{\circ}\text{C/W}$ ,

$\theta_{JB} = 7.1^{\circ}\text{C/W}$ , VALUES DETERMINED PER JEDEC 51-9, 51-12, WEIGHT = 1.9g

注意: このデバイスは静電気放電 (ESD) に敏感です。

LTM9004のRF入力とLO入力を扱うときは適切なESD対策をとることが非常に重要です。

## 発注情報

| 無鉛仕上げ            | トレイ              | 製品マーキング*    | パッケージ                               | 温度範囲          |

|------------------|------------------|-------------|-------------------------------------|---------------|

| LTM9004CV-AA#PBF | LTM9004CV-AA#PBF | LTM9004V AA | 204-Lead (15mm × 22mm × 2.91mm) LGA | 0°C to 70°C   |

| LTM9004IV-AA#PBF | LTM9004IV-AA#PBF | LTM9004V AA | 204-Lead (15mm × 22mm × 2.91mm) LGA | -40°C to 85°C |

| LTM9004CV-AB#PBF | LTM9004CV-AB#PBF | LTM9004V AB | 204-Lead (15mm × 22mm × 2.91mm) LGA | 0°C to 70°C   |

| LTM9004IV-AB#PBF | LTM9004IV-AB#PBF | LTM9004V AB | 204-Lead (15mm × 22mm × 2.91mm) LGA | -40°C to 85°C |

| LTM9004CV-AC#PBF | LTM9004CV-AC#PBF | LTM9004V AC | 204-Lead (15mm × 22mm × 2.91mm) LGA | 0°C to 70°C   |

| LTM9004IV-AC#PBF | LTM9004IV-AC#PBF | LTM9004V AC | 204-Lead (15mm × 22mm × 2.91mm) LGA | -40°C to 85°C |

| LTM9004CV-AD#PBF | LTM9004CV-AD#PBF | LTM9004V AD | 204-Lead (15mm × 22mm × 2.91mm) LGA | 0°C to 70°C   |

| LTM9004IV-AD#PBF | LTM9004IV-AD#PBF | LTM9004V AD | 204-Lead (15mm × 22mm × 2.91mm) LGA | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

この製品はトレイでのみ供給されます。詳細については、<http://www.linear-tech.co.jp/packaging/> をご覧ください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC1} = V_{CC2} = 5\text{V}$ 、 $V_{DD} = 0\text{V}$ 、 $V_{DD} = 3\text{V}$ 、 $V_{CC3} = 3\text{V}$ (LTM9004-AC、LTM9004-AD)、 $V_{CC3} = 5\text{V}$ (LTM9004-AA、LTM9004-AB)、 $P_{LO} = 0\text{dBm}$ 。(Note 3)

| SYMBOL           | PARAMETER                        | CONDITIONS                                                                                                         | MIN | TYP                                                | MAX | UNITS                        |

|------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------|-----|------------------------------|

|                  | RF Input Frequency Range         | No External Matching (High Band)<br>With External Matching (Low Band, Mid Band)                                    |     | 1.5 to 2.7<br>0.7 to 1.5                           |     | GHz<br>GHz                   |

|                  | LO Input Frequency Range         | No External Matching (High Band)<br>With External Matching (Low Band, Mid Band)                                    |     | 1.5 to 2.7<br>0.7 to 1.5                           |     | GHz<br>GHz                   |

|                  | Baseband Frequency Range         | LTM9004-AA<br>LTM9004-AB<br>LTM9004-AC<br>LTM9004-AD                                                               |     | DC to 1.92<br>DC to 4.42<br>DC to 9.42<br>DC to 20 |     | MHz<br>MHz<br>MHz<br>MHz     |

|                  | RF Input Return Loss             | $Z_0 = 50\Omega$ , 1.5GHz to 2.7GHz, Internally Matched                                                            |     | >10                                                |     | dB                           |

|                  | LO Input Return Loss             | $Z_0 = 50\Omega$ , 1.5GHz to 2.7GHz, Internally Matched                                                            |     | >10                                                |     | dB                           |

|                  | RF Input Power for -1dBFS        | RF = 1950MHz                                                                                                       |     | -7.3                                               |     | dBm                          |

|                  | LO Input Power                   |                                                                                                                    |     | -13 to 5                                           |     | dBm                          |

|                  | I/Q Gain Mismatch                |                                                                                                                    |     | 0.2                                                |     | dB                           |

|                  | I/Q Phase Mismatch               |                                                                                                                    |     | 1.5                                                |     | Deg                          |

|                  | LO to RF Leakage                 | RF = 900MHz<br>RF = 1900MHz                                                                                        |     | -60.8<br>-64.6                                     |     | dBm<br>dBm                   |

|                  | RF to LO Isolation               | RF = 900MHz<br>RF = 1900MHz                                                                                        |     | 59.7<br>57.1                                       |     | dB<br>dB                     |

|                  | Maximum DC Offset Voltage, No RF | (Note 5)                                                                                                           |     | 35                                                 |     | mV                           |

|                  | DC Offset Variation              | -40°C to 85°C                                                                                                      |     | 210                                                |     | µV/°C                        |

|                  | Gain Flatness                    | DC to 1.92MHz (LTM9004-AA)<br>DC to 4.42MHz (LTM9004-AB)<br>DC to 9.42MHz (LTM9004-AC)<br>DC to 20MHz (LTM9004-AD) |     | 0.2<br>0.2<br>0.2<br>0.3                           |     | dB<br>dB<br>dB<br>dB         |

|                  | Group Delay Flatness             | DC to 1.92MHz (LTM9004-AA)<br>DC to 4.42MHz (LTM9004-AB)<br>DC to 9.42MHz (LTM9004-AC)<br>DC to 20MHz (LTM9004-AD) |     | 15<br>15<br>15<br>5                                |     | nsec<br>nsec<br>nsec<br>nsec |

| f <sub>LPF</sub> | Rejection                        | LTM9004-AA<br>5MHz<br>10MHz                                                                                        |     | 5.3<br>33.5                                        |     | dB<br>dB                     |

|                  |                                  | LTM9004-AB<br>7.5MHz<br>12.5MHz                                                                                    |     | 1<br>11                                            |     | dB<br>dB                     |

|                  |                                  | LTM9004-AC<br>12.5MHz<br>17.5MHz                                                                                   |     | 0.5<br>1                                           |     | dB<br>dB                     |

|                  |                                  | LTM9004-AD<br>30MHz<br>40MHz                                                                                       |     | 1.5<br>5.5                                         |     | dB<br>dB                     |

| f <sub>LPF</sub> | Lowpass Filter Cutoff Frequency  | 1dB Point (LTM9004-AA)<br>1dB Point (LTM9004-AB)<br>1dB Point (LTM9004-AC)<br>1dB Point (LTM9004-AD)               |     | 4<br>6.3<br>15<br>28                               |     | MHz<br>MHz<br>MHz<br>MHz     |

# LTM9004

## ダイナミック精度

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC1} = V_{CC2} = 5\text{V}$ 、 $V_{DD} = 0\text{V}$ 、 $V_{DD} = 3\text{V}$ 、 $V_{CC3} = 3\text{V}$ (LTM9004-AC、LTM9004-AD)、 $V_{CC3} = 5\text{V}$ (LTM9004-AA、LTM9004-AB)、 $P_{LO} = 0\text{dBm}$ 。

| SYMBOL  | PARAMETER                                                          | CONDITIONS                                                                                                                                                                                   | MIN              | TYP                          | MAX                        | UNITS                                              |

|---------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------|----------------------------|----------------------------------------------------|

| IIP3    | Input 3rd-Order Intercept, 1 Tone                                  |                                                                                                                                                                                              |                  | 22                           |                            | dBm                                                |

| IIP2    | Input 2nd-Order Intercept, 1 Tone                                  |                                                                                                                                                                                              |                  | 58                           |                            | dBm                                                |

| SNR     | Signal-to-Noise Ratio at $-1\text{dBFS}$                           | 1.92MHz (LTM9004-AA)<br>4.42MHz (LTM9004-AB)<br>9.42MHz (LTM9004-AC)<br>20MHz (LTM9004-AD)                                                                                                   | ●<br>●<br>●<br>● | 70.6<br>69.7<br>70.3<br>66.3 | 76.1<br>75.2<br>72<br>68.9 | dB/1.92MHz<br>dB/4.42MHz<br>dB/9.42MHz<br>dB/20MHz |

| SFDR    | Spurious Free Dynamic Range 2nd or 3rd Harmonic at $-1\text{dBFS}$ | LTM9004-AA<br>RF = 1950.5MHz, LO = 1950MHz<br><br>LTM9004-AB<br>RF = 1951MHz, LO = 1950MHz<br><br>LTM9004-AC<br>RF = 1952.5MHz, LO = 1950MHz<br><br>LTM9004-AD<br>RF = 1955MHz, LO = 1950MHz | ●<br>●<br>●<br>● | 50<br>50<br>52.5<br>55       | 63.5<br>65<br>66<br>64     | dB                                                 |

| SFDR    | Spurious Free Dynamic Range 4th or Higher at $-1\text{dBFS}$       | LTM9004-AA<br>RF = 1950.5MHz, LO = 1950MHz<br><br>LTM9004-AB<br>RF = 1951MHz, LO = 1950MHz<br><br>LTM9004-AC<br>RF = 1952.5MHz, LO = 1950MHz<br><br>LTM9004-AD<br>RF = 1955MHz, LO = 1950MHz | ●<br>●<br>●<br>● | 65<br>70<br>70<br>70         | 88<br>91<br>89<br>89       | dB                                                 |

| S/(N+D) | Signal-to-Noise Plus Distortion Ratio at $-1\text{dBFS}$           | LTM9004-AA<br>RF = 1950.5MHz, LO = 1950MHz<br><br>LTM9004-AB<br>RF = 1951MHz, LO = 1950MHz<br><br>LTM9004-AC<br>RF = 1952.5MHz, LO = 1950MHz<br><br>LTM9004-AD<br>RF = 1955MHz, LO = 1950MHz | ●<br>●<br>●<br>● | 51.5<br>51.5<br>53<br>53     | 58.5<br>60<br>61<br>60     | dB                                                 |

| HD2     | 2nd Order Harmonic Distortion Ratio at $-1\text{dBFS}$             | LTM9004-AA<br>RF = 1950.5MHz, LO = 1950MHz<br><br>LTM9004-AB<br>RF = 1951MHz, LO = 1950MHz<br><br>LTM9004-AC<br>RF = 1952.5MHz, LO = 1950MHz<br><br>LTM9004-AD<br>RF = 1955MHz, LO = 1950MHz |                  |                              | 64<br>66<br>66<br>64       | dB                                                 |

| HD3     | 3rd Order Harmonic Distortion Ratio at $-1\text{dBFS}$             | LTM9004-AA<br>RF = 1950.5MHz, LO = 1950MHz<br><br>LTM9004-AB<br>RF = 1951MHz, LO = 1950MHz<br><br>LTM9004-AC<br>RF = 1952.5MHz, LO = 1950MHz<br><br>LTM9004-AD<br>RF = 1955MHz, LO = 1950MHz |                  |                              | 69<br>66<br>67<br>67       | dB                                                 |

## コンバータ特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC1} = V_{CC2} = 5\text{V}$ 、 $V_{DD} = 0\text{V}$ 、 $V_{DD} = 3\text{V}$ 。

$V_{CC3} = 3\text{V}$ (LTM9004-AC、LTM9004-AD)、 $V_{CC3} = 5\text{V}$ (LTM9004-AA、LTM9004-AB)

| SYMBOL | PARAMETER                         | CONDITIONS                | MIN | TYP | MAX       | UNITS |

|--------|-----------------------------------|---------------------------|-----|-----|-----------|-------|

|        | Resolution (No Missing Codes)     |                           | ●   | 14  |           | Bits  |

|        | Integral Linearity Error (Note 4) | Differential Analog Input |     |     | $\pm 1.5$ | LSB   |

|        | Differential Linearity Error      | Differential Analog Input |     |     | $\pm 1$   | LSB   |

## デジタル入力とデジタル出力

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC1} = V_{CC2} = 5\text{V}$ 、 $V_{DD} = 0\text{V}$ 、 $V_{DD} = 3\text{V}$ 。

$V_{CC3} = 3\text{V}$ (LTM9004-AC、LTM9004-AD)、 $V_{CC3} = 5\text{V}$ (LTM9004-AA、LTM9004-AB)

| SYMBOL | PARAMETER | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------|-----------|------------|-----|-----|-----|-------|

|--------|-----------|------------|-----|-----|-----|-------|

### ミキサのロジック入力(MIXENABLE)

|          |                          |                       |   |     |   |               |

|----------|--------------------------|-----------------------|---|-----|---|---------------|

| $V_{IH}$ | High Level Input Voltage | $V_{CC1} = 5\text{V}$ | ● | 2   |   | V             |

| $V_{IL}$ | Low Level Input Voltage  | $V_{CC1} = 5\text{V}$ | ● |     | 1 | V             |

| $I_{IN}$ | Input Current            | $V_{IN} = V_{CC1}$    |   | 120 |   | $\mu\text{A}$ |

|          | Turn On Time             |                       |   | 120 |   | ns            |

|          | Turn Off Time            |                       |   | 750 |   | ns            |

### 1番目のアンプのロジック入力(AMP1ENABLE)

|          |                          |                                                                       |   |      |     |                  |   |

|----------|--------------------------|-----------------------------------------------------------------------|---|------|-----|------------------|---|

| $V_{IH}$ | High Level Input Voltage | $V_{CC2} = 5\text{V}$                                                 | ● | 2.55 | 2   | V                |   |

| $V_{IL}$ | Low Level Input Voltage  | $V_{CC2} = 5\text{V}$                                                 | ● |      | 1.8 | 1.25             | V |

| $R_{IN}$ | Input Pull-Up Resistance | $V_{CC2} = 5\text{V}$ , $V_{AMP1ENABLE} = 0\text{V}$ to $0.5\text{V}$ |   | 25   | 70  | $\text{k}\Omega$ |   |

|          | Turn On Time             |                                                                       |   | 200  |     | ns               |   |

|          | Turn Off Time            |                                                                       |   | 50   |     | ns               |   |

### 2番目のアンプのロジック入力(AMP2ENABLE, LTM9004-AA, LTM9004-AB)

|          |                          |                                                                       |   |                 |                 |                  |

|----------|--------------------------|-----------------------------------------------------------------------|---|-----------------|-----------------|------------------|

| $V_{IH}$ | High Level Input Voltage | $V_{CC3} = 5\text{V}$                                                 | ● | $V_{CC3} - 0.6$ |                 | V                |

| $V_{IL}$ | Low Level Input Voltage  | $V_{CC3} = 5\text{V}$                                                 | ● |                 | $V_{CC3} - 2.1$ | V                |

| $R_{IN}$ | Input Pull-Up Resistance | $V_{CC3} = 5\text{V}$ , $V_{AMP2ENABLE} = 2.9\text{V}$ to $0\text{V}$ |   | 40              | 66              | $\text{k}\Omega$ |

|          | Turn On Time             |                                                                       |   | 4               |                 | $\mu\text{s}$    |

|          | Turn Off Time            |                                                                       |   | 350             |                 | ns               |

### 2番目のアンプのロジック入力(AMP2ENABLE, LTM9004-AC, LTM9004-AD)

|          |                          |                                                                       |   |      |      |     |                  |

|----------|--------------------------|-----------------------------------------------------------------------|---|------|------|-----|------------------|

| $V_{IH}$ | High Level Input Voltage | $V_{CC3} = 3\text{V}$                                                 | ● | 2.55 | 2.25 | V   |                  |

| $V_{IL}$ | Low Level Input Voltage  | $V_{CC3} = 3\text{V}$                                                 | ● |      | 0.7  | 0.4 | V                |

| $R_{IN}$ | Input Pull-Up Resistance | $V_{CC3} = 3\text{V}$ , $V_{AMP2ENABLE} = 0\text{V}$ to $0.5\text{V}$ |   | 60   | 100  | 140 | $\text{k}\Omega$ |

|          | Turn On Time             |                                                                       |   | 200  |      | ns  |                  |

|          | Turn Off Time            |                                                                       |   | 50   |      | ns  |                  |

### ADCのロジック入力(CLK, OE, ADCSHDN, MODE, MUX)

|             |                          |                                        |   |     |     |               |

|-------------|--------------------------|----------------------------------------|---|-----|-----|---------------|

| $V_{IH}$    | High Level Input Voltage | $V_{DD} = 3\text{V}$                   | ● | 2   |     | V             |

| $V_{IL}$    | Low Level Input Voltage  | $V_{DD} = 3\text{V}$                   | ● |     | 0.8 | V             |

| $I_{IN}$    | Input Current            | $V_{IN} = 0\text{V}$ to $V_{DD}$       | ● | -10 | 10  | $\mu\text{A}$ |

| $C_{IN}$    | Input Capacitance        | (Note 6)                               |   | 3   |     | $\text{pF}$   |

| $I_{SENSE}$ | SENSE Input Leakage      | $0\text{V} < \text{SENSE} < 1\text{V}$ | ● | -3  | 3   | $\mu\text{A}$ |

| $I_{MODE}$  | MODE Input Leakage       | $0\text{V} < \text{MODE} < V_{DD}$     | ● | -3  | 3   | $\mu\text{A}$ |

9004fa

# LTM9004

## デジタル入力とデジタル出力

- は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC1} = V_{CC2} = 5\text{V}$ 、 $V_{DD} = 0$ 、 $V_{DD} = 3\text{V}$ 。

$V_{CC3} = 3\text{V}$ (LTM9004-AC、LTM9004-AD)、 $V_{CC3} = 5\text{V}$ (LTM9004-AA、LTM9004-AB)

| SYMBOL                 | PARAMETER                 | CONDITIONS                                        | MIN       | TYP           | MAX | UNITS |

|------------------------|---------------------------|---------------------------------------------------|-----------|---------------|-----|-------|

| ロジック出力                 |                           |                                                   |           |               |     |       |

| $V_{DD} = 3\text{V}$   |                           |                                                   |           |               |     |       |

| $C_{OZ}$               | Hi-Z Output Capacitance   | $\bar{OE} = 3\text{V}$ (Note 6)                   |           | 3             |     | pF    |

| $I_{SOURCE}$           | Output Source Current     | $V_{OUT} = 0\text{V}$                             |           | 50            |     | mA    |

| $I_{SINK}$             | Output Sink Current       | $V_{OUT} = 3\text{V}$                             |           | 50            |     | mA    |

| $V_{OH}$               | High Level Output Voltage | $I_0 = -10\mu\text{A}$<br>$I_0 = -200\mu\text{A}$ | ●<br>2.7  | 2.995<br>2.99 |     | V     |

| $V_{OL}$               | Low Level Output Voltage  | $I_0 = 10\mu\text{A}$<br>$I_0 = 1.6\text{mA}$     | ●<br>0.09 | 0.005<br>0.09 | 0.4 | V     |

| $V_{DD} = 2.5\text{V}$ |                           |                                                   |           |               |     |       |

| $V_{OH}$               | High Level Output Voltage | $I_0 = -200\mu\text{A}$                           |           | 2.49          |     | V     |

| $V_{OL}$               | Low Level Output Voltage  | $I_0 = 1.6\text{mA}$                              |           | 0.09          |     | V     |

| $V_{DD} = 1.8\text{V}$ |                           |                                                   |           |               |     |       |

| $V_{OH}$               | High Level Output Voltage | $I_0 = -200\mu\text{A}$                           |           | 1.79          |     | V     |

| $V_{OL}$               | Low Level Output Voltage  | $I_0 = 1.6\text{mA}$                              |           | 0.09          |     | V     |

## 電源要件

- は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC1} = V_{CC2} = 5\text{V}$ 、 $V_{DD} = 0$ 、 $V_{DD} = 3\text{V}$ 。

$V_{CC3} = 3\text{V}$ (LTM9004-AC、LTM9004-AD)、 $V_{CC3} = 5\text{V}$ (LTM9004-AA、LTM9004-AB) (Note 3)

| SYMBOL          | PARAMETER                         | CONDITIONS                                                                                                                                                              | MIN      | TYP      | MAX         | UNITS |

|-----------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------------|-------|

| $V_{CC1}$       | Mixer Supply Voltage              |                                                                                                                                                                         | ●<br>4.5 | 5.25     |             | V     |

| $V_{CC2}$       | First Amplifier Supply Voltage    |                                                                                                                                                                         | ●<br>4.5 | 5.25     |             | V     |

| $V_{CC3}$       | Second Amplifier Supply Voltage   | LTM9004-AA, LTM9004-AB<br>LTM9004-AC, LTM9004-AD                                                                                                                        | ●<br>2.7 | 4.5<br>3 | 5.25<br>3.5 | V     |

| $V_{DD}$        | ADC Analog Supply Voltage         |                                                                                                                                                                         | ●<br>2.7 | 3        | 3.6         | V     |

| $V_{DD}$        | ADC Digital Output Supply Voltage |                                                                                                                                                                         | ●<br>0.5 | 3        | 3.6         | V     |

| $I_{CC1}$       | Mixer Supply Current              |                                                                                                                                                                         | ●<br>129 | 180      |             | mA    |

| $I_{CC1(SHDN)}$ | Mixer Shutdown Current            | $\text{MIXENABLE} = 0\text{V}$ , $\text{AMPxENABLE} = \text{HIGH}$ ,<br>$\text{ADCSHDN} = 0\text{V}$ , $\bar{OE} = 0\text{V}$                                           | ●<br>10  | 11       |             | mA    |

| $I_{CC2}$       | First Amplifier Supply Current    |                                                                                                                                                                         | ●<br>52  | 63       |             | mA    |

| $I_{CC2(SHDN)}$ | First Amplifier Shutdown Current  | $\text{MIXENABLE} = 5\text{V}$ , $\text{AMP1ENABLE} = 0\text{V}$ ,<br>$\text{AMP2ENABLE} = \text{HIGH}$ , $\text{ADCSHDN} = 0\text{V}$ ,<br>$\bar{OE} = 0\text{V}$      | ●<br>7.5 | 9        |             | mA    |

| $I_{CC3}$       | Second Amplifier Supply Current   | LTM9004-AA, LTM9004-AB                                                                                                                                                  | ●<br>21  | 24       |             | mA    |

| $I_{CC3(SHDN)}$ | Second Amplifier Shutdown Current | LTM9004-AA, LTM9004-AB, $\text{MIXENABLE} = \text{AMP1ENABLE} = 5\text{V}$ , $\text{AMP2ENABLE} = 0\text{V}$ ,<br>$\text{ADCSHDN} = 0\text{V}$ , $\bar{OE} = 0\text{V}$ | ●<br>0.8 | 4        |             | mA    |

| $I_{CC3}$       | Second Amplifier Supply Current   | LTM9004-AC, LTM9004-AD                                                                                                                                                  | ●<br>36  | 44       |             | mA    |

| $I_{CC3(SHDN)}$ | Second Amplifier Shutdown Current | LTM9004-AC, LTM9004-AD, $\text{MIXENABLE} = \text{AMP1ENABLE} = 5\text{V}$ , $\text{AMP2ENABLE} = 0\text{V}$ ,<br>$\text{ADCSHDN} = 0\text{V}$ , $\bar{OE} = 0\text{V}$ | ●<br>0.6 | 4        |             | mA    |

| $I_{DD}$        | ADC Supply Current                |                                                                                                                                                                         | ●<br>273 | 306      |             | mA    |

9004fa

## 電源要件

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC1} = V_{CC2} = 5\text{V}$ 、 $V_{DD} = 0\text{V}$ 、 $V_{DD} = 3\text{V}$ 。

$V_{CC3} = 3\text{V}$ (LTM9004-AC、LTM9004-AD)、 $V_{CC3} = 5\text{V}$ (LTM9004-AA、LTM9004-AB) (Note 3)

| SYMBOL         | PARAMETER               | CONDITIONS                                                                                                  | MIN | TYP  | MAX | UNITS |

|----------------|-------------------------|-------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| $P_{D(SLEEP)}$ | Sleep Power             | MIXENABLE = AMPxENABLE = 0V, ADCSHDN = 3V, $\overline{OE}$ = 3V, No CLK                                     |     | 7    |     | mW    |

| $P_{D(NAP)}$   | Nap Mode Power          | MIXENABLE = AMPxENABLE = 0V, ADCSHDN = 3V, $\overline{OE}$ = 0V, No CLK                                     |     | 33   |     | mW    |

| $P_{D(TOTAL)}$ | Total Power Dissipation | LTM9004-AA, LTM9004_AB,<br>MIXENABLE = AMP1ENABLE = AMP2ENABLE = 5V, ADCSHDN = 0V, $f_{SAMPLE}$ = MAX       |     | 1.83 |     | W     |

|                |                         | LTM9004-AC, LTM9004-AD<br>MIXENABLE = AMP1ENABLE = 5V,<br>AMP2ENABLE = 3V, ADCSHDN = 0V, $f_{SAMPLE}$ = MAX |     | 1.83 |     | W     |

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC1} = V_{CC2} = 5\text{V}$ 、 $V_{DD} = 0\text{V}$ 、 $V_{DD} = 3\text{V}$ 。

$V_{CC3} = 3\text{V}$ (LTM9004-AC、LTM9004-AD)、 $V_{CC3} = 5\text{V}$ (LTM9004-AA、LTM9004-AB)

| SYMBOL       | PARAMETER                                         | CONDITIONS                         | MIN | TYP  | MAX | UNITS  |

|--------------|---------------------------------------------------|------------------------------------|-----|------|-----|--------|

| $f_s$        | Sampling Frequency                                |                                    | ●   | 1    | 125 | MHz    |

| $t_L$        | CLK Low Time                                      | Duty Cycle Stabilizer Off (Note 6) | ●   | 3.8  | 4   | 500    |

|              |                                                   | Duty Cycle Stabilizer Off (Note 6) | ●   | 3    | 4   | 500    |

| $t_H$        | CLK High Time                                     | Duty Cycle Stabilizer Off (Note 6) | ●   | 3.8  | 4   | 500    |

|              |                                                   | Duty Cycle Stabilizer Off (Note 6) | ●   | 3    | 4   | 500    |

| $t_{JITTER}$ | Sample-and-Hold Acquisition Delay Time Jitter     |                                    |     | 0.2  |     | psRMS  |

| $t_{AP}$     | Sample-and-Hold Aperture Delay                    |                                    |     | 0    |     | ns     |

| $t_D$        | CLK to DATA delay                                 | $C_L = 5\text{pF}$ (Note 6)        | ●   | 1.4  | 2.7 | 5.4    |

|              | DATA to CLKOUT Skew                               | $(t_D - t_C)$ (Note 6)             | ●   | -0.6 | 0   | 0.6    |

| $t_C$        | MUX to DATA Delay                                 | $C_L = 5\text{pF}$ (Note 6)        | ●   | 1.4  | 2.7 | 5.4    |

|              | DATA Access Time After $\overline{OE} \downarrow$ | $C_L = 5\text{pF}$ (Note 6)        | ●   |      | 4.3 | 10     |

|              | BUS Relinquish Time                               | (Note 6)                           | ●   |      | 3.3 | 8.5    |

|              | Pipeline Latency                                  |                                    |     | 5    |     | Cycles |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** 全ての電圧値は(注記がない限り)GNDとOGNDを結線したグランドを基準にしている。

**Note 3:** 注記がない限り、 $f_{SAMPLE} = 125\text{MHz}$ 、 $\text{CLKI} = \text{CLKO}$ 。

**Note 4:** 積分非直線性は、実際の伝達曲線のエンドポイントを通る直線からのコードの偏差として定義されている。偏差は量子化幅の中心から測定される。

**Note 5:** DCオフセット電圧は、L0信号が与えられているがRF信号は与えられていない状態での出力コードに対応したDC電圧として定義されている。

**Note 6:** 設計によって保証されているが、テストされない。

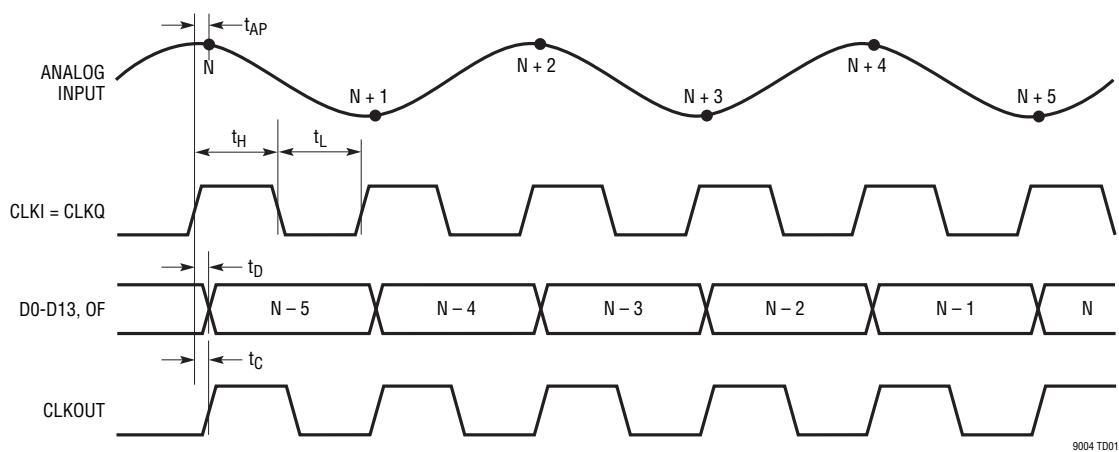

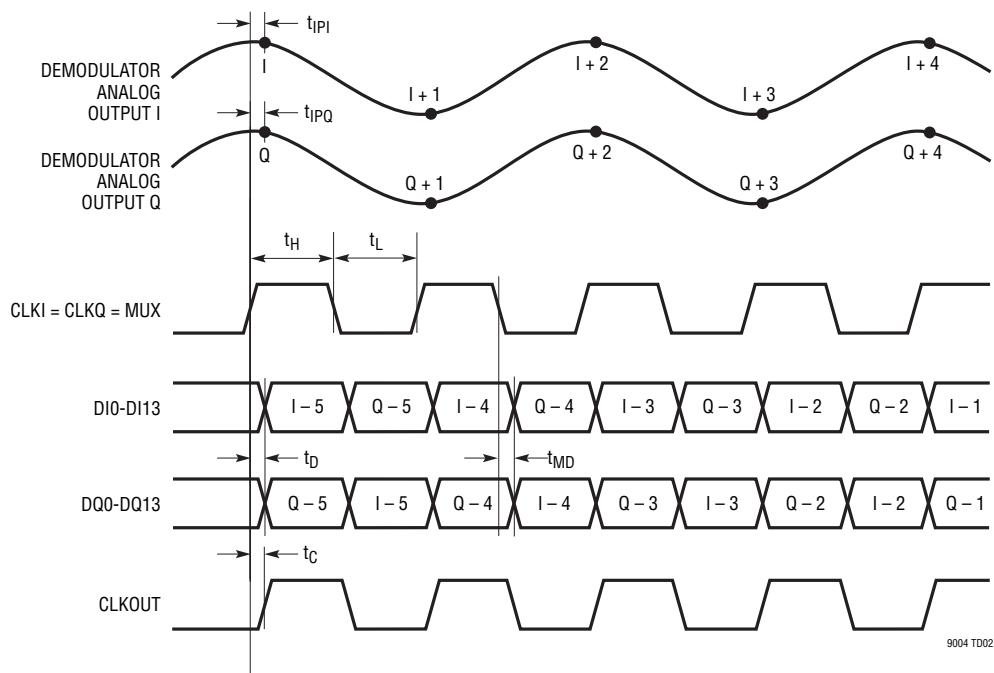

## タイミング図

デュアル・デジタル出力バスのタイミング

多重化されたデジタル出力バスのタイミング

## 標準的性能特性

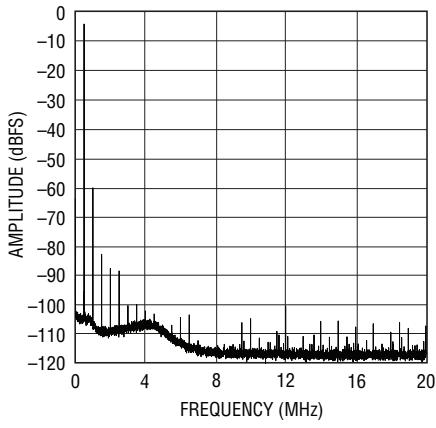

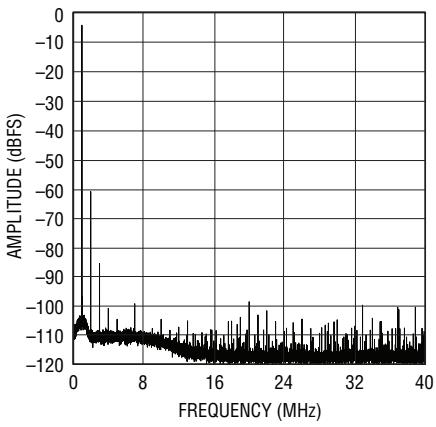

**LTM9004-AA: 64k ポイントの FFT**

$f_{IN} = 700.5\text{MHz}$ , -1dBFS

SENSE =  $V_{DD}$

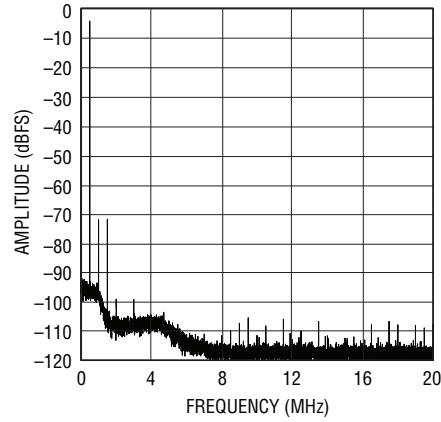

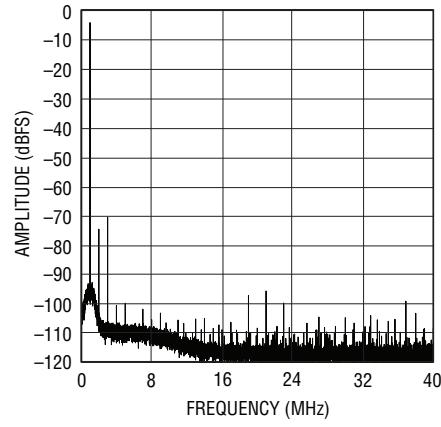

**LTM9004-AA: 64k ポイントの FFT**

$f_{IN} = 1950.5\text{MHz}$ , -1dBFS

SENSE =  $V_{DD}$

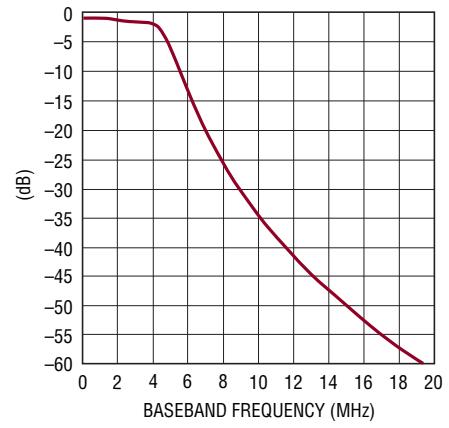

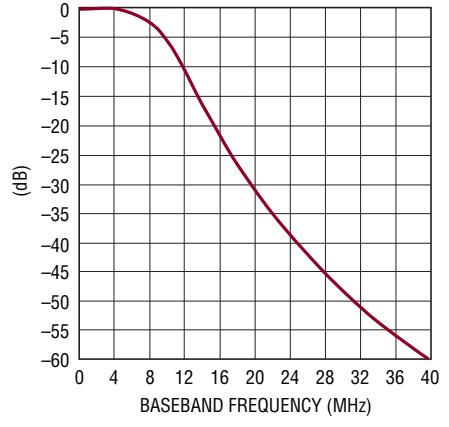

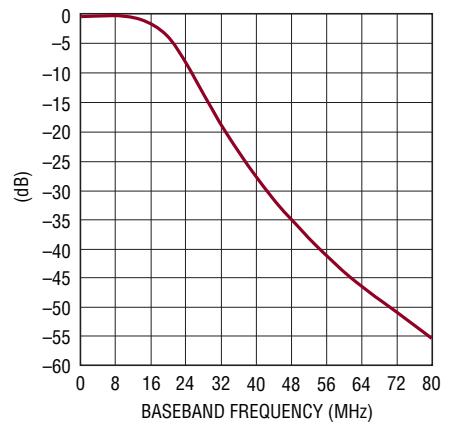

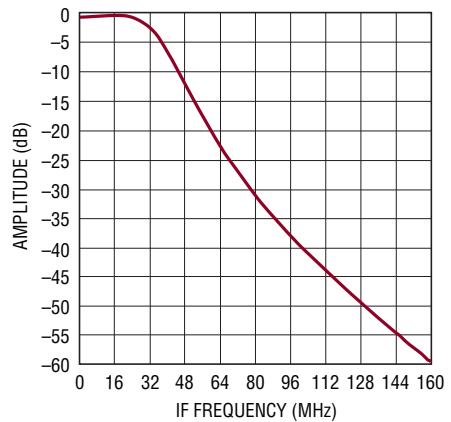

**LTM9004-AA、**

**ベースバンド周波数応答**

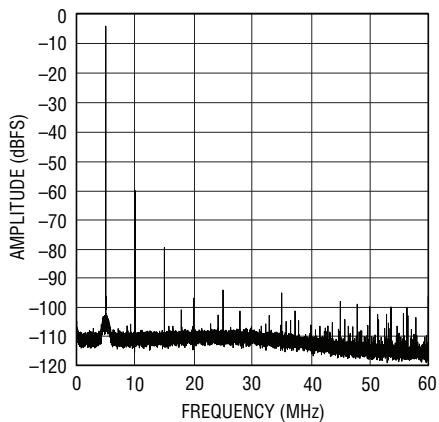

**LTM9004-AB: 64k ポイントの FFT**

$f_{IN} = 701.0\text{MHz}$ , -1dBFS

SENSE =  $V_{DD}$

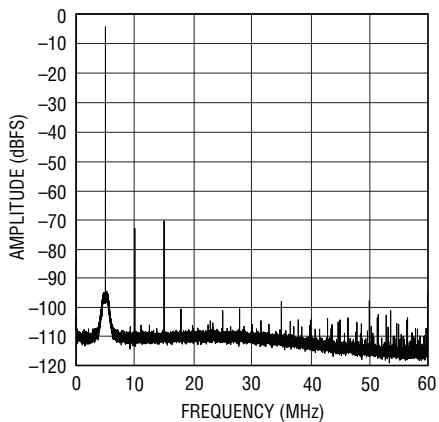

**LTM9004-AB: 64k ポイントの FFT**

$f_{IN} = 1951.0\text{MHz}$ , -1dBFS

SENSE =  $V_{DD}$

**LTM9004-AB、**

**ベースバンド周波数応答**

**LTM9004-AC: 64k ポイントの FFT**

$f_{IN} = 702.5\text{MHz}$ , -1dBFS

SENSE =  $V_{DD}$

**LTM9004-AC: 64k ポイントの FFT**

$f_{IN} = 1952.5\text{MHz}$ , -1dBFS

SENSE =  $V_{DD}$

**LTM9004-AC、**

**ベースバンド周波数応答**

# LTM9004

## 標準的性能特性

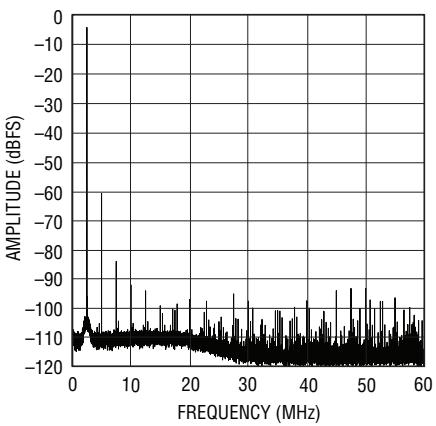

**LTM9004-AD: 64k ポイントの FFT**

$f_{IN} = 705.0\text{MHz}$ , -1dBFS

SENSE =  $V_{DD}$

9004 G07

**LTM9004-AD: 64k ポイントの FFT**

$f_{IN} = 1955.0\text{MHz}$ , -1dBFS

SENSE =  $V_{DD}$

9004 G08

**LTM9004-AD、

ベースバンド周波数応答**

9004 G09

9004fa

## ピン機能

### 電源ピン

**V<sub>CC1</sub>(ピンG5、H2)、V<sub>CC2</sub>(ピンC5、C8、K5、K8)**：ミキサおよび1番目のアンプのアナログ5V電源。規定動作範囲は4.5V～5.25Vです。このピンの電圧はミキサおよびアンプ段にだけ電力を供給し、内部でGNDにバイパスされています。

**V<sub>CC3</sub>(ピンC9、C12、K9、K12)**：2番目のアンプのアナログ電源。LTM9004-AAとLTM9004-ABの場合、規定動作範囲は4.5V～5.5Vです。LTM9004-ACとLTM9004-ADの場合、規定動作範囲は2.7V～3.5Vです。V<sub>CC3</sub>は内部でGNDにバイパスされています。

**V<sub>DD</sub>(ピンD14、F13、G13、J14)**：ADC用アナログ3V電源。規定動作範囲は2.7V～3.6Vです。V<sub>DD</sub>は内部でGNDにバイパスされています。

**OV<sub>DD</sub>(ピンD17、J17)**：デジタル出力ドライバの正電源。規定動作範囲は0.5V～3.6Vです。OV<sub>DD</sub>は内部でOGNDにバイパスされています。

**GND(ピン配置については表を参照)**：アナログ・グランド。

**OGND(ピンC17、K17)**：デジタル出力ドライバのグランド。

### アナログ入力

**RF(ピンE2)**：RF入力ピン。これは50Ωで終端されたシングルエンド入力です。高周波数帯域のための外部整合ネットワークは不要です。700MHz～1.5GHzの低周波数帯域では50Ωへのインピーダンス変換のために、外部直列コンデンサ(およびシャント・コンデンサ)が必要になることがあります(図4を参照)。RFソースがDCブロックされていない場合、直列にブロッキング・コンデンサを使います。そうでないと、デバイスが損傷を受けるおそれがあります。

**LO(ピンH3)**：ローカル発振器の入力ピン。これは50Ωで終端されたシングルエンド入力です。高周波数帯域では外部整合ネットワークは不要です。700MHz～1.5GHzの低周波数帯域では50Ωへのインピーダンス変換のために、外部シャント・コンデンサ(または直列コンデンサ)が必要になることがあります(図6を参照)。LOソースがDCブロックされていない場合、直列にブロッキング・コンデンサを使う必要があります。そうでないと、デバイスが損傷を受けるおそれがあります。

**CLKQ(ピンG14)**：QチャネルADCのクロック入力。立ち上がりエッジで入力のサンプリングが開始されます。CLKQとCLKIと一緒に接続します。

**CLKI(ピンF14)**：IチャネルのADCのクロック入力。立ち上がりエッジで入力のサンプリングが開始されます。CLKQとCLKIと一緒に接続します。

**I<sup>+</sup>\_ADJ(ピンB1)**：Iチャネルの、+ラインのDCオフセット調整ピン。このピンを通して電流をソースまたはシンクしてDCオフセットを調整します。

**I<sup>-</sup>\_ADJ(ピンC1)**：Iチャネルの、-ラインのDCオフセット調整ピン。このピンを通して電流をソースまたはシンクしてDCオフセットを調整します。

**Q<sup>+</sup>\_ADJ(ピンK1)**：Qチャネルの、+ラインのDCオフセット調整ピン。このピンを通して電流をソースまたはシンクしてDCオフセットを調整します。

**Q<sup>-</sup>\_ADJ(ピンL1)**：aQチャネルの、-ラインのDCオフセット調整ピン。このピンを通して電流をソースまたはシンクしてDCオフセットを調整します。

### 制御ピン

**MIXENABLE(ピンE4)**：ミキサ・イネーブル・ピン。MIXENABLE = “H”(入力電圧が2.0Vより上)であれば、ミキサはイネーブルされます。MIXENABLE = “L”(入力電圧が1.0Vより下)であれば、ディスエーブルされます。イネーブル機能が不要なら、このピンをV<sub>CC1</sub>に接続します。

**AMP1ENABLE(ピンD5、L5)**：1番目のアンプのイネーブル・ピン。AMP1ENABLE = “H”またはフロートであれば、各チャネルの1番目のアンプは通常(アクティブ)動作モードになります。AMP1ENABLE = “L”(V<sub>CC2</sub>より最小2.1V下)であれば、1番目のアンプはディスエーブルされます。イネーブル機能が不要なら、このピンをV<sub>CC2</sub>に接続します。

**AMP2ENABLE(ピンC10、L10)**：2番目のアンプのイネーブル・ピン。AMP2ENABLE = “H”またはフロートであれば、各チャネルの2番目のアンプは通常(アクティブ)動作モードになります。AMP2ENABLE = “L”(V<sub>CC3</sub>より最小0.45V下)であれば、2番目のアンプはディスエーブルされます。イネーブル機能が不要なら、このピンをV<sub>CC3</sub>に接続します。

**ADCSHDNQ(ピンJ12)**：QチャネルのADCのシャットダウン・モードの選択ピン。ADCSHDNQとOEQをGNDに接続すると通常動作になり、出力がイネーブルされます。ADCSHDNQをGNDに接続し、OEQをV<sub>DD</sub>に接続すると通常動作になり、出力が高インピーダンスになります。ADCSHDNQをV<sub>DD</sub>に接続し、OEQをGNDに接続するとナップ・モードになり、出力が高インピーダンスになります。ADCSHDNQとOEQをV<sub>DD</sub>に接続するとスリープ・モードになり、出力が高インピーダンスになります。

**ADCSHDNI(ピンD12)**：IチャネルのADCのシャットダウン・モードの選択ピン。ADCSHDNIとOEIをGNDに接続すると

## ピン機能

通常動作になり、出力がイネーブルされます。ADCSHDNIをGNDに接続し、 $\overline{OE}$ をVDDに接続すると通常動作になり、出力が高インピーダンスになります。ADCSHDNIをVDDに接続し、 $\overline{OE}$ をGNDに接続するとナップ・モードになり、出力が高インピーダンスになります。ADCSHDNIと $\overline{OE}$ をVDDに接続するとスリープ・モードになり、出力が高インピーダンスになります。

**SENSEQ(ピンH13)、SENSEI(ピンE13)**：ADCのリファレンスのプログラミング・ピン。通常動作させるにはV<sub>DD</sub>に接続します。外部リファレンスを使うことができます（「ADCのリファレンス」のセクションを参照）。

**MODE(ピンJ13)**：出力のフォーマットとクロック・デューティ・サイクル・スタビライザの選択ピン。MODEは両方のチャネルをコントロールすることに注意してください。MODEをGNDに接続すると、ストレート・バイナリの出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオフします。1/3V<sub>DD</sub>に接続すると、ストレート・バイナリの出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオンします。2/3V<sub>DD</sub>に接続すると、2の補数の出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオンします。V<sub>DD</sub>に接続すると、2の補数の出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがオフします。

**MUX(ピンD13)**：デジタル出力のマルチプレクサ・コントロール。MUX = “H”だと、QチャネルはDQ0～DQ13から出力し、

IチャネルはDI0～DI13から出力します。MUX = “L”だと出力バスが入れ替わり、QチャネルはDI0～DI13から出力し、IチャネルはDQ0～DQ13から出力します。両方のチャネルを1本の出力バスに多重化するにはMUX、CLKQおよびCLKIと一緒に結合します。

**$\overline{OE}$ (ピンK13)**：Qチャネルの出力イネーブル・ピン。ADCSHDNQピンの機能を参照してください。

**$\overline{OE}$ (ピンC13)**：Iチャネルの出力イネーブル・ピン。ADCSHDNIピンの機能を参照してください。

## デジタル出力

**CLKOUT(ピンE12)**：ADCのデータ・レディ・クロック出力。CLKOUTの立ち下がりエッジでデータをラッチします。CLKOUTはCLKQから得られます。同時動作ではCLKQをCLKIに接続します。

**DI0～DI13(ピン配置については表を参照)**：Iチャネル(同相)のADCのデジタル出力。DI13がMSBです。

**DQ0～DQ13(ピン配置については表を参照)**：Qチャネル(直交)のADCのデジタル出力。DQ13がMSBです。

**OF(ピンH12)**：オーバーフロー/アンダーフロー出力。IチャネルまたはQチャネルにオーバーフローまたはアンダーフローが生じると“H”になります。

## ピン配置

|           | A   | B                   | C                   | D                | E      | F    | G    | H      | J                   | K                   | L        | M    |

|-----------|-----|---------------------|---------------------|------------------|--------|------|------|--------|---------------------|---------------------|----------|------|

| <b>1</b>  | ♦ND | ★ <sup>+</sup> _ADJ | ★ <sup>-</sup> _ADJ | ♦ND              | ♦ND    | ♦ND  | ♦ND  | ♦ND    | * <sup>+</sup> _ADJ | * <sup>-</sup> _ADJ | ♦ND      |      |

| <b>2</b>  | ♦ND | ♦ND                 | ♦ND                 | ♦ND              | *F     | ♦ND  | ♦ND  | ★CC1   | ♦ND                 | ♦ND                 | ♦ND      | ♦ND  |

| <b>3</b>  | ♦ND | ♦ND                 | ♦ND                 | ♦ND              | ♦ND    | ♦ND  | ♦ND  | ★O     | ♦ND                 | ♦ND                 | ♦ND      | ♦ND  |

| <b>4</b>  | ♦ND | ♦ND                 | ♦ND                 | ♦ND              | ★IX_EN | ♦ND  | ♦ND  | ♦ND    | ♦ND                 | ♦ND                 | ♦ND      | ♦ND  |

| <b>5</b>  | ♦ND | ♦ND                 | ★CC2                | ★MP1A_EN         | ♦ND    | ♦ND  | ★CC1 | ♦ND    | ♦ND                 | ★CC2                | ★MP1B_EN | ♦ND  |

| <b>6</b>  | ♦ND | ♦ND                 | ♦ND                 | ♦ND              | ♦ND    | ♦ND  | ♦ND  | ♦ND    | ♦ND                 | ♦ND                 | ♦ND      | ♦ND  |

| <b>7</b>  | ♦ND | ♦ND                 | ♦ND                 | ♦ND              | ♦ND    | ♦ND  | ♦ND  | ♦ND    | ♦ND                 | ♦ND                 | ♦ND      | ♦ND  |

| <b>8</b>  | ♦ND | ♦ND                 | ★CC2                | ♦ND              | ♦ND    | ♦ND  | ♦ND  | ♦ND    | ♦ND                 | ★CC2                | ♦ND      | ♦ND  |

| <b>9</b>  | ♦ND | ♦ND                 | ★CC3                | ♦ND              | ♦ND    | ♦ND  | ♦ND  | ♦ND    | ♦ND                 | ★CC3                | ♦ND      | ♦ND  |

| <b>10</b> | ♦ND | ♦ND                 | ★MP2A_EN            | ♦ND              | ♦ND    | ♦ND  | ♦ND  | ♦ND    | ♦ND                 | ♦ND                 | ★MP2B_EN | ♦ND  |

| <b>11</b> | ♦ND | ♦ND                 | ♦ND                 | ♦ND              | ♦ND    | ♦ND  | ♦ND  | ♦ND    | ♦ND                 | ♦ND                 | ♦ND      | ♦ND  |

| <b>12</b> | ♦ND | ♦ND                 | ★CC3                | *HDNI            | ★LKOUT | ♦ND  | ♦ND  | *F     | *HDNQ               | ★CC3                | ♦ND      | ♦ND  |

| <b>13</b> | ❖I3 | ❖I0                 | ❖OE                 | ★UX              | *ENSEI | *DD  | *DD  | *ENSEQ | ★ODE                | ❖OEQ                | ❖Q13     | ❖Q10 |

| <b>14</b> | ❖I8 | ❖I4                 | ❖I1                 | *DD              | ♦ND    | ❖LKI | ❖LKQ | ♦ND    | *DD                 | ❖Q12                | ❖Q8      | ❖Q6  |

| <b>15</b> | ❖I7 | ❖I6                 | ❖I2                 | ♦ND              | ♦ND    | ♦ND  | ♦ND  | ♦ND    | ♦ND                 | ❖Q11                | ❖Q4      | ❖Q5  |

| <b>16</b> | ♦ND | ❖I9                 | ❖I5                 | ❖I10             | ❖I11   | ♦ND  | ♦ND  | ❖Q1    | ❖Q3                 | ❖Q9                 | ❖Q7      | ♦ND  |

| <b>17</b> | ♦ND | ♦ND                 | ★GND                | ★V <sub>DD</sub> | ❖I12   | ❖I13 | ❖Q0  | ❖Q2    | ★V <sub>DD</sub>    | ★GND                | ♦ND      | ♦ND  |

□品を透かして見たLGAパッケージの上面図

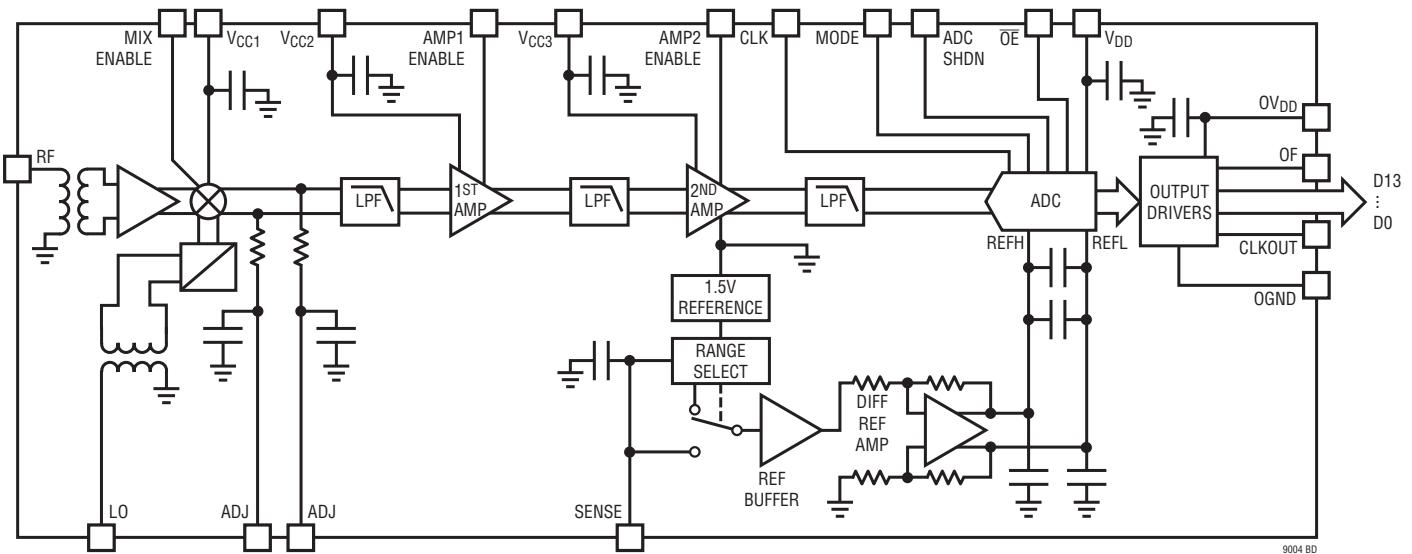

## ブロック図

図1. 機能ブロック図(1チャネルだけ示されている)

## 動作

### 概要

LTM9004は、RF入力周波数が2.7GHzまでのワイヤレス・インフラストラクチャなど、高直線性レシーバのアプリケーション向けのダイレクトコンバージョン・レシーバです。これは、SiP (system in a package) テクノロジーを利用して一体化されたμModule レシーバで、デュアルの高速14ビットA/Dコンバータ、ローパス・フィルタ、チャネル当たり2個の固定利得低ノイズ差動アンプ、およびDCオフセット調整機能付きI/Q復調器を組み合わせています。

ダイレクトコンバージョン・レシーバ・アーキテクチャは従来のスーパー・ヘテロダイインに比べていくつかの長所を備えています。それは、イメージ周波数の信号の影響を受けにくいで、RFフロントエンドのバンドパス・フィルタの要件を緩和します。RFバンドパス・フィルタに要求されるのは、強い帯域外信号を減衰させてそれらがフロントエンドに負担を掛けすぎないよう防ぐことだけです。また、直接変換はIFアンプとバンドパス・フィルタも不要になります。代わりに、RF入力信号はベースバンドに直接変換されます。

ただし、直接変換はそれ固有の実装に関する問題を伴います。受信LO信号はRF信号と同じ周波数ですから、受信アンテナから簡単に放射され、法規上の規定に違反することができます。

レシーバの2次非直線性によって不要のベースバンド信号が生じることもあります。レシーバに入ってくる任意の周波数のトーンは、ベースバンド回路にDCオフセットを生じます。また、レシーバの2次非線形性は、変調信号が(望みの信号であっても)DCの周囲に疑似ランダム・ブロックのエネルギーを発生することを許します。

このため、LTM9004は、I/Q復調段の直後にDCオフセット補正を行います。一旦発生した後、DCオフセットを単純に除去すると厄介な問題が生じます。ベースバンド・アンプの周波数応答はDCまで延びているので、ベースバンド・アンプの必要な利得によりオフセットが増加します。

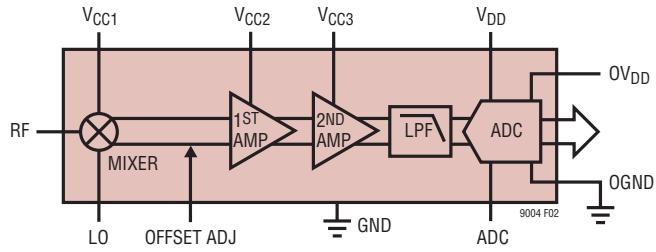

以下のセクションでは各部分の動作を詳細に説明します。μModule テクノロジーにより LTM9004 はカスタム化が可能で、それについては最初のセクションで説明します。残りのセクションのアウトラインは図2に示されている基本的機能要素に従います。

図2. 基本的機能要素(半分だけ示してある)

### セミカスタム・オプション

μModule構造は、アプリケーション固有の標準製品に新しいレベルの柔軟性を与えます。特定のアプリケーション向けに、標準的ADC、アンプおよびRFの各構成要素を(それらのプロセス・テクノロジーに関係なく)統合し、受動部品に適合させることができます。最初の例として、LTM9004-AAは最高125Mspsのレートでサンプリングするデュアル14ビットADCを使って構成されています。アンプは(ミキサの利得を含め)14dBの全電圧利得を与えます。ローパス・フィルタは帯域幅を1.92MHzに制限します。I/Q復調器のRF入力とLO入力には内蔵トランジスタが備わっており、50Ωのシングルエンド入力を与えます。DCオフセットのキャンセルに外部DACを使うことができます。

ただし、リニアテクノロジーのセミカスタム開発プログラムにより他のオプションも可能です。リニアテクノロジーは、ほとんどどんなアプリケーションにも対応する、他のサンプル・レート、分解能、利得およびフィルタ構成を提供するプログラムを用意しています。これらのセミカスタム・デザインは、適切に変更を加えた受動ネットワークと組み合わせた既存の部品をベースにします。次いで、アプリケーションで定義された精確なパラメータに対して最終サブシステムがテストされます。最終的には、同じパッケージに完全に一体化され、精確にテストされ、最適化されたソリューションになります。セミカスタムのレシーバ・サブシステム・プログラムの詳細については、弊社にお問い合わせください。

### ミキサの動作

RF信号はRFトランスクンダクタンス・アンプの入力に与えられ、次に直交LO信号を使ってI/Qベースバンド信号に復調されます。この直交LO信号は高精度90°位相シフタにより外部LOソースから内部で作られます。

## 動作

RFとLOの両方の入力に広帯域内蔵トランジスタが備わっており、シングルエンドのRFとLOのインターフェースが可能です。広い周波数帯域で(1.5GHz～2.7GHz)、RFポートとLOポートの両方が内部で50Ωに整合しています。外付けの整合部品は不要です。低い周波数帯域(700MHz～1.5GHz)では、直列コンデンサまたはシャント・コンデンサの簡単なネットワークをインピーダンス整合ネットワークとして使うことができます。

### IチャネルとQチャネルの位相関係

IチャネルとQチャネルの出力信号間の位相関係は固定されています。LO入力周波数がRF入力周波数より大きい(または小さい)とき、Qチャネルの出力(DQ0～DQ13)はIチャネルの出力(DI0～DI13)より90°だけ位相が遅れ(または進み)ます。

### DCオフセットの調整

各チャネルにはA/Dコンバータの入力に与えられるDCオフセット電圧の調整機能が備わっています。各チャネルには2つの調整端子があるので、同相モードと差動モードのDCオフセットを個別にトリミングすることができます。これらの端子は最大0.3mAのソース電流またはシンク電流を受け入れるように設計されています。2つの端子を流れる電流が等しくないと、差動DCオフセットが生じます。それらが等しいと、DCオフセットは同相のみとなります。一例として、一方の端子から0.1mAをシンクし、他方の端子から0.11mAをシンクすると、差動オフセットは約5.9mV(48LSB)になります。調整端子に5Vの差動電圧を加えることにより、最大約178mV(1457LSB)のDCオフセットを強制することができます。

### アンプの動作

LTM9004の各チャネルは、2段の、DC結合された、低ノイズで低歪みの完全に差動のオペアンプ/ADCドライバで構成されています。各段は、高速の高性能オペアンプと高精度受動部品を使った2ポールのアクティブ・ローパス・フィルタを実装しています。この2段のカスケード構成は、最大利得と位相平坦度を与え、隣接チャネルとブロッカを除去するように設計されています。アンプの範囲内で、異なるカットオフ周波数のローパス応答を設定することができます。たとえば、LTM9004-AAのローパスフィルタは1.92MHzに設定されています。

### ADCの入力ネットワーク

2番目のアンプの出力段とADCの入力段の間の受動ネットワークは、ローパス応答の1次トポロジーを構成しています。

### コンバータの動作

図1に示されているA/Dコンバータ(ADC)は、デュアルのCMOSパイプライン・マルチステップ・コンバータです。パイプライン構成の6つのADC段を備えており、サンプリングされたアナログ入力は6サイクル後にデジタル値になります(タイミング図を参照)。CLK入力はシングルエンドです。ADCはCLK入力ピンの状態で定まる2つのフェーズで動作します。

パイプライン構成の各段は、1個のADC、再構成DAC、および段間残余アンプを備えています。動作時、ADCは各段の入力を量子化し、量子化された値はDACによって入力から差し引かれ、残差を生じます。残差は残差アンプによって増幅されて出力されます。奇数段がその残余を出力しているとき偶数段がその残余を取得するように、またその逆になるように、後に続く段は位相がずれて動作します。

CLKが“L”的とき、アナログ入力が入力のサンプル&ホールド・コンデンサに差動で直接サンプルされます。CLKが“L”から“H”に遷移する瞬間、サンプリングされた入力がホールドされます。CLKが“H”的間、ホールドされた入力電圧はS/Hアンプによってバッファされます。このS/Hアンプはパイプライン構成の最初のADC段をドライブします。初段はCLKのこの“H”フェーズの間にS/Hの出力を取得します。CLKが“L”に戻ると初段はその残余を出力し、この残余が2番目の段によって取得されます。同時に、入力のS/Hは再度アナログ入力を取得します。CLKが“H”に戻ると2番目の段はその残余を出力し、この残余が3番目の段によって取得されます。同様の過程が3番目、4番目、さらに5番目の段で繰り返され、5番目の段の残余は最終評価のために6番目の段のADCに送られます。

初段に続く各ADC段にはフラッシュ誤差とアンプのオフセット誤差を調節するための追加範囲があります。ADCの全段からの結果は、出力バッファに送る前に、それらの結果を補正ロジックで適切に結合できるようにデジタル動作で同期させます。

## アプリケーション情報

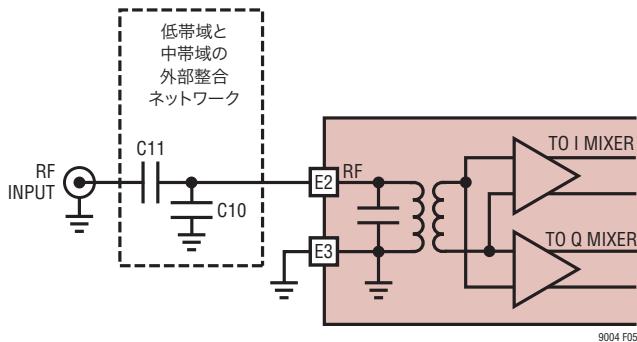

### RF入力

内蔵トランスと高直線性トランスコンダクタンス・アンプによって構成されている、ミキサのRF入力を図3に示します。トランスの1次側はRF入力ピンに接続されています。トランスの2次側はトランスコンダクタンス・アンプの差動入力に接続されています。いかなる場合にも、RF入力ピンにDC電圧を印加してはいけません。トランスの1次側に流れ込むDC電流は内蔵トランスに損傷を与える可能性があります。直列ブロッキング・コンデンサを使ってRF入力ポートをRF信号源にAC結合します。

図3. RF入力のインターフェース

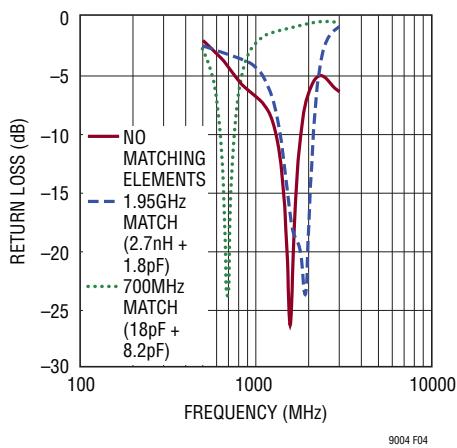

図4. RFポートのリターン損失と周波数

RF入力ポートは1.5GHz～2.7GHzの広い周波数範囲にわたりて内部で整合しており、入力リターン損失は標準で10dBより優れています。この周波数範囲では外部整合ネットワークは不要です。ただし、デバイスが低い周波数で動作するとき

は、図3に示されている整合ネットワークにより、入力リターン損失が改善されます。図4に示されているように、所期の周波数で入力の最適インピーダンス整合を得るために、シャント・コンデンサC10と直列コンデンサC11を選択することができます。低い周波数帯域の動作では、外部整合部品C11が直列DCブロッキング・コンデンサとして機能することができます。

RF入力インピーダンスとS11パラメータを表1に示します(外部整合部品なし)。

表1. RF入力インピーダンス

| 周波数(MHz) | 大きさ  | 位相(°)  | R(Ω) | X(Ω)  |

|----------|------|--------|------|-------|

| 500      | 0.78 | -139.7 | 16.1 | -10.7 |

| 600      | 0.69 | -166.6 | 10.1 | -3.8  |

| 700      | 0.60 | 163.7  | 14.0 | 3.8   |

| 800      | 0.52 | 132.6  | 25.8 | 6.9   |

| 900      | 0.48 | 102.7  | 41.9 | 3.4   |

| 1000     | 0.45 | 77.4   | 58.8 | -4.3  |

| 1100     | 0.42 | 56.6   | 74.9 | -11.4 |

| 1200     | 0.38 | 40.1   | 86.4 | -12.4 |

| 1300     | 0.31 | 25.7   | 87.6 | -7.1  |

| 1400     | 0.22 | 10.9   | 76.8 | -1.4  |

| 1500     | 0.10 | -14.5  | 60.9 | 0.3   |

| 1600     | 0.06 | -132.9 | 45.9 | -0.2  |

| 1700     | 0.19 | -170.7 | 34.6 | -0.4  |

| 1800     | 0.30 | -177.7 | 26.8 | 0.2   |

| 1900     | 0.40 | -172.1 | 21.8 | 1.1   |

| 2000     | 0.47 | -169.4 | 18.7 | 1.9   |

| 2100     | 0.51 | -168.6 | 16.7 | 2.2   |

| 2200     | 0.54 | -169.3 | 15.4 | 2.3   |

| 2300     | 0.55 | -172.0 | 14.7 | 1.7   |

| 2400     | 0.55 | -176.0 | 14.4 | 0.9   |

| 2500     | 0.54 | -178.7 | 14.9 | -0.3  |

| 2600     | 0.52 | -172.3 | 15.9 | -1.6  |

| 2700     | 0.50 | -164.3 | 17.6 | -3.0  |

| 2800     | 0.49 | -155.0 | 19.9 | -4.3  |

| 2900     | 0.48 | -144.7 | 22.9 | -5.4  |

| 3000     | 0.48 | -134.8 | 26.4 | -6.0  |

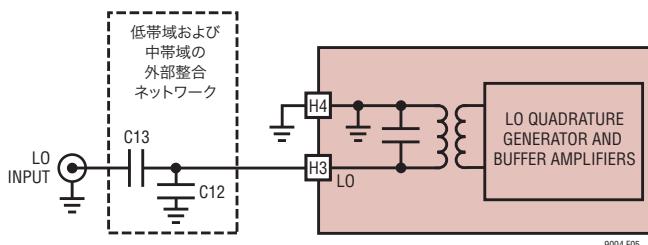

### LO入力ポート

ミキサのLO入力インターフェースを図5に示します。入力は内蔵トランスと高精度直行位相シフタによって構成されており、I/QミキサをドライブするLOバッファ・アンプのために位相のシフ

## アプリケーション情報

トした0°と90°のLO信号を発生します。トランスの1次側はLO入力ピンに接続されています。トランスの2次側はLO直交ジェネレータの差動入力に接続されています。どんな場合にも、この入力ピンにDC電圧を印加してはいけません。トランスの1次側に流れ込むDC電流はトランスに損傷を与える可能性があります。直列ブロッキング・コンデンサを使ってLO入力ポートをLO信号源にAC結合します。

図5. LO入力インタフェース

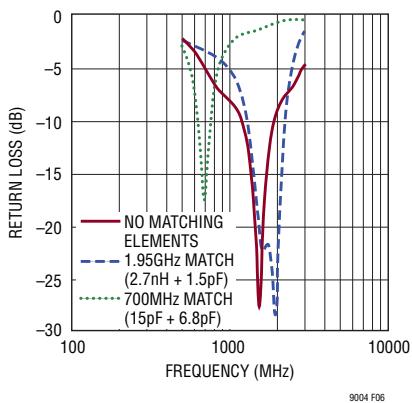

図6. LOのリターン損失と周波数

LO入力ポートは1.5GHz～2.7GHzの広い周波数範囲にわたって内部で整合しており、入力リターン損失は標準で10dBより優れています。この周波数範囲では外部整合ネットワークは不要です。デバイスが低い周波数で動作するときは、図8に示されている整合ネットワークにより、入力リターン損失が改善されます。図6に示されているように、望みの周波数で入力の最適インピーダンス整合を得るために、シャント・コンデンサC12と直列コンデンサC13を選択することができます。低周波数動作では、外部整合部品C13が直列DCブロッキング・コンデンサとして機能することができます。

LO入力インピーダンスとS11パラメータを表2に示します(外部整合部品なし)。

表2. LO入力インピーダンス

| 周波数(MHz) | 大きさ  | 位相(°)  | R(Ω) | X(Ω)  |

|----------|------|--------|------|-------|

| 500      | 0.77 | -143.2 | 14.8 | -10.0 |

| 600      | 0.66 | -172.6 | 10.6 | -2.0  |

| 700      | 0.55 | 154.5  | 17.8 | 5.1   |

| 800      | 0.46 | 119.8  | 33.1 | 5.5   |

| 900      | 0.41 | 88.8   | 50.8 | -0.3  |

| 1000     | 0.39 | 63.9   | 67.5 | -7.4  |

| 1100     | 0.35 | 44.9   | 80.2 | -10.1 |

| 1200     | 0.30 | 31.5   | 83.4 | -7.2  |

| 1300     | 0.23 | 22.7   | 76.9 | -3.1  |

| 1400     | 0.14 | 20.7   | 65.2 | -0.9  |

| 1500     | 0.05 | 47.3   | 53.6 | -0.1  |

| 1600     | 0.08 | 139.3  | 44.1 | 0.3   |

| 1700     | 0.17 | 152.3  | 36.9 | 0.9   |

| 1800     | 0.25 | 154.7  | 31.7 | 1.6   |

| 1900     | 0.31 | 157.5  | 27.9 | 2.0   |

| 2000     | 0.35 | 160.5  | 25.1 | 2.2   |

| 2100     | 0.38 | 164.9  | 23.1 | 2.0   |

| 2200     | 0.41 | 170.3  | 21.4 | 1.4   |

| 2300     | 0.42 | 177.7  | 20.2 | 0.4   |

| 2400     | 0.44 | -173.8 | 19.6 | -1.0  |

| 2500     | 0.46 | -164.6 | 19.7 | -2.6  |

| 2600     | 0.48 | -155.7 | 20.2 | -4.1  |

| 2700     | 0.51 | -147.1 | 21.2 | -5.6  |

| 2800     | 0.54 | -139.2 | 22.8 | -6.8  |

| 2900     | 0.56 | -131.5 | 25.2 | -7.6  |

| 3000     | 0.58 | -124.9 | 27.9 | -7.9  |

## ADCのリファレンス

内部電圧リファレンスは、ピンで選択可能なADCの2つの入力範囲に構成設定することができます。SENSEピンをV<sub>DD</sub>に接続すると既定の範囲が選択され、SENSEピンを1.5Vに接続すると3dB低い範囲が選択されます。外部リファレンスを使って、その出力を直接または抵抗分割器を通してSENSEに与えることができます。ロジック・デバイスを使ってSENSEピンをドライブすることは推奨しません。SENSEピンはできるだけコンバータの近くで適切なレベルに接続します。SENSEピンは、1μFセラミック・コンデンサを使って内部でグランドにバイパスしてあります。

## アプリケーション情報

### イネーブル・インターフェース

ミキサをオンするのに必要なイネーブル電圧は2Vです。ミキサをディスエーブルまたはオフするには、この電圧を1Vより下にします。このピンが接続されていないと、ミキサはディスエーブルされます。ただし、通常動作でこのピンをフロート状態にしておくことは推奨しません。

AMP1ENABLEピンとAMP2ENABLEピンはCMOSロジック入力で、内部プルアップ抵抗を備えています。ピンを“L”にドライブすると、アンプがシップワードダウンし、出力がHi-Zになります。ピンを未接続のままにするか、“H”にドライブすると、デバイスは通常の動作状態になります。偶発的なシャットダウンを防ぐために、このピンのリーコンデンサを制御するよう注意が必要です。シャットダウン状態とアクティブ状態の間のターンオン時間およびターンオフ時間は標準で1μs未満です。

### スリープ・モードとナップ・モード

節電のため、コンバータをシャットダウン・モードまたはナップ・モードにすることができます。ADCSHDNxをGNDに接続すると通常動作になります。ADCSHDNxをV<sub>DD</sub>に接続し、 $\overline{OE}_X$ をV<sub>DD</sub>に接続するとスリープ・モードになり、リファレンスを含む全ての回路がパワードダウンし、ADCの電力損失は標準で1mWになります。スリープ・モードを抜け出すとき、リファレンスのコンデンサを再充電して安定化する必要があるので、出力データが有効になるまで数ミリ秒かかります。ADCSHDNxをV<sub>DD</sub>に接続し、 $\overline{OE}_X$ をGNDに接続するとナップ・モードになり、ADCの電力損失は標準で30mWになります。ナップ・モードでは内蔵リファレンス回路はオンしたままなので、ナップ・モードからの回復はスリープ・モードからの回復よりも速く、標準で100クロック・サイクルかかります。スリープとナップの両方のモードで全てのデジタル出力はディスエーブルされ、Hi-Z状態になります。

チャネルIとチャネルQには独立したADCSHDNピン(ADCSHDNI、ADCSHDNQ)が備わっています。IチャネルはADCSHDNIと $\overline{OE}_I$ によって制御され、QチャネルはADCSHDNQと $\overline{OE}_Q$ によって制御されます。2つのチャネルのナップ・モード、スリープ・モードおよび出力イネーブル・モードは完全に独立しているので、一方のチャネルを動作させながら、他方のチャネルをナップ・モードまたはスリープ・モードすることができます。

ADCSHDNの極性は、MIXENABLE、AMP1ENABLEおよびAMP2ENABLEとは逆であることに注意してください。通常

動作はSHDNピンのロジック“L”レベルによって行われ、“H”レベルによってそれぞれの機能がディスエーブルされます。

個別のコンポーネントを別々にイネーブルまたはシャットダウンすることは推奨しません。これらのピンはテストのために分離されています。

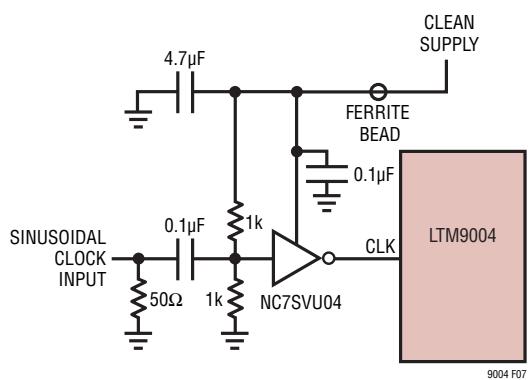

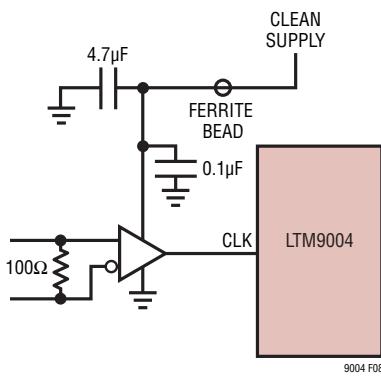

### ADCのクロック入力のドライブ

CLK入力はCMOSまたはTTLレベルの信号で直接ドライブすることができます。CLKピンの前にジッタの小さな方形波発生回路を置いて正弦波のクロックを使うこともできます(図7)。

図7. 正弦波シングルエンドCLKドライバ

ADCのノイズ特性はアナログ入力に依存するのと同程度にクロック信号の品質に依存することがあります。CLK信号に含まれるどんなノイズも新たなアーチャ・ジッタを生じ、このジッタは本来のADCアーチャ・ジッタにRMSとして追加されます。高い入力周波数をデジタル変換する場合など、ジッタに対する要求が厳しいアプリケーションではできるだけ大きな振幅を使います。また、正弦波信号でADCをクロック駆動する場合、クロック信号にフィルタをかけて広帯域ノイズとソースによって生じた歪み積を減らします。

CLKIとCLKQを短絡して同じクロック・ソースでドライブすることを推奨します。2つのチャネルがアナログ入力をサンプリングするタイミングの間に小さな遅延時間を置くのが望ましい場合、CLKIとCLKQを2つの異なった信号でドライブすることができます。この遅延時間が1nsを超えると、デバイスの性能が低下することがあります。CLKIとCLKQは非同期信号でドライブしないでください。

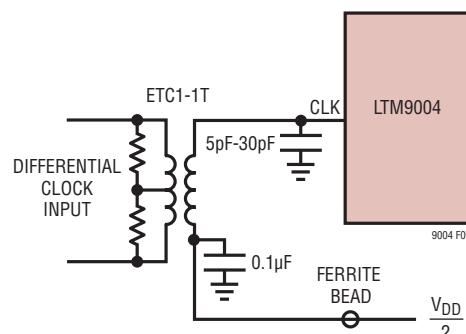

## アプリケーション情報

差動クロックをシングルエンドCLK入力に変換する別の方法を図8と図9に示します。トランスを使うと位相ノイズの増加はありません。LVDSまたはPECLからCMOSへの変換器は70MHz以下ではSNRがほとんど劣化しませんが、140MHzではトランスのソリューションに比べてSNRが劣化します。受信した信号の性質もSNRがどれだけ劣化するかに大きく関係します。WCDMAやOFDMなどの波高率の高い信号では(この場合、公称電力レベルがフルスケールより少なくとも6dB～8dB小さくなります)、これらの変換器の使用の影響は小さくなります。

この例のトランスは使用される信号に適切な終端回路で終端することができます。低い電圧の差動信号が考えられる場合は、1:4のインピーダンス比のトランスの使用が望ましいでしょう。差動信号が別のプレーンから来る場合、センタータップをADCに近いコンデンサを介してグランドにバイパスすることができます。コンデンサを入力に使用するとピーキングが生じることがあり、伝送ラインの長さに依存して、 $10\Omega \sim 20\Omega$ の直列抵抗が必要になることがあります。この抵抗は、近傍のデジタル信号によってクロック・ラインに誘起されることがある高周波ノイズに対するローパス・フィルタおよび反射に対する減衰メカニズムの両方として機能します。

## 最大変換レートと最小変換レート

ADCの最大変換レートは125Mspsです。サンプリング・レートの下限はサンプル&ホールド回路の垂下によって決まります。このADCのパイプライン・アーキテクチャでは、アナログ信号を小容量のコンデンサに保存します。接合部のリーク電流によりコンデンサが放電します。LTM9004の規定最小動作周波数は1Mspsです。

## クロック・デューティ・サイクル・スタビライザ

入力クロックのデューティ・サイクルが50%でなくても、オプションのクロック・デューティ・サイクル・スタビライザ回路により確実に高性能が得られます。ほとんどのアプリケーションにはクロック・デューティ・サイクル・スタビライザの使用を推奨します。クロック・デューティ・サイクル・スタビライザを使うには、外付け抵抗を使ってMODEピンを $1/3V_{DD}$ または $2/3V_{DD}$ に接続します。

この回路はCLKピンの立ち上がりエッジを使ってアナログ入力をサンプリングします。CLKの立ち下がりエッジは無視され、フェーズロック・ループにより内部で立ち下がりエッジが作られます。入力クロックのデューティ・サイクルは40%～60%の範囲で変化することができ、クロック・デューティ・サイクル・スタビライザは内部デューティ・サイクルを50%に保ちます。クロックが長時間オフすると、デューティ・サイクル・スタビライザ回路のPLLが入力クロックにロックするのに100クロック・サイクル必要です。

図8. LVDSまたはPECLからCMOSへの

変換器を使ったCLKドライバ

図9. トランスを使ったLVDSまたはPECLのCLKドライバ

## アプリケーション情報

サンプル・レートを即座に変更する必要のあるアプリケーションでは、クロック・デューティ・サイクル・スタビライザをディスエーブルすることができます。デューティ・サイクル・スタビライザをディスエーブルする場合、サンプリング・クロックのデューティ・サイクルが50%( $\pm 5\%$ )になるように注意してください。

## デジタル出力

アナログ入力電圧、デジタル・データ・ビット、およびオーバーフロー・ビットの相互関係を表3に示します。チャネルIまたはチャネルQにオーバーフローまたはアンダーフローが生じるとOFが“H”になることに注意してください。

表3. 出力コードと入力電圧

| 入力  | OF | D13～D0<br>(オフセット・バイナリ) | D13～D0<br>(2の補数)  |

|-----|----|------------------------|-------------------|

| 過電圧 | 1  | 11 1111 1111 1111      | 01 1111 1111 1111 |

| 最大  | 0  | 11 1111 1111 1111      | 01 1111 1111 1111 |

|     | 0  | 11 1111 1111 1110      | 01 1111 1111 1110 |

|     | 0  | 10 0000 0000 0001      | 00 0000 0000 0001 |

|     | 0  | 10 0000 0000 0000      | 00 0000 0000 0000 |

|     | 0  | 01 1111 1111 1111      | 11 1111 1111 1111 |

|     | 0  | 01 1111 1111 1110      | 11 1111 1111 1110 |

| 最小  | 0  | 00 0000 0000 0001      | 10 0000 0000 0001 |

|     | 0  | 00 0000 0000 0000      | 10 0000 0000 0000 |

| 低電圧 | 1  | 00 0000 0000 0000      | 10 0000 0000 0000 |

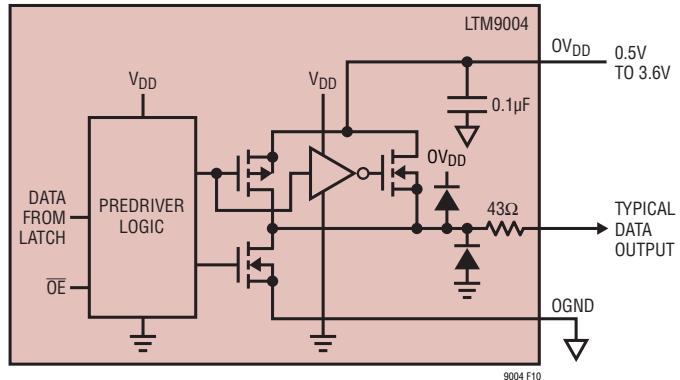

## デジタル出力モード

1個の出力バッファの等価回路を図10に示します。各バッファはOV<sub>DD</sub>とOGNDから給電され、ADCの電源とグランドからは分離されています。出力ドライバにNチャネル・トランジスタが追加されているので低電圧まで動作可能です。出力に直列接続された内部抵抗により、外部回路から見ると出力は50Ωに見えるので、外部の減衰抵抗が不要です。

全ての高速高分解能コンバータの場合と同様、デジタル出力負荷が性能に影響を与えることがあります。デジタル出力と敏感な入力回路の間に生じるおそれのある相互反応を抑えるため、ADCのデジタル出力はできるだけ小さな容量性負荷をドライブするようにします。全速動作では負荷の容量は10pF以下に抑えます。

図10. デジタル出力バッファ

OV<sub>DD</sub>電圧を低くすることも、デジタル出力からの干渉を減らすのに役立ちます。

## データのフォーマット

ADCのパラレル・デジタル出力は、MODEピンを使って、オフセット・バイナリ形式または2の補数形式に設定できます。MODEはIとQの両方のチャネルをコントロールすることに注意してください。MODEをGNDまたは1/3V<sub>DD</sub>に接続するとストレート・バイナリの出力フォーマットが選択されます。MODEを2/3V<sub>DD</sub>またはV<sub>DD</sub>に接続すると2の補数の出力フォーマットが選択されます。外部抵抗分割器を使って1/3V<sub>DD</sub>または2/3V<sub>DD</sub>のロジック値を設定することができます。MODEピンのロジック状態を表4に示します。

表4. MODEピンの機能

| MODEピン             | 出力フォーマット   | クロック・デューティ・サイクル・スタビライザ |

|--------------------|------------|------------------------|

| 0                  | ストレート・バイナリ | オフ                     |

| 1/3V <sub>DD</sub> | ストレート・バイナリ | オン                     |

| 2/3V <sub>DD</sub> | 2の補数       | オン                     |

| V <sub>DD</sub>    | 2の補数       | オフ                     |

## オーバーフロー・ビット

OFがロジック“H”を出力しているとき、コンバータのIチャネルまたはQチャネルにオーバーレンジまたはアンダーレンジが生じています。両方のチャネルは共通のOFピンを共有していることに注意してください。Iチャネルがスリープ・モードまたはナップ・モードのとき、OFはディスエーブルされます。

## アプリケーション情報

### 出力クロック

ADCにはCLKQ入力を遅延させた信号がデジタル出力(CLKOUT)として備わっています。CLKOUTピンの立ち下がりエッジを使ってデジタル出力データをラッチすることができます。チャネルQがスリープ・モードまたはナップ・モードのとき、CLKOUTはディスエーブルされます。

### 出力ドライバの電源

出力専用の電源ピンとグランド・ピンが備わっているので、出力ドライバをアナログ回路から分離することができます。デジタル出力バッファの電源(OV<sub>DD</sub>)は、ドライブされるロジックに給電しているのと同じ電源に接続します。たとえば、1.8V電源から給電されているDSPをコンバータがドライブする場合、OV<sub>DD</sub>を同じ1.8V電源に接続します。

OV<sub>DD</sub>は500mVからデバイスのV<sub>DD</sub>までの任意の電圧で電力供給を受けることができます。OGNDはGND～1Vの任意の電圧で電力供給を受けることができ、OV<sub>DD</sub>より低くなければなりません。ロジック出力はOGNDとOV<sub>DD</sub>の間で振幅します。

### 出力イネーブル

出力イネーブル・ピン( $\overline{OE}$ )を使って出力をディスエーブルすることができます。 $\overline{OE}$ を“H”にすると、OFを含む全てのデータ出力がディスエーブルされます。データのアクセス時間やバスの解放時間は、全速動作時に出力をイネーブルまたはディスエーブルするには遅すぎます。出力のHi-Z状態は長期の休止時に使うことを意図しています。チャネルIとチャネルQには独立した出力イネーブル・ピン( $\overline{OEI}$ ,  $\overline{EQ}$ )が備わっています。

### デジタル出力のマルチプレクサ

ADCのデジタル出力は1本のデータバスに多重化することができます。MUXピンは2本のデータバスを交換するデジタル入力です。MUXが“H”だと、IチャネルはDI0～DI13から出力し、QチャネルはDQ0～DQ13から出力します。MUXが“L”だと出力バスが入れ替わり、IチャネルはDQ0～DQ13から出力し、QチャネルはDI0～DI13から出力します。両方のチャネルを1本の出力バスに多重化するにはMUX、CLKIおよびCLKQと一緒に結合します(多重モードの「タイミング図」を参照)。多重化されたデータはどちらのデータバスでも利用できます(使用しないデータバスは対応するOEピンを使ってディスエーブルすることができます)。

### 設計例 – UMTS アップリンクのFDDシステム

LTM9004をRFフロントエンドと組み合わせて、UMTSバンドのアップリンク・レシーバを構築することができます。RFフロントエンドは、ダイプレクサ、1個または複数のLNAおよびバンドパス・フィルタで構成されます。次に示すのはこのようなフロントエンドの標準的性能の一例です。

|            |               |

|------------|---------------|

| Rx周波数範囲:   | 1920～1980 MHz |

| RF利得:      | 最大15dB        |

| AGCの利得:    | 20dB          |

| ノイズフィギュア:  | 1.6dB         |

| IIP2:      | 50dBm         |

| IIP3:      | 0dBm          |

| P1dB:      | -9.5dBm       |

| 20MHzでの除去: | 2dB           |

| Txバンドでの除去: | 95dB          |

レシーバの最小性能については、3GPP TS25.104 V7.4.0仕様に詳細が示されています。この例では、動作バンドIの中域基地局を使います。

レシーバでは、感度は主要な検討事項です。その要件は、-19.8dB/5MHzの入力SNRに対して≤-111dBmです。つまり、レシーバの入力のところの実効ノイズフロアは≤-158.2dBm/Hzである必要があります。RFフロントエンドの実効ノイズの寄与分がこのように与えられると、LTM9004による最大許容ノイズは-142.2dBm/Hzである必要があります。LTM9004の標準入力ノイズは-148.3dBm/Hzであり、これに基づいて計算するとシステムの感度は-116.7dBmとなります。

一般に、このようなレシーバは、ADCの後に置かれるデジタル化信号のDSPフィルタの恩恵を受けます。この場合、DSPフィルタは、アルファが0.22の64タップRRCローパスであると仮定します。コチャネル干渉信号が存在する状態で動作するには、レシーバに最大感度で十分なダイナミックレンジがなければなりません。UMTS仕様は、-73dBmの最大コチャネル干渉信号を要求しています。LTM9004のIFバスバンド内の-1dBFSの入力レベルは、波高係数が10dBの変調信号では-15.1dBmであることに注意してください。トーン干渉信号は-42.6dBFSのピーク・デジタル化信号レベルに相当します。

## アプリケーション情報

RF AGCが最小利得に設定されている状態で、レシーバはハンドセットからの予期される最大信号を復調できる必要があります。この要件は、LTM9004が-1dBFS以下で対応する必要のある最大信号を最終的に設定します。ハンドセットの+28dBmの平均電力を仮定すると、仕様で要求される最小経路損失は53dBです。すると、最大信号レベルはレシーバの入力では-25dBm、LTM9004の入力では-30dBmです。これは-14.6dBFSのピークに相当します。

UMTSのシステム仕様で詳細に説明されているいくつかのブロッカ信号があります。これらの信号が存在すると、感度が-105dBm以下に劣化することがあります。これらの最初のものは5MHz離れた隣接チャネルであり、-42dBmのレベルです。これは-11.6dBFSのピーク・デジタル化信号レベルに相当します。その結果得られる感度は-112.8dBmです。

レシーバは10MHz以上離れた-35dBmの干渉チャネルにも対抗する必要があります。RFフロントエンドはこのチャネルの除去を行わないので、-6.6dBFSのピークとなり、その結果感度は-109.2dBmになります。

バンド外のブロッカにも対処する必要がありますが、これらは既に対処済みのバンド内のブロッカと同じレベルです。

これら全ての場合に、LTM9004の標準-1dBFSの入力レベルは予期される最大信号レベルを十分上回っています。変調されたチャネルの波高率は10dB～12dB程度になるので、これらの最大のものはモジュールの出力で約-6.5dBFSのピーク電力に達することに注意してください。

最大ブロッキング信号は、受信帯域端を超える20MHz以上のCWトーンで-15dBmです。RFフロントエンドはこのトーンの37dBの除去を行うので、LTM9004の入力で-32dBmになります。この場合も、このレベルの信号はベースバンド・モジュールの感度を下げるとはありません。相当するデジタル化レベルはわずか-41.6dBFS(ピーク)なので、感度に対する影響はありません。

望ましくない信号電力の別のソースはトランスマッタからのリーク電力です。これはFDDアプリケーションなので、ここで説明されているレシーバは同時に動作しているトランスマッタと結合されます。トランスマッタの出力レベルは+38dBm以下であり、送信と受信の分離は95dBであると想定しています。したがって、LTM9004の入力に現れるリーク電力は-42dBmで、

受信信号から少なくとも130MHzオフセットされています。相当するデジタル化レベルはわずか-76.6dBFS(ピーク)なので、感度の低下はありません。

直接変換アーキテクチャの課題の1つは2次直線性です。2次直線性が不十分だと、(要不要に関係なく)どんな信号もDCオフセットやベースバンドの疑似ランダム・ノイズを生じます。上で説明されているブロッキング信号は、この疑似ランダム・ノイズがレシーバのノイズレベルに近づくと、感度を低下させます。システムの仕様は、それぞれの場合にこれらのブロッカが存在するときの感度の低下を許容します。システムの仕様によれば、-35dBmのブロッキング・チャネルは感度を-105dBmに低下させることができます。これは、レシーバの実効入力ノイズを-148.2dBm/Hzに増加させることに相当します。LTM9004の入力によって生じる2次歪みはこのレベルより約18dB下であり、その結果予想される感度は-116.6dBmです。

-15dBmのCWブロッカは2次積も増加させます。この場合、この積はDCオフセットです。DCオフセットはA/Dコンバータが処理できる最大信号を減少させるので、望ましくありません。DCオフセットの影響を緩和する確実な方法の1つは、ベースバンド・モジュールの2次直線性を十分高くすることです。この信号による予測DCオフセットは、ADCの入力のところで1mV未満です。

トランスマッタのリーク電流はシステムの仕様に含まれていないので、この信号による感度の劣化を最小に抑える必要があることに注意してください。LTM9004内で生じる2次歪みは、感度が0.1dB未満になる程度です。

仕様の3次直線性には1つの要件しかありません。2つの干渉信号がある場合、感度は-105dBmより下にならなければなりません。干渉信号は、それぞれ-44dBmのCWトーンおよびWCDMAチャネルです。これらはLTM9004の入力のところにそれぞれ-29dBmで現れます。それらの周波数は望みの周波数から10MHzおよび20MHz離れているので、3次相互変調積はベースバンドになります。この場合も、この積は擬似ランダムノイズとして現れるので、信号対ノイズ比を下げます。したがって、-105dBmの感度では、レシーバの入力を基準にした許容3次歪みは-148.2dBm/Hzです。LTM9004で生じる3次歪みはこのレベルより約23dB下であり、予測される感度の劣化は0.1dB未満です。

## アプリケーション情報

### 電源シーケンシング

V<sub>CC</sub>ピンはミキサと全てのアンプに電源を与え、V<sub>DD</sub>ピンはADCに電源を与えます。ミキサ、アンプおよびADCはLTM9004内の別個の集積回路です。ただし、標準的なやり方以外の電源シーケンシングは考慮されていません。

### 接地とバイパス

LTM9004には全く切れ目の無いグランド・プレーンを備えたプリント基板が必要です。内部グランド・プレーンを備えた多層基板を推奨します。LTM9004のピン配置はフロースルー・レイアウトに最適化されているので、入力とデジタル出力間の相互反応が最小に抑えられます。一列に連続したグランド・パッドによりレイアウトが簡単になり、デジタル信号ラインとアナログ信号ラインをできるだけ分離することができます。

LTM9004は内部でバイパスされており、ADC (V<sub>DD</sub>)、ミキサおよびアンプ (V<sub>CC</sub>) の各電源は共通グランド (GND) に戻ります。デジタル出力電源 (OV<sub>DD</sub>) はOGNDに戻ります。0.1μFのバイパス・コンデンサを2つのOV<sub>DD</sub>ピンのそれぞれに接続します。追加のバイパス・コンデンサはオプションで、電源ノイズが大きいと必要になることがあります。

### 熱伝達

LTM9004が発生する熱の大部分は底面のグランド・パッドを通って伝わります。電気的性能と熱的性能を良くするには、全てのグランド・ピンを面積が十分大きなグランド・プレーンにできるだけ多くのビアを使って接続することが重要です。

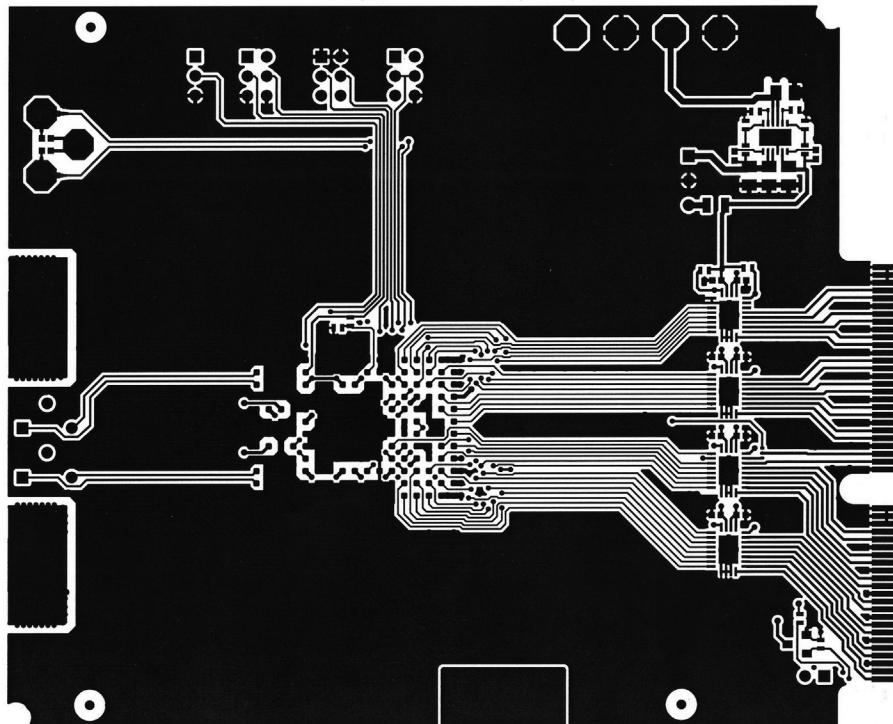

### 推奨レイアウト

LTM9004は高度に一体化されているので、PCB ボードのレイアウトが非常に簡単です。ただし、電気的性能と熱的性能を最適化するにはいくつかのレイアウト上の配慮が依然として必要です。

- グランドにはPCBの大きな銅領域を使用します。これにより基板を通してパッケージ内部の熱が放散するのが助かれられ、基板上の敏感なアナログ信号をシールドするのにも役立ちます。共通グランド (GND) と出力グランド (OGND) はLTM9004では電気的に絶縁されていますが、PCB上でデバイスの下で接続して共通リターン経路を与えることができます。

- 複数のグランド・ビアを使います。できるだけ多くのビアを使うと、基板の熱性能を改善するのに役立ち、基板上のアナログ・トレースとデジタル・トレースを高周波数で分離するのに必要なバリヤを形成します。

- ビアを使って高周波バリヤを作り、アナログ・トレースとデジタル・トレースをできるだけ分離します。これにより、LTM9004の信号対雑音比(SNR)とダイナミックレンジを上げる可能性のあるデジタル・フィードバックが減少します。

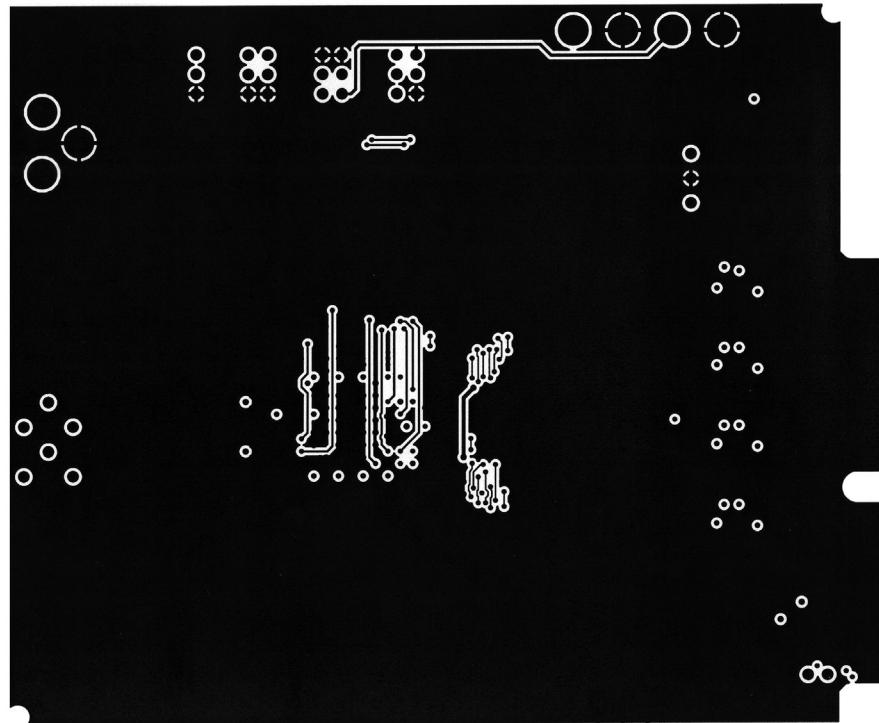

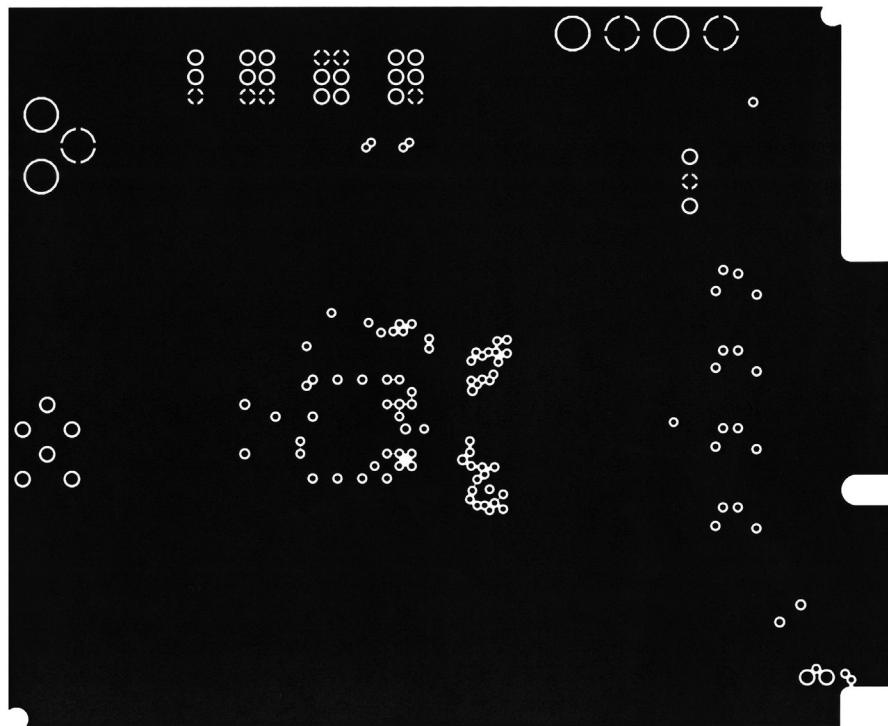

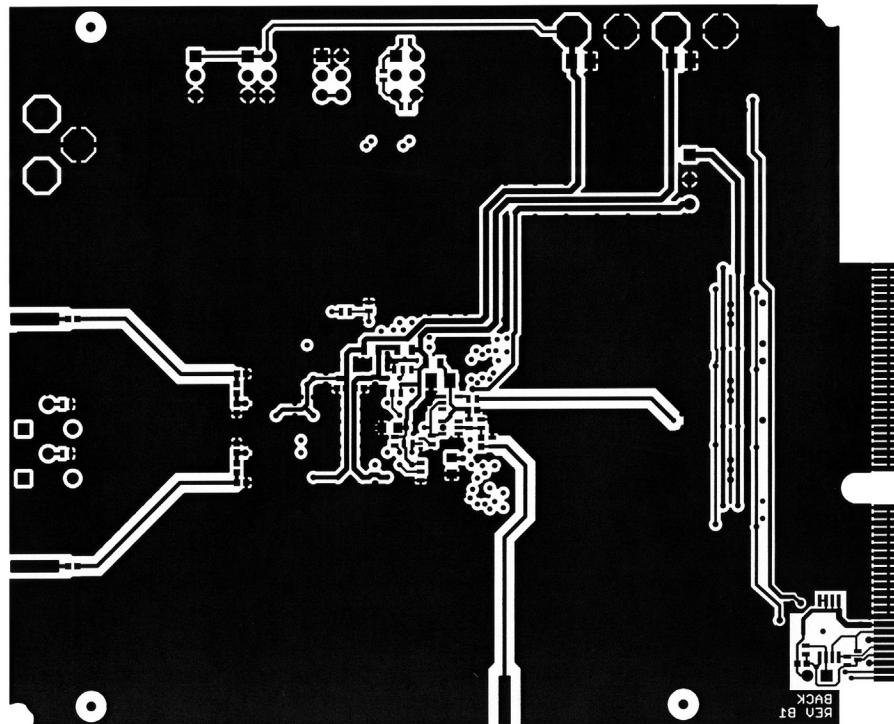

推奨レイアウトの良い例を図11～図14に示します。

ペースト印刷の品質は、高歩留りアセンブリにとって重要な要素です。タイプ3またはタイプ4を使って無洗浄半田ペーストを印刷することを推奨します。半田ステンシルは「アプリケーションノート100」で説明されているガイドラインに従ってデザインします。

LTM9004は鉛ベースまたは錫ベースの半田ペーストで使えるように金仕上げのパッドを採用しています。内部は鉛フリーで、JEDEC (e4) 標準規格に適合しています。材料表は [http://www.linear.com/leadfree/mat\\_dec.jsp](http://www.linear.com/leadfree/mat_dec.jsp) からオンラインで入手できます。

# LTM9004

## アプリケーション情報

図11. レイヤ1

図12. レイヤ2

9004fa

## アプリケーション情報

図13. レイヤ3

図14. レイヤ4

9004fa

# LTM9004

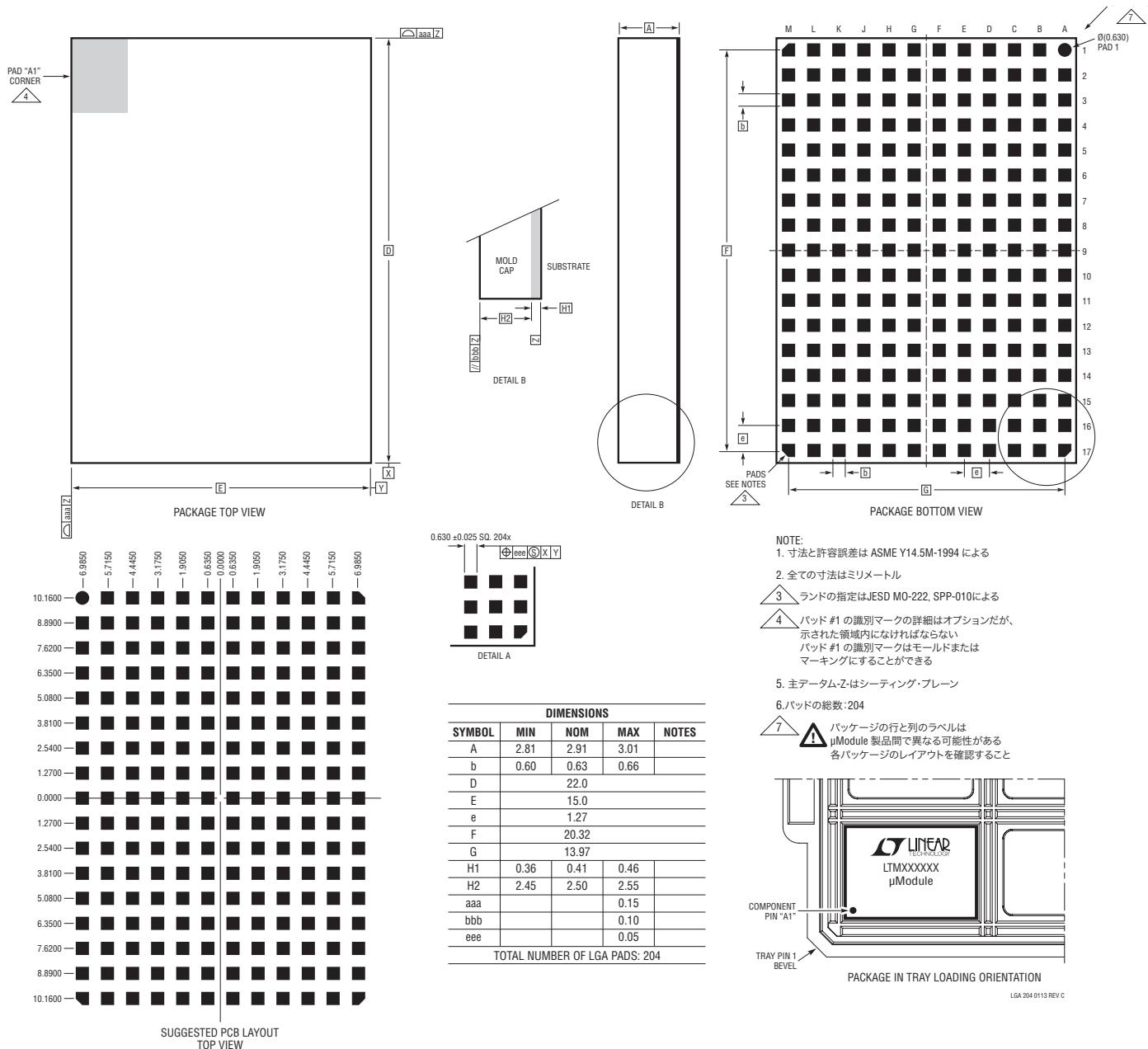

## パッケージ寸法

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

**LGA Package**

**204-Lead (22mm × 15mm × 2.91mm)**

(Reference LTC DWG # 05-08-1822 Rev C)

## 改訂履歴

| Rev | 日付   | 概要                      | ページ番号 |

|-----|------|-------------------------|-------|

| A   | 5/14 | パッケージ図を更新、高さを2.91mmに変更。 | 2、26  |

# LTM9004

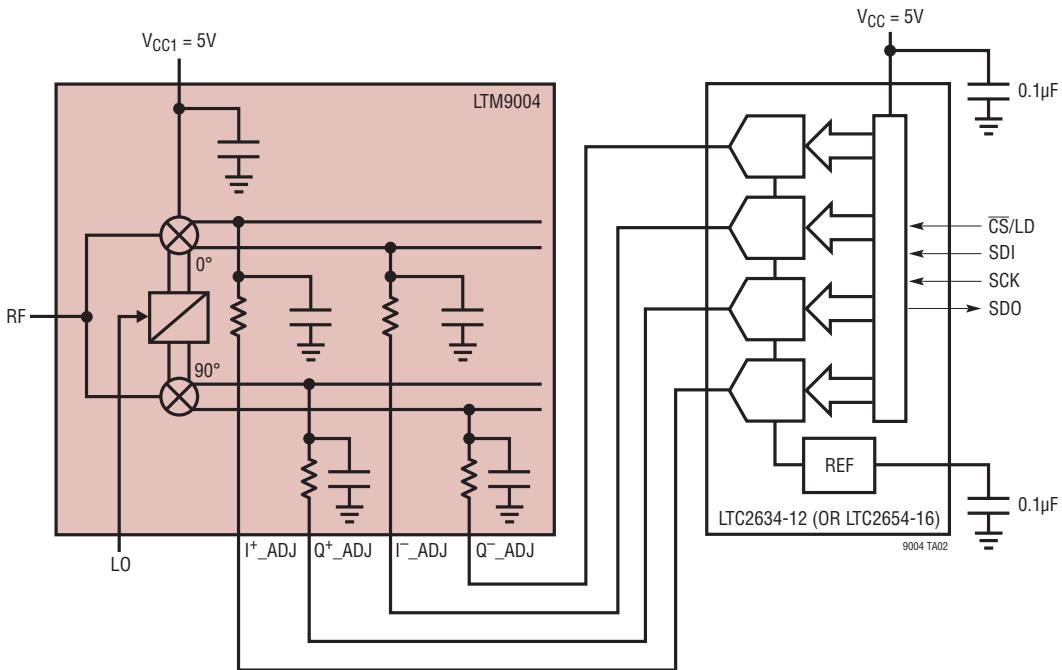

## 標準的応用例

## 関連製品

| 製品番号                    | 概要                                  | 注釈                                                                               |

|-------------------------|-------------------------------------|----------------------------------------------------------------------------------|

| LTC2295                 | デュアルの14ビット、10Msps ADC               | 120mW、SNR:74.4dB、9mm×9mm QFN                                                     |

| LTC2296                 | デュアルの14ビット、25Msps ADC               | 150mW、SNR:74dB、9mm×9mm QFN                                                       |

| LTC2297                 | デュアルの14ビット、40Msps ADC               | 240mW、SNR:74dB、9mm×9mm QFN                                                       |

| LTC2298                 | デュアルの14ビット、65Msps ADC               | 410mW、SNR:74dB、9mm×9mm QFN                                                       |

| LTC2299                 | デュアルの14ビット、80Msps ADC               | 445mW、SNR:73dB、9mm×9mm QFN                                                       |

| LTC2284                 | デュアルの14ビット、105Msps ADC              | 540mW、SNR:72.4dB、SFDR:88dB、64ピンQFN                                               |

| LTC2285                 | デュアルの14ビット、125Msps ADC              | 790mW、SNR:72.4dB、SFDR:88dB、64ピンQFN                                               |

| LT5575                  | 800MHz～2.7GHz高直線性直接変換直交復調器          | IIP2:1.9GHzで60dBm、NF:12.7dB、低いDCオフセット                                            |

| LTC6404-1/<br>LTC6404-2 | 600MHz、低ノイズ、高AC精度、完全差動入出力アンプ/ドライバ   | 3Vまたは5V、1.5nV/ $\sqrt{\text{Hz}}$ 、非常に低い歪み:-92dBC(10MHz)                         |

| LTC6406                 | 3GHz低ノイズ、レール・トゥ・レール入力差動ADCドライバ      | 低ノイズ: 1.6nV/ $\sqrt{\text{Hz}}$ 、低消費電力: 18 $\mu\text{A}$                         |

| LTM9001                 | 16ビット、IF/ベースバンド・レシーバ・サブシステム         | 16ビットの130Msps ADCを内蔵、受動フィルタと固定利得の差動アンプ、11.25mm×11.25mm LGAパッケージ                  |

| LTM9002                 | 14ビット、デュアルチャネルIF/ベースバンド・レシーバ・サブシステム | 14ビットのデュアル125Msps ADCを内蔵、受動フィルタと固定利得の差動アンプ、最大300MHzのIF範囲、15mm × 11.25mm LGAパッケージ |