## 特長

- 16ビット高速ADC、パッシブ・フィルタ、

固定利得差動アンプを内蔵

- 最大300MHzのIF範囲

ローパスおよびバンドパス・フィルタ・バージョン

- 低ノイズ、低歪みアンプ

固定利得:8dB、14dB、20dB、26dB

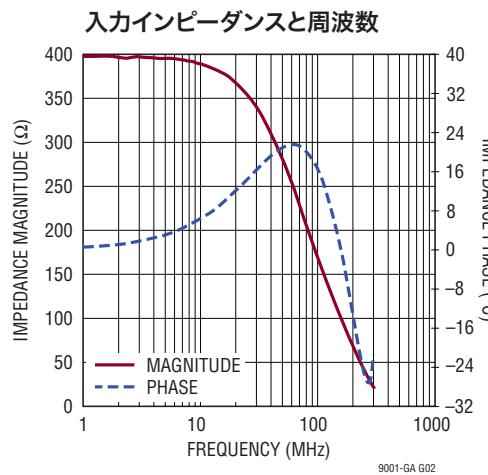

50Ω、200Ωまたは400Ωの入力インピーダンス

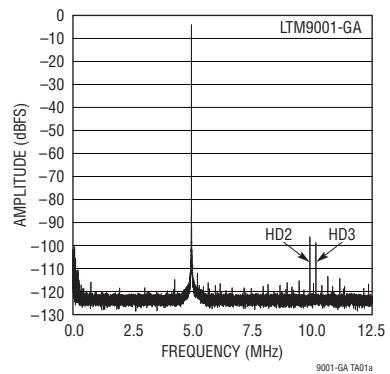

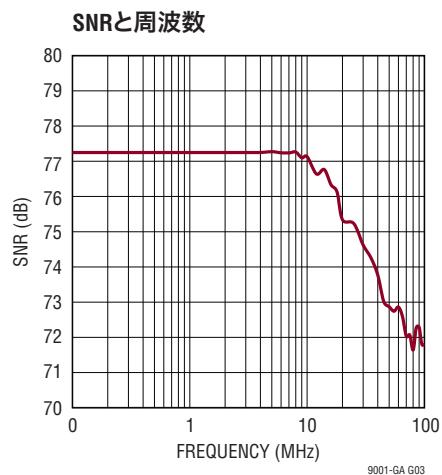

- 78dBのSNR、87dBのSFDR (LTM9001-GA)

- バイパス容量を内蔵、外付け部品不要

- オプションの内部ディザイナー

- オプションのデータ出力ランダマイザ

- 3.3V単一電源

- 消費電力:550mW (LTM9001-GA)

- クロック・デューティ・サイクル・スタビライザ

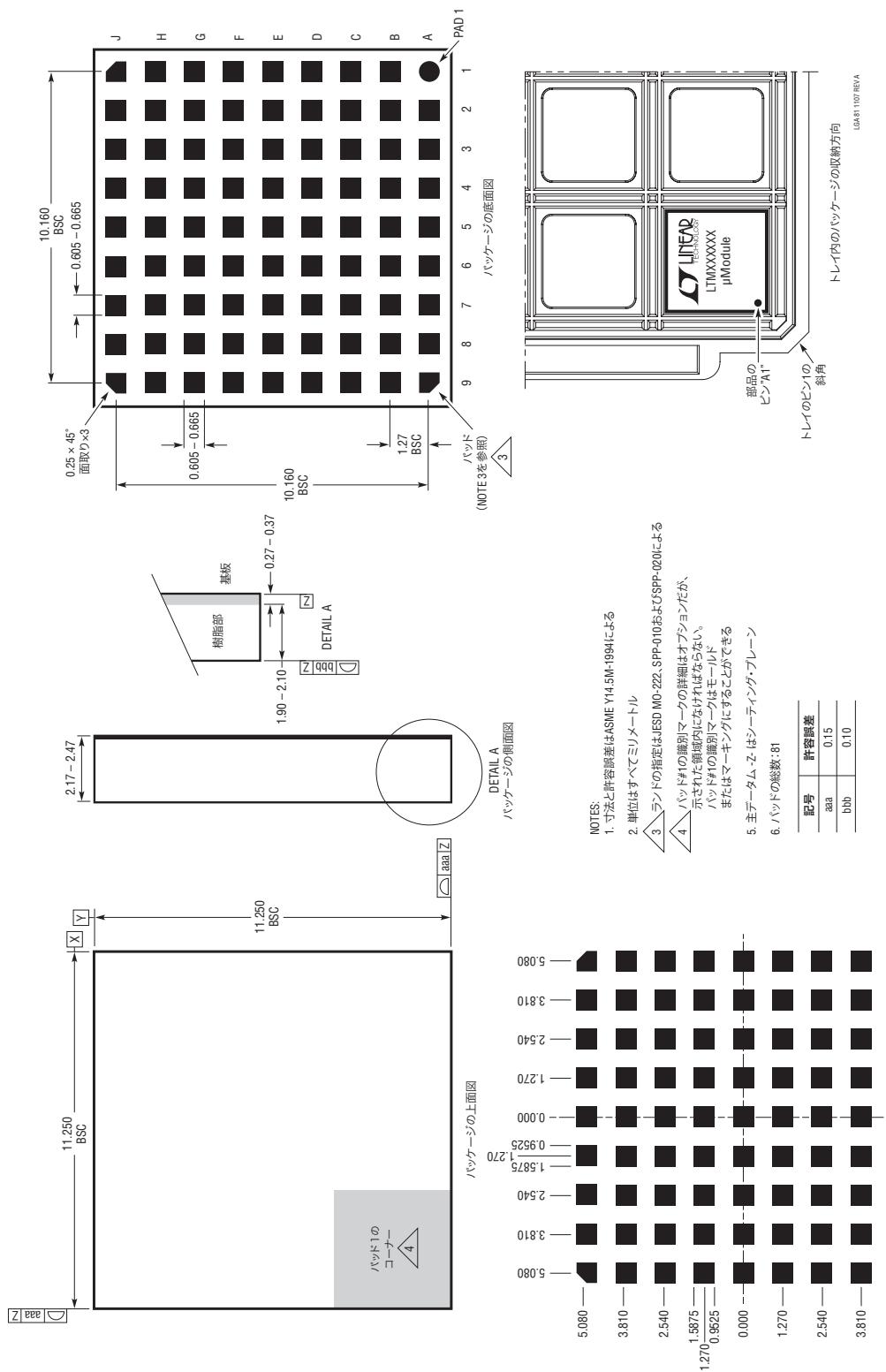

- 11.25mm×11.25mm×2.32mm LGAパッケージ

## アプリケーション

- 通信機器

- 高感度レシーバ

- 画像システム

- スペクトル・アナライザ

- ATE

## 概要

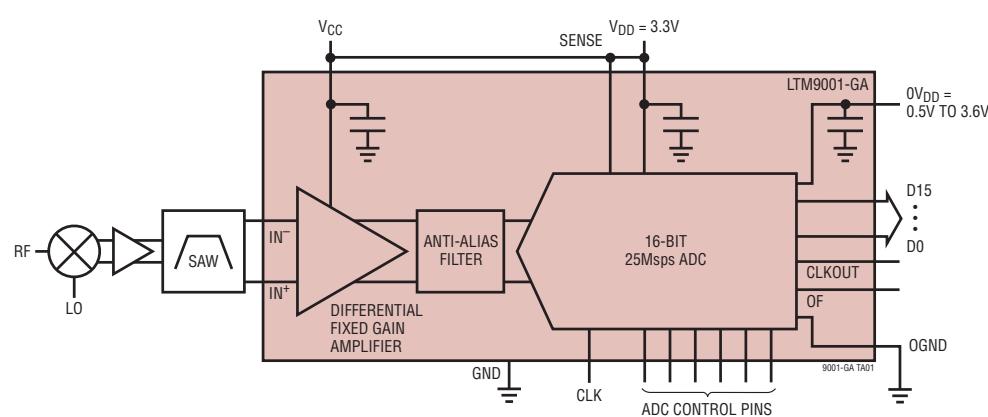

LTM<sup>®</sup>9001は高速16ビットA/Dコンバータ、マッチング・ネットワーク、アンチエイリアス・フィルタ、固定利得の低ノイズ差動アンプを内蔵した集積化SiP(System in a Package)です。このデバイスは、中間周波数(IF)が300MHzまでの広いダイナミック・レンジの信号をデジタル化するために設計されています。アンプはACまたはDC結合入力をドライブできます。ローパスまたはバンドパス・フィルタ・ネットワークは、多様な周波数に対応できます。セミカスタム対応については、弊社にお問い合わせください(表1参照)。

LTM9001は、5MHz時に78dBFSのノイズフロアと87dBのSFDR (LTM9001-GA)のAC性能を有しており、要求の厳しい通信アプリケーションのIFレシーバに最適です。

デジタル出力はシングルエンドCMOSです。独立した出力電源により、0.5V～3.3VのCMOS出力振幅が可能です。

オプションのクロック・デューティ・サイクル・スタビライザにより、広範なクロック・デューティ・サイクルにおいてフルスピードで高性能を実現します。

LT, LTC, LTM, Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。他のすべての商標はそれぞれの所有者に所有権があります。

## 標準的応用例

簡略化されたIFレシーバ・チャネル

64kポイントFFT、f<sub>IN</sub> = 5MHz、

-1dBFS、PGA = 0

# LTM9001-GA

## 絶対最大定格

(Note 1,2)

|                              |                                 |

|------------------------------|---------------------------------|

| 電源電圧 ( $V_{CC}$ )            | -0.3V~3.6V                      |

| 電源電圧 ( $V_{DD}$ )            | -0.3V~4V                        |

| デジタル出力電源電圧 ( $OV_{DD}$ )     | -0.3V~4V                        |

| アナログ入力電流 ( $IN^+$ , $IN^-$ ) | $\pm 10\text{mA}$               |

| デジタル入力電圧                     |                                 |

| (AMPSHDNを除く)                 | -0.3V~( $V_{DD}+0.3\text{V}$ )  |

| デジタル入力電圧                     |                                 |

| (AMPSHDN)                    | -0.3V~( $V_{CC}+0.3\text{V}$ )  |

| デジタル出力電圧                     | -0.3V~( $OV_{DD}+0.3\text{V}$ ) |

| 動作温度範囲                       |                                 |

| LTM9001C                     | 0°C~70°C                        |

| LTM9001I                     | -40°C~85°C                      |

| 保存温度範囲                       | -45°C~125°C                     |

| 最大接合部温度                      | 125°C                           |

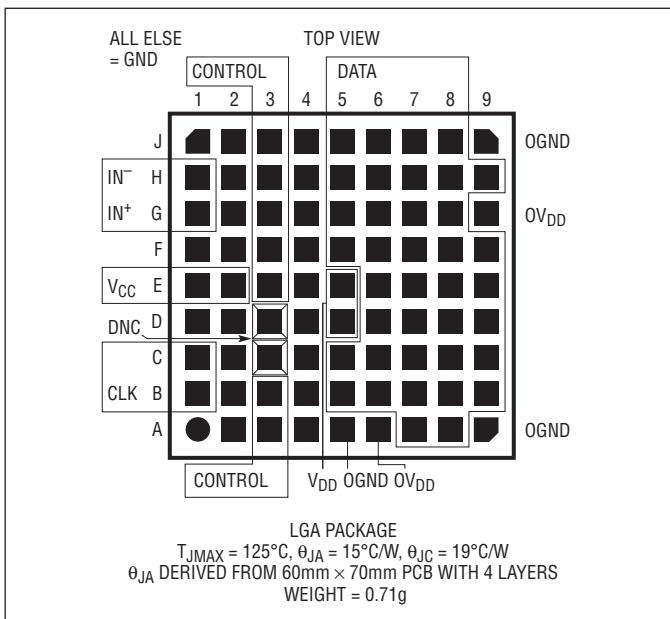

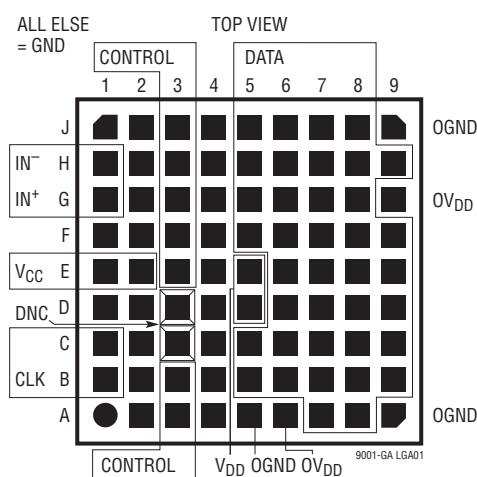

## ピン配置

## 発注情報

| 鉛フリー仕様           | トレイ              | 製品マーキング*    | パッケージ                                   | 温度範囲          |

|------------------|------------------|-------------|-----------------------------------------|---------------|

| LTM9001CV-GA#PBF | LTM9001CV-GA#PBF | LTM9001V-GA | 81-Lead (11.25mm x 11.25mm x 2.3mm) LGA | 0°C to 70°C   |

| LTM9001IV-GA#PBF | LTM9001IV-GA#PBF | LTM9001V-GA | 81-Lead (11.25mm x 11.25mm x 2.3mm) LGA | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー製品のマーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

この製品はトレイでのみ供給されます。詳細については、<http://www.linear-tech.co.jp/packaging/> をご覧ください。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL       | PARAMETER                       | CONDITIONS                               | MIN           | TYP                  | MAX | UNITS                                                      |

|--------------|---------------------------------|------------------------------------------|---------------|----------------------|-----|------------------------------------------------------------|

| $G_{DIFF}$   | Gain                            | DC, LTM9001-GA<br>$f_{IN} = 5\text{MHz}$ | ●<br>7.2<br>8 | 8                    | 8.8 | dB                                                         |

| $G_{TEMP}$   | Gain Temperature Drift          | $V_{IN} = \text{Maximum}$ , (Note 3)     |               | 2                    |     | $\text{mDB}/^\circ\text{C}$                                |

| $V_{INCM}$   | Input Common Mode Voltage Range | $(IN^+ + IN^-)/2$                        |               | 1.0~1.6              |     | V                                                          |

| $V_{IN}$     | Input Voltage Range at -1dBFS   | LTM9001-GA at 5MHz                       |               | 900                  |     | $\text{mV}_{\text{P-P}}$                                   |

| $R_{INDIFF}$ | Differential Input Impedance    | LTM9001-GA                               |               | 400                  |     | $\Omega$                                                   |

| $C_{INDIFF}$ | Differential Input Capacitance  | Includes Parasitic                       |               | 1                    |     | pF                                                         |

| $V_{OS}$     | Offset Error (Note 6)           | Including Amplifier and ADC (LTM9001-GA) | ●<br>-50      | -10                  |     | mV                                                         |

|              | Offset Drift                    | Including Amplifier and ADC              |               | $\pm 10$             |     | $\mu\text{V}/^\circ\text{C}$                               |

|              | Full-Scale Drift                | Internal Reference<br>External Reference |               | $\pm 30$<br>$\pm 15$ |     | $\text{ppm}/^\circ\text{C}$<br>$\text{ppm}/^\circ\text{C}$ |

9001gaf

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL       | PARAMETER                                     | CONDITIONS                     | MIN  | TYP | MAX | UNITS                    |

|--------------|-----------------------------------------------|--------------------------------|------|-----|-----|--------------------------|

| CMRR         | Common Mode Rejection Ratio                   |                                | 60   |     |     | dB                       |

| $I_{SENSE}$  | SENSE Input Leakage Current                   | $0V < SENSE < V_{DD}$ (Note 9) | ● -3 | 3   |     | $\mu\text{A}$            |

| $I_{MODE}$   | MODE Pin Pull-Down Current to GND             |                                |      | 10  |     | $\mu\text{A}$            |

| $I_{OE}$     | $\overline{OE}$ Pin Pull-Down Current to GND  |                                |      | 10  |     | $\mu\text{A}$            |

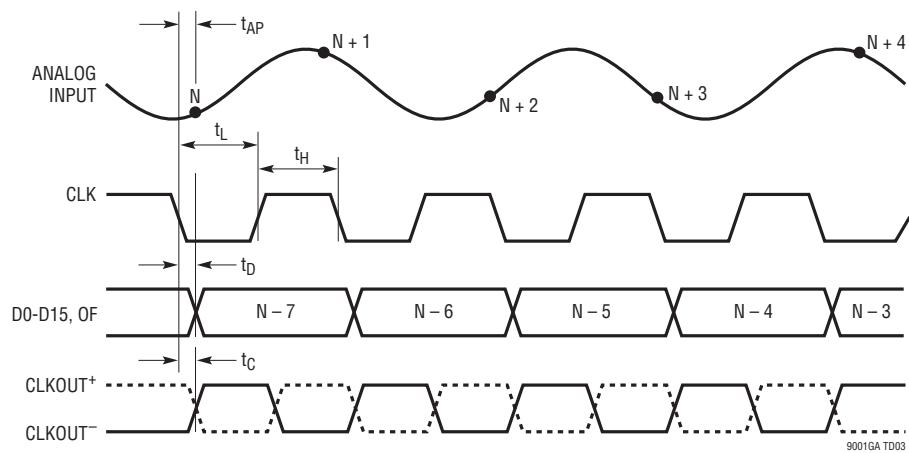

| $t_{AP}$     | Sample-and-Hold Acquisition Delay Time        |                                |      | 1   |     | ns                       |

| $t_{JITTER}$ | Sample-and-Hold Acquisition Delay Time Jitter |                                |      | 70  |     | $\text{fs}_{\text{RMS}}$ |

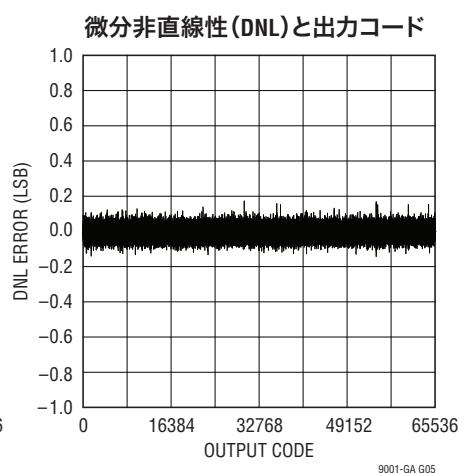

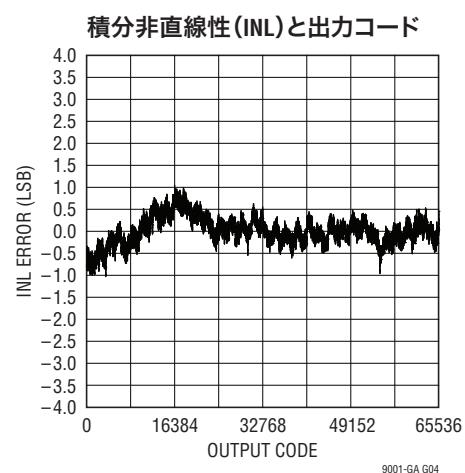

## コンバータの特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

| PARAMETER                     | CONDITIONS                             | MIN         | TYP     | MAX | UNITS                     |

|-------------------------------|----------------------------------------|-------------|---------|-----|---------------------------|

| Resolution (No Missing Codes) |                                        | ● 16        |         |     | Bits                      |

| Integral Linearity Error      | Differential Input LTM9001-GA (Note 5) | ● $\pm 2.4$ | $\pm 8$ |     | LSB                       |

| Differential Linearity Error  | Differential Input                     | ● $\pm 0.3$ | $\pm 1$ |     | LSB                       |

| Transition Noise              | External Reference                     |             | 1       |     | $\text{LSB}_{\text{RMS}}$ |

## ダイナミック精度

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。 $A_{IN} = -1\text{dBFS}$ 。(Note 4)

| SYMBOL  | PARAMETER                                                                             | CONDITIONS                                   | MIN          | TYP          | MAX | UNITS                          |

|---------|---------------------------------------------------------------------------------------|----------------------------------------------|--------------|--------------|-----|--------------------------------|

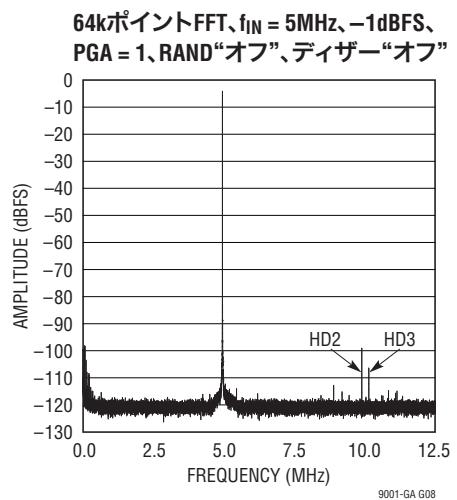

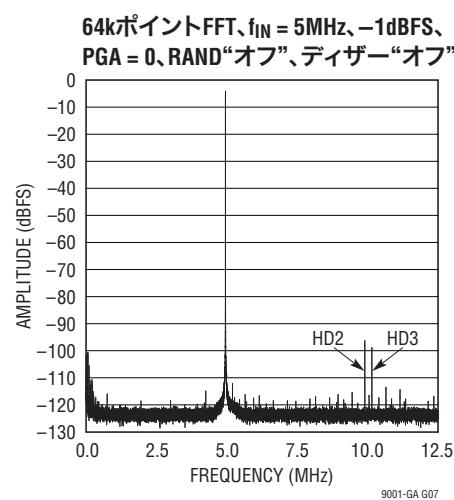

| SNR     | Signal-to-Noise Ratio                                                                 | 5MHz Input (PGA = 0)<br>5MHz Input (PGA = 1) | ● 76<br>75.4 | 78           |     | $\text{dBFS}$<br>$\text{dBFS}$ |

| SFDR    | Spurious Free Dynamic Range, 2nd or 3rd Harmonic                                      | 5MHz Input (PGA = 0)<br>5MHz Input (PGA = 1) | ● 76         | 87<br>89.8   |     | $\text{dBc}$<br>$\text{dBc}$   |

| SFDR    | Spurious Free Dynamic Range 4th or Higher                                             | 5MHz Input (PGA = 0)<br>5MHz Input (PGA = 1) | ● 91         | 100<br>99    |     | $\text{dBc}$<br>$\text{dBc}$   |

| S/(N+D) | Signal-to-Noise Plus Distortion Ratio                                                 | 5MHz Input (PGA = 0)<br>5MHz Input (PGA = 1) | ● 75         | 77.4<br>74.8 |     | $\text{dBFS}$<br>$\text{dBFS}$ |

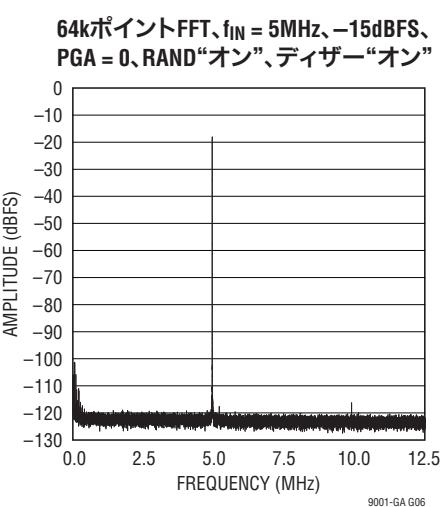

| SFDR    | Spurious Free Dynamic Range at $-15\text{dBFS}$ , Dither "OFF"                        | 5MHz Input (PGA = 0)<br>5MHz Input (PGA = 1) | ● 91         | 105<br>107.5 |     | $\text{dBFS}$<br>$\text{dBFS}$ |

| SFDR    | Spurious Free Dynamic Range at $-15\text{dBFS}$ , Dither "ON"                         | 5MHz Input (PGA = 0)<br>5MHz Input (PGA = 1) | ● 93         | 107<br>109   |     | $\text{dBFS}$<br>$\text{dBFS}$ |

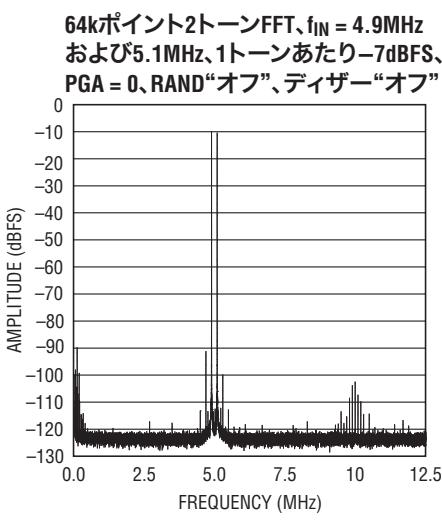

| IMD3    | Third Order Intermodulation Distortion; 1MHz Tone Spacing, 2 Tones at $-7\text{dBFS}$ | $f_{IN} = 5\text{MHz}$                       |              | 85           |     | dB                             |

| IIP3    | Equivalent Third Order Input Intercept Point, 2 Tone                                  | $f_{IN} = 5\text{MHz}$                       |              | 36.5         |     | $\text{dBm}$                   |

# LTM9001-GA

## デジタル入出力

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL                                      | PARAMETER                | CONDITIONS                       | MIN | TYP | MAX      | UNITS         |

|---------------------------------------------|--------------------------|----------------------------------|-----|-----|----------|---------------|

| <b>ロジック入力(DITH、PGA、ADCSHDN、RAND、CKJ、OE)</b> |                          |                                  |     |     |          |               |

| $V_{IH}$                                    | High Level Input Voltage | $V_{DD} = 3.3\text{V}$           | ●   | 2   |          | V             |

| $V_{IL}$                                    | Low Level Input Voltage  | $V_{DD} = 3.3\text{V}$           | ●   |     | 0.8      | V             |

| $I_{IN}$                                    | Input Current            | $V_{IN} = 0\text{V}$ to $V_{DD}$ | ●   |     | $\pm 10$ | $\mu\text{A}$ |

| $C_{IN}$                                    | Input Capacitance        | (Note 7)                         |     |     | 1.5      | pF            |

## ロジック入力(AMPSHDN)

|          |                          |                        |   |   |     |               |

|----------|--------------------------|------------------------|---|---|-----|---------------|

| $V_{IH}$ | High Level Input Voltage | $V_{CC} = 3.3\text{V}$ | ● | 2 |     | V             |

| $V_{IL}$ | Low Level Input Voltage  | $V_{CC} = 3.3\text{V}$ | ● |   | 0.8 | V             |

| $I_{IH}$ | Input High Current       | $V_{IN} = 2\text{V}$   |   |   | 1.3 | $\mu\text{A}$ |

| $I_{IL}$ | Input Low Current        | $V_{IN} = 0.8\text{V}$ |   |   | 0.1 | $\mu\text{A}$ |

| $C_{IN}$ | Input Capacitance        | (Note 7)               |   |   | 1.5 | pF            |

## ロジック出力

### $OV_{DD} = 3.3\text{V}$

|              |                           |                                                                                               |   |     |                    |             |

|--------------|---------------------------|-----------------------------------------------------------------------------------------------|---|-----|--------------------|-------------|

| $V_{OH}$     | High Level Output Voltage | $V_{DD} = 3.3\text{V}, I_0 = -10\mu\text{A}$<br>$V_{DD} = 3.3\text{V}, I_0 = -200\mu\text{A}$ | ● | 3.1 | 3.299<br>3.29      | V<br>V      |

| $V_{OL}$     | Low Level Output Voltage  | $V_{DD} = 3.3\text{V}, I_0 = 10\mu\text{A}$<br>$V_{DD} = 3.3\text{V}, I_0 = 1.6\text{mA}$     | ● |     | 0.01<br>0.1<br>0.4 | V<br>V<br>V |

| $I_{SOURCE}$ | Output Source Current     | $V_{OUT} = 0\text{V}$                                                                         |   |     | -50                | mA          |

| $I_{SINK}$   | Output Sink Current       | $V_{OUT} = 3.3\text{V}$                                                                       |   |     | 50                 | mA          |

### $OV_{DD} = 2.5\text{V}$

|          |                           |                                               |  |      |  |   |

|----------|---------------------------|-----------------------------------------------|--|------|--|---|

| $V_{OH}$ | High Level Output Voltage | $V_{DD} = 3.3\text{V}, I_0 = -200\mu\text{A}$ |  | 2.49 |  | V |

| $V_{OL}$ | Low Level Output Voltage  | $V_{DD} = 3.3\text{V}, I_0 = 1.6\text{mA}$    |  | 0.1  |  | V |

### $OV_{DD} = 1.8\text{V}$

|          |                           |                                               |  |      |  |   |

|----------|---------------------------|-----------------------------------------------|--|------|--|---|

| $V_{OH}$ | High Level Output Voltage | $V_{DD} = 3.3\text{V}, I_0 = -200\mu\text{A}$ |  | 1.79 |  | V |

| $V_{OL}$ | Low Level Output Voltage  | $V_{DD} = 3.3\text{V}, I_0 = 1.6\mu\text{A}$  |  | 0.1  |  | V |

## 電源要件

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL            | PARAMETER                 | CONDITIONS                                      | MIN | TYP   | MAX | UNITS |

|-------------------|---------------------------|-------------------------------------------------|-----|-------|-----|-------|

| $V_{DD}$          | ADC Analog Supply Voltage | (Note 8)                                        | ●   | 3.135 | 3.3 | 3.465 |

| $V_{CC}$          | Amplifier Supply Voltage  |                                                 | ●   | 2.85  |     | V     |

| $I_{CC}$          | Amplifier Supply Current  |                                                 | ●   | 100   | 136 | mA    |

| $P_{SHDN}$        | Total Shutdown Power      | $\text{AMPSHDN} = \text{ADCSHDN} = 3.3\text{V}$ |     |       | 10  | mW    |

| $OV_{DD}$         | Output Supply Voltage     | (Note 8)                                        | ●   | 0.5   | 3.6 | V     |

| $I_{VDD}$         | Analog Supply Current     | LTM9001-GA                                      | ●   | 66    | 80  | mA    |

| $P_{DISS}$        | ADC Power Dissipation     | LTM9001-GA                                      | ●   | 220   | 265 | mW    |

| $P_{DISS(TOTAL)}$ | Total Power Dissipation   | LTM9001-GA                                      |     |       | 550 | mW    |

## タイミング特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。(Note 4)

| SYMBOL | PARAMETER                   | CONDITIONS                | MIN    | TYP | MAX | UNITS |

|--------|-----------------------------|---------------------------|--------|-----|-----|-------|

| $f_S$  | Sampling Frequency (Note 8) | LTM9001-GA                | ● 1    |     | 25  | MHz   |

| $t_L$  | CLK Low Time (Note 7)       | Duty Cycle Stabilizer Off | ● 18.9 | 20  | 500 | ns    |

|        |                             | Duty Cycle Stabilizer On  | ● 5    | 20  | 500 | ns    |

| $t_H$  | CLK High Time (Note 7)      | Duty Cycle Stabilizer Off | ● 18.9 | 20  | 500 | ns    |

|        |                             | Duty Cycle Stabilizer On  | ● 5    | 20  | 500 | ns    |

### CMOS Output Mode

|            |                     |                          |        |     |     |        |

|------------|---------------------|--------------------------|--------|-----|-----|--------|

| $t_D$      | CLK to DATA Delay   | (Note 7)                 | ● 1.3  | 3.1 | 4.9 | ns     |

| $t_C$      | CLK to CLKOUT Delay | (Note 7)                 | ● 1.3  | 3.1 | 4.9 | ns     |

| $t_{SKEW}$ | DATA to CLKOUT Skew | ( $t_C - t_D$ ) (Note 7) | ● -0.6 | 0   | 0.6 | ns     |

|            | Data Latency        |                          |        | 7   |     | Cycles |

**Note 1:**絶対最大定格に記載された値を超えるストレスは、デバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**すべての電圧値はGNDと0GNDが連結されたグランドを基準とする(注記がない場合)。

**Note 3:**利得はADC経由で $\text{IN}^+/\text{IN}^-$ により測定する。

**Note 4:**特に注記がない限り、 $V_{CC} = V_{DD} = 3.3\text{V}$ 、 $f_{SAMPLE}$  = 最大サンプル周波数、入力範囲 = -1dBFS (PGA = 0、差動ドライブ)、AC結合入力。

**Note 5:**積分非直線性は“ベストフィット直線”から伝達曲線へのコードの偏差として定義される。偏差は量子化幅の中心から測定する。

**Note 6:**オフセット誤差は、出力コードを0000 0000 0000 0000と1111 1111 1111 1111の間でふらつかせるのに必要な、 $\text{IN}^+$ ピンと $\text{IN}^-$ ピン間に印加する電圧である。

**Note 7:**設計により保証。テストはされない。

**Note 8:**推奨動作条件。

**Note 9:**リーク電流には起動時に過渡が生じる。抵抗は1kΩ未満に保つこと。

# LTM9001-GA

## タイミング図

## 標準的性能特性

## ピン機能

### 電源ピン

**V<sub>CC</sub>(ピンE1、E2)**: アンプの3.3Vアナログ電源ピン。このピンの電圧はアンプ段のみに電力を供給し、内部でGNDにバイパスされています。

**V<sub>DD</sub>(ピンE5、D5)**: ADCの3.3Vアナログ電源ピン。この電源は内部でGNDにバイパスされています。

**0V<sub>DD</sub>(ピンA6、G9)**: ADC出力ドライバの正電源。この電源は内部でOGNDにバイパスされています。

**GND(ピンA1、A2、A4、B2、B4、C2、C4、D1、D2、D4、E4、F1、F2、F4、G2、G4、H2、H4、J1、J2、J4)**: アナログ・グランド。

**0GND(ピンA5、A9、G8、J9)**: ADC出力ドライバ・グランド。

### アナログ入力

**IN<sup>+</sup>(ピンG1)**: 正(非反転)アンプ入力。

**IN<sup>-</sup>(ピンH1)**: 負(反転)アンプ入力。

**DNC(ピンC3、D3)**: 接続しないこと。これらのピンはテスト用で、PCBに接続してはなりません。未接続パッドに半田付けできますが、十分絶縁されていなければなりません。DNCピンはADC入力の前の信号経路に接続されています。そのため、これらの敏感なノードから他の信号を離すように注意する必要があります。

**NC(ピンの位置についてはピン配置表を参照)**: 非接続。

**CLK(ピンB1)**: クロック入力。サンプリングされたアナログ入力はCLKの立下りエッジでホールドされます。出力データはCLKの立上りエッジでラッチすることができます。

### 制御入力

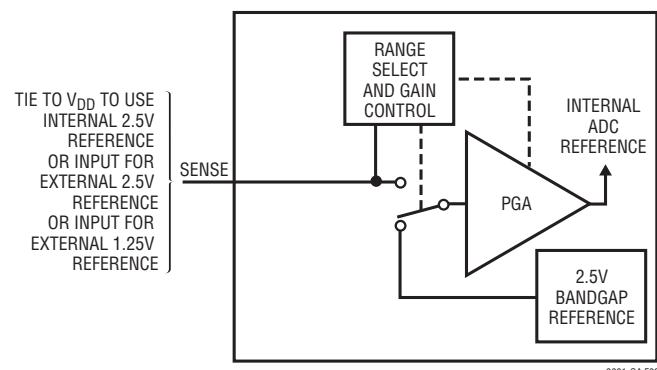

**SENSE(ピンJ3)**: リファレンス・モード選択と外部リファレンス入力。内部2.5Vバンドギャップ・リファレンスを選択するためには、SENSEをV<sub>DD</sub>に接続します。2.5Vまたは1.25Vの外部リファレンスも使用可能で、両方のリファレンス値で最大フル・スケールの入力範囲が設定されます。

**AMPSHDN(ピンH3)**: アンプの電源シャットダウン・ピン。このピンはアナログ・グランド基準のロジック入力です。AMPSHDN = “L”的場合は通常動作です。AMPSHDN = “H”的場合はアンプの消費電力が低減し、標準のアンプ電源電流が3mAになります。

**MODE(ピンG3)**: 出力フォーマットおよびクロック・デューティ・サイクル・スタビライザ選択ピン。MODEを0Vに接続すると、オフセット・バイナリ出力フォーマットが選択され、クロック・デュー

ティ・サイクル・スタビライザがディスエーブルされます。MODEを1/3V<sub>DD</sub>に接続すると、オフセット・バイナリ出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがイネーブルされます。MODEを2/3V<sub>DD</sub>に接続すると、2の補数出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがイネーブルされます。MODEをV<sub>DD</sub>に接続すると、2の補数出力フォーマットが選択され、クロック・デューティ・サイクル・スタビライザがディスエーブルされます。

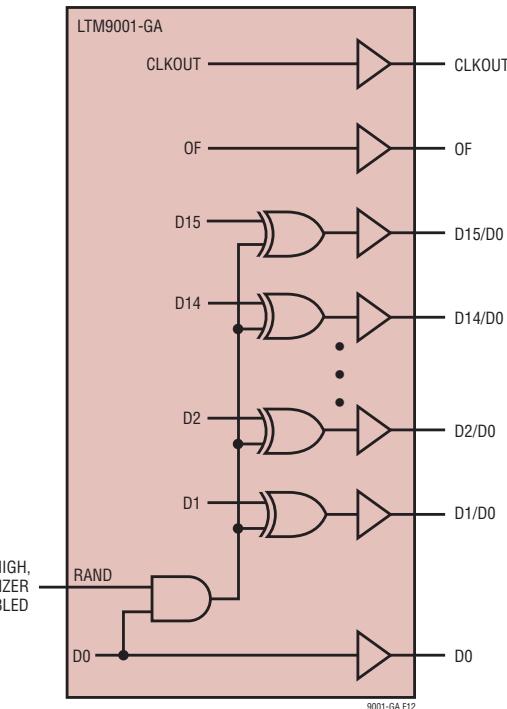

**RAND(ピンF3)**: デジタル出力ランダム化選択ピン。RAND = “L”的場合は通常動作です。RAND = “H”的場合は、D1～D15を選択してD0(LSB)との排他的論理和(XOR)を取ります。LSBと他のすべてのビットの間で再度XOR演算を行って、出力をデコードできます。この動作モードでは、デジタル出力干渉の影響が低減されます。

**PGA(ピンE3)**: プログラマブル・ゲイン・アンプ制御ピン。PGA = “L”的場合は、通常(最大)の入力電圧範囲が選択されます。PGA = “H”的場合は3.5dB狭い入力範囲が選択され、SNRを犠牲にすることで歪み性能をわずかに向上させます。

**ADCSHDN(ピンB3)**: ADCの電源シャットダウン・ピン。ADCSHDN = “L”的場合は通常動作です。ADCSHDN = “H”的場合は、アナログ回路の電力消費が低減し、デジタル出力が高インピーダンス状態になります。

**DITH(ピンA3)**: 内部ディザイナー・イネーブル・ピン。DITH = “L”的場合は内部ディザイナーがディスエーブルされ、DITH = “H”的場合は内部ディザイナーがイネーブルされます。ディザイナー動作の詳細については、本データシートの「内部ディザイナー」を参照してください。

**OE(ピンF5)**: 出力イネーブル・ピン。“L”的場合はデジタル出力ドライバがイネーブルされ、“H”的場合はデジタル出力が高インピーダンス状態になります。

### デジタル出力

**D0～D15(ピンの位置についてはピン配置表を参照)**: デジタル出力。D15がMSBでD0がLSBです。

**CLKOUT<sup>+</sup>(ピンE7)**: 反転データ有効出力。CLKOUT<sup>+</sup>は、サンプル・レートでトグルします。CLKOUT<sup>+</sup>の立上りエッジでデータをラッチします。

**CLKOUT<sup>-</sup>(ピンE6)**: データ有効出力。CLKOUT<sup>-</sup>は、サンプル・レートでトグルします。CLKOUT<sup>-</sup>の立下りエッジでデータをラッチします。

**OF(ピンG5)**: オーバーフロー/アンダーフローのデジタル出力。OFは、オーバーフローまたはアンダーフローが発生すると“H”になります。

## ピン配置

Pin Configuration

|   | 1               | 2               | 3       | 4   | 5               | 6                   | 7      | 8    | 9                |

|---|-----------------|-----------------|---------|-----|-----------------|---------------------|--------|------|------------------|

| J | GND             | GND             | SENSE   | GND | D14             | NC                  | D12    | NC   | OGND             |

| H | IN <sup>-</sup> | GND             | AMPSHDN | GND | NC              | NC                  | NC     | NC   | D11              |

| G | IN <sup>+</sup> | GND             | MODE    | GND | OE              | D15                 | D13    | OGND | OV <sub>DD</sub> |

| F | GND             | GND             | RAND    | GND | OE              | NC                  | D9     | NC   | D10              |

| E | V <sub>CC</sub> | V <sub>CC</sub> | PGA     | GND | V <sub>DD</sub> | CLKOUT <sup>-</sup> | CLKOUT | NC   | D8               |

| D | GND             | GND             | DNC     | GND | V <sub>DD</sub> | NC                  | D6     | NC   | D7               |

| C | NC              | GND             | DNC     | GND | D0              | NC                  | D4     | NC   | D5               |

| B | CLK             | GND             | ADCSHDN | GND | NC              | NC                  | D1     | D3   | NC               |

| A | GND             | GND             | DITH    | GND | OGND            | OV <sub>DD</sub>    | NC     | D2   | OGND             |

LGAピン配置の上面図(部品透過図)

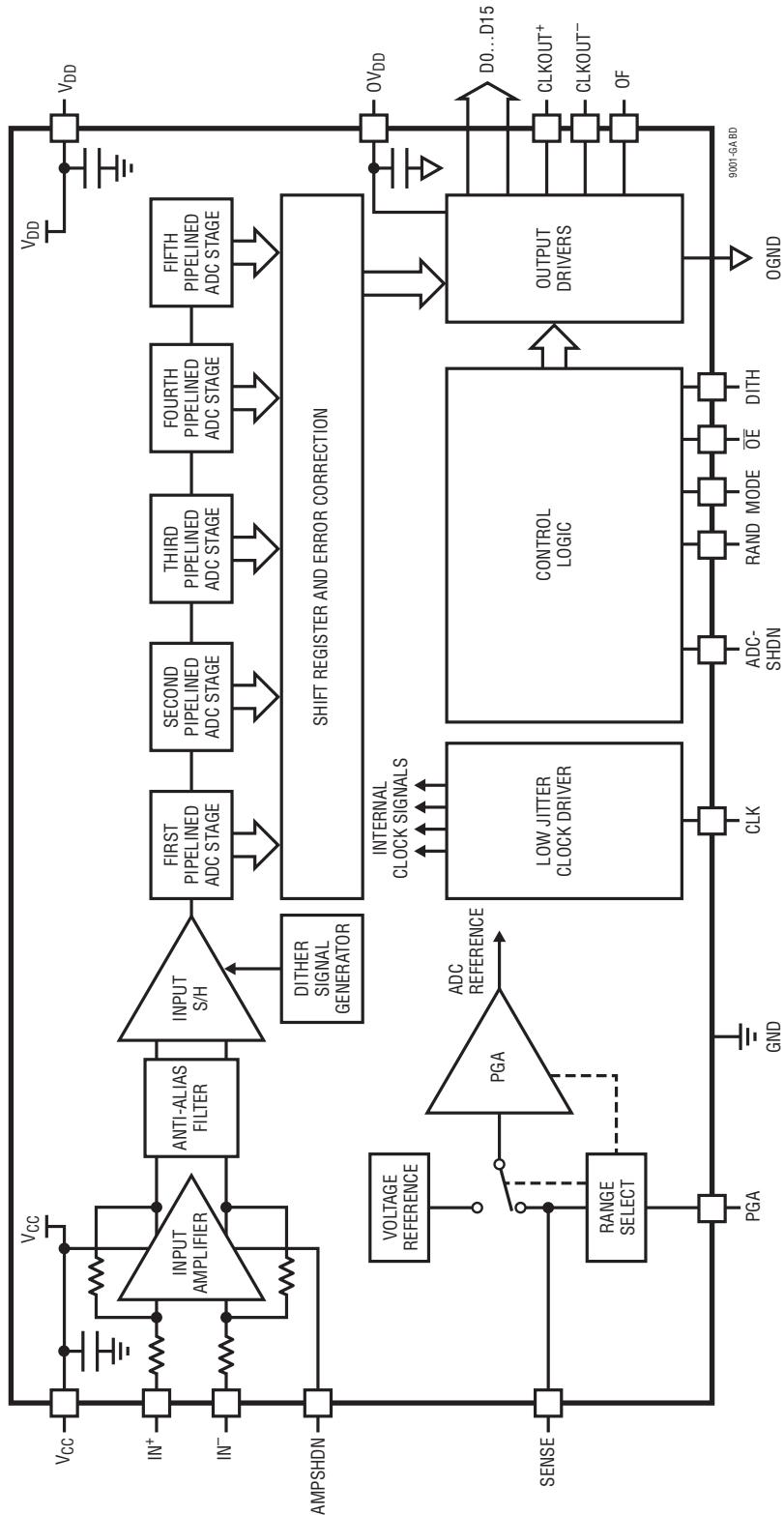

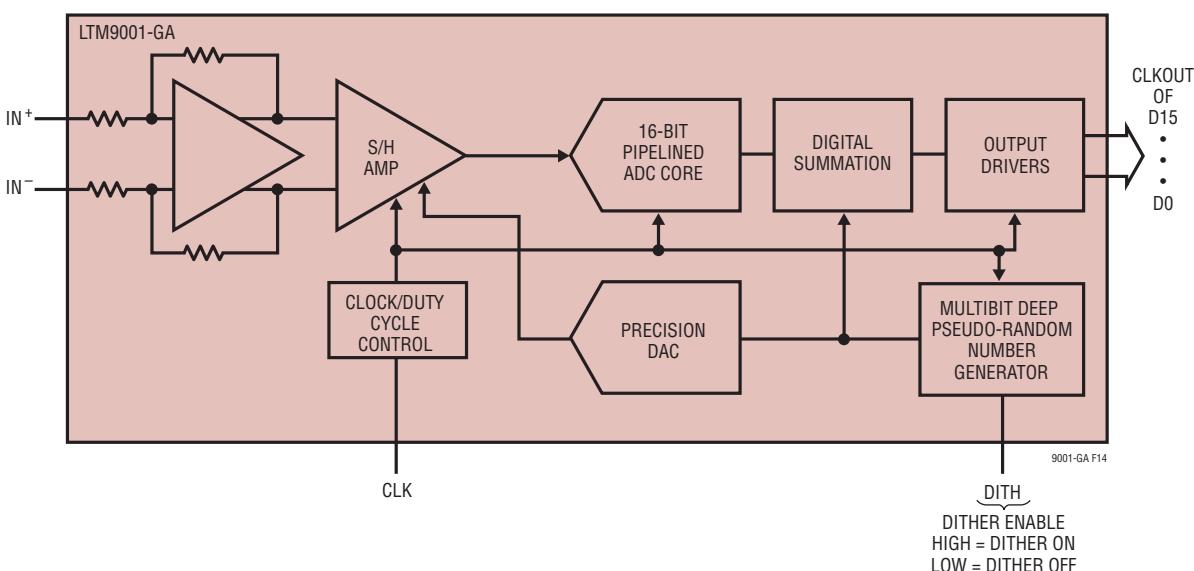

## 機能ブロック図

## 動作

### ダイナミック特性の定義

#### 信号対ノイズ+歪み比

信号対ノイズ+歪み比 [S/(N+D)] は、基本入力周波数の RMS 振幅と ADC 出力における他のすべての周波数成分の RMS 振幅の比です。

#### 信号対ノイズ比

信号対ノイズ比(SNR)は、基本入力周波数のRMS振幅と第5次高調波を除く他のすべての周波数成分のRMS振幅の比です。

#### 全高調波歪み

全高調波歪みは、入力信号のすべての高調波のRMS合計と基本波の比です。帯域外高調波は、DCからサンプリング周波数の1/2までの周波数帯域にエイリアスを発生させます。THDは次式で表されます。

$$\text{THD} = -20 \log \left( \sqrt{(V2^2 + V3^2 + V4^2 + \dots + Vn^2)} / V1 \right)$$

ここで、V1は基本周波数のRMS振幅で、V2からVnは第2次から第n次の高調波の振幅です。

#### 混変調歪み

入力信号が複数のスペクトル成分を含む場合は、伝達関数の非直線性により、THDに加えて混変調歪み(IMD)が発生することがあります。IMDは、異なる周波数の別の正弦波入力が存在することによって発生する正弦波入力の変化です。

周波数faとfbの2つの純粋な正弦波を入力に加えると、伝達関数の非直線性によって、mfa ± nfbの周波数の和と差に歪みが発生する場合があります(mおよびn = 0, 1, 2, 3, …)。

たとえば、3次IMD項には(2fa+fb)、(fa+2fb)、(2fa-fb)、(fa-2fb)が含まれます。3次IMDは、いずれかの入力トーンの RMS 値と最大3次IMD積のRMS値の比として定義されます。

#### スプリアス・フリー・ダイナミックレンジ(SFDR)

RMS入力信号の振幅とピーク・スプリアス・スペクトル成分の RMS 値の比をdBcで表した値。SFDRは、フル・スケールに対しで計算してdBFSで表すこともできます。

#### アパーーチャ遅延時間

アパーーチャ遅延は、ENC<sup>+</sup>が立ち上がり、ENC<sup>-</sup>電圧と等しくなった時点から、入力信号がサンプル・ホールド回路によってホールドされる瞬間までの時間です。あるいは、シングルエンドCLKバージョンの場合は、CLKがV<sub>DD</sub>の0.45倍に達した時点から入力信号がサンプル・ホールド回路によってホールドされる瞬間までの時間です。

#### アパーーチャ遅延ジッタ

変換から変換までのアパーーチャ遅延時間の変動。このランダムな変動が、AC入力をサンプリングする際のノイズになります。ジッタのみが原因の信号対ノイズ比は、次式で求めることができます。

$$\text{SNR}_{\text{JITTER}} = -20 \log (2\pi \cdot f_{IN} \cdot t_{JITTER})$$

#### 概要

LTM9001は、集積化されたSystem in a Package (SiP) μModule<sup>®</sup>レシーバで、高速サンプリング16ビットA/Dコンバータ、マッチング・ネットワーク、アンチエイリアス・フィルタおよび固定利得の低ノイズ差動アンプを備えています。中間周波数(IF)範囲が300MHzまでの高周波の広いダイナミック・レンジの信号をデジタル化するために設計されています。

μModuleはリニアテクノロジー社の登録商標です。

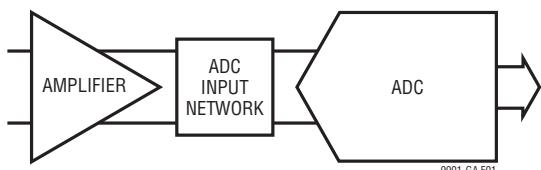

## 動作

以下のセクションでは、LTM9001の機能動作についてさらに詳しく説明します。SiP技術によりLTM9001をカスタマイズすることができます。最初のセクションでは、カスタマイズについて説明します。その後のセクションでは、図1に示す基本的機能要素について説明します。

図1. 基本的機能要素

## セミカスタム・オプション

$\mu$ Moduleの構造は、特定用途向け標準品において画期的な柔軟性を実現します。標準ADCおよびアンプ部品はプロセス技術には関係なく集積可能で、特定のアプリケーションの受動素子に適合します。たとえば、LTM9001-AA(別のデータシートに記載)は、最大130Mspsのレートで16ビットADCサンプリングを行うように構成されています。アンプ利得は、 $200\Omega$ の入力インピーダンスと $233\text{mVp-p}$ の入力範囲で $20\text{dB}$ です。マッチング・ネットワークは、このような条件でアンプ出力とADC間のインターフェースを最適化するように設計されています。さらに、 $162.5\text{MHz} \pm 25\text{MHz}$ の2ポール・バンドパス・フィルタを備えています。

ただし、弊社のセミカスタム開発プログラムを利用すれば、他のオプションも活用できます。リニアテクノロジーは、さまざまな用途向けに、他の速度、分解能、IF範囲、利得およびフィルタ構成を提供するプログラムを用意しています。LTM9001の構成と利用可能なオプションについては、表1を参照してください。このセミカスタム設計は、適切に変更されたマッチング・ネットワークを備えた既存のADCとアンプに基づいています。完成したサブシステムは、アプリケーション用に定義された正確なパラメータでテストされます。最終的には、完全に統合され、正確にテストされた信頼性の高いソリューションになります。セミカスタムのレシーバ・サブシステム・プログラムの詳細については、弊社にお問い合わせください。

表1のオプションの組合せの中には現時点では使用できないものもあり、指定された性能が既存の値と大きく異なる場合があります。LVDSまたはCMOS出力が可能な高速オプションについては、別のデータシートをご覧ください。本データシートでは、ピン配置の異なるCMOS出力のみのバージョンについて説明しています。

## アンプ情報

LTM9001で使用されるアンプは、低ノイズ、低歪みの完全な差動ADCドライバです。アンプはI/O結合に関しては非常に柔軟です。入力ではAC結合またはDC結合が可能です。適正に動作するように、入力同相電圧を $1\text{V} \sim 1.6\text{V}$ にすることを推奨します。入力をAC結合した場合は、入力同相電圧が自動的にバイアスされます。入力信号はシングルエンドまたは差動で、歪み性能にはほとんど差はありません。

## ADC入力ネットワーク

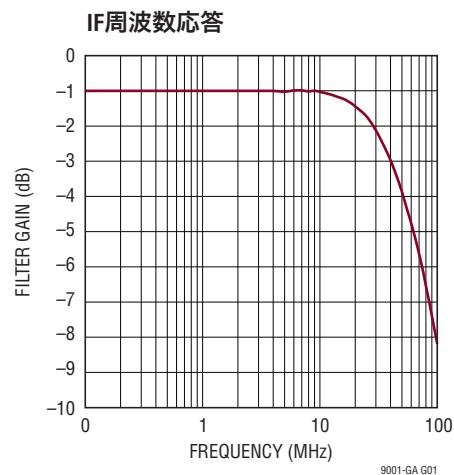

アンプ出力段とADC入力段の間の受動ネットワークを、さまざまなカットオフ周波数と帯域幅を持つバンドパスまたはローパス応答に構成できます。たとえば、LTM9001-GAの場合、帯域幅 $10\text{MHz}$ の1ポール・ローパス・フィルタを備えています。フィルタにより、信号が $10\text{MHz}$ で $0.2\text{dB}$ 減衰され、サブシステムの全体的利得が $7.8\text{dB}$ になることに注意してください。

生産テスト用に、フィルタはADCにDC入力できるように設計されています。

## コンバータ情報

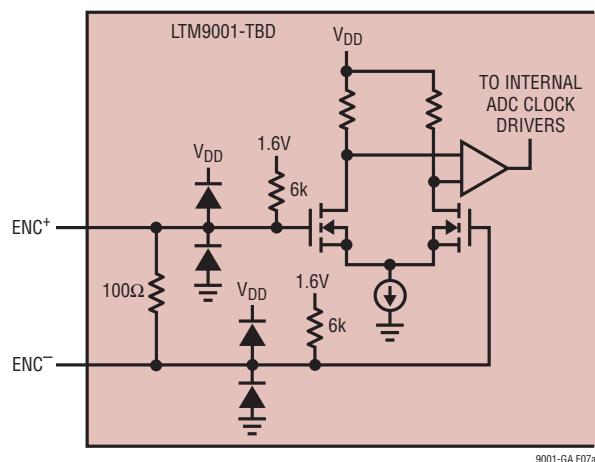

アナログ・デジタル・コンバータ(ADC)は、フロントエンドPGAを備えたCMOSパイプライン多段コンバータです。機能ブロック図に示すように、コンバータには5つのパイプラインADC段があり、サンプリングされたアナログ入力が37サイクル後にデジタル値に変換されます(「タイミング図」を参照)。同相ノイズ除去性能を高めるため、エンコード入力は差動です。

## 動作

表1. セミカスタム・オプション

| AMPLIFIER IF RANGE | AMPLIFIER INPUT IMPEDANCE | AMPLIFIER GAIN | FILTER                 | ADC SAMPLE RATE | ADC RESOLUTION | OUTPUT    | PART NUMBER |

|--------------------|---------------------------|----------------|------------------------|-----------------|----------------|-----------|-------------|

| 300MHz             | 200Ω                      | 20dB           | 162.5MHz BPF, 50MHz BW | 130Msps         | 16-bit         | LVDS/CMOS | LTM9001-AA  |

| 300MHz             | 200Ω                      | 14dB           | 70MHz BPF, 25MHz BW    | 130Msps         | 16-bit         | LVDS/CMOS | LTM9001-AD  |

| 300MHz             | 400Ω                      | 8dB            | DC-300MHz LPF          | 160Msps         | 16-bit         | LVDS/CMOS | LTM9001-BA  |

| 300MHz             | 400Ω                      | 8dB            | DC-10MHz LPF           | 25Msps          | 16-bit         | CMOS      | LTM9001-GA  |

以下の列からオプションの組合せを選択

|           |      |      |         |         |        |           |  |

|-----------|------|------|---------|---------|--------|-----------|--|

| DC-300MHz | 50Ω  | 26dB | LPF TBD | 160Msps | 16-bit | LVDS/CMOS |  |

| DC-140MHz | 200Ω | 20dB | BPF TBD | 130Msps | 14-bit | LVDS/CMOS |  |

| DC-70MHz  | 200Ω | 14dB |         | 105Msps |        | CMOS      |  |

| DC-35MHz  | 400Ω | 8dB  |         | 80Msps  |        | CMOS      |  |

|           | 200Ω | 6dB  |         | 65Msps  |        | CMOS      |  |

|           |      |      |         | 40Msps  |        | CMOS      |  |

|           |      |      |         | 25Msps  |        | CMOS      |  |

|           |      |      |         | 10Msps  |        | CMOS      |  |

## アプリケーション情報

### 入力スパン

LTM9001は固定入力スパンと入力インピーダンスで構成されています。上述したLTM9001-GAのアンプ利得とADC入力ネットワークの場合、ドライバ回路のフル・スケール入力範囲は1000mV<sub>P-P</sub>です。推奨ADC入力スパンは、SENSEピンをV<sub>DD</sub>に接続することにより得ることができます。ただし、SENSEピンにDC電圧を加えることにより、ADC入力スパンを変更できます。

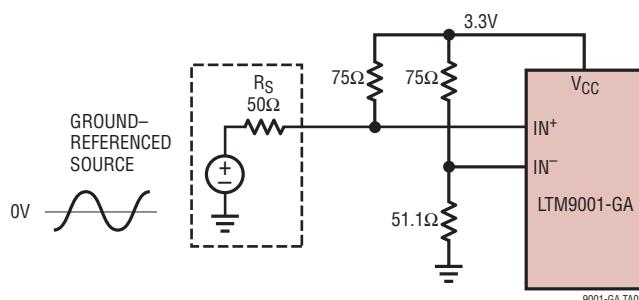

### 入力インピーダンスおよびマッチング

LTM9001の差動入力インピーダンスは50Ω、200Ωまたは400Ωです。アプリケーションによっては、ソースに対してインピーダンスのマッチングを行うために、差動入力を50Ωなどの低インピーダンスに終端する必要があるかもしれません。これにはいくつかの方法があります。

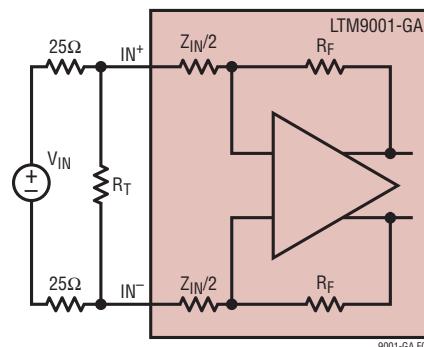

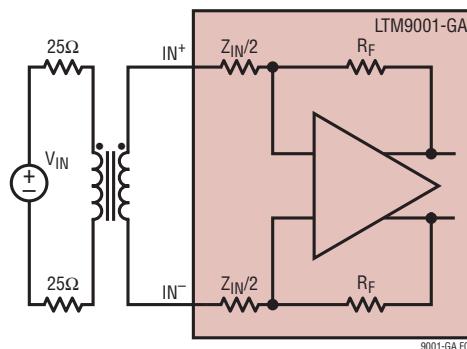

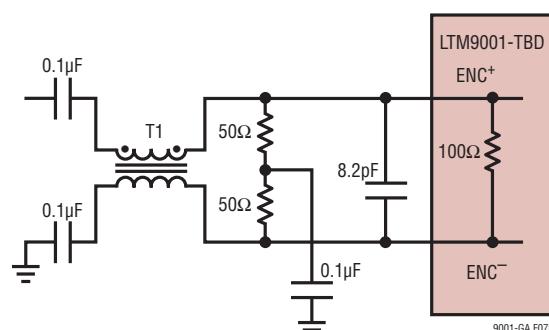

1つは、差動シャント抵抗を使用する方法です(図2)。もう1つは、広帯域トランスを使用する方法です(図3)。どちらの方法でも広帯域のマッチングを行うことができます。終端抵抗またはトランスは、入力のミスマッチによる反射を最小限に抑えるために、入力ピンの近くに配置する必要があります。

表2. 差動アンプの入力終端の値

| $Z_{IN}$ | $R_T$ Figure 2 |

|----------|----------------|

| 400Ω     | 57Ω            |

| 200Ω     | 66.5Ω          |

| 50Ω      | None           |

図2. シャント抵抗を使用した差動50Ω入力インピーダンスの入力終端( $R_T$ 値については表3を参照)

図3. 広帯域トランスを使用した差動50Ω入力インピーダンスの入力終端

## アプリケーション情報

あるいは、周波数の選択やノイズの低減を行うために、入力で狭帯域インピーダンスのマッチングを行なうこともできます。

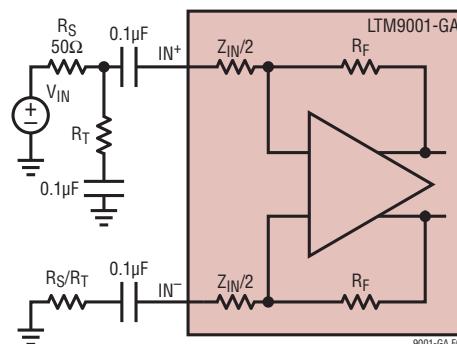

図4では、アンプ入力をバランなしで簡単にシングルエンド入力に構成しています。信号はマッチング・ネットワークを介して1つの入力に供給され、他の入力は同じインピーダンスに接続されています。一般に、シングルエンド入力インピーダンスおよび終端抵抗 $R_T$ は、 $R_S$ 、 $Z_{IN}/2$ および $R_F$ の組合せによって決定します。

表3. シングルエンド・アンプの入力終端の値

| $Z_{IN}$ | $R_T$ Figure 4 |

|----------|----------------|

| 400Ω     | 59Ω            |

| 200Ω     | 68.5Ω          |

| 50Ω      | 150Ω           |

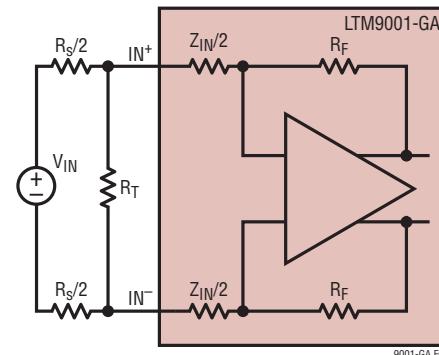

LTM9001のアンプはすべてのソース・インピーダンスで安定しています。次式のように、全体的な差動利得は図5のソース・インピーダンスに影響されます。

$$Av = |V_{OUT}/V_{IN}| = (1000/(R_S + Z_{IN}/2))$$

アンプのノイズ性能もソース・インピーダンスと終端に依存します。たとえば、図3の入力1:4トランスの場合は、入力に6dBの電圧利得を加えることで、入力ノイズフィギュアが改善されます。

## リファレンスおよびSENSEピン動作

図6は、2.5Vバンドギャップ・リファレンス、プログラマブル・ゲイン・アンプ、および制御回路で構成されるコンバータのリファレンス回路です。内部リファレンス、1.25V外部リファレンス、または2.5V外部リファレンスの3つのリファレンス動作モードがあります。内部リファレンスを使用するには、SENSEピンを $V_{DD}$ に接続します。外部リファレンスを使用するには、1.25Vまたは2.5Vのリファレンス電圧をSENSE入力ピンに加えるだけです。SENSEに1.25Vまたは2.5Vを加えると、いずれの場合も最大のフル・スケール・レンジになります。

図4. シャント抵抗を使用した差動50Ω

入力インピーダンスの入力終端

図5. 差動利得の計算

図6. リファレンス回路

## アプリケーション情報

### PGAピン

PGAピンによってADCフロントエンドの2つの利得設定のどちらかを選択します。PGA = “L”的場合は最大入力スパンが選択され、PGA = “H”的場合は3.5dB低い入力スパンが選択されます。高い入力範囲の場合にSNRが最適になります。直線性要件が高いアプリケーションの場合は、低い入力範囲のほうが歪みを改善しますが、SNRは1.8dB低下します。「標準的性能特性」を参照してください。

### クロック入力またはエンコード入力のドライブ

LTM9001には、差動エンコード入力を備えたバージョンとシングルエンド・クロック入力を備えたバージョンがあります。コンバータのノイズ性能は、アナログ入力と同様にエンコード信号の品質に依存する場合があります。エンコード入力は差動でドライブされるもので、主に同相ノイズ源からのノイズ除去を目的としています。それぞれの入力は6kの抵抗を介して1.6Vにバイアスされています。バイアス抵抗によってトランジスト結合ドライブ回路のDC動作点を設定し、シングルエンド・ドライブ回路のロジック・スレッショルドを設定することができます。

エンコード信号に存在するどのようなノイズも、ADC自体が持つアーチャ・ジッタに実効値として加算されることになります。ジッタが重要なアプリケーション(高い入力周波数)の場合は、以下の点を考慮してください。

1. 差動ドライブを使用する。

2. 可能な限り最大の振幅を使用する。トランジスト結合を使用する場合は、高い巻数比を使用して振幅を大きくする。

3. ADCが固定周波数の正弦波信号でクロックされる場合は、エンコード信号をフィルタして広帯域ノイズを低減する。

4. すべての結合ノイズが両方の入力に同相ノイズとして出現するように、両方のエンコード入力において容量と直列抵抗のバランスをとる。

エンコード入力の同相範囲は1.2V~V<sub>DD</sub>です。シングルエンド・ドライブの場合は、それぞれの入力をグランドからV<sub>DD</sub>までドライブすることができます。

エンコード・クロック入力には差動100Ω入力インピーダンスがあります。信号発生器などの50Ω入力の場合は、図7bに示すように、100Ωインピーダンスを追加するとインピーダンスがマッチングします。

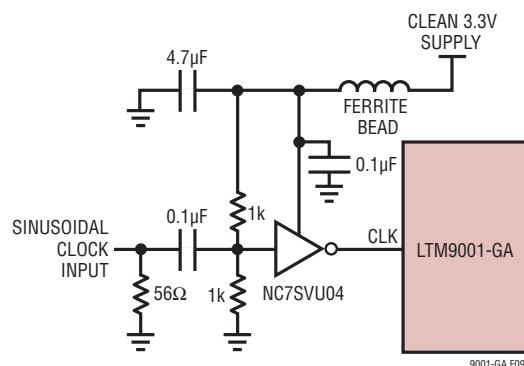

LTM9001-GAのシングルエンドCLK入力は、CMOSレベルまたはTTLレベルの信号で直接ドライブすることができます。CLKピンの前にジッタの小さい方形波発生回路を置いて、正弦波のクロックを使うこともできます(図8)。

図7a. 等価エンコード入力回路

T1 = M/A-COM ETC1-1-13

図7b. トランジスト・ドライブ・エンコード

図8. 正弦波のシングルエンドCLKドライブ

9001gaf

## アプリケーション情報

### 最大および最小エンコード・レート

LTM9001-GAの最大エンコード・レートは25Mspsです。ADCが適正に動作するには、CLK信号のデューティ・サイクルが50% ( $\pm 5\%$ ) である必要があります。ADCの内部回路が適正に動作するために十分なセッティング時間を確保するには、各半周期が18.9ns以上(LTM9001-GA)である必要があります。

入力クロックのデューティ・サイクルが50%でない場合は、オプションのクロック・デューティ・サイクル・スタビライザを使用することができます。この回路はCLKまたはENCの立上りエッジを使用して、アナログ入力をサンプリングします。CLKまたはENCの立下りエッジは無視され、フェーズロック・ループによって内部立下りエッジが生成されます。入力クロックのデューティ・サイクルは30%～70%の範囲で変動する場合があり、クロック・デューティ・サイクル・スタビライザが内部デューティ・サイクルを常に50%に維持します。クロックを長期間オフした場合は、PLLが入力クロックにロック・オンするために、デューティ・サイクル・スタビライザ回路は100クロック・サイクルを必要とします。クロック・デューティ・サイクル・スタビライザを使用するには、外付け抵抗を使用して、MODEピンを1/3V<sub>DD</sub>または2/3V<sub>DD</sub>に接続する必要があります。

サンプル・レートの下限は、サンプル・ホールド回路の垂下によって決定されます。このADCのパイプライン・アーキテクチャは、小さい値のコンデンサに保存されるアナログ信号に依存します。接合部のリーケによってコンデンサが放電されます。仕様では、LTM9001の最小動作周波数は1Mspsです。

### デジタル出力

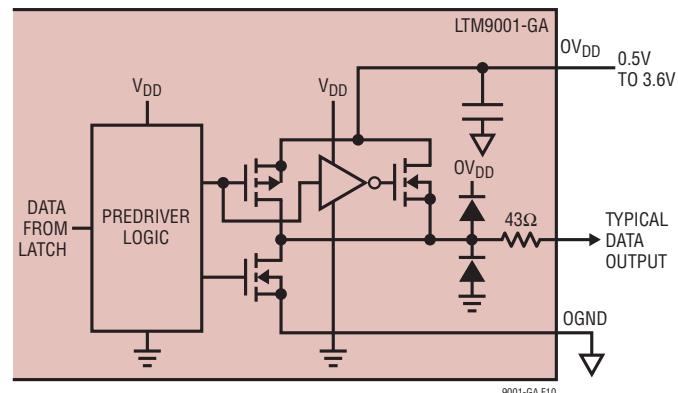

#### デジタル出力バッファ

図9は、CMOSモードでの単一出力バッファの等価回路を示しています。各バッファはADC電源とグランドから絶縁され、OV<sub>DD</sub>およびOGNDから電力供給されます。出力ドライバ内の追加のNチャネル・トランジスタによって、低電圧までの動作が可能です。内部抵抗が出力と直列に接続されると、外部回路から出力が50Ωに見えるようになり、外付けダンピング抵抗は不要になります。

図9. デジタル出力バッファの等価回路

## アプリケーション情報

あらゆる高速・高分解能コンバータと同様に、デジタル出力負荷が性能に影響することがあります。LTM9001のデジタル出力は、デジタル出力と敏感な入力回路の間に発生する可能性がある相互作用を回避するために、容量性負荷のドライブを最小限に抑える必要があります。ALVCH16373 CMOSラッチなどのデバイスを使用して、出力をバッファする必要があります。フルスピードの動作では、容量性負荷を10pF未満に抑える必要があります。出力と直列に接続されている抵抗を使用することもできますが、ADCのチップには43Ωの直列抵抗が内蔵されているため必須ではありません。

OV<sub>DD</sub>の電圧を低くすれば、デジタル出力からの干渉を抑えることができます。

### データ・フォーマット

オフセット・バイナリまたは2の補数フォーマットに、LTM9001のパラレル・デジタル出力を選択できます。フォーマットはMODEピンで選択します。このピンは、中心が0、1/3V<sub>DD</sub>、2/3V<sub>DD</sub>、V<sub>DD</sub>の4レベルのロジック入力を備えています。外付け抵抗分割器を使用して、1/3V<sub>DD</sub>と2/3V<sub>DD</sub>のロジック・レベルを設定できます。表5はMODEピンのロジック状態を示しています。

表5. MODEピンの機能

| MODE               | 出力フォーマット       | クロック・デューティ・サイクル・スタビライザ |

|--------------------|----------------|------------------------|

| 0V(GND)            | Offset Binary  | Off                    |

| 1/3V <sub>DD</sub> | Offset Binary  | On                     |

| 2/3V <sub>DD</sub> | 2's Complement | On                     |

| V <sub>DD</sub>    | 2's Complement | Off                    |

### オーバーフロー・ビット

オーバーフロー出力ビット(OF)は、コンバータがオーバーレンジかアンダーレンジの場合に示されます。OFピンのロジック“H”がオーバーフローまたはアンダーフローを示します。

図10. 機能的に等価なデジタル出力ランダマイザ

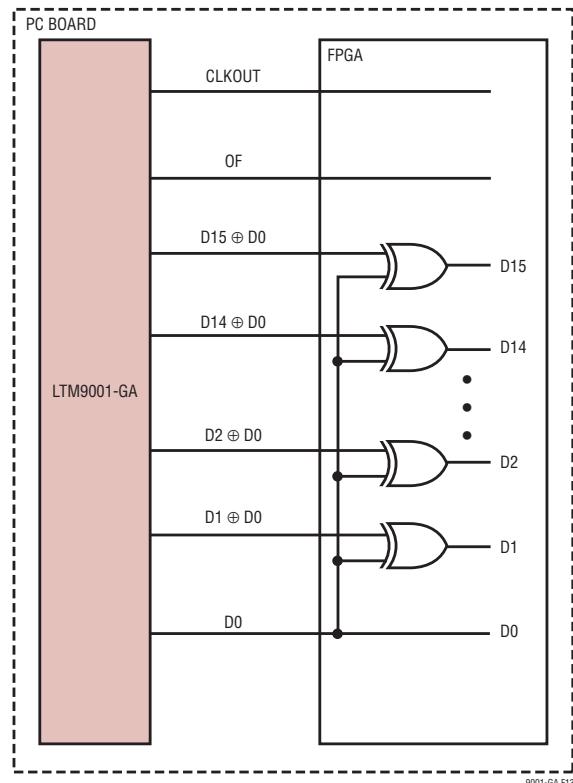

図11. ランダム化デジタル出力のデコード

## アプリケーション情報

### 出力クロック

ADCはデジタル出力として利用できる、遅延エンコード入力を備えています。非反転バージョンのCLKOUT<sup>+</sup>と反転バージョンのCLKOUT<sup>-</sup>の両方があります。CLKOUTピンを使用して、コンバータのデータをデジタル・システムに同期させることができます。これは、正弦波エンコードを使用する場合に必要です。データは、CLKOUT<sup>+</sup>の立下りとCLKOUT<sup>-</sup>の立上りに合わせて更新されます。CLKOUT<sup>+</sup>の立上りエッジまたはCLKOUT<sup>-</sup>の立下りエッジでデータがラッチされる場合があります。

### デジタル出力ランダマイザ

ADCデジタル出力からの干渉が避けられない場合もあります。デジタル出力からの干渉は、容量性または誘導性の結合か、グランド・プレーンを介した結合が原因の場合があります。小さい結合係数であっても、ADC出力スペクトルに識別可能な不要なトーンが発生することがあります。

デジタル出力をチップから伝送する前にランダム化することによって、これらの不要なトーンをランダム化し、ノイズフロアのわずかな上昇と引き換えに不要なトーン振幅を大幅に低減できます。

デジタル出力は、LSBと他のすべてのデータ出力ビットの間で排他的論理和の論理演算を行うことによってランダム化されます(図10を参照)。デコードするには、逆の演算を行います。

つまりLSBと他のすべてのビットの間で排他的論理和演算を行います(図11を参照)。LSB、OF、CLKOUT出力は影響を受けません。出力ランダマイザ機能は、RANDピンが“H”的ときにアクティブになります。

### 出力ドライバ電源

個別の出力用電源ピンとグランド・ピンによって、出力ドライバをアナログ回路から絶縁できます。デジタル出力バッファの電源OV<sub>DD</sub>は、ドライブされるロジックと同じ電源に接続する必要があります。たとえば、1.8V電源から供給を受けるDSPをコンバータがドライブする場合は、OV<sub>DD</sub>を同じ1.8V電源に接続する必要があります。OV<sub>DD</sub>には、3.6V以下の任意のロジック電圧を供給することができます。OGNDには、グランドから1VまでOV<sub>DD</sub>よりも低い電圧を供給できます。ロジック出力はOGNDとOV<sub>DD</sub>の間で振幅します。

### 内部デザイナー

LTM9001は非常に直線性の高い伝達関数を持つ16ビット・レシーバ・サブシステムですが、低い入力レベルでは、伝達関数のわずかな不完全性によって不要なトーンが発生します。伝達関数の小さな誤差は、通常はADC要素のミスマッチが原因です。オプションの内部デザイナー・モードをイネーブルして、ADCの伝達曲線の入力位置をランダム化することで、低い信号レベルのSFDRを改善できます。

## アプリケーション情報

図12に示すように、サンプル・ホールド・アンプの出力はディザーDACの出力に加算されます。ディザーDACは長いシーケンスの擬似ランダム数発生器によってドライブされます。また、ディザーDACに供給されるランダム数はADCの結果から差し引かれます。ディザーDACがADCに対して正確に調整されている場合は、出力にディザー信号はほとんど現れません。リークしたディザー信号はホワイト・ノイズとして現れます。ディザーDACによって、ADCのノイズフロアは、ディザーをオフした場合のノイズフロアと比較して少々上昇します。

ディザー信号をオンした場合に最高のノイズ性能を得るには、 $IN^+$ ピンと $IN^-$ ピンの間に接続された駆動インピーダンスをモジュールのインピーダンスによくマッチングさせる必要があります(表1を参照)。ソース・インピーダンスが抵抗性で、モジュールのインピーダンスの10%であれば、最高の結果が得られます。

### 電源のシーケンス制御

$V_{CC}$ ピンがアンプに電源を供給し、 $V_{DD}$ ピンがADCに電源を供給します。アンプとADCはLTM9001内の個別の集積回路ですが、電源のシーケンス制御の検討事項は通常と同じです。アンプとADCの両方に同じ低ノイズ3.3V電源を使用することを推奨しますが、必要であれば、アンプはより低い電圧レベルで動作させることもできます。同じ3.3Vリニア・レギュレータ

で両方のデバイスを動作させることができますが、 $V_{CC}$ ピンと $V_{DD}$ ピンの間にフェライト・ビーズを配置する必要があります。共通の入力電源がある場合は、追加の電源シーケンス制御回路なしで個別のリニア・レギュレータを使用できます。

### グランドとバイパス

LTM9001には、クリーンで切れ目のないグランド・プレーンを持つプリント回路基板が必要です。内部グランド・プレーンを持つ多層基板を推奨します。LTM9001のピン配置は、フロー・スルー・レイアウト用に最適化されているため、入力とデジタル出力の間の相互作用を最小限に抑えることができます。連続した1列のグランド・パッドは、デジタル信号線とアナログ信号線を可能な限り離してレイアウトすることを容易にします。

LTM9001では、共通グランド(GND)に戻るアンプの電源( $V_{CC}$ )とADCの電源( $V_{DD}$ )が内部でバイパスされています。デジタル出力電源( $OV_{DD}$ )はOGNDに戻ります。追加のバイパス容量はオプションですが、電源ノイズが多い場合には必要なことがあります。

差動入力は平行にし、相互の間隔を小さくします。入力トレイスは、容量とノイズのピックアップを最小限に抑えるためにできるだけ短くします。

図12. 機能的に等価な内部ディザーハ回路のブロック図

## アプリケーション情報

### 熱伝達

LTM9001から発生する熱のほとんどは、底面のグランド・パッドを介して伝達されます。良好な電気的性能と熱的性能を得るために、十分な面積とできる限り多くのビアを持つグランド・プレーンに、すべてのグランド・ピンを接続することが重要です。

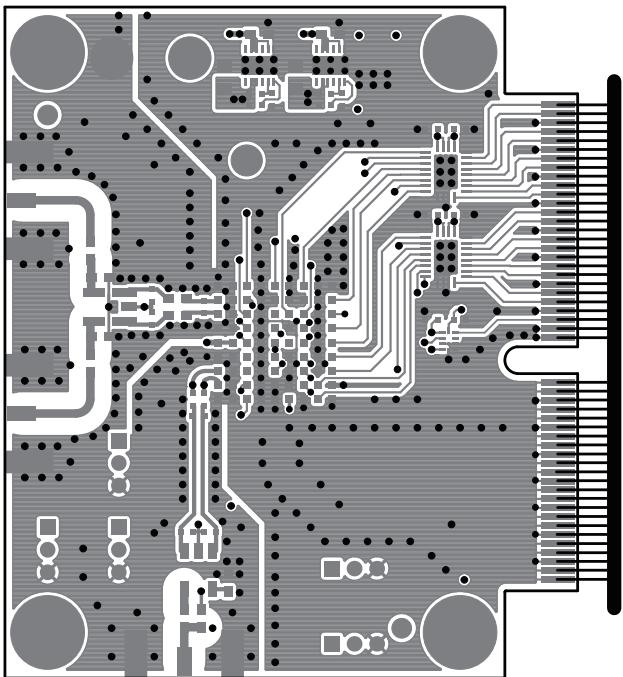

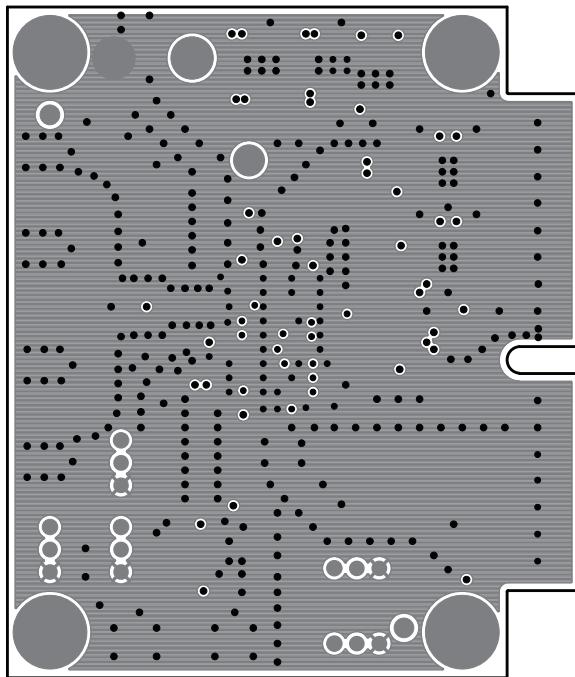

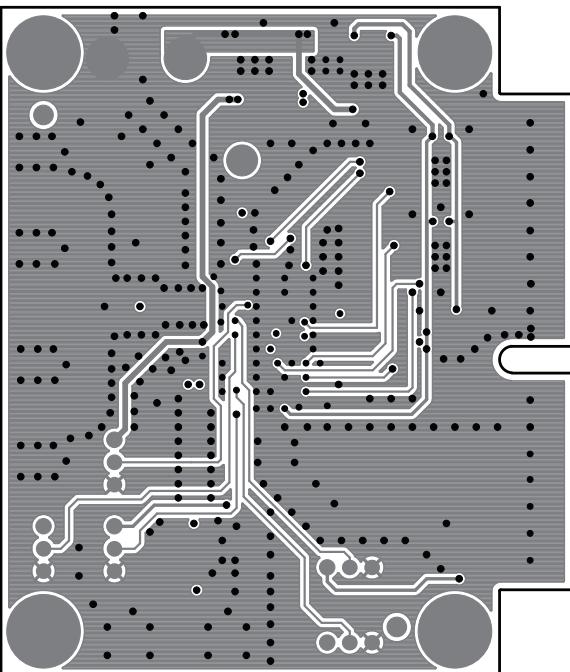

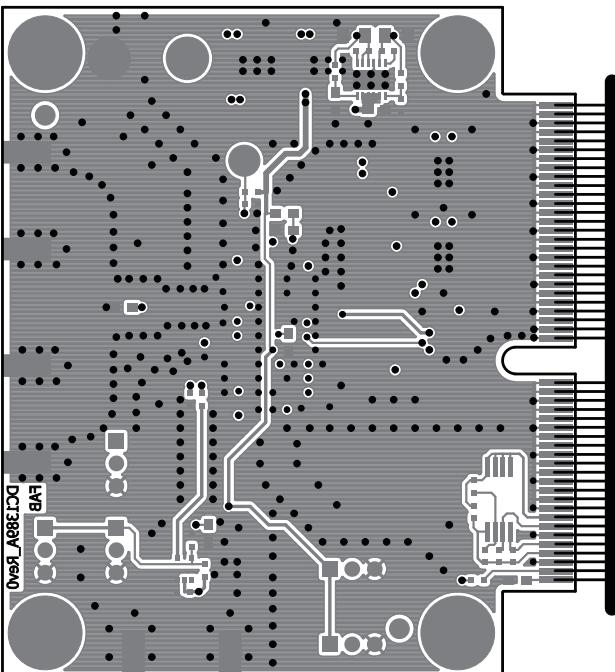

### 推奨レイアウト

LTM9001の高度な集積化により、PCボードのレイアウトが非常にシンプルで容易になります。ただし、電気的性能と熱的性能を最適化するには、レイアウトに関するいくつかの事項を検討する必要があります(図13~16を参照)。

- グランド用に広いPCBの銅領域を使用します。これによって、パッケージの熱がボードを介して放散され、さらに敏感なオンボード・アナログ信号をシールドすることができます。共通グランド(GND)および出力グランド(OGND)はLTM9001内で電気的に絶縁されていますが、共通リターン・パスを提供するためにデバイスの下のPCB上で接続することができます。

- 複数のグランド・ビアを使用します。可能な限り多くのビアを使用することにより、ボードの熱的性能が向上し、高周波数におけるボードでのアナログ・トレースとデジタル・トレースを絶縁するために必要なバリアを作ることができます。

- ビアを使用して高周波バリアを作り、アナログ・トレースとデジタル・トレースを可能な限り分離します。これによって、LTM9001の信号対ノイズ比(SNR)およびダイナミック・レンジを低下させる可能性のあるデジタル帰還を低減できます。

ペースト・プリントの品質は、高歩留りの生産を行うために重要な要素です。タイプ3または4のプリント用無洗浄半田ペーストの使用を推奨します。半田ステンシルの設計は、「アプリケーション・ノート100」のガイドラインに従ってください。「μModuleのLGAパッケージングに関する注意事項およびアセンブリ情報」については [http://www.linear-tech.co.jp/designtools/packaging/μModule\\_Instructions.pdf](http://www.linear-tech.co.jp/designtools/packaging/μModule_Instructions.pdf)をご覧ください。

LTM9001は、鉛ベースまたは錫ベースの半田ペーストを使用するために、金仕上げのパッドを採用しています。本質的に鉛フリーで、JEDEC(e4)規格に準拠しています。規格の詳細については、<http://www.linear.com/design-tools/leadfree/mat-dec.jsp>をご覧ください。

# LTM9001-GA

## アプリケーション情報

図13. 第1層

図14. 第2層

図15. 第3層

図16. 第4層

9001gaf

## パッケージ

**LGA/パッケージ**

**81ピン(11.25mm × 11.25mm × 2.32mm)**

(Reference LTC DWG # 05-08-1809 Rev A)

# LTM9001-GA

## 標準的応用例

グランド基準シングルエンド入力のLTM9001

## 関連製品

| 製品番号                                           | 説明                                                   | 注釈                                   |

|------------------------------------------------|------------------------------------------------------|--------------------------------------|

| LTC2202                                        | 16ビット、10Msps ADC                                     | 140mW、SNR:81.6dB、SFDR:100dB          |

| LTC2203                                        | 16ビット、25Msps ADC                                     | 220mW、SNR:81.6dB、SFDR:100dB          |

| LTC2204                                        | 16ビット、40Msps ADC                                     | 480mW、SNR:79.1dB、SFDR:100dB          |

| LTC2205                                        | 16ビット、65Msps ADC                                     | 610mW、SNR:79dB、SFDR:100dB            |

| LTC2206                                        | 16ビット、80Msps ADC                                     | 725mW、SNR:77.9dB、SFDR:100dB          |

| LTC2207                                        | 16ビット、105Msps ADC                                    | 900mW、SNR:77.9dB、SFDR:100dB          |

| LTC2208                                        | 16ビット、130Msps ADC                                    | 1250mW、SNR:77.7dB、SFDR:100dB         |

| LTC2209                                        | 16ビット、160Msps ADC                                    | 1450mW、SNR:77.1dB、SFDR:100dB         |

| LTC6400-8/LTC6400-14/<br>LTC6400-20/LTC6400-26 | 300MHz IF用低ノイズ低歪み差動アンプ、<br>固定利得8dB、14dB、20dBまたは26dB  | 3V、90mA、OIP3:39.5dBm (300MHz)、NF:6dB |

| LTC6401-8/LTC6401-14/<br>LTC6401-20/LTC6401-26 | 140MHz IF用低ノイズ、低歪み差動アンプ、<br>固定利得8dB、14dB、20dBまたは26dB | 3V、45mA、OIP3:45.5dBm (140MHz)、NF:6dB |

9001gaf