力スケード接続可能な

50MHzシリアル・インターフェース付き

12ビット分解能の48チャネルLED PWMジェネレータ

## 特長

- 入力電圧:3V～5.5V

- 48の独立したPWM出力

- TTL/CMOSロジックの50MHzシリアル・データ・インターフェース

- PWM幅の分解能:12ビット(4096ステップ)

- PWM補正:6ビット(64ステップ)

(設定されたPWM幅の±50%)

- PWM周波数:最大6.1kHz(PWMCK = 25MHz)

- 位相シフト・オプションにより、スイッチング・ノイズを低減

- 3個のLT3595A 16チャネルLEDドライバを直接制御

- 診断情報:同期エラー/オープンLEDのフラグ

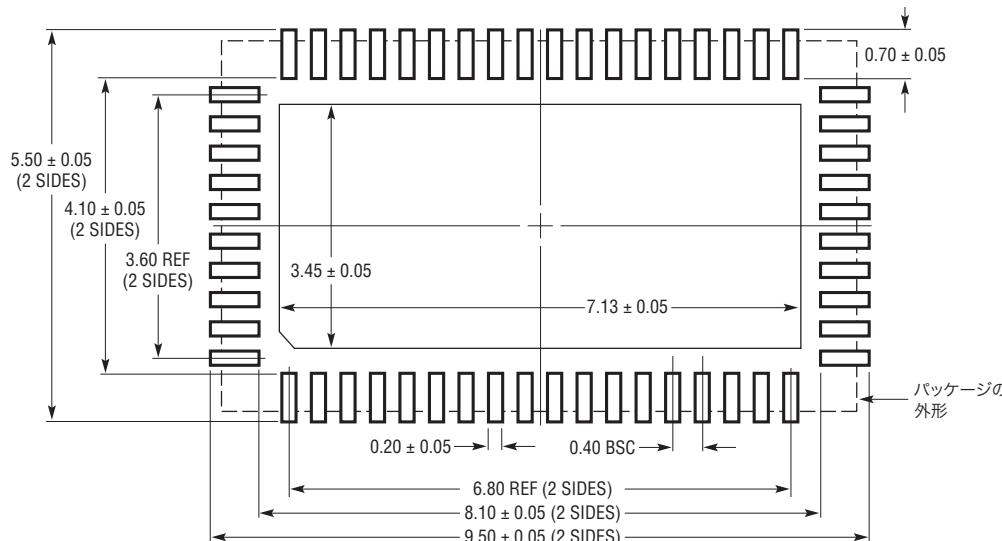

- 56ピン(5mm×9mm×0.75mm)QFNパッケージ

## アプリケーション

- 大画面ディスプレイのLEDバックライト

- モノカラー、マルチカラー、フルカラーのLEDディスプレイ

- LEDの広告塔や看板

- モータ制御

- 産業用制御

- 自動テスト装置

- ロボティクス

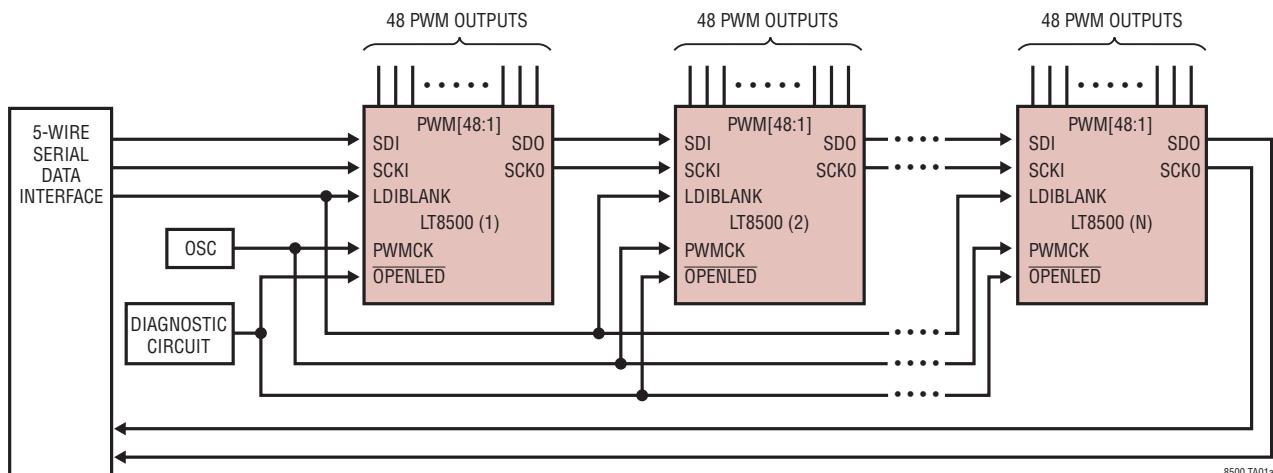

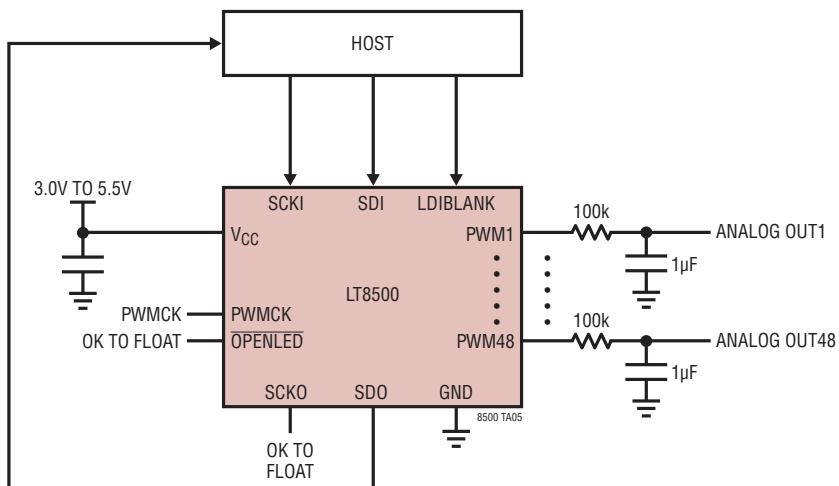

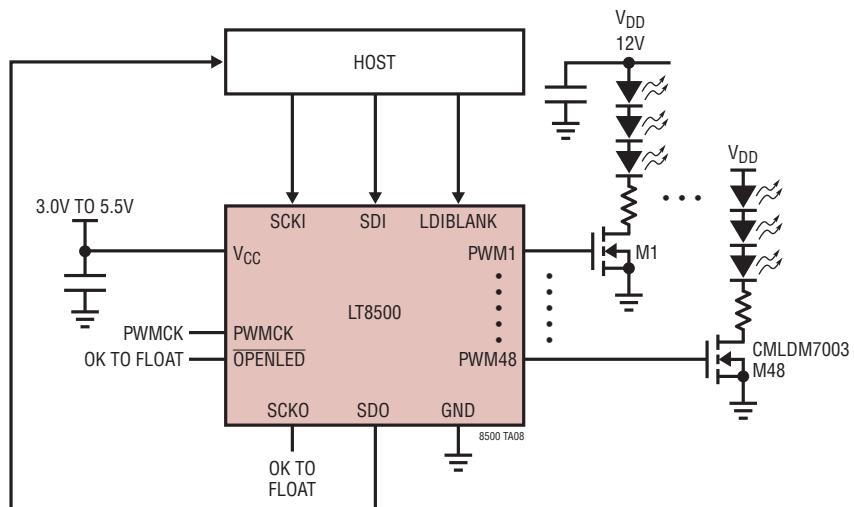

## 標準的応用例

## 概要

LT<sup>®</sup>8500は、48本の独立したチャネルを備えたパルス幅変調(PWM)ジェネレータです。チャネルごとに個別に調整可能な12ビット(4096ステップ)PWMレジスタと6ビット(64ステップ)±50%補正レジスタを搭載しています。シンプルなシリアル・データ・インターフェースを介して全ての制御機能をプログラム可能です。それぞれ16チャネルからなる3つのバンクが120°位相をシフトして動作するように構成することができます。

LT8500は、同期エラーとオープンLEDの2つの診断情報フラグを備えています。これらのフラグは、状態の読み出し時にシリアル・データ・インターフェースを介して追加の状態情報とともに送出されます。カスケード接続可能な50MHzのシリアル・データ・インターフェースはバッファおよびスキー・バランシング機能を備えているので、大画面LCDのダイナミック・バックライトや、モノカラー、マルチカラーおよびフルカラーのLEDディスプレイなど、PWMを多用するアプリケーションに最適です。また、LT8500は3個のLT3595A LEDドライバを制御するにも最適です。

、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴは、リニアテクノロジー社の登録商標です。その他全ての商標の所有権は、それぞれの所有者に帰属します。

## 絶対最大定格

### (Note 1)

|                            |                                          |

|----------------------------|------------------------------------------|

| $V_{CC}$                   | -0.3V ~ 6V                               |

| SDI, SCKI, PWMCK, OPENLED, |                                          |

| LDIBLANK                   | -0.3V ~ 6V または ( $V_{CC} + 0.3V$ ) の小さい方 |

| 動作接合部温度範囲                  |                                          |

| (Note 2)                   | -40°C ~ 125°C                            |

| 保存温度範囲                     | -65°C ~ 150°C                            |

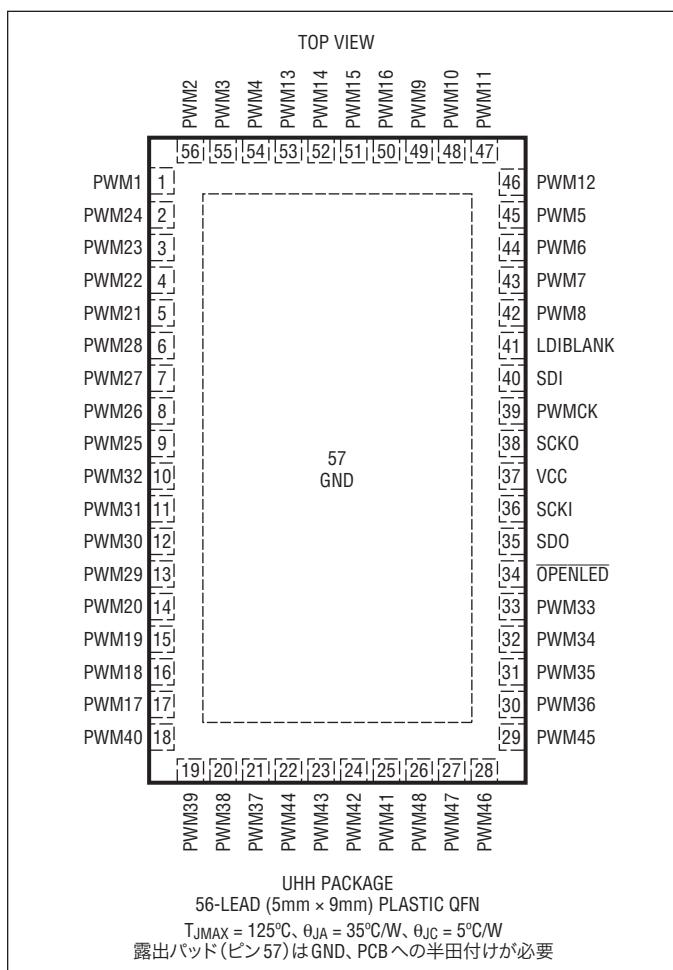

## ピン配置

## 発注情報

| 鉛フリー仕様         | テープアンドリール        | 製品マーキング* | パッケージ                       | 温度範囲          |

|----------------|------------------|----------|-----------------------------|---------------|

| LT8500EUHH#PBF | LT8500EUHH#TRPBF | 8500     | 56-ピン(5mm x 9mm) プラスチック QFN | -40°C ~ 125°C |

| LT8500IUHH#PBF | LT8500IUHH#TRPBF | 8500     | 56-ピン(5mm x 9mm) プラスチック QFN | -40°C ~ 125°C |

より広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度等級は出荷時のコンテナのラベルで識別されます。

鉛ベースの非標準仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー使用の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{CC} = 3.3\text{V}$ 。

| SYMBOL                                                    | PARAMETER                                        | CONDITIONS                                                                                     | MIN    | TYP        | MAX        | UNIT             |

|-----------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------|--------|------------|------------|------------------|

| <b>Supply</b>                                             |                                                  |                                                                                                |        |            |            |                  |

| $V_{CC}$                                                  | $V_{CC}$ Operating Voltage                       |                                                                                                | ●      | 3.0        | 5.5        | V                |

| <b>Digital Inputs:SCKI, SDI, LDIBLANK, OPENLED, PWMCK</b> |                                                  |                                                                                                |        |            |            |                  |

| $V_{IH}$                                                  | Input Logic Levels<br>High Level Voltage         | $V_{CC} = 5\text{V}$<br>$V_{CC} = 3.3\text{V}$                                                 | ●<br>● | 4.0<br>2.7 |            | V<br>V           |

| $V_{IL}$                                                  | Low Level Voltage                                | $V_{CC} = 5\text{V}$<br>$V_{CC} = 3.3\text{V}$                                                 | ●<br>● |            | 1.0<br>0.6 | V<br>V           |

| $I_{IN}$                                                  | Input Current                                    | Pin Voltage = $V_{CC}$ or GND Excluding OPENLED                                                |        | -1         | 1          | $\mu\text{A}$    |

| $R_{PU}$                                                  | OPENLED Pull-Up Resistor                         | $V_{CC} = 5.5\text{V}$                                                                         |        | 70         | 100        | $\text{k}\Omega$ |

| $C_{IN}$                                                  | Input Capacitance (Note 4)                       | Pin to GND                                                                                     |        |            | 3          | $\text{pF}$      |

| <b>Digital Outputs:SCKO, SDO, PWM[48:1]</b>               |                                                  |                                                                                                |        |            |            |                  |

| $V_{OH}$                                                  | SDO, SCKO Output Voltages<br>High Level Voltage  | $I_{OUT} = -6\text{mA}, V_{CC} = 5\text{V}$<br>$I_{OUT} = -3\text{mA}, V_{CC} = 3.3\text{V}$   | ●<br>● | 4.0<br>2.7 |            | V<br>V           |

| $V_{OL}$                                                  | Low Level Voltage                                | $I_{OUT} = 6\text{mA}, V_{CC} = 5\text{V}$<br>$I_{OUT} = 3\text{mA}, V_{CC} = 3.3\text{V}$     | ●<br>● |            | 1.0<br>0.6 | V<br>V           |

| $V_{OH}$                                                  | PWM [48:1] Output Voltages<br>High Level Voltage | $I_{OUT} = -3\text{mA}, V_{CC} = 5\text{V}$<br>$I_{OUT} = -1.5\text{mA}, V_{CC} = 3.3\text{V}$ | ●<br>● | 4.0<br>2.7 |            | V<br>V           |

| $V_{OL}$                                                  | Low Level Voltage                                | $I_{OUT} = 3\text{mA}, V_{CC} = 5\text{V}$<br>$I_{OUT} = 1.5\text{mA}, V_{CC} = 3.3\text{V}$   | ●<br>● |            | 1.0<br>0.6 | V<br>V           |

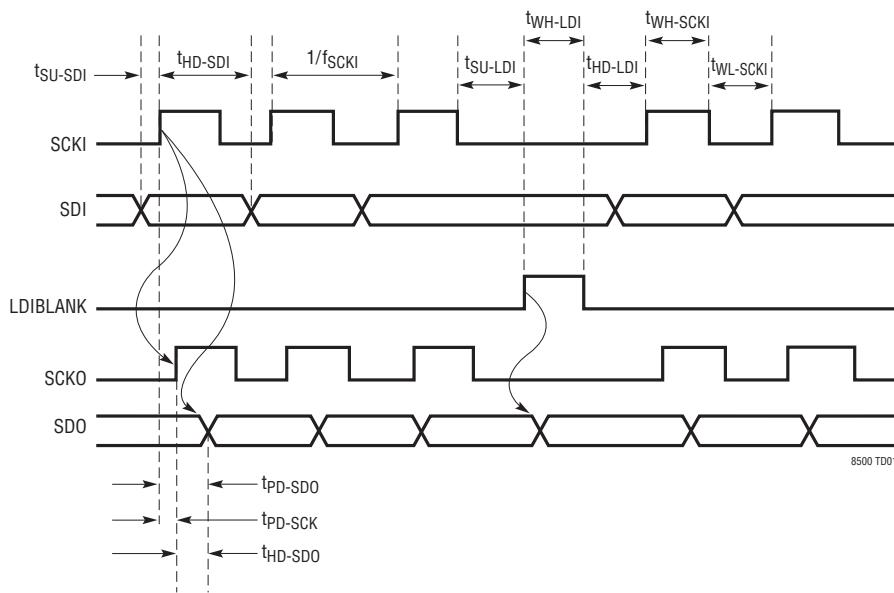

**タイミング特性**

●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{CC} = 3.3\text{V}$ 、全ての入力はレール・トウ・レール。

| SYMBOL         | PARAMETER                                   | CONDITIONS                                                                                               | MIN | TYP    | MAX      | UNIT |

|----------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|--------|----------|------|

| $f_{SCKI}$     | Data Shift Clock Frequency                  | $SCKI \uparrow - SCKI \uparrow$ (Figure 4)                                                               | ●   |        | 50       | MHz  |

| $f_{PWMCK}$    | PWMCK Clock Frequency                       | $PWMCK \uparrow - PWMCK \uparrow$ (Figure 5)                                                             | ●   |        | 25       | MHz  |

| $t_{WH-SCKI}$  | Minimum SCKI High Time (Note 3)             | $SCKI = \text{High}$                                                                                     |     |        | 2        | ns   |

| $t_{WL-SCKI}$  | Minimum SCKI Low Time (Note 3)              | $SCKI = \text{Low}$                                                                                      |     |        | 2        | ns   |

| $t_{WH-LDI}$   | LDIBLANK Pulse Duration<br>(LDI Function)   | $LDIBLANK = \text{High}$ (Figure 4)                                                                      | ●   | 8      | 5,000    | ns   |

| $t_{WH-BLANK}$ | LDIBLANK Pulse Duration<br>(BLANK Function) | $LDIBLANK = \text{High}$ (Figure 4)                                                                      | ●   | 50,000 |          | ns   |

| $t_{SU-SDI}$   | SDI-SCKI Setup Time (Note 3)                | $SDI \uparrow \downarrow - SCKI \uparrow$ (Figure 4)                                                     | ●   | 3      |          | ns   |

| $t_{HD-SDI}$   | SCKI-SDI Hold Time (Note 3)                 | $SCKI \uparrow - SDI \uparrow \downarrow$ (Figure 4)                                                     | ●   | 1.75   |          | ns   |

| $t_{SU-LDI}$   | SCKI-LDIBLANK Setup Time (Note 3)           | $SCKI \uparrow - LDIBLANK \uparrow$ (Figure 4)<br>SCKI 50% Duty Cycle                                    | ●   | 10     |          | ns   |

| $t_{HD-LDI}$   | LDIBLANK-SCKI Hold Time (Note 3)            | $LDIBLANK \downarrow - SCKI \uparrow$ (Figure 4)                                                         | ●   | 5      |          | ns   |

| $t_{PD-SDO}$   | SCKI-SDO Propagation Delay (Note 3)         | $SCKI \uparrow - SDO \uparrow \downarrow$ (Figure 4)                                                     | ●   |        | 15<br>25 | ns   |

| $t_{PD-SCK}$   | SCKI-SCKO Propagation Delay (Note 3)        | $SCKI \uparrow - SCKO \uparrow$ (Figure 4)                                                               | ●   |        | 10<br>20 | ns   |

| $t_{HD-SDO}$   | SCKO-SDO Hold Time (Note 3)                 | $SCKO \uparrow - SDO \uparrow \downarrow$ (Figure 4)                                                     | ●   | 2.75   |          | ns   |

| $t_{DC-SCK}$   | SCKI-SCKO Duty Cycle Change (Note 4)        | Difference Between $SCKI = \text{High Time}$<br>and $SCKO = \text{High Time}$ , $C_{LOAD} = 25\text{pF}$ |     |        | -0.2     | ns   |

## タイミング特性

●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{CC} = 3.3\text{V}$ 、全ての入力はレール・トゥ・レール。

| SYMBOL       | PARAMETER                                     | CONDITIONS                                     | MIN | TYP | MAX | UNIT |

|--------------|-----------------------------------------------|------------------------------------------------|-----|-----|-----|------|

| $t_{PD-PWM}$ | PWMCK-PWM[48:1] Propagation Delay<br>(Note 3) | PWMCK $\uparrow$ – PWM $\downarrow$ (Figure 5) | ●   | 32  | 50  | ns   |

| $t_{R-SD0}$  | SD0, SCK0 Rise Time (Note 4)                  | $C_{LOAD} = 25\text{pF}$ , 30% to 70%          |     | 2   |     | ns   |

| $t_{F-SD0}$  | SD0, SCK0 Fall Time (Note 4)                  | $C_{LOAD} = 25\text{pF}$ , 70% to 30%          |     | 2   |     | ns   |

| $t_{R-PWM}$  | PWM[48:1] Rise Time (Note 4)                  | $C_{LOAD} = 25\text{pF}$ , 30% to 70%          |     | 12  |     | ns   |

| $t_{F-PWM}$  | PWM[48:1] Fall Time (Note 4)                  | $C_{LOAD} = 25\text{pF}$ , 70% to 30%          |     | 12  |     | ns   |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** LT8500Eは、 $0^\circ\text{C} \sim 125^\circ\text{C}$  の接合部温度で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセ

ス・コントロールとの相関で確認されている。LT8500Iは $-40^\circ\text{C} \sim 125^\circ\text{C}$  の全動作接合部温度範囲で保証されている。

**Note 3:** 伝搬遅延、セットアップ/ホールド時間、High持続時間は50%～50%で測定。

**Note 4:** このパラメータは実験値との相関で確認したものであり、量産時の検査には含まれない。

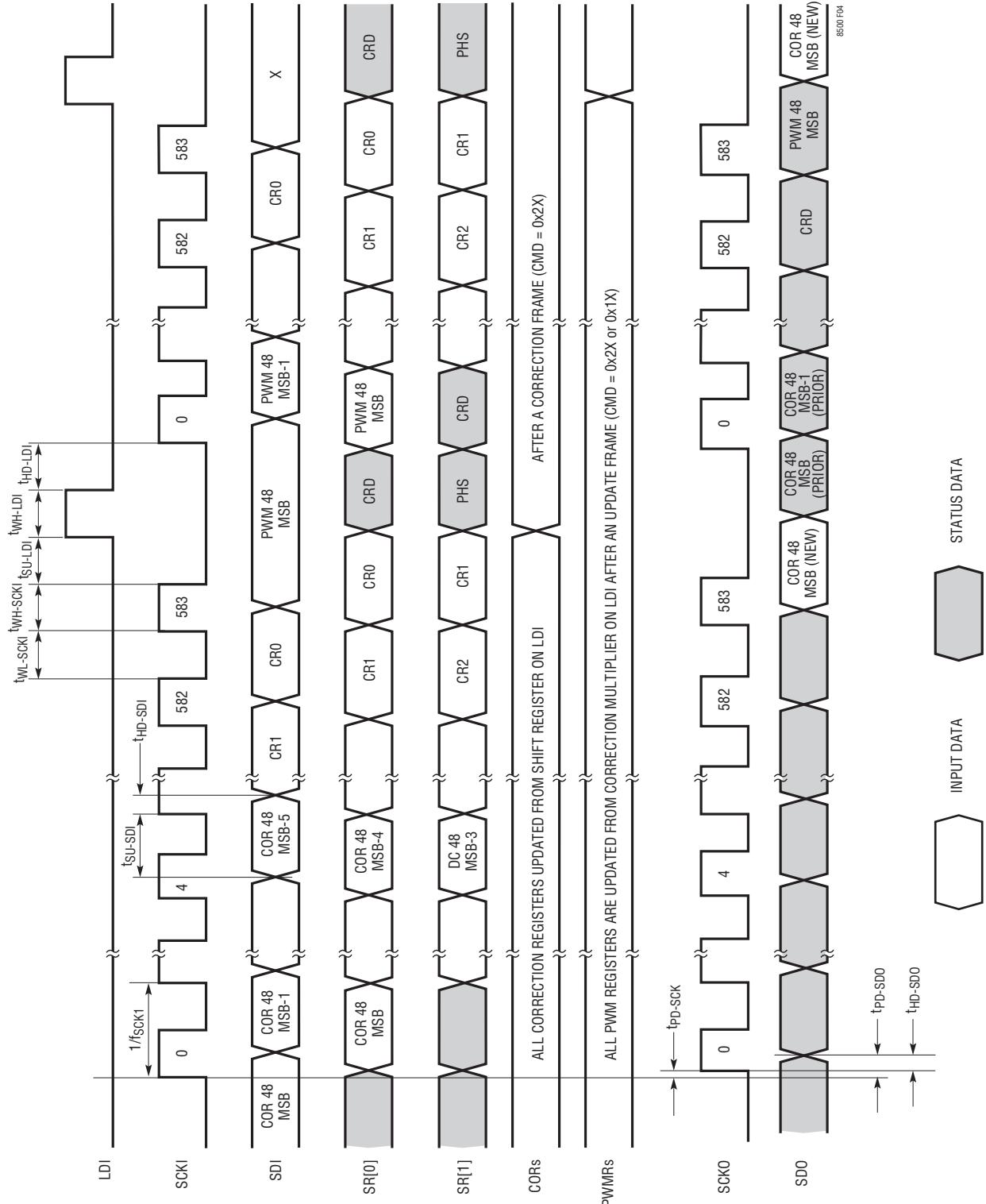

## タイミング図

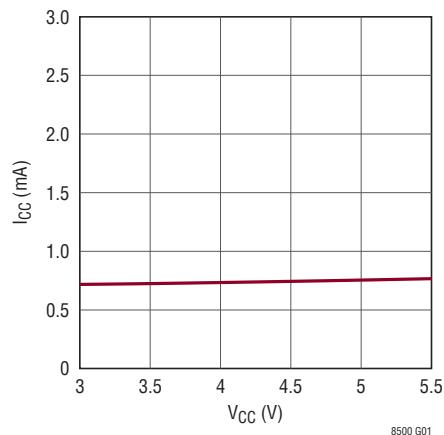

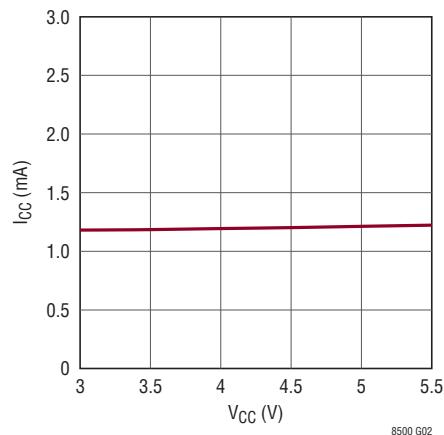

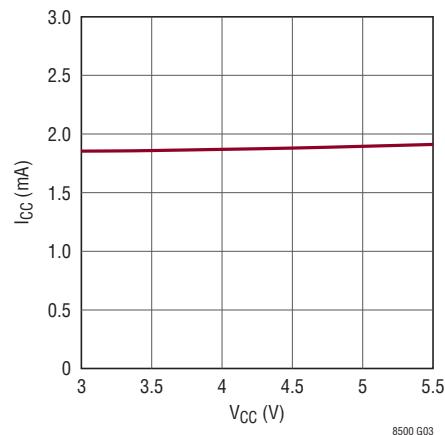

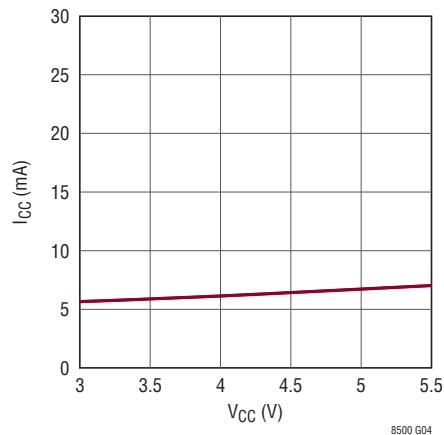

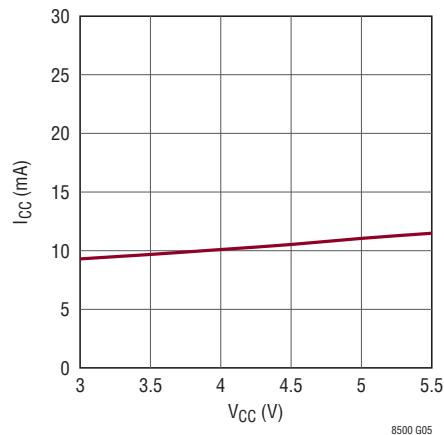

## 標準的性能特性

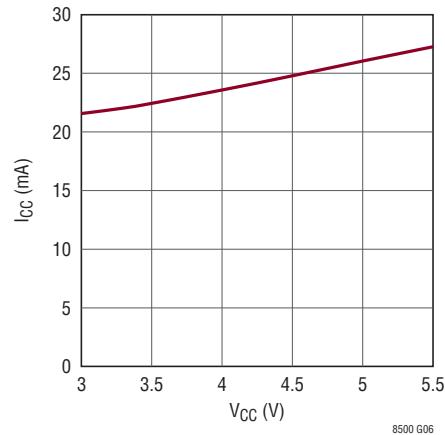

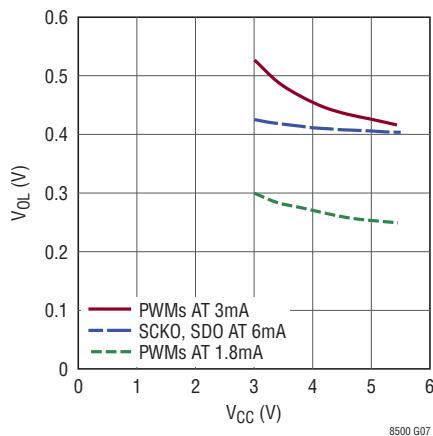

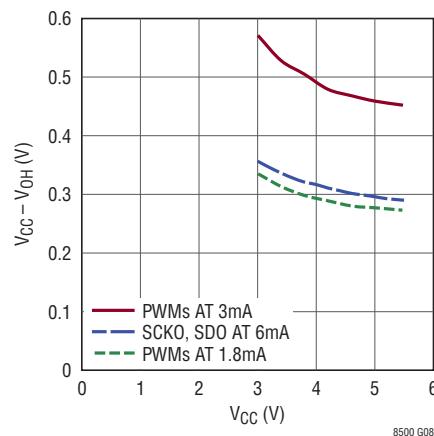

I<sub>CC</sub>とV<sub>CC</sub>のグラフの測定条件: SCK0の負荷: 25pF、PWM出力有効: デューティ・サイクル = 1365/4096、PWMの平均負荷: 10pFI<sub>CC</sub>とV<sub>CC</sub>、SCKI = 0MHz、

SDI = 0MHz、PWMCK = 0MHzI<sub>CC</sub>とV<sub>CC</sub>、SCKI = 0MHz、

SDI = 0MHz、PWMCK = 10MHzI<sub>CC</sub>とV<sub>CC</sub>、SCKI = 0MHz、

SDI = 0MHz、PWMCK = 25MHzI<sub>CC</sub>とV<sub>CC</sub>、SCKI = 12MHz、

SDI = 6MHz、PWMCK = 0MHzI<sub>CC</sub>とV<sub>CC</sub>、SCKI = 20MHz、

SDI = 10MHz、PWMCK = 10MHzI<sub>CC</sub>とV<sub>CC</sub>、SCKI = 50MHz、

SDI = 25MHz、PWMCK = 25MHzV<sub>OL</sub>とV<sub>CC</sub>V<sub>OH</sub>とV<sub>CC</sub>

## ピン機能

**PWM[48:1](ピン1～33, 42～56)：**パルス幅変調(PWM)出力ピン。パルス幅は、PWMRSYNCラッチの値を内部のPWMCKカウンタと比較することで決まります。PWMCKカウンタの値がPWMRSYNC[n]の値よりも小さい場合に、出力がHighになります。PWM周波数は、PWMCKピンに印加される信号によって決まります。

**OPENLED(ピン34)：**オープンLEDの否定入力ピン。この入力は、ステータス・フレームを介して診断情報をホストに渡します。LT3595A LEDドライバと併用する場合、LEDストリング内の少なくとも1つのLEDにオープンがあることを示すLT3595AのOPENLED出力をワイヤードOR(オープン・コレクタ)して、このピンに入力します。ユーザーはLT8500上で、オープンLEDを含むストリングまたはその他のフォールトを含むPWM出力チャネルを特定するセルフ・テストを実行できます。このピンには、チップ内部でV<sub>CC</sub>電源レールにプルアップする100kΩの抵抗が接続されています。

**SDO(ピン35)：**シリアル・データ出力ピン。このピンはシフト・レジスタ(SR)の出力であり、下流のチップにカスケード接続によってデータを送出したり、ホストにデータを戻したりします。

**SCKI(ピン36)：**シリアル・クロック入力ピン。このクロック・ピンはシリアル・インターフェースおよび補正乗算器のPWM値の計算を駆動するタイミングを提供します。このクロックはPWMCKからは独立しています。

**V<sub>CC</sub>(ピン37)：**電源ピン。3.0V～5.5V。コンデンサによりローカルにグランドへバイパスする必要があります。

**SCKO(ピン38)：**シリアル・クロック出力ピン。SCKIをバッファリングしたパス・スルー信号。このピンは、カスケード接続を介してクロックを次のチップまたはホストに送出します。

**PWMCK(ピン39)：**PWMクロック入力ピン。このピンは、PWMの出力タイミングを提供します。各PWM信号は、このクロックのパルスをゼロからPWM同期レジスタ(PWMRSYNC)に格納された計算値までカウントすることで生成されます。このクロックはSCKIからは独立しています。

**SDI(ピン40)：**シリアル・データ入力ピン。このピンは、コマンドを発行し、個々のPWMチャネルを設定するためのシリアル・インターフェース・データを提供します。

**LDIBLANK(ピン41)：**ラッチ・データ・イン/ブランク入力ピン。このピンには、次の2つの機能があります。

**LDI機能：**内部のLDI信号は、LDIBLANKピンに直接接続されています。このピンに対するロジックHighは、常にLDI機能をアサートします。LDIBLANKの立ち上がりエッジで、シフト・レジスタ(SR[7:0])のデコードされたコマンド・フィールド(CMD, CR[7:0])が取り込まれます。LDIBLANKがHighレベルになると、補正乗算器からのデータがPWMレジスタ(PWMR)にラッチされます。LDIBLANKがHighになると、ステータス情報がシフト・レジスタ(SR)にロードされ、次のフレームがSDIにシフト入力されるときに、SDOからシフト出力されます。詳細は動作のセクションを参照してください。

**ブランク機能：**LDIBLANK Highを50μsより長い期間アサートすると、PWM[48:1]出力の全てがオフになり、チップがリセットされます。不注意によるチップのリセットを防ぐには、LDIBLANK Highを5μsより長い期間アサートしないでください。

**GND(露出パッドピン57)：**これはチップのグランド基準です。

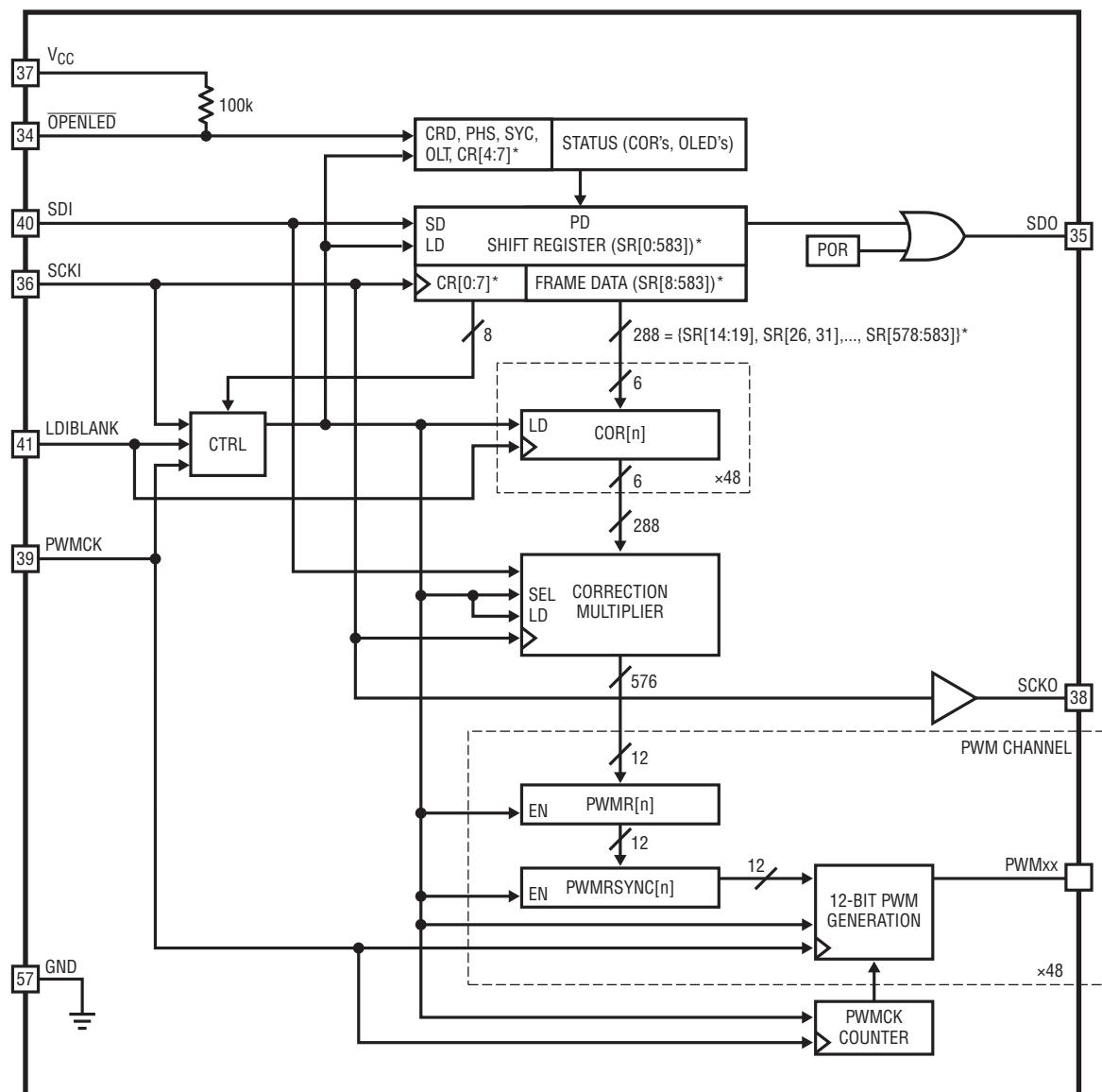

## 機能ブロック図

\*REVERSE INDEXING IS USED TO INDICATE PHYSICAL BIT ORDER.

8500 BD

図1. ブロック図

## 動作

### 概要

LT8500は48個のパルス幅変調出力(PWM[48:1])を制御するものであり、3つのLT3595A LED ドライバを駆動するような制御アプリケーションに適しています。図1のブロック図は、このチップの動作を最もよく表しています。

LT8500に含まれる主なブロックは、584ビットのシフト・レジスタ(SR[0:583])、48個の6ビット補正レジスタ(COR[1:48])、補正乗算器、48本のPWMチャネル、およびPWMCKクロック・カウンタです。各PWMチャネルは対応するPWM<sub>x</sub>出力ピンのデータを格納し、PWMレジスタ(PWMR)とPWM同期レジスタ(PWMRSYNC)を備えています。584ビットのシフト・レジスタの下位8ビットはコマンド・レジスタ(CR[0:7])として使われ、それ以外のビットにはフレーム・データが格納されます。

チャネルのPWMRSYNCレジスタとPWMCKカウンタの値を比較することで、それに対応するPWM出力信号が生成されます。584ビット・シフト・レジスタの入力(SR[0])は、SDI信号に接続されています。SDIは補正乗算器にも入力されます。584ビット・シフト・レジスタの出力(SR[583])は、SDOに接続されます。

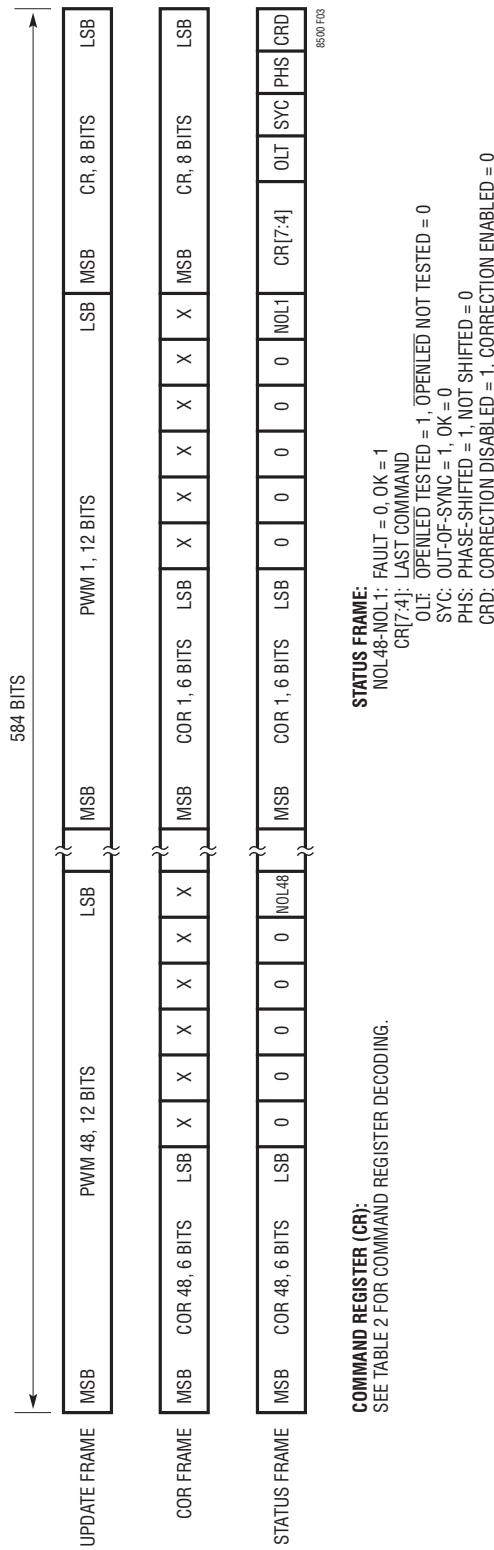

ユーザーはシリアル・インターフェース・ピンのSDI、SCKI、LDIBLANKを制御することで、このデバイスと通信します。コマンド・フレームと呼ばれるシリアル・データ・フレームを、SCKIをクロック信号として、SDIからデバイスにシフト入力します。これと同時に、ステータス・フレームがSDOからシフト出力されます。LDIBLANKピンの立ち上がりエッジでフレームが終了します。1つのフレームは、1本のPWMチャネルあたり12ビットのデータ・フィールドと、その後に続く8ビットのコマンド・フィールドからなり、合計の長さが $(12 \times 48) + 8 = 584$ ビットになります。データは最上位チャネルを先頭に送信され、各フィールドは最上位ビット(MSB)を先頭に送信されます。フレームのフォーマットとタイミングを、それぞれ図3と図4に示します。8つのコマンドがあり、そのうち2つがPWM[48:1]出力を更新するコマンドです。表2にコマンドの概要を示します。本書では、コマンド・フレームをそのフレームが発行するコマンド名で呼ぶことにします。例えば「更新フレーム」や「補正フレーム」などです。

50MHzのSCKIを使用した場合、1フレームを11.7μs(584 SCKI+LDI)で送信できるため、フレーム・レートは85.5kHzになります。PWMCKが25MHzの場合、PWM周期(4096 PWMCK)は164μs、つまりPWM出力周波数6.1kHzが得られます。

48本のPWMチャネルのそれぞれに、12ビットの値をシリアルにロードするには、更新フレームを使用します。LT8500は、これら12ビットのPWMチャネル・データが格納される前に、自動的にスケーリングを適用することができる補正乗算器を搭載しています。補正乗算器は既定で有効であり、入力されるチャネル・データは次式に従ってスケーリングされます。

$$PWM_{OUTn} = CHAN_{n(NOM)} \cdot \left(\frac{2}{3}\right) \cdot \left(\frac{COR_n + 32}{64}\right)$$

ここで、 $PWM_{OUTn}$ は、 $PWM_n$ がHighとなるPWMCKサイクル数、 $CHAN_{n(NOM)}$ はフレーム内の $n$ 番目のチャネル・フィールド、 $COR_n$ はプログラムされた $n$ 番目の補正設定( $COR_n = 0 \sim 63$ )です。表1の計算例を参照してください。

一方、補正乗算器が無効の場合は、入力されるデータが次式のように変更を加えられずに格納されます。

$$PWM_{OUTn} = CHAN_{n(NOM)}$$

補正乗算器は補正レジスタ・ディスエーブル・ビット(CRD)によって無効にします。このビットは補正トグル・コマンド(CMD = 0x7X)によってオン/オフを切り替えます。電源投入後、CRDビットがLowの場合、補正乗算器は既定の有効に設定されます。

補正乗算器によって生成された結果は、更新フレーム後にそれぞれのPWMRSYNCレジスタに移動します。更新フレームによるこの移動は、同期または非同期で動作します。同期更新フレームの場合、データはフレーム終端を示すLDIの次の立ち上がりエッジでPWMRにコピーされます。その後、PWM周期が開始される時点で、PWMRからPWMRSYNCレジスタにコピーされます。PWM周期は、PWMCKの自走カウンタがゼロになった時点から開始されます。これに対して非同期更新フレームは、フレーム終端を示すLDIの次の立ち上がりエッジで、補正乗算器のデータをPWMRを介してPWMRSYNCにも同時にコピーします。

PWMRSYNCレジスタが新しい値で更新されると同時に、PWM出力にもこの更新値が反映されます。前述のとおり、PWMR出力は対応するPWMRSYNCの値とPWMCKカウンタを比較することで生成されます。

## 動作

### 起動

LT8500は電源投入後、LDIBLANKピンがLowならばいつでも通信できます。PWM[48:1]出力は、出力イネーブル・フレームが送信されるまで無効(ロジック0)のままで。起動時の推奨イベント・シーケンスは次のとおりです。

1. 電源を印加し、LDIBLANKをLowに駆動します。オンチップのパワーオン・リセット(POR)がデアサートされると、SDOがLowになります。

2. シリアル・インターフェース上に補正レジスタ・フレーム(CMD = 0x20)を送信します。これによって各チャネルの補正係数を設定します。

3. シリアル・インターフェース上に更新フレーム(CMD = 0x00 またはCMD = 0x10)を送信します。これによって各チャネルのパルス幅を設定します。

4. シリアル・インターフェース上に出力イネーブル・フレーム(CMD = 0x30)を送信します。これによって、PWM[48:1]出力への変調パルス出力が有効になります。

ステップ4よりも前に、PWMクロック(PWMCK)をオンにしておく必要があります。PWM[48:1]の全てのチャネルがオンするPWM周期の開始時点は、フレーム開始前に出力がディスエーブルされていた場合、出力イネーブル・フレームに同期します。

### シリアル・データ・インターフェース

LT8500は、50MHzのカスケード接続可能なシリアル・データ・インターフェースを備え、クロックとデータに対する完全なバッファ機能およびスキュー・バランシング機能を搭載しています。インターフェースには新しい5線式トポロジー(LDIBLANK、SCKI、SDI、SCKO、SDO)が採用され、マイクロコントローラ、デジタル信号プロセッサ(DSP)、フィールド・プログラマブル・ゲート・アレイ(FPGA)などのさまざまなデジタル・コントローラに接続できます。

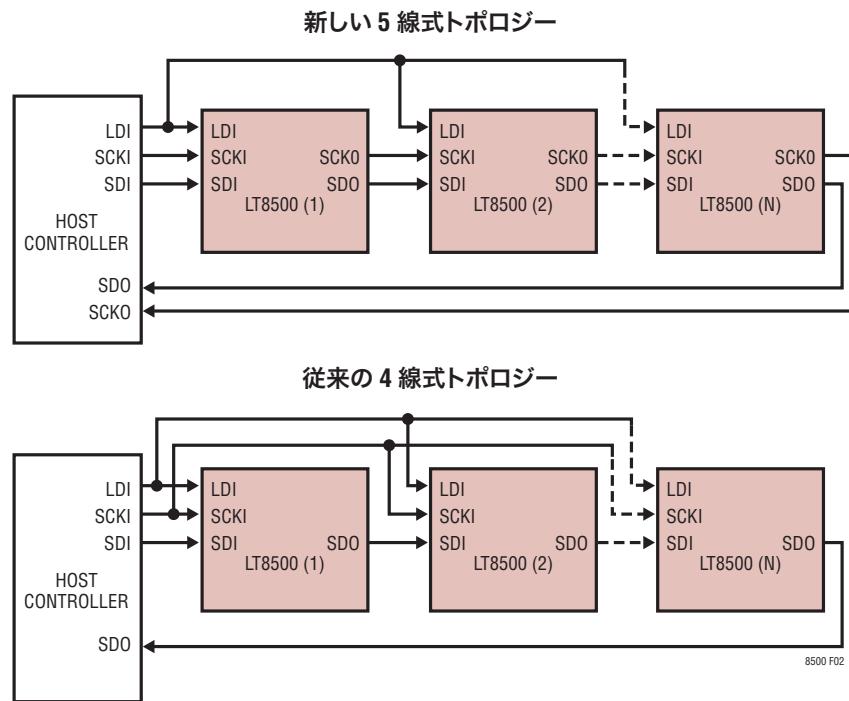

### トポロジー

LT8500は、図2に示す2つのトポロジーによるカスケード接続をサポートします。高速接続および多数のLT8500を接続する場合は、新しい5線式トポロジーの採用を検討してください。低速の場合、および少数のLT8500を接続する場合は、従来の4線式トポロジーの採用を検討してください。いずれのトポロジーを使用する場合も、シグナル・インテグリティ、特にクロックの品質は十分に評価してください。

5線式トポロジーではSCKIのグローバル配線が不要となり、SCKI信号にバッファを挿入する必要がなくなりました。その代わりに、次のチップを駆動するためにSDO信号とともにSCKO信号が設けられています。SCKIとSDIの信号間のチップ内スキューは、チップ内部でバランスが取られます。SCKOとSDOの信号

図2. シリアル・インターフェースのトポロジー

図3. シリアル・データ・フレームのフォーマット

## 動作

図4. シリアル・データ入出力のタイミング図

## 動作

間のチップ外スキーは、これら2つの信号をチップ間で平行配線することにより簡単にバランスを取ることができます。この方法で適切にバランスが取られていれば、SCKO/SDOのタイミングは、カスケード接続された次のチップのSCKI/SDIのタイミング要件を満たすので、より高速のクロックを使用したり、より多くのチップをカスケード接続したりすることができます。ホスト・コントローラはSCKI信号とともにSDI信号を送信し、SCKO信号とともにSDO信号を受信します。コントローラにはSCKIとSCKOの間のスキーが見えるため、カスケード接続されたLT8500の個数とシステムのタイミングにおける制約によっては、2つのクロック・プレーンを使用して動作する必要があります。SCKIとSCKOの間ではデューティ・サイクルも変化するため( $t_{DC-SCK}$ )、SCKIのスピードによって1つのチェーンに含まれるLT8500の個数が制限されます。デューティ・サイクルが変化するのは、SCKIの正のエッジと負のエッジの伝搬遅延にわずかな差があるためです。タイミングが厳しいシステムでは、チップ間でLDIBLANKのスキー・バランスが必要になる場合があります。これを行わない場合は、ホスト側でSCKIとLDIの間の遅延を増やし、LDIに対するSCKIのセットアップおよびホールド時間( $t_{SU-LDI}$ と $t_{HD-LDI}$ )に違反しないようにする必要があります。5線式トポロジーの特徴をまとめると、カスケード接続可能なチップの最大個数の増加、直列データ・インターフェースのクロック周波数の高速化、グローバルSCKI配線が不要になること、SCKI信号へのバッファ挿入の必要性が低減されること、PCBレイアウトの容易化などがあります。カスケード接続するチップが少ない低速のアプリケーションでは、SCKO出力を無視することで5線式トポロジーを4線式トポロジーに簡素化できます。

4線式トポロジーの場合は、LDIBLANKとSCKI信号をグローバル配線する必要がありますが、SDI信号に必要なのはチップ間のローカル配線のみになります。SCKOは無視されます。多数のチップをカスケード接続する場合、または長い基板トレースを使用する場合は、信号スキーを最小限に抑えるために、LDIBLANKとSCKI信号に対し、相応の駆動能力を持ったクロックツリー・バッファを外付けする必要が生じる場合があります。SCKI信号にバッファを挿入したことによる伝搬遅延は、SCKIとSDI信号間にスキーを生じます。通常、このスキーにはバランスが必要になります。SDIとSDO信号は、いずれも送受信に同じSCKI信号を必要とするため、SDIとSDO信号間の伝搬遅延により、カスケード接続可能なチップ数と、直列データ・インターフェースのクロック周波数が制限されます。

## 通信

図3に、SDIに送信されるコマンド・フレームを2つ、SDOより受信されるステータス・フレームを1つ示します。全てのフレー

ムは584ビットの同じ長さで、最上位チャネルを先頭に送信され、各フィールドは最上位ビット(MSB)を先頭に送信されます。コマンド・フレームはSCKI信号とともに送信され、ステータス信号はSCKO信号とともに受信されます。コマンド・フィールドは、表2に従ってフレームの機能を決定します。ステータス・フレームを構成するビットは、最後のコマンドの上位4ビット(CR[7:4])、オープンLEDセルフ・テスト・ビット(OLT)、同期エラー・ステータス・ビット(SYC)、位相シフト・ステータス・ビット(PHS)、補正レジスタ・ディスエーブル・ステータス・ビット(CRD)、各チャネルのOPENLEDフォールト・ビット(NOL[48:1])に加え、これらのそれにつき6ビットを充てている補正レジスタ・ビット(COR[48:1])です。ステータス・フレーム内の未使用ビットはロジック0で埋められます。図3を参照してください。

図4に、シリアル入力信号とシリアル出力信号間のより詳細なタイミング関係を示します。1つの補正レジスタ・フレームに統一、1つの更新フレームがSDI、SCKI、LDIBLANKピンを経て送信されます。同時に、SDO、SCKO、LDIBLANKピンを経て2つのステータス・フレームが受信されます。データ・フレームは、SCKIの立ち上がりエッジでシフト・レジスタSR[0:583]にシフト入力されます。584クロック・サイクル後、データ・ビットは全てシフト・レジスタに格納され、LDI信号を待機します。非同期のLDIBLANK「High」信号によって、デコードされた8ビットのCMDフィールド(CR[7:0])が取り込まれ、これに従ってコマンドが実行されデータが送信されます。同時に、CMDフィールドの上位4ビット(CR[7:4])、ステータス・ビット、CORレジスタ、およびこれらそれについてのオープンLEDフォールト・フラグを含むステータス情報のフレームが584ビット・シフト・レジスタにパラレルにロードされ、次のフレームがシフト入力されるのに合わせてシフト出力されます。

## LDIBLANK = LDI + BLANK

LDIBLANKピンは2つの機能を持つ入力です。機能はピンのロジックHighの持続時間によって決ります。LDIはラッチ・データ入力です。フレームの終端を知らせ、CMDフィールド(CR[7:0])内のコマンドを実行します。BLANK信号はPWM[48:1]出力をオフし、シリアル・インターフェース用のシフト・レジスタを含めデバイスをグローバルにリセットします。LDIBLANKがロジックHighになると、LDIは必ずアサートされます。更に、BLANK信号の最小LDIBLANKパルス幅( $t_{WH-BLANK}$ )よりも長い期間ロジックHighが保たれると、BLANKもアサートされます。ピンがHighに保持される時間がLDIの最大LDIBLANKパルス幅( $t_{WH-LDI}$ )より短い場合、BLANKは決してアサートされません。最大 $t_{WH-LDI}$ と最小 $t_{WH-BLANK}$ の間では、不確定な時点でBLANKがアサートされます。

## 動作

LDI信号の立ち上がりエッジは、常にフレームが終了するものと見なされます。LDIBLNAKの立ち下がりエッジに続く次のSCKIの立ち上がりエッジは、常に新しいフレームが開始されるものと見なされます。ステータス・フレーム内には、デバイスが予期せずLDIを検出した場合にシステムに警告を発する、同期エラー・ステータス・ビット(SYC)があります。エラーは、LDIとSCKIが両方ともHighになった場合、またはフレーム境界( $n \cdot 584$  SCKI)以外でLDIがHighになった場合に発生します。SYCビットは情報提供だけを目的とするものであり、それ以外の影響をデバイスに与えることはありません。SYCビットがセットされている場合、ステータス・フレーム内の他のデータはいずれも信頼できません。また、先行するフレームの効果も不明になります。LT8500は、システムが供給するLDIのタイミングは適正であるものと仮定し、次のSCKIを次のフレームの開始と見なします。

### OPENLED

OPENLEDピンは、ステータス・フレームで状態を示すことで、ホストにステータス情報を提供します。ピンの状態はPWMCKの立ち上がりエッジごとに読み込まれ、2つの方法で報告されます。通常の使用法では、LDIBLANKのLow遷移後、最初のSCKI立ち上がりエッジで、ステータス・フレームにピンから読み込んだ状態が受信されます。この状態は48回複製され、各PWMチャネルのステータス・フレームのLSBに示されます。オンチップのプルアップ抵抗により、標準の状態はロジック「1」になります。

一方、LT8500は、OPENLED状態を、上記と異なる形で報告する、診断セルフ・テスト・フレーム(CMD = 0x5X)をサポートしています。この場合、LT8500はPWM[1]からPWM[48]に、順にそれぞれ64 PWMCKサイクルずつパルスを送出します。OPENLEDピンの状態は、チャネルごとに、そのチャネルに対応するPWMピンがHighである間に読み込まれます。このチャネルごとのデータは、次のフレームがシフト入力されるとともに、ステータス・フレームへとシフト出力されます。更に、ステータス・フレームはオープンLEDテスト・ビット(OLT)をセットします。これは、現在のステータス・フレーム内のOPENLEDのデータがセルフ・テストによって得られたものであることを示します。ステータス・フレームは、次のフレームでは標準の状態表示に戻ります。LT8500をLT3595Aと併用する場合、OPENLEDピンとセルフ・テストによって、オープンLEDフォールトの位置を特定する診断ルーチンを実現できます。アプリケーション情報のセクションの「診断情報フラグ」を参照してください。

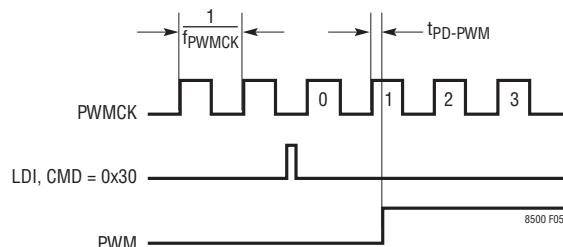

### 出力

電源投入またはリセット後、PWM[48:1]出力は、出力イネーブル・フレームが送信されるまで一切オンしません。12ビット

のPWMCKカウンタは、出力のイネーブル時、PWMCKクロックによる自走カウンタになります。出力イネーブル・フレームが送信されると、図5に示すとおり、LDIBLANKの立ち上がりエッジ後、PWMCKの2番目の立ち上がりエッジで、PWMCKカウンタが1にインクリメントします。既定では、PWMCKカウンタが1のとき、PWMRSYNCの全ての出力(非0の値)がオンします。一方、位相シフト・ビット(PHS)がセットされている場合は、図6のケースA、位相シフト・モードの同期更新の動作に示すように、PWM[48:1]出力がオンします。位相シフト機能については後述します。以降のPWMCKの各立ち上がりエッジでPWMCKカウンタが1ずつインクリメントされます。PWMRSYNCの値がPWMCKカウンタの値と等しくなったPWMチャネルは全てオフします。出力ディスエーブル・フレームはLDI後ただちにPWMCKカウンタをリセットし、LDI後の次のPWMCK立ち上がりエッジで、全てのPWMチャネルをオフします。図5にPWM出力イネーブルのタイミング図を示します。

図5. PWM出力イネーブルのタイミング図

(出力がディスエーブルされていた場合を想定)

### 16チャネル・バンク間の位相差

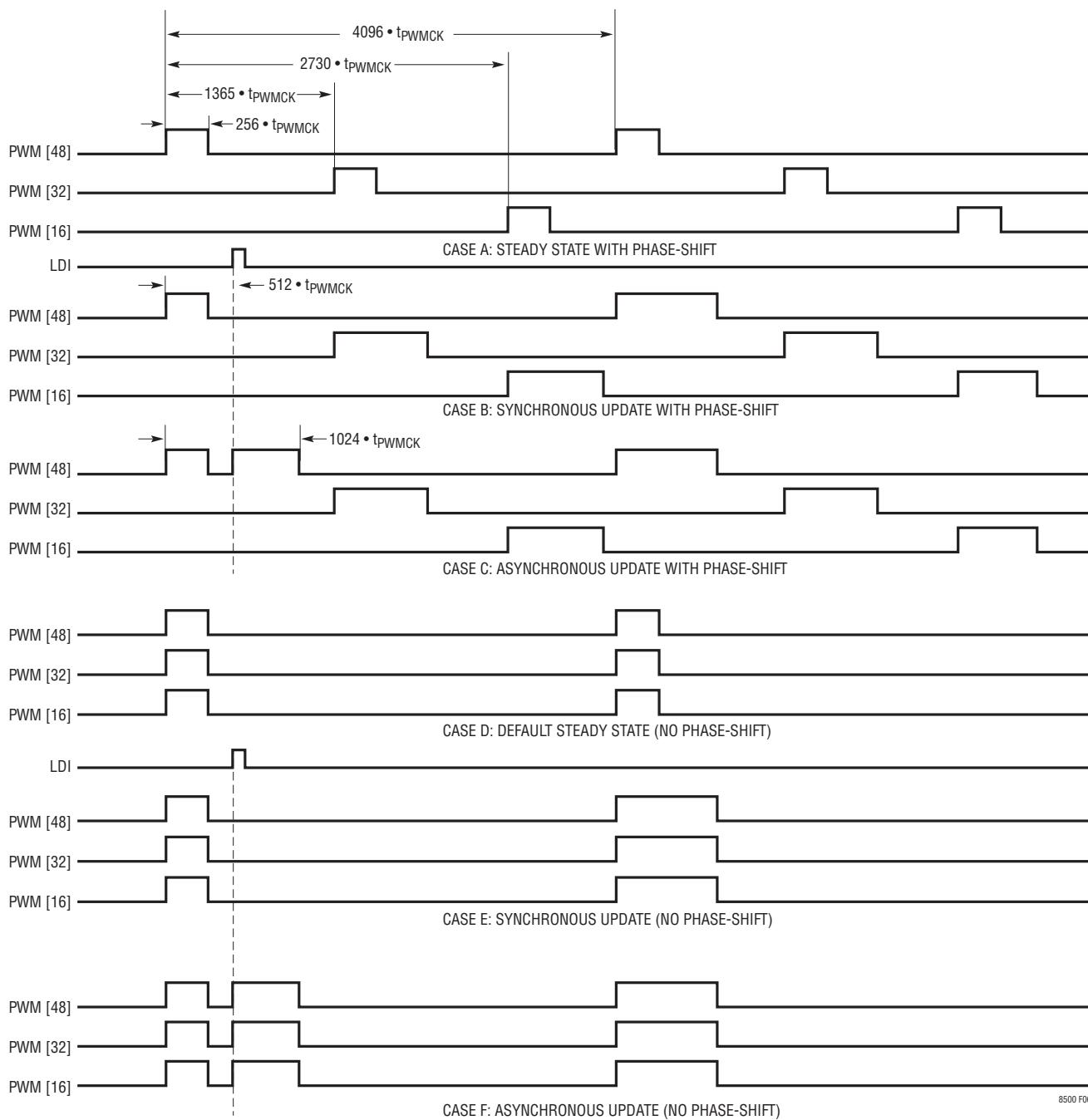

既定では、PWM[48:1]の全てのチャネルの立ち上がりエッジは、PWMCKの、同じく立ち上がりエッジで発生します。この時点から、4096 PWMCKサイクルにわたるPWM周期が開始します。LT8500には、位相シフト・トグル・コマンド(CMD = 0x6X)があります。このコマンドは、48個のピンが同時にスイッチングすることによって生じるシステム・ノイズや電流スパイクを低減するために使用します。このコマンドの機能を図6のケースAに示します。位相シフト・モードでは、PWM[48:1]出力が、PWM周期内で互いに120度位相がずれた、それぞれ16チャネルを含む3つのバンクに分割されます。これは、チャネルPWM[48:33]がPWMCK(1)の立ち上がりエッジでオンした後、PWM周期の1/3の時点に相当するPWMCK(1365)の立ち上がりエッジでチャネルPWM[32:17]がオンし、更に、PWM周期の2/3の時点に相当するPWMCK(2730)の立ち上がりエッジでチャネルPWM[16:1]がオンすることを意味します。

## 動作

表1. 補正を有効(CRD = 0)にした場合のPWM幅の計算例(10進)

| A<br>SDIに送信する<br>PWM更新値 | B<br>プリスケール後のPWM値<br>(A・2/3) | C<br>補正レジスタ(COR)の値 | D<br>乗算器の倍率<br>(C + 32)/64 | E<br>PWM幅(B・D)<br>(t <sub>PWMCK</sub> 単位) |

|-------------------------|------------------------------|--------------------|----------------------------|-------------------------------------------|

| 3                       | 2                            | 63                 | 1.484375                   | 3                                         |

| 120                     | 80                           | 63                 | 1.484375                   | 119                                       |

| 120                     | 80                           | 32                 | 1.0                        | 80                                        |

| 120                     | 80                           | 0                  | 0.5                        | 40                                        |

| 1200                    | 800                          | 63                 | 1.484375                   | 1188                                      |

| 1200                    | 800                          | 32                 | 1.0                        | 800                                       |

| 1200                    | 800                          | 0                  | 0.5                        | 400                                       |

| 4095                    | 2730                         | 63                 | 1.484375                   | 4052                                      |

| 4095                    | 2730                         | 32                 | 1.0                        | 2730                                      |

| 4095                    | 2730                         | 0                  | 0.5                        | 1365                                      |

補正レジスタとPWM更新値のデジタル乗算による

PWM幅の計算

12ビットのPWMチャネル・データは、対応するチャネルのPWM更新値として格納される前に、補正乗算器によって自動的にスケーリングされます。補正乗算器は補正レジスタ・ディスエーブル・ビット(CRD)によって無効にします。このビットは補正トグル・コマンド(CMD = 0x7X)によってオン/オフを切り替えます。補正乗算器が無効の場合は、入力されるデータが次式のように変更を加えられずに格納されます。

$$PWM_{OUTn} = CHAN_{n(NOM)}$$

既定では補正乗算器が有効(CRD = 0)であり、入力されるチャネル・データは次式に従ってスケーリングされます。

$$PWM_{OUTn} = CHAN_{n(NOM)} \cdot \left( \frac{2}{3} \right) \cdot \left( \frac{COR_n + 32}{64} \right)$$

ここで、 $PWM_{OUTn}$ は、 $PWM_n$ がHighとなるPWMCKサイクル数、 $CHAN_{n(NOM)}$ はフレーム内の $n$ 番目のチャネル・フィールド、 $COR_n$ はプログラムされた $n$ 番目の補正設定( $COR_n = 0 \sim 63$ )です。表1の計算例を参照してください。

6ビットのCORの値は、乗算器の倍率として0.5X～1.5X(正確には $(63 + 32) / 64 = 1.484375$ )を設定します。64通りの設定が可能であり、範囲の中央のCOR(倍率1.0Xに相当)は32(0x20)です。乗算器の倍率が1.0より大きい場合にPWMレジスタがオーバーフローするのを避けるために、まずPWM更新の設定値( $CHAN_n$ )がチップ上で2/3倍にプリスケールされます。これは、乗算器の倍率が1.0で、あるチャネルの幅がフルスケールの場合( $CHAN_n = 4095$ 、 $COR_n = 32$ )、 $PWM_{OUTn}$ の幅が4095ではなく、 $4095 \cdot (2/3) = 2730$ になることを意味し

ます。したがって、~1.5倍( $COR_n = 63$ )に設定した補正乗算器の場合、補正後のPWM幅は、 $4095 \cdot (2/3) \cdot 1.484375 = 4052$ になります。 $PWM_{OUTn}$ の幅は、常に最も近い整数に丸められます。表1に、代表的なレジスタ値に対するPWMの計算例を示します。これは、 $CRD = 0$ の場合の最大PWMデューティ・サイクルが4052/4096、 $CRD = 1$ の場合は4095/4096になることを意味します。

## コマンドの解説

LT8500には、表2に示す8つのコマンドが実装されています。コマンド(CMD)は、コマンド・フレームの下位8ビットにエンコードされているため、フレーム全体のシフト入力が完了した時点でシフト・レジスタの下位8ビットに格納されています。コマンド・フィールドはLDIの立ち上がりエッジで実行されます。コマンドとしてデコードされるのは、コマンド・フィールドの上位4ビットだけです。

## 同期更新フレーム:CMD = 0x0X

同期更新フレームは、補正乗算器による処理が完了したフレーム内のデータによって、 $PWM[48:1]$ を更新します。 $PWMR$ は、 $LDIBLANK$ がHighになった時点で更新されます。 $PWMRSYNC$ レジスタには、PWM周期の開始( $PWMCK(1)$ )に同期して $PWMR$ からのデータが書き込まれます。このコマンドは、規定より短い「不完全な」PWMパルスの発生を防ぎます。PWM出力は、 $PWMCK$ の次の立ち上がりエッジで $PWMRSYNC$ レジスタの値によって更新されます。例を図6のケースBとEに示します。

## 動作

表2. コマンド・レジスタのデコード

| CMD (CR[7:0]) | コマンド・フレーム名     | 概要                                       | フレーム・データ      |

|---------------|----------------|------------------------------------------|---------------|

| 0000_xxxx     | 同期更新フレーム       | PWM周期に同期してPWM幅を更新                        | チャネルごとのPWM更新値 |

| 0001_xxxx     | 非同期更新フレーム      | PWM周期に非同期でPWM幅を更新                        | チャネルごとのPWM更新値 |

| 0010_xxxx     | 補正フレーム         | PWM補正係数を設定                               | チャネルごとの補正係数   |

| 0011_xxxx     | 出力イネーブル・フレーム   | PWM出力を有効化                                | ドントケア         |

| 0100_xxxx     | 出力ディスエーブル・フレーム | PWM出力を無効化(Lowに駆動)                        | ドントケア         |

| 0101_xxxx     | セルフ・テスト・フレーム   | セルフ・テストを開始                               | ドントケア         |

| 0110_xxxx     | 位相シフト・トグル・フレーム | 16チャネル・バンクごとの120°位相シフト(PHS)機能のオン/オフを切り替え | ドントケア         |

| 0111_xxxx     | 補正トグル・フレーム     | 乗算器内の補正ディスエーブル(CRD)ビットのオン/オフを切り替え        | ドントケア         |

| 1xxx_xxxx     | 予約済み           | 使用禁止                                     | -             |

### 非同期更新フレーム:CMD = 0x1X

非同期更新フレームは、補正乗算器による処理が完了したフレーム内のデータによって、PWM[48:1]を更新します。PWMRは、LDIBLANKがHighになった時点で更新されます。LDIがHighの場合、このデータはPWMRを介してPWMRSYNCレジスタにもただちに(非同期に)書き込まれます。PWM出力は、PWMCKの次の立ち上がりエッジでPWMRSYNCレジスタの値によって更新されます。例を図6のケースCとFに示します。

### 補正フレーム:CMD = 0x2X

補正フレームは、フレーム内の各チャネルのデータ・フィールド上位6ビットの値によって補正レジスタ(COR)を更新します。CORは、補正乗算器がPWM幅を調整するために使用します。PWM幅は2/3にプリスケールされた後に、乗算器によって0.5～1.5の倍率でスケーリングされます。PWM幅の計算例を表1に示します。一般的なアプリケーションでは、このコマンドをシステム初期化のために使用し、電源投入後に1回だけ実行します。したがって、補正フレームはPWM出力を更新しません。CORの更新は、補正フレームに続く更新フレームによってPWM出力に反映されます。

### 出力イネーブル・フレーム:CMD = 0x3X

出力イネーブル・フレームは、LDIBLANKがHighになってから2番目のPWMCKのエッジで、PWM周期を開始し、PWM出力を有効にします。SDOまたはSCKOには何の影響も与えません。出力イネーブル・フレーム内のデータはコマンドとは無関係ですが、LT8500のデイジー・チェーン接続が適切に動作できるようにします。

### 出力ディスエーブル・フレーム:CMD = 0x4X

出力ディスエーブル・フレームはLDIがHighになるとただちにPWMCKカウンタをリセットし、次のPWCK立ち上がりエッジでPWM出力を無効にします。SDOまたはSCKOには何の影響も与えません。出力ディスエーブル・フレーム内のデータはコマンドとは無関係ですが、LT8500のデイジー・チェーン接続が適切に動作できるようにします。

### セルフ・テスト・フレーム:CMD = 0x5X

セルフ・テスト・フレームは、LT3595Aに接続されたLEDストリングのオープン(切断/開放不良)を識別するなど、PWM[48:1]の各チャネルの診断に使用できます。LDIBLANKがHighに遷移すると、LT8500はPWM[1]からPWM[48]に、順にそれぞれ64 PWMCKサイクルずつパルスを送出します。OPENLEDピンの状態は、チャネルごとに、そのチャネルに対応するPWMピンがHighである間に読み込まれます。このチャネルごとのデータは、その後ステータス・フレームへとシフト出力されます。更に、ステータス・フレームはオープンLEDテスト・ビット(OLT)をセットします。これは、現在のステータス・フレーム内のOPENLEDのデータがセルフ・テストによって得られたものであることを裏付けるものです。その他のコマンドでは、OPENLEDピンの状態が、フレームの最初のSCKIで1回だけ取り込まれます。そして、これがステータス・フレーム内の48チャネル全てに共通の値として報告されます。セルフ・テスト・フレーム内のデータはコマンドとは無関係ですが、LT8500のデイジー・チェーン接続が適切に動作できるようにします。

## 動作

### 位相シフト・トグル・フレーム:CMD = 0x6X

位相シフト・トグル・フレームは位相シフト・ビット (PHS) をトグルします。既定では、このビットはオフです。PHS がセットされると、PWM 出力の立ち上がりエッジが、16 チャネルからなるバンクごとに、互いに 120 度位相がずれるように設定されます。これは、チャネル PWM[48:33] が PWM 周期の始まる立ち上がりエッジ、チャネル PWM[32:17] は PWM 周期の 1/3 が経過した時点、チャネル PWM[16:1] は PWM 周期の 2/3 が経過した時点で起動することを意味します。PHS ビットの状態は、ステータス・フレームごとに毎回返されます。位相シフト・トグル・フレーム内のデータはコマンドとは無関係ですが、LT8500 のデイジー・チェーン接続が適切に動作できるようにします。

### 補正トグル・フレーム:CMD = 0x7X

補正トグル・フレームは補正レジスタ・ディスエーブル・ビット (CRD) をトグルします。既定では、このビットはオフです。CRD がセットされると、補正乗算器内の補正レジスタ (COR) の使用を無効にし、SDI からの入力データを「1」倍します。これによって、更新フレーム内のデータは、変更を加えられずに PWMRSYNC レジスタに到達します。CRD ビットの状態は、ステータス・フレームごとに毎回返されます。補正トグル・フレーム内のデータはコマンドとは無関係ですが、LT8500 のデイジー・チェーン接続が適切に動作できるようにします。

### 代表的ケースにおける PWM 更新の例

図 6 に、各種コマンドが PWM 出力波形に与える効果の例を示します。これらの波形例では、示されている 3 つのチャネルの全てが常に同じ PWM 幅にプログラムされているものとします。各ケースでは、3 つの 16 チャネル・バンク、PWM[48:33]、PWM[32:17]、PWM[16:1] について、それぞれを代表するチャネルを示してあります。

ケース A は、位相シフト・モードの定常状態の動作です。PWM の幅は 256 PWMCK サイクルにプログラムされています。バンク 2 の PWM[48] が、PWM 周期の開始時点で立ち上がっています。バンク 1 の PWM[32] は、バンク 2 の PWM 周期が 1/3 経過した時点、つまり PWMCK の 1365 サイクル後に立ち上がっています。バンク 0 の PWM[16] は、バンク 2 の PWM 周期が 2/3 経過した時点、つまり PWMCK の 2730 サイクル後に立ち上がっています。

ケース B は、ケース A と同様の位相シフト・モードにおける、同期更新フレーム (CMD = 0x0X) の動作です。LDI 信号が、PWM 周期開始から 512 PWMCK サイクルの、PWM[48] がオフになった後に、アクティブに遷移しています。更新フレームが PWM 幅を 1024 にプログラムしますが、同期更新コマンドでは、PWM 周期の開始時点以外では PWM 幅の更新を防止します。このため PWM[48] は次の PWM 周期が始まるまで Low を保持し、新しい周期の開始時点から、更新値である 1024 PWMCK サイクル幅で High に駆動されます。PWM[32] の PWM 周期は PWMCK (1365)、PWM[16] の PWM 周期は PWMCK (2730) から開始し、いずれの幅も 1024 PWMCK サイクルに更新されています。

ケース C は、ケース A と同様の位相シフト・モードにおける、非同期更新フレーム (CMD = 0x1X) の動作です。LDI 信号が、PWM 周期開始から 512 PWMCK サイクルの、PWM[48] がオフになった後に、アクティブに遷移しています。更新フレームが PWM 幅を 1024 にプログラムします。非同期更新であるため、PWM[48] はただちに立ち上がり、PWMCK (1024) まで High を保持しています。PWM[32] と PWM[16] (ならびに全ての PWM) も更新されていますが、位相シフト・モードであるため、立ち上がりエッジが現れるのは、それぞれの PWM 周期が開始する時点です。

ケース D は既定モード (位相シフトなし) の定常状態の動作です。全ての PWM 出力が、PWM 周期が開始する同じ PWMCK のエッジで立ち上がっています。

ケース E は、ケース D と同様に位相シフトを適用しない場合の、同期更新フレーム (CMD = 0x0X) の動作です。LDI 信号が、PWM 周期開始から 512 PWMCK サイクルの、PWM がオフになった後に、アクティブに遷移しています。更新フレームが PWM 幅を 1024 にプログラムしますが、同期更新コマンドでは、PWM 周期の開始時点以外では PWM 幅の更新を防止します。このため PWM は次の PWM 周期が始まるまで Low を保持し、新しい周期の開始時点から、更新値である 1024 PWMCK サイクル幅で High に駆動されます。

ケース F は、ケース D と同様に位相シフトを適用しない場合の、非同期更新フレーム (CMD = 0x1X) の動作です。LDI 信号が、PWM 周期開始から 512 PWMCK サイクルの、PWM がオフになった後に、アクティブに遷移しています。更新フレームが PWM 幅を 1024 にプログラムします。非同期更新であるため、全ての PWM がただちに立ち上がり、PWMCK (1024) まで High を保持しています。

## 動作

図6. 代表的ケースにおけるPWM出力の例

## アプリケーション情報

このセクションではLED調光アプリケーションについて解説しますが、他のアプリケーションにも関連する内容です。LT8500は、3つのLT3595A LEDドライバの駆動などに使用できる、48個のPWM出力を提供します。このデバイスによって、LEDドット補正機能を実現できます。それには、補正レジスタ(COR)と、あらかじめ2/3倍にプリスケールされたPWM更新値との、デジタル乗算を使用します。この演算によって、ドット補正に対応したPWMのデューティ・サイクル値が得られます。補正レジスタ・ディスエーブル・ビットをセットすることにより(CMD = 0x7X)、PWM更新値を(変更することなく)直接書き込むオプションもあります。このビットをセットすると乗算がバイパスされるため、ドット補正を行う場合はチップ外で計算する必要があります。この場合のPWMデューティ・サイクルは、更新フレームによって送信された設定値を4096で割った値になります。デバイスは、各チャネルの $\overline{\text{OPENLED}}$ およびCORデータ、セルフ・テスト(オープンLEDなど)を示すグローバル・ステート・データ、同期エラー、位相シフト・ステータス、直接データ・ステータスを含むステータス・フレームを提供します。ステータス・フレームは、新しいフレームがシフト入力されるたびにシフト出力されます。また、オープンLEDなどのフォールトの原因となっているチャネルを判断する、オンチップ・セルフ・テスト機能(CMD = 0x5X)も搭載しています。 $\overline{\text{OPENLED}}$ ピンとセルフ・テストは、LT3595Aとの併用に特に適しています。このアプリケーションでは、セルフ・テストによってどのチャネルのLEDストリングにオープン個所があるかを特定します。アプリケーション情報のセクションは、一般的なアプリケーションにおいて陥りやすいミスを防ぐための、ガイドラインとして使用してください。

### PWM更新によるグレイスケールの設定

LEDの光度または輝度は、LEDに流れる電流を調整することで変更できますが、色度座標がシフトすることによりLEDチャネル間のカラー・マッチングにも影響を与えます。このため、輝度を調整するより優れた方法として、パルス幅変調(PWM)によるLEDのオン/オフ時間量制御が使用されます。

LT8500は、各チャネルの輝度を独立して調整できます。12ビットのPWMレジスタ(PWMR)をグレイスケール(GS)調光に使用することで、0%～99.98%の4095段階にわたる輝度ステップを実現できます。チャネル $n$ の輝度レベル $GS_n\%$ 、すなわちPWMデューティ・サイクルは、次式に従って計算できます。

$$GS_n\% = \frac{GSR_{n(\text{CALC})}}{4096} \cdot 100\%$$

ここで、 $GSR_{n(\text{CALC})}$ は、計算された $n$ 番目のグレイスケール・レジスタ(PWMRと同じ)設定です( $GSR_{n(\text{CALC})} = 0 \sim 4052$ 、ドット補正有効)。

### ドット補正の設定

LT8500は、各チャネルのPWMデューティ・サイクルを独立して調整できます。デューティ・サイクルの調整はドット補正とも呼ばれ、主にLEDチャネル間の輝度ばらつきを校正するために使用されます。6ビット(64値)のドット補正レジスタ(DCR(CORと同じ))は、次式のように、あらかじめ2/3倍にプリスケールされた各PWMのデューティ・サイクルを0.5X～1.5Xして調整した上で、グレイスケール・レジスタ(GSR)に送信します。

$$PWM_{\text{OUT}n} = \text{CHAN}_{n(\text{NOM})} \cdot \left( \frac{2}{3} \right) \cdot \left( \frac{COR_n + 32}{64} \right)$$

ここで、 $PWM_{\text{OUT}n}$ は $n$ 番目のPWMデューティ・サイクル、 $\text{GSR}_{n(\text{NOM})}$ は $n$ 番目のチャネルに送信されるグレイスケール設定値、 $DCR_n$ はプログラムされた $n$ 番目のドット補正設定( $DCR_n = 0 \sim 63$ )です。

### デバイスのカスケード接続とシリアル・データ・インターフェース・クロックの決定

大画面のLCDバックライトまたはLEDディスプレイ・システムでは、複数のLT8500チップを簡単にカスケード接続できるものであり、LT3595Aなどの全てのLEDドライバとそれらに接続されたLEDストリングを駆動します。LT8500では、クロックのスキー・バランス機能を備え、PCBレイアウトを簡素化する、新しい5線式トポロジーを採用しています。

カスケード化されたフレームを1セット送信するために必要な時間は、1個のLT8500あたり584 SCKIサイクルと、LDIのための1サイクルです。LDIのスキー・バランスが外部で取られていると仮定すると、大画面ディスプレイ・システムのためのシリアル・データ・インターフェースにおける最小クロック周波数 $f_{\text{SCK}}$ は、次式で計算できます。

$$f_{\text{SCK}} = [(n_{\text{CHIPS}} \cdot 584) + 1] \cdot f_{\text{REFRESH}}$$

ここで、 $n_{\text{CHIPS}}$ はカスケード接続されたLT8500の数、 $f_{\text{REFRESH}}$ はシステム全体としてのリフレッシュ・レートです。

### ステータス・フレーム情報

ステータス・フレームは新しいデータ・フレームがSDIからシフト入力されるたびに、その内容が取得され、SDOからシフト出力されます。ステータス・フレームのフォーマットを図5に示します。診断フラグ(SYCとNOL[48:1])を除き、ステータス・フレー

## アプリケーション情報

ムのデータは、ユーザー・インターフェースからのコマンドなしでは変化しません。したがって、このフレームをモニタすることでチップとの通信が適切に行われていることを確認できます。診断情報以外の、次に列挙するステータス情報は、ステータス・フレーム内に継続的に表示されます。各チャネルのドット補正レジスタ(COR[48:1])、オープンLEDテスト・ビット(OLT)、位相シフト・ビット(PHS)、補正レジスタ・ディスエーブル(CRD)ビット。各チャネルに対応するフィールド内には5ビットの未使用領域[5:1]がありますが、いずれも常にロジック0に設定されます。

### 診断情報フラグ

LT8500には、2種類の診断情報フラグ、グローバル同期エラー(SYC)フラグと48個のオープンLEDフラグ(NOL[48:1])があります。

同期エラーは、デバイスが予期せずLDI信号を受信したとき、つまり584 SCKIクロックの受信完了前、またはSCKIがHighの期間に、LDI信号を検出した場合に発生します。これらの事象は、いずれもデータやチップのステートを破壊する可能性があります。SYCビットは全てのステータス・フレームに含まれ、前回のフレームのSCKIの最初の立ち上がりエッジ以降に誤ったLDIを検出した場合に、システムに通知します。フレーム間(SCKIがクロックされていない部分)で複数のLDIが検出されても、これらは同期エラーにはなりません。同期エラーから復帰するために、ユーザーがデータおよびチップのステートを全て書き直さなければならない場合があります。LDI信号はシリアル・インターフェースをリセットします。

OPENLEDビットNOL[48:1]は、LT3595Aとの併用に適しており、3つのLT3595Aが駆動する48個のLEDストリングの少なくとも1つで回路のオープン(切断/開放不良)が検出されたことを示します。LT8500は、3つのLT3595AがそれぞれのLEDストリングのオープンを検出した結果を示す3本のOPENLEDピン信号をワイヤードORするのをモニタします。LT3595Aの1個がLEDストリングのオープンを検出すると、そのLEDストリングのPWMがHighの間はOPENLEDがLowにプルダウンされます。OPENLEDの状態は、(LDI後の)新しいフレームの最初のSCKIの立ち上がりエッジで、LT8500に取り込まれます。SCKIとPWMCKは同期していないため、この方法によるLEDストリングのオープンの検出は、フレーム・レートやPWMデューティ・サイクルに依存する確率関数になります。オープンのLEDストリングに対応するPWMピンがHighの間に新しいフレームが開始されれば、OPENLEDピンがLowに駆動され、これがステータス・レジスタに取り込まれます。しかし、対応するPWMピンがLowの間に新しいフレームが開始された場合、OPENLEDピンはHighにプルアップされ、ステータス・レジスタには既定値であるHighが取り込まれます。

オープンを示すOPENLEDピンのLowが取り込まれた場合、48個のOPENLEDステータス・フラグ(NOL[48:1])は全てクリアされます。ステータス・フレーム、またはポーリング方式でこの状態が検出された場合、ホストはLEDセルフ・テスト(CMD = 0x5X)を要求できます。この機能により、LT8500はオープンがあるとすれば、どのチャネルであるかを判定するテストを実行します。テストでは各PWMピンを1つずつ順にそれぞれ64 PWMCKサイクルの期間Highに駆動し、対応するPWMチャネルのOPENLEDピンの値を取り込みます。これらの結果はステータス・フレーム内のNOLフラグを上書きし、同フレーム内のオープンLEDテスト・ビット(OLT)をセットします。OLTがセットされていることで、このステータス・フレーム内のNOLデータは、チャネルごとの診断結果であることが示されます。次のフレームではOLTビットがクリアされ、再び48個のNOLビットの全てがOPENLEDピンの状態を反映した値になります。

### PCBレイアウトのガイドライン

LT8500を用いたプリント回路基板(PCB)を設計する際は、以下のガイドラインを検討してください。これらのガイドラインは、クロック・スピードとデイジー・チェーンのサイズが増した場合に、更に重要になります。

- 各LT8500へのSDIとSCKIで、配線の長さと遅延を一致させます。

- 各チップへのLDIタイミングが、LDIに対するSCKIのセットアップおよびホールド時間の要件を確実に満たすようにします。5線式トポロジーではデイジー・チェーン内のチップごとにSCKIが遅延するので、チェーン下流の遅延したSCKIと整合させるために、LDIに遅延を追加する必要がある場合があります。動作のセクションのトポロジーの説明を参照してください。

- 通信用の信号(SDI、SCKI、LDI、SDO、SCKO)とPWM信号との間のクロストークを回避します。PWM信号のトグルは低速ではあるものの、全てのエッジが互いに数ナノ秒の間隔で立ち上がる場合があります。

- ホストに戻す信号が長い配線を経由している場合は、バッファを挿入します。

- 高速動作に対応した手法:高周波のクロックおよびデータ・ラインに対しては、標準的な高速PCB設計手法を適用してください。例えば、配線長を短くすること、高速のデータ・ケーブルやトレースをシールドすること、寄生容量を最小限に抑えること、アンテナや反射を低減することなどです。

- VCCピンの近傍にセラミックのバイパス・コンデンサを配置してください。

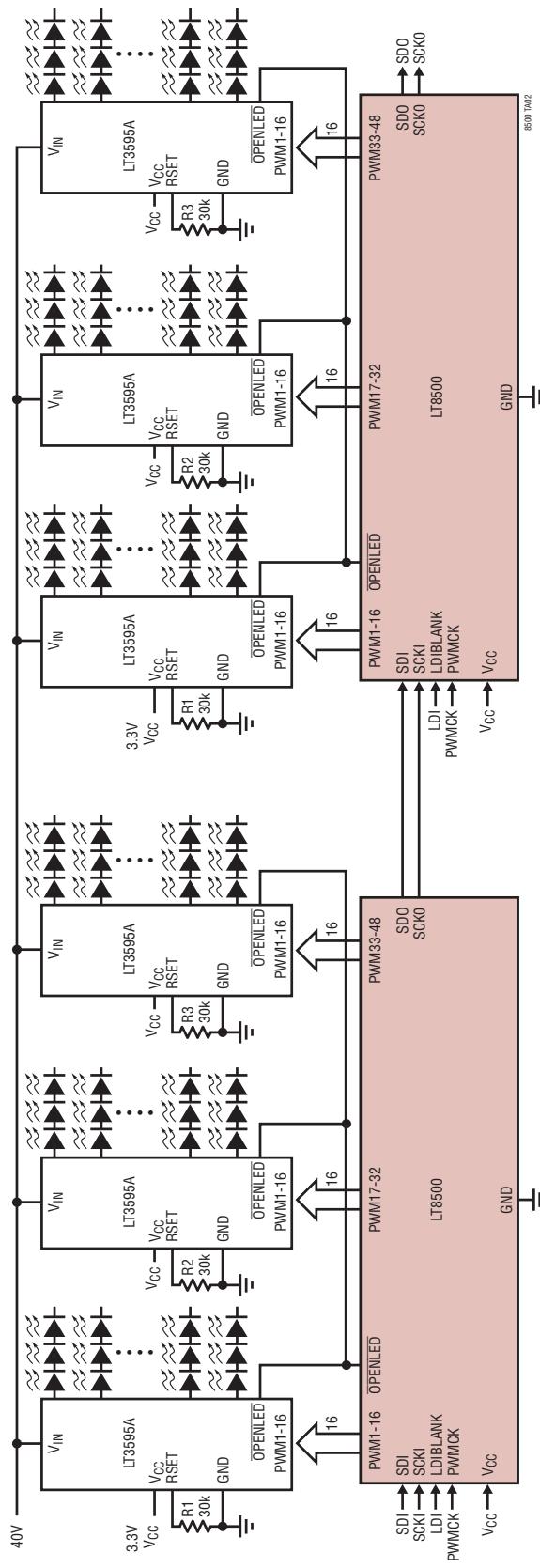

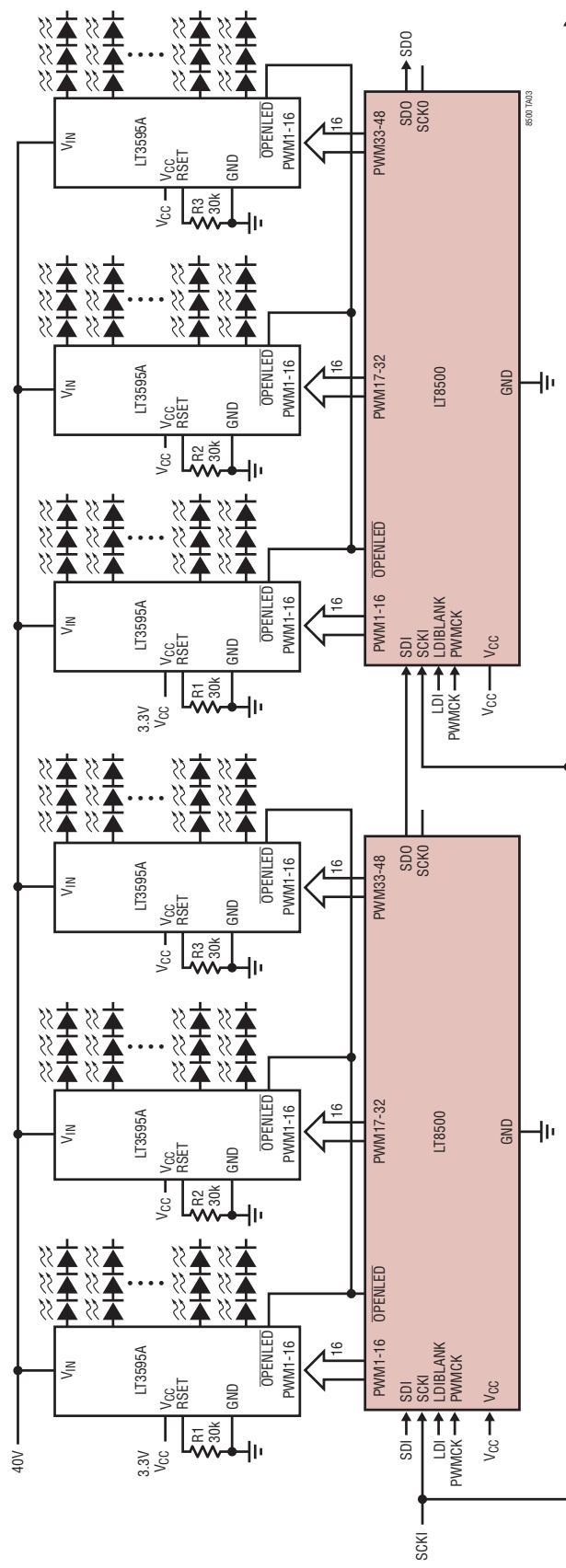

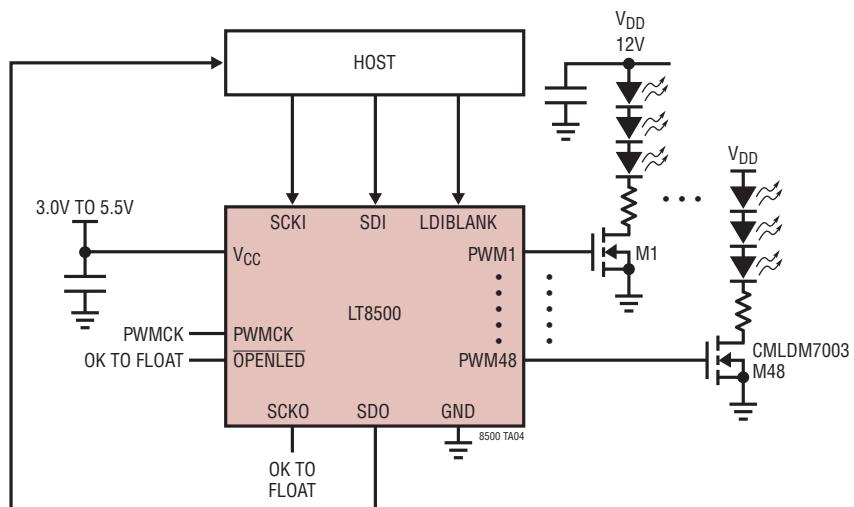

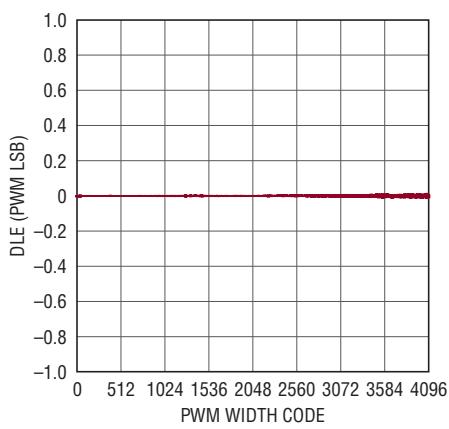

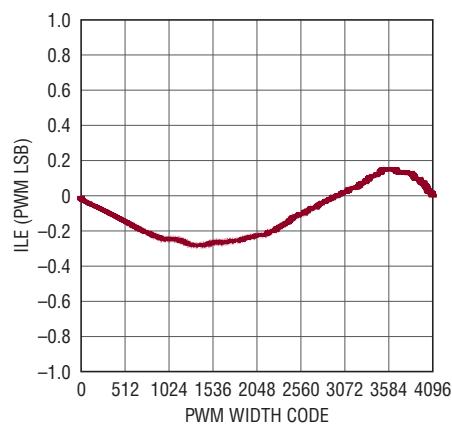

## 標準的応用例

図7～10に、4つの標準的応用例を示します。図7と8は、本データシート既出の5線式および4線式トポロジーによるディジタル・チェーンを示したものです。図9は、1つのLT8500で、48個のLEDストリング(バラスト抵抗付き)を制御する例です。図10は、LT8500を48チャネルのD/Aコンバータ(DAC)として使用する、新しい応用例です。各PWM出力にRC簡易フィルタを使用することで、併記した微分直線性誤差(DLE)や積

分直線性誤差(ILE)のグラフ(図11と図12)からも明らかなように、きわめて優れた誤差特性を示します。このDLEの測定結果は全コード・テストによって得られ、テスト中の $\pm 0.01\%$ 未満のV<sub>CC</sub>電源変動は補償しています。ILEは、上記の補償済みDLE測定結果を単純合計した値です。DLEとILEの測定結果の単位は、PWMのLSBです。

## 標準的应用例

図7.5線式トポロジーでLT3595Aを駆動するLT8500のディイジー・チーン

図8.4 線式トポロジーでLT3595Aを駆動するLT8500のディジタル・チャーン

## 標準的応用例

図9. 単独のLT8500による48個のLEDストリング(バラスト抵抗付き)の( $V_{DD}$ レールからの)駆動

図10. 単独のLT8500による48チャネルD/Aコンバータ(DAC)の実装

図11. DACの微分直線性誤差(DLE)

図12. DACの積分直線性誤差(ILE)

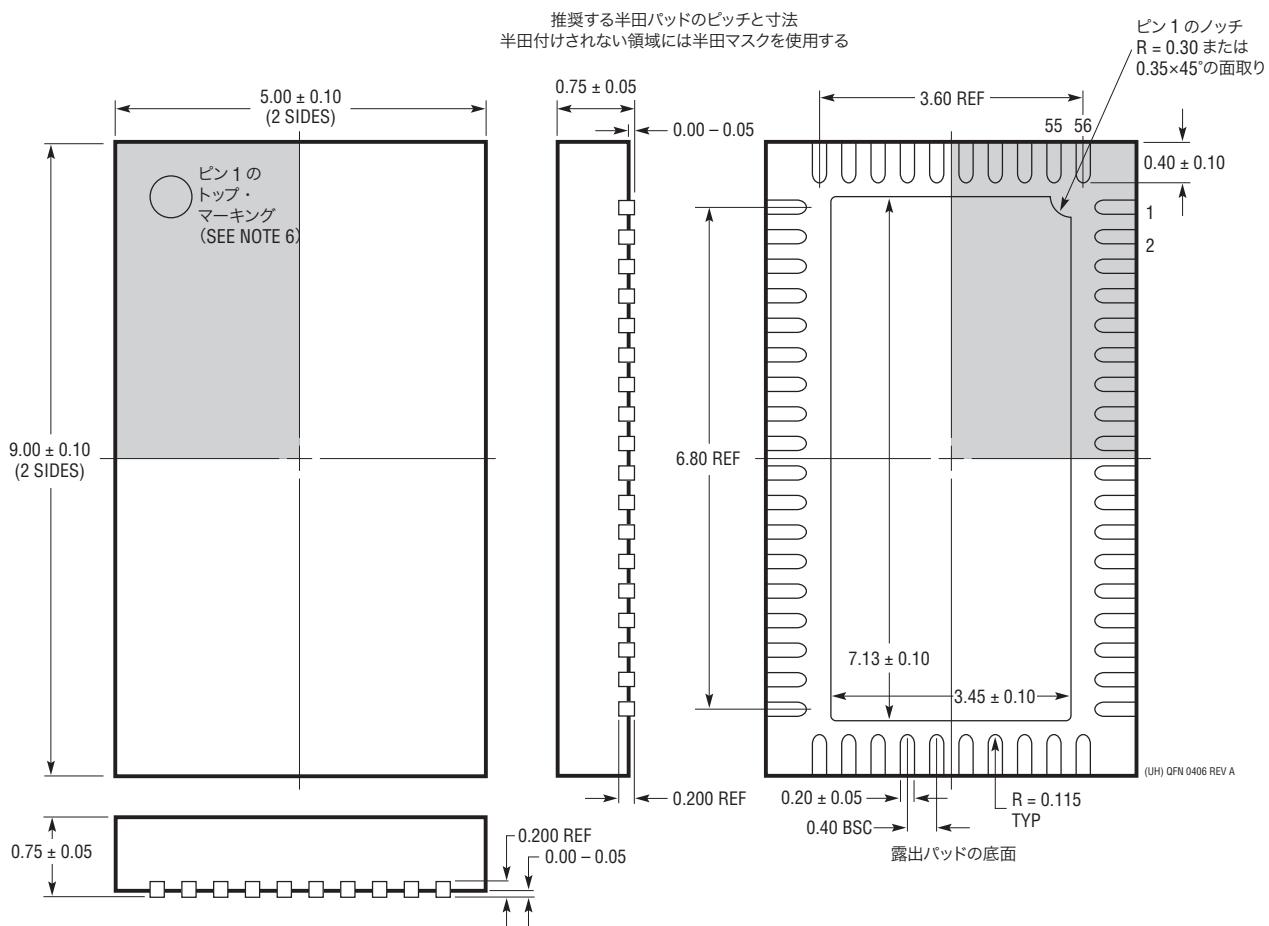

## パッケージ寸法

**UHHパッケージ

56-ピン(5mm×9mm)プラスチックQFN**

(Reference LTC DWG # 05-08-1727 Rev A)

推奨する半田パッドのピッチと寸法

半田付けされない領域には半田マスクを使用する

## NOTE:

1. 図は JEDEC のパッケージ外形ではない

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない。

モールドのバリは(もしあれば)各サイドで 0.15mm を超えないこと

5. 露出パッドは半田めっきとする

6. 網掛けの部分はパッケージのトップとボトムのピン 1 の位置の参考に過ぎない

## 標準的応用例

単独のLT8500による48個のLEDストリング(バラスト抵抗付き)の( $V_{DD}$ レールからの)駆動

## 関連製品

| 製品番号               | 説明                                                                             | 注釈                                                                                                                                                   |

|--------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| LT3746             | 55V、1MHz、32チャネルのフル機能30mA降圧LEDドライバ                                              | $V_{IN(MIN)} = 6V$ 、 $V_{IN(MAX)} = 55V$ 、 $V_{OUT(MAX)} = 13V$ 、<br>調光 = 5,000:1 True Color PWM、 $I_{SD} < 1\mu A$ 、<br>5mm×9mm QFN-56 パッケージ        |

| LT3595/<br>LT3595A | 45V、2.5MHz、16チャネルのフル機能50mA昇圧LEDドライバ                                            | $V_{IN(MIN)} = 4.5V$ 、 $V_{IN(MAX)} = 45V$ 、 $V_{OUT(MAX)} = 45V$ 、<br>調光 = 5,000:1 True Color PWM、 $I_{SD} < 1\mu A$ 、<br>5mm×9mm QFN-56 パッケージ      |

| LT3754             | 60V、1MHz、16チャネルの50mA昇圧LEDドライバ<br>(True Color 3,000:1 の PWM 調光機能および2%の電流整合機能付き) | $V_{IN(MIN)} = 4.5V$ 、 $V_{IN(MAX)} = 40V$ 、 $V_{OUT(MAX)} = 60V$ 、<br>調光 = 3,000:1 True Color PWM、 $I_{SD} < 1\mu A$ 、<br>5mm×5mm QFN-32 パッケージ      |

| LT3598             | 44V、1.5A、2.5MHz、6チャネルの30mA昇圧LEDドライバ                                            | $V_{IN(MIN)} = 3V$ 、 $V_{IN(MAX)} = 30V(40V MAX)$ 、<br>$V_{OUT(MAX)} = 44V$ 、調光 = 1,000:1 True Color PWM、<br>$I_{SD} < 1\mu A$ 、4mm×4mm QFN-24 パッケージ |

| LT3599             | 44V、2A、2.5MHz、4チャネルの120mA昇圧LEDドライバ                                             | $V_{IN(MIN)} = 3V$ 、 $V_{IN(MAX)} = 30V(40V MAX)$ 、<br>$V_{OUT(MAX)} = 44V$ 、調光 = 1,000:1 True Color PWM、<br>$I_{SD} < 1\mu A$ 、4mm×4mm QFN-24 パッケージ |