静止電流9 $\mu$ Aの2A/70Vスイッチ、

PORおよびウォッチドッグ・タイマ付き

SEPIC/昇圧コンバータ

## 特長

- 広い入力電圧範囲: 約1V～60V(起動時は2.5V～32V)

- 低リップルのBurst Mode®動作

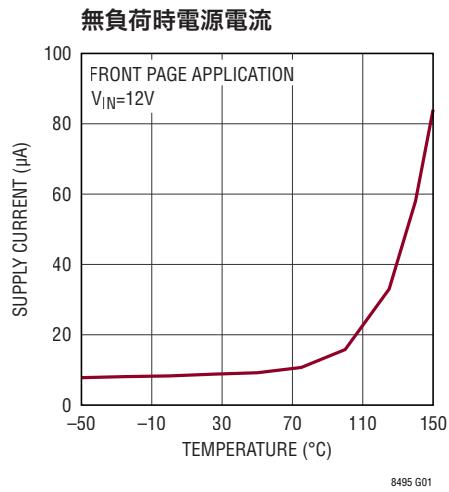

- 12V入力で5.0V出力時の $I_Q = 9\mu$ A

- 出力リップル(標準10mV未満)

- 2種類の電源ピン:

- 効率の向上

- 起動後の最小電源電圧を約1Vに低減してバッテリを長寿命化

- 2A/70Vのパワー・スイッチを内蔵

- $V_{IN}$ 電源を取り外した場合にプログラム可能なウォッチドッグ・タイマが動作可能

- プログラム可能なパワーオン・リセット(POR)タイマ(入力電源電圧が1.3Vまで低下しても $\overline{RST}$ が機能)

- TSSOPパッケージでのFMEAフォルト耐性あり

- 固定周波数のPWM、SEPIC/昇圧/フライバック構成

- プログラム可能なスイッチング周波数:

250kHz～1.5MHz

- SWENピンと $\overline{RSTIN}$ ピンでUVLOをプログラム可能

- 1個のコンデンサでソフトスタートをプログラム可能

- 20ピンTSSOPパッケージ

## アプリケーション

- 自動車のECU電源

- 携帯型製品の電源

- 産業用電源

## 概要

LT®8495は、パワーオン・リセットとウォッチドッグ・タイマを内蔵した可変周波数(250kHz～1.5MHz)のモノリシック・スイッチング・レギュレータです。動作時は静止電流を9 $\mu$ A未満にすることが可能であり、SWEN、WDE、および $\overline{RSTIN}$ が“L”的ときは約0.3 $\mu$ Aです。SEPIC、昇圧、またはフライバック・コンバータとして構成可能なので、低リップルのBurst Mode動作により、低出力電流時に高い効率を維持しつつ、出力リップルを10mV未満に維持できます。このデバイスは、2種類の電源ピン( $V_{IN}$ およびBIAS)により、自動的に最も効率の高い電源で動作することができます。入力電源電圧は、SEPIC構成では最大60V、昇圧構成とフライバック構成では最大32V(ライドスルー電圧は最大60V)にすることができます。起動後は、 $V_{IN}$ の電圧が2.5Vより低くなった場合でも、デバイスはその出力(BIAS)から電流を流すことができる所以、バッテリ寿命が長くなります。

リセットとウォッチドッグのタイムアウト期間は、外付けコンデンサを使用して別個に調整できます。SWENピンに抵抗分割器を使用することにより、プログラム可能な低電圧ロックアウト(UVLO)をコンバータに対して実現します。 $\overline{RSTIN}$ に抵抗分割器を接続することにより、 $\overline{RST}$ ピンをアサートするUVLO制御を行います。

この他に、周波数フォールドバックやソフトスタートなどの機能も内蔵しています。TSSOPでのフォルト耐性により、出力電圧がその設定値を超えて上昇することなく、隣接ピンの短絡または開放が可能です。LT8495は、熱抵抗を低く抑えるための露出パッドを備えた20ピンTSSOPパッケージで供給されます。

LT、LT、LTC、LTM、Linear Technology、LinearのロゴおよびBurst Modeはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

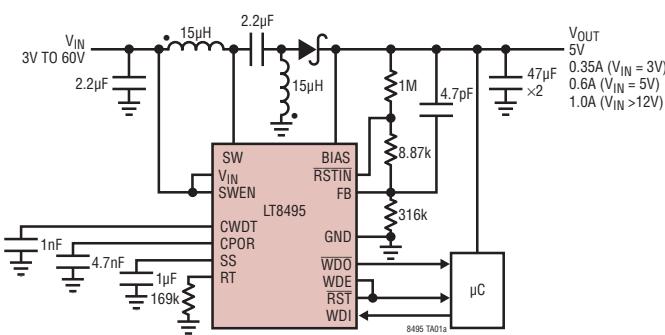

## 標準的応用例

450kHz、5V出力SEPICコンバータ

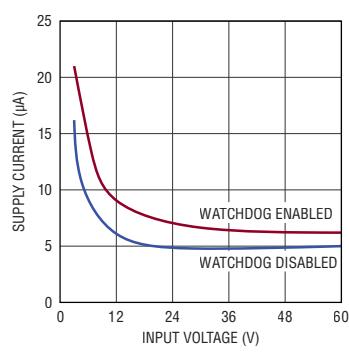

無負荷時電源電流

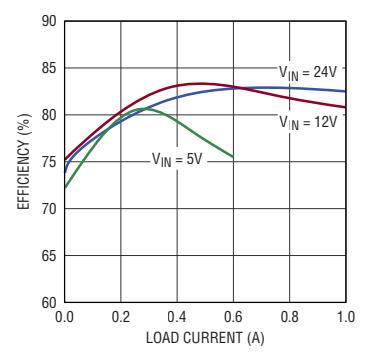

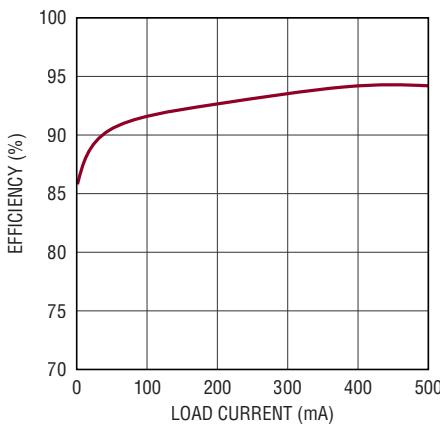

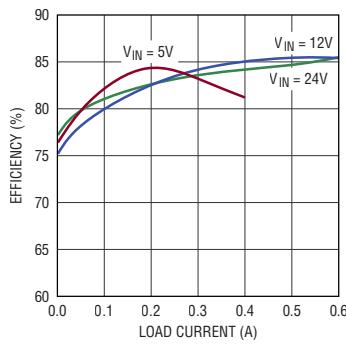

効率

# LT8495

## 絶対最大定格

### (Note 1)

|                            |               |

|----------------------------|---------------|

| V <sub>IN</sub> 、BIASの電圧   | 60V           |

| SWEN、WDE、RSTINの電圧          | 60V           |

| FBの電圧                      | 60V           |

| SWの電圧                      | 70V           |

| WDI、RST、WDOの電圧             | 6V            |

| RTの電圧                      | 6V            |

| CPOR、CWDT、SSの電圧            | 3V            |

| 動作接合部温度範囲                  |               |

| LT8495E、LT8495I (Note 2、3) | -40°C ~ 125°C |

| 保存温度範囲                     | -65°C ~ 150°C |

| リード温度(半田付け、10秒)            |               |

| FEパッケージ                    | 300°C         |

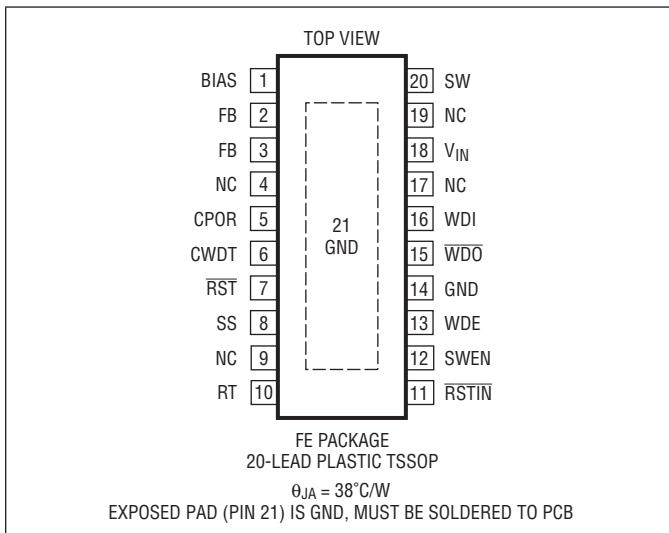

## ピン配置

## 発注情報

| 無鉛仕上げ         | テープアンドリール       | 製品マーキング  | パッケージ                 | 温度範囲           |

|---------------|-----------------|----------|-----------------------|----------------|

| LT8495EFE#PBF | LT8495EFE#TRPBF | LT8495FE | 20-Lead Plastic TSSOP | -40°C to 125°C |

| LT8495IFE#PBF | LT8495IFE#TRPBF | LT8495FE | 20-Lead Plastic TSSOP | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/>をご覧ください。

## 電気的特性

●は全動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、 $V_{IN} = V_{SWEN} = 12\text{V}$ 、 $V_{BIAS} = V_{WDE} = 5\text{V}$ (Note 2)。

| PARAMETER                                                           | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                               |             | MIN                  | TYP                               | MAX                              | UNITS          |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|-----------------------------------|----------------------------------|----------------|

| Minimum $V_{IN}$ Operating Voltages                                 | $V_{BIAS} < 2.5\text{V}$<br>$V_{BIAS} \geq 2.5\text{V}$                                                                                                                                                                                                                                                                                                                                                                                  | ●<br>●      |                      | 2.4                               | 2.5                              | V              |

| Minimum BIAS Operating Voltages                                     | $V_{IN} < 2.5\text{V}$<br>$V_{IN} \geq 2.5\text{V}$                                                                                                                                                                                                                                                                                                                                                                                      | ●<br>●      |                      | 2.4                               | 2.5                              | V              |

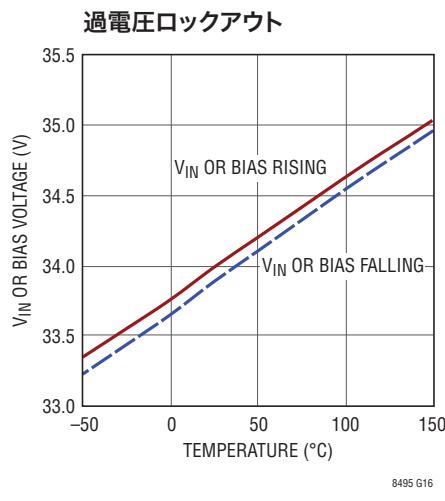

| Power Switch Driver (PSD) Overvoltage Threshold (Note 4)            | $V_{IN}$ or BIAS Rising<br>$V_{IN}$ or BIAS Falling                                                                                                                                                                                                                                                                                                                                                                                      | ●<br>●      | 32.1<br>32           | 34<br>33.9                        | 36.5<br>36.4                     | V              |

| Power Switch Driver (PSD) Overvoltage Threshold Hysteresis (Note 4) |                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |                      | 100                               |                                  | mV             |

| Quiescent Current from $V_{IN}$                                     | $V_{SWEN} = 0\text{V}$ , $V_{WDE} = 0\text{V}$ , $V_{RSTIN} = 0\text{V}$<br>$V_{SWEN} = 5\text{V}$ , $V_{WDE} = 0\text{V}$ , $V_{FB} = V_{RSTIN} = 1.25\text{V}$<br>$V_{SWEN} = 5\text{V}$ , $V_{WDE} = 5\text{V}$ , $V_{FB} = V_{RSTIN} = 1.25\text{V}$<br>$V_{SWEN} = 5\text{V}$ , $V_{WDE} = 0\text{V}$ , $V_{FB} = V_{RSTIN} = 1.25\text{V}$<br>$V_{SWEN} = 5\text{V}$ , $V_{WDE} = 5\text{V}$ , $V_{FB} = V_{RSTIN} = 1.25\text{V}$ | ●<br>●      |                      | 0.3<br>3.0<br>3.1<br>3.0<br>3.1   | 0.9<br>4.8<br>4.9<br>6.2<br>6.3  | $\mu\text{A}$  |

| Quiescent Current from BIAS                                         | $V_{SWEN} = 0\text{V}$ , $V_{WDE} = 0\text{V}$ , $V_{RSTIN} = 0\text{V}$<br>$V_{SWEN} = 5\text{V}$ , $V_{WDE} = 0\text{V}$ , $V_{FB} = V_{RSTIN} = 1.25\text{V}$<br>$V_{SWEN} = 5\text{V}$ , $V_{WDE} = 5\text{V}$ , $V_{FB} = V_{RSTIN} = 1.25\text{V}$<br>$V_{SWEN} = 5\text{V}$ , $V_{WDE} = 0\text{V}$ , $V_{FB} = V_{RSTIN} = 1.25\text{V}$<br>$V_{SWEN} = 5\text{V}$ , $V_{WDE} = 5\text{V}$ , $V_{FB} = V_{RSTIN} = 1.25\text{V}$ |             |                      | 0.07<br>1.7<br>6.00<br>1.7<br>6.0 | 0.5<br>2.8<br>8.5<br>4.0<br>10.0 | $\mu\text{A}$  |

| BIAS to $V_{IN}$ Comparator Threshold                               | $V_{BIAS}-V_{IN}$ , BIAS Rising, $V_{IN} = 12\text{V}$<br>$V_{BIAS}-V_{IN}$ , BIAS Falling, $V_{IN} = 12\text{V}$<br>Hysteresis (Rising-Falling Threshold)                                                                                                                                                                                                                                                                               | ●<br>●<br>● | 0.55<br>0.17<br>0.20 | 0.90<br>0.37<br>0.53              | 1.2<br>0.57<br>0.80              | V              |

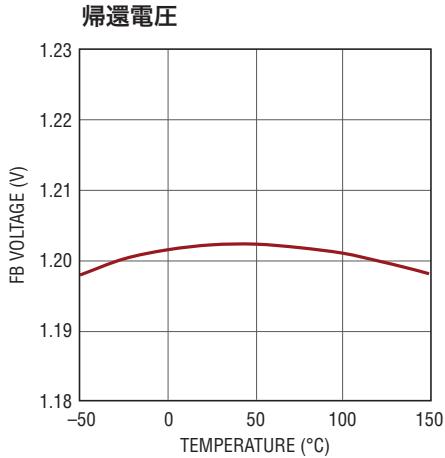

| Feedback Voltage                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                          | ●           | 1.178                | 1.202                             | 1.230                            | V              |

| FB Pin Bias Current (Note 7)                                        | $V_{FB} = 1.202\text{V}$                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                      | 0.1                               | 20                               | nA             |

| FB Voltage Line Regulation                                          | $5\text{V} \leq V_{IN} \leq 32\text{V}$ , $V_{BIAS} = 5\text{V}$<br>$5\text{V} \leq V_{IN} \leq 32\text{V}$ , $V_{BIAS} = 0\text{V}$                                                                                                                                                                                                                                                                                                     |             |                      | 0.2<br>0.2                        | 10<br>10                         | m%/V<br>m%/V   |

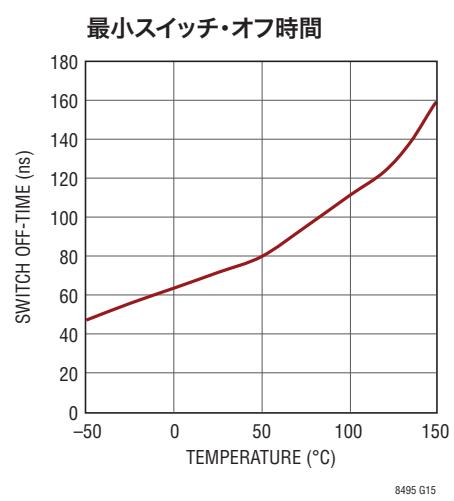

| Minimum Switch Off-Time                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |                      | 70                                |                                  | ns             |

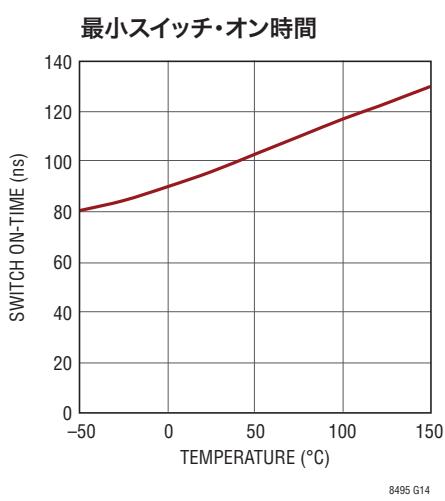

| Minimum Switch On-Time                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |                      | 95                                |                                  | ns             |

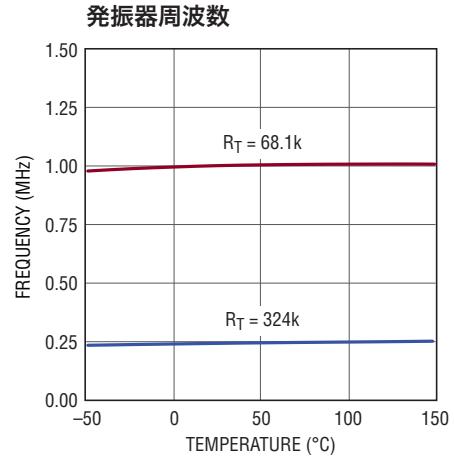

| Switching Frequency                                                 | $R_T = 68.1\text{k}$<br>$R_T = 324\text{k}$                                                                                                                                                                                                                                                                                                                                                                                              | ●<br>●      | 0.92<br>219          | 1.0<br>250                        | 1.06<br>280                      | MHz<br>kHz     |

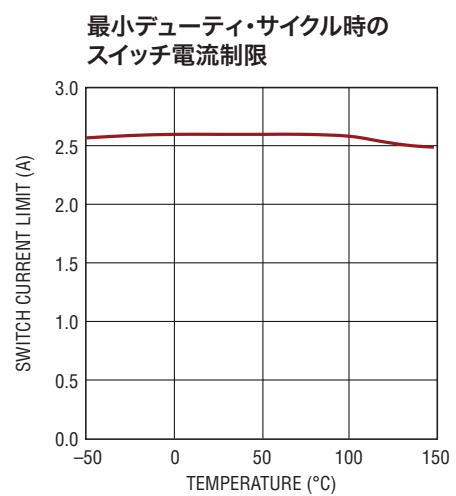

| Switch Current Limit at Min. Duty Cycle (Note 5)                    |                                                                                                                                                                                                                                                                                                                                                                                                                                          | ●           | 2.1                  | 2.55                              | 2.95                             | A              |

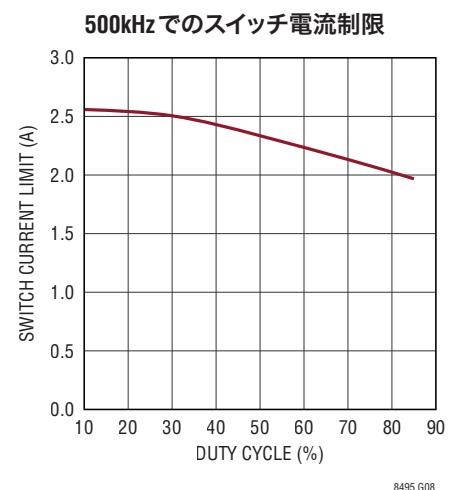

| Switch Current Limit at Max. Duty Cycle (Note 6)                    |                                                                                                                                                                                                                                                                                                                                                                                                                                          | ●           | 1.3                  | 1.85                              | 2.4                              | A              |

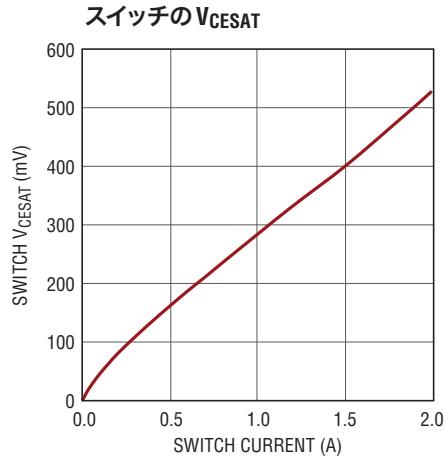

| Switch $V_{CESAT}$                                                  | $I_{SW} = 1.2\text{A}$                                                                                                                                                                                                                                                                                                                                                                                                                   |             |                      | 340                               |                                  | mV             |

| Switch Leakage Current (Note 7)                                     | $V_{SW} = 12\text{V}$ , $V_{SWEN} = 0\text{V}$                                                                                                                                                                                                                                                                                                                                                                                           |             |                      | 0.01                              | 1                                | $\mu\text{A}$  |

| Soft-Start Charging Current (Note 7)                                | $V_{SS} = 100\text{mV}$                                                                                                                                                                                                                                                                                                                                                                                                                  | ●           | 5.2                  | 8.2                               | 12.2                             | $\mu\text{A}$  |

| SWEN Pin Current (Note 7)                                           | $V_{SWEN} = 1.2\text{V}$<br>$V_{SWEN} = 5\text{V}$<br>$V_{SWEN} = 12\text{V}$                                                                                                                                                                                                                                                                                                                                                            |             |                      | 0<br>35<br>240                    | 25<br>200<br>550                 | nA<br>nA<br>nA |

| SWEN Rising Voltage Threshold                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                          | ●           | 0.9                  | 1                                 | 1.1                              | V              |

| SWEN Voltage Hysteresis                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |                      | 30                                |                                  | mV             |

| RSTIN Pin Current (Note 7)                                          | $V_{RSTIN} = 1.2\text{V}$<br>$V_{RSTIN} = 5\text{V}$<br>$V_{RSTIN} = 12\text{V}$                                                                                                                                                                                                                                                                                                                                                         |             |                      | 0<br>35<br>240                    | 25<br>200<br>550                 | nA<br>nA<br>nA |

| RSTIN Threshold as % of $V_{FB}$ Regulation Voltage                 |                                                                                                                                                                                                                                                                                                                                                                                                                                          | ●           | 86                   | 92                                | 97                               | %              |

| RSTIN Low to RST Asserted ( $t_{UV}$ )                              | Step $V_{RSTIN}$ from $1.3\text{V}$ to $0.9\text{V}$                                                                                                                                                                                                                                                                                                                                                                                     | ●           | 8                    | 23                                | 60                               | $\mu\text{s}$  |

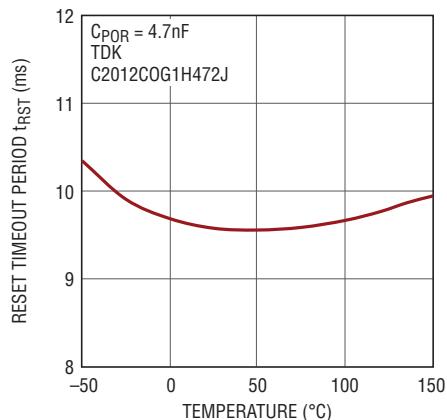

| Watchdog Timeout and Reset Delay Period ( $t_{RST}$ )               | $C_{POR} = 4700\text{pF}$ , Watchdog Timeout Not Occurring at Same Time as the Reset Delay                                                                                                                                                                                                                                                                                                                                               | ●           | 8.5                  | 9.5                               | 11.85                            | ms             |

## 電気的特性

●は全動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。

注記がない限り、 $V_{IN} = V_{SWEN} = 12\text{V}$ 、 $V_{BIAS} = V_{WDE} = 5\text{V}$ (Note 2)。

| PARAMETER                                      | CONDITIONS                                                                                                                                                                       |             | MIN            | TYP               | MAX              | UNITS         |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|-------------------|------------------|---------------|

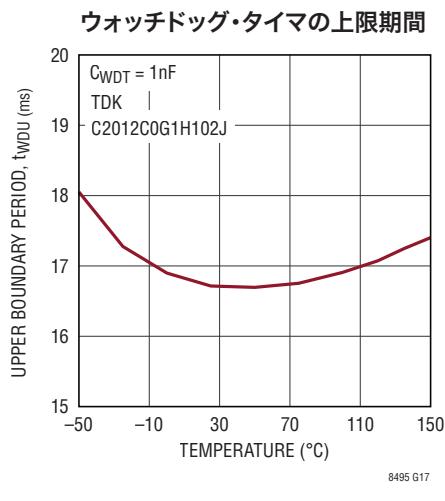

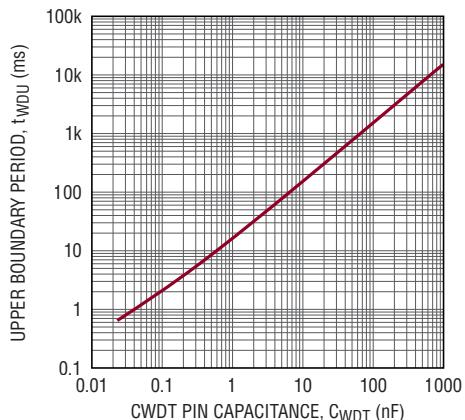

| Watchdog Upper Boundary ( $t_{WDU}$ ) (Note 8) | $C_{WDT} = 1000\text{pF}$                                                                                                                                                        | ●           | 14.9           | 16.7              | 20.9             | ms            |

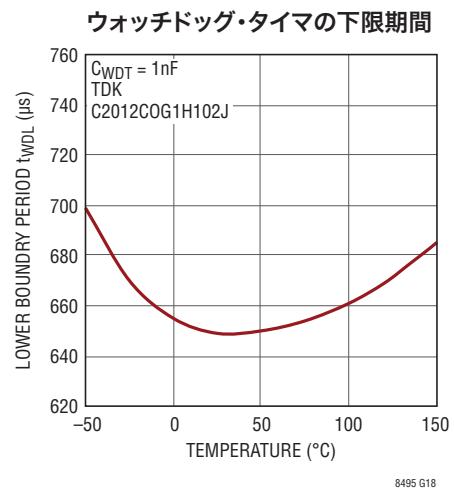

| Watchdog Lower Boundary ( $t_{WDL}$ ) (Note 8) | $C_{WDT} = 1000\text{pF}$                                                                                                                                                        | ●           | 580            | 650               | 812              | $\mu\text{s}$ |

| RST Output Voltage Low                         | $I_{SINK} = 1.25\text{mA}$<br>$I_{SINK} = 100\mu\text{A}, V_{BIAS} = 1.3\text{V}, V_{IN} = 0\text{V}$<br>$I_{SINK} = 100\mu\text{A}, V_{IN} = 1.3\text{V}, V_{BIAS} = 0\text{V}$ | ●<br>●<br>● | 33<br>15<br>15 | 150<br>150<br>150 | mV               | mV            |

| RST Leakage Current                            | $V_{RSTIN} = 1.2\text{V}, V_{RST} = 5\text{V}$                                                                                                                                   | ●           | 0              | 0.3               | 0.3              | $\mu\text{A}$ |

| WD0 Output Voltage Low                         | $I_{SINK} = 1.25\text{mA}$                                                                                                                                                       | ●           | 120            | 420               | 420              | mV            |

| WD0 Leakage Current                            | $V_{WD0} = 5\text{V}$                                                                                                                                                            | ●           | 0              | 0.25              | 0.25             | $\mu\text{A}$ |

| WDI Pin Current                                | $V_{WDI} = 5\text{V}$                                                                                                                                                            |             | 0              | 0.1               | 0.1              | $\mu\text{A}$ |

| WDI Input Rising Threshold                     |                                                                                                                                                                                  | ●           | 0.4            | 0.8               | 1.25             | V             |

| WDI Voltage Hysteresis                         |                                                                                                                                                                                  |             |                | 58                | 58               | mV            |

| WDI Input Pulse Width                          |                                                                                                                                                                                  | ●           | 300            |                   |                  | ns            |

| WDE Pin Current (Note 7)                       | $V_{WDE} = 1.2\text{V}$<br>$V_{WDE} = 5\text{V}$<br>$V_{WDE} = 12\text{V}$                                                                                                       |             | 0<br>35<br>240 | 25<br>200<br>550  | 25<br>200<br>550 | nA            |

| WDE Rising Voltage Threshold                   |                                                                                                                                                                                  | ●           | 0.9            | 1                 | 1.1              | V             |

| WDE Voltage Hysteresis                         |                                                                                                                                                                                  |             |                | 30                | 30               | mV            |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。注記がない限り、電圧値はGNDピンを基準にしている。

**Note 2:** LT8495Eは、 $0^\circ\text{C} \sim 125^\circ\text{C}$ の接合部温度で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT8495Iは、 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の接合部温度で性能仕様に適合することが保証されている。

**Note 3:** このデバイスには、短時間の過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。過熱保護がアクティブなとき、接合部温度は最大動作範囲を超える。規定された最大動作接合部温度を超えた状態で動作が継続すると、デバイスの信頼性を損なう恐れがある。

**Note 4:** 詳細については、「アプリケーション情報」セクションの「電源および動作リミット」を参照してください。

**Note 5:** 設計か、静的テストとの相関によって保証されている電流制限値。高いデューティ・サイクルではスロープ補償により電流制限値が低下する。

**Note 6:** 最大デューティサイクルでの電流制限値は1MHzのスイッチング周波数で測定されている。

**Note 7:** すべての電流の極性の基準はピンに流れ込む方向を正とする。注記がない限り、すべての電圧はグランドを基準にしている。

**Note 8:** この仕様は条件に掲げられているとおりの容量値に対してだけ保証されています。掲げられているとおりの値からの容量値の変化は、それに比例した変化を $t_{RST}$ 、 $t_{WDU}$ および $t_{WDL}$ に生じます。

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

# LT8495

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

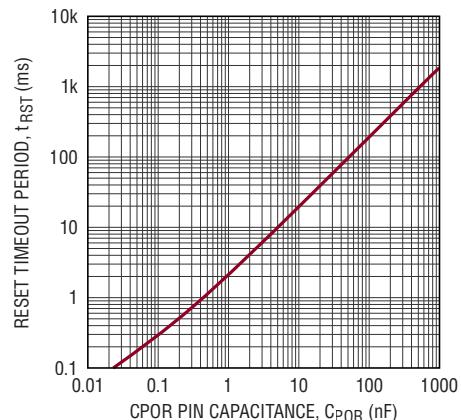

リセット・タイムアウト期間

8495 G19

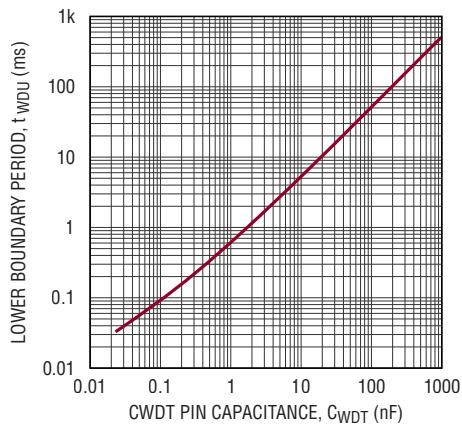

ウォッチドッグ・タイマの上限期間と容量

8495 G20

リセット・タイムアウト期間と容量

8495 G21

ウォッチドッグ・タイマの下限期間と容量

8495 G22

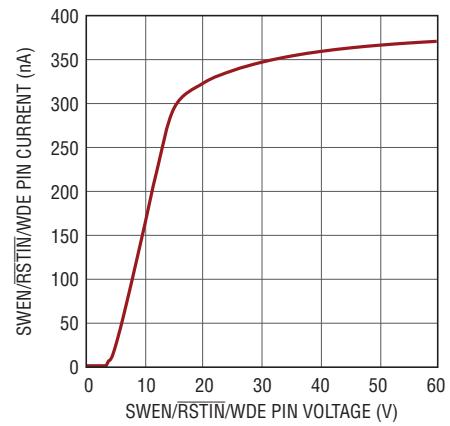

SWEN/RSTIN/WDE ピンの電流

8495 G23

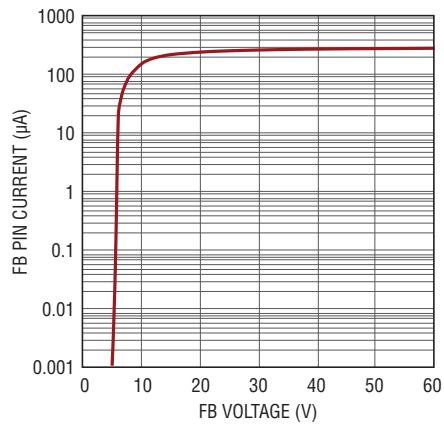

FB ピンの電流

8495 G24

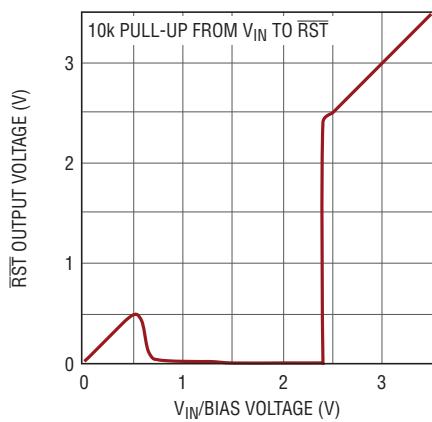

RST 出力電圧と電源電圧

8495 G25

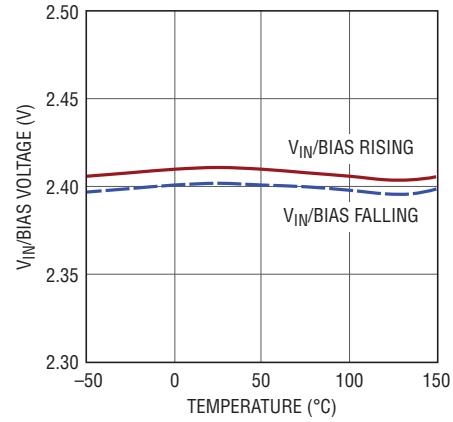

内部UVLO

8495 G26

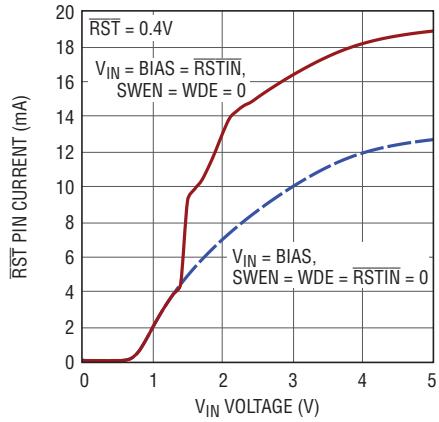

RST ピンの電流と電源電圧

8495 G27

## ピン機能 (TSSOP)

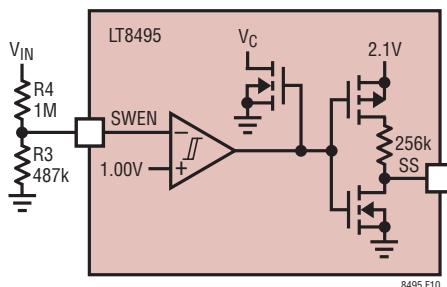

**SS(ピン8)**: ソフトスタート・ピン。ソフトスタート・コンデンサをこのピンに接続します。起動すると、SSピンは(公称) 256k $\Omega$ の抵抗を介して約2.1Vに充電されます。

**RT(ピン10)**: 発振器周波数の設定ピン。このピンとグランドの間に抵抗を接続して、内部発振器周波数を設定します。このピンの容量は最小限に抑えてください。詳細については、「アプリケーション情報」のセクションを参照してください。

**GND(ピン14、露出パッド・ピン21)**: グランド。すべてのピンと露出パッドを、ローカル・グランド・プレーンに直接半田付けします。パッケージの露出した金属パッドにより、グランドへの電気的接触とプリント回路基板への十分な熱的接触の両方が実現されます。

**NC(ピン4、9、17、19)**: 接続なし。これらのピンは内部回路には接続されておらず、フォルト耐性を持たすためにフロートさせたままにする必要があります。

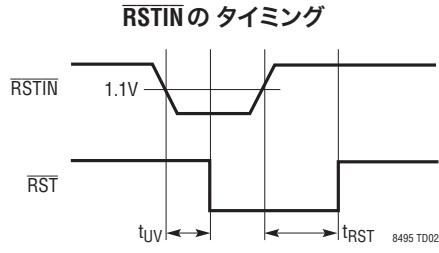

**RSTIN(ピン11)**: リセットの入力リファレンス。RSTINピンに抵抗分割器を接続して、RSTをアサートするためのしきい値電圧を設定します。RSTINの電圧は1.1Vの内部リファレンスと比較されます。RSTINの電圧がリファレンス電圧より低いと、RSTが“L”にアサートされます。

**SWEN(ピン12)**: スイッチ・イネーブル検出ピン。このピンは、スイッチング・レギュレータとソフトスタートをイネーブル/ディスエーブルします。SWENピンに抵抗分割器を接続することで、低電圧ロックアウトを実行することができます。

**WDE(ピン13)**: ウオッチドッグ・タイマのイネーブル・ピン。このピンの電圧を1.1Vより高くして、ウォッチドッグ・タイマ機能をイネーブルします。WDEが“L”的ときはWDO出力ドライバがディスエーブルされて、WDOピンはハイ・インピーダンスになります。

**WDO(ピン15)**: ウォッチドッグ出力。アクティブ“L”的オープンドレイン出力。WDEがイネーブルされていて、マイクロコントローラが適切な信号でLT8495のWDIピンを駆動するのに失敗すると、WDOは“L”にアサートされます。

**WDI(ピン16)**: ウオッチドッグ・タイマの入力ピン。このピンはマイクロコントローラからウォッチドッグ信号を受け取ります。適切な信号が受け取られないと、リセット遅延タイマ期間( $t_{RST}$ )に等しい時間WDOに“L”的パルスが発生します。

**V<sub>IN</sub>(ピン18)**: 電源入力ピン。このピンは通常、DC/DCコンバータの入力に接続します。ローカルにバイパスする必要があります。

**SW(ピン20)**: スイッチ・ピン。これは、内部のNPNパワー・スイッチのコレクタです。このピンに接続されるトレースの面積を小さくしてEMIを最小限に抑えます。

**BIAS(ピン1)**: 電源入力ピン。V<sub>IN</sub>がV<sub>OUT</sub>より高くなる可能性がある場合には、このピンは通常DC/DCコンバータの出力に接続されます。ローカルにバイパスする必要があります。

**FB(ピン2、3)**: 出力電圧帰還ピン。LT8495はFBピンの電圧を1.202Vに安定化します。出力、FBおよびGNDの間に抵抗分割器を接続して安定化出力電圧を設定します。

**CPOR(ピン5)**: WDOおよびRSTのアクティブ遅延期間の設定ピン。外付けコンデンサ(CPOR)をGNDに接続して、この期間( $t_{RST}$ )を設定します。詳細については「アプリケーション情報」のセクションを参照してください。

**CWDT(ピン6)**: ウォッチドッグ・タイマのプログラミング・ピン。このピンとグランドの間にコンデンサ(CWDT)を接続して、ウォッチドッグ・タイマの上限期間( $t_{WDU}$ )と下限期間( $t_{WDL}$ )を調節します。詳細については「アプリケーション情報」のセクションを参照してください。

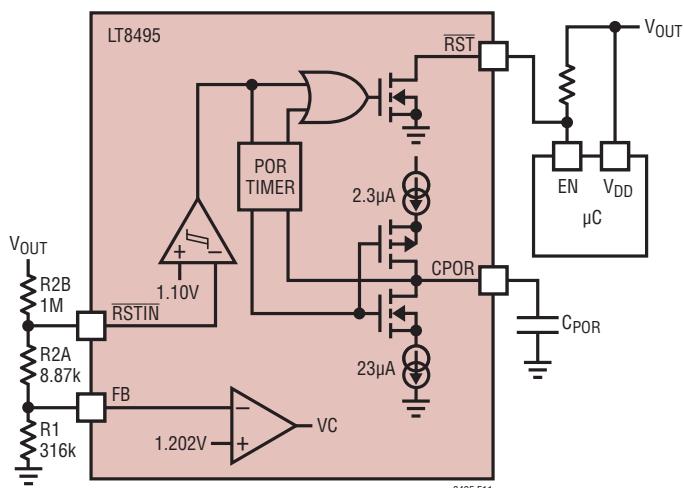

**RST(ピン7)**: アクティブ“L”的オープンドレイン・リセット。RSTINが約1.1Vより低いと、RSTは“L”にアサートされます(「電気的特性」を参照)。RSTINの電圧が上昇した後、CPORピンに接続したコンデンサで設定した期間( $t_{RST}$ )、RSTは“L”にアサートされたままになります。

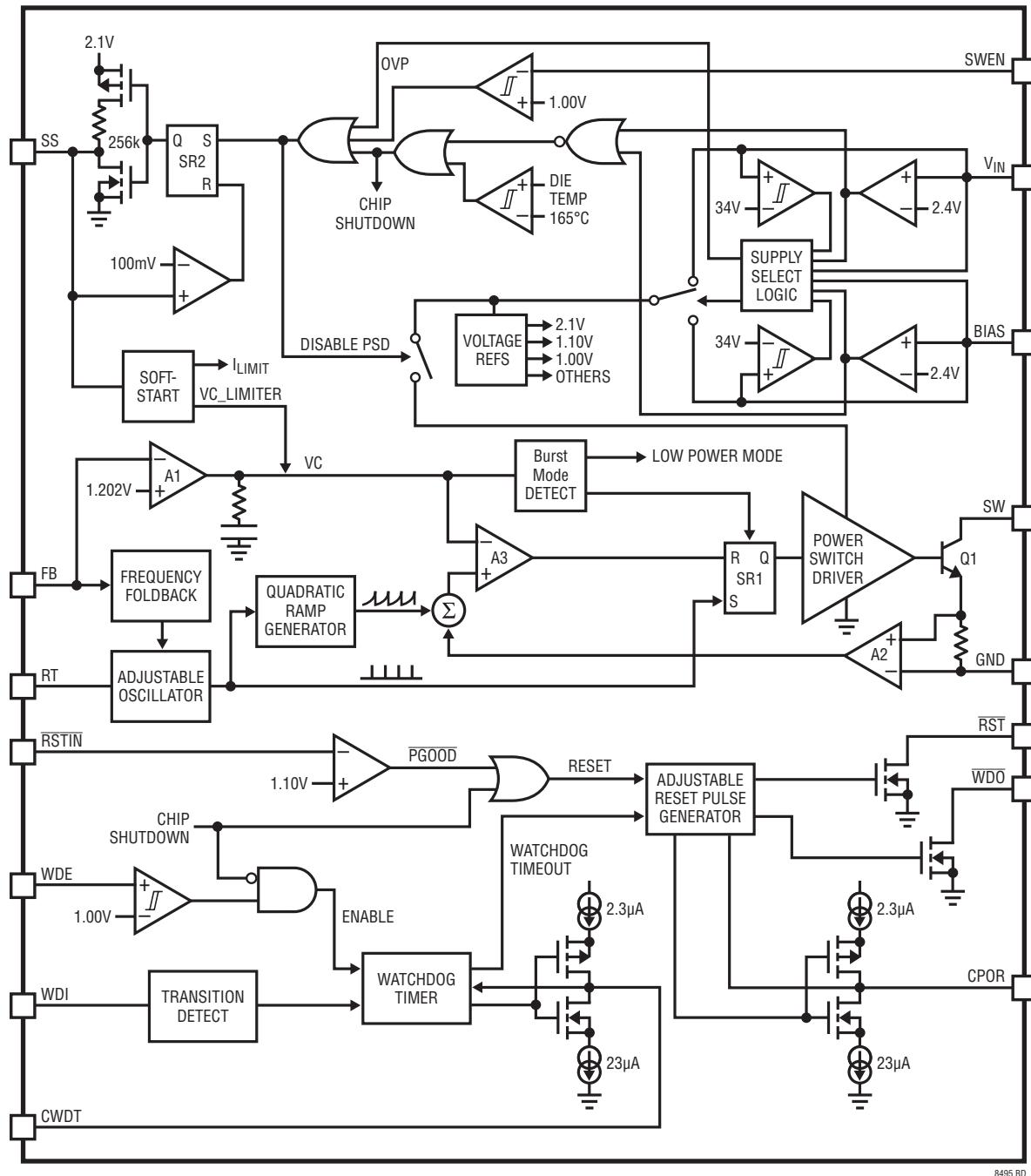

## ブロック図

8495 BD

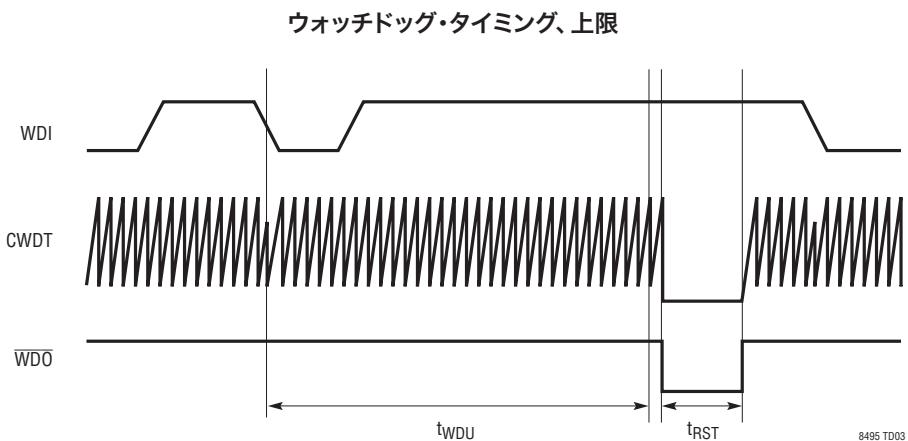

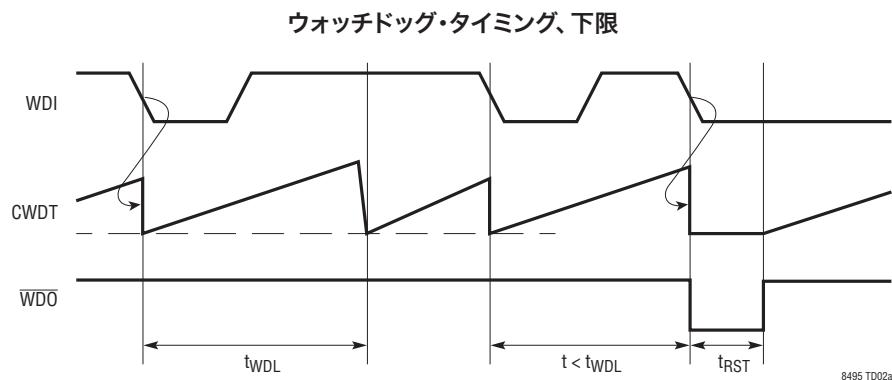

## タイミング図

$t_{STARTUP}$  = TIME REQUIRED TO START UP THE CHIP, APPROXIMATELY 1ms

$t_{DW}$  = TIME REQUIRED TO START UP THE WATCHDOG OR POR TIMER, APPROXIMATELY 200 $\mu$ s

$t_{UV}$  = TIME REQUIRED TO ASSERT RST LOW AFTER RSTIN GOES BELOW ITS THRESHOLD, APPROXIMATELY 23 $\mu$ s

$t_{RST}$  = PROGRAMMED RESET PERIOD

$t_{WDU}$  = WATCHDOG UPPER BOUNDARY PERIOD, APPROXIMATELY 31 RAMPING CYCLES ON CWDT PIN

$t_{WDL}$  = WATCHDOG LOWER BOUNDARY PERIOD, APPROXIMATELY 1 RAMPING CYCLE ON CWDT PIN

8495f

## 動作

LT8495は、パワーオン・リセットとウォッチドッグ・タイマを搭載した固定周波数、電流モードのSEPIC/昇圧/フライバック・レギュレータです。動作については「ブロック図」を参照してください。スイッチング・レギュレーション、ウォッチドッグ・タイマ、およびリセット検出の各機能はそれぞれSWENピン、WDEピンおよびRSTINピンによって制御されます。これらの3つのピンがすべて接地されると、デバイスはシャットダウンし、VINとBIASの電源からは微小な電流が流れるだけです。これら3つのピンのいずれかがそのしきい値より高くなると、デバイスはオンします。

### スイッチング・レギュレータの動作

外付け $R_T$ 抵抗によって周波数が設定される可変発振器がRSラッチをイネーブルし、内部パワースイッチをオンします(ブロック図参照)。アンプとコンバレータは内部検出抵抗を流れるスイッチ電流をモニタし、この電流がVCの電圧によって決まるレベルに達するとスイッチをオフします。エラー・アンプはFBピンに接続された外付け抵抗分割器を介して出力電圧を測定することにより、VC電圧を調整します。エラー・アンプの出力電圧(VC)が上昇すると、出力に供給される電流が増加します。VC電圧が低下すると、供給される電流が減少します。VC電圧のアクティブ・クランプにより電流が制限されます。内部レギュレータが制御回路に電力を供給します。

効率を改善するため、NPNパワー・スイッチ・ドライバ(ブロック図参照)はVINとBIASのいずれか電源電圧の低いほうからNPNベース電流を供給します。ただし、いずれかのピンが2.4V(標準値)より低いか、34V(標準値)より高い場合は、パワー・スイッチはもう片方のピンから電流を引き込みます。両方の電源ピンが2.4Vより低いか、34Vより高い場合は、スイッチング動作が停止されます。

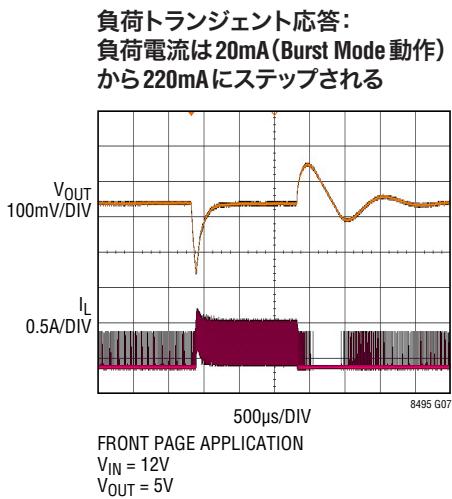

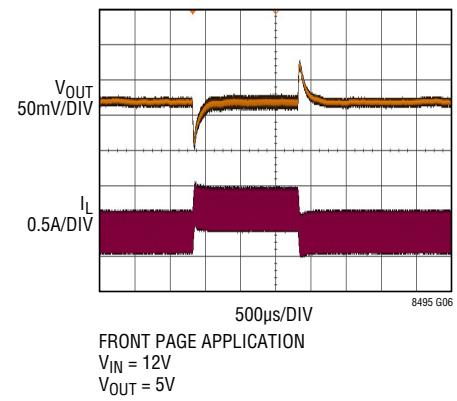

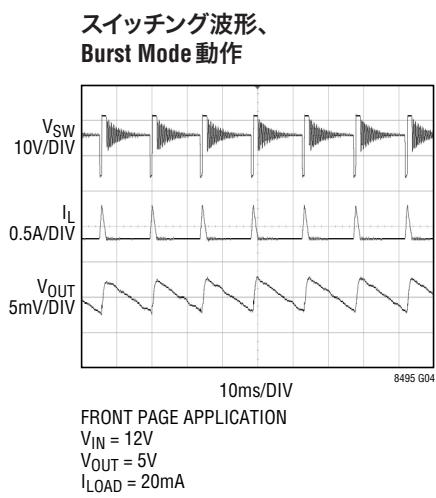

効率をさらに最適化するため、LT8495は軽負荷状態では自動的にBurst Mode動作になります。バーストとバーストの間は、出力スイッチの制御に関連したすべての回路がシャットダウンし、VIN/BIASピンの電源電流は標準で $3\mu A \sim 6\mu A$ 未満に減少します(「電気的特性」表を参照)。

### 起動動作

LT8495の非常にクリーンな起動を可能にするため、いくつかの機能が備わっています。

- 最初に、内部電圧リファレンスによりSWENピンの電圧がモニタされ、精密なターンオンしきい値が与えられます。入

力電源とSWENピンの間に外付け抵抗分割器を接続して、ユーザがプログラム可能な低電圧ロックアウト機能を与えることができます。

- 次に、ソフトスタート回路がスイッチ電流を徐々にランプアップさせます。デバイスがシャットダウン状態から回復すると、まず外付けSSコンデンサが放電します。次いで、256kの内部抵抗がSSピンを約2.1Vに引き上げます。外付けコンデンサをSSピンに接続することにより、このピンの電圧のランプ・レートを設定することができます。このソフトスタート・コンデンサの標準値は $100nF \sim 1\mu F$ の範囲です。

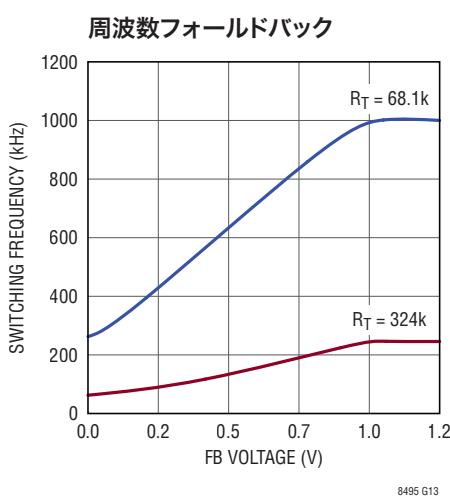

- 最後に、FBピンの電圧が1Vより低いと、周波数フォールドバック回路によって最大スイッチング周波数が下がります。この機能により、デバイスが実現できる最小デューティ・サイクルが減少するので、起動時のスイッチ電流の制御が向上します。

### パワーオン・リセットとウォッチドッグ・タイマの動作

LT8495はパワーオン・リセット(POR)回路とリセット・タイマを備えており、RSTピンを最小時間アサートします。最初にパワーアップすると、オープンドレインのRSTピンがプログラム可能リセット遅延時間の間“L”へアサートされます(タイミング図を参照)。通常動作の間、RSTINピンがそのしきい値を下回るか、またはデバイスが異常状態によってシャットダウン状態になるときも、RSTピンをアサートすることができます。デバイスがシャットダウン状態を抜け出し、RSTINピンがそのしきい値を上回ると、RSTピンは、CPORピンによってプログラム可能リセット遅延時間後リリースされます。

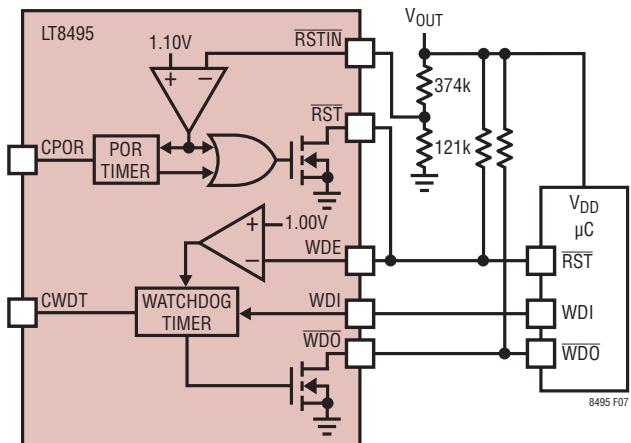

ウォッチドッグ・タイマは一般にマイクロコントローラの動作をモニタします。ウォッチドッグ・タイマは、ロジック信号をWDEピンに与えることによって、イネーブルまたはディスエーブルすることができます。イネーブルされているとき、ウォッチドッグ・タイマが、WD0に“L”的パルスが生じるのを防ぐには、WDIピンに継起する立ち下がりエッジがプログラムされた時間ウィンドウ内に生じることが必要です。したがって、WDIの2つの立ち下がりエッジの間の時間が短すぎると、または長すぎると、WD0ピンに“L”パルスが生じます。WD0ピンが“L”になると、CPORピンによってプログラムされた遅延だけリセット・タイマがWD0ピンを“L”に保ちます。リセット・タイマの時間が経過した後、またはデバイスがシャットダウンすると、WD0ピンは再度“H”になります(タイミング図を参照)。ウィンドウ期間はCWDWピンによって設定できます。

## アプリケーション情報

### 低リップル Burst Mode動作

軽負荷での効率を向上させるため、LT8495レギュレータは低リップルのBurst Mode動作になり、入力静止電流を最小限に抑えながら、出力コンデンサを適切な電圧に充電された状態に保ちます。Burst Mode動作の間、LT8495レギュレータは1サイクルのバーストで電流を出力コンデンサに供給し、それに続くスリープ期間には出力コンデンサから出力電力が負荷に供給されます。スリープ期間には、 $V_{IN}/BIAS$ の静止電流は標準で $3\mu A \sim 6\mu A$ 未満に減少します（「電気的特性」表を参照）。

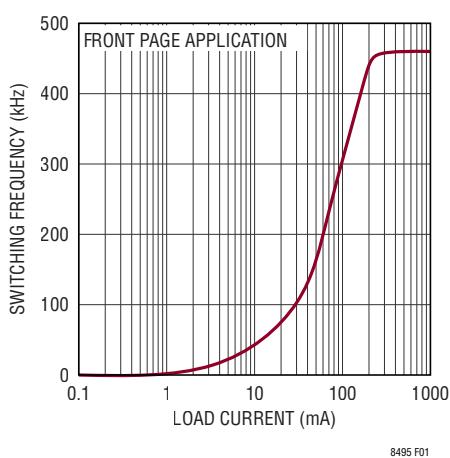

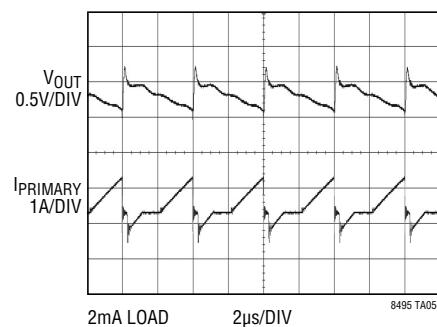

負荷電流が無負荷状態に向かって減少するにつれて、单一電流パルスの周波数が低下（図1参照）することで、LT8495がスリープ・モードで動作する時間の割合が増加し、平均入力電流が減少するので、非常に軽い負荷でも効率が高くなります。

パルスの間隔を最大にすることにより、LT8495の静止電流を最少に抑えます。したがって、軽負荷時の静止電流の性能を最適化するには、帰還抵抗分割器の電流と外付けダイオードの逆電流を最少にする必要があります。これらは負荷電流として出力に現れるからです。より正確に言えば、スリープ期間中、昇圧コンバータではダイオードの逆漏れ電流が出力から入力に流れ、SEPICコンバータでは漏れ電流が出力からグランドに流れます。超低静止電流性能を利用するアプリケーションでは、できるだけ大きな帰還抵抗と漏れ電流の少ないショットキ・ダイオードを使います。

図1. Burst Mode動作でのスイッチング周波数

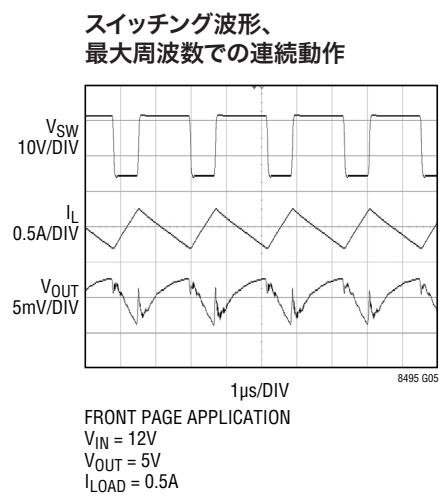

Burst Mode動作では、バースト周波数と各パルスで供給される電荷量が出力容量によって変化することはありません。したがって、出力電圧リップルは出力容量に反比例します。 $47\mu F$ の出力コンデンサを1個使用する標準的アプリケーションでは、出力リップルは約 $10mV$ 、 $47\mu F$ の出力コンデンサを2個使用する場合は出力リップルは約 $5mV$ です（「標準的性能特性」セクションの「スイッチング波形」と「Burst Mode動作」を参照）。出力容量を増やすことにより、出力電圧リップルをさらに減らすことができます。

高い出力負荷では、LT8495レギュレータは $R_T$ 抵抗で設定された周波数で動作し、標準的な電流モード・レギュレータとして動作します。大電流モードと低リップルBurst Mode動作の間の移行はシームレスで、出力電圧を乱しません。

### チップ・イネーブル・ピン

SWEN、WDEおよび $\overline{RSTIN}$ の各ピンはLT8495のいろいろな部分をイネーブルするのに使用されます。3つのピンが全て $0V$ のとき電流状態は最低になり、LT8495の全ての機能がディスエーブルされます。これらのピンのどれでもそれぞれの入力しきい値電圧（「電気的特性」のセクションを参照）より上にすると、LT8495のコア回路がアクティブになります。LT8495のコア回路を起動するには標準で約 $1ms$ を要します（タイミング図を参照）。SWEN、WDEおよび $\overline{RSTIN}$ の詳細に関しては、それぞれ「スイッチング・レギュレータのイネーブル」、「ウォッチドッグ・タイマ」、および「リセット条件」の各セクションを参照してください。

### スイッチング・レギュレータのイネーブル

スイッチング・レギュレータをイネーブルまたはディスエーブルするのにSWENピンが使われます。このピンはウォッチドッグ・イネーブル（WDE）ピン、 $\overline{RST}$ 制御入力（ $\overline{RSTIN}$ ）ピンとは無関係に動作します。SWENの上昇時しきい値は標準 $1V$ で、 $30mV$ のヒステリシスがあります。SWENピンをこのしきい値より低くすることによりスイッチング・レギュレータがディスエーブルされ、NPNパワー・スイッチが無効になります。SWENをしきい値より高くすることにより、スイッチング・レギュレータがイネーブルされます。アクティブなスイッチングを開始する前に、ソフトスタート・コンデンサが急速に放電され、次いでゆっくり充電されるので、レギュレータが徐々に起動します。「常時オン」の動作が必要な場合は、SWENを $V_{IN}$ に接続すること

## アプリケーション情報

ができますが、SWENピンに多少の電流が流れ込む(「標準的性能特性」参照)ので、システムの全体的なバイアス電流が増加します。また、抵抗分割器をSWENに接続することにより、低電圧ロックアウト機能を実装できます(詳細については、「低電圧ロックアウト」を参照)。

### 出力電圧の設定

出力電圧は、出力からFBピン(R2)、FBピンからグランド(R1)に接続された抵抗分割器で設定されます。次式に従って1%精度の抵抗を選択します。

$$R2 = R1 \left( \frac{V_{OUT}}{1.202} - 1 \right)$$

大きな抵抗を選択するほどアプリケーション回路の静止電流が減少することに注意してください。軽負荷アプリケーションでは、デバイスは低消費電流のBurst Mode動作になるので、大きな抵抗を選択することが不可欠です。

### パワー・スイッチのデューティ・サイクル

ループの安定性を維持し、適切な電流を負荷に供給するため、パワーNPN(「ブロック図」のQ1)は各クロック・サイクルの100%の間「オン」に留まることはできません。最大許容デューティ・サイクルは次式で与えられます。

$$DC_{MAX} = \frac{T_P - \text{Minimum Switch Off-Time}}{T_P} \cdot 100\%$$

ここで、 $T_P$ はクロック周期、(「電気的特性」に示されている)最小スイッチ・オフ時間は標準70nsです。

逆に、パワーNPN(「ブロック図」のQ1)は各クロック・サイクルの100%の間オフのままでいることはできず、レギュレーション状態では最小時間(最小スイッチ・オン時間)の間オンします。この最小スイッチ・オン時間により、次式で与えられる最小許容デューティ・サイクルが決まります。

$$DC_{MIN} = \frac{\text{Minimum Switch On-Time}}{T_P} \cdot 100\%$$

ここで、 $T_P$ はクロック周期、(「電気的特性」に示されている)スイッチの最小オン時間は標準95nsです。

動作デューティ・サイクル(DC)がDC<sub>MIN</sub>とDC<sub>MAX</sub>の間になるようにアプリケーションを設計します。通常、V<sub>OUT</sub>が高く、V<sub>IN</sub>が低いほど、DCは増加します。

昇圧構成とSEPIC構成のデューティ・サイクルの式を下に示します。ここで、V<sub>D</sub>はダイオードの順方向電圧降下、V<sub>CESAT</sub>は1.2Aで標準340mVです。

昇圧構成では次のようになります。

$$DC \equiv \frac{V_{OUT} - V_{IN} + V_D}{V_{OUT} + V_D - V_{CESAT}}$$

SEPIC構成では次のようになります。

$$DC \equiv \frac{V_{OUT} + V_D}{V_{IN} + V_{OUT} + V_D - V_{CESAT}}$$

LT8495はデューティ・サイクルがDC<sub>MAX</sub>より高い構成で使用することができますが、実効デューティ・サイクルが減少するよう、不連続導通モードまたはBurst Modeで動作させる必要があります。

### スイッチング周波数の設定

LT8495では、RTピンとグランドの間に接続した1本の抵抗を使用して250kHz～1.5MHzの範囲でスイッチングするよう設定できる固定周波数のPWMアーキテクチャが採用されています。さまざまなスイッチング周波数に対応する必要なR<sub>T</sub>の値を表1に示します。

表1. スイッチング周波数とR<sub>T</sub>の値

| スイッチング周波数(MHz) | R <sub>T</sub> の値(kΩ) |

|----------------|-----------------------|

| 0.25           | 324                   |

| 0.4            | 196                   |

| 0.6            | 124                   |

| 0.8            | 88.7                  |

| 1.0            | 68.1                  |

| 1.2            | 54.9                  |

| 1.4            | 45.3                  |

| 1.5            | 41.2                  |

## アプリケーション情報

### インダクタの選択

**一般的なガイドライン：**LT8495は高い周波数で動作するので小型の表面実装インダクタを使用できます。高効率を実現するには、フェライトなどの高周波用コア材のインダクタを選択して、コア損失を減らします。効率を改善するため、与えられたインダクタンスに対してサイズの大きなインダクタを選択します。 $I^2R$  損失を減らすため、インダクタはDCR（銅線抵抗）が小さく、飽和せずにピーク・インダクタ電流を流すことができるものにします。各インダクタが全スイッチ電流の一部分しか流さない、非結合インダクタを使用したときのSEPIC構成のようなアプリケーションでは、インダクタに要求される処理電流は大きくないことに注意してください。モールド型チョークやチップ・インダクタは、2A～3Aの範囲のピーク・インダクタ電流を担うには一般にコア面積が不十分です。放射ノイズを減らすには、トロイド型インダクタまたはシールドされたインダクタを使用します。シールド・タイプのインダクタンスは電流が増加するにつれて低下し、簡単に飽和するので注意してください。

**最小インダクタンス：**効率とのトレードオフになる可能性がありますが、多くの場合、小さなインダクタを選択して基板スペースを最小限に抑えることを推奨します。インダクタを選択するとき、最小インダクタンスを制限する2つの条件があります。(1) 適切な負荷電流の供給と、(2) 低調波発振の防止です。これらの要件の両方を満たすのに十分な大きさのインダクタンスを選択してください。

**適切な負荷電流：**インダクタの値を小さくするとリップル電流が増加するので、ピーク・スイッチ電流が制限されることにより、負荷( $I_{OUT}$ )に供給できる平均電流が減少します。適切な負荷電流を供給するため、Lは少なくとも次のようにします。

$$L > \frac{DC \cdot V_{IN}}{2(f) \left( I_{LIM} - \frac{V_{OUT} \cdot I_{OUT}}{V_{IN} \cdot \eta} \right)}$$

昇圧構成では上記のようになります。また、

$$L > \frac{DC \cdot V_{IN}}{2(f) \left( I_{LIM} - \frac{V_{OUT} \cdot I_{OUT}}{V_{IN} \cdot \eta} - I_{OUT} \right)}$$

SEPIC構成では、上記のようになります。

ここで、

$$L = L1||L2 \quad (\text{非結合インダクタを使用したSEPIC構成の場合})$$

$$DC = \text{スイッチのデューティ・サイクル} \quad (\text{前のセクションを参照})$$

$$I_{LIM} = \text{スイッチ電流制限、50% デューティ・サイクルで標準約 } 2.35A \quad (\text{「標準的性能特性」のセクションを参照})$$

$$\eta = \text{電力変換効率(高電流時、一般に昇圧構成では } 85\% \sim 90\%, \text{ SEPIC構成では } 80\% \sim 85\%)$$

$$f = \text{スイッチング周波数}$$

$L$ が負の値の場合、出力負荷電流  $I_{OUT}$  が LT8495 のスイッチ電流制限能力を超えていることを示しています。

**低調波発振の防止：**LT8495 の内部スロープ補償回路は、インダクタンスが最小値を超えていれば、デューティ・サイクルが 50% を超えると発生する可能性のある低調波発振を防止するのに役立ちます。50% を超えるデューティ・サイクルで動作するアプリケーションでは、インダクタンスは少なくとも次の値でなければなりません。

$$L > \frac{(V_{IN} - V_{CESAT}) \cdot (2DC - 1)}{0.76 \cdot (1.5 \cdot DC + 1) \cdot f \cdot (1 - DC)}$$

昇圧構成、および、結合されたインダクタを使用したSEPIC構成の場合は上記のようになります。または、

$$L1||L2 > \frac{(V_{IN} - V_{CESAT}) \cdot (2DC - 1)}{0.76 \cdot (1.5 \cdot DC + 1) \cdot f \cdot (1 - DC)}$$

非結合インダクタを使用したSEPIC構成の場合は上記のようになります。

**最大インダクタンス：**インダクタンスが大きすぎると、電流コンパレータ(「ブロック」図の A2)が容易に識別するのが困難なレベルにまでリップル電流が減少する可能性があります。これにより、デューティ・サイクルのジッタが生じたり、レギュレーションが不十分になったりします。最大インダクタンスは次式で計算することができます。

$$L_{MAX} = \frac{V_{IN} - V_{CESAT}}{I_{MIN(RIPPLE)}} \cdot \frac{DC}{f}$$

ここで、 $L_{MAX} = L1||L2$  (非結合インダクタを使用したSEPIC構成の場合)、 $I_{MIN(RIPPLE)} = 150mA$ (標準)です。

## アプリケーション情報

**電流定格:**最後に、効率の損失を招くインダクタの飽和を防ぐため、インダクタの定格はピーク動作電流より大きくする必要があります。

定常状態では、ピーク入力インダクタ電流と平均入力インダクタ電流(連続導通モードのみ)は次式で与えられます。

$$I_{L1(\text{PEAK})} = \frac{V_{\text{OUT}} \cdot I_{\text{OUT}}}{V_{\text{IN}} \cdot \eta} + \frac{V_{\text{IN}} \cdot \text{DC}}{2 \cdot L_1 \cdot f}$$

$$I_{L1(\text{AVG})} = \frac{V_{\text{OUT}} \cdot I_{\text{OUT}}}{V_{\text{IN}} \cdot \eta}$$

これは、昇圧構成、および、非結合インダクタを使用したSEPIC構成の場合です。

非結合インダクタを使用したSEPIC構成の場合、出力インダクタL2のピーク電流と平均電流は次式で与えられます。

$$I_{L2(\text{PEAK})} = I_{\text{OUT}} + \frac{V_{\text{OUT}} \cdot (1 - \text{DC})}{2 \cdot L_2 \cdot f}$$

$$I_{L2(\text{AVG})} = I_{\text{OUT}}$$

結合されたインダクタを使用したSEPIC構成の場合、次のようになります。

$$I_{L(\text{PEAK})} = I_{\text{OUT}} \cdot \left[ 1 + \frac{V_{\text{OUT}}}{V_{\text{IN}} \cdot \eta} \right] + \frac{V_{\text{IN}} \cdot \text{DC}}{2 \cdot L \cdot f}$$

$$I_{L(\text{AVG})} = I_{\text{OUT}} \cdot \left[ 1 + \frac{V_{\text{OUT}}}{V_{\text{IN}} \cdot \eta} \right]$$

注記: 負荷過渡時にインダクタ電流が大きくなる可能性があります。不適切なソフトスタート・コンデンサが使用されると、短絡時と起動時にもインダクタ電流が大きくなる可能性があります。したがって、 $I_L(\text{PEAK})$ は2.95Aのスイッチ電流制限値より大きくなることがあります。RMSインダクタ電流は $I_L(\text{AVG})$ にほぼ等しい値です。十分な飽和電流定格とRMS電流定格を持つインダクタを選んでください。

### コンデンサの選択

出力リップル電圧を最小限に抑えるため、出力には低ESR(等価直列抵抗)のコンデンサを使用します。積層セラミック・コンデンサはESRが非常に低く、小型パッケージのものが入手できるので最適です。X5RやX7Rの誘電体材料は広い電圧範囲と温度範囲にわたって容量を保持するので推奨されます。必ず電圧定格が十分大きなコンデンサを使用してください。定格が2.2μF～20μFのほとんどのコンデンサ(特に0805または0603のケース・サイズ)は望みの出力電圧で容量が大きく

減少します。固体タンタル・コンデンサまたはOS-CONコンデンサを使うこともできますが、セラミック・コンデンサよりも大きなボード面積を占め、ESRが大きくなり、出力リップルが増加します。

セラミック・コンデンサは入力デカップリング・コンデンサとして最適で、LT8495のV<sub>IN</sub>ピンとBIASピンにできるだけ近づけて配置します。ほとんどのアプリケーションでは2.2μF～4.7μFの入力コンデンサで十分です。

### 可聴ノイズ

セラミック・コンデンサは小さく堅牢で、ESRが非常に小さいコンデンサです。ただし、セラミック・コンデンサには圧電特性があるため、LT8495と併用したときに可聴ノイズを発生することがあります。Burst Mode動作のとき、LT8495レギュレータのスイッチング周波数は負荷電流に依存し、非常に軽い負荷ではレギュレータはセラミック・コンデンサを可聴周波数で励起し、可聴ノイズを発生することがあります。LT8495は、Burst Mode動作中は低い電流制限値で動作するため、ノイズは通常は非常に静かです。これが許容できない場合は、高性能のタンタル・コンデンサまたは電解コンデンサを出力に使用してください。

### ダイオードの選択

昇圧構成またはSEPIC構成で使用されるダイオードは、スイッチ・オフ時間中にのみ導通します。スイッチ・オン時間中は、ダイオードに逆電圧がかかります。ピーク逆電圧は、昇圧構成ではV<sub>OUT</sub>と等しく、SEPIC構成では(V<sub>OUT</sub>+V<sub>IN</sub>)と等しくなります。逆電圧定格がピーク逆電圧より大きいダイオードを使用してください。

さらに逆漏れ電流にも配慮が必要です。漏れ電流は負荷電流として出力に現れ、軽負荷条件では効率に顕著な影響を与えます。Burst Mode動作では、インダクタ電流が消滅した後、昇圧ダイオード両端の逆電圧は、昇圧構成ではほぼV<sub>OUT</sub>-V<sub>IN</sub>に等しく、SEPIC構成ではV<sub>OUT</sub>に等しくなります。ダイオードが逆バイアスされる時間の割合は負荷電流が減少するにつれ増加します。

多くの場合、ショットキ・ダイオードは順方向電圧が大きいほど漏れ電流が小さいので、軽負荷での効率と高負荷での効率の間にはトレードオフが生じます。また、逆バイアス定格が大きなショットキ・ダイオードはある特定の出力電圧での漏れ電流が小さいがあるので、ダイオードのサイズと引き換えに卓越したリーキ性能を実現することができます。

## アプリケーション情報

す。最後に、パワー・ショットキ・ダイオードの漏れ電流は、接合部温度とともに指数関数的に増加することにも注意してください。したがって、ショットキ・ダイオードは慎重に選択し、高温での軽負荷時電源電流の過度の増加を防ぐ必要があります。

### ソフトスタート

LT8495は起動時にピーク・スイッチ電流を制限するソフトスタート回路を内蔵しています。スイッチング・レギュレータでは、起動時にV<sub>OUT</sub>がその最終値から大きく外れているため帰還ループが飽和するので、本質的に起動電流が高くなります。レギュレータは出力コンデンサができるだけ速く充電しようとするので、大きなピーク電流が生じます。起動電流は外部コンデンサ(標準で100nF～1μF)をSSピンに接続することによって制限することができます。このコンデンサは、デバイスが起動されると、内部の256k抵抗によって約2.1Vにゆっくり充電されます。SSピンの電圧が約0.8Vより下では、内部電流制限が減少します。こうして、コンデンサが充電するにつれてSSの電圧が徐々にランプすると、電流制限も徐々に増加します。次いで、起動電流を制限しながら出力コンデンサをその最終値に向かって徐々に充電することができます。スイッチング・レギュレータがシャットダウンすると、ソフトスタート・コンデンサは充電が再開される前に自動的に約100mV以下に放電されるので、スイッチング・レギュレーションを再開するたびにソフトスタートが確実に実行されます。

### 電源および動作リミット

LT8495にはV<sub>IN</sub>ピンとBIASピンから電源電流が供給されます。電源電流が最も大きくなるのは、スイッチング・レギュレータがイネーブルされていて(SWENが“H”)、パワー・スイッチがオン、オフにトグルしているときです。軽負荷時、スイッチング・レギュレータはBurst Mode動作になります。Burst Mode動作中は、パワー・スイッチはほとんどトグルせず、入力電流は大幅に減少します(「低リップルBurst Mode動作」セクションを参照)。

**パワー・スイッチ・ドライバ(PSD)の動作範囲:** NPNパワー・スイッチはブロック図に示されているようなパワー・スイッチ・ドライバ(PSD)によって駆動されます。ドライバは、最小動作電圧を上回り、PSD過電圧のしきい値を下回る電源(V<sub>IN</sub>またはBIAS)によって給電する必要があります。これらの電圧は標準でそれぞれ2.4Vと34Vです(「電気的特性」を参照)。

V<sub>IN</sub>とBIASのいずれもこの動作範囲内になければ、PSDとスイッチング・レギュレータは自動的にディスエーブルされます。60Vまでの電圧はPSDに対して有害ではありませんが、説明したように、V<sub>IN</sub>とBIASのいずれも有効な動作範囲にないとき、スイッチング・レギュレーションは自動的にディスエーブルされます。動作条件のいくつかの例については表2を参照してください。

**リセットとウォッチドッグの動作電圧リミット:** リセット回路はV<sub>IN</sub>とBIASのどちらかが1.3Vを上回っている限り、適切に動作します(「リセット条件」のセクションを参照)。ウォッチドッグ・タイマはV<sub>IN</sub>とBIASのどちらかが2.5V～60Vのとき適切に動作します。動作条件のいくつかの例を下の表に示します。

表2. 動作条件の例

| V <sub>IN</sub> (V) | BIAS(V) | リセット回路 | ウォッチドッグ | スイッチング・レギュレータ |

|---------------------|---------|--------|---------|---------------|

| 0                   | 1.3     | X      |         |               |

| 1.3                 | 0       | X      |         |               |

| 1                   | 40      | X      | X       |               |

| 40                  | 40      | X      | X       |               |

| 1                   | 30      | X      | X       | X             |

| 12                  | 40      | X      | X       | X             |

**自動電源選択:** 電力損失を最小にするため、LT8495は電圧が最低の適切な電圧源(V<sub>IN</sub>またはBIAS)から、前の2つのセクションで説明した要件に従って、必要な電流のできるだけ多くを引き出します。この選択は自動的に行われ、V<sub>IN</sub>またはBIASの電圧が変化するのに応じて変化することがあります。

LT8495はV<sub>IN</sub>とBIASの電圧を比較してどちらが低いか判断します。コンパレータには「電気的特性」のセクションに示されているオフセットとヒステリシスがあります。電圧の比較はパワー・スイッチがトグルしているとき連続的に行われます。最新の比較結果はスイッチングが停止するときLT8495の内部でラッチされます。パワー・スイッチがトグルしていない場合、LT8495はV<sub>IN</sub>とBIASの最後の比較結果を使ってどちらの電源が低いか判断します。最初に起動した後、またはサーマル・ロックアウト後、パワー・スイッチがトグルする状態になって新たに電圧を比較できるまでは、LT8495は常にV<sub>IN</sub>が低い方の電源であると判断します。

**SEPICコンバータのBIASの接続:** V<sub>IN</sub>がV<sub>OUT</sub>より上または下になることができるSEPICコンバータの場合、BIASは一般にV<sub>OUT</sub>へ接続されます。これは、V<sub>IN</sub>電圧がV<sub>OUT</sub>より高いとき効率を改善します。SEPIC構成でBIASをV<sub>OUT</sub>に接続すると、V<sub>OUT</sub>がPSDの過電圧しきい値より下に安定化される場合、

## アプリケーション情報

スイッチング・レギュレータは34V(標準的なスイッチ・ドライバの過電圧しきい値)を超える $V_{IN}$ で動作することができます。最後に、BIASを $V_{OUT}$ に接続すると、 $V_{OUT}$ がPSDの動作範囲内に上昇した後、コンバータは2.5Vを下回る $V_{IN}$ 電圧でも動作することができます。これは、バッテリから給電するアプリケーションで非常に便利なことがあります。というのは、バッテリ電圧は放電するにつれて低下するからです。

**昇圧コンバータのBIASの接続:** 昇圧コンバータでは、BIASは一般に $V_{OUT}$ またはグランドに接続されます。BIASを $V_{OUT}$ に接続すると、 $V_{OUT}$ がPSDの動作範囲内に上昇した後、コンバータは $V_{IN} < 2.5V$ で動作することができます。ただし、 $V_{OUT}$ が無負荷状態のとき、 $V_{IN}$ が主入力電源として選択されているにもかかわらず、電圧がもっと高いBIASピンから依然として少量の電流が流れるため、全体の電力損失がわずかに増加します。無負荷状態での昇圧コンバータの電力損失を最小にするには、BIASを代わりにグランドに接続します。

$V_{OUT}$ がPSDの動作範囲より高い昇圧アプリケーションでは、BIASピンは一般に $V_{OUT}$ に接続しません。LT8495は、電圧が高すぎるので、その電流の大半をBIASから引き出すことは決してないので、この接続は効率を改善する助けにはなりません。代わりの選択肢として、BIASピンをグランドまたはPSDの動作範囲内の別の電源に接続します。

**昇圧コンバータの最大 $V_{IN}$ :** 昇圧構成では、インダクタと出力ダイオードを通る $V_{IN}$ から $V_{OUT}$ へのDC経路のため、 $V_{IN}$ は一般に $V_{OUT}$ より高くすることができます。 $V_{IN}$ を $V_{OUT}$ より高くしなければならない場合、インダクタは常に $V_{OUT}$ より低い別の電源から給電する必要があります。別の人方法としては、SEPIC構成を使うことができます。

また、BIASが有効な動作範囲内の別の電源に接続されていない限り、 $V_{IN}$ 電圧がPSDの動作範囲を上回る昇圧構成ではLT8495は動作しません。

**$V_{IN}/BIAS$ のランプ・レート:** スイッチング・コンバータのアプリケーションに最初に給電するとき、 $V_{IN}/BIAS$ のランプ・レートを制限します。 $V_{IN}/BIAS$ のランプ・レートが高いと、コンバータの受動部品に過度の突入電流を生じることができます。このため電流や電圧のオーバーストレスが生じ、受動部品やデバイスに損傷を与えることがあります。500mV/ $\mu$ s以下のランプ・レートでは、部品のパラメータにもよりますが、一般にはこれらの問題が防止されます。また、活線挿入を避けるように注意します。活線挿入は、アクティブな電源電圧がコンバータの入力に「瞬時に」接続されるか、またはスイッチが入れられるとき生じます。活線挿入は非常に高速の入力ランプ・レートを生

じますので、推奨できません。最後に、詳細については、リニアテクノロジー社の「アプリケーションノート88」を参照してください。これは、誘導性のソース・インピーダンスが、セラミック・コンデンサでバイパスされた入力ピンに活線挿入されたとき生じる可能性がある電圧オーバーストレスについて取り上げています。

### ウォッチドッグ・タイマ

LT8495はマイクロコントローラの動作をモニタすることができます。調整可能なウォッチドッグ・タイマを備えています。コードの実行エラーが生じると、ウォッチドッグ・タイマはこれを検出してオープンドレインの $\overline{WDO}$ ピンを“L”にすることができます。 $\overline{WDO}$ を $\overline{RST}$ またはマイクロコントローラの別の入力に接続して、マイクロコントローラをリセットするか割り込みをかけることができます。正しく動作させるには、プルアップ抵抗を $\overline{WDO}$ に接続する必要があることに注意してください。この抵抗は多くの場合既にマイクロコントローラに組み込まれています。

ウォッチドッグ回路はWDIピンの立ち下がりエッジをモニタします。 $\overline{WDO}$ が“L”にならないように、WDIピンの負方向に向かうパルスはプログラムされた時間ウインドウの内部に現れるよう制限されています。コードの実行エラーの間、マイクロコントローラは速すぎるかまたは遅すぎるWDIパルスを発生します。これにより、 $\overline{WDO}$ が“L”にアサートし、マイクロコントローラを強制してプログラムをリセットさせます(「タイミング図」のセクションを参照)。

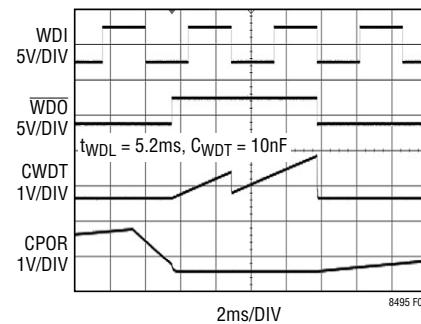

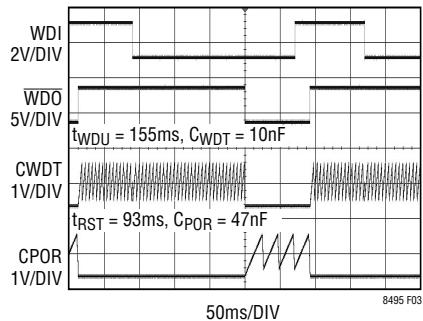

WDIをモニタしている間、任意の2つの立ち下がりエッジの間の時間がウォッチドッグの下限期間 $t_{WDL}$ より短いか(図2を参照)、またはウォッチドッグの上限期間 $t_{WDU}$ より長いと(図3を参照)、 $\overline{WDO}$ はプログラム可能な時間 $t_{RST}$ だけプルダウンされます(「リセット条件」のセクションを参照)。

図2. ウィンドウ・ウォッチドッグ波形

## アプリケーション情報

したがって、通常状態で  $\overline{\text{WDO}}$  を“H”に保つためには、WDI時間を  $t_{\text{WDL}}$  よりは長く、 $t_{\text{WDU}}$  よりは短くする必要があります。ウォッチドッグの上限期間の間に WDIの立ち下がりエッジが生じないときも  $\overline{\text{WDO}}$  は“L”になります。

図3. タイムアウト・ウォッチドッグ波形

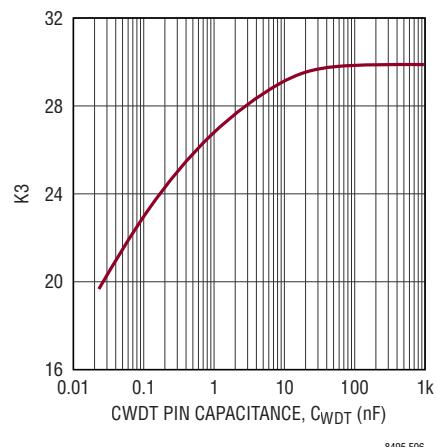

**ウォッチドッグ・タイミング・コンデンサの選択:** ウォッチドッグ・タイミング期間は調整可能で、ソフトウェアの実行に合うように最適化することができます。ウォッチドッグの上限と下限のタイムアウト期間( $t_{\text{WDU}}$  と  $t_{\text{WDL}}$ )は CWDT ピンとグランドの間にコンデンサ  $C_{\text{WDT}}$  を接続することにより調整されます。 $C_{\text{WDT}}$  の値が大きいとき(約 50nF 以上)、 $t_{\text{WDU}}$  は一般に 30 •  $t_{\text{WDL}}$  です。もっと小さい値では、図6に示すようにこの比が減少します。

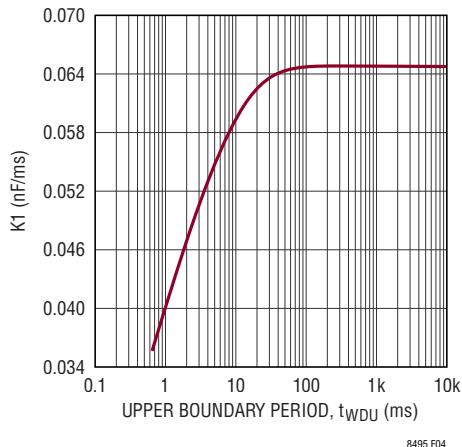

$t_{\text{WDU}}$  と  $t_{\text{WDL}}$  の時間を設定するには、「標準的性能特性」のセクションのウォッチドッグの上限と下限の期間と容量のグラフを参照して、 $C_{\text{WDT}}$  を選択します。必要なコンデンサの値は、次式を使って、ある特定のウォッチドッグ・タイミング期間から計算することができます。

$$C_{\text{WDT}} = K_1 \cdot t_{\text{WDU}}$$

ここで、 $C_{\text{WDT}}$  は nF で表した外付けコンデンサの値、 $t_{\text{WDU}}$  は ms で表した上限期間、 $K_1$  はそれらの比で、標準的な値を図4に示します。上限期間が 50ms を超える場合、 $K_1$  は 0.065nF/ms として近似することができます。

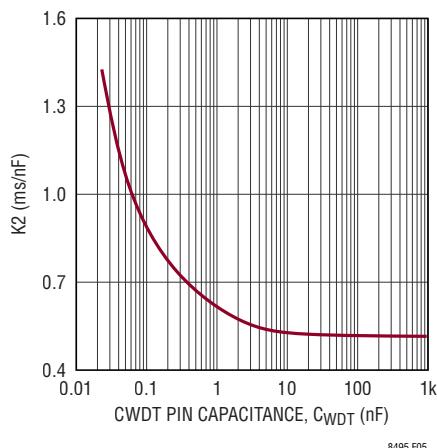

さらに、与えられた  $C_{\text{WDT}}$  コンデンサの値に対するウォッチドッグの下限期間を、次式を使って計算することができます。

$$t_{\text{WDL}} = K_2 \cdot C_{\text{WDT}}$$

ここで、 $t_{\text{WDL}}$  は ms で表した下限期間、 $C_{\text{WDT}}$  は nF で表した外付け容量、 $K_2$  はそれらの比で、標準的な値を図5に示します。 $C_{\text{WDT}}$  の値が 10nF を超える場合、 $K_2$  は 0.52ms/nF として近似することができます。

図4. ウォッチドッグの上限のパラメータ

図5. ウォッチドッグの下限のパラメータ

図6. 上限と下限の比

## アプリケーション情報

与えられた容量CwDTに対して、ウォッチドッグの上限期間(tWDL)と下限期間(tWDL)の関係は一定になります。tWDL期間とtWDL期間の関係は次式で表されます。

$$t_{WDL} = K_3 \cdot t_{WDL}$$

ここで、K3は上限と下限の比で、標準的な値を図6に示します。

CWDTピンを未接続のままにしておくと、最小のウォッチドッグ・タイムアウトは約270μsになります。最大タイムアウトは、漏れ電流の少ないコンデンサのうち入手できる最大容量のものによって制限されます。与えられた容量に対するタイムアウト期間の保証された許容誤差が「電気的特性」のセクションに示されています。タイムアウト期間の精度は、コンデンサの漏れ電流(公称充電電流は2.3μA)とコンデンサの許容誤差にも影響されます。漏れ電流の少ないセラミック・コンデンサを推奨します。

**ウォッチドッグ・タイマの起動:** ウォッチドッグ・タイマによってWDIピンがモニタされないいくつかの状態があります。各状態で、WDIピンのモニタは以下に説明するようにして開始または再開されます。

- ウオッチドッグ・タイマはPORまたはサーマル・ロックアウトの間ディスエーブルされます。PORとサーマル・ロックアウトがクリアされた後、CWDTが0Vからランピングを開始します。CWDTが0Vから約200mVまで充電する間、WDIのエッジは無視されます。

- WDEが“L”的とき、ウォッチドッグはディスエーブルされます。WDEが立ち上がった後、CWDTはランプアップを開始する前に $1\mu s$ ～ $100\mu s$ （標準）必要とすることがあります。CWDTが0Vから約200mVまで充電するまで、WDIのエッジは無視されます。

- $\overline{WDO}$ が“L”にアサートされている間、WDIのエッジはモニタされません。 $\overline{WDO}$ がリリースされ、CWDTがランプアップを開始する前に、CPORの4サイクルが必要です。CWDTが0Vから約200mVまで充電するまで、WDIのエッジは無視されます。

必要なら、RSTピンをWDEに接続して、RSTがリリースされるのとほぼ同時にウォッチドッグ・タイマをイネーブルすることができます。図7に示す例では、RSTがWDEに接続されています。デバイスが起動した後、出力電圧がマイクロコントローラの電源の5Vに向かってランプアップします。 $V_{OUT}$ が4.5Vを超える、したがってRSTINが約1.1Vを超えると、RSTピンとWDEピンは追加のt<sub>RST</sub>の時間“L”に保たれます。t<sub>RST</sub>が経

過後、RSTがリリースされ、WDEが“H”になるので、マイクロコントローラとウォッチドッグ・タイマがほぼ同時にイネーブルされます。

図7. ウォッチドッグの監視

## リセット条件

以下で説明するように、LT8495には3つのリセット条件があります。これら全ての条件は、 $V_{IN}$ またはBIASが1.3Vを上回っている限り、オープンドレインの $\overline{RST}$ ピンを“L”にすることができます。 $\overline{RST}$ ピンを外部のマイクロコントローラや他のデバイスのリセットとして使うことができるよう、プルアップ抵抗を $\overline{RST}$ ピンに接続することができます。調整可能なタイマが $t_{RST}$ だけRSTのリリースを遅らせて、外付けのデバイスのために適切なリセット時間を確保します。

下記の3つのリセット条件があります。

- **POR**:  $V_{IN}$ とBIASの両方が2.4V(標準)より低いと、 $RST$ ピンがアサートされます。これは、LT8495の最初のパワーアップ時に $RST$ をアサートするパワーオン・リセット条件です(タイミング図を参照)。この条件では、スイッチング・レギュレータとウォッчドッグ・タイマがディスエーブルされ、 $C_{WDT}$ 、 $C_{POR}$ およびSSコンデンサがグランドに放電されます。

- **サーマル・ロックアウト**: LT8495のダイが過熱状態になると、 $RST$ ピンが“L”にアサートされます。詳細については「高温に関する検討事項」のセクションを参照してください。この条件では、スイッチング・レギュレータとウォッчドッグ・タイマがディスエーブルされ、 $C_{WDT}$ 、 $C_{POR}$ およびSSコンデンサがグランドに放電されます。詳細については「サーマル・ロックアウト」のセクションを参照してください。

## アプリケーション情報

- RSTINの低電圧ロックアウト:** RSTIN入力が標準1.1Vのしきい値(「電気的特性」表を参照)を下回ると、オープンドレインのRSTが“L”にアサートされます。この機能により、外付け抵抗分割器を使用して低電圧検出回路を構成することができます。このリセット条件は、スイッチング・レギュレータやウォッチドッグ・タイマに影響を与えません。詳細については「低電圧ロックアウト」のセクションを参照してください。

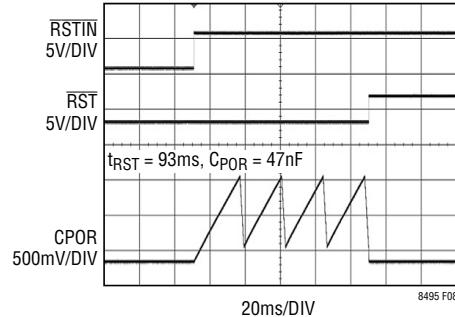

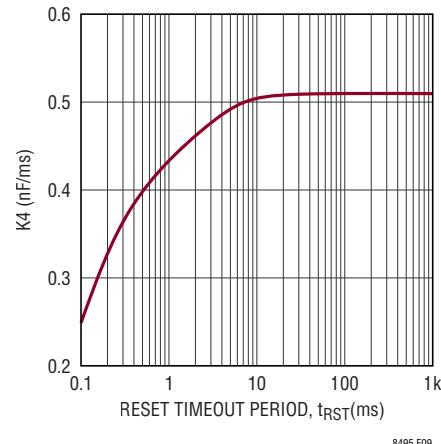

上のリセット条件の全てがもはや満たされなくなった後、プログラム可能なタイマが $t_{RST}$ だけRSTのリリースを遅らせます。RSTをリリースする前に、外付けのCPORコンデンサがランプアップとランプダウンを4サイクル繰り返して $t_{RST}$ の遅延を生じさせます(図8を参照)。 $t_{RST}$ 期間をプログラムするには「標準的性能特性」のセクションの「リセット・タイムアウト期間と容量」のグラフを参照してCPORを選択してください。必要なコンデンサの値は、与えられたリセット・タイムアウト期間に対して次式を使って計算することもできます。

$$C_{POR} = K_4 \cdot t_{RST}$$

ここで、CPORはnFで表した外付けコンデンサの値、 $t_{RST}$ はmsで表したりセット・タイムアウト期間、K4はそれらの比で標準的な値が図9に示されています。リセット・タイムアウト期間が15msを超える場合、K4を0.51nF/msとして近似することができます。前に述べたように、この同じタイマが、ウォッチドッグ・タイムアウトの間WDOがどのくらい長く“L”にアサートされるかを決めるのに使用されます。

一例として、タイムアウト期間 $t_{RST}$ を9.5msにするには、4.7nFのCPORコンデンサ値を選択します。CPORピンを未接続のままにすると、 $t_{RST}$ 期間が約40μsになります。最大期間は、漏れ電流の少ないコンデンサのうち入手できる最大容量のものによって制限されます。与えられた容量に対するタイムアウト期間の保証された許容誤差が「電気的特性」のセクションに示されています。タイムアウト期間の精度は、コンデンサの漏れ電流(公称充電電流は2.3μA)とコンデンサの許容誤差にも影響されます。漏れ電流の少ないセラミック・コンデンサを推奨します。

前に説明したように、ウォッチドッグ・エラーが生じた後、 $t_{RST}$ の間WDOは“L”にアサートされます。この期間は、リセット遅延が測られるのと同様に、CPORピンを4サイクル数えることによって測られます。リセット遅延期間と同時にウォッチドッグ・タイムアウトが発生すると、ウォッチドッグがカウンタの優

図8. リセット・タイマの波形

図9. リセット・タイマのパラメータ

先権を得ます。したがって、CPORピンの4サイクルの間WDOは常に“L”にアサートされ、他方、RST遅延は4サイクルを超えて最大6サイクルまで延長されることがあります。そのため、 $t_{RST}$ が最大50%増加します。

最後に、RSTピンの $t_{RST}$ 遅延はスイッチング・レギュレータやウォッチドッグ・タイマには影響を与えないことに注意してください。スイッチング・レギュレータやウォッチドッグ・タイマはデバイスがもはやPORまたはサーマル・ロックアウト状態でなくなった直後にスタートします。

### 低電圧ロックアウト

SWENピンやRSTINピンを使って低電圧ロックアウト(UVLO)機能を実装することができます。低電圧ロックアウトにより、入力電圧や出力電圧が低すぎるととき、適切な回路をシャットダウンして望ましくない動作を防止できます。

## アプリケーション情報

図10.  $V_{IN}$ 低電圧ロックアウト

**入力UVLO:**  $V_{IN}$ からSWENに抵抗分割器を接続する(図10参照)ことにより、入力低電圧ロックアウト回路を実装します。SWENの高精度の上昇時しきい値は1.0Vで、30mVのヒステリシスがあります(標準値-「電気的特性」参照)。 $V_{IN}$ からSWENに抵抗分割器を接続することにより、LT8495は、 $V_{IN}$ が望みのしきい値より低くなるとスイッチング・レギュレータをディスエーブルするように設定されます。通常、このしきい値は、入力電源が電流制限されているか、または入力電源のソース抵抗が比較的高い状況で使用されます。スイッチング・レギュレータは電源から一定の電力を引き出すため、電源電圧が低下するにつれて電源電流が増加します。この現象は電源からは負の抵抗負荷のように見えるため、電源電圧が低い状態では、電源が電流を制限するか、または低電圧にラッチする原因になることがあります。入力UVLOにより、この問題が発生する恐れのある電源電圧では、レギュレータは動作しません。

図10に示すように、 $V_{IN}$ からSWENに抵抗分割器を接続することにより、下降時の低電圧ロックアウトしきい値が次のように設定されます。

$$V_{IN(UVLO)} = \frac{R3 + R4}{R3} \cdot 0.97V$$

上の式から、図10に示す抵抗分割器の場合は、 $V_{IN}$ ピンの下降時低電圧ロックアウトしきい値は2.96Vになります。 $V_{IN}$ がこのしきい値より低いと、スイッチング・レギュレーションがディスエーブルされて、SSピンが放電し始めます。例えば、R3の値を選択した後、R4は次式を使って計算することができます。

$$R4 = R3 \cdot \left( \frac{V_{IN(UVLO)}}{0.97} - 1 \right) \Omega$$

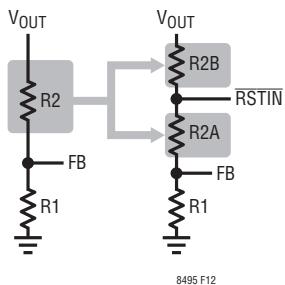

**出力UVLO:**  $\overline{RST}$ ピンと $\overline{RSTIN}$ ピンを図11と図12に示すように接続することにより、出力低電圧ロックアウト(UVLO)回路を実装します。この回路は、 $V_{OUT}$ が必要な電圧を下回るとオーバンドレンの $\overline{RST}$ ピンを“L”にアサートすることにより、 $V_{OUT}$ から給電されるデバイスをリセットします。 $\overline{RST}$ ピンにはプルアップ抵抗が必要ですが、マイクロコントローラに既に内蔵されていることがあるので注意してください。 $\overline{RSTIN}$ ピンのグリッチ耐性のため、 $\overline{RSTIN}$ ピンの立ち下がりエッジから $RST$ が“L”にアサートされるまでに標準23μsの遅延が生じます(「電気的特性」のセクションを参照)。 $\overline{RSTIN}$ がそのしきい値を上回った後、CPORピンのコンデンサによってプログラム可能な遅延時間の間 $RST$ は“L”にアサートされた状態を続けます。

図11.  $\overline{RSTIN}$ リセット・ロックアウト

図12に示されているように、「出力電圧の設定」のセクションで計算されたR2抵抗は2個の抵抗(R2AとR2B)に分割されUVLO機能を実現します。次に、それらの値を計算するには以下の式が使用されます。

$$R2A = R1 \cdot \left( \frac{92\%}{UVLO\%_{NOM}} - 1 \right)$$

$$R2B = R2 - R2A$$

ここで、 $UVLO\%_{NOM}$ は公称 $V_{OUT}$ のパーセントで表した必要な公称UVLOしきい値電圧です。ほとんどのアプリケーションでは、 $UVLO\%_{NOM}$ は89.5%以下にすることを推奨します。 $UVLO\%_{NOM}$ の選択に関する詳細についてはさらに読み進めてください。

## アプリケーション情報

図12. RSTINピンの接続オプション

UVLO%<sub>NOM</sub>を選択するとき、V<sub>OUT</sub>の負荷電流ステップに対するトランジェント応答によってV<sub>OUT</sub>にアンダーシュートが生じる可能性があることを考慮してください。V<sub>OUT</sub>の過度のアンダーシュートにより、RSTINがコンパレータのしきい値より下になり、RSTがアサートする可能性があります。次式にはRSTINコンパレータの最大しきい値(FBリファレンスの97%—「電気的特性」を参照)が含まれ、UVLOしきい値がとりうる最大値が示されています。

$$\text{UVLO\%}_{\text{MAX}} = \text{UVLO\%}_{\text{NOM}} \cdot \frac{97}{92}$$

たとえば、UVLO%<sub>NOM</sub> = 89.5%を選択すると、UVLO%<sub>MAX</sub> = V<sub>OUT</sub>の94.36%となります。したがって、V<sub>OUT</sub>が定常状態の安定化電圧より下に5.64%以上アンダーシュートすると、RSTピンがアサートする可能性があります。もっと大きなマージンが必要であれば、もっと低いUVLO%<sub>NOM</sub>を選択します。

さらに、UVLO%<sub>NOM</sub>の選択は、RSTがアサートされない最小のV<sub>OUT</sub>電圧に影響を与えます。

$$\text{UVLO\%}_{\text{MIN}} = \text{UVLO\%}_{\text{NOM}} \cdot \frac{86}{92}$$

たとえば、UVLO%<sub>NOM</sub> = 89.5%を使用すると、UVLO%<sub>MIN</sub> = V<sub>OUT</sub>の83.66%となります。したがって、V<sub>OUT</sub>がその公称値より16.34%下にならない限り、RSTピンがアサートしない可能性があります。絶対V<sub>OUT</sub> UVLO電圧に関しては、FBのレギュレーション電圧の許容誤差と、R1、R2AおよびR2B抵抗の許容誤差についても検討する必要があることに注意してください。

図11に示されている例では、V<sub>OUT</sub>は5Vに安定化されています。UVLO%を89.5%にしたい場合、計算されたR1、R2A、およびR2Bの値はそれぞれ316k、8.87kおよび1Mです。

**POR UVLO:** LT8495が適切に動作するにはV<sub>IN</sub>とBIASの両方が低すぎるとき(標準で<2.4V)、スイッチング・レギュレータとウォッチドッグ・タイマはディスエーブルされます。詳細は「リセット条件」のセクションを参照してください。

## 高温に関する検討事項

周囲温度が高めの場合は、プリント回路基板のレイアウトに注意して、LT8495が十分放熱できるようにします。パッケージ底面の露出パッドはグランド・プレーンに半田付けする必要があります。このグランドは、サーマル・ビアを使用して、下にある広い銅層に接続してください。これらの層は、LT8495が発生する熱を放散します。ビアを追加すると、熱抵抗をさらに減らすことができます。周囲温度が最大接合部温度の定格に近づくにつれ、最大負荷電流をディレーティングします。LT8495内部の電力損失は、効率の測定結果から全電力損失を計算し、そこからダイオードの損失、FB抵抗の損失、インダクタの損失を差し引くことで概算することができます。ダイの温度は、LT8495の電力損失に、接合部から周囲までの熱抵抗を掛け計算します。

LT8495のほとんどの電力を消費するのは、パワー・スイッチとそのドライバです(ブロック図参照)。スイッチ電流、デューティ・サイクル、出力電圧が大きいほど、ダイの温度が高くなります。入力電源電圧が高いほど、パワー・スイッチ・ドライバの電力損失が大きくなります。パワー・スイッチ・ドライバ(PSD)は、V<sub>IN</sub>およびBIASに印加される適切な最低電圧によって給電されます。BIASを低電圧電源(多くの場合V<sub>OUT</sub>)に接続することにより、LT8495の最高ダイ温度を下げることができます(「自動電源選択」セクションを参照)。

**サーマル・ロックアウト:** ダイの温度が約165°Cに達すると、デバイスはサーマル・ロックアウト状態になり、リセットされます。デバイスはダイの温度が約5°C(公称)低下すると再度インエーブルされます。サーマル・ロックアウト時のデバイスの状態に関する詳細については、「リセット条件」を参照してください。

## フォルト耐性

LT8495は単一のフォルト状態に耐えるように設計されています。隣接する2つのピンを互いに短絡したり、1つのピンをフロート状態のままにしても、V<sub>OUT</sub>が上昇したりLT8495レギュレータが損傷することはありません。

隣接ピンの短絡の影響を表3に、フロート・ピンの影響を表4に、それぞれ示します。フォルト耐性を確保するため、NCピンはフロート状態のままでおく必要があります。隣接ピン間の偶発的短絡に対する最良のフォルト耐性を得るには、BIASピンを1.202Vより高いもの、または出力に接続して、FBからBIASへの短絡時に過電圧を防止します。

## アプリケーション情報

表3. ピン間の短絡の影響(TSSOP)

| ピン名称       | ピン番号  | 出力への影響                              |

|------------|-------|-------------------------------------|

| FB-BIAS    | 1-2   | BIASが出力に接続されていると、出力電圧は約1.202Vに低下する。 |

| CPOR-CWDT  | 5-6   | 出力への影響なし。                           |

| CWDT-RST間  | 6-7   | 出力への影響なし。                           |

| RST-SS     | 7-8   | 影響なしか、または、出力電圧が安定化電圧より低くなる。         |

| RSTIN-SWEN | 11-12 | 出力への影響なし。                           |

| SWEN-WDE   | 12-13 | 出力への影響なし。                           |

| WDE-GND    | 13-14 | 出力への影響なし。                           |

| GND-WDO    | 14-15 | 出力への影響なし。                           |

| WDO-WDI    | 15-16 | 出力への影響なし。                           |

図4. フロートしているピンの影響(TSSOP)

| ピン名称     | ピン番号 | 出力への影響                                                              |

|----------|------|---------------------------------------------------------------------|

| BIAS     | 1    | このピンをフロートさせると、 $V_{IN}$ 電圧と回路構成に応じて、デバイスの性能が低下するか、出力電圧が安定化電圧より低くなる。 |

| FB       | 2～3  | 他のFBパッドが半田付けされていると、影響なし。                                            |

| CPOR     | 5    | 出力への影響なし。                                                           |

| CWDT     | 6    | 出力への影響なし。                                                           |

| RST      | 7    | 出力への影響なし。                                                           |

| SS       | 8    | デバイスが起動した後は影響なし。起動中は、突入電流が増える可能性がある。                                |

| RT       | 10   | 出力電圧が安定化電圧より低くなることがある。                                              |

| RSTIN    | 11   | 出力への影響なし。                                                           |

| SWEN     | 12   | ピンのイネーブル状態が不定になる。出力電圧は安定化電圧より高くはならない。                               |

| WDE      | 13   | 出力への影響なし。                                                           |

| GND      | 14   | 露出パッドが半田付けされていると、影響なし。                                              |

| WDO      | 15   | 出力への影響なし。                                                           |

| WDI      | 16   | 出力への影響なし。                                                           |

| $V_{IN}$ | 18   | このピンをフロートさせると、BIAS電圧と回路構成に応じて、デバイスの性能が低下するか、出力電圧が安定化電圧より低くなる。       |

| SW       | 10   | 出力電圧が安定化電圧より低くなる。                                                   |

| 露出パッド    | 21   | 出力はレギュレーションを維持するが、潜在的にデバイスの性能が下がる。                                  |

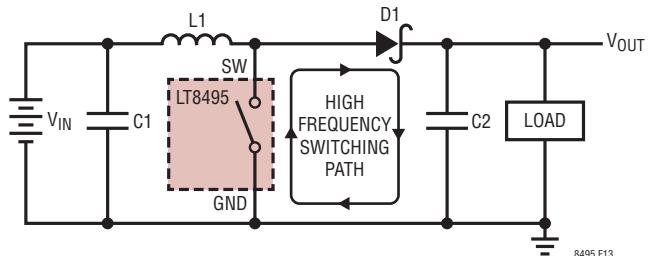

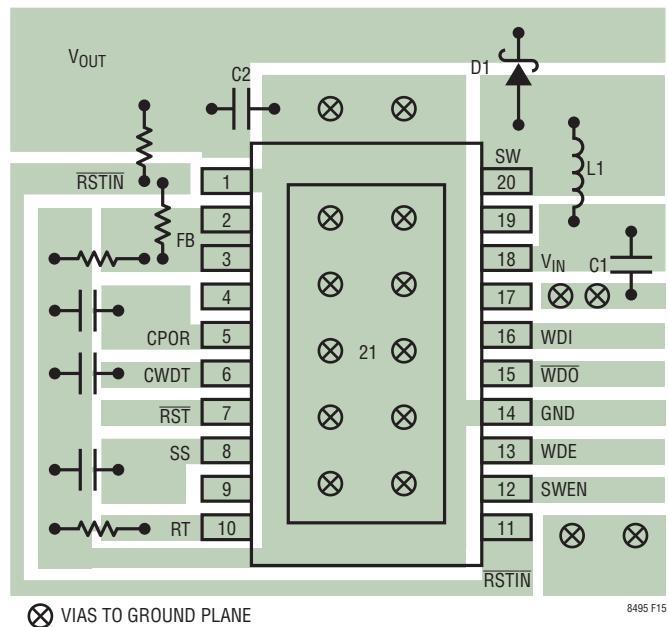

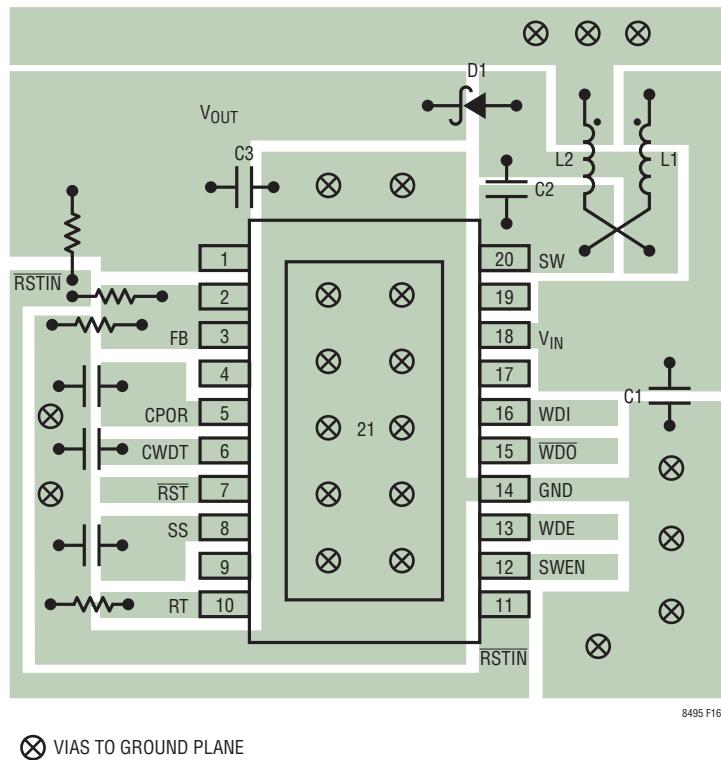

## レイアウトのヒント

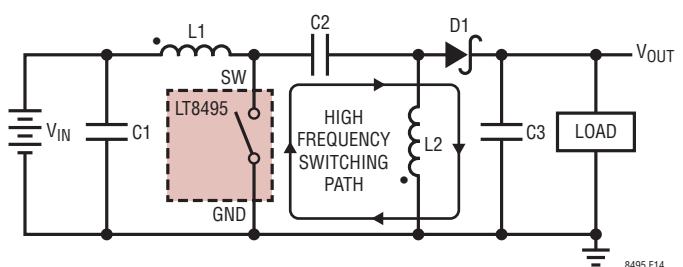

全ての高周波数スイッチャと同様、レイアウトを検討するとき、電気的、熱的、さらにノイズに関する性能を最適化するように注意する必要があります。レイアウトに注意を払わないと、規定された性能が得られません。最大効率を得るために、スイッチの立ち上がり時間と立ち下がり時間は通常5ns～10nsの範囲です。放射ノイズと導通ノイズの両方を防止するため、図13と図14に示されている高速スイッチング電流経路はできるだけ短くします。これは、図15と図16の推奨PCBレイアウトで実現されています。この経路を短くすると、寄生トレース・インダクタンスも減少します。スイッチがオフするとき、この寄生インダクタンスにより、LT8495のスイッチの両端にフライバック・スパイクが発生します。動作時の電流と出力電圧が大きいとき、レイアウトが良くないと、このスパイクはLT8495の絶対最大定格を超える電圧を発生させるおそれがあります。プレーン間のカップリングと全体のノイズを防ぐため、スイッチャ回路の下にもグランド・プレーンを使用します。FBに関連する部品はスイッチ・ノードからできるだけ離して配置します。これらの部品のグランドはスイッチ電流の経路から離します。そうしないと、不安定になり、低調波発振が起きることがあります。

図13. 昇圧構成の高速「こま切れ」スイッチング経路

図14. SEPIC構成の高速「こま切れ」スイッチング経路

## アプリケーション情報

図15. 昇圧構成の推奨部品配置ピン21(露出パッド)は、適切な熱性能を得るために、ローカル・グランド・プレーンに直接半田付けする必要がある。多数のビアを追加のグランド・プレーンに通すと熱性能が改善される

図16. SEPIC構成の推奨部品配置ピン21(露出パッド)は、適切な熱性能を得るために、ローカル・グランド・プレーンに直接半田付けする必要がある。多数のビアを追加のグランド・プレーンに通すと熱性能が改善される

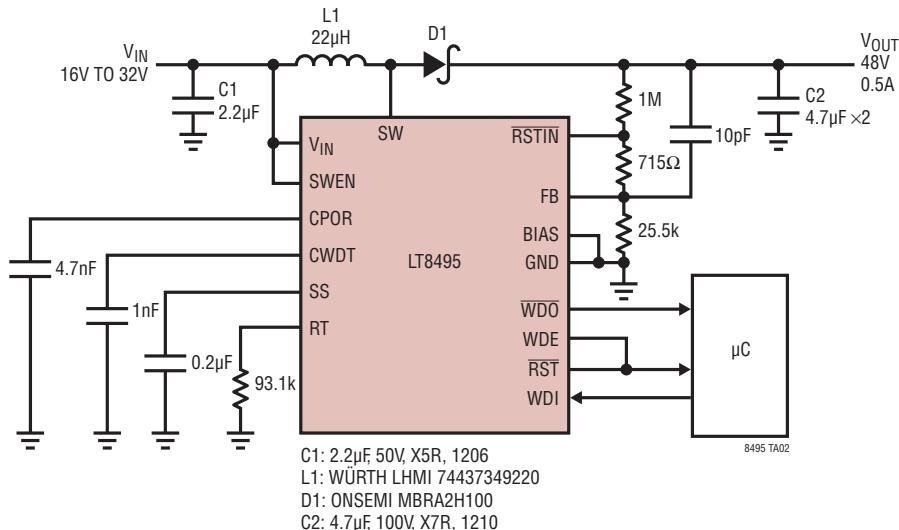

## 標準的応用例

750kHz、16V～32V入力、48V/0.5A出力の昇圧コンバータ

効率、 $V_{IN} = 24V$

8495 TA02b

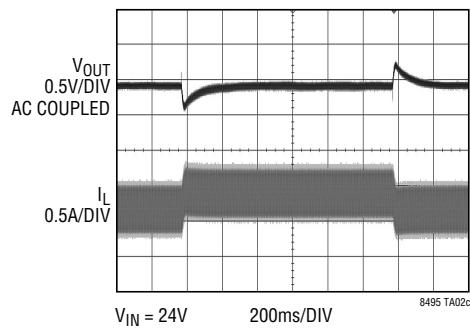

400mAから500mA、さらに

400mAへの出力負荷ステップに

対するトランジェント応答

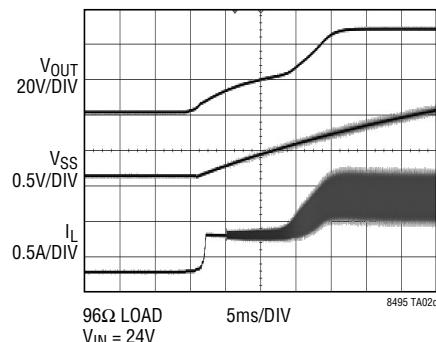

起動波形

## 標準的応用例

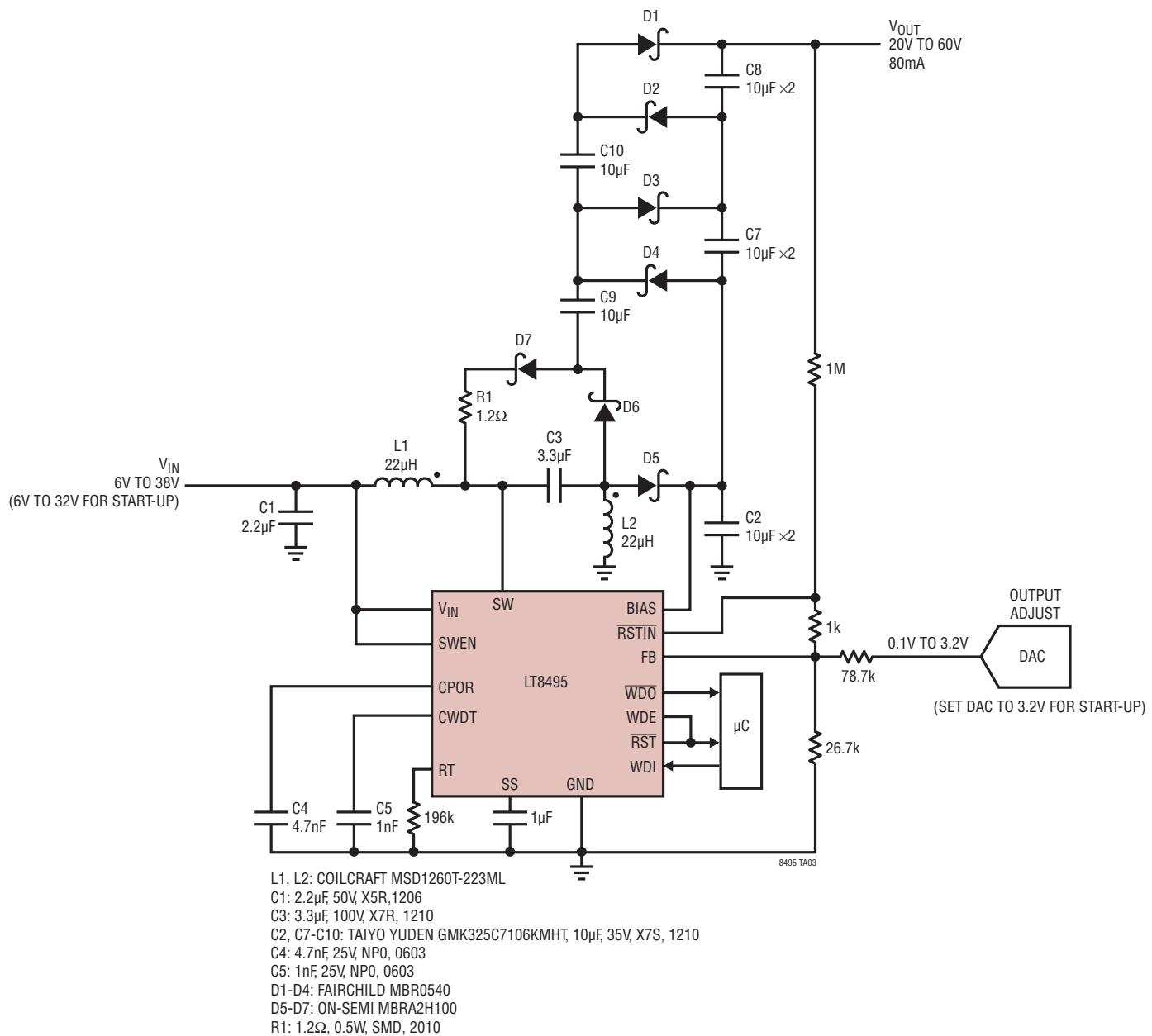

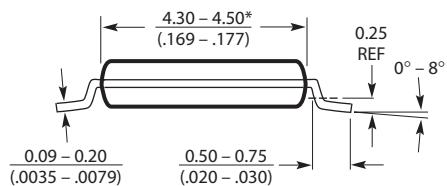

400kHzでスイッチングする、入力電圧範囲と出力電圧範囲が広い、チャージ・ポンプ付きSEPICコンバータ

## 標準的応用例

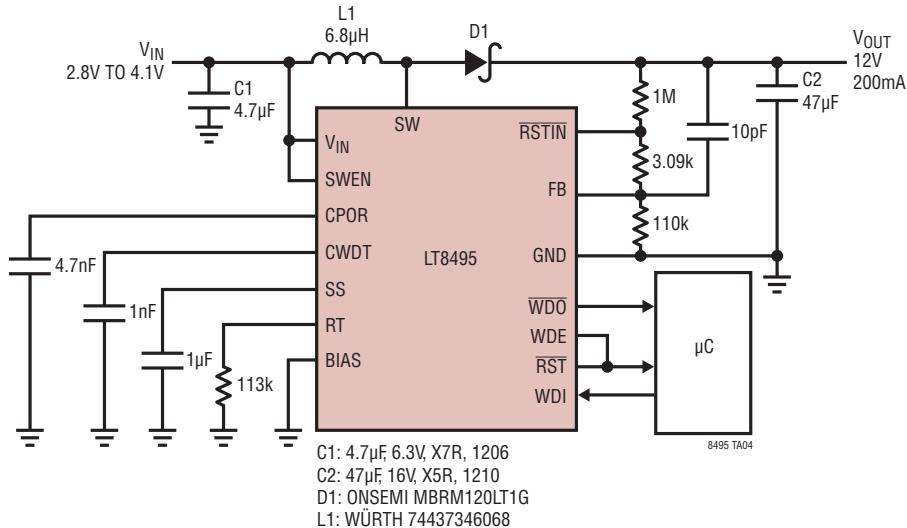

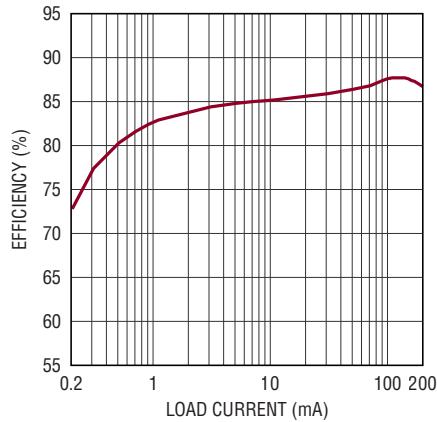

低静止電流、650kHz、リチウムイオン入力/12V出力の昇圧コンバータ

効率、 $V_{IN} = 3.3V$

8495 G17

# LT8495

## 標準的応用例

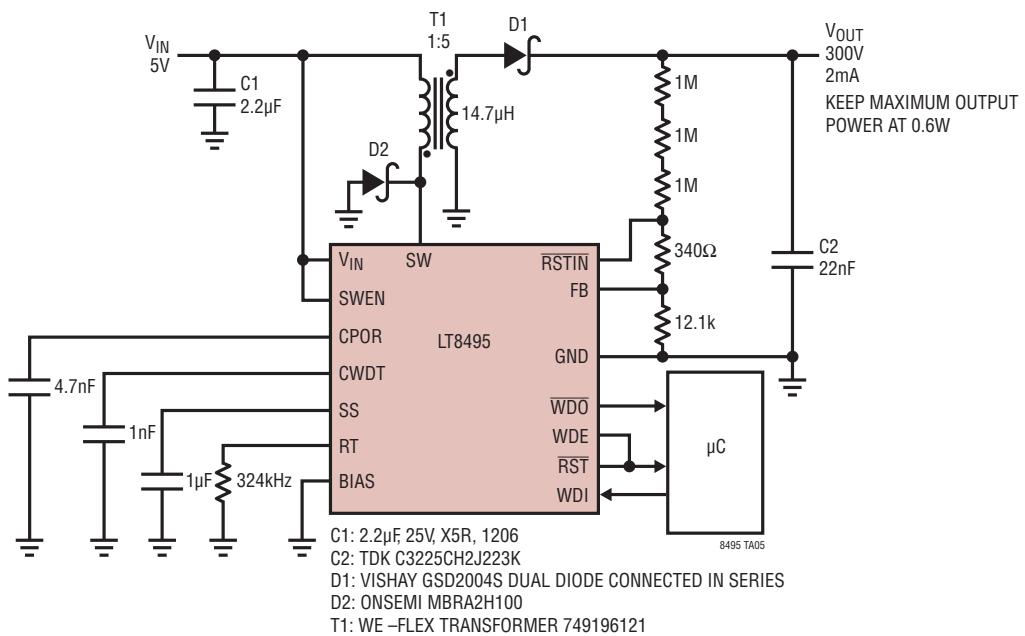

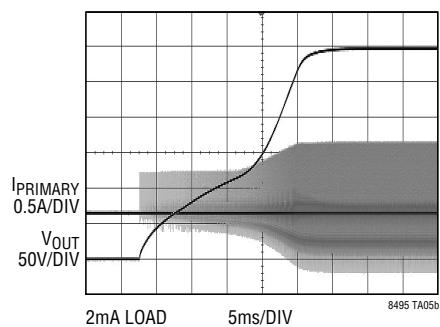

低静止電流、250kHz、5V入力/300V出力のフライバック・コンバータ

危険、高電圧！高電圧技術者のみ操作可

起動波形

スイッチング波形

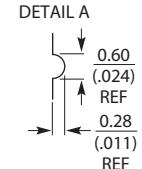

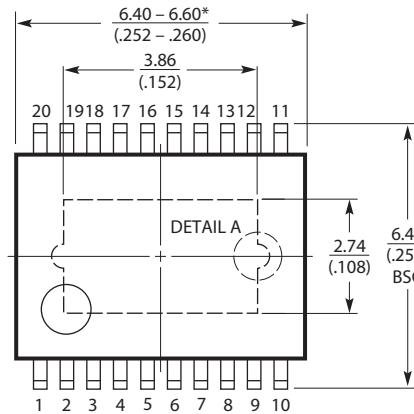

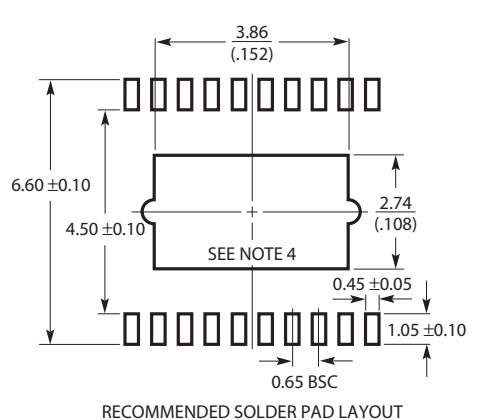

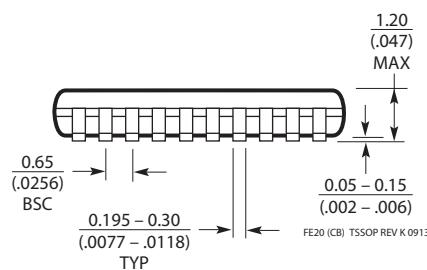

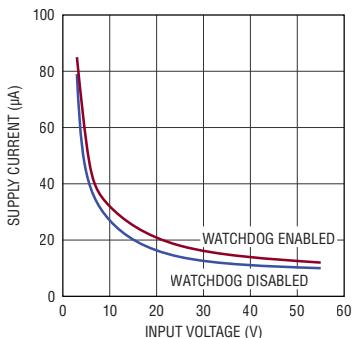

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**FE Package

20-Lead Plastic TSSOP (4.4mm)**

(Reference LTC DWG # 05-08-1663 Rev K)

**Exposed Pad Variation CB**

DETAIL A IS THE PART OF

THE LEAD FRAME FEATURE

FOR REFERENCE ONLY

NO MEASUREMENT PURPOSE

### 注記：

1. 標準寸法：ミリメートル

2. 寸法は  $\frac{\text{ミリメートル}}{(\text{インチ})}$

3. 図は実寸とは異なる

4. 露出パッド接着のための推奨最小PCB メタルサイズ

\* 寸法にはモールドのバリを含まない

モールドのバリは各サイドで 0.150mm(0.006")を超えないこと

# LT8495

## 標準的応用例

450kHz、入力電圧範囲の広い12V出力のSEPICコンバータ

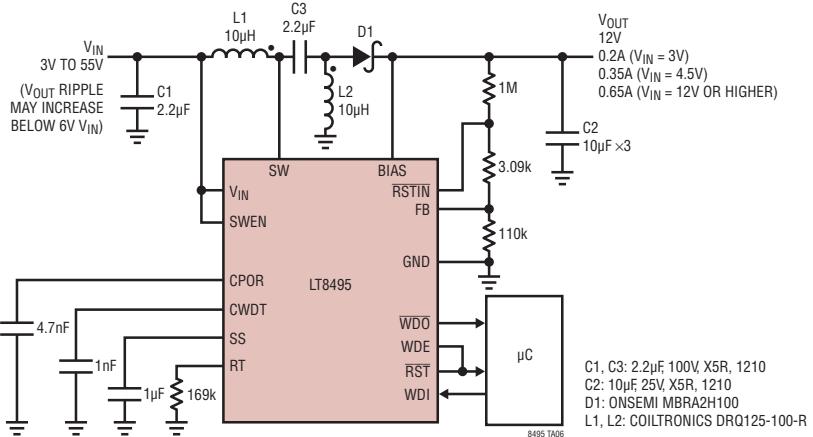

無負荷時電源電流

効率

## 関連製品

| 製品番号             | 説明                                      | 注釈                                                                                                                                                           |

|------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LT8494           | 70V、2A 昇圧/SEPIC、1.5MHz、高効率DC/DCコンバータ    | V <sub>IN(MIN)</sub> = 2.5V、V <sub>IN(MAX)</sub> = 32V、V <sub>OUT(MIN)</sub> = 70V、I <sub>Q</sub> = 9µA、I <sub>SD</sub> = <1µA、TSSOP-20Eパッケージ                |

| LT3580           | 42V、2A 昇圧/反転、2.5MHz、高効率DC/DCコンバータ       | V <sub>IN</sub> : 2.5V ~ 32V、V <sub>OUT(MAX)</sub> = ±40V、I <sub>Q</sub> = 1mA、I <sub>SD</sub> < 1µA、3mm×3mm DFN-8 および MSOP-8Eパッケージ                          |

| LT8580           | 65V、1A 昇圧/反転DC/DCコンバータ                  | V <sub>IN</sub> : 2.55V ~ 40V、V <sub>OUT(MAX)</sub> = ±60V、I <sub>Q</sub> = 1.2mA、I <sub>SD</sub> < 1µA、3mm×3mm DFN-8 および MSOP-8Eパッケージ                       |

| LT8570/ LT8570-1 | 65V、500mA/250mA 昇圧/反転DC/DCコンバータ         | V <sub>IN(MIN)</sub> = 2.55V、V <sub>IN(MAX)</sub> = 40V、V <sub>OUT(MIN)</sub> = ±60V、I <sub>Q</sub> = 1.2mA、I <sub>SD</sub> < 1µA、3×3 DFN-8 および MSOP-8Eパッケージ |

| LT8582           | 40V、デュアル3A、2.5MHz高効率昇圧コンバータ             | V <sub>IN</sub> : 2.5V ~ 40V、V <sub>OUT(MAX)</sub> = ±40V、I <sub>Q</sub> = 2.8µA、I <sub>SD</sub> < 1µA、7mm×4mm DFN-24パッケージ                                   |

| LT8471           | 40V、デュアル3A、マルチトポロジー、高効率DC/DCコンバータ       | V <sub>IN</sub> : 2.6V ~ 50V、V <sub>OUT(MAX)</sub> = ±45V、I <sub>Q</sub> = 2.4mA、I <sub>SD</sub> < 1µA、TSSOP-20Eパッケージ                                        |

| LT3581           | 40V、3.3A、2.5MHz高効率昇圧コンバータ               | V <sub>IN</sub> : 2.5V ~ 40V、V <sub>OUT(MAX)</sub> = ±40V、I <sub>Q</sub> = 1mA、I <sub>SD</sub> < 1µA、4mm×3mm DFN-14 および MSOP-16Eパッケージ                        |

| LT8582           | 40V、デュアル3A 昇圧、反転、SEPIC、2.5MHz高効率昇圧コンバータ | V <sub>IN</sub> : 2.5V ~ 40V、V <sub>OUT(MAX)</sub> = ±40V、I <sub>Q</sub> = 2.1mA、I <sub>SD</sub> < 1µA、7mm×4mm DFN-24パッケージ                                   |

| LT3579/ LT3579-1 | 40V、3.3A 昇圧、反転、SEPIC、2.5MHz高効率昇圧コンバータ   | V <sub>IN</sub> : 2.5V ~ 40V、V <sub>OUT(MAX)</sub> = ±40V、I <sub>Q</sub> = 1mA、I <sub>SD</sub> < 1µA、4mm×5mm QFN-20 および TSSOP-20Eパッケージ                       |

8495f

30

リニアテクノロジー株式会社

〒102-0094 東京都千代田区紀尾井町3-6紀尾井町パークビル8F

TEL 03-5226-7291 • FAX 03-5226-0268 • [www.linear-tech.co.jp/LT8495](http://www.linear-tech.co.jp/LT8495)

LT0415 • PRINTED IN JAPAN

LINEAR

TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 2015