## 特長

- $-3\text{dB}$ 小信号帯域幅:800MHz

- 連続調整可能な利得制御

- dBリニアな利得範囲: $-14\text{dB} \sim +17\text{dB}$

- 240MHzでのOIP3:あらゆる利得設定で35dBm

- ノイズ・フィギュア:最大利得で10dB

- 240MHzでの(IIP3-NF):あらゆる利得で $+8\text{dBm}$

- 入力換算ノイズ: $2.7\text{nV}/\sqrt{\text{Hz}}$

- 差動入出力

- 入力インピーダンス:あらゆる利得で $50\Omega$

- 3V~3.6Vの単一電源動作

- 電源電流:110mA

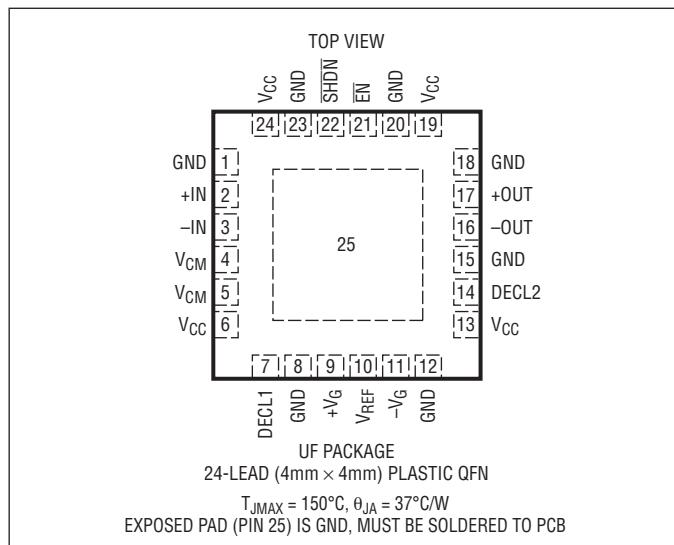

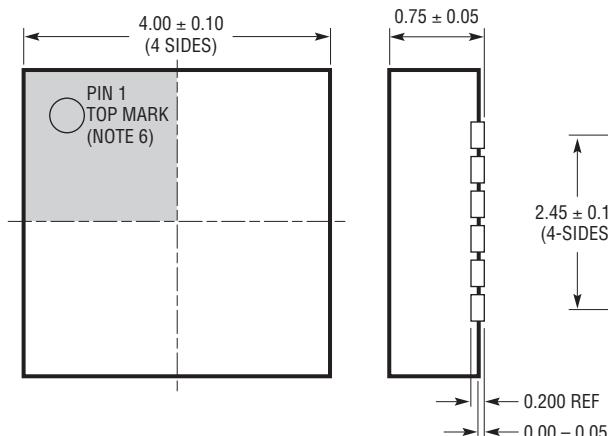

- 4mm×4mm×0.75mmの24ピンQFNパッケージ

## アプリケーション

- IF信号チェーン自動利得制御(AGC)

- 2.5Gおよび3Gセルラー基地局トランシーバ

- WiMAX、WiBro、WLANレシーバ

- 衛星およびGPSレシーバIF

## 概要

LTC<sup>®</sup>6412はdBリニアなアナログ利得制御を備えた完全差動可変ゲイン・アンプ(VGA)です。このデバイスは、1MHz～500MHzのIFレシーバ・チェーンにおけるAC結合動作向けに設計されています。広い出力振幅範囲と31dBの利得制御範囲にわたり、一定したOIP3を実現します。出力ノイズ(NF+利得)も利得に対してフラットなので、240MHzで全利得制御範囲にわたり120dBを超える一定なSFDRを実現します。

LTC6412は、12ビット、14ビット、16ビットADCアプリケーションに使用できるLT<sup>®</sup>5527およびLT5557ダウンコンバーティング・ミキサ、LTC6410-6 IFアンプ、LTC6400/LTC6401/LTC6416 ADCドライバとのインターフェイスに最適です。

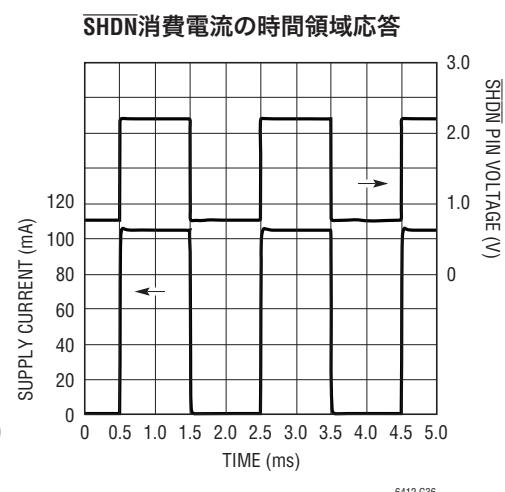

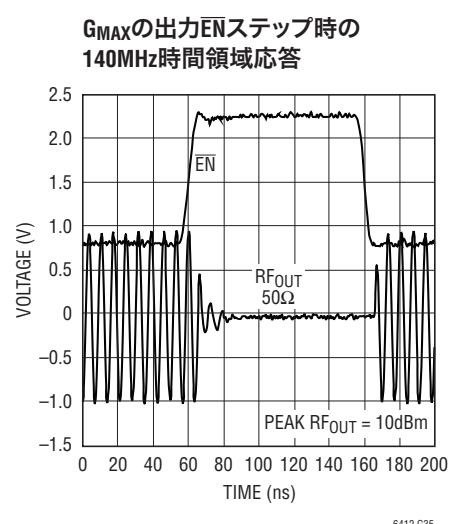

LTC6412はオーバードライブ状態から迅速に回復し、ENピンによって出力信号を素早くディスエーブルできるので、外部からの影響を受けやすい下流部品を保護することができます。SHDNピンをアサートすると、消費電流が1mA未満に減少し、パワーダウン・モードかスリープ・モードになります。

□、LT、LTC、LTM、Linear Technology およびLinearのロゴは、リニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

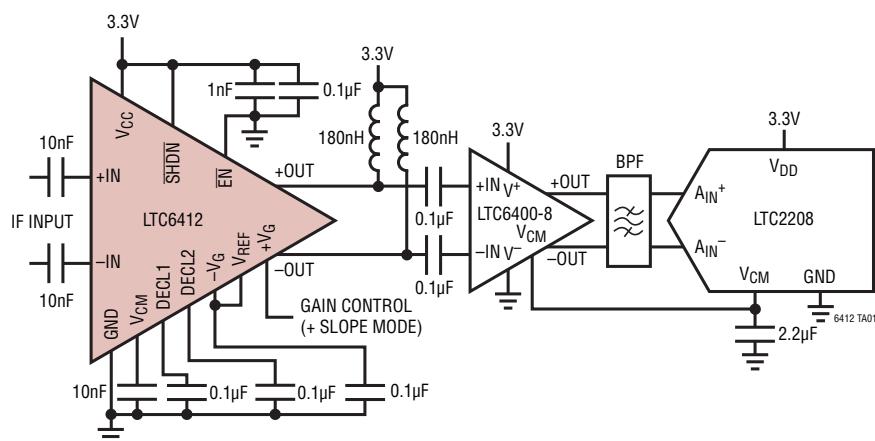

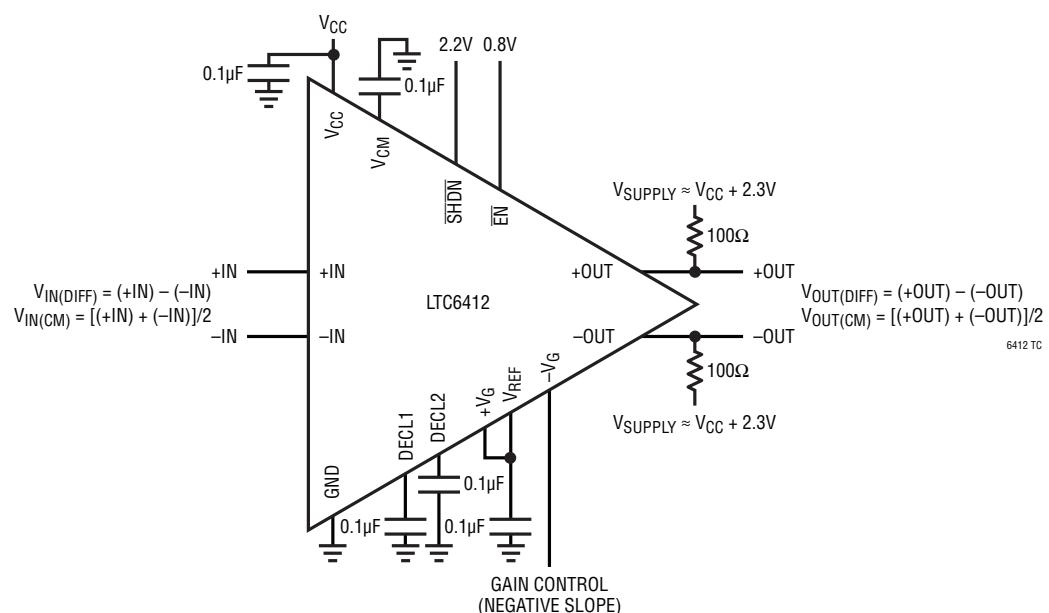

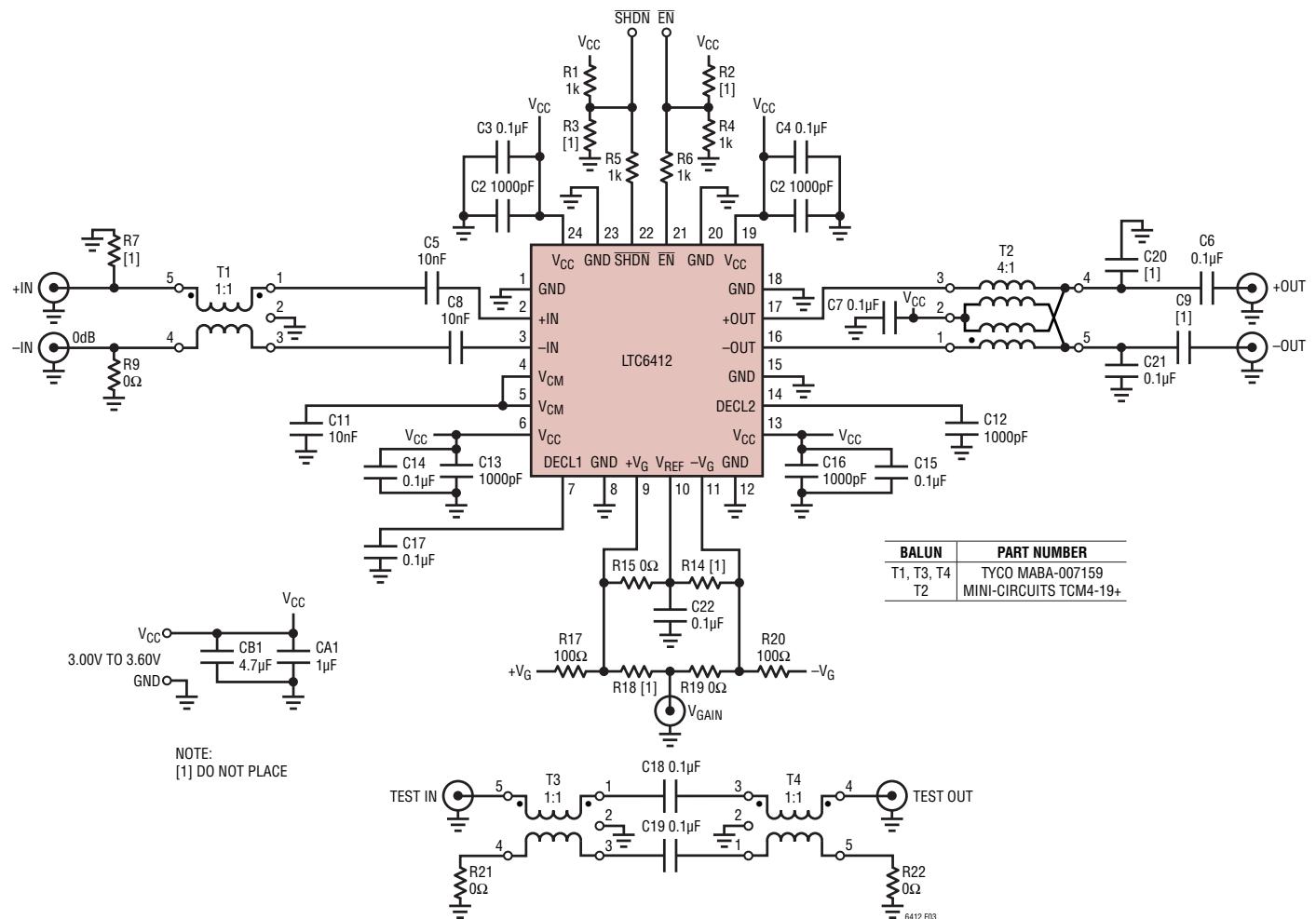

## 標準的應用例

31dB利得制御可能な3.3V完全差動240MHz IFレシーバ・チェーン

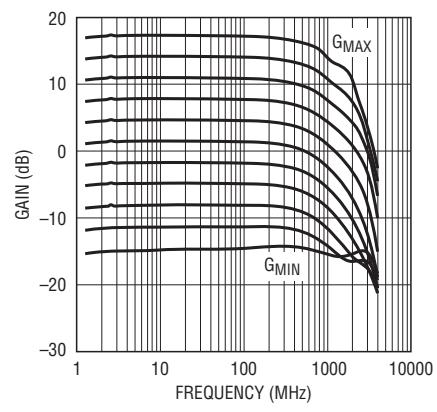

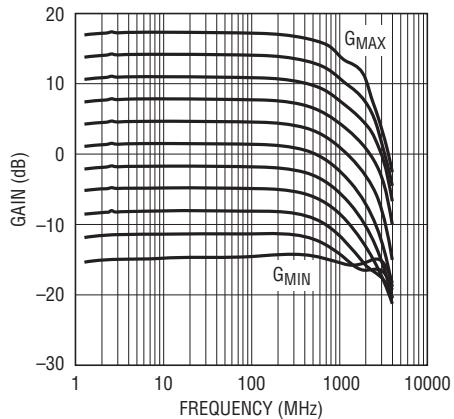

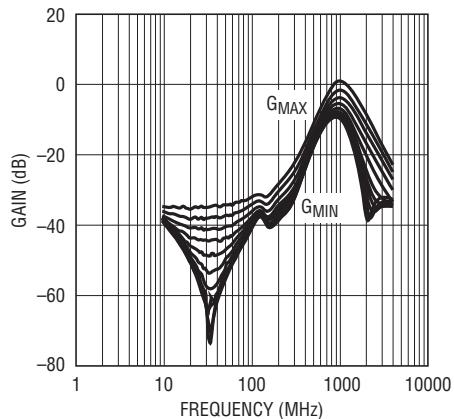

## 利得制御範囲における VGA利得と周波数

## 絶対最大定格

(Note 1)

|                                                                        |                   |

|------------------------------------------------------------------------|-------------------|

| 全電源電圧( $V_{CC}$ からGND) .....                                           | 3.8V              |

| アンプ入力電流(+IN, -IN) .....                                                | $\pm 20\text{mA}$ |

| アンプ出力電流(+OUT, -OUT) .....                                              | $\pm 70\text{mA}$ |

| 入力電流(+ $V_G$ , - $V_G$ , $V_{REF}$ , $\bar{EN}$ , $\bar{SHDN}$ ) ..... | $\pm 10\text{mA}$ |

| 入力電流( $V_{CM}$ , $DECL1$ , $DECL2$ ) .....                             | $\pm 10\text{mA}$ |

| RF入力電力、連続、 $50\Omega$ .....                                            | +15dBm            |

| RF入力電力、100 $\mu\text{s}$ パルス、 $50\Omega$ .....                         | +20dBm            |

| 動作温度範囲(Note 2) .....                                                   | -40°C~85°C        |

| 規定温度範囲(Note 3) .....                                                   | -40°C~85°C        |

| 保存温度範囲 .....                                                           | -65°C~150°C       |

| 接合部温度 .....                                                            | 150°C             |

## ピン配置

## 発注情報

| 鉛フリー仕様         | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲          |

|----------------|------------------|----------|---------------------------------|---------------|

| LTC6412CUF#PBF | LTC6412CUF#TRPBF | 6412     | 24-Lead (4mm x 4mm) Plastic QFN | 0°C to 70°C   |

| LTC6412IUF#PBF | LTC6412IUF#TRPBF | 6412     | 24-Lead (4mm x 4mm) Plastic QFN | -40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛ベースの仕上げ部品に関しては、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## DC電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。DCテスト回路の回路図を使用して測定されたDC電気的性能。

$V_{IN(DIFF)}$ は $(+IN) - (-IN)$ で定義される。 $V_{OUT(DIFF)}$ は $(+OUT) - (-OUT)$ で定義される。 $V_{IN(CM)}$ は $(+IN) + (-IN)$ /2で定義される。

$V_{OUT(CM)}$ は $(+OUT) + (-OUT)$ /2で定義される。注記がない限り、デフォルトの動作条件は、 $V_{CC} = 3.3\text{V}$ 、 $EN = 0.8\text{V}$ 、 $SHDN = 2.2\text{V}$ 、

$+V_G$ は $V_{REF}$ に接続(負の利得スロープ・モード)、 $V_{OUT(CM)} = 3.3\text{V}$ 。差動電力利得は $Z_{SOURCE} = 50\Omega$ 差動、 $Z_{LOAD} = 200\Omega$ 差動で定義。

| SYMBOL          | PARAMETER                                      | CONDITIONS                                                                                     | MIN                 | TYP   | MAX            | UNITS                                        |

|-----------------|------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------|-------|----------------|----------------------------------------------|

| 利得特性            |                                                |                                                                                                |                     |       |                |                                              |

| $G_{MAX}$       | Maximum Differential Power Gain (Note 4)       | $-V_G = 0\text{V}$ , $V_{IN(DIFF)} = 100\text{mV}$                                             | ●<br>16.1<br>15.5   | 17.1  | 18.1<br>18.7   | dB<br>dB                                     |

| $G_{MIN}$       | Minimum Differential Power Gain (Note 4)       | $-V_G = 1.2\text{V}$ , $V_{IN(DIFF)} = 200\text{mV}$                                           | ●<br>-16.2<br>-16.8 | -14.9 | -13.6<br>-13.0 | dB<br>dB                                     |

| $G_{RANGE}$     | Differential Power Gain Range                  | $G_{MAX} - G_{MIN}$                                                                            | ●<br>30.7<br>30.1   | 31.9  | 33.1<br>33.7   | dB<br>dB                                     |

| $TC_{GAIN}$     | Temperature Coefficient of Gain at Fixed $V_G$ | $-V_G = 0\text{V}$ to $1.2\text{V}$                                                            |                     |       | -0.007         | $\text{dB}/^\circ\text{C}$                   |

| $G_{SLOPE}$     | Gain Control Slope                             | $-V_G = 0.2\text{V}$ to $1.0\text{V}$ , 85 Points, Slope of the Least-Square Fit Line          | ●<br>-34.1<br>-34.7 | -32.9 | -31.7<br>-31.1 | $\text{dB}/\text{V}$<br>$\text{dB}/\text{V}$ |

| $G_{CONF(AVE)}$ | Average Conformance Error to Gain Slope Line   | $-V_G = 0.2\text{V}$ to $1.0\text{V}$ , 85 Points, Standard Error to the Least-Square Fit Line |                     | 0.12  | 0.20           | dB                                           |

| $G_{CONF(MAX)}$ | Maximum Conformance Error to Gain Slope Line   | $-V_G = 0.2\text{V}$ to $1.0\text{V}$ , 85 points, Maximum Error to the Least-Square Fit Line  |                     | 0.20  | 0.45           | dB                                           |

## +INおよび-INピン

|                  |                                               |                                                       |               |    |          |                      |

|------------------|-----------------------------------------------|-------------------------------------------------------|---------------|----|----------|----------------------|

| $R_{IN(GMAX)}$   | Differential Input Resistance at Maximum Gain | $-V_G = 0\text{V}$ , $V_{IN(DIFF)} = 100\text{mV}$    | ●<br>49<br>47 | 57 | 65<br>67 | $\Omega$<br>$\Omega$ |

| $R_{IN(GMIN)}$   | Differential Input Resistance at Minimum Gain | $-V_G = 1.2\text{V}$ , $V_{IN(DIFF)} = 200\text{mV}$  | ●<br>49<br>47 | 57 | 65<br>67 | $\Omega$<br>$\Omega$ |

| $V_{INCM(GMAX)}$ | Input Common Mode Voltage at Maximum Gain     | $-V_G = 0\text{V}$ , DC Blocking Capacitor to Input   |               |    | 640      | mV                   |

| $V_{INCM(GMIN)}$ | Input Common Mode Voltage at Minimum Gain     | $-V_G = 1.2\text{V}$ , DC Blocking Capacitor to Input |               |    | 640      | mV                   |

+ $V_G$ 、- $V_G$ 、および $V_{REF}$ ピン

|               |                               |                                                                                                    |                 |     |              |                                      |

|---------------|-------------------------------|----------------------------------------------------------------------------------------------------|-----------------|-----|--------------|--------------------------------------|

| $R_{IH(+VG)}$ | + $V_G$ Input High Resistance | $+V_G = 1.0\text{V}$ , - $V_G$ Tied to $V_{REF}$ ,<br>$R_{IN(+VG)} = 1\text{V}/\Delta I_{IL(+VG)}$ | ●<br>7.8<br>7.2 | 9.2 | 10.6<br>11.6 | $\text{k}\Omega$<br>$\text{k}\Omega$ |

| $R_{IH(-VG)}$ | - $V_G$ Input High Resistance | $-V_G = 1.0\text{V}$ , + $V_G$ Tied to $V_{REF}$ ,<br>$R_{IN(-VG)} = 1\text{V}/\Delta I_{IL(-VG)}$ | ●<br>7.8<br>7.2 | 9.2 | 10.6<br>11.6 | $\text{k}\Omega$<br>$\text{k}\Omega$ |

| $I_{IL(+VG)}$ | + $V_G$ Input Low Current     | $+V_G = 0\text{V}$ , - $V_G$ Tied to $V_{REF}$                                                     | ●<br>-9<br>-10  | -5  | -1<br>-1     | $\mu\text{A}$<br>$\mu\text{A}$       |

| $I_{IL(-VG)}$ | - $V_G$ Input Low Current     | $-V_G = 0\text{V}$ , + $V_G$ Tied to $V_{REF}$                                                     | ●<br>-9<br>-10  | -5  | -1<br>-1     | $\mu\text{A}$<br>$\mu\text{A}$       |

| $V_{REF}$     | Internal Bias Voltage         | $-V_G = 0\text{V}$ , + $V_G$ Tied to $V_{REF}$                                                     | ●<br>590<br>580 | 615 | 640<br>650   | mV<br>mV                             |

## DC電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。DCテスト回路の回路図を使用して測定されたDC電気的性能。

$V_{IN(DIFF)}$ は $(+IN) - (-IN)$ で定義される。 $V_{OUT(DIFF)}$ は $(+OUT) - (-OUT)$ で定義される。 $V_{IN(CM)}$ は $(+IN) + (-IN)$ で定義される。

$V_{OUT(CM)}$ は $(+OUT) + (-OUT)$ で定義される。注記がない限り、デフォルトの動作条件は、 $V_{CC} = 3.3\text{V}$ 、 $\bar{EN} = 0.8\text{V}$ 、 $SHDN = 2.2\text{V}$ 、

$+V_G = V_{REF}$ に接続(負の利得スローブ・モード)、 $V_{OUT(CM)} = 3.3\text{V}$ 。差動電力利得は $Z_{SOURCE} = 50\Omega$ 差動、 $Z_{LOAD} = 200\Omega$ 差動で定義。

| SYMBOL             | PARAMETER                                | CONDITIONS                                    | MIN | TYP | MAX | UNITS |               |

|--------------------|------------------------------------------|-----------------------------------------------|-----|-----|-----|-------|---------------|

| <b>SHDNピン</b>      |                                          |                                               |     |     |     |       |               |

| $V_{IL(SHDN)}$     | SHDN Input Low Voltage                   |                                               | ●   |     | 0.8 | V     |               |

| $V_{IH(SHDN)}$     | SHDN Input High Voltage                  |                                               | ●   | 2.2 |     | V     |               |

| $I_{IL(SHDN)}$     | SHDN Input Low Current                   | $SHDN = 0.8\text{V}$                          | ●   | -60 | -30 | -1    | $\mu\text{A}$ |

| $I_{IH(SHDN)}$     | SHDN Input High Current                  | $SHDN = 2.2\text{V}$                          | ●   | -30 | -15 | -1    | $\mu\text{A}$ |

| <b>ENピン</b>        |                                          |                                               |     |     |     |       |               |

| $V_{IL(\bar{EN})}$ | $\bar{EN}$ Input Low Voltage             |                                               | ●   |     | 0.8 | V     |               |

| $V_{IH(\bar{EN})}$ | $\bar{EN}$ Input High Voltage            |                                               | ●   | 2.2 |     | V     |               |

| $I_{IL(\bar{EN})}$ | $\bar{EN}$ Input Low Current             | $\bar{EN} = 0.8\text{V}$                      | ●   | -60 | -30 | -1    | $\mu\text{A}$ |

| $I_{IH(\bar{EN})}$ | $\bar{EN}$ Input High Current            | $\bar{EN} = 2.2\text{V}$                      | ●   | -30 | -15 | -1    | $\mu\text{A}$ |

| <b>電源</b>          |                                          |                                               |     |     |     |       |               |

| $V_S$              | Operating Supply Range                   |                                               | ●   | 3.0 | 3.3 | 3.6   | V             |

| $I_{S(TOT)}$       | Total Supply Current                     | All $V_{CC}$ Pins Plus $+OUT$ and $-OUT$ Pins | ●   | 110 | 135 | 140   | $\text{mA}$   |

| $I_{S(OUT)}$       | Sum of Supply Current to OUT Pins        | $I_{S(OUT)} = I_{+OUT} + I_{-OUT}$            | ●   | 44  | 55  | 60    | $\text{mA}$   |

| $I_{\Delta(OUT)}$  | Delta of Supply Current to OUT Pins      | Current Imbalance to $+OUT$ and $-OUT$        | ●   | 0.5 | 1.5 | 2.0   | $\text{mA}$   |

| $I_{S(SHDN)}$      | Supply Current in Shutdown               | $I_{S(OUT)}$ at $SHDN = 0.8\text{V}$          | ●   | 0.5 | 1.3 | 2.0   | $\text{mA}$   |

| $PSRR_{MAX}$       | Power Supply Rejection Ratio at Max Gain | $-V_G = 0\text{V}$ , Output Referred          |     | 40  | 53  |       | dB            |

| $PSRR_{MIN}$       | Power Supply Rejection Ratio at Min Gain | $-V_G = 1.2\text{V}$ , Output Referred        |     | 40  | 53  |       | dB            |

## AC電気的特性

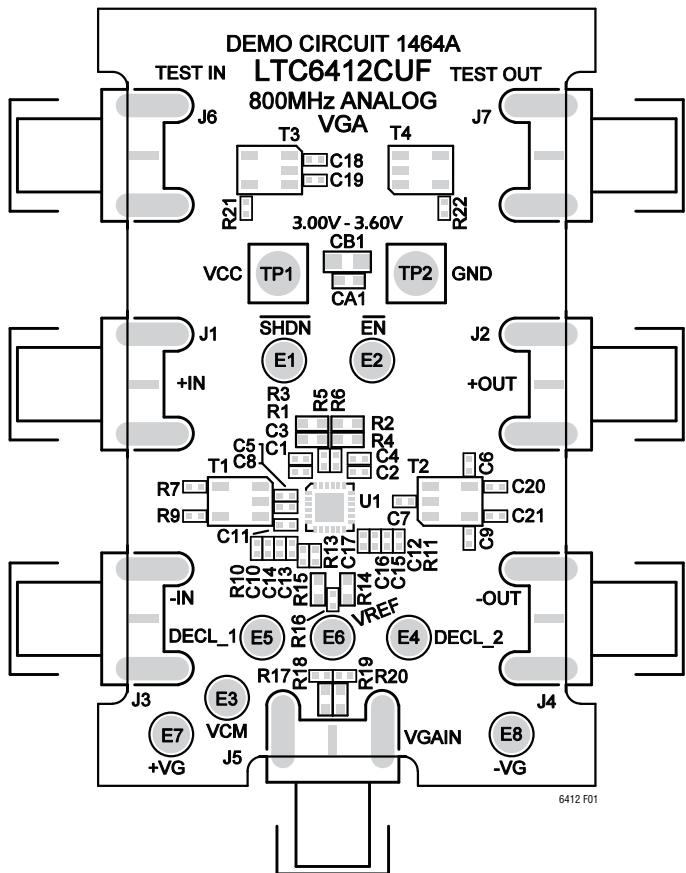

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記のない限り、デモ・ボードDC1464A(図3、テスト回路A)で測定されたAC電気的性能。注記がない限り、デフォルトの動作条件は、 $V_{CC} = 3.3\text{V}$ 、 $\bar{EN} = 0.8\text{V}$ 、 $\bar{SHDN} = 2.2\text{V}$ 、 $+V_G$ は $V_{REF}$ に接続(負の利得スロープ・モード)、 $Z_{SOURCE} = Z_{LOAD} = 50\Omega$ 。

| SYMBOL           | PARAMETER                                           | CONDITIONS                                                                                                                                   | MIN | TYP | MAX | UNITS         |

|------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| <b>小信号</b>       |                                                     |                                                                                                                                              |     |     |     |               |

| $BW_{GMAX}$      | -3dB Bandwidth for Sdd21 at Maximum Gain            | $-V_G = 0\text{V}$ , Test Circuit B                                                                                                          |     | 800 |     | MHz           |

| $BW_{GMIN}$      | -3dB Bandwidth for Sdd21 at Minimum Gain            | $-V_G = 1.2\text{V}$ , Test Circuit B                                                                                                        |     | 800 |     | MHz           |

| Sdd11            | Input Match at $Z_{SOURCE} = 50\Omega$ Differential | $-V_G = 0\text{V}$ to 1.2V, 10MHz-500MHz, Test Circuit B                                                                                     |     | -20 |     | dB            |

| Sdd22            | Output Match at $Z_{LOAD} = 200\Omega$ Differential | $-V_G = 0\text{V}$ to 1.2V, 10MHz-250MHz, Test Circuit B                                                                                     |     | -10 |     | dB            |

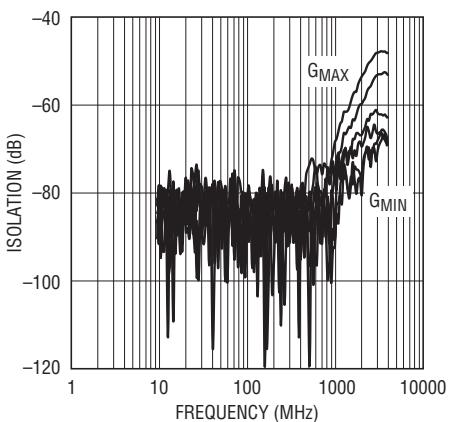

| Sdd12            | Reverse Isolation                                   | $-V_G = 0\text{V}$ to 1.2V, 10MHz-500MHz, Test Circuit B                                                                                     |     | -80 |     | dB            |

| <b>過渡応答</b>      |                                                     |                                                                                                                                              |     |     |     |               |

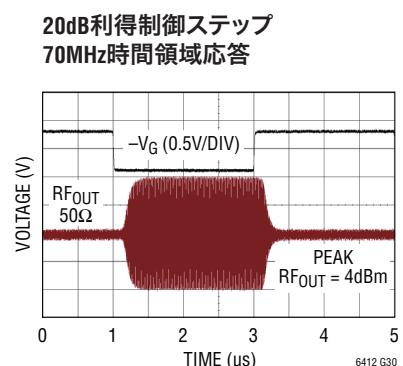

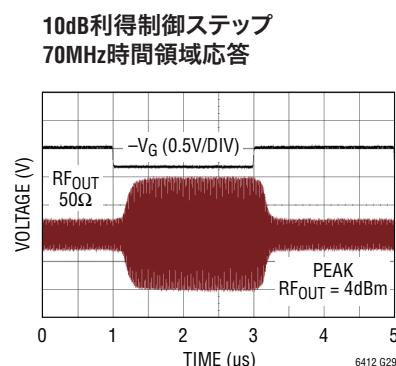

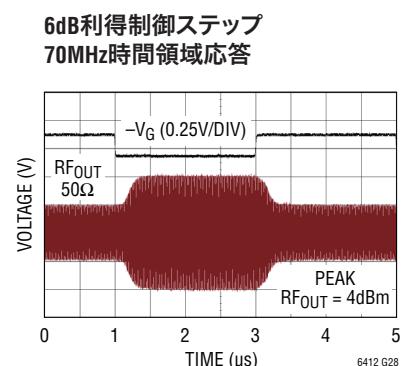

| $t_{STEP(6dB)}$  | 6dB Gain Step Response Time                         | Peak $P_{OUT} = +4\text{dBm}$ , $-V_G = 0.2\text{V}$ to 0.4V, Time to Settle Within 1dB of Final $P_{OUT}$                                   |     | 0.4 |     | $\mu\text{s}$ |

| $t_{STEP(12dB)}$ | 12dB Gain Step Response Time                        | Peak $P_{OUT} = +4\text{dBm}$ , $-V_G = 0.2\text{V}$ to 0.6V, Time to Settle Within 1dB of Final $P_{OUT}$                                   |     | 0.4 |     | $\mu\text{s}$ |

| $t_{STEP(20dB)}$ | 20dB Gain Step Response Time                        | Peak $P_{OUT} = +4\text{dBm}$ , $-V_G = 0.2\text{V}$ to 0.8V, Time to Settle Within 1dB of Final $P_{OUT}$                                   |     | 0.4 |     | $\mu\text{s}$ |

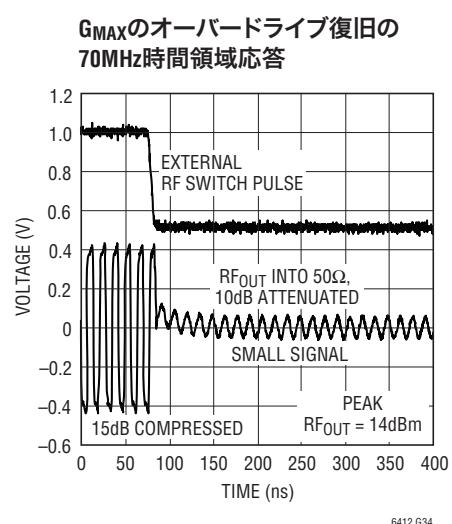

| $t_{OVDR}$       | Overdrive Recovery Time at 70MHz                    | $-V_G = 0\text{V}$ , $P_{IN} = +3\text{dBm}$ to $-17\text{dBm}$ , Time to Settle Within 1dB of Final $P_{OUT}$                               |     | 25  |     | ns            |

| $t_{OFF}$        | Output Amplifier Disable Time                       | $P_{OUT} = 0\text{dBm}$ at $\bar{EN} = 0\text{V}$ , $-V_G = 0\text{V}$ , $\bar{EN} = 0\text{V}$ to 3V, Time for $P_{OUT} \leq -20\text{dBm}$ |     | 25  |     | ns            |

| $t_{ON}$         | Output Amplifier Enable Time                        | $P_{OUT} = 0\text{dBm}$ at $\bar{EN} = 0\text{V}$ , $-V_G = 0\text{V}$ , $\bar{EN} = 3\text{V}$ to 0V, Time for $P_{OUT} \geq -1\text{dBm}$  |     | 20  |     | ns            |

| <b>70MHz信号</b>   |                                                     |                                                                                                                                              |     |     |     |               |

| $G_{MAX}$        | Maximum Gain                                        | $-V_G = 0\text{V}$ , Test Circuit B                                                                                                          |     | 17  |     | dB            |

| $G_{MIN}$        | Minimum Gain                                        | $-V_G = 1.2\text{V}$ , Test Circuit B                                                                                                        |     | -15 |     | dB            |

| $G_{RANGE}$      | Gain Range                                          | $G_{MAX}-G_{MIN}$                                                                                                                            |     | 32  |     | dB            |

| HD2              | Second Harmonic Distortion                          | $P_{OUT} = 0\text{dBm}$ , $-V_G = 0\text{V}$ to 1.0V                                                                                         |     | -80 |     | dBc           |

| HD3              | Third Harmonic Distortion                           | $P_{OUT} = 0\text{dBm}$ , $-V_G = 0\text{V}$ to 1.0V                                                                                         |     | -80 |     | dBc           |

| IM3              | Third-Order Intermodulation                         | $f_1 = 69.5\text{MHz}$ , $f_2 = 70.5\text{MHz}$ , $P_{OUT} = -6\text{dBm/Tone}$ , $-V_G = 0\text{V}$ to 1.0V                                 |     | -90 |     | dBc           |

| OIP3             | Output Third-Order Intercept                        | $f_1 = 69.5\text{MHz}$ , $f_2 = 70.5\text{MHz}$ , $P_{OUT} = -6\text{dBm/Tone}$ , $-V_G = 0\text{V}$ to 1.0V                                 |     | 39  |     | dBm           |

| $P_{1dB_{GMAX}}$ | Output 1dB Compression Point at Max Gain            | $-V_G = 0\text{V}$ (Note 6)                                                                                                                  |     | 13  |     | dBm           |

| $NF_{GMAX}$      | Noise Figure at Maximum Gain                        | $-V_G = 0\text{V}$ (Note 5)                                                                                                                  |     | 10  |     | dB            |

| $NF_{GMIN}$      | Noise Figure at Minimum Gain                        | $-V_G = 1.2\text{V}$ (Note 5)                                                                                                                |     | 42  |     | dB            |

| <b>140MHz信号</b>  |                                                     |                                                                                                                                              |     |     |     |               |

| $G_{MAX}$        | Maximum Gain                                        | $-V_G = 0\text{V}$ , Test Circuit B                                                                                                          |     | 17  |     | dB            |

| $G_{MIN}$        | Minimum Gain                                        | $-V_G = 1.2\text{V}$ , Test Circuit B                                                                                                        |     | -15 |     | dB            |

| $G_{RANGE}$      | Gain Range                                          | $G_{MAX}-G_{MIN}$                                                                                                                            |     | 32  |     | dB            |

| HD2              | Second Harmonic Distortion                          | $P_{OUT} = 0\text{dBm}$ , $-V_G = 0\text{V}$ to 1.0V                                                                                         |     | -80 |     | dBc           |

| HD3              | Third Harmonic Distortion                           | $P_{OUT} = 0\text{dBm}$ , $-V_G = 0\text{V}$ to 1.0V                                                                                         |     | -75 |     | dBc           |

## AC電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記のない限り、デモ・ボードDC1464A(図3、テスト回路A)で測定されたAC電気的性能。注記がない限り、デフォルトの動作条件は、 $V_{CC} = 3.3\text{V}$ 、 $\overline{EN} = 0.8\text{V}$ 、 $\overline{SHDN} = 2.2\text{V}$ 、 $+V_G$ は $V_{REF}$ に接続(負の利得スローブ・モード)、 $Z_{SOURCE} = Z_{LOAD} = 50\Omega$ 。

| SYMBOL               | PARAMETER                                | CONDITIONS                                                                                                              | MIN | TYP | MAX | UNITS |

|----------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| IM3                  | Third-Order Intermodulation              | $f_1 = 139.5\text{MHz}$ , $f_2 = 140.5\text{MHz}$ , $P_{OUT} = -6\text{dBm/Tone}$ , $-V_G = 0\text{V}$ to $1.0\text{V}$ |     | -88 |     | dBc   |

| OIP3                 | Output Third-Order Intercept             | $f_1 = 139.5\text{MHz}$ , $f_2 = 140.5\text{MHz}$ , $P_{OUT} = -6\text{dBm/Tone}$ , $-V_G = 0\text{V}$ to $1.0\text{V}$ |     | 38  |     | dBm   |

| P1dB <sub>GMAX</sub> | Output 1dB Compression Point at Max Gain | $-V_G = 0\text{V}$ (Note 6)                                                                                             |     | 13  |     | dBm   |

| NF <sub>GMAX</sub>   | Noise Figure at Maximum Gain             | $-V_G = 0\text{V}$ (Note 5)                                                                                             |     | 10  |     | dB    |

| NF <sub>GMIN</sub>   | Noise Figure at Minimum Gain             | $-V_G = 1.2\text{V}$ (Note 5)                                                                                           |     | 42  |     | dB    |

### 240MHz信号

|                      |                                          |                                                                                                                         |  |     |  |     |

|----------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|-----|--|-----|

| G <sub>MAX</sub>     | Maximum Gain                             | $-V_G = 0\text{V}$ , Test Circuit B                                                                                     |  | 17  |  | dB  |

| G <sub>MIN</sub>     | Minimum Gain                             | $-V_G = 1.2\text{V}$ , Test Circuit B                                                                                   |  | -14 |  | dB  |

| G <sub>RANGE</sub>   | Gain Range                               | $G_{MAX}$ - $G_{MIN}$                                                                                                   |  | 31  |  | dB  |

| HD2                  | Second Harmonic Distortion               | $P_{OUT} = 0\text{dBm}$ , $-V_G = 0\text{V}$ to $1.0\text{V}$                                                           |  | -70 |  | dBc |

| HD3                  | Third Harmonic Distortion                | $P_{OUT} = 0\text{dBm}$ , $-V_G = 0\text{V}$ to $1.0\text{V}$                                                           |  | -70 |  | dBc |

| IM3                  | Third-Order Intermodulation              | $f_1 = 239.5\text{MHz}$ , $f_2 = 240.5\text{MHz}$ , $P_{OUT} = -6\text{dBm/Tone}$ , $-V_G = 0\text{V}$ to $1.0\text{V}$ |  | -82 |  | dBc |

| OIP3                 | Output Third-Order Intercept             | $f_1 = 239.5\text{MHz}$ , $f_2 = 240.5\text{MHz}$ , $P_{OUT} = -6\text{dBm/Tone}$ , $-V_G = 0\text{V}$ to $1.0\text{V}$ |  | 35  |  | dBm |

| P1dB <sub>GMAX</sub> | Output 1dB Compression Point at Max Gain | $-V_G = 0\text{V}$ (Note 6)                                                                                             |  | 12  |  | dBm |

| NF <sub>GMAX</sub>   | Noise Figure at Maximum Gain             | $-V_G = 0\text{V}$ (Note 5)                                                                                             |  | 10  |  | dB  |

| NF <sub>GMIN</sub>   | Noise Figure at Minimum Gain             | $-V_G = 1.2\text{V}$ (Note 5)                                                                                           |  | 42  |  | dB  |

### 280MHz/320MHz信号

|                      |                                          |                                                                                                      |      |       |      |     |

|----------------------|------------------------------------------|------------------------------------------------------------------------------------------------------|------|-------|------|-----|

| G <sub>MAX</sub>     | Maximum Gain                             | $f = 320\text{MHz}$ , $P_{OUT} = -3\text{dBm}$ , $-V_G = 0\text{V}$                                  |      | 16.9  |      | dB  |

| G <sub>MID</sub>     | Medium Gain                              | $f = 320\text{MHz}$ , $P_{OUT} = -5\text{dBm}$ , $-V_G = 0.6\text{V}$                                |      | 1.5   |      | dB  |

| G <sub>MIN</sub>     | Minimum Gain                             | $f = 320\text{MHz}$ , $P_{OUT} = -5\text{dBm}$ , $-V_G = 1.2\text{V}$                                |      | -14.2 |      | dB  |

| G <sub>RANGE</sub>   | Gain Range                               | $320\text{MHz}$ , $G_{MAX}$ - $G_{MIN}$                                                              | 29.7 | 31.1  | 32.5 | dB  |

| IM3 <sub>GMAX</sub>  | Third-Order Intermodulation at Max Gain  | $f_1 = 280\text{MHz}$ , $f_2 = 320\text{MHz}$ , $P_{OUT} = -3\text{dBm/Tone}$ , $-V_G = 0\text{V}$   |      | -72   |      | dBc |

| IM3 <sub>GMID</sub>  | Third-Order Intermodulation at Mid Gain  | $f_1 = 280\text{MHz}$ , $f_2 = 320\text{MHz}$ , $P_{OUT} = -5\text{dBm/Tone}$ , $-V_G = 0.6\text{V}$ |      | -71   | -65  | dBc |

| IM3 <sub>GMIN</sub>  | Third-Order Intermodulation at Min Gain  | $f_1 = 280\text{MHz}$ , $f_2 = 320\text{MHz}$ , $P_{OUT} = -5\text{dBm/Tone}$ , $-V_G = 1.2\text{V}$ |      | -56   |      | dBc |

| OIP3 <sub>GMAX</sub> | Output Third-Order Intercept at Max Gain | $f_1 = 280\text{MHz}$ , $f_2 = 320\text{MHz}$ , $P_{OUT} = -3\text{dBm/Tone}$ , $-V_G = 0\text{V}$   |      | 31.0  |      | dBm |

| OIP3 <sub>GMID</sub> | Output Third-Order Intercept at Mid Gain | $f_1 = 280\text{MHz}$ , $f_2 = 320\text{MHz}$ , $P_{OUT} = -5\text{dBm/Tone}$ , $-V_G = 0.6\text{V}$ | 26.0 | 30.5  |      | dBm |

| OIP3 <sub>GMIN</sub> | Output Third-Order Intercept at Min Gain | $f_1 = 280\text{MHz}$ , $f_2 = 320\text{MHz}$ , $P_{OUT} = -5\text{dBm/Tone}$ , $-V_G = 1.2\text{V}$ |      | 23.0  |      | dBm |

## AC電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記のない限り、デモ・ボードDC1464A(図3、テスト回路A)で測定されたAC電気的性能。注記がない限り、デフォルトの動作条件は、 $V_{CC} = 3.3\text{V}$ 、 $\overline{EN} = 0.8\text{V}$ 、 $\overline{SHDN} = 2.2\text{V}$ 、 $+V_G$ は $V_{REF}$ に接続(負の利得スロープ・モード)、 $Z_{SOURCE} = Z_{LOAD} = 50\Omega$ 。

| SYMBOL                  | PARAMETER                                | CONDITIONS                                                                                                                 | MIN  | TYP | MAX | UNITS |

|-------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| <b>380MHz信号</b>         |                                          |                                                                                                                            |      |     |     |       |

| $G_{MAX}$               | Maximum Gain                             | $-V_G = 0\text{V}$ , Test Circuit B                                                                                        | 17   |     |     | dB    |

| $G_{MIN}$               | Minimum Gain                             | $-V_G = 1.2\text{V}$ , Test Circuit B                                                                                      | -14  |     |     | dB    |

| $G_{RANGE}$             | Gain Range                               | $G_{MAX}-G_{MIN}$                                                                                                          | 31   |     |     | dB    |

| IM3                     | Third-Order Intermodulation              | $f_1 = 379.5\text{MHz}$ , $f_2 = 380.5\text{MHz}$ ,<br>$P_{OUT} = -6\text{dBm/Tone}$ , $-V_G = 0\text{V}$ to $1.0\text{V}$ | -72  |     |     | dBc   |

| OIP3                    | Output Third-Order Intercept             | $f_1 = 379.5\text{MHz}$ , $f_2 = 380.5\text{MHz}$ ,<br>$P_{OUT} = -6\text{dBm/Tone}$ , $-V_G = 0\text{V}$ to $1.0\text{V}$ | 30   |     |     | dBm   |

| $P_{1\text{dB}}_{GMAX}$ | Output 1dB Compression Point at Max Gain | $-V_G = 0\text{V}$ (Note 6)                                                                                                | 11   |     |     | dBm   |

| $NF_{GMAX}$             | Noise Figure at Maximum Gain             | $-V_G = 0\text{V}$ (Note 5)                                                                                                | 10.5 |     |     | dB    |

| $NF_{GMIN}$             | Noise Figure at Minimum Gain             | $-V_G = 1.2\text{V}$ (Note 5)                                                                                              | 42   |     |     | dB    |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。RF入力電力定格は設計および工学的特性評価により保証されているが、製造時にはテストされない。絶対最大連続RF入力電力は+150dBmを超えないこと。

**Note 2:**LTC6412C/LTC6412Iは、 $-40^\circ\text{C}$ ~ $85^\circ\text{C}$ の温度範囲で動作することが保証されている。

**Note 3:**LTC6412Cは $0^\circ\text{C}$ ~ $70^\circ\text{C}$ の温度範囲で性能仕様に適合することが保証されており、 $-40^\circ\text{C}$ ~ $85^\circ\text{C}$ の拡張温度範囲で性能仕様に適合するように設計され、特性が評価されており、性能仕様に適合すると予想されるが、これらの温度ではテストおよびQAサンプリングは行われない。LTC6412Iは $-40^\circ\text{C}$ ~ $85^\circ\text{C}$ の温度範囲で性能仕様に適合することが保証されている。

**Note 4:**電力利得は、 $Z_{SOURCE} = 50\Omega$ および $Z_{LOAD} = 200\Omega$ で定義。このテスト条件の電圧利得は、明記された電力利得よりも6dB高い。

**Note 5:** $e_n$ は次式で $50\Omega$  NFから計算できる。

$$e_n = \sqrt{4KT(50) (10^{NF/10} - 1)}$$

ここで

$e_n$  = 入力を基準にした $\text{V}/\sqrt{\text{Hz}}$ で表した電圧ノイズ

$NF = 50\Omega$ ノイズ・フィギュア(dB)

$k$  = ポルツマンの定数 =  $1.38 \cdot 10^{-23} \text{J}^\circ\text{K}$

$T$  = 絶対温度( $^\circ\text{K} = ^\circ\text{C} + 273$ )

**Note 6:**入力RF電力の絶対最大定格を満たしながら最小利得状態で出力アンプのP1dB圧縮を行なうことはできない。

## 標準的性能特性

注記のない限り、 $T_A = 25^\circ\text{C}$  および  $V_{CC} = 3.3\text{V}$  におけるテスト回路AとBにおける電気的性能。

11個の利得設定値に対する

差動利得 (Sdd21) と周波数

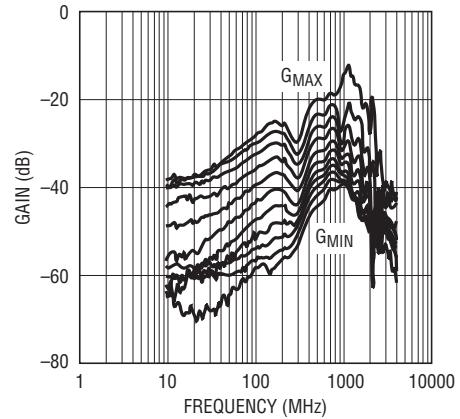

11個の利得設定値に対する

同相利得 (Scc21) と周波数

11個の利得設定値に対する

CM-DM利得 (Sdc21) と周波数

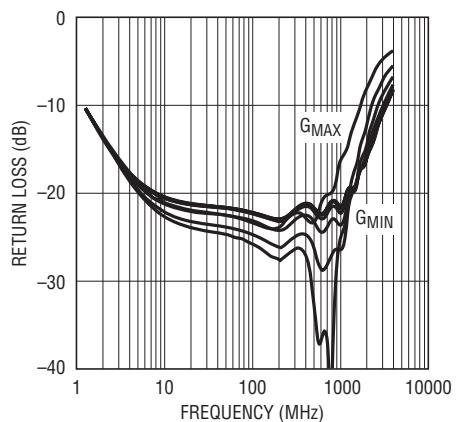

11個の利得設定値に対する

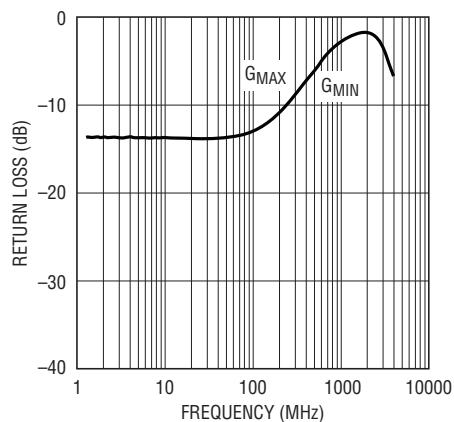

差動入力の整合性 (Sdd11) と周波数

6個の利得設定値に対する

差動出力の整合性 (Sdd22) と周波数

6個の利得設定値に対する

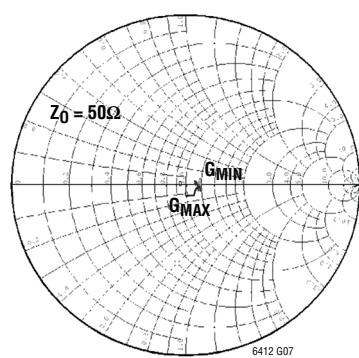

10MHz～500MHzの差動入力

スミス・チャート (Sdd11)

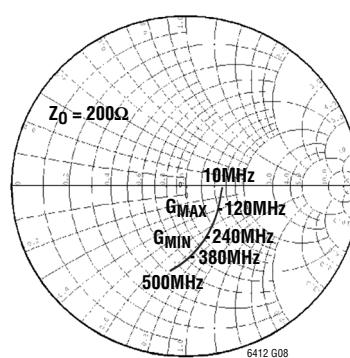

6個の利得設定値に対する

10MHz～500MHzの差動出力

スミス・チャート (Sdd22)

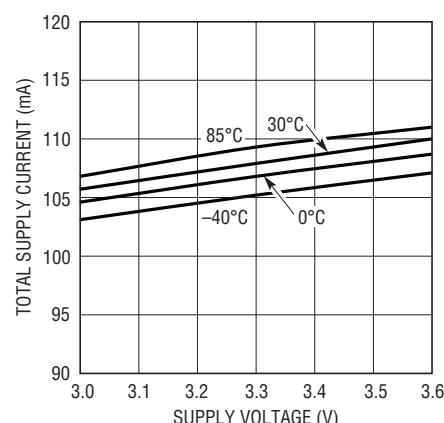

所定温度における

電源電流と電源電圧

## 標準的性能特性

注記のない限り、 $T_A = 25^\circ\text{C}$ および $V_{CC} = 3.3\text{V}$ におけるテスト回路AとBにおける電気的性能。

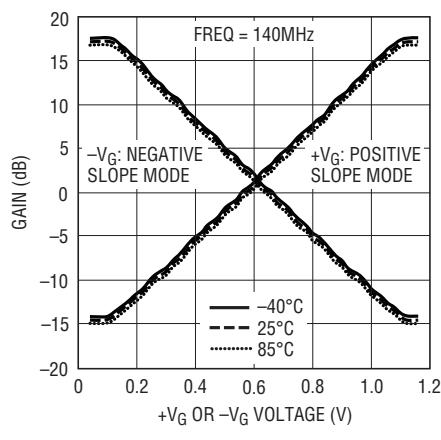

所定温度における差動利得

(Sdd21)と制御電圧

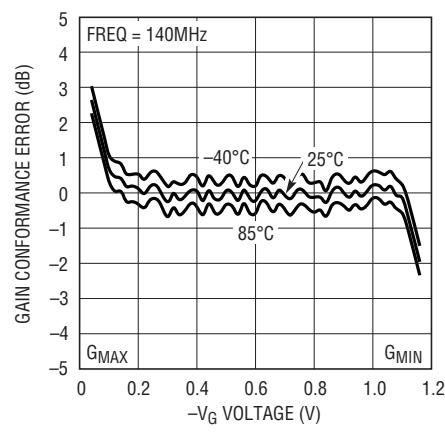

所定温度における利得(Sdd21)

コンフォーマンス誤差と制御電圧

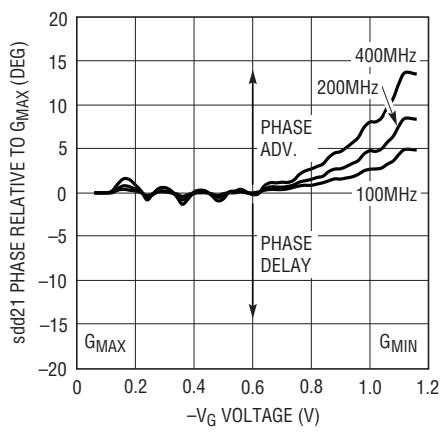

所定周波数における相対位相

(Sdd21)と制御電圧

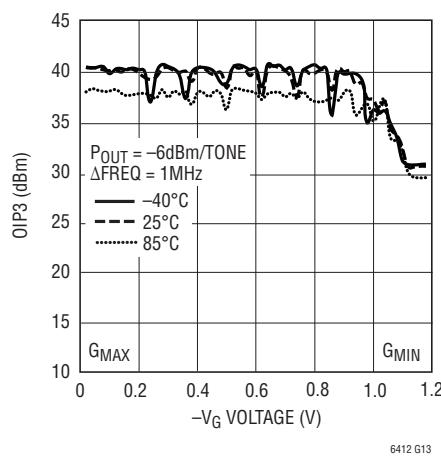

所定温度における

140MHzの出力IP3と制御電圧

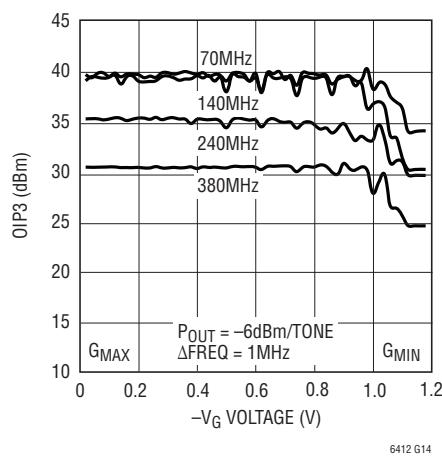

所定周波数における

出力IP3と制御電圧

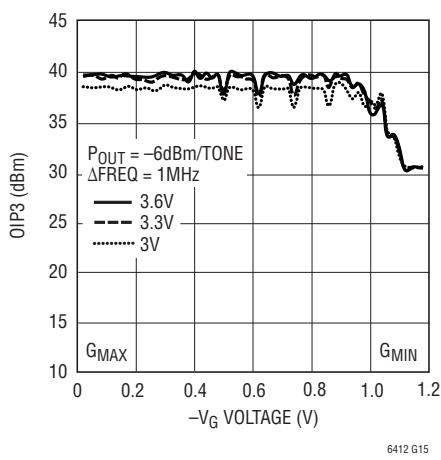

VCCにおける140MHzの

出力IP3と制御電圧

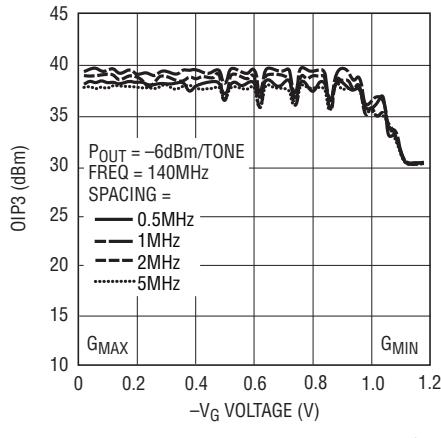

トーン・スペースに対する

出力IP3と制御電圧

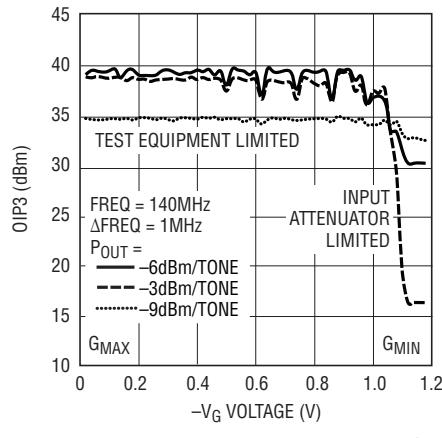

トーンごとの出力電力に対する

出力IP3と制御電圧

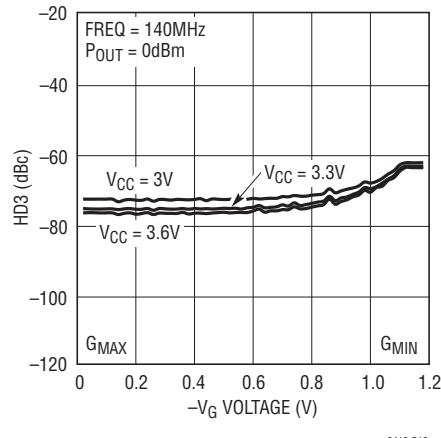

$V_{CC}$ に対する

3次高調波歪みと制御電圧

## 標準的性能特性

注記のない限り、 $T_A = 25^\circ\text{C}$  および  $V_{CC} = 3.3\text{V}$  におけるテスト回路AとBにおける電気的性能。

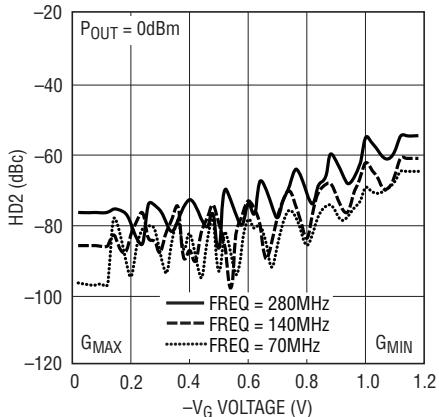

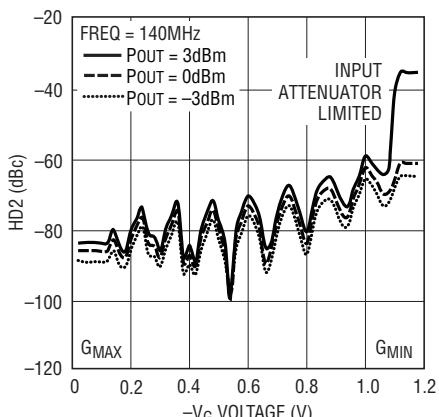

各周波数における2次高調波、歪みおよび制御電圧

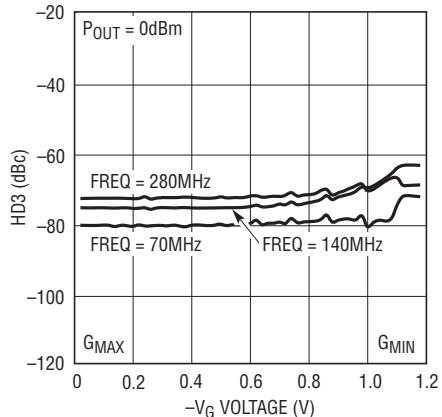

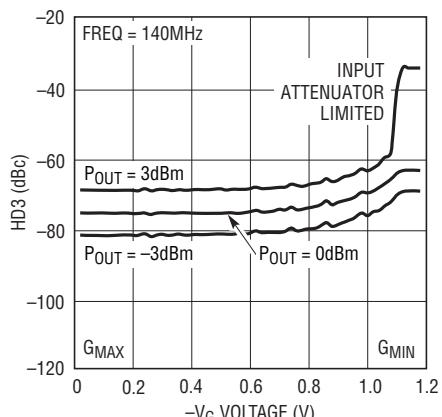

各周波数における3次高調波歪みと制御電圧

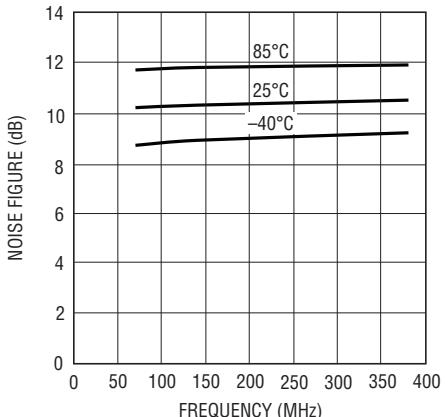

所定温度における $G_{MAX}$ のノイズ・フィギュアと周波数

$P_{OUT}$ に対する2次高調波歪みと制御電圧

$P_{OUT}$ に対する3次高調波歪みと制御電圧

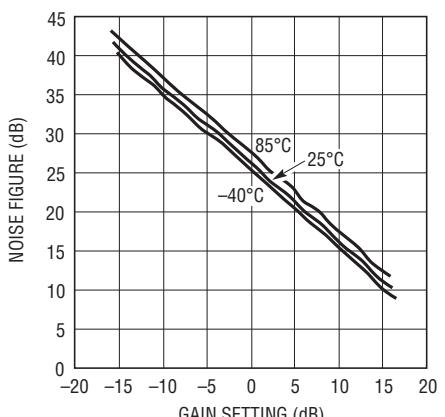

所定温度における140MHzノイズ・フィギュアと利得設定

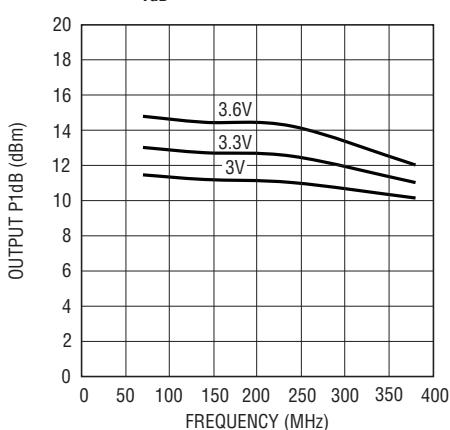

各電源電圧における $G_{MAX}$ の出力 $P_{1dB}$ と周波数

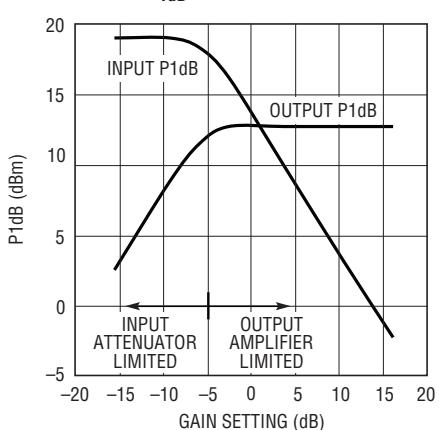

入出力 $P_{1dB}$ と140MHzの利得設定

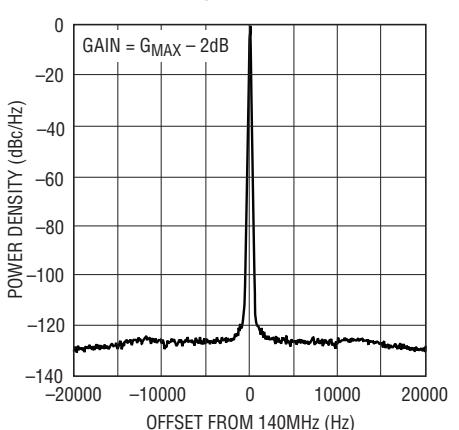

$P_{OUT} = +8\text{dBm}$ の $G_{MAX}$ 近傍の140MHz側波帯ノイズ

## 標準的性能特性

注記のない限り、 $T_A = 25^\circ\text{C}$ および $V_{CC} = 3.3\text{V}$ におけるテスト回路AとBにおける電気的性能。

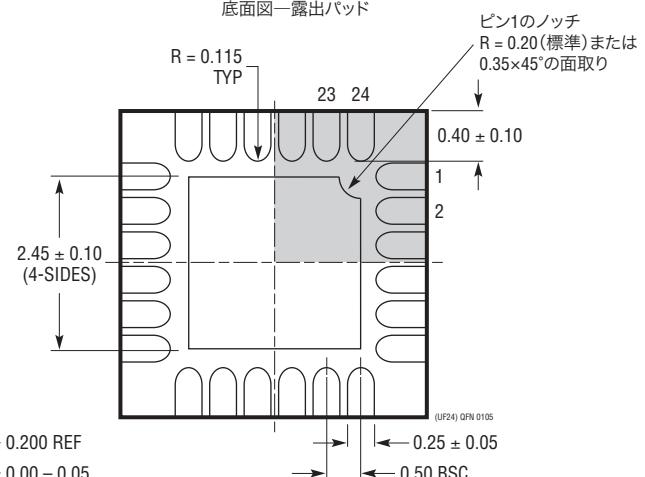

## ピン機能

**GND(ピン1、8、12、15、18、20、23)**: グランド。ピンは内部で互いに接続されています。最良のRF性能を得るには、グランド・ピンはすべてPCボードのグランド・プレーンに接続する必要があります。

**+IN(ピン2)**: 正信号の入力ピン。DCバイアスが内部生成されています。10nF DC阻止コンデンサを推奨します。

**-IN(ピン3)**: 負信号の入力ピン。DCバイアスが内部生成されています。10nF DC阻止コンデンサを推奨します。

**V<sub>CM</sub>(ピン4、5)**: 入力同相電圧ピン。2本のピンが内部で接続されており、+INと-INの差動入力の仮想グランドとして機能しています。ピンに近いところで10nFでグランドへの容量性デカップリングを行うことによって、残留同相入力信号を終端しやすくすることを推奨します。

**V<sub>CC</sub>(ピン6、13、19、24)**: 正電源。4本のピンをすべて同じ電圧(通常、3.3V)に接続する必要があります。ピンに近いところに1000pFおよび0.1μFコンデンサを配置して各ピンをバイパスします。

**DECL1(ピン7)**: デカップリング・ピン。内部ノイズを軽減する役割を果たします。ピンに近いところに0.1μFコンデンサを配置してグランドにバイパスします。

**+V<sub>G</sub>(ピン9)**: 正の利得制御ピン。正モードの利得制御に使用する入力信号ピン。それ以外では、負モードの利得制御用として通常V<sub>REF</sub>に接続されています。10kΩ抵抗で内部的にグランドにプルされています。正の利得スロープ・モードでは、利得制御スロープは140MHzで約+32dB/Vであり、利得制御範囲は、0.1V～1.1Vです。

**V<sub>REF</sub>(ピン10)**: 内部バイアス電圧ピン。通常、正の利得制御時は-V<sub>G</sub>ピンに、負の利得制御時は+V<sub>G</sub>ピンに接続します。利得とV<sub>G</sub>との特性の中間点の電圧を確定します。ピンに近いところに0.1μFコンデンサを配置してグランドにバイパスします。外部リファレンス電圧用としては使用できません。

**-V<sub>G</sub>(ピン11)**: 負の利得制御ピン。負モードの利得制御に使用する入力信号ピン。それ以外では、正モードの利得制御用として通常V<sub>REF</sub>に接続されています。ピンは10kΩ抵抗で内部的にグランドにプルされています。負の利得スロープ・モードでは、利得制御スロープは140MHzで約-32dB/Vであり、利得制御範囲は0.1V～1.1Vです。

**DECL2(ピン14)**: デカップリング・ピン。内部ノイズを軽減する役割を果たします。ピンに近いところに1000pFコンデンサを配置してグランドにバイパスします。

**-OUT(ピン16)**: 負のアンプ出力ピン。DC消費電流をオープン・コレクタ出力デバイスに流すには、センタ・タップをV<sub>CC</sub>に接続した変圧器またはチヨーク・インダクタを推奨します。最良の性能を得るには、-OUTへのDCバイアス電圧をV<sub>CC</sub>の100mV以内にする必要があります。

**+OUT(ピン17)**: 正のアンプ出力ピン。DC消費電流をオープン・コレクタ出力デバイスに流すには、センタ・タップをV<sub>CC</sub>に接続した変圧器またはチヨーク・インダクタを推奨します。最良の性能を得るには、+OUTへのDCバイアス電圧をV<sub>CC</sub>の100mV以内にする必要があります。

**EN(ピン21)**: 出力信号イネーブル・ピン。V<sub>CC</sub>に接続された100kΩにより、このピンは内部的に“H”にプルされます。出力アンプ信号をイネーブルするには、このピンを低電圧にアサートします。出力アンプ・インピーダンスとDC電流はENの状態には影響を受けません。イネーブル機能を使用しないときは、このピンをグランドに接続します。

**SHDN(ピン22)**: シャットダウン・ピン。V<sub>CC</sub>に接続された100kΩにより、このピンは内部的に“H”にプルされます。このピンを低電圧にアサートして回路をシャットダウンし、大幅に電源電流を減少させます。非単調な出力信号動作を防止するには、適切な順番によるENおよびSHDNピンの取り扱いが必要です。詳細は、「アプリケーション情報」を参照してください。シャットダウン機能を使用しないときは、このピンをV<sub>CC</sub>に接続します。

**露出パッド(ピン25)**: グランド。低インダクタンスおよび良好な放熱を得るには、露出パッドにはその下のグランド・プレーンへの多数のビア・ホールを配置します。

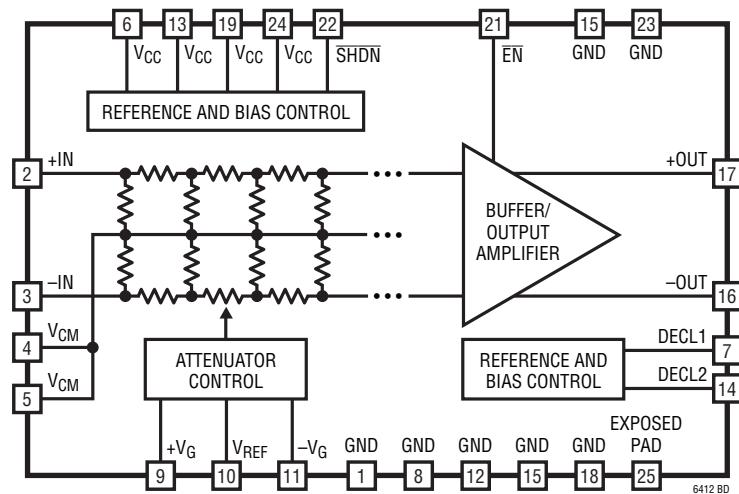

## ブロック図

## DCテスト回路

## 動作

LTC6412では、アンプの可変利得特性を生成するのに補間にによるタップ減衰器回路アーキテクチャを採用しています。このタップ付き減衰器をバッファと出力アンプに使用することで、ブロック図に示すような差動信号パスを形成しています。この回路アーキテクチャにより良好なRF入力電力処理機能が得られ、一定の出力ノイズと出力IP3特性とともにほとんどのIF信号チェーン・アプリケーションに望ましい機能を実現しています。内部制御回路は $\pm V_G$ 端子の利得制御信号を利用して、これを減衰器ラダー向けの制御信号に変換しています。減衰器制御回路によって、dBリニアな利得応答を低速および高速の入力制御信号のいずれの利得レンジに対しても連続的で単調性を維持するとともに、利得に対してもほとんど入力インピーダンスの変動がないようにしています。これらのことことが設計上に考慮されているため、 $\pm 0.1$ dBのリップルと類似のデジタル・ステップの減衰器設計より遅い $0.5\mu\text{s}$ の利得応答を持つ利得対 $V_G$ の特性を実現しています。

特性として見過ごされることの多いアナログ制御のVGAは、利得制御端子のアップコンバーティング振幅変調(AM)ノイズです。VGAは2象限乗算器として動作するので、過度のAM側波帶ノイズの発生を防ぐための最小限の注意が必要です。下表は、LTC6412回路のベースライン $20\text{nV}/\sqrt{\text{Hz}}$ 等価入力制御ノイズの影響と外部制御回路からのノイズの加わったより大きな入力ノイズの影響を示したものです。

| 制御入力全ノイズ電圧<br>( $\text{nV}/\sqrt{\text{Hz}}$ ) | 最大利得付近の $10\text{kHz}$ オフセットにおけるピークAMノイズ(dBc/Hz) |

|------------------------------------------------|--------------------------------------------------|

| 20                                             | -142                                             |

| 40                                             | -136                                             |

| 70                                             | -131                                             |

| 100                                            | -128                                             |

| 200                                            | -122                                             |

ベースライン等価な $20\text{nV}/\sqrt{\text{Hz}}$ 入力ノイズによって公称 $0\text{dBm}$ 出力信号の最大利得における $-147\text{dBm}/\text{Hz}$ 出力ノイズ・フロア付近にワースト・ケースの $-142\text{dBc}/\text{Hz}$ のAM側波帶が発生しているのが分かります。測定可能なAM側波帶ノイズの防止には、一般的に $80\text{nV}/\sqrt{\text{Hz}}$ 未満の入力制御ノイズ電圧が推奨されます。オペアンプ制御回路の出力ノイズ電圧は通常、 $80\text{nV}/\sqrt{\text{Hz}}$ より低いですが、ロー・パワーDAC出力によっては、 $150\text{nV}/\sqrt{\text{Hz}}$ を超えることがあります。通常、 $100\text{nV}/\sqrt{\text{Hz}} \sim 150\text{nV}/\sqrt{\text{Hz}}$ の出力ノイズ範囲を持つDACには、DAC出力部に2:1または3:1の最適な抵抗分割器網を使って同じ比だけノイズ振幅を抑えて対応することができます。AMノイズを最小限に抑えなければならないアプリケーションでは、 $150\text{nV}/\sqrt{\text{Hz}}$ を超えるノイズの多いDACの使用は避けてください。

## アプリケーション情報

### 概要

LTC6412は、直線性の高い、完全な差動動作のアナログ制御による可変利得アンプ(VGA)で、1MHz～500MHzの周波数範囲のアプリケーションに最適化されています。VGAアーキテクチャによって一定のOIP3と出力ノイズ・レベル(NG+利得)が31dBの利得制御範囲にわたって得られるため、全利得範囲で一定のスプリアスのないダイナミック・レンジ(SFDR)を示します。この一定のSFDR特性は、復調器やADCのような信号シンクから上流にあるレシーバIFチェーンでの使用には理想的です。

低電源電圧の条件と完全な差動設計は、コンパクトで低電圧で完全な差動レシーバ・チェーンに使用されている他の多くのLTCのミキサ、アンプおよびADC製品に対応しています。非差動システムでは、50Ω入力インピーダンスと200Ω出力インピーダンスは安価な1:1および4:1バランを使ってシングル・エンドの50Ωポートに簡単に変換されます。

### 利得特性

LTC6412は、連続的に調整可能な-14dB～17dBの利得レンジを提供しており、これは、+VGと-VGに印加される制御電圧に関してdBリニアなものです。これらの制御ピンは、差動信号でも動作可能ですが、シングル・エンド制御信号でVGピンの1つを動作させ、他のVGピンをVREFピンに接続するほうがより一般的です。このようにして、以下に示すような正の利得制御スロープまたは負の利得制御スロープのいずれも簡単に実現することができます。

**負の利得制御スロープ。**+VGをVREFに接続し、利得制御電圧を-VGピンに印加します。-VG電圧が大きくなるにつれて利得は減少します。

**正の利得制御スロープ。**-VGをVREFに接続し、利得制御電圧を+VGピンに印加します。+VG電圧が大きくなるにつれて利得も増加します。

この標準的なシングル・エンド設定に接続すると、アクティブ制御入力範囲は0.1Vから1.1Vです。この制御入力範囲は、最適な低出力抵抗で構成される抵抗分割器を使用して拡大することができます。たとえば、それぞれが1kΩの値を持つ直列抵抗2つで0.2Vから2.2Vに制御入力範囲を拡大し、500Ωのテブナン等価実効ソース抵抗となります。これは+VG/-VG端子の10kΩ入力抵抗と比較すると、比較的小さな負荷効果となります。

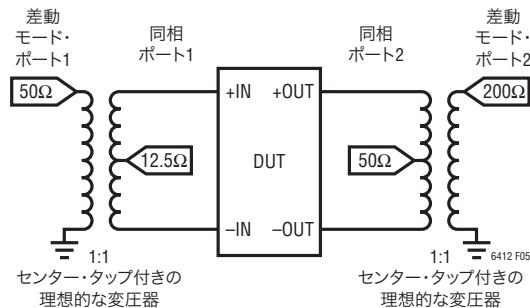

### ポート特性

LTC6412は、動作周波数範囲全体にわたって差動入力インピーダンスが公称50Ω、差動出力インピーダンスが200Ωです。

この入力インピーダンス特性はブロック図に示した差動減衰器ラダーから派生したものです。内部回路でこの減衰器ラダーへのRF接続を制御し、このポートへの最適な同相DC電圧を生成します。差動減衰器ラダーで仮想グランド・ノードを生成しますが、V<sub>CM</sub>ピンにコンデンサによるグランドへのバイパスが必要で、それによって入力ポートに存在する同相信号を効果的に減衰します。図1～4のテスト回路AとBに示すようにDC阻止コンデンサを通して+V<sub>IN</sub>と-V<sub>IN</sub>ピンが入力信号に接続されています。

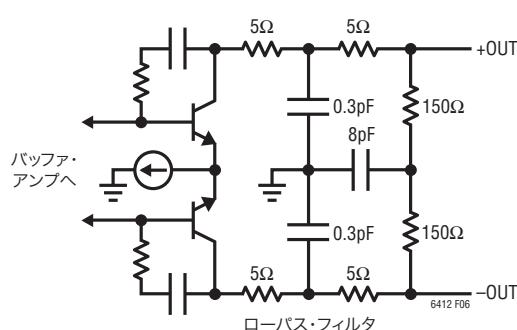

出力インピーダンス特性は、図7に示すオープン・コレクタ等価回路から派生したものです。差動シャント、ローパス・フィルタ、内部帰還の働きにより、動作帯域で200Ω～300Ωの差動出力実効インピーダンスが+OUTピンと-OUTピン間に生じます。+V<sub>OUT</sub>と-V<sub>OUT</sub>ピンがシャント・インダクタまたは変圧器を使用して出力ポートに接続され、電源電圧へのDCパスとなっています。回路出力のDC成分の阻止は、通常、直列コンデンサによって行われます。これらの阻止コンデンサの使用は、出力に磁束変圧器が使用されているときは避けることができます。AC信号とDC電源を出力ピンに結合するための一般的なインダクタとバランtronの方式をいくつか図9に示します。この詳細な説明は、「標準的応用例」を参照してください。

### 電源

電源パスへのインダクタンスは、LTC6412の性能を劣化させることができます。各V<sub>CC</sub>ピンの非常に近いところに低インダクタンスのバイパス・コンデンサを配置することを推奨します。1000pFおよび0.1μFパラレル・コンデンサを推奨します。小さい方をV<sub>CC</sub>に近づけて配置します。どの電源ピンも未接続のままにはしないでください。最良の性能を得るには、+OUTおよび-OUTへのDCバイアス電圧をV<sub>CC</sub>の100mV以内にする必要があります。パッケージ底部の露出パッドは、低インダクタンス、低熱抵抗にてグランドに接続する必要があります。最適な接地方法および電源のデカップリング例に関しては、DC1464A(テスト回路A)の詳細説明を参照してください。高周波数で低インピーダンス電源とグランドを実現しないと発振が生じ、歪みが増大することがあります。

## アプリケーション情報

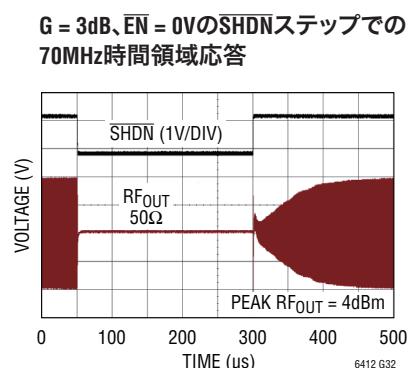

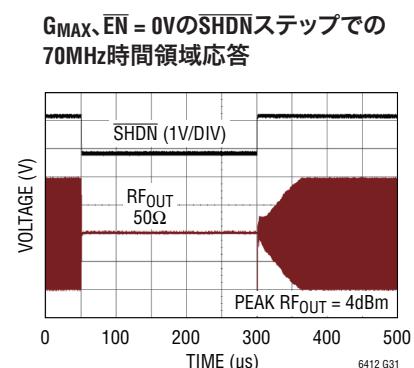

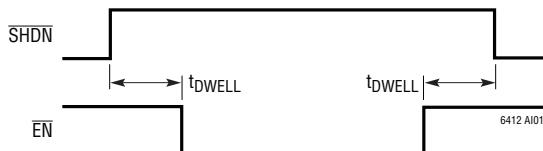

### イネーブル/シャットダウン

$\overline{EN}$ ピンと $\overline{SHDN}$ ピンはいずれも $100\text{k}\Omega$ プルアップ抵抗によって $V_{CC}$ に自己バイアスされているため、デフォルトのオープン・ピンではパワーオンしていますが、出力アンプ信号パスがディスエーブルされています。 $\overline{EN}$ ピンを“L”にプルすると、減衰器ラダーから出力アンプへの信号パスが完成します。 $\overline{EN}$ ピンには、高速ミュート機能、 $\overline{SHDN}$ ピンには低速のパワー・オン/オフ機能があります。

$\overline{SHDN}$ 機能を必要とするアプリケーションでは、出力アンプ信号パスを高い $\overline{EN}$ 電圧でディスエーブルしてから $\overline{SHDN}$ 信号を遷移させることを推奨します。アンプをイネーブルするときは、立ち上がりの $\overline{SHDN}$ 遷移と立ち下がりの $\overline{EN}$ 遷移間に少なくとも $5\text{ms}$ のドウェル・タイムを持たせてVGA経由の非単調出力信号動作を防ぎます。立ち下がり $\overline{SHDN}$ 遷移のときは、これとは逆の遅延シーケンスを推奨しますが、出力信号の振幅が $\overline{EN}$ ピンとは関係なく急に降下するため、それほど不可欠というわけではありません。

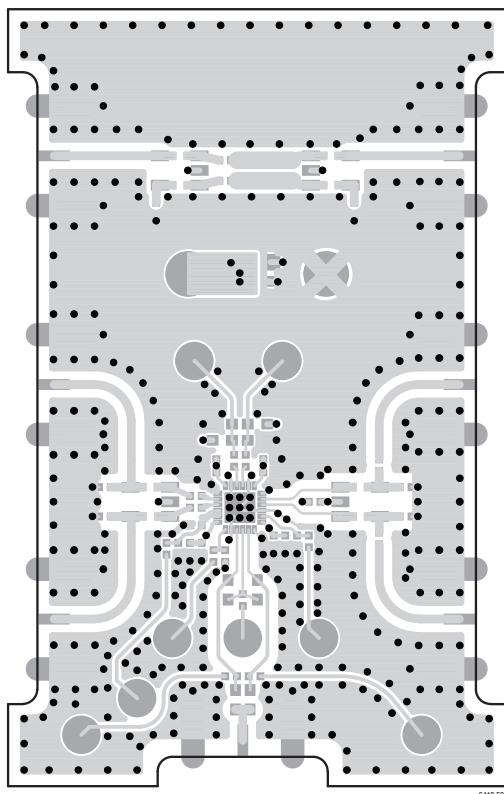

### レイアウト/グランド配線

LTC6412の高周波数性能を生かすには、最適なRFグランド、バイアス・デカップリング、終端に特別な注意を払う必要があります。4層からなる推奨PCBボードの積層状態を下図に示します。これは、1GHzの相対誘電率が $\epsilon_r = 4.2 \sim 4.5$ の1オンス銅被膜のFR-4積層基板です。

|         |                  |                   |

|---------|------------------|-------------------|

| METAL 1 | FR4 12-18 MILS   | RF SIGNAL         |

| METAL 2 | FR4 20-30 MILS   | GROUND PLANE      |

| METAL 3 | FR4 NOT CRITICAL | POWER PLANE       |

| METAL 4 |                  | GND AND LF SIGNAL |

テスト回路Aの最上面の金属とシルク・スクリーンの図で推奨デカップリング・コンデンサ配置、信号配線、グランド配線の様子が分ります。露出パッド直下のグランド・ビアは重要です。できるだけ多くのビアを使用してください。他のグランド・ピンに対してはグランド・ビアはそれほど必須ではありません。

### ESD

LTC6412のI/Oピンはすべて逆バイアス・ダイオードでESD保護されています。どのI/Oピンでも正電源より上でダイオード1つ分の降下が強制されたり、負電源より下でダイオード1つ分の降下が強制されると、これらのダイオードを通じて非常に大きな電流が流れることができます。この電流は $10\text{mA}$ に制限されなければデバイスへの損傷はありません。 $+OUT/-OUT$ ピンには、正電源用に追加の直列ダイオードが装備されており、正電源を上回る約 $2\text{V}$ のオーバーシュートを保持してから大量の電流を流します。

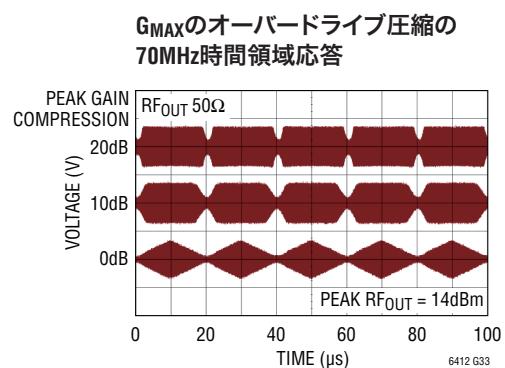

### 信号圧縮特性

図のタイトルに「入出力 $P_{1\text{dB}}$ 」とあるものは、LTC6412VGAの重要な特性を示しています。利得の設定値が $-5\text{dB}$ を超えるときは、出力アンプによってリニア・パワーの処理機能が制限され、利得設定値が $-5\text{dB}$ を下回るときは、入力減衰器ラダーによってリニア・パワーの処理機能が制限されます。その前の段階のミキサまたはアンプの特性が $OP_{1\text{dB}} < 19\text{dBm}$ かつ $OIP_3 < 50\text{dBm}$ の場合は、最小利得値においてリニア入力パワーが制限されても、信号チェーンへの総合的な性能に影響を及ぼすことはありません。

### テスト回路

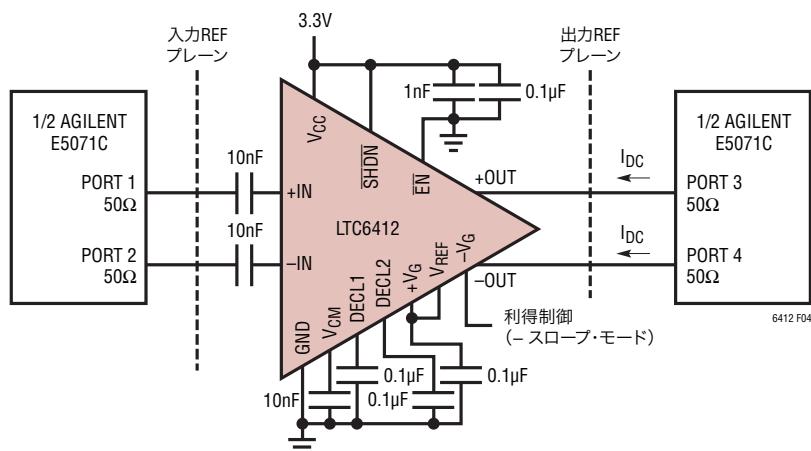

LTC6412の完全な差動動作設計の性質上、このデータシートに記した性能情報を得るには2つのテスト回路が必要です。

テスト回路Aは、DC1464Aであり、入出力バラン変圧器を装備した2ポート・デモ回路によって、2ポート・ネットワーク・アナライザまたはその他のシングル・エンド $50\Omega$ テスト・システムへの直接接続が可能です。バラン変圧器によってLTC6412の高周波数および低周波数性能が制限されますが、70MHz～380MHzの簡単で、十分正確な測定が可能です。利得制御信号を $V_G$ タレットに供給してDC制御測定を行ったり、VGAIN SMAコネクタを通して過渡制御信号を測定したりします。利得制御タレット用のクリップ・リード線はノイズを拾いやすいので、ローパス・フィルタをかけてAMアップコンバージョン・アーチファクトを防ぐ必要があります。 $\pm V_G$ タレット使用時は、

## アプリケーション情報

VGAIN SMA入力からグランドにかけて4.7 $\mu$ Fコンデンサを取り付けることによって効果的なローパス・フィルタとなります。

テスト回路Aの標準的なデータ曲線は、SMAコネクタのプレーンで測定され、入出力バランによるロス(それぞれ約0.5dBおよび1.2dBと推測される)は補正してありません。このデータ・シートで示されている標準的なACデータは、Sdd21やScc21などのミックスト・モードのSパラメータを除き、いずれもテスト回路Aに対応します。

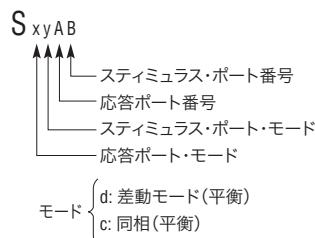

テスト回路Bでは、4ポート・ネットワーク・アナライザを使用してバラン変圧器および関連回路による周波数の制約を超えて差動モードと同相モードのSパラメータと同相Sパラメータの測定を行います。整合した較正セットによりテスト回路Bに示すような測定リファレンス・プレーンが確立されます。出力プレーンはパッケージのエッジで定義されるのに対して、入力プレーンは0402コンデンサの入力ペアのエッジで定義されます。ICのランドとグランドのビア・パターンは、テスト回路Aのそれと同一です。パッケージの直下にあるグランドのビア・パターンは、このデータ・シートで使用しているRF特性を得るために必要なRFグランドを提供します。ミックスト・モードのSパラメータによるSxyABフォームの標準的なデータ曲線はすべてテスト回路Bに対応し、図5および図6の定義に従います。

### 標準的な応用例

グランドと電源のデカップリングの方法はテスト回路Aに提示したレイアウトに厳密に準じる必要がありますが、入出力のネットワークはそれぞれのアプリケーション条件に応じてカスタマイズすることができます。

入力側では、差動ポート・インピーダンスは、すべての利得設定値およびアプリケーション周波数に対して50 $\Omega$ に非常に近い値になっています。差動信号チェーンでは、差動入力信号が約10nFの適切なDC阻止コンデンサを装備した先行する差動出力段から容易に与えられます。VGA用にシングル・エンドの入力信号が使われているときは、差動入力信号に変換するのに適切なバランが必要になります。50 $\Omega$ シングル・エンドから50 $\Omega$ 差動への受動的な変換は、ETC1-1-13またはMABA-007159のような1:1伝送ライン・バランを使用することで最も効率よく行うことができます。これらの1:1バラン・デバイスは比較的廉価で、低損失、広帯域応答および良好な位相マッチングなどの優れた電気的特性を持っています。

図1. DC1464Aの最上面シルクスクリーン。テスト回路A

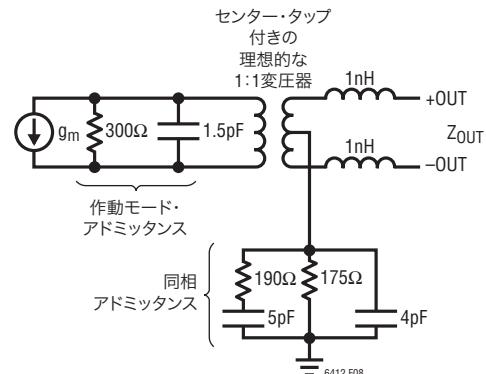

出力側では、差動ポート・アドミッタンスは、すべての利得設定値およびアプリケーション周波数に対して300 $\Omega$ ||1.5pFに非常に近い値になっています。この出力ポート回路は、DC出力電源電流用のパスだけではなく、アプリケーションに必要なバラン、マッチング、あるいはフィルタ機能などの機能を果たす必要があります。したがって、出力回路のデザイン・オプションとしてはさらにバリエーションが多くなります。他の一般的な出力回路を、コンポーネント値を評価する上で必要な若干のデザイン上のガイドラインとともに図9に簡単に示します。最終的なデザイン・シミュレーションでは、図8の小信号等価回路モデルを使用して出力端子の負荷効果を適切に判断します。

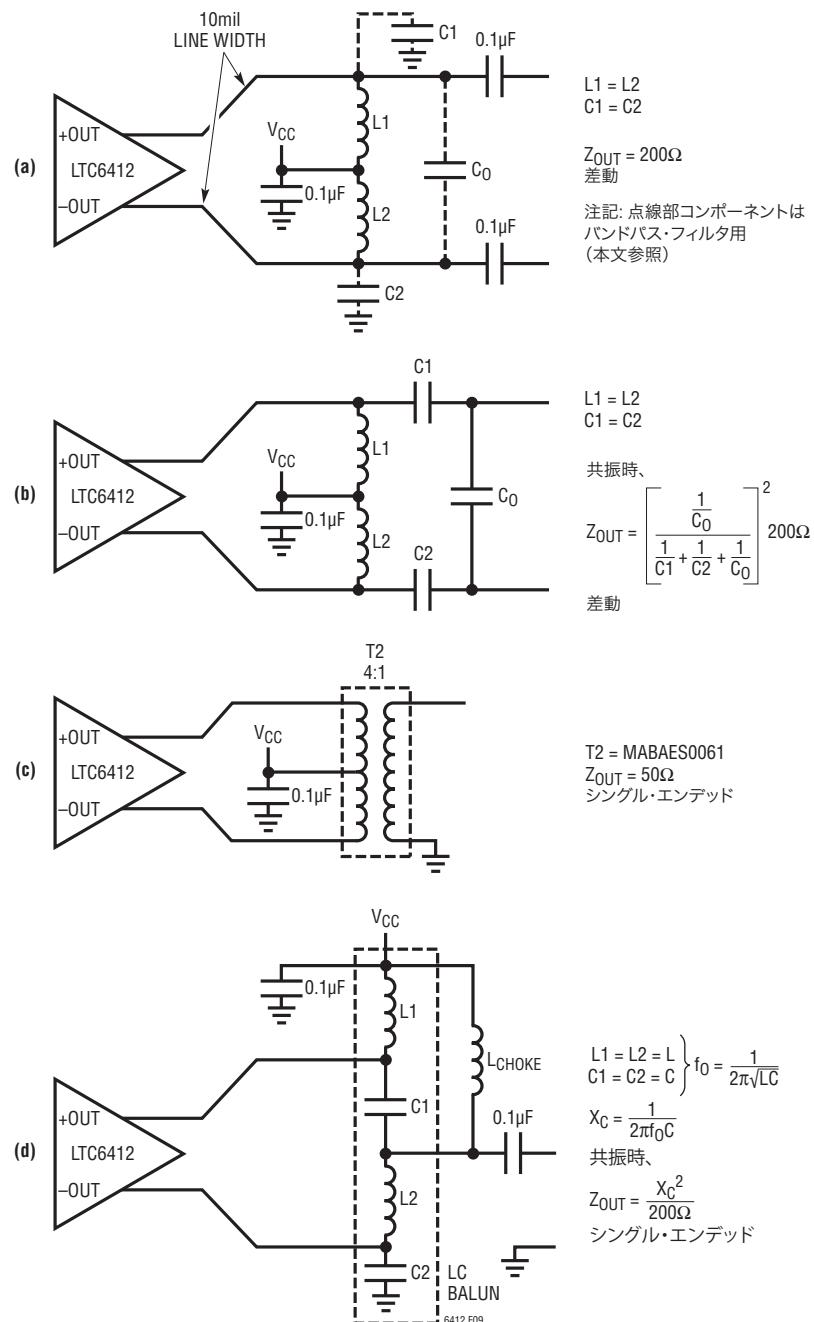

図9の(a)は、L1 = L2の2つの最適なインダクタを使用した最も簡単な差動出力構成で、アプリケーション周波数で出力ノードに負荷を加えることなくDC電源電流を流すことができます。出力ピンのPCBトレース幅は、これらの端子の高いインピーダンス

## アプリケーション情報

図2. DC1464Aの最上面メタル部。テスト回路A

ンスに合わせて細くする必要があります。1オンス銅線で8~10milのトレース幅を選択すれば十分です。0.1 $\mu$ Fコンデンサは、DC成分を阻止する役割を果たし、必要に応じてデカップリングを行います。これらのコンデンサ値は、下は数MHzの周波数まで使用するのに最適で、アプリケーションの周波数が高い場合は、スケールダウンすることができます。

バンドパス・フィルタリングが図9(a)のVGA出力に必要な場合は、対象となる周波数でL1とL2がシャント・コンデンサCOと共振するように設計することができます。 $\omega = 1/\sqrt{C_0(L_1+L_2)}$ 。あるいは、L1=L2が2つの別のコンデンサC1 = C2と共振するように設計することで、同相ノイズにフィルタをかけるようにすることができます。

図9(b)は、チューニングした差動出力にさらにバリエーションを加えたもので、DC阻止コンデンサをタンク・レゾネータ内に入れることでバンドパス・フィルタとしての機能を果たさせ、VGA出力インピーダンスを低い値に変えます。ここでもC0コンデンサを2つの別々の接地されたシャント・コンデンサに分割して同相ノイズを除去することができます。

図9(c)は、50 $\Omega$ シングル・エンド出力を実現するために使用する磁束変圧器を示しています。磁束変圧器は図3に示したような出力伝送ライン変圧器によく見られるような大規模な帯域幅は提供しませんが、シャント・コンデンサ(この図には示されていません)でチューニングを行えば、小さな帯域幅では十分機能します。磁束変圧器を使ったデザインはDC阻止コンデンサが不要になり、厳しい環境でのアプリケーションに魅力的なものとなります。たとえば、MABAES0061などの標準的なRF磁束変圧器を通過しないESDやその他の過渡現象としての電気的に過度なストレスに対してアンプ出力が影響を受けやすい場合などです。

図9(d)は、帯域幅の約15~30%に使えるディスクリートのLCバランを示しています。帯域幅が大きいとここに示した数の部品で実現することが困難になり、帯域幅が小さいと部品の許容性に制約を受けることがあります。これらの制限にもかかわらず、ディスクリートのLCバランは出力回路のソリューションとして費用効果は高いといえます。共振時には、チューニングされた回路では差動からシングル・エンドへの変換とともにインピーダンス変換が得られます。

### DC結合動作

LTC6412は、AC結合動作を念頭に入れて設計されています。固定された入力DC同相電圧とより高いオープン・コレクタ出力DCバイアス・ポイント間の変換のため、DC結合アプリケーションでの使用は実際的ではありません。

## アプリケーション情報

図3. デモ・ボードDC1464Aの回路図。テスト回路A

図4. 4ポート解析図。テスト回路B

## アプリケーション情報

図5. テスト回路Bで報告されたミックスト・モードSパラメータ図

$$S_{xyAB} = \frac{\text{ポートAの}x\text{モード信号出力}}{\text{ポートBの}y\text{モード信号入力}}$$

6412 F06

図6. テスト回路Bで報告されたミックスト・モードSパラメータの定義

図7. 大信号出力等価回路図

図8. 小信号出力等価回路モデル

## アプリケーション情報

図9. 出力AC/DC結合、フィルタおよびバラン回路設計オプション

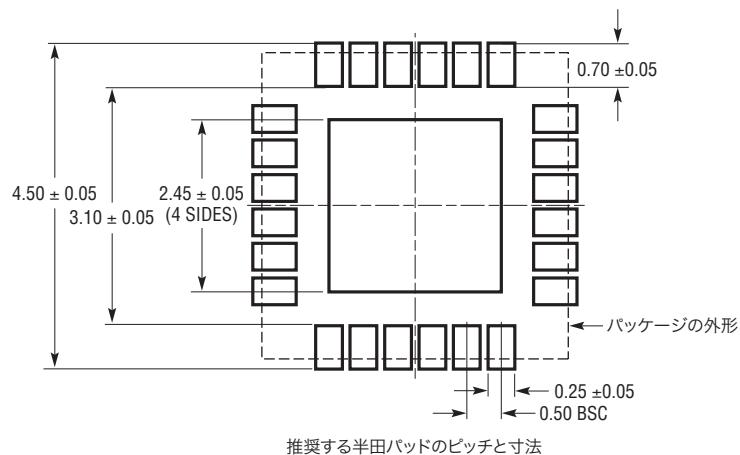

## パッケージ

UFパッケージ

24ピン・プラスチックQFN(4mm×4mm)

(Reference LTC DWG # 05-08-1697)

### 推奨する半田パッドのピッチと寸法

底面図—露出パット

**NOTE:**

NOTE:

1. 図はJEDECのパッケージ寸法M0-220のバリエーション(WGDD-X)とする(未承認)

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージの底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 線掛けの部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

## 改訂履歴 (改訂履歴はRev Aから開始)

| REV | 日付    | 概要                                                           | ページ番号 |

|-----|-------|--------------------------------------------------------------|-------|

| A   | 04/10 | 「電気的特性」のTCGAIN Typicalを $-0.007\text{dB}/^\circ\text{C}$ に変更 | 3     |

# LTC6412

## 関連製品

| 製品番号                                           | 説明                                       | 注釈                                                                                                               |

|------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| <b>固定利得IFアンプ/ADCドライバ</b>                       |                                          |                                                                                                                  |

| LT1993-2、LT1993-4、<br>LT1993-10                | 800MHz差動アンプ/ADCドライバ                      | -72dBc IM3、70MHz 2V <sub>P-P</sub> コンポジット、 $A_V = 2V/V, 4V/V, 10V/V$                                             |

| LTC6400-8、LTC6400-14、<br>LTC6400-20、LTC6400-26 | 1.8GHz低ノイズ、低歪み差動ADCドライバ                  | -71dBc IM3、240MHz 2V <sub>P-P</sub> コンポジット、 $I_S = 90mA, A_V = 8dB, 14dB, 20dB, 26dB$                            |

| LTC6401-8、LTC6401-14、<br>LTC6401-20、LTC6401-26 | 1.3GHz低ノイズ、低歪み差動ADCドライバ                  | -74dBc IM3、140MHz 2V <sub>P-P</sub> コンポジット、 $I_S = 50mA, A_V = 8dB, 14dB, 20dB, 26dB$                            |

| LT6402-6、LT6402-12、<br>LT6402-20               | 300MHz差動アンプ/ADCドライバ                      | -71dBc IM3、20MHz 2V <sub>P-P</sub> コンポジット、 $A_V = 6dB, 12dB, 20dB$                                               |

| LTC6410-6                                      | 1.4GHz差動IFアンプ、<br>入力インピーダンスは設定可能         | OIP3 = 36dBm、70MHz、<br>ミキサIFポートとのフレキシブルなインターフェイス                                                                 |

| LTC6416                                        | 2GHz、16ビット差動ADCバッファ                      | -72dBc IM2、300MHz 2V <sub>P-P</sub> コンポジット、 $I_S = 42mA, e_N = 2.8nV/\sqrt{Hz}, A_V = 0dB, 300MHz \pm 0.1dB$ 帯域幅 |

| LTC6420-20                                     | デュアル1.8GHz低ノイズ、<br>低歪み差動ADCドライバ          | LTC6400-20のデュアル・バージョン、 $A_V = 20dB$                                                                              |

| LTC6421-20                                     | デュアル1.3GHz低ノイズ、<br>低歪み差動ADCドライバ          | LTC6401-20のデュアル・バージョン、 $A_V = 20dB$                                                                              |

| <b>デジタル制御利得のIFアンプ/ADCドライバ</b>                  |                                          |                                                                                                                  |

| LT5514                                         | 超低歪みIFアンプ/ADCドライバ、<br>デジタル制御利得           | OIP3 = 47dBm、100MHz、利得範囲10.5dB～33dB、1.5dB単位                                                                      |

| LT5524                                         | 低歪みIFアンプ/ADCドライバ、デジタル制御利得                | OIP3 = 40dBm、100MHz、利得範囲4.5dB～37dB、1.5dB単位                                                                       |

| LT5554                                         | 高ダイナミック・レンジ7ビット・デジタル制御<br>IF VGA/ADCドライバ | OIP3 = 46dBm、200MHz、利得範囲1.725～17.6dB、0.125dB単位                                                                   |

| <b>ベースバンド差動アンプ</b>                             |                                          |                                                                                                                  |

| LT1994                                         | 低ノイズ、低歪み差動アンプ/ADCドライバ                    | 16ビットSNR、SFDR(1MHz)、レール・トゥ・レール出力                                                                                 |

| LTC6403-1                                      | 低ノイズ、レール・トゥ・レール出力差動アンプ/<br>ADCドライバ       | 16ビットSNR、SFDR(3MHz)、レール・トゥ・レール出力、 $e_N = 2.8nV/\sqrt{Hz}$                                                        |

| LTC6404-1、LTC6404-2                            | 低ノイズ、レール・トゥ・レール出力差動アンプ/<br>ADCドライバ       | 16ビットSNR、SFDR(10MHz)、レール・トゥ・レール出力、<br>$e_N = 1.5nV/\sqrt{Hz}$ 、LTC6404-1はユニティ・ゲイン安定、<br>LTC6404-2は利得2安定          |

| LTC6406                                        | 3GHzレール・トゥ・レール入力差動アンプ/<br>ADCドライバ        | -65dBc IM3(50MHz) 2V <sub>P-P</sub> コンポジット、レール・トゥ・レール入力、<br>$e_N = 1.6nV/\sqrt{Hz}, 18mA$                        |

| LT6411                                         | 低消費電力差動ADCドライバ/<br>利得を選択可能なデュアル・アンプ      | -83dBc IM3(70MHz) 2V <sub>P-P</sub> コンポジット、 $A_V = 1, -1$ または2、16mA、<br>シングル・エンド～差動への変換に優れる                      |

| <b>利得制御用低ノイズDAC</b>                            |                                          |                                                                                                                  |

| LTC2630-10                                     | 低消費電力、内蔵のリファレンス、<br>单一電源10ビットDAC         | SPI入力、2.5V出力レンジ、2:1抵抗分割出力                                                                                        |

| LTC2640-10                                     | 低消費電力、内蔵のリファレンス、<br>单一電源10ビットDAC         | SPI入力、2.5V出力レンジ、2:1抵抗分割出力                                                                                        |

| LTC2641-12                                     | 低ノイズ、低消費電力、单一電源12ビットDAC                  | SPI入力、低グリッチ・インパルス、ゼロ・スケール・パワー・オン                                                                                 |

| LTC2642-12                                     | 低ノイズ、低消費電力、单一電源12ビットDAC                  | SPI入力、低グリッチ・インパルス、ミッド・スケール・パワー・オン                                                                                |

6412fa