# 低ノイズの シングルエンド-差動 コンバータ/ADCドライバ

## 特長

- レール・トゥ・レール入出力

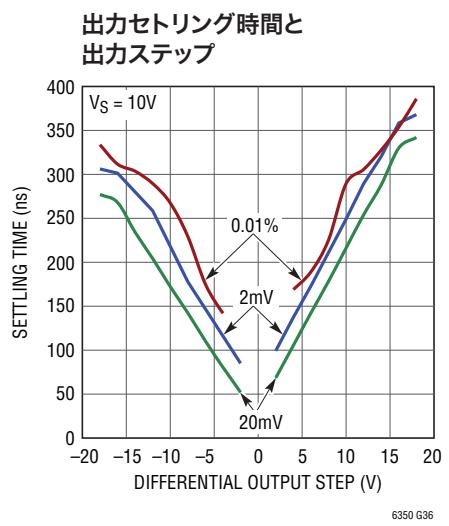

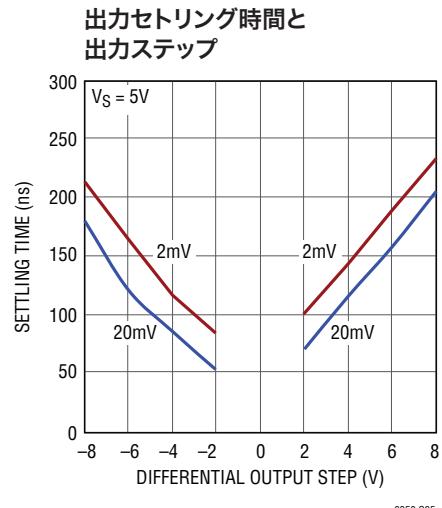

- 高速セトリング時間: 240ns (0.01%、8V<sub>P-P</sub>出力ステップ)

- オペアンプの入力換算ノイズ: 1.9nV/ $\sqrt{\text{Hz}}$

- 高インピーダンス入力

- -3dB帯域幅: 33MHz

- 2.7V~12V電源動作

- 外付け利得抵抗不要

- 消費電流: 4.8mA

- 低消費電力のシャットダウン

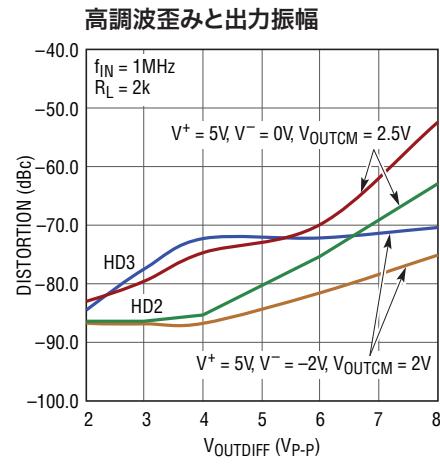

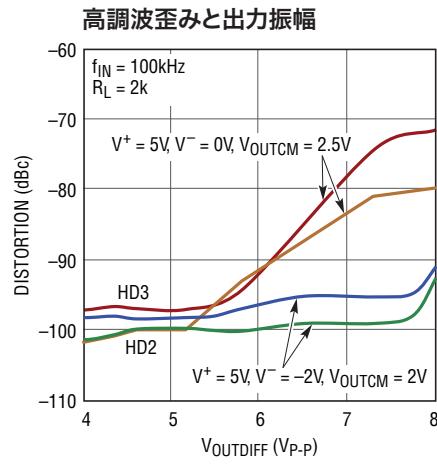

- 低歪み(HD2/HD3): -102dBc/-97dBc

(100kHz、 $V_{\text{OUTDIFF}} = 4V_{\text{P-P}}$ )

- 低いオフセット電圧:  $\pm 400\mu\text{V}$ (最大)

- 高いDC直線性:  $\pm 1\text{LSB}$ (16ビット、8V<sub>P-P</sub>)

- 低い入力電流ノイズ: 1.1pA/ $\sqrt{\text{Hz}}$

- 3mm×3mm 8ピンDFNおよび8ピンMSOPパッケージ

## アプリケーション

- 16ビットおよび18ビットSAR ADCドライバ

- シングルエンドから差動への変換

- 差動ライン・ドライバ

LT、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。5610557、6344773を含む米国特許によって保護されています。

## 概要

LT<sup>®</sup>6350は高速セトリングを特長とするレール・トゥ・レール入出力の低ノイズ、シングルエンド-差動コンバータ/ADCドライバです。このデバイスは、高インピーダンスまたは低インピーダンスのシングルエンド入力信号を、高性能の差動逐次比較レジスタ(SAR)ADCのドライブに適した低インピーダンスの平衡差動出力に変換します。その2オペアンプ方式は非常に低ノイズのオペアンプを特長とし、1MHzの帯域幅にわたって110dBを超えるSNRを達成することができます。

入力オペアンプは入力換算電圧オフセットを全入力範囲にわたって一定した小さい値に保つようにトリミングされているので、 $V_{\text{OS}}$ の急激な変化によって歪み性能が劣化するのを防ぎます。

単一5V電源では、出力は各入力ごとに55mV~4.945Vの範囲でADCをドライブできます。また、負電源を追加すれば、各入力ごとに0V~4.945Vの範囲でADCをドライブできます。出力同相電圧は+IN2ピンに電圧を印加することによって設定されます。

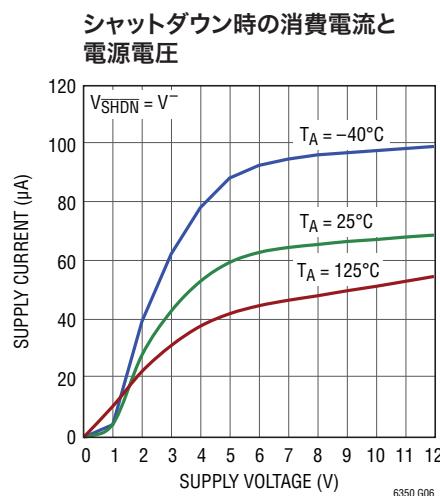

5V電源での消費電流は4.8mAで、シャットダウン・モードではわずか60µAです。

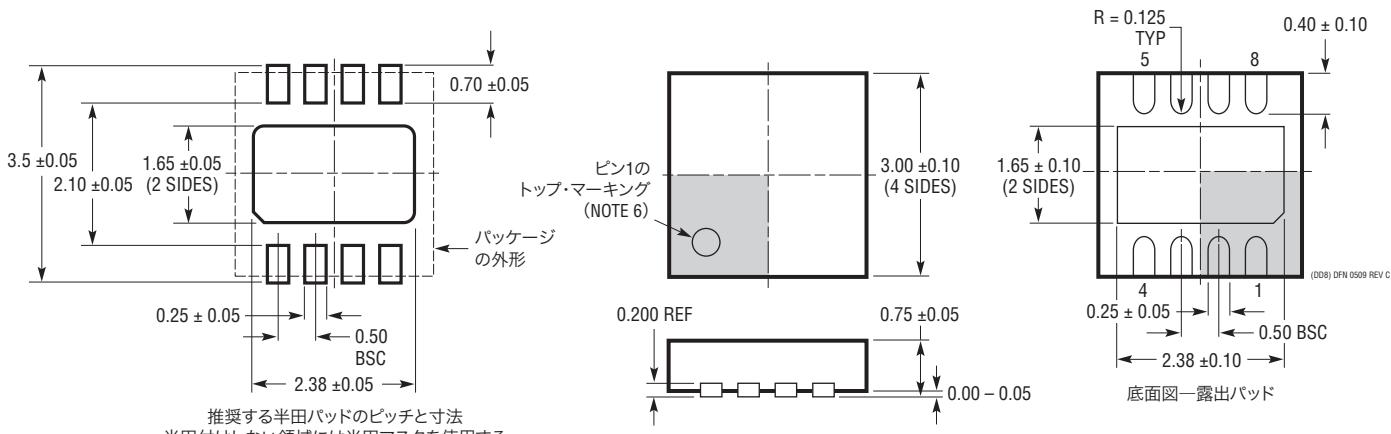

LT6350は3mm×3mmの小型8ピン・リードレスDFNパッケージと8ピンMSOPパッケージで供給され、-40°C~125°Cの温度範囲で動作します。

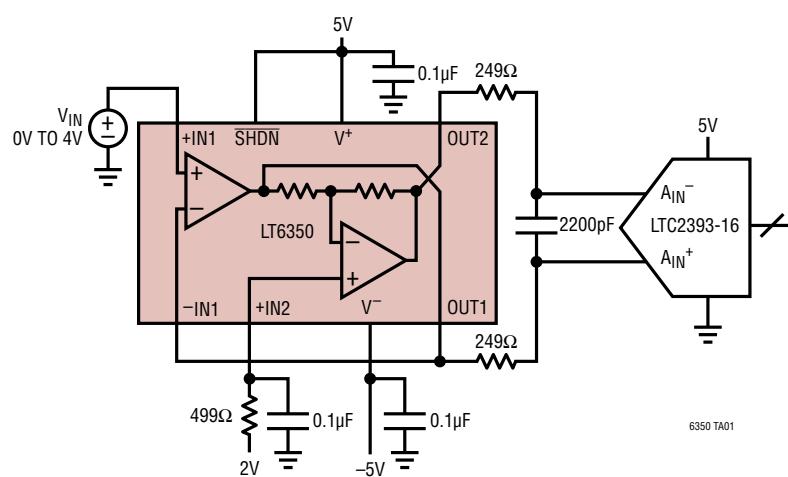

## 標準的応用例

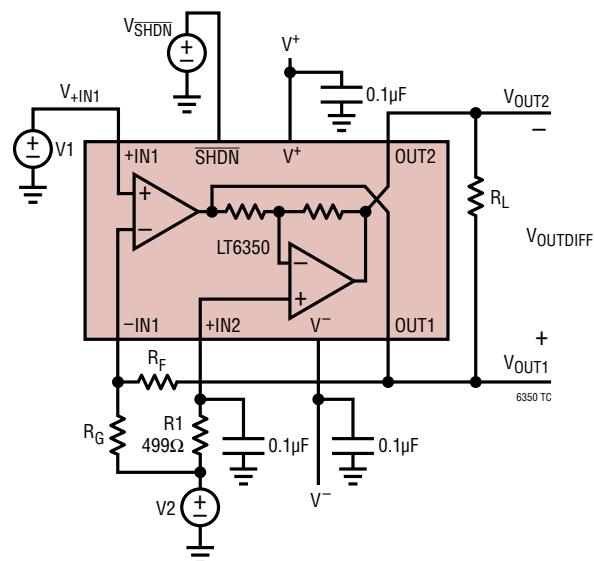

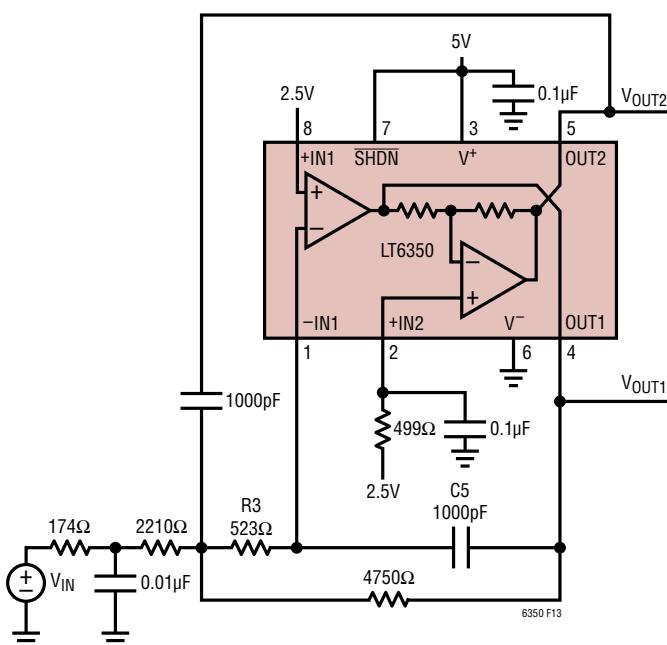

ADCドライバ: シングルエンド入力から差動出力への変換

20kHz正弦波、

-1dBFS 8192ポイントFFT

6350 TA02

6350fc

# LT6350

## 絶対最大定格 (Note 1)

|                                                   |             |

|---------------------------------------------------|-------------|

| 総電源電圧<br>(V <sup>+</sup> -V <sup>-</sup> 間) ..... | 12.6V       |

| 入力電流 (Note 2) .....                               | ±20mA       |

| 出力短絡電流時間<br>(Note 3) .....                        | 無期限         |

| 動作温度範囲<br>(Note 4) .....                          | -40°C~125°C |

|                                      |             |

|--------------------------------------|-------------|

| 規定温度範囲<br>(Note 5) .....             | -40°C~125°C |

| 最大接合部温度 .....                        | 150°C       |

| 保存温度範囲 .....                         | -65°C~150°C |

| リード温度(半田付け、10秒)<br>MSOPパッケージのみ ..... | 300°C       |

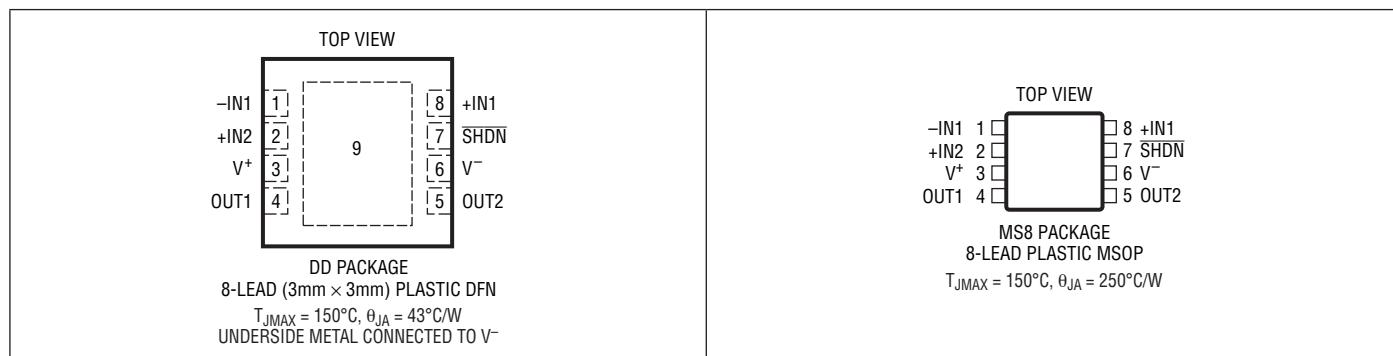

## ピン配置

## 発注情報

| 鉛フリー仕様         | テープアンドリール        | 製品マーキング* | パッケージ                          | 規定温度範囲         |

|----------------|------------------|----------|--------------------------------|----------------|

| LT6350CDD#PBF  | LT6350CDD#TRPBF  | LFJT     | 8-Lead (3mm x 3mm) Plastic DFN | 0°C to 70°C    |

| LT6350IDD#PBF  | LT6350IDD#TRPBF  | LFJT     | 8-Lead (3mm x 3mm) Plastic DFN | -40°C to 85°C  |

| LT6350HDD#PBF  | LT6350HDD#TRPBF  | LFJT     | 8-Lead (3mm x 3mm) Plastic DFN | -40°C to 125°C |

| LT6350CMS8#PBF | LT6350CMS8#TRPBF | LTJV     | 8-Lead Plastic MSOP            | 0°C to 70°C    |

| LT6350IMS8#PBF | LT6350IMS8#TRPBF | LTJV     | 8-Lead Plastic MSOP            | -40°C to 85°C  |

| LT6350HMS8#PBF | LT6350HMS8#TRPBF | LTJV     | 8-Lead Plastic MSOP            | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電氣的特性

- は全規定温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{+\text{IN}1} = V2$  = 電源電圧の中点、 $V_{\text{SHDN}} = V^+$ 、 $R_L = \text{オープン}$ 、 $R_F = \text{短絡}$ 、 $R_G = \text{オープン}$ 。 $V_S$ は $(V^+ - V^-)$ として定義。 $V_{\text{OUTCM}}$ は $(V_{\text{OUT}1} + V_{\text{OUT}2})/2$ として定義。 $V_{\text{OUTDIFF}}$ は $(V_{\text{OUT}1} - V_{\text{OUT}2})$ として定義。図1を参照。

| Symbol       | Parameter                                         | Conditions                                                                                                                                                       | Min                    | Typ                                 | Max            | Units                                |

|--------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------|----------------|--------------------------------------|

| $V_{OSDIFF}$ | Differential Input-Referred Offset Voltage        | $V_S = 5V$<br>$V_{+IN1} = V_2 = \text{Mid-Rail}$<br>$V_{+IN1} = V_2 = V^- + 1.5V \text{ to } V^+ - 0.1V$<br>$V_{+IN1} = V_2 = V^- + 1.5V \text{ to } V^+ - 0.1V$ | -0.4<br>-0.45<br>-0.77 | 0.4<br>$\pm 0.1$<br>0.45<br>1.36    | mV<br>mV<br>mV |                                      |

|              |                                                   | $V_S = 3V$<br>$V_{+IN1} = V_2 = V^- + 1.5V \text{ to } V^+ - 0.1V$<br>$V_{+IN1} = V_2 = V^- + 1.5V \text{ to } V^+ - 0.1V$                                       | -0.45<br>-0.8          | $\pm 0.1$<br>0.45<br>1.36           | mV<br>mV       |                                      |

|              |                                                   | $V_S = 10V$<br>$V_{+IN1} = V_2 = V^- + 1.5V \text{ to } V^+ - 0.1V$<br>$V_{+IN1} = V_2 = V^- + 1.5V \text{ to } V^+ - 0.1V$                                      | -0.52<br>-0.78         | $\pm 0.1$<br>0.52<br>1.48           | mV<br>mV       |                                      |

| $V_{OS1}$    | Input Offset Voltage, Op Amp 1                    | $V_S = 5V$<br>$V_{+IN1} = V^- + 1.5V \text{ to } V^+$<br>$V_{+IN1} = V^- \text{ to } V^+$                                                                        | -0.35<br>-1.5          | $\pm 0.08$<br>$\pm 0.28$            | 0.68<br>1.5    | mV<br>mV                             |

|              |                                                   | $V_S = 3V$<br>$V_{+IN1} = V^- + 1.5V \text{ to } V^+$<br>$V_{+IN1} = V^- \text{ to } V^+$                                                                        | -0.35<br>-1.5          | $\pm 0.08$<br>$\pm 0.32$            | 0.68<br>1.5    | mV<br>mV                             |

|              |                                                   | $V_S = 10V$<br>$V_{+IN1} = V^- + 1.5V \text{ to } V^+$<br>$V_{+IN1} = V^- \text{ to } V^+$                                                                       | -0.68<br>-1.5          | $\pm 0.07$<br>$\pm 0.28$            | 0.68<br>1.5    | mV<br>mV                             |

|              | Input Offset Voltage, Op Amp 2 (Note 6)           | $V_S = 3V, 5V, 10V$<br>$V_{+IN1} = V_2 = V^- + 1.5V \text{ to } V^+ - 0.1V$                                                                                      | -1.0                   | $\pm 0.1$                           | 0.66           | mV                                   |

|              |                                                   | $V_{+IN1} = V_2 = V^- + 1.5V$<br>$V_{+IN1} = V_2 = V^+ - 0.1V$                                                                                                   |                        | 5<br>5.5                            |                | $\mu V/\text{C}$<br>$\mu V/\text{C}$ |

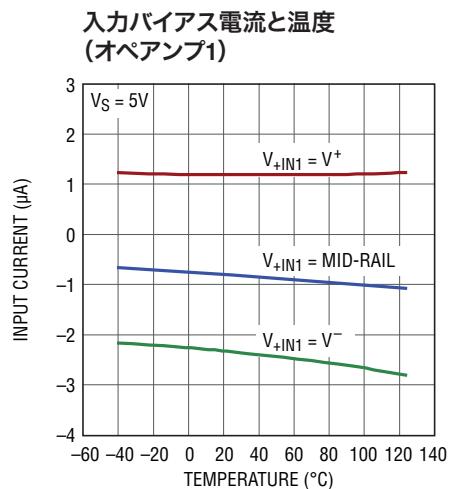

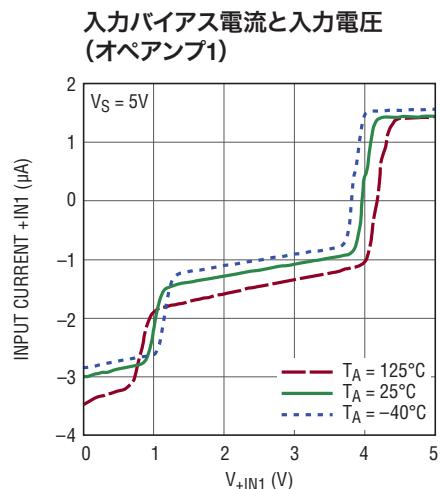

| $I_{B1}$     | Input Bias Current, Op Amp 1 (at $+IN1, -IN1$ )   | $V_{+IN1} = \text{Mid-Supply}$<br>$V_{+IN1} = V^-$<br>$V_{+IN1} = V^+$                                                                                           | -6.8<br>-8.0<br>1.4    | -1.2<br>-3.0<br>2.6                 |                | $\mu A$<br>$\mu A$<br>$\mu A$        |

| $I_{OS1}$    | Input Offset Current, Op Amp 1 (at $+IN1, -IN1$ ) | $V_{+IN1} = \text{Mid-Supply}$<br>$V_{+IN1} = V^-$<br>$V_{+IN1} = V^+$                                                                                           | -1<br>-1<br>-1         | $\pm 0.1$<br>$\pm 0.1$<br>$\pm 0.1$ | 1<br>1<br>1    | $\mu A$<br>$\mu A$<br>$\mu A$        |

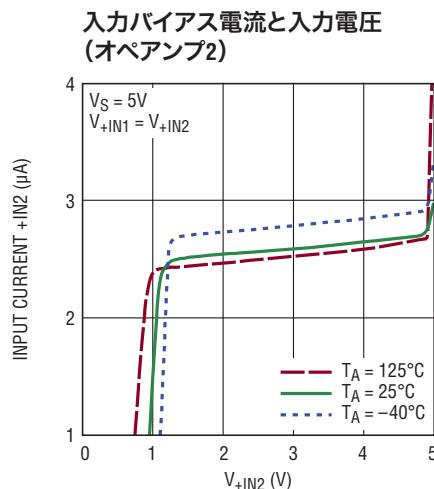

| $I_{+IN2}$   | Input Bias Current, Op Amp 2 (at $+IN2$ )         | $V_{+IN1} = V_2 = \text{Mid-Supply}$                                                                                                                             | -                      | 2.5                                 | 4.4            | $\mu A$                              |

| $I_{OS2}$    | Input Offset Current, Op Amp 2                    | $V_2 = \text{Mid-Supply}$                                                                                                                                        | -                      |                                     | $\pm 0.1$      | $\mu A$                              |

| $e_{n1}$     | Input Voltage Noise Density, Op Amp 1             | Op Amp Input Referred                                                                                                                                            | -                      |                                     | 1.9            | $nV/\sqrt{\text{Hz}}$                |

| $i_{n1}$     | Input Current Noise Density, Op Amp 1             | -                                                                                                                                                                | -                      |                                     | 1.1            | $pA/\sqrt{\text{Hz}}$                |

| $e_{n2}$     | Input Voltage Noise Density, Op Amp 2             | Op Amp Input Referred                                                                                                                                            | -                      |                                     | 2.1            | $nV/\sqrt{\text{Hz}}$                |

| $i_{n2}$     | Input Current Noise Density, Op Amp 2             | -                                                                                                                                                                | -                      |                                     | 1              | $pA/\sqrt{\text{Hz}}$                |

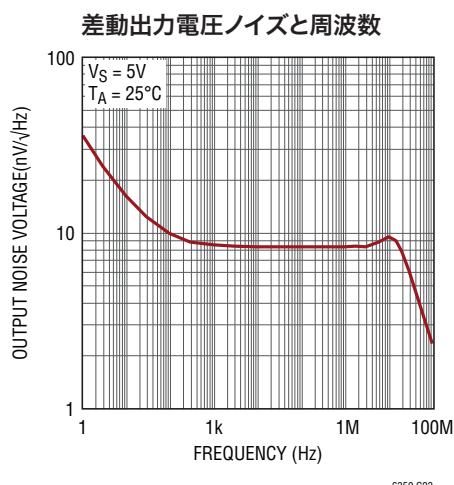

| $e_{n(OUT)}$ | Differential Output Noise Voltage Density         | Total Output Noise Including Both Op Amps and On-Chip Resistors. Input Shorted. $f = 10\text{kHz}$                                                               | -                      |                                     | 8.2            | $nV/\sqrt{\text{Hz}}$                |

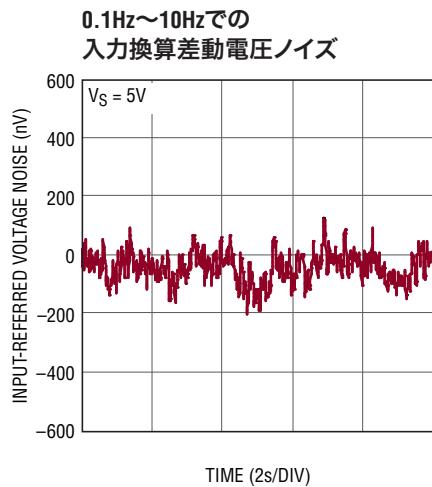

|              | Input Noise Voltage                               | 0.1Hz to 10Hz                                                                                                                                                    | -                      |                                     | 300            | $nV_{P-P}$                           |

| SNR          | Output Signal-to-Noise Ratio                      | $V_{OUTDIFF} = 8V_{P-P}$ , 1MHz Noise Bandwidth                                                                                                                  | -                      |                                     | 110            | dB                                   |

| $V_{+IN1}$   | Input Voltage Range, $+IN1$                       | Guaranteed by CMRR1                                                                                                                                              | -                      | $V^-$                               | $V^+$          | V                                    |

| $V_{+IN2}$   | Input Voltage Range, $+IN2$                       | Guaranteed by CMRR2                                                                                                                                              | -                      | $V^- + 1.5V$                        | $V^+ - 0.1V$   | V                                    |

| $R_{IN}$     | Input Resistance                                  | Single-Ended Input at $+IN1$                                                                                                                                     | -                      |                                     | 4              | $M\Omega$                            |

## 電気的特性

●は全規定温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{+\text{IN}1} = V_2 = \text{電源電圧の中点}$ 、 $V_{\text{SHDN}} = V^+$ 、 $R_L = \text{オープン}$ 、 $R_F = \text{短絡}$ 、 $R_G = \text{オープン}$ 。 $V_S$ は $(V^+ - V^-)$ として定義。 $V_{\text{OUTCM}}$ は $(V_{\text{OUT}1} + V_{\text{OUT}2})/2$ として定義。 $V_{\text{OUTDIFF}}$ は $(V_{\text{OUT}1} - V_{\text{OUT}2})$ として定義。図1を参照。

| SYMBOL                   | PARAMETER                                                                            | CONDITIONS                                                                                                                                                               | MIN              | TYP                      | MAX                                  | UNITS          |   |

|--------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------|--------------------------------------|----------------|---|

| $C_{\text{IN}}$          | Input Capacitance                                                                    | Single-Ended Input at $+\text{IN}1$                                                                                                                                      |                  | 1.8                      |                                      | pF             |   |

| CMRR1                    | Common Mode Rejection Ratio, Op Amp 1                                                | $V_S = 5\text{V}$ , $V_{+\text{IN}1} = V_{-\text{IN}1} = V^- + 1.5\text{V}$ to $V^+$                                                                                     | 82               | 94                       |                                      | dB             |   |

|                          |                                                                                      | $V_S = 5\text{V}$ , $V_{+\text{IN}1} = V_{-\text{IN}1} = V^- + 1.5\text{V}$ to $V^+$                                                                                     | 77               | 94                       |                                      | dB             |   |

|                          |                                                                                      | $V_S = 5\text{V}$ , $V_{+\text{IN}1} = V_{-\text{IN}1} = V^-$ to $V^+$                                                                                                   | 72               | 88                       |                                      | dB             |   |

|                          |                                                                                      | $V_S = 3\text{V}$ , $V_{+\text{IN}1} = V_{-\text{IN}1} = V^-$ to $V^+$                                                                                                   | 67               | 82                       |                                      | dB             |   |

| CMRR2                    | Common Mode Rejection Ratio, Op Amp 2                                                | $V_S = 5\text{V}$ , $V_{+\text{IN}1} = V_2 = V^- + 1.5\text{V}$ to $V^+ - 0.1\text{V}$                                                                                   | 93               | 118                      |                                      | dB             |   |

|                          |                                                                                      | $V_S = 3\text{V}$ , $V_{+\text{IN}1} = V_2 = V^- + 1.5\text{V}$ to $V^+ - 0.1\text{V}$                                                                                   | 85               | 110                      |                                      | dB             |   |

|                          |                                                                                      | $V_S = 10\text{V}$ , $V_{+\text{IN}1} = V_2 = V^- + 1.5\text{V}$ to $V^+ - 0.1\text{V}$                                                                                  | 96               | 118                      |                                      | dB             |   |

| PSRR                     | Power Supply Rejection Ratio<br>( $\Delta V_S / \Delta V_{\text{OSDIFF}}$ )          | $V_S = 2.7\text{V}$ to $12\text{V}$                                                                                                                                      | 80               | 108                      |                                      | dB             |   |

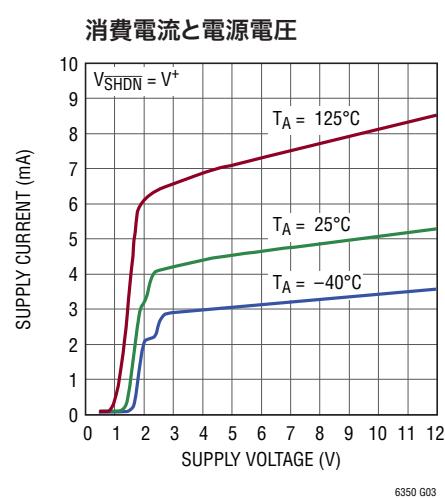

| $V_S$                    | Supply Voltage (Note 7)                                                              |                                                                                                                                                                          | 2.7              | 12                       |                                      | V              |   |

| BAL                      | Output Balance ( $\Delta V_{\text{OUTDIFF}} / \Delta V_{\text{OUTCM}}$ )<br>(Note 8) | $V_{\text{OUTDIFF}} = 2\text{V}$                                                                                                                                         | 50               | 68                       |                                      | dB             |   |

| GAIN                     | Closed-Loop Gain<br>( $\Delta V_{\text{OUTDIFF}} / \Delta (V_{+\text{IN}1} - V_2)$ ) | $\Delta (V_{+\text{IN}1} - V_2) = 4\text{V}$                                                                                                                             | ●                | 2                        |                                      | V/V            |   |

| GAIN <sub>ERR</sub>      | Closed-Loop Gain Error                                                               |                                                                                                                                                                          | ●                | -0.6                     | ±0.08                                | 0.6            | % |

| ΔGAIN <sub>ERR</sub> /ΔT | Closed-Loop Gain Error Drift                                                         |                                                                                                                                                                          | ●                | 3                        |                                      | ppm/°C         |   |

| INL                      | DC Linearity (Note 9)                                                                | $V^+ = 5\text{V}$ , $V^- = 0\text{V}$<br>$V^+ = 5\text{V}$ , $V^- = -2\text{V}$<br>$V^+ = 5\text{V}$ , $V^- = -2\text{V}$ , 16-Bit, $8\text{V}_{\text{P-P}}$             |                  | 230                      |                                      | μV             |   |

|                          |                                                                                      |                                                                                                                                                                          |                  | 125                      |                                      | μV             |   |

|                          |                                                                                      |                                                                                                                                                                          |                  | ±1                       |                                      | LSB            |   |

| $R_{\text{INT}}$         | Internal Resistors                                                                   |                                                                                                                                                                          |                  | 1000                     |                                      | Ω              |   |

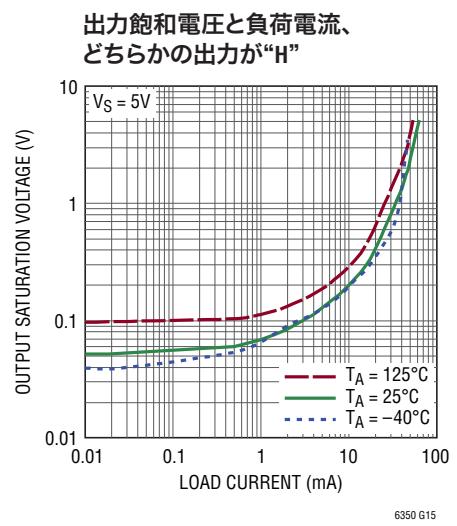

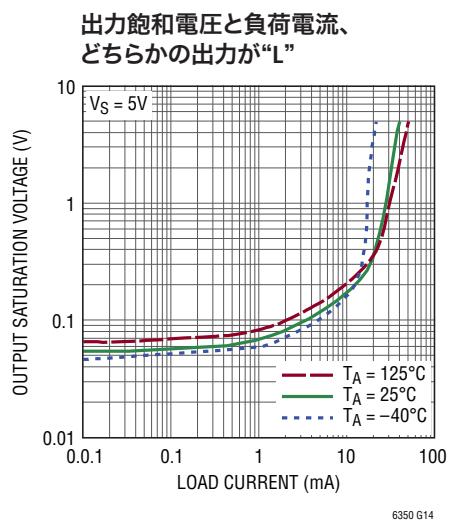

| $V_{\text{OH}}$          | Output Swing to $V^+$ , Either Output<br>(Note 10)                                   | No Load<br>Sourcing 12.5mA                                                                                                                                               | ●<br>●           | 55<br>360                | 170<br>750                           | mV<br>mV       |   |

| $V_{\text{OL}}$          | Output Swing to $V^-$ , Either Output<br>(Note 10)                                   | No Load<br>Sourcing 12.5mA                                                                                                                                               | ●<br>●           | 55<br>260                | 170<br>460                           | mV<br>mV       |   |

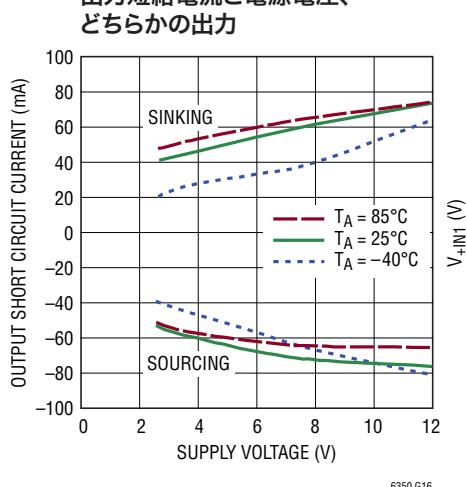

| $I_{\text{SC}}$          | Output Short-Circuit Current                                                         | $V_{+\text{IN}1} = \text{Mid-Rail} \pm 200\text{mV}$ , $V_{-\text{IN}1} = \text{Mid-Rail}$<br>$V_S = 5\text{V}$<br>$V_S = 5\text{V}$<br>$V_S = 3\text{V}$                |                  | ±27<br>±15<br>±15        | ±45<br>±45<br>±40                    | mA<br>mA<br>mA |   |

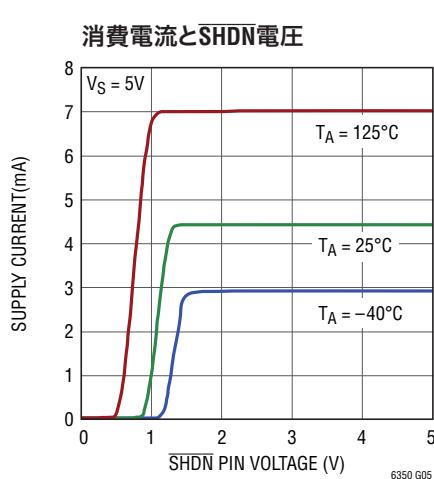

| $V_{\text{IL}}$          | SHDN Input Logic Low                                                                 | $V_S = 2.7\text{V}$ to $12\text{V}$                                                                                                                                      | ●                |                          | $V^- + 0.3$                          | V              |   |

| $V_{\text{IH}}$          | SHDN Input Logic High                                                                | $V_S = 2.7\text{V}$ to $12\text{V}$                                                                                                                                      | ●                |                          | $V^- + 2.0$                          | V              |   |

| $I_{\text{SHDN}}$        | SHDN Pin Current                                                                     | $\overline{\text{SHDN}} = V^+$<br>$\overline{\text{SHDN}} = V^-$                                                                                                         | ●<br>●           | -1<br>-45                | 1<br>-20                             | μA<br>μA       |   |

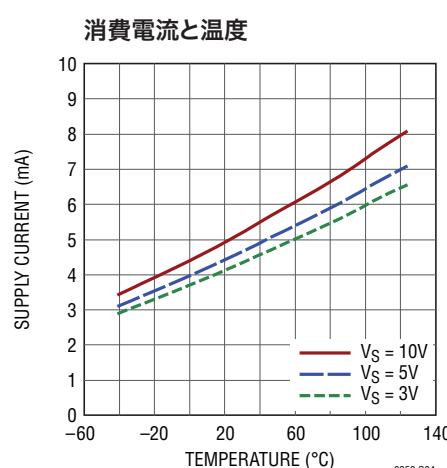

| $I_S$                    | Supply Current                                                                       | $V_S = 3\text{V}$<br>$V_S = 5\text{V}$<br>$V_S = 5\text{V}$<br>$V_S = 10\text{V}$                                                                                        | ●<br>●<br>●<br>● | 4.5<br>5.8<br>4.8<br>5.4 | 8.1<br>mA<br>8.3<br>mA<br>10.4<br>mA | mA             |   |

| $I_{S(\text{SHDN})}$     | Supply Current in Shutdown                                                           | $V_S = 3\text{V}$ , $V_{\text{SHDN}} = V_{\text{IL}}$<br>$V_S = 5\text{V}$ , $V_{\text{SHDN}} = V_{\text{IL}}$<br>$V_S = 10\text{V}$ , $V_{\text{SHDN}} = V_{\text{IL}}$ | ●<br>●<br>●      | 43<br>60<br>70           | 220<br>240<br>260                    | μA<br>μA<br>μA |   |

| GBW                      | Gain-Bandwidth Product<br>Frequency = 1MHz                                           | Op Amp 1 (Noninverting)<br>Op Amp 2 (Inverting)                                                                                                                          |                  |                          | 85<br>115                            | MHz<br>MHz     |   |

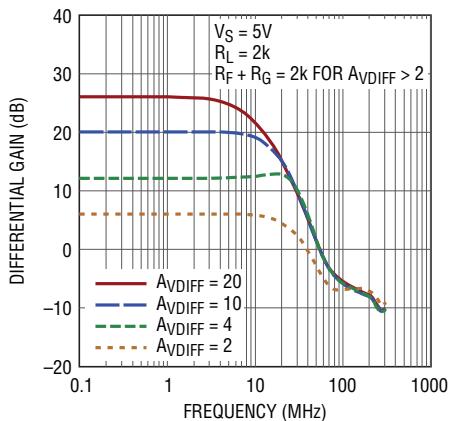

| BW                       | Differential -3dB Small-Signal Bandwidth                                             | $V_{\text{OUTDIFF}} = 100\text{mV}_{\text{P-P}}$<br>$V_{\text{OUTDIFF}} = 100\text{mV}_{\text{P-P}}$                                                                     | ●                | 23<br>19                 | 33                                   | MHz<br>MHz     |   |

## 電気的特性

●は全規定温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{+\text{IN}1} = V2$  = 電源電圧の中点、 $V_{\text{SHDN}} = V^+$ 、 $R_L$  = オープン、 $R_F$  = 短絡、 $R_G$  = オープン。 $V_S$ は $(V^+ - V^-)$ として定義。 $V_{\text{OUTCM}}$ は $(V_{\text{OUT}1} + V_{\text{OUT}2})/2$ として定義。 $V_{\text{OUTDIFF}}$ は $(V_{\text{OUT}1} - V_{\text{OUT}2})$ として定義。図1を参照。

| SYMBOL            | PARAMETER                            | CONDITIONS                                                                                                                  | MIN | TYP               | MAX | UNITS                                |

|-------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|-------------------|-----|--------------------------------------|

| FPBW              | Full-Power Bandwidth (Note 11)       | $V_{\text{OUTDIFF}} = 8\text{V}_{\text{P-P}}$                                                                               |     | 1.6               |     | MHz                                  |

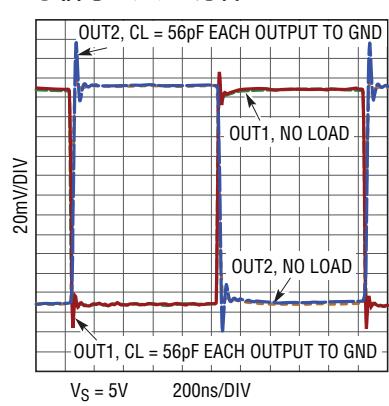

| $C_L$             | Capacitive Load Drive, 20% Overshoot | No Series Output Resistors                                                                                                  |     | 56                |     | pF                                   |

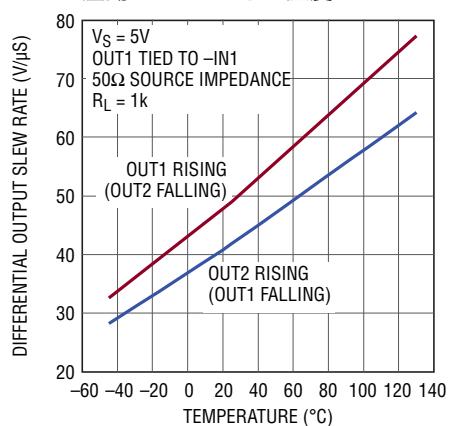

| SR                | Differential Slew Rate               | OUT1 Rising (OUT2 Falling)<br>OUT1 Falling (OUT2 Rising)                                                                    |     | 48<br>41          |     | V/ $\mu\text{s}$<br>V/ $\mu\text{s}$ |

| HD2<br>HD3        | 10kHz Distortion                     | $V_S = 5\text{V}$ , $V_{\text{OUTDIFF}} = 4\text{V}_{\text{P-P}}$ , $R_L = 2\text{k}\Omega$<br>2nd Harmonic<br>3rd Harmonic |     | -115<br>-115      |     | dBc<br>dBc                           |

| HD2<br>HD3        | 100kHz Distortion                    | $V_S = 5\text{V}$ , $V_{\text{OUTDIFF}} = 4\text{V}_{\text{P-P}}$ , $R_L = 2\text{k}\Omega$<br>2nd Harmonic<br>3rd Harmonic |     | -102<br>-97       |     | dBc<br>dBc                           |

| HD2<br>HD3        | 1MHz Distortion                      | $V_S = 5\text{V}$ , $V_{\text{OUTDIFF}} = 4\text{V}_{\text{P-P}}$ , $R_L = 2\text{k}\Omega$<br>2nd Harmonic<br>3rd Harmonic |     | -86<br>-75        |     | dBc<br>dBc                           |

| $t_S$             | Settling Time to a 4V Input Step     | 0.1%<br>0.01%<br>0.0015% ( $\pm 1\text{LSB}$ , 16-Bit, Falling Edge)                                                        |     | 200<br>240<br>350 |     | ns<br>ns<br>ns                       |

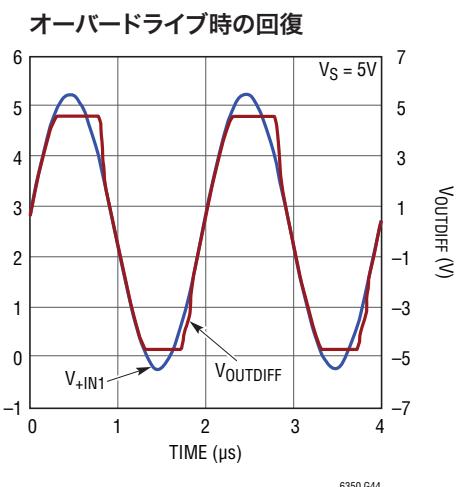

| $t_{\text{OVDR}}$ | Overdrive Recovery Time              | +IN1 to $V^-$ and $V^+$                                                                                                     |     | 200               |     | ns                                   |

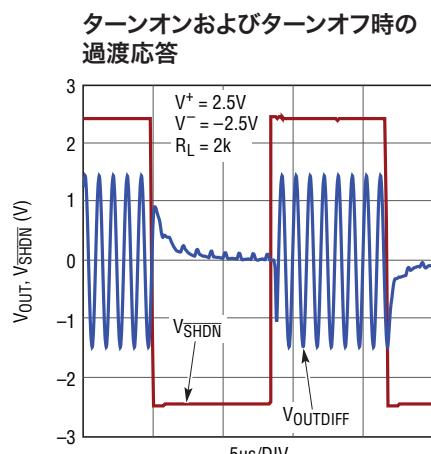

| $t_{\text{ON}}$   | Turn-On Time                         | $V_{\text{SHDN}} = 0\text{V}$ to $5\text{V}$                                                                                |     | 400               |     | ns                                   |

| $t_{\text{OFF}}$  | Turn-Off Time                        | $V_{\text{SHDN}} = 5\text{V}$ to $0\text{V}$                                                                                |     | 400               |     | ns                                   |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**入力は、各電源へのダイオードにより保護されている。さらに、オペアンプ入力+IN1、-IN1、+IN2は、これらのオペアンプ入力のバック・トゥ・バック・ダイオードにより保護されている。入力が電源電圧を超えるか、またはオペアンプの差動入力電圧が $0.7\text{V}$ を超える場合、入力電流は $20\text{mA}$ 未満に制限すること。

**Note 3:**出力が無期限に短絡されるときは、接合部温度を絶対最大定格値以下に抑えるためにヒートシンクが必要な場合がある。

**Note 4:**LT6350C/LT6350Iは、 $-40^\circ\text{C} \sim 85^\circ\text{C}$ の温度範囲で動作することが保証されている。LT6350Hは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の温度範囲で動作することが保証されている。

**Note 5:**LT6350Cは $0^\circ\text{C} \sim 70^\circ\text{C}$ の温度範囲で性能仕様に適合することが保証されている。LT6350Cは $-40^\circ\text{C} \sim 85^\circ\text{C}$ の温度範囲で性能仕様に適合するように設計され、特性が評価されており、性能仕様に適合すると予想されるが、これらの温度ではテストされないし、QAサンプリングも行われない。LT6350Iは $-40^\circ\text{C} \sim 85^\circ\text{C}$ の温度範囲で性能仕様に適合することが保証されている。LT6350Hは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の温度範囲で性能仕様に適合することが保証されている。

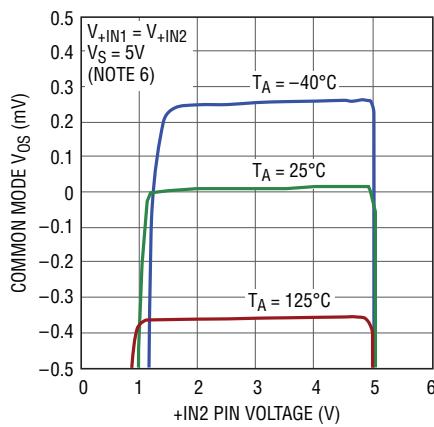

**Note 6:** $V_{0S2}$ は、合計出力同相電圧オフセット(出力同相電圧と $V2$ 電圧の誤差)として測定される。 $V_{0S2}$ には、オペアンプ2の電圧オフセット、 $I_B$ 、 $I_{OS}$ 、および内部抵抗と $499\Omega$ 外付け抵抗 $R1$ の不整合による複合的な影響が含まれる(図1参照)。

**Note 7:**電源電圧範囲は電源除去比テストによって保証されている。

**Note 8:**出力バランスは、利得誤差と利得から次式によって計算される。

$$\text{BAL} = \frac{\text{GAIN}}{\text{GAIN}_{\text{ERR}}}$$

**Note 9:**DCの直線性は、 $V_{+\text{IN}1} = 0.5\text{V}$ 、 $2.5\text{V}$ 、 $4.5\text{V}$ の設定で各入力に対する差動出力を測定し、これら3つのデータ点が形成する直線に最も近い最小二乗値からの最大偏差を計算することによって判定される。

**Note 10:**出力電圧振幅は出力と電源レールの間で測定される。

**Note 11:**フルパワー帯域幅はスルーレートから計算される。FPBW = SR/2π $V_p$

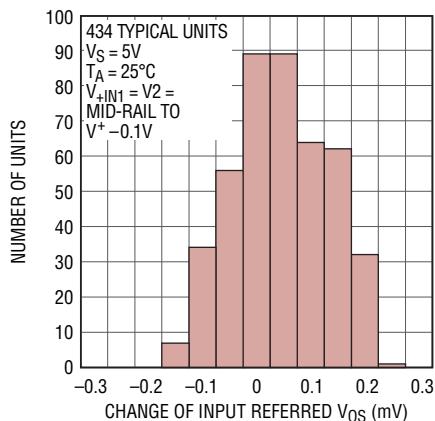

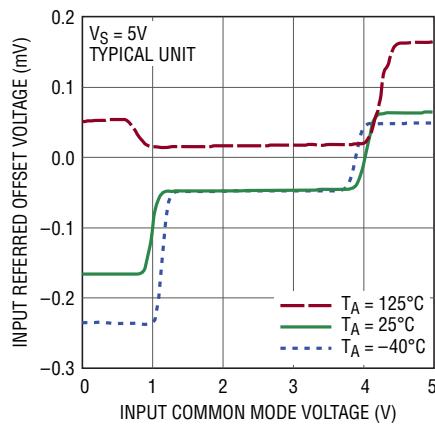

## 標準的性能特性

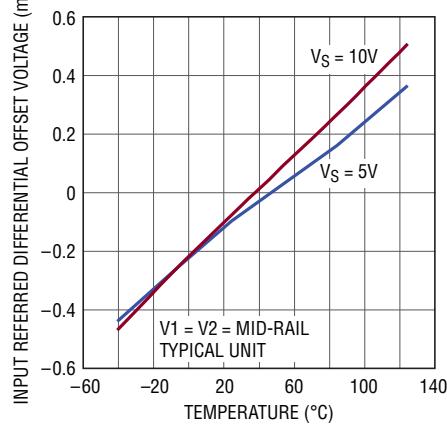

$T_A = 25^\circ\text{C}$ 、 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{+\text{IN}1} = V_2$  = 電源電圧の中点、 $V_{\text{SHDN}} = V^+$ 、 $R_F$  = 短絡、 $R_G$  = オープン、 $R_L$  = オープン。図1を参照。

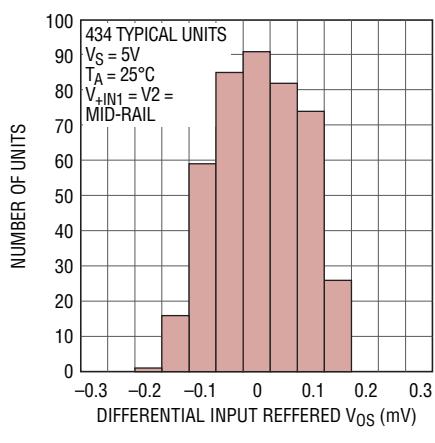

差動 $V_{\text{OS}}$ の変化の分布

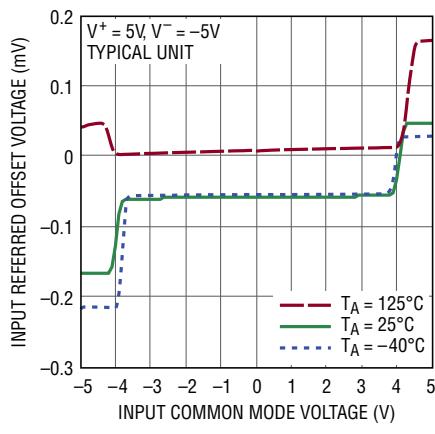

オフセット電圧と入力同相電圧

(オペアンプ1)

オフセット電圧と入力同相電圧

(オペアンプ1)

差動 $V_{\text{OS}}$ の分布

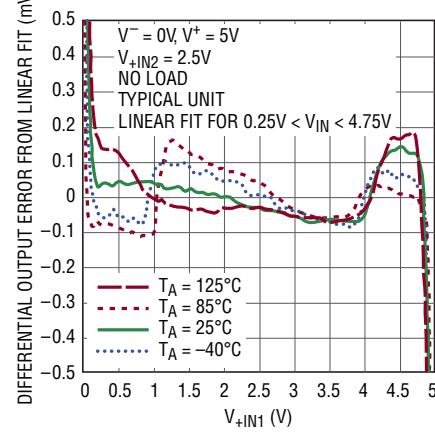

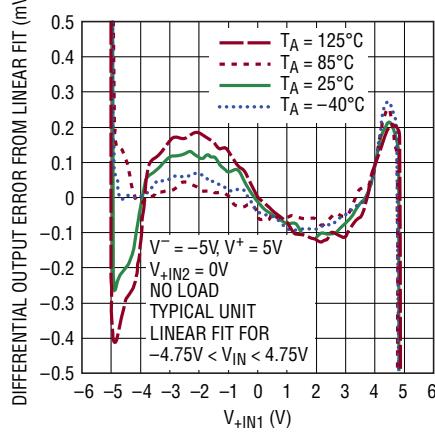

DC直線性

DC直線性

同相 $V_{\text{OS}}$ と入力(+IN2)電圧

差動 $V_{\text{OS}}$ と温度

## 標準的性能特性

$T_A = 25^\circ\text{C}$ 、 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{+\text{IN}1} = V_2$  = 電源電圧の中点、 $V_{\text{SHDN}} = V^+$ 、 $R_F$  = 短絡、 $R_G$  = オープン、 $R_L$  = オープン。図1を参照。

## 標準的性能特性

$T_A = 25^\circ\text{C}$ 、 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{+\text{IN}1} = V_2$  = 電源電圧の中点、 $V_{\text{SHDN}} = V^+$ 、 $R_F$  = 短絡、 $R_G$  = オープン、 $R_L$  = オープン。図1を参照。

## 標準的性能特性

$T_A = 25^\circ\text{C}$ 、 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{+\text{IN}1} = V_2$  = 電源電圧の中点、 $V_{\text{SHDN}} = V^+$ 、 $R_F$  = 短絡、 $R_G$  = オープン、 $R_L$  = オープン。図1を参照。

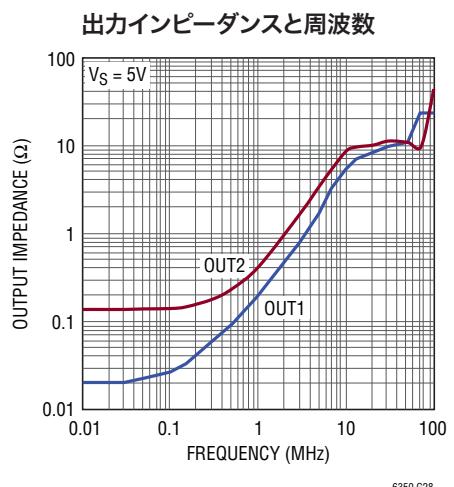

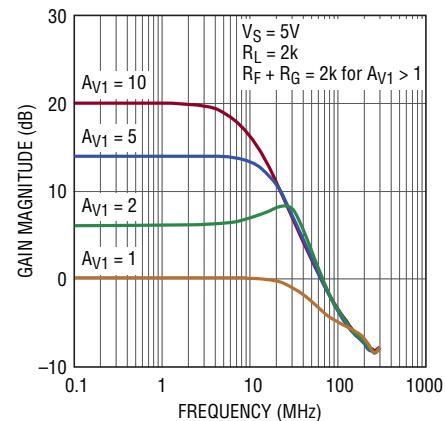

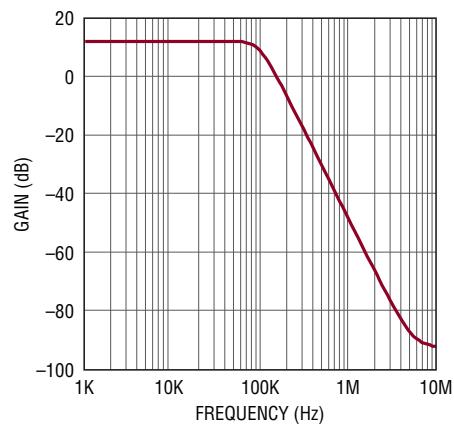

差動周波数応答と利得

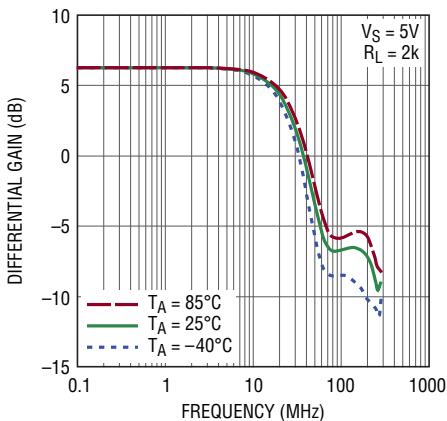

差動周波数応答と温度

閉ループ小信号周波数応答

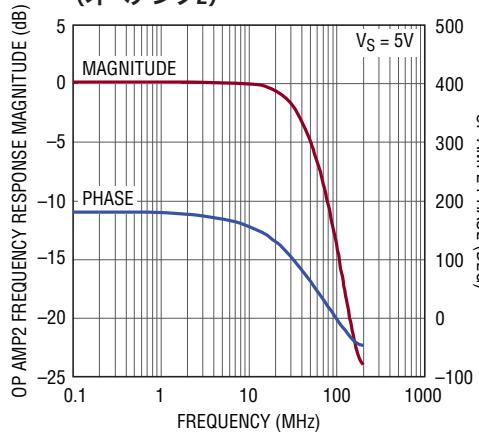

(オペアンプ1)

閉ループ小信号周波数応答

(オペアンプ2)

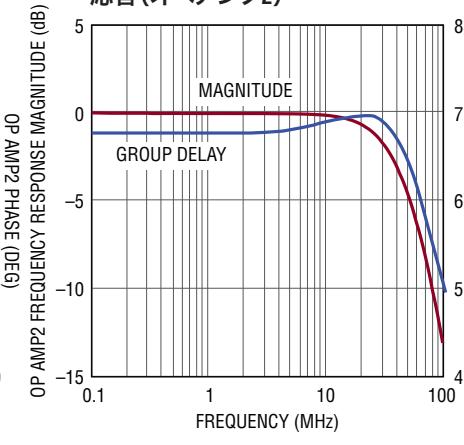

閉ループの振幅とグループ遅延の

応答(オペアンプ2)

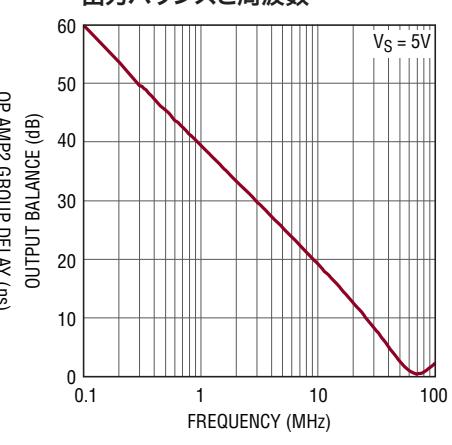

出力バランスと周波数

小信号ステップ応答

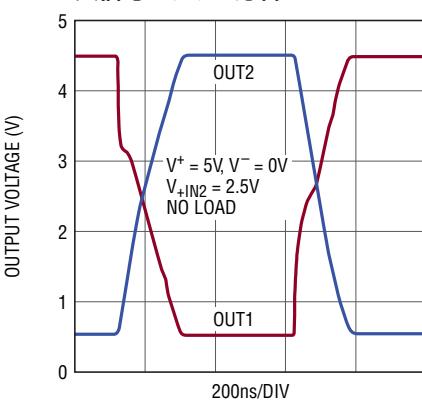

大信号ステップ応答

差動スルーレートと温度

## 標準的性能特性

$T_A = 25^\circ\text{C}$ 、 $V^+ = 5\text{V}$ 、 $V^- = 0\text{V}$ 、 $V_{+\text{IN}1} = V_2$  = 電源電圧の中点、 $V_{\text{SHDN}} = V^+$ 、 $R_F$  = 短絡、 $R_G$  = オープン、 $R_L$  = オープン。図1を参照。

## ピン機能

**-IN1(ピン1):**反転入力。通常、OUT1から帰還を受け取るために使用します。

**+IN2(ピン2):**高インピーダンス入力。通常、リファレンス入力として使用します。

**$V^+$ (ピン3):**正電源。

**OUT1(ピン4):**非反転出力。 $+IN1$ と同位相。

**OUT2(ピン5):**反転出力。

**$V^-$ (ピン6):**負電源。グランドにすることができます。

**SHDN(ピン7):**シャットダウン。“H”に接続するとデバイスがイネーブルされます。“L”に接続するとデバイスはディスエーブルされ、消費電流が $70\mu\text{A}$ 未満になります。

**+IN1(ピン8):**高インピーダンス入力。通常、シングルエンド入力として使用します。

**露出パッド(ピン9、DD8パッケージのみ):** $V^-$ に接続します。

## ブロック図

## DCテスト回路

図1. DCテスト回路

## 動作

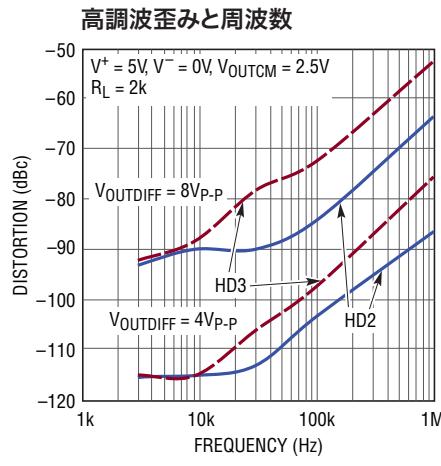

LT6350は低ノイズのシングルエンドー差動コンバータ/ADCドライバです。このデバイスは、低インピーダンスまたは高インピーダンスのシングルエンド入力信号を、高性能差動逐次比較レジスタ(SAR)ADCのドライブに適した低インピーダンスのバランスの取れた差動出力に変換します。標準的な利得2の構成の閉ループ-3dB帯域幅は33MHzです。

LT6350は、ブロック図に示すように2個のオペアンプからなるトポロジーを使用しています。入力側には未設定のオペアンプが備わっており、このオペアンプの両入力と出力はピンに引き出されています。このオペアンプの先にはもう1個のオペアンプが接続されています。このオペアンプは固定配線で、ユニティゲイン・インバータとして最適補償されており、その入力は1個目のオペアンプの出力に接続されています。反転オペアンプの非反転入力はピンに引き出されており、これは出力同相電圧レベルを設定するために使われます。したがって2個のオペアンプの出力は位相が180°ずれており、差動入力アナログ-デジタル・コンバータ用の低インピーダンス差動ドライブを提供します。LT6350の出力振幅はレール・トゥ・レールで、45mAの過渡電流をソースまたはシンクできます。出力は、グランドに対して40pF、差動で20pFをドライブするように設計されています。40pFを超える負荷容量は、少なくとも25Ωの直列抵抗を使用してそれぞれの出力からデカップリングする必要があります。

LT6350の特長は、110dBを超えるSNRを実現するために、極めてノイズの小さいオペアンプを使用している点です。

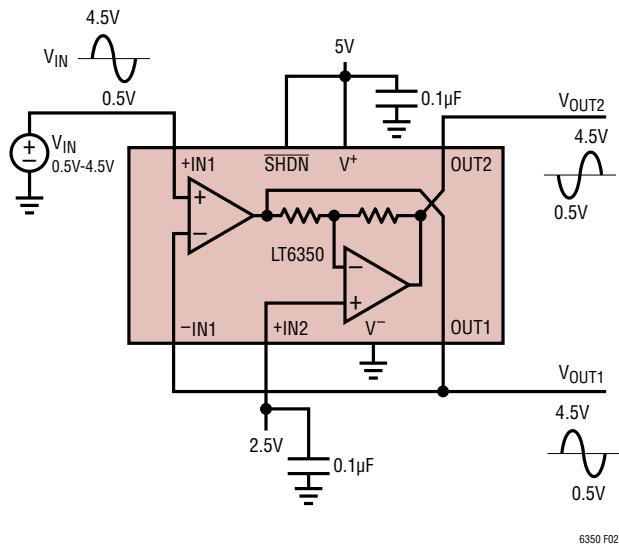

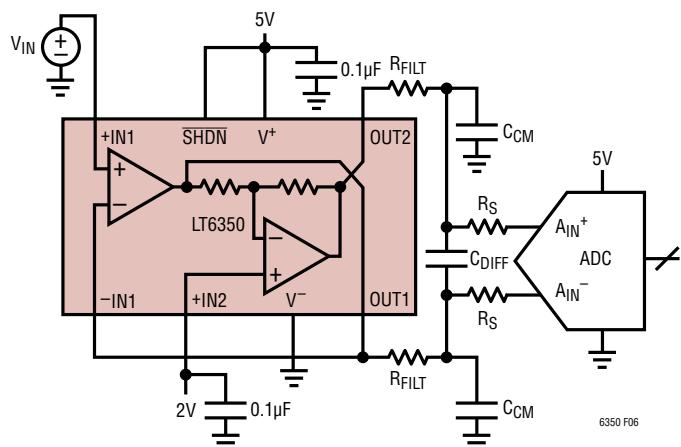

## 基本的接続

LT6350の代表的な使用方法は、高インピーダンスのシングルエンド入力信号を低インピーダンスの差動出力に変換することです。このようなアプリケーションのための構成を図2に示します。ここで、入力オペアンプは、+IN1の高入力インピーダンスの非反転バッファとして配線されています。出力側では、VOUT1が入力に追従し、VOUT2がVOUT1の反転出力となり、全体としての差動利得は2です。入力オペアンプの入力段はレール・トゥ・レールで、両出力もレール・トゥ・レールです。この構成では各出力の標準振幅はレールから55mV以内までで、单一5Vレールから8VP-Pの差動出力が得られます。これは、レールの中間の入力同相電圧を使用する差動入力ADCへの簡単なインターフェースを提供します。

図2. 基本的接続

## 設計式とその他の接続

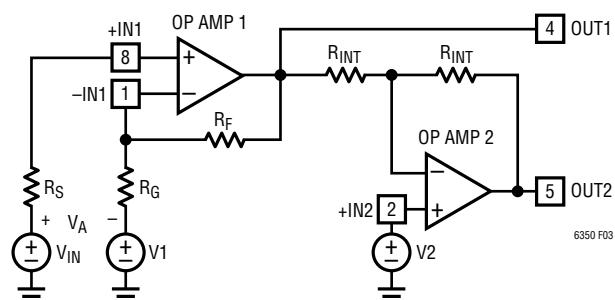

入力オペアンプの出力と両方の入力はLT6350のピンに接続されているので、上記以外の構成とすることも可能です。図3に示す一般的構成を考えます。

通常のオペアンプ解析では、入力電圧をV1、V2、VIN、VAとすると、VOUT1とVOUT2について以下の式が得られます。

$$V_{OUT1} = V_{IN} \cdot (1 + R_F/R_G) - V_1 \cdot (R_F/R_G)$$

$$V_{OUT1} = V_A \cdot (1 + R_F/R_G) + V_1$$

$$V_{OUT2} = -V_{OUT1} + 2 \cdot V_2$$

差動出力電圧と同相出力電圧を以下のように定義します。

$$V_{OUTDIFF} \equiv V_{OUT1} - V_{OUT2}$$

および

$$V_{OUTCM} \equiv (V_{OUT1} + V_{OUT2})/2$$

この定義式にVOUT1とVOUT2の式を結合すると、差動出力電圧と同相出力電圧は次のようにになります。

$$V_{OUTDIFF} = 2 \cdot (V_{IN} \cdot (1 + R_F/R_G) - V_1 \cdot (R_F/R_G) - V_2) \quad (1)$$

$$V_{OUTDIFF} = 2 \cdot (V_A \cdot (1 + R_F/R_G) + V_1 - V_2) \quad (2)$$

$$V_{OUTCM} = V_2 \quad (3)$$

## 動作

つまり、出力同相電圧は $+IN_2$ の電圧のみによって決定されます。しかし、 $+IN_2$ に加えられる電圧は $V_{OUT1}$ 出力の電圧には影響しないので、 $V_1$ と $V_2$ が等しくない時に $V_A = 0$ だと、差動オフセット電圧が発生します。このオフセット電圧の値は、式2から $2 \cdot (V_1 - V_2)$ となります。したがって差動オフセットを最小にするには、ピン $+IN_1$ への入力信号 $V_{IN}$ の中点をピン $+IN_2$ に加える同相電圧に合わせる必要があります。多くの場合、この電圧はADCのリファレンス出力から与えられます。入力値の中点をこのように合わせて $V_1 = V_2$ となるとき、式2は次のようになります。

$$V_{OUTDIFF} = 2 \cdot V_A \cdot (1 + R_F / R_G)$$

「基本的接続」のセクションに示した単純な接続は、図3に示す一般的回路の特殊なケースと見なすことができます。つまり、図3の $R_F$ を短絡して $R_G$ を開放し、 $V_{IN}$ の電圧の中点を電圧 $V_2$ とした場合です。差動利得を2よりも大きくする必要がある時は、式(2)に従って $R_F$ と $R_G$ の値を調整することができます。帰還ネットワークに関する詳細は、次のセクションと「入力アンプ(オペアンプ1)の帰還部品」のセクションに示されています。

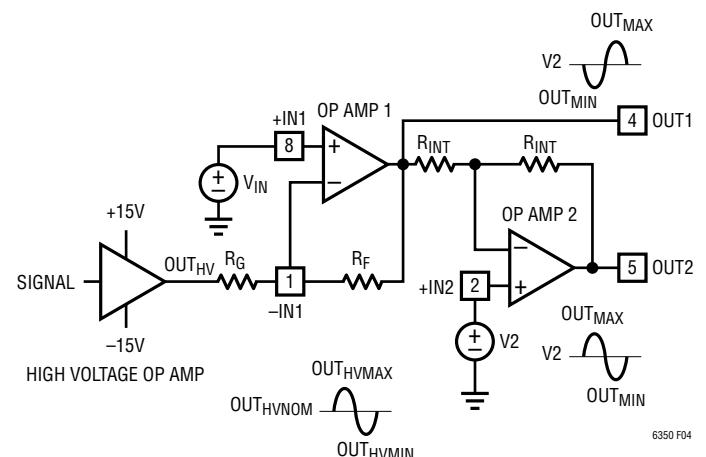

### 反転利得接続／高電圧信号とのインターフェース

上に示した例は $+IN_1$ に入力信号を加えることを前提としていますが、図3の電圧 $V_{IN}$ を固定して $V_1$ に入力信号を加えることによって、入力オペアンプを反転構成で使用することも可能です。入力オペアンプを反転構成で使用するとその入力同相電圧が電圧 $V_{IN}$ に固定され、これによって $V_1$ の入力信号振幅をLT6350の電源レールよりも大きくすることができます。この構成では、好ましくない差動オフセットを防ぐために、次式に従って $V_{IN}$ を選ぶ必要があります。

$$V_{IN} = V_2 / (1 + (R_F / R_G))$$

この場合、式(1)は次のようにになります。

$$V_{OUTDIFF} = -2 \cdot V_1 \cdot (R_F / R_G)$$

$V_1$ の入力について $R_F = R_G$ とすると、この構成の利得は-2となります。

反転利得構成の実際的な応用例としては、5V差動SAR ADCへの高電圧オペアンプのインターフェースがあります。図4に示すように、産業用アプリケーションでは、 $\pm 15V$ レールのオペアンプを介して送られてくる検出信号が使われます。LT6350では、

反転利得構成を使用することによって、高電圧オペアンプを5V ADCに簡単にインターフェースすることができます。クリーンなインターフェースを実現するには、次の3つの条件を満たす必要があります。

1.  $OUT_{HV}$ の中点を $OUT_{HVNOM}$ とした時に $V_{OUTDIFF} = 0$

2.  $OUT_{HV}$ の中点を $OUT_{HVNOM}$ とした時に $V_{OUT1} = V_{OUTCM} = V_2$

3.  $OUT_{HV}$ のフルスケール信号が、LT6350の出力でADCの適切なフルスケール範囲に変換される。

上記の条件を設計式(1)～(3)に適用すると、 $R_F$ と $R_G$ の比率、および $V_{IN}$ の値が求められます。

$$R_F / R_G = (OUT_{MAX} - OUT_{MIN}) / (OUT_{HVMAX} - OUT_{HVMIN})$$

$$V_{IN} = V_2 / (1 + (R_F / R_G)) + (OUT_{HVNOM}) / (1 + (R_G / R_F))$$

図3. 一般的構成

図4. 高電圧信号とのインターフェース

## アプリケーション情報

### 入力アンプ(オペアンプ1)の特性

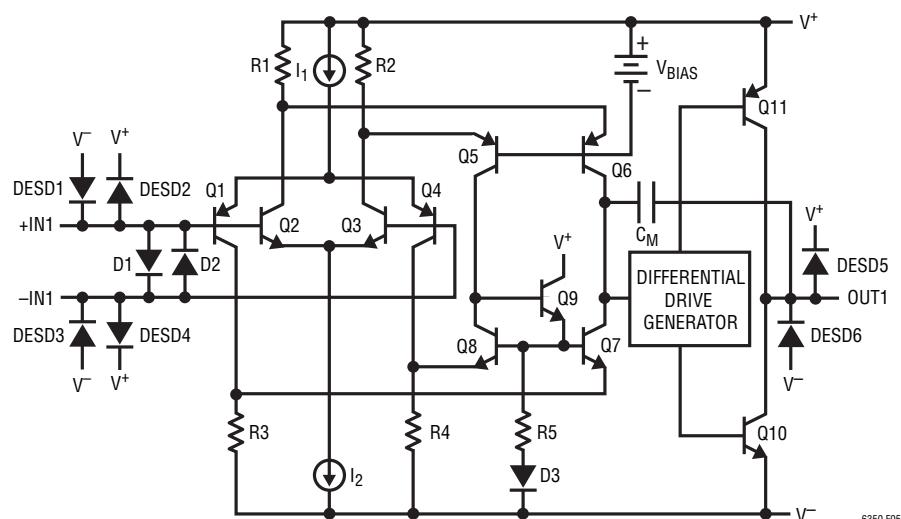

図5はLT6350の入力アンプの簡略回路図です。入力段には、並列で動作するNPNおよびPNP差動ペアがあります。このトポロジーでは、入力振幅を負電源レールから正電源レールまでの全域とすることができます。どちらの差動ペアも、同相電圧がどちらのレールからも少なくとも1.3V離れていれば動作します。同相電圧の振幅が $V^+ - 1.3V$ を超えると電流源 $I_1$ が飽和し、PNP差動ペアQ1/Q4内の電流がゼロになります。帰還はNPN差動ペアQ2/Q3を通じて維持されますが、入力段のトランジスタコンダクタンス $g_m$ は半減します。同相電圧の振幅が負のレールから1.3V以内になると、 $I_2$ にも同様の影響が生じます。入力範囲全体にわたってほぼ一定のオフセット電圧を保つために、精密な2ポイント・アルゴリズムが使われます。

入力同相電圧をレールの中央に合わせると、+IN1入力と-IN1入力には負の入力バイアス電流が流れ込みます。入力同相電圧が負のレールから1.3Vの範囲内にあってQ1/Q4だけがアクティブの時は、この電流の量が増えます。入力同相電圧が正のレールから1.3Vの範囲内にあってQ2/Q3だけがアクティブの時は、この電流の極性が反転します。入力同相範囲全体に

わたる入力バイアス電流の標準的な総変化量は約4 $\mu A$ です。入力バイアス電流のこれらの変化に応じて、ソース抵抗と利得設定抵抗両端の電圧も変化します。LT6350の入力オフセット電流は入力バイアス電流よりも小さいので、入力ピンの有効ソース抵抗と帰還抵抗を整合させれば、入力バイアス電流の変化によって生じる合計オフセット誤差を減らし、歪みを最小限にすることができます。

### 入力アンプ(オペアンプ1)の帰還部品

帰還抵抗を使用してオペアンプ1の利得を設定するときは、帰還抵抗と反転入力-IN1の合計容量で形成されるポールによって安定性が損なわれないように注意する必要があります。たとえばLT6350の差動利得を+4に設定するには、図3の $R_F$ と $R_G$ を $1k\Omega$ に設定します。-IN1の合計容量(LT6350とPC基板)が3pFの場合はループ応答で106MHzに新しいポールが形成され、これによってステップ応答にリングングが生じる可能性があります。-IN1の合計寄生容量と同じ値を持つコンデンサを帰還抵抗と並列に接続すれば、リングングや発振を無くすことができます。

図5. 入力アンプ(オペアンプ1)の簡略回路図

## アプリケーション情報

レイアウト時には、-IN1ピンに生じる寄生容量をできるだけ小さくするために、トレース長をできるだけ短くして-IN1ピンの下のグランド・プレーンを除去することを含め、特別な注意を払う必要があります。

入力バイアス電流によって生じる入力オペアンプのDC電圧オフセットは、 $R_F$ と $R_G$ の並列インピーダンスと+IN1をドライブするソースのインピーダンスを整合させることによって、最小限に抑えることができます。たとえば、標準的な利得2のアプリケーションで入力オペアンプがユニティゲイン・バッファとして設定されている時は、 $R_F = R_S$ とすれば出力の差動オフセットが最小になります。値がゼロ以外の $R_F$ は合計出力ノイズの一因となるので、ノイズ帯域を減らすためにコンデンサを使って $R_F$ をバイパスすることができます。

### 反転アンプ(オペアンプ2)の特性

ピンOUT1、+IN2、およびOUT2のオペアンプは、ユニティゲイン・インバータとして内部的に設定されており、OUT1の反転電圧をピンOUT2に出力します。ピン+IN2に加えられる電圧は、式(3)に従って出力同相電圧を設定します。有効出力同相電圧の範囲は、A/Dコンバータのフルスケール入力範囲によって制限されます。レールの中点付近の出力同相値が最も有効です。したがって、反転バッファに使用されるオペアンプは、主に入力同相範囲がレール・トゥ・レールではないという点で入力オペアンプと異なります。反転オペアンプは、 $V^- + 1.5V$ から $V^+ - 0.1V$ までの入力範囲で機能する入力段を持っています。

反転オペアンプは、利得を-1に設定するために精密に整合された1kの内部抵抗を使用します。出力の振幅中はこれらの抵抗を電流が通過し、LT6350の合計電力損失は大きくなります。静止時消費電力を超えるワーストケースの増加量は、OUT1とOUT2の間に全電源電圧が生じると仮定することによって求められます。この場合の内部帰還ネットワークの電力損失は $V_S^2/2k\Omega$ です。

反転オペアンプの設定はノイズ利得2に固定されているので、内部周波数補償は、反転オペアンプの利得帯域幅積が入力オペアンプのそれよりも大きくなるように調整されています。これにより、標準的な差動利得2の設定でLT6350を使用する時に2個のオペアンプの閉ループ帯域幅をより精密に整合させることが可能になり、そのアプリケーションにおける閉ループ差動帯域幅が広がります。

反転オペアンプの入力換算電圧オフセットは出力同相電圧オフセットに相当し、式(2)に従って差動電圧オフセットの一因となります。これは製造時に $\pm 125\mu V$ 以内にトリミングされています。ピン+IN2への入力バイアス電流によるオフセットへの影響を最小限にするには、すべてのアプリケーションで、ピン+IN2に $499\Omega$ の外付け抵抗を接続する必要があります。詳細については「出力同相電圧の設定」と「オフセットに関する検討事項」のセクションを参照してください。

### 入力保護

LT6350の2個のオペアンプの+入力と-入力の間にはバック・トゥ・バック・ダイオードがあります。入力トランジスタと直列に接続された内部抵抗を入力段に組み込むというのは、差動オーバードライブ状態での過電流から入力トランジスタを保護するためによく使われる手法ですが、LT6350の入力にはこの抵抗がありません。直列抵抗を組み込むと低ノイズ性能が著しく損なわれます。したがって、オペアンプの入力段の電圧が $\pm 0.7V$ を超える可能性がある場合は、保護ダイオードを流れる定常電流を外部的に $\pm 20mA$ に制限する必要があります。入力ダイオードは十分堅牢で、保護抵抗が無くても、アンプのスルーレート・オーバードライブによる過渡電流や一時的なクリッピングを処理できます。

## アプリケーション情報

電源レールを大きく超える入力信号をドライブすると、入力トランジスタが飽和します。飽和するとアンプは位相反転段を失い、出力が反転しようとします。ダイオードD1とD2(図5)は順方向にバイアスされ、入力信号からダイオード電圧降下分以内の電圧に出力を保ちます。入力オーバードライブが非常に大きい場合は、オペアンプ1の出力が反転することがあります。この反転を防ぐには、入力オーバードライブを電源レールを0.5V超えた電圧に制限します。

## 出力電圧範囲

SAR ADCのスイッチトキャパシタ入力段のような純粋な容量性負荷をドライブするときのLT6350の標準出力振幅は、上下の電源レールから55mV以内です。したがって、LT6350は単一5V電源をSAR ADCと共有することができ、2.055V～2.945Vの入力同相電圧を中心とする完全な8V<sub>P-P</sub>差動出力をドライブします。ADCが真の0V基準信号を必要とするようなシステムやADCの入力同相範囲が2.055V未満に制限されるようなシステムでは、LT6350を0Vまで完全に振幅させるために、わずかな負電源を追加することができます。一部のSAR ADCは、各入力のフルスケール入力信号範囲が0V～4Vで入力同相電圧として2Vを使用します。LT6350の出力振幅は、2V同相電圧を中心に差動で7.78V<sub>P-P</sub>です。つまり、失われる振幅はこのようなADCのフルスケール範囲の0.24dBに過ぎません。

## LT6350からA/Dコンバータへのインターフェース

ADCをドライブするときは、LT6350の出力とADCの入力の間にシングル・ポールのパッシブRCフィルタを新たに追加することで、システム性能を改善できる場合があります。これは、ADCのサンプリング・プロセスがADC入力に電荷過渡を生じさせるためで、これはADCのサンプリング・コンデンサのスイッチによるものです。これにより、アンプとサンプリング・コンデンサの間を電荷が移動するときに、アンプの出力が一時的に短絡します。入力信号を正確に表すには、この収集時間が終了する前にこの負荷過渡状態からアンプを回復させ、安定させる必要があります。ドライバ出力のRCネットワークは、ADCのサンプリング時の過渡状態をアンプからデカップリングする助けとなり、アンプの出力段に対する要求を緩和します(図6参照)。ADCへの入力抵抗は、RCフィルタのコンデンサを充電するサンプリング過渡を最小限に抑えます。

図6. ADCのドライブ

## アプリケーション情報

この容量はサンプリング・プロセス中に電荷の大半を提供する役割を果たし、LT6350の出力に取り付けた2本の抵抗は、ADCからの電荷を緩衝して減衰させるために使われます。RCフィルタは、広帯域出力ノイズの帯域を制限するという二次的な利点のために使うこともできます。詳細については「ノイズに関する検討事項」を参照してください。

RC時定数の選択はADCによって異なります。ただし、一般に時定数を長くするとSNRが改善されますが、セトリング時間は長くなります。セトリング時間が長すぎると利得誤差を生じる恐れがあり、フィルタ構成部品が完全に線形でない場合は歪みを生じることもあります。また、抵抗値が小さすぎる場合はサンプリング・プロセスの負荷過渡をうまく緩衝できず、セトリングに要する時間が長くなります。16ビット・アプリケーションでは、通常、1次フィルタのRC時定数の11倍の最小セトリング時間が必要です。

フィルタの直列抵抗は、LT6350の出力を負荷容量からデカップリングする役割も果たします。LT6350の出力は、グランドに対して最大40pF、差動で最大20pFをドライブするように設計されています。フィルタ・コンデンサの値がこれよりも大きい場合は、少なくとも25Ωのフィルタ抵抗を使ってデカップリングする必要があります。

RCフィルタの構成部品は歪みの原因となり得るので、高品質の抵抗やコンデンサを使用する必要があります。歪みを最小限にするには、COG多層セラミック・コンデンサなど、高品質の誘電体を使ったコンデンサを選んでください。金属膜表面実装抵抗は、カーボンタイプの抵抗よりも高い直線性を備えています。

### 出力同相電圧の設定

出力同相電圧は、式(3)に従い、ピン+IN2に加えられた電圧によって設定されます。使用できる出力同相範囲は反転オペアンプの入力同相範囲によって決定され、その値はV<sup>-</sup>+1.5VからV<sup>+</sup>までです。

単一電源のアプリケーションにおけるADCへの最適同相入力範囲は、多くの場合ADCのリファレンスによって決まります。入力同相電圧を設定するための出力ピンがADCにあって、「電気的特性」の表に示されている入力電流を+IN2に供給できれば、そのピンを直接+IN2ピンに接続できます。また、+IN2はLT1790などの外部高精度リファレンスによってドライブすることもできます。

オフセットを最小にするには、すべてのアプリケーションで+IN2ピンに499Ωのドライブ抵抗を接続する必要があります（「オフセットに関する検討事項」を参照）。ドライブ抵抗の公称値が499Ωに満たない場合は、新たに抵抗を追加してその差を埋めることができます。抵抗のノイズ帯域幅は、少なくとも0.1μFのチップ・セラミック・コンデンサを使って+IN2ピンをグランド・プレーンにバイパスすることにより小さくできます（このデータシートの最初のページにある「標準的応用例」を参照）。バイパス・コンデンサは、このピンのAC信号が偶発的に差動信号に変換されるのを防ぐ助けにもなります。

### SHDN

SHDNピン（ピン7）が負の電源レールの300mV以内で“L”になると、LT6350はパワーダウンします。このピンは、ダイオードを介して20μAの内部電流源に接続されています。シャットダウン・スレッショルドより下に引き下げると、このピンから20μAの電流が流れ出します。このピンをオープンのままにするか“H”（V<sup>-</sup>+2Vより上）に引き上げるとデバイスは通常のアクティブ動作となり、ピンに流れ込む電流は逆バイアス・ダイオードの働きによって非常に小さくなります。

## アプリケーション情報

シャットダウン時にはすべてのバイアス電流源がオフになります。OUT1とOUT2の出力ピンそれぞれが、非線形コンデンサが並列に接続されたオープン・コレクタ、および両方の電源に接続されたステアリング・ダイオードとして動作します。非線形コンデンサの動きによって、大きな過渡電圧でドライブされた場合でも出力は少量の過渡電流をシンクまたはソースすることができます。入力の過渡電圧が700mVを超える場合は、+IN1と+IN2との間の入力保護ダイオードに電流が流れます。他のすべての入力にもESD保護ダイオードがあり、加えられた電圧が700mVを超える場合はやはり電流が流れます。出力同士をワイヤOR接続するためにSHDN機能を使用することは推奨しません。

シャットダウン状態とアクティブ状態の間のターンオン時間とターンオフ時間は通常400nsです。

### ESD

LT6350のすべての入力と出力にはESD保護ダイオードが備わっています。これらのダイオードは、通常動作時は逆バイアスされています。入力ピンがどちらかの電源を超えてドライブされると、これらのダイオードに大きな電流が流れます。電流が過渡的なもので100mA以下に制限されれば、デバイスが損傷を受けることはありません。

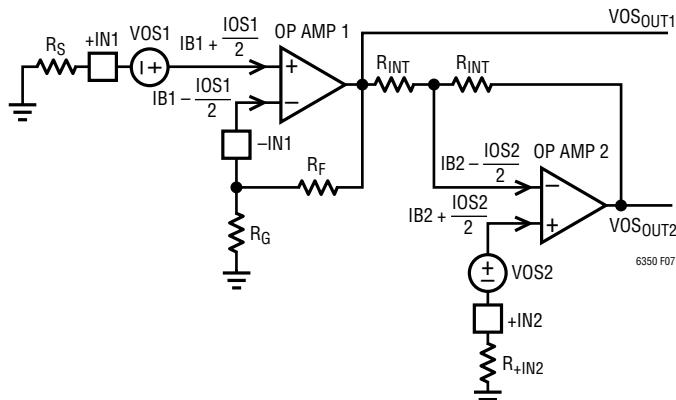

### オフセットに関する検討事項

優れたオフセット性能と歪み性能を実現するために、同相出力電圧と差動出力電圧の両方のオフセットが製造時にトリミングされます。

図7に、DCオフセット電圧を生じるLT6350の構成要素を示します。

図7. オフセットモデル

このようにして生じるピンOUT1とOUT2のDCオフセット電圧は次式で計算できます。

$$\begin{aligned} VOS_{OUT1} = & VOS1 \cdot (1 + R_F/R_G) + IB1 \cdot (R_F - R_S \cdot (1 + R_F/R_G)) \\ & - (IOS1/2) \cdot (R_F + R_S \cdot (1 + R_F/R_G)) \end{aligned}$$

$$\begin{aligned} VOS_{OUT2} = & -VOS_{OUT1} + 2 \cdot VOS2 + IB2 \cdot (R_{INT} - 2 \cdot R_{+IN2}) \\ & - (IOS2/2) \cdot (R_{INT} + 2 \cdot R_{+IN2}) \end{aligned}$$

上の式と式(2)および(3)を使って、出力同相オフセットと出力差動オフセットを求めることができます。同相オフセットは次式で求められます。

$$\begin{aligned} VOS_{CM} = & VOS2 + IB2 \cdot ((R_{INT}/2) - R_{+IN2}) - (IOS2/2) \\ & \cdot (R_{INT}/2) + R_{+IN2} \end{aligned}$$

## アプリケーション情報

オペアンプ2に流れ込む入力バイアス電流はオフセット電流よりはるかに大きいので、 $R_{+IN2}$ を $R_{INT}/2$ とすれば、オペアンプ2の入力電流がオフセットに関してすべてのユニットに与える影響を大幅に減らすことができます。 $R_{+IN2} = R_{INT}/2$ とすると、 $VOS_{CM}$ は次式で示す値に減少します。

$$VOS_{CM} = VOS_2 - (IOS_2/2) \cdot R_{INT}$$

$VOS_{CM}$ は、 $+IN2$ に取り付けられた $499\Omega$ の抵抗によって $\pm 125\mu V$ 以内にトリミングされます。

$VOS_1$ の値は、 $VOS_{DIFF}$ を $\pm 125\mu V$ にするためにトリミングされます。入力同相モードで $VOS_1$ を線形変調するとオペアンプ1の同相除去比仕様を劣化させる懼れがあり、 $VOS_1$ を非線形変調すると非直線性利得誤差(歪み)を生じる懼れがあるので、 $VOS_1$ はできるだけ広い入力同相範囲にわたって低い定数値にトリミングされます。高精度な2ポイント・アルゴリズムが使われ、これによって $VOS_1$ は $V^- + 1.3V \leq V_{+IN1} \leq V^+$ の入力範囲において $\pm 125\mu V$ 以内、 $V^- \leq V_{+IN1} \leq V^+$ の入力範囲において $\pm 300\mu V$ 以内となります。入力範囲を拡張するために $-1.3V$ より下の負の電源を使用することもでき、この場合、 $VOS_1$ はグランドまでの全範囲にわたって $\pm 125\mu V$ 以内となります。

トリミングの結果、同相モードと差動モード両方の最小オフセットは、 $+IN2$ に $499\Omega$ の抵抗を使用した場合に得られます。この抵抗は、ノイズの影響を防ぐためにコンデンサを使ってバイパスすることができます。オフセットに対するオペアンプ1の入力バイアス電流の影響を最小限に抑えるため、利得設定抵抗ネットワーク( $R_G$ と $R_F$ )のインピーダンスをソース・インピーダンスと整合させる必要があります。

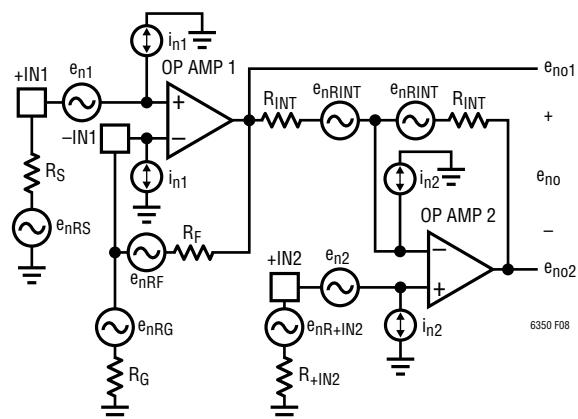

### ノイズに関する検討事項

LT6350の出力ノイズ源を示すモデルを図8に示します。すべてのノイズ源による合計出力ノイズは次式で与えられます。

$$e_{no} = \sqrt{(4 \cdot [e_{n1}^2 + (i_{n1}R_S)^2 + e_{nRS}^2] (1 + (R_F/R_G))^2 + 4 \cdot (i_{n1}R_F)^2 + 4e_{nRF}^2 (1 + (R_F/R_G)) + 4e_{n2}^2 + 4e_{nR+IN2}^2 + 2e_{nRINT}^2 + (i_{n2}R_{INT})^2 + 4 \cdot (i_{n2}R_{+IN2})^2)}$$

LT6350は非常にノイズの小さいオペアンプを使用しており、図2に示す利得2の非反転構成における10kHz時の合計差動出力スポット・ノイズは $8.2nV/\sqrt{Hz}$ です。これは、 $+IN1$ 入力における $1015\Omega$ 抵抗の電圧ノイズに相当します。約1kを超えるソース抵抗の場合は、ソース抵抗による電圧ノイズが出力ノイズの大部分を占めるようになります。約13kよりも大きいソース抵抗は入力電流ノイズと相互に作用し、出力ノイズは抵抗ノイズとアンプの電流ノイズに支配されます。

図8. ノイズモデル

利得設定抵抗 $R_F$ と $R_G$ は、並列に組み合わせるとノイズ計算の観点からはソース抵抗 $R_S$ と同様に動作するので、出力ノイズが大きくなるのを防ぐために値を約1k未満に抑える必要があります。利得抵抗 $R_G$ と帰還抵抗 $R_F$ の値を小さくすれば出力ノイズは確実に小さくなります。しかし、オペアンプ1の負荷が増加す

## アプリケーション情報

るので歪みが大きくなります。オペアンプ1には、オペアンプ2への1k入力抵抗によって内部的に負荷がかかっているので、歪み性能を低下させないために外部負荷は1kを大きく超えないようにする必要があります。

利得2の構成で(オフセットを小さくするため) $R_S$ に等しい $R_F$ を使用すると、 $R_F$ をバイパスすることによって広帯域ノイズを大幅に減らすことができます。出力ノイズを最小にするには、このデータシートの最初のページに示した「標準的応用例」のように、少なくとも $0.1\mu F$ のコンデンサを使って+IN2ピンをバイパスします。あるいは、出力電圧オフセットを許容できるシステムでは、 $R_{+IN2}$ と $R_F$ を省略すれば出力ノイズを最小にできます。ただし、出力オフセット電圧は大きくなります。

図6に示すように、LT6350の出力にシングル・ポールのパッシブRCフィルタ・ネットワークを使用すると出力ノイズ帯域が狭くなり、それによってシステムのSNRが向上します。たとえば出力信号8V<sub>P-P</sub>、信号帯域幅100kHzの標準的なシステムにおいて、 $R_{FILT} = 100\Omega$ 、 $C_{DIFF} = 6.8nF$ のRC出力フィルタを使用すると、出力スポット・ノイズが $8.2nV\sqrt{Hz}$ から $8.4nV\sqrt{Hz}$ へとわずかに増加しますが、全積分ノイズは $47\mu V$ (ノイズ帯域幅が33MHz)から $3.6\mu V$ (ノイズ帯域幅が184kHz)に減少し、SNRも96dBから118dBに向上します。出力フィルタのRC時定数を大きくするとADC入力のセトリング時間が長くなる可能性があるという点に留意してください。セトリングが不完全な場合、利得誤差や、マルチプレクス・システムでの見かけ上のクロストークの増加を招く恐れがあります。

### 出力位相バランス

LT6350のトポロジーでは、非反転段の後に反転段が続きます。このトポロジーは高インピーダンスのシングルエンド入力と低インピーダンスの差動出力を与えます。反転バッファの出力OUT2は、非反転バッファの出力であるOUT1に対してわずかに遅れます。LT6350の場合、DCから差動 $f_{-3dB}$ 周波数に至る入力帯域幅でのOUT1からOUT2への遅れは、このデータシートの「標準的性能特性」にあるグループ遅延曲線に示すように6.8nsでほぼ一定です。この遅延は、差動出力の公称位相180°からのわずかな位相オフセットに相当します。位相オフセットは周波数とともに大きくなります。出力には、位相のアンバランスによって周波数に依存するわずかな同相成分が生じます。この影響の実際的な尺度はバランスの定義に見出すことができ、出力差動信号の存在によって出力同相レベルに生じる変化であると定義されます。

$$\text{バランス} \equiv ((V_{OUTDIFF}/V_{IN})/(V_{OUTCM}/V_{IN}))$$

任意の周波数 $f$ におけるLT6350のバランスは、出力間の遅延 $t_d$ から概算できます。

$$\text{バランス(dB)} \cong 20 \cdot \log((4)/(2 \cdot \pi \cdot f \cdot t_d))$$

この式は、低周波数からバランスが20dB近くになる周波数(LT6350の場合は約10MHz)まで、非常に良く近似します。DCのバランスは、反転バッファの利得を設定する内部抵抗の整合によって制限されます。1%精度で抵抗を整合させると、DCのバランスは52dBに制限されます。差動伝達関数の $f_{-3dB}$ ポイントに近い周波数では、追加の位相遅れと利得ロールオフもバランスに影響してきます。バランスと入力周波数の詳細図については、「標準的性能特性」のバランス曲線を参照してください。

## アプリケーション情報

### 基板レイアウトとバイパス・コンデンサ／ DC1538Aデモボード

単一電源のアプリケーションでは、高品質のX5RまたはX7Rの0.1μFバイパス・コンデンサをV<sup>+</sup>ピンとV<sup>-</sup>ピンの間に直接取り付けることを推奨します。V<sup>-</sup>ピン(DD8パッケージでは露出パッドを含む)は、低インピーダンスのグランド・プレーンに最短経路で直接接続する必要があります。両電源では、V<sup>+</sup>ピンとV<sup>-</sup>ピンをグランドにバイパスするために、高品質のX5RまたはX7Rの0.1μFコンデンサを新たに追加することを推奨します。この場合、経路はできるだけ短くします。寸法の小さい(たとえば0603)表面実装セラミック・コンデンサはリード付きコンデンサよりもはるかに自己共振周波数が高く、LT6350に最適です。

+IN2ピンは、少なくとも0.1μFの高品質セラミック・コンデンサを使用してグランドにバイパスします。これは、推奨されるDCオフセット・バランス抵抗のノイズ帯域幅を狭くするためと、同相リファレンス電圧の変化が差動出力信号に変換されるのを防ぐためです。

-IN1ピンの浮遊寄生容量は、安定性が損なわれて過度のリングングや発振が発生するのを防ぐために、最小限に抑えます。-IN1のトレースはできるだけ短くし、ピンおよびピン・トレース下のグランド・プレーンは除去します。

出力は差動なので、両方の出力から見た(浮遊または意図された)負荷インピーダンスはできるだけバランスさせ、対称にします。これはバランスの取れた動作を保つ助けとなり、出力段における偶数次高調波歪みを最小限に抑えるとともに、同相信号除去とノイズ除去を最大にします。

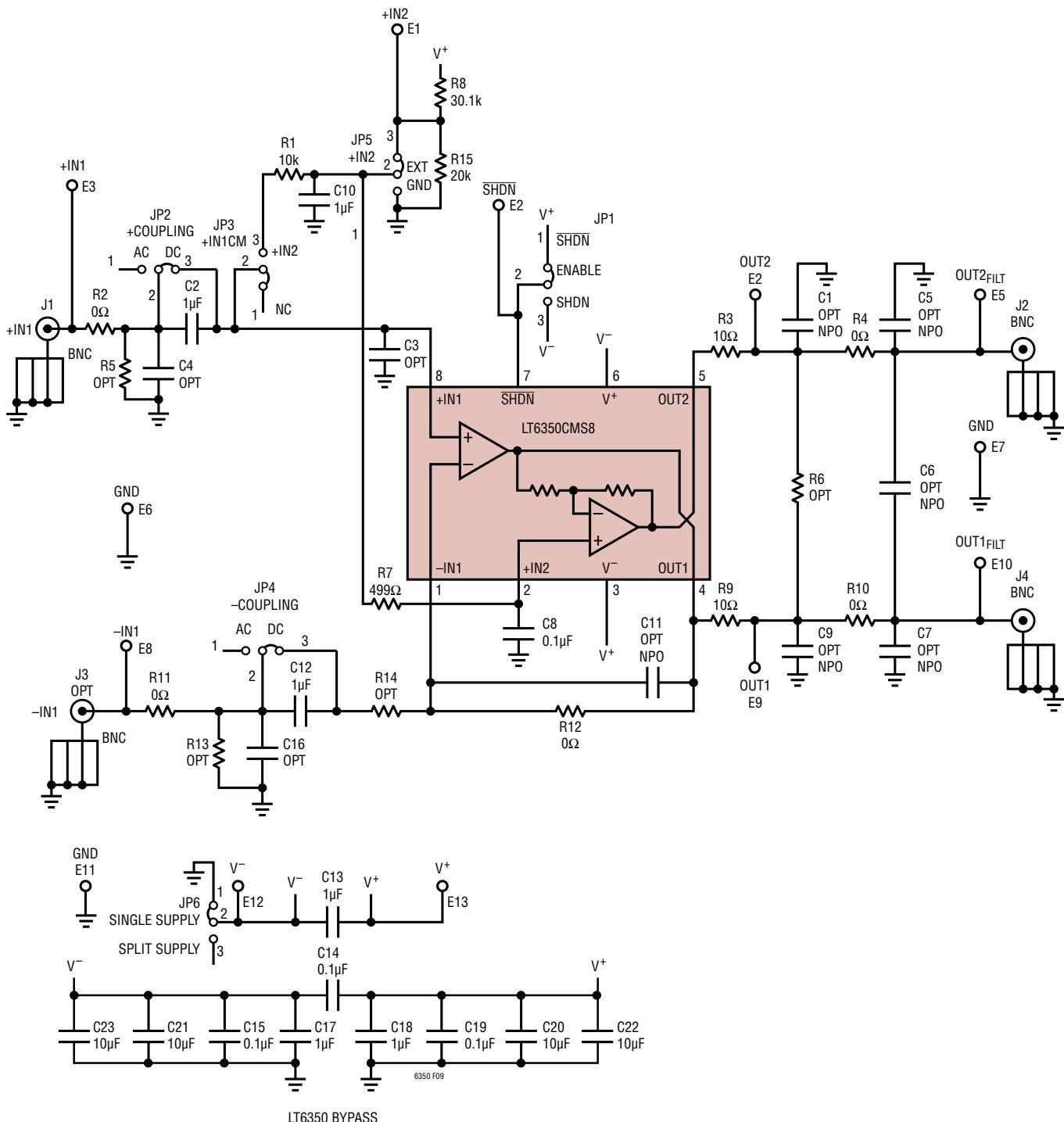

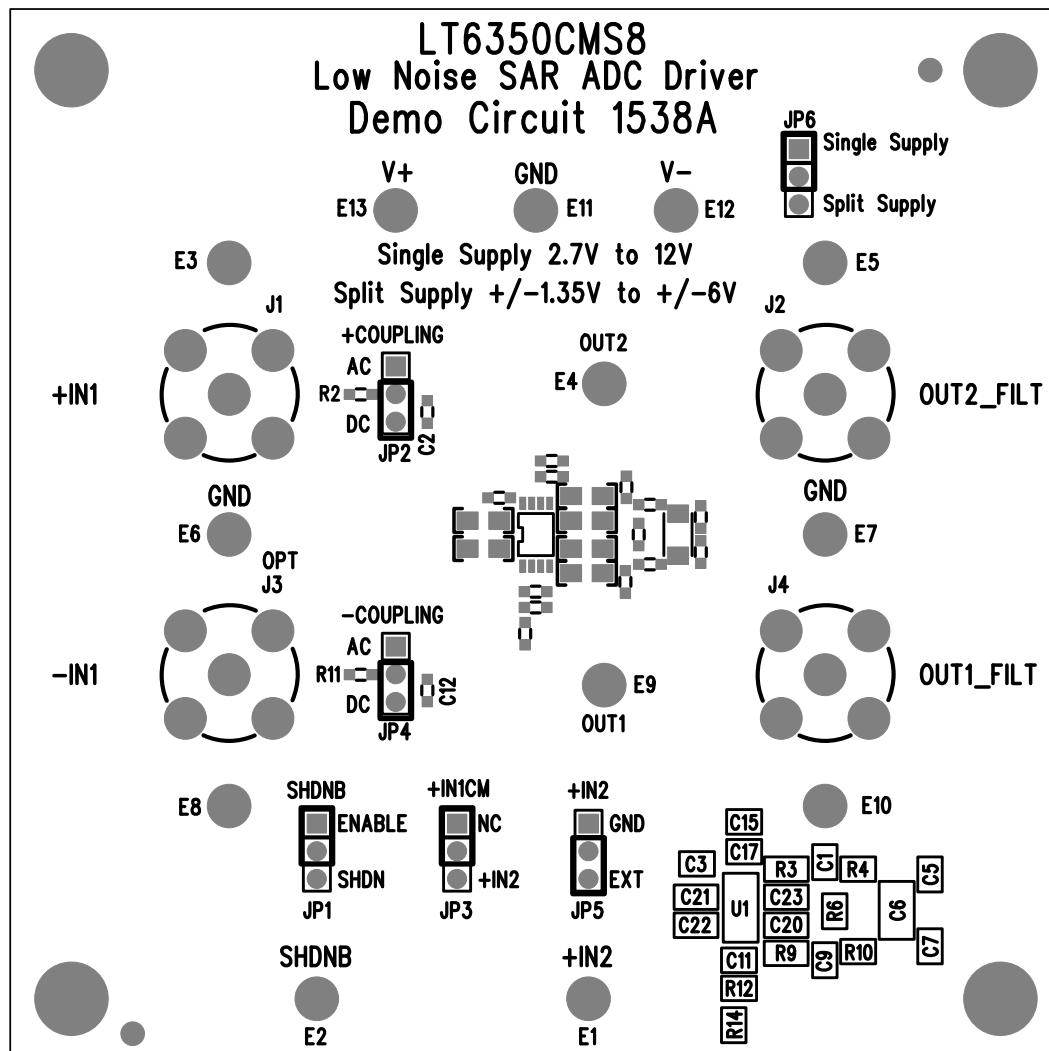

DC1538Aデモボードは、以上のレイアウト手法に従ったLT6350の評価用に設計されています。その回路図と構成部品配置を図9と図10に示します。

## アプリケーション情報

図9. DC1538Aデモボードの回路図

## アプリケーション情報

図10. DC1538Aデモボードのレイアウト

## アプリケーション情報

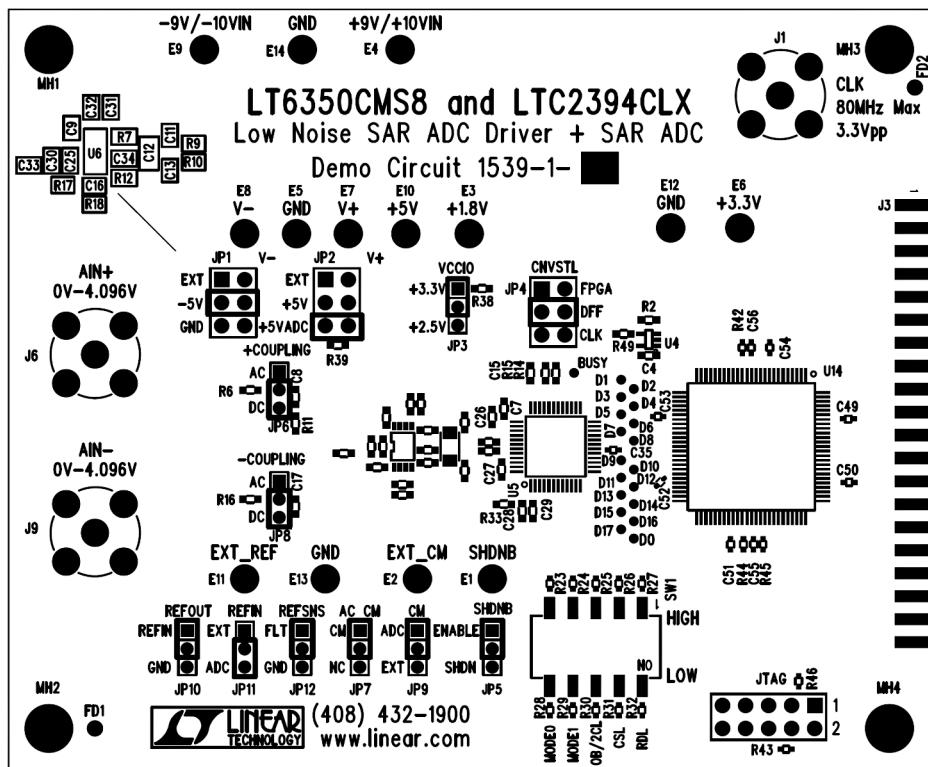

図11. DC1539Aデモボードのレイアウト

### LTC239X-16 / DC1539Aデモボードのドライブ

図11に示すDC1539Aデモボードは、LT6350からLTC239x-16ファミリーの16ビットSAR ADCへのインターフェースのデモ用に開発されました。

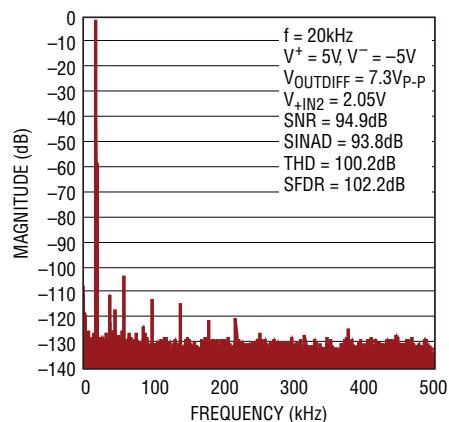

図12のFFTに示すように、DC1539Aでは102.2dBのSFDRを実現することができます。

図12. DC1539AデモボードでLT6350により

LTC2393-16をドライブした時の8192ポイントFFT

## アプリケーション情報

### 100kHz、3次バターワース・フィルタ

LT6350は、反転出力からの帰還信号を組み込んだシングルエンドー差動フィルタとして構成することができます。100kHzの-3dBポイントで差動利得4の3次バターワース・フィルタ特性を与えるような値で構成した回路を図13に示します。10MHzまでのフィルタ出力応答を図14に示します。オプションとして、ソース・インピーダンスを整合させてLT6350の低DC誤差性能を維持するために、2.10kの直列抵抗を+IN1に接続します。抵抗ノイズを減らすために、+IN1ピンは0.1μFのコンデンサでバイパスすることができます。同様のトポロジーについては、LT1567のデータシートとデザインガイドを参照してください。

図13. 100kHz、3次バターワース・フィルタ

図14. 100kHz、3次バターワース・フィルタの応答

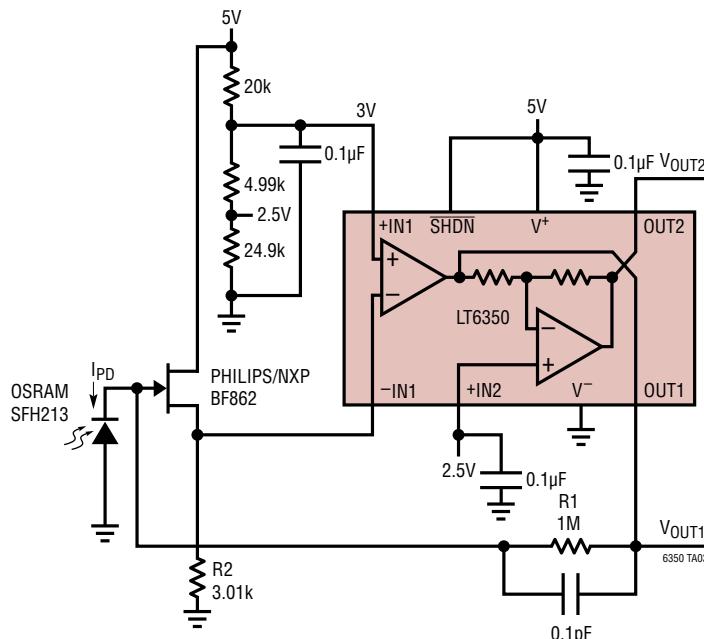

### 低ノイズ、低消費電力の1MΩ単一電源フォトダイオード差動出力トランスインピーダンス・アンプ

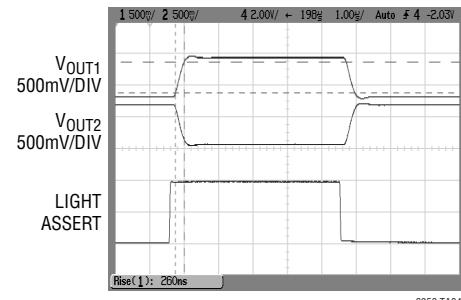

このデータシートの最終ページの「標準的応用例」は、LT6350を差動出力トランスインピーダンス・アンプとして使用したものです。LT6350はBF862超低ノイズJFETのソースを3Vに強制し、R2によりJFETのI<sub>DRAIN</sub>を1mAにします。JFETはソース・フォロワとして機能し、LT6350の入力をバッファして高インピーダンスの帰還素子R1に適したものとします。BF862の最小IDSSは10mAで、ピンチオフ電圧は-0.3V～-1.2Vです。したがって、JFETのゲートとOUT1は、3Vよりピンチオフ電圧1つ分低い電位からわずかに高い電位、すなわち電源電圧の中点である2.5V付近になります。

フォトダイオードに光が当たるとき、通常のトランスインピーダンス・アンプの場合と同様に、電流はOUT1からR1を通って流れ必要があります。低周波数におけるアンプの出力ノイズ密度は帰還抵抗の $130\text{nV}/\sqrt{\text{Hz}}$ によるものが大部分を占め、1MHzでは $210\text{nV}/\sqrt{\text{Hz}}$ に増加します。JFETのg<sub>m</sub>は約 $1/30\Omega$ と高いので、R2による減衰は約1%に過ぎないことに注意してください。3pFのフォトダイオードを使った閉ループ帯域幅の測定値は約1.35MHzです。出力を差動として取り出すと、利得もノイズも倍になります。

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> をご覧ください。

**DD Package**

**8-Lead Plastic DFN (3mm x 3mm)**

(Reference LTC DWG # 05-08-1698 Rev C)

**NOTE:**

- NOTE:-

1. 図はJEDECのパッケージ外形M0-229のバリエーション(WEED-1)になる予定

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのパリを含まない

モールドのパリは(もし、あれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

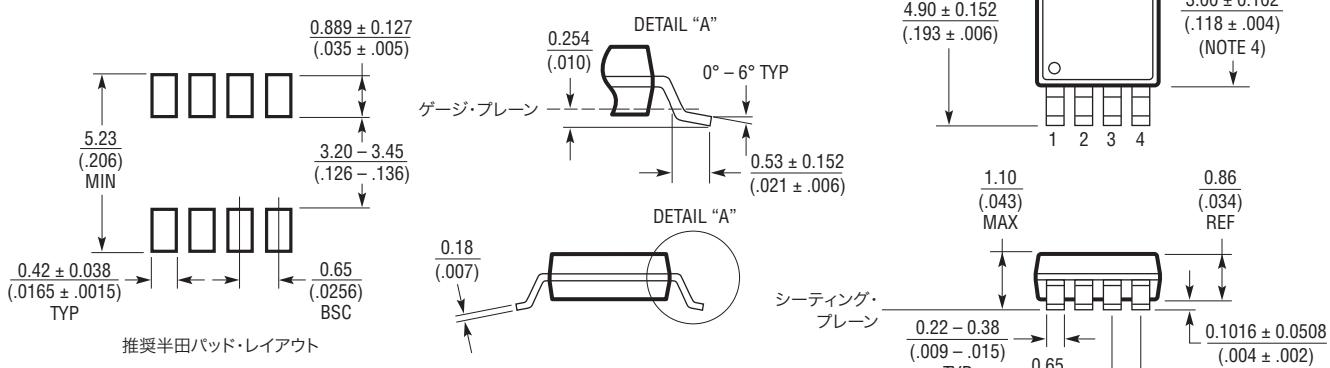

**MS8 Package

8-Lead Plastic MSOP**

(Reference LTC DWG # 05-08-1660 Rev F)

**NOTE:**

2. 図は実寸とは異なる

3. 尺法にはモールドのバリ、突出部、またはゲートのバリを含まない

モールドのバリ、突出部、またはゲートのバリは各サイドで $0.152\text{mm}$ ( $0.006"$ )を超えないこと

4. 尺寸には、リード間のバリまたは突出部を含まない

リード間のバリまたは突起は各サイドで $0.152\text{mm}$ ( $0.006"$ )を超えないこと

5. リードの平坦度(成形後のリードの底面)は最大 $0.102\text{mm}$ ( $0.004"$ )であること

## 改訂履歴 (改訂履歴はRev Aから開始)

| REV | 日付    | 概要                            | ページ番号   |

|-----|-------|-------------------------------|---------|

| A   | 03/10 | 「電気的特性」の $V_{OH}$ の単位を更新      | 4       |

| B   | 05/10 | Note 2を更新<br>「関連製品」を更新        | 5<br>28 |

| C   | 06/13 | 「入力バイアス電流と入力電圧」のグラフの曲線のラベルを修正 | 7       |

## 標準的応用例

低ノイズ、低消費電力の1MΩ単一電源フォトダイオード・トランスインピーダンス・アンプ

$V_{OUTDIFF} = \sim \pm 200mV + I_{PD} \cdot 2M\Omega$

$BW = 1.35MHz$

## 関連製品

| 製品番号                                     | 説明                                           | 注釈                                                                     |

|------------------------------------------|----------------------------------------------|------------------------------------------------------------------------|

| LTC2391-16/<br>LTC2392-16/<br>LTC2393-16 | 16ビットSAR ADC                                 | 250ksps/500ksps/1Msps                                                  |

| LT6202/LT6203                            | シングル/デュアル100MHz、レール・トゥ・レール入出力、超低ノイズ、低消費電力アンプ | ノイズ電圧: $1.9nV/\sqrt{Hz}$ 、消費電流: 3mA/アンプ(最大)、利得帯域幅: 100MHz              |

| LT1806/LT1807                            | シングル/デュアル325MHz、低ノイズ、低歪み、レール・トゥ・レール入出力アンプ    | 2.5V動作、オフセット電圧: 550μV(最大)、ノイズ電圧: $3.5nV/\sqrt{Hz}$                     |

| LTC6403                                  | 200MHz、低ノイズ、低歪み、完全差動入出力アンプ/ドライバ              | 消費電流: 10.8mA、低歪み(3MHz, 2V <sub>P-P</sub> 出力): -95dBc                   |

| LT1468/LT1469                            | シングル/デュアル90MHz、22V/μs、16ビット高精度オペアンプ          | ±5Vおよび±15V動作、VOS ≤ 75μV                                                |

| LTC6246/LTC6247/<br>LTC6248              | シングル/デュアル/クワッド180MHz、レール・トゥ・レール低消費電力オペアンプ    | 消費電流: 1mA/アンプ、ノイズ電圧: $4.2nV/\sqrt{Hz}$                                 |

| LTC1992/LTC1992-X                        | 完全差動入出力アンプ                                   | プログラム可能な利得または固定利得(G = 1, 2, 5, 10)                                     |

| LT1994                                   | 低ノイズ、低歪みの完全差動入出力アンプ/ドライバ                     | 低歪み: -94dBc(2V <sub>P-P</sub> , 1MHz)、消費電流: 13mA、低ノイズ: $3nV/\sqrt{Hz}$ |