入力電流がpAレベルの140V

CMOSレール・トゥ・レール

出力オペアンプ

## 特長

- 電源電圧範囲:  $\pm 4.75V \sim \pm 70V$  (140V)

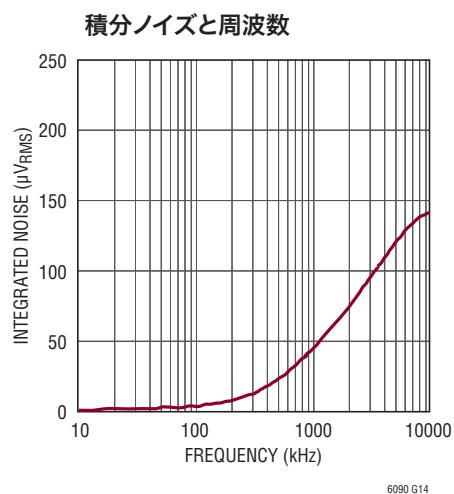

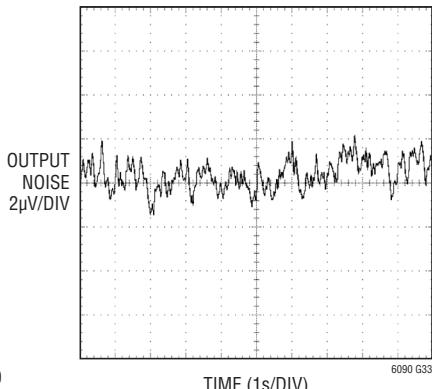

- 0.1Hz～10Hzのノイズ:  $3.5\mu V_{P-P}$

- 入力バイアス電流: 最大  $50pA$

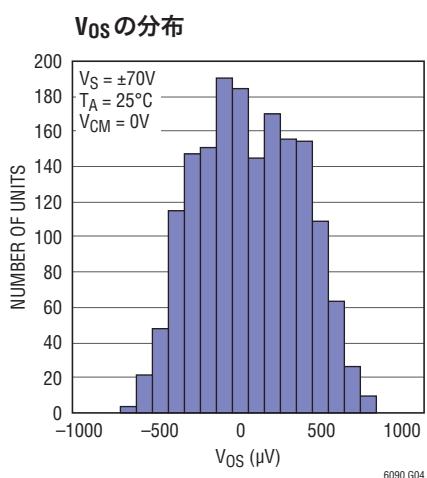

- 低いオフセット電圧: 最大  $1.25mV$

- 低いオフセット・ドリフト: 最大  $\pm 5\mu V/\text{°C}$

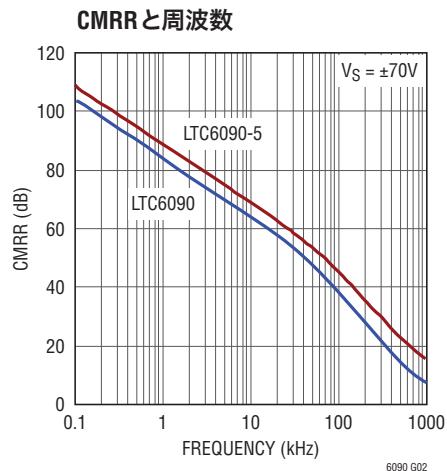

- CMRR: 最少  $130\text{dB}$

- レール・トゥ・レールの出力段

- 出力シンク電流およびソース電流:  $50mA$

- 利得帯域幅積:  $12\text{MHz}$

- スルーレート:  $21V/\mu s$

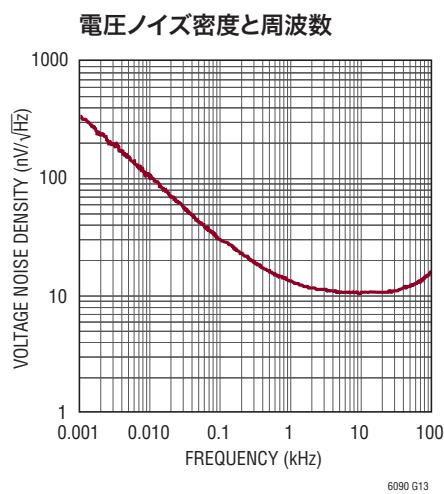

- ノイズ密度:  $11nV/\sqrt{\text{Hz}}$

- サーマル・シャットダウン

- 熱特性が改善されたSOIC-8EパッケージまたはTSSOP-16Eパッケージで供給

## アプリケーション

- ATE(自動試験装置)

- ピエゾ素子ドライバ

- フォトダイオード・アンプ

- 高電圧レギュレータ

- 光通信

## 概要

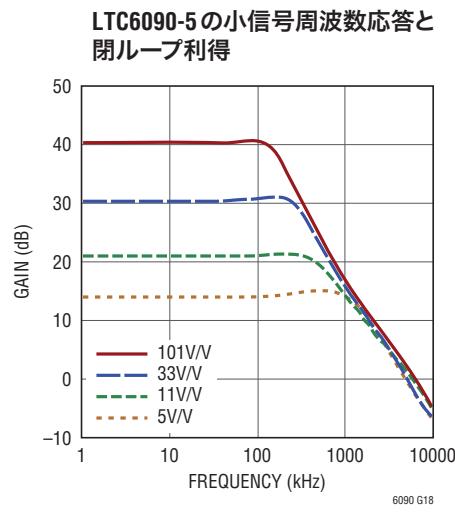

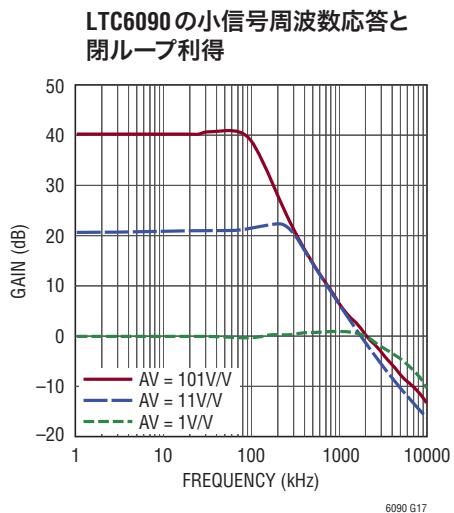

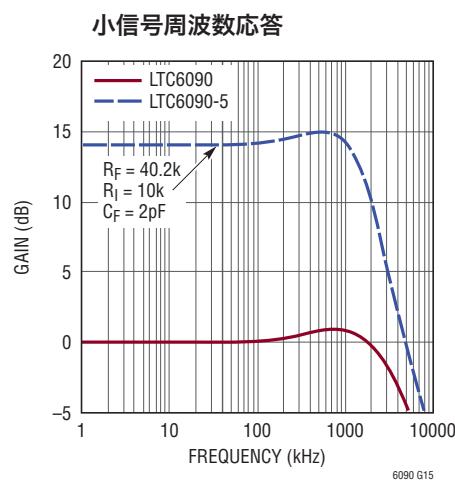

LTC<sup>®</sup>6090/LTC6090-5は、高電圧、高精度のモノリシック・オペアンプです。LTC6090は、単位利得で安定しています。LTC6090-5は、5以上のノイズ利得構成で安定しています。両アンプとも高い開ループ利得、低い入力換算オフセット電圧およびノイズ、pAレベルの入力バイアス電流を特長としており、高電圧、高インピーダンスのバッファ処理あるいは高利得構成に最適です。

これらのアンプは、内部で過熱状態から保護されています。ダイ温度が150°Cに近づくと、高温警告出力(TFLAG)が作動します。出力段は、出力ディスエーブル・ピンであるODを使用してオフにすることができます。ODピンを高温警告出力(TFLAG)に接続することにより、デバイスが安全動作領域から外れると、出力段はディスエーブルされます。これらのピンは、あらゆるロジック・ファミリと容易にインターフェースできます。

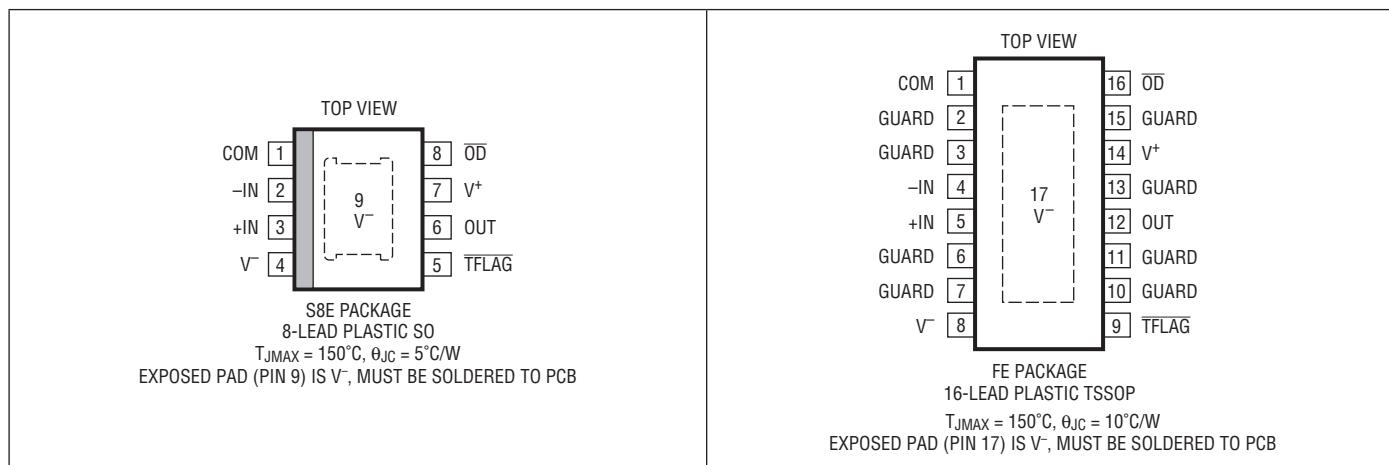

両アンプとも140V 単電源または $\pm 70V$ 両電源で動作可能であり、最大200pFの負荷容量を駆動できます。これらのアンプは、熱抵抗を低く抑えるための露出パッドを備えた8ピンSOパッケージおよび16ピンTSSOPパッケージで供給されます。

**L**、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴは、リニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

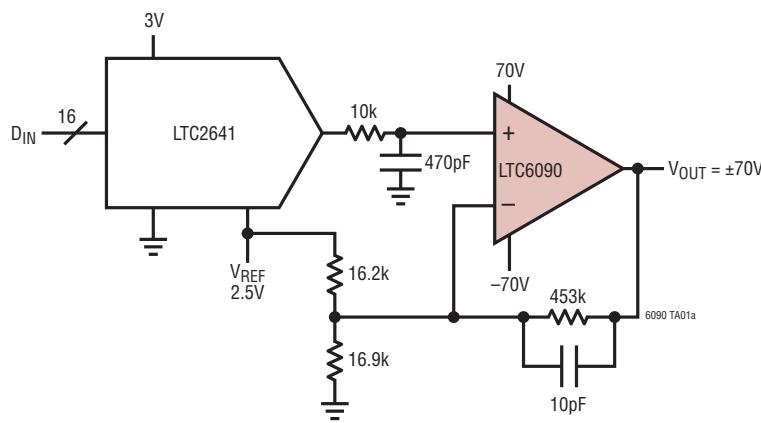

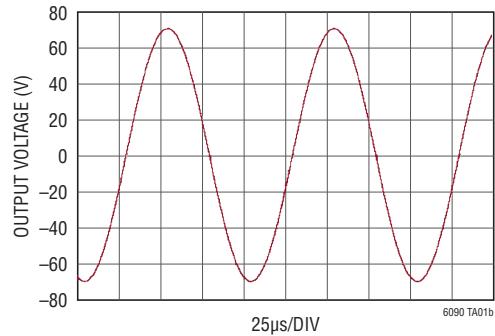

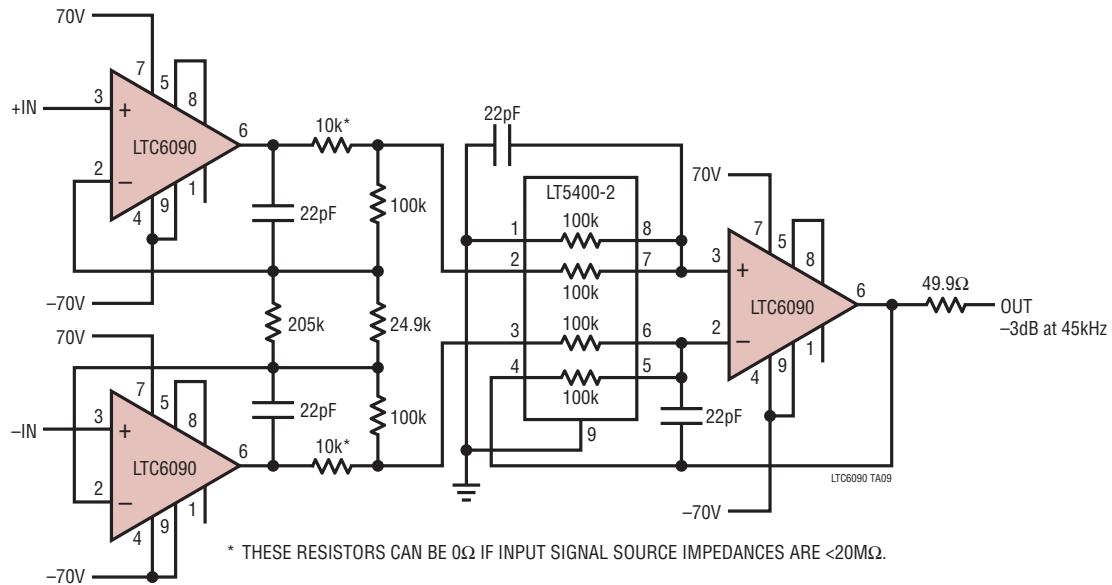

## 標準的応用例

高電圧D/Aコンバータのバッファ・アプリケーション

140V<sub>P-P</sub>の正弦波出力

# LTC6090/LTC6090-5

## 絶対最大定格 (Note 1)

|                           |                              |

|---------------------------|------------------------------|

| 全電源電圧( $V^+ \sim V^-$ )   | 150V                         |

| COMピンの電圧                  | $V^- \sim V^+$               |

| 入力電圧                      |                              |

| $\overline{OD}$ ピン        | $V^- \sim V^+ + 0.3V$        |

| +IN、-INピン                 | $V^- - 0.3V \sim V^+ + 0.3V$ |

| $\overline{OD}$ ピン-COMピン間 | -3V ~ 7V                     |

| 入力電流                      |                              |

| +IN、-INピン                 | $\pm 10mA$                   |

| TFLAG出力電圧                 |                              |

| TFLAGピン                   | $V^- - 0.3V \sim V^+ + 0.3V$ |

| TFLAGピン-COMピン間            | -3V ~ 7V                     |

**低ESD耐性：**このデバイスの出力ピン(OUT)はESD耐性が低くなっています。500Vを超えるESDはデバイスに永久的損傷を与える可能性があります。

|                   |                     |

|-------------------|---------------------|

| 出力電流              |                     |

| 連続(Note 2)        | 50mA <sub>RMS</sub> |

| 動作接合部温度範囲         |                     |

| (Note 3)          | -40°C ~ 125°C       |

| 規定接合部温度範囲(Note 4) |                     |

| LTC6090C          | 0°C ~ 70°C          |

| LTC6090I          | -40°C ~ 85°C        |

| LTC6090H          | -40°C ~ 125°C       |

| 接合部温度(Note 5)     | 150°C               |

| 保存温度範囲            | -65°C ~ 150°C       |

| リード温度(半田付け、10秒)   | 300°C               |

## ピン配置

## 発注情報

| 無鉛仕上げ           | テープアンドリール         | 製品マーキング* | パッケージ                 | 接合部温度範囲        |

|-----------------|-------------------|----------|-----------------------|----------------|

| LTC6090CS8E#PBF | LTC6090CS8E#TRPBF | 6090     | 8-Lead Plastic SO     | 0°C to 70°C    |

| LTC6090IS8E#PBF | LTC6090IS8E#TRPBF | 6090     | 8-Lead Plastic SO     | -40°C to 85°C  |

| LTC6090HS8E#PBF | LTC6090HS8E#TRPBF | 6090     | 8-Lead Plastic SO     | -40°C to 125°C |

| LTC6090CFE#PBF  | LTC6090CFE#TRPBF  | 6090FE   | 16-Lead Plastic TSSOP | 0°C to 70°C    |

| LTC6090IFE#PBF  | LTC6090IFE#TRPBF  | 6090FE   | 16-Lead Plastic TSSOP | -40°C to 85°C  |

| LTC6090HFE#PBF  | LTC6090HFE#TRPBF  | 6090FE   | 16-Lead Plastic TSSOP | -40°C to 125°C |

6090fc

## 発注情報

| 無鉛仕上げ             | テープアンドリール           | 製品マーキング* | パッケージ                 | 接合部温度範囲        |

|-------------------|---------------------|----------|-----------------------|----------------|

| LTC6090CS8E-5#PBF | LTC6090CS8E-5#TRPBF | 60905    | 8-Lead Plastic SO     | 0°C to 70°C    |

| LTC6090IS8E-5#PBF | LTC6090IS8E-5#TRPBF | 60905    | 8-Lead Plastic SO     | -40°C to 85°C  |

| LTC6090HS8E-5#PBF | LTC6090HS8E-5#TRPBF | 60905    | 8-Lead Plastic SO     | -40°C to 125°C |

| LTC6090CFE-5#PBF  | LTC6090CFE-5#TRPBF  | 6090FE-5 | 16-Lead Plastic TSSOP | 0°C to 70°C    |

| LTC6090IFE-5#PBF  | LTC6090IFE-5#TRPBF  | 6090FE-5 | 16-Lead Plastic TSSOP | -40°C to 85°C  |

| LTC6090HFE-5#PBF  | LTC6090HFE-5#TRPBF  | 6090FE-5 | 16-Lead Plastic TSSOP | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は  $T_J = 25^\circ\text{C}$  での値。テスト条件は、注記がない限り  $V^+ = 70\text{V}$ 、

$V^- = -70\text{V}$ 、 $V_{CM} = V_{OUT} = 0\text{V}$ 、 $V_{DD} = \text{開放}$ 。

| SYMBOL                   | PARAMETER                                                      | CONDITIONS                                                                                                  | C-, I-SUFFIXES |                               |                          | H-SUFFIX                      |                          |                                                              | UNITS                        |

|--------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------|-------------------------------|--------------------------|-------------------------------|--------------------------|--------------------------------------------------------------|------------------------------|

|                          |                                                                |                                                                                                             | MIN            | TYP                           | MAX                      | MIN                           | TYP                      | MAX                                                          |                              |

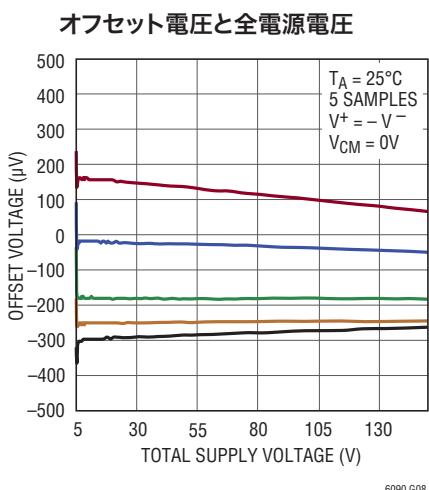

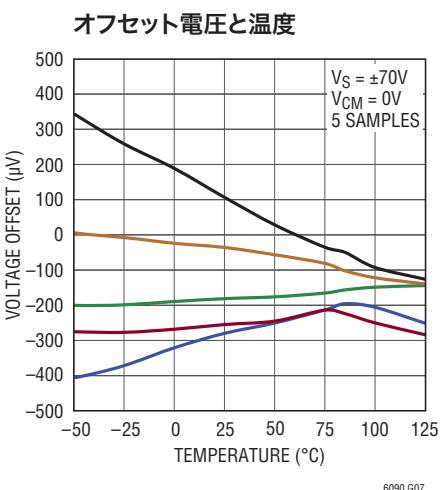

| $V_{OS}$                 | Input Offset Voltage                                           |                                                                                                             | ●              | $\pm 330$<br>$\pm 330$        | $\pm 1000$<br>$\pm 1250$ | $\pm 330$<br>$\pm 330$        | $\pm 1000$<br>$\pm 1250$ | $\mu\text{V}$<br>$\mu\text{V}$                               |                              |

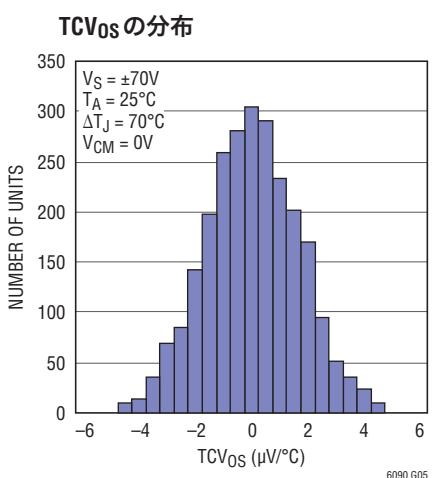

| $\Delta V_{OS}/\Delta T$ | Input Offset Voltage Drift                                     | $T_A = 25^\circ\text{C}$ , $\Delta T_J = 70^\circ\text{C}$                                                  |                | -5                            | $\pm 3$                  | 5                             | -5                       | $\pm 3$                                                      | $\mu\text{V}/^\circ\text{C}$ |

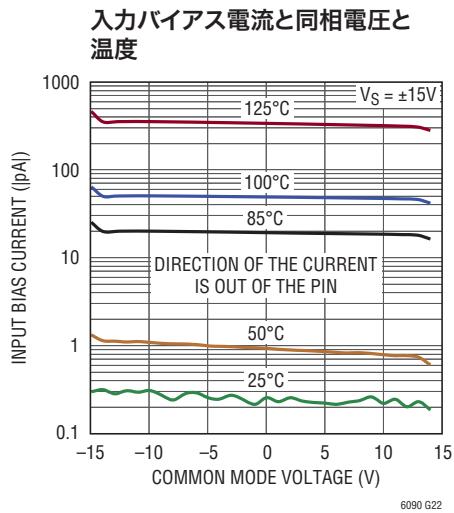

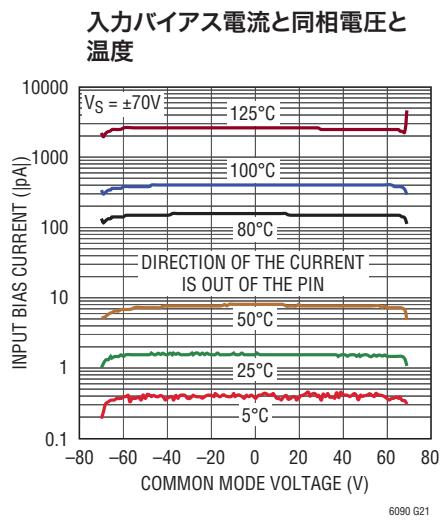

| $I_B$                    | Input Bias Current (Note 6)                                    | Supply Voltage = $\pm 70\text{V}$<br>Supply Voltage = $\pm 15\text{V}$<br>Supply Voltage = $\pm 15\text{V}$ | ●              | 3<br>0.3                      | 50                       | 3<br>0.3                      | 800                      | $\text{pA}$<br>$\text{pA}$<br>$\text{pA}$                    |                              |

| $I_{OS}$                 | Input Offset Current (Note 6)                                  | Supply Voltage = $\pm 15\text{V}$                                                                           | ●              | 0.5                           | 30                       | 0.5                           | 120                      | $\text{pA}$<br>$\text{pA}$                                   |                              |

| $e_n$                    | Input Noise Voltage Density                                    | $f = 1\text{kHz}$<br>$f = 10\text{kHz}$                                                                     |                | 14<br>11                      |                          | 14<br>11                      |                          | $\text{nV}/\sqrt{\text{Hz}}$<br>$\text{nV}/\sqrt{\text{Hz}}$ |                              |

|                          | Input Noise Voltage                                            | 0.1Hz to 10Hz                                                                                               |                | 3.5                           |                          | 3.5                           |                          | $\mu\text{V}_{\text{P-P}}$                                   |                              |

| $i_n$                    | Input Noise Current Density                                    |                                                                                                             |                | 1                             |                          | 1                             |                          | $\text{fA}/\sqrt{\text{Hz}}$                                 |                              |

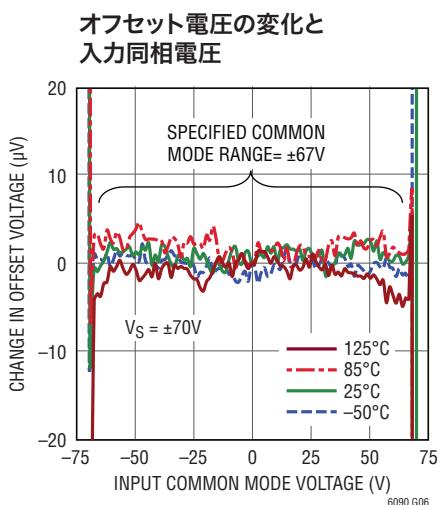

| $V_{CM}$                 | Input Common Mode Range                                        | Guaranteed by CMRR                                                                                          | ●              | $\pm 68$<br>$V^- + 3\text{V}$ | $V^+ - 3\text{V}$        | $\pm 68$<br>$V^- + 3\text{V}$ | $V^+ - 3\text{V}$        | $\text{V}$<br>$\text{V}$                                     |                              |

| $C_{IN}$                 | Common Mode Input Capacitance                                  |                                                                                                             |                | 9                             |                          | 9                             |                          | $\text{pF}$                                                  |                              |

| $C_{DIFF}$               | Differential Input Capacitance                                 |                                                                                                             |                | 5                             |                          | 5                             |                          | $\text{pF}$                                                  |                              |

| $CMRR$                   | Common Mode Rejection Ratio                                    | $V_{CM} = -67\text{V}$ to $67\text{V}$                                                                      | ●              | 130<br>126                    | $> 140$                  | 130<br>126                    | $> 140$                  | $\text{dB}$<br>$\text{dB}$                                   |                              |

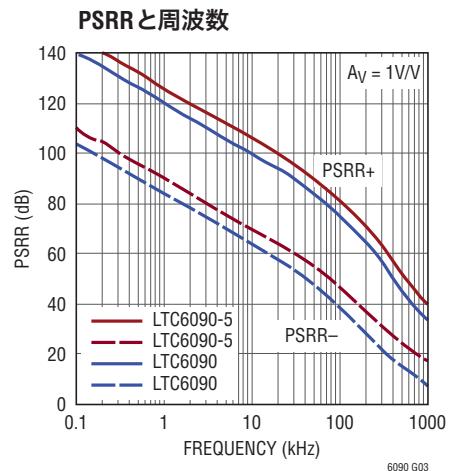

| $PSRR$                   | Power Supply Rejection Ratio                                   | $V_S = \pm 4.75\text{V}$ to $\pm 70\text{V}$                                                                | ●              | 112<br>106                    | $> 120$                  | 112<br>106                    | $> 120$                  | $\text{dB}$<br>$\text{dB}$                                   |                              |

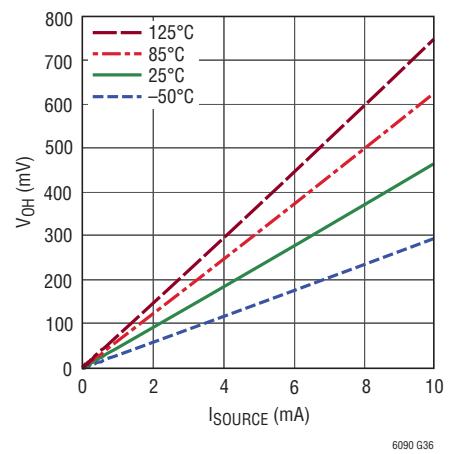

| $V_{OUT}$                | Output Voltage Swing High ( $V_{OH}$ )<br>(Referred to $V^+$ ) | No Load<br>$I_{SOURCE} = 1\text{mA}$<br>$I_{SOURCE} = 10\text{mA}$                                          | ●<br>●<br>●    | 10<br>50<br>450               | 25<br>140<br>1000        | 10<br>50<br>450               | 25<br>140<br>1000        | $\text{mV}$<br>$\text{mV}$<br>$\text{mV}$                    |                              |

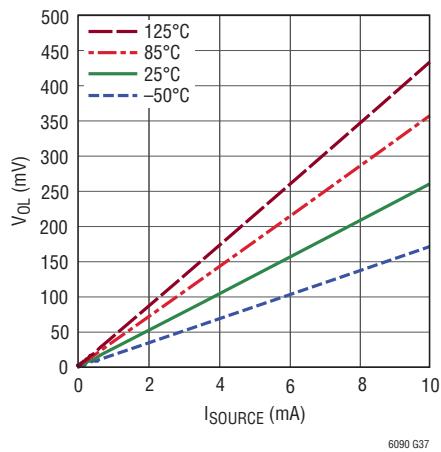

|                          | Output Voltage Swing Low ( $V_{OL}$ )<br>(Referred to $V^-$ )  | No Load<br>$I_{SINK} = 1\text{mA}$<br>$I_{SINK} = 10\text{mA}$                                              | ●<br>●<br>●    | 10<br>40<br>250               | 25<br>80<br>600          | 10<br>40<br>250               | 25<br>80<br>600          | $\text{mV}$<br>$\text{mV}$<br>$\text{mV}$                    |                              |

| $A_{VOL}$                | Large-Signal Voltage Gain                                      | $R_L = 10\text{k}\Omega$ ,<br>$V_{OUT}$ from $-60\text{V}$ to $60\text{V}$                                  | ●              | 1000<br>1000                  | $> 10000$                | 1000<br>1000                  | $> 10000$                | $\text{V/mV}$<br>$\text{V/mV}$                               |                              |

# LTC6090/LTC6090-5

**電気的特性** ●は全動作温度範囲の規格値を意味する。それ以外は $T_J = 25^\circ\text{C}$ での値。テスト条件は、注記がない限り $V^+ = 70\text{V}$ 、 $V^- = -70\text{V}$ 、 $V_{CM} = V_{OUT} = 0\text{V}$ 、 $V_{OD} = \text{開放}$ 。

| SYMBOL                         | PARAMETER                                         | CONDITIONS                                                                                                 | C-,I-SUFFIXES |                           |                    | H-SUFFIX                  |                    |                    | UNITS        |    |

|--------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|---------------------------|--------------------|---------------------------|--------------------|--------------------|--------------|----|

|                                |                                                   |                                                                                                            | MIN           | TYP                       | MAX                | MIN                       | TYP                | MAX                |              |    |

| I <sub>SC</sub>                | Output Short-Circuit Current<br>(Source and Sink) | Supply Voltage = ±70V<br>Supply Voltage = ±15V                                                             | ●             | 50                        | 90                 | 50                        | 90                 | 90                 | mA<br>mA     |    |

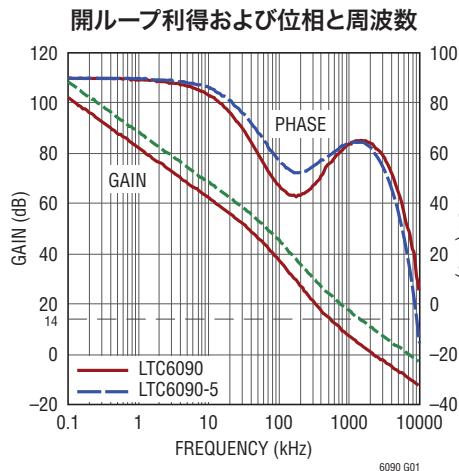

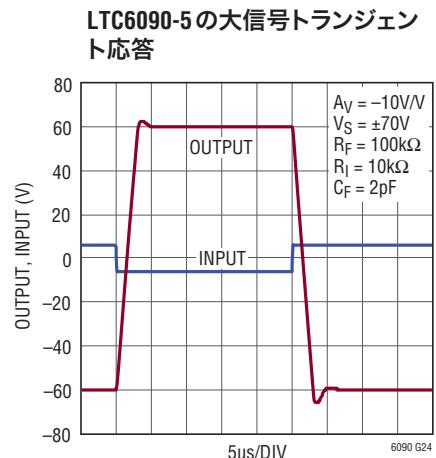

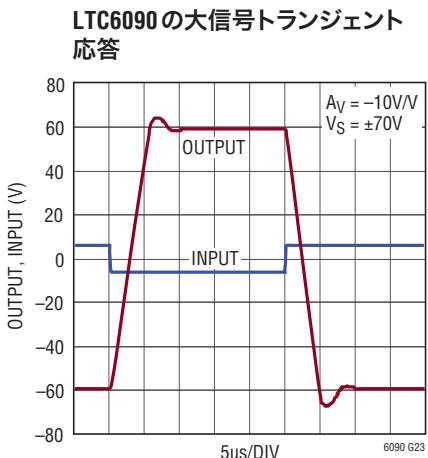

| SR                             | Slew Rate                                         | $A_V = -4$ , $R_L = 10\text{k}\Omega$<br>LTC6090<br>LTC6090-5                                              | ●<br>●        | 10<br>18                  | 21<br>37           | 9<br>16                   | 21<br>37           | 21                 | V/μs<br>V/μs |    |

| GBW                            | Gain-Bandwidth Product                            | $f_{TEST} = 20\text{kHz}$ , $R_L = 10\text{k}\Omega$<br>LTC6090<br>LTC6090-5                               | ●<br>●        | 5.5<br>11                 | 12<br>24           | 5<br>10                   | 12<br>24           | 12                 | MHz<br>MHz   |    |

| Φ <sub>M</sub>                 | Phase Margin                                      | $R_L = 10\text{k}\Omega$ , $C_L = 50\text{pF}$                                                             |               |                           | 60                 |                           |                    | 60                 | Deg          |    |

| FPBW                           | Full Power Bandwidth                              | $V_0 = 125\text{V}_{P-P}$<br>LTC6090<br>LTC6090-5                                                          | ●<br>●        | 20<br>34                  | 40<br>68           | 18<br>32                  | 40<br>68           | 40                 | kHz<br>kHz   |    |

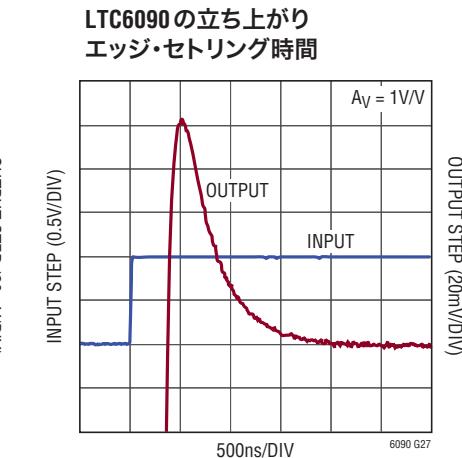

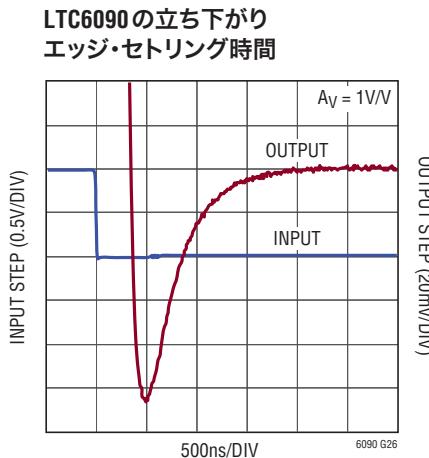

| t <sub>S</sub>                 | Settling Time 0.1%                                | $\Delta V_{OUT} = 1\text{V}$<br>LTC6090, $A_V = 1/\sqrt{\text{V}}$<br>LTC6090-5, $A_V = 5/\sqrt{\text{V}}$ |               |                           | 2<br>2.5           |                           |                    | 2<br>2.5           | μs<br>μs     |    |

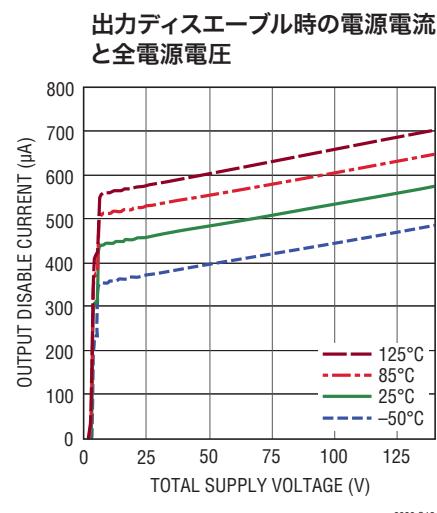

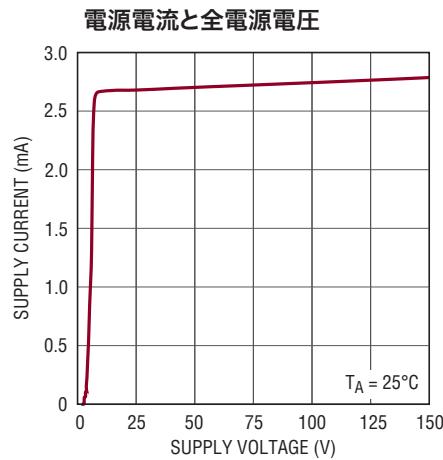

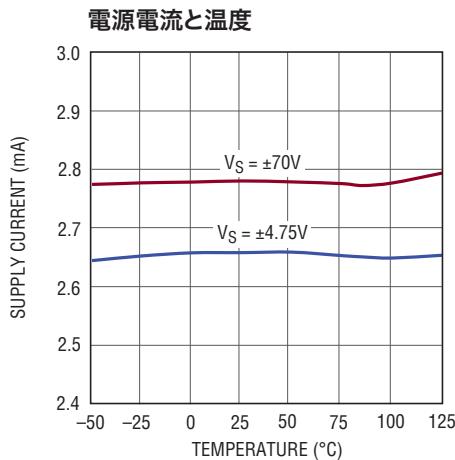

| I <sub>S</sub>                 | Supply Current                                    | No Load                                                                                                    | ●             |                           | 2.8<br>4.3         |                           |                    | 2.8<br>4.3         | mA<br>mA     |    |

| V <sub>S</sub>                 | Supply Voltage Range                              | Guaranteed by the PSRR Test                                                                                | ●             | 9.5                       | 140                | 9.5                       | 140                | 140                | V            |    |

| $\bar{O}_D_H$<br>$\bar{O}_D_L$ | $\bar{O}_D$ Pin Voltage, Referenced to COM Pin    | $V_{IH}$<br>$V_{IL}$                                                                                       | ●<br>●        | COM + 1.8V<br>COM + 0.65V |                    | COM + 1.8V<br>COM + 0.65V |                    | COM + 0.65V        | V<br>V       |    |

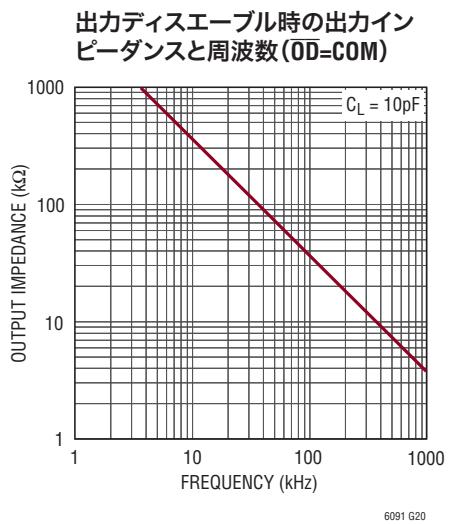

|                                | Amplifier DC Output Impedance, Disabled           | DC, $\bar{O}_D = \text{COM}$                                                                               |               |                           | >10                |                           |                    | >10                | MΩ           |    |

| COM <sub>CM</sub>              | COM Pin Voltage Range                             |                                                                                                            | ●             | V <sup>-</sup>            | V <sup>+</sup> – 5 | V <sup>-</sup>            | V <sup>+</sup> – 5 | V <sup>+</sup> – 5 | V            |    |

| COM <sub>V</sub>               | COM Pin Open Circuit Voltage                      |                                                                                                            | ●             | 17                        | 21                 | 25                        | 17                 | 21                 | 25           | V  |

| COM <sub>R</sub>               | COM Pin Resistance                                |                                                                                                            | ●             | 500                       | 665                | 850                       | 500                | 665                | 850          | kΩ |

| TEMP <sub>F</sub>              | Die Temperature Where TFLAG Is Active             |                                                                                                            |               |                           | 145                |                           |                    | 145                | °C           |    |

| TEMP <sub>PHYS</sub>           | TFLAG Output Hysteresis                           |                                                                                                            |               |                           | 5                  |                           |                    | 5                  | °C           |    |

| I <sub>TFLAG</sub>             | TFLAG Pull-Down Current                           | TFLAG Output Voltage = 0V                                                                                  | ●             | 70                        | 200                | 330                       | 70                 | 200                | 330          | μA |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

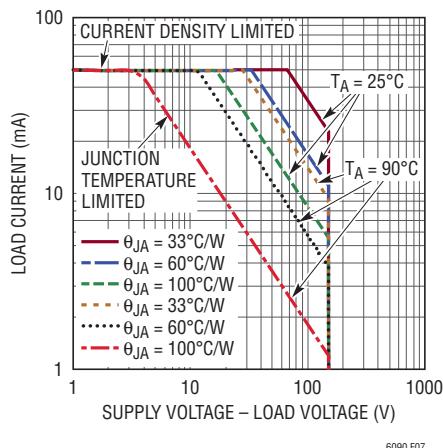

**Note 2:** LTC6090/LTC6090-5は50mAを超えるピーク出力電流を発生することができる。IC内部の電流密度の制限により、デバイスの動作寿命にわたって、出力(ソースまたはシンク)によって供給される連続RMS電流は50mA(絶対最大定格)未満に制限する必要がある。接合部温度を絶対最大定格より下に保つには、適切なヒートシンクが必要になることがある。詳細については、データシートの図7、「電力損失」のセクション、および「安全動作領域」のセクションを参照。

**Note 3:** LTC6090C/LTC6090Iは、-40°C ~ 85°Cの動作接合部温度範囲で動作が保証されている。LTC6090Hは、-40°C ~ 125°Cの動作接合部温度範囲で動作が保証されている。接合部温度範囲を動作条件として規定する対象デバイスは、静止時の電力損失が非常に大きくなる可能性があるデバイスである。

**Note 4:** LTC6090Cは0°C ~ 70°Cで規定の性能を満たすことが保証されている。LTC6090Cは-40°C ~ 85°Cで規定の性能を満たすように設計され、特性が評価されており、規定の性能を満たすと予想されるが、これらの温度ではテストされず、QAサンプリングも行われない。LTC6090Iは-40°C ~ 85°Cで規定の性能を満たすことが保証されている。LTC6090Hは-40°C ~ 125°Cで規定の性能を満たすことが保証されている。

**Note 5:** このデバイスには短時間の過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。規定の最大動作接合部温度を超える動作は推奨されない。

**Note 6:** 入力バイアス電流および入力オフセット電流は、量産時に±15V電源でテストされる。全電源電圧範囲での実際の標準性能については、「標準的性能特性」の曲線を参照。

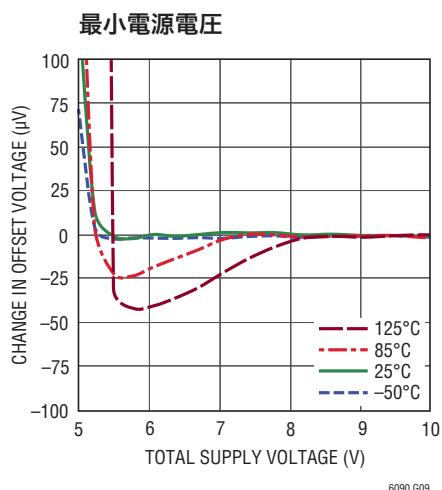

## 標準的性能特性

# LTC6090/LTC6090-5

## 標準的性能特性

## 標準的性能特性

# LTC6090/LTC6090-5

## 標準的性能特性

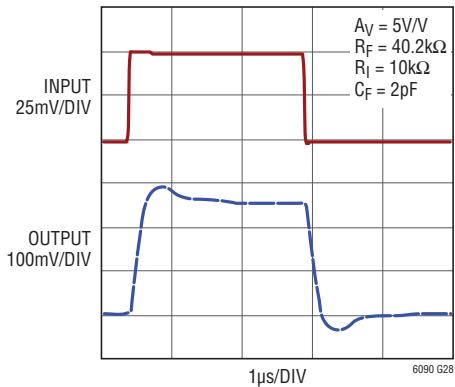

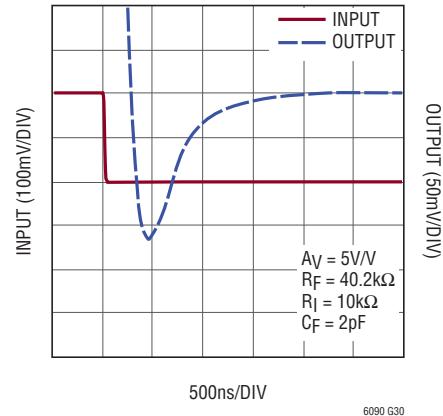

LTC6090-5の

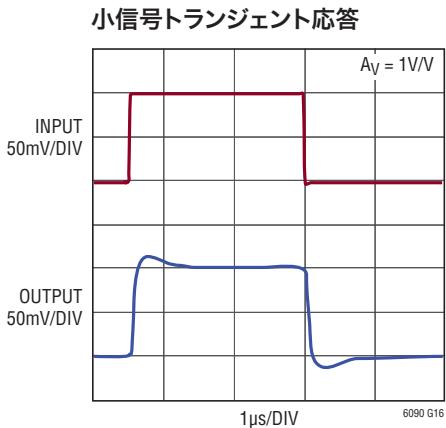

小信号トランジェント応答

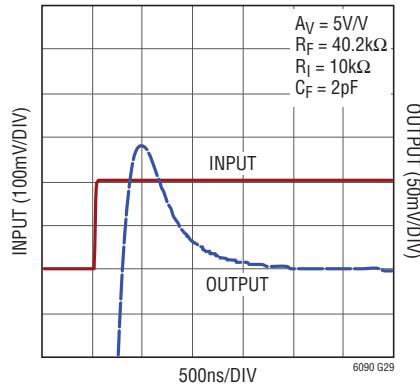

LTC6090-5の立ち上がり

エッジ・セッティング時間

LTC6090-5の立ち下がり

エッジ・セッティング時間

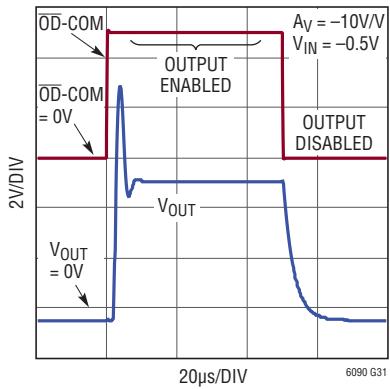

出力ディスエーブル(OD)の

応答時間

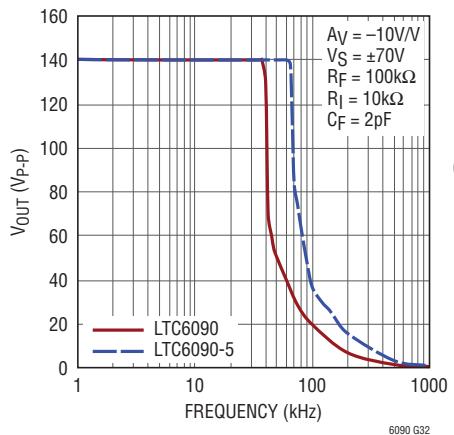

出力電圧振幅と周波数

0.1Hz～10Hzの電圧ノイズ

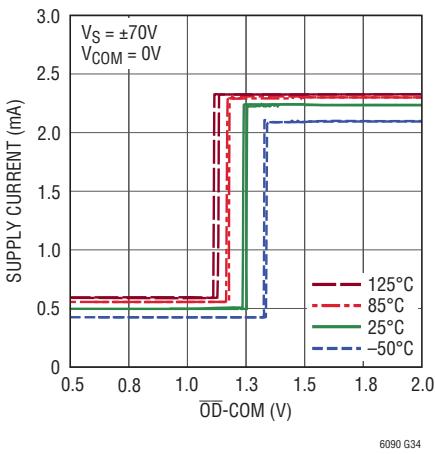

電源電流とODピン電圧

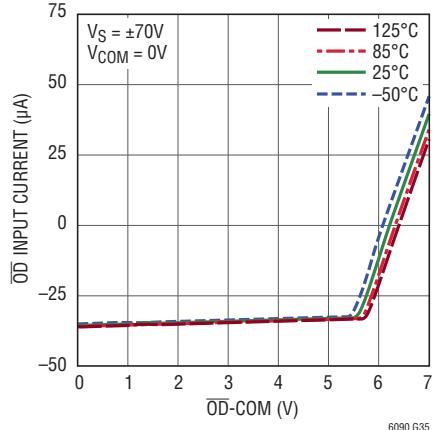

ODピン入力電流とODピン電圧

出力電圧振幅 High ( $V_{OH}$ ) と

負荷電流と温度

## 標準的性能特性

出力電圧振幅 Low ( $V_{OL}$ ) と

負荷電流と温度

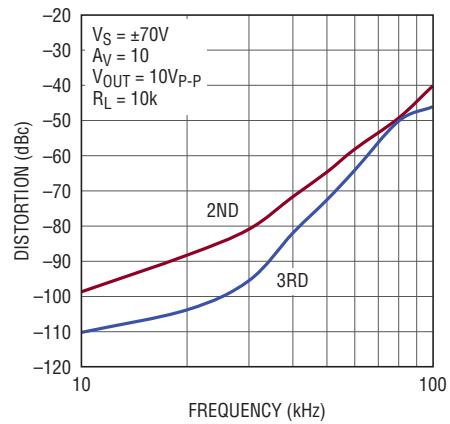

LTC6090 の歪みと周波数

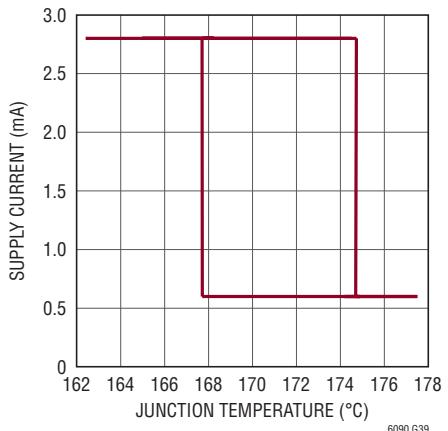

サーマル・シャットダウンの

ヒステリシス

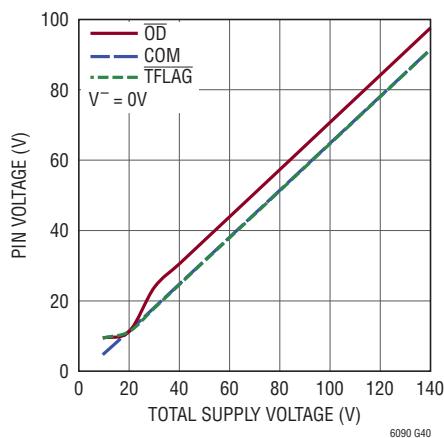

COM、OD、TFLAG の開放回路電圧

開ループ利得

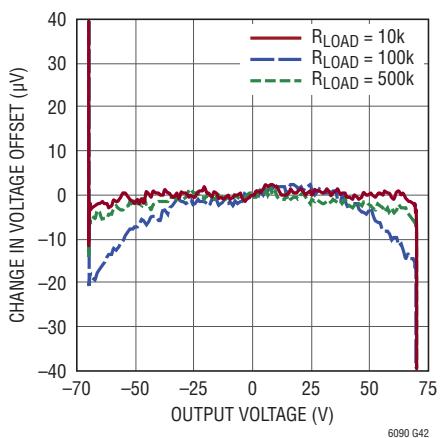

開ループ利得と負荷抵抗

## ピン機能 (S8E/FE)

**COM(ピン1/ピン1)**: COMピンは、 $\overline{OD}$ ピンおよび $\overline{TFLAG}$ ピンと電圧制御回路とのインターフェースをとるために使用します。このピンは低電圧回路のグランドに接続するか、フロートのままにしてください。

**-IN(ピン2/ピン4)**: 反転入力ピン。入力同相範囲は $V^- + 3V \sim V^+ - 3V$ です。絶対最大電圧範囲を超えないようにしてください。

**+IN(ピン3/ピン5)**: 非反転入力ピン。入力同相範囲は $V^- + 3V \sim V^+ - 3V$ です。絶対最大電圧範囲を超えないようにしてください。

**$V^-$ (ピン4、露出パッド・ピン9/ピン8、露出パッド・ピン17)**: 負電源ピン。 $V^-$ ピンにのみ接続してください。熱抵抗を低く抑えるには、このピンを $V^-$ 電源プレーンに接続します。 $V^-$ 電源プレーンへの接続により、デバイスの熱が放散されます。また、この接続は、それ以外のすべての電源プレーンから電気的に絶縁する必要があります。

**$TFLAG$ (ピン5、9/ピン9、17)**: 温度フラグ・ピン。 $\overline{TFLAG}$ ピンは、ダイ温度が $145^\circ C$ を超えると電流を吸い込むオープンドレイン出力です。

**OUT(ピン6/ピン12)**: 出力ピン。このレール・トゥ・レール出力の電圧が $V^-$ より低くなると、ESD保護ダイオードが順方向バイアスになります。OUTピンの電圧が $V^+$ より高くなると、デバイスのダイオードが順方向バイアスになります。OUTピンのダイオードは順方向バイアスにならないようにしてください。過剰な電流によって損傷が生じる可能性があります。

**$V^+$ (ピン7/ピン14)**: 正電源ピン。

**$\overline{OD}$ (ピン8/ピン16)**: 出力ディスエーブル・ピン。アクティブ“L”を入力すると出力段はディスエーブルされます。開放のままにすると、内部プルアップ抵抗によってアンプはイネーブルされます。入力電圧レベルはCOMピンの電圧が基準になります。

**GUARD(非該当/ピン2、3、6、7、10、11、13、15)**: ガード・ピンは、他のピンとの間の表面漏れ距離やピン間隔を広げる役割を果たします。ピン3およびピン6を使用して、入力を囲むガードリングを形成することもできます。

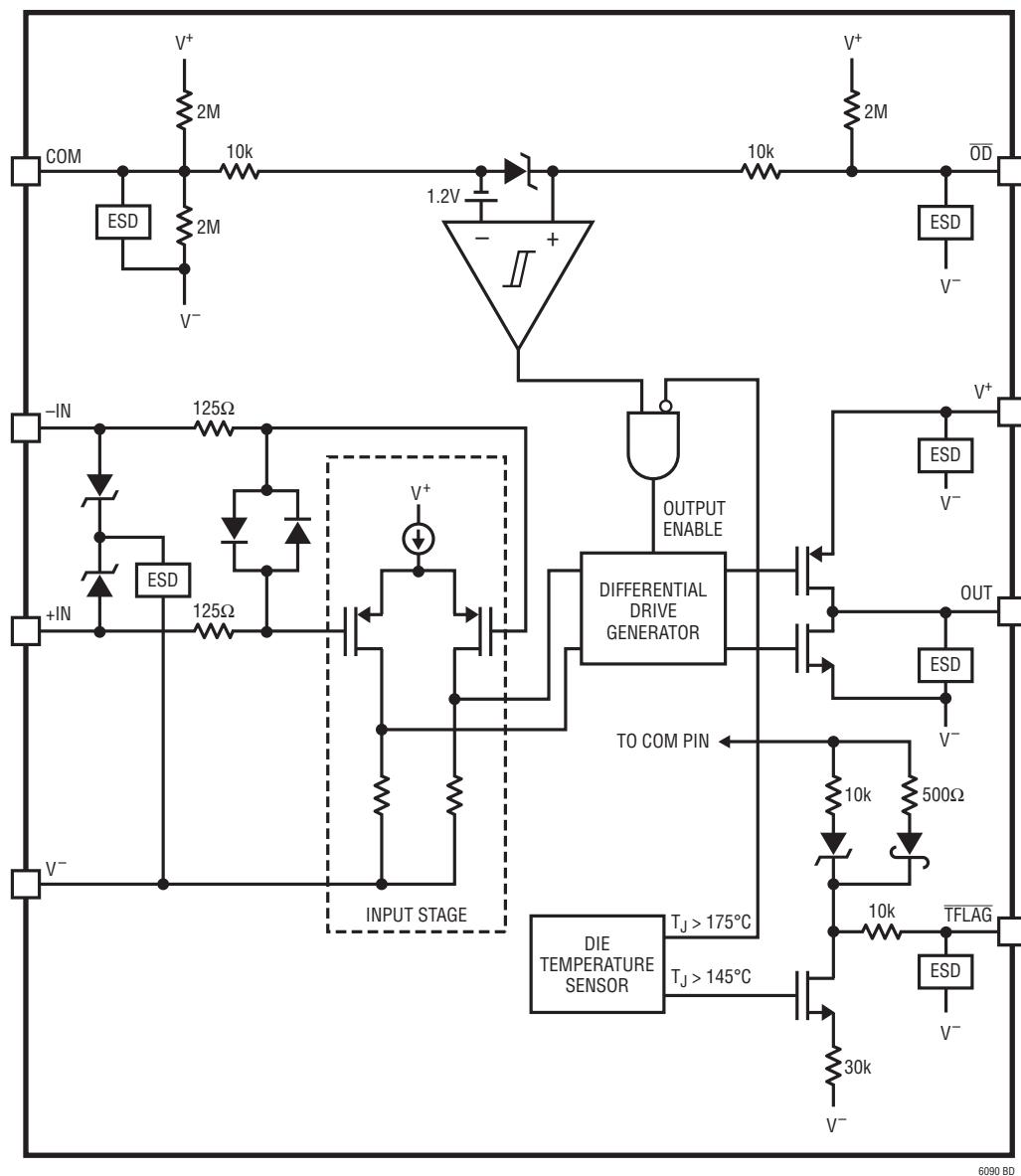

## ブロック図

6090 BD

## アプリケーション情報

### 概要

LTC6090高電圧オペアンプは、140V電源を使用してレール・トゥ・レール出力段をイネーブルする一方で、高精度、低オフセット、低ノイズを維持するリニアテクノロジー独自のプロセスで設計されています。

### 電源

LTC6090は単電源または両電源で動作します。両電源は平衡でも不平衡でもかまいません。たとえば、 $\pm 70V$ 電源を使用することも、100V電源と-40V電源を使用することもできます。单電源アプリケーションの場合は、品質の高い表面実装型の0.1 $\mu F$ セラミック・バイパス・コンデンサをデバイスの近くの電源ピン間に取り付けてください。両電源アプリケーションの場合は、デバイス近くのV<sup>+</sup>とグランド間、およびV<sup>-</sup>とグランド間に品質の高い2つの表面実装型セラミック・コンデンサを使用します。両電源を使用する場合は、電源シーケンシングによる問題は発生しません。

### 入力保護

ブロック図に示すように、LTC6090には、入力素子に対する損傷を防ぐために包括的な保護回路網があります。電流制限抵抗および逆並列ダイオードは、入力が別々に駆動されないようにするためのものです。電圧と電流の関係は、ピン間の電圧差が12Vに達するまでは指数関数と抵抗を合成した関係になります。

ピン間の電圧が12Vになると、ツェナーが導通します。ピンに流れる電流が増加することにより、入力差動電圧は素早く9Vに戻ります。入力とV<sup>-</sup>の間をESDが直撃すると、電圧クランプ回路およびESD保護素子が作動して、入力素子を保護するV<sup>-</sup>への電流経路を確保します。

入力ピン保護回路は、瞬時のESD事象から保護する目的で設計されています。高速(立ち上がり時間が<20ns)で振幅の大きい(>5.5V)入力が繰り返されると、MOSFET入力素子にストレスが繰り返し加わります。こうしたアプリケーションでは、入力間に逆並列接続ダイオード(1N4148)を接続して、振幅を制限してください。

### 帰還抵抗の選択

出力駆動回路の利点を最大限に引き出すには、帰還抵抗を慎重に選ぶことが必要です。 $A_V = -50$ のアンプと5kの帰還抵抗について考えます。入力電圧を1Vとした場合、出力電圧は50Vにまで上昇し、帰還回路には10mAの電流が流れます。出力ステージで消失される電力は、入力ステージへの熱帰

還を生成し、オフセット電圧のシフトを引き起こす可能性があります。したがって、帰還回路の電流を1mAにまで低減する50k帰還抵抗を選択する方が良いことになります。

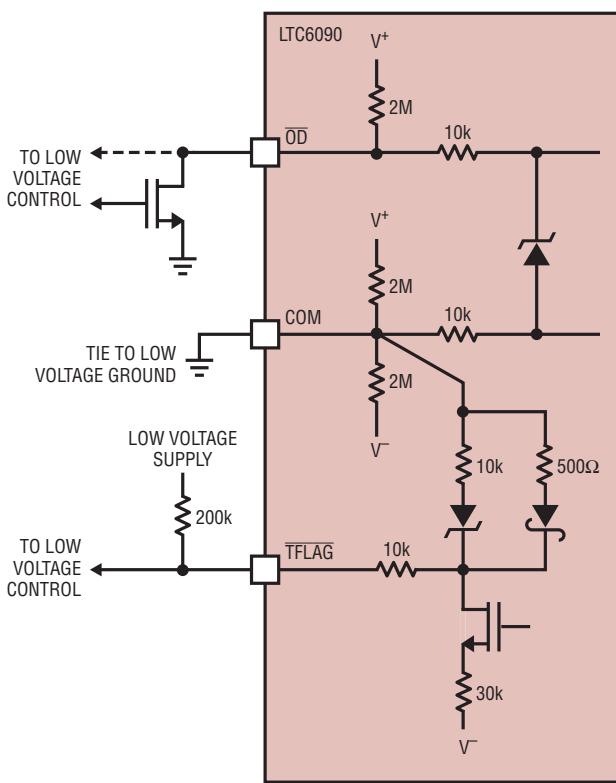

### 低電圧回路とのインターフェース

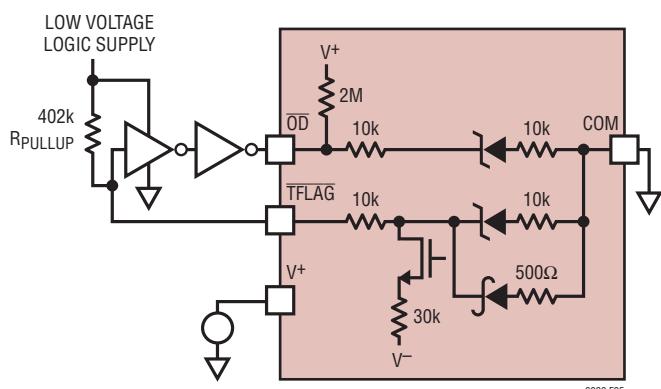

COMピンは、マイクロプロセッサやその他の低電圧ロジック回路との通信に備えて共通の信号グランドを設定する目的で設けられています。COMピンは、図1に示すように低電圧回路のグランドに接続してください。フロート状態のままの場合、デバイス内部の抵抗分割器により、COMピンの電圧は電源の中間電圧より30%高い電圧まで上昇します。COM、OD、TFLAGの各ピンは、デバイス内部のツェナー・ダイオードおよび電流制限抵抗によって過電圧から保護されています。(ODからCOM)および(TFLAGからCOM)の絶対最大電圧リミットを守るように特に注意してください。これらのピンの間の電圧リミットは-3Vと7Vの間に留まる必要があります。

図1. 低電圧回路のインターフェース

## アプリケーション情報

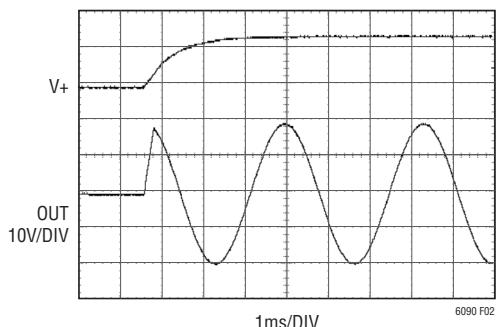

図2. 起動

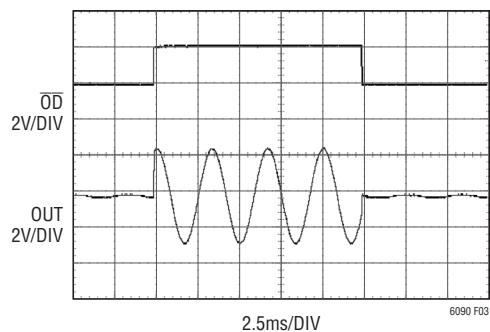

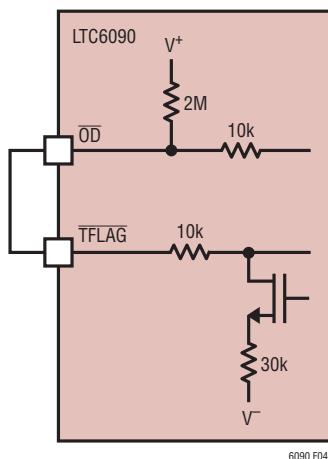

図3. LTC6090の出力ディスエーブル機能

### 出力のディスエーブル

$\overline{OD}$ ピンはアクティブ“L”のディスエーブル・ピンで、 $\overline{OD}$ ピンの電圧を引き上げて出力段をイネーブルする $2M\Omega$ の抵抗が内部に接続されています。 $\overline{OD}$ ピンの電圧は内部のツェナー・ダイオードによって制限されます。 $\overline{OD}$ ピンをCOMピンの0.65V以内にまで下げるとき、出力段はディスエーブルされますが、バイアス回路と入力回路はイネーブルのままであります。この結果、デバイスには $580\mu A$ （標準）のスタンバイ電流が流れます。 $\overline{OD}$ ピンは低電圧駆動回路に直接接続するか、図1に示すようにオープンドレインのNMOSデバイスを接続して使用することもできます。

シャットダウン動作を最も簡単に行うには、COMピンをフロート状態にして、 $\overline{OD}$ ピンをTFLAGピンに接続します。これにより、低電圧制御ピンはフロート状態になるので、ダイの温度が $145^{\circ}C$ に達すると、過熱保護回路によって出力段は安全にシャットダウンします。

( $\overline{OD}$ からCOM)および(TFLAGからCOM)の絶対最大電圧リミットを守るように特に注意してください。これらのピンの間の電圧リミットは-3Vと7Vの間に留まる必要があります。

シャットダウン状態から抜けると、LTC6090のバイアス回路および入力段はすでに起動しており、出力段のみを導通させて適正な出力電圧を駆動する状態になっています。デバイスの起動とシャットダウン状態からの復帰をそれぞれ図2および図3に示します。

### サーマル・シャットダウン

TFLAGピンは、ダイの温度が $145^{\circ}C$ を超えると $200\mu A$ （標準）を吸い込むオープンドレインの出力ピンです。温度センサには $5^{\circ}C$ のヒステリシスがあるので、デバイスはTFLAGピンをディスエーブルする前に $140^{\circ}C$ まで冷却されている必要があります。（ $\overline{OD}$ からCOM）および（TFLAGからCOM）の絶対最大電圧リミットを守るように特に注意してください。これらのピンの間の電圧リミットは-3Vと7Vの間に留まる必要があります。

適切なサーマル・シャットダウン動作を保証するには、出力ディスエーブル・ピン( $\overline{OD}$ )をTFLAGピンにインターフェースするとき、いくつかの注意事項に従う必要があります。

- 既に述べたように、COMピンをフロートさせたままになると、（図4に示されているように） $\overline{OD}$ をTFLAGに接続するだけで、選択された電源電圧に関係なく、サーマル・シャットダウンが適切に動作します。ダイ温度が $145^{\circ}C$ に達すると出力段は安全にディスエーブルされます。サーマル・シャットダウンが適切に動作するには、グランドを基準にして $V_-$ が-3Vより負の側にバイアスされているかぎり、この構成ではCOMピンをグランドに接続することもできます。

- COMピンが接地されているが、 $V_-$ 電源がグランドを基準にして0V～-3V以内にあるとき、図5に示されているように、ロジック・バッファを使って $\overline{OD}$ をロジック“L”に強制する必要があります。図5のプルアップ抵抗( $R_{PULLUP}$ )は、ロジック・バッファに対してロジック“L”を保証するのに十分大きいものを選択する必要があります。ほとんどのCMOSでは、少なくとも $402k$ のプルアップ抵抗値が必要です。代わりにCOMピンをフロートさせれば、ロジック・バッファは不要です。COMがフロート状態であれば、サーマル・シャットダウンを適切に動作させるために、単に $\overline{OD}$ をTFLAGに直接接続することができます。

安全を期すため、独立した第2の過熱しきい値により、内部のダイ温度が $175^{\circ}C$ まで上昇すると、出力段はシャットダウンします。このサーマル・シャットダウン回路には、ダイ温度を $7^{\circ}C$ 冷却することが必要なヒステリシスがあります。デバイスが十分に冷却されると、出力段はイネーブルします。デバイスの接合部温度が $150^{\circ}C$ を超えると、劣化が生じる恐れや信頼性に影響を及ぼす可能性があります。

## アプリケーション情報

図4. TFLAGピンを使用したサーマル・シャットダウン出力の自動ディスエーブル

図5. 単電源アプリケーションの不平衡両電源でTFLAGピンを使った自動サーマル出力ディスエーブル

## 基板のレイアウト

LTC6090は、高性能を維持するために良好なアナログPCBレイアウトを必要とする、高精度、低オフセット、高利得のアンプです。星形に接続されたグランド・プレーンから始めます。グランド・プレーンは、すべての高電圧ビアから離してください。入力などの重要な信号のリード線は長さを短くして、寄生容量を減らしてください。これにより、安定性も向上します。高品質の表面実装型セラミック・コンデンサを使用して電源をバイパスしてください。

高精度オペアンプで生じる典型的なレイアウトの問題の他に、高電圧と大電力の問題があります。高電圧の配線に対する重要な検討事項は、間隔、湿度、および塵です。隣接する導体間に高電圧の電界があると、塵が引き寄せられます。塵によって水分が吸収され、水分が基板の漏れ電流や電気的絶縁破壊の原因となります。

デバイスを半田付けした後にPCBを洗浄することが重要です。半田フラックスには塵がたまるので、漏れ電流の原因になります。溶剤を使用してPCBを洗浄するか、石けんと水だけを使用して残留物を除去することを推奨します。PCBを加熱乾燥すると、残りの水分が除去されます。アプリケーションによっては、漏れ電流の少ない特殊な基板材料を検討することもできます。

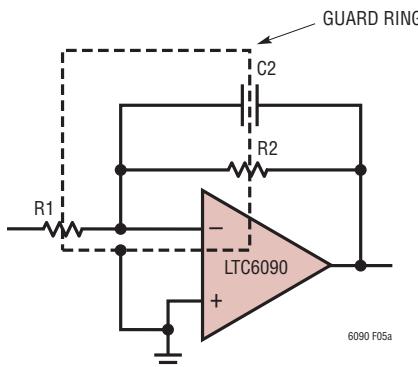

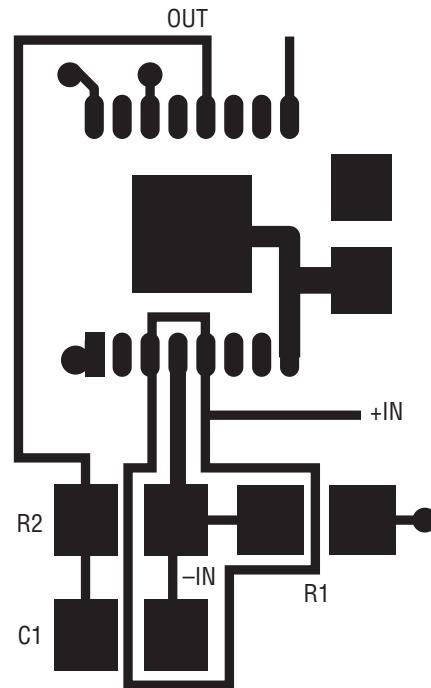

TSSOPパッケージには、ガードリングが必要なアプリケーション用にガード・ピンがあります。-INピンを保護するためのガードリングを使用した回路の回路図とPCBレイアウトの例を図6aおよび図6bにそれぞれ示します。ガードリングは、高インピーダンス・ノードである-INを完全に囲んでいます。PCBレイアウトを簡素化するには、このノードにビアを使用しないようにしてください。さらに、半田マスクをガードリングに沿って後退させ、金属部分を露出させてください。ノード間の間隔を確保するため、TSSOPパッケージの追加ピンの1つを使用して、-INピンの背後にガードリングを配線します。PCBは半田付け後、十分に洗浄して、露出パッド(ピン17)とガードリングの間に半田ペーストが残らないようにする必要があります。

## 電力損失

電源電圧が140Vの場合は、大量の電力を消費する電流を流さないようにします。140Vで10mAを流すと1.4Wの電力を消費するので、この電力を小型のプラスチックSOパッケージで放散する必要があります。電力による熱放散の一助とするため、2つのLTC6090パッケージは、どちらも熱抵抗を低くするための露出パッドを備えています。露出パッドに接続される金属の大きさにより、パッケージの $\theta_{JA}$ が小さくなります。SOパッケージに接続するPCB上の金属面を最適な大きさにすることにより、接合部-周囲雰囲気間熱抵抗を33°C/Wまで下げることができます。最小限の金属を使用した場合、 $\theta_{JA}$ の値は2倍を超える可能性があります(表1参照)。露出パッドの下に金属面がない場合、 $\theta_{JA}$ は120°C/Wまで高くなる可能性があります。

露出パッドには、利用可能な適度な広さのPCB金属面を接続することを推奨します。露出パッドに接続するPCB金属面を広くするほど、熱抵抗は低くなります。露出パッドからV-ピンの電源プレーンまでに複数のビアを使用してください。露出パッドは、V-ピンに電気的に接続されています。さらに、最大接合部温度付近で動作させる場合には、ヒートシンクが必要なことがあります。露出パッドに接続されている金属の面積の関数として熱抵抗がどのように変化するかについては、目安として表1を参照してください。

## アプリケーション情報

図6a. ガードリングを示す回路図

LTC6090は、140Vでのソース電流およびシンク電流が10mAであると規定されています。全電源電圧がデバイスの端子間で降下した場合、1.4Wの電力を熱放散する必要があります。静止電力( $140V \cdot 2.8mA = 0.4W$ )が含まれる場合、全電力損失は1.8Wです。SOパッケージの最適なレイアウトを使用すると、内部のダイ温度は59°C上昇します。最適より劣るレイアウトの場合は、電力損失により、温度上昇が2倍を超える可能性があります。

図6b. TSSOPパッケージのガードリング付きPCBレイアウト

表1. 露出パッドに接続されるPCBの面積によって異なる熱抵抗

| EXAMPLE A                                                                                                     | EXAMPLE B                                                                                                     | EXAMPLE C                                                                                                     | EXAMPLE D                                                                                                     |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| TOP LAYER A                                                                                                   | TOP LAYER B                                                                                                   | TOP LAYER C                                                                                                   | TOP LAYER D                                                                                                   |

| BOTTOM LAYER A                                                                                                | BOTTOM LAYER B                                                                                                | BOTTOM LAYER C                                                                                                | BOTTOM LAYER D                                                                                                |

|                                                                                                               |                                                                                                               |                                                                                                               |                                                                                                               |

|                                                                                                               |                                                                                                               |                                                                                                               |                                                                                                               |

| $\theta_{JA} = 43^\circ\text{C/W}$<br>$\theta_{JC} = 5^\circ\text{C/W}$<br>$\theta_{CA} = 38^\circ\text{C/W}$ | $\theta_{JA} = 50^\circ\text{C/W}$<br>$\theta_{JC} = 5^\circ\text{C/W}$<br>$\theta_{CA} = 45^\circ\text{C/W}$ | $\theta_{JA} = 57^\circ\text{C/W}$<br>$\theta_{JC} = 5^\circ\text{C/W}$<br>$\theta_{CA} = 52^\circ\text{C/W}$ | $\theta_{JA} = 72^\circ\text{C/W}$<br>$\theta_{JC} = 5^\circ\text{C/W}$<br>$\theta_{CA} = 67^\circ\text{C/W}$ |

| MINIMUM BOTTOM LAYER A                                                                                        | MINIMUM BOTTOM LAYER B                                                                                        | MINIMUM BOTTOM LAYER C                                                                                        |                                                                                                               |

|                                                                                                               |                                                                                                               |                                                                                                               |                                                                                                               |

| $\theta_{JA} = 54^\circ\text{C/W}$<br>$\theta_{JC} = 5^\circ\text{C/W}$<br>$\theta_{CA} = 49^\circ\text{C/W}$ | $\theta_{JA} = 57^\circ\text{C/W}$<br>$\theta_{JC} = 5^\circ\text{C/W}$<br>$\theta_{CA} = 52^\circ\text{C/W}$ | $\theta_{JA} = 58^\circ\text{C/W}$<br>$\theta_{JC} = 5^\circ\text{C/W}$<br>$\theta_{CA} = 53^\circ\text{C/W}$ |                                                                                                               |

6090fc

# LTC6090/LTC6090-5

## アプリケーション情報

デバイスの損傷を防ぐため、絶対最大接合部温度( $T_{JMAX} = 150^{\circ}\text{C}$ )を超えないようにする必要があります。接合部温度は次式を使用して求められます。

$$T_J = P_D \cdot \theta_{JA} + T_A$$

ここで、 $P_D$ はパッケージ内での電力損失、 $\theta_{JA}$ は周囲雰囲気から接合部までのパッケージの熱抵抗、 $T_A$ は周囲温度です。たとえば、デバイスの電源電圧が140Vで静止電流が2.8mAであり、出力電圧が負電源レールの電圧より20V高く、出力ソース電流が10mAの場合、デバイスの全電力損失は  $(120\text{V} \cdot 10\text{mA}) + (140\text{V} \cdot 2.8\text{mA}) = 1.6\text{W}$ です。これらの条件下では、周囲温度が次の値を超えないようにする必要があります。

$$T_A = T_{JMAX} - (P_D \cdot \theta_{JA}) = 150^{\circ}\text{C} - (1.6\text{W} \cdot 33^{\circ}\text{C}/\text{W}) = 97^{\circ}\text{C}$$

## 安全動作領域

安全動作領域(SOA)とは、デバイスを確実に動作させることができる電圧、電流、および温度の条件を表したもので。LTC6090のSOAを下の図7に示します。SOAには、デバイスによる電力損失が考慮されます。電力損失に含まれるのは、電源電圧と出力電圧の差と負荷電流との積、および静止電流と電源電圧との積です。

LTC6090は、図7に示す境界線の内側で動作しているときは安全です。接合部-ケース間熱抵抗 $\theta_{JC}$ の定格は、一定値の $5^{\circ}\text{C}/\text{W}$ です。接合部-周囲雰囲気間熱抵抗 $\theta_{JA}$ は、基板レイアウトと追加のヒートシンクによる放熱により異なります。図7の6つのSOA曲線は、SOAにおける $\theta_{JA}$ の直接の影響を示しています。

図7. 安全動作領域

## 大きい抵抗値による安定性

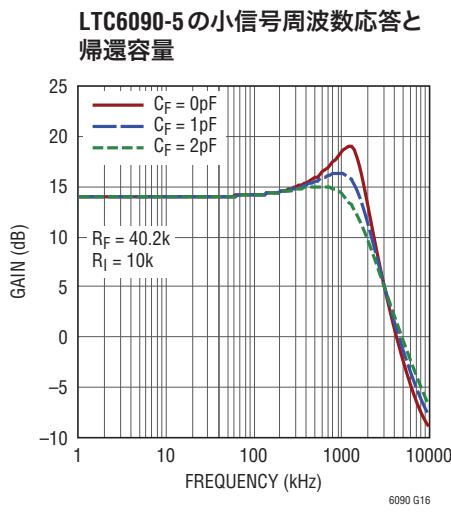

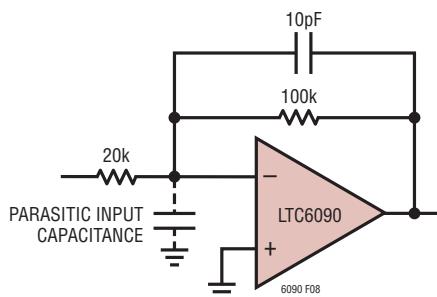

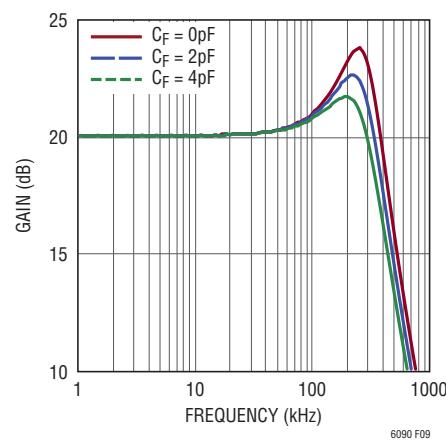

帰還抵抗が大きいと、デバイス固有の入力容量との組み合わせによって追加の極が発生します。この極は安定性に影響し、閉ループ応答でのピーキングの原因になります。ピーキングを軽減するには、図8に示すように、帰還抵抗の両端に小さな帰還コンデンサを取り付けます。これにより、ピーキングおよびオーバーシュートが減少します。さまざまな帰還コンデンサを取り付けた場合の閉ループ応答を図9に示します。

さらに、入力ピンの浮遊容量を最小限に抑えることも必要です。pA入力電流では、PCBのトレースをできるだけ短く、幅を狭く配線します。

図8. ピーキングを減少させるために帰還容量を取り付けた LTC6090

図9. さまざまな帰還コンデンサを取り付けた場合の閉ループ応答

## アプリケーション情報

### スルーレートの増強

LTC6090はスルーレートを21V/ $\mu$ sまで高くするスルーレート増強回路を内蔵しており、この回路によって140Vの全出力電圧範囲に及ぶレール・トゥ・レールでのスルーライングが7 $\mu$ s未満で可能となります。スルーレートを最適化し、セトリング時間を最短にするには、寄生容量を最小限に抑えることが必要です。帰還コンデンサは、スルーレート増強回路に伴うオーバーシュートおよび非直線性を低減します。帰還コンデンサのサイズは、基板、電源電圧、および負荷の具体的な条件に合わせて調整する必要があります。

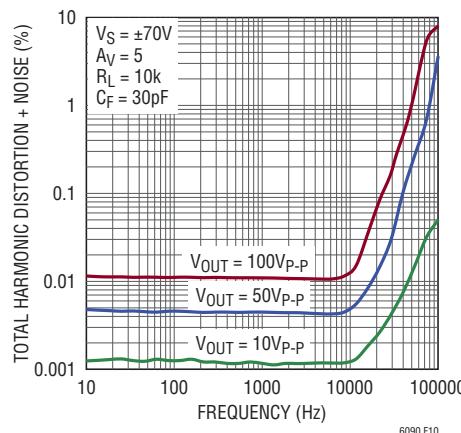

スルーライングは非直線性動作であるため、歪みに影響します。スルーレートとフルパワー帯域幅の関係は、次の関係式で与えられます。

$$SR = V_0 \cdot \omega$$

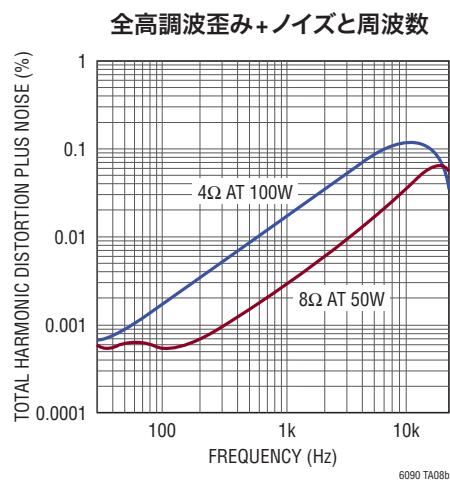

ここで、 $V_0$ は出力電圧のピーク値であり、 $\omega$ は周波数(単位:ラジアン)です。大きな正弦波出力の忠実性はスルーレートによって制限されます。数種類の出力レベルでの歪みと周波数のグラフを図10に示します。

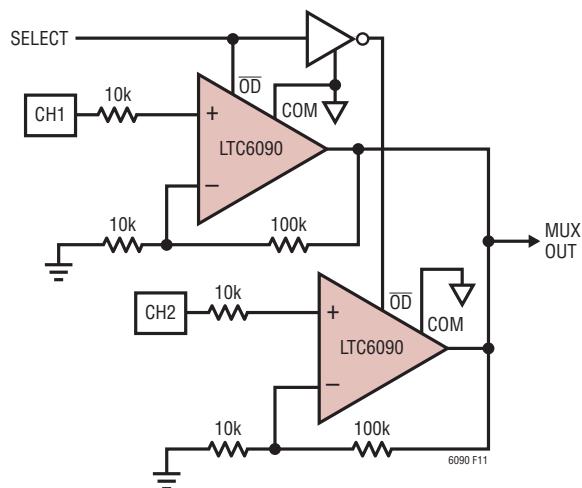

### マルチプレクサ・アプリケーション

いくつかのLTC6090を並べて、図11に示すように高電圧のアナログ・マルチプレクサとして機能させることができます。この配置を使用する場合は、ディスエーブル状態のアンプの非反転入力の信号源に出力が影響するようにすることができます。反転入力と非反転入力は、抵抗および逆並列接続のダイオードによってクランプされます。マルチプレクサ出力からディスエーブル状態のアンプの帰還抵抗を通り、入力を通って非反転入力の信号源に流れる電流の経路があります。たとえば、イネーブル状態のアンプの出力が-70Vであり、ディスエーブル状態のアンプの入力が5Vである場合、2つの抵抗の両端間と入力ピンの両端間の電圧は75Vです。この電流を1mAよりも少なくするには、 $R_{IN}$ と帰還抵抗の合成抵抗を約75kにする必要があります。

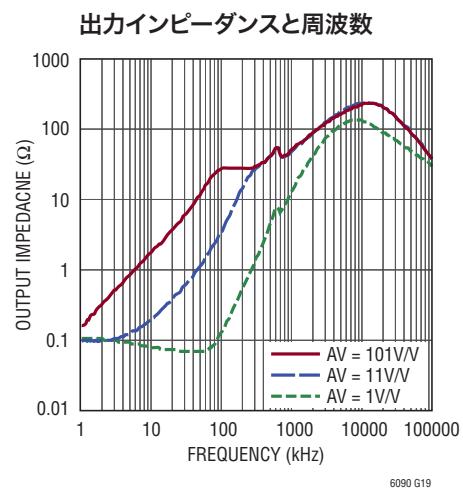

ディスエーブル状態のアンプの出力インピーダンスは、DCで10M $\Omega$ を超えます。AC出力インピーダンスを「標準的性能特性」のセクションに示します。

図10. 出力振幅が大きい場合の歪みと周波数

図11. マルチプレクサ・アプリケーション

# LTC6090/LTC6090-5

## 標準的應用例

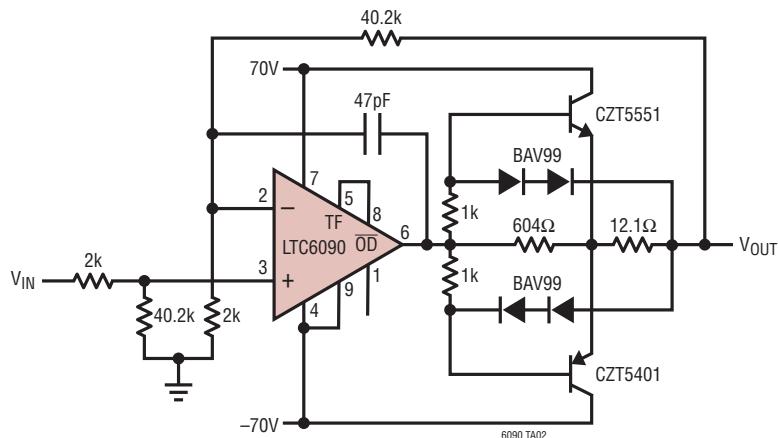

40mAの保護出力ドライバを備えた利得20のアンプ

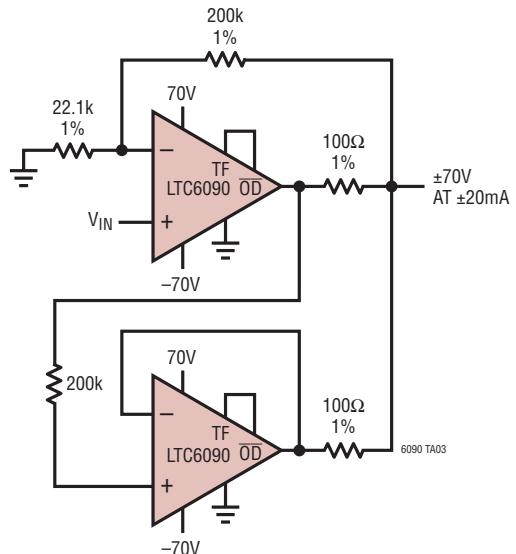

#### 利得が10の保護出力電流ダブル

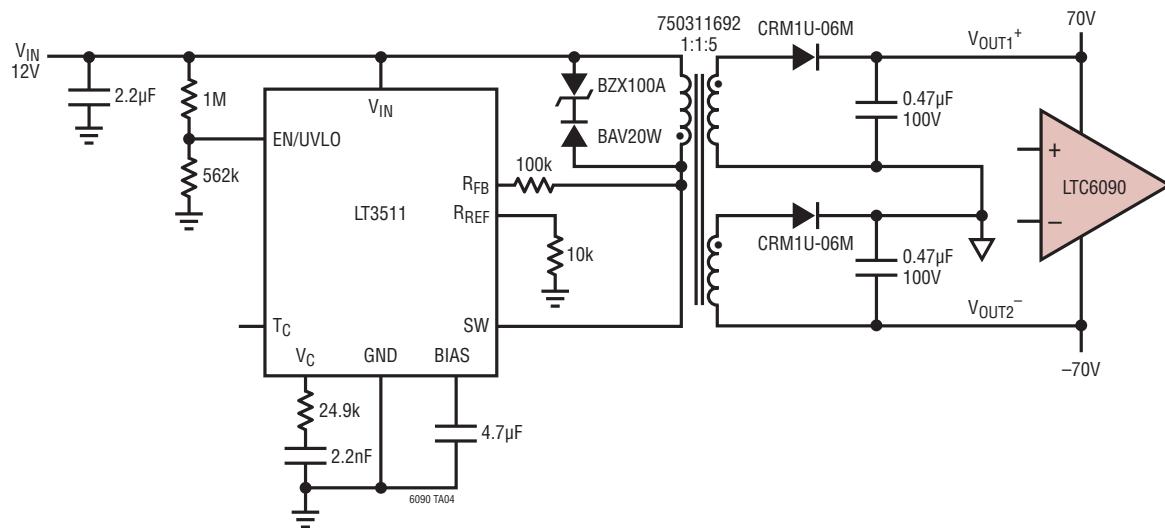

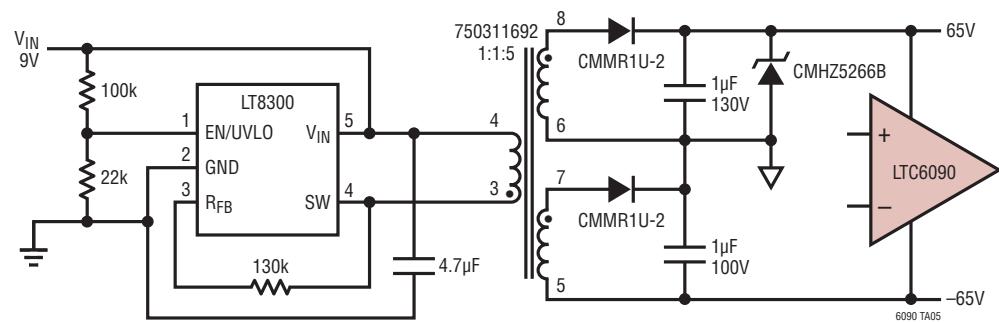

アンプ電源用の12V入力/±70V出力の絶縁型フライバック・コンバータ

アンプ電源用の9V入力/±65V出力の絶縁型フライバック・コンバータ

## 標準的應用例

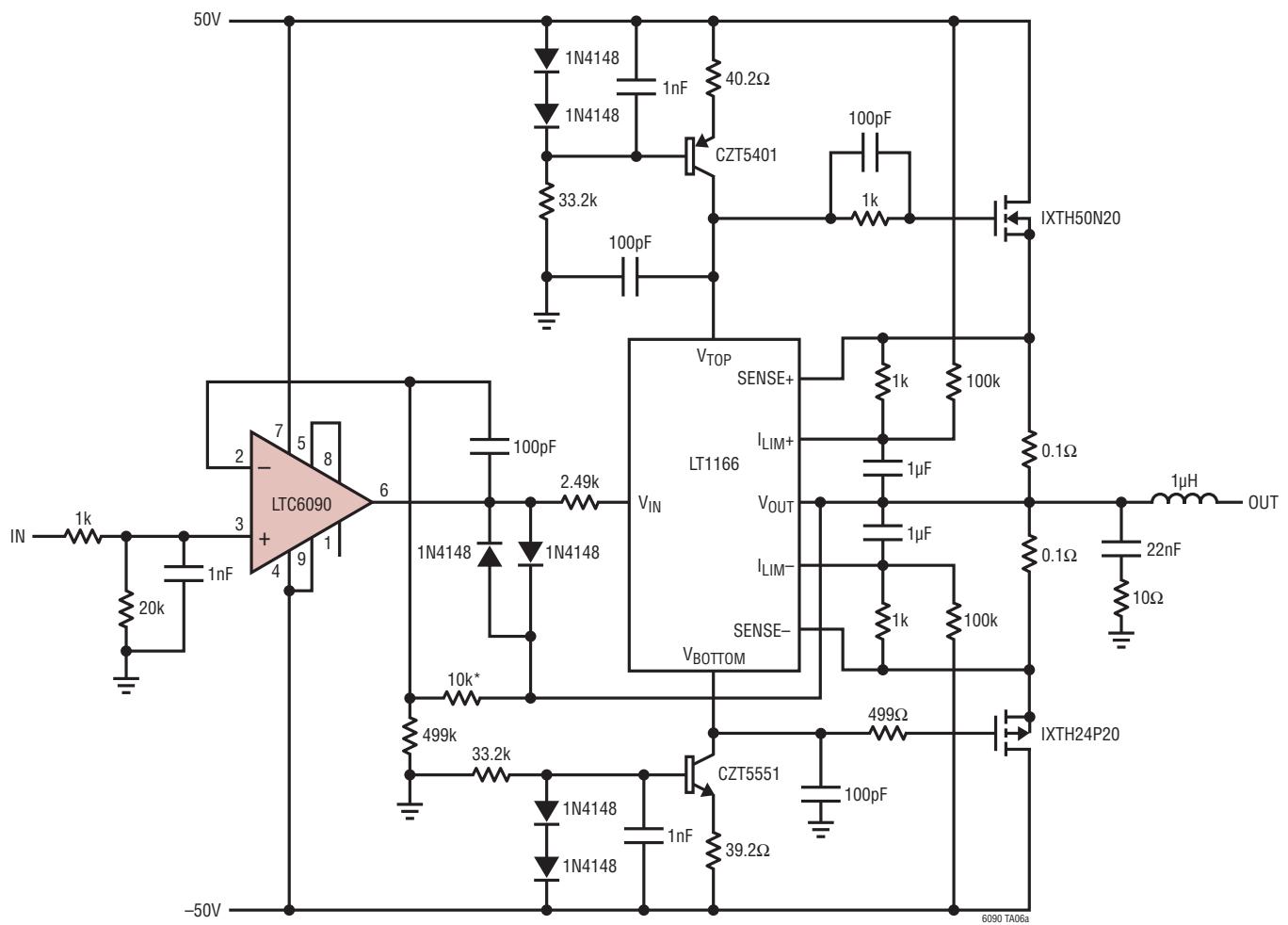

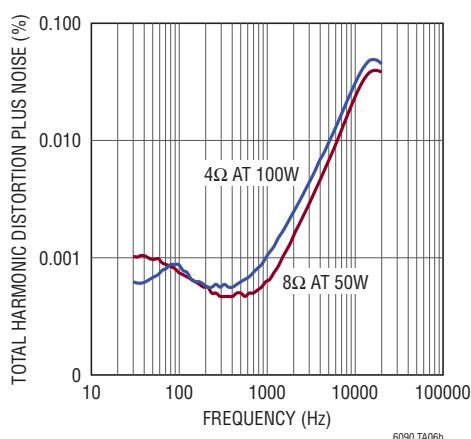

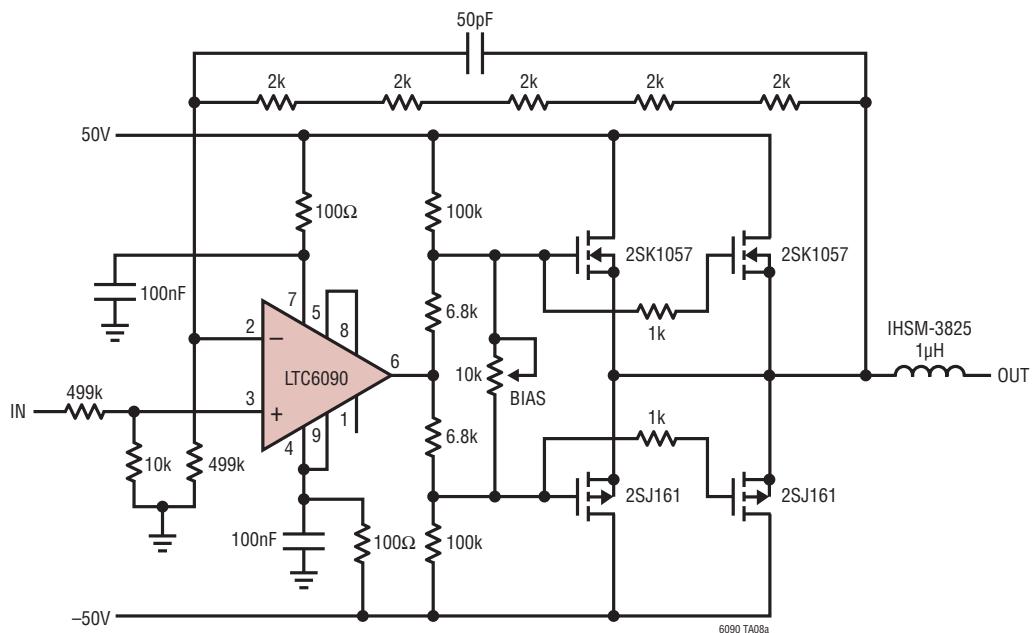

## オーディオ・パワーアンプ

\* USE SEVERAL SERIES RESISTORS TO REDUCE DISTORTION (i.e.  $5 \times 2\text{k}\Omega$ ).

全高調波歪み+ノイズ

アナライザの通過帯域:10Hz～80kHz

# LTC6090/LTC6090-5

## 標準的応用例

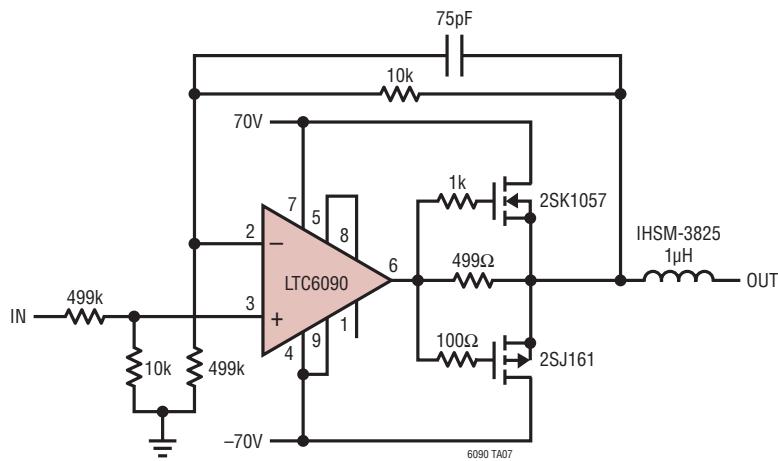

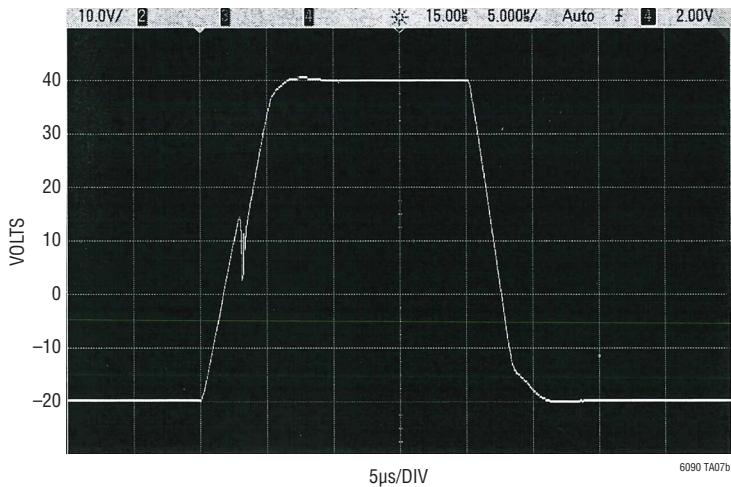

大電流パルス・アンプ

10Ω負荷への60Vステップ応答

## 標準的應用例

## 簡易型の100Wオーディオ・アンプ

SET QUIESCENT SUPPLY CURRENT AT ABOUT 200mA WITH BIAS ADJUSTMENT.

SET QUIESCENT CURRENT TO 100mA IF PARALLEL MOSFETs ARE NOT USED (FOR 8Ω OR HIGHER).

# LTC6090/LTC6090-5

## 標準的応用例

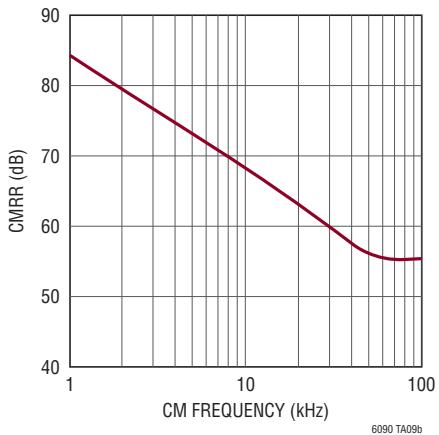

同相範囲の広い利得10の計装用アンプ

入力換算誤差:<1mV(標準)

6090fc

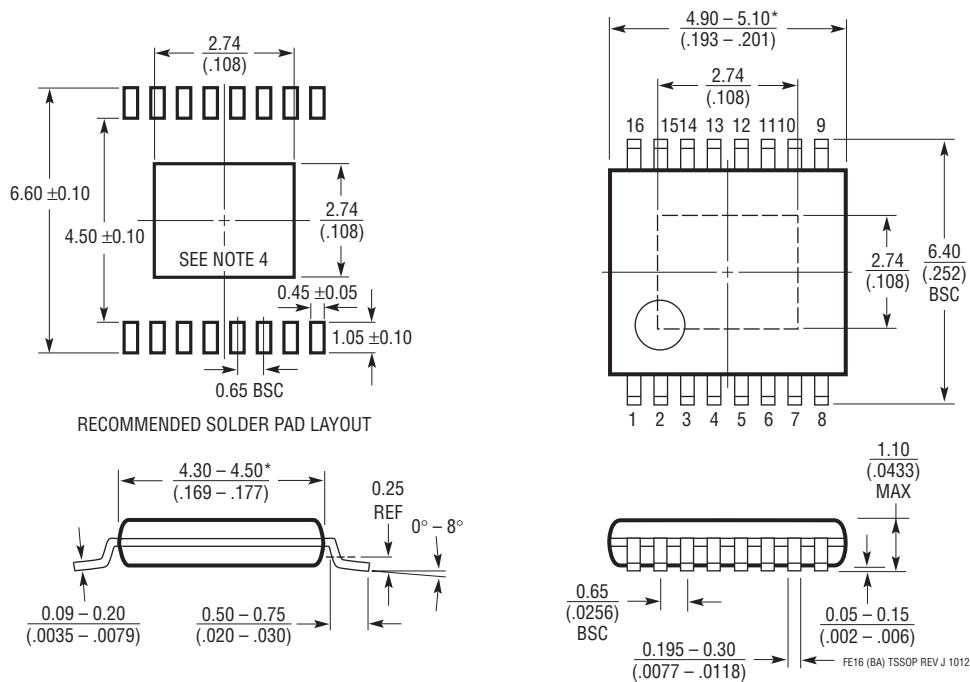

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**FE Package

16-Lead Plastic TSSOP (4.4mm)

(Reference LTC DWG # 05-08-1663 Rev J)

Exposed Pad Variation BA**

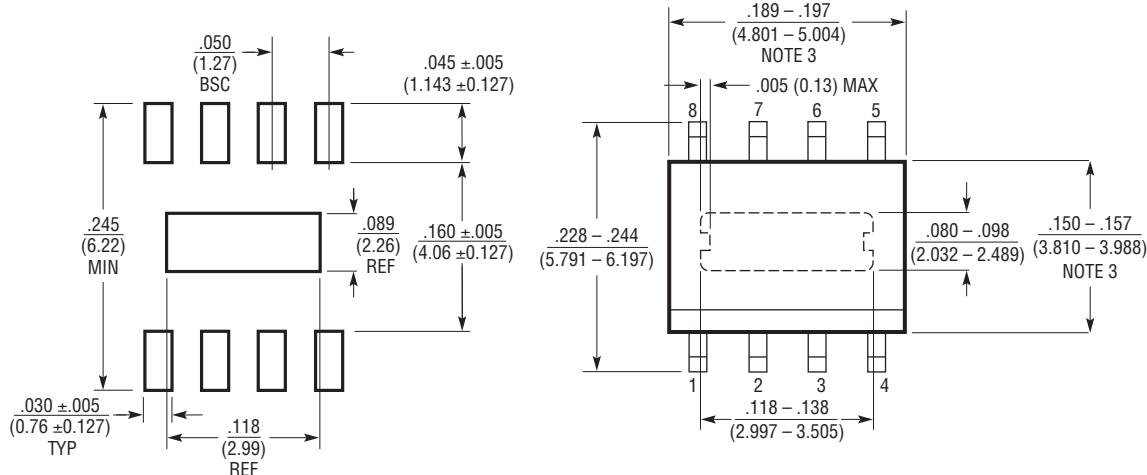

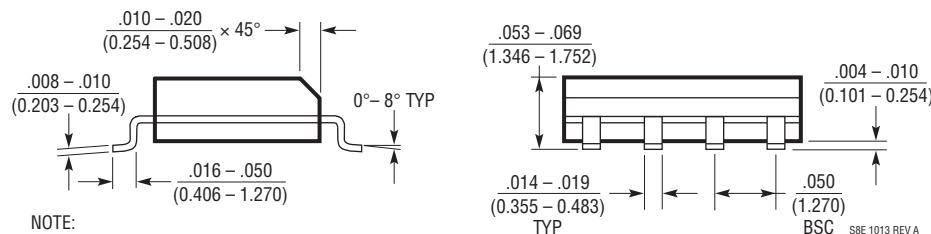

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>を参照してください。

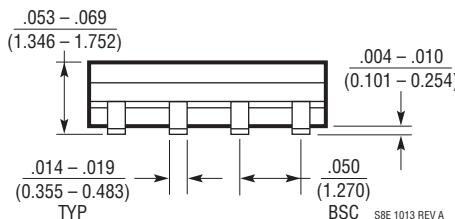

**S8E Package

8-Lead Plastic SOIC (Narrow .150 Inch) Exposed Pad

(Reference LTC DWG # 05-08-1857 Rev A)**

RECOMMENDED SOLDER PAD LAYOUT

NOTE:

1. 寸法はインチ/(ミリメートル)

2. 図は実寸とは異なる

3. これらの寸法にはモールドのバリまたは突出部を含まない

モールドのバリまたは突出部は0.006"(0.15mm)を超えないこと

## 改訂履歴

| REV | 日付    | 概要                   | ページ番号    |

|-----|-------|----------------------|----------|

| A   | 11/12 | ESDに関する記述を追加。        | 2        |

| B   | 9/13  | 図の修正。                | 16、17、18 |

| C   | 6/14  | LTC6090-5の追加、スペックの改良 | 全体       |

# LTC6090/LTC6090-5

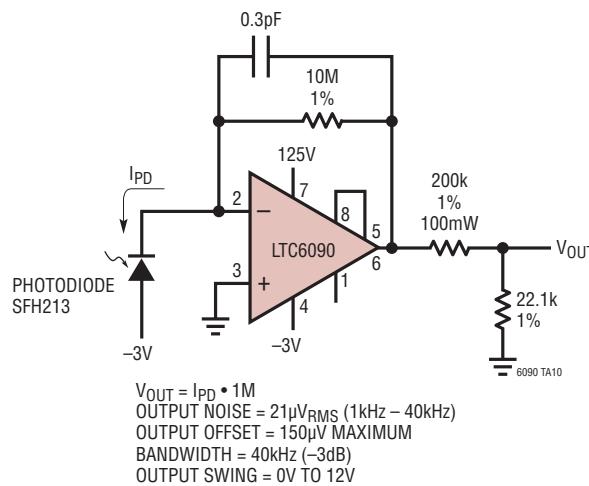

## 標準的応用例

ダイナミックレンジを拡張した1MΩのインピーダンス変換フォトダイオード・アンプ

## 関連製品

| 製品番号                   | 説明                                              | 注釈                                                   |

|------------------------|-------------------------------------------------|------------------------------------------------------|

| <b>アンプ</b>             |                                                 |                                                      |

| LT1990                 | ±250Vの入力電圧範囲、G = 1または10のマイクロパワー差電圧アンプ           | 利得をピンで選択可能: 1または10                                   |

| LT1991                 | 高精度、100µA、利得選択可能アンプ                             | 差電圧アンプ、反転アンプ、および非反転アンプとしてピンで設定可能                     |

| <b>整合した抵抗群</b>         |                                                 |                                                      |

| LT5400                 | 整合したクワッド抵抗回路網                                   | 全温度範囲にわたる優れた整合仕様                                     |

| <b>デジタル/アナログ・コンバータ</b> |                                                 |                                                      |

| LTC2641/LTC2462        | 16ビット電圧出力DAC(3mm×3mm DFN)                       | 全温度範囲で単調性を保証                                         |

| LTC2756                | シリアル18ビットSoftSpan電流出力DAC                        | 18ビットのセトリング時間: 2.1µs<br>18ビットINL誤差の最大値: 全温度範囲で±1 LSB |

| <b>フライバック・コントローラ</b>   |                                                 |                                                      |

| LT3511                 | モノリシック、高電圧、絶縁型フライバック・コンバータ                      | 入力電圧範囲: 4.5V ~ 100V、光カプラ不要                           |

| LT8300                 | 150V/260mAスイッチを備えた100V入力のマイクロパワー絶縁型フライバック・コンバータ | 入力電圧範囲: 6V ~ 100V。1本の外付け抵抗で $V_{OUT}$ を設定            |