# IIP2とDCオフセットを制御する 広帯域IQ復調器

## 特長

- 動作周波数: 400MHz ~ 4GHz

- 高いIIP3: 28.7dBm(700MHz)、25.7dBm(1.95GHz)

- 高いIIP2: 70dBm(700MHz)、60dBm(1.95GHz)

- ユーザが調整可能なIIP2: 最大80dBm

- DCオフセットのゼロ調整をユーザが実行可能

- 高い入力P1dB: 16dBm(1950MHz)

- I/Q帯域幅: 530MHz以上

- イメージ除去比: 43dB(1950MHz)

- ノイズフィギュア: 13.5dB(700MHz)

12.7dB(1.95GHz)

- 変換利得: 2.0dB(700MHz)

2.4dB(1.95GHz)

- トランスを内蔵したシングルエンドのRF

- シャットダウン・モード

- 動作温度範囲( $T_C$ ): -40°C ~ 105°C

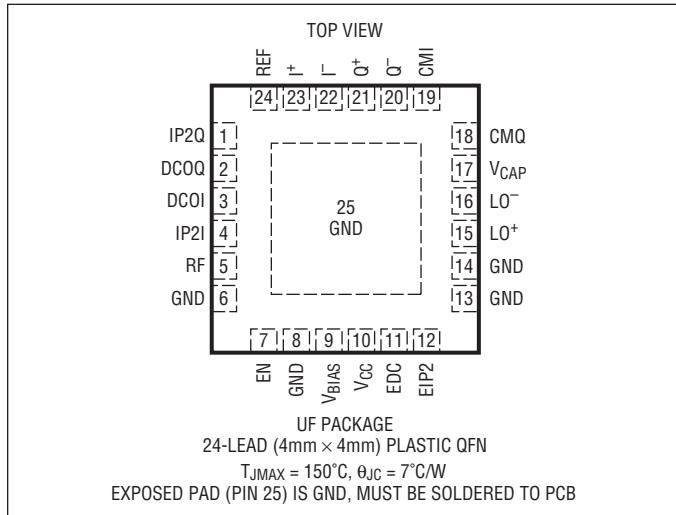

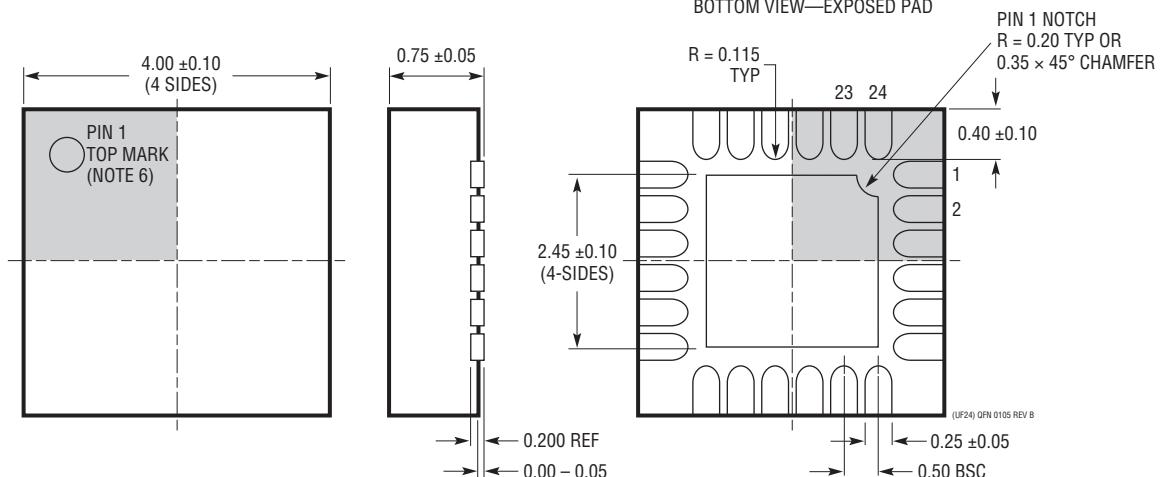

- 4mm×4mmの24ピンQFNパッケージ

## アプリケーション

- LTE/W-CDMA/TD-SCDMA基地局レシーバ

- 広帯域DPDレシーバ

- 2地点間広帯域無線

- 直線性の高い直接変換方式のI/Qレシーバ

- イメージ除去レシーバ

## 概要

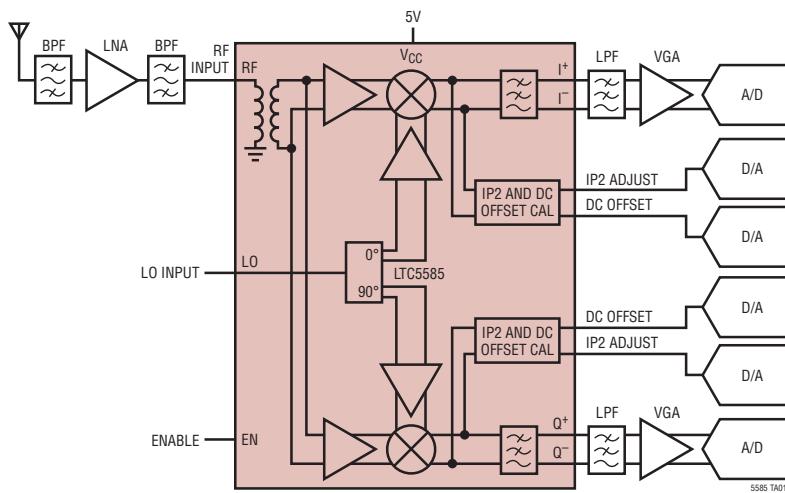

LTC<sup>®</sup>5585は、周波数範囲が400MHz～4GHzの直線性の高いレシーバ・アプリケーション向けに最適化された直接変換方式の直交復調器です。このデバイスは、RF信号をI/Qベースバンド信号に直接変換する、帯域幅が530MHz以上の通信レシーバに適しています。LTC5585は、平衡型I/Qミキサ、LOバッファ・アンプ、および高精度の高周波直交移相器を内蔵しています。広帯域トランスを内蔵しているので、単純な外部LC整合回路を使用して、RF入力でシングルエンドのインターフェースが得られます。さらに、LTC5585はIIP2とDCオフセットを補正するためにアナログ制御電圧インターフェース・ピンを4つ備えているので、システムの較正を大幅に簡略化できます。

LTC5585は直線性が高いので、レシーバに対する優れたスピリアス・フリー・ダイナミックレンジが得られます。この直接変換方式の復調器は、中間周波数(IF)信号処理が不要で、イメージ・フィルタリングやIFフィルタリングに関する対応要件も同様です。これらのI/Q出力は、チャネル選択フィルタ(LPF)またはベースバンド・アンプに直接接続することができます。

**L**、**LT**、**LTC**、**LTM**、**Linear Technology**およびLinearのロゴはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

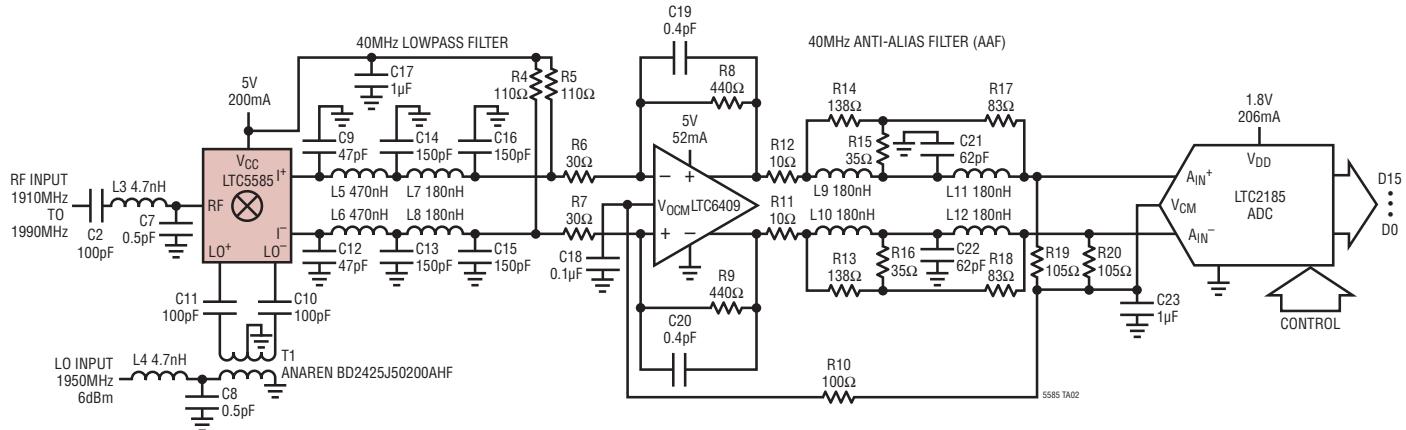

## 標準的応用例

IIP2およびDCオフセット較正付きダイレクトコンバージョン・レシーバ

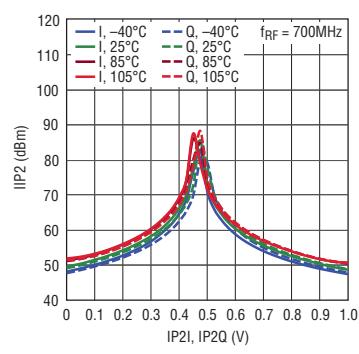

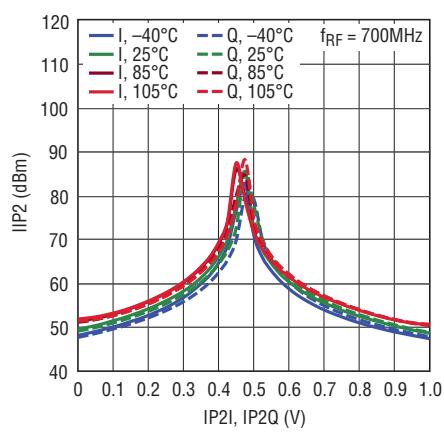

IIP2とIP2I、IP2Qトリム電圧

## 絶対最大定格 (Note 1)

|                                                                             |                                |

|-----------------------------------------------------------------------------|--------------------------------|

| V <sub>CC</sub> 電源電圧                                                        | -0.3V ~ 5.5V                   |

| V <sub>CAP</sub> 電圧                                                         | V <sub>CC</sub> ±0.05V         |

| I <sup>-</sup> 、I <sup>+</sup> 、Q <sup>+</sup> 、Q <sup>-</sup> 、CMI、CMQ の電圧 | 2.5V ~ V <sub>CC</sub> + 0.3V  |

| 他の全てのピンの電圧                                                                  | -0.3V ~ V <sub>CC</sub> + 0.3V |

| L <sub>O</sub> <sup>+</sup> 、L <sub>O</sub> <sup>-</sup> 、RF の入力電力          | 20dBm                          |

| RF 入力の DC 電圧                                                                | ±0.1V                          |

| 最大接合部温度 (T <sub>JMAX</sub> )                                                | 150°C                          |

| 動作温度範囲 (T <sub>c</sub> )                                                    | -40°C ~ 105°C                  |

| 保存温度範囲                                                                      | -65°C ~ 150°C                  |

## ピン配置

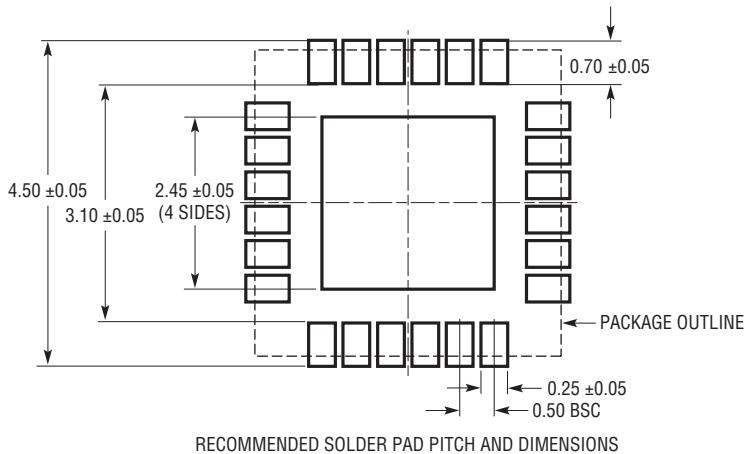

## 発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング | パッケージ                           | 温度範囲           |

|----------------|------------------|---------|---------------------------------|----------------|

| LTC5585IUF#PBF | LTC5585IUF#TRPBF | 5585    | 24-Lead (4mm x 4mm) Plastic QFN | -40°C to 105°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性** 注記がない限り、T<sub>c</sub> = 25°C、V<sub>CC</sub> = 5V、EN = 5V、EDC = EIP2 = 0V、REF = IP2I = IP2Q = DCOI = DCOQ = 0.5V、P<sub>RF</sub> = -5dBm(2トーンのIIP2とIIP3のテストの場合-5dBm/トーン)、P<sub>LO</sub> = 6dBm。(Note 2、3、5、6、9)

| SYMBOL                                                                                                                              | PARAMETER                              | CONDITIONS                                        | MIN        | TYP        | MAX | UNITS |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------|------------|------------|-----|-------|

| f <sub>RF(RANGE)</sub>                                                                                                              | RF Input Frequency Range               | (Note 12)                                         |            | 0.4 to 4.0 |     | GHz   |

| f <sub>LO(RANGE)</sub>                                                                                                              | LO Input Frequency Range               | (Note 12)                                         |            | 0.4 to 4.0 |     | GHz   |

| P <sub>LO(RANGE)</sub>                                                                                                              | LO Input Power Range                   | (Note 12)                                         | 0 to 10    |            |     | dBm   |

| <b>f<sub>RF1</sub> = 700MHz, f<sub>RF2</sub> = 701MHz, f<sub>LO</sub> = 690MHz, L6 = 2.7pF, C19 = 1.0pF, L5 = 12nH, C14 = 5.6pF</b> |                                        |                                                   |            |            |     |       |

| f <sub>RF(MATCH)</sub>                                                                                                              | RF Input Frequency Range               | Return Loss > 10dB                                | 680 to 870 |            |     | MHz   |

| f <sub>LO(MATCH)</sub>                                                                                                              | LO Input Frequency Range               | Return Loss > 10dB                                | 690 to 820 |            |     | MHz   |

| G <sub>V</sub>                                                                                                                      | Voltage Conversion Gain                | Loaded with 100Ω Pull-Up (Note 8)                 | 2.0        |            |     | dB    |

| NF                                                                                                                                  | Noise Figure                           | Double-Side Band (Note 4)                         | 13.5       |            |     | dB    |

| NFBLOCKING                                                                                                                          | Noise Figure Under Blocking Conditions | Double-Side Band, P <sub>RF</sub> = 0dBm (Note 7) | 15.5       |            |     | dB    |

| IIP3                                                                                                                                | Input 3rd Order Intercept              |                                                   | 28.7       |            |     | dBm   |

| IIP2                                                                                                                                | Input 2nd Order Intercept              | Unadjusted, EIP2 = 0V                             | 70         |            |     | dBm   |

| IIP2 <sub>OPT</sub>                                                                                                                 | Optimized Input 2nd Order Intercept    | EIP2 = 5V, IP2I, IP2Q Adjusted for Minimum IM2    | 80         |            |     | dBm   |

| P1dB                                                                                                                                | Input 1dB Compression                  |                                                   | 16         |            |     | dBm   |

| DCOFFSET                                                                                                                            | DC Offset at I/Q Outputs               | Unadjusted, EDC = 0V (Note 13)                    | 4          |            |     | mV    |

| ΔG                                                                                                                                  | I/Q Gain Mismatch                      |                                                   | 0.05       |            |     | dB    |

| Δφ                                                                                                                                  | I/Q Phase Mismatch                     |                                                   | 0.3        |            |     | Deg   |

**電気的特性** 注記がない限り、 $T_C = 25^\circ\text{C}$ 、 $V_{CC} = 5\text{V}$ 、 $EN = 5\text{V}$ 、 $EDC = EIP2 = 0\text{V}$ 、 $REF = IP2I = IP2Q = DCOI = DCQ = 0.5\text{V}$ 、 $P_{RF} = -5\text{dBm}$ (2トーンのIIP2とIIP3のテストの場合-5dBm/トーン)、 $P_{LO} = 6\text{dBm}$ 。(Note 2, 3, 5, 6, 9)

| SYMBOL | PARAMETER             | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------|-----------------------|------------|-----|-----|-----|-------|

| IRR    | Image Rejection Ratio | (Note 10)  | 48  |     |     | dB    |

| LO-RF  | LO to RF Leakage      |            | -64 |     |     | dBm   |

| RF-LO  | RF to LO Isolation    |            | 60  |     |     | dB    |

$f_{RF1} = 1950\text{MHz}$ ,  $f_{RF2} = 1951\text{MHz}$ ,  $f_{LO} = 1940\text{MHz}$ ,  $L6 = 1.2\text{pF}$ ,  $C19 = 5.1\text{nH}$ ,  $L5 = 1.0\text{pF}$ ,  $C13 = 5.1\text{nH}$

|                      |                                     |                                                               |              |  |     |

|----------------------|-------------------------------------|---------------------------------------------------------------|--------------|--|-----|

| $f_{RF(MATCH)}$      | RF Input Frequency Range            | Return Loss > 10dB                                            | 1.6 to 2.1   |  | GHz |

| $f_{LO(MATCH)}$      | LO Input Frequency Range            | Return Loss > 10dB                                            | 1.85 to 2.05 |  | GHz |

| $G_V$                | Voltage Conversion Gain             | Loaded with $100\Omega$ Pull-Up (Note 8)                      | 2.4          |  | dB  |

| NF                   | Noise Figure                        | Double-Side Band (Note 4)                                     | 12.7         |  | dB  |

| IIP3                 | Input 3rd Order Intercept           |                                                               | 25.7         |  | dBm |

| IIP2                 | Input 2nd Order Intercept           | Unadjusted, $EIP2 = 0\text{V}$                                | 60           |  | dBm |

| IIP2 <sub>OPT</sub>  | Optimized Input 2nd Order Intercept | $EIP2 = 5\text{V}$ , $IP2I$ , $IP2Q$ Adjusted for Minimum IM2 | 80           |  | dBm |

| P1dB                 | Input 1dB Compression               |                                                               | 16           |  | dBm |

| DC <sub>OFFSET</sub> | DC Offset at I/Q Outputs            | Unadjusted, $EDC = 0\text{V}$ (Note 13)                       | 7            |  | mV  |

| $\Delta G$           | I/Q Gain Mismatch                   |                                                               | 0.05         |  | dB  |

| $\Delta \phi$        | I/Q Phase Mismatch                  |                                                               | 0.7          |  | Deg |

| IRR                  | Image Rejection Ratio               | (Note 10)                                                     | 43           |  | dB  |

| LO-RF                | LO to RF Leakage                    |                                                               | -49          |  | dBm |

| RF-LO                | RF to LO Isolation                  |                                                               | 58           |  | dB  |

$f_{RF1} = 2150\text{MHz}$ ,  $f_{RF2} = 2151\text{MHz}$ ,  $f_{LO} = 2140\text{MHz}$ ,  $C17 = 1.5\text{pF}$ ,  $L6 = 4.7\text{nH}$ ,  $C19 = 0.5\text{pF}$ ,  $L5 = 5.1\text{nH}$ ,  $C14 = 0.7\text{pF}$

|                        |                                        |                                                               |              |  |     |

|------------------------|----------------------------------------|---------------------------------------------------------------|--------------|--|-----|

| $f_{RF(MATCH)}$        | RF Input Frequency Range               | Return Loss > 10dB                                            | 2.03 to 2.36 |  | GHz |

| $f_{LO(MATCH)}$        | LO Input Frequency Range               | Return Loss > 10dB                                            | 2.05 to 2.18 |  | GHz |

| $G_V$                  | Voltage Conversion Gain                | Loaded with $100\Omega$ Pull-Up (Note 8)                      | 2.3          |  | dB  |

| NF                     | Noise Figure                           | Double-Side Band (Note 4)                                     | 13.0         |  | dB  |

| NF <sub>BLOCKING</sub> | Noise Figure Under Blocking Conditions | Double-Side Band, $P_{RF} = 0\text{dBm}$ (Note 7)             | 14.6         |  | dB  |

| IIP3                   | Input 3rd Order Intercept              |                                                               | 25.9         |  | dBm |

| IIP2                   | Input 2nd Order Intercept              | Unadjusted, $EIP2 = 0\text{V}$                                | 56           |  | dBm |

| IIP2 <sub>OPT</sub>    | Optimized Input 2nd Order Intercept    | $EIP2 = 5\text{V}$ , $IP2I$ , $IP2Q$ Adjusted for Minimum IM2 | 80           |  | dBm |

| P1dB                   | Input 1dB Compression                  |                                                               | 15           |  | dBm |

| DC <sub>OFFSET</sub>   | DC Offset at I/Q Outputs               | Unadjusted, $EDC = 0\text{V}$ (Note 13)                       | 6            |  | mV  |

| $\Delta G$             | I/Q Gain Mismatch                      |                                                               | 0.05         |  | dB  |

| $\Delta \phi$          | I/Q Phase Mismatch                     |                                                               | 1.0          |  | Deg |

| IRR                    | Image Rejection Ratio                  | (Note 10)                                                     | 40           |  | dB  |

| LO-RF                  | LO to RF Leakage                       |                                                               | -50          |  | dBm |

| RF-LO                  | RF to LO Isolation                     |                                                               | 60           |  | dB  |

$f_{RF1} = 2600\text{MHz}$ ,  $f_{RF2} = 2601\text{MHz}$ ,  $f_{LO} = 2590\text{MHz}$ ,  $C17 = 0.5\text{pF}$ ,  $L6 = 2.7\text{nH}$ ,  $L5 = 1.2\text{nH}$ ,  $C14 = 1\text{pF}$

|                        |                                        |                                                               |              |  |     |

|------------------------|----------------------------------------|---------------------------------------------------------------|--------------|--|-----|

| $f_{RF(MATCH)}$        | RF Input Frequency Range               | Return Loss > 10dB                                            | 2.35 to 3.1  |  | GHz |

| $f_{LO(MATCH)}$        | LO Input Frequency Range               | Return Loss > 10dB                                            | 2.47 to 2.65 |  | GHz |

| $G_V$                  | Voltage Conversion Gain                | Loaded with $100\Omega$ Pull-Up (Note 8)                      | 2.3          |  | dB  |

| NF                     | Noise Figure                           | Double-Side Band (Note 4)                                     | 13.6         |  | dB  |

| NF <sub>BLOCKING</sub> | Noise Figure Under Blocking Conditions | Double-Side Band, $P_{RF} = 0\text{dBm}$ (Note 7)             | 15.2         |  | dB  |

| IIP3                   | Input 3rd Order Intercept              |                                                               | 27.5         |  | dBm |

| IIP2                   | Input 2nd Order Intercept              | Unadjusted, $EIP2 = 0\text{V}$                                | 60           |  | dBm |

| IIP2 <sub>OPT</sub>    | Minimum Input 2nd Order Intercept      | $EIP2 = 5\text{V}$ , $IP2I$ , $IP2Q$ Adjusted for Minimum IM2 | 80           |  | dBm |

| P1dB                   | Input 1dB Compression                  |                                                               | 15.5         |  | dBm |

| DC <sub>OFFSET</sub>   | DC Offset at I/Q Outputs               | Unadjusted, $EDC = 0\text{V}$ (Note 13)                       | 8            |  | mV  |

5585fb

**電気的特性** 注記がない限り、 $T_C = 25^\circ\text{C}$ 、 $V_{CC} = 5\text{V}$ 、 $EN = 5\text{V}$ 、 $EDC = EIP2 = 0\text{V}$ 、 $REF = IP2I = IP2Q = DCOI = DCOQ = 0.5\text{V}$ 、 $P_{RF} = -5\text{dBm}$ (2トーンのIIP2とIIP3のテストの場合-5dBm/トーン)、 $P_{LO} = 6\text{dBm}$ 。(Note 2, 3, 5, 6, 9)

| SYMBOL        | PARAMETER             | CONDITIONS | MIN  | TYP | MAX | UNITS |

|---------------|-----------------------|------------|------|-----|-----|-------|

| $\Delta G$    | I/Q Gain Mismatch     |            | 0.05 |     |     | dB    |

| $\Delta \phi$ | I/Q Phase Mismatch    |            | 1.0  |     |     | Deg   |

| IRR           | Image Rejection Ratio | (Note 10)  | 40   |     |     | dB    |

| LO-RF         | LO to RF Leakage      |            | -46  |     |     | dBm   |

| RF-LO         | RF to LO Isolation    |            | 55   |     |     | dB    |

$f_{RF1} = 3500\text{MHz}$ ,  $f_{RF2} = 3501\text{MHz}$ ,  $f_{LO} = 3490\text{MHz}$ ,  $C17 = 0.6\text{pF}$ ,  $L6 = 1.0\text{nH}$ ,  $C13 = 0.7\text{pF}$ ,  $L5 = \text{Short}$ ,  $C14 = \text{Open}$ , Single-Ended LO(図14参照)

|                      |                                   |                                                               |              |  |     |

|----------------------|-----------------------------------|---------------------------------------------------------------|--------------|--|-----|

| $f_{RF(MATCH)}$      | RF Input Frequency Range          | Return Loss > 10dB                                            | 2.88 to 3.97 |  | GHz |

| $f_{LO(MATCH)}$      | LO Input Frequency Range          | Return Loss > 10dB                                            | 2.97 to 3.96 |  | GHz |

| $G_V$                | Voltage Conversion Gain           | Loaded with $100\Omega$ Pull-Up (Note 8)                      | 0.3          |  | dB  |

| NF                   | Noise Figure                      | Double-Side Band (Note 4)                                     | 17.1         |  | dB  |

| IIP3                 | Input 3rd Order Intercept         |                                                               | 28.1         |  | dBm |

| IIP2                 | Input 2nd Order Intercept         | Unadjusted, $EIP2 = 0\text{V}$                                | 52.5         |  | dBm |

| IIP2 <sub>OPT</sub>  | Minimum Input 2nd Order Intercept | $EIP2 = 5\text{V}$ , $IP2I$ , $IP2Q$ Adjusted for Minimum IM2 | 65.9         |  | dBm |

| P1dB                 | Input 1dB Compression             |                                                               | 17.1         |  | dBm |

| DC <sub>OFFSET</sub> | DC Offset at I/Q Outputs          | Unadjusted, $EDC = 0\text{V}$ (Note 13)                       | 16.5         |  | mV  |

| $\Delta G$           | I/Q Gain Mismatch                 |                                                               | 0.04         |  | dB  |

| $\Delta \phi$        | I/Q Phase Mismatch                |                                                               | 1.8          |  | Deg |

| IRR                  | Image Rejection Ratio             | (Note 10)                                                     | 36           |  | dB  |

| LO-RF                | LO to RF Leakage                  |                                                               | -34.7        |  | dBm |

| RF-LO                | RF to LO Isolation                |                                                               | 44.5         |  | dB  |

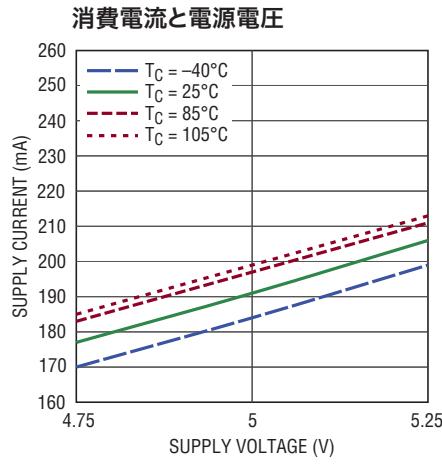

## 電源および他のパラメータ

|                         |                                          |                                                      |                 |     |                              |    |

|-------------------------|------------------------------------------|------------------------------------------------------|-----------------|-----|------------------------------|----|

| $V_{CC}$                | Supply Voltage                           |                                                      | 4.75            | 5.0 | 5.25                         | V  |

| $I_{CC}$                | Supply Current                           | $EDC = EIP2 = 5\text{V}$                             | 180             | 200 | 220                          | mA |

| $I_{CC(\text{LOW})}$    | Supply Current                           | $EDC = EIP2 = 0\text{V}$                             | 170             | 190 | 210                          | mA |

| $I_{CC(\text{OFF})}$    | Shutdown Current                         | $EN < 0.3\text{V}$                                   | 11              | 900 | $\mu\text{A}$                |    |

| $t_{ON}$                | Turn-On Time                             | EN Transition from Logic Low to High (Note 14)       | 0.2             |     | $\mu\text{s}$                |    |

| $t_{OFF}$               | Turn-Off Time                            | EN Transition from Logic High to Low (Note 15)       | 0.8             |     | $\mu\text{s}$                |    |

| $V_{EH}$                | EN, EDC, EIP2 Input High Voltage (On)    |                                                      | 2.0             |     | V                            |    |

| $V_{EL}$                | EN, EDC, EIP2 Input Low Voltage (Off)    |                                                      | 0.3             |     | V                            |    |

| $I_{ENH}$               | EN Pin Input Current                     | $EN = 5.0\text{V}$                                   | 52              |     | $\mu\text{A}$                |    |

| $I_{EDCH}$              | EDC Pin Input Current                    | $EDC = 5.0\text{V}$                                  | 33              |     | $\mu\text{A}$                |    |

| $I_{EIP2H}$             | EIP2 Pin Input Current                   | $EIP2 = 5.0\text{V}$                                 | 50              |     | $\mu\text{A}$                |    |

| $V_{REF}$               | REF Pin Voltage                          | With REF Pin Unloaded                                | 0.5             |     | V                            |    |

| $V_{REF(\text{RANGE})}$ | REF Pin Voltage Range                    | When Driven with External Source                     | 0.4 to 0.7      |     | V                            |    |

| $Z_{REF}$               | REF Input Impedance                      | (Note 11)                                            | 2  1            |     | $\text{k}\Omega  \text{pF}$  |    |

|                         | DCOI, DCOQ, IP2I, IP2Q Pin Voltage       | Unloaded                                             | 0.5             |     | V                            |    |

|                         | DCOI, DCOQ, IP2I, IP2Q Voltage Range     | When Driven with External Source                     | 0 to $2V_{REF}$ |     | V                            |    |

|                         | DCOI, DCOQ, IP2I, IP2Q Impedance         | (Note 11)                                            | 8  1            |     | $\text{k}\Omega  \text{pF}$  |    |

|                         | DCOI, DCOQ, IP2I, IP2Q Settling Time     | For Step Input, Output with 90% of Final Value       | 20              |     | ns                           |    |

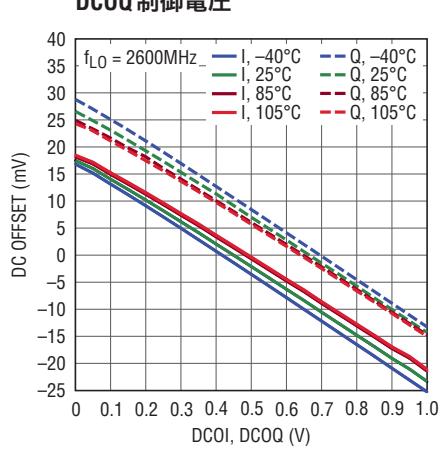

|                         | DC Offset Adjustment Range               | DCOI, DCOQ Swept from 0V to 1V, $EDC = 5\text{V}$    | $\pm 20$        |     | mV                           |    |

|                         | DC Offset Drift Over Temperature         | Unadjusted, $EDC = 0\text{V}$                        | 20              |     | $\mu\text{V}/^\circ\text{C}$ |    |

| $V_{CM}$                | $I^+, I^-, Q^+, Q^-$ Common Mode Voltage |                                                      | $V_{CC} - 1.5$  |     | V                            |    |

| $Z_{OUT}$               | $I^+, I^-, Q^+, Q^-$ Output Impedance    | Single Ended                                         | 100  6          |     | $\Omega  \text{pF}$          |    |

| $BW_{BB}$               | $I^+, I^-, Q^+, Q^-$ Output Bandwidth    | 100 $\Omega$ External Pull-Up, -3dB Corner Frequency | 530             |     | MHz                          |    |

## 電気的特性

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

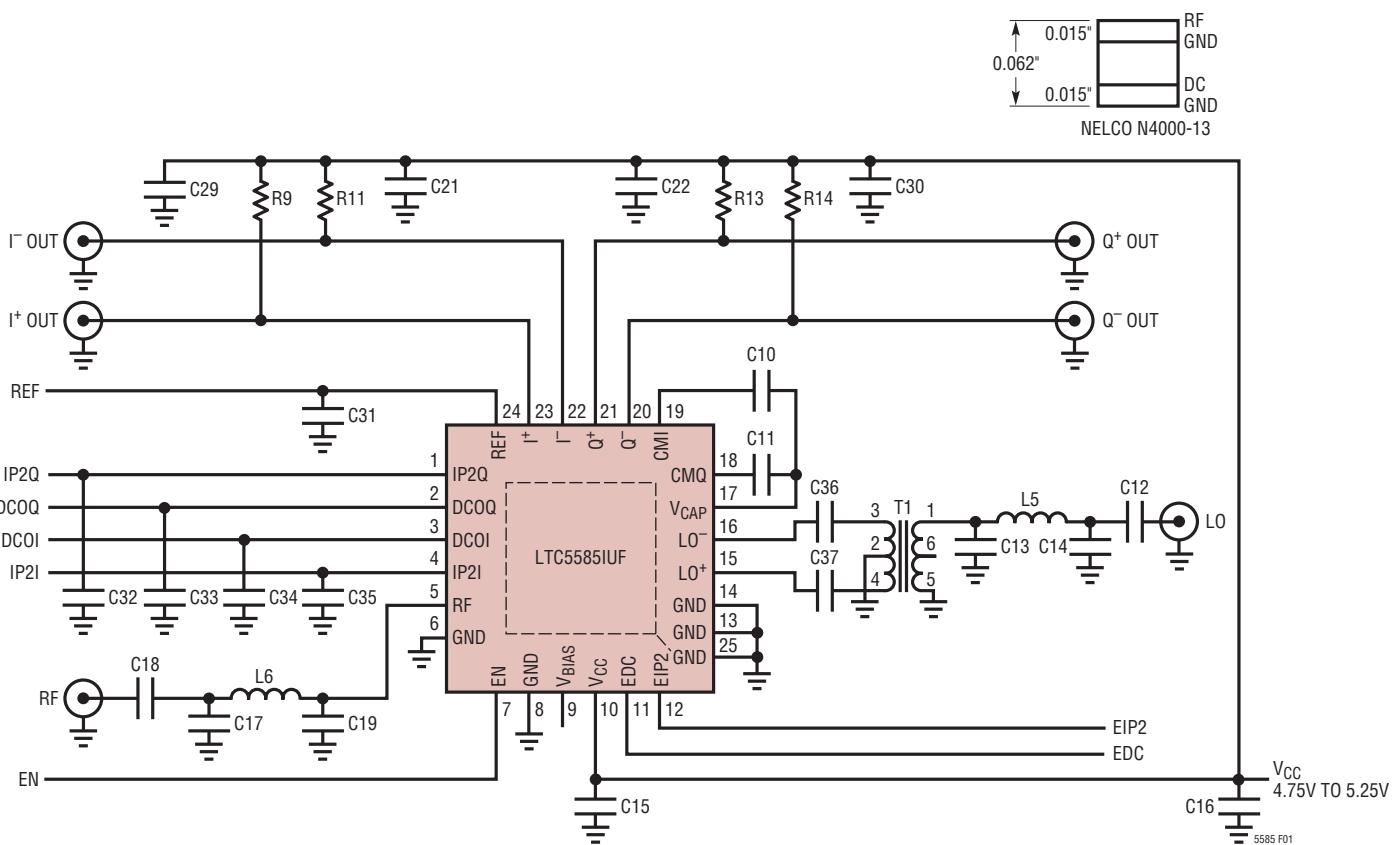

**Note 2:** テストは図1のテスト回路で行われる。

**Note 3:** LTC5585は-40°C～105°Cのケース温度の動作範囲で動作することが保証されている。

**Note 4:** DSBノイズフィギュアは、小信号雑音源を使い、RF入力にはフィルタを使わず、他のRF信号を与えず、15MHzのベースバンド周波数で測定される。

**Note 5:** 示されているRF周波数での性能は、図1の表に示されている、RFおよびL0の外部インピーダンス整合を使って測定される。

**Note 6:** 相補出力(I<sup>+</sup>、I<sup>-</sup>、およびQ<sup>+</sup>、Q<sup>-</sup>)は、180°の位相シフト・コンバインを使って結合される。

**Note 7:** ブロッキング状態のノイズフィギュア(NFBLOCKING)は、f<sub>L0</sub>+1MHzのRF入力信号を使い、60MHzの出力周波数で測定される。RFとL0の両方の入力信号は、ベースバンド出力とともに、適切なフィルタを通す。NFBLOCKINGは、840MHz、2140MHz、および2500MHzのみで測定。

**Note 8:** 電圧変換利得は、(図1のテスト回路を使って測定される)|出力とQ出力の平均電力変換利得から計算される。電力変換利得は、|出力とQ出力に100Ωの差動負荷インピーダンスを使って測定される。

**Note 9:** 図1のテスト回路に示されているように、ベースバンド出力はV<sub>CC</sub>への100Ω外部ブルアップ抵抗を備えている。

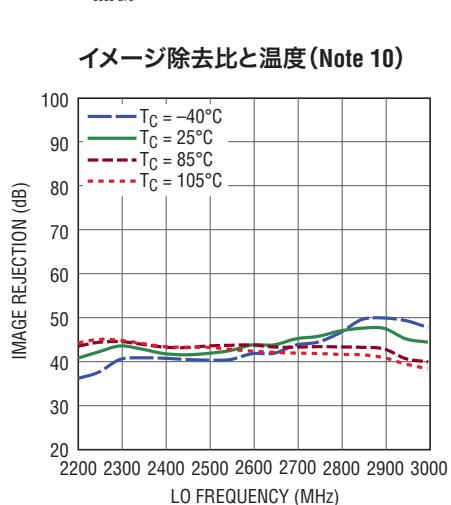

**Note 10:** イメージ除去比は、付録に載せてある方法を使って測定された利得誤差と位相誤差から計算される。

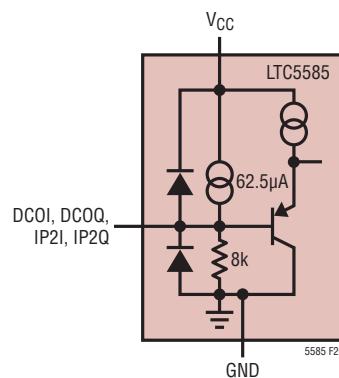

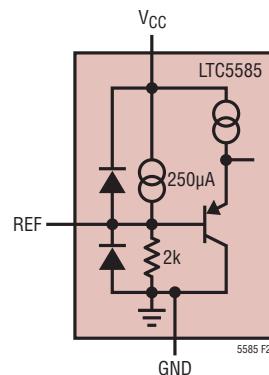

**Note 11:** DCO1、DCOQ、IP2I、IP2Qの各ピンにはグランドへの8k内部抵抗が備わっている。REFピンにはグランドへの2k内部抵抗が備わっている。これらのピンは、未接続状態では内部電流源を介して500mVまでフロートする。これらのピンをドライブするには出力抵抗が小さい電圧源を推奨します。

**Note 12:** これは推奨動作範囲であり、示されている範囲の外側の動作は可能だが、パラメータによっては性能が低下する。

**Note 13:** I<sup>+</sup>とI<sup>-</sup>の間、およびQ<sup>+</sup>とQ<sup>-</sup>の間で差動で測定したDCオフセット。示されている値は特性評価データの分布の絶対値の平均である。

**Note 14:** ベースバンド振幅は最終値の10%以内である。

**Note 15:** ベースバンド振幅はそのオン状態より少なくとも30dB低い。

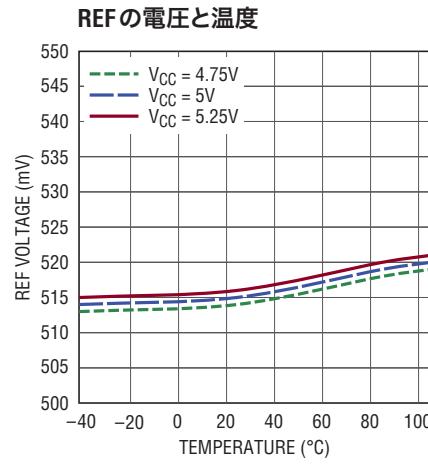

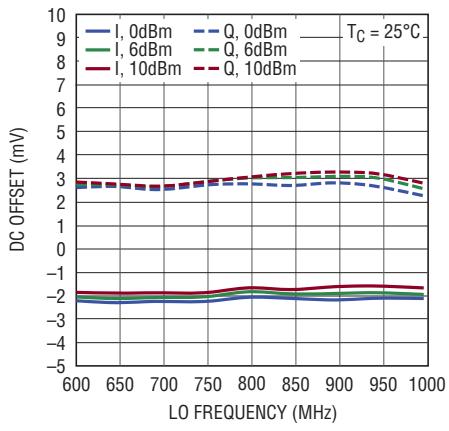

**DC 性能特性** EN = 5V、EDC = 0V および EIP2 = 0V。図1に示されているテスト回路。

5585 G01

5585 G02

## 標準的性能特性

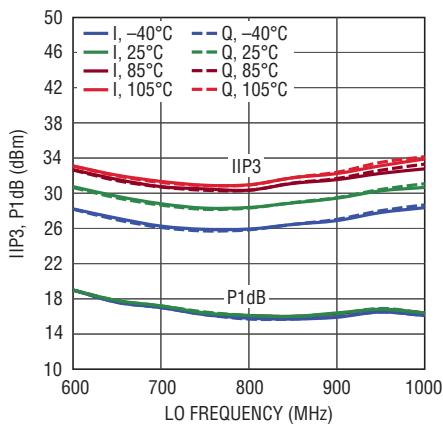

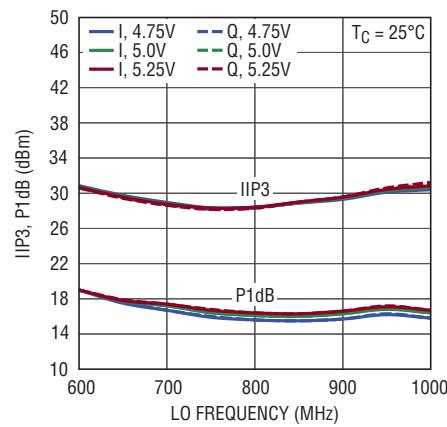

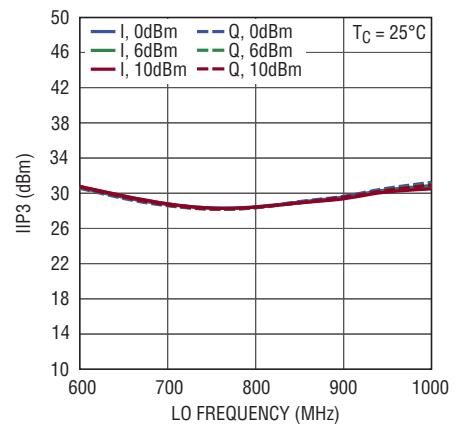

700MHzアプリケーション。注記がない限り、V<sub>CC</sub> = 5V、EN = 5V、EDC = 0V、EIP2 = 0V、REF = 0.5V、T<sub>C</sub> = 25°C、P<sub>LO</sub> = 6dBm、f<sub>LO</sub> = 690MHz、f<sub>RF1</sub> = 700MHz、f<sub>RF2</sub> = 701MHz、f<sub>BB</sub> = 10MHz、P<sub>RF1</sub> = P<sub>RF2</sub> = -5dBm、ベースバンド出力のDCブロックおよびミニ回路PSCJ-2-1 180°コンバインナの影響は測定から除かれている。図1のようにRFポートとLOポートのインピーダンスが整合しているテスト回路。

### IIP3、P1dB と 温度 (T<sub>C</sub>)

5585 G03

### IIP3、P1dB と 電源電圧 (V<sub>CC</sub>)

5585 G04

### IIP3 と LO の 電力

5585 G05

## 標準的性能特性

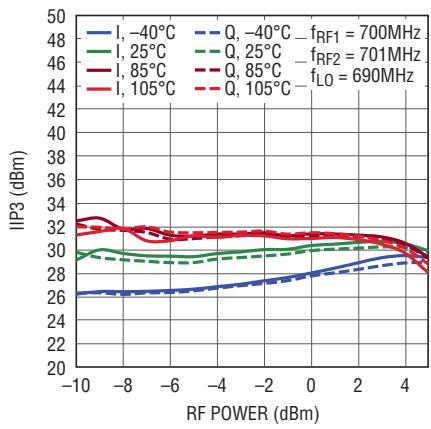

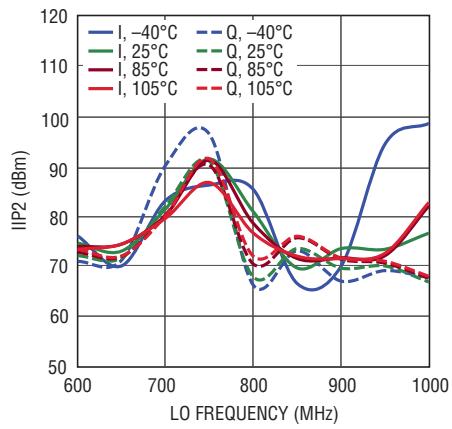

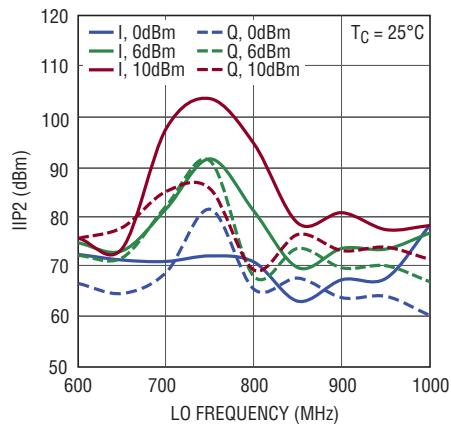

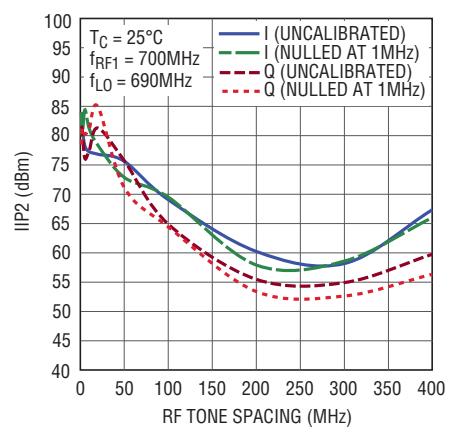

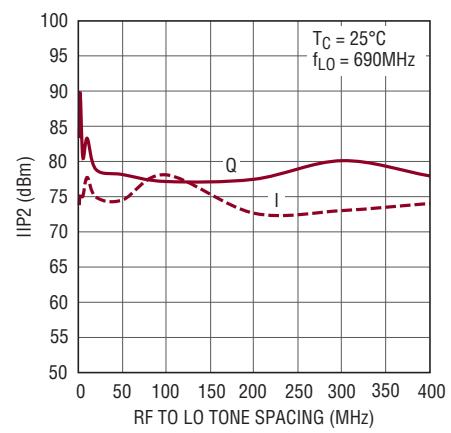

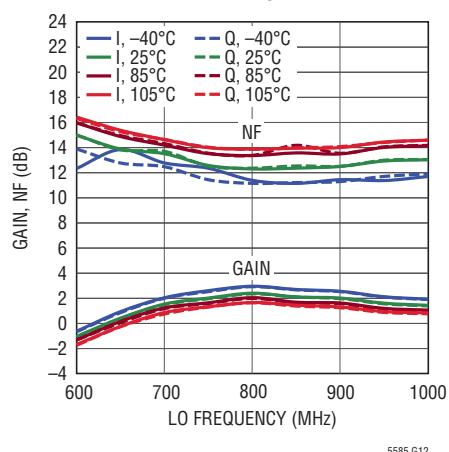

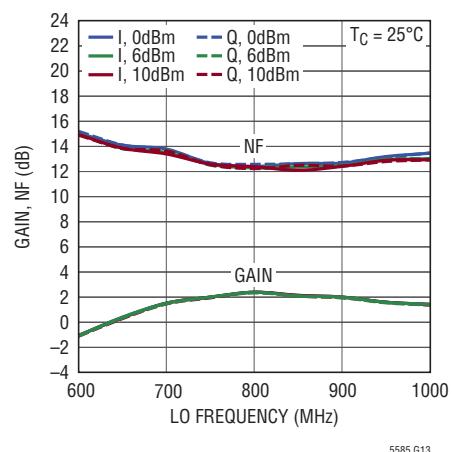

700MHzアプリケーション。注記がない限り、 $V_{CC} = 5V$ 、 $EN = 5V$ 、 $EDC = 0V$ 、 $EIP2 = 0V$ 、 $REF = 0.5V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 6dBm$ 、 $f_{LO} = 690MHz$ 、 $f_{RF1} = 700MHz$ 、 $f_{RF2} = 701MHz$ 、 $f_{BB} = 10MHz$ 、 $P_{RF1} = P_{RF2} = -5dBm$ 、ベースバンド出力のDCブロックおよびミニ回路PSCJ-2-1 180°コンバインナの影響は測定から除かれている。図1のようにRFポートとLOポートのインピーダンスが整合しているテスト回路。

2トーンIIP3とRF電力

未較正のIIP2と温度( $T_C$ )

未較正のIIP2とLO電力

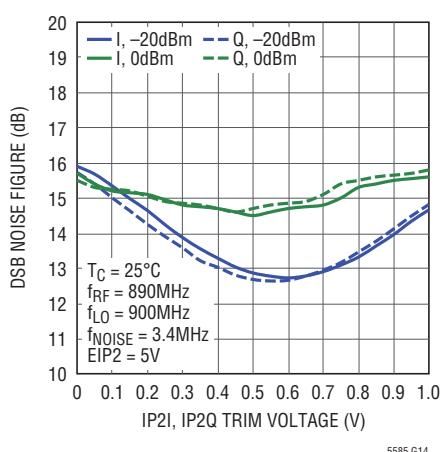

IIP2とIP2I, IP2Qトリム電圧

IIP2とRFトーンの間隔

2x2 Half-IF IIP2とRFからLOへのトーン間隔

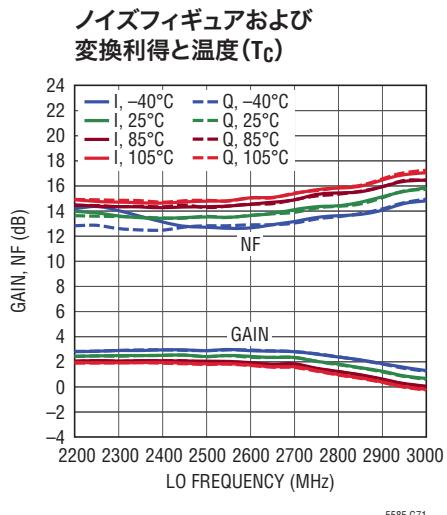

ノイズフィギュアおよび変換利得と温度( $T_C$ )

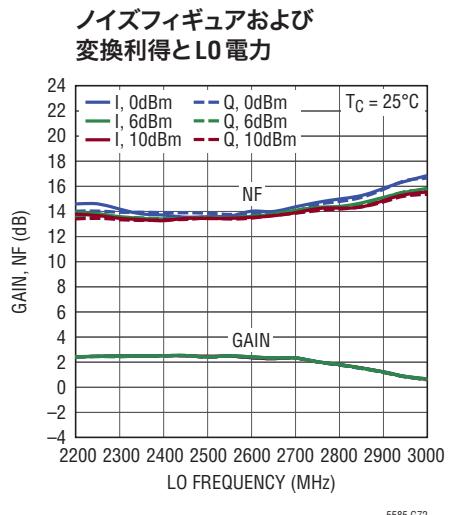

ノイズフィギュアおよび変換利得とLO電力

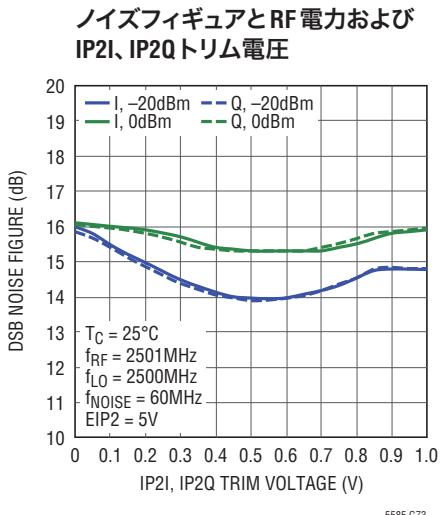

ノイズフィギュアとRF電力およびIP2I, IP2Qトリム電圧

## 標準的性能特性

700MHzアプリケーション。注記がない限り、 $V_{CC} = 5V$ 、 $EN = 5V$ 、 $EDC = 0V$ 、 $EIP2 = 0V$ 、 $REF = 0.5V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 6dBm$ 、 $f_{LO} = 690MHz$ 、 $f_{RF1} = 700MHz$ 、 $f_{RF2} = 701MHz$ 、 $f_{BB} = 10MHz$ 、 $P_{RF1} = P_{RF2} = -5dBm$ 、ベースバンド出力のDCブロックおよびミニ回路PSCJ-2-1 180°コンバイナの影響は測定から除かれている。図1のようにRFポートとLOポートのインピーダンスが整合しているテスト回路。

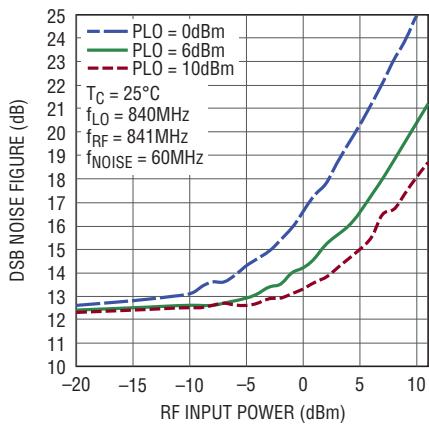

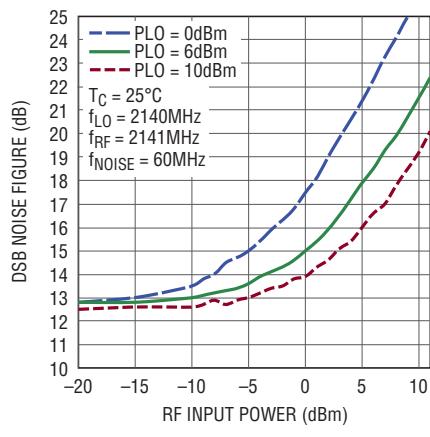

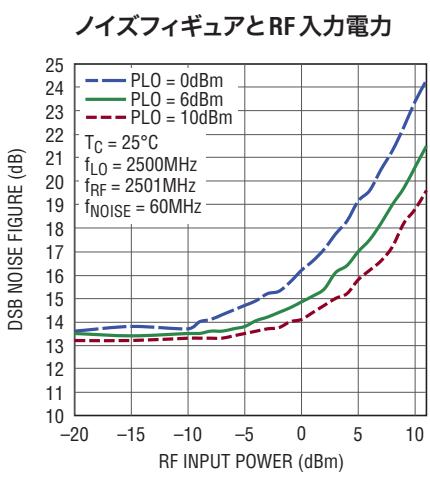

ノイズフィギュアとRF入力電力

( $f_{NOISE} = 60MHz$ )

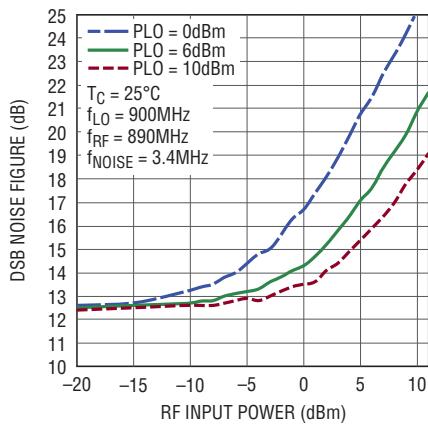

ノイズフィギュアとRF入力電力

( $f_{NOISE} = 3.4MHz$ )

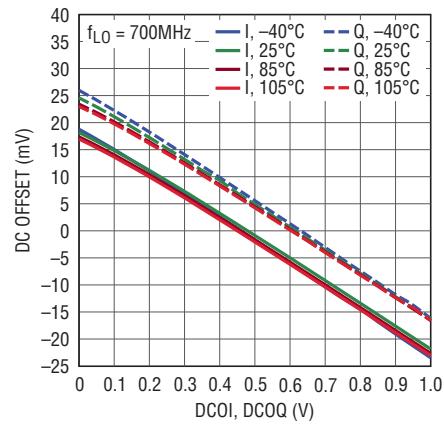

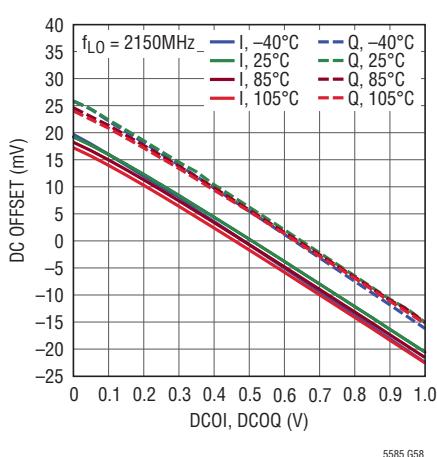

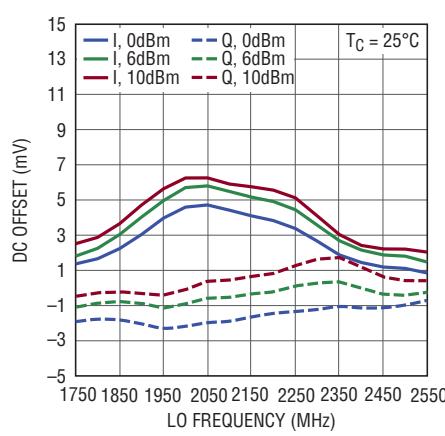

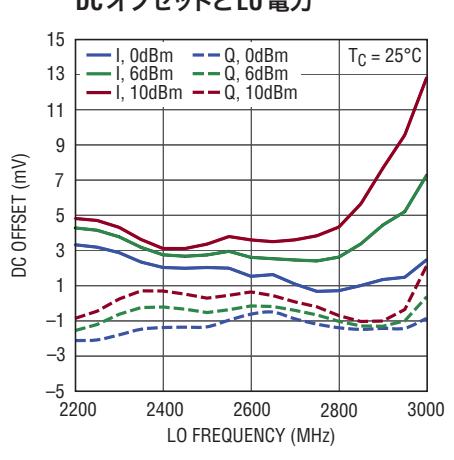

DCオフセットとDCOI、

DCOQ制御電圧

DCオフセットとLO電力

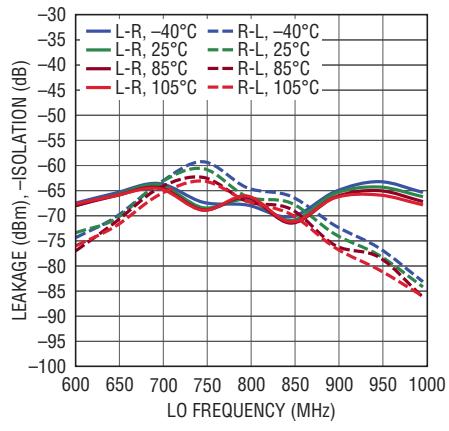

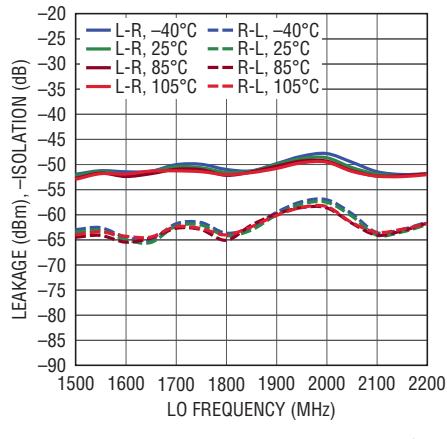

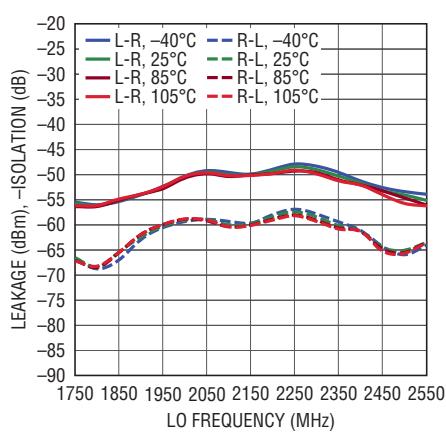

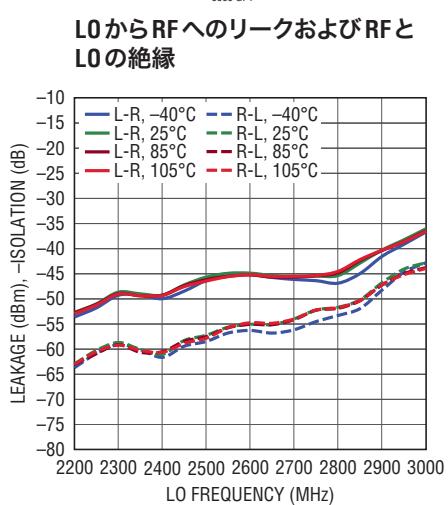

LOからRFへのリークおよび

RFとLOの絶縁

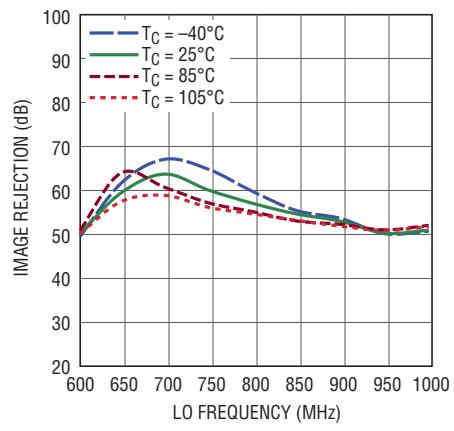

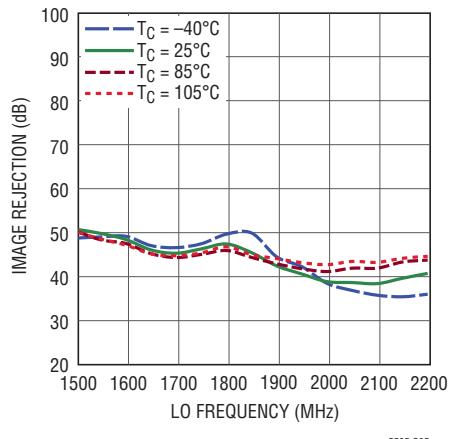

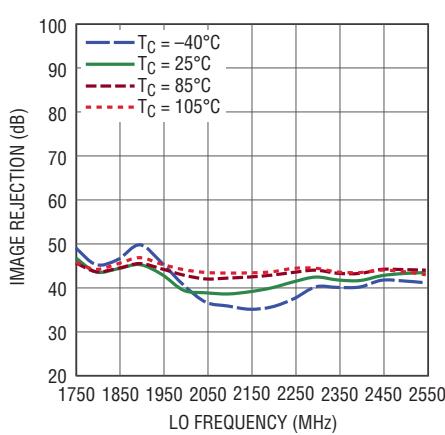

イメージ除去比と温度(Note 10)

## 標準的性能特性

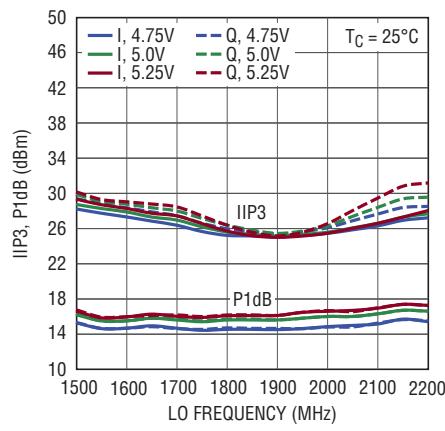

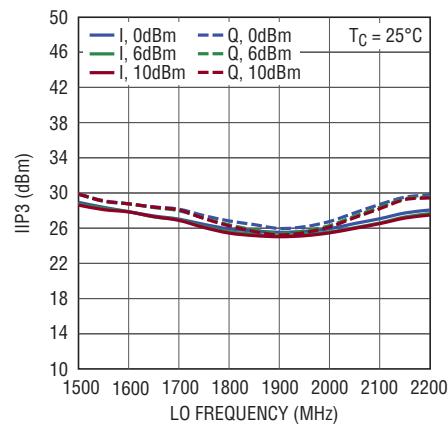

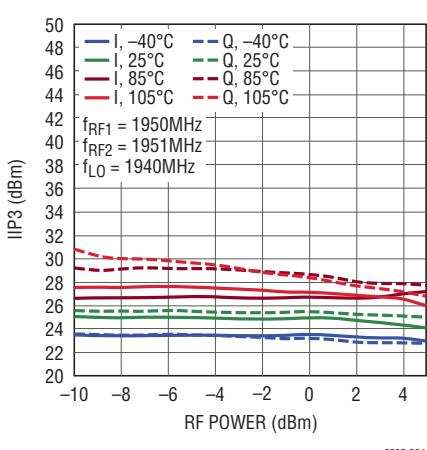

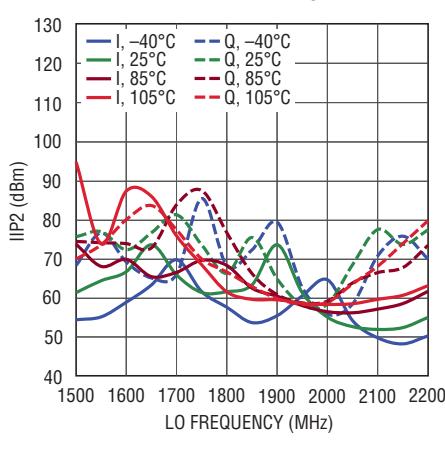

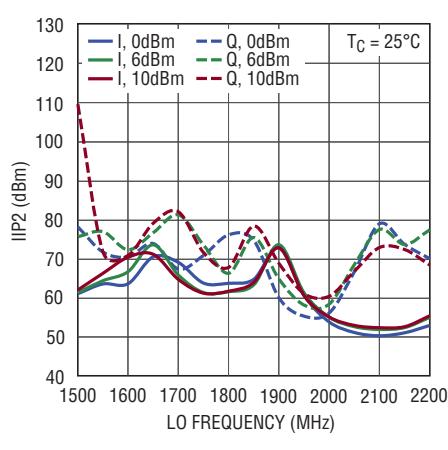

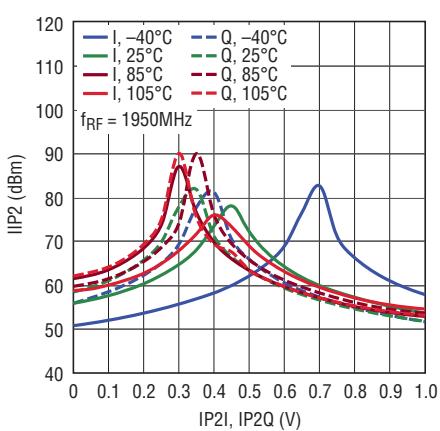

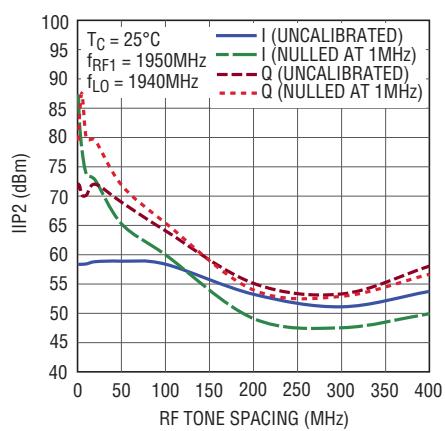

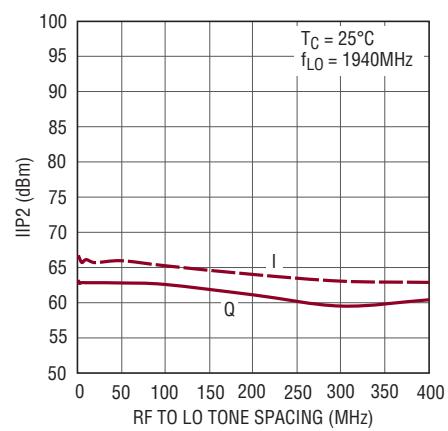

1950MHzアプリケーション。注記がない限り、 $V_{CC} = 5V$ 、 $EN = 5V$ 、 $EDC = 0V$ 、 $REF = 0.5V$ 、 $EIP2 = 0V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 6dBm$ 、 $f_{LO} = 1940MHz$ 、 $f_{RF1} = 1950MHz$ 、 $f_{RF2} = 1951MHz$ 、 $f_{BB} = 10MHz$ 、 $P_{RF1} = P_{RF2} = -5dBm$ 、ベースバンド出力のDCブロックおよびミニ回路PSCJ-2-1 180°コンバイナの影響は測定から除かれている。図1のようにRFポートとLOポートのインピーダンスが整合しているテスト回路。

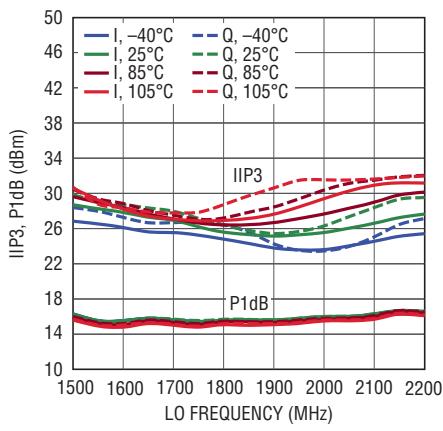

IIP3、P1dBと温度( $T_C$ )

IIP3、P1dBと電源電圧

IIP3とLO電力

2トーンIIP3とRF電力

未較正のIIP2と温度( $T_C$ )

未較正のIIP2とLO電力

IIP2とIP2I、IP2Qトリム電圧

IIP2とRFトーンの間隔

2x2 Half-IF IIP2とRFからLOへのトーン間隔

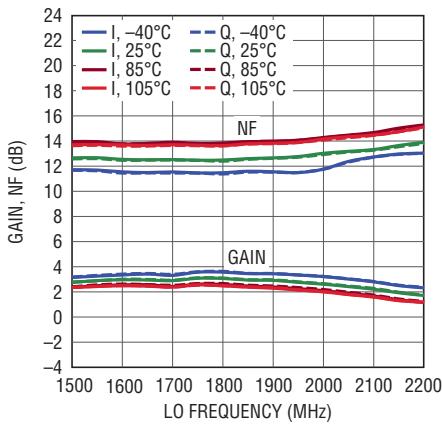

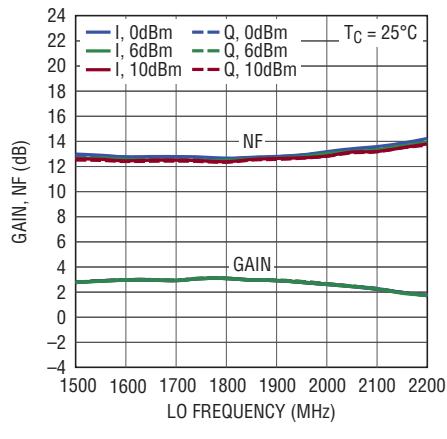

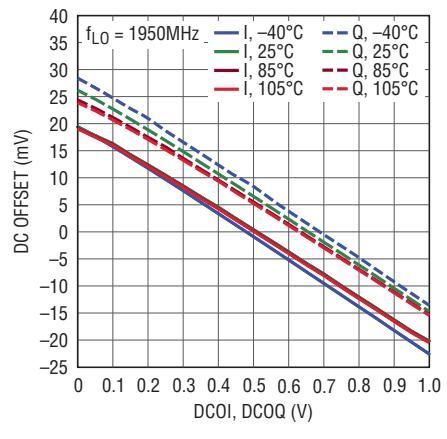

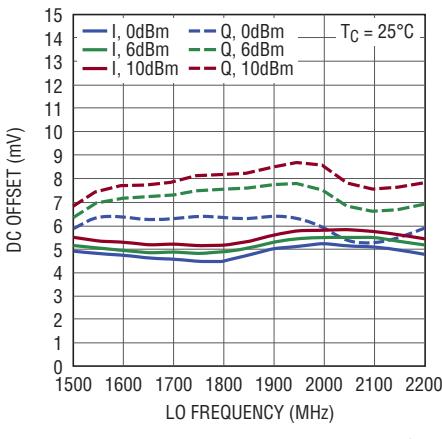

## 標準的性能特性

1950MHzアプリケーション。注記がない限り、 $V_{CC} = 5V$ 、 $EN = 5V$ 、 $EDC = 0V$ 、 $REF = 0.5V$ 、 $EIP2 = 0V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 6dBm$ 、 $f_{LO} = 1940MHz$ 、 $f_{RF1} = 1950MHz$ 、 $f_{BB} = 10MHz$ 、 $P_{RF1} = P_{RF2} = -5dBm$ 、ベースバンド出力のDCブロックおよびミニ回路PSCJ-2-1 180°コンバイナの影響は測定から除かれている。図1のようにRFポートとLOポートのインピーダンスが整合しているテスト回路。

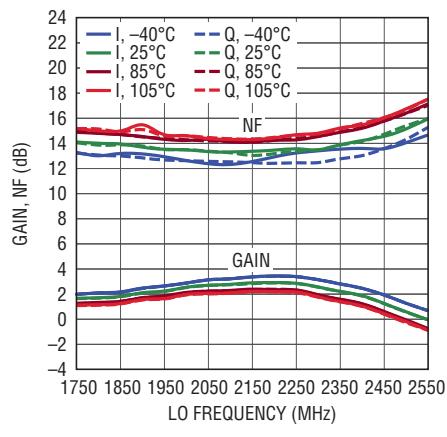

ノイズフィギュアおよび

変換利得と温度( $T_C$ )

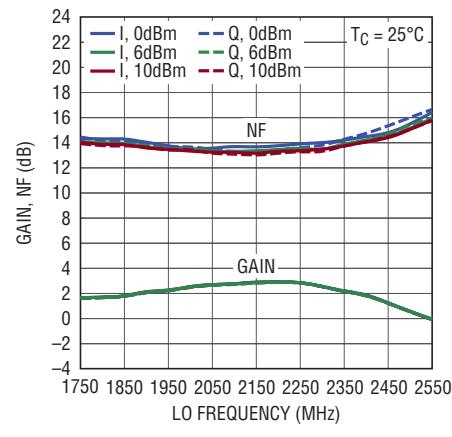

ノイズフィギュアおよび

変換利得とLO電力

DCオフセットとDCOI、

DCOQ制御電圧

DCオフセットとLO電力

LOからRFへのリークおよび

RFとLOの絶縁

イメージ除去比と温度(Note 10)

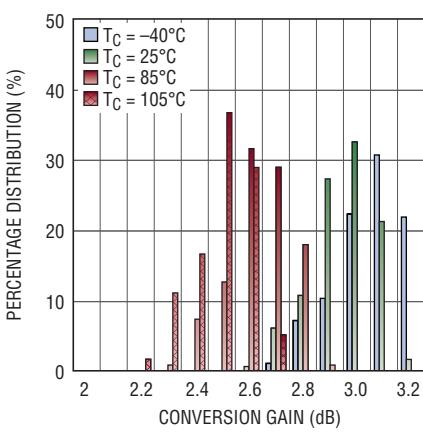

変換利得の分布

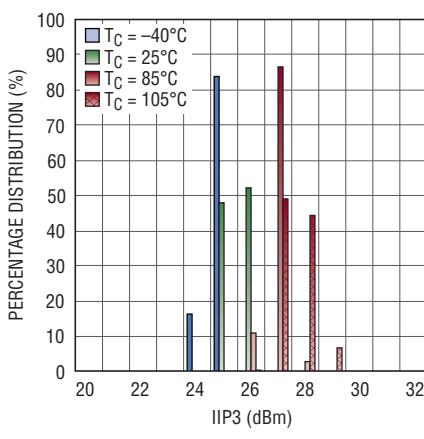

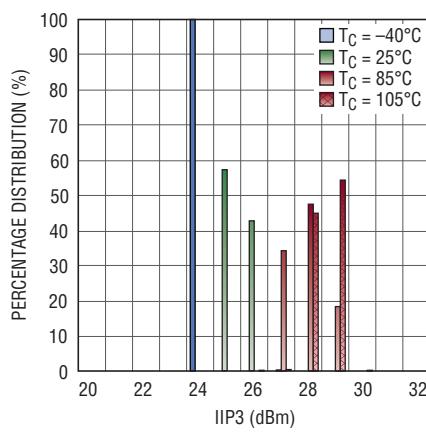

IIP3の分布(I側)

IIP3の分布(Q側)

## 標準的性能特性

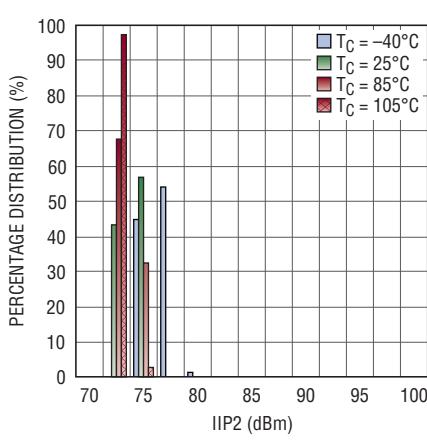

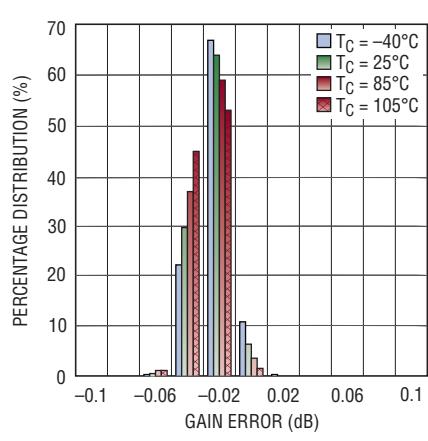

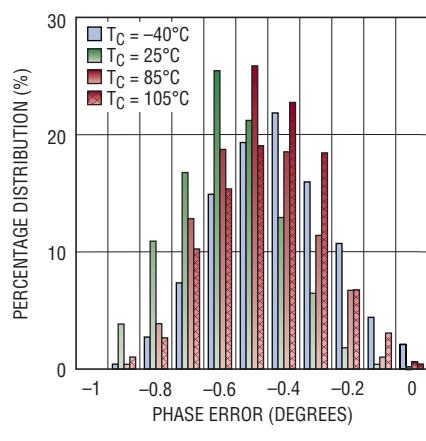

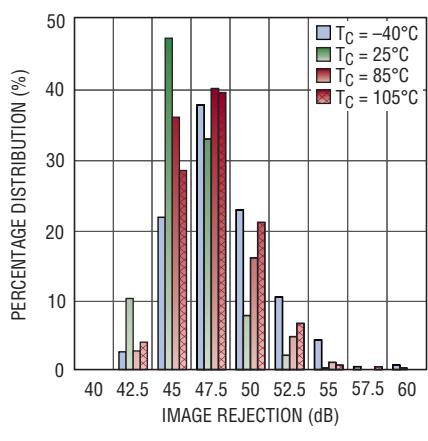

1950MHzアプリケーション。注記がない限り、 $V_{CC} = 5V$ 、 $EN = 5V$ 、 $EDC = 0V$ 、 $REF = 0.5V$ 、 $EIP2 = 0V$ 、 $T_C = 25^{\circ}C$ 、 $P_{LO} = 6dBm$ 、 $f_{LO} = 1940MHz$ 、 $f_{RF1} = 1950MHz$ 、 $f_{RF2} = 1951MHz$ 、 $f_{BB} = 10MHz$ 、 $P_{RF1} = P_{RF2} = -5dBm$ 、ベースバンド出力のDCブロックおよびミニ回路PSCJ-2-1 180°コンバイナの影響は測定から除かれている。図1のようにRFポートとLOポートのインピーダンスが整合しているテスト回路。

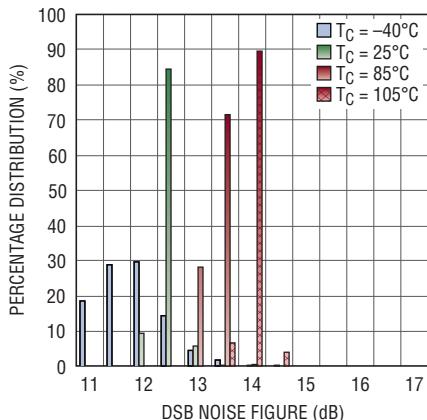

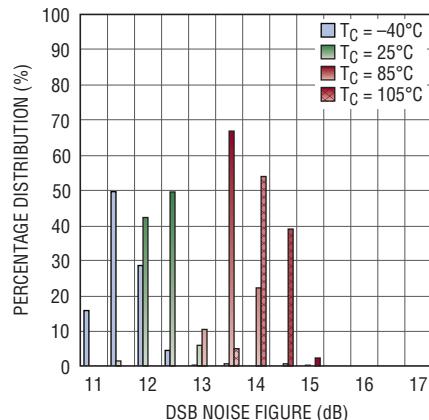

DSBノイズフィギュアの分布(I側)

DSBノイズフィギュアの分布(Q側)

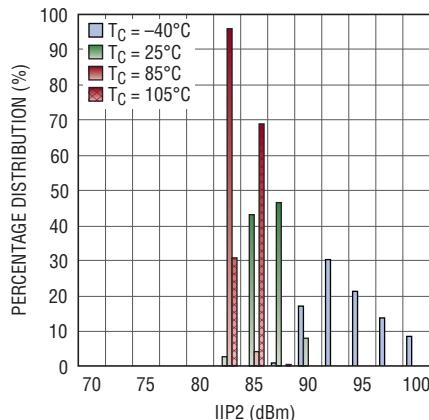

IIP2の分布(I側)

IIP2の分布(Q側)

利得誤差の分布

位相誤差の分布

イメージ除去比の分布 (Note 10)

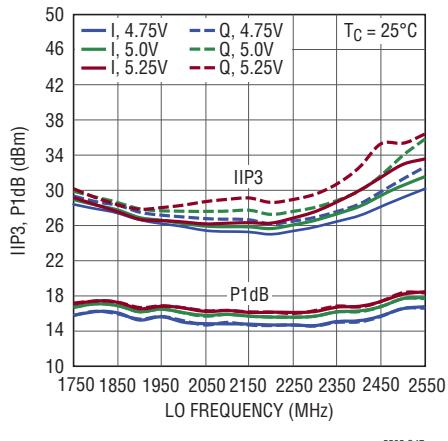

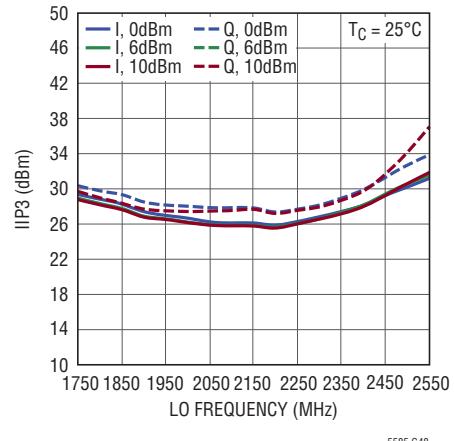

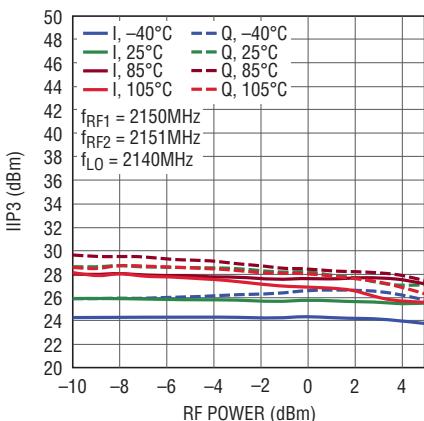

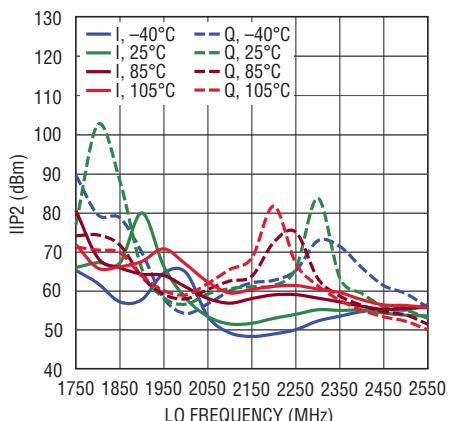

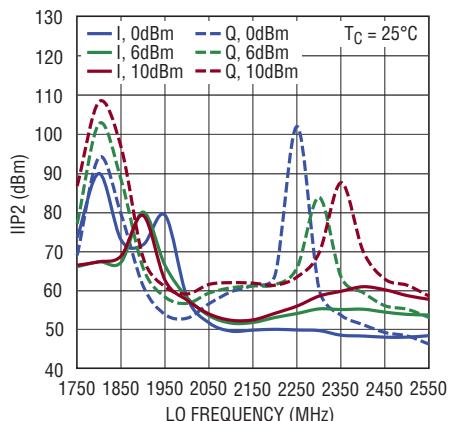

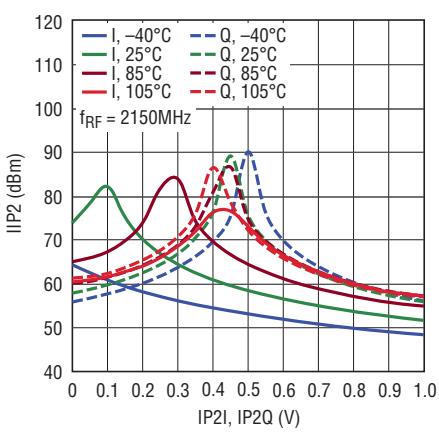

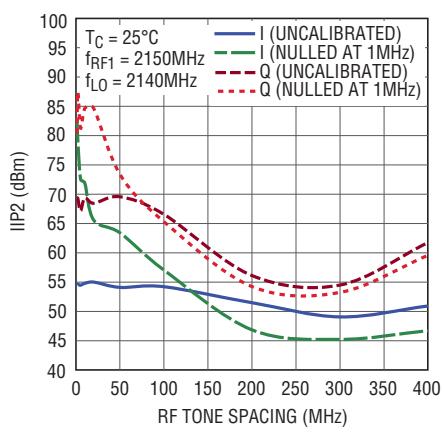

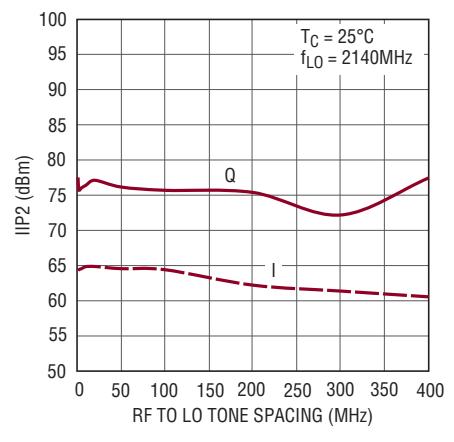

## 標準的性能特性

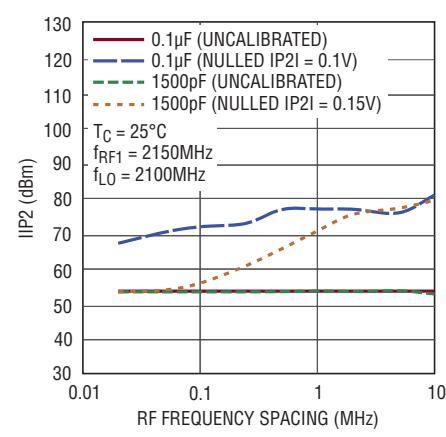

2150MHzアプリケーション。注記がない限り、 $V_{CC} = 5V$ 、 $EN = 5V$ 、 $EDC = 0V$ 、 $EIP2 = 0V$ 、 $REF = 0.5V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 6dBm$ 、 $f_{LO} = 2140MHz$ 、 $f_{RF1} = 2150MHz$ 、 $f_{RF2} = 2151MHz$ 、 $f_{BB} = 10MHz$ 、 $P_{RF1} = P_{RF2} = -5dBm$ 、ベースバンド出力のDCブロックおよびミニ回路PSCJ-2-1 180°コンバイナの影響は測定から除かれている。図1のようにRFポートとLOポートのインピーダンスが整合しているテスト回路。

IIP3、P1dBと温度( $T_C$ )

IIP3、P1dBと電源電圧( $V_{CC}$ )

IIP3とLO電力

2トーンIIP3とRF電力

未較正のIIP2と温度( $T_C$ )

未較正のIIP2とLO電力

IIP2とIP2I、IP2Qトリム電圧

IIP2とRFトーンの間隔

2x2 Half-IF IIP2とRFからLOへのトーン間隔

## 標準的性能特性

2150MHzアプリケーション。注記がない限り、 $V_{CC} = 5V$ 、 $EN = 5V$ 、 $EDC = 0V$ 、 $EIP2 = 0V$ 、 $REF = 0.5V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 6dBm$ 、 $f_{LO} = 2140MHz$ 、 $f_{RF1} = 2150MHz$ 、 $f_{RF2} = 2151MHz$ 、 $f_{BB} = 10MHz$ 、 $P_{RF1} = P_{RF2} = -5dBm$ 、ベースバンド出力のDCブロックおよびミニ回路PSCJ-2-1 180°コンバイナの影響は測定から除かれている。図1のようにRFポートとLOポートのインピーダンスが整合しているテスト回路。

ノイズフィギュアとRF入力電力

ノイズフィギュアおよび

変換利得と温度( $T_C$ )

ノイズフィギュアおよび

変換利得とLO電力

DCオフセットとDCO1、

DCOQ制御電圧

LOからRFへのリークおよびRFと

LOの絶縁

DCオフセットとLO電力

イメージ除去比と温度(Note 10)

## 標準的性能特性

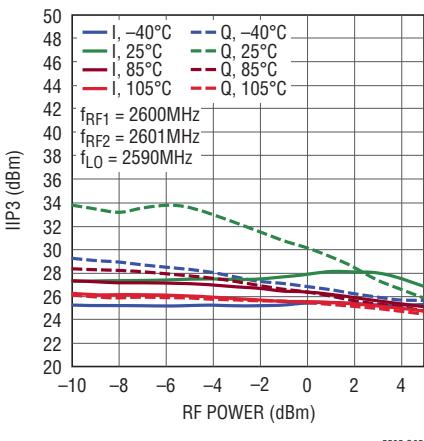

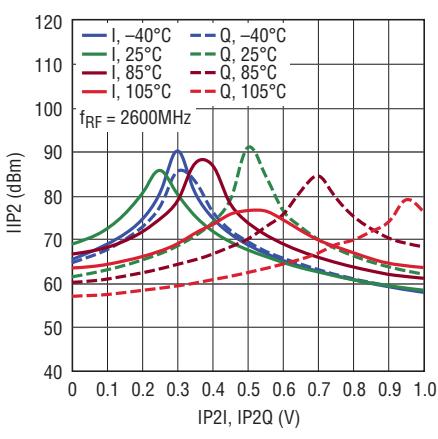

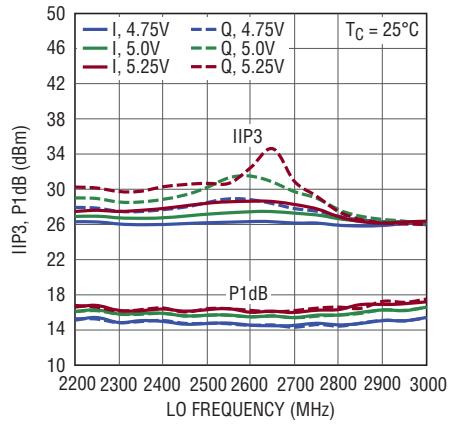

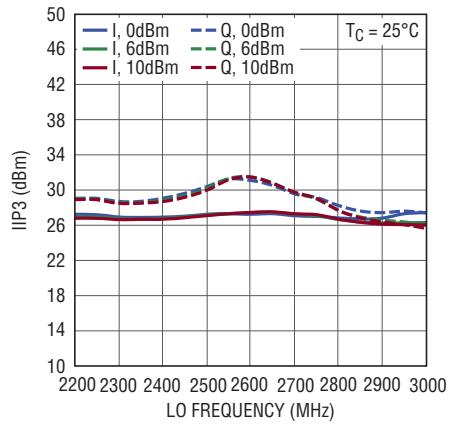

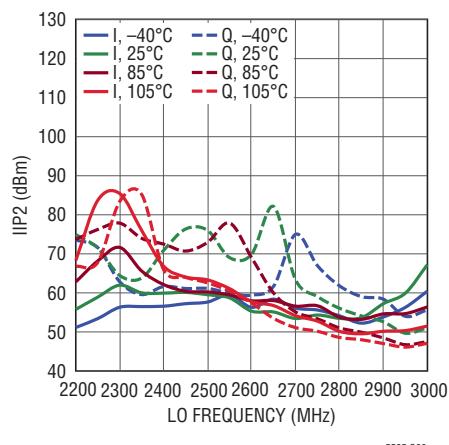

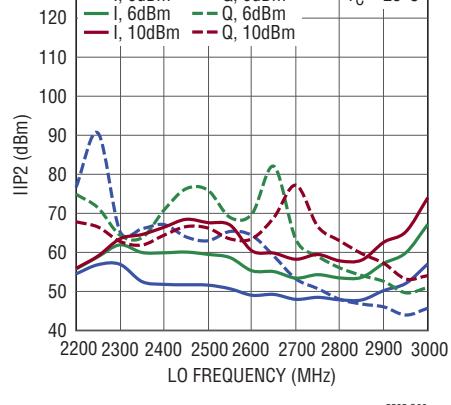

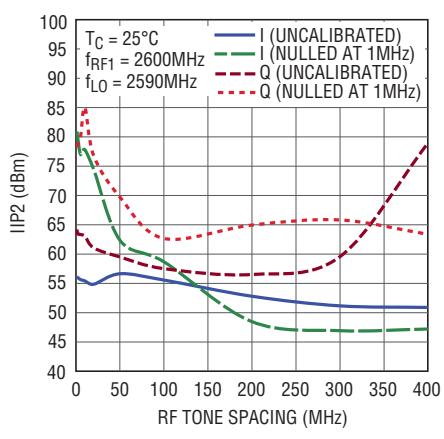

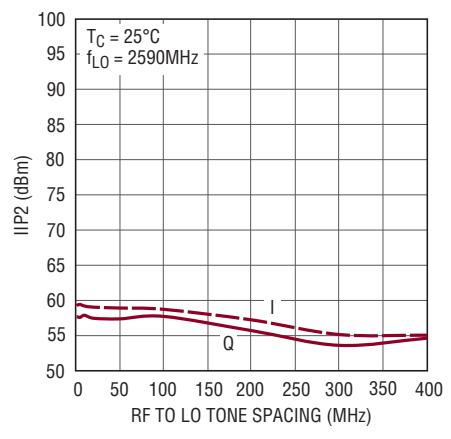

2600MHzアプリケーション。注記がない限り、 $V_{CC} = 5V$ 、 $EN = 5V$ 、 $EDC = 0V$ 、 $EIP2 = 0V$ 、 $REF = 0.5V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 6dBm$ 、 $f_{LO} = 2590MHz$ 、 $f_{RF1} = 2600MHz$ 、 $f_{RF2} = 2601MHz$ 、 $f_{BB} = 10MHz$ 、 $P_{RF1} = P_{RF2} = -5dBm$ 、ベースバンド出力のDCブロックおよびミニ回路PSCJ-2-1 180°コンバイナの影響は測定から除かれている。図1のようにRFポートとLOポートのインピーダンスが整合しているテスト回路。

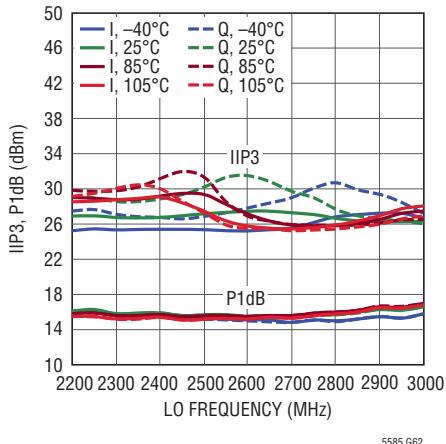

IIP3、P1dBと温度( $T_C$ )

2トーンIIP3とRF電力

IIP2とIP2I、IP2Qトリム電圧

IIP3、P1dBと電源電圧( $V_{CC}$ )

IIP3とLO電力

未較正のIIP2と温度( $T_C$ )

未較正のIIP2とLO電力

IIP2とRFトーンの間隔

2x2 Half-IF IIP2とRFからLOへのトーン間隔

## 標準的性能特性

2600MHzアプリケーション。注記がない限り、 $V_{CC} = 5V$ 、 $EN = 5V$ 、 $EDC = 0V$ 、 $EIP2 = 0V$ 、 $REF = 0.5V$ 、 $T_C = 25^\circ C$ 、 $P_{LO} = 6dBm$ 、 $f_{LO} = 2590MHz$ 、 $f_{RF1} = 2600MHz$ 、 $f_{RF2} = 2601MHz$ 、 $f_{BB} = 10MHz$ 、 $P_{RF1} = P_{RF2} = -5dBm$ 、ベースバンド出力のDCブロックおよびミニ回路PSCJ-2-1 180°コンバイナの影響は測定から除かれている。図1のようにRFポートとLOポートのインピーダンスが整合しているテスト回路。

## ピン機能

**IP2Q、IP2I(ピン1、ピン4)**: QチャネルとIチャネルのIIP2調整用アナログ制御電圧入力。このピンにはデカップリング・コンデンサを推奨します。これらのピンをドライブするには出力抵抗が小さい電圧源を推奨します。使用しない場合、これらのピンは未接続のままにしておきます。

**DCOQ、DCOI(ピン2、ピン3)**: QチャネルとIチャネルのDCオフセットのアナログ制御電圧入力。このピンにはデカップリング・コンデンサを推奨します。これらのピンをドライブするには出力抵抗が小さい電圧源を推奨します。使用しない場合、これらのピンは未接続のままにしておきます。

**RF(ピン5)**: RF入力。外部整合を使って、RF入力周波数範囲全体でリターン損失を小さくします。RFピンは内部トランス巻線を介して内部でグランドに短絡されています。RFピンは1000pFのカップリング・コンデンサでDCブロックします。

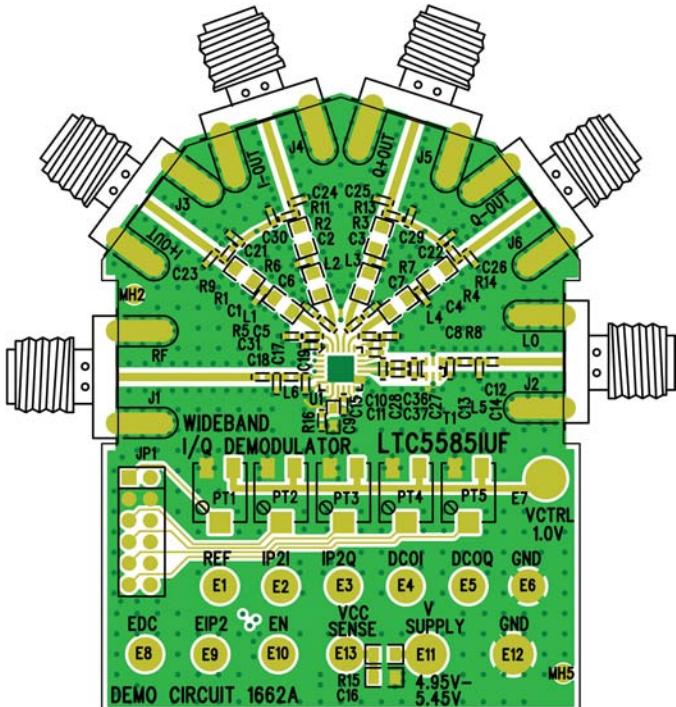

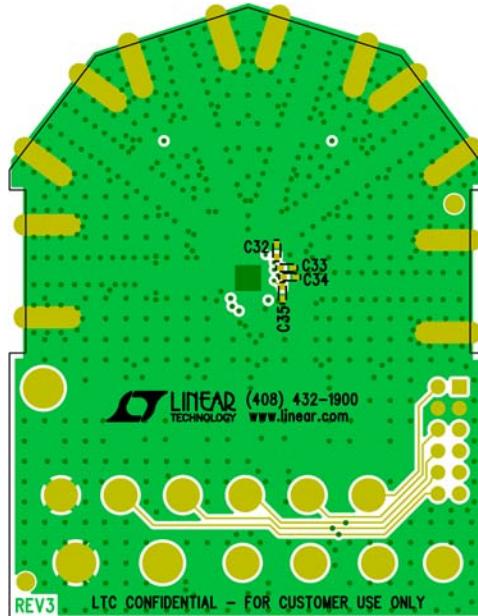

**GND(ピン6、8、13、14、露出パッド・ピン25)**: グランド。これらのピンはプリント回路基板のRFグランド・プレーンに半田付けする必要があります。高周波動作では、裏面の露出パッドのグランド接続に多数のスルーホール・ビアを使い、プリント回路基板のグランド・プレーンに低インダクタンスで接続し、熱的に十分接触させます。図2と図3を参照してください。

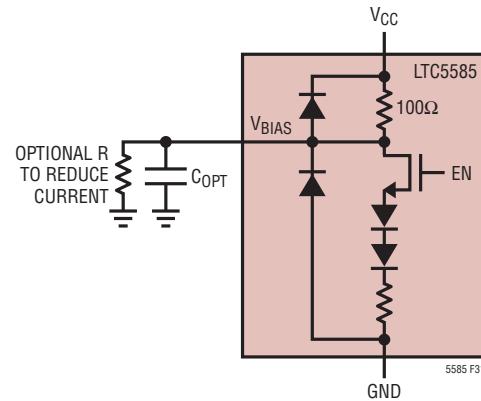

**EN(ピン7)**: イネーブル・ピン。ENピンの電圧がロジック“H”的とき、デバイスは完全にオンし、ロジック“L”的とき完全にオフします。このピンがどこにも接続されていないと(開放回路状態)、内部の200kプルダウン抵抗により、デバイスは確実にディスエーブル状態に留まります。

**V<sub>BIAS</sub>(ピン9)**: このピンを抵抗を介してグランドに引き下げて、デバイスの消費電流を減らすことができます。「アプリケーション情報」を参照してください。

**V<sub>CC</sub>(ピン10)**: 正電源ピン。このピンは並列接続した1000pFと1μFのコンデンサを使ってバイパスします。

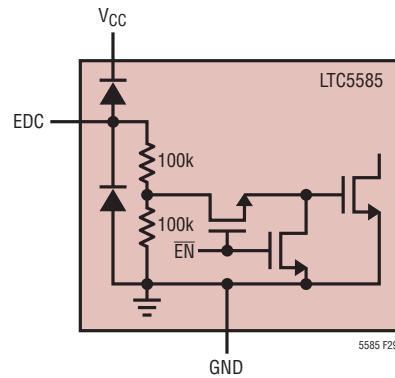

**EDC(ピン11)**: DCオフセット調整モード・イネーブル・ピン。EDCピンの電圧がロジック“H”的とき、DCオフセット制御回路がイネーブルされます。ロジック“L”的とき回路はディスエーブルされます。このピンがどこにも接続されていないと(開放回路状態)、内部の200kプルダウン抵抗により、回路は確実にディスエーブル状態に留まります。

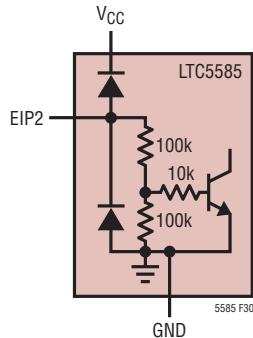

**EIP2(ピン12)**: IP2オフセット調整モード・イネーブル・ピン。EIP2ピンの電圧がロジック“H”的とき、IP2調整回路がイネーブルされます。ロジック“L”的とき回路はディスエーブルされます。このピンがどこにも接続されていないと(開放回路状態)、内部の200kプルダウン抵抗により、回路は確実にディスエーブル状態に留まります。

**LO<sup>+</sup>、LO<sup>-</sup>(ピン15、ピン16)**: LO入力。LO入力周波数範囲全体でリターン損失を減らすには、外部整合が必要です。外部トランスを使って、シングルエンドまたは差動でドライブすることができます。LOピンは1000pFのカップリング・コンデンサでDCブロックします。

**V<sub>CAP</sub>、CMQ、CMI(ピン17、ピン18、ピン19)**: 同相バイパス・コンデンサ・ピン。0.1μFのコンデンサを介して、CMIとCMQをV<sub>CAP</sub>に接続することを推奨します。V<sub>CAP</sub>はデバイス内部でV<sub>CC</sub>に接続されているので、他には何もV<sub>CAP</sub>に接続しないでください。

**I<sup>+</sup>、I<sup>-</sup>、Q<sup>+</sup>、Q<sup>-</sup>(ピン23、ピン22、ピン21、ピン20)**: IチャネルとQチャネルの差動ベースバンド出力ピン。各ピンのDCバイアス・ポイントはV<sub>CC</sub> - 1.5Vです。これらのピンには、V<sub>CC</sub>へのプルアップとして、外部の100Ω抵抗またはインダクタが必要です。

**REF(ピン24)**: アナログ制御電圧ピンの電圧リファレンス入力。このピンにはデカップリング・コンデンサを推奨します。このピンをドライブするには出力抵抗の低い電圧源を推奨します。使用しない場合、このピンは未接続のままにしておきます。

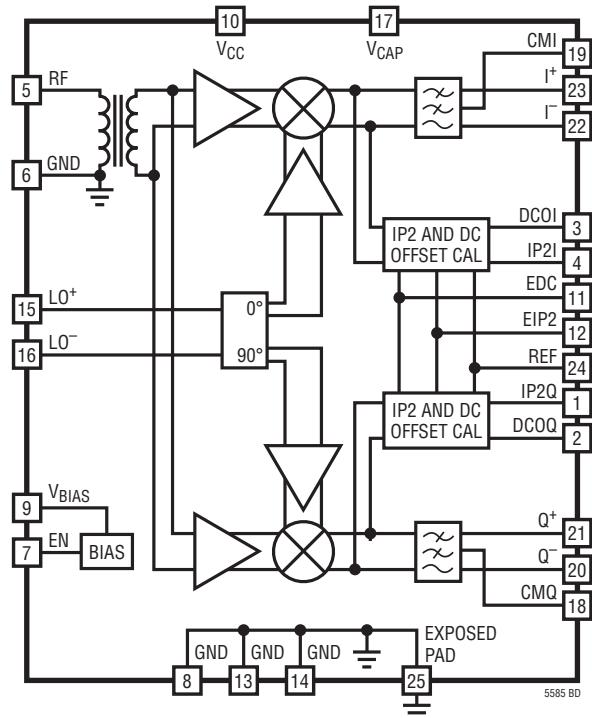

## ブロック図

# LTC5585

## テスト回路

| 周波数範囲   | RFの整合 |       |       | LOの整合 |       |       |

|---------|-------|-------|-------|-------|-------|-------|

|         | C17   | L6    | C19   | C13   | L5    | C14   |

| 700MHz  |       | 2.7pF | 1.0pF |       | 12nH  | 5.6pF |

| 1950MHz |       | 1.2pF | 5.1nH | 5.1nH | 1.0pF |       |

| 2150MHz | 1.5pF | 4.7nH | 0.5pF |       | 5.1nH | 0.7pF |

| 2600MHz | 0.5pF | 2.7nH |       |       | 1.2nH | 1pF   |

| REF DES                 | 値         | サイズ  | メーカー   | REF DES           | 値         | サイズ  | メーカー                      |

|-------------------------|-----------|------|--------|-------------------|-----------|------|---------------------------|

| C10, C11, C31-C35       | 0.1μF     | 0402 | Murata | L5, L6            | See Table | 0402 | Murata                    |

| C12, C15, C18, C36, C37 | 1000pF    | 0402 | Murata | R9, R11, R13, R14 | 100Ω      | 0402 | Vishay                    |

| C13, C14, C17, C19      | See Table | 0402 | Murata | T1                | 4:1       | 0805 | Anaren<br>BD0826J50200A00 |

| C16, C21, C22, C29, C30 | 1μF       | 0402 | Murata |                   |           |      |                           |

図1. テスト回路の回路図

テスト回路

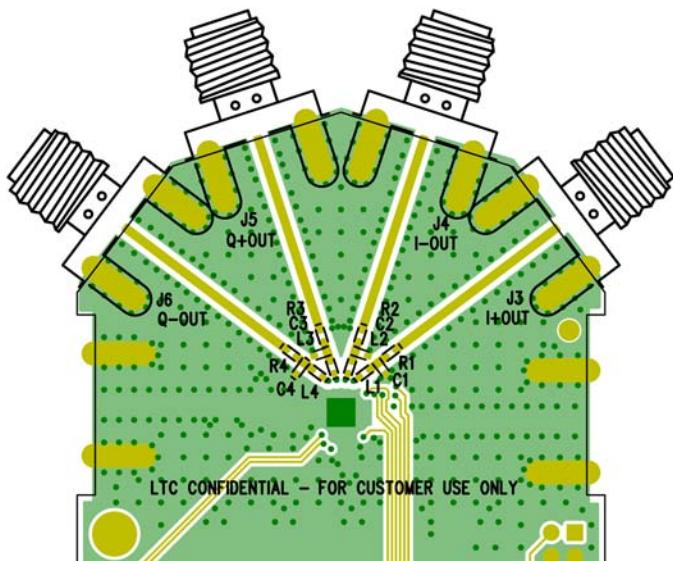

図2. 評価用ボードの部品面

図3. 評価用ボードの裏面

## アプリケーション情報

LTC5585は高ダイナミックレンジのレシーバ・アプリケーション向けに設計されたIQ復調器です。これは、RFトランスコンダクタンス・アンプ、I/Qミキサ、直交LOアンプ、IIP2とDCオフセットの補正回路、およびバイアス回路で構成されています。

動作

LTC5585のブロック図に示されているように、RF信号はRFトランジスタンスコンダクタンス電圧/電流コンバータの入力に与えられ、次に直交LO信号を使ってI/Qベースバンド信号に復調されます。この直交LO信号は高精度90°位相シフタにより内部で発生させます。復調されたI/Q信号は-3dB帯域幅が530MHzのローパス・フィルタで内部処理されます。IチャネルとQチャネルの差動出力は振幅が良く整合しており、それらの位相は90°ずれています。

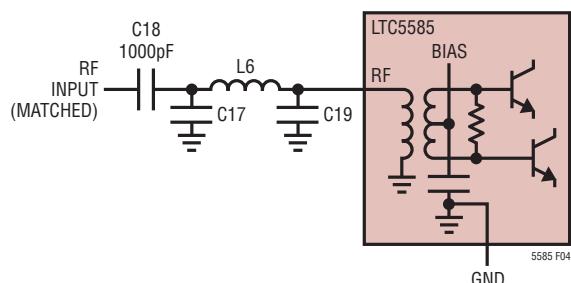

## RF入力ポート

内蔵トランジスタと高直線性トランジスタコンダクタンス・アンプ(電圧/電流コンバータ)によって構成されている、復調器のRF入力を図4に示します。トランジスタの1次側はRF入力ピンに接続されています。トランジスタの2次側はトランジスタコンダクタンス・アンプの差動入力に接続されています。RF入力ピンには外部のDC電

図4. RFピンのインターフェースの簡略回路図

## アプリケーション情報

圧を印加しないでください。トランスの1次側に流れ込むDC電流は内蔵トランスに損傷を与える可能性があります。直列DCブロッキング・コンデンサを使ってRF入力ピンをRF信号源に結合します。

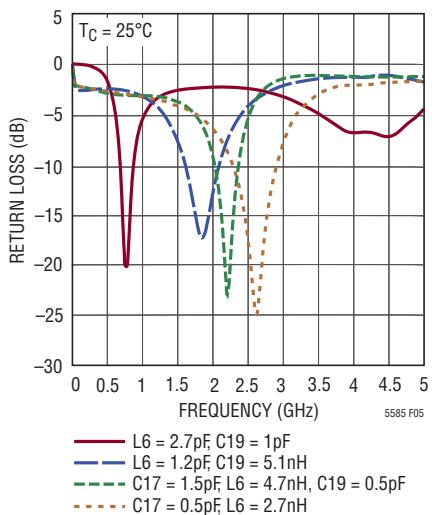

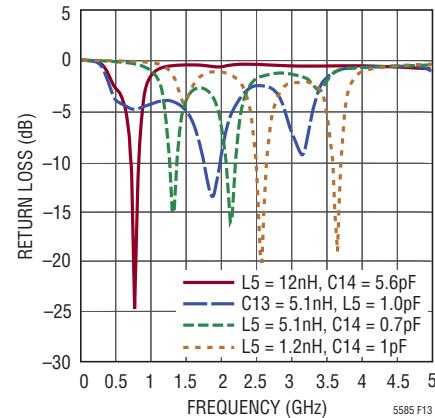

RF入力ポートは、簡単なLC整合を使って、動作周波数範囲にわたって外部で整合させることができます。この方法を使って、16%より良い帯域幅にわたって、10dBより良い入力リターン損失を得ることができます。整合部品の様々な値に対するRF入力のリターン損失を図5に示します。外部整合部品を何も使用しないときのRF入力のインピーダンスおよび入力反射係数を表1に示します。入力の伝送ラインの長さの影響は測定値から除かれています。

図5. RF入力のリターン損失

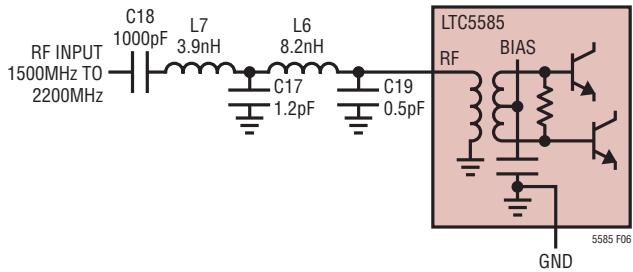

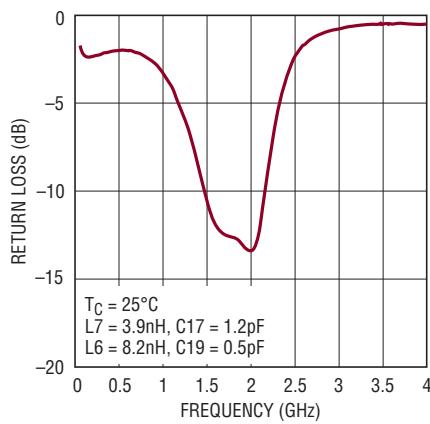

複数のLCセクションを使って、大きな帯域幅を得ることができます。たとえば、帯域幅が約38%、リターン損失が>10dBの2セクションのLC整合を図6に示します。広い帯域幅で整合のとれたRF入力のリターン損失を図7に示します。

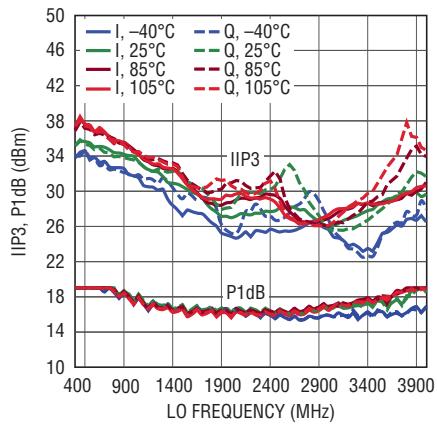

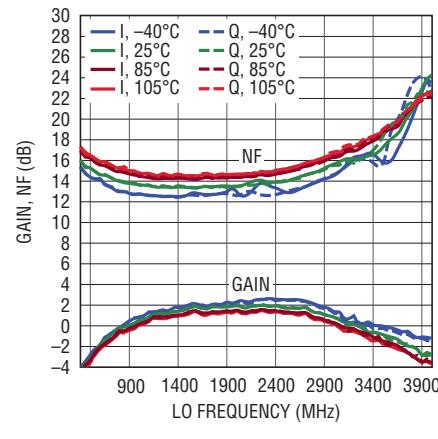

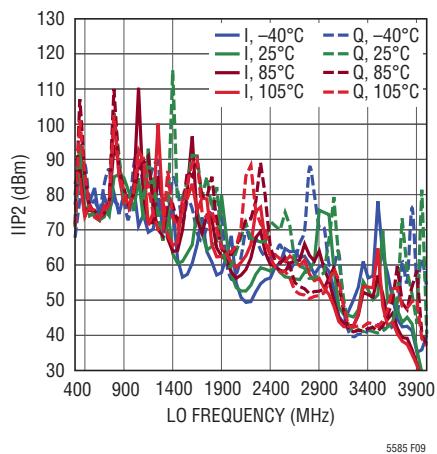

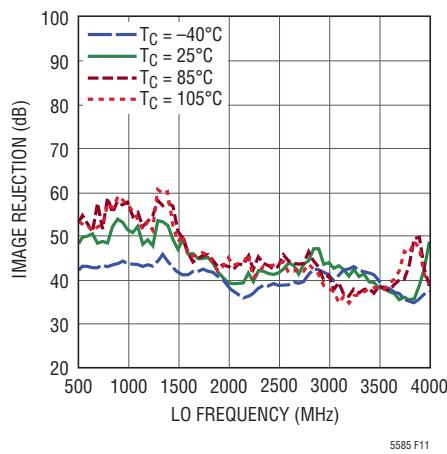

### 広帯域性能

LTC5585の広帯域性能の見当をつけるため、RFポートとLOポートに6dBのパッドを置き、それらのポートを整合させないでおくことができます。この構成設定の測定されたRF性能を、6dBパッドの影響を除いて、図8、9、10、および11に示します。RFトーンの間隔は1MHzで、 $f_{LO}$ は $f_{RF}$ より10MHz下です。変換利得は、インピーダンスが整合した状態に比べて低く、

表1.RF入力インピーダンス

| 周波数(MHz) | 入力インピーダンス( $\Omega$ ) | S11   |          |

|----------|-----------------------|-------|----------|

|          |                       | MAG   | ANGLE(°) |

| 400      | 6.98 + j25.09         | 0.800 | 125.98   |

| 600      | 10.43 + j39.74        | 0.775 | 101.55   |

| 800      | 16.76 + j56.73        | 0.751 | 80.01    |

| 1000     | 28.55 + j77.15        | 0.727 | 61.05    |

| 1200     | 51.47 + j101.03       | 0.706 | 44.29    |

| 1400     | 96.49 + j122.28       | 0.686 | 29.33    |

| 1600     | 171.91 + j112.37      | 0.667 | 15.81    |

| 1800     | 229.92 + j30.89       | 0.648 | 3.45     |

| 2000     | 202.21 - j58.84       | 0.630 | -8.00    |

| 2200     | 145.32 - j91.23       | 0.612 | -18.71   |

| 2400     | 104.82 - j91.69       | 0.594 | -28.49   |

| 2600     | 78.33 - j83.38        | 0.575 | -38.22   |

| 2800     | 61.86 - j73.64        | 0.557 | -47.49   |

| 3000     | 51.27 - j64.65        | 0.538 | -56.32   |

| 3200     | 43.83 - j56.56        | 0.519 | -65.15   |

| 3400     | 38.86 - j49.72        | 0.500 | -73.40   |

| 3600     | 35.17 - j43.6         | 0.481 | -81.68   |

| 3800     | 32.46 - j38.21        | 0.463 | -89.79   |

| 4000     | 30.48 - j33.41        | 0.444 | -97.76   |

図6. 広帯域RF入力の整合

図7. 広帯域整合のRF入力のリターン損失

## アプリケーション情報

図8. 広帯域IIP3およびIP1dB

図10. 広帯域NFと利得

図9. 広帯域IIP2

図11. 広帯域イメージ除去比

それに応じて、P1dB、IIP3、およびNFが高くなります。示されているように、デバイスはその規定動作範囲の外側の周波数でも使用することができますが、変換利得が下がり、NFが増加します。

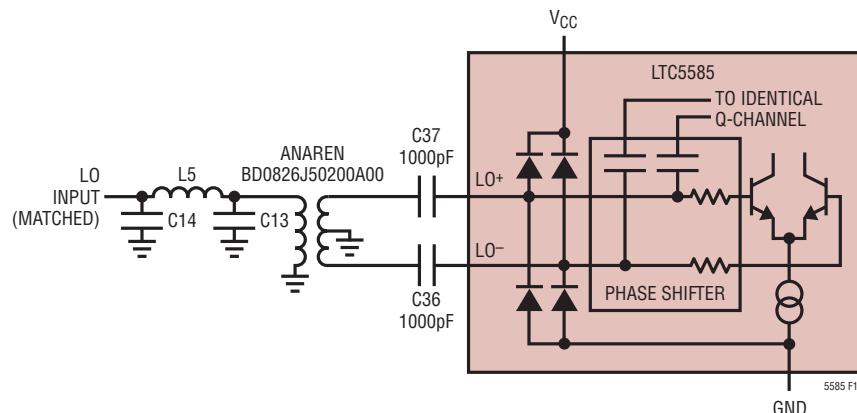

### LO入力ポート

復調器のLO入力インターフェースを図12に示します。入力は高精度直交位相シフタによって構成されており、I/QミキサをドライブするLOバッファ・アンプのために $0^\circ$ と $90^\circ$ の位相のシフトしたLO信号を発生します。LO<sup>+</sup>とLO<sup>-</sup>の入力にはDCブロッキング・コンデンサが必要です。

入力の伝送ラインとバランの影響を除いた、差動LO入力インピーダンスとSパラメータを表2に示します。

整合部品の様々な値に対する、ANARENのBD0826J50200A00 4:1バランを使ったLO入力のリターン損失を図13に示します。

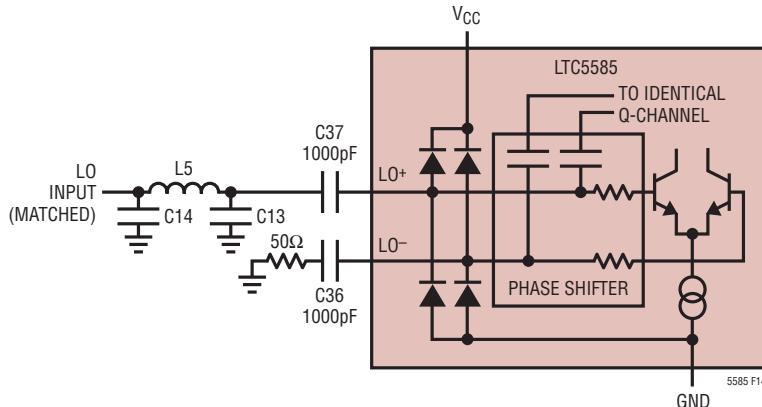

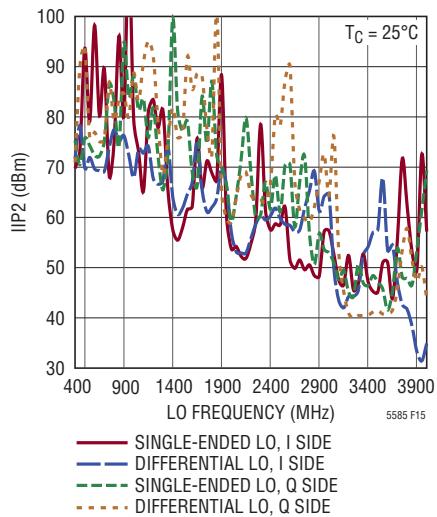

IIP2および大信号NFの最適性能を得るには、ANARENのBD0826J50200A00またはBD2425J50200AHFのような4:1バランを使って、LO入力を差動でドライブします。図14に示されているように、LO入力はLO<sup>+</sup>またはLO<sup>-</sup>のどちらかの入力からシングルエンドでドライブすることもできます。未使用的ポートはDCブロックし、50Ω負荷で終端します。シングルエンドと差動のLOドライブの未較正のIIP2性能の比較を図15に示します。

## アプリケーション情報

図12. 外部整合部品を備えたLO入力インタフェースの簡略回路図

表2.LO入力インピーダンス(差動)

| 周波数(MHz) | 入力<br>インピーダンス( $\Omega$ ) | $S_{11}$ |                     |

|----------|---------------------------|----------|---------------------|

|          |                           | MAG      | ANGLE( $^{\circ}$ ) |

| 400      | $118.18 - j120.02$        | 0.668    | -24.89              |

| 600      | $94.18 - j99.93$          | 0.623    | -31.42              |

| 800      | $78.00 - j85.06$          | 0.583    | -38.17              |

| 1000     | $67.21 - j73.16$          | 0.544    | -44.79              |

| 1200     | $59.71 - j63.49$          | 0.507    | -51.25              |

| 1400     | $54.22 - j55.46$          | 0.471    | -57.63              |

| 1600     | $50.06 - j48.59$          | 0.437    | -64.02              |

| 1800     | $46.80 - j42.69$          | 0.405    | -70.49              |

| 2000     | $44.10 - j37.42$          | 0.374    | -77.28              |

| 2200     | $41.86 - j32.61$          | 0.345    | -84.47              |

| 2400     | $39.98 - j28.16$          | 0.317    | -92.21              |

| 2600     | $38.39 - j23.98$          | 0.291    | -100.65             |

| 2800     | $37.05 - j20.01$          | 0.267    | -109.95             |

| 3000     | $35.92 - j16.21$          | 0.246    | -120.29             |

| 3200     | $34.99 - j12.53$          | 0.228    | -131.76             |

| 3400     | $34.22 - j8.95$           | 0.214    | -144.37             |

| 3600     | $33.61 - j5.45$           | 0.206    | -157.88             |

| 3800     | $33.15 - j2.0$            | 0.204    | -171.85             |

| 4000     | $32.82 + j1.4$            | 0.208    | 174.35              |

図13. LO入力のリターン損失

## アプリケーション情報

図14. シングルエンドLO入力の推奨構成設定

図15. 広帯域IIP2(差動およびシングルエンドのLOドライブ)

### IチャネルとQチャネルの出力

IチャネルとQチャネルの出力信号間の位相関係は固定されています。LO入力周波数がRF入力周波数より高い(または低い)とき、Qチャネルの出力( $Q^+$ 、 $Q^-$ )はIチャネルの出力( $I^+$ 、 $I^-$ )より90°だけ位相が遅れます(または進みます)。

IチャネルとQチャネルの各出力は内部で100Ωの抵抗を通してV<sub>CC</sub>に接続されています。出力の(V<sub>CC</sub> - 1.5V)のDCバイアス電圧を維持するには、外部100Ωプルアップ抵抗または等価15mA DC電流源が必要です。各シングルエンド出力は、6pFの内部コンデンサに並列な100Ωのインピーダンスを備えています。これは、外部の100Ωプルアップ抵抗とともにローパ

ス・フィルタを形成し、その-3dBコーナー周波数は530MHzです。出力は外部負荷にDC結合またはAC結合することができます。電圧変換利得は、外部負荷によって次のように減少します。

$$20\log_{10}\left(\frac{1}{2} + \frac{50\Omega}{R_{PULL-UP} || R_{LOAD(SE)}}\right) \text{dB}$$

出力ポートが $R_{LOAD(SE)}$ によって終端されているとき。たとえば、各出力ピンが50Ω負荷(つまり差動で100Ω)に接続されているとき、利得は6dBだけ減少します。最良のRF性能(NFやIIP2など)を得るには、出力を差動で取り出します(または差動からシングルエンドへの変換を使います)。フィルタや整合のための外部部品を使わないとき、出力応答は負荷容量および出力の全抵抗負荷によって決まります。 $-3\text{dB}$ コーナー周波数( $f_C$ )は次式で与えられます。

$$f_C = [2\pi(R_{LOAD(SE)} || 100\Omega || R_{PULL-UP}) (6\text{pF})]^{-1}$$

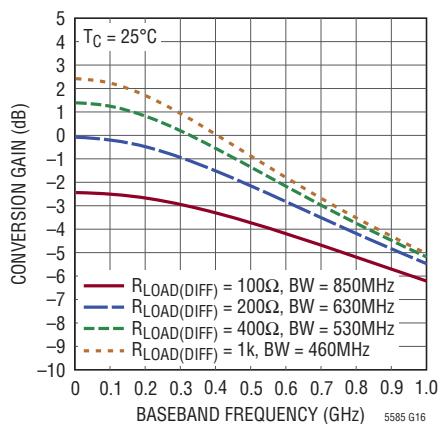

様々な負荷抵抗に対して実際に測定された出力応答を図16に示します。

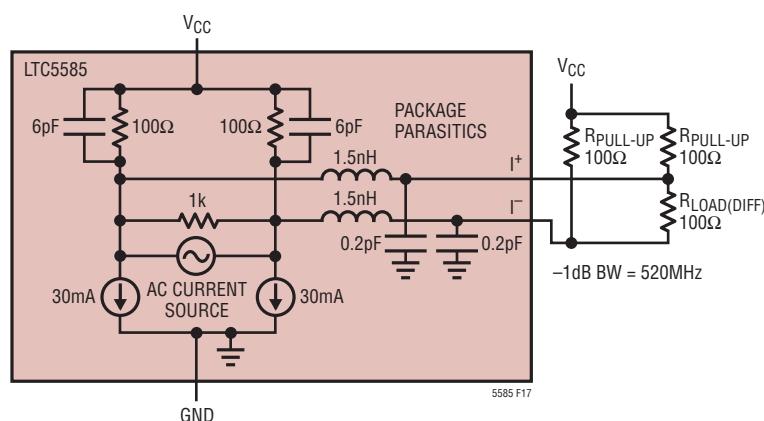

100Ωの差動負荷と100Ωのプルアップ抵抗を使ったI出力とQ出力の簡略モデルを図17に示します。この構成設定の-1dB帯域幅は約520MHz(つまり、無負荷時の-1dB帯域幅の約2倍)です。

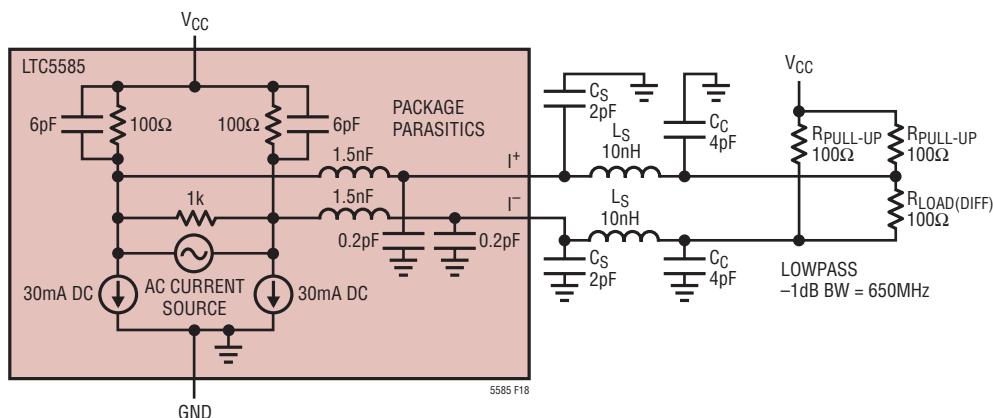

帯域幅を広げるためにLC整合ネットワークを使ったI出力とQ出力の簡略モデルを図18に示します。コンデンサ $C_S$ は、復調器の出力の直ぐ近くの同相LOスイッチング・ノイズをフィルタするのに役立ちます。インダクタ $L_S$ とコンデンサ $C_C$ の組み合わせを使って、出力応答にピークを生じさせて帯域幅を

## アプリケーション情報

図16. 変換利得のベースバンド出力応答( $R_{LOAD(DIFF)} = 100\Omega$ 、 $200\Omega$ 、 $400\Omega$ および $1\text{k}$ 、 $R_{PULL-UP} = 100\Omega$ )

650MHzに広げます。この場合、コンデンサ $C_C$ は、差動モードのコンデンサではなく、同相モードのコンデンサとして選択され、同相モードLOスイッチング・ノイズの除去率を良くします。

出力にAC結合が使われる場合、その結果生じるハイパス・フィルタの $-3\text{dB}$ ロールオフ周波数( $f_C$ )は、外部AC結合容量( $C_{AC}$ )および差動負荷抵抗 $R_{LOAD(DIFF)}$ のRC定数によって定まります。

$$f_C = [2\pi \cdot R_{LOAD(DIFF)} \cdot C_{AC}]^{-1}$$

図17. ベースバンド出力の簡略モデル

図18. 外部のLC整合を使った、帯域幅拡張を示すベースバンド出力の簡略モデル

## アプリケーション情報

復調器の出力が外部負荷にDC結合されるときは注意して、I/Qミキサが適切にバイアスされていることを確認してください。出力からの電流が約6mAを超えると、直線性の性能が大きく劣化することがあります。5V電源で、復調器の同相電圧を3.15Vより上に保つと、確実に最適性能が得られます。出力がV<sub>CC</sub>-1.5Vを超えるDC電圧で外部負荷に接続されているとき、各出力は30mAを超えるシンク電流を流すことはできません。

最良のIIP2性能を達成するには、ベースバンド出力、RFポート、およびLOポート相互の高周波カッピングを最少に抑えることが重要です。ベースバンド出力のトレースをPCBの裏面で配線するとレイアウトが複雑になる可能性がありますが、未較正のIIP2性能を改善することができます。ベースバンド出力をPCBの裏面に置いた別のレイアウトを図19に示します。

図19. ベースバンド出力を裏側に置いた

別のPCBレイアウト

### アナログ制御電圧ピン

DCOI、DCOQ、IP2I、およびIP2Qの各ピンの等価回路を図20に示します。内部の温度補償された62.5μA電流源が、8k抵抗を介して、これらのピンを公称500mVにバイアスします。これらのピンをドライブするには、ソース抵抗が200Ω未満の低インピーダンスの電圧源を推奨します。

図21に示されているように、REFピンはDCOIピンに似ていますが、バイアス電流源は250μAで、内部抵抗は2kです。このピンを未接続のままにすると、500mVに自己バイアスします。このピンをドライブするには、ソース抵抗が200Ω未満の低インピーダンスの電圧源を推奨します。DCOI、DCOQ、IP2I、およびIP2Qの各ピンの制御電圧範囲はREFピンによって設定されます。この範囲は、(内部で印加するか、外部から印加するかに関係なく)0VからREFピンの2倍までです。

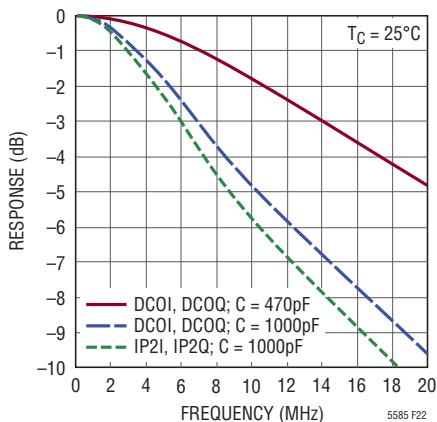

アナログ制御電圧入力に接続される信号ラインに現れるどんなACノイズもデカップリングすることを推奨します。これらのピンの近くに置いたグランドへのシャント・コンデンサにより、適切にフィルタすることができます。たとえば、DCOI、DCOQ、IP2I、およびIP2Qの各ピンの容量の値を1000pFにすると、コーナー周波数は約6MHz～7MHzになります。3900pFの容量値で、同様なコーナー周波数をREFピンで得ることができます。

図20. DCOI、DCOQ、IP2I、およびIP2Qの各ピンの

インターフェースの簡略回路図

図21. REFピンのインターフェースの簡略回路図

## アプリケーション情報

ます。高速の制御応答を必要としない限り、 $0.1\mu F$ など、もっと大きな容量値をこれらのピンに使うことを推奨します。 $50\Omega$ のソースからドライブしたときのピンの入力応答の $-3\text{dB}$ 帯域幅とシャント容量を図22に示します。

図22. DCOI, DCOQ, IP2I, およびIP2Qの各ピンの入力応答帯域幅

## DCオフセット調整回路

ダイレクトコンバージョン・レシーバのRF入力へのLOリークのソースは、そのベースバンド出力のDCオフセットに影響を与えます。LTC5585はDCオフセット調整回路を備えており、このような影響を減らします。EDCピンがロジック“H”的とき回路がイネーブルされ、DCオフセット調整範囲が標準 $\pm 20\text{mV}$ になります。標準的なダイレクトコンバージョン・レシーバのアプリケーションでは、DCオフセットの較正は、受信データが存在せず、レシーバのDCレベルが十分セトリングしているとき定期的に行われます。

## DCオフセット調整の例

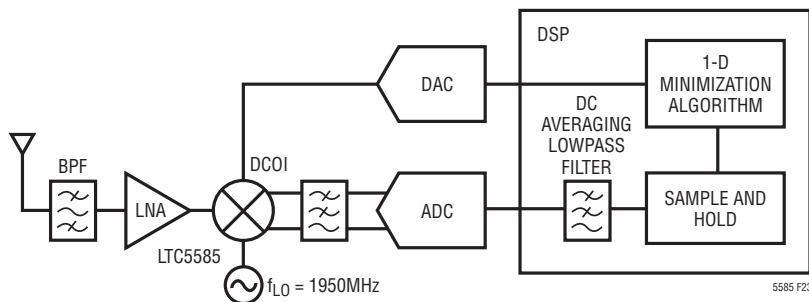

DCオフセット調整のためのDSP帰還経路を備えた標準的なダイレクトコンバージョン受信経路を図23に示します。LTC5585復調器のRF入力へのLOリークのソースは、レシーバのDCオフセットに影響を与えます。これにはスタチックおよびダイナミック両方のDCオフセットが含まれます。結合がボーダーレベルの変化しないリーク経路によるスタチックなものであれば、DCオフセットは一般に高い繰り返しレートで調整する必要はありません。トランスマッタのリークやアンテナの反射によるダイナミックなDCオフセットは、補正するのがもっと困難であり、DSPによるもっと高速の更新が必要です。

復調器のRFポートへのLOリークはベースバンド出力にDCオフセットを生じ、ベースバンド経路の利得により増幅されます。利用可能なADCの電圧ウインドウは増幅されたDCオフセットだけ減少し、ダイナミックレンジが減少します。DSPを使ってこのDCオフセットの値を平均化し、ある更新レートでサンプリングしてから、(新しいDCOIまたはDCOQの制御信号を発生させる前に) 1-D最小化アルゴリズムを適用してオフセットを最小にすることができます。1-D最小化アルゴリズムは、ゴールデン・セクション法、バックトラッキング、ニュートン法など多くの方法で実装することができます。

## IM2調整回路

LTC5585には、IチャネルとQチャネルのIM2レベルの独立した調整回路も備わっています。EIP2ピンがロジック“H”的とき、この回路はイネーブルされ、IP2IとIP2Qのアナログ制御電圧入力はIM2レベルを調整することができます。IM2レベルはベースバンド帯域幅の大きな範囲にわたって効果的に最小化することができます。回路の有効なベースバンド周波数

図23. DCオフセット調整のためのDSP帰還ループを備えたレシーバのブロック図

## アプリケーション情報

数の上限は約200MHzです。この周波数範囲に収まるどんなIM2成分も最小化することができます。この周波数を超えると、IM2補正アンプの利得はかなり低下し、回路はもはやIP2性能を改善しません。IM2調整回路のベースバンド周波数の下限は、CMIピンとCMQピンの同相リファレンス・デカップリング・コンデンサによって設定されます。この周波数より下では、回路はIM2成分を最小にできません。

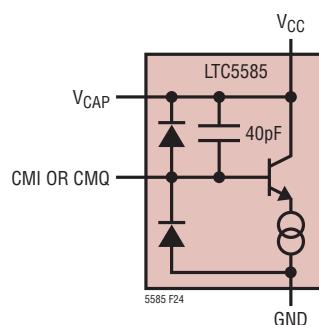

CMIピンのインターフェースを図24に示します(CMQピンのインターフェースも同一)。これらのピンには内部に40pFのV<sub>CC</sub>への容量があり、IP2調整回路のリファレンスを与えます。回路の3dB周波数の下限(f<sub>C</sub>)は次式で設定されます。

$$f_C = [2\pi \cdot 500(40\text{pF} + C_{CM(\text{EXT})})]^{-1}$$

CMIピンまたはCMQピンに外部コンデンサがないと、下限は8MHzです。CMIピンとCMQピンの間に、V<sub>CAP</sub>への0.1μFのコンデンサ(C<sub>CM(EXT)</sub>)を追加して、-3dB周波数を3kHzに下げることができます。0.1μFおよび1500pFの同相デカップリング容量値に対する、RF周波数間隔の関数としてのIIP2を図25に示します。このコンデンサのサイズに対する制限は、IM2回路が動作するイネーブル時間に対する影響以外、実質的ではありません。デバイスがディスエーブルされると、Iミキサと

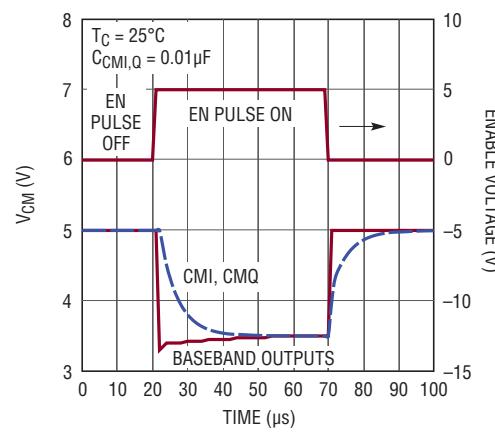

図24. CMIピンおよびCMQピンのインターフェースの等価回路

Qミキサに電流が流れないので、(ベースバンド・アンプのような外部ベースバンド回路によるDC同相電流が流れていないならば)同相出力電圧はV<sub>CC</sub>に等しくなります。デバイスがイネーブルされると、外部デカップリング・コンデンサを500Ω抵抗を介して充電する必要があります。その場合の時定数は本質的に500Ωと同相デカップリング容量値の積です。たとえば、0.01μFコンデンサの場合、この待ち時間は約30μsです。CMIピンとCMQピンが0.01μFのとき、イネーブル・パルスに対する同相出力電圧の応答を図26に示します。

図25. IIP2と同相デカップリング容量

図26. イネーブル・パルスに対する同相出力電圧

## アプリケーション情報

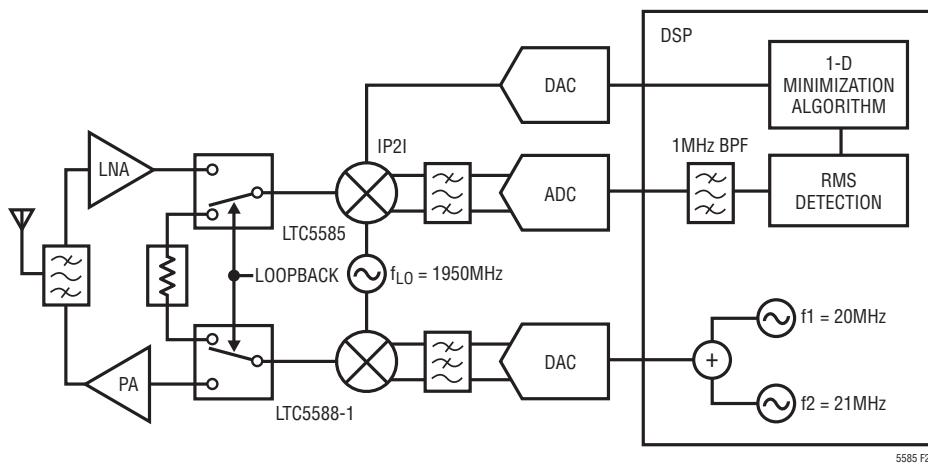

### IM2サプレッションの例

IM2調整回路は、図27に示されているような、トランシーバの標準的ループバック・アプリケーションに使用することができます。この例では、 $f_1 = 20\text{MHz}$ および $f_2 = 21\text{MHz}$ の2トーンSSBソース信号をDSPで発生し、LTC5588-1直交復調器によって、1950MHzのLOソースを使って1970MHzと1971MHzのRFトーンにアップ変換します。LTC5588-1によって生じるIM2成分を除去するため、狭帯域RFフィルタが必要です。ループバック・テストの間、これらのRFトーンは高絶縁スイッチおよびLTC5585復調器の入力への減衰パッドを介して配線されます。次にトーン信号は1950MHzの同じLOソースによってダウン変換され、ベースバンド出力に20MHzと21MHzの2つのトーンおよび1MHzのIM2障害信号を発生します。ベースバンド・チャネルをフィルタして増幅した後、ADCの出力をDSP内の1MHz帯域幅のフィルタによってフィルタし、IM2トーンを分離します。このトーンの電力はDSP内で計算され、次に1-D最小化アルゴリズムを使って、IP2I制御電圧ピンの補正信号を計算します。1-D最小化アルゴリズムは、ゴールデン・セクション法、バックトラッキング、ニュートン法など多くの方法で実装することができます。

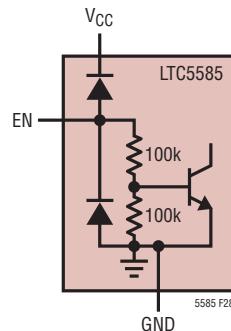

### イネーブル・インターフェース

ENピンの簡略回路図を図28に示します。LTC5585をオンするのに必要なイネーブル電圧は2Vです。デバイスをディスエーブルまたはオフするには、この電圧を0.3Vより低くします。ENピンが接続されていないとデバイスはディスエーブルされます。

EDCピンとEIP2ピンの簡略回路図を図29と図30に示します。

図28. ENピンのインターフェースの簡略回路図

図29. EDCピンのインターフェースの簡略回路図

図27. IM2調整を備えたダイレクトコンバージョン・トランシーバのブロック図。Iチャネルのみ示されている

## アプリケーション情報

図30. EIP2ピンのインターフェースの簡略回路図

EN、EDC および EIP2 の各ピンに加えられる電圧が決して V<sub>CC</sub> を 0.3V 以上超えないようにすることが重要です。そうしないと、ピンに接続されている上側のESD保護ダイオードを通して電源電流がソースされます。いかなる状況でも V<sub>CC</sub> ピンに電源電圧が加えられる前にイネーブルピンに電圧が加わってはなりません。電圧が加わると、デバイスが損傷する恐れがあります。

### 消費電力の低減

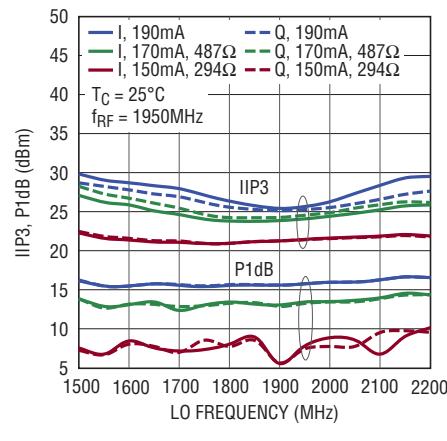

V<sub>BIAS</sub> インタフェースの簡略回路図を図31に示します。V<sub>BIAS</sub> ピンを使って、ミキサのコア・バイアス電流およびデバイスの全消費電力を減らすことができます。たとえば、V<sub>BIAS</sub> ピンから GND に 294Ω を追加すると、DC 電流が 150mA に減少しますが、代価として、IIP3 性能が低下します。IIP3 および P1dB 性能と DC 電流および抵抗値を図32に示します。オプションのコンデンサ(図31の COPT)は、PSRR と IIP2 の改善にわずかしか影響しません。

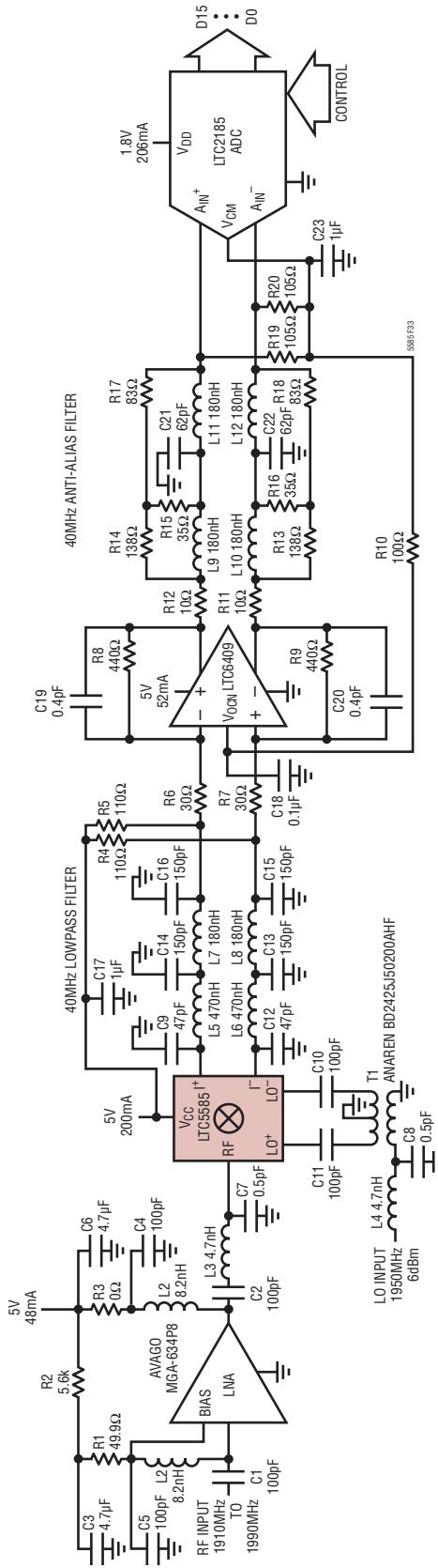

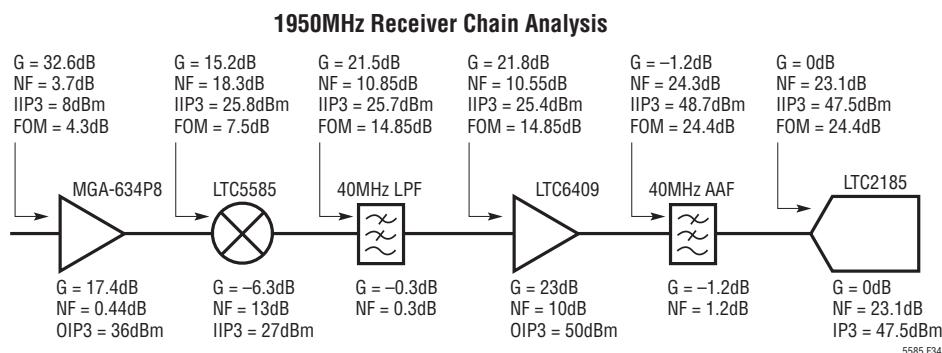

### 1950MHzレシーバ・アプリケーション

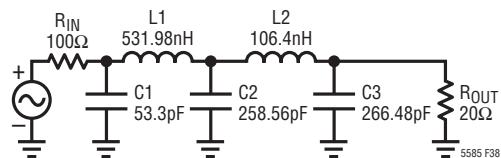

LNA、復調器、ローパス・フィルタ、ADC ドライバ、および ADC を連結した標準的レシーバ・アプリケーションを図33に示します。合計 DC 消費電力は約 2.1W です。RF 入力のフルスケール電力は -6dBm です。不等終端されたチェビシェフ・ローパス・フィルタは、付録に示されている方法を使って設計されています。フィルタ部品の値は、利用可能な部品の値で全体の

図31. V<sub>BIAS</sub>ピンのインターフェースの簡略回路図

図32. IIP3 および P1dB と DC 電流

および V<sub>BIAS</sub> の抵抗値

応答を最良にするように調整されています。ADC ドライバおよびアンチエイリアス・フィルタの影響によるロールオフを補償するには、周波数に対して電圧利得の正の勾配が必要です。図34に示されているチェーンの解析から、IIP3-NFのダイナミックレンジのメリット指標(FOM)はLNA 入力で 4.3dB、復調器の入力で 7.5dB、ADC ドライバ・アンプの入力で 14.85dB です。

## アプリケーション情報

図33. 1950MHzレシーバの簡略回路図(1チャネルのみ示されている)

## アプリケーション情報

図34. 1950MHzレシーバのチェーン解析

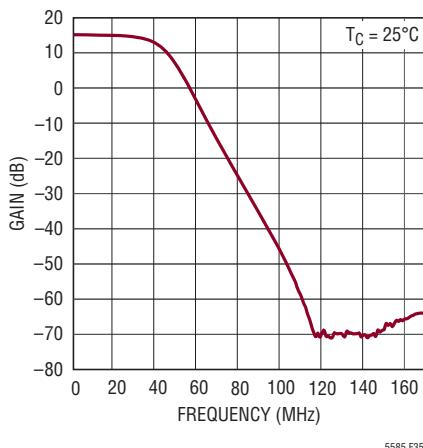

図35. LNAなしのベースバンド利得応答

測定された6次ローパス・ベースバンド応答を図35に示します。

FOMで表したレシーバのスプリアスフリー・ダイナミックレンジ(SFDR)は、以下の式を使って計算することができます。

$$\text{FOM} = \text{IIP3} - \text{NF}$$

$$\text{SFDR} = 2/3(\text{FOM} - \text{P}_0)$$

$$\text{P}_0 = -174\text{dBm} + 10\text{Log}_{10}(\text{BW}|\text{Hz})$$

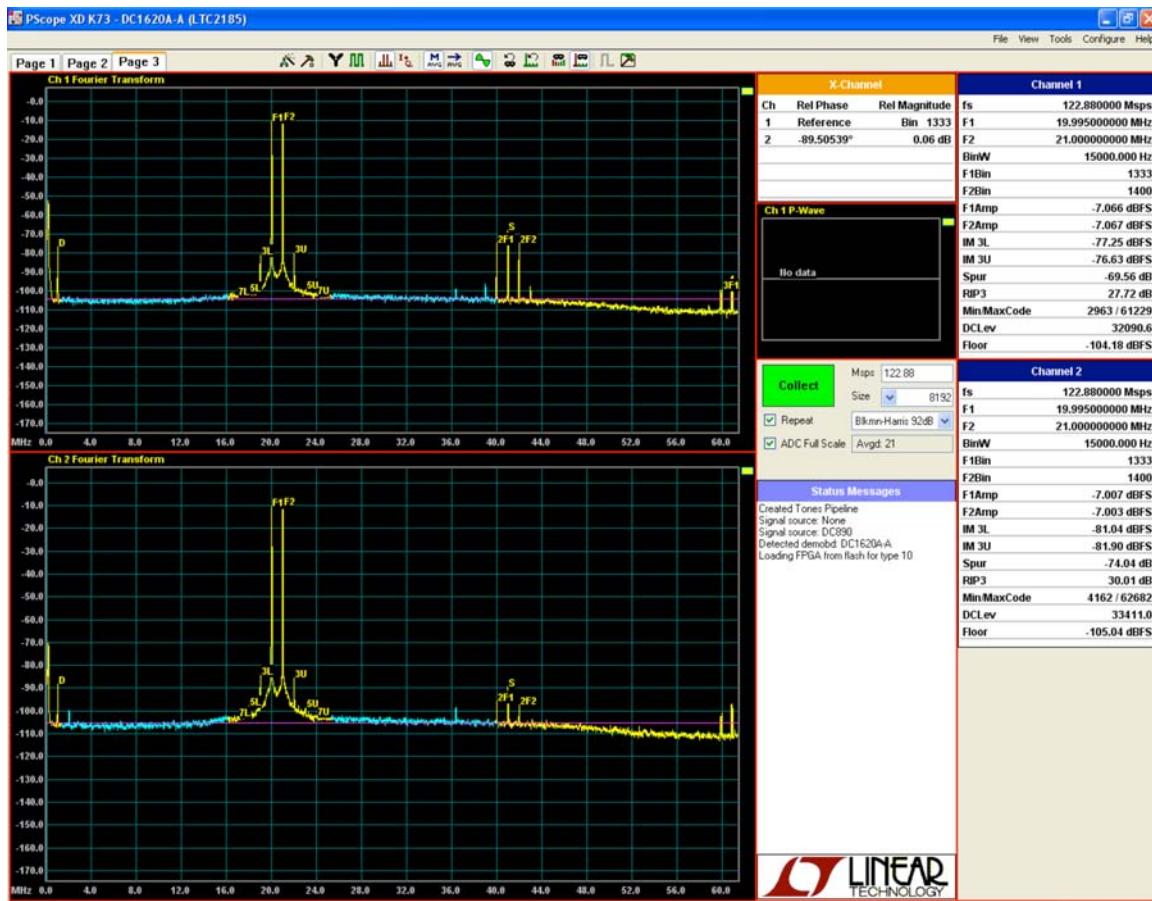

ここで、P<sub>0</sub>は入力ノイズ電力、-174dBmは1Hz帯域幅の入力熱ノイズ電力です。1910MHzで測定された2トーン出力スペクトルを図36に示します。IIP3は2トーンIM3レベルから計算されます。

$$\text{IIP3} = (-7.067 - (-76.63))/2 - 13$$

$$\text{IIP3} = 21.78\text{dBm}$$

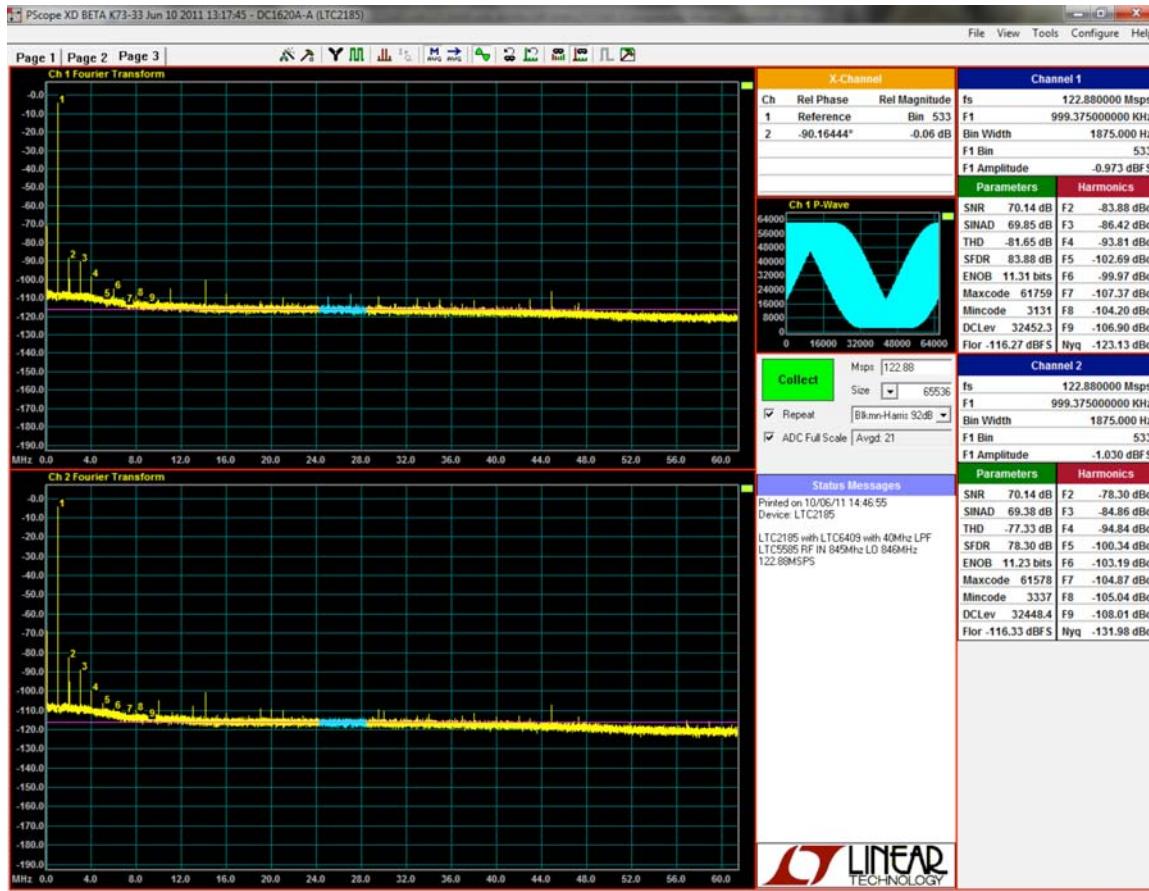

この例では、レシーバのノイズフロアは845MHzでの測定値によって近似しています。この場合、RF信号とLO信号の適切なフィルタ処理が可能でした。図37のテストデータを使うと、レシーバのIチャネル(Ch1)のノイズフィギュアは、-6dBmの入力電力、1875Hzのビン幅、40MHzの帯域幅、および-116.3dBFSの帯域内ノイズフロアの測定値を使って、以下のように計算されます。

$$\text{SNR}_{\text{IN}} = \text{P}_{\text{IN}} - \text{P}_0$$

$$\text{SNR}_{\text{IN}} = -6 - (-174 + 76) = 92\text{dB}$$

$$\text{SNR}_{\text{OUT}} = -10 \text{ Log}_{10}(\text{BinW}/\text{BW}) - \text{Floor}$$

$$\text{SNR}_{\text{OUT}} = -43.3 + 116.3 = 73\text{dB}$$

$$\text{NF} = \text{SNR}_{\text{IN}} - \text{SNR}_{\text{OUT}}$$

$$\text{NF} = 92 - 73 = 19\text{dB}$$

最後に、レシーバのおおよそのスプリアスフリー・ダイナミックレンジは、845MHzと1910MHzで測定したデータを使って、以下のように計算されます。

$$\text{SFDR} = 2(\text{IIP3} - \text{NF} - \text{P}_0)/3$$

$$\text{SFDR} = 2(21.78 - 19 - (-174 + 76))/3$$

$$\text{SFDR} = 67.2\text{dB} (\text{Iチャネル})$$

Qチャネルの測定されたIIP3は2.3dB高いので、SFDRは次のようになります。

$$\text{SFDR} = 68.7\text{dB} (\text{Qチャネル})$$

## アプリケーション情報

図 36.  $f_{RF} = 1909\text{MHz}$  および  $1910\text{MHz}$  の 2トーン・レシーバ・テスト、

$f_{LO} = 1930\text{MHz}$ 。Ch.1 は I チャネル、Ch.2 は Q チャネル。LNA なしでテスト

## アプリケーション情報

図37.  $f_{RF} = 845\text{MHz}$ でのレシーバ・ノイズフロア・テスト、

$f_{LO} = 846\text{MHz}$ 。Ch.1はIチャネル、Ch.2はQチャネル。LNAなしでテスト

## 付録

### 不等終端によるチェビシェフ・フィルタの合成

不等終端を使ってチェビシェフ・フィルタを合成するには、2つの等しく終端されたフィルタを2つの異なるインピーダンス・レベルで合成し、その結果得られるネットワークを、インピーダンス2分法理論を使って結合します[1]。この方法は、対称奇数次フィルタに対してだけ使えます。一般的なローパスのプロトタイプの素子の値は、下に示す方法によって発生させることができます[2]。

$$\beta = \ln \left[ \coth \frac{L_{Ar} |_{dB}}{17.37} \right]$$

$$\gamma = \sinh \left( \frac{\beta}{2n} \right)$$

$$a_k = \sin \frac{\pi(2k-1)}{2n}, k=1,2,\dots,n$$

$$b_k = \gamma^2 + \sin^2 \frac{\pi k}{n}, k=1,2,\dots,n$$

ここで、 $L_{Ar}|_{dB}$  は dB で表したパスバンド・リップル、n はフィルタの次数です。

プロトタイプの素子の値は以下のようにになります。

$$g_1 = \frac{2a_1}{\gamma}$$

$$g_k = \frac{4a_k a_{k-1}}{b_{k-1} g_{k-1}}, k=1,2,\dots,n$$

$$g_{n+1} = 1 \text{ for } n \text{ odd}$$

$$g_{n+1} = \coth^2 \left( \frac{\beta}{4} \right) \text{ for } n \text{ even}$$

最初の素子がコンデンサであると仮定すると、フィルタのコンデンサのプロトタイプ値を所期のカットオフ周波数  $f_C$  までスケールアップすることができます。

$$C_k = \frac{g_k}{2\pi \cdot f_C \cdot R_{IN}}, k=1,3,\dots,n$$

フィルタのインダクタの値は次のように調整できます。

$$L_k = \frac{g_k \cdot R_{IN}}{2\pi \cdot f_C}, k=2,4,\dots,n$$

ここで、 $R_{IN}$  は入力インピーダンスです。終端インピーダンス  $R_{OUT}$  は、n が奇数の場合は  $R_{IN}$  に等しいが、n が偶数の場合は、 $g_{n+1}$  プロトタイプ値に応じて調整します。

対称ネットワークの対称面に沿って素子の値を分割し、次に2つのネットワークを一緒に結合して、対称ネットワークにインピーダンス2分法理論を適用することができます。フィルタ応答は維持されます。

たとえば、 $L_{Ar}|_{dB}=0.2$ dB、 $f_C=40$ MHz、 $R_{IN}=100\Omega$ 、および  $n=5$  であれば、プロトタイプ素子の値およびそれに応じて調整されたフィルタの値は以下のようになります。

**フィルタ1:**  $R_{IN} = R_{OUT} = 100\Omega$

$$g_1 = 1.339 \rightarrow C_1 = 53.3pF$$

$$g_2 = 1.337 \rightarrow L_1 = 531.98nH$$

$$g_3 = 2.166 \rightarrow C_2 = 86.19pF$$

$$g_4 = 1.337 \rightarrow L_2 = 531.98nH$$

$$g_5 = 1.339 \rightarrow C_3 = 53.3pF$$

**フィルタ2:**  $R_{IN} = R_{OUT} = 20\Omega$

$$g_1 = 1.339 \rightarrow C_1 = 266.48pF$$

$$g_2 = 1.337 \rightarrow L_1 = 106.4nH$$

$$g_3 = 2.166 \rightarrow C_2 = 430.93pF$$

$$g_4 = 1.337 \rightarrow L_2 = 106.4nH$$

$$g_5 = 1.339 \rightarrow C_3 = 266.48pF$$

2つのフィルタの1/2の値を使って  $C_2$  の新しい値を計算できるように、インピーダンス2分法理論を  $C_2$  の対称面に対して適用することができます。

$$C_2 \rightarrow \frac{86.19pF}{2} + \frac{430.93pF}{2} = 258.56pF$$

不等終端されたフィルタの最終設計値を図38に示します。

図38. 最終設計の回路図

[1] A.C.Bartlett, "An Extension of a Property of Artificial Lines," Phil.Mag., vol.4, p.902, November 1927.

[2] G. Matthaei, L. Young, and E.M.T.Jones, Microwave Filters, Impedance-Matching Networks, and Coupling Structures, p.99, 1964.

## 付録

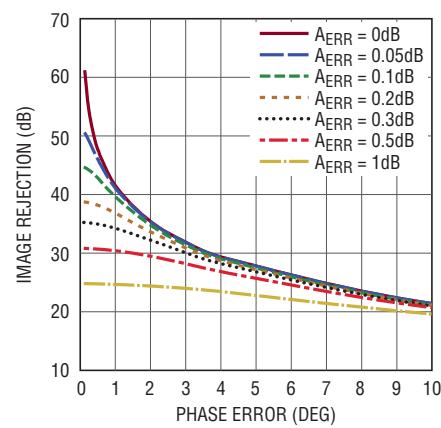

### イメージ除去比の計算

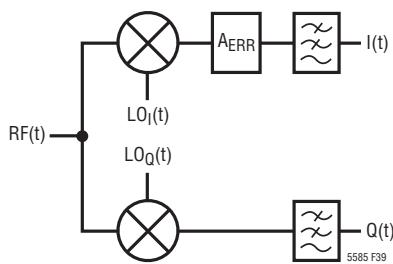

復調器の測定された利得と位相誤差応答からイメージ除去比を計算することができます。図39の信号ダイアグラムを考えます。

図39. 復調器の信号ダイアグラム

ここで、

$$RF(t) = \sin(\omega_{LO} + \omega_{BB})t + \sin(\omega_{LO} - \omega_{IM})t$$

$$LO_I(t) = \cos(\omega_{LO}t + \phi_{ERR})$$

$$LO_Q(t) = \sin(\omega_{LO}t)$$

$\omega_{LO} + \omega_{BB}$  は所期のサイドバンド周波数、 $\omega_{LO} - \omega_{IM}$  はイメージ周波数です。IチャネルとQチャネルの全位相誤差は  $\phi_{ERR}$  として Iチャネルの LO ソースへと一括されます。AERR で表される全利得誤差は、Iチャネルの利得乗算器へ一括されます。

ローパス・フィルタを通した後、I信号とQ信号は次のように書くことができます。

$$I(t) = \frac{A_{ERR}}{2} [\sin(\omega_{BB}t - \phi_{ERR}) - \sin(\omega_{IM}t + \phi_{ERR})]$$

$$Q(t) = \frac{1}{2} [\cos(\omega_{BB}t) + \cos(\omega_{IM}t)]$$

シフトさせたQチャネル信号が次のようになるように、正弦波を余弦波で置き換えることにより、Qチャネルを  $-90^\circ$  シフトさせることができます。

$$Q_{-90}(t) = \frac{1}{2} [\sin(\omega_{BB}t) + \sin(\omega_{IM}t)]$$

I(t)と  $Q_{-90}(t)$  を結合し、 $\omega_{BB}$  を含む項を所期の信号として選択します。

$$\text{desired} = \frac{1}{2} \sin(\omega_{BB}t) + \frac{A_{ERR}}{2} \sin(\omega_{BB}t - \phi_{ERR})$$

同様に、 $\omega_{IM}$  を含む項をイメージ信号として選択します。

$$\text{image} = \frac{1}{2} \sin(\omega_{IM}t) - \frac{A_{ERR}}{2} \sin(\omega_{IM}t + \phi_{ERR})$$

したがって、イメージ除去比(IRR)を次のように書くことができます。

$$\text{IRR}_{\text{dB}} = 10 \log \frac{|\text{desired}|^2}{|\text{image}|^2}$$

$A_{ERR}$  と  $\phi_{ERR}$  を使って書くと、次のようにになります。

$$\text{IRR}_{\text{dB}} = 10 \log \frac{|1 + A_{ERR}^2 + 2A_{ERR} \cos(\phi_{ERR})|}{|1 + A_{ERR}^2 - 2A_{ERR} \cos(\phi_{ERR})|}$$

イメージ除去比を復調器の振幅および位相誤差の関数として図40に示します。

図40. 利得と位相誤差の関数としてのイメージ除去比

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

**UF Package

24-Lead Plastic QFN (4mm × 4mm)**

(Reference LTC DWG # 05-08-1697 Rev B)

NOTE:

1. 図は JEDEC パッケージ外形 MO-220 のバリエーション (WGGD-X) に対するよう提案されている (承認待ち)

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは (もしあれば) 各サイドで 0.15mm を超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

## 改訂履歴

| REV | 日付    | 概要                                         | ページ番号 |

|-----|-------|--------------------------------------------|-------|

| A   | 8/12  | 1950MHzでのL6、C19、L5の整合部品の値を変更               | 3     |

|     |       | 5585のグラフG4の縦軸のラベルを修正                       | 6     |

|     |       | グラフG20を変更                                  | 8     |

|     |       | グラフG30とG35を変更                              | 10    |

|     |       | グラフG44の横軸のラベルを修正                           | 11    |

|     |       | グラフG61を変更                                  | 13    |

|     |       | グラフG78を変更                                  | 15    |

|     |       | 図1のRFとL0の整合表において1950MHzでのL6、C19、L5の部品の値を変更 | 18    |

|     |       | 図5の1.9GHzでのL6とC19の部品の値を変更                  | 20    |

|     |       | 図13の1.9GHzでのL5の部品の値を変更                     | 22    |

|     |       | 「消費電力の低減」の段落タイトルを追加                        | 29    |

|     |       | 図32のタイトルを修正                                | 29    |

|     |       | テキストを「1875Hz」に修正                           | 31    |

|     |       |                                            |       |

| B   | 11/14 | 特長と概要を変更                                   | 1     |

|     |       | 700MHzでのIRRを変更                             | 3     |

|     |       | 3500MHzでのデータと電源電流の条件を挿入                    | 4     |

|     |       | グラフG19の縦軸のラベルを修正                           | 8     |

|     |       | グラフG34の縦軸のラベルを修正                           | 10    |

|     |       | グラフG45の横軸のラベルを修正                           | 11    |

|     |       | グラフG60の縦軸のラベルを修正                           | 13    |

|     |       | グラフG77の縦軸のラベルを修正                           | 15    |

|     |       | 図1のRFの整合表において2150MHzでの表の値を変更               | 18    |

|     |       | 図13のC13とL5の部品の値を変更                         | 22    |

|     |       | テキストを「遅れます(または進みます)。」に変更                   | 23    |

|     |       | 6mAの電流の矢印を削除                               | 24    |

|     |       | 図22のCの値を変更                                 | 26    |

|     |       | 図33のADC出力D15を変更                            | 30    |

|     |       | 標準的応用例のADC出力D15を変更                         | 38    |

# LTC5585

## 標準的応用例

1950MHzレシーバの簡略回路図(Iチャネルのみ示されている)

## 関連製品

| 製品番号                      | 説明                                          | 注釈                                                             |

|---------------------------|---------------------------------------------|----------------------------------------------------------------|

| <b>インフラストラクチャ</b>         |                                             |                                                                |

| LTC5569                   | 300MHz～4GHz、デュアル・アクティブ・ダウンコンバーティング・ミキサ      | 利得:2dB、IIP3:1950MHzで26.7dBm、NF:1950MHzで11.7dB、3.3V/180mA電源     |

| LT5527                    | 400MHz～3.7GHz、5V ダウンコンバーティング・ミキサ            | 利得:2.3dB、IIP3:1900MHzで23.5dBm、NF:1900MHzで12.5dB、5V/78mA電源      |

| LT5557                    | 400MHz～3.8GHz、3.3V ダウンコンバーティング・ミキサ          | 利得:2.9dB、IIP3:1950MHzで24.7dBm、NF:1950MHzで11.7dB、3.3V/82mA電源    |

| LTC6409                   | 10GHz GBW 差動アンプ                             | DC結合、OIP3:140MHzで48dBm、入力ノイズ密度:1.1nV/ $\sqrt{\text{Hz}}$       |

| LTC6412                   | 31dB リニアアナログ制御 VGA                          | OIP3:240MHzで35dBm、連続利得範囲:-14dB～17dB                            |

| LTC554X                   | 600MHz～4GHzのダウンコンバーティング・ミキサのファミリー           | 利得:8dB、IIP3:>25dBm、NF:10dB、3.3V/200mA電源                        |

| LT5554                    | 超低歪みIFデジタル制御 VGA                            | OIP3:200MHzで48dBm、利得範囲:2dB～18dB、利得ステップ:0.125dB                 |

| LT5578                    | 400MHz～2.7GHz アップコンバーティング・ミキサ               | OIP3:900MHzで27dBm、1.95GHzで24.2dBm、RFトランスを内蔵                    |

| LT5579                    | 1.5GHz～3.8GHz アップコンバーティング・ミキサ               | OIP3:2.14GHzで27.3dBm、NF=9.9dB、3.3V電源、シングルエンドのLOおよびRFポート        |

| LTC5590                   | デュアル 600MHz～1.7GHz ダウンコンバーティング・ミキサ          | 利得:8.7dB、IIP3:26dBm、ノイズフィギュア:9.7dB                             |

| LTC5591                   | デュアル 1.3GHz～2.3GHz ダウンコンバーティング・ミキサ          | 利得:8.5dB、IIP3:26.2dBm、ノイズフィギュア:9.9dB                           |

| LTC5592                   | デュアル 1.6GHz～2.7GHz ダウンコンバーティング・ミキサ          | 利得:8.3dB、IIP3:27.3dBm、ノイズフィギュア:9.8dB                           |

| <b>VCO付きRF PLL/シンセサイザ</b> |                                             |                                                                |

| LTC6946-1                 | VCO内蔵の低ノイズ、低スプリアスの整数分周方式 PLL                | 373MHz～3.74GHz、WB位相ノイズフロア:-157dBc/Hz、閉ループ位相ノイズ:-100dBc/Hz      |

| LTC6946-2                 | VCO内蔵の低ノイズ、低スプリアスの整数分周方式 PLL                | 513MHz～4.9GHz、WB位相ノイズフロア:-157dBc/Hz、閉ループ位相ノイズ:-100dBc/Hz       |

| LTC6946-3                 | VCO内蔵の低ノイズ、低スプリアスの整数分周方式 PLL                | 640MHz～5.79GHz、WB位相ノイズフロア:-157dBc/Hz、閉ループ位相ノイズ:-100dBc/Hz      |

| <b>ADC</b>                |                                             |                                                                |

| LTC2145-14                | 14ビット、125Msps 1.8V デュアル ADC                 | SNR:73.1dB、SFDR:90dB、消費電力:95mW/チャネル                            |

| LTC2185                   | 16ビット、125Msps 1.8V デュアル ADC                 | SNR:76.8dB、SFDR:90dB、消費電力:185mW/チャネル                           |

| LTC2158-14                | 14ビット、310Msps 1.8V デュアル ADC、最大電力帯域幅:1.25GHz | SNR:68.8dB、SFDR:88dB、消費電力:362mW/チャネル、入力範囲:1.32V <sub>P-P</sub> |

5585fb