## 特長

- IEEE 802.3at タイプ1およびタイプ2に準拠

- 低電力損失

センス抵抗:  $0.25\Omega$  / チャネル

- 信頼性の極めて高い4ポイントPD検出:

2ポイントの電圧強制

2ポイントの電流強制

- 高容量のレガシー装置を検出

- 1MHzのI<sup>2</sup>C互換シリアル制御インターフェース

- ミッドスパン・バックオフ・タイマ

- 2ペアおよび4ペアの出力電力をサポート

- 複数の電力グレード:

LTC4274A-1:LTPoE++™ 38.7W

LTC4274A-2:LTPoE++ 52.7W

LTC4274A-3:LTPoE++ 70W

LTC4274A-4:LTPoE++ 90W

LTC4274C:PoE 13W

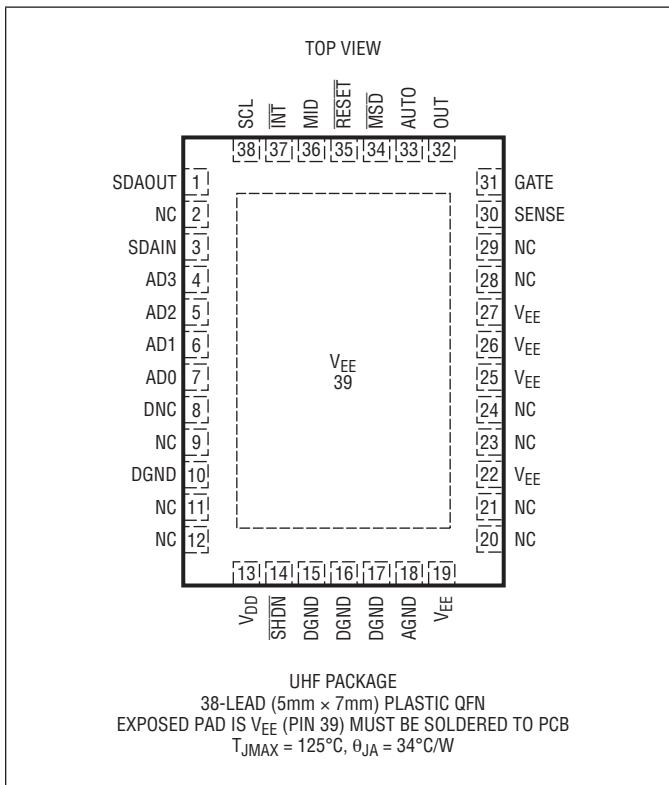

- 38ピン 5mm×7mm QFNパッケージ

## アプリケーション

- LTPoE++ PSEスイッチ/ルータ

- LTPoE++ PSEミッドスパン

- IEEE 802.3at タイプ1 PSEスイッチ/ルータ

- IEEE 802.3at タイプ1 PSEミッドスパン

**L**、**LT**、**LTC**、**LTM**、**Linear Technology**およびLinearのロゴはリニアテクノロジー社の登録商標です。LTPoE++はリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。

## 概要

**LTC®4274A** は、最大90WのLTPoE++の電力をLTPoE++に 対応する受電装置(PD)に供給可能な、シングル給電装置(PSE)コントローラです。独自の検出/分類手法により、LTPoE++のPSEとLTPoE++のPDの間の相互識別を可能にしながら、既存のタイプ1(13W)およびタイプ2(25.5W)のPDとの互換性と相互運用性を維持しています。LTC4274Aは既存のLTC4274の上位互換デバイスです。これらのPSEコントローラは、LTPoE++の電流レベルで熱損失を最小に保つために特に重要な、低 $R_{ON}$ の外部MOSFETと $0.25\Omega$ のセンス抵抗を備えています。

LTC4274Cは、タイプ1(最大13W)のPDに電力を供給する全自動PSEシステム向けのデバイスです。

高度なパワーマネージメントとして、14ビットの電流モニタリングADC、DACでプログラム可能な電流制限、多用途に使える高速シャットダウンなどの機能を備えています。PDの検出は、独自のデュアル・モード4ポイント検出メカニズムを使用して行われ、PDの誤検出を最大限防止できます。LTC4274A/LTC4274Cは、最大1MHzで動作可能なI<sup>2</sup>Cシリアル・インターフェースを備えています。

LTC4274A/LTC4274Cには複数の電力グレードがあり、13W、25.5W、38.7W、52.7W、70Wおよび90Wの電力をPDに供給できます。これらのコントローラは、38ピン 5mm×7mm QFNパッケージで供給されます。

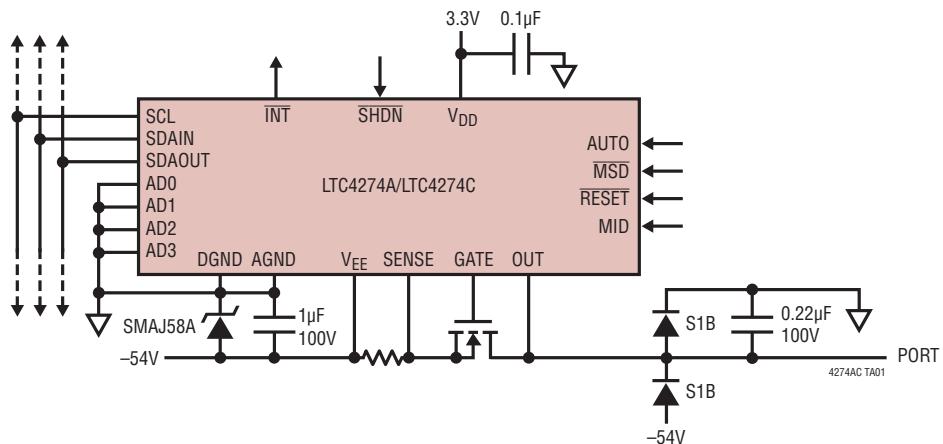

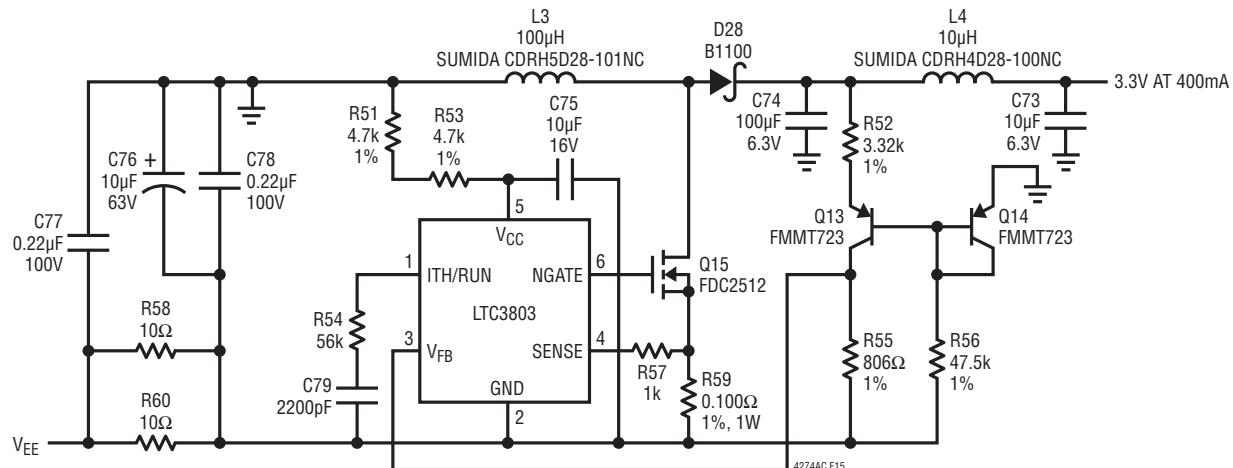

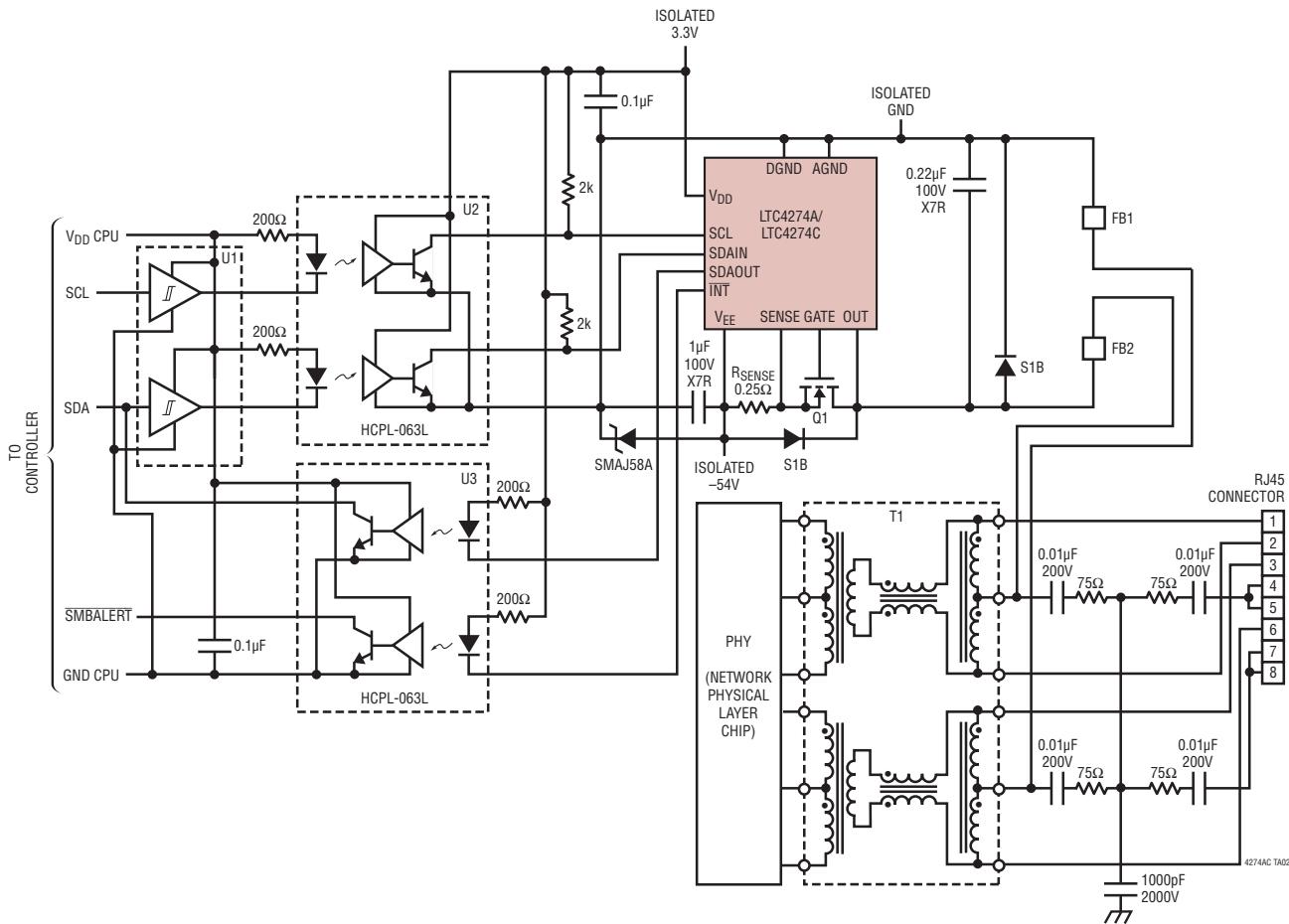

## 標準的応用例

完全なシングルポート・イーサネット高電力源

4274acf0

# LTC4274A/LTC4274C

## 絶対最大定格

### 電源電圧 (Note 1)

|                              |              |

|------------------------------|--------------|

| AGND – V <sub>EE</sub> ..... | -0.3V ~ 80V  |

| DGND – V <sub>EE</sub> ..... | -0.3V ~ 80V  |

| V <sub>DD</sub> – DGND.....  | -0.3V ~ 5.5V |

### デジタル・ピン

SCL、SDAIN、SDAOUT、INT、SHDN、MSD、AD、

RESET、AUTO、MID ..... (DGND – 0.3V) ~ (V<sub>DD</sub> + 0.3V)

### アナログ・ピン

GATE、SENSE、OUT ..... (V<sub>EE</sub> – 0.3V) ~ (V<sub>EE</sub> + 80V)

動作温度範囲..... –40°C ~ 85°C

接合部温度 (Note 2) ..... 125°C

保存温度範囲..... –65°C ~ 150°C

リード温度(半田付け、10秒) ..... 300°C

## ピン配置

## 発注情報

| 鉛フリー仕様             | テープアンドリール            | 製品マーキング | パッケージ                           | 最大電力  | 温度範囲          |

|--------------------|----------------------|---------|---------------------------------|-------|---------------|

| LTC4274CIUHF#PBF   | LTC4274CIUHF#TRPBF   | 4274C   | 38-Lead (5mm x 7mm) Plastic QFN | 13W   | –40°C to 85°C |

| LTC4274AIUHF-1#PBF | LTC4274AIUHF-1#TRPBF | 4274A1  | 38-Lead (5mm x 7mm) Plastic QFN | 38.7W | –40°C to 85°C |

| LTC4274AIUHF-2#PBF | LTC4274AIUHF-2#TRPBF | 4274A2  | 38-Lead (5mm x 7mm) Plastic QFN | 52.7W | –40°C to 85°C |

| LTC4274AIUHF-3#PBF | LTC4274AIUHF-3#TRPBF | 4274A3  | 38-Lead (5mm x 7mm) Plastic QFN | 70W   | –40°C to 85°C |

| LTC4274AIUHF-4#PBF | LTC4274AIUHF-4#TRPBF | 4274A4  | 38-Lead (5mm x 7mm) Plastic QFN | 90W   | –40°C to 85°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $\text{AGND} - V_{EE} = 54\text{V}$ 、 $\text{AGND} = \text{DGND}$ 、 $V_{DD} - \text{DGND} = 3.3\text{V}$ 。(Note 3, 4)

| SYMBOL   | PARAMETER                       | CONDITIONS                                                                                                                     | MIN         | TYP               | MAX            | UNITS |    |

|----------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|----------------|-------|----|

| $V_{EE}$ | Main PoE Supply Voltage         | $\text{AGND} - V_{EE}$<br>For IEEE Type 1 Compliant Output<br>For IEEE Type 2 Compliant Output<br>For LTPoE++ Compliant Output | ●<br>●<br>● | 45<br>51<br>54.75 | 57<br>57<br>57 | V     |    |

|          | Undervoltage Lockout            | $\text{AGND} - V_{EE}$                                                                                                         | ●           | 20                | 25             | V     |    |

|          |                                 |                                                                                                                                |             | 30                |                | V     |    |

| $V_{DD}$ | $V_{DD}$ Supply Voltage         | $V_{DD} - \text{DGND}$                                                                                                         | ●           | 3.0               | 3.3            | V     |    |

|          | Undervoltage Lockout            |                                                                                                                                | ●           |                   | 2.2            | V     |    |

|          | Allowable Digital Ground Offset | $\text{DGND} - V_{EE}$                                                                                                         | ●           | 25                | 57             | V     |    |

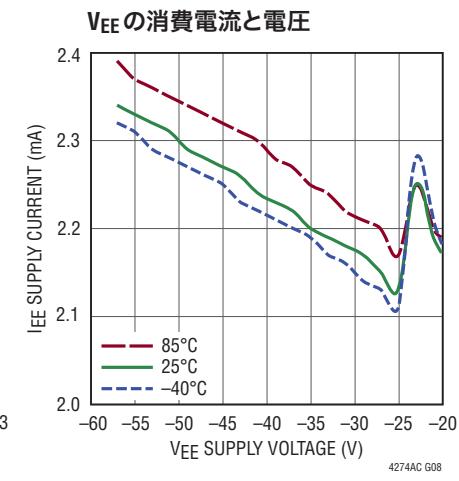

| $I_{EE}$ | $V_{EE}$ Supply Current         | $(\text{AGND} - V_{EE}) = 55\text{V}$                                                                                          | ●           |                   | -2.4           | -5    | mA |

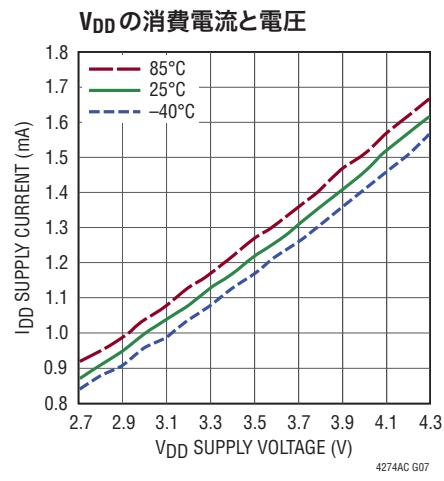

| $I_{DD}$ | $V_{DD}$ Supply Current         | $(V_{DD} - \text{DGND}) = 3.3\text{V}$                                                                                         | ●           |                   | 1.1            | 3     | mA |

## 検出

|          |                                    |                                                                                                         |        |            |            |            |                        |

|----------|------------------------------------|---------------------------------------------------------------------------------------------------------|--------|------------|------------|------------|------------------------|

|          | Detection Current – Force Current  | First Point, $\text{AGND} - V_{OUT} = 9\text{V}$<br>Second Point, $\text{AGND} - V_{OUT} = 3.5\text{V}$ | ●<br>● | 220<br>140 | 240<br>160 | 260<br>180 | $\mu\text{A}$          |

|          | Detection Voltage – Force Voltage  | $\text{AGND} - V_{OUT}, 5\mu\text{A} \leq I_{OUT} \leq 500\mu\text{A}$<br>First Point<br>Second Point   | ●<br>● | 7<br>3     | 8<br>4     | 9<br>5     | V<br>V                 |

|          | Detection Current Compliance       | $\text{AGND} - V_{OUT} = 0\text{V}$                                                                     | ●      |            | 0.8        | 0.9        | mA                     |

| $V_{OC}$ | Detection Voltage Compliance       | $\text{AGND} - V_{OUT}$ , Open Port                                                                     | ●      |            | 10.4       | 12         | V                      |

|          | Detection Voltage Slew Rate        | $\text{AGND} - V_{OUT}, C_{PORT} = 0.15\mu\text{F}$                                                     | ●      |            |            | 0.01       | $\text{V}/\mu\text{s}$ |

|          | Minimum Valid Signature Resistance |                                                                                                         | ●      | 15.5       | 17         | 18.5       | $\text{k}\Omega$       |

|          | Maximum Valid Signature Resistance |                                                                                                         | ●      | 27.5       | 29.7       | 32         | $\text{k}\Omega$       |

## 分類

|             |                                   |                                                                                   |                       |                                     |                               |                                     |                            |

|-------------|-----------------------------------|-----------------------------------------------------------------------------------|-----------------------|-------------------------------------|-------------------------------|-------------------------------------|----------------------------|

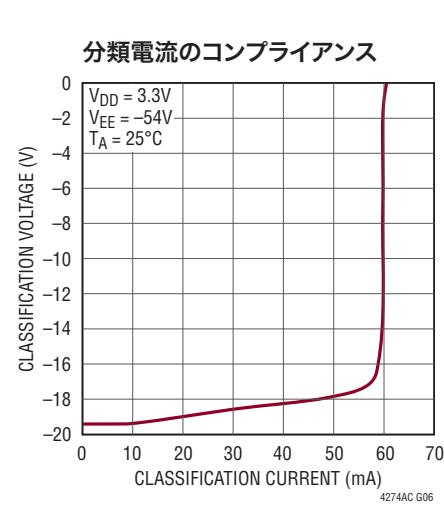

| $V_{CLASS}$ | Classification Voltage            | $\text{AGND} - V_{OUT}, 0\text{mA} \leq I_{CLASS} \leq 50\text{mA}$               | ●                     | 16.0                                | 20.5                          | V                                   |                            |

|             | Classification Current Compliance | $V_{OUT} = \text{AGND}$                                                           | ●                     | 53                                  | 61                            | 67                                  | mA                         |

|             | Classification Threshold Current  | Class 0 – 1<br>Class 1 – 2<br>Class 2 – 3<br>Class 3 – 4<br>Class 4 – Overcurrent | ●<br>●<br>●<br>●<br>● | 5.5<br>13.5<br>21.5<br>31.5<br>45.2 | 6.5<br>14.5<br>23<br>33<br>48 | 7.5<br>15.5<br>24.5<br>34.9<br>50.8 | mA<br>mA<br>mA<br>mA<br>mA |

| $V_{MARK}$  | Classification Mark State Voltage | $\text{AGND} - V_{OUT}, 0.1\text{mA} \leq I_{CLASS} \leq 10\text{mA}$             | ●                     | 7.5                                 | 9                             | 10                                  | V                          |

|             | Mark State Current Compliance     | $V_{OUT} = \text{AGND}$                                                           | ●                     | 53                                  | 61                            | 67                                  | mA                         |

## ゲート・ドライバ

|  |                                 |                                                                                        |        |             |      |    |   |

|--|---------------------------------|----------------------------------------------------------------------------------------|--------|-------------|------|----|---|

|  | GATE Pin Pull-Down Current      | Port Off, $V_{GATE} = V_{EE} + 5\text{V}$<br>Port Off, $V_{GATE} = V_{EE} + 1\text{V}$ | ●<br>● | 0.4<br>0.08 | 0.12 | mA |   |

|  | GATE Pin Fast Pull-Down Current | $V_{GATE} = V_{EE} + 5\text{V}$                                                        |        |             | 30   | mA |   |

|  | GATE Pin On Voltage             | $V_{GATE} - V_{EE}, I_{GATE} = 1\mu\text{A}$                                           | ●      | 8           | 12   | 14 | V |

## 出力電圧の検出

|          |                                    |                                                         |   |     |     |     |                  |

|----------|------------------------------------|---------------------------------------------------------|---|-----|-----|-----|------------------|

| $V_{PG}$ | Power Good Threshold Voltage       | $V_{OUT} - V_{EE}$                                      | ● | 2   | 2.4 | 2.8 | V                |

|          | OUT Pin Pull-Up Resistance to AGND | $0\text{V} \leq (\text{AGND} - V_{OUT}) \leq 5\text{V}$ | ● | 300 | 500 | 700 | $\text{k}\Omega$ |

# LTC4274A/LTC4274C

## 電気的特性

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $\text{AGND} - V_{EE} = 54\text{V}$ 、 $\text{AGND} = \text{DGND}$ 、 $V_{DD} - \text{DGND} = 3.3\text{V}$ 。(Note 3, 4)

| SYMBOL               | PARAMETER                                      | CONDITIONS                                                                                                                                                                                                                            | MIN              | TYP                   | MAX                   | UNITS                    |                      |

|----------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|-----------------------|--------------------------|----------------------|

| <b>電流の検出</b>         |                                                |                                                                                                                                                                                                                                       |                  |                       |                       |                          |                      |

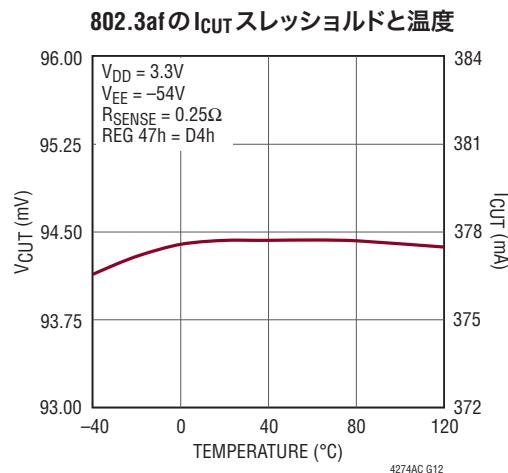

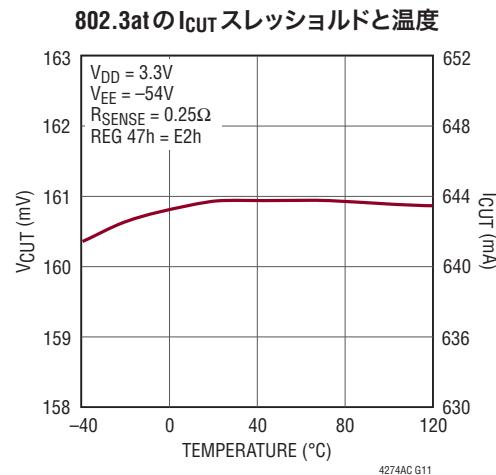

| $V_{CUT}$            | Overcurrent Sense Voltage                      | $V_{SENSE} - V_{EE}$ , $\text{hpen} = 01\text{h}$ , $\text{cut}[5:0] \geq 4$ (Note 12)<br>$\text{cutrng} = 0$<br>$\text{cutrng} = 1$                                                                                                  | ●<br>●           | 9<br>4.5              | 9.38<br>4.69          | 9.75<br>4.88             | mV/LSB<br>mV/LSB     |

|                      | Overcurrent Sense in AUTO Pin Mode             | Class 0, Class 3<br>Class 1<br>Class 2<br>Class 4                                                                                                                                                                                     | ●<br>●<br>●<br>● | 90<br>26<br>49<br>152 | 94<br>28<br>52<br>159 | 98<br>30<br>55<br>166    | mV<br>mV<br>mV<br>mV |

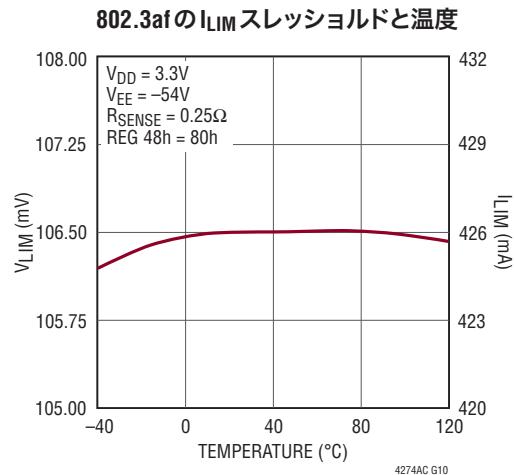

| $V_{LIM}$            | Active Current Limit in 802.3af Compliant Mode | $V_{SENSE} - V_{EE}$ , $\text{hpen} = 01\text{h}$ , $\text{lim} = 80\text{h}$ ,<br>$V_{EE} = 55\text{V}$ (Note 12)<br>$V_{EE} < V_{OUT} < \text{AGND} - 29\text{V}$<br>$\text{AGND} - V_{OUT} = 0\text{V}$                            | ●<br>●           | 102<br>20             | 106<br>50             | 110<br>50                | mV<br>mV             |

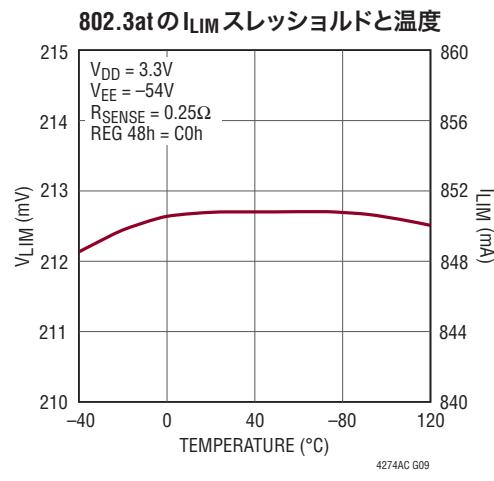

| $V_{LIM}$            | Active Current Limit in High Power Mode        | $\text{hpen} = 01\text{h}$ , $\text{lim} = C0\text{h}$ , $V_{EE} = 55\text{V}$<br>$V_{OUT} - V_{EE} = 0\text{V}$ to $10\text{V}$<br>$V_{EE} + 23\text{V} < V_{OUT} < \text{AGND} - 29\text{V}$<br>$\text{AGND} - V_{OUT} = 0\text{V}$ | ●<br>●<br>●      | 204<br>100<br>20      | 212<br>106<br>50      | 221<br>113<br>50         | mV<br>mV<br>mV       |

| $V_{LIM}$            | Active Current Limit in AUTO Pin Mode          | $V_{OUT} - V_{EE} = 0\text{V}$ to $10\text{V}$ , $V_{EE} = 55\text{V}$<br>Class 0 to Class 3<br>Class 4                                                                                                                               | ●<br>●           | 102<br>204            | 106<br>212            | 110<br>221               | mV<br>mV             |

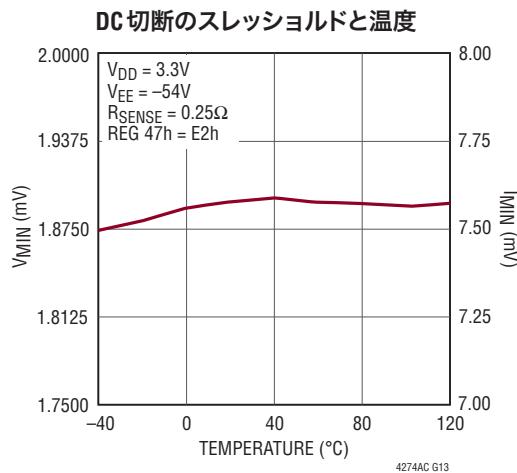

| $V_{MIN}$            | DC Disconnect Sense Voltage                    | $V_{SENSE} - V_{EE}$ , $\text{rdis} = 0$<br>$V_{SENSE} - V_{EE}$ , $\text{rdis} = 1$                                                                                                                                                  | ●<br>●           | 2.6<br>1.3            | 3.8<br>1.9            | 4.8<br>2.41              | mV<br>mV             |

| $V_{SC}$             | Short-Circuit Sense                            | $V_{SENSE} - V_{EE} - V_{LIM}$ , $\text{rdis} = 0$<br>$V_{SENSE} - V_{EE} - V_{LIM}$ , $\text{rdis} = 1$                                                                                                                              | ●<br>●           | 160<br>75             | 200<br>100            | 255<br>135               | mV<br>mV             |

| <b>ポート電流の読み出し</b>    |                                                |                                                                                                                                                                                                                                       |                  |                       |                       |                          |                      |

|                      | Resolution                                     | No Missing Codes, $\text{fast\_iv} = 0$                                                                                                                                                                                               |                  |                       | 14                    | Bits                     |                      |

|                      | LSB Weight                                     | $V_{SENSE} - V_{EE}$                                                                                                                                                                                                                  |                  |                       | 30.5                  | $\mu\text{V}/\text{LSB}$ |                      |

|                      | 50Hz to 60Hz Noise Rejection                   | (Note 7)                                                                                                                                                                                                                              |                  |                       | 30                    | dB                       |                      |

| <b>ポート電圧の読み出し</b>    |                                                |                                                                                                                                                                                                                                       |                  |                       |                       |                          |                      |

|                      | Resolution                                     | No Missing Codes, $\text{fast\_iv} = 0$                                                                                                                                                                                               |                  |                       | 14                    | bits                     |                      |

|                      | LSB Weight                                     | $\text{AGND} - V_{OUT}$                                                                                                                                                                                                               |                  |                       | 5.835                 | $\text{mV}/\text{LSB}$   |                      |

|                      | 50Hz to 60Hz Noise Rejection                   | (Note 7)                                                                                                                                                                                                                              |                  |                       | 30                    | dB                       |                      |

| <b>デジタル・インターフェース</b> |                                                |                                                                                                                                                                                                                                       |                  |                       |                       |                          |                      |

| $V_{ILD}$            | Digital Input Low Voltage                      | $\text{ADn}$ , $\text{SHDN}$ , $\text{RESET}$ , $\text{MSD}$ , $\text{AUTO}$ , $\text{MID}$<br>(Note 6)                                                                                                                               | ●                |                       | 0.8                   | V                        |                      |

|                      | $\text{I}^2\text{C}$ Input Low Voltage         | $\text{SCL}$ , $\text{SDAIN}$ (Note 6)                                                                                                                                                                                                | ●                |                       | 0.8                   | V                        |                      |

| $V_{IHD}$            | Digital Input High Voltage                     | (Note 6)                                                                                                                                                                                                                              | ●                | 2.2                   |                       | V                        |                      |

|                      | Digital Output Low Voltage                     | $I_{SDAOUT} = 3\text{mA}$ , $I_{INT} = 3\text{mA}$<br>$I_{SDAOUT} = 5\text{mA}$ , $I_{INT} = 5\text{mA}$                                                                                                                              | ●<br>●           |                       | 0.4<br>0.7            | V                        |                      |

|                      | Internal Pull-Up to $V_{DD}$                   | $\text{ADn}$ , $\text{SHDN}$ , $\text{RESET}$ , $\text{MSD}$                                                                                                                                                                          |                  |                       | 50                    | $\text{k}\Omega$         |                      |

|                      | Internal Pull-Down to DGND                     | $\text{AUTO}$ , $\text{MID}$                                                                                                                                                                                                          |                  |                       | 50                    | $\text{k}\Omega$         |                      |

## 電気的特性

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $\text{AGND} - \text{V}_{\text{EE}} = 54\text{V}$ 、 $\text{AGND} = \text{DGND}$ 、 $\text{V}_{\text{DD}} - \text{DGND} = 3.3\text{V}$ 。(Note 3, 4)

| SYMBOL              | PARAMETER                                              | CONDITIONS                                                                                                                                   | MIN | TYP | MAX  | UNITS                  |

|---------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------------------------|

| タイミング特性             |                                                        |                                                                                                                                              |     |     |      |                        |

| $t_{\text{DET}}$    | Detection Time                                         | Beginning to End of Detection (Note 7)                                                                                                       | ●   | 270 | 290  | 310                    |

| $t_{\text{DETDLY}}$ | Detection Delay                                        | From PD Connected to Port to Detection Complete (Note 7)                                                                                     | ●   | 300 | 470  | ms                     |

| $t_{\text{CLE}}$    | Class Event Duration                                   | (Note 7)                                                                                                                                     | ●   | 12  |      | ms                     |

| $t_{\text{CLEON}}$  | Class Event Turn-On Duration                           | $C_{\text{PORT}} = 0.6\mu\text{F}$ (Note 7)                                                                                                  | ●   |     | 0.1  | ms                     |

| $t_{\text{ME}}$     | Mark Event Duration                                    | (Notes 7, 11)                                                                                                                                | ●   | 8.6 |      | ms                     |

| $t_{\text{MEL}}$    | Last Mark Event Duration                               | (Notes 7, 11)                                                                                                                                | ●   | 16  | 22   | ms                     |

| $t_{\text{PON}}$    | Power On Delay in AUTO Pin Mode                        | From End of Valid Detect to Application of Power to Port (Note 7)                                                                            | ●   |     | 60   | ms                     |

|                     | Turn On Rise Time                                      | $(\text{AGND} - \text{V}_{\text{OUT}}):10\%$ to 90% of $(\text{AGND} - \text{V}_{\text{EE}})$ , $C_{\text{PORT}} = 0.15\mu\text{F}$ (Note 7) | ●   | 15  | 24   | $\mu\text{s}$          |

|                     | Turn On Ramp Rate                                      | $C_{\text{PORT}} = 0.15\mu\text{F}$ (Note 7)                                                                                                 | ●   |     | 10   | $\text{V}/\mu\text{s}$ |

|                     | Fault Delay                                            | From $\text{I}_{\text{CUT}}$ Fault to Next Detect                                                                                            | ●   | 1.0 | 1.1  | s                      |

|                     | Midspan Mode Detection Backoff                         | $R_{\text{PORT}} = 15.5\text{k}\Omega$ (Note 7)                                                                                              | ●   | 2.3 | 2.5  | 2.7                    |

|                     | Power Removal Detection Delay                          | From Power Removal After $t_{\text{DIS}}$ to Next Detect (Note 7)                                                                            | ●   | 1.0 | 1.3  | 2.5                    |

| $t_{\text{START}}$  | Maximum Current Limit Duration During Port Start-Up    | (Note 7)                                                                                                                                     | ●   | 52  | 62.5 | 66                     |

| $t_{\text{LIM}}$    | Maximum Current Limit Duration After Port Start-Up     | $t_{\text{LIM}}$ Enable = 1 (Notes 7, 12)                                                                                                    | ●   |     | 11.9 | ms                     |

| $t_{\text{CUT}}$    | Maximum Overcurrent Duration After Port Start-Up       | (Note 7)                                                                                                                                     | ●   | 52  | 62.5 | 66                     |

|                     | Maximum Overcurrent Duty Cycle                         | (Note 7)                                                                                                                                     | ●   | 5.8 | 6.3  | 6.7                    |

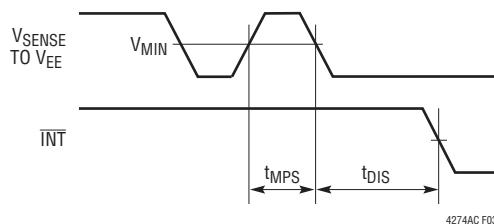

| $t_{\text{MPS}}$    | Maintain Power Signature (MPS) Pulse Width Sensitivity | Current Pulse Width to Reset Disconnect Timer (Notes 7, 8)                                                                                   | ●   | 1.6 | 3.6  | ms                     |

| $t_{\text{DIS}}$    | Maintain Power Signature (MPS) Dropout Time            | (Notes 5, 7)                                                                                                                                 | ●   | 320 | 350  | 380                    |

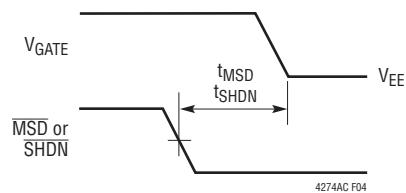

| $t_{\text{MSD}}$    | Masked Shut Down Delay                                 | (Note 7)                                                                                                                                     | ●   |     | 6.5  | $\mu\text{s}$          |

| $t_{\text{SHDN}}$   | Port Shut Down Delay                                   | (Note 7)                                                                                                                                     | ●   |     | 6.5  | $\mu\text{s}$          |

|                     | $\text{I}^2\text{C}$ Watchdog Timer Duration           |                                                                                                                                              | ●   | 1.5 | 2    | 3                      |

|                     | Minimum Pulse Width for Masked Shut Down               | (Note 7)                                                                                                                                     | ●   | 3   |      | $\mu\text{s}$          |

|                     | Minimum Pulse Width for $\text{SHDN}$                  | (Note 7)                                                                                                                                     | ●   | 3   |      | $\mu\text{s}$          |

|                     | Minimum Pulse Width for $\text{RESET}$                 | (Note 7)                                                                                                                                     | ●   | 4.5 |      | $\mu\text{s}$          |

## 電気的特性

● は全動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $\text{AGND} - \text{V}_{\text{EE}} = 54\text{V}$ 、 $\text{AGND} = \text{DGND}$ 、 $\text{V}_{\text{DD}} - \text{DGND} = 3.3\text{V}$ 。(Note 3, 4)

| SYMBOL                      | PARAMETER                     | CONDITIONS                                               | MIN    | TYP       | MAX | UNITS |

|-----------------------------|-------------------------------|----------------------------------------------------------|--------|-----------|-----|-------|

| <b>I<sup>2</sup>C タイミング</b> |                               |                                                          |        |           |     |       |

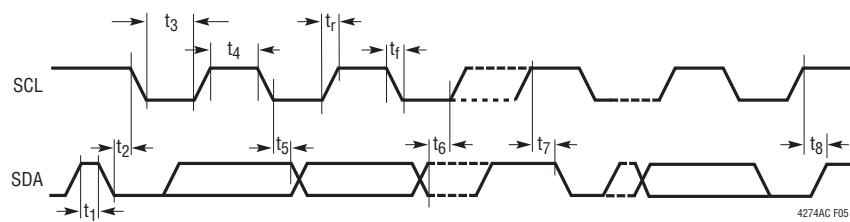

|                             | Clock Frequency               | (Note 7)                                                 |        | 1         |     | MHz   |

| $t_1$                       | Bus Free Time                 | Figure 5 (Notes 7, 9)                                    | ●      | 480       |     | ns    |

| $t_2$                       | Start Hold Time               | Figure 5 (Notes 7, 9)                                    | ●      | 240       |     | ns    |

| $t_3$                       | SCL Low Time                  | Figure 5 (Notes 7, 9)                                    | ●      | 480       |     | ns    |

| $t_4$                       | SCL High Time                 | Figure 5 (Notes 7, 9)                                    | ●      | 240       |     | ns    |

| $t_5$                       | Data Hold Time                | Figure 5 (Notes 7, 9) Data into Chip<br>Data Out of Chip | ●<br>● | 60<br>120 |     | ns    |

| $t_6$                       | Data Set-Up Time              | Figure 5 (Notes 7, 9)                                    | ●      | 80        |     | ns    |

| $t_7$                       | Start Set-Up Time             | Figure 5 (Notes 7, 9)                                    | ●      | 240       |     | ns    |

| $t_8$                       | Stop Set-Up Time              | Figure 5 (Notes 7, 9)                                    | ●      | 240       |     | ns    |

| $t_r$                       | SCL, SDAIN Rise Time          | Figure 5 (Notes 7, 9)                                    | ●      | 120       |     | ns    |

| $t_f$                       | SCL, SDAIN Fall Time          | Figure 5 (Notes 7, 9)                                    | ●      | 60        |     | ns    |

|                             | Fault Present to INT Pin Low  | (Notes 7, 9, 10)                                         | ●      | 150       |     | ns    |

|                             | Stop Condition to INT Pin Low | (Notes 7, 9, 10)                                         | ●      | 1.5       |     | μs    |

|                             | ARA to INT Pin High Time      | (Notes 7, 9)                                             | ●      | 1.5       |     | μs    |

|                             | SCL Fall to ACK Low           | (Notes 7, 9)                                             | ●      | 120       |     | ns    |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** このデバイスには短時間の過負荷状態の間デバイスを保護するための過温度保護機能が備わっている。過温度保護機能がアクティブなとき接合部温度は  $140^\circ\text{C}$  を超える。規定された最大動作接合部温度を超えた状態で動作が継続すると、デバイスの信頼性を損なう恐れがある。

**Note 3:** デバイスのピンに流れ込む電流は全て正。デバイスのピンから流れ出る電流は全て負。

**Note 4:** LTC4274A/LTC4274C はグラウンドを基準にして負電源電圧で動作する。混乱を避けるため、このデータシートの電圧は絶対値で表示されている。

**Note 5:**  $t_{\text{DIS}}$  は IEEE 802.3at 標準規格で定義された  $t_{\text{MPD0}}$  と同じである。

**Note 6:** LTC4274A/LTC4274C のデジタル・インターフェースは DGND を基準にして動作する。すべてのロジック・レベルは DGND を基準にして測定される。

**Note 7:** 設計によって保証されているが、テストされない。

**Note 8:** IEEE 802.3af の規定では、PD が切断されることなくその Maintain Power Signature (MPS) を間欠的に出力するのを許容している。電力供給を受け続けるには、PD はどの  $t_{\text{MPD0}}$  の時間ウィンドウ内でも  $t_{\text{MPS}}$  の間 MPS を出力しなければならない。

**Note 9:**  $V_{\text{ILD}}(\text{MAX})$  および  $V_{\text{IH}}(\text{MIN})$  で測定された値。

**Note 10:** I<sup>2</sup>C トランザクションの進行中にフォルト状態が発生した場合、I<sup>2</sup>C バスに STOP 条件が送信されるまで INT ピンは引き下げられない。

**Note 11:** マーク・イベントでの LTC4274A/LTC4274C の負荷特性：

$7\text{V} < (\text{AGND} - \text{V}_{\text{OUT}}) < 10\text{V}$  または  $\text{I}_{\text{OUT}} < 50\mu\text{A}$

**Note 12:** シリアル・バスの使用およびデバイスの設定レジスタと状態レジスタの詳細について LTC4274A/LTC4274C のソフトウェア・プログラミング・マニュアルを参照。

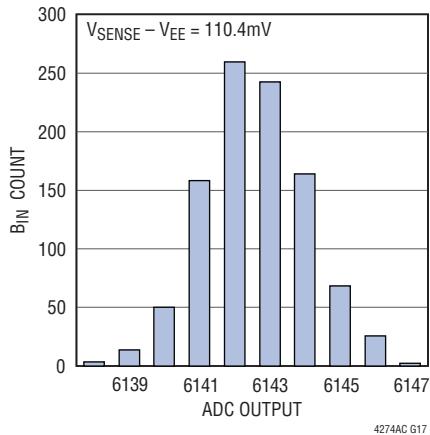

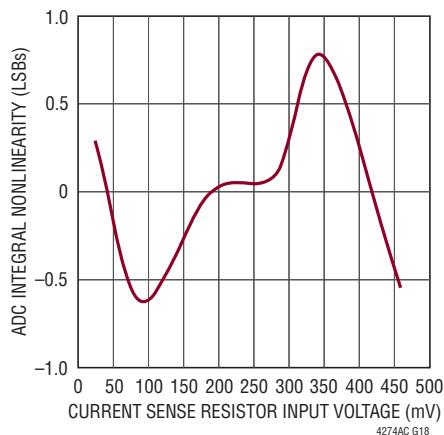

## 標準的性能特性

## 標準的性能特性

## 標準的性能特性

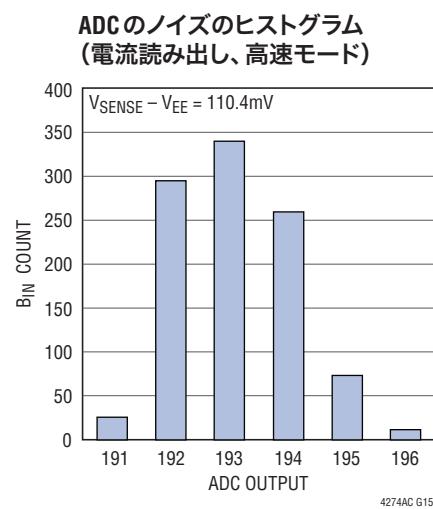

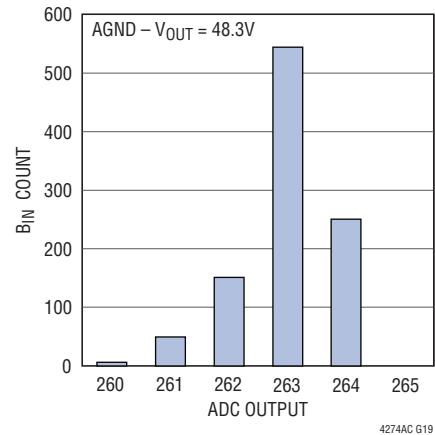

ADCのノイズのヒストグラム

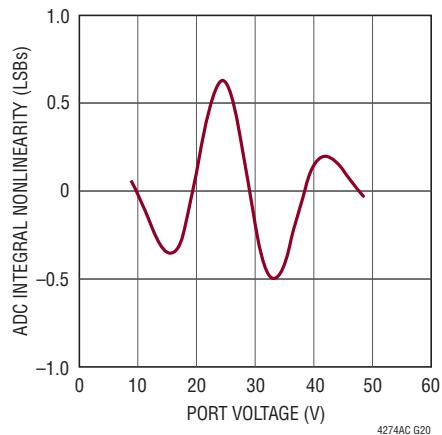

(電流読み出し、低速モード)ADCの積分非直線性

(電流読み出し、低速モード)ADCのノイズのヒストグラム

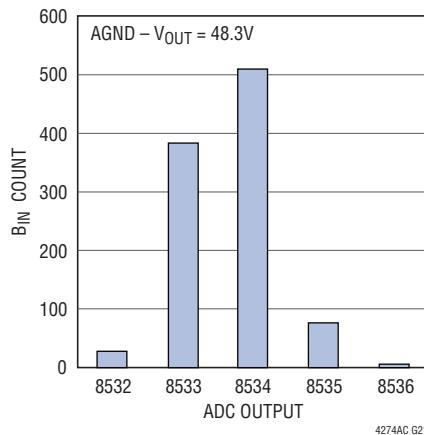

(ポート電圧読み出し、高速モード)ADCの積分非直線性

(電圧読み出し、高速モード)ADCのノイズのヒストグラム

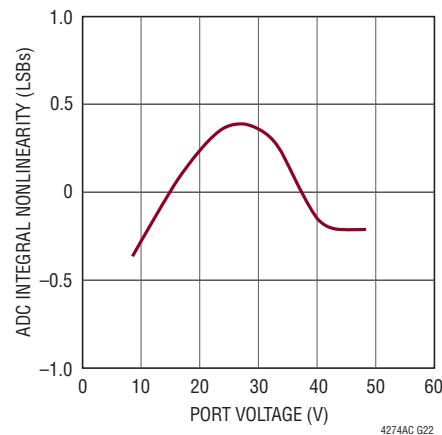

(ポート電圧読み出し、低速モード)ADCの積分非直線性

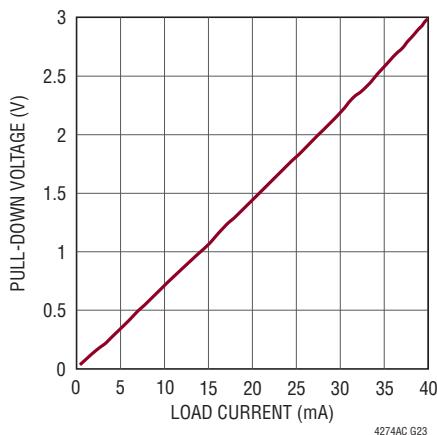

(電圧読み出し、低速モード)INTおよびSDAOUTのプルダウン

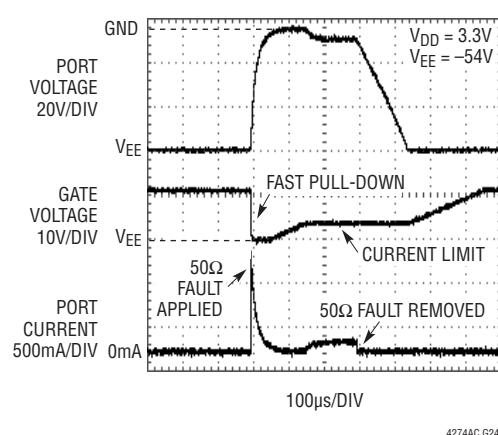

電圧と負荷電流高速プルダウン付き

MOSFETゲート・ドライブ

## テスト・タイミング図

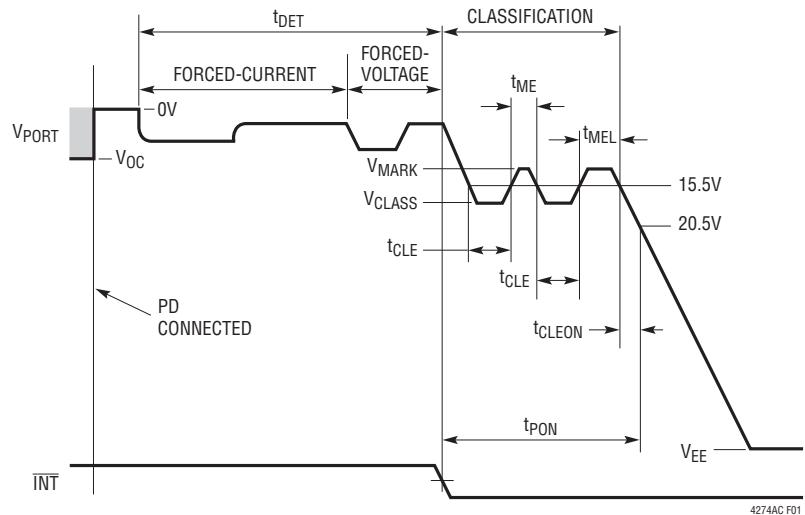

図1. AUTO ピン・モードまたは半自動モードでの検出、分類、ターンオンのタイミング

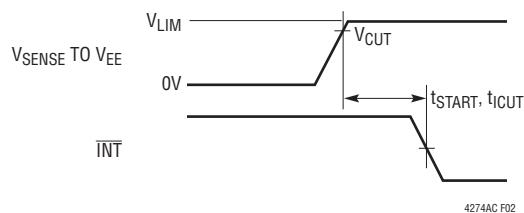

図2. 電流制限のタイミング

図3. DC 切断のタイミング

## テスト・タイミング図

図4. シャットダウン遅延のタイミング

図5. I<sup>2</sup>C インタフェースのタイミング

## I<sup>2</sup>C タイミング図

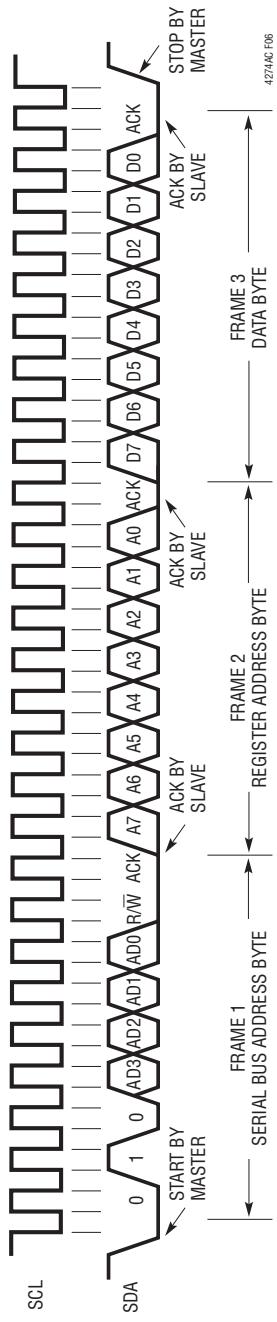

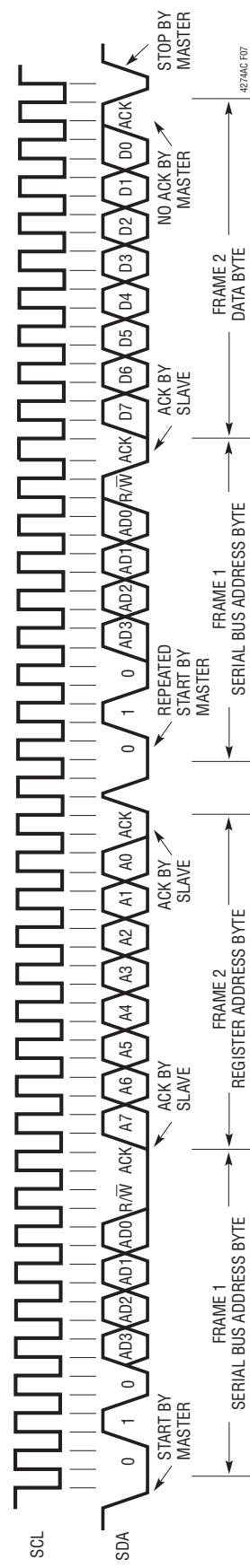

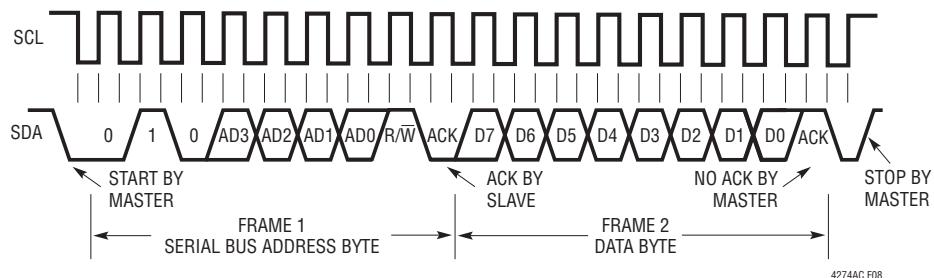

図6. レジスタへの書き込み

図7. レジスタからの読み出し

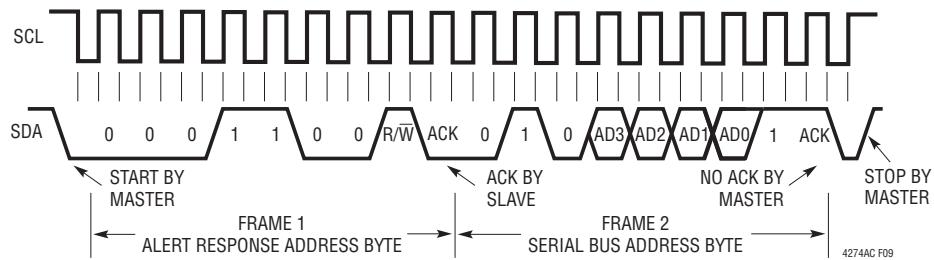

I<sup>2</sup>C タイミング図

図8. 割り込みレジスタの読み出し(ショート・フォーム)

図9. アラート応答アドレスからの読み出し

## ピン機能

**RESET**：アクティブ“L”のデバイス・リセット。 $\overline{\text{RESET}}$ ピンが“L”的とき、LTC4274A/LTC4274Cは非アクティブ状態に保たれ、ポートがオフし、すべての内部レジスタがそれぞれのパワーアップ状態にリセットされます。 $\overline{\text{RESET}}$ が“H”になると、LTC4274A/LTC4274Cは通常動作を開始します。 $\overline{\text{RESET}}$ を外付けコンデンサまたはRCネットワークに接続することで、パワーオンを遅らせることができます。 $\overline{\text{RESET}}$ ピンは内部でフィルタされるので、幅が $1\mu\text{s}$ 未満のグリッチによってLTC4274A/LTC4274Cがリセットされることはありません。内部で $\text{V}_{\text{DD}}$ にプルアップされています。

**MID**：ミッドスパン・モード入力。“H”的とき、LTC4274A/LTC4274Cはミッドスパン・デバイスとして機能します。このピンは内部で $\text{DGND}$ にプルダウンされています。

**INT**：オープン・ドレインの割り込み出力。LTC4274A/LTC4274C内でイベントのいずれか1つが発生すると、 $\overline{\text{INT}}$ は“L”になります。Reset PBレジスタ(1Ah)のビット6またはビット7がセットされると、 $\overline{\text{INT}}$ は高インピーダンス状態に戻ります。 $\overline{\text{INT}}$ 信号を使ってホスト・プロセッサに対して割り込みを発生させることができますので、ソフトウェアによる連続ポーリングは不要です。個々の $\overline{\text{INT}}$ イベントはINT Maskレジスタ(01h)を使ってディスエーブルすることができます。詳細については、LTC4274A/LTC4274Cのソフトウェア・プログラミング・マニュアルを参照してください。 $\overline{\text{INT}}$ ピンが更新されるのは、 $\text{I}^2\text{C}$ のトランザクションとトランザクションの間だけです。

**SCL**：シリアル・クロック入力。 $\text{I}^2\text{C}$ シリアル・インターフェース・バスの高インピーダンス・クロック入力。使用しない場合、SCLは“H”に接続する必要があります。

**SDAOUT**：シリアル・データ出力( $\text{I}^2\text{C}$ シリアル・インターフェース・バスのオープン・ドレイン・データ出力)。LTC4274A/LTC4274Cは2つのピンを使って双方向のSDA機能を実現しているので、 $\text{I}^2\text{C}$ バスのオプトアイソレーションが容易になります。標準的な双方向SDAピンを実現するには、SDAOUTとSDAINを相互接続します。使用しない場合、SDAOUTは接地するか、フローティング状態のままになります。詳細については「アプリケーション情報」のセクションを参照してください。

**SDAIN**：シリアル・データ入力。 $\text{I}^2\text{C}$ シリアル・インターフェース・バスの高インピーダンス・データ入力。LTC4274A/LTC4274Cは2つのピンを使って双方向のSDA機能を実現しているので、

$\text{I}^2\text{C}$ バスのオプトアイソレーションが容易になります。標準的な双方向SDAピンを実現するには、SDAOUTとSDAINを相互接続します。使用しない場合、SDAINは“H”に接続する必要があります。詳細については「アプリケーション情報」のセクションを参照してください。

**AD3**：アドレス・ビット3。アドレス・ピンを“H”または“L”に接続して、LTC4274A/LTC4274Cが応答する $\text{I}^2\text{C}$ シリアル・アドレスを設定します。このアドレスは010A<sub>3</sub>A<sub>2</sub>A<sub>1</sub>A<sub>0</sub>bになります。このピンは内部で $\text{V}_{\text{DD}}$ にプルアップされています。

**AD2**：アドレス・ビット2。AD3を参照してください。

**AD1**：アドレス・ビット1。AD3を参照してください。

**AD0**：アドレス・ビット0。AD3を参照してください。

**NC、DNC**：「NC」または「DNC」と表示されたピンはすべて未接続のままにしておく必要があります。

**DGND**：デジタル・グランド。DGNDは $\text{V}_{\text{DD}}$ 電源のリターンです。

**V<sub>DD</sub>**：ロジック電源。DGNDを基準にした3.3V電源に接続します。 $\text{V}_{\text{DD}}$ は、少なくとも $0.1\mu\text{F}$ のコンデンサを使ってLTC4274A/LTC4274Cの近くでDGNDにバイパスする必要があります。

**SHDN**：アクティブ“L”的シャットダウン・ピン。 $\overline{\text{SHDN}}$ を“L”にすると、内部レジスタの状態に関係なく、ポートがシャットダウンします。 $\overline{\text{SHDN}}$ を“L”にすることは、Reset Pushbuttonレジスタ(1Ah)内のReset Portビットをセットすることに相当します。 $\overline{\text{SHDN}}$ ピンは内部でフィルタされるので、幅が $1\mu\text{s}$ 未満のグリッチによってポートがリセットされることはありません。このピンは内部で $\text{V}_{\text{DD}}$ にプルアップされています。

**AGND**：アナログ・グランド。AGNDは $\text{V}_{\text{EE}}$ 電源のリターンです。

**SENSE**：電流検出入力。SENSEは、SENSEと $\text{V}_{\text{EE}}$ 間の $0.5\Omega$ または $0.25\Omega$ のセンス抵抗を介して外付けMOSFETの電流をモニタします。センス抵抗の両端の電圧が過電流検出スレッショルド $\text{V}_{\text{CUT}}$ を超えるたびに、電流制限フォルト・タイマがカウントアップします。センス抵抗両端の電圧が電流制限スレッショルド $\text{V}_{\text{LIM}}$ に達すると、GATEピンの電圧が下がり、外付けMOSFETの電流を一定に保ちます。詳細については「アプリケーション情報」のセクションを参照してください。

## ピン機能

**GATE**：ゲート・ドライブ。GATEはポートの外付けMOSFETのゲートに接続します。MOSFETをオンすると、ゲート電圧は $V_{EE}$ より12V（標準）高い電圧にドライブされます。電流制限状態の間、GATEの電圧が低下して外付けMOSFETを流れる電流を一定に保ちます。フォルト・タイマが終了すると、GATEはプルダウンされ、MOSFETがオフして、tcUTまたはtSTARTのイベントが記録されます。

**OUT**：出力電圧モニタ。OUTは出力ポートに接続します。電流制限フォールドバック回路は、ドレイン-ソース間の電圧が10Vを超えたときに電流制限スレッショルドを下げることによって外付けMOSFETの電力損失を制限します。OUTから $V_{EE}$ への電圧が2.4V（標準）を下回ると、Power Goodビットがセットされます。ポートがアイドル状態のときは、OUTからAGNDに500kの抵抗が内部接続されます。

**$V_{EE}$** ：主電源入力。AGNDを基準にした-45V～-57V電源に接続します。

**AUTO**：AUTOピン・モード入力。AUTOピン・モードでは、I<sup>2</sup>Cバス上にホスト・コントローラが存在しなくても、LTC4274A/LTC4274CはPDを検出してパワーアップすることができます。AUTOピンの電圧により、LTC4274A/LTC4274Cがリセットされたとき、または $V_{DD}$ のUVLO状態から回復したときの内部レジスタの状態が決まります（LTC4274A/LTC4274Cのソフトウェア・プログラミング・マニュアルを参照）。これらのレジスタのビットの状態は、その後もI<sup>2</sup>Cインターフェースを介して変更することができます。AUTOピンのリアルタイムの状態は、Pin Statusレジスタ（11h）のビット0で読み出されます。このピンは内部でDGNDにプルダウンされています。 $V_{DD}$ またはDGNDのいずれかにローカルに接続する必要があります。

**MSD**：マスク可能なシャットダウン入力。アクティブ“L”。“L”になると、Misc Configレジスタ（17h）内の対応するマスク・ビットがセットされているすべてのポートがリセットされ、SHDNピンを“L”にするのと同等になります。MSDピンは内部でフィルタされるので、幅が1μs未満のグリッチによってポートがリセットされることはありません。このピンは内部で $V_{DD}$ にプルアップされています。

## 動作

### 概要

Power over Ethernet (PoE)は、イーサネット・データ銅配線を通してDC電力を伝送する標準プロトコルです。802.3イーサネット・データ標準規格を策定するIEEEグループは、2003年にPoEによる電力供給機能を追加しました。802.3afと呼ばれるオリジナルのPoE規格は、最大13Wで48VのDC電力供給を可能にします。この最初の規格は広く普及しましたが、13Wでは十分でない場合がありました。IEEEは、2009年に802.3at (PoE+)と呼ばれる新たな標準規格を発表しました。この規格では25Wの電力を供給するために電圧と電流の要件が拡大されています。

IEEE標準規格ではPoE用語も規定しています。ネットワークに電力を供給する装置はPSE（給電装置）と呼ばれ、ネットワークから電力が供給される装置はPD（受電装置）と呼ばれます。PSEには、データと電力を供給するエンドポイント（ネットワーク・スイッチやルータが一般的）と、電力を供給してデータを通過させるミッドスパンの2つのタイプがあります。ミッドスパンは一般に、PoEに対応していない既存のネットワークにPoE機能を追加するために使用されます。PDは一般に、IP電話、ワイヤレス・アクセス・ポイント、防犯カメラなどの機器です。

### PoE++の展開

IEEEのPoE+ 25.5W規格の作成段階からすでに、25.5Wより大きな電力供給に対するかなりの需要があり、そのニーズはさらに高まりつつあることが明らかになってきました。LTC4274Aファミリは、LTPoE++のPDに最大90Wの電力を確実に供給できるようにして、この市場の要求に応えています。LTPoE++規格は、既存のIEEE PoE手法を拡張した信頼性の高い検出および分類機能を与え、既存のタイプ1およびタイプ2のPDに対して下位互換性があり、相互運用可能です。他のプロトコライエタリPoE++ソリューションと異なり、リニアテクノロジーのLTPoE++はPSEとPD間で相互に識別が可能です。このため、LTPoE++のPDは起動時にすでにLTPoE++のPSEを検出しているので、要求した電力を使用できることを知ることができます。LTPoE++のPSEは、LTPoE++のPDと他のあらゆる種類のIEEE準拠のPDを区別できるので、LTPoE++のPSEは既存の装置との互換性ならびに相互運用性を維持することができます。

# LTC4274A/LTC4274C

## 動作

### LTC4274製品ファミリ

LTC4274は、エンドポイントまたはミッドスパンの設計のどちらにも4個のPSEポートを実装する第3世代のクワッドPSEコントローラです。実際、IEEE 802.3at準拠のPSE設計を行うのに必要なすべての回路を内蔵し、必要とするのは外付けパワーMOSFETとセンス抵抗だけなので、内蔵MOSFETを使用する設計と比較して電力損失が最小限に抑えられます。

LTC4274には、異なるPD電力レベルをサポートする3つのグレードがあります。

AグレードのTC4274はPoEの電力供給能力をLTPoE++レベルまで拡張しています。LTPoE++はリニアテクノロジー独自の規格で、LTPoE++準拠のPDに最大90Wを供給可能です。LTPoE++アーキテクチャは、IEEEの物理的な電力ネゴシエーションが38.7W、52.7W、70W、90Wの各電力レベルを含むように拡張されています。AグレードのLTC4274は、BグレードとCグレードの機能も搭載しています。

BグレードのLTC4274はIEEEに完全準拠したタイプ2のPSEで、タイプ1とタイプ2のPDに対して自律的に検出、分類、電力供給を行うことができます。BグレードのLTC4274は、Cグレードの機能もすべて搭載しています。BグレードのLTC4274はレガシー・デバイスであるため、製品番号の末尾に“B”を付けずに販売されています。電力グレードを示す文字が末尾にないデバイスは、Bグレードのデバイスを示します。

CグレードのLTC4274は完全に自律的な802.3atタイプ1のPSEソリューションです。Cグレードのチップセットは、AUTOピン・モードでのみの使用を意図しており、タイプ1のPDに対して自律的に検出、分類、電力供給を行うことができます。タイプ1のPSEとして機能するので、2イベント分類は禁止され、クラス4のPDは自動的にクラス0のPDとして扱われます。

### PoEの基本

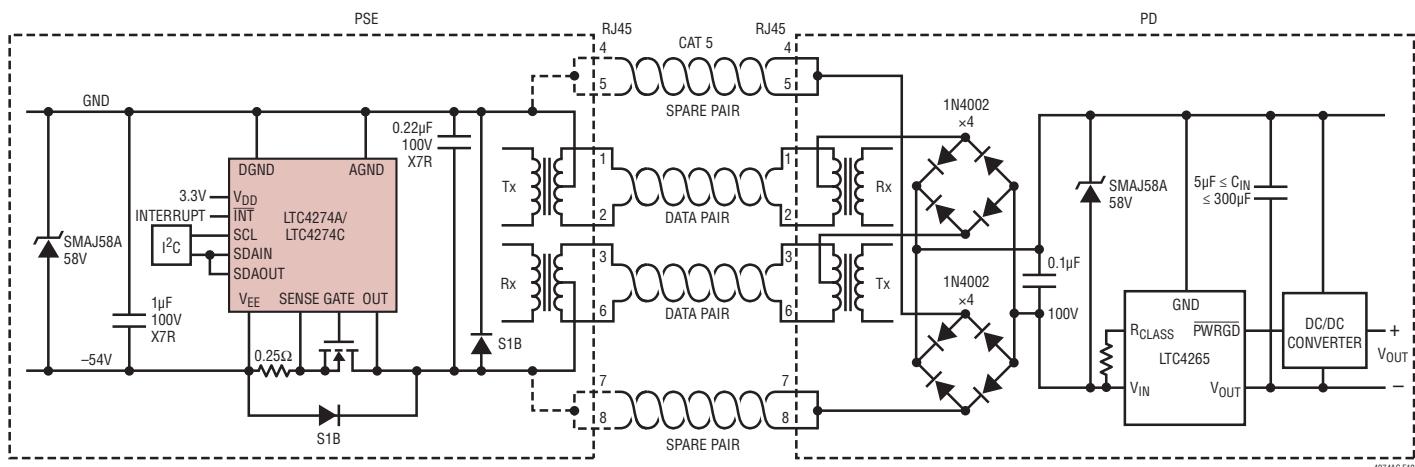

一般的なイーサネット・データは2本または4本の銅のより対線(通称CAT-5ケーブル)で接続し、グランド・ループを避けるために両端をトランス結合にします。PoEシステムは、データ・トランスのセンタータップ間に電圧を印加し、データ伝送に影響を与えることなくPSEからPDに電力を伝送することにより、この結合方式をうまく利用します。ハイレベルなPoEシステムの回路図を図10に示します。

DC電圧が加わることを想定していない従来のデータ機器を損傷しないように、PoE規格ではPSEによる電力の供給と切断の時点を定めたプロトコルが規定されています。有効なPDは入力に固有な $25\text{k}\Omega$ の同相抵抗を必要とします。このようなPDがケーブルに接続されると、PSEはこのシグネチャ抵抗を検出して電源をオンします。その後PDが切断されると、PSEはオープン状態を検出して電源をオフします。電流フォルトや短絡が生じた場合も、PSEは電源をオフします。

図10. Power over Ethernetのシステム図

## 動作

PDが検出されると、PSEはオプションとしてそのPDが消費する最大電力をPSEに知らせる分類シグネチャを探します。PSEはこの情報を使って、複数のポートに対する電力の割り当て、PDの消費電流の監視、またはPSEの供給能力を超える電力を消費するPDの拒絶を行なうことができます。802.3af PSEでは、分類ステップはオプションです。PSEがPDを分類しないことを選択する場合、PSEはPDが13W(802.3afの最大電力)の装置であると想定する必要があります。

### 802.3atの新項目

802.3at標準規格は802.3afを更新したもので、以下の新機能が追加されています。

- PDは最大25.5Wを使用できます。このようなPD(およびそれに対応するPSE)はタイプ2と呼ばれます。従来の13Wの802.3afの装置はタイプ1として分類されます。タイプ1のPDはすべてのPSEに対応しますが、タイプ2のPDを適切に動作させるには、タイプ2のPSEが必要になる場合があります。LTC4274A/LTC4274Cはタイプ1とタイプ2のどちらのPSEの設計でも動作するように設計されており、高電力レベルの非標準の構成にも対応します。

- 分類プロトコルは、タイプ2のPSEがタイプ2のPDを検出でき、タイプ2のPDがタイプ2のPSEに接続されているかどうかを確認できるように拡張されています。2つのバージョンの新しい分類プロトコルが利用できます。それらは、802.3afクラス・パルス・プロトコルの拡張バージョンと、(イーサネット・データ・バスを使用した)既存のLLDPプロトコルと統合した代替手法です。LTC4274A/LTC4274Cは新しいクラス・パルス・プロトコルをフル7サポートすると同時に、(PoE回路ではなくデータ通信レイヤに実装された)LLDPプロトコルと互換性があります。

- フォルト保護の電流レベルとタイミングはフォルト時のMOSFETのピーク電力を低減するように調整されるので、従来の13Wの設計と同じMOSFETを使って新しい25.5Wの電力レベルに達することができます。

### LTPoE++による供給電力の増強

LTC4274Aには、最大90Wの電力をPDに自律的に供給する機能が追加されています。LTPoE++のPDは802.3 LLDPのサポートなしに動作可能で、LTPoE++の物理的な分類だけでLTPoE++のPSEとの電力ネゴシエーションを行なうことができます。これにより、高電力PDの実装を大幅に簡素化します。

LTC4274Aでは、High Power EnableビットとLTPoE++ Enableビットの両方をセットすることにより、LTPoE++の分類をオプションでイネーブル可能です。

LTPoE++の電力供給レベルが上がるのに伴い、レイアウトや部品選択時の制約が厳しくなります。LTC4274Aには4つの電力レベル(-1、-2、-3、および-4)があり、AUTOピン・モードのLTC4274Aはサポートされているレベルまでの電力を自律的に供給することができます。AUTOピンが“H”的場合、供給可能な最大電力が内部回路によって決まります。供給能力を超える電力を要求するPDには、電力は供給されません。

表1. LTPoE++のAUTOピン・モードで供給可能な最大電力量

| デバイス       | ペア | PDへの供給電力 |

|------------|----|----------|

| LTC4274A-1 | 4  | 38.7W    |

| LTC4274A-2 | 4  | 52.7W    |

| LTC4274A-3 | 4  | 70W      |

| LTC4274A-4 | 4  | 90W      |

## アプリケーション情報

## 動作モード

LTC4274A/LTC4274Cは、マニュアル、半自動、AUTOピン、シャットダウンの4つのモードのいずれかで動作できます。

表2. 動作モード

| モード         | AUTO<br>ピン | OPMD | 検出/分類           | パワーアップ  | I <sub>CUT</sub> /I <sub>LIM</sub> の<br>自動設定 |

|-------------|------------|------|-----------------|---------|----------------------------------------------|

| AUTOピン      | 1          | 11b  | リセット時に<br>イネーブル | 自動      | あり                                           |

| 予備          | 0          | 11b  | N/A             | N/A     | N/A                                          |

| 半自動         | 0          | 10b  | ホストにより<br>イネーブル | 要求時     | なし                                           |

| マニュアル       | 0          | 01b  | 要求時に1回          | 要求時     | なし                                           |

| シャット<br>ダウン | 0          | 00b  | ディスエーブル         | ディスエーブル | なし                                           |

- マニュアル・モードでは、ポートはホスト・システムからの指示を待ってアクションをとります。ポートは、ホストから指示されると検出サイクルまたは分類サイクルを1回実行し、Port Statusレジスタでその結果を知らせます。ホスト・システムはいつでもポートに電力のオン/オフを指示することができます。このモードは診断やテストの目的にのみ使用されます。

- 半自動モードでは、ポートは接続されているすべてのPDの検出と分類を繰り返し試みます。ポートはこれらの結果をホストに知らせ、ホストからのコマンドを待ってからポートの電力をオンします。検出が開始される前に、ホストはポートの検出(およびオプションで分類)をイネーブルする必要があります。

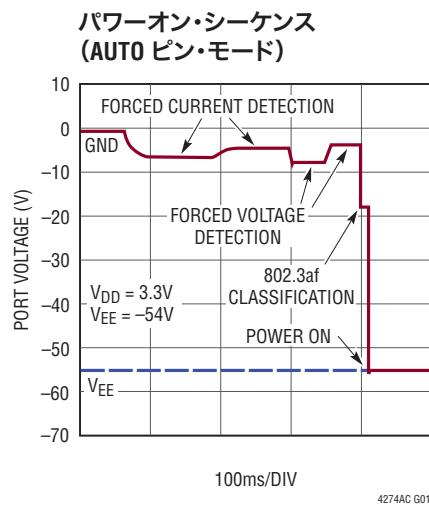

- AUTOピン・モードは、検出に成功するとポートの電力を自動的にオンすること以外は、半自動モードと同じ動作をします。AUTOピン・モードでは、ICUTとILIMの値はLTC4274A/LTC4274Cによって自動的に設定されます。AUTOピン・モードが有効になるのは、リセットまたはパワーアップ時にAUTOピンが“H”であり、かつ、動作中“H”に保持されるときだけです。

- シャットダウン・モードでは、ポートはディスエーブルされており、PDの検出も電力供給も行いません。

LTC4274A/LTC4274Cは、モードに関係なく、電流制限�值を生じたポートへの電力供給を自動的に停止します。また、切断の検出がイネーブルされていると、切断イベントを生じたポートへの電力供給を自動的に停止します。また、ホスト・コントローラはいつでもポートに電力供給の停止を指示することができます。

## リセットとAUTO/MIDピン

LTC4274A/LTC4274Cの初期設定は、リセット時のAUTOピンとMIDピンの状態によって決まります。リセットが生じるのは、パワーアップ時、あるいはRESETピンが“L”になった場合、またはグローバルなReset Allビットがセットされた場合です。パワーアップ後にAUTOやMIDの状態が変化しても、リセットが生じるまではLTC4274A/LTC4274Cのポートの動作は変化しません。

LTC4274A/LTC4274Cは通常、ホスト・コントローラと共に使用されますが、シリアル・インターフェースに接続しないスタンダロン・モードで使用することもできます。ホストが存在しない場合、リセット時にポートが自動的に動作する設定になるように、AUTOピンを“H”に接続する必要があります。ポートは、PDが見つかるまで検出と分類を繰り返し、分類結果に従ってICUTとILIMを設定し、検出に成功すると電力を供給し、PDが切断されると電力供給を停止します。

スタンドアロン(AUTOピン)モード時に検出されたクラスに基づいて自動的に設定される $I_{CUT}$ と $I_{LIM}$ の値を表3に示します。

表3 AUTOピン・モードの $I_{CUT}$ と $I_{IM}$ の値

| クラス             | I <sub>CUT</sub> | I <sub>LIM</sub> |

|-----------------|------------------|------------------|

| クラス 1           | 112mA            | 425mA            |

| クラス 2           | 206mA            | 425mA            |

| クラス 3 または クラス 0 | 375mA            | 425mA            |

| クラス 4           | 638mA            | 850mA            |

AUTOピンが“H”の状態で LTC4274A/LTC4274C がリセットされたときだけ  $I_{CUT}$  と  $I_{UM}$  の値が自動的に設定されます。

スタンドアロン・アプリケーションがミッドスパンの場合は、MIDピンを“H”に接続して正しいミッドスパン検出タイミングが得られるようになります。

檢出

## 検出の概要

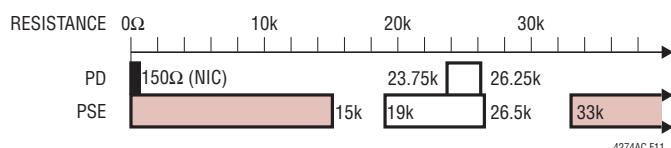

DC電圧に耐えられるように設計されていないネットワーク機器の損傷を防ぐため、PSEは接続された機器が真のPDであることを確認してから電力を供給する必要があります。IEEE規格では、ポートの電圧が10Vより低いとき、有効なPDは $25k\pm5\%$ の同相抵抗を示すことが規定されています。PSEは $19k\sim26.5k$ の範囲の抵抗は受け入れ、 $33k$ より大きいまたは $15k$ より小さい抵抗は拒絶する必要があります(図11の網掛けの部分)。PSEは、受け入れが必要な範囲と拒絶が必要な

## アプリケーション情報

範囲の間の規定されていない部分の抵抗は、受け入れても拒絶しても構いません。特に、PSEはコンピュータの標準ネットワーク・ポートを拒絶する必要があります。これらのポートの多くは同相終端抵抗が $150\Omega$ で、電力が供給されると損傷を受けます(図11の左側の黒の部分)。

図11. IEEE 802.3afのシグネチャ抵抗の範囲

## 4 ポイントの検出

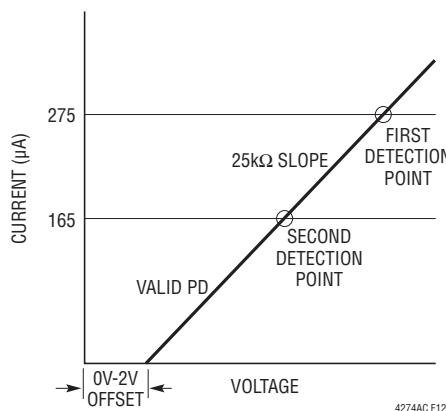

LTC4274A/LTC4274C1は4ポイント検出手法を使ってPDを検出します。電流強制と電圧強制の両方の測定を使ってシグネチャ抵抗をチェックすることにより、誤った適合判定が最小限に抑えられます。最初に、2つのテスト電流を(OUTピンを介して)ポートに強制し、その結果得られる電圧を測定します。検出回路は2つのV-Iポイントの差分を計算し、直列ダイオードやポートのリーク電流に起因するオフセットを除去しながら、抵抗の傾きを求めます(図12を参照)。電流強制による検出が有効なシグネチャ抵抗を示す場合は、2つのテスト電圧をポートに強制し、その結果得られる電流を測定して差分を計算します。両方の手法で有効な抵抗値が得られないと、ポートは有効な検出を知らせることができません。

図12. PDの検出

標準で $17k\sim29k$ のPDシグネチャ抵抗を有効と判定し、対応するPort Statusレジスタで「適合を検出」として知らせます。オープン状態や短絡などのこの範囲外の値も知らせます。最初の電流強制テストでポートが $1V$ より低い値を測定すると、検出サイクルを中断して「短絡」を知らせます。可能な検出結果を表4に示します。

表4. 検出状態

| 測定されたPDシグネチャ          | 検出結果          |

|-----------------------|---------------|

| 未完了またはテストしていない        | 検出状態が不明       |

| $<2.4k$               | 短絡            |

| 容量 $> 2.7\mu F$       | $C_{PD}$ が過大  |

| $2.4k < R_{PD} < 17k$ | $R_{SIG}$ が過小 |

| $17k < R_{PD} < 29k$  | 適合を検出         |

| $>29k$                | $R_{SIG}$ が過大 |

| $>50k$                | オープン状態        |

| 電圧 $> 10V$            | ポート電圧が検出範囲外   |

## 動作モードの詳細

ポートの動作モードにより、LTC4274A/LTC4274Cが検出サイクルを実行する時点が決まります。マニュアル・モードでは、ホストが検出サイクルを指示するまでポートはアイドル状態になります。検出サイクルが指示されるとポートは検出を実行し、その結果を知らせ、アイドル状態に戻って別のコマンドを待ちます。

半自動モードでは、LTC4274A/LTC4274Cは自律的にポートをポーリングしてPDを探しますが、ホストによって指示されるまで電力を供給しません。各検出サイクルの最後にPort Statusレジスタが更新されます。有効なシグネチャ抵抗が検出されて分類がイネーブルされると、ポートはPDを分類してその結果も知らせます。次いで、ポートは少なくとも $100ms$ (ミッドスパン・モードがイネーブルされている場合は2秒)の間待機し、検出サイクルを繰り返してPort Statusレジスタ内のデータが最新のものであることを確認します。

ポートが半自動モードの状態で高電力動作がイネーブルされていると、電流検出の結果が「適合を検出」でない限り、ポートがパワーオン・コマンドに応答してオンすることはありません。「適合を検出」以外の検出結果では、パワーオン・コマンドを受け取るとtSTART フォルトを発生します。ポートが高電力モードでない場合は、コマンドを受け取ったときに検出結果を無視して電力を供給し、LTC4259Aとの下位互換性を維持します。

## アプリケーション情報

AUTOピン・モードの動作は半自動モードに似ていますが、「適合を検出」が通知されて(分類がイネーブルされている場合に)ポートが分類された後、それ以上介入しなくても自動的にパワーオンします。スタンダードアロン(AUTOピン)モードでは、ICUTとILIMのスレッショルドが自動的に設定されます。詳細については「リセットとAUTO/MIDピン」のセクションを参照してください。

AUTOピンが“L”的状態でポートが最初にパワーアップするとき、シャットダウン・モード時、または対応するDetect Enableビットがクリアされているときは、シグネチャ検出回路はディスエーブルされます。

### レガシーPDの検出

オリジナルのIEEE 802.3af標準規格に遡るプロプライエタリPDは、今では一般にレガシー装置と呼ばれています。レガシーPDの1つのタイプは、検出シグネチャとして大きな同相容量(>10F)を使用しています。この範囲の容量を使用するPDは無効であると規定されているので、レガシーPDを検出するPSEはIEEE規格に技術的に準拠していないことに注意してください。

LTC4274A/LTC4274Cは、このタイプのレガシーPDを検出するように設定することができます。レガシーPDの検出はデフォルトではディスエーブルされていますが、手動でイネーブルすることができます。イネーブルされたポートは、有効なIEEE PDまたは高容量のレガシーPDのどちらかを検出したときに「適合を検出」を知らせます。レガシー・モードがディスエーブルされると、有効なIEEE PDのみが認識されます。

## 分類

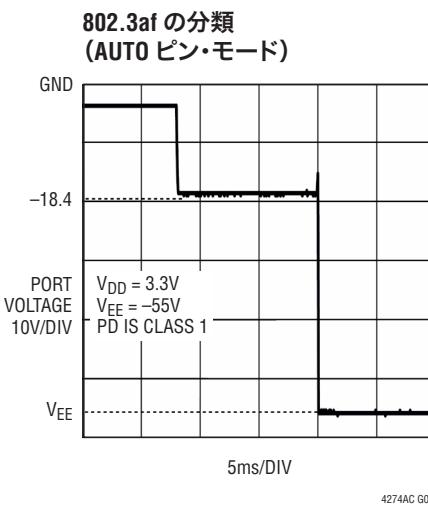

### 802.3afの分類

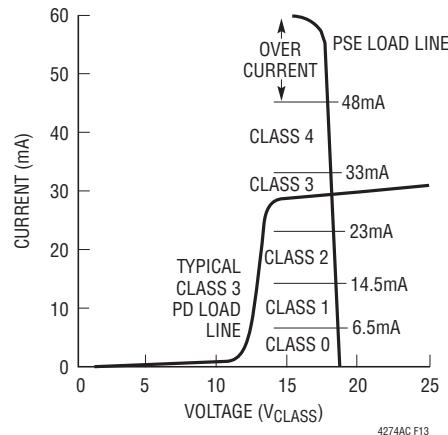

PDは、オプションでPSEに分類シグネチャを送り、動作時に消費する最大電力を知らせることができます。IEEE規格では、このシグネチャをPSEのポート電圧がV<sub>CLASS</sub>の範囲(15.5V～20.5V)内にあるときに流れる定電流と規定しており、この電流レベルは5つの可能なPDクラスの1つを示します。PDの標準負荷曲線を図13に示します。10Vまでは25kΩのシグネチャ抵抗の勾配で始まり、V<sub>CLASS</sub>の範囲では分類シグネチャ電流(この場合、クラス3)に移行します。可能な分類値を表5に示します。

図13. PDの分類

表5. 分類値

| クラス   | 結果                   |

|-------|----------------------|

| クラス 0 | 分類シグネチャなし、クラス3と同様に処理 |

| クラス 1 | 3W                   |

| クラス 2 | 7W                   |

| クラス 3 | 13W                  |

| クラス 4 | 25.5W(タイプ2)          |

分類がイネーブルされていると、半自動またはAUTOピン・モード時、あるいはマニュアル・モードで指示されたときに、検出に成功したサイクルの直後、ポートはPDを分類します。OUTピンを介してポートに12msの間18V(どちらの値も標準値)を印加してその結果生じる電流を測定することでPD分類シグネチャを測定し、Port Statusレジスタによって検出されたクラスを知らせます。LTC4274A/LTC4274CがAUTOピン・モードの場合、さらに分類結果を使ってICUTとILIMのスレッショルドを設定します。詳細については「リセットとAUTO/MIDピン」のセクションを参照してください。

AUTOピンが“L”的状態でポートが最初にパワーアップするとき、シャットダウン・モード時、または対応するClass Enableビットがクリアされているときは、分類回路はディスエーブルされます。

## アプリケーション情報

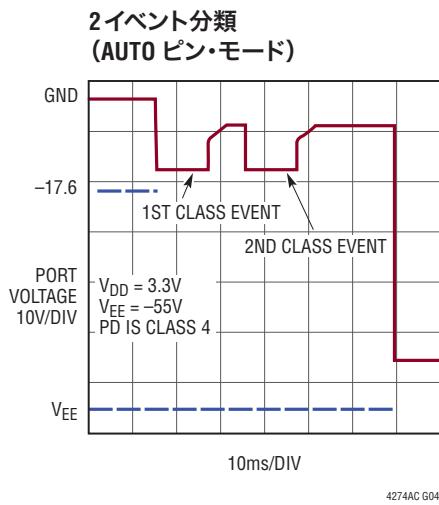

### 802.3atの2イベント分類

802.3at規格では、タイプ2のPDを分類する2つの方法を規定しています。LTC4274Aは、802.3atの2イベント分類をサポートしています。LTC4274Cは2イベント分類をサポートしていません。

1つ目の方法ではイーサネットLLDPデータ・プロトコルに特別なフィールドを追加します。LTC4274A/LTC4274Cにはこの分類方法と互換性がありますが、データ・パスへアクセスできないため直接分類することができません。LLDP分類では、PSEが標準的な802.3af(タイプ1)装置としてのPDへ電力を供給する必要があります。次いでPSEはホストがPDとLLDP通信を行ってPSEポートのデータを更新するまで待機します。LTC4274A/LTC4274Cは $I_{LIM}$ と $I_{CUT}$ のレベルを動作中にいつでも変更できるので、ホストがLLDP分類を完了することができます。

802.3atの2つ目の分類方法は2イベント分類またはピンポン分類と呼ばれ、LTC4274Aによってサポートされています。13Wより大きな電力を要求するタイプ2のPDは通常の802.3af分類のときクラス4を示します。LTC4274Aがクラス4を検出すると、規定された低電圧(マーク電圧と呼ばれ、標準9V)をポートに強制し、一時的に停止してから分類を再開してクラス4の読み出しを確認します(図1)。また、High Power Statusレジスタのビットをセットして、2番目の分類サイクルを実行したことを示します。2番目のサイクルは、タイプ2の電力レベルを供給できるタイプ2のPSEにPDが接続されていることをPDに警告します。

2イベント・ピンポン分類は、ポートのHigh Power Modeレジスタのビットをセットすることによってイネーブルされます。ピンポン分類がイネーブルされたポートはクラス4の装置を検出したときだけ2番目の分類サイクルを実行します。最初のサイクルがクラス0～3を返すと、ポートはタイプ1のPDに接続されているとみなして2番目の分類サイクルを実行しないことに注意してください。

### 無効なタイプ2のクラスの組み合わせ

802.3at規格では、タイプ2のPD分類シグネチャを、連続する2つのクラス4として規定しており、クラス4にクラス0～3が続くシグネチャは有効ではありません。AUTOピン・モードでは、LTC4274Aは1つの例外を除き、分類結果に関係なく検出されたPDに電力を供給します。例外として、PDが無効なタ

イプ2のシグネチャ(クラス4にクラス0～3が続く)を示すと、LTC4274Aは電力を供給しないで検出プロセスを再開します。診断を補うため、Port Statusレジスタは常に最後のクラス・パルスの結果を知らせるので、たとえば、無効なクラス4とクラス2の組み合わせの場合は、High Power Statusレジスタで2番目のクラス・パルスが実行されたこと(最初のサイクルがクラス4を検出したことを意味する)を知らせ、Port Statusレジスタでクラス2を知らせます。

## 電力制御

### 外付けMOSFET、センス抵抗の概要

LTC4274A/LTC4274Cの主な機能は、PSEポートへの電力供給を制御することです。これを行うため、外付けセンス抵抗を流れる電流とOUTピンの出力電圧をモニタしながら、外付けパワーMOSFETのゲート・ドライブ電圧を制御します。この回路は制御されていない $V_{EE}$ 入力電源を制御された状態でポートに接続し、MOSFETの電力損失と $V_{EE}$ バックプレーンの乱れを最小限に抑えながらPDの電力要件を満たします。

LTC4274A/LTC4274Cは $0.25\Omega$ のセンス抵抗を使って電力損失を最小限に抑えるように設計されています。LTC4258/LTC4259Aとの互換性が必要なときのデフォルトである $0.5\Omega$ のセンス抵抗もサポートしています。

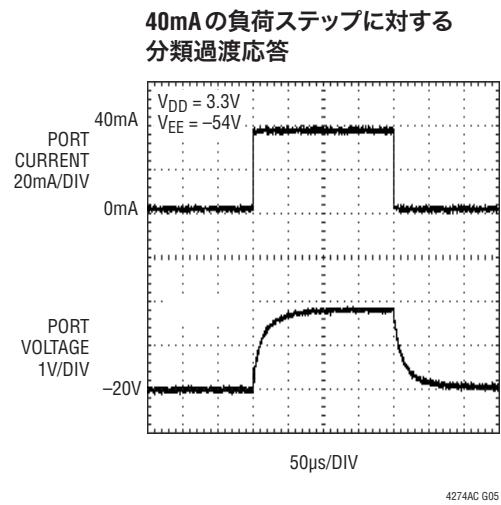

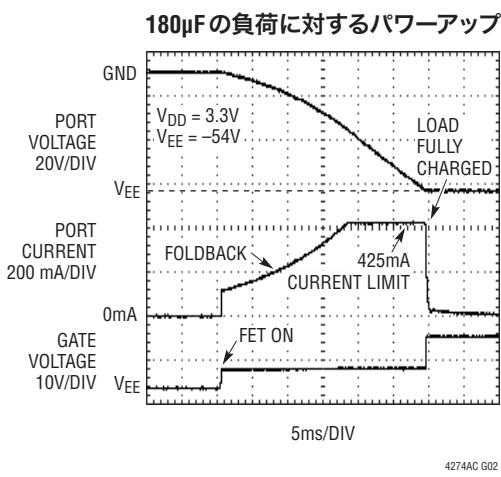

### 突入電流の制御

ポートをオンするコマンドが与えられると、LTC4274A/LTC4274Cはそのポートの外付けMOSFETのGATEピンを制御された状態でランプアップします。通常のパワーアップ環境では、ポート電流が突入電流制限レベル(標準450mA)に達するまでMOSFETのゲート電圧は上昇し、このポイントでGATEピンは規定されたI<sub>INRUSH</sub>電流を維持するようにサーボ制御されます。この突入電流期間の間、タイマ( $t_{START}$ )が作動します。出力の充電が完了するとポート電流が減少するので、GATEピンはMOSFETが完全に導通状態になるまで上昇し続けてそのオン抵抗を最小限に抑えることができます。最終的な $V_{GS}$ は公称12Vです。突入電流期間は $t_{START}$ タイマが終了するまで維持されます。 $t_{START}$ タイマが終了した時点でポート電流が突入電流制限レベルを超えたままだと、ポートはオフに戻って、 $t_{START}$ フォルトが通知されます。

## アプリケーション情報

### 電流制限

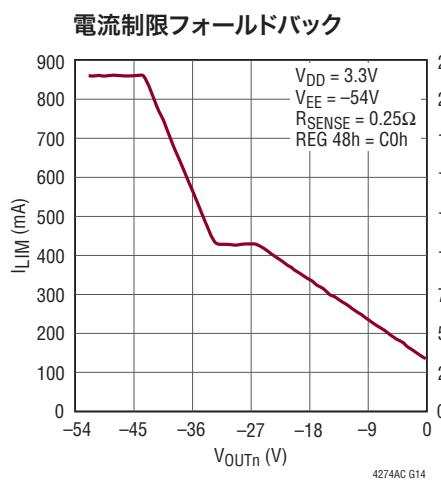

LTC4274A/LTC4274Cのポートには2つの電流制限スレッショルド( $I_{CUT}$ および $I_{LIM}$ )があり、それぞれ対応するタイマ( $t_{CUT}$ および $t_{LIM}$ )を備えています。 $I_{CUT}$ と $I_{LIM}$ のスレッショルドの設定は、PDのクラス、主電源( $V_{EE}$ )の電圧、PSEのタイプ(タイプ1またはタイプ2)、センス抵抗(0.5Ωまたは0.25Ω)、MOSFETのSOA、さらに、システムによるクラスの電流レベルの強制が必要か否かによって変わります。

IEEE規格に従い、LTC4274A/LTC4274Cはポートの電力供給を停止する前の限られた時間で $I_{CUT}$ を超えるポート電流を供給することができる一方で、MOSFETのゲート・ドライブをアクティブに制御してポート電流を $I_{LIM}$ より少なく保ちます。ポートは、 $I_{CUT}$ スレッショルドを超えただけでは電流を制限する動作をしませんが、 $t_{CUT}$ タイマを始動させます。 $t_{CUT}$ タイマが終了する前にポート電流が $I_{CUT}$ 電流スレッショルドを下回ると、 $t_{CUT}$ タイマはカウントダウンしますが、カウントアップの1/16の速度になります。 $t_{CUT}$ タイマが60ms(標準)に達すると、ポートはオフして、ポートの $t_{CUT}$ フォルトがセットされます。これにより、電流制限回路はデューティ・サイクルが約6%を下回る間欠的な過負荷信号を許容することができます。デューティ・サイクルの過負荷状態がこれより長くなるとポートをオフします。

$I_{LIM}$ 電流制限回路は常にイネーブルされており、ポート電流をアクティブに制限しています。 $t_{LIM}$ タイマがイネーブルされるのは、プログラム可能な $t_{LIM}$ フィールドがゼロでないときだけです。このため、 $t_{LIM}$ を $t_{CUT}$ より小さい値に設定することで、より強力にMOSFETを保護し、MOSFETが損傷する前にポートをオフすることができます。ポート電流が $I_{LIM}$ スレッショルドを超えると、 $t_{LIM}$ タイマが始動します。 $t_{LIM}$ タイマが1.7ms(標準)にプログラム可能な $t_{LIM}$ フィールドの値を掛けた値に達すると、ポートはオフして、ポートの $t_{LIM}$ フォルトがセットされます。 $t_{LIM}$ フィールドがゼロのとき、 $t_{CUT}$ タイマは $t_{LIM}$ の動作に追従します。 $t_{CUT}$ タイマは $I_{LIM}$ と $I_{CUT}$ のどちらのイベントにもカウントアップします。

$I_{CUT}$ は通常、 $I_{LIM}$ より小さい値に設定されるので、ポートは小さなフォルトには電流制限なしで耐えることができます。

IEEE規格により、LTC4274A/LTC4274Cはポートのターンオンの突入電流時に $I_{LIM}$ を自動的に425mA(表6の太字で

示した値)に設定し、突入電流期間が完了すると設定された $I_{LIM}$ 値に切り替えます。IEEE準拠を維持するため、 $I_{LIM}$ はタイプ1のPDすべてで425mAに保ち、タイプ2のPDが検出された場合は850mAに保ちます。ポートがオフすると、 $I_{LIM}$ は自動的に425mAにリセットされます。

表6. 電流制限設定の例

| $I_{LIM}$ (mA) | 内部レジスタの設定(16進数)         |                          |

|----------------|-------------------------|--------------------------|

|                | $R_{SENSE} = 0.5\Omega$ | $R_{SENSE} = 0.25\Omega$ |

| 53             | 88                      |                          |

| 106            | 08                      | 88                       |

| 159            | 89                      |                          |

| 213            | 80                      | 08                       |

| 266            | 8A                      |                          |

| 319            | 09                      | 89                       |

| 372            | 8B                      |                          |

| <b>425</b>     | <b>00</b>               | <b>80</b>                |

| 478            | 8E                      |                          |

| 531            | 92                      | 8A                       |

| 584            | CB                      |                          |

| 638            | 10                      | 90                       |

| 744            | D2                      | 9A                       |

| <b>850</b>     | <b>40</b>               | <b>C0</b>                |

| 956            | 4A                      | CA                       |

| 1063           | 50                      | D0                       |

| 1169           | 5A                      | DA                       |

| 1275           | 60                      | E0                       |

| 1488           | 52                      | 49                       |

| 1700           |                         | 40                       |

| 1913           |                         | 4A                       |

| 2125           |                         | 50                       |

| 2338           |                         | 5A                       |

| 2550           |                         | 60                       |

| 2975           |                         | 52                       |

### $I_{LIM}$ フォールドバック

LTC4274A/LTC4274Cは、ポート電圧が通常動作電圧を下回ったときにポート電流を低減する2段のフォールドバック回路を備えています。これにより、拡張された802.3atの電力レベルでも、MOSFETの電力損失は標準的な802.3afのMOSFETにとって安全なレベルに保たれます。電流制限とフォールドバック動作はプログラム可能です。推奨する $I_{LIM}$ レジスタの設定値を表6に示します。

## アプリケーション情報

LTC4274A/LTC4274Cは、802.3at規格の最大値を大幅に超える電流レベルをサポートします。表6の網掛けの部分は、大型の外付けMOSFET、ヒートシンクの追加、 $t_{LIM}$ のイネーブルなどを必要とする可能性のある設定値を示します。

### MOSFETのフォルトの検出

LTC4274A/LTC4274CのPSEポートはかなりのレベルの酷使に耐えられるように設計されていますが、極限状態になると外付けMOSFETが損傷する可能性があります。MOSFETが損傷するとソース-ドレイン間が短絡する可能性があり、これによってオフであるべきポートがオンしているように見えます。また、この状態により、センス抵抗がオープン状態になってポートをオフしますが、LTC4274A/LTC4274CのSENSEピンを異常に高い電圧まで上昇させます。MOSFETが損傷するとゲート-ドレイン間が短絡する可能性もあり、LTC4274A/LTC4274CのGATEピンを異常に高い電圧まで上昇させます。LTC4274A/LTC4274CのOUTピン、SENSEピン、GATEピンは、最大80Vのフォルトまで損傷することなく耐えられるように設計されています。

LTC4274A/LTC4274Cがこれらの状態を180 $\mu$ s以上検出すると、ポートのすべての機能をディスエーブルし、ポートのゲート・ドライブ・プルダウン電流を低減してFET Bad フォルトを知らせます。これは通常、永続的なフォルトですが、ホストはポートをリセットするか、またはポートのリセットでフォルトを解除できない場合はデバイス全体をリセットすることによって回復を試みることができます。MOSFETが実際に損傷していると、直ちにフォルトが返されて、ポートは再びディスエーブルになります。

MOSFETがオープン状態であったり装着されていないことが原因でFET Bad フォルトがトリガされることはありませんが、LTC4274A/LTC4274Cがポートをオンしようすると $t_{START}$  フォルトが生じます。

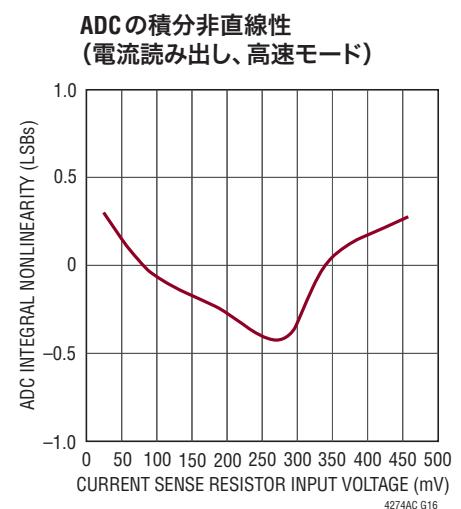

### 電圧と電流の読み出し

LTC4274A/LTC4274Cは内部A/Dコンバータを使ってポートの出力電圧と出力電流を測定します。ポートのデータはポートの電源がオンのときだけ有効です。コンバータには以下の2つのモードがあります。

- 低速モード: 1秒あたり14サンプル、14.5ビットの分解能

- 高速モード: 1秒あたり440サンプル、9.5ビットの分解能

高速モードでは、両方のモードでビットのスケーリングが等しくなるように、下位バイトの最下位の5ビットは0になっています。

### 切断

LTC4274A/LTC4274Cはポートをモニタして、PDに最小規定電流が流れ続けていることを確認します。ポート電流が7.5mA(標準)を下回るたびに切断タイマがカウントアップし、PDが切断されていることを知らせます。 $t_{DIS}$ タイマが終了すると、ポートがオフしてFault EventレジスタのDisconnectビットがセットされます。 $t_{DIS}$ タイマが終了する前に電流が元の状態に戻ると、タイマはリセットし、低電流状態に戻ると最初からカウントを開始します。PDが $t_{DIS}$ より頻繁に最小電流レベルを超える限り、PDには電力が供給され続けます。

推奨しませんが、DC切断機能は、DC Disconnect Enableビットをクリアすることによってディスエーブルすることができます。給電されているポートにはPDが取り去られた後も電力が供給され続けるので、これにより、IEEE規格に組み込まれた保護メカニズムが無効になることに注意してください。給電され続けているポートに、PoEに対応していないデータ機器が接続されると、その機器が損傷する可能性があります。

LTC4274A/LTC4274CはAC切断回路を備えていませんが、LTC4259Aとの互換性を維持するためにAC Disconnect Enableビットを備えています。AC Disconnect Enableビットがセットされると、DC切断が使用されます。

### シャットダウン・ピン

LTC4274A/LTC4274Cはハードウェアの $\overline{SHDN}$ ピンを備えています。 $\overline{SHDN}$ ピンがDGNDに引き下げられると、ポートが直ちにオフします。ポートは、I<sup>2</sup>Cを介して再イネーブルされるか、またはAUTOピン・モードでデバイスがリセットされるまでシャットダウン状態を保ちます。

### マスクされたシャットダウン

LTC4274A/LTC4274Cは待ち時間の短いポート・シェディング機能を備えており、必要に応じて短時間でシステム負荷を低減します。あらかじめ決められた複数のポートをオフすることにより、優先度の高い装置に電力を供給し続けながら、過負荷の主電源の電流を素早く低減することができます。各ポートは優先度の高/低を設定可能で、優先度の低いポートはすべて、 $\overline{MSD}$ ピンが“L”になってから6.5 $\mu$ s以内にシャットダウンします。ポートが $\overline{MSD}$ を介してオフすると、対応するDetection EnableビットとClassification Enableビットがクリアされるので、ホストの指示で検出が再度イネーブルされるまでポートはオフ状態のままでです。

## アプリケーション情報

### シリアル・デジタル・インターフェース

#### 概要

LTC4274A/LTC4274Cは、標準SMBus/I<sup>2</sup>C 2線インターフェースを使ってホストと通信します。LTC4274A/LTC4274Cはスレーブのみのデバイスで、標準SMBusプロトコルを使ってホスト・マスターと通信します。割り込みはINTピンを介してホストに伝えられます。標準的な通信波形とこれらのタイミング関係をタイミング図(図5～図9)に示します。SMBusのデータ・プロトコルの詳細についてはwww.smbus.orgを参照してください。

LTC4274A/LTC4274Cでは、シリアル・インターフェースを機能させるためにV<sub>DD</sub>とV<sub>EE</sub>の両方の電源レールを必要とします。

#### バスのアドレス指定

LTC4274A/LTC4274Cの最初のシリアル・バス・アドレスは010xxxxbで、下位の4ビットはAD3～AD0ピンによって設定されます。これにより、1本のバス上に最大16個のLTC4274A/LTC4274Cを接続することができます。また、すべてのLTC4274A/LTC4274Cがアドレス0110000bに応答することにより、ホストが1回のトランザクションで複数のLTC4274A/LTC4274Cに同じコマンド(通常、設定コマンド)を書き込むことができます。LTC4274A/LTC4274CはINTピンをアサートしていると、SMBus規格に従ってアラート応答アドレス(0001100b)にも応答します。

#### 割り込みとSMBALERT

LTC4274A/LTC4274Cのほとんどのポート・イベントは割り込みをトリガするように設定でき、INTピンをアサートしてホストにイベントへの警告を行います。これにより、ホストがLTC4274A/LTC4274Cをポーリングする必要がなくなり、シリアル・バスのトラフィックが最小限に抑えられてホストCPUのサイクルが節約されます。SMBALERTプロトコル(ARA)を使用しているホストがどのLTC4274A/LTC4274Cが割り込みを発生させたかを判断することにより、複数のLTC4274A/LTC4274Cが共通のINTラインを共有することができます。

#### レジスタの概要

シリアル・バスの使用およびデバイスの設定と状態については、LTC4274A/LTC4274Cのソフトウェア・プログラミング・マニュアルを参照してください。

## 外付け部品の選択

### 電源とバイパス

LTC4274A/LTC4274Cを動作させるには2つの電源電圧が必要です。V<sub>DD</sub>にはDGNDを基準にした3.3V(公称)が必要です。V<sub>EE</sub>には、タイプ1のPSEでは-45V～-57V、タイプ2のPSEでは-51V～-57V、LTPoE++のPSEでは-54.75V～-57VのAGNDを基準にした負電圧が必要です。2つのグラウンドの関係は一定ではなく、AGNDはV<sub>DD</sub>～DGNDの任意のレベルを基準にすることができますが、通常はV<sub>DD</sub>またはDGNDのどちらかに接続します。

V<sub>DD</sub>はLTC4274A/LTC4274Cの大部分の内部回路に電力を供給し、最大3mAを流します。V<sub>DD</sub>からDGNDに、少なくとも0.1μFのセラミック・デカップリング・コンデンサを、各LTC4274A/LTC4274Cデバイスにできるだけ近づけて接続します。

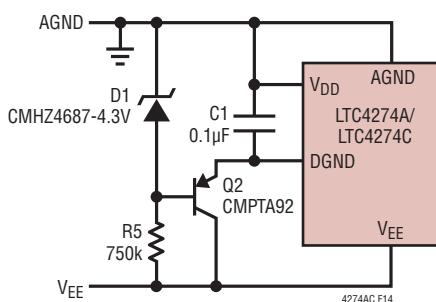

DGNDへの負電源を負のV<sub>EE</sub>電源から生成するための3つの部品から成る低損失レギュレータを図14に示します。V<sub>DD</sub>はAGNDに接続され、DGNDはAGNDを基準にして負になります。このレギュレータは1個のLTC4274A/LTC4274Cデバイスをドライブします。図15では、AGNDより3.3V高い正のV<sub>DD</sub>電源を得るため、この昇圧コンバータ回路のDGNDがAGNDに接続されています。この回路は複数のLTC4274A/LTC4274Cデバイスとオプトカプラーをドライブすることができます。

図14. DGNDへの負のLDO

## アプリケーション情報

図15. 正の  $V_{pp}$  昇圧コンバータ

VEEはPDに電力を供給する主電源です。この電源は比較的大きな電力を供給し、大きな過渡電流を生じやすいので、簡単なロジック電源よりも設計に注意が必要です。最小のIR損失と最大のシステム効率を得るため、VEEを最大振幅(57V)近くに設定し、過渡オーバーシュート/アンダーシュート、温度ドリフト、および使用される個々の電源のライン・レギュレーション仕様を見込んだ十分なマージンを残します。

AGND と VEE の間のバイパス容量は、信頼性の高い動作をさせるために非常に重要になります。出力ポートに短絡が生じると、LTC4274A/LTC4274C が電流を安定化し始めるのに  $1\mu\text{s}$  もの時間を要することがあります。この間は、電流が回路内の小さなインピーダンスによってのみ制限され、通常、高電流スパイクが生じるので、VEE 電源に過渡電圧が生じ、UVLO フォルトによって LTC4274A/LTC4274C がリセットされる可能性があります。誤ったリセットを最小限に抑えるため、 $1\mu\text{F}$  の  $100\text{V X7R}$  コンデンサを VEE ピンの近くに接続することを推奨します。

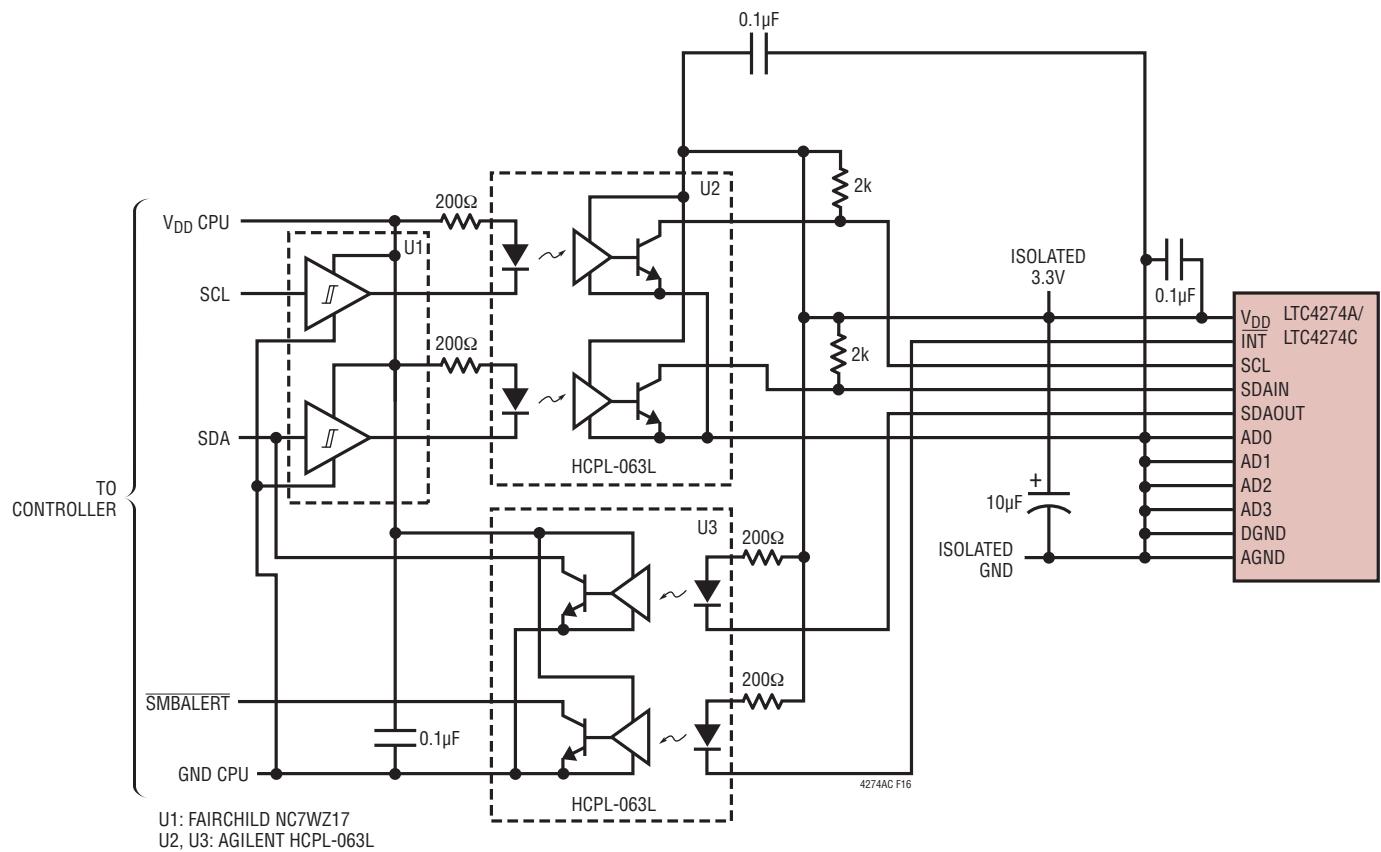

## シリアル・バスの絶縁

LTC4274A/LTC4274Cには分割されたSDAピン(SDAINおよびSDAOUT)が備わっており、双方向のSDAラインのオプトアイソレーションが容易です。

IEEE 802.3 イーサネット規格では、ネットワーク・セグメント (PoE回路を含む)が各ネットワーク・インターフェース装置のシャーシ・グランドから電気的に絶縁されていることを要求しています。ただし、ネットワーク・セグメントは、それらのセグメントが1つの配電システム上の同一建物内にある装置に接続されていれば、相互に絶縁する必要はありません。

小型のPoEスイッチのような簡単な装置の場合、絶縁された主電源を使って装置全体に電力を供給することにより、この絶縁要件を満たすことができます。この方法は、装置がより対線イーサネット以外に電気的に導通したポートを持たない場合に使用することができます。この場合、SDAINピンとSDAOUTピンを相互接続して、標準的なI<sup>2</sup>C/SMBusのSDAピンとして機能させることができます。

装置が大きなシステムの一部であったり、イーサネットに対応していない外部ポートが追加されてたり、あるいは別の何らかの理由により保護されたグランドを基準にする必要がある場合、Power over Ethernetサブシステム(すべてのLTC4274A/LTC4274Cを含む)は、システムの他の部分から電気的に絶縁されている必要があります。標準的な絶縁型シリアル・インターフェースを図16に示します。LTC4274A/LTC4274CのSDAOUTピンは、オプトカプラの入力を直接ドライブするように設計されています。標準のI<sup>2</sup>C/SMBusデバイスは通常、オプトカプラをドライブすることができないので、ホスト・コントローラ側からの信号をバッファするためにU1が使用されています。

## アプリケーション情報

図16. I<sup>2</sup>Cバスのオプトアイソレーション

## アプリケーション情報

### 外付け MOSFET

システムの信頼性にとってパワー MOSFET を慎重に選択することが重要です。弊社では、タイプ1とタイプ2のPSEアプリケーションにおいて信頼性が確認されている Fairchild 社のIRFM120A、FDT3612、FDMC3612 または Philips 社のPHT6NQ10Tを推奨しています。850mA の IEEE の最大規格を超える電流を供給する非標準のアプリケーションでは、放熱や他の MOSFET の設計を考慮する必要があります。これらの推奨デバイス以外の MOSFET を使用する場合には、弊社にお問い合わせください。

### センス抵抗

LTC4274A/LTC4274C は 0.5Ω または 0.25Ω の電流センス抵抗を使用するように設計されています。新規設計では 0.25Ω を使って電力損失を低減することを推奨します。0.5Ω のオプションは、LTC4274A/LTC4274C を LTC4258 や LTC4259A の当座の代替として使用する既存のシステムを対象としたものです。センス抵抗の値が小さくなると熱損失が小さくなります。1本の 0.25Ω 抵抗の代わりに、4本の一般的な 1Ω 抵抗(0402 以上のパッケージ・サイズ)を並列接続して使用することができます。IEEE 規格が要求する  $I_{CUT}$  と  $I_{LIM}$  の精度を満たすため、センス抵抗は許容誤差を  $\pm 1\%$  以下にし、温度係数を  $\pm 200\text{ppm}/^\circ\text{C}$  以下にします。

### ポートの出力コンデンサ

ポートは、起動時や過負荷時の電流制限状態のときに LTC4274A/LTC4274C を安定に保つため、出力の両端に 0.22μF のコンデンサを必要とします。一般的なセラミック・コンデンサは多くの場合大きな電圧係数をもっています。つまり印加電圧が上昇するに従って容量が減少します。この問題を最小限に抑えるためには、少なくとも 100V の定格の X7R セラミック・コンデンサを推奨します。

### ESD/ケーブル放電保護

それぞれ数千ボルトに充電されている可能性がある複数の長いデータ・ケーブルが低インピーダンスの RJ45 ジャックに挿入されたとき、イーサネット・ポートは大きな ESD の影響を受ける可能性があります。損傷を受けないよう保護するため、ポートには一方を AGND に他方を V<sub>EE</sub> に接続した 1 対のクランプ・ダイオードが必要です(図 10)。各 LTC4274A/LTC4274C デバイスの V<sub>EE</sub> から AGND に サージ・サプレッサを追加する必要があります。ポートのこれらのダイオードは有害なサージを電源レールに誘導し、そこでサージ・サプレッサと V<sub>EE</sub> のバイパス容量によってこれらのサージが吸収されます。サージ・サプレッサには、V<sub>EE</sub> 電源の過渡電圧から LTC4274A/LTC4274C を保護するというもう 1 つの利点があります。

S1B ダイオードはポートのクランプ・ダイオードに適しており、SMAJ58A または同等の部品を V<sub>EE</sub> のサージ・サプレッサとして推奨します。

### レイアウトのガイドライン

基板レイアウト、部品の配置および配線のガイドラインの厳格な遵守は、最適な電流読み出し精度、IEEE 準拠、システムの堅牢性、熱損失を達成するために不可欠です。

25.5W を超える電力を供給では、部品やレイアウトに関する制約が厳しくなります。特に MOSFET、センス抵抗、トランジスタの選択は、安全で信頼性の高いシステム運用を行う上で極めて重要です。

すべてのレイアウト・ガイドライン、レイアウト例、BOM (部品表)が必要な場合は、弊社にお問い合わせください。

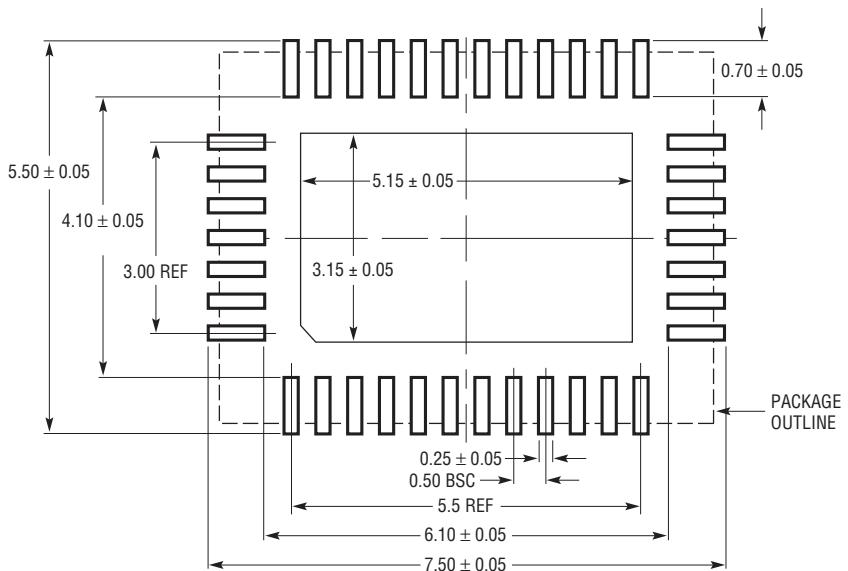

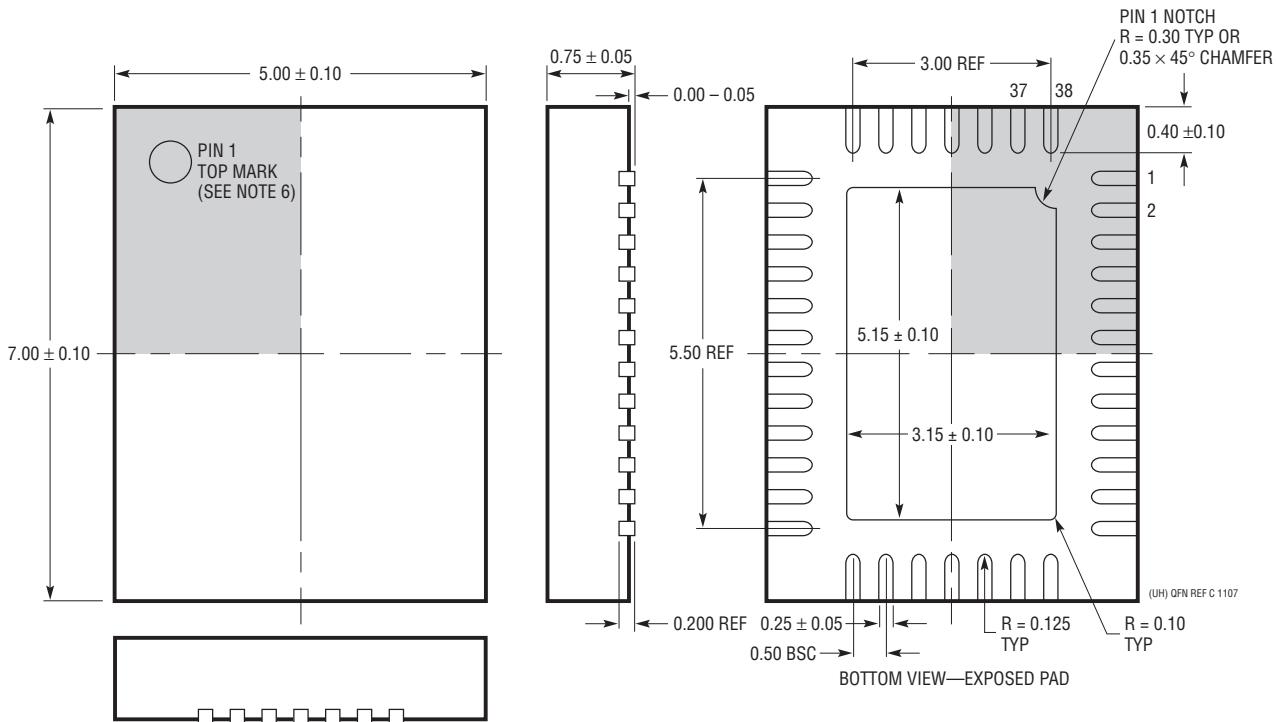

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> をご覧ください。

**UHF Package

38-Lead Plastic QFN (5mm x 7mm)

(Reference LTC DWG # 05-08-1701 Rev C)**

## RECOMMENDED SOLDER PAD LAYOUT APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERS

### 注記:

1. 図は JEDEC のパッケージ外形 MO-220 の

バリエーション WHKD に適合

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで 0.20mm を超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

## 改訂履歴

| REV | 日付   | 概要                                                                                                                                                                                      | ページ番号                                |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| A   | 9/11 | GATEの標準電圧を12Vに変更<br>「デジタル・インターフェース」の $V_{ILD}$ のテキストを改訂<br>「表4. 分類値」のタイトルとこの表への言及を「表5」に変更<br>「電源とバイパス」の電源電圧の数字を改訂<br>「関連製品」セクションのCUT/LIMを $I_{CUT}/I_{LIM}$ に変更<br>ツエナーダイオードにSMAJ58Aを指定 | 3、15、21<br>4<br>20<br>24<br>30<br>30 |

| B   | 1/12 | LTPoE <sup>++</sup> の電力レベルの35W、45Wをそれぞれ38.7W、52.7Wに変更<br>$V_{ILD}$ のI <sup>2</sup> C Input Low VoltageのMAX値を改訂<br>AUTOピン・モードとリセット・ピンの関係を明確化                                             | 1、2、16、17<br>4<br>18                 |

| C   | 8/12 | 表1: 38.7Wと52.7Wに対するツイストペアの要件を、2ペアから4ペアに変更                                                                                                                                               | 17                                   |

## 標準的応用例

1つの完全な絶縁型受電イーサネット・ポート

## 関連製品

| 製品番号               | 説明                                              | 注釈                                                                              |

|--------------------|-------------------------------------------------|---------------------------------------------------------------------------------|

| LTC4270/LTC4271    | 12ポートPoE/PoE+/LTPoE++ PSE コントローラ                | トランスによる絶縁、タイプ1、タイプ2、およびLTPoE++のPDをサポート                                          |

| LTC4266            | IEEE 802.3at 対応のPoEシステム向けクワッド PSE コントローラ        | 2イベント分類、プログラム可能なICUT/IIM                                                        |

| LTC4266A/ LTC4266C | IEEE 802.3at 対応のPoEシステム向けクワッド PSE コントローラ        | 13W～90Wの電力を供給                                                                   |

| LTC4274            | IEEE 802.3at 対応のPoEシステム向けシングル PSE コントローラ        | 2イベント分類、プログラム可能なICUT/IIM                                                        |

| LTC4265            | IEEE 802.3at PD インタフェース・コントローラ                  | 100V、1Aスイッチを内蔵、2イベント分類を認識                                                       |

| LTC4267            | スイッチング・レギュレータ搭載の IEEE 802.3af PD インタフェース        | 100V、400mAスイッチを内蔵、デュアル・レベル突入電流制限、プログラム可能な分類                                     |

| LTC4269-1          | フライバック・スイッチング・レギュレータ搭載の IEEE 802.3at PD インタフェース | 2イベント分類、プログラム可能な分類、同期整流式No-Optoフライバック・コントローラ、スイッチング周波数:50kHz～250kHz、補助電源サポート    |

| LTC4269-2          | フォワード・スイッチング・レギュレータ搭載の IEEE 802.3at PD インタフェース  | 2イベント分類、プログラム可能な分類、同期整流式フォワード・コントローラ、スイッチング周波数:100kHz～500kHz、補助電源サポート           |

| LTC4278            | フライバック・スイッチング・レギュレータ搭載の IEEE 802.3at PD インタフェース | 2イベント分類、プログラム可能な分類、同期整流式No-Optoフライバック・コントローラ、スイッチング周波数:50kHz～250kHz、12V補助電源サポート |

4274acf0