## 特長

- 電源の入ったバックプレーンでボードを安全に挿抜可能

- 10.8V ~ 80V の電源電圧を制御

- フォールドバック電流制限

- 過電流フォルトを検出

- 外付け N チャネル MOSFET をドライブ

- 電源電圧上昇速度をプログラム可能

- 低電圧保護

- ラッチオフ動作モード (LT4256-1)

- 自動リトライ (LT4256-2)

- 8 ピン SO パッケージ

## アプリケーション

- 活線挿入

- 電子回路ブレーカ / 電源バス

- 産業用ハイサイド・スイッチ / 回路ブレーカ

- 24V/48V 産業用 / 警報システム

- 12V、24V および 48V 配電システムに最適

- 48V テレコム・システム

## 説明

LT<sup>®</sup>4256-1/LT4256-2 は、電源の入ったバックプレーンに対し、ボードの安全な挿入 / 引抜きを可能にする高電圧 Hot Swap<sup>TM</sup> コントローラです。内蔵のドライバが外付け N- チャネル MOSFET スイッチをドライブし、10.8V ~ 80V の電源電圧を制御します。

LT4256-1/LT4256-2 は調整可能なアナログ・フォールドバック電流制限機能を搭載しています。プログラム可能な期間を過ぎても電流が電流制限状態にあると、N チャネル MOSFET がオフし、PWRGD 出力が “L” になり、LT4256-2 はタイムアウト遅延後に自動的に再起動します。LT4256-1 は UV ピンが “L” になるまでラッチオフします。

PWRGD 出力は出力電圧がプログラムされたレベルを上回ったことを知らせます。V<sub>CC</sub> からの外付け抵抗ストリングにより、プログラム可能な低電圧保護を提供します。

LT4256 を使用することで LT1641 の設計をアップグレードすることができます。アップグレードされた仕様については、14 ページの表 1 を参照してください。

LT4256-1 と LT4256-2 は 8 ピンの SO パッケージで供給され、LT1641 とピンの互換性があります。

**L**、LTC、LT はリニアテクノロジー社の登録商標です。

Hot Swap はリニアテクノロジー社の商標です。

他のすべての商標はそれぞれの所有者に所有権があります。

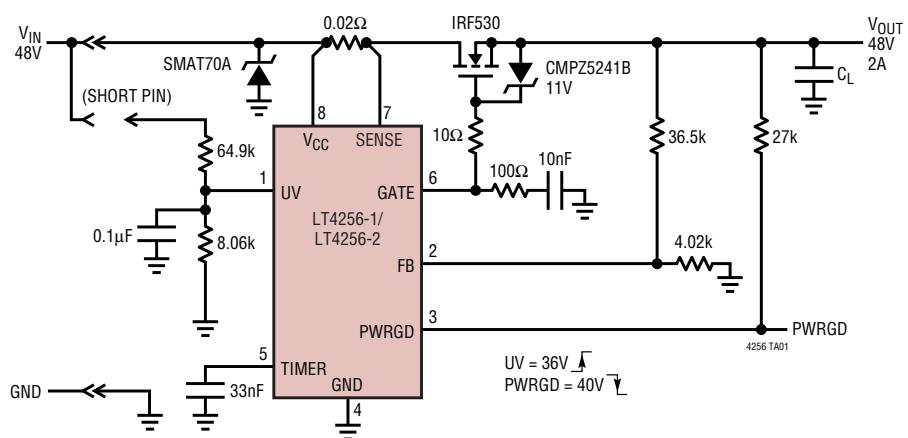

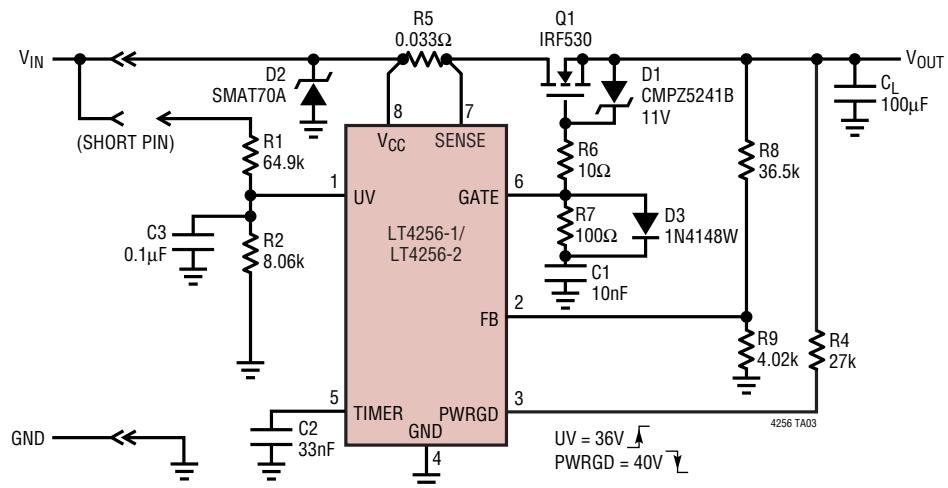

## 標準的応用例

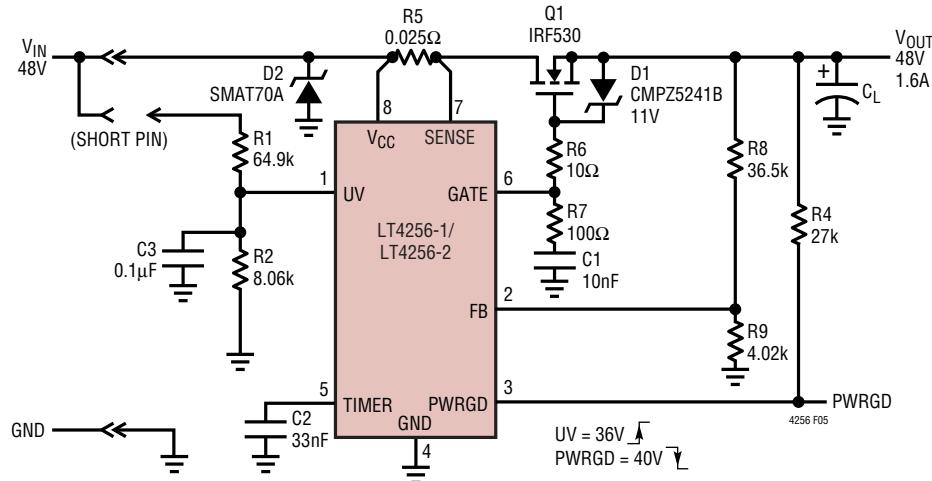

### 48V、2A ホットスワップ・コントローラ

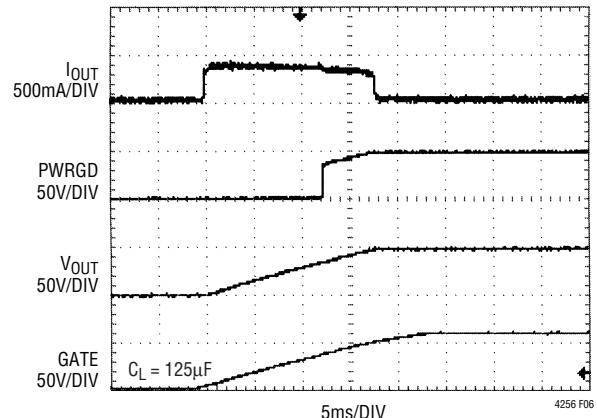

LT4256 起動時の動作

# LT4256-1/LT4256-2

## 絶対最大定格

(Note 1)

|                         |                        |

|-------------------------|------------------------|

| 電源電圧 ( $V_{CC}$ ) ..... | -0.3 ~ 100V            |

| SENSE, PWRGD .....      | -0.3 ~ 100V            |

| GATE (Note 2) .....     | -0.3V ~ $V_{CC} + 10V$ |

| 最大入力電流 (GATE) .....     | 200µA                  |

| FB, UV .....            | -0.3 ~ 44V             |

| TIMER .....             | -0.3V ~ 4.3V           |

| 最大入力電流 (TIMER) .....    | 100µA                  |

| 動作温度範囲                  |                        |

| LT4256C .....           | 0°C ~ 70°C             |

| LT4256I .....           | -40°C ~ 85°C           |

| 保存温度範囲 .....            | -65°C ~ 150°C          |

| リード温度 (半田付け、10秒) .....  | 300°C                  |

## パッケージ/発注情報

| TOP VIEW             | ORDER PART NUMBER                                                                                                                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | LT4256-1CS8<br>LT4256-1IS8<br>LT4256-2CS8<br>LT4256-2IS8                                                                                                                                                 |

| S8 PART MARKING      |                                                                                                                                                                                                          |

|                      | 42561<br>42561I<br>42562<br>42562I                                                                                                                                                                       |

| <b>Order Options</b> | Tape and Reel: Add #TR<br>Lead Free: Add #PBF Lead Free Tape and Reel: Add #TRPBF<br>Lead Free Part Marking: <a href="http://www.linear-tech.co.jp/leadfree/">http://www.linear-tech.co.jp/leadfree/</a> |

より広い動作温度範囲で規定されるデバイスについては、弊社へお問い合わせください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ C$ での値。注記がない限り、 $V_{CC} = 48V$ 。

| SYMBOL            | PARAMETER                                       | CONDITIONS                                                                    | MIN             | TYP          | MAX          | UNITS |

|-------------------|-------------------------------------------------|-------------------------------------------------------------------------------|-----------------|--------------|--------------|-------|

| $V_{CC}$          | Operating Voltage                               |                                                                               | ● 10.8          | 80           |              | V     |

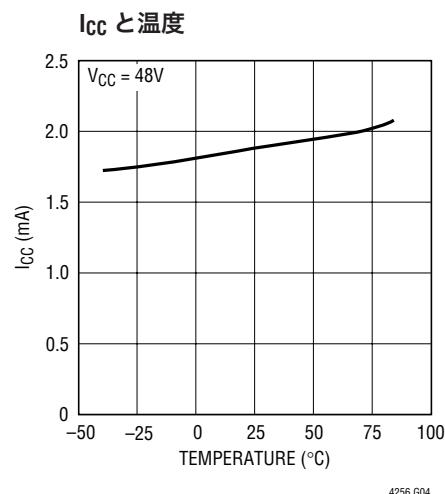

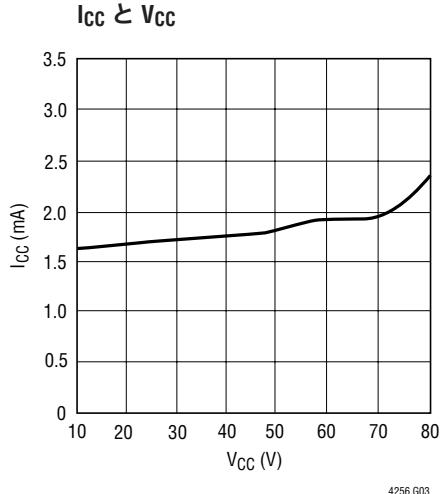

| $I_{CC}$          | Operating Current                               |                                                                               |                 | 1.8          | 3.9          | mA    |

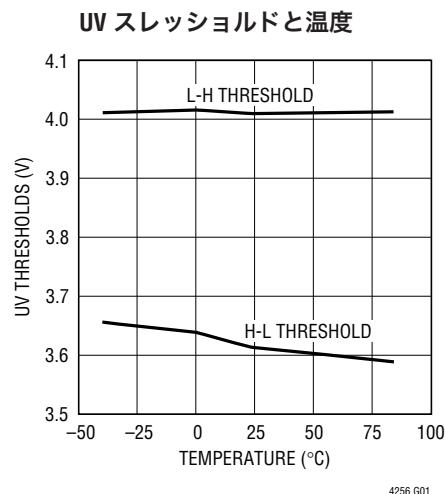

| $V_{UVLH}$        | Undervoltage Threshold                          | $V_{CC}$ Low-to-High Transition                                               | ● 3.96          | 4            | 4.04         | V     |

| $V_{UVHYS}$       | Hysteresis                                      |                                                                               | 0.25            | 0.4          | 0.55         | V     |

| $I_{INUV}$        | UV Input Current                                | UV $\geq 1.2V$<br>UV = 0V                                                     |                 | -0.1<br>-1.5 | -1<br>-3     | µA    |

| $V_{UVRTH}$       | Fault Latch Reset Threshold Voltage             |                                                                               | ● 0.4           | 0.85         | 1.2          | V     |

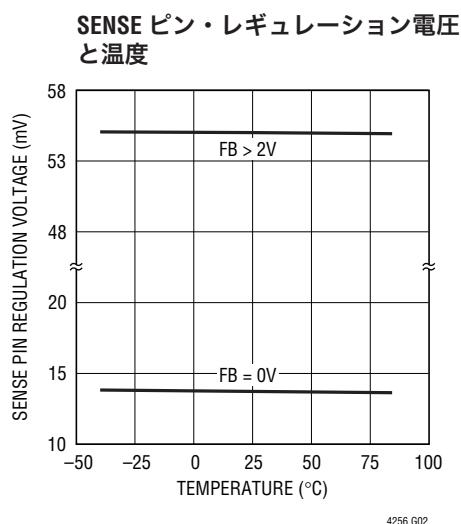

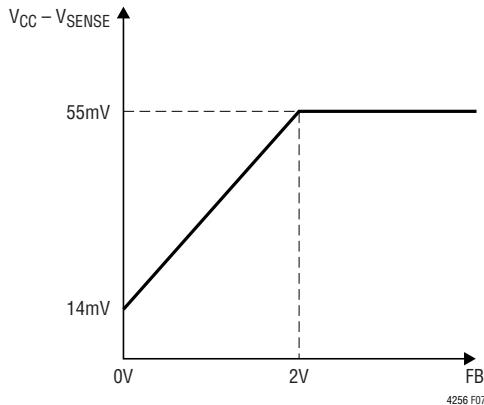

| $V_{SENSETRIP}$   | SENSE Pin Trip Voltage ( $V_{CC} - V_{SENSE}$ ) | FB = 0V<br>FB $\geq 2V$                                                       | ● 5.5<br>● 45   | 14<br>55     | 22<br>65     | mV    |

| $I_{INSNS}$       | SENSE Pin Input Current                         | $V_{SENSE} = V_{CC}$                                                          |                 | 40           | 70           | µA    |

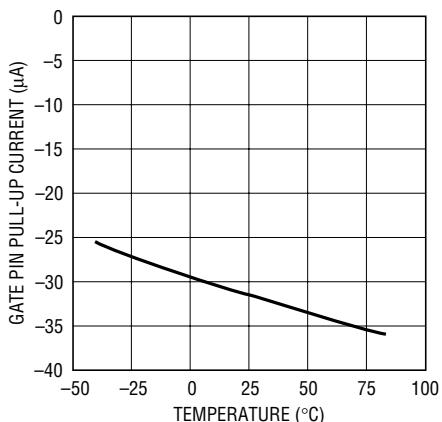

| $I_{PU}$          | GATE Pull-Up Current                            | Charge Pump On, $\Delta V_{GATE} = 7V$                                        | ● -16           | -32          | -63          | µA    |

| $I_{PD}$          | GATE Pull-Down Current                          | Any Fault, $V_{GATE} = 3V$                                                    |                 | 40           | 62           | mA    |

| $\Delta V_{GATE}$ | External N-Channel Gate Drive (Note 2)          | $V_{GATE} - V_{CC}, 10.8V \leq V_{CC} \leq 20V$<br>$20V \leq V_{CC} \leq 80V$ | ● 4.5<br>● 10   | 8.8<br>11.6  | 12.5<br>12.8 | V     |

| $V_{FB}$          | FB Voltage Threshold                            | FB High-to-Low Transition<br>FB Low-to-High Transition                        | ● 3.95<br>● 4.2 | 3.99<br>4.45 | 4.03<br>4.65 | V     |

| $V_{FBHYS}$       | FB Hysteresis Voltage                           |                                                                               | 0.3             | 0.45         | 0.6          | V     |

| $V_{OLPGD}$       | PWRGD Output Low Voltage                        | $I_0 = 1.6mA$<br>$I_0 = 5mA$                                                  |                 | 0.25<br>0.6  | 0.4<br>1     | V     |

| $I_{PWRGD}$       | PWRGD Pin Leakage Current                       | $V_{PWRGD} = 80V$                                                             |                 | 0.1          | 1            | µA    |

| $I_{INFB}$        | FB Input Current                                | FB = 4.5V                                                                     |                 | -0.1         | -1           | µA    |

| $I_{TIMERPU}$     | TIMER Pull-Up Current                           | TIMER = 3V, During Fault                                                      | ● -63           | -105         | -147         | µA    |

| $I_{TIMERPD}$     | TIMER Pull-Down Current                         | TIMER = 3V                                                                    | ● 1.5           | 3            | 5            | µA    |

| $V_{HTIMER}$      | TIMER Shut-Down Threshold                       | $C_{TIMER} = 10nF$                                                            | ● 4.3           | 4.65         | 5            | V     |

| $D_{TIMER}$       | Duty Cycle (RETRY Mode)                         |                                                                               | ● 1.5           | 3            | 4.5          | %     |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = 48\text{V}$ 。

| SYMBOL         | PARAMETER                               | CONDITIONS                          | MIN | TYP | MAX | UNITS         |

|----------------|-----------------------------------------|-------------------------------------|-----|-----|-----|---------------|

| $t_{PHLUV}$    | UV Low to GATE Low                      |                                     |     | 1.7 | 3   | $\mu\text{s}$ |

| $t_{PLHUV}$    | UV High to GATE High                    | $C_{GATE} = 0$                      |     | 6   | 9   | $\mu\text{s}$ |

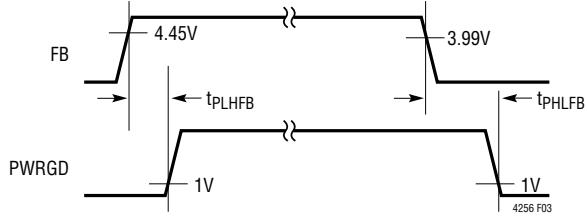

| $t_{PHLFB}$    | FB Low to PWRGD Low                     |                                     |     | 0.8 | 2   | $\mu\text{s}$ |

| $t_{PLHFB}$    | FB High to PWRGD High                   |                                     |     | 3.2 | 5   | $\mu\text{s}$ |

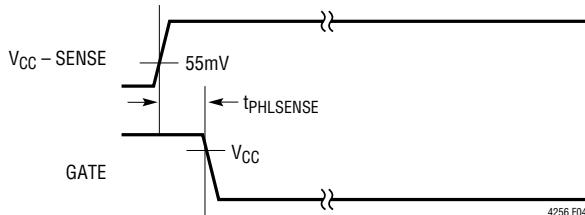

| $t_{PHLSENSE}$ | $(V_{CC} - V_{SENSE})$ High to GATE Low | $V_{CC} - V_{SENSE} = 275\text{mV}$ |     | 1   | 3   | $\mu\text{s}$ |

Note 1: 絶対最大定格はそれを超えるとデバイスの寿命に影響を及ぼす値。

Note 2: 内部クランプによって GATE ピンを制限し、 $V_{CC}$  を 10V 以上上回らないようにする。クランプ電圧を超えてこのピンをドライブすると、デバイスを損傷することがある。

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

# LT4256-1/LT4256-2

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

GATE ピン・プルアップ電流と温度

4256 G07

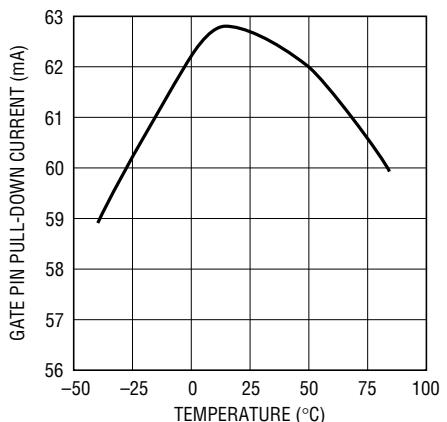

GATE ピン・プルダウン電流と温度

4256 G08

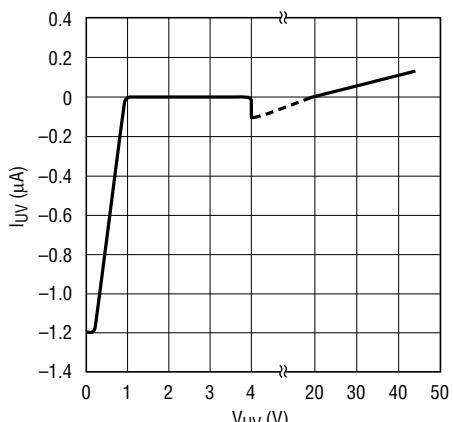

UV ピン電流と UV ピン電圧

4256 G09

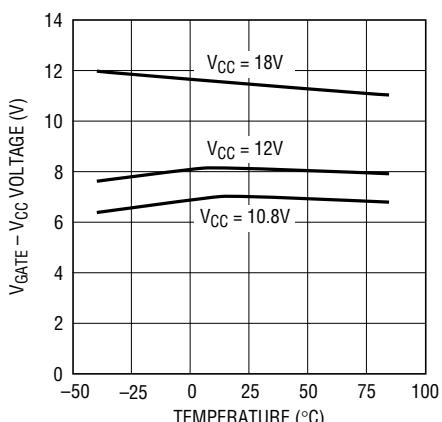

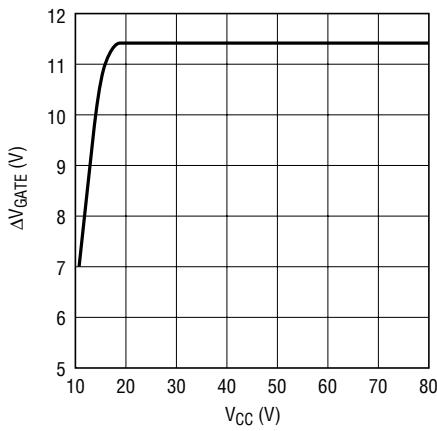

$V_{\text{GATE}} - V_{\text{CC}}$  電圧と温度

4256 G10

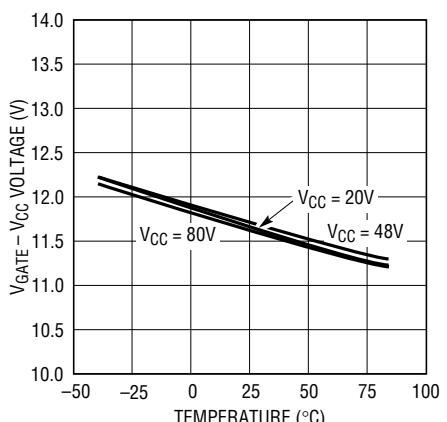

$V_{\text{GATE}} - V_{\text{CC}}$  電圧と温度

4256 G11

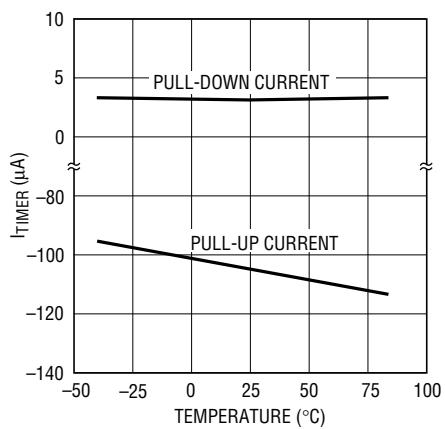

TIMER ピン電流と温度

4256 G12

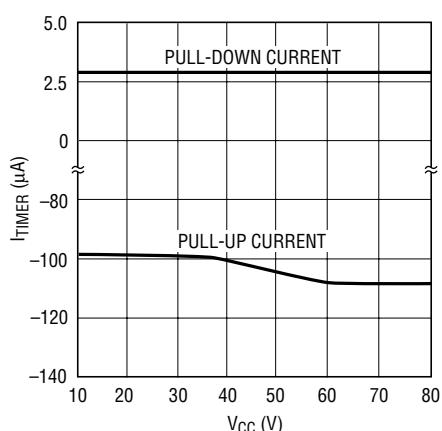

TIMER ピン電流と  $V_{\text{CC}}$

4256 G13

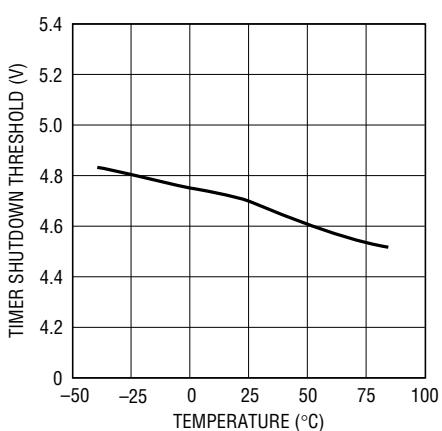

タイマ・シャットダウン・スレッショルドと温度

4256 G14

425612fa

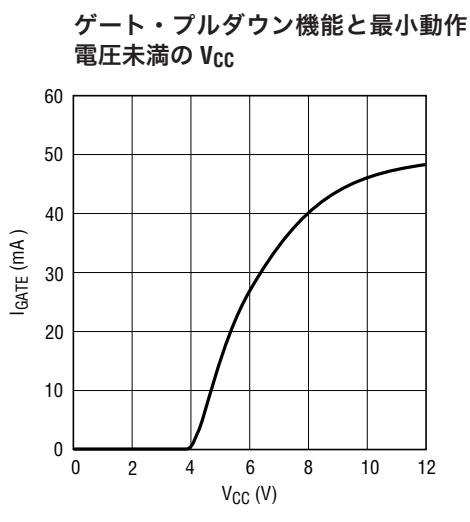

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 。

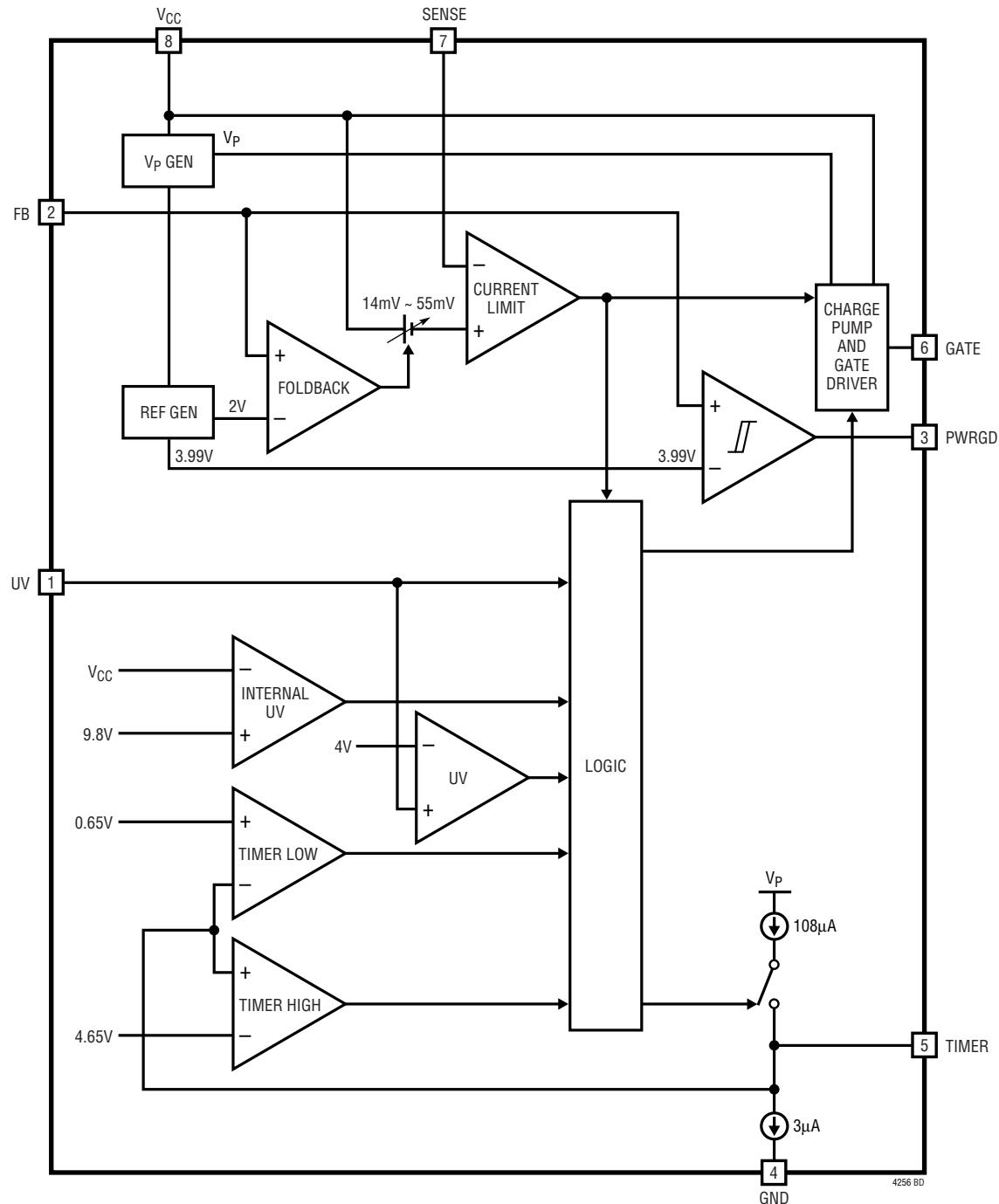

## ピン機能

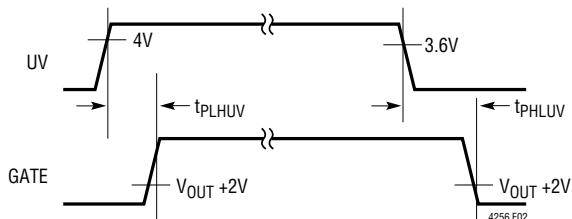

**UV (ピン1)** : 低電圧センス。UVは、出力電圧をイネーブルする入力です。UVが4Vを上回ってドライブされると、GATEは充電を開始し、出力がオンになります。UVが3.6Vを下回ると、GATEが放電し、出力がシャットオフします。

電流制限フォールト後最小限5μsの間UVをパルス信号で“L”にすると、フォールト・ラッチがリセットされ(LT4256-1)、デバイスは再びオン状態になります。このコマンドは、TIMERによって0.65Vを下回るまで放電した後でのみ受け入れられます。UVセンスをディスエーブルするには、UVを5V～44V電圧に接続します。

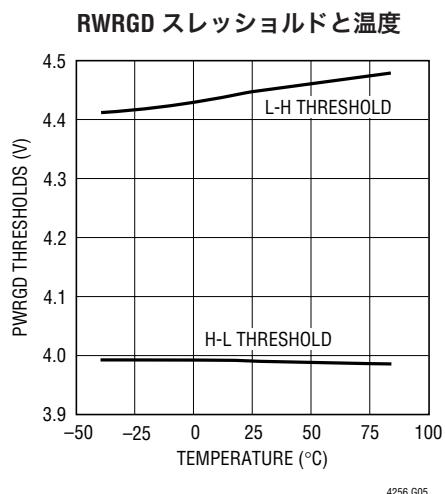

**FB (ピン2)** : パワー・グッド・コンパレータ入力。FBは、外付け抵抗分割器で出力電圧をモニタします。FBの電圧が“H”から“L”になるスレッショルドである3.99Vより低いと、PWRGDは“L”になり、FBが“L”から“H”になるスレッショルドである4.45Vを超えるとPWRGDはリリースされます。

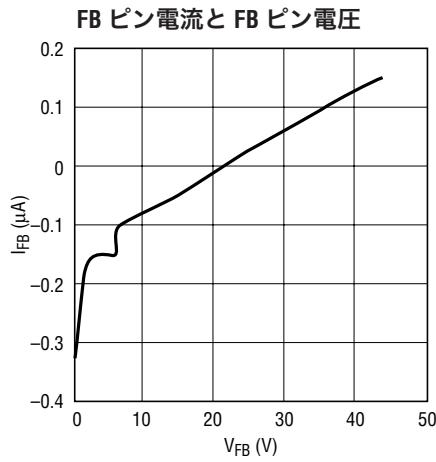

FBの電圧はフォールドバック電流制限値に影響します(図7およびその関連説明を参照)。

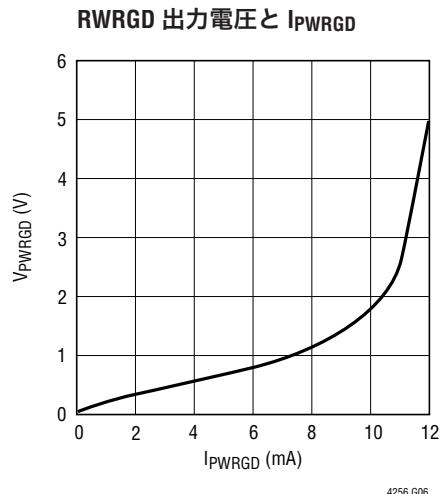

**PWRGD (ピン3)** : パワー・グッド出力。FBの電圧が“H”から“L”になるスレッショルド電圧である3.99Vを下回ると、PWRGDは“L”になります。FBの電圧が“L”から“H”になるスレッショルド電圧を超えると、ハイ・インピーダンス状態となります。外付けプルアップ抵抗でPWRGDをV<sub>CC</sub>より高い電圧または低い電圧に引き上げることができます。

**GND (ピン4)** : デバイスのグランド。最良のパフォーマンスを得るには、このピンをグランド・プレーンに接続する必要があります。

**TIMER (ピン5)** : タイミング入力。TIMERとGND間の外付けタイミング・コンデンサはデバイスが電流制限値内に最大時間とどまっているようにプログラミングします。デバイスが電流制限状態になると、105μA プルアップ電流源はタイミング・コンデンサの充電を開始します。TIMERの電圧が4.65V(標準)になると、GATEは“L”になります。TIMER プルアップ電流がオフし、コンデンサは3μA プルダウン電流によって放電されます。TIMERが0.65V(標準)を下回ると、LT4256-2ではGATEが再びオンします。TIMERが0.65V(標準)より下に放電後は、LT4256-1をリセットするにはUVは“L”にする必要があります。UVを“L”にしないと(LT4256-1

の場合)、GATEはラッチオフのままであり、TIMERはGND近くまで放電されます。出力が短絡状態では、LT4256-2は、3% デューティ・サイクルでオン/オフを繰り返します。

**GATE (ピン6)** : 外付けNチャネルMOSFET用ハイ・サイド・ゲート・ドライブ。内部チャージ・ポンプは、20Vを超えるV<sub>CC</sub>電源電圧では、少なくとも10Vのゲート・ドライブを保証し、10.8V～20VのV<sub>CC</sub>電源電圧では、4.5Vのゲート・ドライブを保証します。GATEの電圧の立ち上がりスロープは、GATE～GNDに接続された外付けコンデンサとチャージ・ポンプ出力の内部32μA プルアップ電流源によって設定されます。

電流制限値に達すると、センス抵抗両端の電圧を一定に保つためにGATE電圧を調整するとともにタイミング・コンデンサの充電が開始します。TIMER電圧が4.65Vを超えると、GATEが“L”にプルされます。

UVが“L”に引き下げられるか、V<sub>CC</sub>電源電圧が外部からプログラミングされた低電圧スレッショルドより下に低下するか、V<sub>CC</sub>が内部UVLOスレッショルド(9.8V)より下に低下する場合もGATEはGNDに引き下げられます。

通常の動作状態では、GATEはV<sub>CC</sub>を超えた最大電圧11.6V(標準)に内部的にクランプします。クランプ電圧を超えてこのピンをドライブすると、デバイスを損傷することがあります。瞬間的な短絡状態では、そのゲート酸化物防止のために外部MOSFETのゲートとソース間にツエナー・ダイオードが必要になります。「アプリケーション情報」を参照してください。

**SENSE (ピン7)** : 電流制限センス入力。V<sub>CC</sub>とSENSE間の供給パスには、センス抵抗が配置されます。FBが2V以上のときに電流制限回路によってセンス抵抗両端の電圧(V<sub>CC</sub>-SENSE)を55mVに安定化させます。FBが2Vより下に低下すると、センス抵抗両端の安定化電圧はFBが0Vのときの14mVにまでリニアに低下します。

電流制限を無効にするには、SENSEをV<sub>CC</sub>に接続します。

**V<sub>CC</sub> (ピン8)** : 入力電源電圧。正常動作時の正の電源入力範囲は、10.8V～80Vです。I<sub>CC</sub>は標準で1.8mAです。内部回路は、9.8V(標準)未満の入力に対しては、LT4256-1/LT4256-2をディスエーブルします。

## ブロック図

# LT4256-1/LT4256-2

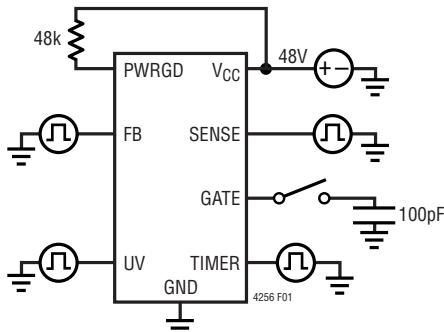

## テスト回路

図 1

## タイミング図

図 2. UV と GATE のタイミング

図 3. V<sub>OUT</sub> と PWRGD のタイミング

図 4. SENSE と GATE のタイミング

## アプリケーション情報

### 活線挿入

電源の入っているバックプレーンに回路基板を挿入するとき、電源バイパス・コンデンサが充電されるので、バックプレーン電源バスから大きなピーク電流が流れることができます。過渡電流により、コネクタ・ピンに恒久的な損傷が生じたり、システム電源にグリッチが発生し、システム内の他の基板がリセットしてしまうことがあります。

LT4256-1/LT4256-2 は、基板の電源電圧を制御された方法でオンにし、電源が供給された状態のバックプレーンへの基板の挿抜を安全に行えるように設計されています。

また、低電圧保護、過電流保護機能を備えているだけではなく、大きな出力に対して出力電源電圧の用意が整っているかどうかをパワーグッド出力信号で示すことができます。

### 電源起動シーケンス

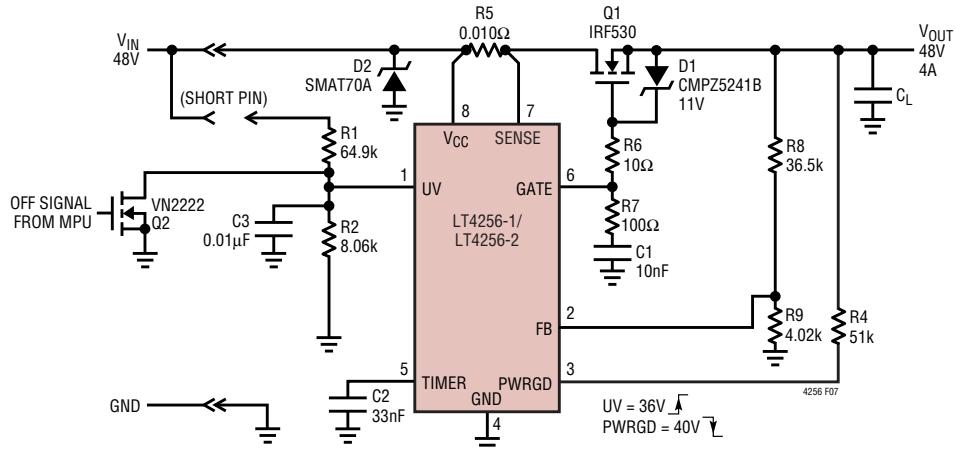

外付け N チャネル MOSFET パス・トランジスタ (Q1) が電源経路に配置され、電源電圧の起動を制御します (図 5)。抵抗 R5 で電流検出を行い、コンデンサ C1 で GATE のスルーレートを制御します。抵抗 R7 で電流制御ループを補償するとともに、抵抗 R6 によって Q1 の高周波発振を防止します。

## アプリケーション情報

図 5. 1600mA、48V アプリケーション

電源ピンが最初に接続された状態になるとき、トランジスタ Q1 はオフしたままです。V<sub>CC</sub> の電圧が外部プログラミングされた低電圧スレッショルドを超えると、V<sub>CC</sub> が 9.8V を超え、TIMER の電圧が 4.65V（標準）未満であれば、トランジスタ Q1 はオンします（図 6）。GATE の電圧は 32μA/C1 のスロープで上昇し、電源の突入電流は以下の値に設定されます。

$$I_{INRUSH} = C_L \cdot 32\mu A/C1 \quad (1)$$

ここで C<sub>L</sub> は、総負荷容量です。

突入電流を軽減するには、C1 を大きくするか、負荷容量を小さくするかのいずれかです。電流センス抵抗 R5 両端の電圧が V<sub>SENSETRIP</sub> に達すると、突入電流は内部電流制限回路によって制限されます。センス抵抗両端の電圧を一定に保つために GATE の電圧が調整され、TIMER の充電が開始します。

FB 電圧が “L” から “H” になる V<sub>FB</sub> スレッショルドを超えると、PWRGD は “H” になります。

## 低電圧検出

LT4256-1/LT4256-2 は UV を使用して V<sub>CC</sub> 電圧をモニタし、いつ負荷をオンにするのが安全かを判断するため、ユーザとしてはスレッショルドを設定する上で最大限の柔軟性が得られます。UV が 3.6V を下回ると、UV が再び 4V を超えるまで GATE は “L” にプルされます。

UV スレッショルドは、絶対に内部 UVLO スレッショルド（標準で 9.8V）を下回らないように設定してください。UV のヒステリシスのメリットが失われ、LT4256-1/LT4256-2 がノイズの影響を受けやすくなるためです（UV

図 6. 起動波形

が 3.6V のスレッショルドのとき、V<sub>CC</sub> は少なくとも 9.8V である必要があります）。UV は、ノイズ・スペイクや容量結合されたグリッチによって誤って LT4256-1/LT4256-2 の出力をシャットダウンするのを防ぐために、C3 でフィルタリングされています。

UV スレッショルドを計算するには、以下の式を使用します。

$$R1 = R2 \left( \frac{V_{THUVLH}}{4V} - 1 \right) \quad (2)$$

$$20k\Omega \leq R1 + R2 \leq 200k\Omega \quad (3)$$

$$V_{THUVLH} = 3.6 \left( 1 + \frac{R1}{R2} \right) \quad (4)$$

ここで、V<sub>THUVLH</sub> は、V<sub>CC</sub> が上昇（L-H）するときの希望する UV スレッショルド電圧です。

## アプリケーション情報

図 7. 電流制限センス電圧と帰還ピン電圧

図 11 は LT4256-1/LT4256-2 をどのようにロジック信号でオフするかを示したものです。これはオープン・ドレイン MOSFET、Q2 (UV ピンに接続) のゲートを “H” にプルすることによって行われます。

### 短絡保護

LT4256-1/LT4256-2 は短絡や過負荷電流に対する保護のために電子回路ブレーカ付きのプログラム可能なフォールドバック電流制限機能を搭載しています。電流制限は  $V_{CC}$  と SENSE の間にセンス抵抗 ( $R_5$ ) を配置することによって設定されます。電流制限スレッショルドは、次の式で計算されます。

$$I_{LIMIT} = 55\text{mV}/R_5 \quad (5)$$

ここで、 $R_5$  はセンス抵抗です。

出力の短絡状態のときパス・トランジスタの過度な電力消費を抑え、入力電源の電圧スパイクを軽減するために、電流は FB で内部的に検出される出力電圧の関数としてフォールドバックします。

FB の電圧が 0V のとき、LT4256-1/LT4256-2 が電流制限されていると、電流制限回路が GATE ピンをドライブしてセンス抵抗両端の電圧降下を 14mV の一定電圧に強制します。FB の出力の増大とともにセンス抵抗両端の電圧が増大し、FB ピンが 2V になるとセンス抵抗両端の電圧が 55mV で一定になります（図 7 を参照）。

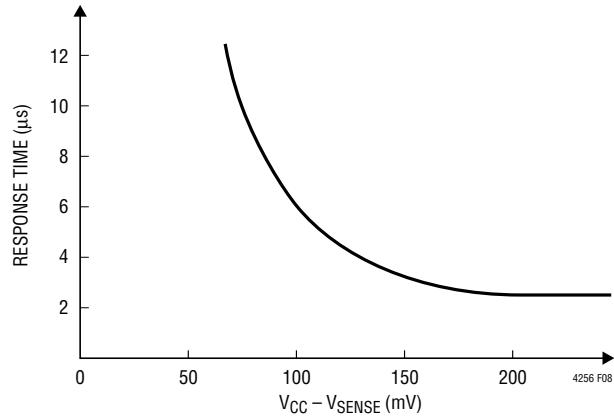

図 8. 過電流に対する応答時間

0.025Ω センス抵抗では、電流制限値は 2200mA に設定され、出力が GND に短絡すると 560mA にフォールドバックします。したがって、短絡状態での MOSFET のピーク電力消費は、105.6W から 26.5W に減少します。電流制限のスレッショルド・エラーを最小限に抑えるためのボード・レイアウトの重要な事項については、「レイアウトの検討事項」の項を参照してください。

過電流の可変応答時間も LT4256-1/LT4256-2 の特徴です。デバイスが GATE 電圧を制御し始めるまでに要する時間は、 $V_{CC}$  と SENSE 間に接続されたセンス抵抗両端の電圧の関数です。電流スパイクや過渡応答による影響を除去することによって電流制限応答の不必要的トリガや MOSFET 消費電流の増加を防ぎます。図 8 は、SENSE のオーバードライブの関数としての応答時間を示したもの

### TIMER

TIMER によってデバイスが電流制限のもとで動作できる最大時間をプログラミングすることができます。電流制限回路がアクティブでないときは、TIMER ピンは  $3\mu\text{A}$  電流源によって GND にプルされます。電流制限回路がアクティブになると、 $108\mu\text{A}$  プルアップ電流源が TIMER に接続され、その回路がアクティブである限り  $105\mu\text{A}/C_{\text{TIMER}}$  のスロープで電圧が上昇します。所定の最大電流制限時間がわかれば、コンデンサ値は、次式のようになります。

$$C[\text{nF}] = 25 \cdot t[\text{ms}]; C = \frac{105\mu\text{A}}{4.65\text{V}} \cdot t \quad (6)$$

## アプリケーション情報

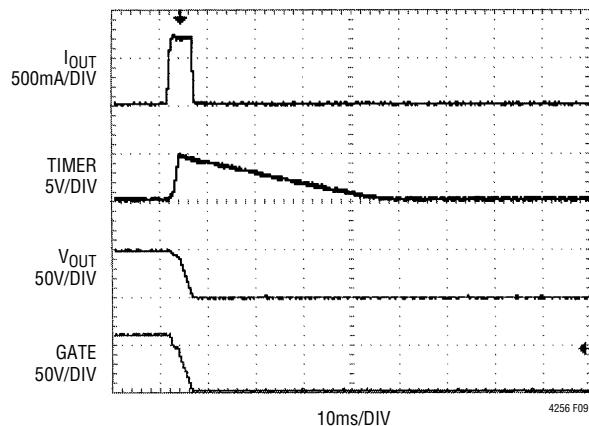

図 9. LT4256-1 電流制限波形

TIMER ピンが 4.65V (標準) に達すると、内部フォールト・ラッチがセットされ、GATE が “L” にプルされ、TIMER は  $3\mu\text{A}$  電流源によって GND に放電されます。TIMER の電圧が 0.65V (標準) 未満に下がるまでデバイスは再びオンすることはありません。

TIMER が上限スレッショルド (標準で 4.65V) を超えると、ピン特性が高インピーダンス電流源から低インピーダンスに変わるために、低インピーダンスによって TIMER が “H” にプルされることのないようにしてください。

なんらかのフォールト状態によって GATE がオフになると、急速放電し、外部 MOSFET をオフにします。図 9 の波形は、電流フォールト後の出力のラッチオフの様子を示したもので (LT4256-1)。タイマが立ち上がると、センス抵抗両端の電圧降下は 55mV に保持されます。TIMER がシャットダウン・スレッショルド (標準で 4.65V) に達すると、回路はラッチ・オフします。

電流制限フォールト後は、LT4256-1 はラッチ・オフします。LT4256-1 のラッチ・オフ後は、デバイスを再起動するこ

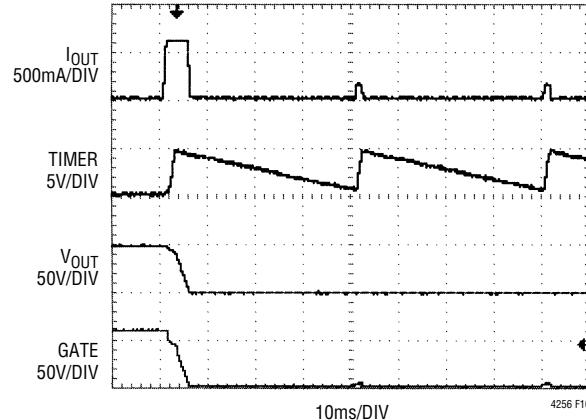

図 10. LT4256-2 電流制限波形

とができます。これは UV をグランドに下げ、その後、“H” にすることによって行われます (このコマンドが有効なのは、TIMER が 0.65V の標準的なスレッショルドを下回るまで放電した後であり、それによってトランジスタ Q1 の過熱を防止しています)。

### 自動再起動

過電流によるフォールト後は、LT4256-2 は自動的に再起動します。それらの波形を図 10 に示します。

LT4256-2 は以下のように機能します。過電流状態が発生すると、GATE ピンがサーボ制御されてセンス抵抗両端の電圧が一定に保たれ、TIMER ピンのコンデンサ C2 が充電を開始します。TIMER ピンの電圧が 4.65V (標準) に達すると、GATE ピンは “L” にプルされます。TIMER ピンの電圧が再度 0.65V (標準) にランプダウンすると、LT4256-2 は再度オンになります。出力部の短絡状態が持続している場合は、このサイクルがいつまでも繰り返されます。短絡状態でのデューティ・サイクルは 3% であり、それによって Q1 が過熱するのを防止します。

# LT4256-1/LT4256-2

## アプリケーション情報

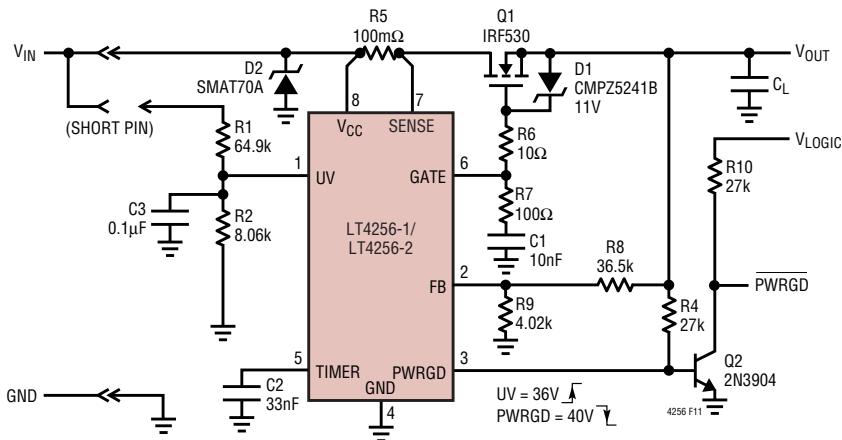

図 11. ロジック信号を使用した LT4256 オン / オフの制御方法

図 12. アクティブ “L” (正論理) イネーブル PWRGD アプリケーション

### パワー・グッド検出

LT4256-1/LT4256-2 にはコンパレータが搭載されており、出力電圧をモニタします。出力電圧は、外付け抵抗ストリッピングを介して FB ピンにより検出されます。コンパレータの出力 (PWRGD) は、オープン・コレクタであり、最大 80V のプル・アップで動作します。

PWRGD を使用してアクティブ “H” (正論理) のイネーブル入力を備えたパワー・モジュールを直接オン / オフすることができます。PWRGD を使用してアクティブ “L” (負論理) のイネーブル入力を備えたパワー・モジュールを制御する方法を図 12 に示します。信号の反転は、トランジスタ Q2 と抵抗 R10 によって行われます。

FB ピンのスレッショルドは、4.45V (“L”から “H”への遷移) と 3.99V (“H”から “L”への遷移) です。PWRGD スレッショルドを計算するには、以下の式を使用します。

$$R8 = \left( \frac{V_{THPWRGD}}{3.99V} - 1 \right) \cdot R9, \text{ high to low} \quad (7)$$

$$20k\Omega \leq R8 + R9 \leq 200k\Omega \quad (8a)$$

$$V_{THPWRGD} = 4.45V \left( 1 + \frac{R8}{R9} \right), \text{ low to high} \quad (8b)$$

## アプリケーション情報

### 電源過渡電圧保護

LT4256-1/LT4256-2 は 100% テスト済みであり、電源電圧が最大 80V まで損傷を受けず、安全であることが保証されています。ただし、電圧過渡が 100V を上回る場合は、恒久的な損傷を与えることがあります。短絡状態では、電源トレースを流れる電流の大規模な変化が 100V を超える誘導電圧過渡を生じさせることができます。電圧過渡を最小限に抑えるためには、広めのトレースまたは厚めのトレース・プレートを使用して電力トレースの寄生インダクタンスを最小限にするとともに  $0.1\mu\text{F}$  バイパス・コンデンサを  $V_{CC}$  と GND の間に配置する必要があります。アプリケーション・ダイアグラムに示すように、入力のサージ・サプレッサ (Transzorb) も過渡電圧による損傷を防止することができます。

### GATE ピン

ゲート・ドライブと  $V_{CC}$  の曲線を図 13 に示します。GATE は  $V_{CC}$  より 12.8V 上の最大電圧にクランプされています。このクランプは、内部チャージ・ポンプ電流をシンクするように設計されています。すべてのアプリケーションに示すように、外付けのツェナー・ダイオードを使用する必要があります。12V の最小入力電源電圧では、最小ゲート・ドライブ電圧は、4.5V です。入力電源電圧が 20V より大きいと、ゲート・ドライブ電圧は少なくとも 10V で、標準スレッショルド MOSFET を使用することができます。12V ~ 15V の範囲のアプリケーションでは、ロジック・レベル MOSFET を使用する必要があります。

図 13.  $\Delta V_{GATE}$  と  $V_{CC}$

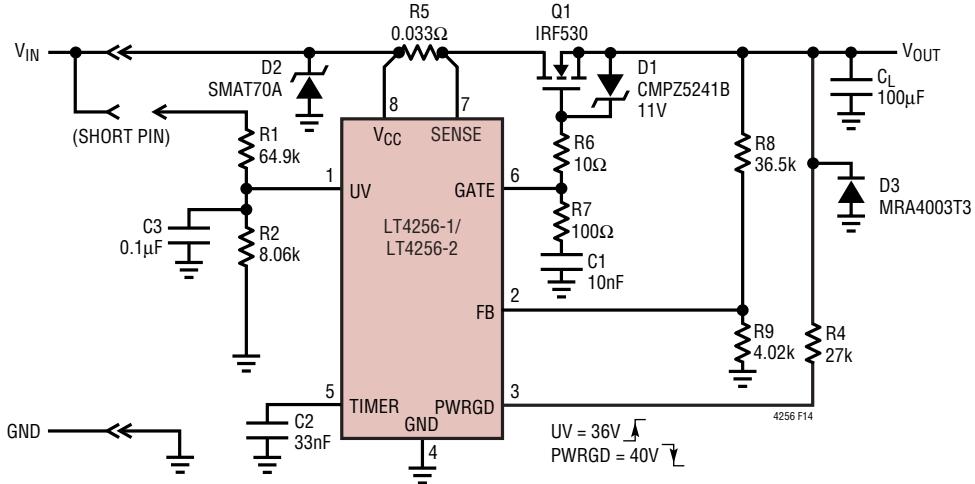

アプリケーションによっては、 $V_{OUT}$  ピンがグランドより下のリングを生じることがあります（寄生トレース・インダクタンスによる）。大電流の場合のアプリケーションでは、特に出力負荷が物理的に LT4256-1/LT4256-2 から離れているときは、これらの過渡現象の影響を受けやすくなります。これは正常な現象であり、LT4256-1/LT4256-2 はグランドより下のリングをある程度許容するように設計されています。ただし、 $V_{OUT}$  が GND より 10V 以上下回るリングを発生するようなアプリケーションでは、LT4256-1 に損傷が発生する恐れがあり、図 14 に示すように GND (アノード) から  $V_{OUT}$  (カソード) にかけて外付けダイオードを回路に追加する必要があります（ダイオードの逆ブレークダウン電圧は  $V_{CC}$  の最大予測電圧よりも高くなければなりません）。LT4256-1/LT4256-2 の GND から  $V_{OUT}$  に直接配置されたコンデンサによって  $V_{OUT}$  のリングを軽減することはできますが、アプリケーションによっては十分な効果が得られないことがあります。

フォールト状態では、LT4256-1/LT4256-2 は、約 60mA をシンクできるスイッチで GATE をプルダウンします。ダイオードの順方向電圧だけ GATE が出力電圧より低下すると、外付けツェナー・ダイオードが順方向にバイアスされ、 $V_{OUT}$  も GND に放電されます。GATE 容量だけでなく、出力容量も LT4256-1/LT4256-2 を通して放電されます。

非常に大きな外付け N チャネル MOSFET を使用するアプリケーションでは、通電しているバックプレーンに最初に挿入したときに MOSFET がオンになる可能性があります (LT4256-1/LT4256-2 がアクティブになり、GATE をプルダウンする前に)。これは、ドレイン電圧が極めて急峻な立ち上がり時間で GND から  $V_{IN}$  に上昇するとき、ドレインとゲート間の容量により強制的に電流が  $R7$  と  $C1$  に流入するためです。この状態を軽減するには、図 15 に示すようにカソードを  $C1$  に接続した状態でダイオード  $D3$  を  $R7$  の両端に配置する必要があります。

# LT4256-1/LT4256-2

## アプリケーション情報

図 14. 負出力電圧保護のダイオード・アプリケーション

### LT1641 アプリケーションでの LT4256 使用上の注意

LT4256 と LT1641 はピンアウトは同じですが、総合的なシステム精度とノイズ耐性改善のためにいくつかの変更が施されています。これらの変更箇所は表 1 に列挙していますので、LT4256 を LT1641 アプリケーションで使用するときはこれらの点を考慮するようにしてください。

### レイアウト上の検討事項

正確な電流センスを行うには、電流センス抵抗へのケルビン接続（標準的なアプリケーション回路では R5）を

推奨します。1 オンス銅箔の最小トレース幅は、アンペアあたり 0.02" で、トレースを妥当な温度に維持します。アンペアあたり 0.03" 以上を推奨します。1 オンス銅箔のシート抵抗は約  $530\mu\Omega/\square$  であることに注意してください。抵抗値が小さいと大電流アプリケーションでの誤差が大きくなります。抵抗分割器を  $V_{CC}$  トレースと GND トレースを短くしてピンの近くに配置すると、ノイズ耐性を大幅に改善することができます。UV および GND 間の  $0.1\mu F$  デカップリング・コンデンサも必須です。

表 1. LT1641 と LT4256 との相違点

| 仕様                 | LT1641     | LT4256      | 備考                                         |

|--------------------|------------|-------------|--------------------------------------------|

| UV スレッショルド         | 1.313V     | 4V          | 1% リファレンスによるノイズ耐性とシステム精度の改善                |

| FB スレッショルド         | 1.233V     | 3.99V       | 1% リファレンスによるノイズ耐性とシステム精度の改善                |

| TIMER 電流           | $\pm 70\%$ | $\pm 40\%$  | より正確な TIMEOUT                              |

| TIMER シャットダウン V    | 1.233V     | 4.65V       | トリップ電圧が高くなり、それによってノイズ耐性が改善                 |

| GATE $I_{PU}$      | $10\mu A$  | $30\mu A$   | より大きな電流により、リークの大きな MOSFET またはパラレル・デバイスにも対応 |

| GATE 抵抗            | $1k\Omega$ | $100\Omega$ | 異なる補償で電流制限ループを実現                           |

| フォールドバック $I_{LIM}$ | 12mV       | 14mV        | 電流制限トリップ・ポイントがやや異なる                        |

| $I_{LIM}$ スレッショルド  | 47mV       | 55mV        | 電流制限トリップ・ポイントがやや異なる                        |

| フォールト・ラッチ・リセット     | 1.233V     | 0.85V       | ノイズ耐性を改善                                   |

| スレッショルド電圧          |            |             |                                            |

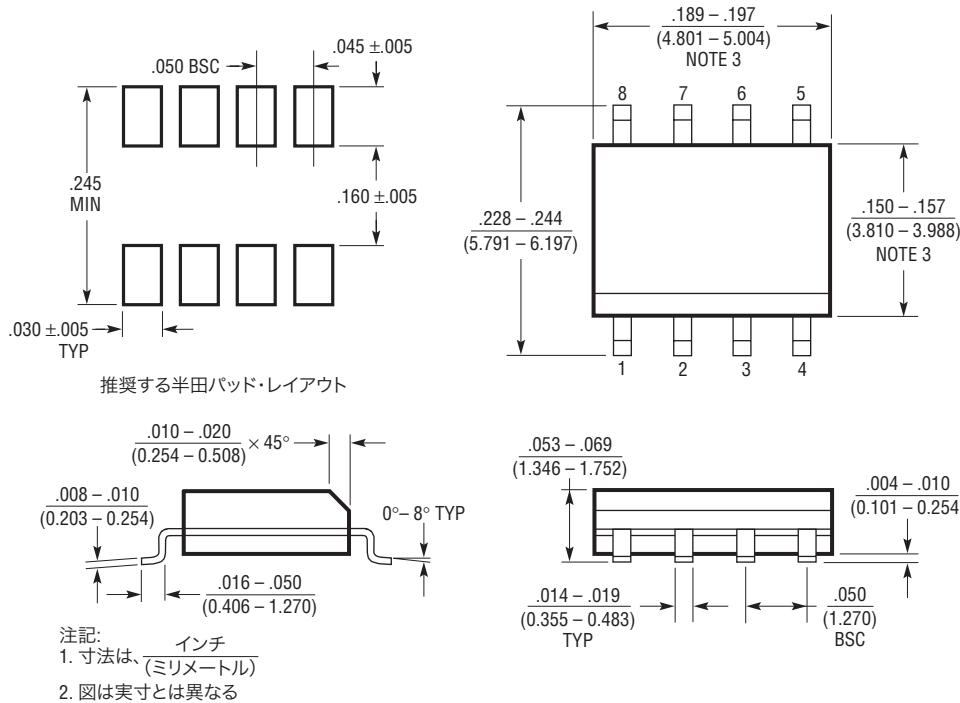

## パッケージ寸法

**S8 パッケージ**

**8 ピン・プラスチック小型（細型 0.150 インチ）**

(Reference LTC DWG # 05-08-1660)

S08 0303

425612fa

# LT4256-1/LT4256-2

## アプリケーション情報

図 15. 高 dv/dt MOSFET ターンオン保護回路

## 関連製品

| 製品番号                | 説明                               | 注釈                                                |

|---------------------|----------------------------------|---------------------------------------------------|

| LT1641-1/LT1641-2   | 正の 48V ホットスワップ・コントローラ、SO-8 パッケージ | 9V ~ 80V で動作、アクティブな電流制限、自動リトライ / ラッチオフ            |

| LTC4211             | シングル・ホットスワップ・コントローラ、マルチ機能電流制御付き  | 2.5V ~ 16.5V、アクティブな突入電流制限、デュアル・レベル回路ブレーカ          |

| LTC4251             | -48V ホットスワップ・コントローラ、SOT-23 パッケージ | -15V からの浮動電源、アクティブな電流制限<br>高速回路ブレーカ               |

| LTC4252-1/LTC4252-2 | -48V ホットスワップ・コントローラ、MSOP パッケージ   | -15V からの浮動電源、アクティブな電流制限<br>パワー・グッド出力              |

| LTC4253             | -48V ホットスワップ・コントローラと電源シーケンサ      | -15V からの浮動電源、アクティブな電流制限<br>3 つの DC/DC コンバータをイネーブル |

| LT4254              | 正の高電圧ホットスワップ・コントローラ              | 10.8V ~ 36V、開回路検出                                 |

425612fa