# マルチフェーズ電流モード昇圧 DC/DCコントローラ

## 特長

- 広い入力電圧範囲:動作電圧範囲:8.5V ~ 36V

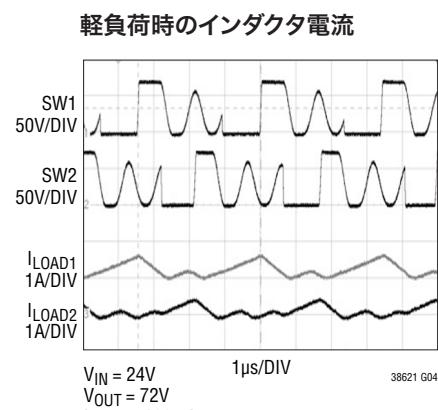

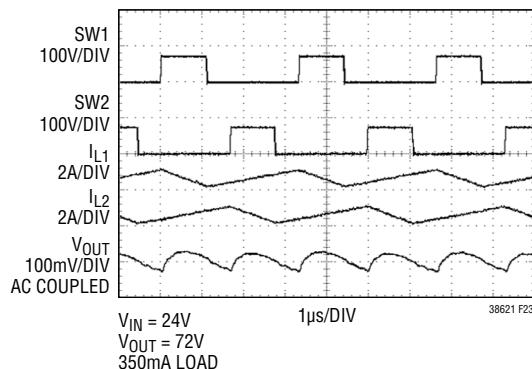

- 2フェーズ動作により入出力容量を低減

- 固定周波数、ピーク電流モード制御

- 高電圧MOSFETのゲート駆動電圧:10V

- 調整可能なスロープ補償利得

- 調整可能な最大デューティサイクル(最大96%)

- 調整可能なリーディングエッジ・ランキング

- $\pm 1\%$  精度の内部電圧リファレンス

- 1本の外付け抵抗でプログラム可能な動作周波数: 75kHz ~ 500kHz

- 位相同期可能な固定周波数(50kHz ~ 650kHz)

- SYNC入力およびCLKOUTにより、2、3、4、6、または12相動作に対応(PHASEMODEでプログラム可能)

- 内部10V LDOレギュレータ

- 24ピン細型SSOPパッケージ

- リードピッチが0.65mmの5mm×5mm QFNパッケージ

- 熱特性が改善された24ピンTSSOPパッケージ

## アプリケーション

- 車載、テレコムおよび産業用電源

## 概要

LTC<sup>®</sup>3862-1は、NチャネルパワーMOSFETを駆動する2相固定周波数電流モード昇圧およびSEPICコントローラです。2相動作により、システムのフィルタリング容量とインダクタンスの要件が軽減されます。

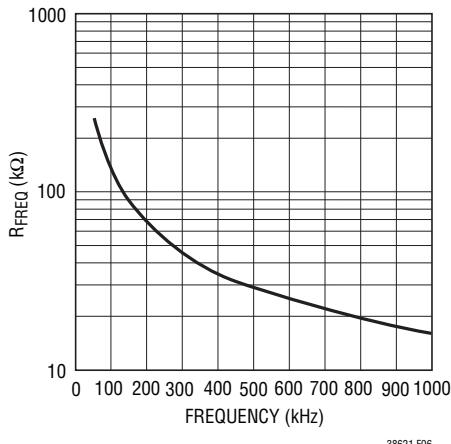

動作周波数は1本の外付け抵抗により75kHz ~ 500kHzの範囲で設定できますが、内部PLLを使用して外部クロックに同期させることもできます。SYNC入力、CLKOUT出力、およびPHASEMODE制御ピンを使用して、2、3、4、6、12相のマルチフェーズ動作が可能です。

この他の特長は、ゲート・ドライバの低電圧ロックアウト保護機能を備えた内部10V LDO、ヒステリシスをプログラム可能な高精度のRUNピンしきい値、ソフトスタート、プログラム可能なリーディングエッジ・ランキングと最大デューティ・サイクルなどです。

| 製品番号      | INTV <sub>CC</sub> | V <sub>IN</sub> オン | V <sub>IN</sub> オフ |

|-----------|--------------------|--------------------|--------------------|

| LTC3862   | 5V                 | 3.3V               | 2.9V               |

| LTC3862-1 | 10V                | 7.5V               | 7.0V               |

| LTC3862-2 | 10V                | 4.4V               | 3.9V               |

LT、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。6144194、6498466、6611131を含む米国特許によって保護されています。

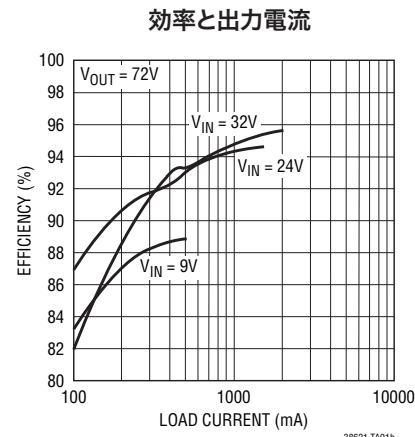

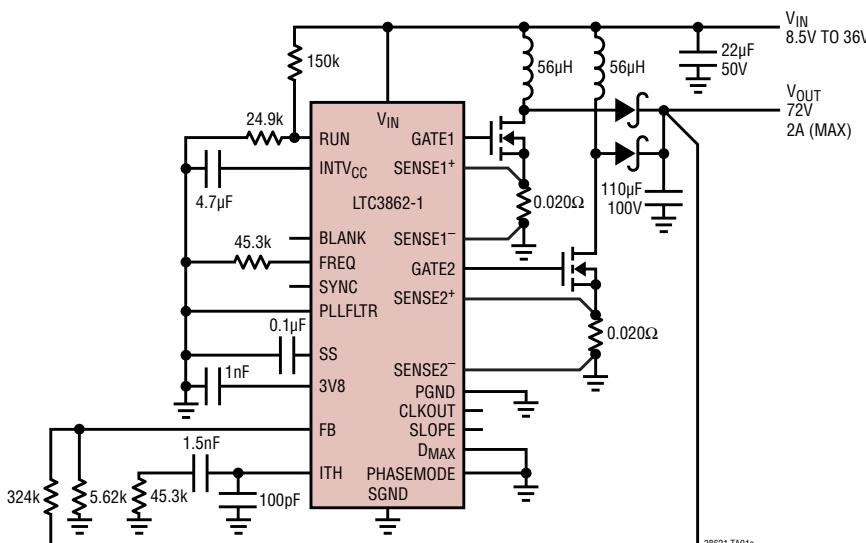

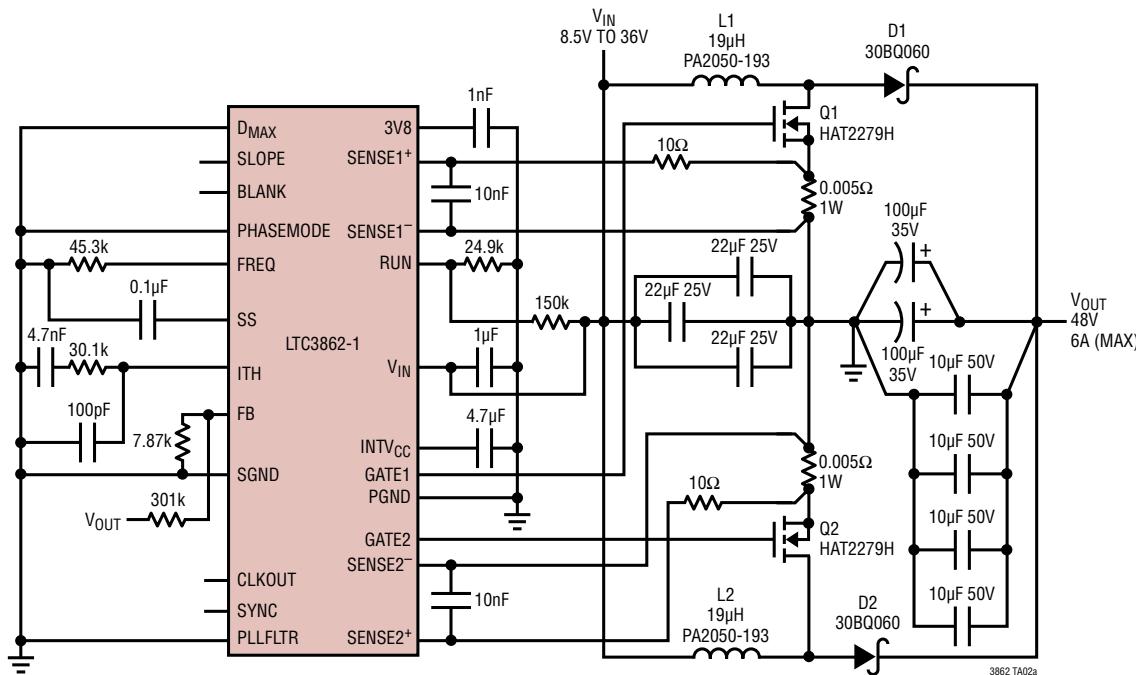

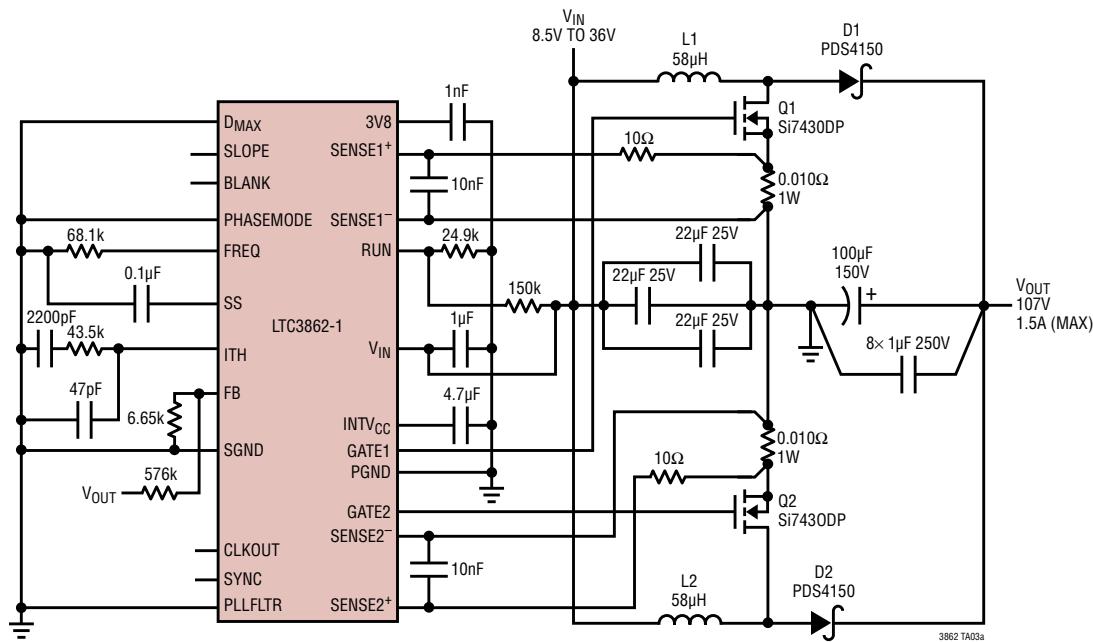

## 標準的応用例

38621fa

# LTC3862-1

## 絶対最大定格 (Note 1、2)

|                                                                                            |                        |                      |                        |

|--------------------------------------------------------------------------------------------|------------------------|----------------------|------------------------|

| 入力電源電圧(V <sub>IN</sub> )                                                                   | -0.3V～40V              | ITH 電圧               | -0.3V～2.7V             |

| INTV <sub>CC</sub> 電圧                                                                      | -0.3V～11V              | FB 電圧                | -0.3V～V <sub>3V8</sub> |

| INTV <sub>CC</sub> LDO の RMS 出力電流                                                          | 50mA                   | FREQ の電圧             | -0.3V～1.5V             |

| RUN の電圧                                                                                    | -0.3V～8V               | 動作接合部温度範囲 (Note 3、4) |                        |

| SYNC の電圧                                                                                   | -0.3V～6V               | LTC3862-1E           | -40°C～85°C             |

| SLOPE、PHASEMODE、D <sub>MAX</sub> 、BLANK の電圧                                                | -0.3V～V <sub>3V8</sub> | LTC3862-1I           | -40°C～125°C            |

| SENSE1 <sup>+</sup> 、SENSE1 <sup>-</sup> 、SENSE2 <sup>+</sup> 、<br>SENSE2 <sup>-</sup> の電圧 | -0.3V～V <sub>3V8</sub> | LTC3862-1H           | -40°C～150°C            |

| SS、PLLFLTR の電圧                                                                             | -0.3V～V <sub>3V8</sub> | 保存温度範囲               | -65°C～150°C            |

|                                                                                            |                        | リフローのピーク・ボディ温度       | 260°C                  |

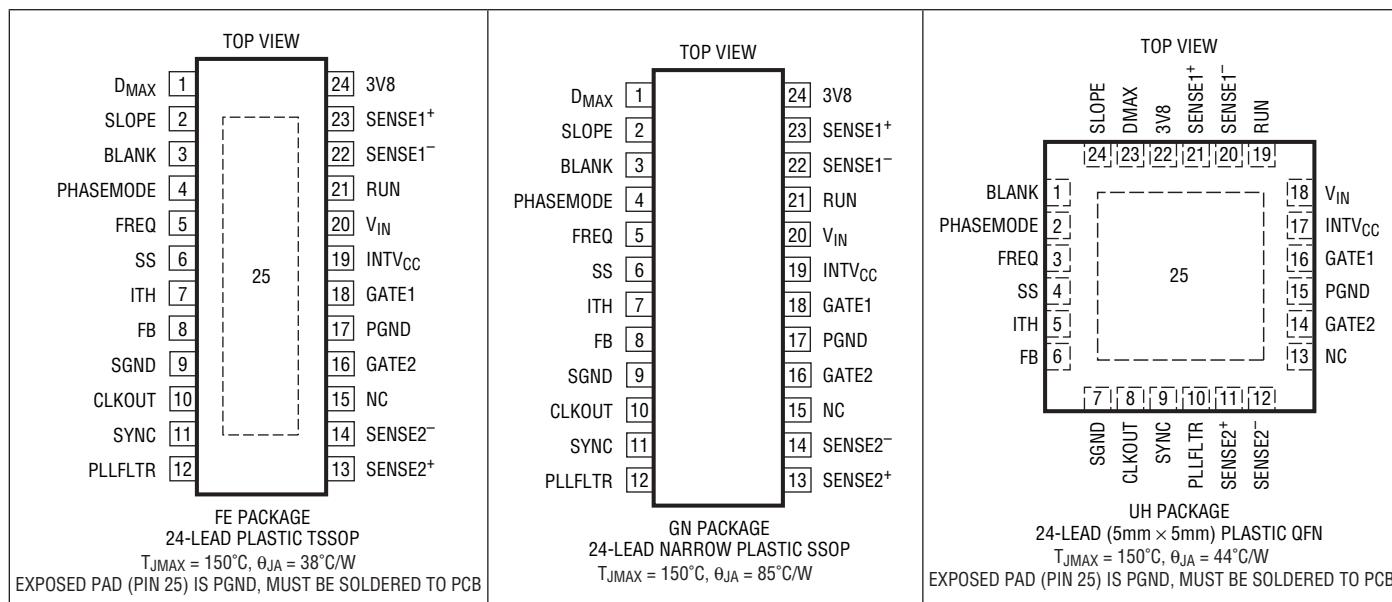

## ピン配置

## 発注情報

| 無鉛仕上げ            | テープアンドリール          | 製品マーキング*    | パッケージ                 | 温度範囲           |

|------------------|--------------------|-------------|-----------------------|----------------|

| LTC3862EFE-1#PBF | LTC3862EFE-1#TRPBF | LTC3862FE-1 | 24-Lead Plastic TSSOP | -40°C to 85°C  |

| LTC3862IFE-1#PBF | LTC3862IFE-1#TRPBF | LTC3862FE-1 | 24-Lead Plastic TSSOP | -40°C to 125°C |

| LTC3862HFE-1#PBF | LTC3862HFE-1#TRPBF | LTC3862FE-1 | 24-Lead Plastic TSSOP | -40°C to 150°C |

| LTC3862EGN-1#PBF | LTC3862EGN-1#TRPBF | LTC3862GN-1 | 24-Lead Plastic SSOP  | -40°C to 85°C  |

| LTC3862IGN-1#PBF | LTC3862IGN-1#TRPBF | LTC3862GN-1 | 24-Lead Plastic SSOP  | -40°C to 125°C |

| LTC3862HGN-1#PBF | LTC3862HGN-1#TRPBF | LTC3862GN-1 | 24-Lead Plastic SSOP  | -40°C to 150°C |

## 発注情報

| 無鉛仕上げ            | テープアンドリール          | 製品マーキング* | パッケージ                         | 温度範囲           |

|------------------|--------------------|----------|-------------------------------|----------------|

| LTC3862EUH-1#PBF | LTC3862EUH-1#TRPBF | 38621    | 24-Lead (5mm×5mm) Plastic QFN | -40°C to 85°C  |

| LTC3862IUH-1#PBF | LTC3862IUH-1#TRPBF | 38621    | 24-Lead (5mm×5mm) Plastic QFN | -40°C to 125°C |

| LTC3862HUH-1#PBF | LTC3862HUH-1#TRPBF | 38621    | 24-Lead (5mm×5mm) Plastic QFN | -40°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。<sup>\*</sup> 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性 (Note 2, 3)

●は規定動作温度範囲での規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $RUN = 2\text{V}$ 、 $SS = \text{開放}$ 。

| SYMBOL                                         | PARAMETER                                                        | CONDITIONS                                                                           | MIN    | TYP            | MAX            | UNITS               |                 |

|------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------|----------------|----------------|---------------------|-----------------|

| <b>電源入力と <math>INTV_{CC}</math> リニア・レギュレータ</b> |                                                                  |                                                                                      |        |                |                |                     |                 |

| $V_{IN}$                                       | $V_{IN}$ Supply Voltage Range                                    |                                                                                      | 8.5    | 36             |                | V                   |                 |

| $I_{VIN}$                                      | $V_{IN}$ Supply Current<br>Normal Mode, No Switching<br>Shutdown | (Note 5)<br>$V_{RUN} = 0\text{V}$                                                    | ●<br>● | 1.8<br>30      | 3.0<br>80      | mA<br>$\mu\text{A}$ |                 |

| $INTV_{CC}$                                    | LDO Regulator Output Voltage                                     |                                                                                      | 9.5    | 10.0           | 10.5           | V                   |                 |

| $dV_{INTVCC(LINE)}$                            | Line Regulation                                                  | $12\text{V} < V_{IN} < 36\text{V}$                                                   |        | 0.002          | 0.02           | %/V                 |                 |

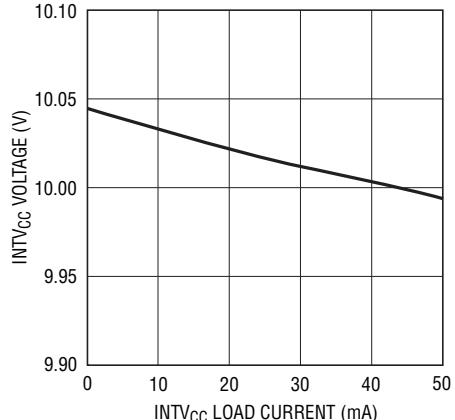

| $dV_{INTVCC(LOAD)}$                            | Load Regulation                                                  | Load = 0mA to 20mA                                                                   |        | -2             |                | %                   |                 |

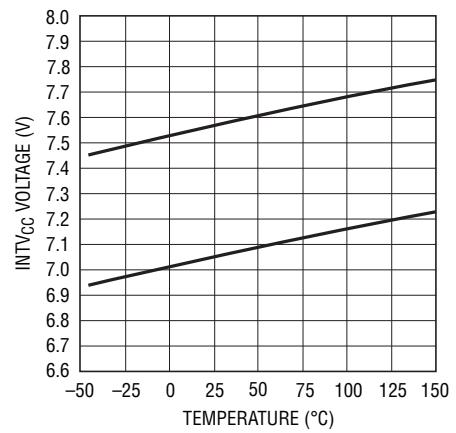

| $V_{UVLO}$                                     | $INTV_{CC}$ UV <sup>+</sup> Voltage                              | Rising $INTV_{CC}$                                                                   |        | 7.5            |                | V                   |                 |

|                                                | $INTV_{CC}$ UV <sup>-</sup> Voltage                              | Falling $INTV_{CC}$                                                                  |        | 7.0            |                | V                   |                 |

| 3V8                                            | LDO Regulator Output Voltage                                     |                                                                                      |        | 3.8            |                | V                   |                 |

| <b>スイッチャ制御ループ</b>                              |                                                                  |                                                                                      |        |                |                |                     |                 |

| $V_{FB}$                                       | Reference Voltage                                                | $V_{ITH} = 0.8\text{V}$ (Note 6) E-Grade (Note 3)<br>I-Grade and H-Grade (Note 3)    | ●<br>● | 1.210<br>1.199 | 1.223<br>1.223 | 1.235<br>1.248      | V               |

| $dV_{FB}/dV_{IN}$                              | Feedback Voltage $V_{IN}$ Line Regulation                        | $V_{IN} = 8.5\text{V}$ to $36\text{V}$ (Note 6)                                      |        |                | $\pm 0.002$    | 0.01                | %/V             |

| $dV_{FB}/dV_{ITH}$                             | Feedback Voltage Load Regulation                                 | $V_{ITH} = 0.5\text{V}$ to $1.2\text{V}$ (Note 6)                                    |        |                | 0.01           | 0.1                 | %               |

| $g_m$                                          | Transconductance Amplifier Gain                                  | $V_{ITH} = 0.8\text{V}$ (Note 6), ITH Pin Load = $\pm 5\mu\text{A}$                  |        |                | 660            |                     | $\mu\text{Mho}$ |

| $f_{0dB}$                                      | Error Amplifier Unity-Gain Crossover Frequency                   | (Note 7)                                                                             |        |                | 1.8            |                     | MHz             |

| $V_{ITH}$                                      | Error Amplifier Maximum Output Voltage<br>(Internally Clamped)   | $V_{FB} = 1\text{V}$ , No Load                                                       |        |                | 2.7            |                     | V               |

|                                                | Error Amplifier Minimum Output Voltage                           | $V_{FB} = 1.5\text{V}$ , No Load                                                     |        |                | 50             |                     | mV              |

| $I_{ITH}$                                      | Error Amplifier Output Source Current                            |                                                                                      |        |                | -30            |                     | $\mu\text{A}$   |

|                                                | Error Amplifier Output Sink Current                              |                                                                                      |        |                | 30             |                     | $\mu\text{A}$   |

| $I_{FB}$                                       | Error Amplifier Input Bias Currents                              | (Note 6)                                                                             |        |                | -50            | -200                | nA              |

| $V_{ITH(PSKIP)}$                               | Pulse Skip Mode Operation ITH Pin Voltage                        | Rising ITH Voltage (Note 6)<br>Hysteresis                                            |        |                | 0.275<br>25    |                     | V<br>mV         |

| $I_{SENSE(ON)}$                                | SENSE Pin Current                                                |                                                                                      |        |                | 0.01           | 2                   | $\mu\text{A}$   |

| $V_{SENSE(MAX)}$                               | Maximum Current Sense Input Threshold                            | $V_{SLOPE} = \text{Float, Low Duty Cycle}$<br>(Note 3)                               | ●      | 65<br>60       | 75<br>75       | 85<br>90            | mV<br>mV        |

| $V_{SENSE(MATCH)}$                             | CH1 to CH2 Maximum Current Sense Threshold Matching              | $V_{SLOPE} = \text{Float, Low Duty Cycle}$ (Note 3)<br>( $V_{SENSE1} - V_{SENSE2}$ ) | ●      | -10            |                | 10                  | mV              |

## 電気的特性 (Note 2, 3)

●は規定動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $\text{RUN} = 2\text{V}$ 、 $\text{SS} = \text{開放}$ 。

| SYMBOL             | PARAMETER                                 | CONDITIONS                                             | MIN | TYP        | MAX        | UNITS                          |               |

|--------------------|-------------------------------------------|--------------------------------------------------------|-----|------------|------------|--------------------------------|---------------|

| <b>RUN/ソフトスタート</b> |                                           |                                                        |     |            |            |                                |               |

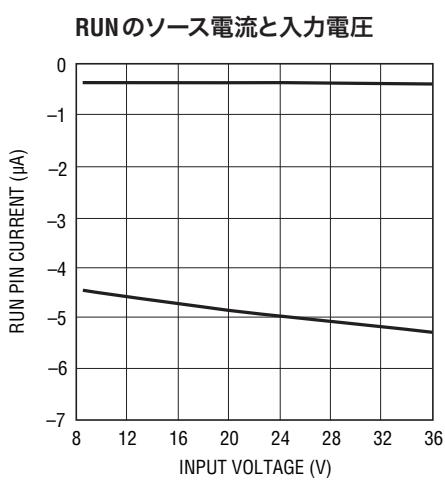

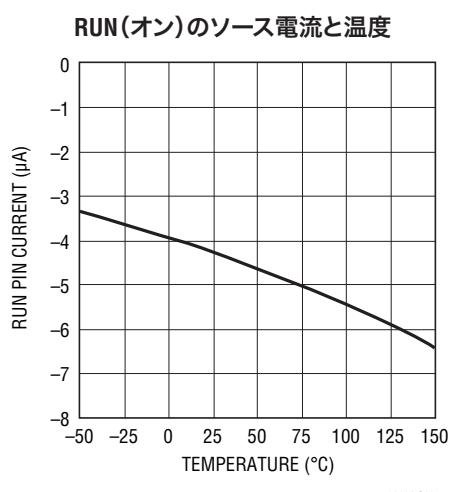

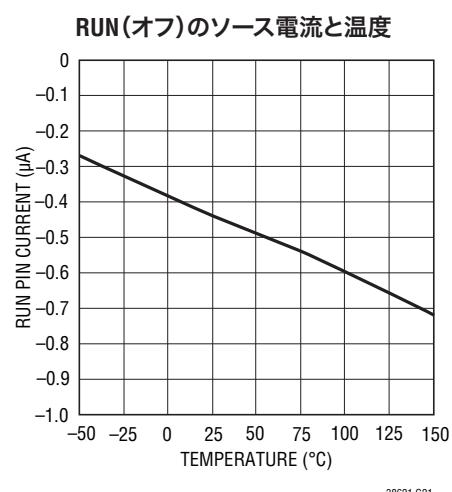

| $I_{RUN}$          | RUN Source Current                        | $V_{RUN} = 0\text{V}$<br>$V_{RUN} = 1.5\text{V}$       |     | -0.5<br>-5 |            | $\mu\text{A}$<br>$\mu\text{A}$ |               |

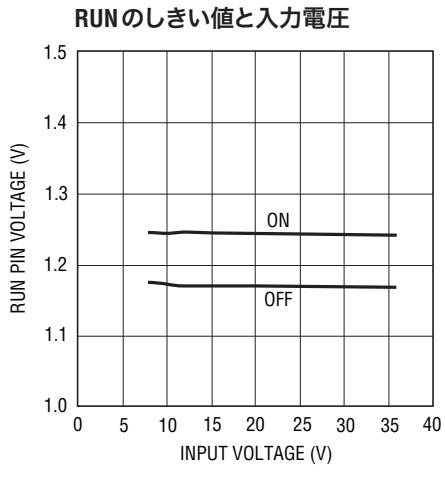

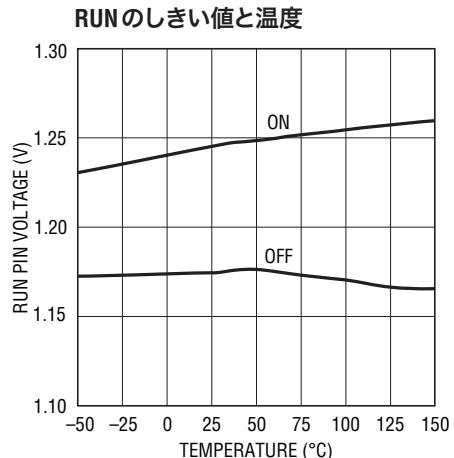

| $V_{RUN}$          | High Level RUN Channel Enable Threshold   |                                                        |     | 1.22       |            | V                              |               |

| $V_{RUNHYS}$       | RUN Threshold Hysteresis                  |                                                        |     | 80         |            | mV                             |               |

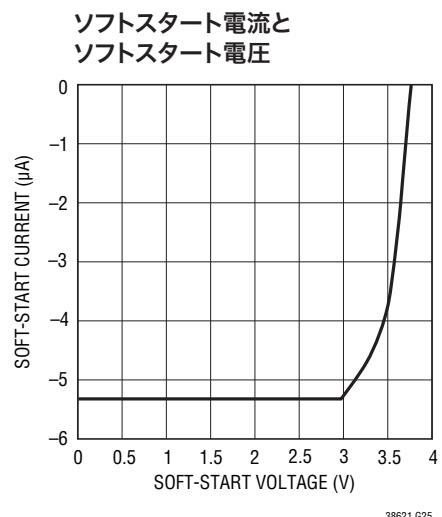

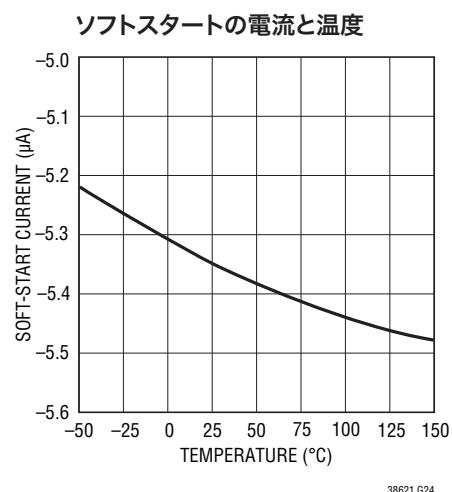

| $I_{SS}$           | SS Pull-Up Current                        | $V_{SS} = 0\text{V}$                                   |     | -5         |            | $\mu\text{A}$                  |               |

| $R_{SS}$           | SS Pull-Down Resistance                   | $V_{RUN} = 0\text{V}$                                  |     | 10         |            | $\text{k}\Omega$               |               |

| <b>発振器</b>         |                                           |                                                        |     |            |            |                                |               |

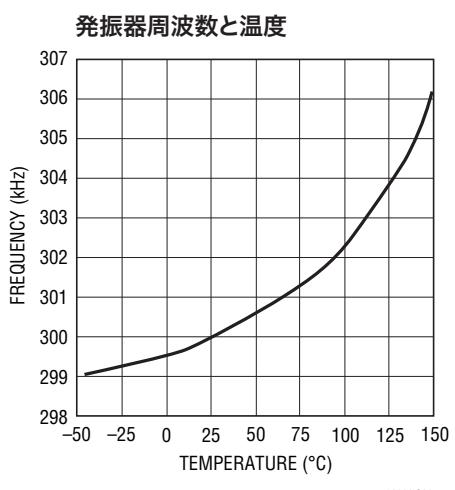

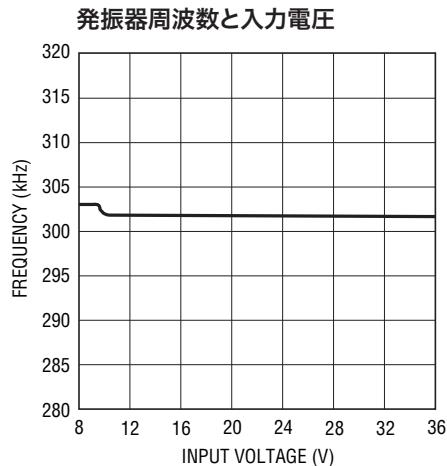

| $f_{OSC}$          | Oscillator Frequency                      | $R_{FREQ} = 45.6\text{k}$<br>$R_{FREQ} = 45.6\text{k}$ | ●   | 280<br>260 | 300<br>300 | 320<br>340                     | kHz           |

|                    | Oscillator Frequency Range                |                                                        |     | 75         |            | 500                            | kHz           |

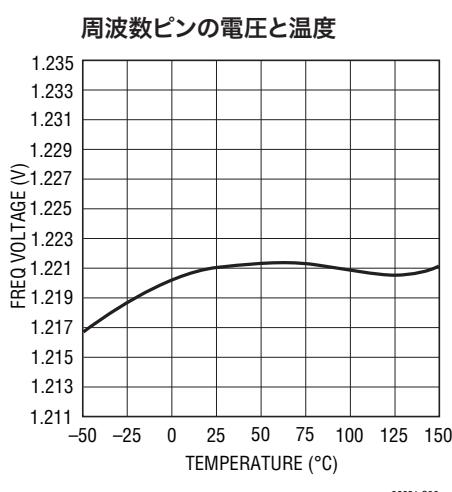

| $V_{FREQ}$         | Nominal FREQ Pin Voltage                  | $R_{FREQ} = 45.6\text{k}$                              |     |            | 1.223      |                                | V             |

| $f_{SYNC}$         | SYNC Minimum Input Frequency              | $V_{SYNC} = \text{External Clock}$                     | ●   |            |            | 50                             | kHz           |

|                    | SYNC Maximum Input Frequency              | $V_{SYNC} = \text{External Clock}$                     |     | 650        |            |                                | kHz           |

| $V_{SYNC}$         | SYNC Input Threshold                      | Rising Threshold                                       |     |            | 1.5        |                                | V             |

| $I_{PLLFLTR}$      | Phase Detector Sourcing Output Current    | $f_{SYNC} > f_{OSC}$                                   |     | -15        |            | $\mu\text{A}$                  |               |

|                    | Phase Detector Sinking Output Current     | $f_{SYNC} > f_{OSC}$                                   |     |            | 15         |                                | $\mu\text{A}$ |

| CH1-CH2            | Channel 1 to Channel 2 Phase Relationship | $V_{PHASEMODE} = 0\text{V}$                            |     |            | 180        |                                | Deg           |

|                    |                                           | $V_{PHASEMODE} = \text{Float}$                         |     |            | 180        |                                | Deg           |

|                    |                                           | $V_{PHASEMODE} = 3\text{V8}$                           |     |            | 120        |                                | Deg           |

| CH1-CLKOUT         | Channel 1 to CLKOUT Phase Relationship    | $V_{PHASEMODE} = 0\text{V}$                            |     |            | 90         |                                | Deg           |

|                    |                                           | $V_{PHASEMODE} = \text{Float}$                         |     |            | 60         |                                | Deg           |

|                    |                                           | $V_{PHASEMODE} = 3\text{V8}$                           |     |            | 240        |                                | Deg           |

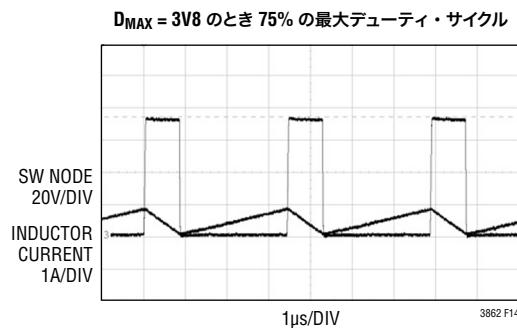

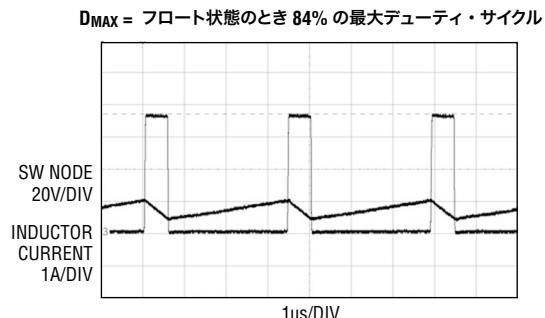

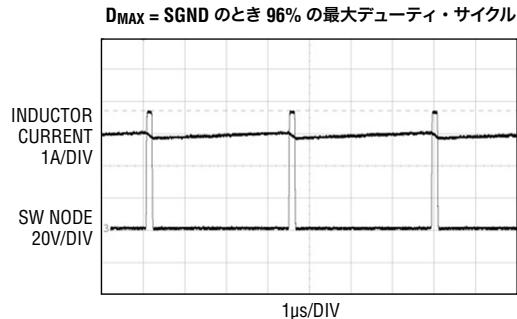

| $D_{MAX}$          | Maximum Duty Cycle                        | $V_{DMAX} = 0\text{V}$ (Note 9)                        |     |            | 96         |                                | %             |

|                    |                                           | $V_{DMAX} = \text{Float}$                              |     |            | 84         |                                | %             |

|                    |                                           | $V_{DMAX} = 3\text{V8}$                                |     |            | 75         |                                | %             |

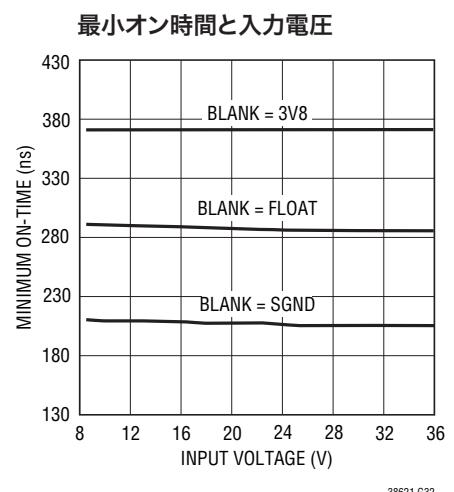

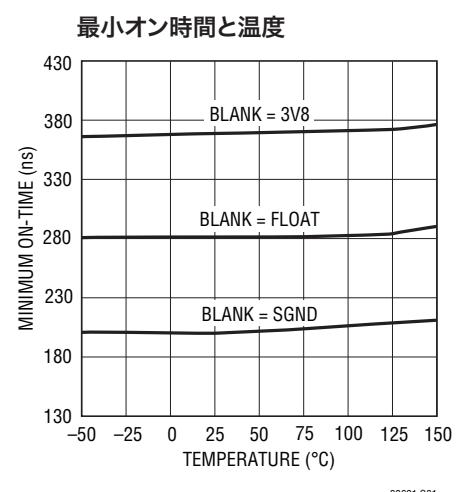

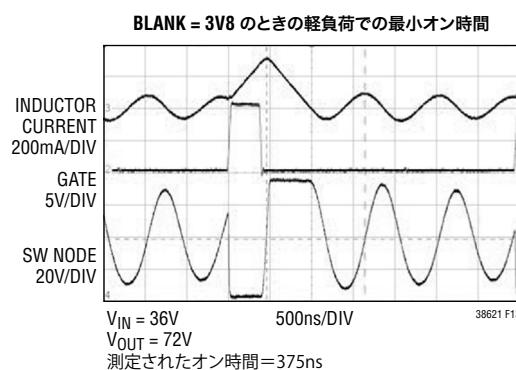

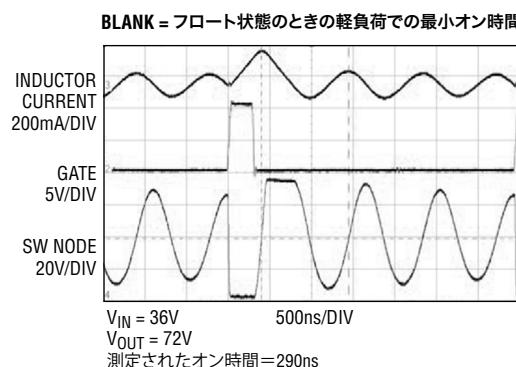

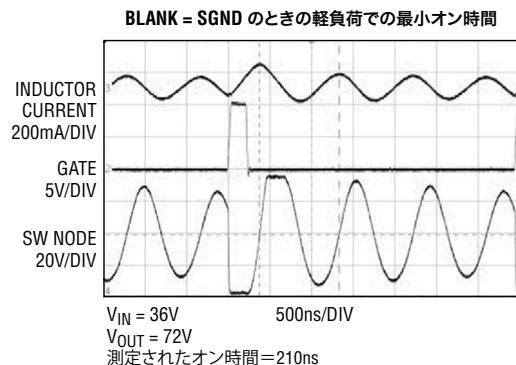

| $t_{ON(MIN)1}$     | Minimum On-Time                           | $V_{BLANK} = 0\text{V}$ (Note 8)                       |     |            | 210        |                                | ns            |

|                    | Minimum On-Time                           | $V_{BLANK} = \text{Float}$ (Note 8)                    |     |            | 290        |                                | ns            |

|                    | Minimum On-Time                           | $V_{BLANK} = 3\text{V8}$ (Note 8)                      |     |            | 375        |                                | ns            |

| <b>ゲート・ドライバ</b>    |                                           |                                                        |     |            |            |                                |               |

| $R_{DS(ON)}$       | Driver Pull-Up $R_{DS(ON)}$               |                                                        |     |            | 3          |                                | $\Omega$      |

|                    | Driver Pull-Down $R_{DS(ON)}$             |                                                        |     |            | 0.9        |                                | $\Omega$      |

| <b>過電圧</b>         |                                           |                                                        |     |            |            |                                |               |

| $V_{FB(OV)}$       | $V_{FB}$ , Overvoltage Lockout Threshold  | $V_{FB(OV)} - V_{FB(NOM)}$ in Percent                  |     | 8          | 10         | 12                             | %             |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** デバイスのピンに流れ込む電流はすべて正。デバイスのピンから流れ出す電流はすべて負。注記がない限り、全ての電圧はグランドを基準にしている。

**Note 3:** LTC3862E-1は $0^\circ\text{C} \sim 85^\circ\text{C}$ の範囲で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 85^\circ\text{C}$ の動作温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3862I-1は $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作温度範囲で動作することが保証されており、LTC3862H-1は $-40^\circ\text{C} \sim 150^\circ\text{C}$ の動作温度範囲で動作することが保証されている。接合部温度が高いと動作寿命が短くなる。接合部温度が $125^\circ\text{C}$ を超えると、動作寿命が短くなる。

**Note 4:** このデバイスには短時間の過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。規定された最大動作接合部温度を超えた動作が継続すると、デバイスの信

頼性を損なう恐れがある。

**Note 5:** 通常動作時の電源電流は外部MOSFETのゲートの充電に必要な電流によって支配される。この電流は電源電圧および使用される外部MOSFETによって変化する。

**Note 6:** このデバイスは、エラーアンプの出力が規定された電圧になるように $V_{FB}$ を調節する帰還ループでテストされる。

**Note 7:** 設計によって保証されているが、テストされない。

**Note 8:** 最小オン時間の条件は、インダクタのピーク・トゥ・ピーク・リップル電流 = 30%に対し規定されている(「アプリケーション情報」のセクションの「最小オン時間の制限」を参照)。

**Note 9:** 最大デューティ・サイクルの制限値は、設定されているスイッチング周波数の12倍の周波数で動作する内部クロックから得られる。詳細については「アプリケーション情報」のセクションを参照してください。

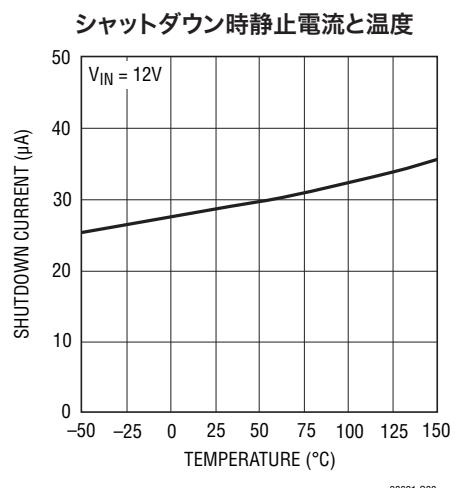

## 標準的性能特性

# LTC3862-1

## 標準的性能特性

IINTV<sub>CC</sub>の入力レギュレーション

38621 G09

IINTV<sub>CC</sub>の負荷レギュレーション

38621 G10

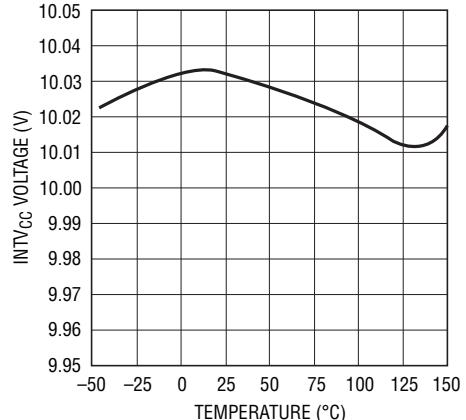

IINTV<sub>CC</sub>と温度

38621 G11

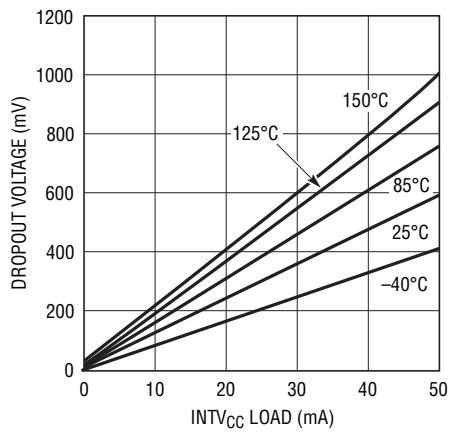

IINTV<sub>CC</sub> LDOの損失電圧と負荷電流、温度

38621 G12

IINTV<sub>CC</sub> UVLOのしきい値と温度

38621 G13

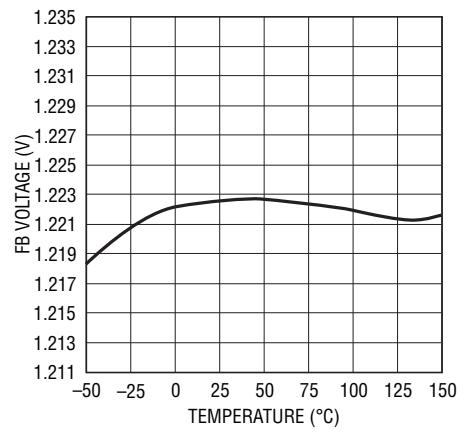

帰還電圧と温度

38621 G14

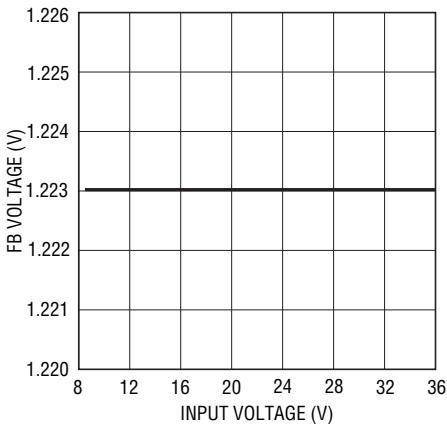

帰還電圧の入力レギュレーション

38621 G15

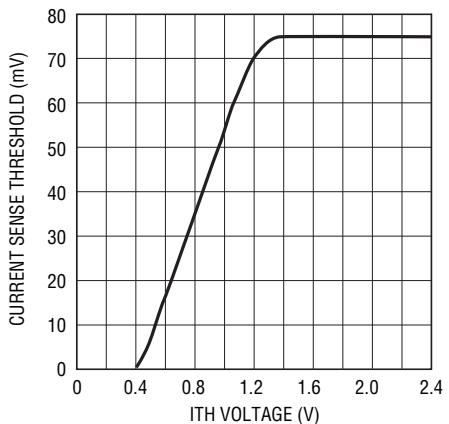

電流センスしきい値とITHの電圧

38621 G16

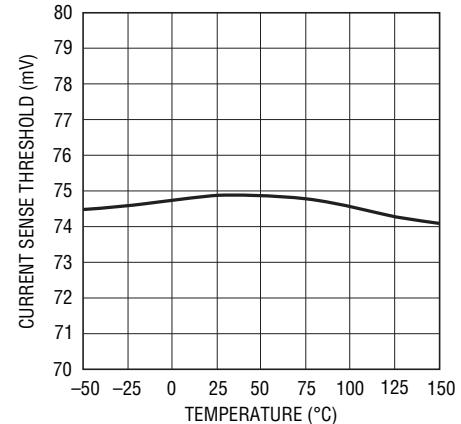

電流センスしきい値と温度

38621 G17

38621fa

## 標準的性能特性

## 標準的性能特性

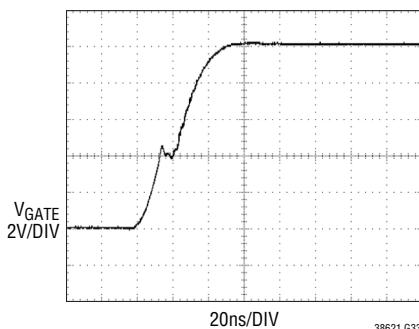

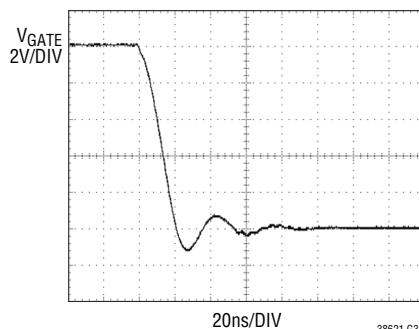

ルネサスのHAT2267Hをドライブするゲートのターンオン波形

$V_{IN} = 24V$

$V_{OUT} = 72V$

$I_{LOAD} = 0.25A$

ルネサスのHAT2267Hをドライブするゲートのターンオフ波形

$V_{IN} = 24V$

$V_{OUT} = 72V$

$I_{LOAD} = 0.25A$

38621fa

## ピン機能 (SSOP/QFN/TSSOP)

**3V8(ピン24/ピン22/ピン24)**: INTV<sub>CC</sub>からの内部3.8V LDOの出力。低電圧のアナログ回路とデジタル回路の電源ピン。低ESRの1nFセラミック・バイパス・コンデンサを、デバイスにできるだけ近づけて、3V8とSGNDの間に接続します。

**BLANK(ピン3/ピン1/ピン3)**: ブランディング時間。このピンをフロートさせると、公称290nsの最小オン時間が与えられます。このピンを3V8に接続すると375nsの最小オン時間が与えられ、SGNDに接続すると210nsの最小オン時間が与えられます。

**CLKOUT(ピン10/ピン8/ピン10)**: マルチフェーズ・システムで複数のLTC3862-1デバイスをデイジーチェーン接続するのに使われるデジタル出力。PHASEMODEピンの電圧が、チャネル1とチャネル2の間およびチャネル1とCLKOUTの間の関係を制御します。

**D<sub>MAX</sub>(ピン1/ピン23/ピン1)**: 最大デューティ・サイクル。このピンは最大デューティ・サイクルをプログラムします。このピンをフロートさせると84%のデューティ・サイクルが与えられます。このピンを3V8に接続すると75%のデューティ・サイクルが与えられ、SGNDに接続すると96%のデューティ・サイクルが与えられます。最大デューティ・サイクルの制限値は、設定されているスイッチング周波数の12倍の周波数で動作する内部クロックから得られます。このため、最大デューティ・サイクルの制限値D<sub>MAX</sub>はきわめて正確です。

**FB(ピン8/ピン6/ピン8)**: エラーアンプの入力。抵抗分割器ネットワークを介してFBピンをV<sub>OUT</sub>に接続し、出力電圧を設定します。

**FREQ(ピン5/ピン3/ピン5)**: FREQからSGNDに接続された抵抗により動作周波数が設定されます。

**GATE1(ピン18/ピン16/ピン18)**: ゲート・ドライブ出力。LTC3862-1はPGNDを基準にした10Vのゲート・ドライブを備えており、高電圧MOSFETをドライブします。このゲート・ピンの電圧の絶対最大定格は、最小-0.3V、最大11Vです。

**GATE2(ピン16/ピン14/ピン16)**: ゲート・ドライブ出力。LTC3862はPGNDを基準にした5Vゲート・ドライブを備えており、スレッショルドがロジックレベルのMOSFETをドライブします。このゲート・ピンの電圧の絶対最大定格は、最小-0.3V、最大11Vです。

**INTV<sub>CC</sub>(ピン19/ピン17/ピン19)**: 内部10V低損失レギュレータ(LDO)の出力。低ESRの4.7nFセラミック・バイパス・コンデンサ(X5Rまたはそれより良いもの)を、デバイスにできるだけ近づけ、INTV<sub>CC</sub>とPGNDの間に接続します。

**ITH(ピン7/ピン5/ピン7)**: エラーアンプの出力。電流コンペレータのトリップしきい値はITH制御電圧に応じて上昇します。ITHピンはコンバータの制御ループを補償するのにも使われます。

**PGND(ピン17/ピン15、露出パッド・ピン25/ピン17、露出パッド・ピン25)**: 電源グランド。このピンは、パワーMOSFETのソースに近づけて接続します。PGNDは、V<sub>IN</sub>とINTV<sub>CC</sub>のそれぞれのバイパス・コンデンサの負端子にも接続します。PGNDは、SGNDピンから電気的に絶縁されています。QFNパッケージとFEパッケージの露出パッドはPGNDに接続されており、電気的な接触と定格の熱性能を確保するためにプリント回路基板のグランドに半田付けする必要があります。

**PHASEMODE(ピン4/ピン2/ピン4)**: PHASEMODEピンの電圧が、チャネル1とチャネル2の立ち上がりゲート信号間およびチャネル1のゲート信号とCLKOUT間の位相関係を制御します。このピンをフロートさせるか、または3V8かSGNDのどちらかに接続すると、CH1、CH2およびCLKOUT間の位相関係が変化します。

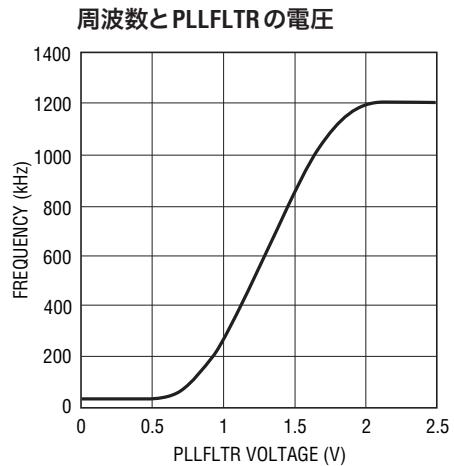

**PLLFLTR(ピン12/ピン10/ピン12)**: PLLローパス・フィルタの入力。外部クロックに同期するとき、このピンがPLLのローパス・フィルタ入力として機能します。PLLFLTRからSGNDに接続された直列抵抗とコンデンサがPLLの帰還ループを補償します。

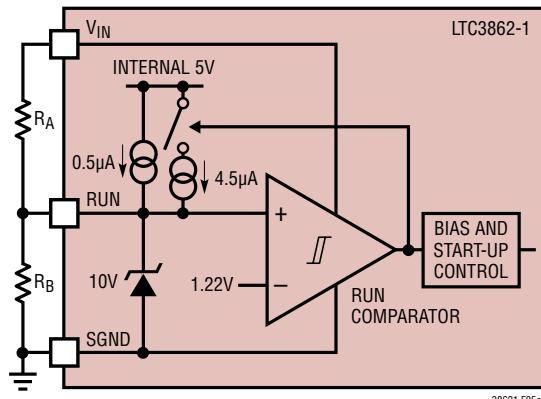

**RUN(ピン21/ピン19/ピン21)**: 実行制御入力。このピンの電圧が1.22Vを超えるとデバイスがオンします。このピンの電圧を1.22Vより下に強制すると、デバイスがシャットダウンします。このピンには0.5μAのプルアップ電流源が備わっています。RUNピンの電圧が1.22Vを超えると、プログラム可能なヒステリシスを与えるために、さらに4.5μAのプルアップ電流がピンに加えられます。

**SENSE1<sup>+</sup>(ピン23/ピン21/ピン23)**: 電流コンペレータの正入力。ピーク電流トリップしきい値を設定するために、ITHピンの電圧が電流コンペレータのオフセットをプログラムします。このピンは、通常、パワーMOSFETのソースのところのセンス抵抗に接続します。

## ピン機能

**SENSE2<sup>+</sup>(ピン13/ピン11/ピン13)**：電流コンパレータの正入力。ピーク電流トリップしきい値を設定するために、ITHピンの電圧が電流コンパレータのオフセットをプログラムします。このピンは、通常、パワーMOSFETのソースのところのセンス抵抗に接続します。

**SENSE1<sup>-</sup>(ピン22/ピン20/ピン22)**：電流コンパレータの負入力。このピンは、通常、センス抵抗の下端に接続します。

**SENSE2<sup>-</sup>(ピン14/ピン12/ピン14)**：電流コンパレータの負入力。このピンは通常センス抵抗の下端に接続します。

**SGND(ピン9/ピン7/ピン9)**：信号グランド。すべての帰還接続とソフトスタート接続をSGNDに戻します。最適な負荷レギュレーションのため、SGNDピンは出力コンデンサの負端子間のPCBの位置にケルビン接続します。

**SLOPE(ピン2/ピン24/ピン2)**：このピンは、内部スロープ補償の利得をプログラムします。このピンをフロートさせると、1.00の正規化されたスロープ補償利得が与えられます。このピンを3V8に接続すると正規化されたスロープ補償が66%

増加し、SGNDに接続すると正規化されたスロープ補償が37.5%減少します。詳細については「アプリケーション情報」を参照してください。

**SS(ピン6/ピン4/ピン6)**：ソフトスタート入力。ソフトスタート動作の場合、このピンとSGNDの間にコンデンサを接続するとエラーアンプの出力がクランプされます。5μAの内部電流源がコンデンサを充電し、コンバータのピーク・スイッチ電流の増加速度を設定します。

**SYNC(ピン11/ピン9/ピン11)**：PLLの同期入力。50kHz～650kHzの外部クロックを与えると、動作周波数がクロックに同期します。SYNCは50kの内部抵抗によってプルダウンされています。SYNCの入力波形の立ち上がりエッジは、閉ループ動作ではGATE1の立ち上がりエッジに揃います。振幅が1.6Vより高いSYNC信号はアクティブ“H”、0.9Vより低い信号はアクティブ“L”とみなされます。

**V<sub>IN</sub>(ピン20/ピン18/ピン20)**：主電源入力。このピンとSGNDの間に低ESRのセラミック・コンデンサを接続します。

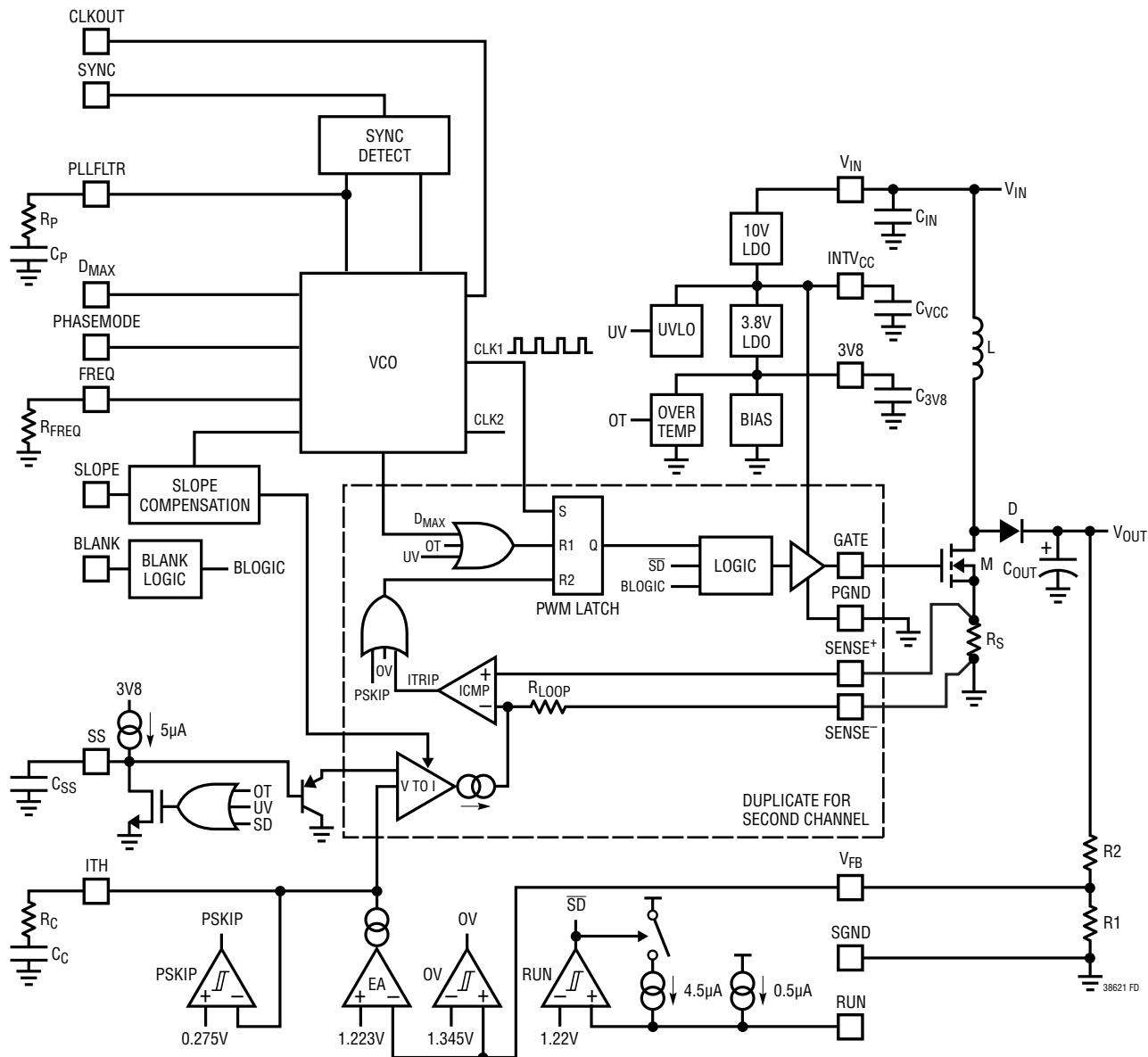

## 機能図

## 動作

### 制御ループ

LTC3862-1は2つのチャネルが180度の位相差で動作する、固定周波数、ピーク電流モード昇圧アキテクチャを採用しています。通常動作時は、各チャネルのクロックがPWMラッチをセットすると対応する外部MOSFETがオンし、メイン電流コンパレータICMPがPWMラッチをリセットするとオフします。ICMPがトリップしてラッチをリセットするピーク・インダクタ電流は、ITHピンの電圧によって制御されます。この電圧はエラーアンプEAの出力です。エラーアンプはV<sub>FB</sub>ピンの出力帰還信号を1.223V内部リファレンスと比較して、ITHピンにエラー信号を生成します。負荷電流が増加するとリファレンス電圧に対してV<sub>FB</sub>ピンの電圧がわずかに下がるので、平均インダクタ電流が新たな負荷電流と一致するまで、EAがITHの電圧を上げます。MOSFETがオフした後、次のクロック・サイクルが開始されるまで、インダクタ電流は昇圧ダイオードを通して出力コンデンサと負荷に流れます。

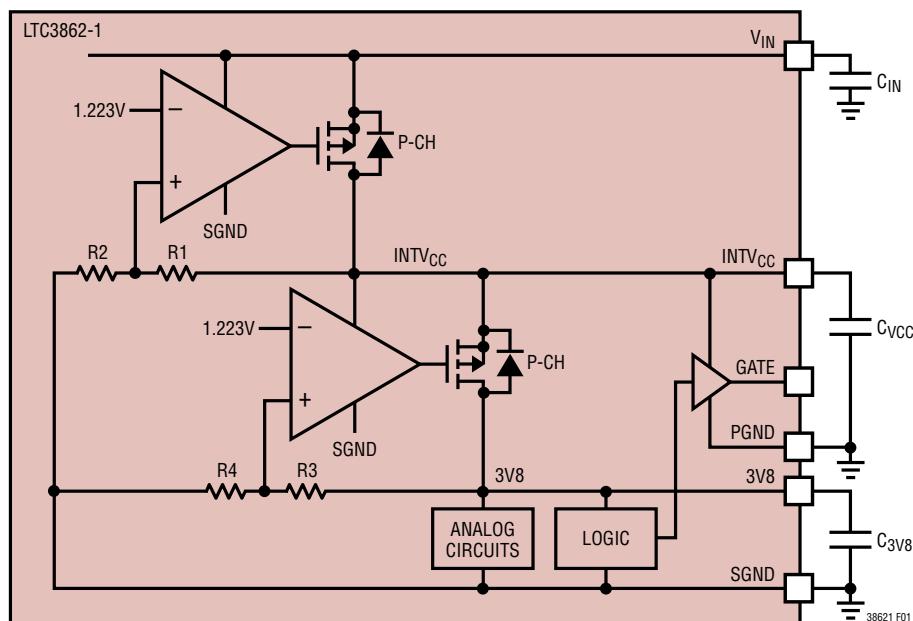

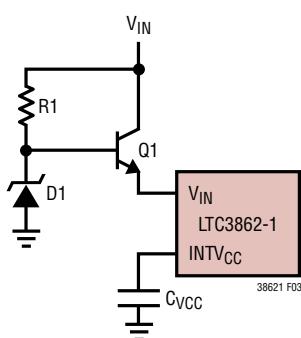

### ゲート・ドライバと制御回路に給電するカスケード接続されたLDO

LTC3862-1はカスケード接続された2個のPMOS出力段低損失電圧レギュレータ(LDO)を備えています。1つはゲート・

ドライブ電源用(INTV<sub>CC</sub>)、1つは低電圧のアナログおよびデジタル制御回路用(3V8)です。この電源を配置したブロック図を図1に示します。

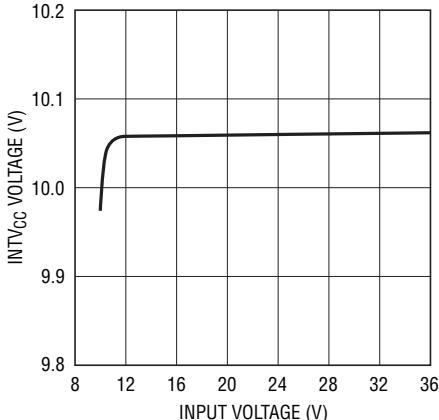

### ゲート・ドライバ電源のLDO(INTV<sub>CC</sub>)

1つ目のLDOの10V出力(INTV<sub>CC</sub>)はV<sub>IN</sub>から給電され、パワーMOSFETのゲート・ドライバに電力を供給します。INTV<sub>CC</sub>ピンは、できるだけデバイス・ピンの近くに配置した最小4.7μFのセラミック・コンデンサ(X5R以上の品質のもの)を使ってPGNDにバイパスします。出力電力レベルを上げるために各チャネルに2個のパワーMOSFETを並列接続する場合や、Q<sub>G</sub>が50nCより大きい1個のMOSFETを使用する場合は、バイパス容量を少なくとも10μFに増やすことを推奨します。

パワーMOSFETが不適切なゲート・ドライバで動作するのを防ぐため、低電圧ロックアウト(UVLO)回路がINTV<sub>CC</sub>レギュレータの出力を検出します。LTC3862-1では、上昇時のUVLOしきい値は標準7.5Vで、ヒステリシスは標準500mVです。LTC3862-1は高電圧パワーMOSFETや高電圧アプリケーション向けに最適化されています。ロジックレベルのパワーMOSFETを必要とするアプリケーションについては、LTC3862のデータシートを参照してください。

注：コンデンサ C<sub>VCC</sub> および C<sub>3V8</sub> はデバイスのピンにできるだけ近づけて配置する

図1. ゲート・ドライバと制御回路に給電するカスケード接続されたLDO

## 動作

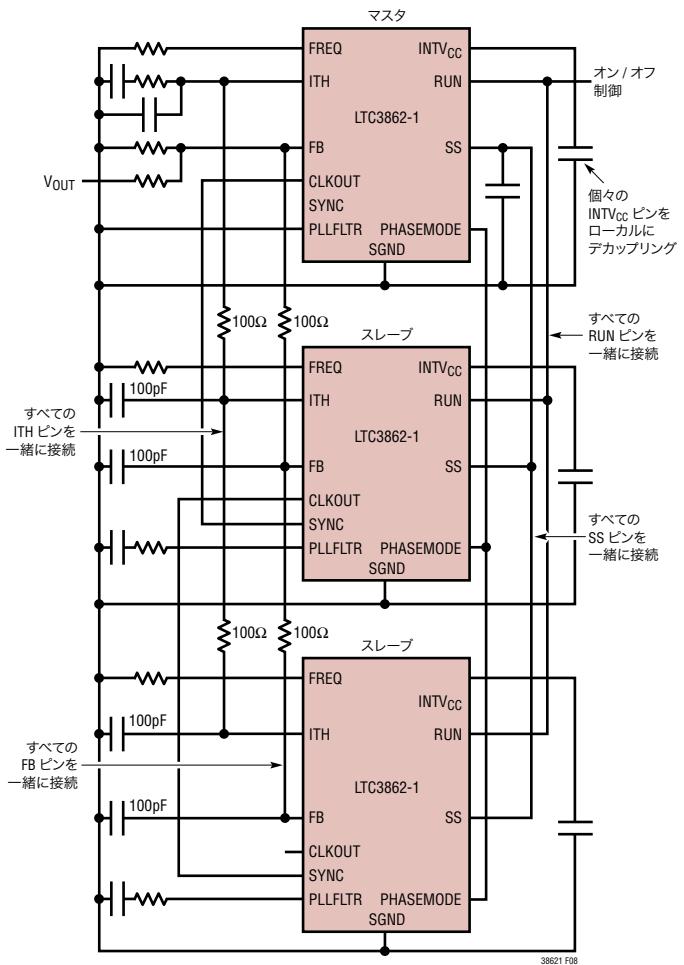

マルチフェーズ・アプリケーションでは、すべてのFBピンと一緒に接続され、すべてのエラーアンプの出力ピン(ITH)と一緒に接続されます。ただし、INTV<sub>CC</sub>ピンは一緒に接続しません。INTV<sub>CC</sub>レギュレータは電流をソースする能力はありませんが、電流をシンクする能力はありません。そのため、複数のINTV<sub>CC</sub>レギュレータの出力を一緒に接続すると、電圧が最も高いレギュレータがすべてのゲート・ドライブと制御回路の電流を供給し、他のレギュレータはオフします。このため、出力電圧が最も高いLDOに熱負荷がかかり、最高ダイ温度を超える可能性があります。LTC3862-1のマルチフェーズ・アプリケーションでは、各INTV<sub>CC</sub>レギュレータの出力を各デバイスにできるだけ近づけて、それぞれのPGNDに個別にバイパスします。

### 低電圧アナログおよびデジタル電源用LDO(3V8)

LTC3862-1に内蔵されている2つ目のLDOは、図1に示されているように、INTV<sub>CC</sub>から給電され、低電圧のアナログおよびデジタル制御回路への電源として機能します。(PMOS出力素子も備えている)このLDOの出力電圧は3.8Vです。ほとんどのアナログおよびデジタル制御回路は内部3V8 LDOから給電されます。3V8ピンは、デバイスのピンのできるだけ近くに配置した1nFのセラミック・コンデンサ(X5R以上の品質のもの)を使ってSGNDにバイパスします。このLDOは外部回路の電源として使うことは意図されていません。

### 熱に関する検討事項とパッケージ・オプション

LTC3862-1は3つのパッケージ・オプションで供給されます。5mm×5mm QFNパッケージ(UH24)の熱抵抗R<sub>TH(JA)</sub>は34°C/W、24ピンTSSOP(FE24)パッケージの熱抵抗は38°C/W、24ピンSSOP(GN24)パッケージの熱抵抗は85°C/Wです。QFNおよびTSSOPパッケージ・オプションのリード・ピッチは0.65mm、GN24オプションのリード・ピッチは0.025インチです。

INTV<sub>CC</sub>レギュレータは全部で最大50mAの電流を供給することができます。そのため、デバイスの最大接合部温度を超え

ないように注意する必要があります。接合部温度は以下の式を使って推算することができます。

$$I_{Q(TOT)} = I_Q + Q_{G(TOT)} \cdot f$$

$$P_{DISS} = V_{IN} \cdot (I_Q + Q_{G(TOT)} \cdot f)$$

$$T_J = T_A + P_{DISS} \cdot R_{TH(JA)}$$

全静止電流(I<sub>Q(TOT)</sub>)は、静止電源電流(I<sub>Q</sub>)とパワーMOSFETのゲート容量の充電に必要な電流を合わせたものです。Q<sub>G(TOT)</sub>の値は、MOSFETのデータシートの「標準的性能特性」のセクションの「V<sub>GS</sub>とQ<sub>G</sub>」のプロットから得られます。電気的仕様に示されている値は(15Vのような)高いV<sub>GS</sub>で測定されている可能性がありますが、ここで関係するのは、10VのINTV<sub>CC</sub>ゲート・ドライブ電圧での値です。

必要な熱解析の一例として、入力電圧範囲が8.5V～24V、出力電圧が72V/1.5Aの2フェーズ昇圧コンバータを検討します。スイッチング周波数は150kHz、最大周囲温度は70°Cです。このアプリケーションに使われるパワーMOSFETはルネサスのHAT2267Hで、標準R<sub>DS(ON)</sub>はV<sub>GS</sub> = 10Vで13mΩです。「V<sub>GS</sub>とQ<sub>G</sub>」のプロットから、V<sub>GS</sub> = 10Vでの全ゲート電荷は30nCです(ゲート電荷の温度係数は高くありません)。各フェーズに1個のパワーMOSFETが使われます。QFNパッケージのオプションでは次のようにになります。

$$I_{Q(TOT)} = 3mA + 2 \cdot 30nC \cdot 150kHz = 12mA$$

$$P_{DISS} = 24V \cdot 12mA = 288mW$$

$$T_J = 70^\circ C + 288mW \cdot 34^\circ C/W = 79.8^\circ C$$

この例では、接合部温度の上昇はわずか9.8°Cです。これらの式は、ゲート充電電流が一般にデバイスの静止電流をどのように支配しているか、また、パッケージ・オプションと基板のヒートシンクの選択がソリューションの熱性能にどのように大きな影響を与えることがあるかを示しています。

## 動作

最大接合部温度を超えないようにするには、最大  $V_{IN}$  での連続モード(重負荷)動作時のデバイスへの入力電源電流をチェックします。デバイスの接合部温度を安全なレベルに保つには、動作周波数とパワー MOSFET のサイズの間にトレードオフが必要になります。最後に、赤外線カメラやサーマルプローブを使って最終 PCB の熱解析を行って、計算を検証することが重要です。オプションとして、図3に示されている外部レギュレータを使って、デバイスの合計電力損失を減らすことができます。

### サーマル・シャットダウン保護

過熱状態(内部または外部)が発生し、ダイ温度が  $170^{\circ}\text{C}$  を超えると、内部サーマル・モニタがゲート・ドライバをシャットダウンし、ソフトスタート・コンデンサをリセットします。このサーマル・センサは  $10^{\circ}\text{C}$  のヒステリシスをもっており、高温での不安定動作を防ぎます。LTC3862-1 の内部サーマル・センサは、短時間の過熱状態の間デバイスを保護することを目的としています。ただし、規定された最大動作接合部温度を超える動作が継続すると、デバイスの劣化を生じることがあります。

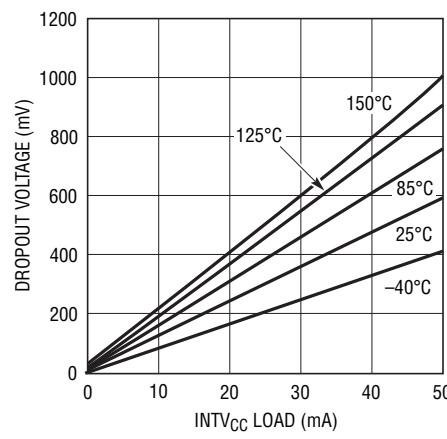

### 低い電源電圧での動作

LTC3862-1 の最小入力電圧は  $8.5\text{V}$  なので、高電圧パワー MOSFET を必要とするアプリケーションに適しています。LTC3862-1 のゲート・ドライバは PMOS のプルアップ素子と NMOS のプルダウン素子で構成されているので、パワー MOSFET のスイッチング時に  $\text{INTV}_{CC}$  の全電圧をゲートに与えることができます。とはいえ、最適なパワー MOSFET を選択するために、最小ゲート・ドライブ電源電圧( $\text{INTV}_{CC}$ )を慎重に決定します。最小ゲート・ドライブ電圧に影響を与える可能性のある重要なパラメータは、最小入力電圧( $V_{IN(MIN)}$ )、LDO の損失電圧、パワー MOSFET の  $Q_G$ 、および動作周波数です。

$\text{INTV}_{CC}$  LDO がドロップアウト状態になるほど入力電圧  $V_{IN}$  が低いと、最小ゲート・ドライブ電源電圧は次のようになります。

$$V_{\text{INTV}_{CC}} = V_{IN(MIN)} - V_{\text{DROPOUT}}$$

LDO の損失電圧は合計ゲート・ドライブ電流とデバイスの静止電流(標準  $3\text{mA}$ )に応じて変動します。LDO の損失電圧と出力電流の関係を示す曲線を図2に示します。LDO の損失電圧の温度係数は約  $6000\text{ppm}/^{\circ}\text{C}$  です。

LDO を流れる合計 Q 電流( $I_{Q(TOT)}$ )は、コントローラの静止電流( $3\text{mA}$ )と全ゲート電荷駆動電流の和です。

$$I_{Q(TOT)} = I_Q + Q_{G(TOT)} \cdot f$$

計算が完了した後、すべての動作条件にわたって(低  $V_{IN}$ 、公称  $V_{IN}$  および高  $V_{IN}$ 、さらに軽負荷から最大負荷まで)ゲート・ドライブ波形とゲート・ドライバ電源電圧( $\text{INTV}_{CC}$  から PGND)を測定し、パワー MOSFET の適正な導通状態を確認することが重要です。パワー MOSFET のデータシートを調べて、測定された  $V_{GS}$  に対する実際の  $R_{DS(ON)}$  を求め、赤外線カメラやサーマル・プローブを使って部品温度を測定し、熱計算を検証します。

図2.  $\text{INTV}_{CC}$  LDO の損失電圧と電流

## 動作

### 高い電源電圧での動作

入力電圧が高い場合、LTC3862-1の内部LDOは大量の電力を消費することがあり、最大接合部温度を超える可能性があります。高い動作周波数や、チャネル当たり複数のパワーMOSFETを使用するなどの条件では、接合部温度が高いレベルまで上昇する可能性があります。熱に関する上記の式が接合部温度の過度の上昇を示す場合、図3に示されているように、常に外部バイアス電源を使ってデバイスの電力損失を減らすことができます。

たとえば、12Vのシステム・レールを利用できれば、LTC3862-1に給電する24Vの主入力電源レールより適しています。また、バイアス電源は別のスイッチング・レギュレータやLDOレギュレータで生成することもできます。LDOレギュレータの一例を図3に示します。適切なツエナー・ダイオードを選択することにより、LDOレギュレータの出力電圧を、10Vより高いが、電力損失をLTC3862-1と図3のQ1の間で分割するのに十分なだけ低く設定することができます。INTV<sub>CC</sub>ピンの絶対最大電圧定格は11Vです。

図3. 外部バイアス電源付きLTC3862-1の使用

### 電源シーケンシング

図1に示すように、LTC3862-1の2個のLDOレギュレータでは、PMOS出力トランジスタにボディ・ダイオードが並列に接続されています。そのため、デバイスのINTV<sub>CC</sub>ピンとV<sub>IN</sub>ピンを別

の電源でバイアスすることができません。INTV<sub>CC</sub>ピンを別の電源で単独にバイアスすると、電源シーケンシング中に起こり得る2つの不良モードのうちのいずれかが生じることがあります。INTV<sub>CC</sub>電源がV<sub>IN</sub>電源よりも前に立ち上がると、大きな電流が外部INTV<sub>CC</sub>電源からLDOのPMOS素子のボディ・ダイオードを通して、入力コンデンサとV<sub>IN</sub>ピンに流れます。この大きな電流によってラッチアップ状態が生じ、デバイスに致命的な損傷を与える可能性があります。

ただし、デバイスへのV<sub>IN</sub>電源がINTV<sub>CC</sub>電源よりも前に立ち上がると、その外部電源INTV<sub>CC</sub>はLTC3862-1の内部LDOの負荷として機能し、LDOはINTV<sub>CC</sub>出力をその短絡電流で充電しようと試みます。このため、LTC3862-1の過度の電力損失と熱的過負荷が生じるおそれがあります。

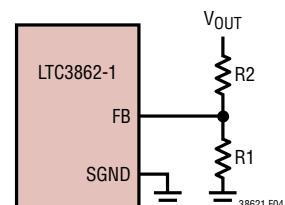

### 出力電圧のプログラミング

出力電圧は次式に従って抵抗分割器によって設定します。

$$V_{OUT} = 1.223V \left( 1 + \frac{R2}{R1} \right)$$

外付け抵抗分割器は図4に示すように出力に接続します。抵抗R1は、通常、通常動作時にV<sub>FB</sub>ピンから流れ出す電流によって生じる出力電圧誤差が、分割器の電流に比べて無視できる程度になるように選択します。エラーアンプの入力バイアス電流による出力電圧誤差が0.5%より小さい場合、R1の最大値は約30kになります。

図4. 抵抗分割器による出力電圧のプログラミング

## 動作

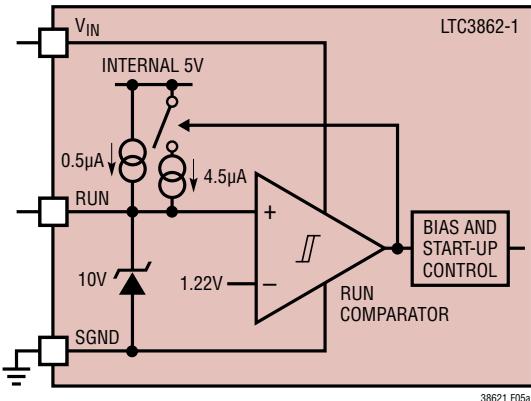

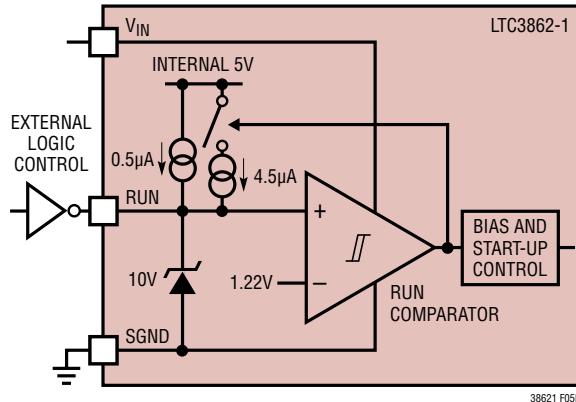

### RUNピンの動作

LTC3862-1の制御回路はRUNピンを使ってオン/オフされます。RUNピンを1.22Vより下に引き下げるときシャットダウン・モードが強制され、これを解放すると0.5μAの電流源がこのピンを引き上げるので、「通常オン」のコンバータを設計することができます。あるいは、RUNピンを外部から引き上げるか、またはロジックで直接ドライブすることもできます。このピンの8Vの絶対最大定格を超えないように注意してください。

RUNピンのコンパレータは入力電圧の検出にも使用できるので、低電圧検出回路を設計することができます。これは、低い入力電圧で入力電流が非常に高いレベルに達することがある昇圧コンバータ・アプリケーションで役立ちます。

$$I_{IN} = \frac{I_{OUT} \cdot V_{OUT}}{V_{IN}}$$

低電圧検出機能の精度を最大にするため、RUNコンパレータの1.22Vの入力しきい値を高精度バンドギャップ・リファレンスから引き出します。RUNコンパレータには80mVのヒステリシスが組み込まれています。RUNピンの電圧が1.22Vを超えると、RUNピンにソースされる電流は0.5μAから5μAの電流に切り替えられます。したがって、以下の式に示されているように、外部分圧器の抵抗の値を使って、ユーザーは上昇時のしきい値とヒステリシスの大きさの両方をプログラムすることができます。

$$V_{IN(ON)} = 1.22V \left( 1 + \frac{R_A}{R_B} \right) - 0.5\mu \cdot R_A$$

$$V_{IN(OFF)} = 1.22V \left( 1 + \frac{R_A}{R_B} \right) - 5\mu \cdot R_A$$

可能なRUNピン制御手法のいくつかを図5に示します。

### 周波数の選択とフェーズロック・ループ

スイッチング周波数の選択は効率と部品サイズの間のトレードオフになります。低周波数動作はMOSFETのスイッチング損失を減らして効率を上げますが、出力リップルを低く抑えるには大きなインダクタと出力コンデンサが必要です。

図5a. RUNピンを使った「通常オン」のコンバータ

図5b. 外部ロジックを使ったオン/オフ制御

図5c. RUNピンを使った入力電圧のターンオンとターンオフのしきい値のプログラミング

## 動作

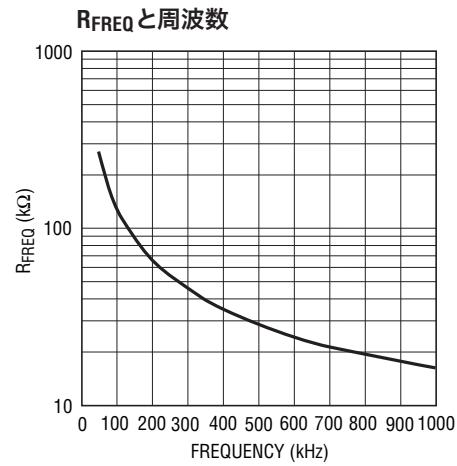

LTC3862-1には固定周波数アーキテクチャが使われており、FREQピンからグランドに接続した1個の抵抗を使って75kHz～500kHzの範囲でプログラムすることができます。FREQピンの抵抗と動作周波数の関係を図6に示します。

図6. FREQピンの抵抗値と周波数

LTC3862-1の動作周波数は次式を使って近似することができます。

$$R_{FREQ} = 5.5096E9(f_{OSC})^{-0.9255}$$

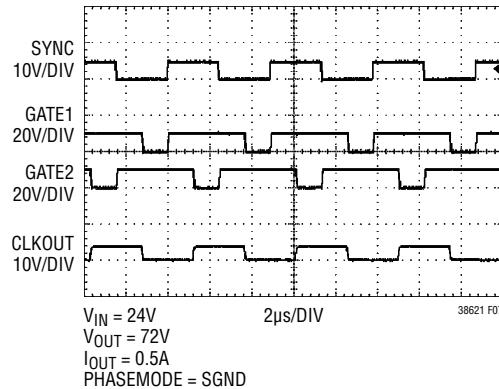

LTC3862-1にはフェーズロック・ループが備わっており、SYNCピンに接続された外部クロック・ソースに内部発振器を同期させることができます。PLLFLTRピンからSGNDに直列RCネットワークを接続して、PLLの帰還ループを補償します。標準的な補償部品は10k抵抗に直列に接続された0.01μFコンデンサです。PLLFLTRピンは位相検出器の出力と電圧制御発振器(VCO)の入力の両方を兼ねています。LTC3862-1の位相検出器はPLLFLTRピンの電圧を調整して、図7に示すように、GATE1の立ち上がりエッジを外部クロック信号のリーディング・エッジに揃えます。GATE2の立ち上がりエッジはPHASEMODEピンの電圧に依存します。LTC3862-1のPLLのキャプチャレンジは50kHz～650kHzです。

図7. PLLを使ったLTC3862-1の外部クロックへの同期

LTC3862-1の動作周波数は外部抵抗を使ってプログラムすることができる所以、同期アプリケーションでは、(外部抵抗で定まる)自走周波数を同期周波数と同じ値に設定することを推奨します。こうすると、デバイスが外部クロックとほぼ同じ周波数で起動するので、同期信号が与えられたとき出力に不連続状態が現れません。また、同期信号が失われたときも、動作周波数が実質的に一定に維持されるようになります。SYNCピンにはグランドに接続された50kの内部抵抗が備わっています。

### マルチフェーズ・アプリケーションでのCLKOUTピンとPHASEMODEピンの利用

LTC3862-1には2つのピン(CLKOUTとPHASEMODE)が備わっており、高電流のマルチフェーズ・アプリケーションで複数のデバイスと一緒にデイジーチェーン接続できるようにします。3フェーズまたは4フェーズのデザインでは、单一の高電流出力を供給できるように追加の電力段を同期させるため、マスター・コントローラのCLKOUT信号をスレーブ・コントローラのSYNC入力に接続します。表1にまとめられているように、チャネル1とCLKOUTの間の位相関係とともにチャネル1とチャネル2の間の位相関係を調節するのにPHASEMODEピンが使われます。GATE1出力の立ち上がりエッジとして定義されているゼロ度を基準にして、位相は計算されます。6フェーズのアプリケーションでは、マスター・コントローラのCLKOUTピンは2番目のコントローラのSYNC入力に接続され、2番目のコントローラのCLKOUTピンは3番目のコントローラのSYNCピンに接続されます。

動作

表1

| PHASEMODE | チャネル1と<br>チャネル2間の<br>位相差 | チャネル1と<br>CLKOUT間の<br>位相差 | アプリケーション    |

|-----------|--------------------------|---------------------------|-------------|

| SGND      | 180°                     | 90°                       | 2フェーズ、4フェーズ |

| フロート      | 180°                     | 60°                       | 6フェーズ       |

| 3V8       | 120°                     | 240°                      | 3フェーズ       |

## マルチフェーズ・アプリケーションで LTC3862-1 のトランスコンダクタンス( $g_m$ )エラーアンプを使用する

LTC3862-1のエラーアンプはトランスコンダクタンス( $g_m$ )アンプであり、DC利得が高いが、出力インピーダンスが高いことを意味します(エラーアンプの出力は差動入力電圧に比例する電流です)。この方式のエラーアンプは複数のデバイスのアンプを並列に接続できるので、マルチフェーズ・ソリューションを実装する作業が大幅に簡素化されます。この場合、図8に示されているように、複数のLTC3862-1のFBピンを(ITHピンと同様に)一緒に接続することができます。合成されたエラーアンプの $g_m$ は、単純に1個のアンプのトランスコンダクタンスのn倍です。つまり  $g_{m(TOT)} = n \cdot 660\mu\text{S}$  であり、ここで、nは並列接続されたアンプの個数です。ITHピンから電流コンパレータの入力への伝達関数は、チャネル間とデバイス間のいずれにおいても正確になるように慎重に設計されています。このようにして、ピーク・インダクタ電流の整合が正確に保たれます。

エラーアンプの出力をバッファしたものによって、電流コンパレータの入力のしきい値が決まります。ゼロ・ピーク電流を表すITH電圧は0.4Vで、電流制限を表す電圧は(低デューティ・サイクルでは)1.2Vです。過負荷状態の間、エラーアンプの出力は、過負荷状態が解消されたときの待ち時間を減らすため、低デューティ・サイクルでは2.6Vにクランプされます。LTC3862-1では特許を取得した回路がスロープ補償信号のリカバリに使われているので、最大ピーク・インダクタ電流がデューティ・サイクルに応じて大きく変動することはありません。

複数のLTC3862-1コントローラを使用するマルチフェーズ・アプリケーションでは、プリント回路基板上のグランド電流によってデバイス間の制御線が乱され、不規則な動作となる可能性があります。こうしたアプリケーションでは、図8に示すように、 $100\Omega$ の抵抗を介してFBピンを互いに接続し、それぞれのスレーブ側FBピンを  $100pF$  のデカップリング・コンデンサを使用して各デバイス付近でグランドに接続する必要があります。

図8. マルチフェーズ動作のためのLTC3862-1のエラーアンプの構成

ソフトスタート

LTC3862-1の起動はSSピンの電圧によって制御されます。内部PNPトランジスタは電流コンパレータのセンスしきい値をソフトスタートの間クランプして、ピーク・スイッチ電流を制限します。PNPのベースはSSピンに接続されており、エミッタは内部のバッファされたITHノードに接続されています(この間、ITHピンの電圧はソフトスタート電圧をトラッキングしないことがあることに注意してください)。内部5 $\mu$ A電流源はソフトスタート(SS)コンデンサを充電し、このコンデンサの電圧が約0.6Vに達するまでピーク・センスしきい値をクランプします。必要なソフトスタート容量の大きさは次式を使って推算することができます。

$$C_{SS} = 5\mu A \left( \frac{t_{SS}}{0.6V} \right)$$

## 動作

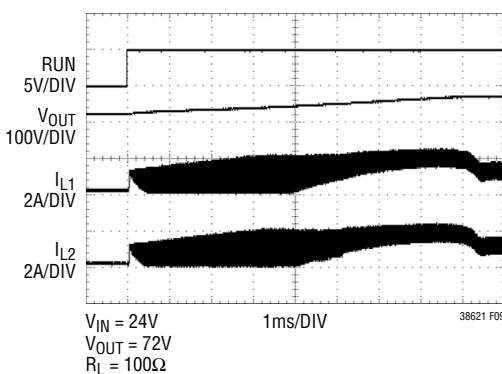

SSピンは内部オープン・ドレインNMOSプルダウン・トランジスタを備えています。このトランジスタは、INTVCCピンの電圧がその低電圧ロックアウトしきい値より低いとき、または過熱状態のときに、RUNピンがLになるとオンします。複数のLTC3862-1デバイスを使うマルチフェーズ・アプリケーションでは、すべてのSSピンと一緒に接続し、1個の外部コンデンサを使ってソフトスタート時間をプログラムします。この場合、ソフトスタート・コンデンサへ流れ込む電流は $I_{SS} = n \cdot 5\mu A$ となります。ここで、nは一緒に接続されるSSピンの個数です。LTC3862-1の2フェーズ・アプリケーションの起動波形を図9に示します。

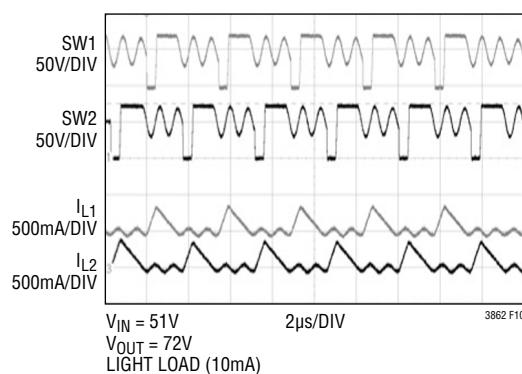

### 軽負荷時のパルス・スキップ動作

負荷電流が減少するにつれ、コントローラは不連続モード(DCM)に入ります。ピーク・インダクタ電流はコントローラの最小オン時間に達するまで減少することができます。負荷電流がさらに減少すると、出力の安定化を維持するためパルス・スキップが発生しますが、これは正常な動作です。このモードでのコントローラの最小オン時間は約210nsであり(ブランギング時間はその最小値に設定されます)、その大部分はリーディングエッジ・ブランギングです。LTC3862-1のパルス・スキップの開始点のスイッチング波形を図10に示します。

### プログラム可能なスロープ補償

CCMで動作している電流モード昇圧レギュレータでは、50%を超えるデューティ・サイクルの場合、低調波発振を避けるためにスロープ補償を追加する必要があります。LTC3862-1の

場合、このランプ補償は内部にありますが、ユーザーによって調整可能です。ランプ補償の波形が内部で固定されているので、インダクタ値と動作周波数が通常いくらか制約されます。たとえば、内部スロープ補償の大きさが固定されている場合、大きすぎるインダクタが使われるとスロープ補償の効果が大きくなりすぎて、コンバータが不安定になる可能性があります。同様に、小さすぎるインダクタが使われると、内部ランプ補償が低調波発振を防ぐのに不十分なことがあります。

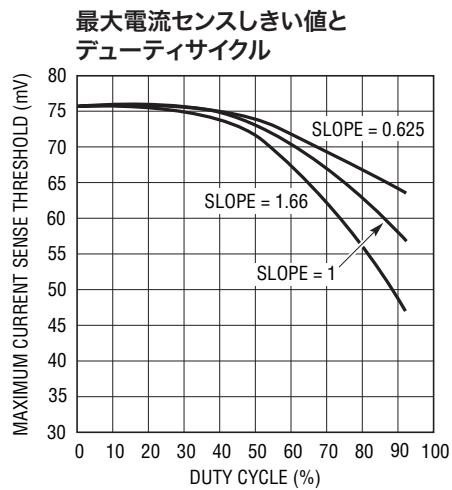

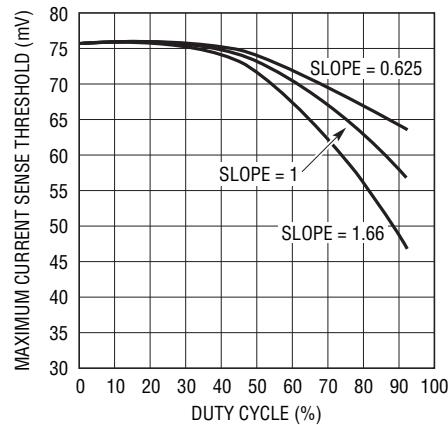

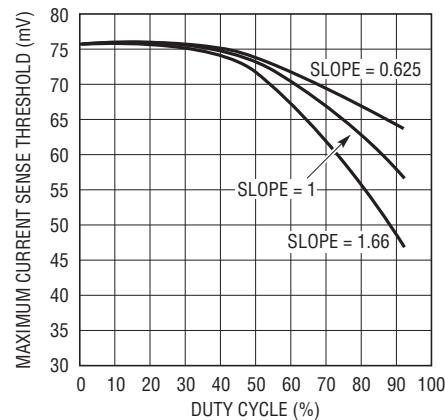

さまざまなインダクタンスの性能を最適化するため、LTC3862-1にはユーザーがスロープ補償の利得をプログラムすることのできるピンが備わっています。SLOPEピンがフロート状態のとき、正規化されたスロープ利得は1.00です。SLOPEピンをグランドに接続すると、正規化された利得が0.625に減少し、3V8電源に接続すると、正規化されたスロープ利得が1.66に増加します。

正規化されたスロープ補償の利得が1.00に設定されているとき、従来の設計と同様に、設計式は20%~40%のインダクタ・リップル電流を想定しています。ただし、応用回路によっては、選択されたインダクタに対して、1.00の正規化された利得が最適ではないことがあります。インダクタのリップル電流が40%を超える場合、SLOPEピンを3V8電源に接続することにより、正規化されたスロープ利得を1.66に増加することができます(66%の増加)。インダクタのリップル電流が20%を下回る場合、SLOPEピンをSGNDに接続することにより、正規化されたスロープ利得を0.625に減少させることができます(37.5%の減少)。

図9. LTC3862-1を使った昇圧コンバータの標準的起動波形

図10. パルス・スキップ開始時の LTC3862-1 の軽負荷スイッチング波形

## 動作

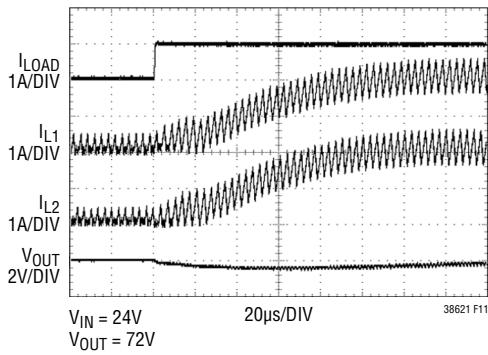

スロープ補償の効果を調べるには、負荷ステップを出力に与え、負荷電流のリーディング・エッジとトレーリング・エッジの間のインダクタ電流の振る舞いをサイクルごとにモニタします。入力電圧をその全範囲で変化させ、サイクルごとのスイッチ・ノードの不安定性や低調波発振の兆候を調べます。スロープ補償が低すぎると、コンバータは過度のジッタや(最悪の場合は)低調波発振による悪影響を受けることがあります。内部電流センス信号に過度のスロープ補償が与えられると、制御ループの位相マージンが損なわれます。適切に補償されたループのインダクタ電流波形を図11に示します。

SENSE<sup>+</sup>からSENSE<sup>-</sup>のしきい値がデューティ・サイクルによって大きく変動しないようにするために、LTC3862-1には特許を取得した回路が備わっており、これによって加えられたスロープ補償の大部分がリカバリされます。ただし、図12に示されているように、このセンスしきい値はプログラムされたスロープ利得に応じて変動します。データシートの75mVの(SENSE<sup>+</sup>からSENSE<sup>-</sup>を差し引いた電圧の)標準規定値は、低デューティ・サイクル時の1.00の正規化されたスロープ利得で測定されます。正規化されたスロープ利得が1.00ではないアプリケーションの場合、図12を使ってセンス抵抗の正しい値を求めます。

### プログラム可能なブランкиングと最小オン時間

LTC3862-1のBLANKピンにより、ユーザーはSENSEピンのリーディングエッジ・ブランкиングの大きさをプログラムすることができます。BLANKピンをSGNDに接続すると、最小オン時間が210nsになり、フロートさせると290nsに増加し、3V8

電源に接続すると375nsになります。電流コンパレータの伝播遅延(標準25ns)とロジック回路の伝播遅延(10ns～15ns)は本来小さいので、最小オン時間の大半はこのリーディングエッジ・ブランкиングによります。

リーディングエッジ・ブランкиングの目的は、パワーMOSFETのターンオンのリーディングエッジでSENSEピンのノイズを取り除くことです。パワーMOSFETのターンオンの間、ゲート・ドライブ電流、スイッチ・ノードの寄生容量の放電、昇圧ダイオードの電荷の回復、およびdi/dtの高い経路の寄生直列インダクタンスのすべてが、電流コンパレータを誤ってトリップさせる可能性があるオーバーシュートと高周波数ノイズの原因となります。LTC3862-1がtしているアプリケーションの範囲は広いので、内部リーディングエッジ・ブランкиング時間を1つの値に固定するすれば、最長の遅延時間を使用する必要があったでしょう。ブランク時間をプログラムする手段が与えられているので、ユーザーはアプリケーションごとにSENSEピンのフィルタリングを最適化することができます。昇圧コンバータの最小オン時間に対するプログラム可能なリーディングエッジ・ブランкиング時間の影響を図13に示します。

### プログラム可能な最大デューティ・サイクル

一定の周波数と低出力リップル電圧を維持するため、シングルエンド昇圧(またはフライバックまたはSEPIC)コンバータは、サイクルごとに最小限の時間スイッチをオフする必要があります。このオフ時間により、エネルギーをインダクタから出力コンデンサと負荷に渡すことができ、過度のリップル電流とリップル電圧を防ぎます。昇圧コンバータやSEPICコンバー

図11. 適切に補償された制御ループのインダクタ電流波形

図12. ピーク・センスしきい値に対するスロープ利得の影響

## 動作

図13. 最小オン時間に対する

リーディングエッジ・ブランкиングの影響

タのようなインダクタをベースにしたトポロジーでは、特に低い  $V_{IN}$  から高い  $V_{OUT}$  へのアプリケーションの場合、最大デューティ・サイクルができるだけ 100% に近づけるのが望ましいでしょう。ただし、トランジistorをベースにしたソリューションでは、主スイッチのオフ時間の間  $V \cdot sec$  のリセットが必要なため、最大デューティ・サイクルを 100% に近づけるのは望ましくありません。

図14. 異なるデューティ・サイクル・リミットでの

スイッチ・ノードの波形

これらの異なるアプリケーションの要件を満たすため、LTC3862-1は最大デューティ・サイクルをプログラムする簡単な方法を備えています。 $D_{MAX}$  ピンを SGND に接続すると、最大デューティ・サイクルが 96% に制限されます。 $D_{MAX}$  ピンをフロートさせるとデューティ・サイクルが 84% に制限され、3V8 電源に接続すると 75% に制限されます。昇圧コンバータのスイッチ・ノードの波形に対する最大デューティ・サイクル制限の影響を図 14 に示します。

## 動作

2、3、4、6および12フェーズの動作を行うために、LTC3862-1はスイッチング周波数の12倍で動作する発振器を備えています。ゲート・ドライバの動作周波数を得るために、デジタル・カウンタを使って基本発振器周波数を分周します。**最大デューティ・サイクル・リミット**はこのデジタル・カウンタから得られるので、**最大デューティ・サイクルのパーセンテージ**はプロセスの許容誤差や温度によって変化することはありません。

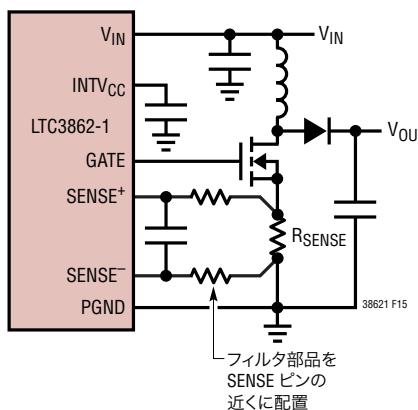

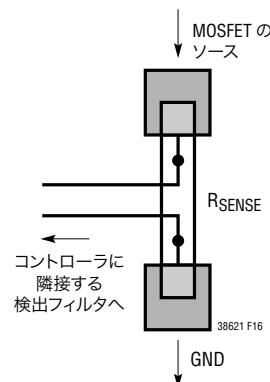

### SENSE<sup>+</sup>ピンとSENSE<sup>-</sup>ピン

SENSE<sup>+</sup>ピンとSENSE<sup>-</sup>ピンは、各チャネルのCMOS電流コンペレータへの高インピーダンス入力です。公称値として、これらのピンに流れ込む、またはこれらのピンから流れ出すDC電流はありません。これらのピンからSGNDにESD保護ダイオードが接続されていますが、高温でも、SENSE<sup>+</sup>ピンとSENSE<sup>-</sup>ピンに流れ込む漏れ電流は1μA未満です。

LTC3862-1にはリーディングエッジ・ブランкиングが備わっているので、外部RCフィルタなしで適切に動作します。ただし、外部フィルタを使う場合は、図15に示すように、フィルタ部品はデバイスのSENSE<sup>+</sup>ピンとSENSE<sup>-</sup>ピンの近くに配置します。正と負の検出ノードの配線は、図16に示すように、互いに並列にセンス抵抗の下にケルビン接続します。基板の他の場所で電流を検出すると、電流センス素子に寄生インダクタンスと寄生容量が追加されることがあります、センス・ピンでの情報を劣化させ、プログラムされた電流制限が予測できなくなります。PCBのビアを使ってSENSE<sup>-</sup>ラインをグランド・プレーンに接続

図15. 電流検出フィルタの適切な部品配置

続いたくなりますが、そうしないでください。このように接続すると、予期せぬ動作をすることがあります。

センス抵抗は、図16に示すように、短く、幅の広いPCBトレースを使って、パワーMOSFETのソースとグランド・ノードに接続します。理想的には、センス抵抗の下の端子は出力コンデンサの負端子に隣接させます。というのは、この経路はスイッチ、昇圧ダイオード、出力コンデンサおよびセンス抵抗で形成される高di/dtループの一部だからです。インダクタ電流は三角波なので、インダクタの配置はそれほど他に影響を与えません。

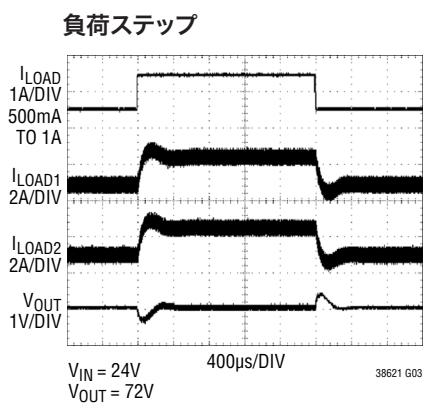

### 負荷過渡応答のチェック

レギュレータのループ応答は負荷電流の過渡応答を観察すればチェックできます。スイッチング・レギュレータはDC(抵抗性)負荷電流のステップに応答するのに数サイクルを要します。負荷ステップが発生すると、V<sub>OUT</sub>はΔI<sub>LOAD</sub>(ESR)に等しい大きさだけシフトします。ここで、ESRはC<sub>OUT</sub>の等価直列抵抗です。またΔI<sub>LOAD</sub>は、C<sub>OUT</sub>の充電または放電を開始して、帰還誤差信号を生成します。この信号により、レギュレータは電流の変化に適応してV<sub>OUT</sub>をその定常状態の値に戻すよう強制されます。この回復期間に(安定性に問題があることを示す)過度のオーバーシュートやリンギングが発生しないか、V<sub>OUT</sub>をモニタすることができます。

ITHピンが備わっているので、制御ループ動作を最適化できるだけでなく、DC結合され、ACフィルタを通した閉ループ応

図16. ケルビン接続を使ったSENSE<sup>+</sup>とSENSE<sup>-</sup>のトレースのセンス抵抗への接続

## 動作

答のテスト・ポイントが与えられます。このテスト・ポイントでのDCステップ、立ち上がり時間、およびセトリングは、閉ループ応答を正確に反映します。2次特性が支配的なシステムを想定すれば、位相マージンや減衰係数は、このピンで見られるオーバーシュートのパーセンテージを使用して概算することができます。このピンの立ち上がり時間を調べることにより、帯域幅も概算できます。

ITHの直列 $R_C-C_C$ フィルタにより、支配的なポール-ゼロ・ループ補償が設定されます。昇圧コンバータとフライバック・コンバータの伝達関数には右半平面のゼロが含まれており、十分な位相マージンを維持するため、通常はループのクロスオーバー周波数を大幅に下げる必要があります。最終のPCレイアウトが完了し、特定の出力コンデンサのタイプと値が決まつたら、通常、 $R_C-C_C$ フィルタの値を多少修正して(推奨値の0.5倍~2倍)過渡応答を最適化することができます。出力コンデンサの実効ESRとバルク容量はループの利得と位相に大きく影響するので、出力コンデンサの構成は前もって選択しておく必要があります。立ち上がり時間が1μs~10μsの、全負荷電流の20%~80%の出力電流パルスによっ

て、帰還ループを開くことなく全体的なループの安定性を判断することができる出力電圧波形とITHピンの波形が発生します。高速負荷ステップを発生させる実用的な方法として、出力コンデンサの両端に直接パワーMOSFETと負荷抵抗を接続し、適切な信号発生器でそのゲートをドライブします。出力電流のステップ変化によって生じる初期出力電圧ステップは、帰還ループの帯域幅内にない場合があるため、位相マージンを決定するのにこの信号を使用することはできません。このため、ITHピンの信号を調べる方が確実です。この信号は帰還ループ内にあり、フィルタを通して補償された制御ループ応答です。ループの利得は $R_C$ を大きくすると増加し、ループの帯域幅は $C_C$ を小さくすると拡大します。 $C_C$ を減少させるのと同じ比率で $R_C$ を増加させるとゼロの周波数は変化しないので、帰還ループの最も重要な周波数範囲で位相シフトが一定に保たれます。出力電圧のセトリングの様子は閉ループ・システムの安定性に関係し、電源全体の実際の性能を表します。適切に補償された昇圧コンバータの負荷ステップ応答を図17に示します。

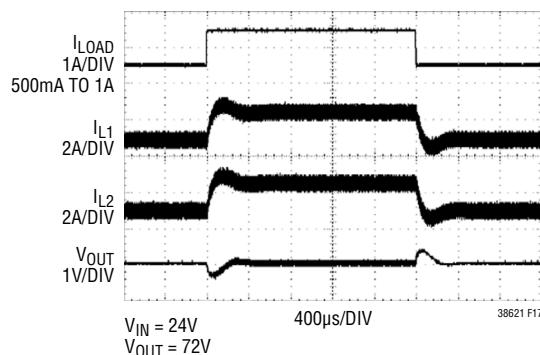

図17. 適切に補償された昇圧コンバータの負荷ステップ応答

## アプリケーション情報

### 標準的な昇圧応用回路

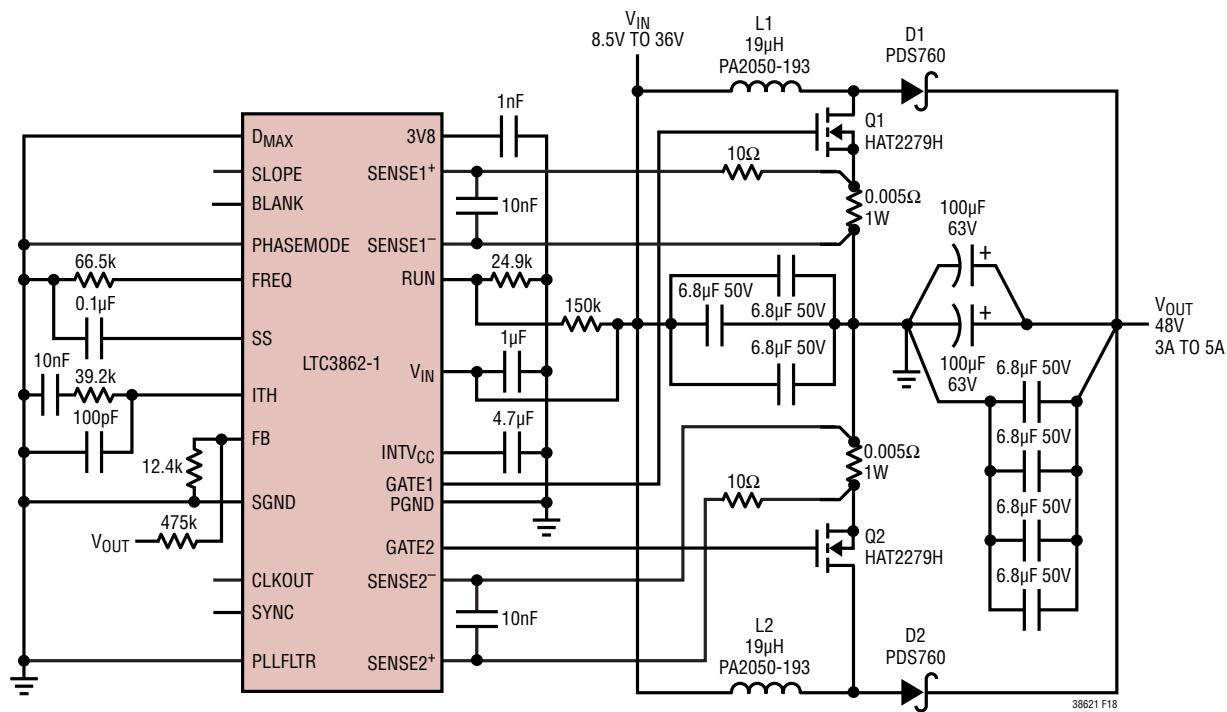

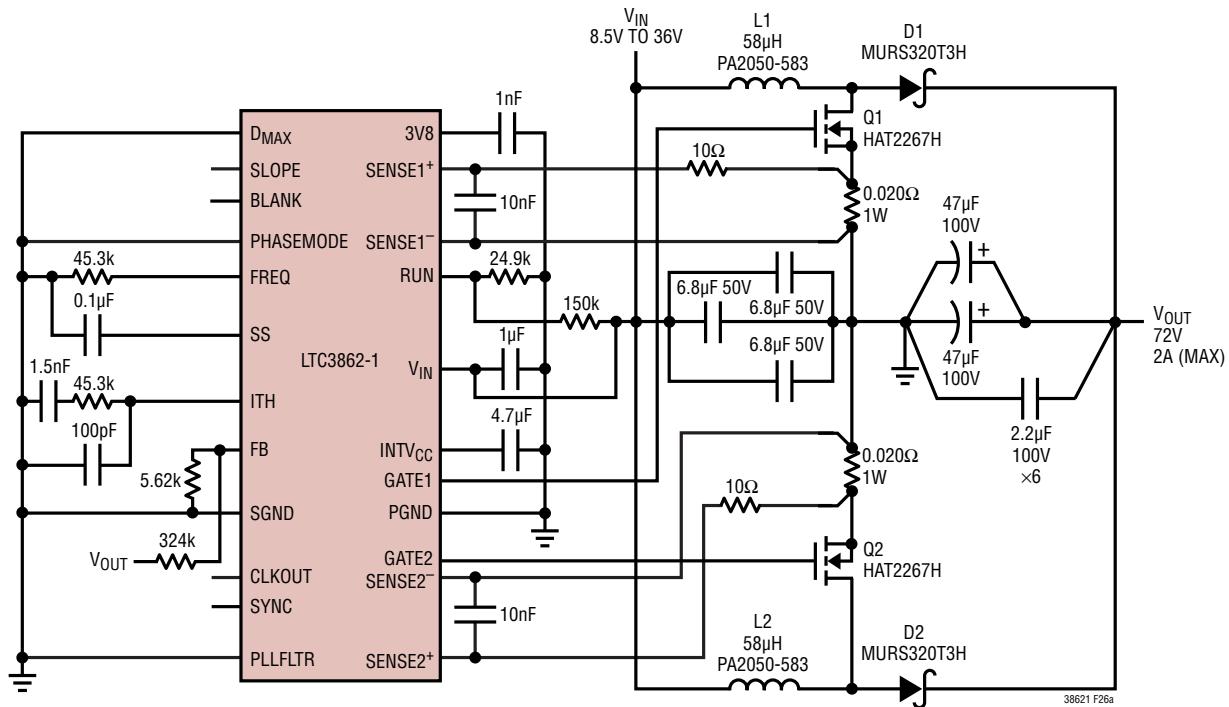

基本的な2フェーズ、シングル出力のLTC3862-1の応用回路を図18に示します。外付け部品の選択は負荷と入力電源の特性に基づいて行います。

### デューティ・サイクルに関する検討事項

連続導通モード(CCM)で動作している昇圧コンバータでは、主スイッチのデューティ・サイクルが次のようにになります。

$$D = \left( \frac{V_0 + V_F - V_{IN}}{V_0 + V_F} \right) = t_{ON} \cdot f$$

ここで、 $V_F$ は昇圧ダイオードの順方向電圧です。CCMで動作している所定のアプリケーションの最小オン時間は次のようにになります。

$$t_{ON(MIN)} = \frac{1}{f} \left( \frac{V_0 + V_F - V_{IN(MAX)}}{V_0 + V_F} \right)$$

与えられた入力電圧範囲と出力電圧では、アプリケーションの最小オン時間が制御デバイスの最小オン時間にどれほど近づくかを知ることが重要です。LTC3862-1の最小オン時間は、BLANKピンを使って210ns～375nsにプログラムすることができます。

### 最小オン時間の制限

シングルエンドの昇圧コンバータでは、2つの定常状態により、コントローラが最小オン時間で動作することがあります。最初の状態は入力電圧が出力電圧に近い場合です。 $V_{IN}$ が $V_{OUT}$ に近づくと、インダクタ両端の電圧がスイッチのオフ時間の間にゼロに近づきます。この動作条件ではコンバータが不安定になり、可聴周波数において高いリップル電圧で出力が発振する恐れがあります。入力電圧が出力電圧に近づくか、出力電圧を超える可能性のあるアプリケーションでは、昇圧コンバータの代わりに、SEPICまたは昇降圧トポロジーの使用を検討してください。

コントローラが最小オン時間で動作する可能性のある2つ目の状態は、深い不連続モードで軽負荷の場合です。負荷電流が減少するにつれ、コントローラの最小オン時間のリミットに達するまで、スイッチのオン時間が低減します。出力電流がさらに減少すると、パルス・スキップ状態になります。これは通常、効率のよい状態で、出力を安定化状態に保つためにサイクルがスキップされます。

図18. 標準的な2フェーズ、シングル出力の昇圧コンバータの応用回路

## アプリケーション情報

### 最大デューティ・サイクルの制限

もう1つの動作上の限界は、入力電圧が低く、出力電圧が高い高デューティ・サイクルで発生します。この場合、次のようになります。

$$D_{MAX} = \left( \frac{V_0 + V_F - V_{IN(MIN)}}{V_0 + V_F} \right)$$

シングルエンドの昇圧コンバータは、入力のインダクタから出力のコンデンサにエネルギーを移せるようにするため、サイクルごとに最小オフ時間を必要とします。この最小オフ時間でコンバータの最大デューティ・サイクルを表すことができます。上記の式を変形して、与えられた最小入力または最大デューティ・サイクルに対する最大出力電圧を得ることができます。

$$V_{O(MAX)} = \frac{V_{IN}}{1-D_{MAX}} - V_F$$

上記の  $D_{MAX}$  の式は、応用回路の最大デューティ・サイクルを決める最初のガイドラインとして使うことができます。ただし、インダクタ、入力と出力のコンデンサ、パワー MOSFET、センス抵抗およびコントローラで生じる損失(ゲート・ドライブ損失)はすべてデューティ・サイクルの増加の要因となります。これらの損失の影響として、与えられた最小入力電圧に対する最大出力電圧が低下します。

応用回路の最初の計算が完了したら、回路が正しく動作することを検証するため、回路のプロトタイプを作製し、入力電圧範囲全体にわたり、軽負荷から最大負荷まで、全温度範囲にわたって測定することが重要です。

### ピーク入力電流と平均入力電流

LTC3862-1の制御回路は入力電流を(パワーMOSFETのソースの抵抗によって)測定するので、パワーMOSFETのサイズを適切なものにするため、出力電流を入力に反映させる必要があります。出力電力は理想的には入力電力に等しいという事実に基づくと、最大平均入力電流は次のようになります。

$$I_{IN(MAX)} = \frac{I_{O(MAX)}}{1-D_{MAX}}$$

各インダクタのピーク電流は次のとおりです。

$$I_{IN(PK)} = \frac{1}{n} \cdot \left( 1 + \frac{\chi}{2} \right) \cdot \frac{I_{O(MAX)}}{1-D_{MAX}}$$

ここで、nは位相数を表し、 $\chi$ はインダクタのピーク・トゥ・ピーク電流のパーセンテージを表します。たとえば、インダクタのリップル電流の設計目標が30%であれば、 $\chi = 0.30$ となり、ピーク電流は平均電流より15%大きくなります。

### インダクタの選択

入力電圧範囲、動作周波数およびリップル電流が与えられたら、次式を使ってインダクタの値を求めることができます。

$$L = \frac{V_{IN(MIN)}}{\Delta I_L \cdot f} \cdot D_{MAX}$$

ここで、

$$\Delta I_L = \frac{\chi}{n} \cdot \frac{I_{O(MAX)}}{1-D_{MAX}}$$

$\Delta I_L$ に大きな値を選ぶと低い値のインダクタを使用できますが、出力電圧リップルが高くなり、コア損失が大きくなり、入力と出力のコンデンサのリップル電流定格が高くなります。妥当な出発点は、30%のインダクタ・リップル電流( $\chi = 0.3$ )です。つまり、次のようになります。

$$\Delta I_L = \frac{0.3}{n} \cdot \frac{I_{O(MAX)}}{1-D_{MAX}}$$

インダクタの飽和電流定格は、過負荷状態の間のワーストケースのピーク・インダクタ電流より高くなければなりません。 $I_{O(MAX)}$ を最大定格負荷電流とすると、通常、最大電流制限値( $I_{O(CL)}$ )は  $I_{O(MAX)}$  よりいくらかの割合で(たとえば30%)大きくなるように選びます。

$$I_{O(CL)} = 1.3 \cdot I_{O(MAX)}$$

## アプリケーション情報

これを(電流が測定されている)入力に反映させ、リップル電流を計算に入れると、次のようにインダクタの最小飽和電流定格が得られます。

$$I_{L(SAT)} \geq \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{1.3 \cdot I_{D(MAX)}}{1 - D_{MAX}}$$

インダクタの飽和電流定格は、最小入力電圧(このときデューティ・サイクルと入力電流が最大になります)、最大出力電流および最大予想コア温度で決めます。市販されているほとんどのインダクタの飽和電流定格は高温で低下します。安全動作を検証するため、1)ワーストケースの動作条件、2)最大許容周囲温度、および、3)最終筐体内に実装される電源を使って、インダクタのコアと巻線の温度特性を評価することを推奨します。熱特性の評価は、熱電対を巻線/コアの構造に密着させ、または熱電対を巻線自体の中に埋め込んで行うことができます。

シングルエンドの昇圧コンバータは短絡に対して保護されておらず、出力が短絡した状態では、出力電流は入力電源の能力によってのみ制限されることに注意してください。短絡保護された昇圧コンバータを必要とするアプリケーションについては、SEPICコンバータまたはフォワード・コンバータのトポロジーを検討してください。

### パワー MOSFET の選択

INTV<sub>CC</sub>の電圧で設定されるピーク・トゥ・ピークのゲート・ドライブ・レベルは、LTC3862-1では通常の動作条件で10Vです。パワー MOSFET の選択基準には、R<sub>DSON</sub>、ゲート電荷 Q<sub>G</sub>、ドレイン-ソース間の降伏電圧 BV<sub>DSS</sub>、最大連続ドレイン電流 I<sub>D(MAX)</sub>、および熱抵抗 R<sub>TH(JA)</sub> と R<sub>TH(JC)</sub> (接合部から周囲と接合部からケースの両方) が含まれます。

LTC3862-1のゲート・ドライバはPMOSのプルアップ素子とNMOSのプルダウン素子で構成されているので、パワー MOSFET のスイッチング時に INTV<sub>CC</sub> の全電圧をゲートに与えることができます。とはいえ、最小ゲート・ドライブ電圧でもパワー MOSFET を完全に導通させるのに十分であることを確認する必要があります。MOSFET のデータシートを注意して調べ、MOSFET の R<sub>DSON</sub> が 10V の公称 INTV<sub>CC</sub> 電圧以下で規定されていることを確認します。アプリケーションが 5V 定格のパワー MOSFET を必要とする場合は、LTC3862 のデータシートを参照してください。

アプリケーションの実際の最大スイッチ電圧と比較して、MOSFET の BV<sub>DSS</sub> 仕様にも十分注意を払ってください。シングル・プローブと高帯域オシロスコープを使い、MOSFET のスイッチング波形をドレイン端子で直接チェックします。ドレイン電圧のリングが MOSFET の BV<sub>DSS</sub> に近づかないようにします。高周波数での過度のリングは、通常、MOSFET、昇圧ダイオード、出力コンデンサ、センス抵抗、およびこれらの部品を接続している PCB トレースを含む、高 di/dt 電流経路内の直列インダクタンスが大きすぎることを示しています。

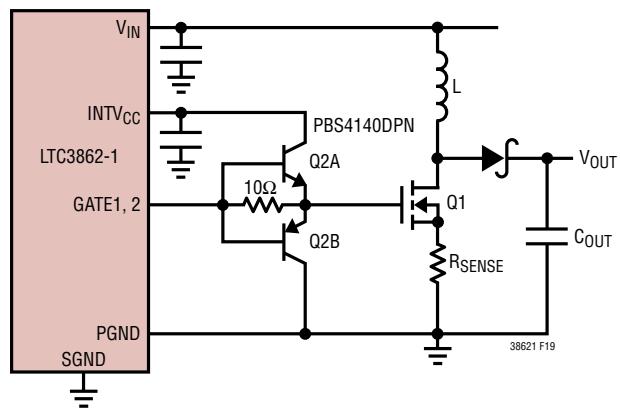

寄生リード・インダクタンスや不適切な PCB レイアウトにより、MOSFET Q1 のターンオン、ターンオフ時にこの MOSFET のゲートでトランジエント電圧スパイクが発生することがあります。このような電圧スパイクは LTC3862-1 の GATE ピンの絶対最大電圧定格を超える可能性があります。GATE ピンの電圧の絶対最大定格は、最小 -0.3V、最大 11V です。このため、図 19 に示すように、MOSFET のゲートの近くに外付けバッファを追加することを推奨します。

図 19. 外付けバッファ回路

最後に、アバランシェ・エネルギー定格(EAS)について、MOSFET メーカーのデータシートをチェックします。MOSFET によってはボディ・ダイオードのアバランシェ定格が定められていないものがあり、V<sub>DS</sub> がデバイスの BV<sub>DSS</sub> を超えると(たとえわずか数分の 1 ボルトであっても)、致命的な不具合を生じることがあります。アバランシェ定格が定められている MOSFET は、ターンオフ過渡時のデバイスの BV<sub>DSS</sub> に近いドレイン-ソース間の高周波数リングに対する耐性がより優れています。

## アプリケーション情報

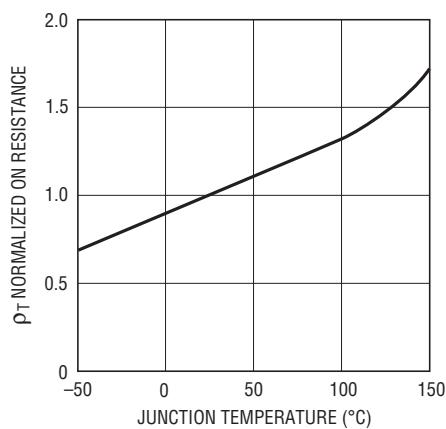

### パワー MOSFET のスイッチング損失と導通損失および接合部温度の計算

パワー MOSFET の接合部温度を計算するには、デバイスによって消費される電力を知る必要があります。この電力損失は、デューティ・サイクル、負荷電流、および( $R_{DS(ON)}$ )の正の温度係数による)接合部温度に応じて変動します。そのため、十分正確な値を決めるには何回かの反復計算が通常必要です。

n フェーズのマルチフェーズ昇圧コンバータ内の MOSFET による電力損失は次のとおりです。

$$P_{FET} = \left( \frac{I_{O(MAX)}}{n \cdot (1 - D_{MAX})} \right)^2 \cdot R_{DS(ON)} \cdot D_{MAX} \cdot \rho_T + k \cdot V_{OUT}^2 \cdot \frac{I_{O(MAX)}}{n \cdot (1 - D_{MAX})} \cdot C_{RSS} \cdot f$$

上式の最初の項はデバイスの  $I^2R$  損失を表し、2番目の項はスイッチング損失を表します。定数  $k = 1.7$  はゲート・ドライブ電流に反比例する経験的に得られる係数で、「1/電流」の次元をもっています。

$\rho_T$  の項は MOSFET の  $R_{DS(ON)}$  の温度係数を表しており、標準で  $0.4\%/^\circ\text{C}$  です。標準的なパワー MOSFET の温度に対する正規化された  $R_{DS(ON)}$  の変化を図 20 に示します。

図20. 正規化されたパワー MOSFET の  $R_{DS(ON)}$  と温度

パワー MOSFET 内で消費される既知の電力から、次式を使って接合部温度を求めることができます。

$$T_J = T_A + P_{FET} \cdot R_{TH(JA)}$$

この式で使われている  $R_{TH(JA)}$  にはデバイスの  $R_{TH(JC)}$  およびケースから周囲温度までの熱抵抗  $R_{TH(CA)}$  が通常含まれます。次に、 $T_J$  のこの値を反復計算に使用された元の仮定値と比べることができます。

導通損失を減らすため、 $R_{DS(ON)}$  が非常に低いパワー MOSFET を選びたくなります。ただし、そうすると、ゲート電荷  $Q_G$  が通常非常に高くなり、スイッチング損失とゲート・ドライブ損失が増加します。スイッチング損失は出力電圧の 2乗に比例して増加するので、出力電圧が低いアプリケーションでは一般に MOSFET の導通損失の方が大きくなり、出力電圧が高いアプリケーションでは一般に MOSFET のスイッチング損失の方が大きくなります。高い出力電圧では、一般に  $R_{DS(ON)}$  が高く  $Q_G$  が低い MOSFET を使うことによって最高効率が得られます。上の式は 2つの部分(導通およびスイッチング)に簡単に分けることができ、異なった MOSFET の性能を比較するため、スプレッドシートに入力することができます。

### 電流制限のプログラミング

LTC3862-1 のピーク検出電圧しきい値は、低デューティ・サイクルおよび 1.00 の正規化されたスロープ利得では  $75\text{mV}$  であり、SENSE<sup>+</sup> から SENSE<sup>-</sup> まで測定されます。デューティ・サイクルとスロープ利得の変化に伴うセンスしきい値の変化を図 21 に示します。

図21. デューティ・サイクルとスロープ利得による最大検出電圧の変化

## アプリケーション情報

電流制限値が最大負荷電流より30%高くなるように選択された昇圧コンバータでは、MOSFETとセンス抵抗のピーク電流は次のようにになります。

$$I_{SW(MAX)} = I_{R(SENSE)} = \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{1.3 \cdot I_{O(MAX)}}{1 - D_{MAX}}$$

次いで、センス抵抗値は次のようにになります。

$$R_{SENSE} = \frac{V_{SENSE(MAX)} \cdot n \cdot (1 - D_{MAX})}{1.3 \cdot \left(1 + \frac{\chi}{2}\right) \cdot I_{O(MAX)}}$$

ここでも、係数nは使用される位相数、 $\chi$ はインダクタのリップル電流のパーセンテージを表します。数字1.3は電流制限が最大負荷電流( $I_{O(MAX)}$ )を超える係数を表します。たとえば、電流制限が最大負荷電流を50%超える必要があれば、1.3の係数を1.5で置き換えます。

センス抵抗の平均電力損失は次のように簡単に計算することができます。

$$P_{R(SENSE)} = \left( \frac{1.3 \cdot I_{O(MAX)}}{n \cdot (1 - D_{MAX})} \right)^2 \cdot R_{SENSE} \cdot D_{MAX}$$

この式では、センス抵抗の温度係数が想定されていません。選択された抵抗の温度係数が大きければ、ワーストケースの高抵抗値を式に代入します。

抵抗の温度は次式を使って計算することができます。

$$T_D = T_A + P_{R(SENSE)} \cdot R_{TH(JA)}$$

## 出力ダイオードの選択

効率を最大にするには、順方向の電圧降下が小さく、逆方向の漏れ電流が小さい高速スイッチング・ダイオードが必要です。昇圧コンバータの出力ダイオードはスイッチのオフ時間に電流を流します。ダイオードが耐えなければならないピーク逆電圧は、レギュレータの出力電圧に等しくなります。通常動作の平均順方向電流は出力電流に等しく、ピーク電流はピーク・インダクタ電流に等しくなります。

$$I_{D(Peak)} = \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

平均ダイオード電流は出力電流に等しいとはいえ、デューティ・サイクルが非常に高い( $V_{IN}$ が低く $V_{OUT}$ が高い)アプリケーションでは、図22に示されているように、ピーク・ダイオード電流が平均の数倍になることがあります。この場合、ダイオード・メーカーのデータシートをチェックして、そのピーク電流定格が上の式のピーク電流を超えていることを確認します。さらに、ダイオードの電力損失を計算するときは、平均出力電流ではなく、ピーク電流で測定された順方向電圧( $V_F$ )の値を使います。過剰な電力がダイオードの直列抵抗で消費されますが、式の中で平均出力電流と順方向電圧が使われたら、

図22. デューティ・サイクルの高いアプリケーションのダイオード電流波形

## アプリケーション情報

この過剰な電力は計算に入れられないでしょう。最後に、この追加の電力損失は、ダイオードの電流定格、パッケージの種類、およびヒートシンクの方法を決定するのに重要です。

ダイオードの電力損失は次のように近似されます。

$$P_D = I_{D(Peak)} \cdot V_{F(Peak)} \cdot (1 - D_{MAX})$$

ダイオードの接合部温度は次のとおりです。

$$T_J = T_A + P_D \cdot R_{TH(JA)}$$

この式で使われる  $R_{TH(JA)}$  にはデバイスの  $R_{TH(JC)}$  および基板から筐体内の周囲温度までの熱抵抗が通常含まれます。適切なダイオードが選択され、回路性能が検証されたら、サーマルプローブまたは赤外線カメラを使って、すべての動作条件にわたってパワー部品の温度を測定し、熱設計に問題がないことを確認します。

最後に、過度なリングングや電力損失の増加を防ぐため、ダイオードのリード長を短くし、スイッチ・ノードの適切なレイアウトを守ってください(「基板レイアウトのチェックリスト」を参照)。

## 出力コンデンサの選択

昇圧コンバータ・アプリケーション向けに出力コンデンサの正しい組み合わせを選択するときは、ESR(等価直列抵抗)、ESL

(等価直列インダクタンス)およびバルク容量が与える影響を考慮する必要があります。標準的な昇圧コンバータにおいて、これらの3つのパラメータが出力電圧リップル波形に与える影響を図23に示します。

部品の選択は、(出力電圧のパーセンテージで表示された)最大許容リップル電圧と、このリップルをESRのステップと充放電  $\Delta V$  の間でどのように分割すべきかの検討から始めます。説明を簡単にするため、最大出力リップルとして2%を選択し、ESRのステップと充放電  $\Delta V$  の間で等分します。この百分率リップルはアプリケーションの要件に応じて変化しますが、以下の式は簡単に修正できます。

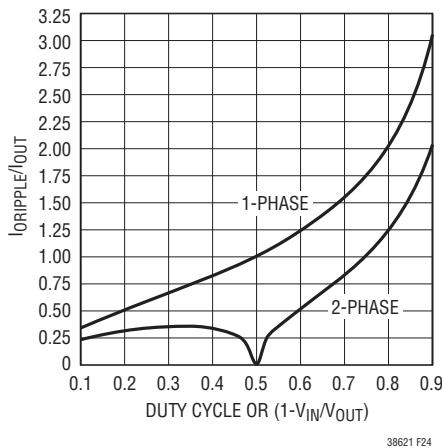

マルチフェーズ動作の主要な利点の1つは、昇圧ダイオードによって出力コンデンサに供給されるピーク電流の減少です。その結果、コンデンサのESRの要件が緩和されます。全リップル電圧に対する割合が1%の場合、出力コンデンサのESRは次式を使って求めることができます。

$$ESR_{COUT} \leq \frac{0.01 \cdot V_{OUT}}{I_{D(Peak)}}$$

ここで、

$$I_{D(Peak)} = \frac{1}{n} \cdot \left( 1 + \frac{\chi}{2} \right) \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

図23. 昇圧コンバータのスイッチング波形

## アプリケーション情報

係数nは位相数を表し、係数 $\chi$ はインダクタのリップル電流のパーセンテージを表します。

バルク容量の場合、全出力リップルに対して1%と想定すると、必要最小容量はおよそ次のようにになります。

$$C_{OUT} \geq \frac{I_{O(MAX)}}{0.01 \cdot n \cdot V_{OUT} \cdot f}$$

多くの設計で、必要なESRを得るために使用するコンデンサと、バルク容量を満たすために使用するコンデンサの種類が異なります。たとえば、低ESRのセラミック・コンデンサを使うとESRのステップを最小に抑えることができますが、一方で、電解コンデンサを使って必要なバルク容量を得ることができます。

出力コンデンサの電圧定格は、コンデンサの最大温度を計算に入れた十分なディレーティングを行ったうえで、最大出力電圧より大きくなればなりません。

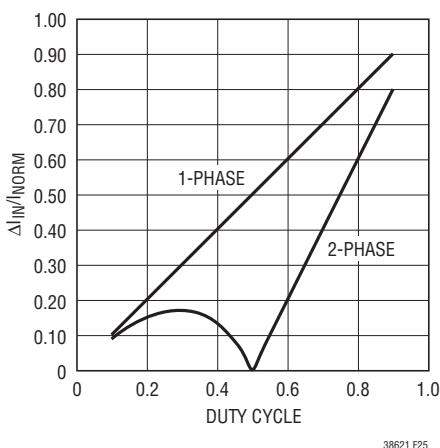

出力コンデンサのリップル電流は方形波なので、このコンデンサのリップル電流の要件は、デューティ・サイクル、位相数および最大出力電流に依存します。デューティ・サイクルと正規化された出力コンデンサ・リップル電流の相関関係を図24に示します。出力コンデンサのリップル電流定格を選択するには、最初に、出力電圧と入力電圧の範囲に基づいてデューティ・サイクルの範囲を定めます。図24を参照して、最大負荷電流の

パーセンテージとして、正規化されたワーストケースの高リップル電流を選択します。

出力リップル電流は、出力電圧のところに並列に接続された様々なコンデンサの間で分割されます。セラミック・コンデンサ(特にX5RとX7R)は一般にESRが低いことで知られていますが、これらのコンデンサは電圧係数が比較的高いという弱点があります。したがって、リップル電流全体がセラミック・コンデンサを流れると想定するのは安全ではありません。アルミ電解コンデンサはバルク容量が大きいので一般に選択されますが、ESRは比較的高くなります。その結果、いくらかのリップル電流がこのコンデンサを流れます。コンデンサに流れ込むリップル電流がそのRMS定格を超えるとコンデンサは発熱し、実効容量が減少し、その信頼性に悪影響を与えます。与えられた式を使って出力コンデンサの構成が決まつたら、十分な熱性能を検証するために個々のコンデンサのケース温度を測定します。

### 入力コンデンサの選択

昇圧コンバータの入力コンデンサの電圧定格は、最大入力電圧をゆとりを持って超えるようにします。セラミック・コンデンサは過電圧状態を比較的耐えることができますが、アルミ電解コンデンサはそうではありません。入力コンデンサに過度のストレスを与える可能性のある過電圧過渡に関して、入力電圧の特性を必ず評価してください。

図24. 昇圧コンバータの出力コンデンサの正規化されたリップル電流(RMS)

## アプリケーション情報

入力コンデンサの値はソース・インピーダンスに応じて変動し、一般に、ソース・インピーダンスが高いほど、必要な入力容量が大きくなります。必要な入力容量の大きさはデューティ・サイクルによっても大きく影響されます。高いデューティサイクルで動作する高出力電流アプリケーションは、DC電流とリップル電流の両方で、入力電源に大きな負担を負わせることがあります。

マルチフェーズ昇圧コンバータの入力リップル電流は連続しており、複数のインダクタの間で分割されるので、(出力リップル電流に比べて)比較的少なくなります。それでも、特にデューティ・サイクルの高いアプリケーションでは、入力コンデンサに大きなストレスが加わることがあります。正規化された入力リップル電流を図25に示します。ここで、

$$I_{INORM} = \frac{V_{IN}}{L \cdot f}$$

図25. 正規化された入力ピーク・トゥ・ピーク・リップル電流

## 設計例

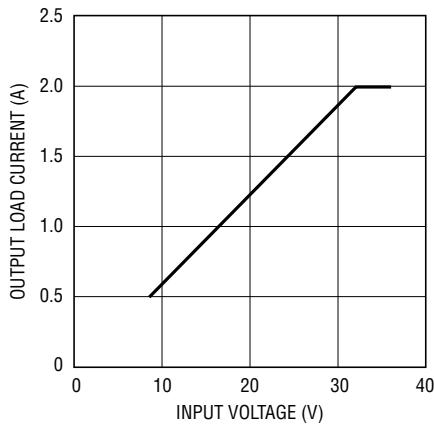

図26aに示されているLTC3862-1の応用回路について検討します。出力電圧は72V、入力電圧範囲は8.5V～36Vです。入力電圧が24Vのとき最大出力電流は1.5A、入力電圧が32Vのとき最大出力電流は2Aです。32Vより低い場合、電流制限により最大負荷が直線的に減少し、8.5Vの入力電圧で0.5Aになります(図26bを参照)。

- (出力で1.5Aが得られる) デューティ・サイクルの範囲は次のとおりです。

$$D_{MAX} = \left( \frac{V_0 + V_F - V_{IN}}{V_0 + V_F} \right) = \left( \frac{72V + 0.5V - 24V}{72V + 0.5V} \right) = 66.9\%$$

$$D_{MIN} = \left( \frac{72V + 0.5V - 36V}{72V + 0.5V} \right) = 50.3\%$$

- 動作周波数は300kHzになるように選択されているので、その周期は3.33μsです。図6から、FREQピンからグランドに接続されている抵抗は45.3kです。

- CCMで動作しているこのアプリケーションの最小オン時間は次のとおりです。

$$t_{ON(MIN)} = \frac{1}{f} \cdot \left( \frac{V_0 + V_F - V_{IN(MAX)}}{V_0 + V_F} \right) = \frac{1}{300\text{kHz}} \cdot \left( \frac{72V + 0.5V - 36V}{72V + 0.5V} \right) = 1.678\mu\text{s}$$

最大DC入力電流は次のとおりです。

$$I_{IN(MAX)} = \frac{I_{O(MAX)}}{1 - D_{MAX}} = \frac{1.5\text{A}}{1 - 0.669} = 4.5\text{A}$$

# LTC3862-1

## アプリケーション情報

図26a. 8.5V～36V入力、72V/2A出力の2フェーズ昇圧コンバータの応用回路

図26b. 出力電流と入力電圧

4. 40%のリップル電流が選択されているので、各インダクタのピーク電流は次のようにになります。

$$I_{IN(PK)} = \frac{1}{n} \cdot \left(1 - \frac{\chi}{2}\right) \cdot \frac{I_0(MAX)}{1 - D_{MAX}} \\ = \frac{1}{2} \cdot \left(1 + \frac{0.4}{2}\right) \cdot \frac{1.5A}{1 - 0.669} = 2.7A$$

5. インダクタのリップル電流は次のとおりです。

$$\Delta I_L = \frac{\chi}{n} \cdot \frac{I_0(MAX)}{1 - D_{MAX}} = \frac{0.4}{2} \cdot \frac{1.5A}{1 - 0.669} = 0.9A$$

6. したがって、インダクタの値は次のようになります。

$$L = \frac{V_{IN(MIN)}}{\Delta I_L \cdot f} \cdot D_{MAX} = \frac{24V}{0.9A \cdot 300kHz} \cdot 0.669 \\ = 59.5\mu H$$

7. 最大負荷電流より30%高い電流制限の場合、次のようになります。

$$I_{O(CL)} = 1.3 \cdot I_0(MAX) = 1.3 \cdot 1.5A = 1.95A$$

したがって、インダクタの飽和電流定格は次の値を超える必要があります。

$$I_{L(SAT)} \geq \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{1.3 \cdot I_0(MAX)}{1 - D_{MAX}} \\ = \frac{1}{2} \cdot \left(1 + \frac{0.4}{2}\right) \cdot \frac{1.3 \cdot 1.5A}{1 - 0.669} = 3.5A$$

## アプリケーション情報

選択されたインダクタの値は57.8 $\mu$ H、製品番号はPA2050-583、メーカーはPulse Engineeringです。このインダクタの飽和電流定格は5Aです。

8. このアプリケーション用に選択されたパワーMOSFETはRenesasのHAT2267Hです。このMOSFETの標準 $R_{DS(ON)}$ は、 $V_{GS} = 10V$ では13m $\Omega$ です。 $BVDSS$ は最小80Vで定格が規定されており、最大連続ドレイン電流は25Aです。標準ゲート電荷は $V_{GS} = 10V$ で30nCです。最後に重要なこととして、このMOSFETの絶対最大アバランシェ・エネルギー定格EASは30mJであり、致命的な故障なしにアバランシェを起こすことができる事を示しています。

9. デバイス全体の静止電流、デバイスの電力損失および最大接合部温度はおよそ以下のとおりです。

$$\begin{aligned} I_{Q(TOT)} &= I_Q + 2 \cdot Q_{G(TOT)} \cdot f \\ &= 3mA + 2 \cdot 30nC \cdot 300kHz = 21mA \end{aligned}$$

$$P_{DISS} = 24V \cdot 21mA = 504mW$$

$$T_J = 70^\circ C + 504mW \cdot 34^\circ C/W = 87.1^\circ C$$

10. インダクタのリップル電流は40%になるように選択され、最大負荷電流は1.5Aです。最大負荷電流より30%上に設定された電流制限の場合、最大スイッチ電流とセンス抵抗の電流は次のとおりです。

$$\begin{aligned} I_{SW(MAX)} &= I_{R(SENSE)} = \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{1.3 \cdot I_{O(MAX)}}{1 - D_{MAX}} \\ &= \frac{1}{2} \cdot \left(1 + \frac{0.4}{2}\right) \cdot \frac{1.3 \cdot 1.5A}{1 - 0.669} = 3.5A \end{aligned}$$

11. LTC3862-1の最大電流センスしきい値は、デューティ・サイクルが低く、正規化されたスロープ利得が1.0のとき、75mVです。図21を利用すると、デューティ・サイクルが70%で正規化されたスロープ利得が1のとき、最大検出電圧は68mVに低下するので、センス抵抗は次のように計算されます。

$$R_{SENSE} = \frac{V_{SENSE(MAX)}}{I_{SW(MAX)}} = \frac{68mV}{3.5A} = 19.4m\Omega$$

このアプリケーションでは、各フェーズに20m $\Omega$ 、1Wの表面実装抵抗が使われています。

12. 電流制限でのセンス抵抗の電力損失は次のとおりです。

$$\begin{aligned} P_{R(SENSE)} &= \left( \frac{1.3 \cdot I_{O(MAX)}}{n \cdot (1 - D_{MAX})} \right)^2 \cdot R_{SENSE} \cdot D_{MAX} \\ &= \left( \frac{1.3 \cdot 1.5}{2 \cdot (1 - 0.669)} \right)^2 \cdot 0.020 \cdot 0.669 \\ &= 0.12W \end{aligned}$$

13. 昇圧ダイオードの平均電流は出力電流の1/2 ( $1.5A/2 = 0.75A$ )ですが、各ダイオードのピーク電流は次のようにになります。

$$\begin{aligned} I_{D(Peak)} &= \frac{1}{n} \cdot \left(1 + \frac{\chi}{2}\right) \cdot \frac{I_{O(MAX)}}{1 - D_{MAX}} \\ &= \frac{1}{2} \cdot \left(1 + \frac{0.4}{2}\right) \cdot \frac{1.5A}{1 - 0.669} = 2.7A \end{aligned}$$

このアプリケーション用に選択されたダイオードはON SemiconductorのMURS320T3Hです。この表面実装ダイオードの最大平均順方向電流は140°Cで3A、最大逆電圧は200Vです。最大順方向電圧降下は25°Cで0.875V、150°Cで0.71Vです(直列抵抗の正の温度係数はダイオードの順方向電圧の負の温度係数によって補償されます)。

ダイオードの電力損失はおよそ次のとおりです。

$$\begin{aligned} P_D &= I_{D(Peak)} \cdot V_{F(Peak)} \cdot (1 - D_{MAX}) \\ &= 2.7A \cdot 0.71V \cdot (1 - 0.669) = 0.64W \end{aligned}$$

14. このアプリケーションの2種類の出力コンデンサ(低ESRセラミック・コンデンサとバルク蓄電のためのアルミ電解コンデンサ)は並列に接続されています。ESRの全リップル電圧に対して1%の場合、合成された出力容量の最大ESRはおよそ次のようになります。

$$ESR_{COUT} \leq \frac{0.01 \cdot V_{OUT}}{I_{D(Peak)}} = \frac{0.01 \cdot 72V}{2.7A} = 0.267\Omega$$

## アプリケーション情報

バルク容量の場合、全出力リップルに対して1%と想定すると、必要最小容量はおよそ次のようにになります。

$$C_{\text{OUT}} \geq \frac{I_{\text{O}(\text{MAX})}}{0.01 \cdot n \cdot V_{\text{OUT}} \cdot f} = \frac{1.5\text{A}}{0.01 \cdot 2 \cdot 72\text{V} \cdot 300\text{kHz}} \\ = 3.45\mu\text{F}$$

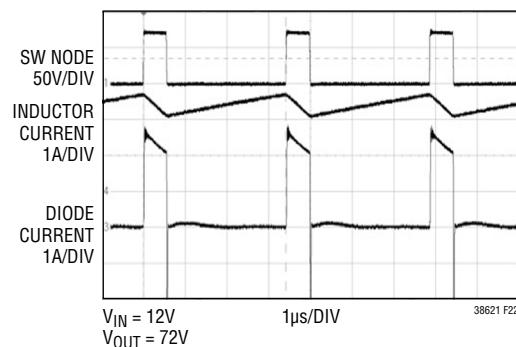

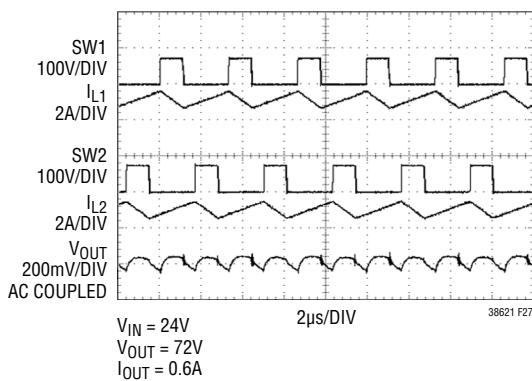

このアプリケーションでは、低ESRと適切なリップル電流定格の両方を得るために(図24を参照)、2個の47μF、100Vのアルミニウム電解コンデンサが、6個の2.2μF、100Vのセラミック・コンデンサと並列に接続されています。この応用回路のスイッチング波形を図27に示します。

図27. 72V出力の昇圧コンバータにおける

LTC3862-1のスイッチング波形

## PC基板レイアウトのチェックリスト

プリント回路基板をレイアウトするときは、以下のチェックリストを使用してコンバータが適切に動作するようにします。

1. 低電力アプリケーションでは、2層PC基板で十分です。ただし、電力レベルが高い場合は多層PC基板を推奨します。回路の下に切れ目のないグランド・プレーンを使用し、部品を適切に配置するのが、スイッチング・ノイズが動作に影響を与えないようにする最も簡単な方法です。

2. MOSFETとダイオードからの電力を放散させるのを助けるため、パワー部品に最も近い層にグランド・プレーンを配置します。MOSFETとダイオードからPC基板への熱拡散を最大化するため、これらの部品にはパワー・プレーンを使用します。

3. すべてのパワー部品を狭い領域に配置します。これにより、高電流ループの大きさが最小になります。センス抵抗、パワーMOSFET、昇圧ダイオードおよび出力コンデンサで形成されるdi/dtが高いループは、EMIを防ぐためにできるだけ小さくします。

4. 入力コンデンサ、出力コンデンサ、および電流センス抵抗を、グランド・プレーンに接続されるパッド間の距離が最小になるように配置します。INTVCC、3V8およびVINのコンデンサはできるだけLTC3862-1の近くに置きます。

5. INTVCCのデカップリング・コンデンサは、デバイスと同じ層で、INTVCCピンとPGNDピンのできるだけ近くに配置します。低ESRの4.7μF～10μFの(X5R以上の品質の)セラミック・コンデンサを使います。

6. グランドに接続されるすべてのパッドにグランド・プレーンへのローカル・ビアを使います。パワー部品にはビアを複数使います。

7. 小信号部品は基板上の高周波数のスイッチング・ノードから離して配置します。LTC3862-1のピン配置は、部品配置を簡単にするため、注意深く設計されています。すべてのパワー部品をすべての小信号部品から離して、デバイスの一方の側に配置することができます。

8. QFNパッケージの底面の露出領域は内部でPGNDに接続されていますが、高電流の主経路としては使用しないでください。

9. MOSFETは基板のセンス抵抗と同じ層に配置します。MOSFETのソースは短く幅の広いPCBトレースを使ってセンス抵抗に接続します。

## アプリケーション情報

10. 出力の抵抗分割器はデバイスにできるだけ近づけて配置し、下側の抵抗をFBとSGNDの間に接続します。上側の抵抗を出力コンデンサの上側の端子に接続するPCBトレースは、どの高周波数スイッチング・ノードも避けて配線します。

11. インダクタはピーク電流モード制御トポロジーでは電流源のように動作するので、その基板上の配置はdi/dtの高い部品ほど問題にはなりません。

12. SENSE<sup>+</sup>とSENSE<sup>-</sup>のPCBトレースは、間隔を最小に保ちながら互いに並行にセンス抵抗まで配線します。これらのトレースはレイアウトで高周波数スイッチング・ノードを避けます。これらのPCBトレースは、PCBの寄生抵抗のIR電圧降下による検出誤差を防ぐため、センス抵抗のパッドの内部にケルビン接続します。

13. センス抵抗とSENSE<sup>+</sup>ピンおよびSENSE<sup>-</sup>ピンの間に外付けRCフィルタが使われる場合、これらのフィルタ部品はデバイスのSENSE<sup>+</sup>ピンおよびSENSE<sup>-</sup>ピンにできるだけ近づけて配置します。SENSE<sup>-</sup>ラインは、電流センス抵抗が接地されているポイントでのみ接地されるようにします。

14. MOSFETのドレイン・ノード(SW1、SW2)を、敏感な小信号ノード、特に反対チャネルの電流検出信号から遠ざけてください。スイッチ・ノードは、スルーレートがグランドを基準にして1V/nsを超えることがあるので、LTC3862-1の「出力側」に保ちます。

15. デバイスの端子間でドレイン-ソース間電圧を直接個別に測定することにより、パワーMOSFETへのストレスをチェックします。誘導性リンクに注意してください。これはMOSFETの最大電圧定格を超えることがあります。このリンクを避けることができず、デバイスの最大定格を超えているなら、電圧定格がもっと高いMOSFETを選択するか、スナバの使用を検討します。

16. LTC3862-1を外部クロックに同期させるときは、ロジック・ゲートのような低インピーダンスのソースを使ってSYNCピンをドライブし、リードができるだけ短くします。

# LTC3862-1

## 標準的応用例

24V入力、48V/6A出力の2フェーズ昇圧コンバータの応用回路

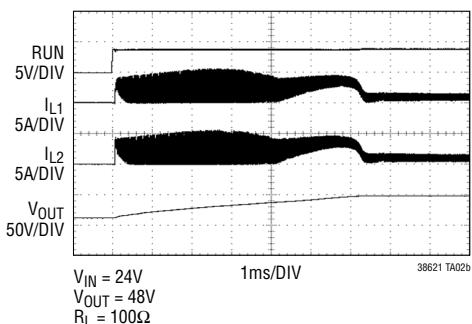

起動

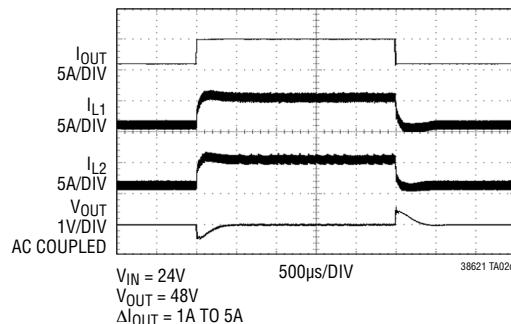

負荷ステップ

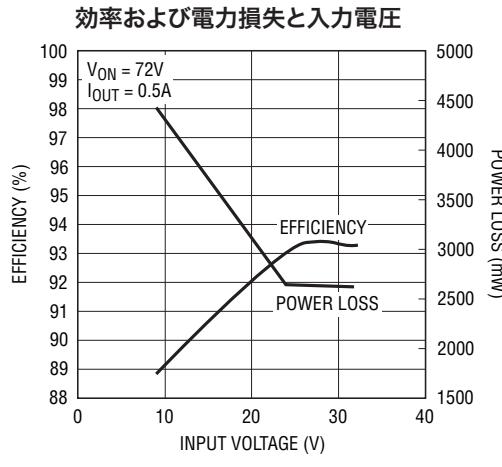

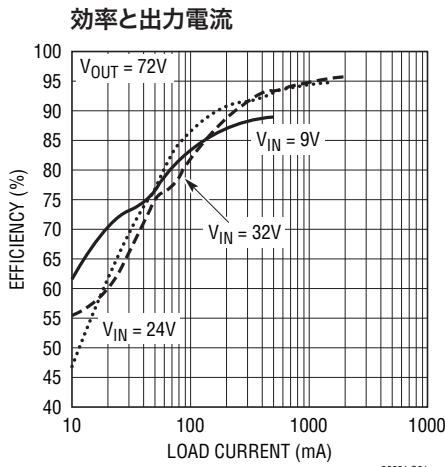

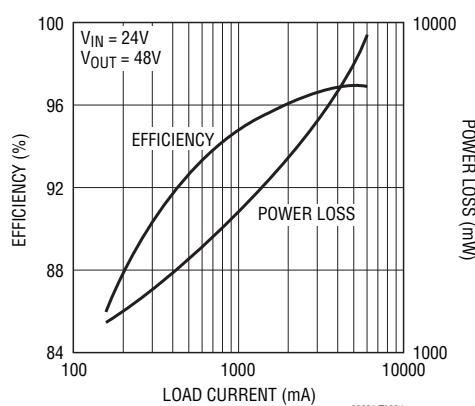

効率

38621fa

## 標準的応用例

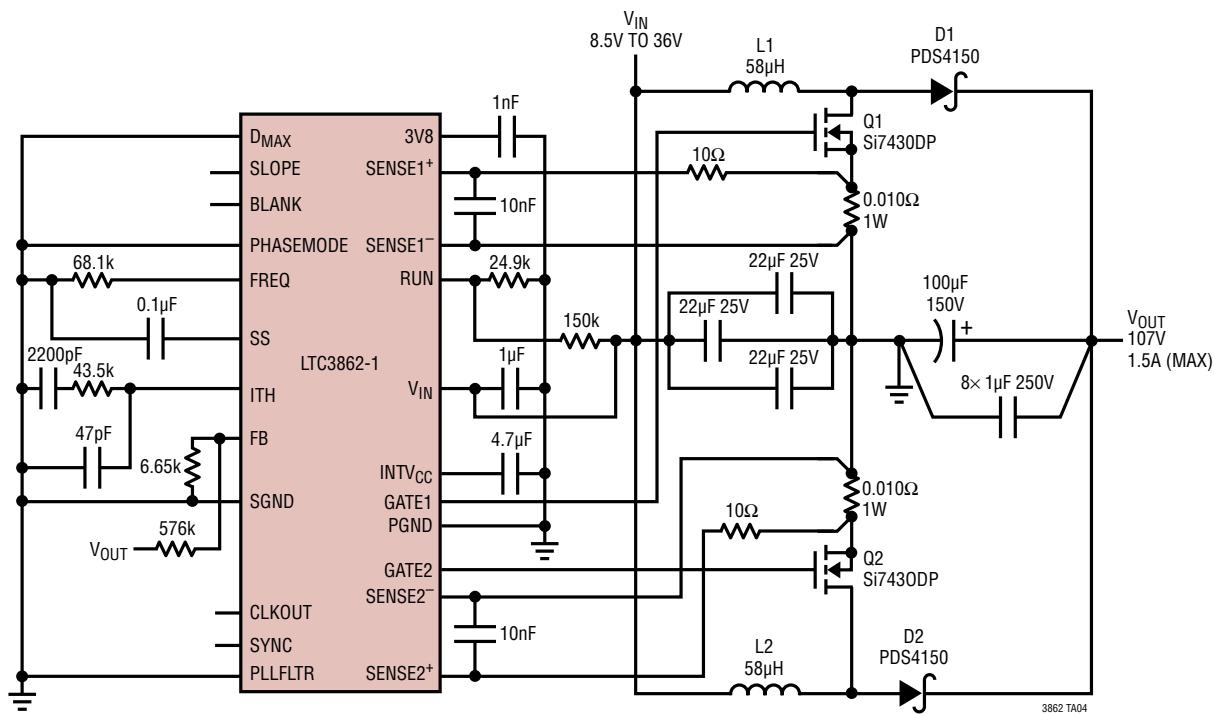

24V入力、107V/1.5A出力の2フェーズ昇圧コンバータの応用回路

L1, L2: CHAMPS TECHNOLOGIES HRPQA2050-57

PULSE ENGINEERING PA2050-583

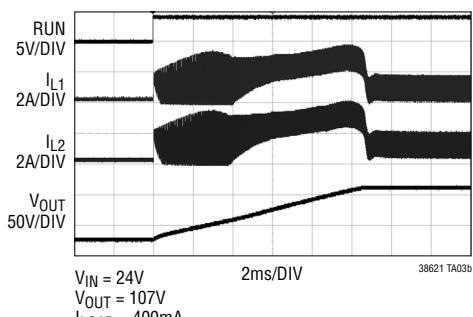

## 起動

V<sub>IN</sub> = 24V

V<sub>OUT</sub> = 107V

I<sub>LOAD</sub> = 400mA

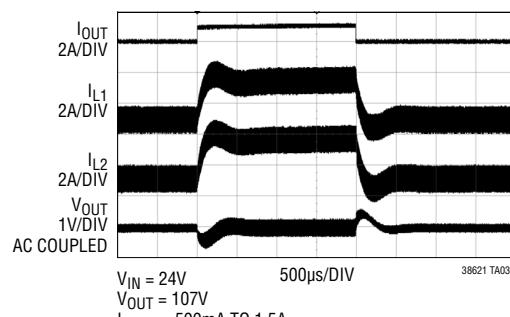

## 負荷ステップ

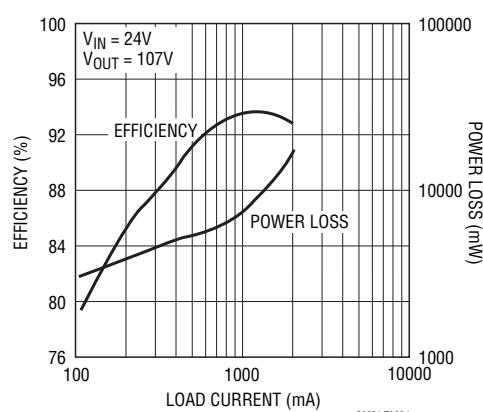

## 効率

38621fa

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

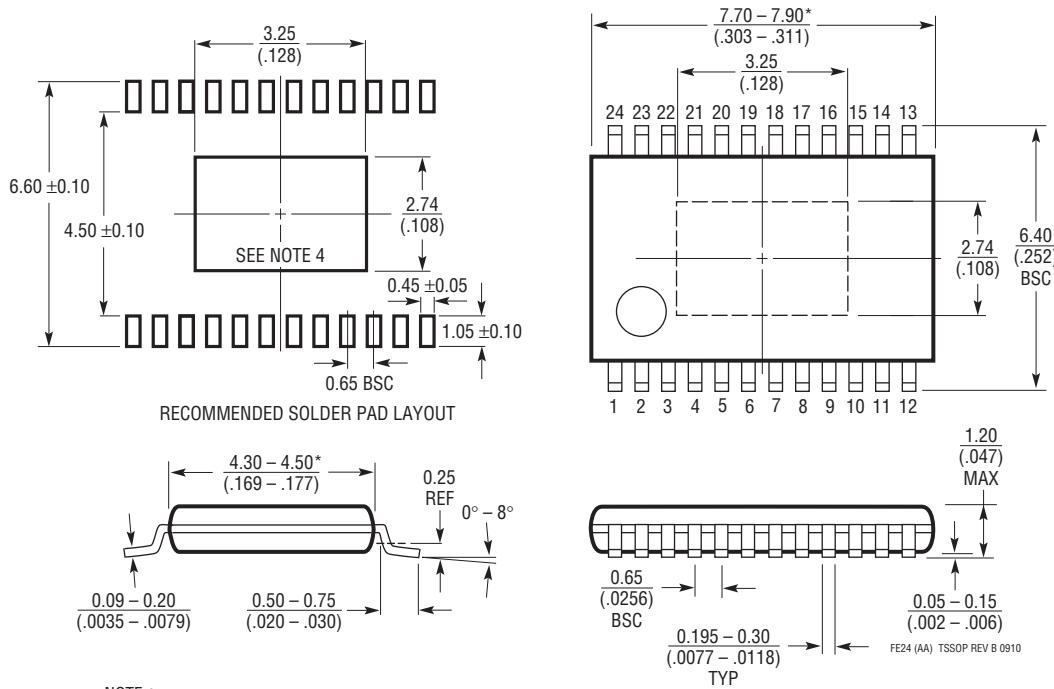

**FE Package

24-Lead Plastic TSSOP (4.4mm)**

(Reference LTC DWG # 05-08-1771 Rev B)

**Exposed Pad Variation AA**

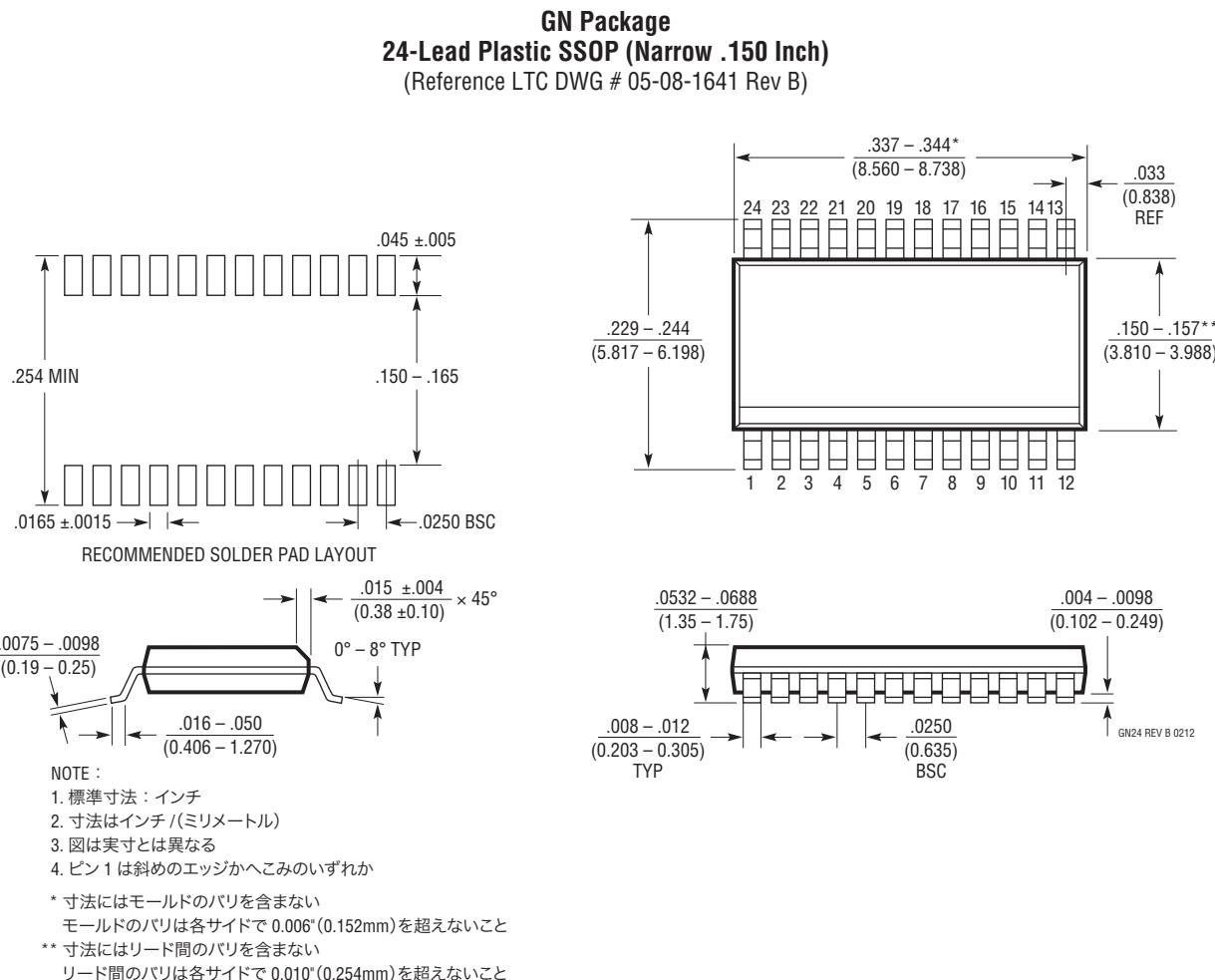

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

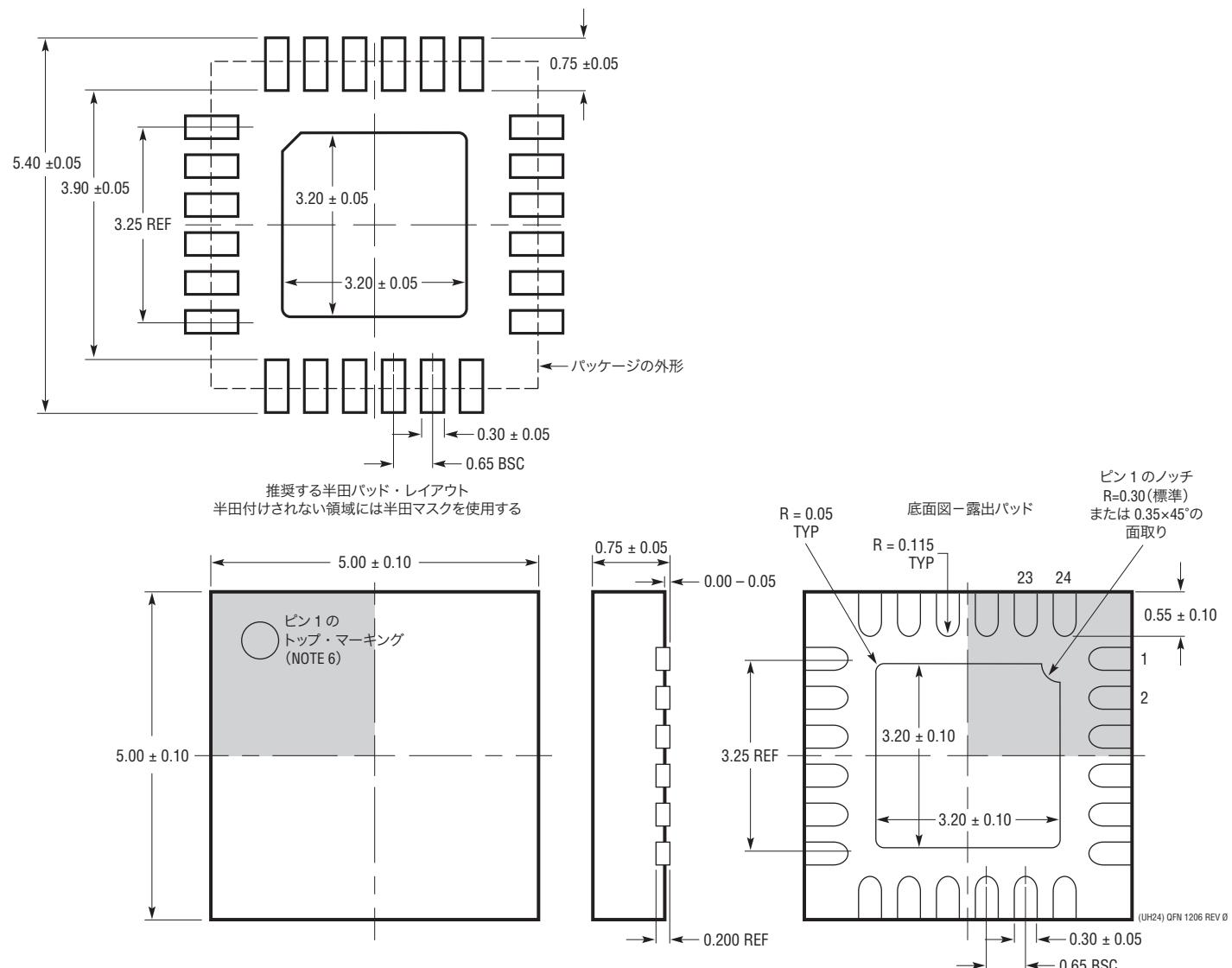

**UH Package

24-Lead Plastic QFN (5mm × 5mm)**

(Reference LTC DWG # 05-08-1747 Rev A)

NOTE :

1. 図は JEDEC のパッケージ外形ではない

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで 0.20mm を超えないこと

5. 露出パッドは半田メッキとする

6. 网掛けの部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

## 改訂履歴

| REV | 日付    | 概要                                           | ページ番号                |

|-----|-------|----------------------------------------------|----------------------|

| A   | 12/13 | 比較表を追加。<br>Note 9を追加。<br>ピン番号を追加。<br>回路図を追加。 | 1<br>4<br>9、10<br>40 |

# LTC3862-1

## 標準的応用例

入力が24V、出力が107V/5Aの2フェーズ昇圧コンバータの応用回路

L1, L2: CHAMPS TECHNOLOGIES HRPQA2050-57

PULSE ENGINEERING PA2050-583

## 関連製品

| 製品番号                  | 説明                                    | 注釈                                                                                                                                                            |

|-----------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3787/<br>LTC3787-1 | シングル出力、デュアル・チャネル、マルチフェーズ同期整流式昇圧コントローラ | 4.5V(起動後は最低2.5V) ≤ V <sub>IN</sub> ≤ 38V、V <sub>OUT</sub> :最大60V、動作周波数:50kHz～900kHz、4mm×5mm QFN-28 および SSOP-28パッケージ                                           |

| LTC3788/<br>LTC3788-1 | デュアル出力、マルチフェーズ同期整流式昇圧コントローラ           | 4.5V(起動後は最低2.5V) ≤ V <sub>IN</sub> ≤ 38V、V <sub>OUT</sub> :最大60V、固定周波数:50kHz～900kHz、5mm×5mm QFN-32 および SSOP-28パッケージ                                           |

| LTC3786               | 低消費電流の同期整流式昇圧コントローラ                   | 4.5V(起動後は最低2.5V) ≤ V <sub>IN</sub> ≤ 38V、V <sub>OUT</sub> :最大60V、固定動作周波数:50kHz～900kHz、3mm×3mm QFN-16 および MSOP-16Eパッケージ                                        |

| LT3757A               | 昇圧、フライバック、SEPIC および 反転コントローラ          | 2.9V ≤ V <sub>IN</sub> ≤ 40V、電流モード制御、プログラム可能な動作周波数:100kHz～1MHz、3mm×3mm DFN-10 および MSOP-10Eパッケージ                                                               |

| LTC3859AL             | 低静止電流、トリプル出力、降圧/降圧/昇圧同期整流式DC/DCコントローラ | すべての出力はコールド・クランク時でもレギュレーション状態を維持、4.5V(起動後は最低2.5V) ≤ V <sub>IN</sub> ≤ 38V、V <sub>OUT(BUCKS)</sub> :最大24V、V <sub>OUT(BOOST)</sub> :最大60V、I <sub>Q</sub> = 28μA |

| LTC3789               | 高効率同期整流式4スイッチ昇降圧DC/DCコントローラ           | 4V ≤ V <sub>IN</sub> ≤ 38V、0.8V ≤ V <sub>OUT</sub> ≤ 38V、4mm×5mm QFN-28 および SSOP-28パッケージ                                                                      |

38621fa