## 差動出力検出機能を備えた、 高速、高精度のデュアル降圧 DC/DC コントローラ

### 特長

- 広い入力電圧範囲: 4.5V ~ 38V、出力電圧: 0.6V ~ 5.5V

- チャネル1では全温度範囲で  $\pm 0.67\%$  の出力電圧精度、

差動出力電圧検出、デバイスから離れたグランドで最大

$\pm 500\text{mV}$  のライン損失を許容

- 独立したチャネル2での出力精度:  $\pm 1\%$

- 制御されたオン時間の谷電流モード制御

- 高速負荷トランジエント応答

- トランジエント検出(DTR)により出力電圧のオーバー<sup>+</sup>

シートを低減

- 周波数を 200kHz ~ 2MHz にプログラム可能、外部クロック

に同期可能

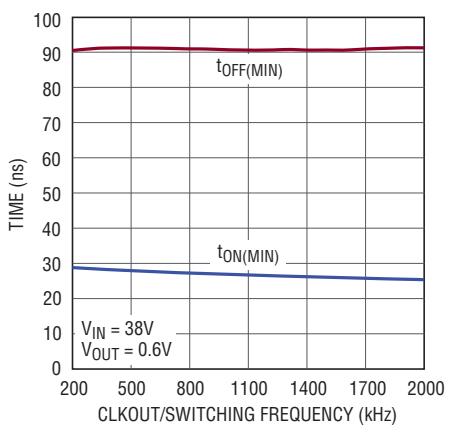

- $t_{ON(MIN)} = 30\text{ns}$ ,  $t_{OFF(MIN)} = 90\text{ns}$

- RSENSE またはインダクタの DCR による電流検出

- 過電圧保護と電流制限フォールドバック

- パワーグッド出力電圧モニタ

- 出力電圧トラッキングと調整可能なソフトスタート

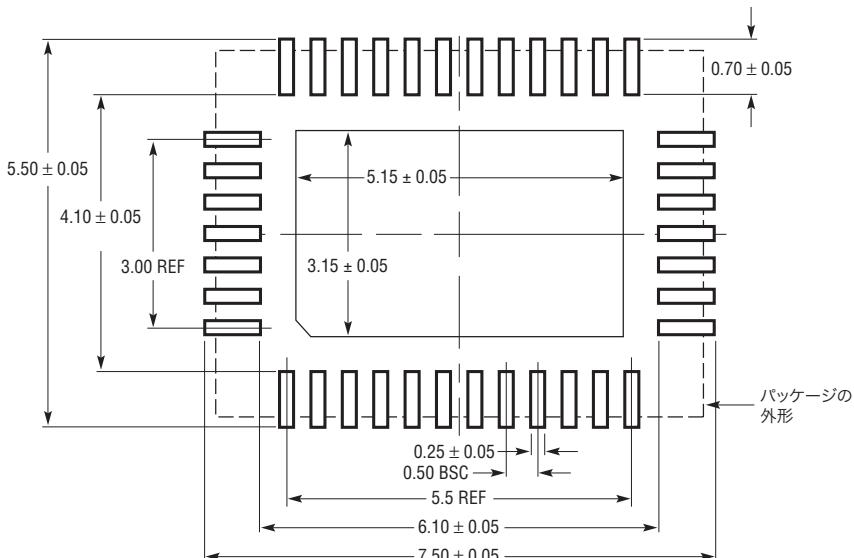

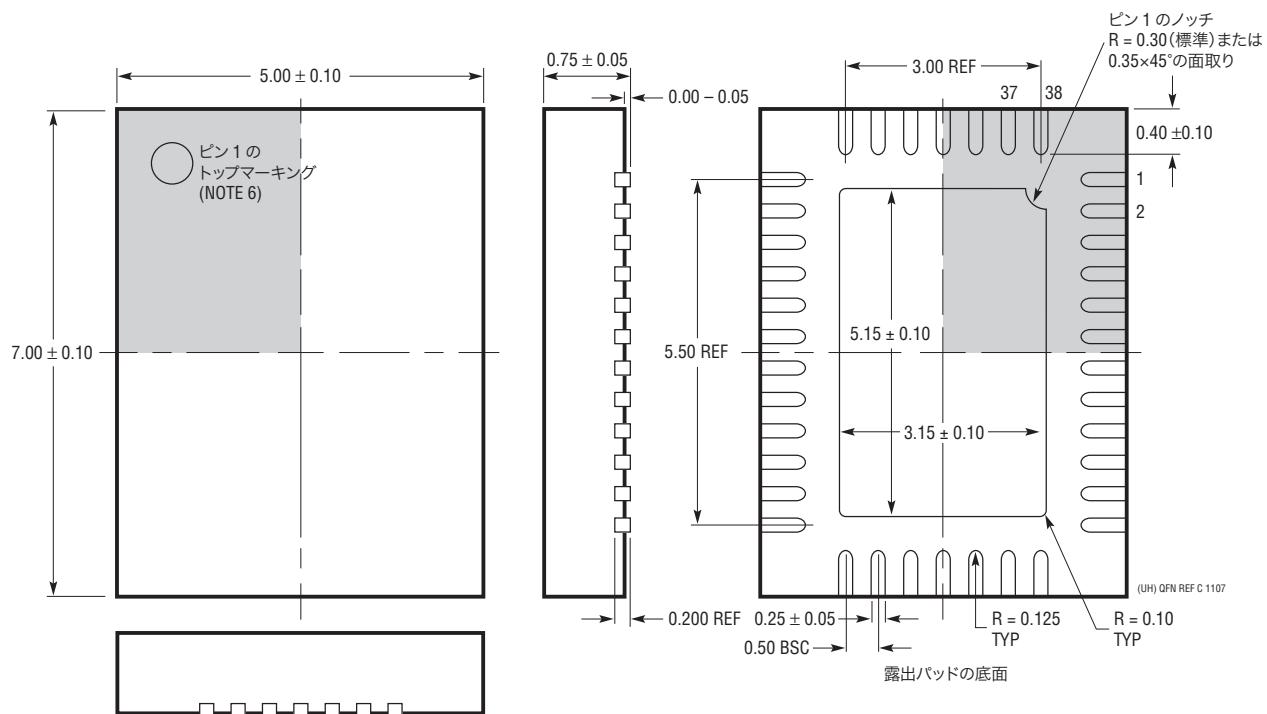

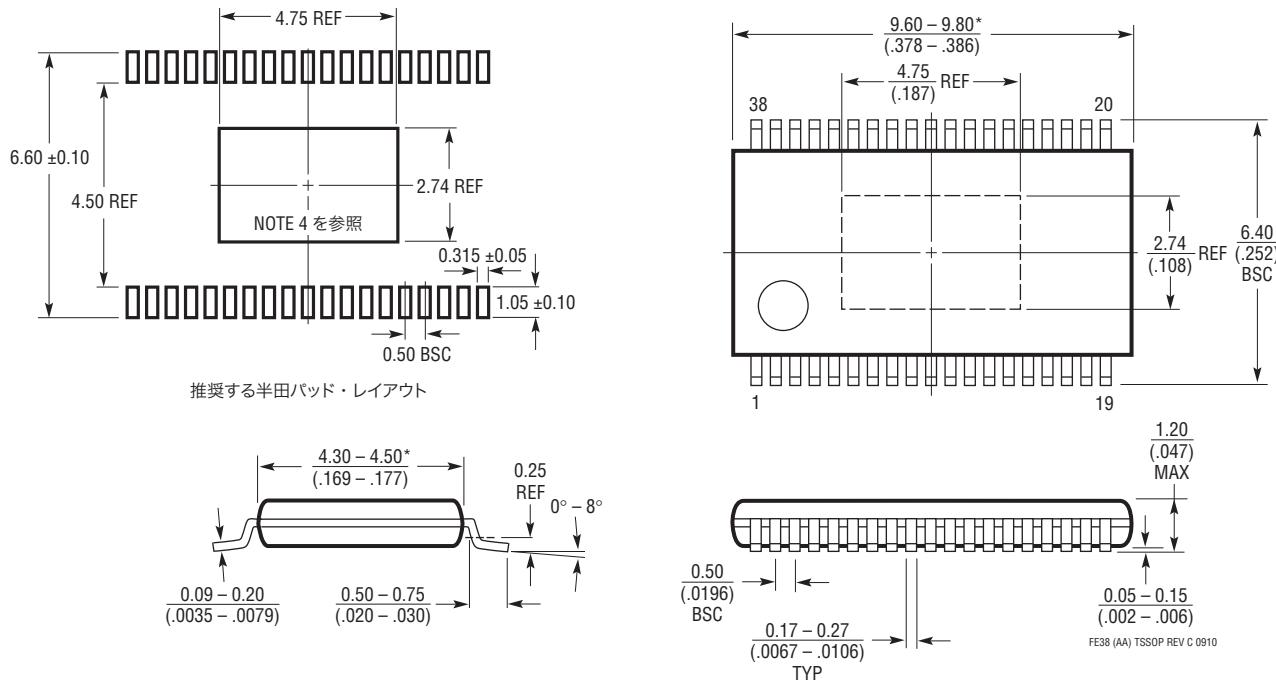

- 熱特性が改善された 38 ピン (5mm × 7mm) QFN および

TSSOP パッケージ

### アプリケーション

- 分散給電システム

- ポイントオブロード・コンバータ

- コンピュータ・システム

- データ通信システム

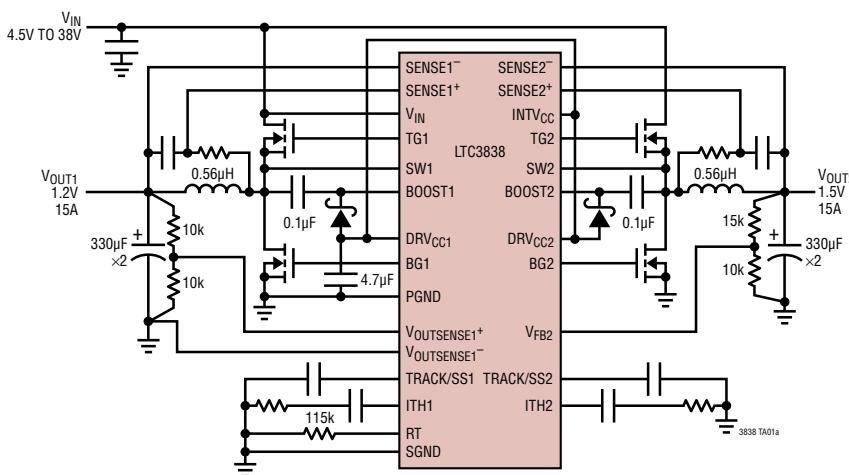

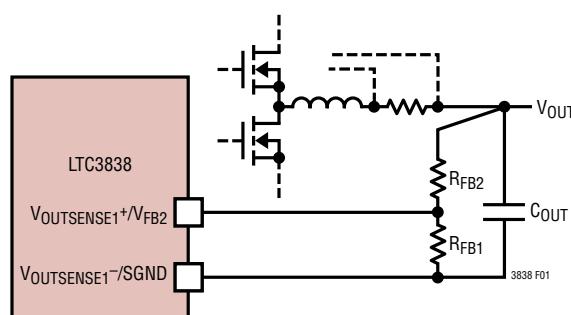

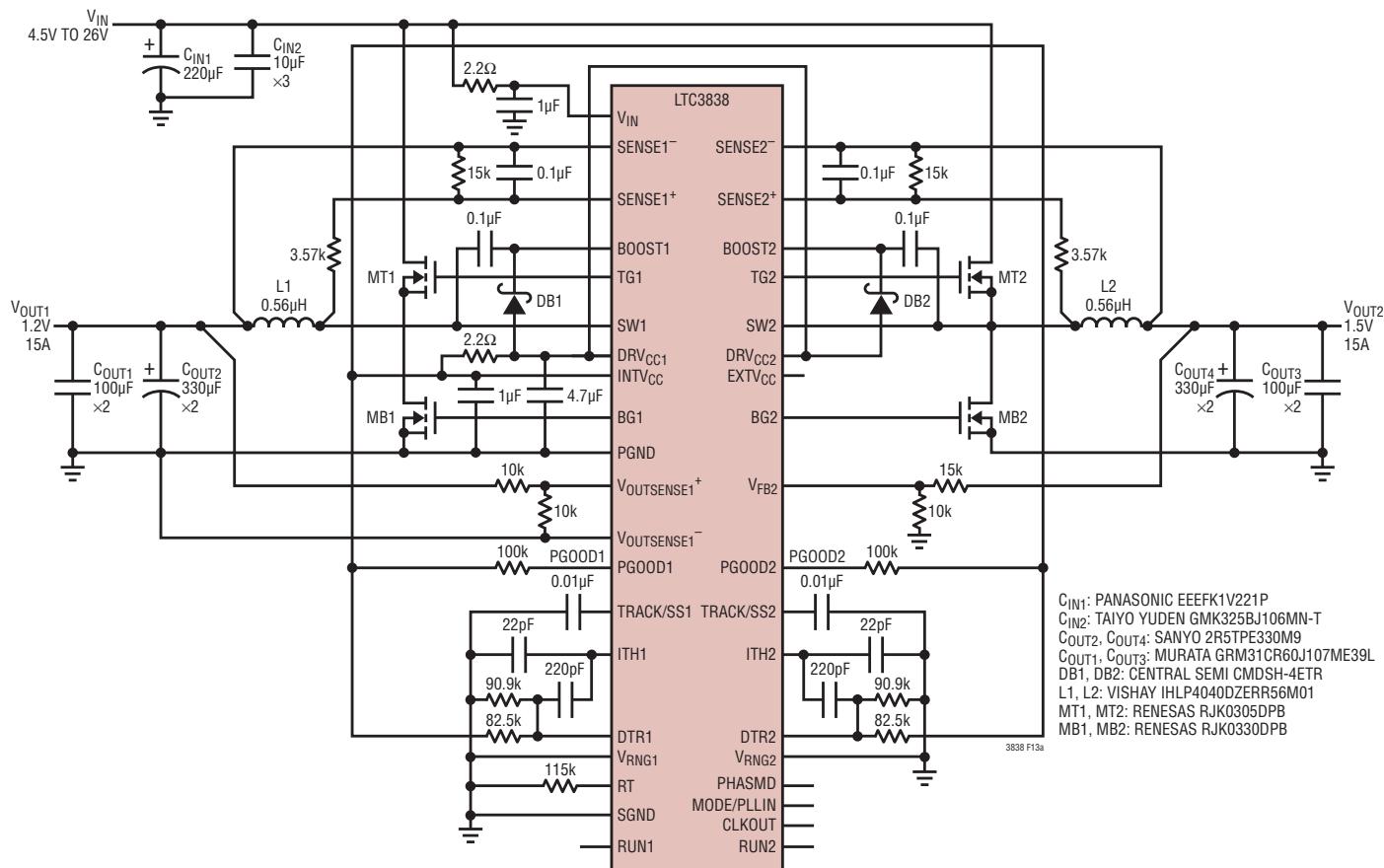

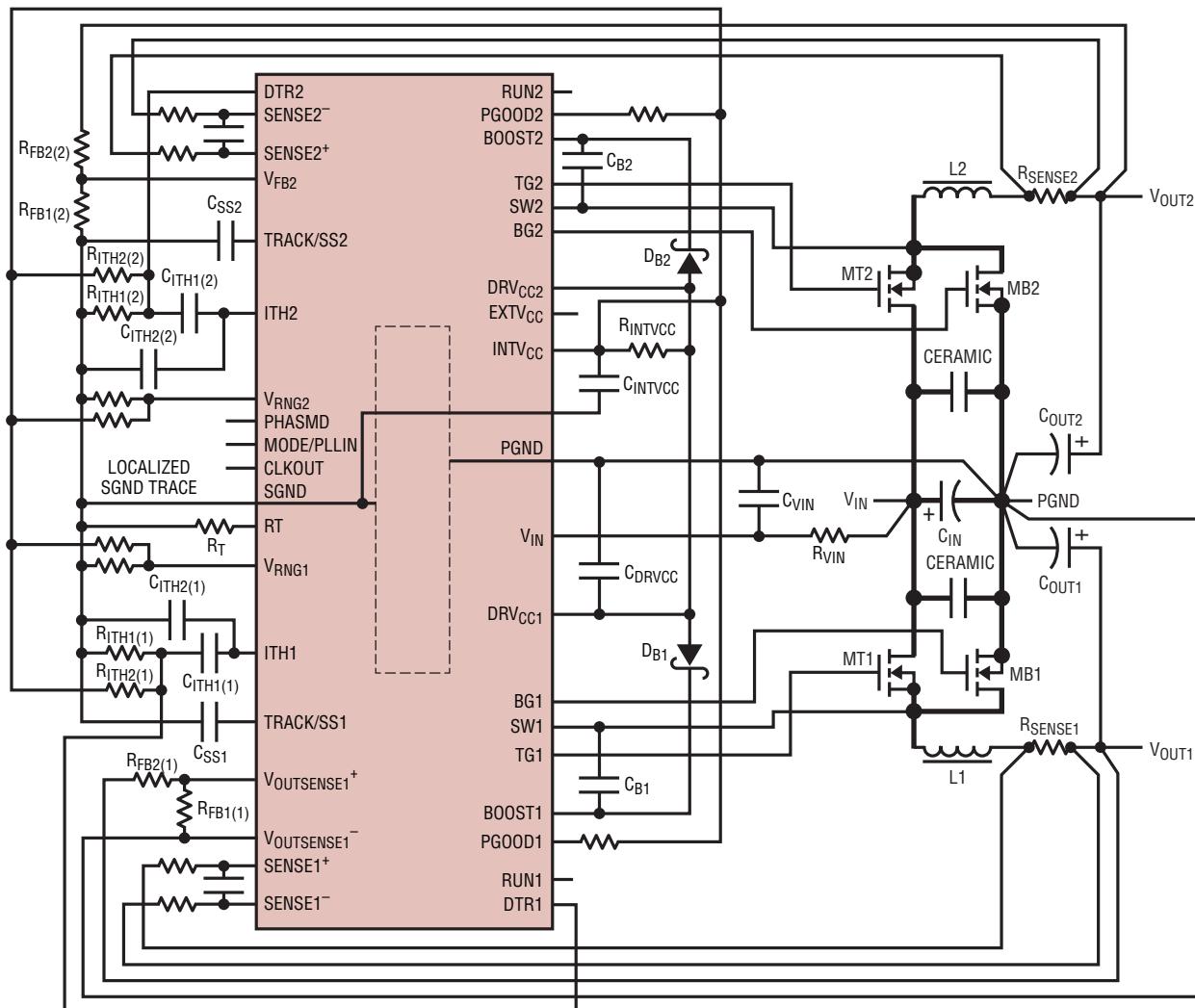

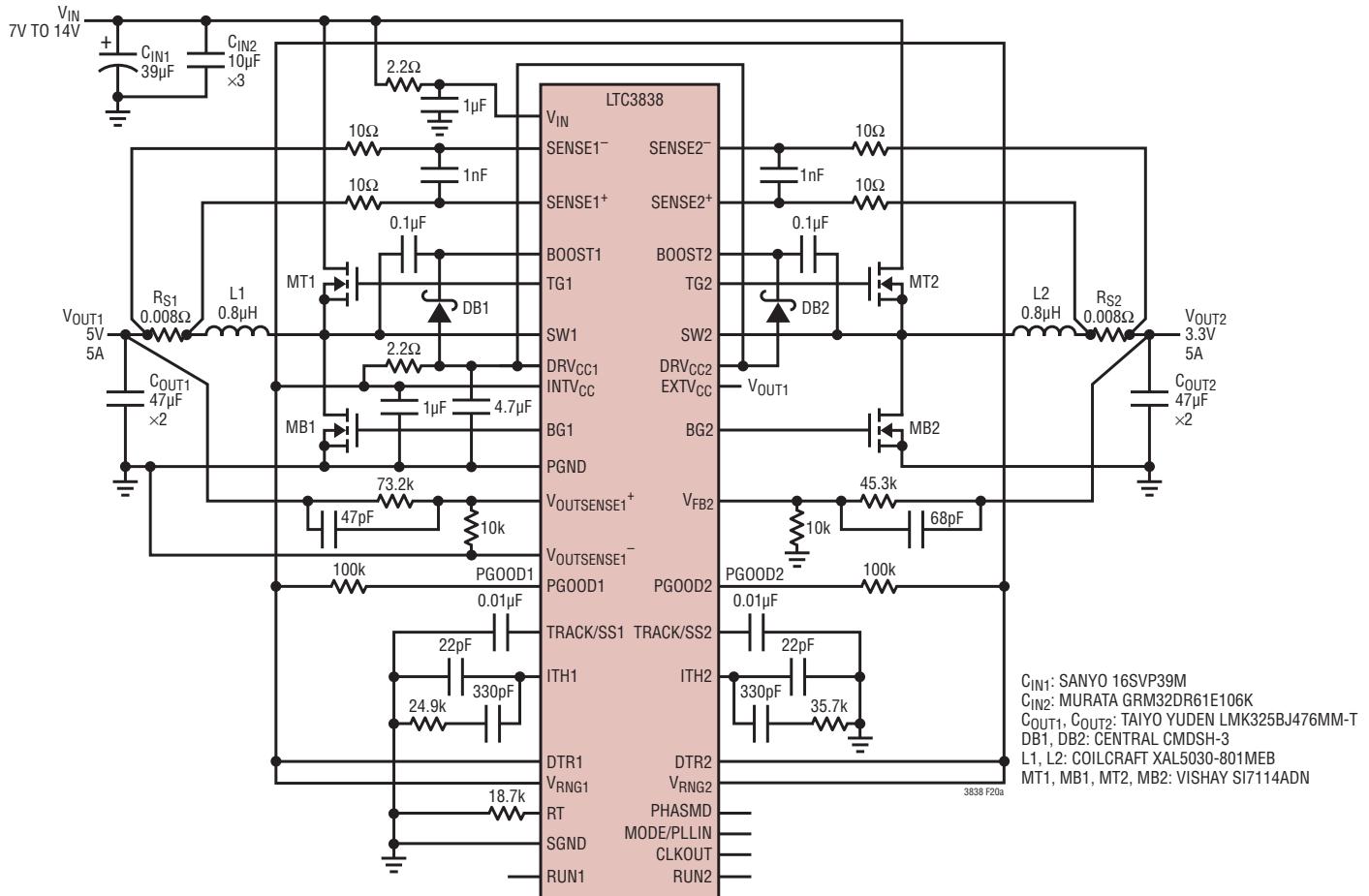

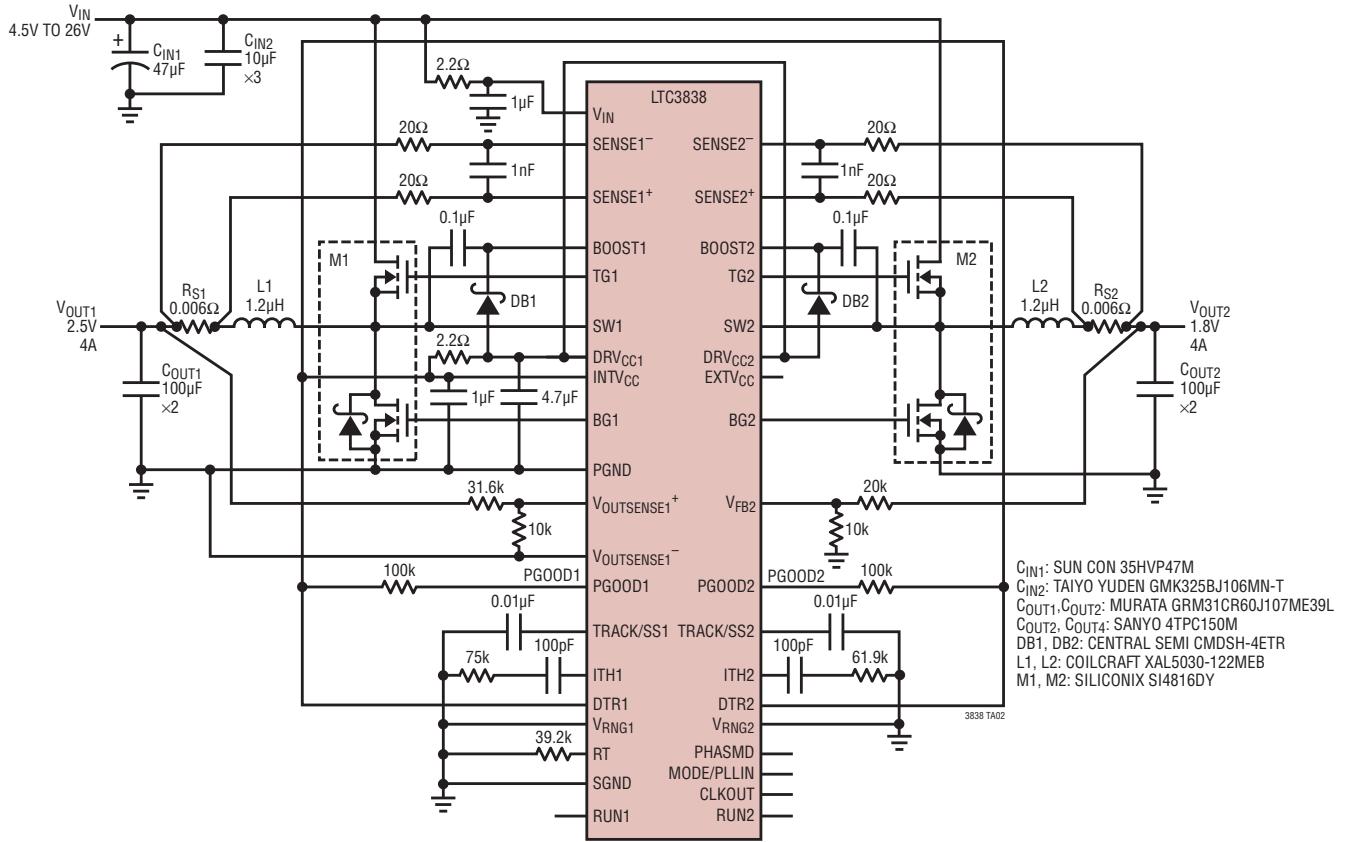

### 標準的応用例

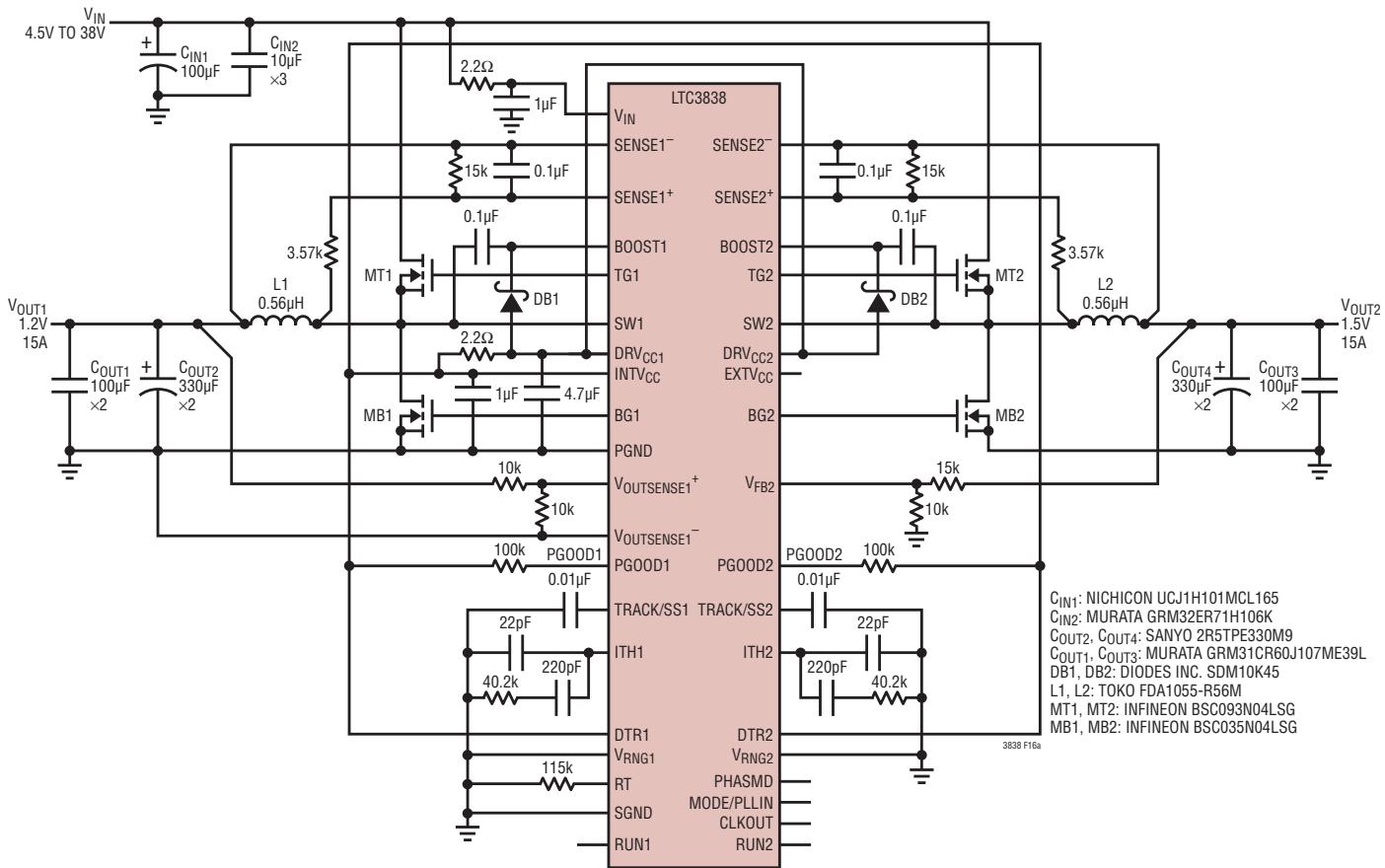

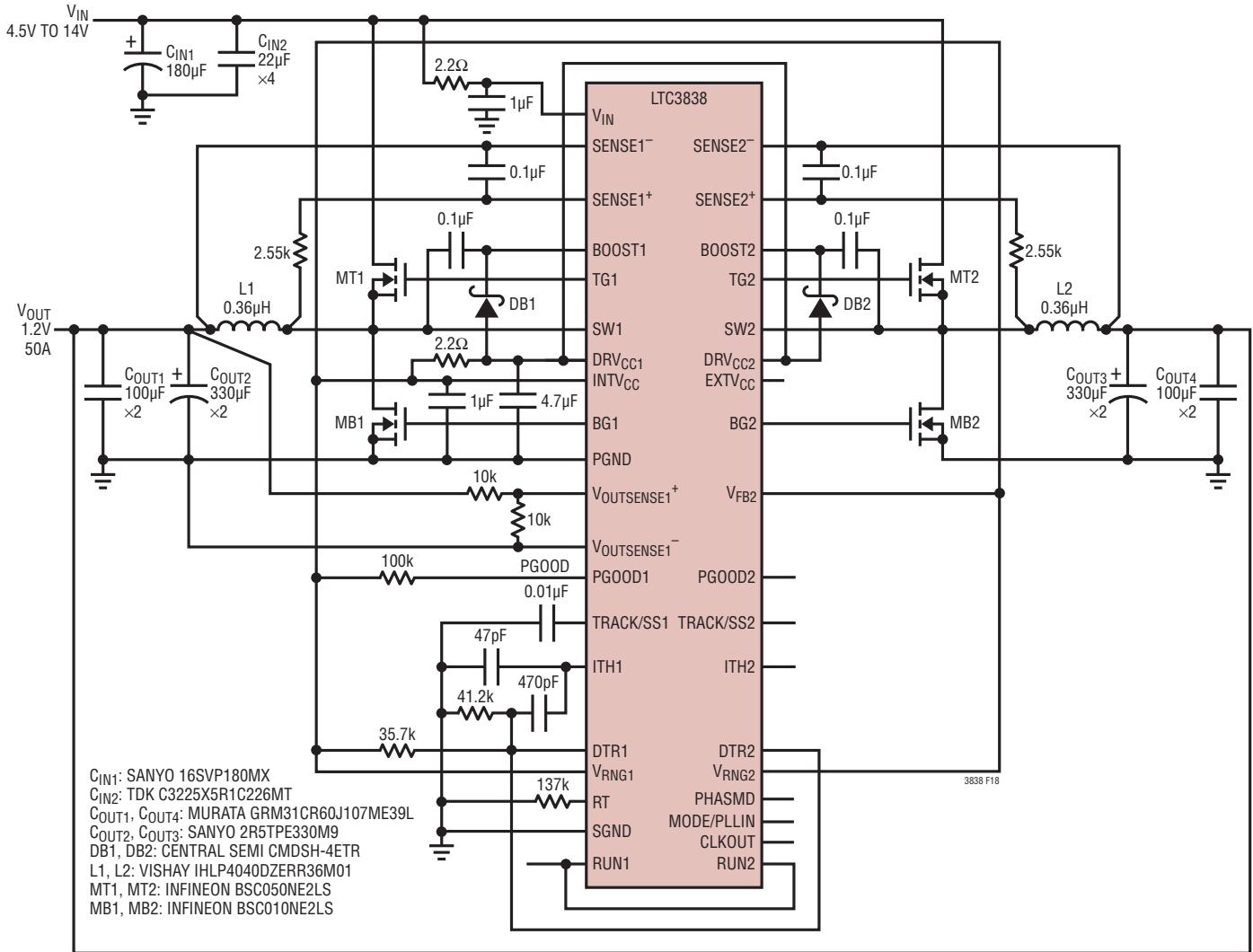

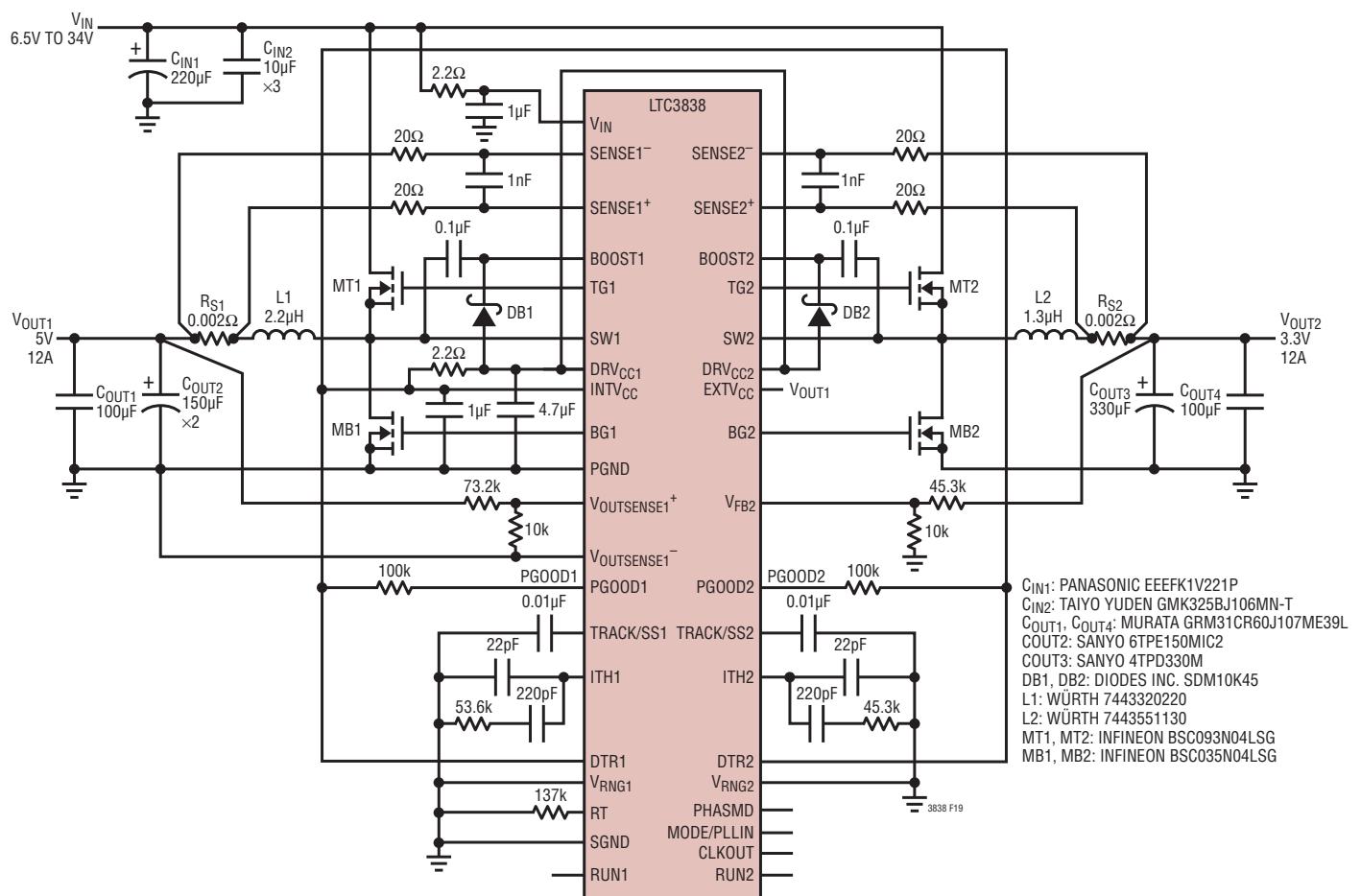

1.2V/1.5V、15A出力、350kHz、DCR 検出、降圧コンバータ(設計図全体については図16を参照)

3838f16a

## 絶対最大定格 (Note 1)

|                                                                                                                                                          |             |                                                                             |                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------|-------------------------------|

| $V_{IN}$ 電圧                                                                                                                                              | -0.3V ~ 40V | TRACK/SS1、TRACK/SS2 の電圧                                                     | -0.3V ~ 5V                    |

| BOOST1、BOOST2 の電圧                                                                                                                                        | -0.3V ~ 46V | DTR1、DTR2、PHASMD、RT、 $V_{RNG1}$ 、 $V_{RNG2}$ 、 $V_{FB2}$ 、<br>ITH1、ITH2 の電圧 | -0.3V ~ ( $INTV_{CC}$ + 0.3V) |

| SW1、SW2 の電圧                                                                                                                                              | -5V ~ 40V   | 動作接合部温度範囲 (Note 2, 3, 4)                                                    | -40°C ~ 125°C                 |

| INTV <sub>CC</sub> 、DRV <sub>CC1</sub> 、DRV <sub>CC2</sub> 、EXTV <sub>CC</sub> 、PGOOD1、<br>PGOOD2、RUN1、RUN2、(BOOST1-SW1)、<br>(BOOST2-SW2)、MODE/PLLIN の電圧 | -0.3V ~ 6V  | 保存温度範囲                                                                      | -65°C ~ 150°C                 |

| $V_{OUTSENSE1^+}$ 、 $V_{OUTSENSE1^-}$ 、SENSE1 <sup>+</sup> 、SENSE2 <sup>+</sup> 、<br>SENSE1 <sup>-</sup> 、SENSE2 <sup>-</sup> の電圧                        | -0.6V ~ 6V  | リード温度 (半田付け、10秒)                                                            |                               |

|                                                                                                                                                          |             | FE パッケージ                                                                    | 300°C                         |

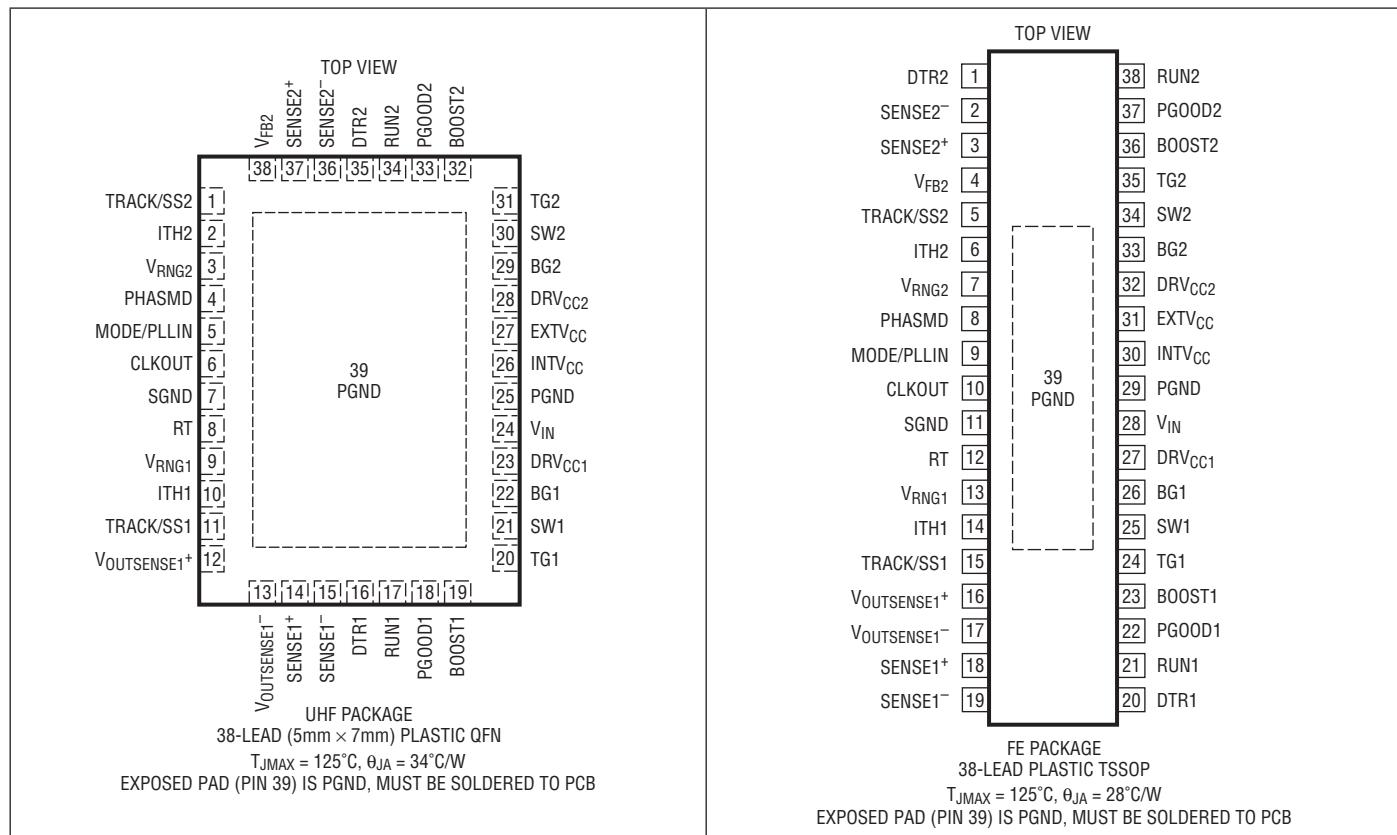

## ピン配置

## 発注情報

| 無鉛仕上げ           | テープアンドリール         | 製品マーキング*  | パッケージ                           | 温度範囲           |

|-----------------|-------------------|-----------|---------------------------------|----------------|

| LTC3838EUHF#PBF | LTC3838EUHF#TRPBF | 3838      | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 125°C |

| LTC3838IUHF#PBF | LTC3838IUHF#TRPBF | 3838      | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 125°C |

| LTC3838EFE#PBF  | LTC3838EFE#TRPBF  | LTC3838FE | 38-Lead Plastic TSSOP           | -40°C to 125°C |

| LTC3838IFE#PBF  | LTC3838IFE#TRPBF  | LTC3838FE | 38-Lead Plastic TSSOP           | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性** ●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 15\text{V}$ (Note 3)。

| SYMBOL                      | PARAMETER                                                                                               | CONDITIONS                                                                                                                                                                                                                    | MIN         | TYP                      | MAX               | UNITS                    |             |

|-----------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------|-------------------|--------------------------|-------------|

| <b>メイン制御ループ</b>             |                                                                                                         |                                                                                                                                                                                                                               |             |                          |                   |                          |             |

| $V_{IN}$                    | Input Voltage Operating Range                                                                           |                                                                                                                                                                                                                               | 4.5         | 38                       |                   | V                        |             |

| $V_{OUT1,2(\text{REG})}$    | Regulated Output Voltage Operating Range                                                                | $V_{OUT1}$ Regulated Differentially with Respect to $V_{OUTSENSE1^+}$ , $V_{OUT2}$ Regulated with Respect to SGND                                                                                                             | 0.6         | 5.5                      |                   | V                        |             |

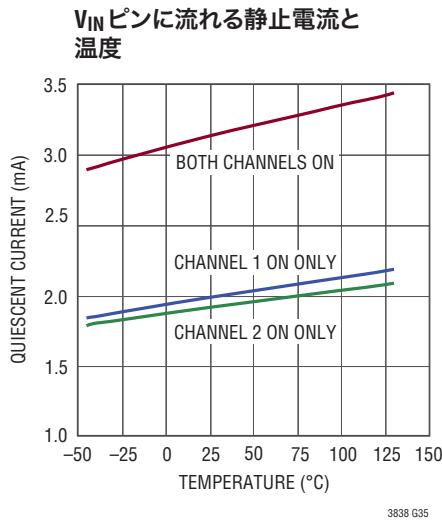

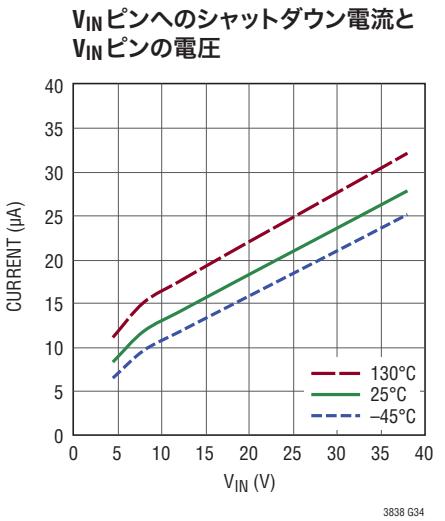

| $I_Q$                       | Input DC Supply Current<br>Both Channels Enabled<br>Only One Channel Enabled<br>Shutdown Supply Current | MODE/PLLIN = 0V, No Load<br>RUN1 or RUN2 (But Not Both) = 0V<br>RUN1 = RUN2 = 0V                                                                                                                                              |             | 3<br>2<br>15             |                   | mA<br>mA<br>μA           |             |

| $V_{OUTSENSE1(\text{REG})}$ | Regulated Differential Feedback Voltage on Channel 1 ( $V_{OUTSENSE1^+} - V_{OUTSENSE1^-}$ )            | ITH1 = 1.2V (Note 5)<br>$T_A = 25^\circ\text{C}$<br>$T_A = 0^\circ\text{C}$ to $85^\circ\text{C}$<br>$T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                                                                         | ●<br>●<br>● | 0.5985<br>0.596<br>0.594 | 0.6<br>0.6<br>0.6 | 0.6015<br>0.604<br>0.606 | V<br>V<br>V |

|                             | Regulated Differential Feedback Voltage on Channel 1 Over Line, Load and Common Mode                    | $V_{IN} = 4.5\text{V}$ to $38\text{V}$ , ITH1 = 0.5V to 1.9V (Note 5),<br>$-0.5\text{V} < V_{OUTSENSE1^-} < 0.5\text{V}$<br>$T_A = 0^\circ\text{C}$ to $85^\circ\text{C}$<br>$T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$ |             | 0.594<br>0.591           | 0.6<br>0.6        | 0.606<br>0.609           | V<br>V      |

| $V_{FB2(\text{REG})}$       | Regulated Feedback Voltage on Channel 2                                                                 | ITH2 = 1.2V (Note 5)<br>$T_A = 25^\circ\text{C}$<br>$T_A = 0^\circ\text{C}$ to $85^\circ\text{C}$<br>$T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                                                                         | ●<br>●<br>● | 0.597<br>0.594<br>0.592  | 0.6<br>0.6<br>0.6 | 0.603<br>0.606<br>0.608  | V<br>V<br>V |

|                             | Regulated Feedback Voltage on Channel 2 Over Line, Load                                                 | $V_{IN} = 4.5\text{V}$ to $38\text{V}$ , ITH2 = 0.5V to 1.9V (Note 5)<br>$T_A = 0^\circ\text{C}$ to $85^\circ\text{C}$<br>$T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                                                    |             | 0.592<br>0.588           | 0.6<br>0.6        | 0.608<br>0.612           | V<br>V      |

| $I_{VOUTSENSE1^+}$          | $V_{OUTSENSE1^+}$ Input Bias Current                                                                    | $V_{OUTSENSE1^+} - V_{OUTSENSE1^-} = 0.6\text{V}$                                                                                                                                                                             |             |                          | $\pm 5$           | $\pm 25$                 | nA          |

| $I_{VOUTSENSE1^-}$          | $V_{OUTSENSE1^-}$ Input Bias Current                                                                    | $V_{OUTSENSE1^+} - V_{OUTSENSE1^-} = 0.6\text{V}$                                                                                                                                                                             |             |                          | -25               | -50                      | μA          |

| $I_{VFB2}$                  | $V_{FB2}$ Input Bias Current                                                                            | $V_{FB2} = 0.6\text{V}$                                                                                                                                                                                                       |             |                          | -5                | $\pm 50$                 | nA          |

| $g_m(\text{EA})_{1,2}$      | Error Amplifier Transconductance                                                                        | ITH = 1.2V (Note 5)                                                                                                                                                                                                           |             |                          | 1.7               |                          | mS          |

| $t_{ON(\text{MIN})1,2}$     | Minimum Top Gate On-Time                                                                                | $V_{IN} = 38\text{V}$ , $V_{OUT} = 0.6\text{V}$ , $R_T = 20\text{k}$ (Note 6)                                                                                                                                                 |             |                          | 30                |                          | ns          |

| $t_{OFF(\text{MIN})1,2}$    | Minimum Top Gate Off-Time                                                                               | (Note 6)                                                                                                                                                                                                                      |             |                          | 90                |                          | ns          |

**電気的特性** ●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 15\text{V}$ (Note 3)。

| SYMBOL                     | PARAMETER                                                                                             | CONDITIONS                                                                                                                                                                                                                                             |             | MIN            | TYP                | MAX                 | UNITS               |

|----------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|--------------------|---------------------|---------------------|

| <b>電流検出</b>                |                                                                                                       |                                                                                                                                                                                                                                                        |             |                |                    |                     |                     |

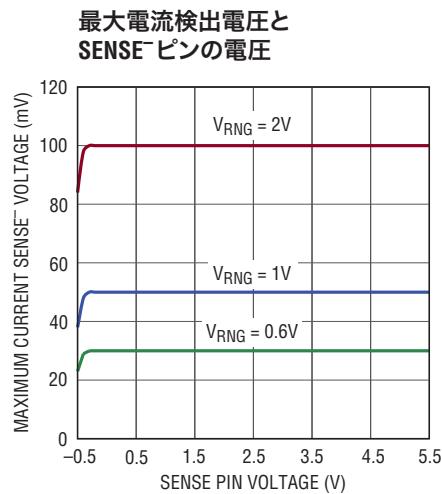

| $V_{SENSE(\text{MAX})1,2}$ | Maximum Valley Current Sense Threshold ( $V_{SENSE1,2^+} - V_{SENSE1,2^-}$ )                          | $V_{RNG} = 2\text{V}$ , $V_{FB} = 0.57\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$<br>$V_{RNG} = 0\text{V}$ , $V_{FB} = 0.57\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$<br>$V_{RNG} = \text{INTV}_{CC}$ , $V_{FB} = 0.57\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$ | ●<br>●<br>● | 80<br>21<br>39 | 100<br>30<br>50    | 120<br>40<br>61     | mV                  |

| $V_{SENSE(\text{MIN})1,2}$ | Minimum Valley Current Sense Threshold ( $V_{SENSE1,2^+} - V_{SENSE1,2^-}$ ) (Forced Continuous Mode) | $V_{RNG} = 2\text{V}$ , $V_{FB} = 0.63\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$<br>$V_{RNG} = 0\text{V}$ , $V_{FB} = 0.63\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$<br>$V_{RNG} = \text{INTV}_{CC}$ , $V_{FB} = 0.63\text{V}$ , $V_{SENSE^-} = 2.5\text{V}$ |             |                | -50<br>-15<br>-25  | mV                  |                     |

| $I_{SENSE1,2^+}$           | SENSE1,2 <sup>+</sup> Pins Input Bias Current                                                         | $V_{SENSE^+} = 0.6\text{V}$<br>$V_{SENSE^+} = 5\text{V}$                                                                                                                                                                                               |             |                | $\pm 5$<br>1       | $\pm 50$<br>$\pm 2$ | nA<br>$\mu\text{A}$ |

| $I_{SENSE1,2^-}$           | SENSE1,2 <sup>-</sup> Pins Input Bias Current (Internal 500k Resistor to SGND)                        | $V_{SENSE^-} = 0.6\text{V}$<br>$V_{SENSE^-} = 5\text{V}$                                                                                                                                                                                               |             |                | 1.2<br>10          |                     | $\mu\text{A}$       |

| <b>起動とシャットダウン</b>          |                                                                                                       |                                                                                                                                                                                                                                                        |             |                |                    |                     |                     |

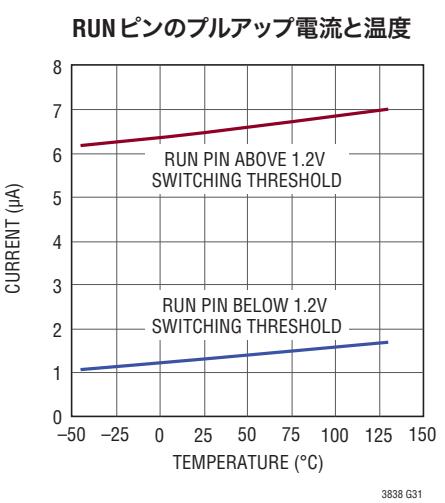

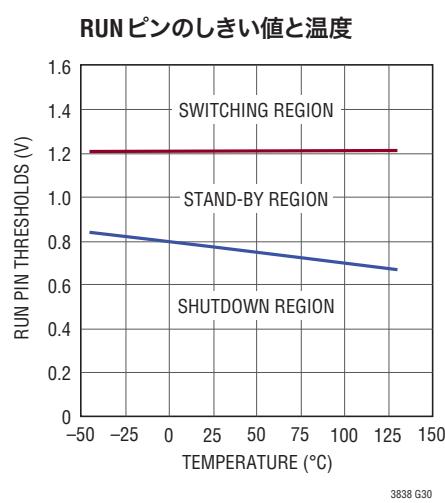

| $V_{RUN1,2}$               | RUN Pin On Threshold                                                                                  | $V_{RUN1,2}$ Rising                                                                                                                                                                                                                                    | ●           | 1.1            | 1.2                | 1.3                 | V                   |

|                            | RUN Pin On Hysteresis                                                                                 | $V_{RUN1,2}$ Falling from On Threshold                                                                                                                                                                                                                 |             |                | 100                |                     | mV                  |

| $I_{RUN1,2}$               | RUN Pin Pull-Up Current when Off                                                                      | $\text{RUN1,2} = \text{SGND}$                                                                                                                                                                                                                          |             |                | 1.2                |                     | $\mu\text{A}$       |

|                            | RUN Pin Pull-Up Current Hysteresis                                                                    | $I_{RUN1,2(\text{HYS})} = I_{RUN1,2(\text{ON})} - I_{RUN1,2(\text{OFF})}$                                                                                                                                                                              |             |                | 5                  |                     | $\mu\text{A}$       |

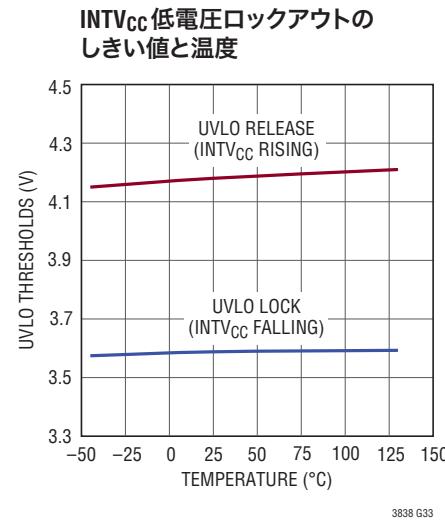

| UVLO                       | INTV <sub>CC</sub> Undervoltage Lockout                                                               | INTV <sub>CC</sub> Falling<br>INTV <sub>CC</sub> Rising                                                                                                                                                                                                | ●<br>●      | 3.3<br>4.2     | 3.7<br>4.2         | 4.5                 | V                   |

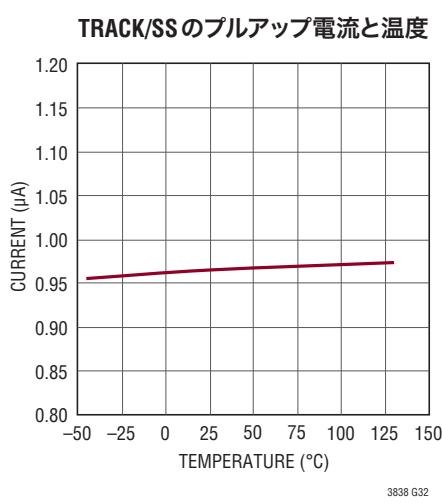

| $I_{TRACK/SS1,2}$          | Soft-Start Pull-Up Current                                                                            | $0\text{V} < \text{TRACK/SS1,2} < 0.6\text{V}$                                                                                                                                                                                                         |             |                | 1                  |                     | $\mu\text{A}$       |

| <b>周波数とクロック同期</b>          |                                                                                                       |                                                                                                                                                                                                                                                        |             |                |                    |                     |                     |

|                            | Clock Output Frequency (Steady-State Switching Frequency)                                             | $R_T = 205\text{k}$<br>$R_T = 80.6\text{k}$<br>$R_T = 18.2\text{k}$                                                                                                                                                                                    |             | 450            | 200<br>500<br>2000 | 550                 | kHz                 |

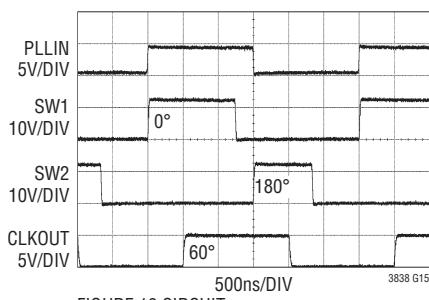

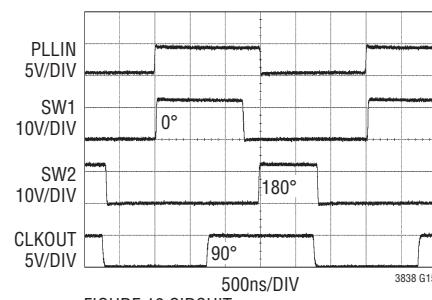

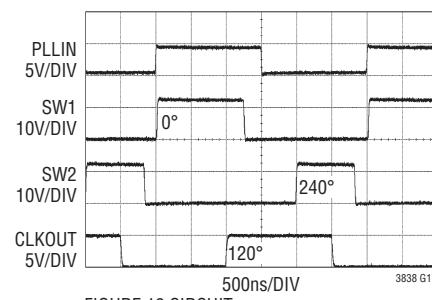

|                            | Channel 2 Phase (Relative to Channel 1)                                                               | PHASMD = SGND<br>PHASMD = Floating<br>PHASMD = INTV <sub>CC</sub>                                                                                                                                                                                      |             |                | 180<br>180<br>240  |                     | Deg                 |

|                            | CLKOUT Phase (Relative to Channel 1)                                                                  | PHASMD = SGND<br>PHASMD = Floating<br>PHASMD = INTV <sub>CC</sub>                                                                                                                                                                                      |             |                | 60<br>90<br>120    |                     | Deg                 |

| $V_{PLLIN(H)}$             | Clock Input High Level Into MODE/PLLIN                                                                |                                                                                                                                                                                                                                                        |             |                | 2                  |                     | V                   |

| $V_{PLLIN(L)}$             | Clock Input Low Level Into MODE/PLLIN                                                                 |                                                                                                                                                                                                                                                        |             |                |                    | 0.5                 | V                   |

| $R_{MODE/PLLIN}$           | MODE/PLLIN Input DC Resistance                                                                        | With Respect to SGND                                                                                                                                                                                                                                   |             |                | 600                |                     | $\text{k}\Omega$    |

| <b>ゲート・ドライバ</b>            |                                                                                                       |                                                                                                                                                                                                                                                        |             |                |                    |                     |                     |

| $R_{TG(UP)1,2}$            | TG Driver Pull-Up On Resistance                                                                       | TG High                                                                                                                                                                                                                                                |             |                | 2.5                |                     | $\Omega$            |

| $R_{TG(DOWN)1,2}$          | TG Driver Pull-Down On Resistance                                                                     | TG Low                                                                                                                                                                                                                                                 |             |                | 1.2                |                     | $\Omega$            |

| $R_{BG(UP)1,2}$            | BG Driver Pull-Up On Resistance                                                                       | BG High                                                                                                                                                                                                                                                |             |                | 2.5                |                     | $\Omega$            |

| $R_{BG(DOWN)1,2}$          | BG Driver Pull-Down On Resistance                                                                     | BG Low                                                                                                                                                                                                                                                 |             |                | 0.8                |                     | $\Omega$            |

| $t_D(TG/BG)1,2$            | Top Gate Off to Bottom Gate On Delay Time                                                             | (Note 6)                                                                                                                                                                                                                                               |             |                | 20                 |                     | ns                  |

| $t_D(BG/TG)1,2$            | Bottom Gate Off to Top Gate On Delay Time                                                             | (Note 6)                                                                                                                                                                                                                                               |             |                | 15                 |                     | ns                  |

**電気的特性** ●は規定動作接合部温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN} = 15\text{V}$ (Note 3)。

| SYMBOL                               | PARAMETER                                          | CONDITIONS                                              | MIN | TYP  | MAX | UNITS         |

|--------------------------------------|----------------------------------------------------|---------------------------------------------------------|-----|------|-----|---------------|

| <b>内部 <math>V_{CC}</math> レギュレータ</b> |                                                    |                                                         |     |      |     |               |

| $V_{DRVCC1}$                         | Internally Regulated $DRV_{CC1}$ Voltage           | $6\text{V} < V_{IN} < 38\text{V}$                       | 5.0 | 5.3  | 5.6 | V             |

|                                      | $DRV_{CC1}$ Load Regulation                        | $I_{DRVCC1} = 0\text{mA}$ to $-100\text{mA}$            |     | -1.5 | -3  | %             |

| $V_{EXTVCC}$                         | $EXTV_{CC}$ Switchover Voltage                     | $EXTV_{CC}$ Rising                                      | 4.4 | 4.6  | 4.8 | V             |

|                                      | $EXTV_{CC}$ Switchover Hysteresis                  |                                                         |     | 200  |     | mV            |

|                                      | $EXTV_{CC}$ to $DRV_{CC2}$ Voltage Drop            | $V_{EXTVCC} = 5\text{V}$ , $I_{DRVCC2} = -100\text{mA}$ |     | 200  |     | mV            |

| <b>PGOOD 出力</b>                      |                                                    |                                                         |     |      |     |               |

| OV                                   | PGOOD Overvoltage Threshold                        | $V_{FB1,2}$ Rising, with Respect to Regulated Voltage   | 5   | 7.5  | 10  | %             |

| UV                                   | PGOOD Undervoltage Threshold                       | $V_{FB1,2}$ Falling, with Respect to Regulated Voltage  | -5  | -7.5 | -10 | %             |

|                                      | PGOOD Threshold Hysteresis                         | $V_{FB1,2}$ Returning to Reference Voltage              |     | 2    |     | %             |

| $V_{PGOOD(L)1,2}$                    | PGOOD Low Voltage                                  | $I_{PGOOD} = 2\text{mA}$                                |     | 0.1  | 0.3 | V             |

| $t_{D(PGOOD)1,2}$                    | Delay from $V_{FB}$ Fault (OV/UV) to PGOOD Falling |                                                         |     | 50   |     | $\mu\text{s}$ |

|                                      | Delay from $V_{FB}$ Good to PGOOD Rising           |                                                         |     | 20   |     | $\mu\text{s}$ |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** 接合部温度( $T_J$  ( $^\circ\text{C}$ ))は周囲温度( $T_A$  ( $^\circ\text{C}$ ))および電力損失( $P_D$  (W))から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

ここで、 $\theta_{JA}$  ( $^\circ\text{C/W}$ )はパッケージの熱インピーダンスである。

**Note 3:** LTC3838は $T_J$ が $T_A$ にはば等しくなるようなパルス負荷条件でテストされる。LTC3838Eは $0^\circ\text{C} \sim 85^\circ\text{C}$ の動作接合部温度範囲で仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3838Iは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲で仕様に適合することが保証されている。これらの仕様を満たす最大周囲温度は、基板レイアウト、パッケージの定格熱インピーダンスおよび他の環境要因と関連した特定の動作条件によって決まるに注意。

**Note 4:** このデバイスには短時間の過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。この保護が動作しているときは、最大定格接合部温度を超える。規定された絶対最大動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうか、またはデバイスに永続的損傷を与える恐れがある。

**Note 5:** LTC3838は、規定されたエラーアンプ出力電圧(ITH1,2)が得られるように( $V_{OUTSENSE1^+} - V_{OUTSENSE1^-}$ )または $V_{FB2}$ を調整する帰還ループでテストされる。

**Note 6:** 遅延時間は、上側ゲート(TG)および下側ゲート(BG)が最小負荷を駆動する状態で、50%のレベルを使用して測定される。

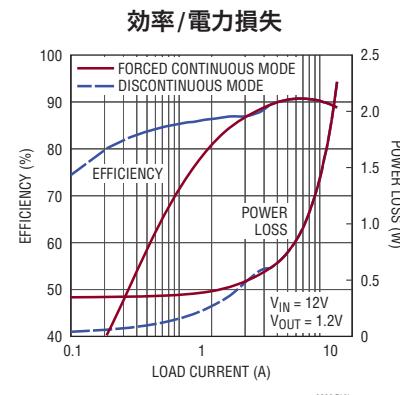

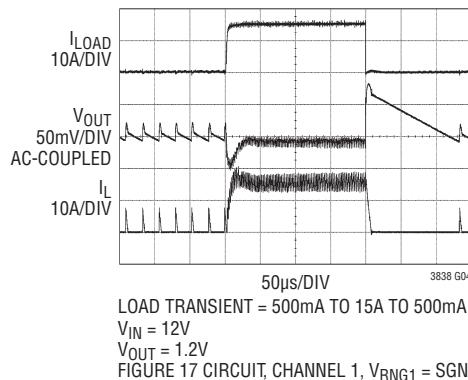

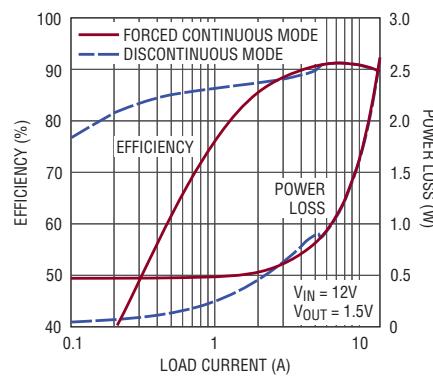

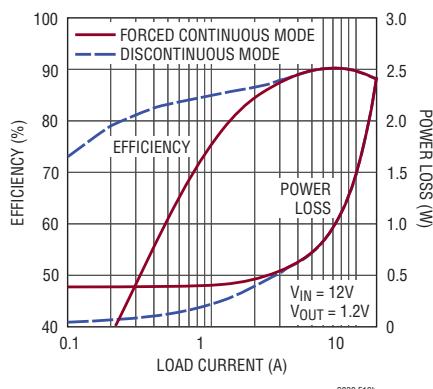

## 標準的性能特性

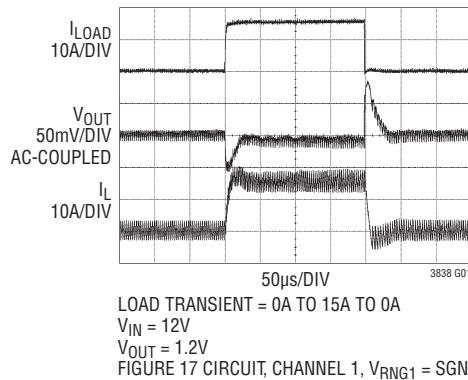

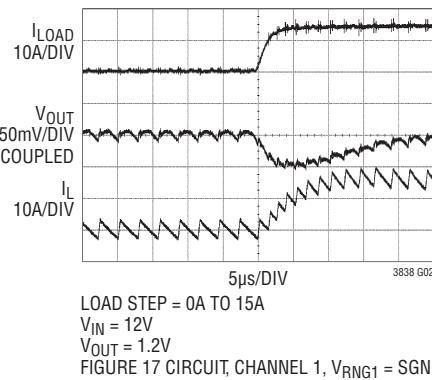

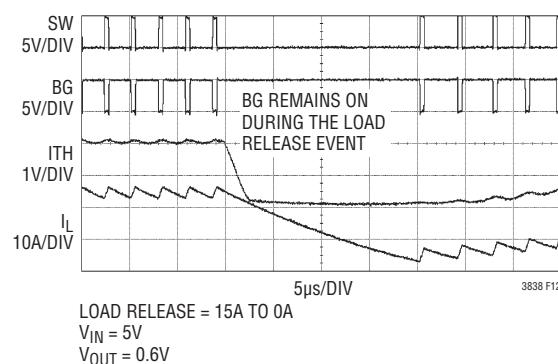

**トランジエント応答

(強制連続モード)**

**負荷ステップ

(強制連続モード)**

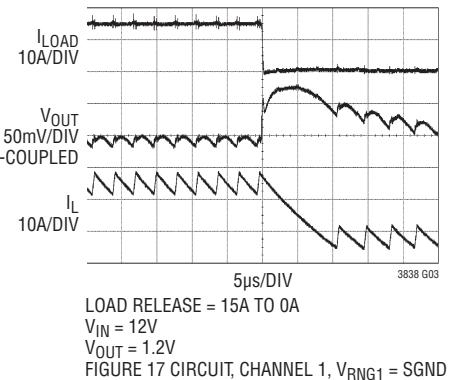

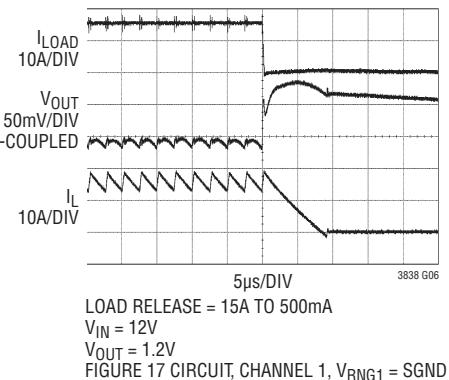

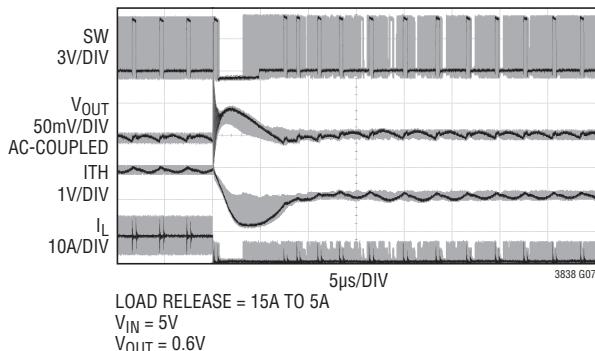

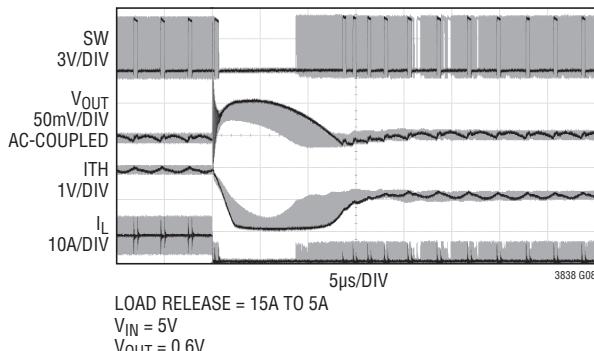

**負荷解放

(強制連続モード)**

**トランジエント応答

(不連続モード)**

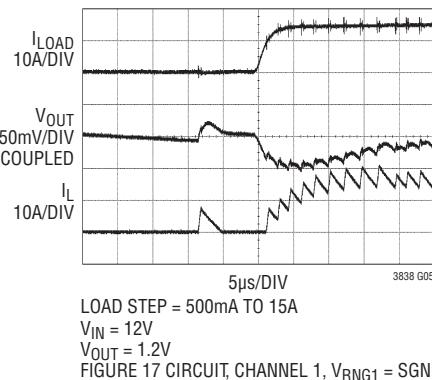

**負荷ステップ

(不連続モード)**

**負荷解放

(不連続モード)**

**トランジエント検出(DTR)機能イネーブル時の

負荷解放**

**トランジエント検出(DTR)機能ディスエーブル

時の負荷解放**

## 標準的性能特性

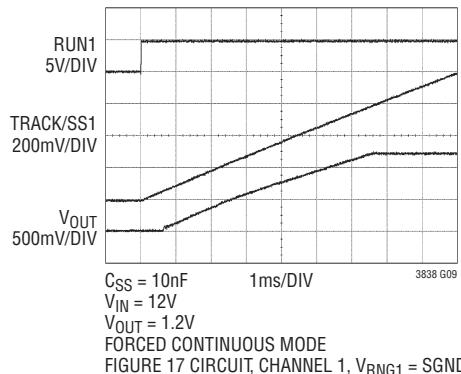

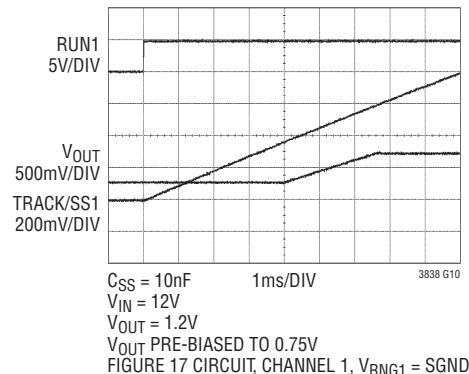

### 通常のソフトスタート

### 出力がプリバイアスされた状態までのソフトスタート

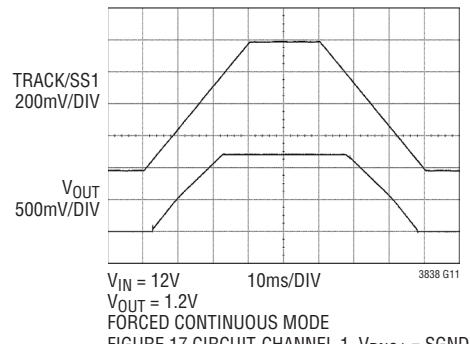

### 出力トラッキング

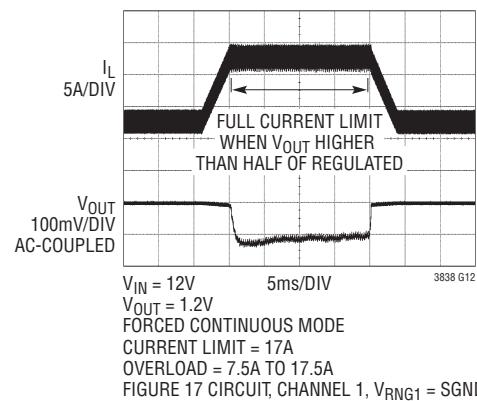

### 過電流保護

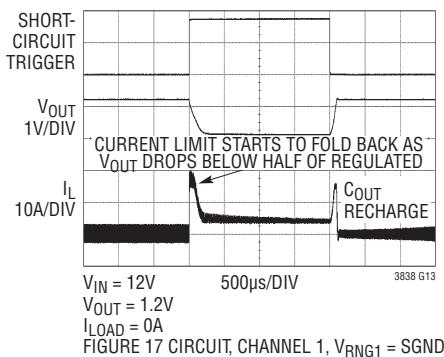

### 短絡保護

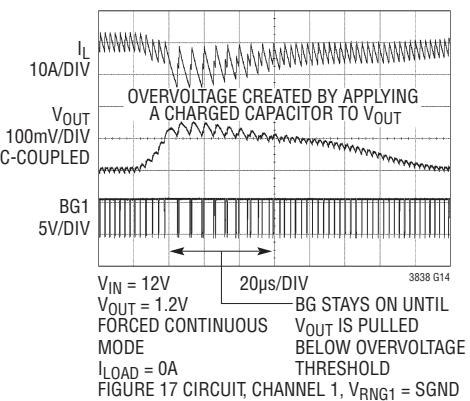

### 過電圧保護

### 位相関係: PHASMD = グランド

### 位相関係: PHASMD = フロート

### 位相関係: PHASMD = INTVCC

## 標準的性能特性

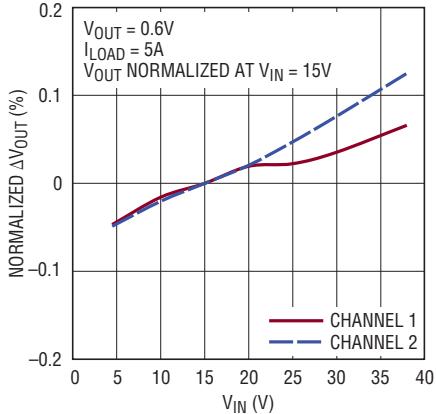

### 出力レギュレーションと入力電圧

3838 G18

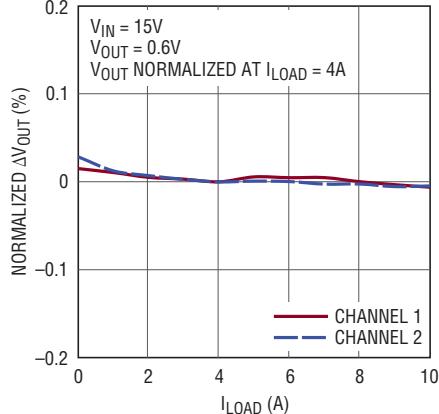

### 出力レギュレーションと負荷電流

3838 G19

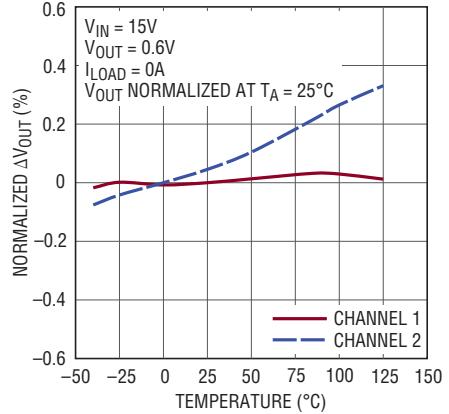

### 出力レギュレーションと温度

3838 G20

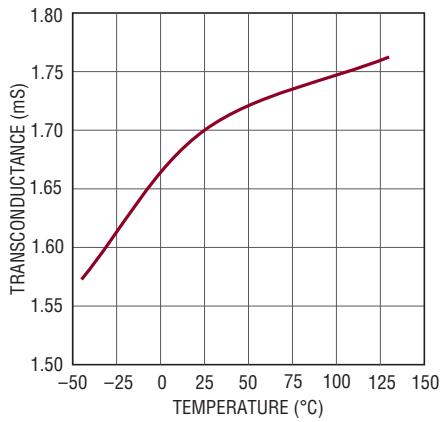

### エラーアンプのトランジスタコンダクタンスと温度

3838 G27

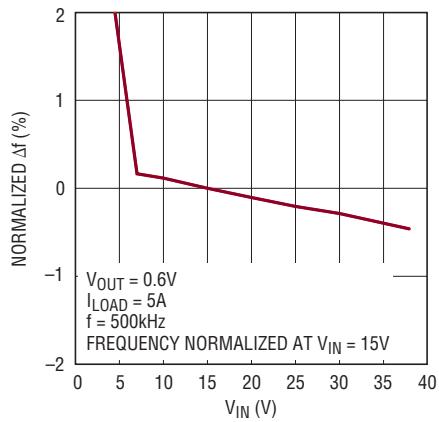

### CLKOUT/スイッチング周波数と入力電圧

3838 G21

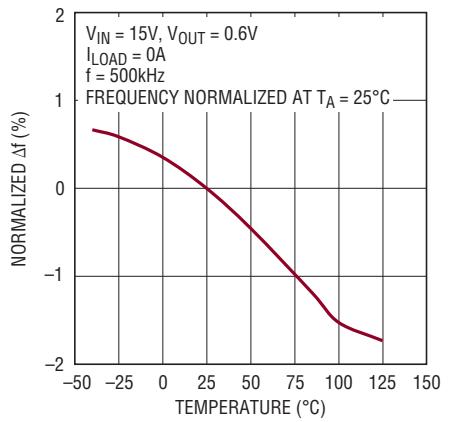

### CLKOUT/スイッチング周波数と温度

3838 G23

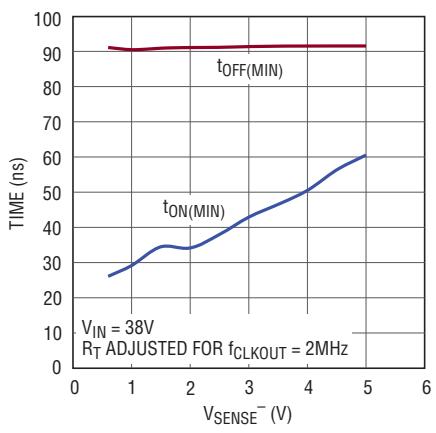

### t<sub>ON(MIN)</sub>およびt<sub>OFF(MIN)</sub>とV<sub>OUT</sub>(SENSE<sup>-</sup>ビンの電圧)

3838 G24

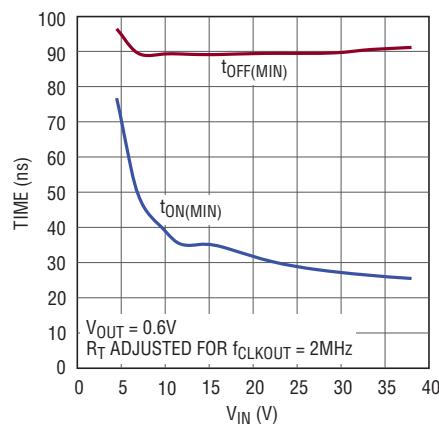

### t<sub>ON(MIN)</sub>およびt<sub>OFF(MIN)</sub>とV<sub>IN</sub>ビンの電圧

3838 G25

### t<sub>ON(MIN)</sub>およびt<sub>OFF(MIN)</sub>とスイッチング周波数

3838 G26

## 標準的性能特性

## ピン機能 (QFN/TSSOP)

**PHASMD(ピン4/ピン8)：**位相セレクタ入力。このピンにより、チャネルとCLKOUT信号の位相関係が決まります。ゼロ位相をTG1の立ち上がりエッジとして定義した場合、次のようにになります。このピンをSGNDに接続すると、TG2が180°に、CLKOUTが60°にロックされます。このピンをINTVCCに接続すると、TG2が240°に、CLKOUTが120°にロックされます。このピンをフロート状態にすると、TG2が180°に、CLKOUTが90°にロックされます。

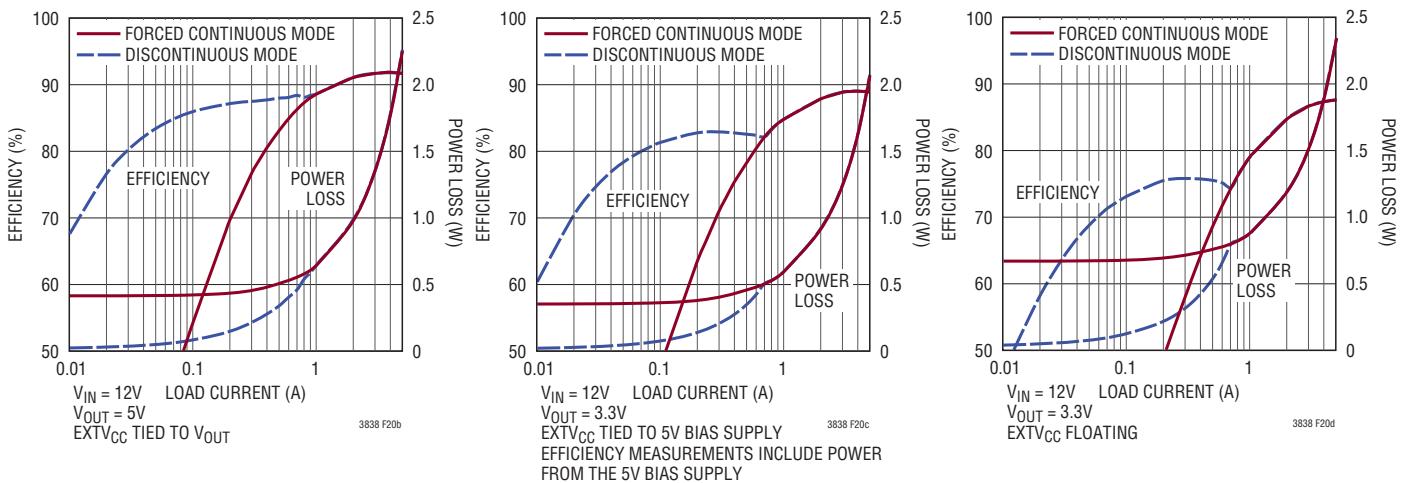

**MODE/PLLIN(ピン5/ピン9)：**動作モードの選択または外部クロックの同期入力。このピンをINTVCCに接続すると、強制連続モード動作が選択されます。このピンをSGNDに接続すると、不連続モード動作が可能になります。このピンに外部クロックを与えると、両方のチャネルが強制連続モードで動作し、外部クロックに同期します。

**CLKOUT(ピン6/ピン10)：**内部クロック発生器のクロック出力。その出力レベルの振幅はINTVCCからSGNDまでです。MODE/PLLINピンにクロック入力が存在すると、CLKOUTは入力クロックに同期し、その位相はPHASMDピンによって設定されます。MODE/PLLINにクロックが入力されないと、周波数はRTピンによって設定されます。別のコントローラに同期させるため、そのコントローラのMODE/PLLINピンに接続することができます。

**SGND(ピン7/ピン11)：**信号グランド。すべての小信号用アナログ部品および補償用部品は、このグランドに接続します。SGNDは1本のPCBトレースを使って露出パッドおよびPGNDピンに接続します。

**RT(ピン8/ピン12)：**クロック発生器の周波数設定ピン。スイッチング周波数を200kHz～2MHzの範囲に設定するには、RTとSGNDの間に外付け抵抗を接続します。周波数を確実にロックするには、MODE/PLLINに入力する外部クロックをこの設定周波数の±30%以内にします。RTピンがフロート状態の場合、周波数は200kHzよりわずかに低い値に内部で設定されます。

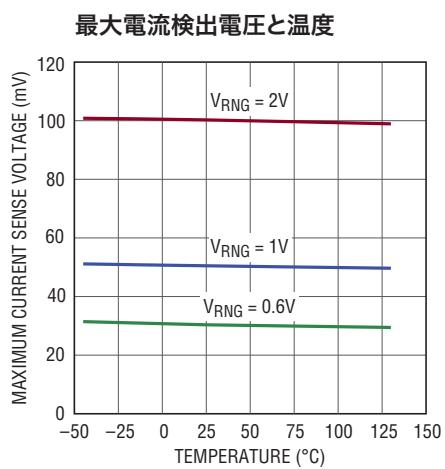

**VRNG1、VRNG2(ピン9、3/ピン13、7)：**電流検出電圧範囲の入力。0.6V～2Vに設定すると、VRNG<sub>1,2</sub>に印加される電圧は、SENSE1、2<sup>+</sup>とSENSE1、2<sup>-</sup>の間の最大検出電圧の20倍、つまり、いずれのチャネルの場合も( $V_{SENSE}^+ - V_{SENSE}^-$ ) = 0.05 • VRNGとなります。VRNGをSGNDに接続すると、そのチャネルは、0.6VのVRNGに相当する30mVの最大検出電圧で動作し、INTVCCに接続すると、1VのVRNGに相当する50mVの最大検出電圧で動作します。

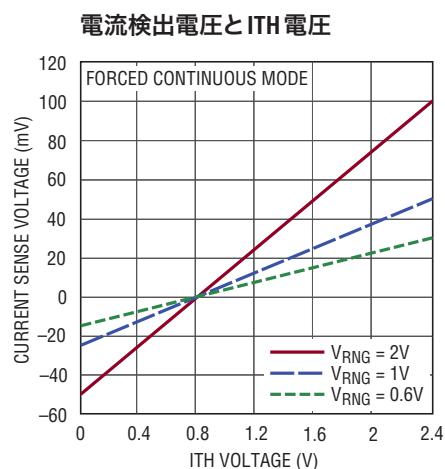

**ITH1、ITH2(ピン10、2/ピン14、6)：**電流制御しきい値。このピンはエラーアンプの出力であり、スイッチング・レギュレータの補償点です。電流コンバレータのしきい値はこの制御電圧に応じて増加します。電圧範囲は0V～2.4Vで、0.8Vがゼロ検出電圧(インダクタ谷電流がゼロ)に相当します。

**TRACK/SS1、TRACK/SS2(ピン11、1/ピン15、5)：**外部トラッキングとソフトスタート入力。LTC3838は、帰還電圧( $V_{OUTSENSE1}^+ - V_{OUTSENSE1}^-$ ) および $V_{FB2}$ を、0.6Vと、TRACK/SS1、2ピンの電圧のそれれいづれか低い方に安定化します。各TRACK/SSピンには、温度に依存しない1μAの内部プルアップ電流源が接続されています。このピンとグランドの間に接続したコンデンサにより、最終的な安定化出力電圧までのランプ時間が設定されます。あるいは、別の電源をこのピンに接続すると、出力が起動時に別の電源をトラッキングすることができます。

**V<sub>OUTSENSE1</sub><sup>+</sup>(ピン12/ピン16)：**チャネル1の差動出力検出アンプの(+)入力。このピンは、V<sub>OUT1</sub>の出力コンデンサの正端子と負端子との間の帰還抵抗分割器に接続します。公称動作時、LTC3838は差動出力電圧V<sub>OUT1</sub>を、帰還抵抗分割器の比で分圧した0.6Vに安定化しようとします。

## ピン機能 (QFN/TSSOP)

**VOUTSENSE<sub>1</sub>- (ピン13/ピン17)**：チャネル1の差動出力検出アンプの(-)入力。このピンはVOUT<sub>1</sub>の出力負荷コンデンサの負端子に接続します。

**SENSE1<sup>+</sup>、SENSE2<sup>+</sup>(ピン14、37/ピン18、3)**：差動電流検出コンパレータの(+)入力。ITHピンの電圧、およびSENSE<sup>-</sup>ピンとSENSE<sup>+</sup>ピンの間の制御されたオフセットによって、電流コンパレータの作動しきい値が設定されます。このコンパレータは、RSENSEによる検出またはインダクタのDCRによる検出に使用できます。RSENSEによる検出では、SENSE<sup>+</sup>ピンをRSENSEの(+)端子にケルビン(4線)接続します。DCRによる検出では、インダクタ両端間に接続されたDCR検出コンデンサと検出抵抗の接続点にSENSE<sup>+</sup>ピンを接続します。

**SENSE1<sup>-</sup>、SENSE2<sup>-</sup>(ピン15、36/ピン19、2)**：差動電流検出コンパレータの(-)入力。このコンパレータは、RSENSEによる検出またはインダクタのDCRによる検出に使用できます。RSENSEによる検出では、SENSE<sup>-</sup>ピンをRSENSEの(-)端子にケルビン(4線)接続します。DCRによる検出では、インダクタのVOUTノード接続点に接続されているDCR検出コンデンサにSENSE<sup>-</sup>ピンを接続します。これらのピンは、上側MOSFETのオン時間を調整するための出力電圧検出ピンとしても機能します。各SENSE<sup>-</sup>ピンとSGNDの間には追加の500k内部抵抗があるので、これらのピンへのインピーダンスはSENSE<sup>+</sup>ピンとは異なります。

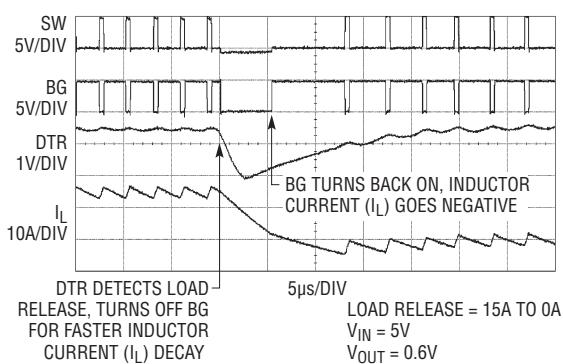

**DTR1、DTR2(ピン16、35/ピン20、1)**：オーバーシュートを低減するための負荷解放トランジエント検出ピン。負荷電流が急激に減少した場合に、このDTRピンの電圧がINTVCCの電圧の半分より低くなると、下側ゲート(BG)がオフすることにより、インダクタ電流が急速にゼロまで減少するので、VOUTのオーバーシュートが低減されます。(詳細については、「アプリケーション情報」のセクションの「負荷解放時のトランジエントの検出」を参照してください。) 2.5μAの内部電流源により、このピンの電圧はINTVCCの電圧に向かって上昇します。DTR機能をディスエーブルするには、DTRピンをそのままINTVCCに接続します。

**RUN1、RUN2(ピン17、34/ピン21、38)**：実行制御入力。内蔵の絶対温度比例式(PTAT) プルアップ電流源(25°Cで約1.2μA)は、このピンに常時接続されています。RUN1ピンおよびRUN2ピンの電圧をしきい値電圧(25°Cで約0.8V)より低くすると、INTVCCおよびDRVCCのすべてのバイアスがシャットダウンし、LTC3838はマイクロパワー・シャットダウン・モードになります。一方のRUNピンの電圧をこのしきい値より高くすると、内部のバイアス電源および特定のチャネルの回路がオンになります。1つのRUNピンの電圧が上昇して1.2Vを超えると、対応するチャネルのTGドライバおよびBGドライバがオンになり、温度に依存しない追加の5μA プルアップ電流源がこのRUNピンに内部で接続されます。RUNピンは最大50μAの電流を吸い込むことや、強制的に6V以下の電圧にすることが可能です。

**PGOOD1、PGOOD2(ピン18、33/ピン22、37)**：パワーグッド・インジケータの出力。このオープンドレインのロジック出力は、50μsのパワーバッドマスキング遅延の後、出力電圧がレギュレーション点を中心とした±7.5%の範囲から外れると、グランド電位に低下します。レギュレーション点に戻る場合、パワーグッド表示までには非常に短時間の遅延があり、電圧範囲の両側には約2%のヒステリシスがあります。

**BOOST1、BOOST2(ピン19、32/ピン23、36)**：上側MOSFETドライバの昇圧されたフロート電源。ブーストストラップ・コンデンサC<sub>B</sub>の(+)端子をこのピンに接続します。BOOSTピンはV<sub>IN</sub>により、ダイオードの電圧降下分だけDRVCCより低い電圧、つまり(DRVCC - V<sub>D</sub>)と(V<sub>IN</sub> + DRVCC - V<sub>D</sub>)の間で振幅します。

**TG1、TG2(ピン20、31/ピン24、35)**：上側のゲート・ドライバ出力。TGピンは、上側のNチャネル・パワーMOSFETのゲートを、V<sub>DRVCC</sub>の電圧振幅により、SWからBOOSTまでの電圧範囲で駆動します。

## ピン機能 (QFN/TSSOP)

**SW1、SW2(ピン21、30/ピン25、34)：**インダクタへのスイッチ・ノードの接続ピン。電圧振幅は、ダイオードの電圧降下分だけグランドより低い電圧から $V_{IN}$ までです。ポートストラップ・コンデンサ $C_B$ の(-)端子をこのノードに接続します。

**BG1、BG2(ピン22、29/ピン26、33)：**下側のゲート・ドライバ出力。BGピンは、下側のNチャネル・パワーMOSFETのゲートをPGNDからDRVCCまでの電圧範囲で駆動します。

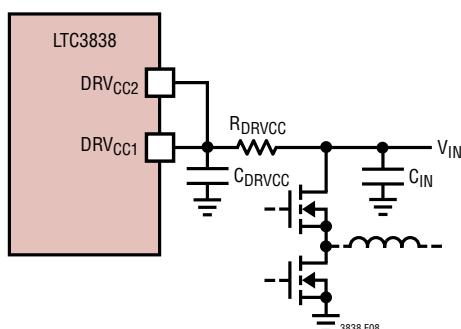

**DRVCC1、DRVCC2(ピン23、28/ピン27、32)：**下側のゲート・ドライバの電源。DRVCC1は、5.3Vの内部レギュレータの出力であります。DRVCC2は、EXTVCCスイッチの出力であります。通常、2つのDRVCCピンはPCB上で互いに短絡されており、最小 $4.7\mu F$ のセラミック・コンデンサ $C_{DRVCC}$ でPGNDに減結合します。

**$V_{IN}$ (ピン24/ピン28)：**入力電源。電源電圧の可能な範囲は4.5V～38Vです。ノイズ耐性を増すには、RCフィルタを使用してこのピンをSGNDに減結合します。このピンの電圧は上側ゲートのオン時間を調整するためにも使用されるので、このピンはRCフィルタを介して主電力の入力電源に接続することを推奨します。

**PGND(ピン25、露出パッドのピン39/ピン29、露出パッドのピン39)：**電源グランド。このピンは、下側のNチャネル・パワーMOSFETのソース、 $C_{DRVCC}$ の(-)端子、および $C_{IN}$ の(-)端子のできるだけ近くに接続します。露出パッドとPGNDピンはICの下に1本のPCBトレースを通してSGNDピンに接続します。電気的性能と定格熱性能を得るため、露出パッドは回路基板に半田付けする必要があります。

**INTVCC(ピン26/ピン30)：**内部回路の電源入力(ゲート・ドライバは含まない)。通常、SGNDへのデカップリングRCフィルタ(標準で $2\Omega$ と $1\mu F$ )を介してDRVCCピンから給電します。

**EXTVCC(ピン27/ピン31)：**外部電源入力。EXTVCCが切り替え電圧(標準で4.6V)を超えると、このピンは内部スイッチによってDRVCC2に接続され、内部レギュレータがシャットダウンします。そのため、INTVCCとゲート・ドライバはEXTVCCから電力を供給されます。 $V_{IN}$ ピンには引き続き電源を供給する必要がありますが、流れる電流は最小限で済みます。

**$V_{FB2}$ (ピン38/ピン4)：**チャネル2のエラーアンプ帰還入力。このピンは、 $V_{OUT2}$ からの外付けの帰還抵抗分割器にエラーアンプを接続します。公称動作時、LTC3838は $V_{OUT2}$ を、帰還抵抗分割器の比で分圧した0.6Vに安定化しようとします。

このピンをINTVCCに短絡すると、チャネル2のエラーアンプはディスエーブルされ、ITH2ピンは内部でITH1ピンに接続されます。(この結果、TRACK/SS2は機能しなくなり、PGOOD2ピンの電圧は常に“L”になります)。こうすることにより、このデバイスは2相、単一出力電圧の降圧コントローラとして機能することが可能であり、ITH出力および補償のため、2つのチャネルが**単一の**チャネル1のエラーアンプを使用します。

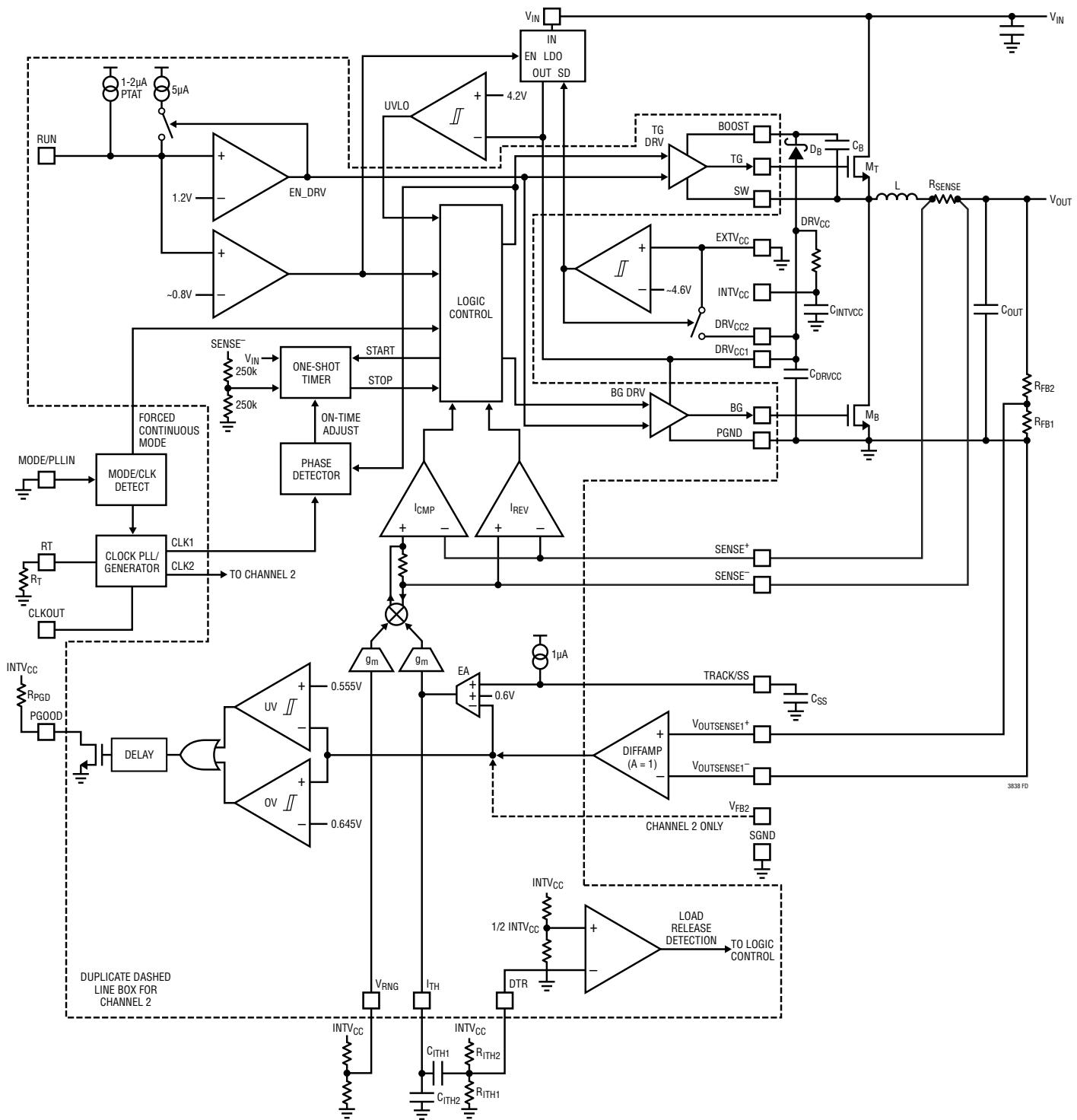

## 機能図

## 動作（「機能図」を参照）

### メイン制御ループ

LTC3838は、オン時間が制御された谷電流モードの降圧DC/DCデュアル・コントローラで、2つのチャネルが位相のずれた状態で動作します。各チャネルは、メインと同期の両方のNチャネルMOSFETを駆動します。2つのチャネルは、2つの独立した安定化出力となるよう構成されるか、単一出力に合成されます。

上側MOSFETはワンショット・タイマによって決定された時間だけオンします。ワンショット・タイマの時間は、固定スイッチング周波数を維持するように制御されます。上側MOSFETがオフすると、短い遅延時間の後に下側MOSFETがオンします。この遅延、つまり不動作時間は、上側と下側の両方のMOSFETが同時にオンになり、そのために $V_{IN}$ から電源グランドへ直接流れるシートスルー電流が生じないようにするための時間です。次のスイッチング・サイクルが開始されるのは、ITHピンおよびVRNGピンの電圧によって設定された作動レベルよりインダクタ電流が少なくなったことを電流コンパレータICMPが検出した時点です。下側MOSFETは即座にオフになり、上側MOSFETは再びオンになって、ワンショット・タイマが再起動され、サイクルが繰り返されます。シートスルー電流を防ぐため、上側MOSFETがオンする前の短いデッドタイム遅延も備えています。この瞬間にインダクタ電流はその「谷」に達して、再び上昇し始めます。

インダクタ電流は、SENSE<sup>+</sup>とSENSE<sup>-</sup>間の電圧を検出することによって決まります。検出するには、インダクタに直列に接続した抵抗を直接使用するか、インダクタの両端に接続したRCフィルタを介してインダクタのDC抵抗性(DCR)電圧降下を間接的に検出します。電流コンパレータの作動レベルICMPは、ITHピンの電圧に比例し、約0.8VのITH電圧に相当するゼロ電流しきい値を備えています。

エラーアンプ(EA)は、帰還信号を0.6Vの内部リファレンス電圧と比較することにより、このITH電圧を調整します。チャネル1では、差電圧アンプ(DIFFAMP)が差動帰還信号( $V_{OUTSENSE1^+} - V_{OUTSENSE1^-}$ )をEAのシングルエンド入力に変換します。チャネル2では、SGNDを基準にして $V_{FB2}$ を直接使用します。出力電圧は、帰還電圧が0.6Vの内部リファレンスと等しくなるように安定化されます。負荷電流が増加または減少すると、リファレンスと比べて差動帰還電圧が瞬間的に降下または上昇します。EAは、その後、平均インダクタ電流

が負荷電流と再度一致するまでITH電圧つまりインダクタの谷電流設定値を上下させます。これにより、出力電圧は安定化電圧に戻ります。

LTC3838はトランジエント検出(DTR)ピンを特徴としており、ITH電圧の一次導関数をモニタすることにより、「負荷解放」状態、つまり負荷電流が突然低下するトランジエント状態を検出します。この状態が検出されると、下側ゲート(BG)がオフになり、下側MOSFETのボディ・ダイオードをインダクタ電流が流れるので、SWノードの電圧をボディ・ダイオードの順方向電圧の分だけPGNDより低くすることができます。これにより、インダクタの両端により低い負の差動電圧( $V_{SW} - V_{OUT}$ )が発生するので、インダクタ電流は急速に0まで低下し、したがって $V_{OUT}$ のオーバーシュートを小さくすることができます。詳細については、「アプリケーション情報」の「負荷解放時のトランジエントの検出」を参照してください。

### 差動出力検出

このデュアル・コントローラの第1のチャネルは、差動出力電圧の検出機能を特徴としています。出力電圧は外部で抵抗分割され、コントローラの帰還電圧が生成されます。内部の差電圧アンプ(DIFFAMP)は、出力の遠隔グランド・リファレンスを基準にしてこの帰還電圧を検出し、差動帰還電圧を生成します。この方式では、デバイス付近のグランドと遠隔出力のグランド間のグランド・オフセットを除去できるので、より正確な出力電圧が得られます。チャネル1では、デバイス付近のグランド(SGND)を基準にした遠隔出力グランドのずれが最大±500mVまで許容されます。

### DRV<sub>CC</sub>/EXTV<sub>CC</sub>/INTV<sub>CC</sub>電源

DRV<sub>CC1,2</sub>は下側MOSFETドライバの電源です。通常、2つのDRV<sub>CC</sub>ピンはPCB上で互いに短絡されており、最小4.7μFのセラミック・コンデンサC<sub>DRVCC</sub>でPGNDに減結合します。上側MOSFETドライバは、フロート状態のブートストラップ・コンデンサ(C<sub>B1</sub>, C<sub>B2</sub>)からバイアスされます。このコンデンサは、上側MOSFETがオフしてSWピンの振幅が小さくなると、外付けのショットキ・ダイオードを介して各サイクル中に再充電されます。

DRV<sub>CC</sub>には、次の2つの手段で電源を供給できます。1つは、 $V_{IN}$ から給電され、DRV<sub>CC1</sub>に5.3Vを出力可能な内部の低ド

## 動作 (「機能図」を参照)

ロップアウト(LDO)リニア電圧レギュレータです。もう1つは、EXTV<sub>CC</sub>ピンをDRV<sub>CC2</sub>に短絡可能な内部のEXTV<sub>CC</sub>スイッチ(オン抵抗が約2Ω)です。

EXTV<sub>CC</sub>ピンの電位がEXTV<sub>CC</sub>切り替え電圧(標準4.6Vで200mVのヒステリシスあり。「電気的特性」の表を参照)より低くなると、内部の5.3V LDOがイネーブルされます。EXTV<sub>CC</sub>ピンをこのEXTV<sub>CC</sub>切り替え電圧より高い外部電圧源に接続すると、LDOがシャットダウンされ、内部のEXTV<sub>CC</sub>スイッチによりEXTV<sub>CC</sub>ピンがDRV<sub>CC2</sub>ピンに短絡されるので、DRV<sub>CC</sub>とINTV<sub>CC</sub>の電源は外部電圧源によって供給されます。これにより、全体的な効率が向上し、LDOで消費される電力で生じる内部自己発熱が減少します。この外部電源は、(降圧コンバータの出力を切り替え電圧の上限値である4.8Vより高く設定している場合は)降圧コンバータ自体の出力にしてもかまいません。VINピンには引き続き電源を供給する必要がありますが、流れる電流は最小限で済みます。

ゲート・ドライバ以外のほとんどの内部制御回路の電源は、INTV<sub>CC</sub>ピンから供給されます。INTV<sub>CC</sub>の電源は、結線した複数のDRV<sub>CC</sub>ピンから供給できますが、SGNDとの間に接続した外付けのRCフィルタを介しています。これはスイッチングに起因するノイズを除去するためです。

### シャットダウンと起動

RUN1ピンおよびRUN2ピンには、これらのピンの電圧を高くる絶対温度比例式(PTAT)電流源(25°Cで約1.2μA)がそれぞれ内蔵されています。RUN1ピンとRUN2ピンの両方の電圧を一定のしきい値電圧(25°Cで約0.8V)より低くすると、INTV<sub>CC</sub>およびDRV<sub>CC</sub>のすべてのバイアスがシャットダウンされ、LTC3838はVINピンに最小のI<sub>Q</sub>が流れるマイクロパワー・シャットダウン・モードになります。LTC3838のDRV<sub>CC</sub>が(内部の5.3V LDOレギュレータまたはEXTV<sub>CC</sub>を介して)起動状態にバイアスされ、さらにINTV<sub>CC</sub>の対応するチャネルの内部回路が起動状態にバイアスされるのは、内部のプルアップ電流によるか、またはロジック・ゲート出力などの外部電圧源で直接駆動することにより、2つのRUNピンのいずれかまたは両方が0.8Vのしきい値より高くなったときです。

それぞれのチャネルのRUNピンの電圧が1.2Vに上昇するまで、LTC3838のチャネルはスイッチングを開始しません。RUNピンの電圧が1.2Vより高くなると、対応するチャネルのTGドライバとBGドライバがイネーブルされ、TRACK/SSが解放

されます。温度に依存しない追加の5μA プルアップ電流が各チャネルのRUNピンに内部で接続されます。TG、BGおよび追加の5μA プルアップ電流をオフにするには、RUNピンの電圧を1.2Vより約100mV 低くする必要があります。これらの組み込まれた電流ヒステリシスと電圧ヒステリシスにより、ノイズに起因する微小変動性の誤ったオンまたはオフを防止します。RUNピンのこのような機能により、外付けの抵抗分圧器をVINから接続して入力低電圧ロックアウト(UVLO)を設定できます。

チャネルの出力電圧(V<sub>OUT</sub>)の起動はTRACK/SSピンの電圧によって制御されます。TRACK/SSピンの電圧が0.6Vの内部リファレンスより低いと、(差動)帰還電圧は0.6VのリファレンスではなくTRACK/SSピンの電圧に安定化されます。TRACK/SSピンと信号グランドの間に外付けのコンデンサを接続することにより、TRACK/SSピンを使用して出力電圧のソフトスタート起動時間を設定できます。温度に依存しない内部の1μA プルアップ電流源がこのコンデンサを充電し、TRACK/SSピンに電圧ランプを発生します。TRACK/SS電圧がグランドから0.6Vまで直線的に上昇すると、スイッチングが開始され、V<sub>OUT</sub>はその最終値まで滑らかに上昇し、帰還電圧は0.6Vになります。TRACK/SSは0.6Vを超えて上昇し続けますが、約3.7Vでクランプされます。

あるいは、TRACK/SSピンを使用して、マスター・スレーブ構成のように外部電源を追跡することもできます。通常、このためにはマスター電源とTRACK/SSピン間に抵抗分割器を接続することが必要です(「アプリケーション情報」のセクションを参照)。

TRACK/SSは、対応するチャネルのRUNピンの電圧が(ヒステリシスを考慮した上で)1.2Vのしきい値より低くなるか、INTV<sub>CC</sub>ピンの電圧またはDRV<sub>CC1, 2</sub>のいずれかのピンの電圧がそれぞれの低電圧ロックアウト(UVLO)しきい値より低くなると、内部で“L”になります。

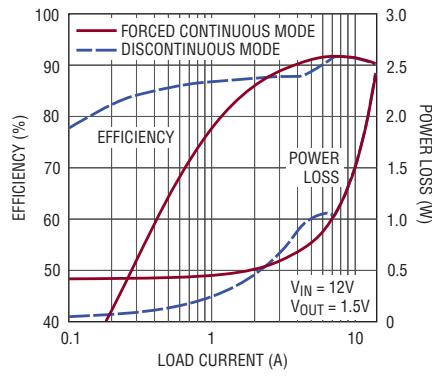

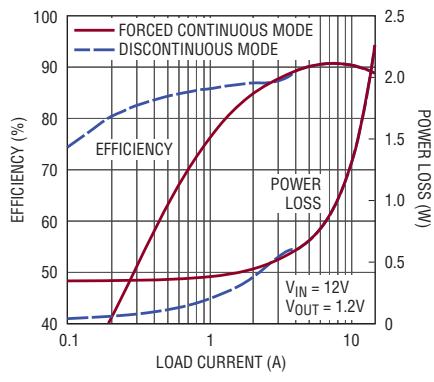

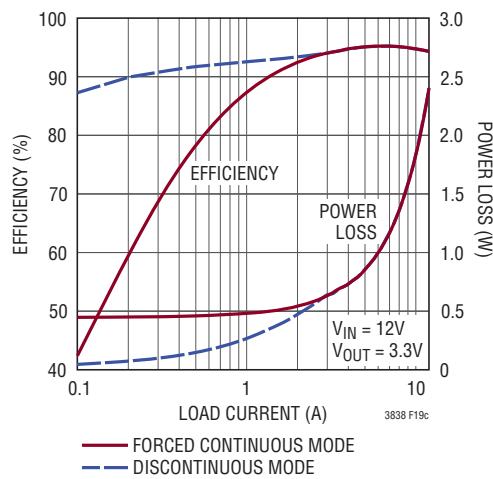

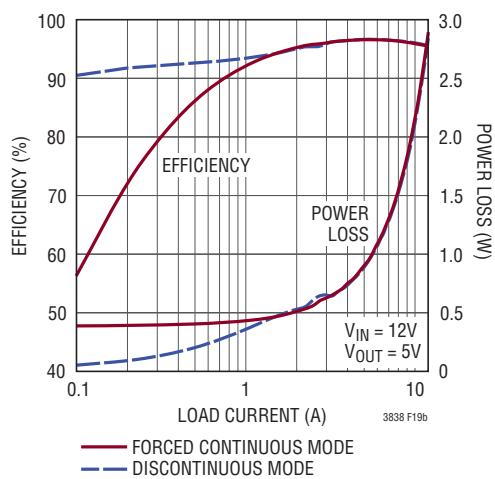

### 軽負荷電流動作

MODE/PLLINピンをINTV<sub>CC</sub>に接続するか外部クロックをMODE/PLLINに入力すると、LTC3838は連続モードで動作するように強制されます。負荷電流が全負荷のピーク・トゥ・ピークのリップルの1/2より小さいと、インダクタ電流は0まで低下するか、負の値になることがあります。これにより、固定周波数動作が可能ですが、その代償として軽負荷時の効率が低下します。

## 動作（「機能図」を参照）

MODE/PLLINピンを開放のままにするか、または信号グランドに接続すると、該当チャネルは不連続モード動作に移行します。このモードでは、インダクタ電流が0に近づくと、電流反転コンパレータ( $I_{REV}$ )が下側のMOSFET( $M_B$ )をオフするので、負のインダクタ電流が流れなくなり、軽負荷時の効率が向上します。このモードでは、両方のスイッチを長期にわたってオフにしておくことができます。出力コンデンサが負荷電流によって放電して出力電圧が低下すると、最終的にEAがITH電圧をゼロ電流レベル(0.8V)より高くして、新しいスイッチング・サイクルを開始します。

## パワーグッドと�オルト保護

各PGOODピンは、オープンドレインの内部NチャネルMOSFETに接続されています。このピンは、外付け抵抗または電流源を使用して最大6V(たとえば、 $V_{OUT1,2}$ または $DRV_{CC}$ )まで電圧を高くすることができます。帰還電圧が0.6Vのリファレンス電圧から±7.5%の範囲を外れると、過電圧コンパレータ(OV)または低電圧コンパレータ(UV)によりMOSFETがオンになり、PGOODピンは“L”になります。PGOODピンは、該当チャネルのRUNピン電圧が(ヒステリシスを考慮した上で)1.2Vのしきい値より低くなるか、低電圧ロックアウト(UVLO)の状態になると“L”になります。チャネル1の帰還電圧は $V_{OUTSENSE1}^+$ を介して $V_{OUTSENSE1}^-$ を基準にした差動で検出されますが、チャネル2では $V_{FB2}$ を介してSGNDを基準にして検出されます。

帰還電圧が±7.5%の範囲内に入ると、オープンドレインNMOSがオフし、外部電源によってPGOODピンの電圧は高くなります。PGOODピンは帰還電圧が範囲内に入ると即座にパワーグッドを示します。ただし、チャネルの帰還電圧が範囲を外れた場合には、そのPGOODが“L”になるまで内部に50μsの遅延が存在します。過電圧(OV)状態では、 $M_T$ がオフすると遅延なしで即座に $M_B$ がオンし、過電圧状態が解消されるまでオン状態が保持されます。

出力がグランドに短絡するなど、出力が安定化電圧の1/2より低くなると、フォールドバック電流制限が作動します。帰還電圧が0Vに近づくと、ITHピンの内部クランプ電圧が2.4Vから約1.27Vに低下することにより、インダクタの谷電流レベルが最大値の約30%に減少します。フォールドバック電流制限は起動時にはディスエーブルされます。

## 周波数の選択と外部クロックへの同期

内部発振器(クロック発生器)は、固定する個々のチャネルに、位相が交互に入れ替わる内部クロック信号を供給します。各スイッチング・チャネルのスイッチング周波数および位相は、上側MOSFETのターンオン時間(オン時間)をワンショット・タイマを介して調整することにより、別々に制御されます。これは、上側MOSFETのターンオン信号とその内部リファレンス・クロック間の位相関係を位相検出器によって検出することで実現されます。また、ワンショット・タイマの時間間隔は、上側MOSFETがオンするときの立ち上がりエッジが各チャネルの内部リファレンス・クロック信号に常に同期するように、サイクルごとに調整されます。

内部発振器の周波数は、RTピンと信号グランド(SGND)の間に抵抗 $R_T$ を接続することにより、200kHz～2MHzの範囲に設定できます。RTピンは内部で1.2Vに安定化されています。

周波数または干渉に関する要件が厳しいアプリケーションでは、MODE/PLLINピンに接続された外部クロック発生源を使用し、クロックの位相同期ループ(クロックPLL)を介して内部のクロック信号に同期させることができます。LTC3838は、外部クロックに同期しているときは強制連続モードで動作します。同期を正常に行うには、外部クロック周波数を内部発振器周波数の±30%以内にする必要があります。クロック入力レベルは“H”的場合は2V以上で、“L”的場合は0.5V以下にします。MODE/PLLINピンには600kΩのプルダウン抵抗が内蔵されています。

## マルチチップ動作

PHASMDピンは、表1に示すように、2つのチャネルの内部リファレンス・クロック信号、ならびにCLKOUT信号の間の相対的な位相を決定します。表に記載されている位相は、チャネル1の内部リファレンス・クロック信号の立ち上がりエッジとして定義されている0°を基準にしています。CLKOUT信号を使用して、单一の大電流出力または異なる出力に電力を供給するマルチフェーズ電源ソリューションで追加のパワーレベルを同期することができます。

## 動作 (「機能図」を参照)

マルチチップ・ソリューションを使って、最大12相動作のシステムを構成することができます。チャネルの位相を交互に入れ替える標準構成を表2に示します。

表1

| PHASMD | SGND | フロート | INTV <sub>CC</sub> |

|--------|------|------|--------------------|

| チャネル1  | 0°   | 0°   | 0°                 |

| チャネル2  | 180° | 180° | 240°               |

| CLKOUT | 60°  | 90°  | 120°               |

表2

| 位相の数 | LTC3838の数        | ピンの接続<br>[ピン名称(デバイスの番号)]                                                                                                                                                                                                                                                     |

|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2    | 1                | PHASMD(1) = フロートまたはSGND                                                                                                                                                                                                                                                      |

| 3    | 2、または1 + LTC3833 | PHASMD(1) = INTV <sub>CC</sub><br>MODE/PLLIN(2) = CLKOUT(1)                                                                                                                                                                                                                  |

| 4    | 2                | PHASMD(1) = フロート<br>PHASMD(2) = フロートまたはSGND<br>MODE/PLLIN(2) = CLKOUT(1)                                                                                                                                                                                                     |

| 6    | 3                | PHASMD(1) = SGND<br>PHASMD(2) = SGND<br>MODE/PLLIN(2) = CLKOUT(1)<br>PHASMD(3) = フロートまたはSGND<br>MODE/PLLIN(3) = CLKOUT(2)                                                                                                                                                    |

| 12   | 6                | PHASMD(1) = SGND<br>PHASMD(2) = SGND<br>MODE/PLLIN(2) = CLKOUT(1)<br>PHASMD(3) = フロート<br>MODE/PLLIN(3) = CLKOUT(2)<br>PHASMD(4) = SGND<br>MODE/PLLIN(4) = CLKOUT(3)<br>PHASMD(5) = SGND<br>MODE/PLLIN(5) = CLKOUT(4)<br>PHASMD(6) = フロートまたはSGND<br>MODE/PLLIN(6) = CLKOUT(5) |

## 单一出力 PolyPhase 構成

LTC3838を2相、单一出力の降圧コントローラとして使用するには、以下のようにします。V<sub>FB2</sub>ピンをINTV<sub>CC</sub>に接続します。これにより、チャネル2のエラーアンプがディスエーブルされ、ITH2ピンは内部でITH1ピンに接続されます。補償用R-C部品をITH1ピンに接続します。ITH2ピンは開放のままでおくことも、外部でITH1ピンと短絡しておくこともできます。TRACK/SS2ピンとPGOOD2ピンは機能しなくなるので、開放のままでかまいません。RUN1、RUN2、DTR1、DTR2、VRNG1およびVRNG2の各ピンは、引き続き2つのチャネル

として個別に機能するので、单一出力アプリケーションの場合には、外部で短絡する必要があります。2つのチャネルの位相が180°ずれるように、PHASMDはSGNDまたはフロートに設定します。入力コンデンサからのピーク電流は、使用する位相の数で実質的に分割され、電力損失は実効値電流の2乗に比例するので、効率の低下が大幅に抑えられる可能性があります。2相出力の実現により、入力経路の電力損失を最大75%低減できます。

3相以上の单一出力コンバータを構成するには、LTC3838またはLTC3833デバイスを追加します。最初のデバイスは、前述した2相の場合と同様に接続します。追加する必要があるのはLTC3838の1チャネルのみである場合は、追加する位相に対してチャネル1を使用してください。

- ITH1ピンを最初のデバイスのITH1ピンに接続します。

- RUN1ピンを最初のデバイスの2つのRUNピンに接続します。

- V<sub>OUTSENSE1</sub><sup>+</sup>ピンを最初のデバイスのV<sub>OUTSENSE1</sub><sup>+</sup>ピンに接続します。

- V<sub>OUTSENSE1</sub><sup>-</sup>ピンを最初のデバイスのV<sub>OUTSENSE1</sub><sup>-</sup>ピンに接続します。

- TRACK/SS1ピンを最初のデバイスのTRACK/SS1ピンに接続します。

両方のチャネルが必要な場合は、追加するLTC3838デバイスを最初のLTC3838デバイスと同じ方法で接続して、2番目のチャネルのエラーアンプをディスエーブルする必要があります。

- V<sub>FB2</sub>ピンをデバイス自体のINTV<sub>CC</sub>に接続します。

- ITH1ピンを最初のデバイスのITH1ピンに接続します。

- 2つのRUNピンを最初のデバイスの2つのRUNピンに接続します。

- V<sub>OUTSENSE1</sub><sup>+</sup>ピンを最初のデバイスのV<sub>OUTSENSE1</sub><sup>+</sup>ピンに接続します。

- V<sub>OUTSENSE1</sub><sup>-</sup>ピンを最初のデバイスのV<sub>OUTSENSE1</sub><sup>-</sup>ピンに接続します。

- TRACK/SS1ピンを最初のデバイスのTRACK/SS1ピンに接続します。

## アプリケーション情報

必要な出力電圧と動作周波数が決定すると、外付け部品の選択は負荷要件が主体となり、インダクタと電流検出方法(検出抵抗 $R_{SENSE}$ またはインダクタのDCRによる検出)の選択が始まります。次に、パワーMOSFETを選択します。最後に、入力と出力のコンデンサを選択します。

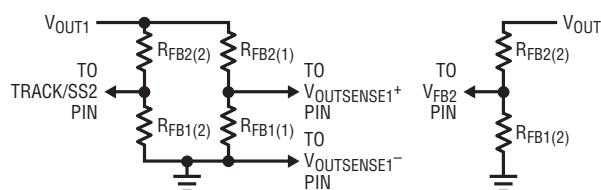

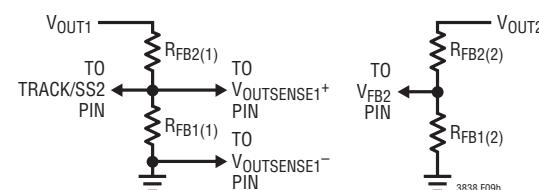

### 出力電圧の設定

図1に示すように、安定化出力とそのグランド・リファレンスの間に外付けの抵抗分割器を使用して出力電圧を設定します。チャネル1では、抵抗分割器は $V_{OUTSENSE1}^+$ ピンによって引き出され、グランド・リファレンスは $V_{OUTSENSE1}^-$ ピンによってデバイスから離れた場所で検出されて、この電圧は差動で検出されます。チャネル2では、抵抗分割器は $V_{FB2}$ ピンによって引き出され、電圧はSGNDピンの信号グランドが基準になります。引き出された(差動)帰還電圧を内部リファレンスの0.6Vに安定化することにより、得られる出力電圧は次式のようになります。

$$V_{OUT1} - V_{OUTSENSE1}^- = 0.6V \cdot (1 + R_{FB2}/R_{FB1})$$

および

$$V_{OUT2} = 0.6V \cdot (1 + R_{FB2}/R_{FB1})$$

たとえば、 $V_{OUT1}$ を5Vに設定し、出力のグランド・リファレンスがSGNDを基準にして-0.5Vの電位である場合、出力の絶対値はSGNDを基準にして4.5Vになります。最小(差動)出力電圧は内部リファレンスの0.6Vに制限され、最大出力電圧は5.5Vです。

$V_{OUTSENSE1}^+$ ピンは高インピーダンスのピンであり、nAレンジの漏れ電流以外入力バイアス電流は流れません。 $V_{OUTSENSE1}^-$ ピンからは約30μAの電流が流れ出します。 $V_{FB2}$ ピンは準高インピーダンスのピンであり、このピンから流れるバイアス電流は最小限で済みます。

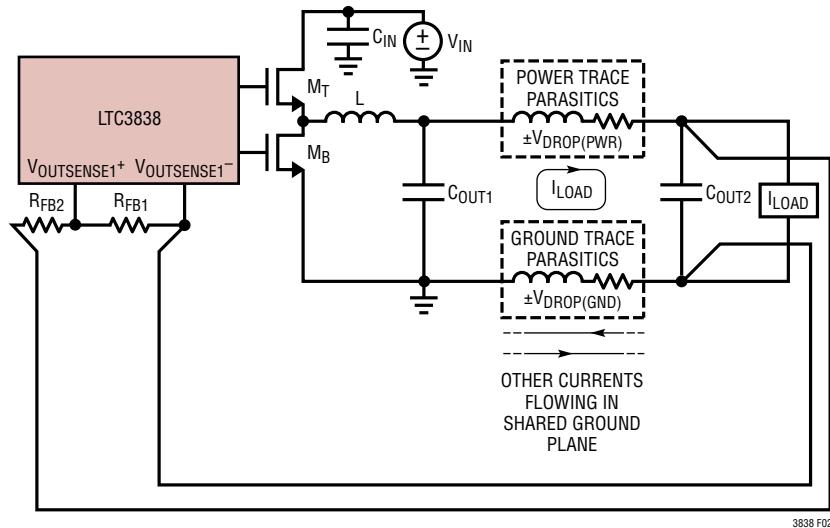

差動出力検出により、線路損失の大きい大電力の分散システムでより正確な出力レギュレーションが可能です。寄生素子による電源ラインとグランド・ラインの電位変動を図2に示します。これらの変動は、グランド・プレーンを共有するマルチアプリケーション・システムではさらに大きくなる可能性があります。差動出力検出を行わないと、これらの変動は安定化出力電圧の誤差として直接反映されます。LTC3838のチャネル1の差動出力検出では、出力の電力ラインおよびグランド・ラインでの変動を最大±500mVまで補正できます。

LTC3838のチャネル1の差動出力検出方式は、従来の方式とはまったく異なります。従来の方式では、安定化出力とグランド・リファレンスが差電圧アンプによって直接検出され、この差電圧アンプの出力が外付け抵抗分割器によって分圧されてエラーアンプ入力に供給されます。この従来の方式は、差動アンプの同相入力範囲によって制限され、通常は出力電圧の低い範囲に差動検出が制限されます。

LTC3838のチャネル1では、抵抗で分割された帰還電圧を差動で検出することにより、継ぎ目のない差動出力検出が可能で、これにより、0.6V～5.5Vの全出力範囲での差動検出が可能になります。差動アンプ(DIFFAMP)は帯域幅が8MHzと

図1. 出力電圧の設定

## アプリケーション情報

**図2. 共有グランド・プレーンを備えた大電力分散システムでの

線路損失のばらつきを補正するために使用した差動出力検出**

十分に大きいので、メイン・ループ補償およびトランジエント動作には影響しません。

帰還電圧( $V_{OUTSENSE1+}$ または $V_{FB2}$ )へのノイズ結合を防ぐため、抵抗分割器は $V_{OUTSENSE1+}$ ピンおよび $V_{OUTSENSE1-}$ ピン、または $V_{FB2}$ ピンおよびSGNDピンの近くに配置してください。遠隔出力のトレースおよびグランド・トレースは、遠隔出力への差動対としてまとめて配線します。最高の精度を得るには、遠隔出力およびグランドへのこれらのトレースを目的のレギュレーション点のできるだけ近くで接続します。

### スイッチング周波数の設定

動作周波数の選択は、効率と部品サイズとの間の兼ね合いです。動作周波数を低くするとMOSFETのスイッチング損失が減少することで効率が上がりますが、出力リップル電圧を低く抑えるにはインダクタンスや容量を大きくすることが必要です。逆に、動作周波数を高くすると効率は下がりますが部品サイズは小さくなります。

LTC3838のスイッチング周波数は、RTピンと信号グランドとの間に抵抗を接続することにより、200kHz～2MHzの範囲に

設定できます。この抵抗の値は次式に従って選択することができます。

$$R_T [\text{k}\Omega] = \frac{41550}{f [\text{kHz}]} - 2.2$$

クロックPLLとスイッチング・チャネルを含むコントローラ・システム全体の同期範囲は、この設定周波数を中心とした±30%以上です。したがって、外部クロック同期を行う場合は、外部クロック周波数がこのRTで設定する周波数から±30%の範囲内に入るようになります。同期の余裕を最大にするには、RTによる設定周波数を外部クロックと同じにすることを推奨します。詳細については、「位相と周波数の同期」のセクションを参照してください。

### インダクタの値の計算

動作周波数が高いほど小さい値のインダクタとコンデンサを使用できるという意味で、動作周波数とインダクタの選択には相関関係があります。MOSFETのゲート電荷損失のために、一般に周波数が高いほど効率が低下します。この基本的な二律背反事項に加えて、リップル電流と低電流動作に対するインダクタ値の影響も考慮しなければなりません。

## アプリケーション情報

インダクタの値は、リップル電流に直接影響を与えます。インダクタのリップル電流  $\Delta I_L$  は、インダクタンスまたは周波数が高くなると減少し、 $V_{IN}$  が高くなると増加します(次式)。

$$\Delta I_L = \left( \frac{V_{OUT}}{f \cdot L} \right) \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

大きな値の  $\Delta I_L$  を受け入れれば、低いインダクタンスを使用できますが、出力電圧リップル、出力コンデンサの ESR 損失、およびコア損失が大きくなります。リップル電流を設定するための妥当な出発点は、 $\Delta I_L = 0.4 \cdot I_{MAX}$  です。 $\Delta I_L$  が最大になるのは、入力電圧が最大のときです。リップル電流が規定の最大値を超えないことを保証するには、次式に従ってインダクタンスを選択します。

$$L = \left( \frac{V_{OUT}}{f \cdot \Delta I_{L(MAX)}} \right) \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

### インダクタのコアの選択

$L$  の値が分かつたら、インダクタの種類を選択する必要があります。基本的な2種類は鉄粉とフェライトです。鉄粉タイプの飽和曲線は緩やかで、フェライトのように急激には飽和しませんが、鉄粉タイプのインダクタの方がコア損失が大きくなります。フェライトを使用した設計ではコア損失がきわめて小さく、高いスイッチング周波数に適しているため、設計目標を飽和の防止と銅損失に集中することができます。

インダクタ値が同じ場合、コア損失はコア・サイズではなく、選択したインダクタンスに大きく依存します。インダクタンスが大きくなると、コア損失は減少します。インダクタンスを大きくするには、ワイヤの巻数を増やす必要があるため、銅損失は残念ながら増加します。

フェライト・コアの材質は**急激**に飽和します。つまり、設計ピーク電流を超えると、インダクタンスは突然低下します。その結果、インダクタのリップル電流が急増し、そのため出力電圧リップルが増加します。コアは絶対に飽和させないでください。

大電流、低電圧アプリケーション用に設計されたさまざまなインダクタを、スミダ電機、パナソニック、Coilcraft、東光、Vishay、Pulse、Würthなどのメーカーから入手できます。

### 電流検出ピン

インダクタ電流は、内部の電流コンパレータの入力である SENSE<sup>+</sup>ピンと SENSE<sup>-</sup>ピン間の電圧を介して検出されます。SENSE ピンの入力電圧範囲は-0.5V ~ 5.5V です。通常動作時にこれらのピンをフロート状態にしないよう注意してください。SENSE<sup>+</sup>ピンは、準高インピーダンス入力です。SENSE<sup>-</sup>ピンが 1.1V より低い電圧から上昇して 1.4V より低い電圧にとどまつた場合、それに対応するチャネルの SENSE<sup>+</sup>ピンにはバイアス電流は流れません。ただし、SENSE<sup>-</sup>ピンの電圧が 1.4V から下降して 1.1V より高い電圧にとどまつた場合、対応する SENSE<sup>+</sup>ピンには小電流(約 1μA)が流れます。このような電流は SENSE<sup>-</sup>ピンにも存在します。ただし、各 SENSE<sup>-</sup>ピンには、その他に SGND との間に 500k の抵抗が内蔵されています。これによって生じる電流( $V_{OUT}/500k$ )が、SENSE<sup>-</sup>ピンに流れ込む全電流の中心になります。RSENSE または DCR によるインダクタ電流の検出を設計する場合には、SENSE<sup>+</sup>ピンと SENSE<sup>-</sup>ピンの電流を考慮に入れる必要があります。

### 電流制限の設定

電流検出コンパレータの SENSE<sup>+</sup> と SENSE<sup>-</sup> 間の最大作動電圧(つまり「検出電圧」)は、ITH がその最大値(2.4V)でクラシプされている場合、VRNG ピンに印加されている電圧で設定され、次式で与えられます。

$$V_{SENSE(MAX)} = 0.05V_{RNG}$$

谷電流モード制御ループにより、インダクタ電流の谷が 0.05VRNG を超えることはありません。実際には、デバイスと外付け部品の値の許容誤差を考慮するために十分な余裕をとります。電流制限時には ITH が 2.4V に近づくことに注意してください。

外付け抵抗分割器を INTV<sub>CC</sub> に接続して使用すると VRNG ピンの電圧を 0.6V ~ 2V の範囲に設定できるので、その結果最大検出電圧は 30mV ~ 100mV になります。このように電圧範囲が広いので、さまざまなアプリケーションが可能です。VRNG ピンを SGND と INTV<sub>CC</sub> のいずれかに接続して内部のデフォルト設定を強制することもできます。VRNG を SGND に接続すると、デバイスの設定は VRNG が 0.6V の場合と等価になります。VRNG ピンを INTV<sub>CC</sub> に接続すると、デバイスの設定は VRNG が 2V の場合と等価になります。

## アプリケーション情報

### RSENSEによるインダクタ電流の検出

LTC3838は、値の小さい直列の電流検出抵抗(RSENSE)またはインダクタのDC抵抗(DCR)を介してインダクタ電流を検出するように構成できます。2つの電流検出方式のどちらを選択するかは、主として設計上、コスト、消費電力、精度のどれを探るかで決まります。DCRによる検出は高価な電流検出抵抗を省くことができ、特に大電流のアプリケーションで電力効率が高いので普及しつつあります。ただし、電流検出抵抗からは、コントローラの最も正確な電流制限値が得られます。

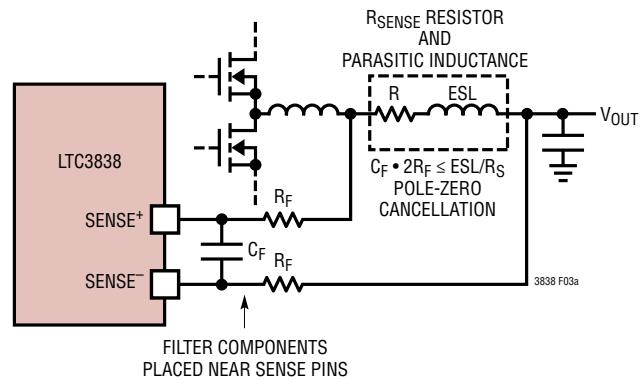

標準的なRSENSEによるインダクタ電流の検出方式を図3aに示します。フィルタ部品( $R_F$ ,  $C_F$ )はデバイスの近くに配置する必要があります。図3bに示すように、正と負の検出トレースは差動対として互いに近づけて配線し、検出抵抗の下でケルビン(4線)接続する必要があります。電流を他の場所で検出すると、実質的に寄生インダクタンスが電流検出素子に付加されて検出端子での情報が劣化するので、設定した電流制限値が予測できない値になることがあります。

RSENSEは必要な最大出力電流に基づいて選択します。最大電流 $I_{OUT(MAX)}$ 、 $V_{RNG}$ によって設定される最大検出電圧 $V_{SENSE(MAX)}$ 、および最大インダクタ・リップル電流 $\Delta I_L(MAX)$ が与えられると、RSENSEの値は次式で選択できます。

$$R_{SENSE} = \frac{V_{SENSE(MAX)}}{I_{OUT(MAX)} - \frac{\Delta I_L(MAX)}{2}}$$

逆に、RSENSEと $I_{OUT(MAX)}$ が与えられると、上式から $V_{SENSE(MAX)}$ を求めることができるので、 $V_{RNG}$ の電圧も得られます。最大出力電流を確保するには、さまざまな動作条件や外付け部品の許容誤差でのLTC3838のばらつきを考慮して、計算時に十分な余裕をとる必要があります。

電流検出ループにはPCBノイズが存在する可能性があるので、良好な信号対雑音比を得るために、電流検出電圧リップル $\Delta V_{SENSE} = \Delta I_L \cdot R_{SENSE}$ も設計時に確認しておく必要があります。一般に、適度に良好なPCBレイアウトを得るには、RSENSEとインダクタDCRのいずれの検出アプリケーションの

図3a. RSENSEによる電流検出

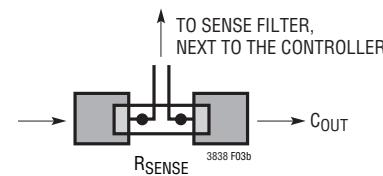

図3b. 検出抵抗を備えた検出ラインの配置

場合でも、出発点の控えめな値として10mVの $\Delta V_{SENSE}$ を推奨します。

電流密度の高い現在のソリューションでは、検出抵抗の値は1mΩに満たないことがあります。ピーカ検出電圧がわずか20mVになります。さらに、最大2MHzの動作でインダクタのリップル電流が50%を超えることも普通になってきています。これらの条件では、検出抵抗の寄生インダクタンス両端の電圧降下がより大きく関連してきます。PCBの検出トレースに結合した容量性および誘導性のノイズの影響を軽減するために、デバイスの近くに小さなRCフィルタを配置する方法が従来から使われてきました。標準的なフィルタは並列の1000pFコンデンサに接続された2個の直列10Ω抵抗で構成され、時定数は20nsとなります。

この同じRCフィルタを(小さな修正を加えて)使って、寄生インダクタンスが存在するときの電流検出信号の抵抗成分を抽出することができます。たとえば、100%の負荷で動作する

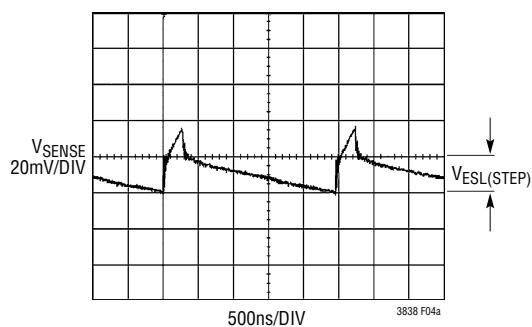

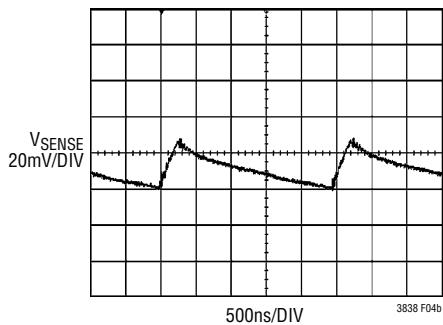

## アプリケーション情報

1.2V/15Aのコンバータの場合、実装面積が2010の2mΩ検出抵抗の両端の電圧波形を図4aに示します。この波形は純粹に抵抗性の成分と純粹に誘導性の成分を重ね合わせたものです。これは、差動での測定結果を得るために、オシロスコープの2つのプローブと波形計算を使用して測定しています。インダクタのリップル電流および上側スイッチのオン時間とオフ時間の追加測定に基づき、寄生インダクタンスの値は次式によつて0.5nHであると計算されました。

$$ESL = \frac{V_{ESL(STEP)}}{\Delta I_L} \cdot \frac{t_{ON} \cdot t_{OFF}}{t_{ON} + t_{OFF}}$$

ここで、 $V_{ESL(STEP)}$ はESLによって生じた電圧ステップで、図4aに示します。また、 $t_{ON}$ および $t_{OFF}$ は、それぞれ上側MOSFETのオン時間およびオフ時間です。寄生インダクタンスを検出抵抗で割った値( $L/R$ )に近くなるようにRC時定数

図4a. 検出抵抗の両端で直接測定した電圧波形

図4b. 検出抵抗フィルタの後に測定した電圧波形。

$C_F = 1000\text{pF}$ ,  $R_F = 100\Omega$

を選択すると、得られる波形は、図4bに示すように、やはり抵抗性があるように見えます。小さい $V_{SENSE(MAX)}$ を使うアプリケーションでは、検出抵抗メーカーのデータシートを調べて、寄生インダクタンスの情報がないか確認してください。データが存在しない場合には、検出抵抗の両端で電圧降下を直接測定してESLステップの大きさを求め、上式を使用してESLを決定します。ただし、フィルタをかけすぎないようにしてください。RC時定数をインダクタの時定数以下にして $V_{RSENSE}$ のリップル電圧を十分高く保ちます。

$SENSE1^-$ ピンと $SENSE2^-$ ピンは、上側ゲートのオン時間 $t_{ON}$ を調整するために出力電圧を検出する目的にも使用されます。このため、各 $SENSE^-$ ピンとSGNDの間には500kの付加的な抵抗が内蔵されているので、対応する $SENSE^+$ ピンとの間にはインピーダンスの不整合が存在します。 $R_F$ 両端の電圧降下により、検出電圧にはオフセットが生じます。たとえば、 $R_F = 100\Omega$ の場合、 $V_{OUT} = V_{SENSE^-} = 5\text{V}$ では、検出電圧のオフセットは $V_{SENSE(OFFSET)} = V_{SENSE^-} \cdot R_F/500\text{k} = 1\text{mV}$ です。このような小さいオフセットは電流制限に対して害がないように見えますが、電流反転検出( $I_{REV}$ )には影響があり、不連続モードで過剰な負のインダクタ電流が生じる可能性があります。その他に、 $V_{SENSE(MAX)} = 30\text{mV}$ では、わずか1mVのオフセットによってゼロ電流のITH電圧が大幅にシフトします(シフト量は $(2.4\text{V} - 0.8\text{V}) \cdot 1\text{mV}/30\text{mV} = 53\text{mV}$ )。シフト量が大きすぎると、ITHフォールドバックのために、出力が短絡した後に出力電圧がそのレギュレーション値に戻らない場合があります。したがって、フィルタ抵抗 $R_F$ の値を大きくした場合は、各 $SENSE^+$ ピンとSGNDの間に、外付けの500k抵抗を使用して、対応する $SENSE^-$ ピンの内部500k抵抗とバランスをとることを推奨します。

上記の説明は、一般に、 $I_{OUT(MAX)} > 10\text{A}$ かつ値の小さいインダクタが使用されている高密度/大電流のアプリケーションに当てはまります。 $I_{OUT(MAX)} < 10\text{A}$ のアプリケーションで

## アプリケーション情報

は、 $R_F$ を $10\Omega$ に、 $C_F$ を $1000\text{pF}$ に設定します。これにより妥当な出発点が与えられます。

フィルタ部品はデバイスの近くに配置する必要があります。正と負の検出トレースは差動ペアとして配線し、センス抵抗にケルビン(4線)接続する必要があります。

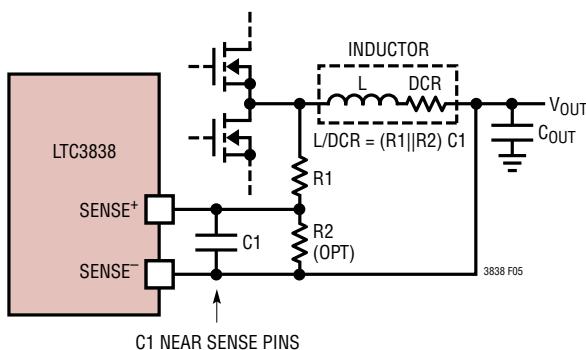

### DCRによるインダクタ電流検出

高負荷電流時に高効率が必要なアプリケーションでは、図5に示すように、LTC3838はインダクタのDCR両端の電圧降下を検出することができます。インダクタのDCRは値の小さいDC巻線抵抗を表し、値の小さい最近の大電流インダクタでは $1\text{m}\Omega$ より小さいことがあります。

このようなインダクタを必要とする大電流アプリケーションでは、検出抵抗による導通損失はDCRによる検出に比べると数ポイントの効率低下になると考えられます。

インダクタのDCRはインダクタの両端にRCフィルタを接続して検出します。このフィルタは、通常、図5に示すように1個または2個の抵抗( $R_1$ および $R_2$ )と1個のコンデンサ( $C_1$ )で構成されます。外付けの( $R_1||R_2$ )・ $C_1$ の時定数が正確に $L/DCR$ の時定数に等しくなるように選択すると、外付けコンデンサ両端の電圧降下は、インダクタのDCR両端の電圧降下に $R_2/(R_1+R_2)$ を掛けた値に等しくなります。したがって、DCRが目標の検出抵抗より大きいときは、 $R_2$ を使用して検出端子両端の電圧の大きさを変更することができます。電流制限値は $V_{RNG}$ ピンを介して設定できるので、 $R_2$ はオプションとすることができます。 $C_1$ は通常、 $0.01\mu\text{F} \sim 0.47\mu\text{F}$ の範囲に入るよう

に選択します。これにより、 $R_1||R_2$ はおよそ $2\text{k}\Omega \sim 4\text{k}\Omega$ に強制されるので、SENSEピンの入力バイアス電流によって生じる可能性がある誤差が減少します。

影響を受けやすい小信号ノードにノイズが結合しないように、抵抗 $R_1$ はスイッチング・ノードの近くに配置します。コンデンサ $C_1$ はデバイスのピンの近くに配置します。

DCR電流検出設計の第一歩は、インダクタのDCRを決定することです。メーカの最大値(通常は $25^\circ\text{C}$ で与えられる値)が分かっている場合は、その値を使用します。この値は抵抗の温度係数(約 $0.4\%/\text{°C}$ )を考慮して大きくします。インダクタ温度 $T_L$ の控えめな値は $100^\circ\text{C}$ です。インダクタのDCRは良質なRLCメータを使用して測定することができますが、DCRの許容誤差は常に同じとは限らず、温度によって変化します。詳細については、メーカのデータシートを参照してください。

DCRの値から、 $V_{SENSE(MAX)}$ は次式で容易に計算されます。

$$V_{SENSE(MAX)} = DCR_{MAX(25^\circ\text{C})} \cdot \left[ 1 + 0.4\% (T_{L(MAX)} - 25^\circ\text{C}) \right] \cdot \left( I_{OUT(MAX)} - \frac{\Delta I_L}{2} \right)$$

$V_{SENSE(MAX)}$ が、 $V_{RNG}$ ピンによって設定されるLTC3838の最大検出電圧の範囲内( $30\text{mV} \sim 100\text{mV}$ )である場合、RCフィルタに必要なのは $R_1$ だけです。 $V_{SENSE(MAX)}$ の方が大きい場合は、 $R_2$ を使用して最大検出電圧値を下げ、範囲内に入ることができます。

図5.DCRによる電流検出

## アプリケーション情報

R1での最大電力損失はデューティ・サイクルと関係があり、連続モード時に最大入力電圧で発生します(次式)。

$$P_{LOSS}(R1) = \frac{(V_{IN(MAX)} - V_{OUT}) \cdot V_{OUT}}{R1}$$

R1の電力定格がこの値より大きいことを確認します。軽負荷時に高い効率が必要な場合は、DCRによる検出とRSENSEによる検出のどちらを使うか決定するときに、この電力損失を考慮します。軽負荷での電力損失は、R1によって生じる余分なスイッチング損失のため、検出抵抗を使う場合よりDCR回路網を使う方がやや高いことがあります。ただし、DCRによる検出では検出抵抗が取り除かれるので、導通損失が減少し、重負荷時の効率が高くなります。ピーク効率はどちらの方法でもほぼ同じです。

電流検出信号の信号対雑音比を良好に保つには、10mVの $\Delta V_{SENSE}$ から始めます。DCR検出アプリケーションでは、実際のリップル電圧は次式で求められます。

$$\Delta V_{SENSE} = \frac{V_{IN} - V_{OUT}}{R1 \cdot C1} \cdot \frac{V_{OUT}}{V_{IN} \cdot f}$$

### パワー MOSFET の選択

LTC3838 コントローラの各チャネルには2つの外付けNチャネル・パワー MOSFETを選択する必要があります。1つは上側(メイン)スイッチ用であり、もう1つは下側(同期)スイッチ用です。ゲート駆動レベルはDRVCC電圧により設定されます。この電圧は通常5.3Vです。MOSFETのBV<sub>DSS</sub>の仕様にも十分注意を払ってください。ほとんどのロジック・レベルMOSFETは、30V以下に制限されています。

パワー MOSFET の選択基準には、オン抵抗 $R_{DS(ON)}$ 、ミラー容量 $C_{MILLER}$ 、入力電圧、および最大出力電流が含まれます。ミラー容量 $C_{MILLER}$ は、MOSFETのメーカーのデータシートに通常記載されているゲート電荷曲線から推定することができます。 $C_{MILLER}$ は、曲線がほぼ平坦な区間の水平軸に沿つ

たゲート電荷の増分(または、メーカーのデータシートに規定されている場合にはパラメータ $Q_{GD}$ )を、規定の $V_{DS}$ テスト電圧で割ったものに等しくなります。

$$C_{MILLER} \equiv \frac{Q_{GD}}{V_{DS(TEST)}}$$

このデバイスが連続モードで動作しているとき、上側MOSFETと下側MOSFETのデューティ・サイクルは、次式で与えられます。

$$D_{TOP} = \frac{V_{OUT}}{V_{IN}}$$

$$D_{BOT} = 1 - \frac{V_{OUT}}{V_{IN}}$$

最大出力電流でのMOSFETの電力損失は、次式で与えられます。

$$P_{TOP} = D_{TOP} \cdot I_{OUT(MAX)}^2 \cdot R_{DS(ON)(MAX)} (1 + \delta) + V_{IN}^2 \cdot \left( \frac{I_{OUT(MAX)}}{2} \right) \cdot C_{MILLER} \left[ \frac{R_{TG(UP)}}{V_{DRVCC} - V_{MILLER}} + \frac{R_{TG(DOWN)}}{V_{MILLER}} \right] \cdot f$$

$$P_{BOT} = D_{BOT} \cdot I_{OUT(MAX)}^2 \cdot R_{DS(ON)(MAX)} \cdot (1 + \delta)$$

ここで、 $\delta$ は $R_{DS(ON)}$ の温度依存性、 $R_{TG(UP)}$ はTGのプルアップ抵抗、 $R_{TG(DOWN)}$ はTGのプルダウン抵抗です。 $V_{MILLER}$ はミラー効果の $V_{GS}$ 電圧であり、MOSFETのデータシートから図表によって読み取ります。

$I^2R$ 損失は両方のMOSFETに共通していますが、上側のNチャネルの式には遷移損失の追加項があり、これは入力電圧が高いときに最も高くなります。 $V_{IN} < 20V$ では、大電流での効率は一般に大きいMOSFETを使用すると向上しますが、 $V_{IN} > 20V$ では遷移損失が急激に上昇し、 $R_{DS(ON)}$ が大きく $C_{MILLER}$ が小さいMOSFETを使用した方が実際には効率が高くなる点に達します。同期MOSFETの損失は、上側スイッチのデューティ・ファクタが低くなる高入力電圧時か、または同期スイッチが周期の100%近くオンになる短絡時に、最も大きくなります。

## アプリケーション情報

MOSFETの場合、 $(1 + \delta)$ の項は、パワーMOSFETデータシートでの正規化された  $R_{DS(ON)}$  と温度の曲線の形で通常は与えられます。低電圧MOSFETでは、 $R_{DS(ON)}$  のおよそのパーセント値変化として  $0.5\text{%/}^{\circ}\text{C}$  を使用して  $\delta$  を推定できます。

$$\delta = 0.005\text{%/}^{\circ}\text{C} \cdot (T_J - T_A)$$

ここで、 $T_J$  は MOSFET の推定接合部温度、 $T_A$  は周囲温度です。

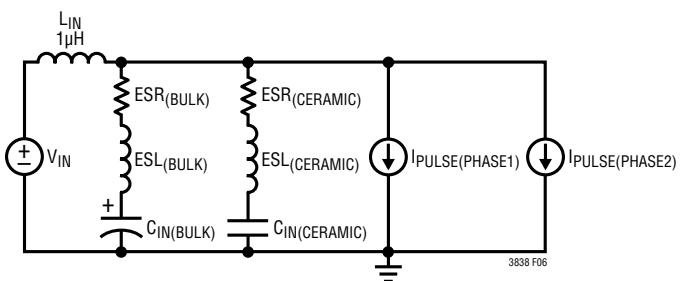

### $C_{IN}$ の選択

連続モードでは、上側のNチャネルMOSFETのソース電流は、デューティ・サイクルが  $V_{OUT}/V_{IN}$  の方形波になります。大きいトランジエント電圧の発生を防止するには、最大実効値(RMS)電流に対応するサイズの低ESR入力コンデンサを使用する必要があります。ワーストケースの RMS 電流は単相のアプリケーションを想定することで発生します。コンデンサの最大RMS電流は次式で与えられます。

$$I_{RMS} \approx I_{OUT(MAX)} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

この式は  $V_{IN} = 2V_{OUT}$  のときに最大になります。ここで、 $I_{RMS} = I_{OUT(MAX)}/2$  です。設計ではこの単純なワーストケース条件がよく使用されます。条件を大きく振っても値は改善されないからです。コンデンサ・メーカーが定めるリップル電流定格は、多くの場合、わずか2000時間の動作寿命に基づいています。このため、コンデンサをさらにディレーティングすること、つまり要求条件よりも高い温度定格のコンデンサを選択することを推奨します。設計でのサイズまたは高さの要件を満たすため、数個のコンデンサを並列に接続することもできます。LTC3838は動作周波数が高いため、 $C_{IN}$  には、デバイスおよびパワー・スイッチの近くにも追加のセラミック・コンデンサを並列に使用して、高周波のスイッチング・ノイズをバイパスさせます。通常は複数のX5RまたはX7Rセラミック・コンデンサを導電性ポリマー・タイプやアルミ电解タイプの大容量コンデンサと並列に配置します。セラミック・コ

ンデンサはESRが低いので、ほとんどのRMSリップル電流を吸収できます。セラミック・コンデンサのリップル電流定格はメーカーによっては必ずしも規定されていませんが、セラミック・コンデンサは過剰なリップル電流によっても故障する可能性があります。疑問点がある場合は、必ずメーカーに問い合わせてください。

図6は、これらのコンデンサのそれぞれでリップル電流を計算するための簡易回路モデルを表しています。入力電源とコンバータの入力の間にある入力インダクタンス( $L_{IN}$ )は、コンデンサを流れるリップル電流に影響します。入力インダクタンスが小さいと、より多くのリップル電流が入力電源から流れ出るようになるので、入力コンデンサを流れるリップル電流は少なくなります。

このモデルを使ったシミュレーションでは、一方の位相が最大負荷状態で他方の位相が無負荷状態の場合での定常状態のときのリップル電流を調べます。これは、一般に、リップル電流にとってワーストケースになります。それは、一方の位相からのリップル電流が他方の位相からのリップル電流によって相殺されないからです。

与えられた回路モデルによるシミュレーションでは、コンデンサに流れるRMS電流を超える十分な余裕を持ったRMS定格の大容量コンデンサを選択することも必要であることに注意してください。 $V_{IN}$ の電圧範囲が低い場合は、導電性ポリマー・タイプ(三洋のOS-CONなど)を使用することができます。リップル電流定格が高くESRが低いことがその理由です。高い電圧定格も

図6. 入力コンデンサのリップル電流

シミュレーションの回路モデル

## アプリケーション情報

必要とする範囲の広い $V_{IN}$ の場合は、減衰量を大きくするために容量を増やすことができるので、アルミ電解コンデンサが適しています。すべてのリップル電流を単独で処理できるほど大きなリップル電流定格をもつアルミ電解コンデンサは、非常に大型になります。ただし、セラミック・コンデンサを並列に接続すると、アルミ電解コンデンサはESRが大きいので、そこで吸収されるRMSリップル電流はごく一部になります。ただし、アルミ電解コンデンサを流れるリップル電流がその定格を超えないようにすることは非常に重要です。定格を超えるとかなりの熱が発生し、それによって時間の経過とともにコンデンサ内部の電解質が乾燥して容量が低下し、ESRが増大するからです。

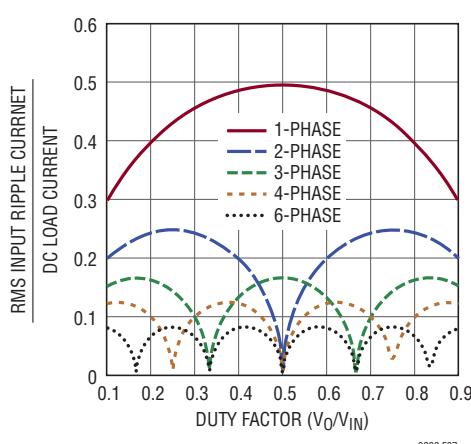

PolyPhase動作の利点は、RMS電流が減少することと、それによって入力コンデンサの電力損失が小さくなることです。さらに、PolyPhaseシステムではピーク電流が減少するので、入力保護ヒューズの抵抗、バッテリ抵抗、およびPC基板の配線抵抗による各損失も減少します。正確な式の詳細については、「アプリケーションノート77」の大電流アプリケーション用の高効率高密度PolyPhaseコンバータを参照してください。DC出力電流で正規化された入力コンデンサのRMSリップル電流と、デューティ・サイクルとのグラフを図7に示します。複数のチャネルが同一でそれらの位相が完全に交互に入れ替わっていると仮定すると、このグラフを使用して、マルチフェーズ・

アプリケーションでのコンデンサの最大RMS電流を推定できます。

図7は、より多くの位相を使用すると、リップル電流が相殺されることにより、入力コンデンサを流れるリップル電流が減少することを示しています。ただし、LTC3838で位相が正確に交互に入れ替わるのは定常状態のときだけなので、トランジエントRMS電流は、指定された位相数の曲線より大きくなる可能性があります。したがって、アプリケーションの固有の負荷状況を考慮してコンデンサを選択することを推奨します。入力コンデンサのRMS電流定格は、前述の単相アプリケーションのワーストケースに近い値を選択するのが常に最も安全です。この値は、コントローラのチャネルが同時にオンに切り替わるときに生じる損失を想定して計算されます。

ただし、複数の位相のオン時間がすべての時間で一致する場合には、通常、入力コンデンサをこのようなワーストケースの条件に対応するサイズにする必要はありません。負荷ステップが生じている間、オン時間の重複は、特にデューティ・サイクルが低いときにはほんの少しの時間しか生じません。スイッチ・ノードが数サイクルにわたって重なるトランジエント事象が生じても、コンデンサが損傷することはありません。ほとんどのアプリケーションでは、入力コンデンサを100%の定常状態の負荷に対応するサイズにすれば十分です。たとえば、マイクロプロセッサの負荷はオン時間の重複を頻繁に生じる可能性があり、リップル電流が大きくなりますが、負荷電流が $I_{OUT(MAX)}$ の100%になることはほとんどありません。ワーストケースの負荷電流を使用すると、トランジエント状態に対して既に余裕を持たせていることになります。

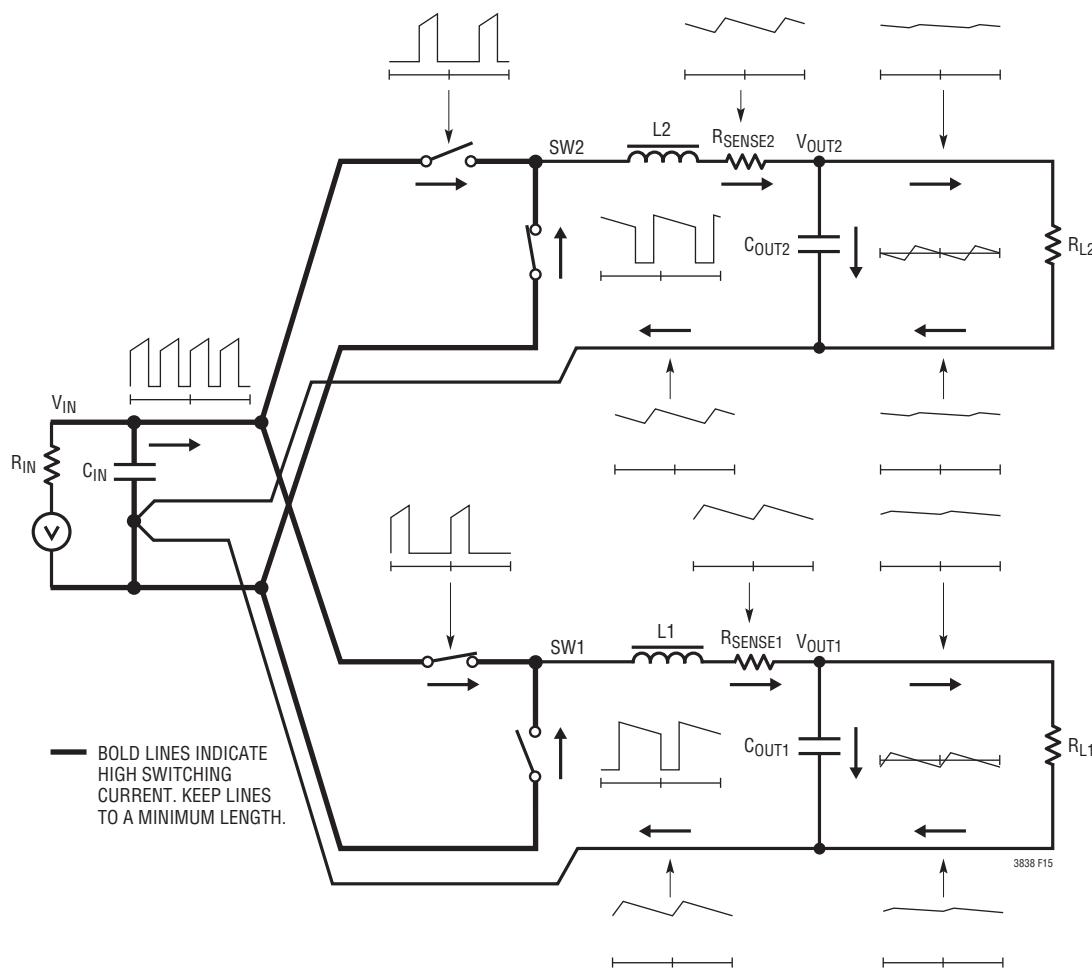

上側MOSFETの $V_{IN}$ 電圧源は互いに近づけて配置し、 $C_{IN}$ を共有するようにしてください。電圧源と $C_{IN}$ を離すと、 $V_{IN}$ に望ましくない電圧共振や電流共振が生じる可能性があります。

小さい( $0.1\mu F \sim 1\mu F$ )バイパス・コンデンサをデバイスの $V_{IN}$ ピンとグランドの間に、デバイスに近づけて配置することを推奨します。 $C_{IN}$ と $V_{IN}$ ピンの間に $2.2\Omega \sim 10\Omega$ の抵抗を配置することも推奨します。こうすると、2つのチャネルのスイッチング・ノイズの分離度を高めることができるからです。

図7. 正規化されたRMS入力リップル電流

## アプリケーション情報

### C<sub>OUT</sub>の選択

出力容量C<sub>OUT</sub>は、電圧リップルを最小限に抑えるために、主に等価直列抵抗(ESR)に基づいて選択します。連続モードでの出力電圧リップルΔV<sub>OUT</sub>は次式によって求められます。

$$\Delta V_{OUT} \leq \Delta I_L \left( R_{ESR} + \frac{1}{8 \cdot f \cdot C_{OUT}} \right)$$

ここで、fは動作周波数、ΔI<sub>L</sub>はインダクタを流れるリップル電流です。ΔI<sub>L</sub>は入力電圧に応じて増加するため、出力リップルは入力電圧が最大のとき最大になります。一般に、C<sub>OUT</sub>のESR要件を満たせば、RMS電流定格は、通常はリップル電流によって要求される定格をはるかに上回ります。

マルチフェーズの単一出力アプリケーションでは、特定の負荷条件でのリップル要件を検討することを推奨します。定常状態では、LTC3838の各位相が交互に入れ替わり、リップルが出力で互いに相殺されるので、C<sub>OUT</sub>のリップルは減少します。トランジエントの間、位相が完全に交互に入れ替わっていないと、リップルの相殺が機能しない可能性があります。ワーストケースのΔI<sub>L</sub>は、高速トランジエント時に重なった個々の位相のΔI<sub>L</sub>の合計ですが、こうしたリップルは、負荷トランジエント自体の影響を打ち消す傾向があり、持続時間はごく短時間です。たとえば、負荷電流の急激な増加時には、位相が揃って全インダクタ電流が増加し、V<sub>OUT</sub>が電圧低下状態から急速に上昇します。

小さい出力容量を選択すると、放電期間のためにリップル電圧が増加しますが、ESRが非常に小さいコンデンサを使用して補償することにより、リップル電圧を維持できます。

ESRおよびRMS電流処理の要件を満たすには、複数のコンデンサを並列に配置することが必要な場合があります。乾式タンタル、特殊ポリマー、アルミ電解およびセラミックの各コンデンサはすべて表面実装パッケージで入手できます。特殊ポリマー・コンデンサはESRは非常に小さいのですが、他のタイプに比べて容量密度が低くなっています。タンタル・コンデンサは容量密度が最高ですが、スイッチング電源に使用するにはサージ・テストが実施されているタイプのみを使用することが重要です。アルミ電解コンデンサはESRがかなり大きいの

ですが、リップル電流定格および長期信頼性に対して配慮すれば、コスト重視のアプリケーションに使うことができます。

セラミック・コンデンサは優れた低ESR特性を備えていますが、電圧係数が高く可聴圧電効果を示すことがあります。また、セラミック・コンデンサはQ値が高いので、配線インダクタンスがあると大きなリングングを引き起こす場合があります。入力コンデンサとして使用する場合は、突入電流によって生じるリングングとスイッチングがパワー・スイッチとコントローラに対する過電圧障害の原因にならないように注意する必要があります。

スイッチング周波数が高い場合は、出力リップルを低減してEMIフィルタリングの効果を上げるために、ESLが低く(それに応じて自己共振周波数が高い)小さい値のコンデンサをESLが高く大きい値のコンデンサと並列に配置しなければならない場合があります。これにより、対象となる全周波数スペクトルで、良好なノイズ・フィルタリングとEMIフィルタリングを実現することができます。セラミック・コンデンサは一般に良好な高周波性能を備えていますが、性能を最適化するためには小さいセラミック・コンデンサを大きいセラミック・コンデンサと並列に接続しなければならないことがあります。

高性能のスルーホール・コンデンサを使用することもできますが、セラミック・コンデンサを並列に追加して、リードのインダクタンスの影響を低減することを推奨します。高周波デカップリング・コンデンサを負荷の電力ピンにできるだけ近づけて配置することも忘れないでください。

### 上側MOSFETドライバの電源(C<sub>B</sub>、D<sub>B</sub>)

BOOSTピンに接続されている外付けのブートストラップ・コンデンサC<sub>B</sub>は、上側のMOSFETのゲート駆動電圧を供給します。このコンデンサは、スイッチ・ノードが“L”になると、ダイオードD<sub>B</sub>を介してDRV<sub>CC</sub>から充電されます。上側MOSFETがオンすると、スイッチ・ノードの電圧はV<sub>IN</sub>まで上昇し、BOOSTピンの電圧はおよそV<sub>IN</sub> + INTV<sub>CC</sub>まで上昇します。BOOSTピンのコンデンサは、上側MOSFETが必要とするゲート電荷の約100倍を蓄積する必要があります。ほとんどのアプリケーションでは、0.1μF～0.47μFのX5RまたはX7Rの誘電体コン

## アプリケーション情報

デンサで十分です。DRV<sub>CC</sub>のコンデンサであるC<sub>DRVCC</sub>がすべての動作条件で上側MOSFETのゲートとBOOSTピンのコンデンサに電荷を供給できるように、BOOSTのコンデンサはC<sub>DRVCC</sub>の10%より大きくしないことを推奨します。負荷ステップに応答する可変周波数は優れたトランジエント性能を示しますが、瞬時のゲート駆動能力が高いことが必要です。ゲート電荷の必要量は、周波数が高くデューティ・ファクタの低いアプリケーションで、負荷ステップが大きいときや起動時に最大になります。

### DRV<sub>CC</sub> レギュレータとEXTV<sub>CC</sub> 電源

LTC3838は、V<sub>IN</sub>電源からDRV<sub>CC</sub>に電力を供給するPMOS低ドロップアウト(LDO)リニア・レギュレータを備えています。このLDOは、DRV<sub>CC1</sub>ピンでの出力を5.3Vに安定化します。LDOは100mAの最大電流を供給可能であり、4.7μF以上のセラミック・コンデンサでグランドにバイパスする必要があります。MOSFETゲート・ドライバが必要とする大きなトランジエント電流を供給し、チャネル間の相互作用を最小限に抑えるため、十分なバイパスが必要です。

大きなMOSFETが高い周波数で駆動される高入力電圧のアプリケーションでは、特にLDOがアクティブでDRV<sub>CC</sub>を供給している場合、LTC3838の最大接合部温度定格を超える恐れがあります。この場合にはデバイスの電力損失が最大になり、V<sub>IN</sub>・I<sub>DRVCC</sub>にほぼ等しくなります。「効率に関する検討事項」のセクションで説明されているように、ゲート充電電流は動作周波数に依存します。接合部温度は「電気的特性」のNote 2に与えられている式を使って推定することができます。たとえば、LDOを使用している場合、LTC3838のDRV<sub>CC</sub>電流は、FEパッケージではT<sub>A</sub> = 70°Cで38V電源から52mA未満に制限されます。

$$T_J = 70^\circ\text{C} + (52\text{mA})(38\text{V})(28^\circ\text{C}/\text{W}) = 125^\circ\text{C}$$

最大接合部温度を超えないようにするには、連続導通モード動作時の入力電源電流を最大V<sub>IN</sub>で検査する必要があります。

EXTV<sub>CC</sub>ピンに印加された電圧が上昇して切り替え電圧(標準で4.6V)を超えると、V<sub>IN</sub>のLDOがオフし、EXTV<sub>CC</sub>は内部スイッチによりDRV<sub>CC2</sub>ピンに接続されます。EXTV<sub>CC</sub>に印加された電圧が切り替え電圧よりヒステリシス(約200mV)を超えて高い電圧で推移する限り、このスイッチはオンのままです。

EXTV<sub>CC</sub>を使用すると、MOSFETドライバと制御回路への電力を、通常動作時にはLTC3838のスイッチング・レギュレータ出力V<sub>OUT</sub>から得ることができ、出力が非レギュレーション状態のとき(起動時、短絡時など)にはLDOから得ることができます。規定よりも多くの電流をEXTV<sub>CC</sub>から供給する必要がある場合は、EXTV<sub>CC</sub>ピンとDRV<sub>CC</sub>ピンの間にショットキ・ダイオードを外付けすることができます。EXTV<sub>CC</sub>ピンには6Vを超える電圧を印加しないようにし、EXTV<sub>CC</sub>の値はV<sub>IN</sub>よりも小さくなるようにしてください。

ドライバ電流および制御電流に起因するV<sub>IN</sub>電流は、(デューティ・サイクル)/(スイッチャの効率)に比例するため、スイッチング・コンバータ出力からDRV<sub>CC</sub>に電力を供給すれば効率と熱特性を大幅に改善できます。

EXTV<sub>CC</sub>ピンを5V電源に接続すると、前の例の接合部温度は125°Cから次の値にまで下がります。

$$T_J = 70^\circ\text{C} + (52\text{mA})(5\text{V})(28^\circ\text{C}/\text{W}) = 77^\circ\text{C}$$

ただし、3.3Vなど他の低電圧出力の場合、コンバータ出力からDRV<sub>CC</sub>の電力を得るには追加回路が必要です。

以下に、EXTV<sub>CC</sub>に対して可能な4つの接続方法を示します。

1. EXT<sub>VCC</sub>を開放のままにします(または接地します)。こうすると、5.3Vの内部LDOからINT<sub>VCC</sub>に電力が供給されるため、入力電圧が高いときに効率が最大で10%ほど低下します。

2. EXT<sub>VCC</sub>をスイッチング・コンバータ出力(V<sub>OUT</sub>)に直接接続します。この出力電圧は、切り替え電圧の上限(4.8V)より高い電圧です。こうすると最高の効率が得られます。

3. EXT<sub>VCC</sub>を外部電源に接続します。4.8V以上の外部電源を利用できる場合は、それがMOSFETのゲート駆動要件を十分満足しているという前提で、外部電源を使用してEXT<sub>VCC</sub>に電力を供給することができます。

4. 出力を電源とする昇圧回路網にEXT<sub>VCC</sub>を接続します。3.3Vなど他の低電圧コンバータでは、4.8Vより高い電圧に昇圧した、出力から得られる電圧にEXT<sub>VCC</sub>を接続することにより、効率を改善できます。

## アプリケーション情報

主な入力電源が5.3Vを超えることのないアプリケーションでは、図8に示すように、DRVCC1ピンとDRVCC2ピンを(1Ω～2Ωのような)小さい抵抗を介してVIN入力に接続し、ゲート充電電流によって生じる電圧降下を最小限に抑えます。これにより、LDOが無効になり、ドロップアウト電圧によってDRVCCが低くなりすぎないようにすることができます。DRVCC電圧が外付けMOSFETのRDS(ON)テスト電圧(ロジック・レベルのデバイスの場合は標準で4.5V)より高いことを確認してください。

図8.  $V_{IN} \leq 5.3V$ での設定

## 入力低電圧ロックアウト(UVLO)

LTC3838は、入力が低電圧状態の場合にコントローラを保護するのに役立つ2つの機能を備えています。内部のUVLOコンパレータは、INTVCCとDRVCCの電圧を絶えずモニタし、十分な電圧が存在することを保証します。コンパレータは内部のUVLO信号をイネーブルします。これにより、INTVCCピンとDRVCC1,2ピンがいずれもそれぞれのUVLOしきい値より高くなるまで、2つのチャネルのスイッチング動作がロックアウトされます。INTVCCの(UVLOを解除するための)上昇時しきい値は標準で4.2Vであり、(UVLOを再イネーブルするための)0.5Vの下降時ヒステリシスがあります。DRVCC1,2のUVLOしきい値はINTVCCのUVLOしきい値よりも低い値ですが、十分なゲート駆動電圧が加わらない状態でパワーMOSFETがオンしないように、MOSFETの標準のしきい値電圧より高い値になっています。

通常、 $V_{IN} > 6V$ の場合は、 $V_{IN}$ とSGNDの間に接続した外付けの抵抗分割器をRUNピンで使用することにより、 $V_{IN}$ 電源をモニタしてUVLOを設定できます。抵抗分割器を設計するには、2つのRUNピンの両方に2つのレベルのしきい値電圧があることに注意してください。1.2Vの高精度のゲート駆動イネーブルしきい値電圧を使用して、1つのチャネルのスイッチングを開始するVINを設定します。2つのRUNピンの両方に抵抗分割器を使用している場合は、 $V_{IN}$ の値が十分低く、RUNピンの電圧が両方とも約0.8Vのしきい値より低くなると、デバイスはINTVCCおよびDRVCCのすべてのバイアスをシャットダウンして、マイクロパワー・シャットダウン・モードになります。

RUNピンのバイアス電流はRUNピンの電圧により異なります。バイアス電流の変化を考慮に入れる必要があるのは、外付け抵抗分割器のUVLO回路を設計するときです。内蔵の絶対温度比例式(PTAT)プルアップ電流源(25°Cで約1.2μA)は、このピンに常時接続されています。1つのRUNピンの電圧が上昇して1.2Vを超えると、対応するチャネルのTG駆動回路およびBG駆動回路がオンになり、温度に依存しない追加の5μAプルアップ電流源がこのRUNピンに内部で接続されます。このRUNピンの電圧を、80mVのヒステリシスの分を加味して1.2Vより低くすると、対応するチャネルのTGおよびBGはオフになり、追加の5μAプルアップ電流は切り離されます。

1つのRUNピンの電圧が増加して標準で3Vを超えると、そのバイアス電流は逆方向に流れ始め、そのRUNピンに流れ込みます。いずれのRUNピンも50μAを超える電流を吸い込むことはできないことに留意してください。シンク電流が50μAのときにRUNピンの電圧が6Vをわずかに超えた場合でも、障害状態を防ぐため、低インピーダンスの電圧源によってRUNピンが強制的に6Vより高い電圧になることはありません。

## ソフトスタートとトラッキング

LTC3838には、コンデンサを使って自力でソフトスタートを行うか、または別のチャネルや外部電源の出力を追跡する能力があります。ソフトスタート機能およびトラッキング機能は、コントローラの最大出力電流を制限することによってではなく、TRACK/SSピンの電圧のランプ・レートに従って出力ランプ電圧を制御することによって実現されることに注意してください。

## アプリケーション情報

ソフトスタートを自力で行うようにチャネルを構成するときは、コンデンサをそのTRACK/SSピンに接続します。TRACK/SSはRUNピンの電圧が1.2Vを超えてUVLOが解除されるまで“L”的ままであり、1.2Vを超えた時点で、1μAの内部電流が、TRACK/SSピンに接続されているソフトスタート・コンデンサC<sub>SS</sub>を充電します。スムーズなソフトスタートまたはトラッキングを保証するため、この段階の間は電流制限フォールドバックがディスエーブルされます。ソフトスタートまたはトラッキングの範囲は、TRACK/SSピンが0V～0.6Vの電圧範囲になるように定められます。合計ソフトスタート時間は次のように計算できます。

$$t_{SS}(\text{SEC}) = 0.6(V) \cdot \frac{C_{SS}(\mu\text{F})}{1(\mu\text{A})}$$

外部電源を追跡するように特定の1チャネルを設定する場合は、外部電源とTRACK/SSピンの間に抵抗分割器を使用するとランプ・レートを適切な値に調整できます。一般的な実装形態は、同時トラッキングと比例トラッキングの2つです。同時トラッキングの場合は、外部電源からの分圧比を差動帰還電

圧の分圧比と同じにします。比例トラッキングは、差動帰還とは異なる比を使用することによって実現できます。

引き続き1μAのソフトスタート・コンデンサ充電電流が流れているので、小さなオフセット誤差が生じることに注意してください。この誤差を最小限に抑えるには、トラッキング抵抗分割器の値として、このオフセット誤差を無視できるのに十分なほど小さい値を選択します。

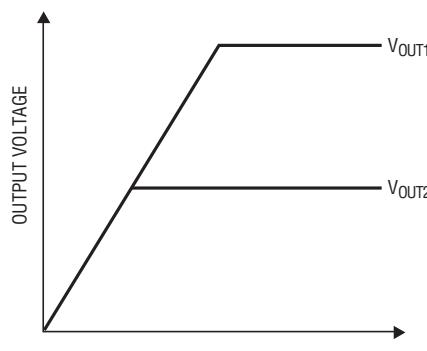

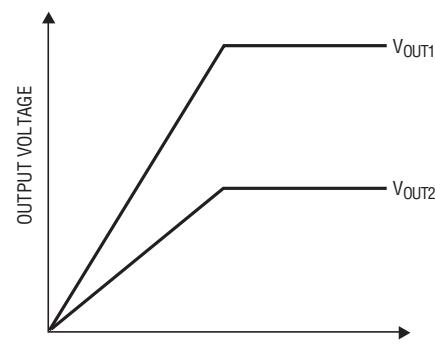

LTC3838では、2つのチャネルの出力が電圧の上昇および下降を互いにどのように追跡するかをユーザが設定できます。以下の説明では、V<sub>OUT1</sub>はマスター・チャネルとしてLTC3838の出力1を指し、V<sub>OUT2</sub>はスレーブ・チャネルとしてLTC3838の出力2を指します。ただし、実際には、どちらのチャネルもマスターとして使用することができます。

LTC3838では、さまざまな抵抗を選択することにより、図9の2つのモードを含むさまざまなトラッキング・モードを実現することができます。同時トラッキングを実現するには、追加の抵抗分割器をV<sub>OUT1</sub>に接続し、その中点をスレーブ・チャネルのTRACK/SSピンに接続します。この分割器の比は、図9bに示

Coincident Tracking

Ratiometric Tracking

図9a. 出力トラッキングの2つの異なるモード

Coincident Tracking Setup

Ratiometric Tracking Setup

図9b. 同時トラッキングおよび比例トラッキングの設定

## アプリケーション情報

すスレーブ・チャネルの帰還分割器の比と同じにします。このトラッキング・モードでは、V<sub>OUT1</sub>をV<sub>OUT2</sub>より高く設定する必要があります。比例トラッキングを実現するには、マスタ・チャネルの帰還分割器を使用してスレーブ・チャネルのTRACK/SS電圧を供給することもできます。追加の分割器を使用する場合は、マスタ・チャネルの帰還分割器と同じ比にするからです。

では、どちらのモードを設定すべきでしょうか。どちらのモードもほとんどの実用アプリケーションに使えますが、いくつかの妥協点が存在します。比例モードでは抵抗対を1つ節約できますが、同時モードでは出力のレギュレーションが向上します。

マスタ・チャネルの出力が(たとえば、過渡的な負荷状態で)動的に変化すると、スレーブ・チャネルの出力も影響を受けます。出力をさらに安定化するには、比例トラッキング・モードではなく同時トラッキング・モードを使用してください。

### 位相と周波数の同期

EMIとスイッチング・ノイズの制御性能向上が求められるアプリケーションや特殊な同期要求が存在するアプリケーション向けに、LTC3838では、上側MOSFETがオンするタイミングをMODE/PLLINピンに入力される外部クロック信号に同期させることができます。適切な周波数ロックおよび位相ロックを確実に行うため、入力されるクロック信号は、RTで設定された周波数の±30%以内にする必要があります。クロック信号レベルは、通常はV<sub>PLLIN(H)</sub> > 2VかつV<sub>PLLIN(L)</sub> < 0.5Vに適合する必要があります。MODE/PLLINピンには内部に600kΩのプルダウン抵抗があり、このピンが開放状態の場合に不連続電流モード動作になるようにしています。

LTC3838では、広範囲にわたるV<sub>IN</sub>、V<sub>OUT</sub>、およびR<sub>T</sub>で設定されたスイッチング周波数fに対して位相ロックおよび周波数ロックを維持するため、V<sub>IN</sub>とV<sub>OUT</sub>の電圧およびR<sub>T</sub>を使用して上側ゲートのオン時間を調整します。

$$t_{ON} \approx \frac{V_{OUT}}{V_{IN} \cdot f}$$

オン時間はスイッチング・レギュレータの出力電圧の関数なので、必要なオン時間を設定するために、この出力はSENSE-ピンで測定されます。ほとんどのアプリケーションでは、SENSE-ピンをレギュレータ付近の出力点に接続します。レギュレータから離れた場所で安定化された出力点は、線路損失により、レギュレータ付近の出力点とは電位が大幅に異なることがあります。近くのグランドに対する近くの出力の電位が、通常はt<sub>ON</sub>の計算に必要なV<sub>OUT</sub>であるからです。

ただし、このV<sub>OUT</sub>で設定されるオン時間が、周波数ロックおよび位相ロックを維持するために必要なオン時間とは大幅に異なる状況が存在する可能性があります。たとえば、スイッチング・レギュレータでの効率が低いと、内部で設定されたオン時間よりも必要なオン時間の方が大幅に長くなることがあります(「効率に関する検討事項」を参照)。安定化されたV<sub>OUT</sub>の値が比較的小さい場合は、それに比例して大きな誤差が発生する可能性があります。これは、共用のグランド・プレーンを流れる他の電流によって、近くのグランドと遠くのグランドとの間に電位差が生じることが原因です。

必要に応じて、R<sub>T</sub>抵抗の値、V<sub>IN</sub>ピンの電圧、場合によってはSENSEピンの同相電圧を外部で設定し、このような系統的な誤差を補正することができます。システムに部品や動作条件のばらつきを補正するための十分な範囲を持たせるか、または外部クロックに同期させるための目標は、V<sub>IN</sub>、V<sub>OUT</sub>、およびR<sub>T</sub>によって設定されるオン時間を定常状態のオン時間に近い値に設定することです。各SENSE-ピンにはSGNDとの間に500kΩの内部抵抗がありますが、SENSE+ピンにはないことに注意してください。

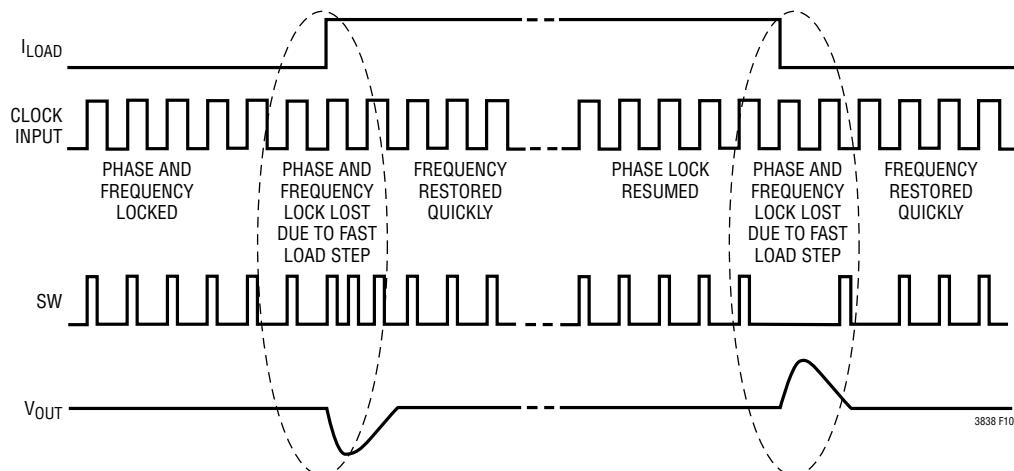

電源電圧または負荷電流の動的トランジエント状態(たとえば、負荷ステップや負荷解放)では、より高速なトランジエント応答を実現するために、上側のスイッチが応答時に多少頻繁にオンします。これは、LTC3838のオン時間が制御された谷電流モード・アーキテクチャの利点です。ただし、この過程では、当然のことながら位相ロックとさらに周波数ロックも瞬間に外れることがあります。比較的変化が遅い場合は、位相ロックと周波数ロックを引き続き維持できます。スルーレートが高い大幅な負荷ステップの場合は、位相ロックはシステムが定常状態に戻るまで解除されたままです(図10参照)。位相ロックが完全に再開されるまでに最大で数百マイクロ秒かかることがあります。周波数ロックは通常、位相ロックが回復するよりかなり前に短時間で回復します。

軽負荷の条件では、位相と周波数の同期はMODE/PLLINピンの設定に依存します。外部クロックを入力した場合、同期はアクティブになります。外部クロックを入力しない場合、MODE/PLLINをINTV<sub>CC</sub>に接続した場合は、R<sub>T</sub>で設定された周波数で強制連続モードで動作します。MODE/PLLINピンをSGNDに接続した場合、LTC3838は軽負荷では不連続モードで動作し、負荷が増加すると、R<sub>T</sub>で設定された周波数で連続導通モードに切り替わります。不連続導通時のTGオン時間は、連続/不連続導通の負荷電流境界でヒステリシスを発

## アプリケーション情報

図10. トランジエント状態での位相ロック動作と周波数ロック動作

生させるため、意図的に若干( $V_{IN}$ 、 $V_{OUT}$ 、および $f$ から計算した連続導通オン時間の約1.2倍)に延長されます。

(最小オン時間に近い)非常に短いオン時間をアプリケーションが必要とする場合は、システムがその全周波数同期範囲を維持できないことがあります。最小オン時間に近づくと、無負荷または軽負荷の条件では位相/周波数ロックが解除される場合もあります。その条件では、TG/BGの不動作時間のためにSWのオン時間がTGのオン時間より実質的に長くなります。これについては、「最小オン時間、最小オフ時間、およびドロップアウト動作」で詳しく説明します。

### 最小オン時間、最小オフ時間、およびドロップアウト動作

最小オン時間は、LTC3838のTG(上側ゲート)ピンを“H”、つまり「オン」状態に維持できる最小時間です。最小オン時間は、スイッチング・レギュレータの動作条件に依存しており、 $V_{IN}$ ピンおよび $V_{OUT}$ ピンの電圧、ならびに外付け抵抗 $R_T$ の値の関数です。30nsという最小オン時間を達成できるのは、 $V_{IN}$ をその最大値である38Vに接続しているときに、 $V_{OUT}$ ピンをその最小値である0.6Vに接続した場合です。 $V_{OUT}$ の値がこれより大きい場合や $V_{IN}$ の値がこれより小さい場合、達成できる最小オン時間は長くなります。谷モード制御アーキテクチャではオン時間を短くすることができるので、LTC3838は降圧比の高いアプリケーションに適しています。

**実効**オン時間は、このTGオン時間とは異なる場合があります。前者はSWノードのパルス幅によって決定されますが、後者はスイッチング・レギュレータの負荷条件だけでなく、外付け部品にも依存するからです。この違いにつながる要因の1つは、パワーMOSFETの特性です。たとえば、上側のパワーMOSFETのターンオン遅延がターンオフ遅延より大幅に短い場合、実効オン時間はTGオン時間より長くなり、最小の実効オン時間はより大きい値に制限されます。

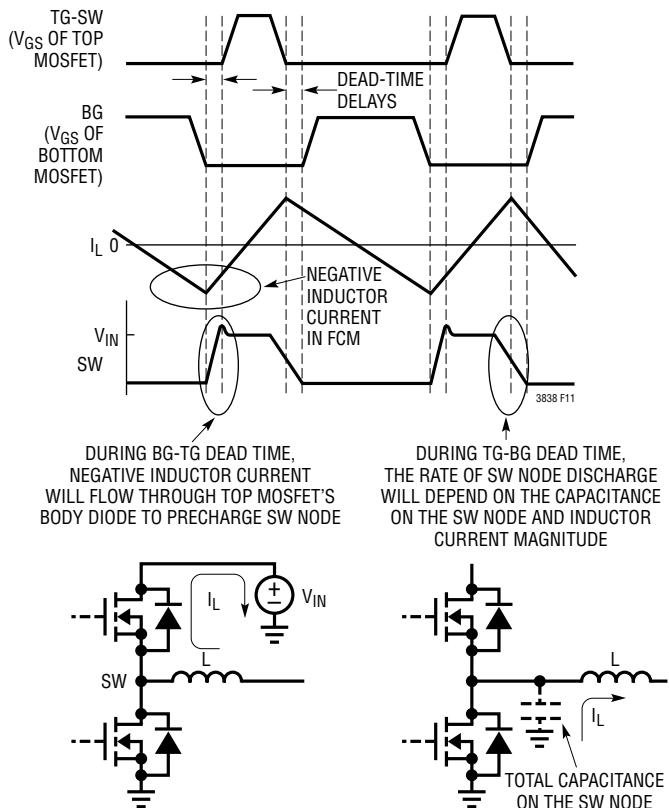

強制連続モードでは、図11に示すように、TGの「オン」状態とBGの「オン」状態の間の不動作時間が原因で、軽負荷動作では実効オン時間がさらに長くなります。BGがオフしてからTGがオンするまでの不動作時間の間、インダクタ電流は逆方向に流れ、TGが実際にオンになる前にSWノードを充電して“H”になります。逆方向の電流は通常は小さいので、立ち上がりエッジは緩やかになります。立ち下がりエッジでは、上側FETがオフしてから下側FETがオンするまでに、SWノードは長時間“H”的状態にとどまります。これは、SWノードを“L”にするためのピーク・インダクタ電流が軽負荷では小さいためです。SWノードの立ち上がりエッジと立ち下がりエッジが緩やかになつた結果、実効オン時間は長くなり、TGオン時間では完全に制御できなくなります。最小オン時間に近づくと、これが原因で軽負荷時にある程度の位相ジッタが生じることがあります。負荷電流が増加するとエッジは急になり、位相ロック動作が改善されます。

## アプリケーション情報

図11. 強制連続モード動作での軽負荷時のオン時間の延長

連続モード動作では、最小オン時間の制限により、最小デューティ・サイクルは次のようにになります。

$$D_{MIN} = f \cdot t_{ON(MIN)}$$

ここで、 $t_{ON(MIN)}$ はスイッチング・レギュレータの実効最小オン時間です。この式が示すように、動作周波数を下げると、最小デューティ・サイクルの制約が緩和されます。LTC3838が可能な最小オン時間が、スイッチング周波数を維持するためにデューティ・サイクルによって要求されるオン時間より長い場合、スイッチング周波数が減少してデューティ・サイクルを維持する必要がありますが、出力電圧は引き続き安定化状態を維持します。この動作は、サイクルをスキップしてリップルが大きくなるという、固定周波数のスイッチング・レギュレータで典型的に見られる動作よりも通常は望ましいものです。

「標準的性能特性」の $t_{ON(MIN)}$ の曲線は、 $V_{IN} = 38V$ 、 $V_{OUT} = 0.6V$ 、あるいは設定 $f = 2MHz$ (つまり、 $R_T = 18k$ )という極端なケースで、TGおよびBGの負荷を最小にして測定されて

います。さまざまな $V_{IN}$ 、 $V_{OUT}$ 、あるいは $f$ を使用したアプリケーションでは、実現可能な $t_{ON(MIN)}$ は一般的に大きくなります。また、軽負荷での周波数ロックおよび位相ロックを保証するには、不動作時間(「電気的特性」の $t_D(TG/BG) + t_D(BG/TG)$ )を考慮して十分な余裕をとる必要があります。

比較的短いオン時間が必要なアプリケーションでは、パワーMOSFETを選ぶときに注意する必要があります。オン時間が不十分なためにMOSFETのゲートを完全にオンすることができないと、 $R_{DS(ON)}$ が大きくなるので、かなりの放熱と効率低下が生じる可能性があります。このことは、パワーMOSFETが早期に故障する原因となる可能性もあります。

最小オフ時間は、TGピンの電圧が“L”になってから速やかに“H”に戻るまでの最小時間です。この最小オフ時間には、BG(下側ゲート)がオンしてからオフに戻るまでの時間と、TGがオフになってからBGがオフになるまでの不動作時間による遅延と、BGがオフになってからTGがオフになるまでの不動作時間による遅延が含まれます。LTC3838で実現できる最小オフ時間は90nsです。

スイッチング・レギュレータの**実効**最小オフ時間、つまりSWノードが“L”にとどまることができる最短時間は、この最小オフ時間とは異なる場合があります。実効最小オフ時間に影響する主な要因は、 $Q_g$ やオン/オフ時の遅延など、上側および下側のパワーMOSFETの電気的特性です。これらの特性により、SWノードの実効最小オフ時間は長くなることも短くなることもあります。大サイズの( $Q_g$ の大きい)パワーMOSFETは、ゲートの充放電時間が長くなるため、通常は実効最小オフ時間が長くなる傾向があります。これに対して、オン時の遅延とオフ時の遅延の均衡がとれていないと、実効最小オフ時間は短くなることがあります。

最小オフ時間の制限により、最大デューティ・サイクルは次のようにになります。

$$D_{MAX} = 1 - f \cdot t_{OFF(MIN)}$$

ここで、 $t_{OFF(MIN)}$ はスイッチング・レギュレータの実効最小オフ時間です。動作周波数を下げると、最大デューティ・サイクルの制約が緩和されることがあります。

## アプリケーション情報

たとえば、入力電圧が低下したために最大デューティ・サイクルに達すると、出力はレギュレーション不能状態になります。ドロップアウトを避けるための最小入力電圧は次のとおりです。

$$V_{IN(MIN)} = \frac{V_{OUT}}{D_{MAX}}$$

ドロップアウトの開始時には、2つの不連続なオフ時間を生じる約500mVの $V_{IN}$ の領域があります。1つは最小オフ時間であり、もう1つは最小オフ時間より約40ns～60ns長いオフ時間です。この2次オフ時間は、内部電流コンパレータが作動するときの追加の遅延によるものです。2つのオフ時間の平均値は、出力をレギュレーション状態に保つために必要なデューティ・サイクルになります。SWノードのジッタは大きい場合があり、外部クロックに同期しているときは特に顕著ですが、出力電圧リップルは比較的小さい値にとどまります。

### フォルト状態:電流制限と過電圧

電流モード・コントローラの最大インダクタ電流は、最大検出電圧によって制限されます。LTC3838では、最大検出電圧は $V_{RNG}$ ピンの電圧で制御されます。谷電流モード制御では、最大検出電圧と検出抵抗によって最大許容インダクタ谷電流が決まります。対応する出力電流制限値は、次式で得られます。

$$I_{LIMIT} = \frac{V_{SENSE(MAX)}}{R_{SENSE}} + \frac{1}{2} \cdot \Delta I_L$$

この電流制限値を確認して、 $I_{LIMIT(MIN)} > I_{OUT(MAX)}$ となるようにします。電流制限値は、ワーストケースの効率で最大出力電力を発生するのに必要なインダクタ電流より大きくなります。

一般に、ワーストケースの効率になるのは、 $V_{IN}$ と周囲温度とともに最大の場合です。想定されるMOSFETの接合部温度と、MOSFETスイッチを加熱する要因である $I_{LIMIT}$ の値に整合性がとれているか確認することが重要です。

グランドへの短絡が発生した場合に電流をさらに制限するため、LTC3838はフォールドバック電流制限回路を内蔵しています。出力の低下が50%を超えた場合は、最大検出電圧は次第に低下し、帰還電圧が0Vに達すると最大値の約1/4になります。

帰還電圧が0.6Vの安定化目標値の7.5%を超えると、過電圧(OV)状態と見なされます。このような過電圧状態では、上側MOSFETは直ちにオフし、下側MOSFETは過電圧状態が解消されるまで無期限にオンのままになります。過電圧状態が解消されるのは、帰還電圧が7.5%のしきい値より標準で2%のヒステリシス以上低い値に再度低下するときです。過電圧状態の間、電流制限は動作しません。過電圧状態が持続し、BGが長時間オン状態になると、インダクタと下側MOSFETを流れる電流が最大定格を超えて、負荷を保護するためにインダクタとMOSFETが犠牲になる場合があります。

### OPTI-LOOP補償

ITHピンを使ってOPTI-LOOP補償を行えば、幅広い負荷と出力コンデンサに対してトランジメント応答を最適化することができます。ITHピンにより、制御ループ動作を最適化できるだけでなく、DC結合され、ACフィルタを通した閉ループ応答のテスト・ポイントも得られます。このテスト・ポイントでのDCステップ、立ち上がり時間、およびセトリングは、閉ループ応答を正確に反映します。2次特性が支配的なシステムを想定すれば、位相余裕や減衰係数は、このピンで見られるオーバーシュートのパーセンテージを使用して推定することができます。

ITHピンに直列の $R_{ITH-CITH1}$ フィルタを外付けすることにより、支配的なポールゼロ・ループ補償が設定されます。PCBのレイアウトを完了し、特定の出力コンデンサの種類と容量値を決定したら、これらの値を調整してトランジメント応答を最適化することができます。出力コンデンサのさまざまな種類と値によってループ帰還係数の利得と位相が決まるので、まず出力コンデンサを選択する必要があります。

高周波ノイズを減衰するため、ITHピンとSGNDの間に小さいコンデンサ $C_{ITH2}$ を追加することができます。この $C_{ITH2}$ を追加するとループ利得特性にポールが追加されるので、大きすぎるとシステムの安定性に影響することがあります。このコンデンサを選択するときは、追加されるポールが相当な余裕を持ってループ帯域幅より高くなるようにします。

## アプリケーション情報

レギュレータのループ応答は負荷トランジェント応答を見て確認することもできます。立ち上がり時間が $1\mu\text{s} \sim 10\mu\text{s}$ の全負荷電流の20%~100%の出力電流パルスによって、帰還ループを開くことなく全体的なループの安定性を判断することができる $V_{\text{OUT}}$ 波形とITH電圧のトランジェント応答波形が発生します。OPTI-LOOP補償の詳細な説明については、「アプリケーション・ノート76」を参照してください。