## 特長

- 広い $V_{IN}$ 範囲: 4.5V~38V

- ライン・フィードフォワード補償

- 短い最小オン時間:  $t_{ON(MIN)} < 30\text{ns}$

- 強力なMOSFETドライバを内蔵

- リーディングエッジ変調電圧モード制御

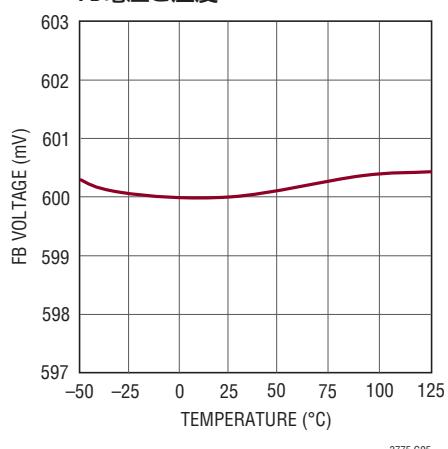

- 全温度範囲で $\pm 0.75\%$ の0.6Vリファレンス電圧精度

- $V_{OUT}$ 範囲: 0.6V~0.8 $V_{IN}$

- サイクルごとのピーク電流制限をプログラム可能

- センス抵抗または $R_{DS(ON)}$ による電流検出

- プログラム可能なソフトスタート

- 同期可能な固定周波数: 250kHz~1MHz

- パルススキップ動作モード

または強制連続動作モードを選択可能

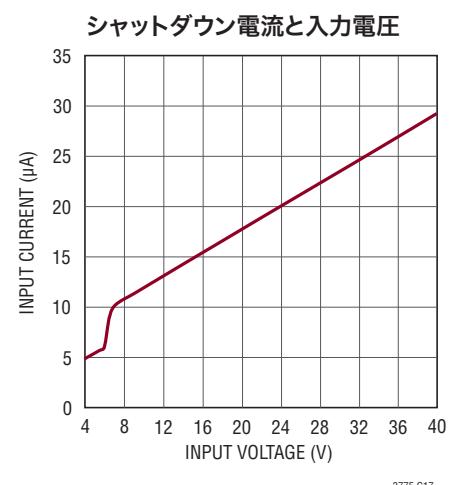

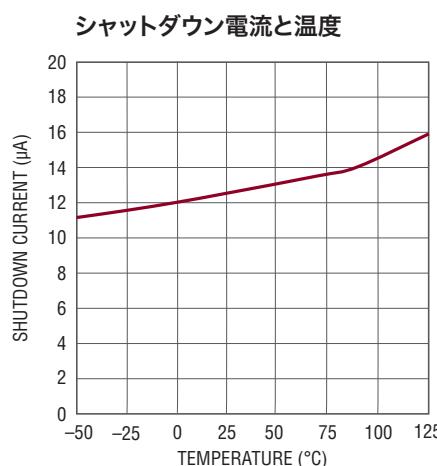

- 低シャットダウン電流: 14 $\mu\text{A}$ (標準)

- 熱特性が改善された16ピンMSOP

および3mm×3mm QFNパッケージ

## アプリケーション

- 車載用システム

- テレコムおよび産業用電源

- ポイントオブロード・アプリケーション

## 概要

LTC®3775は、4.5V~38Vの入力電源電圧すべてNチャネルのパワーMOSFET段をドライブする、高効率同期整流式降圧スイッチングDC/DCコントローラです。特許取得済みのライン・フィードフォワード補償回路と高帯域幅エラー・アンプにより、非常に高速な入力および負荷過渡応答を実現します。

最小オン時間が30nsと短いので、高い降圧比を達成でき、極めて低いデューティ・サイクルが可能です。MOSFETの $R_{DS(ON)}$ による電流検出により、効率が最大になります。代わりにセンス抵抗を使用して、さらに高い電流制限精度を達成することも可能です。トップおよびボトムMOSFETの両端の電圧を連続的にモニタすることにより、外付け抵抗で設定可能なインダクタ電流をサイクルごとに制御できます。

ソフトスタート機能により、起動時のデューティ・サイクルを制御し、出力電圧をスムーズにランプアップします。動作周波数は250kHz~1MHzの範囲でユーザ設定可能で、外部クロックに同期することも可能です。

**L**、**LT**、**LTC**、**LTM**、**Linear Technology**およびLinear Technologyのロゴはリニアテクノロジー社の登録商標です。No RSENSEとUltraFastはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。5408150、5481178、5705919、6580258、5847554、5055767を含む米国特許によって保護されています。

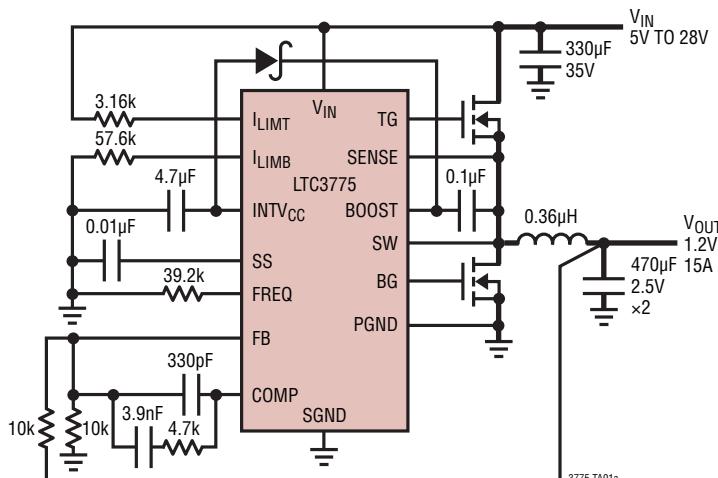

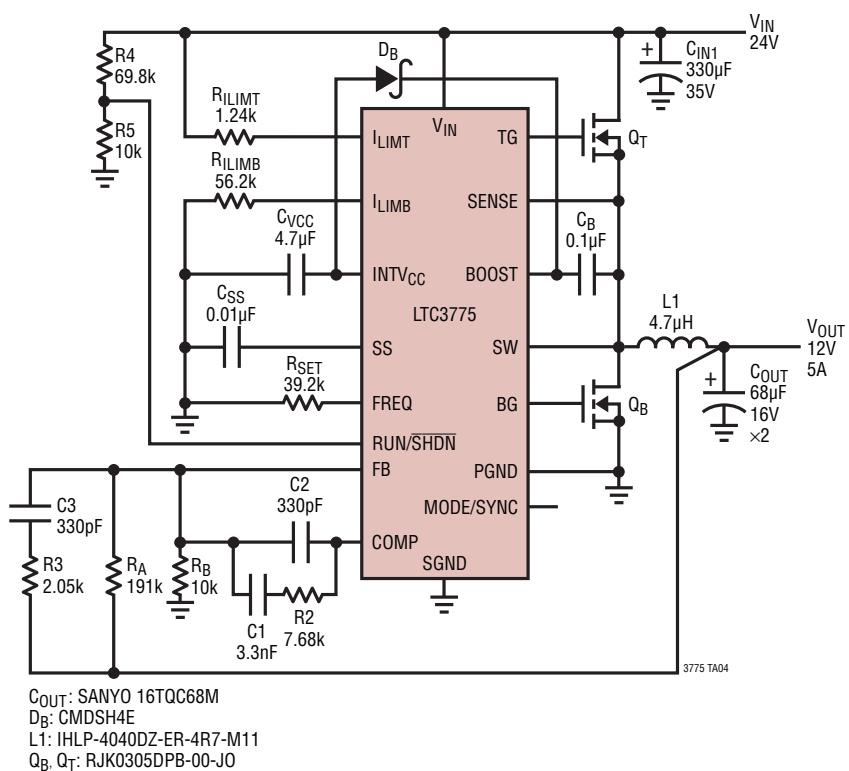

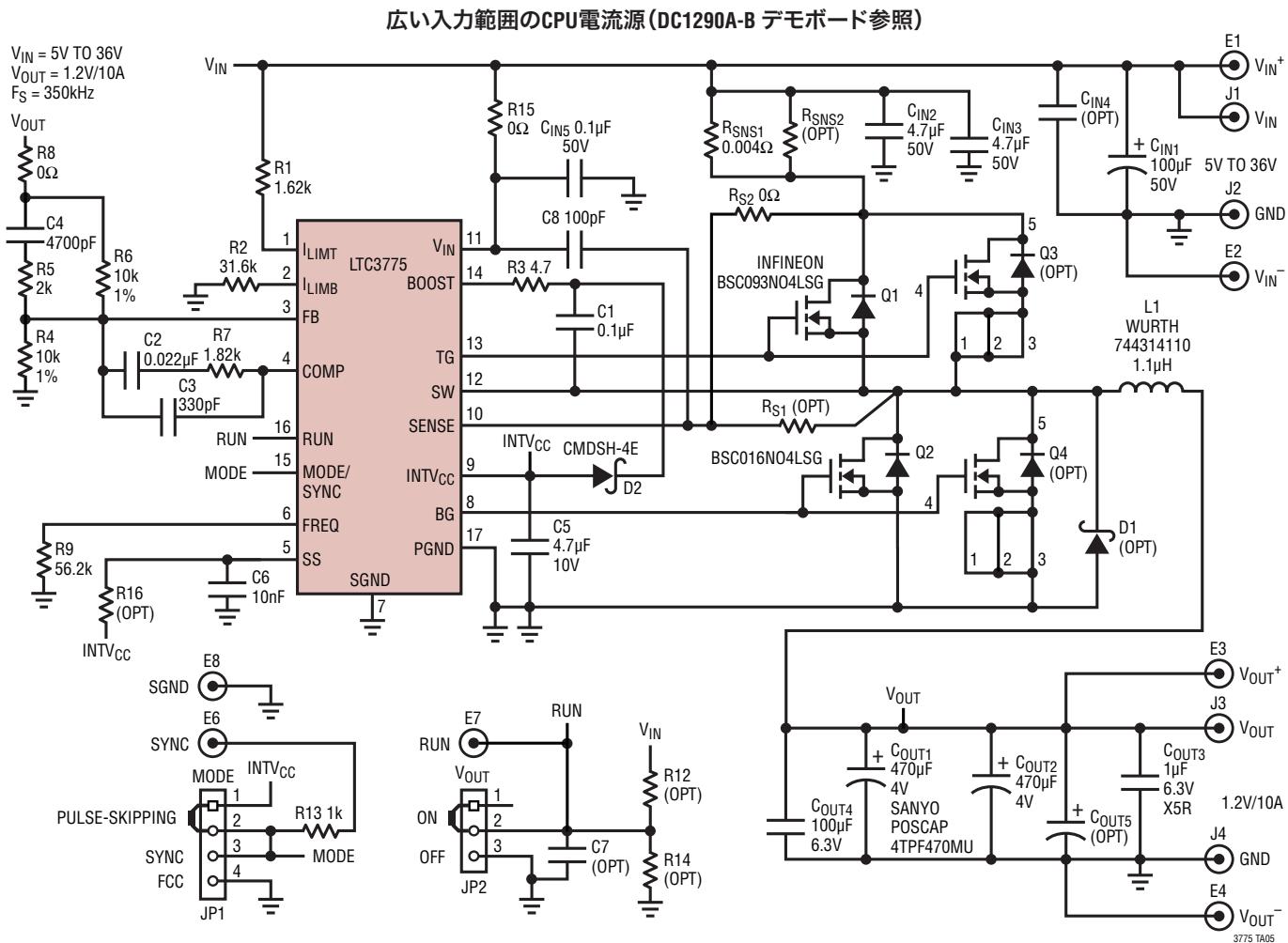

## 標準的応用例

3775fa

# LTC3775

## 絶対最大定格

(Note 1)

電源電圧

|             |                 |

|-------------|-----------------|

| $V_{IN}$    | -0.3V~40V       |

| BOOST       | -0.3V~46V       |

| BOOST-SW    | -0.3V~6V        |

| SW          | -5V~40V         |

| $I_{LIMIT}$ | -0.3V~ $V_{IN}$ |

| SENSE       | -5V~ $V_{IN}$   |

| $INTV_{CC}$ | -0.3V~6V        |

|                       |                    |

|-----------------------|--------------------|

| RUN/ $\bar{SHDN}$     | -0.3V~6V           |

| FB、MODE/SYNC          | -0.3V~ $INTV_{CC}$ |

| FREQ, $I_{LIMB}$ , SS | -0.3V~ $INTV_{CC}$ |

| $INTV_{CC}$ RMS電流     | 50mA               |

| 動作接合部温度範囲 (Note 2)    | -40°C~125°C        |

| 保存温度範囲                | -65°C~150°C        |

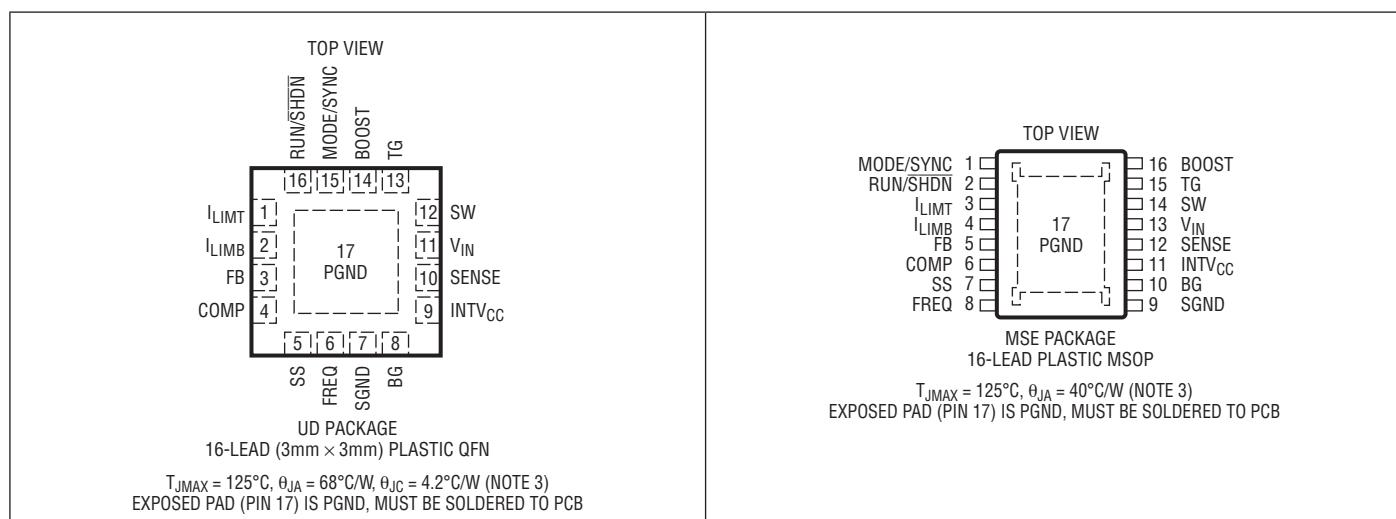

## ピン配置

## 発注情報

| 鉛フリー仕様          | テープアンドリール         | 製品マーキング* | パッケージ                           | 温度範囲           |

|-----------------|-------------------|----------|---------------------------------|----------------|

| LTC3775EUD#PBF  | LTC3775EUD#TRPBF  | LDJK     | 16-Lead (3mm × 3mm) Plastic QFN | -40°C to 85°C  |

| LTC3775IUD#PBF  | LTC3775IUD#TRPBF  | LDJK     | 16-Lead (3mm × 3mm) Plastic QFN | -40°C to 125°C |

| LTC3775EMSE#PBF | LTC3775EMSE#TRPBF | 3775     | 16-Lead Plastic MSOP            | -40°C to 85°C  |

| LTC3775IMSE#PBF | LTC3775IMSE#TRPBF | 3775     | 16-Lead Plastic MSOP            | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛ベース仕様の製品の詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作接合部温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 2)。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $V_{RUN} = 5\text{V}$ 。

| SYMBOL                                                 | PARAMETER                                                              | CONDITIONS                                                          | MIN | TYP             | MAX             | UNITS                          |

|--------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------|-----|-----------------|-----------------|--------------------------------|

| <b>Input Supply</b>                                    |                                                                        |                                                                     |     |                 |                 |                                |

| $V_{IN}$                                               | $V_{IN}$ Supply Voltage                                                |                                                                     | ●   | 4.5             | 38              | V                              |

| $I_{VIN}$                                              | Input DC Supply Current                                                | $V_{FB} = 0.7\text{V}$ (Note 5)<br>$V_{RUN} = 0\text{V}$            |     | 3.5<br>14       | 1.22<br>1.25    | mA<br>$\mu\text{A}$            |

| <b>RUN/SHDN Pin</b>                                    |                                                                        |                                                                     |     |                 |                 |                                |

| $V_{RUN}$                                              | RUN/SHDN Pin Enable Threshold                                          |                                                                     |     | 1.19            | 1.22            | 1.25                           |

| $V_{SHDN}$                                             | RUN/SHDN Pin Shutdown Threshold                                        | $V_{RUN/SHDN}$ Rising                                               |     | 0.74            |                 | V                              |

| $V_{SHDN(HYST)}$                                       | RUN/SHDN Pin Shutdown Threshold Hysteresis                             |                                                                     |     | 140             |                 | mV                             |

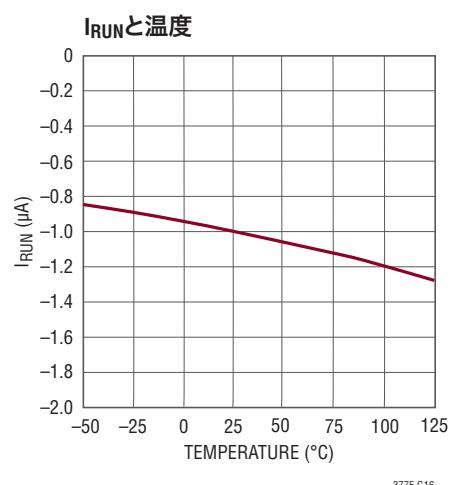

| $I_{RUN}$                                              | RUN/SHDN Pin Source Current                                            | $V_{RUN/SHDN} = 0\text{V}$<br>$V_{RUN/SHDN} = 1.5\text{V}$          |     | -1<br>-5        | -1<br>-5        | $\mu\text{A}$<br>$\mu\text{A}$ |

| <b>Error Amplifier</b>                                 |                                                                        |                                                                     |     |                 |                 |                                |

| $V_{FB}$                                               | Feedback Pin Voltage                                                   |                                                                     | ●   | 0.597<br>0.5955 | 0.600<br>0.6045 | V<br>V                         |

| $\Delta V_{FB}$                                        | Feedback Voltage Line Regulation                                       | $4.5\text{V} < V_{IN} < 38\text{V}$                                 |     | ±0.01           |                 | %/V                            |

| $\Delta V_{OUT}$                                       | Output Voltage Load Regulation                                         | $1\text{V} < V_{COMP} < 2\text{V}$ (Note 6)                         |     | 0.01            | 0.1             | %                              |

| $I_{FB}$                                               | FB Pin Input Current                                                   | $V_{FB} = 0.6\text{V}$                                              |     | -50             | 50              | nA                             |

| $I_{COMP}$                                             | COMP Pin Output Current                                                | Sourcing, $V_{COMP} = 0\text{V}$<br>Sinking, $V_{COMP} = 2\text{V}$ |     | -0.5<br>1       | -1<br>60        | mA<br>mA                       |

| $f_{0dB}$                                              | Error Amplifier Unity-Gain Crossover Frequency                         | (Note 6)                                                            |     | 25              |                 | MHz                            |

| <b>Soft-Start</b>                                      |                                                                        |                                                                     |     |                 |                 |                                |

| $I_{SS}$                                               | SS Pin Source Current                                                  | $V_{SS} = 0\text{V}$                                                |     | -1              |                 | $\mu\text{A}$                  |

| $R_{SS}$                                               | SS Pin Pull-Down Resistance in Current Limit                           |                                                                     |     | 1.3             |                 | k $\Omega$                     |

| <b>Current Limit</b>                                   |                                                                        |                                                                     |     |                 |                 |                                |

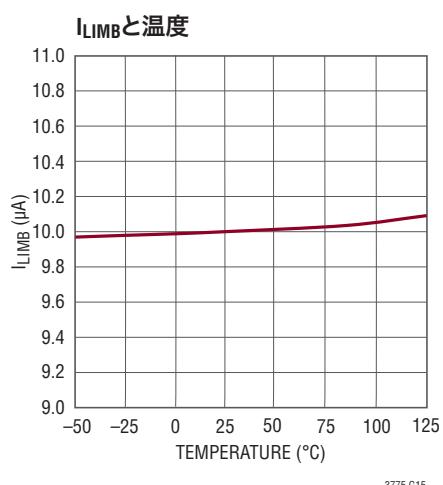

| $I_{LIMB}$                                             | $I_{LIMB}$ Source Current                                              | $V_{ILIMB} = 1\text{V}$                                             | ●   | -9              | -10             | -11                            |

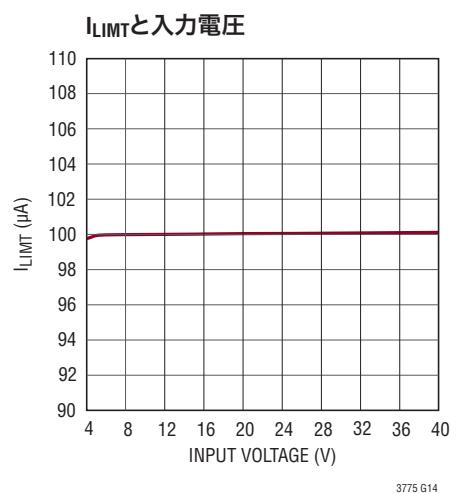

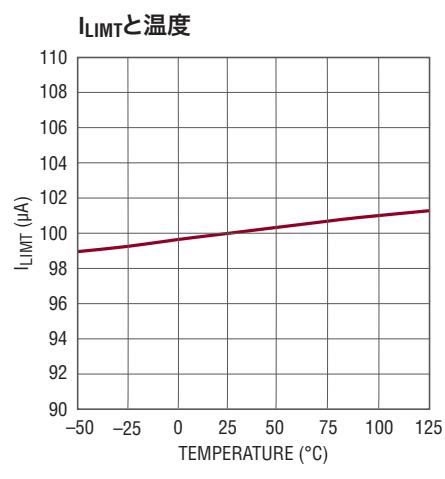

| $I_{LIMIT}$                                            | $I_{LIMIT}$ Sink Current                                               | $V_{ILIMIT} = 12\text{V}$                                           | ●   | 90              | 100             | 110                            |

| $I_{SENSE}$                                            | SENSE Pin Input Current                                                |                                                                     |     |                 | 1               | $\mu\text{A}$                  |

| $V_{ILIMIT(MAX)}$                                      | Topside Current Limit Threshold ( $V_{IN}$ -SENSE)                     | $V_{ILIMIT} = 0.1\text{V}$                                          | ●   | 90              | 100             | 110                            |

| $V_{ILIMB(MAX)}$                                       | Bottom Side Current Limit Threshold (PGND-SW)                          | $V_{ILIMB} = 0.5\text{V}$                                           | ●   | 80              | 100             | 120                            |

| <b>INTV<sub>CC</sub> Low Dropout Voltage Regulator</b> |                                                                        |                                                                     |     |                 |                 |                                |

| $INTV_{CC}$                                            | LDO Regulator Output Voltage                                           |                                                                     |     | 4.9             | 5.2             | 5.5                            |

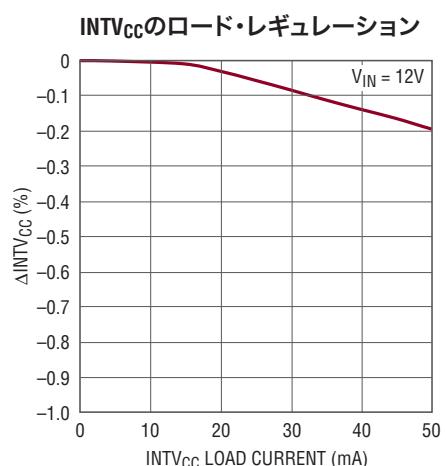

| $\Delta V_{INTVCC(LINE)}$                              | INTV <sub>CC</sub> Line Regulation                                     | $7.5\text{V} < V_{IN} < 38\text{V}$                                 |     | 0.01            |                 | %/V                            |

| $\Delta V_{INTVCC(LOAD)}$                              | INTV <sub>CC</sub> Load Regulation                                     | $\Delta I_{INTVCC} = 0\text{mA}$ to $20\text{mA}$                   |     | -1              | -0.1            | %                              |

| $V_{DROPOUT}$                                          | INTV <sub>CC</sub> Regulator Dropout Voltage ( $V_{IN} - V_{INTVCC}$ ) | $I_{INTVCC} = 20\text{mA}$                                          |     | 0.35            |                 | V                              |

| $V_{UVLO}$                                             | INTV <sub>CC</sub> UVLO Voltage                                        | INTV <sub>CC</sub> Rising Hysteresis                                |     | 3.0<br>0.5      | 3.6<br>0.5      | 4.2<br>V                       |

## 電気的特性

●は全動作接合部温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値(Note 2)。注記がない限り、 $V_{IN} = 12\text{V}$ 、 $V_{RUN} = 5\text{V}$ 。

| SYMBOL            | PARAMETER                                                                | CONDITIONS                               |   | MIN  | TYP | MAX | UNITS      |

|-------------------|--------------------------------------------------------------------------|------------------------------------------|---|------|-----|-----|------------|

| <b>Oscillator</b> |                                                                          |                                          |   |      |     |     |            |

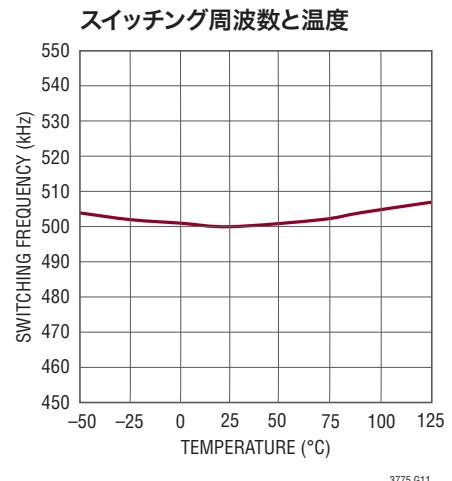

| $f_{OSC}$         | Oscillator Frequency                                                     | $R_{SET} = 39.2\text{k}$                 | ● | 425  | 500 | 575 | kHz        |

| $f_{HIGH}$        | Maximum Oscillator Frequency                                             |                                          | ● | 1000 |     |     | kHz        |

| $f_{LOW}$         | Minimum Oscillator Frequency                                             |                                          | ● |      | 250 |     | kHz        |

| $f_{SYNC}$        | External Sync Frequency Range                                            | With Reference to Free Running           |   | -20  | 20  |     | %          |

| $t_{ON(MIN)}$     | TG Minimum On-Time                                                       | (Notes 6, 8) $V_{MODE/SYNC} = 0\text{V}$ |   |      | 30  |     | ns         |

| $t_{OFF(MIN)}$    | TG Minimum Off-Time                                                      | (Note 6)                                 |   |      | 300 |     | ns         |

| $DC_{MAX}$        | Maximum TG Duty Cycle                                                    | $f_{OSC} = 500\text{kHz}$                | ● | 90   |     |     | %          |

| $V_{MODE}$        | MODE/SYNC Threshold                                                      | MODE/SYNC Rising                         |   |      | 1.2 |     | V          |

| $V_{MODE(HYST)}$  | MODE/SYNC Hysteresis                                                     |                                          |   |      | 430 |     | mV         |

| $R_{MODE/SYNC}$   | MODE/SYNC Input Resistance to SGND                                       |                                          |   |      | 50  |     | k $\Omega$ |

| <b>Driver</b>     |                                                                          |                                          |   |      |     |     |            |

| $BG\ R_{UP}$      | Bottom Gate (BG) Pull-Up On-Resistance                                   |                                          |   |      | 2.5 |     | $\Omega$   |

| $TG\ R_{UP}$      | Top Gate (TG) Pull-Up On-Resistance                                      |                                          |   |      | 2.5 |     | $\Omega$   |

| $BG\ R_{DOWN}$    | Bottom Gate (BG) Pull-Down On-Resistance                                 |                                          |   |      | 1.0 |     | $\Omega$   |

| $TG\ R_{DOWN}$    | Top Gate (TG) Pull-Down On-Resistance                                    |                                          |   |      | 1.5 |     | $\Omega$   |

| $BG, TG\ t_{2D}$  | Bottom Gate Off to Top Gate On Delay<br>Top Switch-On Delay Time         | $C_L = 3300\text{pF}$ (Note 7)           |   |      | 15  |     | ns         |

| $TG, BG\ t_{1D}$  | Top Gate Off to Bottom Gate On Delay<br>Synchronous Switch-On Delay Time | $C_L = 3300\text{pF}$ (Note 7)           |   |      | 15  |     | ns         |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また長期にわたって、絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** LTC3775は $T_J$ が $T_A$ にほぼ等しいパルス負荷条件でテストされている。LTC3775Eは $0^\circ\text{C} \sim 85^\circ\text{C}$ の接合部温度範囲で仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LTC3775Iは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲で保証されている。これらの仕様と調和する最大周囲温度は、基板レイアウト、パッケージの定格熱抵抗および他の環境要因と関連した特定の動作条件によって決まることに注意。

接合部温度( $T_J$ 、単位:  $^\circ\text{C}$ )は周囲温度( $T_A$ 、単位:  $^\circ\text{C}$ )および電力損失( $P_D$ 、単位: W)から次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA})$$

ここで、 $\theta_{JA}$ (単位:  $^\circ\text{C}/\text{W}$ )はパッケージの熱抵抗である。

**Note 3:** UDパッケージの露出パッドをPC基板に半田付けしないと、熱抵抗が $68^\circ\text{C}/\text{W}$ よりもはるかに大きくなる。

**Note 4:** デバイスのビンに流れ込む電流はすべて正。デバイスのビンから流れ出す電流はすべて負。注記がない限り、すべての電圧はグランドを基準にしている。

**Note 5:** 通常動作時の消費電流の大部分は、外付けMOSFETのゲートを充放電するのに必要な電流である。この電流は電源電圧と使用される外付けMOSFETによって異なる。

**Note 6:** 設計によって保証されており、テストされない。

**Note 7:** 立ち上がりおよび立ち下がり時間は10%と90%のレベルを使用して測定する。遅延時間および非重複時間は50%レベルを使用して測定する。

**Note 8:** LTC3775のリーディングエッジ変調アーキテクチャには、TGの最小パルス幅の要件はない。TGの最小パルス幅は、SWノードの立ち上がりおよび立ち下がり時間によって制限される。

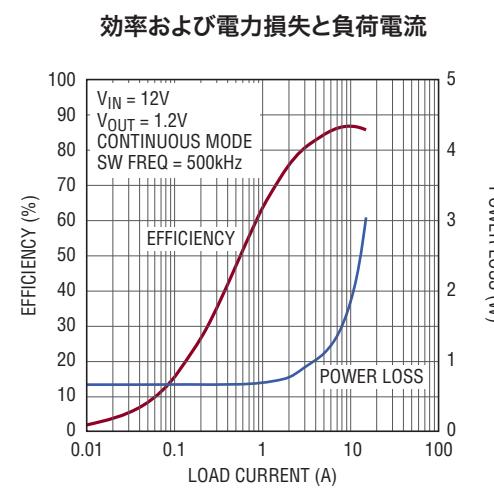

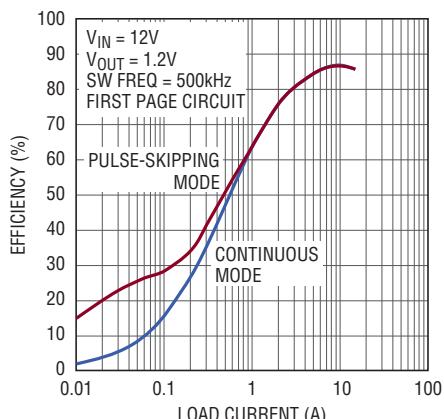

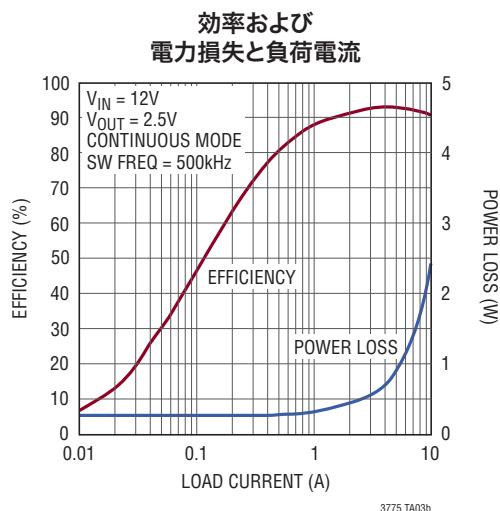

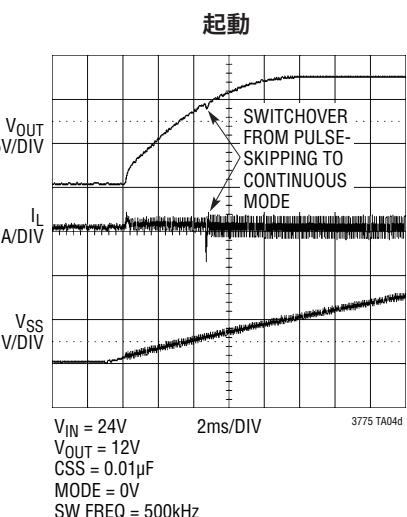

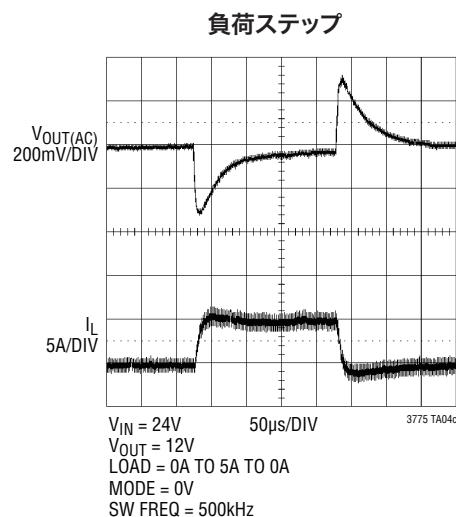

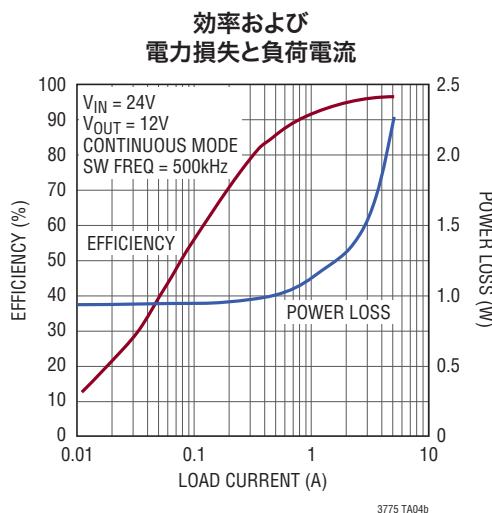

## 標準的性能特性

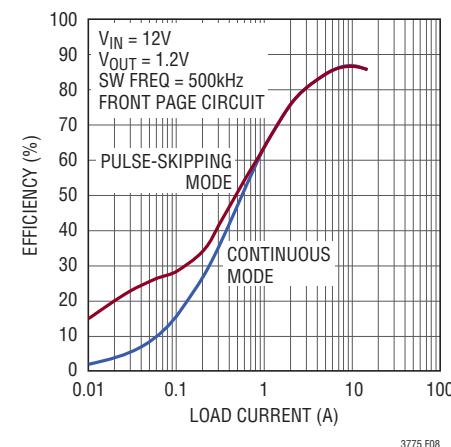

効率と負荷電流

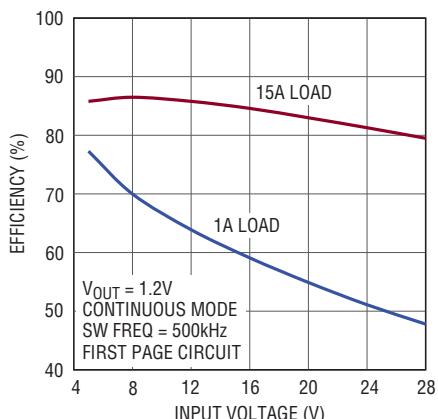

効率と入力電圧

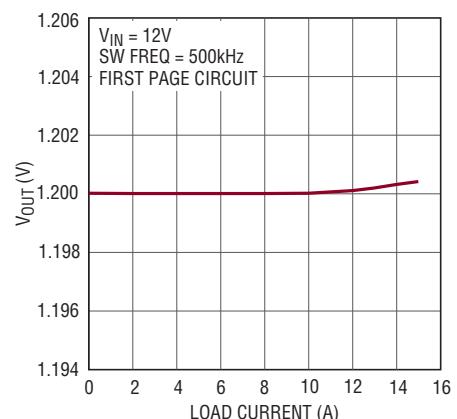

ロード・レギュレーション

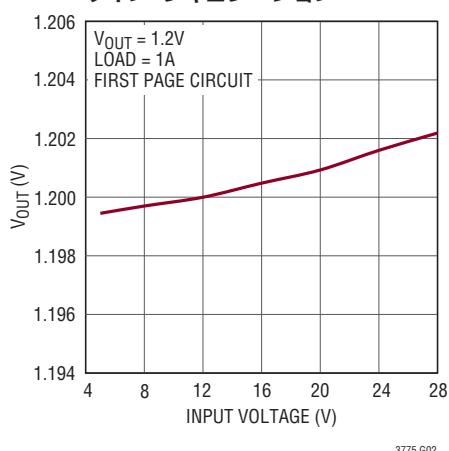

ライン・レギュレーション

FB電圧と温度

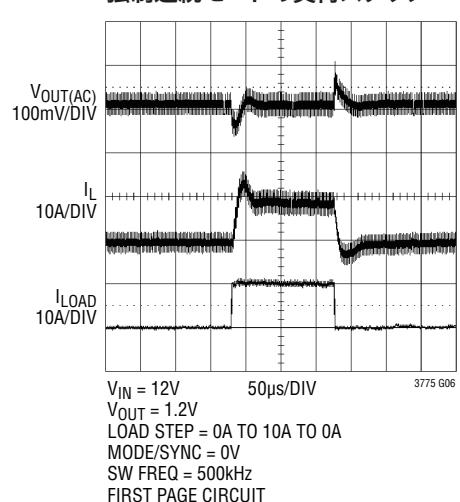

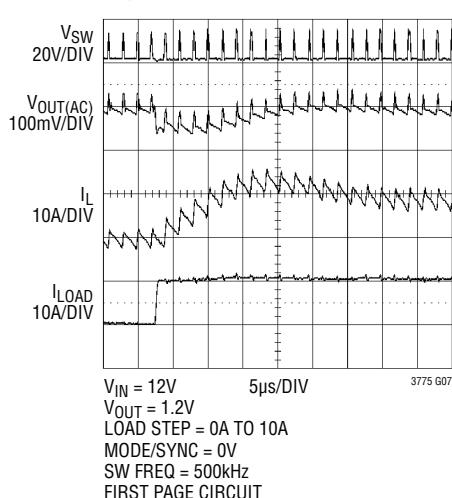

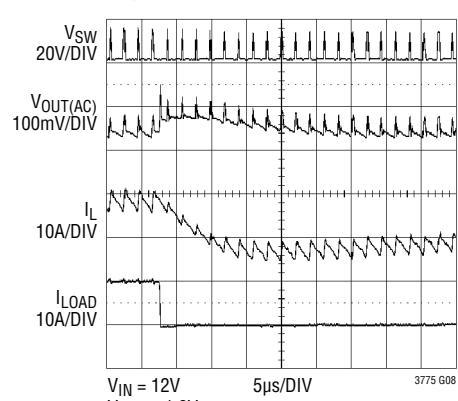

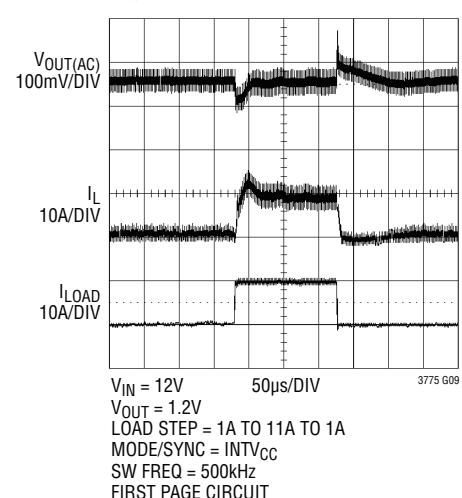

強制連続モードの負荷ステップ

強制連続モードの立ち上がり

負荷ステップ

強制連続モードの立ち下がり

負荷ステップ

パルススキップ・モードの

負荷ステップ

3775fa

## 標準的性能特性

## 標準的性能特性

## ピン機能 (QFN/MSOP)

**I<sub>LIMT</sub>(ピン1/ピン3)**: トップサイド電流制限の設定ポイント。このピンは100µAのプルダウン電流源を備えていて、V<sub>IN</sub>に接続された外付け抵抗によってトップサイド電流制限スレッショルドを設定することができます。「アプリケーション情報」の「電流制限」を参照してください。

**I<sub>LIMB</sub>(ピン2/ピン4)**: ボトムサイド電流制限の設定ポイント。このピンは10µAのプルアップ電流源を備えていて、SGNDに接続された外付け抵抗によってボトムサイド電流制限スレッショルドを設定することができます。「アプリケーション情報」の「電流制限」を参照してください。

**FB(ピン3/ピン5)**: エラーアンプの入力。FBピンはV<sub>OUT</sub>からSGNDに接続された抵抗分割器に接続します。帰還ループ補償ネットワークもこのピンに接続します。

**COMP(ピン4/ピン6)**: エラーアンプの出力。COMPピンとFBピンの間にRCネットワークを使用して、過渡応答が最適になるように帰還ループを補償します。

**SS(ピン5/ピン7)**: ソフトスタート。このピンを外付けコンデンサCSSに接続してソフトスタート機能を実現します。SSピンの電圧が0.6Vの内部リファレンスより低いと、LTC3775はV<sub>FB</sub>の電圧を0.6VのリファレンスではなくSSピンの電圧に制御します。

**FREQ(ピン6/ピン8)**: 周波数の設定ピン。このピンからSGNDに抵抗を接続して内部発振器の自走周波数を設定します。抵抗値の選択の詳細については、「アプリケーション情報」を参照してください。

**SGND(ピン7/ピン9)**: 信号グランド。すべての内部低電力回路のリターンはSGNDピンになります。帰還およびソフトスタートの全ての接続点のリターンはSGNDになります。SGNDは、V<sub>OUT</sub>のバイパス・コンデンサの負端子近くの一点にケルビン接続します。

**BG(ピン8/ピン10)**: ボトム・ゲート・ドライブ。このピンは、ボトムNチャネル同期スイッチMOSFETのゲートをドライブします。このピンはPGNDからINTV<sub>CC</sub>まで振幅します。

**INTV<sub>CC</sub>(ピン9/ピン11)**: 5.2Vの内部レギュレータの出力。ゲート・ドライバおよび制御回路はこの電圧から電力供給されます。このピンは、容量が4.7µF以上の低ESRセラミック・コンデンサ(温度特性がX5R以上)を使用して電源グランドにバイパスします。

**SENSE(ピン10/ピン12)**: トップサイド電流検出入力。このピンは、MOSFETのR<sub>DS(ON)</sub>による電流検出の場合はコンバータのスイッチ・ノードに接続します。あるいは、より高精度な電流

制限を行うため、このピンをトップMOSFETのドレインに接続された検出抵抗に接続することもできます。

**V<sub>IN</sub>(ピン11/ピン13)**: 主入力電源。このピンは、容量が1µF以上の低ESRセラミック・コンデンサ(温度特性がX5R以上)を使用してPGNDにバイパスします。

**SW(ピン12/ピン14)**: スイッチ・ノード。このピンは上側のパワーMOSFETのソースに接続します。このピンは、ボトムサイド電流制限コンパレータおよびゼロクロス逆電流コンパレータの入力としても使用されます。

**TG(ピン13/ピン15)**: トップ・ゲート・ドライブ。このピンはトップNチャネルMOSFETのゲートをドライブします。TGドライバはBOOSTピンから給電されそのリターン経路はSWピンなので、トップMOSFETは真にフロート状態でドライブされます。

**BOOST(ピン14/ピン16)**: トップ・ゲート・ドライバ電源。このピンは、0.1µFの低ESRセラミック・コンデンサを使用してSWにデカップリングします。INTV<sub>CC</sub>からBOOSTにショットキー・ダイオードを外付けすることにより、BOOSTにフローティング・チャージポンプ電源が形成されます。他の外部電源は不要です。

**MODE/SYNC(ピン15/ピン1)**: パルススキップ・モード・イネーブル/同期ピン。この多機能ピンは、パルススキップ・モードのイネーブル/ディスエーブル制御と内部発振器の同期用外部クロック入力として機能します。このピンを1.2V(DC)以下にするか外部のロジックレベルの同期信号でドライブすると、パルススキップ・モードがディスエーブルされ、連続動作に強制されます。このピンを1.2V以上にすると、パルススキップ・モード動作がイネーブルされます。このピンは、SGNDに接続された50kのプルダウン抵抗を備えています。

**RUN/SHDN(ピン16/ピン2)**: イネーブル/シャットダウン入力。このピンを1.22V以上にすると、コントローラがイネーブルされます。このピンを1.22V以下に強制すると、ドライバ出力が“L”になります。このピンを0.74V以下にすると、LTC3775はシャットダウン・モードに強制されます。シャットダウン時には、INTV<sub>CC</sub>レギュレータと大部分の内部回路がオフするので、消費電流は14µA以下に減少します。このピンは1µAのプルアップ電流源を備えているので、フロート状態のままにされてもLTC3775をパワーアップさせることができます。

**PGND(露出パッド・ピン17/露出パッド・ピン17)**: 電源グランド(露出パッド)。このピンはBGドライバのリターンです。PGNDは、ボトム・パワーMOSFETのソースとV<sub>IN</sub>およびINTV<sub>CC</sub>のバイパス・コンデンサに接続します。PGNDはSGNDから電気的に絶縁されています。QFNおよびMSOPパッケージの露出パッドはPGNDに接続されています。

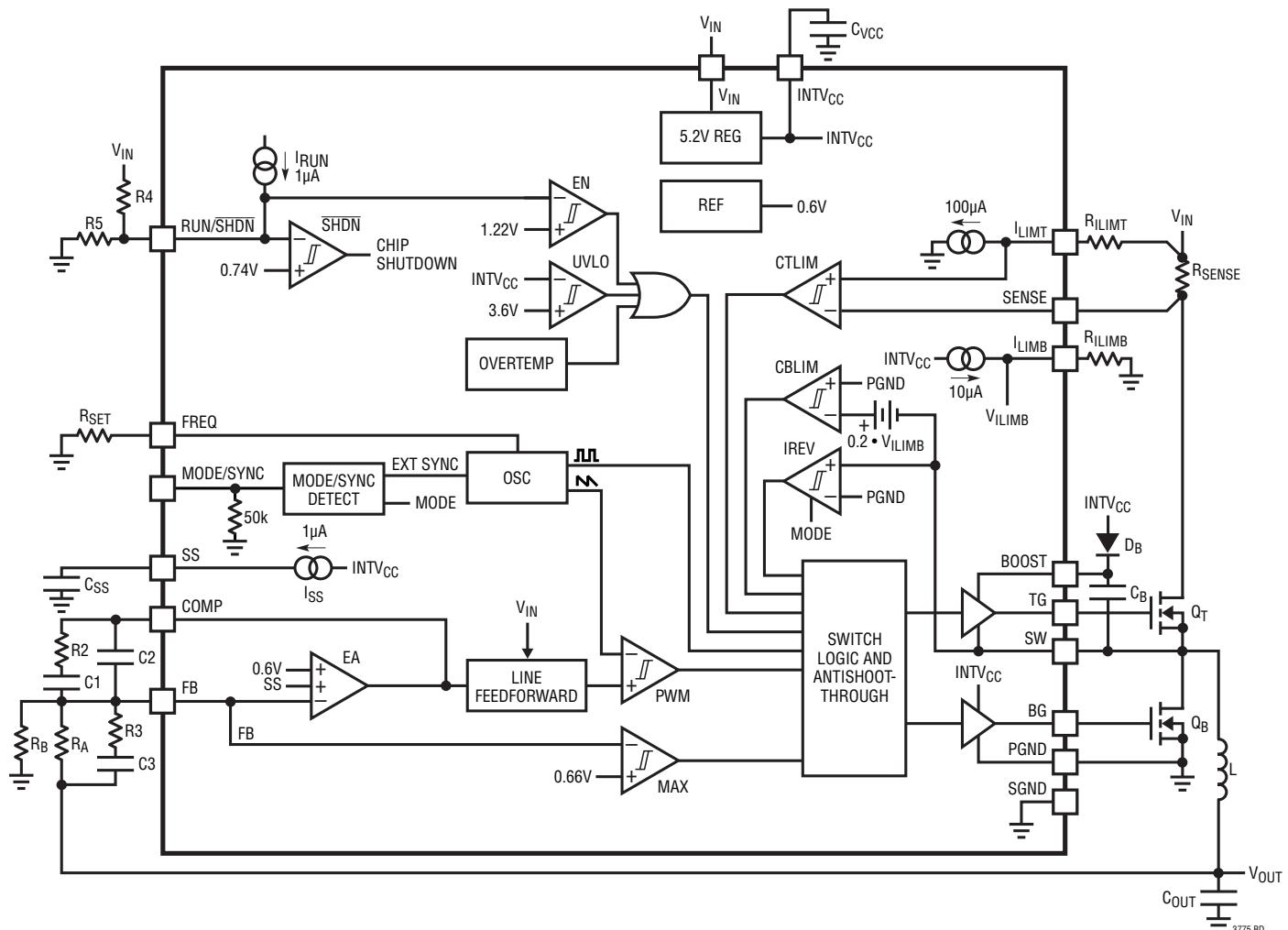

## ブロック図

## アプリケーション情報

### 動作(「ブロック図」を参照)

LTC3775は、DC/DC降圧コンバータ用の固定周波数、電圧モード・コントローラです。2個の外付けNチャネルMOSFETを用いた同期整流式スイッチング・アーキテクチャに使用するように設計されています。回路動作については、「ブロック図」を参照してください。

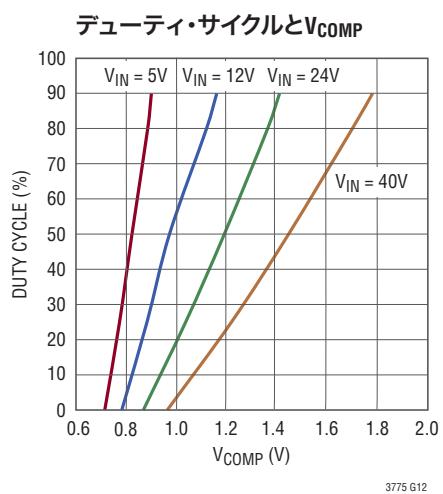

LTC3775には電圧モード制御が使用されており、デューティ・サイクルはエラーアンプの出力によって直接制御されます。エラーアンプは、V<sub>FB</sub>ピンの電圧を0.6Vの内部リファレンスと比較することによってCOMPピンの電圧を調整します。負荷電流が増加すると、リファレンスに比べて帰還電圧が低下します。すると、COMP電圧が上昇し、LTC3775の出力帰還電圧が再度リファレンス電圧に等しくなるまでデューティ・サイクルが増加します。

通常動作時は、PWMコンパレータの状態が変化するとトップMOSFETがオンし、内部発振器によってオフします。PWMコンパレータは、(ライン・フィードフォワード乗算器によって「補償」された後の)エラーアンプの出力を発振器によって生成される鋸波と比較することにより、適切なデューティ・サイクルを維持します。トップMOSFETがオフすると、ボトムMOSFETがオンし、次のサイクルが開始されるまで、または、パルススキップ・モード動作がイネーブルされている場合には、逆電流コンパレータによってインダクタ電流が反転したと判定されるまでオン状態に留まります。

### 帰還制御

LTC3775は、内部の帰還オペアンプを使用してV<sub>OUT</sub>の出力電圧を検出します(「ブロック図」を参照)。これは、低インピーダンス出力を備え、開ループ利得が80dBで、利得帯域幅積が25MHzの真のオペアンプです。正入力は0.6Vの内部リファレンスに接続されており、負入力はFBピンに接続されています。その出力はCOMPに接続されており、さらにライン・フィードフォワード回路に接続され、ここからPWM発生器に送られます。

定常状態では、「ブロック図」に示すように、スイッチング・リギュレータの出力は次式で求められます。

$$V_{\text{OUT}} = V_{\text{REF}} \cdot \left( 1 + \frac{R_A}{R_B} \right)$$

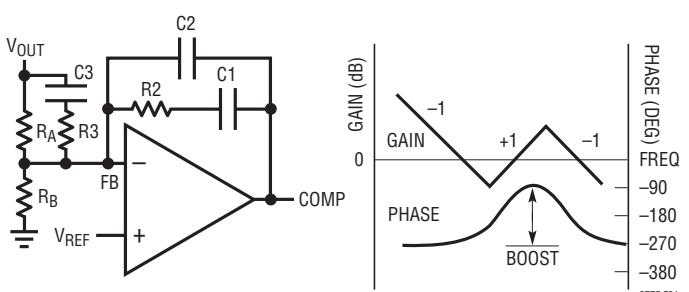

トランスコンダクタンス(g<sub>m</sub>)アンプを使用する多くのリギュレータとは異なり、LTC3775は、FBピンを仮想グランドとする反転加算アンプ・トポロジーを使用して設計されています。これにより、帰還利得を外付け部品によって正確に制御することができます。さらに、電圧帰還アンプの場合、ポールとゼロの位置を柔軟に選択できます。特に、「タイプ3」の補償を使用することができるるので、LCポール周波数で位相ブーストが得られ、制御ループの位相マージンが大幅に改善されます。

LTC3775の標準的な回路の場合、帰還ループは、ライン・フィードフォワード回路、変調器、外付けインダクタ、出力コンデンサ、補償ネットワークを備えた帰還アンプで構成されます。これらの部品全てがループ動作に影響を与えるので、ループ補償の観点から考慮する必要があります。変調器は、内部PWM発生器、出力MOSFETドライバおよび外付けMOSFET自体で構成されます。変調器の利得は入力電圧に従って直線的に変化します。ライン・フィードフォワード回路はこの利得の変化を補償し、入力電圧に関係なく、エラーアンプの出力からインダクタ入力までの利得を一定にします。帰還ループの観点からは、ライン・フィードフォワード回路と変調器の組み合わせはCOMPからインダクタ入力への線形電圧伝達関数のように見え、30V/Vにほぼ等しい利得があります。標準的ループ補償周波数ではAC動作に問題は無く、スイッチング周波数の1/2で大きな位相シフトが生じます。

外付けインダクタ/出力コンデンサの組み合わせにより、ループ動作への影響がさらに大きくなります。これらの部品により、出力に2次のLCロールオフが生じ、180°の位相シフトを伴います。このロールオフによってPWM波形がフィルタされ、必要なDC出力電圧が得られますが、この位相シフトによって帰還ループの安定化の課題が生じるので、周波数補償を行う必要があります。周波数が高くなると、出力コンデンサのリアクタンスがそのESRに近づき、コンデンサによるロールオフが停止して-20dB/decadeと90°の位相シフトが残ります。

## アプリケーション情報

タイプ3のアンプを図1に示します。このアンプの伝達関数は次式から求められます。

$$\frac{V_{COMP}}{V_{OUT}} = \frac{- (1 + sR2C1) [1 + s(R_A + R3)C3]}{sR_A (C1 + C2) (1 + s(C1||C2)R2) (1 + sC3R3)}$$

エラーアンプのRCネットワークとフィードフォワード部品R3およびC3によって2つのポールとゼロの対が生じ、システムのユニティゲイン周波数f<sub>C</sub>での位相ブーストが得られます。理論的には、ゼロとポールはf<sub>C</sub>の周囲に対称に配置され、ゼロとポールの間の開きはf<sub>C</sub>で必要な位相ブーストが得られるように調整されます。ただし、実際には、クロスオーバー周波数がLCのダブルポール周波数よりはるかに高い場合、この周波数補償の手法では通常、ユニティゲイン帯域幅内に位相の減少箇所が生じるので、条件付き安定性に関する何らかの問題が生じます。

条件付き安定性が問題になる場合、エラーアンプのゼロを低い周波数に移動して位相が減少ないようにします。次式を使用して帰還補償部品の値を計算することができます。

f<sub>SW</sub> = スイッチング周波数

$$f_{LC} = \frac{1}{2\pi\sqrt{LC_{OUT}}}$$

$$f_{ESR} = \frac{1}{2\pi R_{ESR} C_{OUT}}$$

以下のように選択します。

$$f_C = \text{クロスオーバー周波数} = \frac{f_{SW}}{10}$$

$$f_{Z1(ERR)} = f_{LC} = \frac{1}{2\pi R2C1}$$

$$f_{Z2(RES)} = \frac{f_C}{5} = \frac{1}{2\pi(R_A + R3)C3}$$

$$f_{P1(ERR)} = f_{ESR} = \frac{1}{2\pi R2(C1||C2)}$$

$$f_{P2(RES)} = 5f_C = \frac{1}{2\pi R3C3}$$

周波数f<sub>C</sub>での必要なエラーアンプの利得は以下のようになります。

$$\begin{aligned} A_{V(CROSSOVER)} &\approx 40 \log \sqrt{1 + \left(\frac{f_C}{f_{LC}}\right)^2} - 20 \log \sqrt{1 + \left(\frac{f_C}{f_{ESR}}\right)^2} - 20 \log(A_{MOD}) \\ &\approx 20 \log \frac{R2}{R_A} \cdot \frac{\left(1 + \frac{f_{LC}}{f_C}\right) \left(1 + \frac{f_{P2(RES)}}{f_C} + \frac{f_{P2(RES)} - f_{Z2(RES)}}{f_{Z2(RES)}}\right)}{\left(1 + \frac{f_C}{f_{ESR}} + \frac{f_{LC}}{f_{ESR} - f_{LC}}\right) \left(1 + \frac{f_{P2(RES)}}{f_C}\right)} \end{aligned}$$

ここで、A<sub>MOD</sub>は変調器およびラインのフィードフォワード利得で、次のようになります。

$$A_{MOD} \approx \frac{V_{IN(MAX)} \cdot DC_{MAX}}{V_{SAW}} = \frac{40V \cdot 0.95}{1.25V} \approx 30V/V$$

抵抗R<sub>A</sub>の値とポールおよびゼロの位置が決まると、C1、R2、C2、R3、C3の各値は上式から求めることができます。

スイッチング電源の帰還ループの補償は複雑な作業になります。このデータシートに示すアプリケーションには標準的値が示されており、示された電源部品用に最適化されています。類似した電源部品も使用できますが、主要な電源部品の1つでも値を大きく変更すると、性能が大幅に低下する可能性があります。安定性は回路基板のレイアウトにも左右されます。算出した部品の値を検証するため、全ての新規回路設計は試作して安定性のテストをする必要があります。

図1. タイプ3のアンプの補償

## アプリケーション情報

### 出力過電圧保護

過電圧コンパレータMAXは、過渡的なオーバーシュート(10%以上)や、出力に過電圧を生じる恐れのあるより深刻な状態からデバイスを保護します。このような場合、過電圧状態が解消されるまでトップMOSFETはオフし、ボトムMOSFETはオンします。

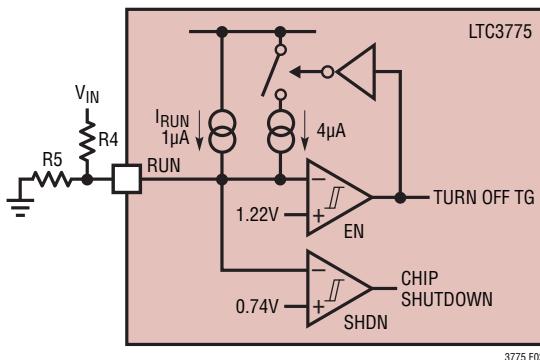

### 実行/シャットダウン

RUN/SHDNピンを0.74V以下にすることにより、LTC3775を静止電流が14 $\mu$ A以下の低消費電力シャットダウン・モードにすることができます。RUN/SHDNピンは、スレッショルドが1.22Vの高精度外部UVLO(低電圧ロックアウト)入力として使用することができます。このピンが1.22V以下の場合、ドライバ出力は“L”に保たれます。「ブロック図」に示す外付け抵抗分割器R4およびR5を使用し、V<sub>IN</sub>に基づいてUVLOレベルを設定することができます。スイッチングが開始されるV<sub>IN</sub>電圧は次式から求められます。

$$\text{UVLO(Upper)} = 1.22V \cdot (1 + R4/R5) - (1\mu A \cdot R4)$$

RUN/SHDNピンは、このピンがフロート状態のままにされた場合、自動的にオンするように1 $\mu$ Aのプルアップを備えています。この1 $\mu$ Aのプルアップ電流は上記のUVLOの計算に含まれています。RUN/SHDNが1.22Vを上回ると、このプルアップ電流は5 $\mu$ Aまで増加します。これにより、UVLOスレッショルドに若干のヒステリシスが与えられます。下側のUVLOレベルは次のようにになります。

$$\text{UVLO(Lower)} = 1.22V \cdot (1 + R4/R5) - (5\mu A \cdot R4)$$

したがって、ヒステリシスの値は次のように求められます。

$$\text{UVLO(Hysteresis)} = 4\mu A \cdot R4$$

図2. RUNピンの制御

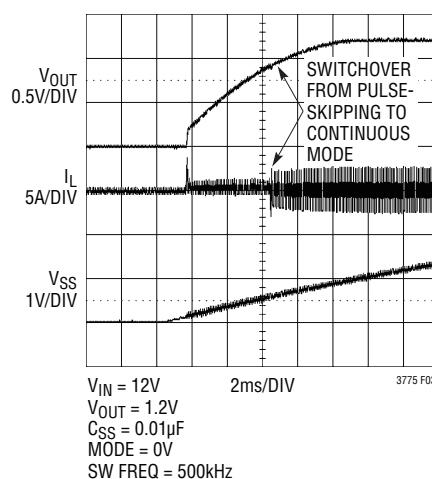

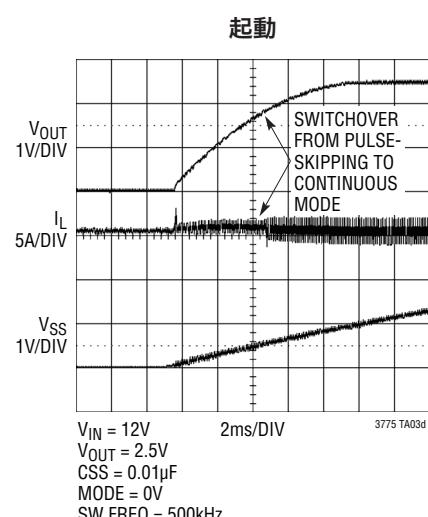

### ソフトスタート

LTC3775には、起動時に出力電圧を滑らかに上昇させるソフトスタート回路が搭載されています。SSピンには、GNDに接続する外付けコンデンサC<sub>SS</sub>が必要で、容量は必要なソフトスタート時間によって決ります。1 $\mu$ Aの内部電流源がC<sub>SS</sub>を充電します。SSピンの電圧が0.6Vの内部リファレンスより低い間は、LTC3775はV<sub>FB</sub>の電圧を0.6VのリファレンスではなくSSピンの電圧に制御します。SS電圧が0Vから0.6V、さらにそれ以上に直線的に上昇するにつれ、出力電圧V<sub>OUT</sub>がゼロからその最終値まで滑らかに上昇します。合計ソフトスタート時間は次のように算出できます。

$$t_{\text{SOFTSTART}} = \frac{0.9 \cdot C_{\text{SS}}}{1\mu A}$$

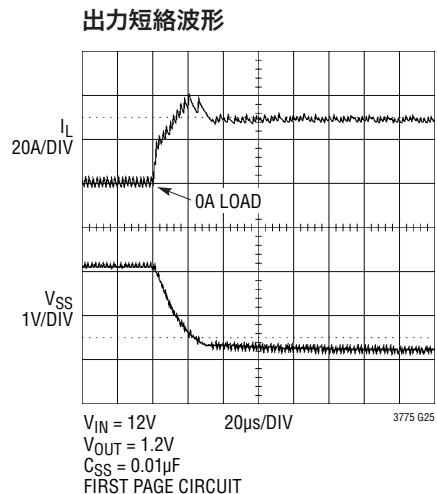

SSピンは、LDOの低電圧状態(INTV<sub>CC</sub> < 3.6V)、シャットダウン(RUNピン < 1.22V)、過温度状態(T<sub>J</sub> > 165°C)、電流制限の各状態の間に“L”になります。

トップまたはボトムのいずれかの電流制限コンパレータがトリップすると、インダクタ電流が電流制限の設定値近くに安定するまで、SSピンは“L”状態に留まります。フォールトが解消されると、SSは充電を開始し、次第にデューティ・サイクルを増加させ出力電圧を上昇させます。SSピンは電流を制限するので、電源の起動時に過電流状態にならないようにすることが重要です。そうしないと、V<sub>OUT</sub>が正常に起動しません。

図3. LTC3775を使用した降圧コンバータの標準的な起動波形

## アプリケーション情報

プリバイアスされたV<sub>OUT</sub>が放電しないように、LTC3775は、MODE/SYNCピンによって選択されたモードに関係なく、SS = 0.54Vまでは常にパルススキップ・モードでスイッチングを開始します。したがって、パワーアップ時にV<sub>OUT</sub>が0Vを上回っていると、V<sub>OUT</sub>は(無負荷時の場合)SS電圧がV<sub>OUT</sub>に達するまでプリバイアスされた電圧に保たれ、その後、V<sub>OUT</sub>はSSの上昇をトラッキングします。SSが0.54Vを上回ると、LTC3775は選択されたモードに戻ります。

### 固定スイッチング周波数

部品サイズと個々のアプリケーションの効率およびノイズを最適化するため、FREQピンからグランドに接続される外付け抵抗を使用して内部発振器を250kHz～1MHzに設定することができます。内部発振器はMODE/SYNCピンに接続された外部クロックに同期させることも可能で、設定された自走周波数の±20%の範囲にロックすることができます。外部クロックにロックすると、パルススキップ・モード動作が自動的にディスエーブルされます。固定周波数動作には、高精度な動作周波数のためのインダクタとコンデンサの値を選択可能のこと、帰還ループも同様に厳密に規定可能など、多くの利点があります。回路に生じるノイズは常に既知の周波数になります。低調波発振やスロープ補償など、固定周波数電流モードのスイッチャで一般に頭痛の種となる問題は、LTC3775のような電圧モードの設計では生じません。

### サーマル・シャットダウン

LTC3775は、デバイスの接合部温度が165°Cを超えるとドライバ出力を“L”にする熱検出器を搭載しています。サーマル・シャットダウン回路には25°Cのヒステリシスがあります。

### 電流制限

LTC3775はサイクルごとの電流制限回路を内蔵しており、最大出力電流をユーザーによって設定されるレベルに制限します。電流制限回路は、それぞれトップMOSFETとボトムMOSFETの電圧降下をモニタする2つのコンパレータCTLIMとCBLIMで構成されています。MOSFETの実効抵抗R<sub>DSON</sub>はMOSFETがオンのときは小さいので、ドレイン-ソース間の電圧降下は流れる電流に比例します。また、精度を高めるため、検出抵抗を使用してトップサイド電流をモニタすることもできます。

2つのコンパレータを備える利点は、動作デューティ・サイクルに関係なく、連続モニタとインダクタ電流のサイクルごとの制御が可能ことです。高デューティ・サイクルの動作では、トップMOSFET(Q<sub>T</sub>)が大部分の時間オン状態です。したがって、高デューティ・サイクルの動作時には、ハイサイドのコンパレータが出力電流を制限する必要があります。ローサイドのMOSFETをモニタするコンパレータが1つのだけのアーキテクチャでは、高デューティ・サイクルの動作時に出力電流を効率的に制限することができません。逆に、低デューティ・サイクルの動作時には、ローサイドのコンパレータが出力電流を制限する必要があります。もう1つの一般的な電流検出手法では、インダクタと直列接続された検出抵抗を使用して連続モニタを可能にします。ただし、この手法では、電流制限コンパレータの同相範囲によってV<sub>OUT</sub>の範囲が制限されます。LTC3775ではこのようにV<sub>OUT</sub>が制約されることはありません。

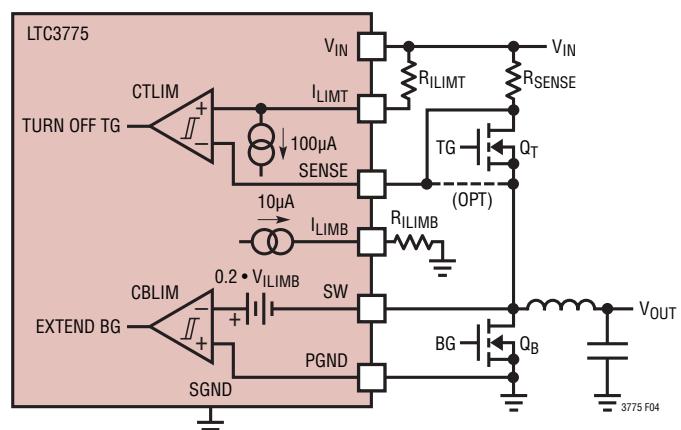

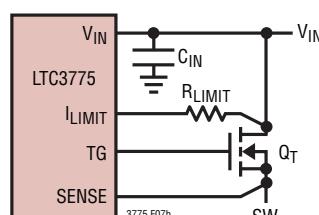

電流制限回路を図4に示します。トップ電流制限コンパレータCTLIMは、TGが“H”的とき、トップMOSFET(Q<sub>T</sub>)を介して電流をモニタします。Q<sub>T</sub>がオンのときにインダクタ電流が電流制限スレッショルドを超えると、Q<sub>T</sub>が瞬時にオフしてボトムMOSFET(Q<sub>B</sub>)をオンします。SENSEピンはCTLIMの入力です。上側のMOSFETのR<sub>DSON</sub>が電流の検出に使用されるアプリケーションでは、SENSEピンをQ<sub>T</sub>のソース(SWノード)に接続します。または、高精度の電流検出を行う場合には、こ

図4. LTC3775の電流制限回路

## アプリケーション情報

のピンをQTのドレインに接続された検出抵抗に接続します。CTLIMのリファレンス入力はILIMTピンに接続されています。ILIMTピンからVINに外付け抵抗RILIMTを接続して、電流制限スレッショルドを設定します。SENSEピンの電圧はインダクタ電流が増加するに従って低下します。SENSEピンの電圧がILIMTピンの電圧を下回ると、CTLIMがトリップすることにより、TGが“L”になってQTをオフします。

ボトム電流制限コンパレータCBLIMは、BGが“H”的とき、ボトムMOSFET(QB)を通過する電流をモニタします。QBがオンのときにインダクタ電流が電流制限スレッショルドを超えていると、電流がスレッショルドを下回るまでQBはオン状態を保ちます。SWピンはCBLIMの入力です。CBLIMのリファレンス入力はILIMBピンの電圧から供給されます。ILIMBピンからSGNDに外付け抵抗RILIMBを接続して、電流制限スレッショルドを設定します。

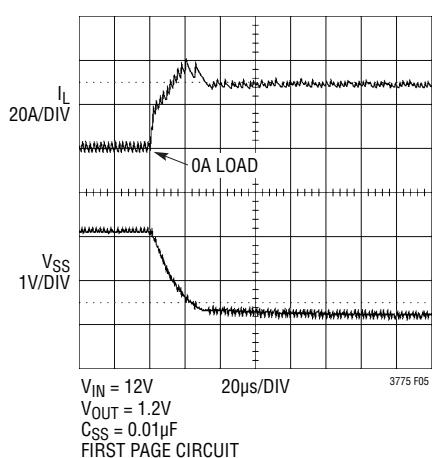

QBがオンのとき、PGNDからSWにインダクタ電流が(正の負荷電流として)流れます。したがって、SWノードは負の電圧になります。LTC3775は、SWピンの電圧を反転させてからILIMBピンの(1/5に)減衰させた電圧と比較します。CBLIMがトリップするとBGが“H”に保たれ、インダクタ電流がスレッショルドを下回るまでTGは“L”に保たれます。出力過負荷時の標準的な波形を図5に示します。

図5. 出力過負荷時の標準的な波形

### 電流制限のブランкиング時間

LTC3775の電流制限回路は、SWノードの“L”から“H”および“H”から“L”的遷移に続く短いブランкиング時間を特長としています。これにより、SWノードにリングが生じたときに電流制限回路が誤ってトリップしないようにします。

トップ・ゲートTGが“H”になると、トップサイド・コンパレータCTLIMは200nsの間待機してからオンしてSENSE電圧をモニタします。同様に、ボトム・ゲートBGが“H”になると、ボトムサイド・コンパレータCBLIMは200nsの間待機してからオンしてSW電圧をモニタします。これは、電流制限時には、TGおよびBGの最小パルス幅が200nsよりもわずかに長くなることを意味します。ただし、これらのブランкиング時間によって制御ループのデューティ・サイクル能力が制限されることはありません。LTC3775の制御ループは、TGのオン時間がわずか30nsで動作することができます。

トップサイドに検出抵抗が用いられている場合、LTC3775はCTLIMのブランкиング時間を200nsから100nsに自動的に短縮します。CBLIMのブランкиング時間は200nsのままであります。SWノードよりもリングが少ないトップMOSFETのドレインにSENSEピンを接続するので、検出抵抗を使用したときにブランкиング時間を短縮することができます。LTC3775は、BGが“H”的ときにSENSEピンが( $V_{IN}$ に等しい)高い電圧に保たれることを確認することにより、検出抵抗が用いられていることを検知します。SENSEピンがSWノードに接続されている場合、BGが“H”的ときにSENSEは0Vになります。

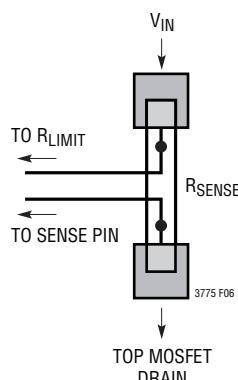

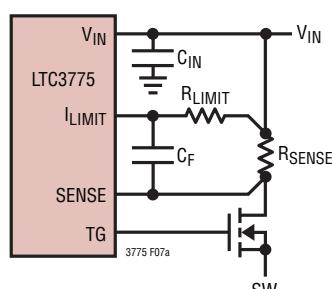

### 電流検出入力ピン

SENSEピンとILIMTピンはトップ電流制限コンパレータCTLIMの入力です。トップ電流制限スレッショルドは、ILIMTピンに接続された抵抗RILIMTとILIMTピンの100 $\mu A$ のプルダウン電流源によって設定されます。RILIMTはLTC3775の近くに配置し、RILIMTの他端は(図6に示すように)検出抵抗の下のケルビン検出接続点までSENSEのトレースに沿って配線します。検出抵抗は、トップ・パワーMOSFETのドレインと $V_{IN}$ ノードに、短く幅の広いPCBトレースを使用して接続します。理想的には、図7aに示すように、検出抵抗の上側の端子は入力コンデンサの正端子に隣接させます。この経路は、検出抵抗、トップ・パワーMOSFET、インダクタ、および出力コンデンサによって形成される高di/dtのループの一部です。

## アプリケーション情報

電流制限コンパレータはリーディングエッジ・ブランкиングを備えているので、適正に動作させるためにRCフィルタを外付けする必要はありません。ただし、SENSEピンとI<sub>LIMIT</sub>ピンの間にコンデンサ(C<sub>F</sub>)を追加することによる外付けフィルタの設計は可能です。フィルタ部品はSENSEピンとI<sub>LIMIT</sub>ピンの近くに配置します。

R<sub>DSON</sub>検出を用いる場合、図7bに示すように、ケルビン検出接続はSENSEピンとR<sub>LIMIT</sub>抵抗からそれぞれトップパワーMOSFETのソース端子とドレイン端子に配線します。ソース端子がスイッチングしているので、外付けRCフィルタを追加することはできません。

図6. トップサイド電流制限検出用のケルビン検出接続

図7a. トップサイド電流検出用の外付けフィルタ

図7b. トップサイドR<sub>DSON</sub>検出用のケルビン接続

ボトムサイド電流制限スレッショルドは、I<sub>LIMB</sub>ピンからSGNDに接続された抵抗R<sub>ILIMB</sub>とI<sub>LIMB</sub>ピンの10μAのプルアップ電流源によって設定されます。I<sub>LIMB</sub>の電圧は、ボトム電流制限コンパレータCBLIMの入力に印加される前に内部で1/5に減衰されます。この電圧は安定していなければなりません。R<sub>ILIMB</sub>は、I<sub>LIMB</sub>ピンからLTC3775のSGNDピンの近くの安定したグランドに接続します。CBLIMの他方の入力はSWピンに接続されています。SWピンはボトム・ゲート・ドライバとも共有されているので、ボトムMOSFET(Q<sub>B</sub>)のドレインの近くに接続します。

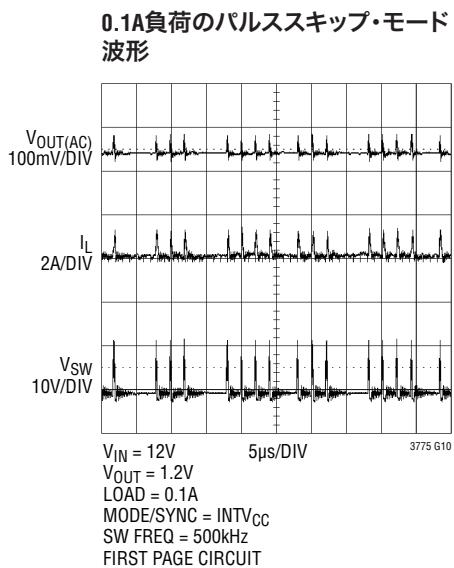

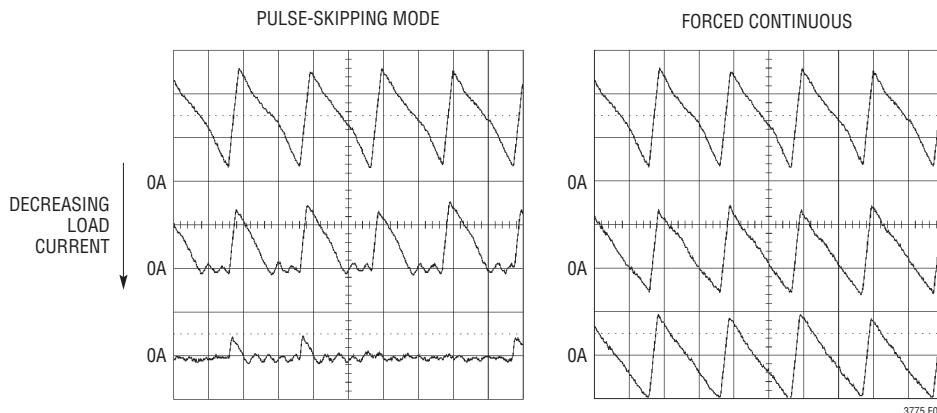

## パルススキップ・モード

LTC3775は、MODE/SYNCピンで選択可能な2つのモード(パルススキップ・モードまたは強制連続モード)のうちの1つで動作することができます。図8に示すように、軽負荷時に効率を上げる必要がある場合にパルススキップを選択します。このモードでは、逆電流による効率の損失を最小限に抑えるため、インダクタ電流が反転するときにボトムMOSFETをオフします。負荷電流が減少すると(図9を参照)、レギュレーションを維持するために、最小オン時間(50ns)に達するまでデューティ・サイクルが低下します。負荷がこのポイントを下回ると、LTC3775はレギュレーションを維持するためにサイクルをスキップし始めます。これにより、周波数が低下し、ゲート電荷損失を最小限に抑えることによって効率が改善されます。

強制連続モードでは、トップMOSFETがオフのときにはボトムMOSFETが常にオンになるので、低電流時にインダクタ電流を反転させることができます。このモードでは、スイッチングによって効率が低下しますが、低負荷電流時に過渡応答が良

図8. パルススキップ時の効率/強制連続モード

## アプリケーション情報

図9. パルススキップ・モードと強制連続モードのインダクタ電流波形の比較

好になる、固定周波数動作を行う、電流のシンク時にレギュレーションを維持できるなどの利点があります。各モードの軽負荷時の効率については、図8を参照してください。

パルススキップ・モードでは、LTC3775の逆電流コンパレータIREVは、ボトム・ゲートBGが“H”的ときにゼロクロスを検出するためSWピンをモニタします。インダクタ電流が反転してSWの電圧がGNDを上回るとBGがオフします。BGが最初にオンしたとき、SWノードのリンギングによって誤ったトリップが生じないように、ボトムサイド電流制限のブランкиングと同様、200nsのブランкиング時間があります。特定の軽負荷状態で、TGのオン時間が短いと、IREVのブランкиング時間内にインダクタ電流が反転することがありますが、LTC3775がBGをオフするのはブランкиング時間が終了してからです。

小さい値のインダクタが使用されるアプリケーションの場合、インダクタ・リップル電流の $di/dt$ が高くなり、ボトムMOSFET(Q<sub>B</sub>)の寄生直列インダクタンスおよびPCBトレースのインダクタンスと結びついて、Q<sub>B</sub>のR<sub>DSON</sub>の電圧降下に対抗する電圧が生成されます。これにより、インダクタ電流が反転する前にIREVが早めにトリップする可能性があります。SWピンをQ<sub>B</sub>のドレインの近くに接続することにより、PCBトレースの寄生直列インダクタンスを最小限に抑えることができます。

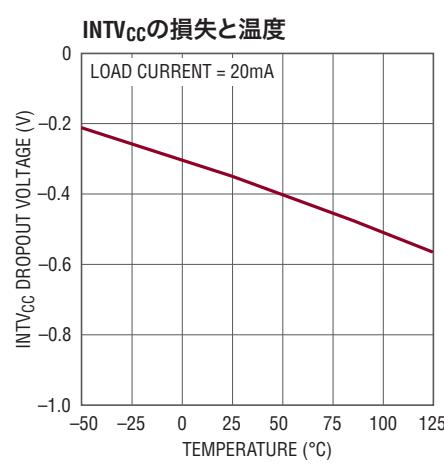

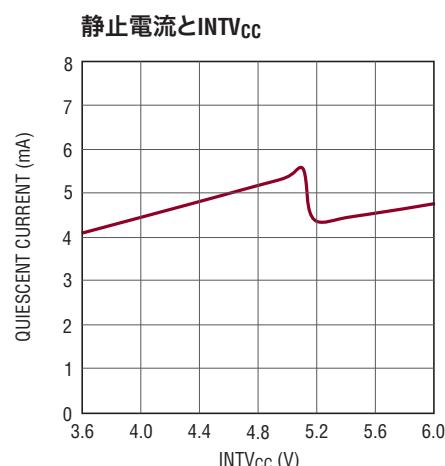

### INTVCCレギュレータ

LTC3775は、V<sub>IN</sub>電源からINTVCCピンに電力を供給するPチャネル低損失リニア・レギュレータ(LDO)を備えています。INTVCCはゲート・ドライバとLTC3775の内部回路のほとんどに電力を供給します。V<sub>IN</sub>が6.5Vを上回ると、LDOはINTVCC

ピンの電圧を5.2Vに安定化します。INTVCCピンは、少なくとも4.7μFの低ESRセラミック・コンデンサ(温度特性がX5R以上)を使用してグランドにバイパスする必要があります。MOSFETゲート・ドライバが必要とする大きな過渡電流を供給するには、十分なバイパスが必要です。

内部の低電圧ロックアウト(UVLO)がINTVCCの電圧をモニタし、LTC3775のゲート・ドライブ電圧が十分であることを確認します。INTVCC電圧が3.1VのUVLOスレッショルドを下回る場合には、ゲート・ドライブ出力は“L”的ままです。

### 熱に関する検討事項

LTC3775は、熱抵抗R<sub>TH(JA)</sub>が68°C/Wの3mm×3mm QFNパッケージ(UD16)と熱抵抗R<sub>TH(JA)</sub>が40°C/WのMSOPパッケージ(MSE16)で提供されます。どちらのパッケージもリード・ピッチは0.5mmです。

このレギュレータは最大50mAのゲート・ドライブ負荷電流を供給できます。予測されるLDO負荷電流は、外付けMOSFETのゲート電荷要件から次のように計算できます。

$$I_{INTVCC} = (f_{SW}) \cdot (Q_{G(QT)} + Q_{G(QB)}) + 3.5\text{mA}$$

ここで、

3.5mAはLTC3775の静止電流

Q<sub>G(QT)</sub>はトップMOSFETの総ゲート電荷

Q<sub>G(QB)</sub>はボトムMOSFETの総ゲート電荷

f<sub>SW</sub>はスイッチング周波数

## アプリケーション情報

$Q_G$ の値は、MOSFETのデータシートの「標準的性能特性」の  $V_{GS}$  と  $Q_G$  の曲線から求めます。電気的仕様に記載されている値は、10Vなどの高い  $V_{GS}$  で測定されていることがあります、重要なのは5VのINTV<sub>CC</sub>ゲート・ドライブ電圧時の値です。

LTC3775の最大接合部温度を決して超えないように注意する必要があります。接合部温度は以下の式を使用して概算することができます。

$$P_{DISS} = V_{IN} \cdot I_{INTVCC}$$

$$T_J = T_A + P_{DISS} \cdot R_{TH}(JA)$$

必要な熱解析の例として、入力電圧が24V、出力電圧が3.3Vの15A降圧コンバータを考えます。スイッチング周波数は500kHz、最大周囲温度は70°Cです。このアプリケーションに使用されるパワーMOSFETはVishay SiliconixのSi7884DPで、標準  $R_{DS(ON)}$  は  $V_{GS} = 4.5V$  で  $7.5m\Omega$ 、 $V_{GS} = 10V$  で  $5.5m\Omega$  です。 $V_{GS}$  と  $Q_G$  のプロットから、 $V_{GS} = 5V$  での総ゲート電荷は  $18.5nC$  です（ゲート電荷の温度係数は小さい）。トップサイドとボトムサイドにそれぞれ1個のパワーMOSFETが使用されています。UDパッケージの場合には以下のようになります。

$$I_{INTVCC} = 3.5mA + 2 \cdot 18.5nC \cdot 500kHz = 22mA$$

$$P_{DISS} = 24V \cdot 22mA = 528mW$$

$$T_J = 70^\circ C + 528mW \cdot 68^\circ C/W = 105.9^\circ C$$

この例では、接合部温度は35.9°C上昇します。これらの式から、ゲート充電電流が通常、デバイスの静止電流を左右していることと、動作周波数の選択と基板の放熱がソリューションの熱性能に大きな影響を与える可能性があることが分ります。

最大接合部温度を超えないようにするには、最大  $V_{IN}$  の連続モード（重負荷）動作時のデバイスの入力電源電流をチェックする必要があります。安全な接合部温度を維持するため、動作周波数とパワーMOSFETのサイズのトレードオフが必要になる場合があります。

最後に、赤外線カメラやサーマル・プローブを使用した最終的なPCBの熱解析を行うことにより、計算値を検証することが重要です。

### 低電源電圧での動作

LTC3775の最小入力電圧は4.5Vです。LTC3775のゲート・ドライバはPMOSプルアップおよびNMOSプルダウン素子で構成されているので、パワーMOSFETのスイッチング時に全INTV<sub>CC</sub>電圧をゲートに印加することができます。それでも、最適なパワーMOSFETを選択するために、最小ゲート・ドライブ電源電圧（INTV<sub>CC</sub>）は注意して決める必要があります。最小ゲート・ドライブ電圧に影響を与える可能性がある重要なパラメータは、最小入力電圧（ $V_{IN(MIN)}$ ）、LDOの損失電圧、パワーMOSFETの  $Q_G$ 、および動作周波数です。

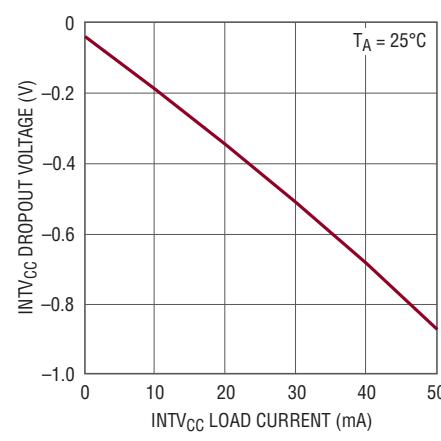

入力電圧  $V_{IN}$  が、INTV<sub>CC</sub> LDOがドロップアウト状態になるほど十分に低いと、最小ゲート・ドライブ電源電圧は次のようになります。

$$V_{INTVCC} = V_{IN(MIN)} - V_{DROPOUT}$$

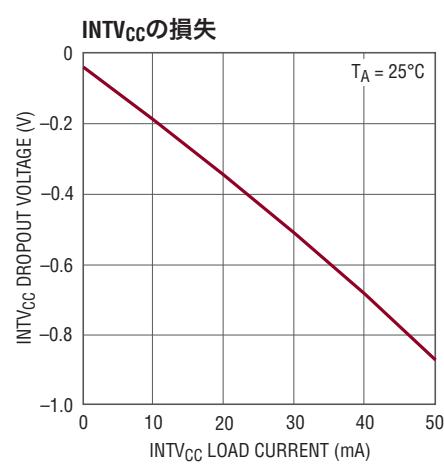

LDOの損失電圧は、総ゲート・ドライブ電流およびデバイスの静止電流（標準3.5mA）と相関関係があります。LDOの損失電圧と出力電流のグラフを図10に示します。LDOの損失電圧の温度係数は約6000ppm/°Cです。総静止電流の計算の詳細については、「INTV<sub>CC</sub>レギュレータ」および「熱に関する検討事項」を参照してください。

図10. INTV<sub>CC</sub> LDOの損失電圧と電流

## アプリケーション情報

計算が完了した後は、全ての動作条件(低V<sub>IN</sub>、公称V<sub>IN</sub>、高V<sub>IN</sub>、および軽負荷から最大負荷まで)でゲート・ドライブ波形とゲート・ドライバの電源電圧(INTV<sub>CC</sub>-PGND間)を測定し、パワーMOSFETが十分に導通していることを確認することが重要です。パワーMOSFETのデータシートを参照し、測定したV<sub>GS</sub>の実際のR<sub>DS(ON)</sub>を確認し、赤外線カメラやサーマル・プローブを使用して部品温度を測定することによって熱の計算値を検証します。

### 高電源電圧での動作

高入力電圧時には、LTC3775の内部LDOが大きな電力を消費することがあるので、最大接合部温度を超える可能性があります。高動作周波数や2個以上のパワーMOSFETが並列に使用されるなどの状態では、接合部温度が高レベルまで上昇する可能性があります。最大接合部温度を超えないようにするには、最大V<sub>IN</sub>での連続導通モード動作時の入力消費電流をチェックする必要があります。最大接合部温度の計算については「熱に関する検討事項」を参照してください。

### 低デューティ・サイクルの動作

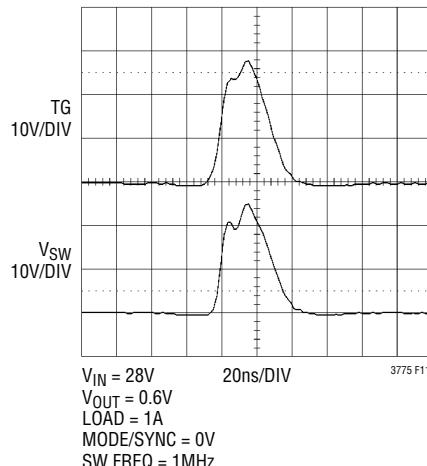

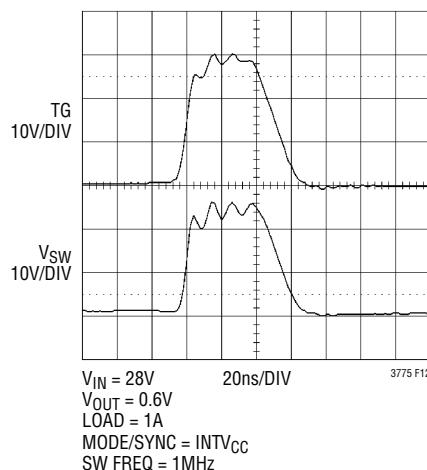

LTC3775はリーディングエッジ変調アーキテクチャを用いています。PWMコンパレータがトリップするとトップMOSFETがオンするので、トップMOSFETの最小オン時間はPWMコンパレータの伝播遅延には左右されません。この時間はゲート・ドライバの内部遅延とパワーMOSFETのゲートの立ち上がり/立ち下がり時間によってのみ制限されます。これにより、LTC3775は、降圧比が大きな非常に低いデューティ・サイクルのアプリケーションでの動作が可能になります。強制連続モード動作の最小オン時間の波形を図11に示します。

パルススキップ・モードを選択すると、LTC3775は軽負荷時にコントローラがパルスをスキップするのを許すので、スイッチング損失が低減し、効率が改善されます。パルススキップ・モード時の最小オン時間の波形を図12に示します。

TGのオン時間がトップサイド電流制限コンパレータCTLIMのブランкиング時間より短いと、通常動作時にトップサイド・コンパレータがトリップすることはありません。R<sub>DS(ON)</sub>の検出のブランкиング時間は200ns、検出抵抗を使用している場合には100nsです。TGのオン時間がトップサイド・ブランкиング時間より短い場合、LTC3775は、ボトム電流制限コンパレ

図11. 強制連続モード時の

最小オン時間の波形

図12. パルススキップ・モード時の

最小オン時間の波形

タCBLIMによってインダクタ電流をモニタします。CBLIMがトリップすると、LTC3775はパルスをスキップし始め、同時にソフトスタート・コンデンサをプルダウンしてデューティ・サイクルを制限します。V<sub>OUT</sub>が十分に低下すると、TGのオン時間はCTLIMをオンにするのに十分なだけ長くなり、ピークインダクタ電流を制限します。アプリケーション回路の最大V<sub>IN</sub>での最小オン時間は次のようにになります。

$$t_{ON(MIN)} = \frac{V_{OUT}}{f_{SW} \cdot V_{IN(MAX)}}$$

## アプリケーション情報

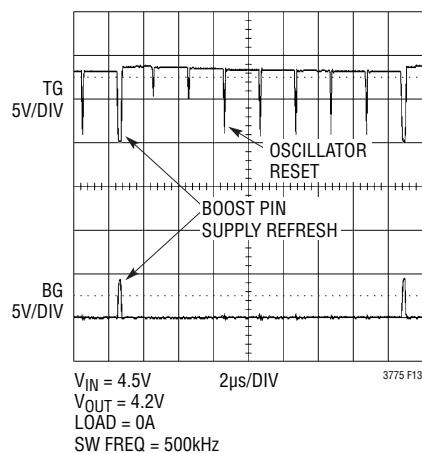

### 高デューティ・サイクルの動作

最大デューティ・サイクルは、LTC3775の内部発振器のリセット時間、PWMコンパレータの伝播遅延、およびBOOSTピンの電源リフレッシュ・レートによって制限されます。最小オフ時間は標準で300nsです。

トップMOSFETドライバはフローティング・ブートストラップ・コンデンサ $C_B$ からバイアスされます。このコンデンサは通常、トップMOSFETがオフしているとき、各オフ・サイクルの間に外付けダイオードを介して再充電されます。入力電圧 $V_{IN}$ が $V_{OUT}$ に近い電圧まで低下すると、コントローラがドロップアウト状態になり、トップMOSFETを連続してオンしようとします。ブートストラップ・コンデンサ $C_B$ の電荷がなくならないように、LTC3775はカウンタを内蔵しており、8サイクルごとに200nsの間ボトムMOSFETをオンしてブートストラップ・コンデンサをリフレッシュします。BOOSTピンの200nsの電源リフレッシュを行う最大デューティ・サイクルの動作を図13に示します。

図13. 最大デューティ・サイクルの波形

### 外付け部品の選択

#### 動作周波数

動作周波数とインダクタの値の選択は、効率と部品サイズのトレードオフになります。低周波数の動作では、MOSFETのスイッチング損失とゲート電荷損失が減少するので効率が改善されます。ただし、所定の値のリップル電流で低周波数の動作をさせるには大きなインダクタンスを必要とするので、インダクタのサイズが大きくなつてコストが高くなります。リップル電流の増加を許容した場合、同じ出力リップルを維持するのに大きな出力コンデンサが必要になることがあります。 $V_{IN}$ と $V_{OUT}$

の降圧比が大きなコンバータの場合、もう1つの検討事項はLTC3775の最小オン時間です（「最小オン時間の検討事項」のセクションを参照）。動作周波数の最後の検討事項はノイズに敏感な通信システムに関するもので、多くの場合、敏感な周波数域にスイッチング・ノイズが入らないようにすることが求められます。

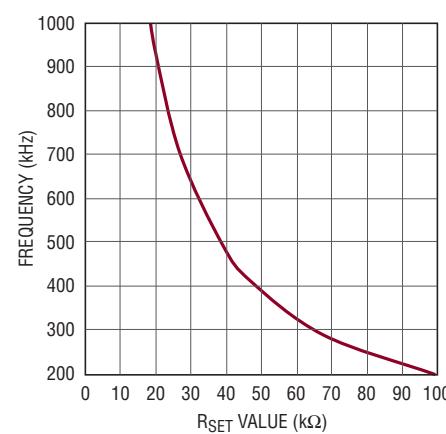

LTC3775には固定周波数アーキテクチャが使用されており、図14に示すように、FREQピンからグランドに1本の抵抗を接続して250kHz～1MHzの範囲で設定することができます。FREQピンの公称電圧は1.22Vで、このピンから流れる電流を使用して内部発振器のコンデンサを充放電します。所定の動作周波数に対する $R_{SET}$ の値は、図14または次式から選択することができます。

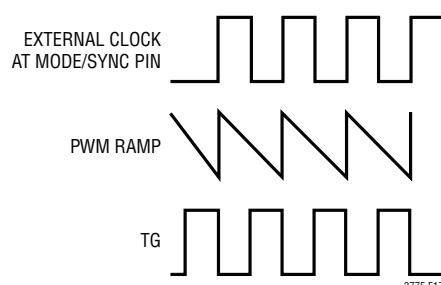

$$R_{SET}(\text{k}\Omega) = \frac{19500}{f(\text{kHz})}$$

発振器はMODE/SYNCピンに印加される外部クロックに同期させることもできます。この場合、周波数はFREQピンによって設定された自走周波数の±20%の範囲です。この同期モードでは、パルススキップ・モード動作はディスエーブルされます。機能を作動させるためには、クロックの“H”レベルは、少なくとも約25nsの間1.5Vを超える必要があります。ボトムMOSFETは外部クロックの立ち上がりエッジの直後にオンします。

図14. 周波数設定抵抗( $R_{SET}$ )の値

#### トップMOSFETドライバの電源

BOOSTピンに接続した外付けブートストラップ・コンデンサ $C_B$ は、トップサイドMOSFETのゲート・ドライブ電圧を供給します。このコンデンサは、スイッチ・ノードが“L”的ときにINTVCCからダイオード $D_B$ を介して充電されます。トップ

## アプリケーション情報

MOSFETがオンすると、スイッチ・ノードは $V_{IN}$ まで上昇し、BOOSTピンは約 $V_{IN} + INTV_{CC}$ まで上昇します。昇圧コンデンサは、トップMOSFETが必要とするゲート電荷の少なくとも100倍を蓄積する必要があります。ほとんどのアプリケーションでは、 $0.1\mu F \sim 1\mu F$ のX5RまたはX7Rの誘電体を使用したコンデンサで十分です。ショットキー・ダイオード $D_B$ の逆ブレーカダウン電圧は $V_{IN(MAX)}$ より大きくななければなりません。

### パワーMOSFETの選択

LTC3775は2個の外付けNチャネル・パワーMOSFETを必要とします。1個はトップ(メイン)スイッチ用で、もう1個はボトム(同期)スイッチ用です。パワーMOSFETの重要なパラメータは、スレッショルド電圧 $V_{(GS)TH}$ 、ブレークダウン電圧 $V_{(BR)DSS}$ 、最大電流 $I_{DS(MAX)}$ 、オン抵抗 $R_{DS(ON)}$ 、および入力容量です。

ゲート・ドライブ電圧は5.2VのINTV<sub>CC</sub>電源によって設定されます。したがって、LTC3775のアプリケーションではロジックレベル・スレッショルドのMOSFETを使用する必要があります。INTV<sub>CC</sub>電圧が5Vより低くなると予想される場合、サブロジック・レベルのスレッショルドのMOSFETを検討します。ほとんどのロジックレベルMOSFETは30V以下に制限されているので、 $V_{(BR)DSS}$ の規格によく注意してください。最大入力電圧より大きな $V_{(BR)DSS}$ 定格のMOSFETを選択し、過渡とスパイクのためにある程度のマージンを含めます。

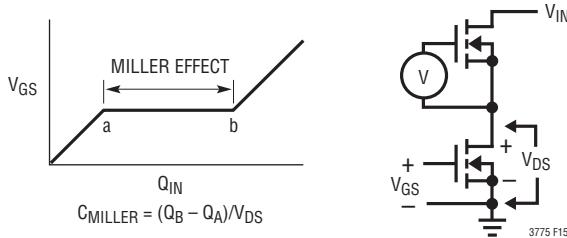

MOSFETの入力容量は複数の構成要素が組み合わされたものですが、ほとんどのデータシートに含まれる標準的「ゲート電荷」曲線(図15)から得られます。この曲線は、コモンソースの電流源負荷段のゲートに一定の入力電流を強制し、時間に対してゲート電圧をプロットして作成されたものです。最初のスロープは、ゲート-ソース間およびゲート-ドレン間容量の影響によるものです。この曲線の平坦な部分は、ドレン電

圧が低下するときのドレン-ゲート間容量のミラー乗算効果の結果です。上側のスロープは、ドレン-ゲート間蓄積容量とゲート-ソース間容量によるものです。ミラー電荷(曲線が平坦なaからbまでの水平軸のクーロン値の増加分)は特定の $V_{DS}$ ドレン電圧に対して規定されていますが、曲線で規定される $V_{DS}$ 値に対するアプリケーションの $V_{DS}$ の比を掛けることにより、異なった $V_{DS}$ 電圧に対して補正することができます。容量 $C_{MILLER}$ を推定するには、製造元のデータシートでa点からb点までのゲート電荷の変化を求め、規定された $V_{DS}$ 電圧で割ります。 $C_{MILLER}$ はトップMOSFETの過渡損失項を決める最も重要な選択基準ですが、MOSFETのデータシートで直接規定されていません。 $C_{RSS}$ と $C_{OS}$ は規定されていることがあります、これらのパラメータの定義は記載されていません。

コントローラが連続モードで動作している場合、トップMOSFETとボトムMOSFETのデューティ・サイクルは以下の式で求められます。

$$\begin{aligned} \text{トップ・ゲートのデューティ・サイクル} &= \frac{V_{OUT}}{V_{IN}} \\ \text{ボトム・ゲートのデューティ・サイクル} &= \left( \frac{V_{IN} - V_{OUT}}{V_{IN}} \right) \end{aligned}$$

最大出力電流でのトップMOSFETとボトムMOSFETの電力損失は以下の式で求められます。

$$\begin{aligned} P_{TOP} &= \frac{V_{OUT}}{V_{IN}} \left( I_{OUT(MAX)}^2 \right) \left( \rho_{T(TOP)} \right) \left( R_{DS(ON)(MAX)} \right) \\ &\quad + V_{IN}^2 \left( \frac{I_{OUT(MAX)}}{2} \right) \left( R_{DR} \right) \left( C_{MILLER} \right) \cdot \\ &\quad \left( \frac{1}{INTV_{CC} - V_{TH(IL)}} + \frac{1}{V_{TH(IL)}} \right) \cdot f_{SW} \\ P_{BOT} &= \frac{V_{IN} - V_{OUT}}{V_{IN}} \left( I_{OUT(MAX)}^2 \right) \left( \rho_{T(TOP)} \right) \left( R_{DS(ON)(MAX)} \right) \end{aligned}$$

ここで、

$R_{DR}$  = トップ・ドライバの実効抵抗

$V_{TH(IL)}$  = MOSFETのデータシートで規定された

規定ドレン電流時の標準ゲート・スレッショルド電圧

図15. ゲート電荷特性

## アプリケーション情報

$C_{MILLER}$  = MOSFETのデータシートのゲート電荷曲線を使用して算出したミラー容量

$f_{SW}$  = スイッチング周波数

両方のMOSFETに導通損失( $I^2R$ )の項がありますが、トップサイドNチャネルの式には遷移損失の項が追加されています。これは入力電圧が最大のとき最も大きくなります。 $V_{IN} < 12V$ では、高電流のときの効率は一般に大型のMOSFETを使用すると向上しますが、 $V_{IN} > 12V$ では遷移損失が急激に増加し、実際には $C_{MILLER}$ が小さくて $R_{DS(ON)}$ が大きなデバイスを使用する方が効率が高くなるポイントにまで達します。ボトムMOSFETの損失は、トップ・スイッチのデューティ・ファクタが低い高入力電圧時、またはボトム・スイッチが周期の100%近い時間オンになる短絡時に最も大きくなります。

### ショットキー・ダイオードの選択

SWノード(カソード)とボトムMOSFETのソース(アノード)の間に接続されたオプションのショットキー・ダイオードは、パワーMOSFETスイッチの導通期間の間隙に生じるデッドタイムの間導通します。これは、ボトムMOSFETのボディー・ダイオードがデッドタイムの間オンして電荷を蓄積しないようにするためです。電荷が蓄積すると効率がわずかに(約1%)低下することがあります。このダイオードは、デューティ・サイクルのほんの一部だけオンるので、最大負荷電流の約1/2~1/5の定格にすることができます。このダイオードが効果を発揮するには、ダイオードとボトムMOSFETの間のインダクタンスをできるだけ小さくする必要があるので、これらの部品は必ずPC基板の同じ層に互いに隣接させて配置します。

### 入力コンデンサの選択

入力バイパス・コンデンサには3つの主要な要件があります。トップMOSFETがオンしたときの電源電圧の低下を最小限に抑えるためにESRが小さくなくてはならないこと、RMS電流能力が入力のリップル電流に十分に耐えなければならないこと、そして、入力電源が対応できるまで入力電圧を維持するのに十分な容量でなければならぬことです。一般に、最初の2つのパラメータを満たすコンデンサ(特に非セラミック・タイプ)は、容量に依存する垂下を限度内に抑えるのに必要な容量よりも大きな容量を備えています。入力コンデンサの電圧定格は最大入力電圧の少なくとも1.4倍にします。

連続モードでは、トップNチャネルMOSFETのソース電流は、ほぼデューティ・サイクルが $V_{OUT}/V_{IN}$ の方形波になります。コンデンサの最大RMS電流は次式で求められます。

$$I_{RMS} \approx I_{OUT(MAX)} \frac{\sqrt{V_{OUT}(V_{IN}-V_{OUT})}}{V_{IN}}$$

この式は $V_{IN} = 2V_{OUT}$ のとき最大値をとります。ここで、 $I_{RMS} = I_{OUT}/2$ です。大きく変化させてもそれほど状況が改善されないので、通常、この単純なワーストケース条件が設計に使用されます。

コンデンサの製造元のリップル電流定格は多くの場合わずか2000時間の寿命によって規定されていることに注意してください。このため、コンデンサをさらにディレーティングする、もしくは要求条件よりも高い温度定格のコンデンサを選択することを推奨します。サイズまたは高さの設計要件を満たすため、複数のコンデンサを並列に接続することもできます。疑問点については必ず製造元に問い合わせてください。

中程度の電圧(20V~35V)のセラミック・コンデンサ、タンタル・コンデンサ、OS-CONコンデンサ、さらにスイッチャ定格の電解コンデンサを入力コンデンサに使用できますが、それぞれ短所があります。セラミック・コンデンサは容量の電圧係数が大きく、可聴圧電効果が生じることがあります。タンタル・コンデンサはサーボに対する定格が定められている必要があります。OS-CONコンデンサはインダクタンスが大きくケースのサイズが大きくなるので表面実装の適用に制約があります。また電解コンデンサはESRが大きく、ドライアウトするので複数個を並列に使用することが必要になる場合があります。三洋電機のOS-CON SVP、SVPDシリーズ、POSCAP TQCシリーズのコンデンサ、またはパナソニックのWAシリーズやCornell DubilierのSPVシリーズのアルミ電解コンデンサを数個の高性能セラミック・コンデンサと並列に接続して使用することによって、低ESRと大きなバルク容量を実現する効果的な手段が得られます。

### 出力コンデンサの選択

$C_{OUT}$ の選択は、主に電圧リップルと負荷ステップに対する過渡応答を最小限に抑えるために必要なESRによって決まります。出力リップル $\Delta V_{OUT}$ はほぼ次式のように制限されます。

$$\Delta V_{OUT} \leq \Delta I_L \left( ESR + \frac{1}{8 \cdot f_{SW} \cdot C_{OUT}} \right)$$

ここで、 $\Delta I_L$ はインダクタのリップル電流です。

## アプリケーション情報

$\Delta I_L$ は次式を使用して算出することができます。

$$\Delta I_L = \frac{V_{OUT}}{L \cdot f_{SW}} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

$\Delta I_L$ は入力電圧に従って増加するので、出力リップル電圧は最大入力電圧時に最も高くなります。一般に、ESRの要件が満たされれば、その容量はフィルタリングに対して十分であり、必要なRMS電流定格を備えています。

高性能スルーホール・コンデンサについては、三洋電機、パナソニック、Cornell Dubilierなどの製造元が検討対象になります。三洋電機製OS-CON半導体誘電体コンデンサは、ESRとサイズの積が良い値を示します。OS-CONコンデンサと並列にセラミック・コンデンサを追加して、リード・インダクタンスの影響を相殺することを推奨します。

表面実装のアプリケーションでは、アプリケーションのESRまたは過渡電流処理要件を満たすため、複数のコンデンサの並列接続が必要になることがあります。アルミ電解コンデンサと乾式タンタル・コンデンサの両方とも表面実装タイプが提供されています。新しい特殊ポリマ表面実装コンデンサもESRが非常に小さいのですが、体積あたりの容量密度がはるかに低くなっています。タンタル・コンデンサの場合、スイッチング電源に使用するためのサージ・テストが実施されていることが不可欠です。優れた出力コンデンサの選択肢としては、三洋電機のPOSCAP TPD、POSCAP TPB、AVX TPS、AVX TPSV、KemetのT510シリーズの表面実装タンタル・コンデンサ、KemetのAO-CAPまたはパナソニックのSPシリーズの特殊ポリマ表面実装コンデンサなどがあり、高さ2mm～4mmのケースで供給されます。他のコンデンサとしては、ニチコンのPLシリーズ、そしてSpragueの595Dシリーズがあります。それ以外の特定の推奨製品に関しては、製造元に問い合わせてください。

### インダクタの選択

LTC3775の標準的なアプリケーション回路のインダクタは、必要なリップル電流、サイズ、および飽和電流定格に基づいて選択します。インダクタは、ピーク電流制限スレッショルド以下で飽和しないものにします。

インダクタ値によってリップル電流が設定されます。この値は通常、予測最大負荷電流の約40%に選択されます。リップル電流が小さくなると、インダクタのコア損失、出力コンデンサのESR損失、および出力電圧リップルが減少します。周波数が低くリップル電流が小さい場合に最大効率が得られます。ただし、高効率を実現するには大きなインダクタを必要とするので、負荷過渡時により大きな出力電圧の変化が生じます。部品サイズ、効率、動作周波数の間でトレードオフを行います。リップル電流が規定の制限値の場合、インダクタ値は次式を使用して求めることができます。

$$L = \frac{V_{OUT}}{f_{SW} \cdot \Delta I_{L(MAX)}} \cdot \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

$L$ の値が分かったら、次にインダクタの種類を選択します。高効率のコンバータは、一般に低コストの鉄粉コアで生じるコア損失を許容できないため、より高価なフェライト、モリペーマロイ、またはKool M $\mu$ ®コアを使用することになります。高電流、低電圧アプリケーション用に設計された様々なインダクタが、スミダ電機、パナソニック、Coiltronics、Coilcraft、Tokoなどの製造元から入手できます。インダクタの飽和電流の計算については「電流制限の設定」を参照してください。

### 電流制限の設定

検出抵抗を使用して電流検出を行う場合、トップサイド電流制限は $R_{ILIMIT}$ を次のように設定することによって設定することができます。

$$R_{ILIMIT} = CF \cdot R_{SENSE} \cdot \frac{I_{O(MAX)} + 0.5 \cdot \Delta I_L}{I_{LIMIT(MIN)}}$$

ここで、

$R_{SENSE}$  = 検出抵抗の値

$I_{O(MAX)}$  = 最大出力電流

$\Delta I_L$  = インダクタのリップル電流（「出力コンデンサの選択」を参照してください。）

$I_{LIMIT(MIN)}$  =  $I_{LIMIT}$ ピンの90 $\mu$ Aの最小プルダウン電流

$CF$  = 補正係数。安全マージンを確保し $R_{SENSE}$ の許容誤差を考慮するために、 $CF = 1.2$ の値を使用するのが妥当です。

## アプリケーション情報

トップサイドMOSFET  $R_{DS(ON)}$  の検出を使用する場合、 $R_{ILIMIT}$  の値は次式から算出されます。

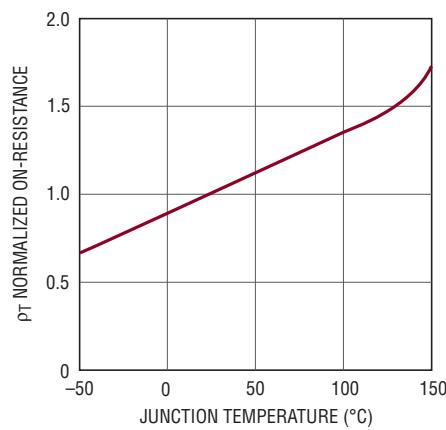

$$R_{ILIMIT} = \rho_T \cdot R_{DS(ON)(QT)(MAX)} \cdot \frac{I_{O(MAX)} + 0.5 \cdot \Delta I_L}{I_{LIMIT(MIN)}}$$

$R_{DS(ON)(QT)(MAX)}$  は、通常25°Cで規定されるMOSFETの最大オン抵抗です。 $\rho_T$ の項は正規化係数(25°Cで1)で、温度によるオン抵抗の大きな変化を表しており、図16に示されているように通常約0.5%/°Cです。100°Cの最大接合部温度の場合、 $\rho_T = 1.4$ の値を使用するのが妥当です。

ボトムサイド電流制限は、 $R_{ILIMB}$ を次のように設定することによって設定することができます。

$$R_{ILIMB} = 5 \cdot \rho_T \cdot R_{DS(ON)(QB)(MAX)} \cdot \frac{I_{O(MAX)} + 0.5 \cdot \Delta I_L}{I_{LIMB(MIN)}}$$

ここで、 $I_{LIMB(MIN)} = I_{LIMB}$ ピンの9μAの最小プルアップ電流です。

この結果得られる $R_{ILIMIT}$ および $R_{ILIMB}$ の値は、実際の回路でチェックして電流制限が予測通りに起動することを確認します。 $R_{DS(ON)}$ の値が小さいMOSFETを使用する回路で電流検出を行う場合には、注意してチェックする必要があります。PCBトレースの抵抗と寄生インダクタンスにより、実際の電流制限スレッショルドが大幅に変化することがあります。SENSE、SW、およびPGNDの接続箇所のPCBトレースが短くなるように注意する必要があります。

電流制限の設定では、過負荷状態のときにインダクタに流れるワーストケースのピーク電流も決定します。インダクタの飽和電流定格は、以下のようなワーストケースのピーク・インダクタ電流よりも大きくする必要があります。

$$I_{L(SAT)} \geq \frac{I_{LIMIT(MAX)} \cdot R_{ILIMIT}}{R_{SENSE(MIN)}}$$

または、

$$I_{L(SAT)} \geq \frac{I_{LIMIT(MAX)} \cdot R_{ILIMIT}}{R_{DS(ON)(QT)(MIN)}}$$

または、

$$I_{L(SAT)} \geq \frac{(0.2 \cdot I_{LIMB(MAX)}) \cdot R_{ILIMB}}{R_{DS(ON)(QB)(MIN)}}$$

$I_{LIMIT(MAX)} = I_{LIMT}$ ピンの110μAの最大プルダウン電流

$I_{LIMB(MAX)} = I_{LIMB}$ ピンの11μAの最大プルアップ電流

$R_{DS(ON)(QT)(MIN)}$  および  $R_{DS(ON)(QB)(MIN)}$  はパワー MOSFETの最小オン抵抗です。MOSFETのデータシートでは通常、 $R_{DS(ON)}$ の公称値と最大値が規定されていますが、最小値は規定されていません。 $R_{DS(ON)}$ の最小値は、最大値が標準値を上回っている分と同じだけ標準値を下回る値であると仮定するのが妥当です。詳細なガイドラインについては MOSFETの製造元にお問い合わせください。

インダクタの飽和電流定格は、最大入力電圧、最大出力電流、および最大予測コア温度で決まります。市販のインダクタのほとんどの飽和電流定格は高温時に低下します。安全動作を検証するには、1)ワーストケースの動作条件、2)最高許容周囲温度、3)電源が最終的な筐体に実装されているという条件で、インダクタのコア/巻線温度の特性評価を行うことが得策です。温度の特性評価は、巻線/コアの構造体に熱電対を密着させるか、または巻線自体の中に熱電対を埋め込むことによって行うことができます。

図16. 標準的なMOSFETの $R_{DS(ON)}$ と温度

## アプリケーション情報

### MODE/SYNCピン

MODE/SYNCピンには2つの機能があり、動作モードの設定、またはスイッチング周波数の外部クロックへの同期に使用することができます。MODE/SYNCピンが1.2Vより上のとき、パルススキップ・モードがイネーブルされます。このピンが1.2Vより下のとき、連続モードに強制されます。

このピンをフロート状態のままにすると、50kの内部プルダウン抵抗により、デフォルトで強制連続モードが選択されます。LTC3775は、パワーアップ時にはこのモード選択を無効にしてパルススキップ・モードで動作し、プリバイアスされた出力コンデンサの放電を防止します。

LTC3775の内部発振器は、1.5V以上の外部クロック信号に同期させることができます。MODE/SYNCピンが“L”から“H”に遷移すると、発振器の鋸波波形を(“H”に)リセットしてTGを“L”に強制します(図17を参照)。外部発振周波数はR<sub>SET</sub>抵抗によって設定された周波数の±20%以内でなければなりません。そうでないと、デバイスは自走モードに戻ります。内部発振器は、2番目のクロック遷移を認識すると外部クロックにロックします。外部同期が検出されると、LTC3775は強制連続モードで動作します。

### PC基板のレイアウト・チェックリスト

プリント回路基板をレイアウトするときには、以下のチェックリストを使用してLTC3775が正しく動作するようにします。レイアウトでは、以下の項目をチェックしてください。

1. 信号グランドと電源グランドを分離します。信号グランドにはLTC3775のSGNDピンとV<sub>OUT</sub>の(-)端子が接続されています。電源グランドには、オプションのショットキー・ダイオードのアノード、ボトムサイドMOSFETのソース、および入力コンデンサの(-)端子が接続されています。信号グランドは出力コンデンサの(-)端子に接続します。また、出力コン

デンサの(-)端子は入力コンデンサの(-)端子にできるだけ近づけるようにします。

2. トップNチャネルMOSFETによって形成される高di/dtのループ、ボトムMOSFET、およびC<sub>IN</sub>コンデンサはリードとPCトレースを短くし、高周波ノイズと誘導性リンクによる電圧ストレスを最小限に抑えます。

3. トップサイドMOSFETのドレインをC<sub>IN</sub>の(+)端子に直接接続し、ボトムサイドMOSFETのソースをC<sub>IN</sub>の(-)端子に直接接続します。このコンデンサはMOSFETにAC電流を供給します。

4. C<sub>INTVCC</sub>のセラミック・デカップリング・コンデンサはデバイスに隣接させて、INTVCCとSGNDの間に配置します。同様にC<sub>B</sub>コンデンサもデバイスに隣接させて、BOOSTとSWの間に配置します。

5. 小信号部品は高周波スイッチング・ノード(BOOST、SW、TG、およびBG)から離して配置します。

6. 最適なロード・レギュレーションと真のリモート検出を実現するため、出力抵抗分割器の上側は出力コンデンサの上側へ個別に接続し(ケルビン接続)、dV/dtの大きなどのトレースからも離しておきます。高インピーダンスのFBノードへのトレースを短くするため、分割器の抵抗はLTC3775の近くに配置します。

7. 複数のスイッチング・パワー・コンバータが同じ入力電源に接続されているアプリケーションでは、LTC3775の入力フィルタ・コンデンサが他のコンバータと共有されていないことを確認します。別のコンバータからのAC入力電流によって大きな入力電圧リップルが生じ、これがLTC3775の動作に影響を与えることがあります。LTC3775のC<sub>IN</sub>と実際の電源V<sub>IN</sub>の間の数インチのPCトレースまたは配線(Lが約100nH)により、入力ノイズの影響を十分抑えることができます。

図17. 外部同期

## アプリケーション情報

8. トップ電流制限設定抵抗 $R_{ILIMIT}$ はLTC3775の近くに配置し、 $R_{ILIMIT}$ の他端は検出抵抗の下のケルビン検出接続点までのSENSEのトレースに沿って配線します。

9. ボトム電流制限設定抵抗 $R_{ILIMB}$ はLTC3775の近くに配置し、 $R_{ILIMB}$ の他端はSGNDに接続します。

10. SWピンはボトムMOSFETのドレインに接続します。

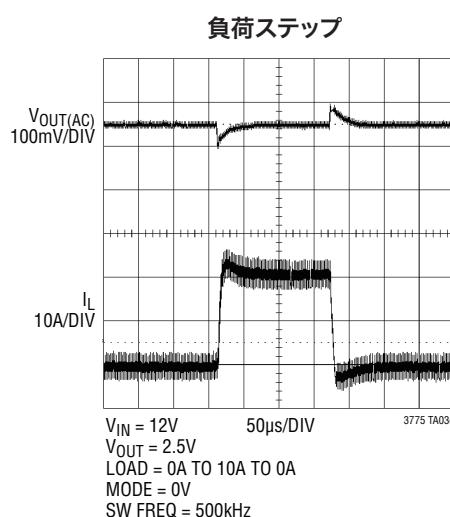

## 過渡応答のチェック

全ての新しいLTC3775のPCB回路は、帰還ループが適正に動作していることを検証するために過渡テストを行う必要があります。レギュレータのループ応答は負荷電流過渡応答を観察することによってチェックできます。スイッチング・レギュレータはDC(抵抗性)負荷電流のステップに応答するのに数サイクルを要します。負荷ステップが発生すると、 $V_{OUT}$ は $\Delta I_{LOAD} \cdot (ESR)$ だけシフトします。ここで、ESRはCOUTの等価直列抵抗です。さらに、 $\Delta I_{LOAD}$ によりCOUTの充放電が始まって帰還誤差信号を発生し、レギュレータを電流変化に適応させて $V_{OUT}$ を定常値に回復させます。この回復時間に、安定性に問題があることを示す過度のオーバーシュートやリンギングが発生しないか $V_{OUT}$ をモニタします。

過渡応答の測定には、正確に測定することと、回路をテストするための適切な過渡を発生させることの2つ課題があります。出力を測定するには、出力コンデンサの両端をオシロスコープのプローブで直接測定します。高周波プロービングの適切な手法を使用します。プローブに付いた6インチのグランド・リードは使用しないでください。プローブの先端に適合した、短いグランド・クリップ付きアダプタを使用し、グランド経路のインダクタンスが測定される過渡信号より大きなスパイクを生じさせないようにします。プローブ先端の標準的グランド・シールドは標準的な出力コンデンサのリード幅に合った間隔になっています。一般に、この測定はオシロスコープの20MHzの帯域制限を有効にして、高周波ノイズを制限して行うのがベストです。20MHz以上のエネルギーは一般に放射されるだけで伝導せず、出力コンデンサに生じても負荷に影響しないので、マイクロプロセッサのメーカーは通常、20MHz以下のリップルだけ規定しています。

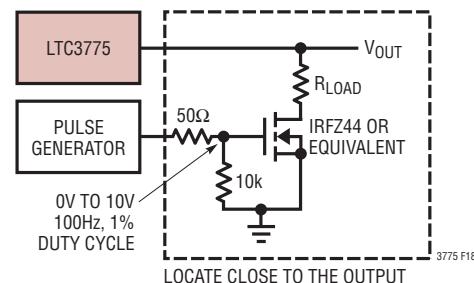

信号の測定方法が分ったので、次に測定対象が必要になります。理想的な状況は、テストに実際の負荷を使用し、出力を観測しながらその負荷をオン/オフすることです。これが実際的でない場合には、電流ステップ発生器が必要になります。この発生器は、数ナノ秒でオン/オフして標準的なスイッチング・ロジック負荷をシミュレートできなければならないので、LTC3775と過渡信号発生器の間の浮遊インダクタンスと長いクリップ・リードを最小限に抑える必要があります。

シンプルな過渡信号発生器の例を図18に示します。負荷素子には必ず非誘導性の抵抗を使用してください。電力抵抗の多くは誘導性の螺旋状パターンを使用しており、ここでの用途には適していません。シンプルな解決策として、1/4Wの薄膜抵抗を10個使用し、それらを並列に接続して必要な値を得ます。これにより、非誘導性の抵抗負荷が得られ、連続動作では2.5Wを、あるいは、1%のデューティ・サイクルのパルスでは250Wを消費することができ、ほとんどのLTC3775の回路にとって十分です。MOSFETと抵抗はLTC3775の回路の出力にできるだけ近づけて半田付けし、信号発生器は1%のデューティ・サイクルで100Hzのパルスを発生するように設定します。これにより、過渡が100μsで間隔が10msのパルスがLTC3775に供給されます。これは負荷抵抗を低い温度に保ちながら正負両方の遷移に対する全体の過渡回復時間を観測するのに十分な信号です。

図18. 過渡負荷発生器

## アプリケーション情報

### 設計例

設計例として、仕様が $V_{IN} = 5V \sim 26V$ (公称12V)、 $V_{OUT} = 1.2V \pm 5\%$ 、 $I_{OUT(MAX)} = 15A$ 、 $f = 500kHz$ の電源を取り上げます。

まず、最大 $V_{IN}$ で発生する最小オン時間を検証します。

$$t_{ON(MIN)} = \frac{1.2V}{(26V)(500kHz)} = 92.3ns$$

検出抵抗による検出時に、最小オン時間はトップ電流制限コンパレータの100nsのブランкиング時間より短くなります。高 $V_{IN}$ 時には、コントローラはボトムMOSFETの $R_{DS(ON)}$ の検出が支配的になります。

次に、最小 $V_{IN}$ で発生する最大デューティ・サイクルを検証します。

$$\text{Maximum Duty Cycle} = \frac{1.2V}{5V} = 24\%$$

これはLTC3775の最大デューティ・サイクル90%を下回ります。

次に、動作周波数を500kHzにする $R_{SET}$ を計算します。

$$R_{SET} = \frac{19500}{500} = 39k$$

次に、最大 $V_{IN}$ で約40%のリップル電流になるようにインダクタ値を選択します。

$$L = \frac{1.2V}{(500kHz)(0.4)(15A)} \left(1 - \frac{1.2}{26}\right) = 0.38\mu H$$

標準値に最も近い $0.36\mu H$ を選択します。

この結果、最大リップル電流は次のようになります。

$$\Delta I_L = \frac{1.2V}{(500kHz)(0.36\mu H)} \left(1 - \frac{1.2}{26}\right) = 6.4A$$

次に、トップMOSFETスイッチとボトムMOSFETスイッチを選択します。各MOSFETのドレインには全電源電圧26V(最大)にリンクギングを加えた電圧が加わるので、30VのMOSFETを選択して安全のためのマージンを確保します。

トップMOSFETがオンするのは短時間なので、ルネサステクノロジのRJK0305DPB( $R_{DS(ON)} = 13m\Omega$ (最大)、 $C_{MILLER} = Q_{GD}/10V = 150pF$ 、 $V_{GS(TH)} = 2.5V$ 、 $\theta_{JA} = 40^{\circ}C/W$ )で十分です。 $\rho_{100^{\circ}C} = 1.4$ での電流制限時の電力損失をチェックします。

$$\begin{aligned} P_{TOP} &= \frac{1.2V}{26V} \left( (15A)^2 \cdot 1.4 \cdot 13m\Omega \right) \\ &+ (26V)^2 \left( \frac{15A}{2} \right) (2.5\Omega) (150pF) \\ &\left( \left( \frac{1}{5.2-2.5} \right) + \frac{1}{2.5} \right) 500kHz \\ &= 0.19W + 0.73W = 0.92W \end{aligned}$$

さらに、MOSFETの予測 $T_J$ を再度確認します。

$$T_J = 70^{\circ}C + (0.92W) (40^{\circ}C/W) = 107^{\circ}C$$

公称電流では接合部温度は大幅に下回りますが、この解析から放熱に注意を払うことが必要なことが分ります。

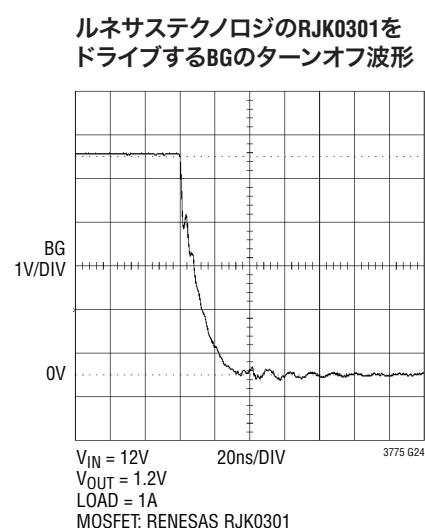

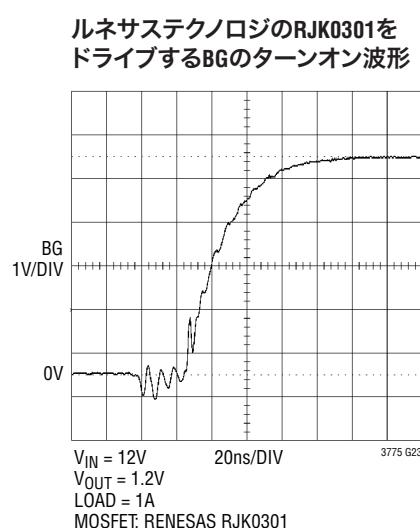

同期MOSFETには、ルネサステクノロジのRJK0301DPB( $R_{DS(ON)} = 4m\Omega$ (最大)、 $\theta_{JA} = 40^{\circ}C/W$ )を選択します。

$$P_{BOT} = \frac{26V - 1.2V}{26V} \left( (15A)^2 \cdot 1.4 \cdot 4m\Omega \right) = 1.26W$$

さらに、MOSFETの予測 $T_J$ を再度確認します。

$$T_J = 70^{\circ}C + (1.26W) (40^{\circ}C/W) = 120^{\circ}C$$

次に、INTVCCのLDO電流を計算します。

$$I_{INTVCC} = (500kHz) (8nC + 32nC) + 3.5mA = 23.5mA$$

さらに、LTC3775の $T_J$ を再度確認します。

$$T_J = 70^{\circ}C + (23.5mA) (26V) (68^{\circ}C/W) = 112^{\circ}C$$

次に、3mΩの検出抵抗を使用して電流制限抵抗を設定します

$$R_{ILIMT} = 1.2 \cdot 3m\Omega \cdot \frac{15A + 0.5 \cdot 6.4A}{90\mu A} = 728\Omega$$

$$R_{ILIMB} = 5 \cdot 1.4 \cdot 4m\Omega \cdot \frac{15A + 0.5 \cdot 6.4A}{9\mu A} = 56.62k$$

その次に高い標準値 $732\Omega$ および $57.6k$ を使用します。

## アプリケーション情報

検出抵抗の±1%の許容誤差に基づくワーストケースのピーク・インダクタ電流は次のようにになります。

$$I_{L(SAT)} \geq \frac{110\mu A \cdot 732\Omega}{2.97m\Omega} = 27.1A$$

入力RMS電流は $V_{IN(MIN)} = 5V$ および $I_{OUT(MAX)} = 15A$ のとき最大になります。

$$I_{RMS} \approx 15A \frac{\sqrt{1.2V(5V-1.2V)}}{5V} = 6.4A$$

$C_{IN}$ には85°Cのときに6.4A以下のRMS電流定格のものを選択します。出力コンデンサには、インダクタの電流リップルと負荷

ステップによる出力電圧の変化を最小限に抑えるため、2個の低ESRのOS-CONコンデンサ(それぞれ470μFと5mΩ)を使用します。リップル電圧は次のようにになります。

$$V_{OUT(RIPPLE)} = 6.4A \cdot \left( \frac{0.005}{2} + \frac{1}{8 \cdot 500kHz \cdot 470\mu F \cdot 2} \right) \\ = 17.7mV$$

ただし、0A～15Aの負荷ステップにより、出力電圧は少なくとも次のように変化します。

$$\Delta V_{OUT(STEP)} = (15A)(0.0025\Omega) = 37.5mV$$

# LTC3775

## 標準的応用例

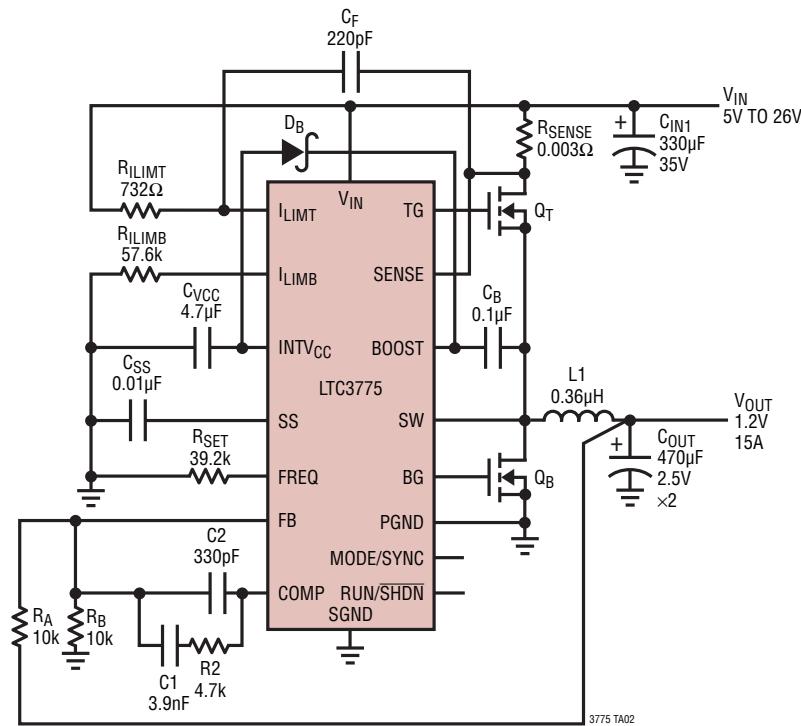

5V～26Vの入力、1.2V/15Aの出力(500kHz)

C<sub>OUT</sub>: SANYO 2R5TPD470M5

D<sub>B</sub>: CMDSH4E

L1: IHLP-4040DZ-ER-R36-M11

Q<sub>B</sub>: RJK0301DPB-00-J0

Q<sub>T</sub>: RJK0305DPB-00-J0

## 標準的応用例

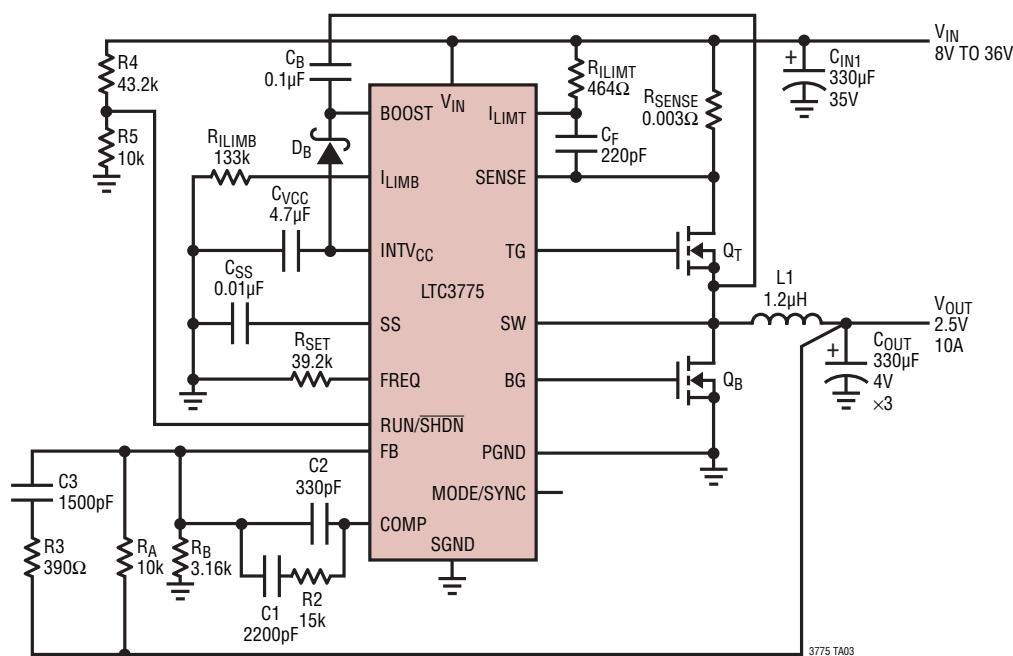

8V～36Vの入力、2.5V/10Aの出力(500kHz)

C<sub>OUT</sub>: SANYO 4TPD330M

D<sub>B</sub>: CMDSH4E

L1: TOKO FDA1254-1R2M

Q<sub>B</sub>, Q<sub>T</sub>: INFINEON BSZ097N04LS

3775 TA03

# LTC3775

## 標準的応用例

24Vの入力、12V/5Aの出力(500kHz)

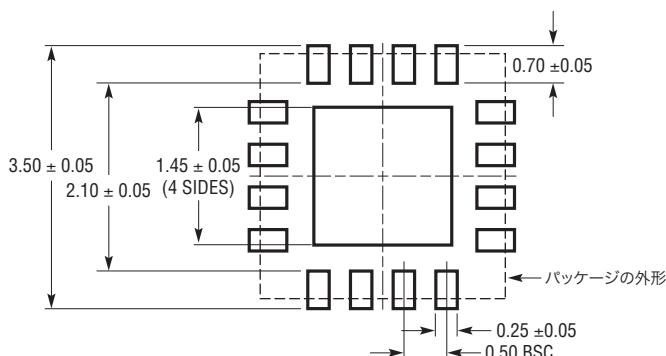

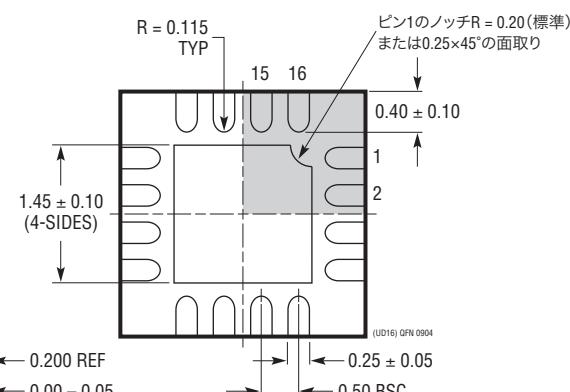

## パッケージ

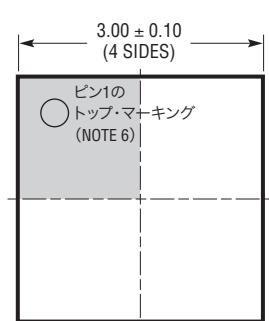

**UDパッケージ

16ピン・プラスチックQFN(3mm×3mm)

(Reference LTC DWG # 05-08-1691)**

推奨する半田パッドのピッチと寸法

底面図—露出パッド

## NOTE:

1. 図面はJEDECのパッケージ外形MO-220バリエーション(WEED-2)に適合

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のピン1の位置の参考に過ぎない

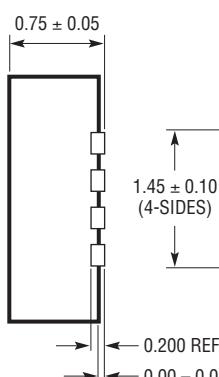

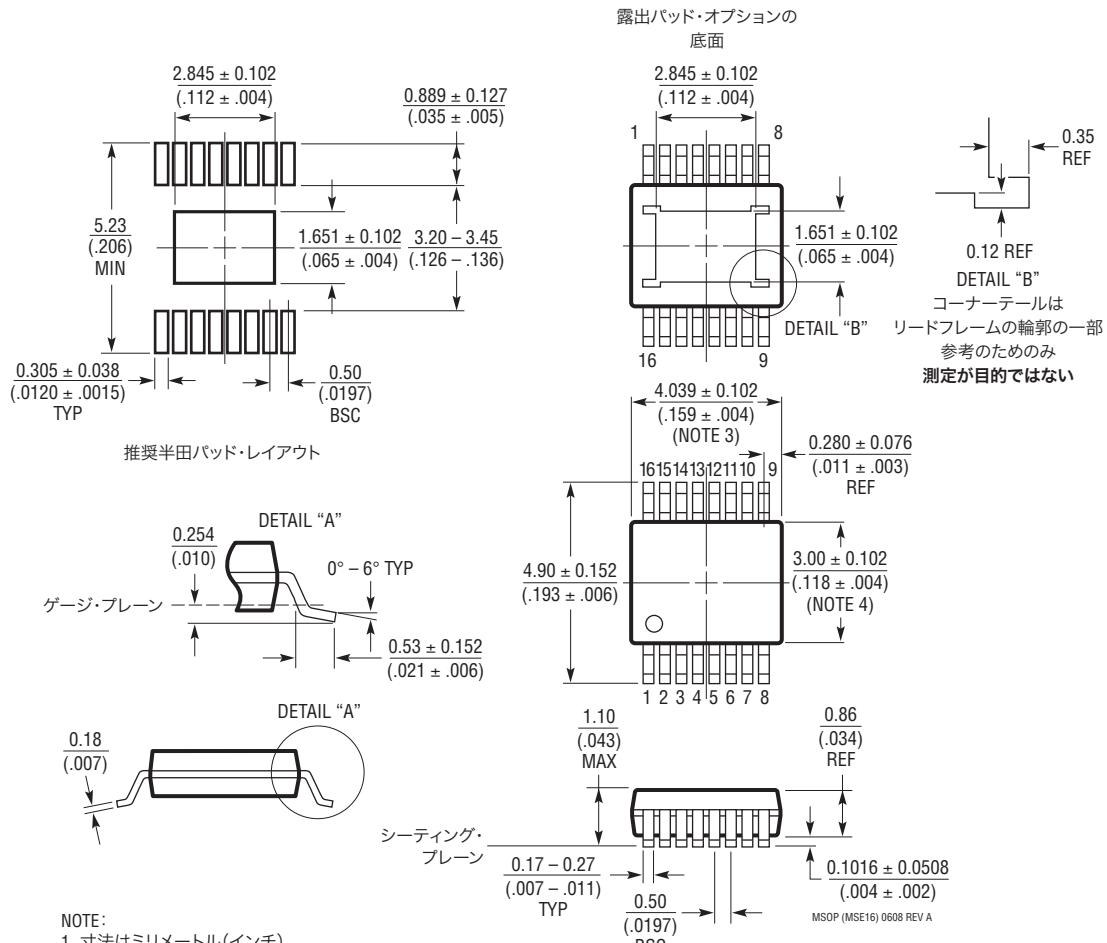

## パッケージ

MSEパッケージ

16ピン・プラスティックMSOP、露出ダイ・パッド

(Reference LTC DWG # 05-08-1667 Rev A)

- NOTE: TYP (.0197) → |

1. 寸法はミリメートル(インチ)

2. 図は実寸とは異なる

3. 寸法にはモールドのバリ、突出部、またはゲートのバリを含まない

モールドのバリ、突出部、またはゲートのバリは、各サイドで0.152mm(0.006")を超えないこと

4. 寸法にはリード間のバリ、または突出部を含まない

リード間のバリまたは突出部は、各サイドで0.152mm(0.006")を超えないこと

5. リードの平坦度(成形後のリードの底面)は最大0.102mm(0.004")を超えないこと

## 改訂履歴 (Rev Aよりスタート)

| REV | 日付   | 概要                       | ページ番号 |

|-----|------|--------------------------|-------|

| A   | 8/10 | MSOPパッケージを追加、データシート全体に反映 | 1~34  |

# LTC3775

## 標準的応用例

## 関連製品

| 製品番号                                | 説明                                                          | 注釈                                                                                                                                                          |

|-------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3854                             | 実装面積の小さい、広い入力電圧範囲の同期整流式降圧DC/DCコントローラ                        | 固定動作周波数:400kHz, 4.5V ≤ V <sub>IN</sub> ≤ 38V, 0.8V ≤ V <sub>OUT</sub> ≤ 5.25V, 2mm×3mm QFN-12パッケージ                                                          |

| LTC3851A/<br>LTC3851A-1             | 広い入力電圧範囲の同期整流式降圧DC/DCコントローラ                                 | フェーズロック可能な固定動作周波数:250kHz~750kHz, 4V ≤ V <sub>IN</sub> ≤ 38V, 0.8V ≤ V <sub>OUT</sub> ≤ 5.25V, MSOP-16E, 3mm×3mm QFN-16およびSSOP-16パッケージ                       |

| LTC3878/<br>LTC3879                 | オン時間が一定のNo RSENSE™同期整流式降圧DC/DCコントローラ                        | 極めて高速な過渡応答, t <sub>ON(MIN)</sub> = 43ns, 4V ≤ V <sub>IN</sub> ≤ 38V, 0.8V ≤ V <sub>OUT</sub> ≤ 0.9V <sub>IN</sub> , SSOP-16, MSOP-16Eおよび3mm×3mm QFN-16パッケージ |

| LTC3850/<br>LTC3850-1/<br>LTC3850-2 | デュアル、2フェーズ、高効率同期整流式降圧DC/DCコントローラ, RSENSEまたはDCR電流検出およびトラッキング | フェーズロック可能な固定動作周波数:250kHz~780kHz, 4V ≤ V <sub>IN</sub> ≤ 30V, 0.8V ≤ V <sub>OUT</sub> ≤ 5.25V                                                                |

| LTC3860                             | 差動アンプとスリーステート出力ドライブを備えた、デュアル、マルチフェーズ同期整流式降圧DC/DCコントローラ      | パワーブロック、DRMOSドライブまたは外部MOSFETを使用した動作、3V ≤ V <sub>IN</sub> ≤ 24V, t <sub>ON(MIN)</sub> = 20ns                                                                 |

| LTC3853                             | トリプル出力、マルチフェーズ同期整流式降圧DC/DCコントローラ, RSENSEまたはDCR電流検出およびトラッキング | フェーズロック可能な固定動作周波数:250kHz~750kHz, 4V ≤ V <sub>IN</sub> ≤ 24V、出力電圧:最大13.5V                                                                                    |

3775fa