## 特長

- あらゆるサイズのコンデンサを充電

- 電圧レギュレーション・モードで低ノイズ出力

- 無負荷時の安定動作

- 8V以下のV<sub>CC</sub>に対してレール・トゥ・レール動作を行う

2A MOSFETゲート・ドライバを内蔵

- 選択可能な内部ゲート・ドライブ電圧クランプ:

5.6Vまたは10.5V

- ユーザが選択可能な過電圧/低電圧検出

- 出力電圧を容易に調整可能

- 1次側または2次側出力電圧センス

- 広い入力V<sub>CC</sub>電圧範囲: 5V~24V

- 4mm × 5mm 20ピンQFNパッケージと

20ピンTSSOPパッケージ

## アプリケーション

- 高電圧安定化電源

- 高電圧コンデンサ・チャージャ

- プロフェッショナル・フォトフラッシュ・システム

- 緊急用ストロボ

- セキュリティ/インベントリー制御システム

- 雷管

## 概要

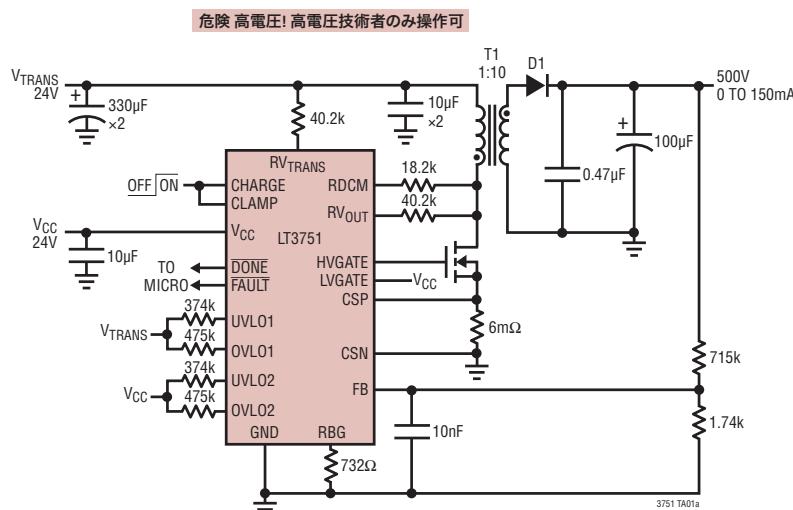

LT<sup>®</sup>3751は、大型のコンデンサをユーザが調整可能な目標電圧まで高速充電するように設計された、高入力電圧が可能なフライバック・コントローラです。目標電圧はトランスの巻数比と3本の外付け抵抗によって設定されます。また、オプションとして、帰還ピンを使用して低ノイズの高電圧安定化出力を供給することができます。

LT3751は、最低4.75Vまで効率的な動作を可能にするレール・トゥ・レールMOSFETゲート・ドライバを内蔵しています。106mVという低い差動電流センス・スレッシュホールド電圧により、ピークスイッチ電流を高精度で制限します。また、V<sub>CC</sub>とV<sub>TRANS</sub>の両方に対して過電圧ロックアウトと低電圧ロックアウトをユーザが選択可能なので、保護機能がさらに追加されています。標準的なアプリケーションでは、1秒以内に1000μFコンデンサを500Vまで充電できます。

CHARGEピンを使用して、新しい充電サイクルを開始し、ON/OFF制御を行なうことができます。DONEピンは、コンデンサが設定値に達し、デバイスが充電を停止したことを知らせます。FAULTピンは、V<sub>CC</sub>電圧またはV<sub>TRANS</sub>電圧のいずれかがユーザ設定の電源許容誤差を超えたことによってLT3751がシャットダウンしていることを知らせます。

□、LT、LTC、LTM、Linear TechnologyおよびLinearのロゴはリニアテクノロジー社の登録商標です。ThinSOTはリニアテクノロジー社の商標です。その他すべての商標の所有権は、それぞれの所有者に帰属します。6518733および6636021を含む米国特許によって保護されています。

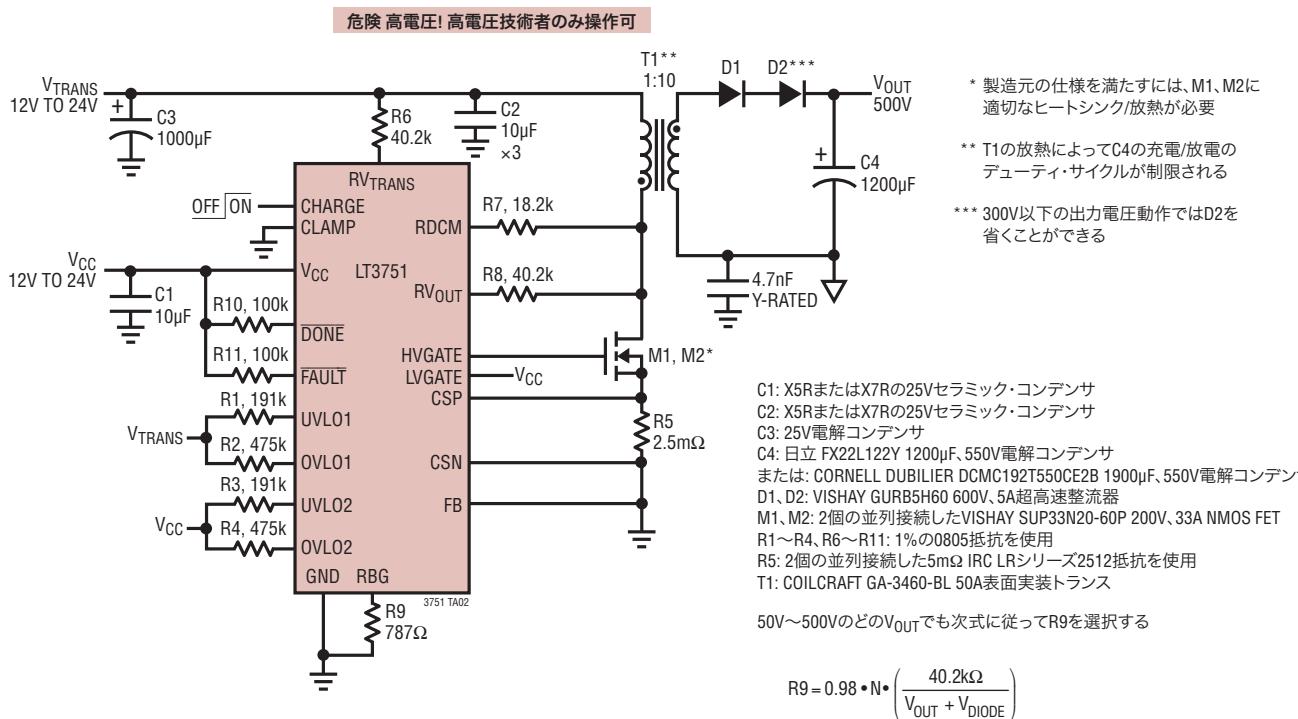

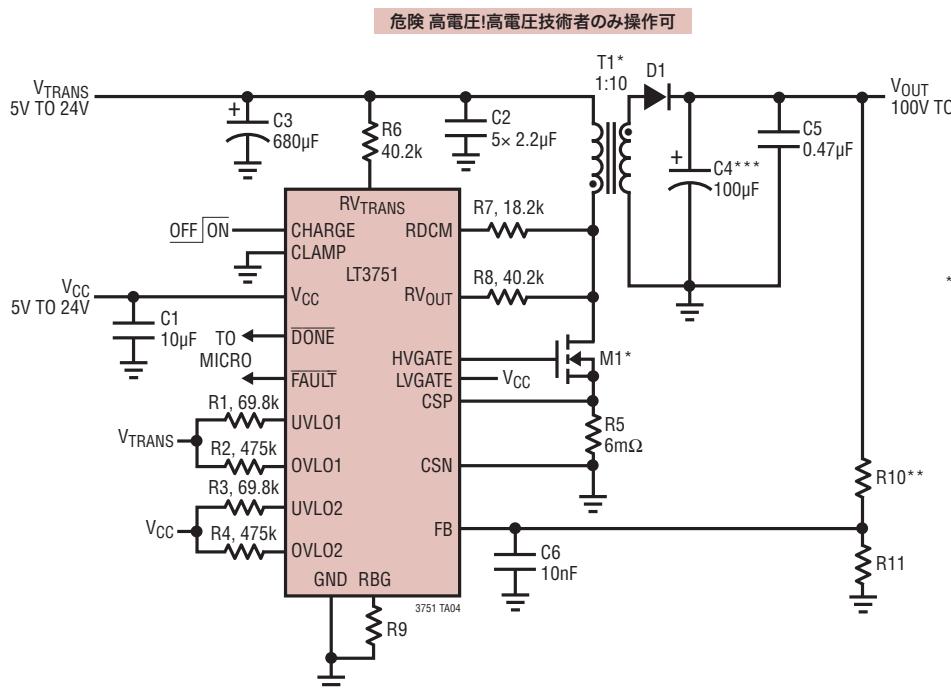

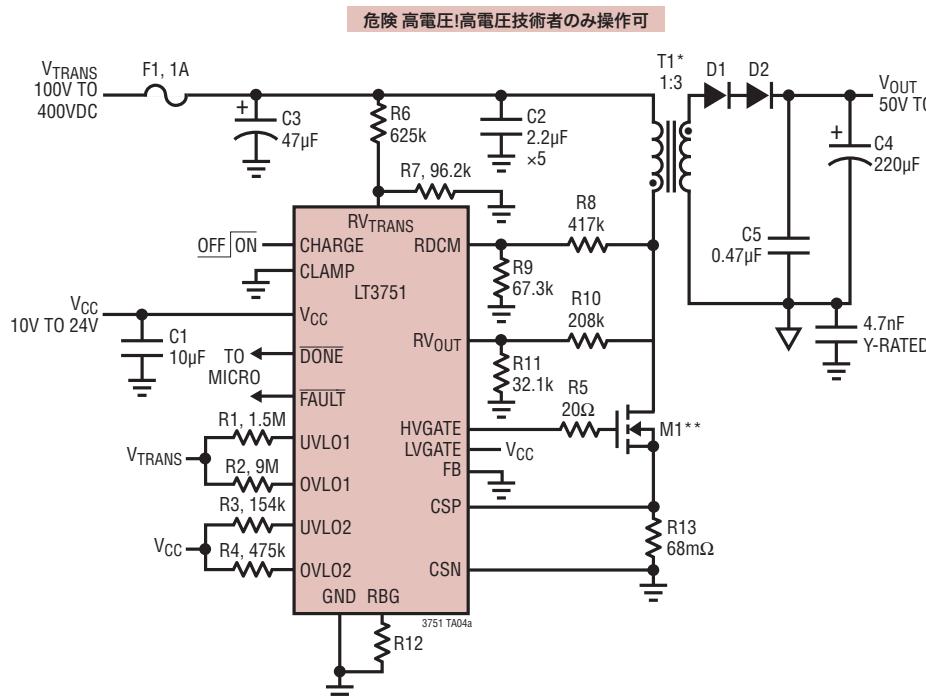

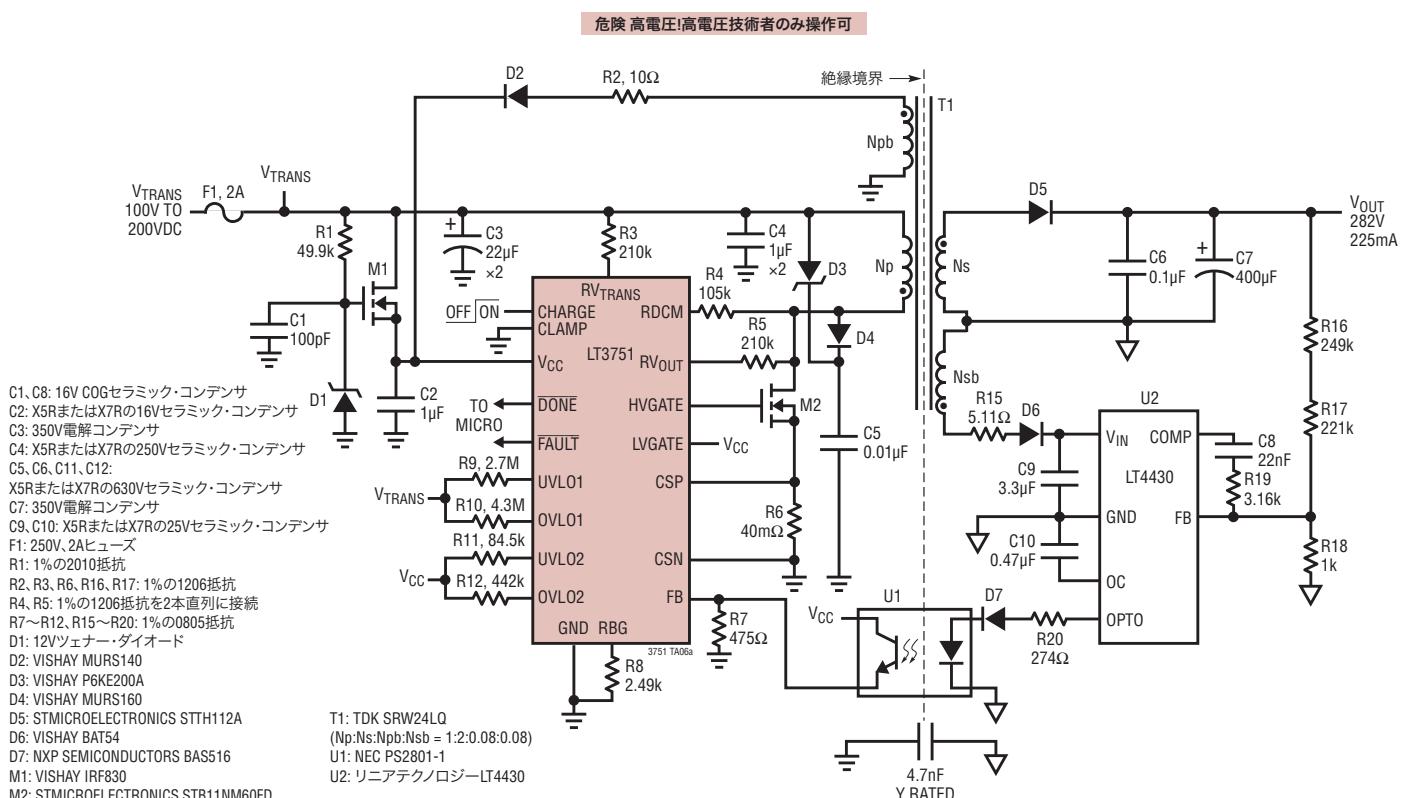

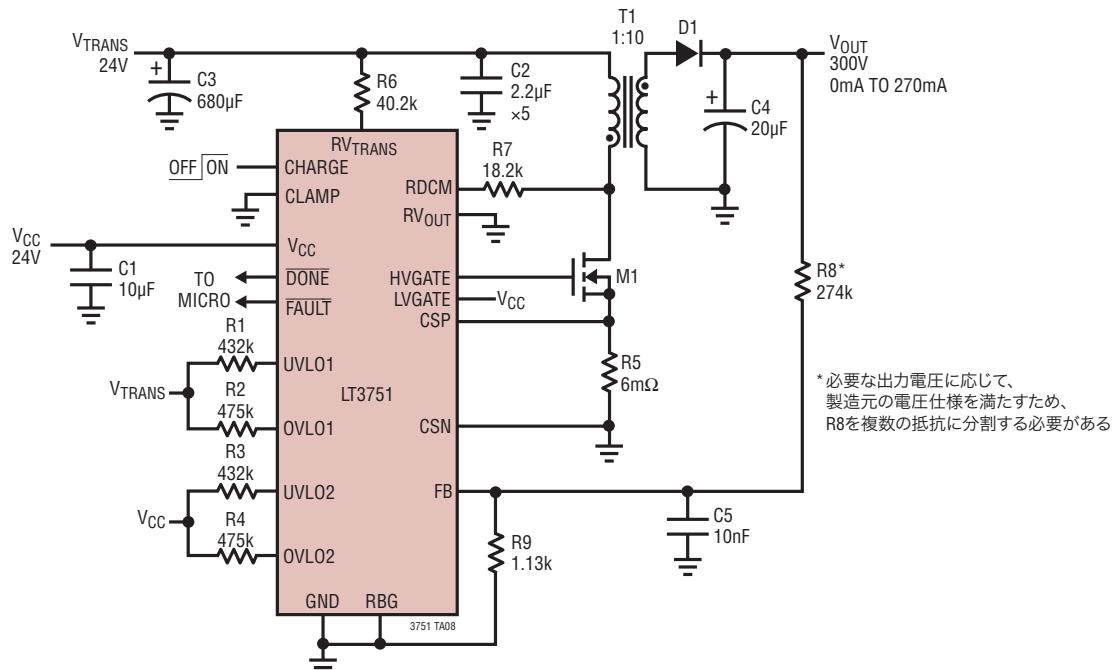

## 標準的応用例

## 絶対最大定格 (Note 1)

|                        |           |                      |             |

|------------------------|-----------|----------------------|-------------|

| $V_{CC}$ 、CHARGE、CLAMP | 24V       | $RV_{OUT}$ ピンに流れ込む電流 | $\pm 10mA$  |

| DONE、FAULT             | 24V       | RDCMピンに流れ込む電流        | $\pm 10mA$  |

| LVGATE (Note 8)        | 24V       | UVL01ピンに流れ込む電流       | $\pm 1mA$   |

| $V_{CC}$ –LVGATE       | 8V        | UVL02ピンに流れ込む電流       | $\pm 1mA$   |

| HVGATE                 | Note 9    | OVL01ピンに流れ込む電流       | $\pm 1mA$   |

| RBG、CSP、CSN            | 2V        | OVL02ピンに流れ込む電流       | $\pm 1mA$   |

| FB                     | 5V        | 最大接合部温度              | 125°C       |

| DONEピンに流れ込む電流          | $\pm 1mA$ | 動作温度範囲 (Note 2)      | -40°C~125°C |

| FAULTピンに流れ込む電流         | $\pm 1mA$ | 保存温度範囲               | -65°C~125°C |

| $RV_{TRANS}$ ピンに流れ込む電流 | $\pm 1mA$ |                      |             |

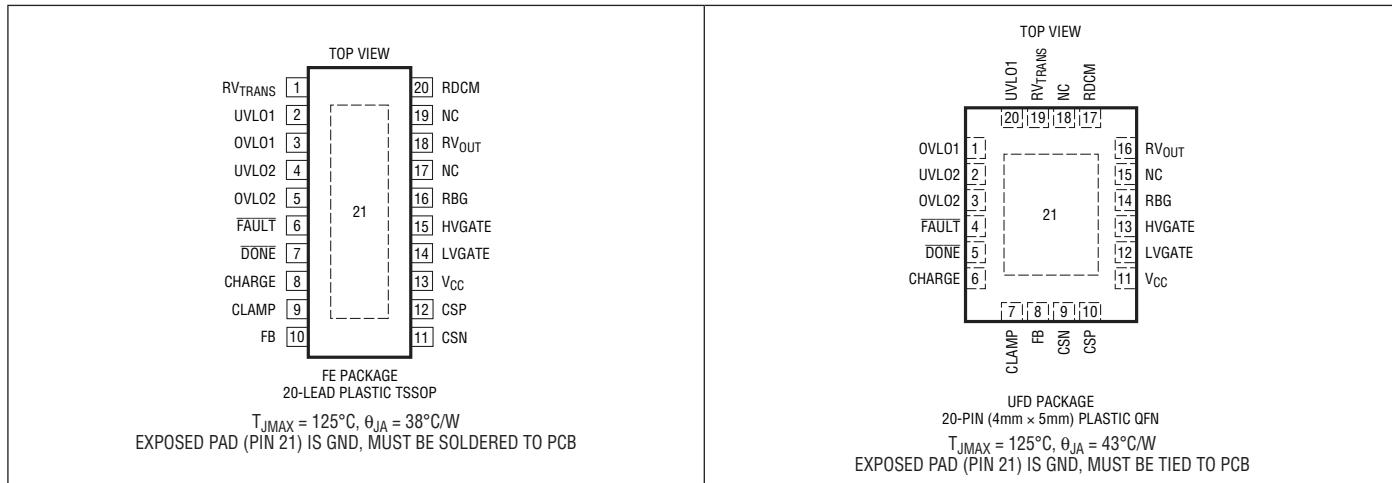

## ピン配置

## 発注情報

| 鉛フリー仕様        | テープアンドリール       | 製品マーキング* | パッケージ                          | 温度範囲           |

|---------------|-----------------|----------|--------------------------------|----------------|

| LT3751EFE#PBF | LT3751EFE#TRPBF | LT3751FE | 20-Lead Plastic TSSOP          | -40°C to 125°C |

| LT3751IFE#PBF | LT3751IFE#TRPBF | LT3751FE | 20-Lead Plastic TSSOP          | -40°C to 125°C |

| LT3751EUF#PBF | LT3751EUF#TRPBF | 3751     | 20-Pin (4mm x 5mm) Plastic QFN | -40°C to 125°C |

| LT3751IUF#PBF | LT3751IUF#TRPBF | 3751     | 20-Pin (4mm x 5mm) Plastic QFN | -40°C to 125°C |

| 鉛ベース仕様        | テープアンドリール       | 製品マーキング* | パッケージ                          | 温度範囲           |

| LT3751EFE     | LT3751EFE#TR    | LT3751FE | 20-Lead Plastic TSSOP          | -40°C to 125°C |

| LT3751IFE     | LT3751IFE#TR    | LT3751FE | 20-Lead Plastic TSSOP          | -40°C to 125°C |

| LT3751EUF     | LT3751EUF#TR    | 3751     | 20-Pin (4mm x 5mm) Plastic QFN | -40°C to 125°C |

| LT3751IUF     | LT3751IUF#TR    | 3751     | 20-Pin (4mm x 5mm) Plastic QFN | -40°C to 125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。 \*温度グレードは出荷時のコンテナのラベルで識別されます。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = \text{CHARGE} = 5\text{V}$ 、 $\text{CLAMP} = 0\text{V}$ 。注記がない限り、 $5\text{V}$   $V_{TRANS}$ 電源から $RV_{TRANS}$ 、 $RV_{OUT}$ 、 $R_{DCM}$ に $25\text{k}\Omega$ 抵抗が個別に接続されている。(Note 2)

| PARAMETER                                           | CONDITIONS                                                                                                    | MIN          | TYP            | MAX       | UNITS                                           |    |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------|----------------|-----------|-------------------------------------------------|----|

| $V_{CC}$ Voltage                                    |                                                                                                               | ● 4.75       | 24             |           | V                                               |    |

| $RV_{TRANS}$ Voltage                                | (Note 3)                                                                                                      | ● 4.75       | 65             |           | V                                               |    |

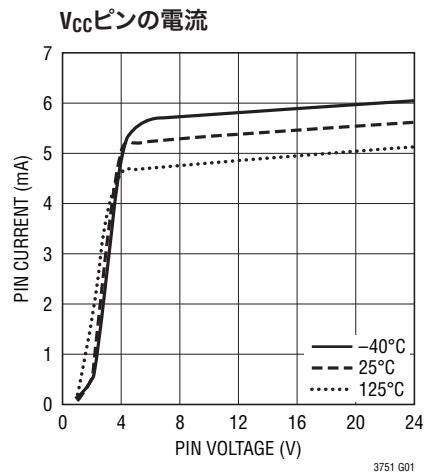

| $V_{CC}$ Quiescent Current                          | Not Switching, $\text{CHARGE} = 5\text{V}$<br>Not Switching, $\text{CHARGE} = 0.3\text{V}$                    |              | 5.5<br>0       | 8<br>1    | mA<br>$\mu\text{A}$                             |    |

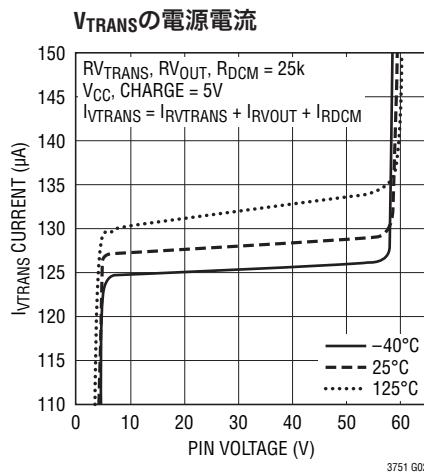

| $RV_{TRANS}$ , $R_{DCM}$ Quiescent Current          | (Note 4)<br>Not Switching, $\text{CHARGE} = 5\text{V}$<br>Not Switching, $\text{CHARGE} = 0.3\text{V}$        | ● 35         | 40<br>0        | 45<br>1   | $\mu\text{A}$<br>$\mu\text{A}$                  |    |

| $RV_{OUT}$ Quiescent Current                        | (Note 4)<br>Not Switching, $\text{CHARGE} = 5\text{V}$<br>Not Switching, $\text{CHARGE} = 0.3\text{V}$        | ● 42         | 47<br>0        | 52<br>1   | $\mu\text{A}$<br>$\mu\text{A}$                  |    |

| $UVLO1$ , $UVLO2$ , $OVLO1$ , $OVLO2$ Clamp Voltage | Measured at 1mA into Pin, $\text{CHARGE} = 0\text{V}$                                                         |              | 55             |           | V                                               |    |

| $RV_{TRANS}$ , $RV_{OUT}$ , $R_{DCM}$ Clamp Voltage | Measured at 1mA into Pin, $\text{CHARGE} = 0\text{V}$                                                         |              | 60             |           | V                                               |    |

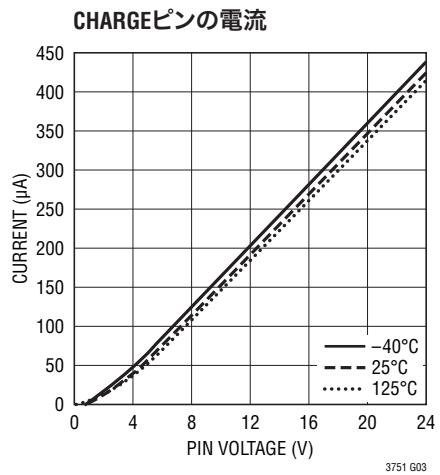

| CHARGE Pin Current                                  | $\text{CHARGE} = 24\text{V}$<br>$\text{CHARGE} = 5\text{V}$<br>$\text{CHARGE} = 0\text{V}$                    |              | 425<br>60<br>1 |           | $\mu\text{A}$<br>$\mu\text{A}$<br>$\mu\text{A}$ |    |

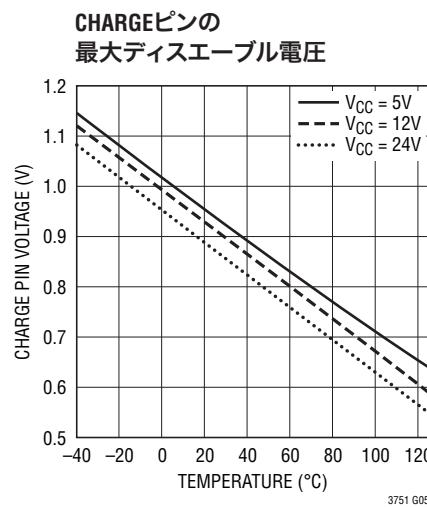

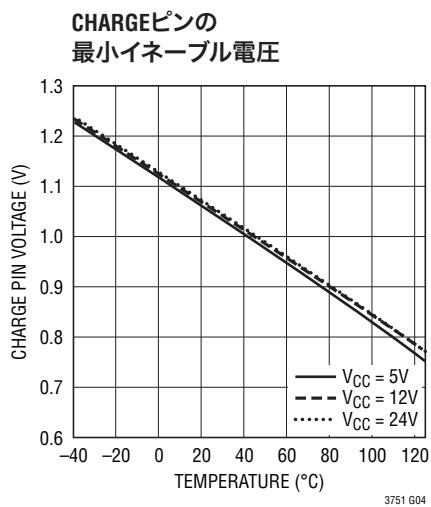

| CHARGE Minimum Enable Voltage                       |                                                                                                               | ● 1.5        |                |           | V                                               |    |

| CHARGE Maximum Disable Voltage                      | $I_{VCC} \leq 1\mu\text{A}$                                                                                   | ●            |                | 0.3       | V                                               |    |

| Minimum CHARGE Pin Low Time                         |                                                                                                               |              | 20             |           | $\mu\text{s}$                                   |    |

| One-Shot Clock Period                               |                                                                                                               | ● 32         | 38             | 44        | $\mu\text{s}$                                   |    |

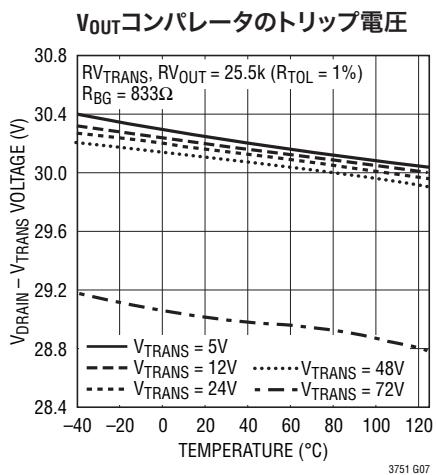

| $V_{OUT}$ Comparator Trip Voltage                   | Measured at RBG Pin                                                                                           | ● 0.955      | 0.98           | 1.005     | V                                               |    |

| $V_{OUT}$ Comparator Overdrive                      | 2 $\mu\text{s}$ Pulse Width,<br>$RV_{TRANS}$ , $RV_{OUT} = 25\text{k}\Omega$<br>$R_{BG} = 0.83\text{k}\Omega$ |              | 20             | 40        | mV                                              |    |

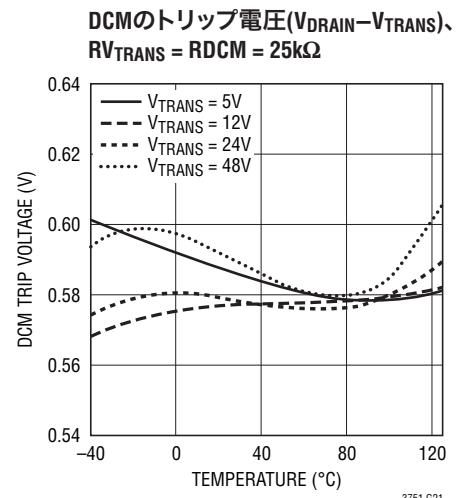

| DCM Comparator Trip Voltage                         | Measured as $V_{DRAIN} - V_{TRANS}$ , $R_{DCM} = 25\text{k}\Omega$ , $V_{CC} = 4.75\text{V}$ (Note 5)         |              | 350            | 600       | 900                                             | mV |

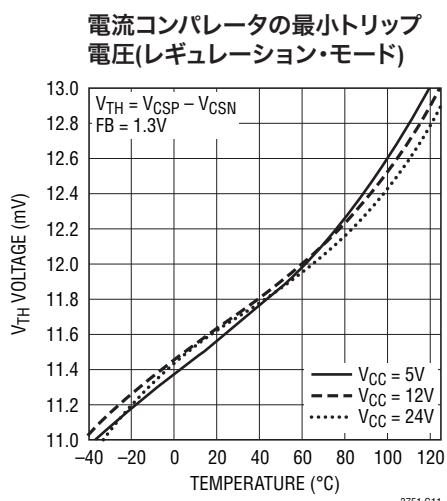

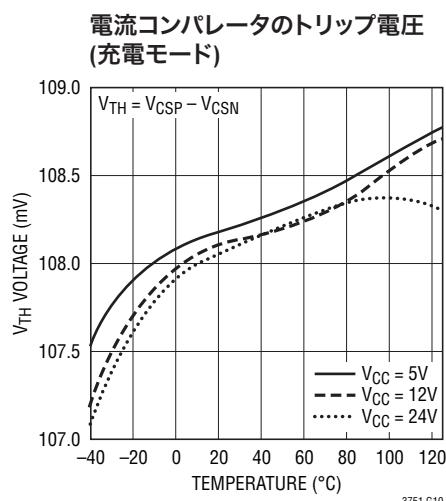

| Current Limit Comparator Trip Voltage               | FB Pin = 0V<br>FB Pin = 1.3V                                                                                  | ● 100<br>● 7 | 106<br>11      | 112<br>15 | mV<br>mV                                        |    |

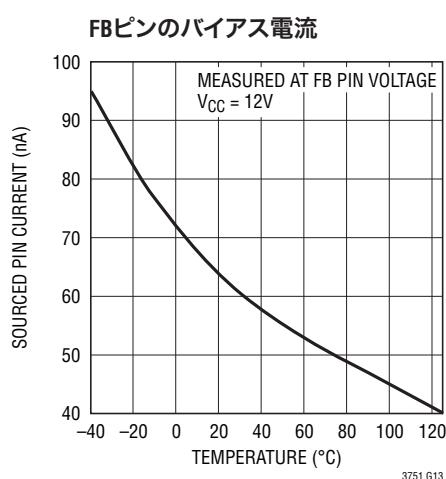

| FB Pin Bias Current                                 | Current Sourced from FB Pin, Measured at FB Pin Voltage                                                       |              | 64             | 300       | nA                                              |    |

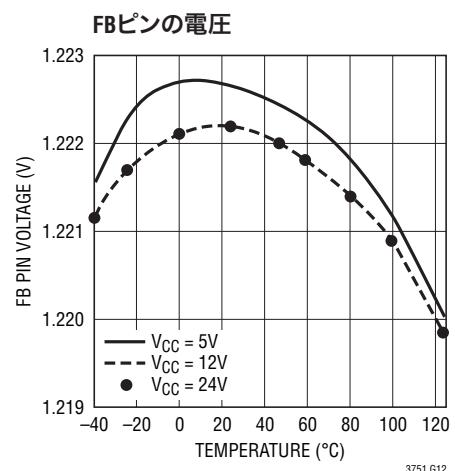

| FB Pin Voltage                                      | (Note 6)                                                                                                      | ● 1.19       | 1.22           | 1.25      | V                                               |    |

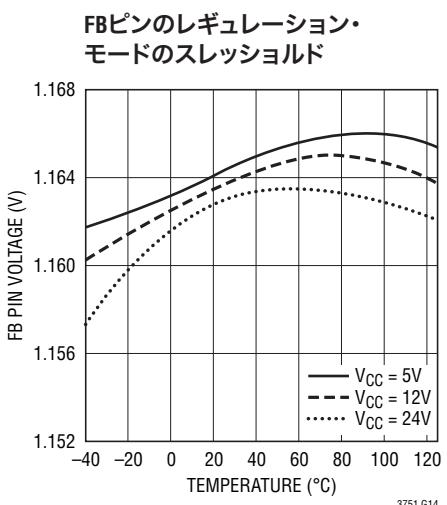

| FB Pin Charge Mode Threshold                        |                                                                                                               |              | 1.12           | 1.16      | 1.2                                             | V  |

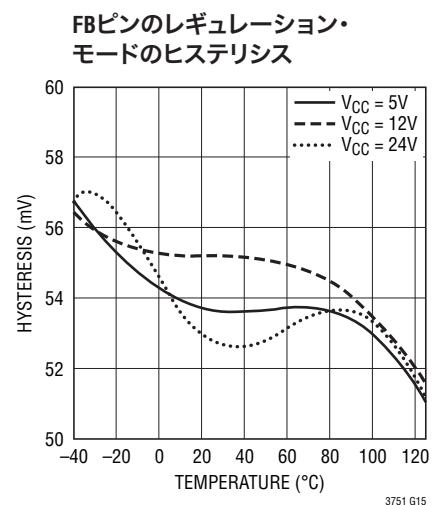

| FB Pin Charge Mode Hysteresis                       | (Note 7)                                                                                                      |              | 55             |           | mV                                              |    |

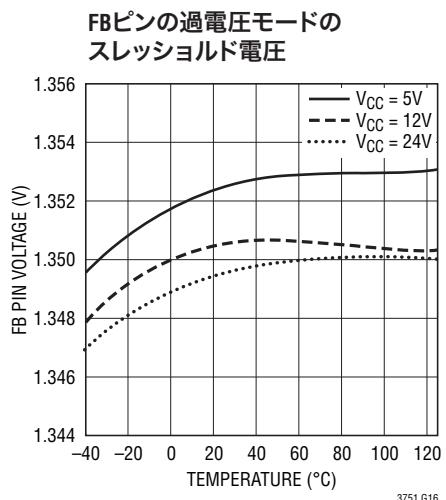

| FB Pin Overvoltage Mode Threshold                   |                                                                                                               |              | 1.29           | 1.34      | 1.38                                            | V  |

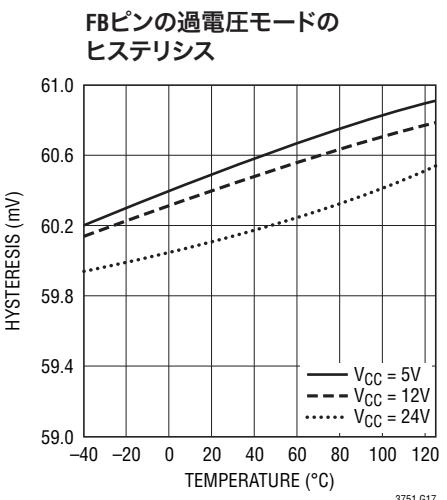

| FB Pin Overvoltage Hysteresis                       |                                                                                                               |              | 60             |           | mV                                              |    |

| DONE Output Signal High                             | 100 $\text{k}\Omega$ to 5V                                                                                    |              | 5              |           | V                                               |    |

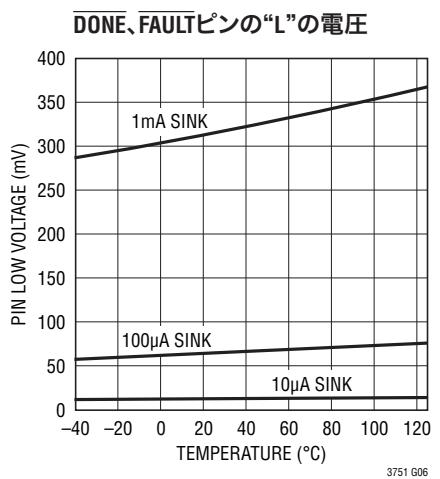

| DONE Output Signal Low                              | 100 $\text{k}\Omega$ to 5V                                                                                    |              | 40             | 200       | mV                                              |    |

| DONE Leakage Current                                | DONE = 5V                                                                                                     |              | 5              | 200       | nA                                              |    |

| FAULT Output Signal High                            | 100 $\text{k}\Omega$ to 5V                                                                                    |              | 5              |           | V                                               |    |

| FAULT Output Signal Low                             | 100 $\text{k}\Omega$ to 5V                                                                                    |              | 40             | 200       | mV                                              |    |

| FAULT Leakage Current                               | FAULT = 5V                                                                                                    |              | 5              | 200       | nA                                              |    |

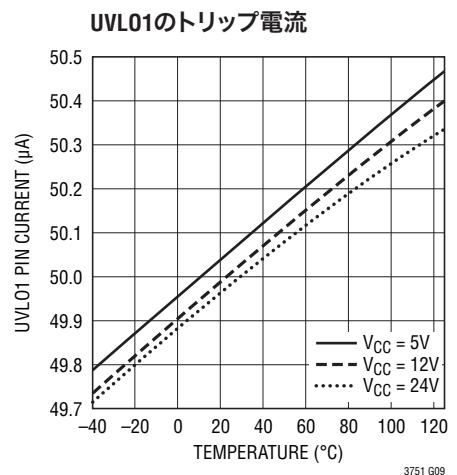

| UVLO1 Pin Current                                   | UVLO1 Pin Voltage = 1.24V                                                                                     | ● 48.5       | 50             | 51.5      | $\mu\text{A}$                                   |    |

| UVLO2 Pin Current                                   | UVLO2 Pin Voltage = 1.24V                                                                                     | ● 48.5       | 50             | 51.5      | $\mu\text{A}$                                   |    |

| OVLO1 Pin Current                                   | OVLO1 Pin Voltage = 1.24V                                                                                     | ● 48.5       | 50             | 51.5      | $\mu\text{A}$                                   |    |

| OVLO2 Pin Current                                   | OVLO2 Pin Voltage = 1.24V                                                                                     | ● 48.5       | 50             | 51.5      | $\mu\text{A}$                                   |    |

## 電気的特性

●は全動作温度範囲の規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{CC} = \text{CHARGE} = 5\text{V}$ 、 $\text{CLAMP} = 0\text{V}$ 。注記がない限り、 $5\text{V}$   $V_{TRANS}$ 電源から $RV_{TRANS}$ 、 $RV_{OUT}$ 、 $RDCM$ に $25\text{k}\Omega$ 抵抗が個別に接続されている。(Note 2)

| PARAMETER                       | CONDITIONS                                                                                                                                                                                         | MIN                   | TYP                      | MAX   | UNITS            |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|-------|------------------|

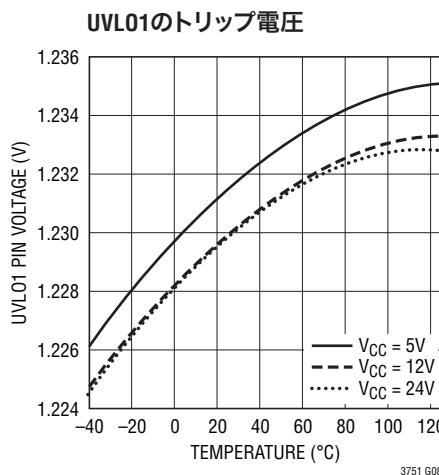

| UVLO1 Threshold                 | Measured from Pin to GND                                                                                                                                                                           | ● 1.195               | 1.225                    | 1.255 | V                |

| UVLO2 Threshold                 | Measured from Pin to GND                                                                                                                                                                           | ● 1.195               | 1.225                    | 1.255 | V                |

| OVLO1 Threshold                 | Measured from Pin to GND                                                                                                                                                                           | ● 1.195               | 1.225                    | 1.255 | V                |

| OVLO2 Threshold                 | Measured from Pin to GND                                                                                                                                                                           | ● 1.195               | 1.225                    | 1.255 | V                |

| Gate Minimum High Time          |                                                                                                                                                                                                    |                       | 0.7                      |       | $\mu\text{s}$    |

| Gate Peak Pull-Up Current       | $V_{CC} = 5\text{V}$ , LVGATE Active<br>$V_{CC} = 12\text{V}$ , LVGATE Inactive                                                                                                                    |                       | 2.0<br>1.5               |       | A                |

| Gate Peak Pull-Down Current     | $V_{CC} = 5\text{V}$ , LVGATE Active<br>$V_{CC} = 12\text{V}$ , LVGATE Inactive                                                                                                                    |                       | 1.2<br>1.5               |       | A                |

| Gate Rise Time                  | $10\% \rightarrow 90\%$ , $C_{GATE} = 3.3\text{nF}$ (Note 8)<br>$V_{CC} = 5\text{V}$ , LVGATE Active<br>$V_{CC} = 12\text{V}$ , LVGATE Inactive                                                    |                       | 40<br>55                 |       | ns<br>ns         |

| Gate Fall Time                  | $90\% \rightarrow 10\%$ , $C_{GATE} = 3.3\text{nF}$ (Note 8)<br>$V_{CC} = 5\text{V}$ , LVGATE Active<br>$V_{CC} = 12\text{V}$ , LVGATE Inactive                                                    |                       | 30<br>30                 |       | ns<br>ns         |

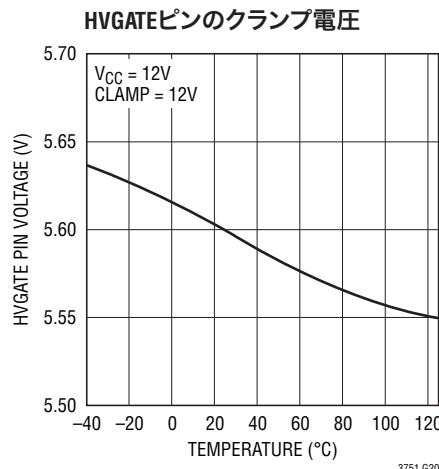

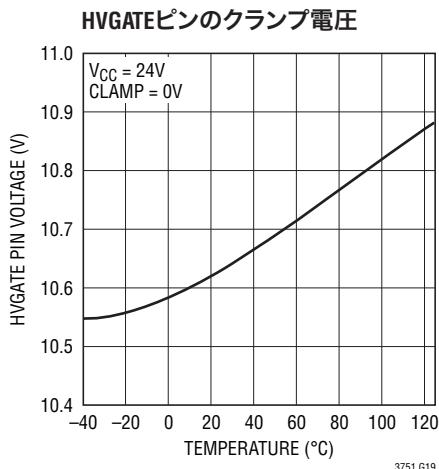

| Gate High Voltage               | (Note 8):<br>$V_{CC} = 5\text{V}$ , LVGATE Active<br>$V_{CC} = 12\text{V}$ , LVGATE Inactive<br>$V_{CC} = 12\text{V}$ , LVGATE Inactive, CLAMP Pin = 5V<br>$V_{CC} = 24\text{V}$ , LVGATE Inactive | 4.98<br>10<br>5<br>10 | 5<br>10.5<br>5.6<br>10.5 | 11.5  | V<br>V<br>V<br>V |

| Gate Turn-Off Propagation Delay | $C_{GATE} = 3.3\text{nF}$<br>25mV Overdrive Applied to CSP Pin                                                                                                                                     |                       | 180                      |       | ns               |

| Gate Voltage Overshoot          |                                                                                                                                                                                                    |                       | 500                      |       | mV               |

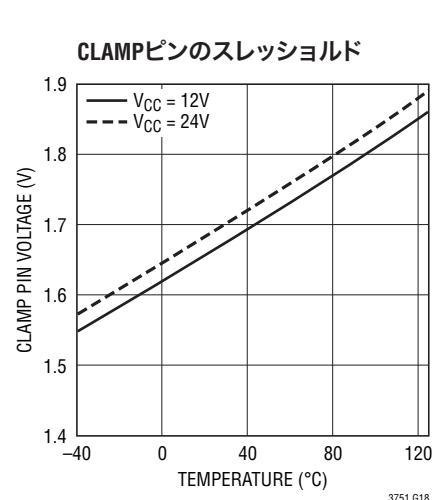

| CLAMP Pin Threshold             |                                                                                                                                                                                                    |                       | 1.6                      |       | V                |

**Note 1:**絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:**LT3751Eは $0^\circ\text{C} \sim 125^\circ\text{C}$ の接合部温度で性能仕様に適合することが保証されている。 $-40^\circ\text{C} \sim 125^\circ\text{C}$ の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT3751Iは $-40^\circ\text{C} \sim 125^\circ\text{C}$ の全動作接合部温度範囲で保証されている。

**Note 3:**60Vの内部クランプが、 $RV_{TRANS}$ 、 $RDCM$ 、 $RV_{OUT}$ 、 $UVLO1$ 、 $UVLO2$ 、 $OVLO1$ および $OVLO2$ に接続されている。ピン電流が絶対最大定格を超えないように抵抗を使用する。

**Note 4:**ピン電圧が内部クランプ電圧より高くなるにつれ、電流が増加する。

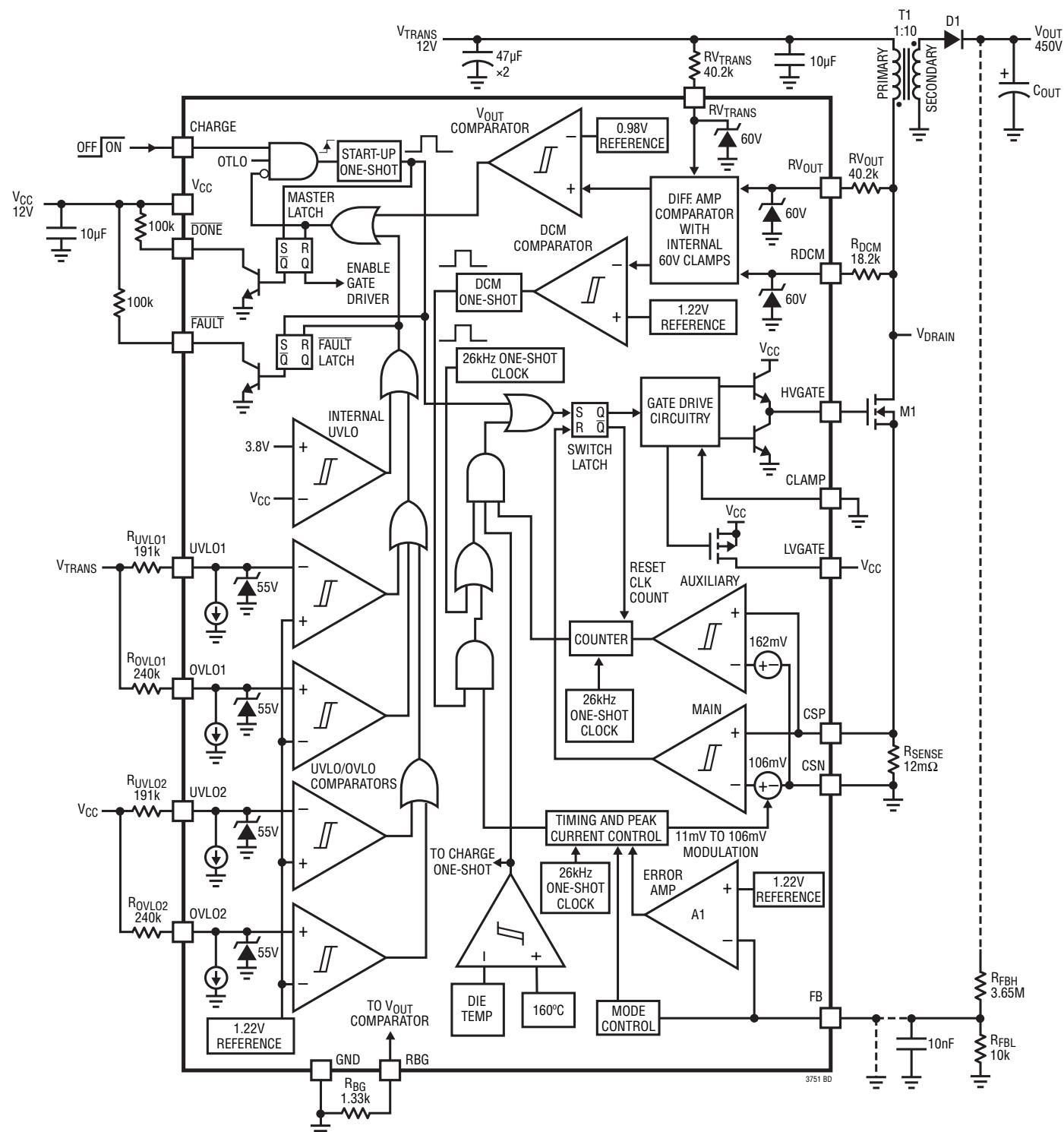

**Note 5:** $V_{TRANS}$ と $V_{DRAIN}$ の定義に関しては、「ブロック図」を参照。

**Note 6:**出力電圧の低ノイズ・レギュレーションを確保するには出力電圧からFBピンに抵抗分圧器を接続する必要がある。この回路構成ではFBピンを接地しない。FBピンの正しい回路構成については、「標準的応用例」の回路図を参照。

**Note 7:**帰還ピンには内部ヒステリシスがあり、充電のみのモードと低ノイズ・レギュレーション・モードの間の境界を定めている。

**Note 8:** $V_{CC} \geq 8\text{V}$ 以下のとき、LVGATEをHVGATEと並列に使う(LVGATEはアクティブ)。使用しない場合、LVGATEは $V_{CC}$ に接続する(LVGATEは非アクティブ)。

**Note 9:**HVGATEには正または負の電圧源または電流源を印加してはならない。印加すると、永続的損傷を与えることがある。

## 標準的性能特性

## 標準的性能特性

## 標準的性能特性

## ピン機能 (TSSOP/QFN)

**RV<sub>TRANS</sub>(ピン1/ピン19)**:トランス電源検出ピン。抵抗をRV<sub>TRANS</sub>ピンとV<sub>TRANS</sub>電源の間に接続します。RV<sub>TRANS</sub>抵抗の適切な大きさに関しては表2を参照してください。V<sub>TRANS</sub>の最小動作電圧は4.75Vです。

**UVL01(ピン2/ピン20)**:V<sub>TRANS</sub>の低電圧ロックアウト・ピン。V<sub>TRANS</sub>が以下の値を下回ると、低電圧ロックアウトを検出します。

$$V_{UVL01} = 1.225 + 50\mu A \cdot R_{UVL01}$$

そして、FAULTラッチを“L”にトリップし、スイッチングをディスエーブルします。V<sub>TRANS</sub>がV<sub>UVL01</sub>を上回った後、CHARGEピンをトグルするとスイッチングが再起動します。

**OVL01(ピン3/ピン1)**:V<sub>TRANS</sub>の過電圧ロックアウト・ピン。V<sub>TRANS</sub>が以下の値を上回ると、過電圧ロックアウトを検出します。

$$V_{OVL01} = 1.225 + 50\mu A \cdot R_{OVL01}$$

そして、FAULTラッチを“L”にトリップし、スイッチングをディスエーブルします。V<sub>TRANS</sub>がV<sub>OVL01</sub>を下回った後、CHARGEピンをトグルするとスイッチングが再起動します。

**UVL02(ピン4/ピン2)**:V<sub>CC</sub>の低電圧ロックアウト・ピン。V<sub>CC</sub>が以下の値を下回ると、低電圧ロックアウトを検出します。

$$V_{UVL02} = 1.225 + 50\mu A \cdot R_{UVL02}$$

そして、FAULTラッチを“L”にトリップし、スイッチングをディスエーブルします。V<sub>CC</sub>がV<sub>UVL02</sub>を上回った後、CHARGEピンをトグルするとスイッチングが再起動します。

**OVL02(ピン5/ピン3)**:V<sub>CC</sub>の過電圧ロックアウト・ピン。V<sub>CC</sub>が以下の値を上回ると、過電圧ロックアウトを検出します。

$$V_{OVL02} = 1.225 + 50\mu A \cdot R_{OVL02}$$

そして、FAULTラッチを“L”にトリップし、スイッチングをディスエーブルします。V<sub>CC</sub>がV<sub>OVL02</sub>を下回った後、CHARGEピンをトグルするとスイッチングが再起動します。

**FAULT(ピン6/ピン4)**:オープンコレクタの通知ピン。V<sub>TRANS</sub>またはV<sub>CC</sub>のどちらかがユーザーが選択した電圧範囲を超えるか、あるいは内部UVLO条件が発生すると、トランジスタがオンします。デバイスはスイッチングを停止します。このピンには適切なプルアップ抵抗または電流源が必要です。

## ピン機能

**DONE(ピン7/ピン5)**: オープンコレクタの通知ピン。目標の出力電圧(充電モード)に達するか、あるいは~~FAULT~~ピンが“L”になると、トランジスタがオンします。このピンには適切なプルアップ抵抗または電流源が必要です。

**CHARGE(ピン8/ピン6)**: 充電ピン。1.5Vより高い電圧にドライブすると、新しい充電サイクルを開始する(充電モード)か、またはデバイスをイネーブルします(レギュレーション・モード)。充電を中止し、デバイスをシャットダウンするには、このピンを0.3V以下にします。ターンオン・ランプ・レートは10ns～10msにします。V<sub>CC</sub>を使ってCHARGEピンを直接ランプさせないでください。V<sub>CC</sub>を使ってランプさせると、LT3751は正しく初期化しないことがあります。

**CLAMP(ピン9/ピン7)**: 内部クランプ電圧選択ピン。5.6Vの内部ゲート・ドライバ・クランプを起動するには、このピンをV<sub>CC</sub>に接続します。10.5Vの内部ゲート・ドライバ・クランプを起動するには、このピンをグランドに接続します。

**FB(ピン10/ピン8)**: 帰還レギュレーション・ピン。このピンを使って低ノイズ電圧レギュレーションを実現します。抵抗分割器がこのピンから出力に接続されると、FBは内部で1.22Vに安定化されます。FBピンはフロート状態にしてはなりません。FBピンは抵抗分割器またはグランドのどちらかに接続します。

**CSN(ピン11/ピン9)**: 負の電流検出ピン。外付けNMOS FETのソース電流を検出します。適切なケルビン検出を行うため、R<sub>SENSE</sub>のローカルなグランド接続点に接続します。電流制限値は106mV/R<sub>SENSE</sub>によって設定されます。

**CSP(ピン12/ピン10)**: 正の電流検出ピン。NMOS FETのソース電流を検出します。NMOS FETのソース端子と電流検出抵抗をこのピンに接続します。充電モードでは電流制限値は106mV/R<sub>SENSE</sub>に固定されます。レギュレーション・モードでは電流制限値は最小11mV/R<sub>SENSE</sub>まで減らすことができます。

**V<sub>CC</sub>(ピン13/ピン11)**: 入力電源ピン。高グレード(X5R以上)のセラミック・コンデンサを使ってローカルにバイパスする必要があります。V<sub>CC</sub>の最小動作電圧は4.75Vです。

**LVGATE(ピン14/ピン12)**: 低電圧ゲート・ピン。8Vより低いV<sub>CC</sub>で動作しているとき、NMOS FETのゲート端子をこのピンに接続します。内部ゲート・ドライバは電圧をV<sub>CC</sub>レールまでドライブします。8Vより高いV<sub>CC</sub>で動作しているときは、このピンをV<sub>CC</sub>に直接接続します。

**HVGATE(ピン15/ピン13)**: 高電圧ゲート・ピン。全てのV<sub>CC</sub>動作電圧で、NMOS FETのゲート端子をこのピンに接続します。内部ゲート・ドライバが、スイッチング・サイクルごとに、電圧をV<sub>CC</sub>～2Vまでドライブします。

**RBG(ピン16/ピン14)**: バイアス発生ピン。0.98V/R<sub>BG</sub>によって設定されるバイアス電流を発生します。R<sub>DCM</sub>、R<sub>VOUT</sub>およびR<sub>VTRANS</sub>に適した抵抗値に相当するR<sub>BG</sub>を選択します。

**NC(ピン17、19/ピン15、18)**: NC。

**R<sub>VOUT</sub>(ピン18/ピン16)**: 出力電圧検出ピン。出力コンデンサの電圧に比例する電流を発生します。以下のように、このピンとNMOS FETのドレインの間に抵抗を接続します。

$$V_{OUT} = 0.98 \cdot N \cdot \left( \frac{R_{VOUT}}{R_{BG}} \right) - V_{DIODE}$$

これはR<sub>VOUT</sub>がR<sub>VTRANS</sub>に等しく設定されているときで、それ以外は次のようにになります。

$$V_{OUT} = N \cdot \left[ 0.98 \cdot \frac{R_{VOUT}}{R_{BG}} + V_{TRANS} \left( \frac{R_{VOUT}}{R_{VTRANS}} - 1 \right) \right] - V_{DIODE}$$

ここで、V<sub>DIODE</sub> = ダイオードD1の順方向電圧降下です(「ブロック図」を参照)。

**R<sub>DCM</sub>(ピン20/ピン17)**: 不連続モード検出ピン。外付けNMOS FETのドレインが20μA・R<sub>DCM</sub>+V<sub>TRANS</sub>に等しくなるときを検出し、次の充電サイクルを開始します。このピンとV<sub>DRAIN</sub>の間に、R<sub>VTRANS</sub>ピンの抵抗の0.45倍に等しい抵抗を接続します。

**GND(ピン21/ピン21)**: グランド。ローカル・グランド・プレーンに直接接続します。

## ブロック図

## 動作

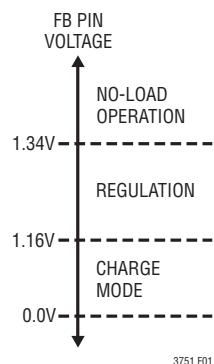

LT3751は高速で効率の良い高電圧コンデンサ・チャージャ・コントローラとして、または高電圧、低ノイズの電圧レギュレータとして使うことができます。FBピンの電圧により、充電モード、低ノイズ・レギュレーション、無負荷動作の3つの主要なモードの1つが決まります(図1を参照)。

Figure 1. FB Pin Modes

### 充電モード

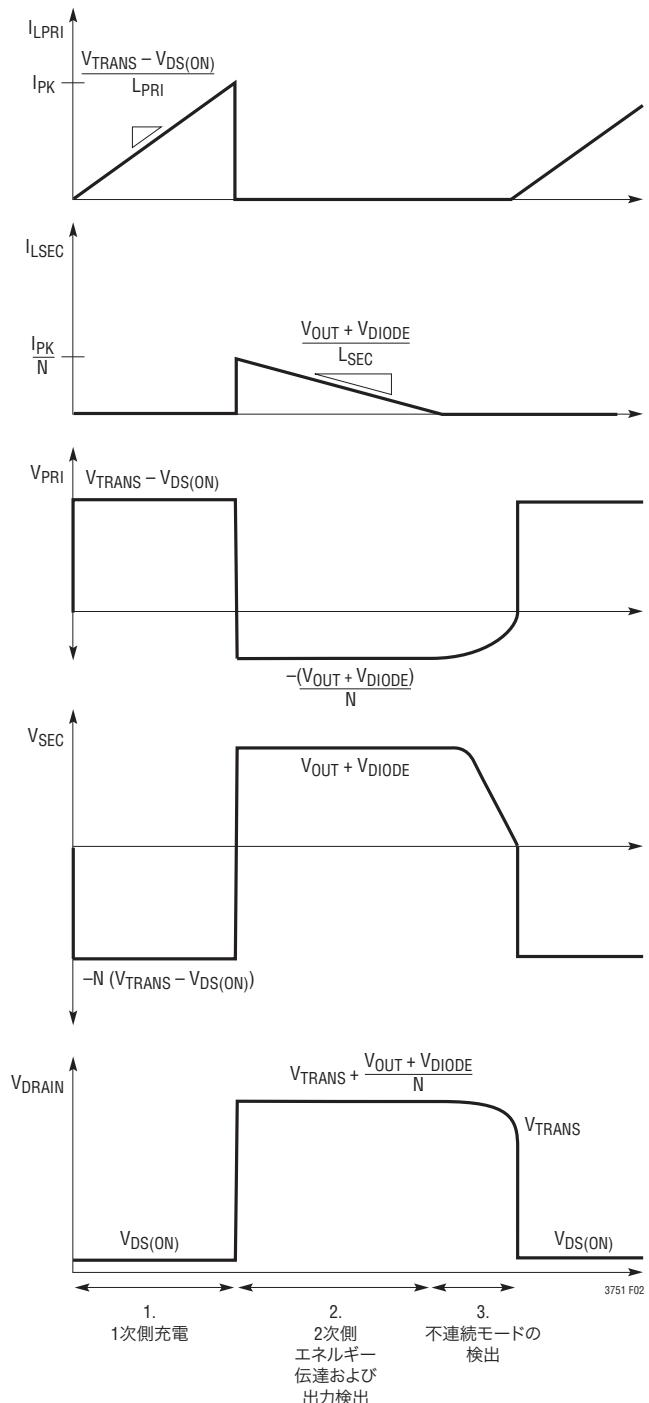

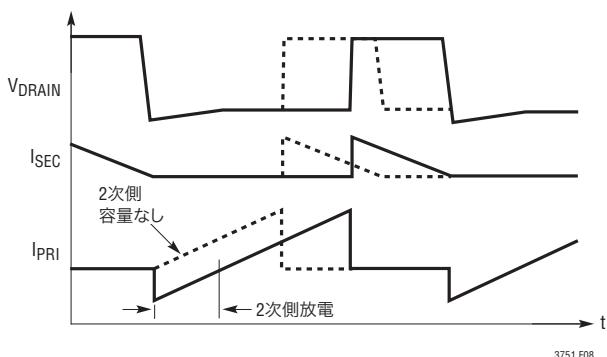

FBピンの電圧が1.16Vを下回ると、LT3751は高速コンデンサ・チャージャとして動作します。充電動作には、充電モードの定常状態動作の4つの基本状態があります(図2を参照)。

#### 1. 起動

最初のスイッチング・サイクルはCHARGEピンが“H”に引き上げられてから約2 $\mu$ s後に開始されます。このフェーズの間、起動ワンショットにより、マスタ・ラッチが外付けNMOS FETをオンして最初のスイッチング・サイクルを開始できるようになります。起動後、目標出力電圧に達するまで、またはフォールト状態が発生するまで、マスタ・ラッチはスイッチング・イネーブル状態を維持します。

LT3751はトランジスタの1次電流が暴走状態にならないように保護する回路を使用しており、DCMコンパレータが十分なヘッドルームを確保するまで起動モードを維持します。詳細については「起動保護」を参照してください。

#### 2. 1次側充電

NMOSスイッチのラッチがセットされると、LVGATEの使用状態に応じて、ゲート・ドライバがゲート・ピンを高電圧アプリケーションではV<sub>CC</sub>-2Vまで急速充電し、低電圧アプリケーションではちょうどV<sub>CC</sub>まで充電します(LVGATEの適切な使用法に関しては、「アプリケーション情報」を参照)。ゲート・ドライバの出力が“H”的とき、外付けNMOS FETがオンし、1次

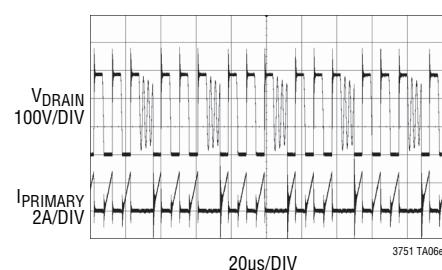

図2. 理想的な充電波形

## 動作

巻線の両端に $V_{TRANS} - V_{DS(ON)}$ を強制します。その結果、1次コイルの電流が $(V_{TRANS} - V_{DS(ON)}) / L_{PRI}$ のレートで直線的に上昇します。入力電圧は2次巻線にミラーリングされた $-N \cdot (V_{TRANS} - V_{DS(ON)})$ で、この電圧がダイオードを逆バイアスして2次巻線に電流が流れないようにします。こうして、エネルギーがトランスのコアに蓄積されます。

### 3. 2次側エネルギー伝達

電流制限に達すると、電流制限コンパレータがNMOSスイッチのラッチをリセットし、デバイスは第3フェーズの動作(2次側エネルギー伝達)に移行します。トランスのコアに蓄積されたエネルギーがダイオードを順方向にバイアスし、電流が出力コンデンサに流れ込みます。この間、出力電圧(ダイオードの電圧降下は無視)は1次コイルに逆反射されます。目標出力電圧に達すると、 $V_{OUT}$ コンパレータがマスター・ラッチをリセットし、DONEピンが“L”になります。それ以外の場合、デバイスは次のフェーズの動作に移行します。

### 4. 不連続モードの検出

出力コンデンサへの2次側エネルギー伝達の間、 $(V_{OUT} + V_{DIODE})/N$ が1次巻線の両端に現れます。エネルギーのないトランスはDC電圧を保持することができないので、1次巻線両端の電圧はゼロまで低下します。つまり、NMOS FETのドレインは $V_{TRANS} + (V_{OUT} + V_{DIODE})/N$ から $V_{TRANS}$ まで低下します。ドレイン電圧が $V_{TRANS} + 20\mu A \cdot R_{DCM}$ まで下がると、DCMコンパレータがNMOSスイッチのラッチをセットし、新しいスイッチング・サイクルが開始されます。目標出力電圧に達するまで、ステップ2~4が繰り返されます。

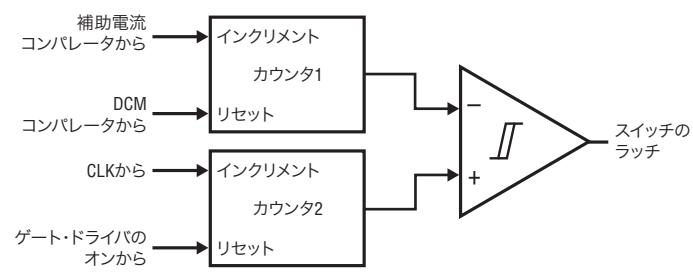

### 起動保護

起動時に、出力電圧が非常に低い(または短絡している)と、LT3751のV<sub>DRAIN</sub>ノードの電圧はDCMコンパレータをトリップさせるのに通常十分ではありません。起動モードのデバイスは26kHzの内部クロックと補助電流コンパレータを使います。起動回路の簡略ブロック図を図3に示します。

図3. 起動保護回路

CHARGEピンをトグルすると常に起動ワンショットが発生し、外部スイッチをオンして充電過程を開始します。起動ワンショットの後、LT3751は、DCMコンパレータがワンショットを発生するか、または起動保護回路の出力が“H”になるか、どちらか先に起きる方を待ちます。スイッチのドレイン・ノード(V<sub>DRAIN</sub>)がDCMコンパレータのスレッショルドを下回ると(「通常の境界モードへの移行」を参照)、DCMコンパレータは決して作動せず、起動回路が支配的になります。

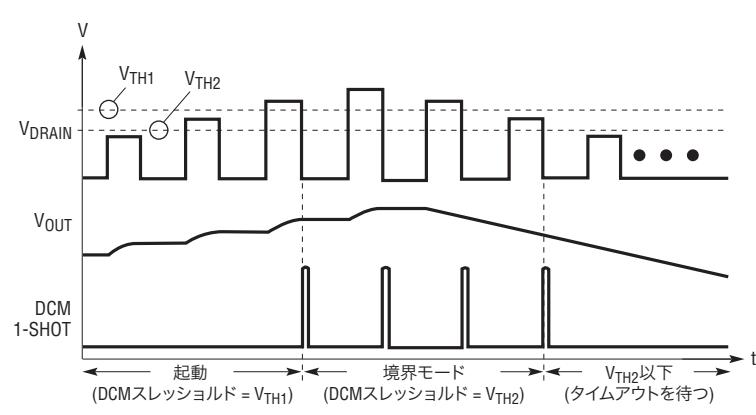

図4. DCMコンパレータのスレッショルド

## 動作

非常に低い出力電圧では、境界モードのスイッチング・サイクルの周期はかなり大きくなるので、トランジスタのコアに蓄積されたエネルギーは次のクロック・サイクルまでに消耗しません。この状況では、クロックは2次巻線の電流がゼロに達する前に別のスイッチング・サイクルを開始するので、LT3751は連続モードの導通状態に移行します。通常、これは問題ではありませんが、2次側のエネルギー伝達時間がCLKの周期よりはるかに長いと、1次側電流に大きなオーバーシュートが生じる可能性があります。これは、スイッチがオンしたとき1次電流の開始点がゼロではなく、また電流コンパレータのスピードが無限ではないためです。

LT3751の起動回路には、トリップ・レベルが通常のトリップ・レベルより50%高い補助電流コンパレータが追加されています。補助電流コンパレータがトリップするたびに、スイッチング・サイクルとスイッチング・サイクルの間に必要なクロック・カウントが1だけインクリメントされます。これにより、2次側エネルギー伝達の時間を増やすことができます。

図3のカウンタ1は、1番目のDCMコンパレータのワンショットが発生するとその最大カウントに設定されます。約500μsの最大カウントの間に通常の境界モードの動作でDCMワンショットが始動しないと、LT3751は再度起動モードに移行し、カウントはゼロに戻されます。

カウンタ1は起動時にゼロに初期化されることに注意してください。このように、起動回路の出力は1クロック後に“H”になります。カウンタ2はゲート・ドライバが“H”になるとリセットされます。これは、補助電流コンパレータが必要なクロック・カウントをインクリメントするまで、または前項のステップ2～4で説明されている通常動作を維持するのに十分なだけV<sub>DRAIN</sub>が高くなるまで、繰り返されます。

### 通常の境界モードへの移行

LT3751のDCMコンパレータには2つのスレッショルドがあり、デバイスが起動モードと通常の境界モードのどちらのモードにあるかによって決まり、またモード・ラッチの状態によっても決まります。LT3751は、境界モードのスイッチングでは、DCM検出電圧(V<sub>DRAIN</sub>)がΔDCMコンパレータ・スレッショルド(ΔV<sub>DRAIN</sub>)だけV<sub>TRANS</sub>を超えることが必要です。

$$\Delta V_{DRAIN} = (40\mu A + I_{OFFSET}) \cdot R_{DCM} - 40\mu A \cdot R_{VTRANS}$$

ここで、I<sub>OFFSET</sub>はモードによって異なります。DCMワンショット信号はスイッチ・ノード(V<sub>DRAIN</sub>)の負エッジによってトリガされ、2次巻線のエネルギーが消耗したことを知らせます。これが起きるためには、その負エッジの前にV<sub>DRAIN</sub>がV<sub>TRANS</sub> + ΔV<sub>DRAIN</sub>を超える必要があります。そうでないと、DCMコンパレータは次のスイッチング・サイクルを開始するワンショットを発生しません。デバイスは無期限にこの状態に固定されたままになるところですが、500μsの最大タイムアウト経過後DCMコンパレータがワンショットを発生しないと、LT3751は起動保護回路を使ってスイッチングをジャンプスタートさせます。

テスト回路の電圧クランプが出力に加えられている状態のV<sub>DRAIN</sub>ノードの標準的波形を図4に示します。V<sub>TH1</sub>は起動スレッショルドで、I<sub>OFFSET</sub>を40μAに強制することにより内部で設定されます。最初のDCMワンショットが始動すると、モード・ラッチが境界モードに設定されます。次いで、モード・ラッチはクロック・カウントを最大(500μs)に設定し、DCMコンパレータのスレッショルドをV<sub>TH2</sub> (I<sub>OFFSET</sub> = 20μA)まで下げます。これにより、起動モードと境界モードの動作の間に必要なヒステリシスが求められます。

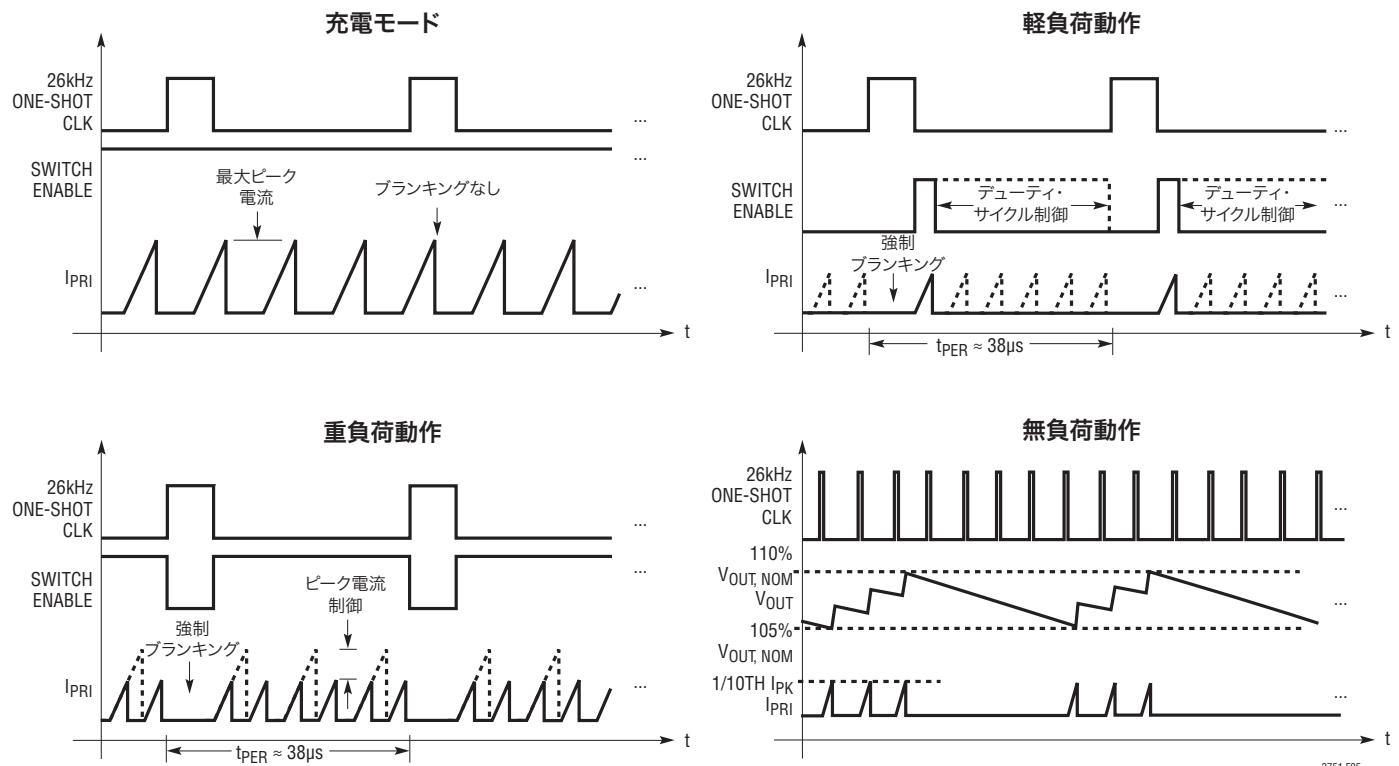

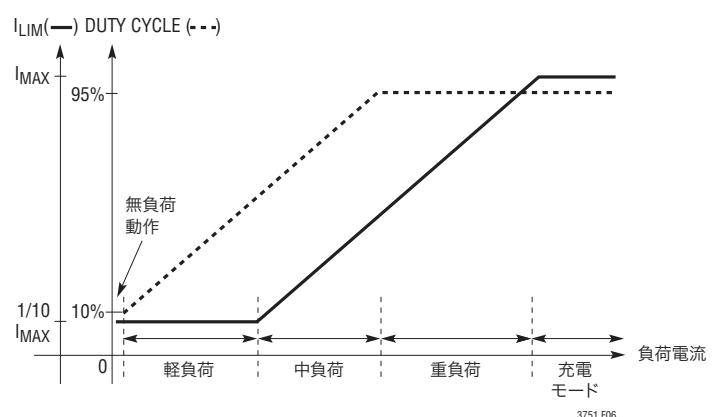

### 低ノイズ・レギュレーション

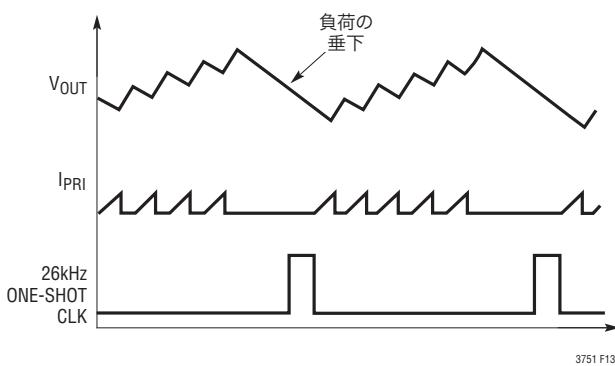

抵抗分割器を出力ノードからLT3751のFBピンに追加することにより、低ノイズ電圧レギュレーションを実現することができます。起動時(FBピンが1.16V以下)、LT3751は充電モードになり、出力コンデンサを急速に充電します。FBピンが1.16V～1.34Vのスレッショルド範囲になると、デバイスは低ノイズ・レギュレーション・モードに移行します。レギュレーション・モードでのスイッチング方法はコンデンサ充電モードで使われる方法によく似ていますが、ピーク電流とデューティ・サイクルの制御手法を追加しています。両方の安定化手法の定常状態の動作を図5に示します。両方の手法を組み合わせて、広い負荷範囲と電源範囲にわたって安定した低ノイズ動作を実現する方法を図6に示します。

重負荷状態の間、LT3751はピーク1次電流をその最大値(106mV/R<sub>SENSE</sub>)に設定し、最大デューティ・サイクルを約95%に設定します。これにより、最大電力の供給が可能になります。軽負荷では反対のことが起き、LT3751はピーク1次電流をその最大値の約1/10まで下げ、デューティ・サイクルを10%以下に調節します。LT3751はピーク電流モード制御とデューティ・サイクル制御を組み合わせて、中程度の負荷を制御します。

## 動作

図5. 動作モード(定常状態)

図6. 安定化手法

## 動作

### 周期的リフレッシュ

LT3751がパルス幅制御モードに移行するとき、内部ワンショット・クロックが“H”だと内部回路がスイッチングを停止します。クロックは1/20のデューティ・サイクルで、1.5μsの最小ブランкиング時間で動作します。このリセット・パルスはオーディオ・スペクトル内のスイッチング周波数成分を大きく減らすようにタイミングが設定され、全ての負荷条件でアクティブです。各リセット・パルスは少なくとも1エネルギー・サイクルを保証します。LT3751が無負荷動作に移行するのを防ぐには最小負荷が必要です。

### 重負荷動作

LT3751は高出力負荷条件ではピーク電流モード制御に移行します。制御ループが各リセット・パルスの間のスイッチ・サイクル数を最大にします。制御回路は境界モードで動作するので、共振境界モードの周期は変化するピーク1次電流とともに変化します。

$$\text{Period} = I_{PK} \cdot L_{PRI} \cdot \left[ \frac{1}{V_{TRANS}} + \frac{N}{V_{OUT}} \right]$$

電力出力はピーク1次電流に比例します。

$$P_{OUT} = \frac{1/2 \cdot I_{PK}}{\left[ \frac{1}{V_{TRANS}} + \frac{N}{V_{OUT}} \right]}$$

非常に小さい負荷電流ではノイズが問題になります。LT3751は低い方のピーク電流制限値を最大レベルの1/10に設定することにより、この問題を解決し、デューティ・サイクル制御を使い始めます。

### 軽負荷動作

LT3751はデューティ・サイクル制御を使って、トランス(機械的)とセラミック・コンデンサ(圧電効果)の両方の可聴ノイズを大きく減らします。内部制御回路は、20kHzより大きい、オーディオ・スペクトルを外れた周期レートにワンショットの条件を強制します。次いで、リフレッシュ・ループが、正しい出力電圧を維持するのに必要なパルス数を決定します。デューティ・サイクル制御の使用法を図5に示します。

### 無負荷動作

LT3751は非常に小さい負荷条件で低ノイズ・リフレッシュを維持することができます。特定の負荷電流スレッショルド以下では(軽負荷動作)、出力電圧が上昇し続け、暴走状態が生じる可能性があります。これは、周期的リフレッシュ回路によって周期的ワンショットが強制されるからです。設計により、LT3751はFBピンに対応した過電圧保護機能を搭載しています。

FBピンの電圧が1.34V(±20mV)を超えると、LT3751は無負荷動作に移行します。無負荷動作はワンショット・クロックでリセットすることはしません。代わりに、パルス列は完全に負荷によって左右されます。これらのバーストは非同期であり、長時間の無作動状態を含むことができます。これにより無負荷状態でのリフレッシュが可能になりますが、可聴ノイズと電圧リップルが増加します。無負荷状態で動作するときは、出力電圧が公称出力電圧より10%高くなることに注意してください。

## アプリケーション情報

LT3751のチャージャ・コントローラはコンデンサの充電のみに最適化することも、低ノイズ・レギュレーションのアプリケーションに最適化することもできます。設計プロセスを手助けするためにはいくつかの式が用意されています。

### 安全上の注意

高電圧に充電された大容量のコンデンサは、不適切に扱われると致死量のエネルギーを放出する可能性があります。LT3751を使ってアプリケーションを設計するときは、適切な安全対策を遵守することが特に重要です。最初に、設計者が出力コンデンサを安全に放電させられる放電回路を作ります。次に、高電圧ノードと隣接するトレースとの間に十分なスペースを確保して、プリント回路基板の電圧ブレーカダウン要件を満たします。

### 動作モードの選択

LT3751をコンデンサ・チャージャとして動作させるには、FBピンをGNDに接続します。このモードでは、LT3751は境界モード動作を使用してピーク1次電流で出力を充電します。これによって最大電力供給が実現し、最高速の充電時間になります。出力が、RVOUTピンとRBGピンによって設定される所期の出力電圧に達すると、電力供給が停止されます。

LT3751を低ノイズの電圧レギュレータとして動作させるには、抵抗分割器をFBピンからVOUTとGNDに接続します(適切な設計手順に関しては、「低ノイズ・レギュレーション」を参照)。LT3751はピーク電流とデューティ・サイクルの両方の変調を使った電圧レギュレータとして動作し、異なる負荷条件に合わせて出力電流を変化させます。

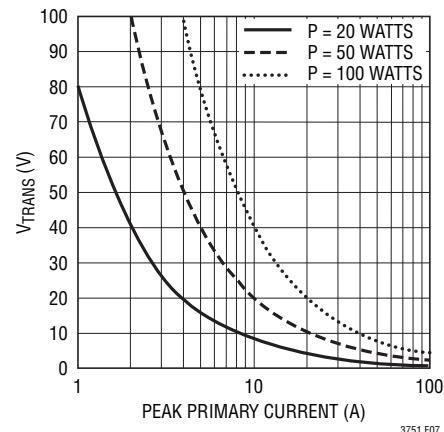

### 部品のパラメータの選択

ほとんどの設計は、V<sub>TRANS</sub>、V<sub>OUT</sub>、C<sub>OUT</sub>、および充電時間t<sub>CHARGE</sub>(コンデンサ・チャージャ)またはP<sub>OUT,MAX</sub>(レギュレータ)のどちらかの初期選択から開始します。次いで、これらの設計情報は、トランジスタの巻数比(N)、ピーク1次電流(I<sub>PK</sub>)、および1次インダクタンス(L<sub>PRI</sub>)を選択するのに使われます。所定のV<sub>TRANS</sub>とI<sub>PK</sub>の最大電力出力の大体の目安として図7を使うことができます。

図7. 最大電力出力

### トランジスタの巻数比の選択

トランジスタの巻数比(N)は入力電圧と出力電圧に基づいて選択します。Nの値が小さいほど充電時間が短くなり使用可能な出力電力が大きくなります。NをV<sub>OUT</sub>/V<sub>TRANS</sub>の比より大幅に小さくすると、NMOS FETのドレインのフライバック電圧が上昇し、出力ダイオードを流れる電流が増加することに注意してください。容量の増加(N<sup>2</sup> • C<sub>SEC</sub>)が1次側に影響するので、巻数比(N)を大幅に大きくしてなりません。最適な選択は、NがV<sub>OUT</sub>/V<sub>TRANS</sub>に等しくなるようにすることです。

$$N \leq \frac{V_{OUT}}{V_{TRANS}}$$

### コンデンサ・チャージャのI<sub>PK</sub>の選択

LT3751をコンデンサ・チャージャとして動作させる場合、必要なコンデンサ充電時間(t<sub>CHARGE</sub>)および初期設計情報に基づいてI<sub>PK</sub>を選択します。

$$I_{PK} = \frac{(2 \cdot N \cdot V_{TRANS} + V_{OUT}) \cdot C_{OUT} \cdot V_{OUT}}{\text{Efficiency} \cdot V_{TRANS} \cdot (t_{CHARGE} - t_d)}$$

コンバータの効率は出力電圧範囲にわたって変化します。I<sub>PK</sub>の式は充電時間全体にわたる平均効率に基づいています。いくつかの要因により、充電時間が長くなることがあります。効率は支配的要因であり、トランジスタの巻線抵抗、コア損失、リレー・インダクタンス、およびトランジスタのR<sub>DS</sub>によって主に影響を受けます。ほとんどのアプリケーションは全体の効率が70%を超えます。

## アプリケーション情報

合計伝播遅延時間( $t_d$ )は効率に影響を与える2番目に支配的な要因で、ゲート・ドライバのオン/オフ伝播遅延と2次巻線の容量に関連した放電時間の和です。合計伝播遅延を減らす2つの効果的な方法があります。まず、2次巻線の総容量(特に問題になるダイオード容量)を減らします。2番目に、NMOS FETのゲートに必要な総電荷を減らします。大きな2次側容量の影響を図8に示します。

2次巻線容量に蓄積されるエネルギーは $(1/2) \cdot C_{SEC} \cdot V_{OUT}^2$ です。このエネルギーは、ダイオードが順方向の導通を遮断すると、1次側に反射されます。反射された容量がNMOS FETの総ドレイン容量より大きいと、NMOSパワー・スイッチのドレインは負になり、その本来のボディー・ダイオードが導通します。このエネルギーが消費されるのにいくらかの時間を要するので、合計伝播遅延が増加します。

図8. 2次巻線の容量の影響

レギュレータの最大 $I_{PK}$ の選択

レギュレーション・モードの $I_{PK}$ パラメータは、コンデンサ・チャージャのアプリケーションの場合の充電時間ではなく、必要な最大出力電力に基づいて計算されます。

$$I_{PK} = 2 \cdot \frac{P_{OUT(AVG)}}{\text{Efficiency}} \cdot \left( \frac{1}{V_{TRANS}} + \frac{N}{V_{OUT}} \right)$$

LT3751のレギュレーション回路は、出力負荷電流に基づいてピーク電流を変化させることに注意してください。出力電力が最大化される充電モードまたは重負荷状態でのみ最大 $I_{PK}$ に達します。

## トランスの設計

トランスの1次側インダクタンス( $L_{PRI}$ )は、必要な $V_{OUT}$ と前に計算した $N$ および $I_{PK}$ のパラメータによって決まります。次式を使って $L_{PRI}$ を選択します。

$$L_{PRI} = \frac{3\mu\text{s} \cdot V_{OUT}}{I_{PK} \cdot N}$$

前の式は、 $V_{OUT}$ コンパレータがフライバック波形を検出して $\overline{DONE}$ ピンのラッチをトリップするのに十分な時間を保証します。 $L_{PRI}$ を計算するのに使われた電圧よりも大幅に高い電圧で $V_{OUT}$ を動作させると、暴走状態が生じて出力コンデンサを過充電する可能性があります。

$L_{PRI}$ の式はほとんどのレギュレータ・アプリケーションに対応します。所定の $V_{TRANS}$ と $V_{OUT}$ に対して $I_{PK}$ と $N$ の両方を大幅に増やすと、リフレッシュ周期内に最大 $I_{PK}$ に達しないことに注意してください。これにより、最大出力電力が予期される値より小さくなります。こうならないようにするには、次式の条件を維持します。

$$L_{PRI} < \frac{38\mu\text{s}}{I_{PK} \cdot \left[ \frac{1}{V_{TRANS}} + \frac{N}{V_{OUT}} \right]}$$

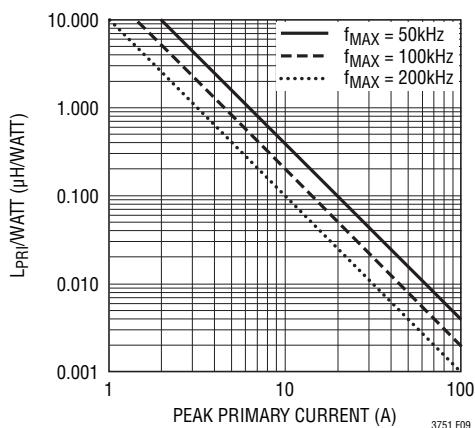

$L_{PRI}$ の上側の制約は $V_{TRANS}$ を上げて設計プロセスをやり直すことによって減らすことができます。最良のレギュレーションは100kHzを超える境界モード周波数で動作するときに得られます(境界モードの定義については、「動作」を参照)。

図9は必要な出力電力レベルで動作しているときの最大境界モード・スイッチング周波数を示しており、 $L_{PRI}/P_{OUT}$  ( $\mu\text{H}/\text{ワット}$ )に正規化されています。出力電力、境界モード周波数、 $I_{PK}$ 、および1次側インダクタンスの関係は、設計プロセスを通してガイドラインとして使うことができます。

## アプリケーション情報

表1. 推奨トランジ

| MANUFACTURER                                 | PART NUMBER      | SIZE L × W × H (mm) | MAXIMUM $I_{PRI}$ (A) | $L_{PRI}$ ( $\mu$ H) | URNS RATIO (PRI:SEC) |

|----------------------------------------------|------------------|---------------------|-----------------------|----------------------|----------------------|

| Coilcraft<br>www.coilcraft.com               | DA2033-AL        | 17.4 × 24.1 × 10.2  | 5                     | 10                   | 1:10                 |

|                                              | DA2034-AL        | 20.6 × 30 × 11.3    | 10                    | 10                   | 1:10                 |

|                                              | GA3459-BL        | 32.65 × 26.75 × 14  | 20                    | 5                    | 1:10                 |

|                                              | GA3460-BL        | 32.65 × 26.75 × 14  | 50                    | 2.5                  | 1:10                 |

|                                              | HA4060-AL        | 34.29 × 26.75 × 14  | 2                     | 300                  | 1:3                  |

|                                              | HA3994-AL        | 34.29 × 28.75 × 14  | 5                     | 7.5                  | 2:1:3:3*             |

| Würth Elektronik/Midcom<br>www.we-online.com | 750032051        | 28.7 × 22 × 11.4    | 5                     | 10                   | 1:10                 |

|                                              | 750032052        | 28.7 × 22 × 11.4    | 10                    | 10                   | 1:10                 |

|                                              | 750310349        | 36.5 × 42 × 23      | 20                    | 5                    | 1:10                 |

|                                              | 750310355        | 36.5 × 42 × 23      | 50                    | 2.5                  | 1:10                 |

| Sumida<br>www.sumida.com                     | C8117            | 23 × 18.6 × 10.8    | 5                     | 10                   | 1:10                 |

|                                              | C8119            | 32.2 × 27 × 14      | 10                    | 10                   | 1:10                 |

|                                              | PS07-299         | 32.5 × 26.5 × 13.5  | 20                    | 5                    | 1:10                 |

|                                              | PS07-300         | 32.5 × 26.5 × 13.5  | 50                    | 2.5                  | 1:10                 |

| TDK<br>www.tdk.com                           | DCT15EFD-U44S003 | 22.5 × 16.5 × 8.5   | 5                     | 10                   | 1:10                 |

|                                              | DCT20EFD-U32S003 | 30 × 22 × 12        | 10                    | 10                   | 1:10                 |

|                                              | DCT25EFD-U27S005 | 27.5 × 33 × 15.5    | 20                    | 5                    | 1:10                 |

\*トランジには3つの2次巻線がある(巻数比はPRI:SEC1:SEC2:SEC3で示される)

図9. 最大スイッチング周波数

$R_{VTRANS}$ 、 $R_{VOUT}$ 、および $R_{DCM}$ の選択

$R_{VTRANS}$ は、DCMコンパレータと $V_{OUT}$ コンパレータの両方の同相リファレンス電圧を設定します。トランジの電源電圧 $V_{TRANS}$ の範囲と最大トリップ電圧 $\Delta V_{DRAIN}$  ( $V_{DRAIN} - V_{TRANS}$ )に基づき、表2から $R_{VTRANS}$ を選択してください。

$R_{VTRANS}$ ピンは40 $\mu$ Aの内部電流源に接続されています。ピン電圧が60Vの内部ツェナー・クランプより高くなるにつれて、ピン電流が増加します。LT3751は、 $R_{VTRANS}$ ピンの電流を250 $\mu$ Aに制限することにより、60Vの内部ツェナー・クランプよりも高い $V_{TRANS}$ で動作させることができます。200Vより高い $V_{TRANS}$ で動作するには、抵抗分割器を使う必要があります。

表2.  $R_{VTRANS}$ 、 $R_{VOUT}$ 、 $R_{DCM}$ の推奨値

| $V_{TRANS}$ の範囲 (V) | $\Delta V_{DRAIN}$ の範囲 (V) | $R_{VTRANS}$ (k $\Omega$ )              | $R_{VOUT}$ (k $\Omega$ )                | $R_{DCM}$ (k $\Omega$ ) |

|---------------------|----------------------------|-----------------------------------------|-----------------------------------------|-------------------------|

| 4.75 to 55          | 0 to 5                     | 5.11                                    | 5.11                                    | 2.32                    |

| 4.75 to 60          | 2.5 to 50                  | 25.5                                    | 25.5                                    | 11.5                    |

|                     | 5 to 80                    | 40.2                                    | 40.2                                    | 18.2                    |

| 8 to 80             | 8 to 160                   | 80.6                                    | 80.6                                    | 36.5                    |

| 80 to 200           | 2mA • $R_{VOUT}$           | $\frac{V_{TRANS} - 55 \text{ V}}{0.25}$ | $\frac{V_{TRANS} - 55 \text{ V}}{0.25}$ | 0.86 • $R_{VTRANS}$     |

| >200                | 抵抗分割器による                   | 抵抗分割器使用                                 | 抵抗分割器使用                                 | 抵抗分割器使用                 |

## アプリケーション情報

100V～400VのV<sub>TRANS</sub>で動作する応用例を2つ示します（「標準的応用例」のセクションを参照）。400Vより高いV<sub>TRANS</sub>を使用する応用例については、弊社へお問合せください。

コンデンサ・チャージャのアプリケーションにはRV<sub>OUT</sub>が必要ですが、レギュレータのアプリケーションでは省略することができます。V<sub>OUT</sub>コンパレータは、レギュレータのアプリケーションの補助的な保護策として使用することができます。V<sub>OUT</sub>コンパレータを保護用に使用する場合は、V<sub>OUT,TRIP</sub>を安定化電圧より15%～20%高く設計してください。RV<sub>OUT</sub>抵抗を使用しない場合はRV<sub>OUT</sub>ピンをグランドに接続します。

R<sub>DCM</sub>は、RV<sub>TRANS</sub>に対して適切な値にする必要があります。R<sub>DCM</sub>の選択が不適切だと、低入力電圧において望ましくないスイッチング動作を引き起こす恐れがあります。R<sub>DCM</sub>の値を決めるには表2を使用してください。

RV<sub>TRANS</sub>、RV<sub>OUT</sub>、およびR<sub>DCM</sub>の寄生容量は最小限に抑える必要があります。これらのノードの容量は、V<sub>OUT</sub>コンパレータとDCMコンパレータの応答速度を低下させます。抵抗とピンの距離はできるだけ短くしてください。これらのピンとその関連部品の下にあるグランド・プレーンとパワー・プレーンは、すべて除去することを推奨します（このセクションの末尾に示す推奨基板レイアウトを参照）。

### R<sub>BG</sub>の選択

R<sub>BG</sub>はトリップ電流（0.98/R<sub>BG</sub>）を設定し、RV<sub>OUT</sub>の選択に直接関係します。最大精度は100μA～2mAのトリップ電流範囲で得られ、表2を使用してRV<sub>OUT</sub>を選択すればこの基準を満たすことができます。R<sub>BG</sub>の値を決定するには次式を使用します（V<sub>TRANS</sub> ≤ 80V）。

$$R_{BG} = 0.98 \cdot N \cdot \left( \frac{RV_{OUT}}{V_{OUT,TRIP} + V_{DIODE}} \right)$$

V<sub>OUT</sub>コンパレータを使用しないときは、R<sub>BG</sub>ピンをグランドに接続します。80Vを超えるV<sub>TRANS</sub>で動作するときのR<sub>BG</sub>の計算については、弊社へお問合せください。

### NMOSスイッチの選択

ゲート電荷が最小で、オン抵抗が電流制限および電圧ブレーカダウンの要件を満たす外付けNMOSパワー・スイッチを選択します。ゲートは各充電サイクルの間、公称V<sub>CC</sub>～2Vまでドライブされます。この電圧はNMOS FETの最大ゲート-ソース間電圧定格を超えないようにしますが、チャネルは十分高くしてオン抵抗を最小限に抑えます。

同様に、NMOS FETの最大ドレイン-ソース間電圧定格が、V<sub>TRANS</sub> + V<sub>OUT</sub>/Nまたはリーク・インダクタンス・スパイクの大きさのどちらか大きい方を超える必要があります。最大瞬時ドレイン電流定格は選択された電流制限値を超える必要があります。スイッチング周期は出力電圧に従って短くなるので、NMOS FETを流れる平均電流は出力がほぼ充電されたとき最大になり、次のように求められます。

$$I_{AVG,M} = \frac{I_{PK} \cdot V_{OUT(PK)}}{2(V_{OUT(PK)} + N \cdot V_{TRANS})}$$

推奨外付けNMOSトランジスタについては、表3を参照してください。

表3. 推奨NMOSトランジスタ

| MANUFACTURER                                                                                | PART NUMBER  | I <sub>D</sub> (A) | V <sub>DS(MAX)</sub> (V) | R <sub>DS(ON)</sub> (mΩ) | Q <sub>G(TOT)</sub> (nC) | PACKAGE            |

|---------------------------------------------------------------------------------------------|--------------|--------------------|--------------------------|--------------------------|--------------------------|--------------------|

| Fairchild Semiconductor<br><a href="http://www.fairchildsemi.com">www.fairchildsemi.com</a> | FDS2582      | 4.1                | 150                      | 66                       | 11                       | SO-8               |

|                                                                                             | FQB19N20L    | 21                 | 200                      | 140                      | 27                       | D <sup>2</sup> PAK |

|                                                                                             | FQP34N20L    | 31                 | 200                      | 75                       | 55                       | TO-220             |

|                                                                                             | FQD12N20L    | 12                 | 200                      | 280                      | 16                       | DPAK               |

|                                                                                             | FQB4N80      | 3.9                | 800                      | 3600                     | 19                       | D <sup>2</sup> PAK |

| On Semiconductor<br><a href="http://www.onsemi.com">www.onsemi.com</a>                      | MTD6N15T4G   | 6                  | 150                      | 300                      | 15                       | DPAK               |

|                                                                                             | NTD12N10T4G  | 12                 | 100                      | 165                      | 14                       | DPAK               |

|                                                                                             | NTB30N20T4G  | 30                 | 200                      | 81                       | 75                       | D <sup>2</sup> PAK |

|                                                                                             | NTB52N10T4G  | 52                 | 100                      | 30                       | 72                       | D <sup>2</sup> PAK |

| Vishay<br><a href="http://www.vishay.com">www.vishay.com</a>                                | Si7820DN     | 2.6                | 200                      | 240                      | 12.1                     | 1212-8             |

|                                                                                             | Si7818DN     | 3.4                | 150                      | 135                      | 20                       | 1212-8             |

|                                                                                             | SUP33N20-60P | 33                 | 200                      | 60                       | 53                       | TO-220             |

## アプリケーション情報

表4. 推奨出力ダイオード

| MANUFACTURER                                                                                | PART NUMBER | I <sub>F(AV)</sub> (A) | V <sub>RRM</sub> (V) | T <sub>RR</sub> (ns) | PACKAGE            |

|---------------------------------------------------------------------------------------------|-------------|------------------------|----------------------|----------------------|--------------------|

| Central Semiconductor<br><a href="http://www.centralsemi.com">www.centralsemi.com</a>       | CMR1U-10M   | 1                      | 1000                 | 100                  | SMA                |

|                                                                                             | CMSH2-60M   | 2                      | 60                   |                      | SMA                |

|                                                                                             | CMSH5-40    | 5                      | 40                   |                      | SMC                |

| Fairchild Semiconductor<br><a href="http://www.fairchildsemi.com">www.fairchildsemi.com</a> | ES3J        | 3                      | 600                  | 35                   | SMC                |

|                                                                                             | ES1G        | 1                      | 400                  |                      | SMA                |

|                                                                                             | ES1J        | 1                      | 600                  |                      | SMA                |

| On Semiconductor<br><a href="http://www.onsemi.com">www.onsemi.com</a>                      | MURS360     | 3                      | 600                  | 75                   | SMC                |

|                                                                                             | MURA260     | 2                      | 600                  |                      | SMA                |

|                                                                                             | MURA160     | 1                      | 600                  |                      | SMA                |

| Vishay<br><a href="http://www.vishay.com">www.vishay.com</a>                                | USB260      | 2                      | 600                  | 30                   | SMB                |

|                                                                                             | US1G        | 1                      | 400                  |                      | SMA                |

|                                                                                             | US1M        | 1                      | 1000                 |                      | SMA                |

|                                                                                             | GURB5H60    | 5                      | 600                  |                      | D <sup>2</sup> PAK |

### ゲート・ドライバ動作

LT3751のゲート・ドライバは、選択可能な10.5Vまたは5.6Vの内部クランプを備えており、(LVGATEを使った)電流能力は最大2Aです。10.5V動作ではCLAMPピンをグランドに接続し、5.6V動作ではCLAMPピンをV<sub>CC</sub>に接続します。NMOS FETの製造元の最大V<sub>GS</sub>定格を超えないクランプ電圧を選択します。5.6Vのクランプは、ロジック・レベルのFETを使うとき、LT3751の電力損失を減らして効率を上げるのにも使うことができます。ゲート・ドライバの標準的オーバーシュート電圧はクランプ電圧より0.5V高い値です。

LT3751のゲート・ドライバはLVGATEピンを介したPMOSプルアップ・デバイスも内蔵しています。PMOSプルアップ・ドライバは8V以下のV<sub>CC</sub>アプリケーションにだけ使います。8Vを超えるV<sub>CC</sub>でLVGATEを動作させると、デバイスに永続的損傷を与えます。HVGATEに接続するとLVGATEはアクティブになり、レール・トゥ・レールのゲート・ドライバ動作が可能になります。これは低V<sub>CC</sub>アプリケーションに特に有効で、NMOS FETのドライブ能力を改善することができます。また、HVGATEだけを使うときの1.5Aに対して、大きな2A電流能力が確保されると立上り時間が短くなります。

### 出力ダイオードの選択

出力ダイオードは最大反復逆電圧(V<sub>RRM</sub>)および平均順方向電流(I<sub>F(AV)</sub>)に基づいて選択します。出力ダイオードのV<sub>RRM</sub>は、V<sub>OUT</sub>+N•V<sub>TRANS</sub>を超えるようにします。出力ダイオードのI<sub>F(AV)</sub>は、I<sub>PK</sub>/2N(平均短絡電流)を超えるようにします。平均ダイオード電流は出力電圧とも相関関係があります。

$$I_{AVG} = \frac{I_{PK} \cdot V_{TRANS}}{2 \cdot (V_{OUT} + N \cdot V_{TRANS})}$$

最大平均ダイオード電流は低出力電圧で生じ、出力電圧が上昇するにつれ減少します。逆回復時間、逆バイアス・リーク電流および接合容量についても検討します。全て全体の充電効率に影響を与えます。ダイオード逆回復時間が長すぎると、出力コンデンサが大きく放電し、充電時間が長くなることがあります。逆回復時間が100ns未満のダイオードを選択します。逆バイアスが大きいときのダイオードのリーク電流は出力コンデンサの電荷を流出させるので、充電時間が長くなります。逆バイアス・リーク電流が最も小さなダイオードを選択します。ダイオードの接合容量は1次側に反射され、NMOS FET本来のダイオードの導通期間にエネルギーが失われます。接合容量が最も小さなダイオードを選択します。逆回復時間が十分で、様々な出力電圧に対応するいくつかの推奨出力ダイオードを表4に示します。

### 電流制限値の設定

正の電流検出ピン(CSP)から負の電流検出ピン(CSN)に接続した検出抵抗により、最大ピーク・スイッチ電流が設定されます。最大電流制限値は公称106mV/R<sub>SENSE</sub>です。電流検出抵抗の電力定格は次の値を超える必要があります。

$$P_{RSENSE} \geq \frac{I_{PK}^2 \cdot R_{SENSE}}{3} \left( \frac{V_{OUT(PK)}}{V_{OUT(PK)} + N \cdot V_{TRANS}} \right)$$

## アプリケーション情報

さらに、ピーク電流制限値が検出されてから、ゲートが“L”状態に遷移するまでに約180nsの伝播遅延があります。この遅延により、ピーク電流制限値が( $V_{TRANS}$ )(180ns)/ $L_{PRI}$ だけ増加します。

検出抵抗のインダクタンス( $L_{RSENSE}$ )は電流制限誤差のもう1つの要因です。 $L_{RSENSE}$ は電流コンパレータへの入力オフセット電圧( $V_{OS}$ )を生じて、電流コンパレータを早めにトリップします。 $V_{OS}$ は次のように計算することができます。

$$V_{OS} = V_{TRANS} \cdot \left( \frac{L_{RSENSE}}{L_{PRIMARY}} \right)$$

電流制限値の変化は $V_{OS}/R_{SENSE}$ となります。トランスの1次側に大きなdi/dtを使うアプリケーションでは誤差がもっと大きくなります。インダクタンスが非常に小さい(< 2nH)検出抵抗を使うことを推奨します。インダクタンスを減らすために複数の抵抗を並列に接続することができます。

検出ラインの配置にも注意を払います。負のリターン・ライン(CSN)は抵抗の下側端子までを専用トレースにする必要があります。CSNをグランド・プレーンにいいかげんに配線すると電流制限値が不正確になることがあります。充電プロファイルが生じることもあります。

### DONEピンとFAULTピンの設計

DONEピンとFAULTピンには、適切なプルアップ抵抗が電流源が必要です。これらのピンへの流入電流は、いずれも1mAに制限してください。ほとんどのアプリケーションには100kΩのプルアップ抵抗を使用することを推奨します。DONEピンとFAULTピンは、低出力状態でともに“L”にラッチされ、どちらかのラッチをリセットする場合はCHARGEピンを切り替える必要があります。フォールト状態になった場合もDONEピンは“L”になります。3つめの非ラッチ状態は、CHARGEピンが“H”になる起動時に発生します。この起動状態では、数マイクロ秒間にわたってDONEピンもFAULTピンも“L”になります。これは、内部電源レールがその適正値に向けてまだランプアップ中であることを示しています。これらの通知ピンには、起動時の通知動作をなくすために外付けのRCフィルタを追加することができます。RCフィルタの時定数は5μs～20μsにしてください。

### 低電圧/過電圧ロックアウト

LT3751はVCCと $V_{TRANS}$ の両方に、ユーザーがプログラム可能な低電圧ロックアウトおよび過電圧ロックアウト機能を備えています。抵抗値の適切な選択には、「ピン機能」の式を使います。低電圧/過電圧ロックアウト・コンパレータがトリップすると、マスタ・ラッチがディスエーブルされ、電力供給が停止され、FAULTピンが“L”になります。

適切な電源用バールク・コンデンサを使って、通常のスイッチング動作時に誤ってトリップを生じる電源電圧リップルを減らします。低電圧/過電圧ロックアウト・ピンは入力インピーダンスが大きいので、誤ったトリップを防ぐために追加のフィルタリングが必要となる場合があります。UVLO1、UVLO2、OVLO1、OVLO2の各ピンとグランドとの間に100pF～1nFのコンデンサを個別に接続することができます。低電圧ロックアウトをディスエーブルするには、UVLO1ピンとUVLO2ピンをVCCに直接接続します。過電圧ロックアウトをディスエーブルするには、OVLO1ピンとOVLO2ピンをグランドに直接接続します。

LT3751は内部ツエナー・クランプ・ダイオードを備えており、 $V_{TRANS}$ が55V以上で動作するとき、シャットダウン時にデバイスを保護します。電源電圧は必ず直列抵抗を使ってUVLO1、UVLO2、OVLO1およびOVLO2に供給し、絶対最大ピン電流を超えないようにします。ピン電流は次式を使って計算することができます。

$$I_{PIN} = \frac{V_{APPLIED} - 55V}{R_{SERIES}}$$

シャットダウン時には、 $R_{VTRANS}$ 、 $R_{VOUT}$ 、 $R_{DCM}$ 、UVLO1、UVLO2、OVLO1およびOVLO2の各電流は、 $V_{TRANS}$ がツエナー・クランプ電圧以上で動作するとき大きく増加し、外付けの直列ピン抵抗に反比例することに注意してください。

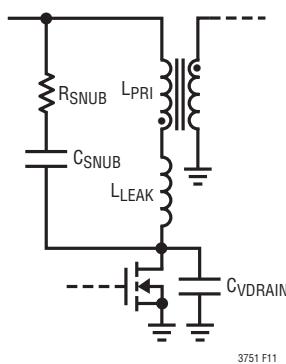

### NMOSスナバの設計

トランスのリーク・インダクタンスは、ターンオフの遷移の間パワーNMOSスイッチのドレインに寄生電圧スパイクを生じます。トランスのリーク・インダクタンスの影響はピーク1次電流が大きいときほど顕著になります。電圧スパイクのワーストケースの大きさは、リーク・インダクタンスと $V_{DRAIN}$ ノードの総容量に蓄積されるエネルギーによって決まります。

$$V_{D,LEAK} = \sqrt{\frac{L_{LEAK} \cdot I_{PK}^2}{C_{VDRAIN}}}$$

## アプリケーション情報

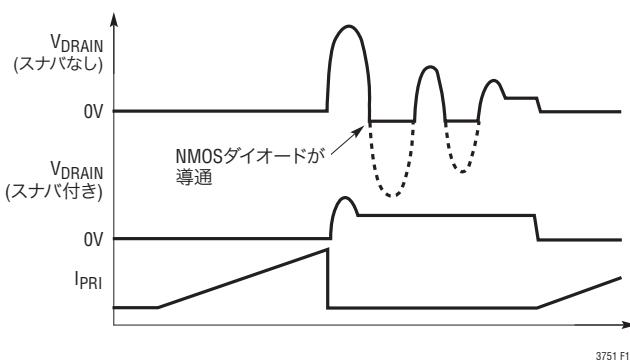

$V_{D,LEAK}$ が大きいと、2つの問題が生じことがあります。まず、スパイクの大きさによっては、 $V_{(BR)DSS}$ が過剰に高いNMOS FETが必要になり、結局 $R_{DS(ON)}$ が大きくなります。2番目に、 $V_{DRAIN}$ ノードは（場合によってはグランドを下回る）リングを生じて、DCMコンパレータを誤ってトリップさせ、またはNMOSスイッチに損傷を与えます（図11を参照）。両方の問題とも、スナバを使って解決することができます。リーク・インダクタンスが問題を引き起こす場合、図10に示されているように、1次巻線と並列にRCスナバを使うことを推奨します。必要なリーク・スパイク電圧、既知のリーク・インダクタンス、および $1\mu\text{s}$ 以下のRC時定数に基づいて $C_{SNUB}$ と $R_{SNUB}$ の大きさを決めます。そうしないと、リーク電圧スパイクが $V_{OUT}$ コンパレータを誤ってトリップし、充電を早く停止しきることがあります。

図11はRCスナバの効果を示しており、電圧スパイクが低下し、セトリング時間が短くなっています。

図10. RCスナバ回路

図11. RCスナバの効果

## 低ノイズ・レギュレーション

LT3751は、抵抗分圧器を出力ノードからFBピンに使うとき低ノイズの安定化された出力電圧を供給するオプションを備えています。トランジスタ、NMOSパワー・スイッチ、出力ダイオード、および検出抵抗を設計するには、「部品のパラメータの選択」を参照してください。以下の式を使って、電力損失および必要な出力電圧に基づいて帰還抵抗の値を選択します。

$$R_{FBH} = \frac{(V_{OUT} - 1.22)^2}{P_D}; \text{ トップ帰還抵抗}$$

$$R_{FBL} = \left( \frac{1.22}{V_{OUT} - 1.22} \right) \cdot R_{FBH}; \text{ ボトム帰還抵抗}$$

$R_{FBH}$ は、出力電圧と使われるタイプに応じて、小さい値の抵抗をいくつか直列に接続することが必要になる可能性があります。これにより、アーケ放電の発生と帰還抵抗の損傷の危険が減少します。帰還抵抗を安全に動作させるには、製造元の定格電圧の規定を調べます。

LT3751の周期的リフレッシュの最小周波数の制限値は23kHzです。これにより、オーディオ・スペクトル内のスイッチング周波数成分が大幅に減少します。LT3751は無負荷で動作可能ですが、レギュレーション方式が無負荷動作に切り替わり、可聴ノイズと出力電圧リップルが増加します。最小負荷電流で動作させることにより、これを防ぐことができます。

## 最小負荷電流

無負荷動作に移行するのを避けるため、周期的リフレッシュ回路は平均最小負荷電流を必要とします。通常、帰還抵抗はこの最小負荷電流を供給するのに十分な値にします。

$$I_{LOAD(MIN)} \geq \frac{L_{PRI} \cdot I_{PK}^2 \cdot 23\text{kHz}}{100 \cdot V_{OUT}}$$

$I_{PK}$ は最大電力供給時のピーク1次電流です。最小負荷電流が供給されないと、LT3751は無負荷動作に移行します。無負荷動作はアプリケーションが暴走状態になるのを防ぎますが、出力電圧が公称安定化電圧を10%上回ります。

## アプリケーション情報

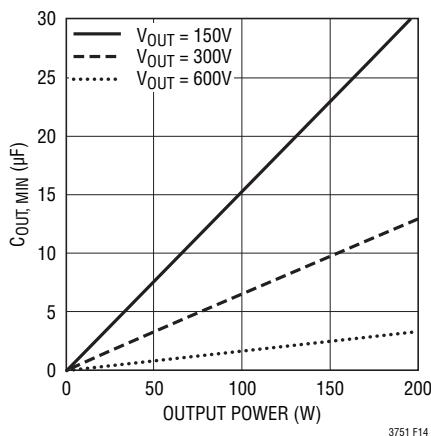

## 大信号の安定性

可聴ノイズが懸念される場合、大信号の安定性が問題になることがあります。ワンショット・クロックおよび出力電圧リップルによって問題が起きる場合を図12は示しています。1クロック周期内に、出力電圧リップルがエラーアンプの安定化の範囲(FBピンを基準にして約6mV)を超えないように負荷を制限する必要があります。

発振が起きるかまたは可聴ノイズが発生する場合、出力容量を増やします。図13を使って、所定の出力容量で低可聴ノイズ動作を維持するための最大負荷を決定します。FBピンからグランドに小さなコンデンサを追加して、FBピンに注入されるリップルを下げることもできます。

図12. 電圧リップル安定性の制約

図13.  $C_{OUT,MIN}$  と出力電力

## 小信号の安定性

LT3751のエラーアンプは動作範囲を広げるために内部で補償されていますが、コンバータの出力ノードが支配的ポールになることが必要です。支配的出力ポールが高い周波数に移動して内部帰還のポールとゼロに近づく重負荷状態では、一般的に小信号の安定性が制約されます。帰還ループは出力ポール周波数が200Hz以下に留まって小信号の安定性を確保する必要があります。これにより、大信号の制約より小さな値の  $R_{LOAD}$  が可能になります。したがって、大信号の制約が満たされれば小信号の問題は生じません。

## 基板のレイアウト

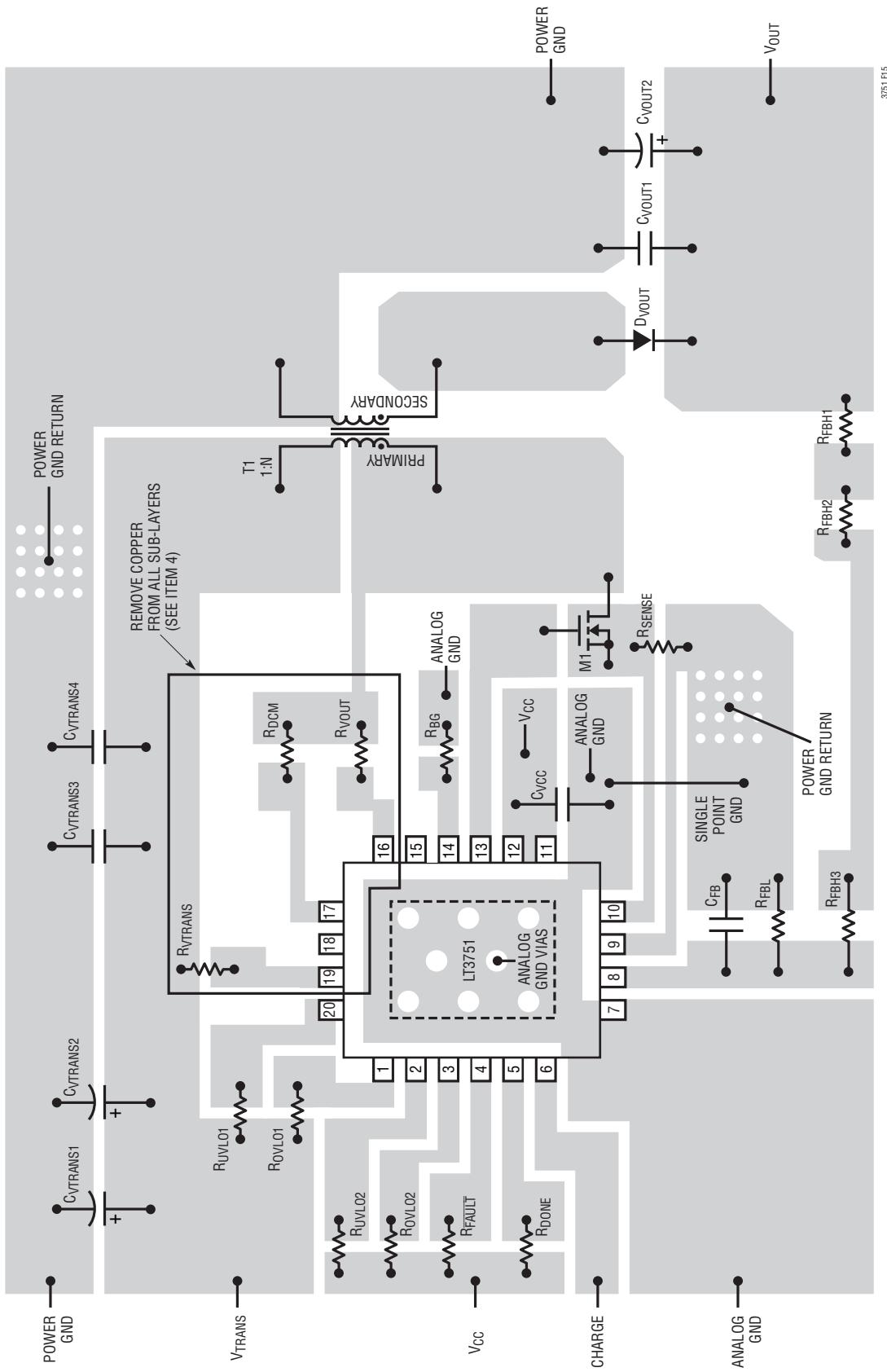

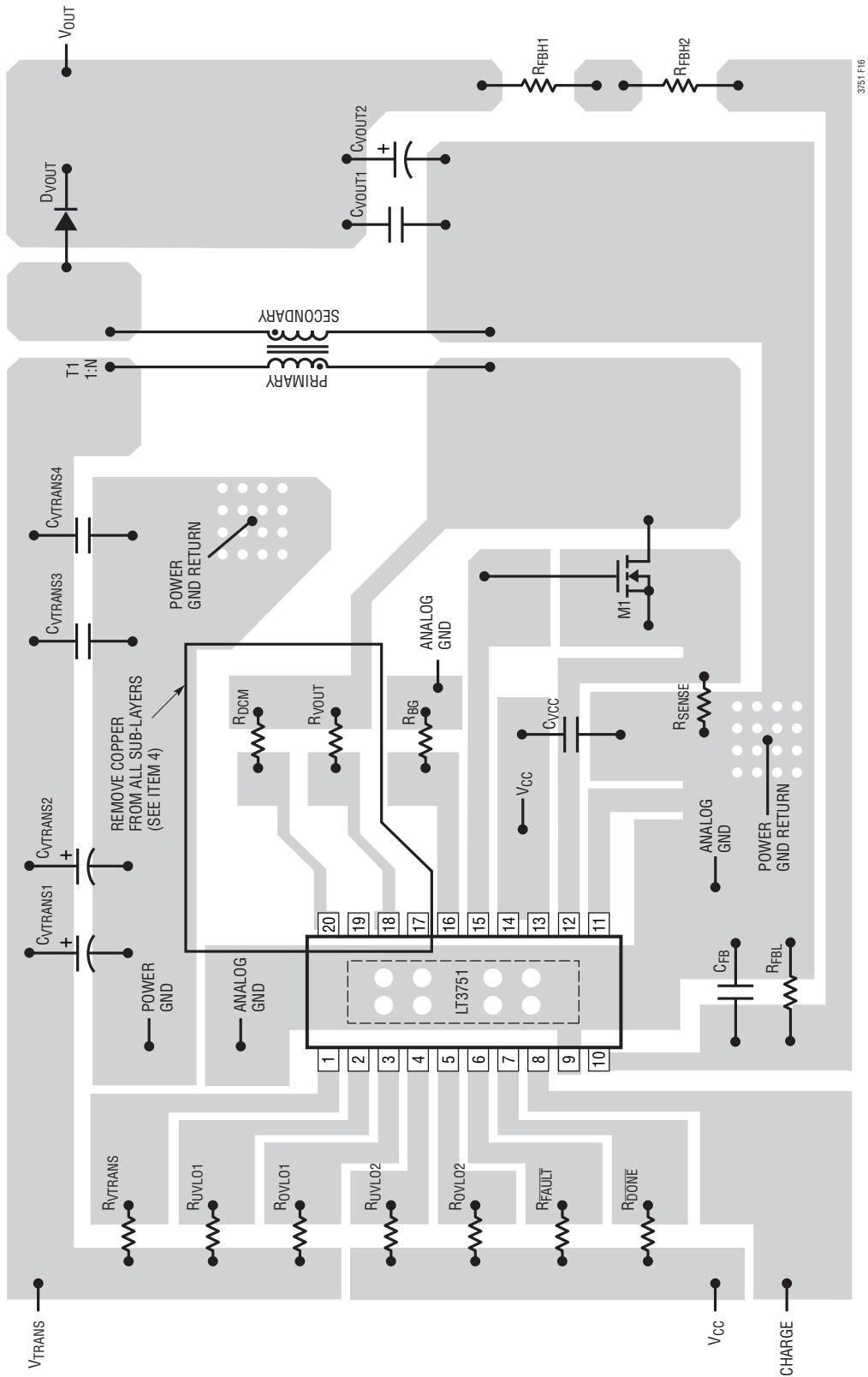

LT3751は高電圧で動作するので、ボードのレイアウトには細心の注意を払い、以下の点を守る必要があります。

1. 2次巻線の高電圧端の面積を最小限に抑えます。

2. ブレークダウン電圧の要件を満たすため、全ての高電圧ノード(NMOS FETのドレイン、 $V_{OUT}$  およびトランジスタの2次巻線)に十分なスペースを確保します。

3.  $C_{VTRANS}$ 、T1の1次側、およびNMOS FETのドレインで形成される電気経路をできるだけ短くします。この経路を長くすると、T1のリーク・インダクタンスが実質的に増加し、NMOS FETのドレインに過電圧状態を生じるおそれがあります。

4.  $R_{DCM}$  と  $R_{VOUT}$  のパッドおよびトレースの下のグランドまたはパワー・プレーンを取り除いて、 $R_{VOUT}$  ピンと  $R_{DCM}$  ピンの合計ノード容量を減らします。寄生容量はこれらのピンに望ましくない動作を生じることがあります。

5. 露出パッド(ピン21)の下にサーマル・ビアを追加して、LT3751の熱性能を改善します。これらのビアはグランド・プレーンの広い領域に直接接続するようにします。

6. 絶縁されたアプリケーションでは、出力側グランドと1次側グランドを直流的に絶縁する必要があります。両方のグランド・プレーンの間に十分な間隔をとって、電圧の安全性要件を満たす必要があります。

## アプリケーション情報

図14. QFNパッケージの推奨ボード・レイアウト(実寸とは異なる)

図15. TSSOPパッケージの推奨ボード・レイアウト(実寸とは異なる)

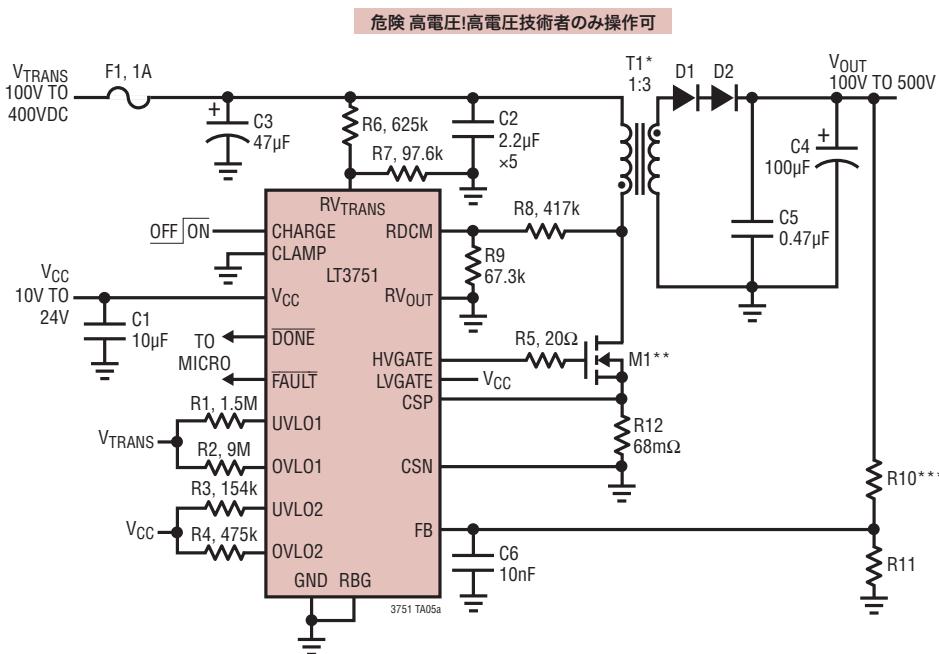

## 標準的応用例

## 42Aコンデンサ・チャージャ

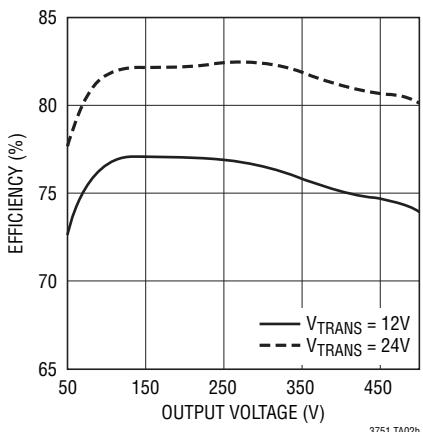

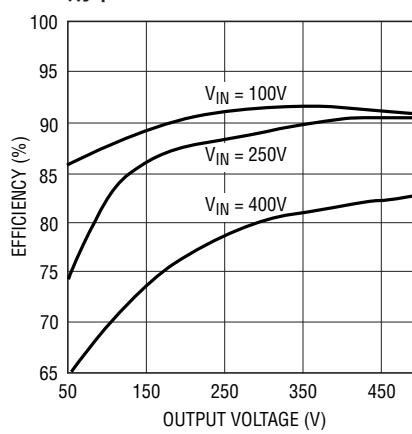

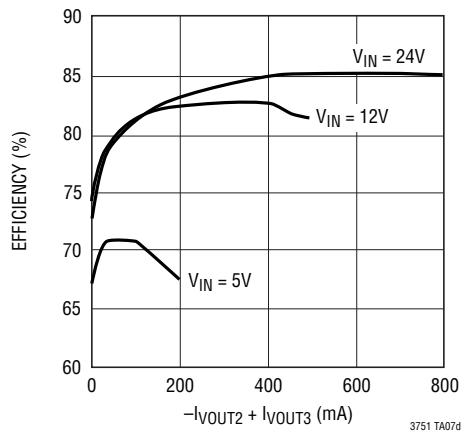

効率

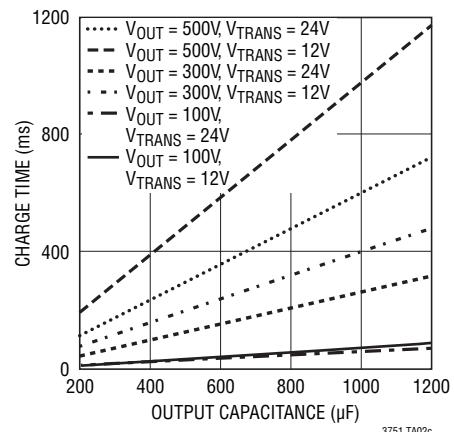

出力コンデンサの充電時間

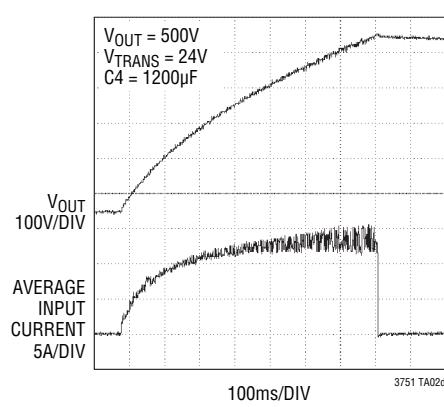

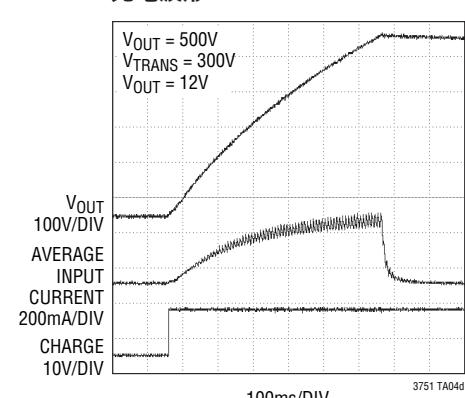

充電波形

## 標準的応用例

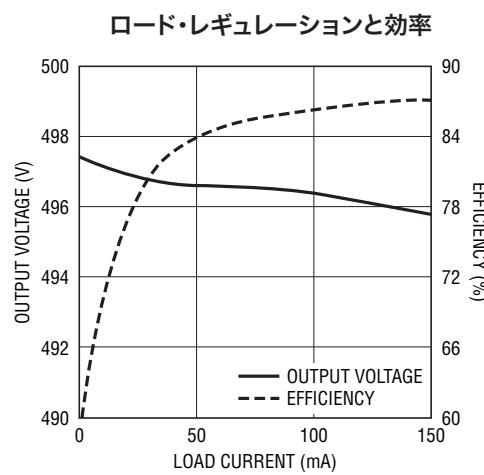

## 高電圧レギュレータ

\* 製造元の仕様を満たすには、M1およびT1に適切なヒートシンク/放熱が必要

\*\* 必要な出力電圧に応じて、製造元の電圧仕様を満たすため、R10を複数の抵抗に分割する必要がある。

\*\*\* 「アプリケーション情報」に記載されている大信号の安定性の判定基準を満たすように、C4の大きさを決める必要がある

C1: X5RまたはX7Rの25Vセラミック・コンデンサ

C2: X5RまたはX7Rの25Vセラミック・コンデンサ

C3: 25V電解コンデンサ

C5: TDK CKG57NX7R2J474M

D1: VISHAY US1M 1000V

M1: FAIRCHILD FQP34N20L

R1～R4, R6～R9, R11: 1%の0805抵抗を使用

R5: IRC LRシリーズ2512抵抗

R10: 200V 1206抵抗を使用

T1: COILCRAFT GA3459-AL

## 推奨部品値

| $V_{OUT}$<br>(V) | $I_{OUT(MAX)}$ (mA)<br>AT $V_{TRANS} = 5V$ ,<br>5% $V_{OUT}$ DEFLECTION | $I_{OUT(MAX)}$ (mA)<br>AT $V_{TRANS} = 24V$ ,<br>5% $V_{OUT}$ DEFLECTION | $R9$<br>(k $\Omega$ ) | $R11$<br>(k $\Omega$ ) | $R10$<br>(k $\Omega$ ) |

|------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------|------------------------|------------------------|

| 100              | 180                                                                     | 270                                                                      | 3.32                  | 0.383                  | 30.9                   |

| 200              | 110                                                                     | 315                                                                      | 1.65                  | 0.768                  | 124                    |

| 300              | 75                                                                      | 245                                                                      | 1.10                  | 1.13                   | 274                    |

| 400              | 55                                                                      | 200                                                                      | 0.825                 | 1.54                   | 499                    |

| 500 <sup>†</sup> | 40                                                                      | 170                                                                      | Tie to GND            | 1.74                   | 715                    |

<sup>†</sup>トランジスの1次側インダクタンスにより、 $V_{OUT}$ コンパレータの動作が $V_{OUT} = 400V_{MAX}$ に制限される。400V以上で $V_{OUT}$ を動作させるときは、 $RV_{OUT}$ と $RBG$ をグランドに接続する。

## 標準的応用例

## 1.6A高入力電圧、絶縁型コンデンサ・チャージャ

\* 必要な出力電力レベルを確保するため、T1には適切な熱管理が必要

\*\* 製造元の仕様を満たすには、M1に適切なヒートシンク/放熱が必要

50V～500Vのどの出力電圧でもR12を次式のよう設定する

$$R12 = \frac{0.98}{\frac{V_{OUT,TRIP}}{3 \cdot R10} + 40\mu A \cdot 2}$$

C1: X5RまたはX7Rの25Vセラミック・コンデンサ

C2: X5RまたはX7Rの630Vセラミック・コンデンサ

C3: 450V ILLINOIS CAP 476CKE450MQW

C4: 50V～500Vの電解コンデンサ

C5: TDK CKG57NX7R2J474M

D1, D2: VISHAY US1M 1000V

F1: BUSSMANN PCB-1-R

M1: FAIRCHILD FQB4N80

R1, R2: 1%の1206抵抗を2本直列に接続

R3～R5, R9, R12: 1%の0805抵抗

R6, R10: 0.1%の1206抵抗を3本直列に接続

R7, R11: 0.1%の0805抵抗

R8: 1%の1206抵抗を3本直列に接続

R13: 1%のIRC LRシリーズ1206抵抗

T1: COILCRAFT HA4060-AL

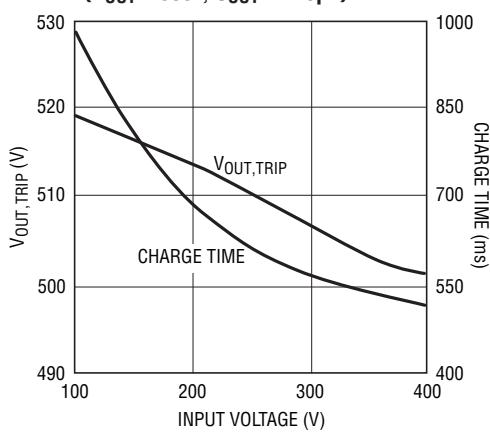

出力トリップ電圧と充電時間

( $V_{OUT} = 500V$ ,  $C_{OUT} = 220\mu F$ )

効率

充電波形

## 標準的応用例

## 高入力電圧、高出力電圧レギュレータ

\* 必要な出力電力レベルを確保するため、T1には適切な熱管理が必要

\*\* 製造元の仕様を満たすには、M1に適切なヒートシンク/放熱が必要

\*\*\* 必要な出力電圧に応じて、製造元の電圧仕様を満たすため、R10を複数の抵抗に分割する必要がある

C1: X5RまたはX7Rの25Vセラミック・コンデンサ

C2: X5RまたはX7Rの630Vセラミック・コンデンサ

C3: 450V ILLINOIS CAP 476CKE450MQW

C4: 50V~500Vの電解コンデンサ

C5: TDK CKG57NXR2J474M

C6: X5RまたはX7Rの6.3Vセラミック・コンデンサ

D1, D2: VISHAY US1M 1000V

F1: BUSSMANN PCB-1-R

M1: FAIRCHILD FQB4N80

R1, R2: 1%の1206抵抗を2本直列に接続

R3~R5, R7, R9, R11: 1%の0805抵抗

R6, R8: 1%の1206抵抗を3本直列に接続

R10: 1%の1206抵抗

R12: 1%のIRC LRシリーズ1206抵抗

T1: COILCRAFT HA4060-AL

## 推奨部品値

| $V_{OUT}$ (V) | $I_{OUT(MAX)}$ (mA)<br>AT $V_{TRANS} = 100V$ ,<br>1% $V_{OUT}$ DEFLECTION | $I_{OUT(MAX)}$ (mA)<br>AT $V_{TRANS} = 400V$ ,<br>1% $V_{OUT}$ DEFLECTION | $R_{10}$ (k $\Omega$ ) | $R_{11}$ (k $\Omega$ ) |

|---------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------|------------------------|

| 100           | 55                                                                        | 130                                                                       | 30.9                   | 0.383                  |

| 200           | 110                                                                       | 150                                                                       | 124                    | 0.768                  |

| 300           | 95                                                                        | 175                                                                       | 274                    | 1.13                   |

| 400           | 80                                                                        | 130                                                                       | 499                    | 1.54                   |

| 500           | 65                                                                        | 140                                                                       | 715                    | 1.74                   |

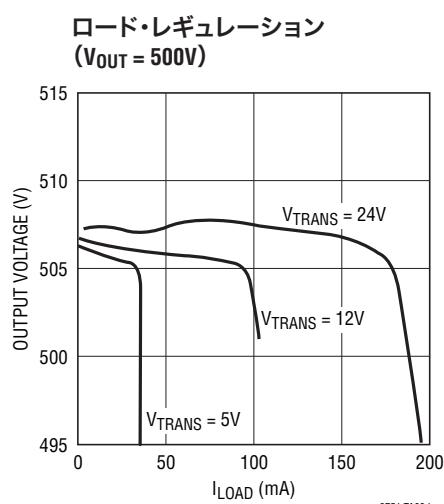

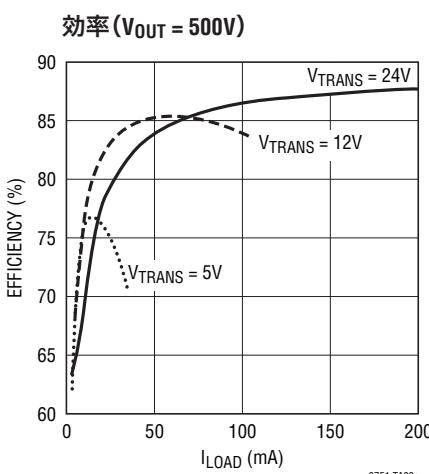

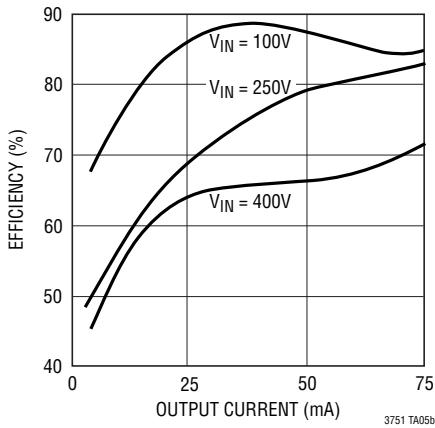

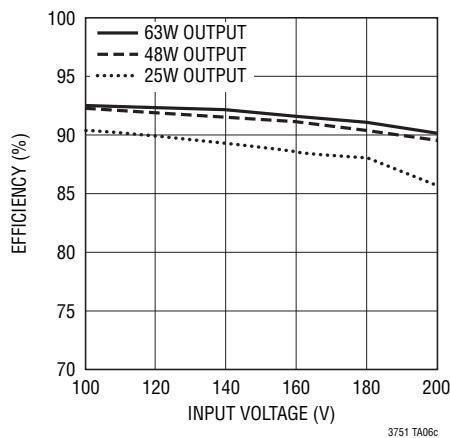

## 効率

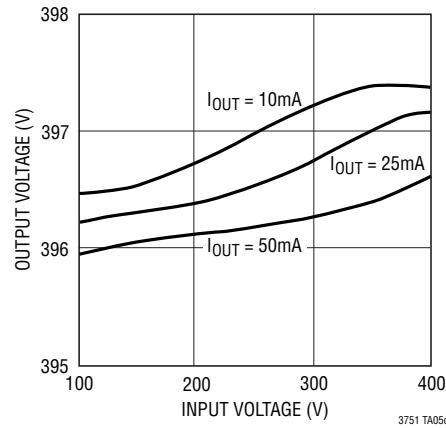

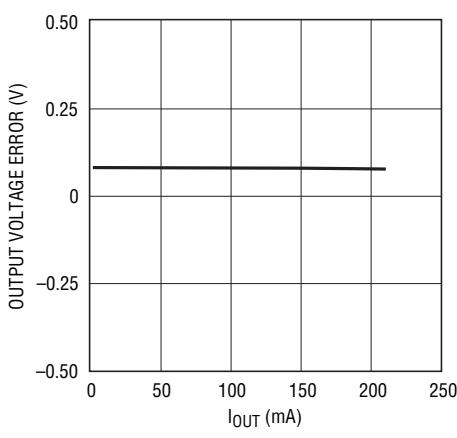

## ライン・レギュレーション

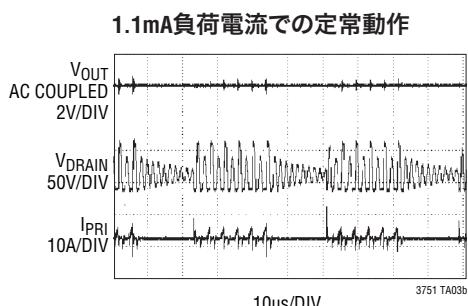

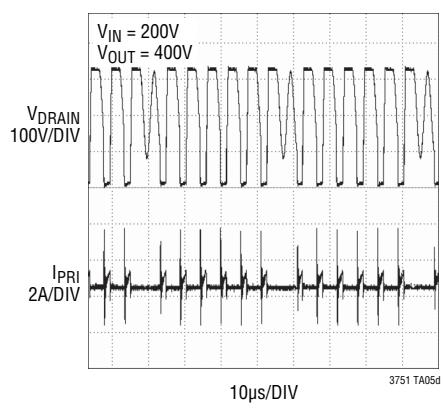

## 50mA負荷電流での定常動作

## 標準的応用例

## 絶縁型282V電圧レギュレータ

## ロード・レギュレーション

## 効率

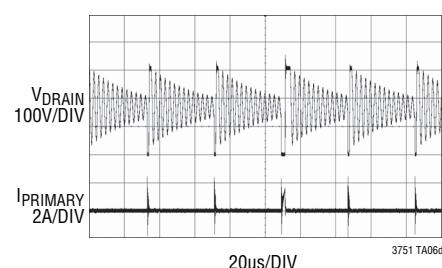

## 7.1mA負荷電流での定常動作

## 225mA負荷電流での定常動作

## 標準的応用例

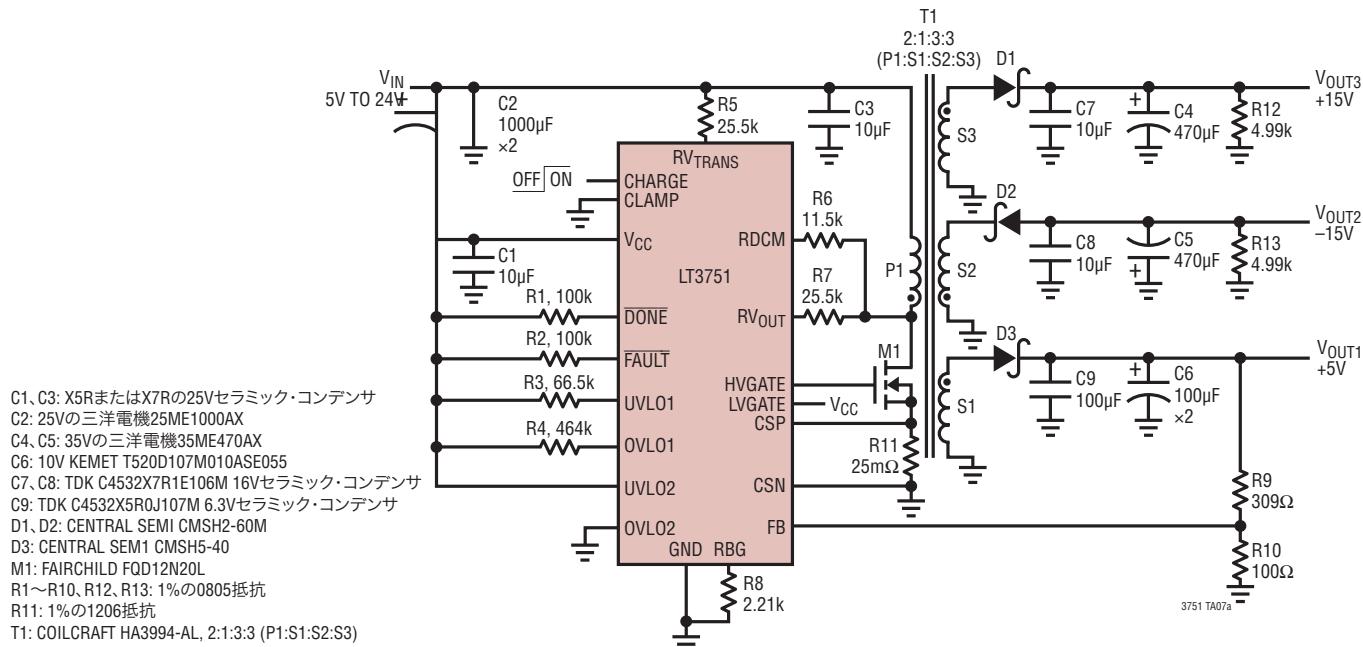

## 広入力電圧範囲、15Wトリプル出力電圧レギュレータ

## 最大出力条件

| V <sub>CC</sub><br>(V) | P <sub>OUT(MAX)</sub><br>(W) | I <sub>OUT(MAX)</sub> * (mA) |                   |                   |

|------------------------|------------------------------|------------------------------|-------------------|-------------------|

|                        |                              | V <sub>OUT1</sub>            | V <sub>OUT2</sub> | V <sub>OUT3</sub> |

| 5                      | 6.5                          | 750                          | 300               | 300               |

| 12                     | 10                           | 1750                         | 300               | 300               |

| 24                     | 13                           | 2500                         | 300               | 300               |

\*他の出力電流は全て0mAに設定

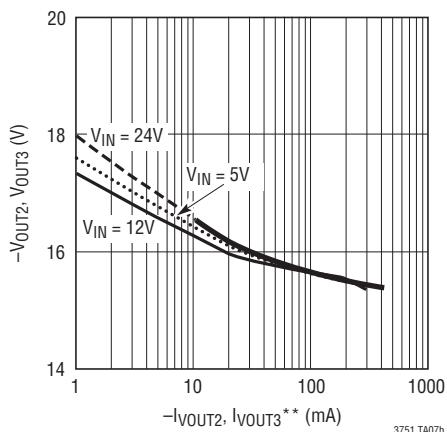

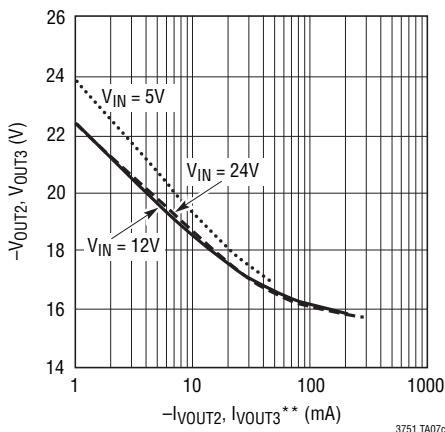

クロス・レギュレーション

(I<sub>VOUT1</sub> = 100mA)クロス・レギュレーション

(I<sub>VOUT1</sub> = 500mA)効率 (I<sub>VOUT1</sub> = 500mA)\*\*V<sub>OUT2</sub>とV<sub>OUT3</sub>の双方からそれぞれ等しい電流をソース/シンクする

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

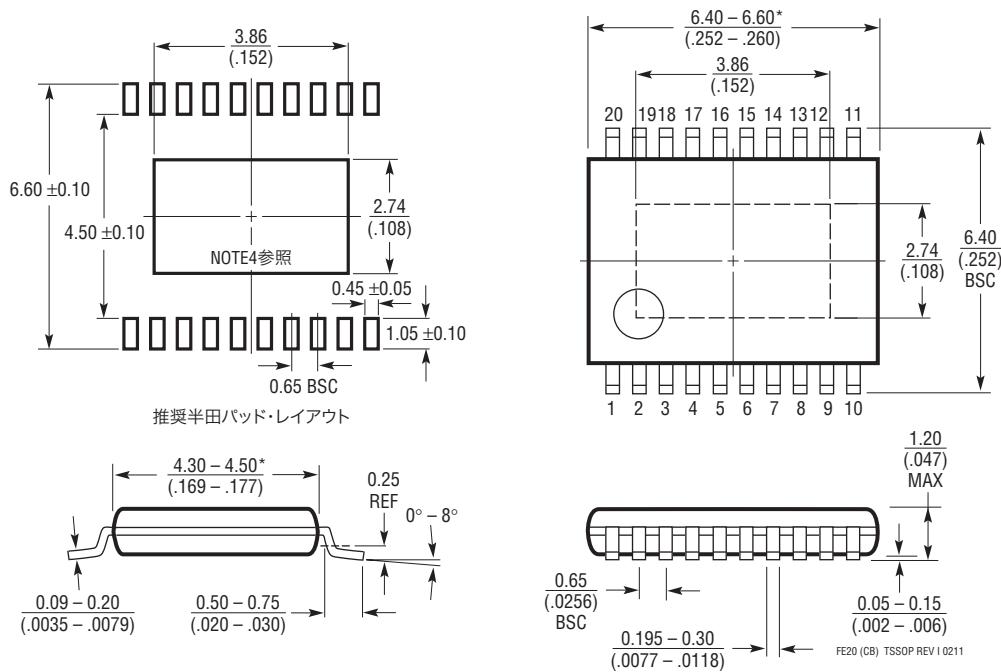

FEパッケージ

20ピン・プラスチックTSSOP(4.4mm)

(Reference LTC DWG # 05-08-1663 Rev I)

露出パッドのバリエーションCB

## NOTE:

1. 標準寸法: ミリメートル

2. 寸法は  $\frac{\text{ミリメートル}}{\text{(インチ)}}$

3. 図は実寸とは異なる

4. 露出パッド接着のための推奨最小PCBメタルサイズ

\* 寸法にはモールドのバリを含まない

モールドのバリは各サイドで0.150mm(0.006")を超えないこと

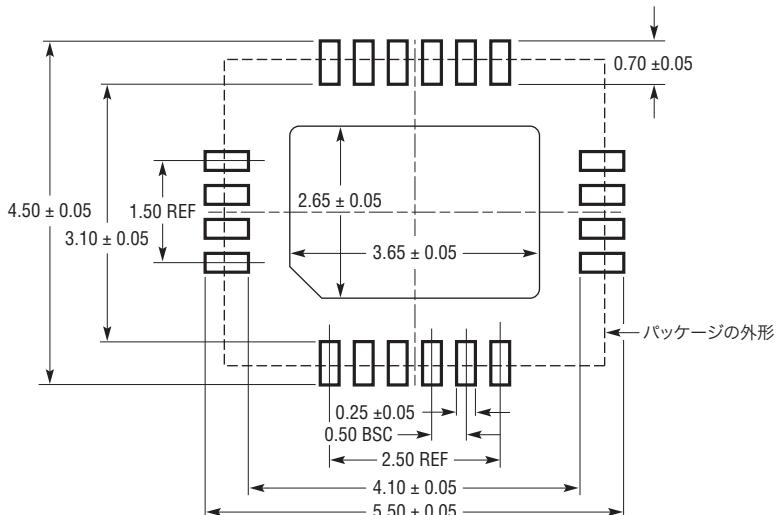

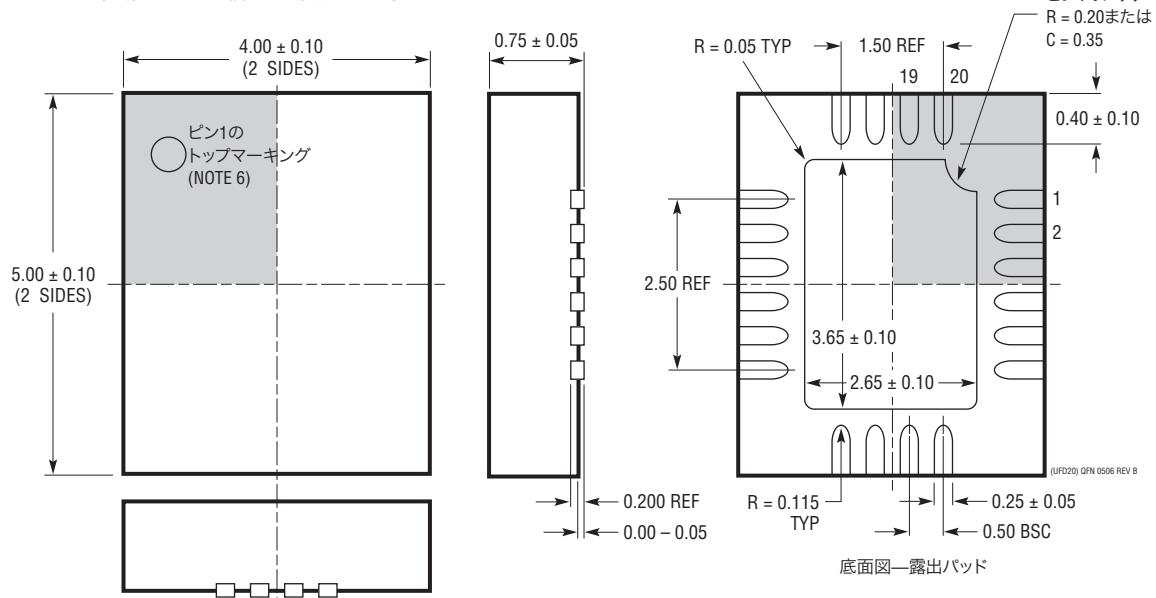

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>をご覧ください。

UFDパッケージ

20ピン・プラスチックQFN(4mm×5mm)

(Reference LTC DWG # 05-08-1711 Rev B)

推奨する半田パッドのピッチと寸法

半田付けされない領域には半田マスクを使用する

底面図—露出パッド

## NOTE:

- NOTE:

1. 図はJEDECパッケージ外形M0-220のバリエーション(WXXX-X)にするよう提案されている

2. 図は実寸とは異なる

3. すべての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで0.15mmを超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面の

ピン1の位置の参考に過ぎない

## 改訂履歴 (改訂履歴はRev Bから開始)

| REV | 日付   | 概要                                                                                                           | ページ番号                      |

|-----|------|--------------------------------------------------------------------------------------------------------------|----------------------------|

| B   | 5/10 | 「ピン機能」のFAULT(ピン6/ピン4)の記述を更新<br>「ピン機能」のDONE(ピン7/ピン5)の記述を更新<br>ブロック図を改訂<br>「アプリケーション情報」セクションを改訂<br>標準的応用例の図を改訂 | 7<br>8<br>9<br>17、18<br>30 |

| C   | 6/12 | 「アプリケーション情報」セクションを改訂<br>回路図のR8の値を3.40kから2.21kに修正<br>FEパッケージの図を更新                                             | 20<br>30<br>31             |

## 標準的応用例

## 安定化された300V電源

C1: X5RまたはX7Rの25Vセラミック・コンデンサ

C2: X5RまたはX7Rの25Vセラミック・コンデンサ

C3: 25V電解コンデンサ

C4: ルビコン330Vフォトフラッシュ・コンデンサ

D1: VISHAY US1M 1000V

M1: FAIRCHILD FQP34N20L

R1～R4: 1%の0805抵抗を使用

R5: IRC LRシリーズ2512抵抗

T1: スミダ電機PS07-299、20Aトランジスタ

C5: 10nF

## 関連製品

| 製品番号                                    | 説明                                                                  | 注釈                                                                                                                                 |

|-----------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| LTC3225                                 | 150mAスーパー・キャパシタ・チャージャ                                               | V <sub>IN</sub> : 2.75V～5.5V、直列接続された2個のスーパー・キャパシタを4.8Vまたは5.3Vまで充電                                                                  |

| LT3420/LT3420-1                         | 1.4A/1A、フォトフラッシュ・コンデンサ・チャージャ、自動トップオフ付き                              | 220μFを5Vから320Vまで3.7秒で充電、V <sub>IN</sub> : 2.2V～16V、I <sub>SD</sub> < 1μA、10ピンMSパッケージ                                               |

| LT3468/LT3468-1/<br>LT3468-2            | 1.4A、1A、0.7A、フォトフラッシュ・コンデンサ・チャージャ                                   | V <sub>IN</sub> : 2.5V～16V、充電時間: LT3468では4.6秒(0Vから320V、100μF、V <sub>IN</sub> = 3.6V)、I <sub>SD</sub> < 1μA、ThinSOT™パッケージ           |

| LT3484-0/LT3484-1/<br>LT3484-2          | 1.4A、0.7A、1A、フォトフラッシュ・コンデンサ・チャージャ                                   | V <sub>IN</sub> : 1.8V～16V、充電時間: LT3484-0の場合4.6秒(0Vから320V、100μF、V <sub>IN</sub> = 3.6V)、I <sub>SD</sub> < 1μA、2mm×3mm 6ピンDFNパッケージ  |

| LT3485-0/LT3485-1/<br>LT3485-2/LT3485-3 | 1.4A、0.7A、1A、2A、フォトフラッシュ・コンデンサ・チャージャ、出力電圧モニタおよび内蔵IGBT付き             | V <sub>IN</sub> : 1.8V～10V、充電時間: LT3485-0の場合3.7秒(0Vから320V、100μF、V <sub>IN</sub> = 3.6V)、I <sub>SD</sub> < 1μA、3mm×3mm 10ピンDFNパッケージ |

| LT3585-0/LT3585-1/<br>LT3585-2/LT3585-3 | 1.2A、0.55A、0.85A、1.7A、フォトフラッシュ・コンデンサ・チャージャ、調節可能な入力電流および内蔵IGBTドライバ付き | V <sub>IN</sub> : 1.5V～16V、充電時間: LT3585-3の場合3.3秒(0Vから320V、100μF、V <sub>IN</sub> = 3.6V)、I <sub>SD</sub> < 1μA、3mm×2mm DFN-10パッケージ  |

| LT3750                                  | コンデンサ・チャージャ・コントローラ                                                  | V <sub>IN</sub> : 3V～24V、充電時間: 300ms(0Vから300V、100μF) MSOP-10パッケージ                                                                  |