# フォルト保護されたデュアルLDO内蔵の40V、400mA降圧スイッチング・レギュレータ

## 特長

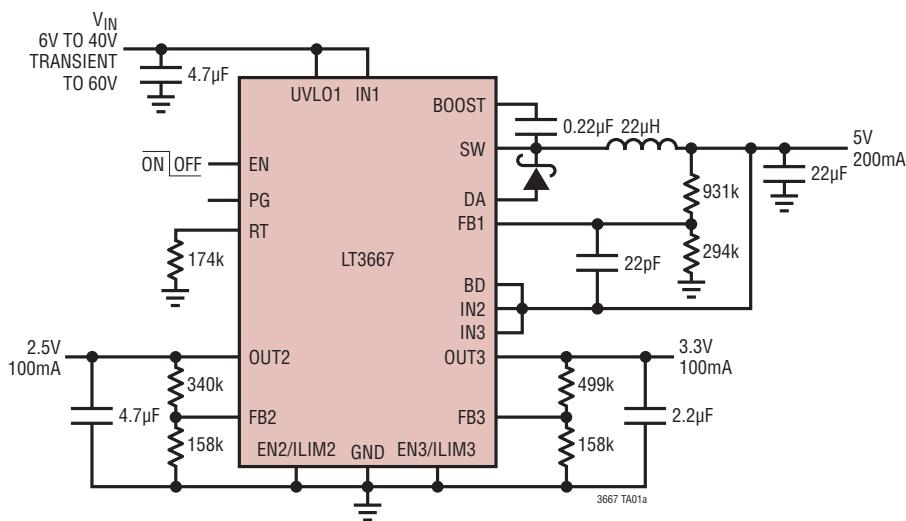

- 単一入力から3つの出力を供給するのに必要なインダクタは1個のみ

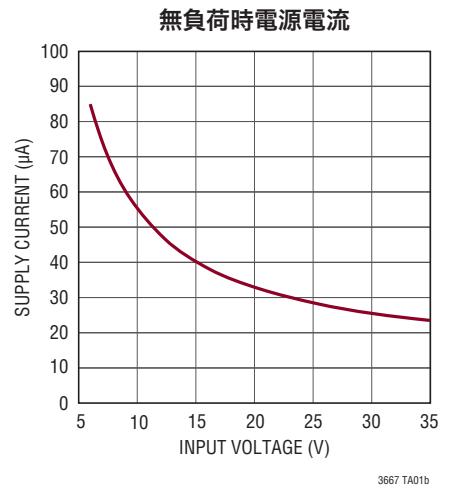

- 入力12V、出力5V、3.3V、2.5V、無負荷での $I_Q = 50\mu A$

- 降圧レギュレータ：

- 低リップル(15mVp-p未満)Burst Mode®動作

- パワー・スイッチ内蔵の400mA出力

- 動作入力電圧範囲:4.3V～40V(最大60V)

- デュアル低ドロップアウト・リニア・レギュレータ

- プログラム可能な電流制限回路を内蔵した200mA出力

- 入力電圧範囲:1.6V～45V

- フォルト保護:最大±45V

- 調整可能なスイッチング周波数:250kHz～2.2MHz

- 300kHz～2.2MHzの範囲で同期可能

- プログラム可能な低電圧ロックアウト

- パワーグッド・インジケータ

- 熱特性が改善された16ピンMSOPおよび24ピン(3mm×5mm)QFNパッケージで供給

## アプリケーション

- 自動車用バッテリのレギュレーション

- ポータブル機器の電源

- 産業用電源

- フォルト保護されたセンサ電源

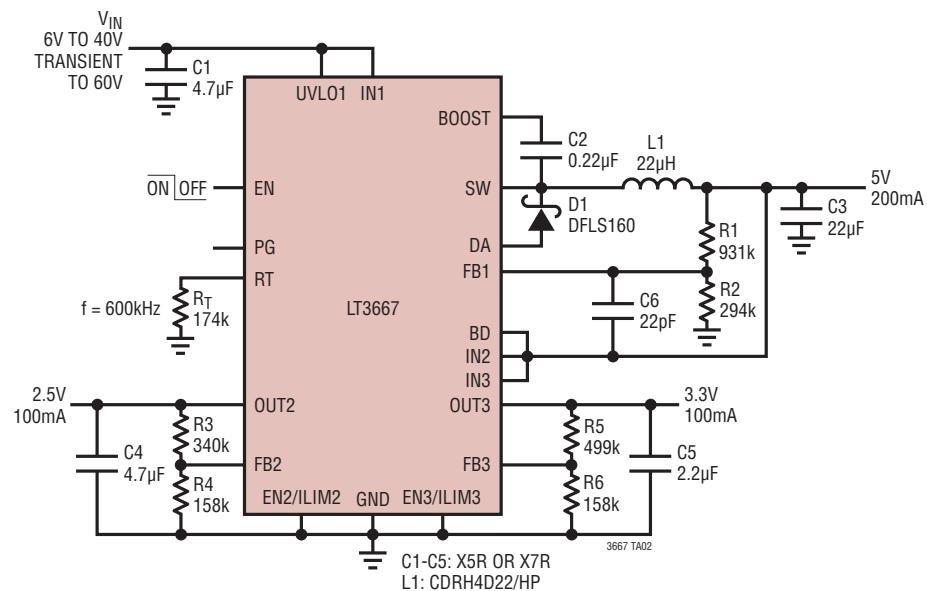

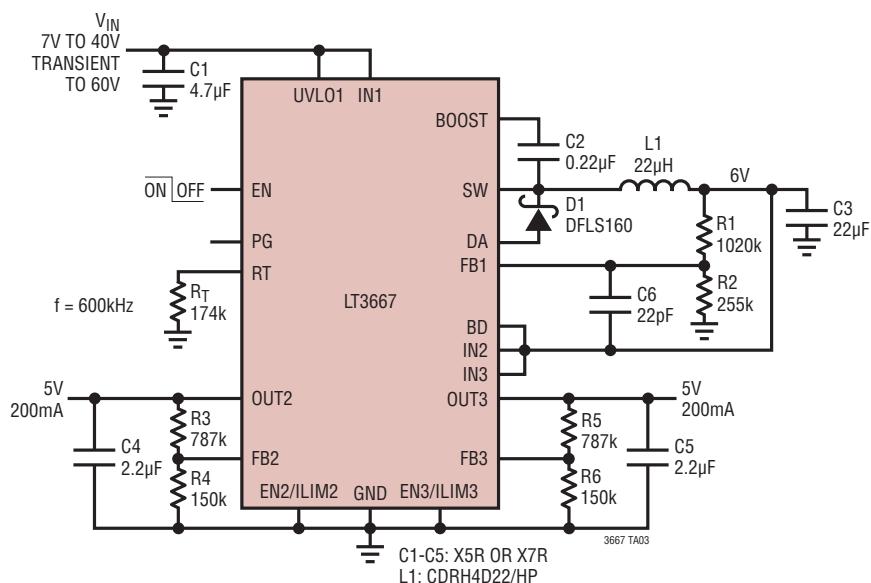

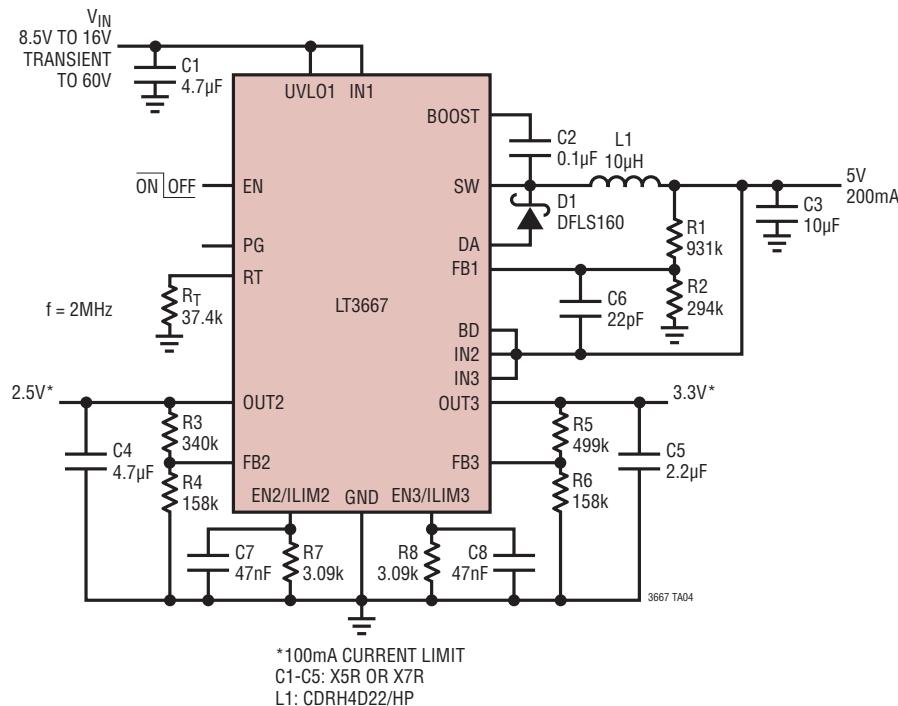

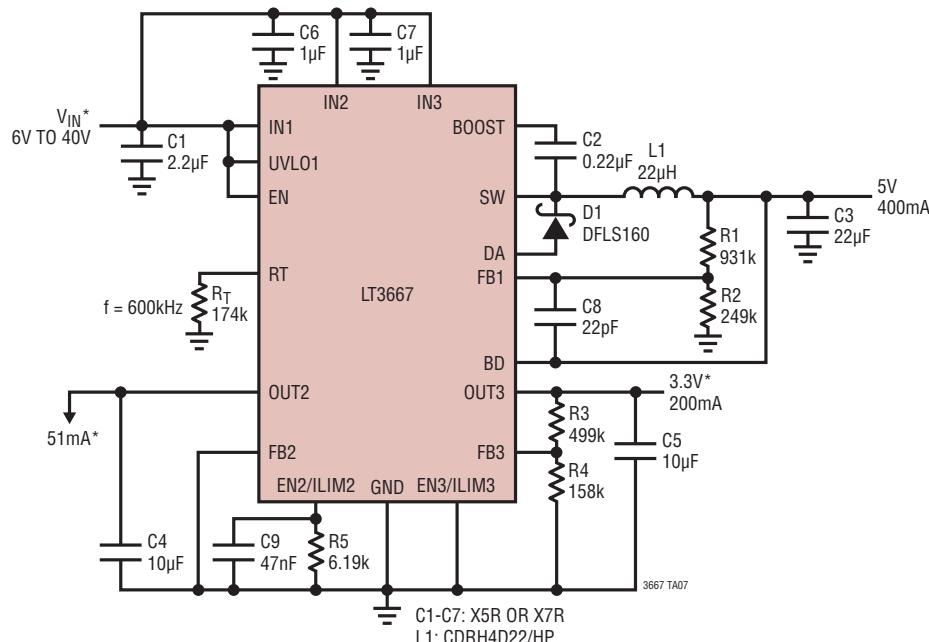

## 標準的応用例

## 絶対最大定格 (Note 1, 2)

|                                |           |                         |               |

|--------------------------------|-----------|-------------------------|---------------|

| FB2, FB3の電圧                    | $\pm 45V$ | RTの電圧                   | 2V            |

| OUT2, OUT3の電圧                  | $\pm 45V$ | FB1の電圧                  | 6V            |

| IN2, IN3(QFN)の電圧               | $\pm 45V$ | EN2/ILIM2, EN3/ILIM3の電圧 | 4V            |

| OUT2 – IN2間の電圧差                | $\pm 45V$ | PGの電圧                   | 30V           |

| OUT3 – IN3/BD間の電圧差(MSOP)       | $\pm 45V$ | PG1, PG2, PG3の電圧(QFN)   | 30V           |

| OUT3 – IN3間の電圧差(QFN)           | $\pm 45V$ | SYNCの電圧(QFN)            | 6V            |

| IN1, EN, UVLO1(QFN)の電圧(Note 3) | 60V       | 動作接合部温度範囲(Note 4, 5)    |               |

| IN1の逆電圧                        | -0.3V     | EグレードおよびIグレード           | -40°C ~ 125°C |

| ENピンの電流                        | -1mA      | Hグレード                   | -40°C ~ 150°C |

| IN3/BD(MSOP)の電圧                | 30V       | 保存温度範囲                  | -65°C ~ 150°C |

| BD(QFN)の電圧                     | 30V       | リード温度(半田付け, 10秒)        |               |

| BOOSTピンの電圧                     | 50V       | MSOPパッケージのみ             | 300°C         |

| SWピンを超えるBOOSTピンの電圧             | 30V       |                         |               |

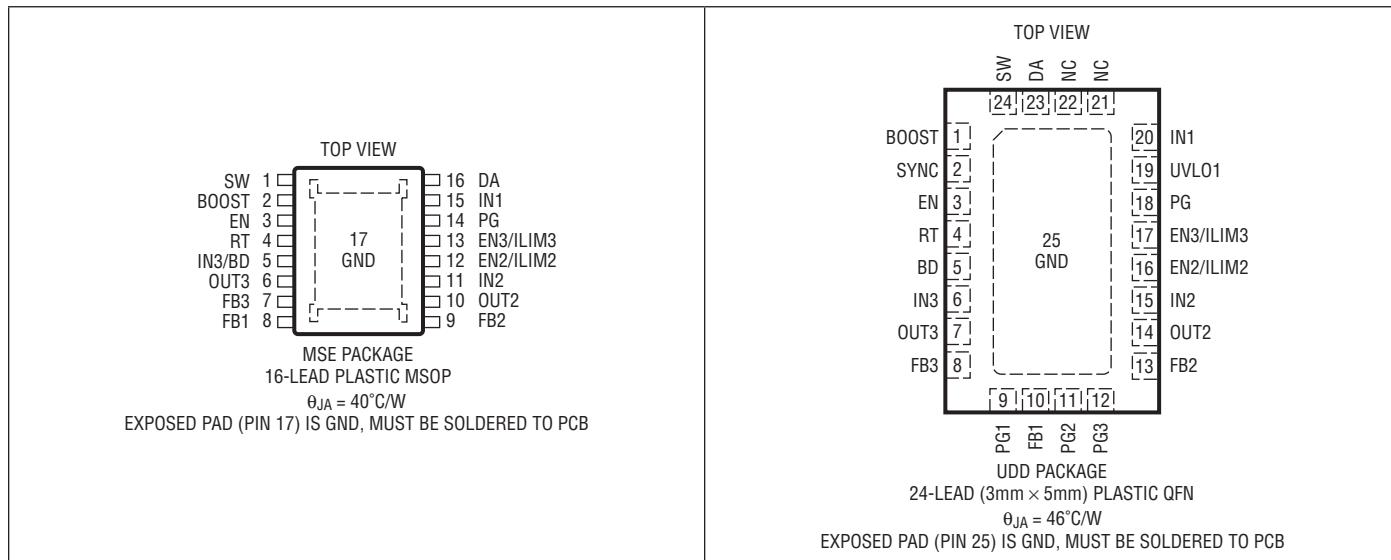

## ピン配置

## 発注情報

| 無鉛仕上げ          | テープアンドリール        | 製品マーキング* | パッケージ                           | 温度範囲           |

|----------------|------------------|----------|---------------------------------|----------------|

| LT3667EMSE#PBF | LT3667EMSE#TRPBF | 3667     | 16-Lead Plastic MSOP            | -40°C to 125°C |

| LT3667IMSE#PBF | LT3667IMSE#TRPBF | 3667     | 16-Lead Plastic MSOP            | -40°C to 125°C |

| LT3667HMSE#PBF | LT3667HMSE#TRPBF | 3667     | 16-Lead Plastic MSOP            | -40°C to 150°C |

| LT3667EUDD#PBF | LT3667EUDD#TRPBF | LGFH     | 24-Lead (3mm × 5mm) Plastic QFN | -40°C to 125°C |

| LT3667IUDD#PBF | LT3667IUDD#TRPBF | LGFH     | 24-Lead (3mm × 5mm) Plastic QFN | -40°C to 125°C |

| LT3667HUDD#PBF | LT3667HUDD#TRPBF | LGFH     | 24-Lead (3mm × 5mm) Plastic QFN | -40°C to 150°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛仕上げの製品の詳細については、弊社または弊社代理店にお問い合わせください。

無鉛仕上げの製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/>をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/>をご覧ください。

## 電気的特性 ● は全動作温度範囲での規格値を意味する。それ以外は $T_A=25^\circ\text{C}$ での値。注記がない限り、 $V_{IN1}=12\text{V}$ 。(Note 4)

| PARAMETER                               | CONDITIONS                                                                                                      | MIN | TYP        | MAX     | UNITS         |   |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|------------|---------|---------------|---|

| $V_{IN1}$ Undervoltage Lockout (Note 6) | $V_{IN2} = 0\text{V}$ , $V_{IN3} = 0\text{V}$                                                                   | ●   | 4          | 4.3     | V             |   |

| $V_{IN1}$ Overvoltage Lockout           |                                                                                                                 | ●   | 40         | 42      | V             |   |

| $V_{IN2}$ Undervoltage Lockout (Note 6) | $V_{IN1} = 3.5\text{V}$ , $V_{IN3} = 0\text{V}$                                                                 | ●   | 4          | 4.3     | V             |   |

| UVLO1 Threshold Voltage                 | Pin Voltage Falling                                                                                             | ●   | 0.95       | 1       | 1.05          | V |

| UVLO1 Pin Hysteresis                    |                                                                                                                 |     | 75         |         | mV            |   |

| UVLO1 Pin Current                       | $V_{UVLO1} = 1\text{V}$                                                                                         |     | 1          | 30      | nA            |   |

| Quiescent Current from IN1              | $V_{EN} = 0.3\text{V}$<br>$V_{EN} = 12\text{V}$ , $V_{IN2} = 0\text{V}$ , Not Switching                         | ●   | 0.01<br>13 | 1<br>30 | $\mu\text{A}$ |   |

| Quiescent Current from IN2              | $V_{EN} = 0.3\text{V}$<br>$V_{EN} = 12\text{V}$ , $V_{IN1} = 0\text{V}$ , $V_{IN2} = 5\text{V}$                 | ●   | 0.01<br>38 | 1<br>80 | $\mu\text{A}$ |   |

| Quiescent Current from IN1 + IN2        | $V_{EN} = 0.3\text{V}$ , $V_{IN2} = 5\text{V}$<br>$V_{EN} = 12\text{V}$ , $V_{IN2} = 5\text{V}$ , Not Switching | ●   | 0.01<br>40 | 1<br>90 | $\mu\text{A}$ |   |

| Quiescent Current from IN3              | $V_{EN} = 0.3\text{V}$ , $V_{IN3} = 5\text{V}$<br>$V_{EN} = 12\text{V}$ , $V_{IN3} = 5\text{V}$                 | ●   | 0.01<br>25 | 1<br>60 | $\mu\text{A}$ |   |

| EN Pin Current                          | $V_{EN} = 12\text{V}$                                                                                           |     | 0.6        | 2       | $\mu\text{A}$ |   |

| EN Input Threshold                      |                                                                                                                 |     | 0.3        | 1.1     | V             |   |

### パワーグッド・ピン PG (MSOP)、PG1、PG2、PG3 (QFN)

|                                            |                                                          |   |           |           |               |

|--------------------------------------------|----------------------------------------------------------|---|-----------|-----------|---------------|

| Leakage Current                            | $V_{PG} = 5\text{V}$ , $V_{PG1/2/3} = 5\text{V}$         |   | 0.1       | 1         | $\mu\text{A}$ |

| Output Voltage Low                         | $I_{PG} = 40\mu\text{A}$ , $I_{PG1/2/3} = 40\mu\text{A}$ | ● | 0.2       | 0.3       | V             |

| Threshold as % of $V_{FB}$ (FB1, FB2, FB3) | Pin Voltage Falling<br>Pin Voltage Rising                |   | 88<br>108 | 90<br>110 | %             |

| PG1 Threshold Hysteresis                   | Measured at FB1 Pin                                      |   | 30        |           | mV            |

| PG2/PG3 Threshold Hysteresis               | Measured at FB2/FB3 Pin                                  |   | 20        |           | mV            |

電気的特性 ●は全動作温度範囲での規格値を意味する。それ以外は $T_A = 25^\circ\text{C}$ での値。注記がない限り、 $V_{IN1} = 12\text{V}$ 。(Note 4)

| PARAMETER                                                                           | CONDITIONS                                                                                                                                 | MIN         | TYP               | MAX                | UNITS             |                   |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|--------------------|-------------------|-------------------|

| <b>スイッチング・レギュレータ</b>                                                                |                                                                                                                                            |             |                   |                    |                   |                   |

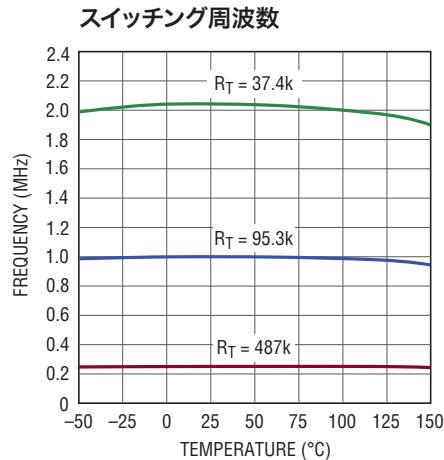

| Switching Frequency                                                                 | $R_T = 37.4\text{k}$<br>$R_T = 102\text{k}$<br>$R_T = 487\text{k}$                                                                         | ●<br>●<br>● | 1.8<br>0.8<br>220 | 2.0<br>0.94<br>243 | 2.1<br>1.1<br>275 | MHz<br>MHz<br>kHz |

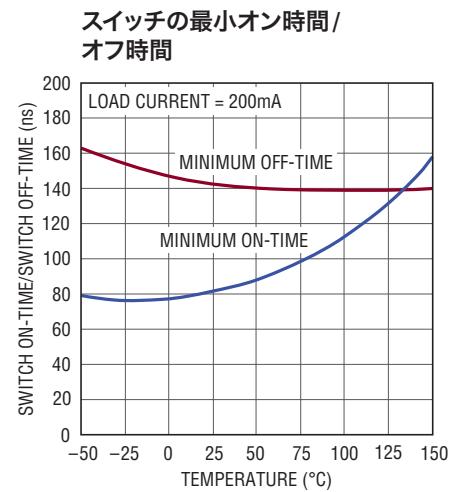

| Minimum Switch Off-Time                                                             |                                                                                                                                            | ●           |                   | 120                | 170               | ns                |

| Switch Current Limit (Note 7)                                                       | 5% Duty Cycle, $V_{IN} = 5\text{V}$ , $V_{FB1} = 0\text{V}$<br>90% Duty Cycle, $V_{IN} = 5\text{V}$ , $V_{FB1} = 0\text{V}$                | ●<br>●      | 600<br>450        | 750<br>550         | 950<br>750        | mA<br>mA          |

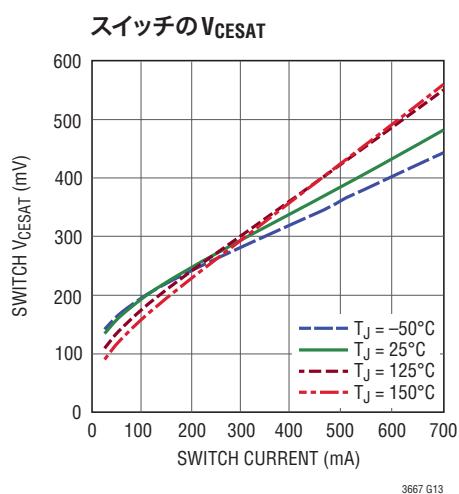

| Switch $V_{CESAT}$                                                                  | $I_{SW} = 200\text{mA}$                                                                                                                    |             |                   | 300                |                   | mV                |

| DA Pin Current to Stop Switching                                                    |                                                                                                                                            | ●           | 420               | 500                | 650               | mA                |

| Switch Leakage Current                                                              | $V_{SW} = 0\text{V}$                                                                                                                       |             |                   | 0.05               | 2                 | μA                |

| Boost Schottky Diode Forward Voltage                                                | $I_{BOOSTDIODE} = 50\text{mA}$ , $V_{IN} = \text{NC}$ , $V_{BOOST} = 0\text{V}$                                                            |             |                   | 900                |                   | mV                |

| Boost Schottky Diode Reverse Leakage                                                | $V_{REVERSE} = 12\text{V}$ , $V_{IN} = \text{NC}$                                                                                          |             |                   | 0.04               | 4                 | μA                |

| Minimum Boost Voltage (Note 8)                                                      |                                                                                                                                            | ●           |                   | 1.7                | 2.5               | V                 |

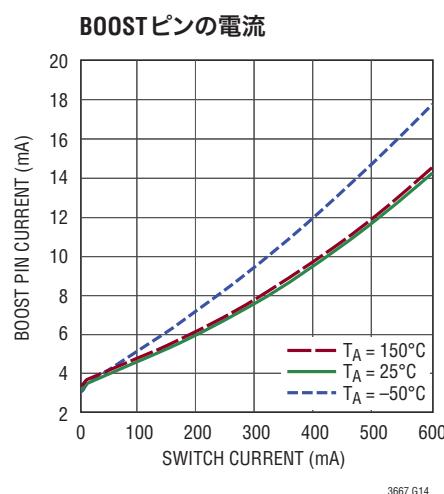

| BOOST Pin Current                                                                   | $I_{SW} = 200\text{mA}$ , $V_{BOOST} = 15\text{V}$                                                                                         |             |                   | 10                 | 16                | mA                |

| Feedback Voltage (FB1)                                                              |                                                                                                                                            | ●<br>●      | 1.188<br>1.176    | 1.2<br>1.2         | 1.212<br>1.224    | V<br>mV           |

| FB1 Pin Bias Current                                                                | Pin Voltage = 1.2V                                                                                                                         | ●           |                   | 0.1                | 20                | nA                |

| Reference Voltage Line Regulation                                                   | $4.2\text{V} < V_{IN1} < 40\text{V}$                                                                                                       |             |                   | 0.001              | 0.005             | %/V               |

| SYNC High Level Input Voltage                                                       |                                                                                                                                            | ●           | 1.2               |                    |                   | V                 |

| SYNC Low Level Input Voltage                                                        |                                                                                                                                            | ●           |                   | 0.5                |                   | V                 |

| SYNC Input Frequency                                                                |                                                                                                                                            |             |                   | 0.3                | 2.2               | MHz               |

| <b>各LDOレギュレータ</b>                                                                   |                                                                                                                                            |             |                   |                    |                   |                   |

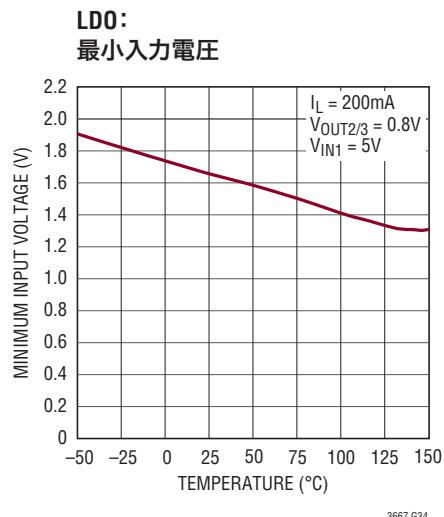

| Minimum Input Voltage                                                               | $I_{LOAD} = 200\text{mA}$                                                                                                                  | ●           |                   | 1.6                | 2.2               | V                 |

| Feedback Voltage (FB2/FB3)                                                          | $V_{IN} = 2.2\text{V}$ , $I_{LOAD} = 1\text{mA}$<br>$2.2\text{V} < V_{IN} < 15\text{V}$ , $1\text{mA} < I_{LOAD} < 200\text{mA}$           | ●<br>●      | 792<br>784        | 800<br>816         | 808<br>816        | mV<br>mV          |

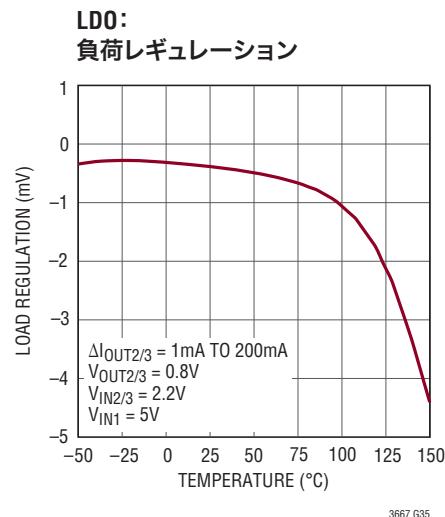

| Load Regulation (Note 12)                                                           | $V_{IN} = 2.2\text{V}$ , $I_{LOAD} = 1\text{mA}$ to $200\text{mA}$                                                                         | ●           |                   | 0.2                | 5                 | mV                |

| Reference Voltage Line Regulation (Note 12)                                         | $2.2\text{V} < V_{IN2,3} < 45\text{V}$                                                                                                     |             |                   | 0.005              | 0.01              | %/V               |

| Dropout Voltage (Notes 9, 10), $V_{IN} = V_{OUT(\text{NOMINAL})}$                   | $I_{LOAD} = 1\text{mA}$<br>$I_{LOAD} = 1\text{mA}$                                                                                         | ●           |                   | 70                 | 165<br>210        | mV<br>mV          |

|                                                                                     | $I_{LOAD} = 50\text{mA}$<br>$I_{LOAD} = 50\text{mA}$                                                                                       | ●           |                   | 230                | 300<br>400        | mV<br>mV          |

|                                                                                     | $I_{LOAD} = 100\text{mA}$<br>$I_{LOAD} = 100\text{mA}$                                                                                     | ●           |                   | 280                | 400<br>450        | mV<br>mV          |

|                                                                                     | $I_{LOAD} = 200\text{mA}$<br>$I_{LOAD} = 200\text{mA}$                                                                                     | ●           |                   | 340                | 650<br>750        | mV<br>mV          |

| GND Pin Current, $V_{IN} = V_{OUT(\text{NOMINAL})} + 0.6\text{V}$<br>(Notes 10, 11) | $I_{LOAD} = 0\text{mA}$<br>$I_{LOAD} = 50\text{mA}$<br>$I_{LOAD} = 200\text{mA}$                                                           | ●<br>●<br>● | 40<br>1<br>5      | 90<br>2<br>10      |                   | μA<br>mA<br>mA    |

| Quiescent Current $I_{IN2}$ with LDO2 Disabled                                      | $V_{IN1} = 0\text{V}$ , $V_{IN2} = 12\text{V}$ , $V_{EN2}/I_{LIM2} = 2\text{V}$                                                            |             |                   | 13                 | 20                | μA                |

| Quiescent Current $I_{IN3}$ with LDO3 Disabled (QFN)                                | $V_{IN1} = 16\text{V}$ , $V_{IN3} = 12\text{V}$ , $V_{EN3}/I_{LIM3} = 2\text{V}$                                                           |             |                   | 0.2                | 1                 | μA                |

| Quiescent Current $I_{IN3/BD}$ with LDO3 Disabled (MSOP)                            | $V_{IN1} = 16\text{V}$ , $V_{IN3/BD} = 12\text{V}$ , $V_{EN3}/I_{LIM3} = 2\text{V}$                                                        |             |                   | 1.2                | 2                 | μA                |

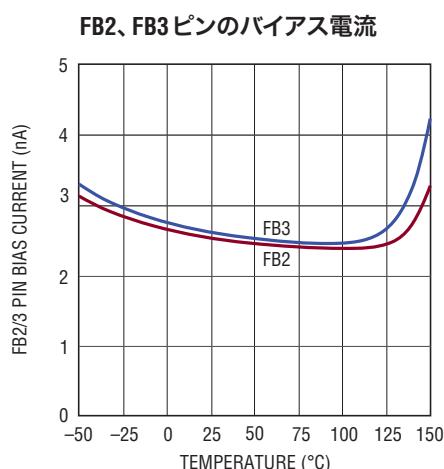

| FB2 Pin Bias Current (Note 12)                                                      | $V_{IN2} = 12\text{V}$                                                                                                                     | ●           |                   | -3                 | ±40               | nA                |

| FB3 Pin Bias Current (Note 12)                                                      | $V_{IN3} = 12\text{V}$                                                                                                                     | ●           |                   | -3                 | ±40               | nA                |

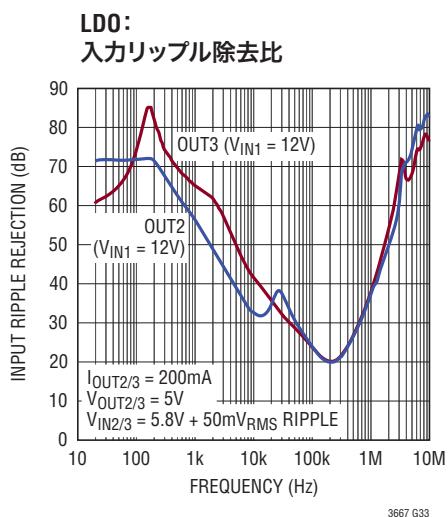

| Ripple Rejection (Note 12)                                                          | $V_{IN} - V_{OUT} = 2\text{V}$ (Avg), $V_{RIPPLE} = 0.5\text{V}_{\text{P-P}}$ ,<br>$f_{RIPPLE} = 120\text{Hz}$ , $I_{LOAD} = 200\text{mA}$ |             | 60                | 85                 |                   | dB                |

3667fb

**電気的特性** ●は全動作温度範囲での規格値を意味する。それ以外は $T_A=25^\circ\text{C}$ での値。注記がない限り、 $V_{IN1}=12\text{V}$ 。(Note 4)

| PARAMETER                                | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                           | MIN              | TYP                       | MAX                   | UNITS                                                    |                                                          |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------|-----------------------|----------------------------------------------------------|----------------------------------------------------------|

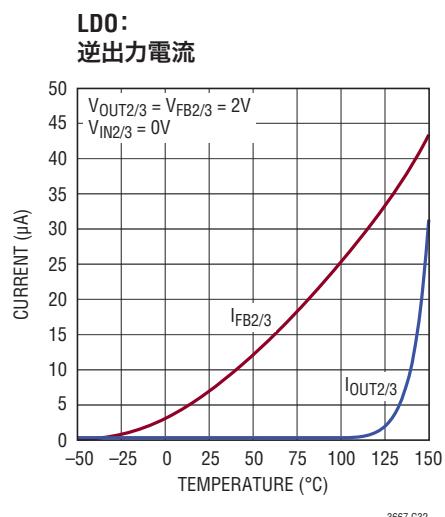

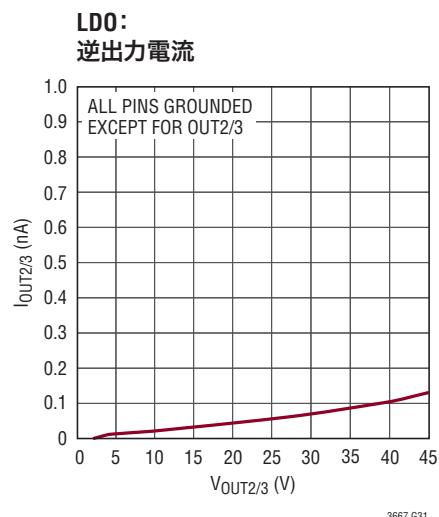

| Reverse Output Current (Note 13)         | $V_{OUT2} = 1.2\text{V}$ , $V_{IN1} = V_{IN2} = V_{IN3} = 0\text{V}$<br>$V_{OUT3} = 1.2\text{V}$ , $V_{IN1} = V_{IN2} = V_{IN3} = 0\text{V}$                                                                                                                                                                                                                                                         |                  | 5<br>5                    | 40<br>40              | $\mu\text{A}$<br>$\mu\text{A}$                           |                                                          |

| Input Reverse Leakage Current LDO2       | $V_{IN2} = -45\text{V}$ , $V_{IN1} = V_{IN3} = V_{OUT2} = 0\text{V}$                                                                                                                                                                                                                                                                                                                                 | ●                |                           | 300                   | $\mu\text{A}$                                            |                                                          |

| Input Reverse Leakage Current LDO3 (QFN) | $V_{IN3} = -45\text{V}$ , $V_{IN1} = V_{IN2} = V_{OUT3} = 0\text{V}$                                                                                                                                                                                                                                                                                                                                 | ●                |                           | 300                   | $\mu\text{A}$                                            |                                                          |

| Internal Current Limit (Note 12)         | $V_{IN2} = 2.2\text{V}$ , $V_{OUT2} = 0\text{V}$ , EN2/ILIM2 Pin Grounded<br>$\Delta V_{OUT2} = -5\%$<br>$V_{IN3} = 2.2\text{V}$ , $V_{OUT3} = 0\text{V}$ , EN3/ILIM3 Pin Grounded<br>$\Delta V_{OUT3} = -5\%$                                                                                                                                                                                       |                  | 300<br>220<br>300<br>220  |                       | $\text{mA}$<br>$\text{mA}$<br>$\text{mA}$<br>$\text{mA}$ |                                                          |

| Externally Programmed Current Limit      | $R_{EN/ILIM} = 31.6\text{k}$ , $V_{OUT2/3} = 5\text{V}$ , $V_{IN2/3} \geq 5.6\text{V}$<br>$R_{EN/ILIM} = 6.19\text{k}$ , $V_{OUT2/3} = 5\text{V}$ , $V_{IN2/3} \geq 5.6\text{V}$<br>$R_{EN/ILIM} = 6.19\text{k}$ , $V_{OUT2/3} = 5\text{V}$ , $5.6\text{V} \leq V_{IN2/3} \leq 15\text{V}$<br>$R_{EN/ILIM} = 1.54\text{k}$ , $V_{OUT2/3} = 5\text{V}$ , $5.6\text{V} \leq V_{IN2/3} \leq 15\text{V}$ | ●<br>●<br>●<br>● | 9.5<br>47<br>48.45<br>176 | 10<br>51<br>51<br>197 | 10.5<br>55<br>53.55<br>230                               | $\text{mA}$<br>$\text{mA}$<br>$\text{mA}$<br>$\text{mA}$ |

| LDO Disable Threshold                    | $V_{EN/ILIM}$ Rising                                                                                                                                                                                                                                                                                                                                                                                 |                  | 0.9                       | 1                     | 1.2                                                      | V                                                        |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに回復不可能な損傷を与える可能性がある。長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える恐れがある。

**Note 2:** 正電流はピンに流れ込み、負電流はピンから流れ出す。最小値と最大値は絶対値を意味する。

**Note 3:** IN1 ピン、UVLO1 ピンおよびEN ピンの絶対最大電圧は、1 秒の非反復性トランジエントで 60V、連続動作では 40V である。

**Note 4:** LT3667E は、0°C ~ 125°C の接合部温度で性能仕様に適合することが保証されている。-40°C ~ 125°C の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの相関で確認されている。LT3667I は-40°C ~ 125°C の動作接合部温度範囲で動作することが保証されている。LT3667H は-40°C ~ 150°C の動作接合部温度範囲で動作することが保証されている。

**Note 5:** このデバイスには短時間の過負荷状態の間デバイスを保護するための過熱保護機能が備わっている。過熱保護がアクティブなとき、接合部温度は最大動作接合部温度を超える。規定された最大動作接合部温度を超えた状態で動作が継続すると、デバイスの信頼性を損なう恐れがある。

**Note 6:** これは、内部バイアス回路をレギュレーション状態に保つのに必要な電圧である。

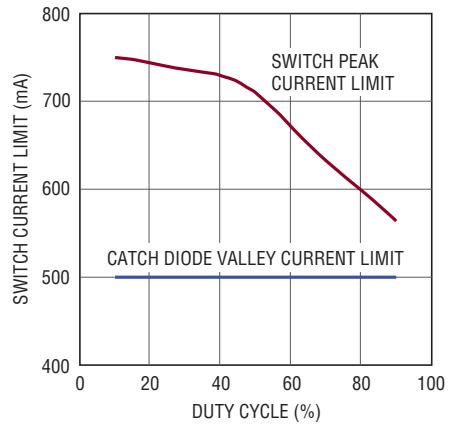

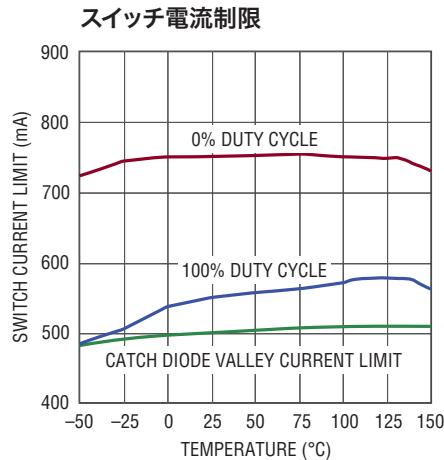

**Note 7:** 設計か、静的テストとの相関によって保証されている電流制限値。高いデューティ・サイクルではスロープ補償により電流制限値が低下する。

**Note 8:** これは、スイッチが完全に飽和するのを保証するのに必要な、昇圧コンデンサの最小電圧である。

**Note 9:** ドロップアウト電圧は、規定出力電流でレギュレーションを維持するのに必要な、入力-出力間の最小電圧差である。LDO がドロップアウト時には、出力電圧は ( $V_{IN}-V_{DROP}$ ) に等しくなる。

**Note 10:** 最小入力電圧の要件を満たすため、LT3667 は  $V_{OUT}$  を 5V に設定する外付け抵抗分割器(下側 80.6k、上側 422k)を使用した状態でテストされ、仕様が規定されている。外付け抵抗分割器によって 9.93μA の DC 負荷が出力に追加される。この外部電流は GND ピンの電流に算入されない。

**Note 11:** GND ピンの電流は  $V_{IN}=V_{OUT}(\text{NOMINAL})+0.6\text{V}$  および電流源負荷でテストされる。ドロップアウト時には、GND ピンの電流は増加する。

**Note 12:** LT3667 は FB2(FB3) ピンを OUT2(OUT3) ピンに接続した条件でテストされ、仕様が規定されている。

**Note 13:** 逆出力電流は、IN2(IN3) ピンを接地し、OUT2(OUT3) ピンを定格出力電圧に強制した状態でテストされる。この電流は OUT2(OUT3) ピンに流れ込み、GND ピンから流れ出す。

## 標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

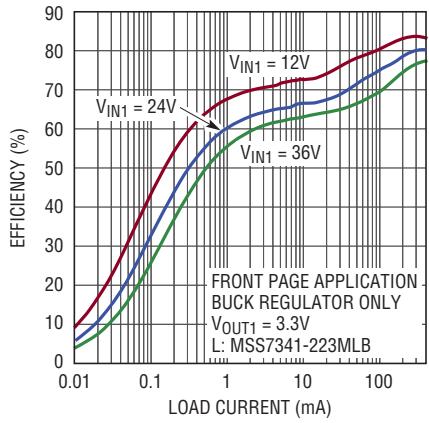

効率、 $V_{\text{OUT}} = 3.3\text{V}$

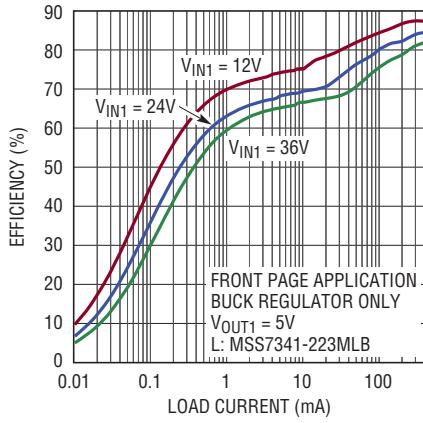

効率、 $V_{\text{OUT}} = 5\text{V}$

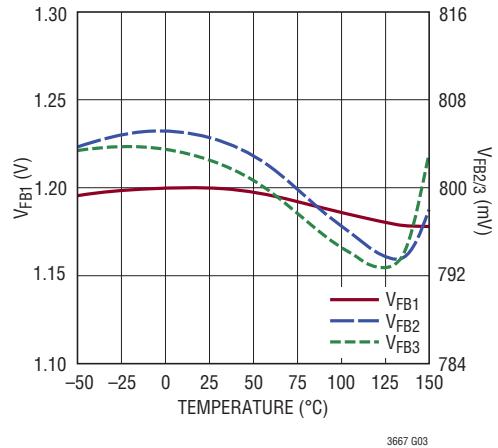

$V_{\text{FB}1/2/3}$  と 温度

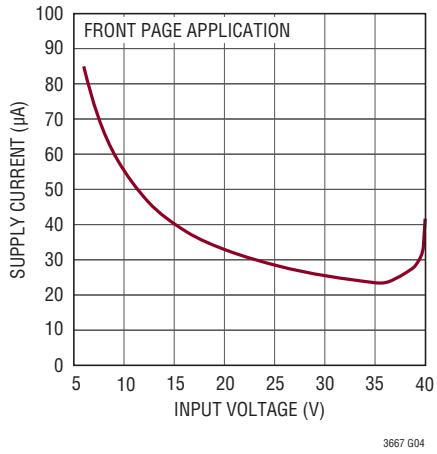

無負荷時電源電流

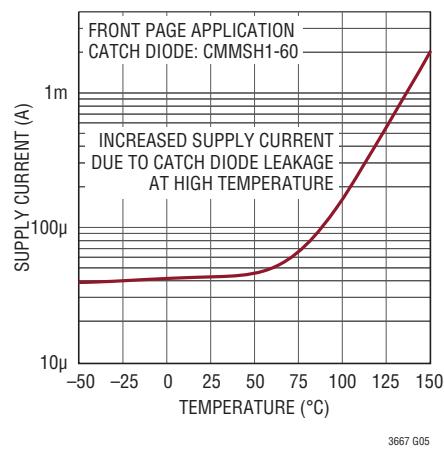

無負荷時電源電流

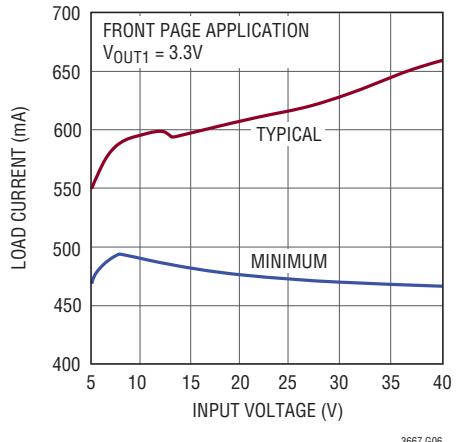

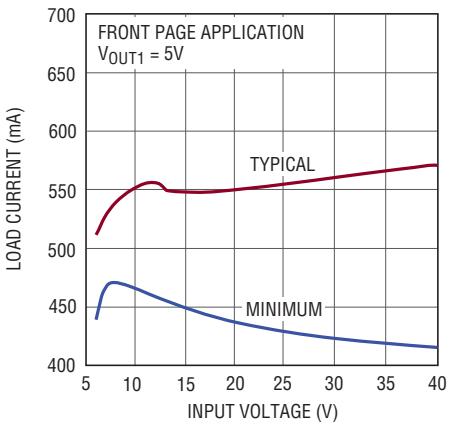

最大負荷電流

最大負荷電流

スイッチング・レギュレータ

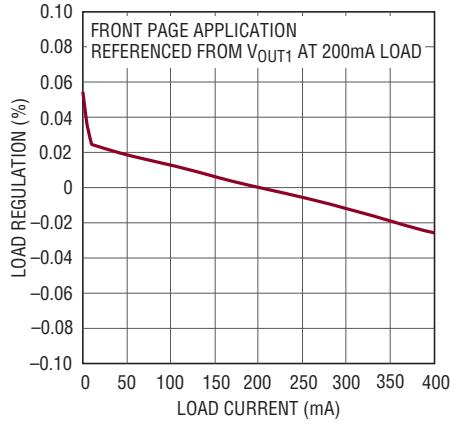

負荷レギュレーション

スイッチ電流制限

**標準的性能特性** 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

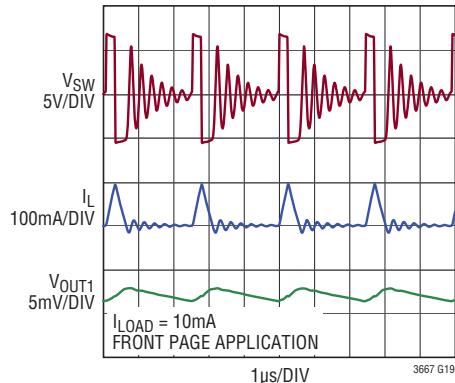

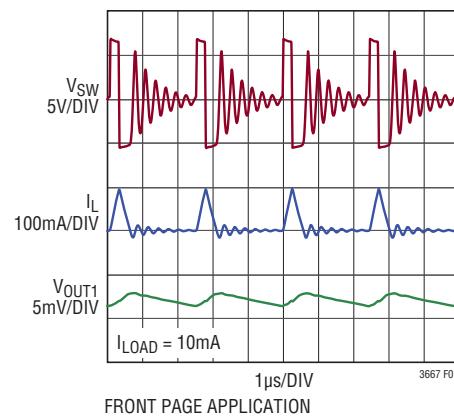

スイッチング波形、

Burst Mode動作

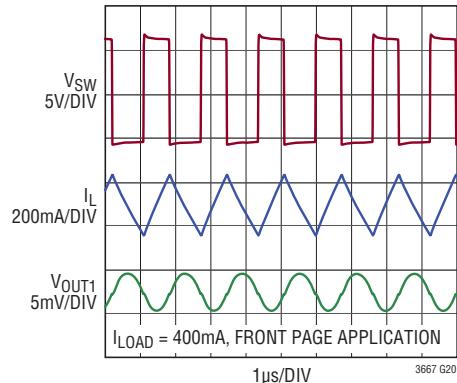

スイッチング波形、最大周波数での

連続動作

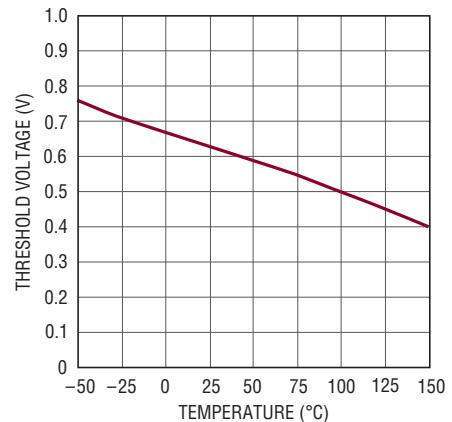

ENのしきい値

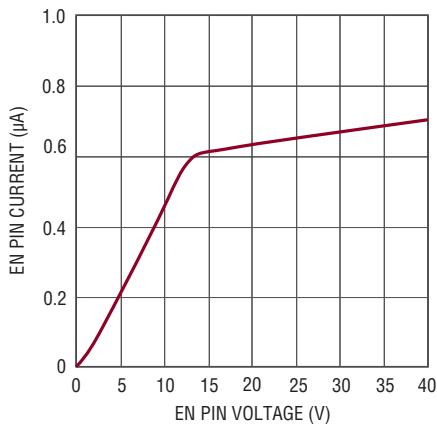

ENピンの電流

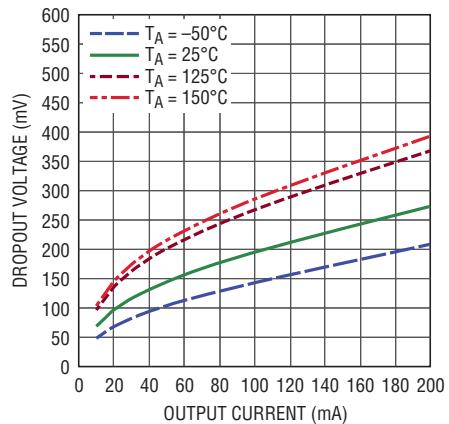

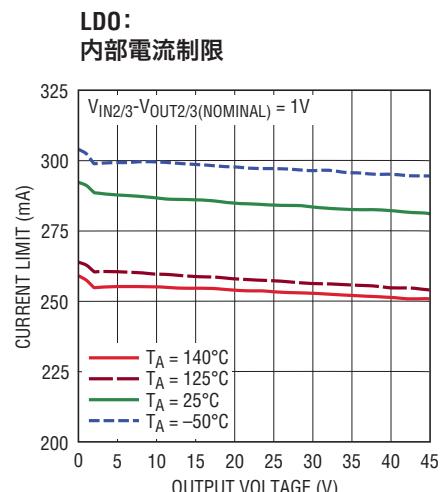

LDO:

標準ドロップアウト電圧

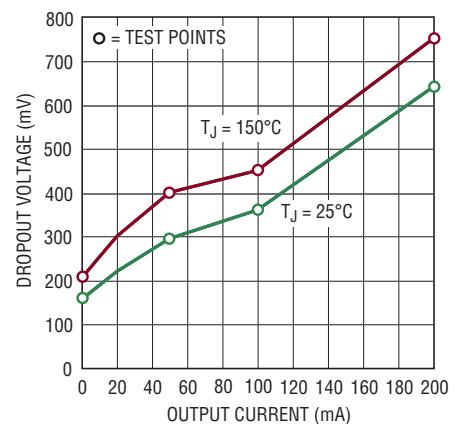

LDO:

保証されたドロップアウト電圧

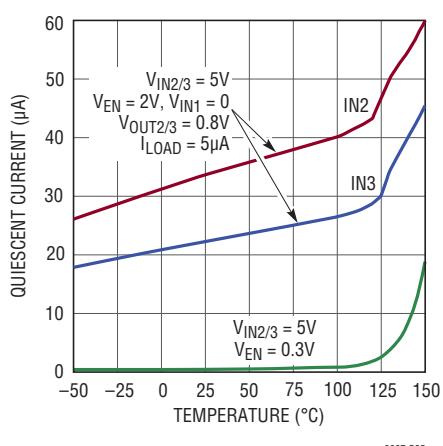

LDO:

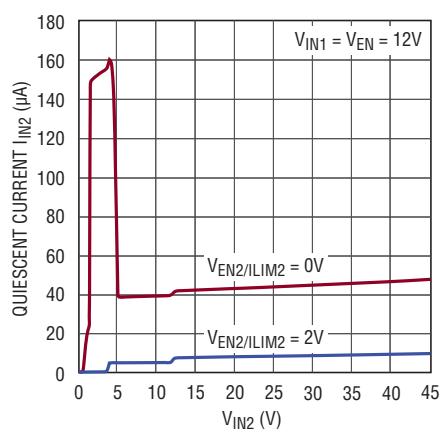

IN2, IN3の静止電流

LDO:

IN2の5V静止電流

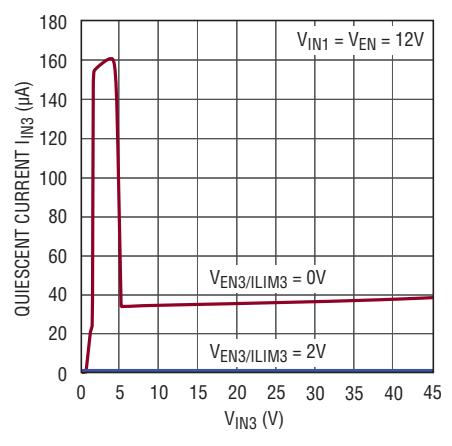

LDO:

IN3の5V静止電流

**標準的性能特性** 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

標準的性能特性 注記がない限り、 $T_A = 25^\circ\text{C}$ 。

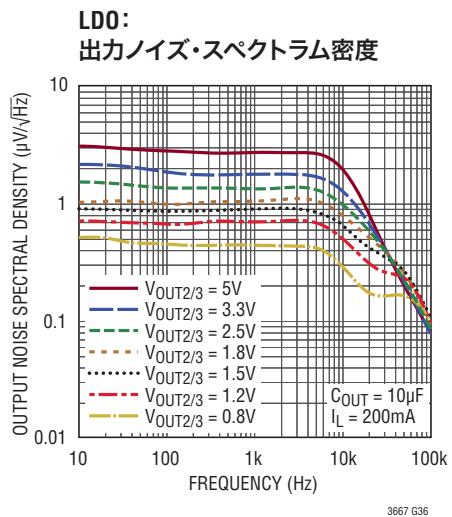

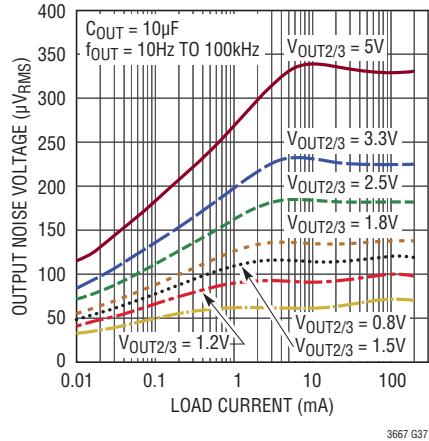

**LD0:

RMS出力ノイズ**

**LD0:

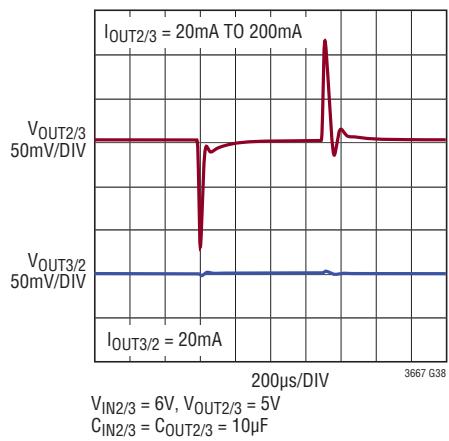

チャネル間絶縁**

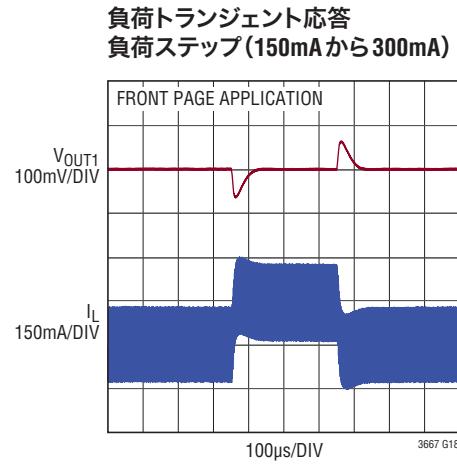

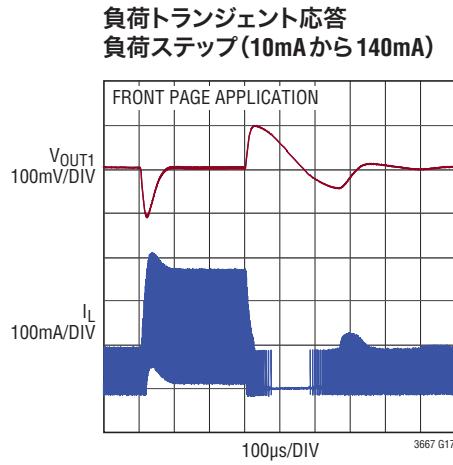

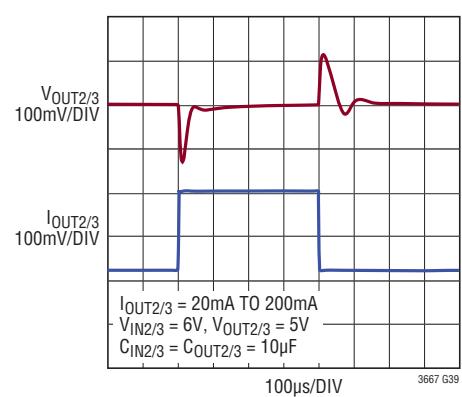

**LD0:

トランジエント応答**

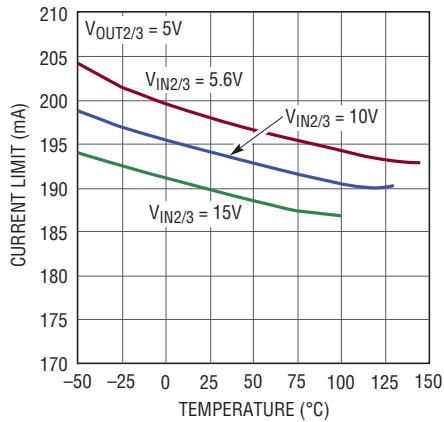

**LD0:外部電流制限、

$R_{\text{EN}}/\text{ILIM} = 1.54\text{k}$**

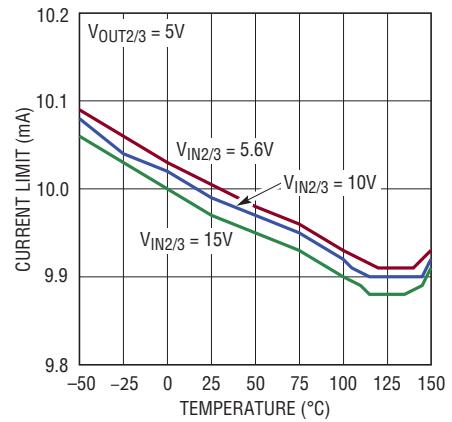

**LD0:外部電流制限、

$R_{\text{EN}}/\text{ILIM} = 6.19\text{k}$**

**LD0:外部電流制限、

$R_{\text{EN}}/\text{ILIM} = 31.6\text{k}$**

## ピン機能 (MSOP/QFN)

**SW(ピン1/ピン24)**: SWピンは、内部パワー・スイッチの出力です。このピンは、インダクタ、キャッチ・ダイオードおよび昇圧コンデンサに接続します。

**BOOST(ピン2/ピン1)**: このピンは、入力電圧より高いドライブ電圧をスイッチング・レギュレータの内蔵バイポーラNPNパワー・スイッチに与えるのに使用します。BOOSTとSWの間にコンデンサ(標準0.22μF)を接続します。

**SYNC(ピン2、QFNのみ)**: これは外部クロック同期入力です。低出力負荷での低リップルBurst Mode動作では、このピンを接地します。同期させるにはクロック・ソースに接続します。詳細については、「アプリケーション情報」の「同期」のセクションを参照してください。

**EN(ピン3/ピン3)**: ENピンはLT3667をシャットダウン・モードにするのに使用されます。グランドに接続すると、LT3667はシャットダウンします。通常動作時は1V以上の電圧に接続します。ENピンがグランドより低い電圧に引き下げられる場合には、直列抵抗を使ってピンの電流を1mAに制限します。

**RT(ピン4/ピン4)**: 発振器の抵抗入力。このピンとグランドの間に抵抗を接続して、スイッチング周波数を設定します。

**BD(ピン5、QFNのみ)**: このピンは、内部昇圧ダイオードのアノードに接続されています。また、このピンは、BDが3.2Vより高いと、LT3667の内部レギュレータに電流を供給します。

**OUT3(ピン6/ピン7)、OUT2(ピン10/ピン14)**: これらのピンは2個のLDOの出力です。安定させるには、最小2.2μFのセラミック出力コンデンサで発振を防ぐ必要があります。

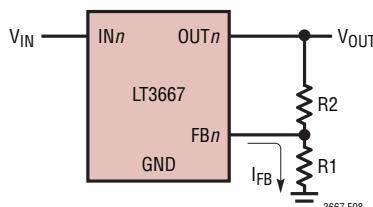

**FB3(ピン7/ピン8)、FB2(ピン9/ピン13)**: LT3667の2個のLDOは、FB2ピンとFB3ピンを0.8Vに安定化します。帰還抵抗分割器のタップをこれらのピンに接続します。

**FB1(ピン8/ピン10)**: LT3667のスイッチング・レギュレータは、FB1ピンを1.2Vに安定化します。帰還抵抗分割器のタップをこのピンに接続します。

**PG1(ピン9、QFNのみ)**: PG1ピンは、内部ウインドウ・コンパレータのオープン・ドレイン出力です。PG1は、FB1ピンが最終レギュレーション電圧の10%以内になるまで“L”に保たれ

ます。VIN1またはVIN2が最小入力電圧より高く、ENが“H”的場合、PG1出力は有効です。

**IN2(ピン11/ピン15)、IN3/BD(ピン5、MSOP)、IN3(ピン6、QFN)**: これらのピンは、2個のLDOの入力です。また、IN3/BDも内部昇圧ダイオードのアノードに接続されており、IN3/BDが3.2Vより高いときにLT3667の内部レギュレータに電流を供給します。

**PG2(ピン11、QFNのみ)**: PG2ピンは、内部ウインドウ・コンパレータのオープン・ドレイン出力です。PG2は、FB2ピンが最終レギュレーション電圧の10%以内になるまで“L”に保たれます。VIN1またはVIN2が最小入力電圧より高く、ENが“H”的場合、PG2出力は有効です。

**EN2/ILIM2(ピン12/ピン16)、EN3/ILIM3(ピン13/ピン17)**: 高精度電流制限の設定ピン。これらは、2個のLDOの出力電力PNPの1/799の大きさの電流ミラーPNPのコレクタに接続されています。これらのピンは電流制限アンプの入力でもあります。電流制限しきい値は、EN2/ILIM2ピンとGNDの間およびEN3/ILIM3ピンとGNDの間に抵抗を接続することによって設定されます。安定化するには、47nFのコンデンサをこれらの抵抗と並列接続する必要があります。このピンの抵抗値の設定方法の詳細については、「動作」のセクションを参照してください。これらのピンのいずれも使用しない場合には、GNDに接続します。LDOをディスエーブルするには、LDOのEN/ILIMピンを1.2Vより高くなります。

**PG3(ピン12、QFNのみ)**: PG3ピンは、内部ウインドウ・コンパレータのオープン・ドレイン出力です。PG3は、FB3ピンが最終レギュレーション電圧の10%以内になるまで“L”に保たれます。VIN1またはVIN2が最小入力電圧より高く、ENが“H”的場合、PG3出力は有効です。

**PG(ピン14/ピン18)**: PGピンは、内部ウインドウ・コンパレータのオープン・ドレイン出力です。PGは、FB1、FB2およびFB3ピンが最終レギュレーション電圧の10%以内になるまで“L”に保たれます。VIN1またはVIN2が最小入力電圧より高く、ENが“H”的場合、PG出力は有効です。

## ピン機能 (MSOP/QFN)

**IN1(ピン15/ピン20)**: IN1ピンは、内部レギュレータおよび内部パワー・スイッチに電流を供給します。このピンはローカルにバイパスする必要があります。

**DA(ピン16/ピン23)**: このピンには、キャッチ・ダイオード(「ブロック図」のD1)のアノードを接続します。内部回路がキャッチ・ダイオードを介して電流を検出することにより、過負荷状態での周波数フォールドバックが行われます。

**GND(露出パッド・ピン17/露出パッド・ピン25)**: GNDは、すべての内部回路のグランドであり、キャッチ・ダイオード(D1)で使用される電源グランドでもあります。露出パッドはPCBに半田付けする必要があります。

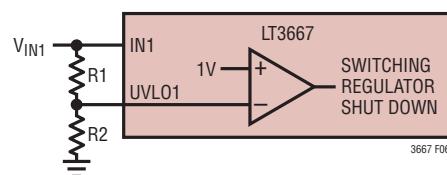

**UVLO1(ピン19、QFNのみ)**: このピンの1Vの高精度しきい値電圧は、高精度低電圧ロックアウト(UVLO)として機能することができます。UVLO1ピンの電圧がこのしきい値を超えると、スイッチング・レギュレータのみが動作します。LDOはこのピンの影響を受けません。

**NC(ピン21、22、QFNのみ)**: これらのピンは内部で接続されていないので、開放のままにするか、またはグランドに接続することができます。

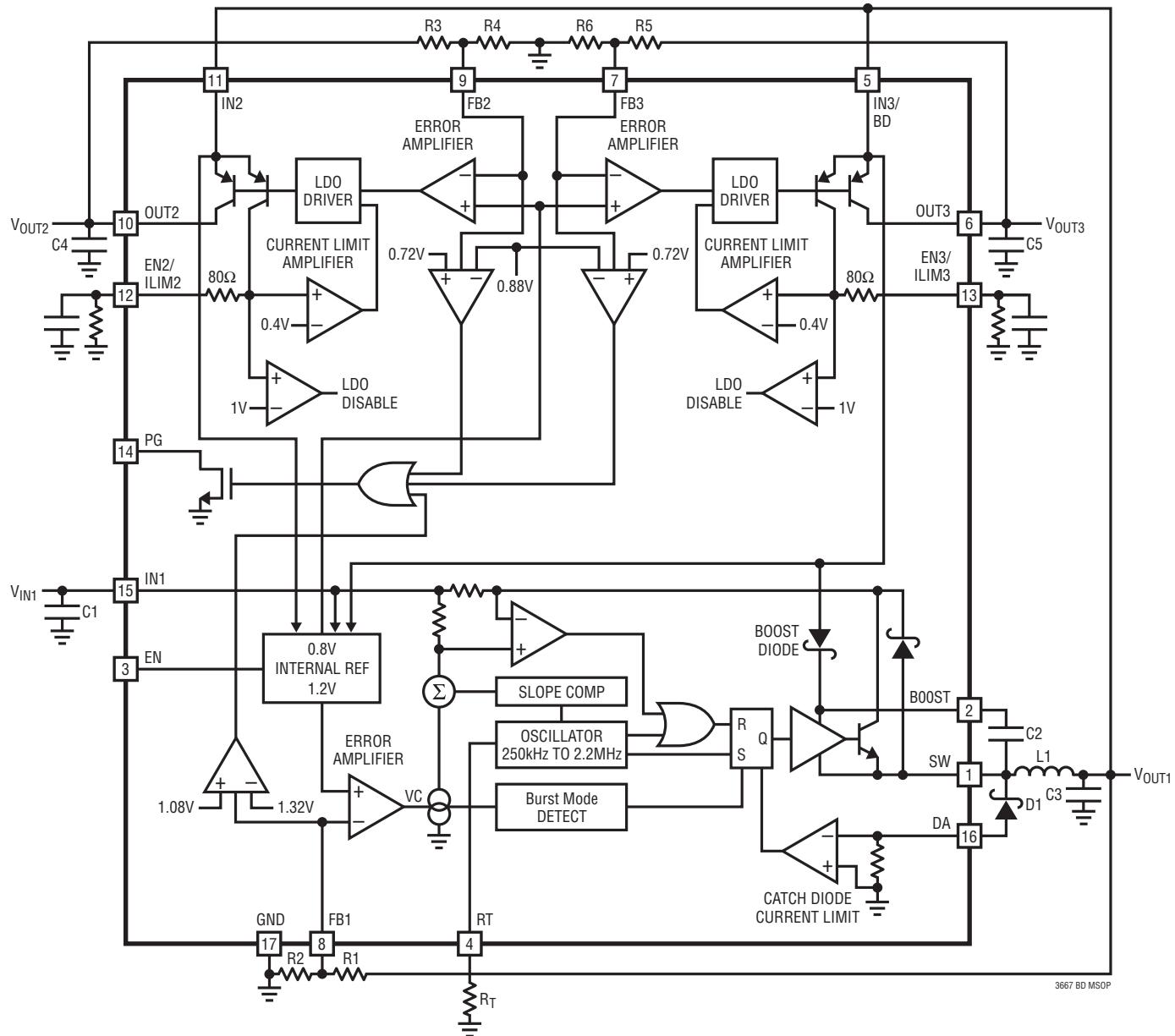

## ブロック図 (MSOP)

3667 BD MSOP

# LT3667

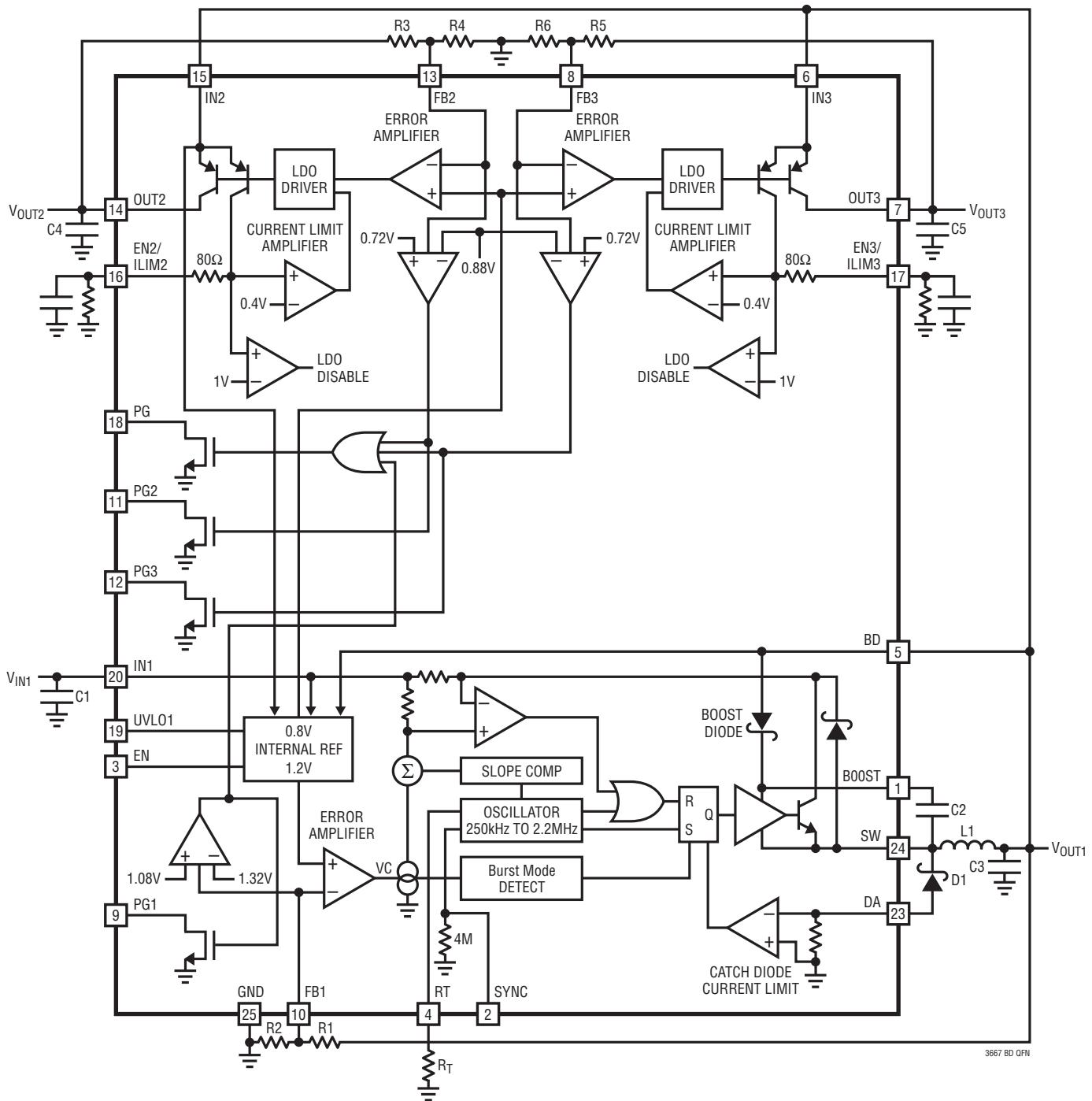

ブロック図 (QFN)

3667fb

## 動作

LT3667は、400mA降圧スイッチング・レギュレータと2個の200mA低ドロップアウト・レギュレータを組み合わせたデバイスです。「ブロック図」を参照すると、動作をよく理解できます。

降圧レギュレータの部分は、固定周波数の電流モード降圧レギュレータです。周波数が $R_T$ で設定される発振器により、RSフリップフロップがセットされ、内部のパワースイッチがオンします。アンプおよびコンパレータはIN1ピンとSWピン間を流れる電流をモニタし、この電流がVCの電圧によって決まるレベルに達するとスイッチをオフします。エラーアンプはFB1ピンに接続された外付け抵抗分割器を介して出力電圧を測定し、VCノードをサーボ制御します。エラーアンプの出力が増加すると出力に供給される電流が増加します。エラーアンプの出力が減少すると供給される電流が減少します。

別のコンパレータがキャッチ・ダイオードを通じて流れる電流をモニタし、電流が500mAのボトム電流制限値を超えると動作周波数を下げます。この周波数フォールドバックは、高い入力電圧での短絡出力など、フォルト状態の出力電流を制御するのに役立ちます。したがって、出力へ供給可能な最大電流は、スイッチの電流制限とキャッチ・ダイオードの電流制限の両方によって制限されます。

内部レギュレータが制御回路に電力を供給します。このバイアス・レギュレータは、通常IN1ピンから電力を供給されますが、3.2Vより高い外部電圧にIN3/BDピン(MSOP)またはBDピン(QFN)を接続すると、BIAS電源は外部ソース(通常は安定化出力電圧)から供給されます。これにより効率が改善されます。

スイッチ・ドライバは、IN1ピンまたはBOOSTピンのどちらかで動作します。外付けのコンデンサを使って、入力電源より高い電圧をBOOSTピンに発生させます。これにより、ドライバは内蔵のNPNパワー・スイッチを飽和させ、高い効率で動作させることができます。

効率をさらに最適化するため、LT3667は軽負荷状態ではBurst Mode動作に自動的に切り替わります。バーストとバーストの間では、出力スイッチの制御に関連したすべての回路がシャットダウンし、入力電源電流が50µA(LDOから流れる電流を含む)に低下します。

スイッチング・レギュレータは、トランジエント時にIN1が42V(標準)を超えるとスイッチング動作をディスエーブルする過電圧保護機能を備えています。したがって、最大60Vのトランジエント入力電圧に耐えることができます。

スイッチング・レギュレータは、UVLO1ピンによって個別にシャットダウンすることもできます。UVLO1ピンは、外付け抵抗分割器によるプログラム可能な低電圧ロックアウトを実行するのに使用できます。

LDOのブロックは、低ドロップアウト電圧で電流制限機能を備えた、マイクロパワー、低ノイズ200mAリニア・レギュレータで、最小2.2µFの低ESRセラミック出力コンデンサを使って高速トランジエント応答を実現します。各出力電流制限は1つの抵抗で個別に設定可能で、EN2/ILIM2ピンまたはEN3/ILIM3ピンを“H”にすると、対応するLDOがシャットダウンします。内部保護回路には、バッテリ逆接続保護、逆出力保護、逆電流保護、フォールドバックによる電流制限などの機能があります。

内部リファレンス電圧回路は、IN1ピンとIN2ピンによって形成されます。これにより、IN2のLDOが個別に動作し、LDOの出力OUT2をスイッチング・レギュレータに供給することができます。

ENピンを使ってLT3667をシャットダウン状態にすることにより、入力電流を1µA未満に低減します。

LT3667は、出力電圧が公称値の±10%であるかどうかを示す3個のパワーグッド・ウィンドウ・コンパレータを備えています。これらのコンパレータの出力は、対応する出力がレギュレーション状態のときにオフになるオープン・ドレイン・トランジスタなので、外付け抵抗でパワーグッド・ピンを“H”に引き上げることができます。PGピンには混合されたパワーグッド信号が出力されますが、QFNパッケージでは、さらにピンPG1、PG2およびPG3を介して各パワーグッド信号にアクセスすることができます。LT3667がイネーブルされていてIN1またはIN2が最小入力電圧より高いと、パワーグッドは有効です。

過負荷状態では、内部熱制限によってLT3667が保護されます。

## アプリケーション情報

### スイッチング・レギュレータ

#### FB1の抵抗回路網

LT3667のスイッチング・レギュレータの出力電圧は、スイッチング・レギュレータの出力とFB1ピンの間の抵抗分割器で設定されます。次式に従って抵抗値を選択します。

$$R1=R2\left(\frac{V_{OUT1}}{1.2V}-1\right)$$

参照名については、LT3667の「ブロック図」を参照してください。出力電圧の精度を保つため、誤差1%の抵抗を推奨します。大きな抵抗を選択するほどアプリケーション回路の静止電流が減少することに注意してください。

#### スイッチング周波数の設定

LT3667レギュレータでは、RTピンとグランドの間に接続した1本の抵抗を使用して250kHz～2.2MHzの範囲でスイッチングするよう設定できる固定周波数のPWMアーキテクチャが採用されています。望みのスイッチング周波数の設定に必要なRT値を表1に示します。

表1. スイッチング周波数とRTの値

| SWITCHING FREQUENCY (MHz) | R <sub>T</sub> VALUE (kΩ) |

|---------------------------|---------------------------|

| 0.25                      | 475                       |

| 0.3                       | 383                       |

| 0.4                       | 274                       |

| 0.5                       | 215                       |

| 0.6                       | 174                       |

| 0.8                       | 124                       |

| 1                         | 95.3                      |

| 1.2                       | 75                        |

| 1.4                       | 61.9                      |

| 1.6                       | 51.1                      |

| 1.8                       | 43.2                      |

| 2                         | 37.4                      |

| 2.2                       | 32.4                      |

#### 動作周波数のトレードオフ

動作周波数の選択は、効率、部品サイズ、最小ドロップアウト電圧、および最大入力電圧の間のトレードオフになります。高周波数動作の利点は、小さな値のインダクタとコンデンサを使用できることです。不利な点は、効率が下がり、最大入力電圧が下がり、ドロップアウト電圧が大きくなることです。与えられたアプリケーションで許容できる最高スイッチング周波数(f<sub>SW</sub>(MAX))は、次のように計算することができます。

$$f_{SW(MAX)} = \frac{V_{OUT1} + V_D}{t_{ON(MIN)}(V_{IN1} - V_{SW} + V_D)}$$

ここで、V<sub>IN1</sub>は標準入力電圧、V<sub>OUT1</sub>は出力電圧、V<sub>D</sub>はキャッチ・ダイオードの電圧降下(約0.5V)、V<sub>SW</sub>は内部スイッチの電圧降下(最大負荷で約0.5V)です。この式は、高いV<sub>IN1</sub>/V<sub>OUT1</sub>比に対応するには、スイッチング周波数を下げる必要がありますことを示しています。

また、周波数を下げるとき、ドロップアウト電圧を小さくすることができます。LT3667のスイッチには有限の最小オン時間と最小オフ時間があるため、入力電圧範囲はスイッチング周波数に依存します。このスイッチは、約150nsの最小時間でオンし、約170nsの最小時間でオフすることができます(最小オン時間は温度に大きく依存することに注意)。最小オン時間と最小オフ時間を考慮すると、達成できる最小と最大のデューティ・サイクルは次のようになります。

$$DC_{MIN} = f_{SW} \cdot t_{ON(MIN)}$$

$$DC_{MAX} = 1 - f_{SW} \cdot t_{OFF(MIN)}$$

ここで、f<sub>sw</sub>はスイッチング周波数、t<sub>ON(MIN)</sub>はスイッチの最小オン時間(約150ns)、t<sub>OFF(MIN)</sub>はスイッチの最小オフ時間(約170ns)です。これらの式は、スイッチング周波数が低下するにつれ、デューティ・サイクルの範囲が増加することを示しています。

スイッチング周波数の選択が適切だと、適切な入力電圧範囲が可能になり(「入力電圧範囲」のセクションを参照)、インダクタとコンデンサの値が小さく保たれます。

## アプリケーション情報

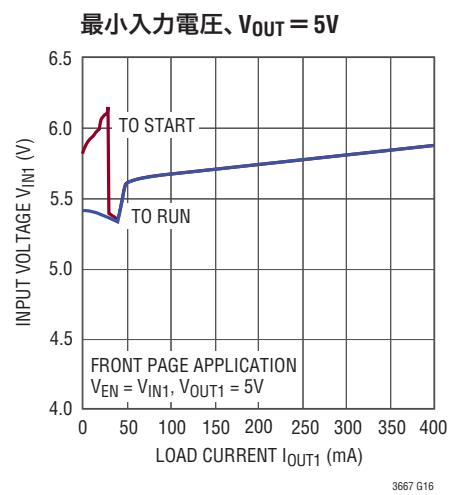

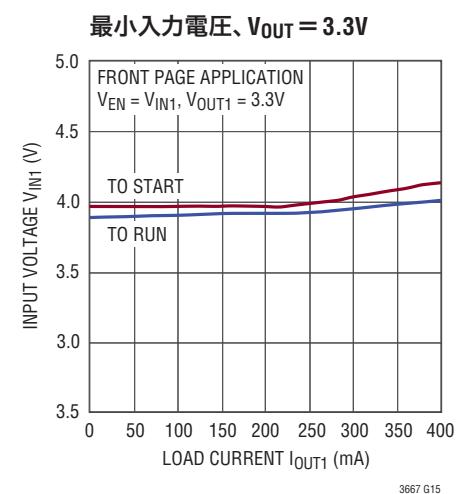

### 入力電圧範囲

最小入力電圧は、LT3667の4.3Vの最小動作電圧または(前のセクションで説明した)最大デューティ・サイクルのどちらかによって決まります。デューティ・サイクルによる最小入力電圧は次のとおりです。

$$V_{IN1(MIN)} = \frac{V_{OUT1} + V_D}{1 - f_{SW} \cdot t_{OFF(MIN)}} - V_D + V_{SW}$$

ここで、 $V_{IN1(MIN)}$ は最小入力電圧、 $V_{OUT1}$ は出力電圧、 $V_D$ はキャッチ・ダイオードの電圧降下(約0.5V)、 $V_{SW}$ は内部スイッチの電圧降下(最大負荷で約0.5V)、 $f_{SW}$ はスイッチング周波数、 $t_{OFF(MIN)}$ はスイッチの最小オフ時間(約170ns)です。スイッチング周波数が高いほど、最小入力電圧が増加することに注意してください。ドロップアウト電圧を小さくしたい場合は、低いスイッチング周波数を使用します。

通常動作時に許容される最高 $V_{IN1}$ ( $V_{IN1(OP-MAX)}$ )は最小デューティ・サイクルによって制限され、次式で与えられます。

$$V_{IN1(OP-MAX)} = \frac{V_{OUT1} + V_D}{f_{SW} \cdot t_{ON(MIN)}} - V_D + V_{SW}$$

ここで、 $V_{OUT1}$ は出力電圧、 $V_D$ はキャッチ・ダイオードの電圧降下(約0.5V)、 $V_{SW}$ は内部スイッチの電圧降下(最大負荷で約0.5V)、 $f_{SW}$ はスイッチング周波数、 $t_{ON(MIN)}$ はスイッチの最小オン時間(約150ns)です。

ただし、選択されたスイッチング周波数に関係なく、LT3667は $V_{IN1}$ ピンとBOOSTピンの絶対最大定格までの入力に耐えます。このようなトランジエントの間に $V_{IN1}$ が $V_{IN1(OP-MAX)}$ より高くなると、デバイスはパルスをスキップして出力レギュレーションを維持します。出力電圧リップルとインダクタ電流リップルが通常動作時より大きくなります。LT3667は、最大60Vの入力トランジエント電圧にも確実に耐えますが、 $V_{IN1}$ が $V_{OVLO}$ (過電圧ロックアウト、標準42V)より高いときにはスイッチングを停止して、出力をレギュレーション状態から外します。

起動、短絡などの過負荷状態の間、特にスイッチが既に最小オン時間で動作している場合に、インダクタ・ピーク電流はLT3667の最大電流制限に到達し、さらにそれを超えることさえあります。インダクタの谷電流が公称500mAを超えると、キャッチ・ダイオードによる電流制限回路により、スイッチが再びオンになるのが防止されます。

### インダクタの選択と最大出力電流

与えられた入力電圧と出力電圧に対して、インダクタ値とスイッチング周波数によってリップル電流が決まります。リップル電流は、 $V_{IN1}$ または $V_{OUT1}$ が高いほど増加し、インダクタンスが大きくスイッチング周波数が高いほど減少します。

最初に選択するインダクタの値としては、次の値が適切です。

$$L = (V_{OUT1} + V_D) \cdot \frac{2.4}{f_{SW}}$$

ここで、 $f_{SW}$ はMHzが単位のスイッチング周波数、 $V_{OUT1}$ は出力電圧、 $V_D$ はキャッチ・ダイオードの電圧降下(約0.5V)、 $L$ はμHが単位のインダクタ値です。インダクタのRMS電流定格は最大負荷電流より大きくなければならず、その飽和電流は約30%大きくなければなりません。フォルト状態(起動または短絡時)や高入力電圧(>30V)で堅牢な動作を実現するには、飽和電流を900mAより大きさします。高い効率を保つには、直列抵抗(DCR)が0.3Ωより小さく、コア材が高周波アプリケーション向けのものにする必要があります。いくつかのメーカーを表2に示します。

表2. インダクタ・メーカー

| VENDOR           | URL                                                      |

|------------------|----------------------------------------------------------|

| Coilcraft        | <a href="http://www.coilcraft.com">www.coilcraft.com</a> |

| Sumida           | <a href="http://www.sumida.com">www.sumida.com</a>       |

| Toko             | <a href="http://www.tokoam.com">www.tokoam.com</a>       |

| Würth Elektronik | <a href="http://www.we-online.com">www.we-online.com</a> |

| Coiltronics      | <a href="http://www.cooperet.com">www.cooperet.com</a>   |

| Murata           | <a href="http://www.murata.com">www.murata.com</a>       |

## アプリケーション情報

この簡単なデザイン・ガイドでは、特定のアプリケーションに最適のインダクタの選択肢を常に与えるとは限りません。一般則として、出力電圧が低くスイッチング周波数が高いほど、小さいインダクタ値を必要とします。アプリケーションが必要とする負荷電流が400mA未満なら、もっと小さなインダクタ値を使用することができます。このため、物理的に小さいインダクタを使用することや、DCRの小さいものを使用して効率を高めることができます。ただし、通常、インダクタンスを10 $\mu$ Hより小さくしてはなりません。

上述の簡単な一般則と異なるインダクタンスの場合、最大負荷電流は入力電圧に依存することに注意してください。また、インダクタンスが小さいと不連続モード動作になることがあります。最大負荷電流がさらに減少します。最大出力電流と不連続モード動作の詳細については、「アプリケーションノート44」を参照してください。最後に、デューティ・サイクルが50%を超える場合( $V_{OUT1}/V_{IN1} > 0.5$ )、低調波発振を防ぐためにインダクタンスを最小限に抑える必要があります。

$$L_{MIN} = (V_{OUT1} + V_D) \cdot \frac{2}{f_{SW}}$$

ここで、 $f_{SW}$ はMHzが単位のスイッチング周波数、 $V_{OUT1}$ は出力電圧、 $V_D$ はキャッチ・ダイオードの電圧降下(約0.5V)、 $L_{MIN}$ は $\mu$ Hが単位のインダクタ値です。

### キャッチ・ダイオード

キャッチ・ダイオード(「ブロック図」のD1)はスイッチのオフ時間の間だけ電流を流します。最高の性能を得るには、1Aのショットキ・ダイオードを使用します。

ピーク逆電圧は、過電圧保護しきい値を下回ると、 $V_{IN1}$ に等しくなります。この機能により、 $V_{IN1}$ がOVLO(最大44V)よりも高いときにはスイッチがオフに保たれます。40Vの最大動作電圧までの入力では、逆電圧定格が入力電圧よりも高いダイオードを使用します。最大60Vの入力でのトランジエントが予想される場合には、逆電圧定格が44Vの最大OVLOよりも少しでも高いダイオードを使用します。高い周囲温度で動作する場合、逆漏れ電流が小さいショットキ・ダイオードの使用を検討してください。例えば、Diodes Inc.のSBR1U40LPまたはDFLS160、ON SemiのMBRM140、Central SemiconductorのCMMSH1-60はキャッチ・ダイオードに最適です。

### 入力コンデンサ

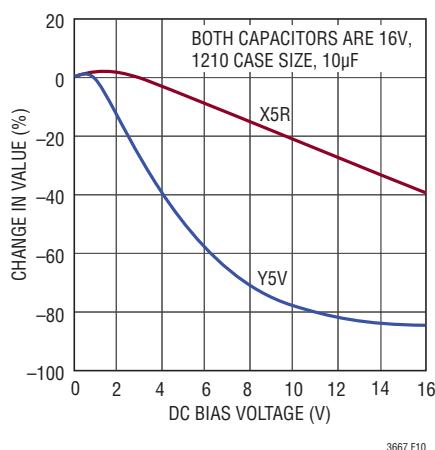

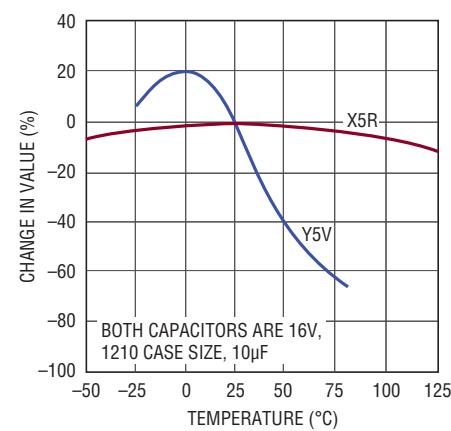

X7RまたはX5Rタイプのセラミック・コンデンサを使って、LT3667回路の入力をバイパスします。Y5Vタイプは、温度や印加される電圧が変化すると性能が低下するので使用しないでください。LT3667をバイパスするには1 $\mu$ F～4.7 $\mu$ Fのセラミック・コンデンサが適しており、リップル電流を容易に処理できます。低いスイッチング周波数を使用すると(オン時間が長くなるので)、大きな入力容量が必要になることに注意してください。入力電源のインピーダンスが高いか、長い配線やケーブルによる大きなインダクタンスが存在する場合、追加のバルク容量が必要になることがあります。これには性能の高かない電解コンデンサを使用することができます。降圧レギュレータには、立ち上がり時間と立ち下がり時間の短いパルス電流が入力電源から流れます。その結果として生じるLT3667での電圧リップルを減らし、周波数が非常に高いこのスイッチング電流を狭い範囲のループに押し込めてEMIを最小限に抑えるために、入力コンデンサが必要です。1 $\mu$ Fのコンデンサをこの用途に使用できますが、LT3667の近くに配置できる場合に限ります(「PCBレイアウト」のセクションを参照)。セラミック入力コンデンサに関する2つ目の注意点は、LT3667の最大入力電圧定格に関することです。セラミック入力コンデンサは、トレースやケーブルのインダクタンスと結合して、質の良い(減衰の小さな)タンク回路を形成します。LT3667の回路を通電中の電源に差し込むと、入力電圧に公称値の2倍のリンギングが生じてLT3667の電圧定格を超える恐れがあります。この状況は容易に避けられます(「安全な活線挿入」のセクションを参照)。

### 出力コンデンサと出力リップル

出力コンデンサには2つの基本機能があります。出力コンデンサは、インダクタとともに、LT3667が発生する方形波をフィルタにしてDC出力を生成します。この機能では出力コンデンサは出力リップルを決定するので、スイッチング周波数でのインピーダンスが小さいことが重要です。2番目の機能は、トランジエント負荷を満たしてスイッチング・レギュレータの制御ループを安定させるためにエネルギーを蓄えることです。セラミック・コンデンサは、等価直列抵抗(ESR)が非常に小さいので最良のリップル性能が得られます。出発点としては、次の値が適当です。

$$C_{OUT1} = \frac{50}{V_{OUT1} \cdot f_{SW}}$$

## アプリケーション情報

ここで、 $f_{SW}$ の単位はMHz、 $C_{OUT1}$ は $\mu F$ が単位の推奨出力容量です。X5RまたはX7Rのタイプを使用してください。この選択により、出力リップルが小さくなり、トランジエント応答が良くなります。出力とFB1ピンの間の位相リード・コンデンサ(標準22pF)と組み合わせて、もっと大きな値のコンデンサを使用すると、トランジエント性能を改善することができます。大きな出力コンデンサには大きな位相リード・コンデンサを使用するように注意してください。スペースとコストを節約するため、もつと小さな値の出力コンデンサを使用することもできますが、トランジエント性能が低下します。

コンデンサを選択するときは、データシートを注意深く調べて、動作条件(加えられる電圧や温度)での実際の容量を確認してください。物理的に大きなコンデンサまたは電圧定格が高いコンデンサが必要なことがあります。表3にいくつかのコンデンサ・メーカーを示します。

表3. コンデンサ・メーカー

| VENDOR      | URL                                                          |

|-------------|--------------------------------------------------------------|

| Panasonic   | <a href="http://www.panasonic.com">www.panasonic.com</a>     |

| Kemet       | <a href="http://www.kemet.com">www.kemet.com</a>             |

| Sanyo       | <a href="http://www.sanyovideo.com">www.sanyovideo.com</a>   |

| Murata      | <a href="http://www.murata.com">www.murata.com</a>           |

| AVX         | <a href="http://www.avxcorp.com">www.avxcorp.com</a>         |

| Taiyo Yuden | <a href="http://www.taiyo-yuden.com">www.taiyo-yuden.com</a> |

### 可聴ノイズ

セラミック・コンデンサは小さく堅牢で、ESRが非常に小さいコンデンサです。ただし、セラミック・コンデンサには圧電特性があるため、LT3667と一緒に使用すると問題が発生することがあります。Burst Mode動作のとき、LT3667のスイッチング周波数は負荷電流に依存し、非常に軽い負荷ではLT3667はセラミック・コンデンサを可聴周波数で励起し、可聴ノイズを発生することがあります。LT3667は、Burst Mode動作中は低い電流制限値で動作するため、ノイズは通常は非常に静かです。それでも許容できない場合、高性能のタンタル・コンデンサまたは電解コンデンサを出力に使用します。

### 低リップル Burst Mode動作

軽負荷での効率を向上させるため、LT3667は低リップル Burst Modeで動作し、入力静止電流を最小限に抑えながら、出力コンデンサを適切な電圧に充電された状態に保ちます。LT3667は、Burst Mode動作の間1サイクルのバーストで電流を出力コンデンサに供給し、それに続くスリープ期間には出力コンデンサから出力電力を負荷に供給します。LT3667は1個の低電流パルスで電力を出力に供給するので、標準的のアプリケーションでは出力リップルが5mV以下に保たれます。負荷電流が無負荷状態に向かって減少するにつれ、LT3667がスリープ・モードで動作する時間の割合が増加し、平均入力電流が大きく減少するので非常に小さい負荷でも効率が高くなります。Burst Mode動作の間、スイッチング周波数はプログラマされた周波数より低くなることに注意してください。

大きい出力負荷(表紙のアプリケーションでは50mA以上)では、LT3667は $R_T$ 抵抗で設定された周波数で動作し、標準的 PWMモードで動作します。PWMと低リップル Burst Mode動作の間の移行はシームレスで、出力電圧を乱しません。

図1.Burst Mode動作

## アプリケーション情報

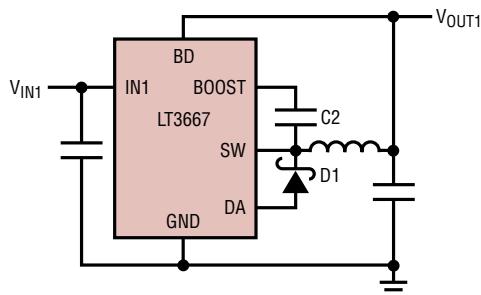

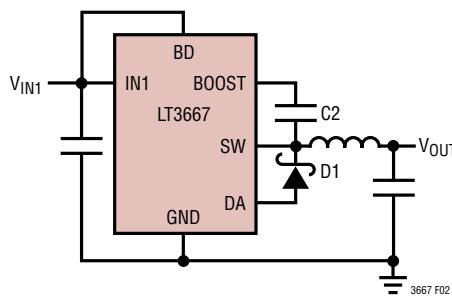

### BOOSTピンとBD、IN3/BDピンに関する検討事項

入力電圧より高い昇圧電圧を発生させるため、コンデンサC2と内部昇圧ショットキ・ダイオード（「ブロック図」を参照）が使用されます。ほとんどの場合、 $0.22\mu F$ のコンデンサで問題なく動作します。昇圧回路の2通りの構成方法を図2に示します。最高の効率を得るには、BOOSTピンの電圧をSWピンより1.9V以上高くする必要があります。2.2V以上の出力の場合は、標準回路（図2a）が最適です。2.2V～2.5Vの出力には、 $0.47\mu F$ の昇圧コンデンサを使用します。出力電圧が2.2Vより低い場合、昇圧ダイオードを入力（図2b）または2.2Vより高い別の外部電源に接続することができます。ただし、電圧の低い方の電圧源からBOOSTピンの電流とBDピンの静止電流が供給されるので、図2aの回路の方が効率が高くなります。また、BOOSTピンとBDピンの最大電圧定格を超えないようにします。

LT3667のアプリケーションの最小動作電圧は、前のセクションで説明されているように、最小入力電圧（4.3V）と最大デューティ・サイクルによって制限されます。正しく起動するために、最小入力電圧は昇圧回路によっても制限されます。入力電圧をゆっくり上昇させると、昇圧コンデンサが満充電されないことがあります。昇圧コンデンサはインダクタに蓄えられた

(2a) For  $V_{OUT1} \geq 2.2V$

(2b) For  $V_{OUT1} < 2.2V$ ;  $V_{IN1} < 25V$

図2. 昇圧電圧を発生させる2つの回路

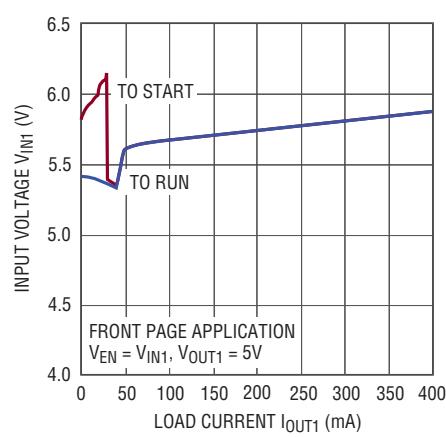

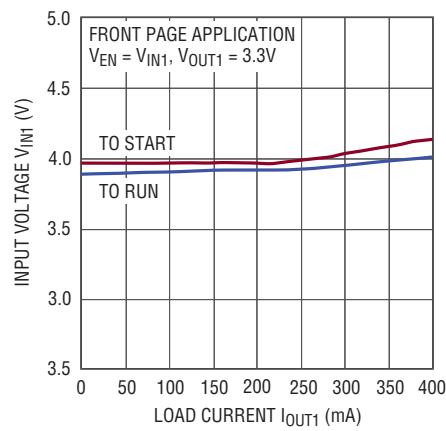

エネルギーによって充電されるので、昇圧回路を適切に動作させるため、回路はいくらかの最小負荷電流を必要とします。この最小負荷は、入力電圧、出力電圧、および昇圧回路の構成により異なります。回路が起動した後は、最小負荷電流は通常ゼロになります。起動および動作に必要な最小負荷電流と入力電圧の関係をプロットしたものを図3に示します。多くの場合、放電した出力コンデンサがスイッチャの負荷となるので、スイッチャは起動できます。プロットは、 $V_{IN1}$ が非常にゆっくり上昇するワーストケースの状態を示しています。起動電圧が低い場合は昇圧ダイオードを $V_{IN1}$ に接続できますが、こうすると、入力電圧範囲はBOOSTピンの絶対最大定格の半分に制限されます。

図3. 最小入力電圧は出力電圧、負荷電流および昇圧回路に依存する

## アプリケーション情報

### 同期(QFNのみ)

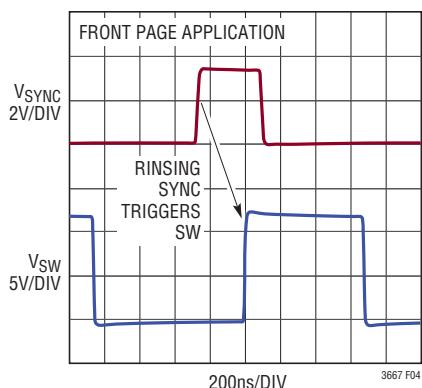

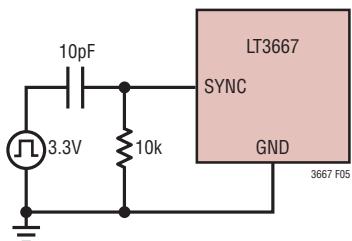

SYNCピンにデジタル・クロック信号を接続することにより、LT3667の発振器を外部周波数に同期させることができます。この場合、図4に示すように、LT3667はSWノードをこのクロック信号の立ち上がりエッジに同期させます。方形波の振幅は、0.5Vより下の谷と1.2Vより上(最大6V)の山が必要で、オン時間とオフ時間が50nsを下回ってはなりません。SYNCの立ち上がりエッジと、スイッチの最小オフ時間にある程度起因するSWの立ち上がりエッジの間には、標準280nsの時間遅延があります。SWの立ち下がりエッジはSYNCの立ち下がりエッジに影響されるので、SYNCのクロック信号のデューティ・サイクルのオン時間ができるだけ短く保つように調整することを推奨します。あるいは、図5に示すAC結合を使ってクロック信号のオン時間を短くすることができます。

図4. 同期信号の波形

図5.SYNCクロック信号のAC結合の例

LT3667は、外部クロックに同期しているときは低出力負荷でもBurst Mode動作になりますが、バースト・パルスはクロック信号に同期します。同期が不要な場合、SYNCピンを接地する必要があります。このピンは1.2V(ロジック“H”)より高い電圧に接続することもできますが、SYNCからグランドに4M抵抗が内蔵されており、この抵抗に電流が流れることに注意してください。

LT3667は300kHz～2.2MHzの範囲にわたって同期させることができます。R<sub>T</sub>抵抗は、スイッチング周波数を最低同期入力より20%低く設定するように選択します。たとえば、同期信号が360kHzの場合は、300kHzになるようにR<sub>T</sub>を選択します。また、低調波発振を防ぐスロープ補償がR<sub>T</sub>によって設定されるので、最小インダクタ値はR<sub>T</sub>で決まる周波数を使用して計算する必要があります。

### UVLO1ピン(QFNのみ)

LT3667のスイッチング・レギュレータの部分は、UVLO1ピンを介して個別にディスエーブルすることができます。UVLO1コンパレータの下降しきい値は1Vで、75mVのヒステリシスがあります。V<sub>IN1</sub>とV<sub>IN2</sub>が4.3Vを下回るとUVLO1ピンは無効になるので、内部低電圧ロックアウトがLT3667をシャットダウン状態に保ちます。

図6に示すように、IN1からUVLO1に抵抗分割器を追加すると、V<sub>IN1</sub>が次式で与えられるしきい値電圧V<sub>IN</sub>(UVLO1)より高いときだけスイッチング・レギュレータをイネーブルするように、LT3667が設定されます。

$$V_{IN(UVLO1)} = \frac{R1+R2}{R2} \cdot 1V$$

コンパレータのヒステリシスのため、入力がV<sub>IN</sub>(UVLO1)をわずかに上回るまでスイッチング・レギュレータはイネーブルされないことに注意してください。

図6.UVLO1ピンにより、プログラム可能な低電圧ロックアウトまたはスイッチング・レギュレータの個別のディスエーブルが可能

### 短絡入力保護と逆入力保護

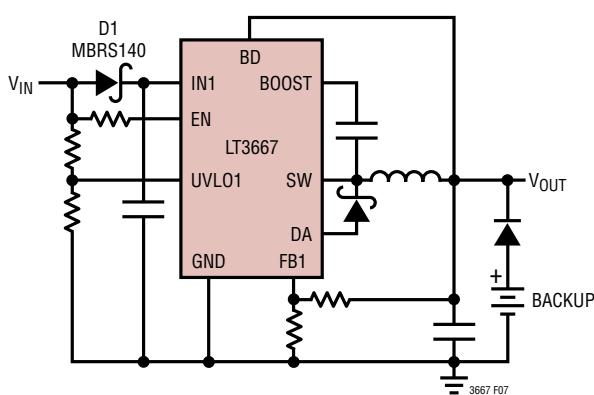

過度に飽和しないようにインダクタを選択すれば、スイッチング・レギュレータは出力短絡に耐えます。LT3667に入力が加わっていなくても出力が高い電圧に保たれるシステムでは、考慮すべき状況がもう1つあります。この状況は、バッテリ充電アプリケーション、またはバッテリや他の電源がスイッチング・レギュレータの出力とダイオードOR接続されているバッテリ・バックアップ・システムで発生することができます。IN1ピンを

## アプリケーション情報

フロート状態にすることができる場合で、ENピンとUVLO1ピンが(ロジック信号によって、あるいはIN1に接続されているために)高い電圧に保たれないと、SWピンを介してLT3667の内部回路に静止電流が流れます。この状態で数μAの電流を許容できるシステムであれば、問題ありません。ENピンまたはUVLO1ピンが接地されると、SWピンの電流は実質的に0.7μAに低下します。ただし、出力が高い電圧に保たれた状態でIN1ピンを接地すると、ENとUVLO1には関係なく、出力からSWピンおよびIN1ピンを通って、LT3667内部の寄生ダイオードに電流が流れる可能性があります。入力電圧が存在しているときにのみ動作し、短絡入力や逆入力から保護する回路を図7に示します。代わりに、「アプリケーション情報」のセクションの「LDO」に示すように、OUT2のLDOからスイッチング・レギュレータに給電することができます。

図7. ダイオードD1は、出力に接続されたバックアップ用バッテリが短絡入力によって放電するのを防ぐ。また、逆入力から回路を保護する。この場合、ENピンの抵抗がこのピンから流れる電流を制限する。LT3667は入力が与えられているときだけ動作する

## LDO

### FB2/FB3抵抗回路網

図8に示すように、LT3667の各LDOの出力電圧は、LDOの出力とFB2/FB3ピンの間の抵抗分割器で設定されます。各FB2/FB3ピンのピン電流 $I_{FB}$ (25°Cで3nA、150°Cで±40nA)が各ピンから流れ出す結果、次のようにになります。

$$V_{OUT} = 0.8V \left( \frac{R2}{R1} + 1 \right) - I_{FB} \cdot R2$$

FB2/FB3ピンの電流によって生じる出力電圧の誤差を最小限に抑えるため、R1の値が160kより大きくならないようにして最小5μAの負荷電流を確保します。整理し直してR2を求めるところのようになります。

$$R2 = \frac{0.8V - V_{OUT}}{I_{FB} - 0.8V/R1}$$

小さな抵抗を選択するほどアプリケーション回路の静止電流が増加することに注意してください。

図8. 各LDOの出力電圧の設定

## アプリケーション情報

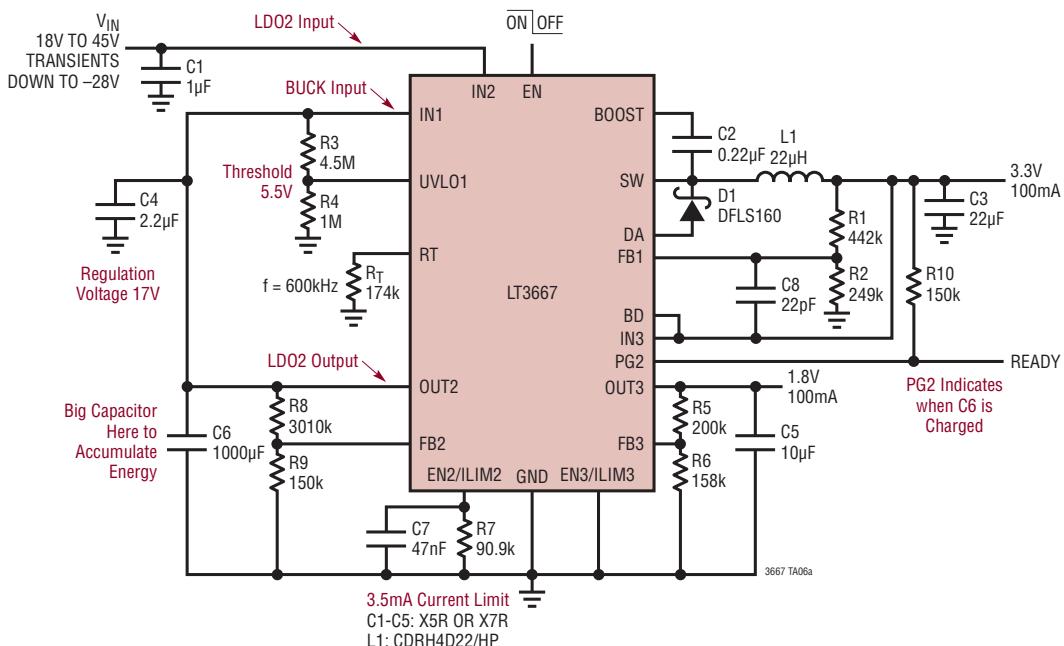

### 入力電源

LT3667の内部バイアスと内部リファレンス回路は、IN1ピンとIN2ピンによって形成されます。これにより、スイッチング・レギュレータの入力IN1をLDOの出力OUT2に接続することができます。これにより、LDOのプログラム可能な電流制限を使用することによって、IN2の電源をスイッチング・レギュレータの高起動電流からシールドすることができます。「標準的応用例」のセクションにこのようなアプリケーションの例が示されていますが、これもLDOの逆電圧保護の利点を生かしています。

### 入力容量と安定性

各LDOは、標準で $1\mu\text{F} \sim 10\mu\text{F}$ の範囲の入力コンデンサで安定します。この入力コンデンサは、対応する入力ピンのできるだけ近くに配置する必要があります。入力-出力間の電圧差が小さい状態で動作し、大きな負荷トランジェントが発生するアプリケーションでは、入力電圧の低下を防止し、レギュレータがドロップアウト状態にならないように、入力コンデンサの値を大きくすることが必要な場合があります。

超低ESRのセラミック・コンデンサを使用してもかまいません。ただし、電源からLDOの入力およびグランドまでのワイヤが長い場合は、小容量の入力コンデンサを使用すると、不安定になることがあります。この原因は、ワイヤのインダクタンスと入力コンデンサによって形成される共振LCタンク回路であり、LDOの不安定性の結果ではありません。

アプリケーションの安定化に必要な最小入力容量も、電源の出力インピーダンスに応じて変化します。LDOの出力に追加のコンデンサを接続することも効果的です。ただし、このためには、追加の入力バイパスに比べて1桁大きい容量のコンデンサが必要です。また、電源とLDOの間に直列抵抗を接続することもアプリケーションの安定化に役立ちます。 $0.1\Omega \sim 0.5\Omega$ 程度の小さな抵抗で十分です。このインピーダンスは、ドロップアウト電圧を犠牲にしてLCタンク回路を減衰させます。より良い代替手段は、入力にセラミック・コンデンサの代わりに高ESRのタンタル・コンデンサまたは電解コンデンサを使用することです。

### 出力容量、トランジェント応答、安定性

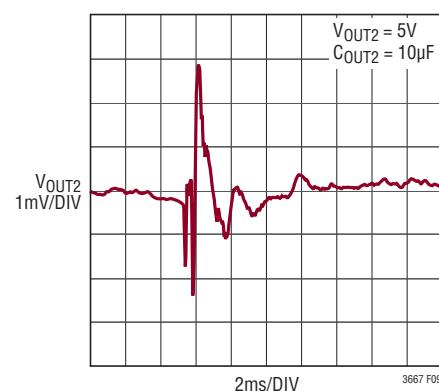

LT3667の各LDOは広範な出力コンデンサで安定します。出力コンデンサのESRは、特に小容量のコンデンサの場合、安

定性に影響を与えます。発振を防止するため、最小 $2.2\mu\text{F}$ の出力コンデンサを使用してください。出力電圧が $2.5\text{V}$ より低いアプリケーションや入力電圧と出力電圧の差が $20\text{V}$ を超えるアプリケーションでは、少なくとも $10\mu\text{F}$ の出力コンデンサが必要です。さらに、出力コンデンサのESRは $3\Omega$ を超えてはなりません。

LT3667はマイクロパワー・デバイスであり、出力負荷トランジェント応答は出力容量に応じて変化します。出力容量の値を大きくすると、特に低出力電圧に対して、負荷電流の大きな変化に対するピーク変動が減り、トランジェント応答が改善されます。LT3667によって電力を供給される個々の部品のデカップリングに使用されるバイパス・コンデンサにより、出力コンデンサの実効値が増加します。負荷電流トランジェントが大きなアプリケーションでは、多くの場合、バルクのタンタル・コンデンサと低ESRのセラミック・コンデンサを並列接続することによって、最適に減衰された応答が得られます。

セラミック・コンデンサの中には圧電効果を示すものがあることに注意してください。圧電デバイスは、圧電加速度計やマイクロホンの動作原理と同様、機械的応力によって端子間に電圧を発生します。セラミック・コンデンサでは、システムの振動や熱トランジェントによって応力が生じます。その結果発生した電圧によってかなりの大きさのノイズが生じます。セラミック・コンデンサを鉛筆で軽くたたくと図9の波形が生じます。同様の振動を発生させると、出力電圧ノイズが増加したように見えることがあります。

図9. セラミック・コンデンサを軽くたたくことにより生じるノイズ

## アプリケーション情報

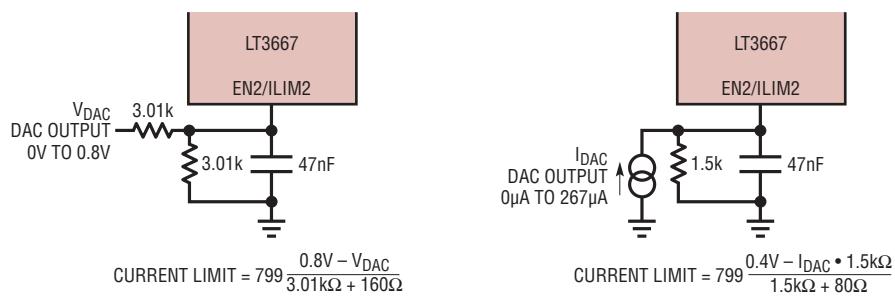

### 外部設定可能な電流制限、イネーブル

各EN/ILIMピン(EN2/ILIM2およびEN3/ILIM3)は、対応するLDOの出力を1:799の比で反映するPNPのコレクタです(「ブロック図」を参照)。EN2/ILIM2ピンとEN3/ILIM3ピンは、高精度電流制限アンプの入力でもあります。出力負荷が対応する電流制限アンプの入力電圧を0.4Vまで上昇させるポイントまで大きくなると、電流制限アンプが、出力電圧に関係なく、入力を0.4Vにクランプするように出力のレギュレーションを制御します。LDOの電流制限しきい値(ILIMIT)は、対応するEN/ILIMからグランドに抵抗(R<sub>IMAX</sub>)を接続することにより、次のように設定されます。

$$R_{IMAX} = \frac{799 \cdot 0.4V}{I_{LIM}} - 80\Omega$$

安定性を維持するため、各EN/ILIMピンにはグランドとの間に47nFのコンデンサが必要です。

入力-出力間の電圧差が10Vを超える場合、フォールドバック電流制限によって内部電流レベルの制限値が小さくなり、外部設定可能な電流制限よりも優先される可能性があります。「標準的性能特性」のセクションの内部電流制限と入力-出力間の電圧差のグラフを参照してください。

外部電流制限を行う必要がない場合には、対応するEN/ILIMピンをグランドに接続する必要があります。この場合、コンデンサは不要です。

各LDOは、EN/ILIMピンを1.2V(標準1V)より高くすることにより、個別にシャットダウンすることができます。この場合、特定の動作条件でLDOがシャットダウンするまでこのピンが最大500μA(このピンを駆動する回路が供給する必要がある値)を流す点に注意してください。LDOのイネーブル/ディスエーブルにEN/ILIMピンのみが使用される場合、このピンにコンデンサは不要です。

### 過負荷からの回復

LT3667の各LDOは安全動作領域保護機能を備えており、入力-出力間の電圧差が増加するにつれて電流制限値が減少し、入力-出力間電圧のすべての値についてパワー・トランジスタを安全動作領域内に保ちます。各LDOは、デバイスのブレークダウンまでの入力-出力間のすべての電圧値で、ある程度の出力電流を供給します。LDOに最初に電源が印加されるとき、入力電圧が上昇して出力が入力に追随するので、

レギュレータは非常に重い負荷で起動することができます。起動時に入力電圧が上昇しているときは入力-出力間の電圧差が小さいので、レギュレータは大きな出力電流を供給することができます。入力電圧が高いと、出力の短絡状態を解除しても出力電圧が回復しないという問題が発生する可能性があります。この問題は、出力負荷が重い場合に、入力電圧が高く、出力電圧が低いと発生します。このような状況が発生しやすいのは、短絡状態が解消した直後か、入力電圧が既に投入された状態の後にEN/ILIMピンを介してLDOがイネーブルされた場合です。このような場合、出力電圧を上げるため、レギュレータはパワー・デバイスを安全動作領域の外側(高電圧および大電流)で動作させなければならなくなります。この状況は安全動作領域保護によって回避されるので、出力は低電圧でスタックします。基本的に、このような負荷の負荷曲線は出力電流曲線と2点で交わるので、レギュレータの安定出力動作点が2つになります。このように2つの交点があると、出力を回復するには、入力電源を一度0Vにしてから再度立ち上げる必要があります。

### 保護機能

LT3667のLDOは、逆入力電圧、逆出力電圧および逆出力-入力電圧に対して保護します。電流制限保護と熱過負荷保護の機能は、LDOの出力の電流過負荷状態に対してLDOを保護します。通常動作では、最大動作接合部温度を超えてはなりません。LT3667のIN2ピンとIN3ピン(QFNのみ)は45Vの逆電圧に耐えます。デバイスに流れる電流は300μA未満(標準で10μA未満)に制限され、OUT2やOUT3に負電圧は出力されません。LDOは出力がグランドより低い電圧に引き下げられても損傷を受けることはありません。入力が開放状態のままか、または接地されている場合、対応する出力をグランドより45V下げることができます。出力からパス・トランジスタを介して電流が流出することはできません。ただし、出力電圧を設定する抵抗分割器に電流が流れますが、この抵抗分割器によって制限されます。電流は、分割器の下側の抵抗とFB2/FB3ピンの内部クランプから、分割器の上側の抵抗を通って、OUT2/OUT3をグランドより低い電圧に引き下げている外部回路に流れます。入力が電圧源によって給電される場合、出力は電流制限能力に等しい電流をソースし、LT3667は熱制限によって自己を保護します。出力をグランドより低い電圧にすると、外部設定可能な電流制限の精度が低下することに注意してください。

## アプリケーション情報

「標準的応用例」のセクションに示すように、これらの保護機能を使って、スイッチング・レギュレータの入力を保護することができます。

### 共通

#### セラミック・コンデンサの特性

セラミック・コンデンサを使用する際には、特に注意が必要です。セラミック・コンデンサは様々な誘電体を使用して製造されており、それぞれ温度や印加される電圧によって動作が異なります。最も一般的な誘電体は、Z5U、Y5V、X5R、X7RのEIA 温度特性コードで規定されています。Z5UとY5Vの誘電体は小型のパッケージで高C-V積を低成本で実現していますが、図10と図11のY5Vに見られるように、電圧係数と温度係数が大きくなります。5Vのレギュレータに使用する場合、16V 10 $\mu$ FのY5Vコンデンサは、印加されたDCバイアス電圧と動作温度範囲で1 $\mu$ F～2 $\mu$ Fの小さな実効値になる可能性があります。X5RとX7Rの誘電体を使用するとさらに安定した特性が得られるので、これらは入力コンデンサと出力コンデンサとして使用するのにより適しています。X7Rタイプはより広い温度範囲にわたって動作し、温度安定性が優れています。X5Rタイプは安価で大きな値のものが入手可能です。X5RやX7Rのコンデンサを使用する場合でも注意が必要です。X5RとX7Rのコードは動作温度範囲と全温度範囲での最大容量変化を規定しているだけです。X5RとX7RのコンデンサのDC

バイアスによる容量変化はY5VやZ5Uのコンデンサに比べると小さいですが、それでもコンデンサの容量が適切なレベルを下回るほど変化することがあります。コンデンサのDCバイアス特性は部品のケース・サイズが大きいほど良くなる傾向がありますが、動作電圧で期待する容量が保てるかを検証する必要があります。

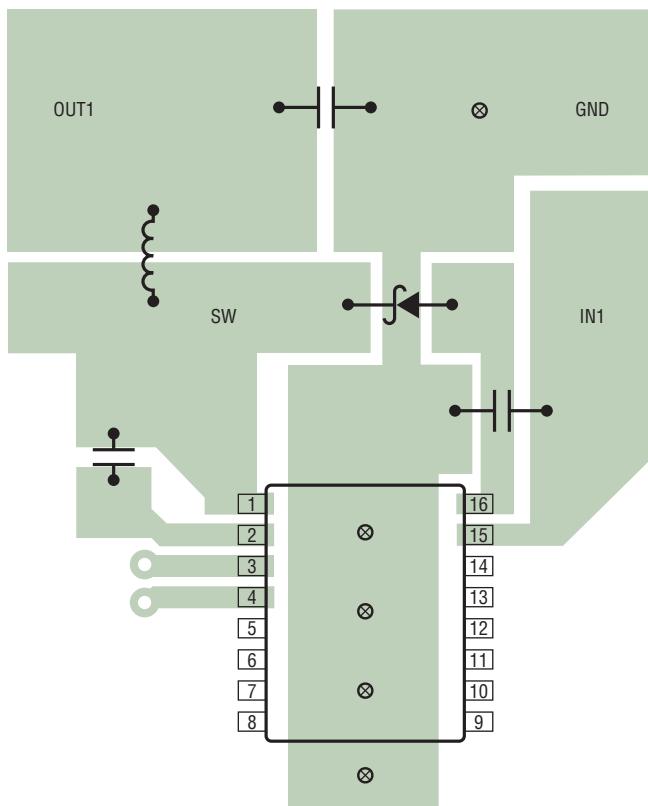

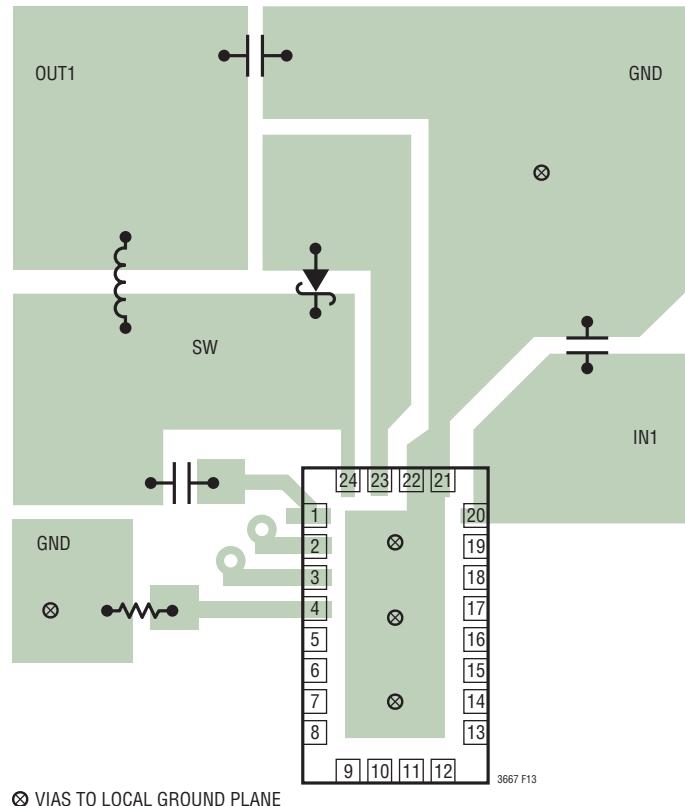

#### PCBレイアウト

適切に動作させ、EMIを最小にするには、プリント回路基板のレイアウト時に注意が必要です。推奨部品配置と、トレース、グランド・プレーン、およびビアの位置を図12および図13に示します。LT3667のIN1ピン、SWピン、GNDピンおよびDAピン、キャッチ・ダイオード、および入力コンデンサに大きなスイッチング電流が流れることに注意してください。これらの部品が形成するループはできるだけ小さくしてください。これらの部品とインダクタおよび出力コンデンサは回路基板の同じ側に配置し、それらをその層で接続します。これらの部品の下には切れ目のないローカル・グランド・プレーンを配置します。

SWノードとBOOSTノードはできるだけ小さくします。グランド・トレースがSWノードとBOOSTノードからシールドするように、FB1ノード、FB2ノードおよびFB3ノードは小さく保ちます。露出パッドは、ヒートシンクとして機能できるように半田付けする必要があります。(「高温に関する検討事項」のセクションを参照。)

図10. セラミック・コンデンサのDCバイアス特性

図11. セラミック・コンデンサの温度特性

## アプリケーション情報

図12. 適切な低EMI動作を保証する優れた

PCBレイアウト(MSOP)

## 安全な活線挿入

セラミック・コンデンサはサイズが小さく、堅牢でインピーダンスが低いので、LT3667の回路の入力バイパス・コンデンサに適しています。ただし、通電中の電源にLT3667が差し込まれると、これらのコンデンサが問題を生じることがあります。低損失のセラミック・コンデンサは電源に直列の浮遊インダクタと結合して、減衰の小さなタンク回路を形成し、LT3667の入力ピンの電圧に公称入力電圧の2倍に達するリンクギングを生じる可能性があり、LT3667の定格を超えてデバイスを傷める恐れがあります。入力電源の制御が十分でない場合や、ユーザがLT3667を通電中の電源に差し込む場合、このようなオーバーシュートを防ぐように入力回路網を設計する必要があります。詳細については、「アプリケーションノート88」を参照してください。

図13. 適切な低EMI動作を保証する優れた

PCBレイアウト(QFN)

## 高温に関する検討事項

LT3667の電力処理能力は、125°C(Eグレード、Iグレード)および150°C(Hグレード)の最大定格接合部温度によって制限されます。

スイッチング・レギュレータ内部の電力損失は、効率測定から計算される総電力損失からインダクタの損失を差し引いて、推測することができます。高い周囲温度では、外部ショットキ・ダイオードの漏れ電流がかなり大きくなり(「標準的性能特性」を参照)、スイッチング・レギュレータの静止電流が増加することに注意してください。

## アプリケーション情報

各LDOの電力損失は2つの要素からなります。各パワー・デバイスの電力損失は次のとおりです。

$$P_{\text{PASS}} = (V_{\text{IN}} - V_{\text{OUT}}) \cdot I_{\text{OUT}}$$

ここで、 $P_{\text{PASS}}$ は電力損失、 $V_{\text{IN}}$ は入力電圧、 $V_{\text{OUT}}$ は出力電圧、 $I_{\text{OUT}}$ は出力電流です。LDOのパワーPNPトランジスタのベース電流が内部でグランドに流れますが、これがグランド電流の大部分を占めます。各LDOでは、これによって次の電力損失 $P_{\text{GND}}$ が生じます。

$$P_{\text{GND}} = V_{\text{IN}} \cdot I_{\text{GND}}$$

ここで、 $V_{\text{IN}}$ は入力電圧、 $I_{\text{GND}}$ は対応するパワー・デバイスによって生成されるグランド電流です。GNDピンの電流はパワーPNPの電流利得によって決まりますが、これを計算するための標準値は40です。

$$I_{\text{GND}} = \frac{I_{\text{OUT}}}{40}$$

総電力損失は、スイッチング・レギュレータの電力損失と上記の2つのLDOの損失の合計に等しくなります。

LT3667は、過負荷状態でデバイスを保護する熱制限機能を備えています。接合部温度がサーマル・シャットダウンしきい値に達すると、LT3667は、LDOをシャットダウンしてスイッチングを停止し、過熱による内部損傷を防止します。通常状態を継続する場合、最大動作接合部温度を超えないようにしてください。接合部-周囲間の熱抵抗のすべての発生源や熱源の近くなどを慎重に検討してください。LT3667のどちらのパッケージにも露出パッドがあり、ヒートシンクとして機能するように、グランド・プレーンに半田付けする必要があります。熱抵抗を小さく保つには、グランド・プレーンができるだけ広げ、LT3667の下や近くから回路基板内および裏側の追加グランド・プレーンまでサーマル・ビアを追加します。

ダイ温度の上昇分は、LT3667の電力損失に、接合部-周囲間の熱抵抗を掛けて計算します。例：表紙の「標準的応用例」で、出力電流が最大、入力電圧が12V、最大周囲温度が85°Cの場合、最大接合部温度は何度になるでしょうか？

「標準的性能特性」から分かるように、スイッチング・レギュレータの効率は400mAの出力電流で85%に近づきます。これから次の電力損失 $P_{\text{LOSS}}$ が得られます。

$$P_{\text{LOSS}} = 5V \cdot 400\text{mA} \cdot \left( \frac{1}{0.85} - 1 \right) = 353\text{mW}$$

(計算を簡単にし、控えめにするため、この電力がすべてLT3667で消費されると仮定します。) LDOパワー・デバイスの電力損失は次のとおりです。

$$P_{\text{PASS2}} = (5V - 2.5V) \cdot 100\text{mA} = 250\text{mW}$$

$$P_{\text{PASS3}} = (5V - 3.3V) \cdot 100\text{mA} = 170\text{mW}$$

100mAの負荷電流では、2.5mAの最大グランド電流が見込まれます。したがって、相当する電力損失は次のようにになります。

$$P_{\text{GND2}} = P_{\text{GND3}} = 5V \cdot 2.5\text{mA} = 12.5\text{mW}$$

最終的に、総電力損失は次のようになります。

$$\begin{aligned} P_{\text{TOT}} &= P_{\text{LOSS}} + P_{\text{PASS2}} + P_{\text{PASS3}} + P_{\text{GND2}} + P_{\text{GND3}} \\ &= 786\text{mW} \end{aligned}$$

熱抵抗が約40°C/WのMSOPパッケージを使用すると、この総電力損失は接合部温度を周囲から次の値だけ上昇させます。

$$0.786\text{W} \cdot 40^{\circ}\text{C}/\text{W} = 32^{\circ}\text{C}$$

最大周囲温度を85°Cと仮定すると、最大接合部温度は次のようにになります。

$$T_{\text{JMAX}} = 85^{\circ}\text{C} + 32^{\circ}\text{C} = 117^{\circ}\text{C}$$

### リニアテクノロジー社の他の出版物

「アプリケーションノート」の19、35、および44には、降圧レギュレータやその他のスイッチング・レギュレータの詳細な説明と設計情報が記載されています。LT1376のデータシートには、出力リップル、ループ補償、および安定性のテストに関するさらに広範な説明が記載されています。「デザインノート318」には、降圧レギュレータを使ってバイポーラ出力電源を生成する方法が示されています。

# LT3667

## 標準的応用例

5V、3.3Vおよび2.5V降圧コンバータ

デュアル5V/200mA降圧コンバータ

## 標準的応用例

100mA LDO電流制限付き、5V、3.3Vおよび2.5V降圧コンバータ

## デジタル/アナログ・コンバータによるLDO電流制限の設定

## 標準的応用例

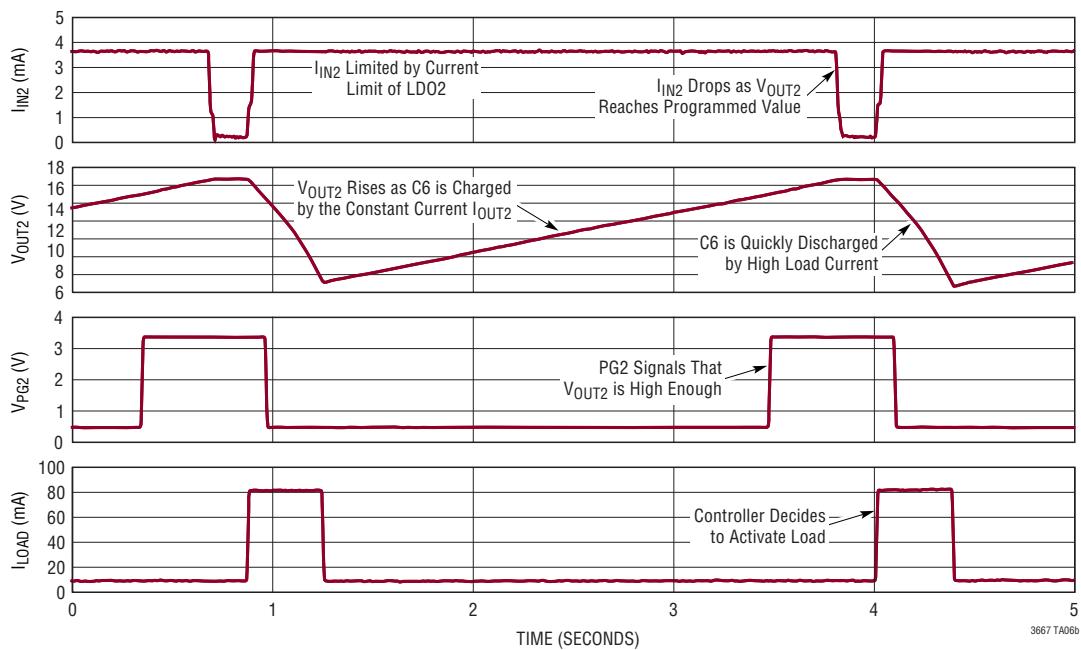

このアプリケーションにより、小さな入力電流で大電流パルス負荷をサポート可能になります。スイッチング・レギュレータは OUT2 の LDO2 から給電され、この電流は 3.5mA に制限されるように設定されています。PG2 は「レディ」信号として機能し、コントローラ(図示されていない)に C6 が 17V (LDO2 のレギュレーション電圧)まで充電されていることを知らせます。する

と、コントローラはスイッチング・レギュレータから大電流を流す負荷をオンすることができます。

LDO2 は 3.5mA しか供給できないので、C6 を短時間で放電して  $V_{OUT2} (= V_{IN1})$  を下げます。スイッチング・レギュレータは、 $V_{IN1}$  が  $R3$  と  $R4$  で設定された 5.5V の低電圧ロックアウトしきい値を下回るまで、設定された出力電圧を維持します。

**4mA～20mAの電流ループ用パルス電源。

OUT2はスイッチング・レギュレータに給電し、低い電圧でUVLO1によってオフに保たれる**

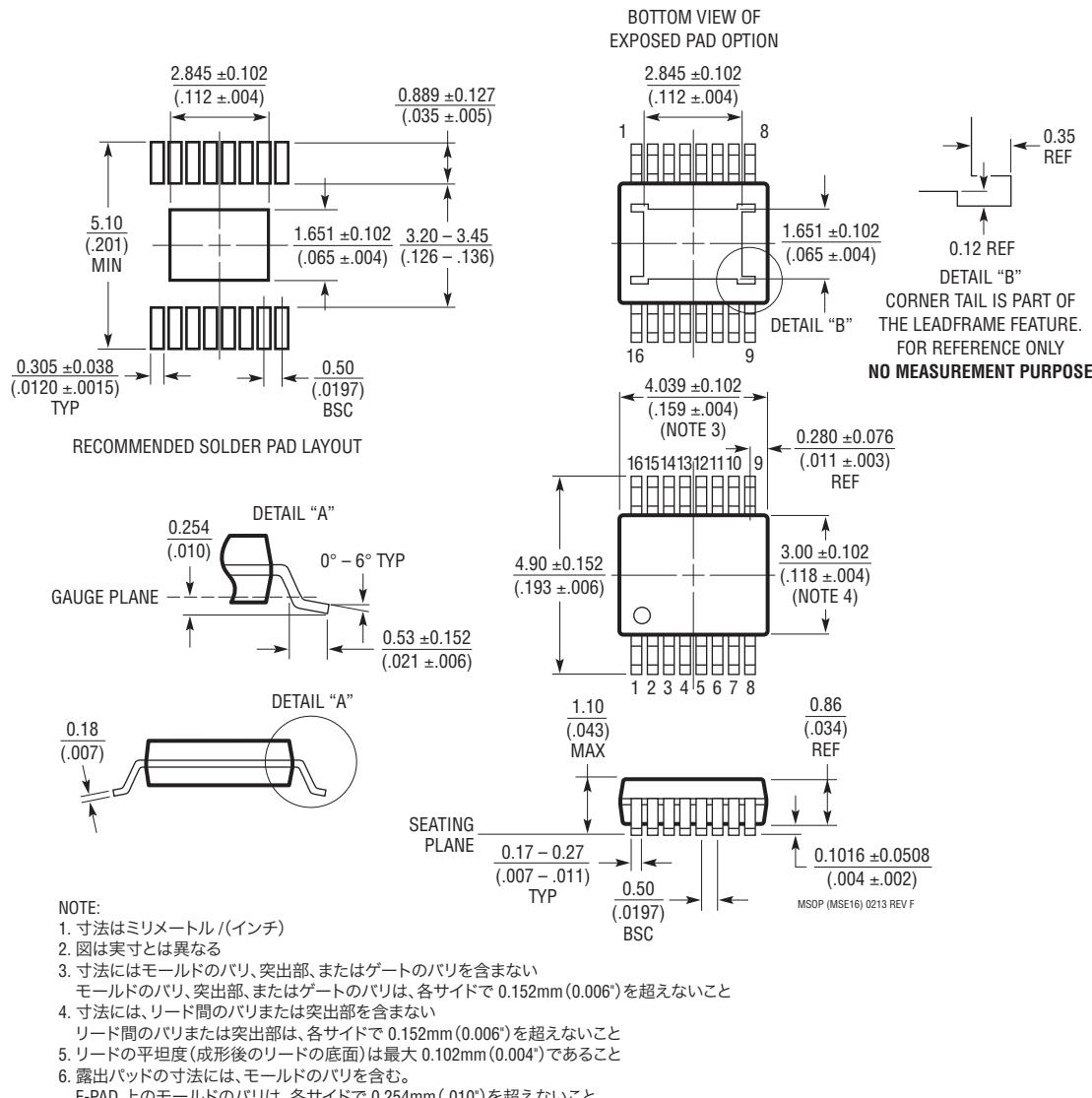

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/>を参照してください。

**MSE Package

16-Lead Plastic MSOP, Exposed Die Pad**

(Reference LTC DWG # 05-08-1667 Rev F)

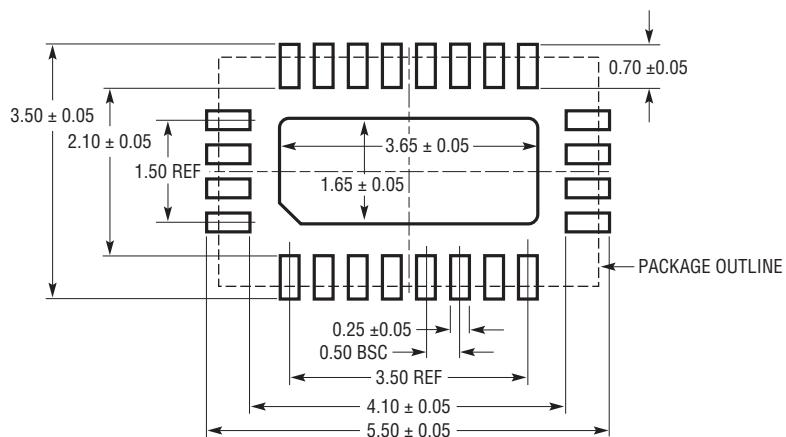

## パッケージ

最新のパッケージ図面については、<http://www.linear-tech.co.jp/designtools/packaging/> を参照してください。

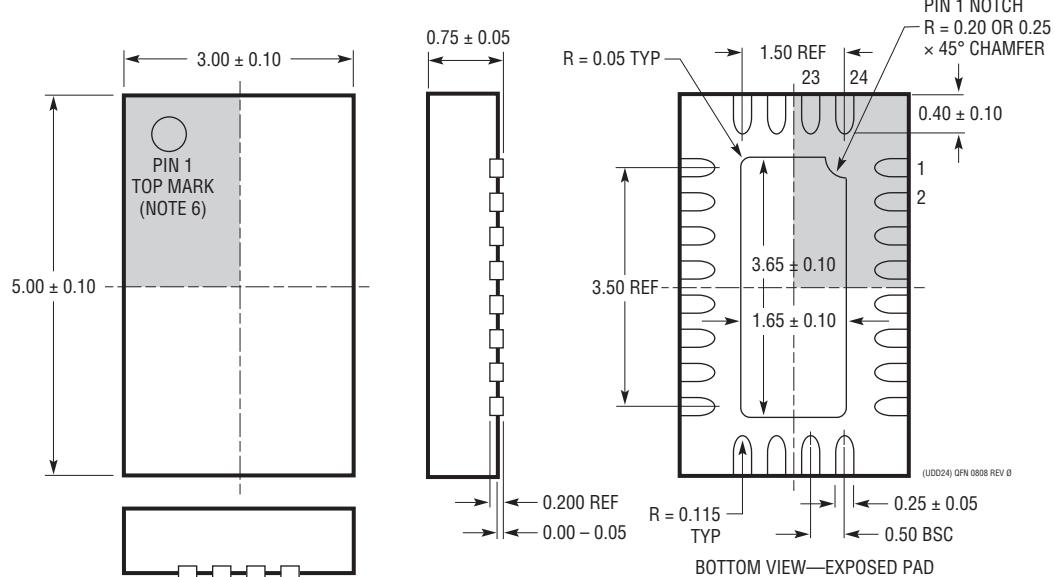

**UDD Package**

**24-Lead Plastic QFN (3mm × 5mm)**

(Reference LTC DWG # 05-08-1833 Rev 0)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

**NOTE:**

1. 図は JEDEC のパッケージ外形ではない

2. 図は実寸とは異なる

3. 全ての寸法はミリメートル

4. パッケージ底面の露出パッドの寸法にはモールドのバリを含まない

モールドのバリは(もしあれば)各サイドで 0.15mm を超えないこと

5. 露出パッドは半田メッキとする

6. 網掛けの部分はパッケージの上面と底面のピン 1 の位置の参考に過ぎない

## 改訂履歴

| REV | 日付    | 概要                                                                                             | ページ番号         |

|-----|-------|------------------------------------------------------------------------------------------------|---------------|

| A   | 4/14  | 発注情報のMS16EパッケージにHグレードを追加。                                                                      | 3             |

| B   | 11/14 | Externally Programmable Current Limitのスペックを明確化。<br>「スイッチング周波数の設定」の説明文を文法的に修正。<br>標準的応用例の図を明確化。 | 5<br>16<br>29 |

## 標準的応用例

## 5V、3.3Vおよび51mA出力のレギュレータ

\*DERATE OUTPUT CURRENT AT HIGHER AMBIENT TEMPERATURES

AND INPUT VOLTAGES TO MAINTAIN JUNCTION TEMPERATURE

BELOW THE ABSOLUTE MAXIMUM

## 関連製品

| 製品番号           | 説明                                                                                      | 注釈                                                                                                                             |

|----------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| LT3500         | LDOコントローラを備えた36V(40V <sub>MAX</sub> )、2A(I <sub>OUT</sub> )、2.2MHz降圧スイッチング・レギュレータ       | V <sub>IN</sub> :3V～36V、V <sub>OUT(MIN)</sub> =0.8V、I <sub>Q</sub> =2.5mA、I <sub>SD</sub> <12μA、3mm×3mm DFN-10およびMSOP-16Eパッケージ |

| LT1939         | LDOコントローラを備えた25V、2A(I <sub>OUT</sub> )、2.2MHz降圧スイッチング・レギュレータ                            | V <sub>IN</sub> :3V～25V、V <sub>OUT(MIN)</sub> =0.8V、I <sub>Q</sub> =2.5mA、I <sub>SD</sub> <12μA、3mm×3mm DFN-10およびMSOP-16Eパッケージ |

| LT3694         | デュアルLDOコントローラを備えた36V(70V <sub>MAX</sub> )、2.6A(I <sub>OUT</sub> )、2.5MHz降圧スイッチング・レギュレータ | V <sub>IN</sub> :4V～36V、V <sub>OUT(MIN)</sub> =0.8V、I <sub>Q</sub> =1mA、I <sub>SD</sub> <1μA、4mm×5mm QFN-28およびTSSOP-20Eパッケージ   |

| LT3507/LT3507A | LDOコントローラを備えた36V、2.5MHz、トリプル(2.4A+1.5A+1.5A(I <sub>OUT</sub> ))高効率降圧DC/DCコンバータ          | V <sub>IN</sub> :4V～36V、V <sub>OUT(MIN)</sub> =0.8V、I <sub>Q</sub> =7mA、I <sub>SD</sub> =1μA、5mm×7mm QFN-38パッケージ               |

| LT3970         | 静止電流が2.5μAの40V、350mA(I <sub>OUT</sub> )、2.2MHz降圧スイッチング・レギュレータ                           | V <sub>IN</sub> :4.2V～40V、V <sub>OUT(MIN)</sub> =1.2V、I <sub>Q</sub> =2.5μA、I <sub>SD</sub> <1μA、3mm×2mm DFNおよびMSOP-10パッケージ    |

| LT3502/LT3502A | 40V、500mA(I <sub>OUT</sub> )、1.1MHz/2.2MHz降圧スイッチング・レギュレータ                               | V <sub>IN</sub> :3V～40V、V <sub>OUT(MIN)</sub> =0.8V、I <sub>Q</sub> =1.5mA、I <sub>SD</sub> <1μA、2mm×2mm DFN-8およびMSOP-10Eパッケージ   |