# DDR 終端向け $\pm 6A$ モノリシック 同期整流式降圧レギュレータ

## 特長

- 出力電流:  $\pm 6A$

- 入力電圧範囲: 2.25V ~ 5.5V

- 出力電圧精度:  $\pm 10mV$

- 最小 0.5V の低出力電圧向けに最適化

- 高効率

- 内蔵バッファによる  $V_{TTR} = V_{DDQIN} \cdot 0.5$

- シャットダウン電流:  $< 1\mu A$

- 調整可能なスイッチング周波数: 最大 4MHz

- オプションの内部補償

- 内部ソフトスタート

- パワーグッド状態出力

- 入力過電圧保護

- 熱特性が改善された 24 ピン 3mm × 5mm QFN パッケージ

## アプリケーション

- DDR の終端

- DDR、DDR2、DDR3 の各規格に対応

- トラッキング電源

## 概要

LTC<sup>®</sup>3617 は、固定周波数電流モード・アーキテクチャを採用した高効率モノリシック同期整流式降圧レギュレータです。2.25V ~ 5.5V の入力電圧範囲で動作し、0.5 • V<sub>DDQIN</sub> の安定化出力電圧を供給し、最大 6A の負荷電流をソースおよびシンクします。内部アンプが 0.5 • V<sub>DDQIN</sub> の VTTR 出力電圧を供給し、 $\pm 10mA$  の出力電流が可能です。

4MHzまでの動作周波数を外部設定可能なので、小型の表面実装インダクタを使用できます。スイッチング・ノイズに敏感なアプリケーションでは、最大 4MHz の外部クロックに同期させることができます。

LTC3617 は強制連続モード動作によってノイズと RF 干渉を低減します。外部補償を調整できるので、広範な負荷と出力コンデンサに対して過渡応答を最適化することができます。

内部同期スイッチにより、効率が向上し、外付けキャッチ・ダイオードが不要なので、外付け部品数とボードスペースを最小限に抑えます。LTC3617 は熱特性が改善されたリードレス 24 ピン 3mm × 5mm QFN パッケージで供給されます。

**L**、**T**、**LTC**、**LTM**、**Linear Technology**、**Linear** のロゴおよび **Burst Mode** はリニアテクノロジー社の登録商標です。その他全ての商標の所有権は、それぞれの所有者に帰属します。6580258、5481178、6498466、6611131 をはじめとする米国特許によって保護されています。

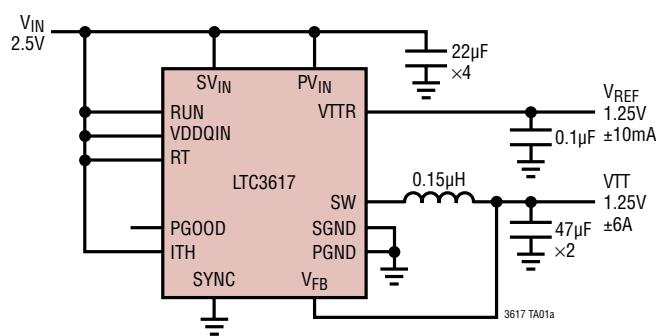

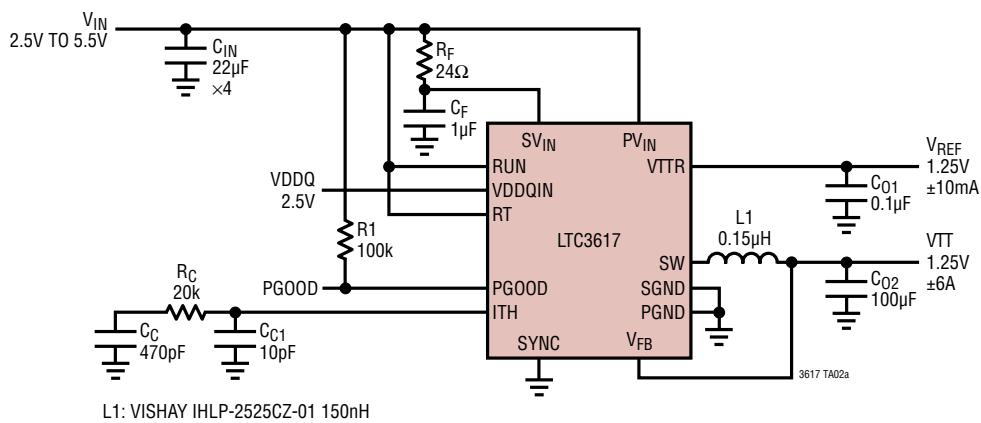

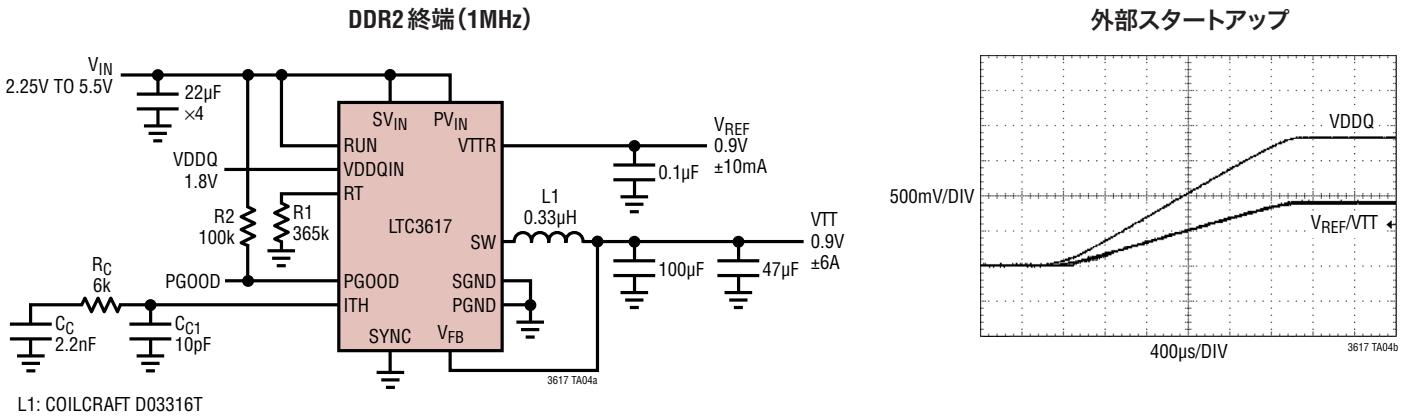

## 標準的応用例

## 絶対最大定格

(Note 1)

|                                       |                                 |

|---------------------------------------|---------------------------------|

| PV <sub>IN</sub> 、SV <sub>IN</sub> 電圧 | -0.3V～6V                        |

| SWの電圧                                 | -0.3V～(PV <sub>IN</sub> + 0.3V) |

| ITH、RT、SYNCの電圧                        | -0.3V～(SV <sub>IN</sub> + 0.3V) |

| VTTR、RUN、V <sub>FB</sub> の電圧          | -0.3V～(SV <sub>IN</sub> + 0.3V) |

| VDDQIN、PGOODの電圧                       | -0.3V～6V                        |

| 動作接合部温度範囲                             | -40°C～125°C                     |

| (Note 2、8)                            | -65°C～150°C                     |

| 保存温度                                  | -65°C～150°C                     |

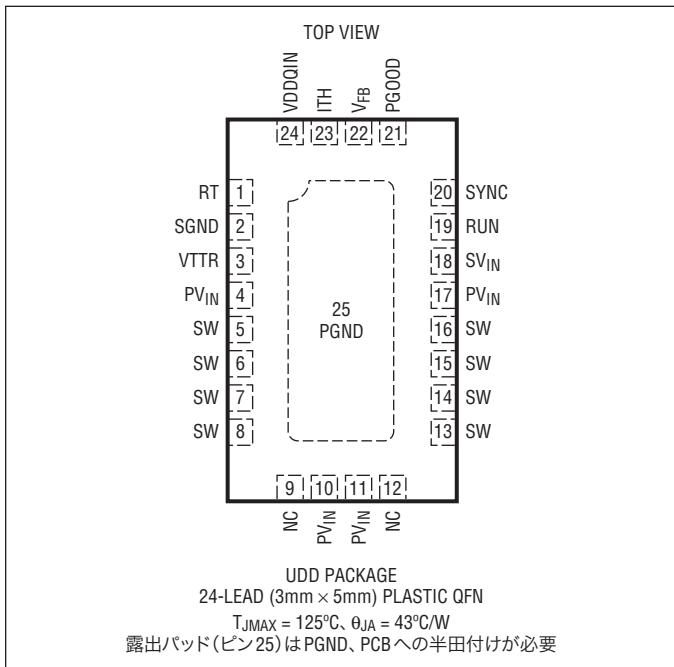

## ピン配置

## 発注情報

| 鉛フリー仕様          | テープアンドリール         | 製品マーキング* | パッケージ                   | 温度範囲        |

|-----------------|-------------------|----------|-------------------------|-------------|

| LTC3617EUDD#PBF | LTC3617EUDD#TRPBF | LFXC     | 24-ピン(3mm×5mm)プラスチックQFN | -40°C～125°C |

| LTC3617IUDD#PBF | LTC3617IUDD#TRPBF | LFXC     | 24-ピン(3mm×5mm)プラスチックQFN | -40°C～125°C |

さらに広い動作温度範囲で規定されるデバイスについては、弊社または弊社代理店にお問い合わせください。\* 温度グレードは出荷時のコンテナのラベルで識別されます。

非標準の鉛ベース仕様の製品マーキングの詳細については、弊社または弊社代理店にお問い合わせください。

鉛フリー仕様の製品マーキングの詳細については、<http://www.linear-tech.co.jp/leadfree/> をご覧ください。

テープアンドリールの仕様の詳細については、<http://www.linear-tech.co.jp/tapeandreel/> をご覧ください。

**電気的特性** ●は全動作接合部温度範囲の規格値を意味する。それ以外はT<sub>A</sub> = 25°Cでの値。注記がない限り、PV<sub>IN</sub> = SV<sub>IN</sub> = 3.3V、RT = SV<sub>IN</sub>。 (Note 1、2、8)

| SYMBOL            | PARAMETER                                         | CONDITIONS                                                   | MIN    | TYP           | MAX          | UNITS   |

|-------------------|---------------------------------------------------|--------------------------------------------------------------|--------|---------------|--------------|---------|

| V <sub>IN</sub>   | Input Voltage Operating Range                     |                                                              | ●      | 2.25          | 5.5          | V       |

| V <sub>UVLO</sub> | Undervoltage Lockout Threshold                    | SV <sub>IN</sub> Ramping Down<br>SV <sub>IN</sub> Ramping Up | ●<br>● | 1.7           | 2.2          | V       |

| V <sub>OVLO</sub> | Overvoltage Lockout Threshold                     | SV <sub>IN</sub> Ramping Up<br>Hysteresis                    |        | 6.5<br>250    | 7            | V<br>mV |

| VTTR              | VTTR Output Voltage with Line and Load Regulation | VDDQIN = 1.5V, Load = ±10mA                                  | ●      | 0.49 • VDDQIN | 0.5 • VDDQIN | V       |

|                   | VTTR Maximum Output Current                       |                                                              |        |               | ±10          | mA      |

| V <sub>FB</sub>   | Feedback Voltage Accuracy                         | VDDQIN = 1.5V (Note 3)                                       | ●      | VTTR - 10     | VTTR         | mV      |

| I <sub>FB</sub>   | Feedback Input Current                            | V <sub>FB</sub> = 0.75V                                      | ●      |               | ±30          | nA      |

## 電気的特性

●は全動作接合部温度範囲の規格値を意味する。それ以外は  $T_A = 25^\circ\text{C}$  での値。注記がない限り、 $P_{V_{IN}} = SV_{IN} = 3.3\text{V}$ 、 $RT = SV_{IN}$ 。(Note 1, 2, 8)

| SYMBOL                   | PARAMETER                                                             | CONDITIONS                                                                                                            | MIN         | TYP         | MAX          | UNITS                          |

|--------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------|-------------|--------------|--------------------------------|

| $\Delta V_{FB(LINEREG)}$ | Feedback Voltage Line Regulation                                      | $SV_{IN} = PV_{IN} = 2.25\text{V}$ to $5.5\text{V}$ ,<br>$VDDQIN = 1.5\text{V}$ (Notes 3, 4)                          |             |             | 0.2          | %/V                            |

| $\Delta V_{FB(LOADREG)}$ | Feedback Voltage Load Regulation                                      | $ITH$ from $0.5\text{V}$ to $0.9\text{V}$ (Notes 3, 4)<br>$V_{ITH} = SV_{IN}$ (Note 5)                                |             |             | 0.25<br>0.25 | %<br>%                         |

| $I_Q$                    | Input DC Supply Current<br>Active Mode<br>Shutdown                    | $V_{FB} = 0.6\text{V}$ , $VDDQIN = 1.5\text{V}$ (Note 6)<br>$SV_{IN} = PV_{IN} = 5.5\text{V}$ , $V_{RUN} = 0\text{V}$ |             | 1100<br>0.1 | 1            | $\mu\text{A}$<br>$\mu\text{A}$ |

| $R_{DS(ON)}$             | Top Switch On-Resistance                                              | $PV_{IN} = 3.3\text{V}$                                                                                               |             | 35          |              | $\text{m}\Omega$               |

|                          | Bottom Switch On-Resistance                                           | $PV_{IN} = 3.3\text{V}$                                                                                               |             | 25          |              | $\text{m}\Omega$               |

| $I_{LIM}$                | Top Switch Positive Peak Current Limit                                | Sourcing (Note 7), $V_{FB} = 0.5\text{V}$                                                                             | 8           | 10          | 14           | A                              |

|                          | Top Switch Negative Peak Current Limit                                | Sinking (Note 7)                                                                                                      | -12         | -8          | -5           | A                              |

| $g_m(EA)$                | Error Amplifier Transconductance                                      | $-5\mu\text{A} < I_{ITH} < 5\mu\text{A}$ (Note 4)                                                                     |             | 200         |              | $\mu\text{S}$                  |

| $I_{EA0}$                | Error Amplifier Maximum Output Current                                | (Note 4)                                                                                                              |             | $\pm 30$    |              | $\mu\text{A}$                  |

| $t_{SS}$                 | Internal Soft-Start Time                                              | $V_{FB}$ from $0.075\text{V}$ to $0.675\text{V}$ ,<br>$VDDQIN = 1.5\text{V}$                                          | 0.4         | 0.85        | 2            | ms                             |

| $f_{osc}$                | Oscillator Frequency<br>Internal Oscillator Frequency                 | $R_T = 370\text{k}$<br>$V_{RT} = SV_{IN}$                                                                             | 0.8<br>1.8  | 1<br>2.25   | 1.2<br>2.7   | MHz<br>MHz                     |

| $f_{SYNC}$               | Synchronization Frequency Range                                       |                                                                                                                       |             | 0.3         | 4            | MHz                            |

| $V_{SYNC}$               | SYNC Input Threshold High Voltage<br>SYNC Input Threshold Low Voltage |                                                                                                                       |             | 1.2         |              | V<br>V                         |

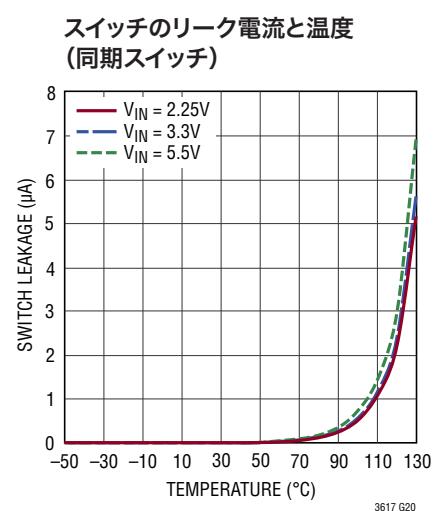

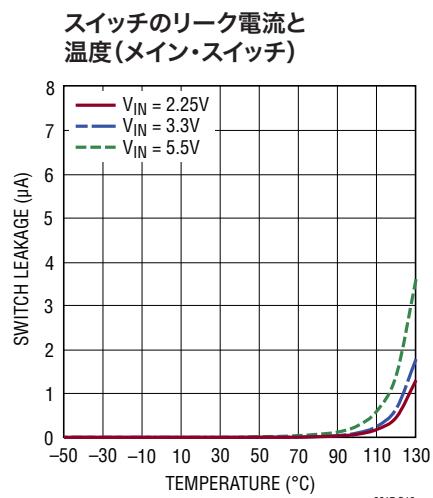

| $I_{SW(LKG)}$            | Switch Leakage Current                                                | $SV_{IN} = PV_{IN} = 5.5\text{V}$ , $V_{RUN} = 0\text{V}$                                                             |             | 0.1         | 1            | $\mu\text{A}$                  |

| $PGOOD$                  | Power Good Voltage Windows                                            | $VDDQIN = 1.5\text{V}$ , Entering Window<br>$V_{FB}$ Ramping Up<br>$V_{FB}$ Ramping Down                              | -3.5<br>3.5 | -5<br>5     |              | %<br>%                         |

|                          |                                                                       | $VDDQIN = 1.5\text{V}$ , Leaving Window<br>$V_{FB}$ Ramping Up<br>$V_{FB}$ Ramping Down                               |             | 8<br>-8     | 10<br>-10    | %<br>%                         |

| $t_{PGOOD}$              | Power Good Blanking Time                                              | Entering and Leaving Window                                                                                           | 70          | 105         | 140          | $\mu\text{s}$                  |

| $R_{PGOOD}$              | Power Good Pull-Down On-Resistance                                    |                                                                                                                       | 8           | 17          | 33           | $\Omega$                       |

| $V_{RUN}$                | RUN voltage                                                           | Input High<br>Input Low                                                                                               | ●<br>●      | 1           | 0.4          | V<br>V                         |

**Note 1:** 絶対最大定格に記載された値を超えるストレスはデバイスに永続的損傷を与える可能性がある。また、長期にわたって絶対最大定格条件に曝すと、デバイスの信頼性と寿命に悪影響を与える可能性がある。

**Note 2:** LTC3617は $T_J$ が $T_A$ にほぼ等しいバ尔斯負荷条件でテストされる。LTC3617Eは、 $0^\circ\text{C}$ ～ $85^\circ\text{C}$ の動作接合部温度範囲で性能仕様に適合することが保証されている。 $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度範囲での仕様は、設計、特性評価および統計学的なプロセス・コントロールとの関連で確認されている。LTC3617Iは $-40^\circ\text{C}$ ～ $125^\circ\text{C}$ の動作接合部温度の全範囲で仕様に適合することが保証されている。最大周囲温度は、基板レイアウト、パッケージの定格熱抵抗および他の環境要因と関連した特定の動作条件によって決まるに注意。接合部温度( $T_J$ (単位: $^\circ\text{C}$ ))は、周囲温度( $T_A$ (単位: $^\circ\text{C}$ ))および電力損失( $P_D$ (単位:W))から、次式に従って計算される。

$$T_J = T_A + (P_D \cdot \theta_{JA}) \quad \text{ここで、} \theta_{JA} \text{ (単位: } ^\circ\text{C/W}) \text{ はパッケージの熱インピーダンス。}$$

**Note 3:** このパラメータは、 $V_{FB}$ を誤差アンプの中点( $V_{ITH} = 0.75\text{V}$ )にサーボ制御する帰還ループでテストされている。

**Note 4:**  $ITH$ ピンによる外部補償。

**Note 5:**  $ITH$ ピンを $SV_{IN}$ に接続すると、内部補償が有効になる。

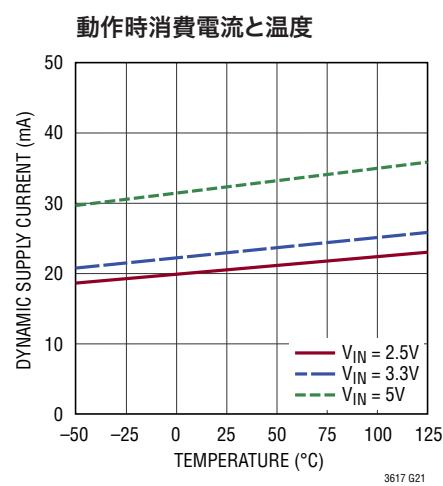

**Note 6:** スイッチング周波数で供給される内部ゲート電荷により動作時消費電流が増加する。

**Note 7:** ソース・モードの平均出力電流は $SW$ ピンから流れ出す。シンク・モードの平均出力電流は $SW$ ピンに流れ込む。

**Note 8:** このデバイスには短時間の過負荷状態の間デバイスを保護するための過温度保護機能が備わっている。過温度保護機能がアクティブなとき接合部温度は $125^\circ\text{C}$ を超える。規定された最高動作接合部温度を超えた動作が継続すると、デバイスの信頼性を損なうおそれがある。

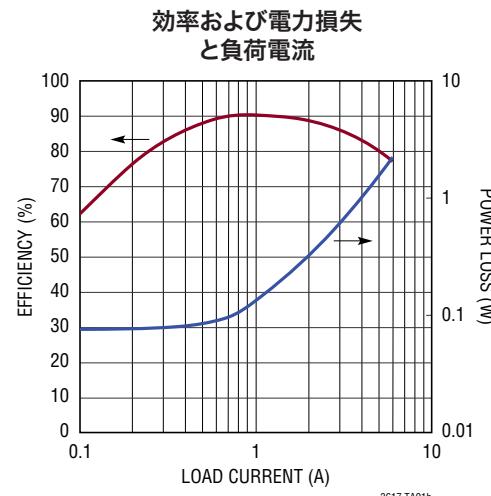

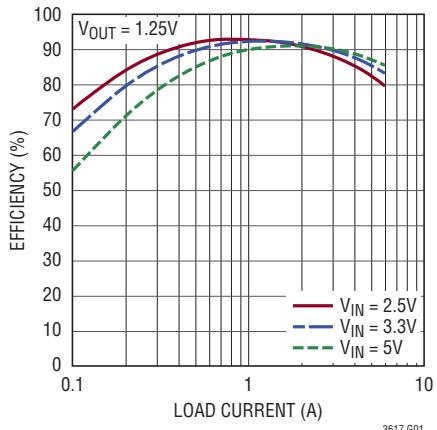

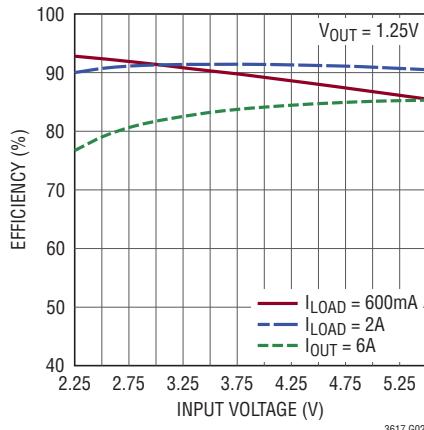

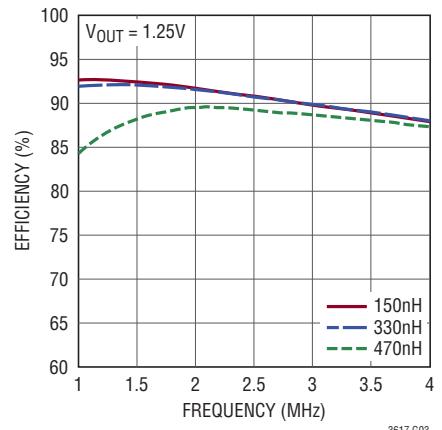

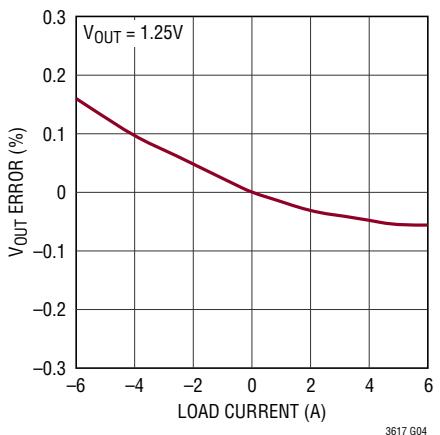

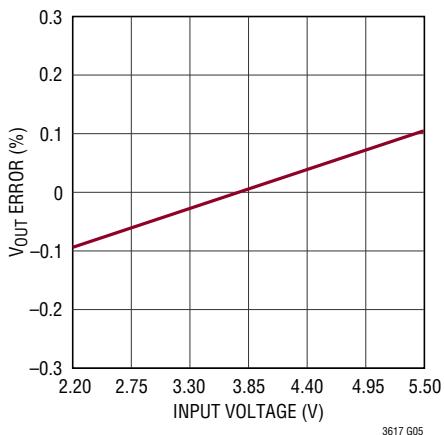

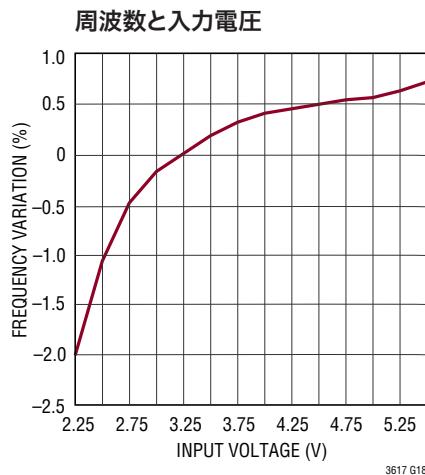

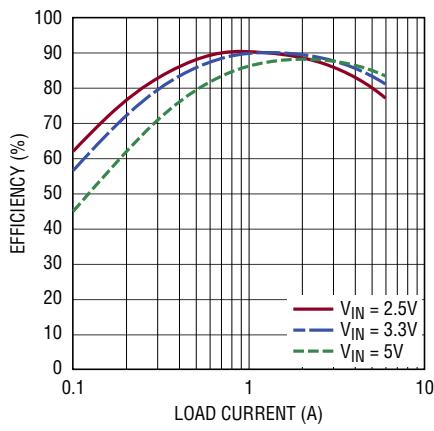

## 標準的性能特性

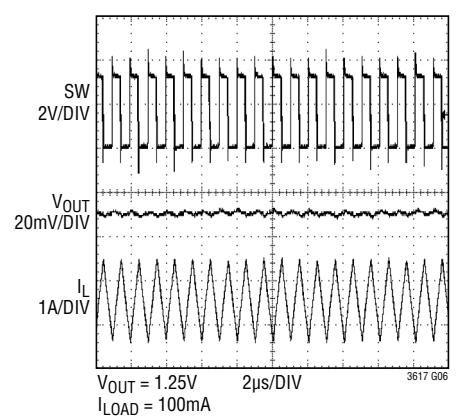

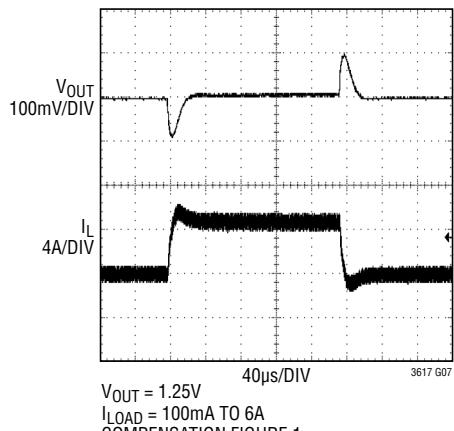

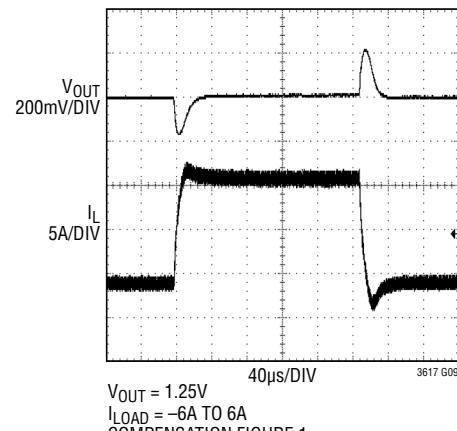

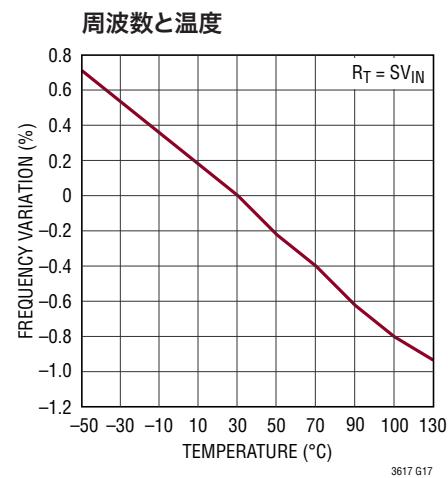

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 3.3\text{V}$ 、 $f_0 = 1\text{MHz}$ 。

効率と負荷電流

効率と入力電圧

効率と周波数

負荷レギュレーション

ライン・レギュレーション

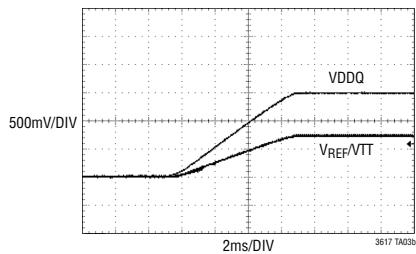

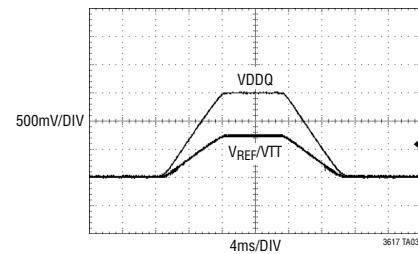

出力電圧と時間

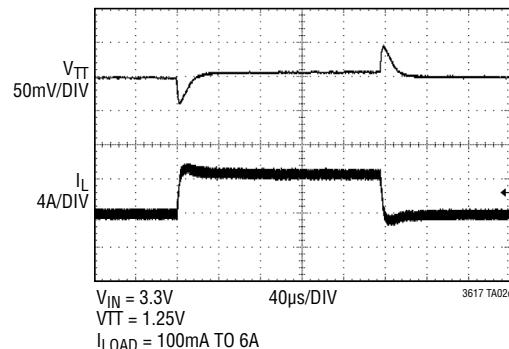

負荷ステップ過渡

負荷ステップ過渡

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 3.3\text{V}$ 、 $f_0 = 1\text{MHz}$ 。

## 標準的性能特性

注記がない限り、 $T_A = 25^\circ\text{C}$ 、 $V_{IN} = 3.3\text{V}$ 、 $f_0 = 1\text{MHz}$ 。

## ピン機能

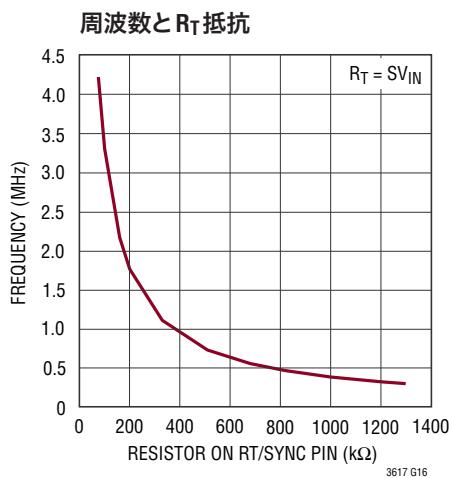

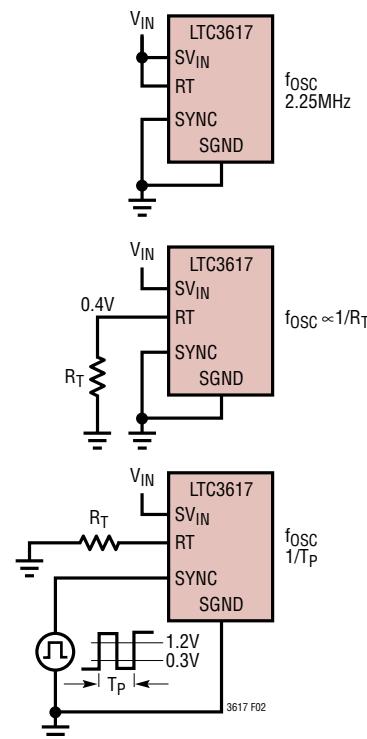

**RT(ピン1) :** 発振器の周波数。このピンにより、次の2つの方

法で固定スイッチング周波数を設定できます。

1. RTからグランドに抵抗を接続すると、抵抗の値に基づいて

スイッチング周波数が設定されます。

2. RTピンをSV<sub>IN</sub>に接続すると内部の2.25MHz発振器の周

波数が有効になります。

**SGND(ピン2) :** 信号グランド。全ての小信号用部品と補償用

部品はこのグランドに接続し、このグランド自体はPGNDに一

点接続します。

**VTTR(ピン3) :** 電圧バッファ出力。内部電圧バッファからの出

力です。電圧値はVDDQIN • 0.5に等しくなります。電流出力

能力は±10mAです。VTTRは出力電圧を設定する誤差アン

プのリファレンス電圧としても使用されます。V<sub>FB</sub>は、VTTRに

レギュレートされます。このピンの容量が0.1μFを超えないよ

うにしてください。

**PV<sub>IN</sub>(ピン4、10、11、17) :** 入力電源。PV<sub>IN</sub>は内部のPチャネ

ル・パワーMOSFETのソースに接続されています。このピンは

SV<sub>IN</sub>からは独立しており、同じ電圧またはより低い電圧の電

源に接続することができます。

**SW(ピン5、6、7、8、13、14、15、16) :** スイッチ・ノード。インダ

クタへの接続。これらのピンは内部のパワーMOSFETスイッ

チのドレインに接続されています。

**NC(ピン9、12) :** グランドに接続するか、オープンのままにす

ることができます。

**SV<sub>IN</sub>(ピン18) :** 信号用入力電源。このピンは内部制御回路

に電力を供給し、低電圧ロックアウト・コンパレータによってモ

ニタされます。

**RUN(ピン19) :** イネーブル入力。このピンをHighにすると

LTC3617がイネーブルされ、グランドにするとレギュレータが

シャットダウンされます。シャットダウン時には全機能がディス

エーブルされ、デバイスに流れる消費電流は1μA未満になり

ます。

**SYNC(ピン20) :** 外部同期入力。このピンにクロック信号を印

加すると、スイッチング周波数がこのクロック信号に同期しま

す。外部クロックを使用しない場合は、フローティングまたはグ

ランドに接続できます。

**PGOOD(ピン21) :** パワーグッド・ピン。このオープン・ドレン

出力は、スタートアップ時およびFB電圧がパワーグッド電圧

ウインドウから外れている場合、SGNDに引き下げられます。

FB電圧が増加し、パワーグッド・ウインドウ内に100μsよりも

長い期間留まると、PGOODピンがリリースされます。FB電圧

がパワーグッド・ウインドウから100μsよりも長い期間外れる

と、PGOODピンがLowに引き下げられます。

パワーグッド・ウインドウはVDDQINピンの電圧に連動します。

シャットダウン状態では、PGOOD出力はアクティブにプルダ

ウンされるので、外部抵抗を介して出力コンデンサを放電す

るのに使用することができます。

**V<sub>FB</sub>(ピン22) :** 帰還電圧の入力。出力に接続された外部抵抗

分割器からの帰還電圧を検出します。

**ITH(ピン23) :** 誤差アンプ補償。電流コンパレータのスレッショ

ルドはこの制御電圧に応じて増加します。このピンをSV<sub>IN</sub>に接

続すると内部補償が有効になります。

**VDDQIN(ピン24) :** 外部リファレンス入力。レギュレート電圧

であるVTTRとV<sub>FB</sub>は、内部抵抗分割器によって、この入力に印

加される電圧の1/2に等しい値に設定されます。

**PGND(露出パッドのピン25) :** 電源グランド。このピンは内部

Nチャネル・パワーMOSFETのソースに接続されています。こ

のピンは、C<sub>IN</sub>とC<sub>OUT</sub>の(-)端子に近づけて接続してください。

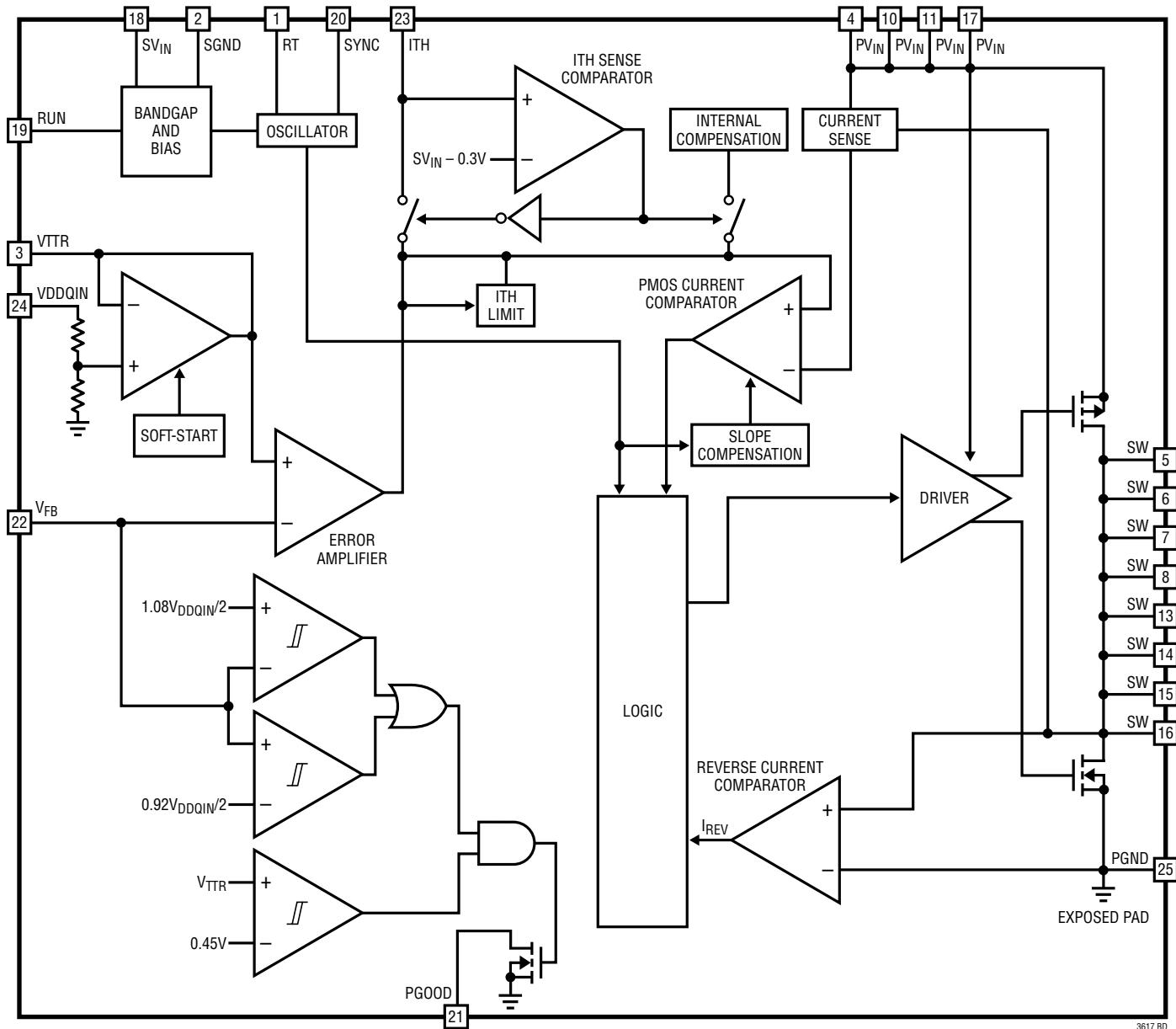

## 機能ブロック図

3617 BD

3617fa

## 動作

### メイン制御ループ

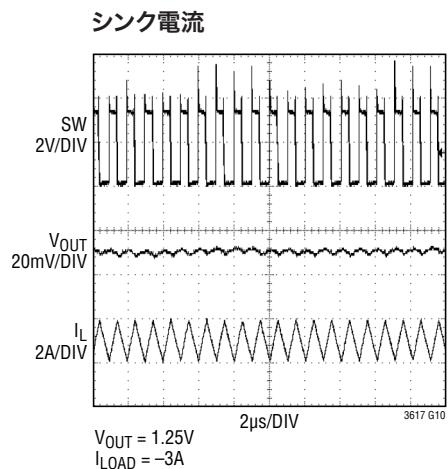

LTC3617はモノリシック、固定周波数、電流モードの降圧DC/DCコンバータです。通常動作時、内部のトップ・パワースイッチ(PチャネルMOSFET)が各クロック・サイクルの始点でオンします。電流コンパレータがトリップしてトップ・パワースイッチをオフするまで、インダクタを流れる電流が増加します。電流コンパレータがトリップする場合のピーク・インダクタ電流は、ITHピンの電圧によって制御されます。誤差アンプは、V<sub>FB</sub>ピンに接続された抵抗分割器からの帰還信号を、VTTRピンのリファレンス電圧と比較することによってITHピンの電圧を調節します。VTTRは、VDDQINピンの1/2の電圧に等しいオペアンプ・バッファ出力です。負荷電流が増加すると、リファレンスに比べて帰還電圧が低下します。誤差アンプは平均インダクタ電流が新しい負荷電流に釣り合うまでITH電圧を上昇させます。ITHピンの標準電圧範囲は0.2V～1.05Vで、0.575Vがゼロ電流に対応します。

トップ・パワースイッチがオフすると、ボトム電流リミットに達するか、次のクロック・サイクルが開始されるまで同期ボトム・パワースイッチ(NチャネルMOSFET)がオンします。ボトム電流リミットは標準で-10Aに設定されます。

RTがSV<sub>IN</sub>に接続されていると、動作周波数は既定で2.25MHzになります。あるいは、RTピンとグランドの間に接続された外部抵抗によっても、RTピンに印加するクロック信号によって、動作周波数を設定することができます。スイッチング周波数は300kHz～4MHzに設定することができます。

過電圧コンパレータと低電圧コンパレータは、出力電圧が設定ポイントから±8% (標準)を超えて変化すると、PGOOD出力をLowに引き下げます。

### VTTR電圧バッファ出力

内部の高精度オペアンプ・バッファは、VDDQIN・0.5に等しいVTTRピン電圧を生成します。VTTRには最大10mAのソースおよびシンク能力があり、最大0.1μFのバイパス・コンデンサで安定します。約20mAの短絡電流リミットが設定されており、オペアンプの損傷を防いでいます。VTTRは、出力電圧を制御する誤差アンプのリファレンス電圧としても使用されます。したがって、このピンに対する大きな過渡電圧は出力時の動きに影響を与えます。

### V<sub>IN</sub>過電圧保護

内部パワーMOSFETデバイスを過渡電圧スパイクから保護するために、LTC3617はV<sub>IN</sub>ピンの過電圧状態を連続してモニタします。V<sub>IN</sub>が6.5Vを超えると、レギュレータは両方のMOSFETをオフして動作を一時停止します。過電圧状態が解消されると、レギュレータはソフトスタート機能を実行します。

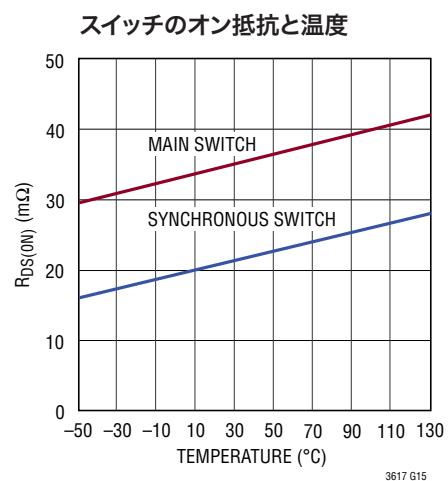

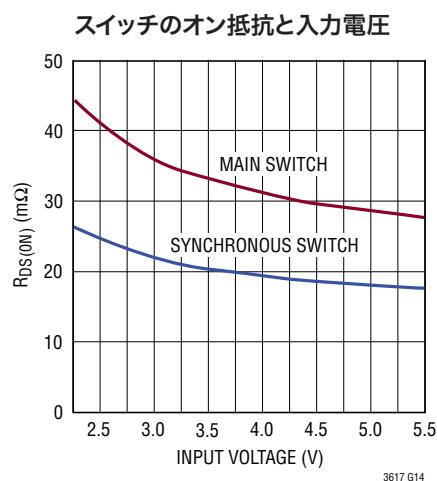

### 低電源動作

LTC3617は2.25Vの入力電源電圧まで動作するように設計されています。低い入力電源電圧で考慮すべきことは、PチャネルとNチャネルのパワースイッチのR<sub>DS(ON)</sub>が増加することです。ユーザーは、低い入力電圧でLTC3617が100%デューティ・サイクルで使用されるときの電力損失を計算して、サーマル・リミットを超えないようにする必要があります。「標準的性能特性」のグラフを参照してください。

### 短絡保護

電流コンパレータがトップ・パワースイッチをオフする場合のピーク・インダクタ電流は、ITHピンの電圧によって制御されます。

出力電流が増加すると、誤差アンプは平均インダクタ電流が新しい負荷電流に釣り合うまで、ITHピンの電圧を上昇させます。通常動作では、LTC3617は最大ITHピン電圧を、標準10Aのピーク・インダクタ電流に対応する約1.05Vにクランプします。

出力がグランドに短絡すると、インダクタ電流は1スイッチング・サイクルの間非常にゆっくり減衰します。電流暴走が発生しないように、インダクタ電流には第2の電流リミットが設定されています。ボトムMOSFETを介して測定されるインダクタ電流が標準12Aを超えて増加すると、トップ・パワーMOSFETがオフに保たれ、インダクタ電流がこのリミットを下回るまでスイッチング・サイクルをスキップします。

# LTC3617

## アプリケーション情報

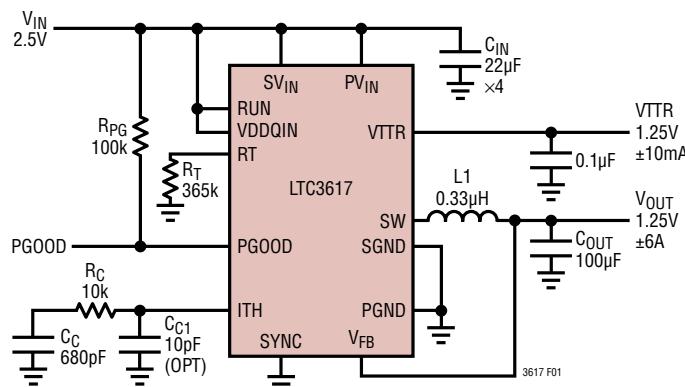

LTC3617の基本的な応用回路を図1に示します。

### 動作周波数

動作周波数の選択には、効率と部品サイズの間のトレードオフが必要です。動作周波数を高くすると、小さい値のインダクタとコンデンサを使うことができます。

低い周波数で動作させると内部ゲートの充電による損失が減り、効率が改善されるものの、出力電圧リップルを低く抑えるには、インダクタンスや容量の値を大きくする必要があります。

LTC3617の動作周波数は、RTピンとグランド間に接続した外部抵抗によって決まります。この抵抗の値により、発振器内の内部タイミング・コンデンサを充放電するのに使われるランプ電流が設定されます。この抵抗の値は次式を使って計算することができます。

$$R_T = \frac{3.82 \cdot 10^{11} \text{Hz}}{f_{\text{OSC}} (\text{Hz})} \Omega - 16 \text{k}\Omega$$

最大4MHzの周波数も可能ですが、LTC3617の最小オン時間により、動作デューティ・サイクルの最小値が制限されます。最小オン時間は標準80nsであるため、最小デューティ・サイクルは  $80\text{ns} \cdot f_{\text{OSC}}(\text{Hz}) \cdot 100\%$  になります。

図1. 2.5V入力、1.25V/±6A出力、1MHz動作

RTピンをSVINに接続すると、内部動作周波数は既定の2.25MHz±20%に設定されます。

### 周波数同期

SYNCピンに方形波クロック信号を印加することにより、LTC3617の内部発振器を外部周波数に同期させることができます。同期動作の間、トップ・スイッチのターンオンは外部周波数ソースの立ち下がりエッジにロックします。同期周波数範囲は300kHz～4MHzです。

RTピンの抵抗によって設定する周波数は、外部クロック周波数と同じにしてください。これにより、クロック信号を印加または遮断した際に内部発振器が適正に調整されます。

図2. スイッチング周波数の設定

## アプリケーション情報

### インダクタの選択

与えられた入力電圧と出力電圧に対するリップル電流は、インダクタの値と動作周波数によって決まります。リップル電流  $\Delta I_L$  は  $V_{IN}$  が高いほど増加し、インダクタンスが高いほど減少します。

$$\Delta I_L = \left( \frac{V_{OUT}}{f_{SW} \cdot L} \right) \cdot \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

リップル電流を小さくすると、インダクタのコア損失、出力コンデンサのESR損失、出力電圧リップルが減少します。リップル電流を選択するための妥当な出発点は  $\Delta I_L = 0.3 \cdot I_{OUT(MAX)}$  です。最大  $V_{IN}$  でリップル電流が最大になります。リップル電流が規定された最大値を超えないよう、次式に従ってインダクタンスを選択してください。

$$L = \left( \frac{V_{OUT}}{f_{SW} \cdot \Delta I_{L(MAX)}} \right) \cdot \left( 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right)$$

### インダクタのコアの選択

$L$  の値が求まつたら、次にインダクタの種類を選択します。実際のコア損失は、インダクタ値が同じならばコア・サイズは無関係ですが、選択したインダクタンスに大きく依存します。インダクタンスが大きいほどコア損失が減少します。インダクタンスを大きくするにはワイヤの巻数を増やす必要があり、よって銅損失が増加してしまいます。

フェライトを使ったタイプはコア損失がきわめて低いため高いスイッチング周波数に適しており、設計目標を銅損失と飽和防止に集中することができます。フェライト・コアの材質は「ハードに」飽和します。つまり、設計ピーク電流を超えるとインダクタンスが急激に減少します。

このため、インダクタのリップル電流が急増して、最終的に出力電圧リップルが増加します。フェライト・コアは、決して飽和させないでください。

コアの材質と形状が異なると、インダクタのサイズ/電流の関係および価格/電流の関係が変化します。フェライトやパーマロイを素材とするトロイド・コアやシールドされたポット型コアは小型で、エネルギー放射は大きくありませんが、同等の特性を有する鉄粉コアのインダクタより通常は高価です。使用するインダクタの種類の選択は、主として価格とサイズの要件や放射フィールド/EMIの要件に依存します。表1に、LTC3617のアプリケーションで適切に動作する標準的な表面実装インダクタの例を示します。

### 入力コンデンサ( $C_{IN}$ )の選択

連続モードでは、トップPチャネルMOSFETのソース電流は、デューティ・サイクルが  $V_{OUT}/V_{IN}$  の方形波になります。大きな入力過渡電圧を防止するには、 $V_{IN}$  には最大RMS電流に対応できるサイズの低ESRコンデンサを使用する必要があります。

コンデンサの最大RMS電流は次式で与えられます。

$$I_{RMS} = I_{OUT(MAX)} \cdot \frac{V_{OUT}}{V_{IN}} \cdot \sqrt{\left( \frac{V_{IN}}{V_{OUT}} - 1 \right)}$$

この式は、 $V_{IN} = 2 \cdot V_{OUT}$  のとき最大値をとります。ここで、 $I_{RMS}$  は  $I_{OUT}/2$  です。大きく変化させてもそれほど状況が改善されないため、設計では一般的にこの単純なワーストケース条件が使用されます。コンデンサ・メーカーの規定するリップル電流定格は多くの場合2000時間だけの寿命試験に基づいているので、コンデンサを更にディレーティングするか、必要とされるよりも高い温度定格のコンデンサを選択することを推奨します。設計でのサイズまたは高さの要件に適合させるため、複数のコンデンサを並列に接続することもできます。

## アプリケーション情報

表1. 標準的な表面実装インダクタ

| インダクタンス<br>( $\mu$ H)                      | DCR<br>(m $\Omega$ ) | 飽和電流(A) | 寸法(mm)     | 高さ<br>(mm) |

|--------------------------------------------|----------------------|---------|------------|------------|

| <b>Vishay IHLP-2525CZ-01</b>               |                      |         |            |            |

| 0.10                                       | 1.5                  | 60      | 6.5 × 6.9  | 3          |

| 0.15                                       | 1.9                  | 52      | 6.5 × 6.9  | 3          |

| 0.20                                       | 2.4                  | 41      | 6.5 × 6.9  | 3          |

| 0.22                                       | 2.5                  | 40      | 6.5 × 6.9  | 3          |

| 0.33                                       | 3.5                  | 30      | 6.5 × 6.9  | 3          |

| 0.47                                       | 4                    | 26      | 6.5 × 6.9  | 3          |

| <b>Sumida CDMC6D28 Series</b>              |                      |         |            |            |

| 0.2                                        | 2.5                  | 21.7    | 7.25 × 6.5 | 3          |

| 0.3                                        | 3.2                  | 15.4    | 7.25 × 6.5 | 3          |

| 0.47                                       | 4.2                  | 13.6    | 7.25 × 6.5 | 3          |

| <b>Cooper HCM0703 Series</b>               |                      |         |            |            |

| 0.22                                       | 2.8                  | 40      | 6.8 × 7.1  | 3.0        |

| 0.47                                       | 4.2                  | 26      | 6.8 × 7.1  | 3.0        |

| 0.68                                       | 5.5                  | 25      | 6.8 × 7.1  | 3.0        |

| <b>Würth Electronik WE-HC744310 Series</b> |                      |         |            |            |

| 0.24                                       | 1.8                  | 40      | 7 × 6.9    | 3.0        |

| 0.52                                       | 3.7                  | 20      | 7 × 6.9    | 3.0        |

| <b>Coilcraft SLC7530 Series</b>            |                      |         |            |            |

| 0.100                                      | 0.123                | 20      | 7.5 × 6.7  | 3          |

| 0.188                                      | 0.100                | 21      | 7.5 × 6.7  | 3          |

| 0.272                                      | 0.100                | 14      | 7.5 × 6.7  | 3          |

| 0.350                                      | 0.100                | 11      | 7.5 × 6.7  | 3          |

| 0.400                                      | 0.100                | 8       | 7.5 × 6.7  | 3          |

出力コンデンサ( $C_{OUT}$ )の選択

$C_{OUT}$ の選択は通常、電圧リップルおよび負荷ステップ過渡を最小限に抑えるために必要なESRによって決まります(低ESRセラミック・コンデンサについては次のセクションで説明します)。一般に、ESRの要件が満たされれば、その容量はフィルタリング機能にも十分です。出力リップル  $\Delta V_{OUT}$  は次式で求められます。

$$\Delta V_{OUT} \leq \Delta I_L \cdot \left( ESR + \frac{1}{8 \cdot f_{SW} \cdot C_{OUT}} \right)$$

ここで、 $f_{OSC}$ は動作周波数、 $C_{OUT}$ は出力容量、 $\Delta I_L$ はインダクタを流れるリップル電流です。 $\Delta I_L$ は入力電圧に応じて増加するため、出力リップルは入力電圧が最大のとき最大になります。

表面実装のアプリケーションでは、アプリケーションに必要な容量、ESRまたはRMS電流を扱うための要件を満たすべく、複数のコンデンサの並列接続が必要になることがあります。アルミ電解、特殊ポリマー、セラミック、および乾式タンタルの各コンデンサは全て表面実装パッケージで入手できます。

タンタル・コンデンサでは最大の容量密度が得られますが、ESRが大きくなりうるので、スイッチング電源で使用するにはサーボテストが実行される必要があります。ESRが著しく大きいアルミ電解コンデンサも、リップル電流定格および長期信頼性に配慮すれば、コストがきわめて重視されるアプリケーションに適用できる場合が多いです。

## 入力と出力のセラミック・コンデンサ

セラミック・コンデンサは最もESRが小さく費用対効果が高いものの、電圧係数と温度係数も高く、容量密度は低く、可聴圧電効果を呈します。更に、セラミック・コンデンサの高いQがトレース・インダクタンスを伴って、大きなリンクギングを引き起こす場合があります。

ESRが非常に小さいため、スイッチング・レギュレータとしての使用には適していますが、入出力の全てにセラミック・コンデンサを使用する場合は細心の注意が必要です。

セラミック・コンデンサは温度の影響を受けやすいので、設計者は動作温度の全範囲でループの安定性を確認する必要があります。大きな温度係数と電圧係数の影響を最小限に抑えるため、X5RまたはX7Rのセラミック・コンデンサのみを使用してください。

入力にセラミック・コンデンサを使用し、ACアダプタなどの長いコードを通して給電すると、出力の負荷ステップによってVINピンにリンクギングが発生する場合があります。このリンクギングは、よくても出力に結合してループの不安定性と誤認され、最悪の場合には、デバイスに損傷を与えるほど大きくなるおそれがあります。

## アプリケーション情報

セラミック・コンデンサのESRは非常に小さいため、代わりに入力コンデンサと出力コンデンサが電荷保存の要件を満たす必要があります。負荷ステップ発生時には、帰還ループがスイッチ電流を増加させて負荷を十分に支えられるようになるまで、出力コンデンサが即座に電流を供給する必要があります。帰還ループが応答するための所要時間は、補償部品と出力コンデンサのサイズに依存します。負荷ステップに応答するには通常、3~4スイッチング・サイクルを要しますが、出力が直線的に低下するのは最初のサイクルのみです。出力の垂下( $V_{DROOP}$ )は通常、最初のサイクルの直線的な電圧低下の約2~4倍です。ただし、この動きは補償部品の値に依存して変化することがあります。したがって、およそ以下の出力コンデンサのサイズを出発点に検討を開始することを推奨します。

$$C_{OUT} \approx \frac{3.5 \cdot \Delta I_{OUT}}{f_{SW} \cdot V_{DROOP}}$$

これは近似式であり、デューティ・サイクルや負荷ステップの要件によっては、更に大きな容量が必要になる場合があります。

ほとんどのアプリケーションでは、電源インピーダンスが非常に小さいため、入力コンデンサは単に高周波をバイパスするために必要とされます。

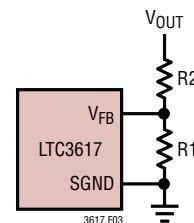

## 出力電圧のプログラミング

ほとんどのアプリケーションでは、 $V_{OUT}$ が $V_{FB}$ に直接接続されます。この場合、出力電圧は $V_{DDQIN}$ ピンの電圧の半分になります。

$$V_{OUT} = \frac{V_{DDQIN}}{2}$$

出力との関係をこれとは異なるものに設定する必要がある場合、 $V_{OUT}$ と $V_{FB}$ の間に外部抵抗分割器が使用できます。この場合の出力電圧は、次式に従って設定されます。

$$V_{OUT} = \frac{V_{DDQIN}}{2} \cdot \left( 1 + \frac{R2}{R1} \right)$$

図3. 出力電圧の設定

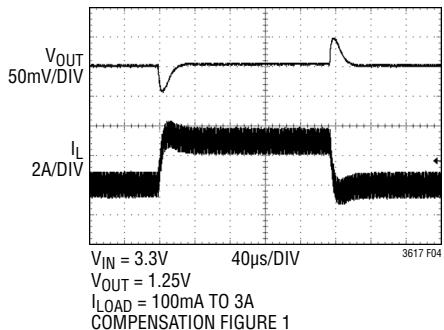

## 内部補償と外部補償

レギュレータのループ応答は、負荷電流の過渡応答を測定することで確認できます。スイッチング・レギュレータはDC負荷電流ステップに対して応答するのに数サイクルを要します。負荷ステップが発生すると、 $V_{OUT}$ は $\Delta I_{LOAD} \cdot ESR$ だけ変動します。ここで、 $ESR$ は $C_{OUT}$ の等価直列抵抗です。 $\Delta I_{LOAD}$ は $C_{OUT}$ の充放電も開始し、これが帰還誤差信号を発生することで、レギュレータを電流変化に適応させ、 $V_{OUT}$ を定常値に回復させます。この回復期間に $V_{OUT}$ をモニタして、過度のオーバーシュートやリンギングが発生していないければ、ループの安定性に問題がないことを確認できます。デバイスに用意されているITHピンにより、広い範囲の出力容量に対して過渡応答を最適化できます。

図1でITHに接続されている外部部品( $R_C$ と $C_C$ )は、ほとんどのアプリケーションで適切な補償動作が得られるため、検討の出発点として使用できます。PCBの最終レイアウトが完了し、出力コンデンサの種類と容量値が具体的に決定したら、これらの値を多少変更して過渡応答を最適化できます。出力コンデンサのさまざまな種類と値によってループの利得と位相が決まるので、まず出力コンデンサを選択する必要があります。ループの利得は $R_C$ を大きくすると増加し、ループの帯域幅は $C_C$ を小さくすると広くなります。 $C_C$ を減少させるのと同じ比率で $R_C$ を増加させればゼロ周波数が変化しないので、最も重要な周波数範囲での帰還ループの位相シフトを一定に保つことができます。出力電圧のセトリング特性は、閉ループ・システムの安定性に関係します。外部コンデンサ $C_{C1}$ (図1)はループの安定化には必要ありませんが、そのノードに結合している可能性のある高周波ノイズを除去するのに役立ちます。

## アプリケーション情報

標準的応用例に示した最初の回路では、ステップ応答を改善するために、より高速の補償回路を使用しています。

しかし待ってください。大容量の( $>1\mu\text{F}$ )電源バイパス・コンデンサが接続されている負荷のスイッチが入れられると、更に大きな過渡が発生します。放電しきったバイパス・コンデンサが実質的に $C_{\text{OUT}}$ と並列接続状態になるため、 $V_{\text{OUT}}$ が急激に低下します。負荷スイッチの抵抗が小さく、かつ短時間で駆動されると、どのようなレギュレータでも出力電圧の急激なステップ変化を防止できるほど素早く電流供給を変えることはできません。デューティ・サイクルと負荷ステップの要件によっては、更に大きな出力容量が必要になる場合があります。

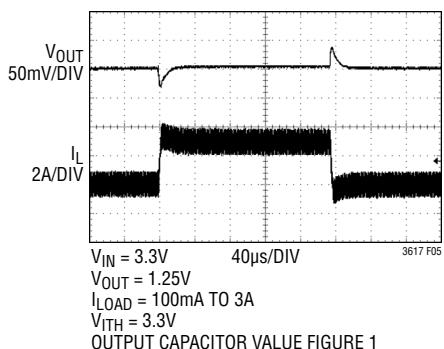

### 内部補償

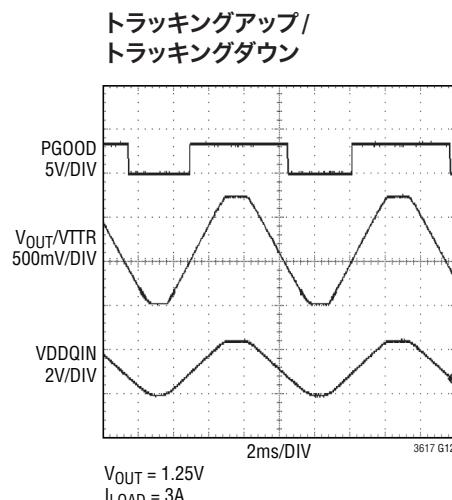

LTC3617には固定内部ループ補償ネットワークを使用するオプションがあり、所要の外部部品点数と設計時間を削減できます。この内部ループ補償ネットワークは、ITHピンをSVINに

接続することで選択できます。ただし、内部補償を選択すると、0Vへのトラッキングダウン時に出力電圧が不安定になる場合があります。

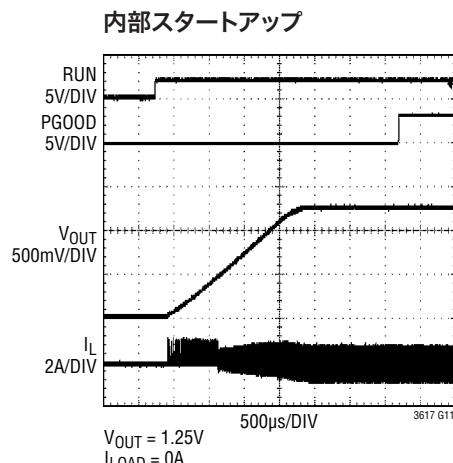

### シャットダウンとソフトスタート

RUNピンを使ってLTC3617をシャットダウンできます。RUNピンをSGNDに接続すると、レギュレータは低消費電流( $I_Q < 1\mu\text{A}$ )のシャットダウン状態になります。

RUNピンをHighに引き上げると、VTTRピン電圧を約850mV/msというゆっくりとした速度でランプアップする内部ソフトスタート機能を使用してレギュレータをイネーブルできます。このスタートアップでは、VTTRピンの電圧が約0.45Vを超えるまでレギュレータが不連続モードで動作します。

RUNピンをLowに引き下げた場合、レギュレータは両方のパワーMOSFETを遮断する前に、インダクタのピーク電流を強制的に0A近辺まで放電させます。

### 出力パワーグッド

LTC3617のPGOOD出力は、 $17\Omega$ (標準値)のオープン・ドレンのプルダウンMOSFETによって駆動されます。このMOSFETは、スタートアップから3ms~4ms後、および出力電圧が $0.5 \cdot V_{\text{DDQIN}} \pm 5\%$ (標準値)以内になるとターンオフします。これによってPGOODの電圧は外部プルアップ抵抗(標準値100k)を介して上昇します。出力電圧がレギュレーション・ウインドウである $0.5 \cdot V_{\text{DDQIN}} \pm 8\%$ (標準値)の範囲を外れるか、VTTRピンが0.45Vを下回ると、オープン・ドレン出力はLowに引き下げられ、PGOODピン電圧が低下します。過渡状態または $V_{\text{OUT}}$ が動的に変化している間にPGOODに無用なグリッチが生ずることのないように、LTC3617のPGOODの立ち下がりエッジには、約105μsのフィルタ時間が設定されています。

### 効率に関する検討事項

スイッチング・レギュレータの効率は「出力電力÷入力電力×100%」で表されます。個々の損失を解析して、効率を制限する要素がどれであり、また何が変化すれば最も効率が改善されるかを判断できる場合がよくあります。効率は次式で表すことができます。

$$\text{効率} = 100\% - (L_1 + L_2 + L_3 + \dots)$$

ここで、 $L_1$ 、 $L_2$ などは入力電力に対するパーセンテージで表した個々の損失です。

図4. 負荷ステップ過渡(外部補償)

図5. 負荷ステップ過渡(内部補償)

## アプリケーション情報

回路内の電力を消費する全ての要素で損失が生じますが、損失の大部分は2つの主な損失要因によって生じます。 $V_{IN}$ の消費電流による損失と $I^2R$ 損失です。非常に低い負荷電流では $V_{IN}$ の消費電流による損失が効率の損失を支配するのに對して、中程度から高い負荷電流では $I^2R$ 損失が効率の損失を支配します。標準的な効率曲線では、非常に低い負荷電流での効率曲線は誤解を与えかねません。というのは、実際の電力損失は通常大したことはないからです。

1.  $V_{IN}$ の消費電流は2つの要素からなります。「電気的特性」で与えられているDCバイアス電流および内部のメイン・スイッチと同期スイッチのゲート充電電流です。内部パワーMOSFETスイッチのゲート容量をスイッチングすると、ゲート充電電流が流れます。ゲートが“L”から“H”、そして再び“L”に切り替わるたびに、 $V_{IN}$ からグランドに微小電荷 $dQ$ が移動します。したがって、 $dQ/dt$ はゲート充電により $V_{IN}$ に流入する電流であり、一般にDCバイアス電流より大きくなります。DCバイアス損失とゲート電荷損失は両方とも $V_{IN}$ に比例するので、それらの影響は電源電圧が高くなると顕著になります。

2.  $I^2R$ 損失は内部スイッチの抵抗 $R_{SW}$ と外部インダクタの抵抗 $R_L$ から計算されます。連続モードでは、インダクタ $L$ を流れる平均出力電流は、メイン・スイッチと同期スイッチの間で「こま切れ」にされます。したがって、SWピンを見たときの直列抵抗は、次式のとおり、トップMOSFETとボトムMOSFETの両方の $R_{DS(ON)}$ およびデューティ・サイクル(DC)の関数になります。

$$R_{SW} = (R_{DS(ON)TOP})(DC) + (R_{DS(ON)BOT})(1 - DC)$$

トップMOSFETとボトムMOSFETの $R_{DS(ON)}$ は、いずれも「標準的性能特性」の曲線から求めることができます。 $I^2R$ 損失を求めるには、単に $R_{SW}$ を $R_L$ に加え、その結果に平均出力電流の2乗を掛けます。

$C_{IN}$ や $C_{OUT}$ のESRによる損失やインダクタのコア損失など、他の損失は、一般に全損失の2%以下に過ぎません。

### 熱に関する検討事項

LTC3617は効率が高いため、ほとんどのアプリケーションで大きな発熱はありません。

ただし、LTC3617が、高い周囲温度、(ドロップアウトの場合のように)低い電源電圧、高いデューティ・サイクルで動作する高電流アプリケーションでは、放熱がデバイスの最大接合部温度を超えることがあります。接合部温度が約160°Cに達すると、両方のパワースイッチがオフし、SWノードが高インピーダンスになります。

LTC3617が最大接合部温度を超えるのを防ぐには、若干の熱解析が必要です。温度上昇は次式で与えられます。

$$T_{RISE} = (P_D) \cdot (\theta_{JA})$$

ここで、 $P_D$ はレギュレータの電力損失、 $\theta_{JA}$ はダイの接合部から周囲温度への熱抵抗です。接合部温度 $T_J$ は次式で与えられます。

$$T_J = T_A + T_{RISE}$$

ここで、 $T_A$ は周囲温度です。

一例として、LTC3617を $V_{IN} = 3.3V$ 、 $I_{OUT} = 6A$ 、 $f = 1MHz$ 、 $V_{OUT} = 1.25V$ のDDRアプリケーションで使用する場合について検討します。パワーMOSFETの等価抵抗 $R_{SW}$ は次のようになります。

$$\begin{aligned} R_{SW} &= R_{DS(ON)TOP} \cdot \frac{V_{OUT}}{V_{IN}} + R_{DS(ON)BOT} \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \\ &= 35m\Omega \cdot \frac{1.25}{3.3} + 25m\Omega \cdot \left(1 - \frac{1.25}{3.3}\right) = 28.79m\Omega \end{aligned}$$

無負荷の1MHz動作時の $V_{IN}$ 電流は約22mAであり、これにはスイッチング損失と内部バイアス電流損失、遷移損失、インダクタのコア損失、アプリケーション内の他の損失が含まれます。したがって、デバイスによる総電力損失は次のとおりです。

$$\begin{aligned} P_D &= I_{OUT}^2 \cdot R_{SW} + V_{IN} \cdot I_{VIN} \quad (\text{無負荷時}) \\ &= 36A^2 \cdot 28.79m\Omega + 3.3V \cdot 22mA = 1.11W \end{aligned}$$

QFN 3mm×5mmパッケージの接合部から周囲温度への熱抵抗 $\theta_{JA}$ は、約43°C/Wです。したがって、周囲温度25°Cで動作するレギュレータの接合部温度は、およそ次の値になります。

$$T_J = 1.11W \cdot 43°C/W + 25°C = 73°C$$

## アプリケーション情報

この接合部温度は、25°Cにおける $R_{DS(ON)}$ から計算したものであることに注意が必要です。この抵抗も温度とともに増加するため、接合部温度をより大きな $R_{DS(ON)}$ を使って再計算することになります。73°Cでは $R_{SW}$ が15%増加すると仮定して再計算すると、新たな接合部温度は79°Cになります。したがって、実際の接合部温度が絶対最大定格の125°Cを超えないことを安全に判断できます。

非常に低い入力電圧では、スイッチ抵抗( $R_{DS(ON)}$ )が増加するので、接合部温度は更に高くなることに注意してください。高い周囲温度および低い入力電圧で最大負荷電流を使うことは推奨しません。

LTC3617の熱性能を最大にするには、露出パッドをグランド・プレーンに半田付けする必要があります。「PCボードのレイアウトのチェックリスト」を参照してください。

### 設計例

設計例として、以下の仕様のアプリケーションにLTC3617を使用する場合を考えます。

$V_{IN} = 2.5V$ 、 $V_{OUT} = 1.25V$ 、 $I_{OUT(MAX)} = 6A$ 、

$I_{OUT(MIN)} = 200mA$ 、 $f = 2.6MHz$  です。

最初に、タイミング抵抗を計算します。

$$R_T = \frac{3.82^{11}Hz}{2.6MHz} - 16k = 130k\Omega$$

次に、最大 $V_{IN}$ で約33%のリップル電流になるようにインダクタ値を計算します。

$$L = \left( \frac{1.25V}{2.6MHz \cdot 2A} \right) \cdot \left( 1 - \frac{1.25V}{2.5V} \right) = 0.12\mu H$$

0.1μHの標準値のインダクタを使用すると、最大リップル電流は以下のようになります。

$$\Delta I_L = \left( \frac{1.25V}{2.6MHz \cdot 0.1\mu H} \right) \cdot \left( 1 - \frac{1.25V}{2.5V} \right) = 2.4A$$

$C_{OUT}$ は、出力電圧リップルの要件を満たすESRとループの安定性に必要なバルク容量に基づいて選択します。この設計では、X5RまたはX7R誘電体による100μFセラミック・コンデンサを使用します。

次の最大電流定格を満たせるように $C_{IN}$ を選択します。

$$I_{RMS} = 6A \cdot \frac{1.25V}{2.5V} \cdot \sqrt{\left( \frac{2.5V}{1.25V} - 1 \right)} = 3A_{RMS}$$

ほとんどのアプリケーションでは、 $P_{VIN}$ は10μF～22μFコンデンサを4個使用してデカップリングすれば十分です。 $V_{FB}$ ピンを直接 $V_{OUT}$ ピンに接続すると、出力電圧は $V_{DDQIN}$ ピンの半分になります。この設計例の全回路を図1に示します。

### PCボードのレイアウトのチェックリスト

プリント回路基板をレイアウトするときには、以下のチェックリストを使用して LTC3617 が正しく動作するようにします。

1. グランド・プレーンの使用を推奨します。グランド・プレーン層を使用しない場合は、信号グランドと電源グランドを分離し、小信号用部品は1点でSGNDピンに戻し、この1点をLTC3617の近くでPGNDピンに接続します。

2. 入力コンデンサ( $C_{IN}$ )の(+)端子は $P_{VIN}$ ピンにできるだけ近づけ、(-)端子は露出パッド(PGND)にできるだけ近づけて接続します。このコンデンサは内部パワーMOSFETにAC電流を供給します。

3. スイッチング・ノードSWは、ノイズに敏感な小信号ノードの全てから離します。

4. 全ての層の全ての未使用領域を銅で覆います。銅で覆うことにより、電力部品の温度上昇を抑えることができます。最高の性能を得るには、この銅領域をPGND(露出パッド)に接続します。

5.  $V_{FB}$ ピンを $V_{OUT}$ ピンに直接接続します。

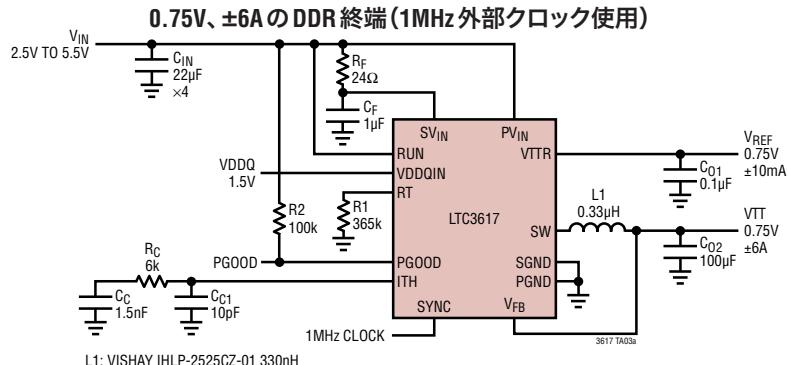

## 標準的応用例

1.25V、±6AのDDRメモリ終端電源(2.25MHz)

効率と負荷電流

負荷ステップ応答

## 標準的応用例

### 外部スタートアップ

### 出力トラッキングアップ/トラッキングダウン

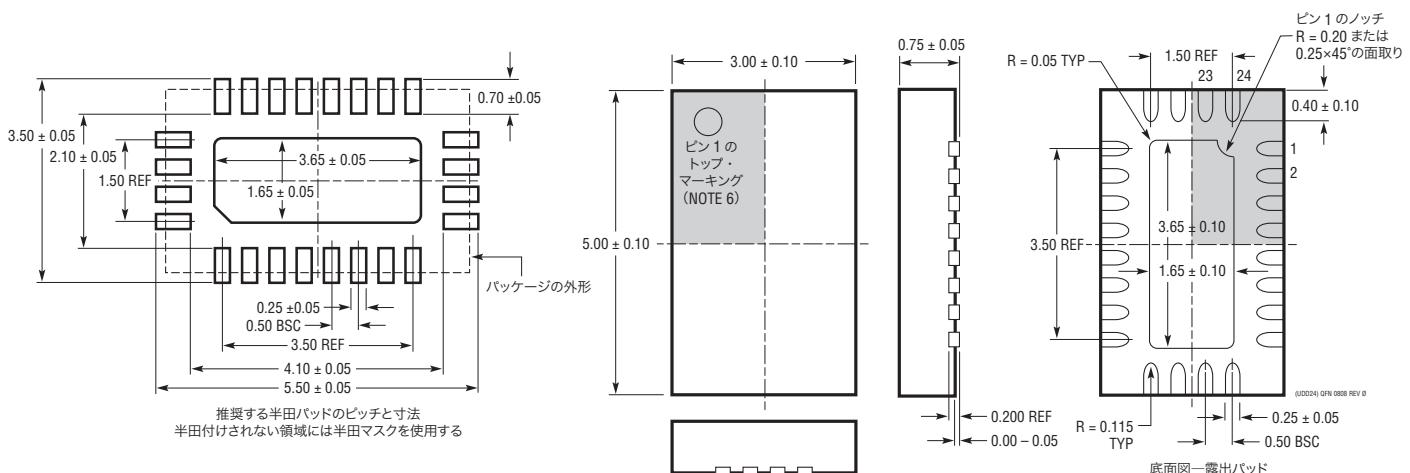

## パッケージ

**UDDパッケージ

24ピン・プラスチックQFN (3mm×5mm)

(Reference LTC DWG # 05-08-1833 Rev Ø)**

## 改訂履歴

| REV | 日付   | 概要                                                              | ページ番号            |

|-----|------|-----------------------------------------------------------------|------------------|

| A   | 7/11 | 「メイン制御ループ」セクションを更新<br>「出力パワーグッド」セクションを更新<br>「標準的応用例」とグラフの目盛りを更新 | 9<br>14<br>18、20 |

## 標準的応用例

## 関連製品

| 製品番号     | 説明                                                                        | 注釈                                                                                                                                                                     |

|----------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3616  | 5.5V、6A (I <sub>OUT</sub> )、4MHz 同期整流式降圧DC/DCコンバータ                        | 効率95%、V <sub>IN(MIN)</sub> = 2.25V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.6V、I <sub>Q</sub> = 70μA、I <sub>SD</sub> < 1μA、3mm×5mm QFN24 パッケージ            |

| LTC3612  | 5.5V、3A (I <sub>OUT</sub> )、4MHz 同期整流式降圧DC/DCコンバータ                        | 効率95%、V <sub>IN(MIN)</sub> = 2.25V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.6V、I <sub>Q</sub> = 70μA、I <sub>SD</sub> < 1μA、3mm×4mm QFN-20 TSSOP20E パッケージ  |

| LTC3418  | 5.5V、8A (I <sub>OUT</sub> )、4MHz 同期整流式降圧DC/DCコンバータ                        | 効率95%、V <sub>IN(MIN)</sub> = 2.25V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 380μA、I <sub>SD</sub> < 1μA、5mm×7mm QFN-38 パッケージ          |

| LTC3415  | 5.5V、7A (I <sub>OUT</sub> )、1.5MHz 同期整流式降圧DC/DCコンバータ                      | 効率95%、V <sub>IN(MIN)</sub> = 2.5V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.6V、I <sub>Q</sub> = 450μA、I <sub>SD</sub> < 1μA、5mm×7mm QFN-38 パッケージ           |

| LTC3416  | 5.5V、4A (I <sub>OUT</sub> )、4MHz 同期整流式降圧DC/DCコンバータ                        | 効率95%、V <sub>IN(MIN)</sub> = 2.25V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 64μA、I <sub>SD</sub> < 1μA、TSSOP20E パッケージ                 |

| LTC3413  | 5.5V、3A (I <sub>OUT</sub> シンク/ソース)、2MHz モノリシック同期整流式レギュレータ (DDR/QDRメモリ終端用) | 効率90%、V <sub>IN(MIN)</sub> = 2.25V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = V <sub>REF</sub> /2、I <sub>Q</sub> = 280μA、I <sub>SD</sub> < 1μA、TSSOP16E パッケージ |

| LTC3412A | 5.5V、2.5A (I <sub>OUT</sub> )、4MHz 同期整流式降圧DC/DCコンバータ                      | 効率95%、V <sub>IN(MIN)</sub> = 2.5V、V <sub>IN(MAX)</sub> = 5.5V、V <sub>OUT(MIN)</sub> = 0.8V、I <sub>Q</sub> = 60μA、I <sub>SD</sub> < 1μA、4mm×4mm QFN-16 TSSOP16E パッケージ   |